Patents

Literature

190results about How to "Solve the large amount of calculation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

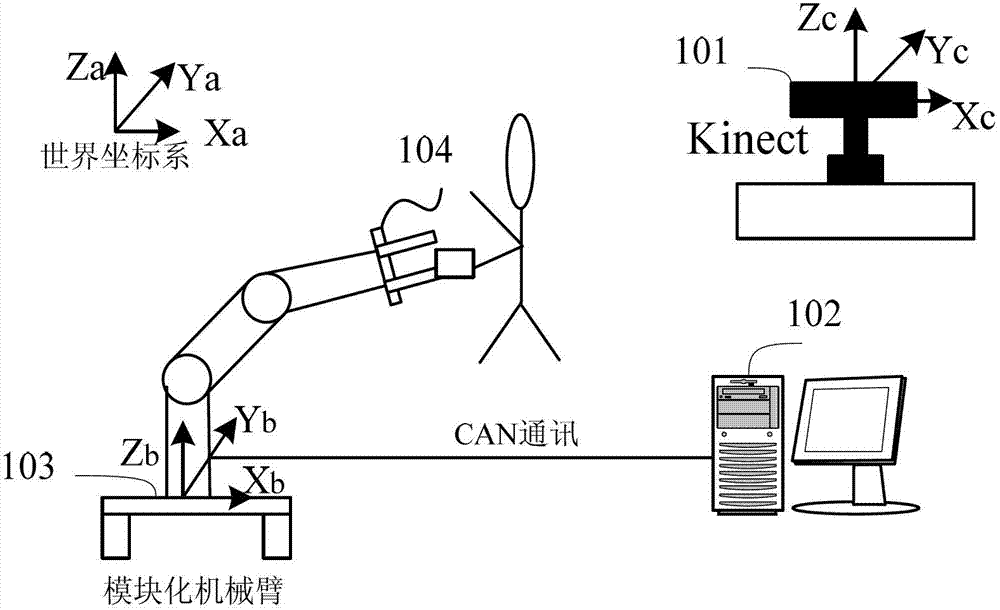

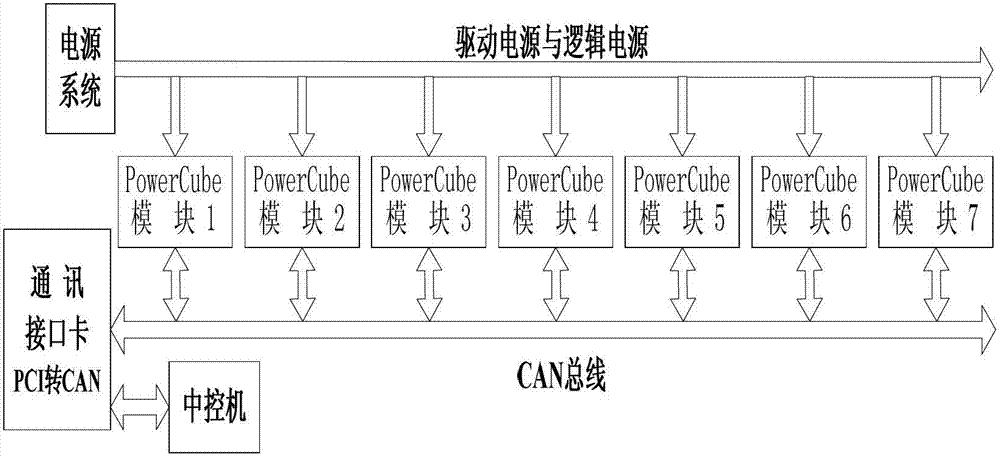

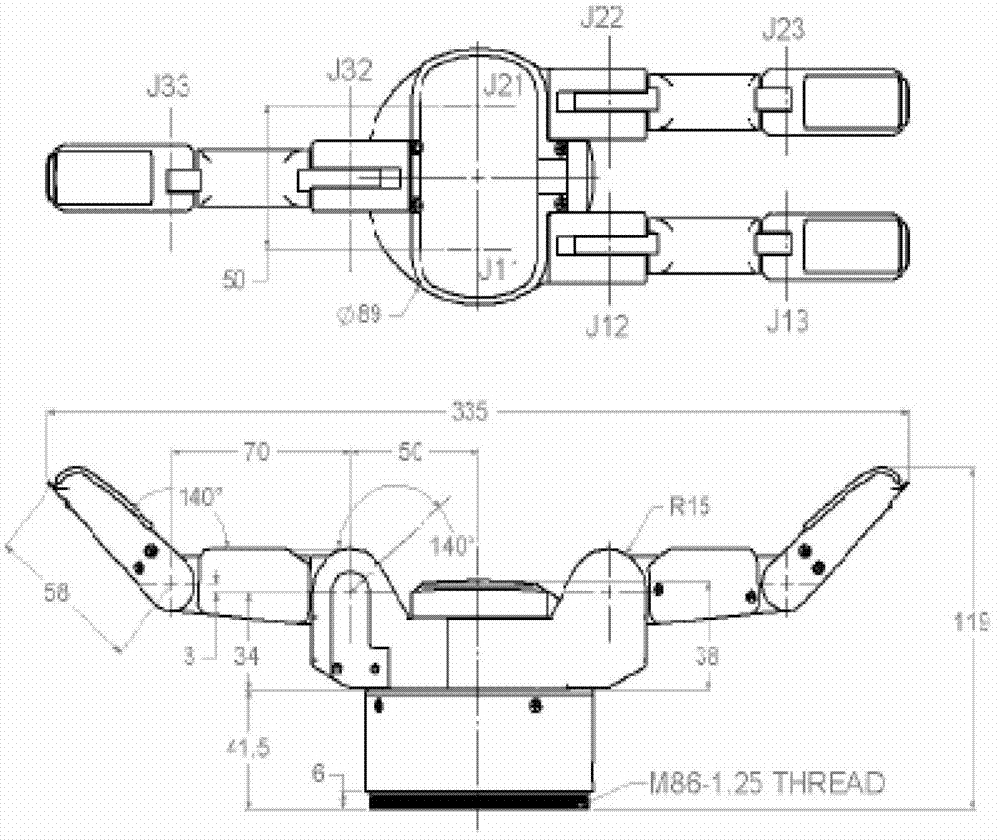

Man-machine cooperation device and method based on Kinect video camera

InactiveCN103170973AImprove noise immunitySolve the large amount of calculationProgramme-controlled manipulatorHuman bodyMan machine

The invention discloses a man-machine cooperation device and method based on a Kinect video camera. The man-machine cooperation device and method based on the Kinect video camera is mainly based on a Kinect video camera which is launched by the Microsoft Corporation recently so as to achieve detecting and tracking of a human body target. The man-machine cooperation device and method based on the Kinect video camera can accurately judge the position of a target object and the intention of a tester by utilizing Kinect human skeleton detecting technology, and therefore the risks which occur in the process of handover are avoided. Besides, a rail rapid transit (RRT) algorithm based on working space is provided to achieve route planning. Through repeated experimental verification, the system can conduct interpersonal handover safely.

Owner:UNIV OF SHANGHAI FOR SCI & TECH

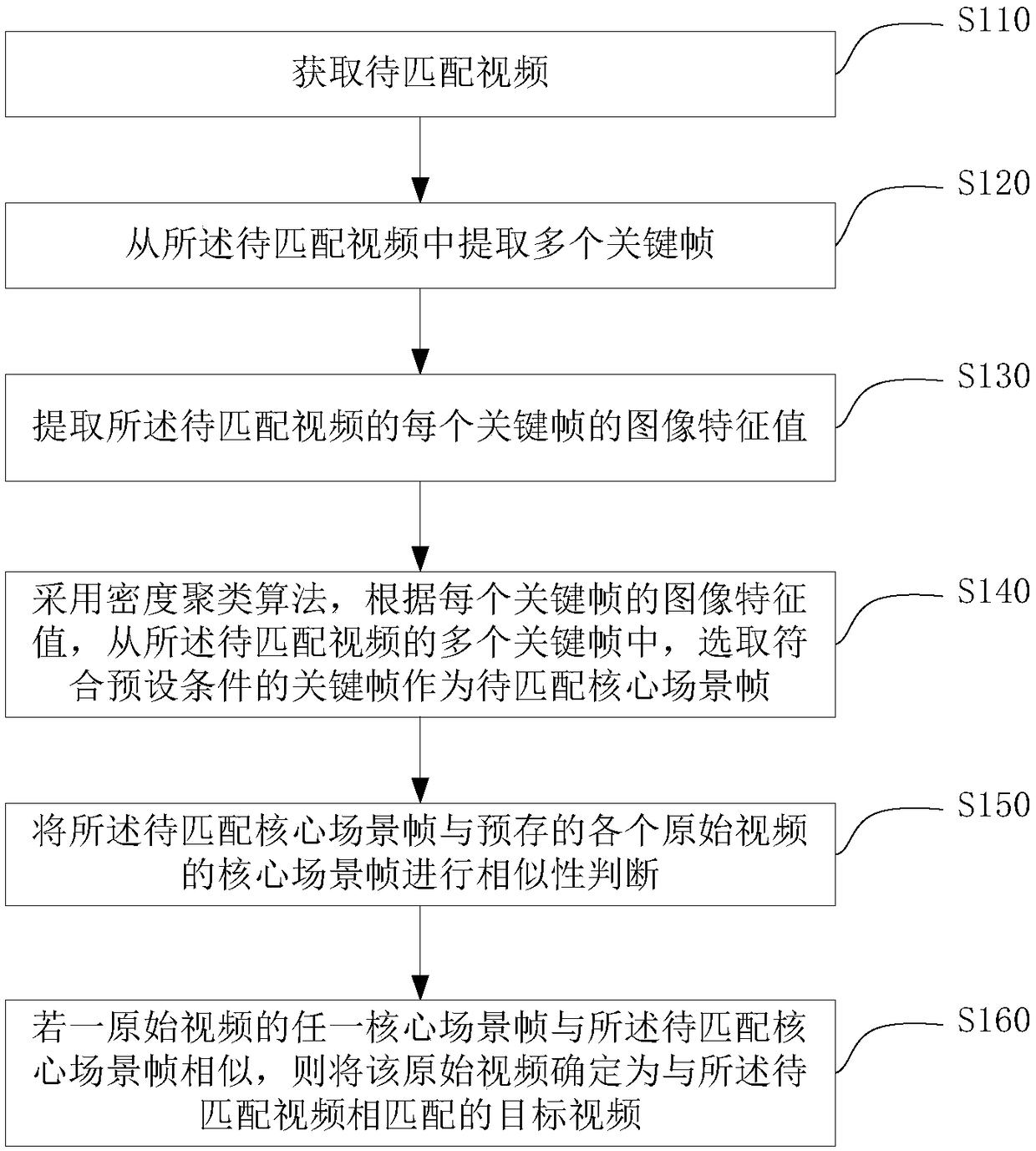

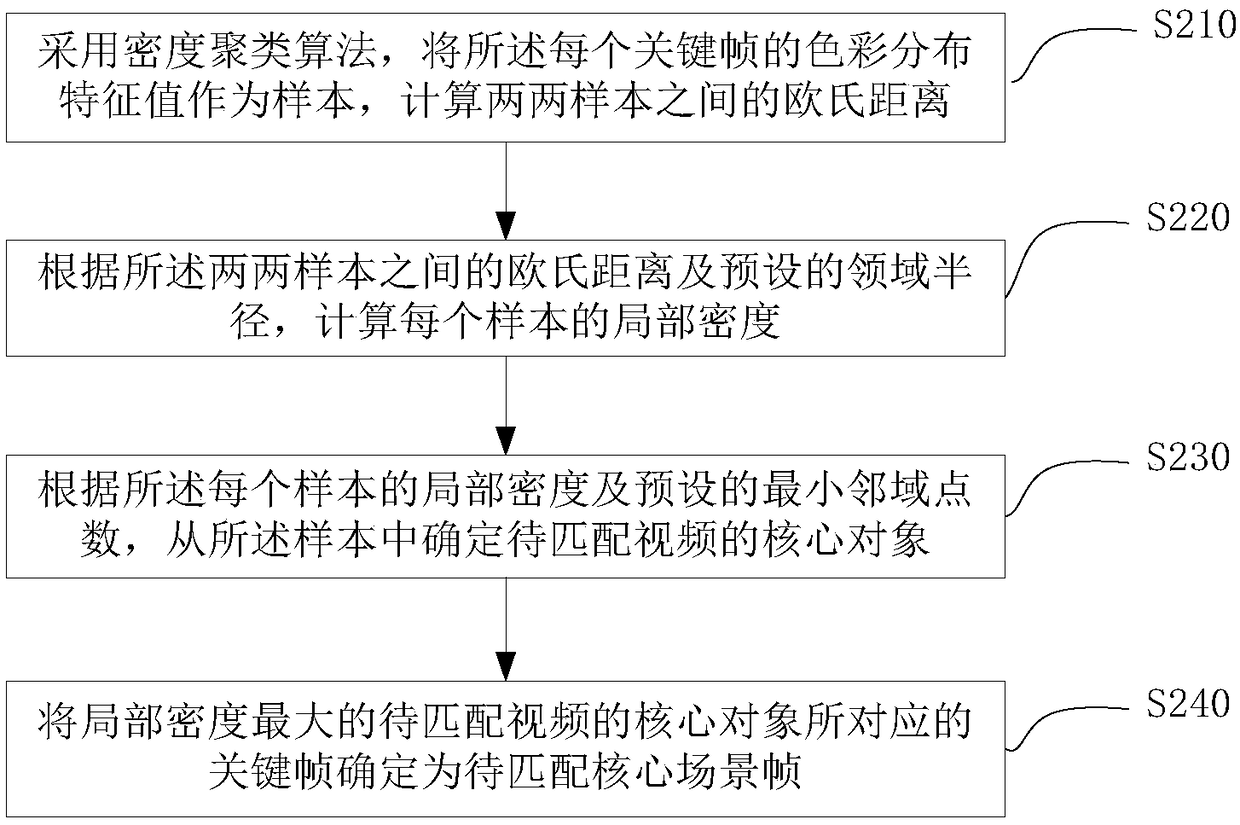

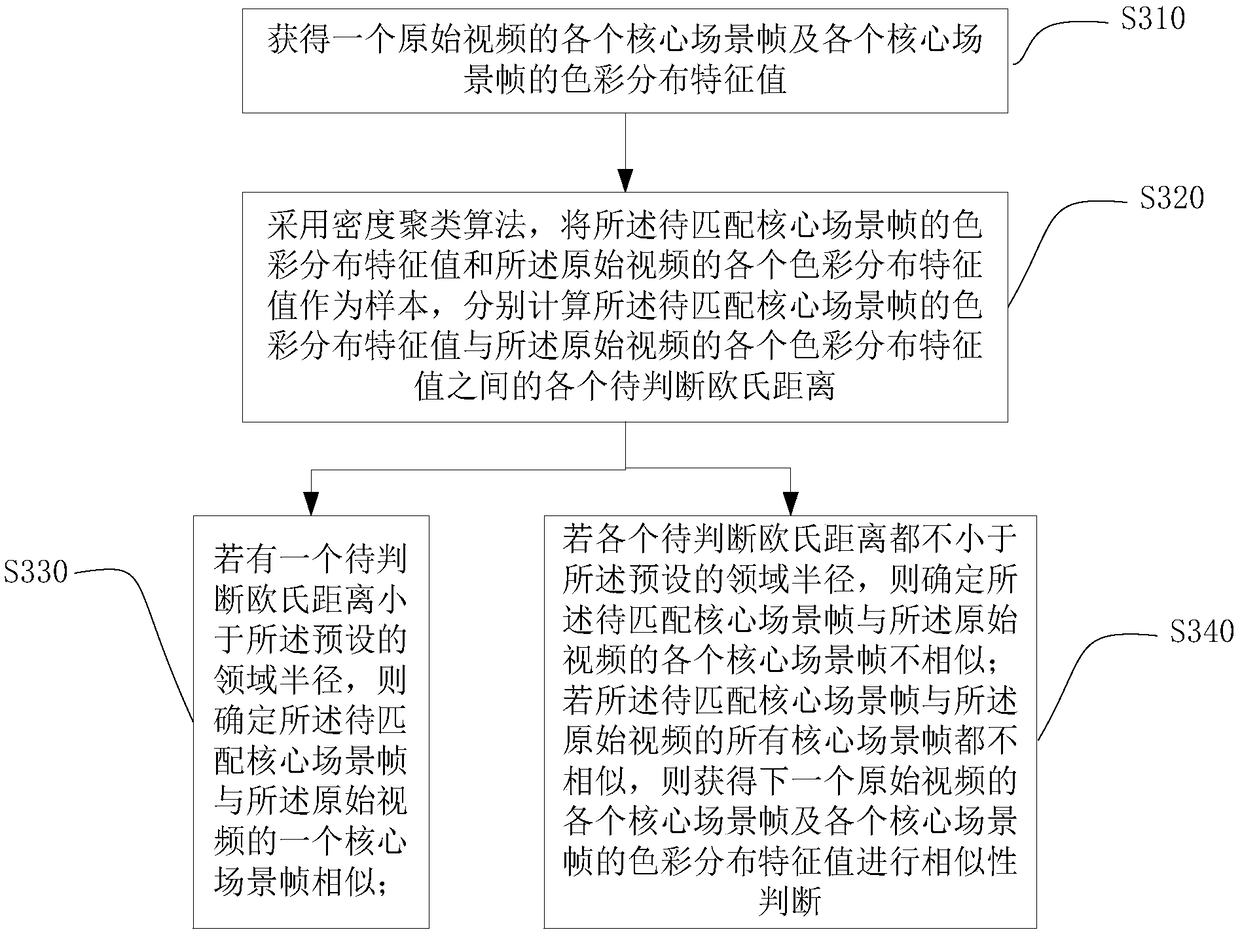

Video matching, retrieving, classifying and recommending method and device and electronic device

ActiveCN108416013AThe method of implementing classificationSolve the large amount of calculationCharacter and pattern recognitionSpecial data processing applicationsCluster algorithmImaging Feature

The embodiment of the invention provides a video matching, retrieving, classifying and recommending method and device and an electronic device. The video matching method includes the steps of acquiring a to-be-matched video; extracting a plurality of key frames from the to-be-matched video; extracting an image feature value of each key frame of the to-be-matched video; using a density clustering algorithm for selecting a key frame in line with preset conditions from the key frames of the to-be-matched video according to the image feature value of each key frame as a core scene frame to be matched; comparing the similarity between the core scene frame to be matched with pre-stored core scene frames of each original video; if any one core scene frame of an original video is similar to the core scene frame to be matched, determining the original video as a target video which is matched with the to-be-matched video. According to the embodiment, the problem of large computational amount dueto too many long video frames and frequent scene switching is solved.

Owner:BEIJING QIYI CENTURY SCI & TECH CO LTD

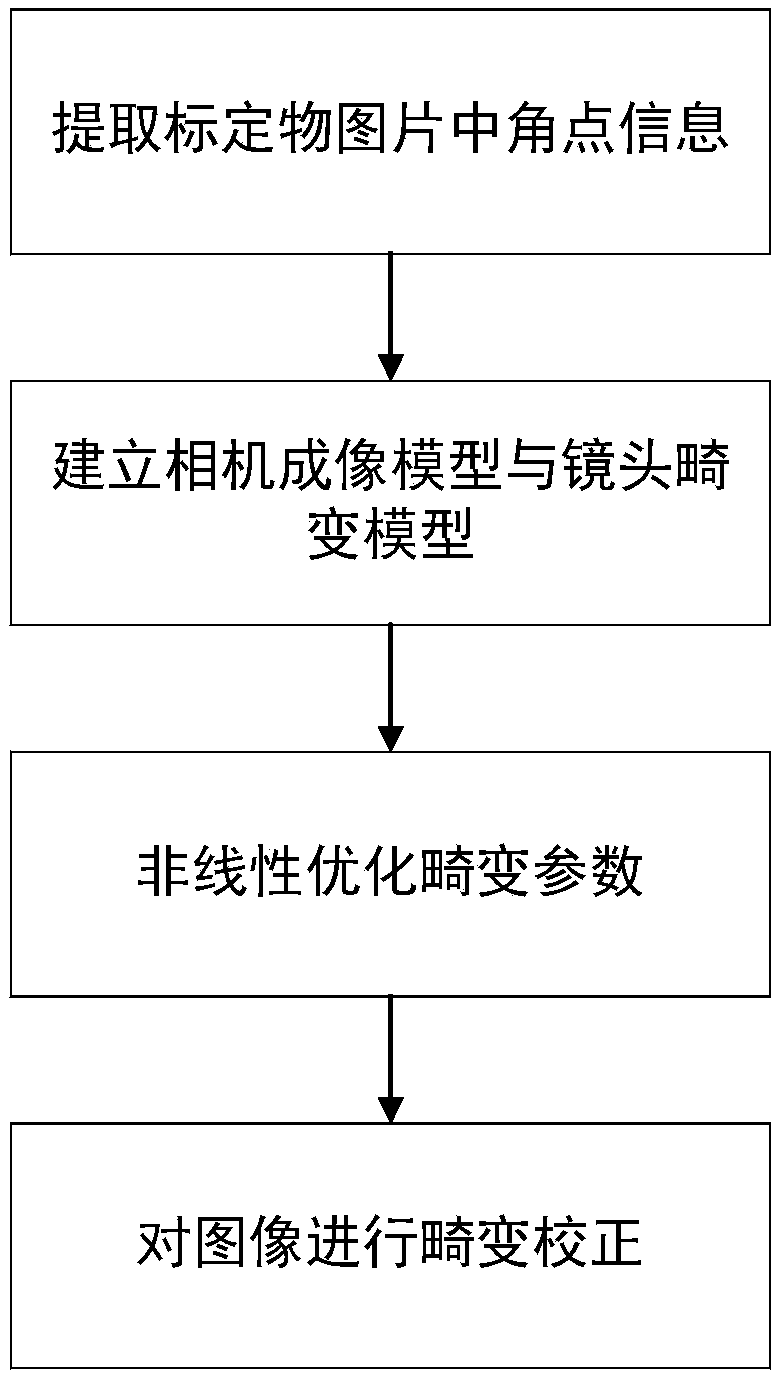

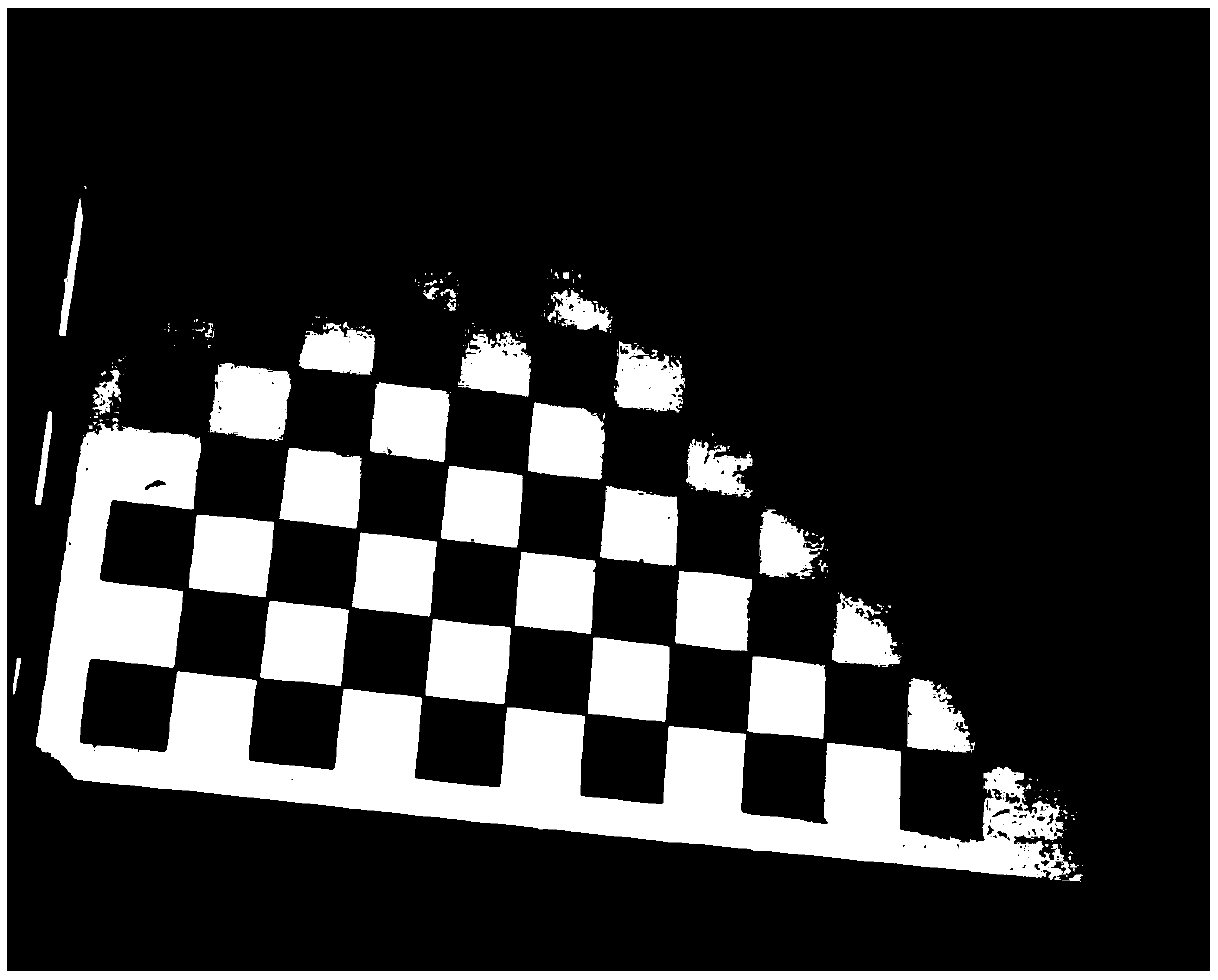

Robust lens distortion correction method

InactiveCN108876749ASolve complexitySolve the large amount of calculationImage enhancementImage analysisFeature extractionAngular point

The invention discloses a robust lens distortion correction method. The invention provides a method for separating lens distortion from camera parameters to be solved separately. The method comprisesthe following steps of: performing a feature extraction from a checkerboard calibration object by firstly performing angular point detection utilizing a Shi-Tomasi operator, then performing screeningaccording to the specific characteristics of symmetry and large variance of the checkerboard angular point, and finally obtaining an sub-pixel coordinate with accurate checkerboard angular point by utilizing a sub-pixel optimization algorithm; establishing a camera imaging model and a lens distortion model to obtain an optimized objective function with respect to a distortion parameter; and solving the distortion parameter by utilizing a nonlinear optimization algorithm for distortion correction. According to the robust lens distortion correction method, a calculation of all main distortion parameters can be accomplished with only one calibration object image containing the checkerboard, the model is simple, the calculation efficiency and stability are high, the application adaptability isgood in an industrial field, and the calculation accuracy is comparable to a traditional method.

Owner:NANJING HUICHUAN IND VISUAL TECH DEV +1

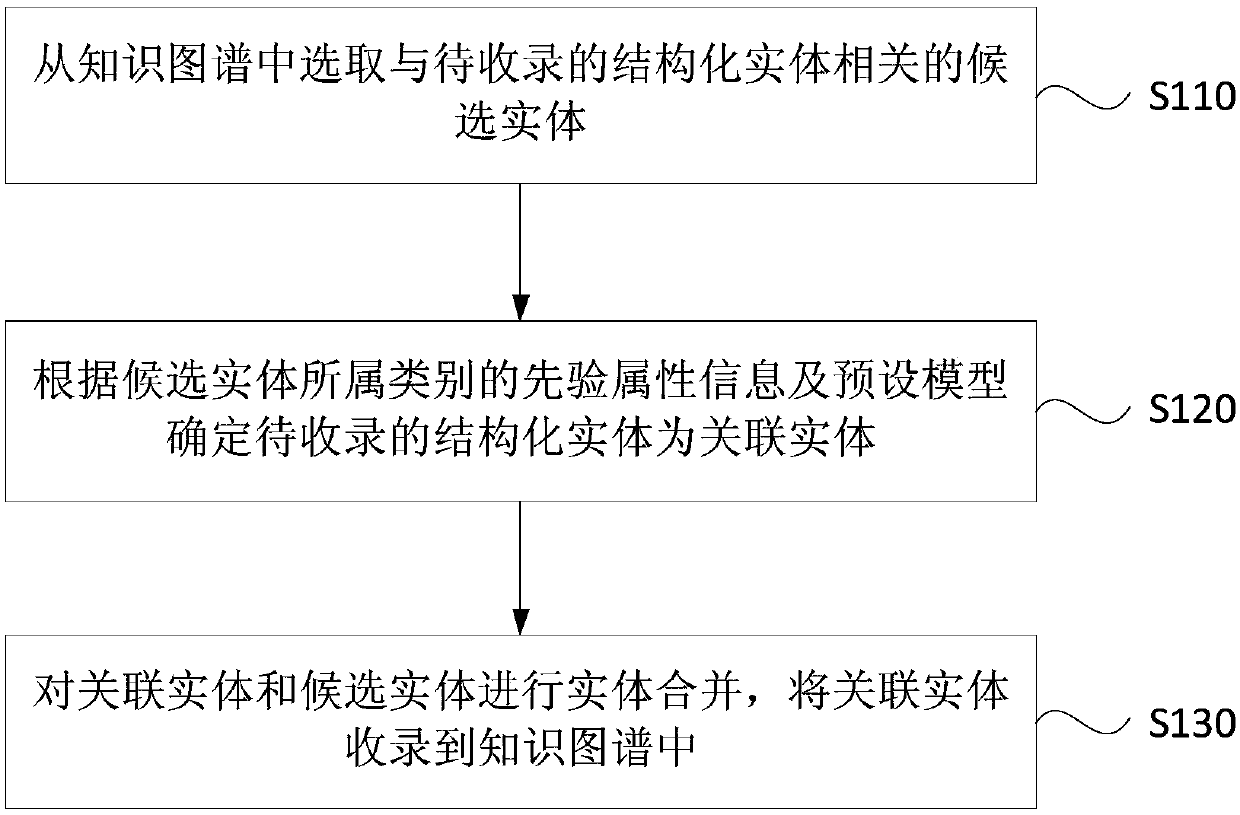

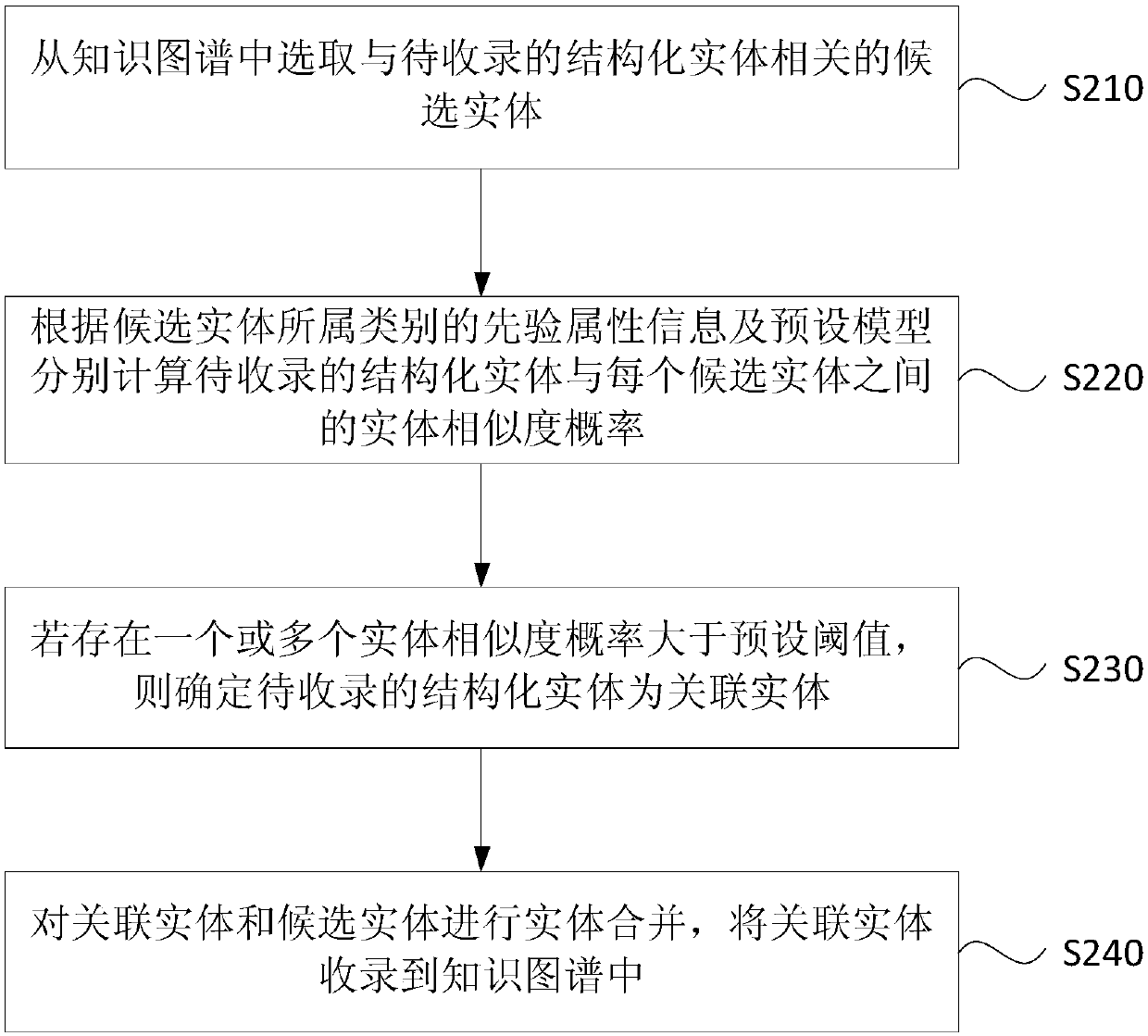

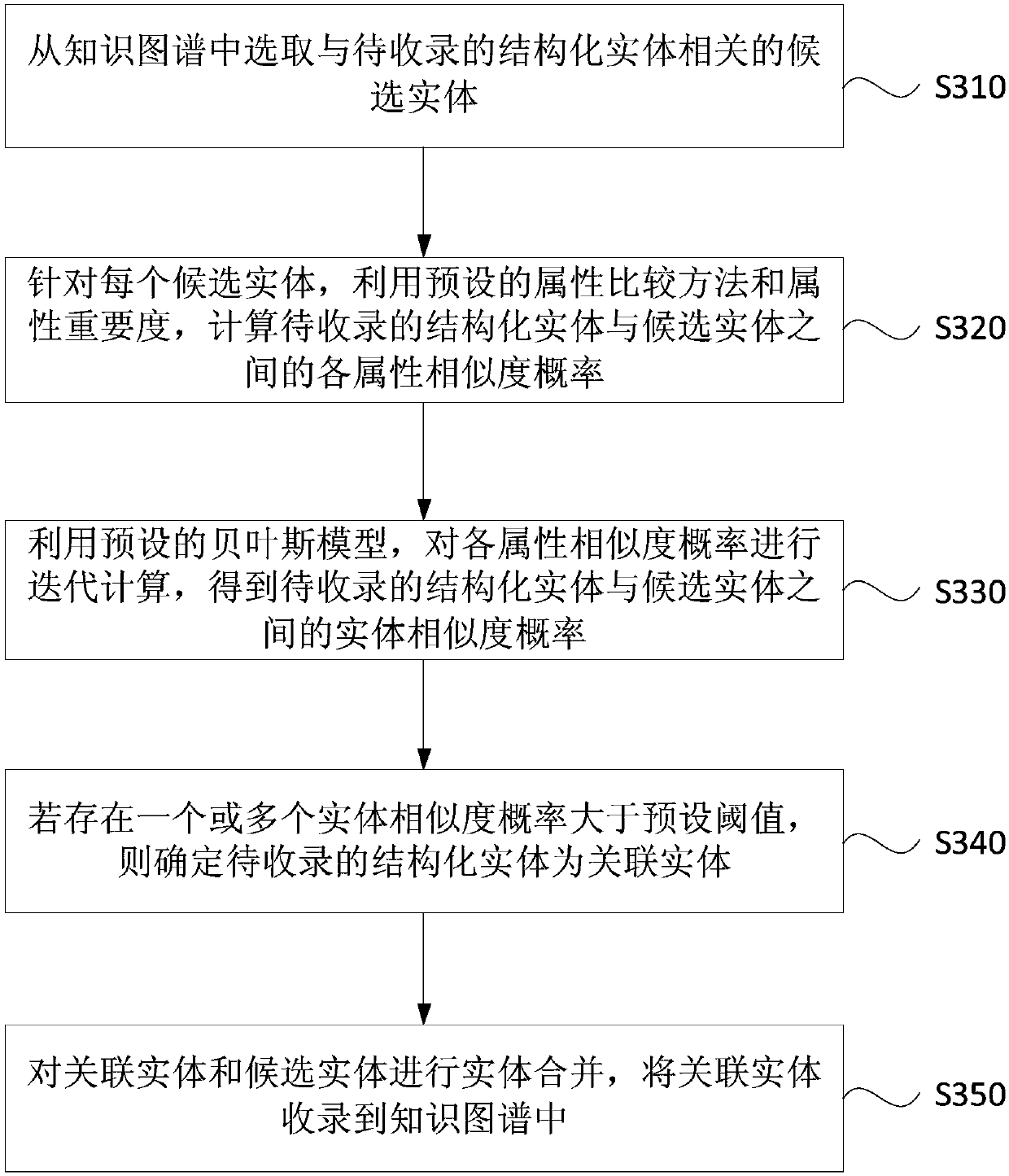

Structured entity recording method and device, server and storage medium

ActiveCN108038183ASimple and efficient collectionImprove efficiencyMathematical modelsWeb data indexingKnowledge graphData mining

The embodiment of the invention discloses a structured entity recording method and device, a server and a storage medium. The structured entity recording method comprises the steps that candidate entities related to structured entities to be recorded are selected from a knowledge graph, the structured entities to be recorded are determined as associated entities according to priori attribute information of the type to which the candidate entities belong and a preset model, the associated entities and the candidate entities are merged, and the associated entities are recorded into the knowledgegraph. According to the embodiment of the invention, the problems are solved that when an existing knowledge map records entities, since entity analysis is conducted on existing entities in the knowledge graph once in the process of adding one entity, the calculation amount is large, the consumed time is long, and the accuracy of entity analysis is not high; the candidate entities are selected, and then prior knowledge is utilized to fuse the preset model so that the efficiency and accuracy of entity association can be effectively improved; the calculation amount is reduced, and therefore theknowledge graph can easily and efficiently record the structured entities.

Owner:BEIJING BAIDU NETCOM SCI & TECH CO LTD

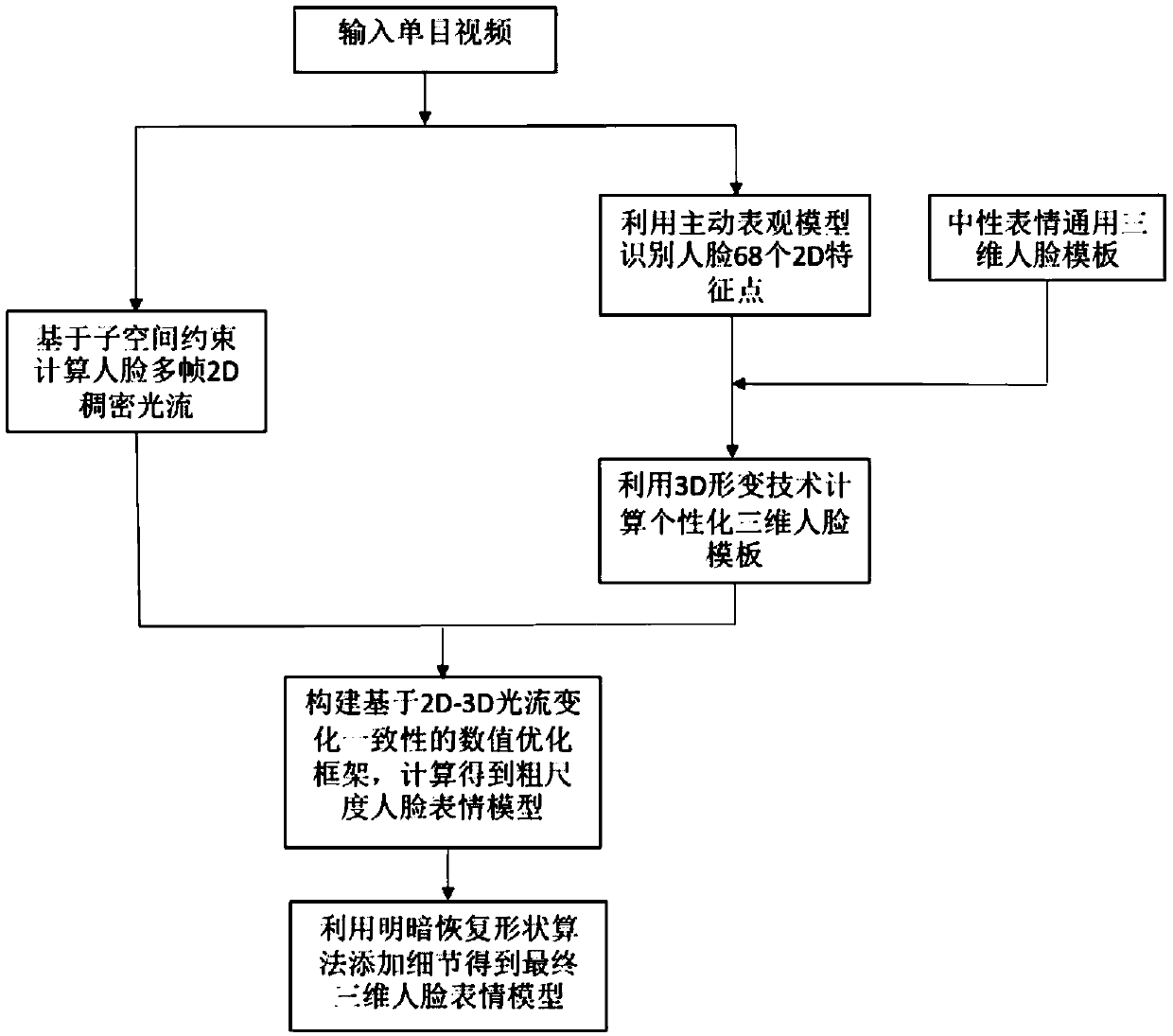

Method for reconstructing a three-dimensional facial expression model based on a monocular video

ActiveCN109584353ASolve the large amount of calculationResolution rangeImage enhancementDetails involving processing stepsPattern recognitionPersonalization

The invention discloses a method for reconstructing a three-dimensional facial expression model based on a monocular video. Extra multi-angle shooting is not needed, A universal 3D face model is directly driven from a neutral expression image frame in an input monocular video to deform so as to generate a personalized three-dimensional face template; and expressing the deformation of the three-dimensional face expressions corresponding to different frames as the change of the personalized three-dimensional face template in the 3D vertex flow of the three-dimensional space, and solving the coarse-scale geometric model of the face expressions through the consistency with the change of the 2D optical flow. While the shape accuracy of a coarse-scale reconstruction model is improved by utilizing dense optical flow, the shooting requirement of an input video is broadened, details are added on a recovered coarse-scale face model through a light and shade recovery shape technology so as to recover fine-scale face geometric data, and a three-dimensional face geometric model with high fidelity is reconstructed.

Owner:BEIHANG UNIV

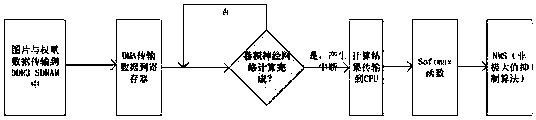

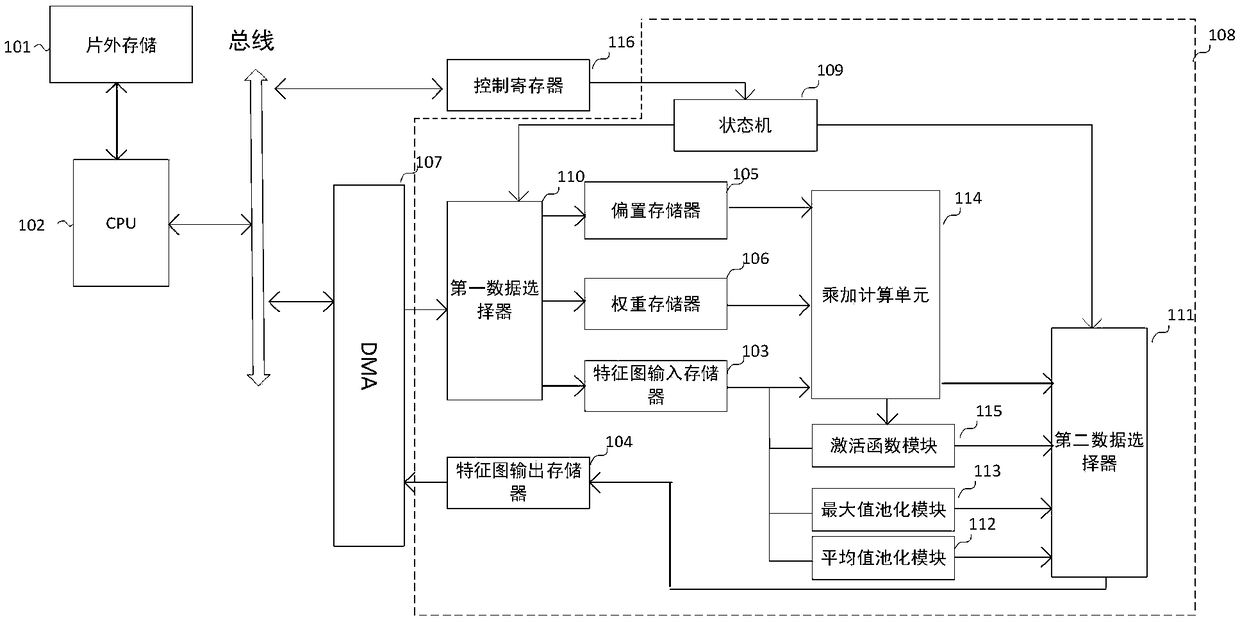

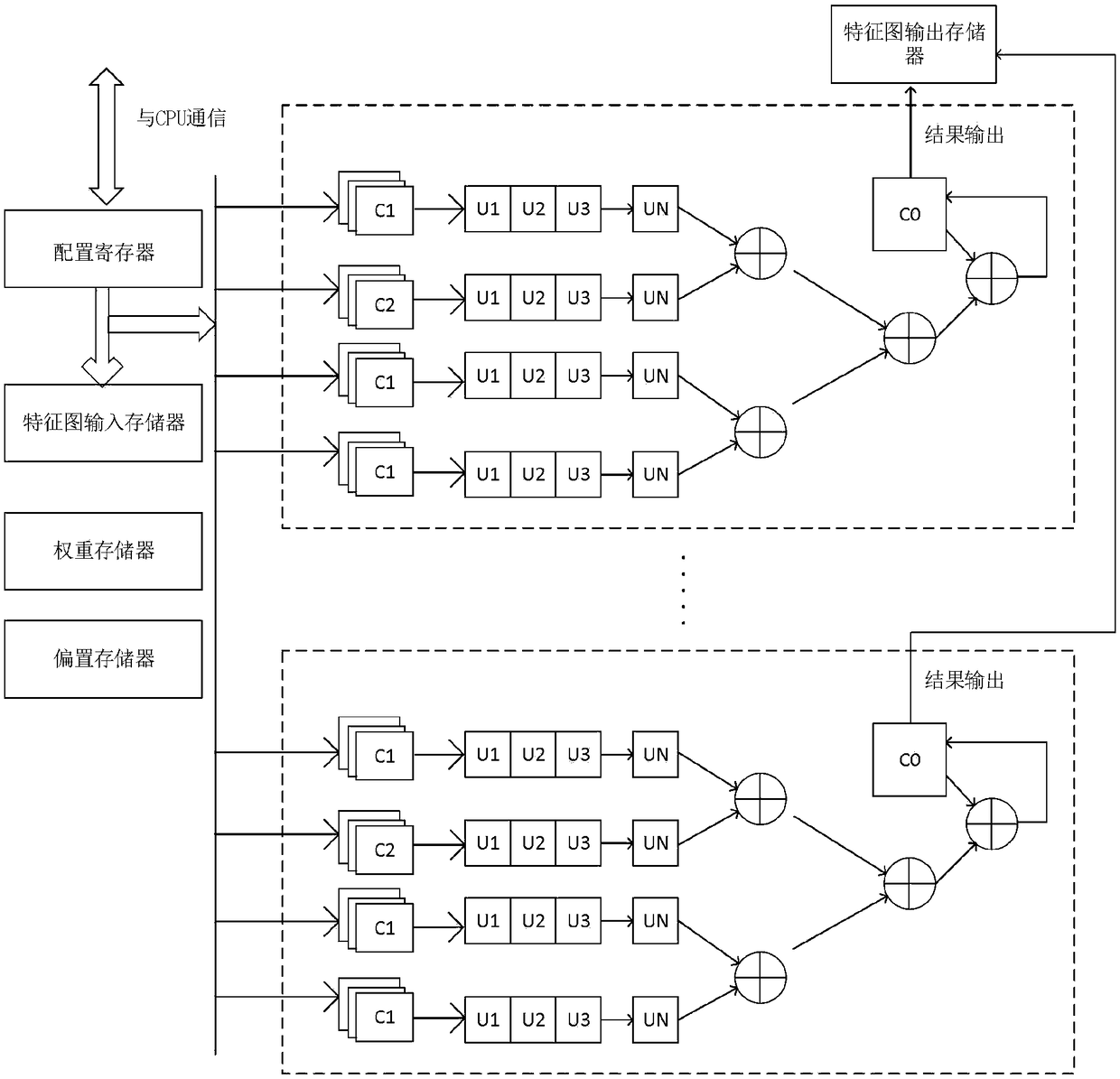

A convolution neural network accelerator based on PSoC

ActiveCN109102065ASolve the large amount of calculationImprove Parallel Processing EfficiencyNeural architecturesPhysical realisationNeural network systemActivation function

This patent discloses a convolution neural network accelerator based on PSoC device, including an off-chip memory, a CPU, a feature map input memory, a feature Map Output Memory, a bias memory, a weight memory, a direct memory access to the same number of cells as neurons. The calculation unit comprises a first-in first-out queue, a state machine, a data selector, an average pooling module, a maximum pooling module, a multiplication and addition calculation module and an activation function module, wherein the calculations in the multiplication and addition calculation module are executed in parallel, and can be used for a convolution neural network system of various architectures. The invention fully utilizes the programmable part in the PSoC (Programmable System on Chip) device to realize the convolution neural network calculation part with large calculation amount and high parallelism, and utilizes the CPU to realize the serial algorithm and the state control.

Owner:GUANGDONG UNIV OF TECH +1

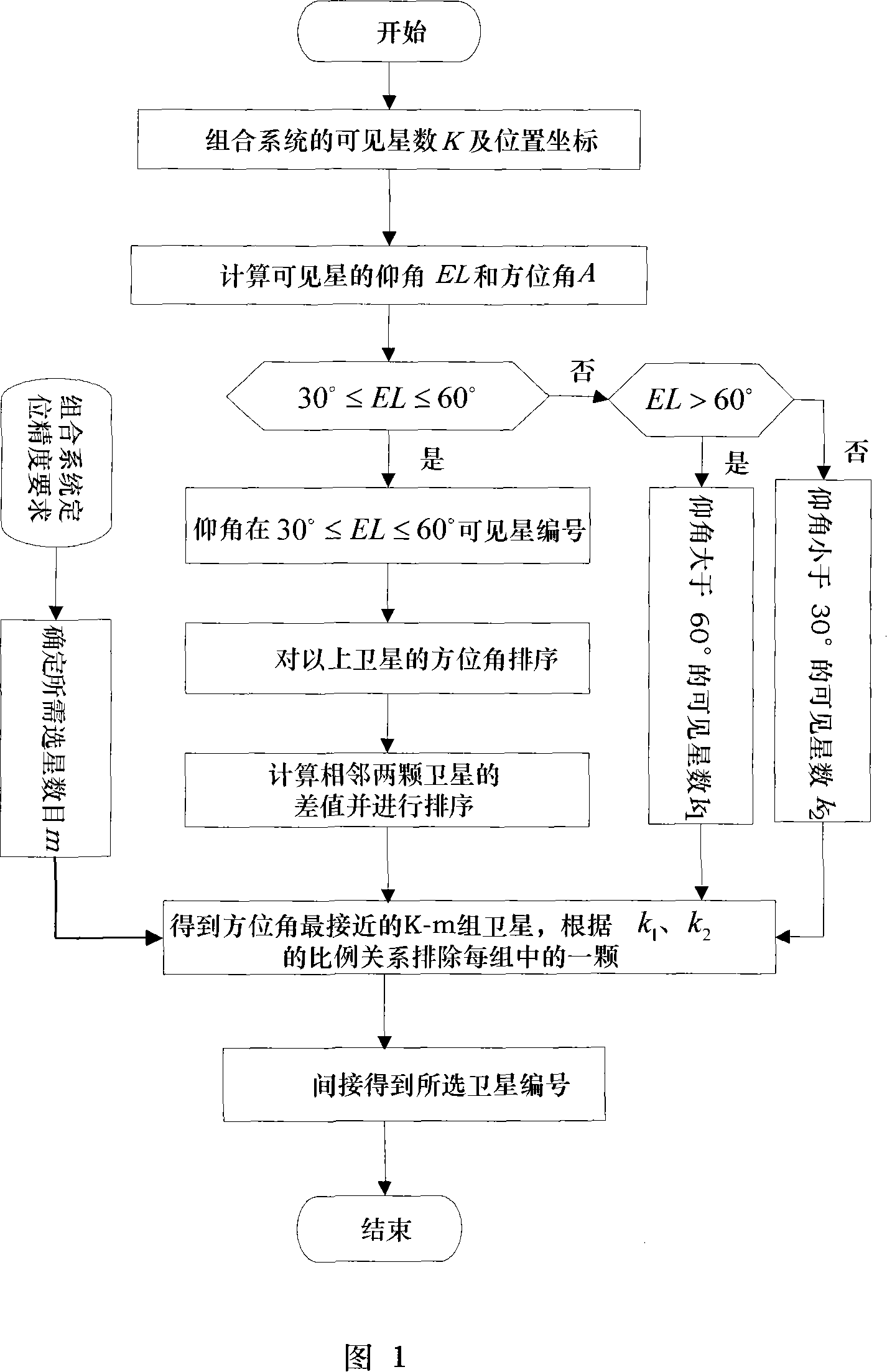

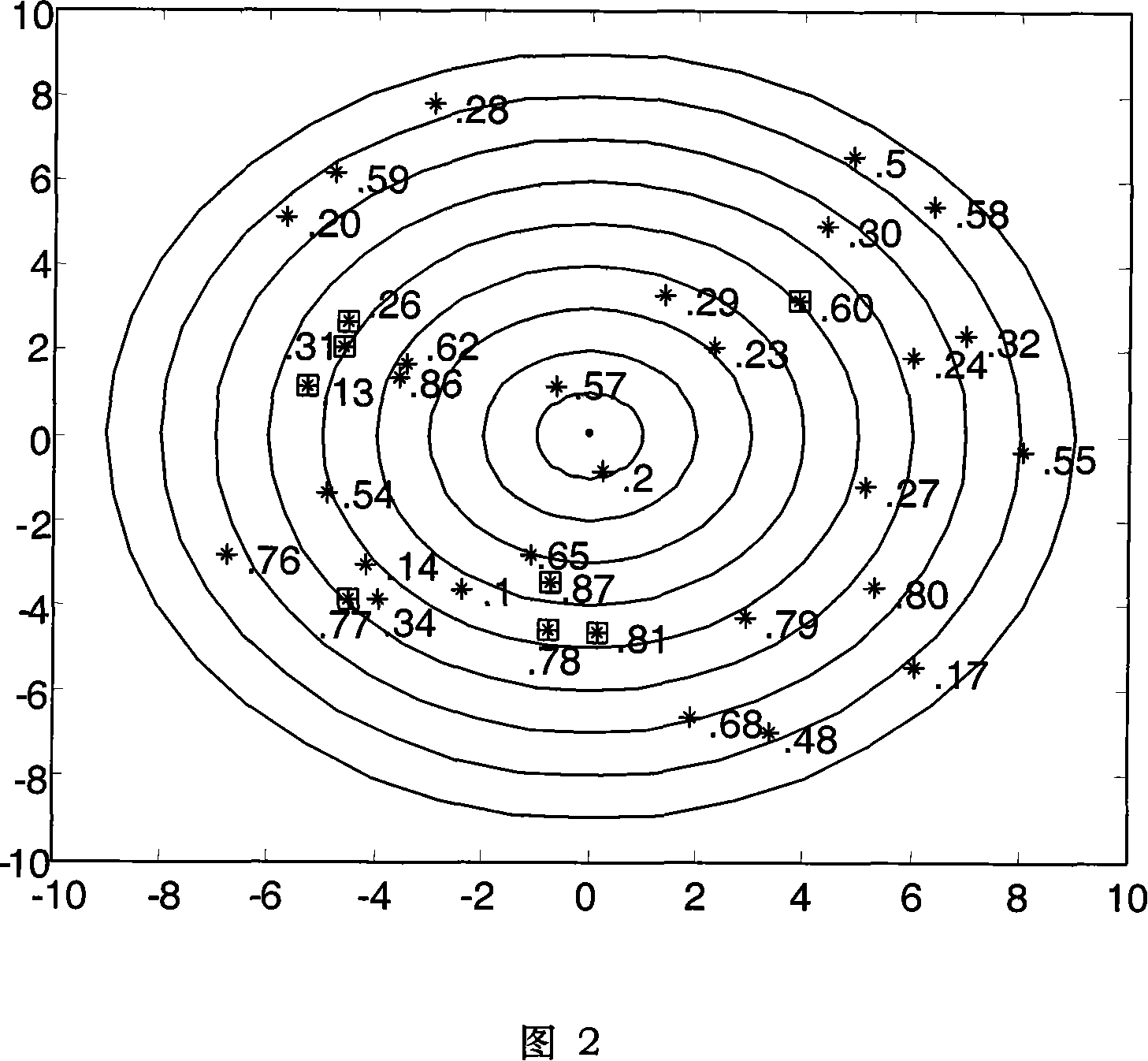

Quick satellite selection method for combined satellite navigation system

InactiveCN101149428ASolve the large amount of calculationStar selection is simpleBeacon systems using radio wavesPosition fixationAzimuthEnvironmental geology

This invention provides a quick satellites choosing method for together fitted satellites system. It chooses satellites indirectly in this way: first, confirm the number of satellites in need. Then calculate the quadrant elevation and azimuth angle of visible satellites, set them to different parts and choose a group of satellites which has a medium quadrant elevation. Disposal the azimuth angle of the choosing satellites, combine the quadrant elevation information to remove some improper satellites. This satellite choosing method is quick, convenience and needs less calculation than the traditional one. Even it is not as precise as before, but it makes the navigational computer working more easily and guarantee the precision of together fitted navigation.

Owner:BEIHANG UNIV

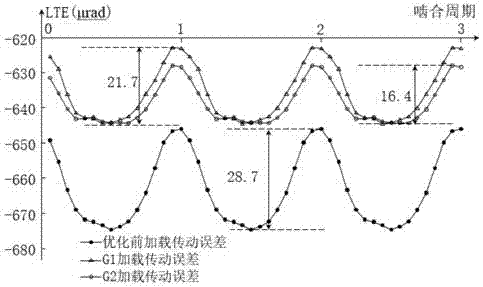

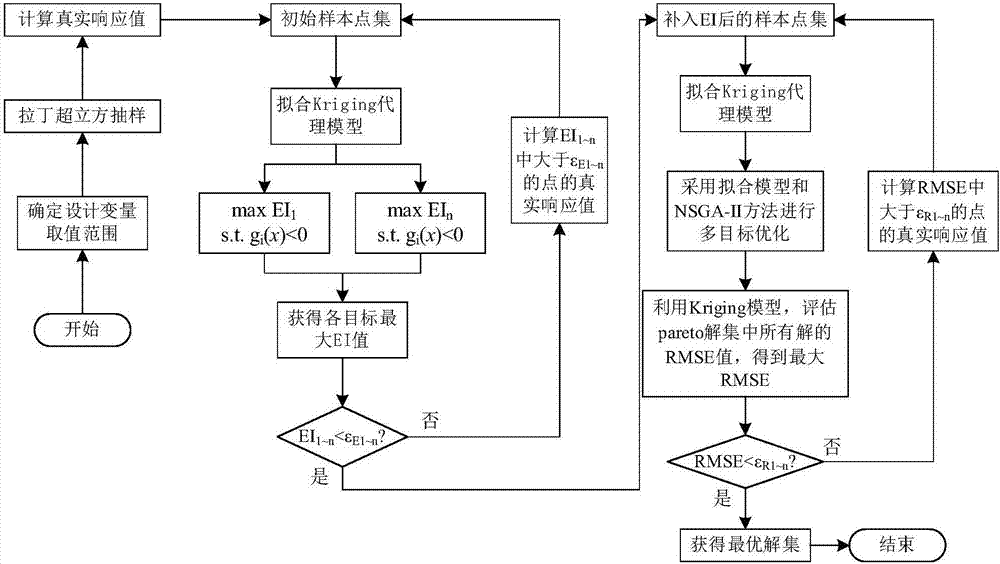

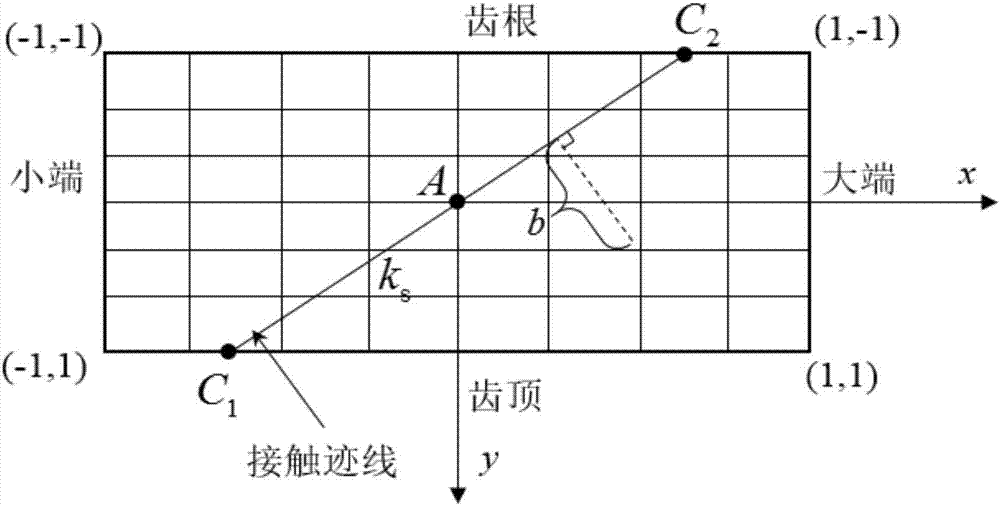

Spiral bevel gear tooth surface loading performance multi-objective optimization method

ActiveCN107577876AImprove loading effectAvoid broken teethSpecial data processing applicationsMathematical modelRooted tooth

The invention relates to a spiral bevel gear tooth surface loading performance multi-objective optimization method. The method is characterized by comprising the following steps that firstly, a mathematical model of a spiral bevel gear tooth surface loading performance multi-objective optimization problem is established, and test design sample points are obtained; secondly, a tooth surface loadingcontact analysis method considering tooth root bending stress is established, tooth surface loading contact analysis is conducted on the test design sample points, target functions corresponding to the test design sample points and response values of the target functions are obtained, and then an initial sample point set including the test design sample points and the corresponding response values is obtained; thirdly, a Kriging proxy model is fitted on the basis of the initial sample point set, the mathematical model of the spiral bevel gear tooth surface loading performance multi-objectiveoptimization problem is solved, and the optimal solution set of the spiral bevel gear tooth surface loading performance multi-objective optimization problem is obtained. The method is high in calculation efficiency, high in calculation accuracy and capable of being widely applied to spiral bevel gear tooth surface loading performance multi-objective optimization.

Owner:TSINGHUA UNIV +1

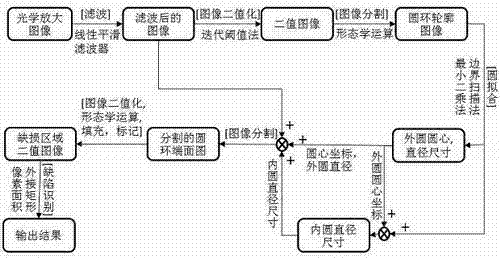

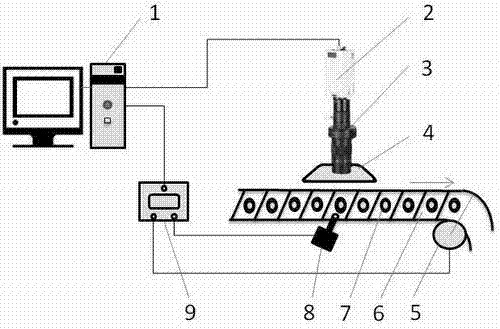

Method and system for detecting and screening end defects in circular parts

ActiveCN103499590ASolve the large amount of calculationSolve the speed problemOptically investigating flaws/contaminationPneumatic pressureOptical amplifier

The invention relates to a method and a system for detecting and screening end defects in circular parts. The system comprises an optical amplifier, a control computer, a controller, a pneumatic nozzle device, a step motor and a conveyor belt. The method includes the steps of 1, photographing a circular part to be detected by the optical amplifier to obtain an optically amplifier image of the end of the circular part to be detected; 2, subjecting the optically amplified image to image processing and defect recognition by the control computer, and judging whether the circular part is qualified or not according to defect conditions; 3, allowing the controller to receive a command of controlling the computer, control the pneumatic nozzle device to operate, remove unqualified parts, and control the conveyor belt to convey next part to a detection position. The method and the system have the advantages that end defects in circular parts can be reflected truly, whether an object is qualified or not can be judged accurately, automation level is high, and detection efficiency is improved.

Owner:FUZHOU UNIVERSITY

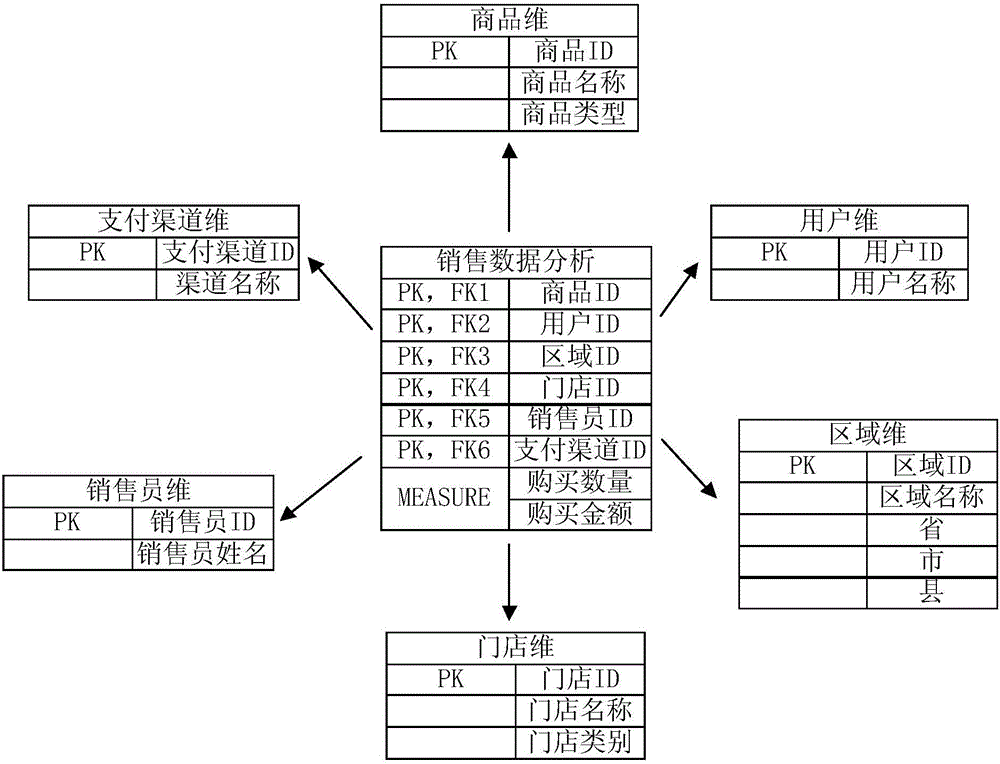

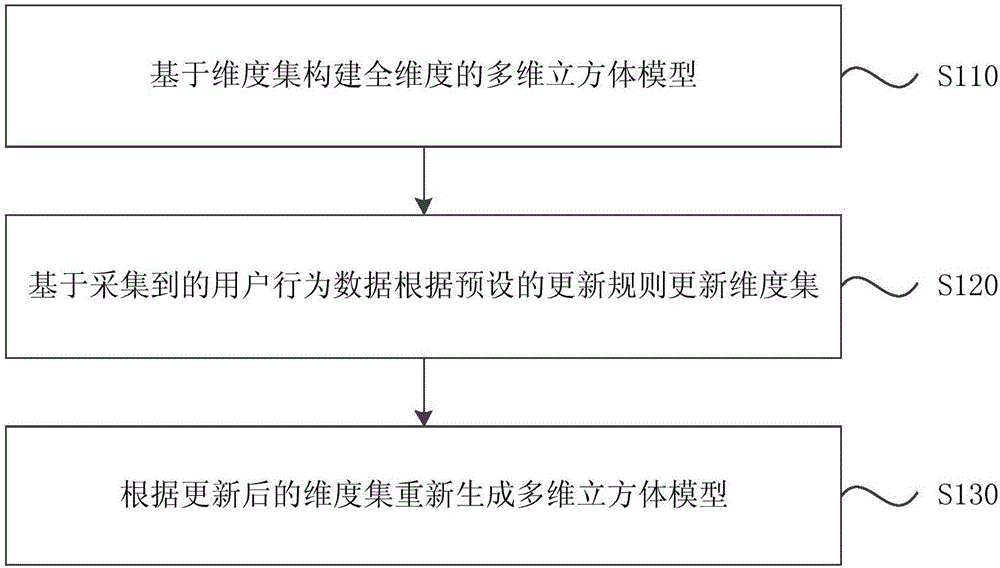

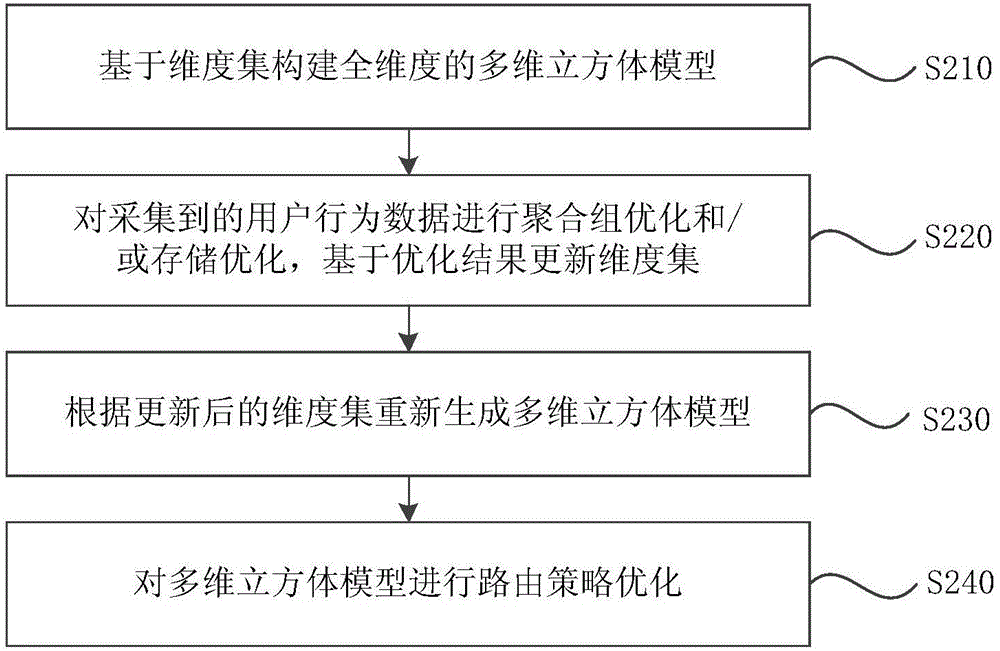

Method and device for optimizing multidimensional cube model

ActiveCN106600067AAchieve automatic optimizationPracticalDatabase distribution/replicationForecastingService modelData dimension

The invention discloses a method and a device for optimizing a multidimensional cube model. The method for optimizing a multidimensional cube model comprises the following steps: building an all-dimension multidimensional cube model based on a dimension set, wherein the dimension set includes all data dimensions in a service model; updating the dimension set based on acquired user behavior data and according to preset updating rules; and regenerating a multidimensional cube model according to the updated dimension set. According to the technical scheme of the invention, the dimension set is updated based on the acquired user behavior data, and then, a multidimensional cube is regenerated. The problem that the updating of a multidimensional cube at present requires a large amount of calculation and depends on the experience of the designer is solved. A multidimensional cube can be updated automatically. Updating of the dimension set based on the operation data in a database is closer to the actual need of users. Thus, the updated multidimensional cube model is smarter and more practical.

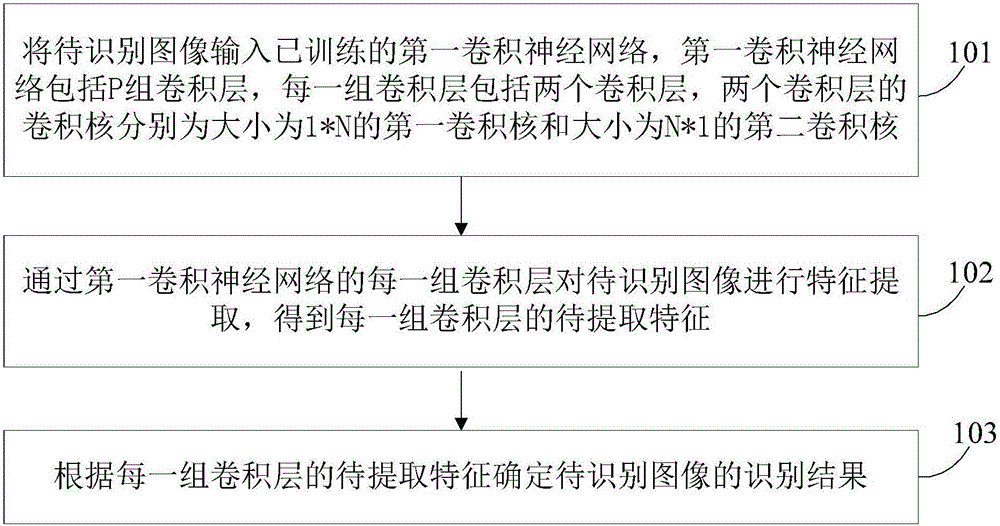

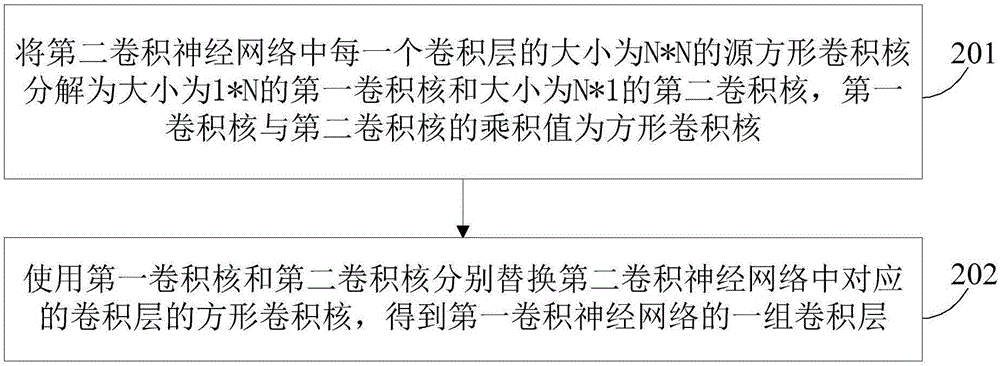

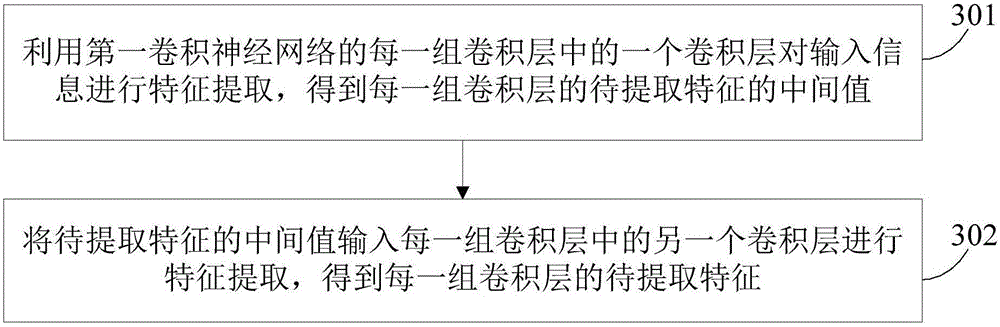

Image identification method and apparatus

InactiveCN106682736ASolve the large amount of calculationSolve the costCharacter and pattern recognitionNeural learning methodsConvolutionImage identification

The invention discloses an image identification method and apparatus. The image identification method includes the steps: inputting an image to be identified into a trained first convolution neural network which includes P groups of convolution layers, wherein each group of convolution layers includes two convolution layers; the sizes of the convolution cores of the two convolution layers are respectively a 1*N first convolution core and an N*1 second convolution core; by means of each group of convolution layers in the first convolution neural network, extracting the characteristics of the image to be identified and obtaining the characteristics, of each group of convolution layers, to be extracted; and according to the characteristics, of each group of convolution layers, to be extracted, determining the identifying result of the image to be identified. The technical scheme of the image identification method and apparatus solves the problem that in the related technologies, a square convolution core causes high computational complexity and high computing cost.

Owner:BEIJING XIAOMI MOBILE SOFTWARE CO LTD

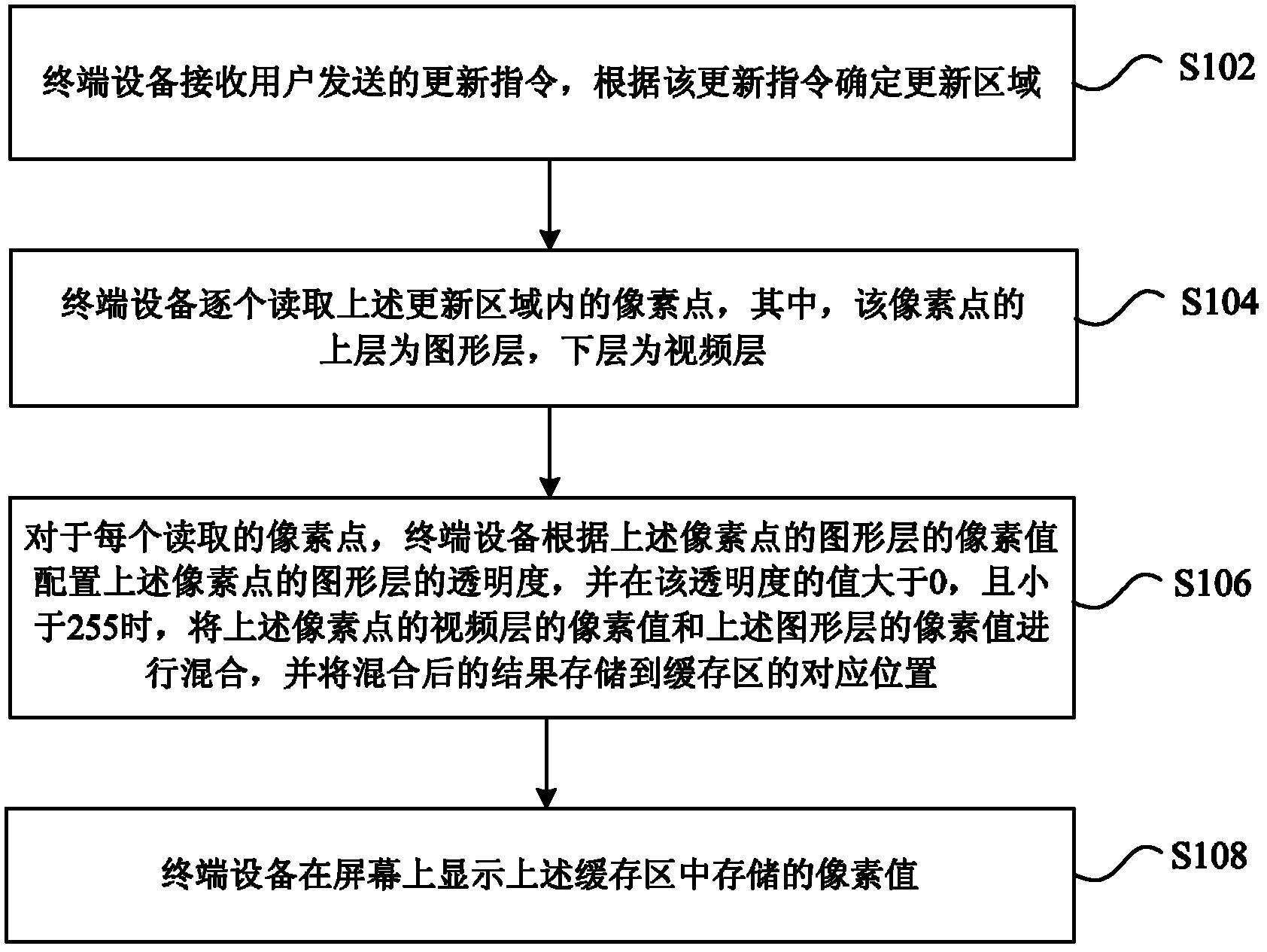

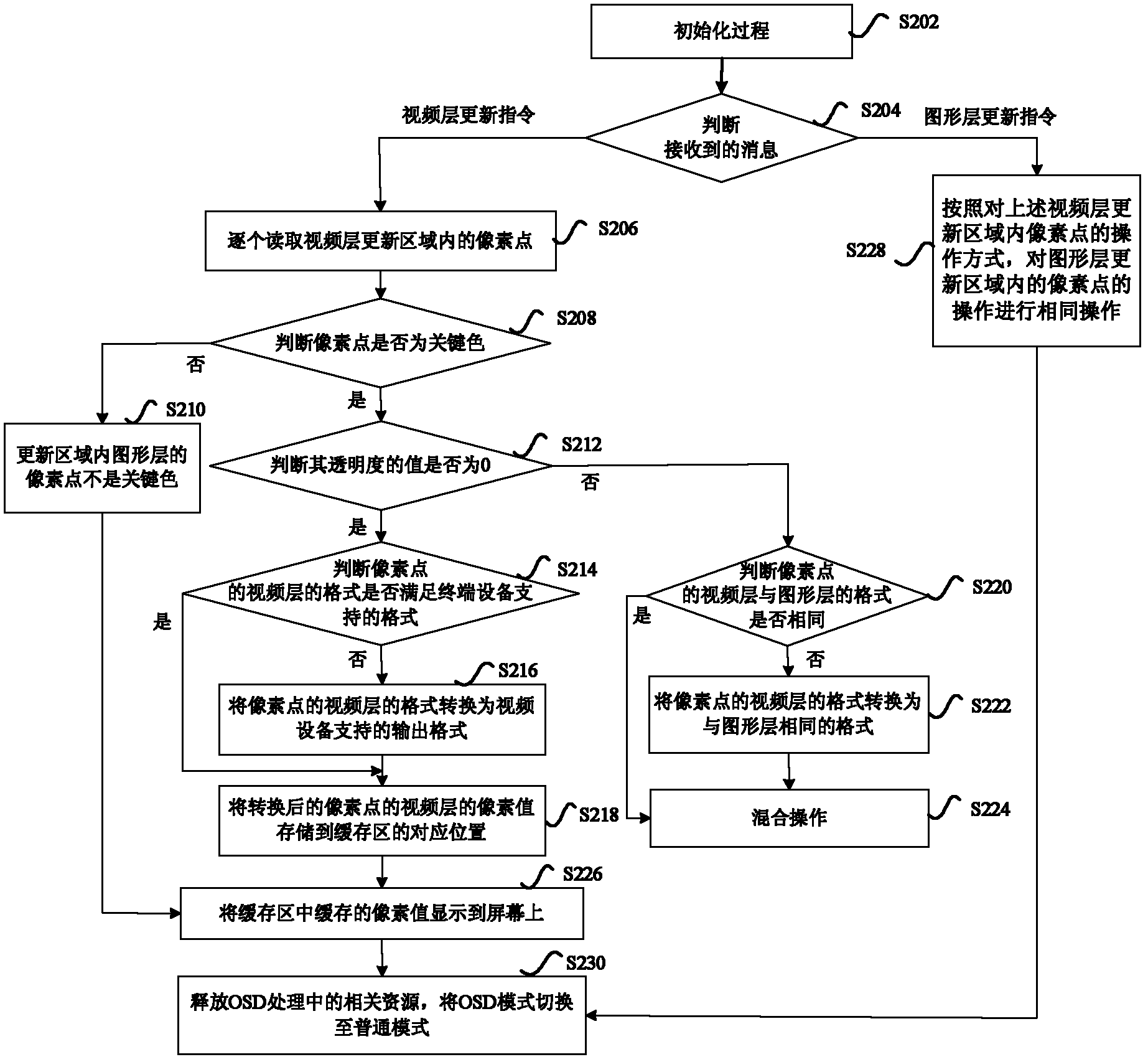

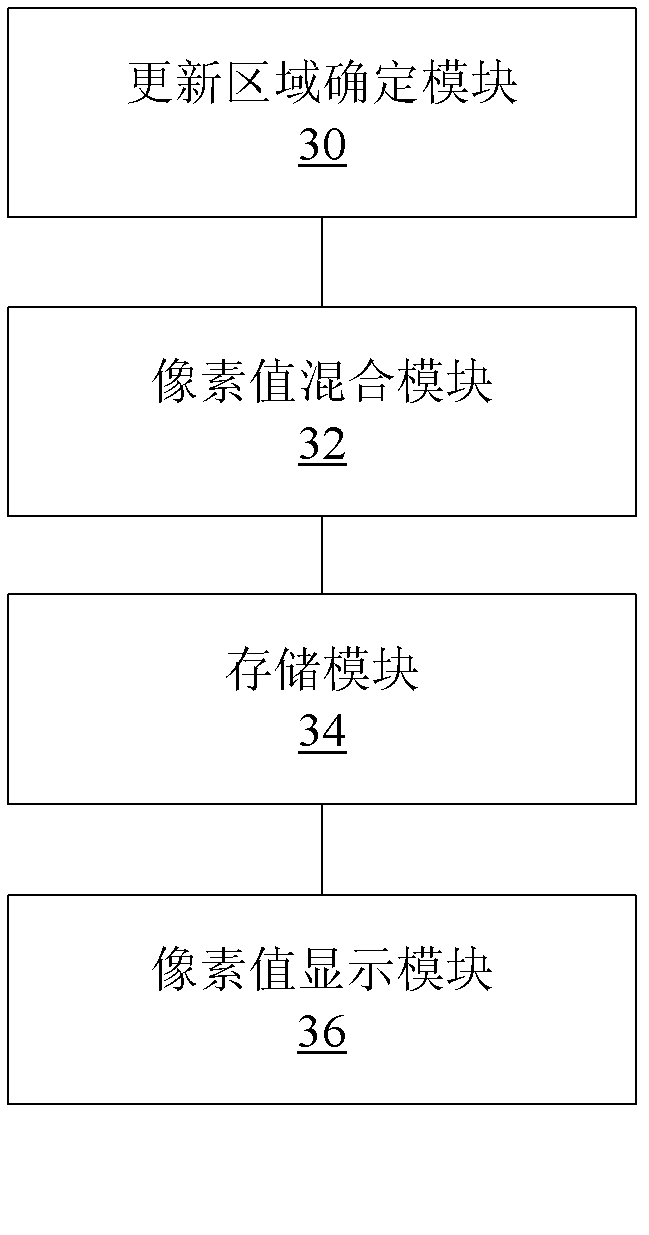

Screen content display method and screen content display device

ActiveCN103259989ASolve the large amount of calculationImprove experienceTelevision system detailsCathode-ray tube indicatorsGraphicsDisplay device

The invention discloses a screen content display method and a screen content display device. The screen content display method includes a first step of receiving an updating instruction sent by a user and confirming an updated area according to the updating instruction, a second step of reading pixel points in the updated area one by one, wherein the upper layer of the pixel points is a image layer and the lower layer of the pixel points is a video layer, a third step of configuring the transparency of the image layer of the pixel points according to the pixel value of the image layer of the pixel points for the pixel points which are read, mixing the pixel value of the video layer of the pixel points with the pixel value of the image layer when the transparency value is bigger than 0 and smaller than 255, and storing a mixed result to a corresponding position of a cache region, and a fourth step of displaying the pixel values stored in the cache region on a screen. Through adoption of the screen content display method, the problem in the prior art that calculated amount of screen contents is large in the displaying process is solved. Consequently, calculation procedures are simplified, power consumption of the device is reduced and user experience is improved.

Owner:ZTE CORP

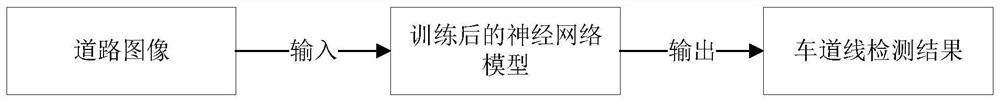

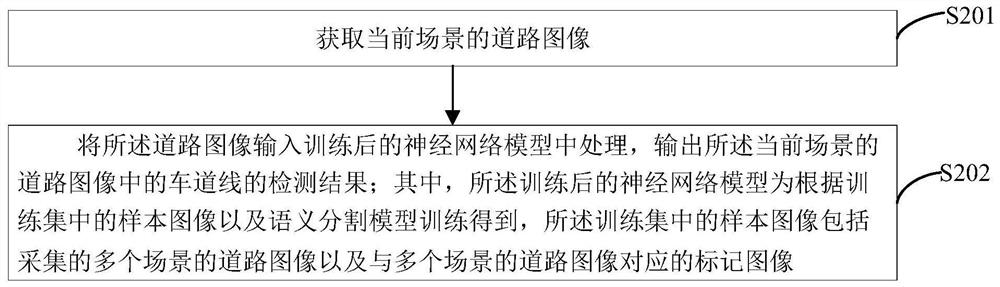

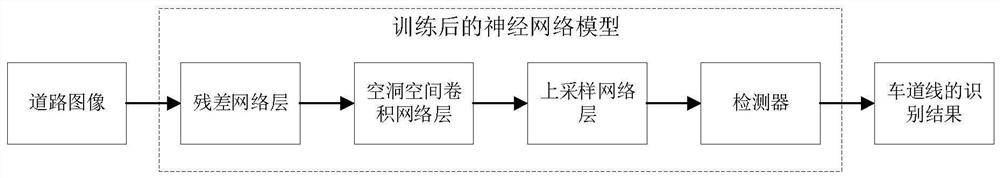

Lane line detection method and device, terminal equipment and readable storage medium

PendingCN112528878ASolve the large amount of calculationSolve the speed problemCharacter and pattern recognitionNeural architecturesSample graphComputer graphics (images)

The invention is applicable to the technical field of computer vision and image processing, and provides a lane line detection method and device, terminal equipment and a readable storage medium. Inputting the road image into a trained neural network model for processing, and outputting a detection result of a lane line in the road image of the current scene; wherein the trained neural network model is obtained by training according to sample images in a training set and a semantic segmentation model, and the sample images in the training set comprise collected road images of a plurality of scenes and marked images corresponding to the road images of the plurality of scenes. According to the method and the device, the problems that most of deep learning models used for lane recognition atpresent are relatively large in calculation amount, relatively complex in model and unfavorable for meeting the requirement on real-time performance in an actual application scene of an automatic driving task can be solved.

Owner:SHENZHEN INST OF ADVANCED TECH CHINESE ACAD OF SCI

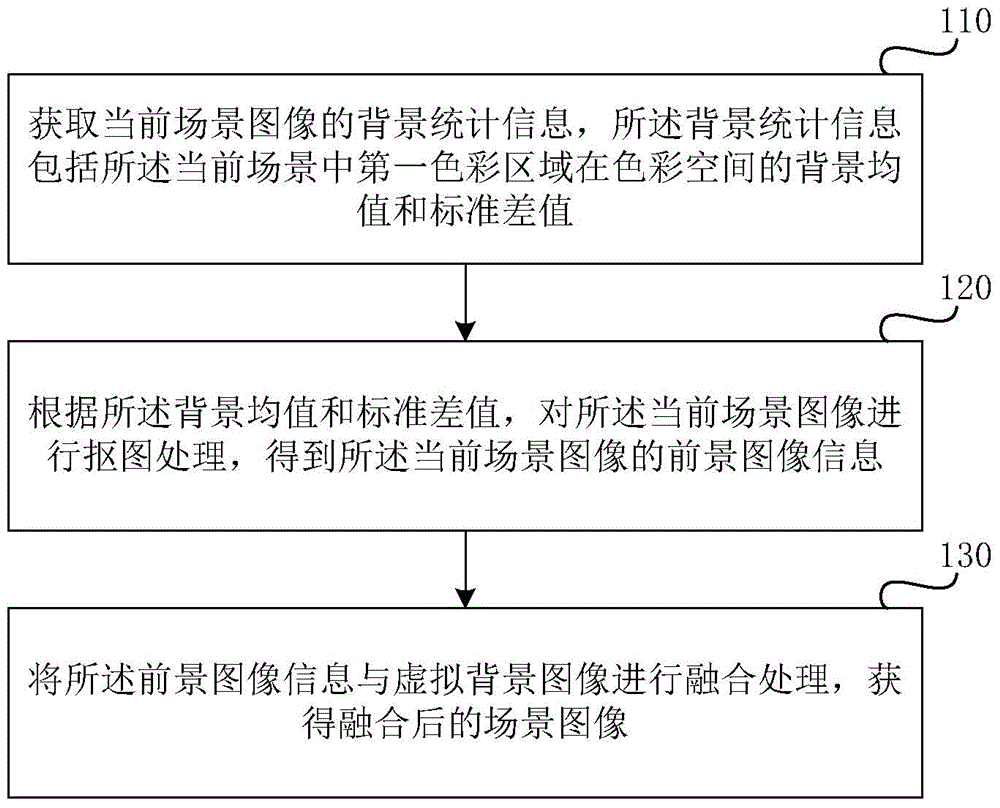

Image processing method, device and equipment

ActiveCN106251286ASolve the large amount of calculationAchieving real-time fusionImage enhancementImage analysisImaging processingBackground image

The invention relates to an image processing method and device. The image processing method comprises the steps of acquiring background statistical information of the current scene image, wherein the background statistical information comprises a background mean value and a standard deviation value of a first color area of the current scene in a color space to which the first color area belongs; carrying out matting processing on the current scene image according to the background mean value and the standard deviation value, and acquiring foreground image information of the current scene image; and carrying out fusion processing on the foreground image information and a virtual background image so as to acquire a fused scene image.

Owner:SUPERD CO LTD

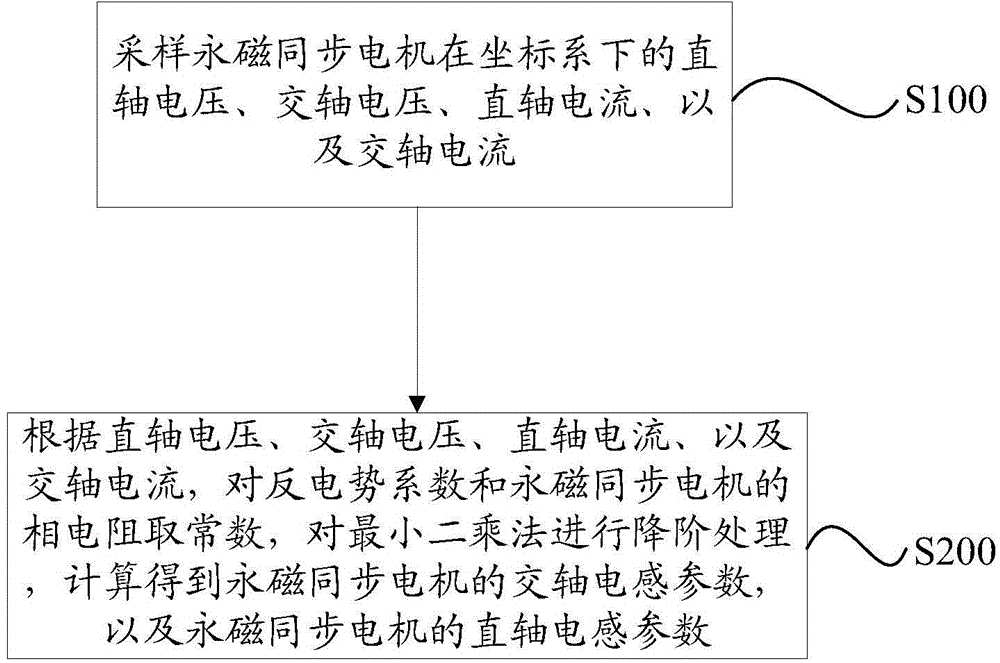

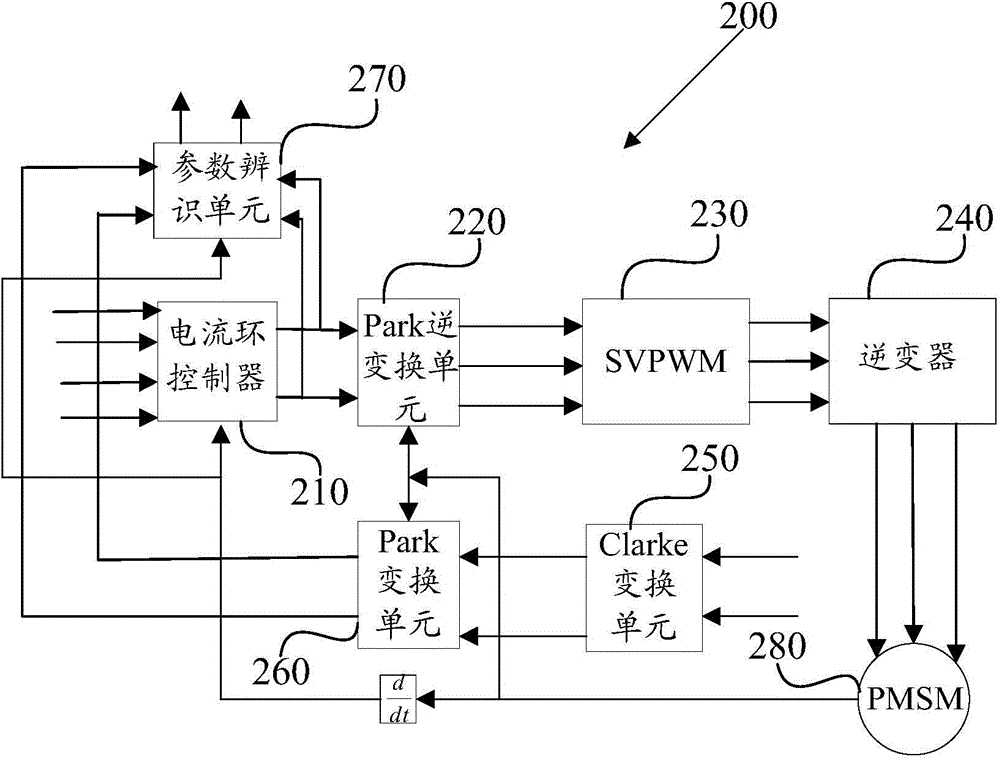

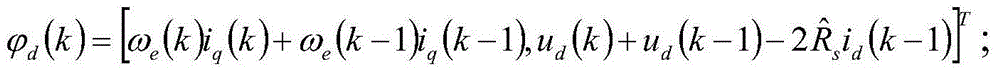

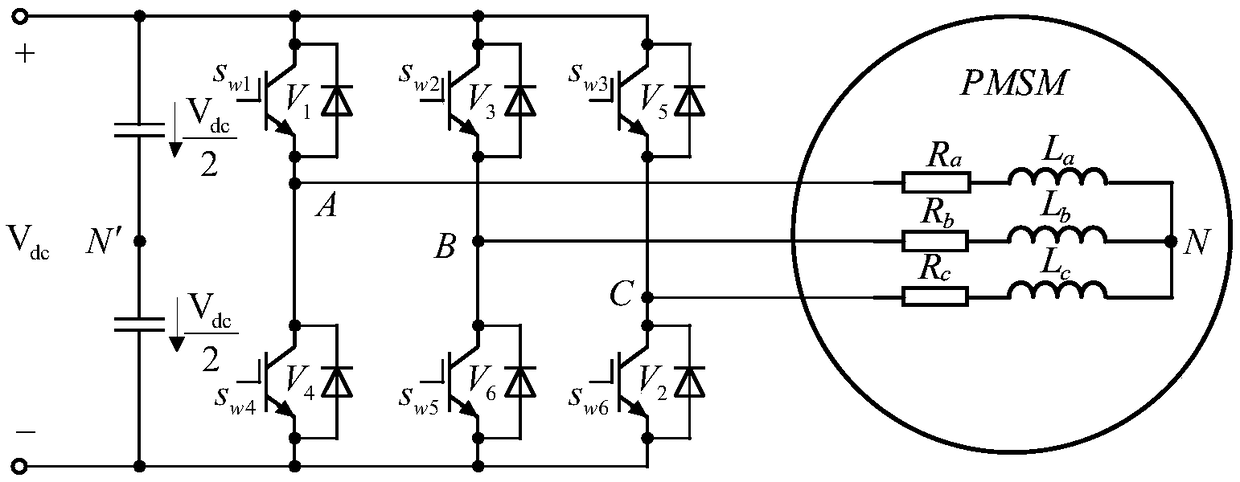

Permanent magnet synchronous motor d-axis and q-axis induction parameter on-line identification method and system

ActiveCN104836499ASolve the large amount of calculationSmall amount of calculationElectronic commutation motor controlVector control systemsOrder reductionPermanent magnet synchronous motor

The invention discloses a permanent magnet synchronous motor d-axis and q-axis induction parameter on-line identification method and a system. The method comprises sampling a d-axis voltage u<d), a q-axis voltage u<q>, a d-axis current i<d> and a q-axis current i<q> of a permanent magnet synchronous motor in a dq coordinate system; and, according to the d-axis voltage u<d), the q-axis voltage u<q>, the d-axis current i<d> and the q-axis current i<q>, regarding the back electromotive force efficient and a phase resistance R<s> of the permanent magnet synchronous motor as constants, performing order reduction processing on a least square method, and calculating to obtain a q-axis induction parameter L<q> of the permanent magnet synchronous motor and a d-axis induction parameter L<d> of the permanent magnet synchronous motor. According to the d-axis voltage u<d), the q-axis voltage u<q>, the d-axis current i<d>, the q-axis current i<q> and an order reduction calculation model based on the least square method, the q-axis induction parameter L<q> and the d-axis induction parameter L<d> of the permanent magnet synchronous motor are calculated, and then the problem of the large calculated amount in an existing method for achieving permanent magnet synchronous motor parameter on-line identification based on the least square method is effectively solved.

Owner:GREE ELECTRIC APPLIANCES INC

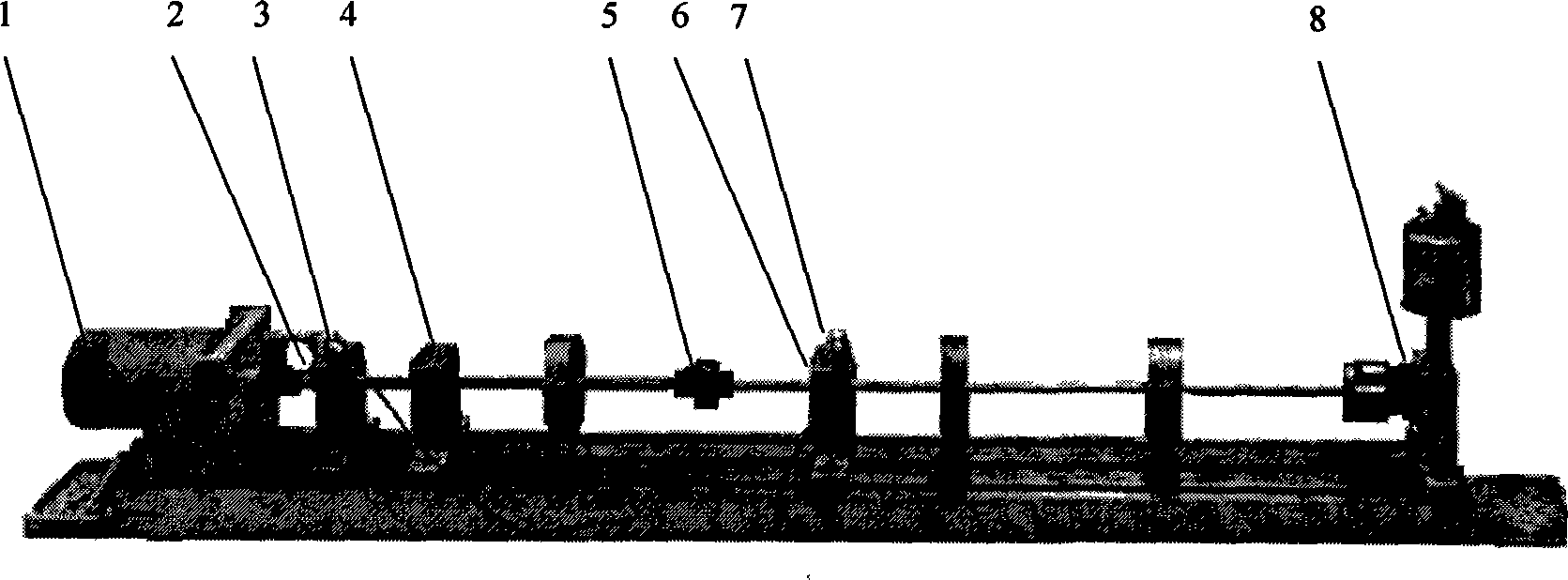

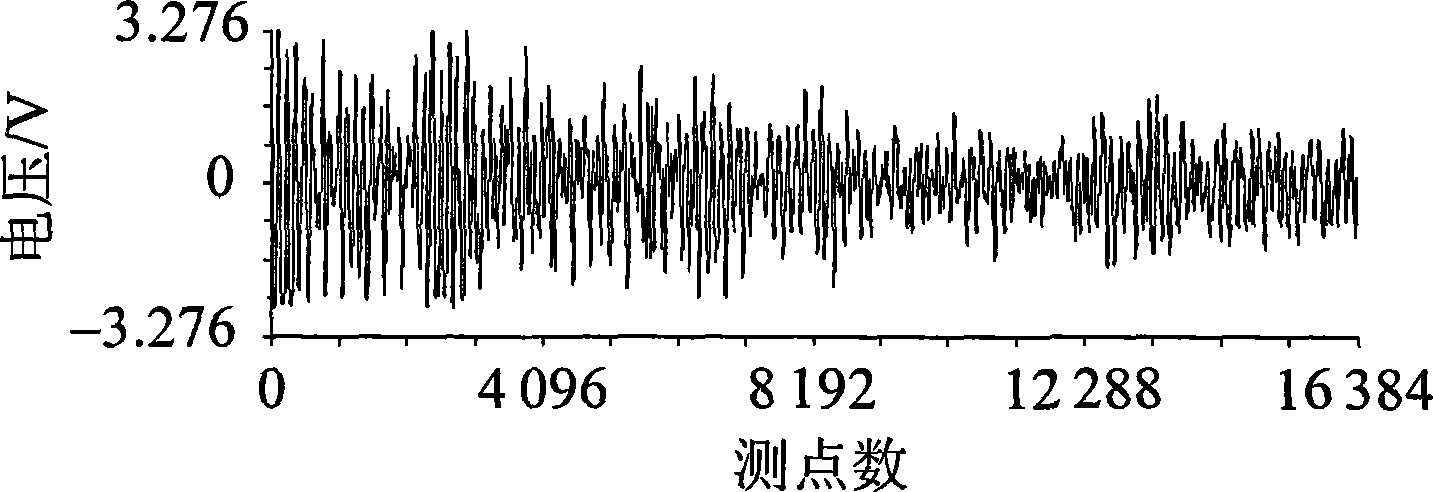

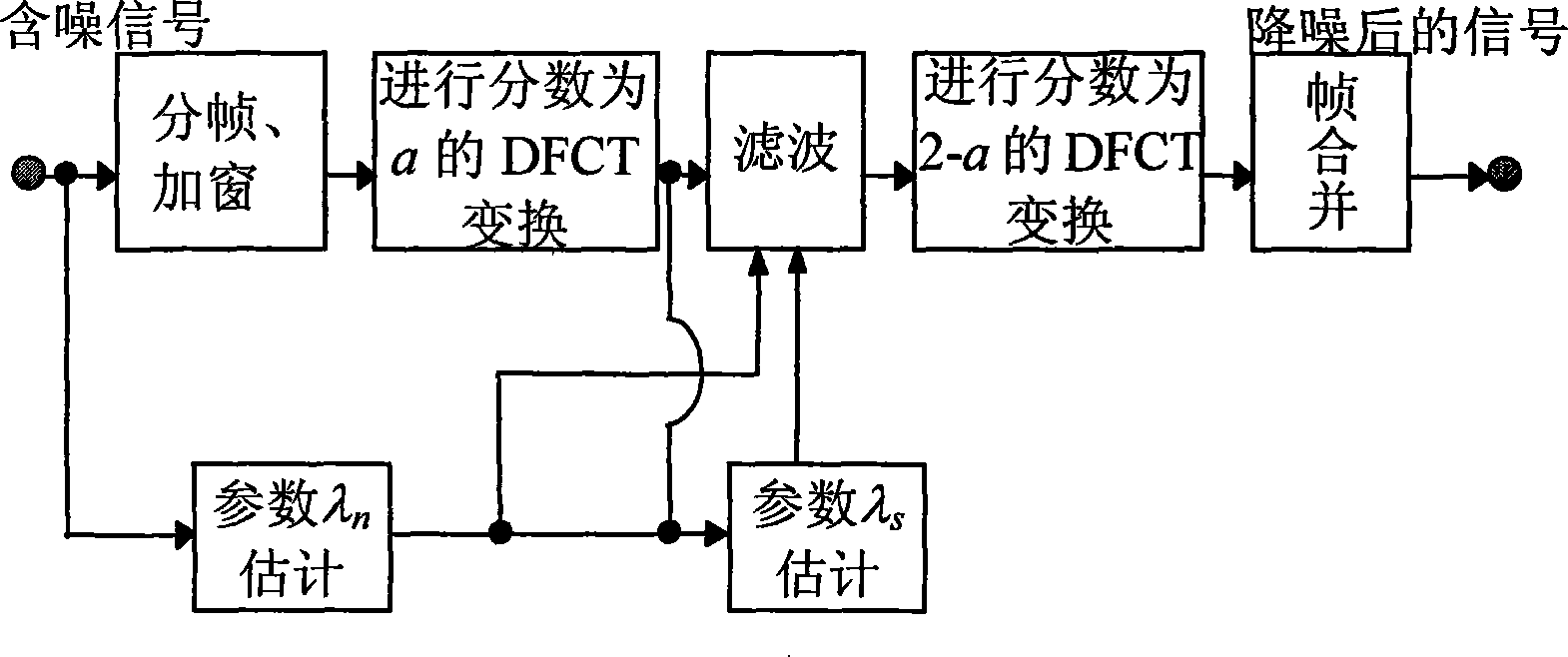

Method for denoising bump-scrape acoustic emission signal based on discrete fraction cosine transform

InactiveCN101251446AImprove noise reductionRobustSubsonic/sonic/ultrasonic wave measurementStructural/machines measurementAcoustic emissionDiscrete cosine transform

The invention relates to a rubbing sound emission signal denoising method based on discrete fraction cosine transform. The invention comprises the technical proposal that: a sound emission signal is extracted from an emission sensor of a friction point and superimposed with noise; the signal comprising noise is sampled, quantized and subframed and added with windows to obtain a discrete time sequence; the sequence is carried out discrete fraction Fourier transform with the fraction a to obtain F(k), then the signal after being filtered is carried out the discrete fraction Fourier transform with the fraction 2-a and the combination of frames; the signal after being denoised is output. The rubbing sound emission signal denoising method solves the disadvantages that a sound emission source has diversity, transient property and a noise source has complexity and can not gain satisfactory effect. The rubbing sound emission signal denoising method can obtain good denoising effect to the rubbing sound emission signal under the environment of a plurality of nonstationary noise, strengthen the sound emission signal, has robustness to the diversity and transient property of the sound emission source and the complexity of the noise source, effectively solves the problem of the large calculation amount in the prior method and has wide applicability.

Owner:邓艾东

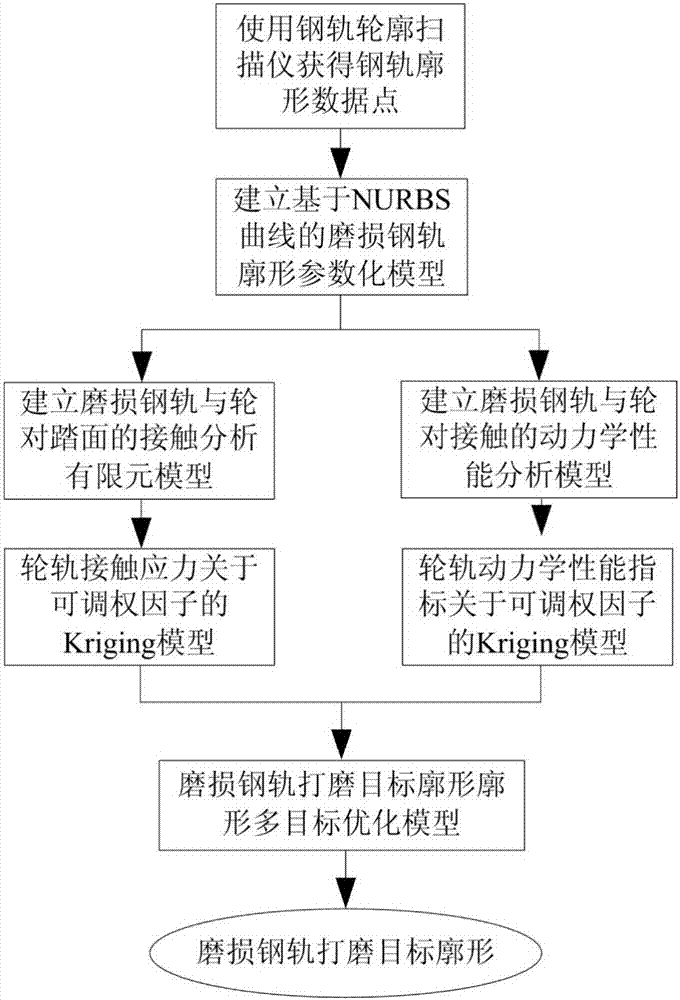

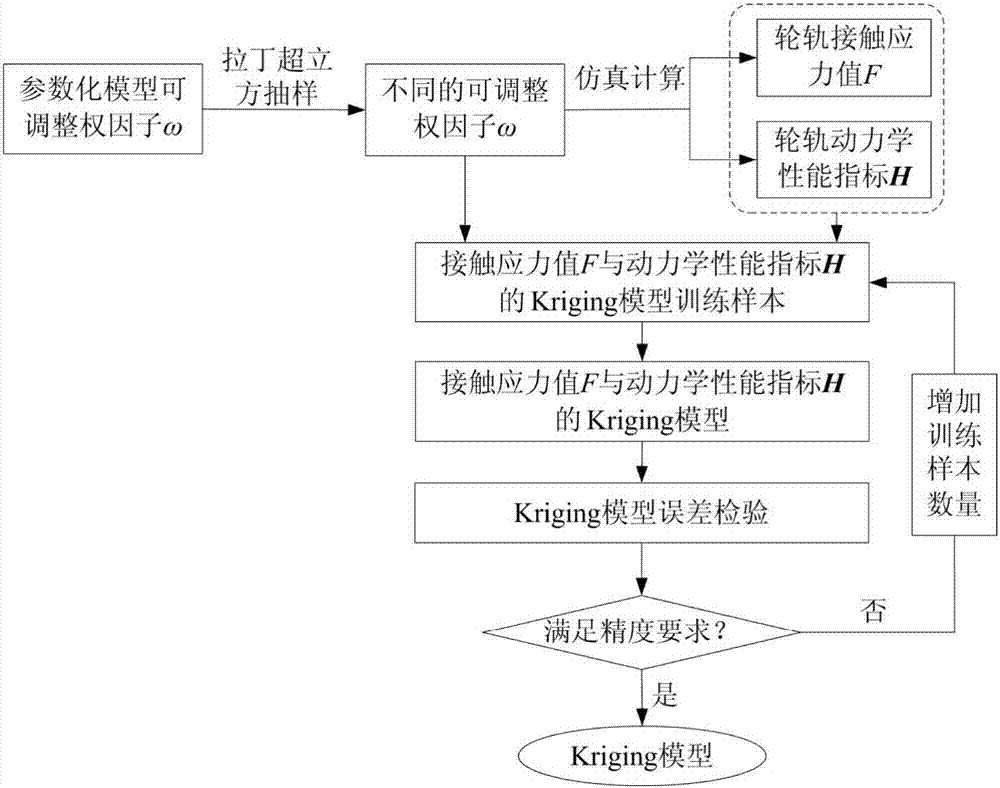

Worn steel rail polishing target profile rapid design method

ActiveCN106951657AQuick calculationAccurate calculationGeometric CADDesign optimisation/simulationRail profilePerformance index

The invention relates to a worn steel rail polishing target profile rapid design method. The worn steel rail polishing target profile rapid design method comprises constructing a parameterized model of a worn profile by means of a cubic NURBS curve; establishing a Kriging model of the worn steel rail polishing target profile performance by taking an adjustable weight factor of the NURBS parameterized model of the worn steel rail profile as the design variable and taking the wheel-rail contact stress and the wheel-rail dynamics performance index as dependent variables; establishing an optimization design model of the steel rail polishing target profile by taking the adjustable weight factor as the design variable and taking the Kriging model of the steel rail polishing target profile performance as the target function, and achieving the optimal design of the worn steel rail polishing target profile. According to the invention, the polishing target profile of any worn steel rail can be designed rapidly, and the worn steel rail polishing target profile rapid design method is characterized by being high in design efficiency and accurate in design result, and the problem that when a steel rail needs to be polished, the accuracy of the polishing target profile needs to be checked repeatedly by means of a numerical simulation method, and therefore the design efficiency is low is solved.

Owner:XI'AN PETROLEUM UNIVERSITY

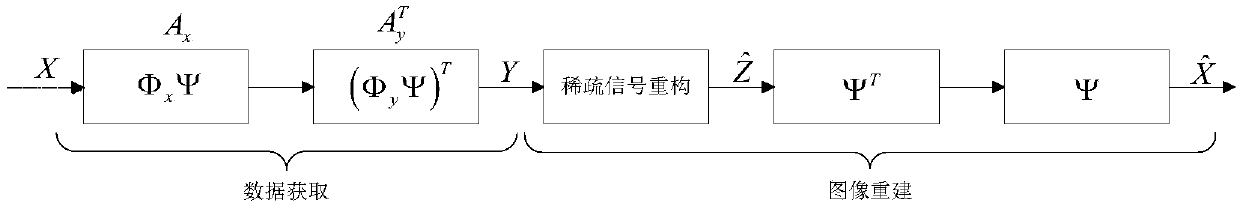

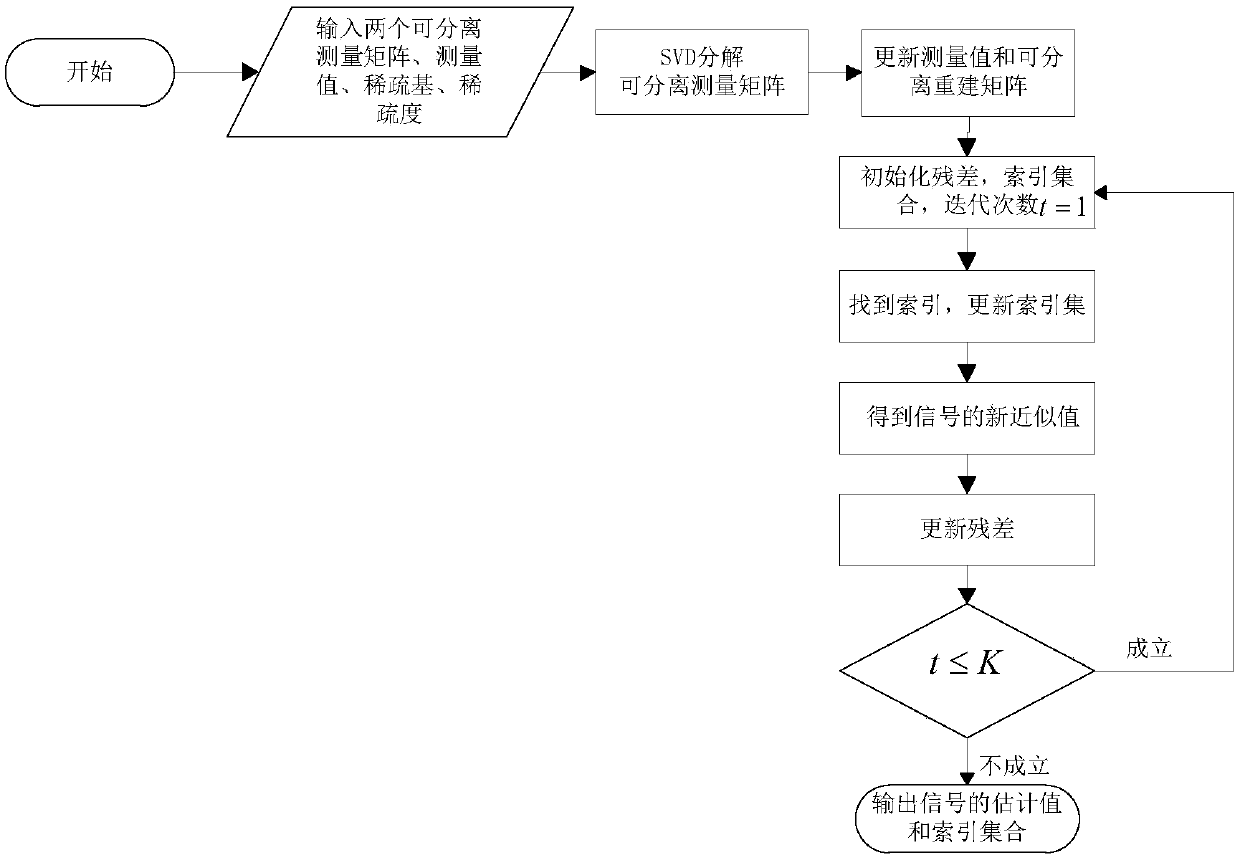

Two-dimensional orthogonal matching pursuit optimization algorithm based on singular value decomposition

ActiveCN108832934ASolve storage problemsSolve the large amount of calculationCode conversionSingular value decompositionSignal-to-noise ratio (imaging)

The invention discloses a two-dimensional orthogonal matching pursuit optimization algorithm based on singular value decomposition. The algorithm comprises acquiring a row measurement matrix, a columnmeasurement matrix, measurement values, a sparse base and signal sparseness. SVD decomposition is executed on two measurement matrixes, the measurement matrixes and the measurement values are updated, a residual, an index set and an optimized sensing matrix are initialized, an index is found, and new approximation of a signal is computed; the residual is further updated, continuous iterations areperformed, and at last the estimated value of the signal and the index set are output. According to the algorithm provided by the invention, separation of the measurement matrix in front-end information collection and rebuilt matrix in rear-end rebuilding are achieved, and thus the algorithm is applicable to a common separable linear system. The two measurement matrixes are subjected to SVD decomposition, so that the two optimized rebuilt matrixes are acquired, correlation between the measurement values is effectively eliminated, and the rebuilding signal to noise ratio and the robustness ofthe algorithm are significantly improved. Furthermore, the separable operator is used in the design of the measurement matrixes, and thus the algorithm can be applied to the building process of the large-scale image.

Owner:ANHUI UNIVERSITY

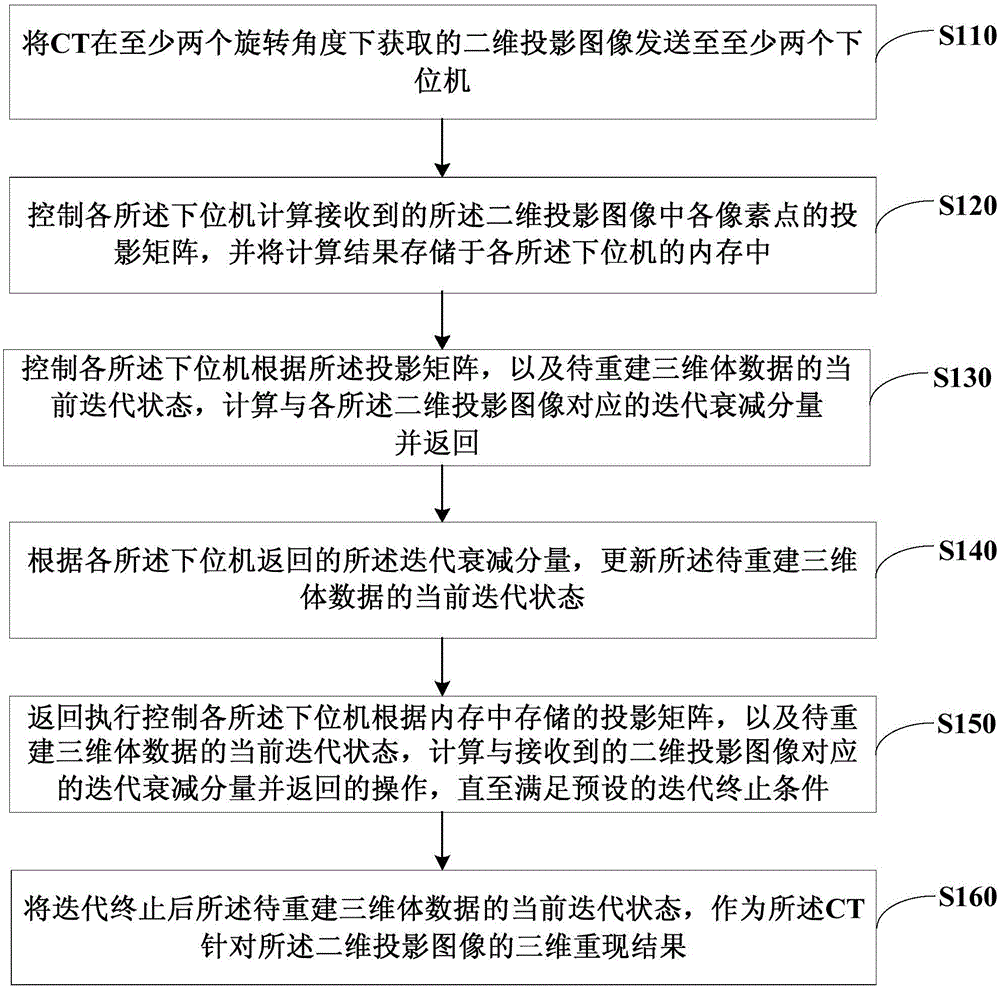

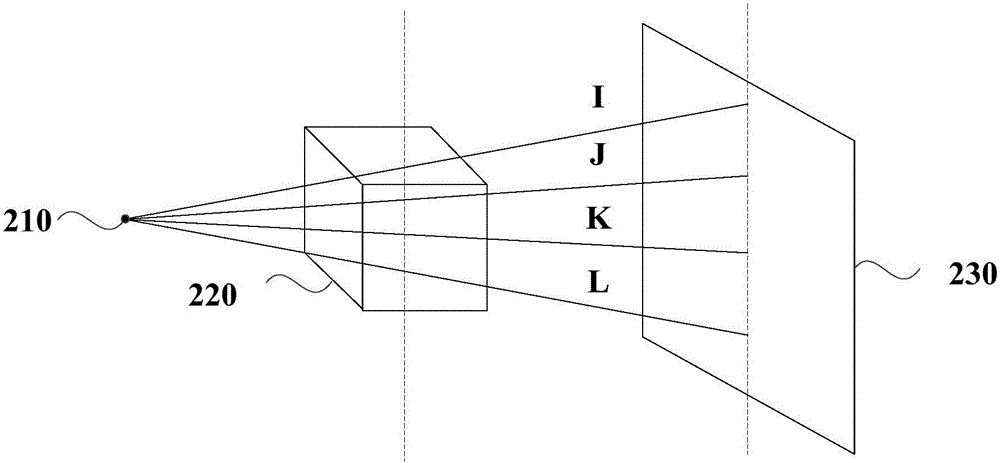

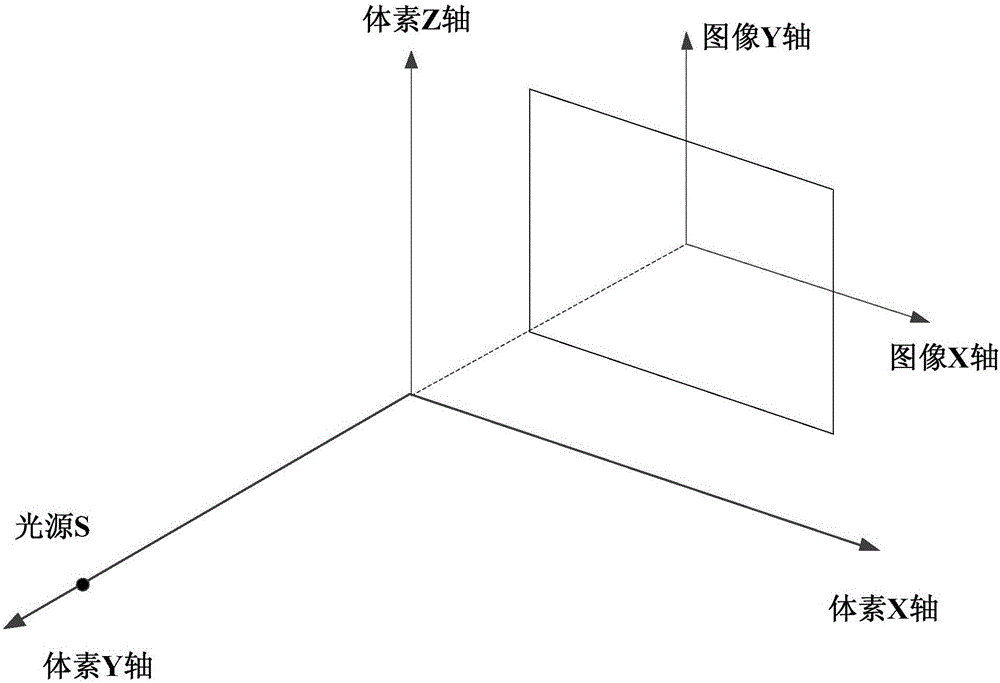

CT three-dimensional reconstructing method and system

ActiveCN106846465ASolve the large amount of calculationSolve efficiency problems3D modellingUltrasound attenuationHat matrix

The embodiment of the invention discloses a CT three-dimensional reconstructing method and system. The method comprises the steps of sending two-dimensional projection images obtained by CT at at least two rotation angles to at least two lower computers; controlling projection matrixes of all pixel points in the two-dimensional projection images received by all the lower computers through calculation, and storing the calculation result into memories of all the lower computers; according to the projection matrixes and the current iteration state of three-dimensional body data to be reconstructed, controlling all the lower computers to calculate an iterative attenuation weight and returning; according to the iterative attenuation weight, updating the current iteration state; returning to execute control over the projection matrixes and the current iteration state which are stored in the memories of all the lower computer, and calculating an iterative attenuation weight and returning till a preset ending condition is met; adopting a current iteration state after iteration ends as a three-dimensional representing result of a CT. By utilizing multiple lower computers to conduct distributed parallel calculation, the problems of low calculating efficiency, low reuse performance of calculating result and the like are overcome, and the three-dimensional reconstructing image quality is guaranteed.

Owner:SHENZHEN INST OF ADVANCED TECH

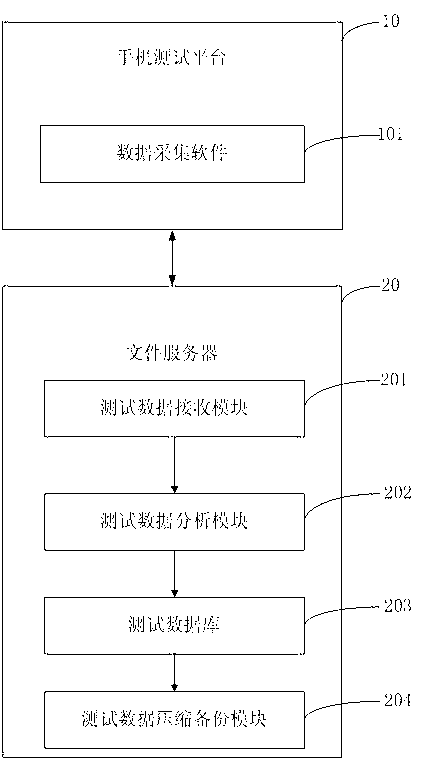

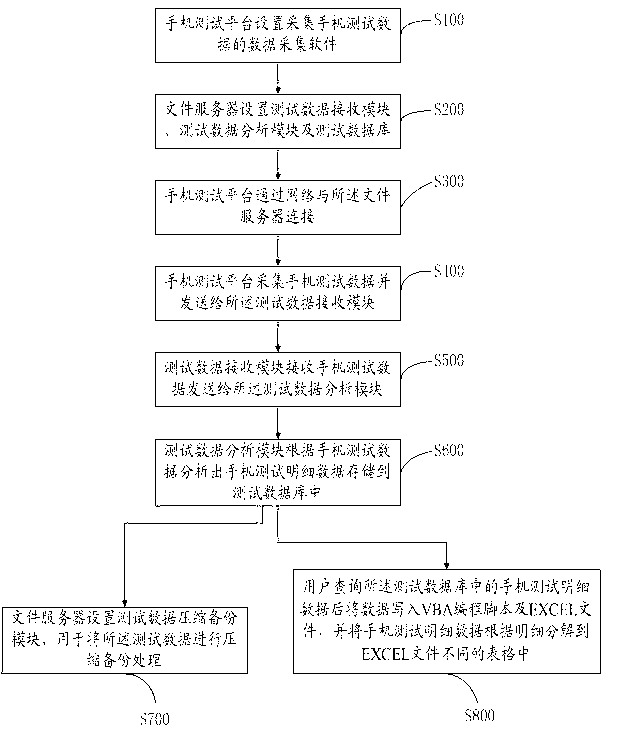

System and method for integrating mobile phone test data

ActiveCN102984325ASolve the large amount of calculationSolve efficiency problemsSubstation equipmentData switching networksComputer hardwareTest platform

Disclosed are a system and a method for integrating mobile phone test data. The system comprises a mobile phone test platform and a file server. The mobile phone test platform is connected with the file server through a network. Data acquisition software used for acquiring the mobile phone test data is arranged in the mobile phone test platform. The file server comprises a test data receiving module, a test data analyzing module and a test database. The test data receiving module receives the mobile phone test data acquired by the mobile phone test platform, and the test data analyzing module analyzes mobile phone test detail data according to the mobile phone test data and saves the mobile phone test detail data into the test database. The system and the method for integrating the mobile phone test data can automatically acquire the mobile phone test data of a mobile phone in the process of testing in real time, and automatically extract the mobile phone test detail data from the test data to classify and gather the mobile phone test detail data. Thus, the problems that, in the prior art, manual acquisition and analysis of the mobile phone test data is large in computing amount and low in efficiency and accuracy are solved, and timeliness of mobile phone test data acquisition is ensured.

Owner:HUIZHOU TCL MOBILE COMM CO LTD

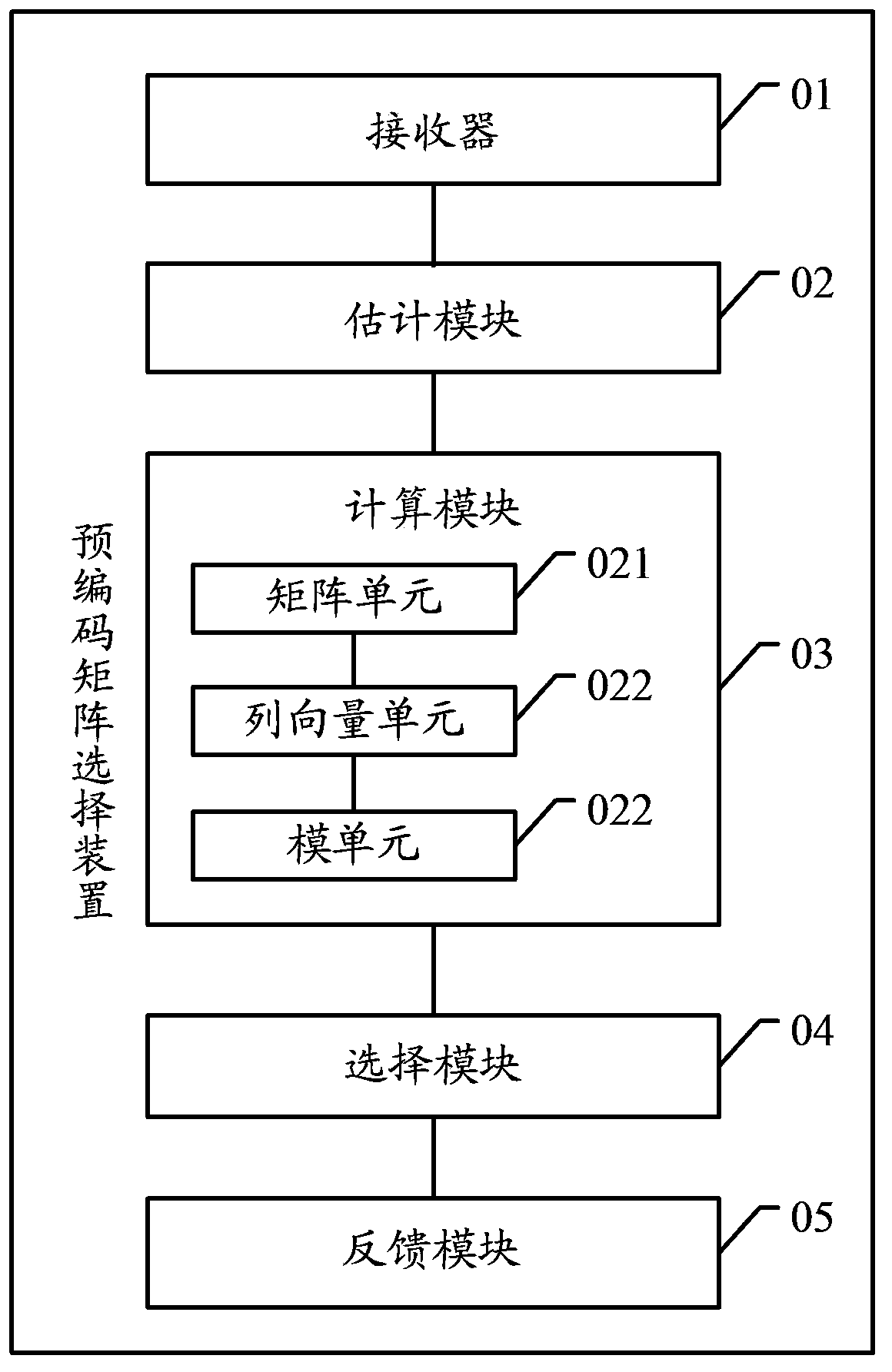

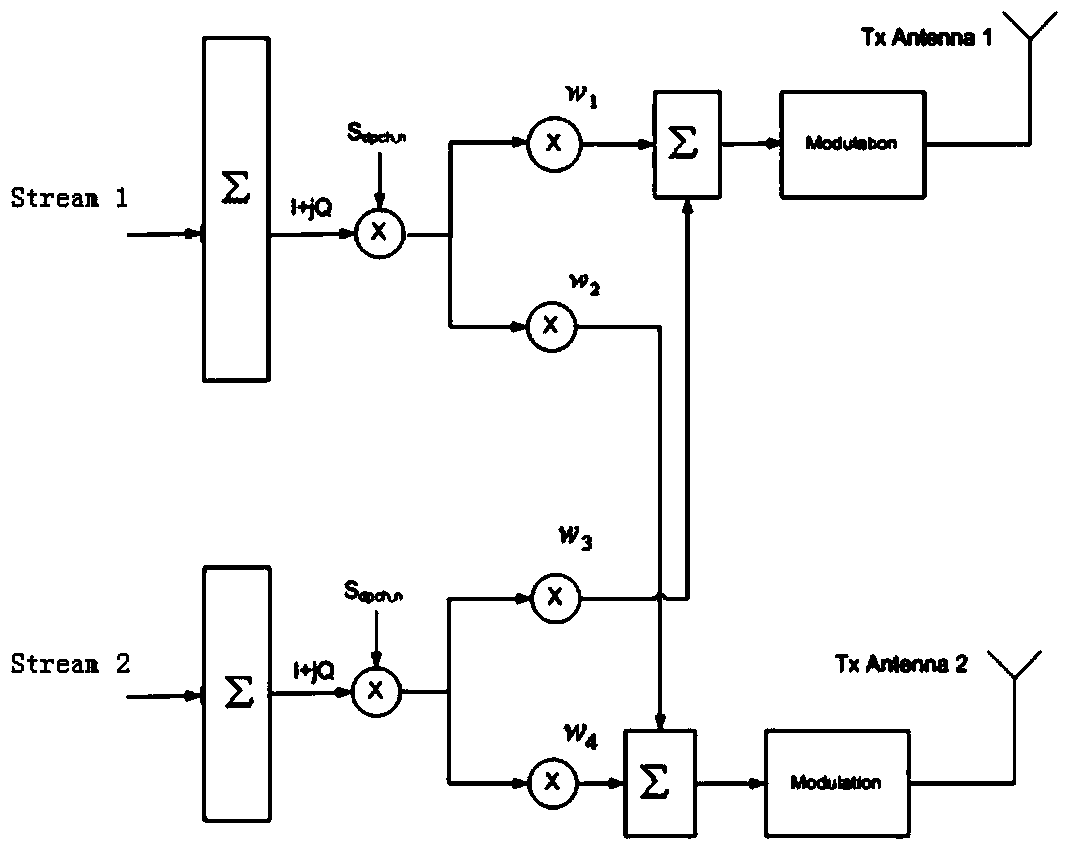

Pre-coding matrix selection method, device and system

InactiveCN103634071ASimplify the selection processSmall amount of calculationError prevention/detection by diversity receptionCurrent channelEngineering

The embodiment of the invention discloses a pre-coding matrix selection method, a device and a system. The method comprises the steps that pilot frequency information sent by a sending end is received through the current channel; according to the pilot frequency information, an equivalent channel matrix of the current channel is estimated; inner product and modulo operation are respectively carried out on the equivalent channel matrix and each pre-coding matrix in a preset pre-coding codebook collection, so as to acquire a number of module values; the pre-coding matrix corresponding to the maximum module value in a number of module values is selected as a target matrix; and the target matrix is fed back to the sending end, so that the sending end selects the target matrix to carry out pre-coding on a signal sent through the current channel. The embodiment of the invention further discloses a pre-coding matrix selection device and system. According to the invention, the pre-coding matrix selection method, device and system are provided; a pre-coding selection process can be simplified; the calculation amount in the pre-coding selection process is reduced; and the problems of large calculation amount and complicated operation of the pre-coding matrix selection method in the prior art, are solved.

Owner:HUAWEI TECH CO LTD

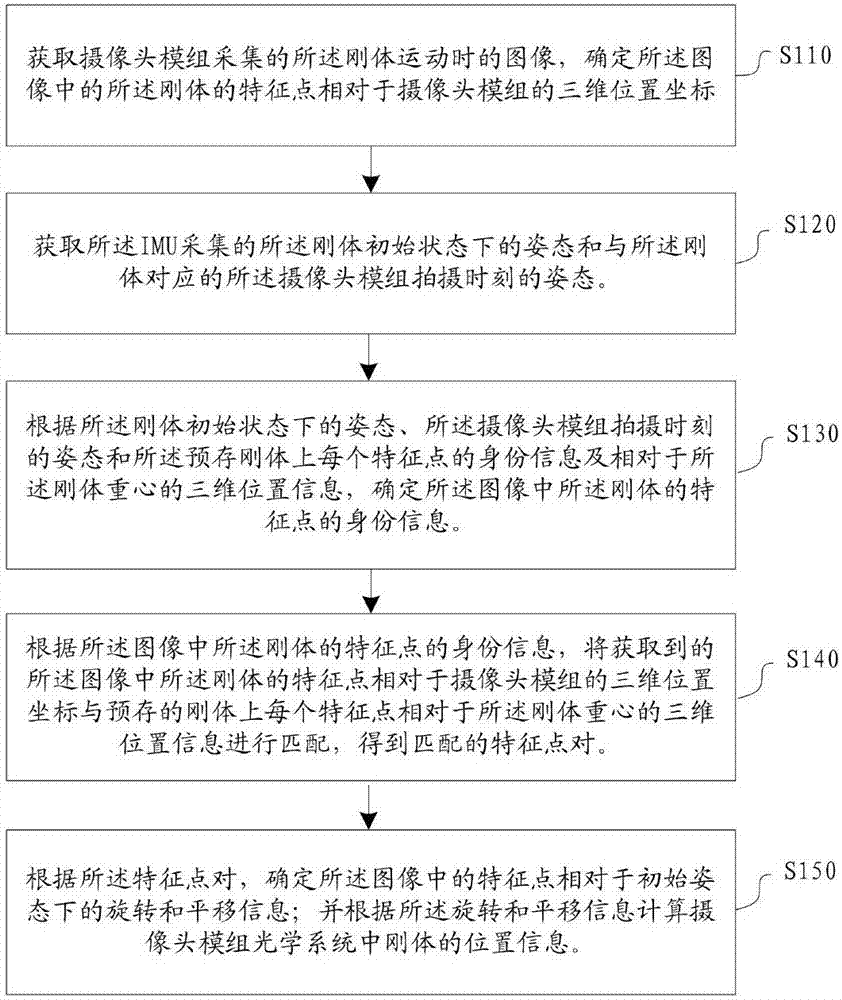

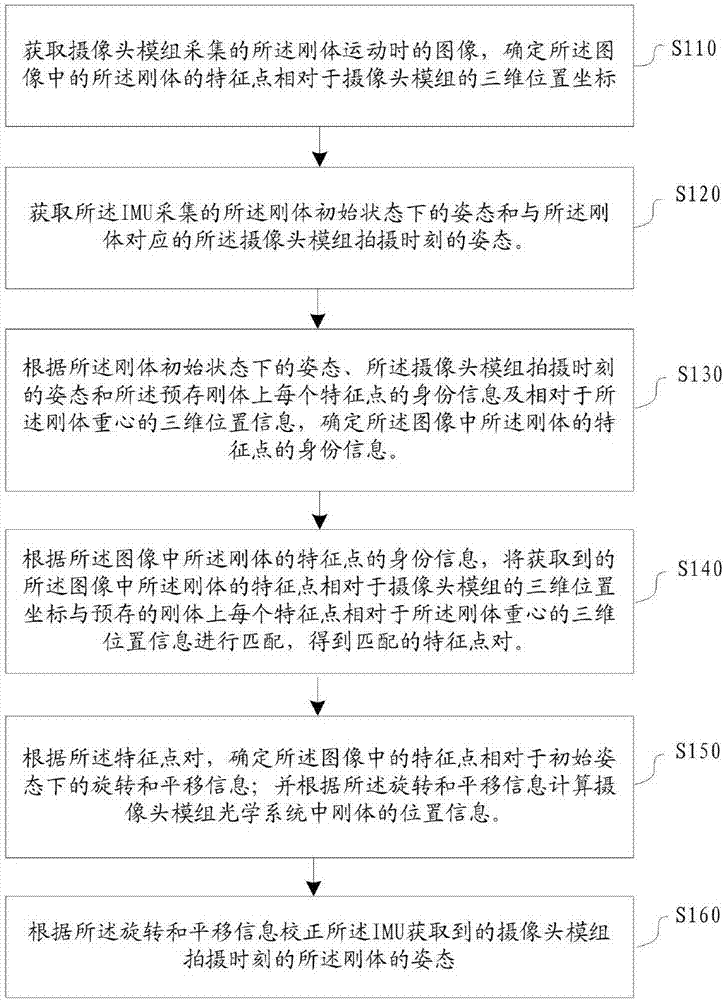

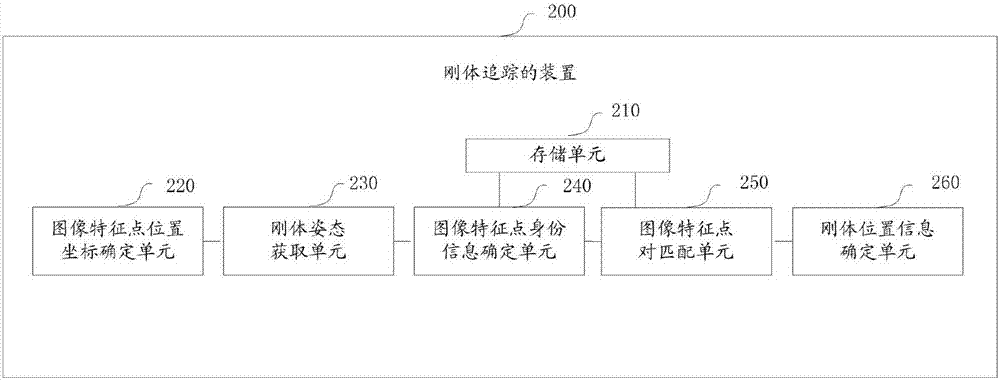

Method, device and system for tracking rigid body

ActiveCN107316319ASolve the large amount of calculationAddress limitationsImage enhancementImage analysisSpatial positioningImage resolution

The invention discloses a method, a device and a system for tracking a rigid body. The method comprises steps of acquiring an image, acquired by a camera, of a rigid body and determining a three-dimensional coordinate of feature points in the image relative to the camera; acquiring an initial posture, acquired by an IMU, of the rigid body and a rigid body posture corresponding to a shooting period of the camera, and determining identity information of feature points of the image; according to the identity information of the feature points, obtaining matched feature point pairs; according to the matched feature point pairs, calculating rotation and translation information of the feature points in the image; and according to the rotation and translation information, calculating position information of the rigid body in an optical system. According to the invention, problems of big calculated amount of the current feature matching algorithm and severe limitation of application scenes are solved; a problem of low space positioning precision caused by low resolution of images acquired by the camera in the computer graphics-based tracking algorithm is solved; an objective of complementing advantages of the computer graphics-based tracking algorithm and the IMU-based tracking algorithm is achieved; and tracking precision of the rigid body is improved.

Owner:BEIJING PICO TECH

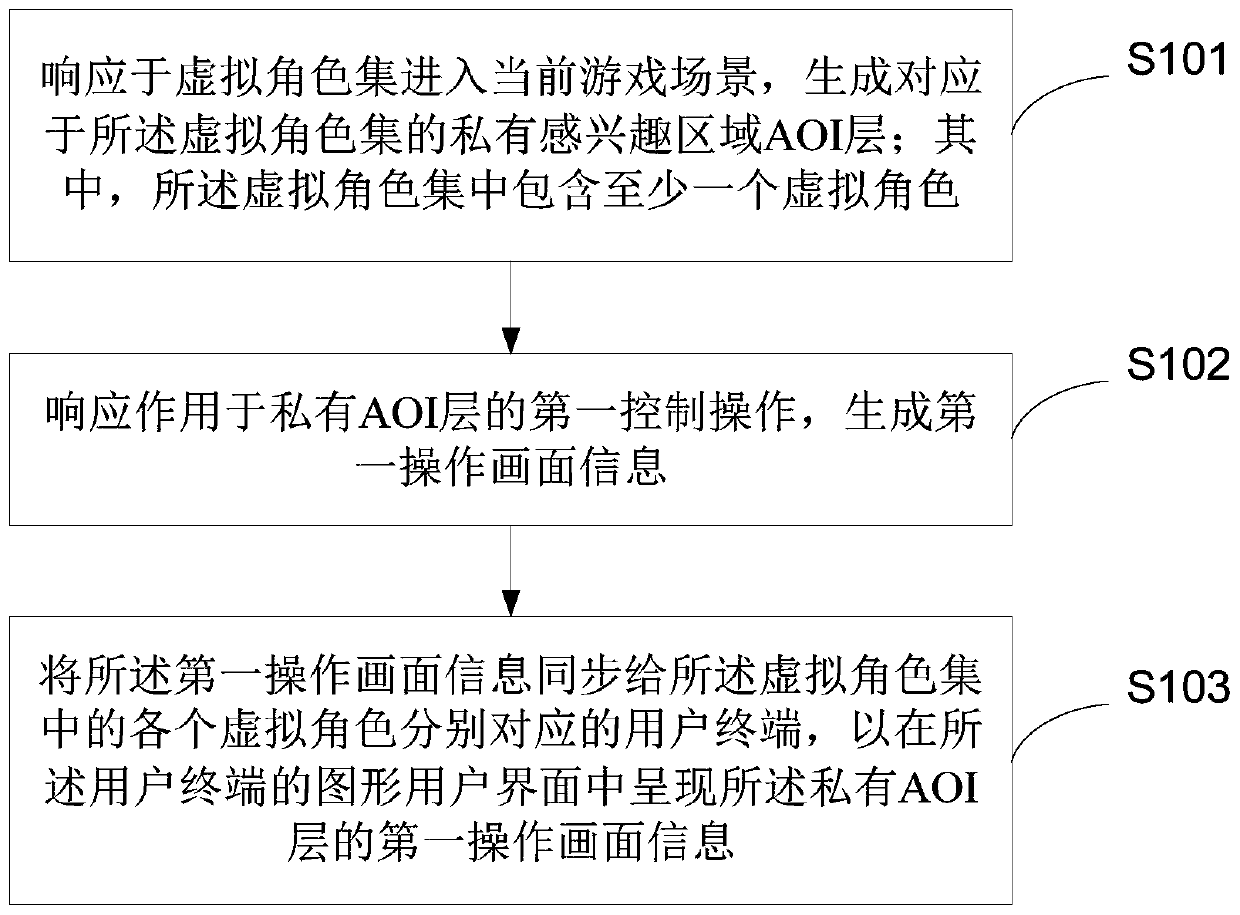

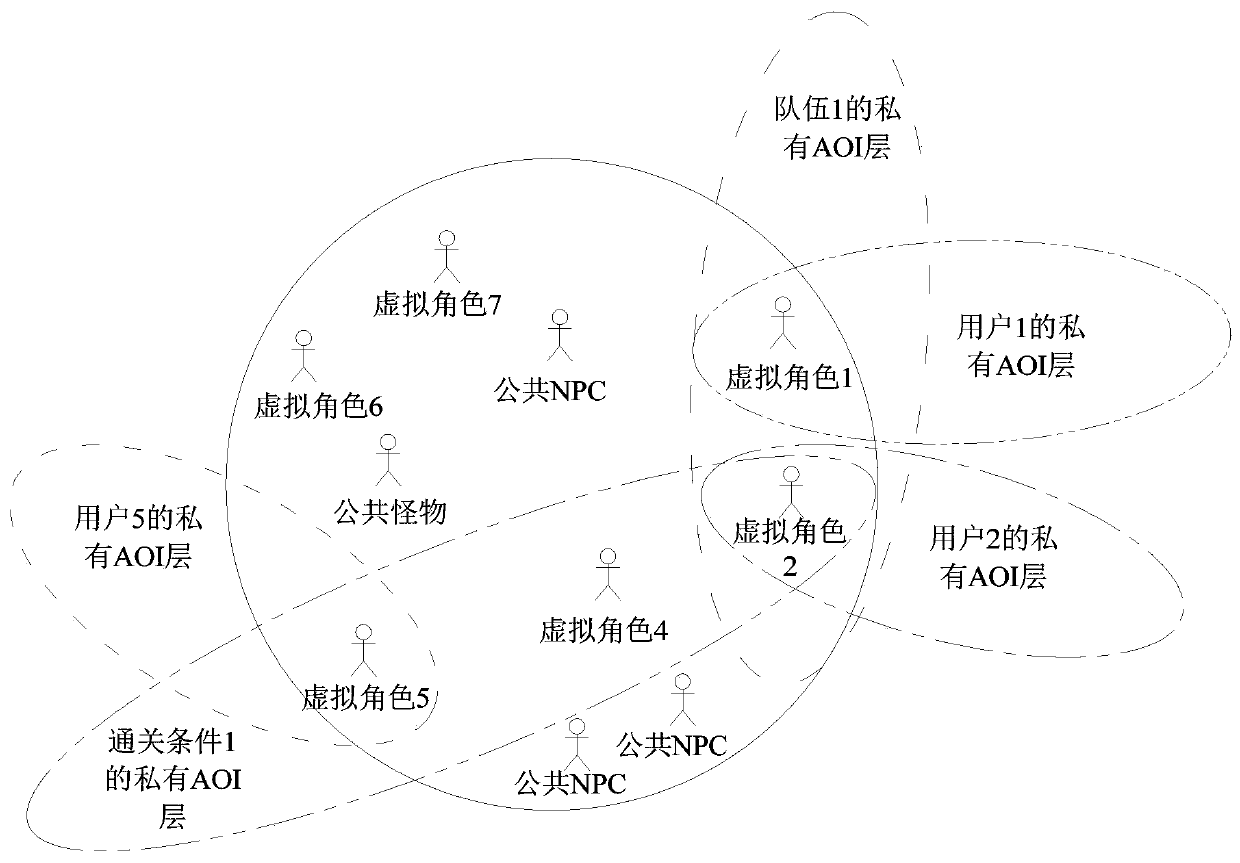

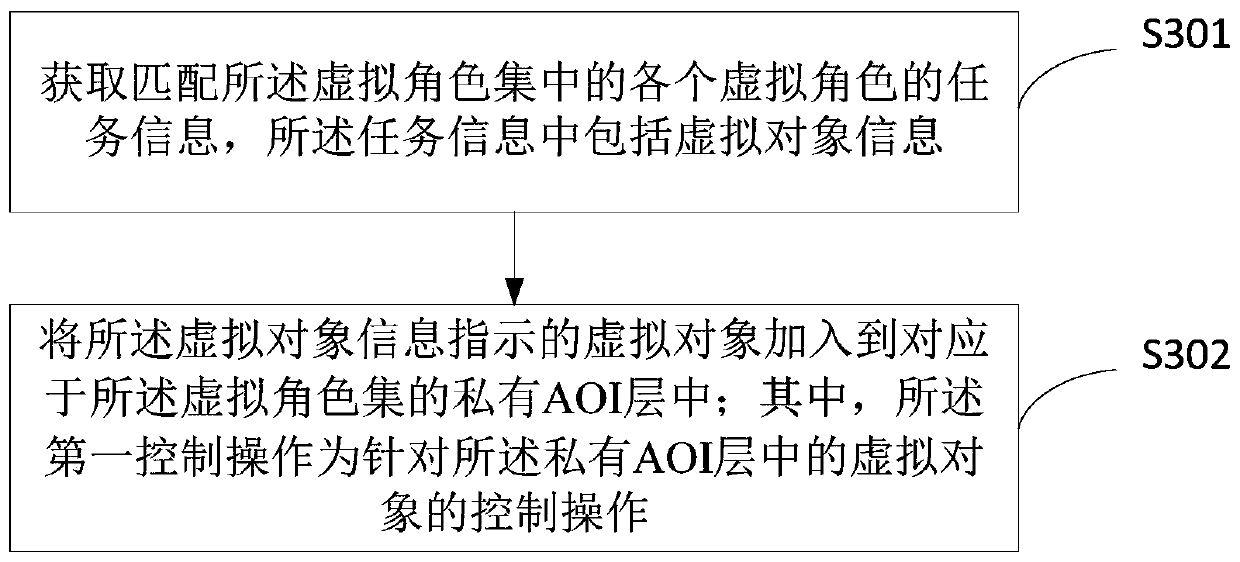

Display control method and device in game, electronic equipment and storage medium

ActiveCN110404262AMeet the needs of actual operationSolve the large amount of calculationVideo gamesGraphicsGraphical user interface

The invention provides a display control method and device in a game, electronic equipment and a storage medium. The display control method is applied to a server which can respond operation of user terminals, and provides operation image information of the game in a graphical user interface for the user terminals. The display control method comprises the steps that virtual character sets are responded to enter a current game scene, a privately-owned area-of-interest AOI layer corresponding to the virtual character sets is generated; the virtual character sets comprise contain at least one virtual character; a first control operation acting on the privately-owned AOI layer is responded, and a first operation image information is generated; and the first operation image information is synchronized to the user terminals corresponding to the virtual characters in the virtual character sets correspondingly, and the operation image information of the privately-owned AOI layer is presented on the graphical user interface of the user terminals. According to the display control method and device in the game, the electronic equipment and the storage medium, under the premise of meeting practical operation requirements of users, the problem of large calculated amounts of the server is solved.

Owner:NETEASE (HANGZHOU) NETWORK CO LTD

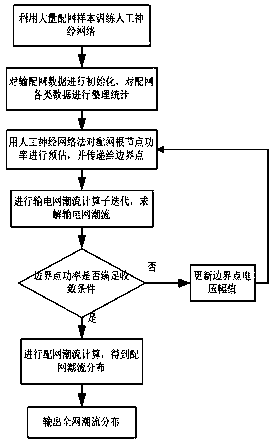

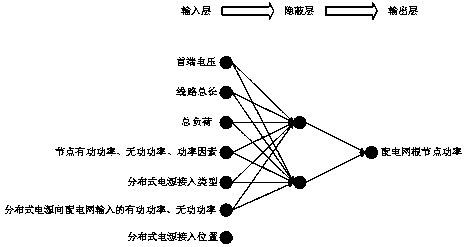

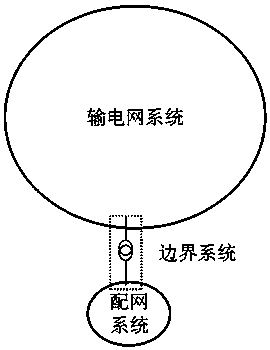

Artificial neural network-based global power flow calculation method of transmission network

ActiveCN108599172AReduce the number of power flow iterationsSolve the problem of large amount of calculationAc networks with different sources same frequencyVoltage amplitudePower flow

The invention relates to an artificial neural network-based global power flow calculation method of a transmission network. The artificial neural network is trained by using a large quantity of samples of distribution networks, so as to predict an accurate power at a boundary of the transmission network, then a global power flow calculation method with the predicted boundary power and a voltage amplitude as coordinational variables is built, therefore, the number of power flow iteration of the transmission network is lowered. Under the conditions of a normal power grid and distributed power supply, the number of power flow iteration of the transmission network is lowered remarkably, power flow convergence speed is improved, and the method is suitable for global power flow calculation of the large-scale transmission network at present.

Owner:FOSHAN POWER SUPPLY BUREAU GUANGDONG POWER GRID

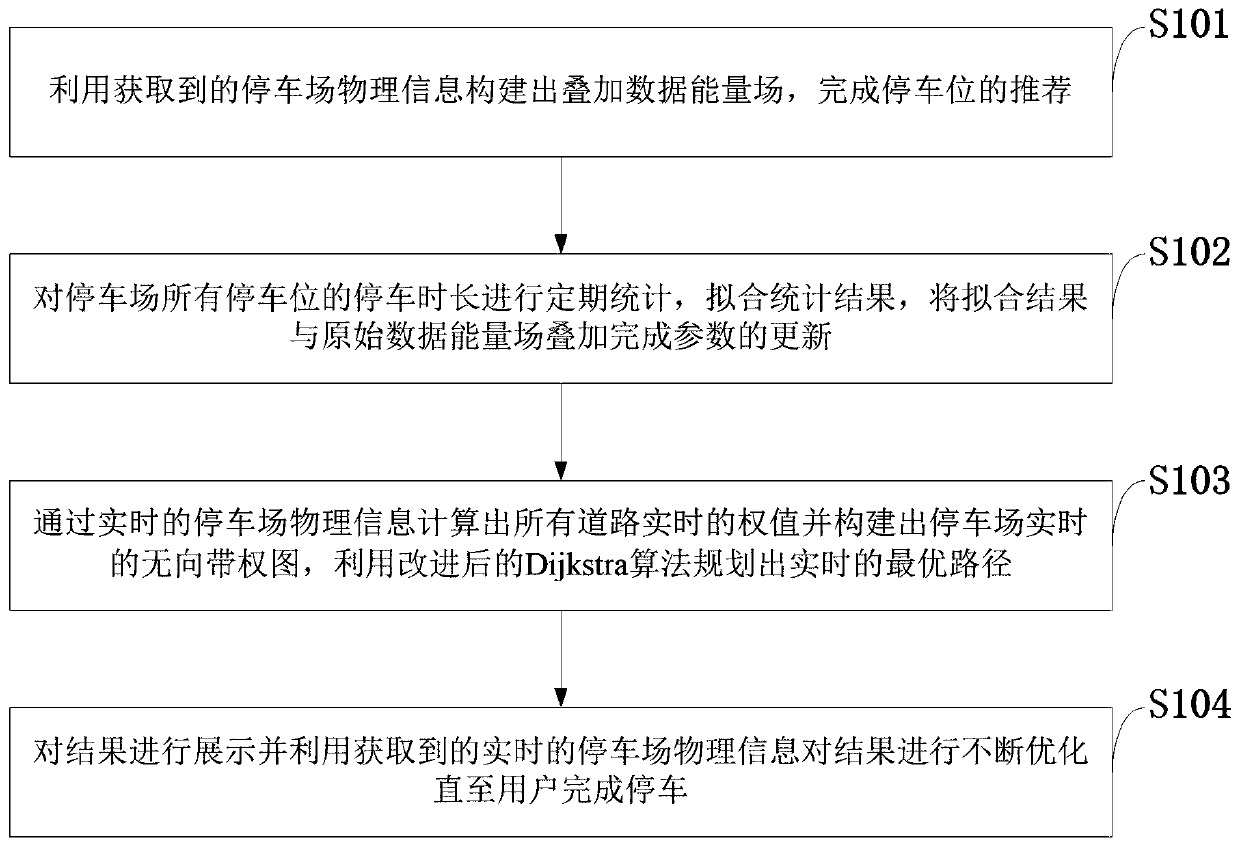

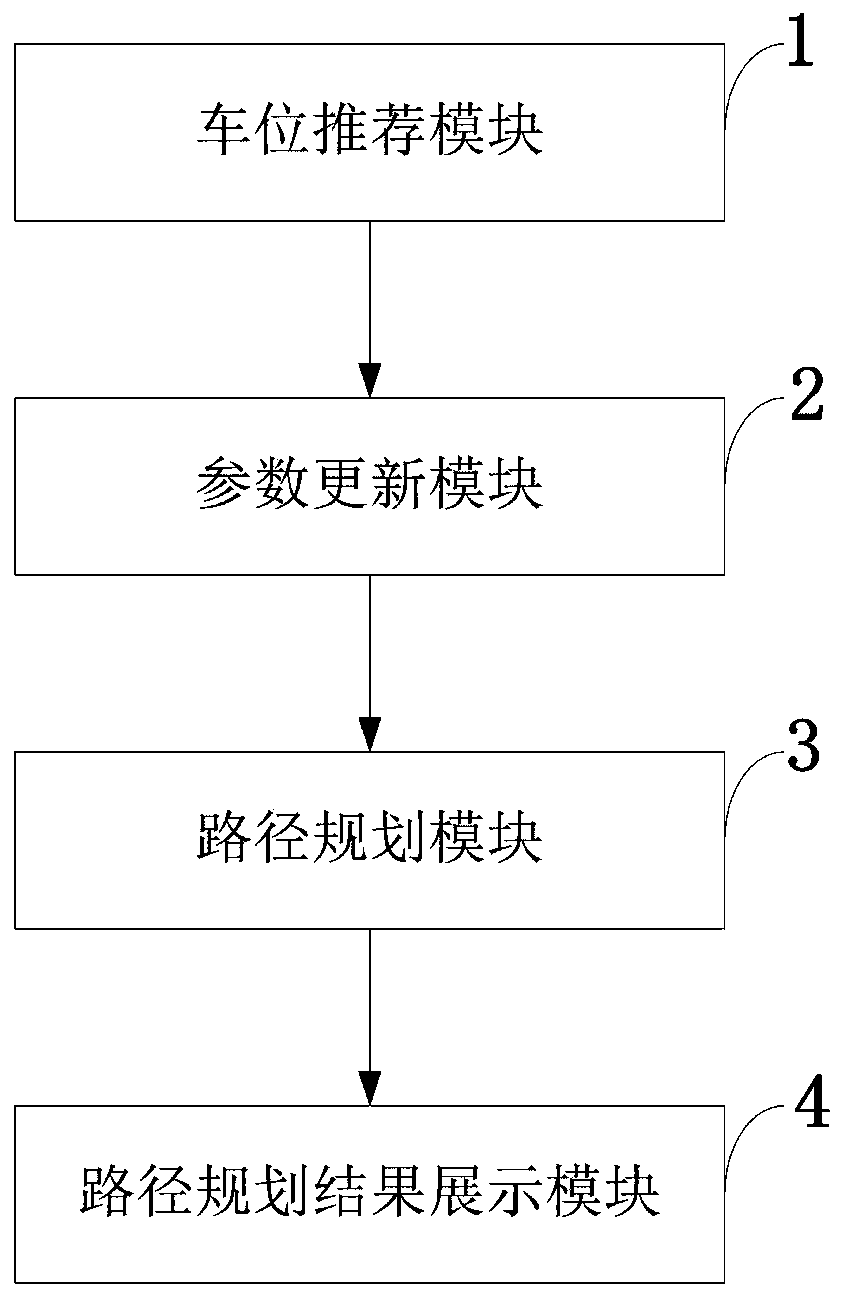

Intelligent parking control method and system, storage medium, computer program and terminal

ActiveCN111402616AMeet real-time requirementsSolve the large amount of calculationDetection of traffic movementIndication of parksing free spacesOriginal dataSimulation

The invention belongs to the field of parking lot path planning in intelligent transportation, and discloses an intelligent parking control method and system, a storage medium, a computer program anda terminal. The method comprises the following steps: constructing a superposed data energy field through the obtained physical information of a parking lot, and completing the recommendation of parking spaces; performing regular statistics on the parking duration of all parking spaces of the parking lot, fitting a statistical result, and superposing the fitting result and the original data energyfield to complete parameter updating; calculating real-time weights of all roads through real-time physical information of the parking lot, constructing a real-time undirected weighted graph of the parking lot, and planning a real-time optimal path by using an improved Dijkstra algorithm; and displaying the result and continuously optimizing the result by utilizing the obtained real-time physicalinformation of the parking lot until a user finishes parking. According to the invention, the problems caused by many parking spaces and irregular distribution of parking spaces in large parking lotsare effectively solved, and the method has better dynamics and real-time performance.

Owner:XIDIAN UNIV

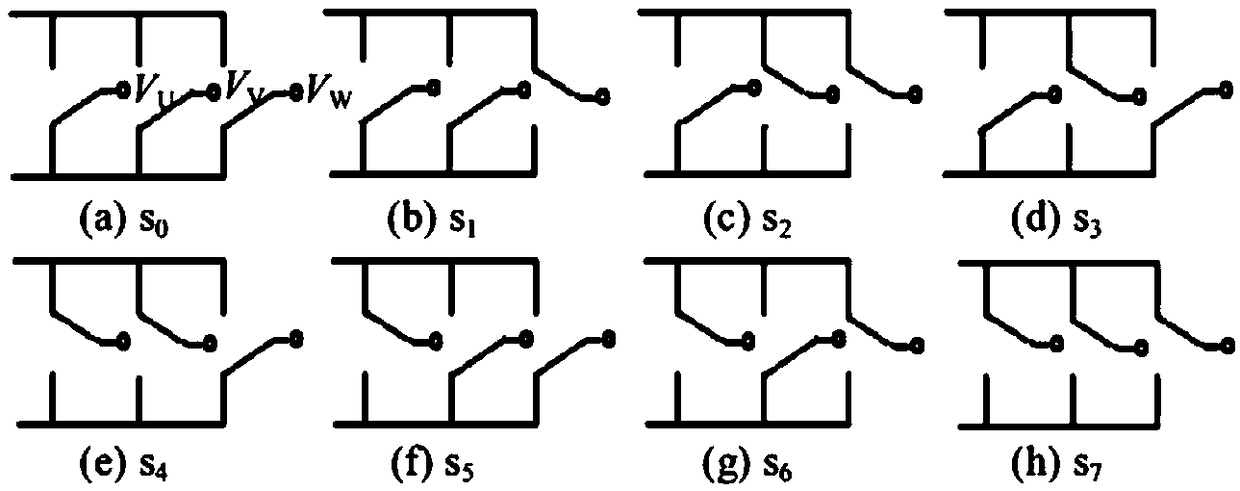

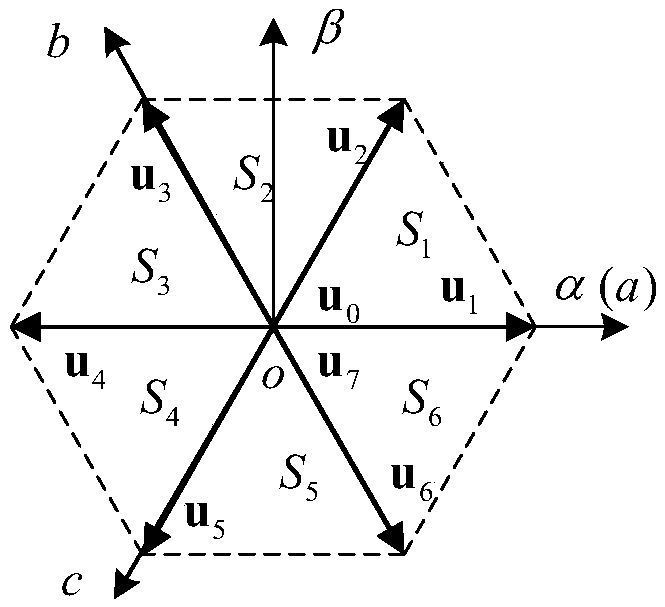

A pulse width modulation method and device based on an equivalent zero vector

InactiveCN109039133AReduce common mode voltageSmall amount of calculationAc-dc conversionThree phase converterCarrier signal

The invention relates to a pulse width modulation method and device based on an equivalent zero vector, belonging to the technical field of power electronic converters. The invention determines the action time of the modulated wave space vector according to a space vector algorithm, adopts the adjacent symmetrical vector with equal time to replace the zero vector in the modulated wave space vector, and ensures the voltage output of the three-phase converter to achieve the effect of reducing the common-mode voltage of the converter port on the basis of the voltage output of the three-phase converter. The invention completely retains the existing space vector calculation part, obtains the carrier signal by calculating the voltage instruction through the space vector algorithm, and greatly saves the calculation amount and improves the efficiency compared with an existing vector modulation method for reducing the common-mode voltage.

Owner:ZHANGJIAKOU WIND & SOLAR POWER ENERGY DEMONSTRATION STATION CO LTD +2

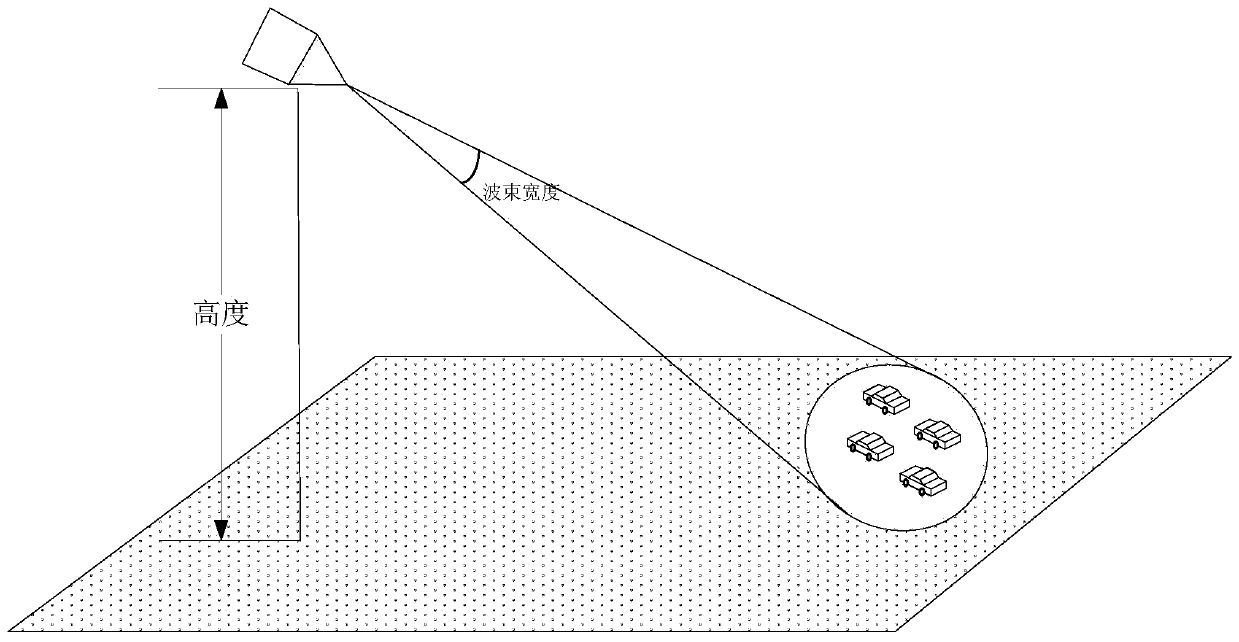

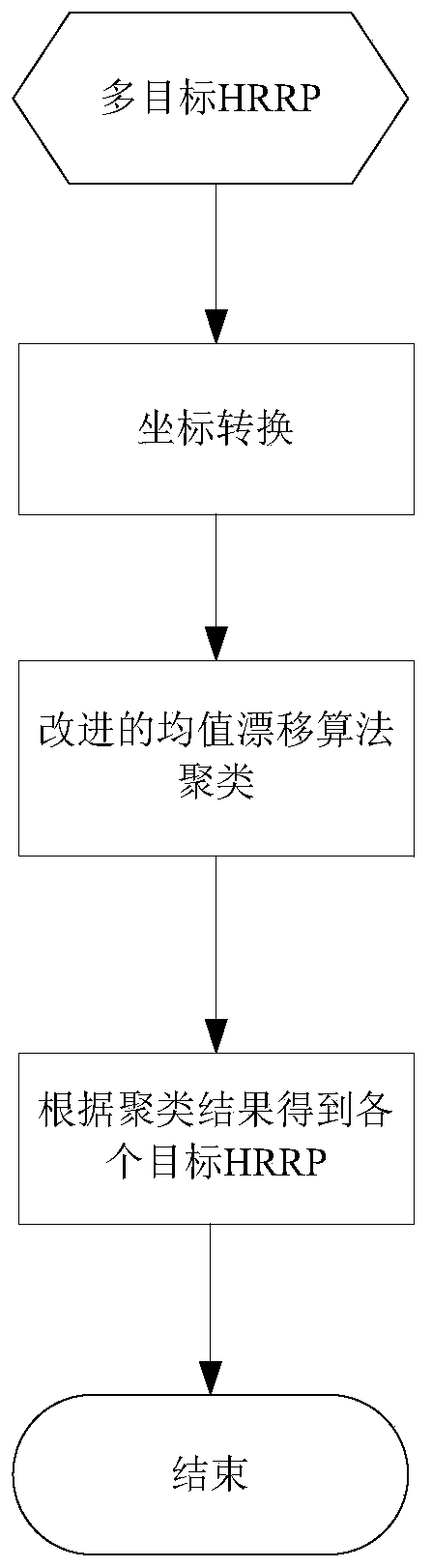

Group target identification method based on high-resolution range-profile and single-pulse measurement angle

ActiveCN110018461AImprove iteration efficiencySolve the large amount of calculationWave based measurement systemsCharacter and pattern recognitionCluster algorithmRadar

The invention relates to a group target identification method based on a high-resolution range-profile and a single-pulse measurement angle. The method is used for radar group target identification. For the disadvantages that the traditional group target identification method requires each sub-target to move relative to a radar and the computation burden is comparatively large, the invention provides the group target identification method based on the high-resolution range-profile and the single-pulse measurement angle. Based on the high-resolution range-profile and the single-pulse measurement angle information, the clustering is accomplished by adopting a mean value drifting clustering algorithm on a two-dimensional plane, and HRRPs of various sub-targets are extracted without utilizingmovement information of the target; the method has no constraint on a condition whether each sub-target is in movement, and a requirement of requiring each sub-target to move relative to the radar inthe traditional method is solved. By utilizing scattering point amplitude information, the method improves the traditional mean value drifting clustering algorithm from two aspects: initial value selection and sample weight, the iteration efficiency of the mean value drifting algorithm is improved, and the problem that the traditional method is large in computation burden is solved.

Owner:CNGC INST NO 206 OF CHINA ARMS IND GRP

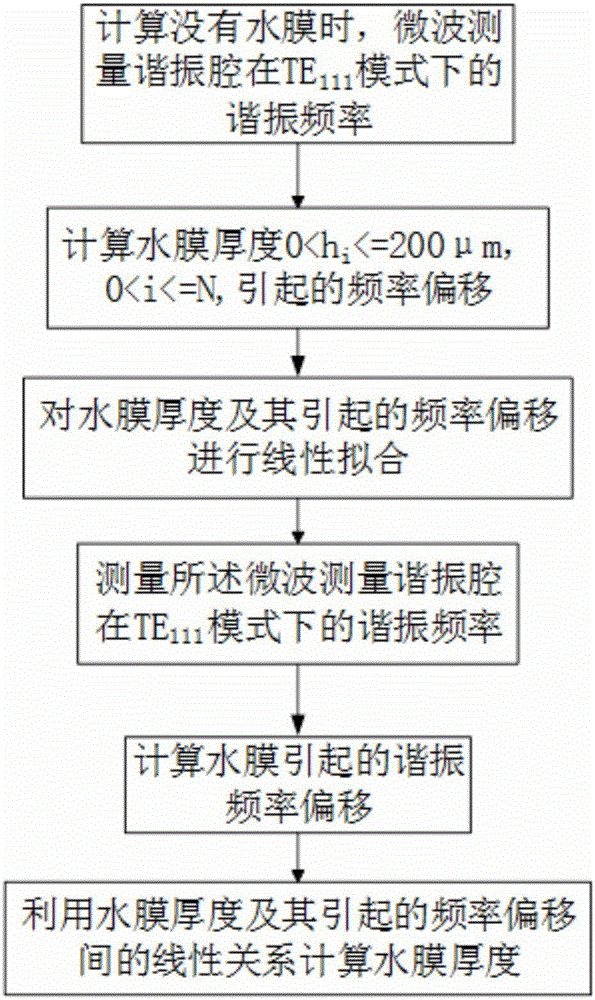

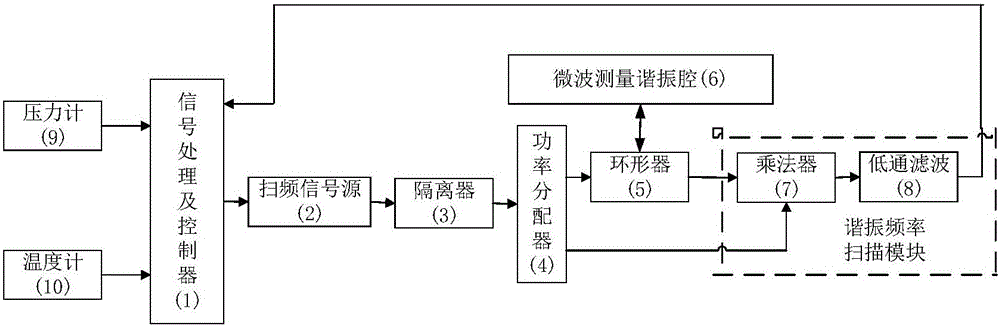

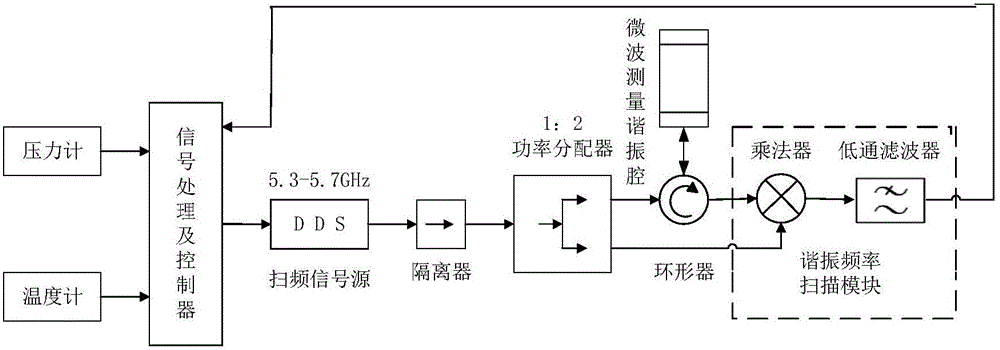

Method for measuring inner wall water film thickness of microwave humidity sensor on basis of linear fitting

InactiveCN105928955AQuick measurementAccurate measurementUsing wave/particle radiation meansMoisture content investigation using microwavesObservational errorOptoelectronics

The invention discloses a method for measuring the inner wall water film thickness of a microwave humidity sensor on the basis of linear fitting. The measuring method comprises the following steps that the resonant frequency of a microwave measurement resonant cavity in a TE111 mode on the condition that no water film exists is calculated; the water film thickness and the corresponding frequency deviation caused by the water film thickness are calculated, wherein 0<hi<=200 micrometers, and 0<i<=N; linear fitting is conducted on the water film thickness hi and the corresponding frequency deviation deltaf<w-1,i> caused by the water film thickness; the resonant frequency of the microwave measurement resonant cavity in the TE111 mode is measured; the resonant frequency deviation caused by the water film is calculated; the water film thickness is calculated through a linear relation between the water film thickness and the frequency deviation caused by the water film thickness. According to the method, the water film thickness hi and the corresponding frequency deviation deltaf<w-1,i> caused by the water film thickness present the linear relation on the basis of the work of the cylindrical waveguide resonant cavity in the TE111 mode, the inner wall water film thickness of a wet steam humidity sensor is quickly and accurately measured, and convenient conditions are provided for eliminating measuring errors brought by the water film thickness on a humidity measuring result and improving the humidity measuring precision.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

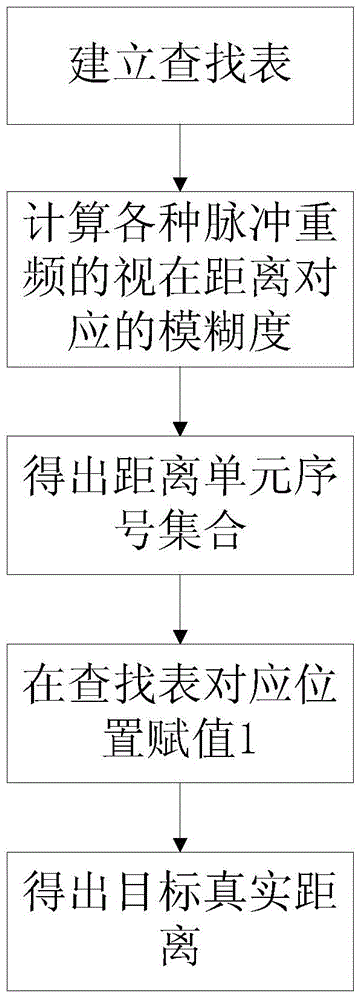

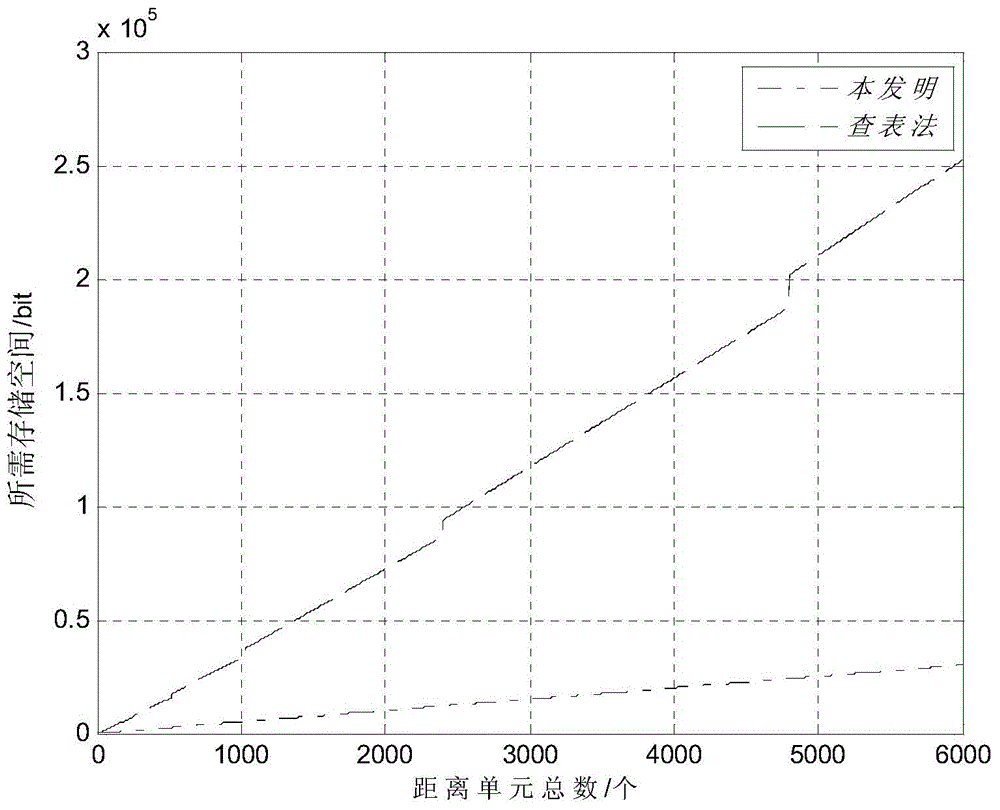

Pulse Doppler radar ranging improvement method based on one-dimensional set method

InactiveCN104375139ASolve the large amount of calculationThe calculation process is simpleRadio wave reradiation/reflectionEcho signalEnvironmental geology

The invention relates to a pulse Doppler radar ranging improvement method based on a one-dimensional set method. The method includes the steps of establishing a finding table, and making each numerical value in the finding table be 0; obtaining the apparent distance threshold s[i] and the maximum fuzzy degree f[i] corresponding to the ith pulse repetition frequency P[i] of a radar transmitting signal; obtaining the apparent distance x[i] corresponding to the ith pulse repetition frequency P[i] of the radar transmitting signal according to a target echo signal; renewing the maximum fuzzy degree f[i] corresponding to the apparent distance threshold s[i] to obtain the renewed maximum fuzzy degree f[xi] corresponding to the apparent distance threshold s[i]; obtaining the qth element r[iq] of the distance unit sequence number set (please see the specifications), wherein the qth element r[iq] of the distance unit sequence number set (please see the specifications) is equal to the sum of x[i] and the product of q and q[i], and q is equal to 0, 1, 2...f[xi]; renewing the numerical value (please see the specifications) in the ith row and the R[i]th line of the finding table as 1, wherein R[i] is equal to r[i0], r[i1], r[i2]...r[if[xi]]; making j sequentially be 1, 2...N, and obtaining the distance A between a target and the pulse Doppler radar if the sum y[j] of all the numerical values in the jth line in the finding table is larger than or equal to L.

Owner:XIDIAN UNIV

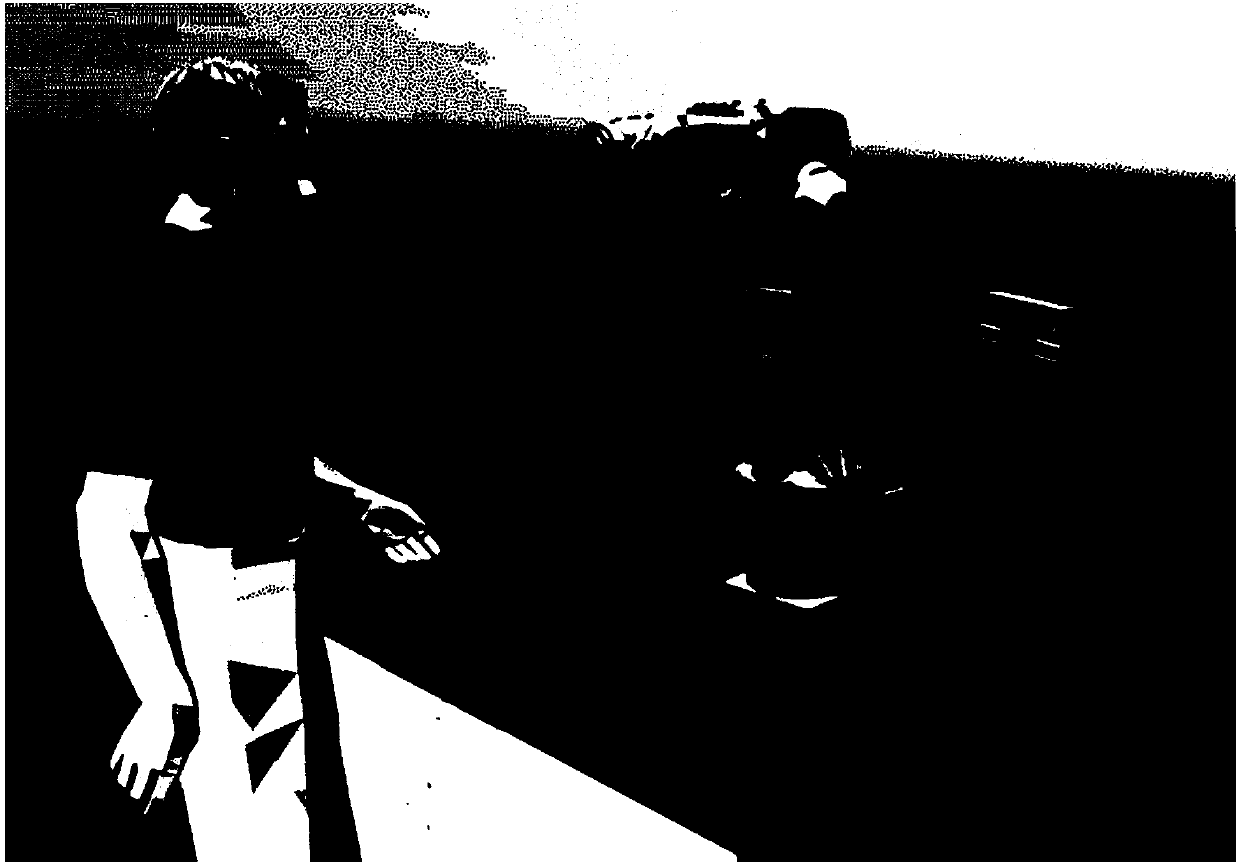

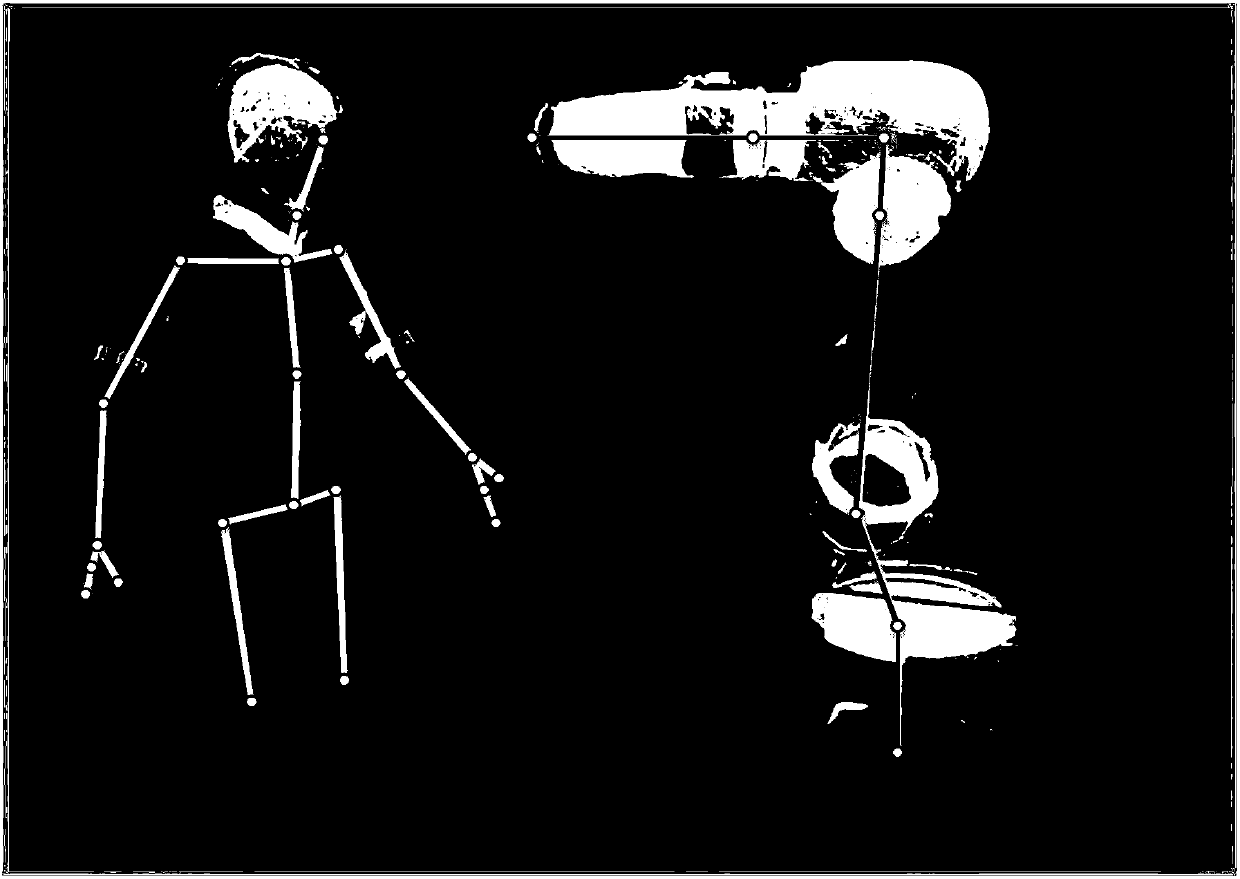

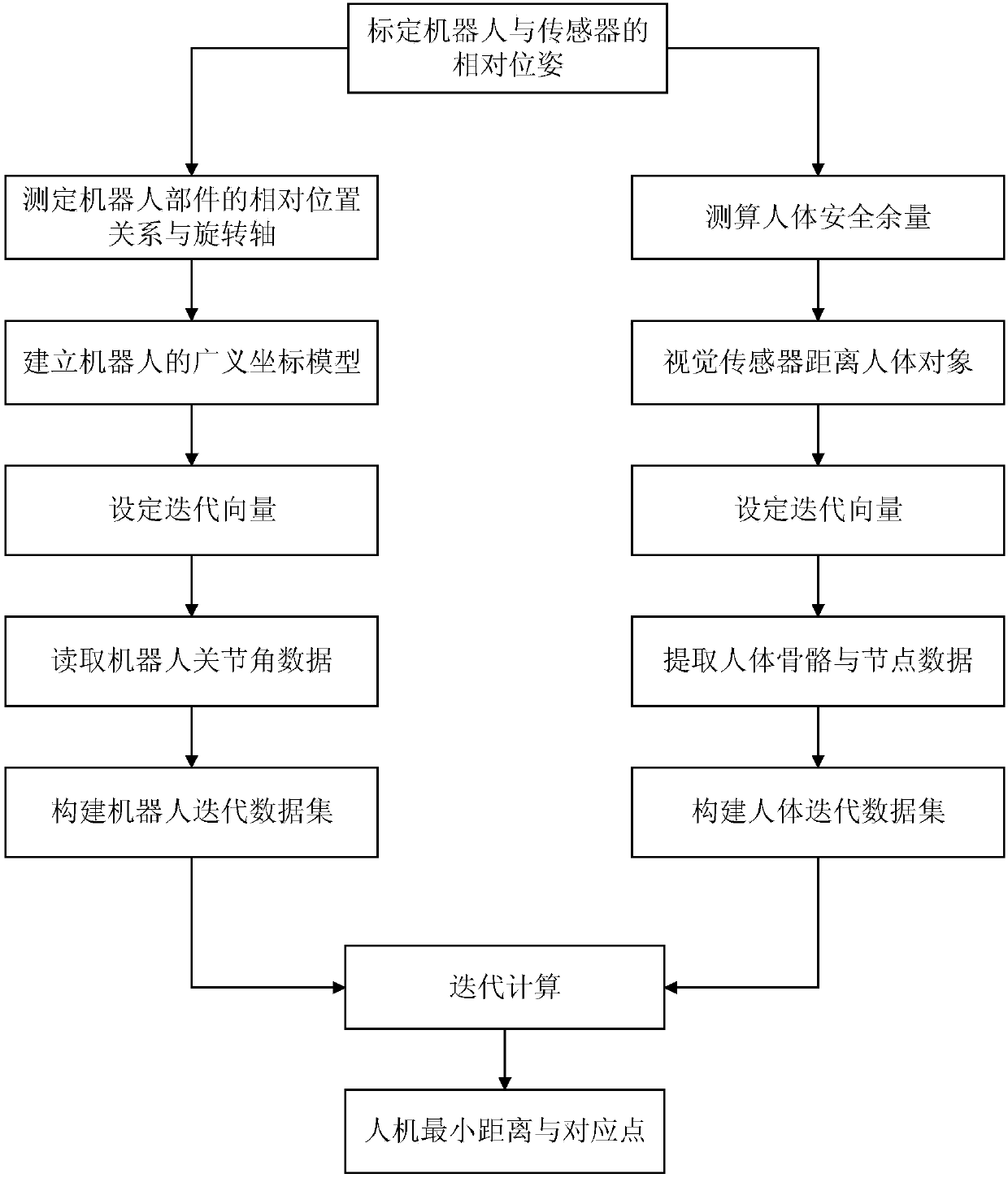

Method for measuring and calculating human-robot minimum distance in collaborative environment

The invention discloses a method for measuring and calculating the human-robot minimum distance in a collaborative environment. According to the relative position relation and the rotating axes of theparts of a robot, a generalized motion model of the robot is established. Meanwhile, a motion node iteration data set of the robot with a minimum human-robot distance is constructed. Meanwhile, the image data of the human-robot cooperation space is collected through a 3D visual sensor, so that the human body information in the collaborative environment is tracked and identified. The skeleton nodedata of a human body are extracted, and a human skeleton node iteration data set with the minimum human-robot distance is constructed. According to the obtained iteration data set, the minimum distance between the human body and the robot in the collaborative environment, and the space coordinates of corresponding points are calculated in the iterative manner. According to the invention, based onthe method for measuring and calculating the human-robot minimum distance in the collaborative environment, an accurate and easy-to-achieve human-robot distance calculation model is built in real time. After that, a human-robot minimum distance and a corresponding point in the collaborative environment are calculated in real time. The safety of the robot can be improved. The human-robot minimum distance in the environment can be efficiently tracked in real time.

Owner:SOUTHEAST UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com