Patents

Literature

203results about "Electromagnetic wave demodulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

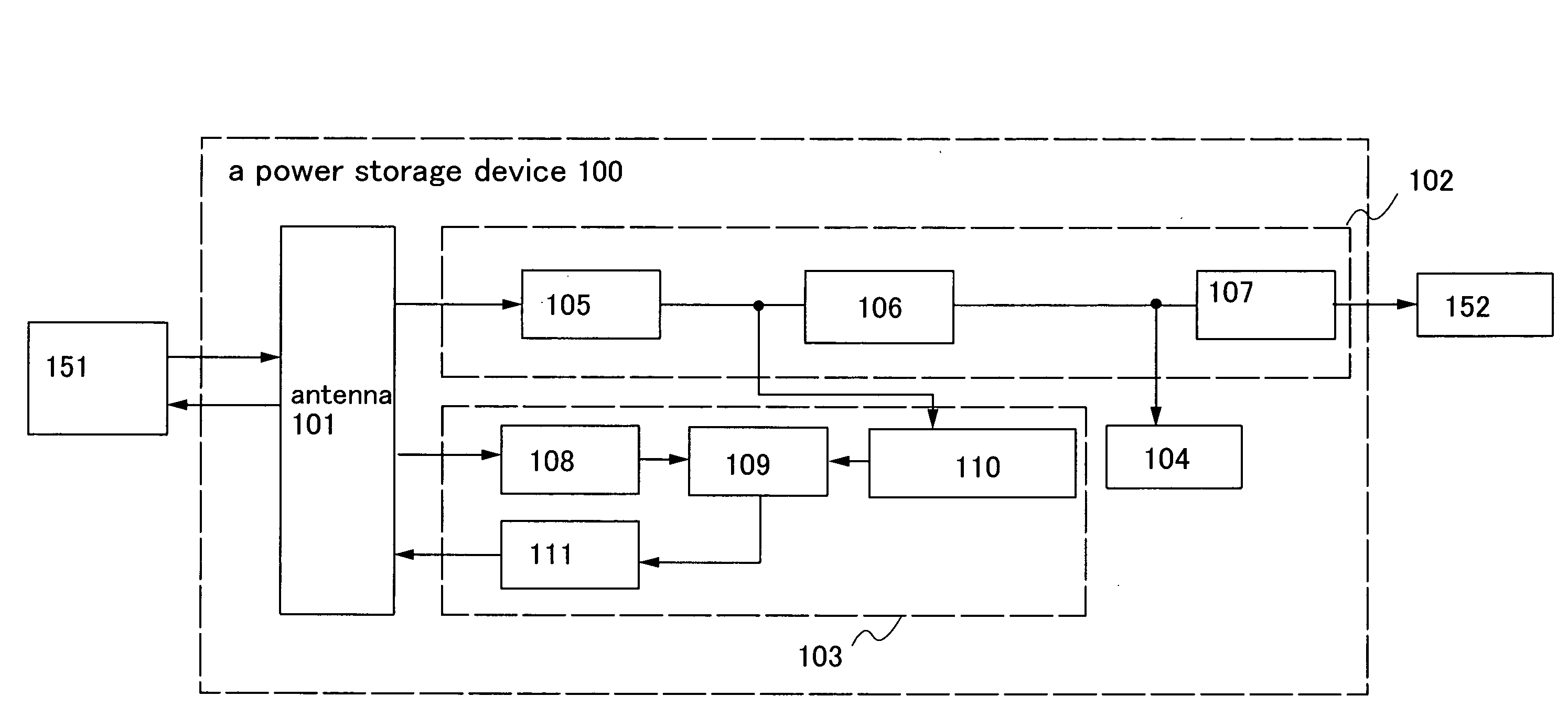

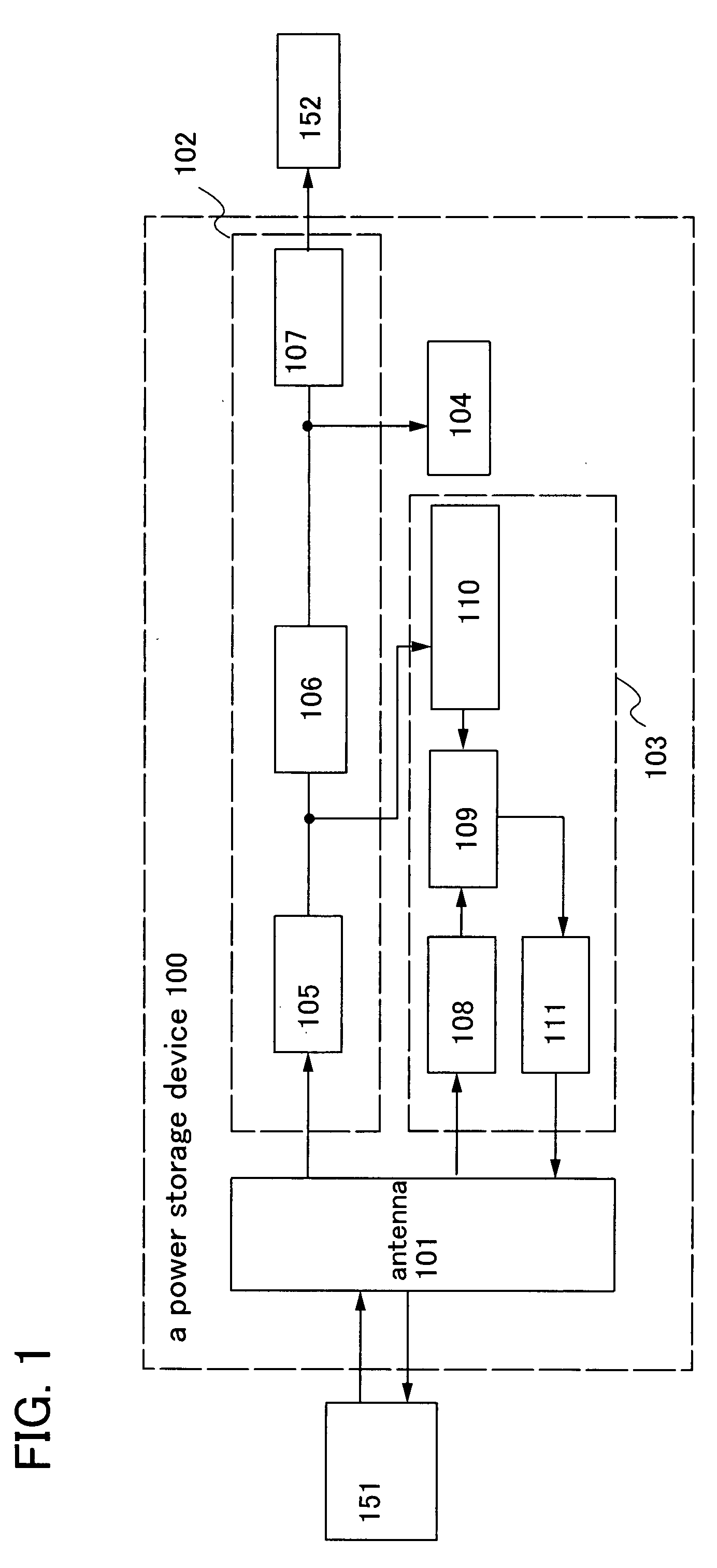

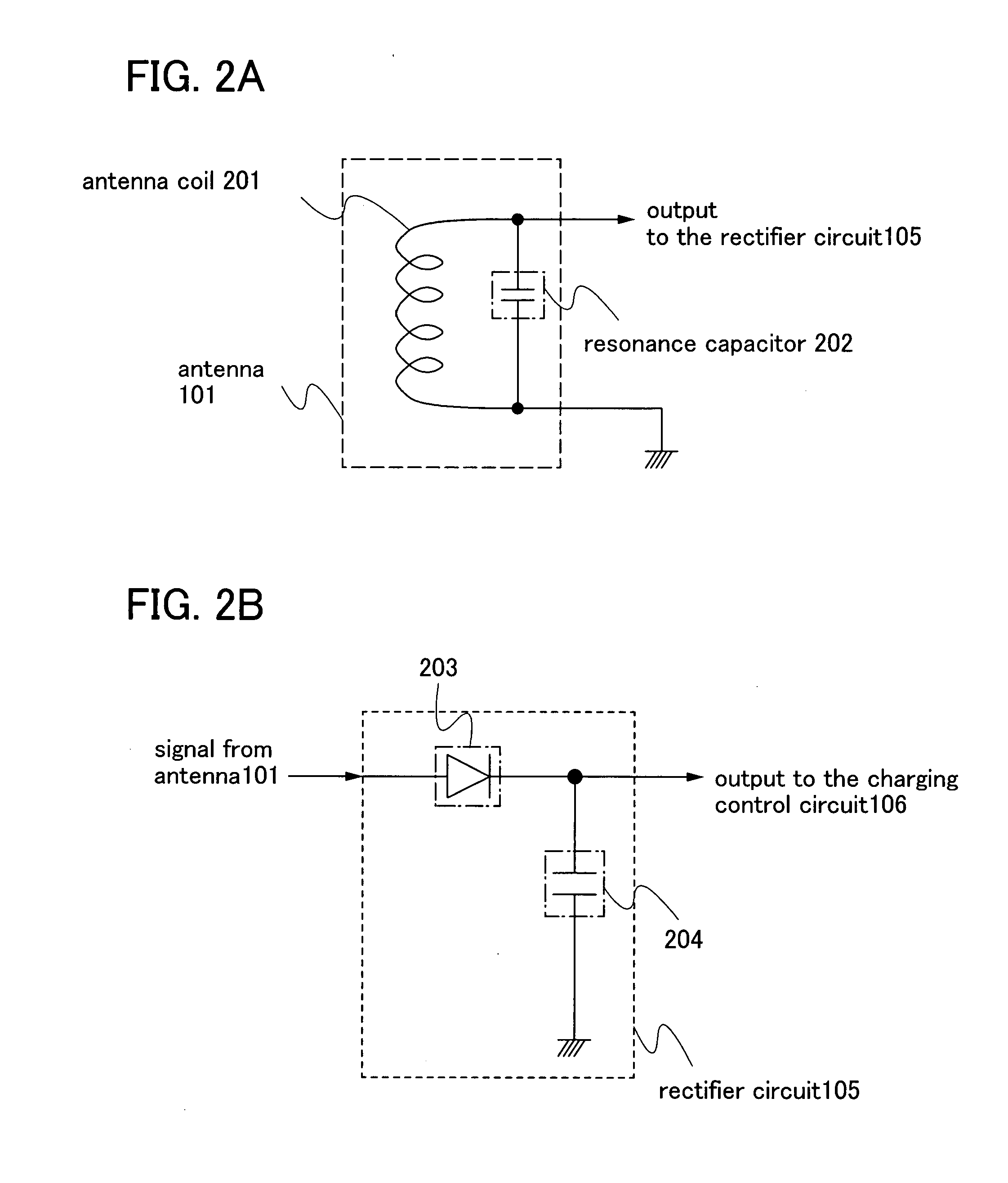

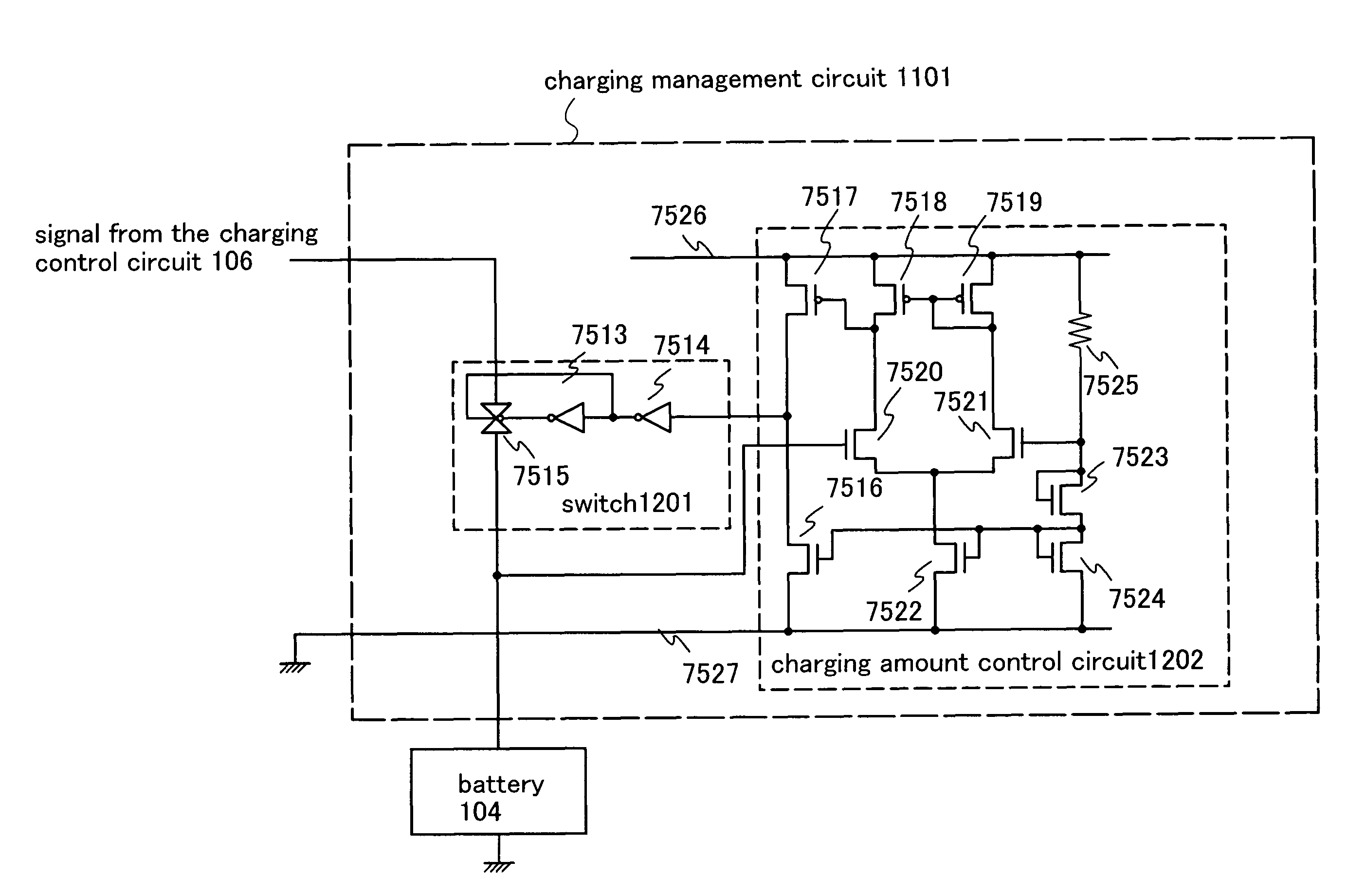

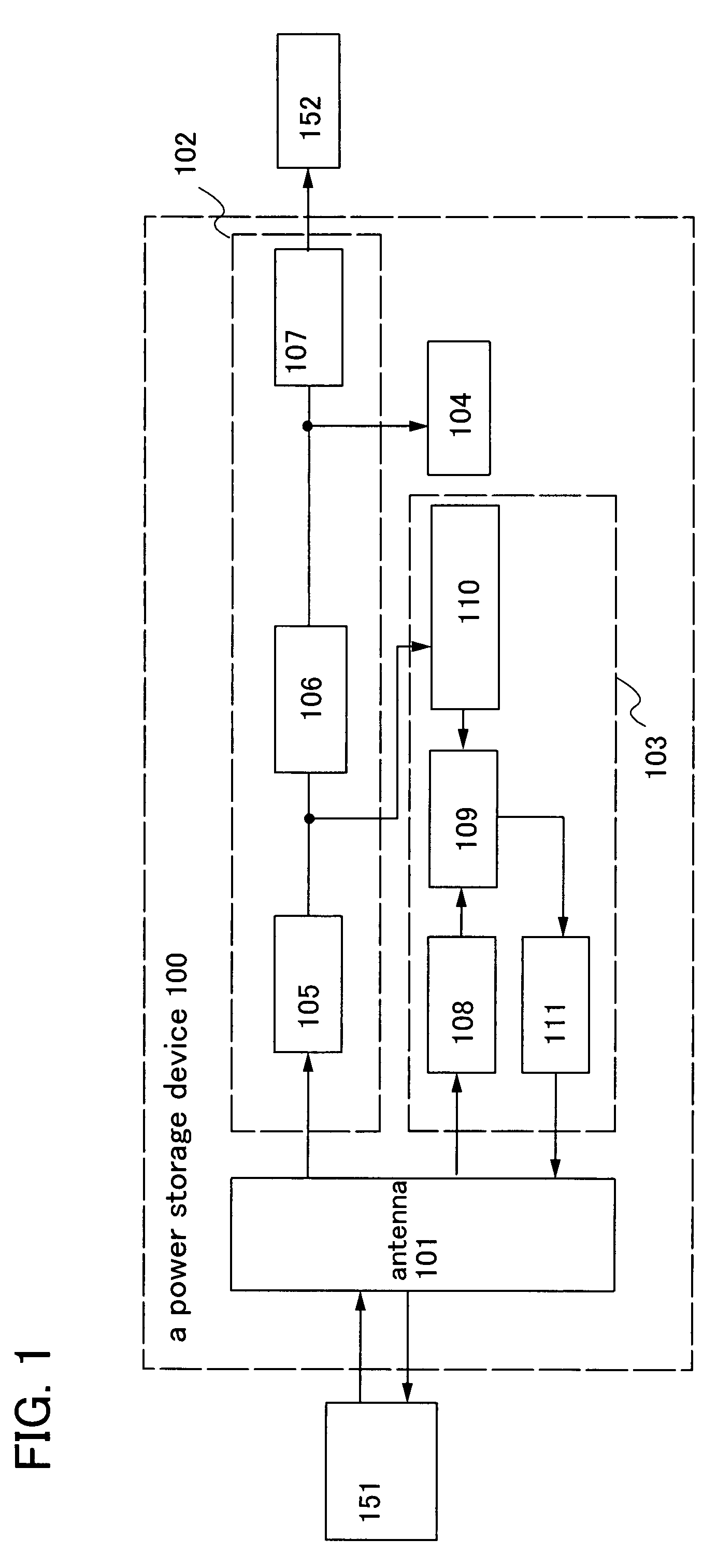

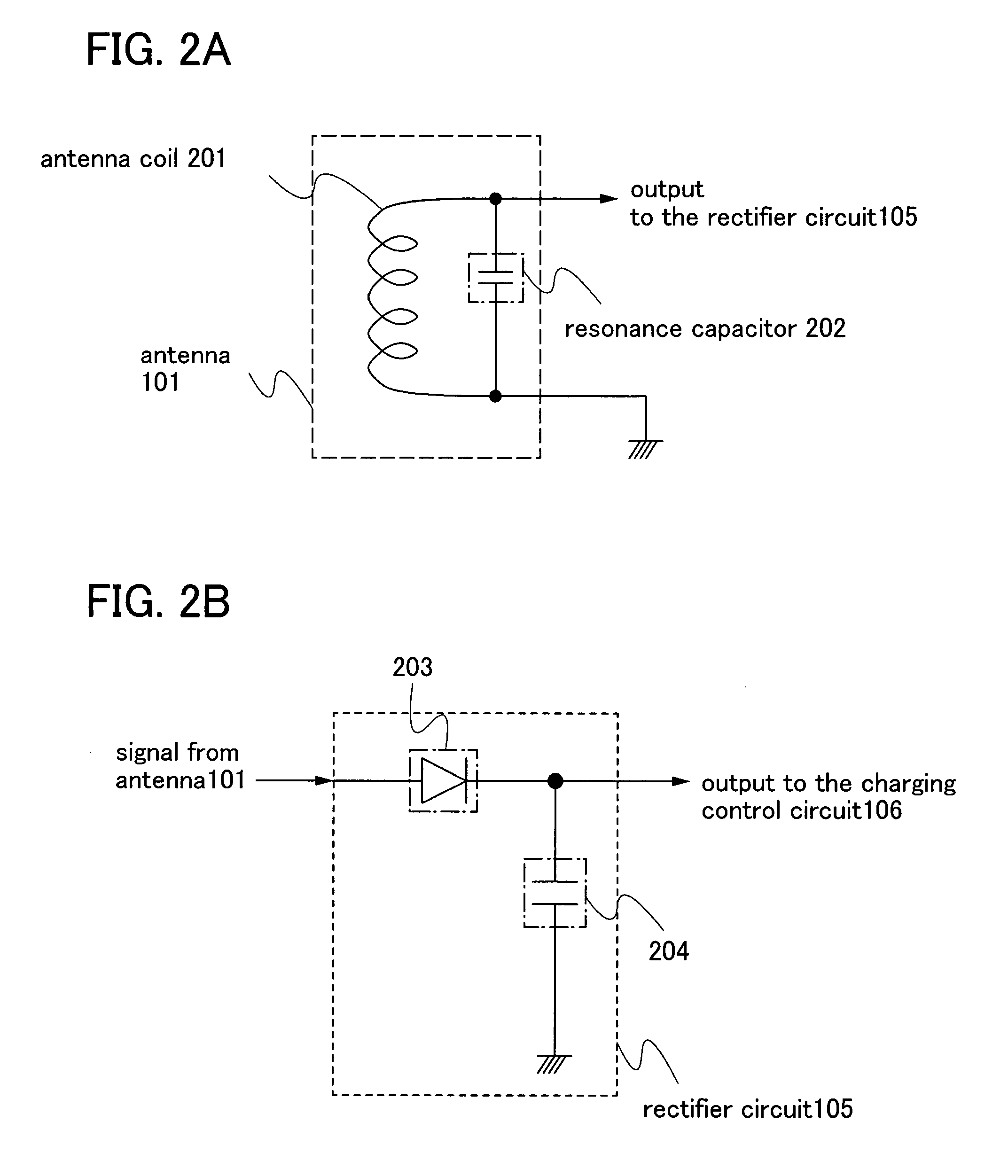

Power storage device and semiconductor device provided with the power storage device

InactiveUS20080252254A1Increase powerShort timeNear-field transmissionElectromagnetic wave systemElectric power systemPower flux

An object is to provide a power storage device provided with a battery that is a power storage means, for safe and accurate supply of electric power in a short period of time for drive power supply voltage without checking remaining capacity of the battery or changing batteries with deterioration over time of the battery for drive power supply voltage. The power storage device is provided with a battery that is a power storage means as a power supply for supplying electric power and a counter circuit for counting charging time of the power storage means. An electromagnetic wave with electric field intensity, magnetic field intensity, and power flux density per unit time which are transmitted from a power feeder are controlled, and the power storage means is efficiently charged using the electromagnetic wave in a short period of time.

Owner:SEMICON ENERGY LAB CO LTD

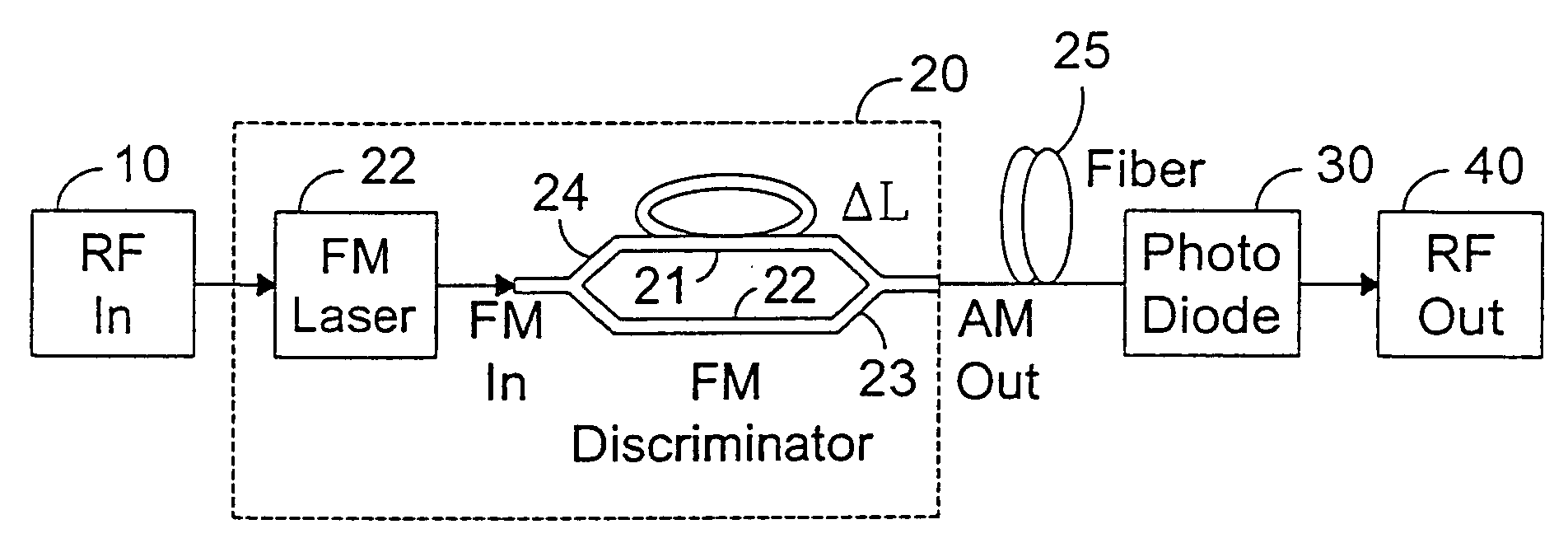

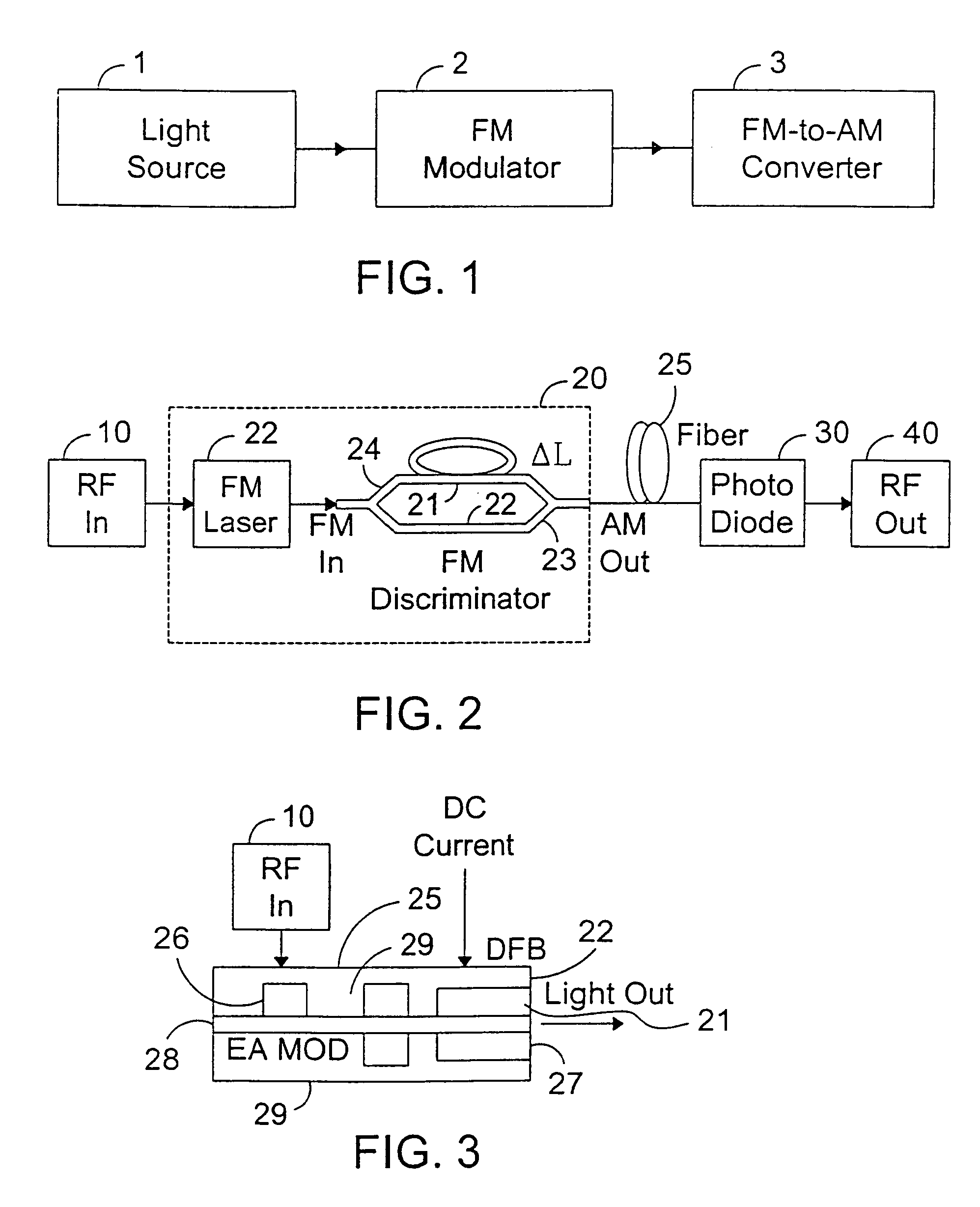

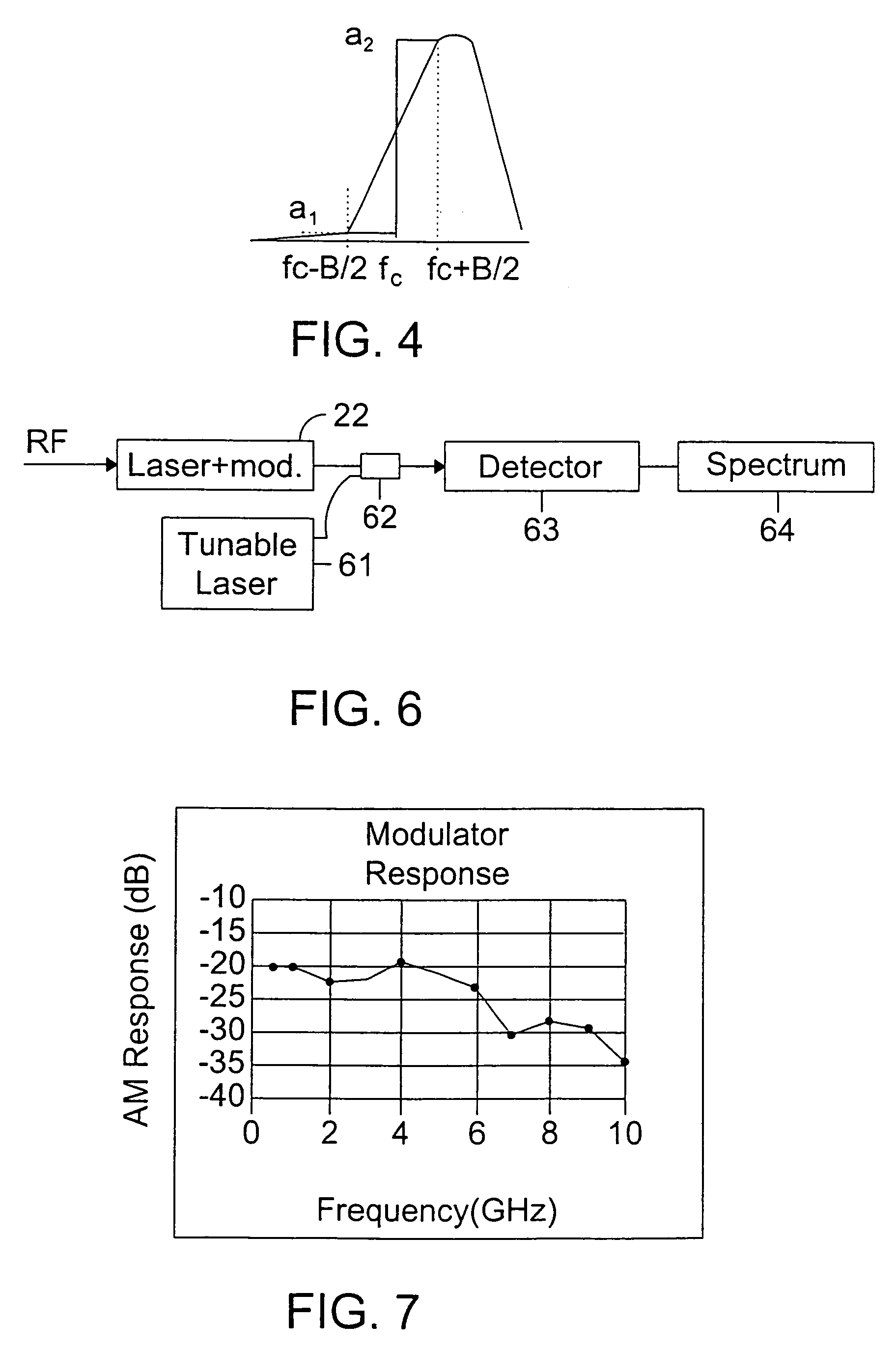

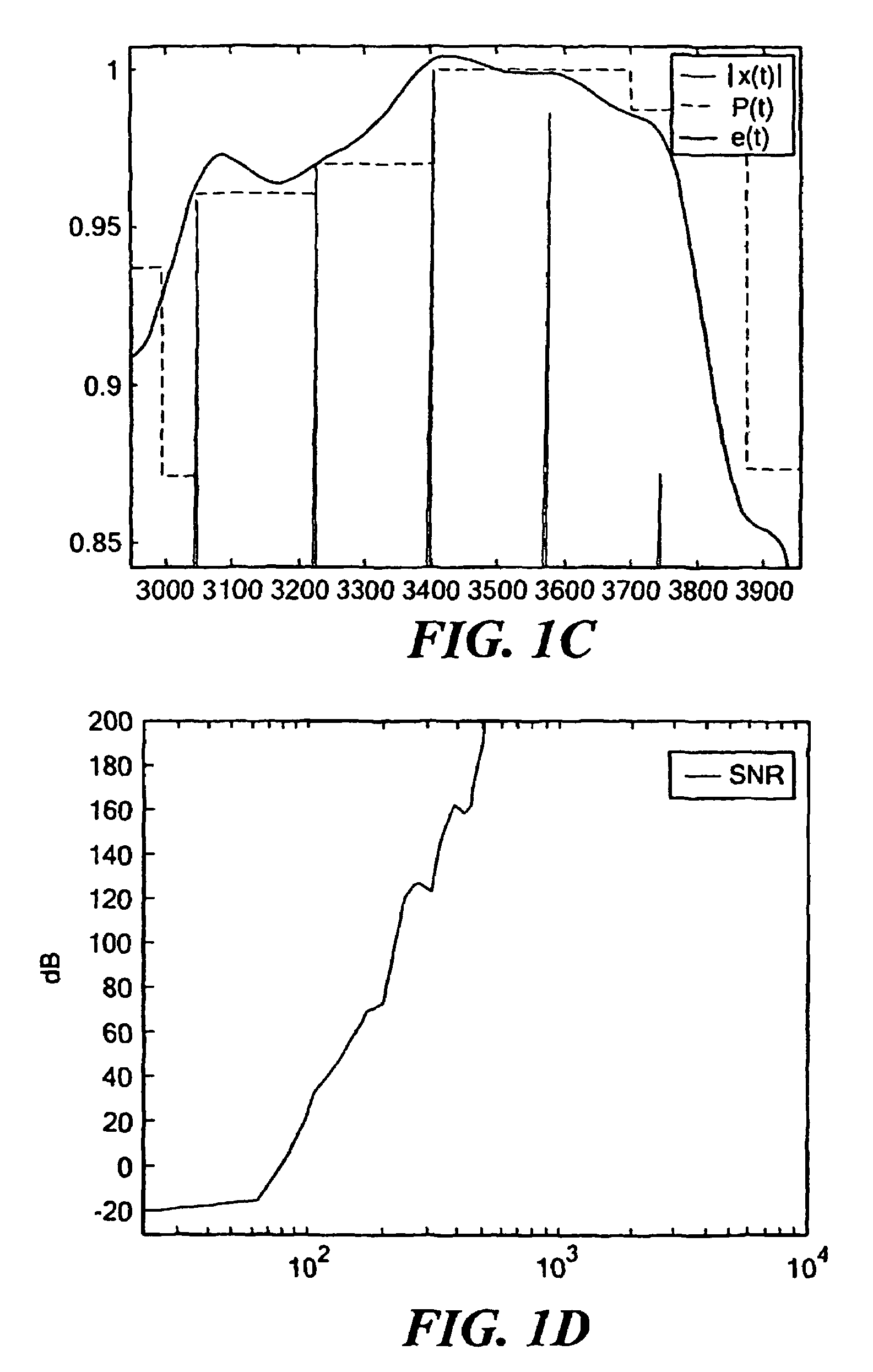

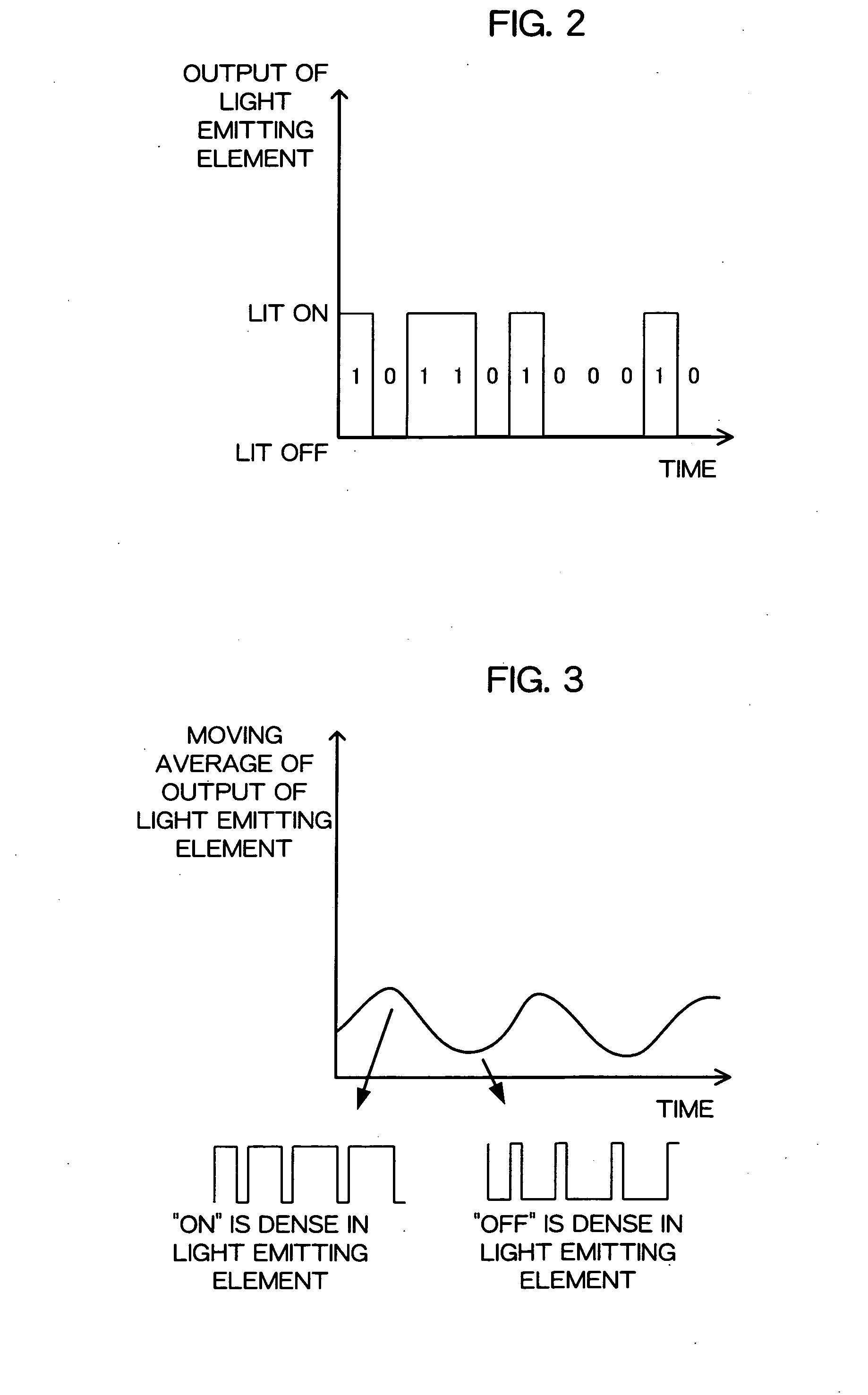

System and method for generating analog transmission signals

InactiveUS7076170B2Overcomes drawbackImprove dynamic rangeLaser detailsCoupling light guidesLow noiseDiscriminator

An RF-lightwave transmitter performs successive conversions of an information-bearing input signal in order to generate an output signal suitable for transmission in a wireless communications system. The transmitter includes a high-efficiency FM laser connected to a FM discriminator. In operation, the laser converts an RF signal into a frequency-modulated optical signal, and the discriminator converts this signal into an amplitude-modulated optical signal. The discriminator performs its conversion using a high slope-efficiency linear transfer function which ensures that the AM optical signal varies in accordance with a desired operational performance. The transmitter also includes a photodiode which converts the AM signal output from the optical discriminator back into an RF signal for transmission. Experimental results demonstrated that a transmitter of this type is able to realize greater than 10 dB RF insertion gain at less than 0 dBm optical power, with a high spurious-free dynamic range and low noise. A signal processor embodied within the transmitter may be used in a purely optical communication systems or may be used for other types of RF-photonics applications such as those expected for use in next-generation systems.

Owner:UNIV OF MARYLAND BALTIMORE COUNTY

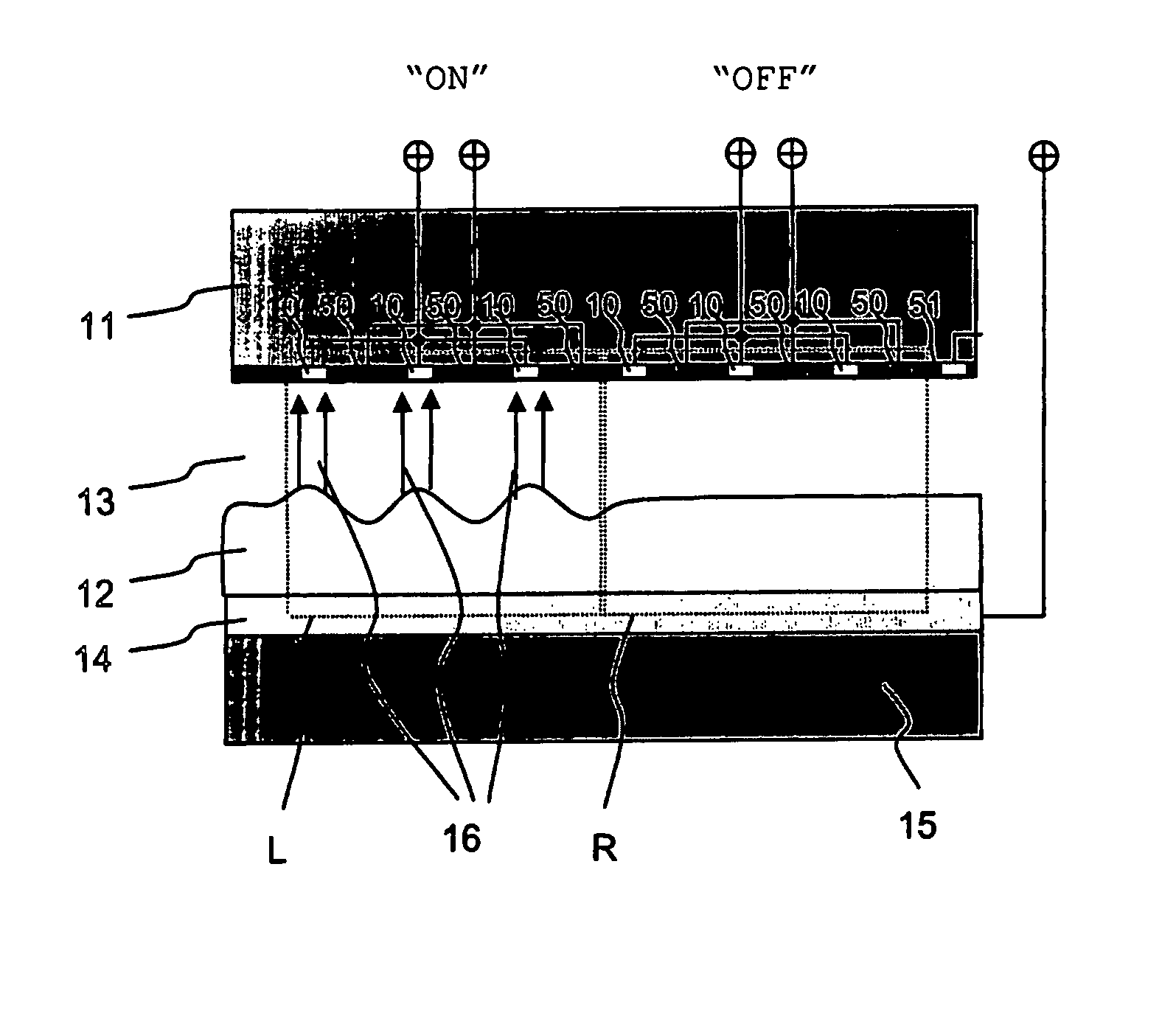

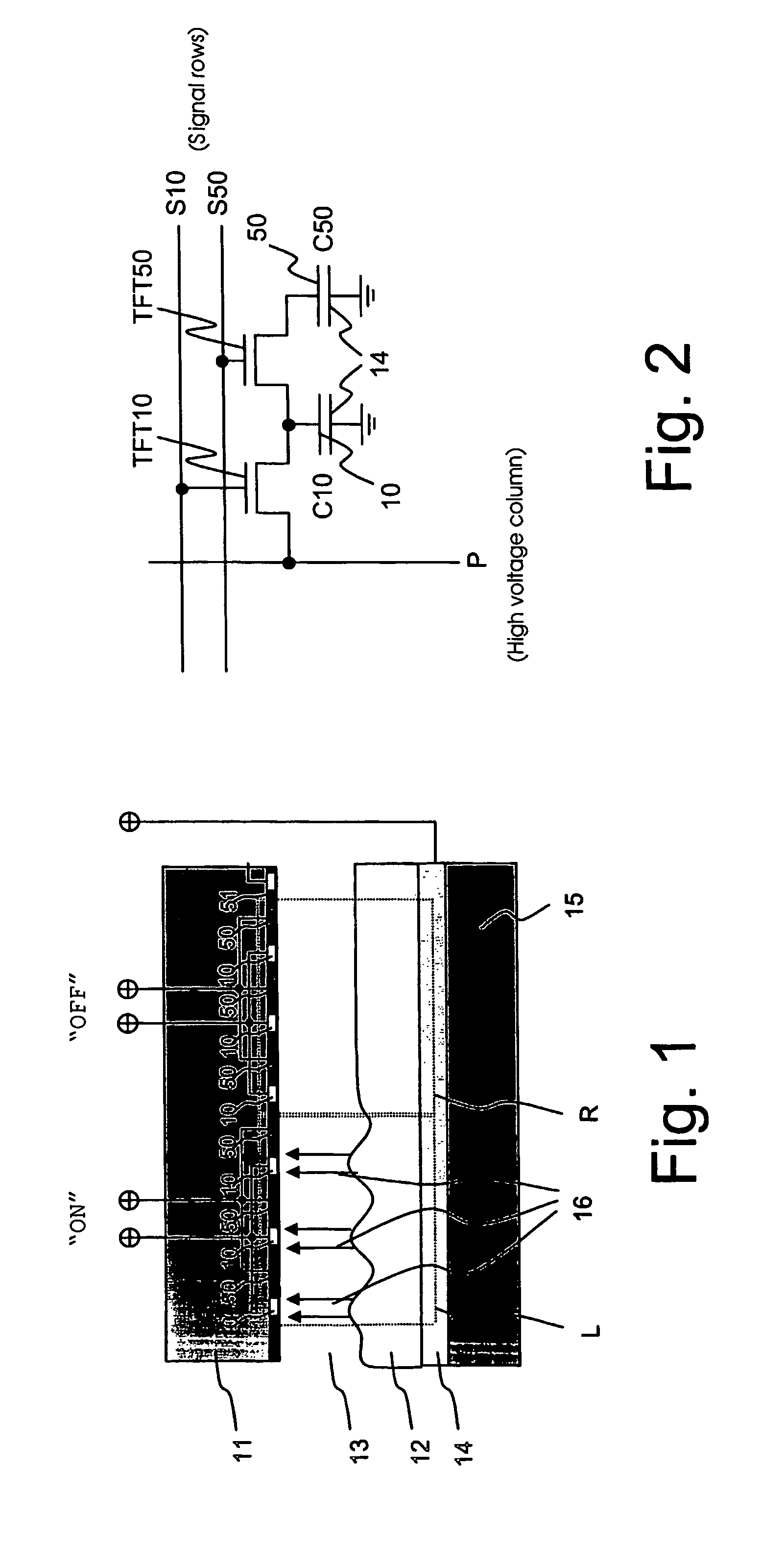

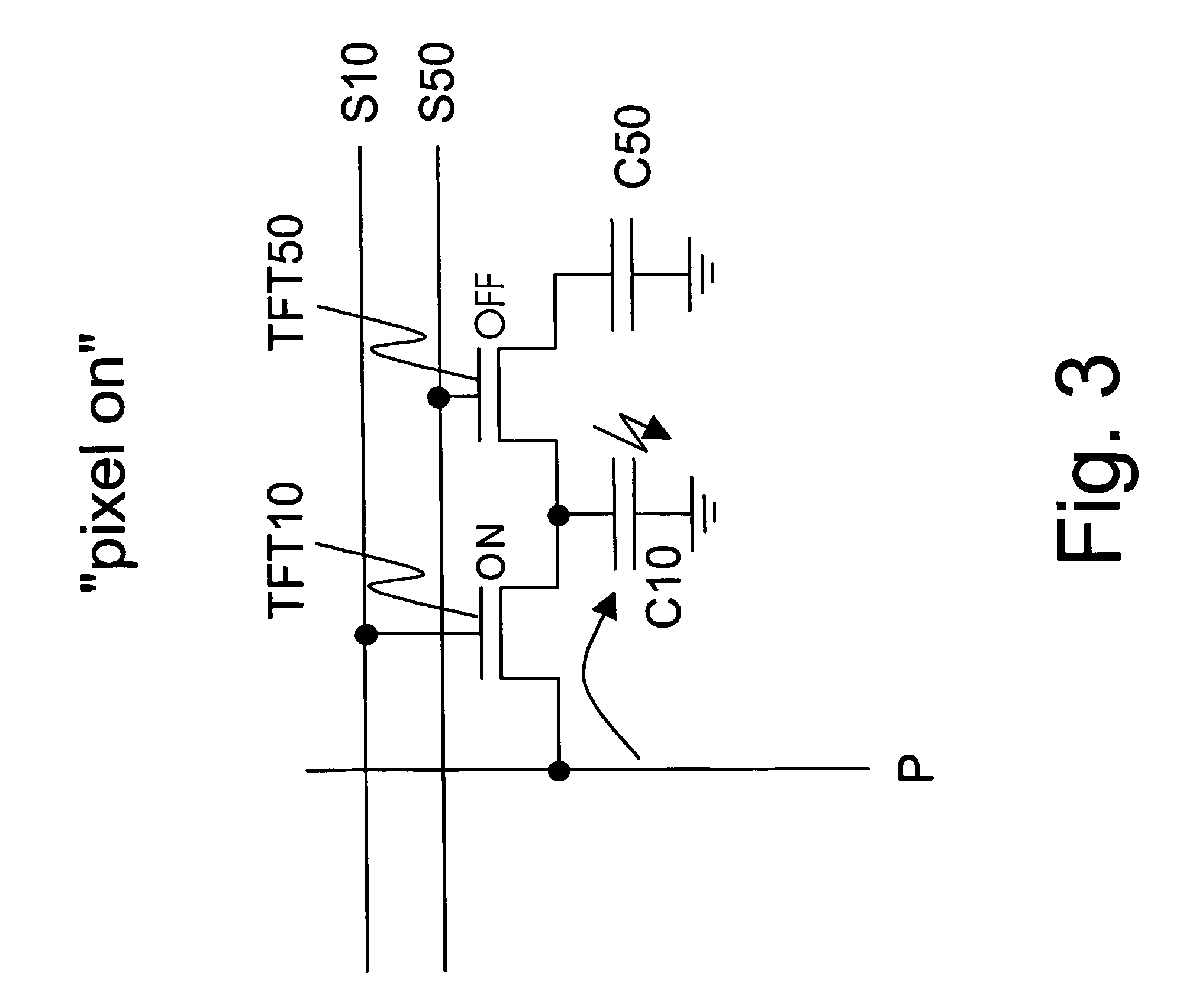

Electrical device utilizing charge recycling within a cell

InactiveUS7567372B2Increase power consumptionGood optical performanceStatic indicating devicesSemiconductor/solid-state device manufacturingElectricityElectrical battery

The invention relates to an electrically controlled device, which device comprises at least one electrically and individually controllable cell (L,R) with at least two separate electrode structures (10,50) arranged within the cell, each of the electrode structures capable of storing electric charges (C10,C50). The device further comprises a charge transfer mechanism (P,S10,S20,TFT10,TFT50) to transfer electric charges in a temporally controlled manner between the at least two separate electrode structures (10,50), and that for at least one of the electrode structures within the cell, the charge transfer mechanism comprises substantially the only means for providing electrical power and / or electrical driving. The invention reduces the power consumption of the electrode structures by use of a new type of in-cell type charge recycling. The invention is especially suitable to be used in light modulator components based on the use of electrically deformable viscoelastic materials.

Owner:NOKIA CORP

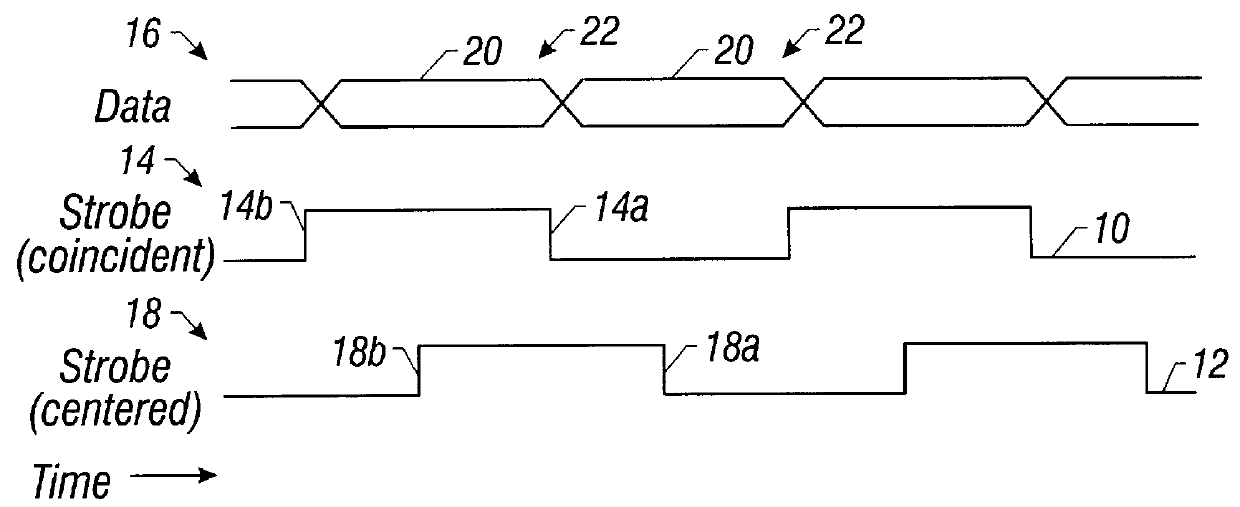

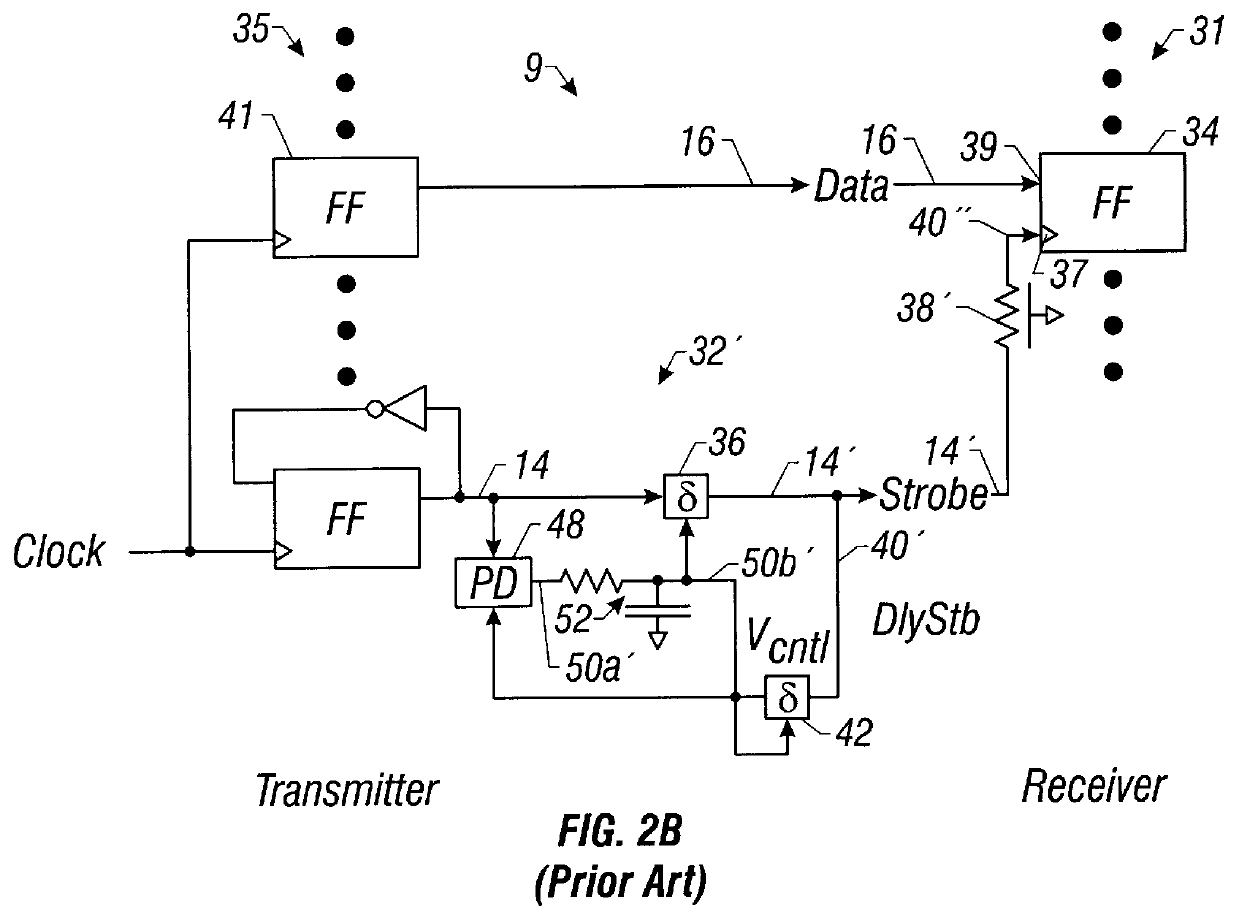

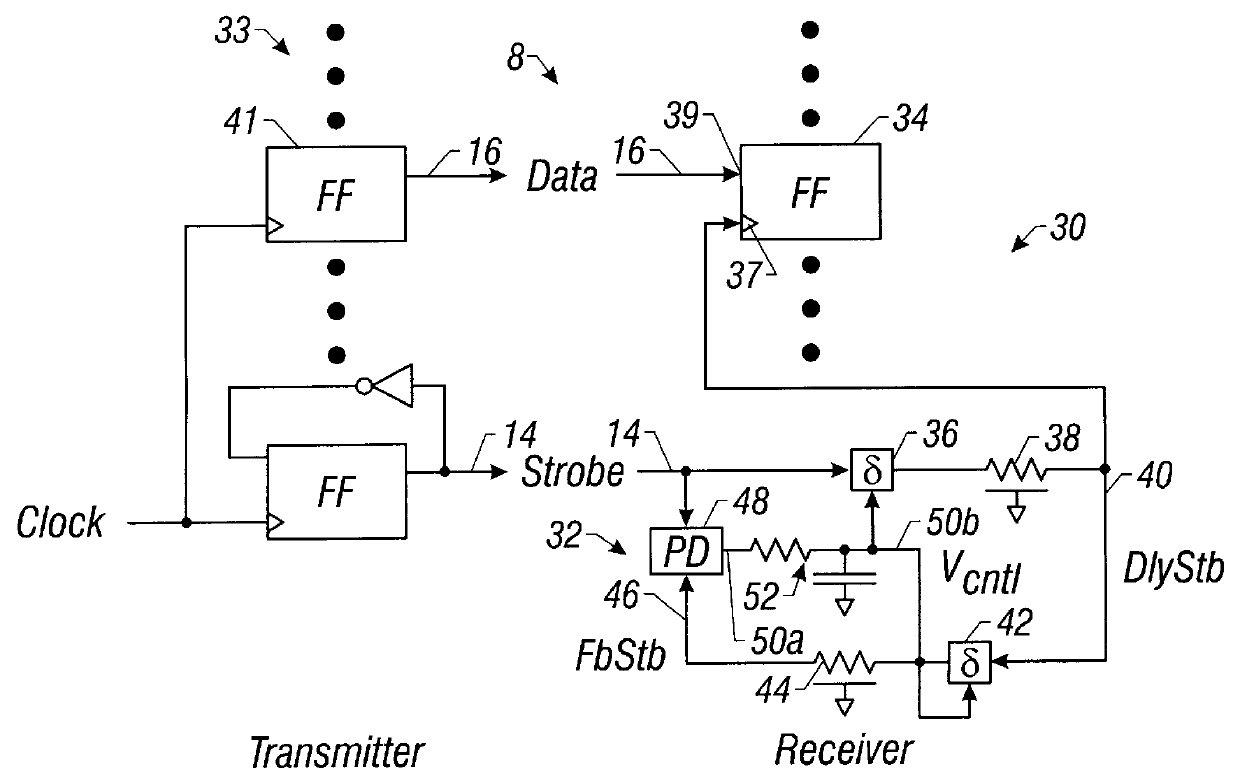

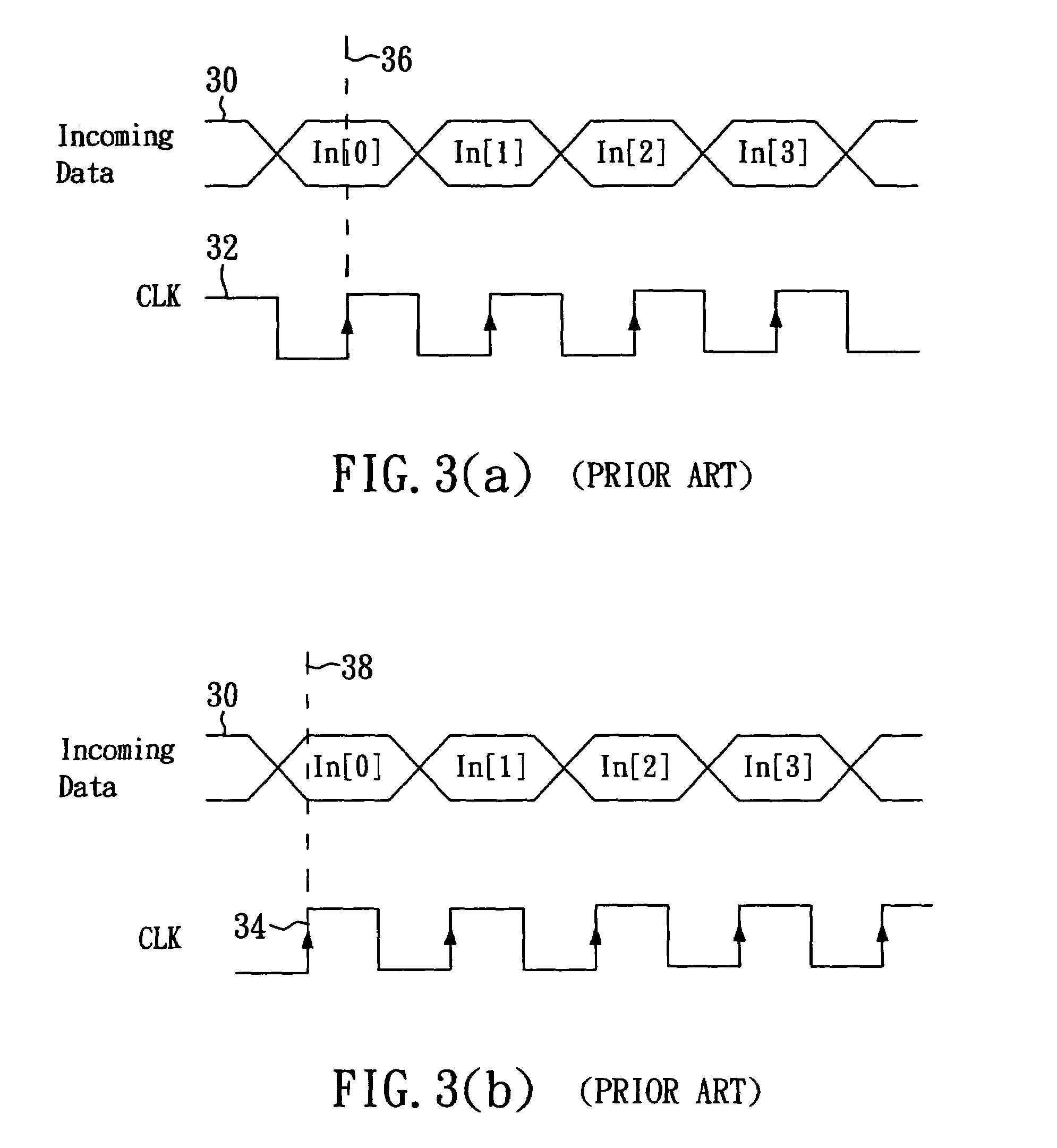

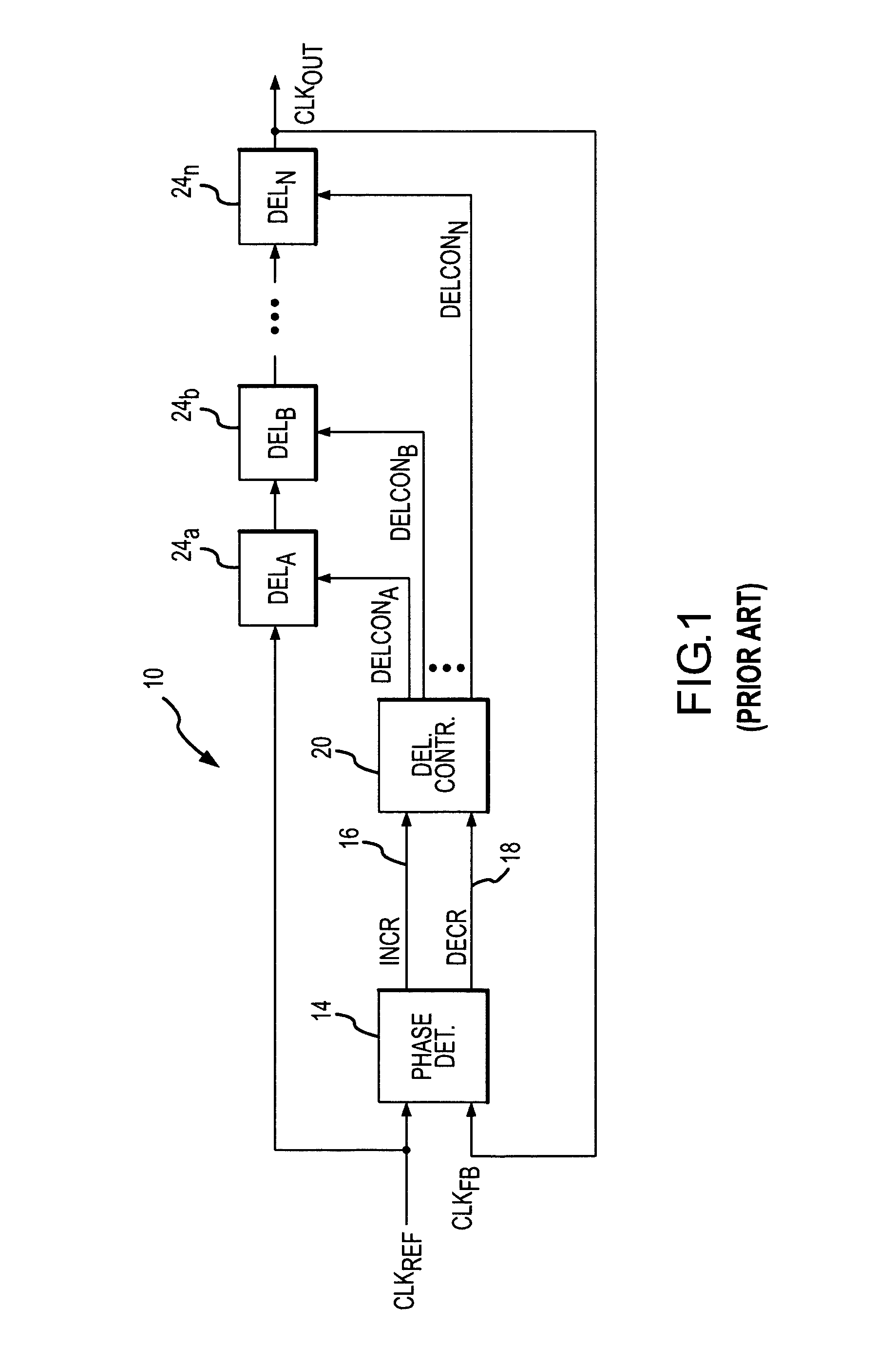

Timing control for input/output testability

InactiveUS6085345AMultiple input and output pulse circuitsPulse automatic controlPhase differenceDelay-locked loop

Circuitry added to chips that use source synchronous techniques reduces difficulties associated with testing the chips. The circuitry increases the ability to use source synchronous techniques for data transmission. The circuitry is implemented in a delayed-lock loop (DLL) in either a transmitter (driver) or a receiver. The DLL measures the phase difference between a strobe signal and a delayed strobe signal. The DLL can be externally controlled by a source selectable input which allows the delay of the delayed strobe signal to be varied to test Tsetup and Thold in the receiver without varying the timings of the strobe signal and the data signals supplied to the chips. A timing measurement circuit having the strobe signal, the delayed strobe signal, and reference signals as inputs may be used to calibrate the phase difference between the strobe signal and delayed strobe signal.

Owner:INTEL CORP

Power storage device and semiconductor device provided with the power storage device

InactiveUS7764046B2Increase powerShort timeNear-field transmissionElectromagnetic wave systemElectrical field strengthElectrical battery

An object is to provide a power storage device provided with a battery that is a power storage means, for safe and accurate supply of electric power in a short period of time for drive power supply voltage without checking remaining capacity of the battery or changing batteries with deterioration over time of the battery for drive power supply voltage. The power storage device is provided with a battery that is a power storage means as a power supply for supplying electric power and a counter circuit for counting charging time of the power storage means. An electromagnetic wave with electric field intensity, magnetic field intensity, and power flux density per unit time which are transmitted from a power feeder are controlled, and the power storage means is efficiently charged using the electromagnetic wave in a short period of time.

Owner:SEMICON ENERGY LAB CO LTD

Method and apparatus for acquiring a frequency without a reference clock

InactiveUS6856206B1Error detection/prevention using signal quality detectorPulse automatic controlData streamEvaluation Interval

A clock and data recovery system acquires a clock embedded in an input data stream by detecting the occurrence of transitions in the input data stream falling into a predetermined phase zone of a sample clock used to sample the input data stream. A control circuit counts how many evaluation intervals have at least one transition in the predetermined phase zone. The control circuit determines if lock is achieved according to the count. If it is determined that lock is not achieved, an output of a variable oscillator circuit used in the clock recovery operation is adjusted until the number of evaluation intervals having one or more transitions in the predetermined phase zone is below a level indicating lock.

Owner:SKYWORKS SOLUTIONS INC

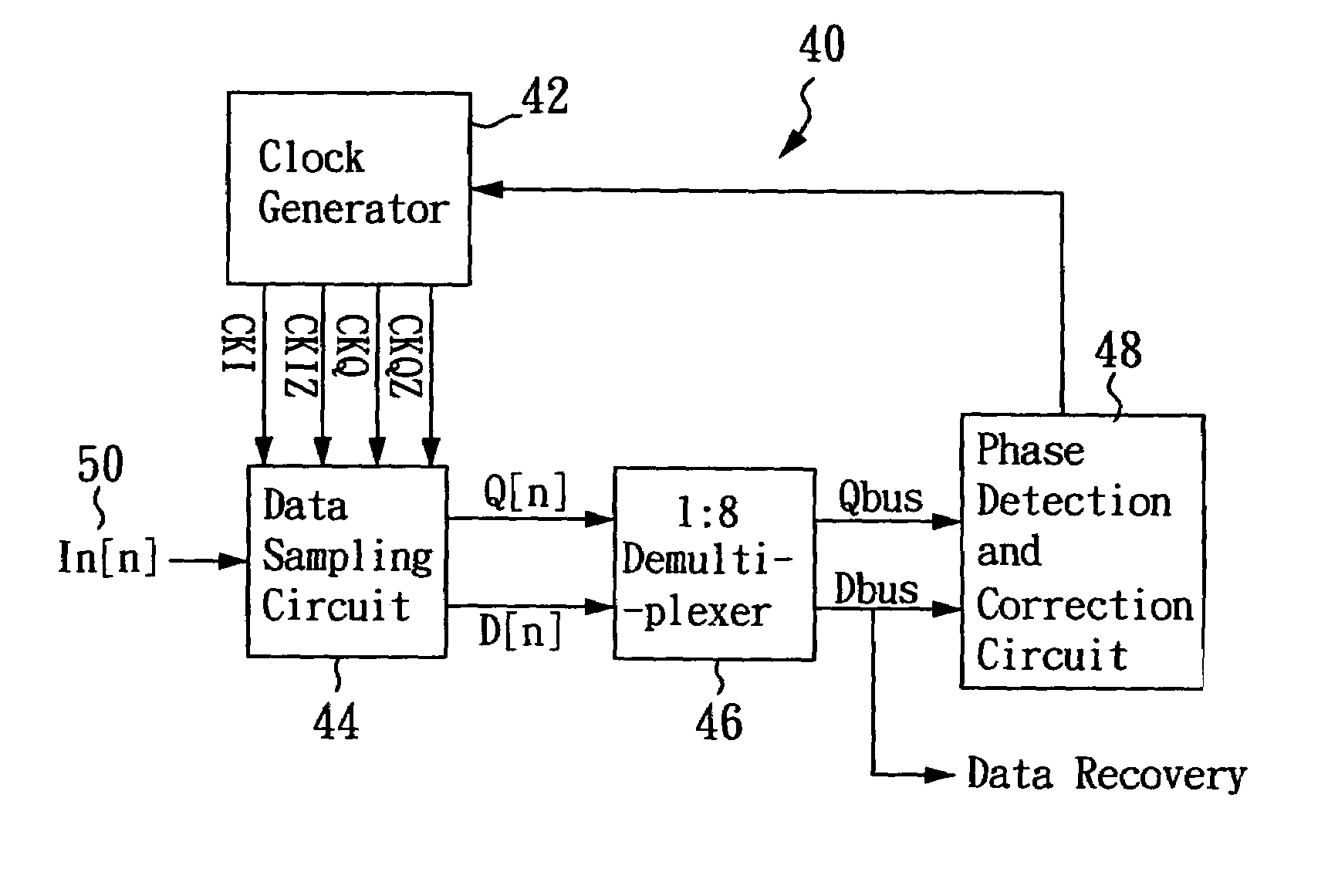

Data recovery circuit, phase detection circuit and method for detecting and correcting phase conditions

ActiveUS7310397B2Reduce frequencyPulse automatic controlVoltage-current phase angleData streamData recovery circuit

In the data recovery circuit of the invention, a first group of sampling clock pulses is used for sampling approximately the central portions of the data bits in an incoming data stream to produce a first sampled data stream, while a second group of sampling clock pulses is used for sampling approximately the transition portions between every two adjacent data bits in the incoming data stream to produce a second sampled data stream. By detecting the resemblance of each bit in the second sampled data stream to the corresponding two adjacent bits in the first sampled data stream, a phase detection and correction circuit determines an early condition or a late condition for the phases of the sampling clocks and produces a signal to correct the phases of the sampling clocks by shifting the phases backwards or forwards. According to the invention, sampling clocks with lower frequencies can be used for sampling, and the phase error can be corrected to obtain the correct data recovery.

Owner:XUESHAN TECH INC

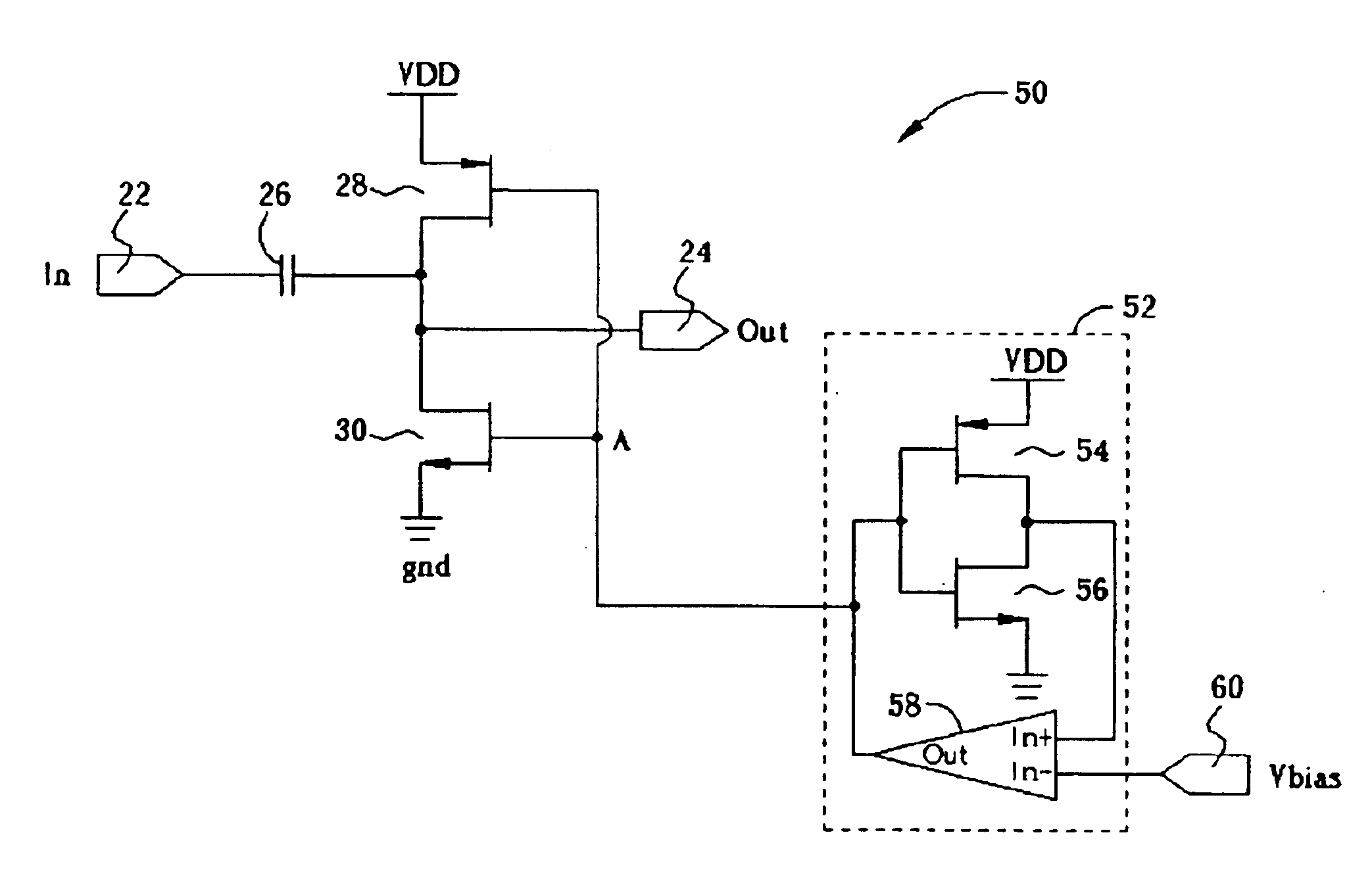

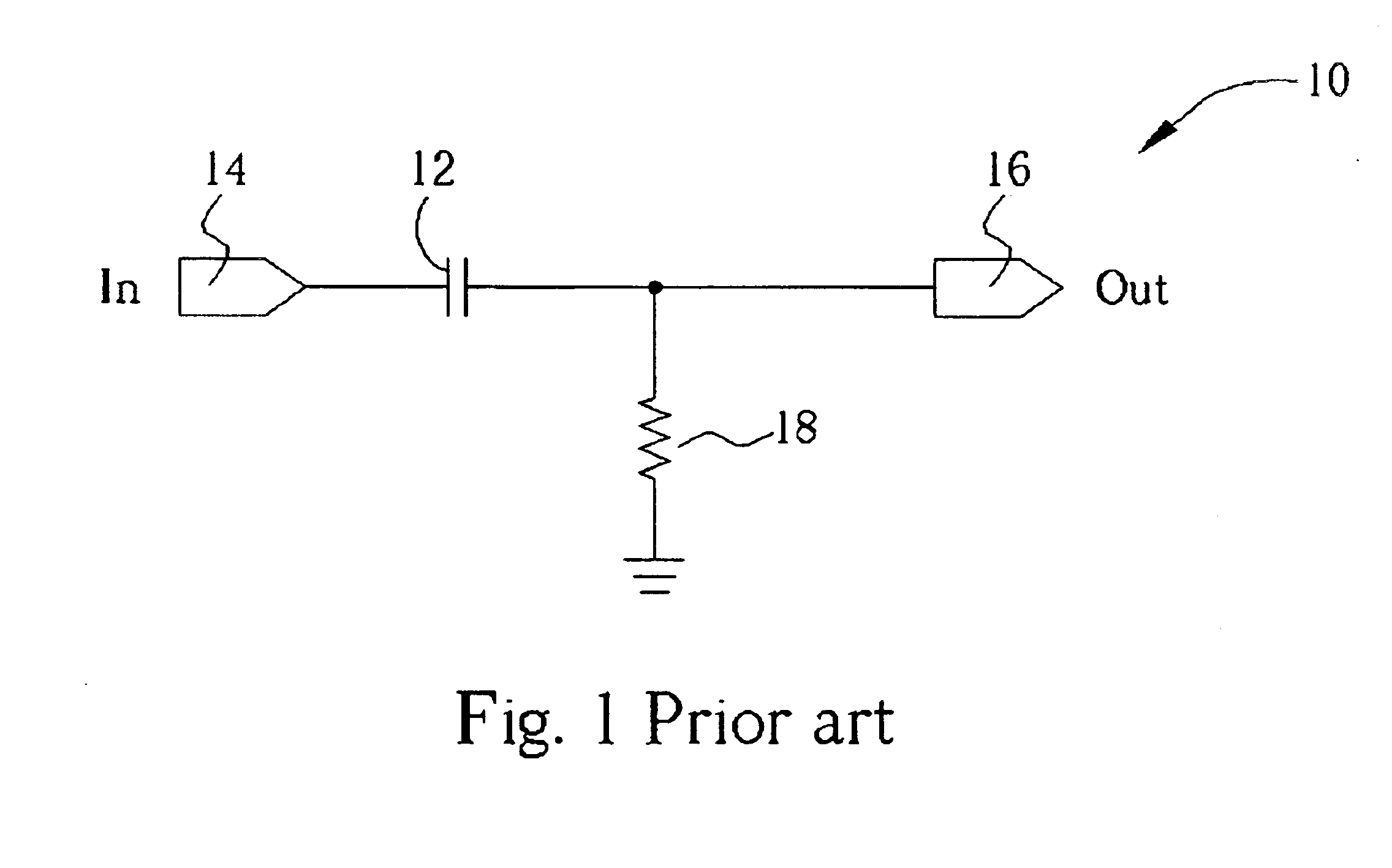

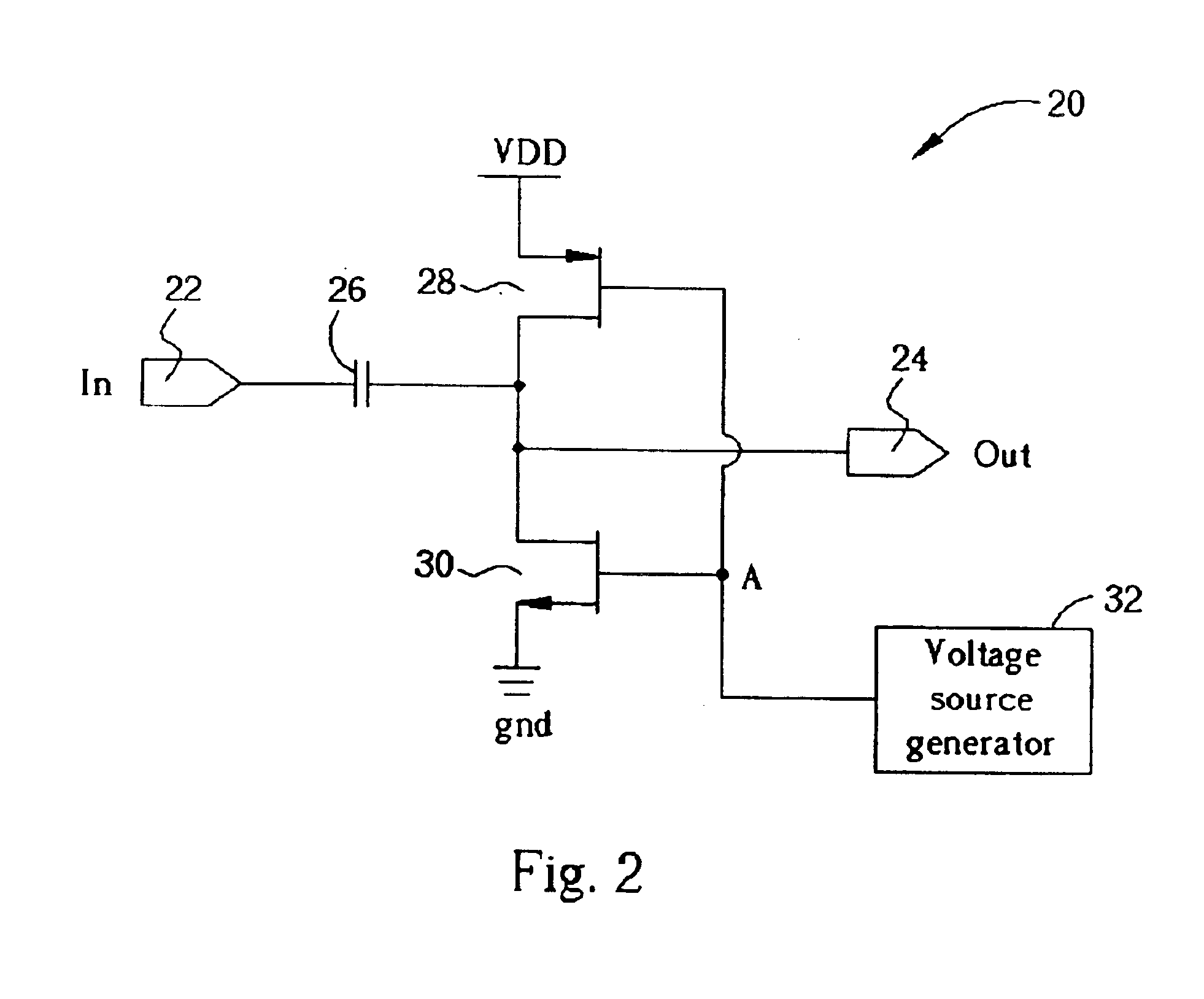

On-chip high-pass filter with large time constant

InactiveUS6882216B2Large time constantLow corner frequencyElectrical measurementsOscillations generatorsEngineeringVoltage source

An on-chip high-pass filter with large time constant comprising a capacitor, a first transistor having a first terminal connected to a first voltage source and a second terminal connected to the capacitor, and a second transistor having a first terminal connected to the second terminal of the first transistor and a second terminal connected to ground, wherein the first transistor and the second transistor are for operating as a large-resistance resistor. The electrical equivalent large-resistance resistor and the capacitor together form a high-pass filter between the input port and the output port.

Owner:REALTEK SEMICON CORP

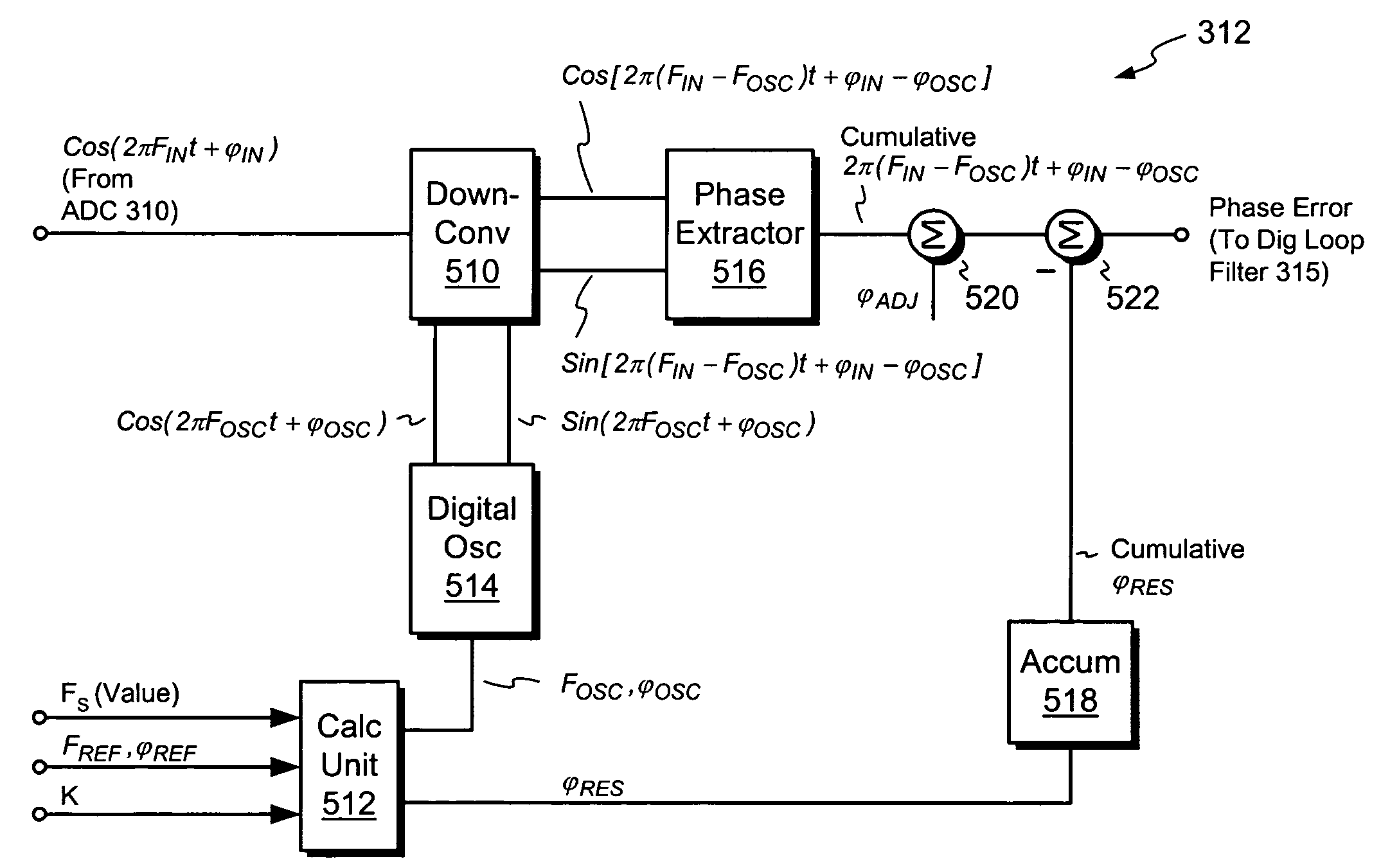

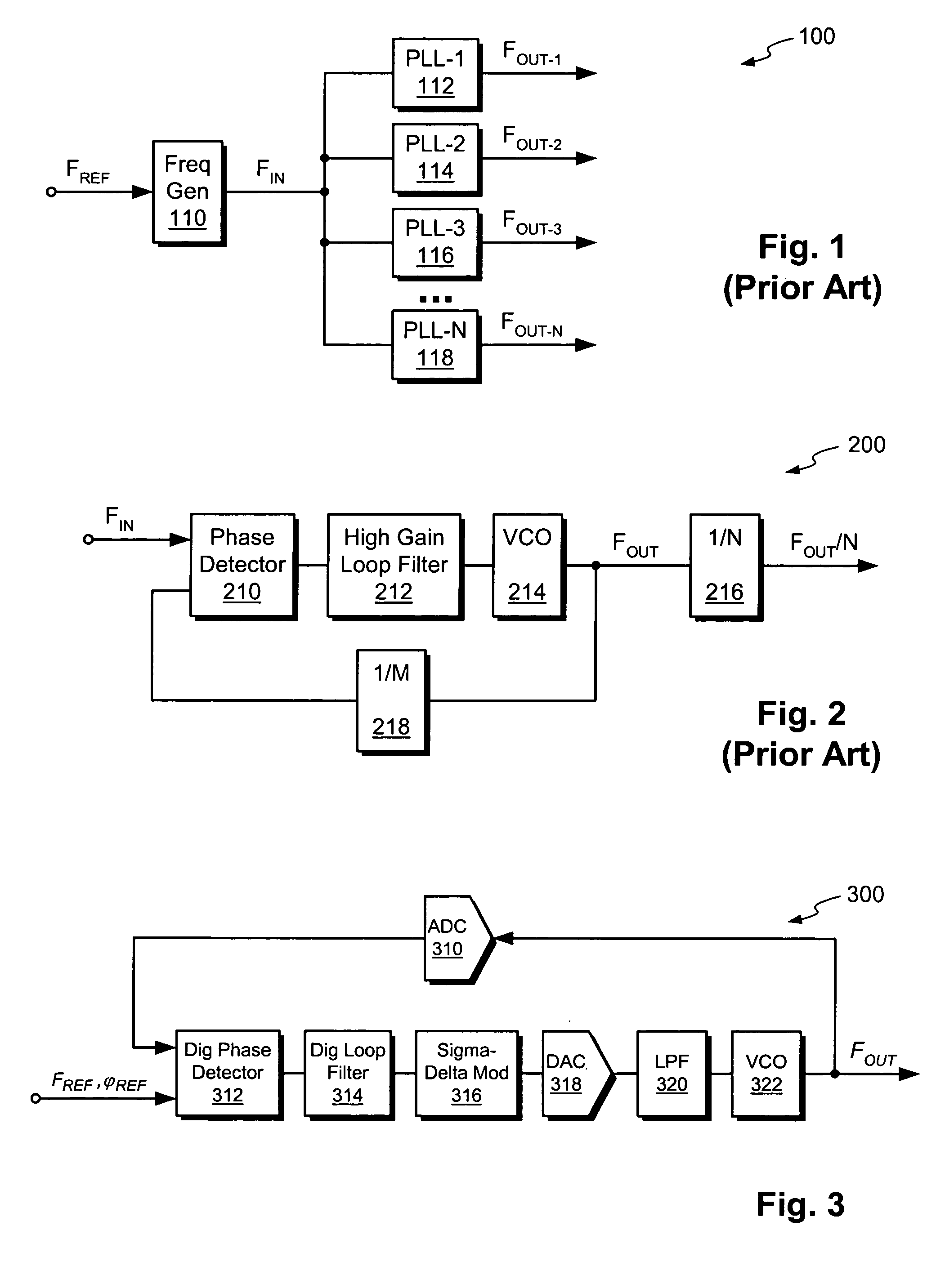

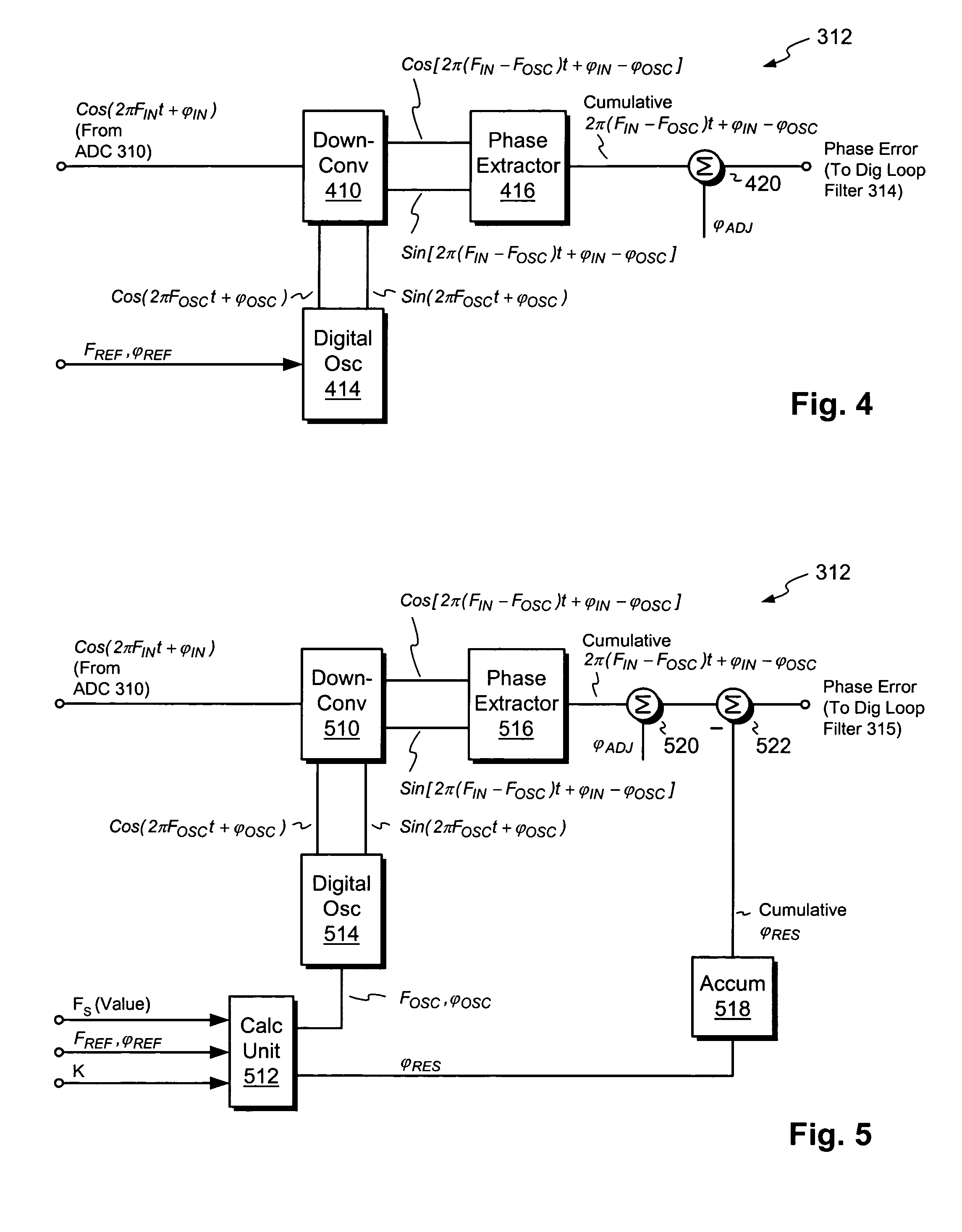

Digital phase detector

A high performance phase detector includes a local digital oscillator for generating a digital reference signal of programmable frequency and phase. The phase detector accumulates a difference in phase between the digital reference signal and a sampled input signal to produce a measure of phase error. The phase detector can be advantageously used in a frequency synthesizer to produce signals with low phase noise and accurate phase control. Synthesizers of this type can further be used to as building blocks in ATE systems and other electronic systems for generating low jitter clocks and waveforms.

Owner:TERADYNE

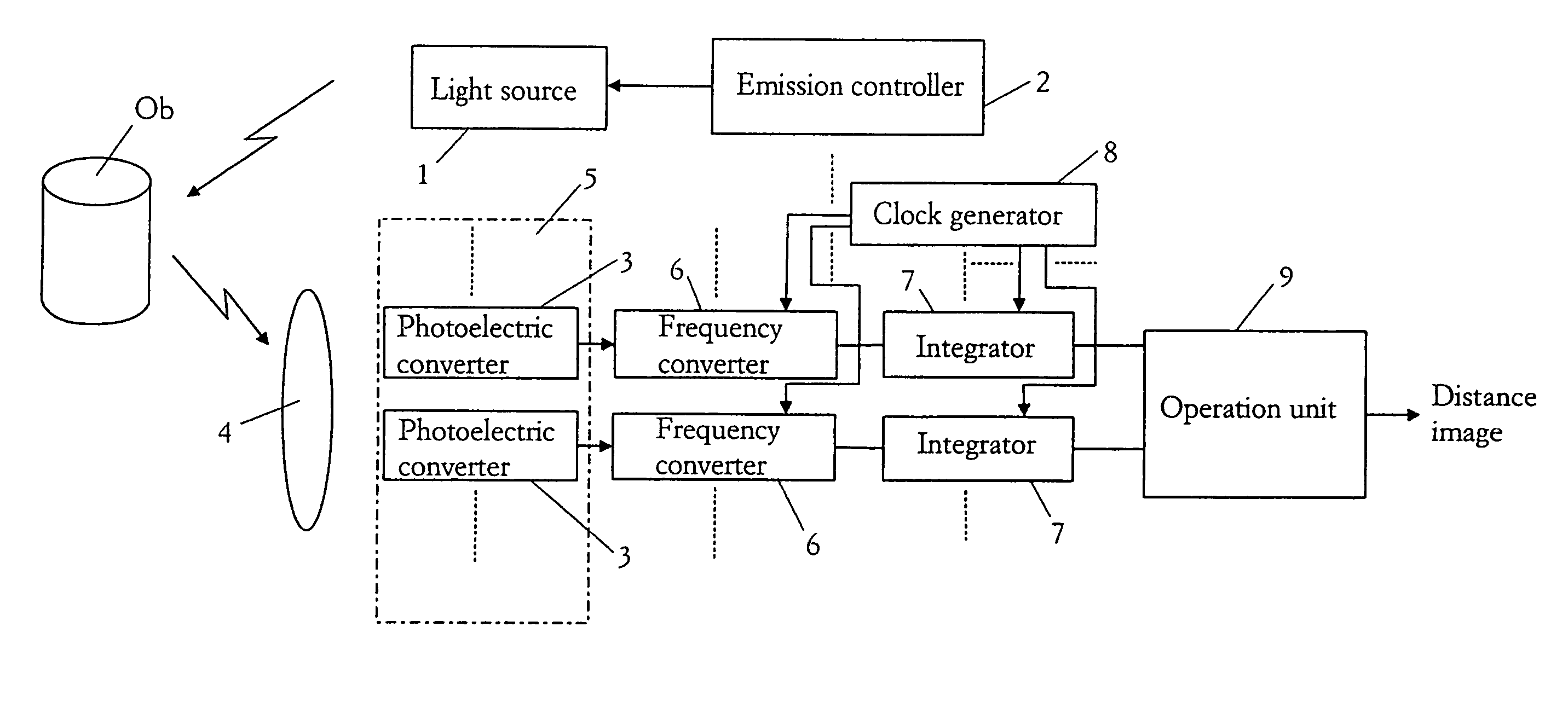

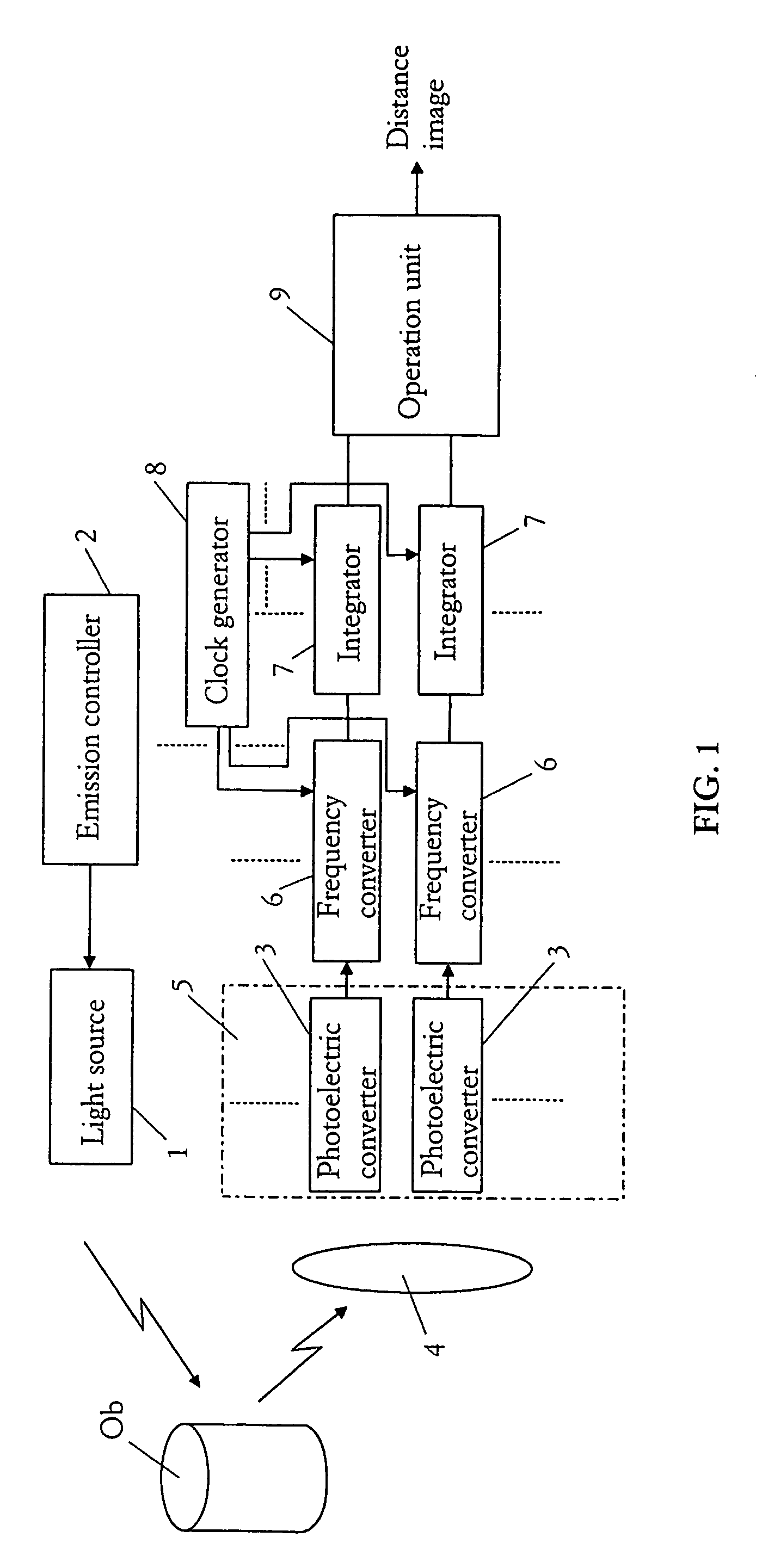

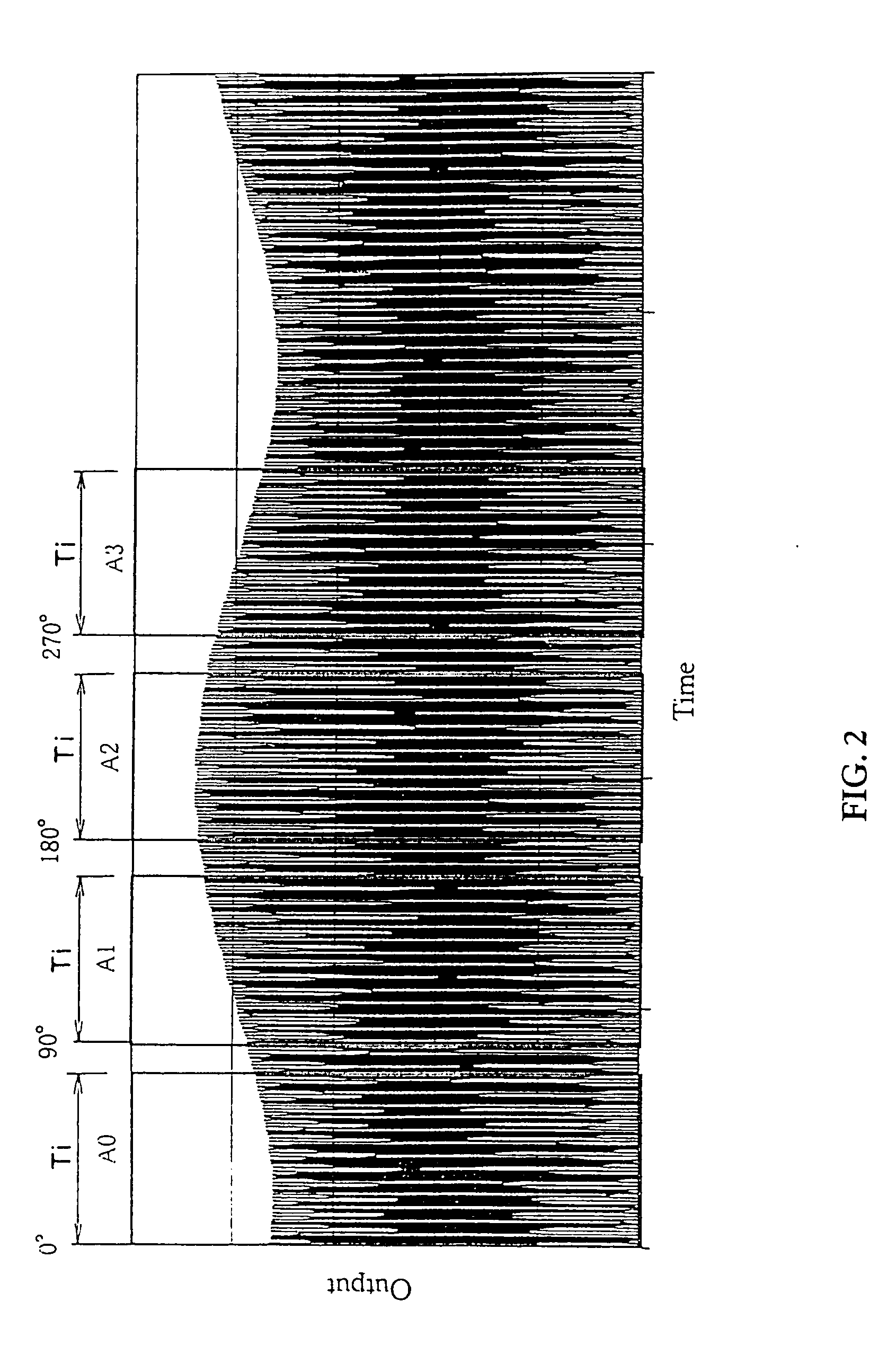

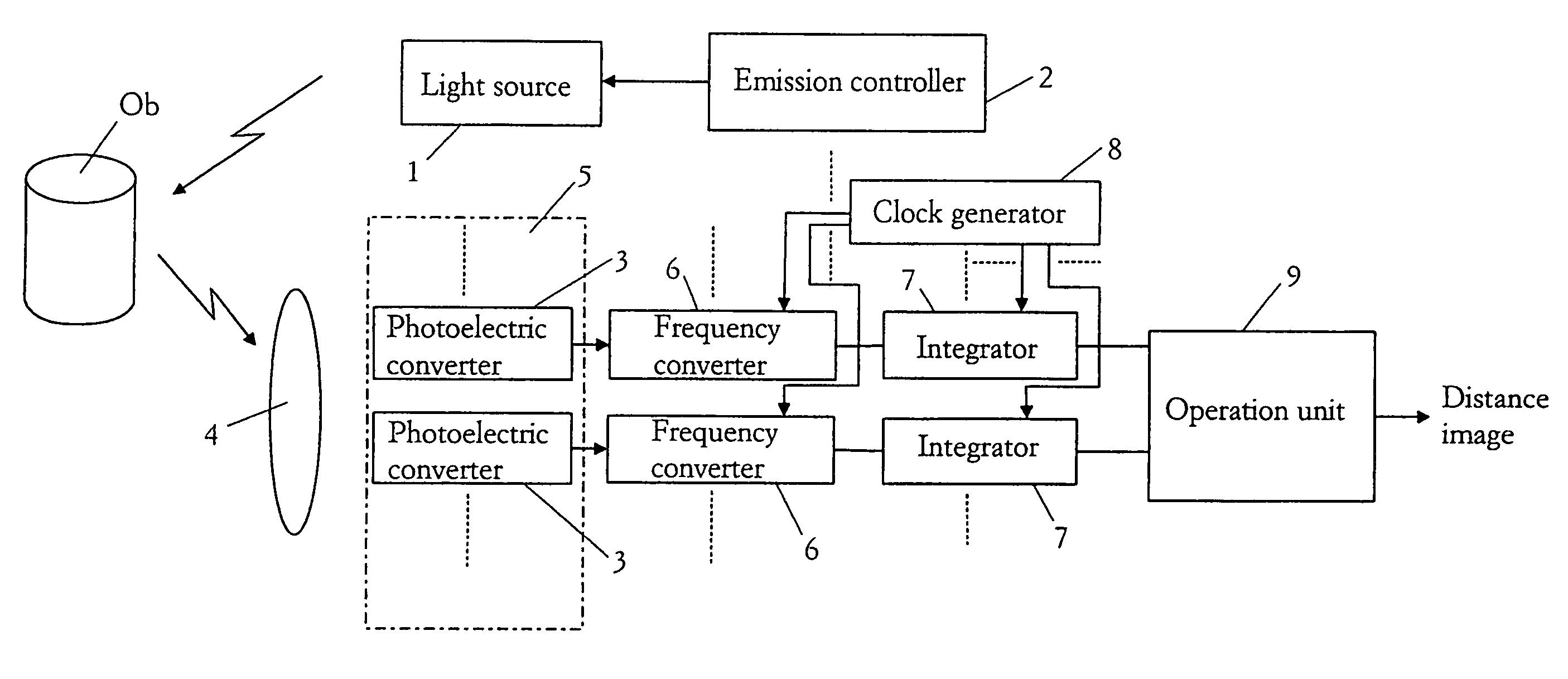

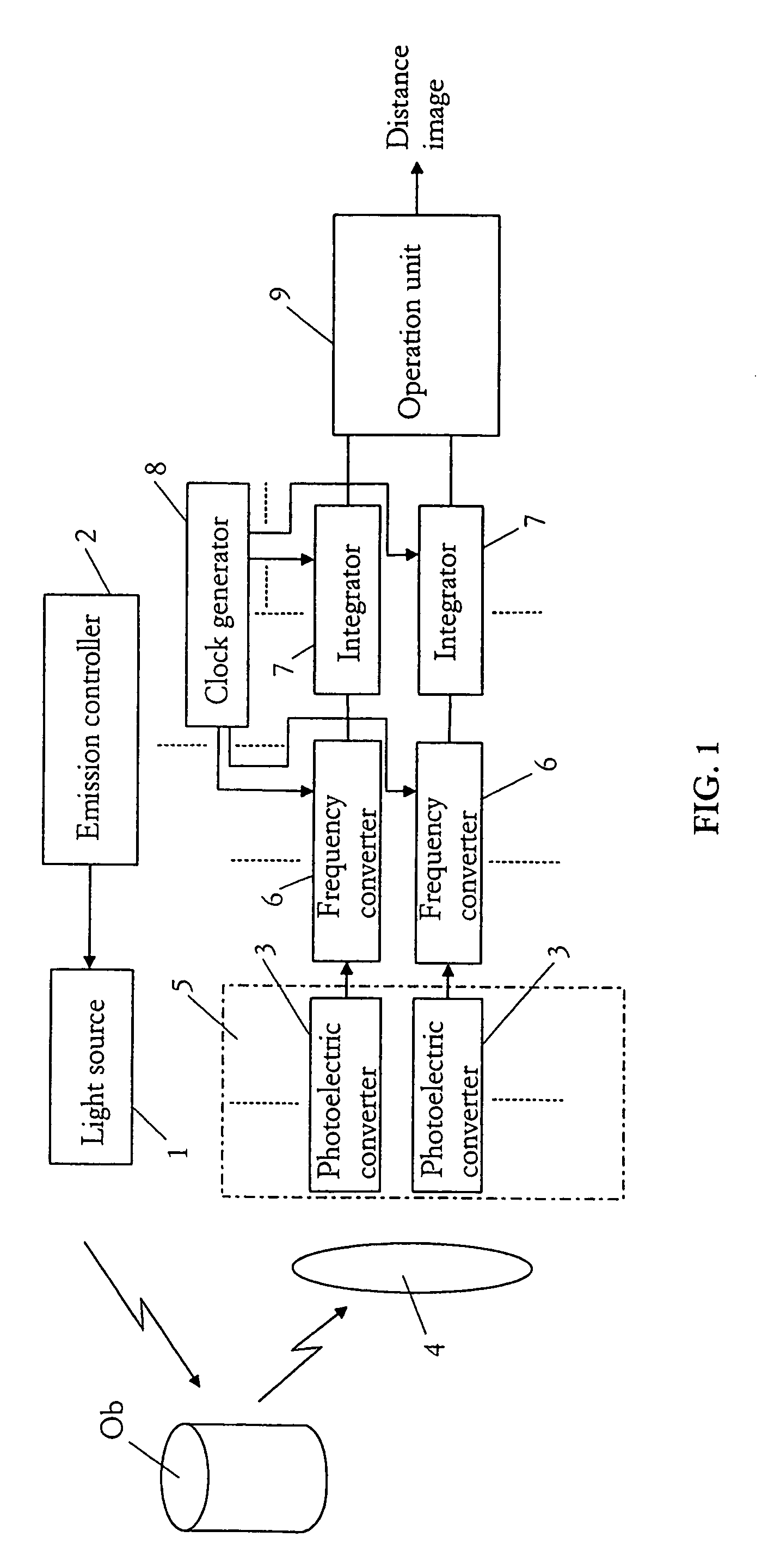

Spatial information detecting device using intensity-modulated light

InactiveUS20050145773A1Accurately detecting informationHigh speed responseTelevision system detailsPhotometry using reference valueLocal oscillator signalIntegrator

A spatial information detecting device using an intensity-modulated light is provided. This device comprises a photoelectric converter for receiving a light from a space into which a light intensity-modulated at a predetermined emission frequency is being irradiated, and generating an electrical output corresponding to an intensity of received light; a local oscillator circuit for outputting a local oscillator signal having a local oscillator frequency different from the emission frequency; a sensitivity controller for mixing the local oscillator signal with the electrical output to frequency convert the electrical output into a beat signal having a lower frequency than the emission frequency; an integrator for performing integration of said beat signal at a predetermined timing; and an analyzer for detecting information concerning the space according to an output of the integrator. According to this device, it is possible to accurately detect the spatial information without using a switching element having high-speed response at the light receiving side.

Owner:MATSUSHITA ELECTRIC WORKS LTD

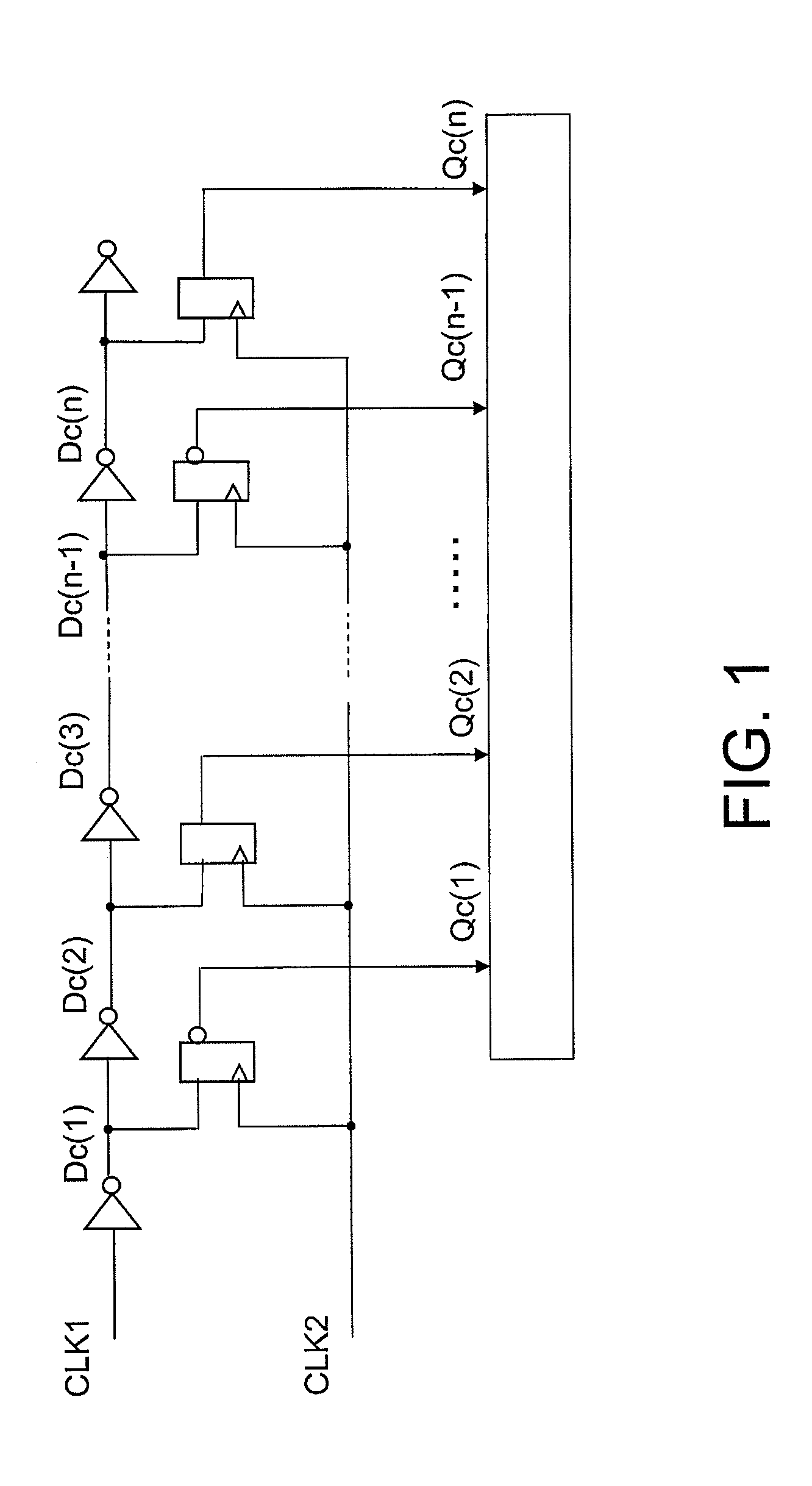

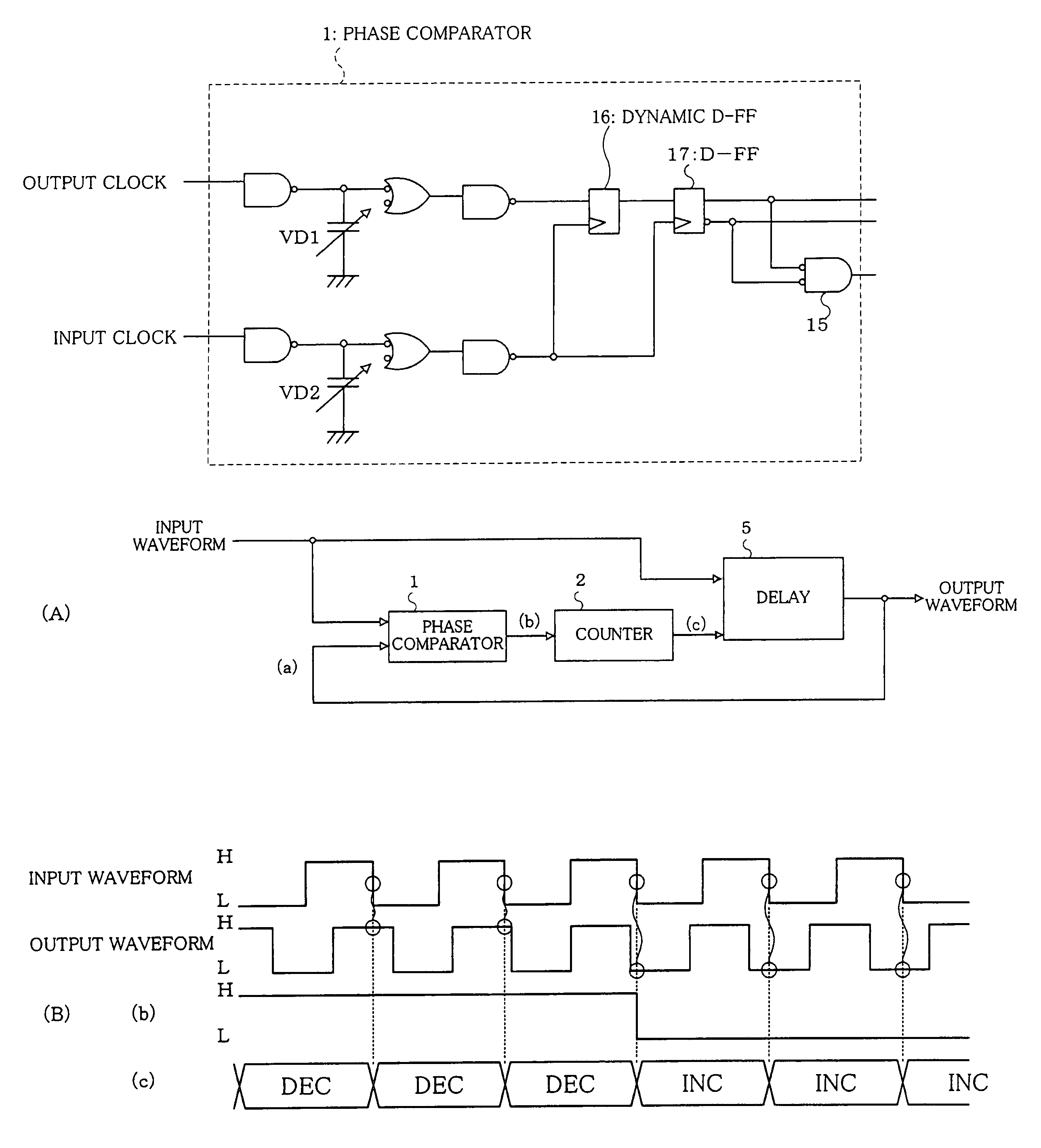

Digital phase comparator

ActiveUS20110304357A1Reducing area consumptionReduce circuit areaMultiple input and output pulse circuitsPulse automatic controlPhase differenceComparator

A digital phase comparator is provided in which first phase difference signals and second phase difference signals are used as digital phase difference information. The first phase difference signals are generated by sampling a second clock signal with a first group of clock signals having regular intervals. The second phase difference signals are generated, using a second group of clock signals and a first group of signals which are obtained by delaying a second clock signal and a first signal generated by performing a logic operation on the first phase difference signal respectively at different regular intervals, by sampling the second group of clock signals with the first group of signals.

Owner:NEC CORP

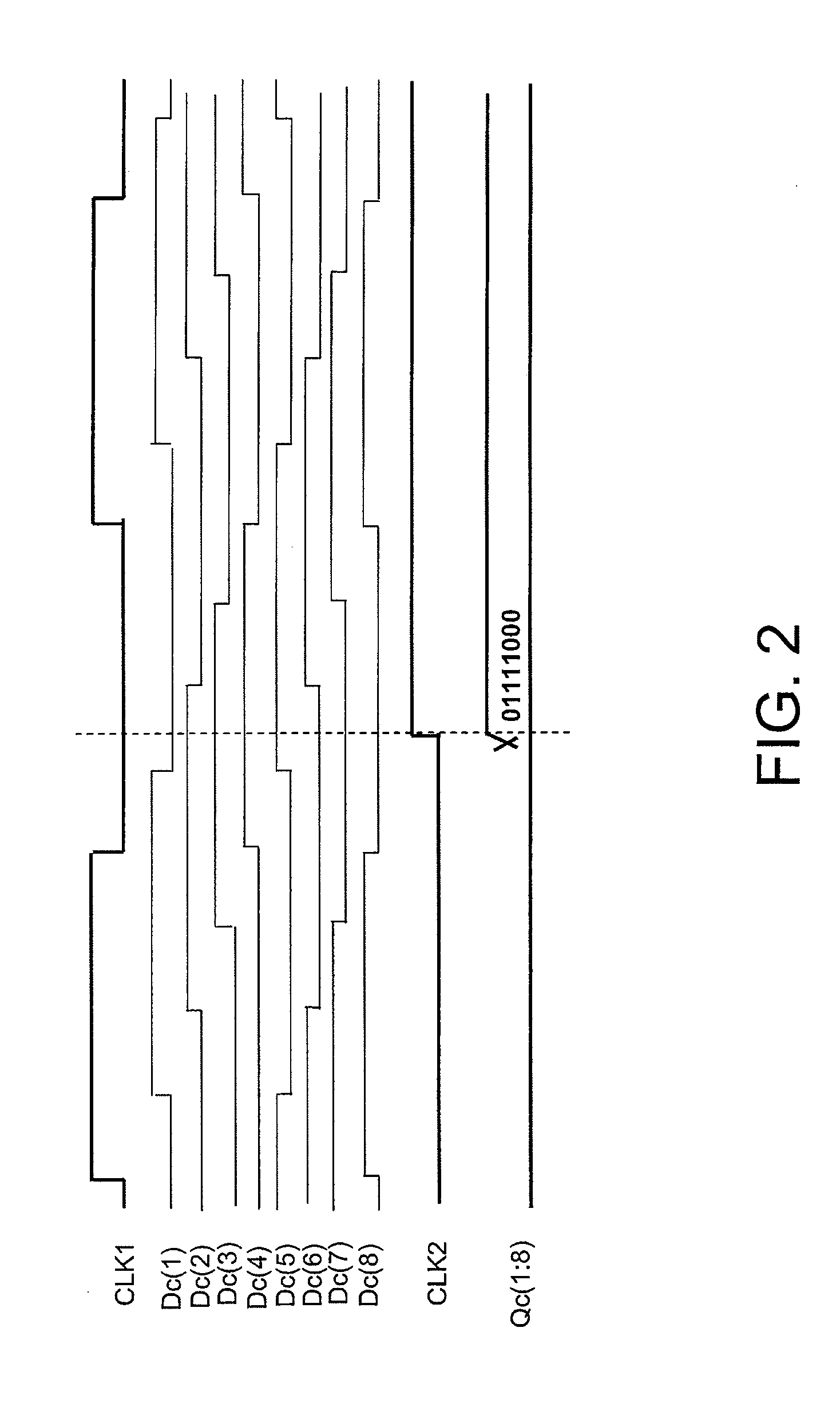

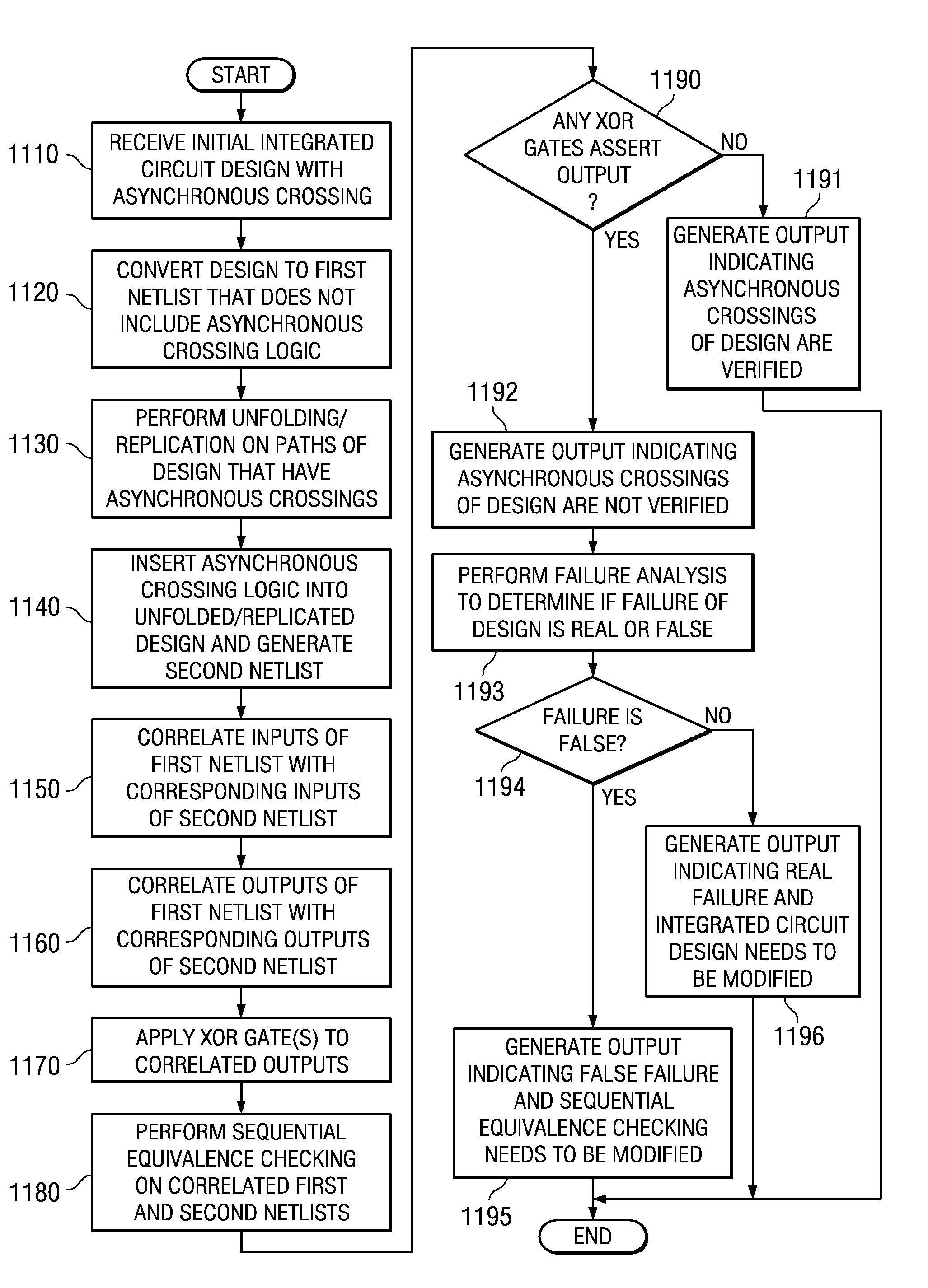

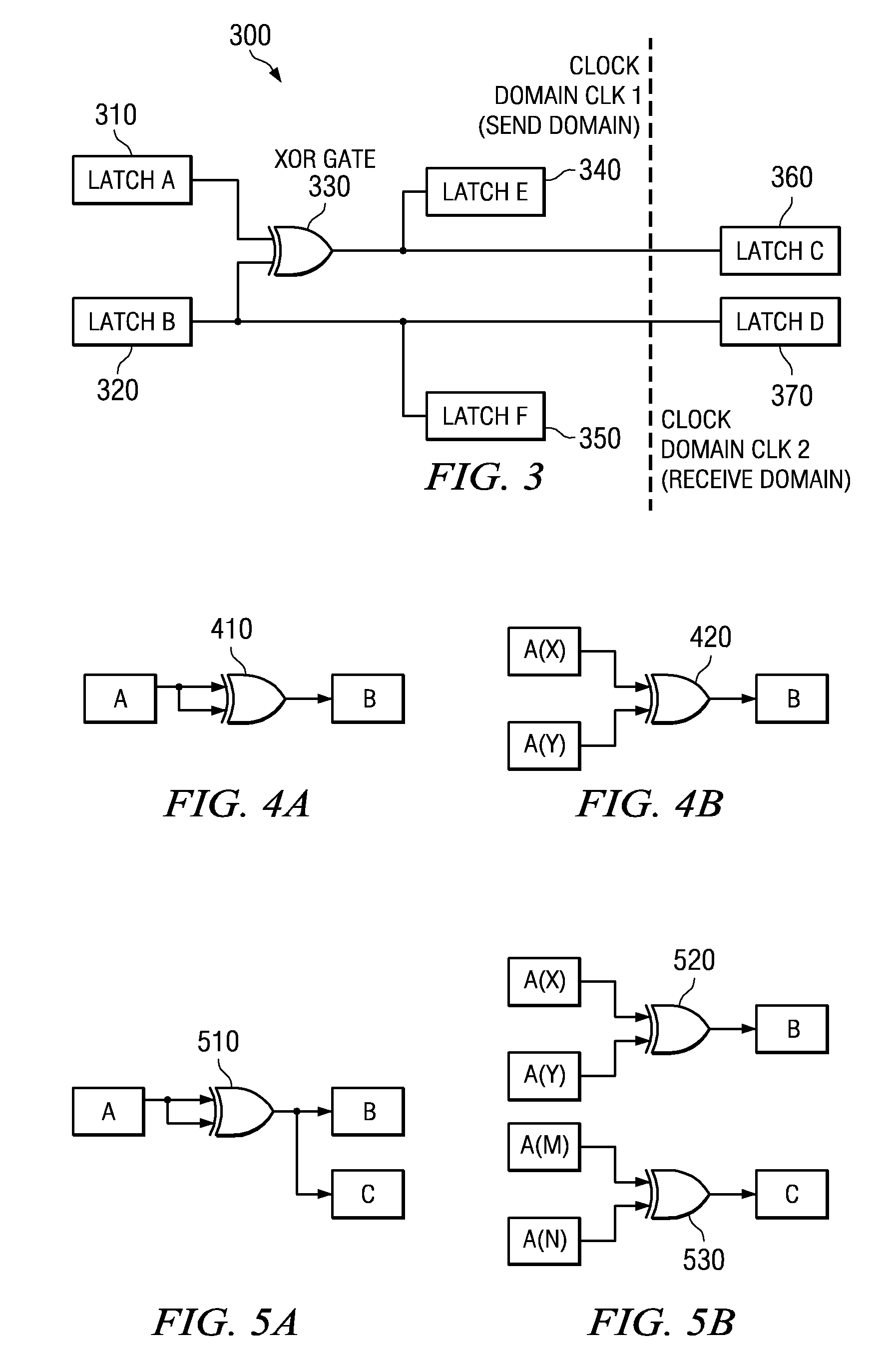

Sequential equivalence checking for asynchronous verification

ActiveUS7882473B2Component separationAnalogue computers for electric apparatusMaximum latencyArrival time

Mechanisms for performing sequential equivalence checking for asynchronous verification are provided. A first model of the integrated circuit design is provided that has additional logic in it to reflect the possible variance in behavior of the asynchronous crossings. A second model of the integrated circuit design is provided that does not have this asynchronous behavior logic but instead correlates to the simplest synchronous model that is usually used for non-asynchronous functional verification tasks. Sequential equivalence checking is performed to verify that the two models are input / output equivalent. In order to address non-uniform arrival times of bus strands, logic is provided for identifying bus strands that have transitioning bits, determining a representative delay for these strands, comparing the representative delays for all of the bus strands to determine the maximum delay for the entire bus, and applying this maximum delay to one of the models.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

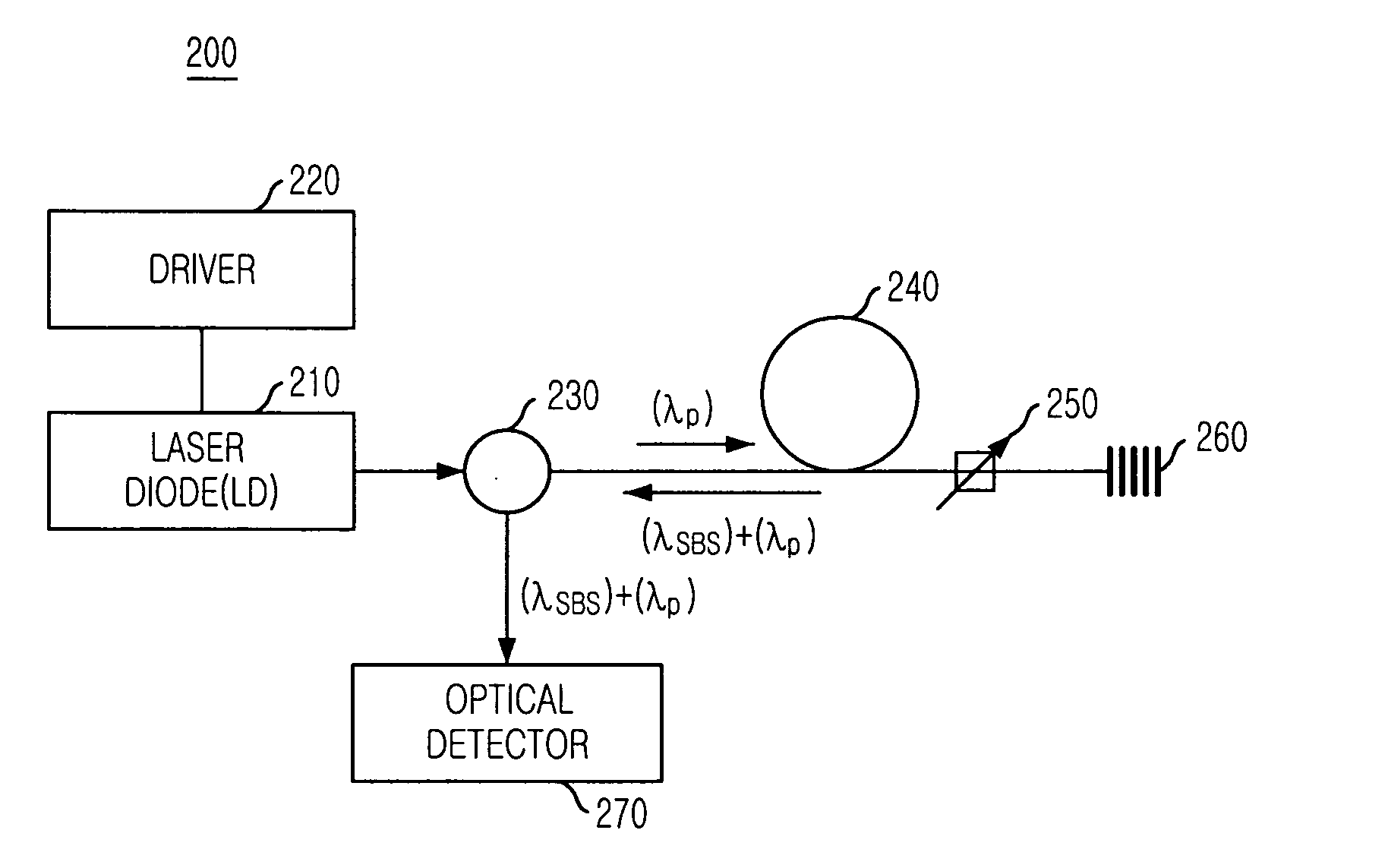

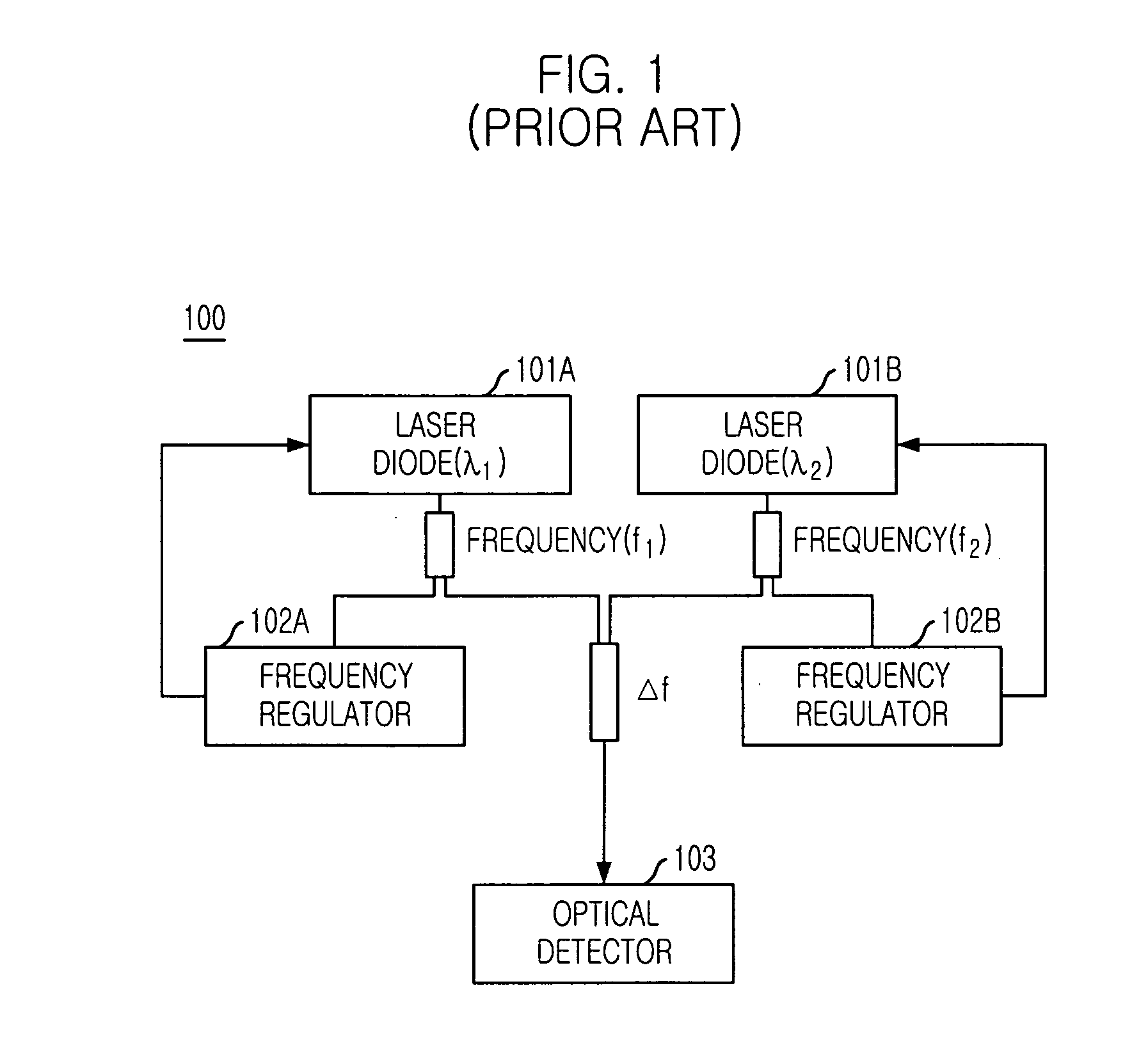

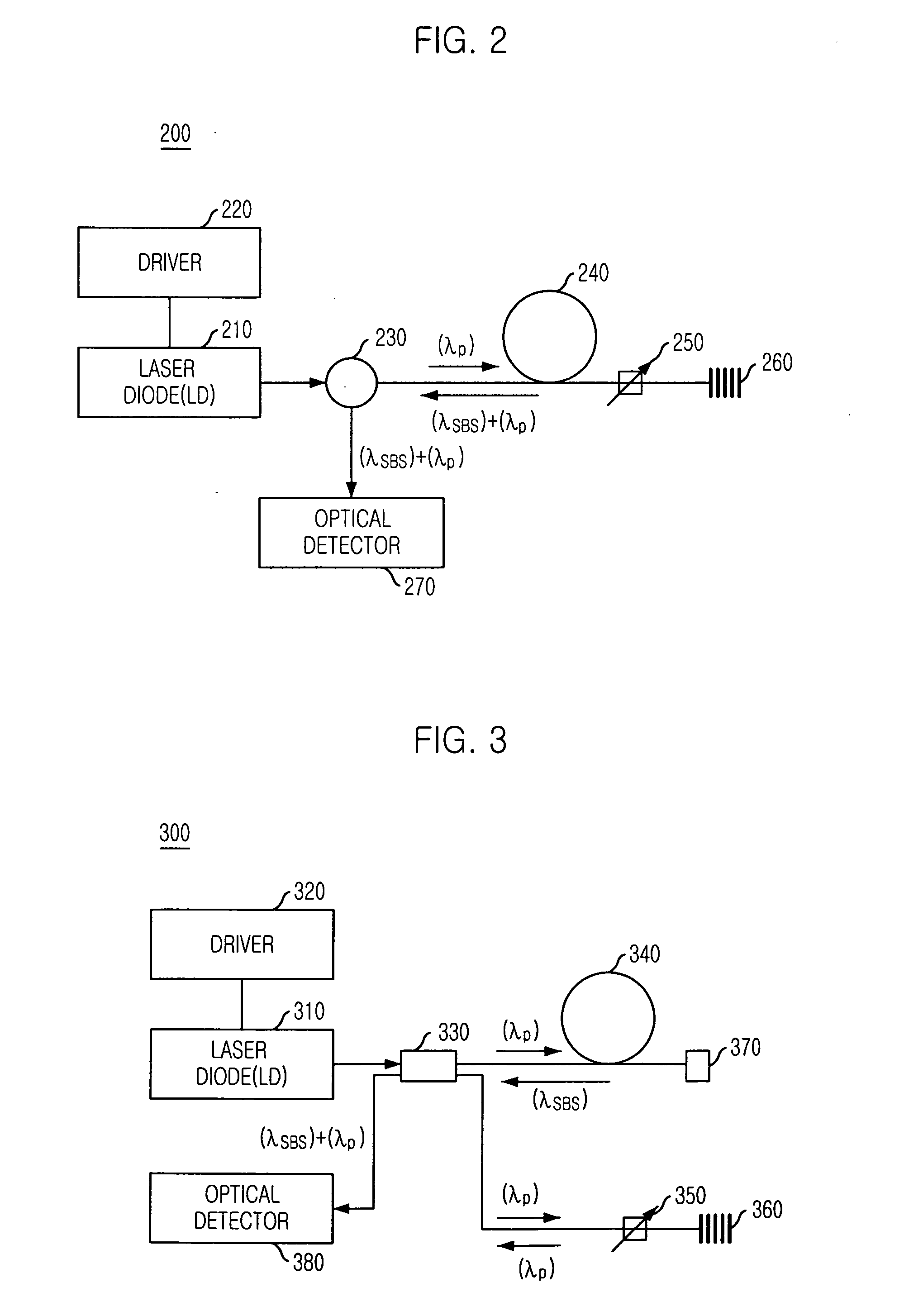

Apparatus and method for generating optical carrier for microwave and millimeterwave photonics system

InactiveUS20050141582A1High optical densityLaser using scattering effectsUsing optical meansPhotonicsAmplitude control

Owner:INTELLECTUAL DISCOVERY CO LTD

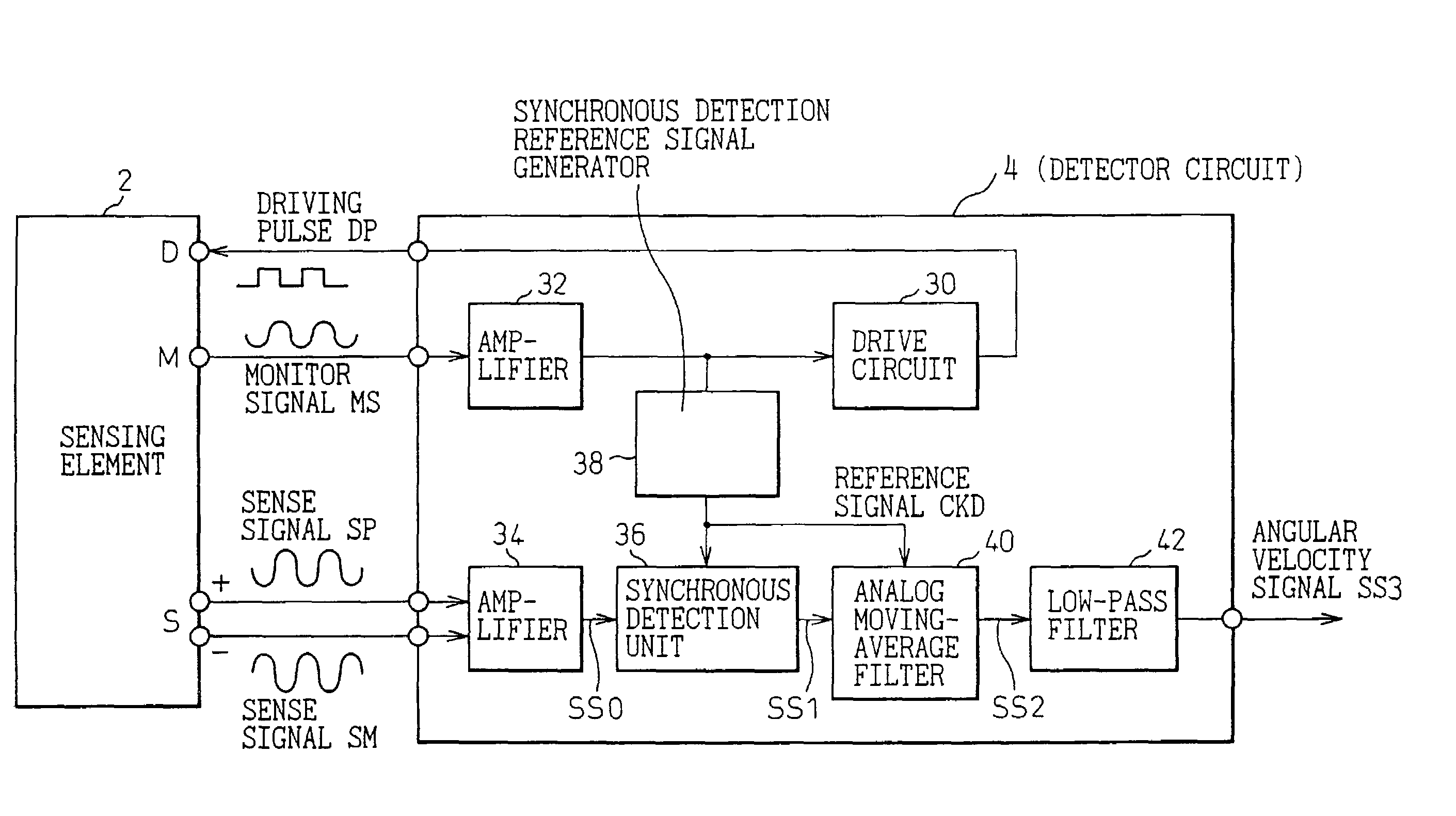

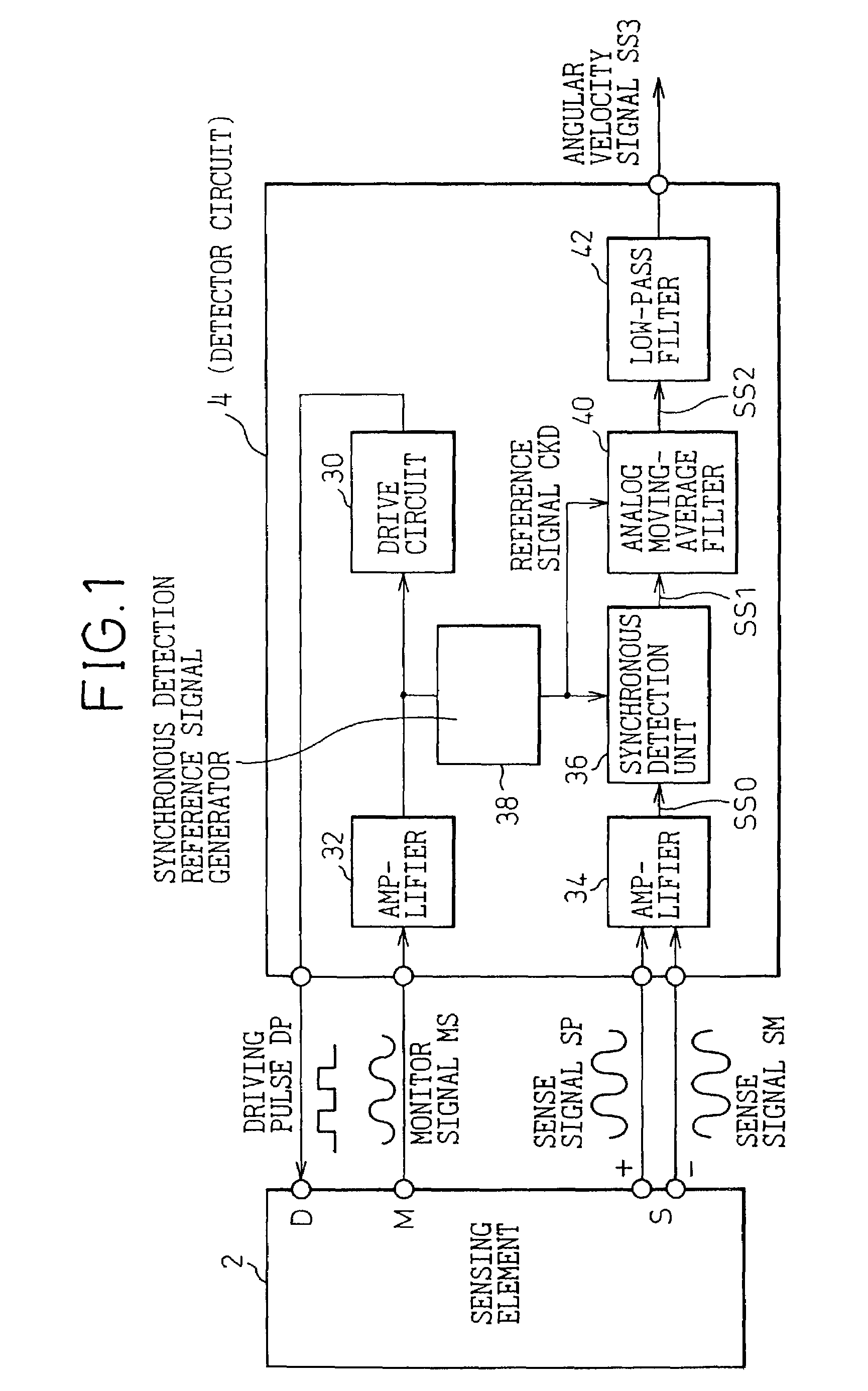

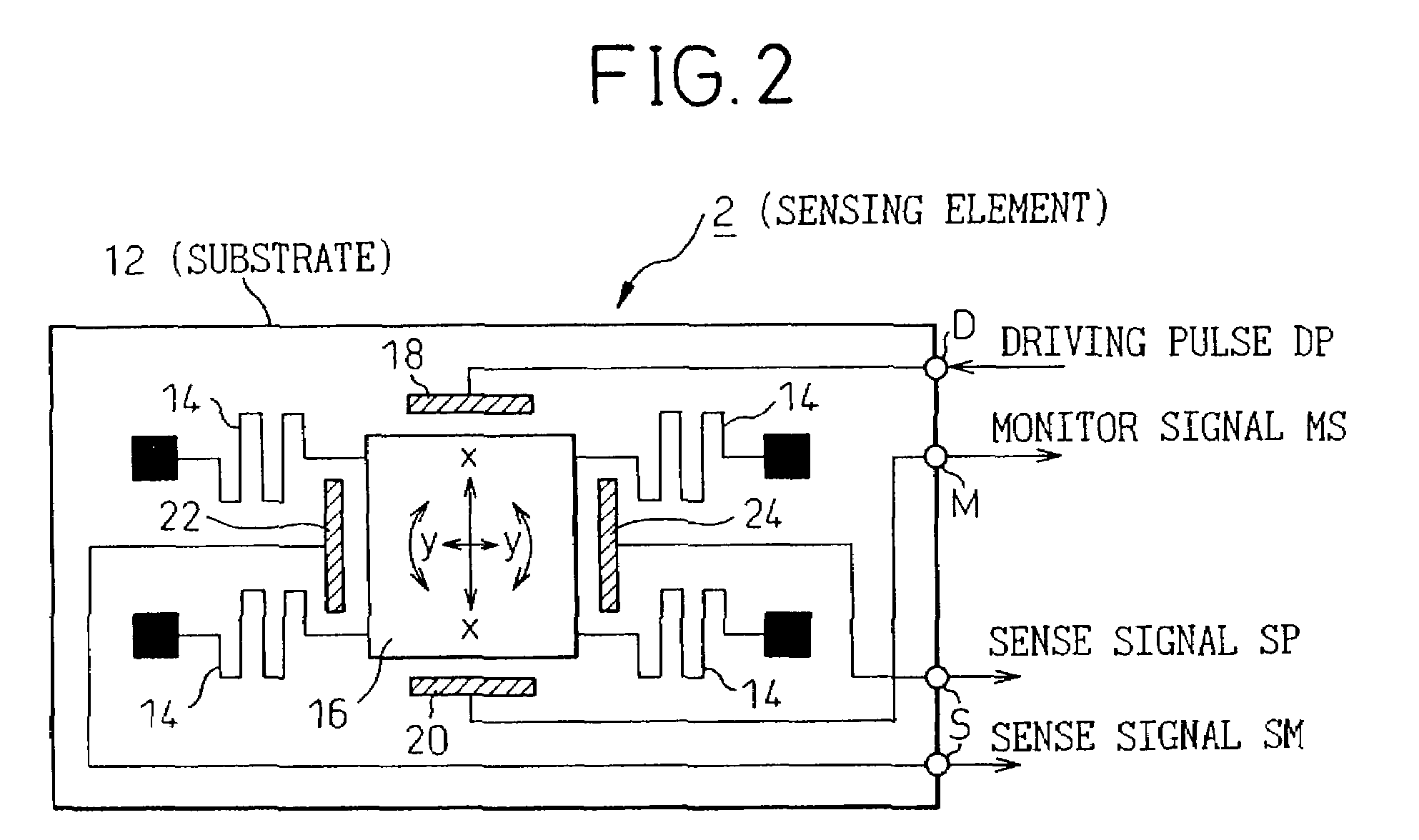

Synchronous detection method and device, and sensor signal detector

ActiveUS7068744B2Effectively minimizedMinimize high-frequency noiseAcceleration measurement using interia forcesError preventionMoving averageGyroscope

The present invention is intended to efficiently minimize high-frequency noise stemming from synchronous detection without the necessity of a low-pass filter that requires a large time constant. A vibratory gyroscope includes a synchronous detection unit that detects a sense signal sent from a sensing element using a reference signal synchronous with a monitor signal. In the vibratory gyroscope, an analog moving-average filter that produces a moving average of the detection signal by sampling the detection signal during one cycle of the reference signal is used to remove high-frequency noise components from the detection signal, which is detected to be synchronous with the reference signal, without the necessity of a CR filter that requires a large time constant. Consequently, unnecessary noise components whose frequencies are equal to the frequency of the reference signal and those of its harmonics, and which stem from synchronous detection, can be efficiently attenuated owing to an infinite attenuation frequency band offered by the analog moving-average filter.

Owner:DENSO CORP

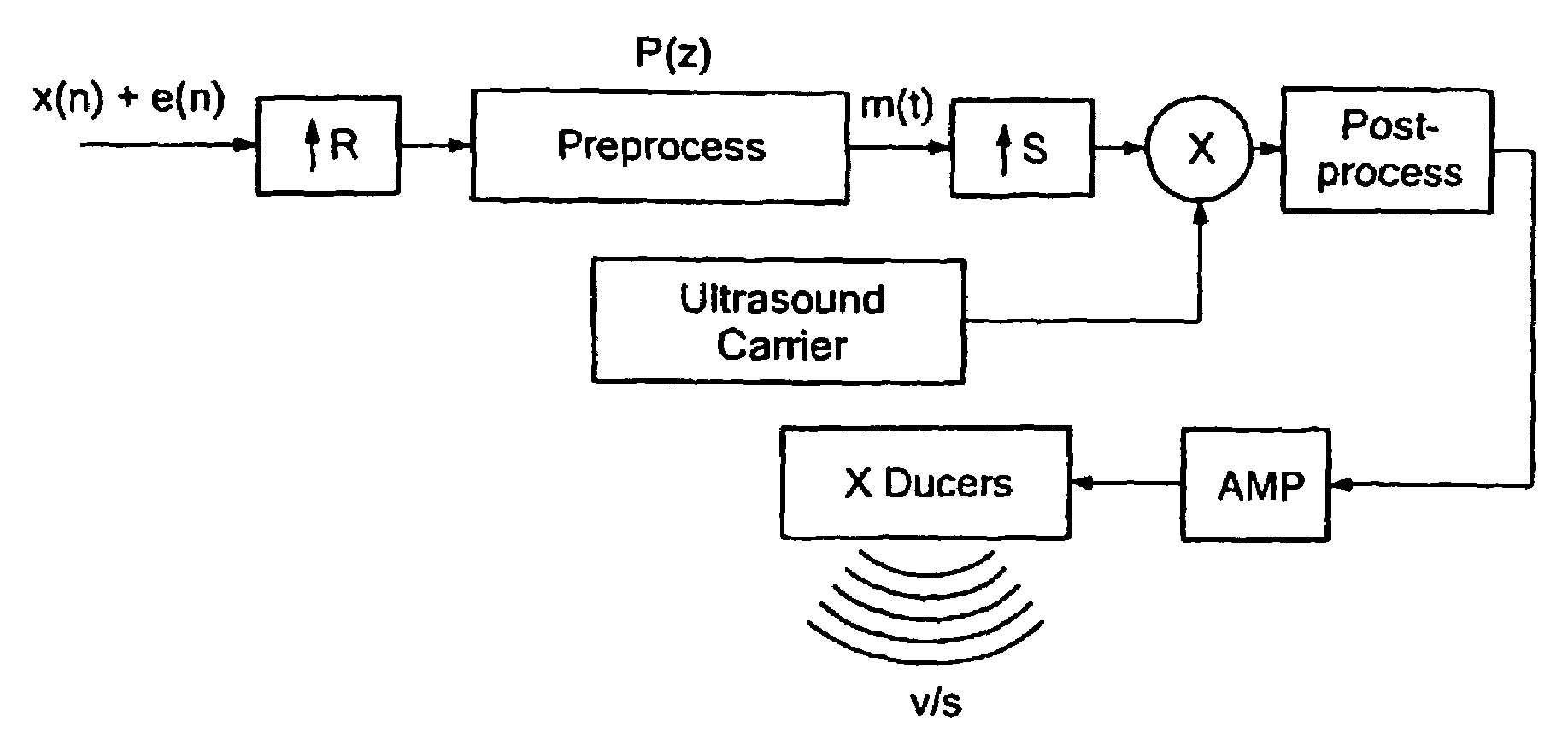

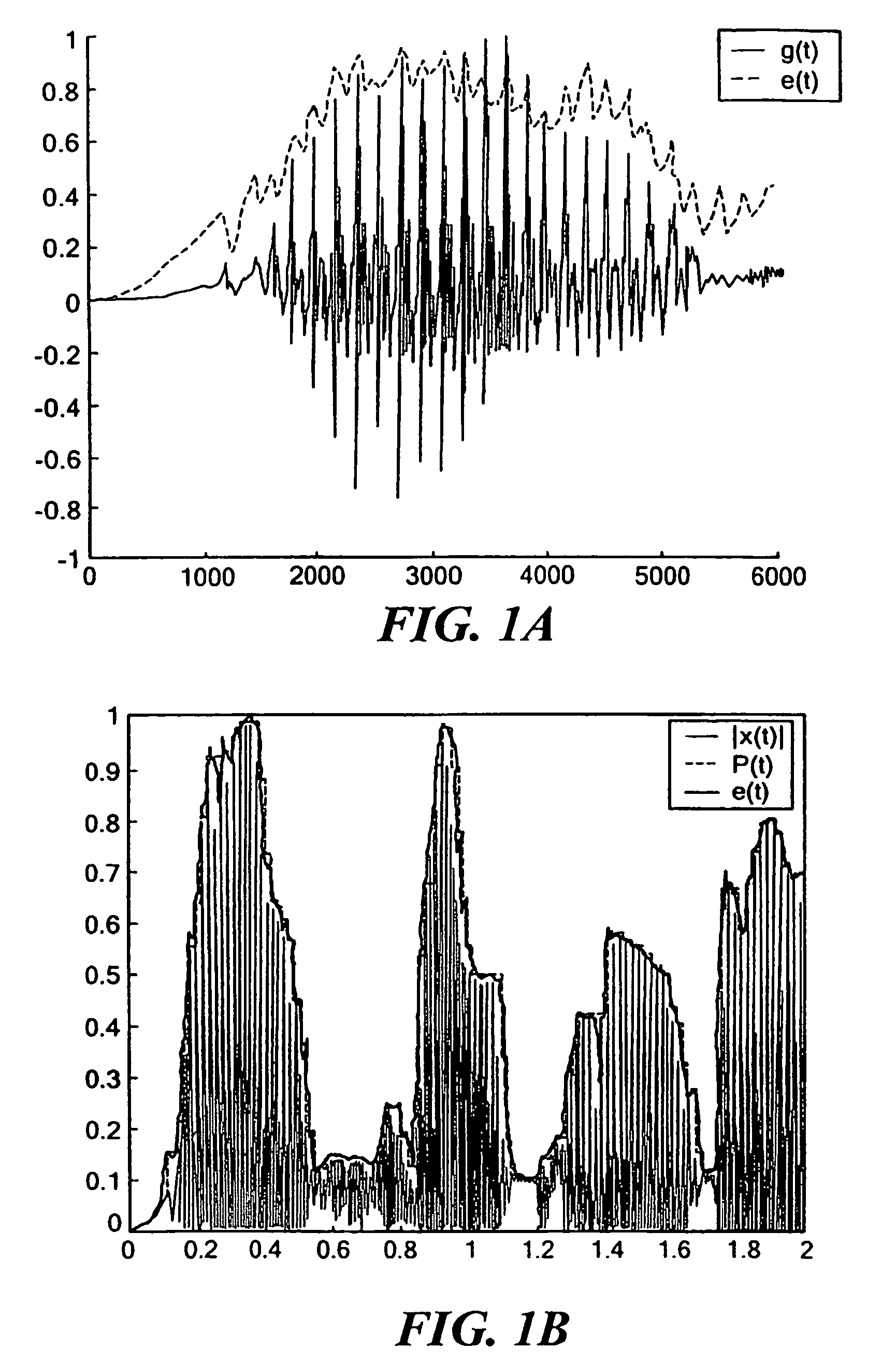

Parametric array modulation and processing method

ActiveUS7596228B2Near-field transmissionSonic/ultrasonic/infrasonic transmissionSonificationParametric array

A system using the nonlinearity of a propagation medium to demodulate an ultrasonic wave having audio modulated onto the ultrasonic frequency, audio signal processing circuitry providing a delayed audio signal and an envelope signal which is a function of peaks of the audio signal over a predetermined interval. The delayed audio signal and the envelope signals are combined with the delay in the audio allowing the envelope signal to accurately be aligned with the audio signal in the combination.

Owner:POMPEI FRANK JOSEPH

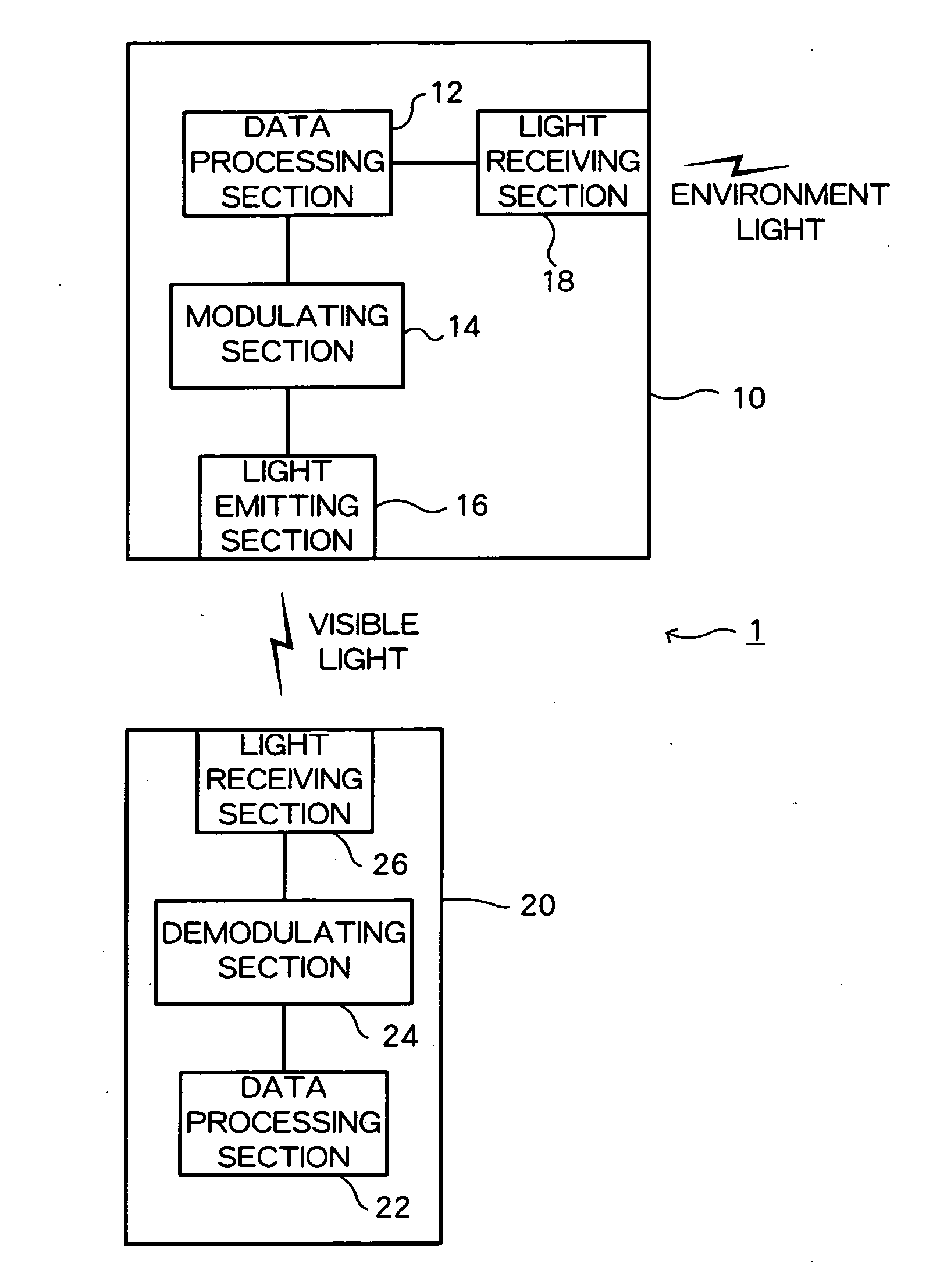

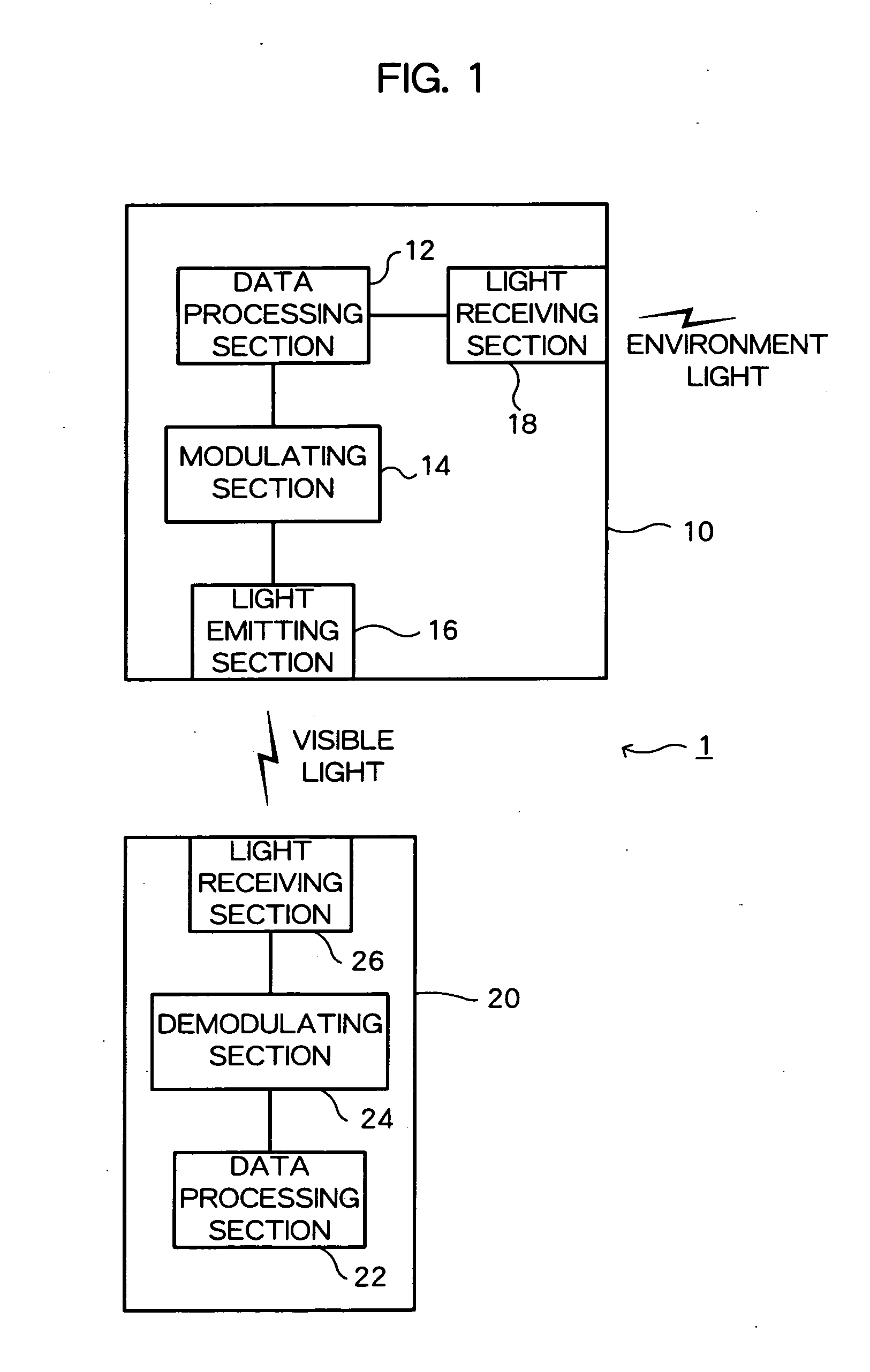

Optical transmitter and optical receiver

InactiveUS20060275041A1Fine-tuned adjustmentIncrease redundancyClose-range type systemsDiversity/multi-antenna systemsComputer hardwareData stream

In an optical transmitter provided with an LED that transmits a transmission bit stream as an optical signal by varying the luminance of visible light to be irradiated according to an input transmission bit stream, plural scramble data streams each having a different mark ratio are stored in a scramble data stream storage, and a light-control bit stream to which the mark ratio of the transmission bit stream is changed by performing a reversible bit operation on the transmission bit stream using a scramble data stream chosen among the stored scramble data streams. The light-control bit stream is then outputted to the LED.

Owner:KYOCERA CORP

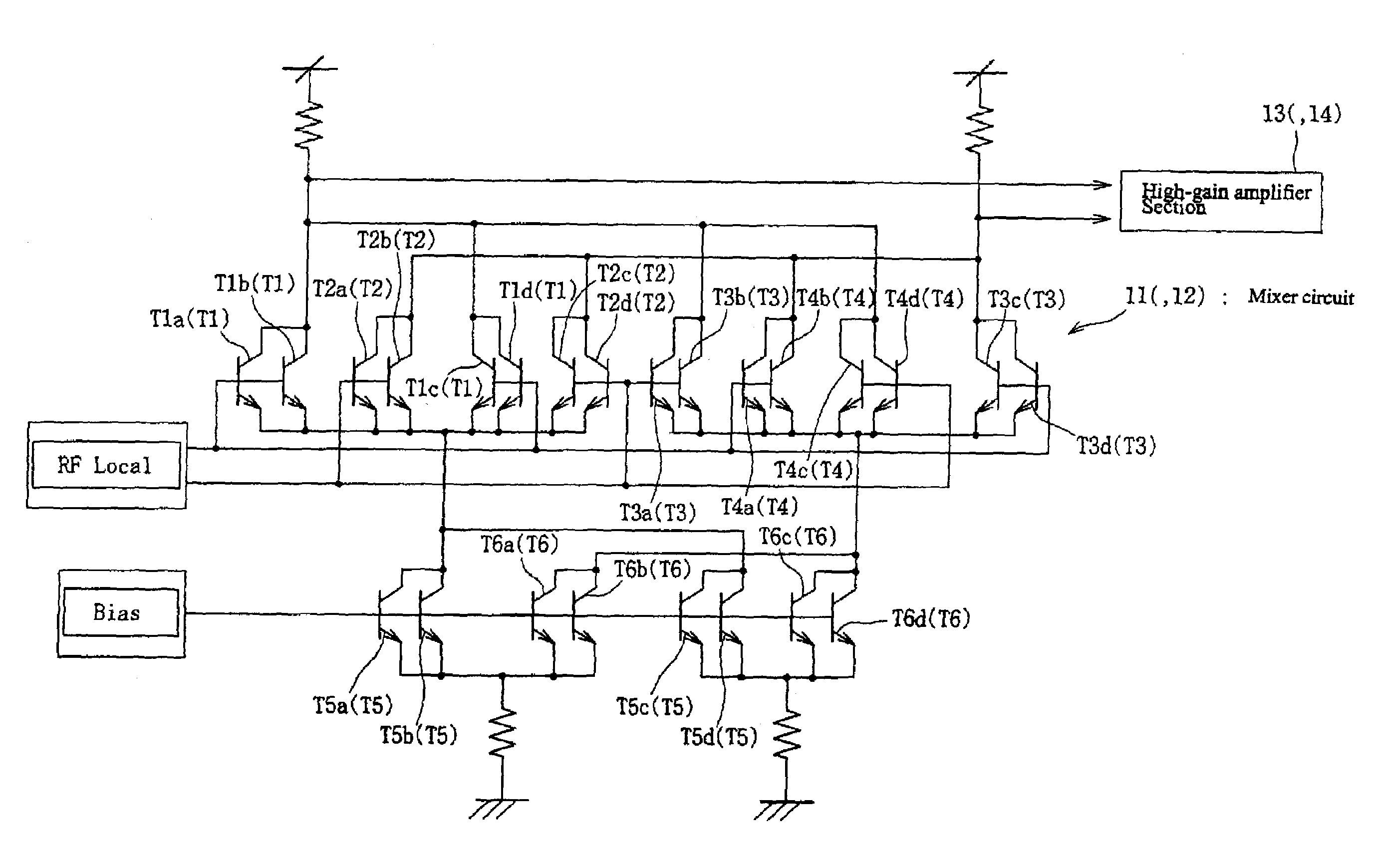

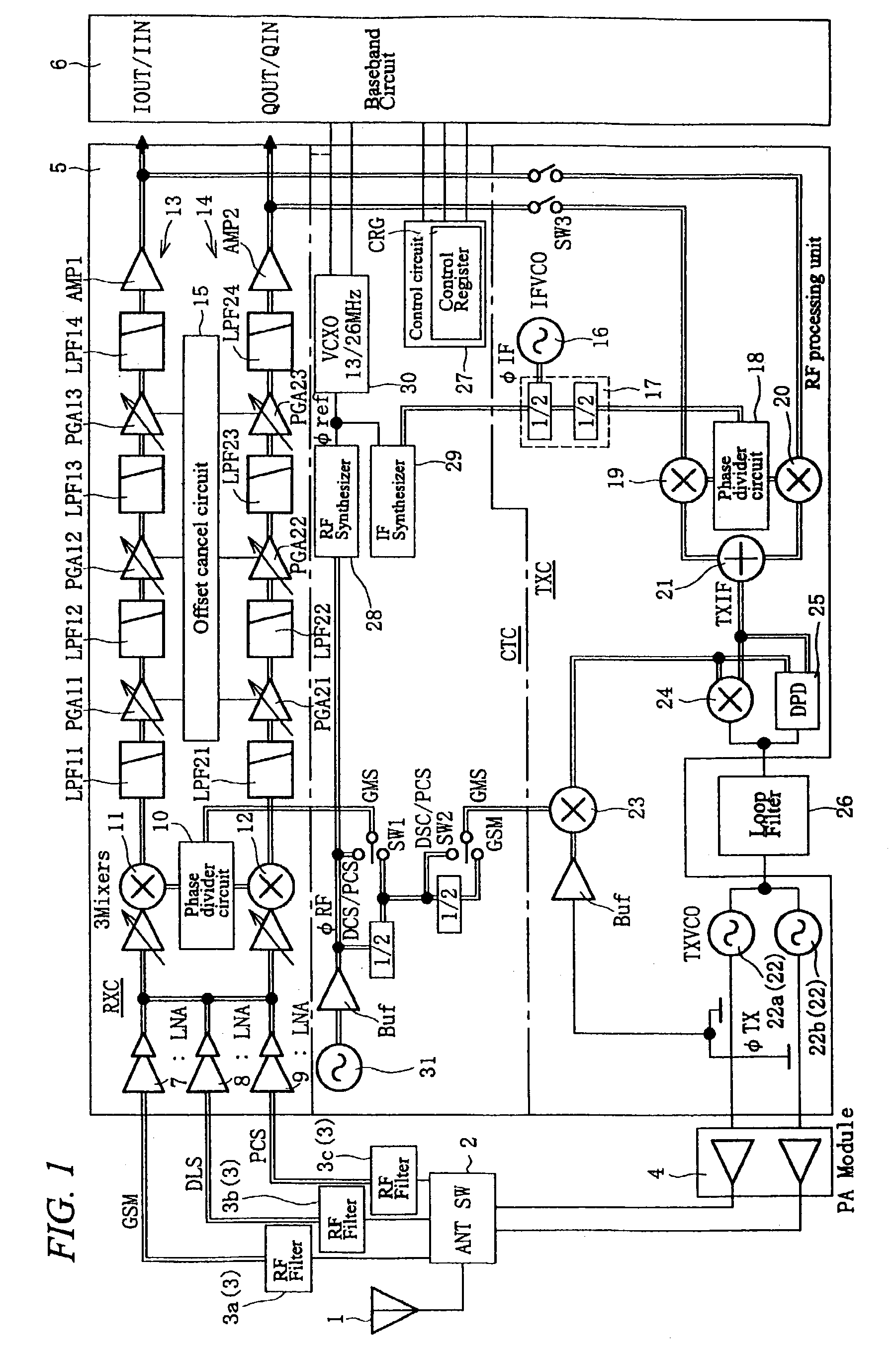

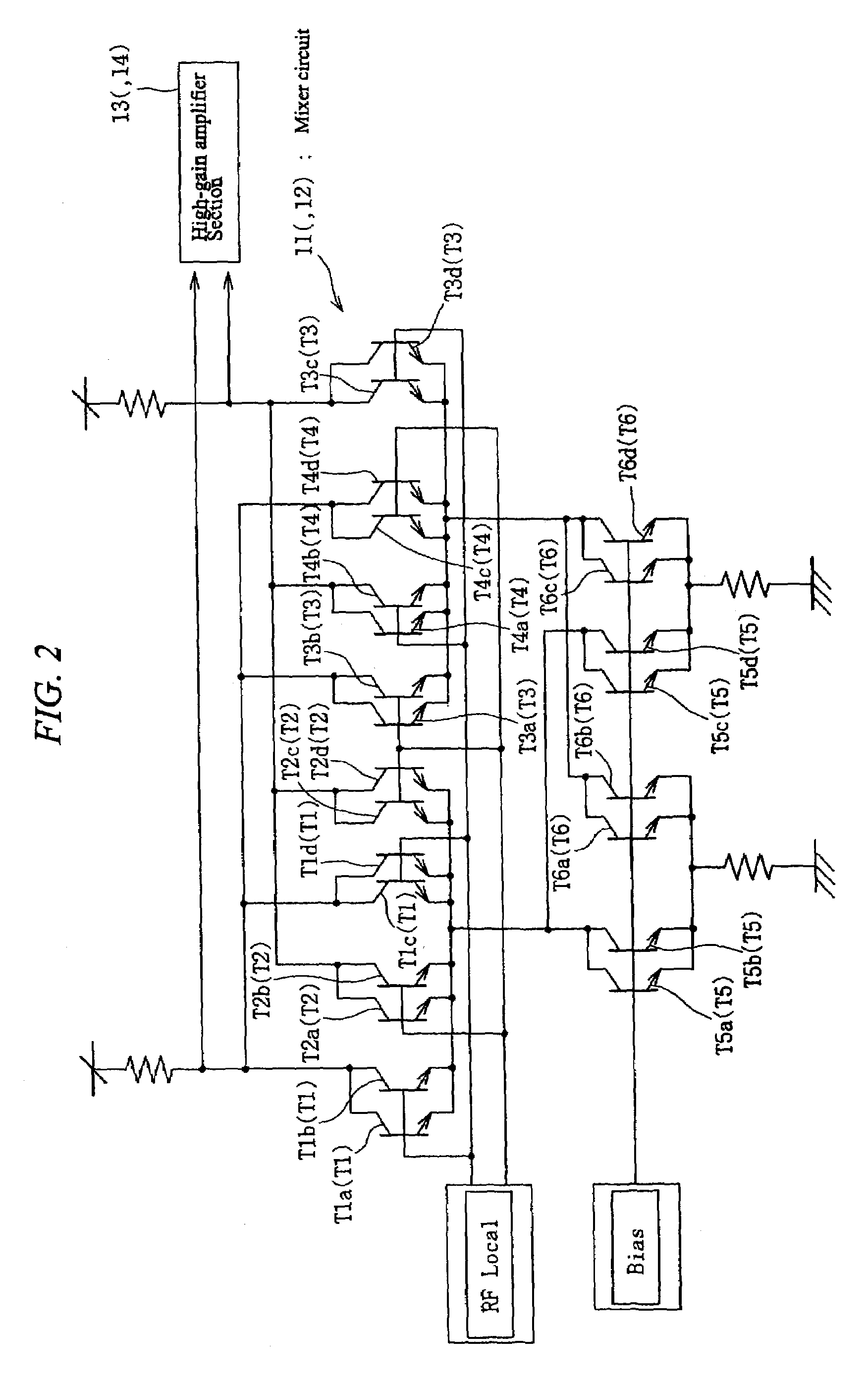

Semiconductor integrated circuit device

InactiveUS7050779B2Prevent DC offsetImprove receiver sensitivityModulation transference balanced arrangementsSolid-state devicesGilbert cellSemiconductor chip

The thermal interference due to the self heating of transistors constituting a gilbert cell circuit is reduced, thereby largely improving the receiving sensitivity to signals. A mixer circuit composed of a gilbert cell circuit comprises transistors T1 to T6. Each of the transistors T1 to T4 is con figured so that four transistors may be connected in parallel. In a layout on a semiconductor chip, four transistors T1a to T1d and T2a to T2d respectively constituting the transistors T1 and T2 are respectively separated into two pairs, and the respective two pairs are laid out in a crisscross shape so that they are crossed with each other. Similarly, four transistors T3a to T3d and T4a to T4d respectively constituting the transistors T3 and T4 are respectively separated into two pairs, and the respective two pairs are laid out in a crisscross shape so that they are crossed with each other. Thus, the thermal influence applied on the transistors T1 to T4 is uniformed.

Owner:HITACHI LTD +1

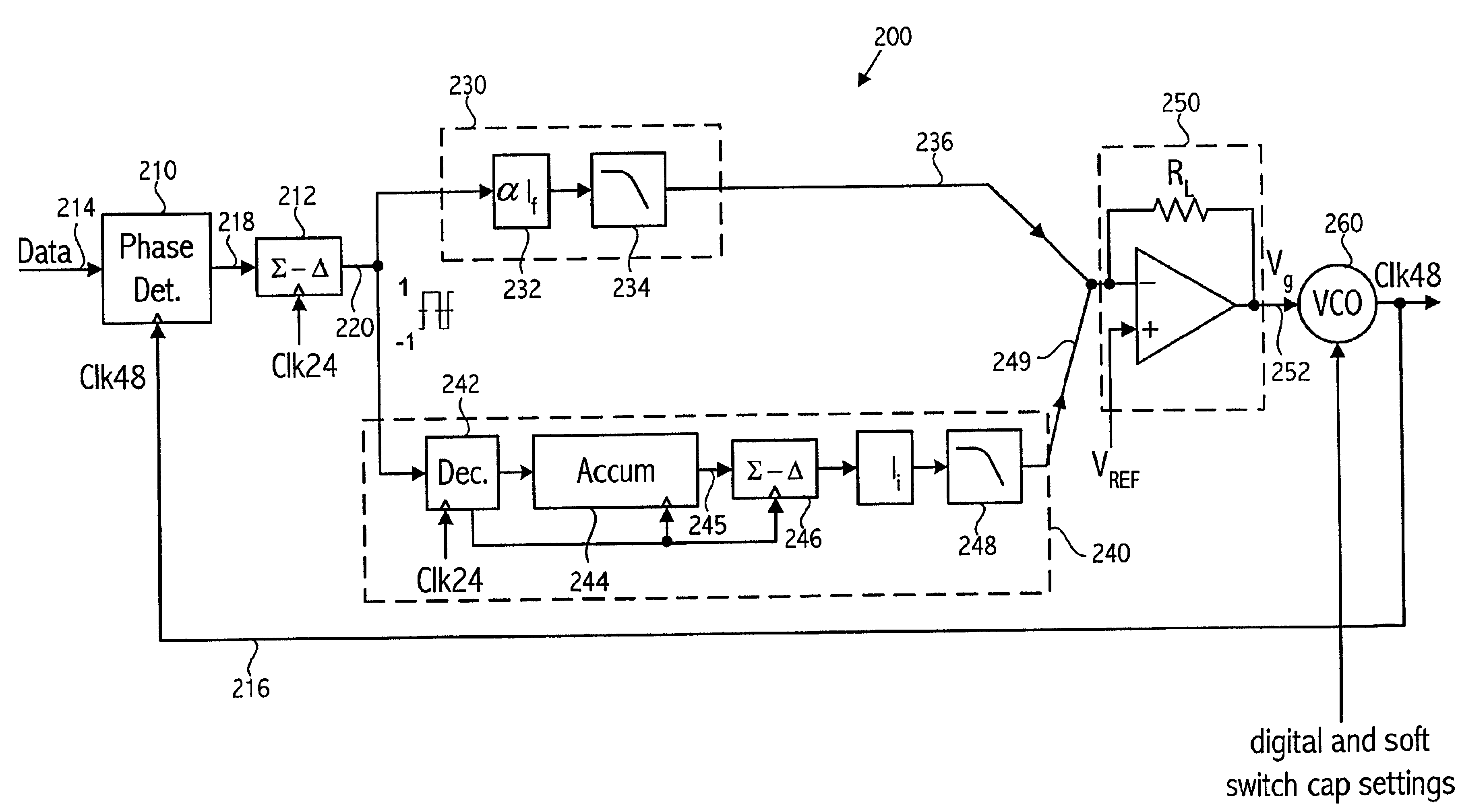

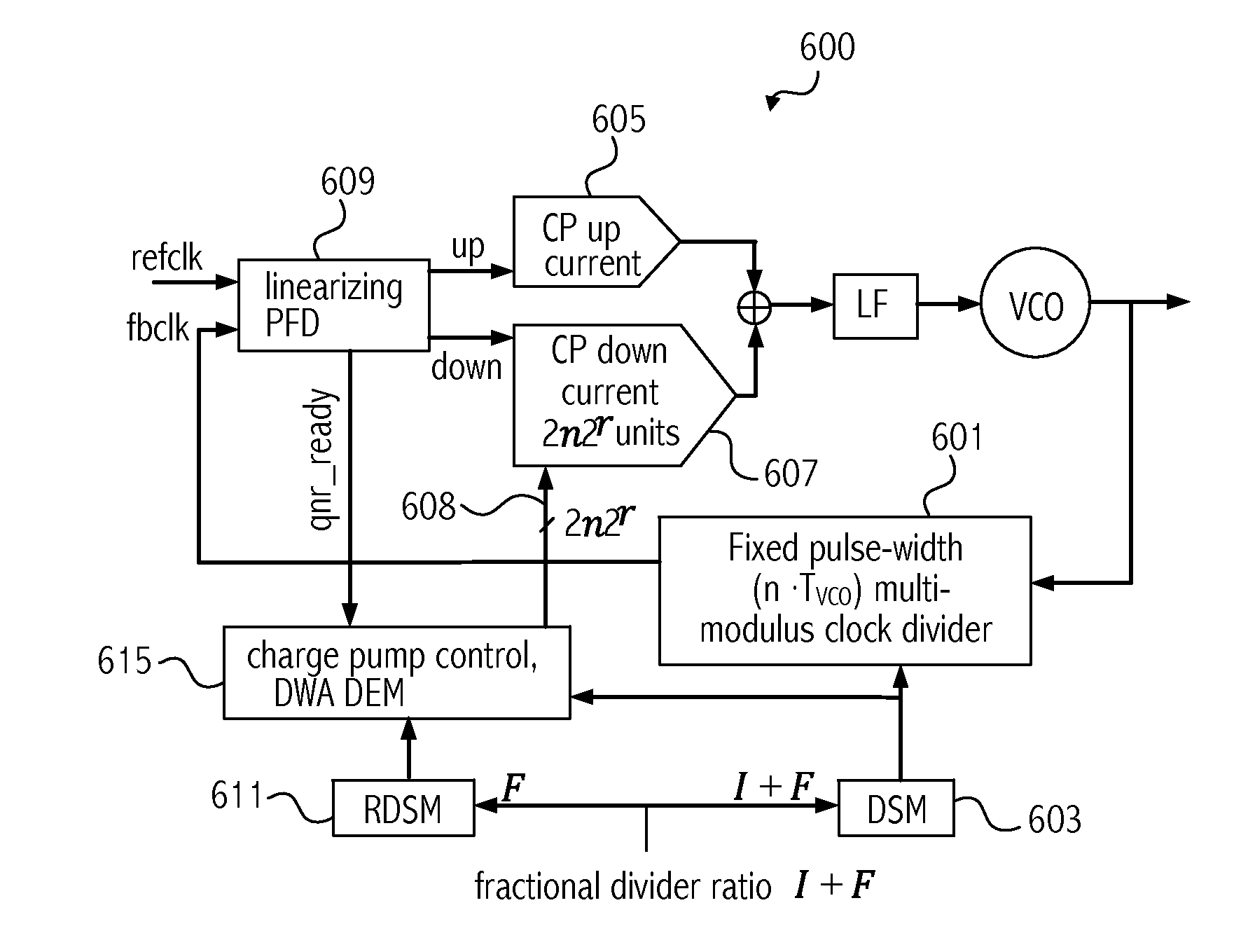

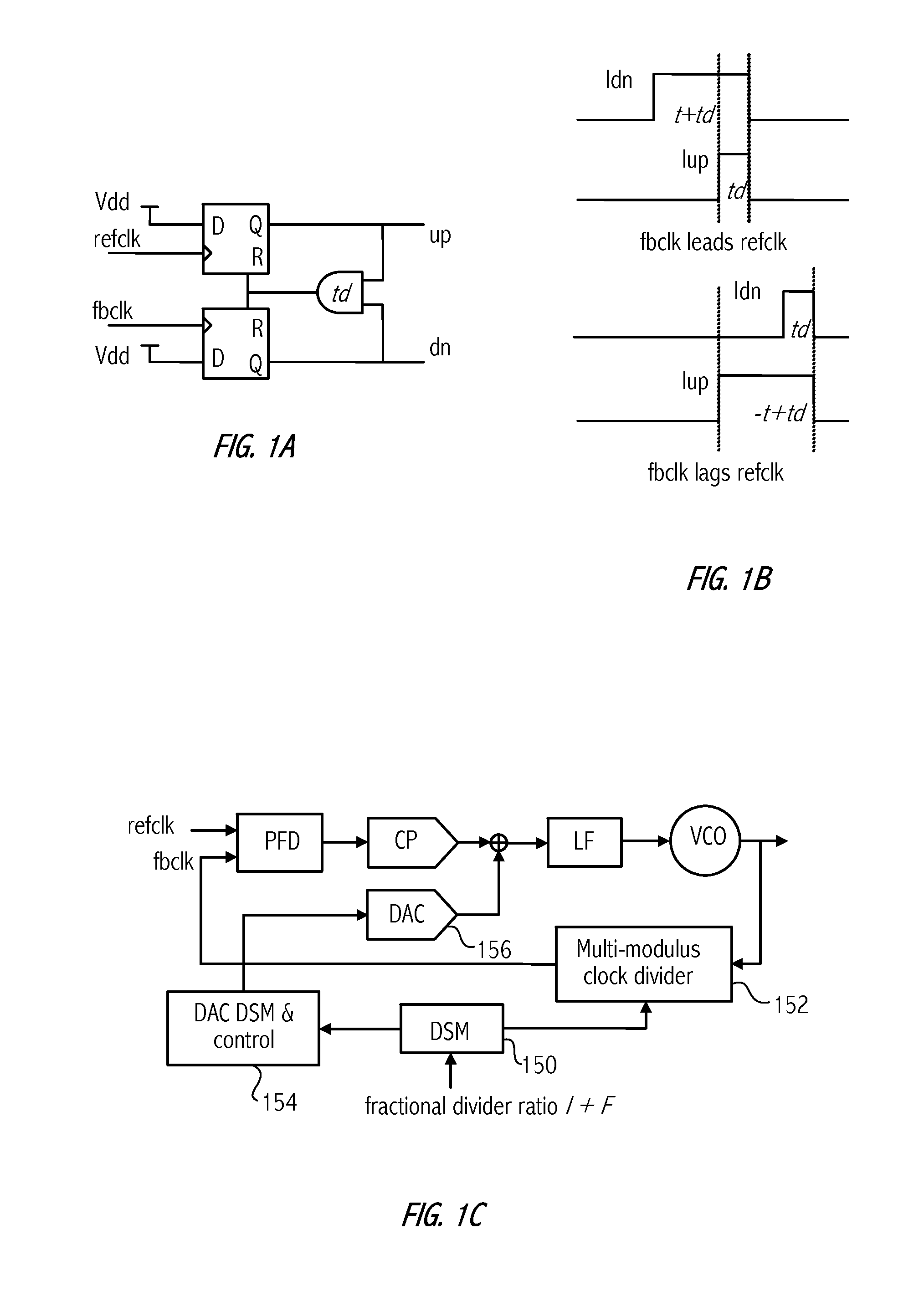

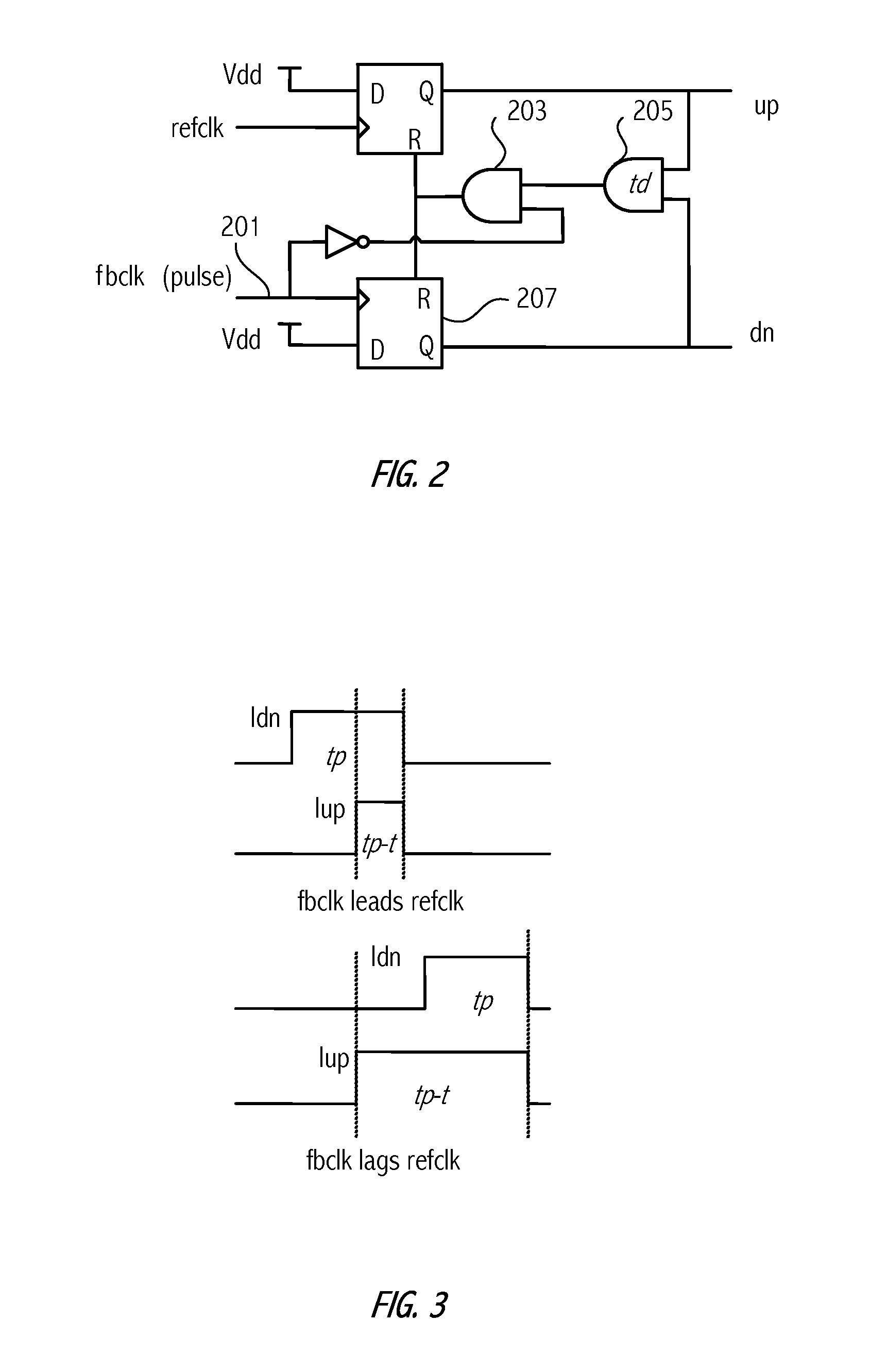

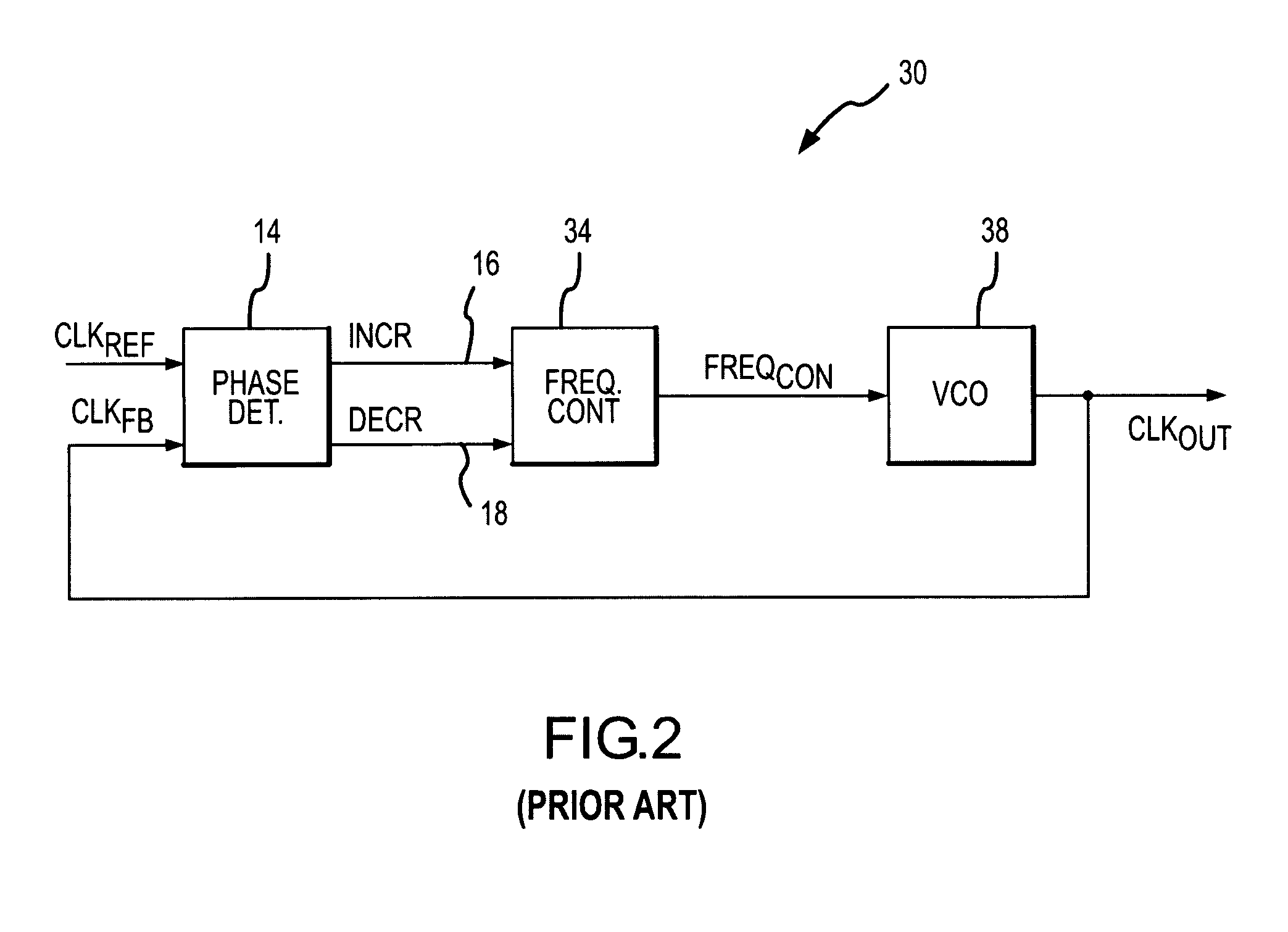

Method and apparatus for charge pump linearization in fractional-n plls

ActiveUS20110234272A1Pulse automatic controlVoltage-current phase anglePhase frequency detectorLinearity

Efficient techniques improve the linearity of a charge pump in fractional-N PLLs. A feedback clock pulse several VCO clock periods wide is formed and supplied to a phase frequency detector (PFD). The down pulse generated by the PFD is fixed to eliminate the nonlinearity associated with up and down current source mismatch. The up pulse is made to fall when the down pulse falls, that is, when the feedback clock pulse falls.

Owner:SILICON LAB INC

Spatial information detecting device using intensity-modulated light and a beat signal

InactiveUS7119350B2Accurate detectionHigh speed responseTelevision system detailsSolid-state devicesElectricityIntegrator

A spatial information detecting device using an intensity-modulated light is provided. This device comprises a photoelectric converter for receiving a light from a space into which a light intensity-modulated at a predetermined emission frequency is being irradiated, and generating an electrical output corresponding to an intensity of received light; a local oscillator circuit for outputting a local oscillator signal having a local oscillator frequency different from the emission frequency; a sensitivity controller for mixing the local oscillator signal with the electrical output to frequency convert the electrical output into a beat signal having a lower frequency than the emission frequency; an integrator for performing integration of said beat signal at a predetermined timing; and an analyzer for detecting information concerning the space according to an output of the integrator. According to this device, it is possible to accurately detect the spatial information without using a switching element having high-speed response at the light receiving side.

Owner:MATSUSHITA ELECTRIC WORKS LTD

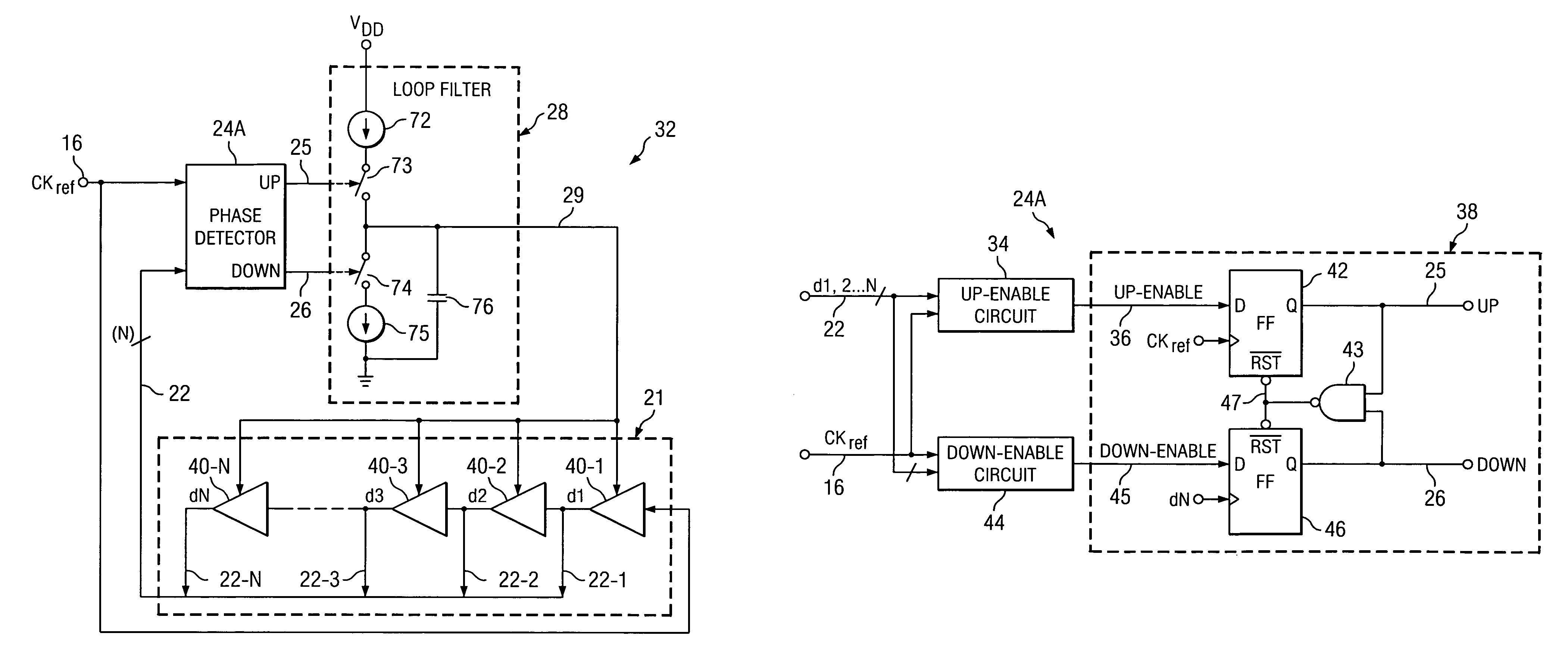

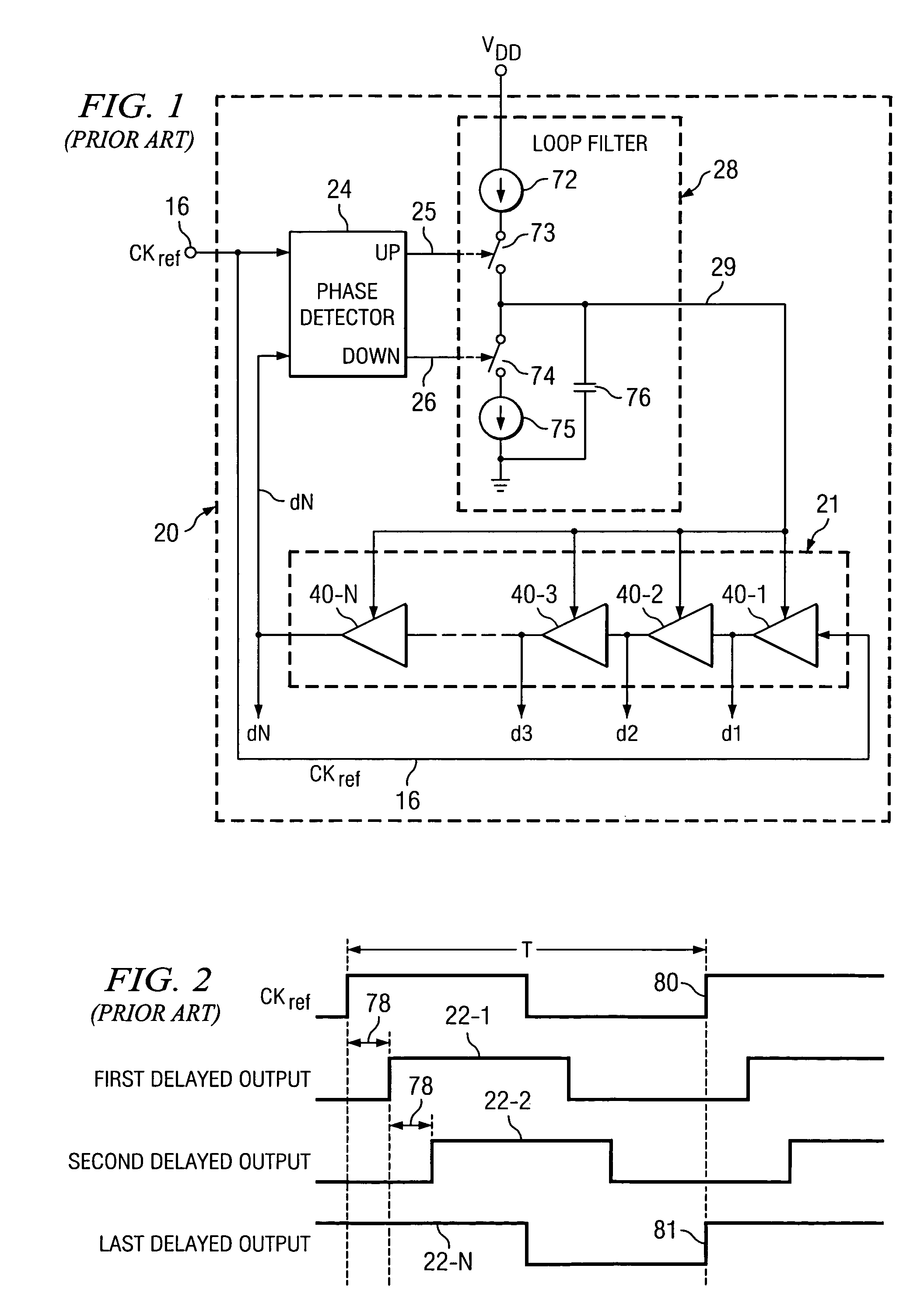

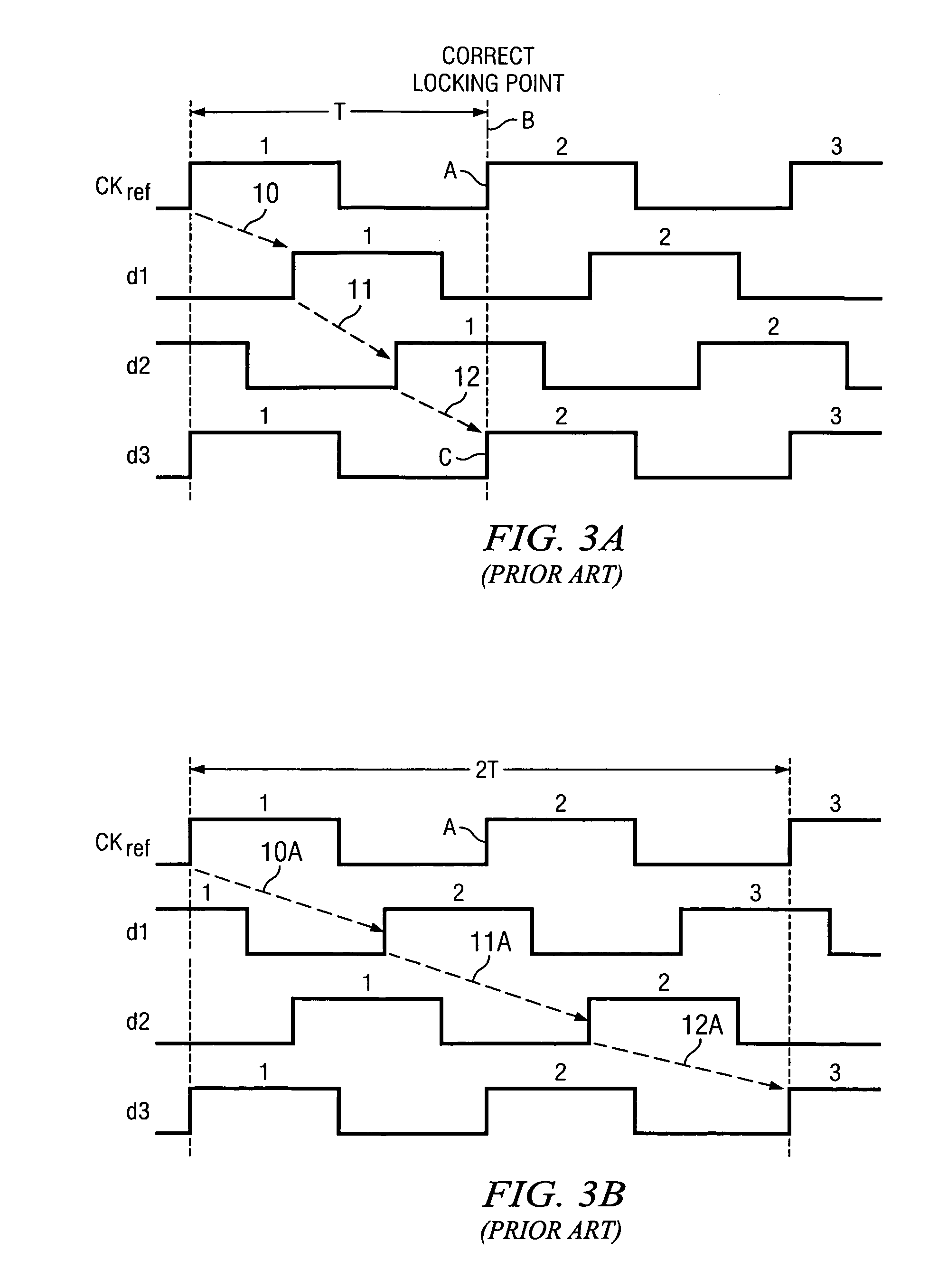

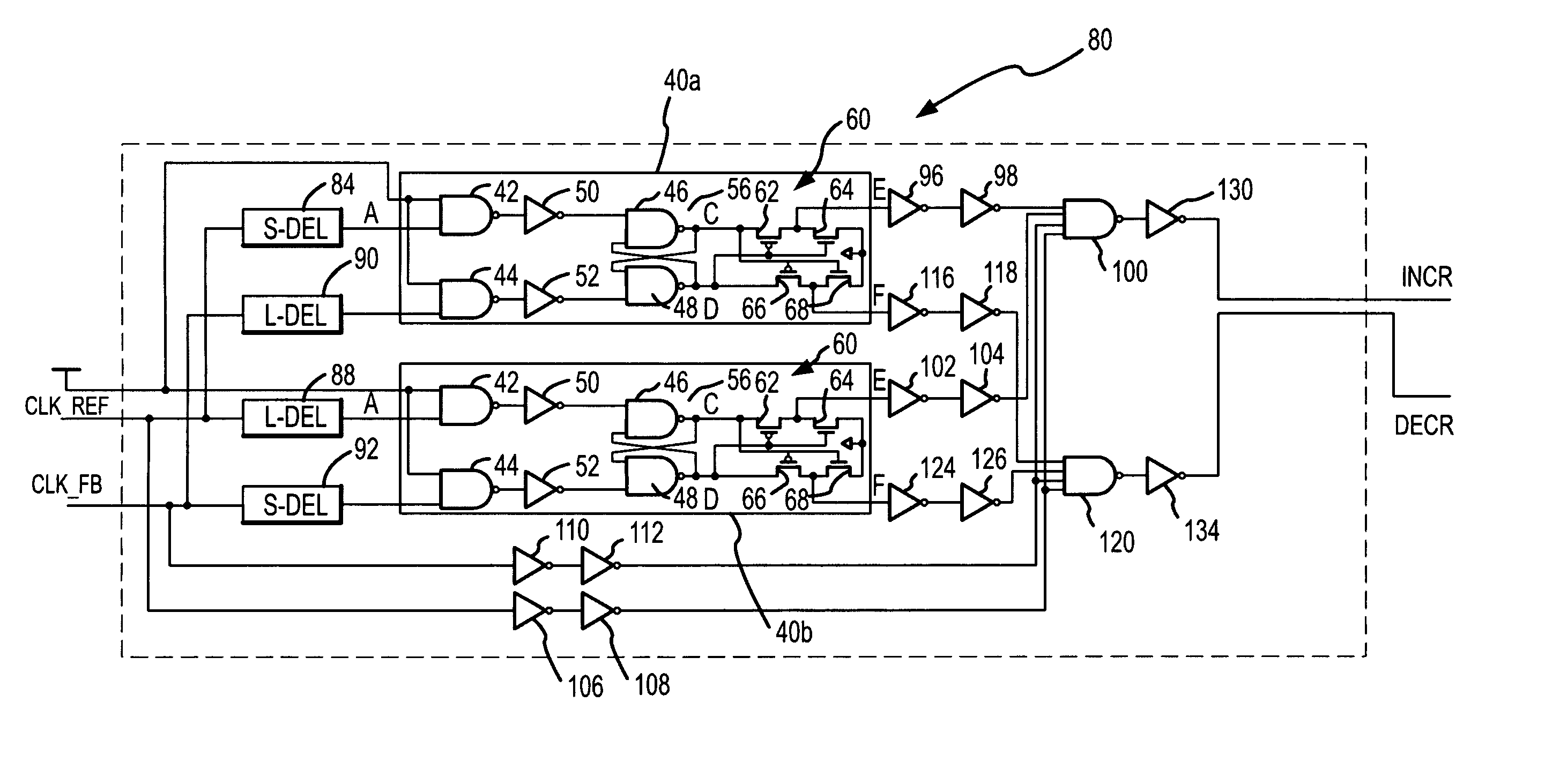

False-lock-free delay locked loop circuit and method

ActiveUS7034591B2Avoid the needReliably establishPulse automatic controlElectrical measurementsPhase detectorControl signal

A phase detector in a delay locked loop circuit operates to determine the status of propagation of a first pulse of a reference clock signal (CKref) through a delay line (21). A first control signal (DOWN) is produced a in response to represent a first time at which the first pulse has progressed entirely through the delay line (21) and a later second time at which a next second pulse of the reference clock signal (CKref) arrives at a first input of the phase detector (24A). The delay of the delay line (21) is reduced in response to the first control signal (DOWN). A second control signal (UP) is produced in response to the status to represent a third time at which the second pulse of the reference clock signal (CKref) arrives at the first input of the phase detector (24A) and a later fourth time at which the first pulse of the reference clock signal (CKref) has progressed to the end of the delay line (21) and is used to increase the delay of the delay line (21).

Owner:SAMSUNG ELECTRONICS CO LTD +1

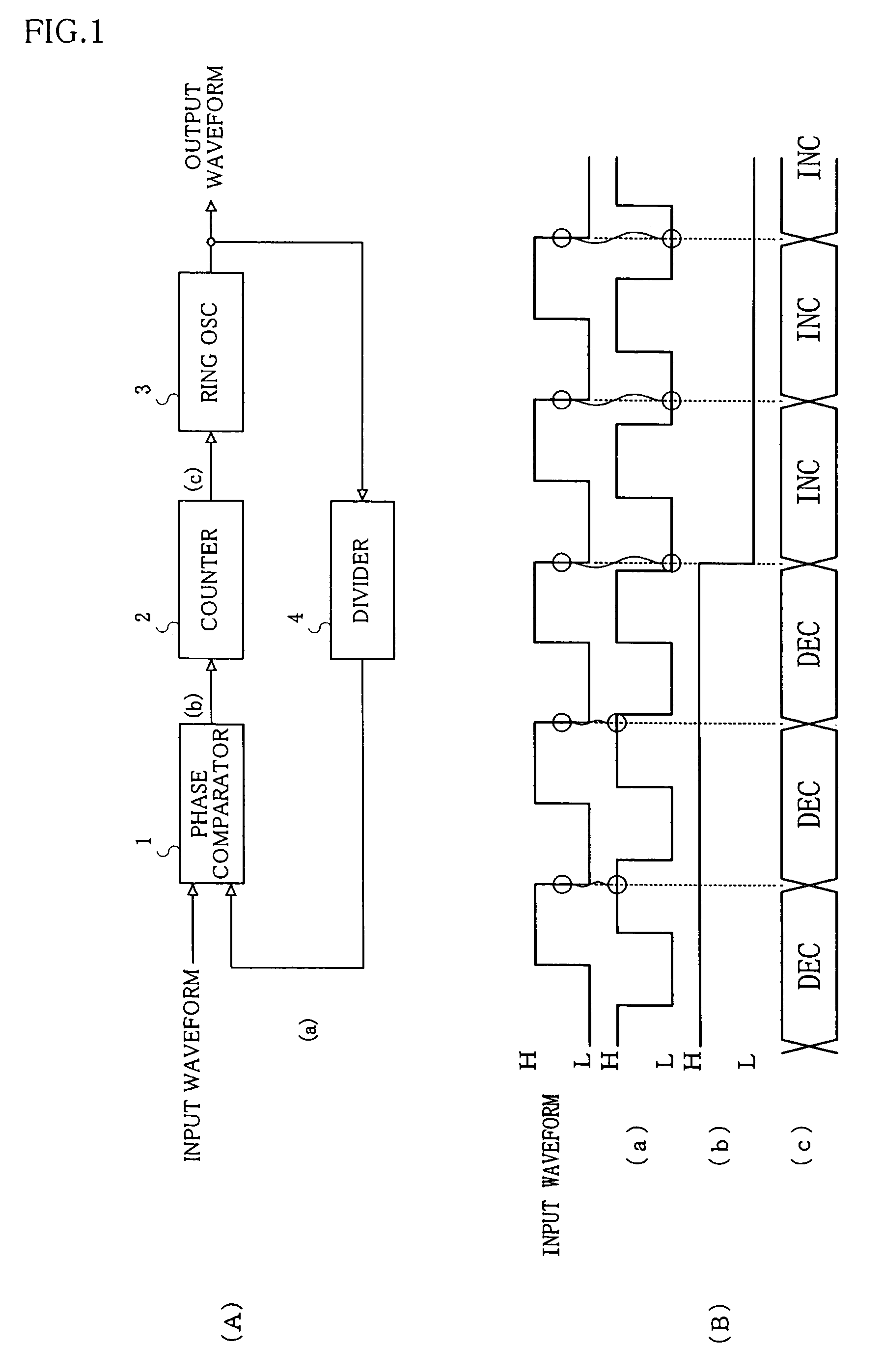

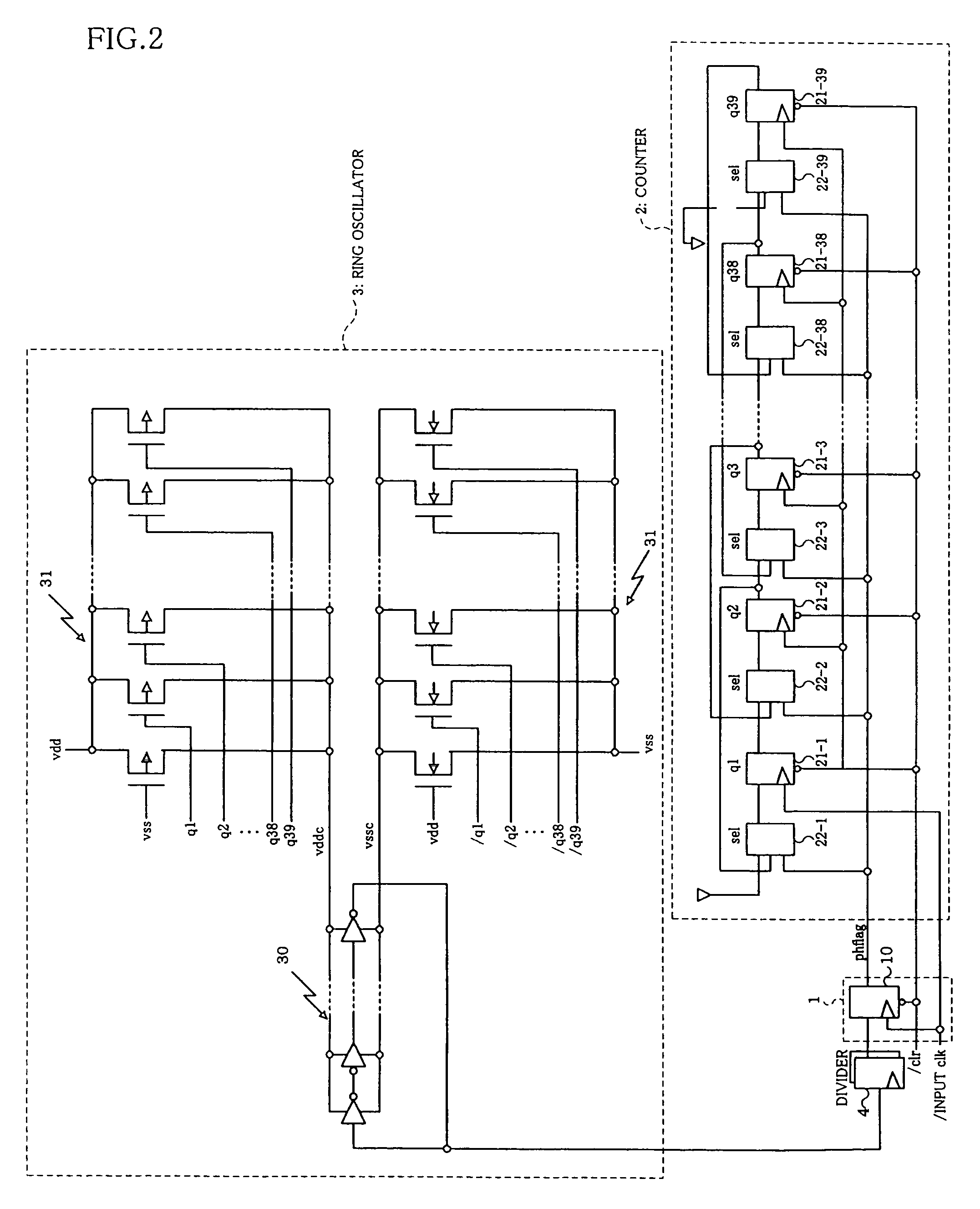

Phase-locked loop circuit, delay locked loop circuit, timing generator, semiconductor test instrument, and semiconductor integrated circuit

InactiveUS7492198B2Enhanced output signalReduce output signalPulse automatic controlVoltage-current phase anglePhase locked loop circuitControl signal

A PLL and DLL are designed such that the power consumption is reduced, the size is reduced, the band width of the locked loop is increased, and the reliability is improved. There are provided a phase comparator for measuring the value of a feedback signal in synchronism with an input signal and outputting a phase signal representing the lead or lag of the phase of the feedback signal, a counter for increasing by one the number of bits representing “H” in a control signal when the phase signal represents the lead of the phase or decreasing by one the number of bits representing “H” in the control signal when the phase signal represents the lag of the phase, and a ring oscillator for increasing the oscillation period when the number of bits representing “H” in the control signal increases or decreasing the oscillation period when the number of bits representing “H” decreases.

Owner:ADVANTEST CORP

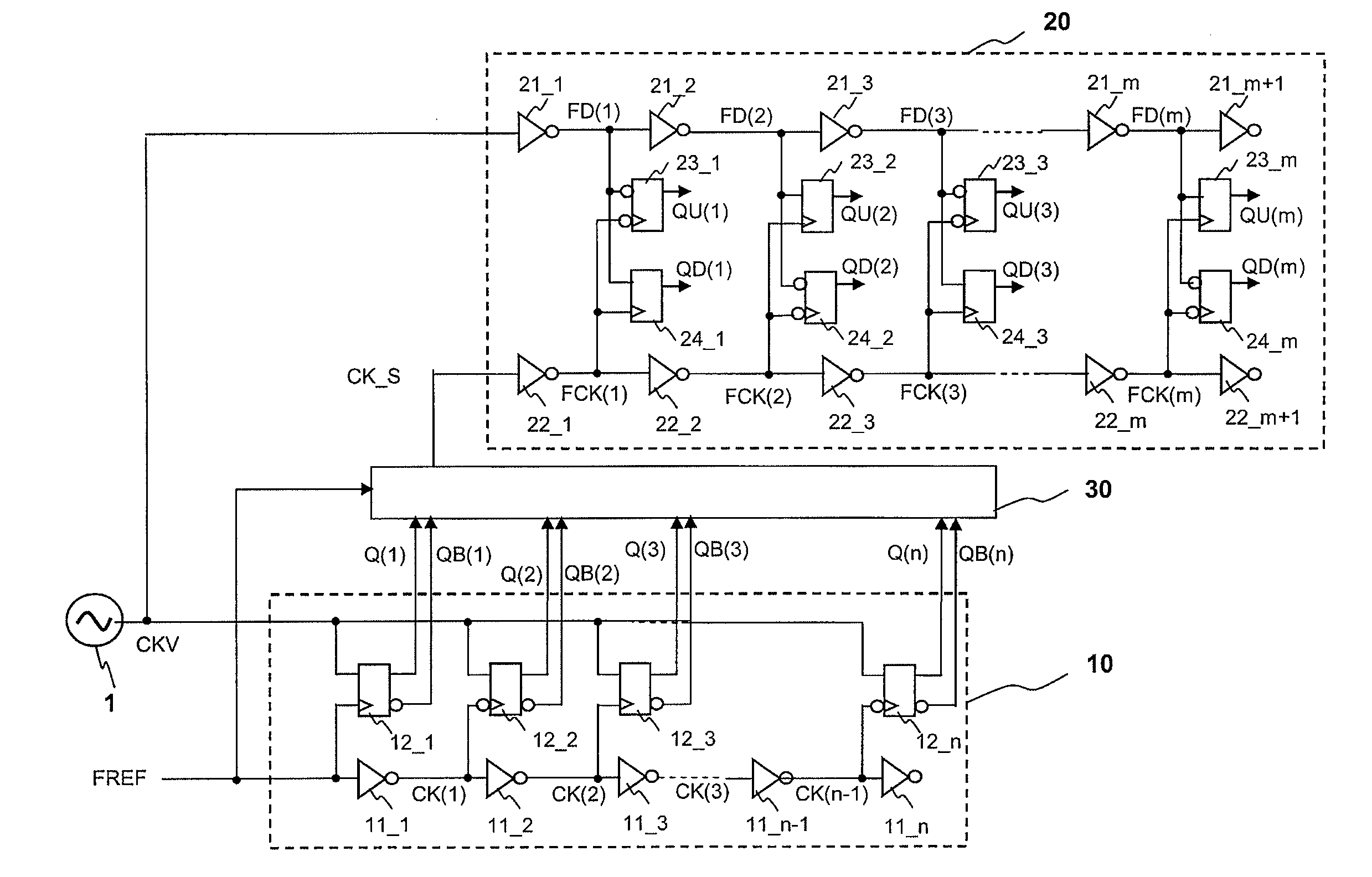

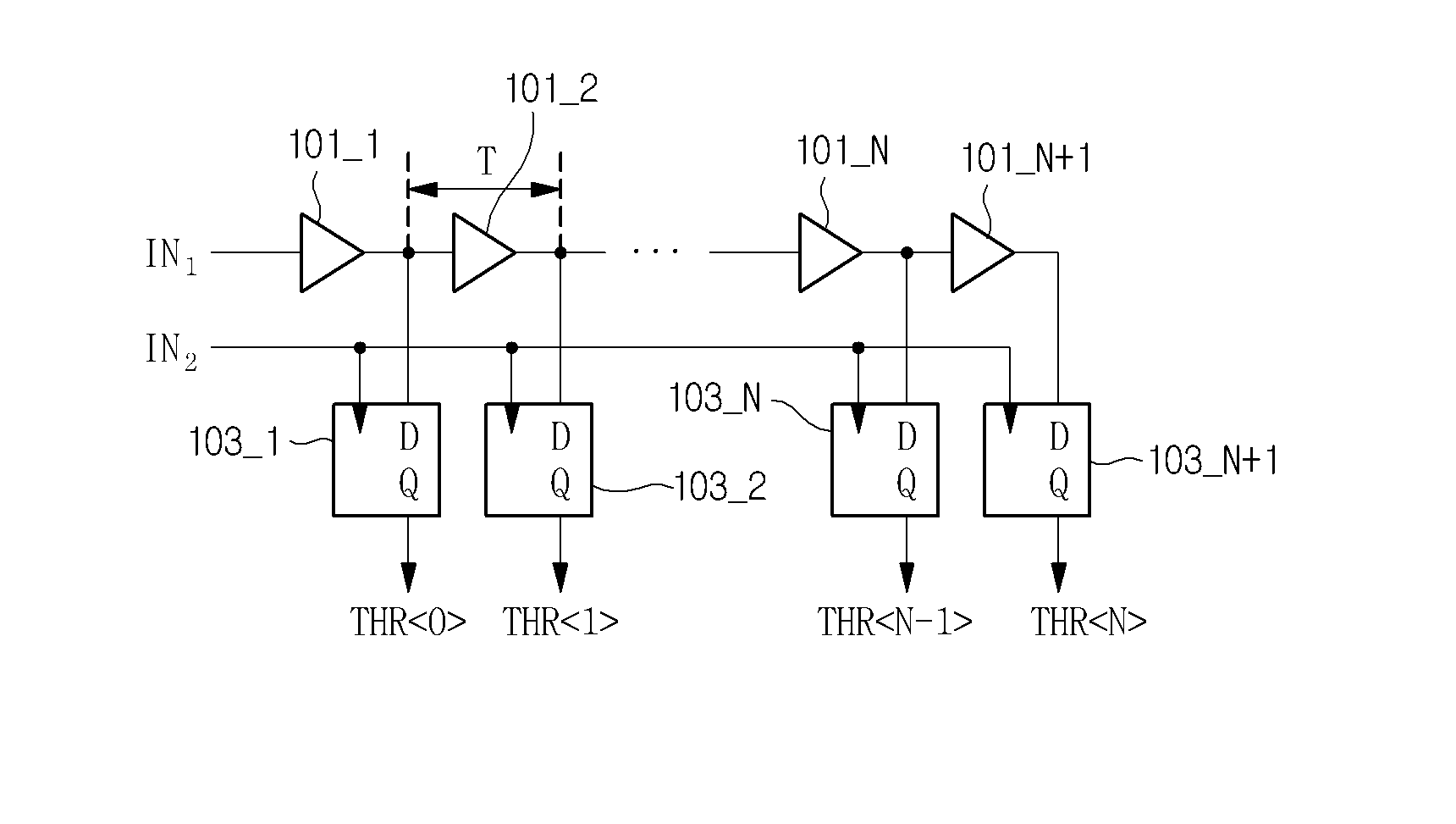

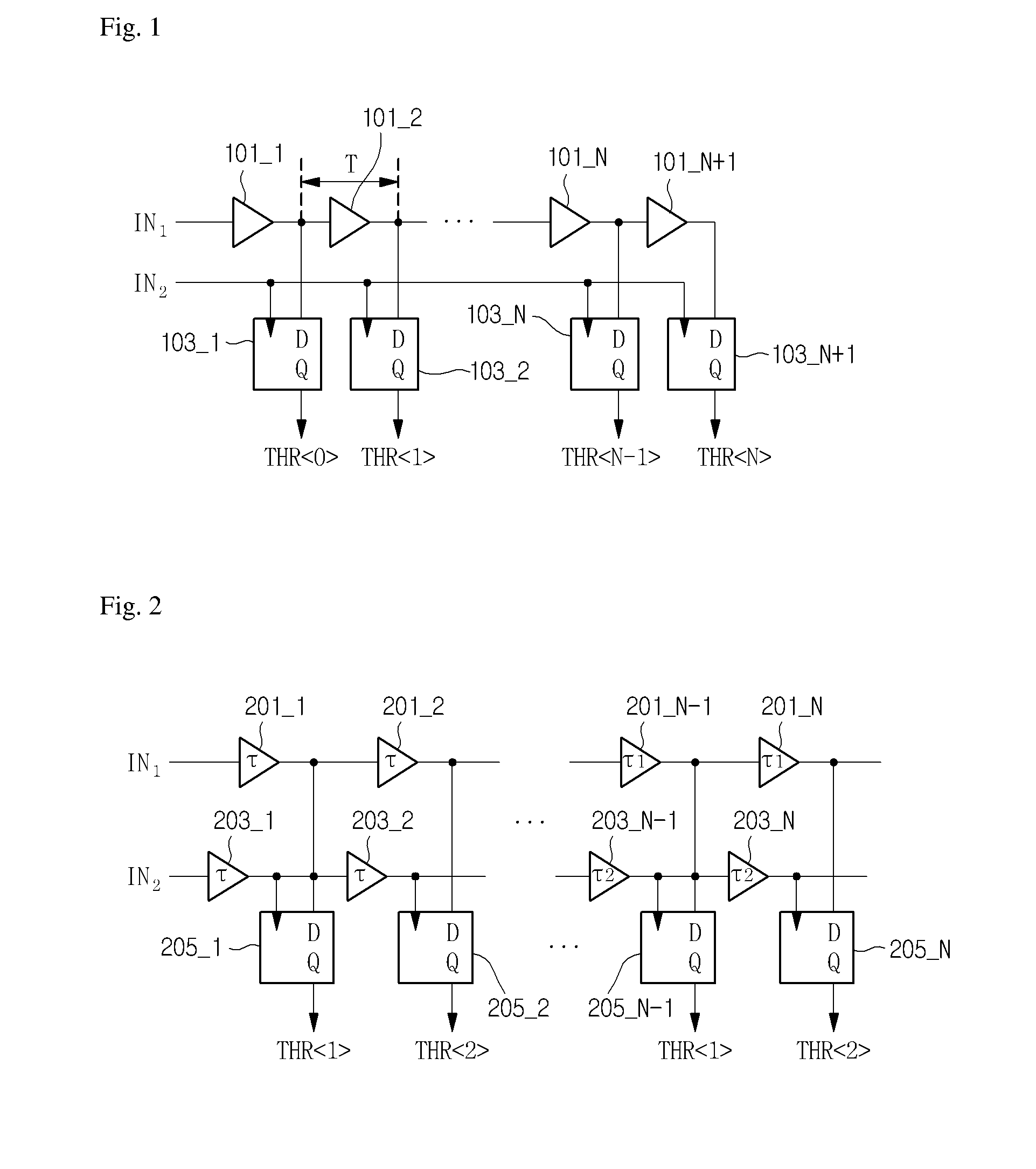

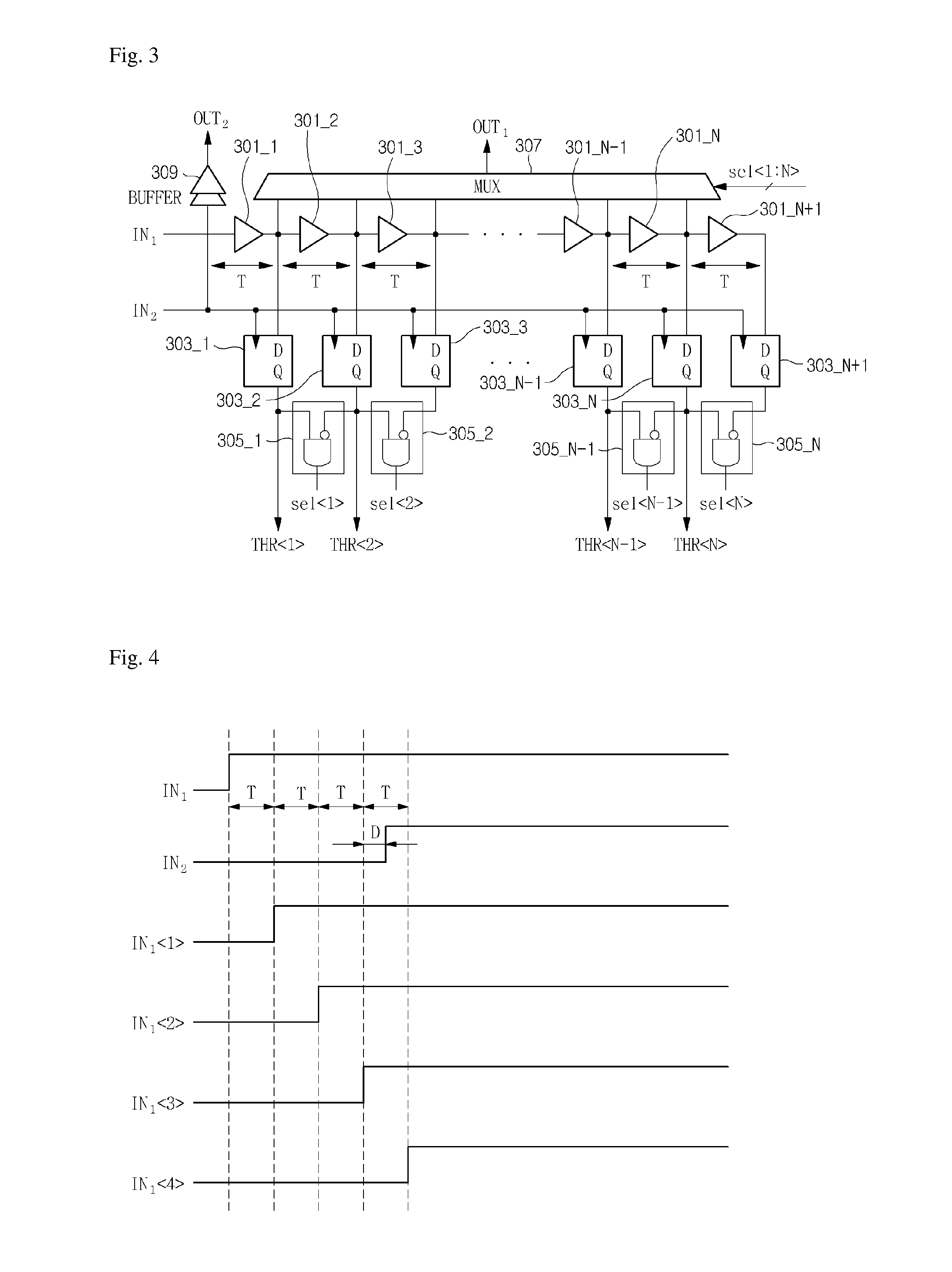

Phase-digital converter having hierarchical structure

InactiveUS20090028274A1Small sizeHigh resolutionAnalogue/digital conversionMultiple-port networksDigital down converterPhase difference

A time to digital converter having a hierarchical structure is provided. The time to digital converter includes: a plurality of delay stages for sequentially delaying a first signal for a specific delay time; a plurality of flip-flops for comparing delay signals of the first signal delayed by the delay stages with a second signal, and generating different outputs before and after a phase difference between the delay signals of the first signal and the second signal becomes smaller than a resolution of the phase detector; a selection signal generator for generating a selection signal for selecting a signal most similar to the second signal among the delay signals of the first signal from the outputs of the flip-flops; and a Multiplexer (MUX) for receiving the delay signals of the first signal and the selection signal, and outputting the signal most similar to the second signal among the delay signals of the first signal.

Owner:KOREA UNIV IND & ACADEMIC CALLABORATION FOUND

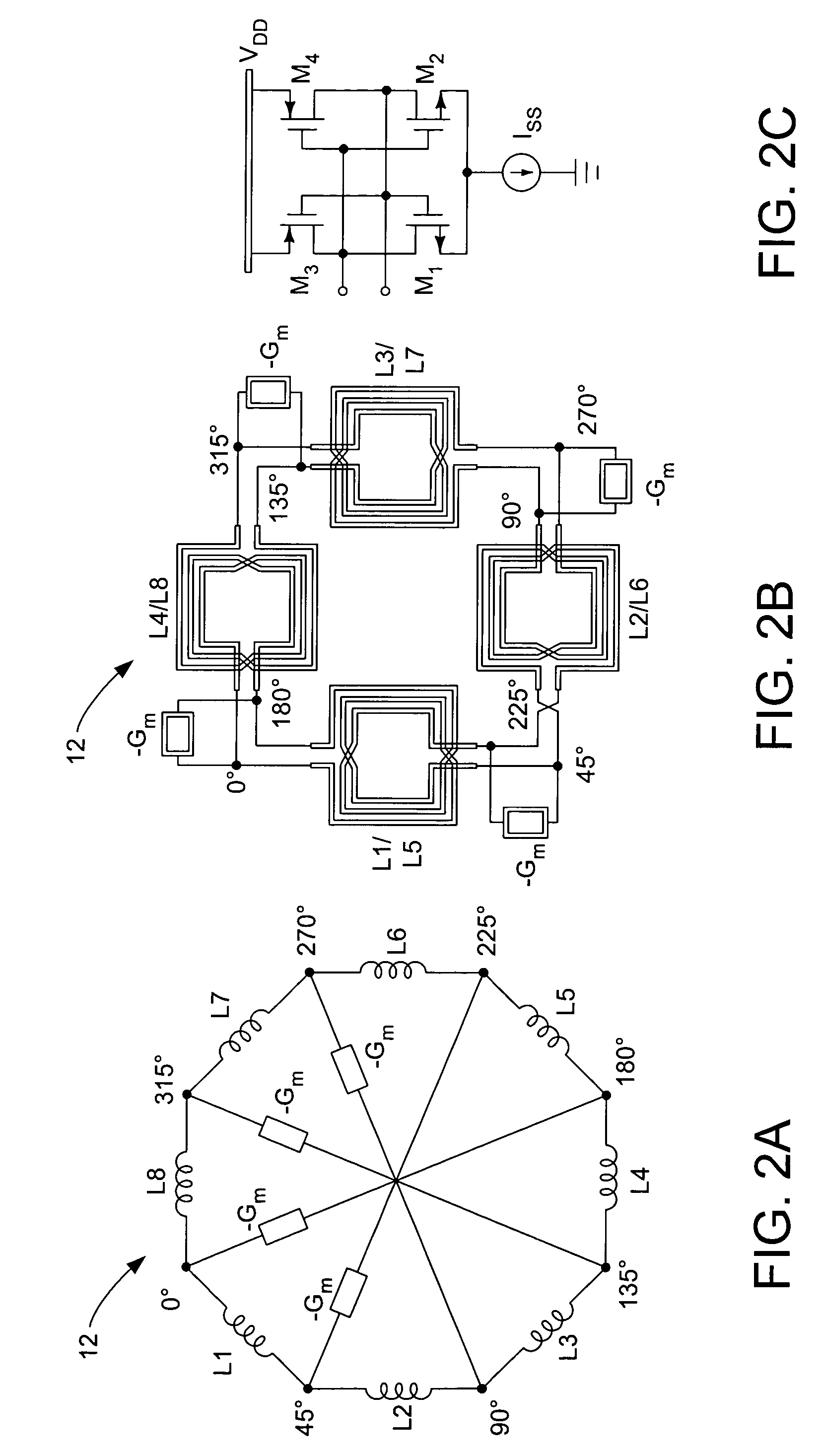

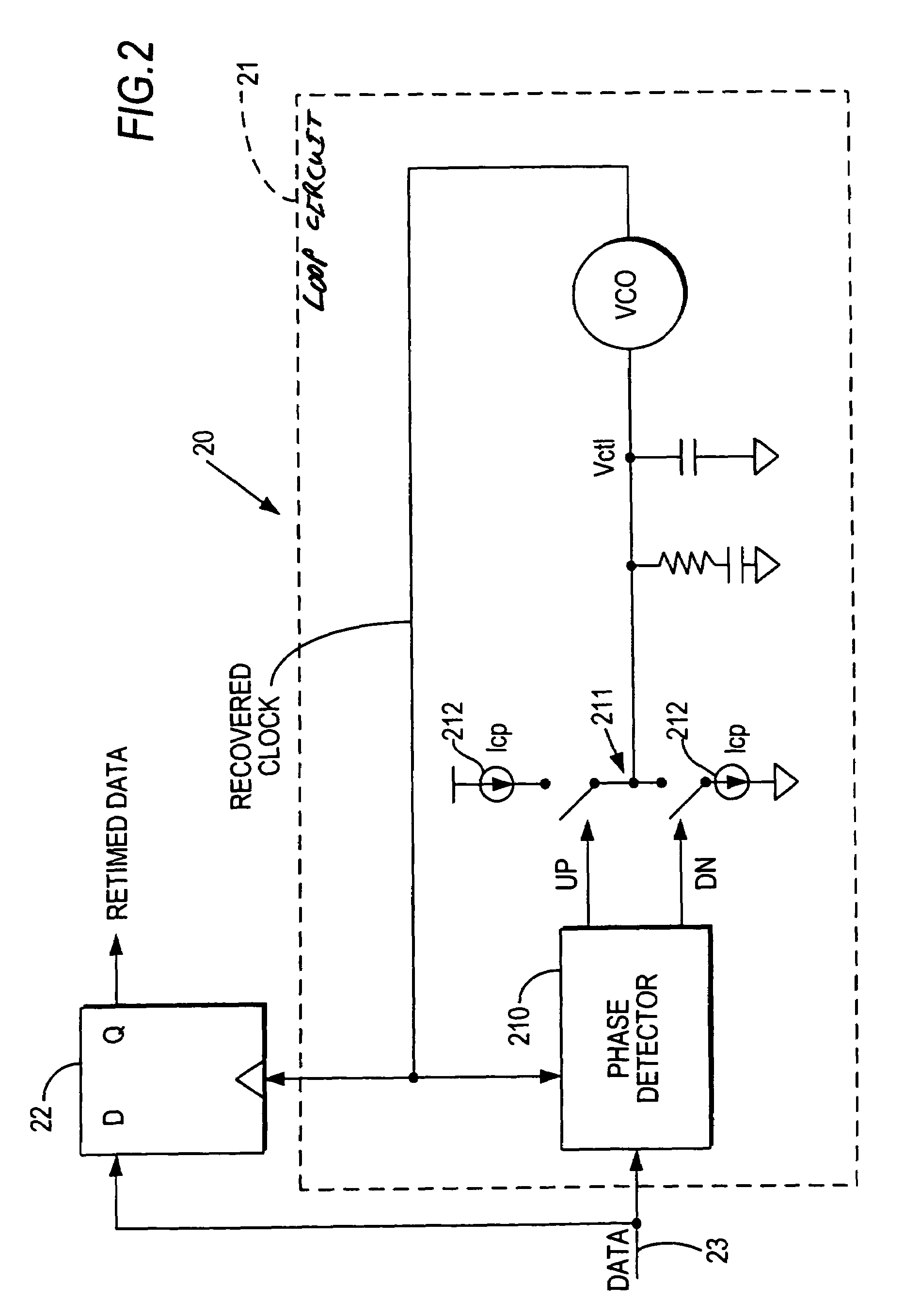

High-speed clock and data recovery circuit

A 40-Gb / s clock and data recovery (CDR) circuit incorporates a quarter-rate phase detector and a multi-phase voltage controlled oscillator to re-time and de-multiplex a 40-Gb / s input data signal into four 10-Gb / s output data signals. The circuit is fabricated in 0.18 μm CMOS technology.

Owner:RGT UNIV OF CALIFORNIA

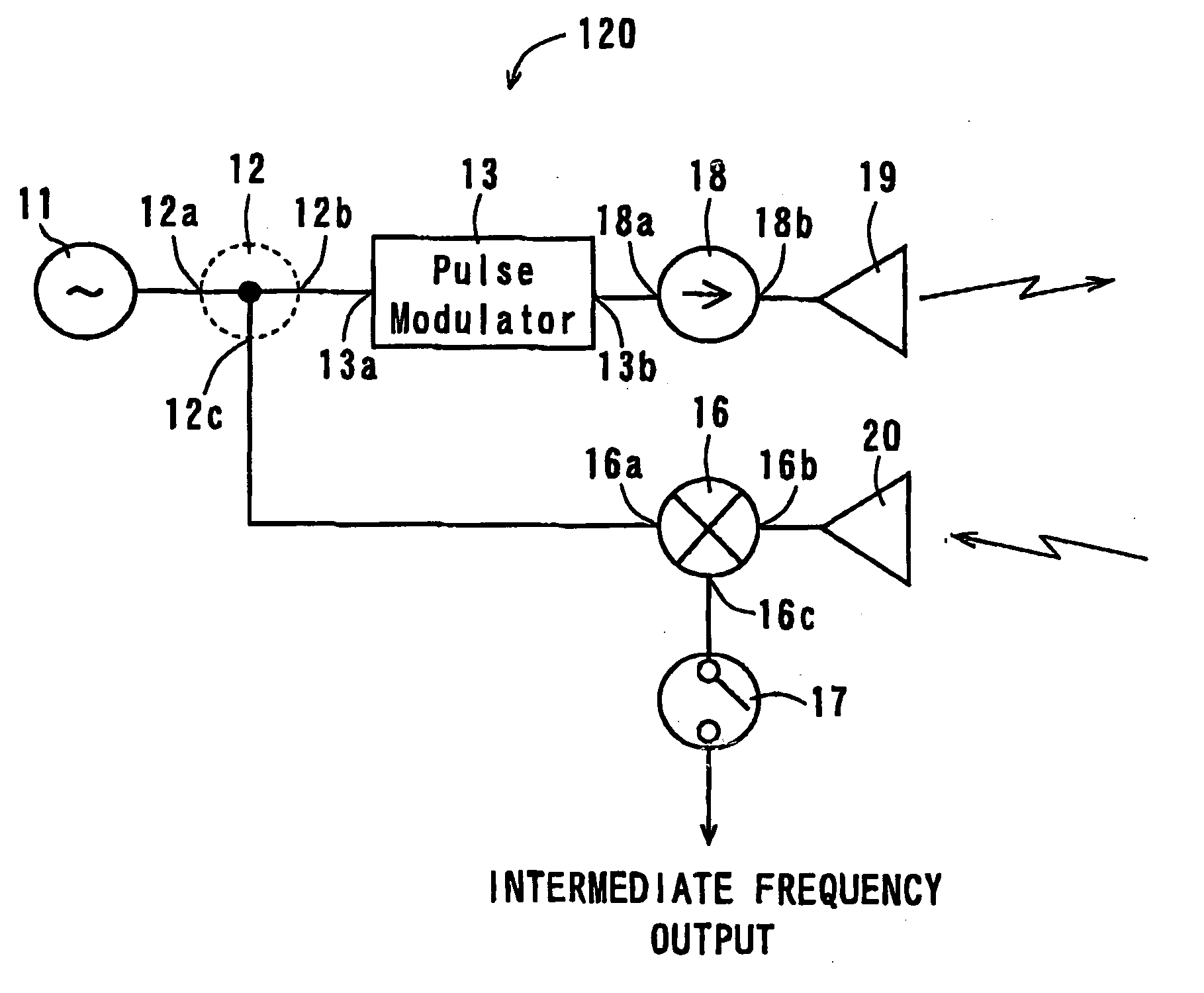

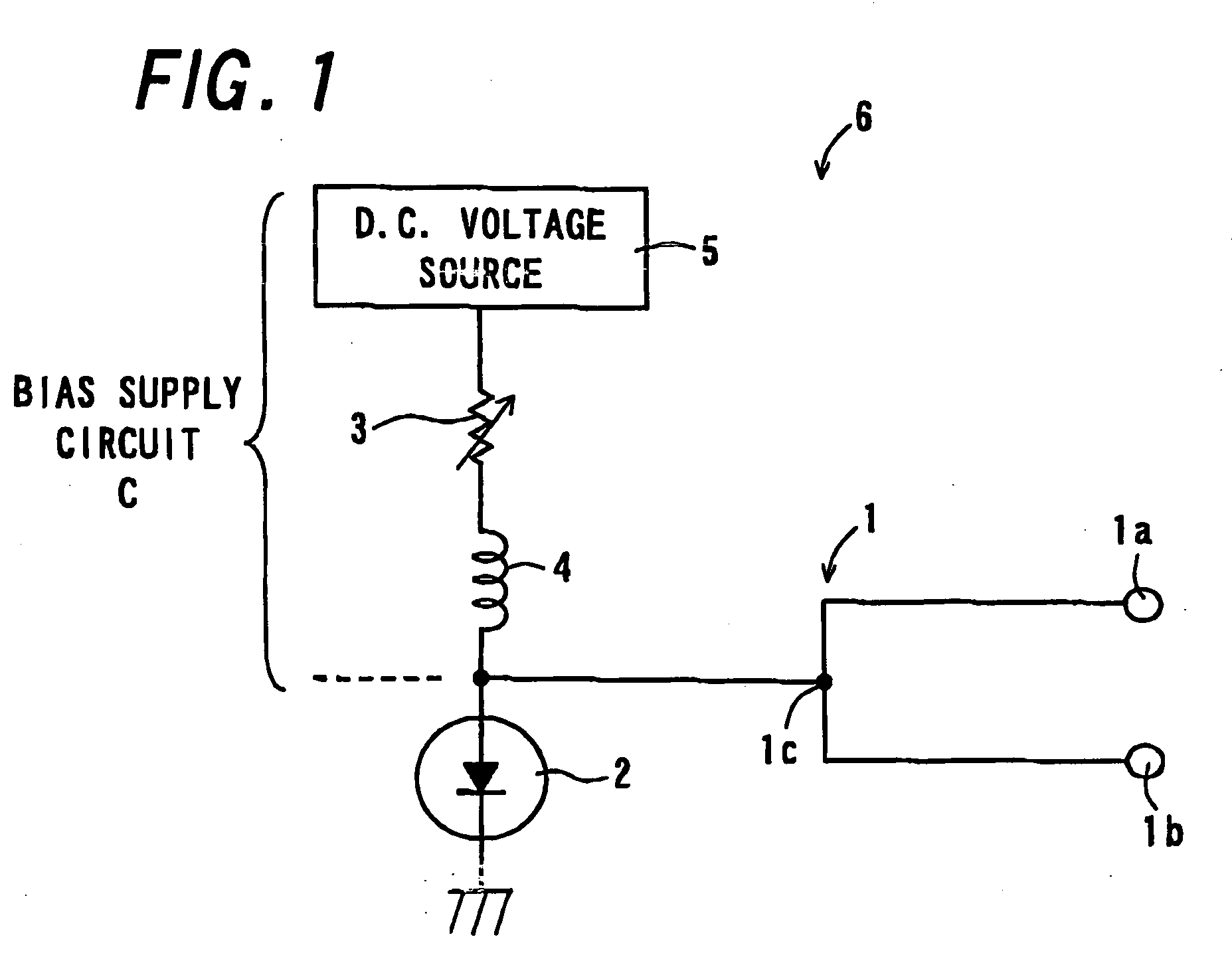

Mixer, High-Frequency transmitting/receiving apparatus having the same, radarapparatus having the high-frequency transmitting/receiving apparatus, and vehicle equipped with radar apparatus

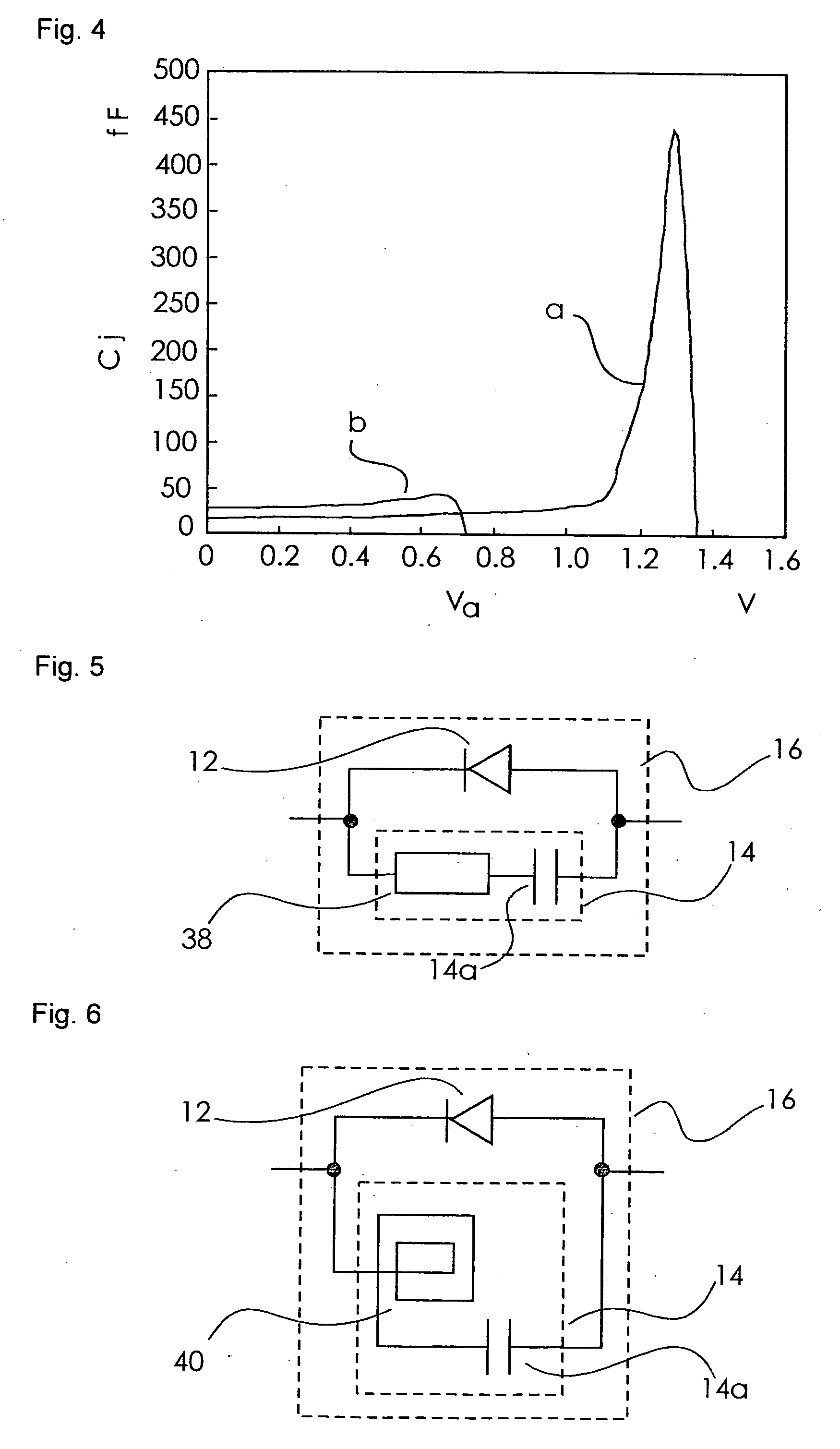

InactiveUS20060214842A1Easy to controlRadio wave reradiation/reflectionElectromagnetic wave demodulationSchottky barrierRadar

A mixer capable of keeping mixing characteristics tuned satisfactorily is provided. A coupler includes two input ends, and one or two output ends. At the output end is disposed a Schottky-barrier diode acting as a high-frequency detection element. Connected to the Schottky-barrier diode is a bias supply circuit having a trimmable chip resistor acting as a pre-set variable resistor, for controlling a bias current which passes through the Schottky-barrier diode. By adjusting the resistance of the trimmable chip resistor, it is possible to control a bias current passing through the Schottky-barrier diode, and thereby keep mixing characteristics tuned satisfactorily.

Owner:KYOCERA CORP

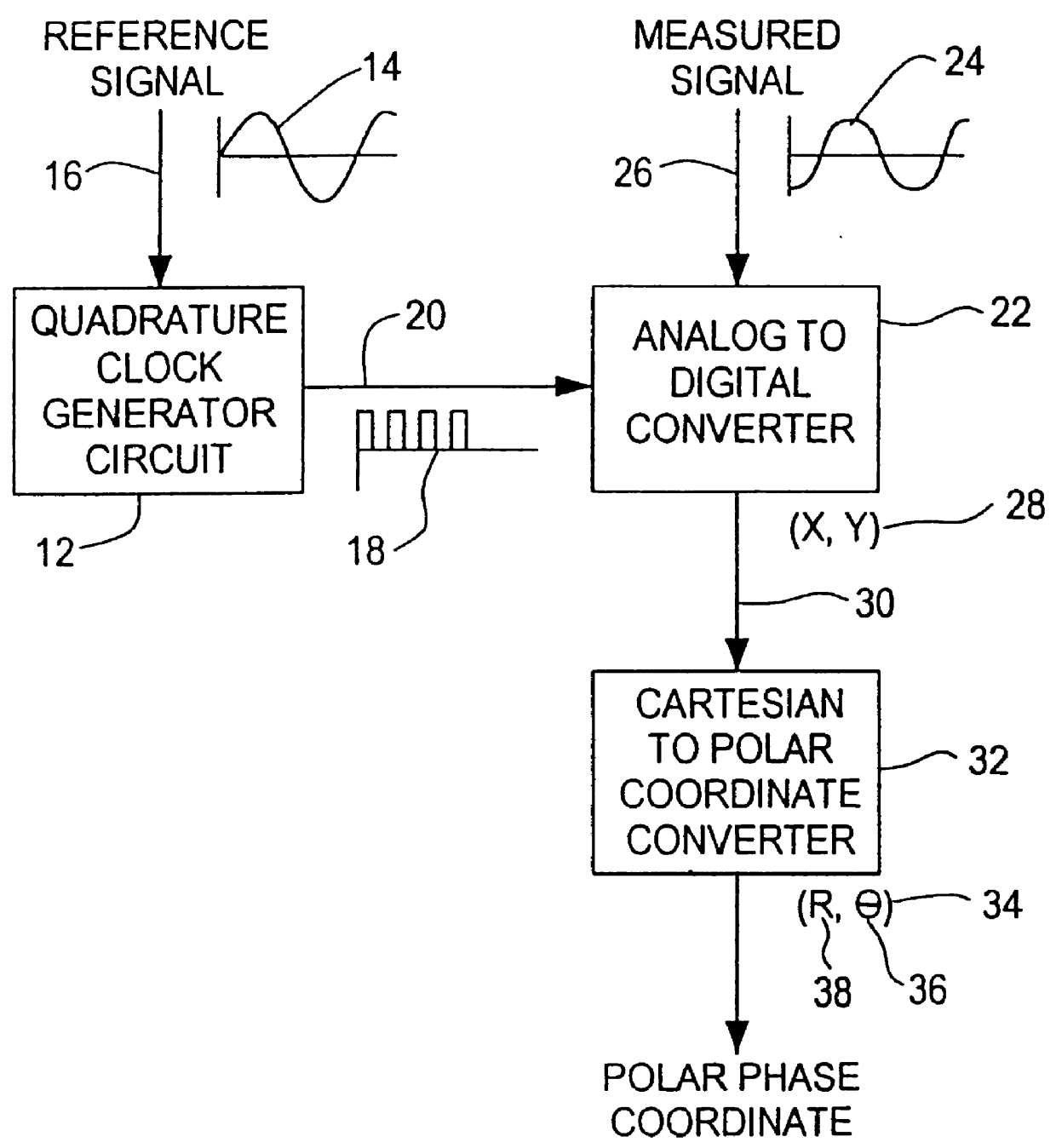

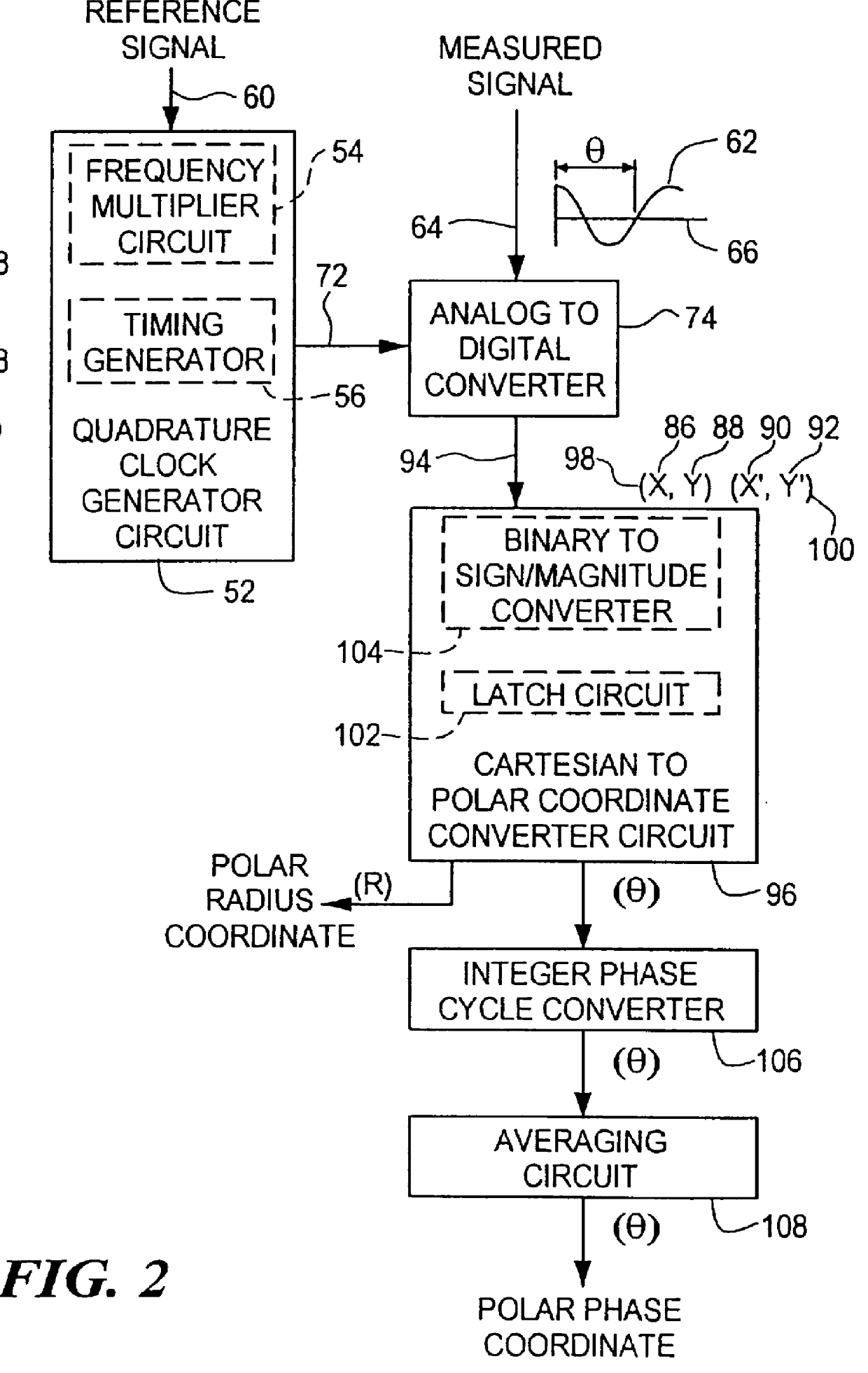

Digital phase measuring system and method

InactiveUS6049297ALow costFast processingElectric signal transmission systemsVoltage-current phase anglePhase differencePhysics

A digital phase measuring system and method for measuring the phase difference between two signals including generating quadrature clock signals for a first reference signal, converting a second measured signal from analog to digital form by sampling the second measured signal using the quadrature clock signals to produce quadrature cartesian samples of the measured signal, and converting the quadrature cartesian samples to polar coordinates to define the polar phase coordinate representative of the phase difference between the two signals.

Owner:VISIDYNE

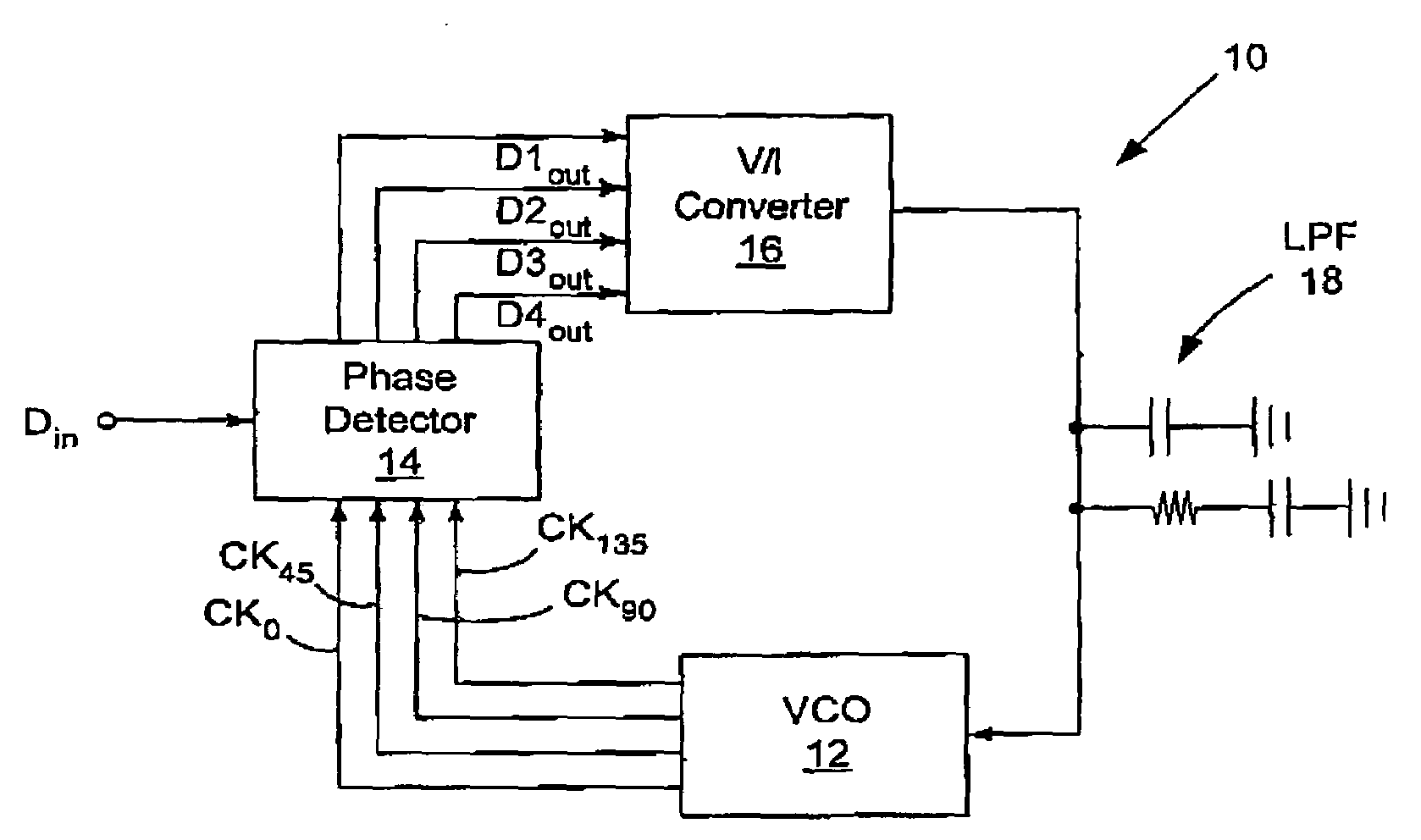

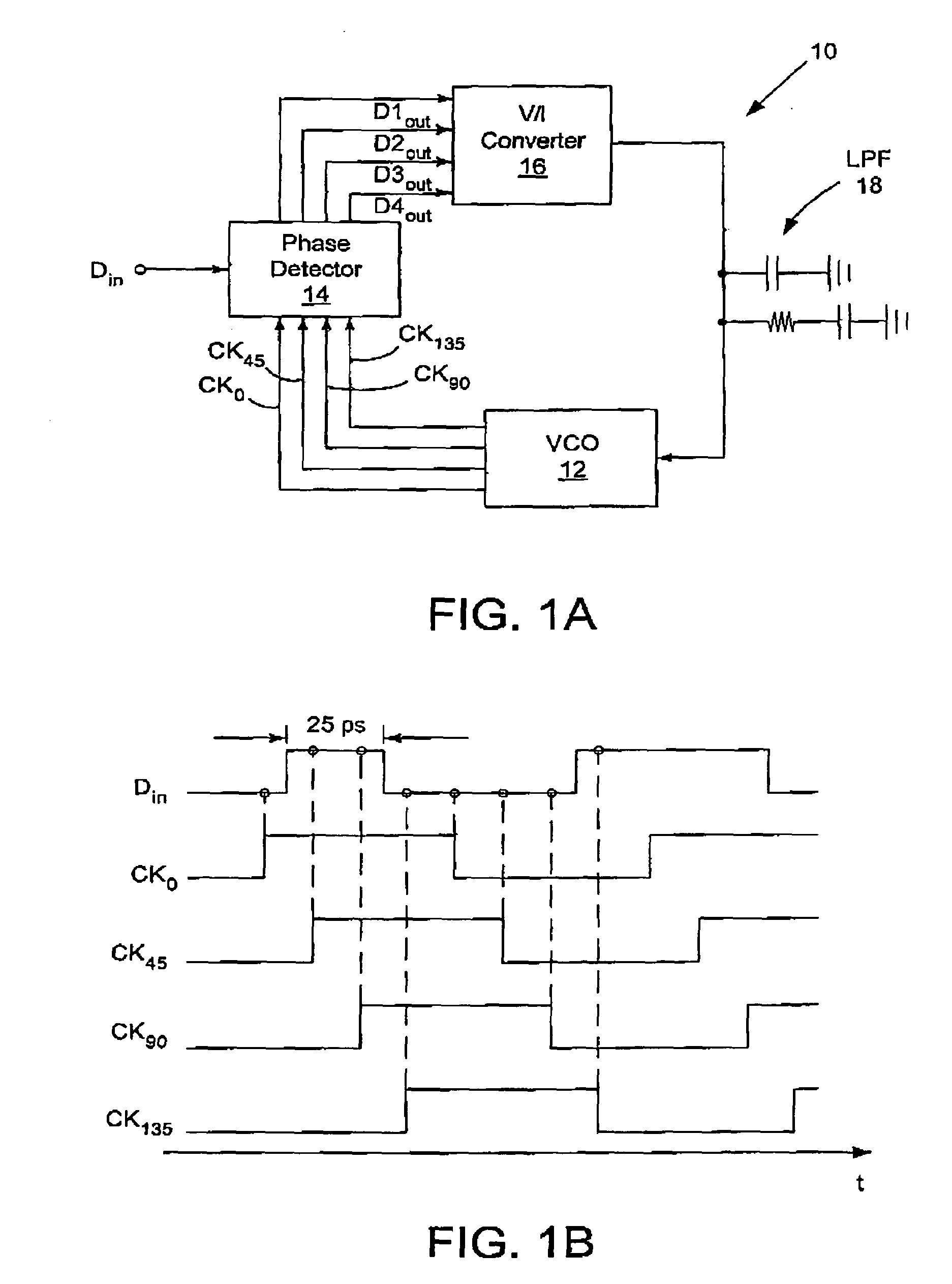

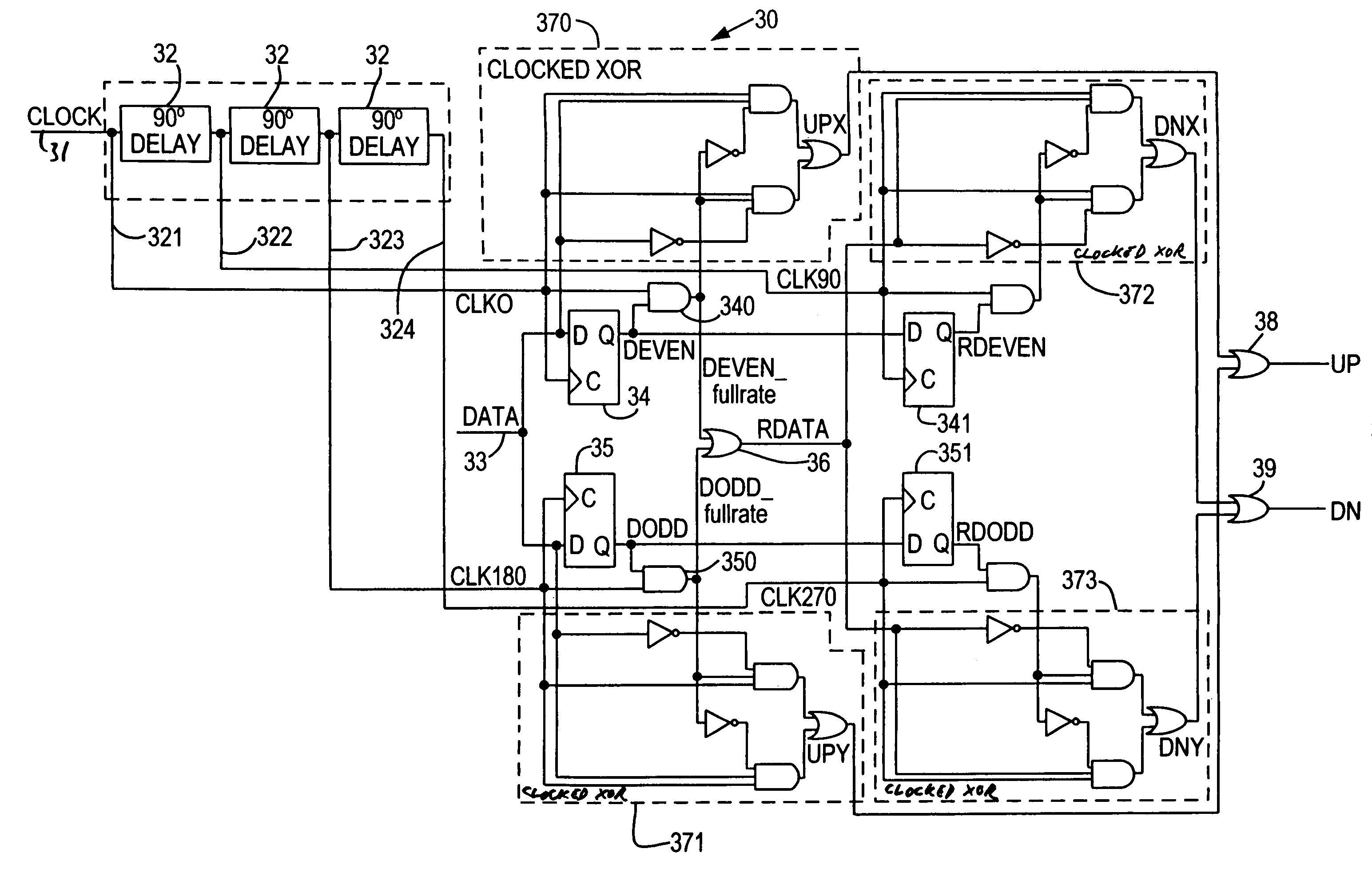

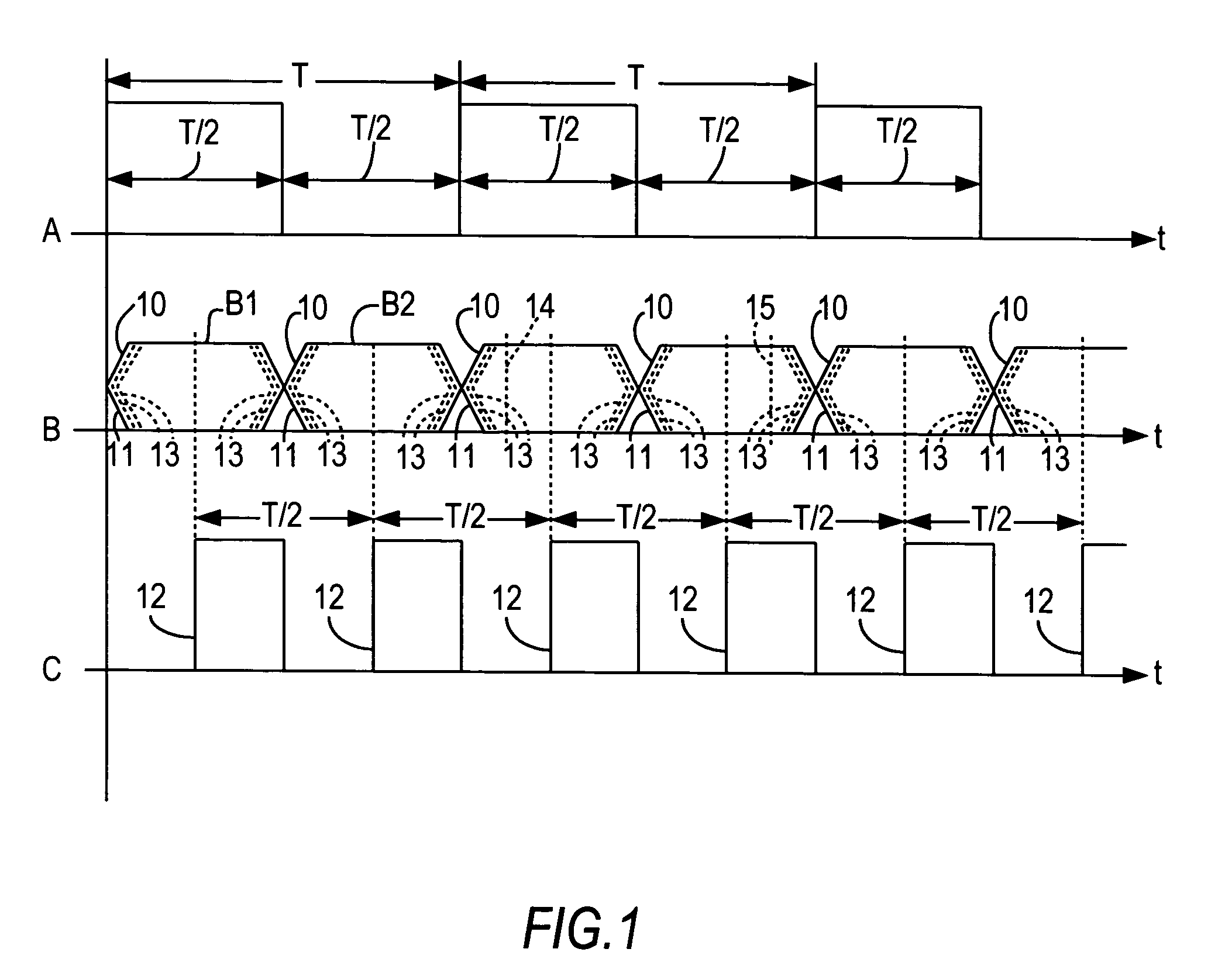

Half-rate linear quardrature phase detector for clock recovery

InactiveUS6970020B1Minimize jitterMinimizing control signalVoltage-current phase angleSingle output arrangementsPhase detectorControl signal

A half-rate linear phase detector is particularly well-suited to clock data recovery in a serial data interface. The phase detector uses a quadrature clock to process different portions of the incoming data with different phases of the clock. The resulting component signals can be combined to provide the expected UP and DOWN phase detector output control signals. The phase detector output signals are balanced and of uniform width, minimizing oscillator control signal ripple in the clock data recovery circuit, while the linearity of the phase detector makes its output predictable.

Owner:ALTERA CORP

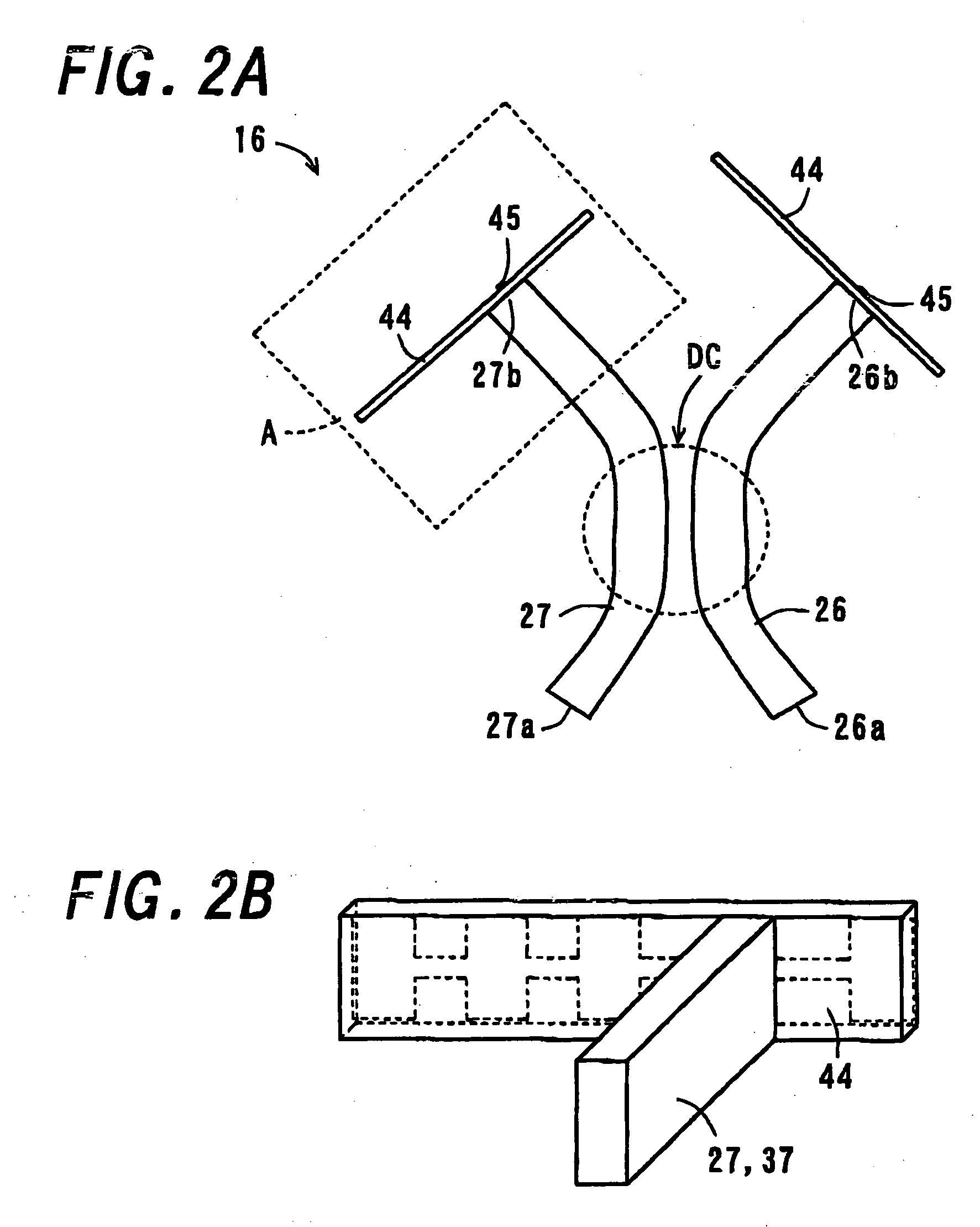

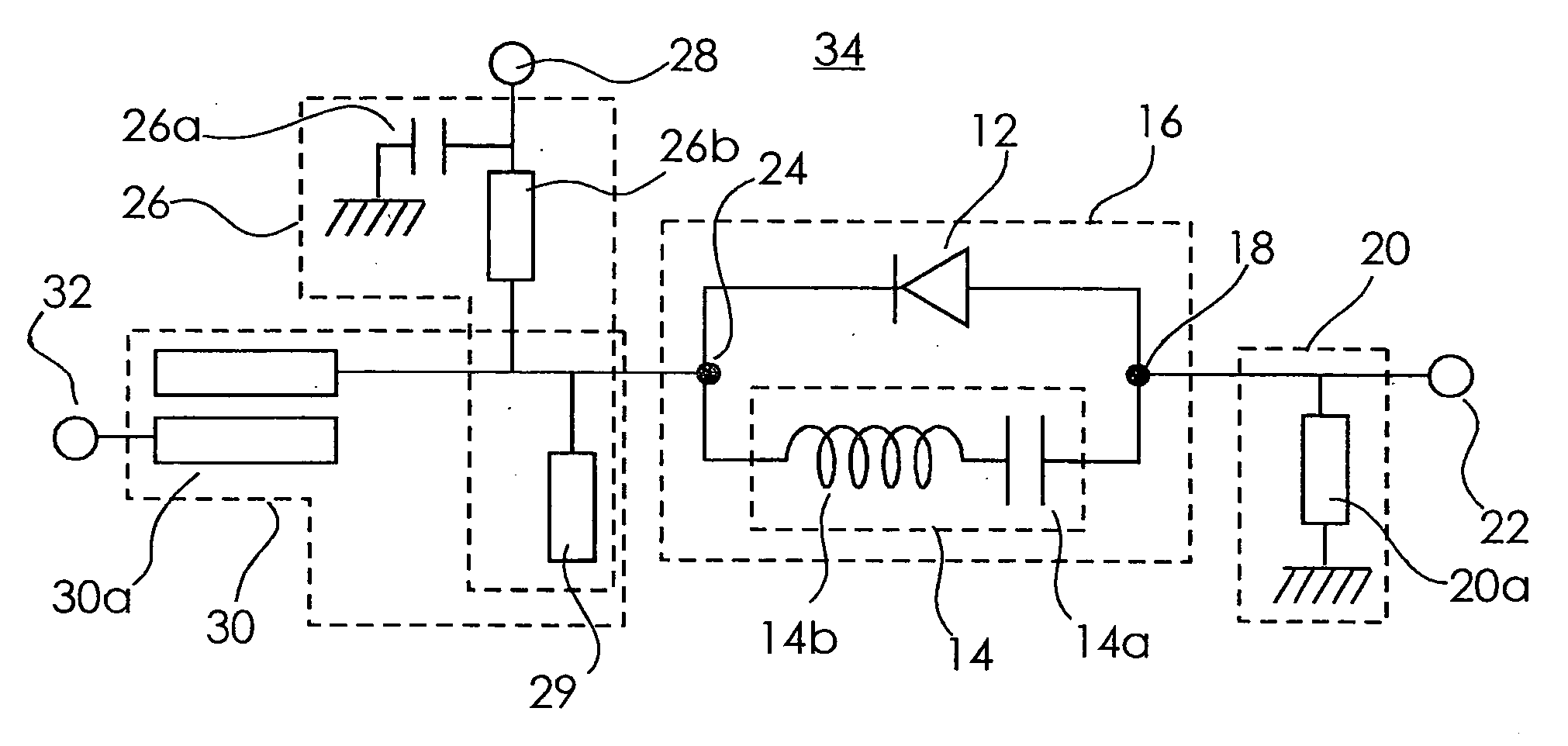

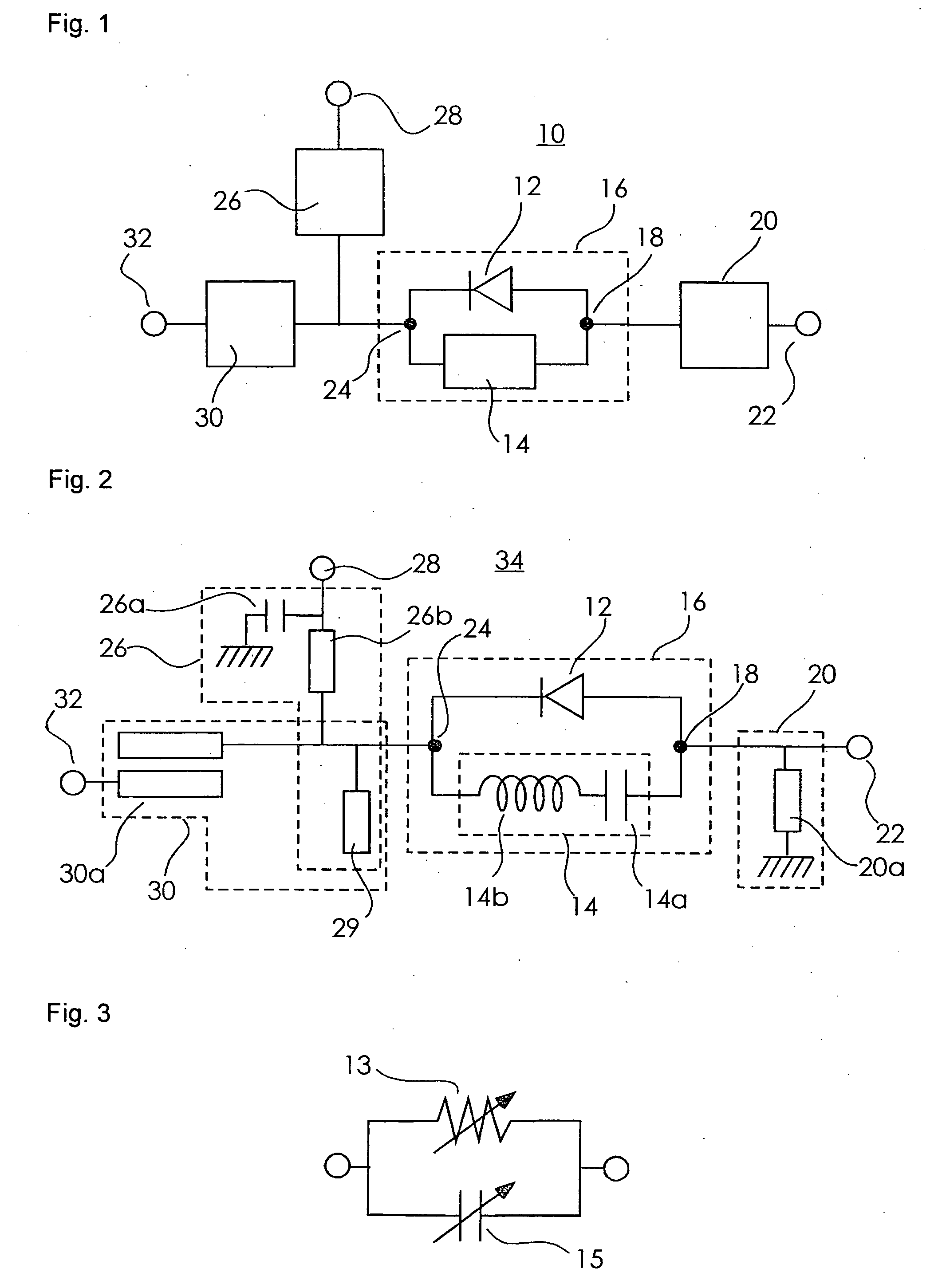

Diode mixer

ActiveUS20060040637A1Improve conversion efficiencyImprove noise characteristicsModulation transference by diodesTransmissionEngineeringInductor

A diode mixer comprises a mixer diode section which has a first circuit including an inductor and a capacitor connected in series and a diode connected in parallel with the first circuit and which includes a first connecting portion to which one end of the first circuit and the anode of the diode are connected, and a second connecting portion to which the other end of the first inductor circuit and the cathode of the diode are connected; an LO signal port connected to the first connecting portion via a first branching circuit and receiving an LO signal; an IF signal port connected to the mixer diode section via a second branching circuit; and an RF signal port connected to the mixer diode section through a third branching circuit. The inductor and the capacitive component of the diode constitute a resonant circuit.

Owner:ARIGNA TECH LTD

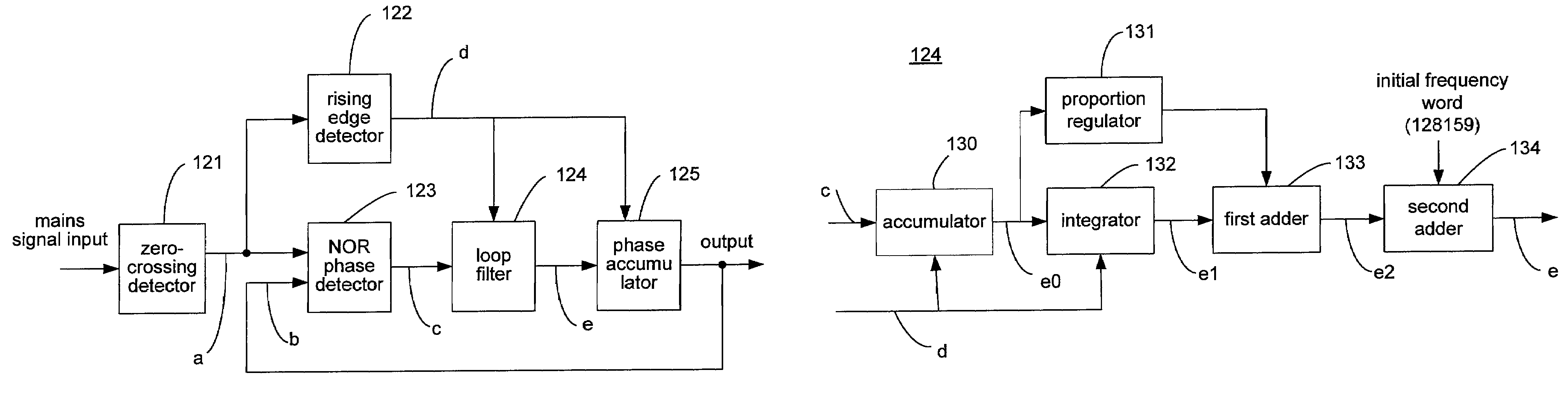

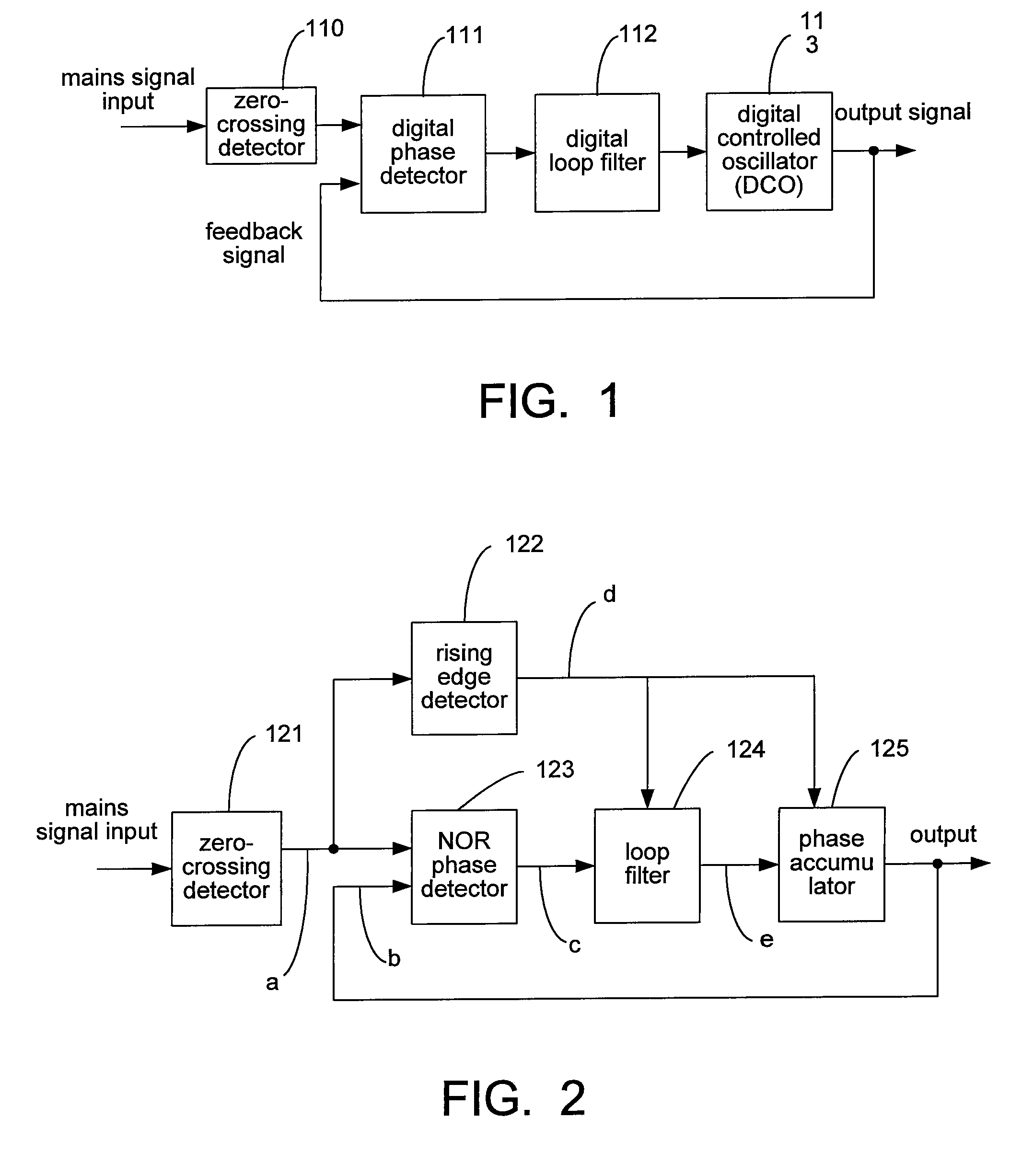

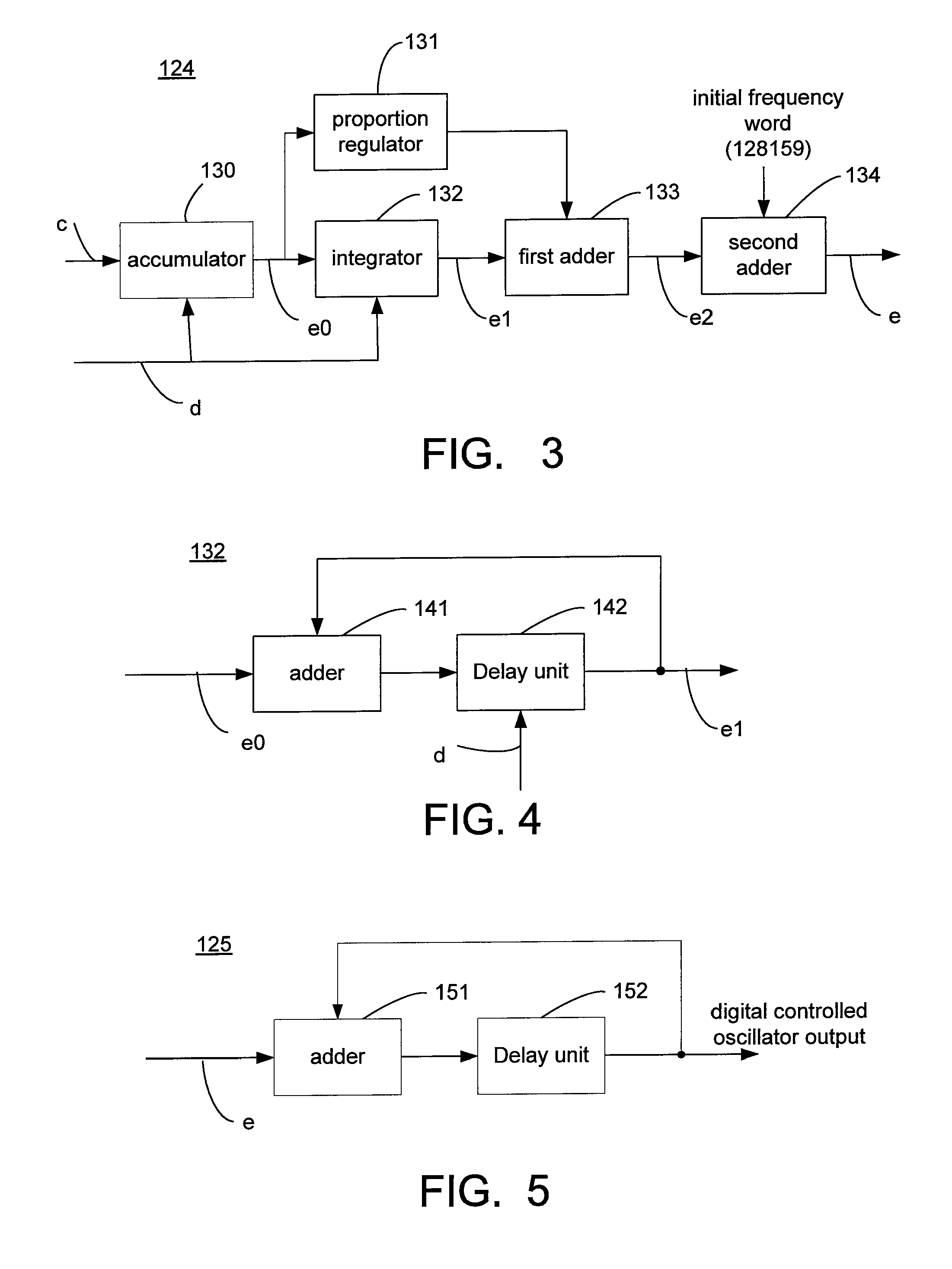

Mains phase detection apparatus

InactiveUS7646225B2Easy to detectOvercome deficienciesPulse automatic controlElectrical measurementsElectricityLoop filter

The present invention relates to an apparatus for accurately detecting a mains phase. The apparatus is constructed with a zero-crossing detector, a digital phase detector, a digital loop filter, and a digital controlled oscillator (DCO) of a direct digital synthesized (DDS) manner. The present apparatus employs an all-digital loop architecture and a high sampling clock to recover a signal with a phase orthogonal with the mains signal and a frequency the same as the mains signal. And jitters in the recovered signal are less than 10 us. The present apparatus is capable of implementing signal tracking of a zero frequency error and a zero phase in a wide range, and can provide a detection result of excellent performance for the power line carrier communication, mains frequency detection, etc.

Owner:MIARTECH

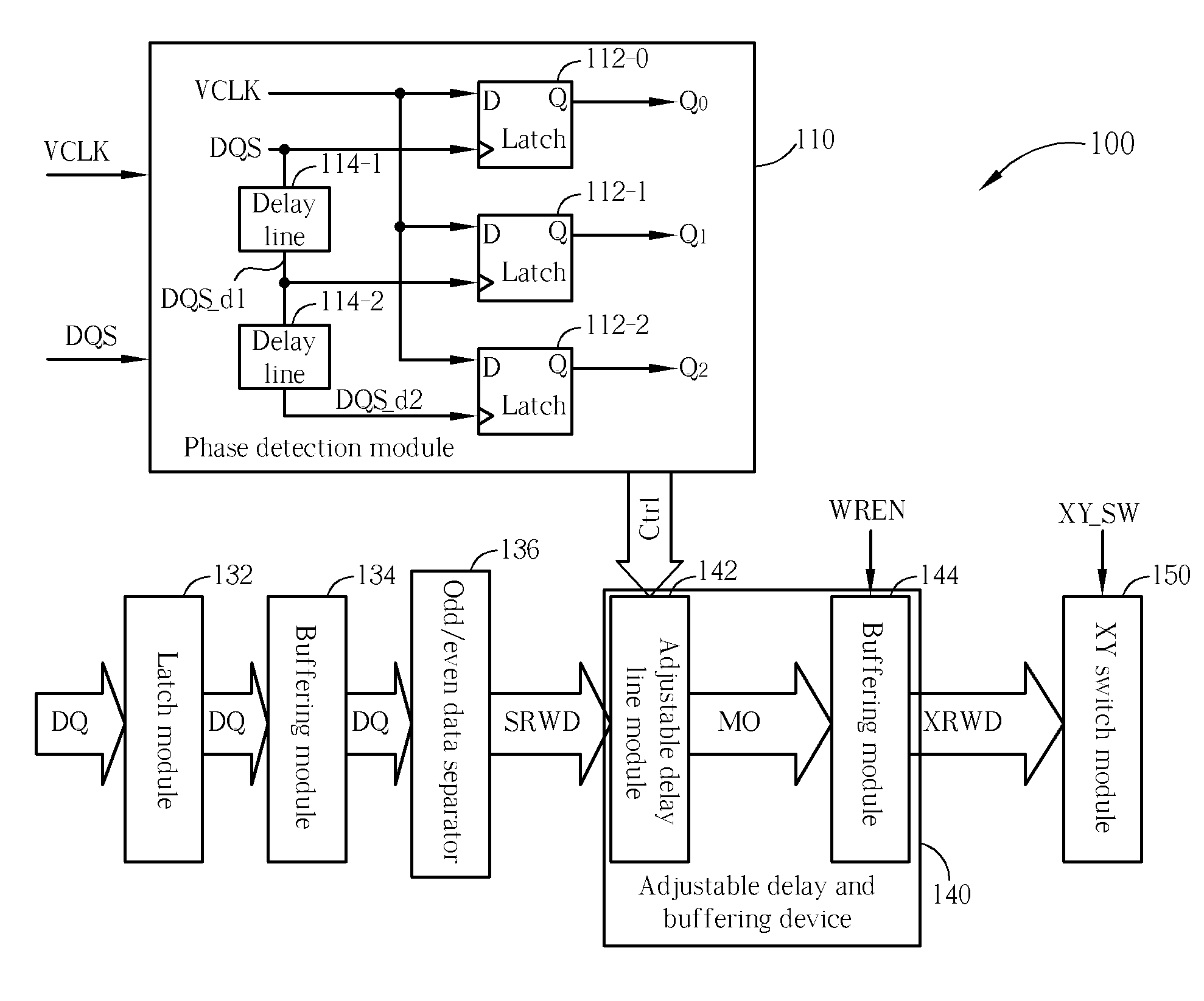

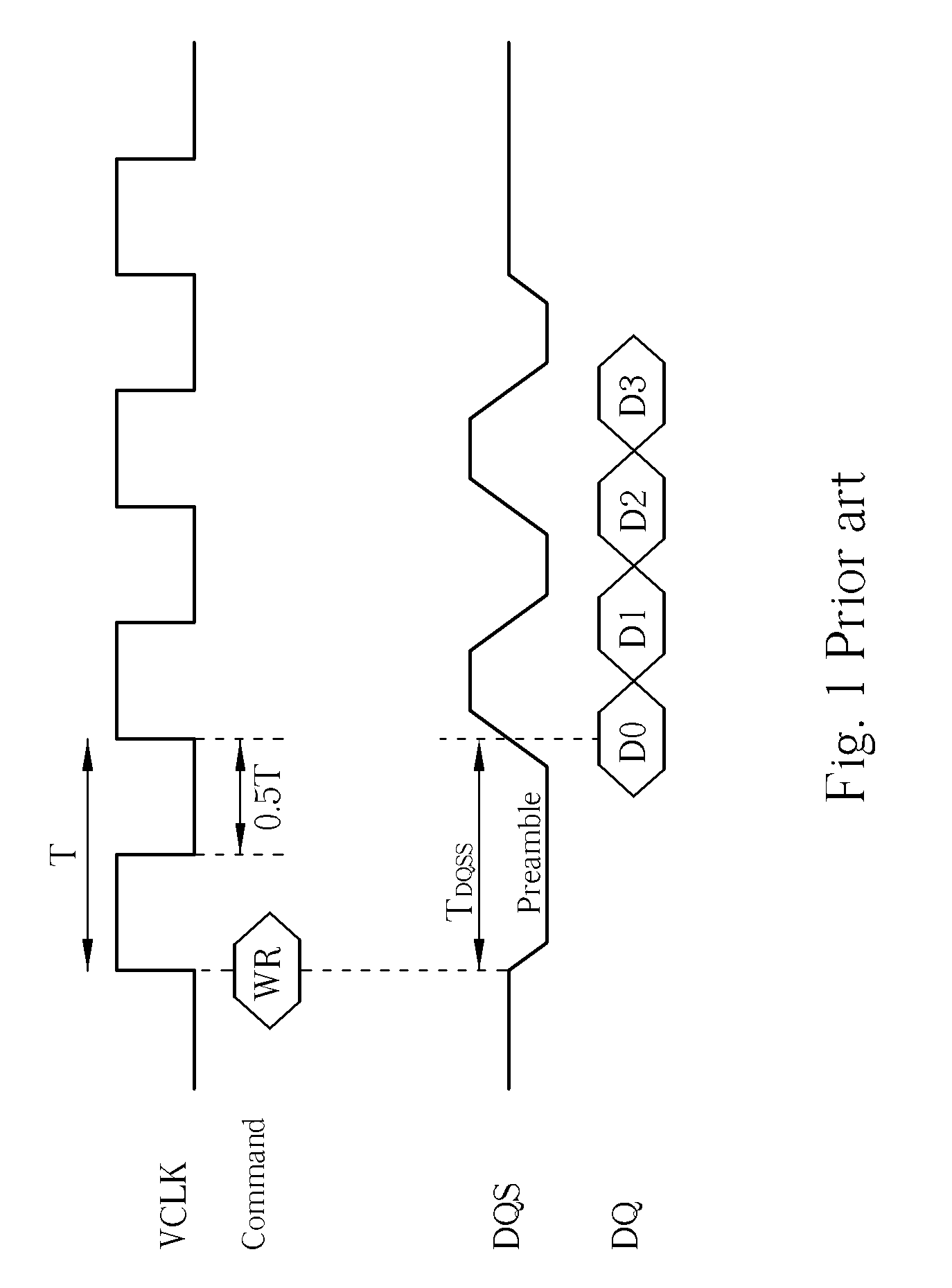

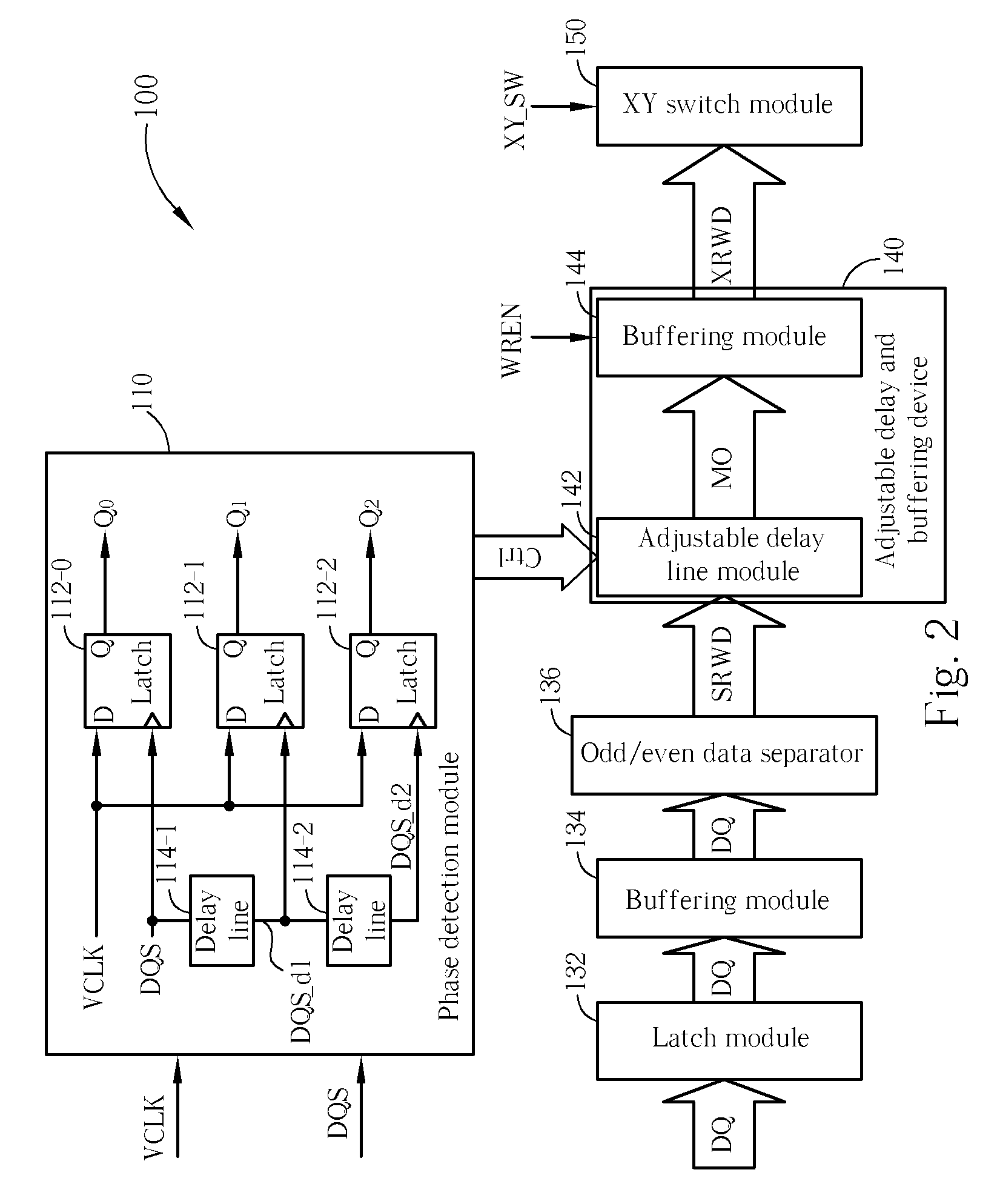

Phase detection method, memory control method, and related device

A phase detection method for detecting a phase difference between a data strobe signal and a clock signal, includes: latching the clock signal according to the data strobe signal to generate a phase lead / lag detection result; delaying the data strobe signal to generate a plurality of delayed data strobe signals; latching the clock signal according to the delayed data strobe signals to generate a plurality of phase detection results corresponding to the delayed data strobe signals, respectively; and if the phase lead / lag detection result indicates that the data strobe signal leads the clock signal, utilizing the phase detection results to represent the phase difference between the data strobe signal and the clock signal. A memory control method and a memory control circuit respectively corresponding to the phase detection method are further provided.

Owner:NAN YA TECH

Phase detector and method having hysteresis characteristics

InactiveUS7119583B2Voltage-current phase angleOscillations comparator circuitsHysteresisPhase detector

Owner:ROUND ROCK RES LLC