Patents

Literature

51results about How to "Improve appearance yield" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for cutting sapphire substrate LED chip through lasers

InactiveCN107538136AAvoid twinsAvoid chippingLaser beam welding apparatusSemiconductor devicesScriberOptoelectronics

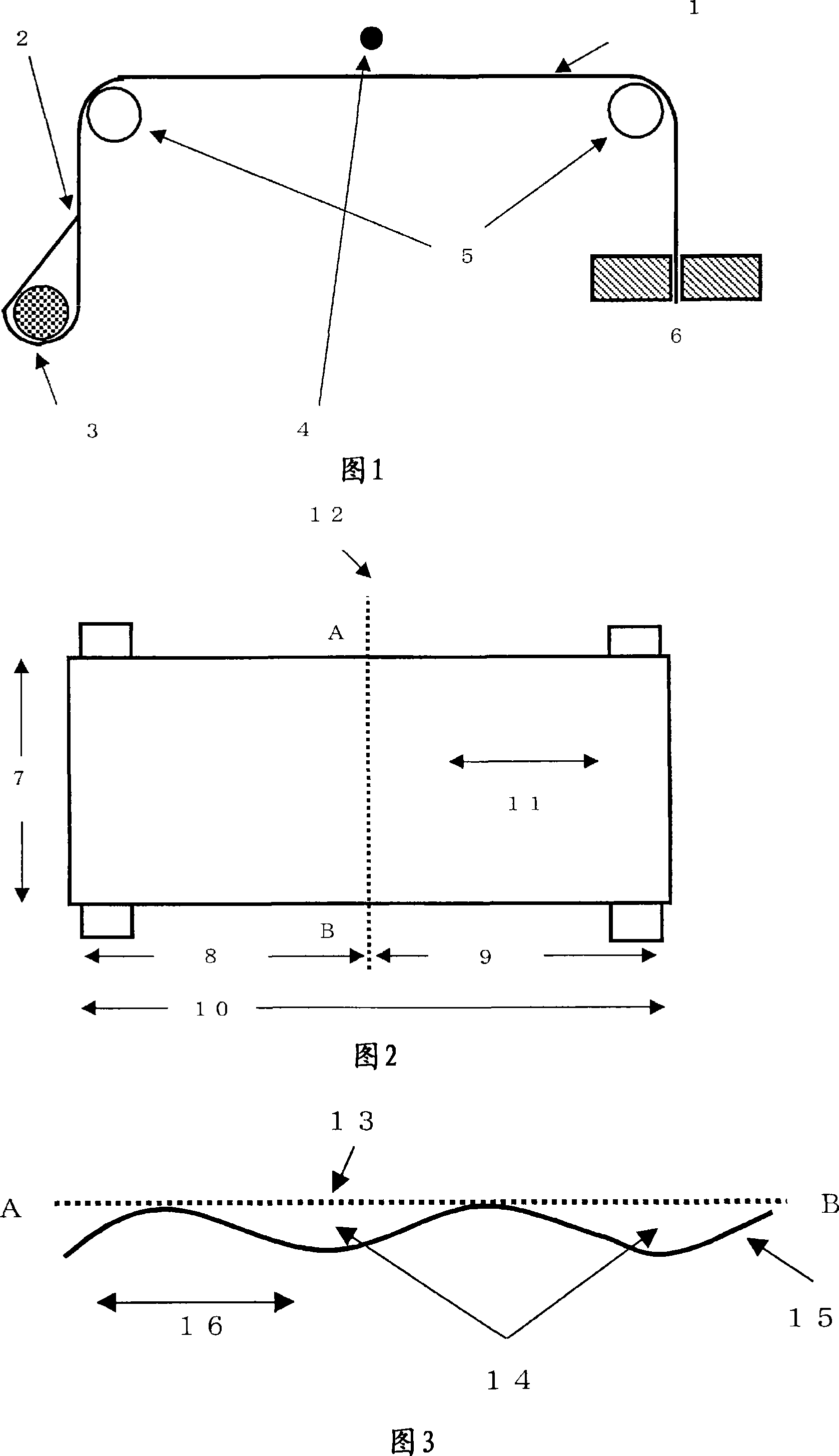

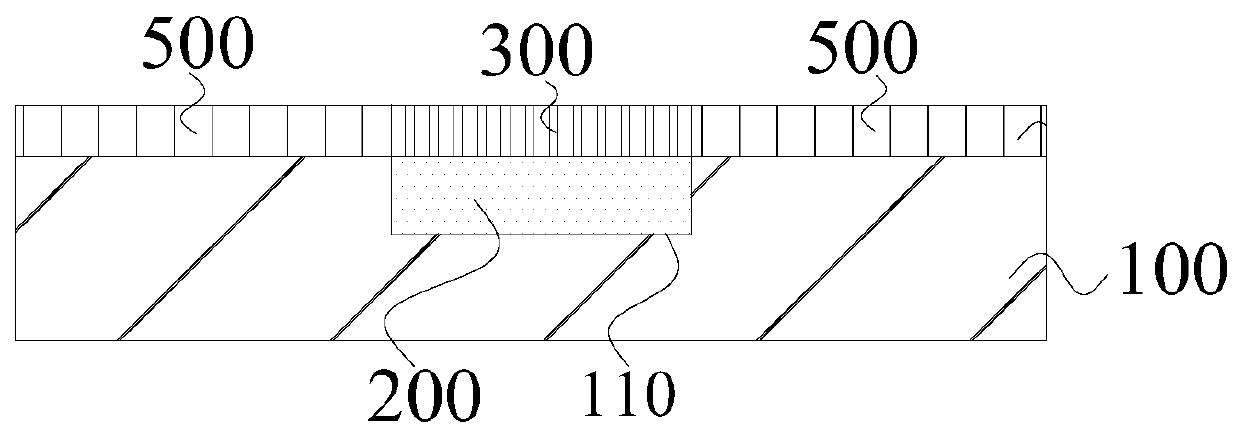

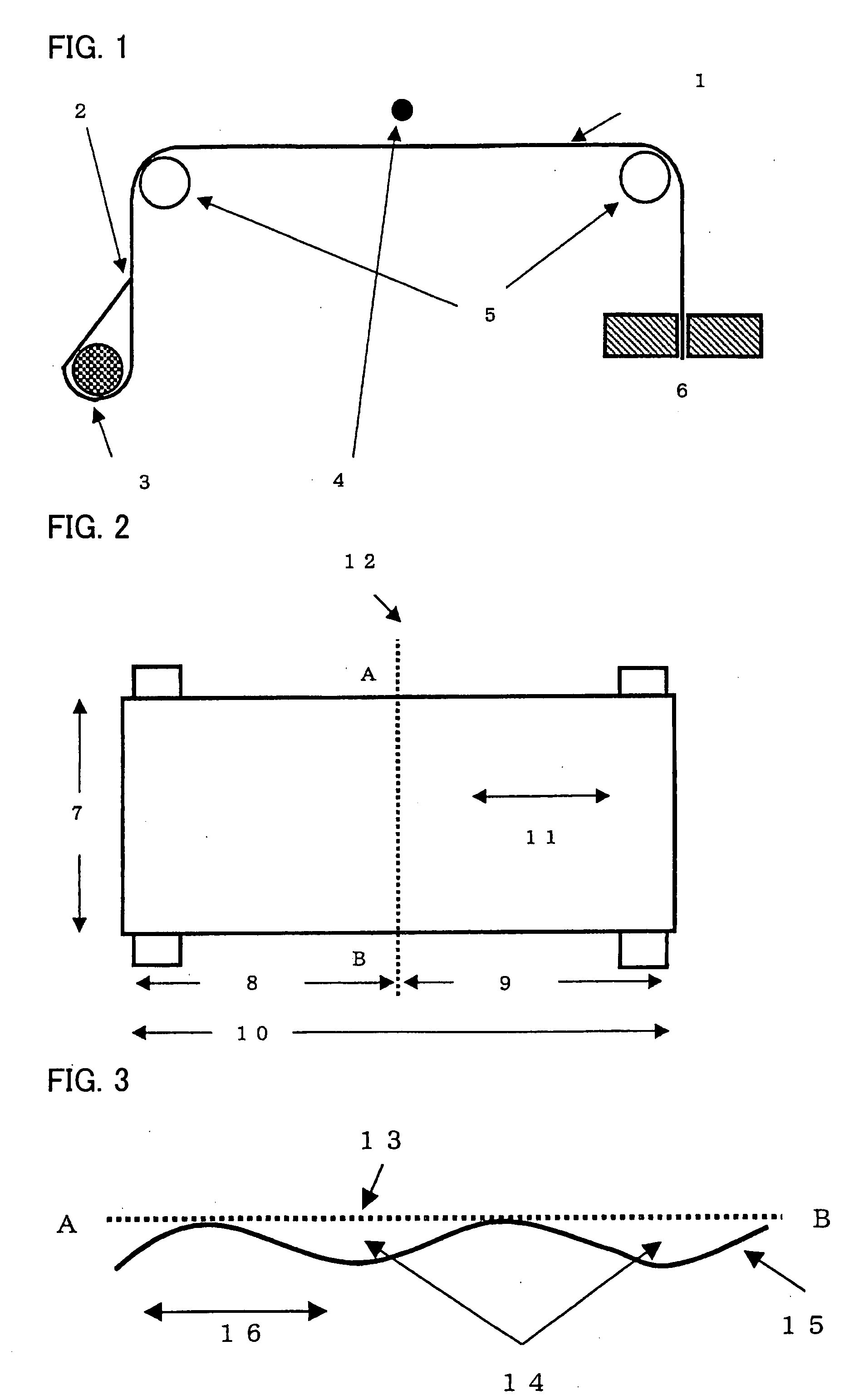

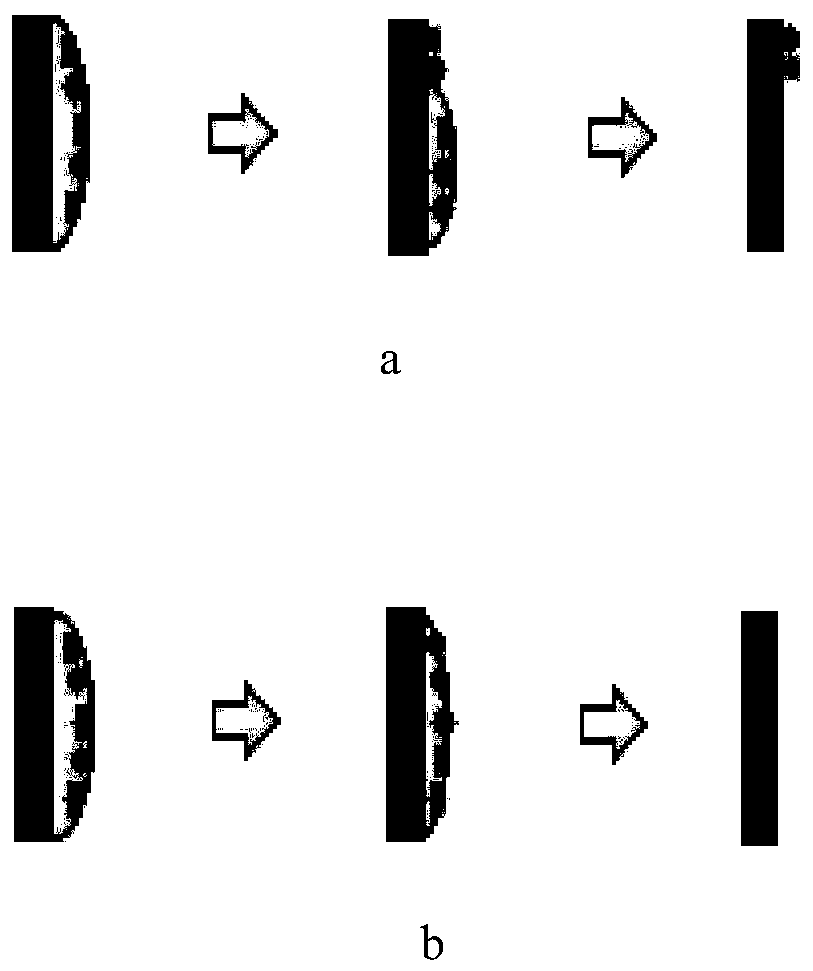

According to a method for cutting a sapphire substrate LED chip through lasers, a paddle with the depth being 20-40 [mu]m is cut in the face, with an electrode, of a wafer through an ultraviolet laserwafer scriber; and modified layers are formed in the mode that an invisible laser wafer scriber is utilized to act on the interior of the wafer, that is, the different modified layers are formed in the mode that the lasers are focused on the positions, with different depths, of the wafer through adjustment of the laser focus depth of the invisible laser wafer scriber, and cracks generated throughstress releasing of the modified layers can be connected together. The sapphire substrate wafer machined through the method is cleaved in the direction of the cracks through a piece cleavage machine,so that the sapphire substrate wafer is cut into independent light emitting units, and thus, cutting is completed. According to the method for cutting the sapphire substrate LED chip through the lasers, the sapphire substrate wafer with the large thickness and size is cut, the cutting yield of the sapphire substrate wafer can be effectively increased, the cut chip is prevented from generating thephenomena of crystal twin, edge breakage and oblique cracking, and the appearance yield rate of the cut chip is effectively increased.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

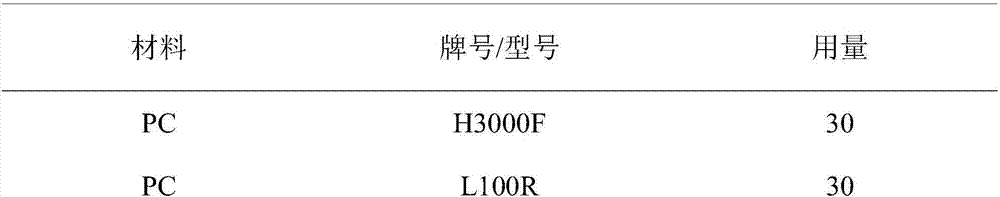

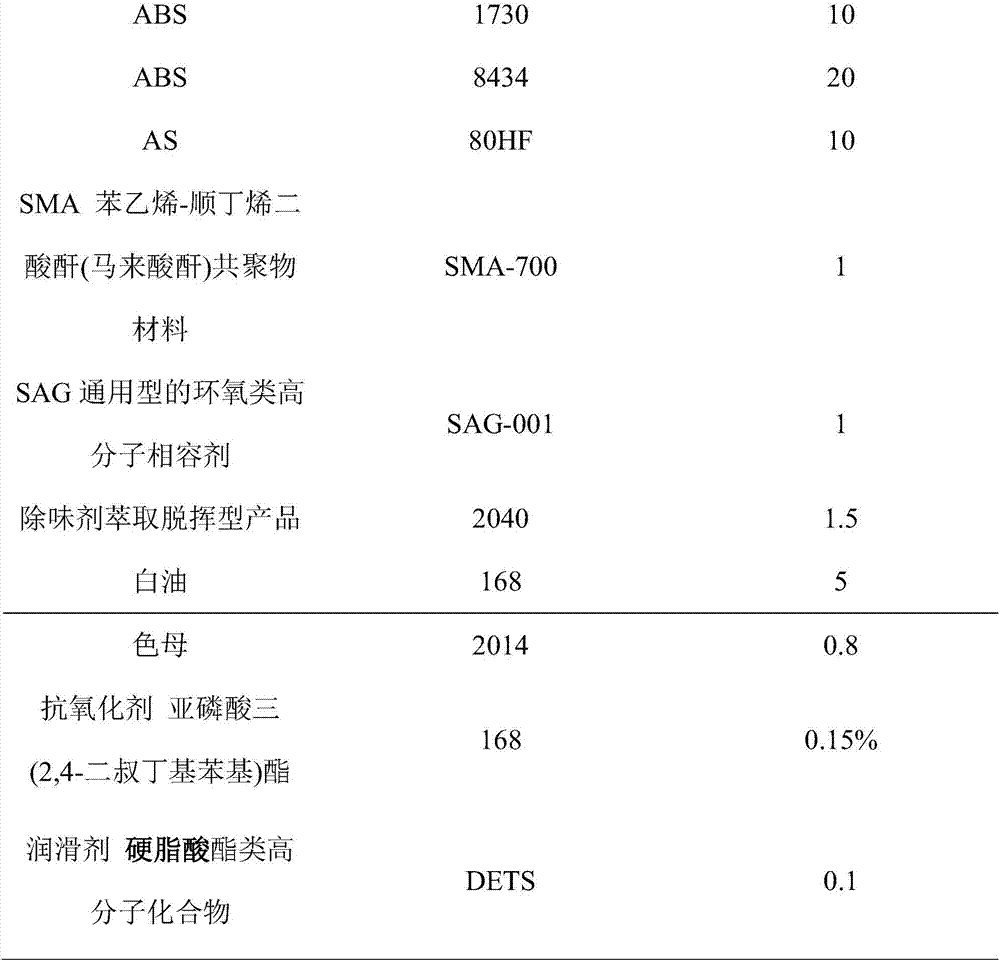

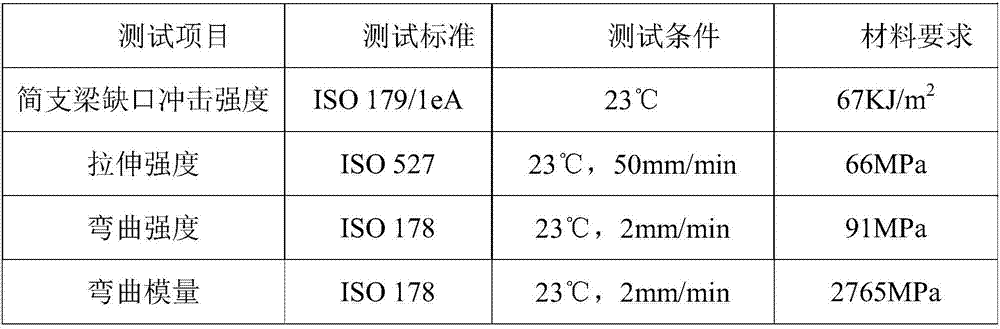

Low-odor spray-coating-free PC/ABS (polycarbonate/acrylonitrile butadiene styrene) material and preparation method thereof

The invention discloses a low-odor spray-coating-free PC / ABS (polycarbonate / acrylonitrile butadiene styrene) material and a preparation method thereof. The material is prepared from the following ingredients including 40 to 80phr of PC, 20 to 60phr of ABS, 5 to 10phr of AS, 0 to 1phr of lubricating agents, 1 to 1.5phr of deodorants, 0.5 to 1phr of heat stabilizers, 0.5 to 1phr of color masterbatch, 0 to 10phr of compatibilizers, 0 to 5phr of processing auxiliary agents, 0.1 to 0.5phr of antioxidants and 0 to 5phr of ultraviolet light absorbers. The material has the low odor and spray-coating-free appearance requirements; the odor grade is lower than or equal to 3.0; the appearance luster is good; the blackness is high; the thermal stability is high; the defects of flowing marks, melting and connecting wires, silver silks and the like cannot be easily generated; the spraying work procedure is omitted; the good spray-coating-free effect is achieved; through the creative selection on raw materials and auxiliary agents and the process innovation, a low-odor spray-coating-free PC / ABS material is produced, and is obviously superior to similar products in the market.

Owner:太仓市华鼎塑料有限公司

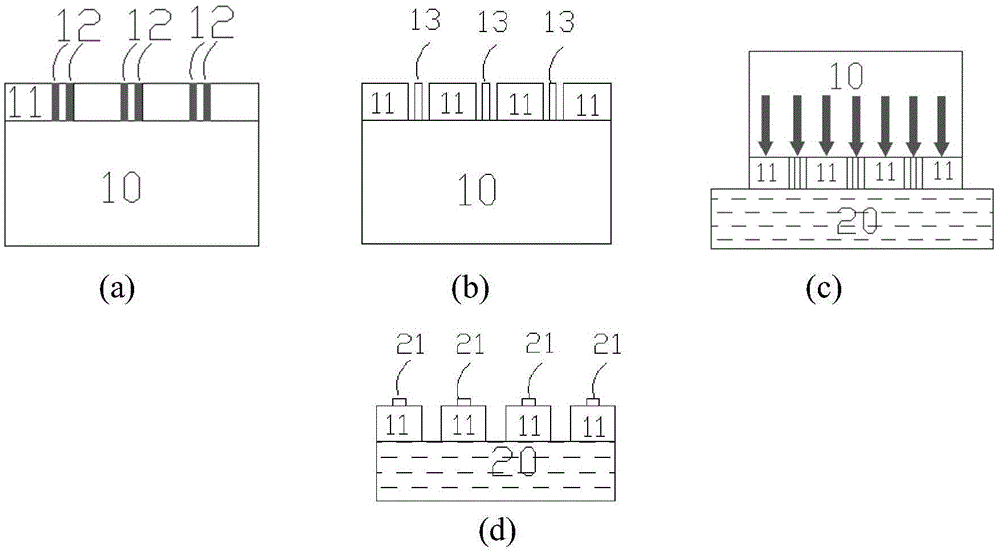

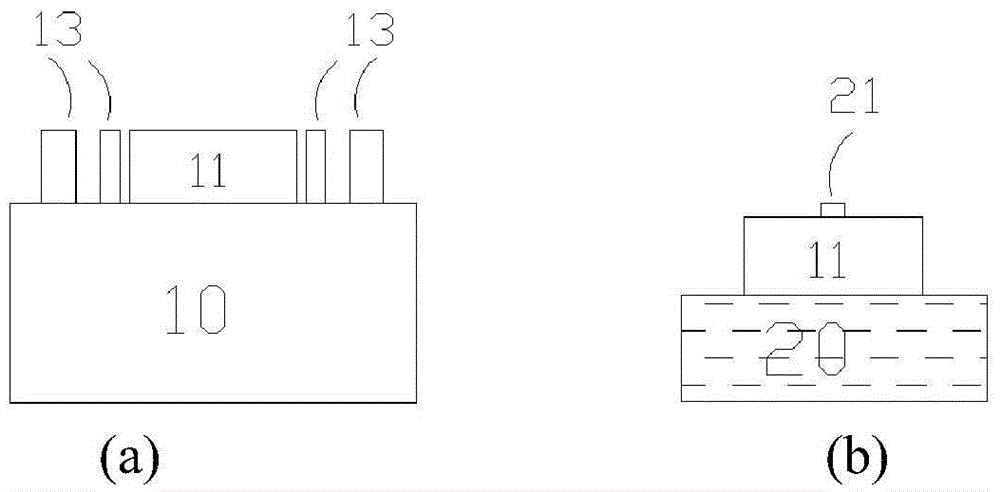

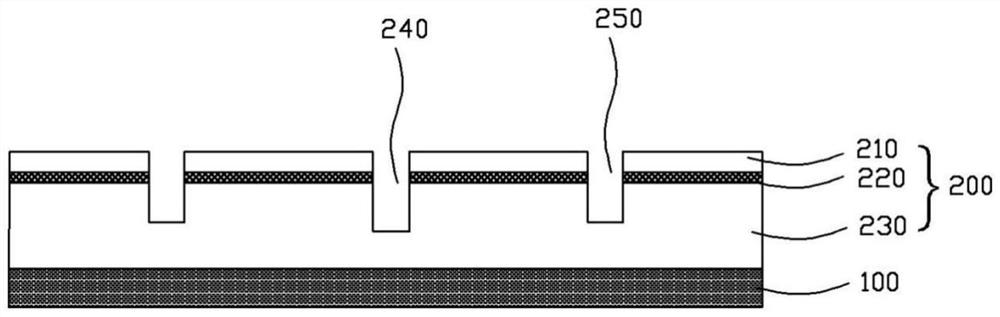

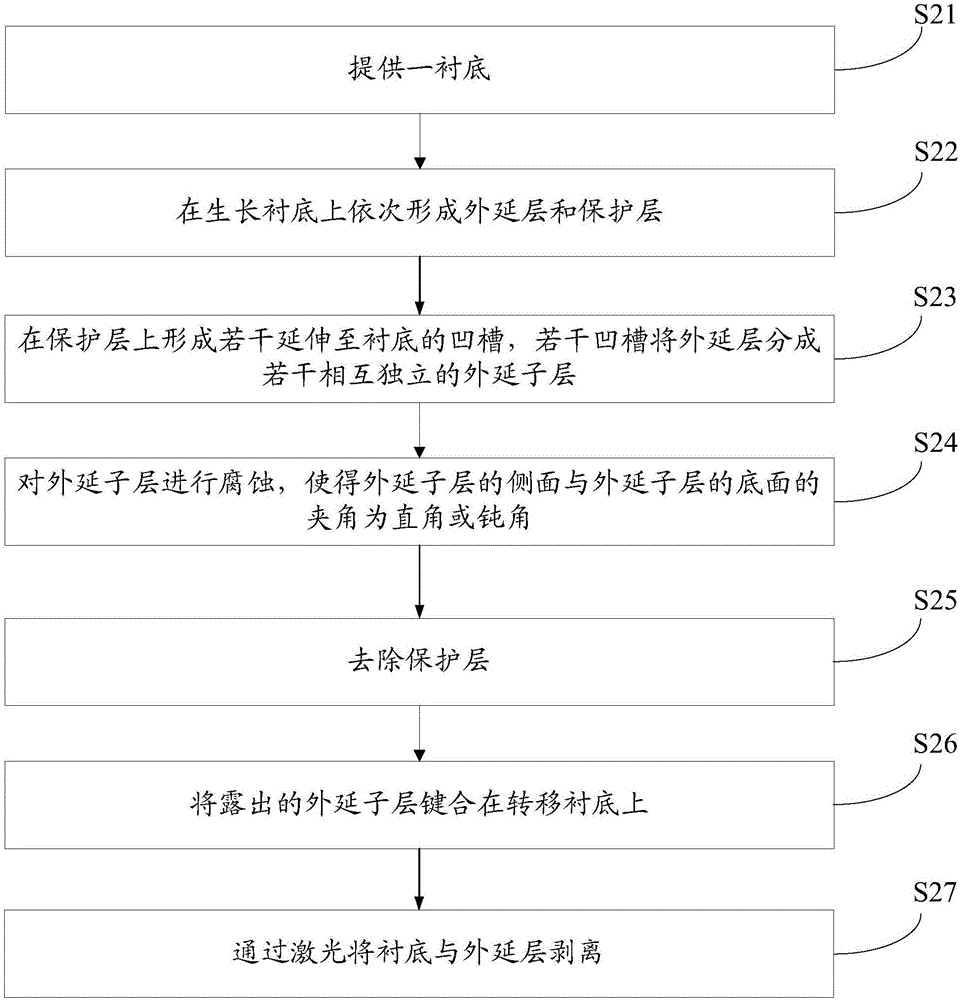

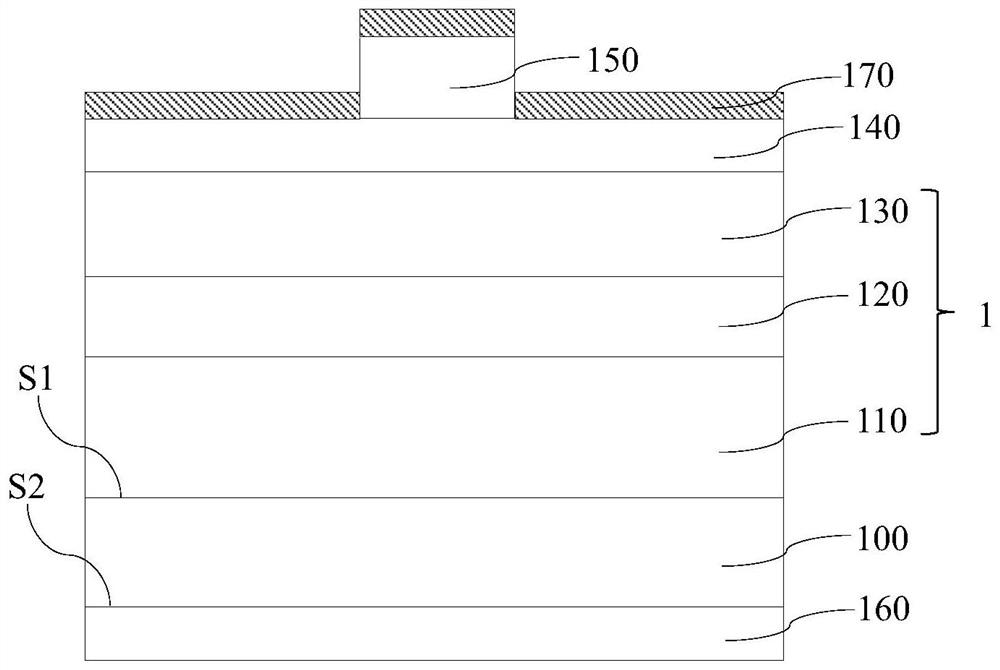

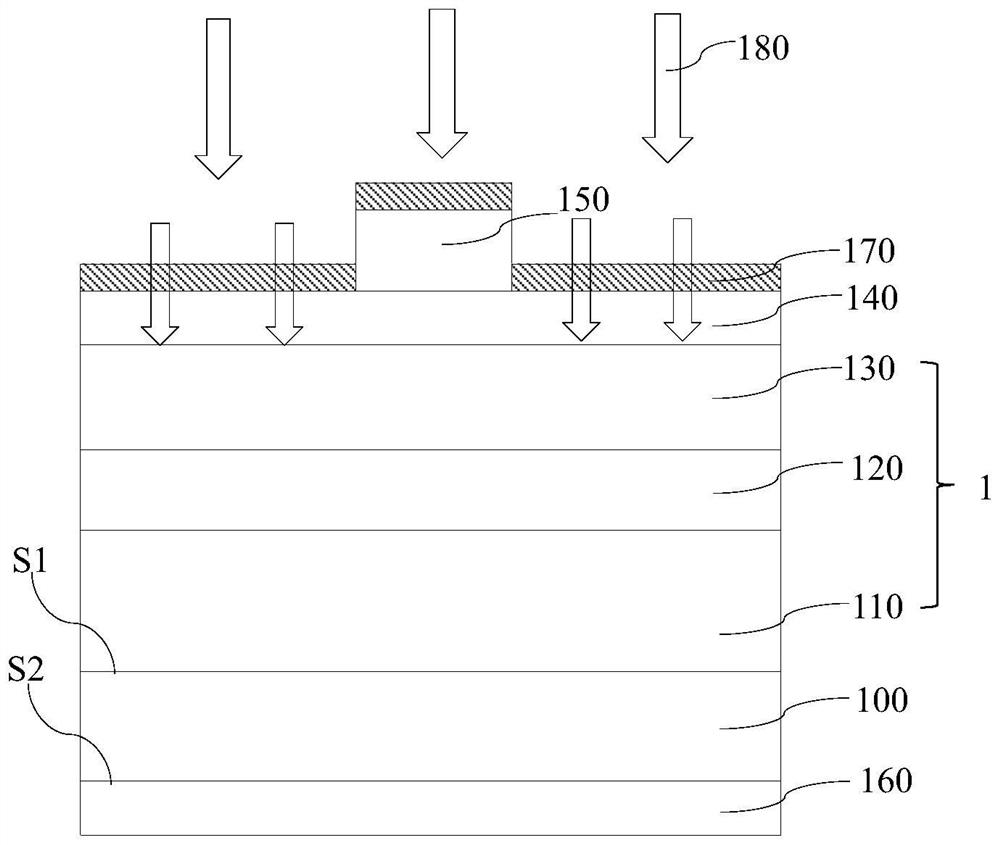

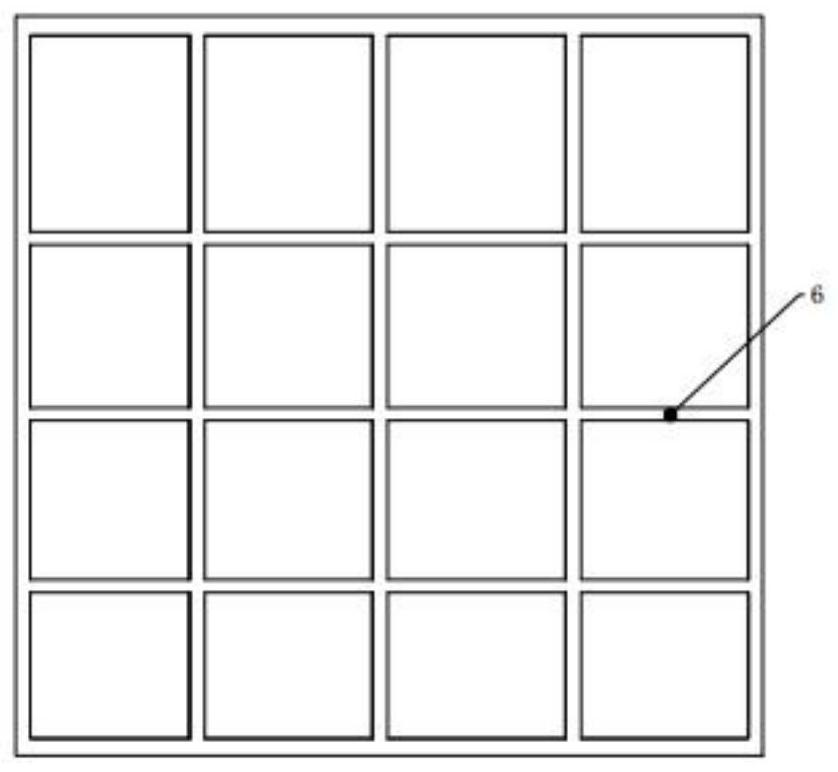

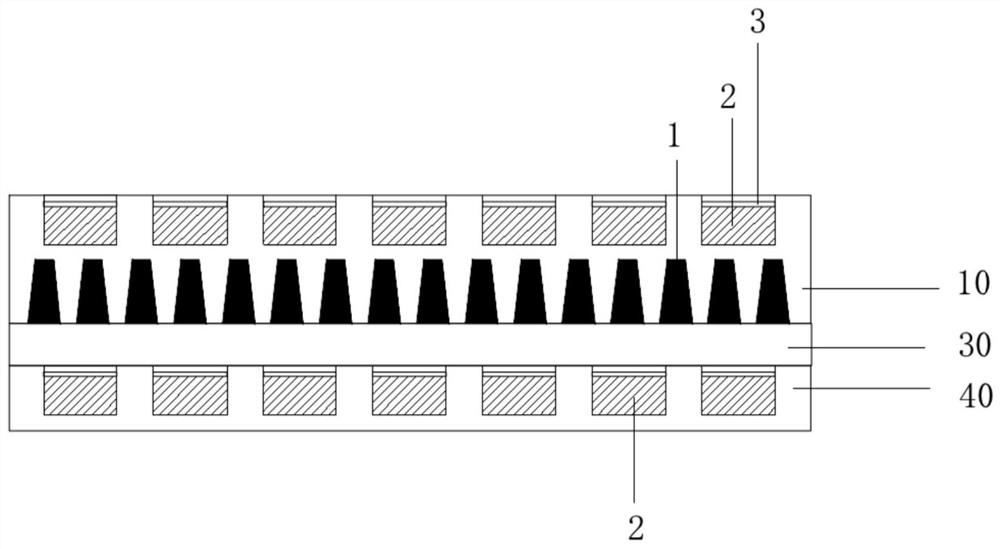

Vertically structured LED chip preparation method

InactiveCN105655452AImprove yieldImprove appearance yieldSemiconductor devicesOhmic contactEngineering

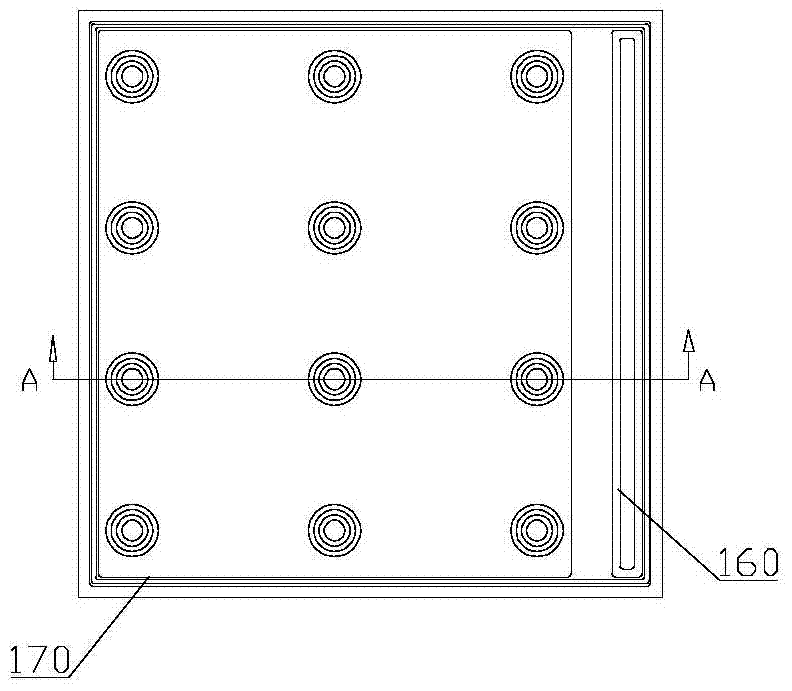

The invention discloses a vertically structured LED chip preparation method. The method comprises the steps of 1) obtaining an LED epitaxial layer of an LED structure on a heterogeneous substrate according to the epitaxial growth method; 2) forming multiple interlaced grooves on the upper surface of the LED epitaxial layer through the laser machining process so as to form a cylindrically surrounded gallium nitride high-pressure gas release sacrificial region; 3) successively preparing an ohmic contact layer and a first bonding material layer on the LED epitaxial layer, and preparing a second bonding material layer on a bonding substrate; 4) bonding the first bonding material layer on the LED epitaxial layer and the second bonding material layer on the bonding substrate together, and removing the heterogeneous substrate through the laser lift-off process; 5) etching the lifted-off LED epitaxial layer onto an N-GaN surface, removing the gallium nitride material outside the cylindrically surrounded gallium nitride high-pressure gas release sacrificial region and the effective region of the LED epitaxial layer based on the wet etching technology, and finally completing the preparation of a passivation layer and an N electrode. In this way, a vertically structured LED chip can be obtained.

Owner:XI AN JIAOTONG UNIV

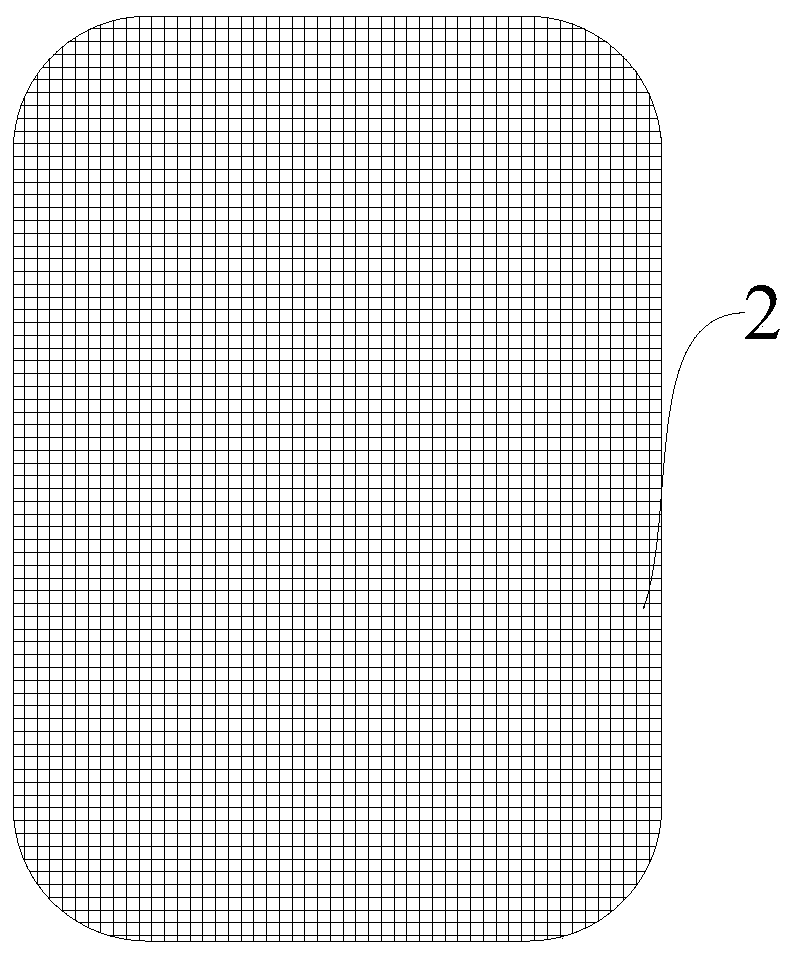

Polyimide film

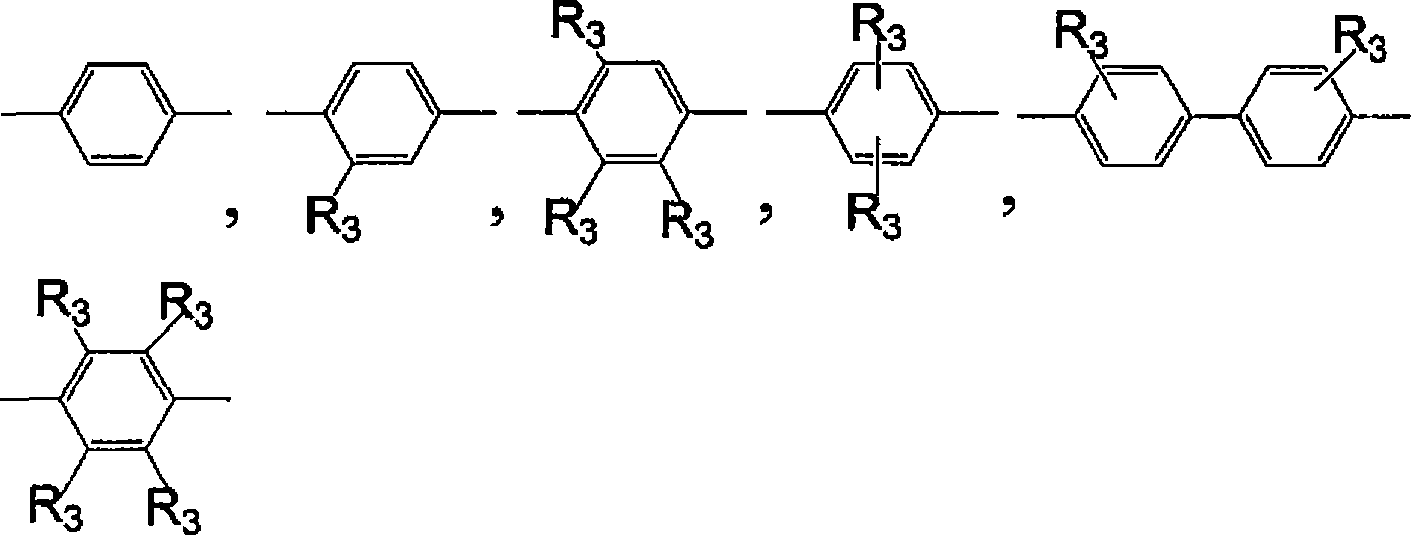

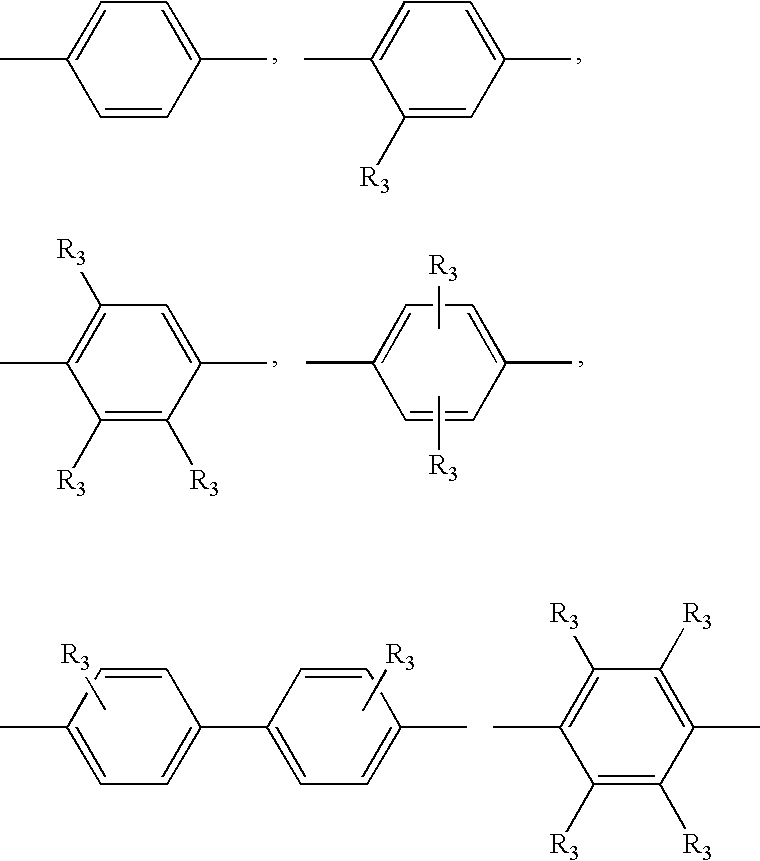

ActiveCN101146850AImprove appearance yieldSuppresses dimensional changesPrinted circuit aspectsCircuit susbtrate materialsWrinkle skinDynamic viscoelasticity

The present invention provides a polyimide film with a small rate of dimensional change in the manufacturing process when used in FPC. In particular, the object is to produce a metal-clad laminate with few abnormal parts such as wrinkles, and obtain dimensional change at a high yield. FPC with a small rate can solve this problem with the following polyimide film, which is a polyimide film having a tan δ peak temperature equal to or greater than 320° C. and less than 380° C. in the measurement of dynamic viscoelasticity, and is characterized in that : The maximum slack of the film is 13mm or less.

Owner:KANEKA CORP

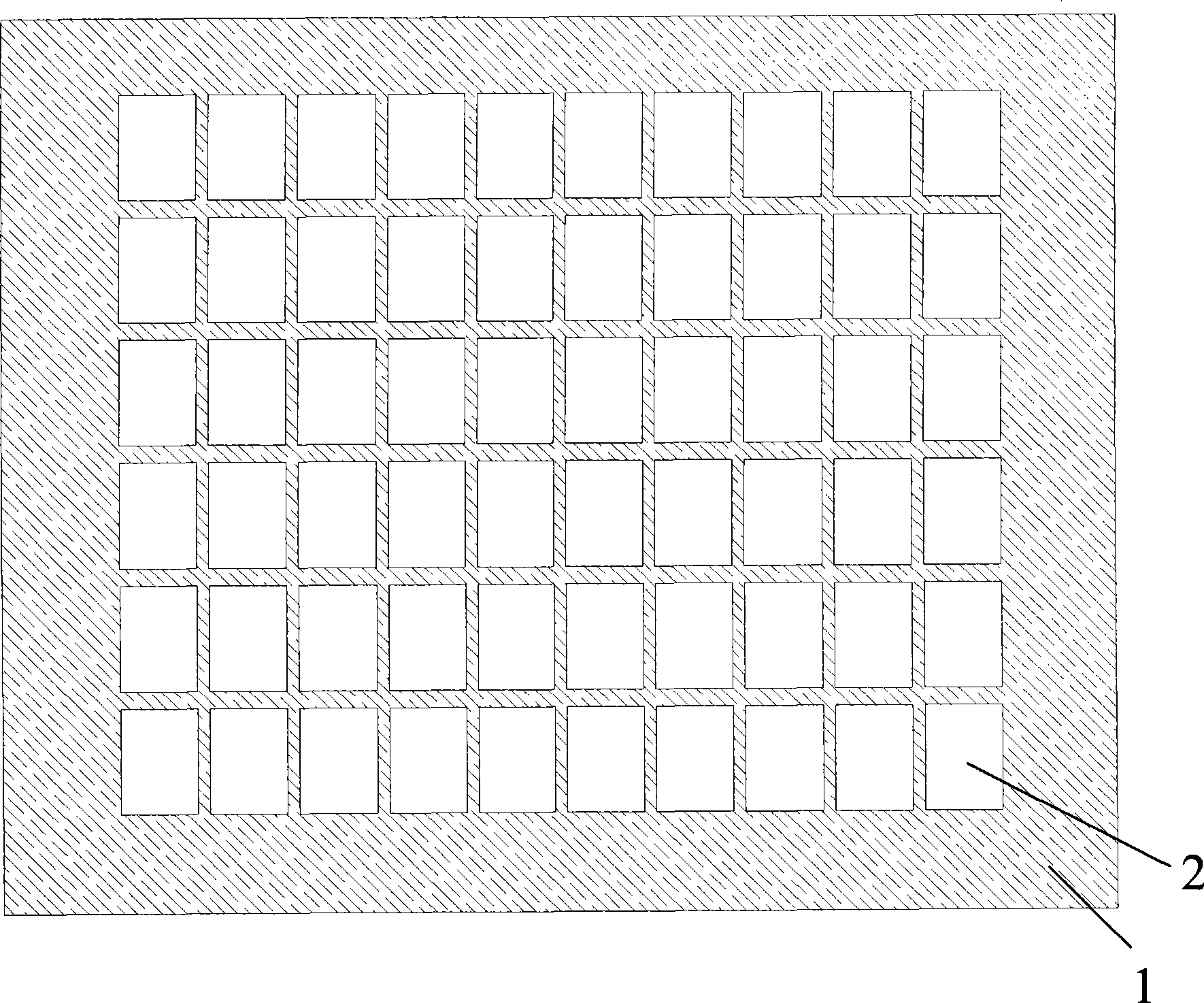

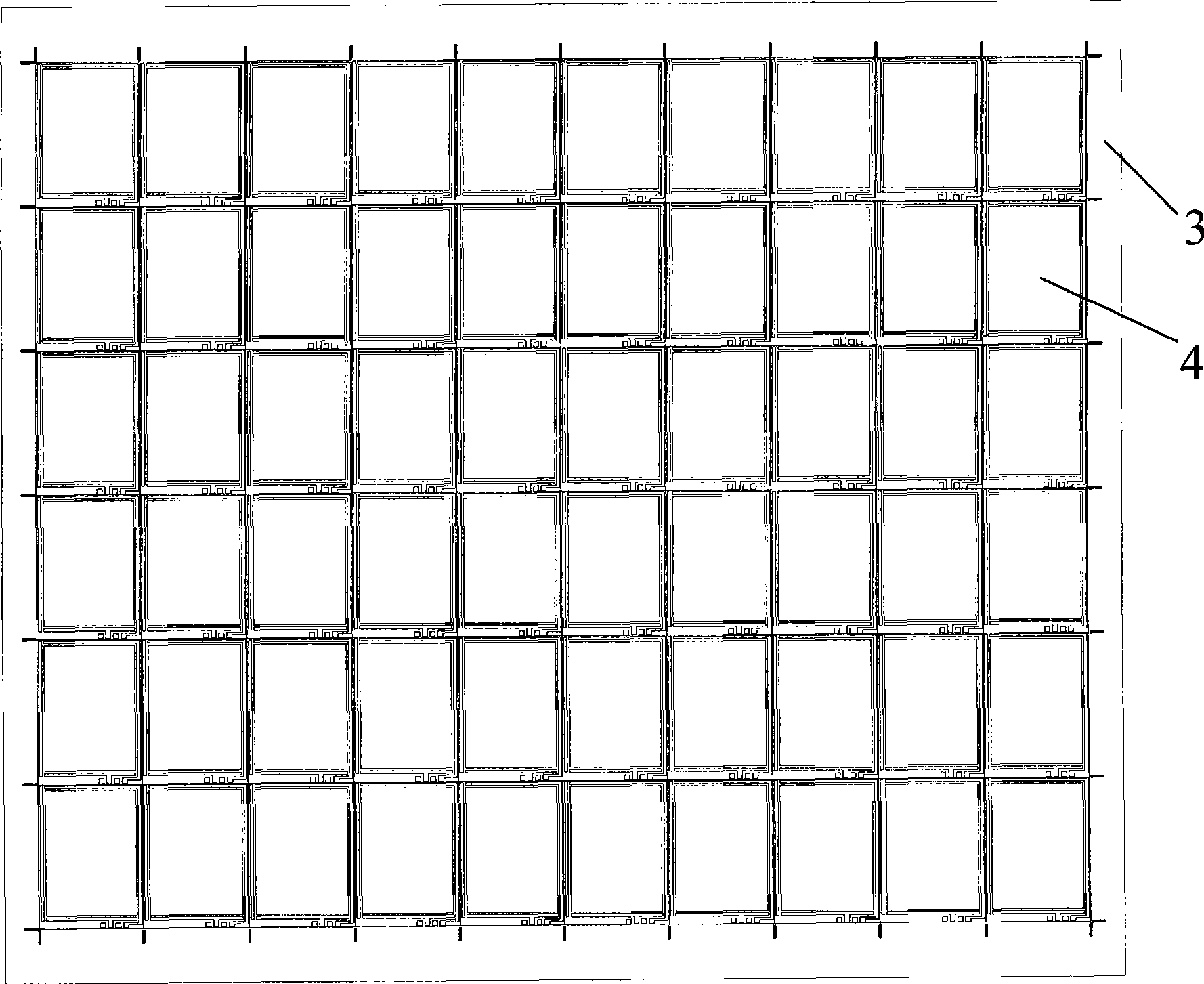

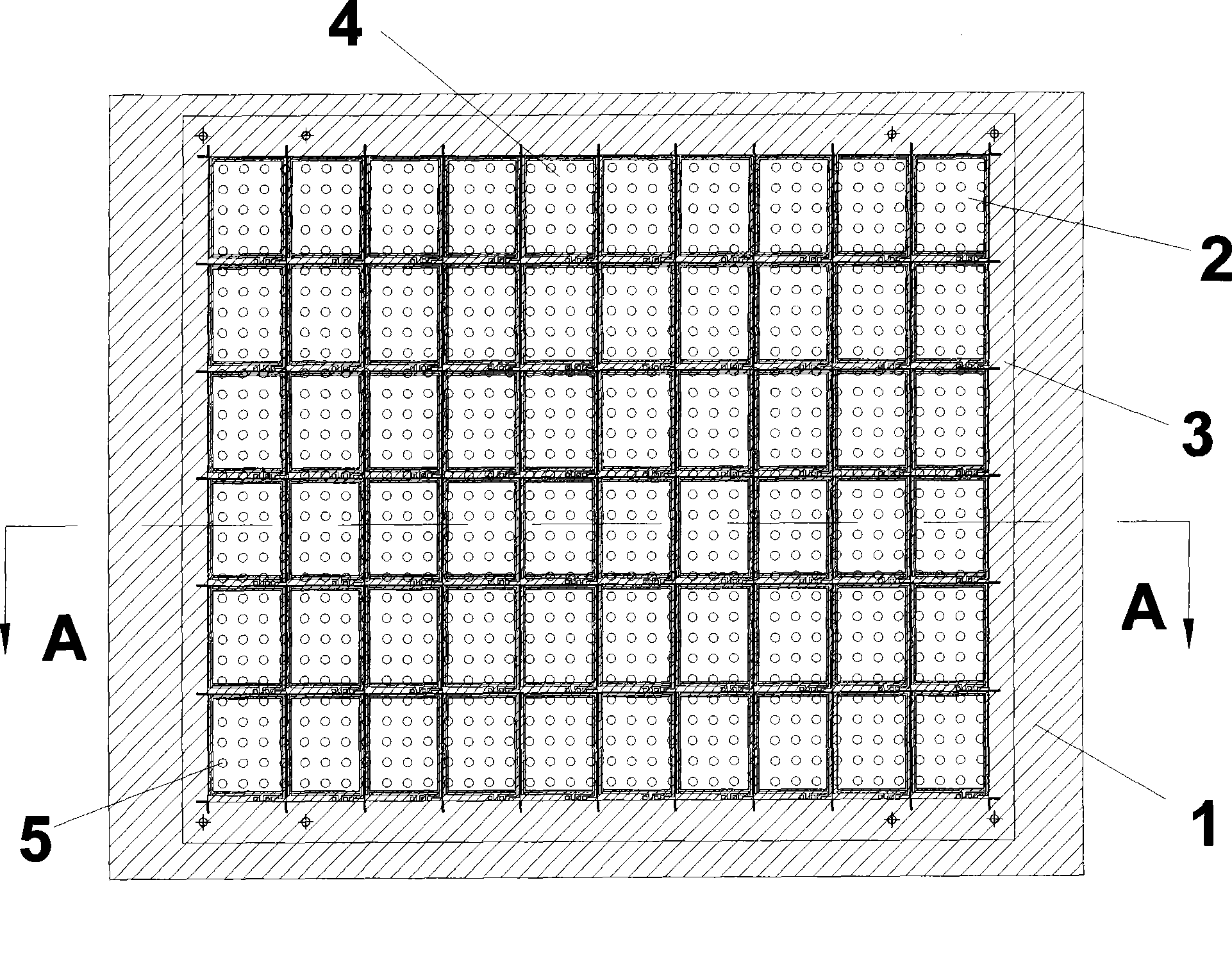

Manufacturing process of laminated film mold

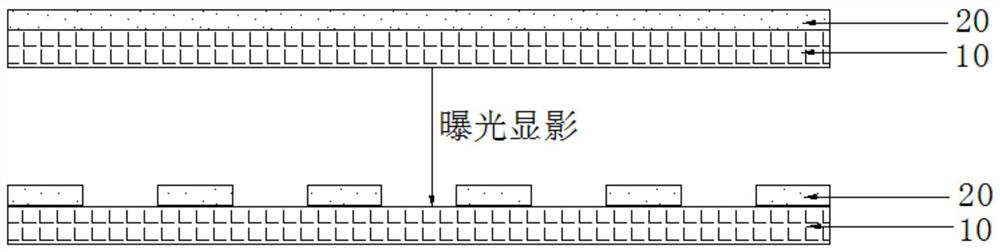

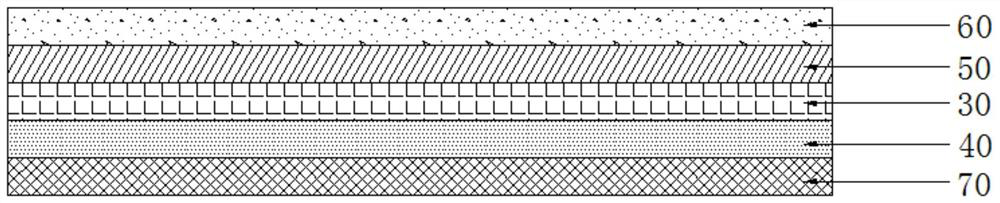

PendingCN112060422ANeat edgesNo aliasingPhotomechanical apparatusDomestic articlesAdhesive glueCoating

The invention discloses a manufacturing process of a laminated film mold. The manufacturing process of the laminated film mold comprises the following steps of (1) preparing a shading film, namely, coating a photosensitive material on a PET base material, and exposing and developing to obtain the shading film with a required texture pattern; (2) preparing a texture film, namely, applying UV glue on a texture female die substrate, covering the UV glue with a PET film, transferring the required texture on the PET film through transfer printing machine impressing and UV photocuring, and separating the texture female die substrate from the PET film to obtain a PET texture film; (3) laminating the texture surface of the shading film prepared in the step (1) with the non-texture surface of the PET texture film prepared in the step (2), and defoaming and cutting to obtain a semi-finished product of the film mold; and (4) performing PVD coating on the texture surface of the PET texture film ofthe semi-finished product of the film mold to obtain a finished product of the film mold. The film mold has the advantages of being good in toughness, high in precision, high in yield and simple in process.

Owner:伯恩创盛技术研发(惠州)有限公司

Casing of electronic equipment, manufacture method of casing of electronic equipment and electronic equipment

ActiveCN110512254AWith ceramic textureImprove appearance yieldAnodisationMolten spray coatingDie castingMetallic substrate

The invention provides a casing of electronic equipment, a manufacture method of the casing of the electronic equipment and the electronic equipment. The casing of the electronic equipment comprises ametal base material, a coating and a first anodic oxidation layer, wherein the coating is arranged on one surface of the metal base material and comprises aluminum or aluminum alloy; and the first anodic oxidation layer is applied to the surface, away from the metal base material, of the coating. According to the casing of the electronic equipment, one aluminum or aluminum alloy coating is formedon the surface of the metal base material made of die-casting aluminum alloy and other materials, conventional anodic oxidation treatment can be conducted, accordingly, the casing has a ceramic texture, the appearance yield is enhanced, and the manufacture cost is low.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

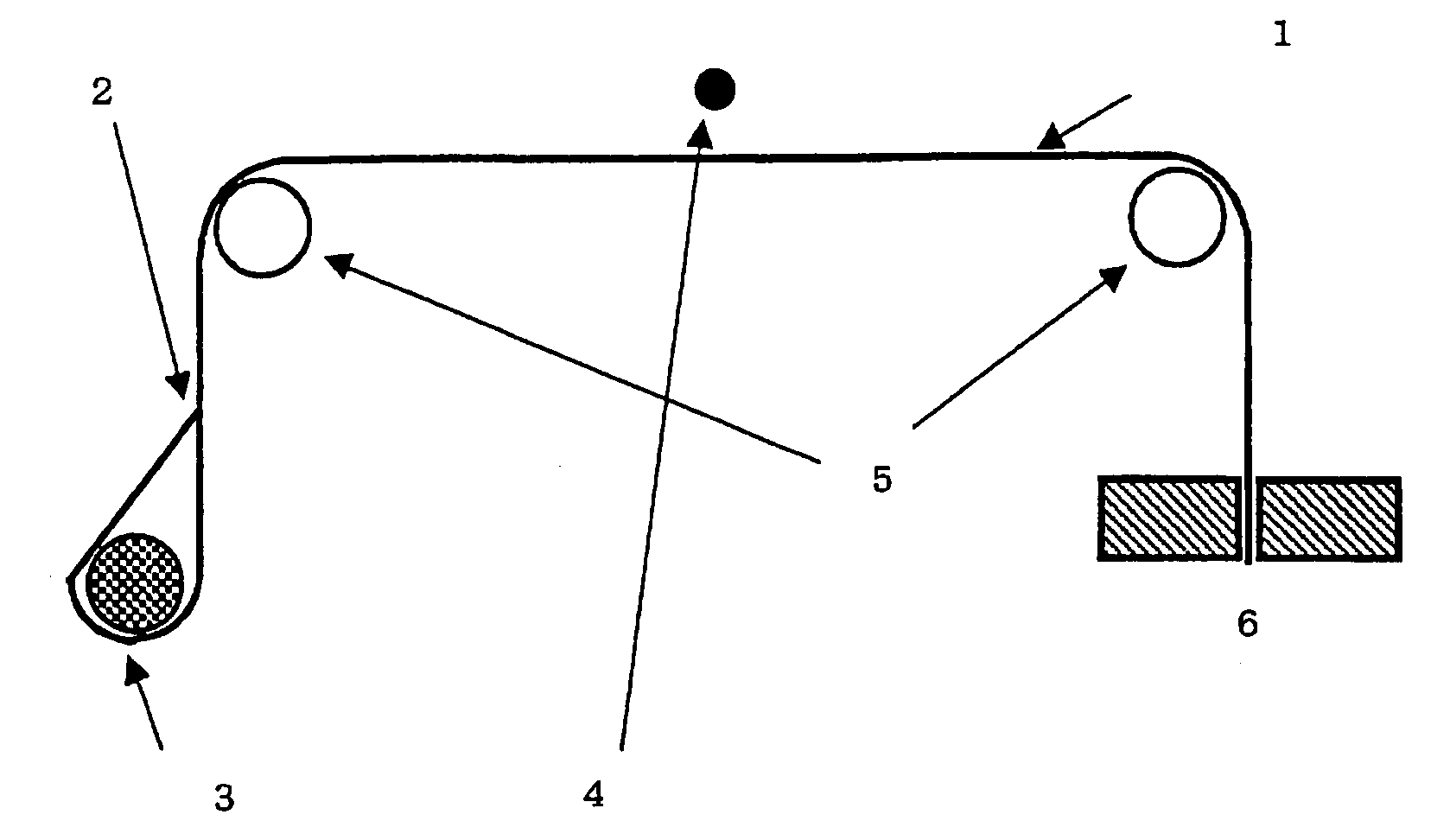

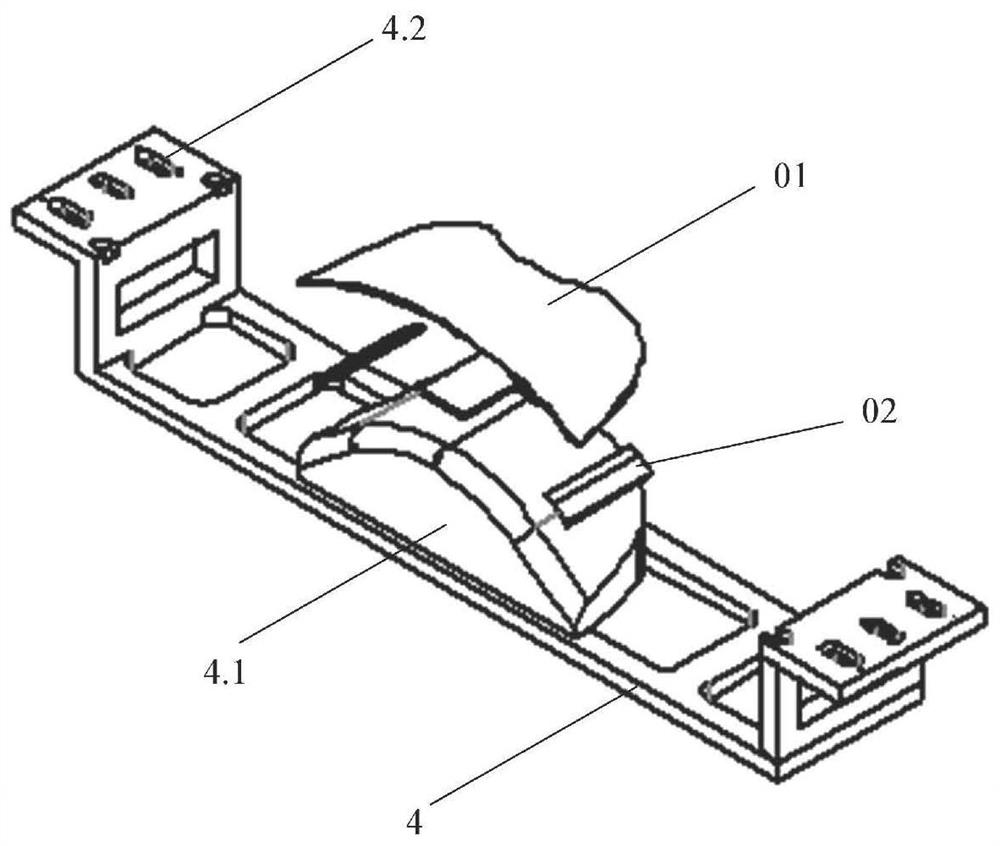

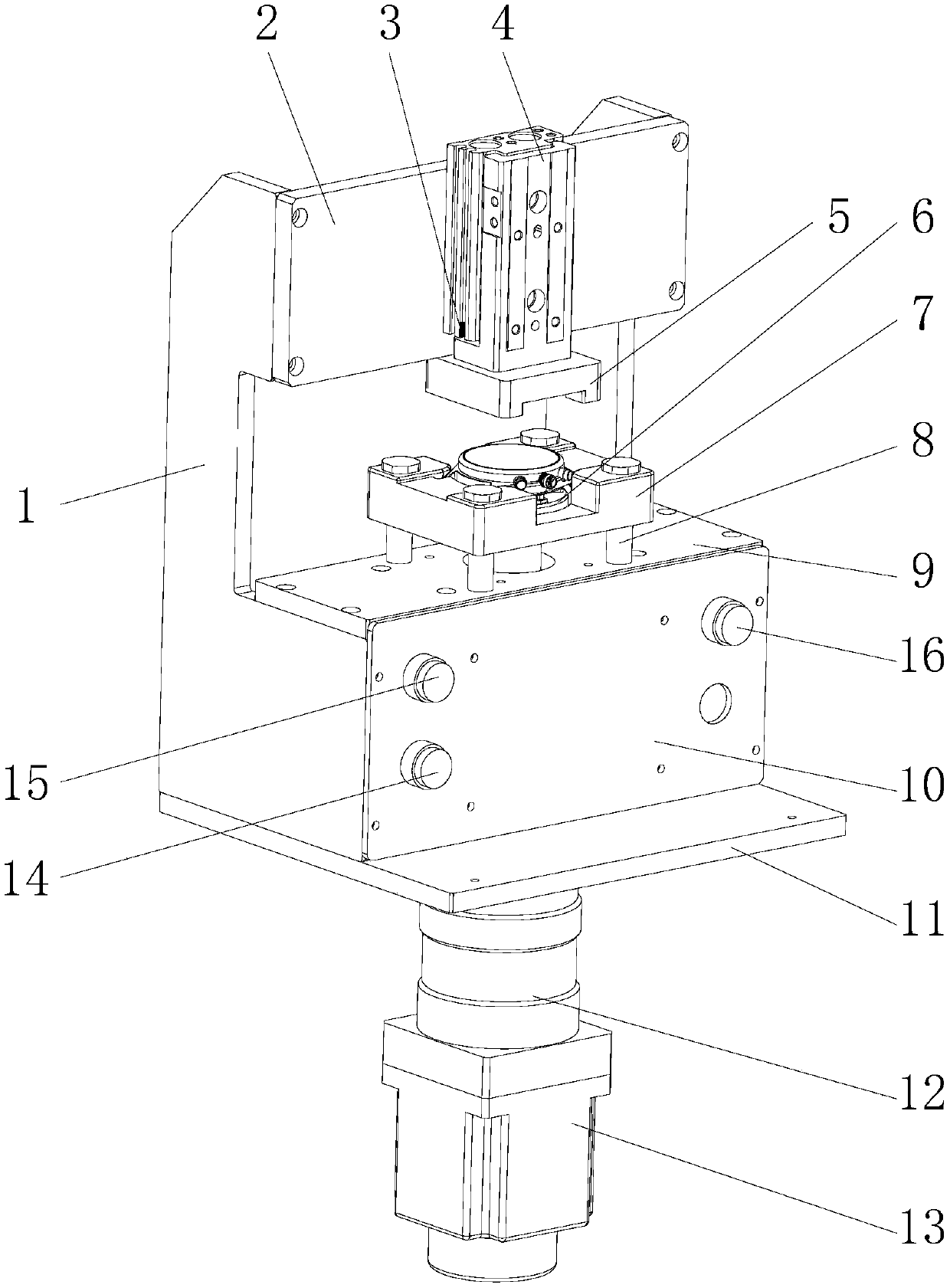

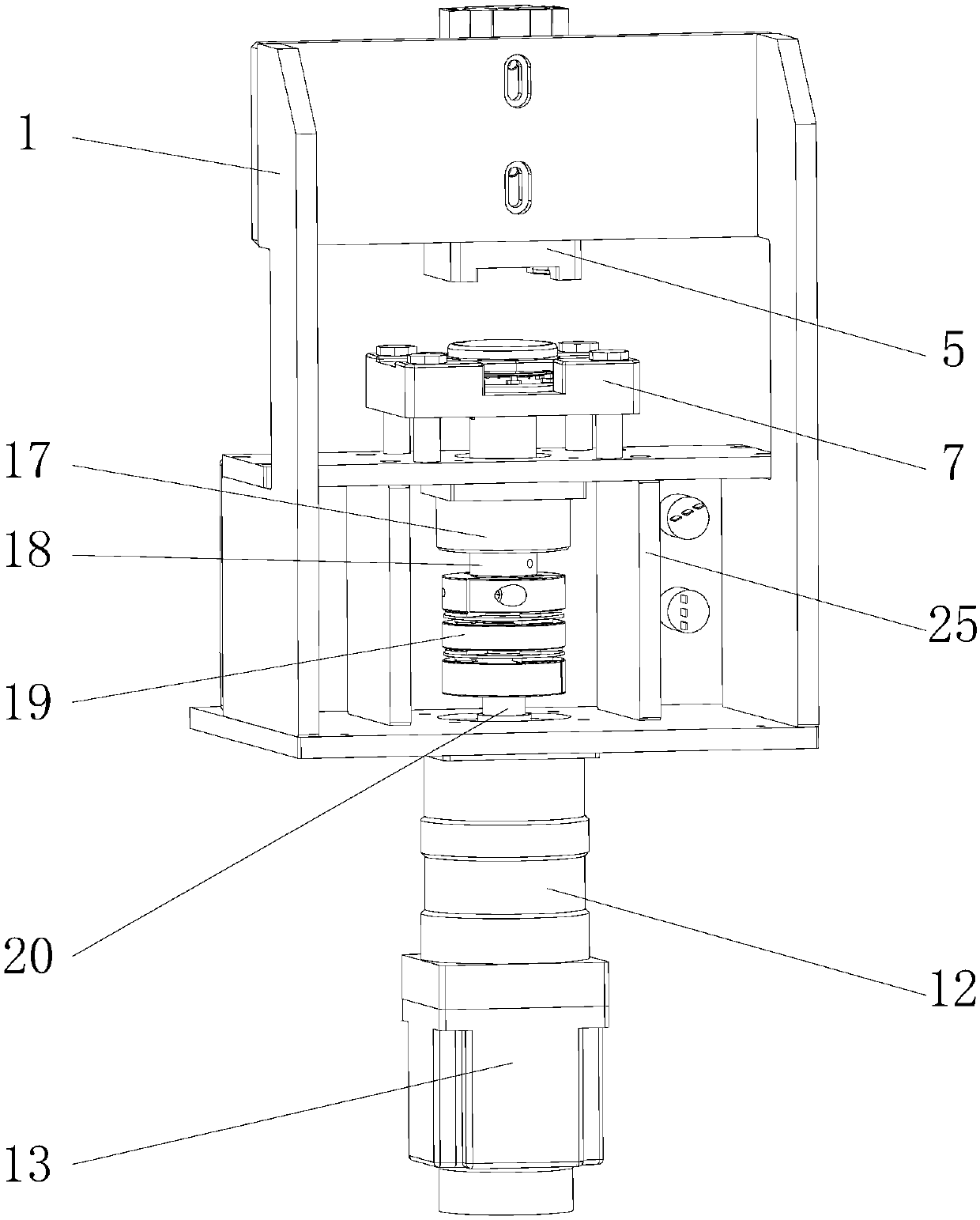

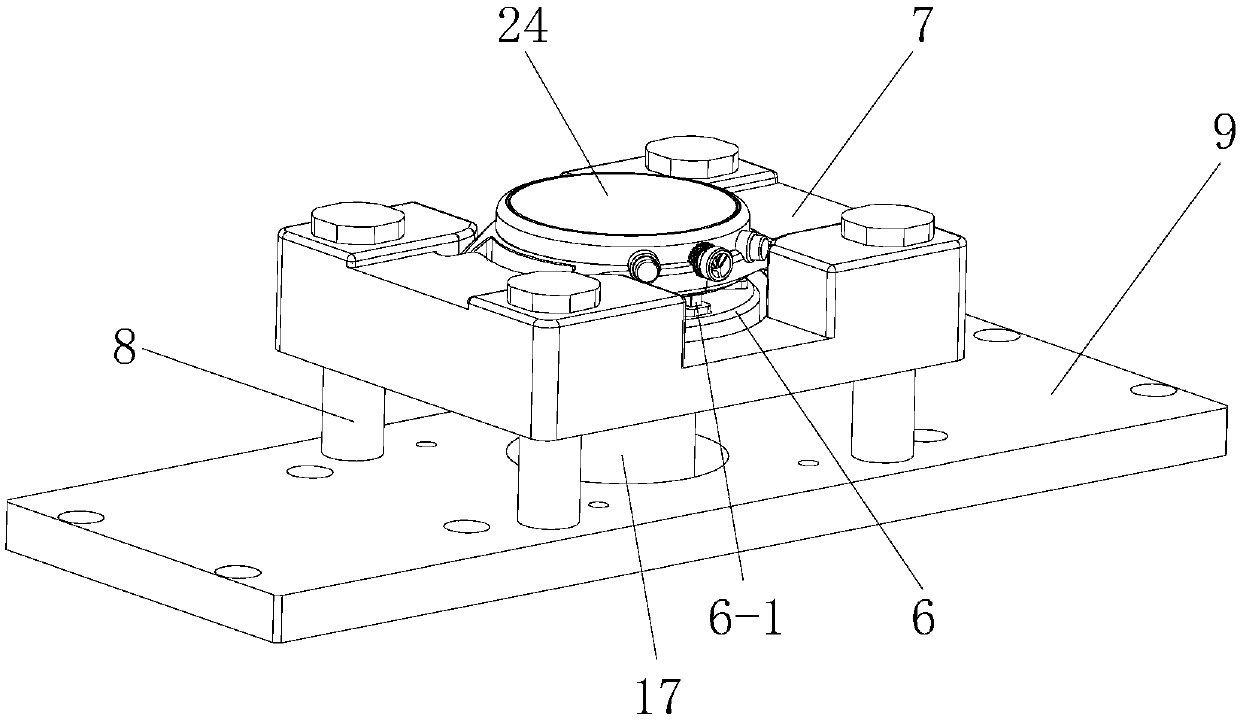

Automatic watch case disassembling and assembling equipment

ActiveCN106736459AReduce fatigueImprove work efficiencyMetal working apparatusDrive shaftEngineering

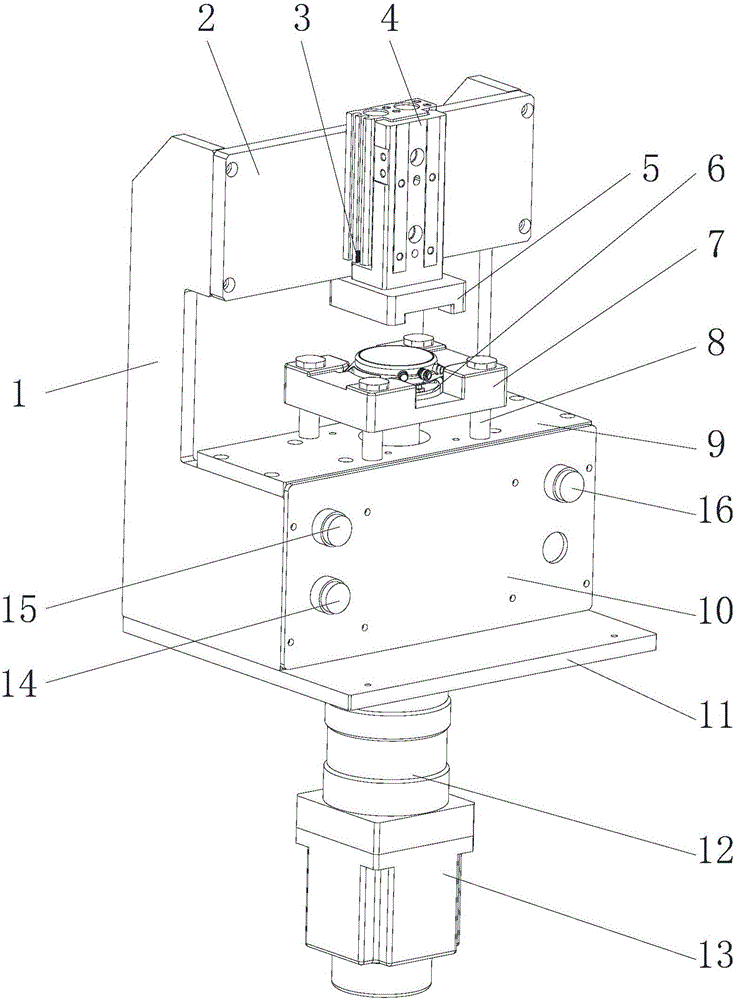

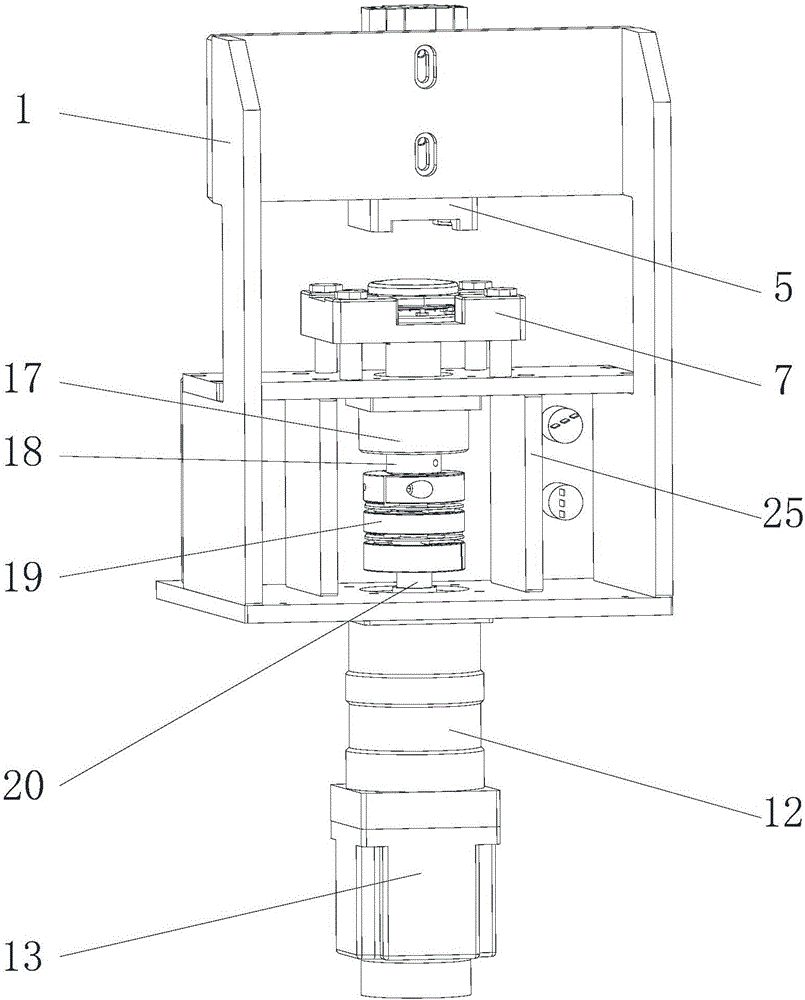

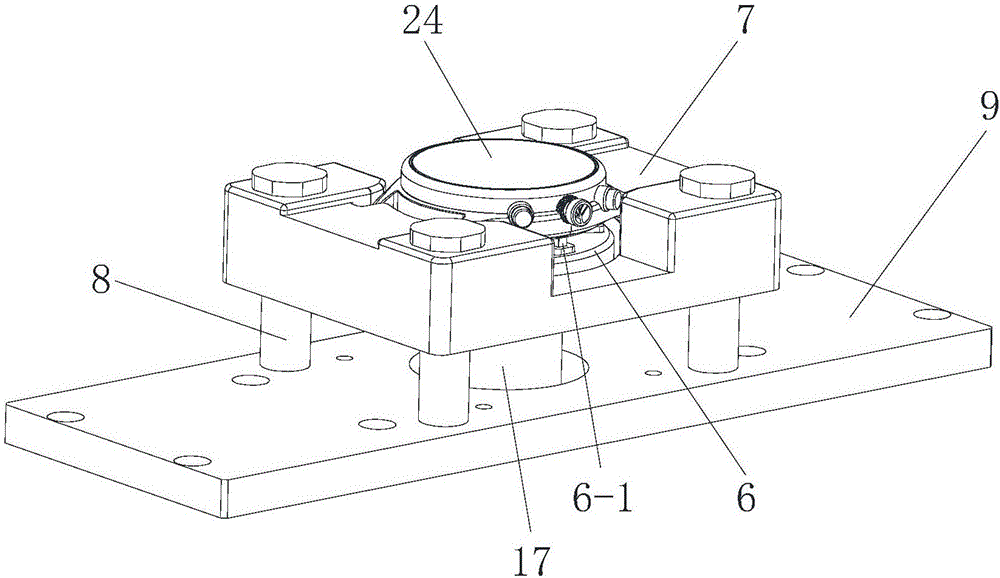

The invention discloses automatic watch case disassembling and assembling equipment which solves the technical problems that in the prior art, a rear watch case needs to be manually disassembled and assembled, the labor intensity is high, operation efficiency is low, and the assembling effect is not ideal. The automatic watch case disassembling and assembling equipment comprises a frame, a watch case fixing block is fixedly mounted in the frame, a watch head to be disassembled and assembled is positioned in the watch case fixing block, and a rear watch head case is placed downwards; a vertical through hole is formed in the watch case fixing block, a watch case disassembling and assembling block is mounted in the through hole and can rotate relative to the watch case fixing block, and a plurality of upward positioning claws are arranged on the watch case disassembling and assembling block and stretch into clamping grooves in the rear watch head case. A servo motor is mounted in the frame, and a transmission shaft of the servo motor is connected with the watch case disassembling and assembling block and drives the watch case disassembling and assembling block to rotate, so that the rear watch head case is disassembled and assembled.

Owner:GEER TECH CO LTD

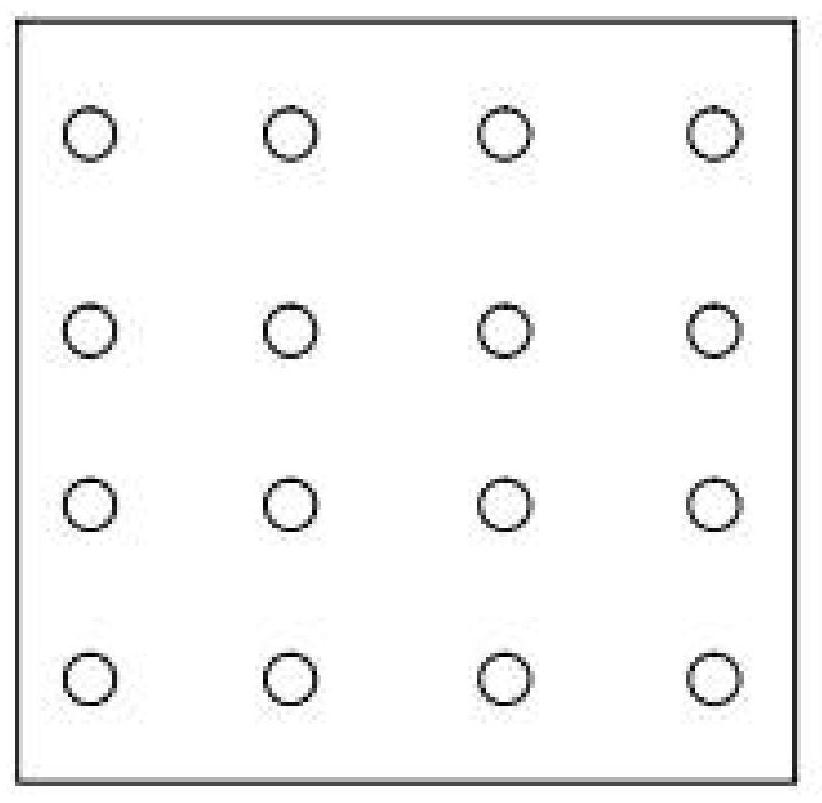

Method for manufacturing touch screen

InactiveCN101458582AReduce incidenceImprove appearance yieldInput/output processes for data processingNewton's ringsLaser

The invention relates to a method for manufacturing a touch screen. The touch screen includes a conducting film and a conducting glass. The manufacturing method includes steps as follows: dividing some active regions on the conducting film; providing a cutting mat frame that a window shape corresponding to the active region is cut on the cutting mat using laser; putting the cutting mat frame level on a combined machine, then putting the conducting film level on the cutting mat frame for combining with the conducting glass; the combined machine inhaling between the cutting mat frame and the conducting film through a platform surface air vent. The method can absorb the conducting film for forming phenomenon that the conducting film shows down, accordingly reduces occurrence rate of Newton's ring and increases the touch screen appearance yield.

Owner:SHANGHAI CHENXING ELECTRONICS SCI & TECH CO LTD

Polyimide Film

InactiveUS20090069531A1Improve appearance yieldShrinking and dimensional changePrinted circuit aspectsDynamic viscoelasticityPolyimide membrane

A polyimide film which, when used in FPC production, is reduced in dimensional change during the production steps. In particular, a metal-clad laminate apt to have abnormal parts such as rumples is produced from the film, and an FPC reduced in dimensional change is obtained in high yield. The polyimide film has a tan δ peak temperature within a range of 320° C. or more and lower than 380° C. in measuring a dynamic viscoelasticity, and is characterized by having a maximum sag of 13 mm or less.

Owner:KANEKA CORP

Display module, manufacturing method thereof and display device

ActiveCN113436530AIncrease the pressing areaImprove appearance yieldIdentification meansDigital data processing detailsDisplay deviceEngineering

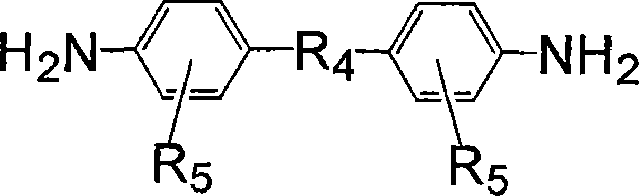

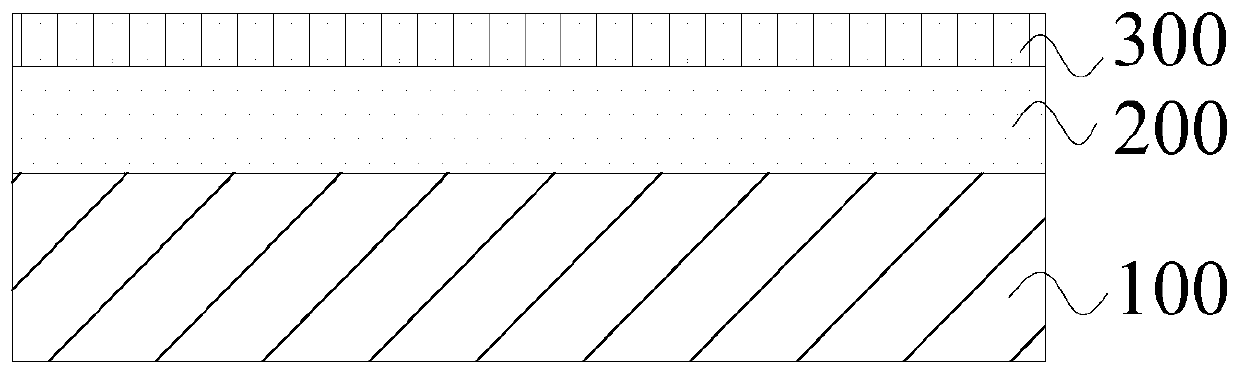

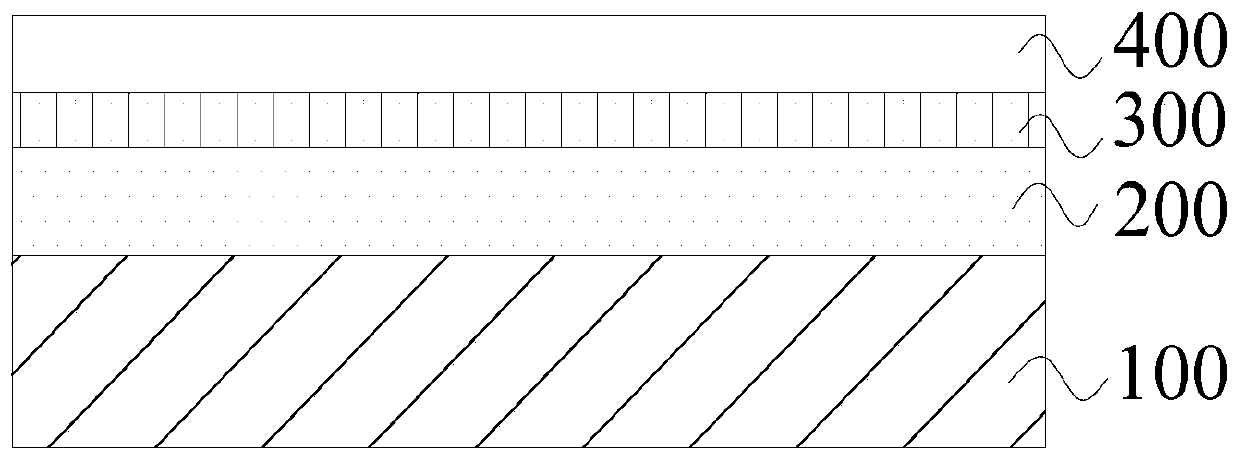

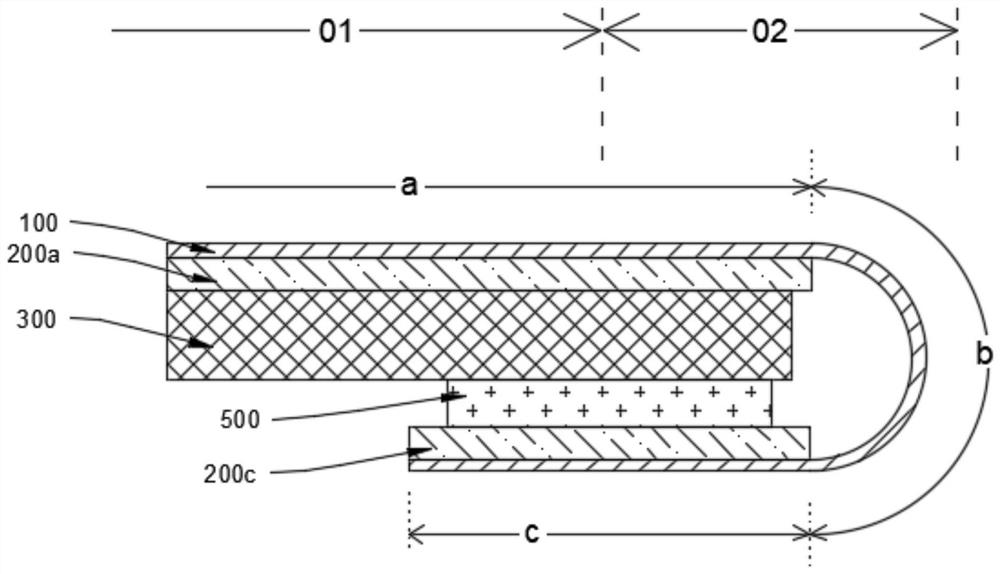

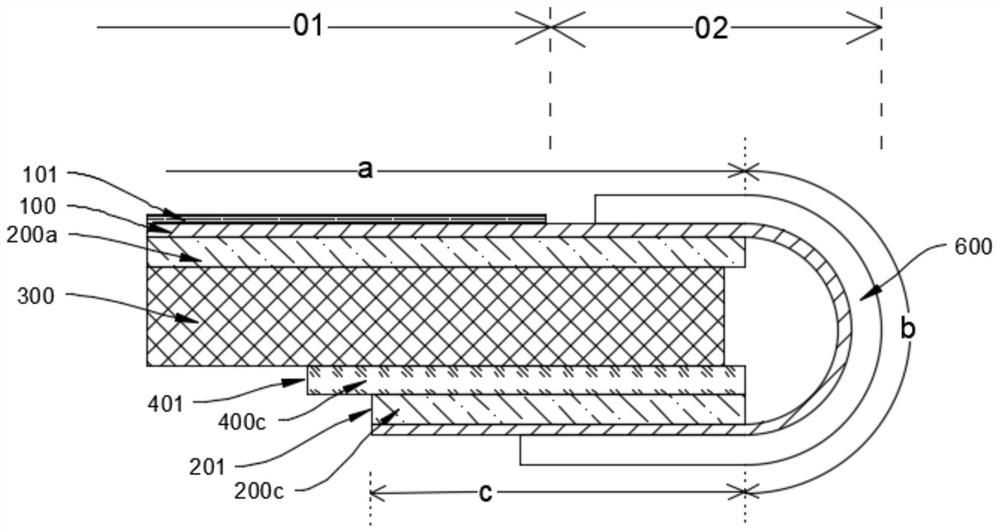

The invention provides a display module, a manufacturing method thereof and a display device. The display module comprises a substrate, a display function layer, a supporting layer, a buffer layer and a first bonding layer. The substrate comprises a display section, a bending section and an extension section; the supporting layer is arranged on one side, far away from the display function layer, of the substrate, and comprises a first supporting layer arranged close to the extension section and a second supporting layer arranged on the display section; the buffer layer is arranged on one side, deviating from the substrate, of the second supporting layer; the first bonding layer is arranged between the first supporting layer and the buffer layer; and the distance from one end, far away from the non-display area, of the first bonding layer to the non-display area is larger than or equal to the distance from one end, far away from the non-display area, of the buffer layer to the non-display area. The technical problem that the appearance of a display module product is affected due to the fact that a buffer layer is excessively thinned in order to achieve a narrow frame effect in an existing terminal bending process, so that a bonding layer on the display module is impressed obviously is solved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

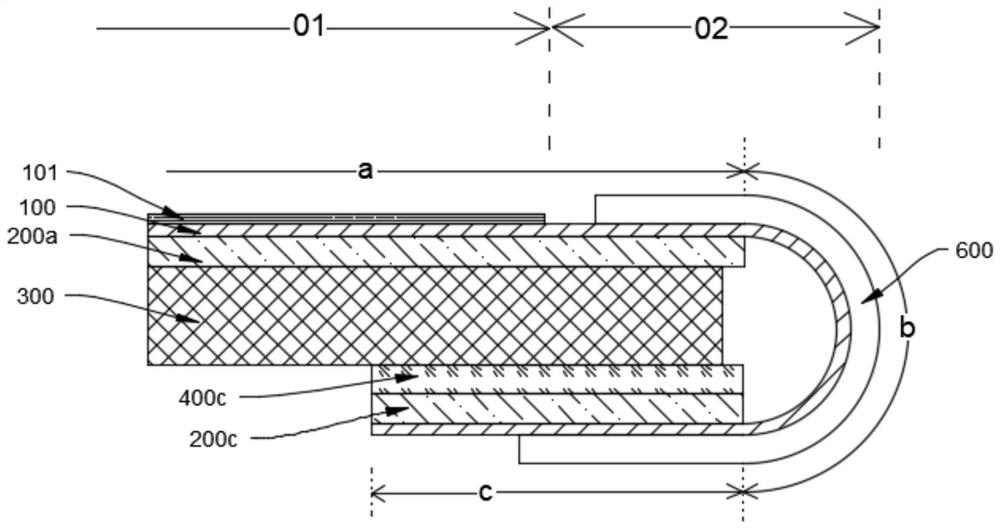

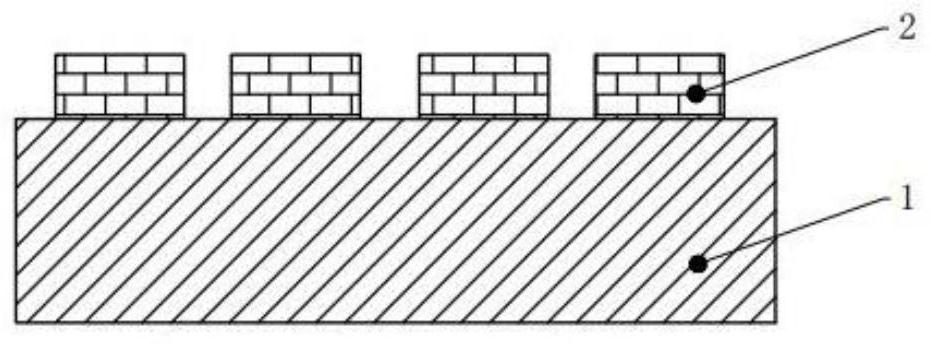

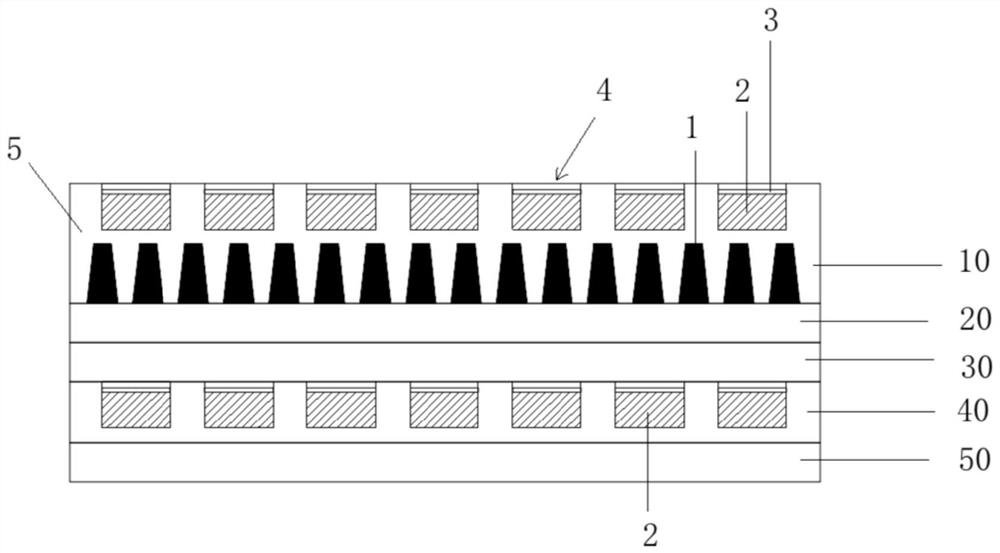

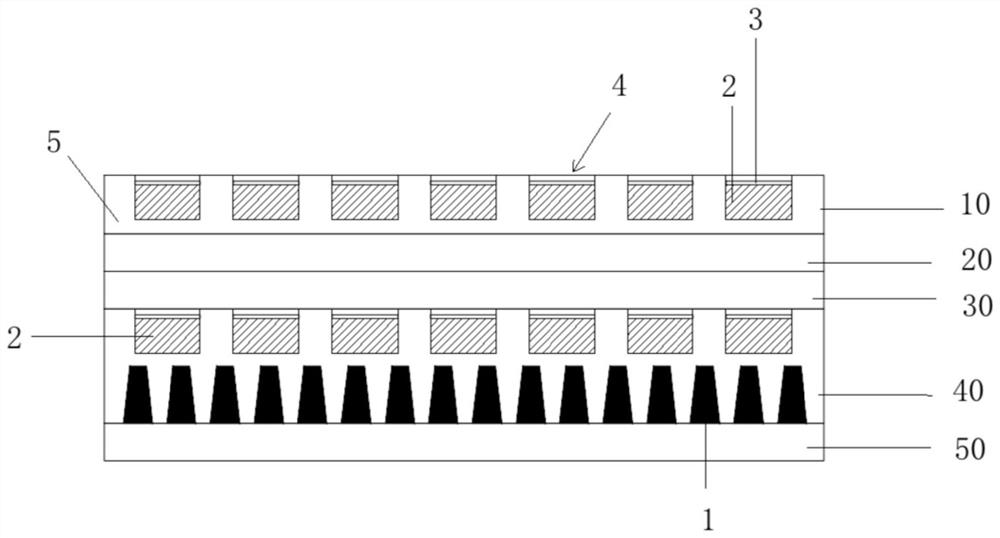

Light-emitting diode device and preparation method thereof

ActiveCN112335060AReduce areaReduce persistent accumulationSolid-state devicesSemiconductor devicesEngineeringLight-emitting diode

The invention discloses a light-emitting diode device and a preparation method thereof, which are not only suitable for light-emitting diode devices with a vertical structure, but also for other series of light-emitting diode devices such as a horizontal structure and a high-voltage structure. The light emitting diode device includes a substrate and a plurality of mesa structures located on the upper surface of the substrate. The mesa structure includes a light emitting diode mesa located in a light emitting area and a cutting area mesa located in a cutting area. The light emitting diode mesaand the cutting area mesa are arranged at intervals, and the cutting area Including the cutting channel and the spacer area, the reflective metal layer, the sacrificial layer and the first insulatinglayer inside the cutting channel are distributed in a trapezoid shape. This trapezoidal distribution method effectively improves the continuous direction of the stress at the cutting channel and reduces the continuous accumulation of stress Therefore, the stress lines and the abnormalities of easy peeling and falling off of the semiconductor epitaxial layer are reduced or eliminated, and the appearance yield of the light emitting diode device can be effectively improved, and the product quality of the light emitting diode device can be improved.

Owner:XIAMEN SANAN OPTOELECTRONICS TECH CO LTD

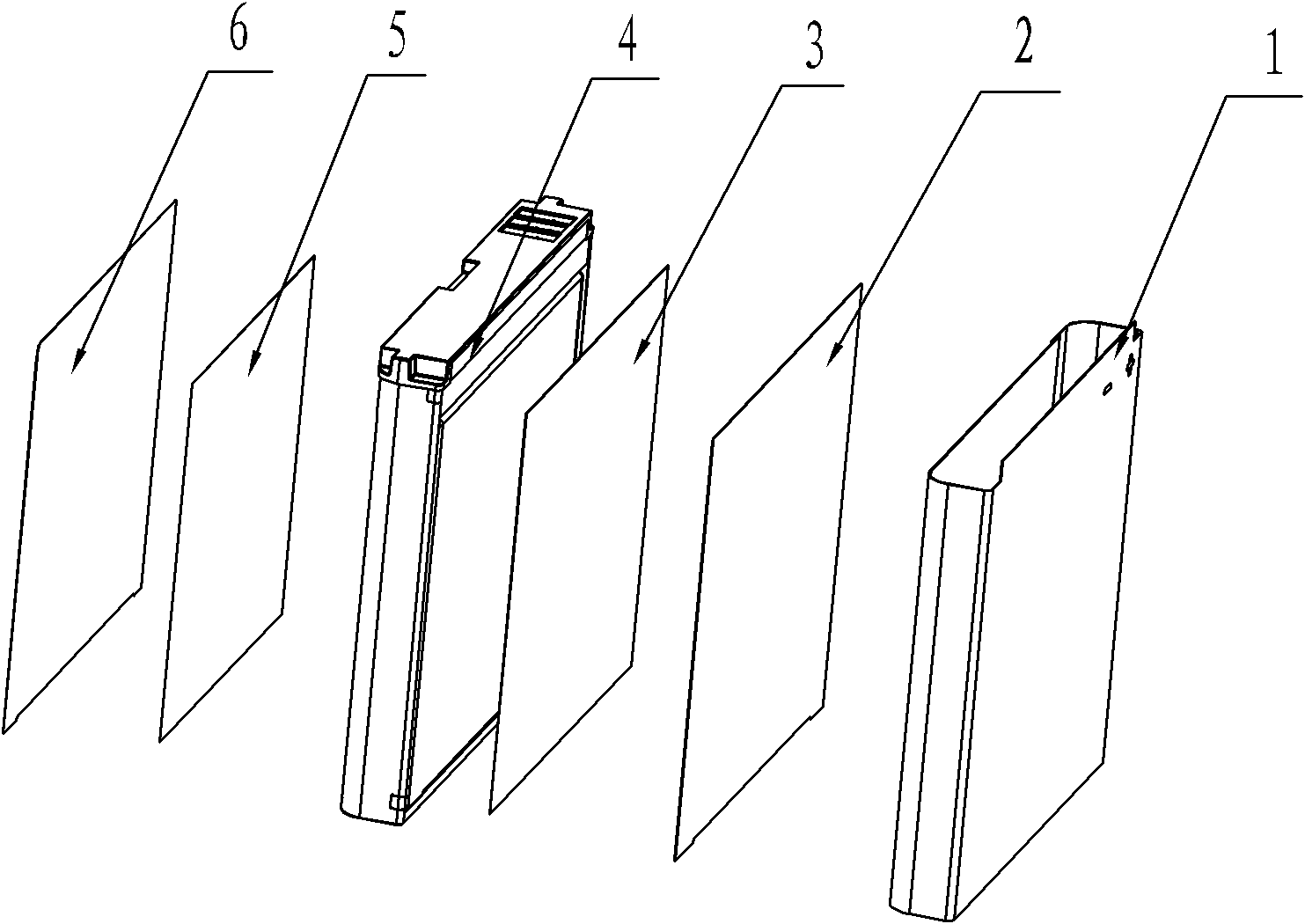

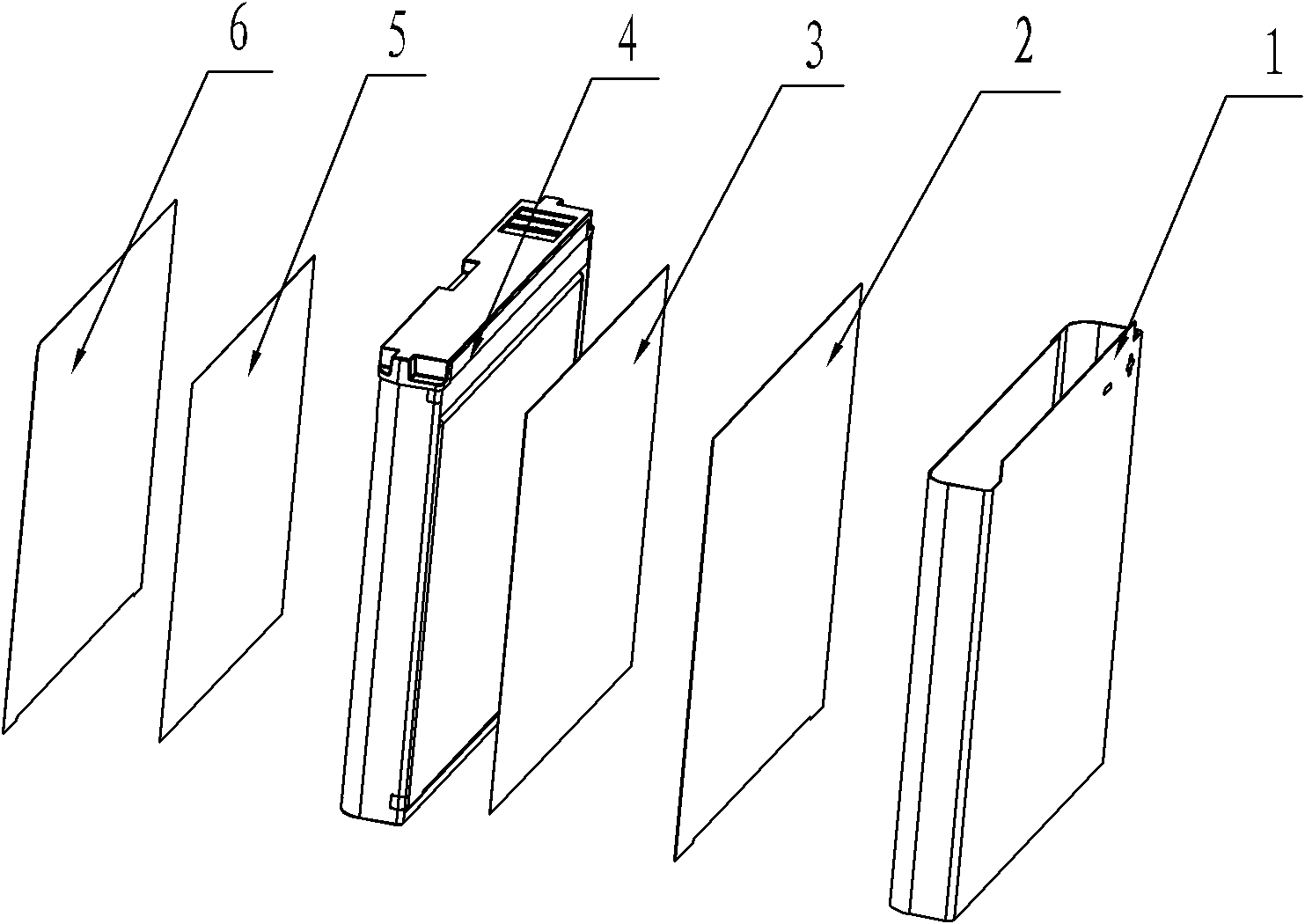

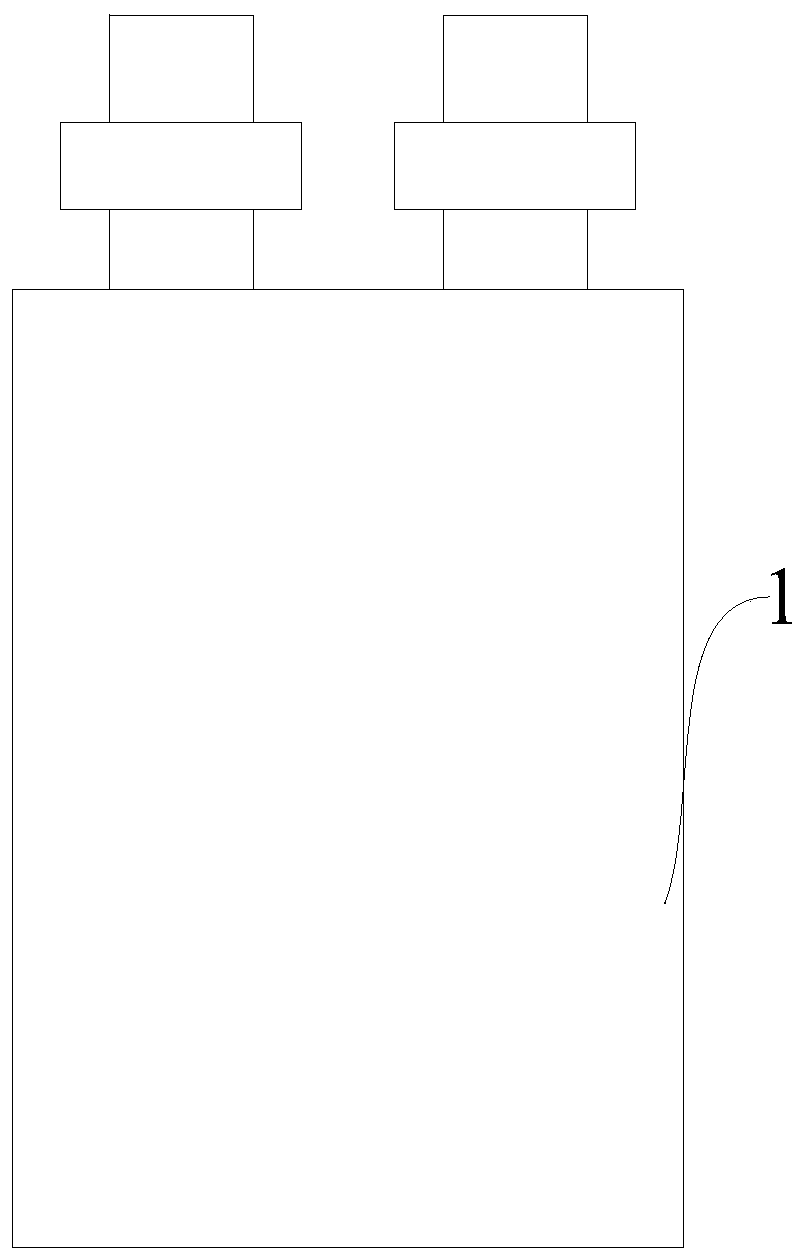

Low-pressure hot-melting and injection-molding assembly process for polymer lithium ion battery

InactiveCN101916880AAvoid stab woundsImprove appearance yieldFinal product manufactureCell component detailsPolymer scienceWork in process

The invention discloses a low-pressure hot-melting and injection-molding assembly process for a polymer lithium ion battery, which comprises the following steps of: first encapsulating a polymer lithium ion battery cell welded with a protective plate into a plastic frame; then performing low-pressure hot-melting and injection-molding to form a polymer lithium ion battery semi-finished product; next pasting a stainless steel wafer on the upper and lower surfaces of the polymer lithium ion battery semi-finished product respectively, and connecting the stainless steel wafers and a polymer lithium ion battery semi-finished product body by using double faced adhesive tapes; and finally attaching labels to the outside of the stainless steel wafer. Through the process, the appearance of the polymer mobile phone battery manufactured by low-pressure hot-melting and injection-molding technology is more attractive, while the yield is improved.

Owner:TIANJIN LISHEN BATTERY

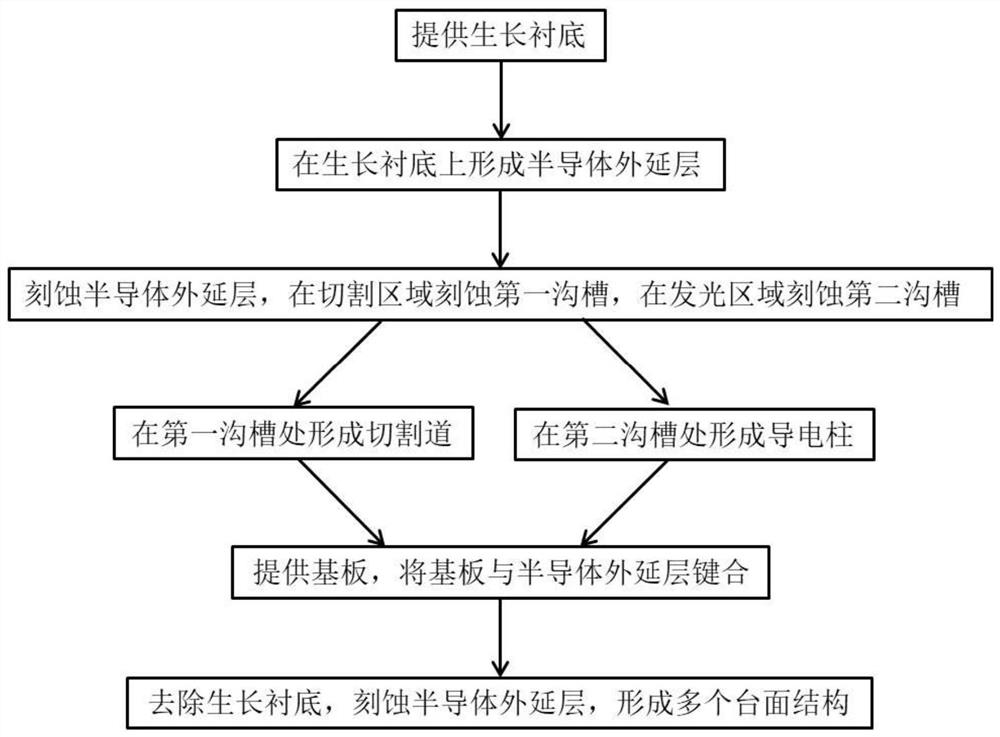

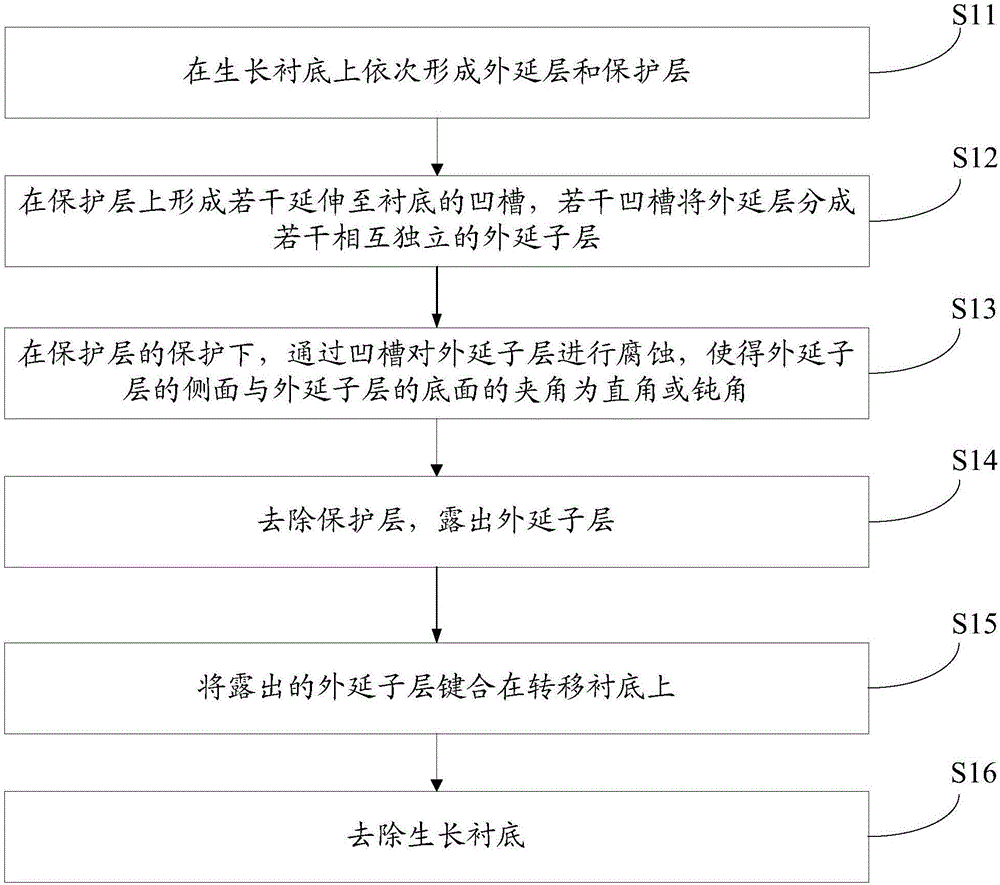

Manufacturing method of light-emitting diode

ActiveCN106449901AImprove appearance yieldNot easy to damageSemiconductor devicesManufacturing technologyEngineering

The invention discloses a manufacturing method of a light-emitting diode, and belongs to the technical field of photoelectron manufacturing. The method comprises the steps as follows: an epitaxial layer and a protection layer are sequentially formed on a growth substrate; a plurality of grooves extending to the substrate are formed in the protection layer; epitaxial sub-layers are corroded through the grooves under the protection of the protection layer and the protection layer is removed; the exposed epitaxial sub-layers are bonded on a transfer substrate and the growth substrate is removed; the epitaxial layer is divided into independent epitaxial sub-layers through forming the protection layer on the epitaxial layer and forming the grooves extending to the substrate in the protection layer, and the epitaxial sub-layers are corroded through the grooves, so that the included angle between the side surface and the bottom surface of each epitaxial sub-layer is a right angle or an obtuse angle; and the exposed included angle of each epitaxial sub-layer is the right angle or the obtuse angle and is not easily damaged after the epitaxial sub-layers are bonded on the transfer substrate and the growth substrate is removed, thereby improving the appearance yield of an LED chip.

Owner:HC SEMITEK ZHEJIANG CO LTD

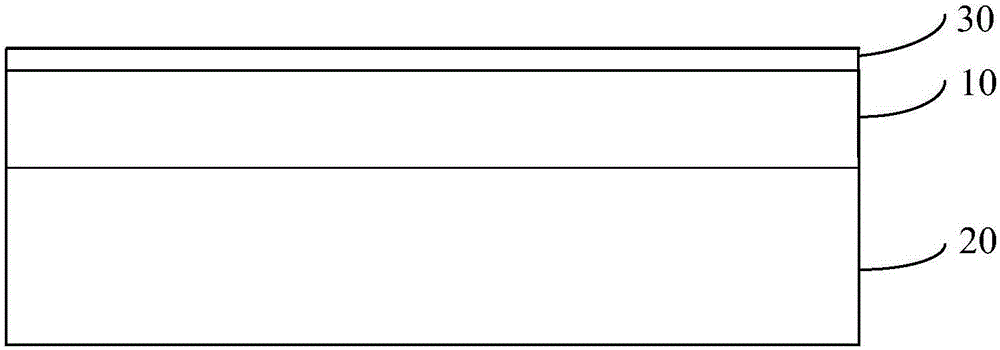

Solar cell reworking sheet coating technology

InactiveCN106098861AHigh refractive indexMitigate visual differencesFinal product manufactureSemiconductor devicesRefractive indexEngineering

A solar cell reworking sheet coating technology employs a bilayer film technology. The refractive index of a first layer film is higher than the refractive index of a second layer film, and the thickness of the first layer film is 25-40mm. The technology provided by the invention can effectively reduce the proportion of bad cell appearances caused by re-flocking.

Owner:ALTUSVIA ENERGY TAICANG

Method for improving manufacturing yield of LED chip

ActiveCN112447890AImprove manufacturing yieldSimple process operationSemiconductor devicesPhysicsThin membrane

The invention discloses a method for improving the manufacturing yield of an LED chip. The method comprises the steps: firstly carrying out the growth of a wafer epitaxial layer, then carrying out thecorrosion of a second highly-doped pGaP window layer to form an exposed region, and then depositing an oxide film; and then evaporating an ITO film on the surface of the epitaxial layer, continuouslymanufacturing a P-surface electrode and an N-surface electrode, finally evaporating a protective film on the surface of the P-surface electrode, then performing cutting, ultrasonically removing the protective film through hot water after cutting, and finally cleaning and expanding the film of the chip to form independent single core particles. According to the method, preparation of the LED chipis effectively achieved, the light-emitting effect of the chip is improved, MgF2 / CaF2 films alternately grow on the surface of the wafer, the light-emitting surface is smooth, the problems that in thecutting process, a diamond knife makes direct contact with an ITO film, and corner breakage, cracks and the like are likely to be generated are solved, the product quality and reliability are greatlyimproved, chippings and water stain and dirt residues in the cutting process are avoided, the product appearance yield is increased, and high practicability is achieved.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

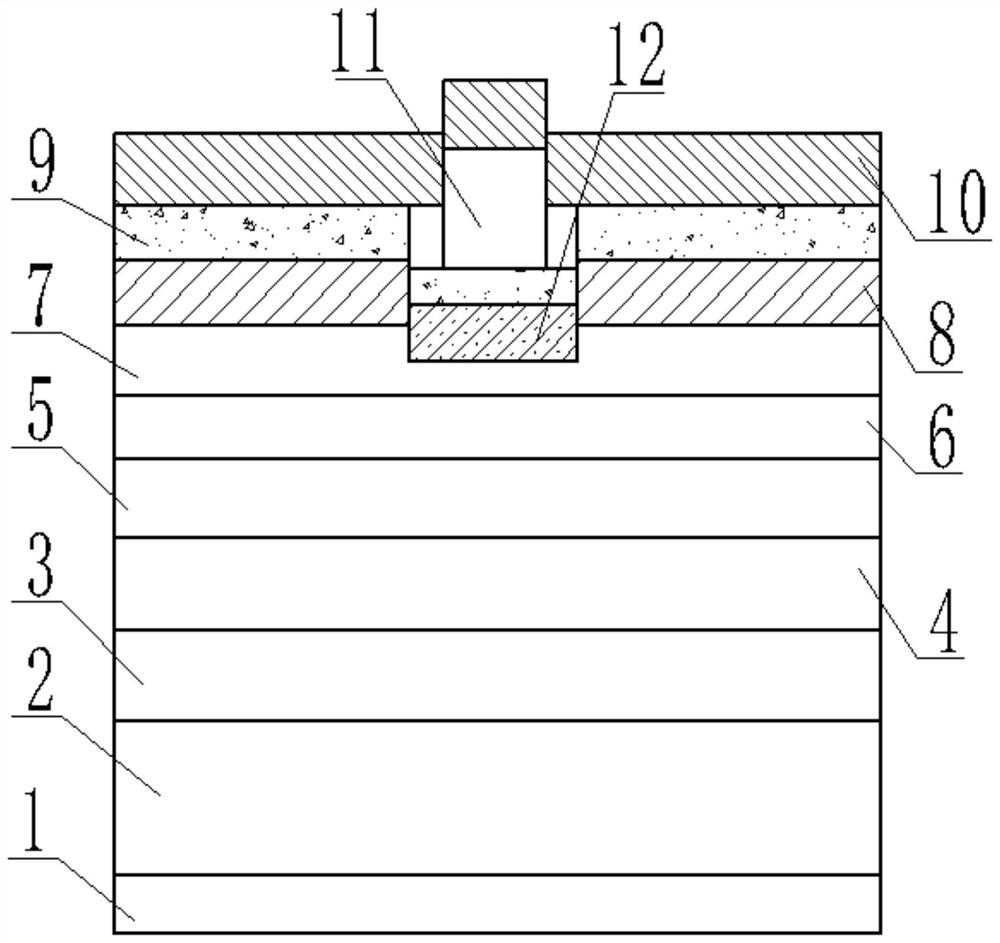

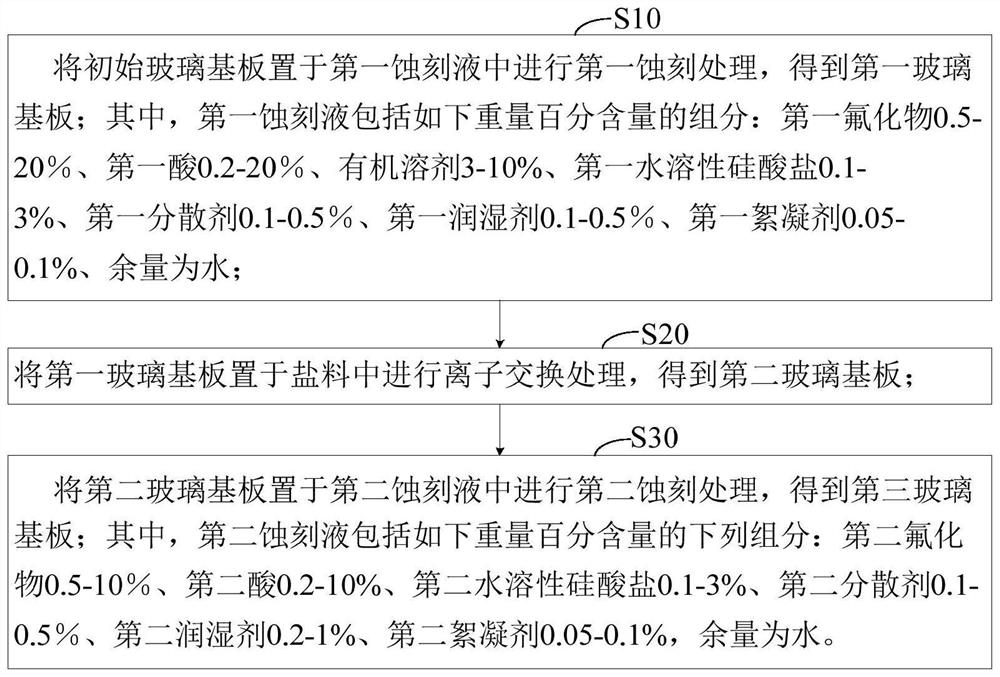

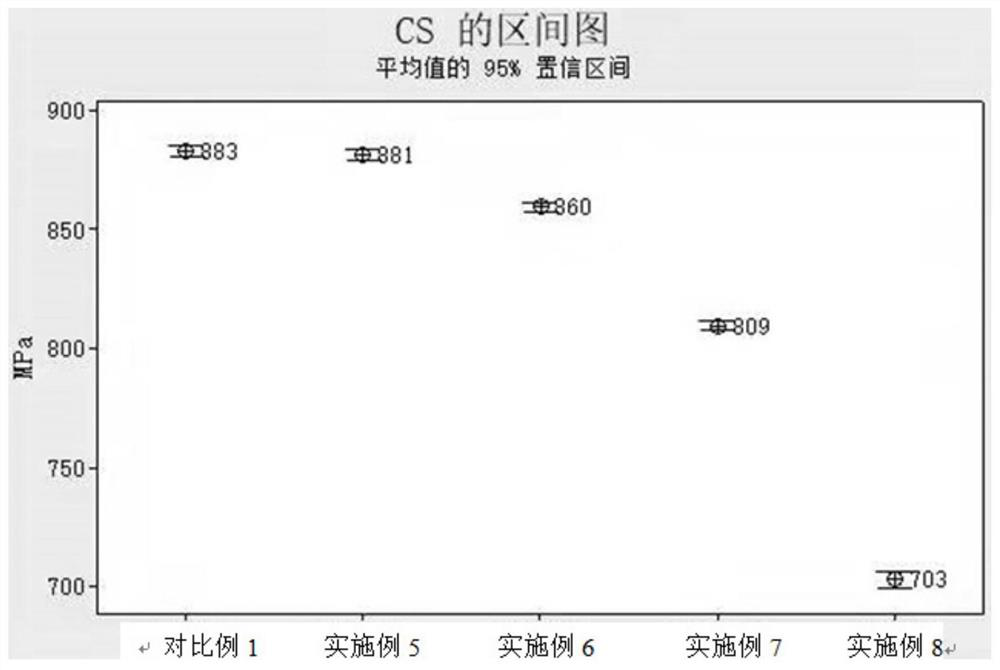

Glass strengthening method, glass substrate, and etching material for glass

PendingCN114455858ALittle change in thicknessImprove mechanical propertiesIon exchangeImpact resistance

The invention relates to the technical field of glass processing, and provides a glass strengthening method which comprises the following steps: putting an initial glass substrate into a first etching solution for first etching treatment to obtain a first glass substrate; placing the first glass substrate in a salt material for ion exchange treatment to obtain a second glass substrate; the second glass substrate is placed in a second etching solution for second etching treatment, and a third glass substrate is obtained. The method comprises the following steps: passivating microcracks generated in the manufacturing and appearance processing processes of an initial glass substrate through first etching treatment, and then forming an ion exchange layer with a certain depth on the surface of a first glass substrate through ion exchange treatment; and finally, passivating microcracks generated by ion exchange and releasing stress concentration formed by ion exchange through second etching treatment, so that the glass substrate strengthened by the glass strengthening method is good in mechanical property and has very strong impact resistance. In addition, the glass strengthening method is simple in process, easy to control and low in production cost.

Owner:LILING KIBING ELECTRONIC GLASS CO LTD

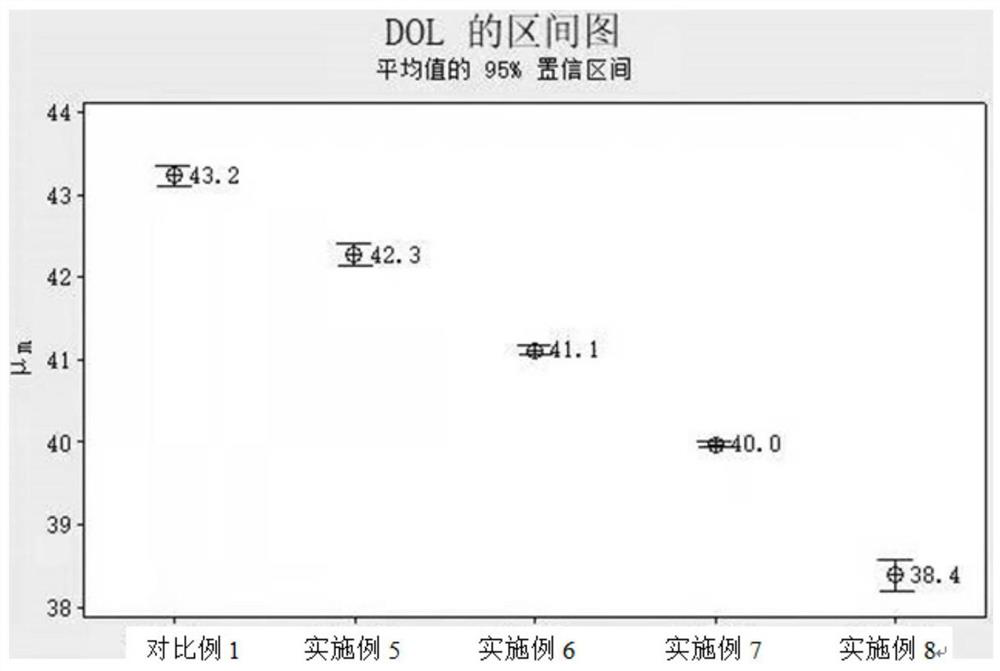

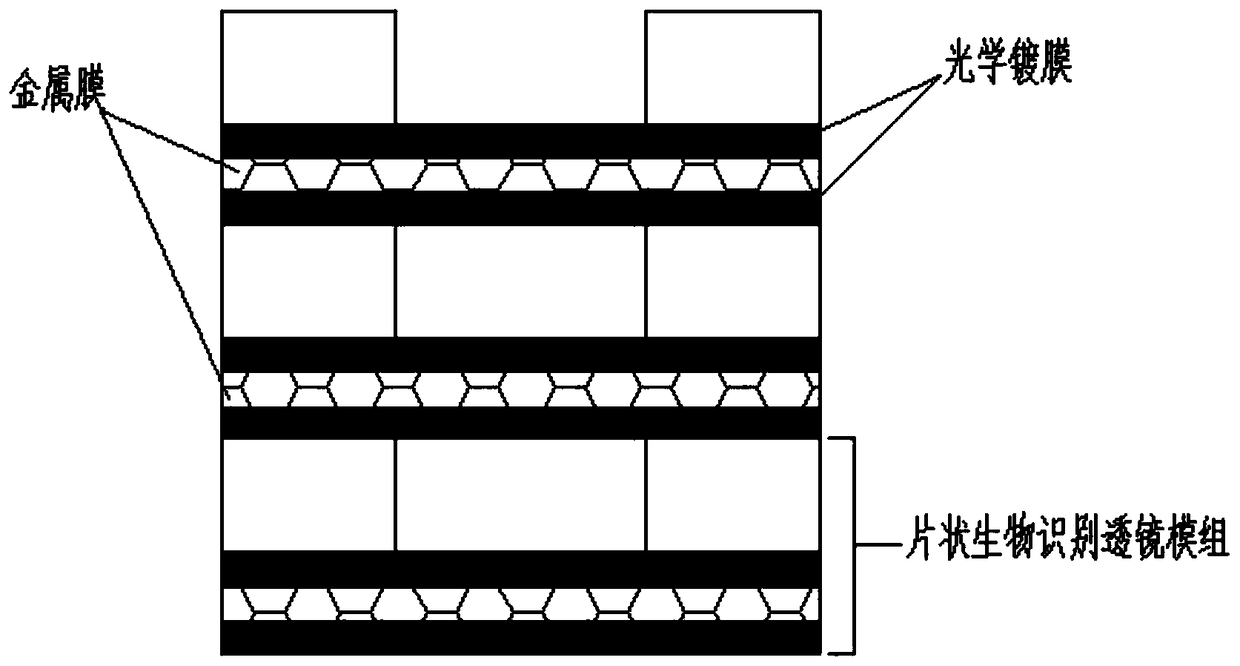

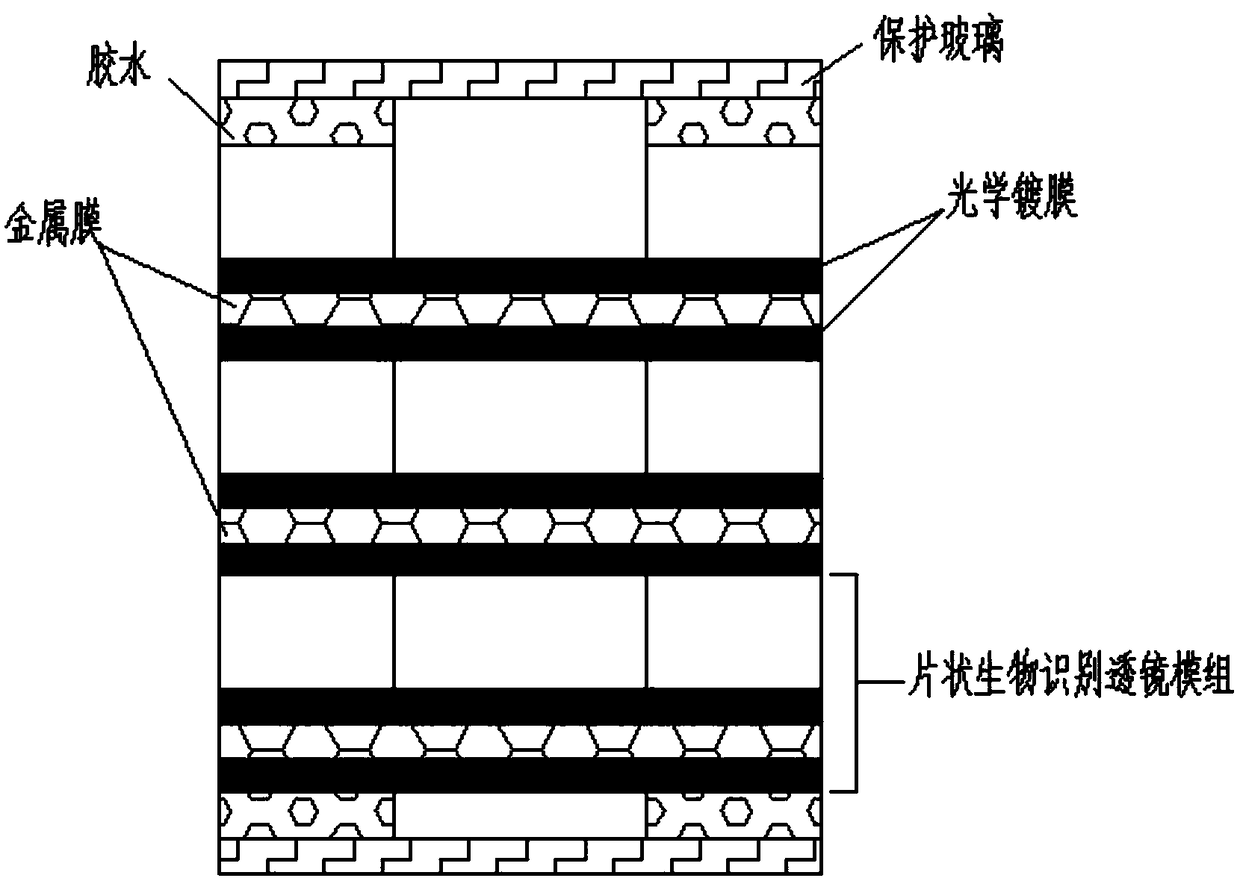

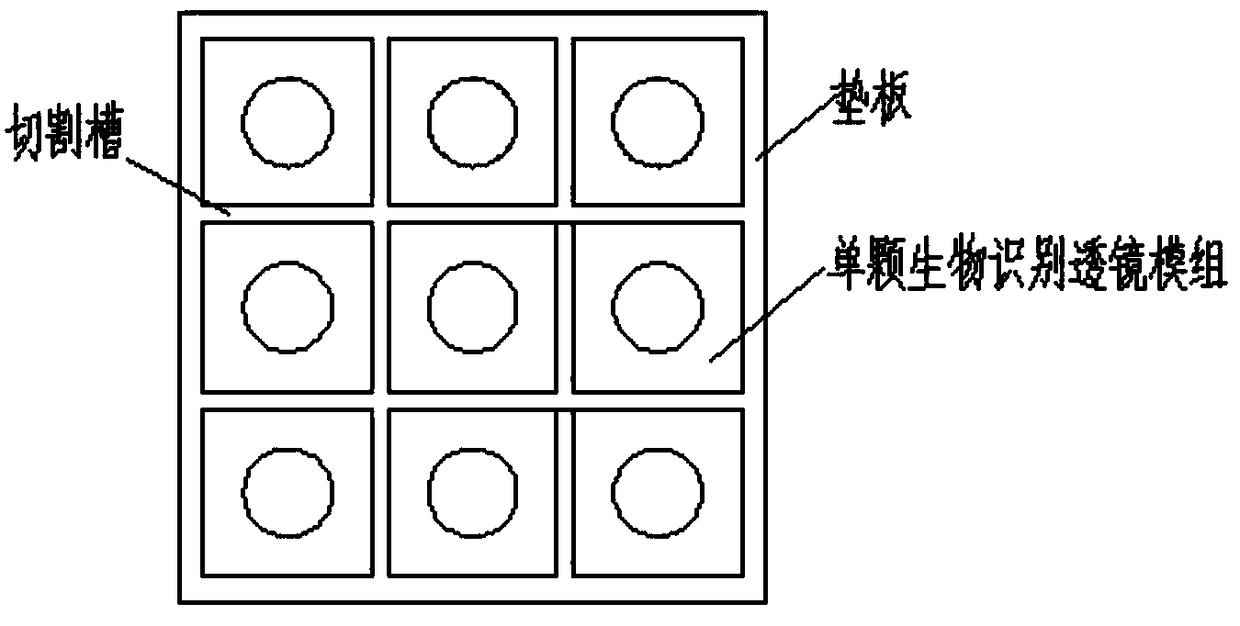

Processing technology of multilayer superimposed biological recognition lens module

InactiveCN109445004AImprove alignment accuracyImprove machining accuracyLensSuperimpositionProtective glasses

The invention discloses a processing technology of a multilayer superimposed biological recognition lens module. The processing technology comprises the following steps of step 1, superimposition of the biological recognition lens module; step 2, pasting of protective glass; step 3, cutting of a metal blade; step 4, cylindrical processing of the single multilayer biological recognition lens module; step 5, degumming processing; and step 6, ultrasonic cleaning. The processing technology of the multilayer superimposed biological recognition lens module has the advantages that the processing precision is high, the non-defective product rate of the appearance is high, and the technology is novel.

Owner:HANGZHOU MDK OPTO ELECTRONICS CO LTD

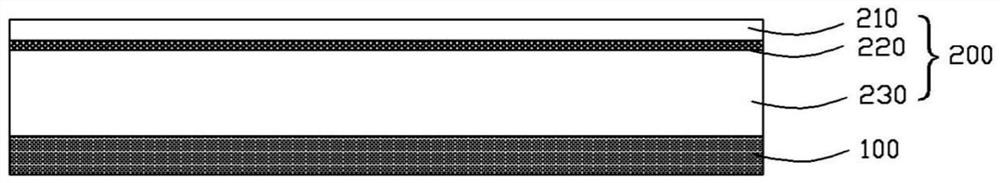

Light emitting diode and manufacturing method

ActiveCN113875032AAvoid etchingImprove appearance yieldSemiconductor devicesPhysical chemistryActive layer

The invention discloses a light-emitting diode and a manufacturing method, and the light-emitting diode comprises: a substrate which is provided with a first surface and a second surface which are opposite to each other; a semiconductor epitaxial laminated layer which comprises a first conductive type semiconductor layer, an active layer and a second conductive type semiconductor layer which are laminated on the first surface of the substrate; a side wall which is formed on the edge of the semiconductor epitaxial laminated layer, wherein the side wall is provided with a coarsening structure, and the coarsening structure comprises a bulge; an etching barrier layer which is located on the upper surface, far away from the substrate, of the semiconductor epitaxial laminated layer. The etching barrier layer can prevent etching liquid from etching the upper surface of the semiconductor epitaxial laminated layer in the side wall coarsening process, the appearance yield of the semiconductor light-emitting diode is improved, and the photoelectric property of the light-emitting diode is improved.

Owner:TIANJIN SANAN OPTOELECTRONICS

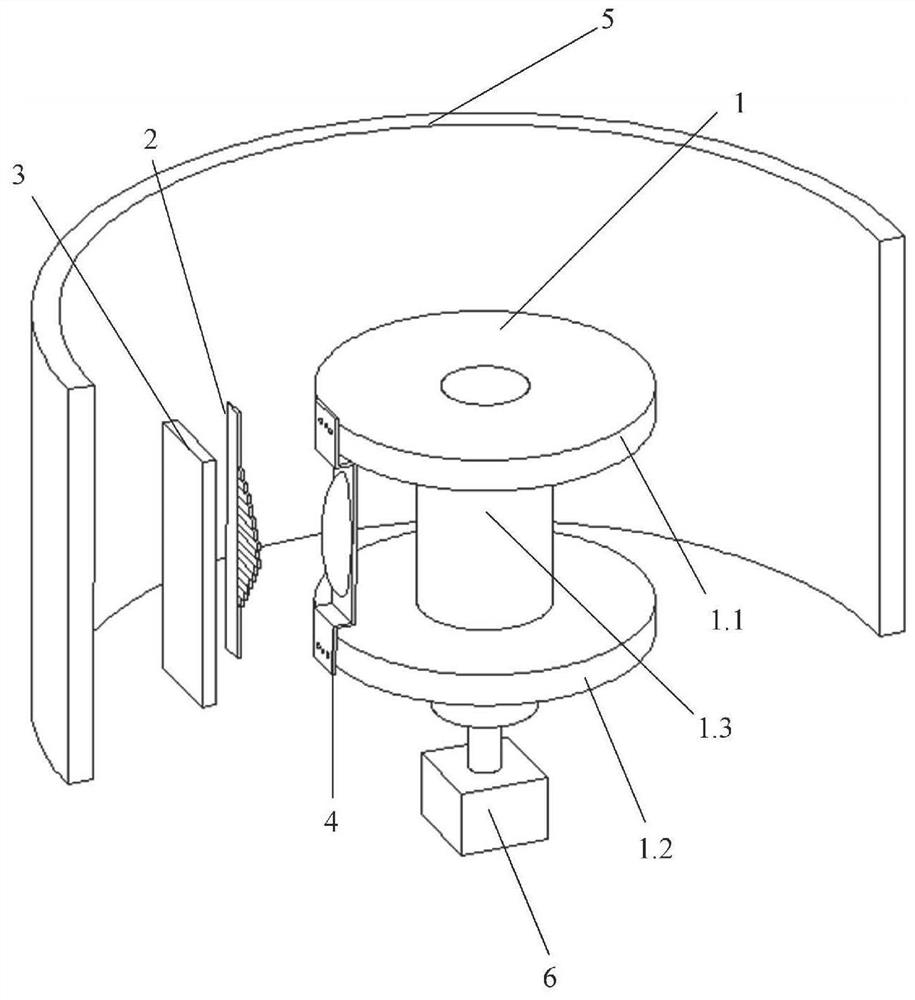

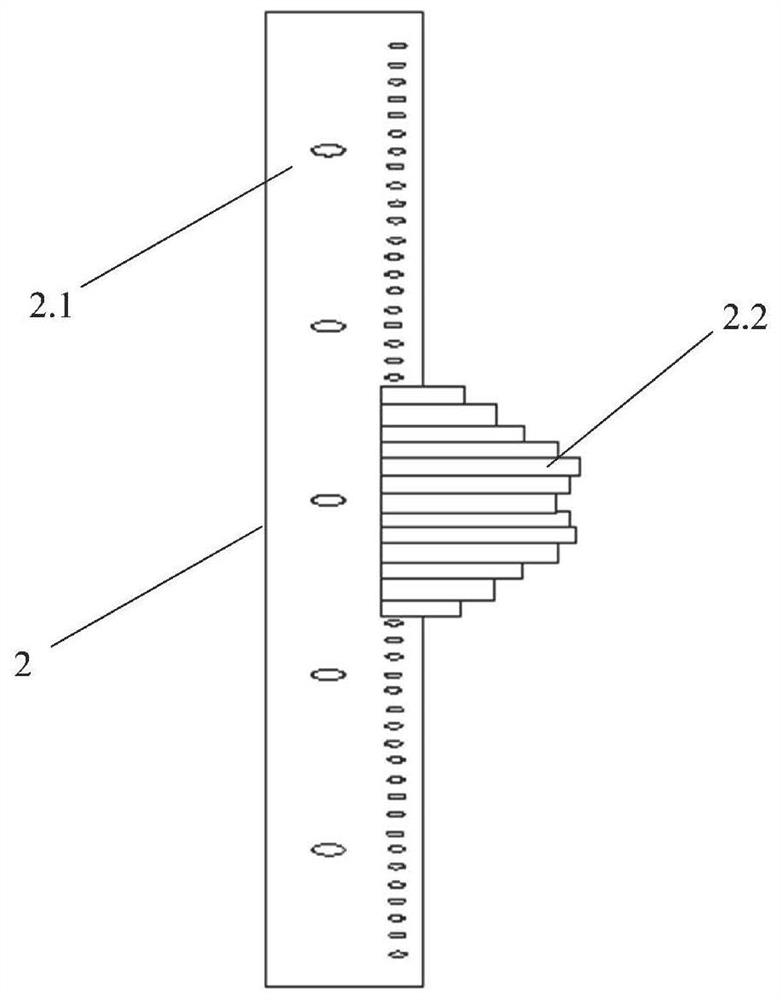

A curved glass coating device, coating process and coating product

The invention provides a curved glass coating device, a coating process and a coating product, which include a rotatable workbench, a power source for driving the workbench, a hanging plate set on the workbench, and a hanger The plate is opposite to the target spray head and the correction component arranged between the hanging plate and the target spray head, the rotation axis direction of the worktable is parallel to its own length direction; The end is fixed with the workbench, and the hanging plate includes a bump set in the middle for placing the curved glass, and the bump and the curved glass are fixedly connected by an adhesive member, and the correction part includes a correction plate and a tooth piece arranged in the same plane And the plane is perpendicular to the line connecting the spraying center of the nozzle of the target material and the geometric center of the bump. The coating device of the invention has simple structure, simplified coating process steps and convenient operation. The spectral wavelength of the coating product is 380-1100nm, the light transmittance is greater than 94%, and the film thickness is uniform.

Owner:LENS TECH

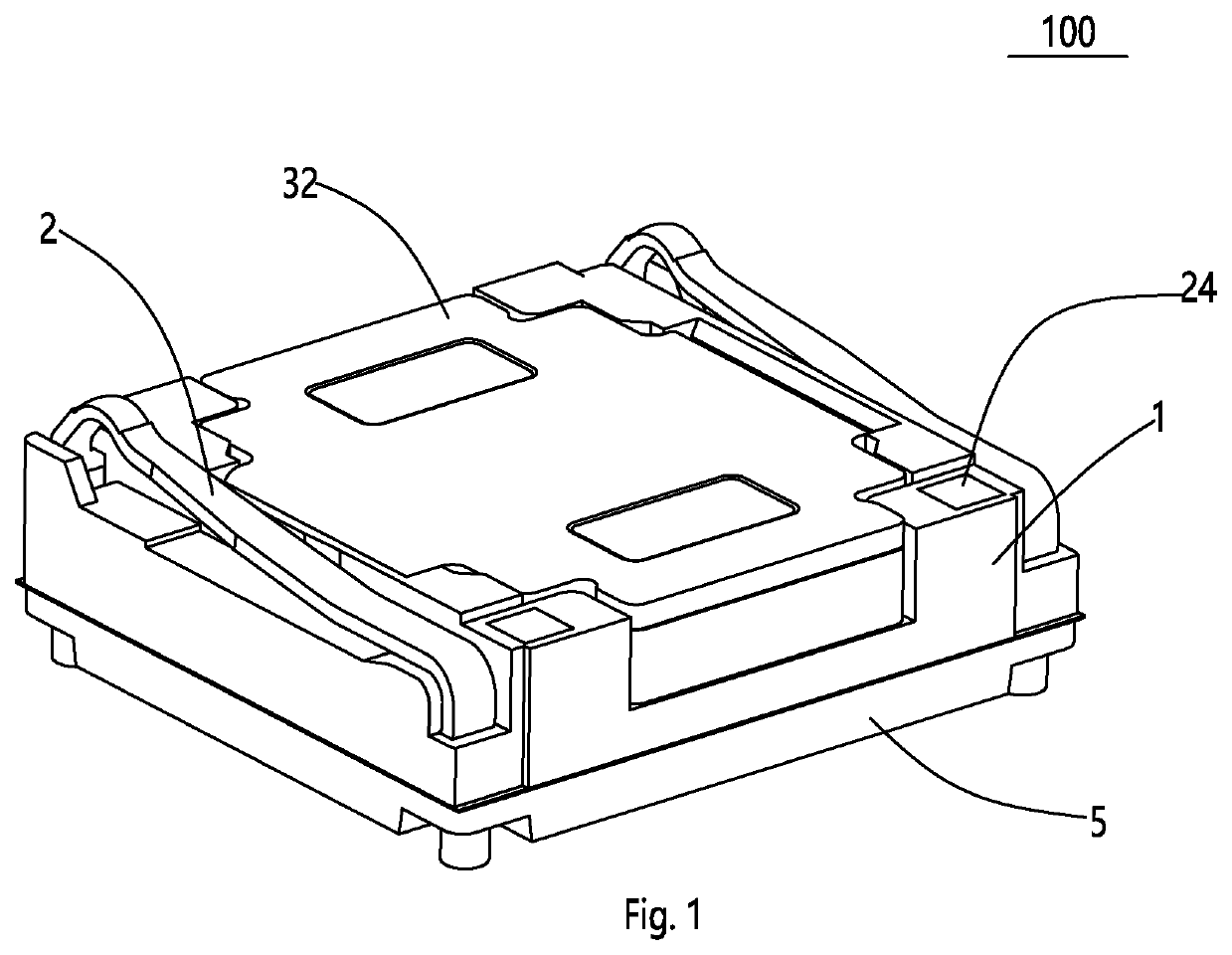

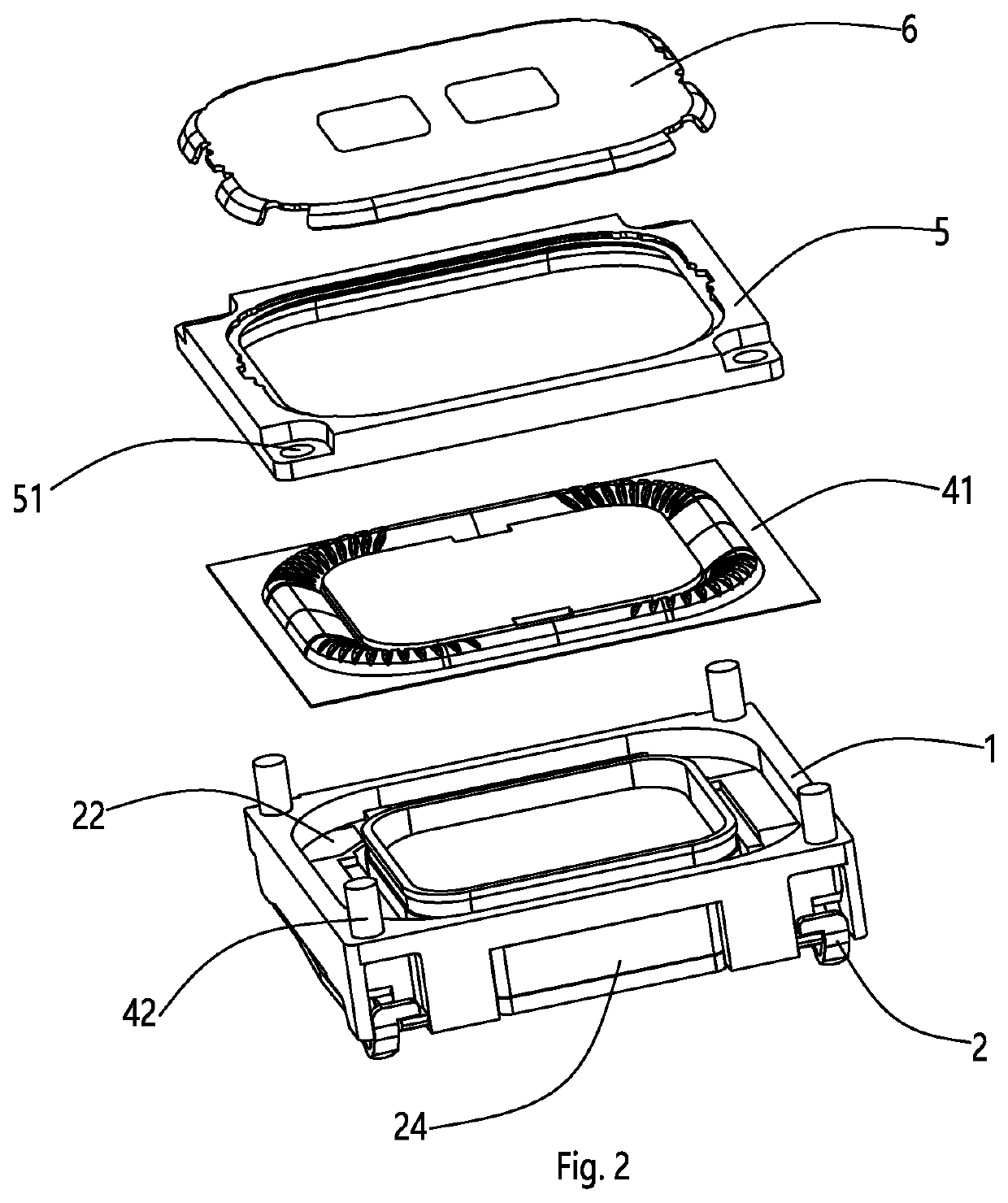

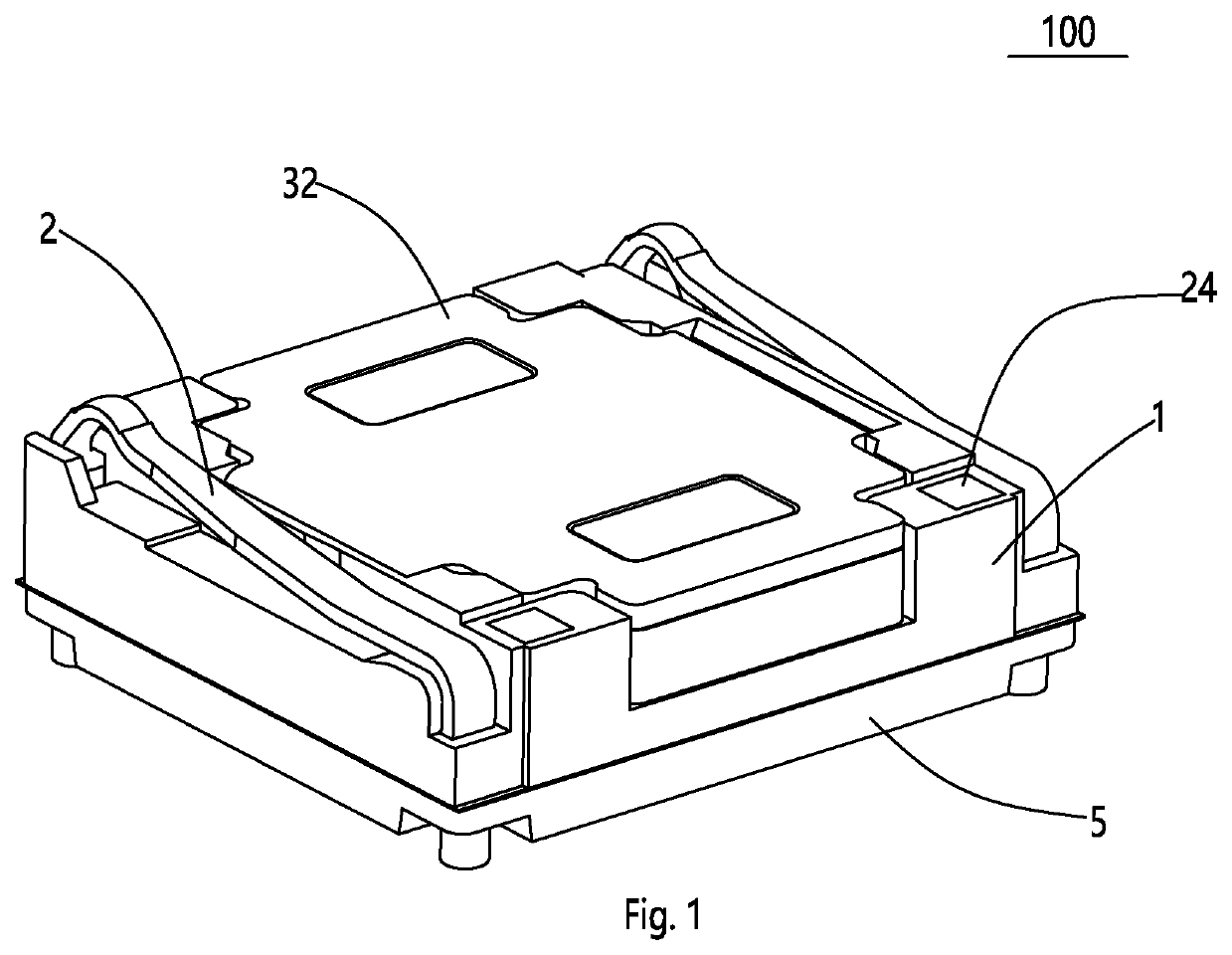

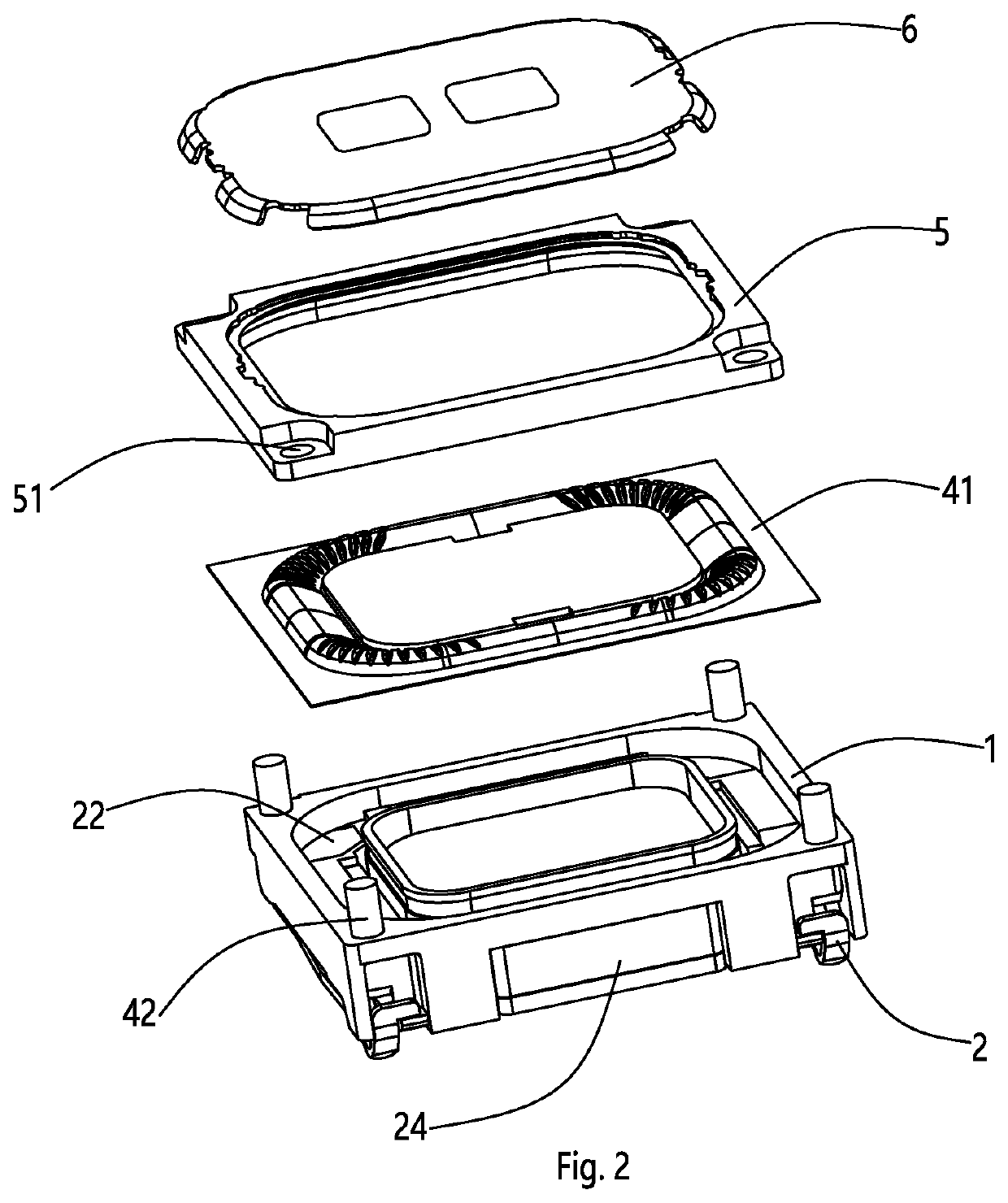

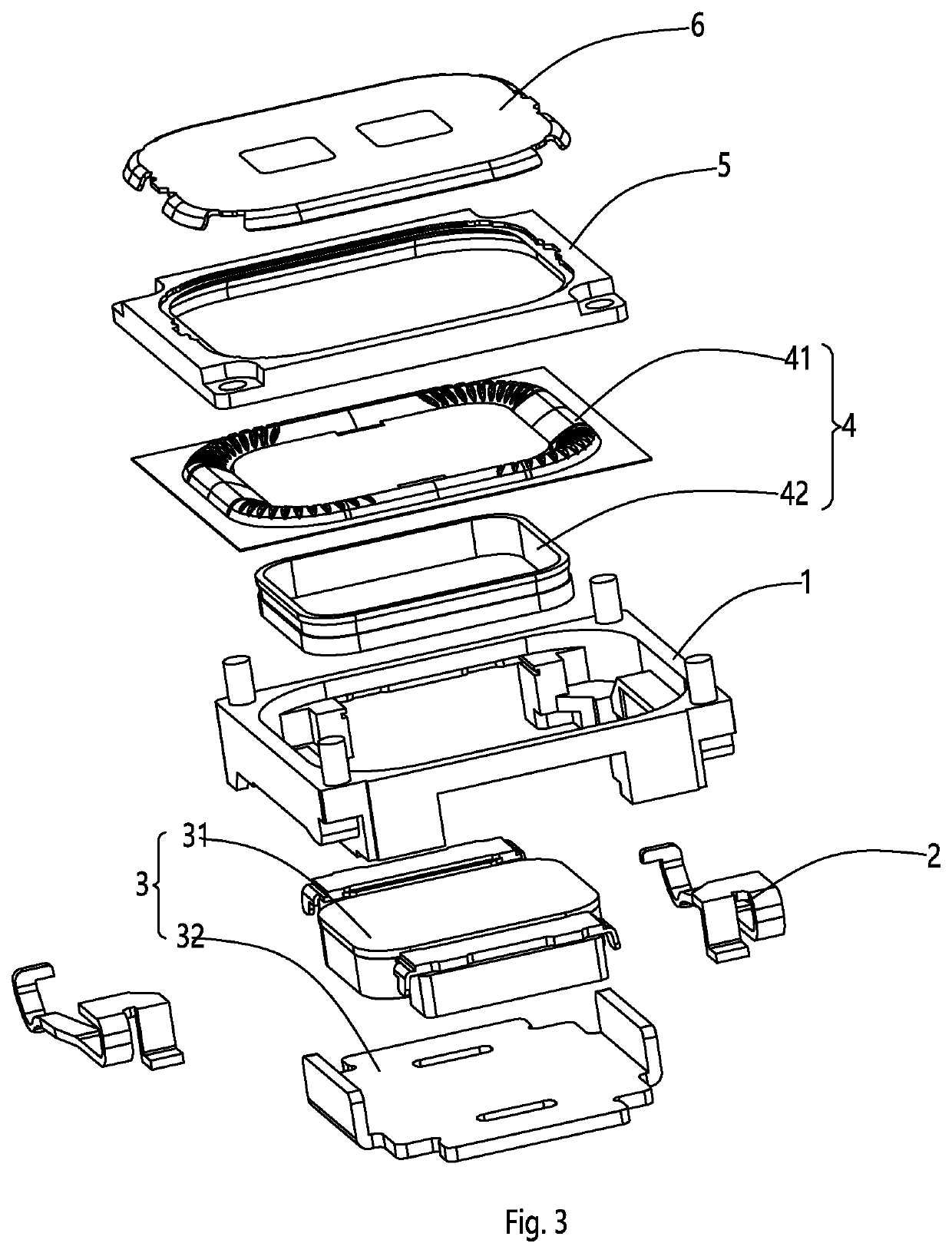

Speaker assembly

ActiveUS10764690B2Improve appearance yieldLoudspeakersCircuit lead arrangements/reliefElectrical connectionEngineering

The present disclosure provides a speaker assembly. The speaker assembly includes an electrical connector, and the electrical connector includes a body part and a second pad part connected with the body part. In this way, we can measure flux or test pure tone and performance of the finished product through the second pad part during assembling of the speaker assembly of the structure, so as to prevent the body part from being scratched caused by contact in the traditional test process, thus improving the appearance yield of the finished product.

Owner:AAC TECH PTE LTD

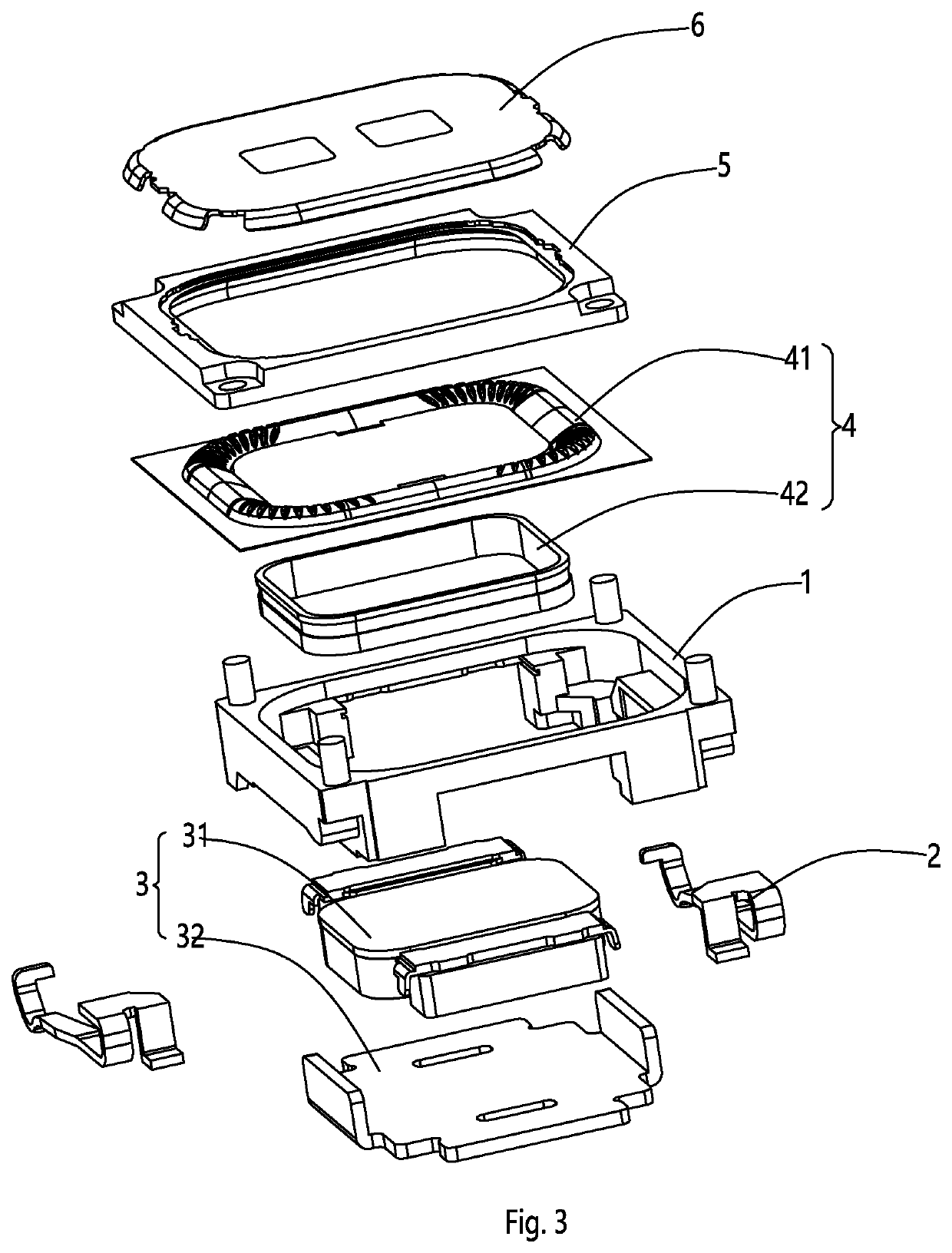

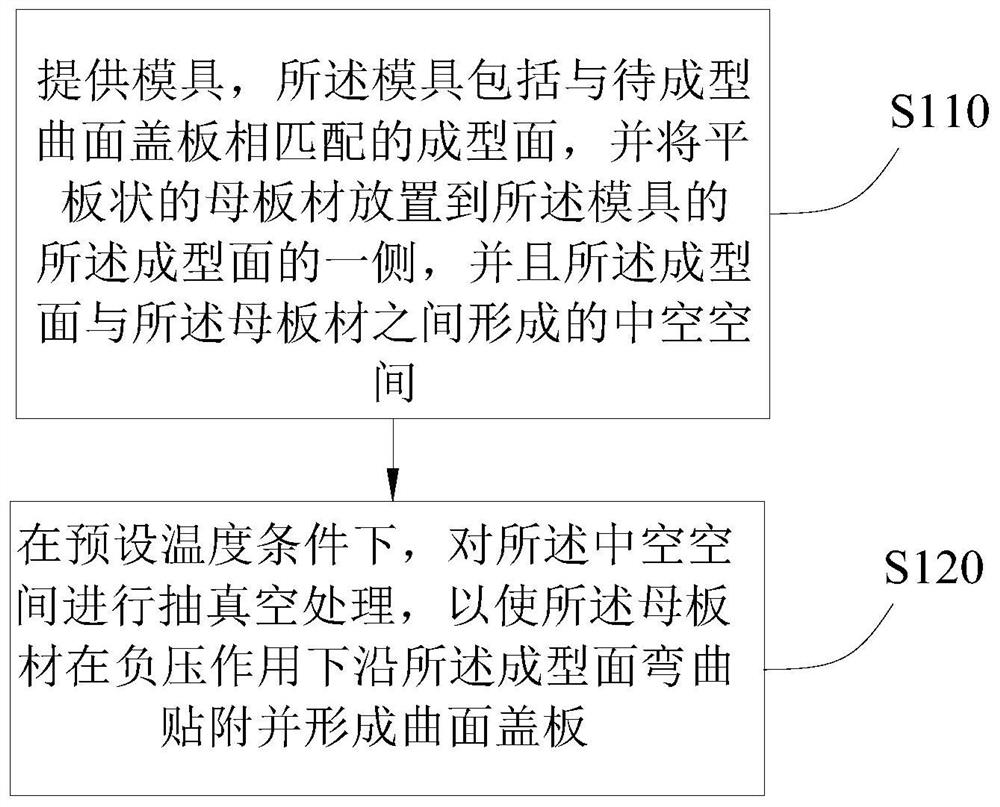

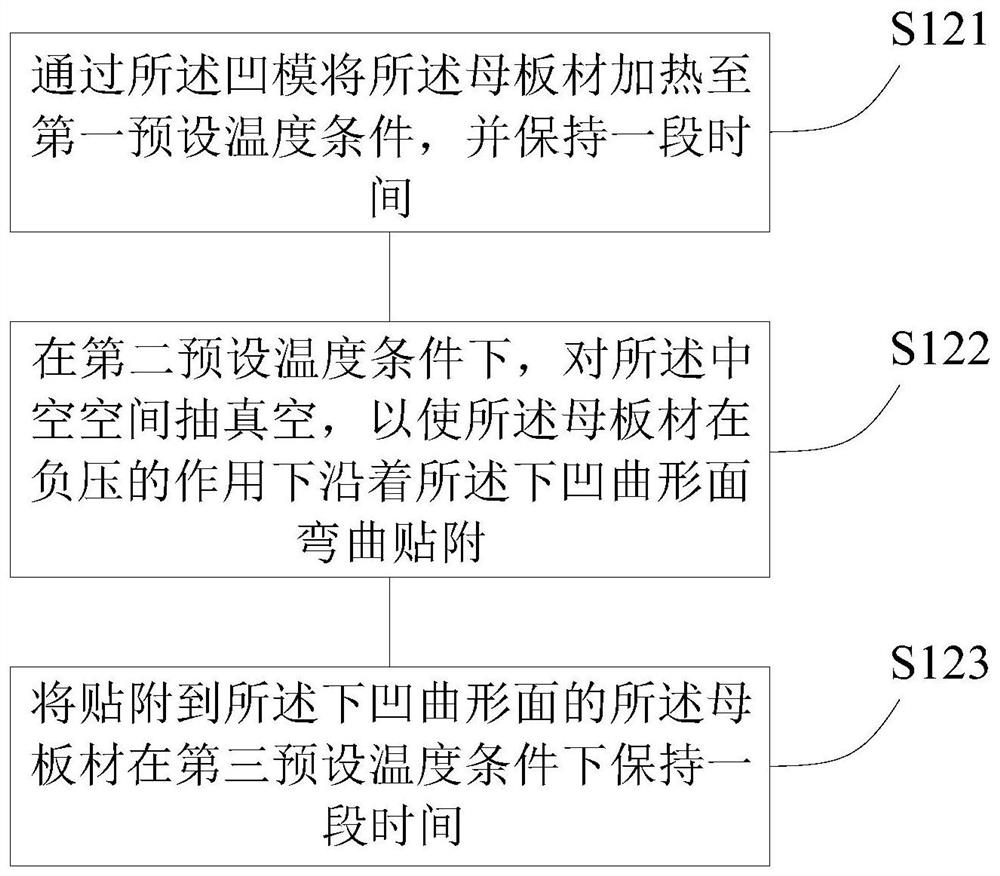

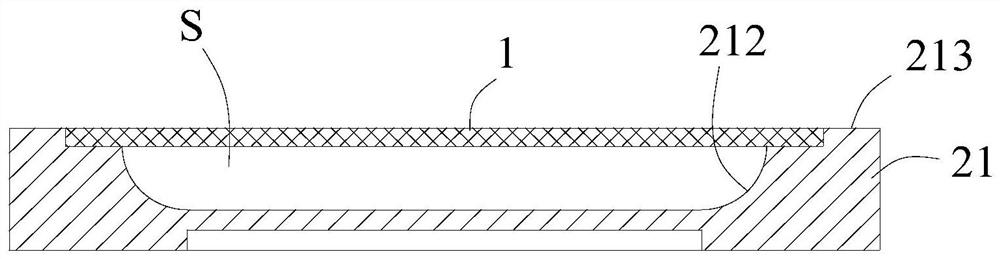

Forming method and forming device of curved-surface cover plate

PendingCN112174499AImprove appearance yieldReduce wearGlass reforming apparatusMoulding devicePumping vacuum

The invention discloses a forming method and a forming device for a curved surface cover plate. The invention provides the forming method for the curved surface cover plate, which comprises the stepsthat a mold is provided, the mold comprises a forming surface matched with a to-be-formed curved surface cover plate, a flat-plate-shaped mother plate is placed on one side of the forming surface of the mold, and a hollow space is formed between the forming surface and the mother plate; and under a preset temperature condition, the hollow space is subjected to vacuumizing treatment, so that the mother plate is bent and attached along the forming surface under the action of negative pressure to form a curved-surface cover plate.

Owner:KUNSHAN NEW FLAT PANEL DISPLAY TECH CENT

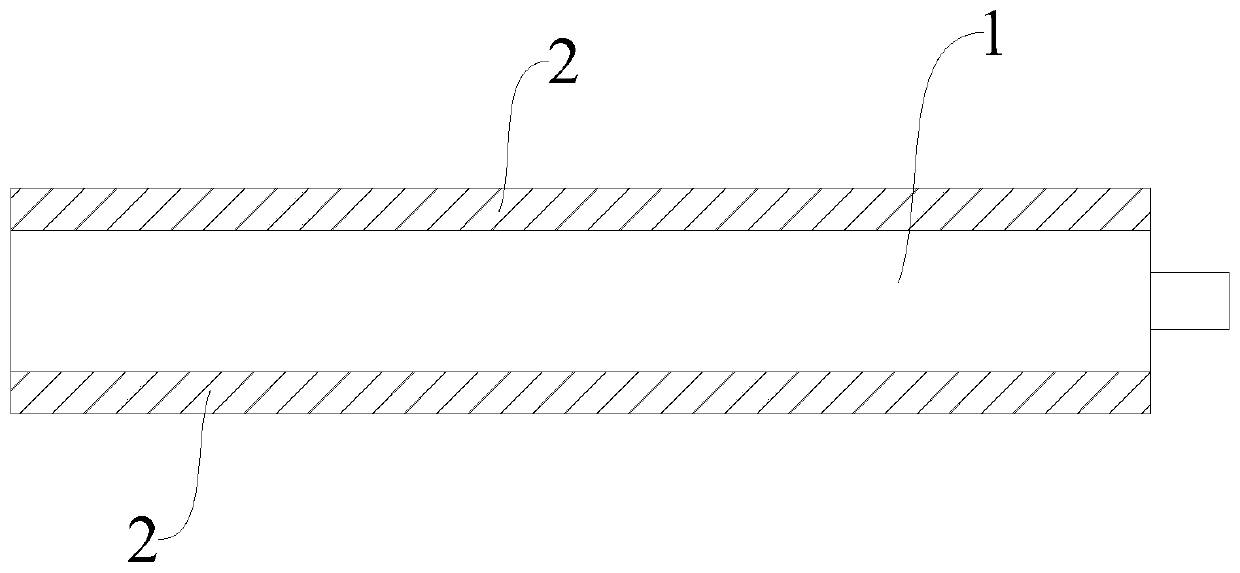

High-flatness soft package lithium ion battery and preparation method thereof

PendingCN111584928AImprove flatnessImprove appearance yieldFinal product manufactureElectrolyte accumulators manufactureEngineeringLithium-ion battery

The invention belongs to the technical field of soft package lithium ion batteries, and particularly relates to a high-flatness soft package lithium ion battery and a preparation method thereof. The preparation method comprises the steps that a positive plate, a diaphragm and a negative plate are subjected to Z-shaped lamination and tab welding, and a bare battery cell is obtained; the upper surface and the lower surface of the bare battery cell are respectively provided with a plastic partition plate, the length and the width of each plastic partition plate are 1 to 2 mm smaller than those ofthe bare battery cell, the thickness of each plastic partition plate is 0.5to 1 mm, the chamfer of each plastic partition plate is 1.5 to 2 mm, and the surfaces of the plastic partition plates are provided with net-shaped gaps and are uniformly distributed; and the bare battery cell with the plastic partition plates is put into an aluminum-plastic film, top side sealing, liquid injecting, formingand capacity grading are carried out to acquire the high-flatness soft package lithium ion battery. According to the invention, the flatness of the battery cell can be improved, and high flatness canbe permanently maintained; and the method has the advantages of simplicity and convenience in operation, low cost, easiness in large-scale production, improvement of the appearance yield of the battery cell, great reduction of the production cost and the like.

Owner:TIANNENG SAFT ENERGY JOINT CO

Cutting method of GaAs-based LED chip

The invention relates to a cutting method of a GaAs-based LED chip. The cutting method comprises the following specific steps: (1) grinding a front-end semi-finished product COW of the GaAs-based LEDchip; (2) evaporating an ohmic contact metal film layer on the N surface of the COW; (3) corroding the ohmic contact metal film layer on the N surface of the COW to form a cutting channel; (4) coatingthe P surface of the COW with a curing adhesive; (5) transferring the COW to ICP etching equipment, and carrying out ICP dry etching; (6) covering the N surface of the COW with a blue film; and (7) removing the curing adhesive on the P surface of the COW to obtain the independent chip. According to the method, the ICP etching technology is adopted to cut the N surface of the front process semi-finished product COW of the GaAs-based LED chip, the ohmic contact metal film layer is adopted as a mask to perform ICP dry etching, the cutting efficiency is high, the phenomena of P collapse and N collapse do not occur, and the appearance yield is 10-20% higher than that obtained through mechanical cutting.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

A watch case automatic disassembly device

ActiveCN106736459BReduce fatigueImprove work efficiencyMetal working apparatusDrive shaftEngineering

Owner:GEER TECH CO LTD

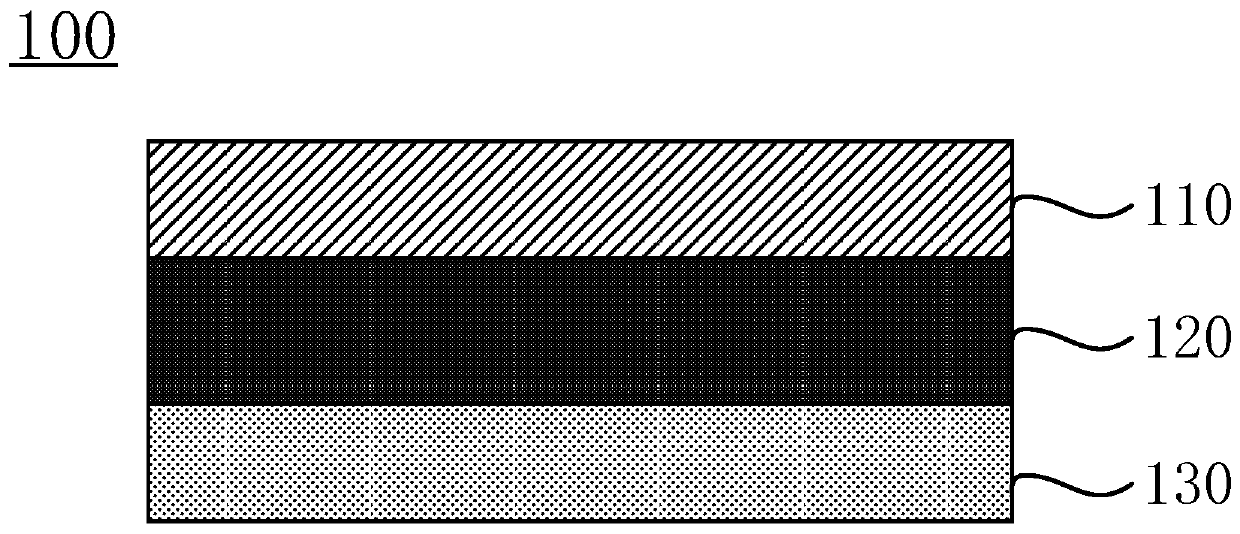

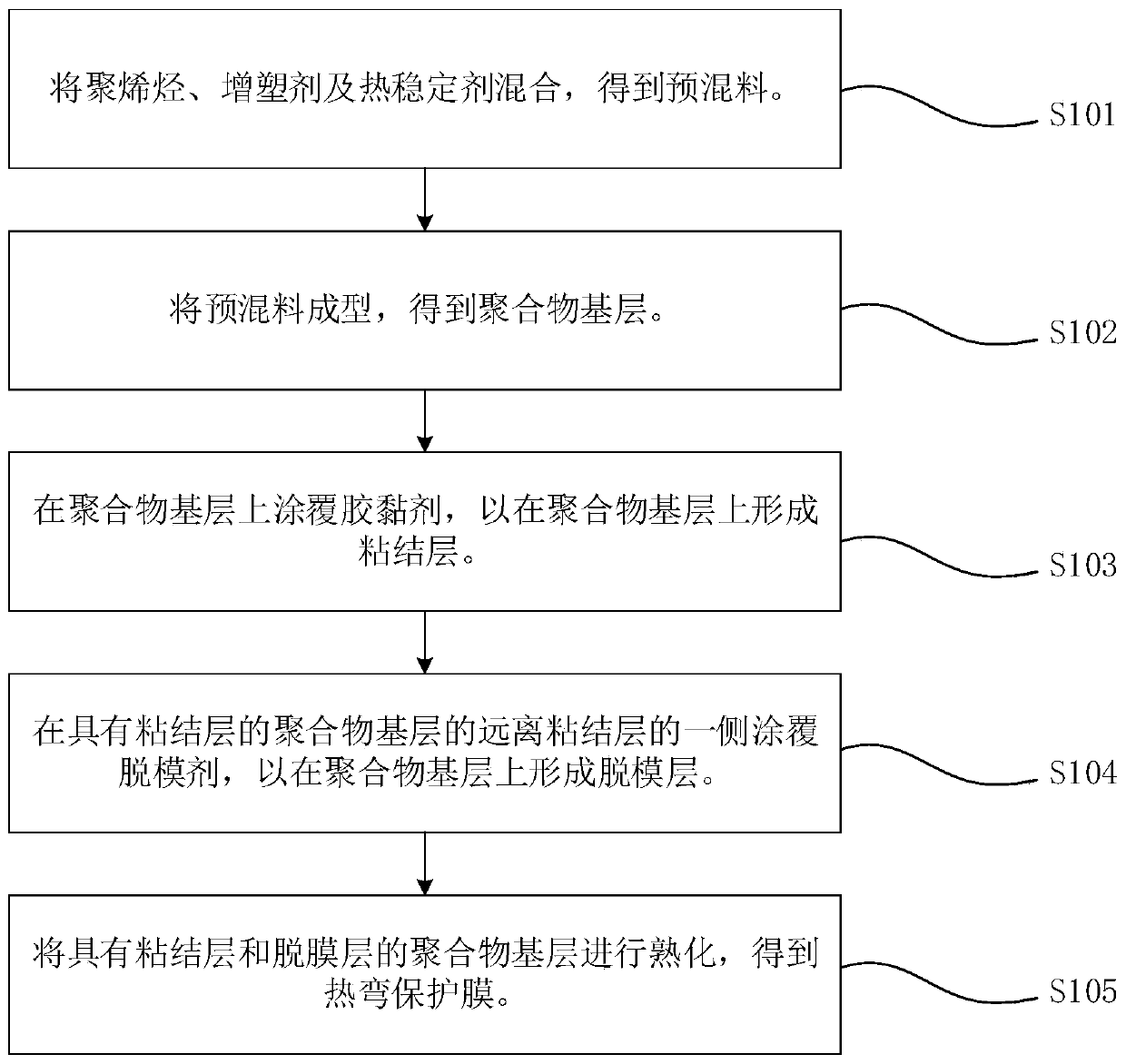

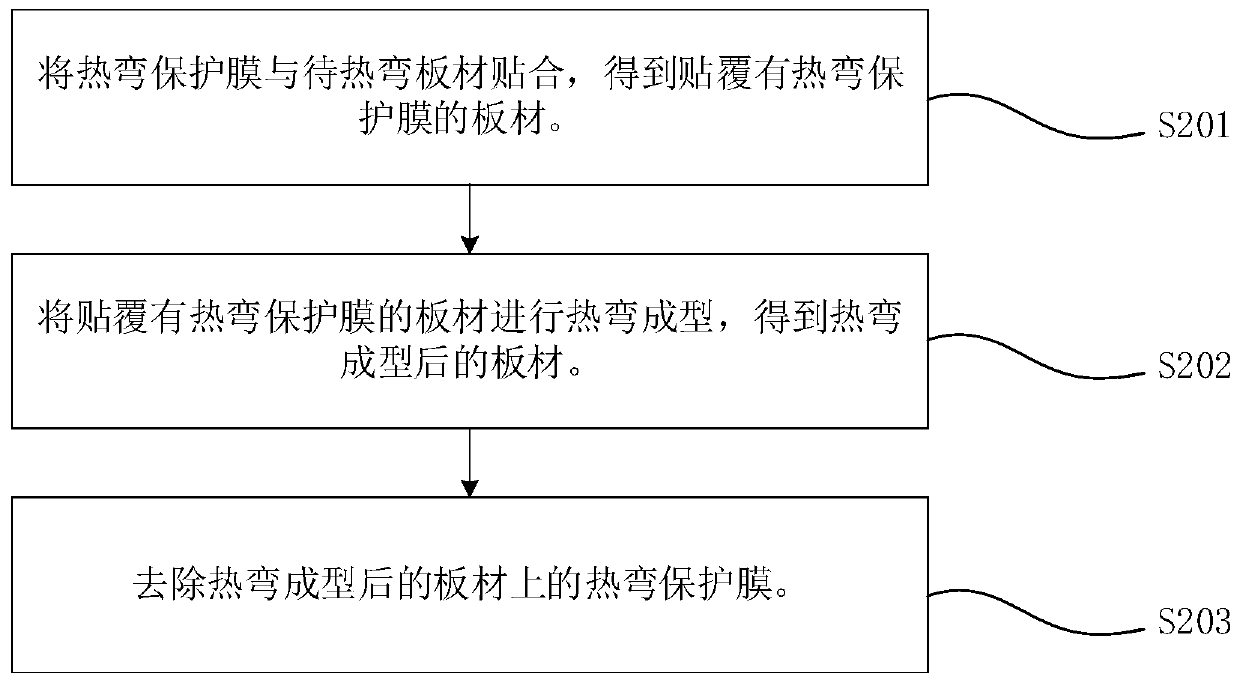

Hot bending protective film as well as preparation method and application thereof

The invention relates to a hot bending protective film as well as a preparation method and an application thereof. The hot bending protective film comprises a polymer base layer; raw materials for preparing the polymer base layer comprise polyolefin, a plasticizer and a heat stabilizer; the weight ratio of the polyolefin to the plasticizer to the heat stabilizer is 100:(20-80):(1-10). The hot bending protective film has high flexibility and can be well attached to a to-be-hot-bent plate, so that a sufficient buffering effect is achieved in the hot bending process, the plate is protected, meanwhile, reduction of point defects caused by the fact that dust or other particles contaminate the plate in the production environment can be facilitated, and the yield of the appearance surface of theplate is increased.

Owner:GUANGDONG OPPO MOBILE TELECOMM CORP LTD

Clearance groove machining method and 3D substrate product

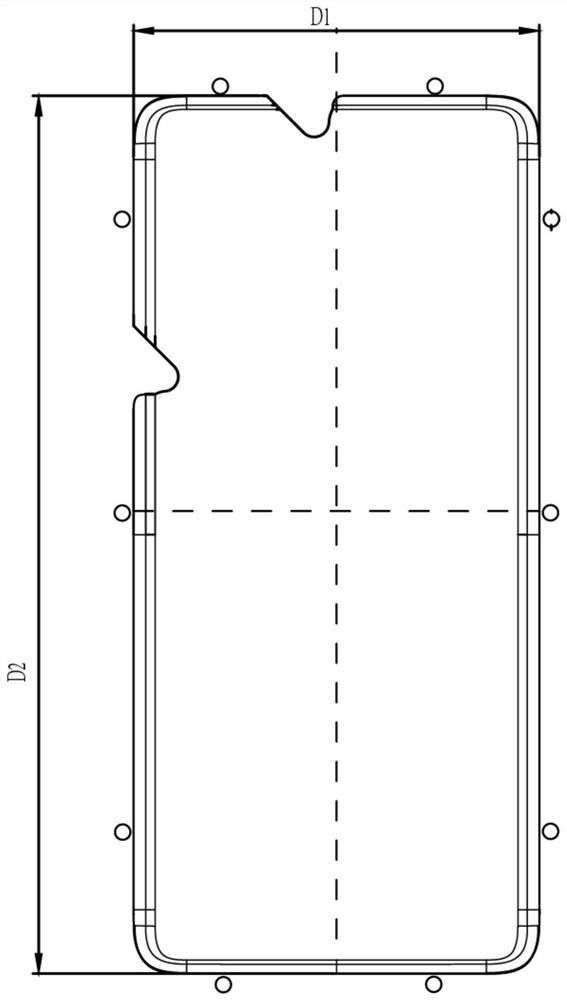

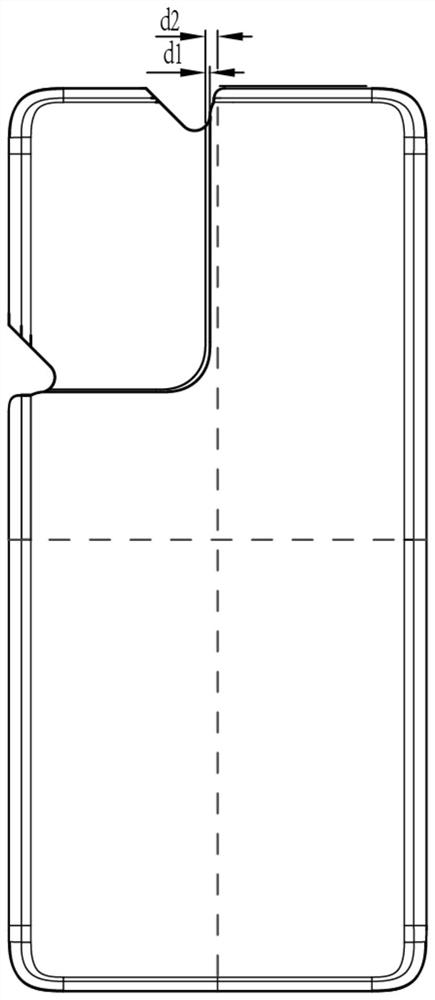

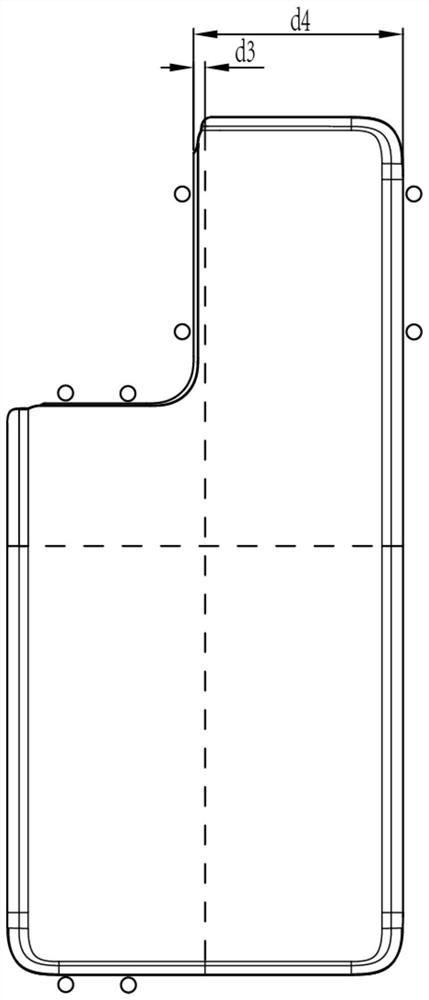

ActiveCN113698085AImprove appearance yieldGuaranteed stabilityGlass reforming apparatusGlass severing apparatusStructural engineeringMachining

The invention discloses a clearance groove machining method, a 3D substrate product clearance groove machining method and a 3D substrate product. The clearance groove machining method comprises the following steps that the length D1 of the long side of a product to be machined and the width D2 of the short side of the product to be machined are detected, the center point and the center line of the product to be machined are fitted according to the length D1 and the width D2, a CNC rough cutting curve is fitted according to d2, d2 = d1 + sigma, d1 is the distance between the groove long side of an L-shaped clearance groove and the center line, and sigma is tolerance; and the distance d4 between the long side of the L-shaped clearance groove roughly cut according to the rough cutting curve and the long side of the 3D product is detected, the allowance d needing fine trimming is calculated, a CNC fine cutting curve is fitted according to the allowance d, and the L-shaped clearance groove is cut according to the CNC fine cutting curve. According to the clearance groove machining method, the two-time CNC tool connecting position accuracy during CNC machining can be achieved, the tool connecting mark proportion is close to 0%, and the product appearance yield is increased.

Owner:WEIDALI IND CHIBI CO LTD +1

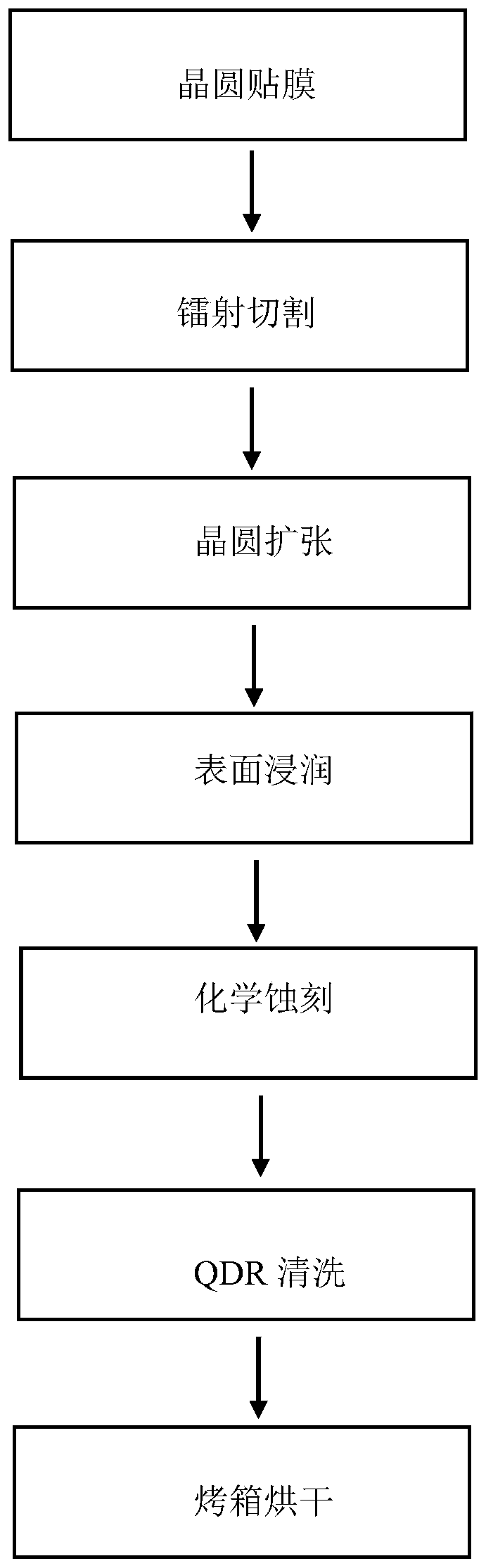

Processing method of chip after laser cutting

ActiveCN111192817AImprove wettabilityImproves staying on chip surfaceSemiconductor/solid-state device manufacturingEtchingWafer

The invention discloses a processing method of a chip after laser cutting. The method comprises the steps of: performing laser cutting and wafer expanding processing on a chip to form a plurality of independent chips, soaking the chips in a surfactant solution for a period of time, removing the chips from the surfactant solution, soaking the chips in an etching solution, etching a burning melt onthe edges of the chips through the etching solution, cleaning the etched chips, removing the residual etching solution on the surfaces of the etched chips, and drying the cleaned chips. After the chipis subjected to laser cutting and before the chip is etched, the surface active agent is adopted to improve the wettability of the surface of the chip, so that on one hand, burnt and melted particlesare prevented from being stuck back to the surface of the chip in the etching process; and on the other hand, the burnt and melted material particles are prevented from being attached to the surfaceof the chip in the process of conveying the etched chip to the cleaning link, so that the condition that the burnt and melted material particles stay on the surface of the chip in the subsequent etching and cleaning process is improved, and the appearance yield of products is improved.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

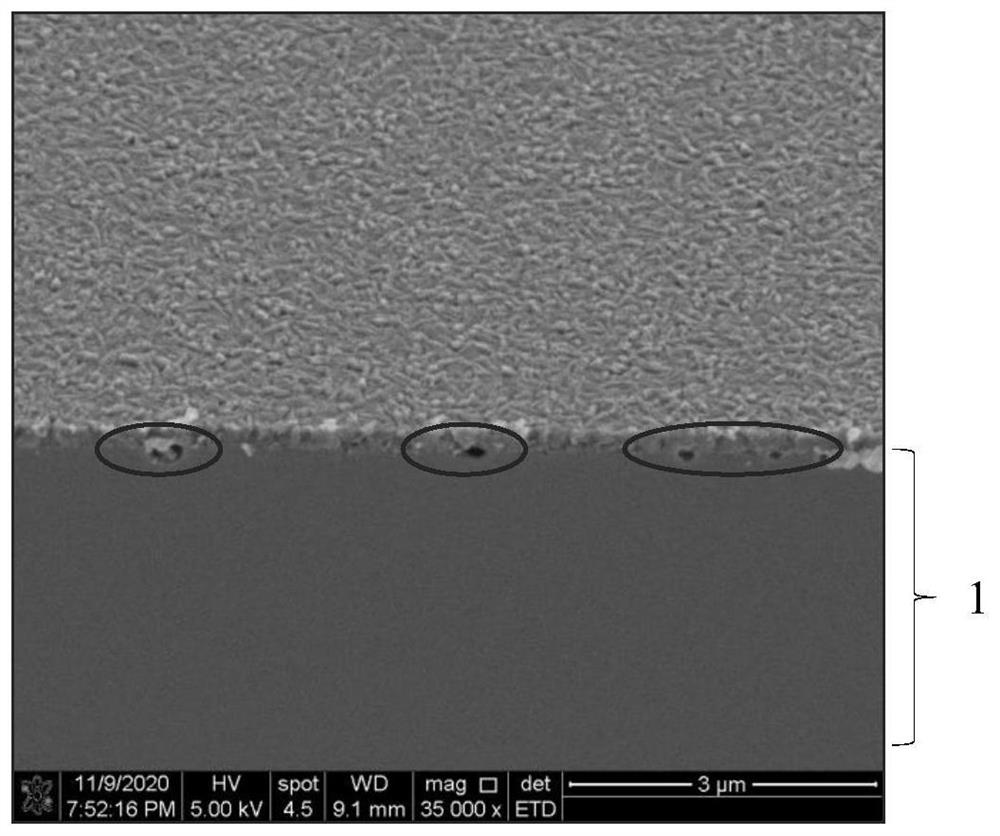

led chip and its growth method

ActiveCN103972351BImprove adhesionImprove leakage yieldSemiconductor devicesSemiconductorMaterials science

The invention provides an LED chip and a growing method of the LED chip. The LED chip comprises a metal layer and an insulating layer, wherein the metal layer and the insulating layer are overlaid. The LED chip further comprises an adhesion layer. The adhesion layer is arranged between the metal layer and the insulating layer and is a material layer containing Ni or a material layer containing Ti. The adhesion layer made of materials of Ni or Ti is additionally arranged between the metal layer and the insulating layer of the LED chip so that adhesive power between the meta layer and the insulating layer can be improved. The electric leakage yield of semiconductor products is improved to more than 98 percent, and the appearance yield is improved to more than 99 percent.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

Speaker Assembly

ActiveUS20200045467A1Improve appearance yieldLoudspeakersCircuit lead arrangements/reliefElectrical connectionEngineering

The present disclosure provides a speaker assembly. The speaker assembly includes an electrical connector, and the electrical connector includes a body part and a second pad part connected with the body part. In this way, we can measure flux or test pure tone and performance of the finished product through the second pad part during assembling of the speaker assembly of the structure, so as to prevent the body part from being scratched caused by contact in the traditional test process, thus improving the appearance yield of the finished product.

Owner:AAC TECH PTE LTD

Touch screen integrated with anti-peeping function and production process thereof

PendingCN114153333ABad masking appearanceImprove appearance yieldInput/output processes for data processingProcess engineeringComputer science

The invention belongs to the technical field of touch control, and discloses a touch screen integrated with an anti-peeping function and a production process thereof, an anti-peeping structure is integrated in a touch screen structure, according to different types of touch screen structures, one or two layers of base materials can be saved, a UV adhesive layer is filled, and the purposes of overall thinning, manufacturing process and cost saving and the like can be achieved; and in combination with the peep-proof structure, part of poor appearance of the touch screen can be shielded, so that the appearance yield of the touch screen is indirectly improved.

Owner:ANHUI JINGZHUO OPTICAL DISPLAY TECH CO LTD