Patents

Literature

30results about How to "Improve resistivity uniformity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for improving uniformity of axial resistivity of czochralski silicon and obtained monocrystalline silicon

ActiveCN102912424AImprove uniformityGood prospects for industrial applicationPolycrystalline material growthBy pulling from meltMolten siliconSeed crystal

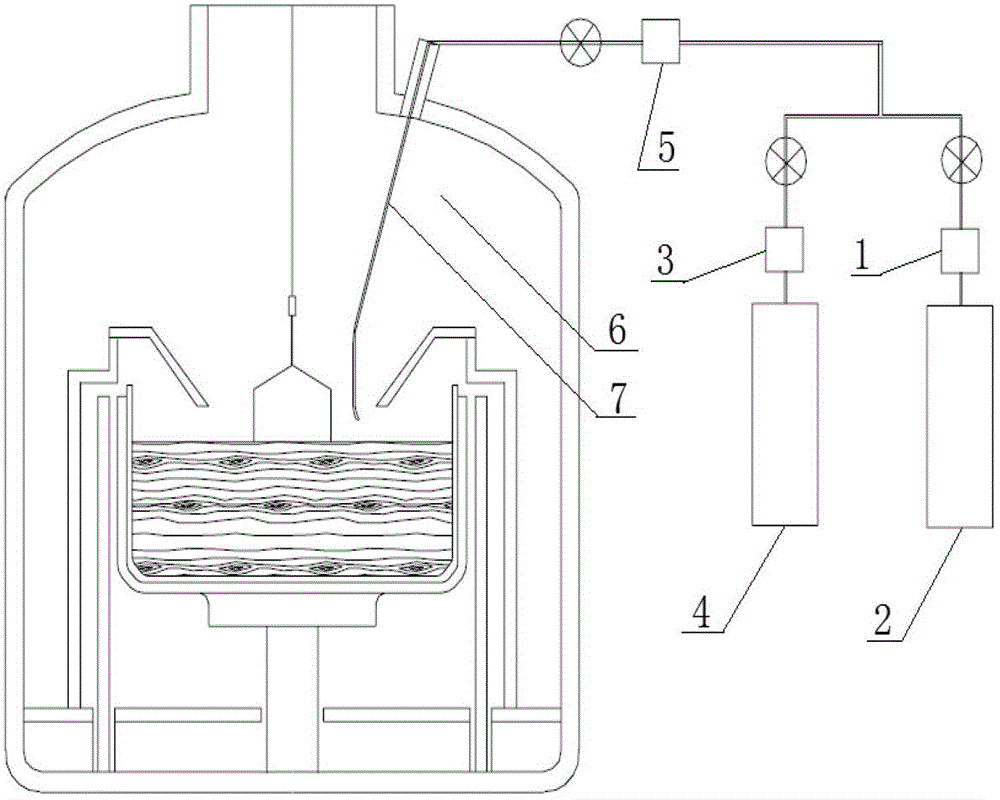

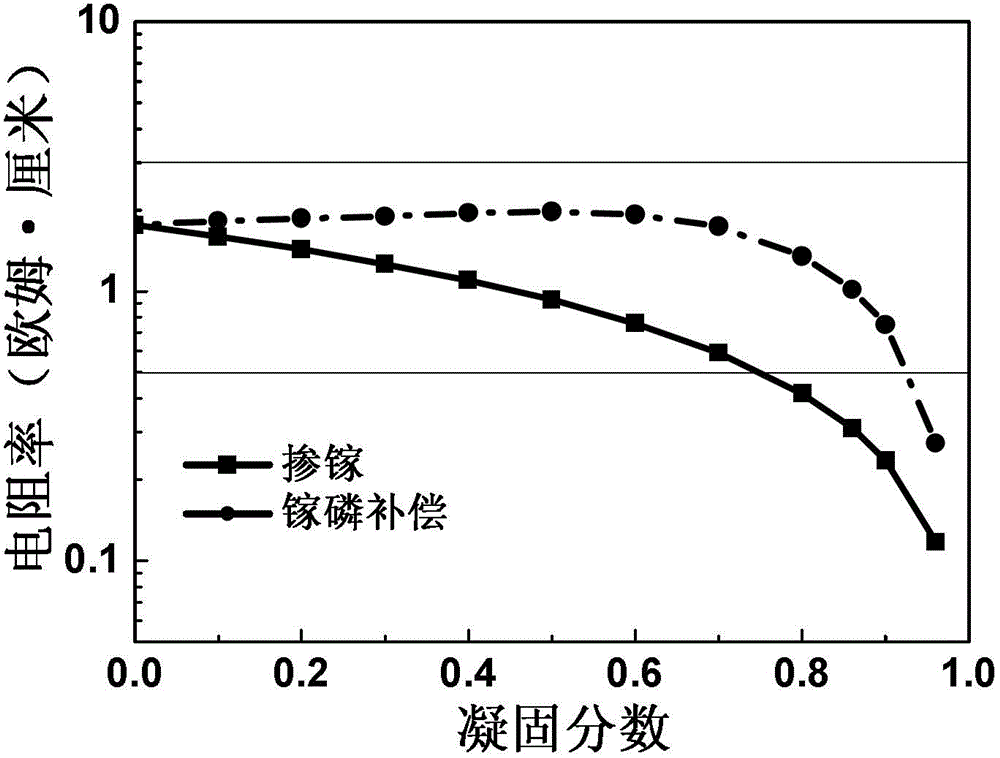

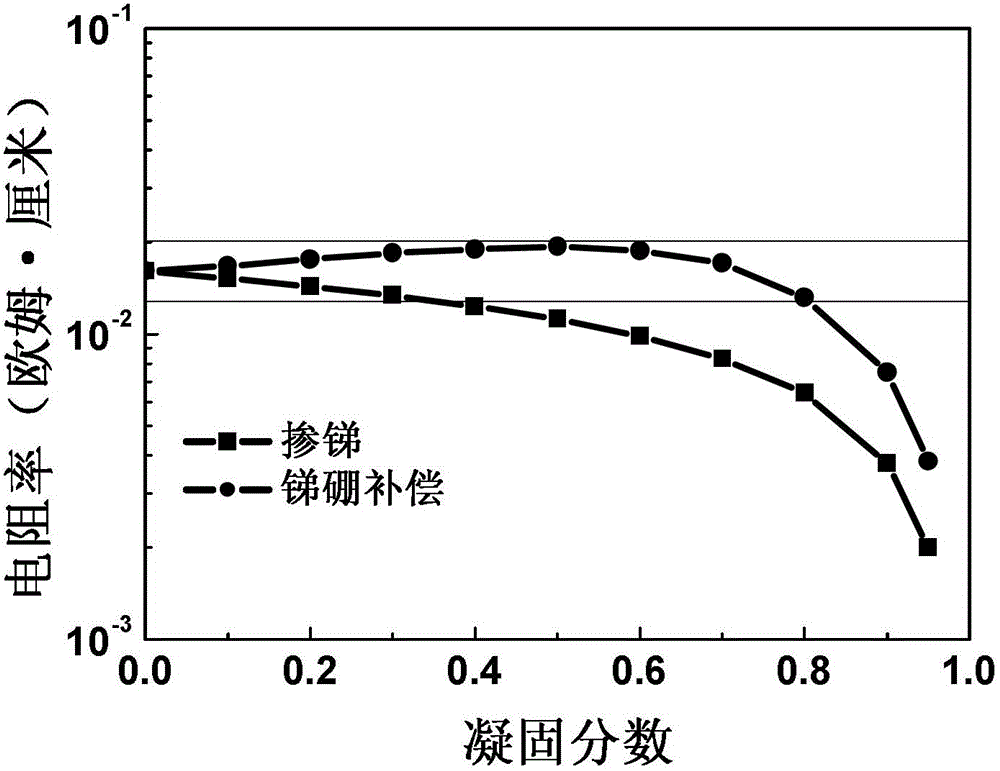

The invention discloses a method for improving the uniformity of axial resistivity of czochralski silicon. The method comprises the steps as follows: (1) melting a polycrystalline silicon raw material and a solid doping agent in an argon atmosphere to obtain stable molten silicon; (2) introducing seed crystals into the stable molten silicon, and conducting constant diameter growth on the crystals after necking and shouldering processes; and (3) during the constant diameter growth period, adding dopant gas with the conductive type opposite to that of the solid doping agent until the growth of the czochralski silicon is fulfilled. According to the method, the type and the usage amount of the dopant gas are convenient to control, various required impurity concentration distributions can be obtained, the utilization rate of the czochralski silicon is increased, and the uniformity of the resistivity of the czochralski silicon is remarkably improved.

Owner:ZHEJIANG UNIV

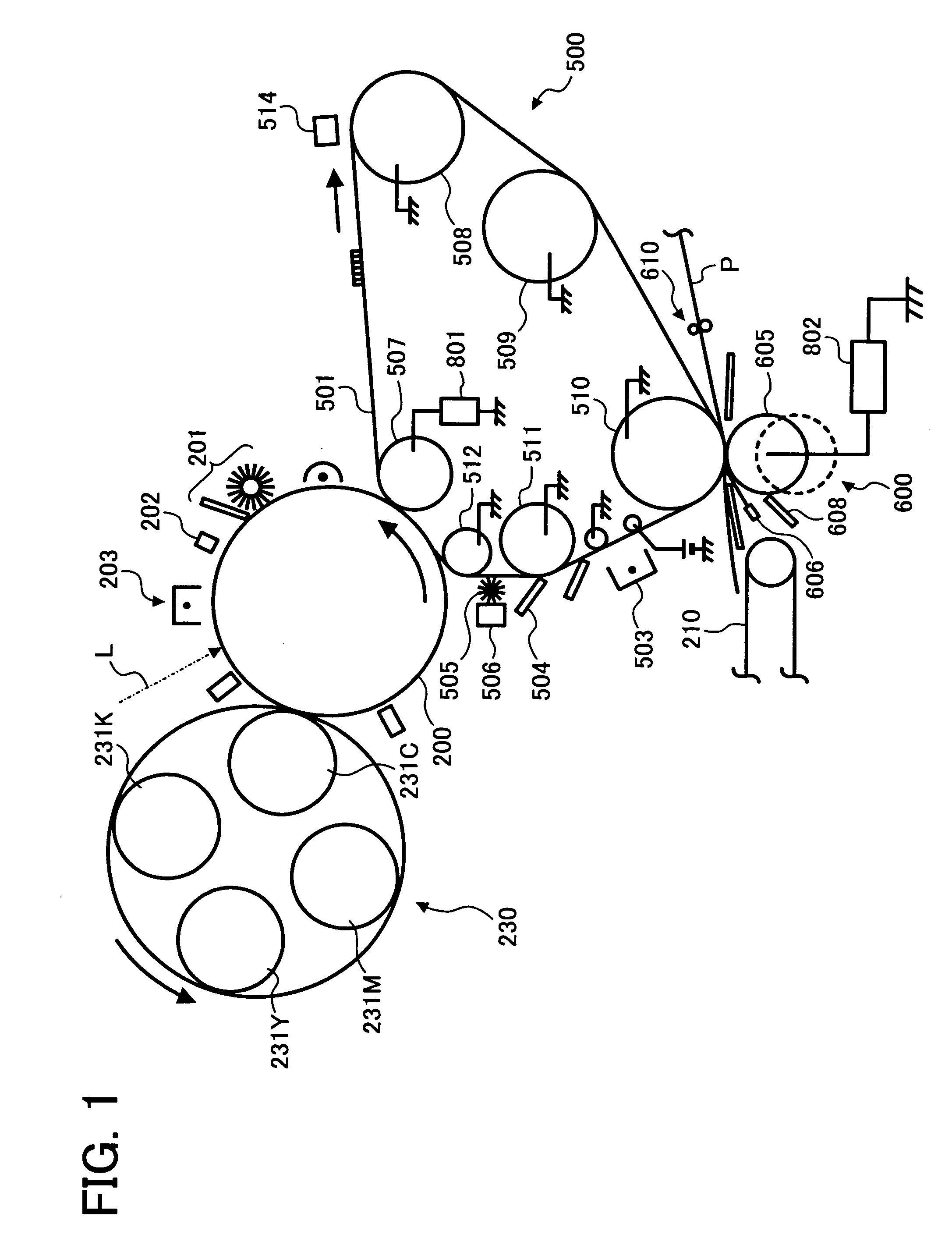

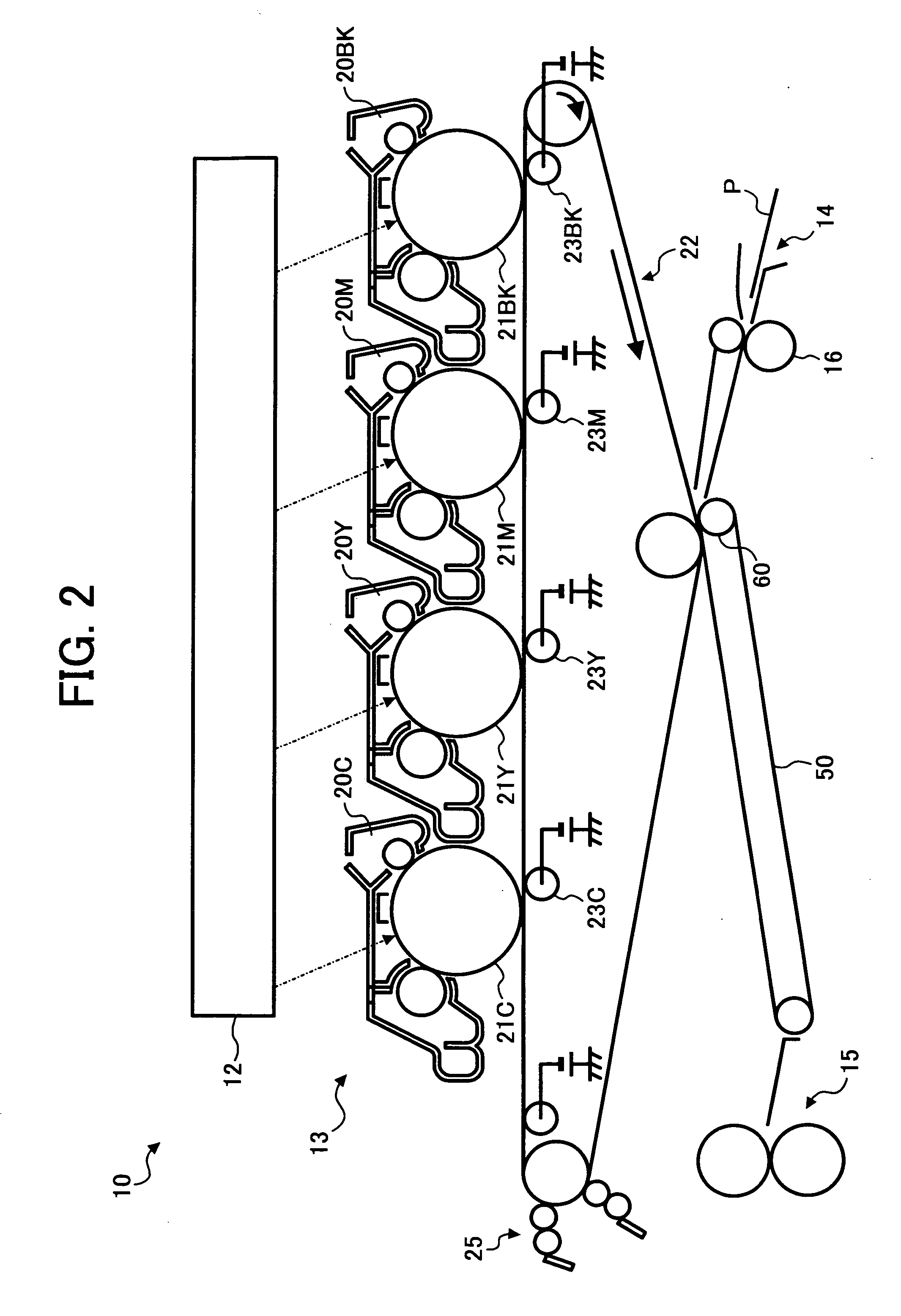

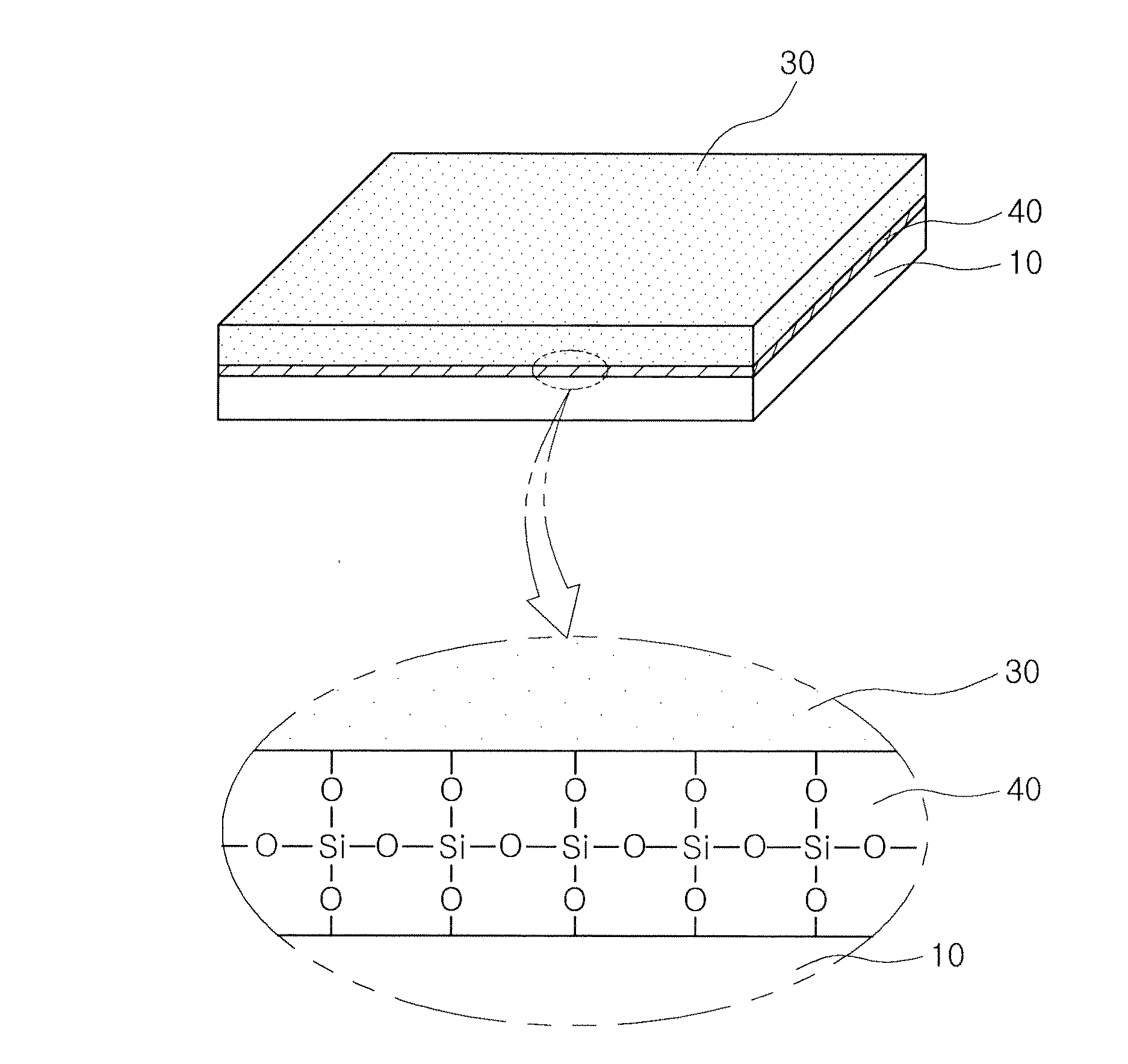

Intermediate transfer medium, film forming liquid for the intermediate transfer medium and image forming apparatus using intermediate transfer medium

InactiveUS20050136245A1Good resistivity uniformityImprove resistivity uniformitySynthetic resin layered productsElectrographic process apparatusCarbon blackWater soluble

An intermediate transfer medium including a layer which includes an acidic carbon black including volatile components of from 3.5 to 8.0% by weight; at least one of a water soluble resin having a weight average molecular weight of from 3,000 to 30,000, and a resin dispersant having a weight average molecular weight of from 3,000 to 300,000 which is selected from the group consisting of polyamide acids, polyimides, and block copolymer including a unit containing at least one of a polyamide acid and a polyimide; and a binder resin, wherein a weight ratio (CB / R) of the carbon black (CB) to the at least one (R) of the water soluble resin and the resin dispersant is from 3 / 1 to 10 / 1. A film forming liquid for use in preparing the layer, and an image forming apparatus using the intermediate transfer medium are also provided.

Owner:RICOH KK

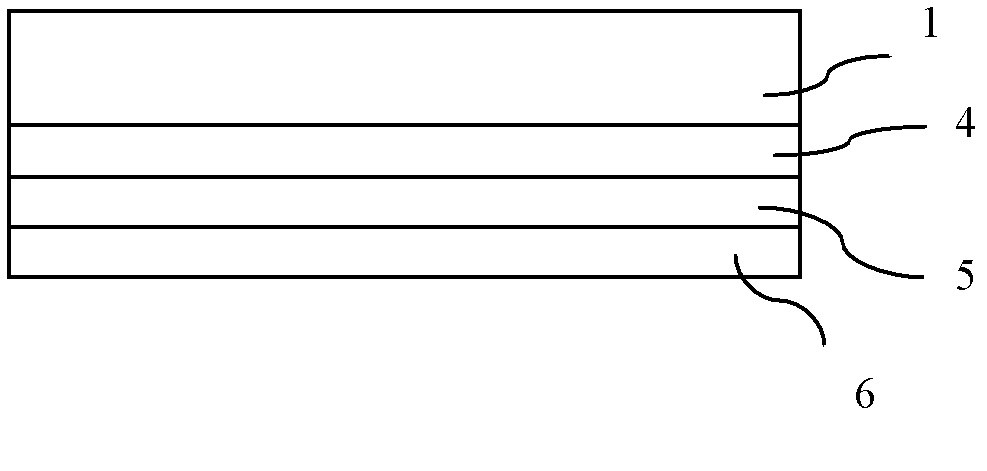

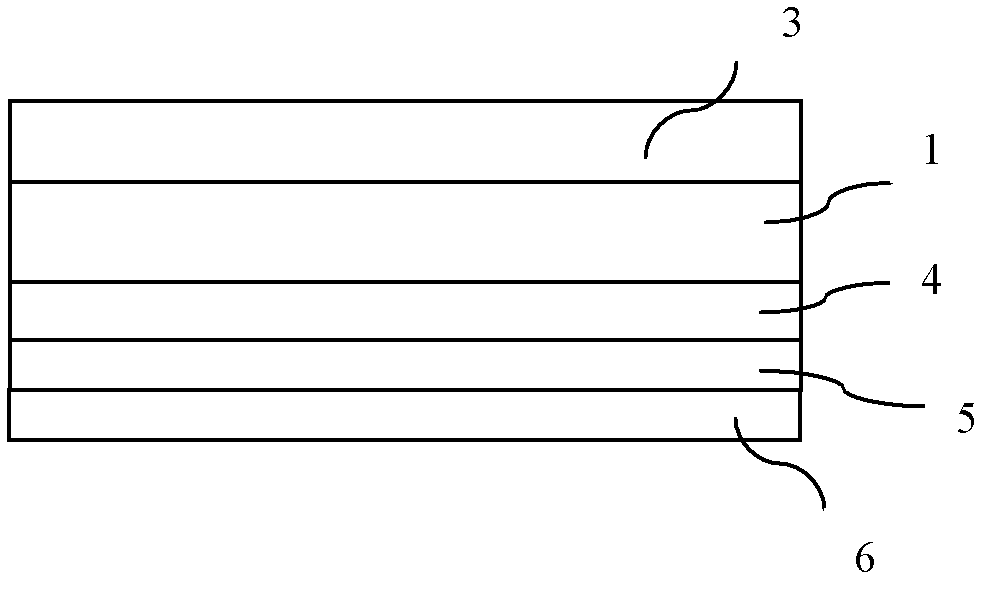

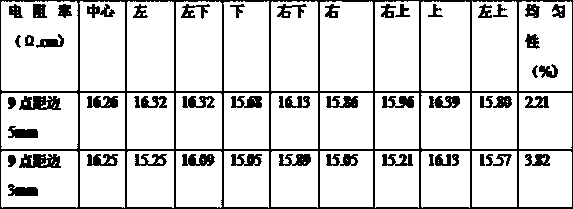

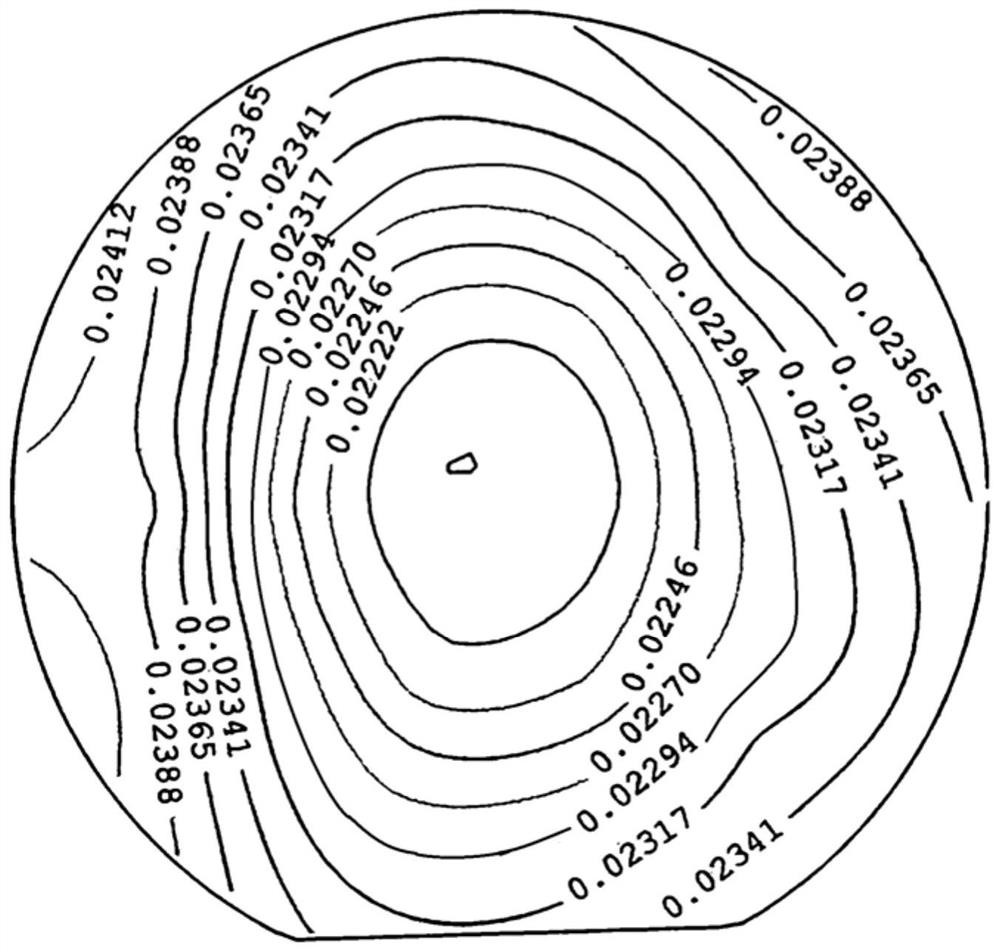

Method for improving electrical resistivity evenness of P-type silicon epitaxial wafer for CCD

InactiveCN104282535AImprove resistivity uniformityAdvance the development processSemiconductor/solid-state device manufacturingRadiation controlled devicesP type siliconTwo step

The invention relates to a method for improving the electrical resistivity evenness of a P-type silicon epitaxial wafer for a CCD. The method includes the steps that an intrinsic layer is prepared before a needed epitaxial layer grows, so that impurities on the edges of the surface and the back face of a substrate and impurities in a furnace cavity of an epitaxial furnace are isolated from volatilizing and escaping to the needed epitaxial layer; meanwhile, the harmful impurities adsorbed to the surface is resolved by increasing temperature, the impurities in a reaction furnace cavity are removed out through continuously-changed air flow, a passive doping source is effectively restrained, then the needed parameter epitaxial layer grows, and therefore the epitaxial layer with the high electrical resistivity evenness is acquired. According to the method, the substrate covered silicon technology, the two-step epitaxial growth technology and the temperature and flow change blowing technology are organically combined, parameters of the prepared silicon epitaxial wafer can meet the requirements of a substrate material of the large-area-array and high-integration-density CCD, the electrical resistivity evenness of the epitaxial wafer can be higher than 99%, and the research process of the high-performance CCD is greatly promoted.

Owner:CHINA ELECTRONICS TECH GRP NO 46 RES INST

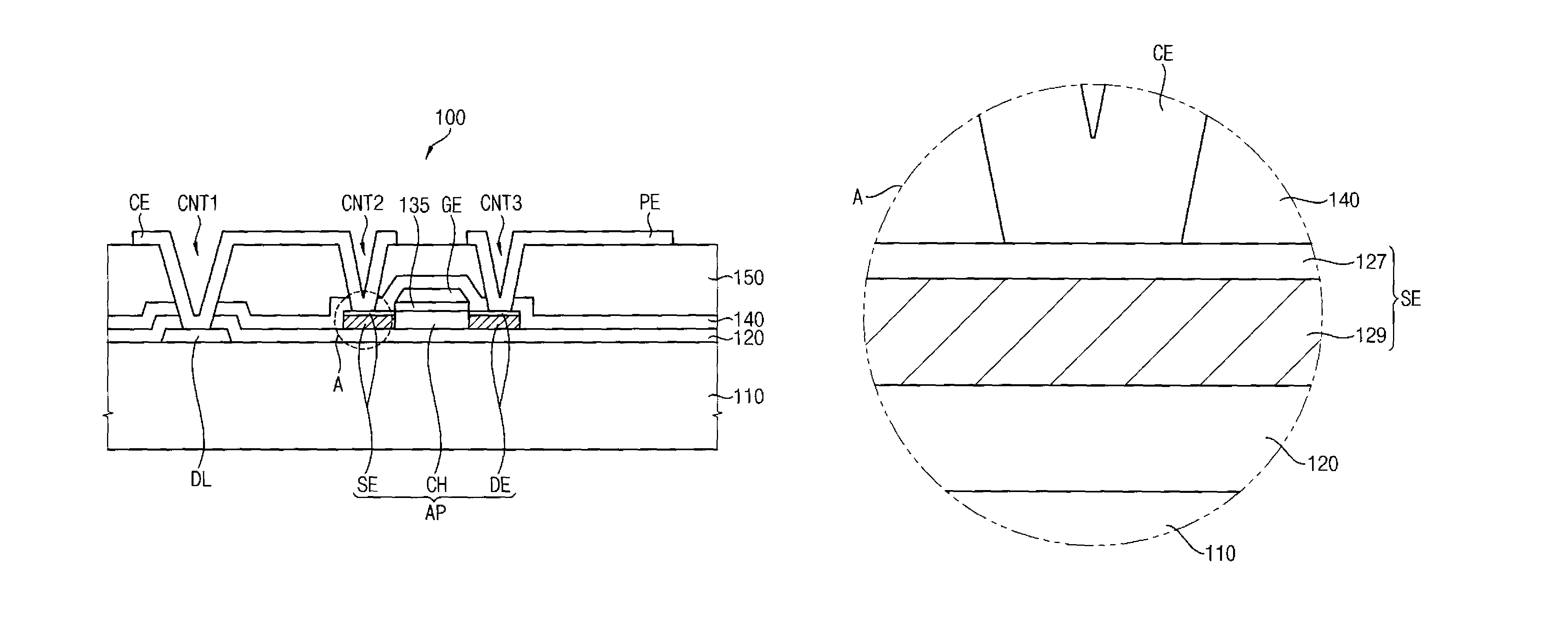

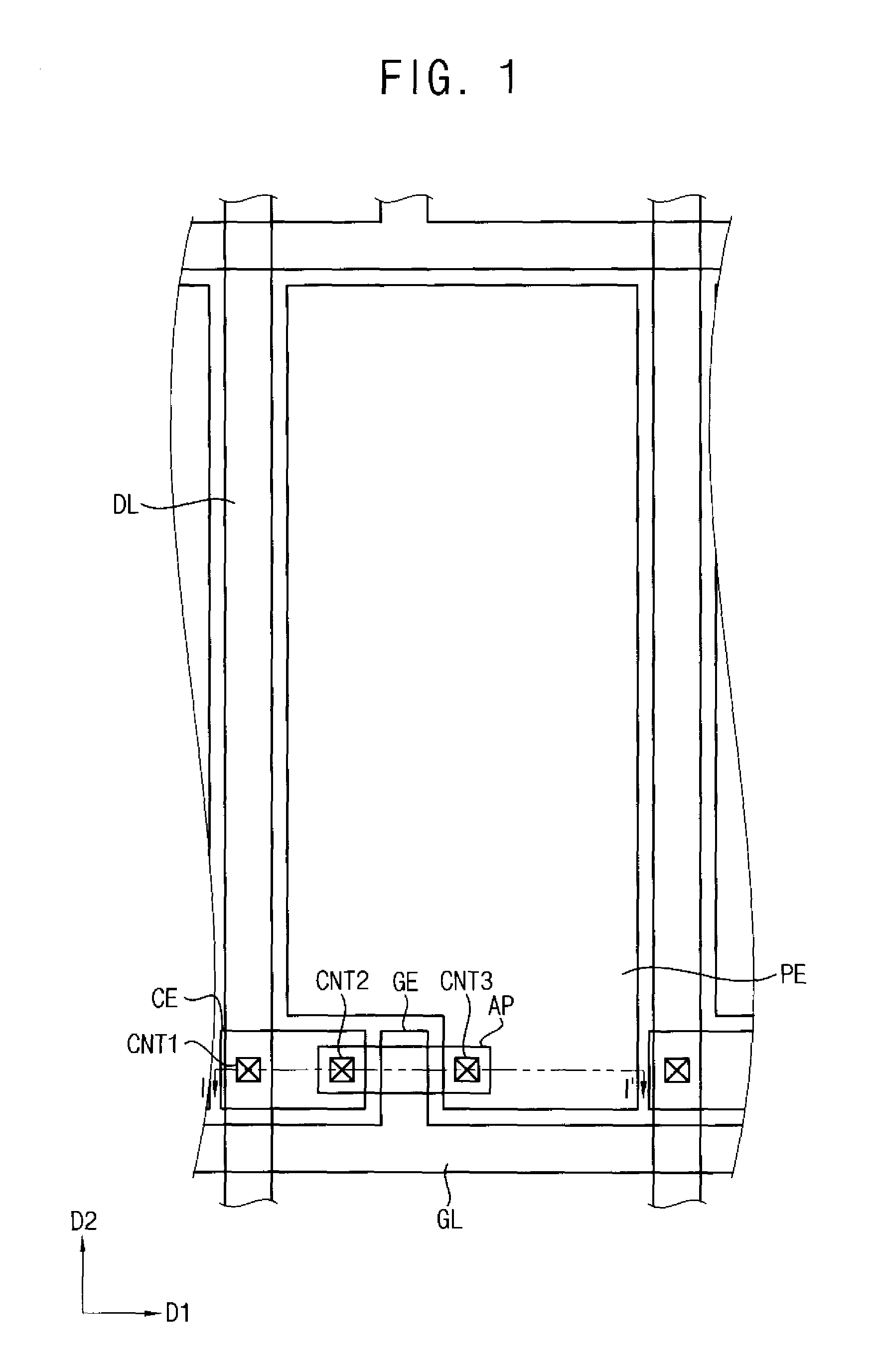

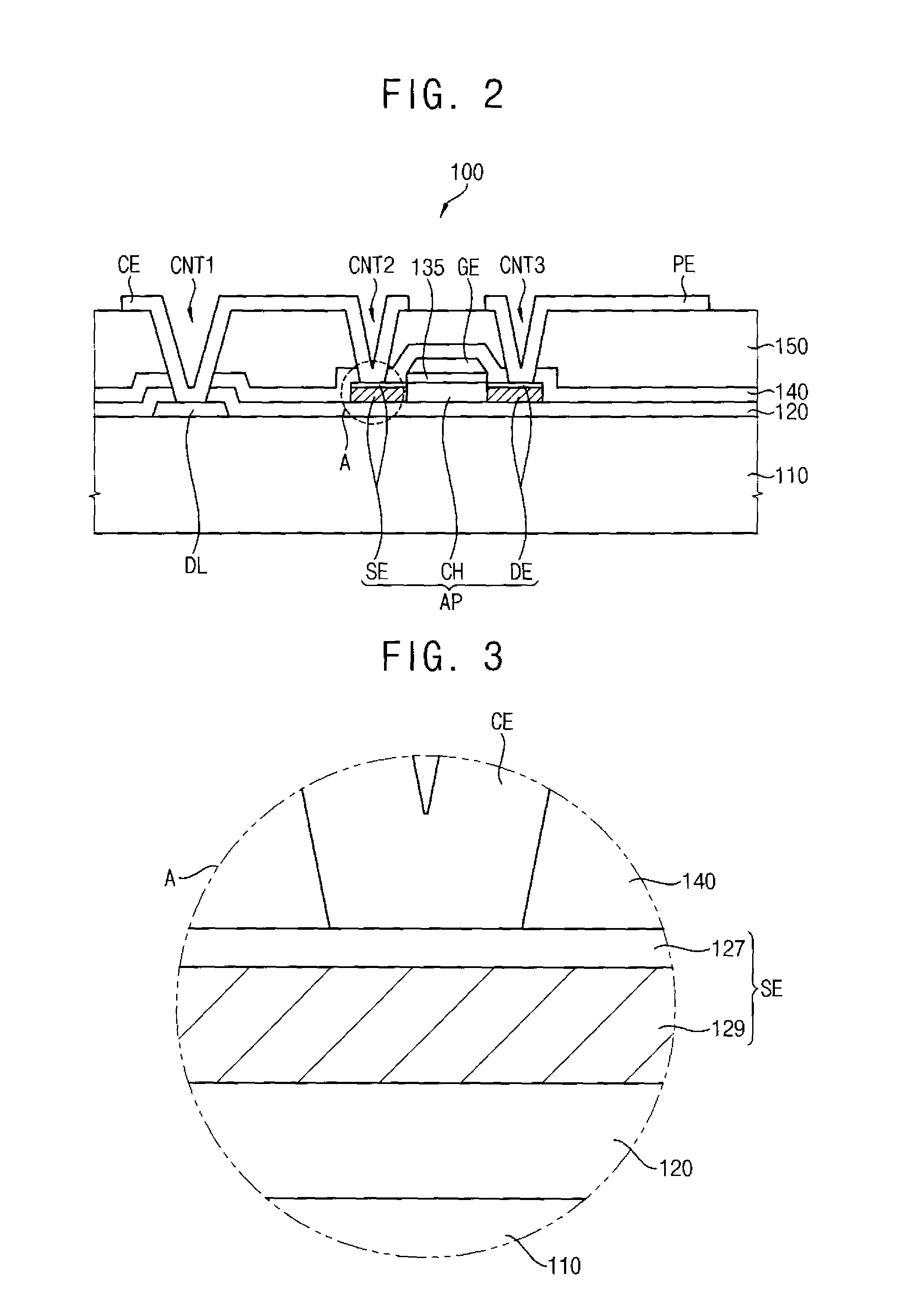

Thin film transistor substrate and method of manufacturing the same

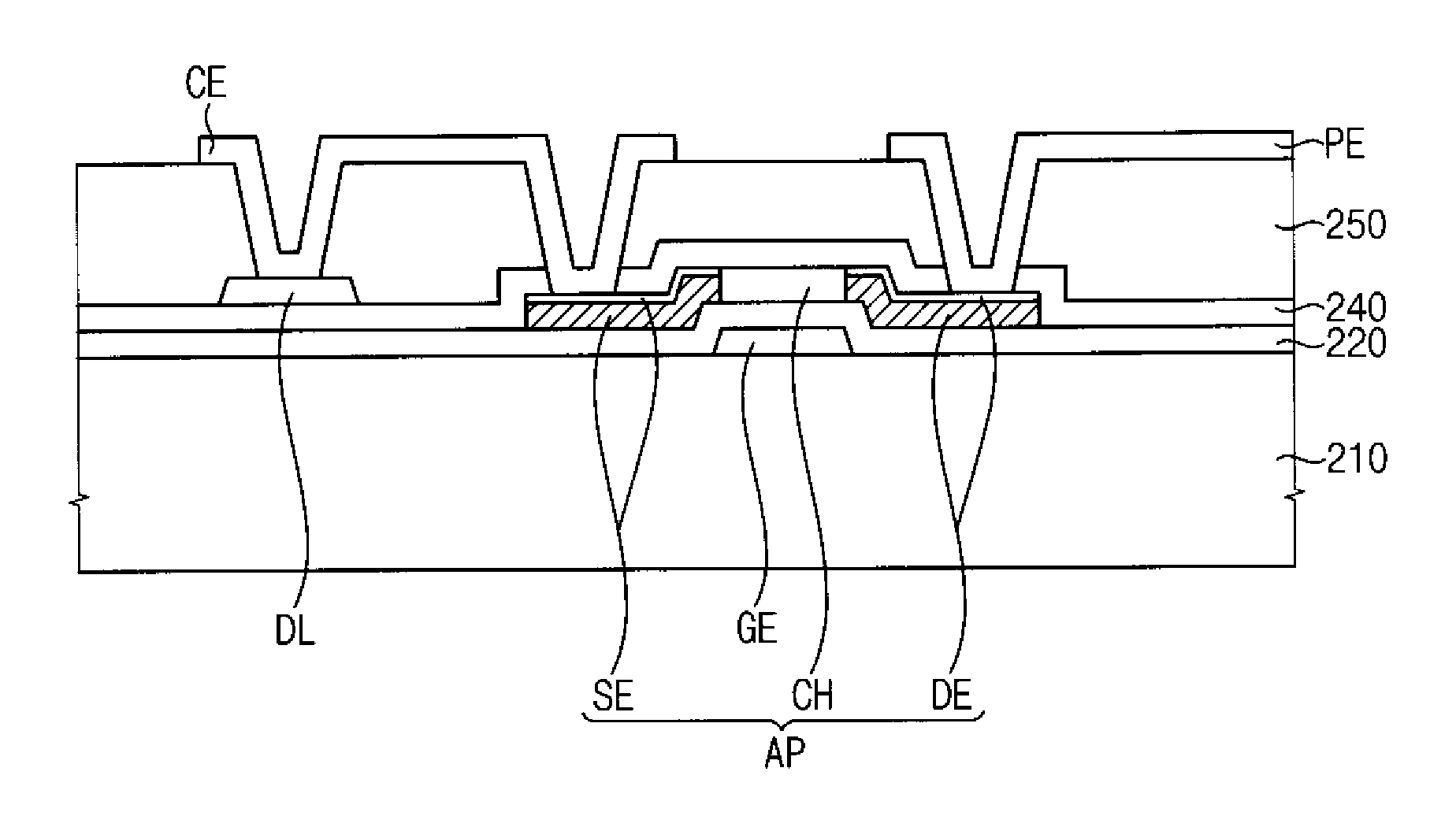

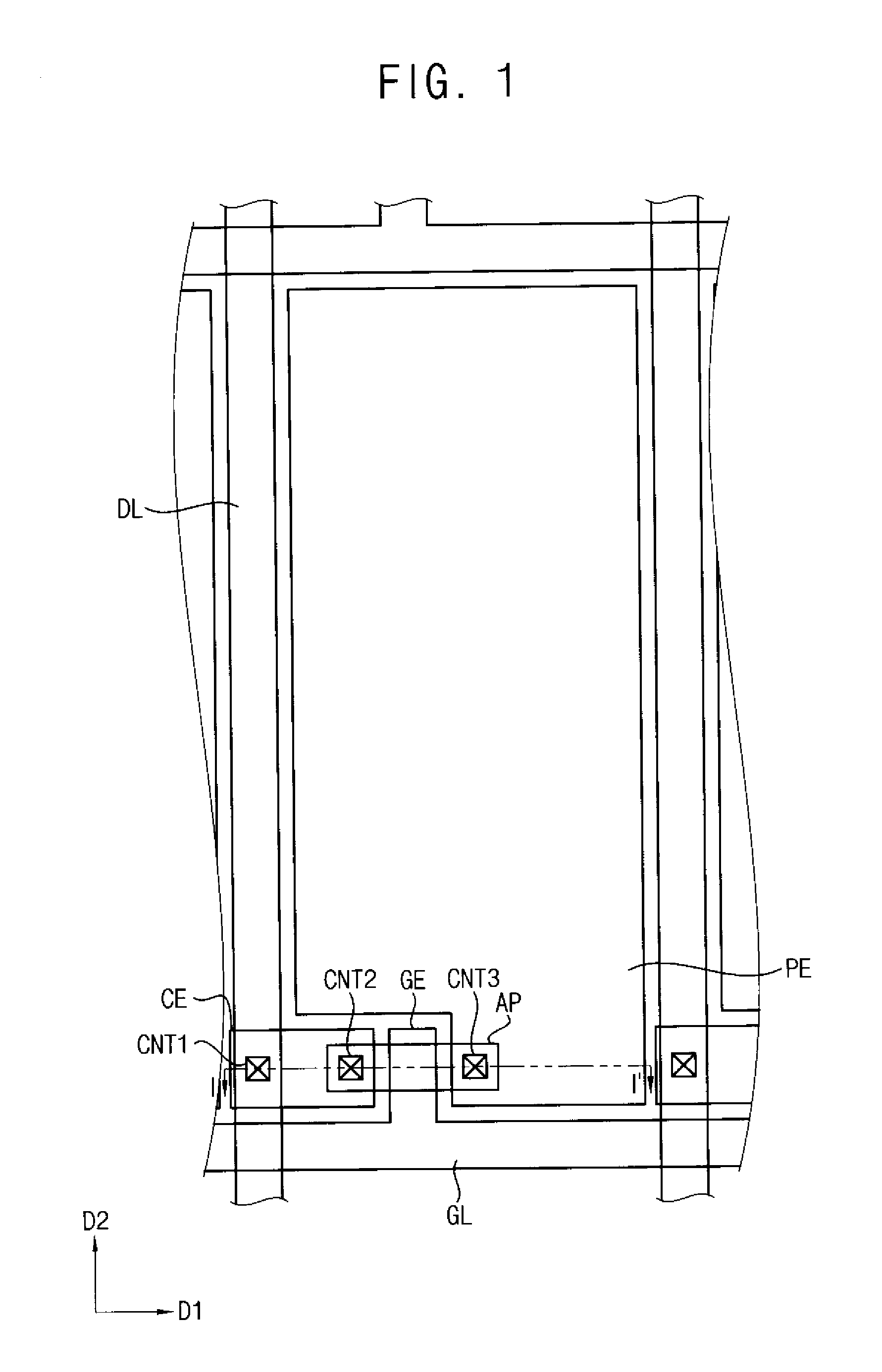

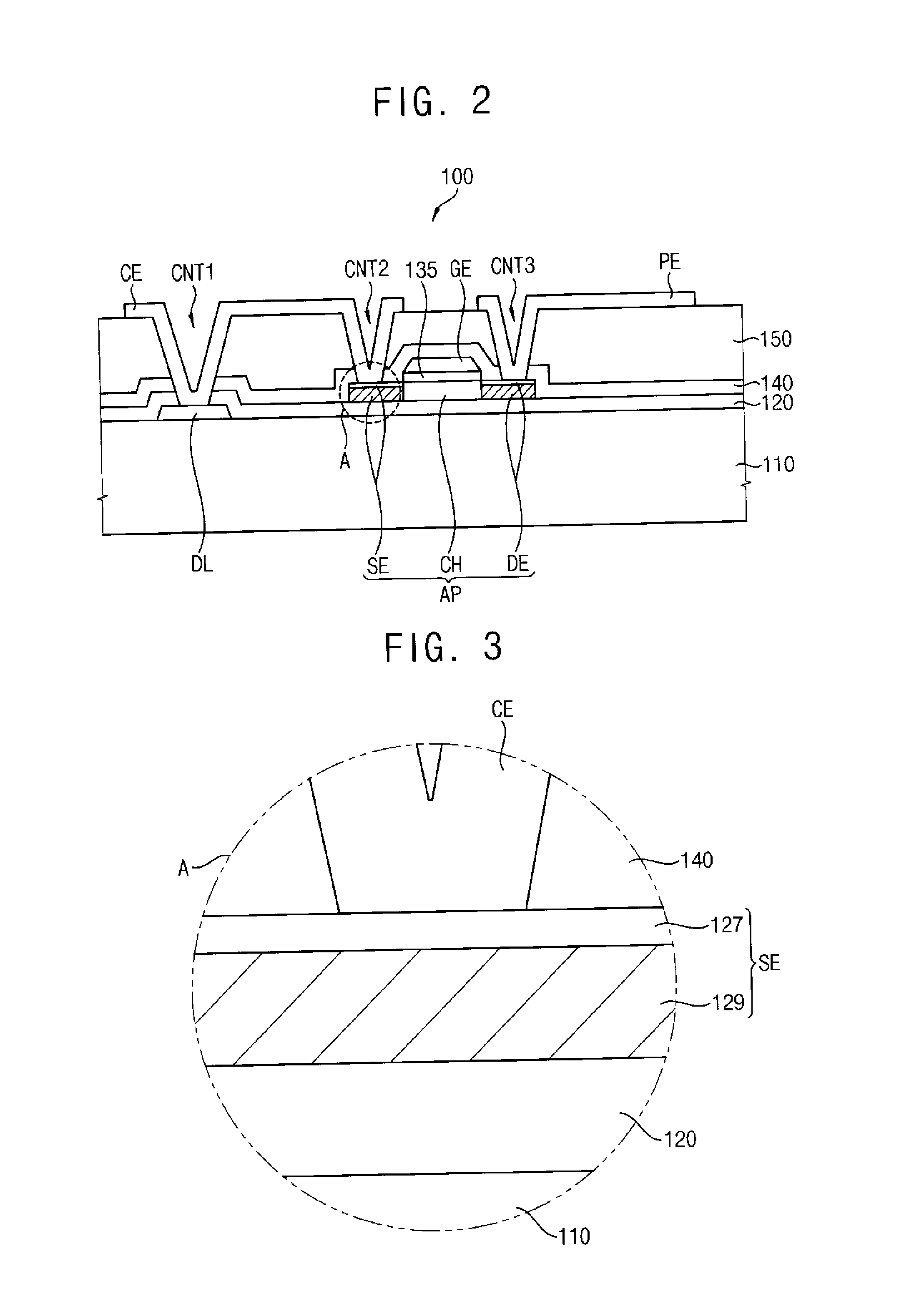

ActiveUS20140054579A1Reduce resistanceImprove the immunityTransistorSemiconductor/solid-state device manufacturingEngineeringTransistor

A thin film transistor substrate includes a base substrate, an active pattern, a gate insulation pattern and a gate electrode. The active pattern is disposed on the base substrate. The active pattern includes a source electrode, a drain electrode, and a channel disposed between the source electrode and the drain electrode. The gate insulation pattern and the gate electrode overlap with the channel. The gate insulation pattern is disposed between the channel and the gate electrode. The source electrode and the drain electrode each include a fluorine deposition layer.

Owner:SAMSUNG DISPLAY CO LTD

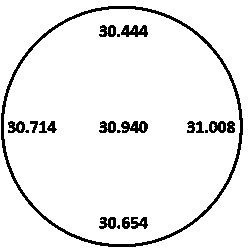

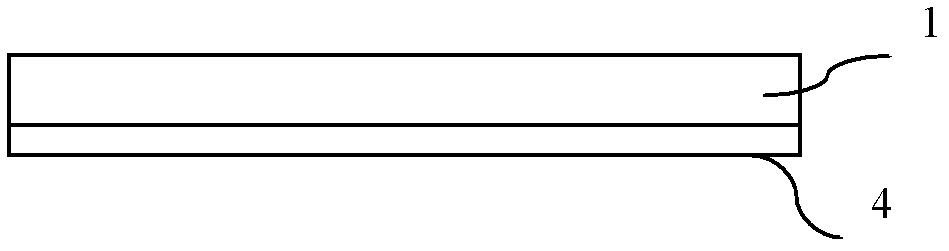

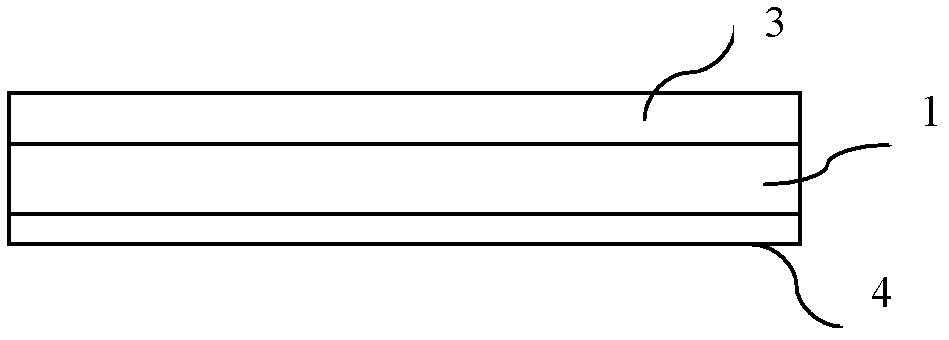

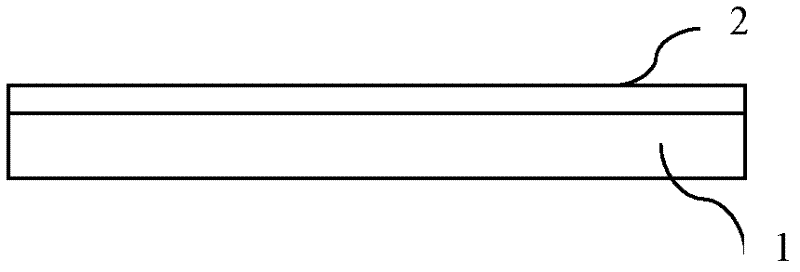

Epitaxial wafer substrate capable of reducing auto-doping during epitaxy, epitaxial wafer and semiconductor device

InactiveCN102324406AImprove resistivity uniformityAvoid enteringSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceSilicon dioxide

The invention discloses an epitaxial wafer substrate capable of reducing auto-doping during epitaxy. The epitaxial wafer substrate comprises a substrate body, and is characterized in that: the back surface of the substrate body is provided with a silicon dioxide layer. When an epitaxial layer generated by using the epitaxial wafer substrate capable of reducing the auto-doping during epitaxy is used, the resistivity uniformity numerical value can be less than 1.5 percent. Compared with an epitaxial layer which is generated by not using the epitaxial wafer substrate capable of reducing the auto-doping during epitaxy, the epitaxial layer which is generated by using the epitaxial wafer substrate capable of reducing the auto-doping during epitaxy has higher epitaxial layer resistance uniformity. By using the epitaxial wafer substrate capable of reducing the auto-doping during epitaxy, the follow-up production cost can be reduced, and the product quality can be improved.

Owner:SHANGHAI JINGMENG SILICON CORP

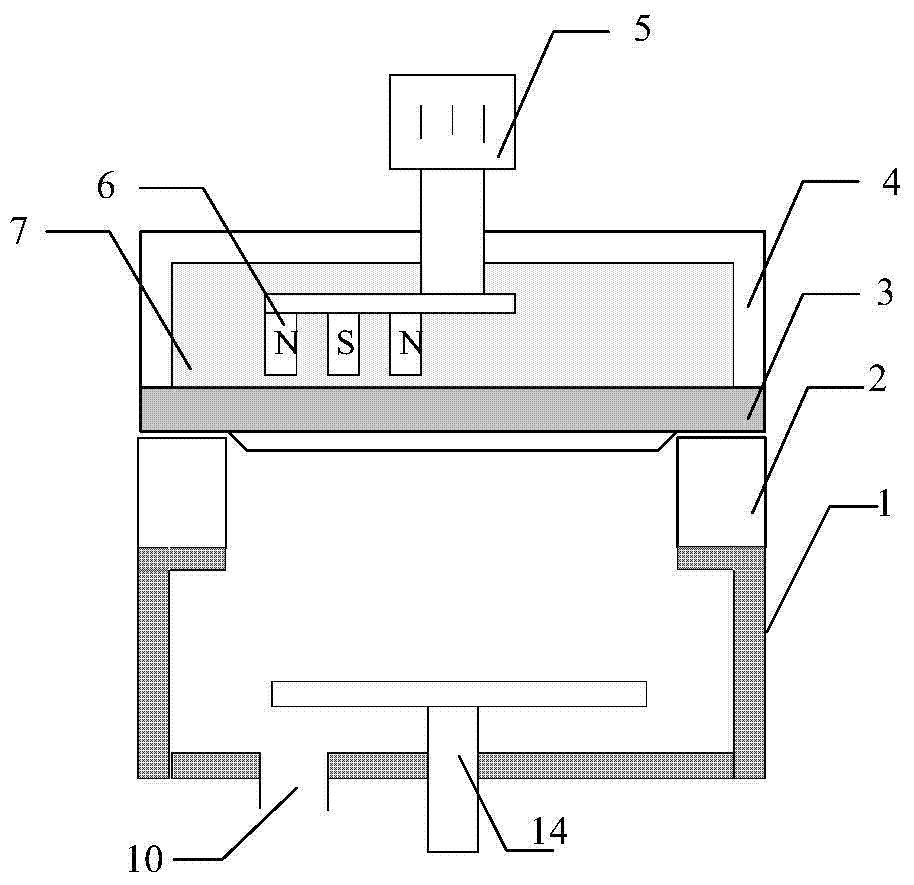

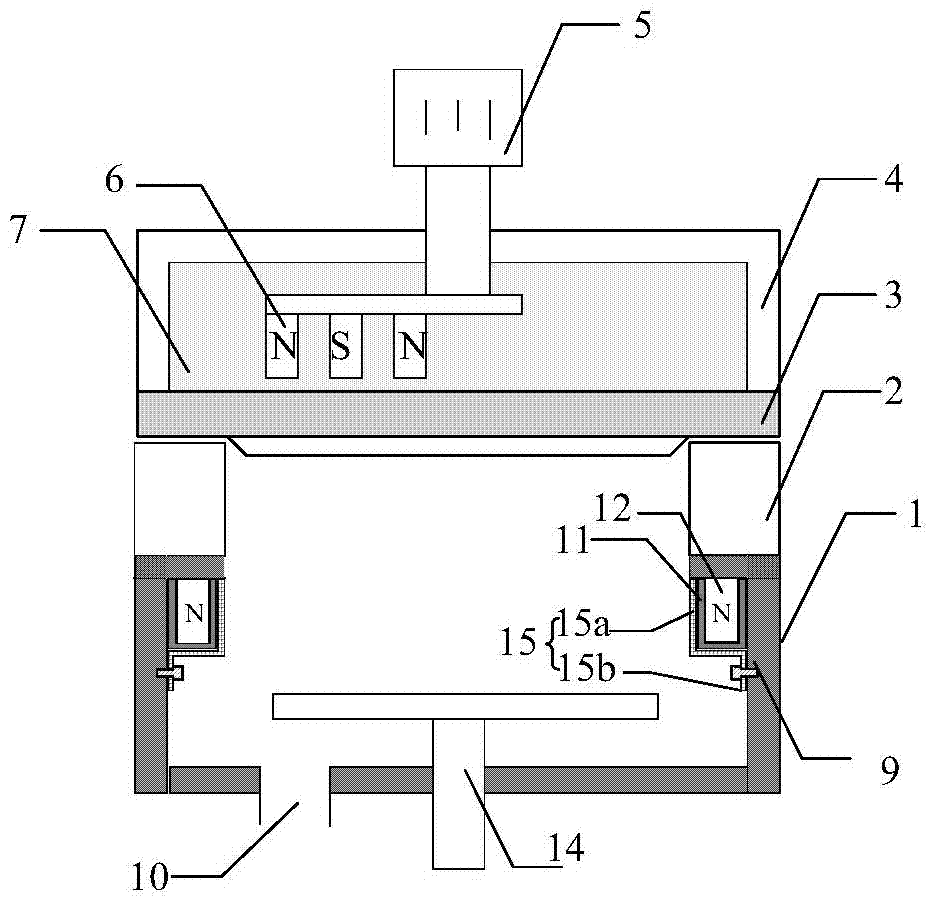

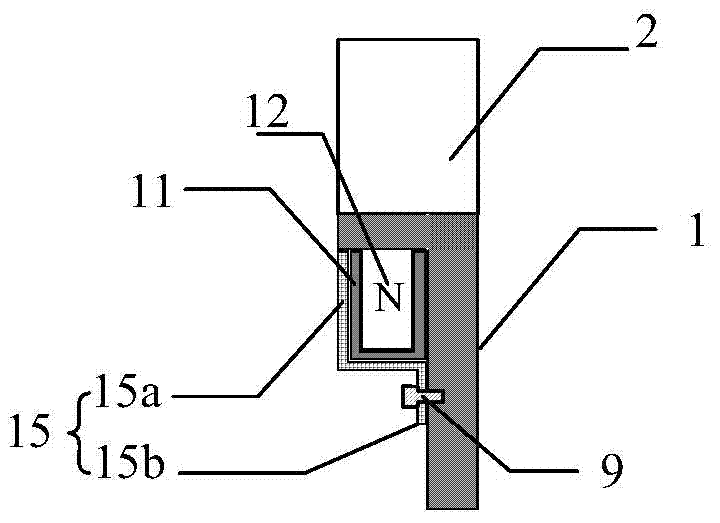

Sputtering apparatus

InactiveCN104746025AIncrease the magnetic field strengthHigh resistivityVacuum evaporation coatingSputtering coatingSputteringElectrical resistance and conductance

The invention provides a sputtering apparatus, which comprises a technology chamber, a magnetron and a pedestal for bearing a substrate, the magnetron and the pedestal are arranged in the technology chamber, the magnetron is positioned over the pedestal, wherein the sputtering apparatus also comprises a magnetic element, the magnetic element is arranged at a preset position in the technology chamber for increasing the magnetic field intensity of the preset position; and the preset position is determined according to a material of a target material between the magnetron and the pedestal. When the sputtering apparatus is used for depositing a film layer on the substrate, target material atoms or molecules move by deflecting the preset position, resistivity of the film layer at the preset position is increased, resistivity uniformity of the deposited film layer can be integrally improved, and the film thickness uniformity and the square resistance uniformity of the film layer is improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

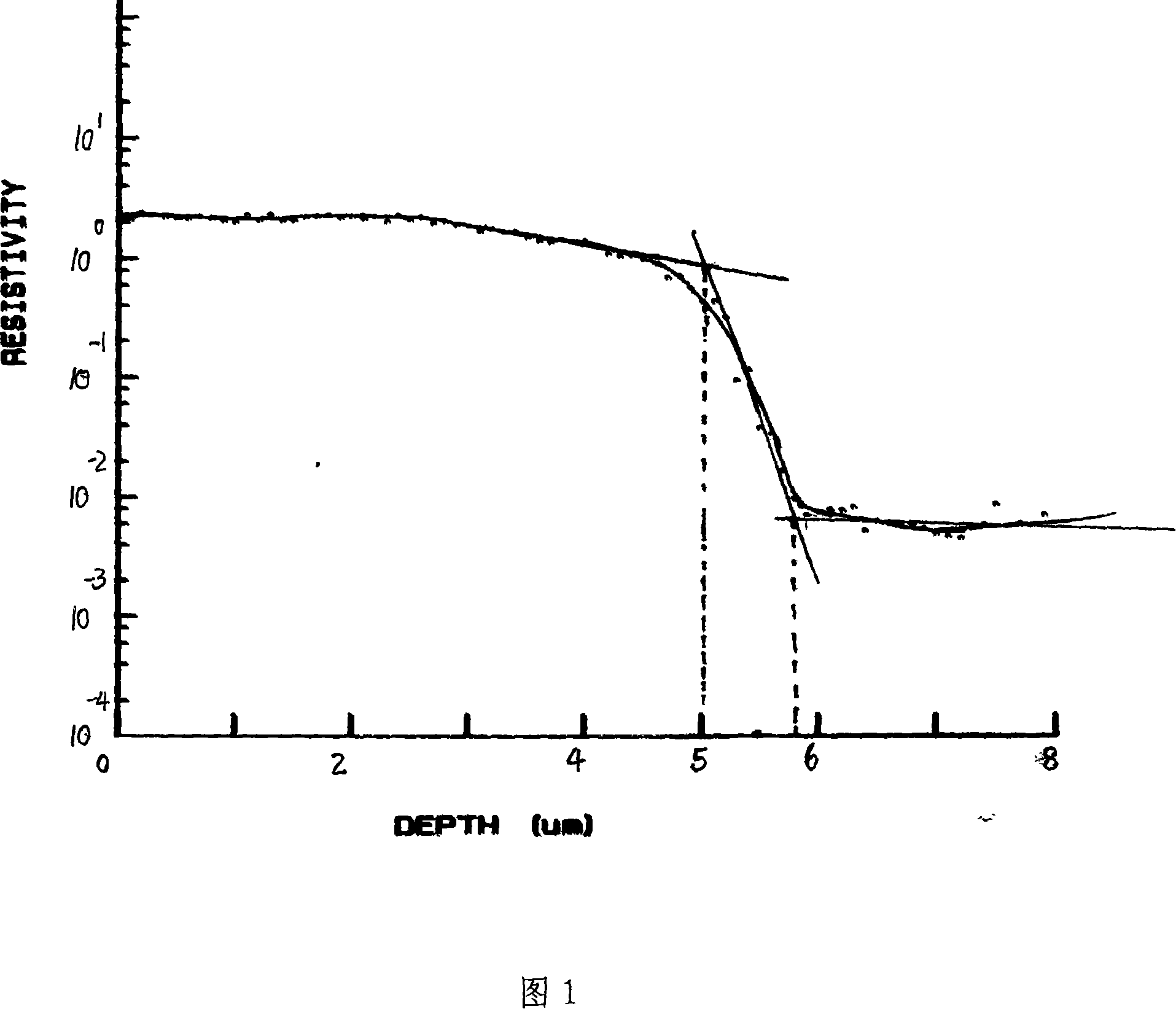

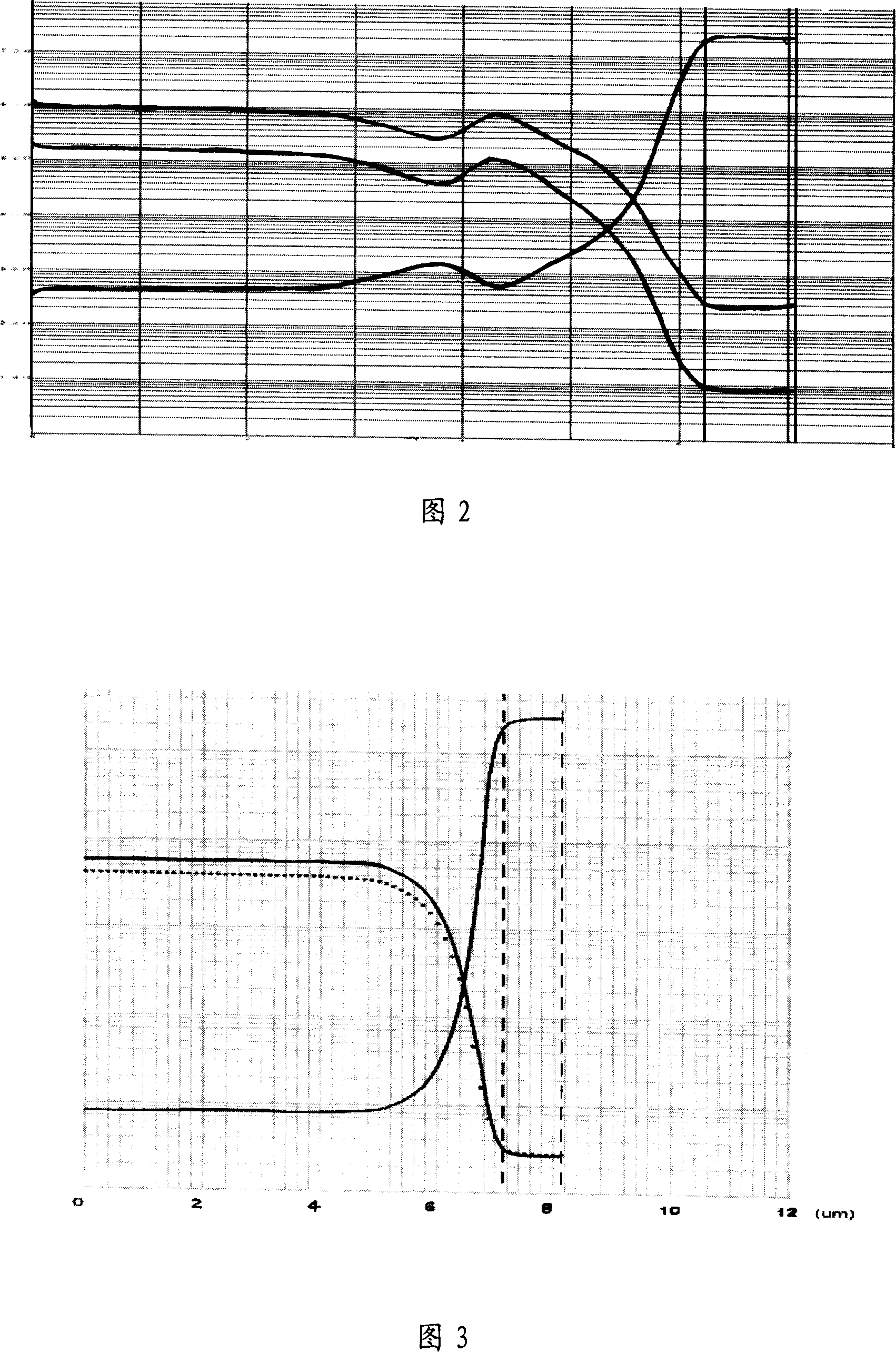

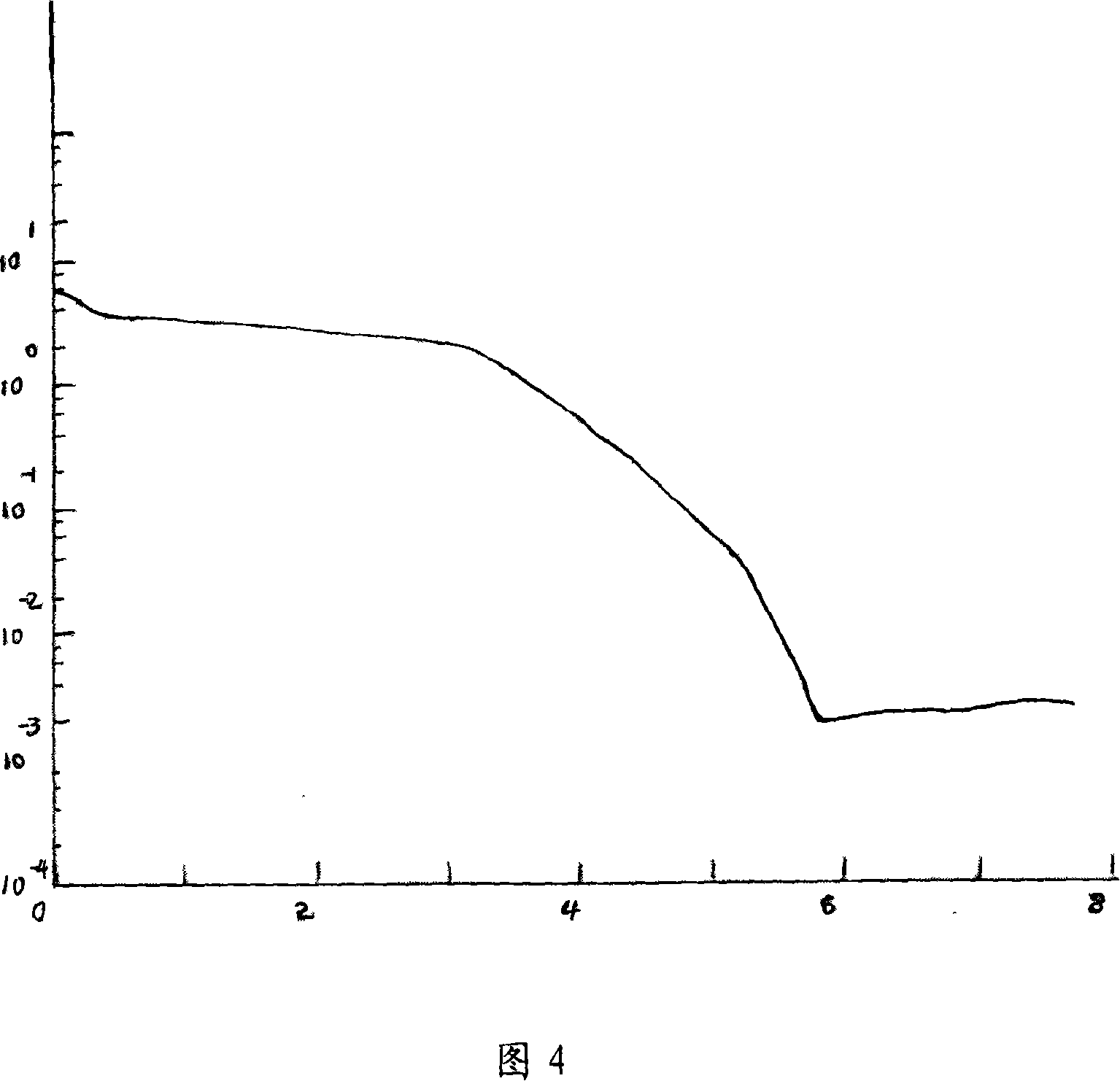

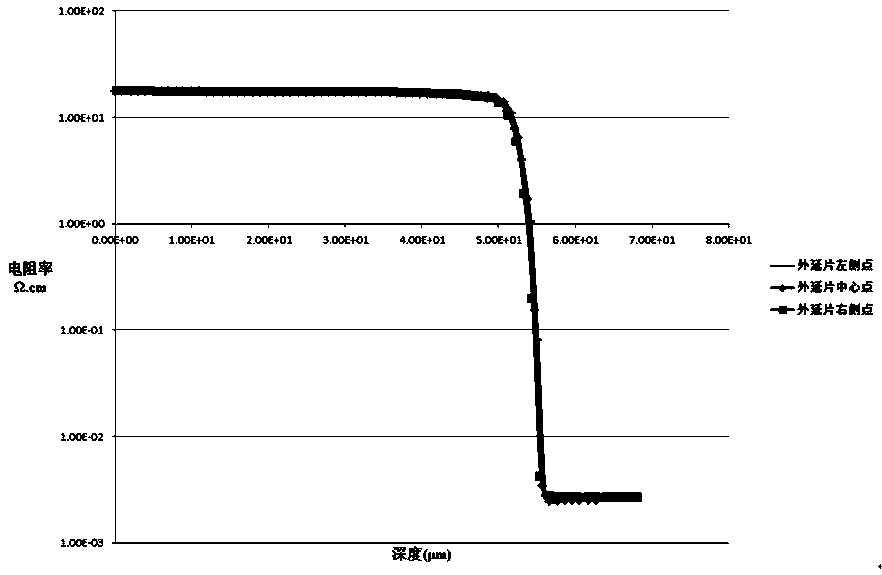

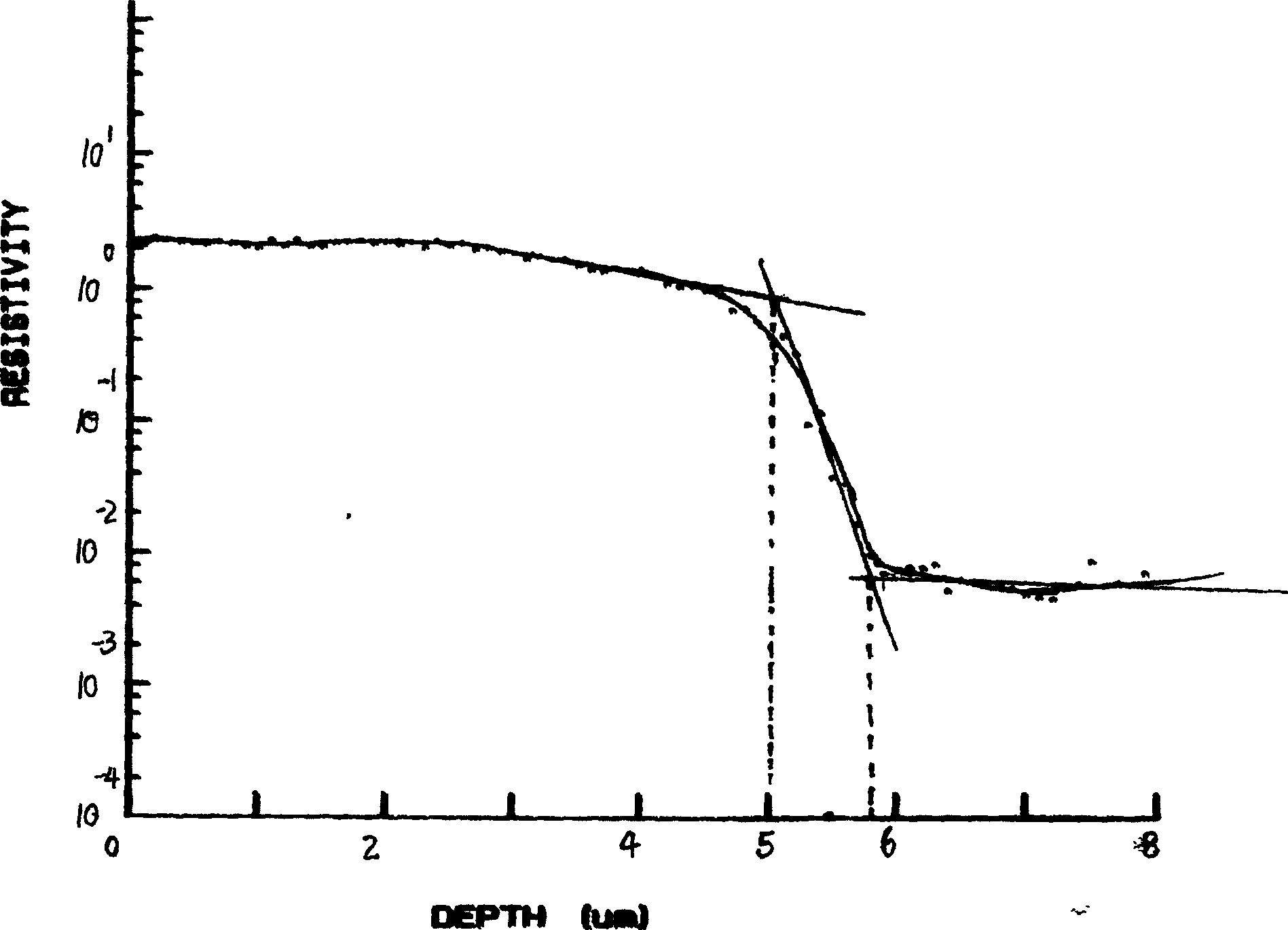

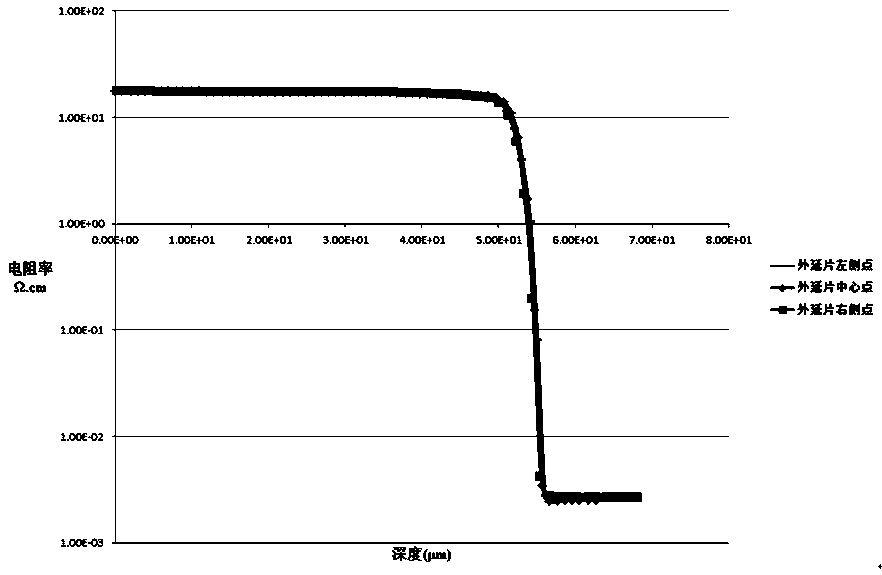

Control method for epitaxial layer transition zone on re-mixed arsenic underlay

ActiveCN101110356AResistivity gradient increasesHigh resistivitySemiconductor/solid-state device manufacturingMemory effectGrow light

The invention discloses a control method for an external extension transition section on a heavy doping arsenic underlay, which adopts chemical vapor deposition technology to grow light doping thin silicon extension layer at two times on a n-type heavy doping arsenic silicon underlay. After the growing of a first own extension layer, reduce the temperature to 870 to 930 DEG C. and take it out. During the process, remove the memory effect by putting in a HCI erosion base. After the completion of erosion, place the piece in furnace under the temperature of 870 to 930 DEG C. and then grow the residual extension layer. By checking and comparing the extension layer made with ordinary method and the method in the invention via an extension resistance analyzer, it is proved that the extension layer made of the method in the invention has steepy transition section and resistance of the extension layer has excellent evenness.

Owner:HEBEI POSHING ELECTRONICS TECH

Method for improving uniformity of axial resistivity of czochralski silicon and obtained monocrystalline silicon

ActiveCN102912424BThe dosage is easy to controlIncrease profitPolycrystalline material growthBy pulling from meltDopantArgon atmosphere

The invention discloses a method for improving the uniformity of axial resistivity of czochralski silicon. The method comprises the steps as follows: (1) melting a polycrystalline silicon raw material and a solid doping agent in an argon atmosphere to obtain stable molten silicon; (2) introducing seed crystals into the stable molten silicon, and conducting constant diameter growth on the crystals after necking and shouldering processes; and (3) during the constant diameter growth period, adding dopant gas with the conductive type opposite to that of the solid doping agent until the growth of the czochralski silicon is fulfilled. According to the method, the type and the usage amount of the dopant gas are convenient to control, various required impurity concentration distributions can be obtained, the utilization rate of the czochralski silicon is increased, and the uniformity of the resistivity of the czochralski silicon is remarkably improved.

Owner:ZHEJIANG UNIV

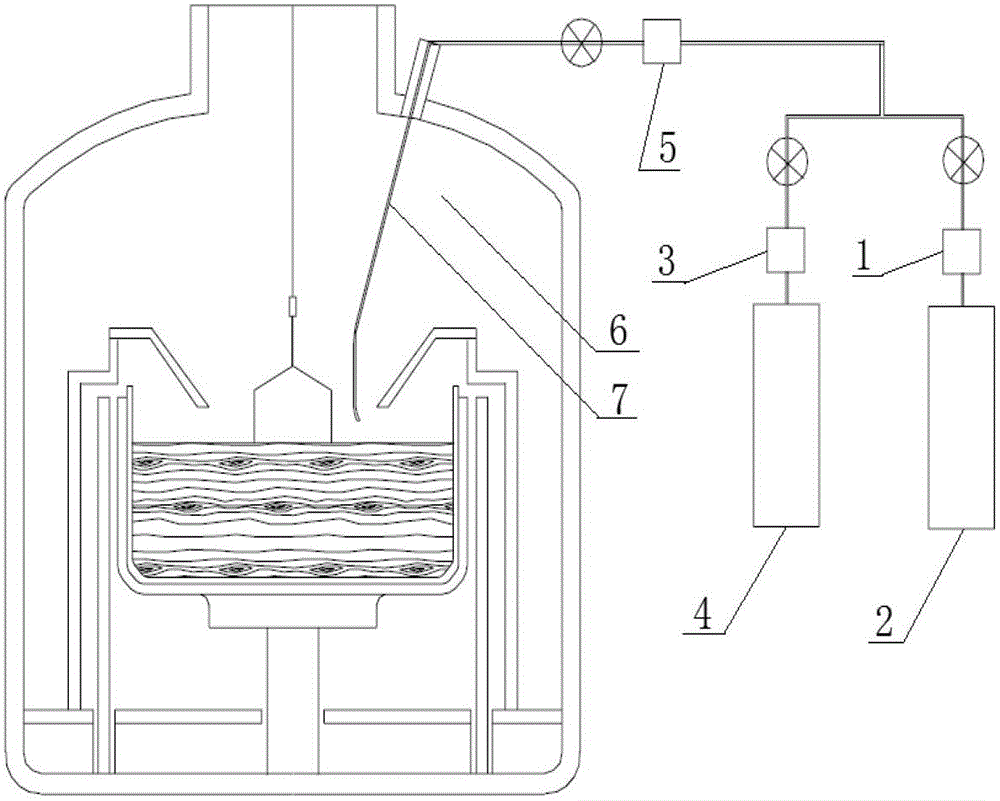

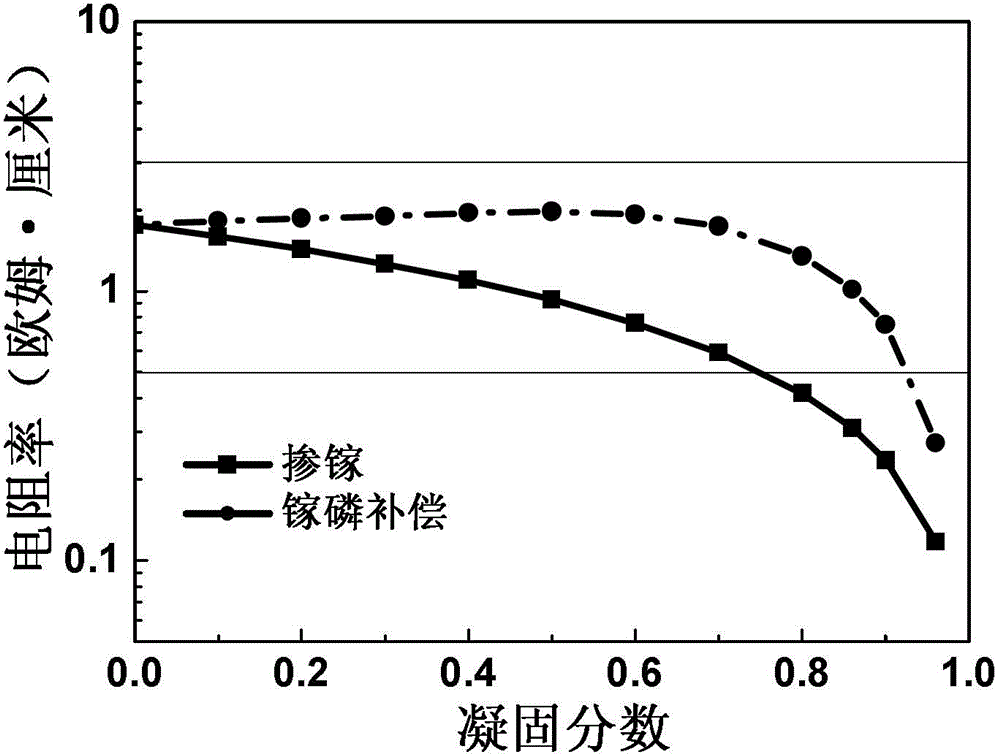

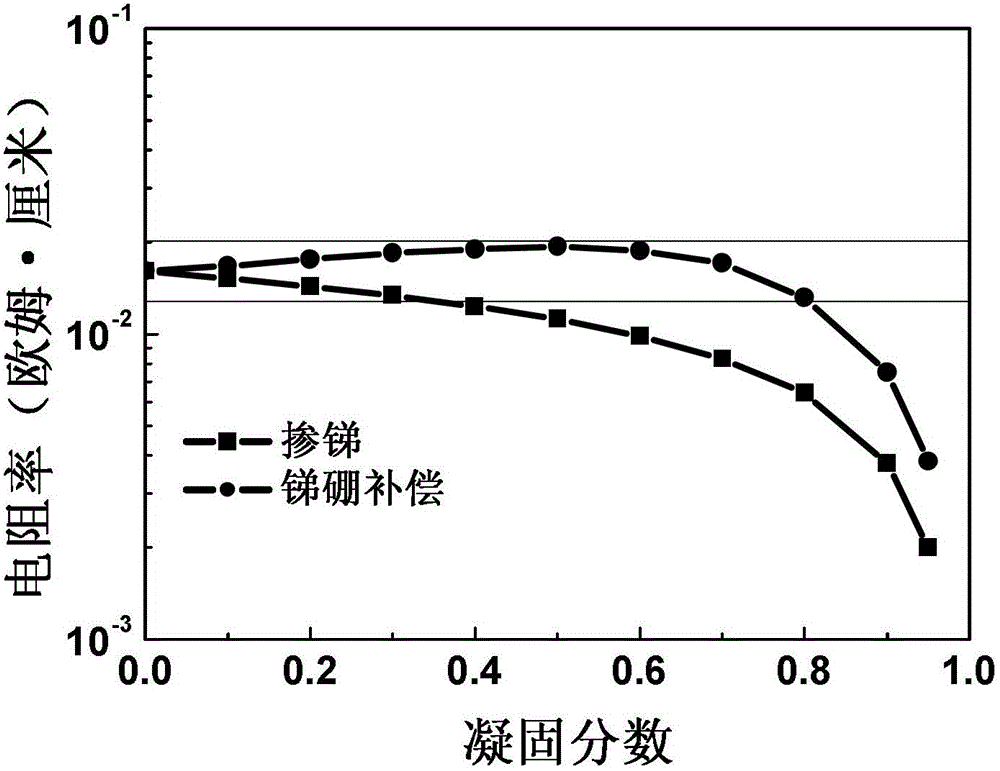

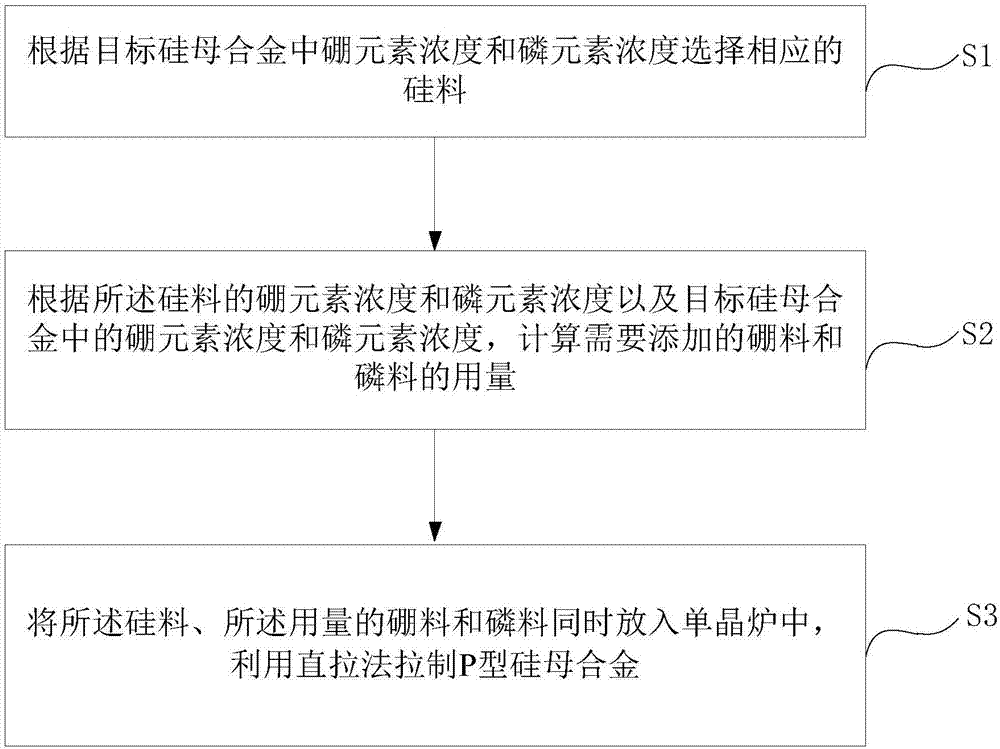

P-type silicon mother alloy production method

InactiveCN107419328AImprove uniformityReduce dosagePolycrystalline material growthBy pulling from meltP type siliconDopant

The invention discloses a P-type silicon mother alloy production method, which comprises the steps of selecting a corresponding silicon material according to the boron element concentration and the phosphorus element concentration in target silicon mother alloy; calculating the amount of boron material and phosphorus material which are need to be added according to the boron element concentration and the phosphorus element concentration of the silicon material, and the boron element concentration and the phosphorus element concentration in the target silicon mother alloy; putting the silicon material, the amount of boron material and phosphorus material simultaneously into a single crystal furnace, and pulling to prepare the P-type silicon mother alloy by using a Czochralski method. The P-type silicon mother alloy production method can improve the uniformity of the P-type mother alloy resistivity, reduce the amount of boron dopants and reduce the resistivity levels, thereby reducing the production cost.

Owner:JINKO SOLAR CO LTD +1

Electrode paste composition, electrode for electronic device using the same, and method of manufacturing the same

InactiveUS20130130020A1Improve resistivity uniformityImprove conductivityMaterial nanotechnologyConductive materialOptoelectronicsGraphene

There is provided an electrode paste composition, an electrode for an electronic device using the same, and a method of manufacturing the same. The electrode for an electronic device includes: a substrate; a thin film layer formed on the substrate, the thin film layer including reduced graphene oxide (rGO); and an oxide layer formed between the substrate and the thin film layer. The electrode for an electronic device may have excellent uniform resistivity and electrical conductivity since the electrode is formed by coating the substrate with a solution containing graphene oxide having superior dispersibility and reducing the graphene oxide.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

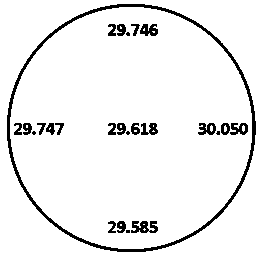

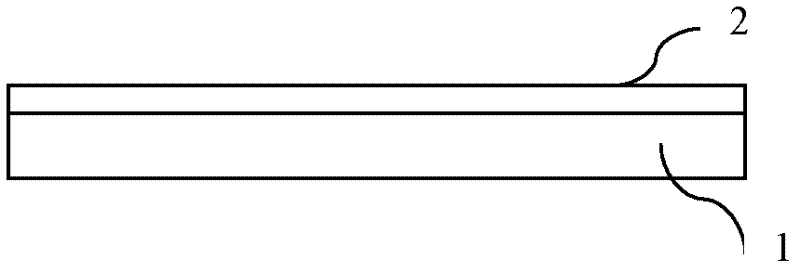

Substrate, epitaxial wafer and semiconductor device

InactiveCN102324435AReduced resistivity uniformityReduce subsequent production costsSemiconductor devicesPolycrystalline siliconSemiconductor

The invention discloses a substrate. The substrate comprises a substrate body and is characterized in that a first silicon dioxide layer is arranged at the back side of the substrate body; a polycrystalline silicon layer is arranged on the surface of the first silicon dioxide layer; and a second polycrystalline silicon layer is arranged on the surface of the polycrystalline layer. The invention has another advantage of being capable of improving the flatness of an epitaxial wafer and increasing the resistivity uniformity of an epitaxial layer.

Owner:SHANGHAI JINGMENG SILICON CORP

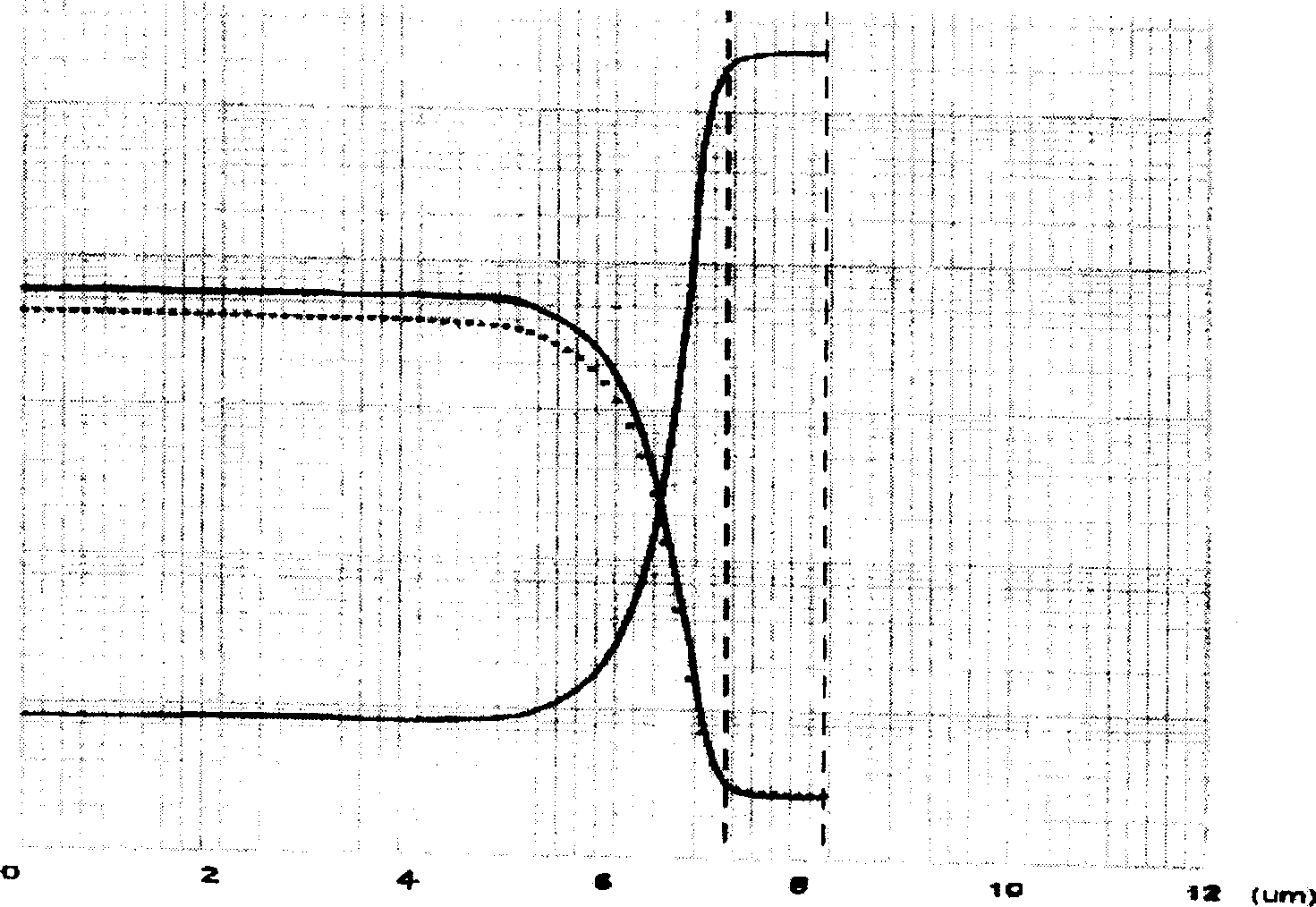

Manufacturing method of silicon epitaxial wafer for 8-inch VDMOS power tube

ActiveCN110660649APrevent proliferationGuaranteed uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryElectric resistivity

The invention discloses a manufacturing method of a silicon epitaxial wafer for an 8-inch VDMOS power tube, which comprises the steps of (1) selecting an As-doped substrate, wherein the resistivity ofthe substrate is less than or equal to 0.004 omega.cm; (2) growing a first epitaxial layer, wherein the first epitaxial layer grows on the surface of the substrate at the growth temperature of 1040-1080 DEG C and the growth rate of less than or equal to 1.5[mu]m / min, and purging the cavity with hydrogen after the growth of the first epitaxial layer is completed; and (3) and growing a second epitaxial layer, wherein second epitaxial layer grows on the surface of the first epitaxial layer at the growth temperature of 1040-1060 DEG C and the growth rate of 2-3[mu]m / min. According to the invention, the proper substrate is selected, the device and epitaxial requirements are met, the resistivity uniformity of the epitaxial layer is effectively improved, the deviation between the edge and the central region transition region is reduced, and the yield of the die is improved.

Owner:NANJING GUOSHENG ELECTRONICS

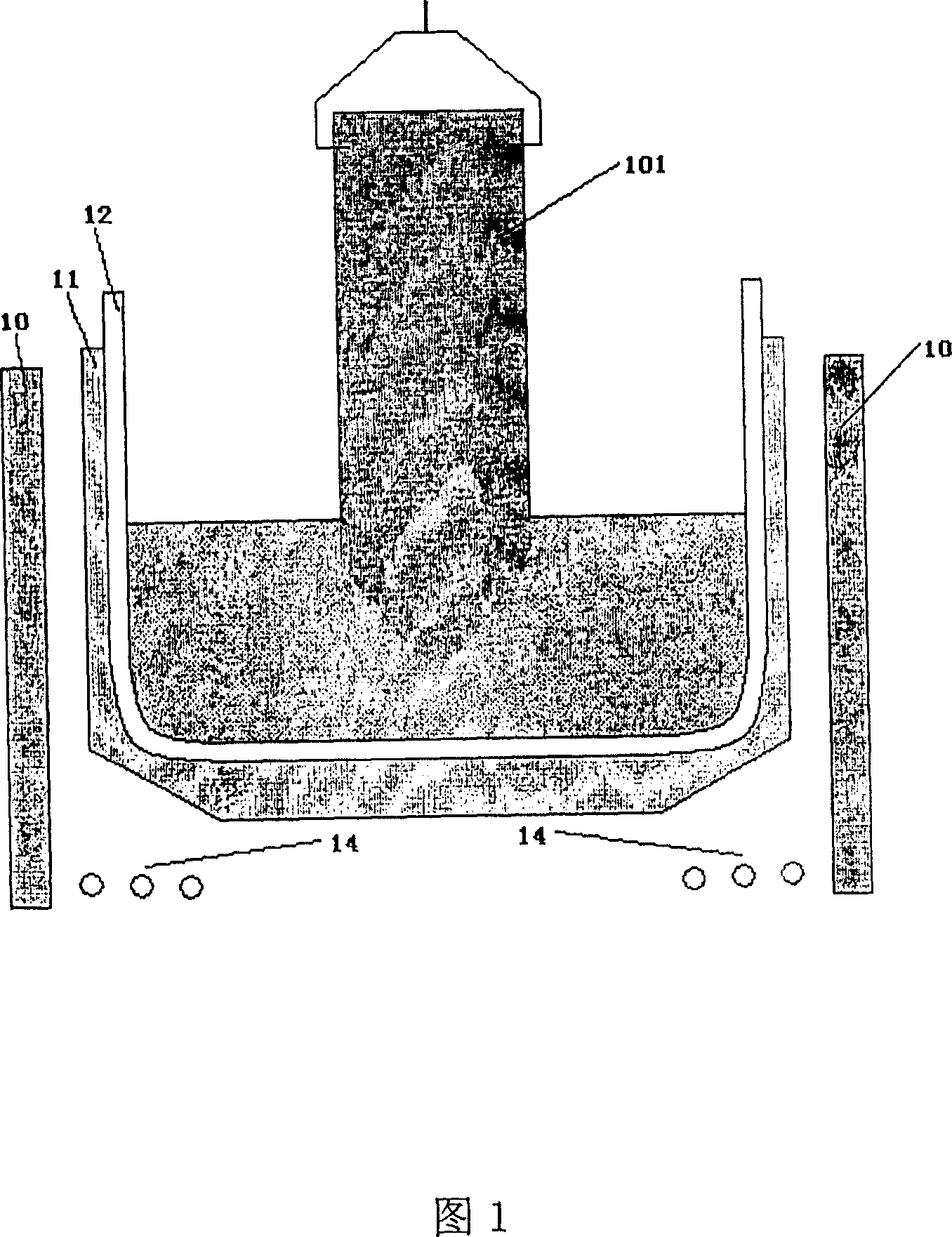

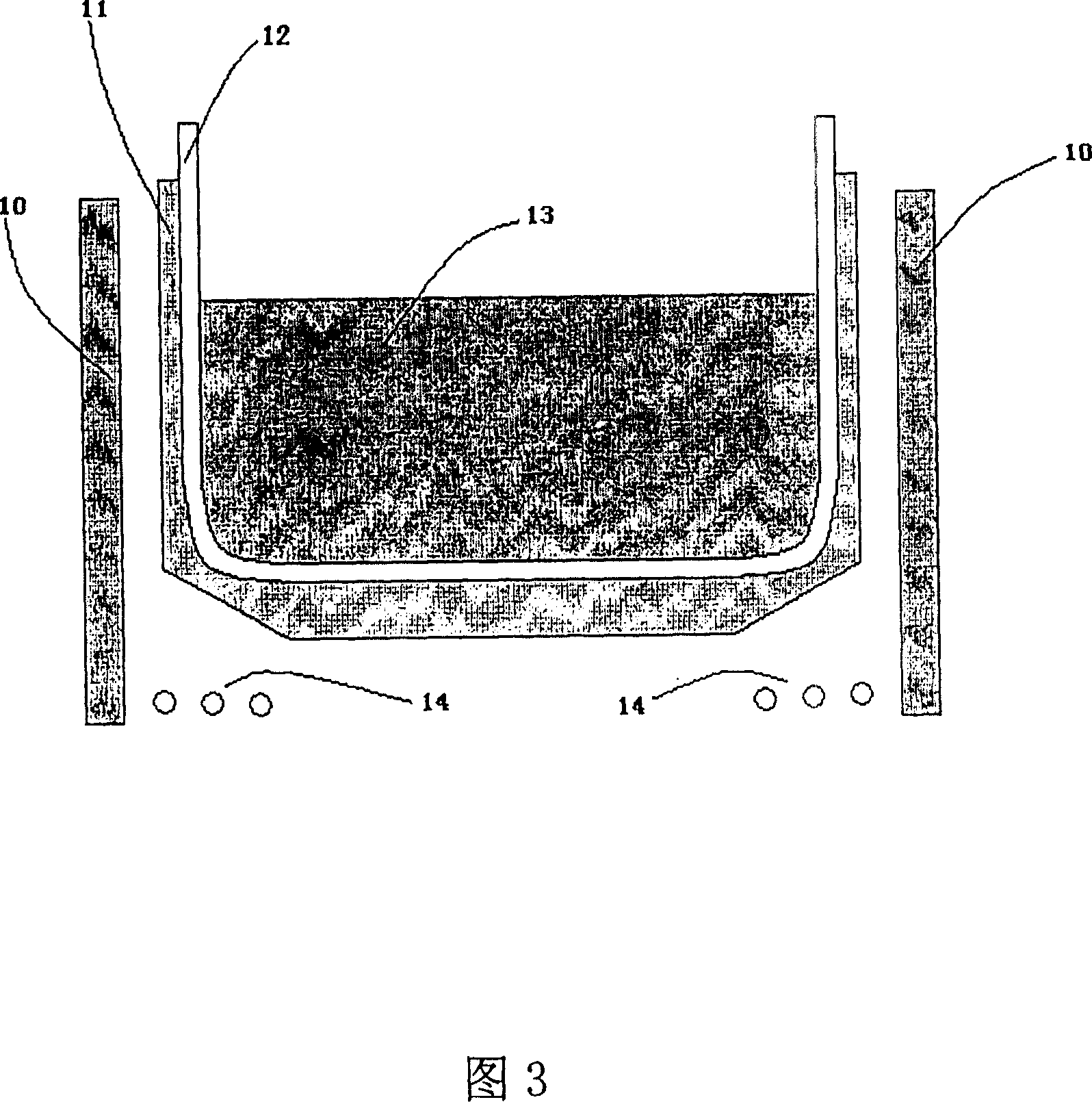

Apparatus for growing crystal by repeating adding material and method thereof

InactiveCN1327040CQuality improvementHigh resistivityPolycrystalline material growthBy pulling from meltCrucibleMaterial consumption

An apparatus and method for recharge raw material in the crystal growth. Use a feed tube to recharge raw material in a crucible. Cover the lower end of the tube with a plate. The plate is made of the same raw material as the charge in the crucible. Load the raw material in the tube, and then lower the tube into the melt in crucible. When the plate is melted, the raw material in the tube is droped into the crucible. It can be recharged using the feed tube after pulling a ingot, sequentially multiple ingots can be grown by using one crucible. In this apparatus and methods, there are not limited for the shape and size of the raw material, and increase the quantity of the raw material with one time. This apparatus and method can improve productivity, product quality and yield. Lowering material consumption, energy and cost.

Owner:袁建中

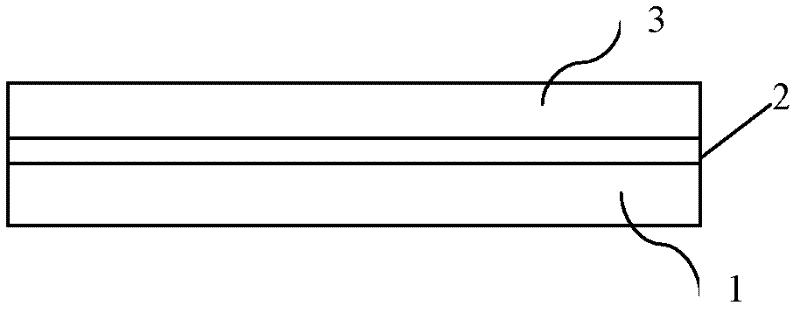

Method for producing novel substrate, epitaxial wafer and semiconductor device

InactiveCN102412124ALow growth temperatureImprove resistance uniformitySemiconductor/solid-state device manufacturingCrystallographyDevice material

The invention discloses a method for producing a novel substrate. The novel substrate comprises a substrate body and is characterized in that: the surface of the substrate body is provided with a monocrystalline silicon layer; and the monocrystalline silicon layer is formed by depositing monocrystalline silicon which is generated by reacting trichlorosilane and hydrogen at the temperature of between 900 and 1,050 DEG C on the surface of the substrate body. The resistance uniformity of the epitaxial wafer which is produced by using the novel substrate is less than 1.5 percent. Compared with the epitaxial wafer which is not produced by using the novel substrate, the epitaxial wafer has the advantages that the resistance uniformity value of the epitaxial wafer can be reduced by 1 percent. By using the novel substrate, the subsequent production cost can be reduced and product quality can be improved.

Owner:SHANGHAI JINGMENG SILICON CORP

Control method for epitaxial layer transition zone on re-mixed arsenic underlay

ActiveCN100485873CLow impurity contentSteep transition zoneSemiconductor/solid-state device manufacturingMemory effectGrow light

Owner:HEBEI POSHING ELECTRONICS TECH

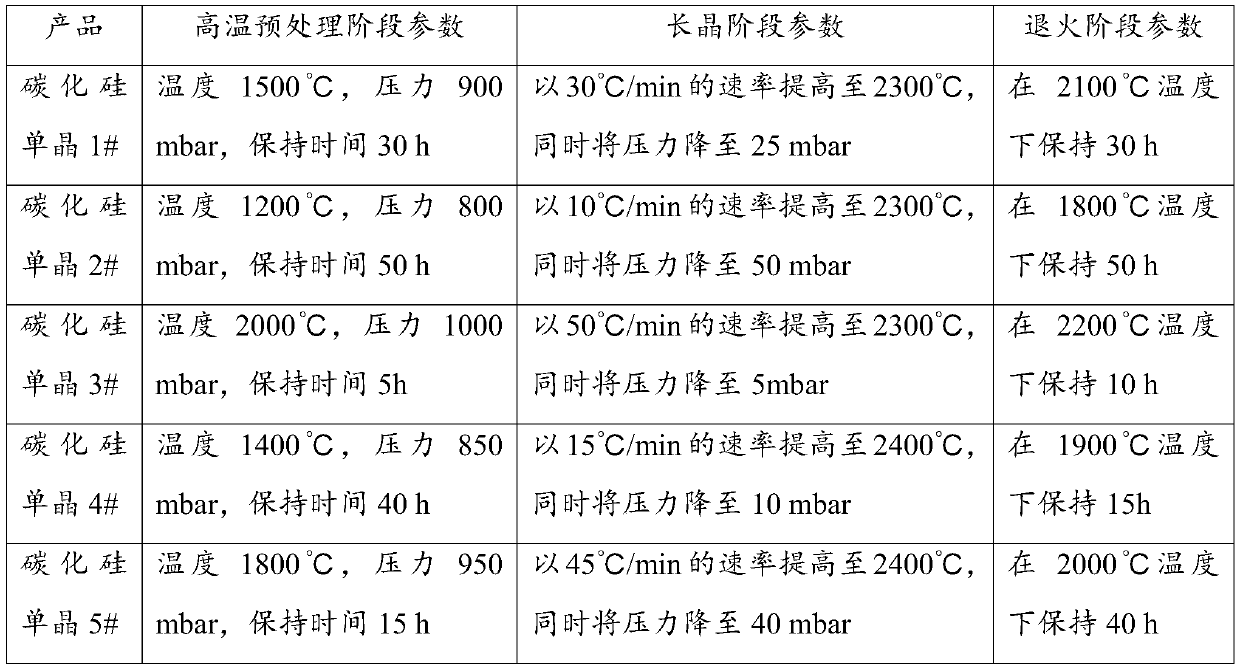

A kind of growth of SIC crystal for off-axis substrate and preparation method of n-type SIC substrate with high electrical uniformity

ActiveCN106012002BConducive to diameter expansionGuaranteed anglePolycrystalline material growthFrom condensed vaporsSingle crystal substrateOptoelectronics

The invention relates to a method for growth of a SiC crystal for an off-axis substrate and a method for preparing an N type SiC substrate with high electric uniformity. A deviating SiC seed crystal is adopted, a mechanism of controlling facet growth by a seed crystal asymmetric bonding way is used, and a SiC single-crystal material having the diameter increased by 20 mm than a standard diameter is obtained through an atmosphere guide plate. The asymmetrical rounding work is performed, and the SiC single-crystal material without facets is obtained. The N type SiC single-crystal substrate material with low defect density and electrical deviation of 3.5% or less can be obtained by the method.

Owner:SHANDONG UNIV

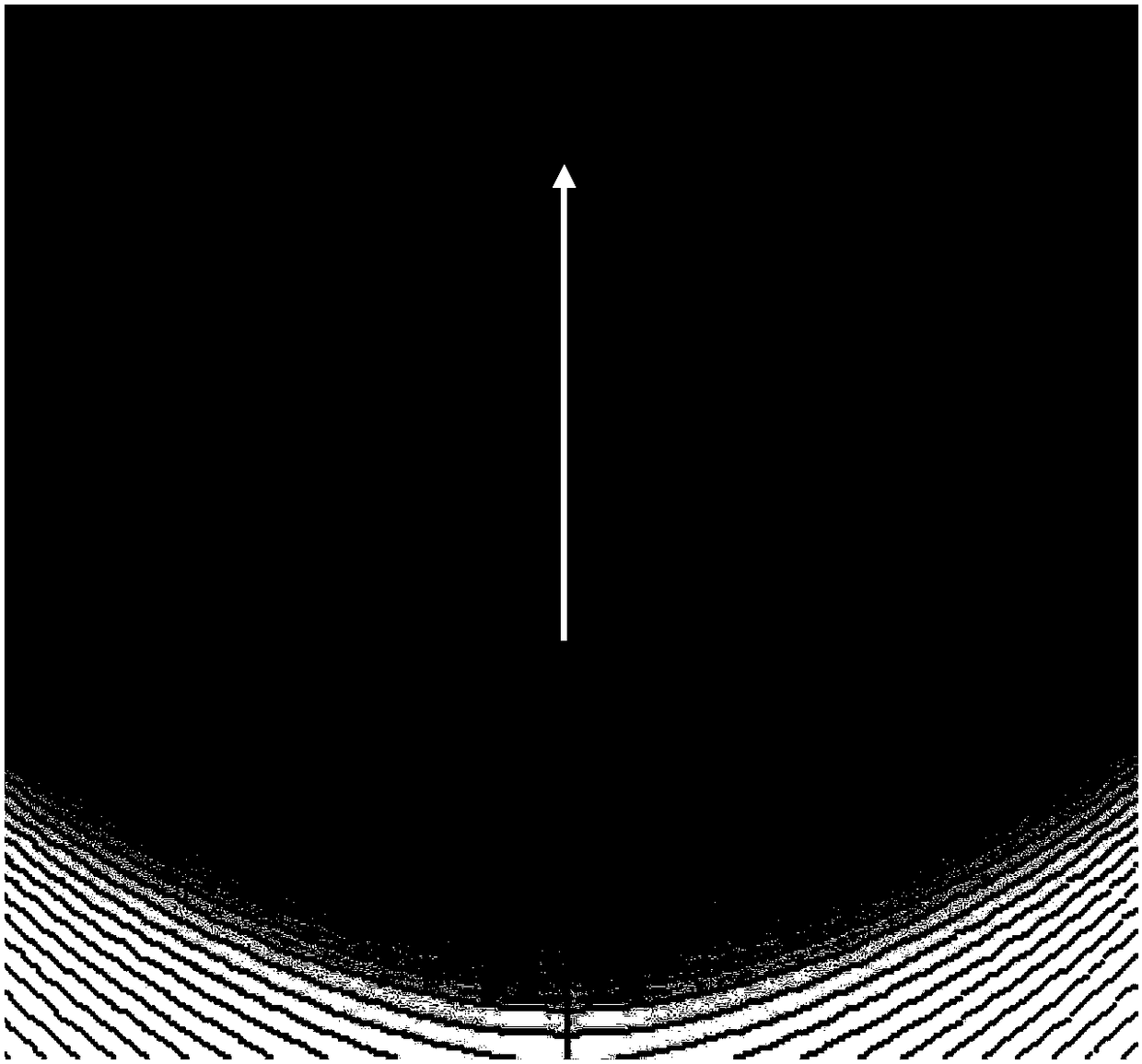

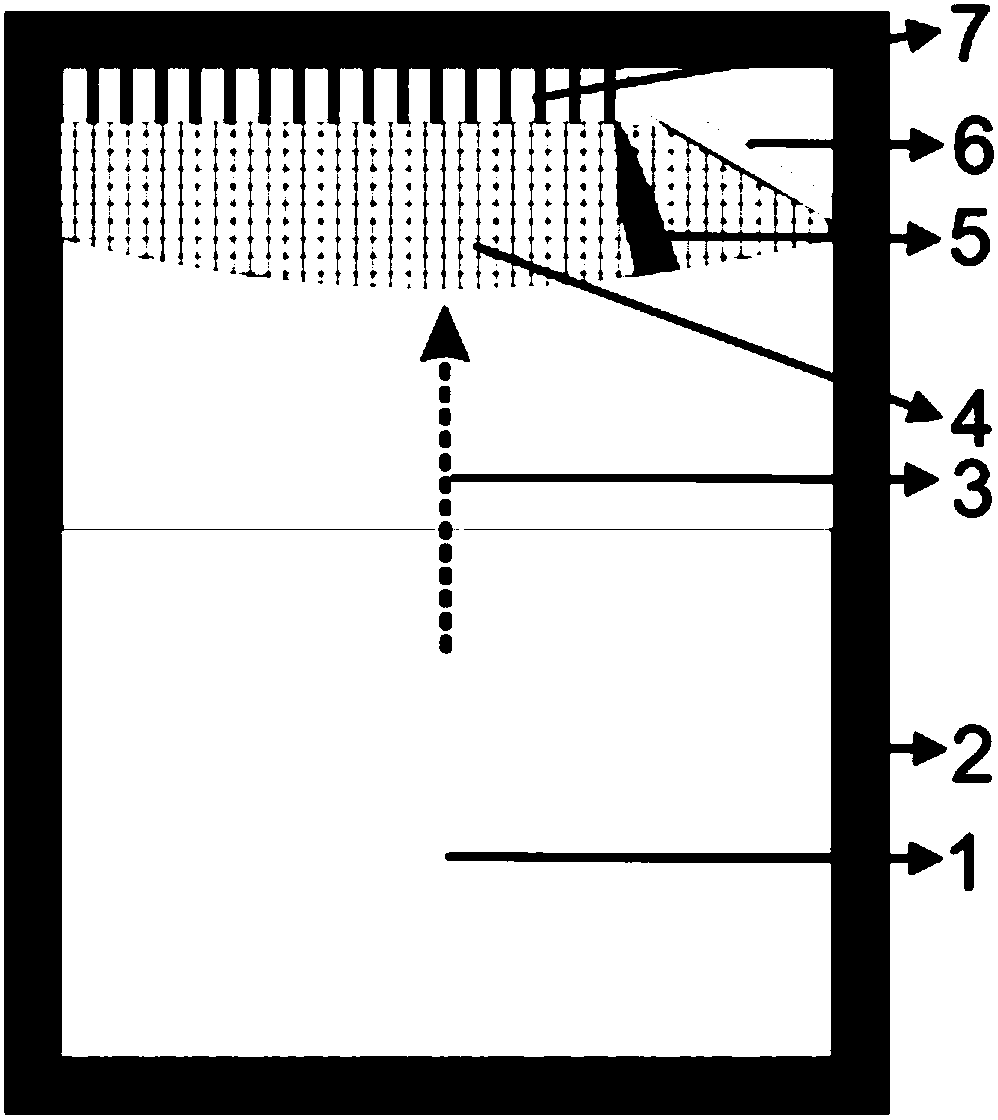

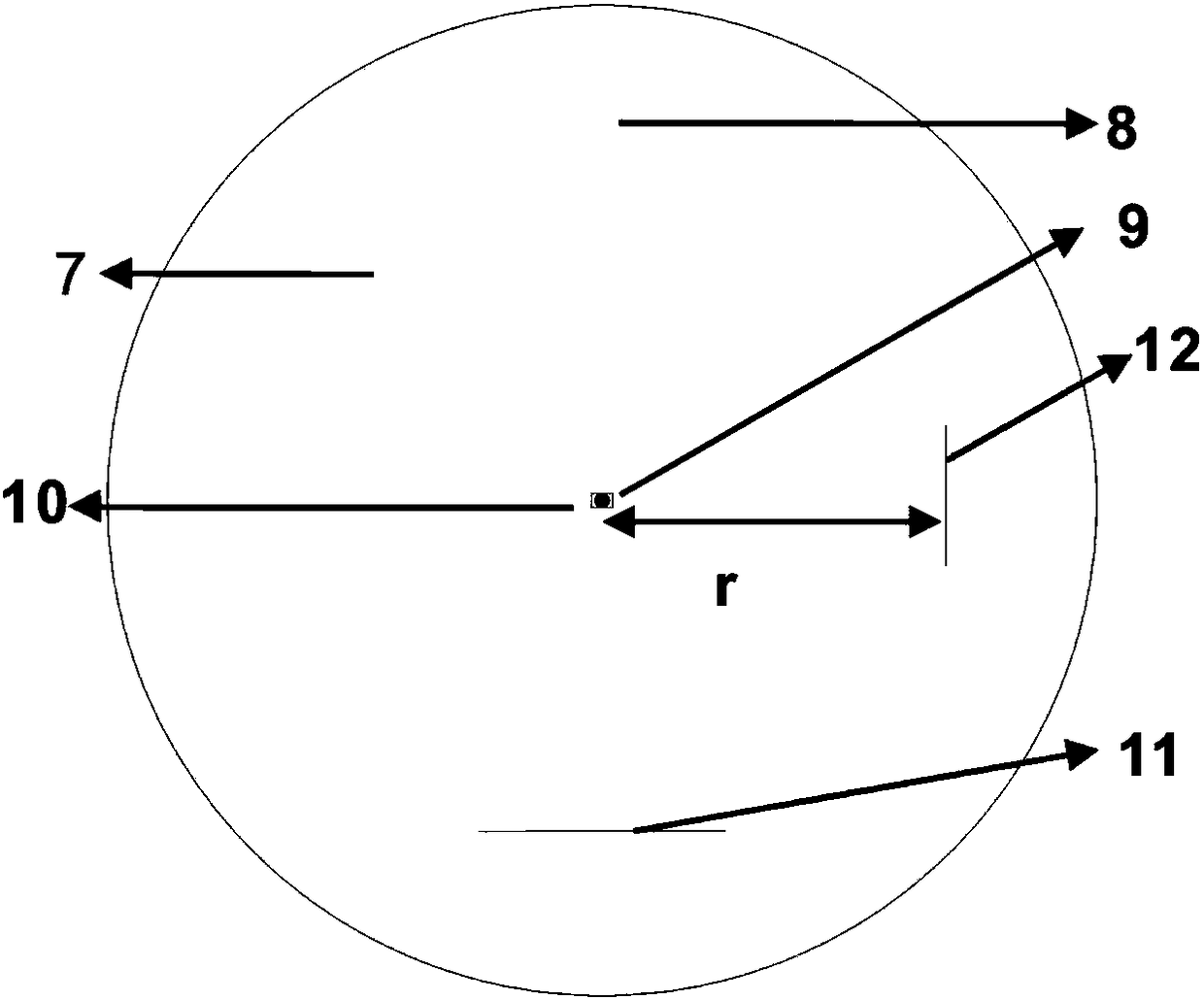

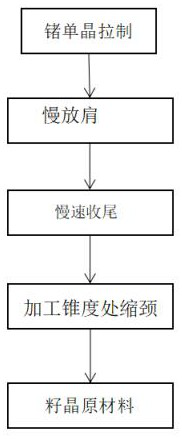

Manufacturing and processing method for improving seed crystal defects of germanium single crystal

PendingCN113957520AImprove resistivity uniformityReduce dislocation densityPolycrystalline material growthBy pulling from meltPhysical chemistrySeed crystal

The invention discloses a manufacturing and processing method for improving seed crystal defects of a germanium single crystal, and belongs to the field of crystal processing. The manufacturing and processing method for improving the seed crystal defects of the germanium single crystal comprises the following steps: step 1, drawing a single crystal with a proper size according to the size of a seed crystal chuck and the required size; step 2, necking a section at a taper part needing to be processed in the later period through more detailed manual control; and step 3, adopting slow shouldering, wherein the shouldering speed ranges from 10 mm / h to 15 mm / h, and the shouldering angle is larger than 45 degrees. The resistivity uniformity of the germanium seed crystal is greatly improved, the dislocation density and internal defects of the seed crystal are reduced, and a high-quality seed crystal raw material grows.

Owner:云南驰宏国际锗业有限公司

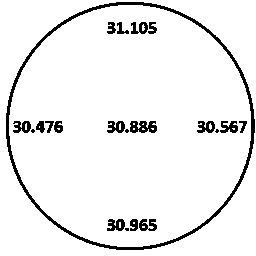

Novel substrate, epitaxial wafer and semiconductor device

InactiveCN102332465ALow growth temperatureImprove resistance uniformitySemiconductor devicesSemiconductorSemiconductor device

The invention discloses a novel substrate, which comprises a substrate body, and the novel substrate is characterized in that a monocrystalline silicon layer is arranged on the surface of the substrate body. The resistivity uniformity of an epitaxial layer produced with the novel substrate in the invention can be less than 1.5 percent. Compared with the resistivity uniformity value of an epitaxial layer which is not produced with the novel substrate in the invention, the resistivity uniformity value of the epitaxial layer in the invention can be decreased by one percent. By means of using the novel substrate in the invention, the subsequent production cost can be reduced, and the quality of products can be increased.

Owner:SHANGHAI JINGMENG SILICON CORP

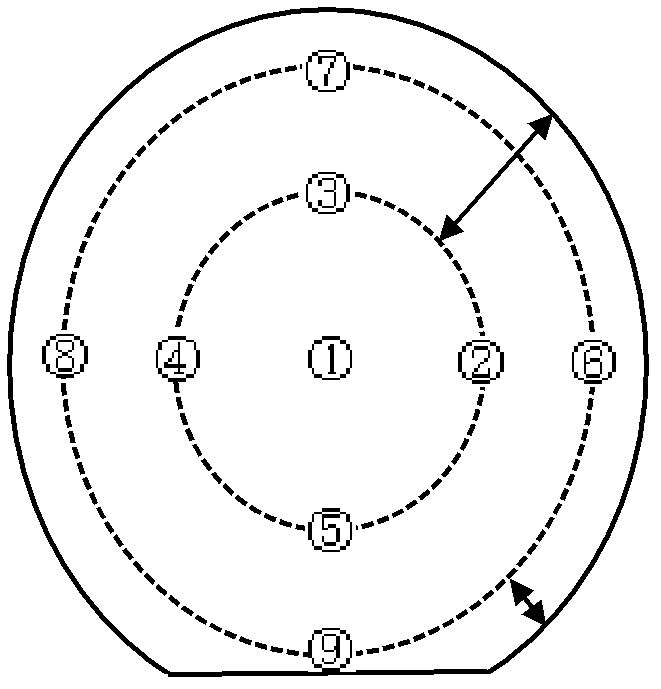

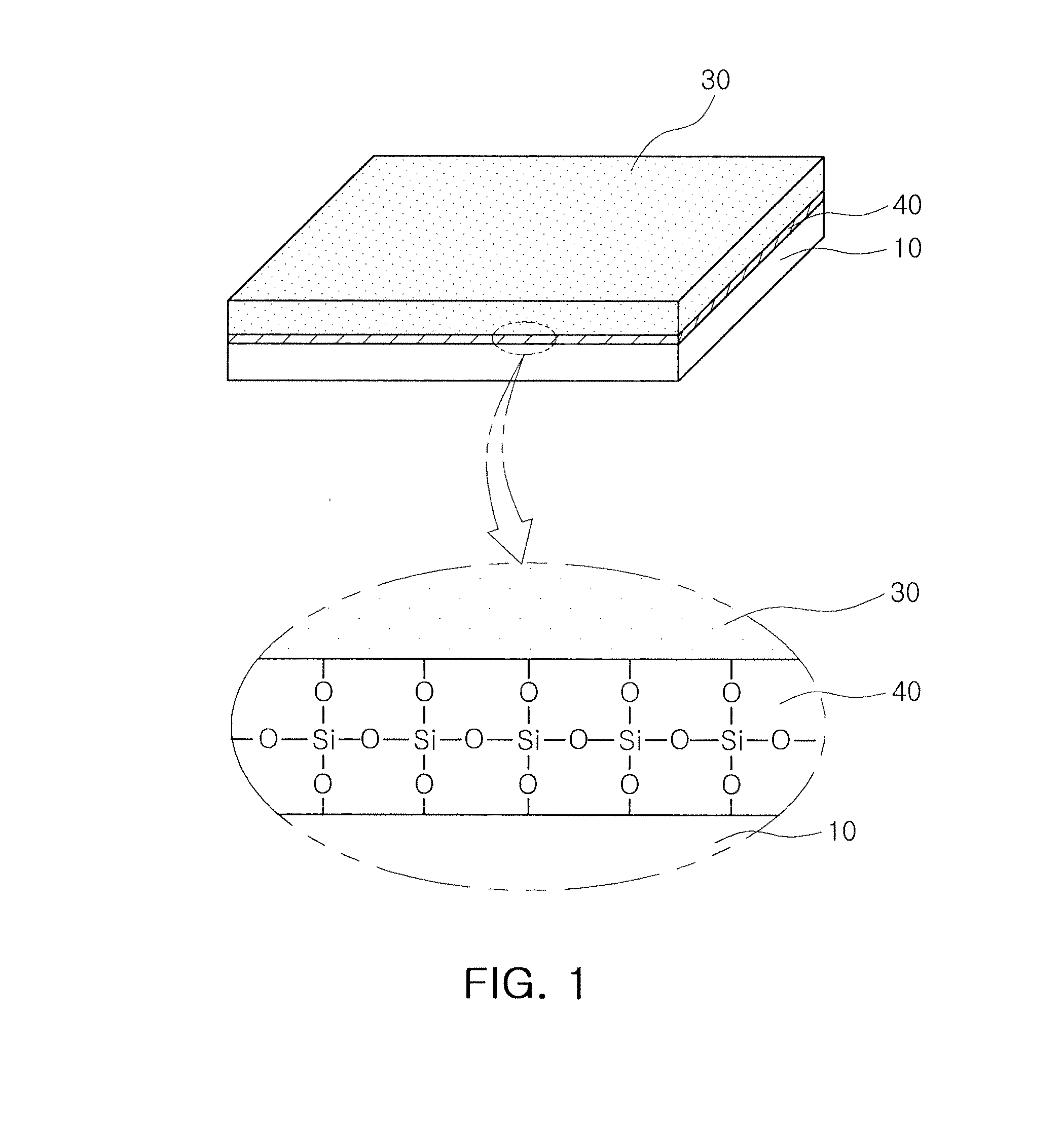

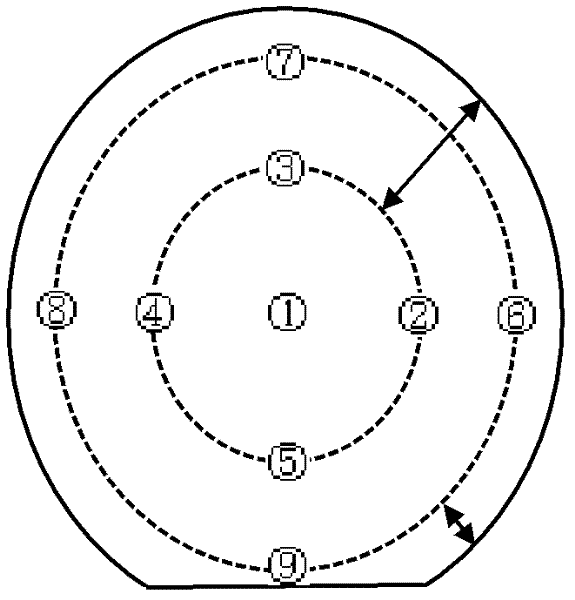

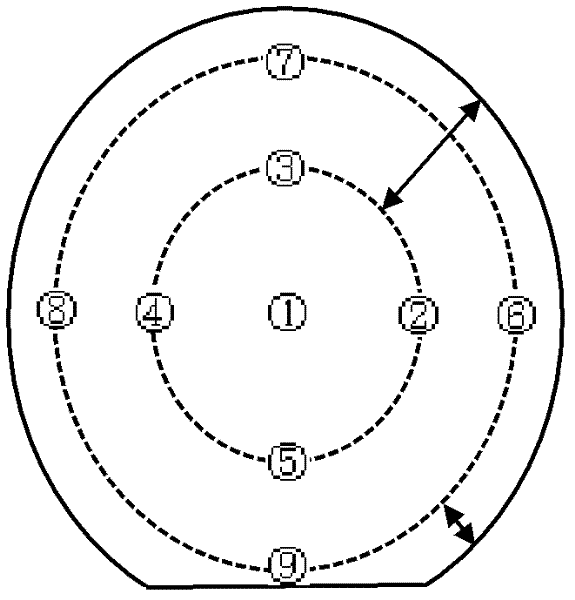

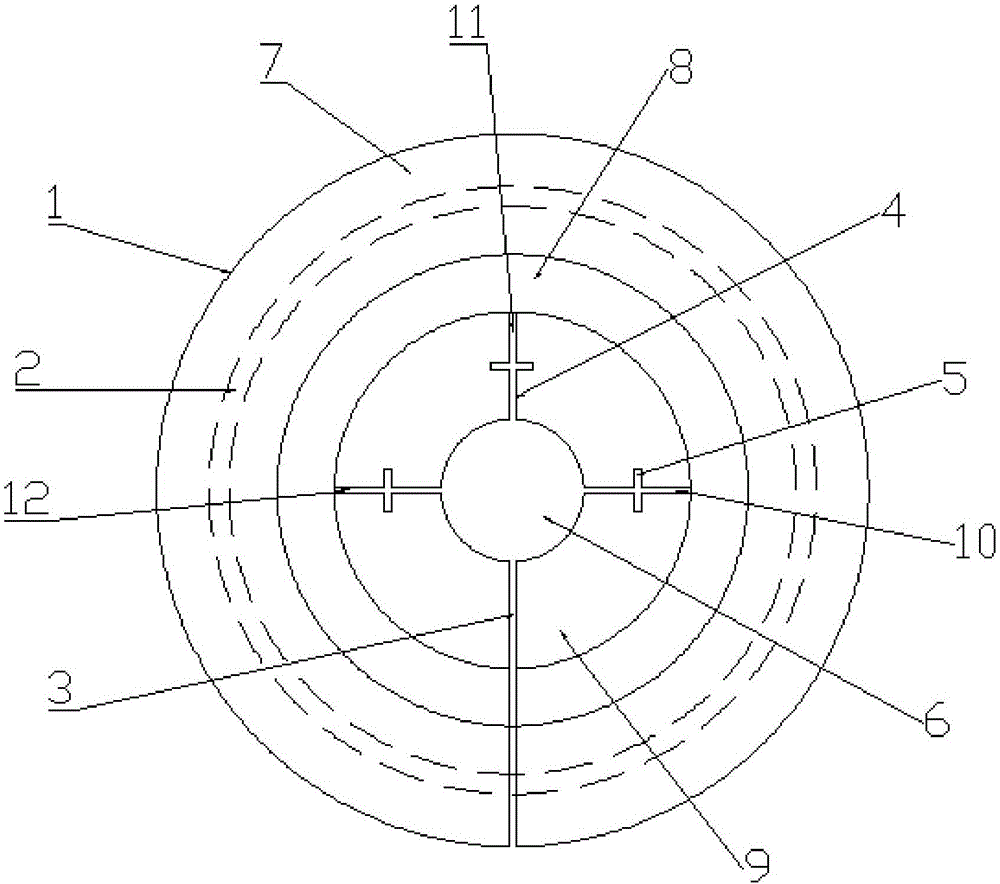

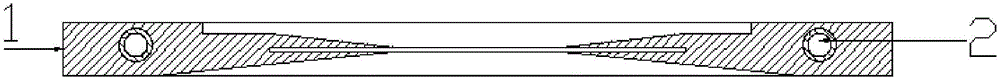

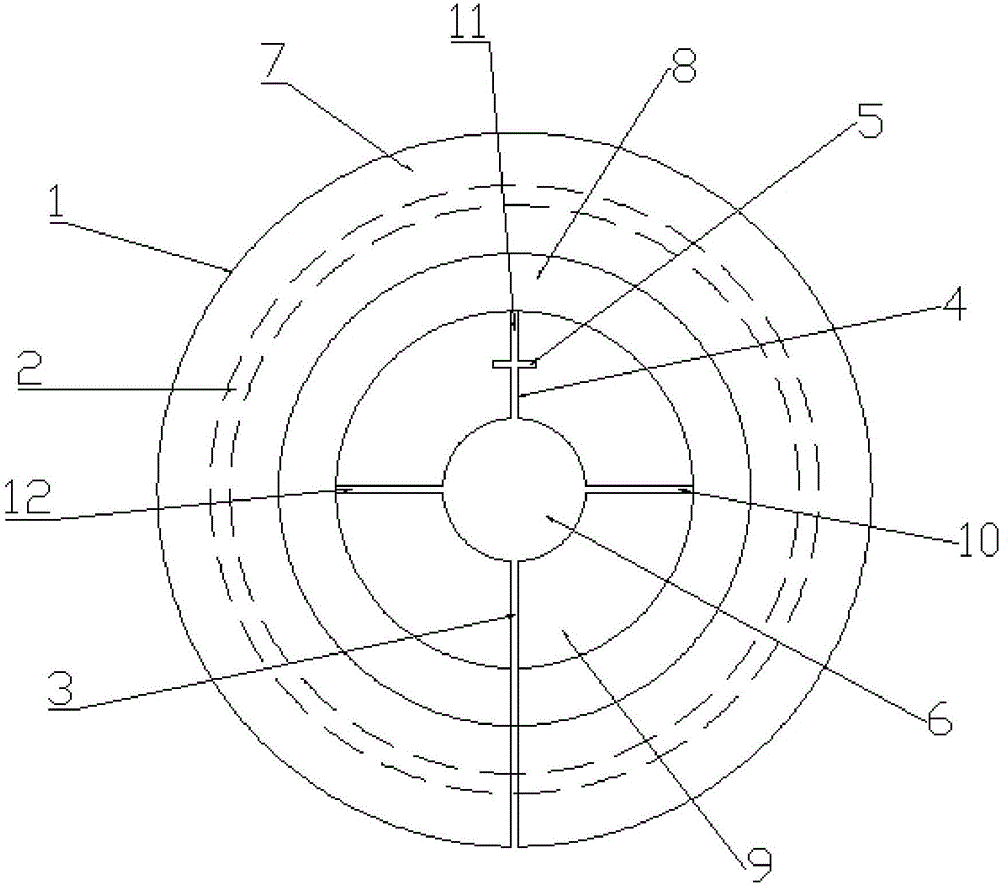

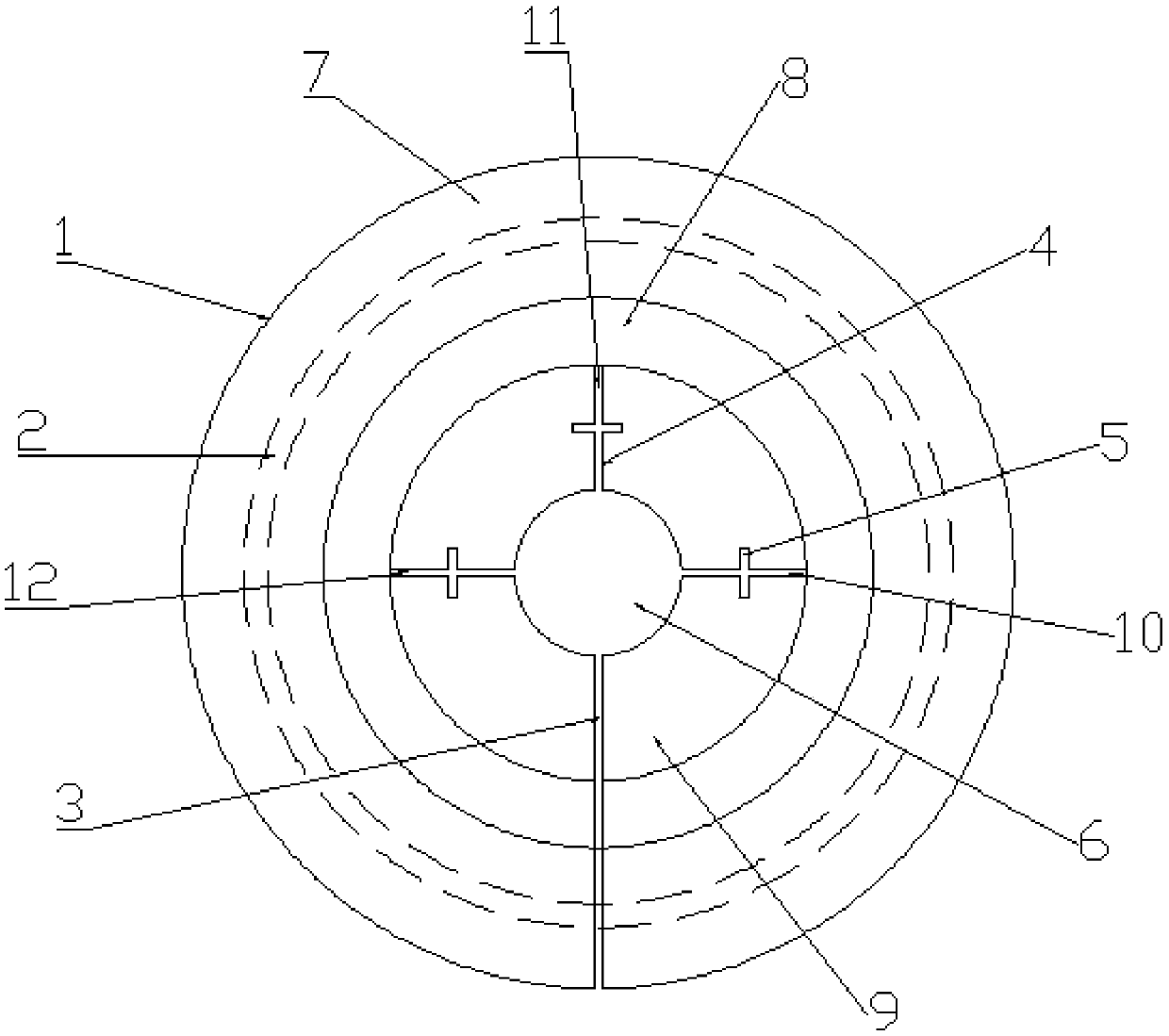

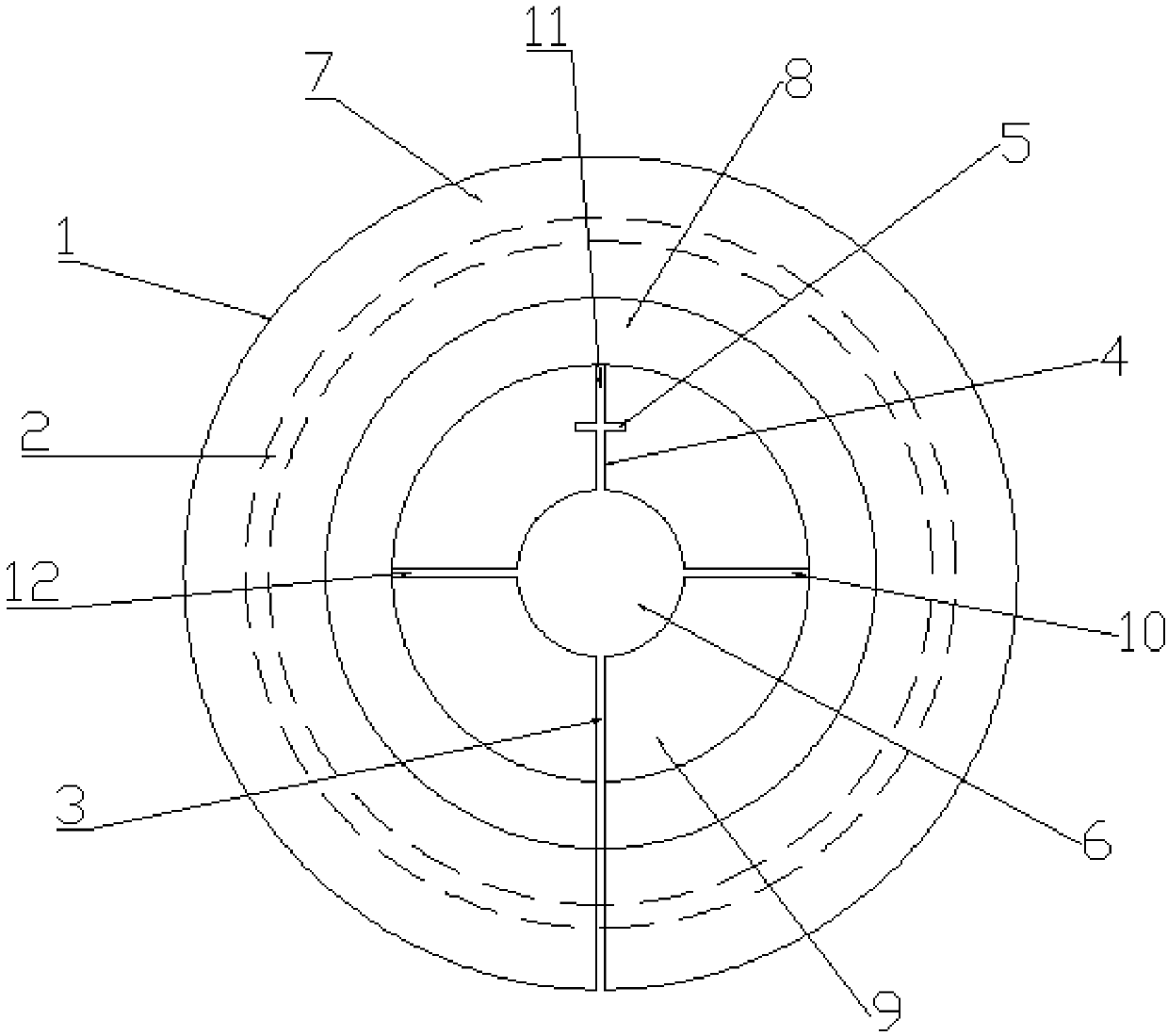

Coil structure for improving zone-melting radial resistivity uniformity

ActiveCN106087035AImprove the radial resistivity uniformity of zone meltingIncreasing the thicknessPolycrystalline material growthCoil arrangementsZone meltingSingle crystal

The invention provides a coil structure for improving the zone-melting radial resistivity uniformity. The coil structure comprises a coil main body, a cooling water pipeline, a main seam, a plurality of sub seams and a plurality of transverse seams, wherein the coil main body is a flat plate coil; the upper surface of the coil main body is sunken into the inside of the coil into a centrosymmetric step structure; a coil hole is formed in the geometric center part of the coil main body; the cooling water pipeline is positioned inside a step at the outermost layer of the coil main body; the main seam is arranged on the coil main body in the radial direction and penetrates through the upper surface and the lower surface of the coil main body; the plurality of sub seams are arranged on the step surface at the innermost layer of the coil main body and penetrate through the upper surface and the lower surface of the step surface; the transverse seams are partially or all arranged on the sub seams; the transverse seams are perpendicular to the respective sub seam. The coil structure for improving the zone-melting radial resistivity uniformity has the advantage that due to the adaption of the technical scheme, the zone-melting silicon single-crystal radial resistivity uniformity can be simultaneously improved.

Owner:ZHONGHUAN ADVANCED SEMICON MATERIALS CO LTD +1

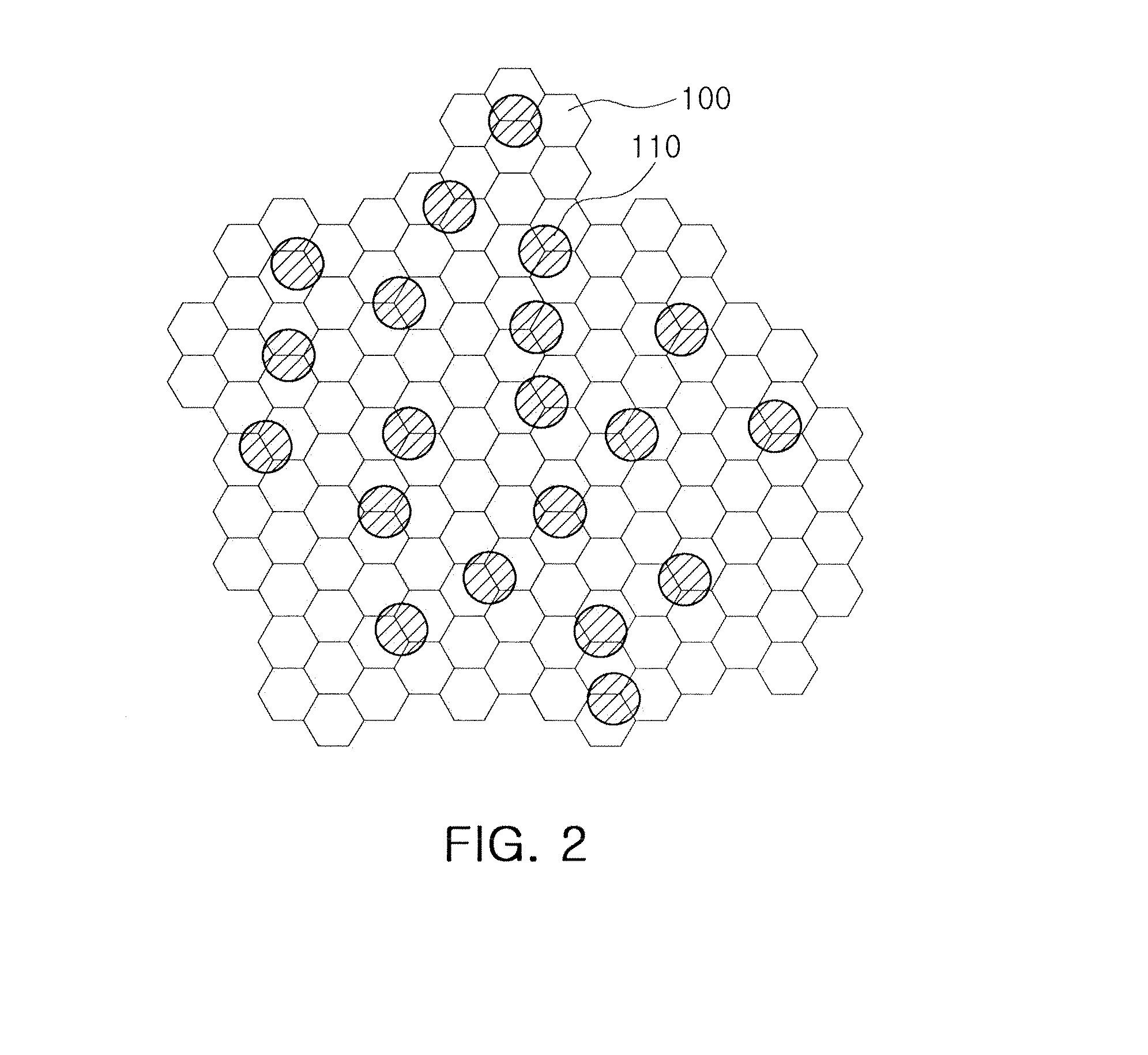

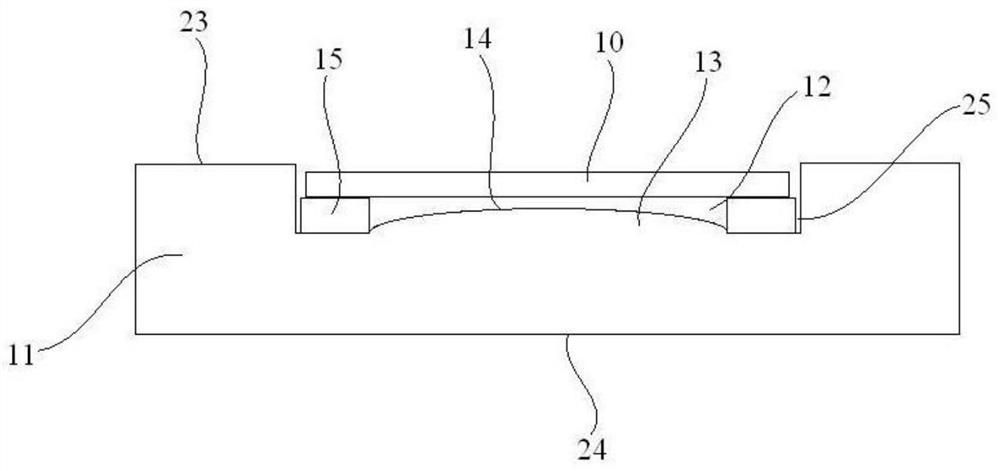

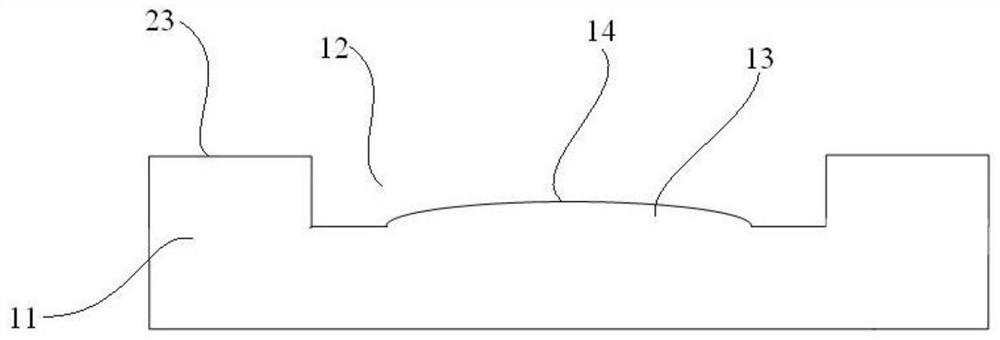

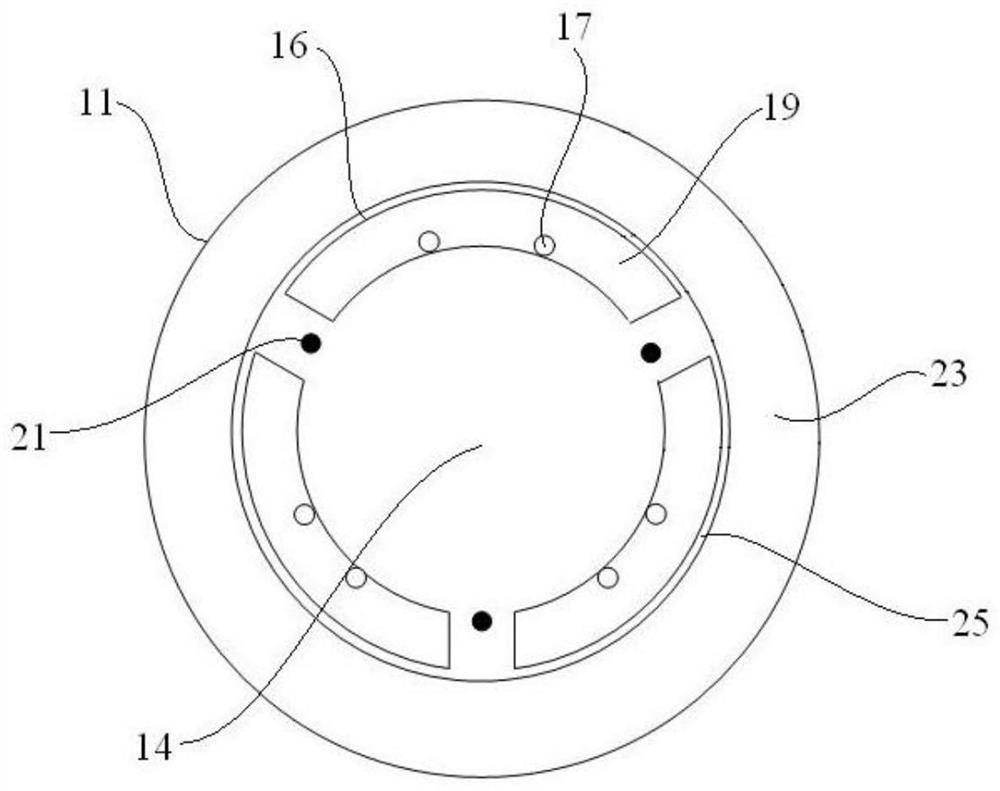

Tray of semiconductor processing equipment and semiconductor processing equipment

PendingCN111863700AImprove temperature uniformityImprove resistivity uniformitySemiconductor/solid-state device manufacturingPhysicsEngineering

The invention provides a tray of semiconductor processing equipment and the semiconductor processing equipment. The tray of the semiconductor processing equipment comprises a tray body and a supporting part, an accommodating groove for accommodating a wafer is formed in the tray body, the accommodating groove comprises a convex part positioned on the bottom surface of the accommodating groove, theupper surface of the convex part is an arc surface, and the distance between a point on the arc surface and the bottom surface of the accommodating groove is gradually reduced from the center of thearc surface to the edge so as to reduce the temperature difference between the center of the tray and the edge of the tray; the supporting part is arranged on the tray body and surrounds the peripheryof the arc surface, the supporting part is used for supporting the wafer, and a gap is formed between the wafer and the arc surface, so that the heat conduction efficiency of the tray to the edge ofthe wafer is reduced. According to the tray of the semiconductor processing equipment and the semiconductor processing equipment provided by the invention, the temperature uniformity of the wafer in the semiconductor technological process can be improved, so that the resistivity uniformity of an epitaxial layer is improved.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

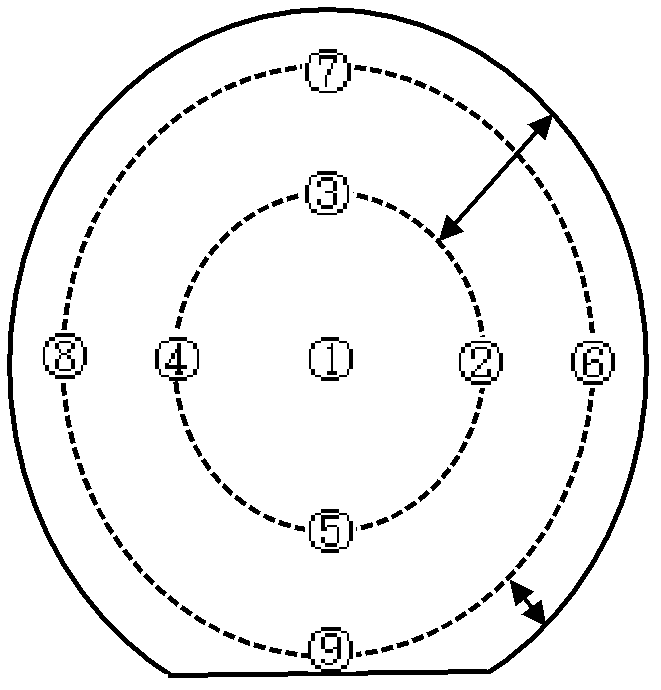

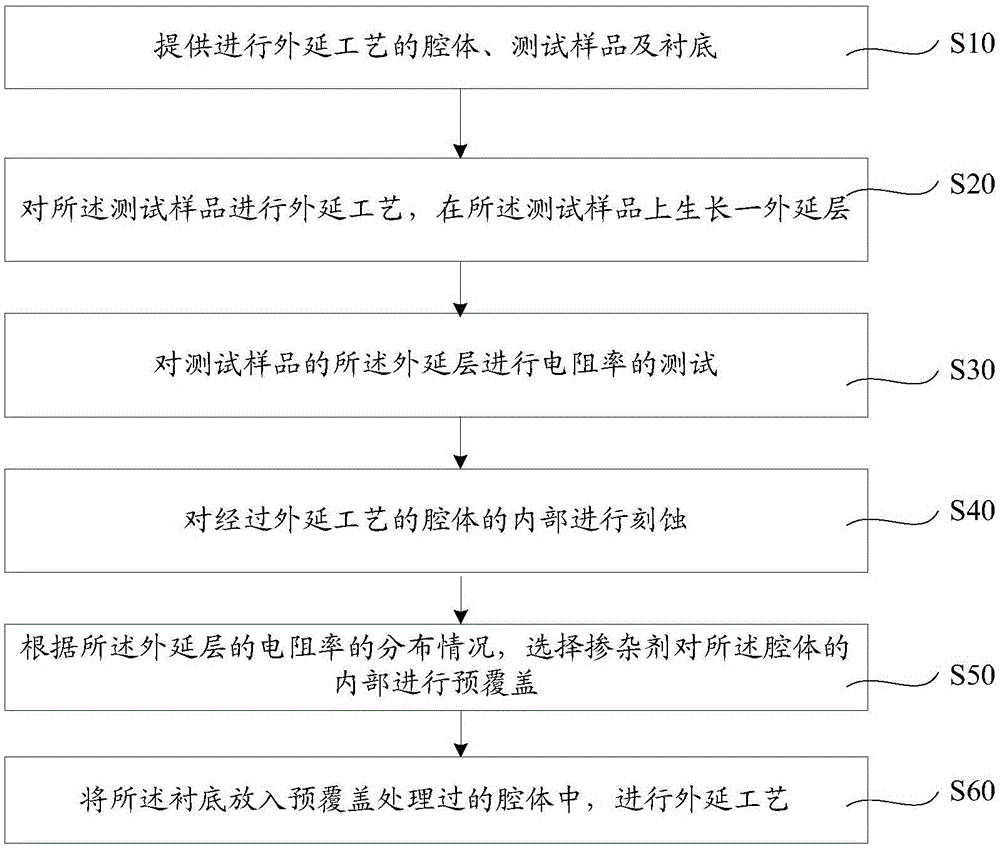

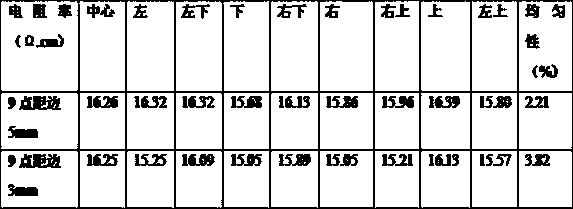

Method for Improving the Uniformity of Resistivity of Epitaxial Layer

ActiveCN103996608BImprove resistivity uniformityChange in resistivity uniformitySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingDopantTest sample

The invention provides a method for improving the uniformity of the electrical resistivity of an epitaxial layer. According to the method for improving the uniformity of the electrical resistivity of the epitaxial layer, pre-covering is conducted inside a cavity with a selected dopant according to the distribution condition of the electrical resistivity of the epitaxial layer grown on a test sample, namely, a film containing the dopant is grown inside the cavity, and then epitaxy processing is conducted on a substrate. In the epitaxy process, the dopant on the internal side wall of the pre-covered cavity and a base can be diffused out under the influence of high temperature, and thus the concentration of the dopant gas on the edge of the substrate can be changed; the dopant gas enters the epitaxial layer, the distribution of the electrical resistivity of the epitaxial layer is changed, the influence of doping on the uniformity of the electrical resistivity of the epitaxial layer is reduced, and the qualified rate of products is increased.

Owner:ADVANCED SEMICON MFG CO LTD

Thin film transistor substrate including a fluorine layer in an active pattern

ActiveUS8791460B2Improve resistivity uniformityImproving a reduction of specific resistance of a signal electrodeTransistorTransistorElectrical and Electronics engineering

A thin film transistor substrate includes a base substrate, an active pattern, a gate insulation pattern and a gate electrode. The active pattern is disposed on the base substrate. The active pattern includes a source electrode, a drain electrode, and a channel disposed between the source electrode and the drain electrode. The gate insulation pattern and the gate electrode overlap with the channel. The gate insulation pattern is disposed between the channel and the gate electrode. The source electrode and the drain electrode each include a fluorine deposition layer.

Owner:SAMSUNG DISPLAY CO LTD

A coil structure for improving the uniformity of radial resistivity in zone melting

ActiveCN106087035BIncreasing the thicknessWell mixedPolycrystalline material growthCoil arrangementsZone meltingEngineering

The invention provides a coil structure for improving the zone-melting radial resistivity uniformity. The coil structure comprises a coil main body, a cooling water pipeline, a main seam, a plurality of sub seams and a plurality of transverse seams, wherein the coil main body is a flat plate coil; the upper surface of the coil main body is sunken into the inside of the coil into a centrosymmetric step structure; a coil hole is formed in the geometric center part of the coil main body; the cooling water pipeline is positioned inside a step at the outermost layer of the coil main body; the main seam is arranged on the coil main body in the radial direction and penetrates through the upper surface and the lower surface of the coil main body; the plurality of sub seams are arranged on the step surface at the innermost layer of the coil main body and penetrate through the upper surface and the lower surface of the step surface; the transverse seams are partially or all arranged on the sub seams; the transverse seams are perpendicular to the respective sub seam. The coil structure for improving the zone-melting radial resistivity uniformity has the advantage that due to the adaption of the technical scheme, the zone-melting silicon single-crystal radial resistivity uniformity can be simultaneously improved.

Owner:ZHONGHUAN ADVANCED SEMICON MATERIALS CO LTD +1

A method for suppressing the formation of carbon inclusion defects in the growth of conductive silicon carbide crystals

ActiveCN110331438BInhibitionReduce excessPolycrystalline material growthFrom condensed vaporsCarbide siliconWafering

The invention discloses a method for suppressing the formation of carbon inclusion defects in the growth of conductive silicon carbide crystals. It uses carbon powder, silicon powder and nitrogen as raw materials to synthesize nitrogen-containing silicon carbide powder, and then uses the nitrogen-containing silicon carbide powder as raw material to grow silicon carbide single crystals to obtain silicon carbide crystals. The invention uses nitrogen-containing silicon carbide powder to grow silicon carbide crystals, which can make nitrogen doping more evenly distributed in the gas phase components, so that the resistivity uniformity in the wafer is better, and solves the problem that nitrogen gas cannot permeate due to nitrogen gas being introduced from the outside. Uniformity, resulting in poor uniformity of N doping concentration in the wafer, which in turn leads to poor uniformity of wafer resistivity. Therefore, the method for suppressing carbon inclusion defects in conductive silicon carbide crystals provided by the present invention is suitable for growing conductive silicon carbide crystals, especially suitable for preparing large-diameter conductive silicon carbide crystals, and has broad market application prospects.

Owner:HEBEI POSHING ELECTRONICS TECH

A method for manufacturing silicon epitaxial wafers for 8-inch vdmos power tubes

ActiveCN110660649BPrevent proliferationGuaranteed uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesPhysical chemistryEngineering

The invention discloses a manufacturing method of a silicon epitaxial wafer for an 8-inch VDMOS power tube, which comprises the steps of (1) selecting an As-doped substrate, wherein the resistivity ofthe substrate is less than or equal to 0.004 omega.cm; (2) growing a first epitaxial layer, wherein the first epitaxial layer grows on the surface of the substrate at the growth temperature of 1040-1080 DEG C and the growth rate of less than or equal to 1.5[mu]m / min, and purging the cavity with hydrogen after the growth of the first epitaxial layer is completed; and (3) and growing a second epitaxial layer, wherein second epitaxial layer grows on the surface of the first epitaxial layer at the growth temperature of 1040-1060 DEG C and the growth rate of 2-3[mu]m / min. According to the invention, the proper substrate is selected, the device and epitaxial requirements are met, the resistivity uniformity of the epitaxial layer is effectively improved, the deviation between the edge and the central region transition region is reduced, and the yield of the die is improved.

Owner:NANJING GUOSHENG ELECTRONICS

Preparation method of high-quality semi-insulating silicon carbide single crystal and substrate doped with a small amount of vanadium

ActiveCN109280966BHighly stable resistivityImprove thermal stabilityPolycrystalline material growthAfter-treatment detailsSemiconductor materialsHigh resistivity

The invention discloses preparation methods of high-quality semi-insulating silicon carbide single crystal doped with a small amount of vanadium and a high-quality semi-insulating silicon carbide single crystal substrate doped with a small amount of vanadium, and belongs to the field of semiconductor materials. The preparation method of the semi-insulating silicon carbide single crystal comprisesthe steps: removing impurities of a thermal field device, mixing materials, performing crystal growth and conducting annealing treatment. The preparation method of the semi-insulating silicon carbidesingle crystal has low technical cost and capital cost, and the resistivity of the prepared silicon carbide single crystal depends on residual shallow energy level impurities and a small amount of vanadium element; since lattice positions are occupied by the impurities, the impurities have high thermal stability, it means that the crystal can have highly stable resistivity; and since the silicon carbide single crystal substrate prepared from the silicon carbide single crystal has high resistivity uniformity and low stress, so that the silicon carbide single crystal substrate has excellent surface quality, and the stability and consistency of the substrate quality in the subsequent epitaxial process are ensured.

Owner:SICC CO LTD

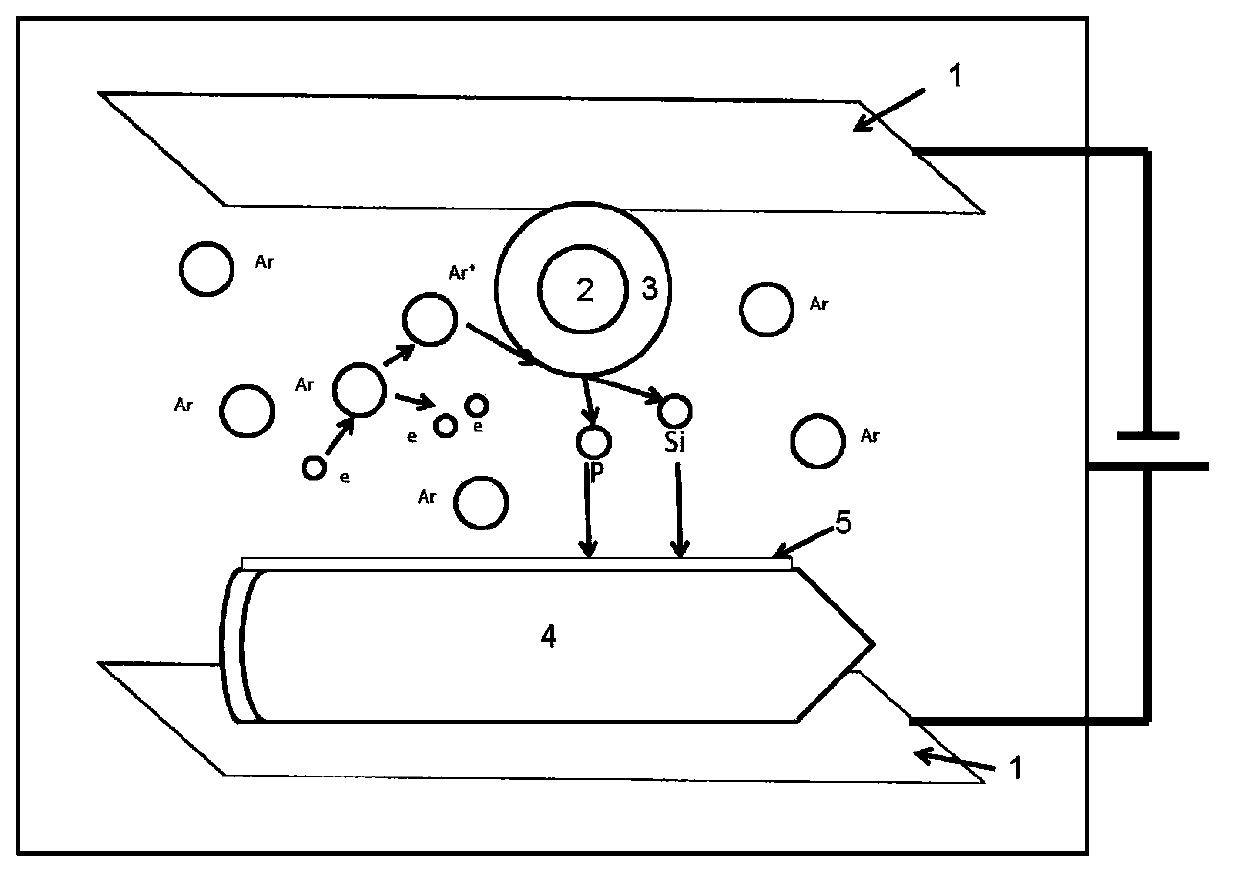

Preparation method for doped float zone silicon crystal

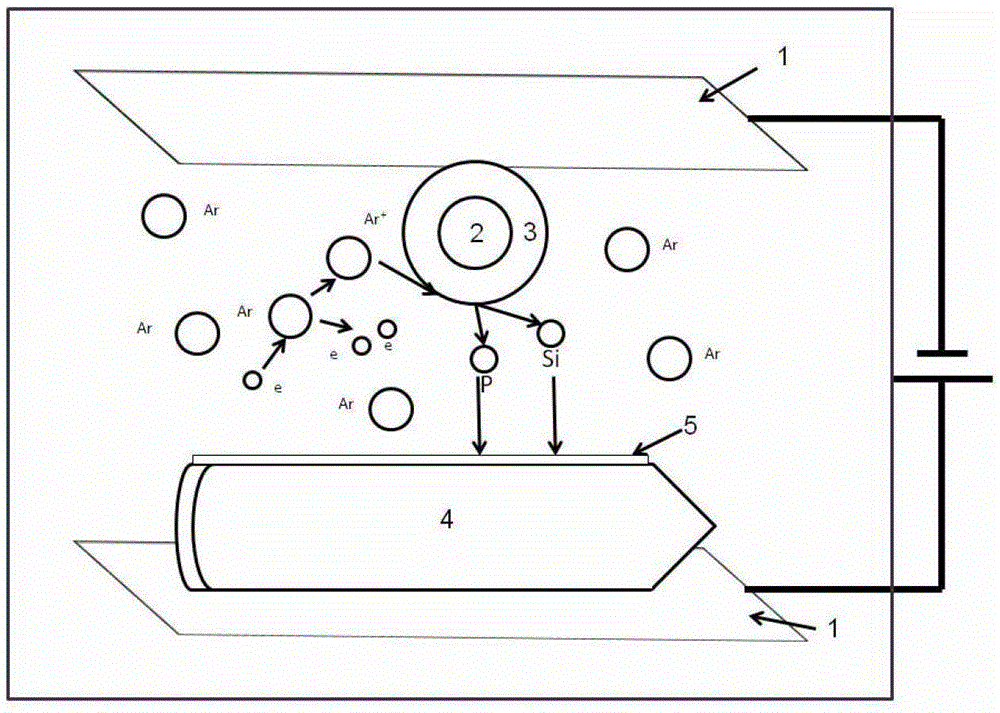

ActiveCN103866375ALow costIncrease productivityBy zone-melting liquidsVacuum evaporation coatingIonizationCorrosion

The invention relates to a preparation method for a doped float zone silicon crystal. The method comprises that: (1) cone grinding, corrosion, cleaning and drying are performed on a polysilicon material; (2) the polysilicon material is fixed in a cavity of a magnetron sputtering apparatus, a phosphorus-silicon-doped target is arranged, vacuumizing is performed to achieve 5*10<-3> Pa, argon gas is introduced to achieve the pressure in the cavity of 1 Pa, a high voltage of 500 Kv is applied between the two electrodes, argon ions produced through ionization continuously bombard the target, the phosphorus atoms and the silicon atoms in the target obtain energy, sputter, and deposit on the surface of the polysilicon to form a layer of a uniform and compact phosphorus / silicon film, the sputtering is performed for 30-90 min and then is stopped, the sputtering chamber is opened to rotate the polysilicon 180 DEG, the steps are repeated, and the sputtering is continuously performed for the same time; and (3) the polysilicon material is taken out and placed into a float zone silicon crystal furnace, the seed crystal and the polysilicon are centered, steps of vacuumizing, argon gas introduction, preheating, fusion splicing, narrow neck shrinking and crystal diameter achieving are sequentially performed until the equal diameter is maintained, and the ending step is performed. The preparation method has characteristics of low-cost, high production efficiency and no toxicity and harm, wherein the uniformities of the radial resistivity and the axial resistivity are good.

Owner:GRINM SEMICONDUCTOR MATERIALS CO LTD

A method for preparing doped zone molten silicon single crystal

ActiveCN103866375BLow and controllable resistivityLow costBy zone-melting liquidsVacuum evaporation coatingFloat-zone siliconSeed crystal

The invention relates to a preparation method for a doped float zone silicon crystal. The method comprises that: (1) cone grinding, corrosion, cleaning and drying are performed on a polysilicon material; (2) the polysilicon material is fixed in a cavity of a magnetron sputtering apparatus, a phosphorus-silicon-doped target is arranged, vacuumizing is performed to achieve 5*10<-3> Pa, argon gas is introduced to achieve the pressure in the cavity of 1 Pa, a high voltage of 500 Kv is applied between the two electrodes, argon ions produced through ionization continuously bombard the target, the phosphorus atoms and the silicon atoms in the target obtain energy, sputter, and deposit on the surface of the polysilicon to form a layer of a uniform and compact phosphorus / silicon film, the sputtering is performed for 30-90 min and then is stopped, the sputtering chamber is opened to rotate the polysilicon 180 DEG, the steps are repeated, and the sputtering is continuously performed for the same time; and (3) the polysilicon material is taken out and placed into a float zone silicon crystal furnace, the seed crystal and the polysilicon are centered, steps of vacuumizing, argon gas introduction, preheating, fusion splicing, narrow neck shrinking and crystal diameter achieving are sequentially performed until the equal diameter is maintained, and the ending step is performed. The preparation method has characteristics of low-cost, high production efficiency and no toxicity and harm, wherein the uniformities of the radial resistivity and the axial resistivity are good.

Owner:GRINM SEMICONDUCTOR MATERIALS CO LTD

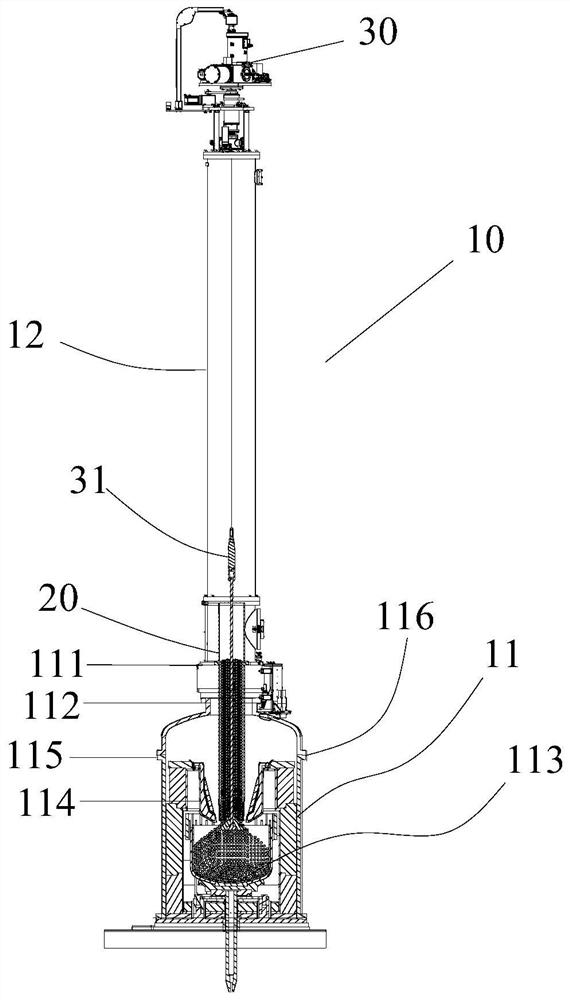

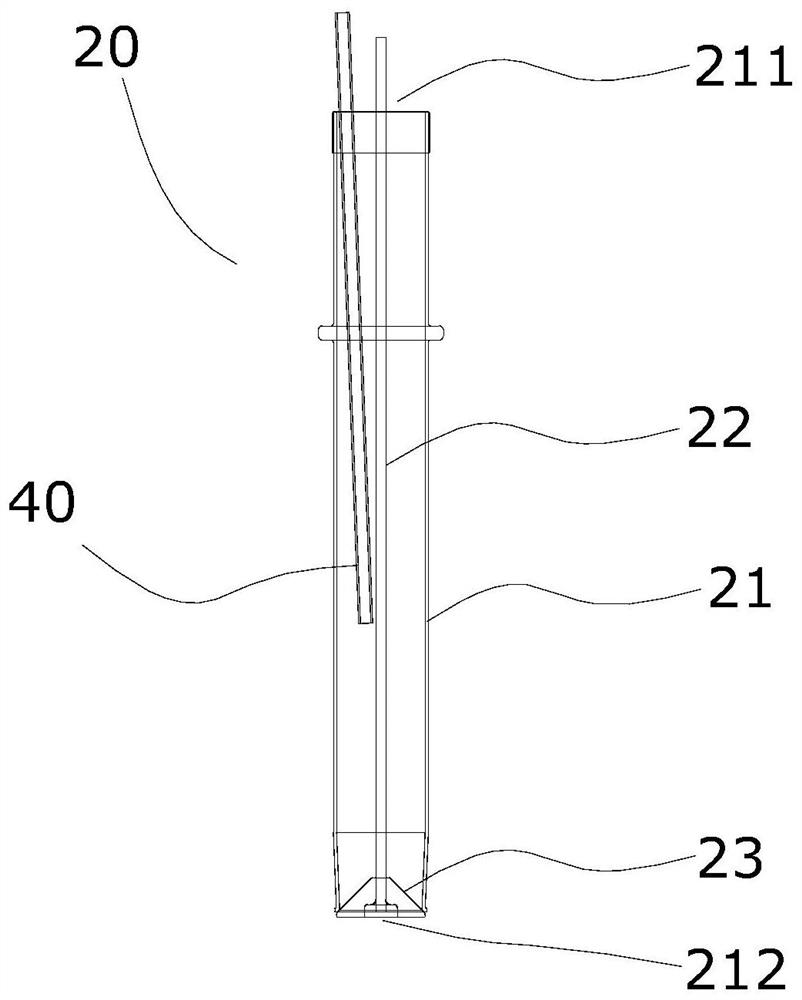

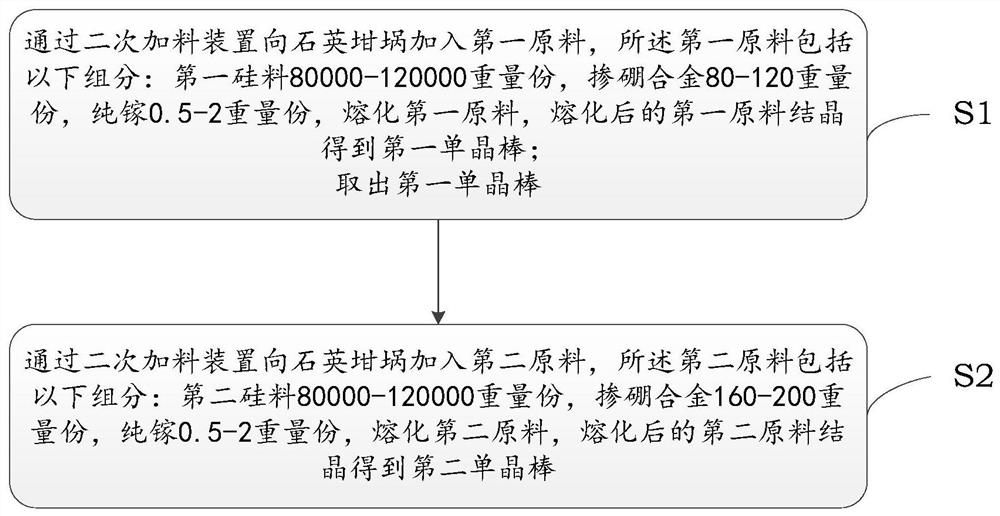

Boron-gallium co-doped single crystal preparation equipment and preparation method thereof

ActiveCN112760704AExtend your lifeImprove efficiencyPolycrystalline material growthFinal product manufacturePhysical chemistryAlloy

The invention relates to boron-gallium co-doped single crystal equipment and a preparation method thereof. The equipment comprises a single crystal furnace, a secondary feeding device, a pulling device and a single feeding tubule, the preparation method comprises the following steps that S1, adding a first raw material into the single crystal furnace through the secondary feeding device, wherein the first raw material comprises, by weight, 80000-120000 parts of a first silicon material, 80-120 parts of boron-doped alloy and 0.5-2 parts of pure gallium, melting the first raw material and crystallizing the melted first raw material to obtain a first single crystal rod; taking out the first single crystal rod from a quartz crucible; s2, adding a second raw material into the single crystal furnace through the secondary feeding device, wherein the second raw material comprises, by weight, 160000-200000 parts of a second silicon material, 160-200 parts of boron-doped alloy and 0.5-2 parts of pure gallium, melting the second raw material, and crystallizing the melted second raw material to obtain a second single crystal rod.

Owner:JA SOLAR +1

A high-quality semi-insulating silicon carbide single crystal and substrate doped with a small amount of vanadium

ActiveCN109280965BAchieving semi-insulating propertiesImprove resistivity uniformityPolycrystalline material growthAfter-treatment detailsDopantSemiconductor materials

The invention discloses high-quality semi-insulating silicon carbide single crystal doped with a small amount of vanadium and a silicon carbide single crystal substrate, and belongs to the field of semiconductor materials. The semi-insulating silicon carbide single crystal comprises shallow energy level impurities, a low-concentration deep energy level dopant and a very small amount of intrinsic point defects, wherein the shallow energy level impurities are compensated by the deep energy level dopant and the intrinsic point defects together, the concentration of the deep energy level dopant issmaller than that of the deep energy level dopant in the doped semi-insulating silicon carbide single crystal, and the concentration of the intrinsic point defects is the primary concentration of theintrinsic point defects in the silicon carbide single crystal at room temperature; and the stability of the electrical properties of the silicon carbide single crystal is not affected by the concentration of the intrinsic point defects. The semi-insulating silicon carbide single crystal has highly stable resistivity and high resistivity uniformity, and the silicon carbide single crystal substrateprepared from the silicon carbide single crystal has high resistivity uniformity and low stress, so that the silicon carbide single crystal substrate has excellent surface quality, and the stabilityand consistency of subsequent epitaxial quality are ensured.

Owner:SICC CO LTD