Patents

Literature

38results about How to "Reduce the chance of electric leakage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

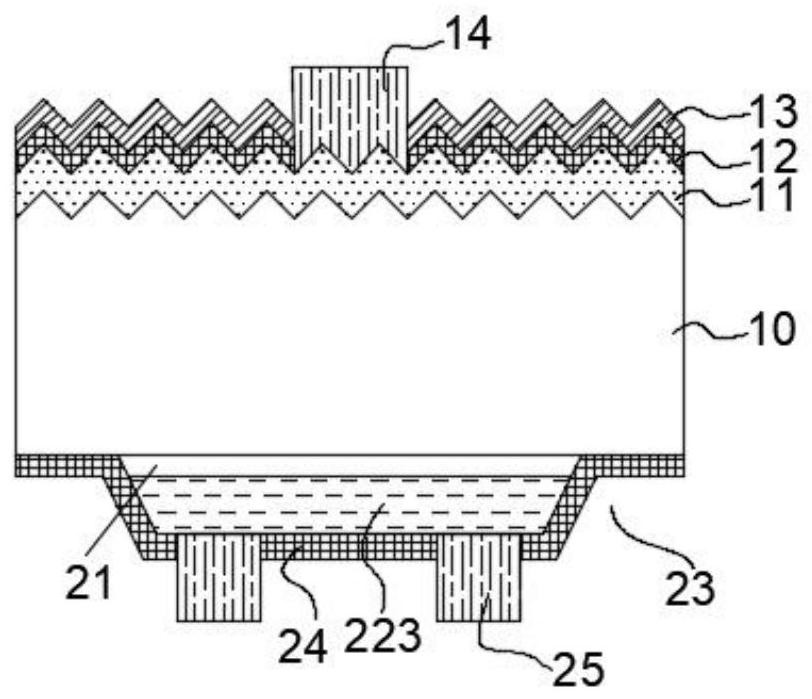

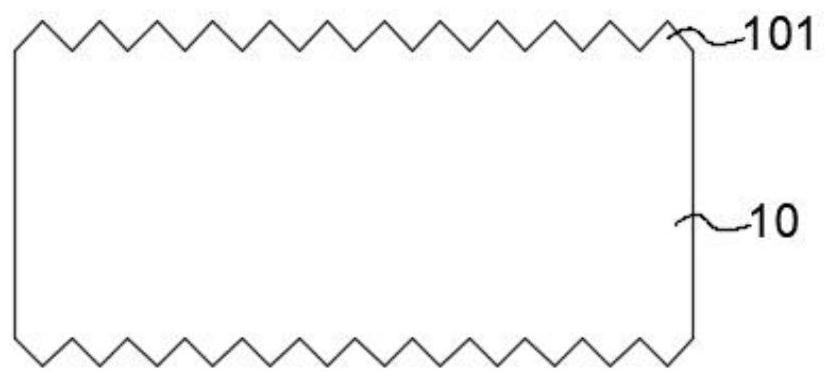

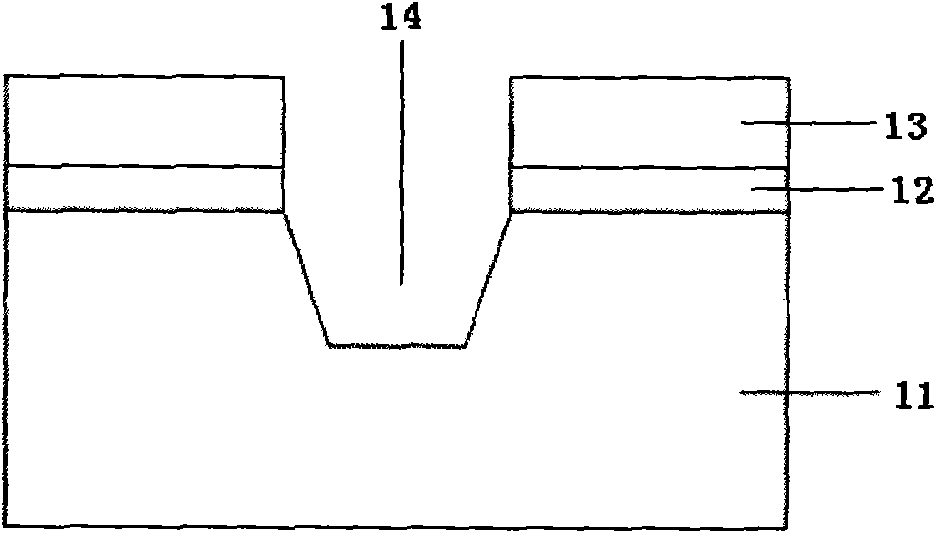

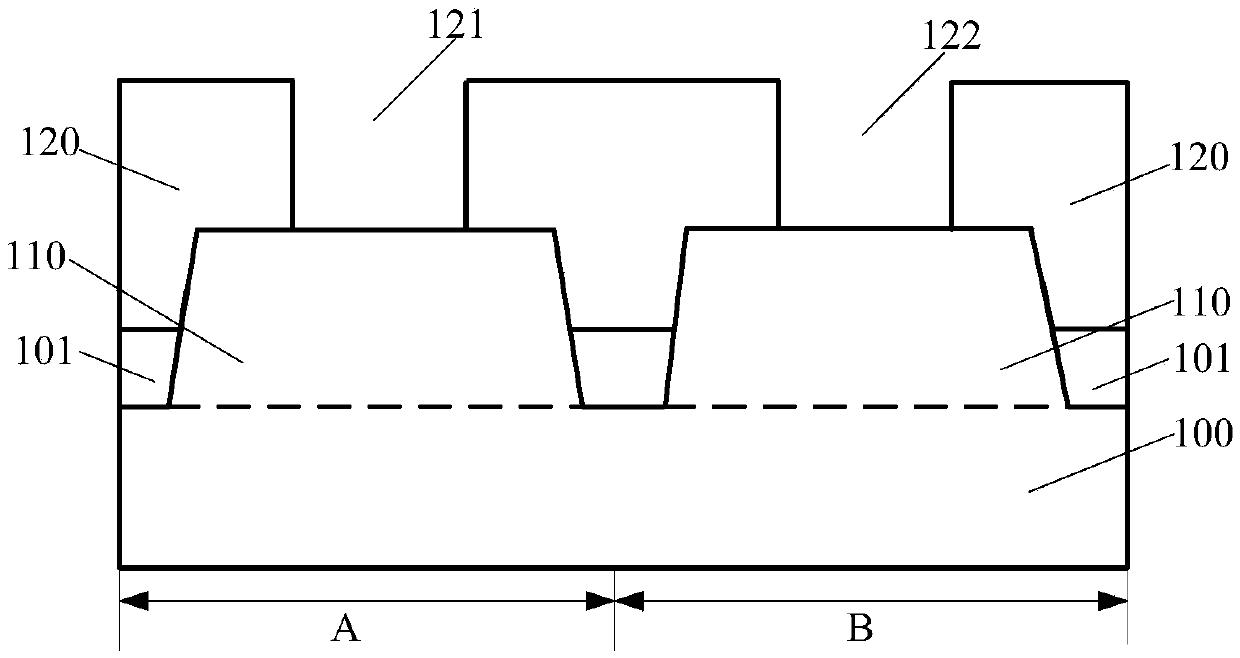

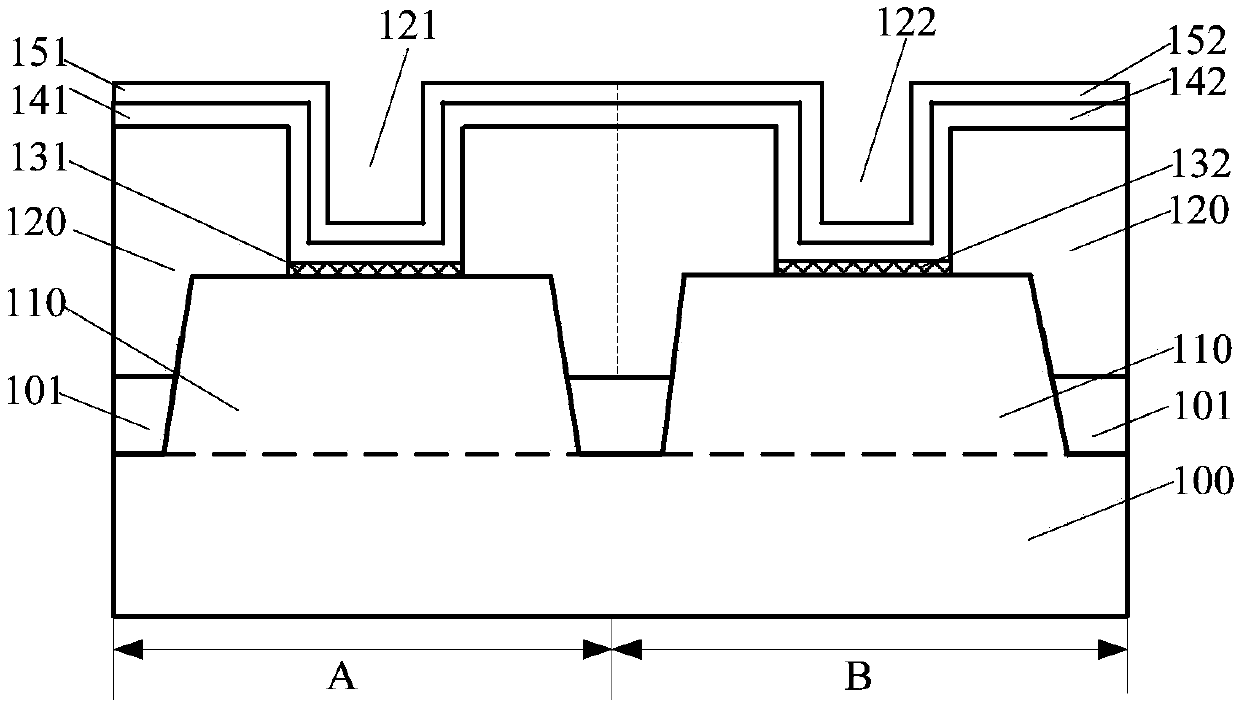

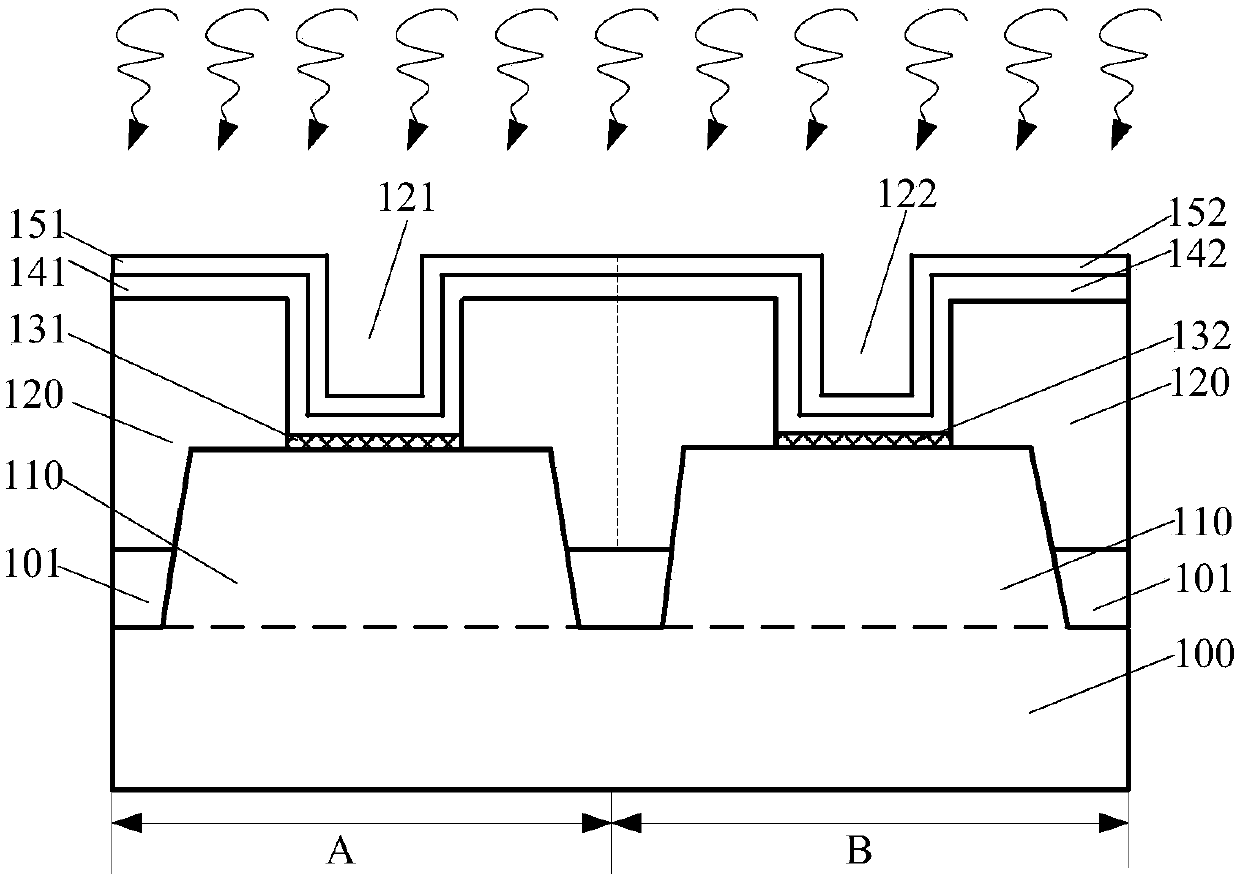

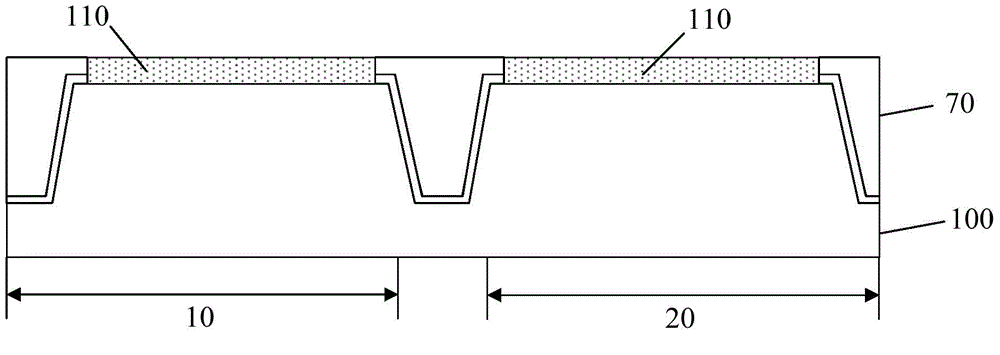

Solar cell and manufacturing method thereof

ActiveCN112885925AImprove work efficiencyReduce the chance of electric leakageFinal product manufacturePhotovoltaic energy generationAmorphous siliconEngineering

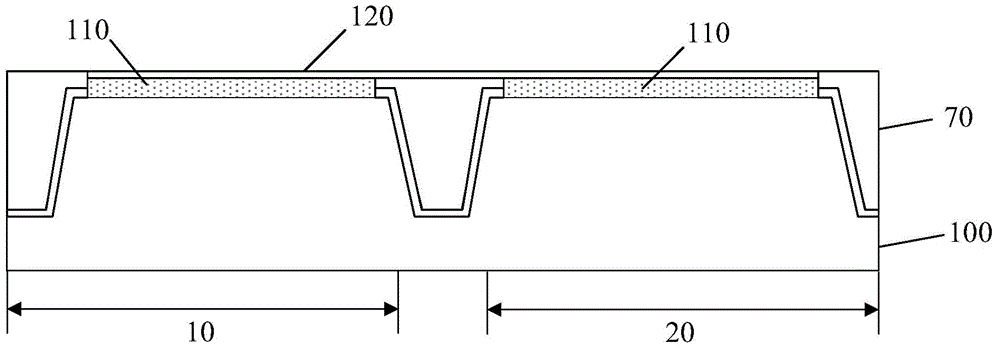

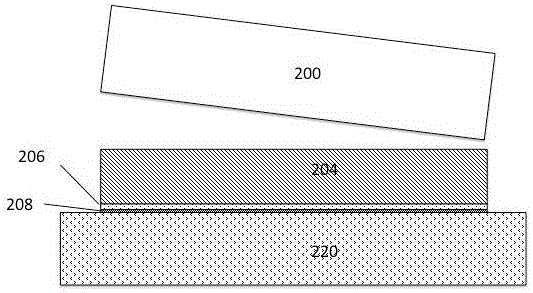

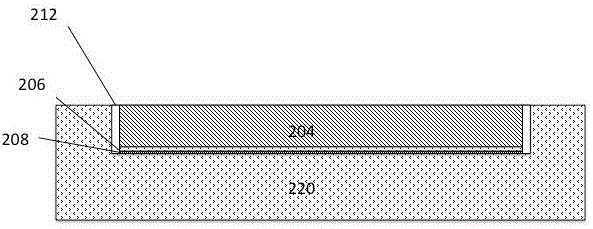

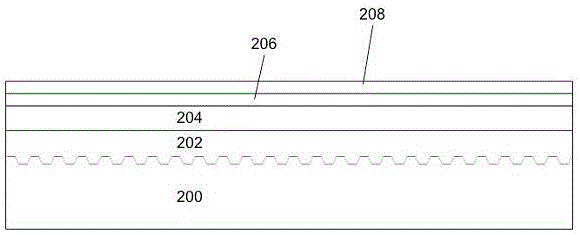

The invention discloses a solar cell and a manufacturing method thereof, relates to the technical field of photovoltaics, and aims to conveniently form an isolation part and reduce the probability of electric leakage of the solar cell. The manufacturing method of the solar cell comprises the following steps of: providing a silicon substrate; forming a tunneling layer on the back surface of the silicon substrate; forming an amorphous silicon layer on the tunneling layer; processing the first part of the amorphous silicon layer to form a doped polycrystalline silicon region and an amorphous silicon region surrounding the doped polycrystalline silicon region; removing the amorphous silicon region and the tunneling layer covered by the amorphous silicon region; and acquiring a passivation contact structure and an isolation part surrounding the passivation contact structure. The solar cell and the manufacturing method thereof provided by the invention are used for solar cell manufacturing.

Owner:TAIZHOU LERRISOLAR TECH CO LTD

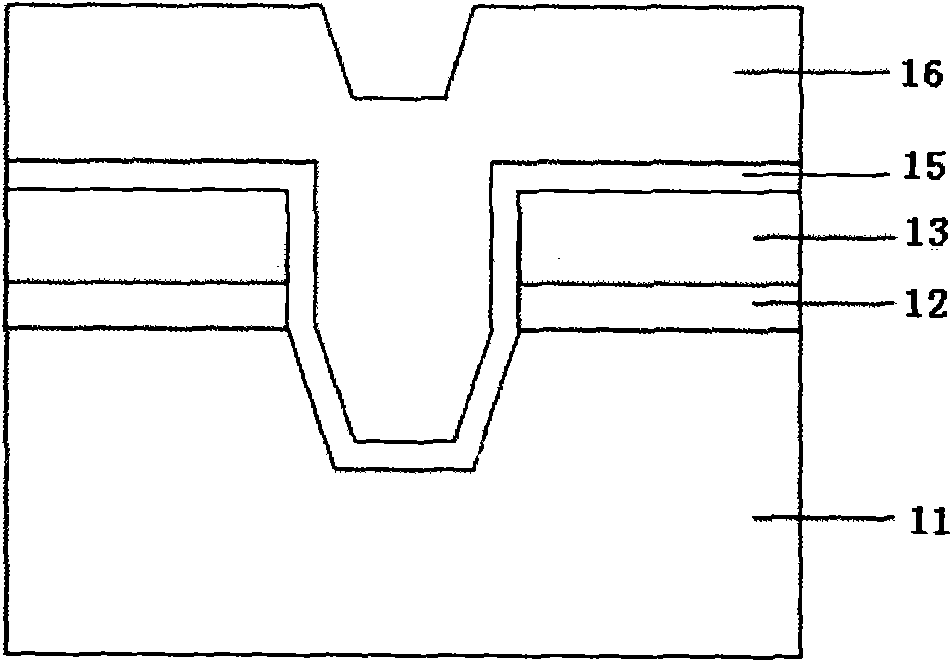

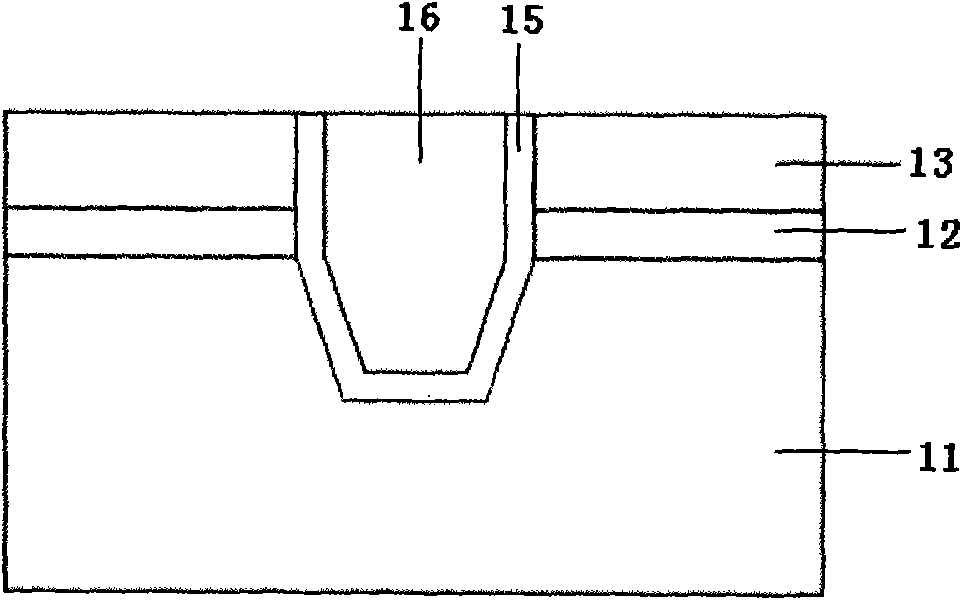

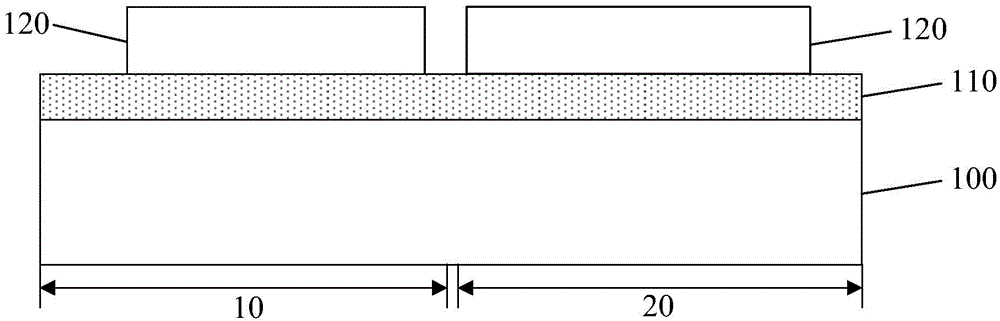

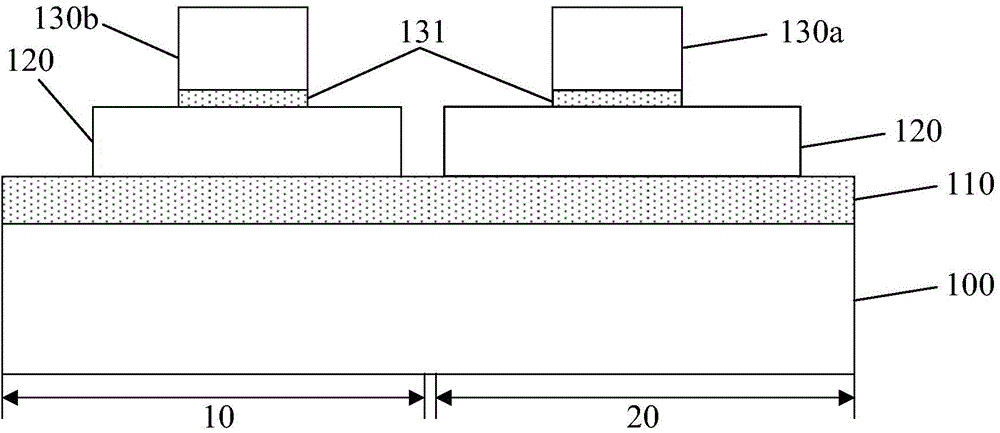

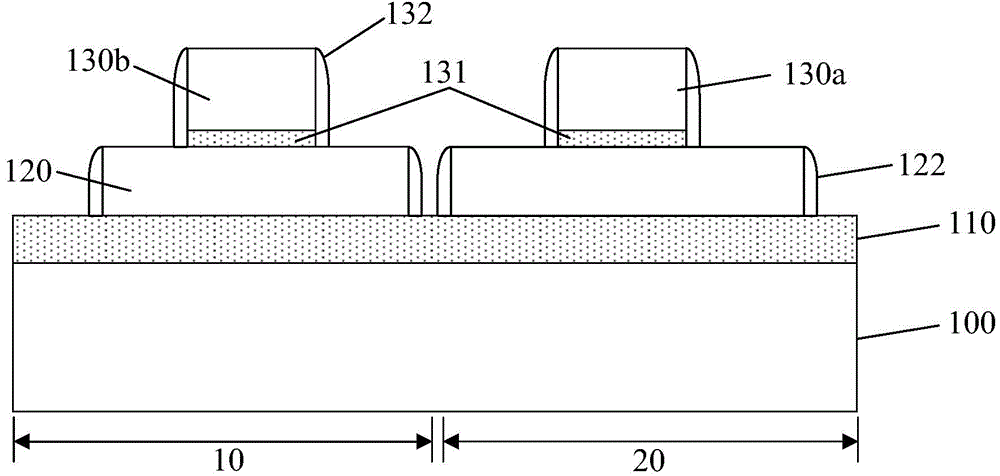

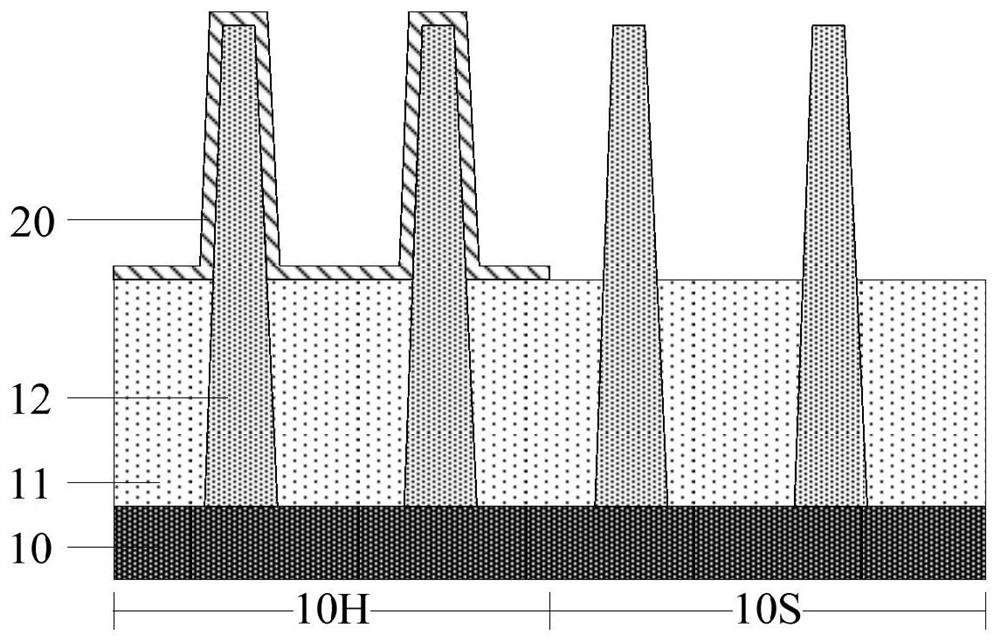

Fabricating method of shallow trench isolation structure

InactiveCN101673702AReduce the chance of electric leakageImprove electrical performanceSemiconductor/solid-state device manufacturingEtchingOxide

A fabricating method of a shallow trench isolation structure of the invention comprises the following steps: forming a pad oxide layer and a hard mask layer in sequence on the surface of a substrate;etching the pad oxide layer and the hard mask layer in sequence to form an opening; depositing oxide layers on the surface of the hard mask layer and in the opening; removing the oxide layer on the surface of the hard mask layer and part of the oxide layer on the surface of the substrate by etching and forming self-aligned spacers at two sides of the opening; taking the self-aligned spacers as masks and etching a shallow trench in the substrate; removing the self-aligned spacers to fully expose the sharp top corner of the shallow trench; generating linear oxides in the shallow trench to fullyround the sharp top corner of the shallow trench in the process; filling insulating media in the shallow trench; and removing the hard mask layer and the pad oxide layer to form the shallow trench isolation structure. By adopting the method of the invention, the rounding top corner can be formed at the top of the shallow trench isolation structure to avoid leakage current from occurring.

Owner:GRACE SEMICON MFG CORP

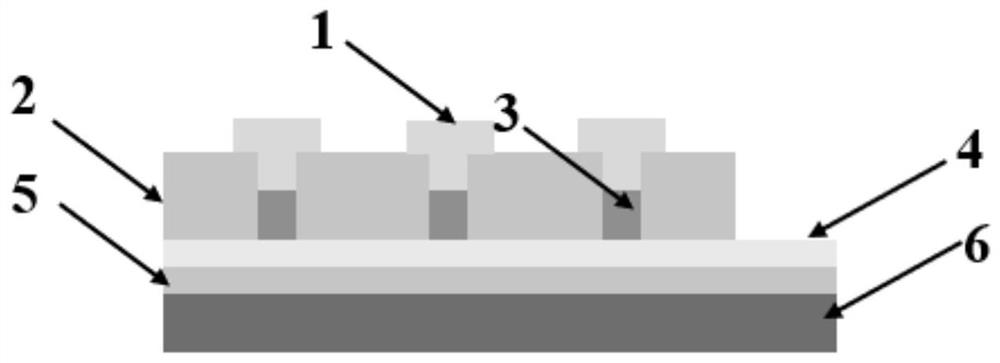

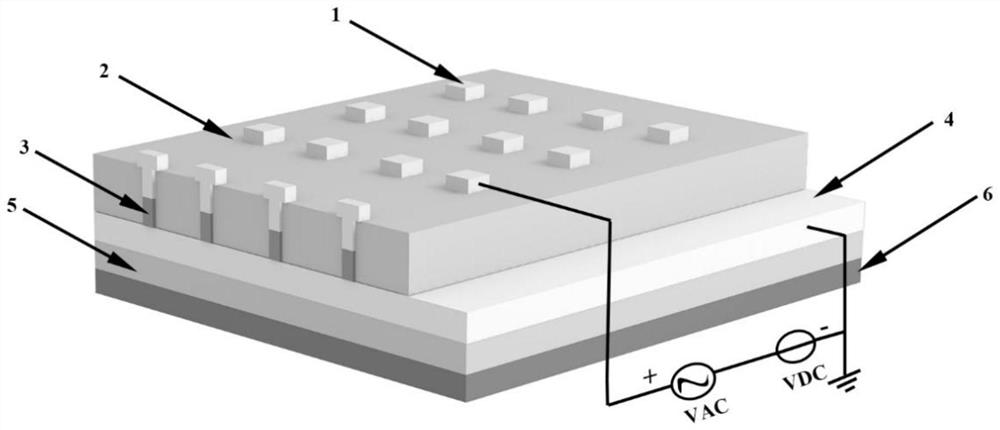

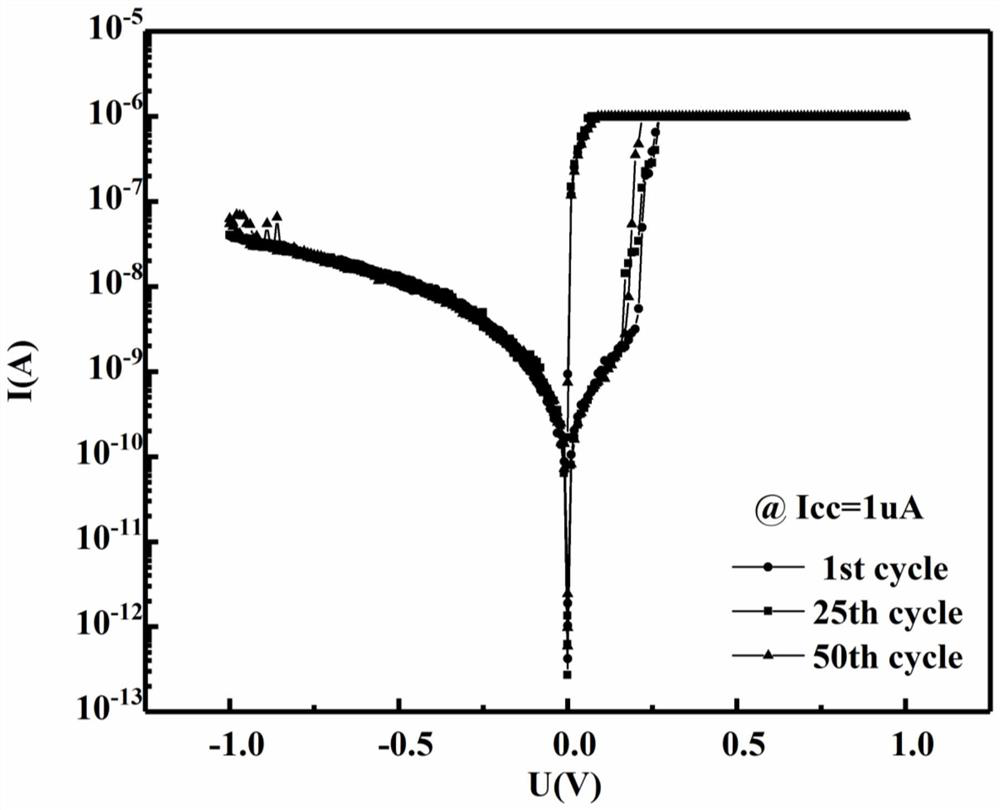

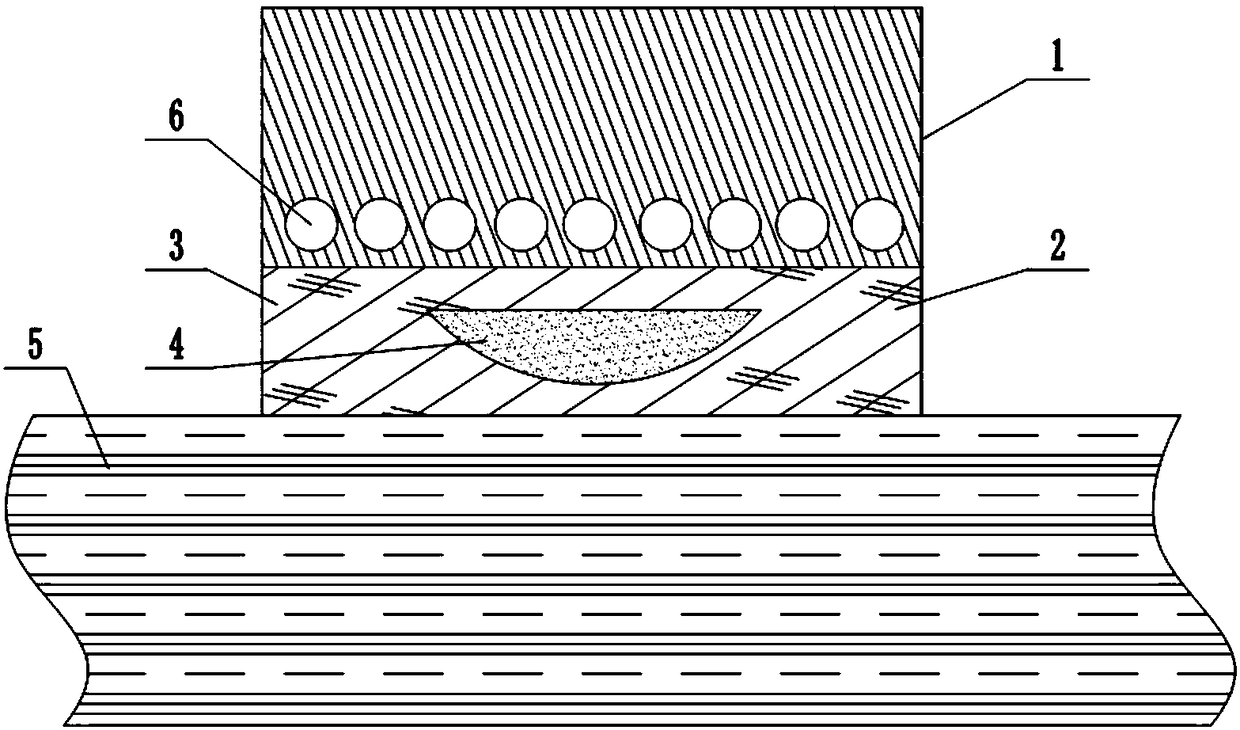

Volatile and nonvolatile CuxO memristor and regulation and control method thereof

ActiveCN112289930AHigh activityEasy to controlElectrical apparatusEngineeringCondensed matter physics

The invention belongs to the technical field of microelectronic devices, and discloses a volatile and nonvolatile CuxO memristor and a regulation and control method thereof. The volatile and nonvolatile CuxO memristor comprises a lower electrode layer (4), a functional layer (3) and an upper electrode layer (1) stacked from bottom to top, the functional layer (3) is a CuxO functional layer, x is larger than 1.8 and smaller than 2, and the functional layer is deposited to enable the functional layer to be in contact with the lower electrode layer; and the upper electrode layer is deposited on the functional layer. The key structure and composition of the memristor are improved, CuxO serves as a functional layer, x is larger than 1.8 and smaller than 2, the chemical proportion is close to Cu2O, the volatile and nonvolatile CuxO memristor can be obtained, the CuxO memristor is based on Cu vacancy modulation, Cu vacancies can be induced through simple limiting current to construct synapsesand conductive wires, and volatility and non-volatility are achieved.

Owner:HUAZHONG UNIV OF SCI & TECH

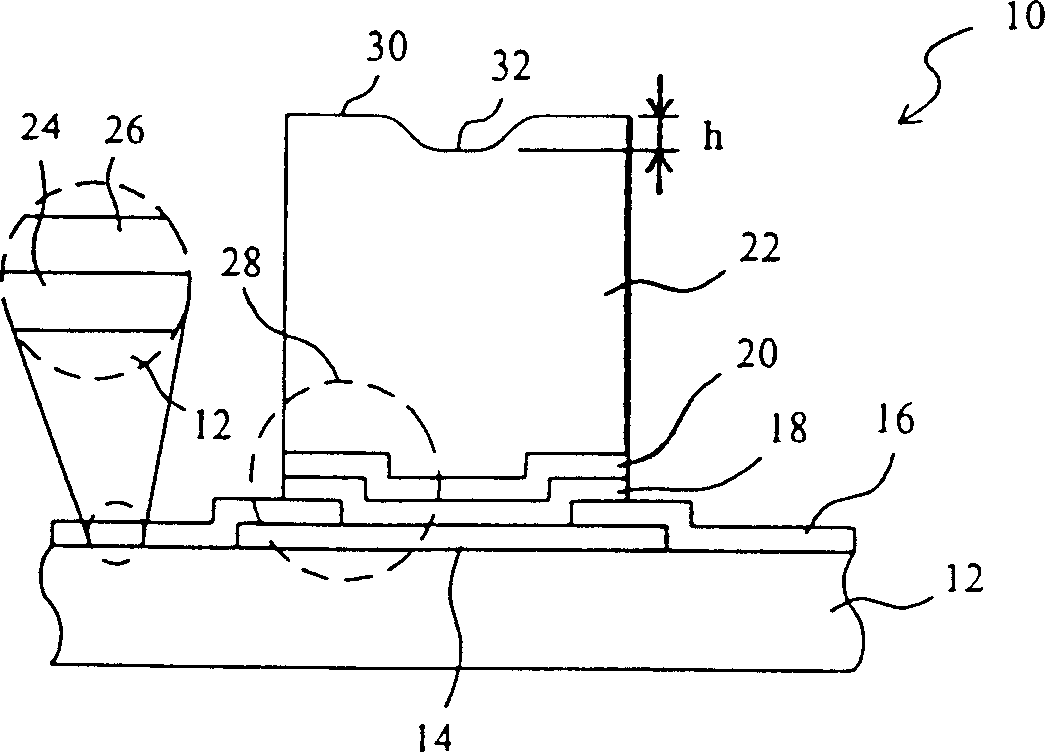

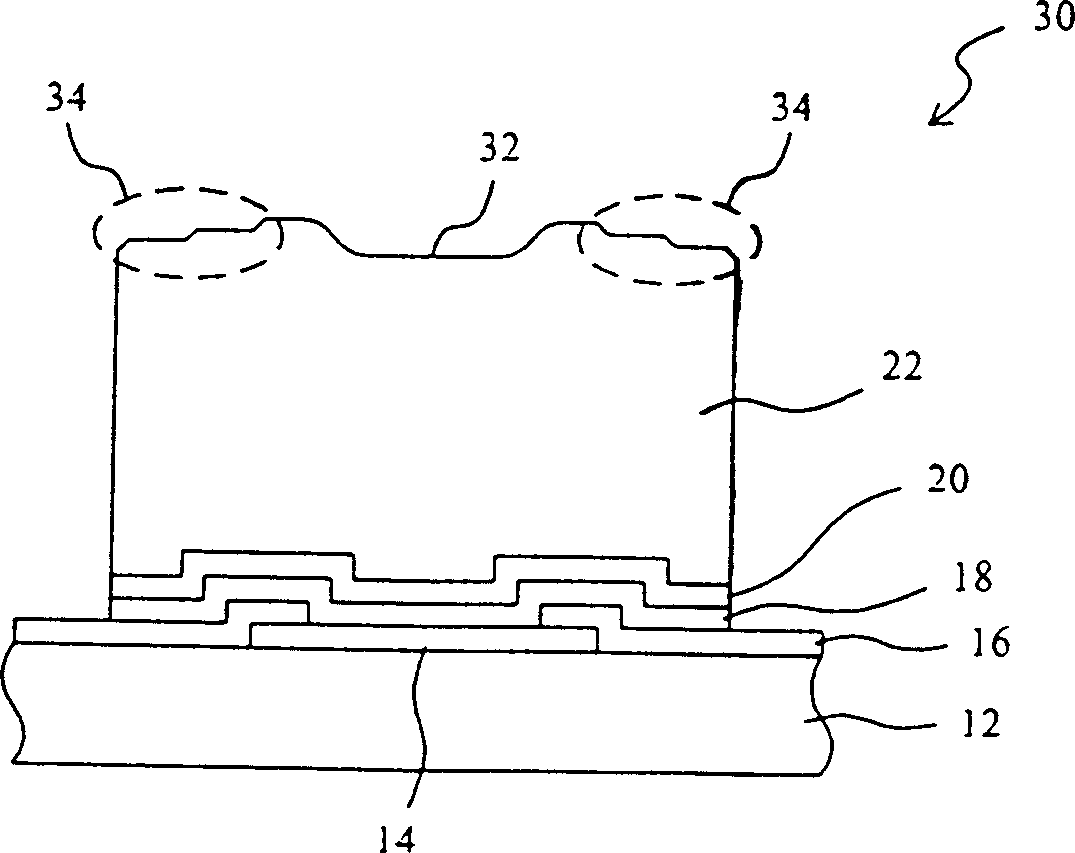

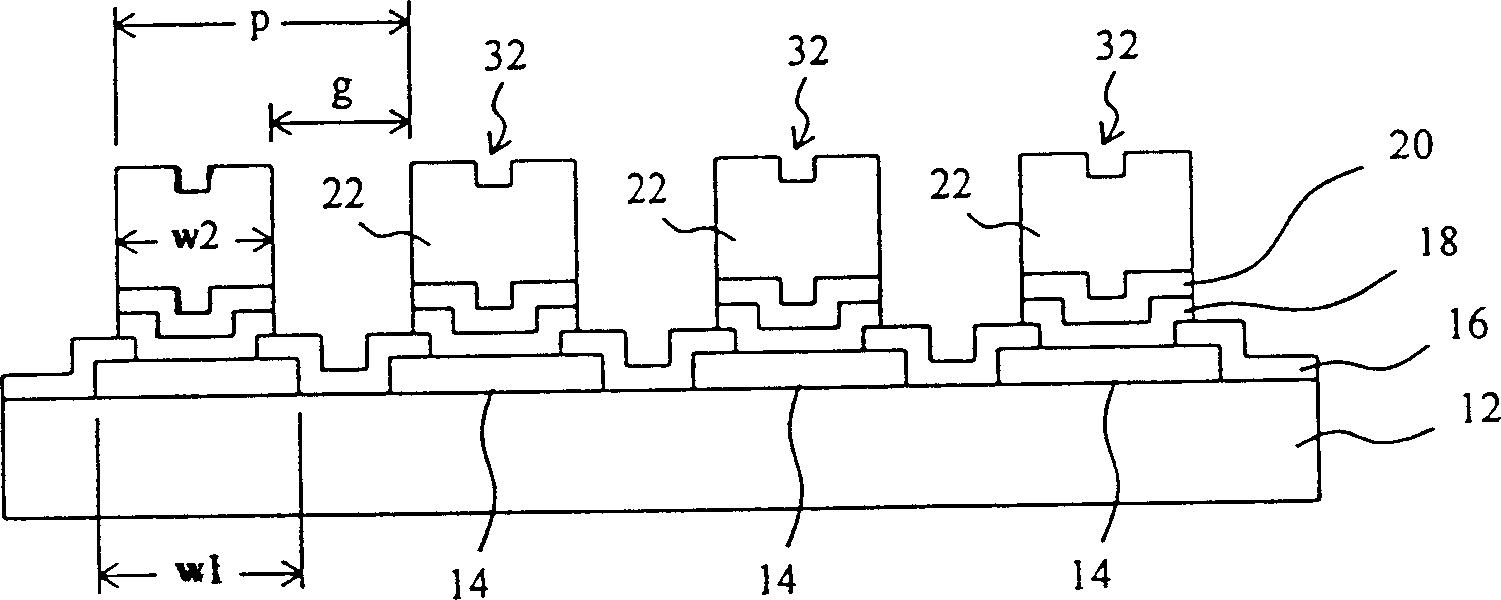

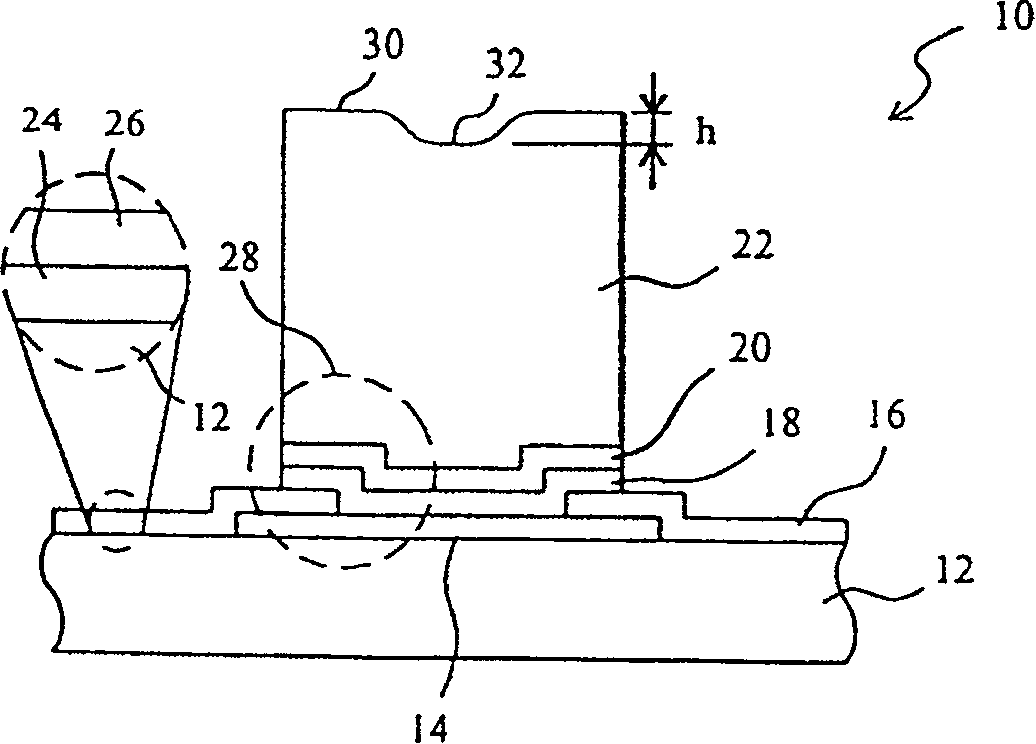

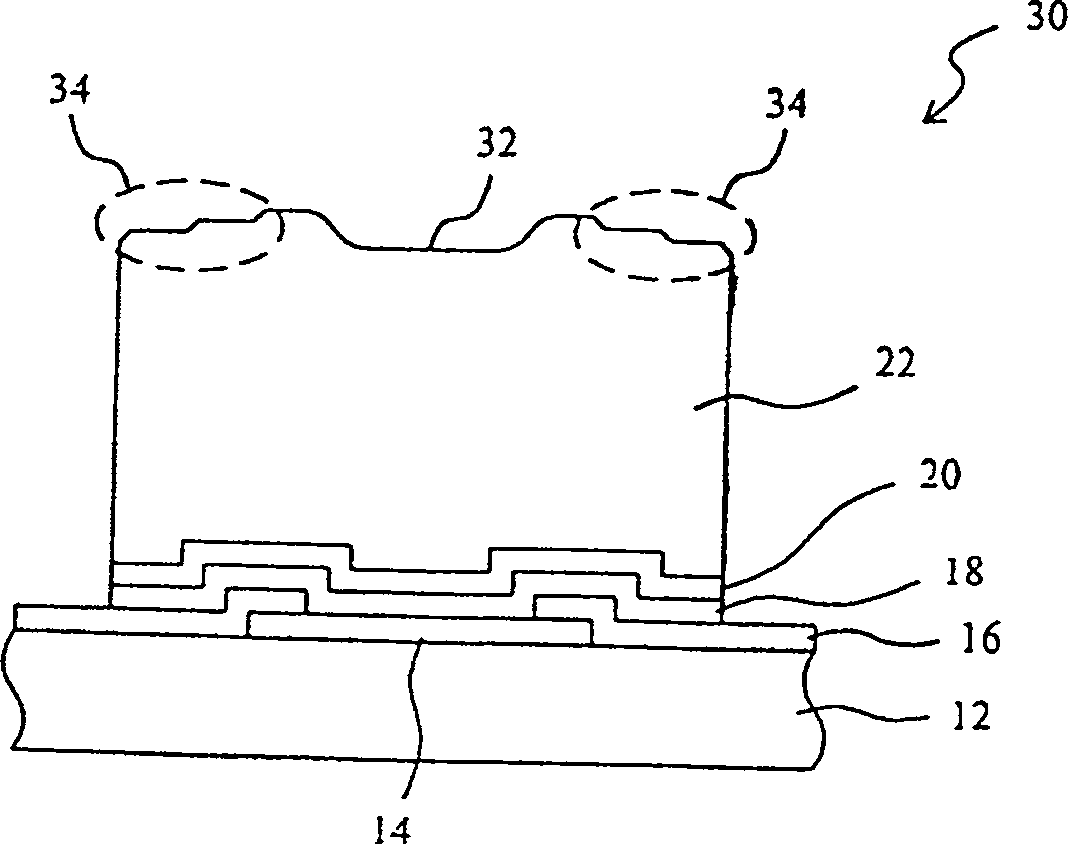

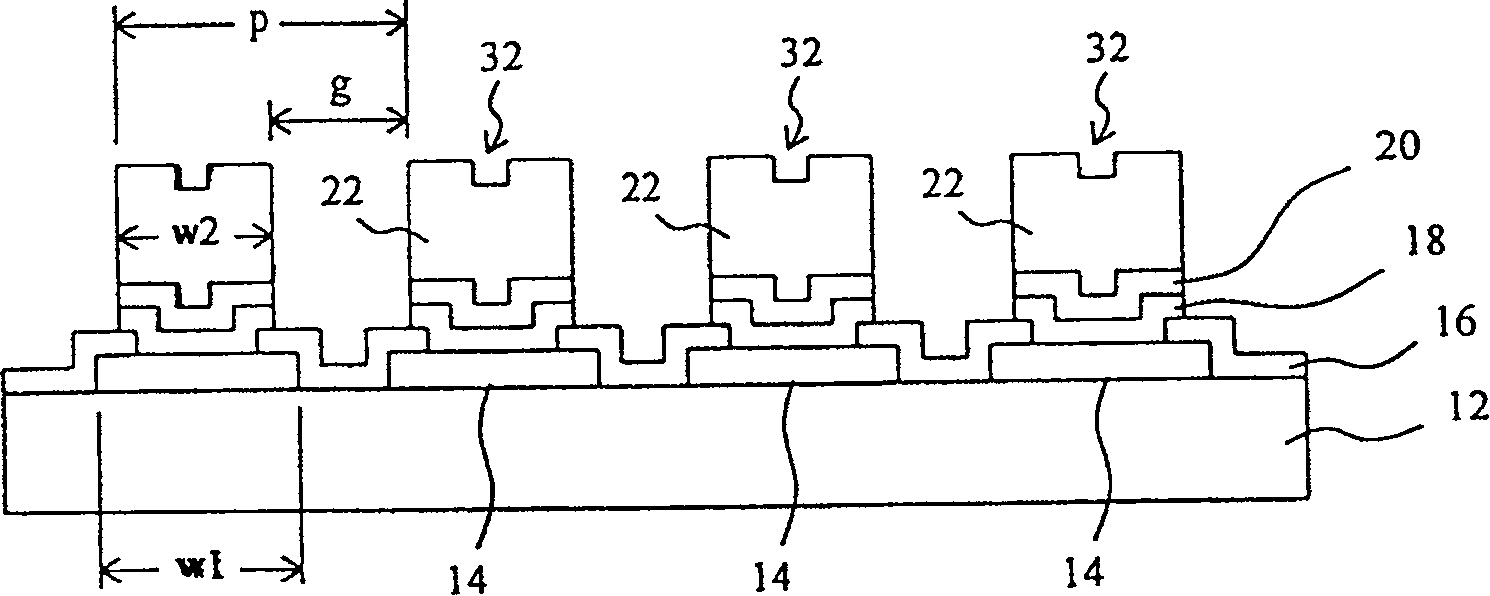

Technique and structure for making convex

InactiveCN1862771AHigh mechanical strengthIncrease effective areaSemiconductor/solid-state device detailsSolid-state devicesCamUltimate tensile strength

This invention relates to cam creation technique and its structure. It includes a sheath with flat surface, the sheath is covered on a joint mat on the plaque to form a contact surface with one open through the sheath, and one cam on the contact surface and the flat surface is formed. The contact mat can be reduced because of the flat surface of the sheath. The mechanical strength of the sheath on the contact mat is strengthened; the cam will has large efficient area when stitching. Selecting space of different directivity conduction membrane is large, short circuit and electric leakage probability is little, so the stitching good ratio and conducting quality of the cam is improved.

Owner:ELAN MICROELECTRONICS CORPORATION

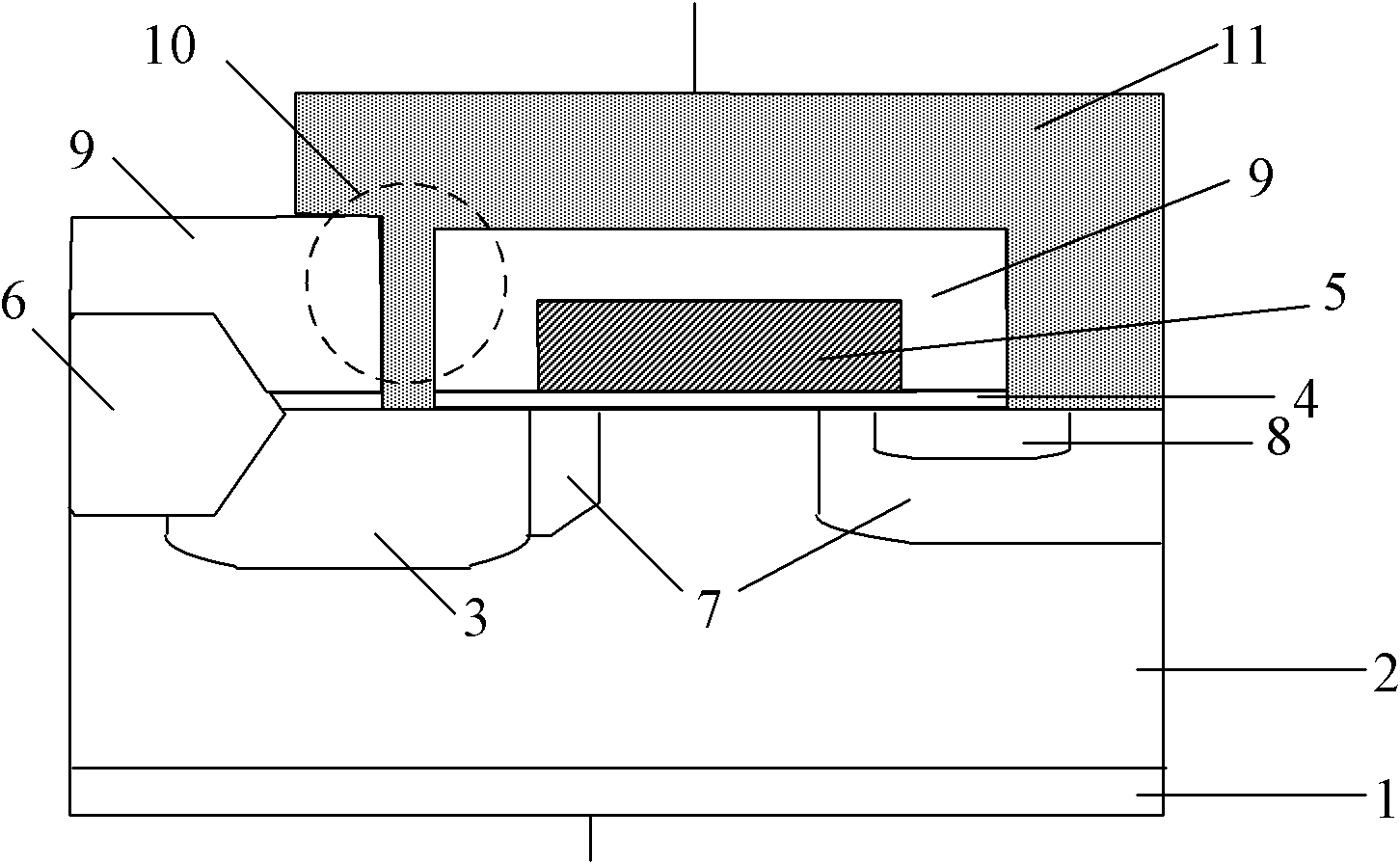

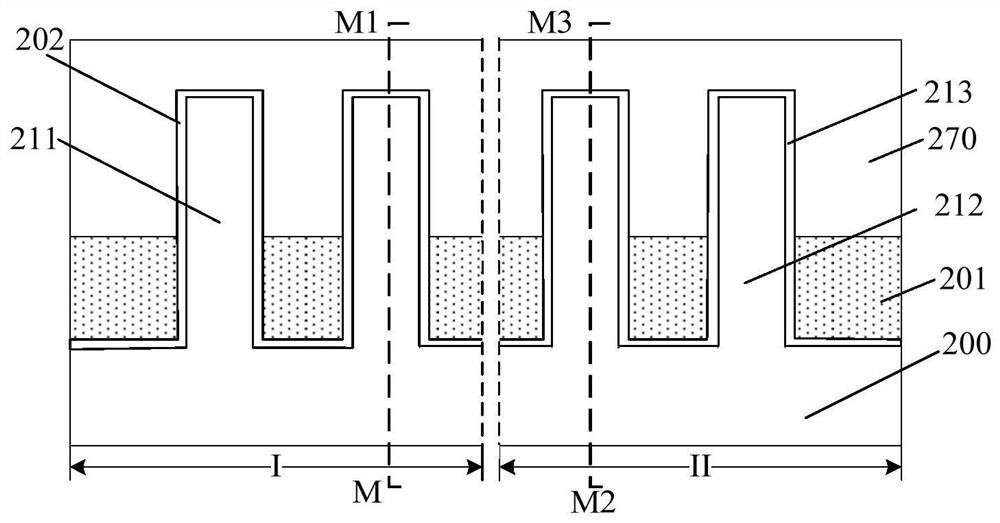

DRAM device and manufacturing method thereof

ActiveCN105529328AReduce manufacturing difficultyImprove compatibilityTransistorSemiconductor/solid-state device manufacturingEngineeringDeep trench

The invention provides a DRAM device and a manufacturing method thereof. The manufacturing method of the DRAM device comprises steps that, a substrate is provided; a first grid electrode and a second grid electrode are formed; source electrodes or drain electrodes of a logic transistor and a channel transistor are formed, a dielectric layer and a metal layer are formed, and the dielectric layer and the source electrode or the drain electrode of the channel transistor commonly form a capacitor. The DRAM device comprises the substrate, the channel transistor, the capacitor and the logic transistor, wherein the dielectric layer and the metal layer are sequentially arranged on the source electrode or the drain electrode of the transistor, and the source electrode or the drain electrode, the dielectric layer and the metal layer are used for forming the capacitor. The method and the device are advantaged in that, the dielectric layer and the metal layer are formed on the source electrode or the drain electrode of the channel transistor for forming the capacitor, a problem that a special deep trench for forming a capacitor is formed in a substrate in the prior art can be solved, the manufacturing process is simplified, manufacturing complexity is reduced, and compatibility with the routine manufacturing flow can be better.

Owner:SEMICON MFG INT (SHANGHAI) CORP

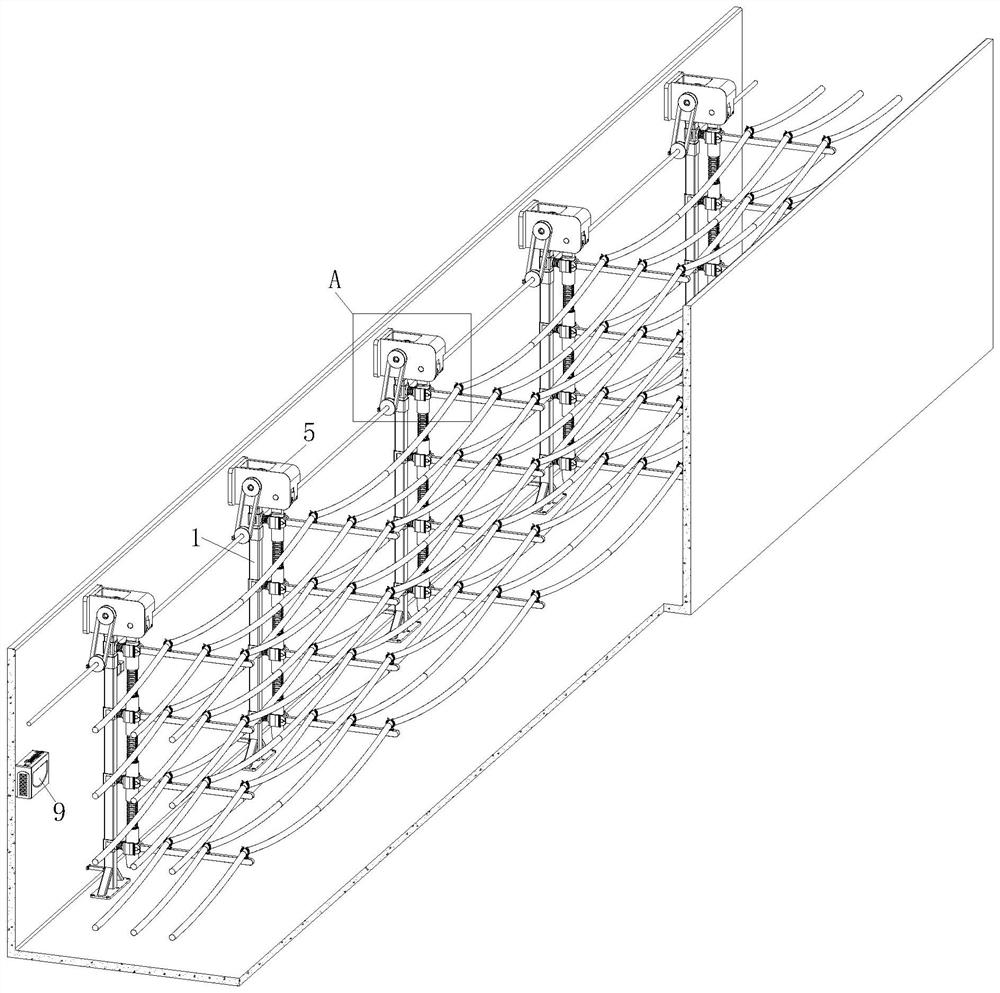

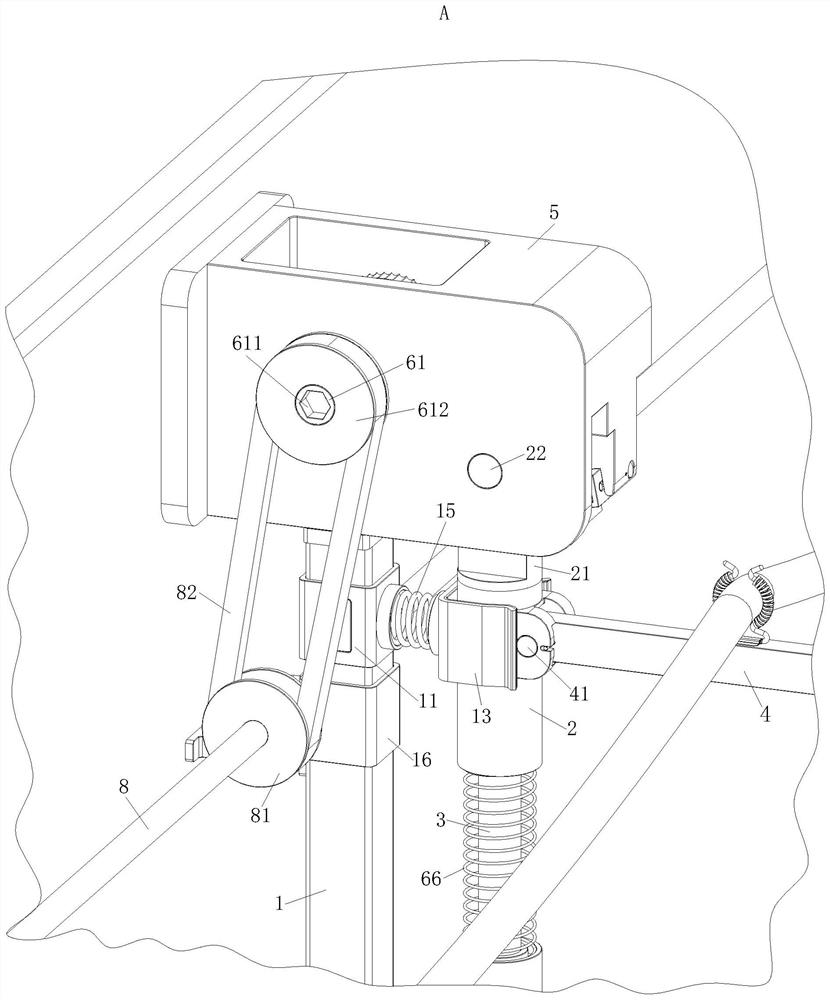

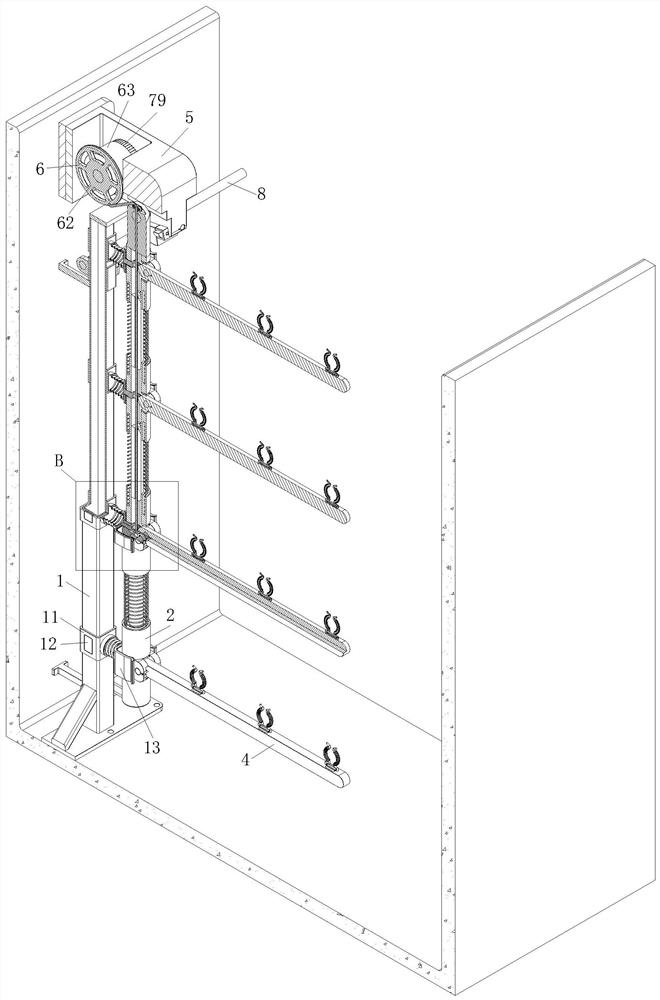

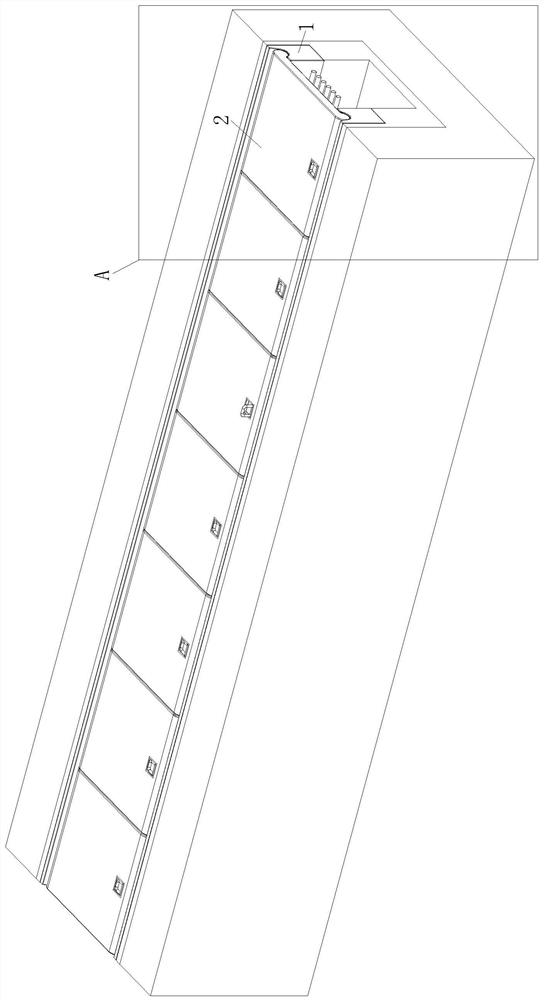

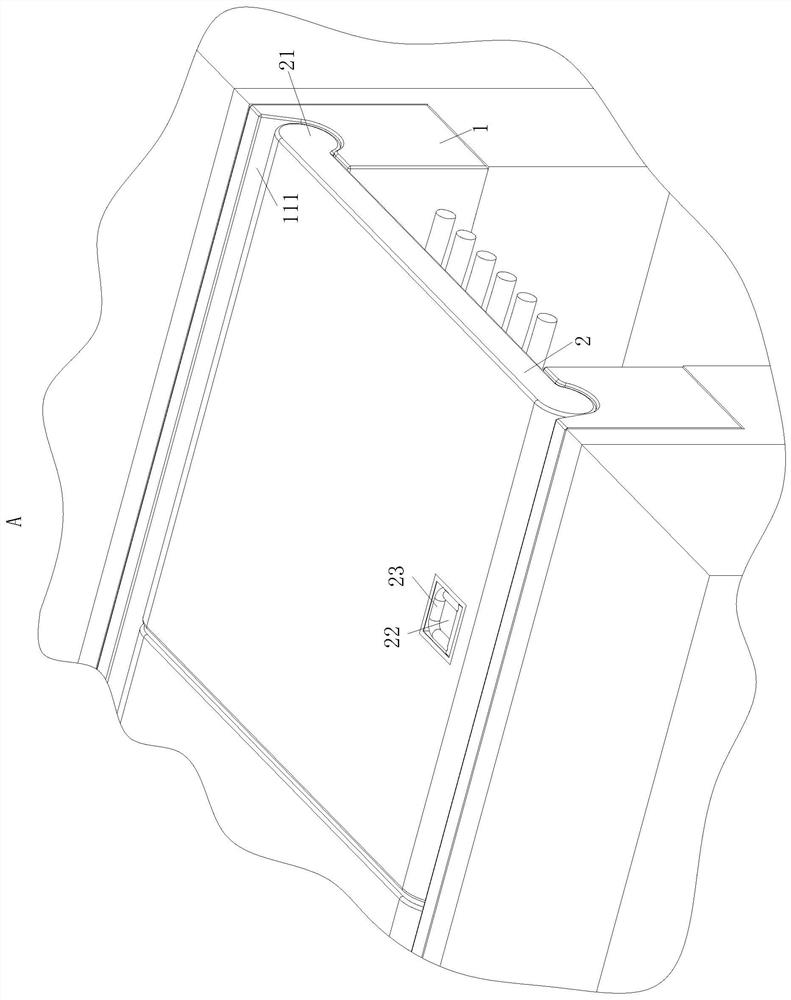

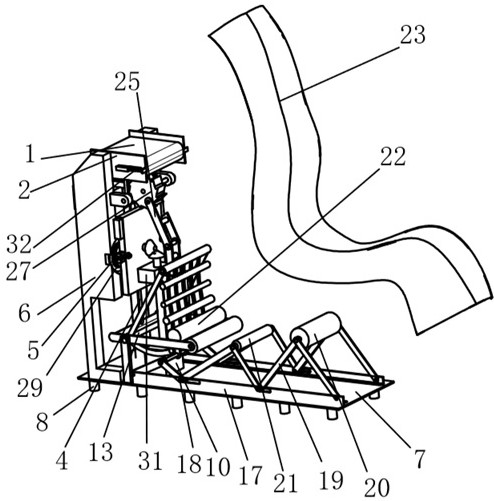

Shrinkage turnover type intelligent cable trench support

InactiveCN114784740AIncrease distanceReliable rotationCable installations on groundCable installations in underground tubesElectric power equipmentPower equipment

The invention belongs to the technical field of power equipment, and particularly relates to a contraction turnover type intelligent cable trench support which comprises a stand column, a sliding cylinder, a sliding rod and a connecting piece. The connecting piece is rotated above the ground through the power part, so that a worker is prevented from stretching into a cable trench to install or overhaul a cable, the risk that the worker falls into the cable trench is reduced, the difficulty of installation and overhaul is reduced, installation and overhaul of the cable are facilitated, and the working efficiency is improved. The power part enables the farthest sliding cylinder to abut against the opening of the cable trench, so that the side wall of the cable trench provides supporting force for the sliding cylinder, the stability of the connecting pieces is improved, the distance between the connecting pieces is increased, the operation space is increased, and the cable can be conveniently installed or overhauled. The power part enables the sliding cylinder to contract upwards, so that the distance between the end of the connecting piece and the first rotating shaft is reduced, reliable rotation of the connecting piece is achieved, and reliable work of the cable trench support is achieved.

Owner:周盼

Electric automobile front cabin mounting bracket and electric automobile

PendingCN111731394AReduce the chance of electric leakageLow costBraking action transmissionElectric propulsion mountingIn vehicleElectrical battery

The invention discloses an electric automobile front cabin mounting bracket and an electric vehicle, and belongs to the technical field of electric vehicles. A first mounting area and a second mounting area are connected in the first direction, the first mounting area is used for supporting and fixing one, two or three of a power distribution unit, a vehicle-mounted charger, a motor control unit and a battery, and the second mounting area is used for supporting and fixing the rest of the power distribution unit, the vehicle-mounted charger, the motor control unit and the battery; a vacuum boosting main cylinder is arranged above the joint of the first mounting area and the second mounting area in the second direction; the first direction is perpendicular to the second direction; a strengthweakening structure is arranged at the joint of the first mounting area and the second mounting area; the maximum breaking stress capable of being borne by the joint in the second direction is lowerthan a preset breaking stress value, the maximum breaking stress capable of being borne by other positions of the first mounting area and the second mounting area in the second direction is higher than the preset breaking stress value, and the mounting bracket can effectively avoid the vacuum boosting main cylinder and is low in cost.

Owner:上海元城汽车技术有限公司

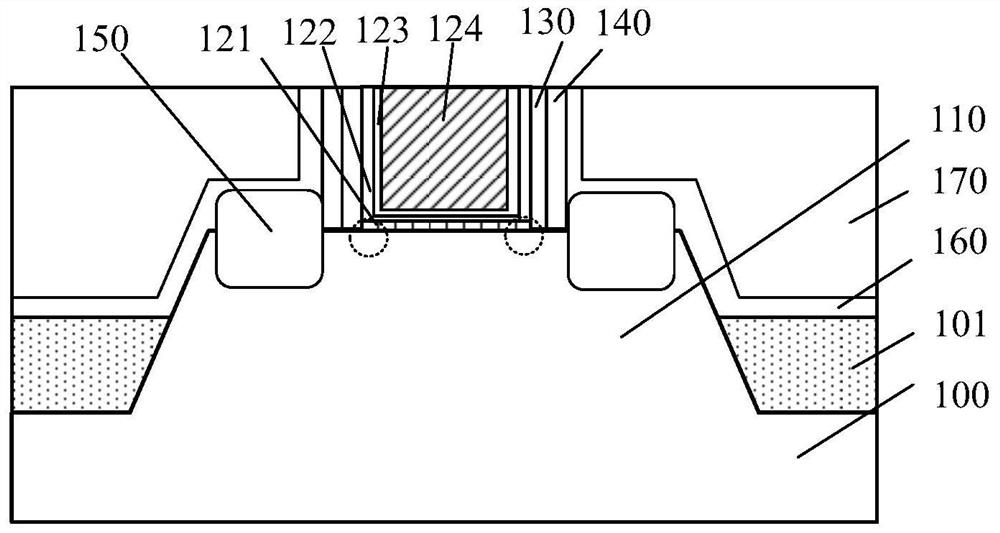

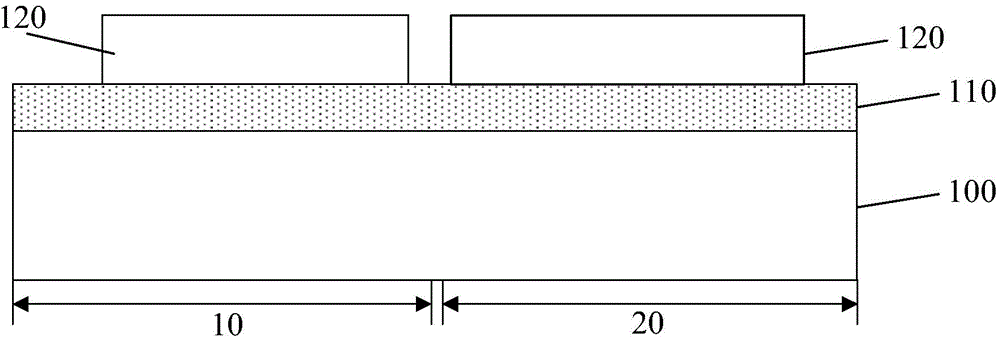

Semiconductor device and forming method thereof

InactiveCN109585546AImprove performanceReduce the chance of electric leakageSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsSemiconductor

The invention provides a semiconductor device and a forming method thereof. The method comprises the following steps that a substrate is provided; a dielectric layer is formed on the substrate, wherein a first gate opening which penetrates through the dielectric layer is formed in the dielectric layer; a first interface layer is formed at the bottom of the first gate opening; a first gate dielectric layer is formed on the side walls and the bottom of the first gate opening, wherein the first gate dielectric layer is located on the first interface layer; annealing treatment is carried out on the first interface layer; after annealing treatment is carried out, a first gate electrode layer located on the first gate dielectric layer is formed in the first gate opening; first through holes areformed in the dielectric layer on the two sides of the first gate electrode layer; and a first source drain doping layer is formed in the substrate at the bottoms of the first through holes. Accordingto the method, the performance of the semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Technique and structure for making convex

InactiveCN100405548CHigh mechanical strengthIncrease effective areaSemiconductor/solid-state device detailsSolid-state devicesCamUltimate tensile strength

This invention relates to cam creation technique and its structure. It includes a sheath with flat surface, the sheath is covered on a joint mat on the plaque to form a contact surface with one open through the sheath, and one cam on the contact surface and the flat surface is formed. The contact mat can be reduced because of the flat surface of the sheath. The mechanical strength of the sheath on the contact mat is strengthened; the cam will has large efficient area when stitching. Selecting space of different directivity conduction membrane is large, short circuit and electric leakage probability is little, so the stitching good ratio and conducting quality of the cam is improved.

Owner:ELAN MICROELECTRONICS CORPORATION

High voltage semiconductor device

ActiveCN107799595BPrevent penetrationIncrease kinetic energySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialVoltage drop

The invention provides a high voltage semiconductor device. The high-voltage semiconductor device comprises a substrate; a source electrode zone and a drain electrode are arranged in the substrate andare isolated by an isolation structure; the first metal layer is arranged on the substrate and comprises a first metal layer main body which is electrically connected to the source area and the drainarea and a plurality of first metal stop blocks which are arranged right above the isolation structure; the second metal layer is stacked on the first metal layer; the second metal layer main body iselectrically connected to the source zone or drain zone, and the plurality of second metal stop blocks are arranged right above the isolation structure, wherein a stacking part is arranged between each first metal stop block and the corresponding second metal block; a via hole is arranged between the first metal layer and the second metal layer; the via hole is arranged in a stacking part of thefirst metal stop block and the second metal stop block. The high voltage semiconductor device can prevent stray electrons from permeating to the isolation structure and can reduce rates of break through voltage drop and electricity leakage.

Owner:NUVOTON

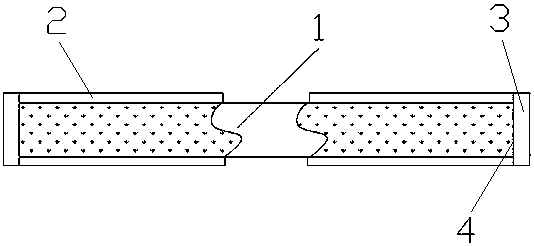

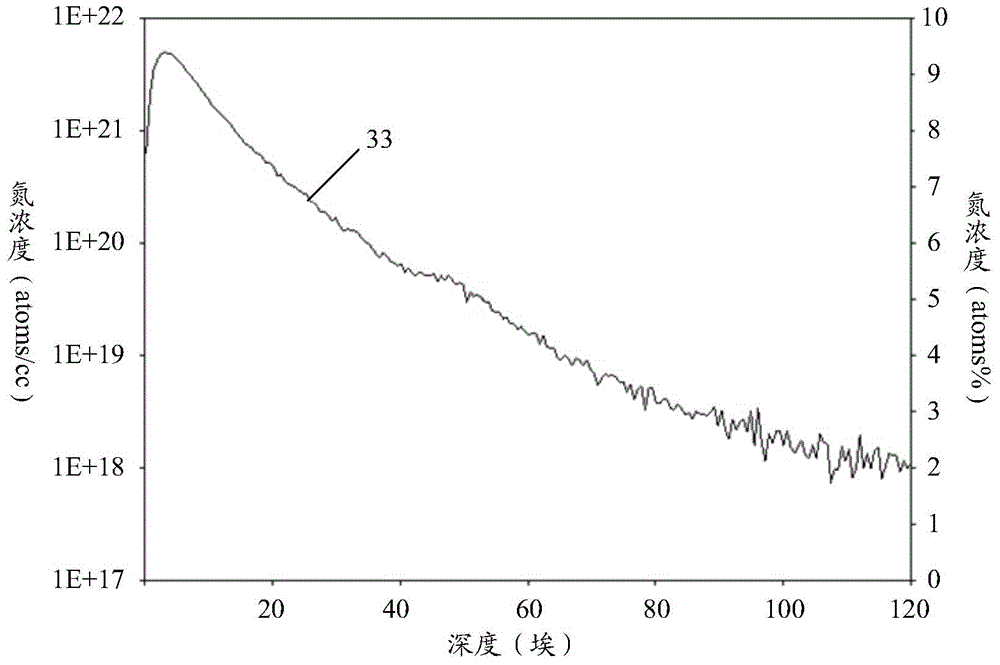

A photovoltaic cell resistant to high temperature and high humidity environment

ActiveCN106449779BImprove performanceReduce the possibilityFinal product manufacturePhotovoltaic energy generationPhotoelectric conversionSilicon chip

The invention relates to a photovoltaic cell for high temperature high moisture environment resistance, belongs to the solar energy photovoltaic generation production field and solves a problem of photoelectric conversion rate decrease caused by the PID effect because of the high temperature high moisture environment. The photovoltaic cell comprises a crystal silicon substrate, wherein a front side and a back side of the crystal silicon substrate are respectively plated with a layer of an antireflection film. The photovoltatic cell is characterized in that a silicon chip edge of the crystal silicon substrate is plated with an edge protection film, the edge protection film is connected with the antireflection films, and the crystal silicon substrate is completely sealed through the edge protection film and the antireflection films so as to realize complete isolation from the external environment. The photovoltatic cell is advantaged in that properties of reasonable structure design, strong reliability, good economics, light weight and practicality are realized, and the problem of photoelectric conversion rate decrease caused by the PID effect because of the high temperature high moisture environment can be effectively solved.

Owner:HUADIAN ELECTRIC POWER SCI INST CO LTD

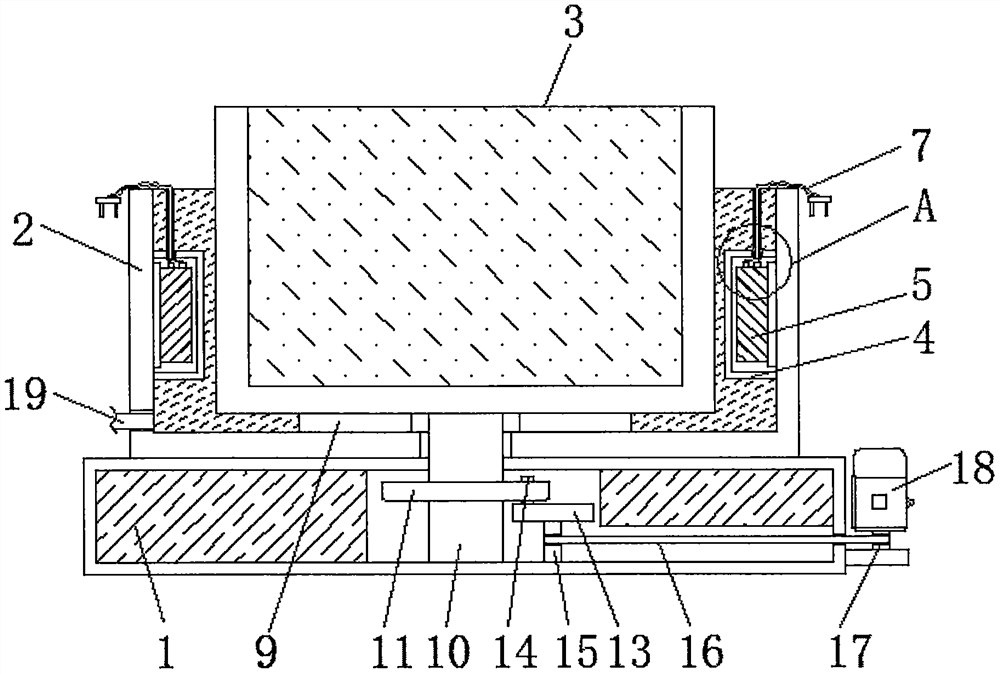

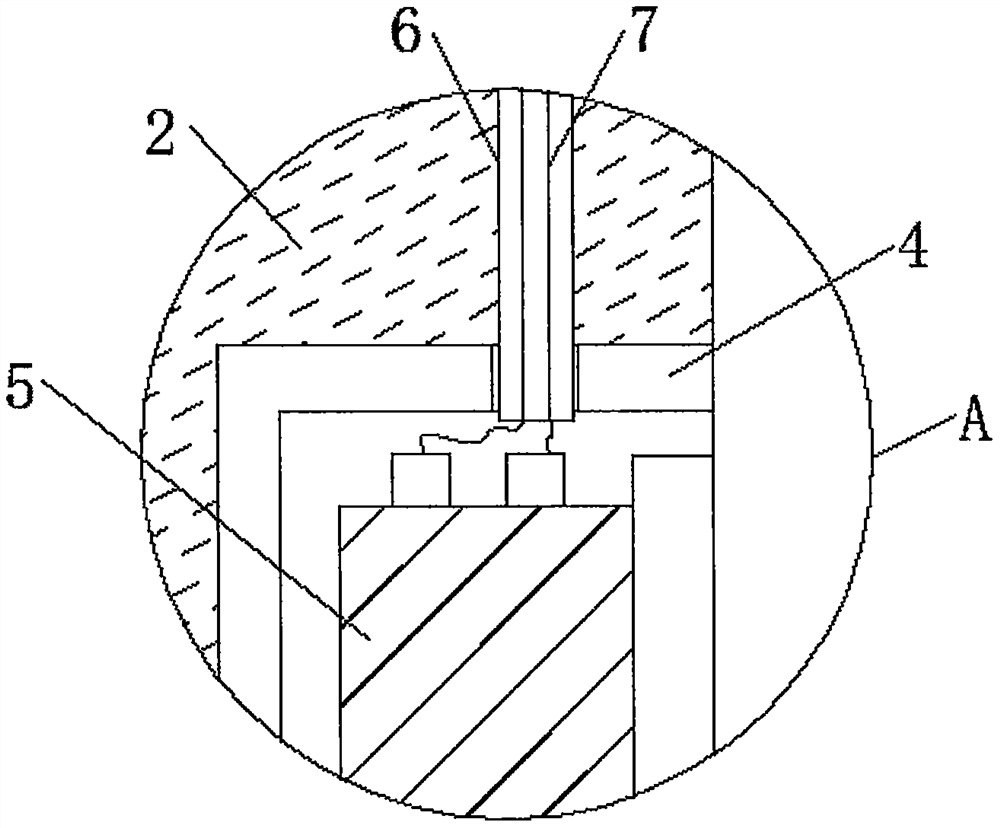

Water temperature heating device used for culture pond and capable of preventing electric leakage due to water entry

InactiveCN111887200AImprove sealingEnsure normal farmingPisciculture and aquariaThermodynamicsElectric machine

The invention discloses a water temperature heating device used for a culture pond and capable of preventing electric leakage due to water entry. The device comprises a base, a water inlet, a motor and a drainage pipe, wherein an outer box body is arranged above the base; an inner box body is arranged in the outer box body; a mounting box is arranged between the outer box body and the inner box body; the mounting box is mounted on the inner wall of the outer box body; a second rotating shaft is fixedly connected to the interior of a connecting plate; the right side of the second rotating shaftis connected with a third rotating shaft through a transmission belt; and a heat conduction piece is arranged between the mounting box and an electric heating plate. According to the water temperature heating device used for the culture pond and capable of preventing electric leakage due to water entry, the heat conduction piece is arranged between the mounting box and the electric heating plateand is provided with a first cooling fin, a heat conduction rod and a second cooling fin, and the ends, connected with the first cooling fin and the second cooling fin, of the heat conduction rod arecoated with heat conduction silicone grease, so that heat of the electric heating plate can be rapidly transmitted outwards, and the water heating progress is accelerated.

Owner:UNIV FOR SCI & TECH ZHENGZHOU

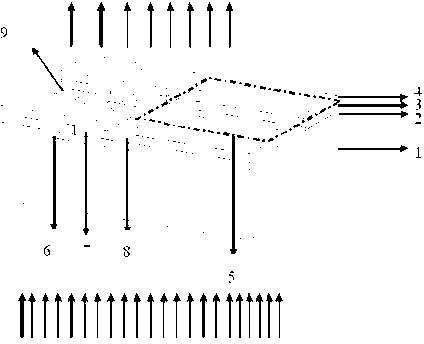

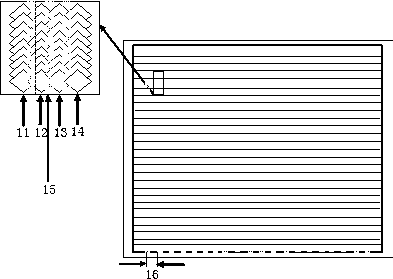

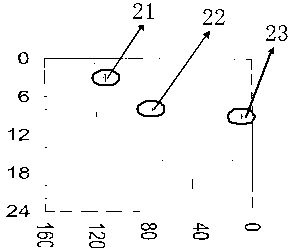

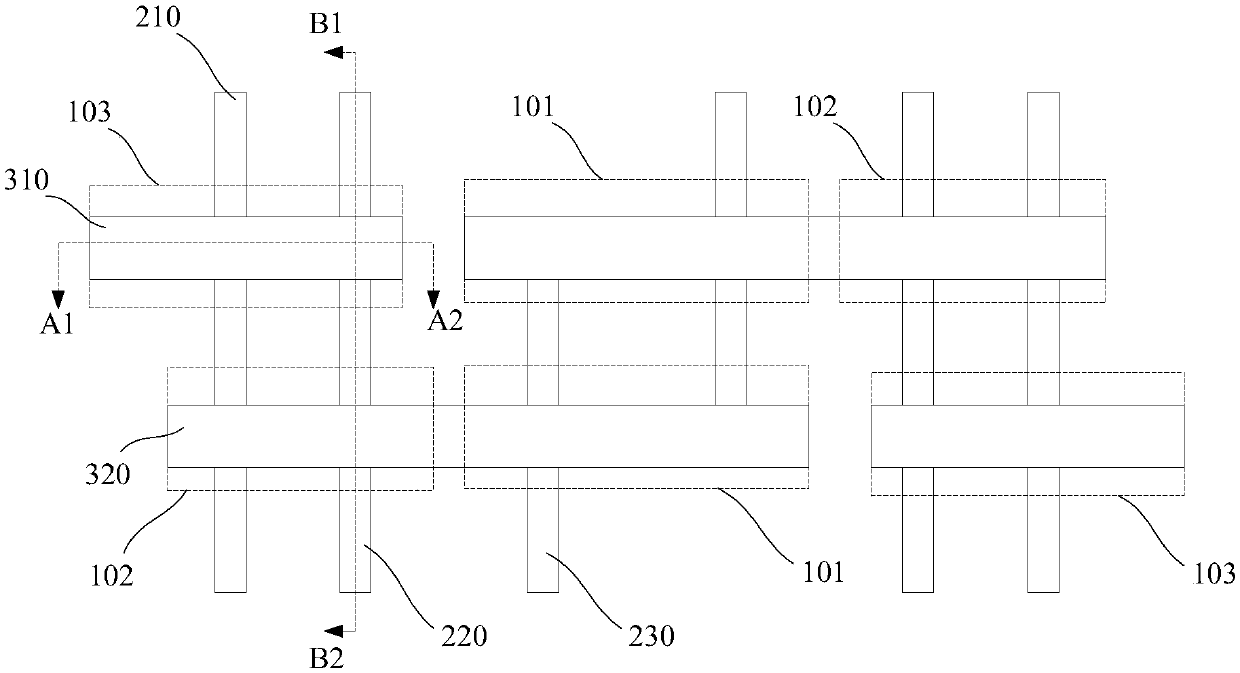

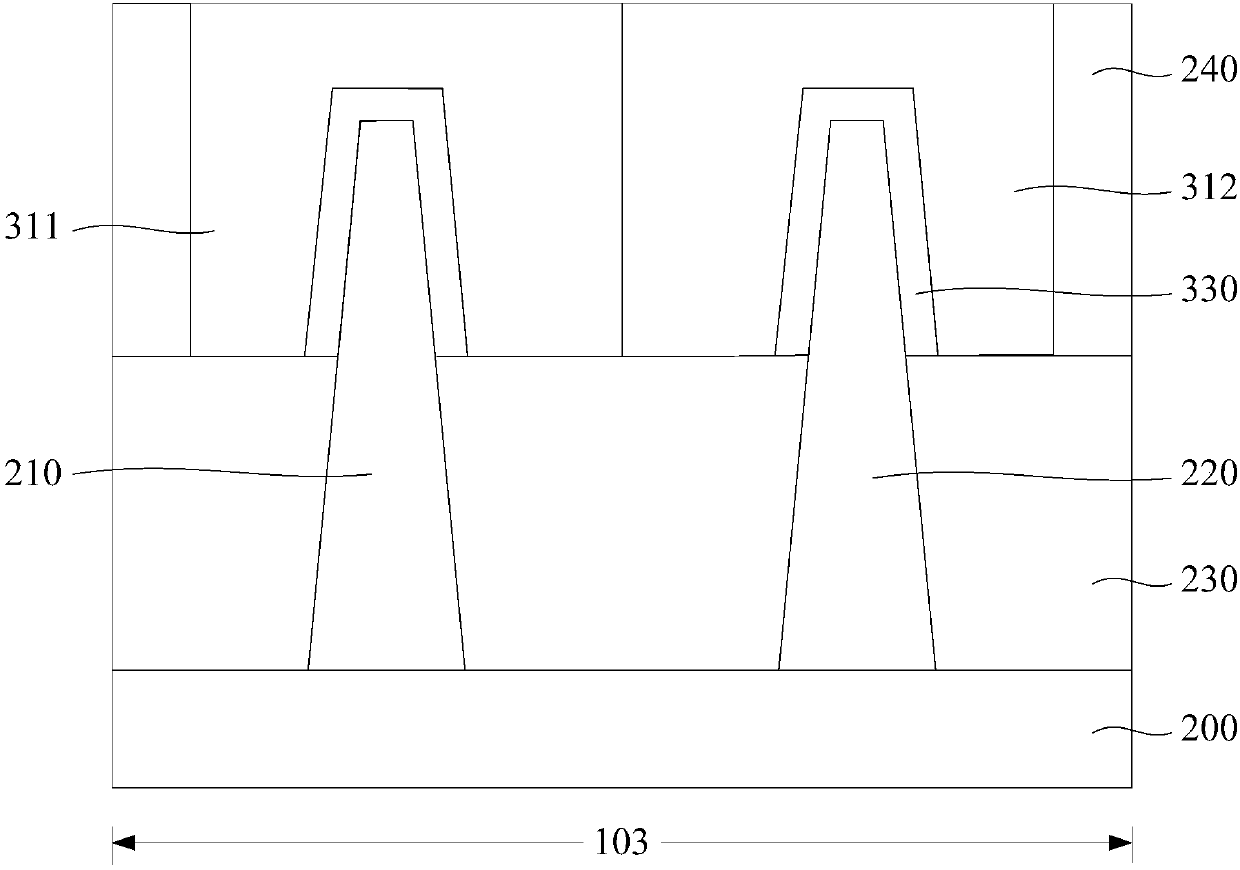

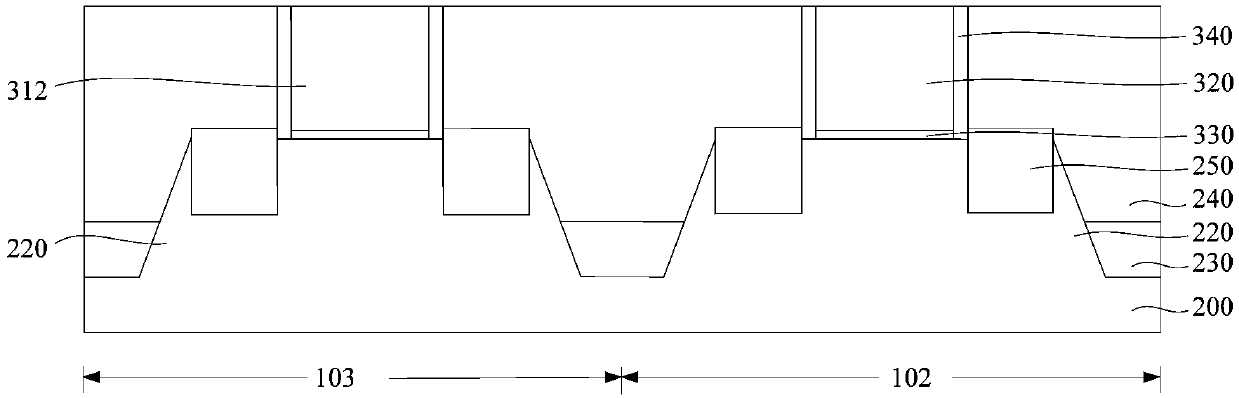

Etching method for improving power of light-transmitting solar cell module

InactiveCN102254996BGuaranteed light transmissionReduce the chance of electric leakageFinal product manufactureSemiconductor devicesElectrical batteryTransmittance

The invention relates to a scribing method for improving the power of a light-transmitting solar cell assembly, and belongs to the technical field of solar cell applications. Under the condition that the light-transmitting performance of the light-transmitting solar cell module remains unchanged, the purpose of improving the power of the module is achieved by optimizing the light-transmitting scribing method. The width of the optical groove (9) is used to adjust the number of scribed light-transmitting grooves per unit area, and to reduce the number of scribed light-transmitting grooves on the basis of ensuring that the light-transmitting performance remains unchanged, so as to reduce the impact on the film during the scribing process. Leakage caused by damage to the edge of the layer, so that the light transmittance of the component can be kept unchanged, and the power generation can be greatly improved. The present invention analyzes the source of leakage, aims at reducing the probability of leakage, optimizes the way of marking, and does not change much in equipment adjustment, so it has the characteristics of good controllability and flexible change mode, and is the best way to achieve high transparency. An efficient way to rate high power products.

Owner:BAODING TIANWEI GRP CO LTD

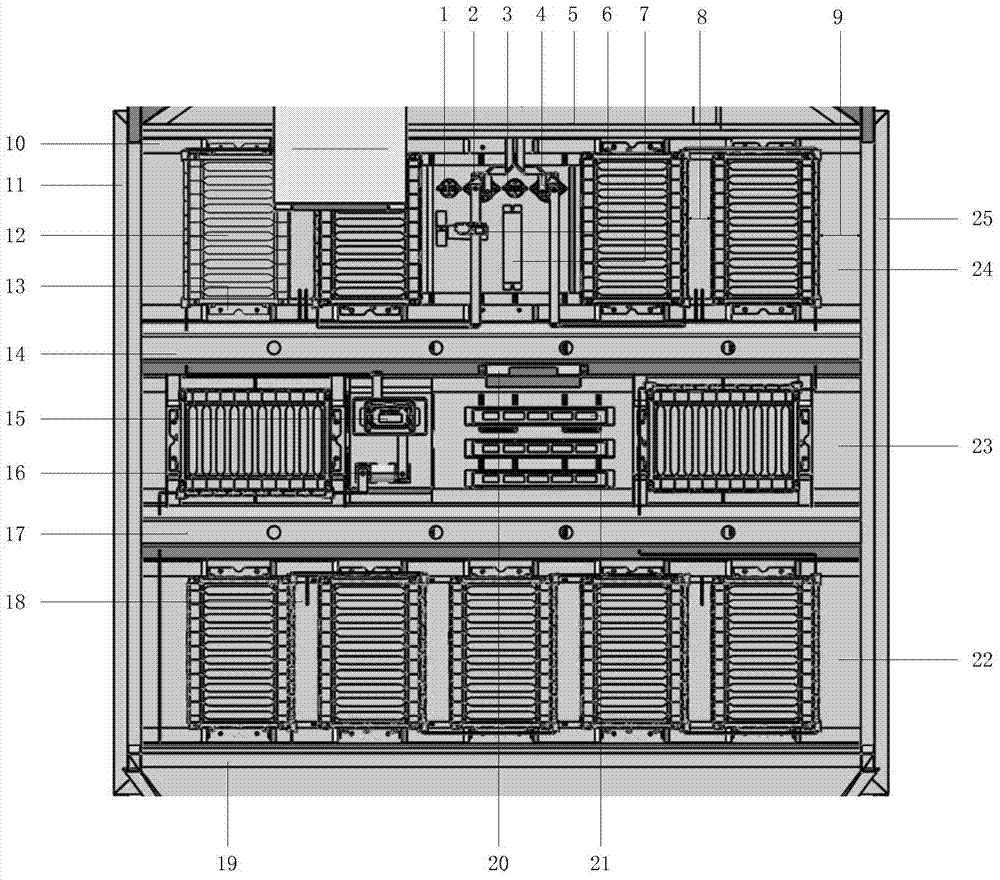

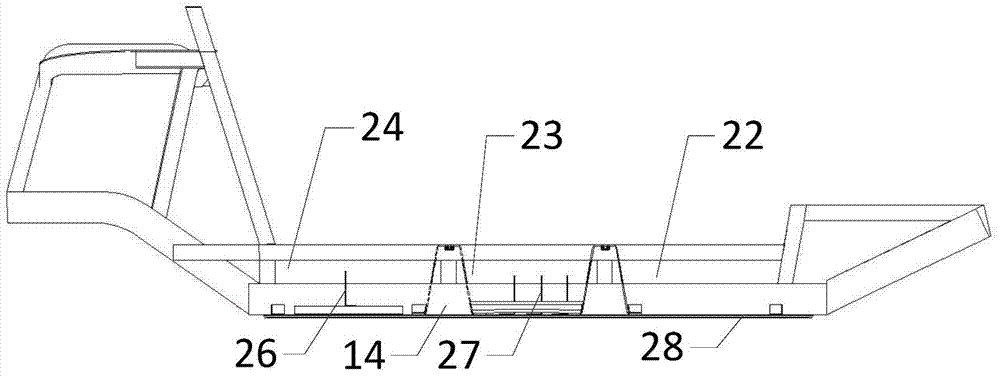

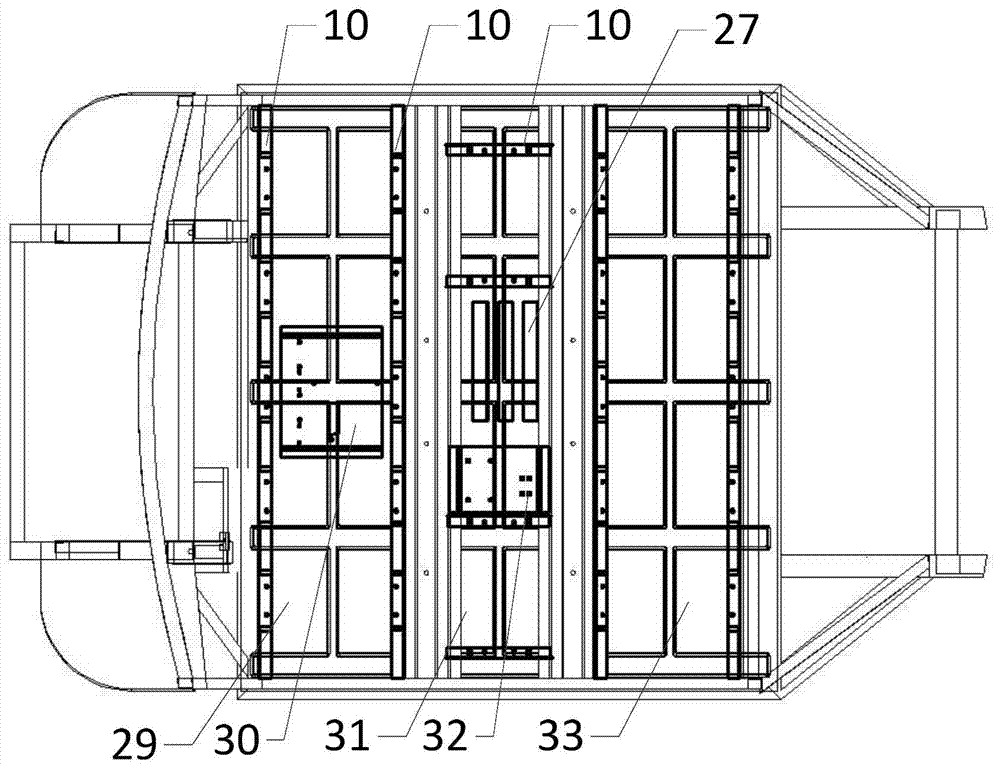

A layout structure of a power battery pack for a distributed four-wheel hub motor driving an electric vehicle

ActiveCN105128644BEnsure safetyAchieve lightweightElectric propulsion mountingMotor driveElectric-vehicle battery

The invention provides an arrangement structure of a power battery pack of a distributed four-wheel hub motor driven electric vehicle. Space. According to the layout requirements of ergonomics, the body structure, the installation structure of the seat, and the layout requirements of the internal cells and electrical components of the power battery, the battery pack is designed to be laid flat between the upper floor and the lower floor, and the lower surface is determined. Ensure that the minimum ground clearance and longitudinal passing angle of the vehicle meet the relevant requirements of the vehicle design. Through reasonable arrangement and simple fixing method, the present invention ensures that the power has the largest volume, ensures the utilization rate of the internal space of the power battery, and is beneficial to the reasonable distribution of the front and rear axle loads of the vehicle. In addition, the power battery pack and the vehicle body The high strength of the connection structure improves the stability of the power battery pack and is conducive to the stable operation of the car.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

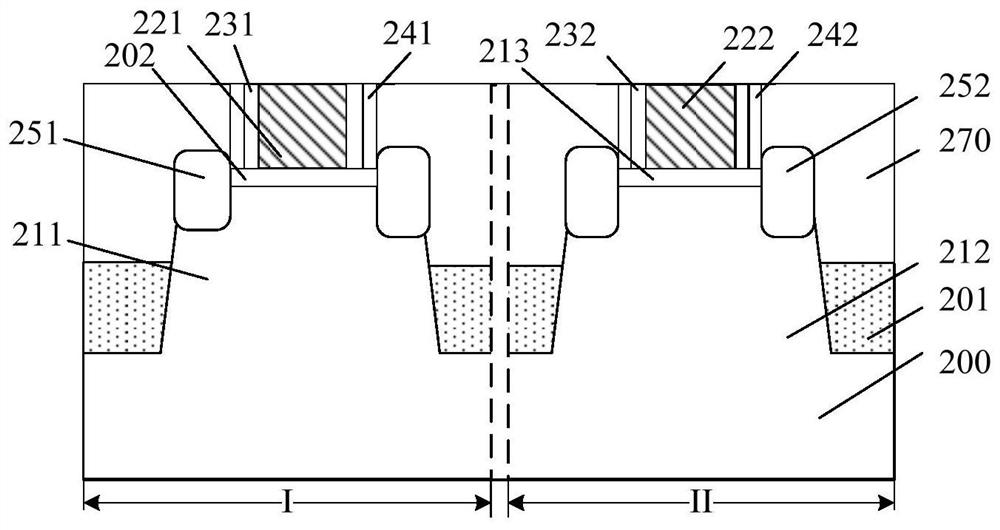

Gate structure forming method and gate structure

InactiveCN105529255AReduce the chance of electric leakageImprove electrical stabilitySemiconductor devicesPhysicsElectrical stability

The invention provides a gate structure forming method and a gate structure. The gate structure forming method comprises the steps of: providing a substrate; forming a first oxidation layer; forming a nitride layer; forming a first gate, so that the first oxidation layer and the nitride layer positioned in a first region form a gate dielectric layer of an input / output MOS device; and forming a second gate on a substrate in a second region. The gate structure comprises a substrate, a first oxidation layer positioned on the substrate in the first region, the nitride layer positioned on the surface of the first oxidation layer, the first gate positioned on the nitride layer in the first region, and the second gate positioned on the substrate in the second region, wherein the nitride layer is formed by carrying out nitrogen treatment on the first oxidation layer. The gate structure forming method and the gate structure have the beneficial effects of reducing probability of electric leakage of the gate dielectric layer, increasing electrical stability of the gate dielectric layer, and reducing thickness of the equivalent oxidation layer under the condition that the physical thickness of the gate dielectric layer of the input / output MOS device is unchanged.

Owner:SEMICON MFG INT (SHANGHAI) CORP

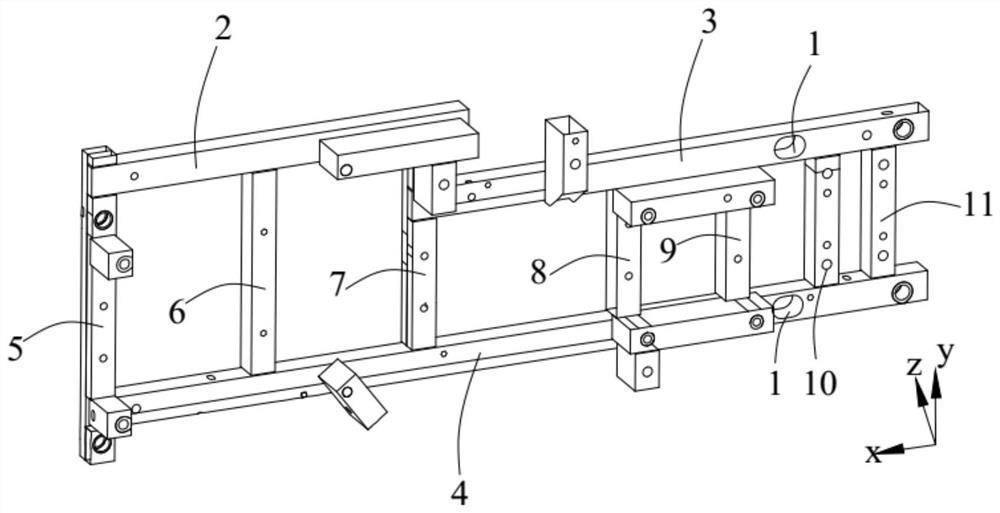

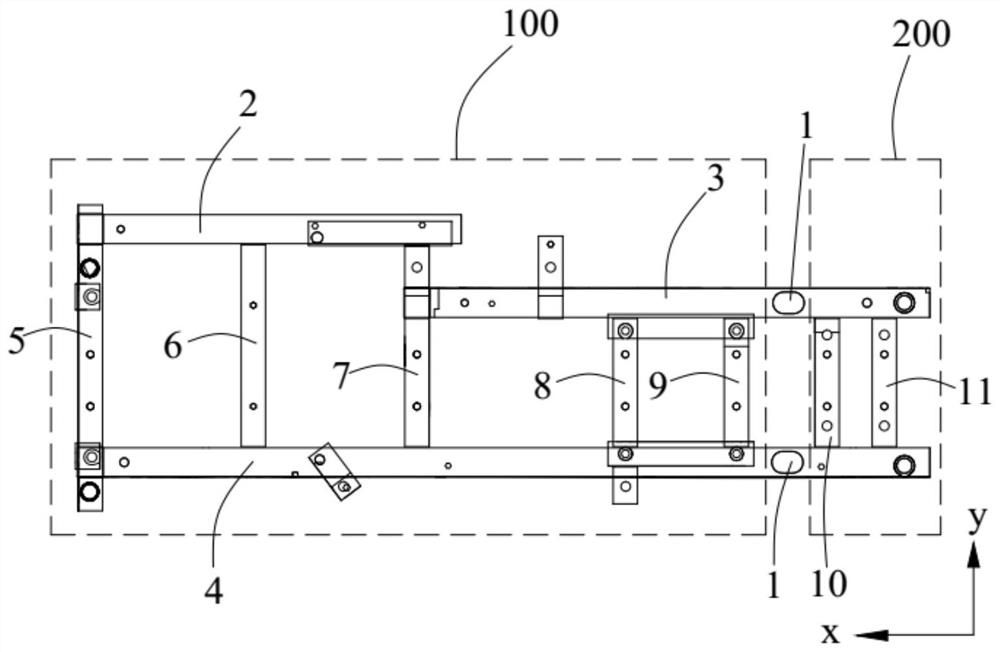

Cable trench cover plate assembly and use method thereof

InactiveCN113991582AIncrease the difficulty of workIncreased chance of falling into cable trenchesCable installations on groundCable installations in underground tubesArchitectural engineeringStructural engineering

The invention belongs to the technical field of cable trench accessories, and particularly relates to a cable trench cover plate assembly and a use method thereof. The cable trench cover plate assembly comprises a supporting part, a covering part and a mounting mechanism. By arranging the mounting mechanism, before the covering part is mounted, a cable is mounted on the covering part through the mounting mechanism, so that a worker is prevented from lying on the ground and stretching the body into a cable trench to mount the cable, the risk that the worker falls into the cable trench is reduced, the probability that the worker is injured is reduced, meanwhile, the cable installation difficulty is reduced, and cable installation is facilitated; and the cable is suspended below the covering part, so that the distance between the cable and accumulated water at the bottom of the cable trench is increased, the probability that the cable is soaked by the accumulated water is reduced, the aging of a cable insulator is prevented from being accelerated due to soaking of the cable, the aging speed of the insulator is reduced, the service life of the cable is prolonged, the probability of electric leakage of the cable is reduced, and the safety of pedestrians and vehicles on the road surface is ensured.

Owner:王树合

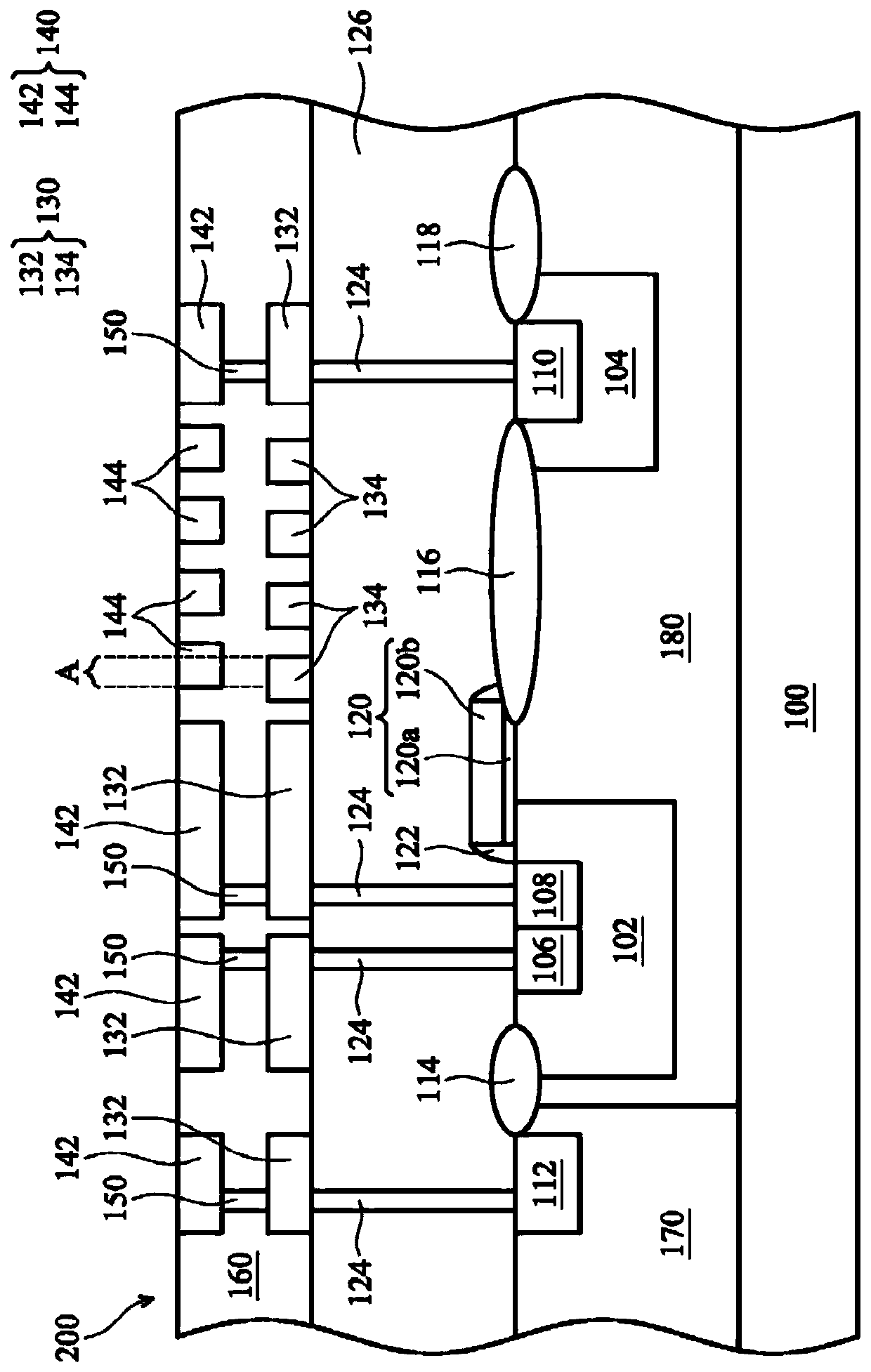

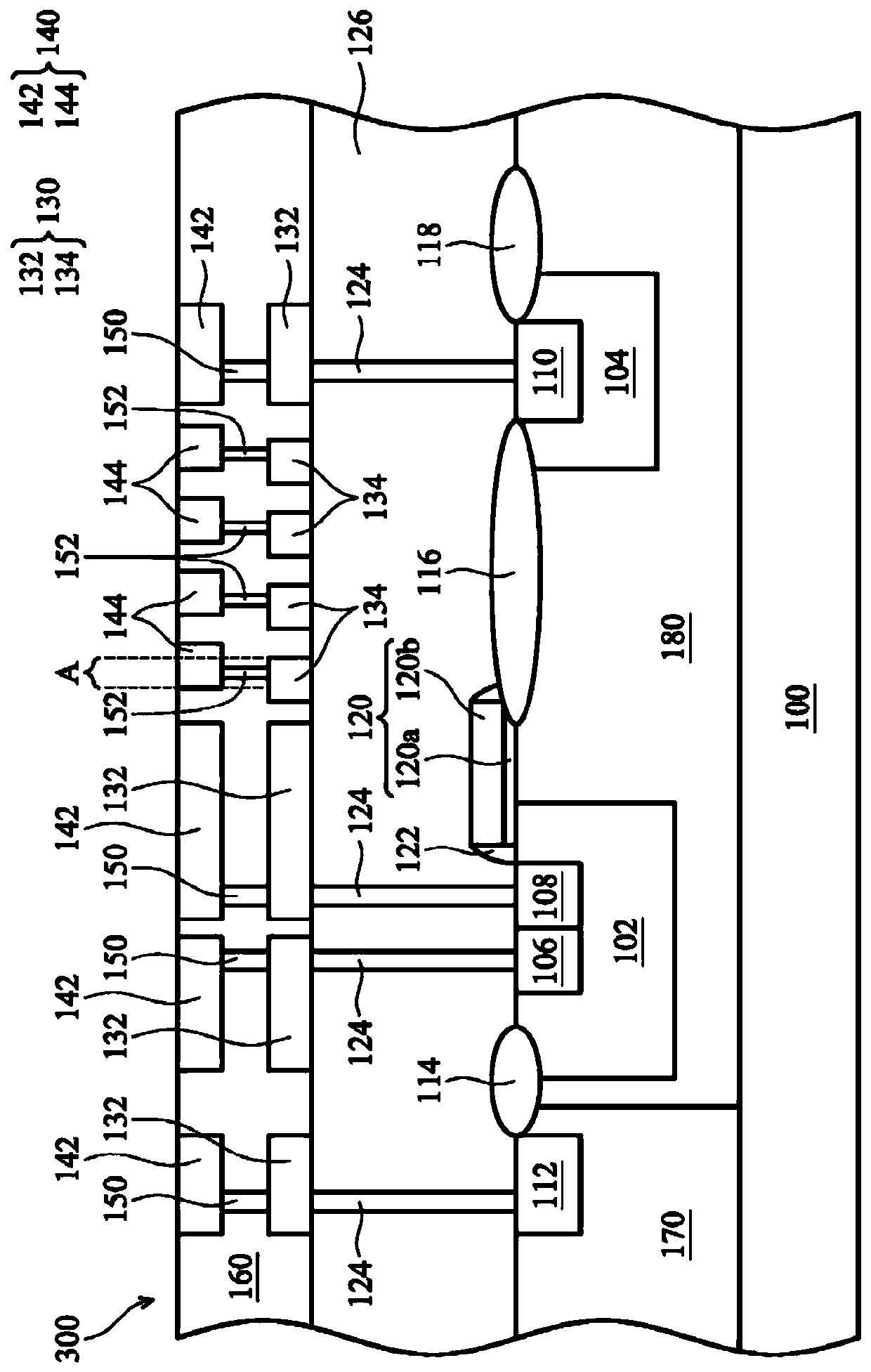

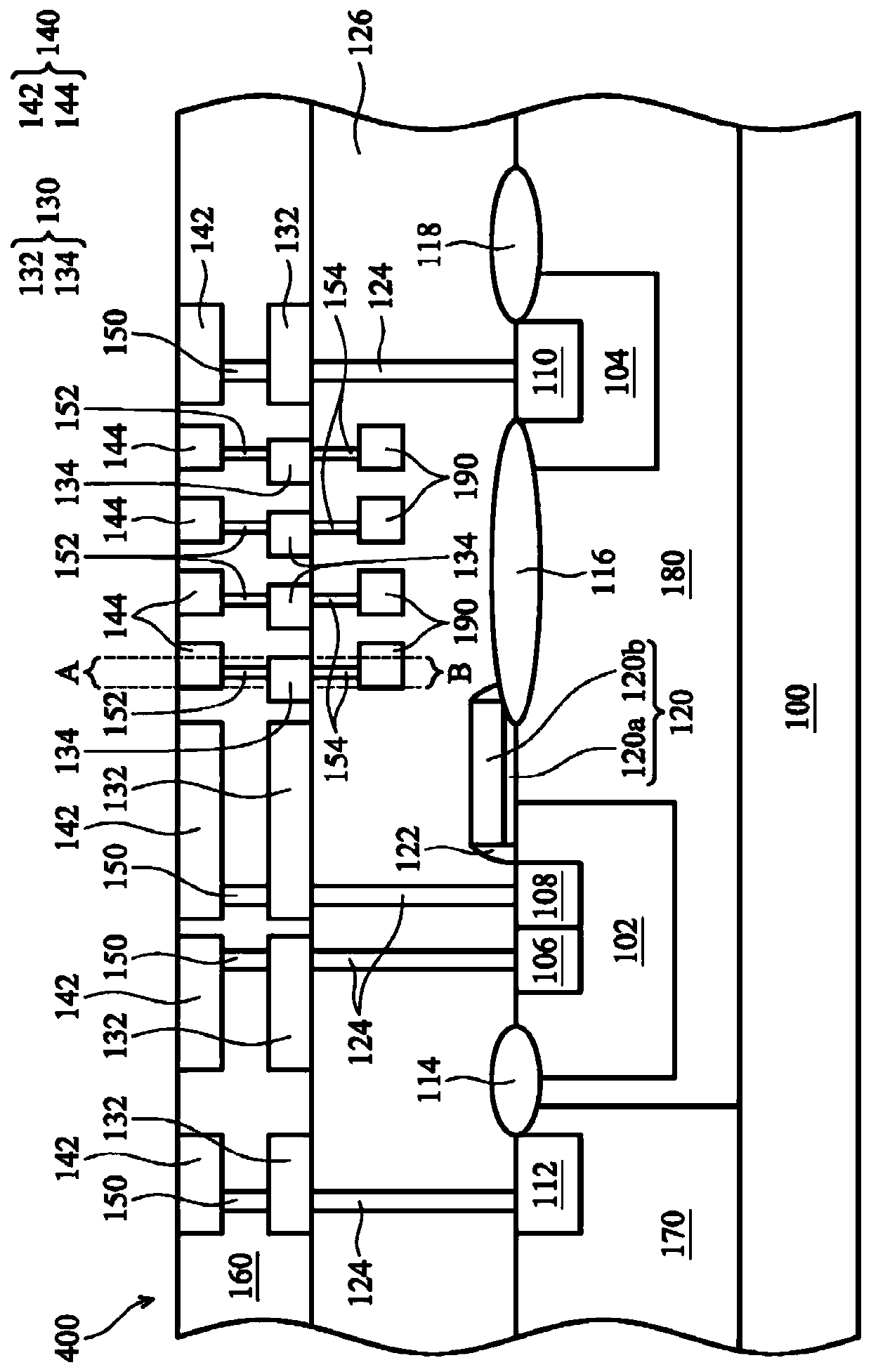

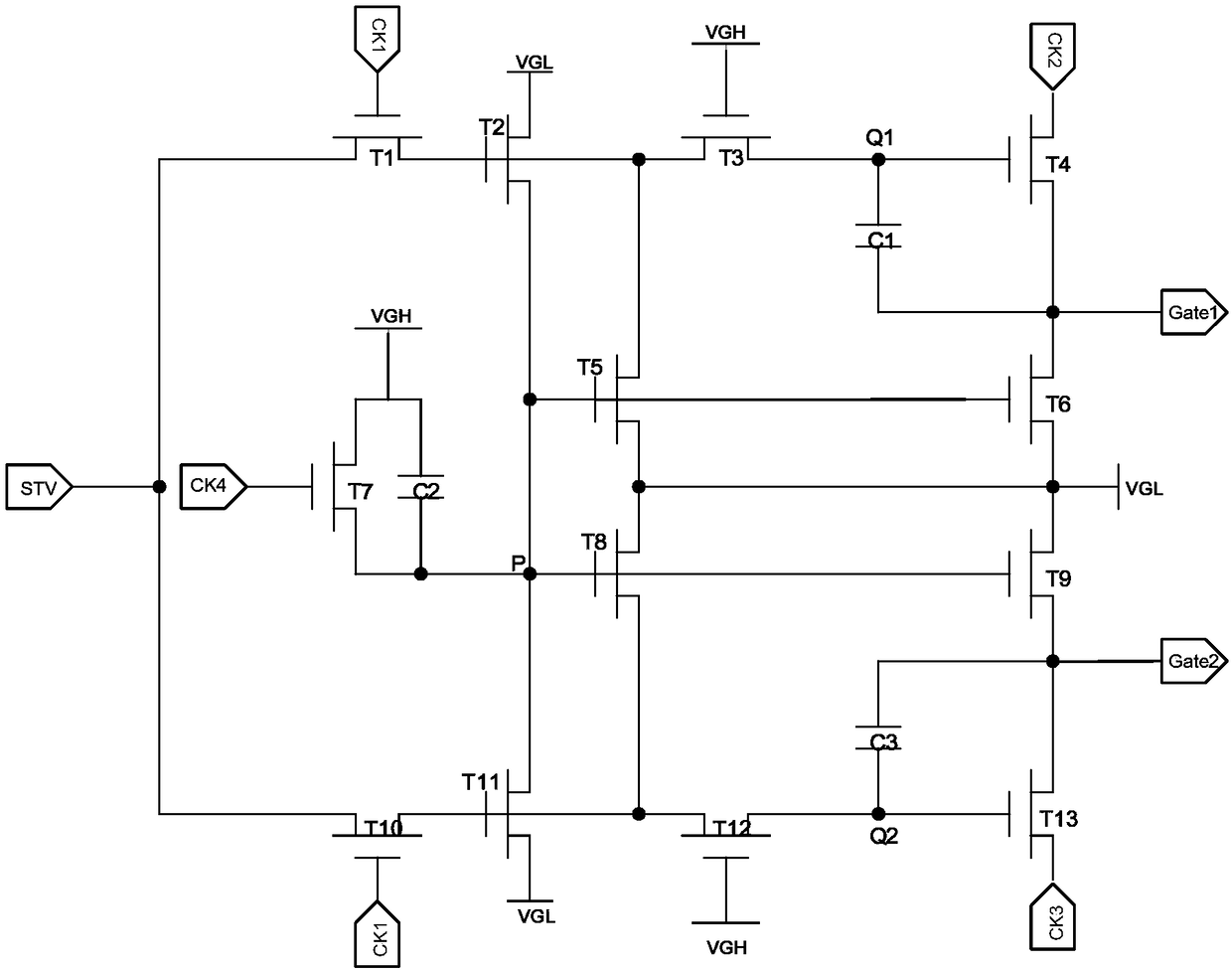

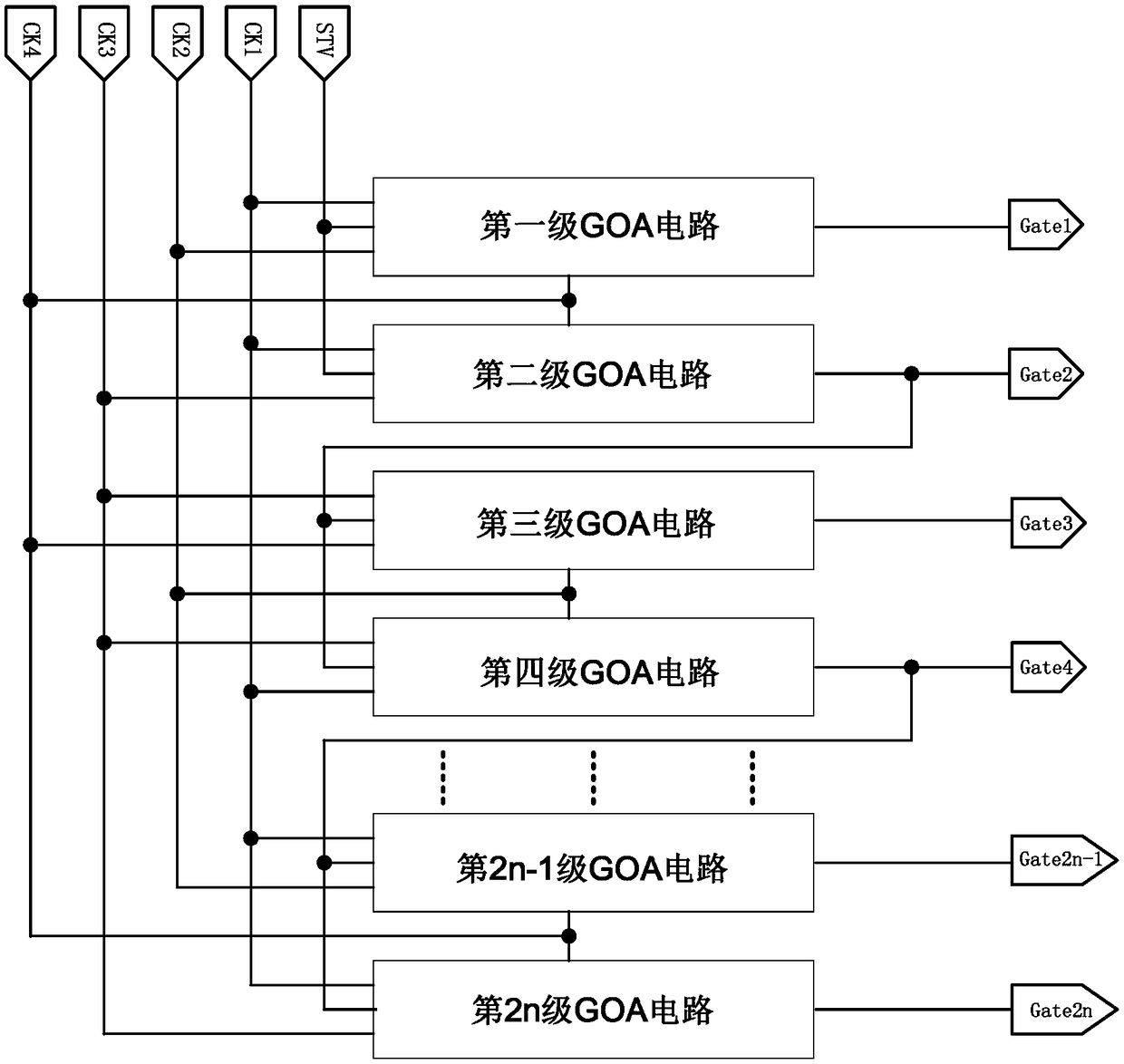

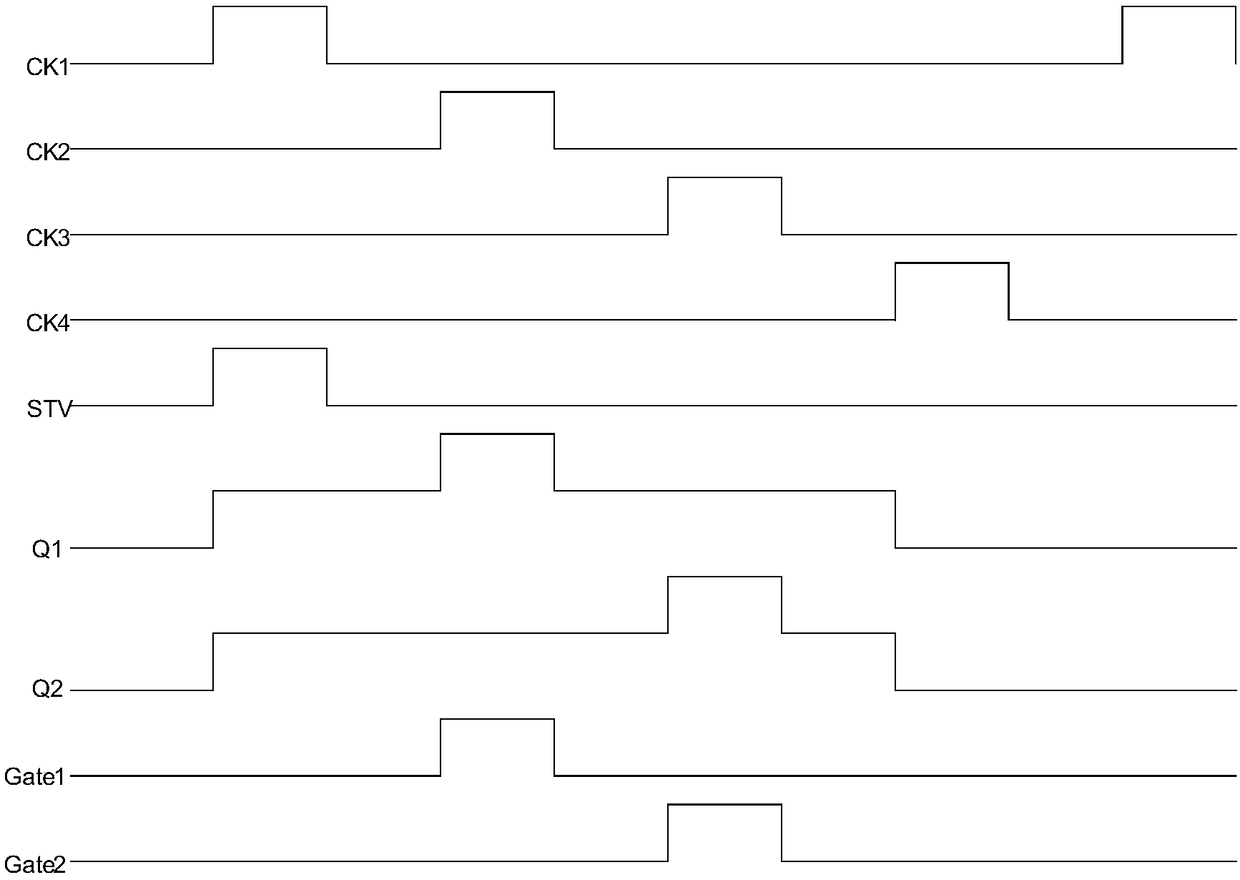

A two-stage single mos tube goa scanning drive circuit and display panel

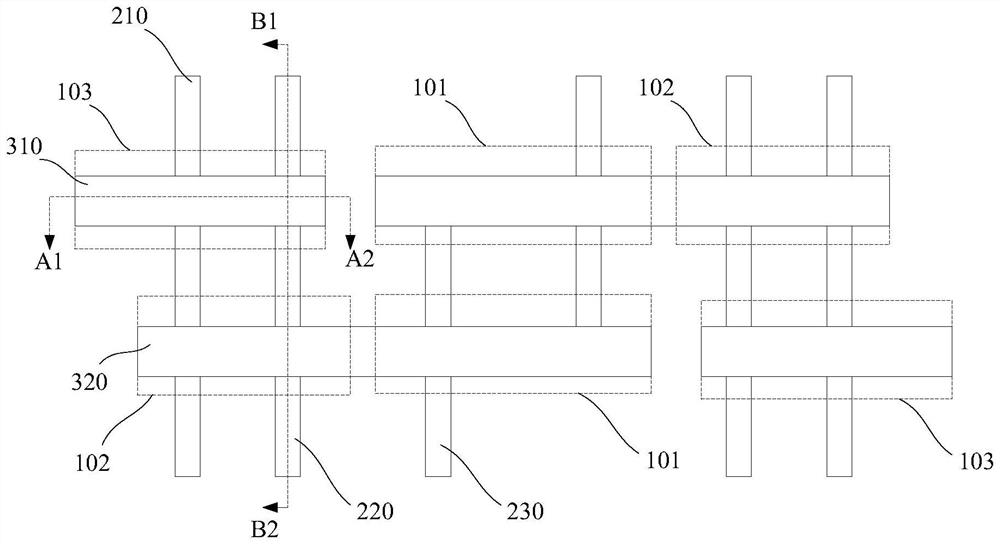

ActiveCN106023940BReduce the risk of failureReduce the chance of electric leakageStatic indicating devicesControl signalInput control

The invention discloses a two-stage single MOS tube GOA scanning driving circuit and a display panel. In each group of scanning driving units of the two-stage single MOS tube GOA scanning driving circuit, the level transmission signal input signal inputted by the level transmission signal input end of the input control circuit of a first scanning driving line and a second scanning driving line are set as signals with different time sequences, and the level transmission signal control signals inputted by the level transmission signal input end of the input control circuit are set as signals with different time sequences. Through the above mode, the Q point leakage probability outputted by the control scanning signal in the circuit can be reduced, and the purpose of reducing circuit failure risk is achieved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

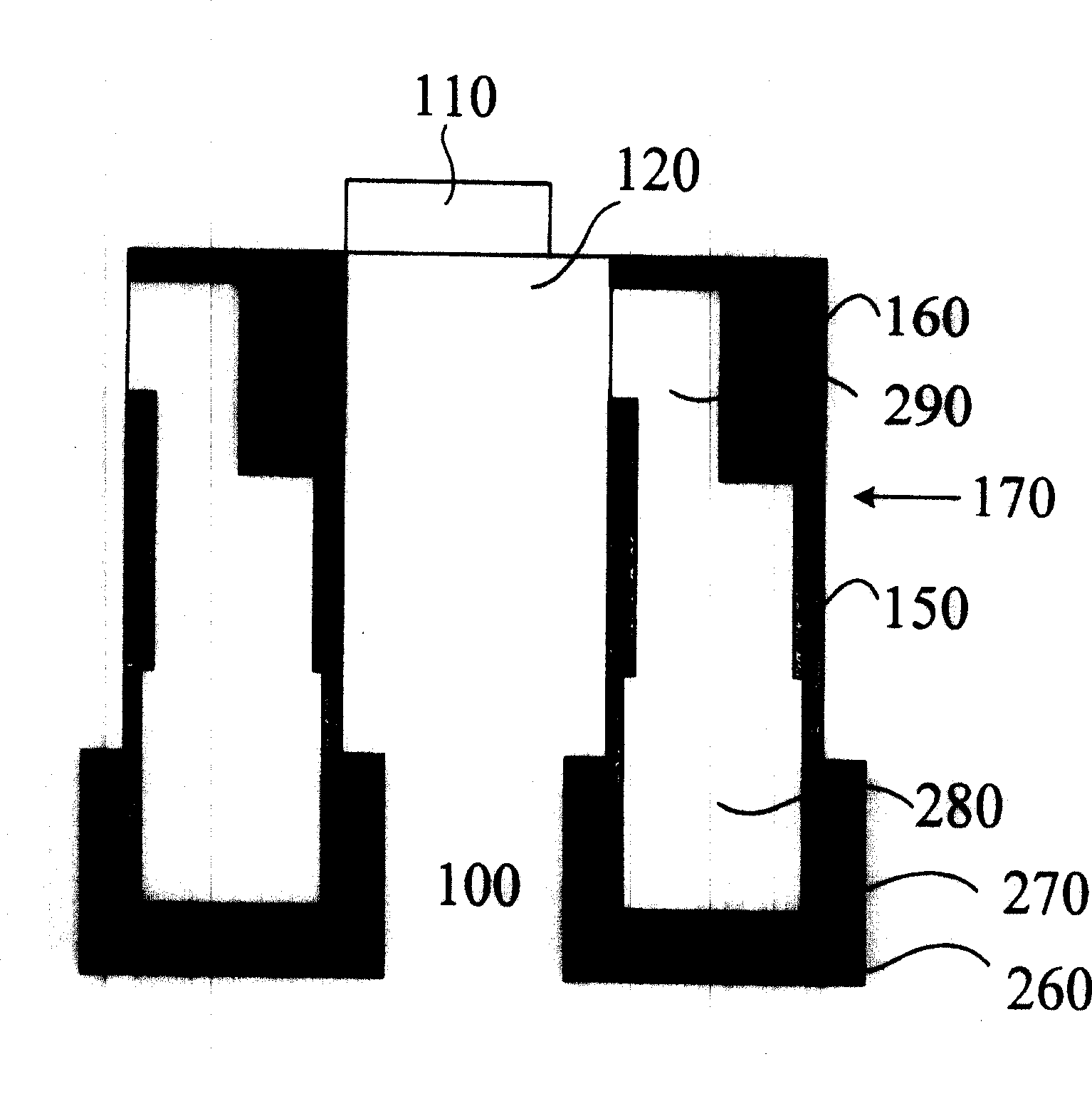

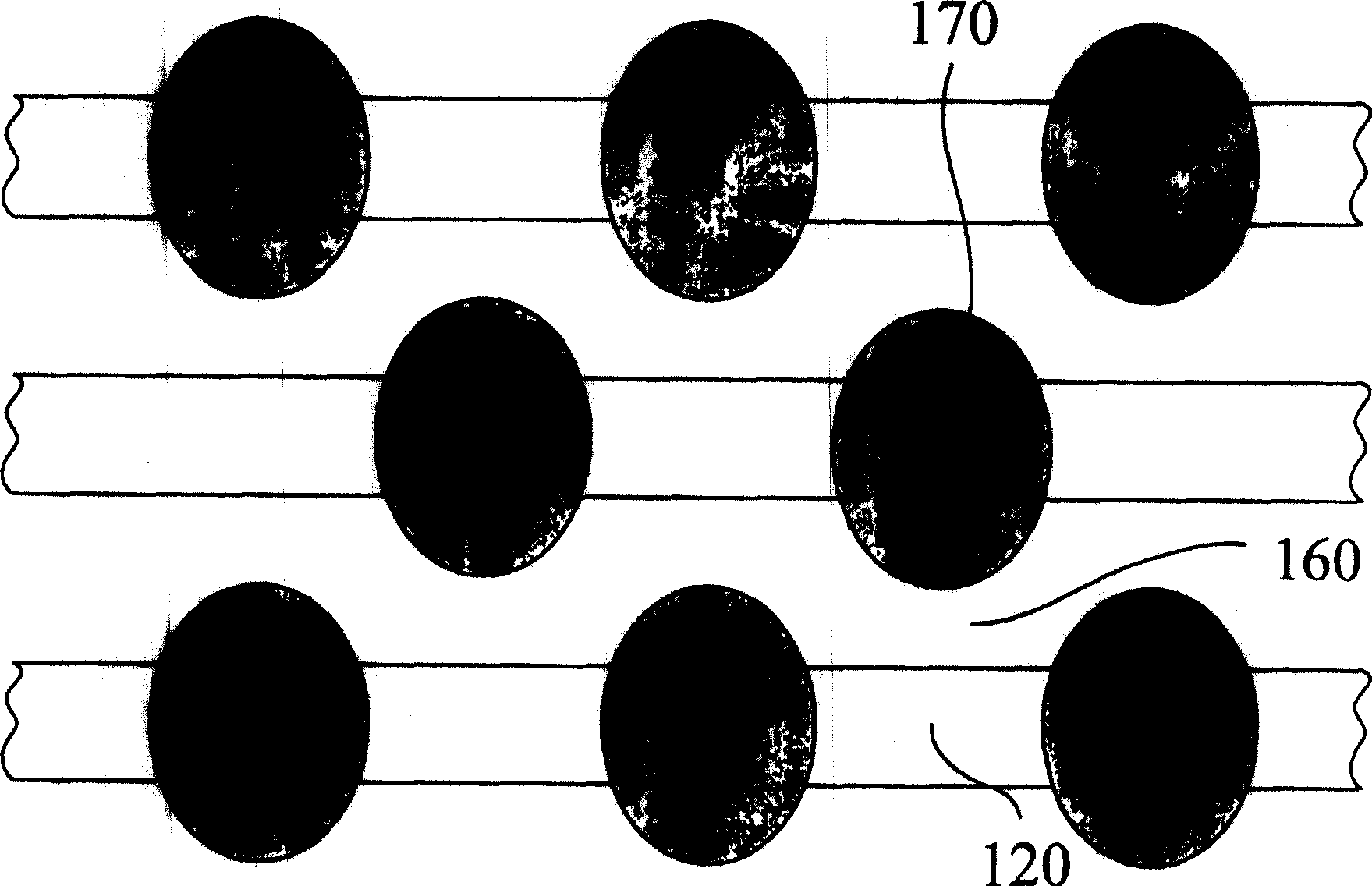

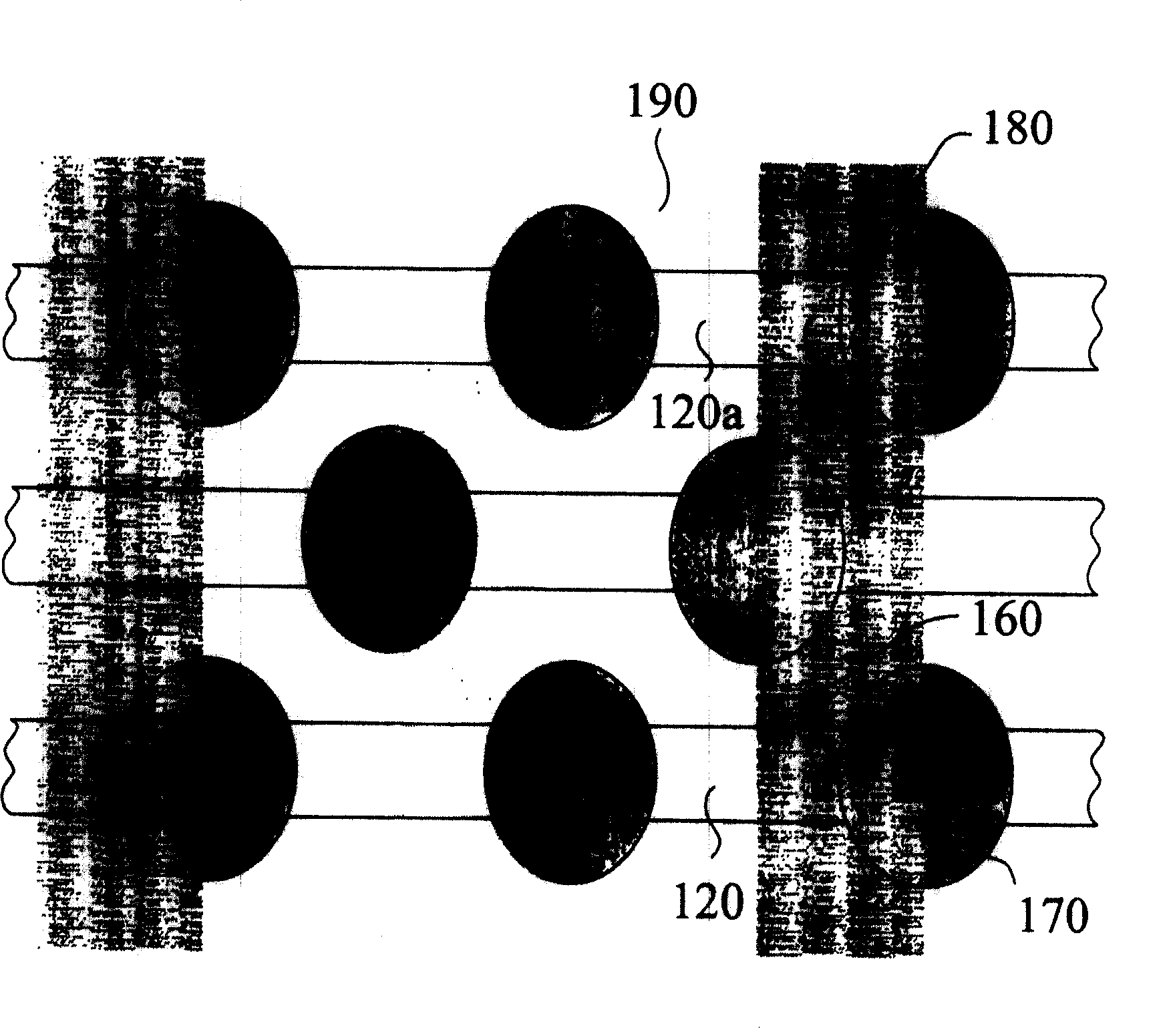

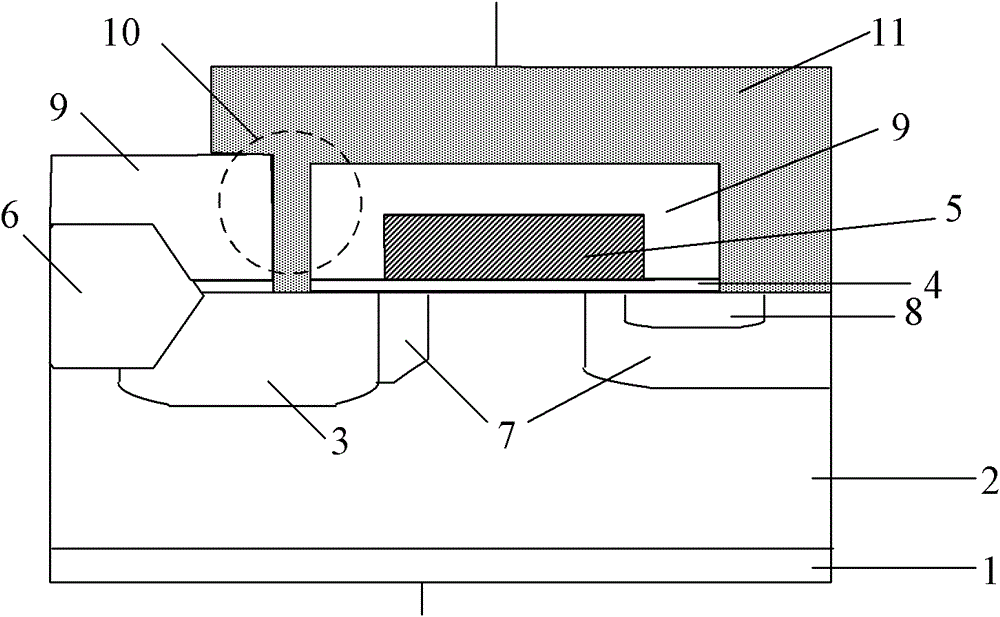

A kind of flip-chip structure light-emitting diode and its preparation method

ActiveCN103579447BShort circuit is easy to eliminateReduce the chance of electric leakageSemiconductor devicesElectricityQuantum well

The invention discloses a light-emitting diode of an inversion structure and a manufacturing method of the light-emitting diode of the inversion structure, and relates to the field of the photoelectric technology. The light-emitting diode comprises a metal supporting substrate, a P-type semiconductor layer, a quantum well light-emitting layer, an N-type semiconductor layer and a non-doped layer which are sequentially overlapped from bottom to top. The light-emitting diode is structurally characterized in that an N-type ohmic contact metal layer, an insulating film and a reflection metal layer are arranged between the metal supporting substrate and the P-type semiconductor layer, multiple layers of metal are arranged above and around the reflection metal layer and extend to the side to serve as a P-type electrode, the metal supporting substrate is connected with the N-type semiconductor layer through the N-type ohmic contact metal layer to serve as an N-type electrode. Compared with the prior art, the light-emitting diode of the inversion structure and the manufacturing method of the light-emitting diode of the inversion structure can effectively avoid electricity leakage of the lateral wall of a chip of the light-emitting diode, improve the reliability of the chip, reserve the advantages of an original vertical-type LED structure, and give the efficiency of the vertical-type LED structure into full play.

Owner:TONGFANG OPTO ELECTRONICS +1

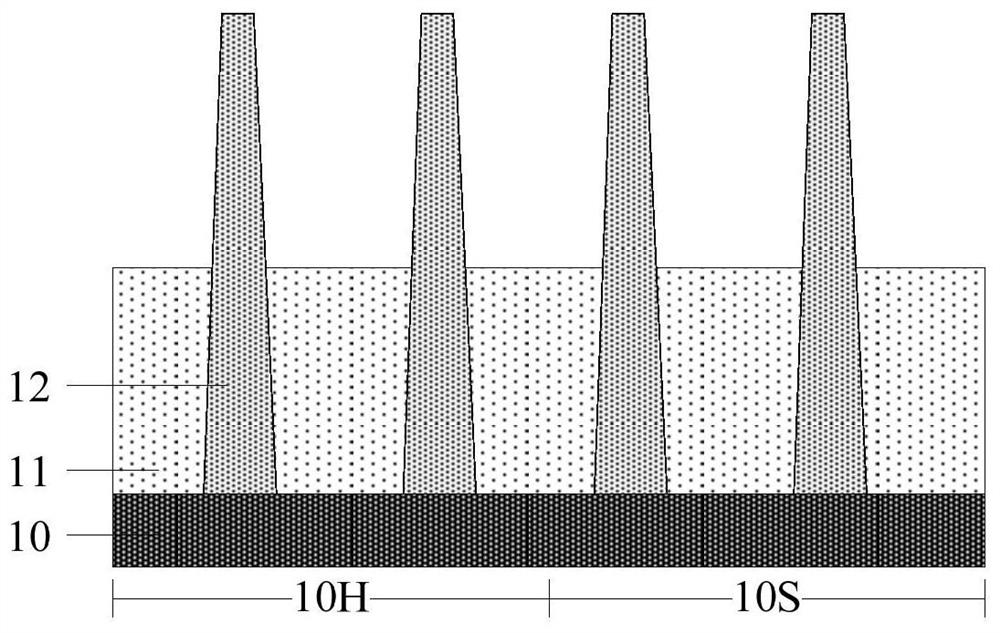

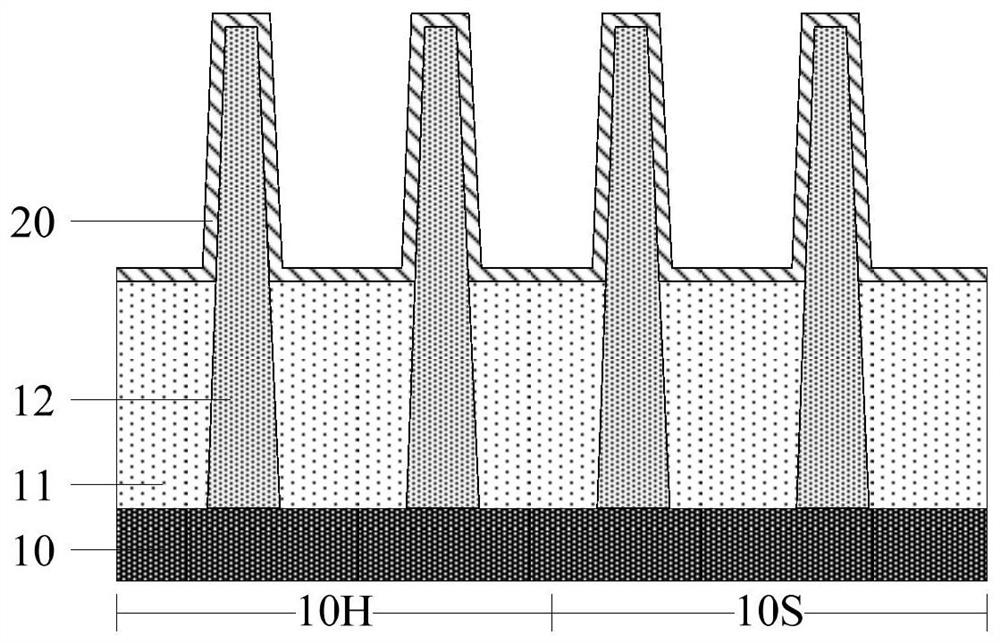

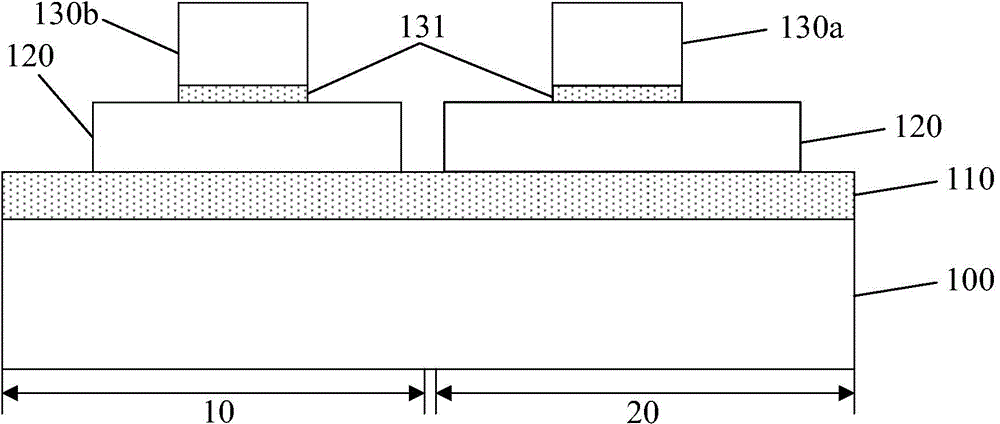

Semiconductor structures and methods of forming them

ActiveCN110120415BSimple processPrevent openingSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureIsolation layer

A semiconductor structure and its forming method, the forming method comprising: providing a substrate and fins protruding from the substrate, the number of the fins is at least two, and the fins are exposed on the substrate An isolation layer is provided, the isolation layer covers part of the sidewall of the fin, the isolation layer has a dummy gate across the fin, and the dummy gate covers part of the top and part of the sidewall of the fin; A dielectric layer is formed on the isolation layer, and the dielectric layer covers the sidewalls of the dummy gate; part of the dummy gate is removed to expose part of the tops of some number of fins, and a penetrating through the dielectric layer is formed in the dielectric layer. an opening in the layer thickness; forming an insulating layer that fills the opening. The present invention can form a semiconductor structure with a required number of channel regions on the basis of multiple positions where channel regions can be formed, thereby simplifying the process of forming a semiconductor structure with a specific number of channel regions.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

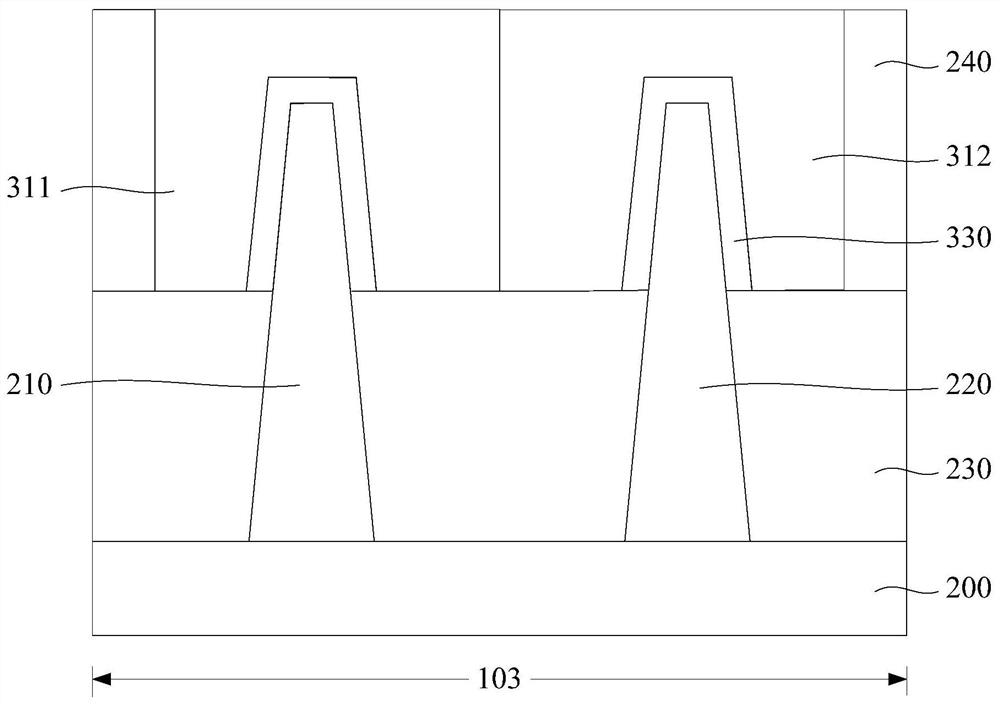

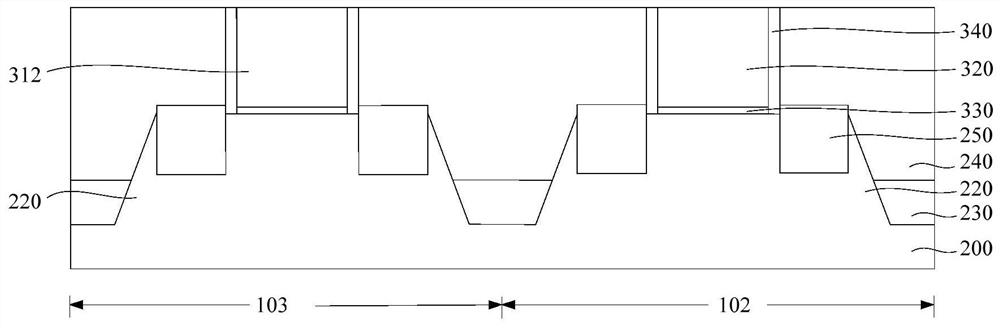

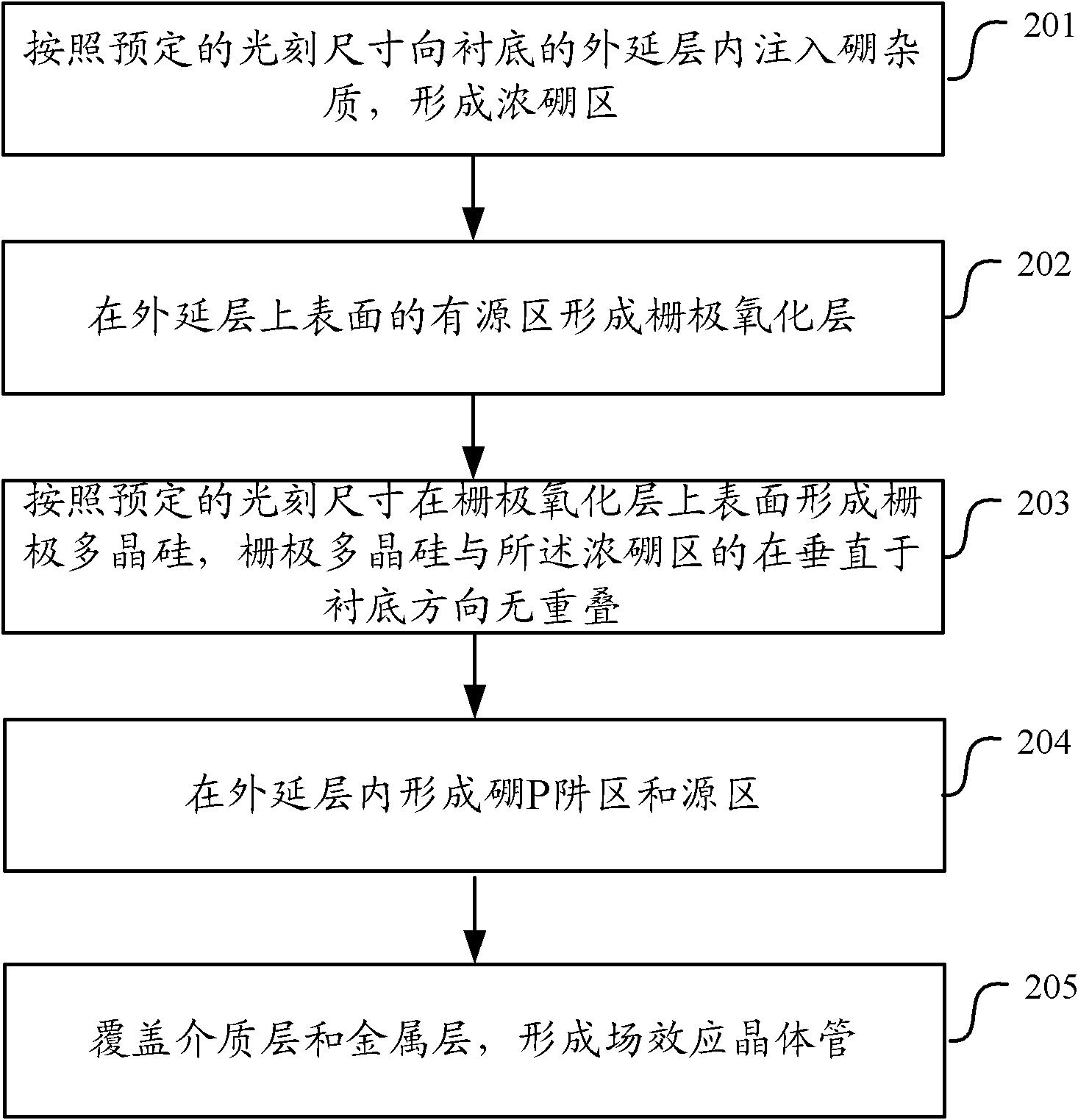

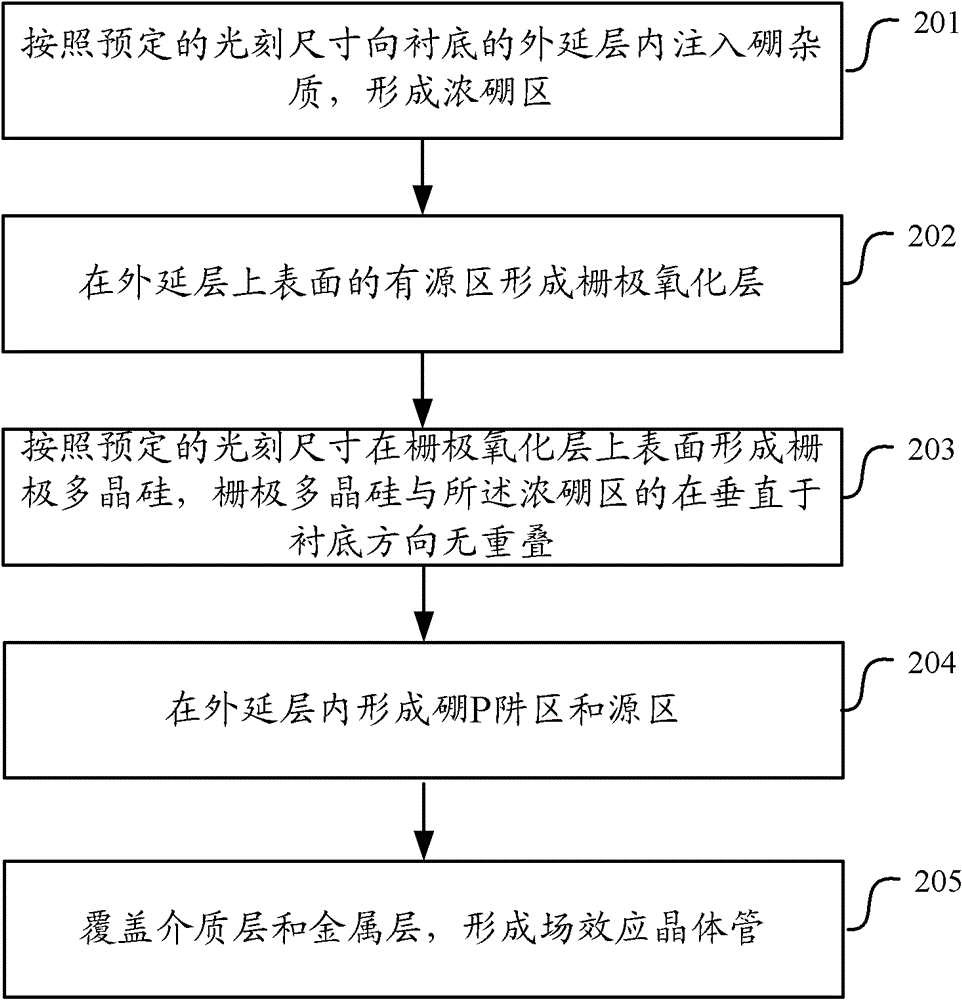

Field effect transistor and manufacturing method thereof

InactiveCN102916038APrevent leakageReduce the chance of electric leakageSemiconductor/solid-state device manufacturingSemiconductor devicesGate oxideField-effect transistor

The embodiment of the invention relates to the field of semiconductor technology, in particular to a field effect transistor and a manufacturing method thereof. The manufacturing method comprises the following steps: boron impurity is injected to an epitaxial layer of a substrate according to preset photoetching size to form a thick boron region; a gate oxide layer is formed in the active region of the upper surface of the epitaxial layer; gate polycrystalline silicon is formed on the upper surface of the gate oxide layer according to the preset photoetching size, and the gate polycrystalline silicon and the thick boron region are not superposed in the direction of being vertical to the substrate; and a boron P well region and a source region are formed in the epitaxial layer; and a dielectric layer and a metal layer are covered, and the field effect transistor is formed. With the adoption of the field effect transistor and a manufacturing method thereof, provided by the embodiment of the invention, through ensuring that the thick boron region and the gate polycrystalline silicon does not coincide, the gate-source leakage is avoided from being generated between the gate and the source through the boron impurity heavily-doped part of the gate oxide layer, so that the gate-source leakage probability of products is reduced.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

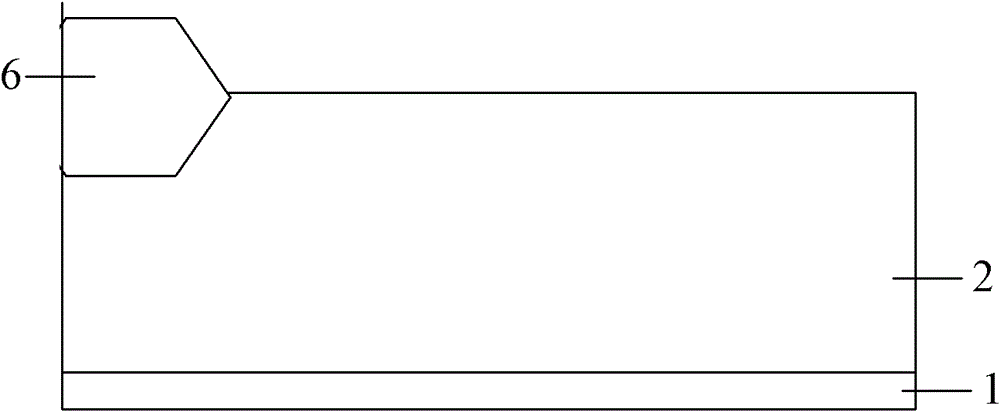

A canal step channel unit transistor and its manufacture method

InactiveCN100505214CIncrease channel lengthIncrease channel distanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSilicon

A trench step channel (Trench Step Channel, TSC for short) unit transistor and its manufacturing method are used to increase the channel length of the transistor, and the transistor includes a selectively grown step silicon layer. Wherein the step silicon crystal layer is located above the active element area of the transistor.

Owner:PROMOS TECH INC

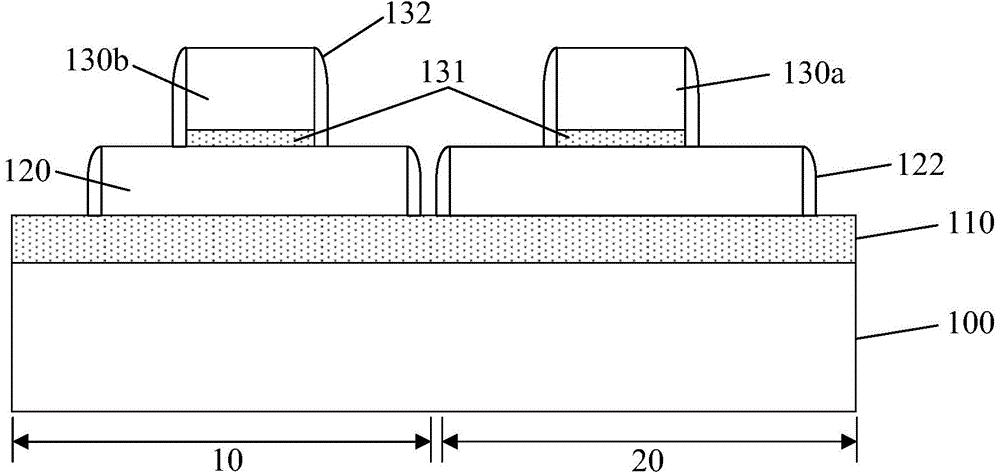

Semiconductor device and method of forming the same

ActiveCN110164767BImprove performanceExtend your lifeSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricDevice material

A semiconductor device and a method for forming the same, the method comprising: providing a substrate, the substrate has a first region, the substrate has a first fin and a first dummy gate structure, and the first dummy gate structure includes a first dummy gate layer; Form a dielectric layer covering the sidewall surface of the first dummy gate structure on the substrate; remove the first dummy gate layer, and form a first gate opening in the dielectric layer; form an interface layer at the bottom of the first gate opening; The sidewall and bottom of the opening form a gate dielectric layer on the interface layer; a sacrificial layer is formed on the gate dielectric layer, the top surface of the sacrificial layer is lower than the top surface of the first fin, and the sacrificial layer exposes the top and part of the side of the first fin The gate dielectric layer on the wall surface; the interface layer under the gate dielectric layer exposed by the sacrificial layer is annealed to increase the thickness of the interface layer not covered by the sacrificial layer; the sacrificial layer is finally removed; and then formed on the surface of the gate dielectric layer The gate electrode layer filling the first gate opening. The method improves the performance of semiconductor devices.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

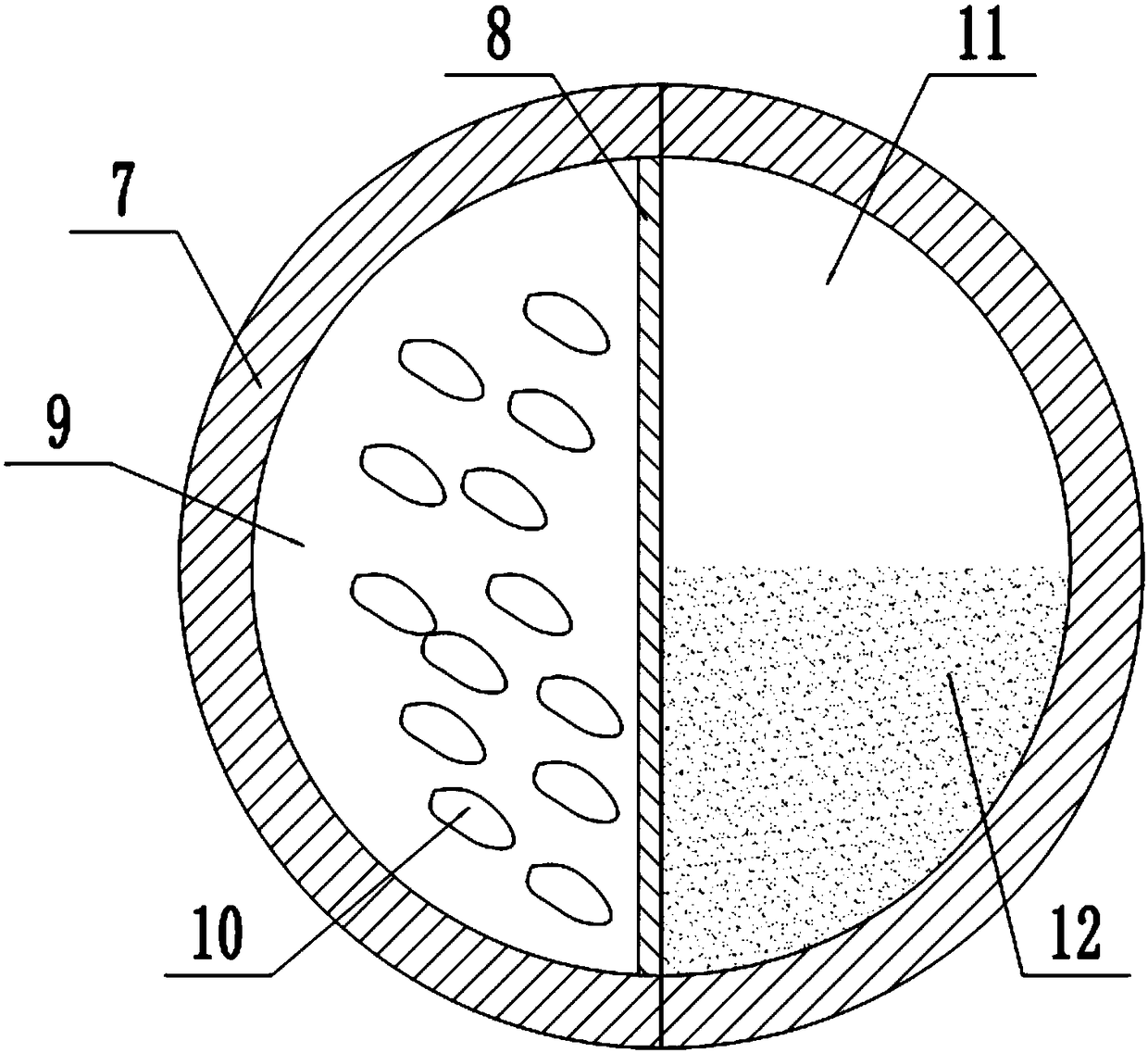

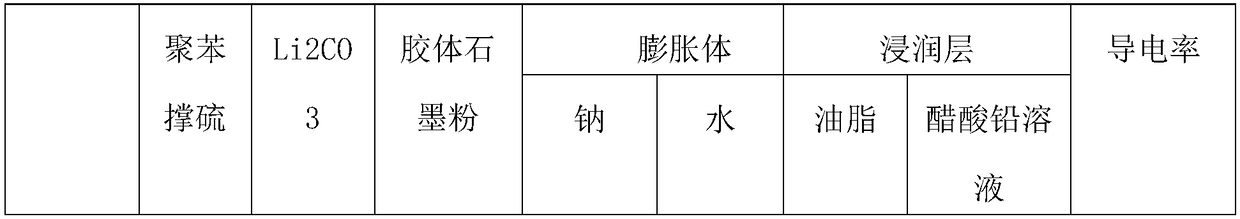

Solid electrolyte used for horizontal battery production

InactiveCN108258329AImprove conductivityImprove the lubrication effectLead-acid accumulatorsElectrolyte immobilisation/gelificationSolid state electrolyteGraphite

The invention relates to the field of battery production, and discloses a solid electrolyte used for horizontal battery production. The solid electrolyte comprises the following components in parts bymass: 80 to 91 parts of a polyhenylene high-molecular organic polymer, 9 to 16 parts of a lithium salt and 1.5 to 4 parts of graphite powder. The graphite powder in the scheme has high electrical conductivity, abrasion resistance and lubricating property, the electrical conductivity of the solid electrolyte can be improved, and then the electrical conductivity of each part of the solid electrolyte is relatively balanced, so that the electrical conductivity is promoted. Through the scheme, the space structure is adjusted by selecting appropriate lithium salt, and through the combined action ofthe polyhenylene high-molecular organic polymer and the lithium salt, the electrical conductivity activation energy is reduced, so that an ion channel of a one-dimensional structure is realized, theleakage probability of the solid electrolyte is reduced, and guarantee is provided for the electrical conductivity of the solid electrolyte.

Owner:GUANGZHOU ZHUOYUE POWER NEW ENERGY CO LTD

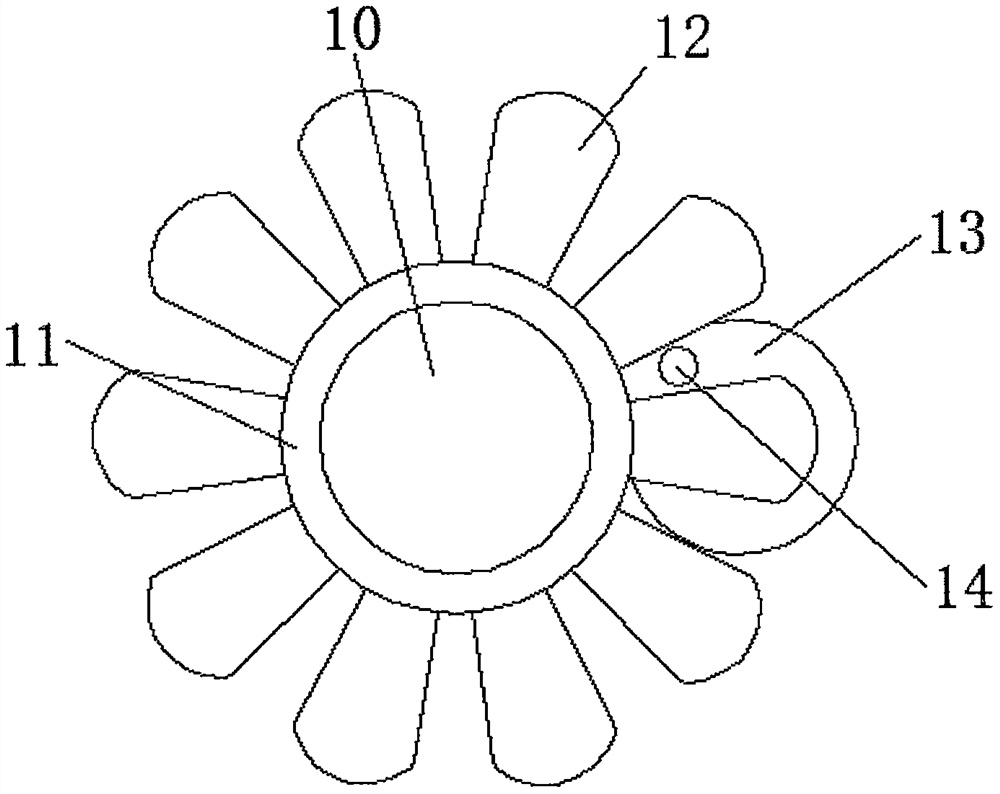

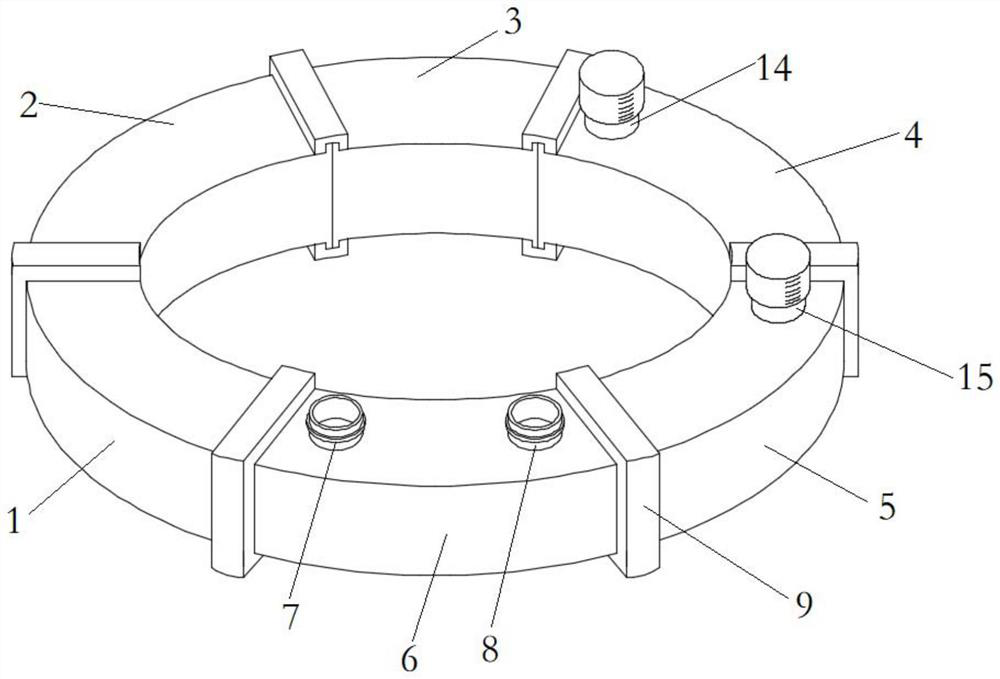

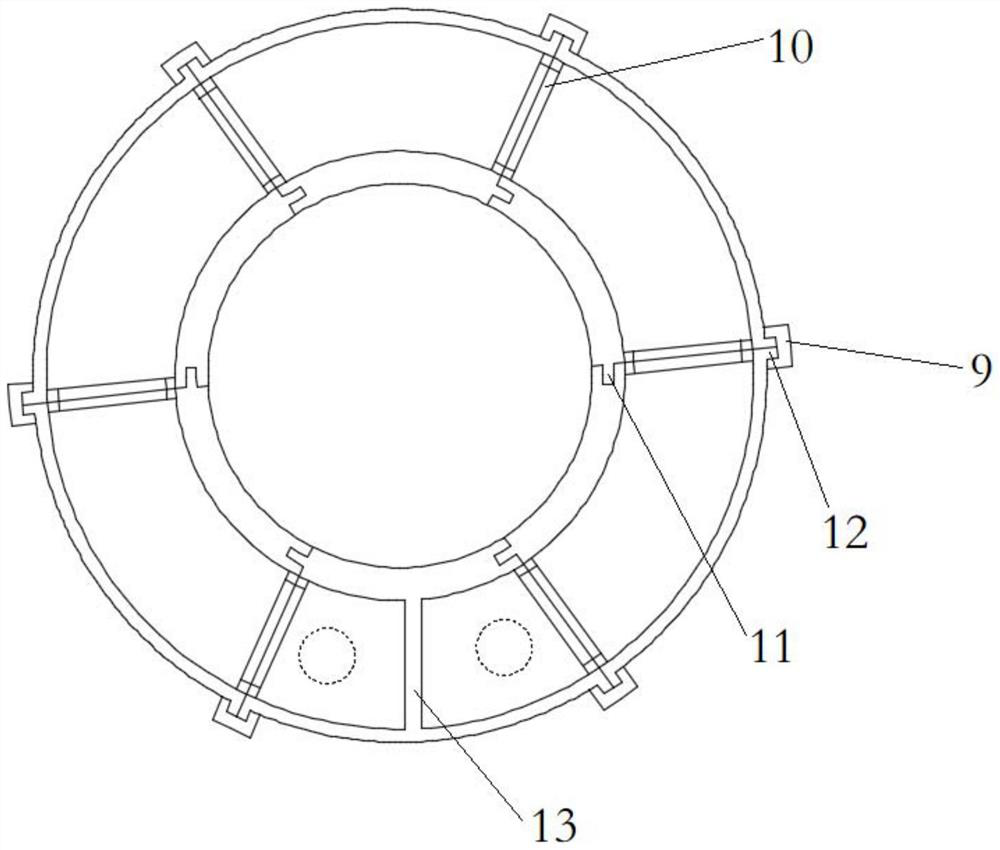

A ring-shaped multifunctional water purifier

ActiveCN109912090BReduce volumeHigh degree of integrationWater contaminantsMultistage water/sewage treatmentActivated carbonSewage treatment

The invention relates to the field of sewage treatment and in particular relates to a water purifier. An annular multifunctional water purifier comprises a water purifier, wherein the water purifier comprises a shell of which the cross section takes the shape of a circular ring; the shell comprises at least six tube sections which are connected in sequence; at least one filtering net is arranged between two adjacent tube sections; at least six tube sections comprise a first tube section in which quartz sand is stored, a second tube section in which activated carbon is stored, a third tube section, a fourth tube section and a fifth tube section in which a soft water resin is stored, and a sixth tube section as a purified water area. Due to the design, the annular multifunctional water purifier is provided, functions of multiple water purification modules are integrated, the purifier is small in size, high in integration degree and convenient to mount and use, and an effect of multiple functions can be achieved; in addition, due to adoption of an annular pipeline, the purifier is easy to modularize and mount; due to adoption of a photocatalyst, the purification efficiency can be improved, photocatalysts which are high in price can be recycled, and thus the cost can be lowered.

Owner:CENT SOUTH UNIV

Semiconductor structure and forming method thereof

ActiveCN110120415ASimple processPrevent openingSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureIsolation layer

The invention discloses a semiconductor structure and a forming method thereof. The forming method comprises the following steps: providing a substrate and at least two fin parts protruding out of thesubstrate, wherein the substrate exposed out of the fin parts is provided with an isolation layer, the isolation layer covers part of the side walls of the fin parts, the isolation layer is providedwith pseudo grids crossing the fin parts, and the pseudo grids cover part of the tops and part of the side walls of the fin parts; forming a dielectric layer on the isolation layer, wherein the dielectric layer covers the side walls of the pseudo gates; removing a part of the pseudo gates, exposing a part of the tops of a part of the fin parts, and forming an opening penetrating through the thickness of the dielectric layer in the dielectric layer; and forming an insulating layer filling the opening. According to the invention, the semiconductor structure of which the number of the channel regions meets the requirement can be formed on the basis of a plurality of positions where the channel regions can be formed, so that the technological process of forming the semiconductor structure witha specific number of channel regions can be simplified.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

A kind of field effect transistor and its manufacturing method

InactiveCN102916038BPrevent leakageReduce the chance of electric leakageSemiconductor/solid-state device manufacturingSemiconductor devicesGate oxideField-effect transistor

The embodiment of the invention relates to the field of semiconductor technology, in particular to a field effect transistor and a manufacturing method thereof. The manufacturing method comprises the following steps: boron impurity is injected to an epitaxial layer of a substrate according to preset photoetching size to form a thick boron region; a gate oxide layer is formed in the active region of the upper surface of the epitaxial layer; gate polycrystalline silicon is formed on the upper surface of the gate oxide layer according to the preset photoetching size, and the gate polycrystalline silicon and the thick boron region are not superposed in the direction of being vertical to the substrate; and a boron P well region and a source region are formed in the epitaxial layer; and a dielectric layer and a metal layer are covered, and the field effect transistor is formed. With the adoption of the field effect transistor and a manufacturing method thereof, provided by the embodiment of the invention, through ensuring that the thick boron region and the gate polycrystalline silicon does not coincide, the gate-source leakage is avoided from being generated between the gate and the source through the boron impurity heavily-doped part of the gate oxide layer, so that the gate-source leakage probability of products is reduced.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

Semiconductor structure and forming method thereof

PendingCN114823670AImprove performancePlay a protective effectTransistorSolid-state devicesGate dielectricSemiconductor structure

The invention discloses a semiconductor structure and a forming method thereof, and the method comprises the steps: providing a substrate which comprises a substrate and a fin part protruding out of the substrate, the substrate comprises a first region used for forming a first device and a second region used for forming a second device, and the working voltage of the first device is greater than the working voltage of the second device; forming a first gate oxide layer covering the fin portions of the first region and the second region in a shape-preserving manner, the first gate oxide layer located in the second region being used for forming a gate dielectric layer of a second device; a second gate oxide layer covering the first gate oxide layer in a shape-preserving mode is formed, and the second gate oxide layer and the first gate oxide layer located in the first area are used for forming a gate dielectric layer of the first device; and carrying out gate dielectric layer thinning treatment, wherein the gate dielectric layer thinning treatment comprises the step of removing the second gate oxide layer in the second region. According to the scheme, the consumption of the fin parts in the second region in the process is reduced, and the width uniformity and height uniformity of the fin parts in the first region and the second region are further improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Embedded DRAM device and formation method thereof

InactiveCN105529329AReduce manufacturing difficultyImprove compatibilityTransistorSemiconductor/solid-state device manufacturingEngineeringDeep trench

The invention discloses an embedded DRAM device and a formation method thereof. The formation method of the embedded DRAM device comprises steps that, a substrate is provided; a first grid electrode, a second grid electrode, a source electrode and a drain electrode are formed; a logic transistor and a channel transistor are formed, a dielectric layer and a metal layer are sequentially formed on the source electrode or the drain electrode of the channel transistor, and a capacitor is further formed. The embedded DRAM device comprises the substrate, the channel transistor, the capacitor and the logic transistor, wherein the dielectric layer and the metal layer are sequentially arranged on the source electrode or the drain electrode of the channel transistor, and the source electrode or the drain electrode, the dielectric layer and the metal layer form the capacitor. The method and the device are advantaged in that, the dielectric layer and the metal layer are formed on the source electrode or the drain electrode of the channel transistor for forming the capacitor, a problem that a special deep trench for forming a capacitor is formed in a substrate in the prior art can be solved, the manufacturing process is simplified, manufacturing complexity is reduced, and compatibility with the routine manufacturing flow can be better.

Owner:SEMICON MFG INT (SHANGHAI) CORP

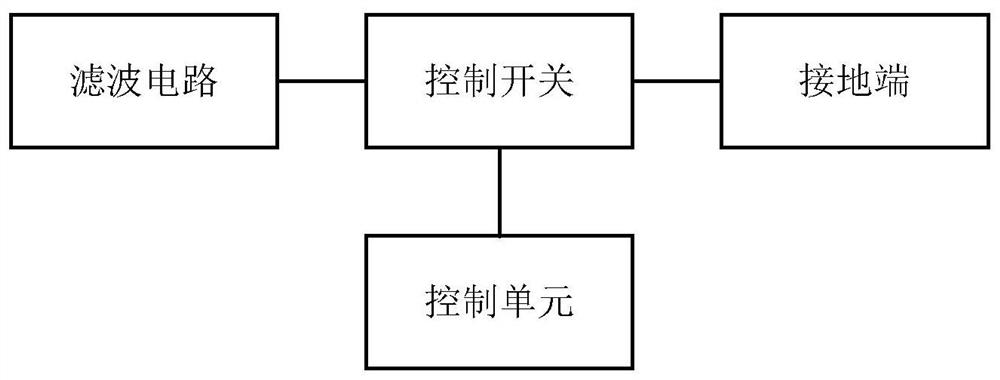

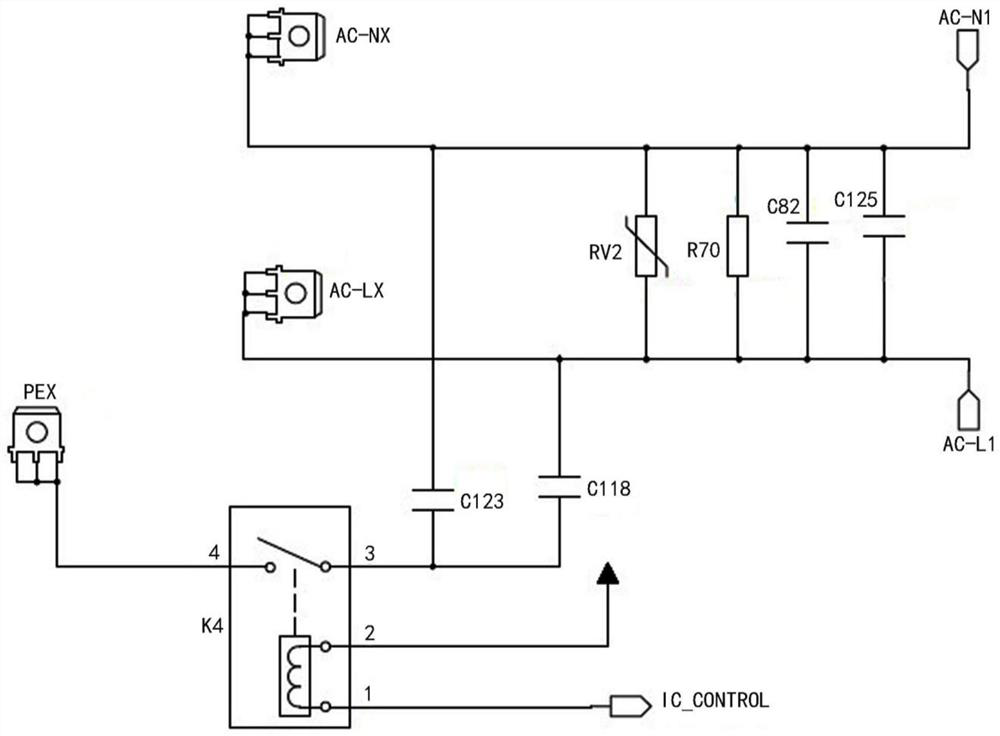

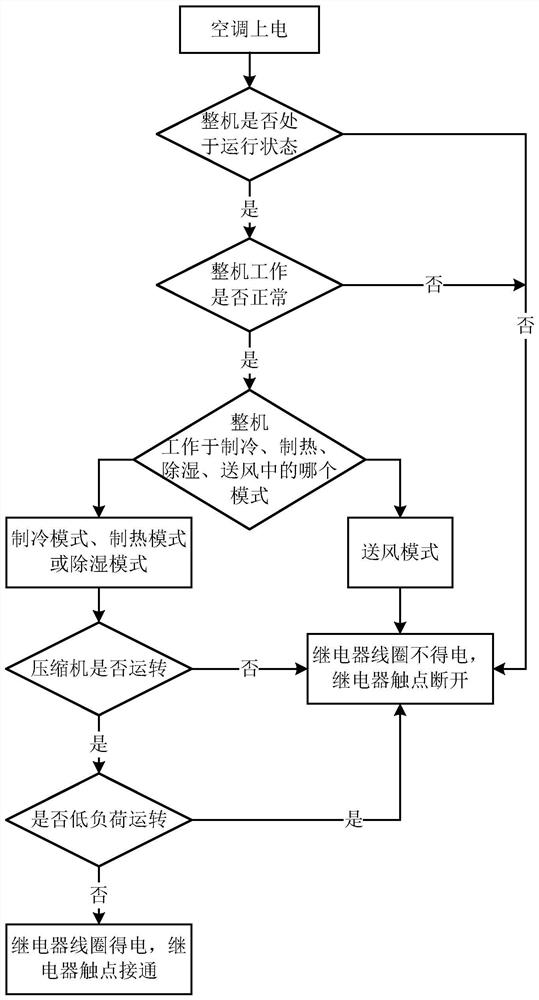

An anti-leakage control device, an air conditioner and an anti-leakage control method thereof

ActiveCN111397173BShorten the timeReduce leakage currentMechanical apparatusSpace heating and ventilation safety systemsCapacitanceControl cell

The invention discloses an anti-leakage control device, an air conditioner and an anti-leakage control method thereof. The device comprises: a control switch, arranged between a filter circuit and a grounding terminal, for switching on or off the filter circuit under the control of a control unit; The path between the circuit and the ground terminal is used to disconnect the path between the filter circuit and the ground terminal to prevent the filter circuit from leaking to the ground terminal; the control unit is used to determine the operating parameters of the air conditioner when the air conditioner is powered on, and The on or off of the control switch is controlled according to the operating parameters of the air conditioner; the operating parameters of the air conditioner include: working state and / or operating mode. The solution of the present invention can solve the problem of high safety risk in use in the way of improving the anti-electromagnetic interference ability of the inverter air conditioner by connecting Y capacitors in series between the neutral line and the ground, and achieve the effect of reducing the safety risk in use.

Owner:GREE ELECTRIC APPLIANCES INC

An energy-saving massage seat

ActiveCN110547957BReduce harmReduce the chance of electric leakageSuction-kneading massageRatchetHuman body

The invention discloses an energy-saving massage seat, which includes a bottom plate, and is characterized in that: the left side of the upper surface of the bottom plate is fixedly connected with a main bracket; the inner side of the top of the main bracket is fixedly connected with a headrest bracket, and the headrest bracket The inner side is slidingly connected with a headrest, and the headrest and the headrest support are elastically connected by springs, the upper part of the main support right side is fixedly connected with a first ratchet support, and the inboard of the first ratchet support is connected with a ratchet through the rotation of the ratchet shaft. The energy-saving massage seat, by setting a single servo motor and lowering the position of the servo motor, reduces the probability of leakage and reduces the damage caused by radiation to the human body. When sitting on the seat, it can make full use of its own weight to massage the waist, thereby reducing the number of motors used, solving the problem of high radiation and reducing the energy consumption of the seat, making the whole device more environmentally friendly.

Owner:佛山市康倍家具有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com