Patents

Literature

58results about How to "Increase nitrogen concentration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

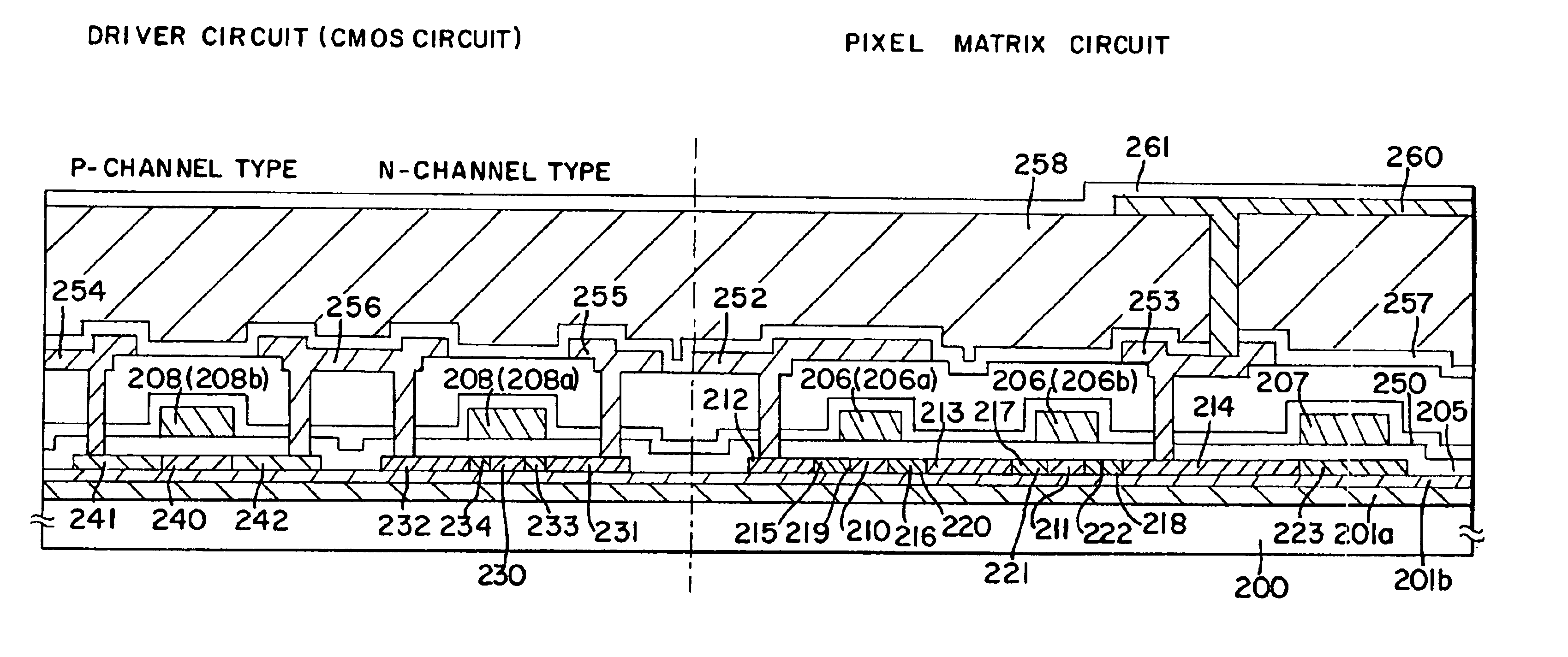

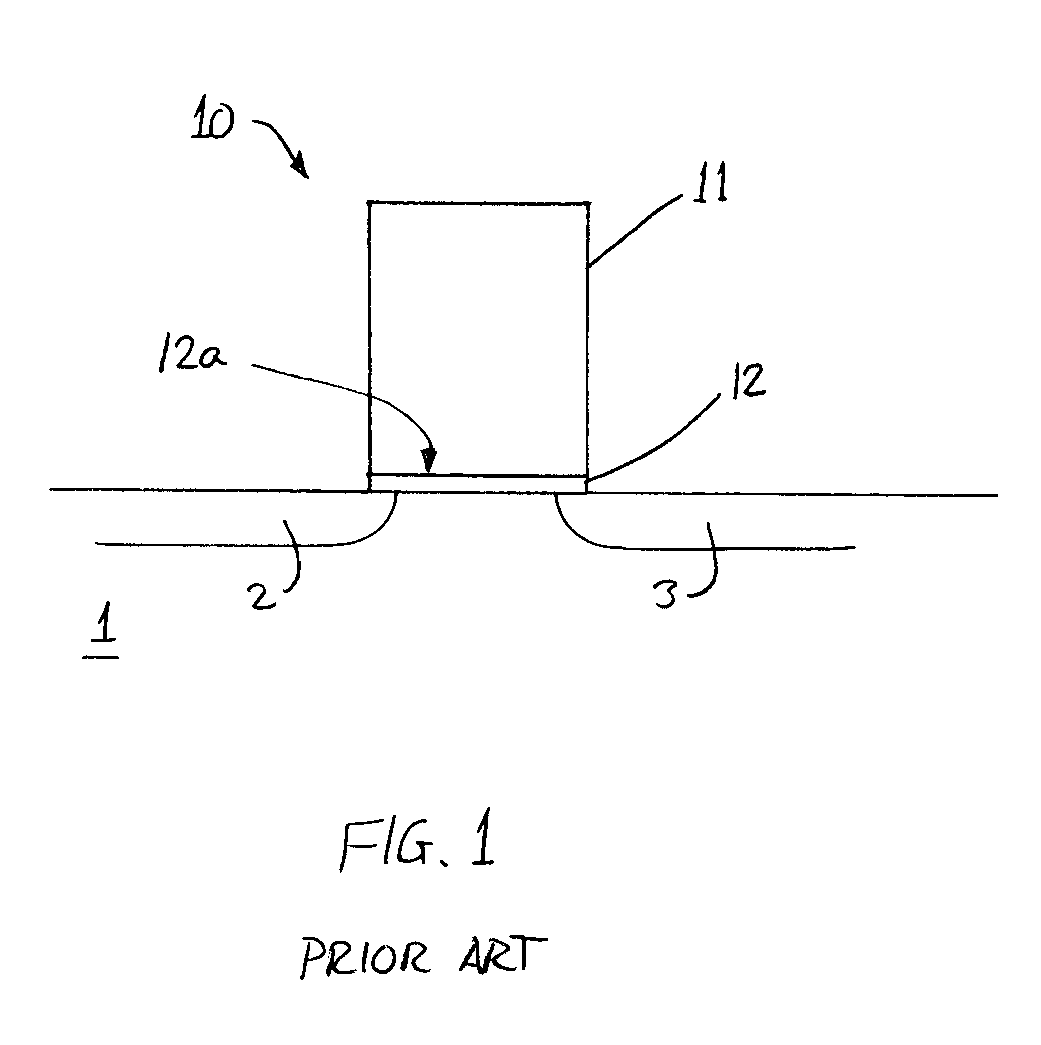

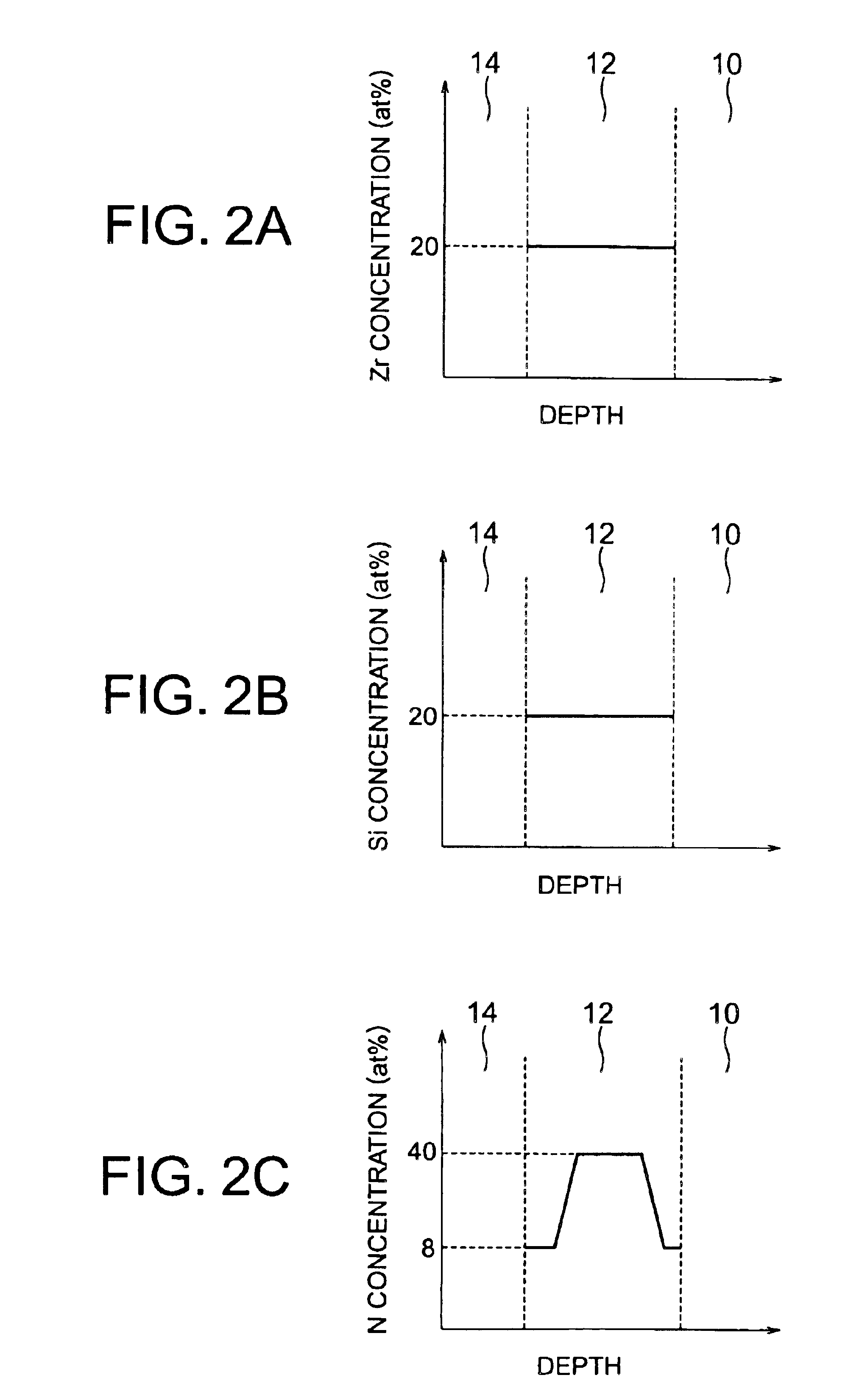

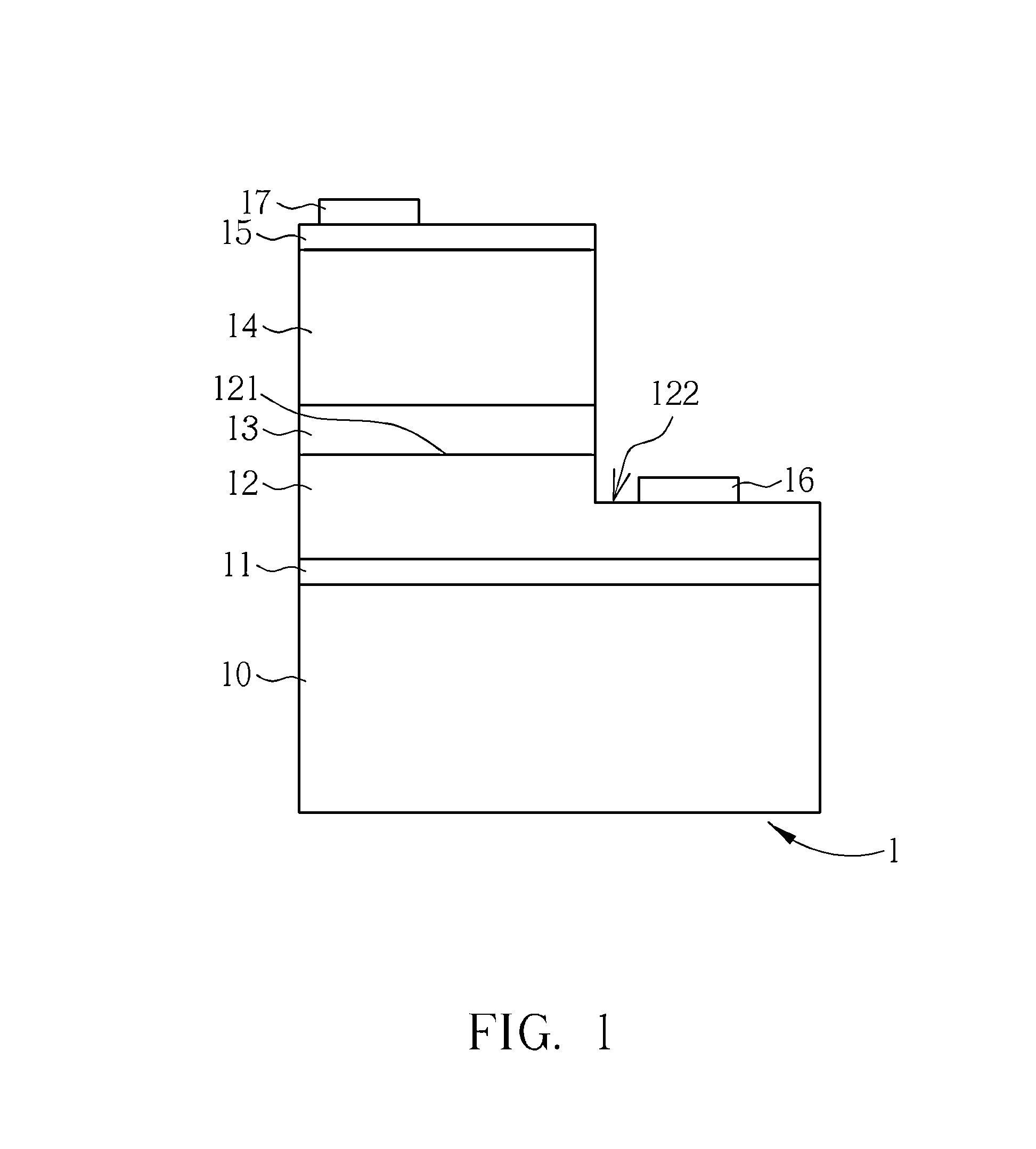

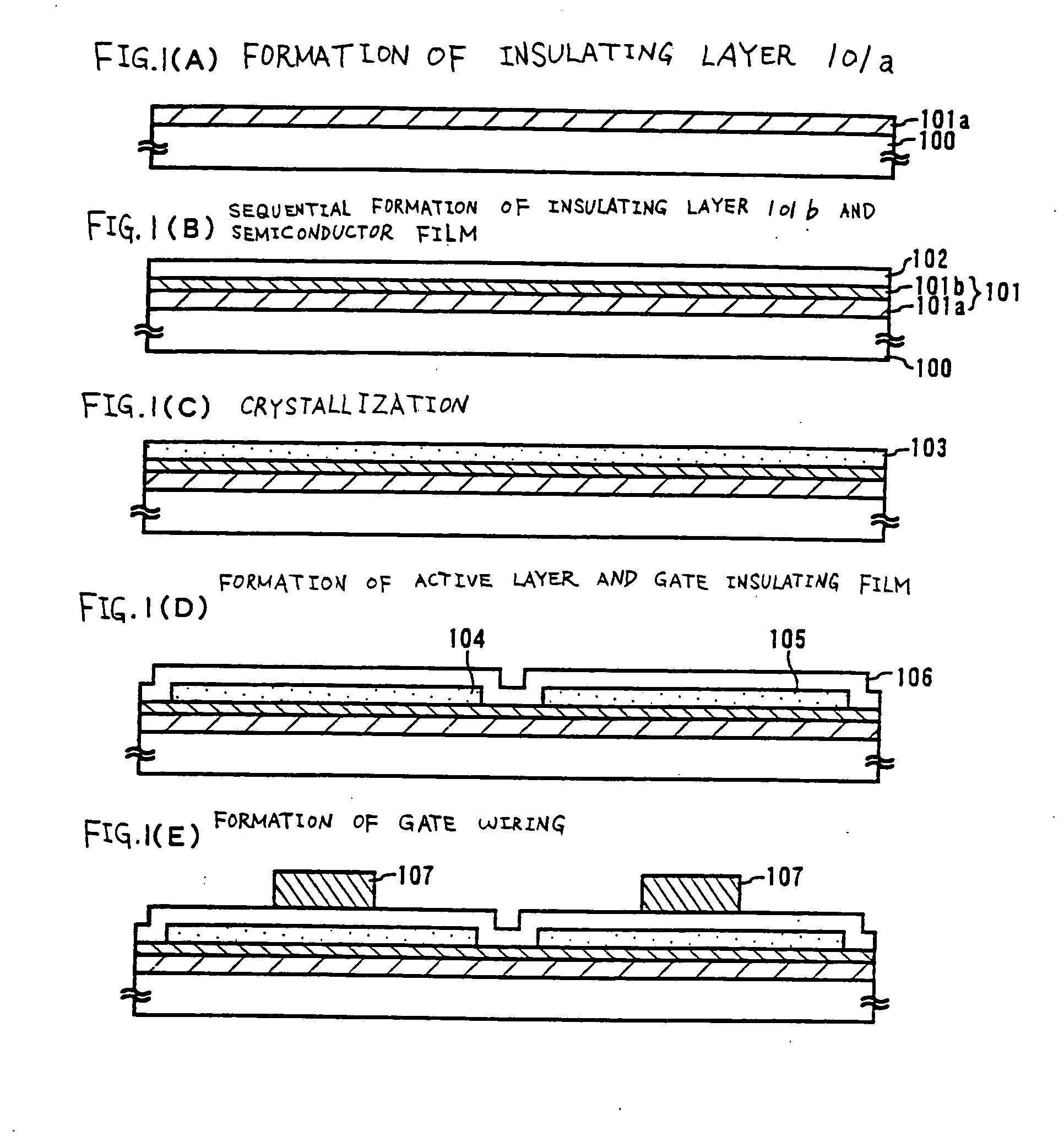

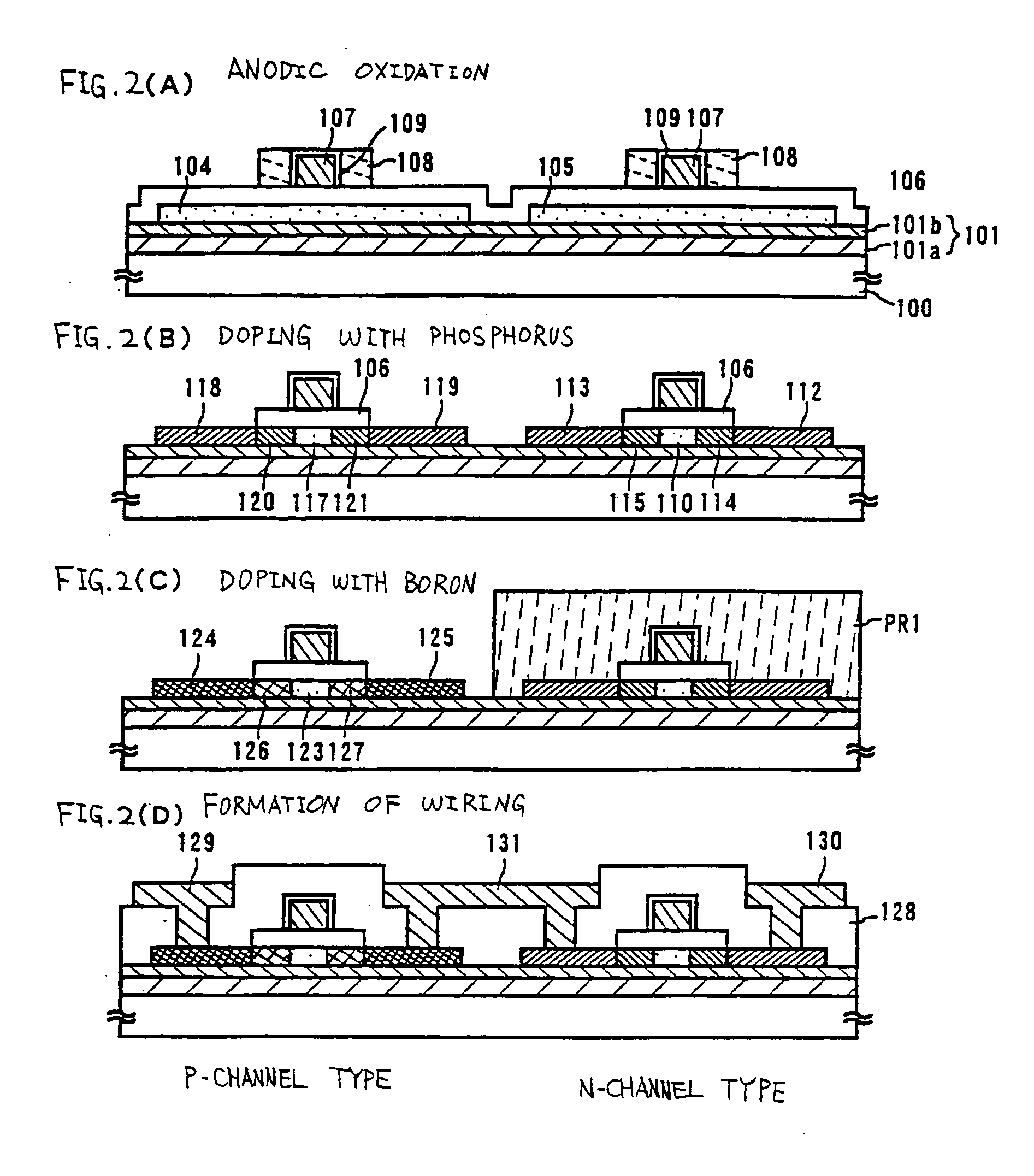

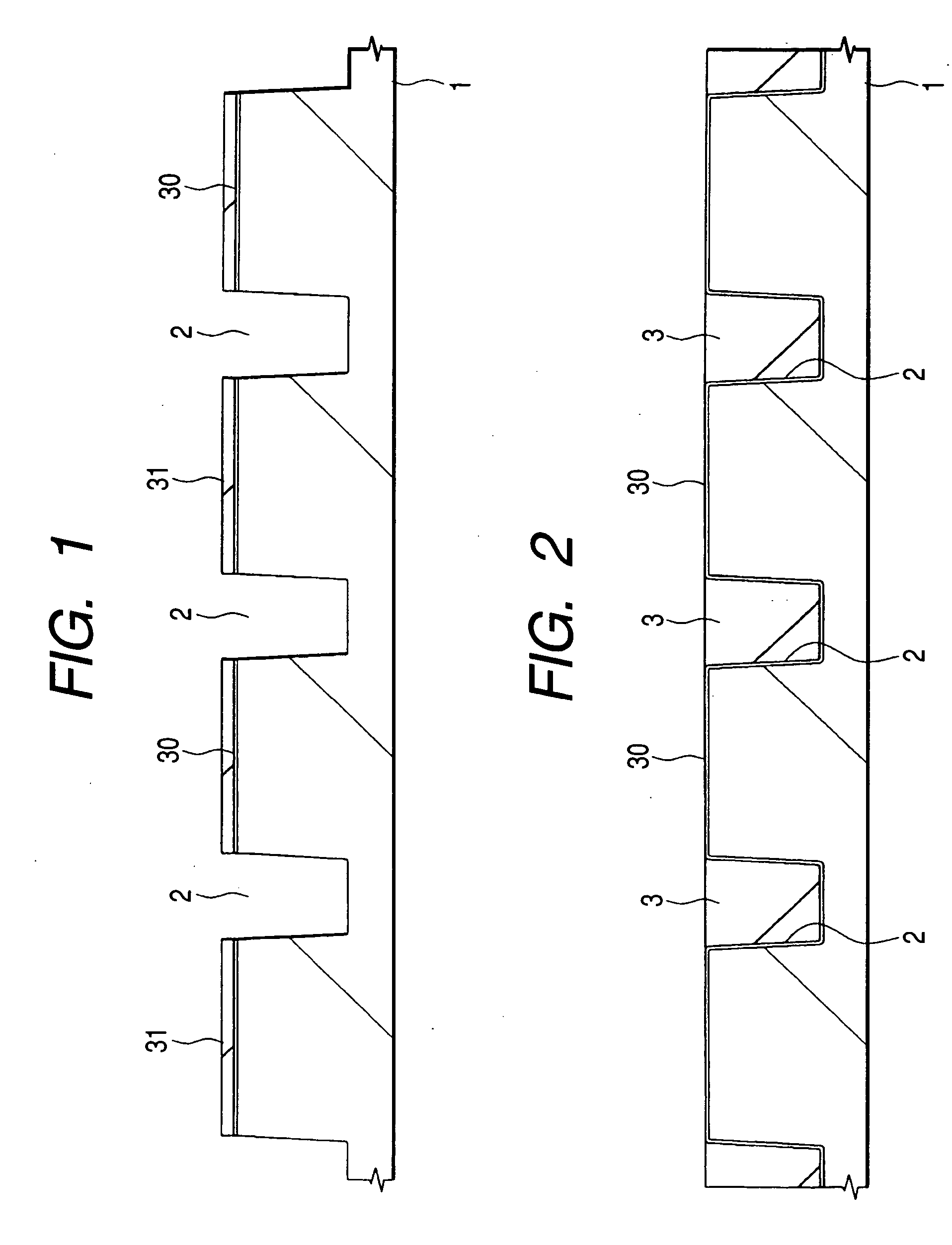

Semiconductor device and method for manufacturing the same

InactiveUS6858898B1Improve reliabilityEliminate the problemTransistorSemiconductor/solid-state device detailsDevice materialSilicon oxide

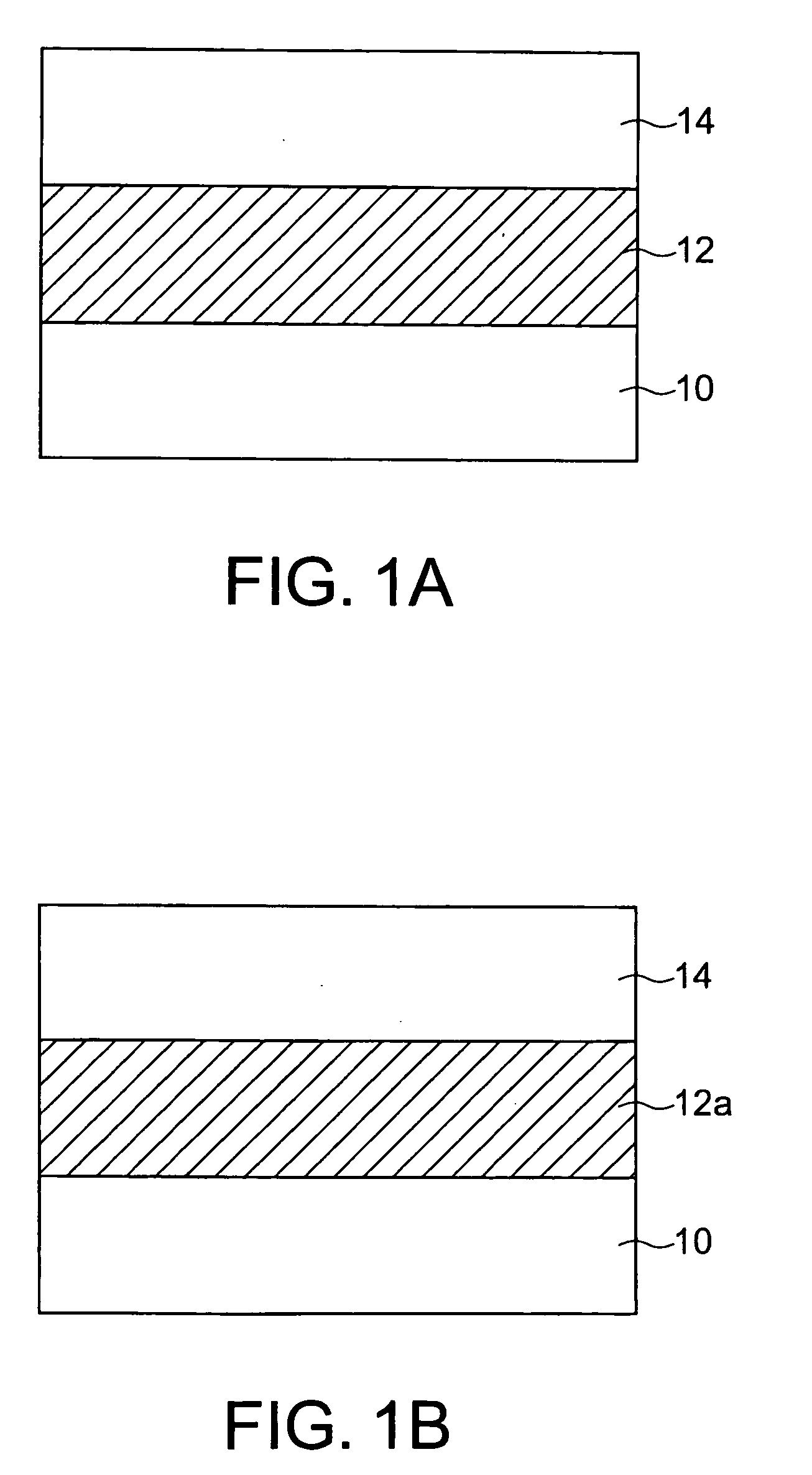

An object of the present invention is to prevent the deterioration of a TFT (thin film transistor). The deterioration of the TFT by a BT test is prevented by forming a silicon oxide nitride film between the semiconductor layer of the TFT and a substrate, wherein the silicon oxide nitride film ranges from 0.3 to 1.6 in a ratio of the concentration of N to the concentration of Si.

Owner:SEMICON ENERGY LAB CO LTD

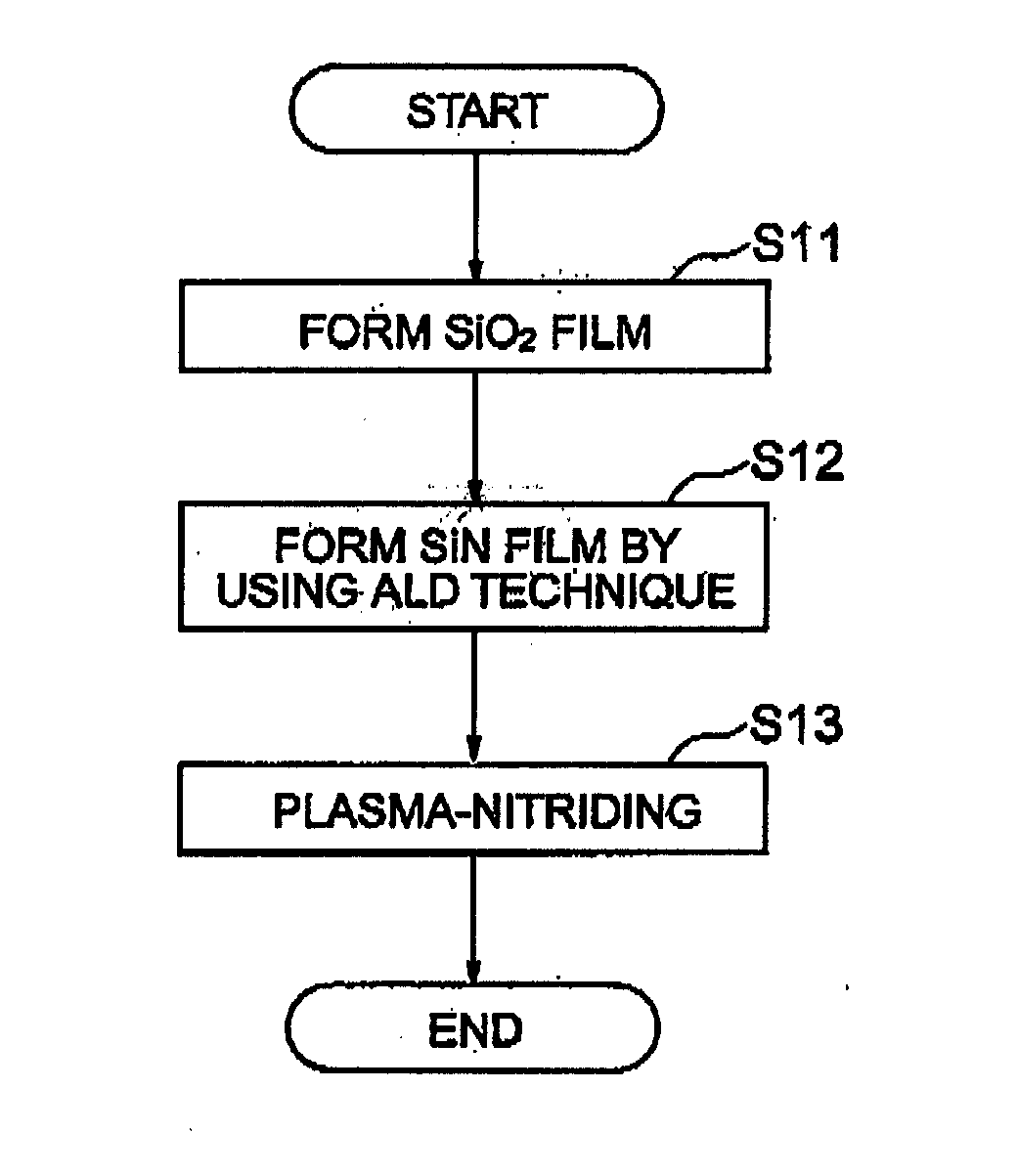

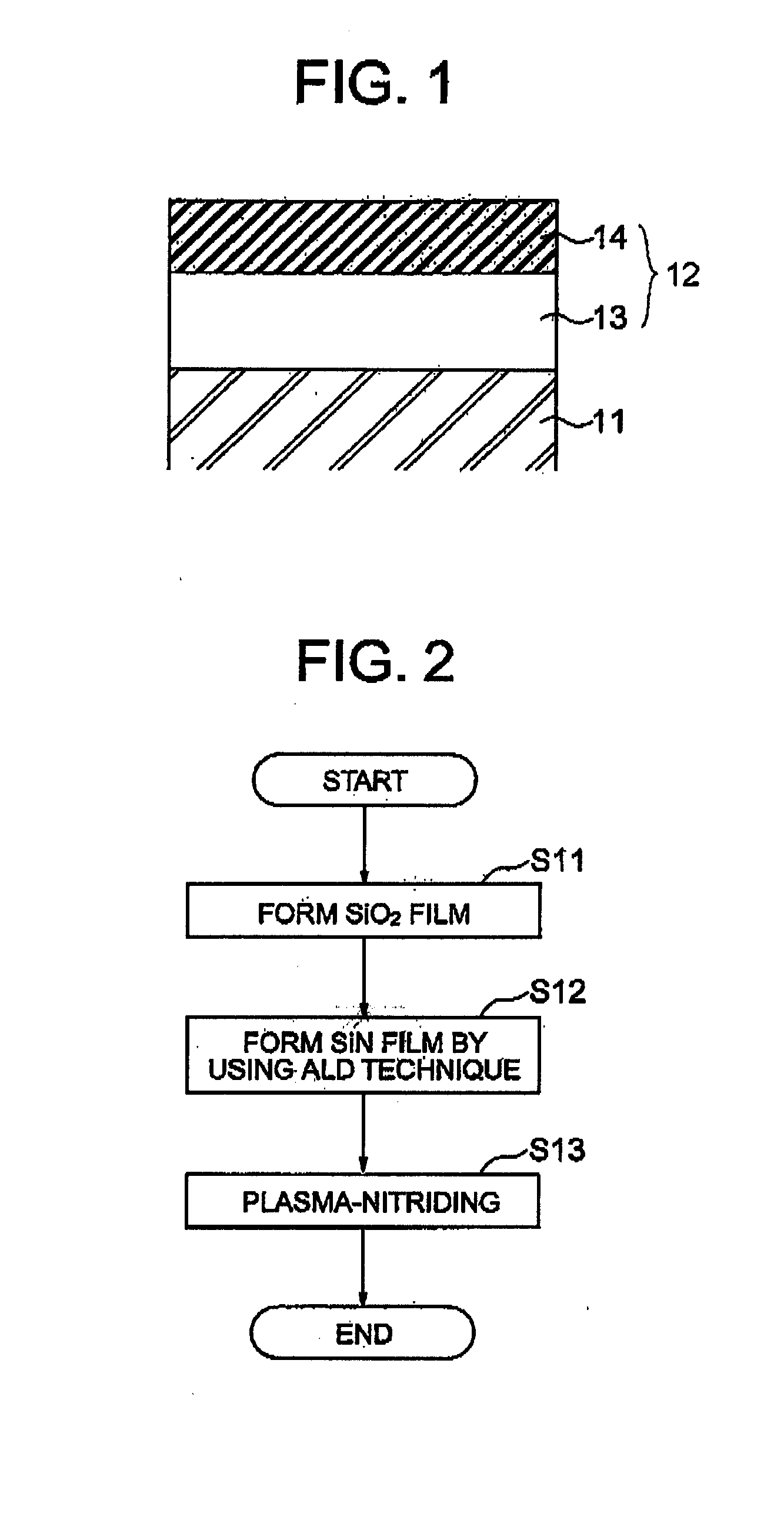

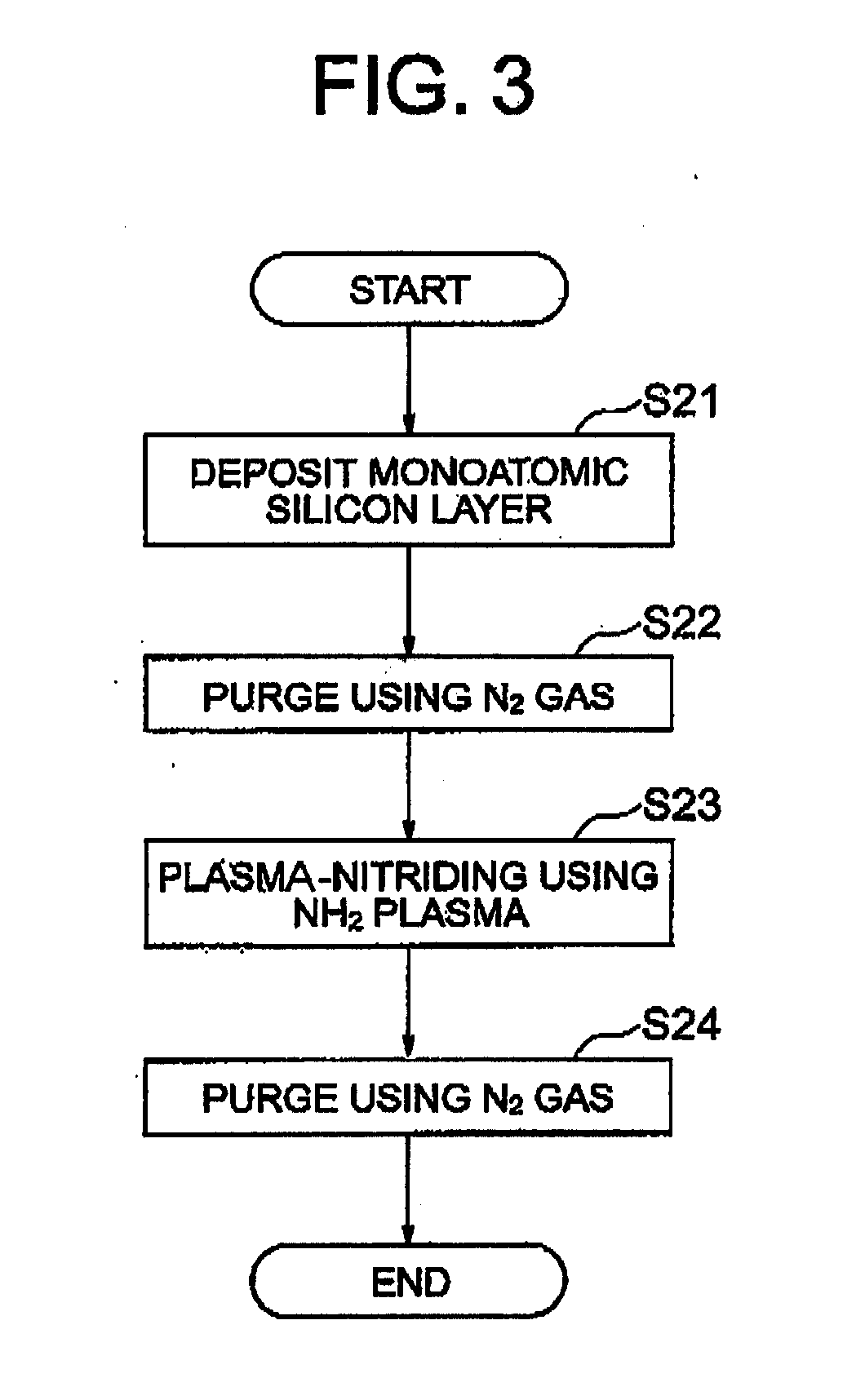

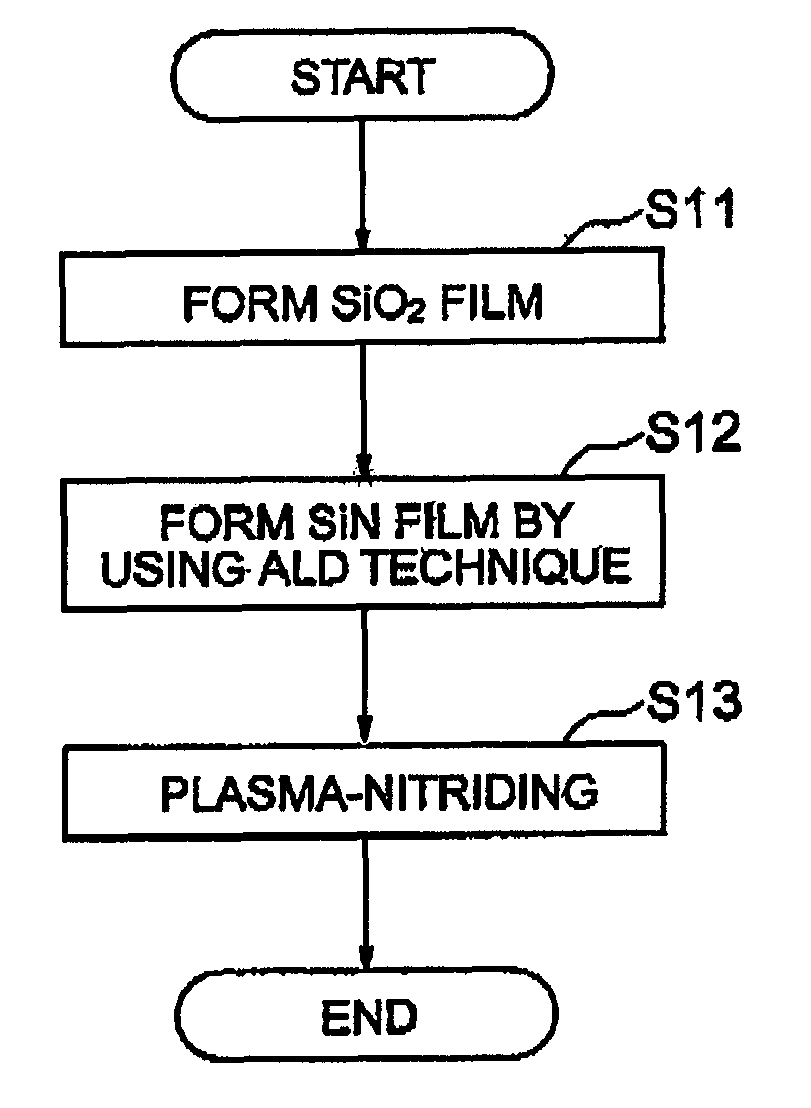

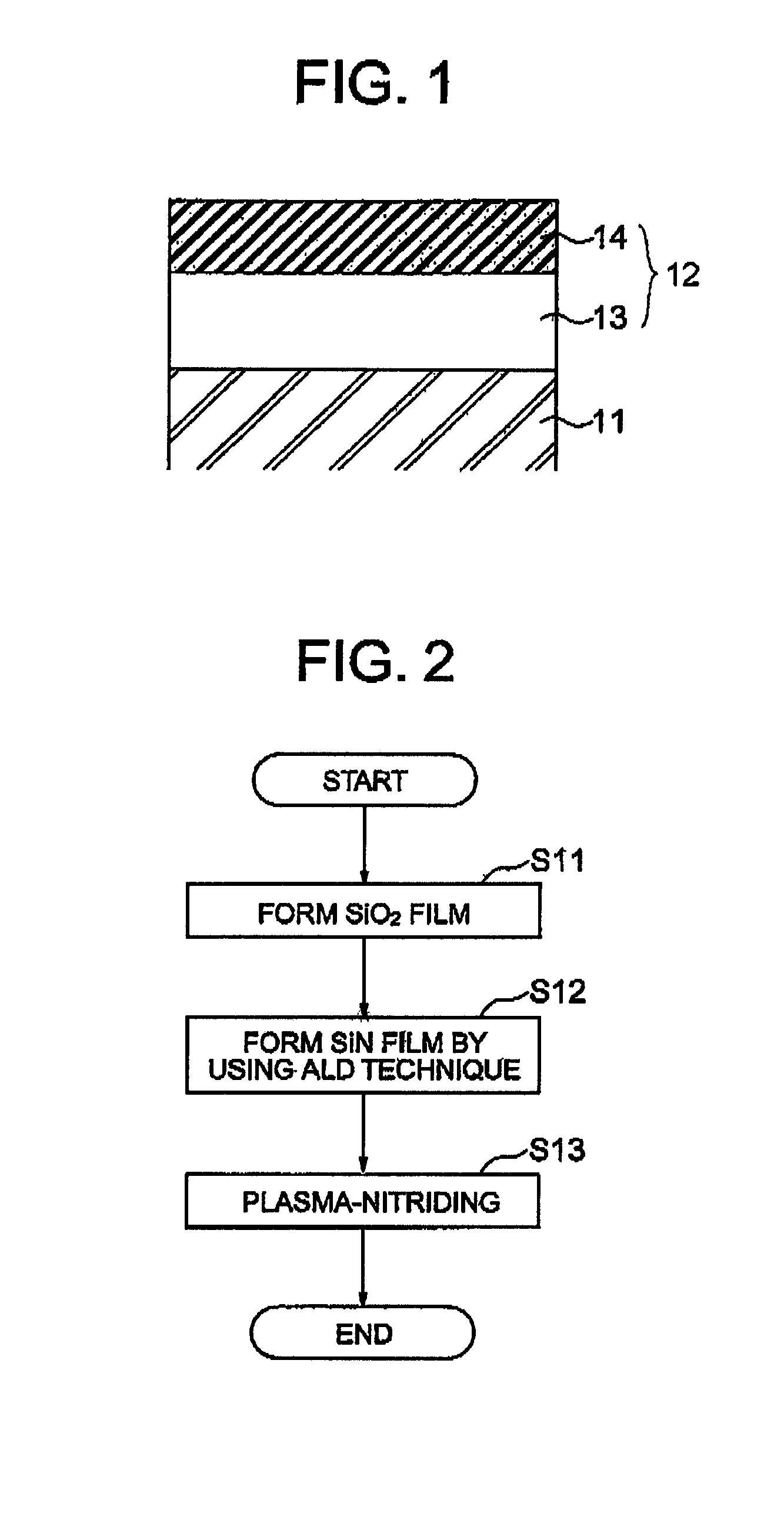

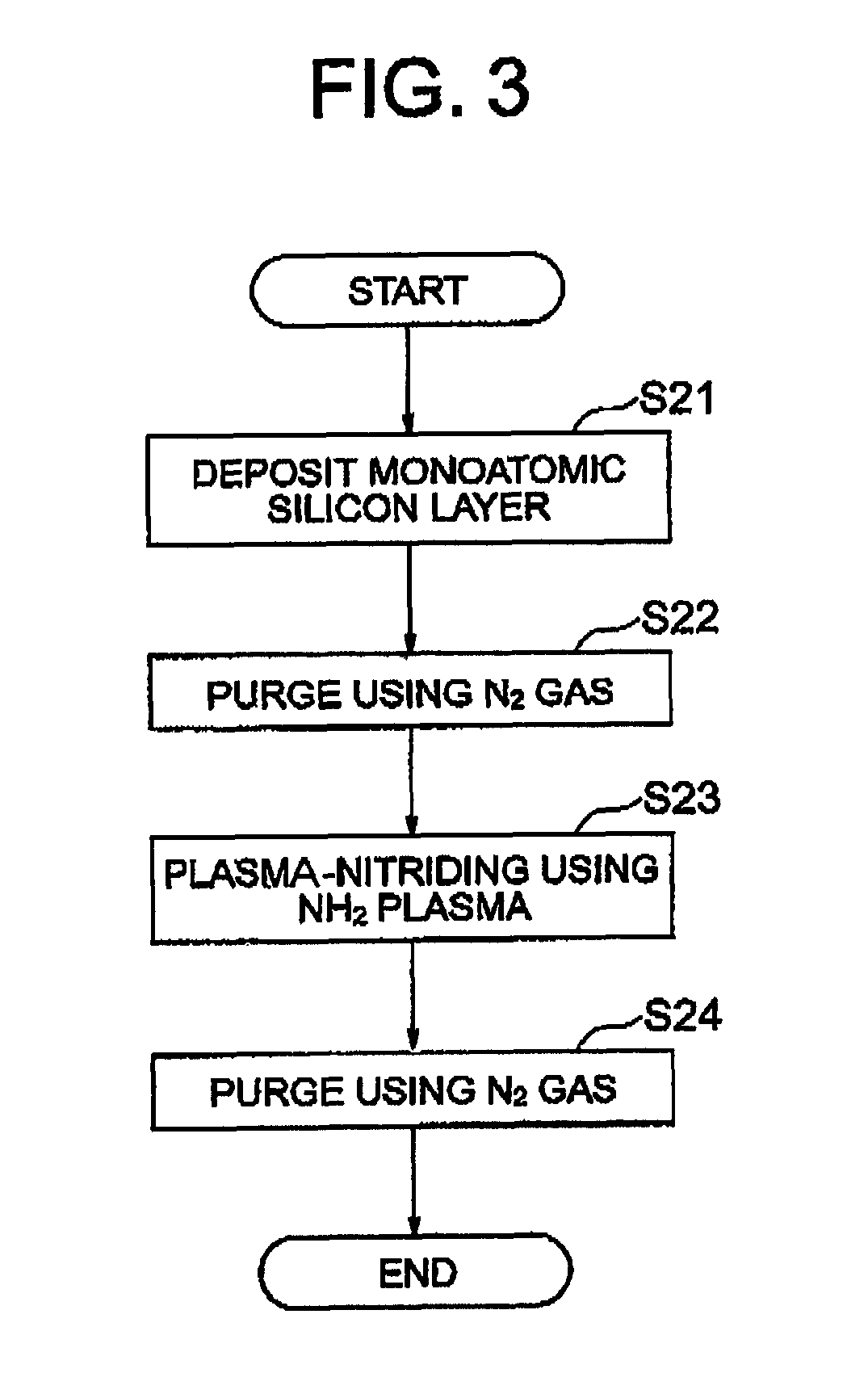

Method for manufacturing a semiconductor device having a nitrogen-containing gate insulating film

InactiveUS20070238316A1Superior characteristicLow nitrogen concentrationSemiconductor/solid-state device manufacturingPlasma nitridationNitrogen

A method for manufacturing a semiconductor device includes the steps of: forming a SiO2 layer on a silicon substrate; forming on the SiO2 layer an SiN film having a N / Si composition ratio smaller than the stoichiometric composition ratio of SiN by using the ALD technique; and performing a plasma-nitriding process on the SiN layer at a substrate temperature of 550 degrees C. or below.

Owner:PS4 LUXCO SARL

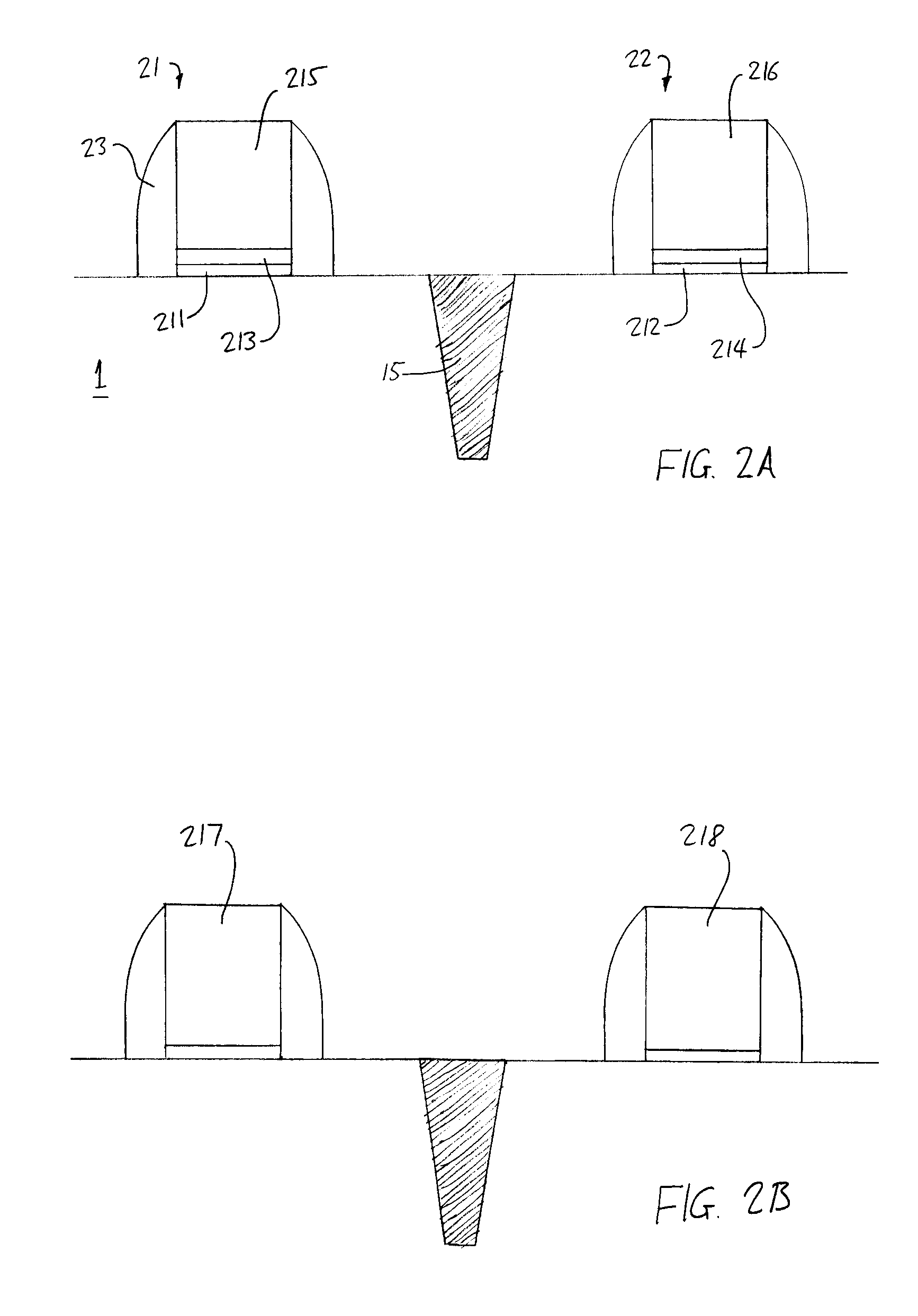

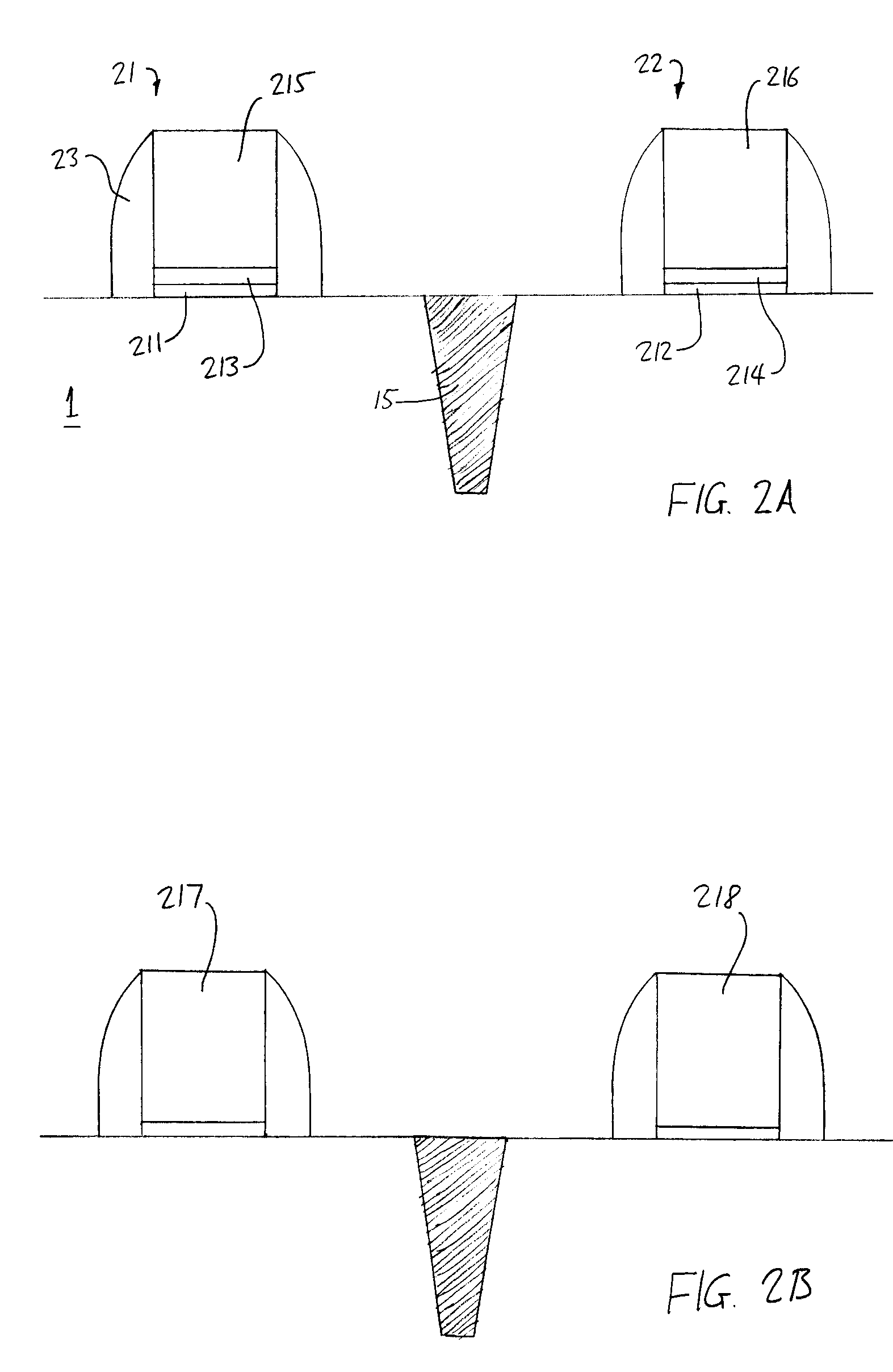

Temperature stable metal nitride gate electrode

InactiveUS7023064B2Eliminate the effects ofIncrease nitrogen concentrationSemiconductor/solid-state device detailsSolid-state devicesGate dielectricNitrogen

An integrated circuit is provided including an FET gate structure formed on a substrate. This structure includes a gate dielectric on the substrate, and a metal nitride layer overlying the gate dielectric and in contact therewith. This metal nitride layer is characterized as MNx, where M is one of W, Re, Zr, and Hf, and x is in the range of about 0.7 to about 1.5. Preferably the layer is of WNx, and x is about 0.9. Varying the nitrogen concentration in the nitride layer permits integration of different FET characteristics on the same chip. In particular, varying x in the WNx layer permits adjustment of the threshold voltage in the different FETs. The polysilicon depletion effect is substantially reduced, and the gate structure can be made thermally stable up to about 1000° C.

Owner:GLOBALFOUNDRIES U S INC

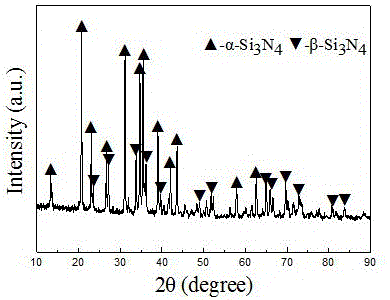

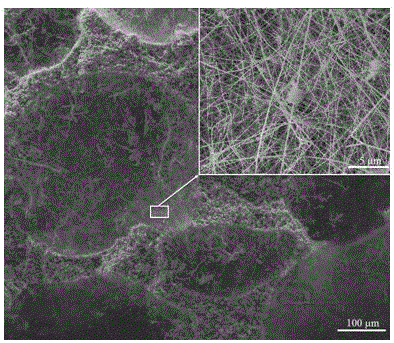

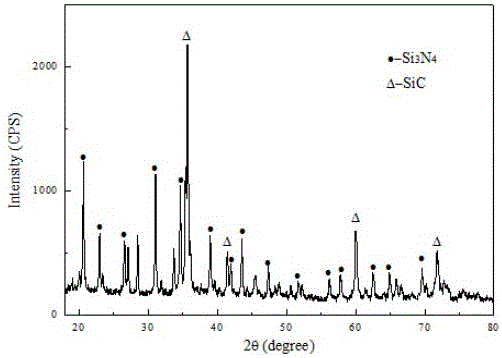

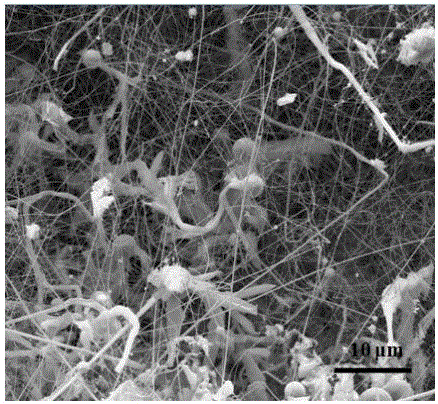

Nanowire self-reinforced porous silicon nitride ceramic and preparation method thereof

The invention relates to a nanowire self-reinforced porous silicon nitride ceramic and a preparation method thereof. The technical scheme is as follows: the preparation method comprises the following steps: using 70-80 wt% of silicon powder, 5-10 wt% of catalyst and 10-20 wt% of nitrogen source as raw materials, adding deionized water which accounts for 20-30 wt% of the raw materials, and stirring to obtain a ceramic slurry; adding foam prepared by adding a foaming agent (accounting for 10-20 wt% of the raw materials) into the ceramic slurry, and continuously stirring for 30-60 minutes to obtain a ceramic foam slurry; pouring the ceramic foam slurry into a mold, standing in a nitrogen environment, drying, and demolding to obtain a ceramic body; in a nitrogen atmosphere, heating the ceramic body to 1100-1150 DEG C, and keeping the temperature; heating to 1200-1600 DEG C, and keeping the temperature; and naturally cooling to obtain the nanowire self-reinforced porous silicon nitride ceramic. The method has the advantages of simple technique, low cost, high utilization ratio of raw materials and controllable process. The prepared product has the advantages of uniform pore size, uniform pore size distribution and high mechanical strength.

Owner:WUHAN UNIV OF SCI & TECH

Temperature stable metal nitride gate electrode

ActiveUS20050280099A1Reduced polysilicon depletion effectStable temperatureSemiconductor/solid-state device detailsSolid-state devicesGate dielectricNitrogen

An integrated circuit is provided including an FET gate structure formed on a substrate. This structure includes a gate dielectric on the substrate, and a metal nitride layer overlying the gate dielectric and in contact therewith. This metal nitride layer is characterized as MNx, where M is one of W, Re, Zr, and Hf, and x is in the range of about 0.7 to about 1.5. Preferably the layer is of WNx, and x is about 0.9. Varying the nitrogen concentration in the nitride layer permits integration of different FET characteristics on the same chip. In particular, varying x in the WNx layer permits adjustment of the threshold voltage in the different FETs. The polysilicon depletion effect is substantially reduced, and the gate structure can be made thermally stable up to about 1000° C.

Owner:GLOBALFOUNDRIES US INC

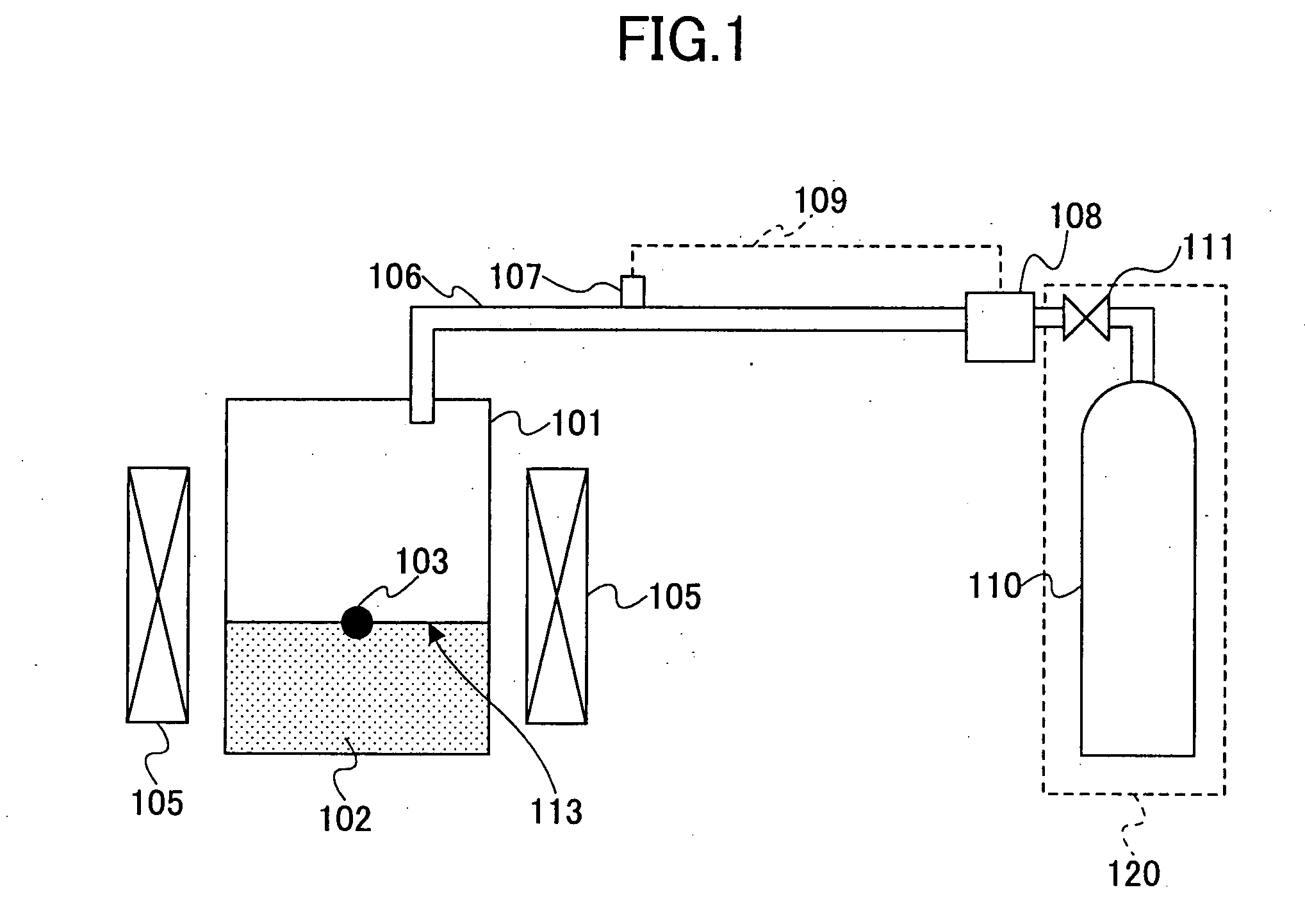

Group III nitride crystal, crystal growth process and crystal growth apparatus of group III nitride

InactiveUS20070194408A1Inhibition formationCrystal growth is stablePolycrystalline material growthFrom normal temperature solutionsNitrogenSupersaturation

A crystal growth method of a group III nitride includes the steps of forming a melt mixture of an alkali metal and a group III element in a reaction vessel, and growing a crystal of a group III nitride formed of the group III element and nitrogen from the melt mixture in the reaction vessel, wherein the step of growing the crystal of the group III nitride is conducted while controlling an increase rate of degree of supersaturation of a group III nitride component in the melt mixture in a surface region of the melt mixture.

Owner:SUMITOMO CHEM CO LTD

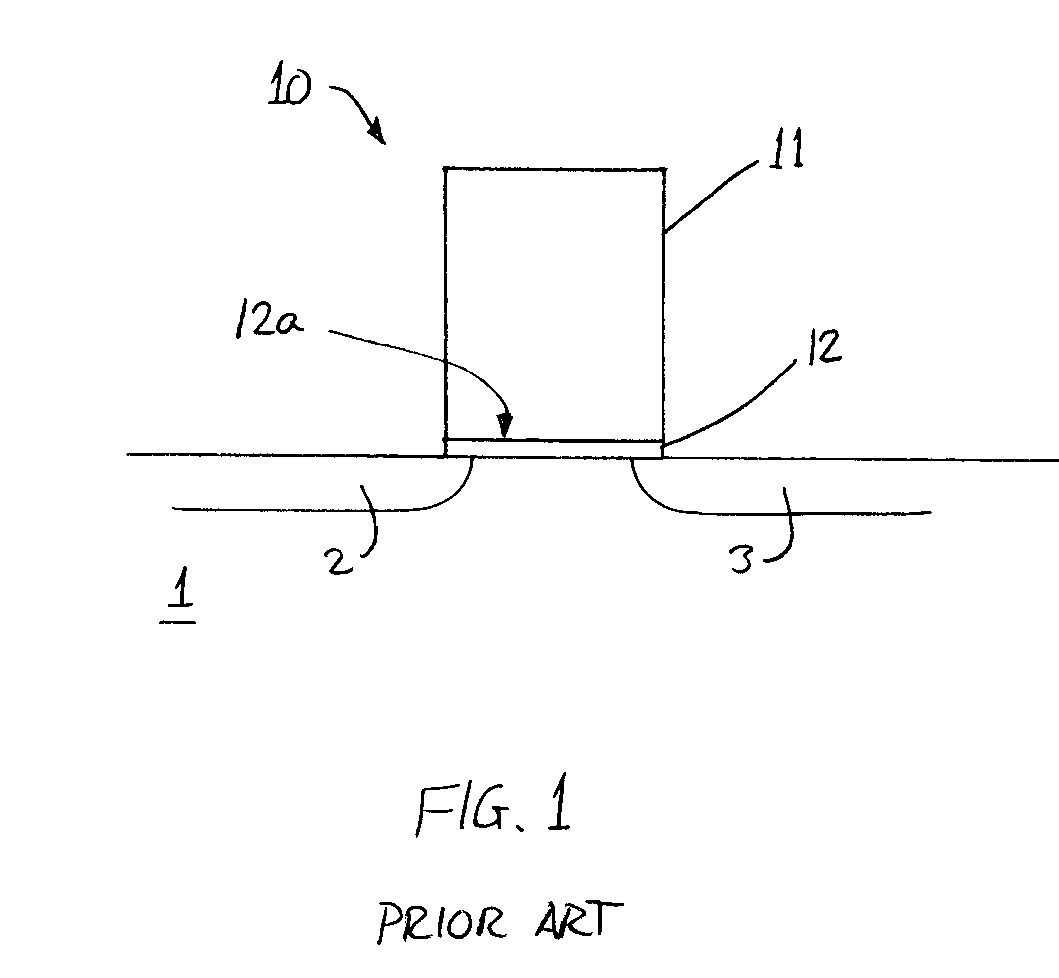

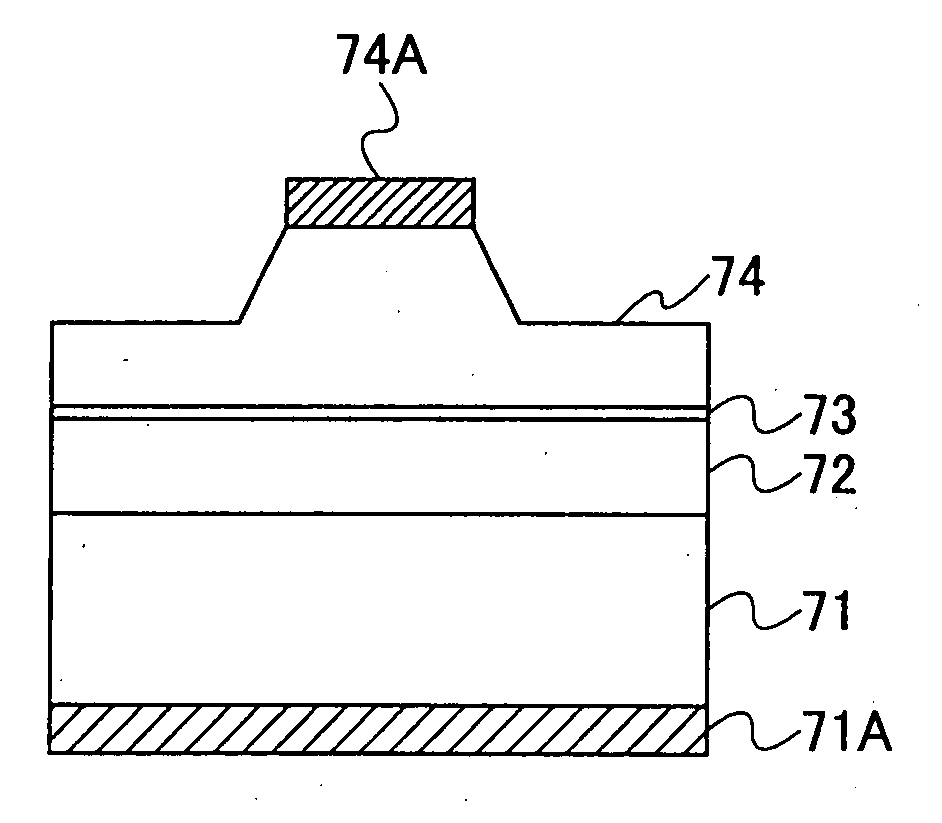

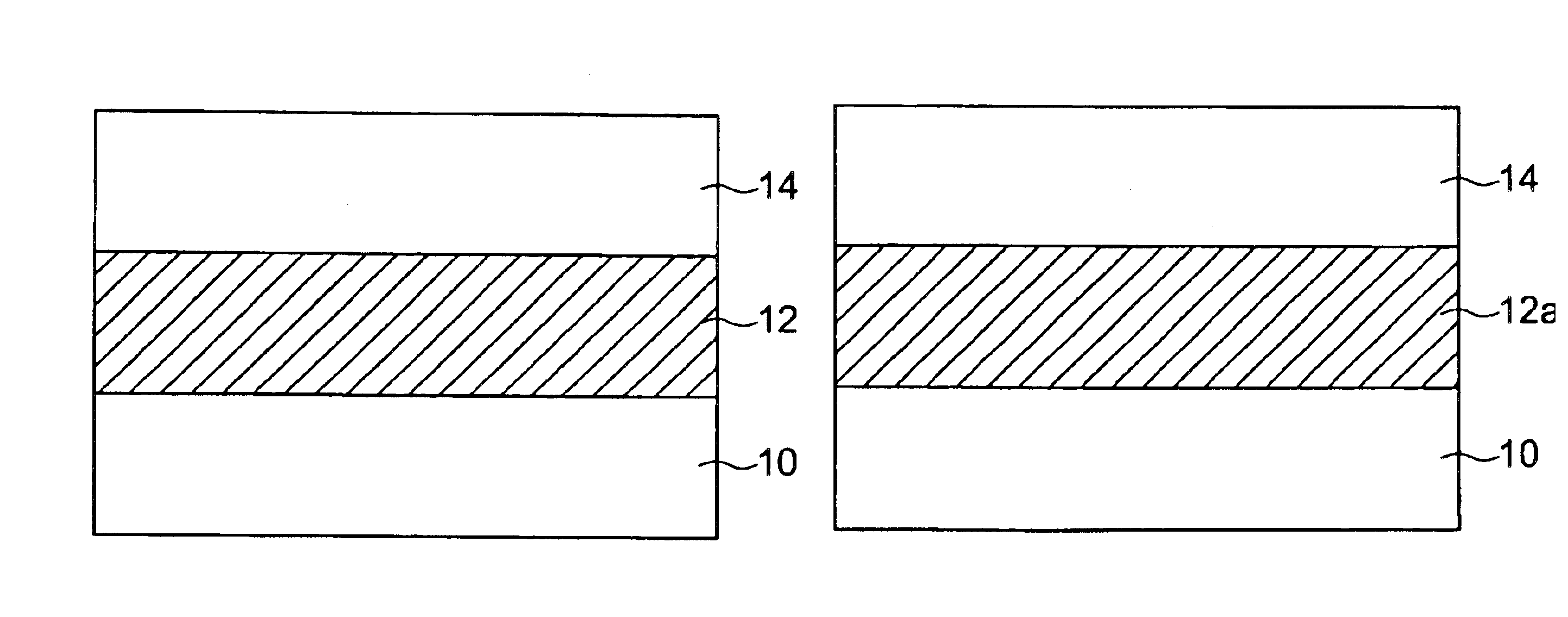

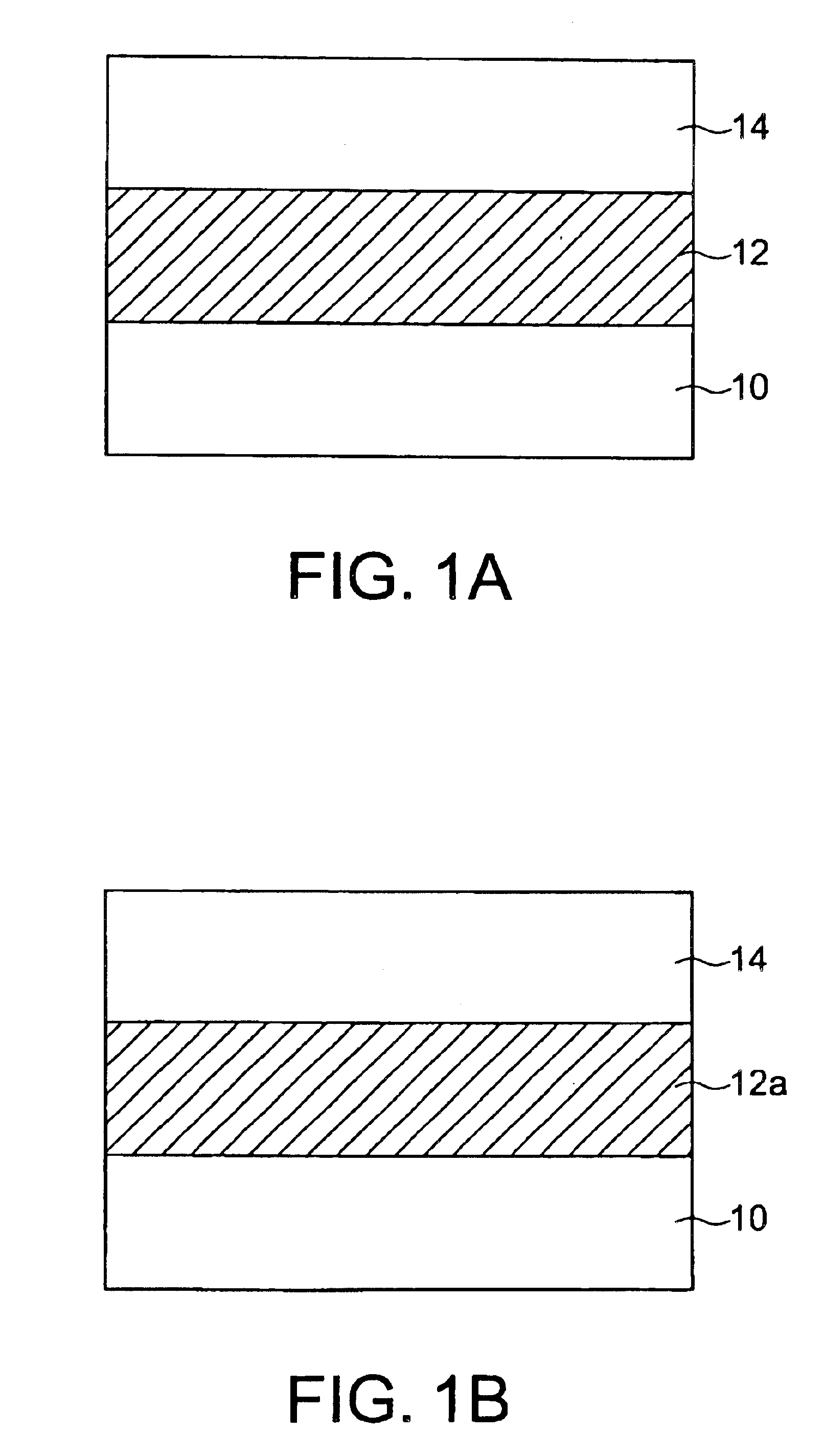

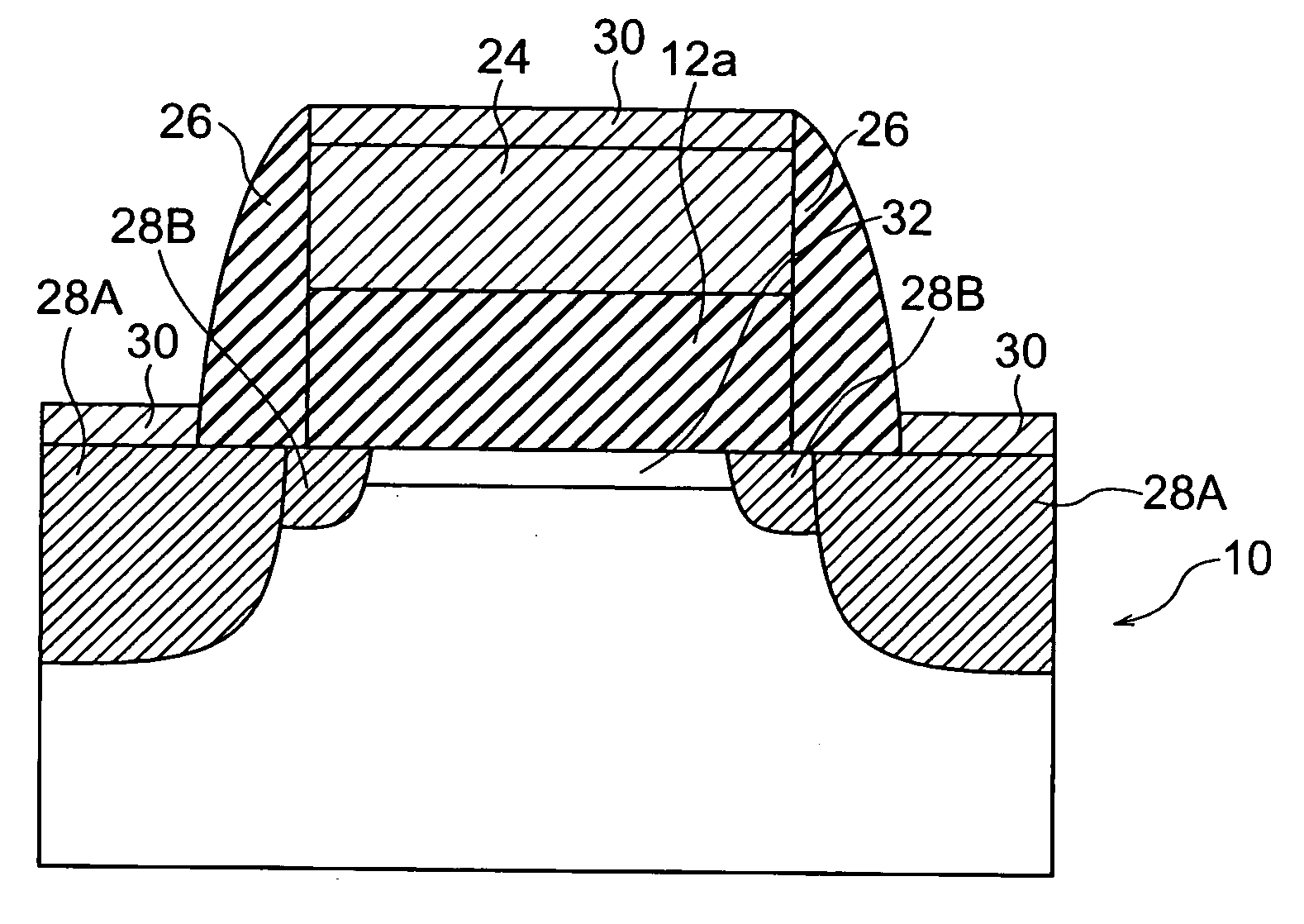

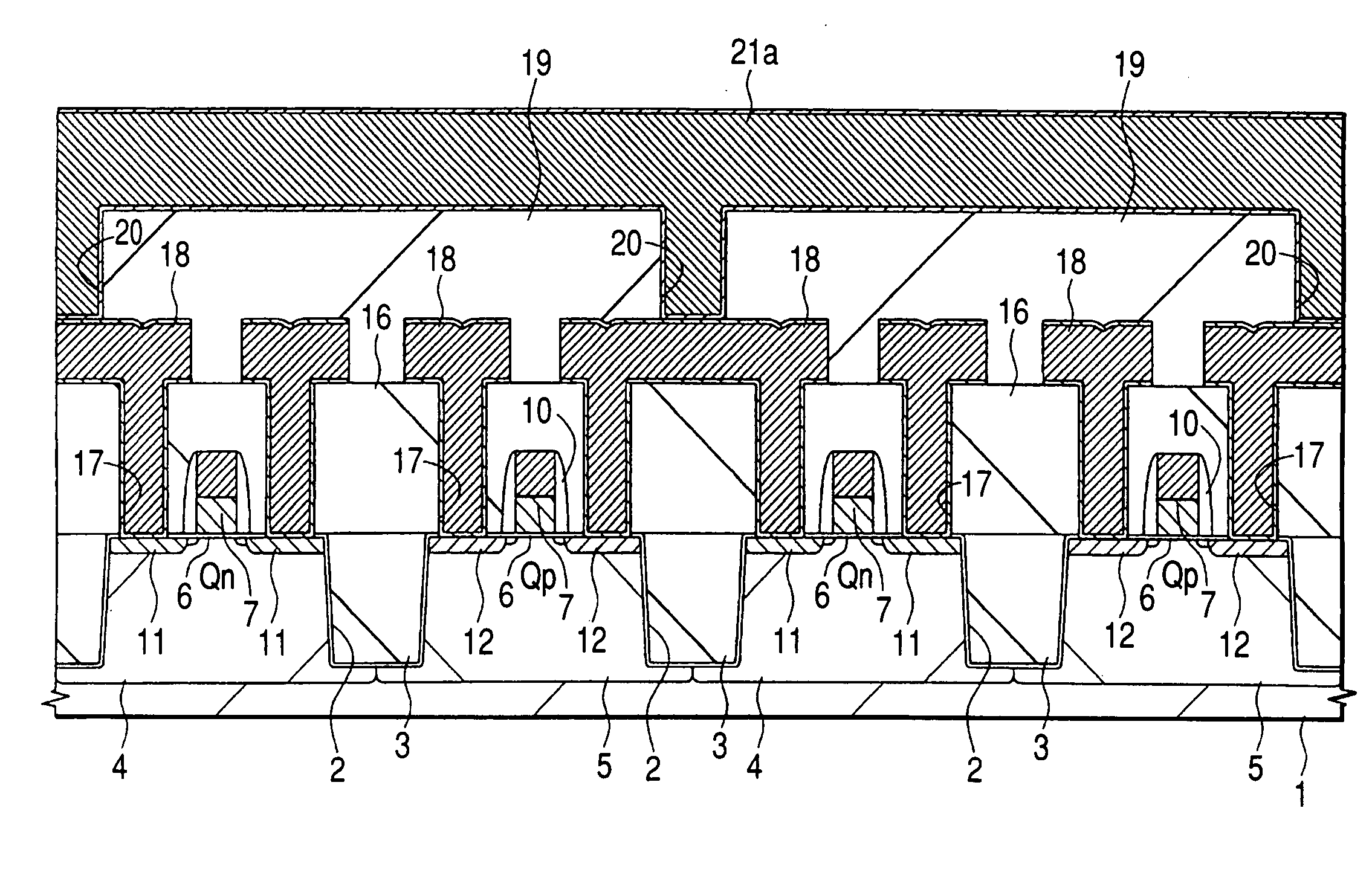

Semiconductor device and method of manufacturing the same

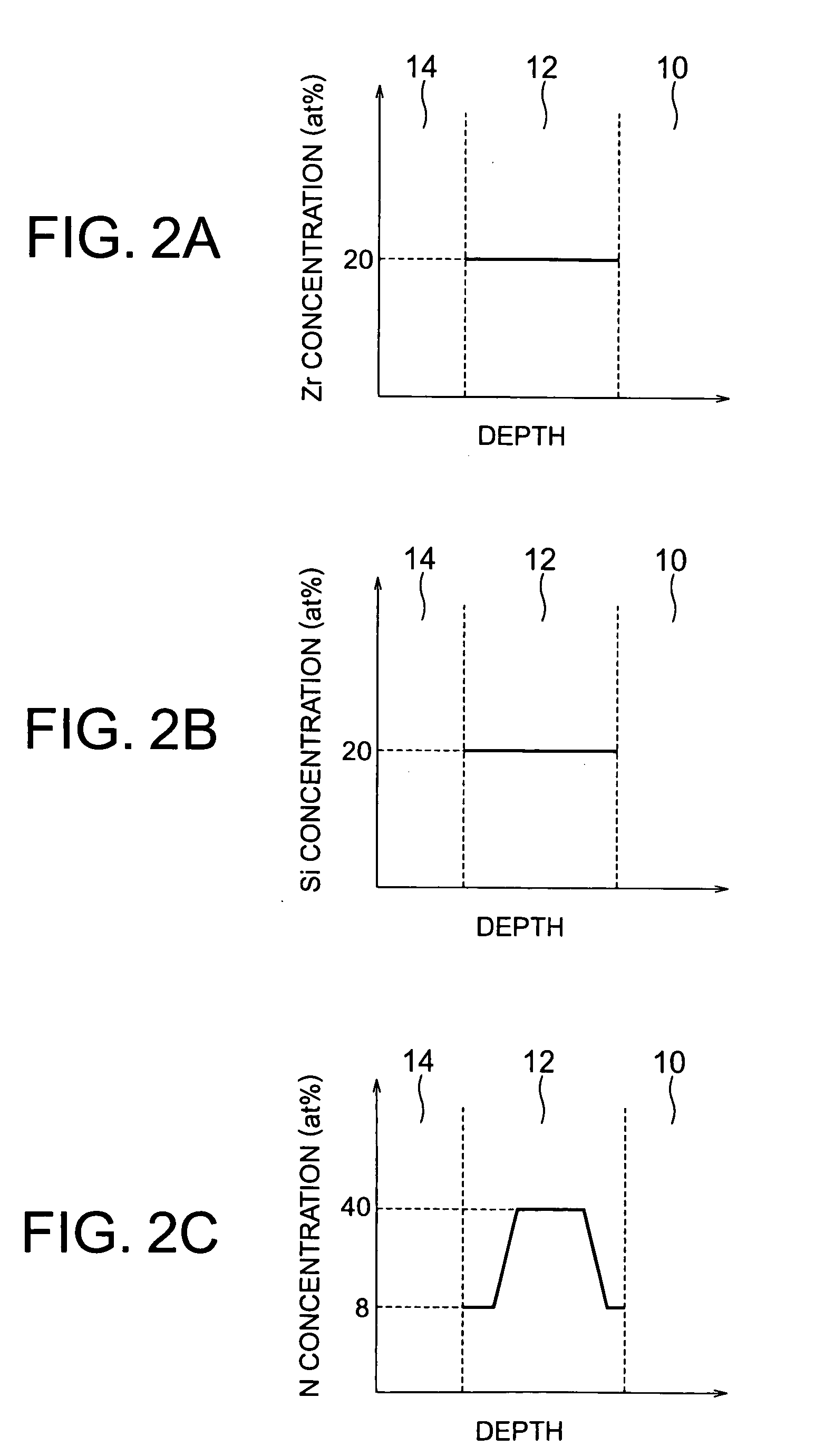

ActiveUS6849908B2Increase nitrogen concentrationVacuum evaporation coatingSputtering coatingGate dielectricNitrogen

A good interface characteristic can be maintained, and a leakage current of a dielectric film can be decreased. A semiconductor device according to one aspect of the present invention includes: a semiconductor substrate; a gate dielectric film containing at least nitrogen and a metal, the gate dielectric film being formed on the semiconductor substrate, and including a first layer region contacting the semiconductor substrate, a second layer region located at a side opposite to that of the first layer region in the gate dielectric film, and a third layer region located between the first and second layer regions, a maximum value of a nitrogen concentration in the third layer region being higher than maximum values thereof in the first and second layer regions; a gate electrode contacting the second layer region; and a pair of source and drain regions formed at both sides of the gate dielectric film in the semiconductor substrate.

Owner:KIOXIA CORP

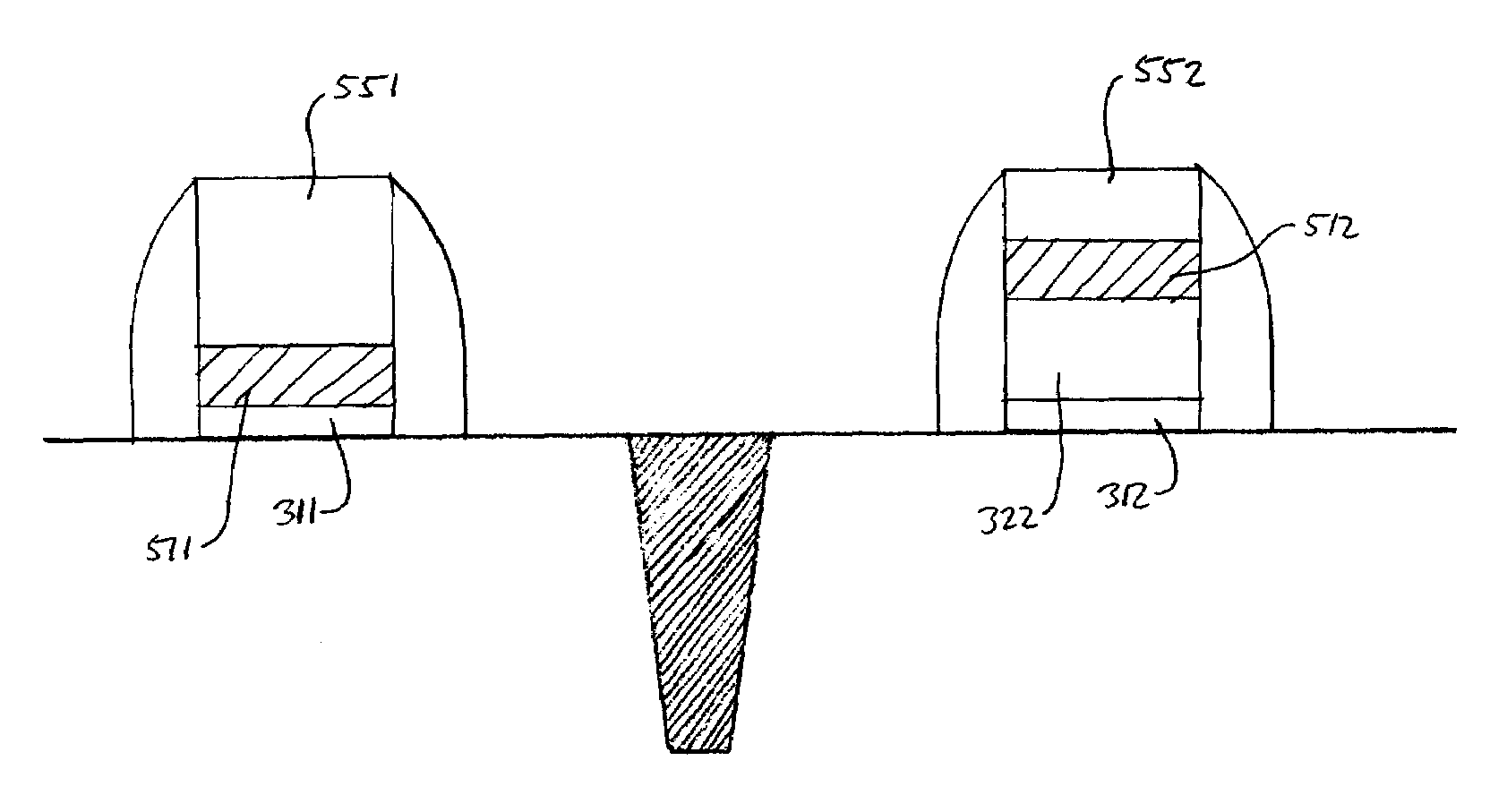

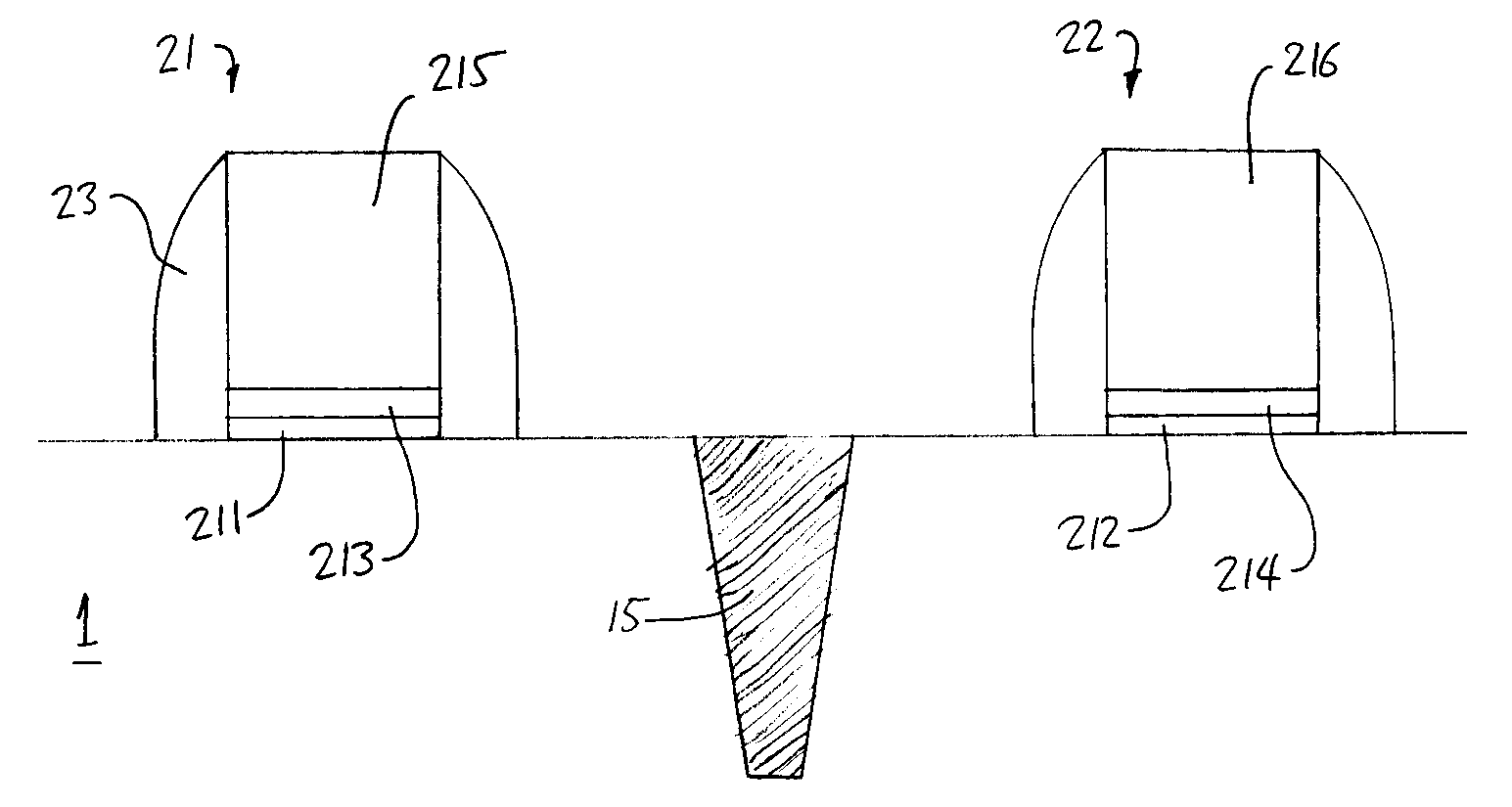

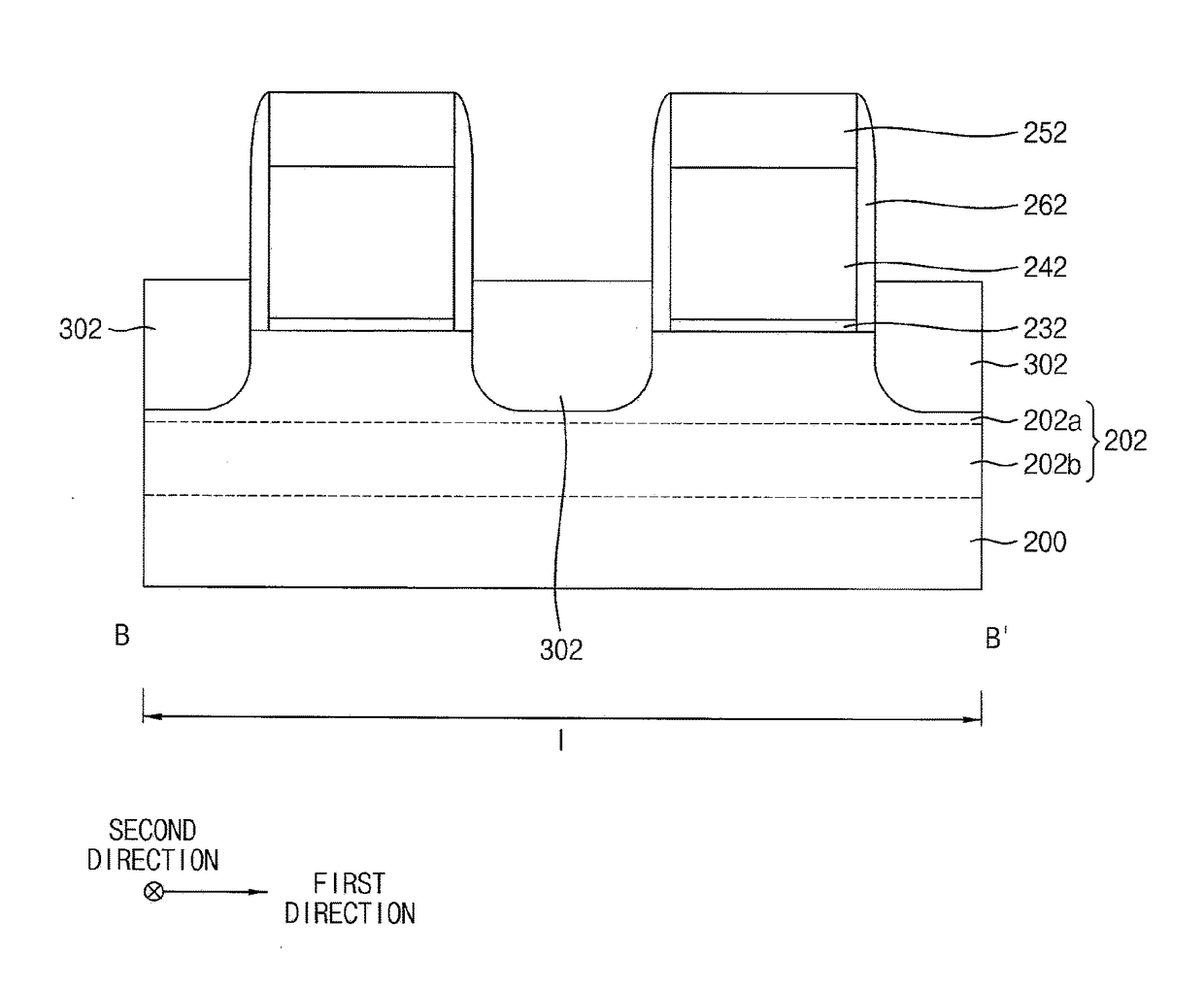

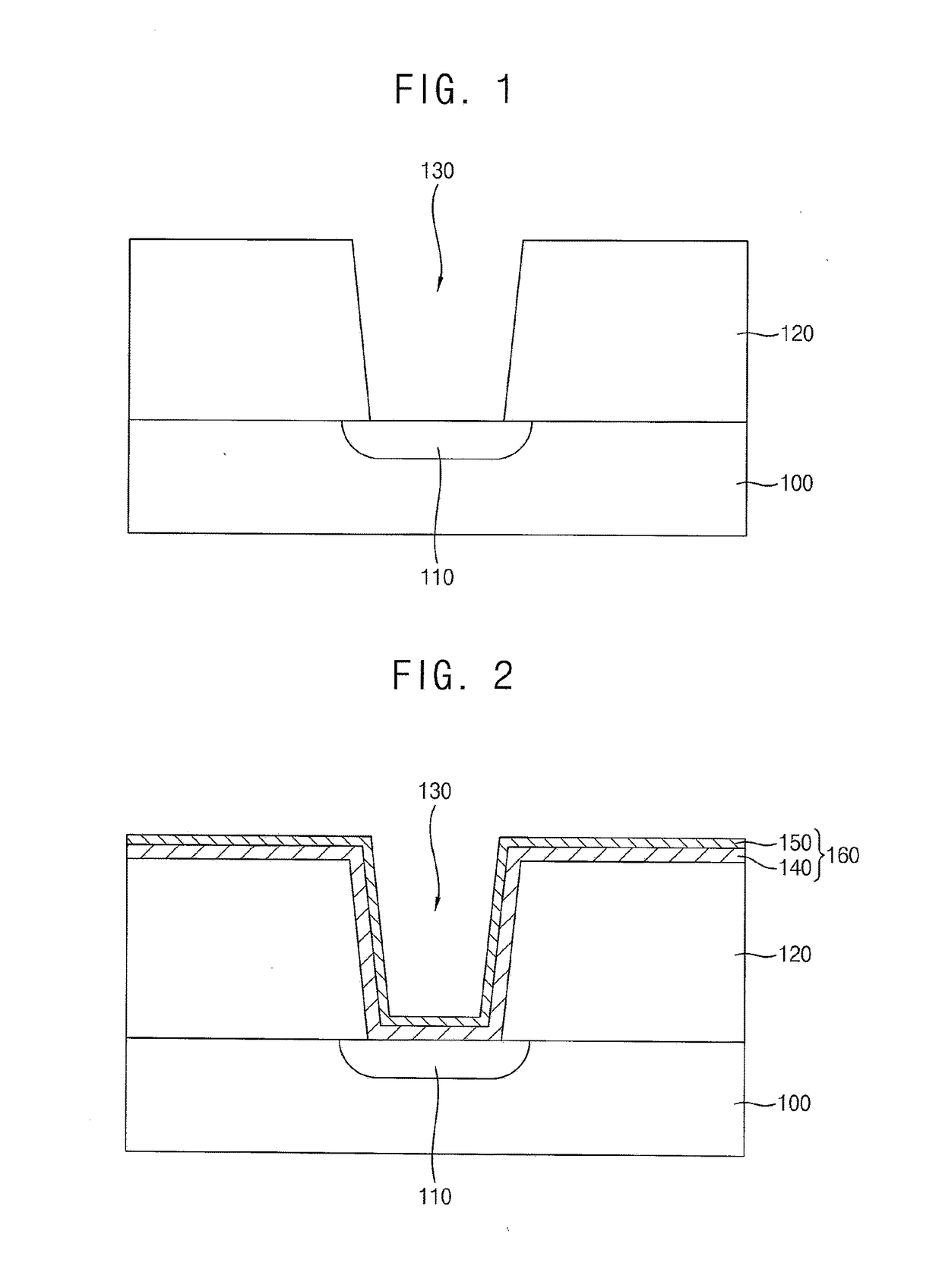

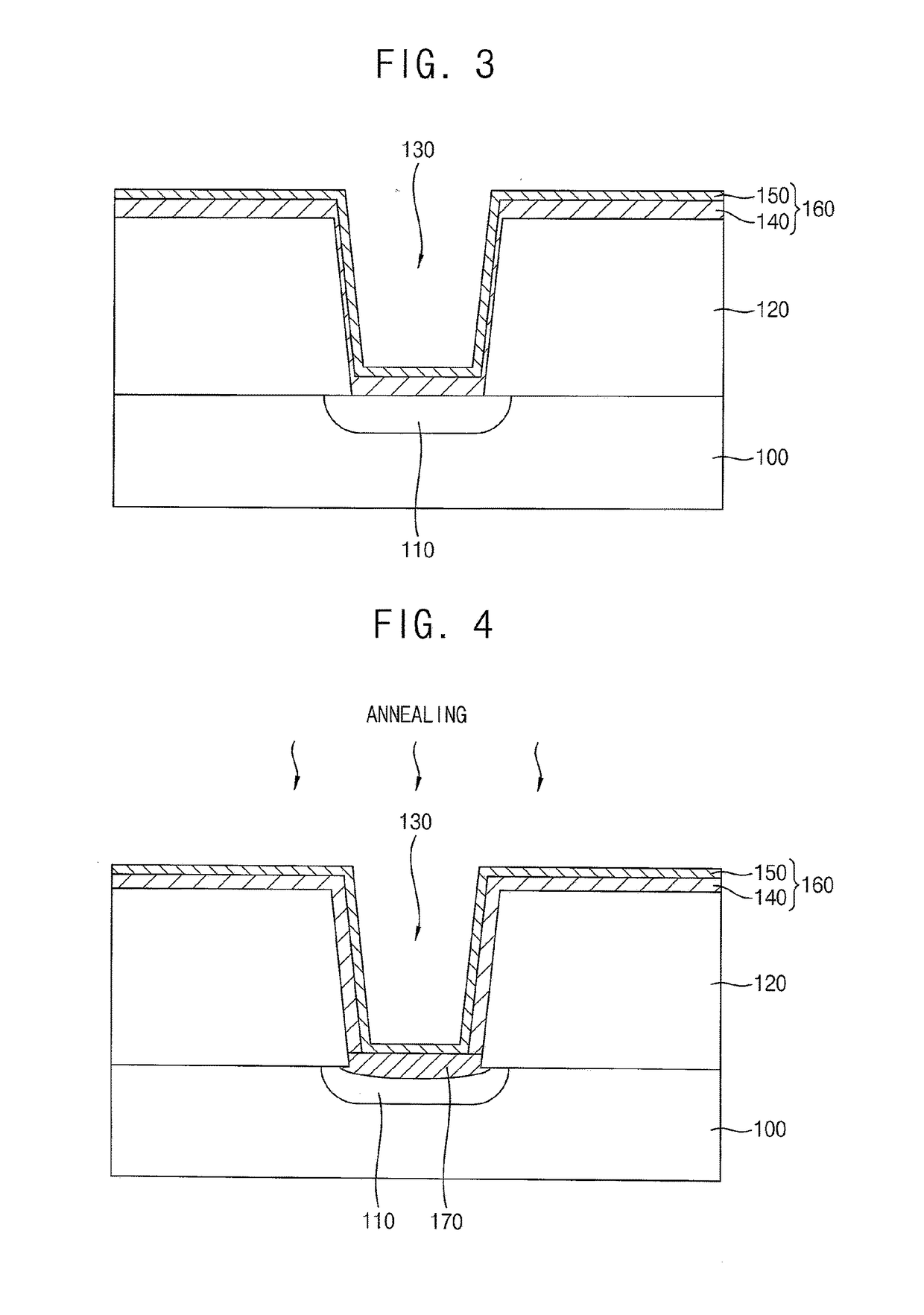

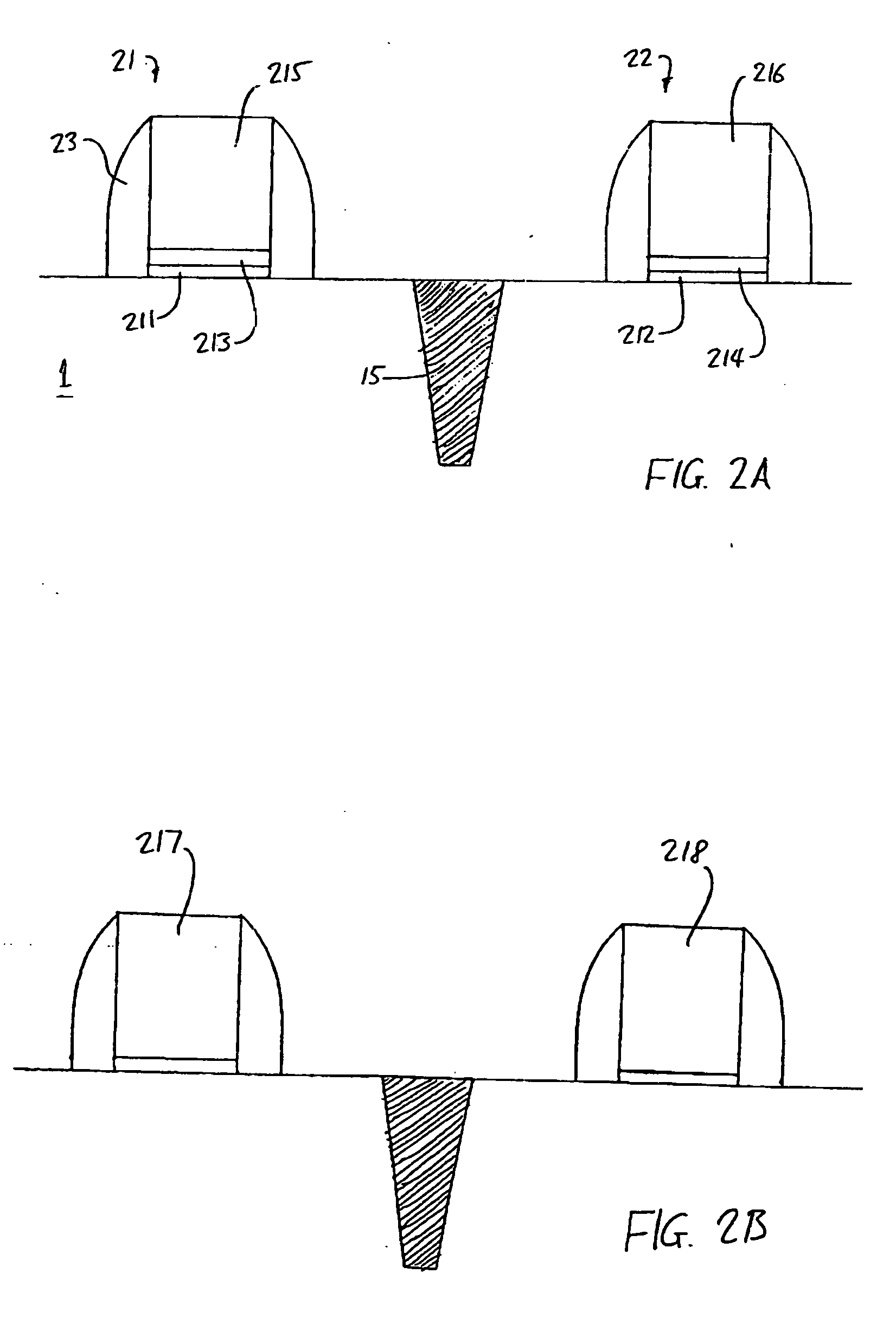

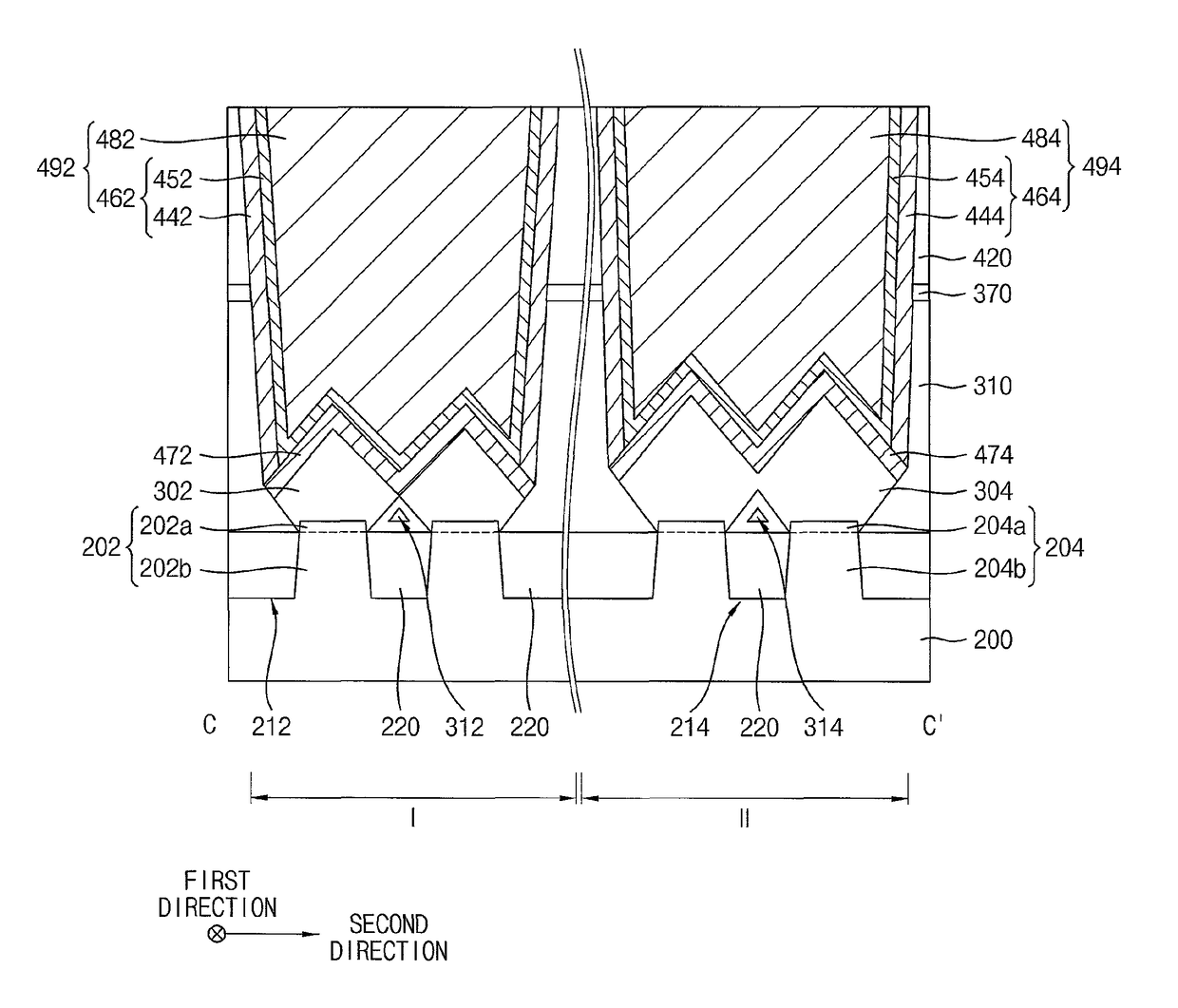

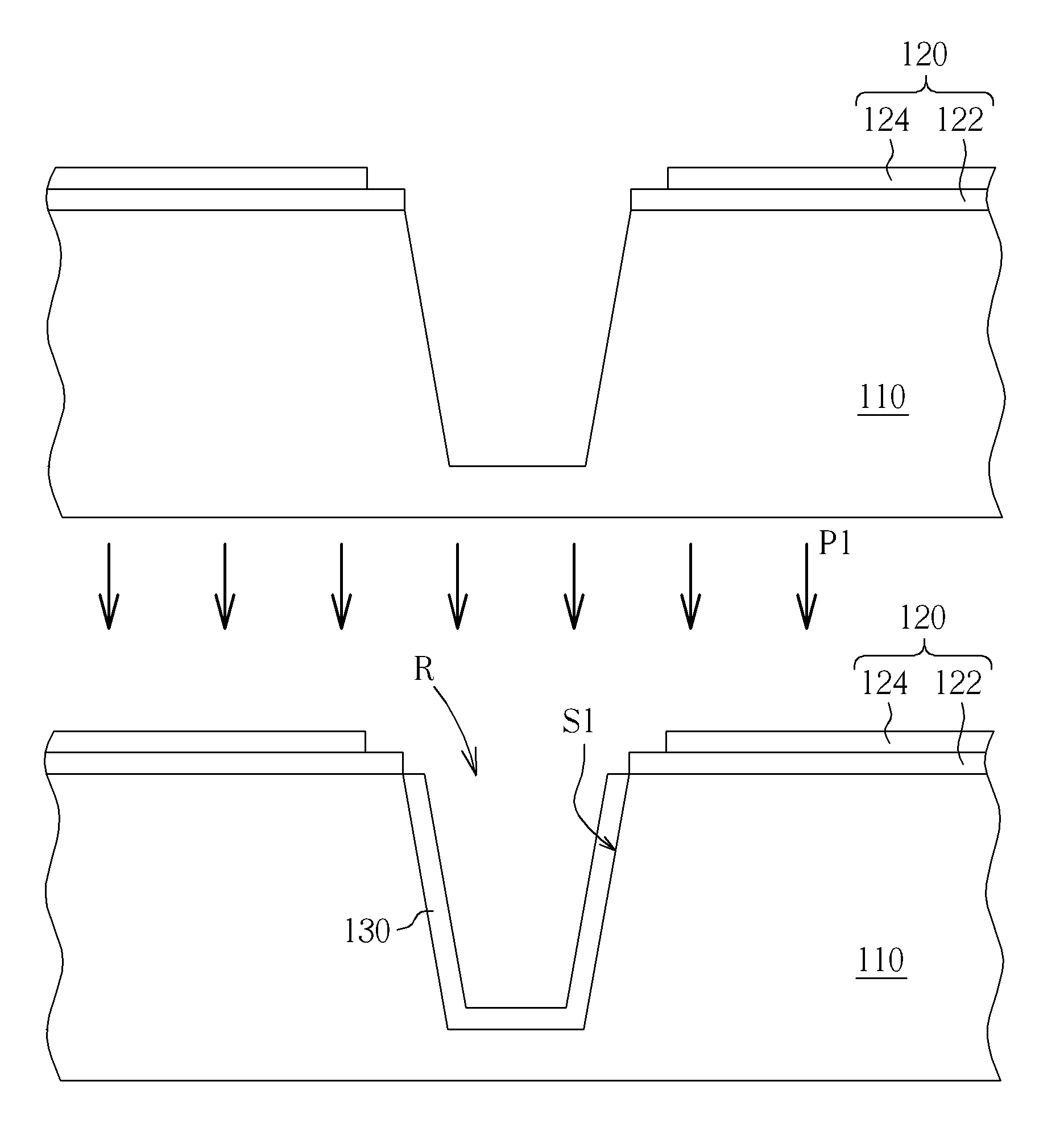

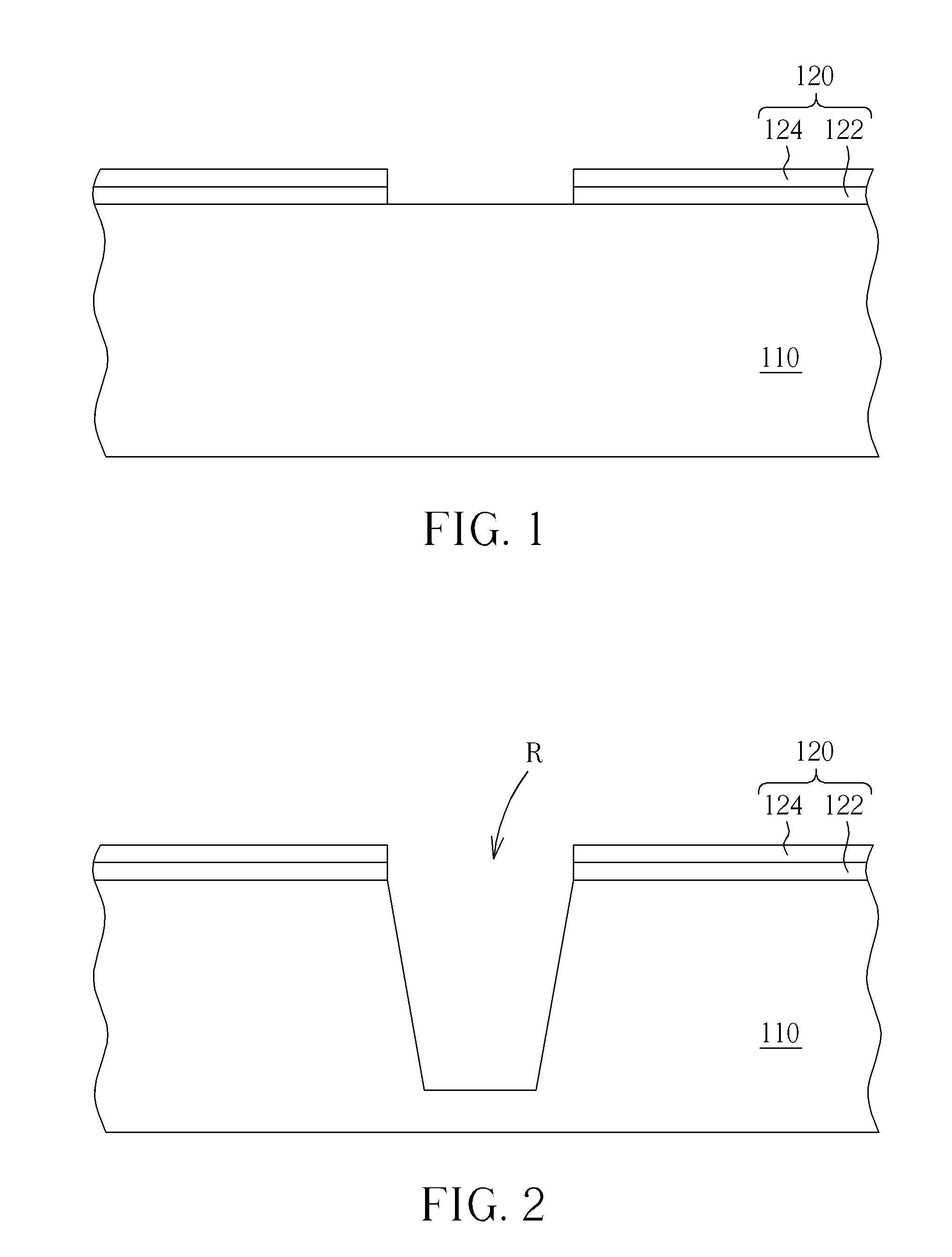

Semiconductor device including contact plug and method of manufacturing the same

ActiveUS20170077248A1Increase nitrogen concentrationIncrease in sizeSemiconductor/solid-state device detailsSolid-state devicesDevice materialMetal silicide

A semiconductor device includes an active fin partially protruding from an isolation pattern on a substrate, a gate structure on the active fin, a source / drain layer on a portion of the active fin adjacent to the gate structure, a source / drain layer on a portion of the active fin adjacent to the gate structure, a metal silicide pattern on the source / drain layer, and a plug on the metal silicide pattern. The plug includes a second metal pattern, a metal nitride pattern contacting an upper surface of the metal silicide pattern and covering a bottom and a sidewall of the second metal pattern, and a first metal pattern on the metal silicide pattern, the first metal pattern covering an outer sidewall of the metal nitride pattern. A nitrogen concentration of the first metal pattern gradually decreases according to a distance from the outer sidewall of the metal nitride pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

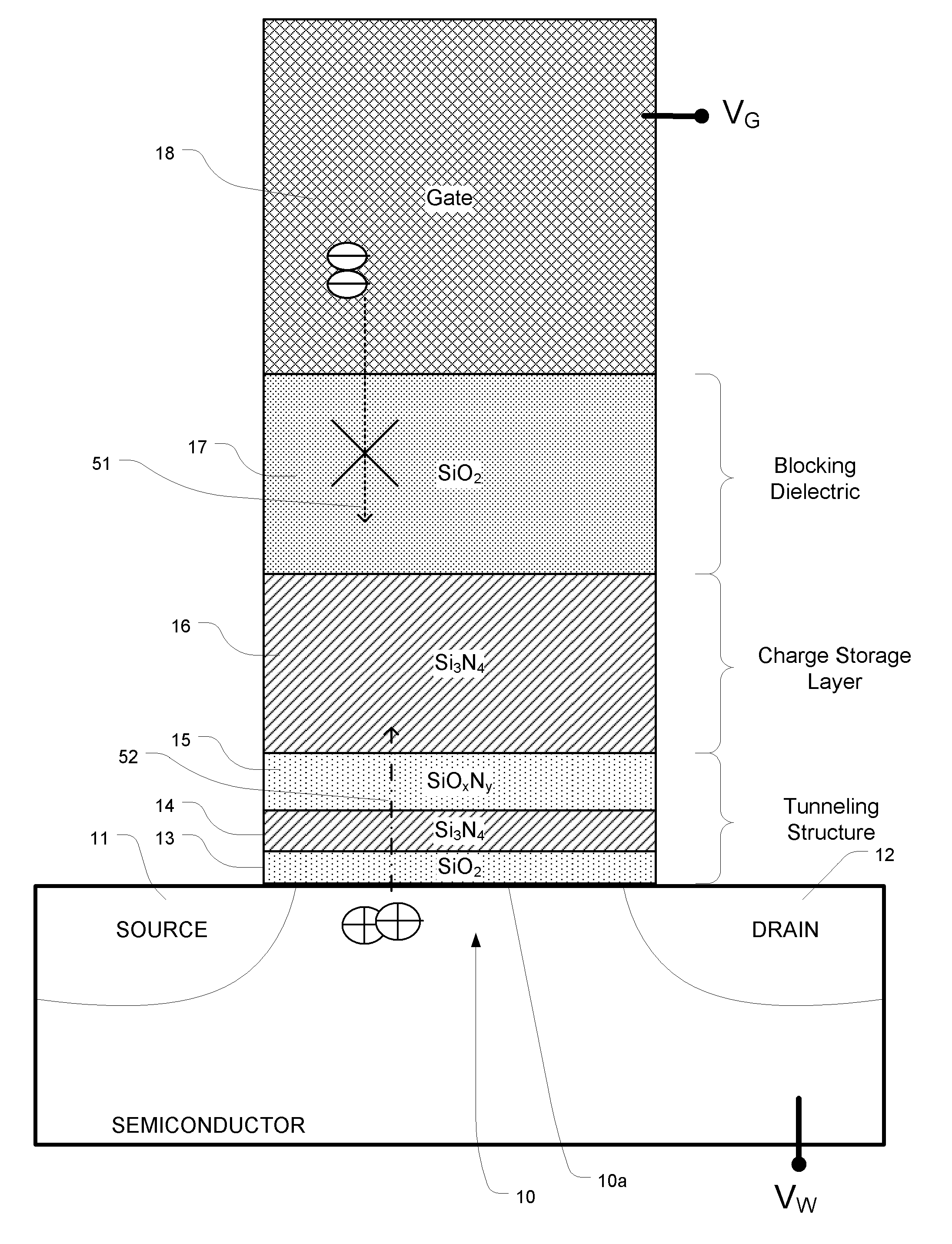

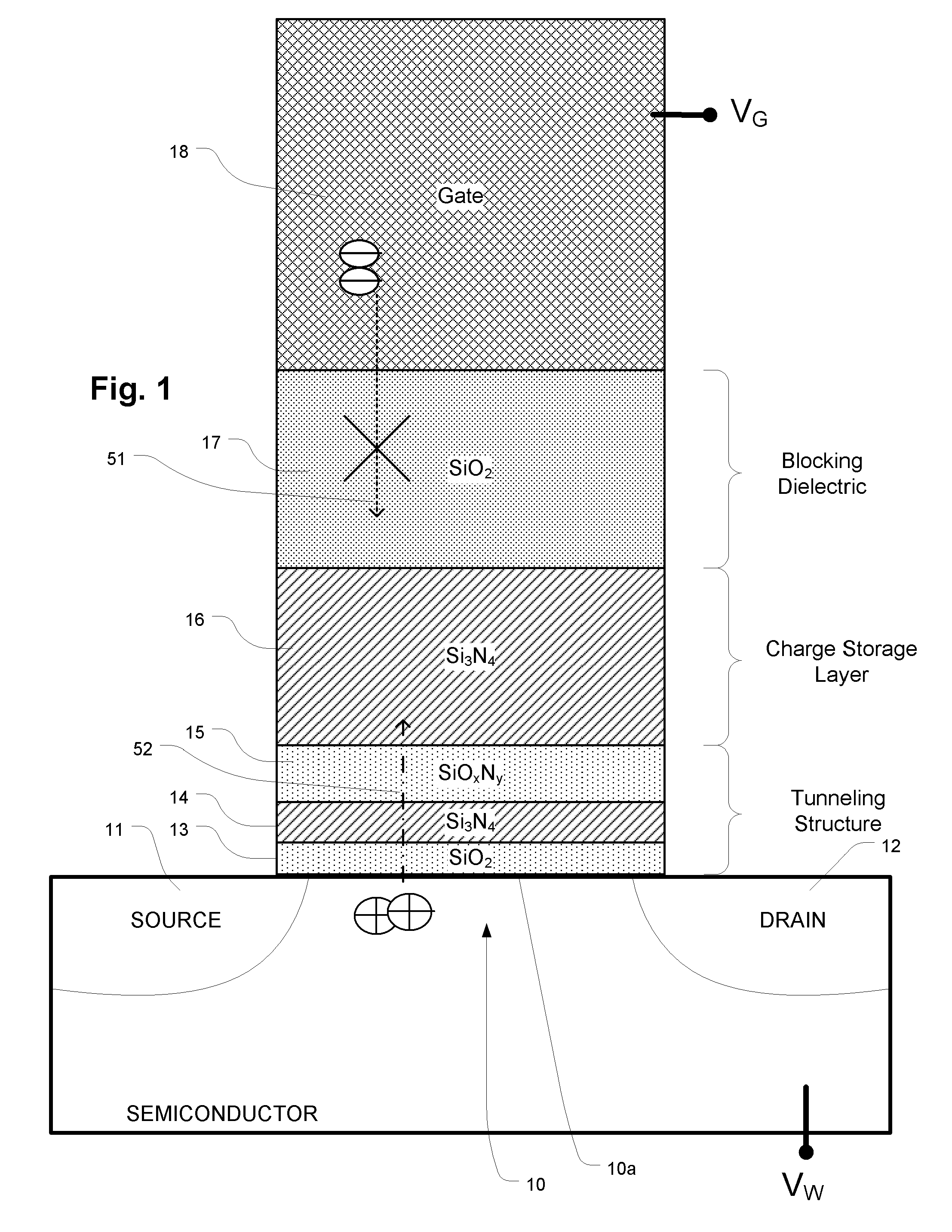

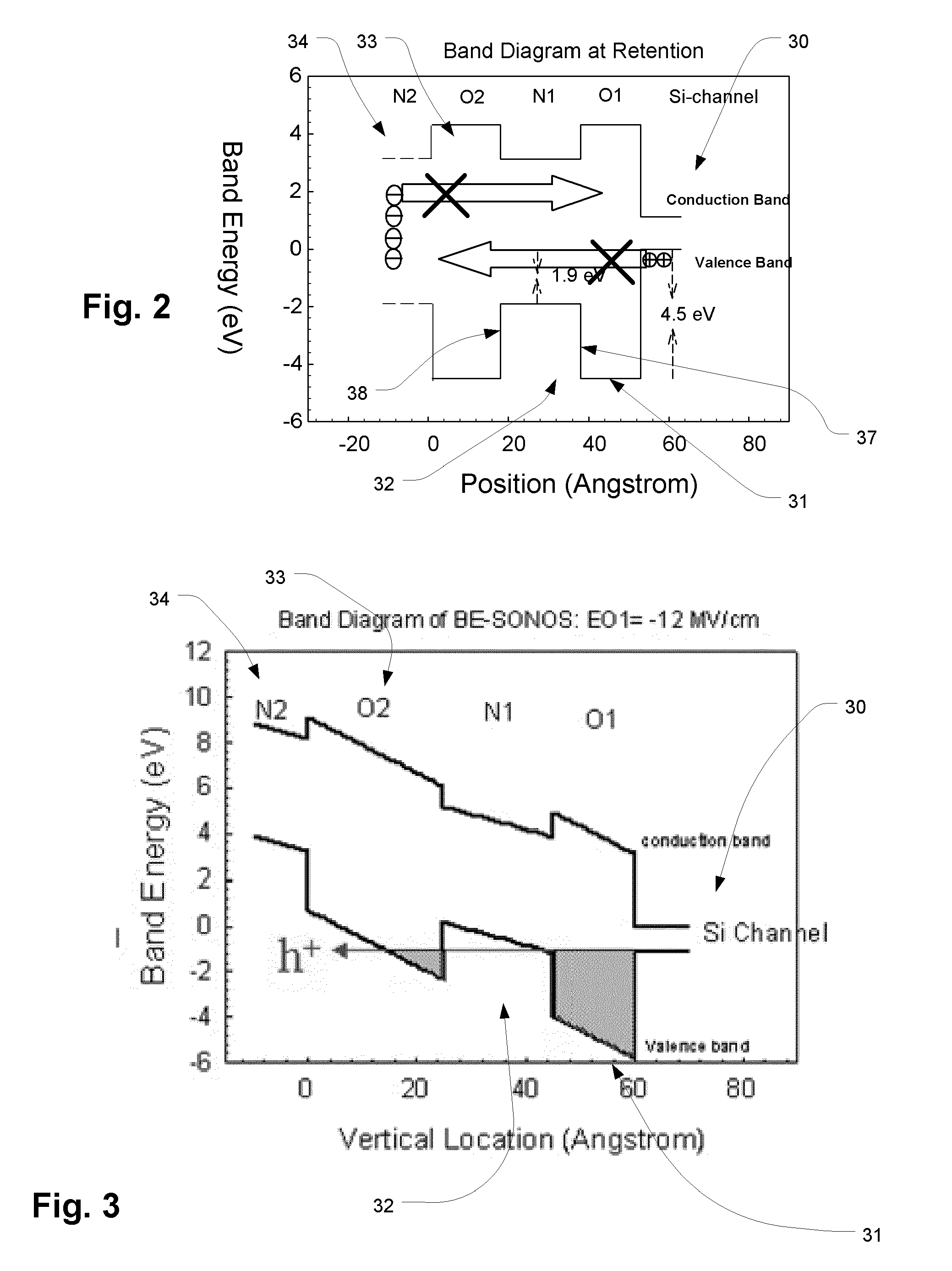

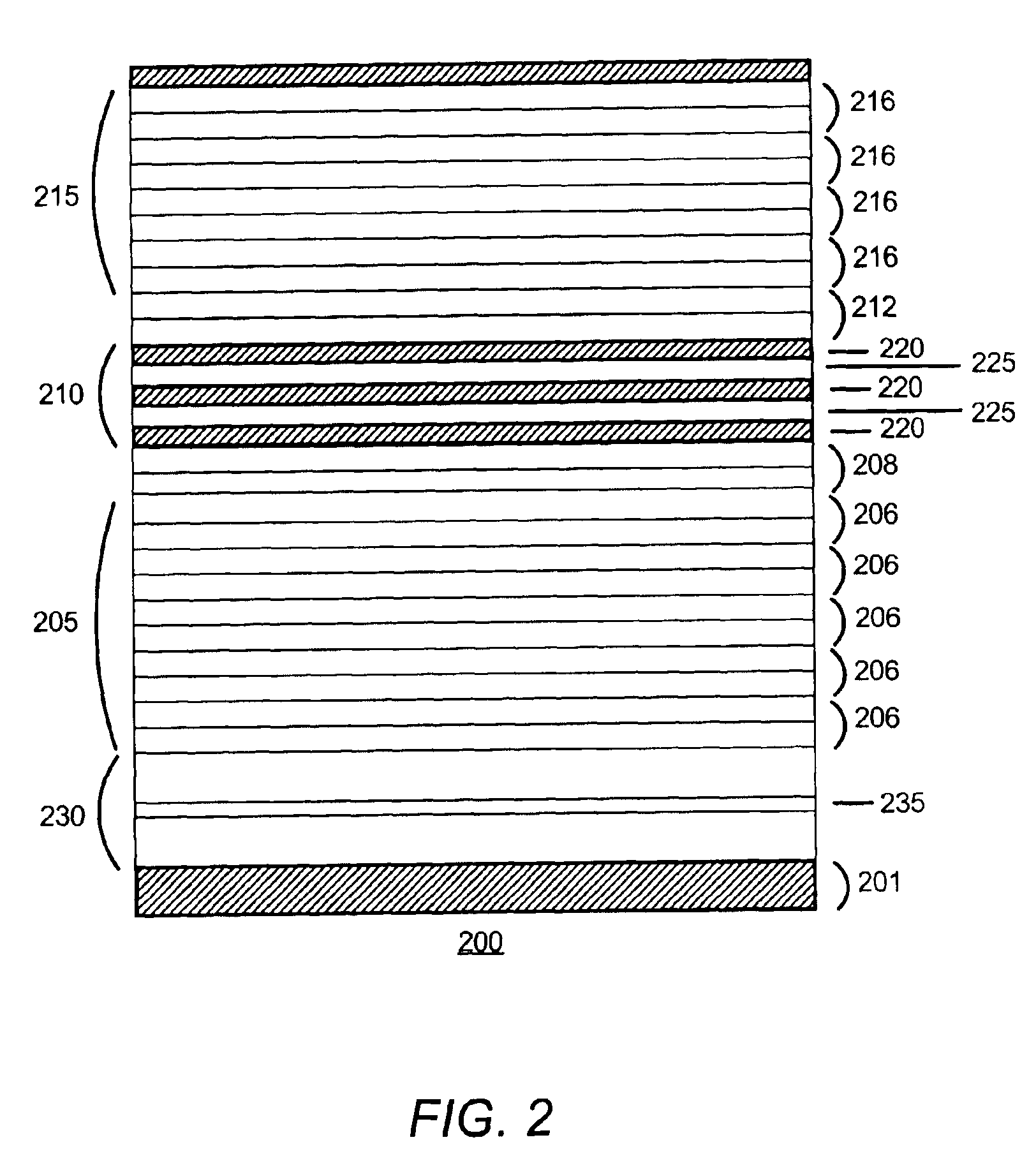

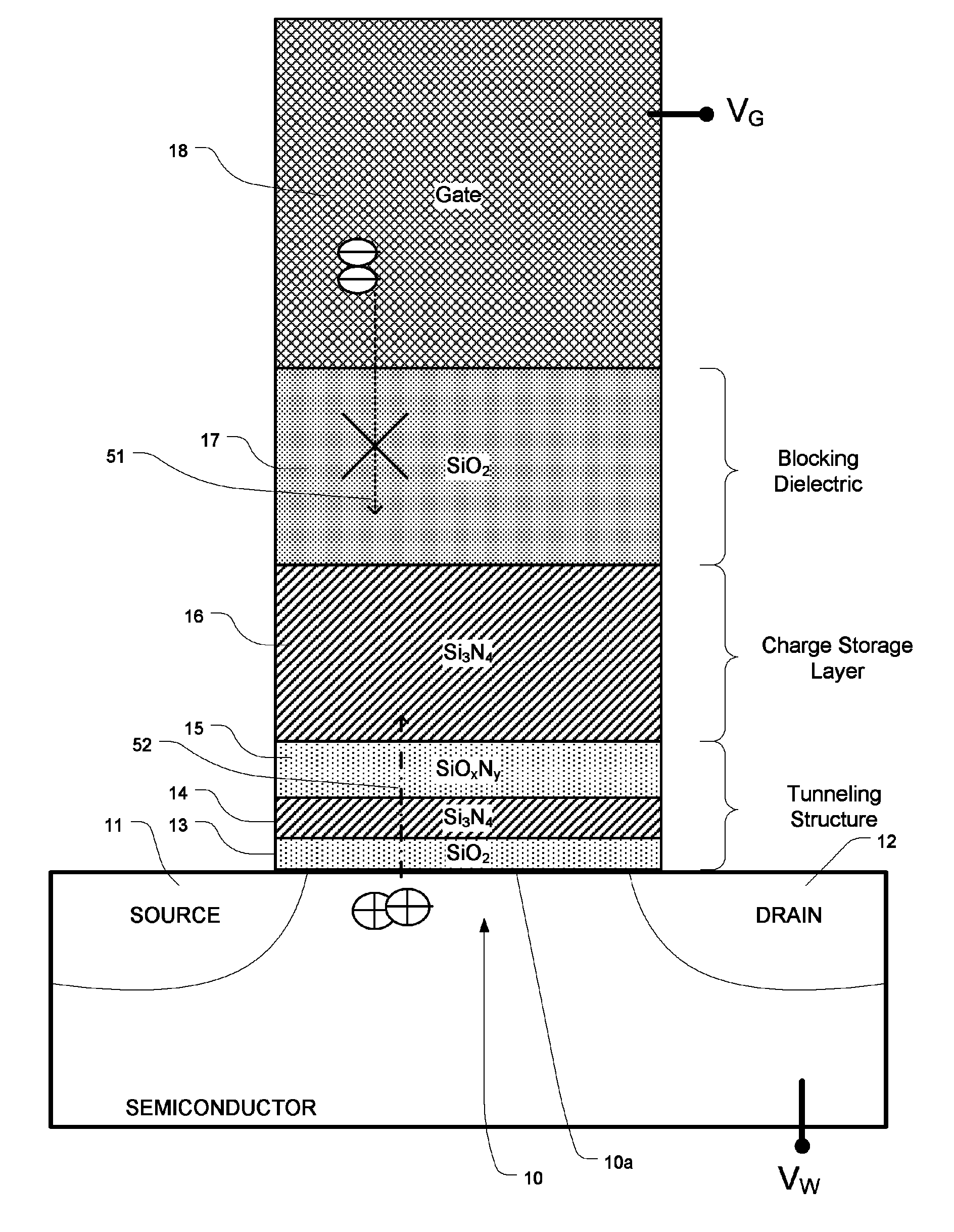

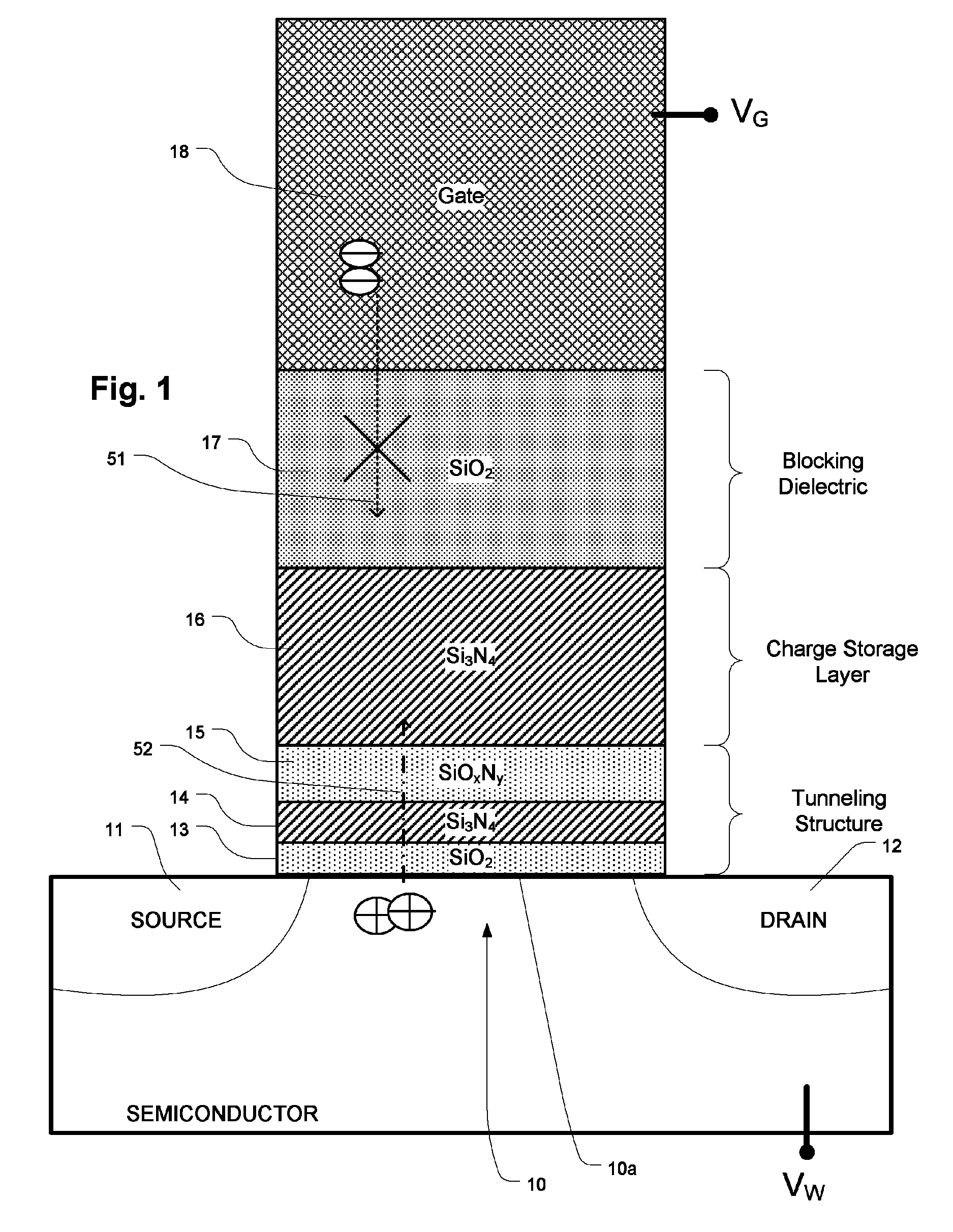

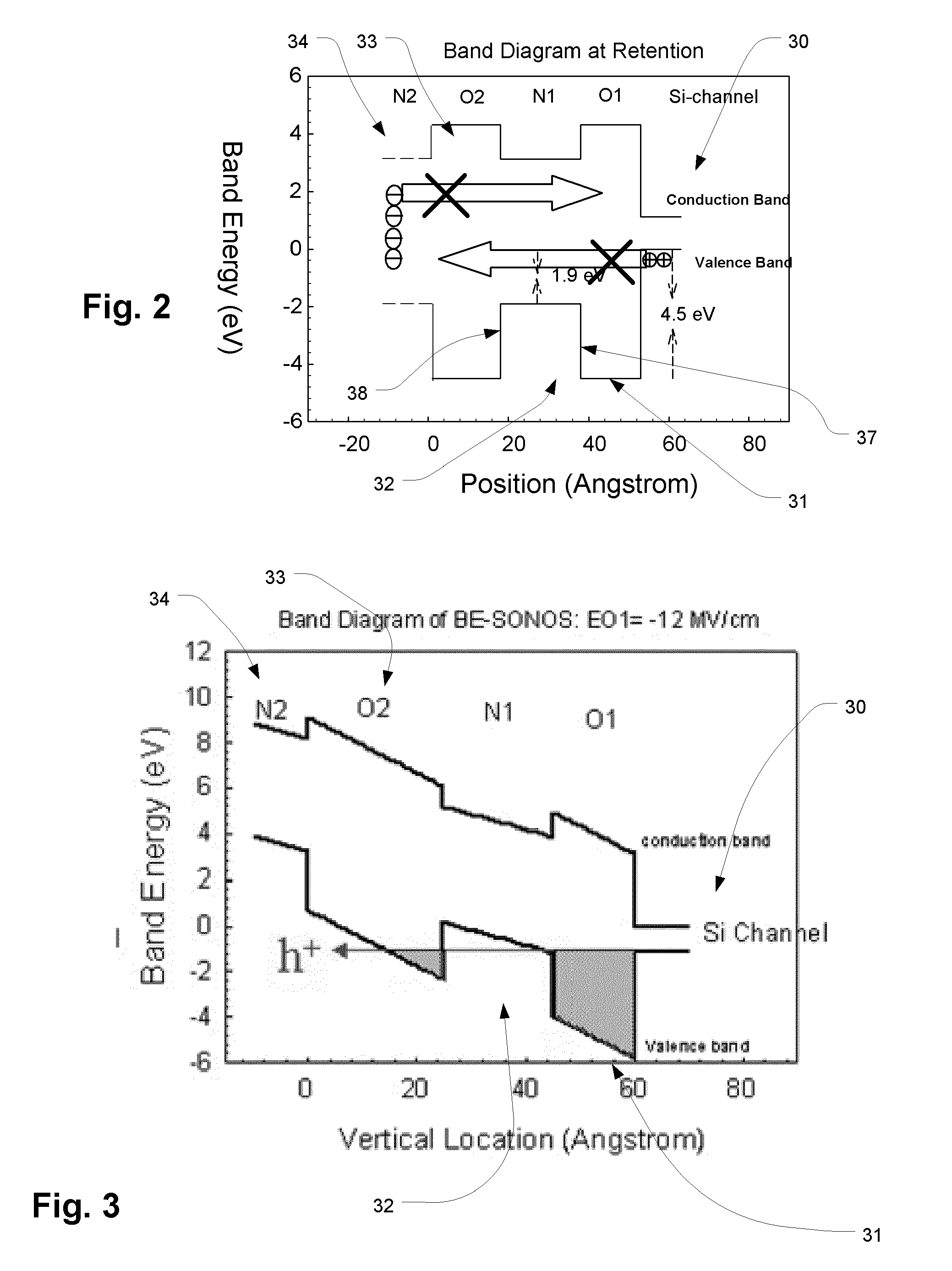

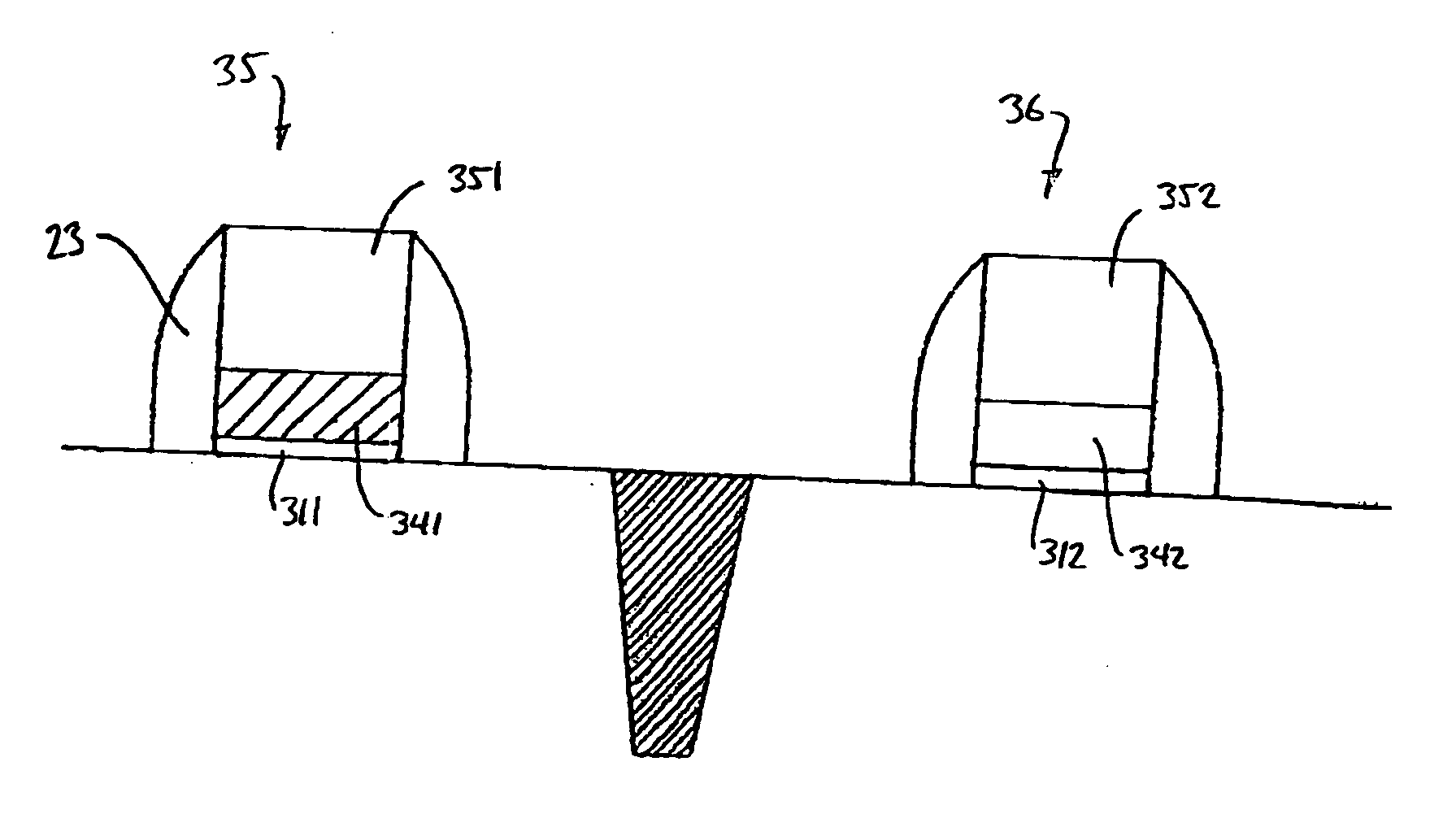

Charge trapping memory cell having bandgap engineered tunneling structure with oxynitride isolation layer

ActiveUS20110075486A1Increase erasing speedSolve the lack of heightSolid-state devicesRead-only memoriesTrappingIsolation layer

A band gap engineered, charge trapping memory cell includes a charge storage structure including a trapping layer. a blocking layer, and a dielectric tunneling structure including a thin tunneling layer, a thin bandgap offset layer and a thin isolation layer comprising silicon oxynitride. The memory cell is manufactured using low thermal budget processes.

Owner:MACRONIX INT CO LTD

Process for producing fine calcium carbonate by wet carbon solidification method using industrial flue

InactiveCN1491894AIncrease nitrogen concentrationLow input costCalcium/strontium/barium carbonatesNitrogen purification/separationCalcium hydroxideCo2 absorption

The wet carbon fixing process of producing fine calcium carbonate with industrial fume includes a two-step alkali absorption-metathesis regeneration process to absorb CO2 in fume to form soluble carbonate quickly, synthesis with calcium hydroxide suspension after being digested and filtered to form homogeneous calcium carbonate, deposition, washing, filtering and stoving to obtain final product. On the other hand, gas after carbon fixation is dewatered and deoxidized to obtain high purity nitrogen, which may be led to nitridize furnace to synthesize nitride product. The present invention can recover low content CO2 in fume to purify fume and reduce pollution while utilizing nitrogen in fume.

Owner:UNIV OF SCI & TECH BEIJING

Semiconductor device and method of manufacturing the same

ActiveUS20040164329A1Increase nitrogen concentrationTransistorVacuum evaporation coatingGate dielectricNitrogen

A good interface characteristic can be maintained, and a leakage current of a dielectric film can be decreased. A semiconductor device according to one aspect of the present invention includes: a semiconductor substrate; a gate dielectric film containing at least nitrogen and a metal, the gate dielectric film being formed on the semiconductor substrate, and including a first layer region contacting the semiconductor substrate, a second layer region located at a side opposite to that of the first layer region in the gate dielectric film, and a third layer region located between the first and second layer regions, a maximum value of a nitrogen concentration in the third layer region being higher than maximum values thereof in the first and second layer regions; a gate electrode contacting the second layer region; and a pair of source and drain regions formed at both sides of the gate dielectric film in the semiconductor substrate.

Owner:KIOXIA CORP

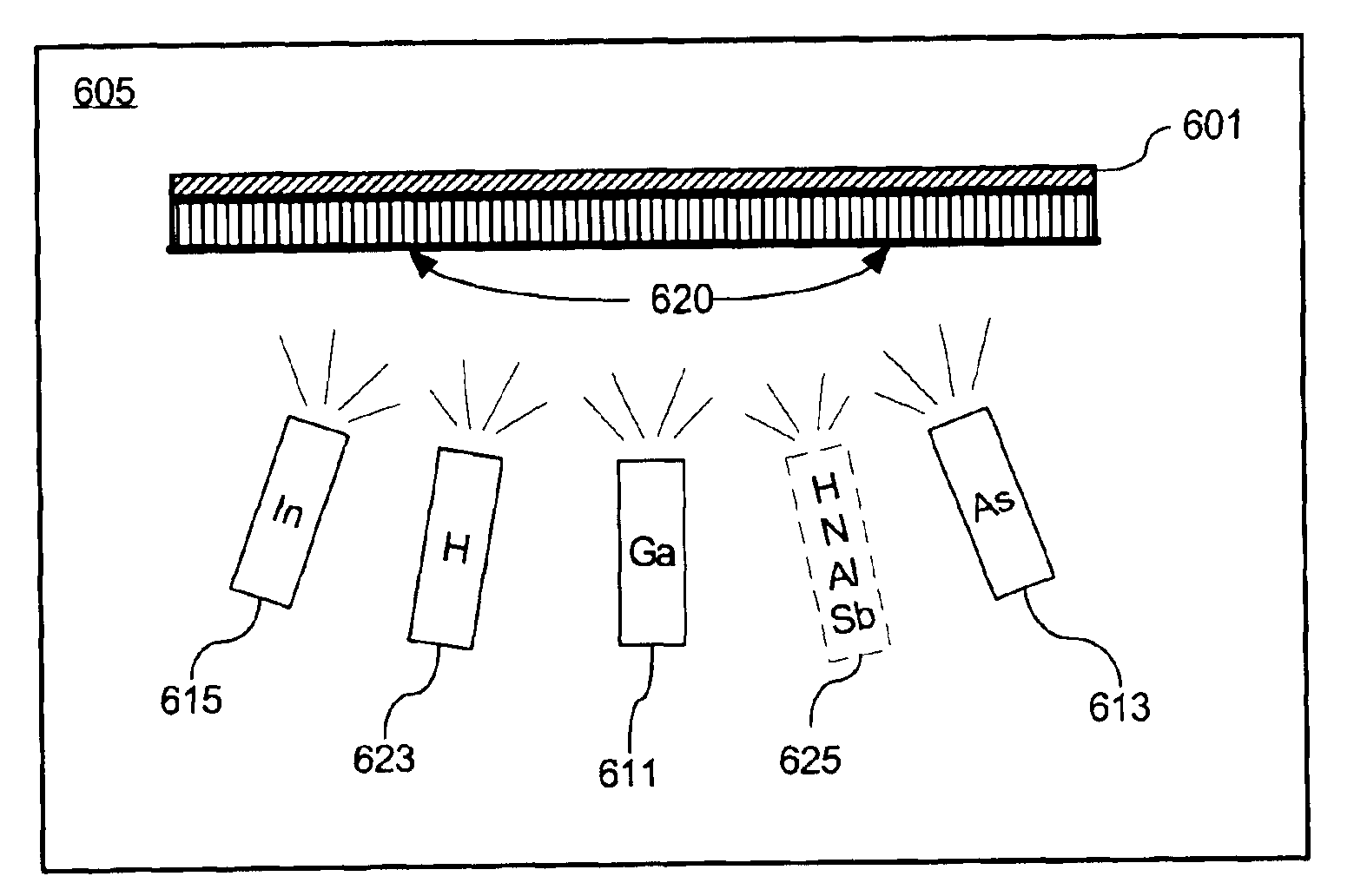

Atomic hydrogen as a surfactant in production of highly strained InGaAs, InGaAsN, InGaAsNSb, and/or GaAsNSb quantum wells

InactiveUS6858519B2Avoid phase separationSimple materialLaser detailsSemiconductor/solid-state device manufacturingIndiumQuantum well

Atomic hydrogen flux impinging on the surface of a growing layer of III-V compounds during VCSEL processing can prevent three-dimensional growth and related misfit dislocations. Use of hydrogen during semiconductor processing can allow, for example, more indium in InGaAs quantum wells grown on GaAs. Atomic hydrogen use can also promote good quality growth at lower temperatures, which makes nitrogen incorporated in a non-segregated fashion producing better material. Quantum wells and associated barriers layers can be grown to include nitrogen (N), aluminum (Al), antimony (Sb), and / or indium (In) placed within or about a typical GaAs substrate to achieve long wavelength VCSEL performance, e.g., within the 1260 to 1650 nm range.

Owner:II VI DELAWARE INC

Silicon nitride nanowire reinforced porous silicon carbide material and preparation method thereof

The invention relates to a silicon nitride nanowire reinforced porous silicon carbide material and a preparation method of the silicon nitride nanowire reinforced porous silicon carbide material. The invention adopts the technical scheme as follows: taking 40-70 wt% of a silicon carbide powder, 15-35 wt% of a silicon powder, 1-5 wt% of a catalyst and 10-20 wt% of a nitrogen source as raw materials, additionally adding 20-30 wt% of deionized water, stirring to obtain a ceramic slurry; adding a foaming agent, which is 10-20 wt% of the raw materials, into the ceramic slurry, continuously stirring for 30-60 minutes to obtain a ceramic foam slurry; pouring the ceramic foam slurry into a mold, standing in a nitrogen environment, drying, demolding to obtain a ceramic body; putting the ceramic body in the nitrogen atmosphere, raising the temperature to 1100-1150 DEG C, and preserving heat; raising the temperature again to 1200-1600 DEG C, preserving heat; naturally cooling to obtain the silicon nitride nanowire reinforced porous silicon carbide material. The process is simple, the cost is low, the utilization ratio of the raw materials is high, the process is easy to control, the size of pores of a prepared product is even, the pore distribution is uniform, and the mechanical strength is high.

Owner:武汉塑之源科技有限公司

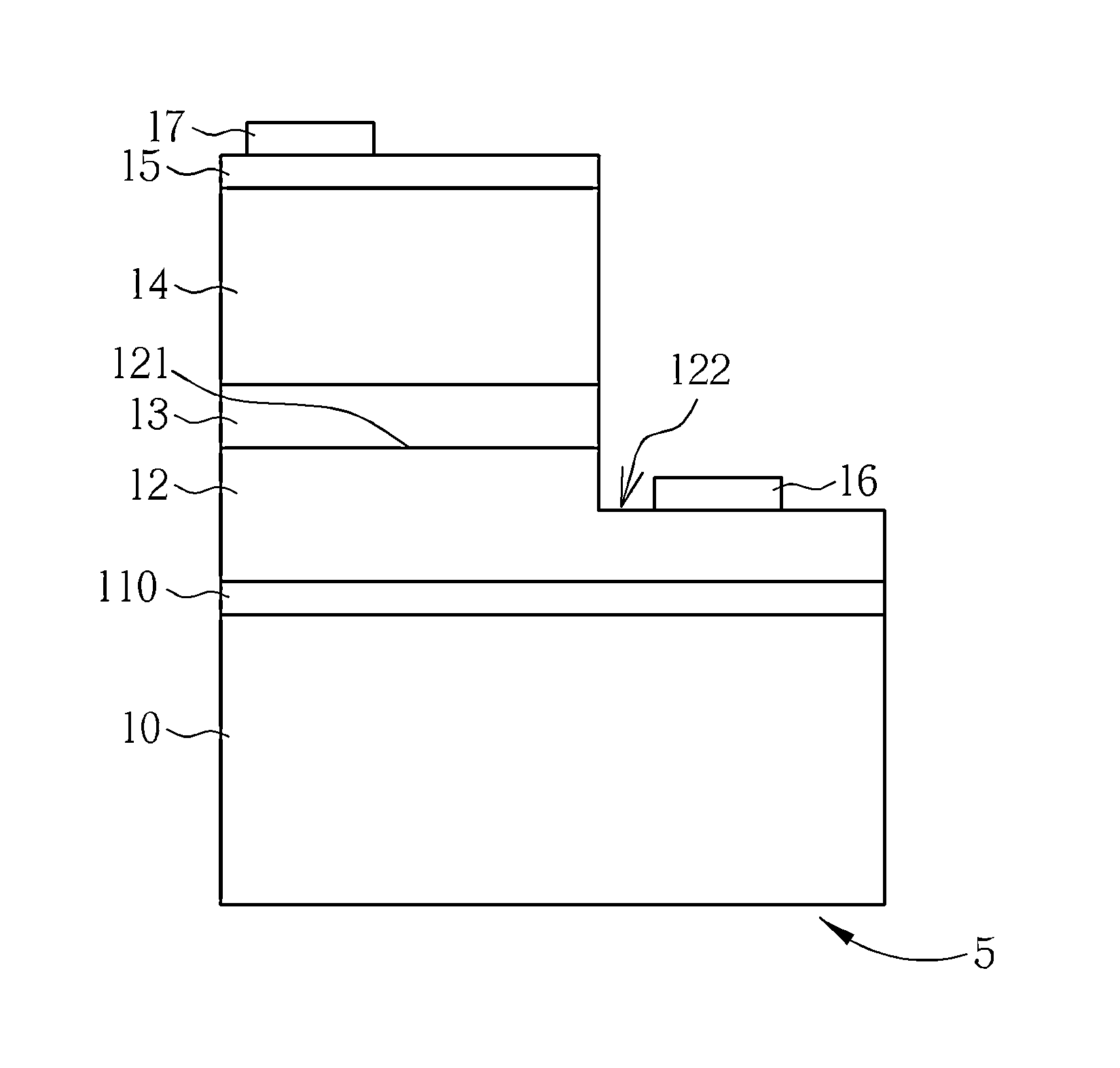

Nitride-based light-emitting device

InactiveUS20140017840A1Increase concentrationReduce total nitrogen concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesNitrogenNitride

A nitride-based light-emitting device includes a substrate and a plurality of layers formed over the substrate in the following sequence: a nitride-based buffer layer formed by nitrogen, a first group III element, and optionally, a second group III element, a first nitride-based semiconductor layer, a light-emitting layer, and a second nitride-based semiconductor layer.

Owner:EPISTAR CORP

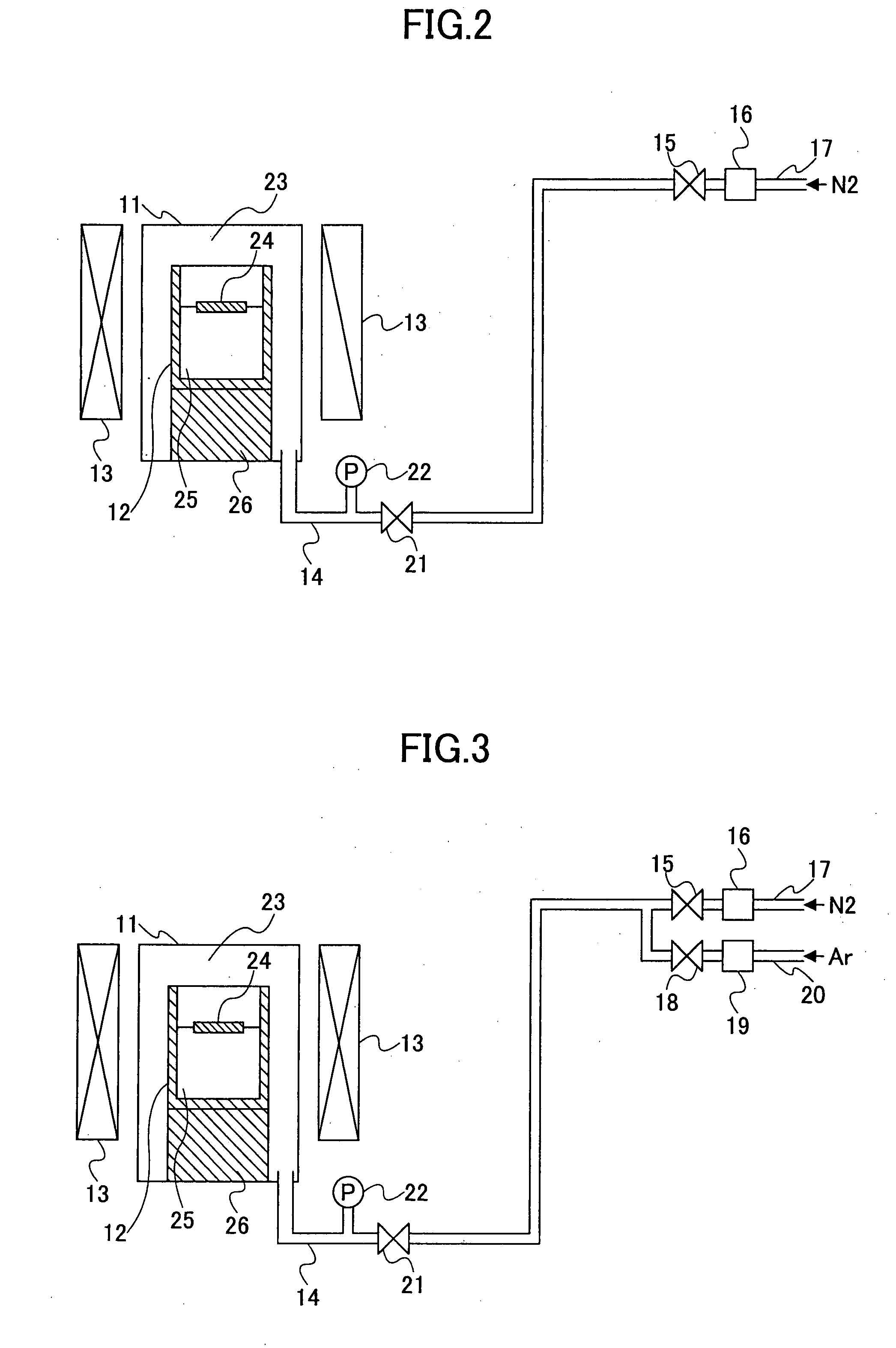

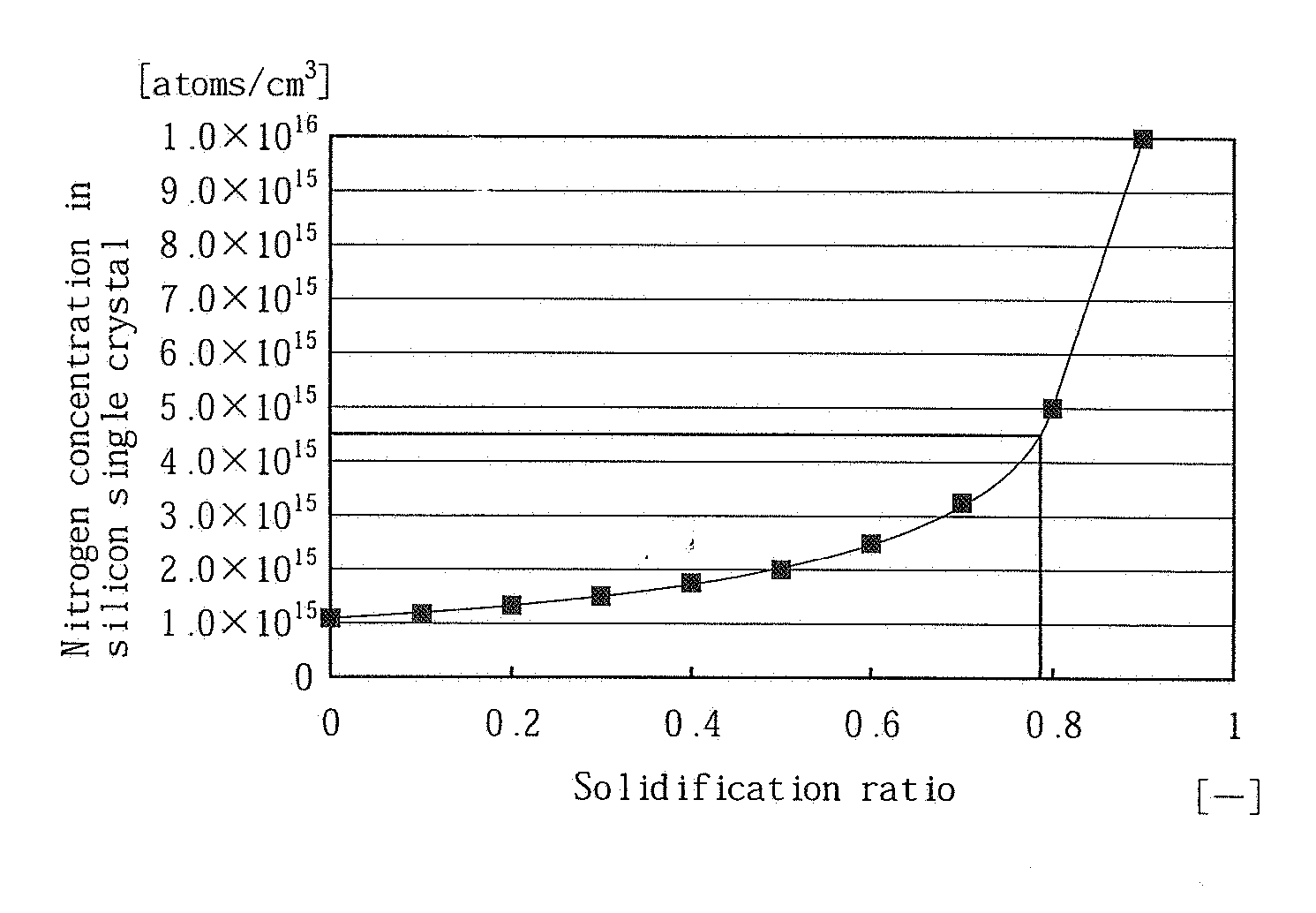

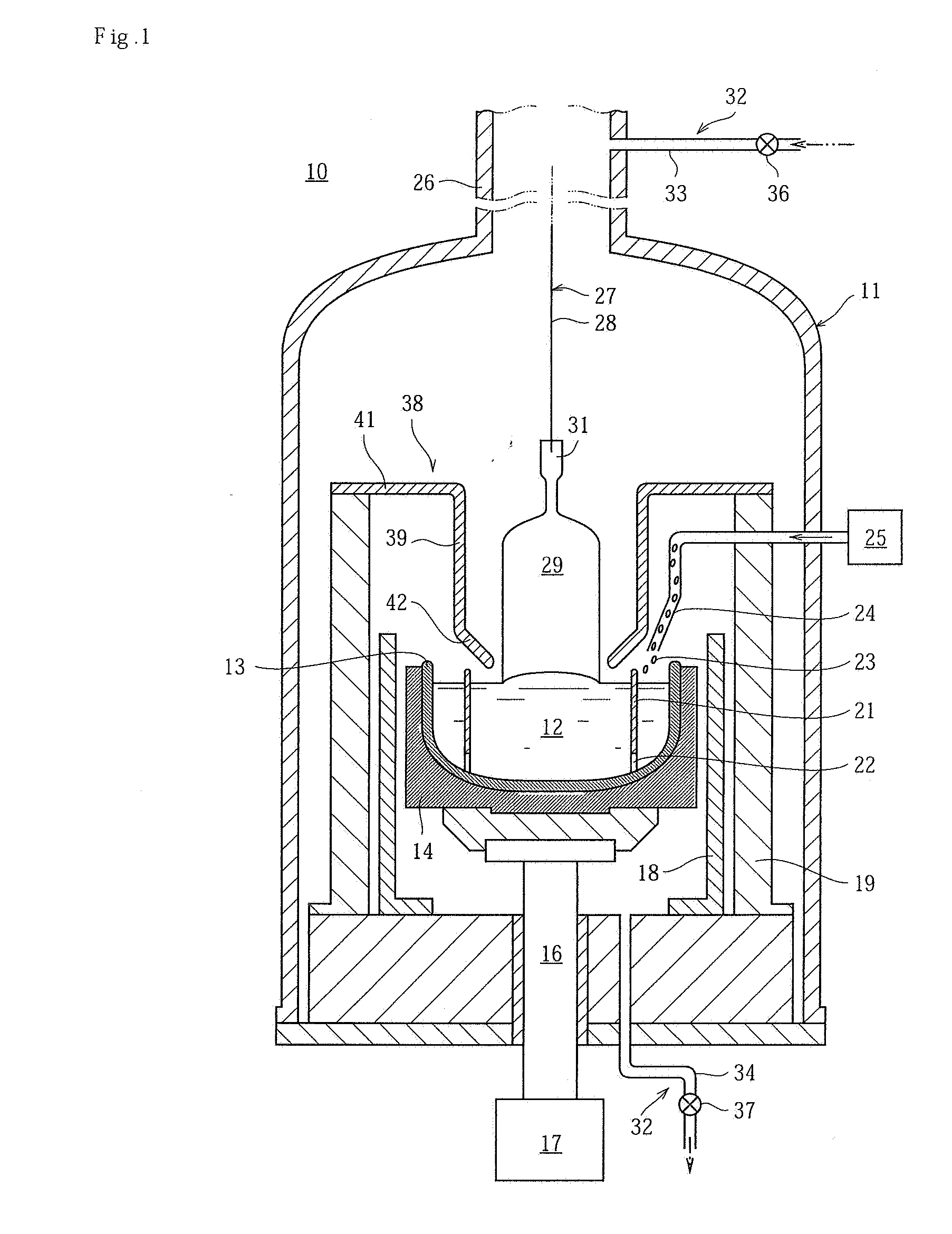

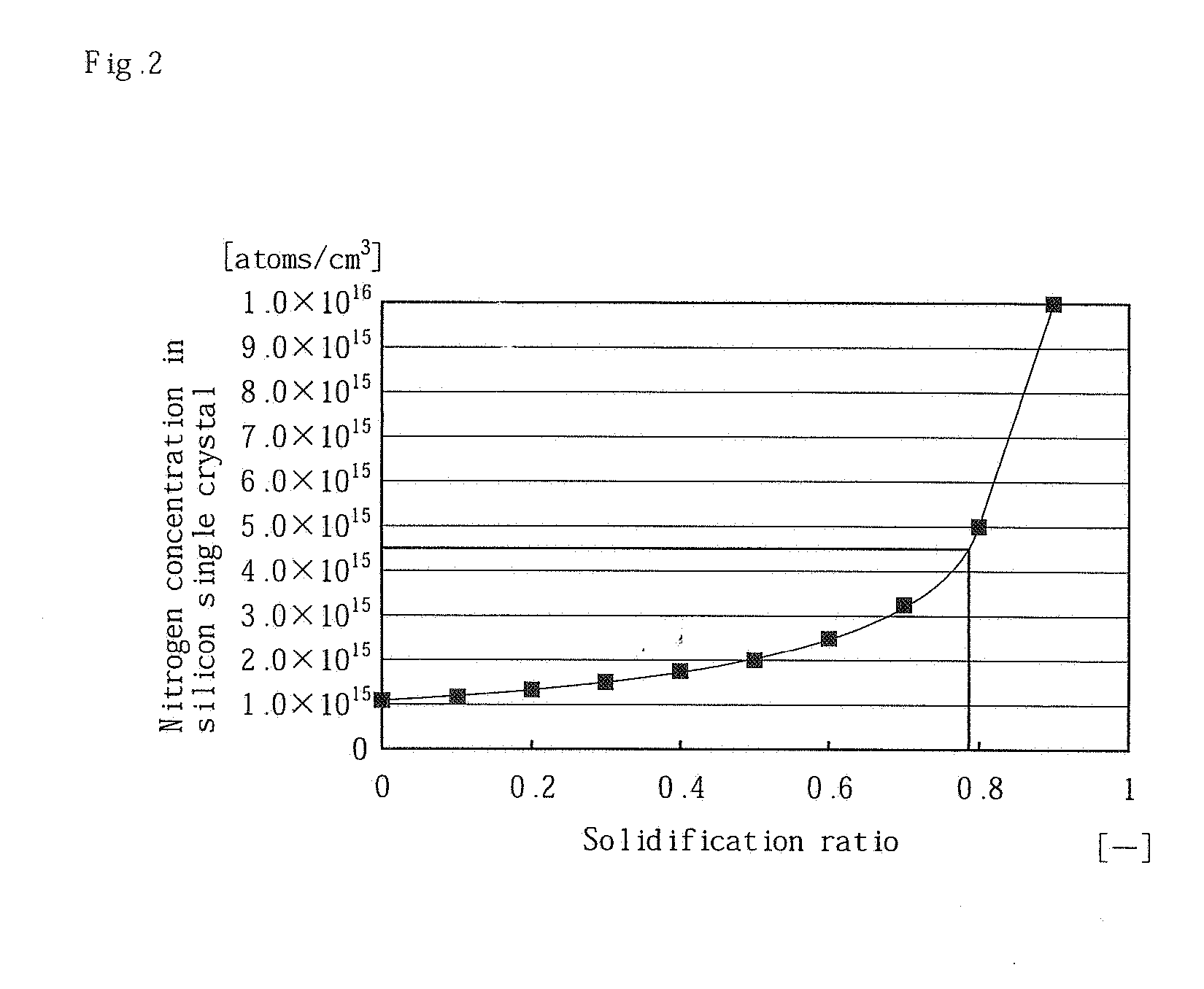

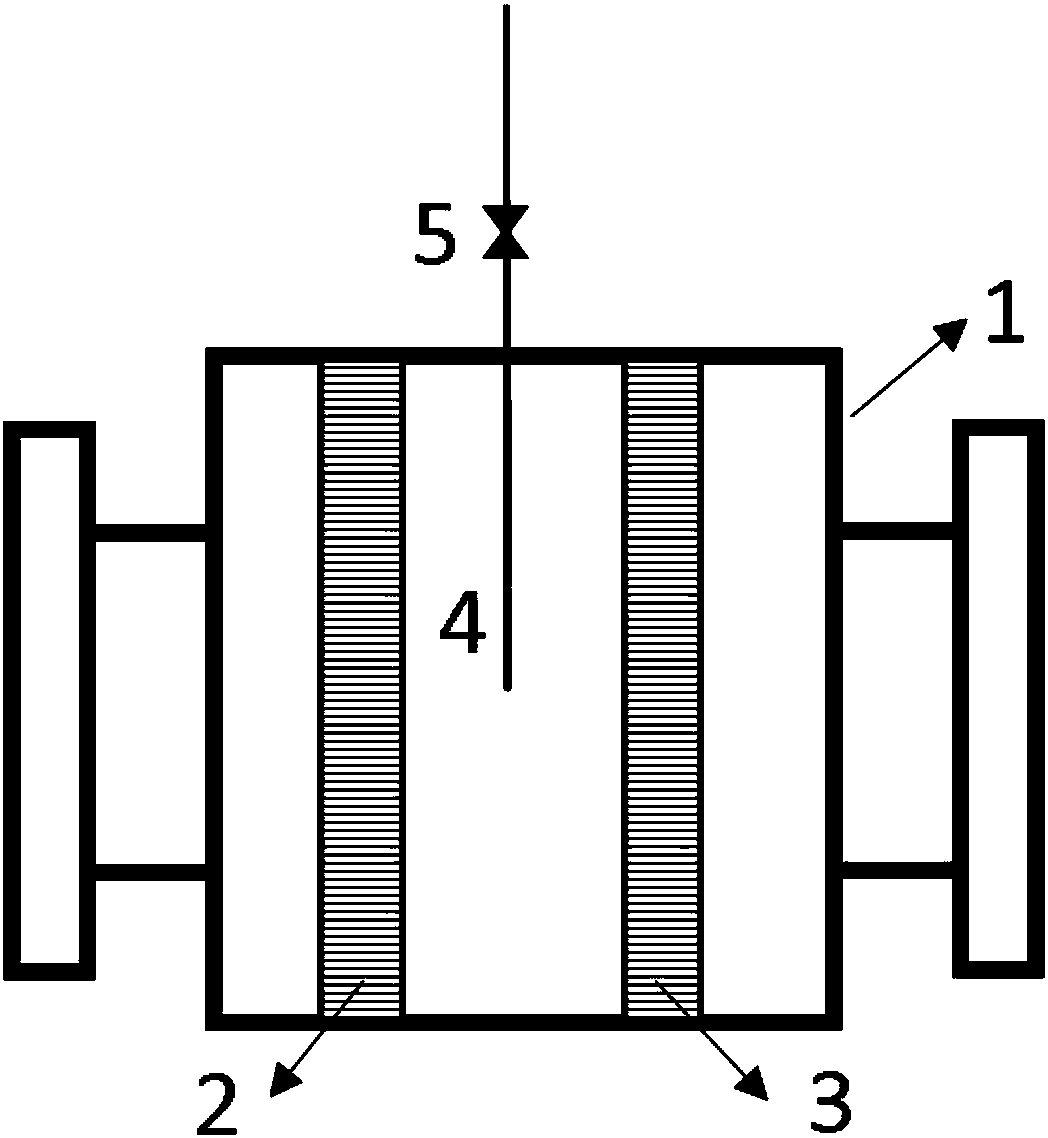

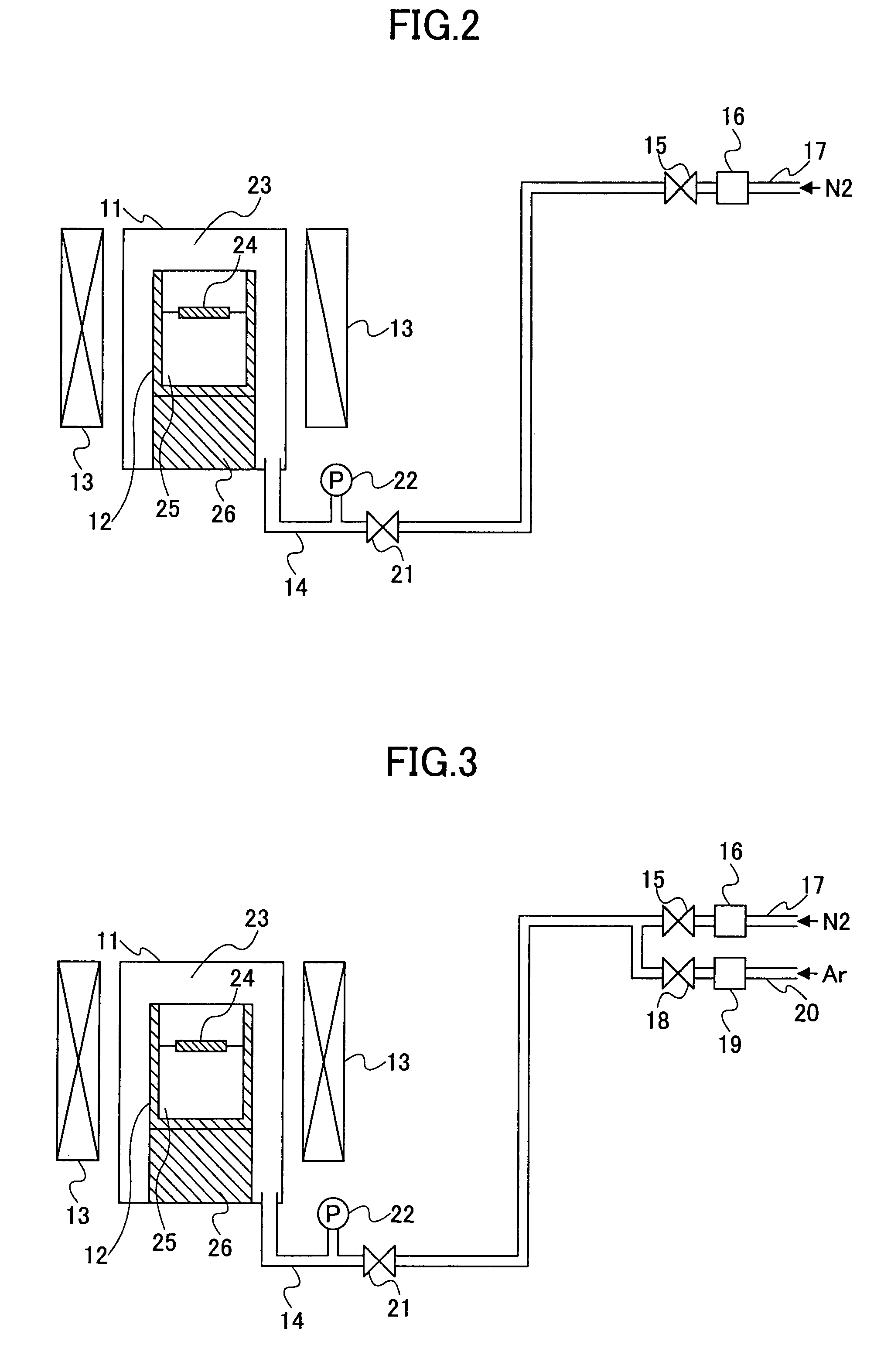

Method For Manufacturing Nitrogen-Doped Silicon Single Crystal

InactiveUS20060254499A1Increase nitrogen concentrationLimited amountPolycrystalline material growthSemiconductor/solid-state device manufacturingHigh concentrationNitrogen doped

There is provided an improvement in a method for manufacturing a silicon single crystal in which nitrogen is doped at a rate which is not smaller than 1×1015 atoms / cm3 and less than 4.5×1015 atoms / cm3 by pulling up a silicon single crystal 29 from a silicon melt 12 which is stored in a quartz crucible 13 and contains nitrogen, wherein the single crystal is pulled up while supplying a silicon raw material 23 which does not contain nitrogen into the silicon melt 12 in such a manner that the liquid level position of the silicon melt stored in the quartz crucible is maintained constant in accordance with the amount of growth of the single crystal. The amount of nitrogen contained in a pulled-up silicon single crystal is controlled, and hence a uniform nitrogen concentration can be obtained along the axial direction of the single crystal. The pull-up length of the silicon single crystal in which nitrogen is doped at a high concentration can be increased.

Owner:SUMCO CORP

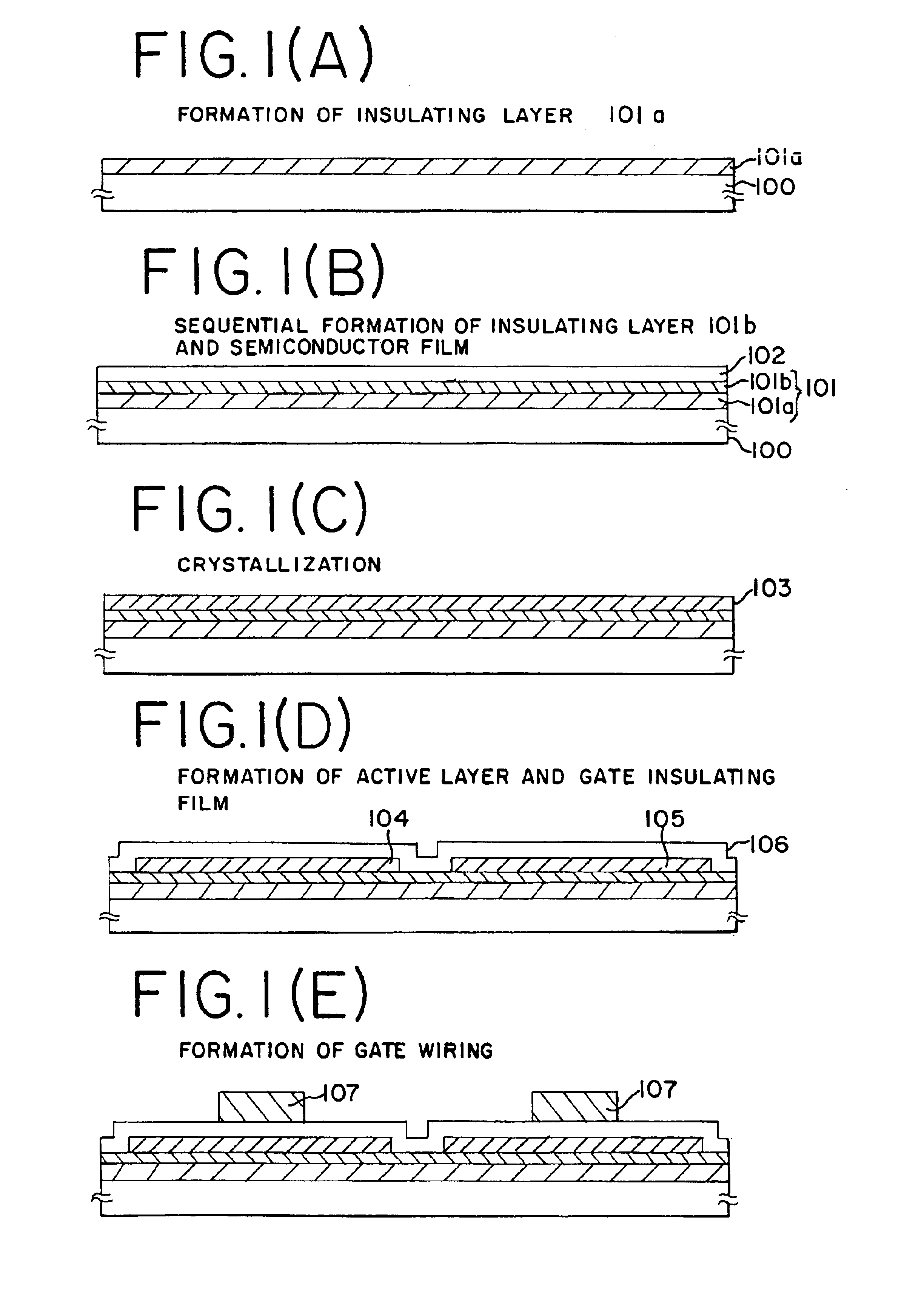

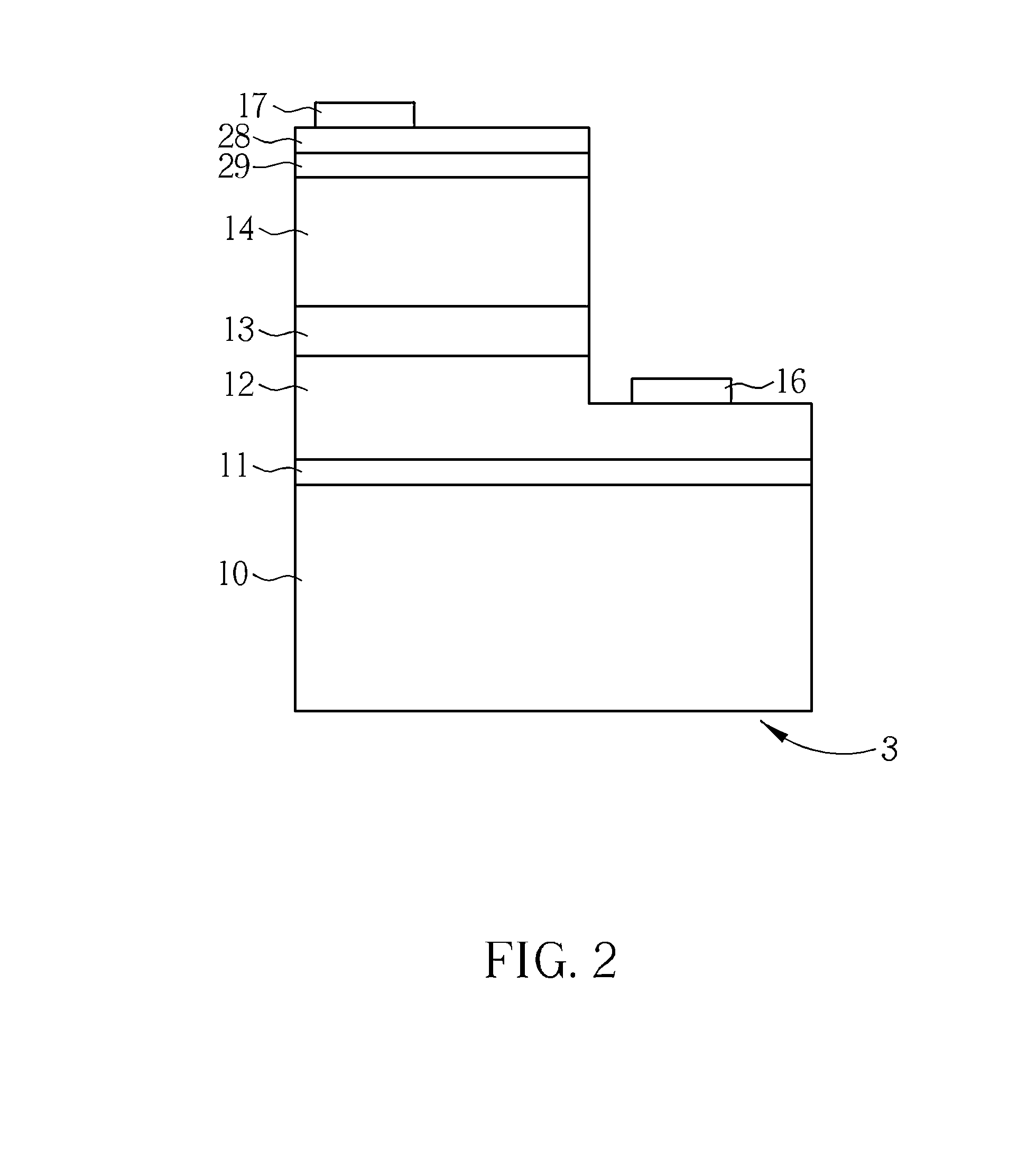

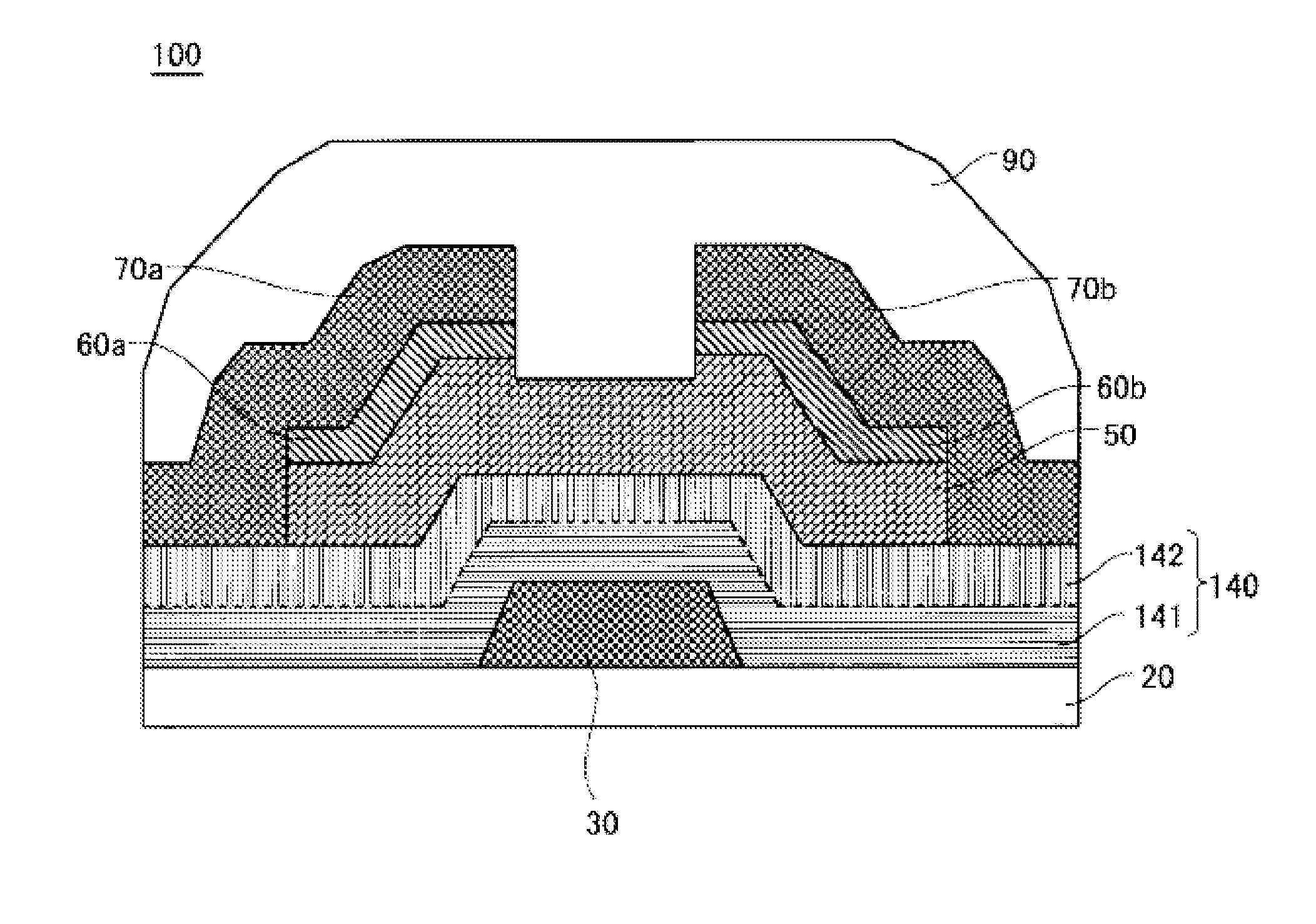

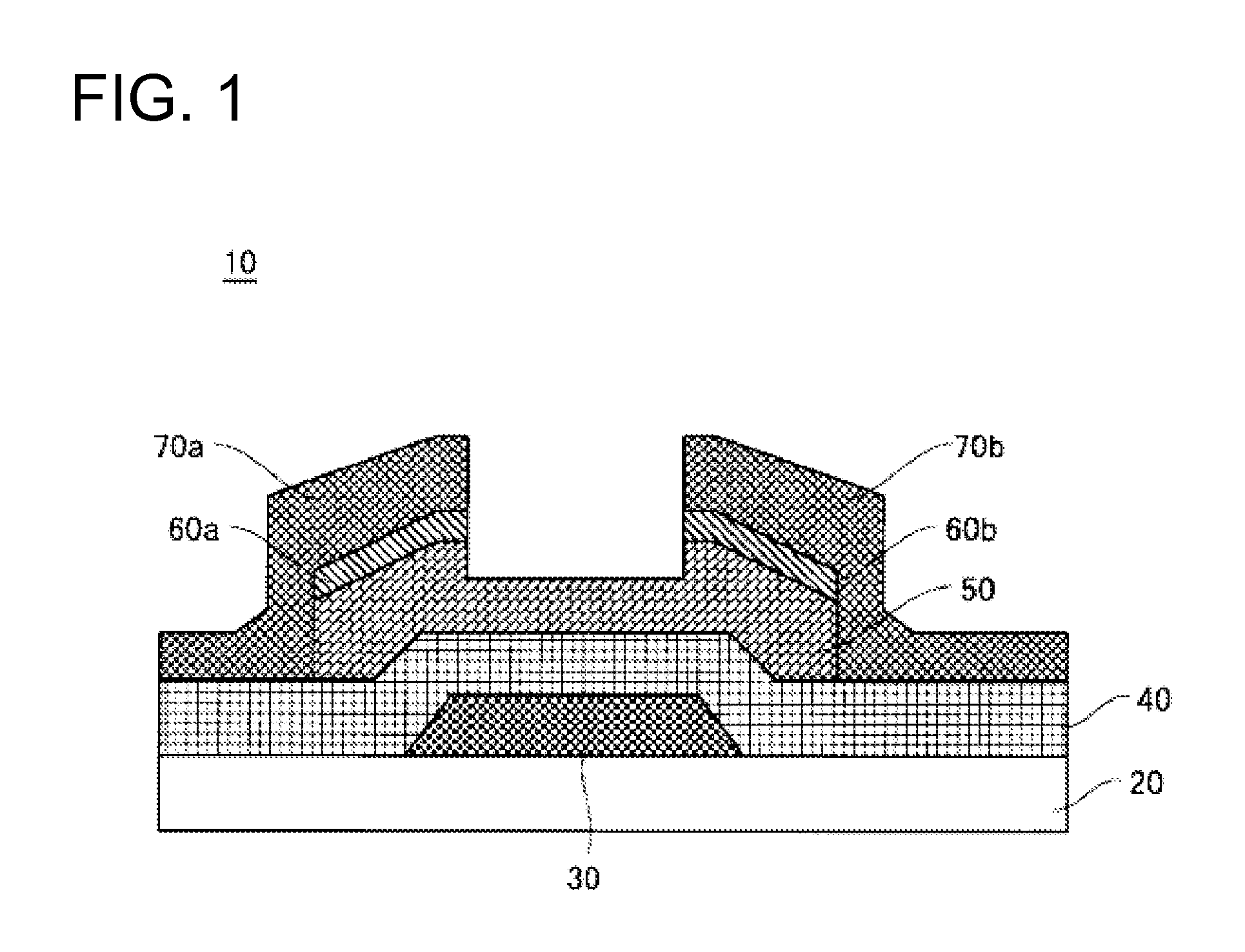

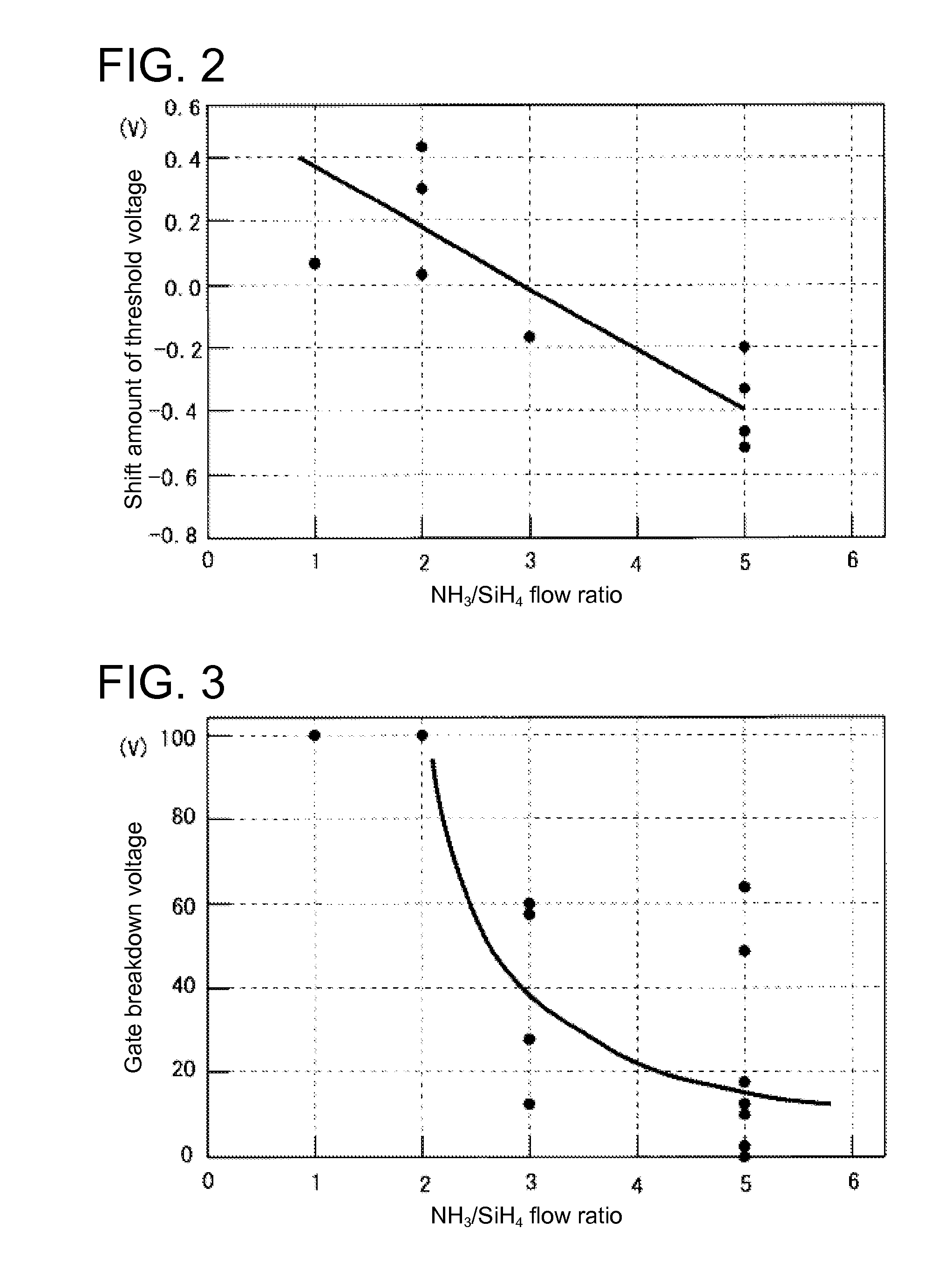

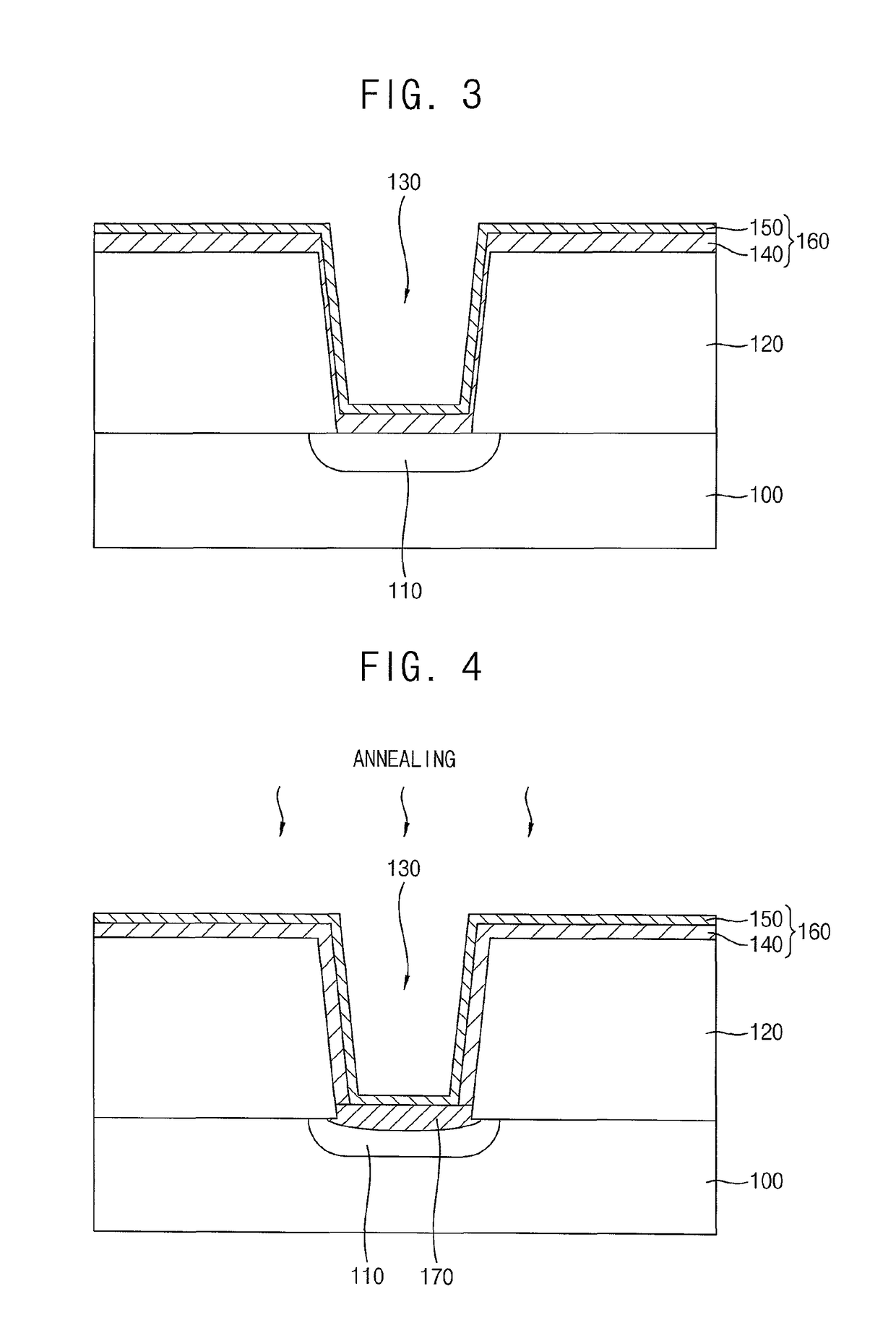

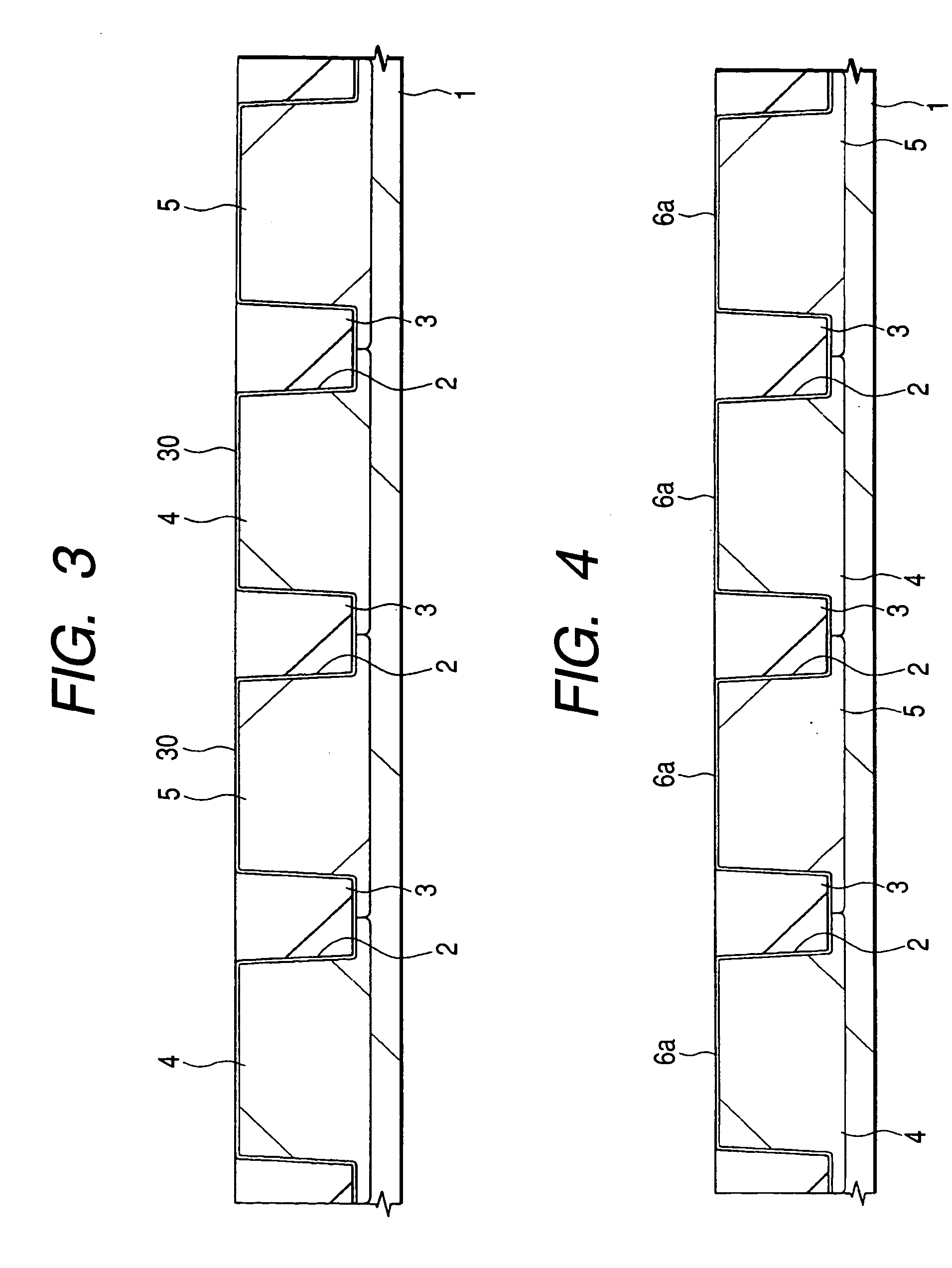

Thin film transistor and method for producing the same

InactiveUS20120104403A1Increase in amount of threshold can be suppressedHigh dielectric breakdown voltageTransistorSemiconductor/solid-state device manufacturingBlock effectNitrogen

An object of the present invention is to provide a thin film transistor having a gate insulating film for suppressing a shift amount of a threshold voltage generated by use under a high temperature environment. In a thin film transistor having a channel layer made of microcrystalline silicon, a gate insulating film 140 is a film obtained by laminating a first silicon nitride film 141 having a nitrogen concentration of 6×1021 atoms / cc or less and a second silicon nitride film 142 having a nitrogen concentration higher than 6×1021 atoms / cc. Therefore, the second silicon nitride film 142 increases the blocking effect against mobile ions entering from a glass substrate 20 to make the mobile ions less likely to be stored in an interface with a channel layer 50. The first silicon nitride film 141 increases the dielectric breakdown voltage of the gate insulating film 140.

Owner:SHARP KK

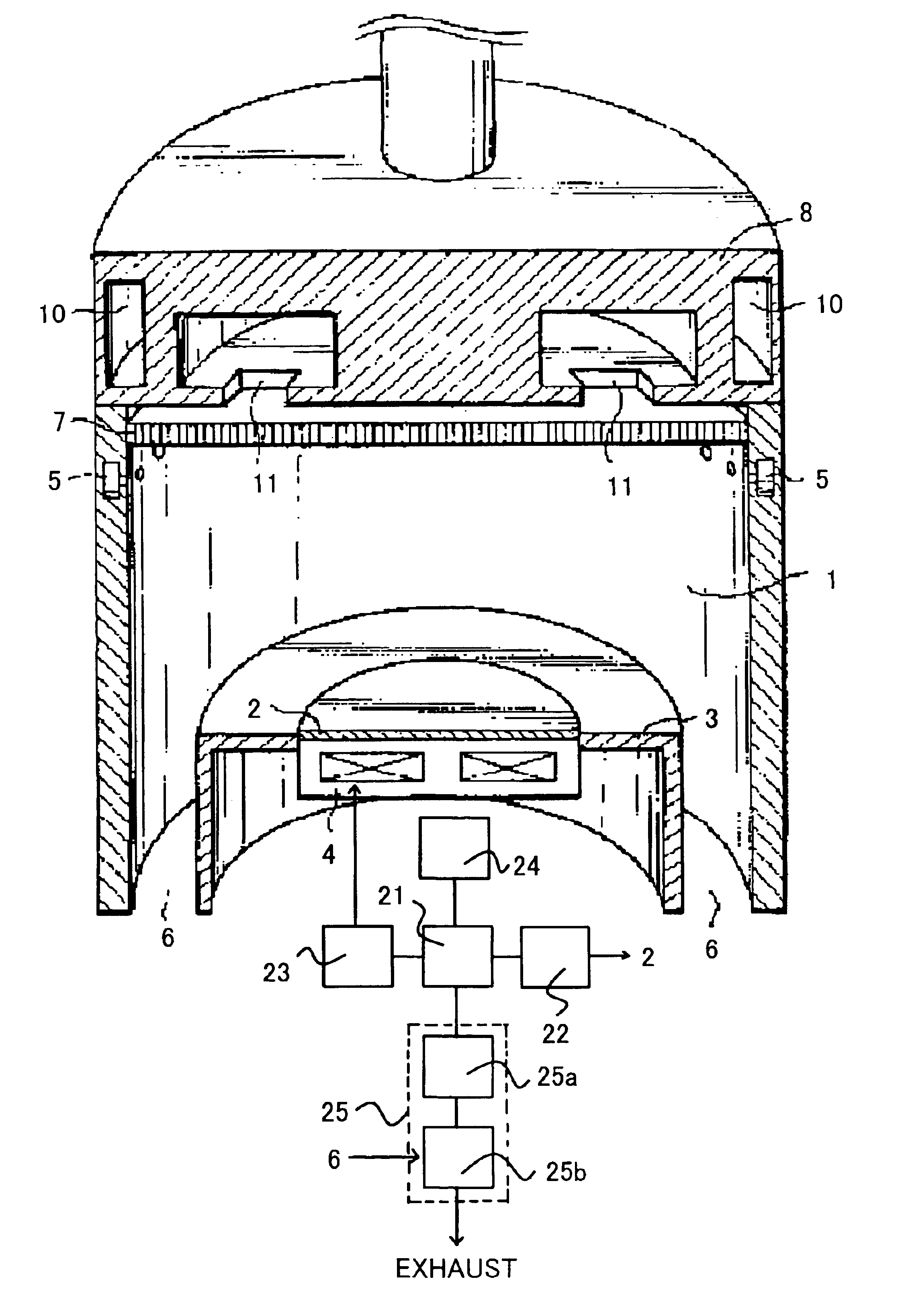

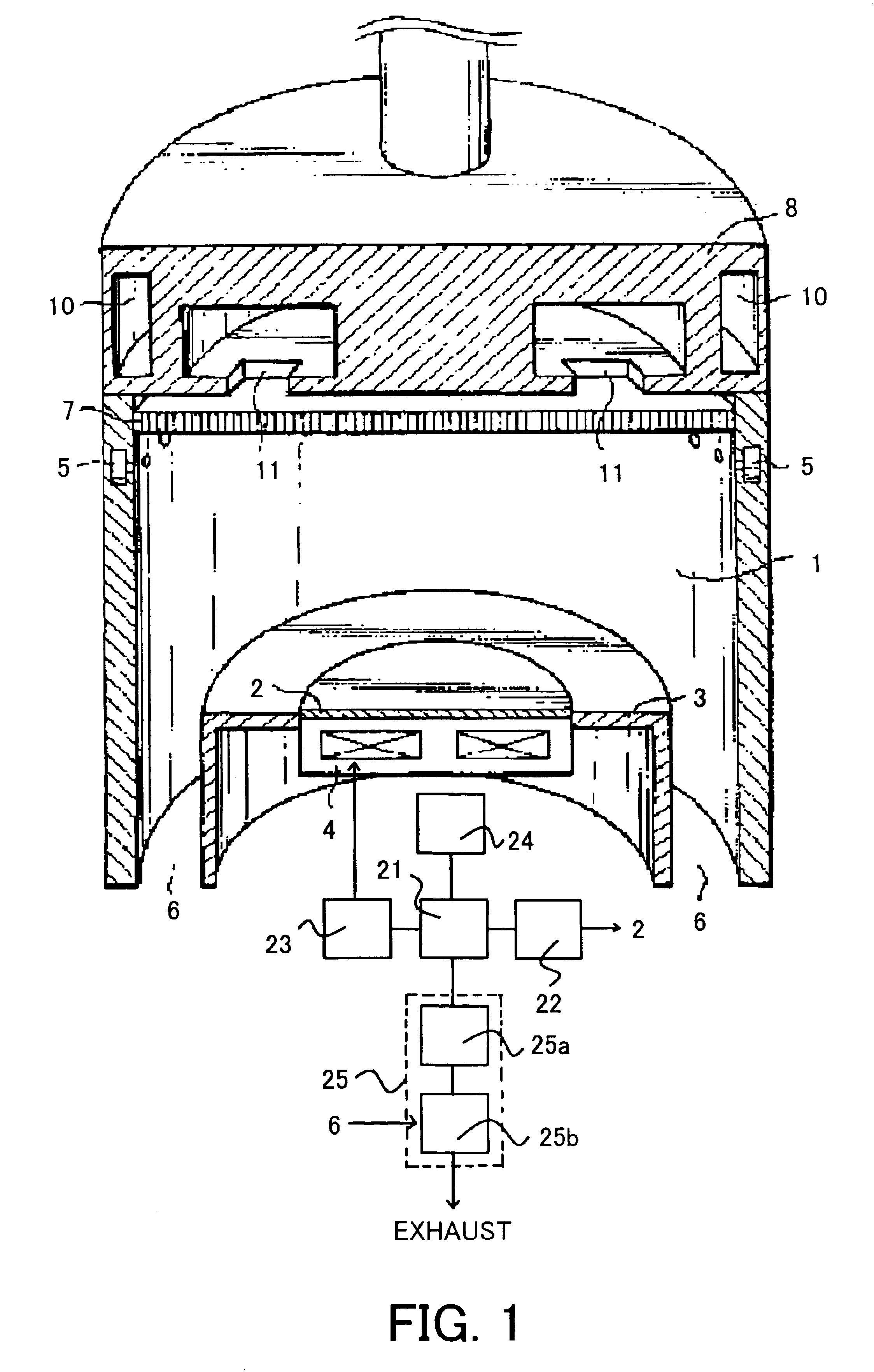

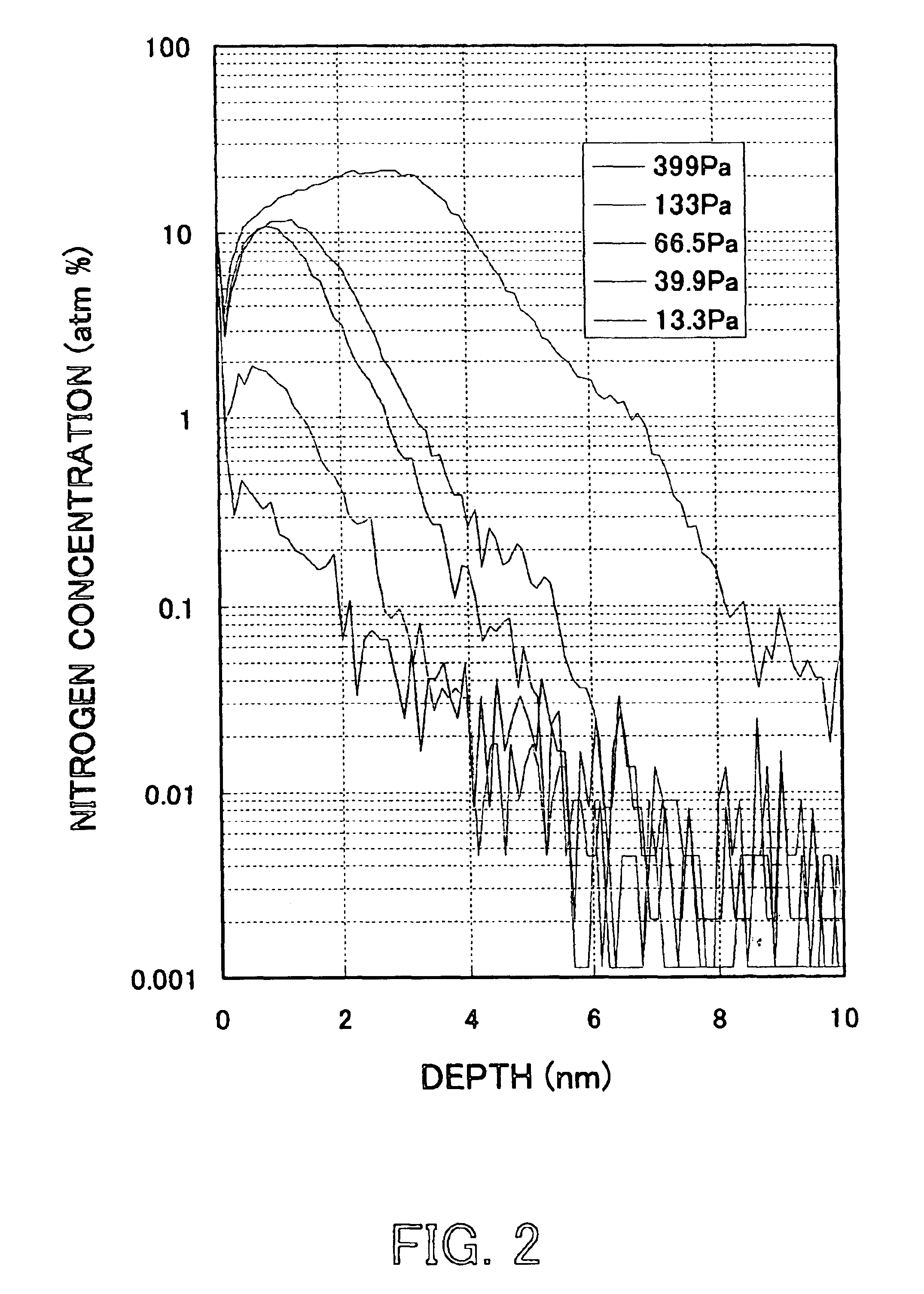

Surface modification method

InactiveUS6916678B2Increase nitrogen concentrationQuick modificationElectric discharge tubesSemiconductor/solid-state device manufacturingNitrogenMixed gas

A method for modifying a surface of a substrate to be processed, by utilizing plasma includes the steps of adjusting a temperature of the substrate from 200° C. to 400° C., introducing gas including nitrogen atoms or mixture gas including inert gas and the gas including nitrogen atoms into a plasma process chamber, adjusting pressure in the plasma process chamber above 13.3 Pa, generating plasma in the plasma process chamber, and injecting ions equal to or smaller than 10 eV in the plasma into the substrate to be processed.

Owner:CANON KK

Charge trapping memory cell having bandgap engineered tunneling structure with oxynitride isolation layer

ActiveUS8169835B2Solve the lack of heightAvoid insufficient thicknessSolid-state devicesRead-only memoriesTrappingIsolation layer

A band gap engineered, charge trapping memory cell includes a charge storage structure including a trapping layer. a blocking layer, and a dielectric tunneling structure including a thin tunneling layer, a thin bandgap offset layer and a thin isolation layer comprising silicon oxynitride. The memory cell is manufactured using low thermal budget processes.

Owner:MACRONIX INT CO LTD

Temperature stable metal nitride gate electrode

InactiveUS20060040439A1Eliminate the effects ofIncrease nitrogen concentrationSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricNitrogen

An integrated circuit is provided including an FET gate structure formed on a substrate. This structure includes a gate dielectric on the substrate, and a metal nitride layer overlying the gate dielectric and in contact therewith. This metal nitride layer is characterized as MNx, where M is one of W, Re, Zr, and Hf, and x is in the range of about 0.7 to about 1.5. Preferably the layer is of WNx, and x is about 0.9. Varying the nitrogen concentration in the nitride layer permits integration of different FET characteristics on the same chip. In particular, varying x in the WNx layer permits adjustment of the threshold voltage in the different FETs. The polysilicon depletion effect is substantially reduced, and the gate structure can be made thermally stable up to about 1000° C.

Owner:GLOBALFOUNDRIES INC

Method for manufacturing a semiconductor device having a nitrogen-containing gate insulating film

InactiveUS8105959B2Increase nitrogen concentrationImprove featuresSemiconductor/solid-state device manufacturingPower semiconductor deviceNitrogen

A method for manufacturing a semiconductor device includes the steps of: forming a SiO2 layer on a silicon substrate; forming on the SiO2 layer an SiN film having a N / Si composition ratio smaller than the stoichiometric composition ratio of SiN by using the ALD technique; and performing a plasma-nitriding process on the SiN layer at a substrate temperature of 550 degrees C. or below.

Owner:PS4 LUXCO SARL

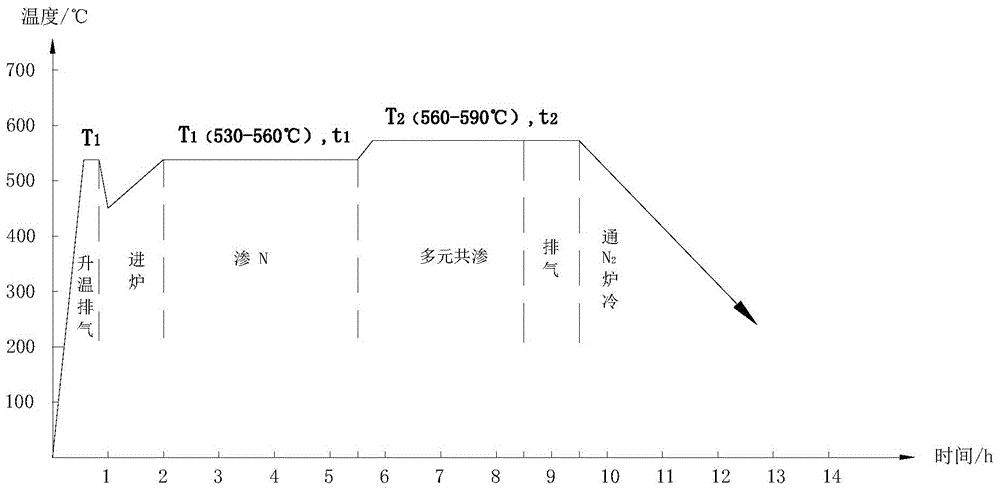

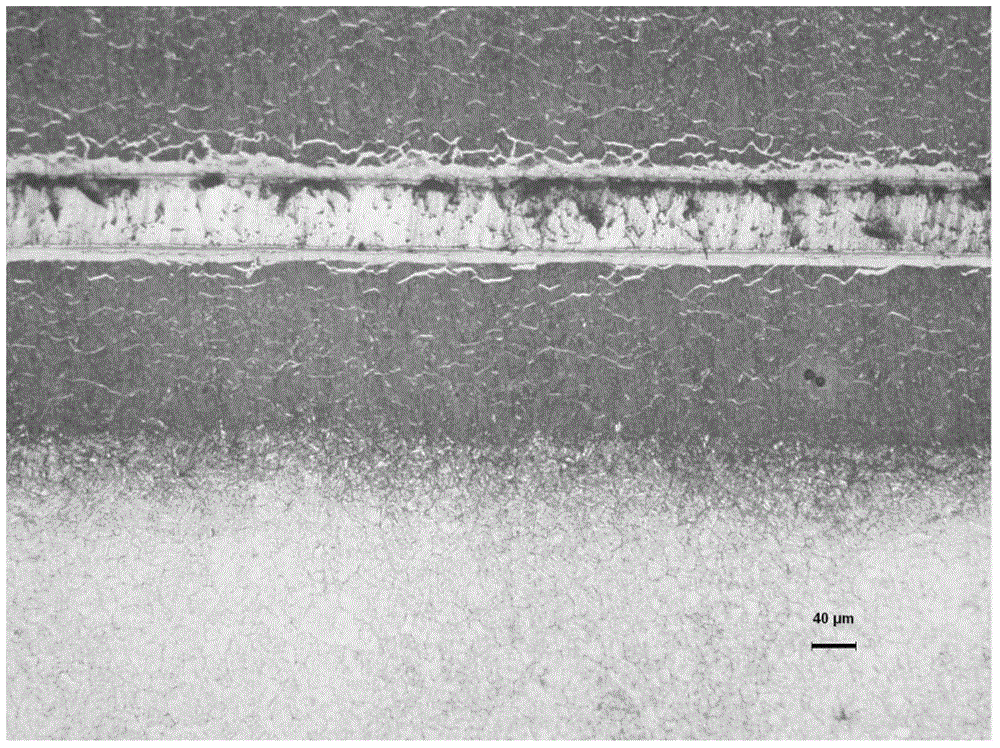

Aluminum extrusion die and surface strengthening and toughening treatment process

ActiveCN103981482AThe hardness gradient is more gentle thanDelay peeling timeSolid state diffusion coatingRare earthHardness

The invention relates to an aluminum extrusion die and its surface strengthening and toughening treatment process. The process aims to improve surface strengthening and toughening performance of the aluminum extrusion die. By a two-stage process of doping of N before multi-element penetration of O-S-N, thicknesses of a strengthened layer and a diffusion layer in a penetration layer are both increased at different levels in comparison with an isothermal method, and it is ensured that bonding ability of the penetration layer and a matrix is better. Hardness gradient of the penetration layer is milder, penetration layer peeling time is put off, and life of the die is effectively prolonged. In addition, based on the two-stage process, thickness and strength of the diffusion layer are both raised effectively by the use of a Ce / La rare earth compound for catalysis and by the use of an NH4Cl powder for cleaning and penetration treatments; and an antifriction complex phase layer containing Fel-xS and Fe3O4 phases and a strengthened layer containing Fe2-3N, gamma'-Fe4N and other high hardness and toughness phases can be obtained. Thus, the penetration layer satisfies ideal wearing layer conditions of tribological requirements.

Owner:FUJIAN NANPING ALUMINUM

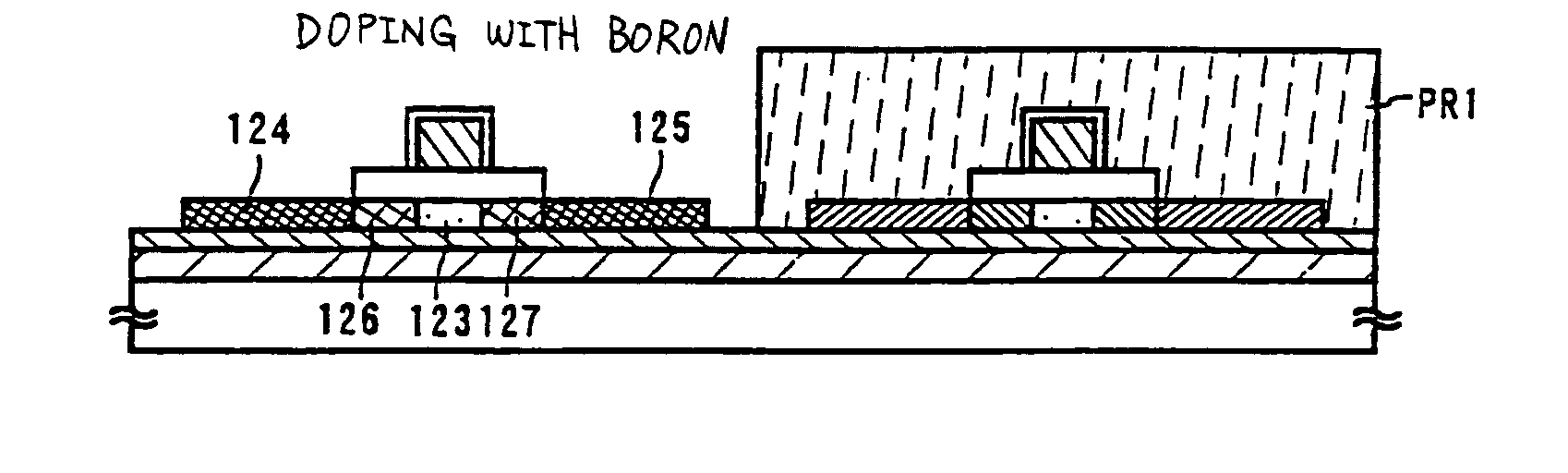

Semiconductor device and method for manufacturing the same

InactiveUS20050116294A1Improve reliabilityEliminate the problemTransistorSolid-state devicesDevice materialSilicon oxide

An object of the present invention is to prevent the deterioration of a TFT (thin film transistor). The deterioration of the TFT by a BT test is prevented by forming a silicon oxide nitride film between the semiconductor layer of the TFT and a substrate, wherein the silicon oxide nitride film ranges from 0.3 to 1.6 in a ratio of the concentration of N to the concentration of Si.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device including contact plug and method of manufacturing the same

ActiveUS10134856B2Increase nitrogen concentrationLower resistanceTransistorSemiconductor/solid-state device detailsDevice materialMetal silicide

A semiconductor device includes an active fin partially protruding from an isolation pattern on a substrate, a gate structure on the active fin, a source / drain layer on a portion of the active fin adjacent to the gate structure, a source / drain layer on a portion of the active fin adjacent to the gate structure, a metal silicide pattern on the source / drain layer, and a plug on the metal silicide pattern. The plug includes a second metal pattern, a metal nitride pattern contacting an upper surface of the metal silicide pattern and covering a bottom and a sidewall of the second metal pattern, and a first metal pattern on the metal silicide pattern, the first metal pattern covering an outer sidewall of the metal nitride pattern. A nitrogen concentration of the first metal pattern gradually decreases according to a distance from the outer sidewall of the metal nitride pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

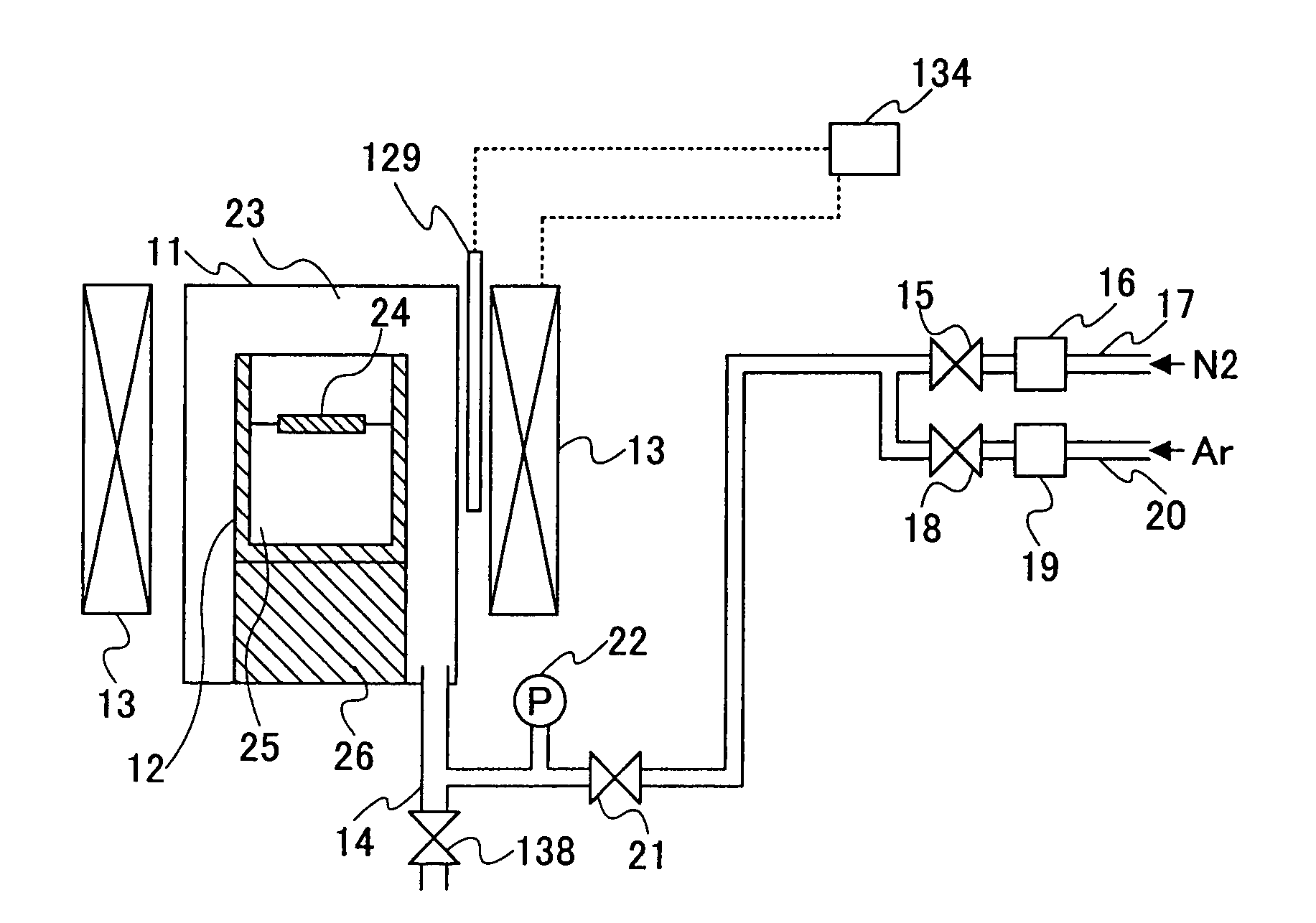

Method of manufacturing a semiconductor integrated circuit device

InactiveUS20050020018A1Increase nitrogen concentrationConcentration of nitrogen near the interface between the film and the substrate can be increasedTransistorSolid-state devicesNitrogen plasmaPeak value

A method of manufacturing a semiconductor integrated circuit device comprising forming a silicon oxide film as thin as 5 nm or less on the surfaces of p type wells and n type wells by wet oxidizing a substrate, heating the substrate in an atmosphere containing about 5% of an NO gas to introduce nitrogen into the silicon oxide film so as to form a silicon oxynitride film, exposing the substrate to a nitrogen plasma atmosphere to further introduce nitrogen into the silicon oxynitride film in order to form a silicon oxynitride gate insulating film having a first peak concentration near the interface with the substrate and a second peak concentration near the surface thereof. Thereby, the concentration of nitrogen in the gate insulating film is increased without raising the concentration of nitrogen near the interface between the substrate and the gate insulating film to a higher level than required.

Owner:RENESAS ELECTRONICS CORP

Semiconductor process

ActiveUS8889523B2Improve device performanceReduce total nitrogen concentrationSemiconductor/solid-state device manufacturingMetallurgySemiconductor package

Owner:UNITED MICROELECTRONICS CORP

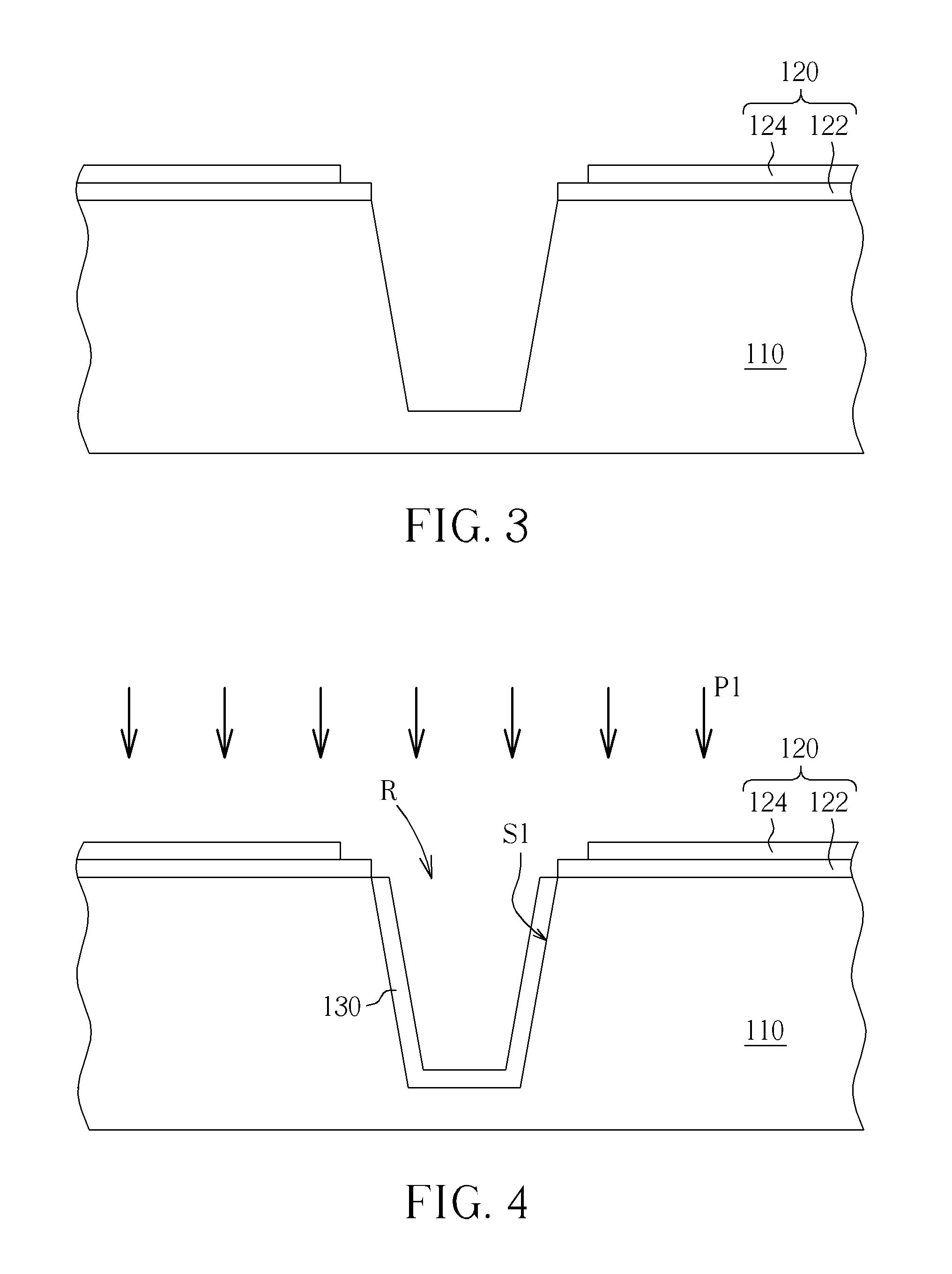

Flame arrester with self-cleaning function

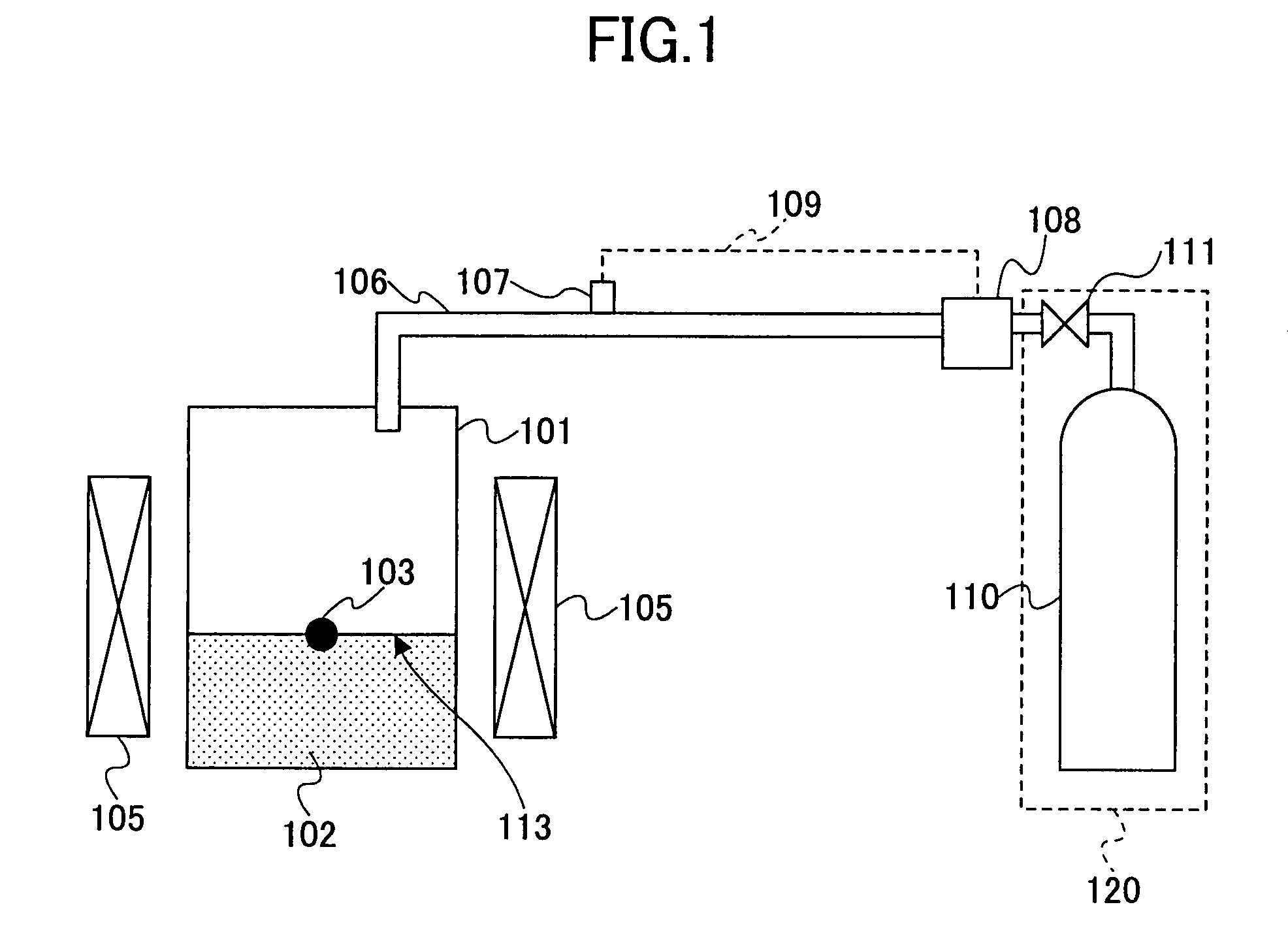

PendingCN110013630AAchieve self-cleaning effectReduce the temperatureFire rescueCleaning using gasesFlame arresterFlame propagation

The invention relates to a flame arrester with a self-cleaning function. The flame arrester mainly solves the problem that a flame arrester in the prior art is likely to be blocked. The flame arresterwith the self-cleaning function comprises a flame arrester shell, at least two flame retardant elements, a gas injection channel and a gas throttle valve, the flame retardant elements are distributedon the two sides in the flame arrester, a gas injection channel is arranged between the flame retardant elements, a gas injection pipeline is arranged on the gas injection channel, and a gas throttlevalve is arranged on the portion, outside the flame arrester shell, of the gas injection pipeline. By adopting the technical scheme, the problem is well solved, and the flame arrester can be used forarresting flame propagation.

Owner:CHINA PETROLEUM & CHEM CORP +1

Group III nitride crystal, crystal growth process and crystal growth apparatus of group III nitride

InactiveUS7981213B2Inhibition formationCrystal growth is stablePolycrystalline material growthFrom normal temperature solutionsNitrogenGroup element

A crystal growth method of a group III nitride includes the steps of forming a melt mixture of an alkali metal and a group III element in a reaction vessel, and growing a crystal of a group III nitride formed of the group III element and nitrogen from the melt mixture in the reaction vessel, wherein the step of growing the crystal of the group III nitride is conducted while controlling an increase rate of degree of supersaturation of a group III nitride component in the melt mixture in a surface region of the melt mixture.

Owner:SUMITOMO CHEM CO LTD

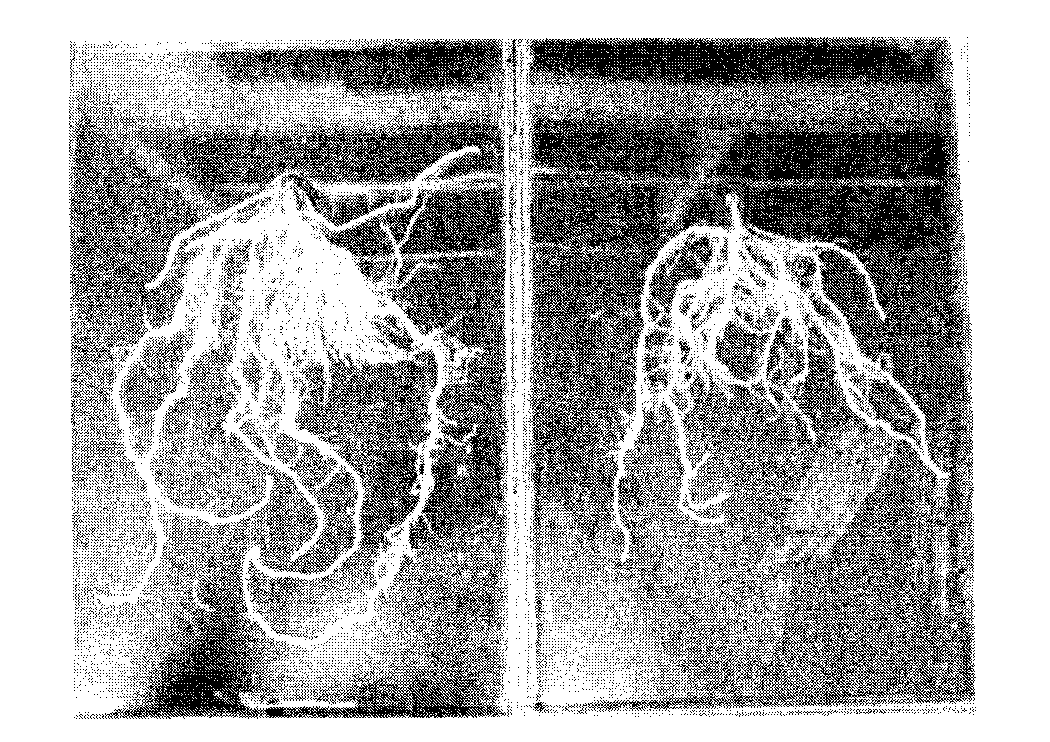

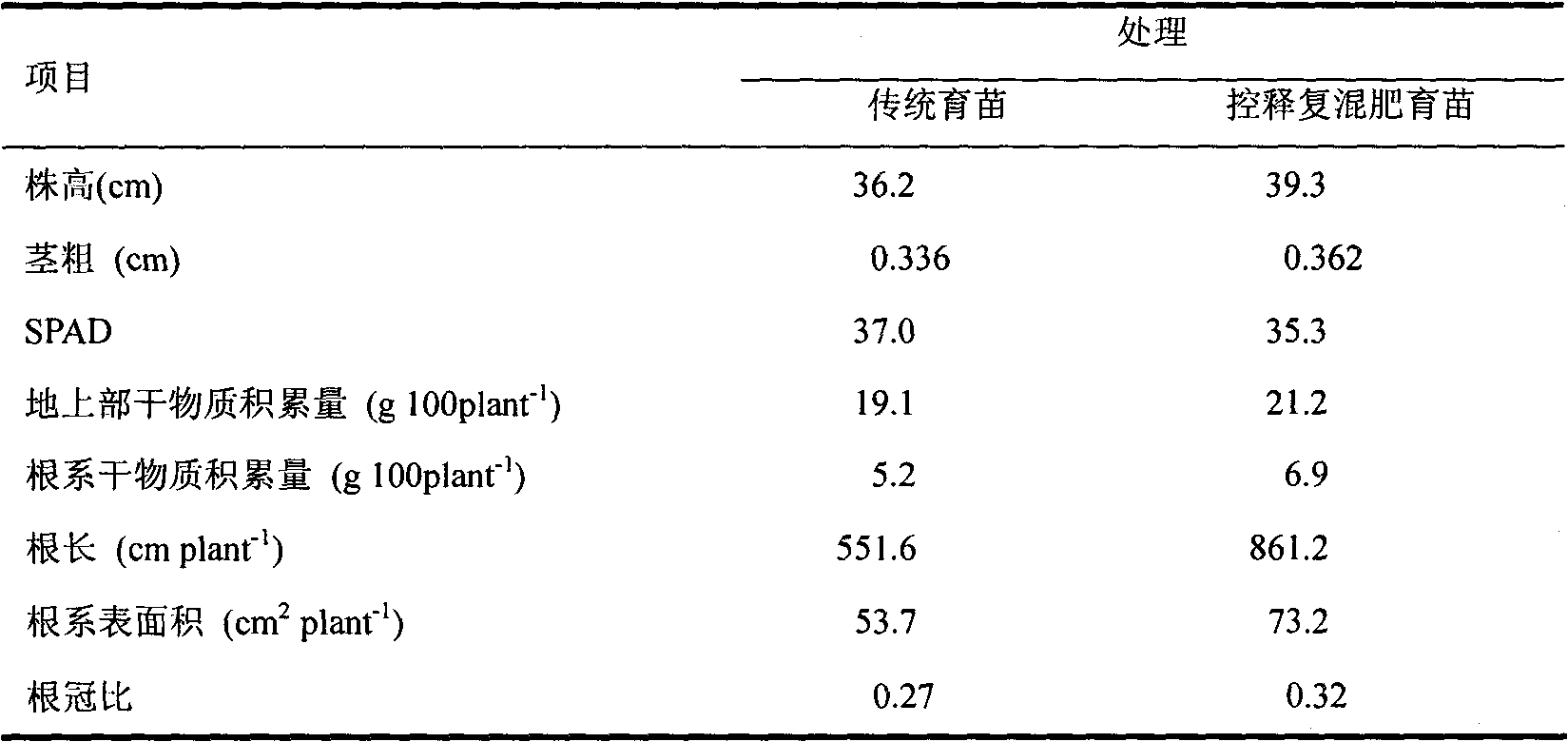

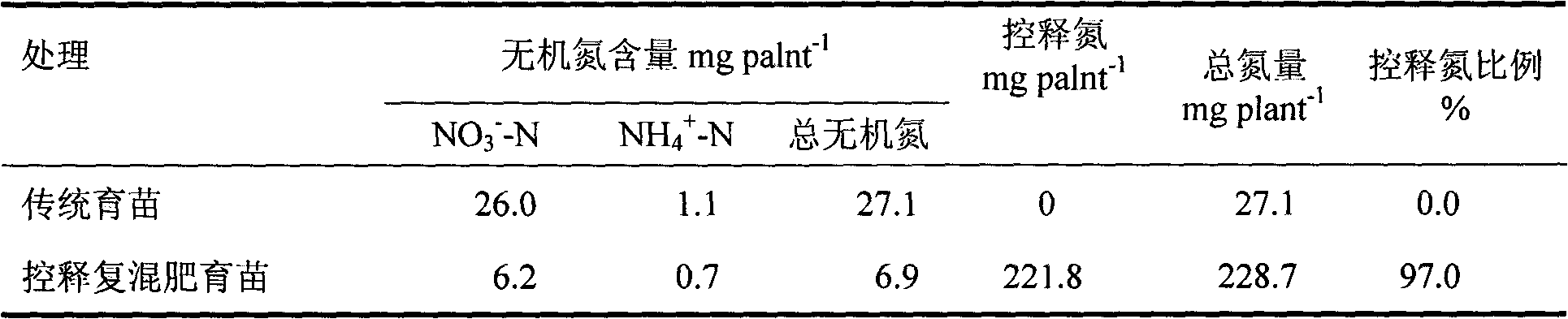

Controlled release compound fertilizer for corn seedling and preparation method thereof

InactiveCN102199046BReduce dosageMeet nutrient needsClimate change adaptationExcrement fertilisersCoated ureaNitrogen fertilization

The invention discloses a controlled release compound fertilizer for corn seedling and a preparation method thereof. The seedling controlled release compound fertilizer comprises coated urea, phosphate fertilizer and potash fertilizer. Nutrient contents are that: 16-24% of N, 11-16% of P2O5, 8-12% of K2O, and preferred is 20% of N, 14% of P2O5 and 10% of K2O, wherein N:P2O5:K2O equals to 1.0:0.7:0.5. The coated urea contains a fertilizer core of common large granule urea, a coating material of polyethylene or polyurethane and 42% of nitrogen, and has an initial stage leaching rate larger than 0 and less than 2% and a release period of 50-70 d; the phosphate fertilizer is granular heavy calcium superphosphate with a P2O5 content of 40-44%; The potash fertilizer is granular potassium sulfate with a K2O content of 50-52%; and the coated urea, granular heavy calcium superphosphate and granular potassium sulfate all have a particle diameter of 3.0-4.0mm. The seedling controlled release compound fertilizer can promote early growth stage of corn, advance fertility process, raise output, reduce nitrogen amount used in early growth stage of corn and nitrogen discharge into environment, increase nitrogen utilization rate. Therefore, the seedling controlled release compound fertilizer has high economic, social and ecologic benefits.

Owner:CHINA AGRI UNIV

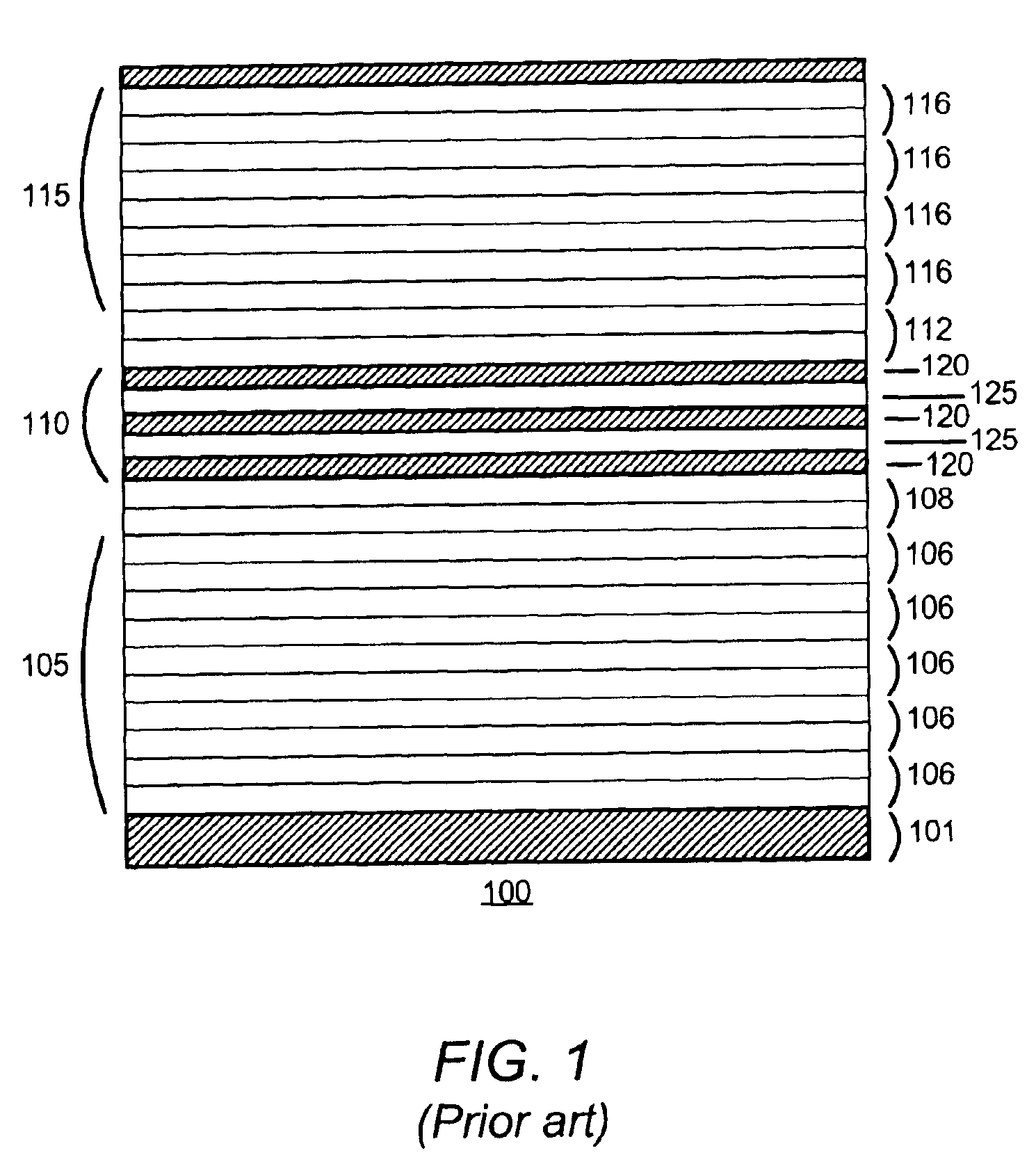

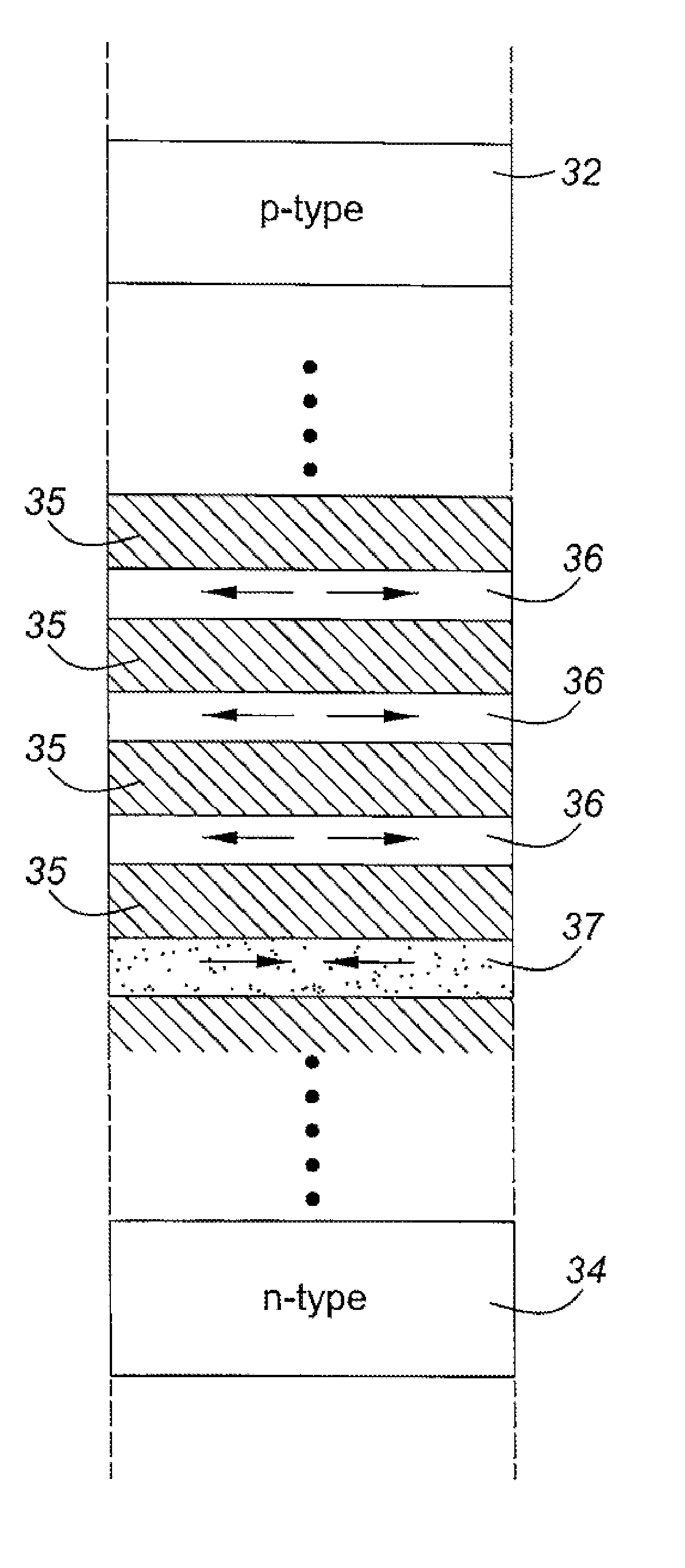

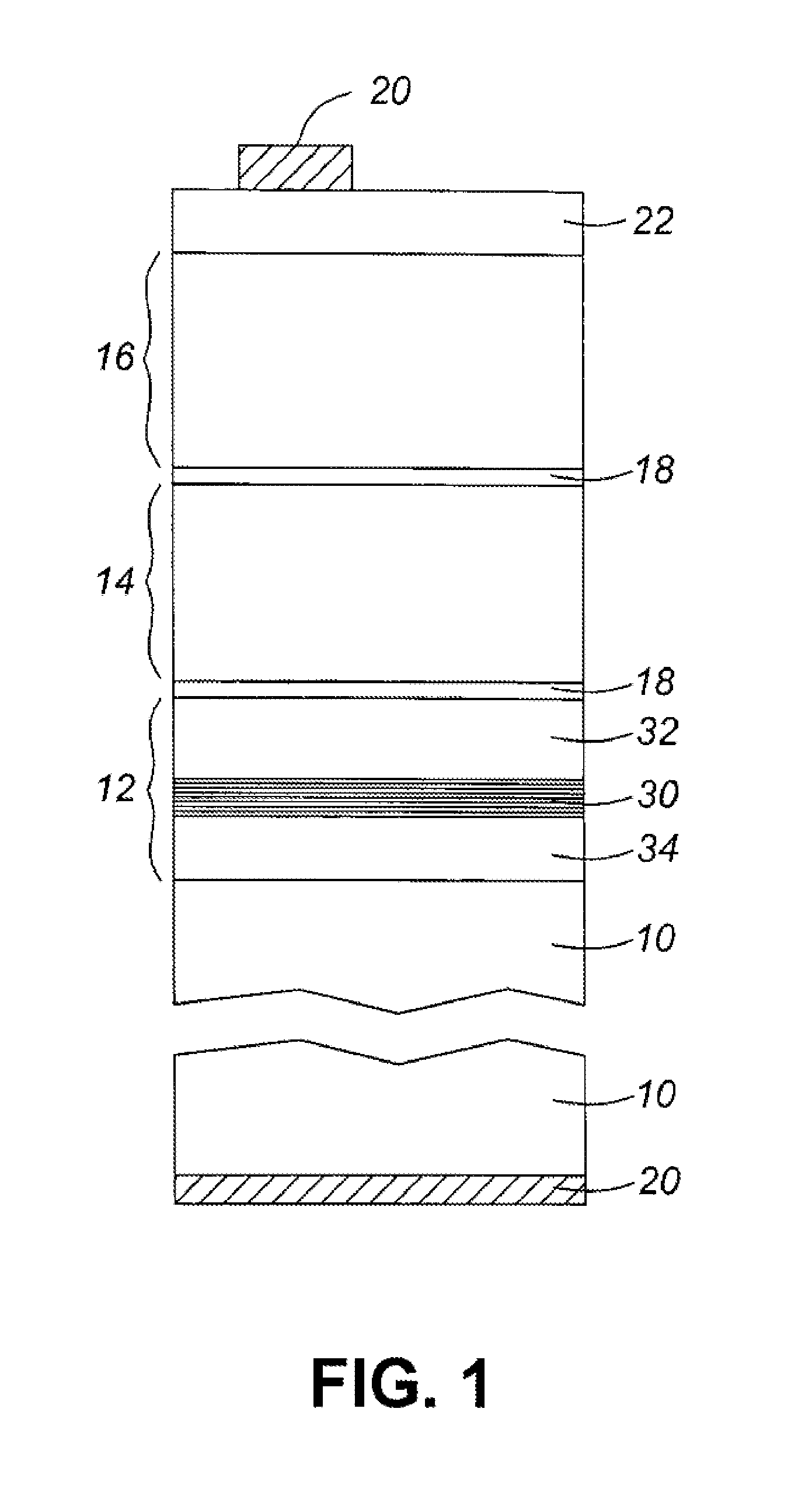

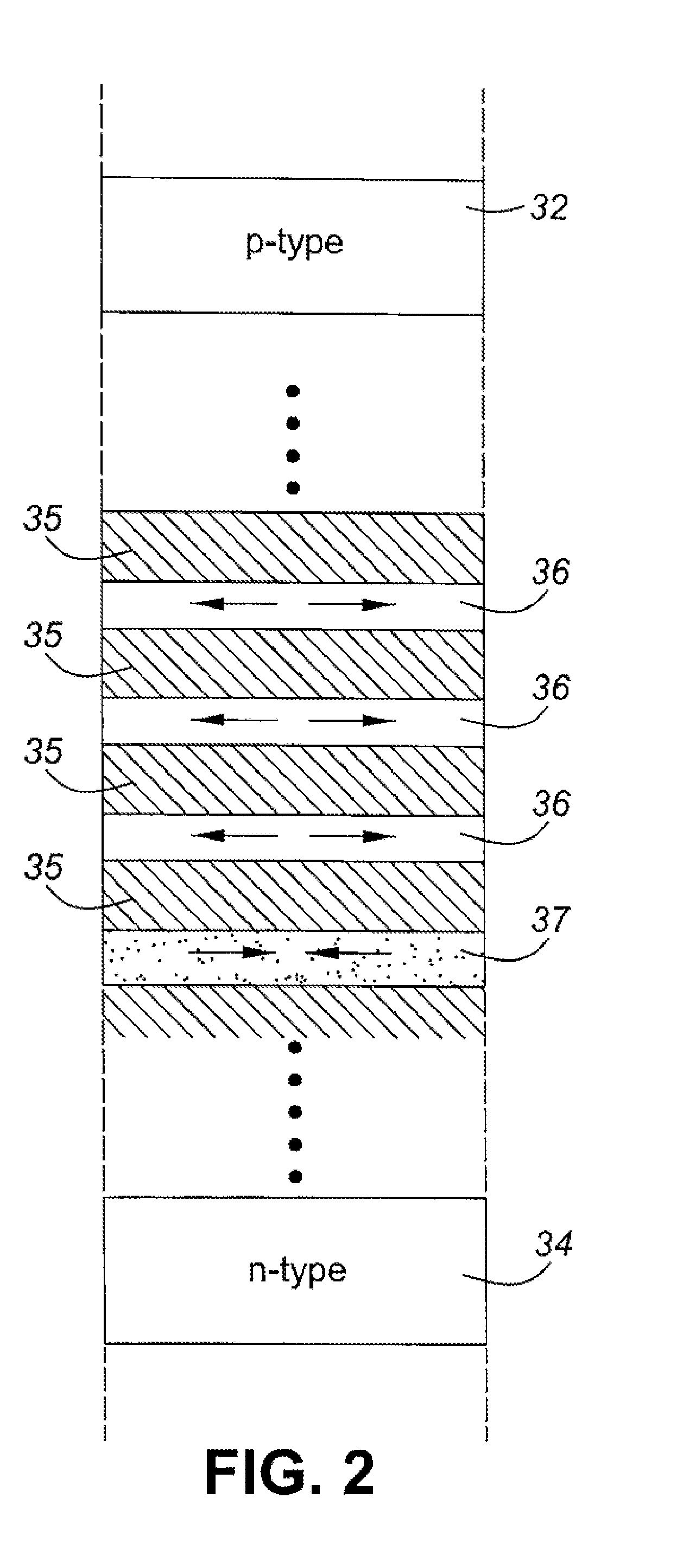

Photovoltaic junction for a solar cell

ActiveUS9368662B2Maximum stress differential between wells and barriers is much reducedReduce impactSemiconductor/solid-state device manufacturingNanoopticsOptical propertySolar cell

A photovoltaic junction for a solar cell is provided. The photovoltaic junction has an intrinsic region comprising a multiple quantum well stack formed from a series of quantum wells separated by barriers, in which the tensile stress in some of the quantum wells is partly or completely balanced by compressive stress in the others of the quantum wells. The overall elastostatic equilibrium of the multiple quantum well stack may be ensured by engineering the structural and optical properties of the quantum wells only, with the barriers having the same lattice constant as the materials used in the oppositely doped semiconductor regions of the junction, or equivalently as the actual lattice size of the junction or intrinsic region, or the bulk or effective lattice size of the substrate. Alternatively, the barriers may contribute to the stress balance.

Owner:LUMENTUM OPERATIONS LLC

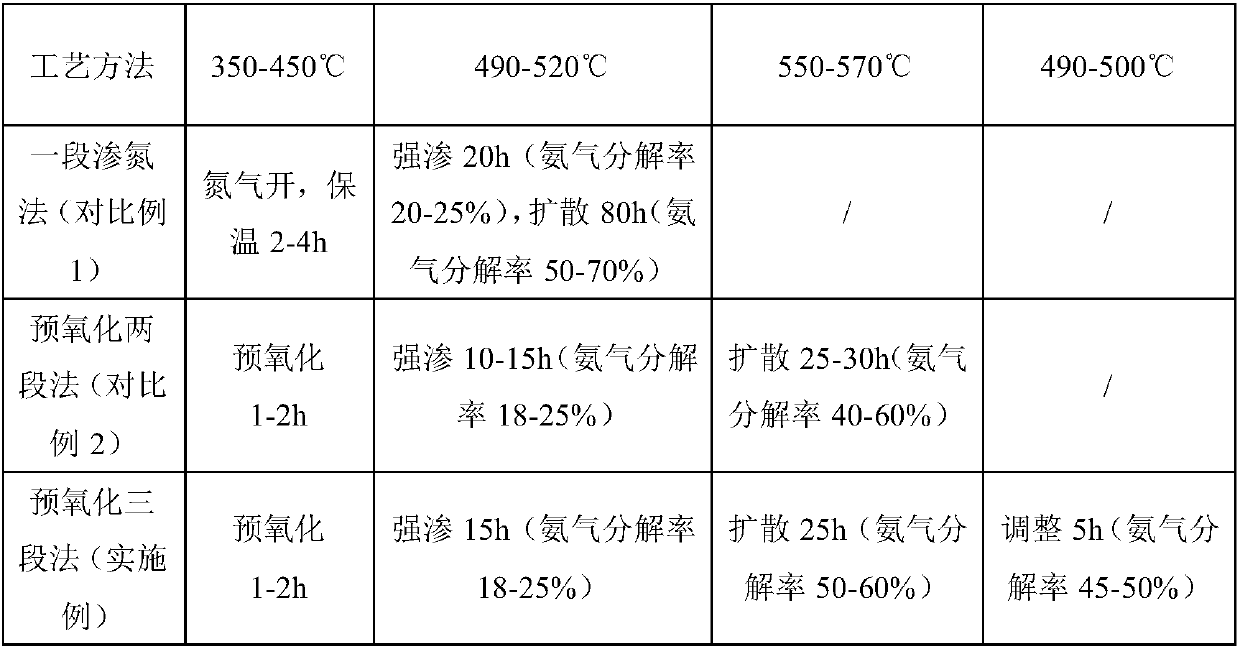

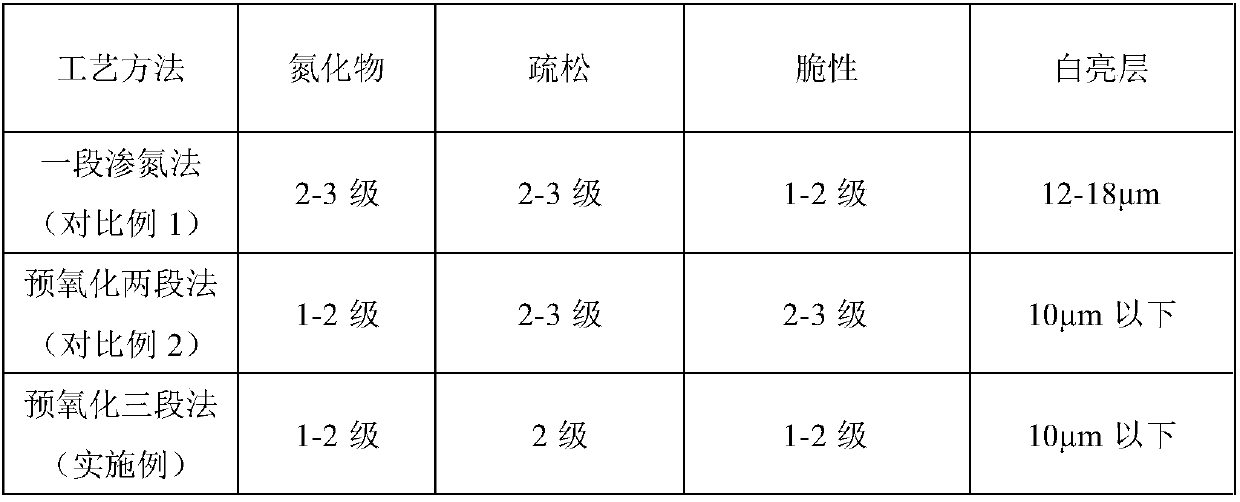

Process method for improving surface quality of quenched-and-tempered steel nitrided members

ActiveCN109252133AAvoid accumulationImprove wear resistanceSolid state diffusion coatingDecompositionNitriding

The invention relates to the technical field of heat treatment processes and particularly relates to a process method for improving surface quality of quenched-and-tempered steel nitrided members. Themethod specifically adopts a preoxidation three-stage-process rapid nitriding process and comprises three stages, i.e., rigid-nitriding intense nitriding, diffusion and adjusting nitrogen feeding. Intense nitriding is carried out in a nitriding environment with low ammonia gas decomposition rate, so that the nitrogen concentration of workpiece surfaces is increased; diffusion is carried out in anitriding environment with high ammonia gas decomposition rate, so that the accumulation of surface nitrides is avoided; the rate and temperature of decomposition of ammonia gas are lowered, and the nitrogen concentration of the workpiece surfaces is adjusted. Through an improvement on a nitriding process, the surface hardness of workpieces is improved to 650HV1 to 680HV1, the surface brittlenessis a level 2 or less, and 80% or more of results display that the surfaces of the workpieces are free of obvious brittle cracks.

Owner:CHANGZHOU TIANSHAN HEAVY IND MACHINERY