Patents

Literature

33 results about "Proton implantation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

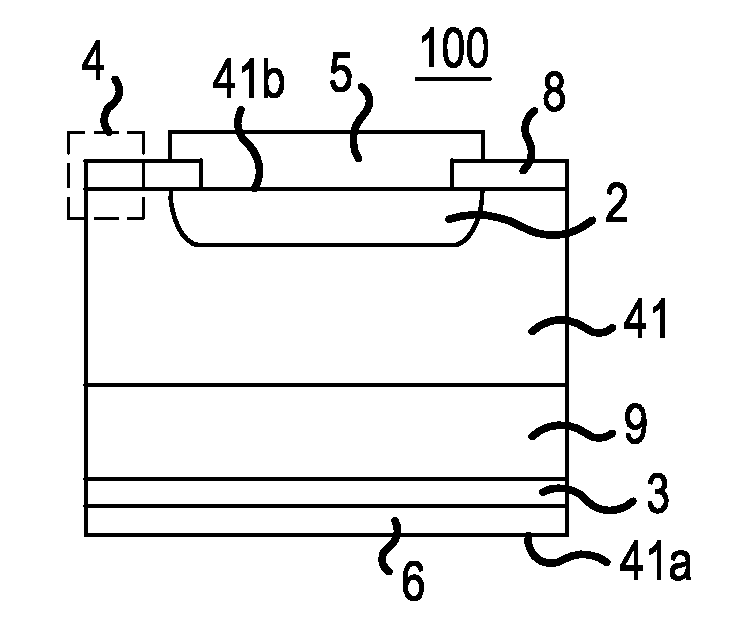

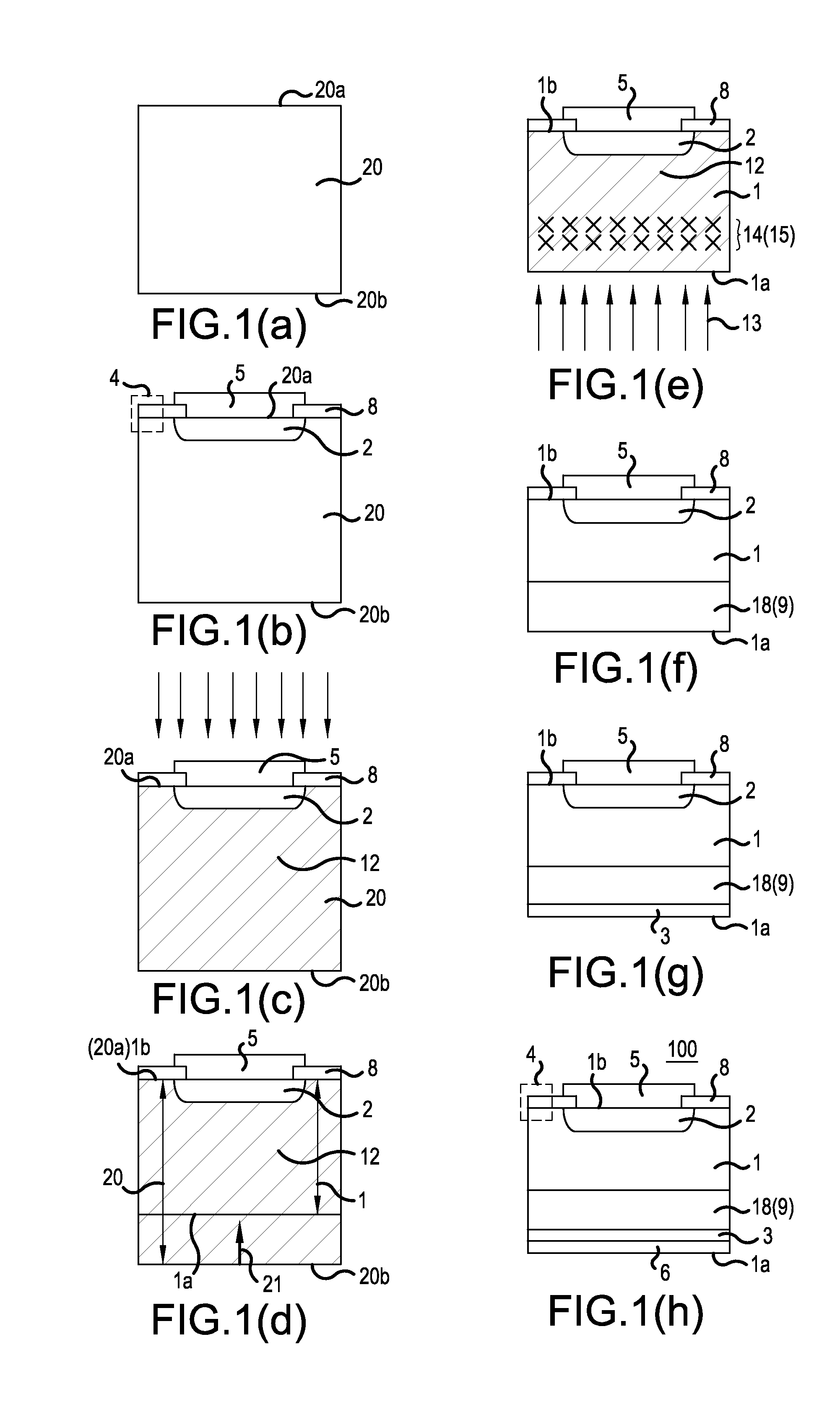

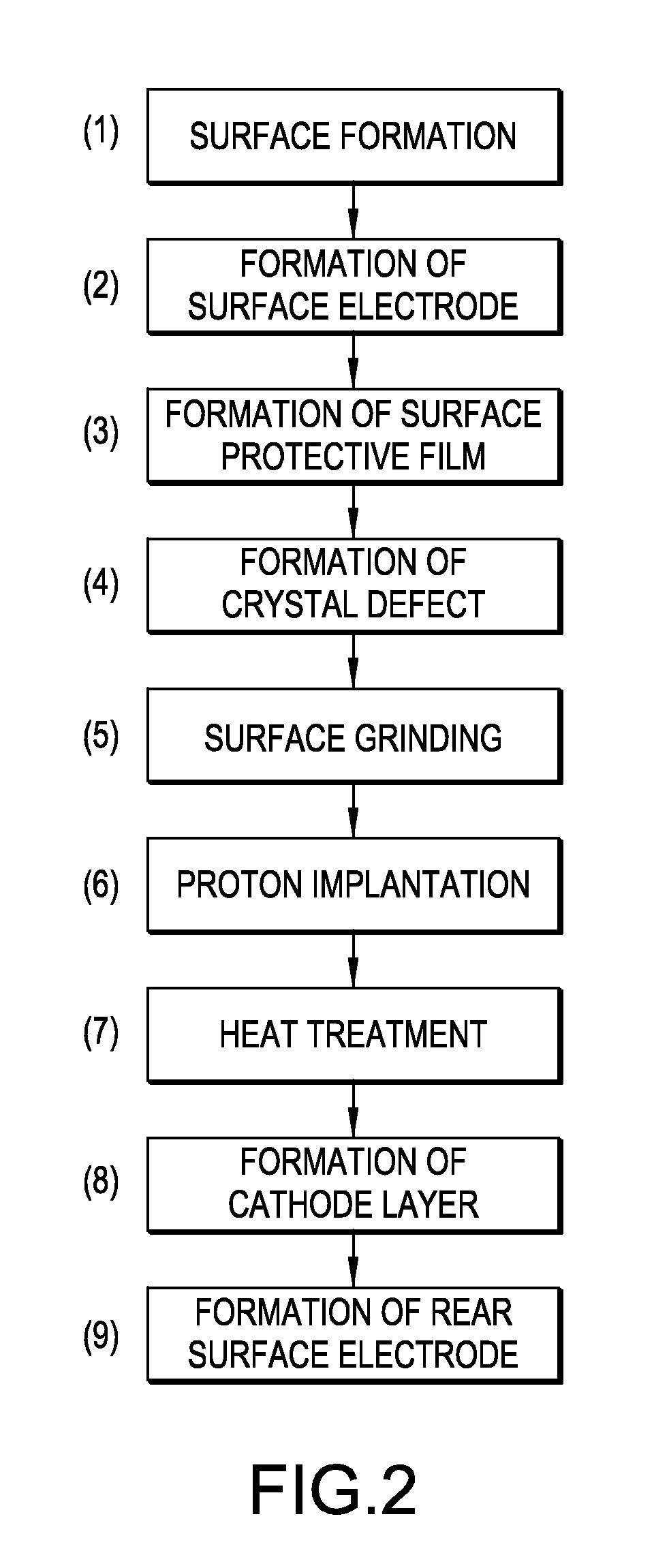

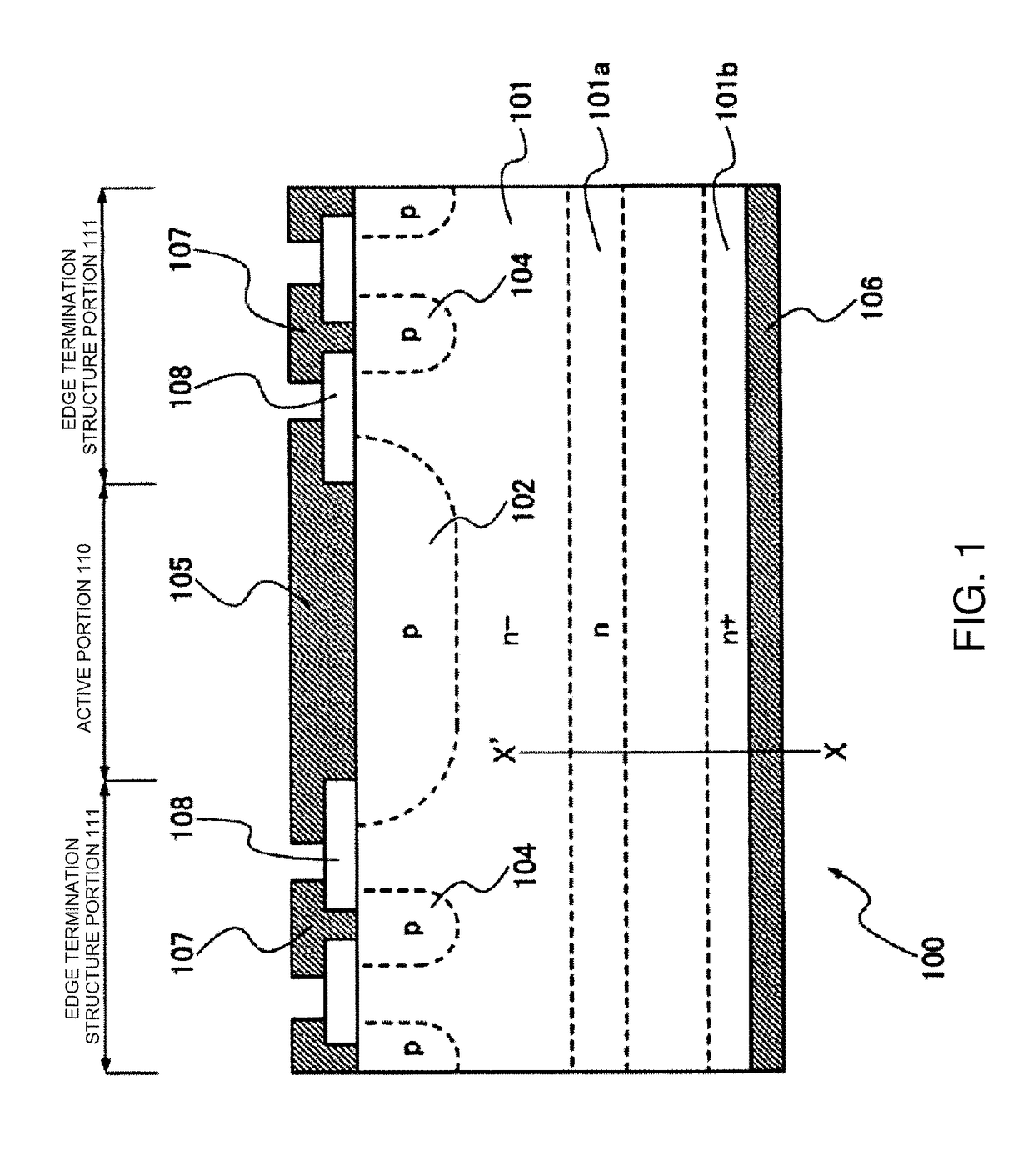

Semiconductor device and method for producing semiconductor device

ActiveUS20140246755A1Limited amountIncrease spawn rateSemiconductor/solid-state device manufacturingSemiconductor devicesProton implantationGeneration rate

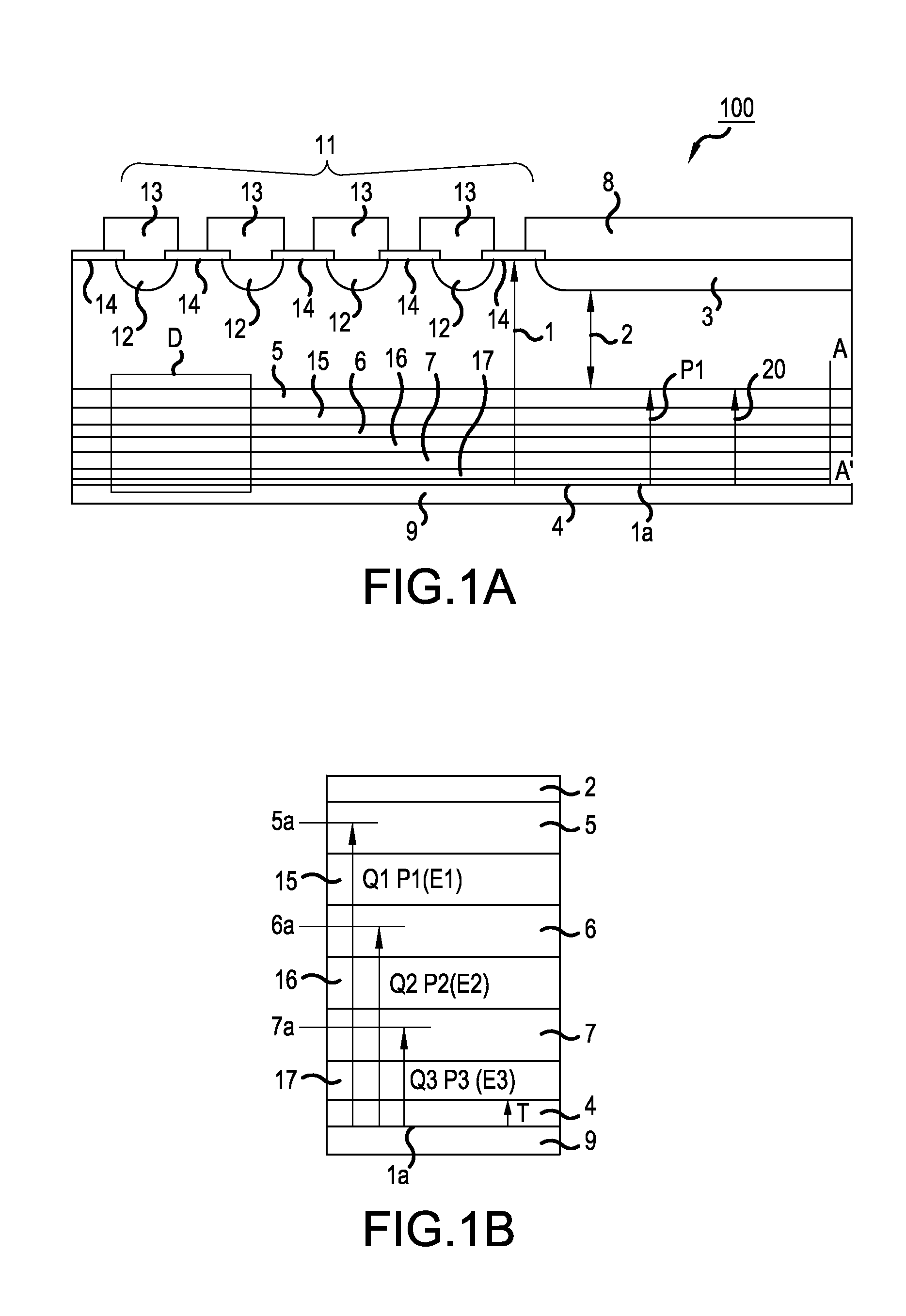

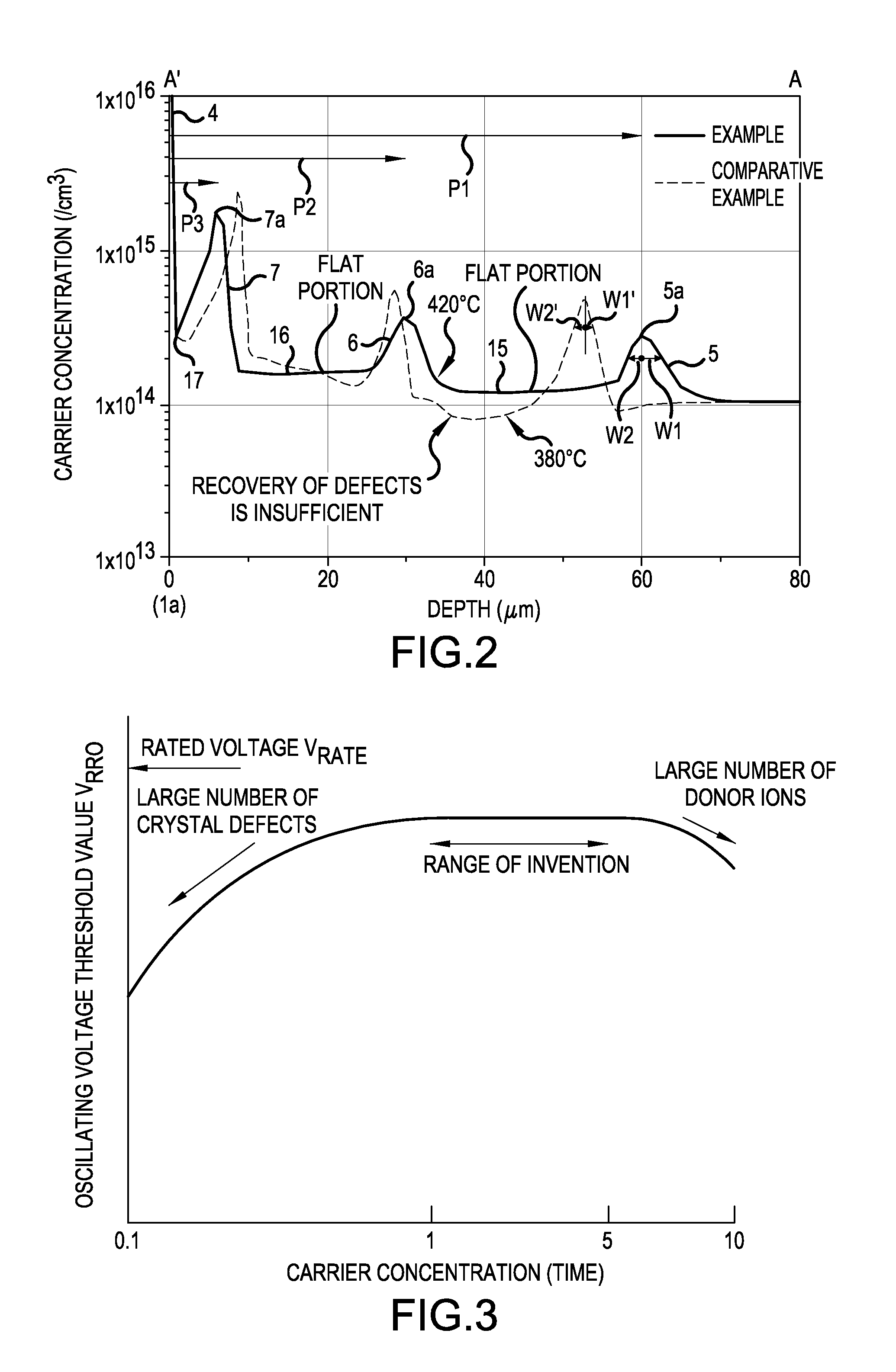

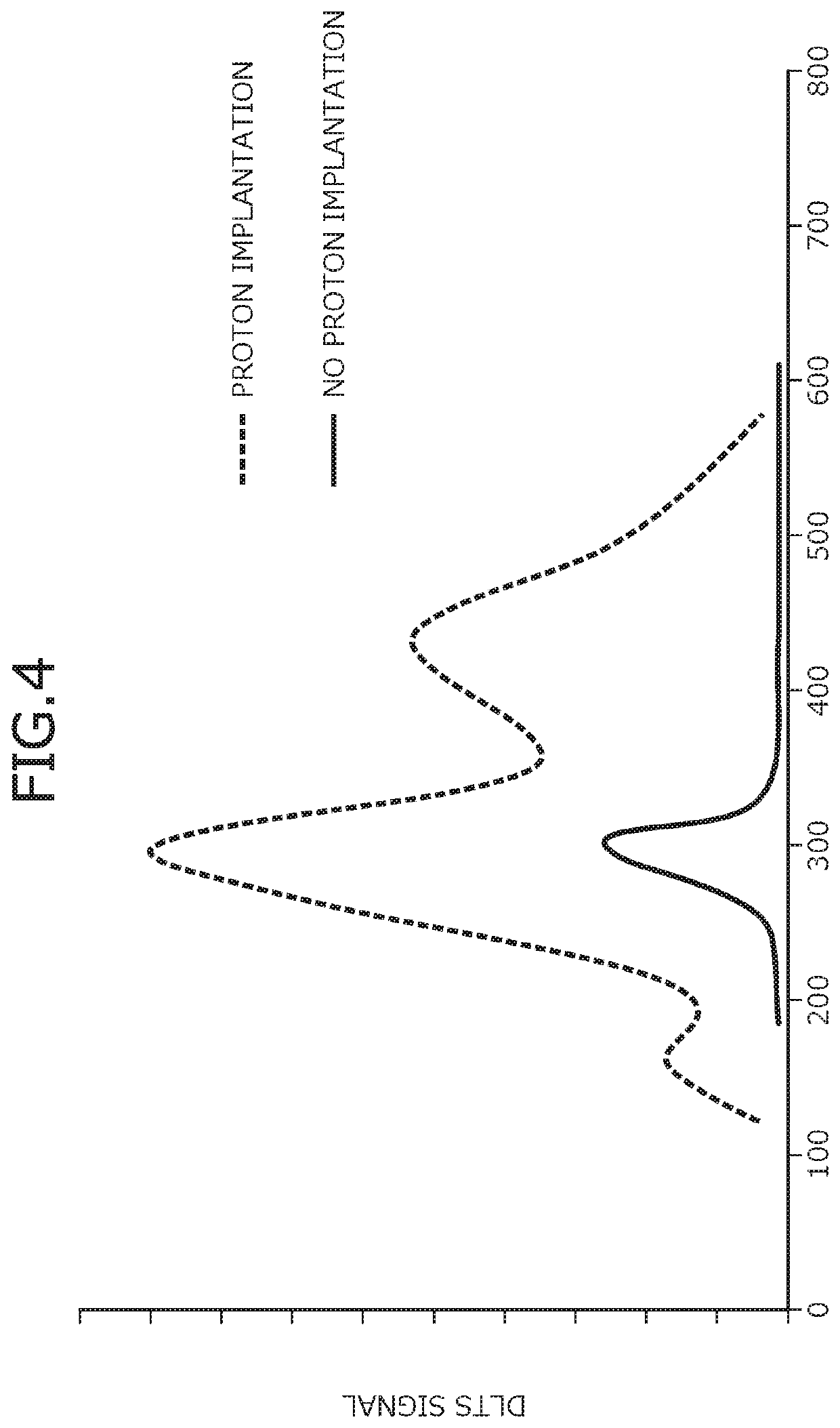

Hydrogen atoms and crystal defects are introduced into an n− semiconductor substrate by proton implantation. The crystal defects are generated in the n− semiconductor substrate by electron beam irradiation before or after the proton implantation. Then, a heat treatment for generating donors is performed. The amount of crystal defects is appropriately controlled during the heat treatment for generating donors to increase a donor generation rate. In addition, when the heat treatment for generating donors ends, the crystal defects formed by the electron beam irradiation and the proton implantation are recovered and controlled to an appropriate amount of crystal defects. Therefore, for example, it is possible to improve a breakdown voltage and reduce a leakage current.

Owner:FUJI ELECTRIC CO LTD

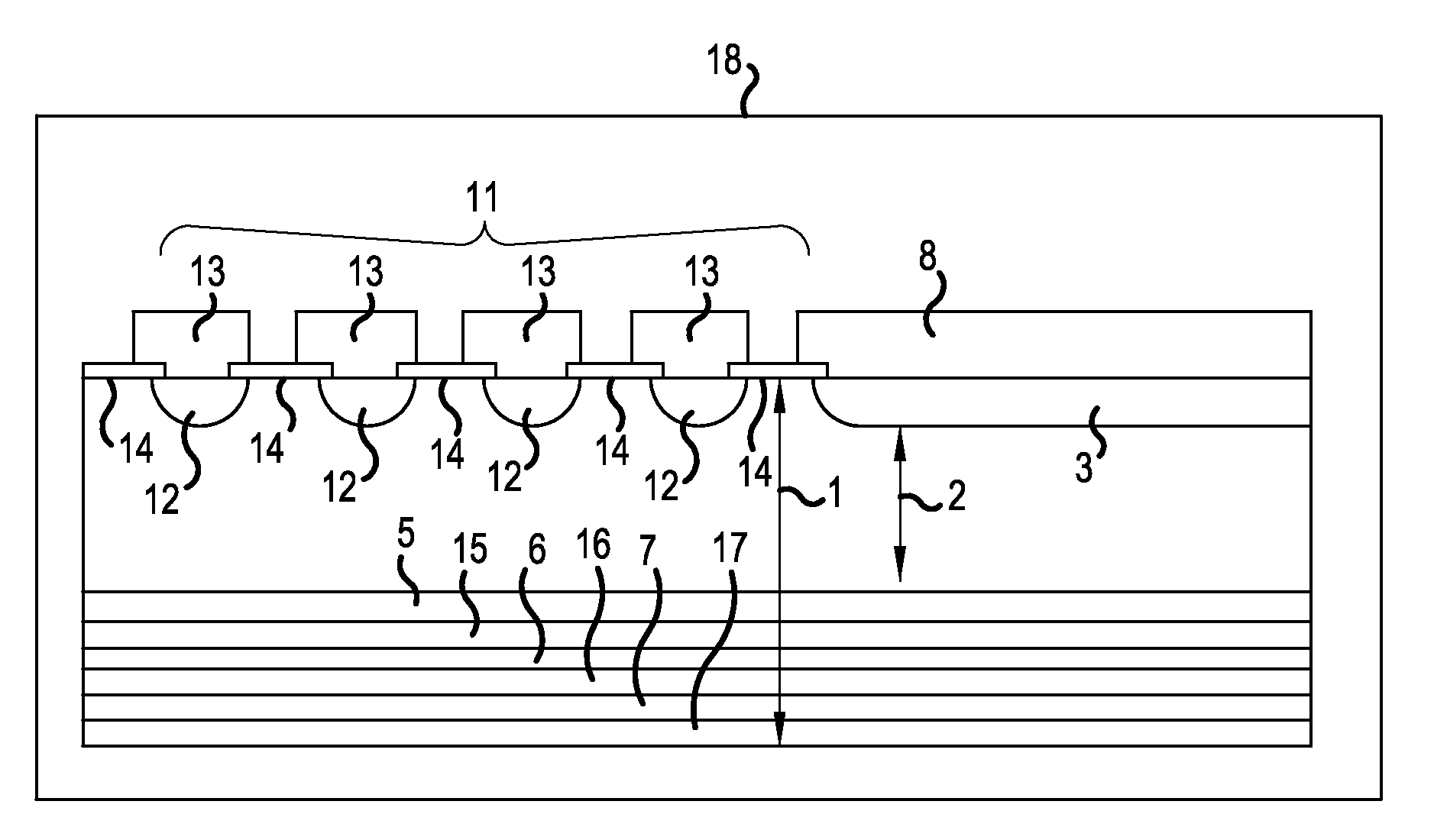

Semiconductor device and method for manufacturing the same

ActiveUS20150179441A1Suppress of depletion layerReduce power lossTransistorSemiconductor/solid-state device manufacturingProton implantationCharge carrier

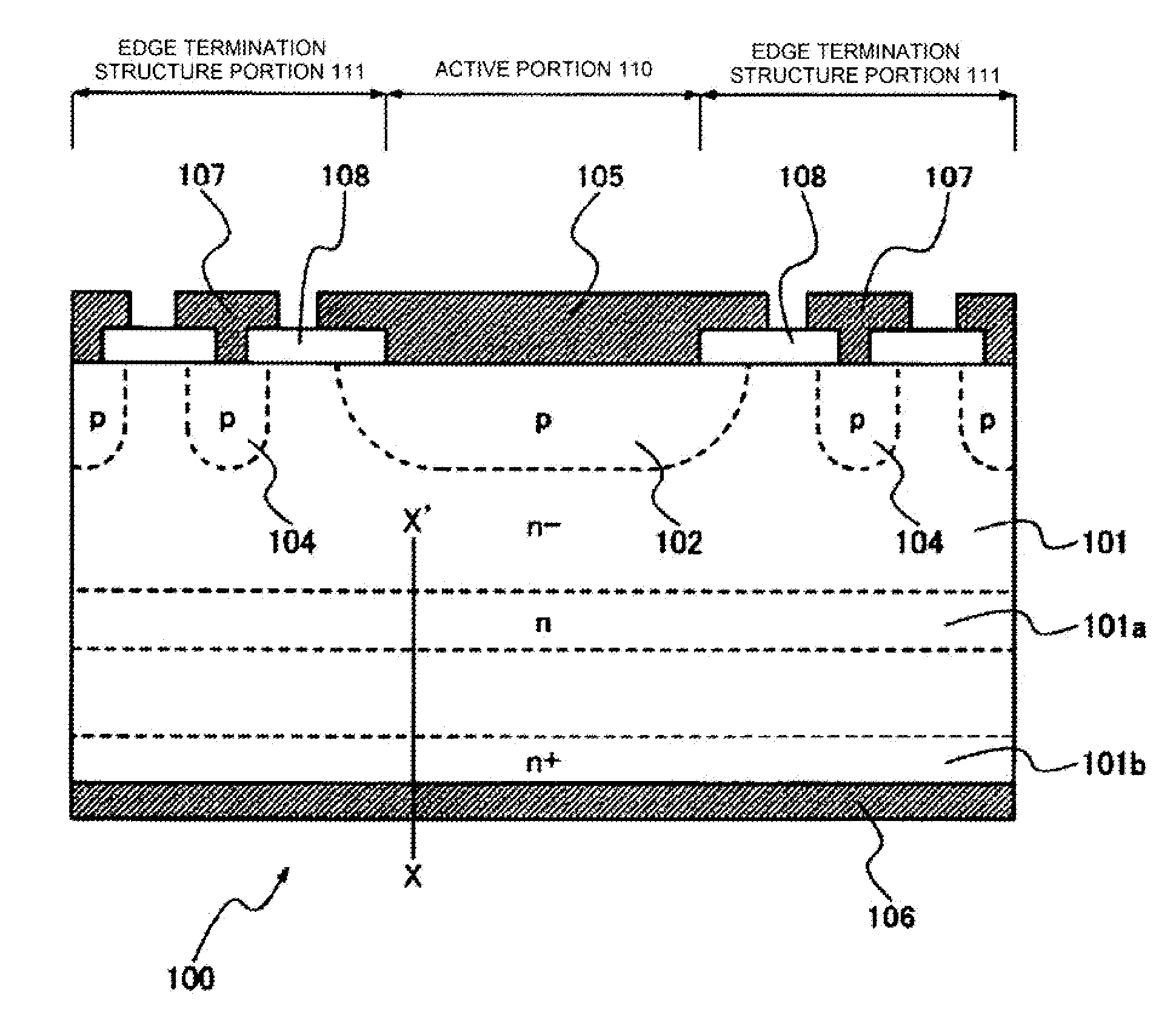

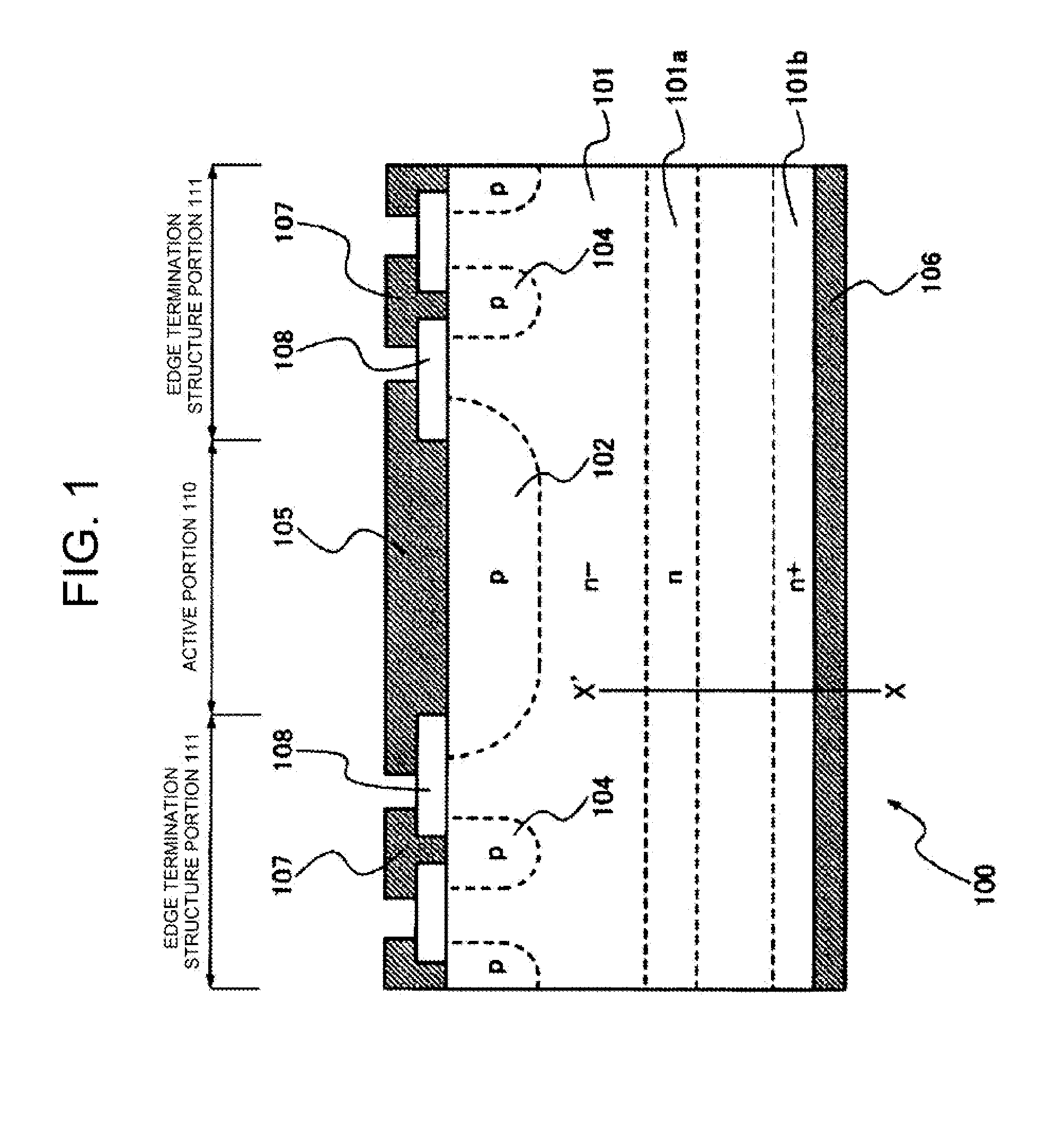

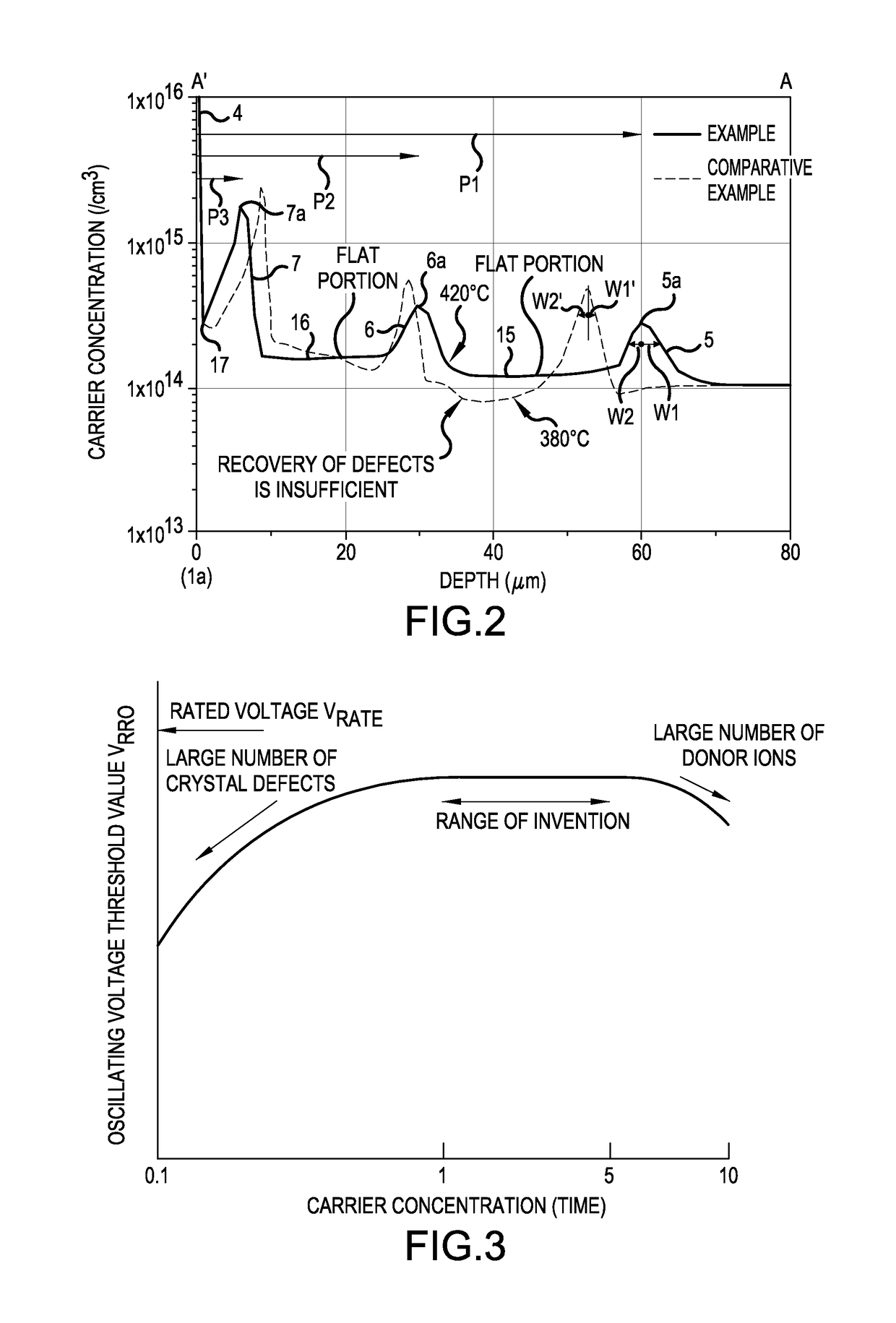

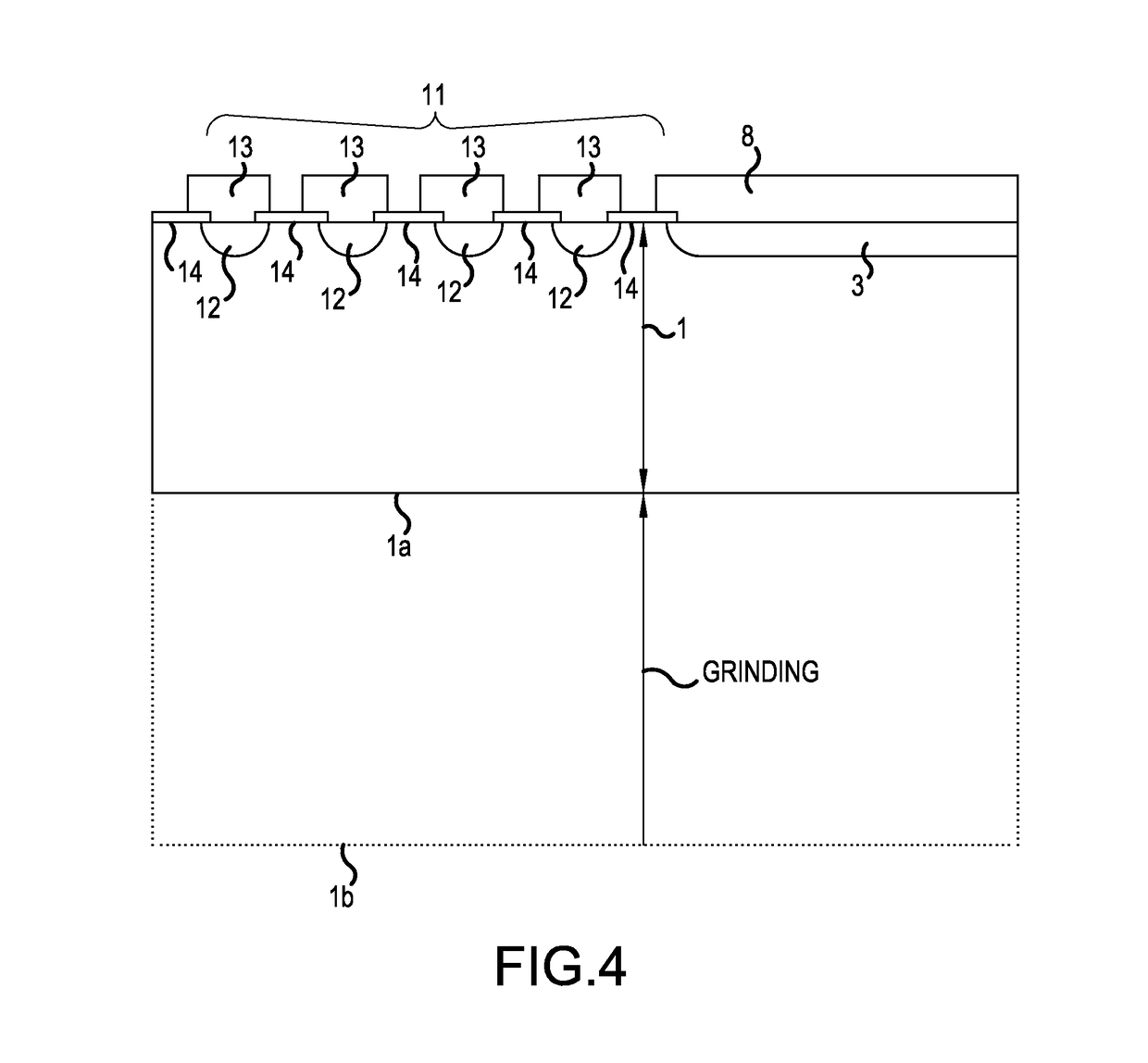

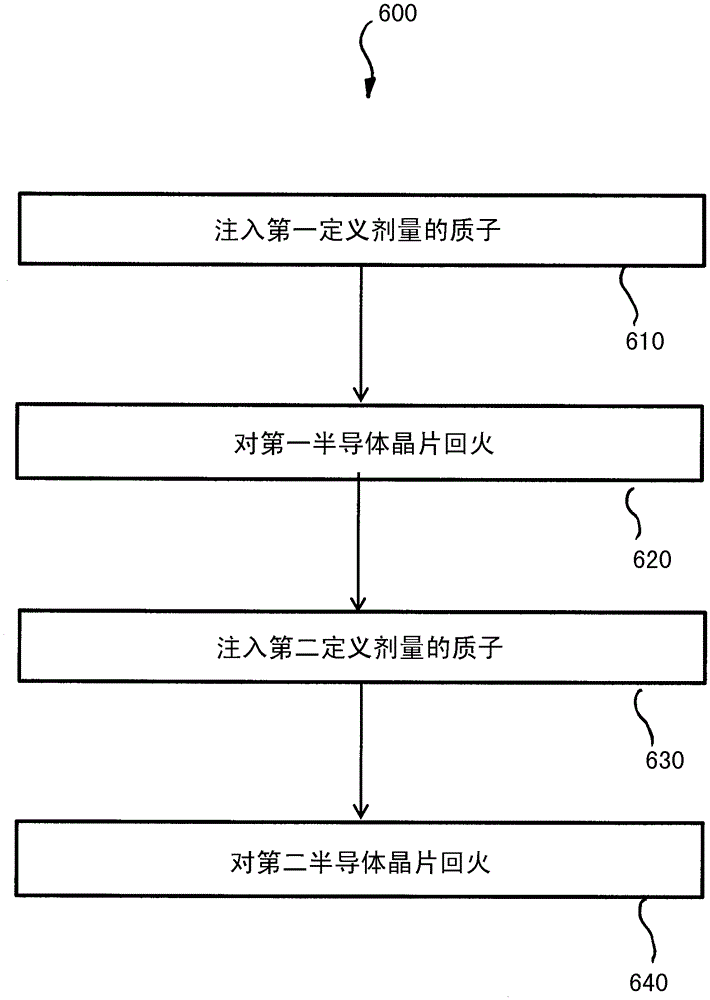

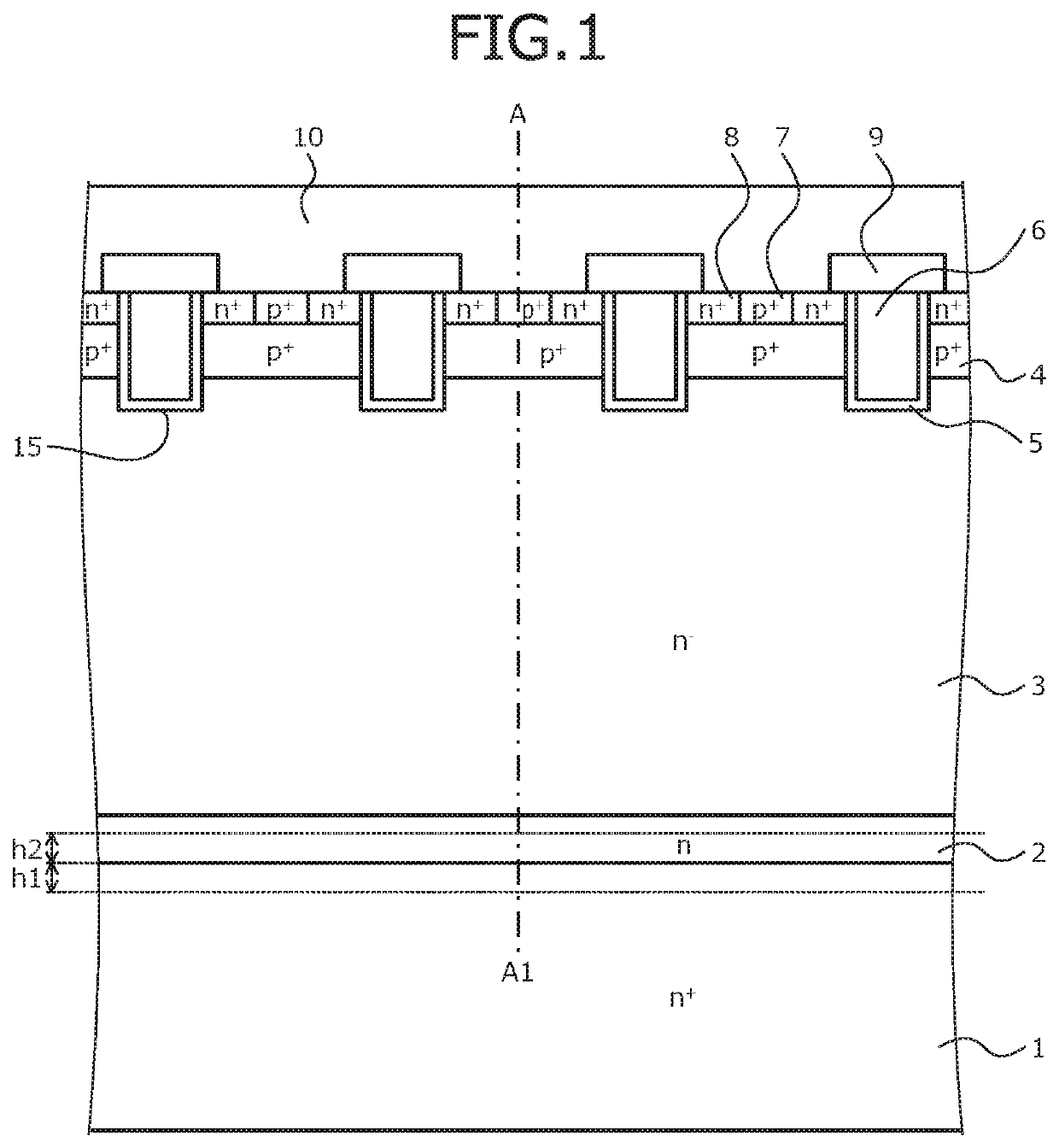

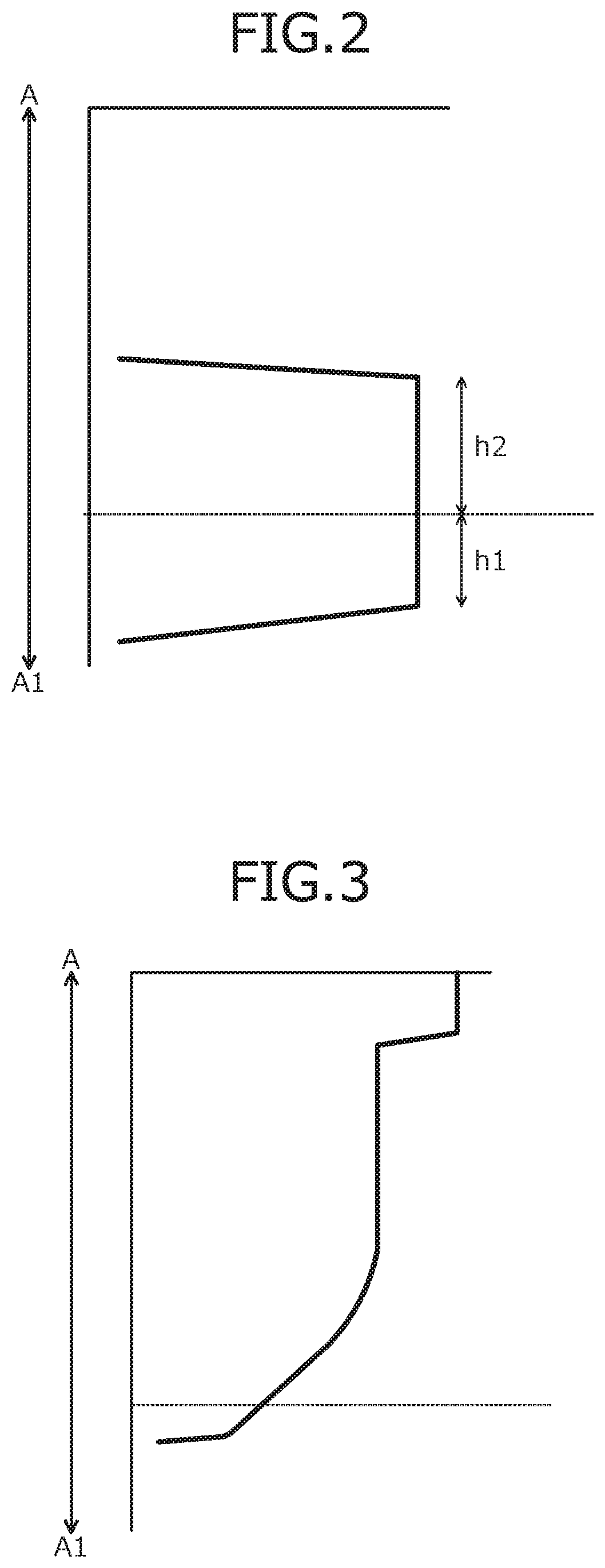

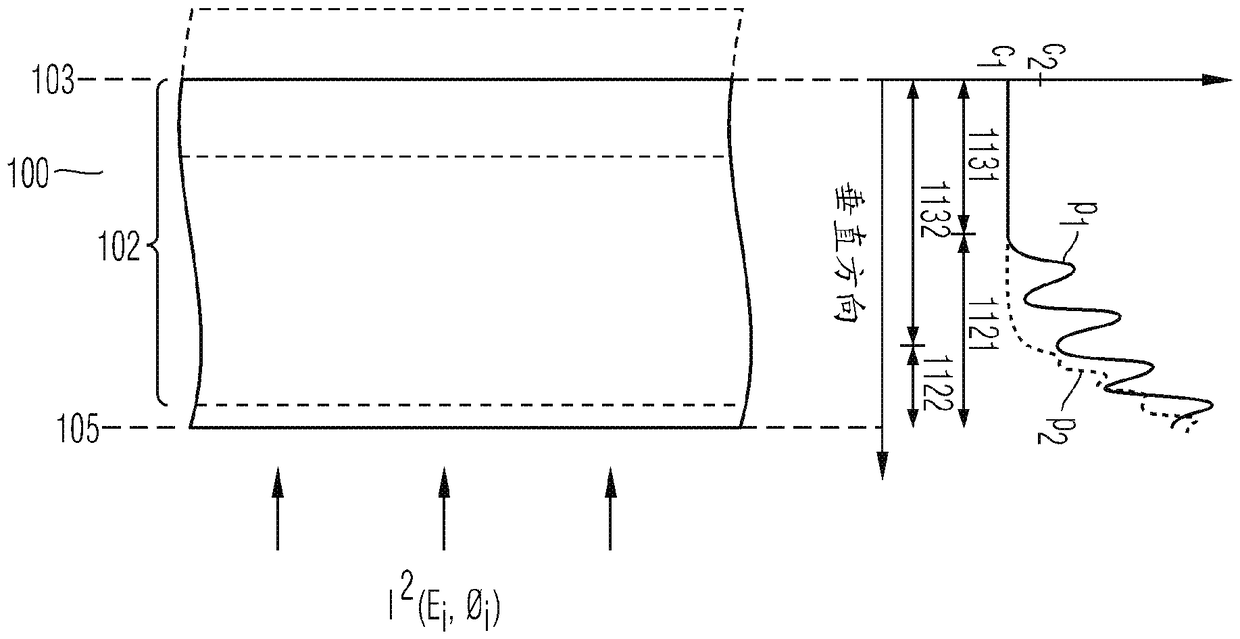

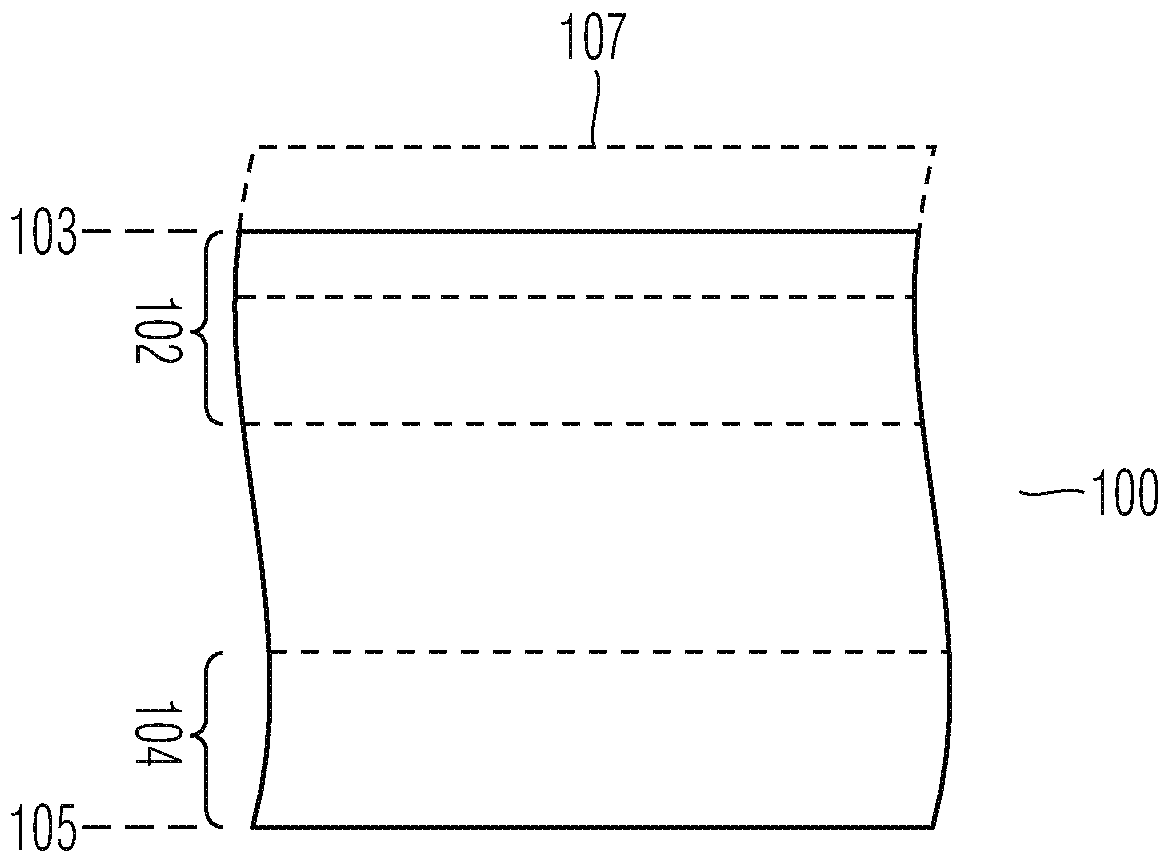

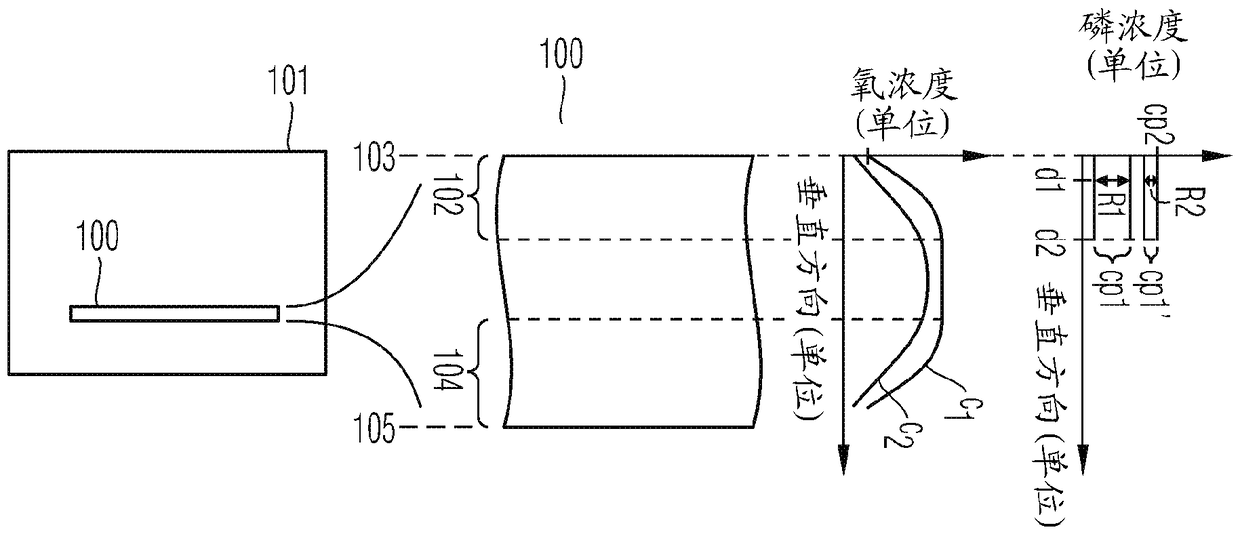

A semiconductor device is disclosed in which proton implantation is performed a plurality of times to form a plurality of n-type buffer layers in an n-type drift layer at different depths from a rear surface of a substrate. The depth of the n-type buffer layer, which is provided at the deepest position from the rear surface of the substrate, from the rear surface of the substrate is more than 15 μm. The temperature of a heat treatment which is performed in order to change a proton into a donor and to recover a crystal defect after the proton implantation is equal to or higher than 400° C. In a carrier concentration distribution of the n-type buffer layer, a width from the peak position of carrier concentration to an anode is more than a width from the peak position to a cathode.

Owner:FUJI ELECTRIC CO LTD

Production method for a semiconductor device

ActiveUS20150050798A1Without increasing crystal defectInhibit deteriorationSemiconductor/solid-state device manufacturingSemiconductor devicesProton implantationHydrogen atmosphere

A method for producing a semiconductor device includes providing a semiconductor substrate having a first conductivity type; implanting protons through a rear surface of the semiconductor substrate of the first conductivity type; and forming a first semiconductor region of the first conductivity type in the semiconductor substrate by performing an annealing process in an annealing furnace in a hydrogen atmosphere having a volume concentration of hydrogen that is equal to or greater than 0.5% and less than 4.65%, the first semiconductor region having a higher impurity concentration than that of the semiconductor substrate after the implantation step. The method reduces crystal defects in the generation of donors during proton implantation and improves the rate of change into a donor.

Owner:FUJI ELECTRIC CO LTD

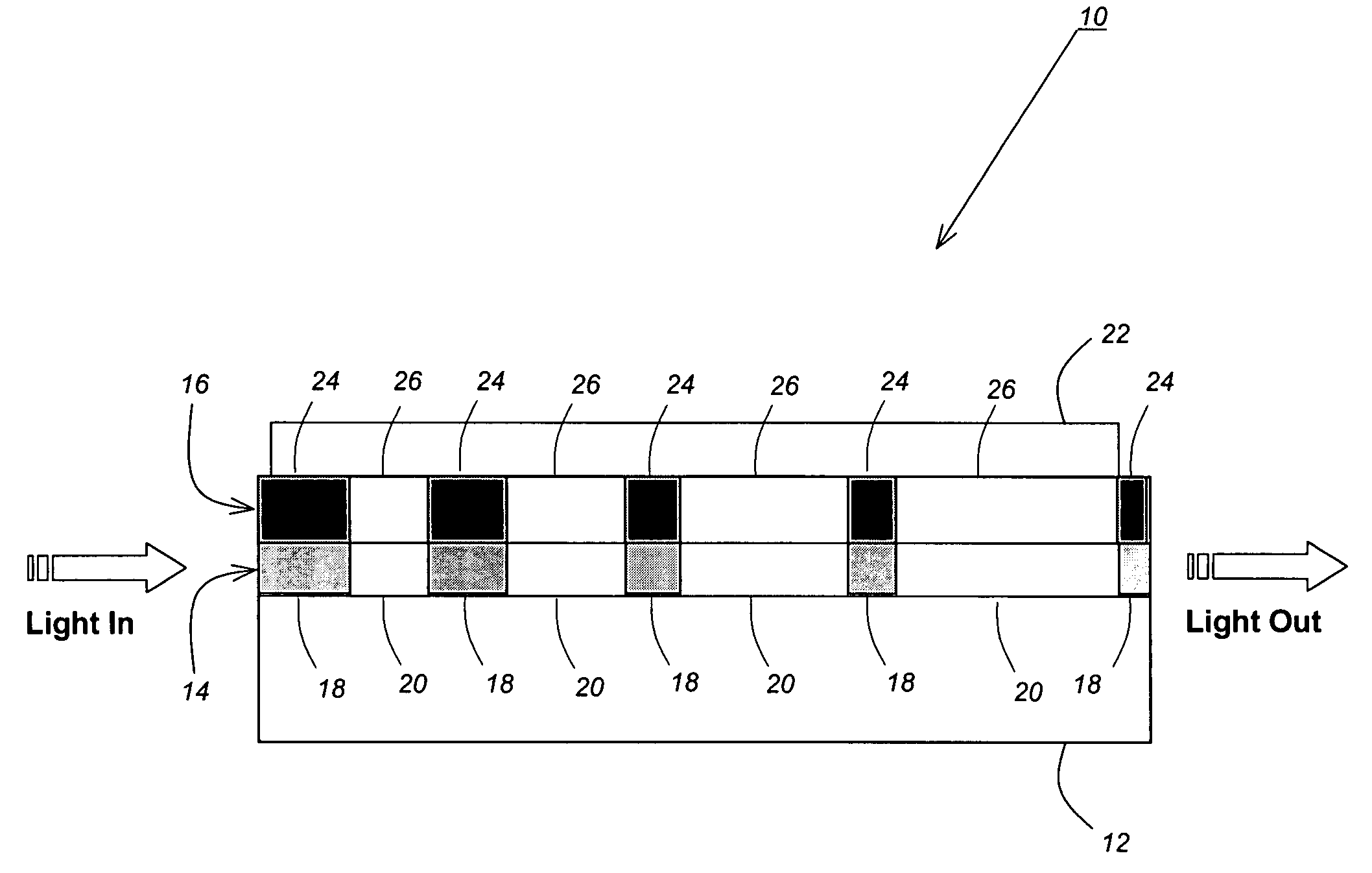

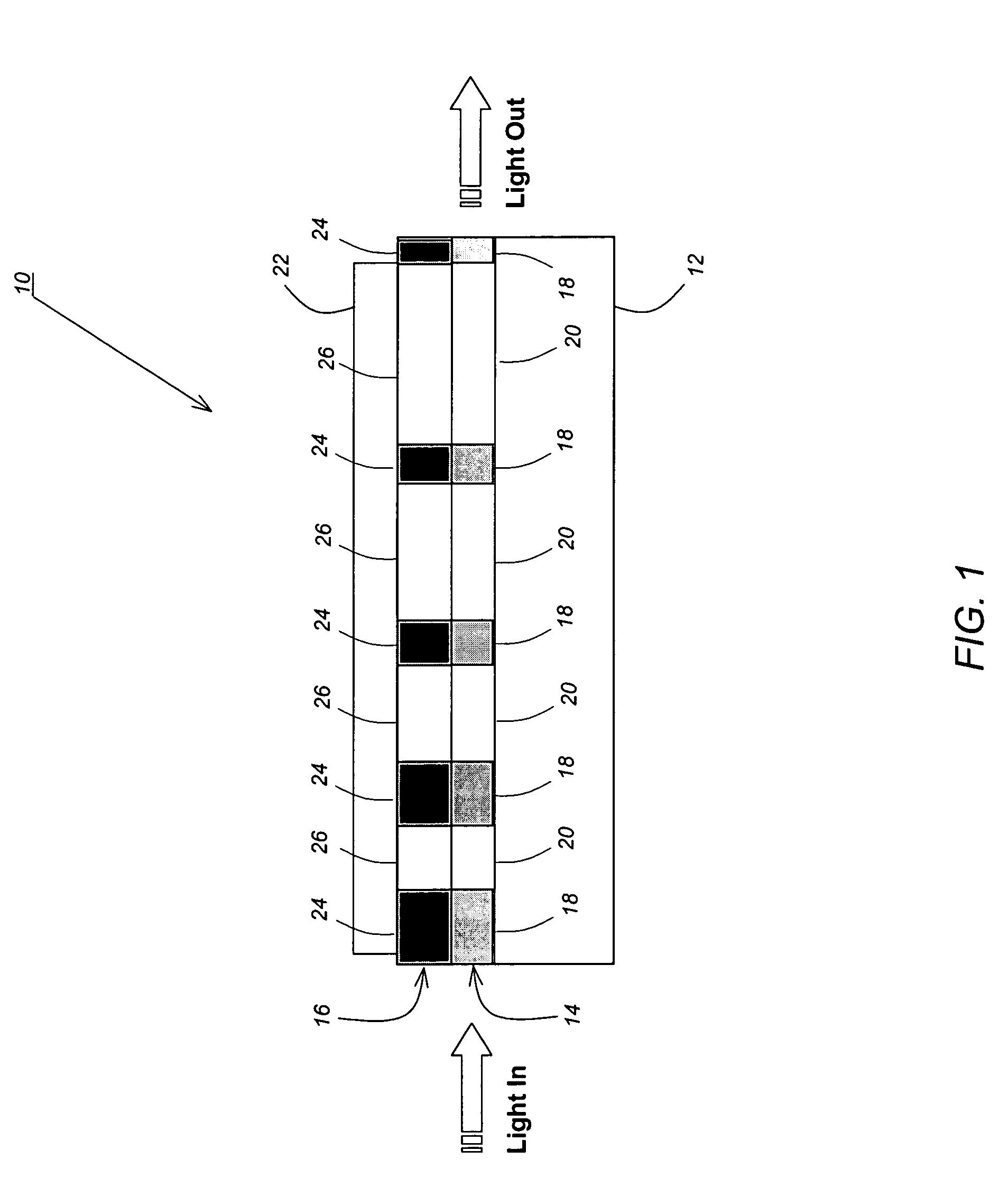

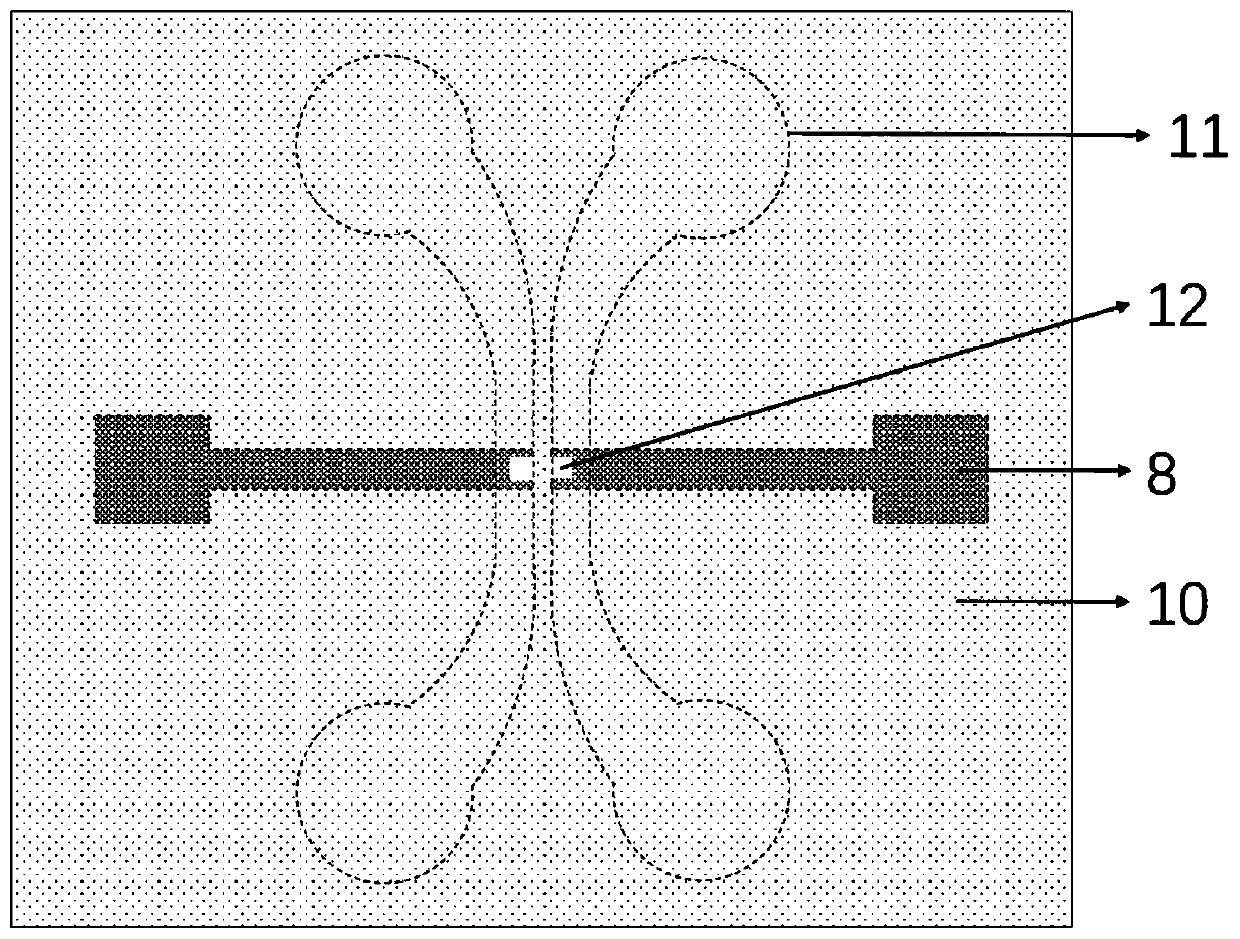

Methods for forming index guided vertical cavity surface emitting lasers

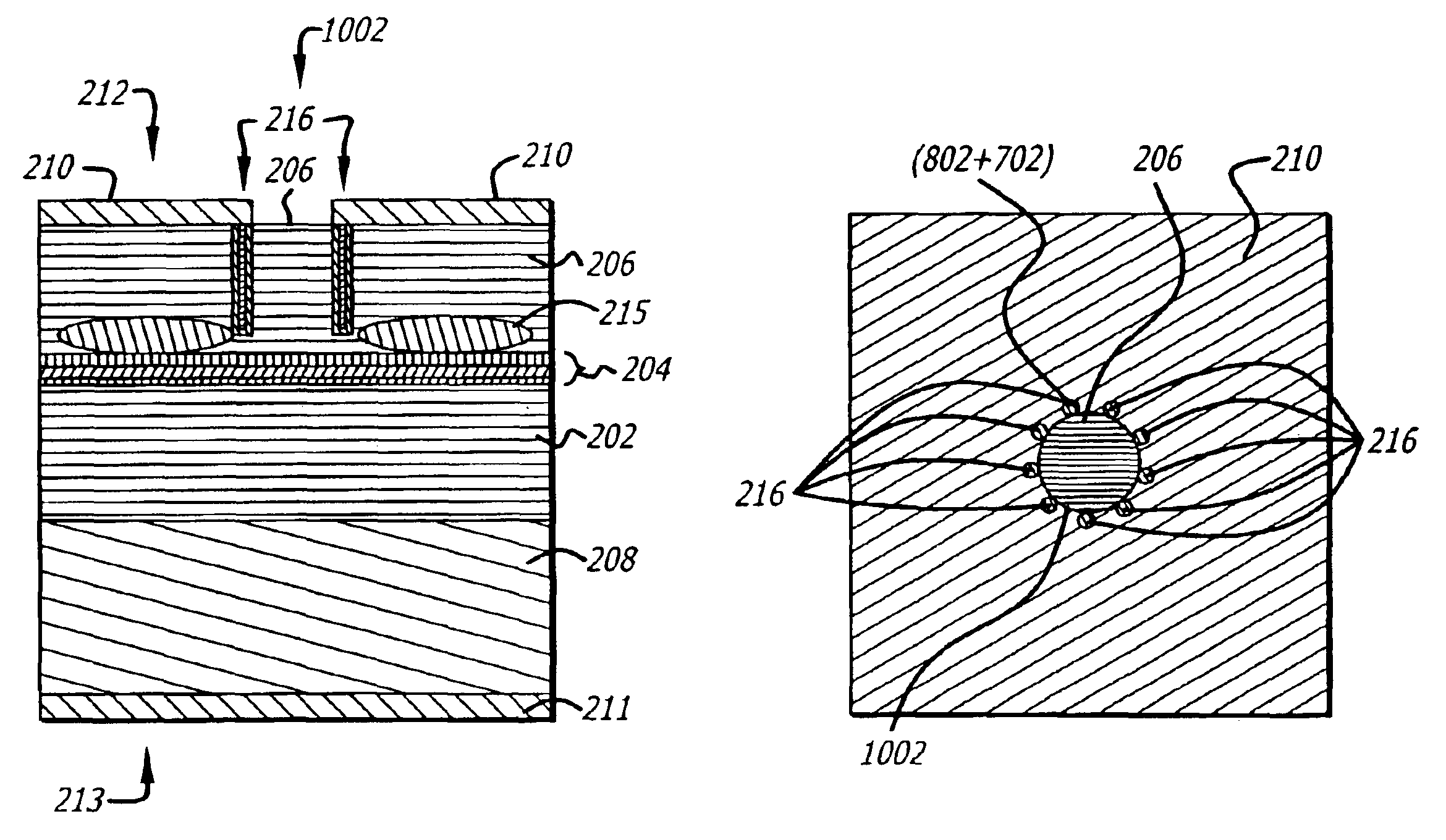

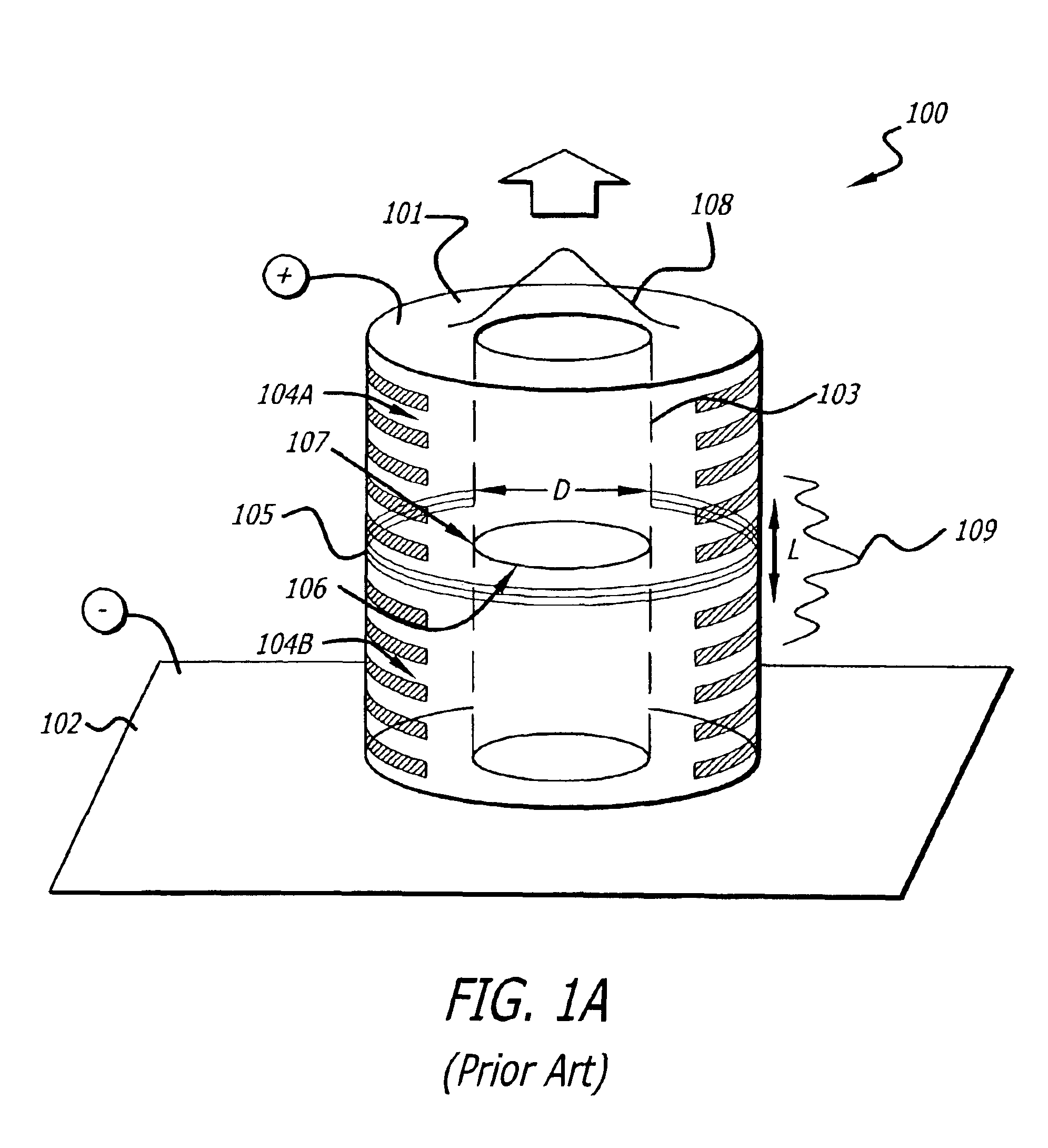

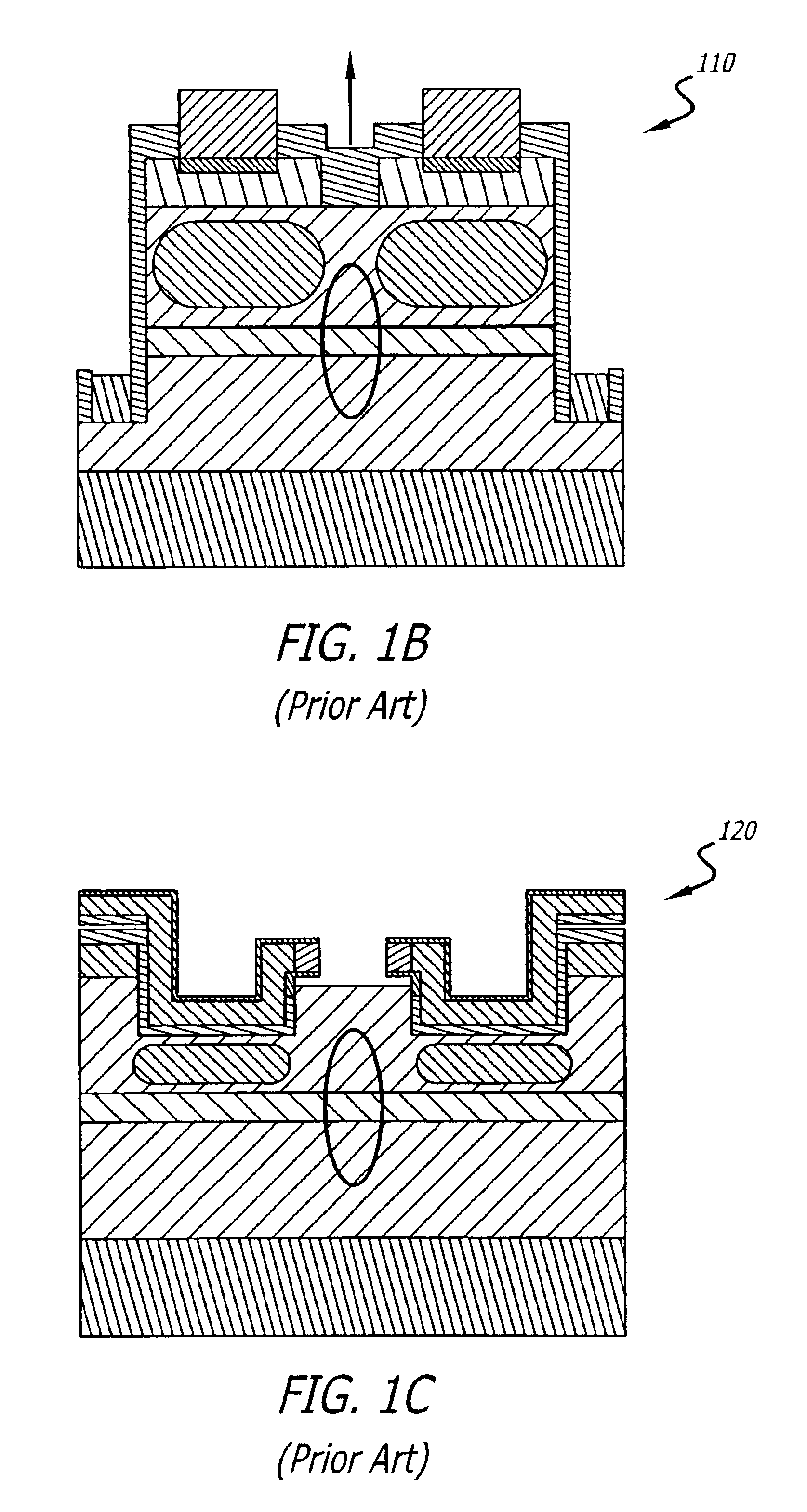

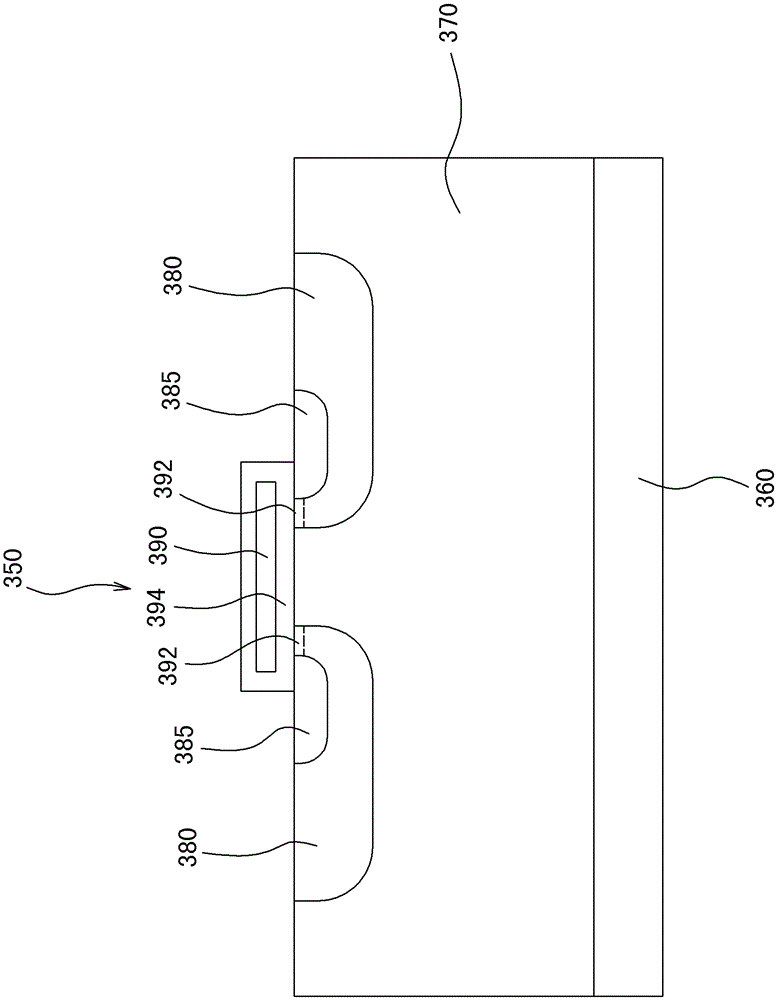

InactiveUS6852558B2Improved implantMinimizes thermal lensing effectOptical wave guidanceLaser detailsVertical-cavity surface-emitting laserCurrent limiting

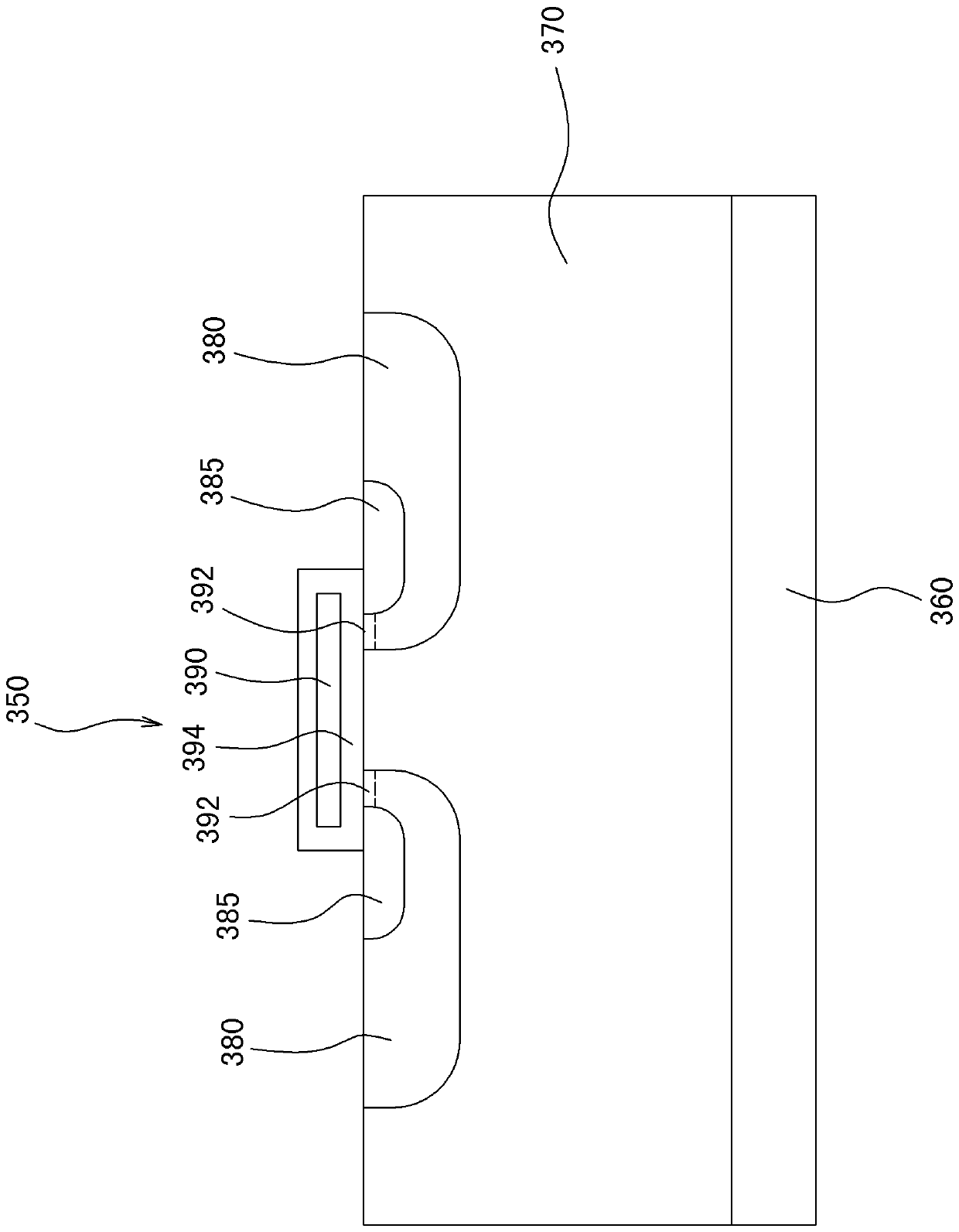

Planar index guided vertical cavity surface emitting laser (PIG VCSEL) utilizes index guiding to provide improved optical confinement and proton implantation to improve current confinement. Index guiding is achieved by etching index guide openings (holes or partial ridges) around the optical confinement region and may be adjusted by varying the etched volume of the index guide openings (holes and partial ridges). The top contact surface area is increased in the PIG VCSEL thereby lowering contact and device resistance to improve VCSEL performance further. The PIG VCSEL is a substantially planarized device for ease of manufacture.

Owner:LUMENTUM OPERATIONS LLC

Semiconductor device and method for producing semiconductor device

ActiveUS9276071B2Limited amountIncrease spawn rateSemiconductor/solid-state device manufacturingSemiconductor devicesGeneration rateProton implantation

Hydrogen atoms and crystal defects are introduced into an n− semiconductor substrate by proton implantation. The crystal defects are generated in the n− semiconductor substrate by electron beam irradiation before or after the proton implantation. Then, a heat treatment for generating donors is performed. The amount of crystal defects is appropriately controlled during the heat treatment for generating donors to increase a donor generation rate. In addition, when the heat treatment for generating donors ends, the crystal defects formed by the electron beam irradiation and the proton implantation are recovered and controlled to an appropriate amount of crystal defects. Therefore, for example, it is possible to improve a breakdown voltage and reduce a leakage current.

Owner:FUJI ELECTRIC CO LTD

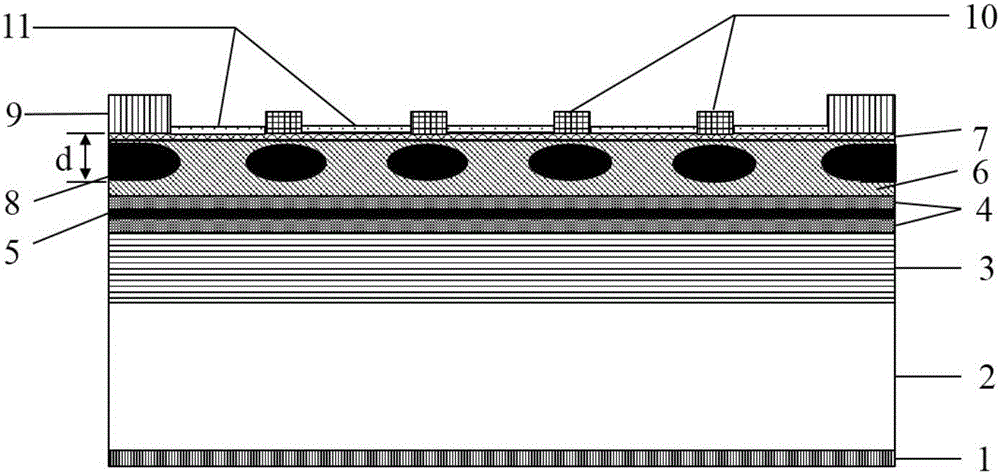

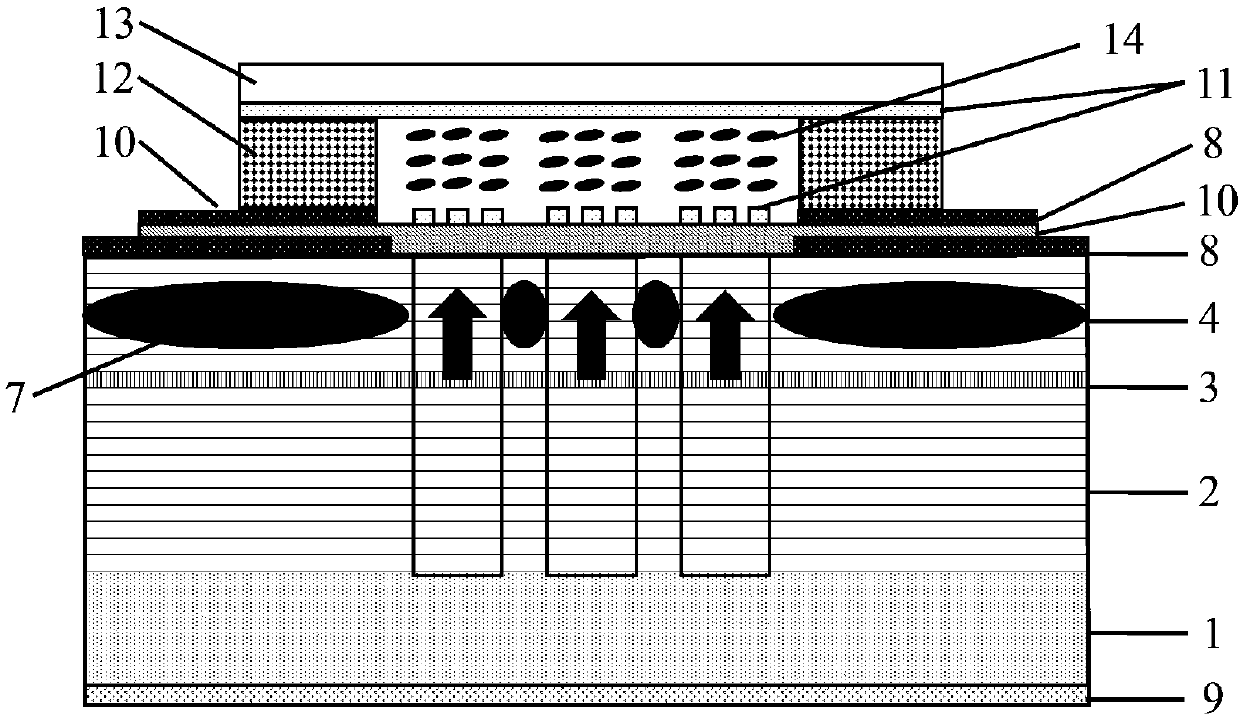

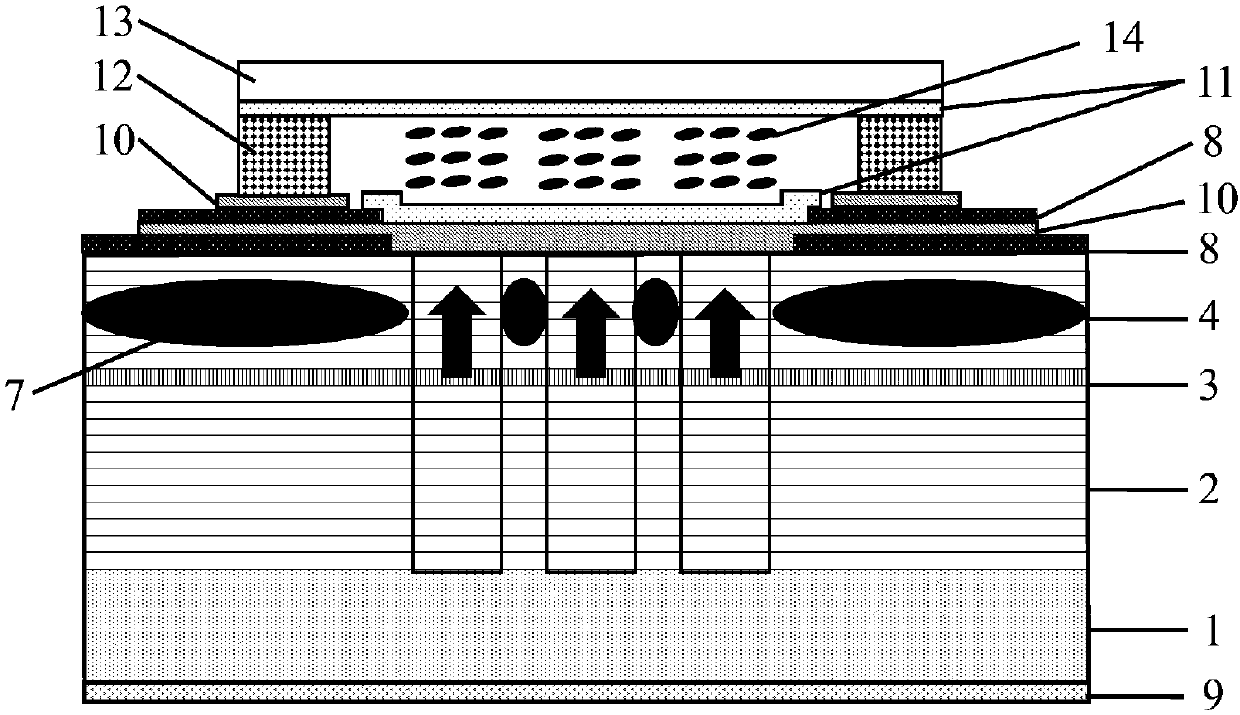

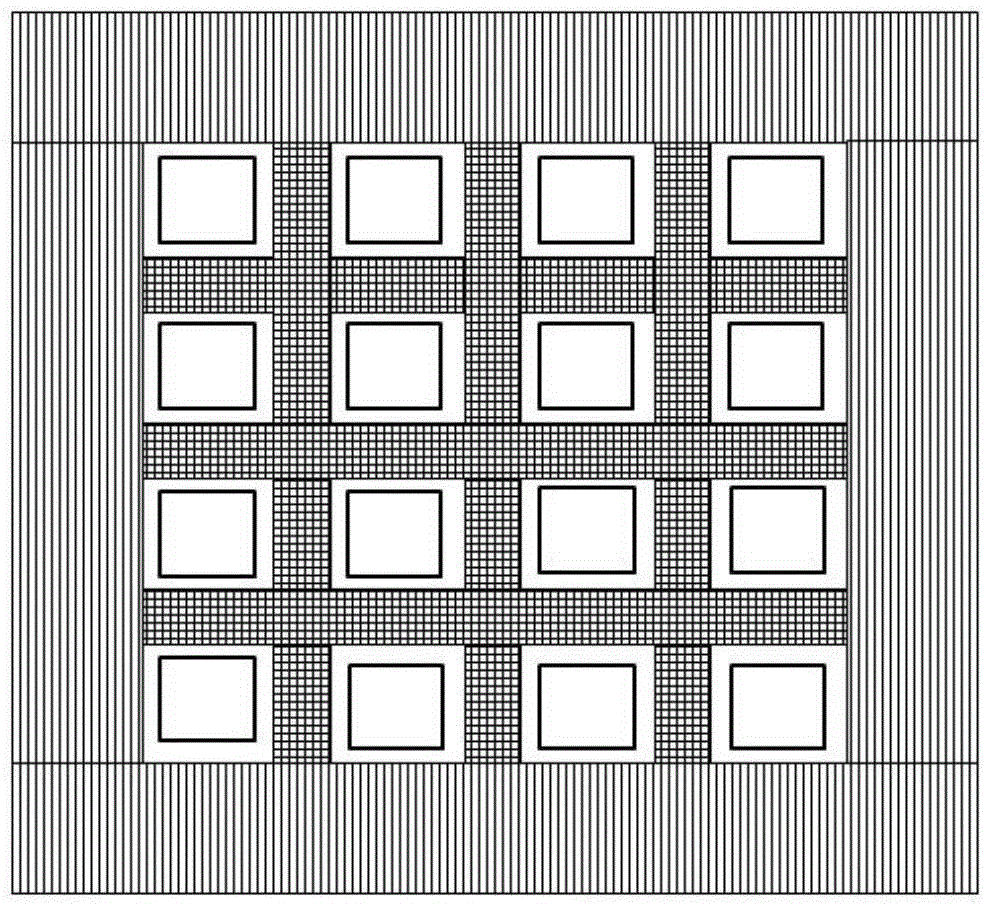

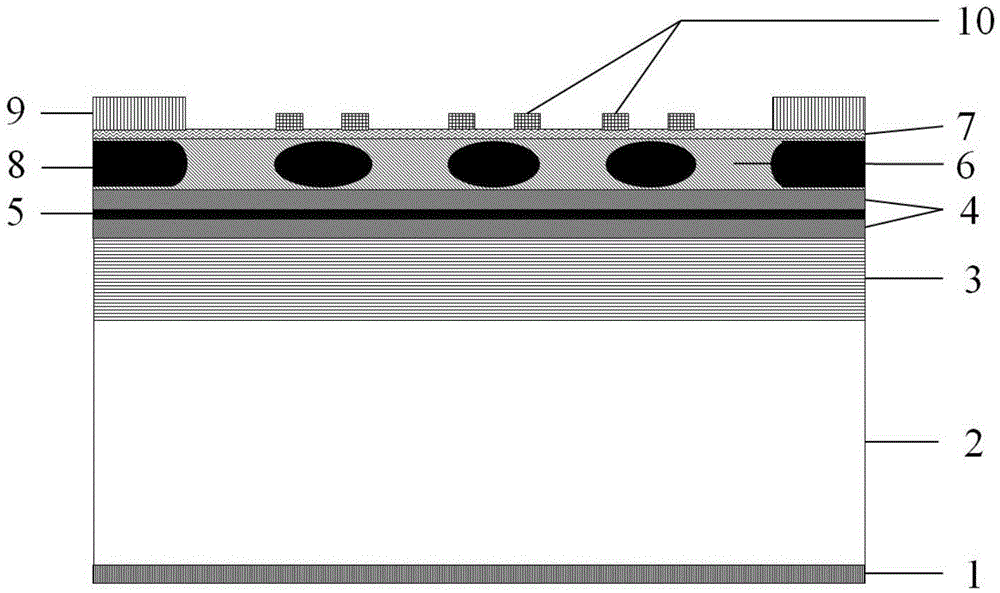

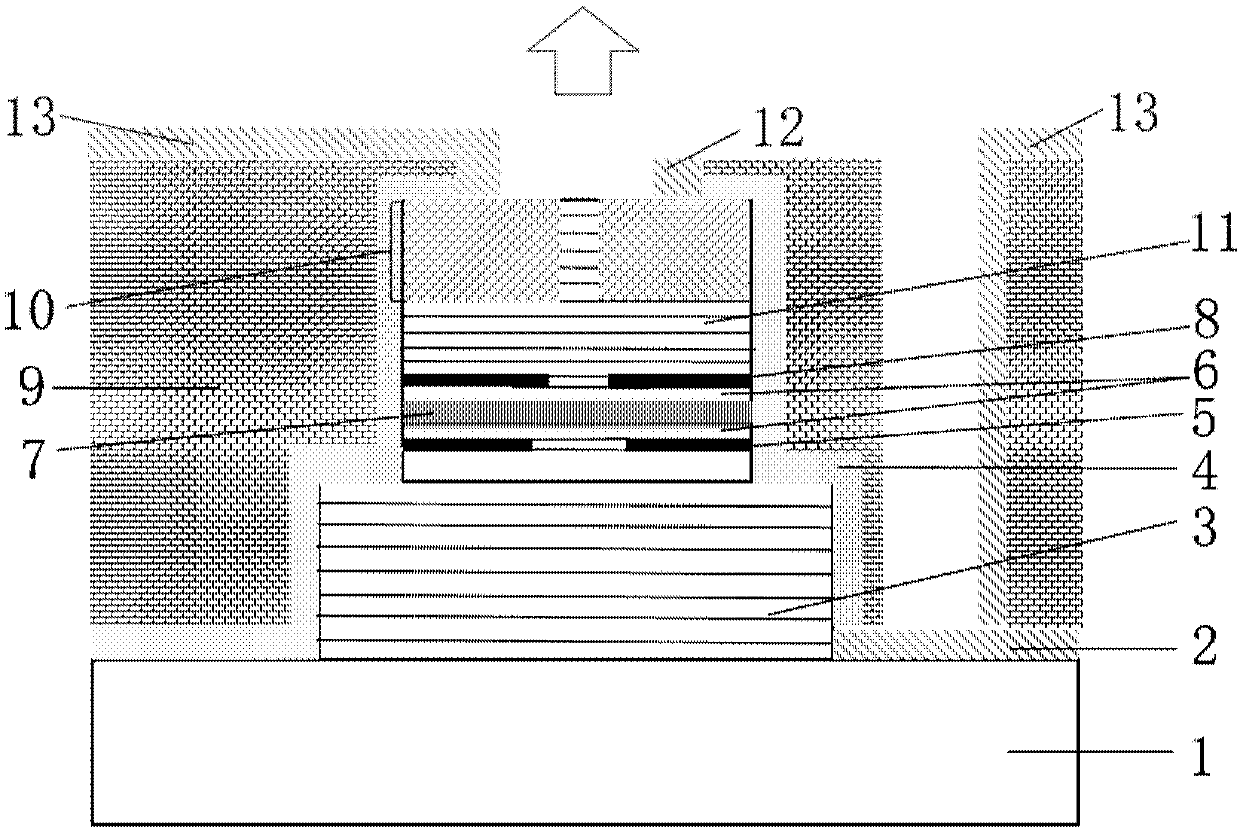

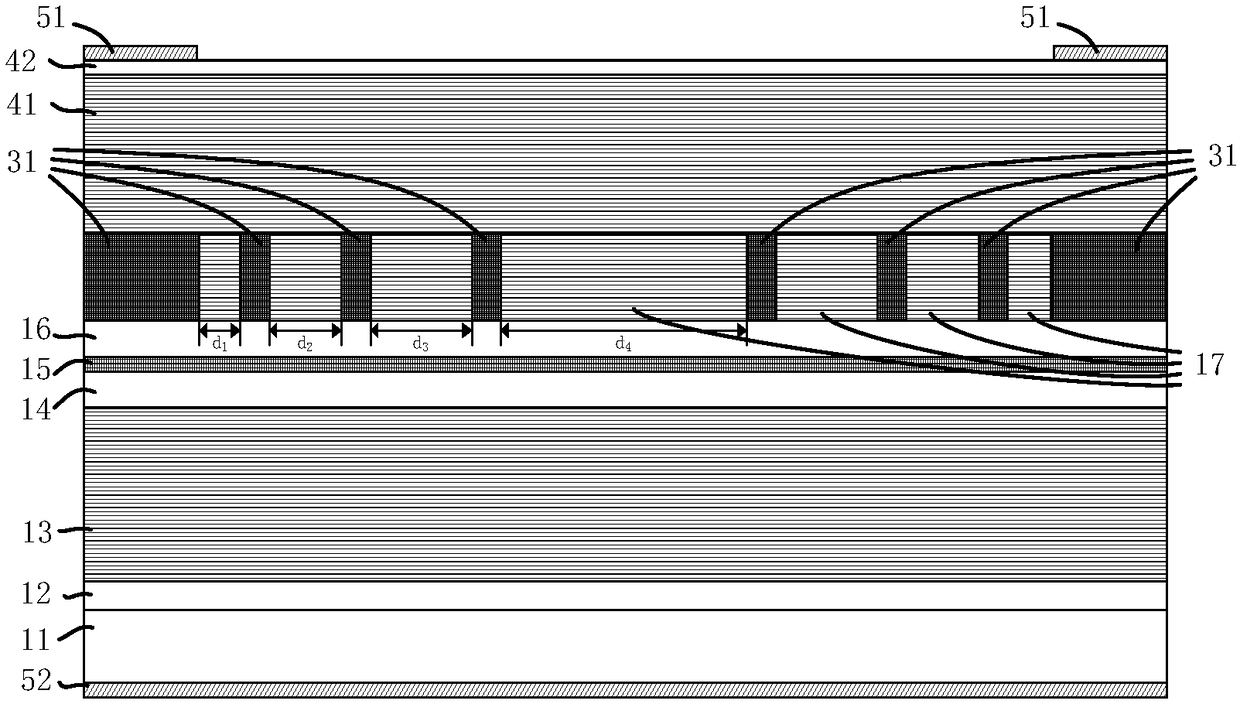

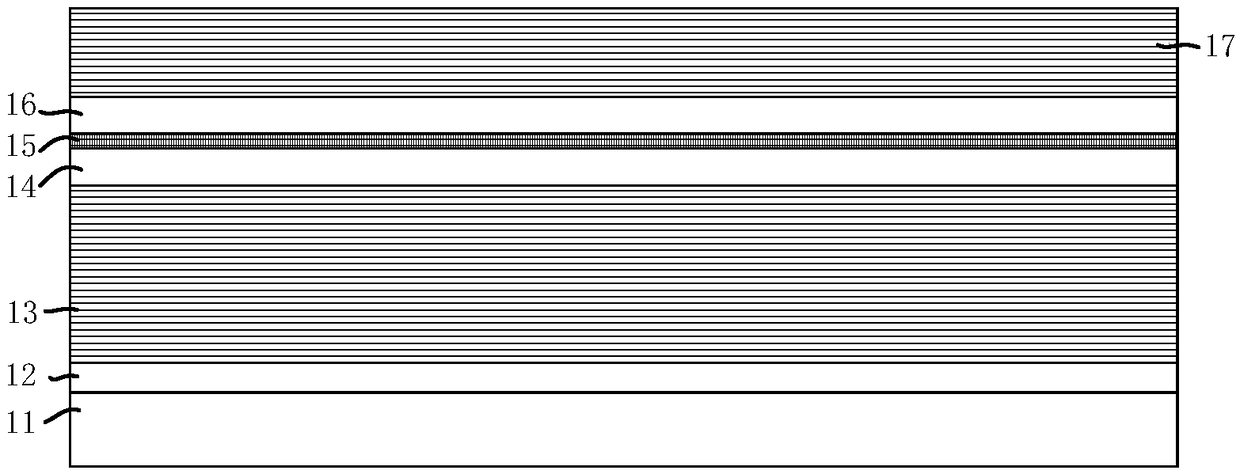

High-beam-quality large-scale VCSEL in-phase coupled array

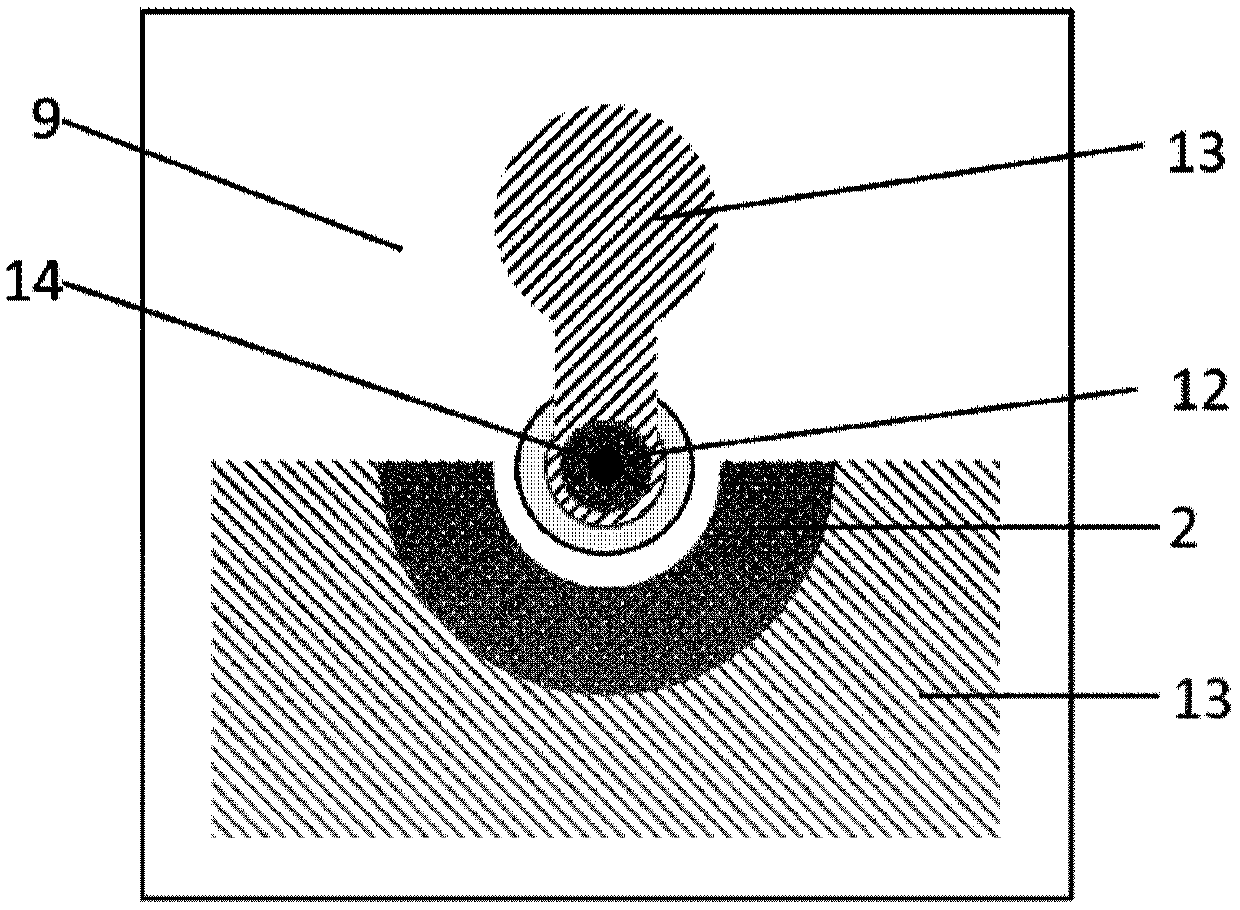

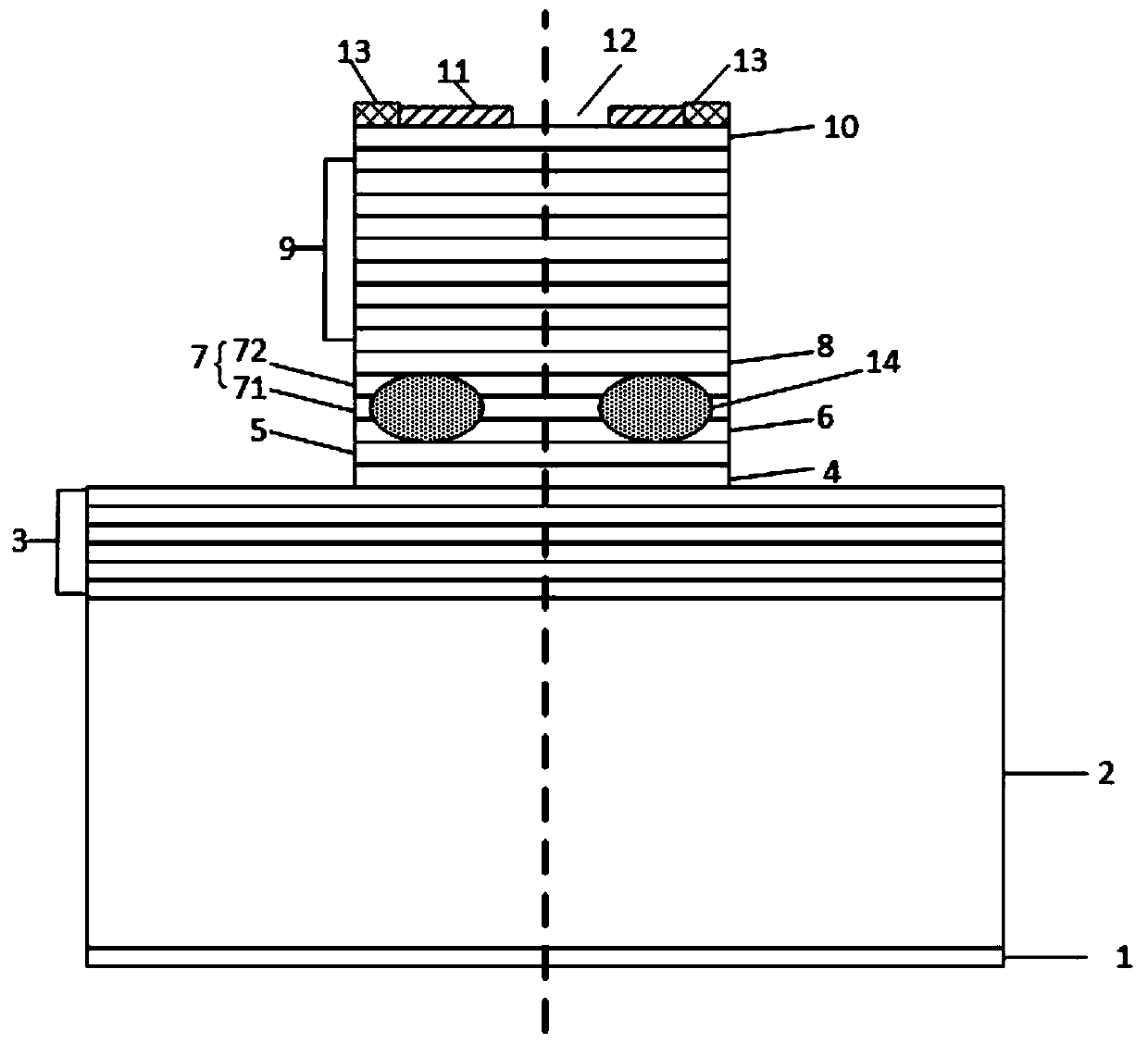

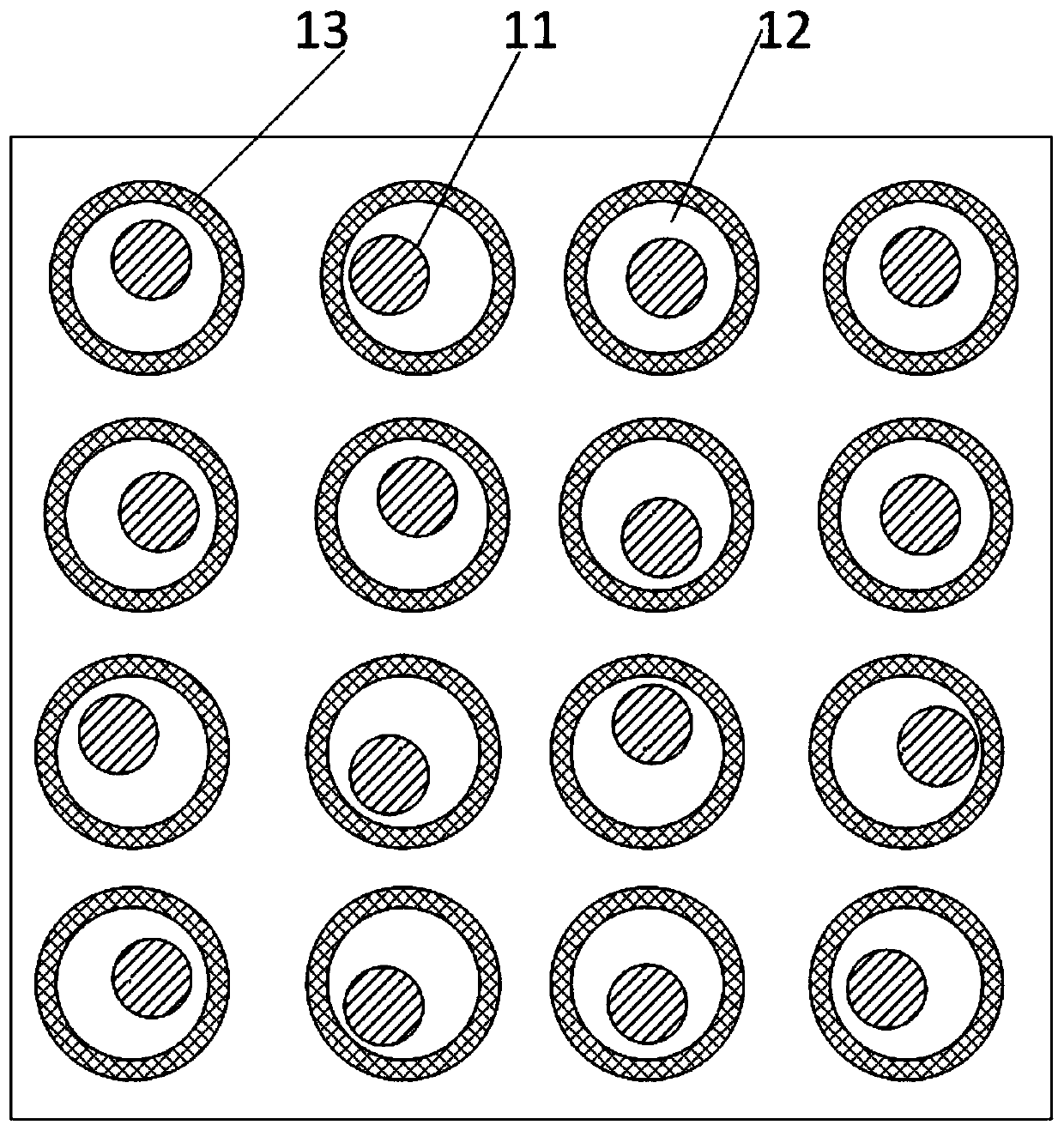

InactiveCN106654857ALow costSimple processLaser detailsSemiconductor lasersFiber-optic communicationLaser printing

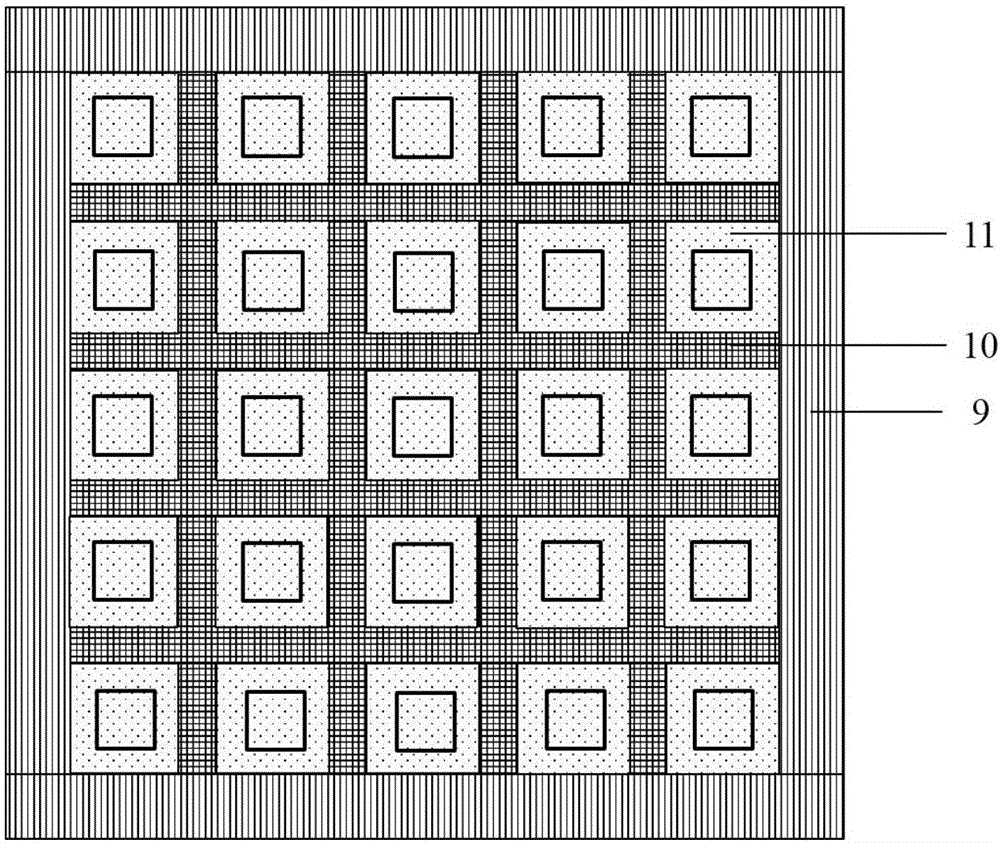

The invention discloses a high-beam-quality large-scale VCSEL in-phase coupled array and belongs to the field of semiconductor laser unit technology. The high-beam-quality large-scale VCSEL in-phase coupled array is provided with grid electrodes. A proton injection method is adopted to realize electrical isolation between light-out units. When a device operates, the effective refractive index of each light outlet region is lower than the effective refractive index of each interval region, and a special anti-waveguide structure is formed. The grid electrodes in the interval regions further enlarge anti-waveguide refractive index steps, so that in-phase coupling difficulty is lowered. By properly adjusting proton injection depth d and unit spacing, the array satisfies in-phase laser emission conditions, and the in-phase coupled array can be realized. By reasonably designing the array unit spacing and the proton injection depth d, in-phase laser output can be obtained, the beam quality of the array is improved, and the array can be applied to the fields of free space optical interconnection, laser radar, laser printing, optical fiber communication, optical pumping, etc.

Owner:BEIJING UNIV OF TECH

Photonic device with segmented absorption design

ActiveUS7050689B2Decrease maximum local temperatureImprove cooling effectOptical waveguide light guideLaser cooling arrangementsHigh absorptionProton implantation

A photonic device designed with an intermittent absorption profile along a waveguide. The absorption profile is divided into low-absorption and high-absorption segments that are distributed axially in order to decrease the maximum local temperature in the device. The distribution of low-absorption segments can be controlled through techniques such as proton implantation or selective-area quantum well intermixing. The lengths of low-absorption and high-absorption segments can be adjusted to optimize heat dissipation along the device length.

Owner:LUMENTUM OPERATIONS LLC

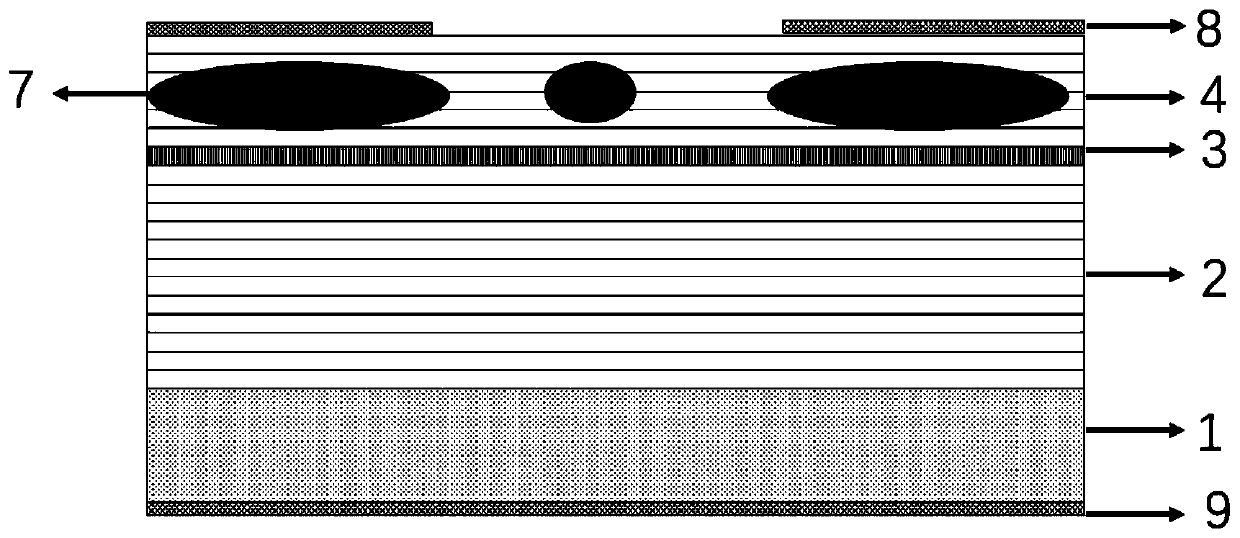

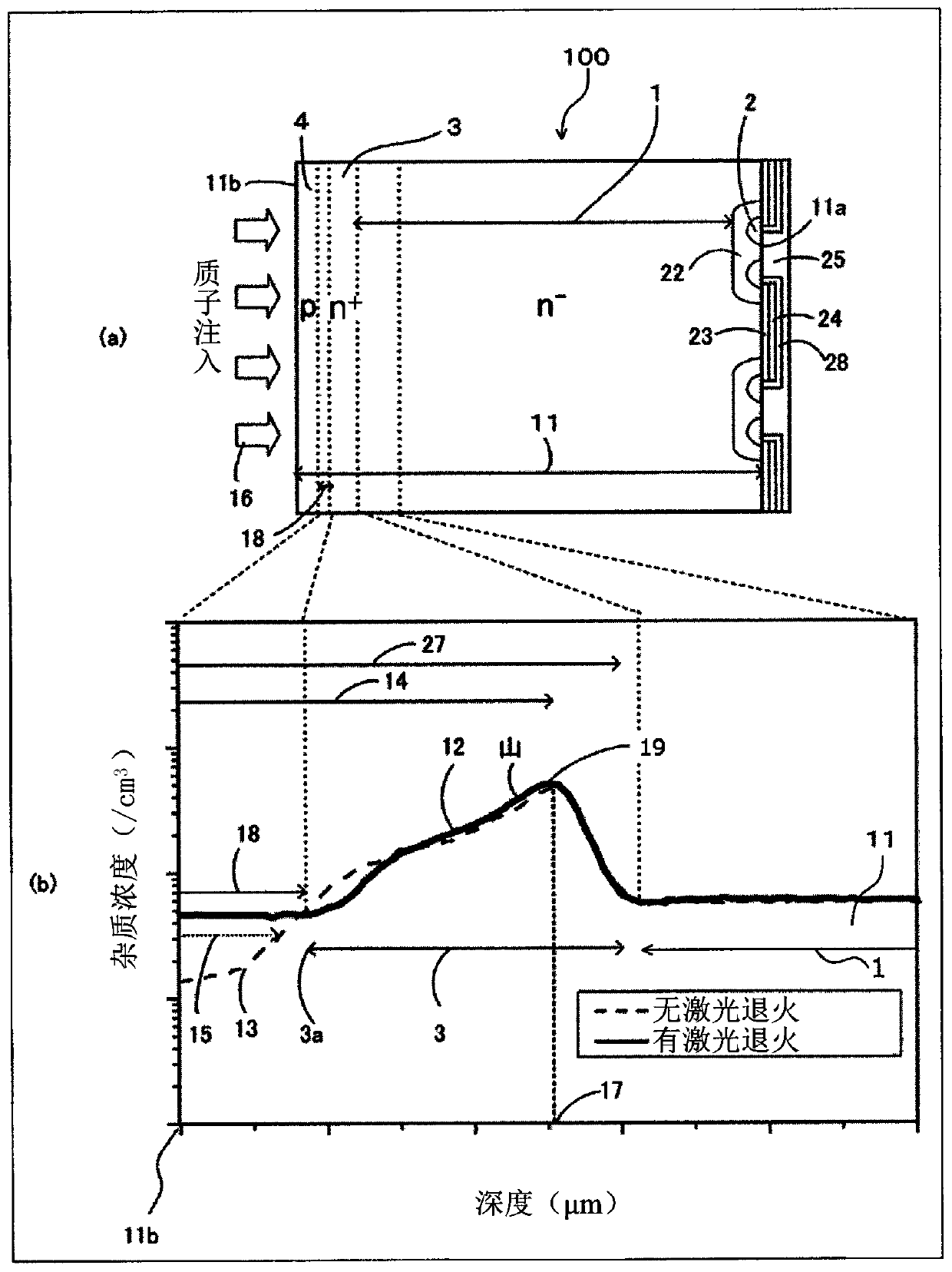

Semiconductor device and method for producing same

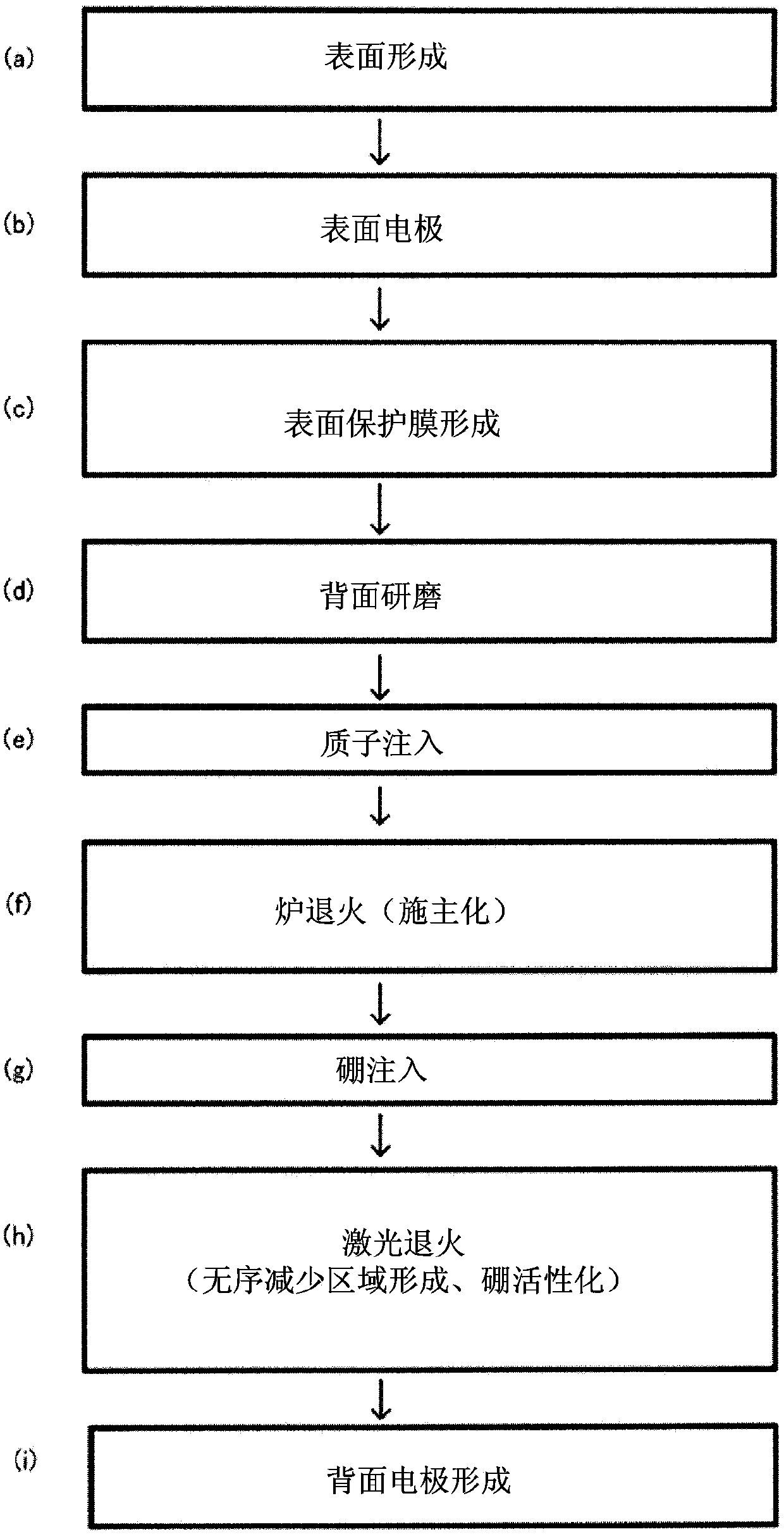

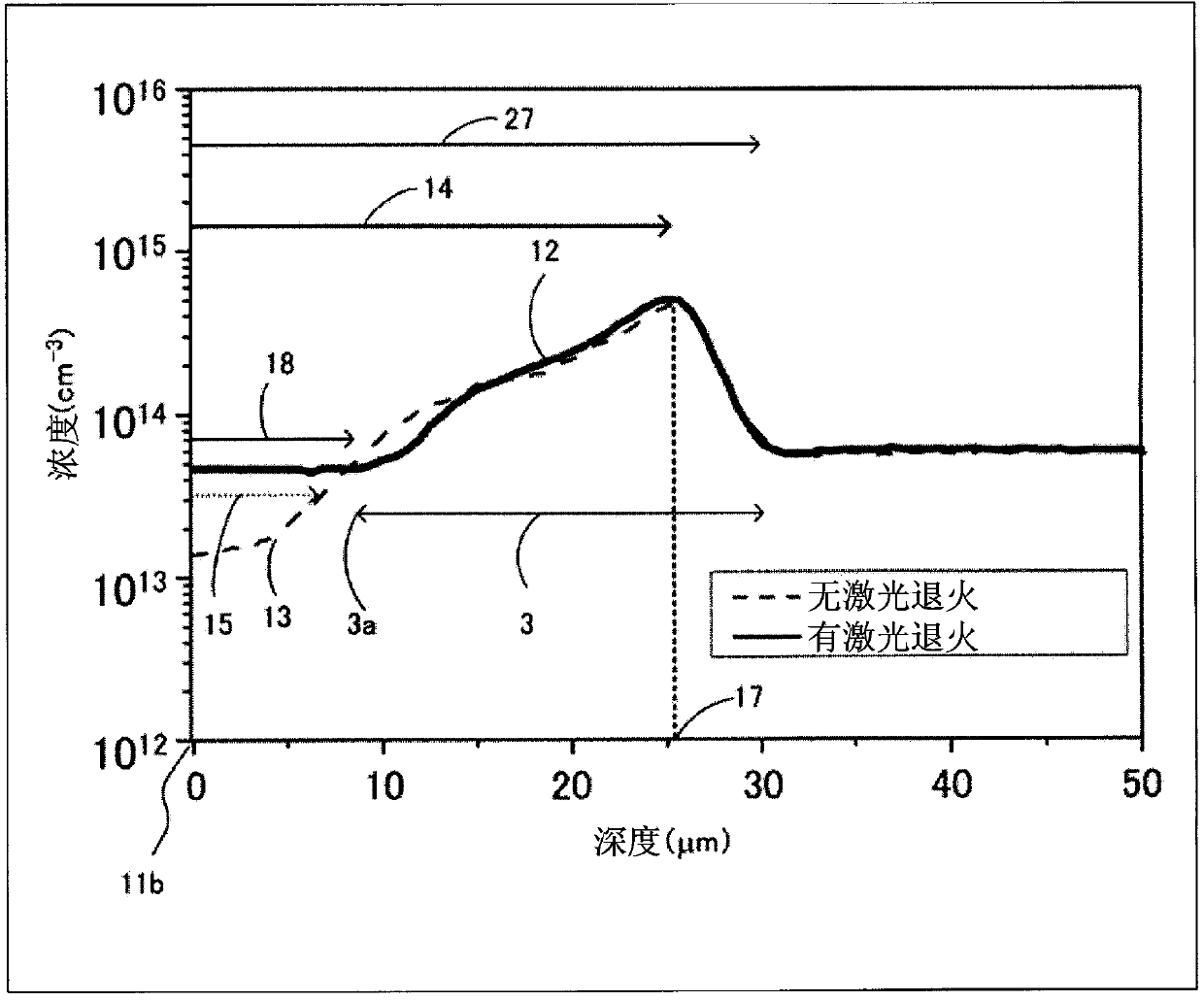

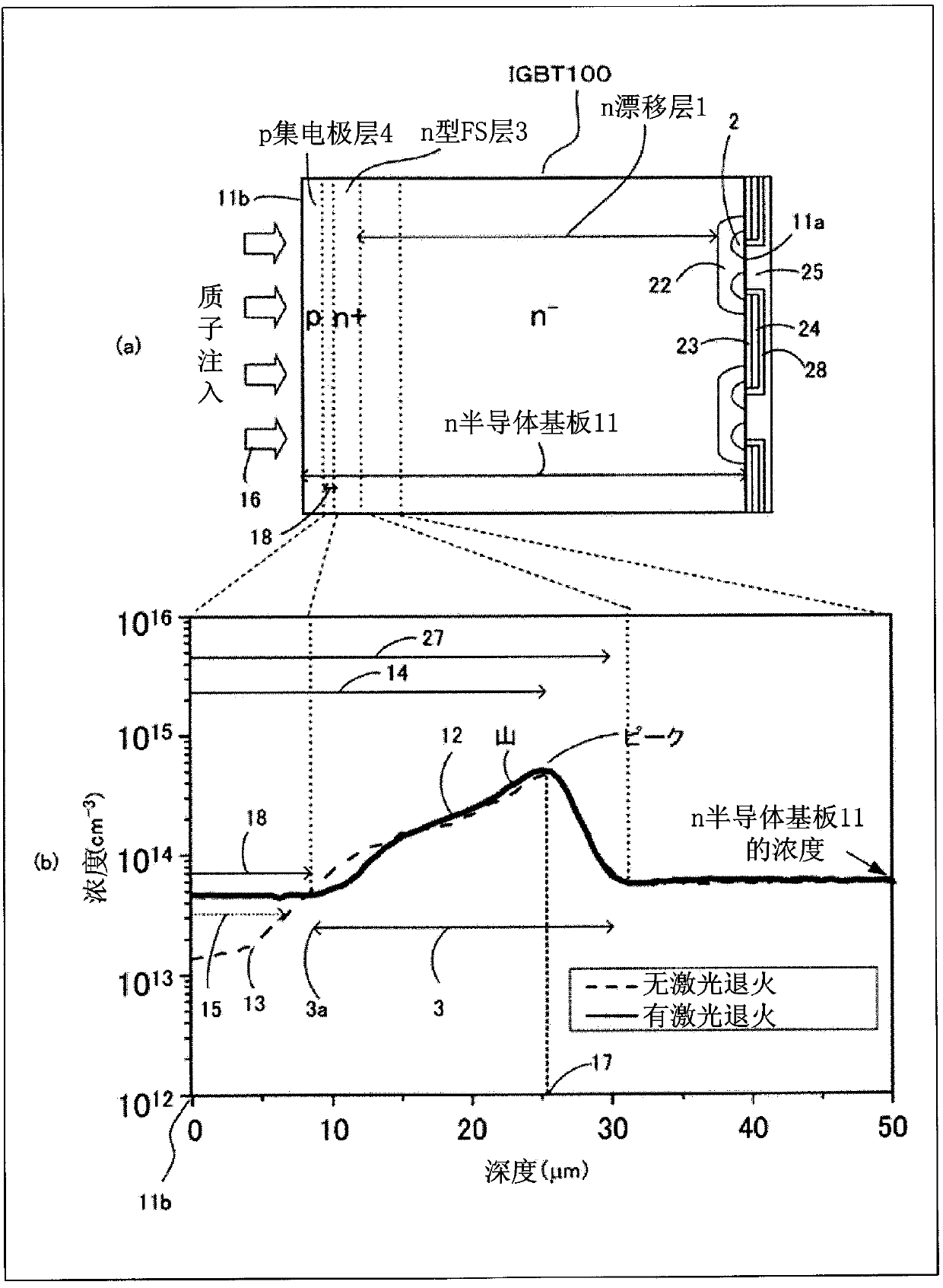

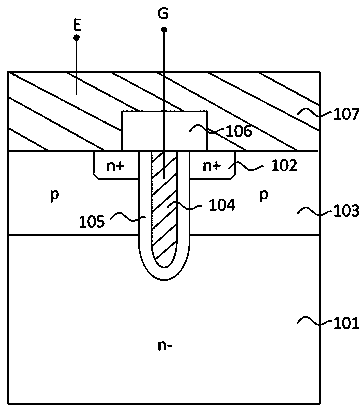

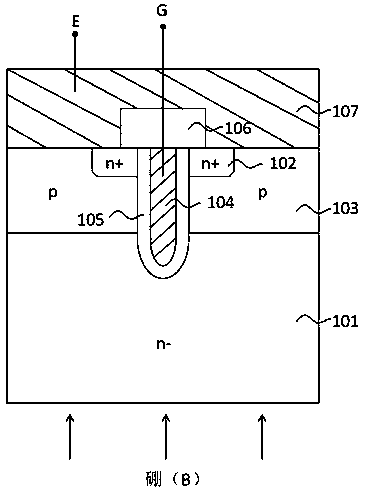

ActiveCN103999225AIncrease the on-resistanceImprove leakage currentTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceProton implantation

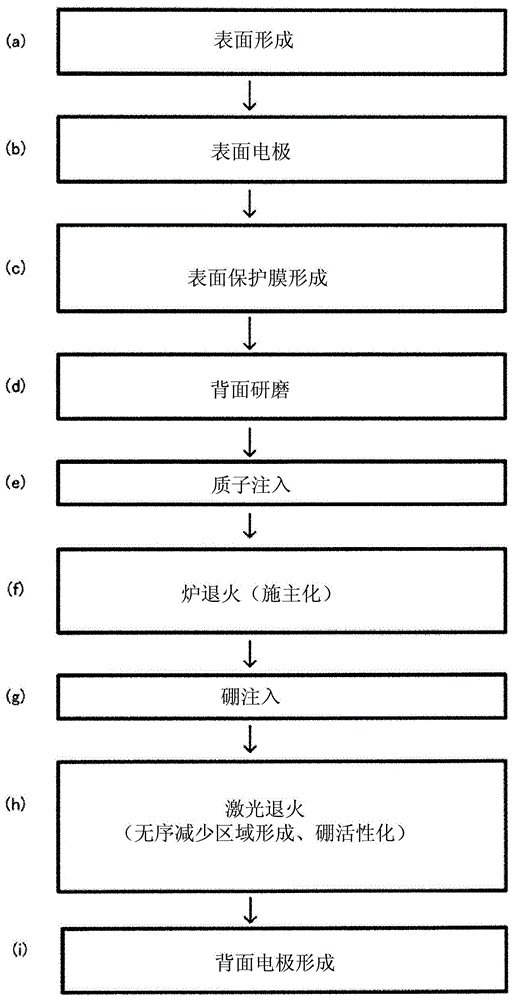

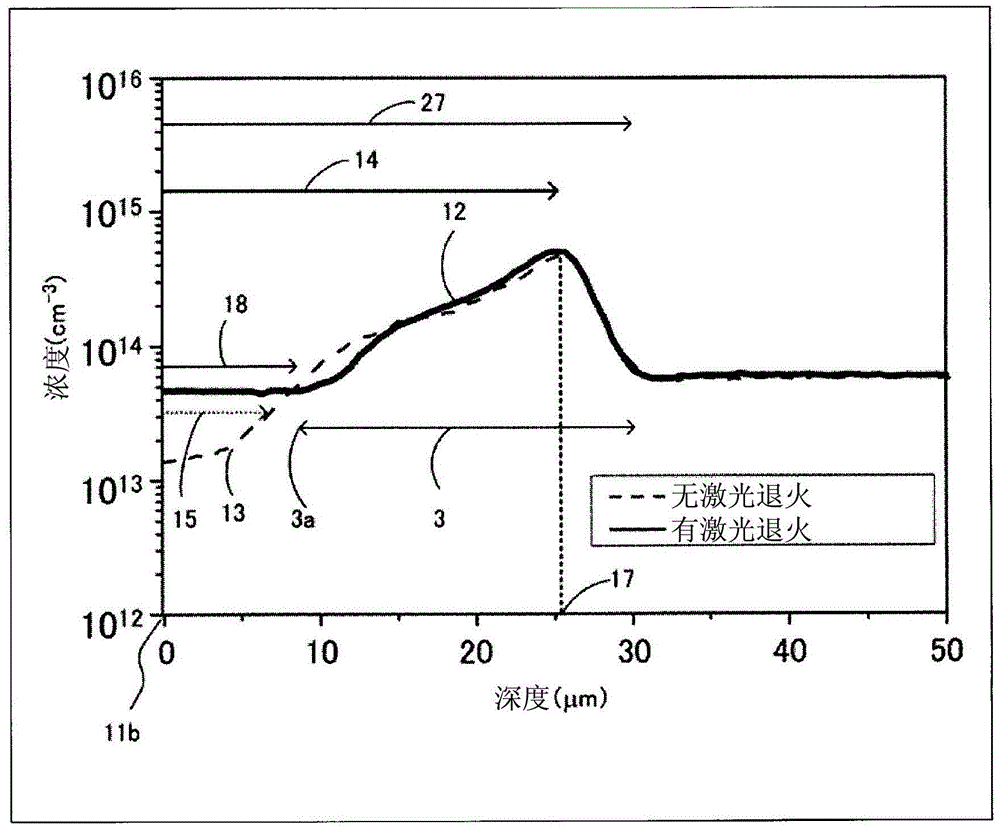

A method of producing a seminconductor device is disclosed in which, after proton implantation is performed, a hydrogen-induced donor is formed by a furnace annealing process to form an n-type field stop layer. A disorder generated in a proton passage region is reduced by a laser annealing process to form an n-type disorder reduction region. As such, the n-type field stop layer and the n-type disorder reduction region are formed by the proton implantation. Therefore, it is possible to provide a stable and inexpensive semiconductor device which has low conduction resistance and can improve electrical characteristics, such as a leakage current, and a method for producing the semiconductor device.

Owner:FUJI ELECTRIC CO LTD

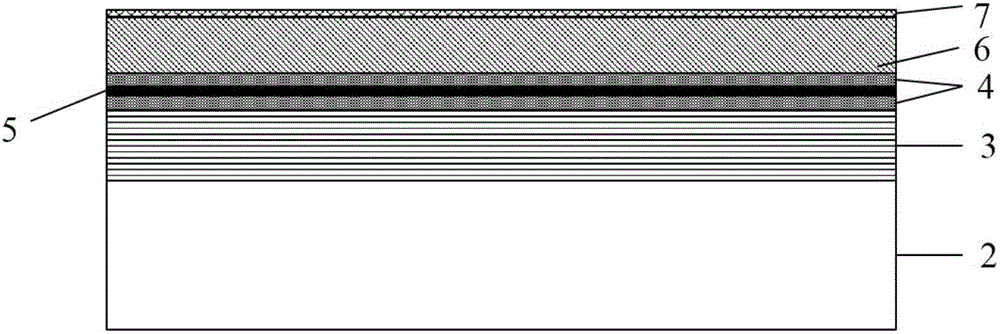

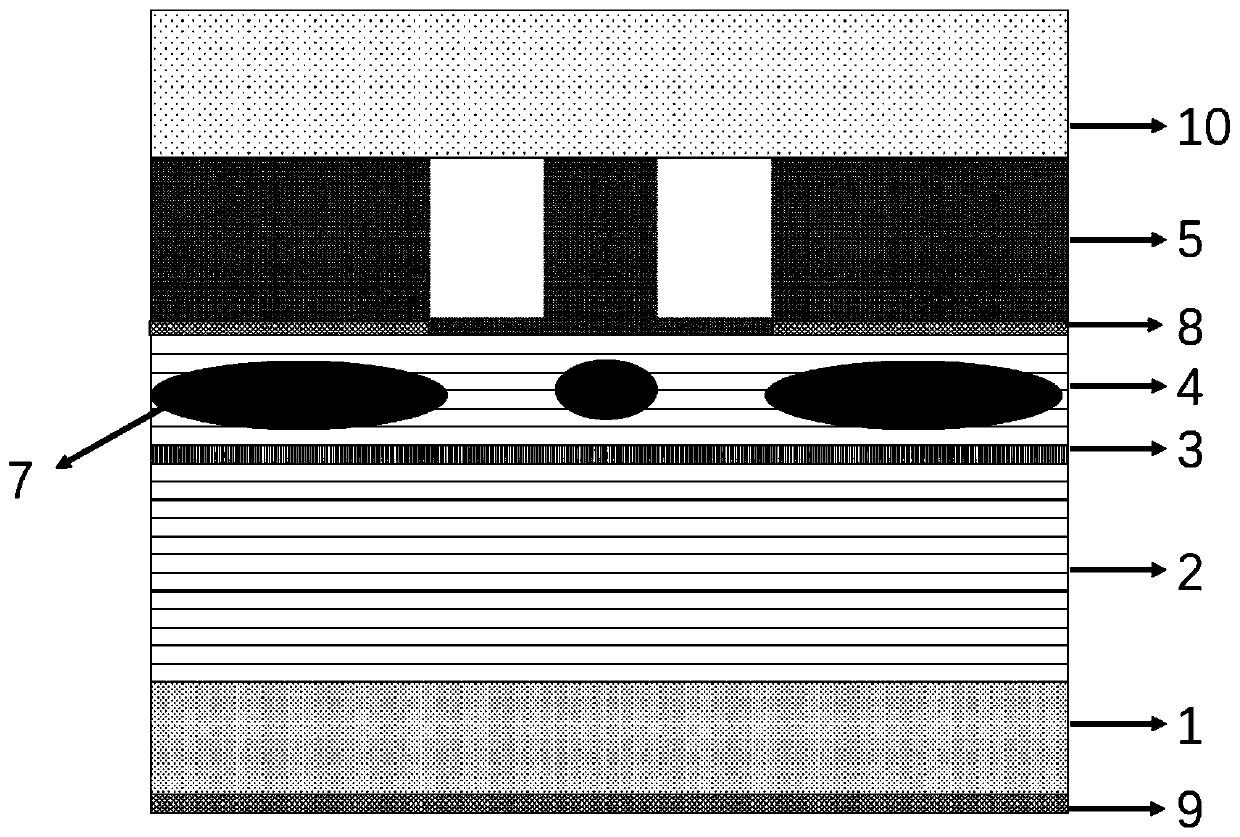

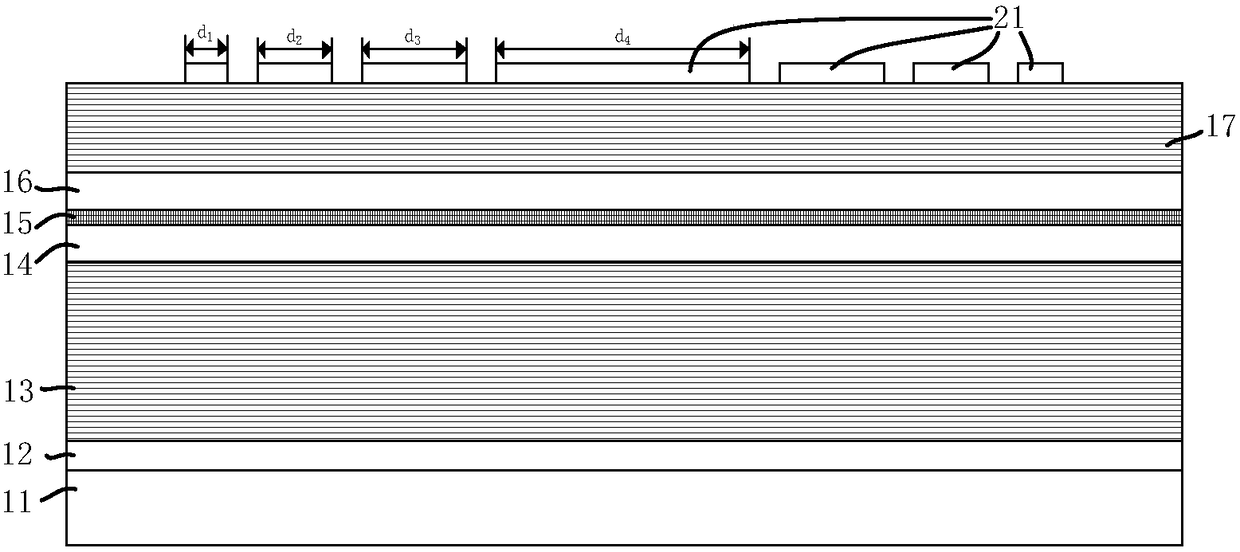

Optical beam scanning chips integrated on VCSEL coupled array and optical phase shifter array sheet

ActiveCN107611779ASolve the lack of separationImprove reliabilitySemiconductor laser arrangementsLaser active region structureProton implantationEvaporation

The invention discloses optical beam scanning chips integrated on VCSEL coupled array and a surface optical phase shifter array sheet, and belongs to the cross technical field of semi-conductor lasertechnologies and optical beam scanning technologies. A proton implantation technology, a photonic crystal or cavity induction reverse waveguide technology and the like are adopted, coupling among VCSEL array units is achieved, and coherent light with the same power can be generated by each array unit. By using characteristics of the VCSEL array plane structure, through technologies such as photolithography, sputtering, PECVD, ICP and evaporation, a transmissive optical phase shifter array is integrated on the surfaces of the VCSEL coupled array, and accordingly the optical beam scanning chipswith small size, compact structure and high integration level are obtained. The problems such as large size, low reliability and complex installation due to space separation of a laser source and thephase shifter array in a traditional optical phased array beam scanning device are solved, and the application prospects of the optical phase shifter sheet are wide.

Owner:BEIJING UNIV OF TECH

Liquid detection chip system for optical phase differences based on VCSEL (vertical-cavity surface-emitting laser) coupling array

ActiveCN110433878AReduce volumeWide detection rangeLaser detailsPhase-affecting property measurementsVertical-cavity surface-emitting laserPhase difference

The invention discloses a liquid detection chip system for optical phase differences based on a VCSEL (vertical-cavity surface-emitting laser) coupling array and belongs to the technical field of cross of semiconductor laser emitter techniques and biochemical detection techniques. By using techniques such as proton injection, cavity induction reverse waveguide or photonic crystals, preparation ofthe VCSEL coupling array can be achieved. By using processes such as PECVD (plasma enhanced chemical vapor deposition), photoetching, sputtering, reactive ion etching, wet etching and bonding, a microfluidic structure is integrated on the surface of the VCSEL coupling array. By using a microfluidic technique on the upper surface of the VCSEL coupling array, a liquid to be tested is introduced above VCSEL coupling array units, then light beam coupling phase differences of VCSEL units are changed, laser beams are derived, the refractive index of a liquid can be calculated by measuring deflectionangles of laser beams, and detection on liquid refractive indexes can be achieved.

Owner:BEIJING UNIV OF TECH

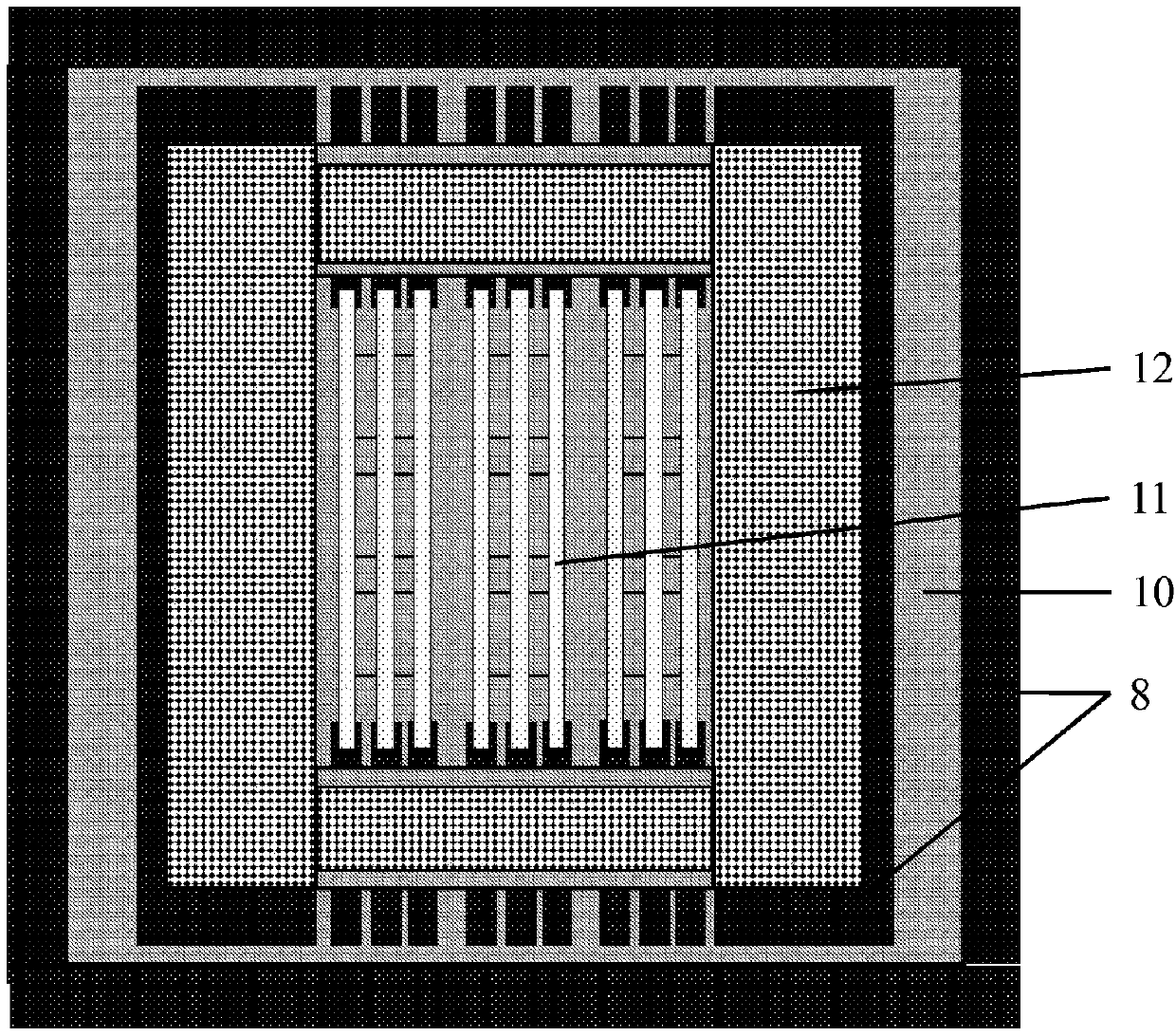

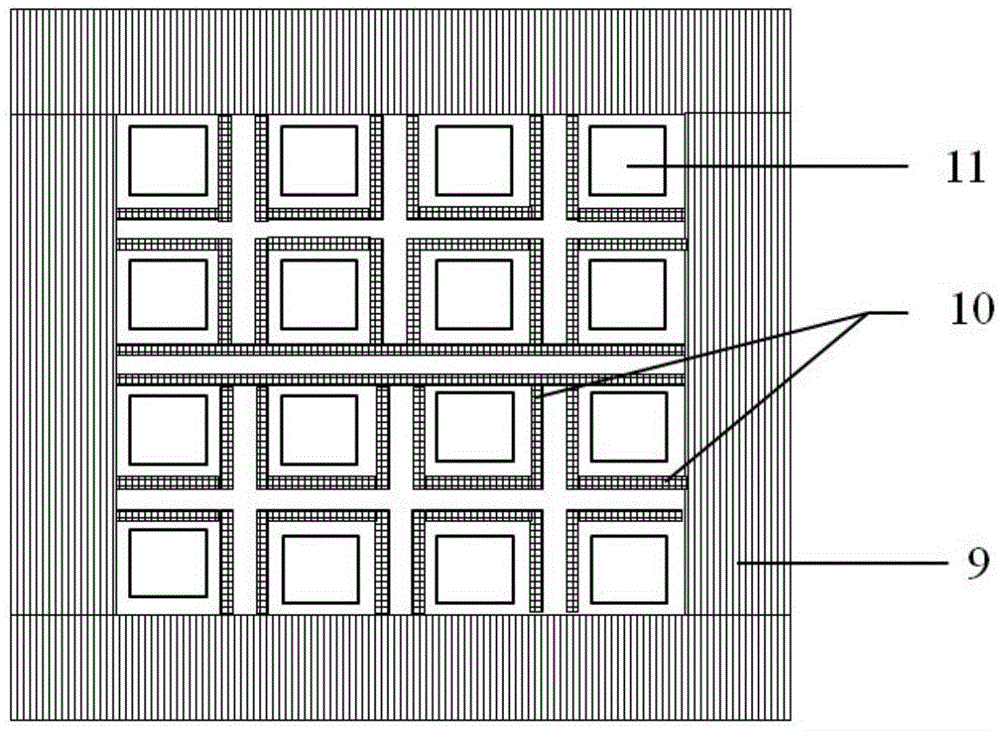

Double-grid electrode for high-beam-quality large-power VCSEL (Vertical Cavity Surface Emitting Laser) same-phase coupling array

ActiveCN105655867AIncrease optical powerHigh beam qualityLaser detailsSemiconductor lasersVertical-cavity surface-emitting laserProton implantation

The invention discloses a double-grid electrode for a high-beam-quality large-power VCSEL (Vertical Cavity Surface Emitting Laser) same-phase coupling array. By adoption of the double-grid electrode, the problem of non-uniform current spreading of the large-scale VCSEL array can be solved, and simultaneously the problem of same-phase mode absorption in the traditional single-grid electrode also can be solved, so that the array can obtain high-power same-phase output. The double-grid electrode comprises a large electrode with an external frame and an electrode with double internal grids. The double-grid electrode disclosed by the invention has the advantages that the VCSEL array is prepared by adopting a multiple-proton implantation mode, the problem of mode absorption in the single-grid electrode can be solved by reasonably designing the spacing of array elements and the novel double-grid electrode, and high-power output can be obtained while guaranteeing same-phase laser output, so that the beam quality of the array is greatly improved; and the double-grid electrode can be applied in the fields such as free-space optical interconnection, laser radar, laser printing, optical-fiber communication and optical pumping and the like.

Owner:BEIJING UNIV OF TECH

Production method for a semiconductor device

ActiveUS9530672B2Accelerates generation and extinctionIncrease generationSemiconductor/solid-state device manufacturingSemiconductor devicesProton implantationHydrogen atmosphere

A method for producing a semiconductor device includes providing a semiconductor substrate having a first conductivity type; implanting protons through a rear surface of the semiconductor substrate of the first conductivity type; and forming a first semiconductor region of the first conductivity type in the semiconductor substrate by performing an annealing process in an annealing furnace in a hydrogen atmosphere having a volume concentration of hydrogen that is equal to or greater than 0.5% and less than 4.65%, the first semiconductor region having a higher impurity concentration than that of the semiconductor substrate after the implantation step. The method reduces crystal defects in the generation of donors during proton implantation and improves the rate of change into a donor.

Owner:FUJI ELECTRIC CO LTD

Production method for semiconductor device

ActiveUS9947761B2Accelerates generation and extinctionIncrease generationTransistorSemiconductor/solid-state device manufacturingProton implantationHydrogen atmosphere

A method for producing a semiconductor device includes an implantation step of performing proton implantation from a rear surface of a semiconductor substrate of a first conductivity type and a formation step of performing an annealing process for the semiconductor substrate in an annealing furnace to form a first semiconductor region of the first conductivity type which has a higher impurity concentration than the semiconductor substrate after the implantation step. In the formation step, the furnace is in a hydrogen atmosphere and the volume concentration of hydrogen is in the range of 6% to 30%. Therefore, it is possible to reduce crystal defects in the generation of donors by proton implantation. In addition, it is possible to improve the rate of change into a donor.

Owner:FUJI ELECTRIC CO LTD

Vertical-cavity surface-emitting semiconductor laser structure

ActiveCN111435781AImprove uniformityImprove performanceLaser detailsSemiconductor lasersVertical-cavity surface-emitting laserProton implantation

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Vertical cavity surface emitting laser and manufacturing method thereof

PendingCN111478179AImplementing Tunable FunctionsSimple preparation processLaser detailsLaser active region structureVertical-cavity surface-emitting laserProton implantation

The invention discloses a vertical cavity surface emitting laser. The vertical cavity surface emitting laser comprises a first electrode, a substrate, a first reflector layer, a quantum dot layer, a first limiting layer, a transition layer, a doping layer, a second limiting layer, a second reflector layer, an embossment layer and a second electrode which are sequentially stacked from bottom to top. Proton implantation regions are distributed in the transition layer and the doped layer, the embossment layer comprises an etching region and a non-etching region, and the intersection point of thecenter line of the vertical cavity surface emitting laser and the embossment layer is located in the etching region or the non-etching region. Different modes of lasing of the VCSEL array unit are realized by introducing the offset of the non-coaxial embossment layer, the wavelength of the long-wavelength VCSEL can be adjusted, the manufacturing process is simple, and the problem that the center of a surface embossment needs to be strictly aligned with the center of a VCSEL tabletop in the design and preparation process of an existing surface embossment technology is solved. The invention further provides a manufacturing method of the vertical cavity surface emitting laser with the advantages.

Owner:长春中科长光时空光电技术有限公司

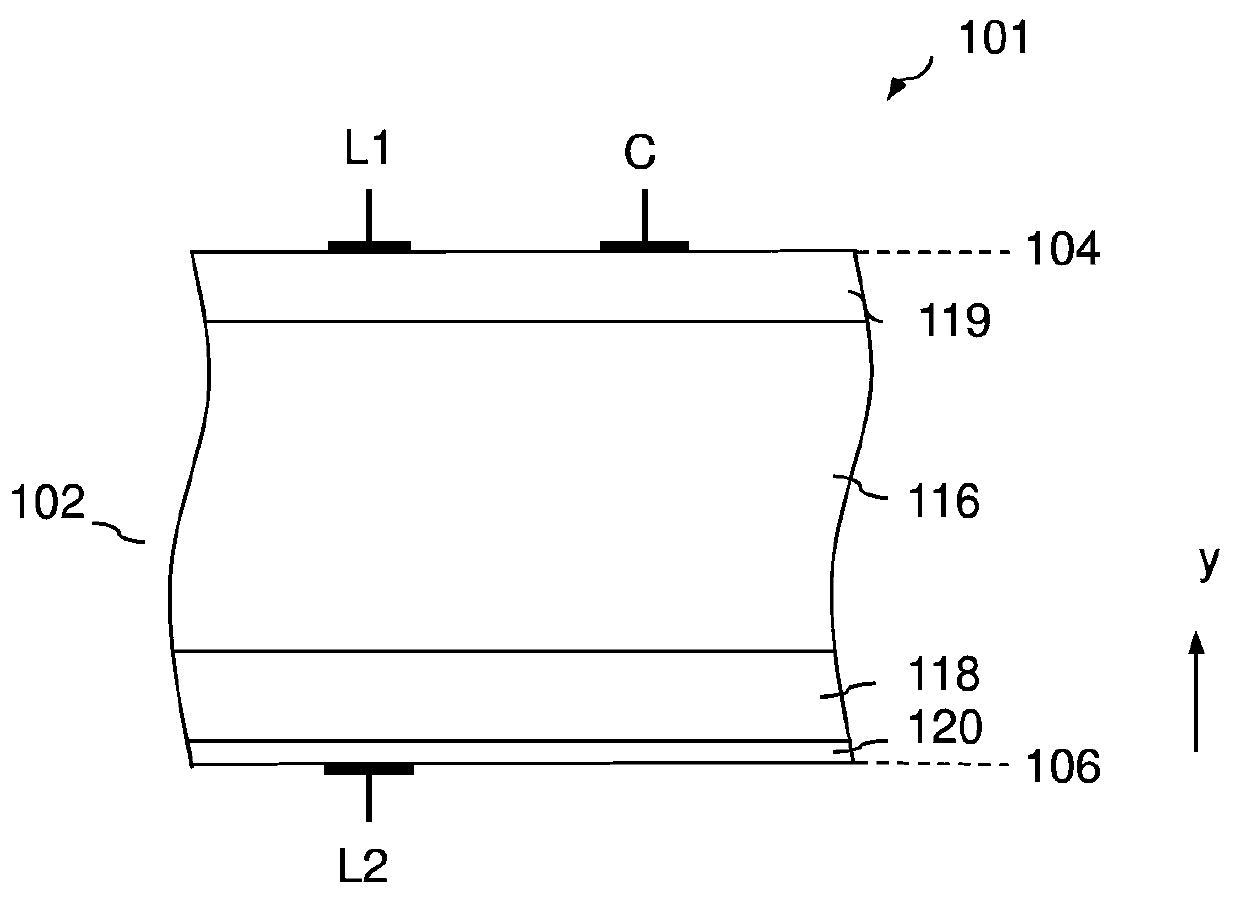

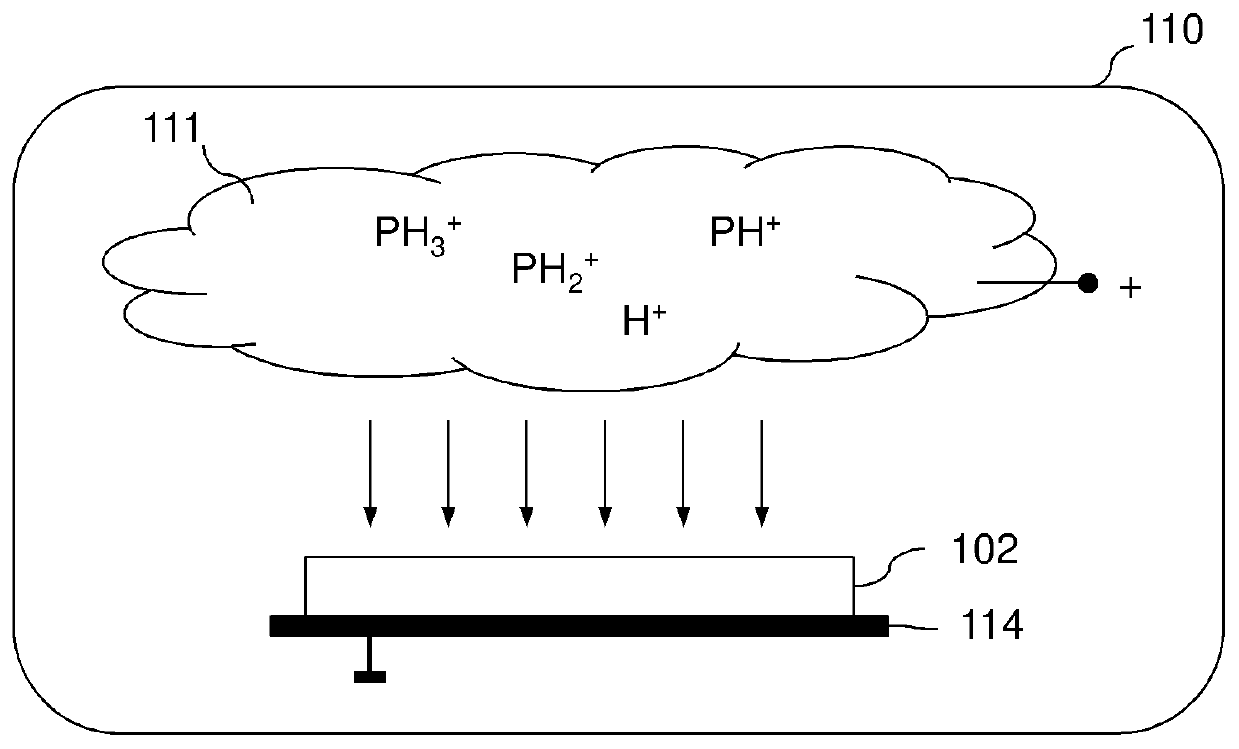

Method for manufacturing semiconductor device

The present disclosure relates to a method for manufacturing a semiconductor device. The method includes introducing at least one first dopant into a semiconductor body (102) through a first surface (104) of the semiconductor body (102). One or more proton implants are then performed. The method also includes introducing a second dopant into the semiconductor body (102) through a second surface (106) opposite the first surface (104) using a plasma-based ion implantation method, wherein the plasma-based ion implantation method is carried out using a composite of the second dopant and hydrogen as a process gas.

Owner:INFINEON TECH AG

Semiconductor device and method for manufacturing the same

ActiveUS10176986B2Suppress of depletion layerReduce power lossTransistorSemiconductor/solid-state device manufacturingPower semiconductor deviceProton implantation

A semiconductor device is disclosed in which proton implantation is performed a plurality of times to form a plurality of n-type buffer layers in an n-type drift layer at different depths from a rear surface of a substrate. The depth of the n-type buffer layer, which is provided at the deepest position from the rear surface of the substrate, from the rear surface of the substrate is more than 15 μm. The temperature of a heat treatment which is performed in order to change a proton into a donor and to recover a crystal defect after the proton implantation is equal to or higher than 400° C. In a carrier concentration distribution of the n-type buffer layer, a width from the peak position of carrier concentration to an anode is more than a width from the peak position to a cathode.

Owner:FUJI ELECTRIC CO LTD

Semiconductor device and manufacturing method thereof

ActiveCN103999225BIncrease the on-resistanceImprove leakage currentTransistorSemiconductor/solid-state device manufacturingElectrical resistance and conductanceProton implantation

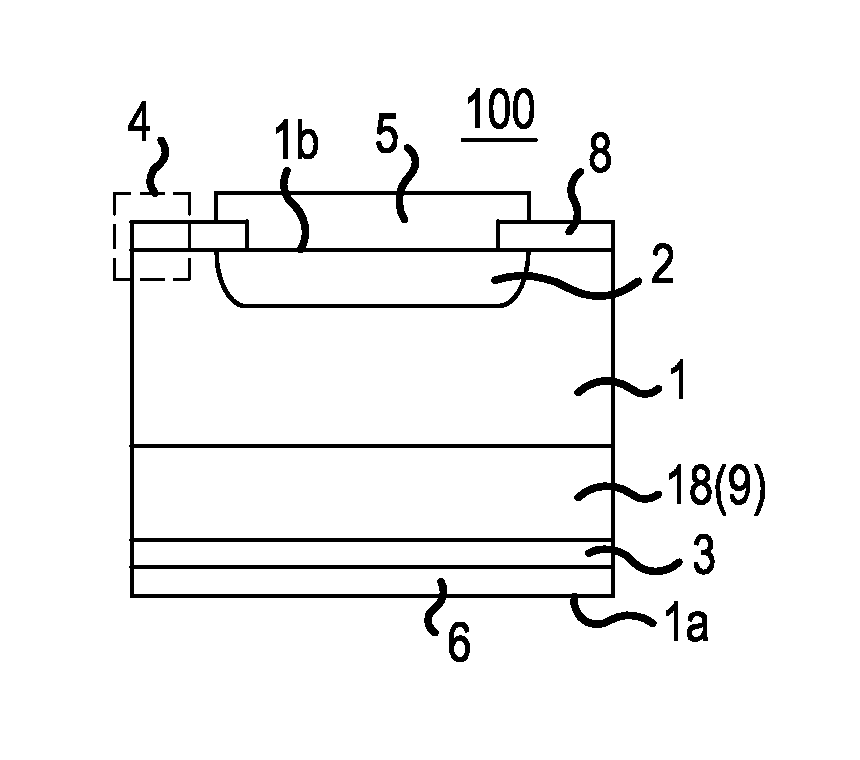

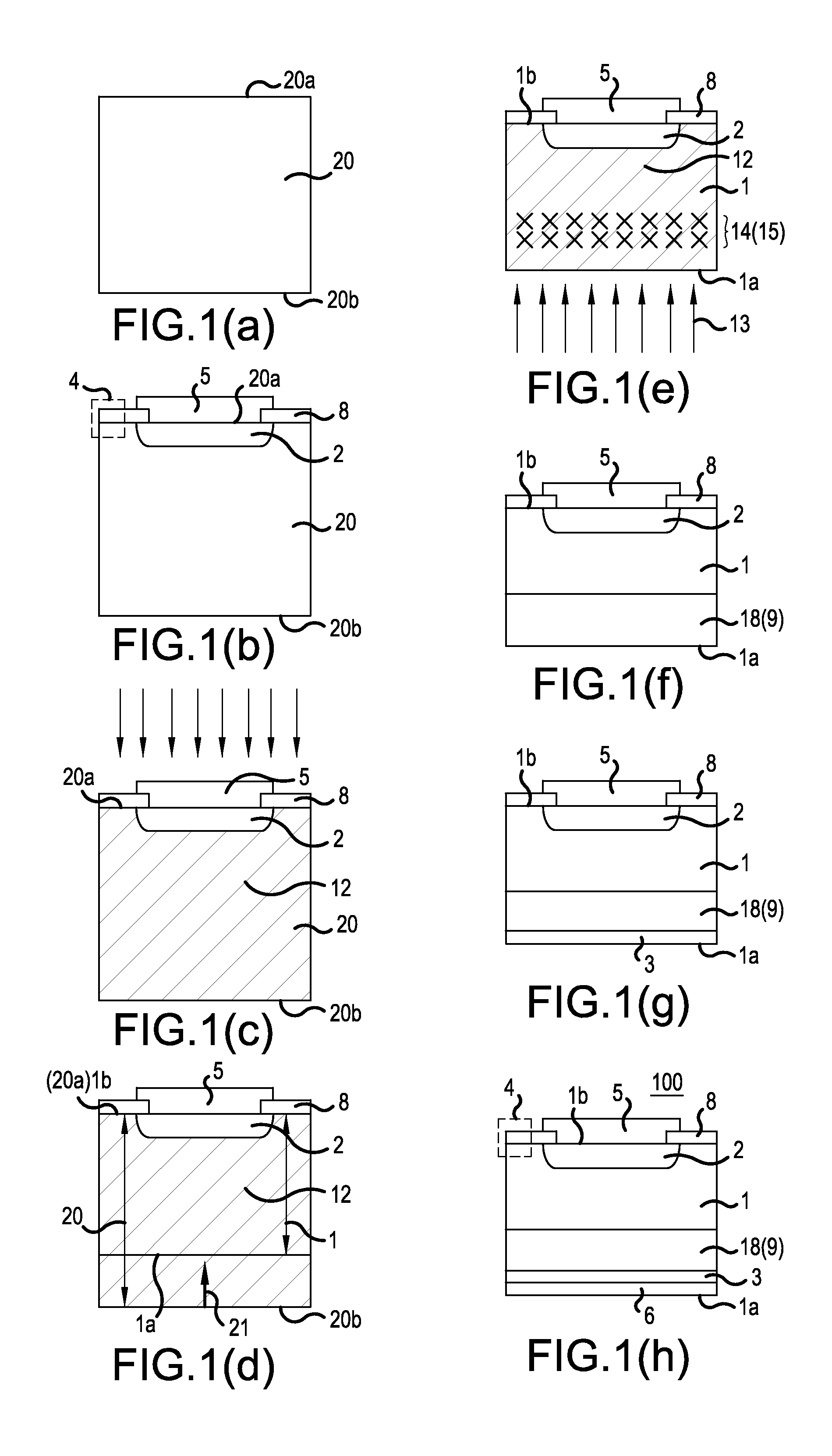

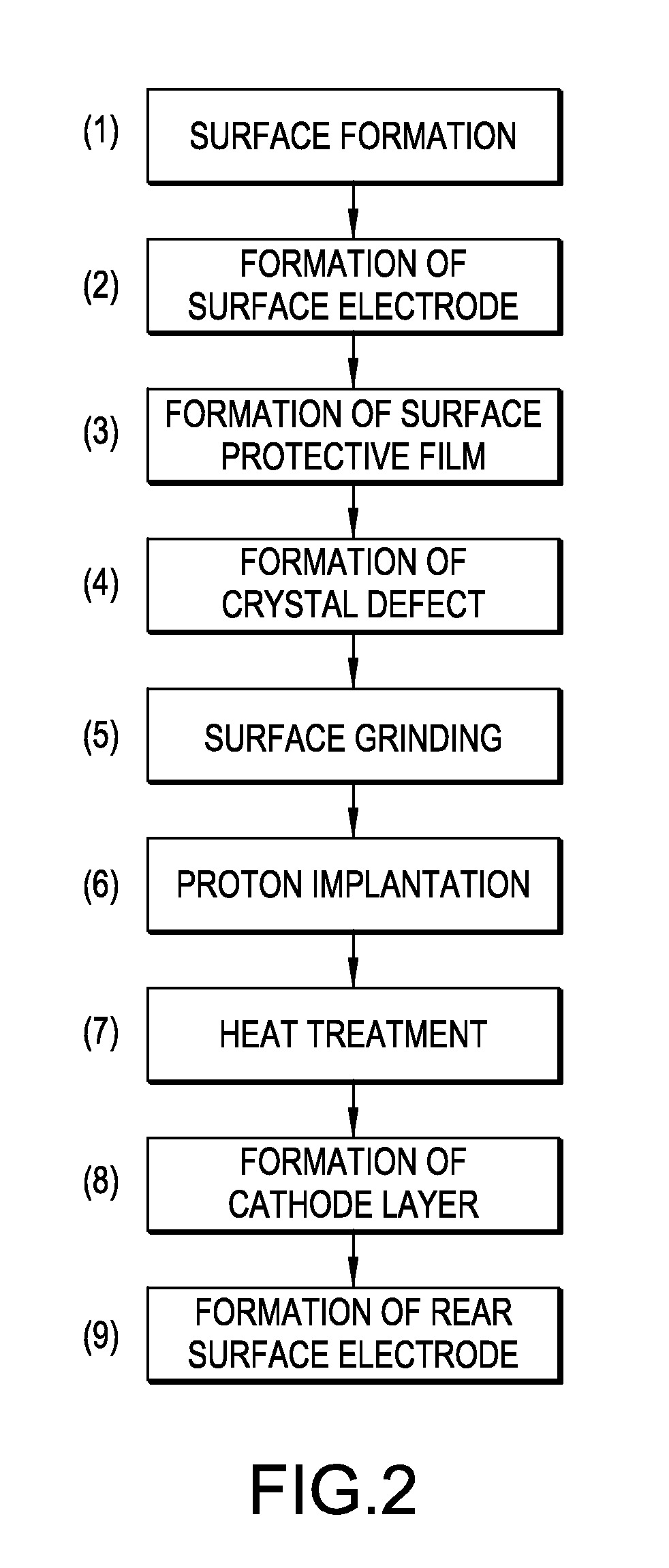

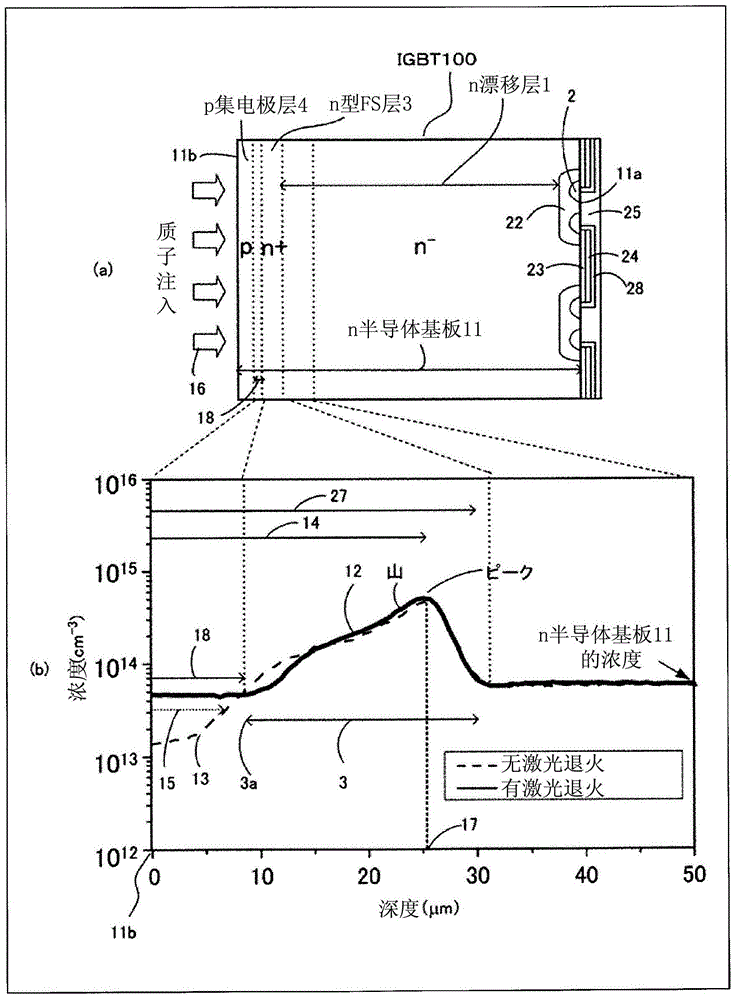

After the proton implantation (16), hydrogen-induced donors are formed by furnace annealing treatment, thereby forming an n-type electric field stop layer (3), and the disorder generated in the proton passing region (14) is further reduced by laser annealing treatment, thereby forming an n-type disordered Sequentially reduce the area (18). In this way, the present invention can provide an n-type electric field stop layer (3) based on proton injection (16) and an n-type disorder-reducing region (18), which has low on-resistance and can improve electrical characteristics such as leakage current, and is stable and inexpensive. Semiconductor device and manufacturing method thereof.

Owner:FUJI ELECTRIC CO LTD

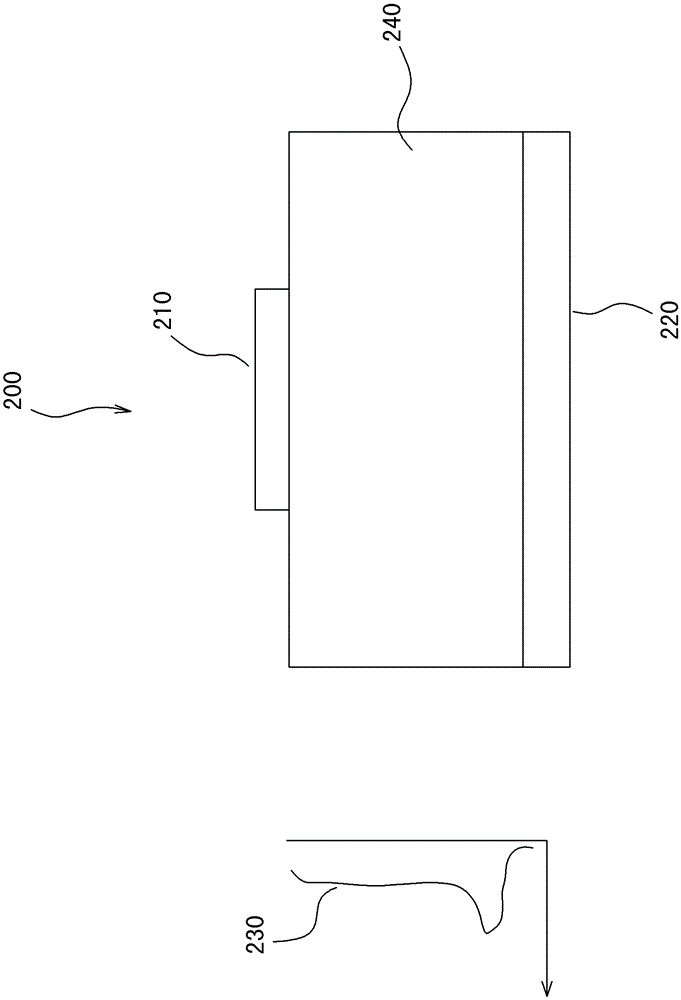

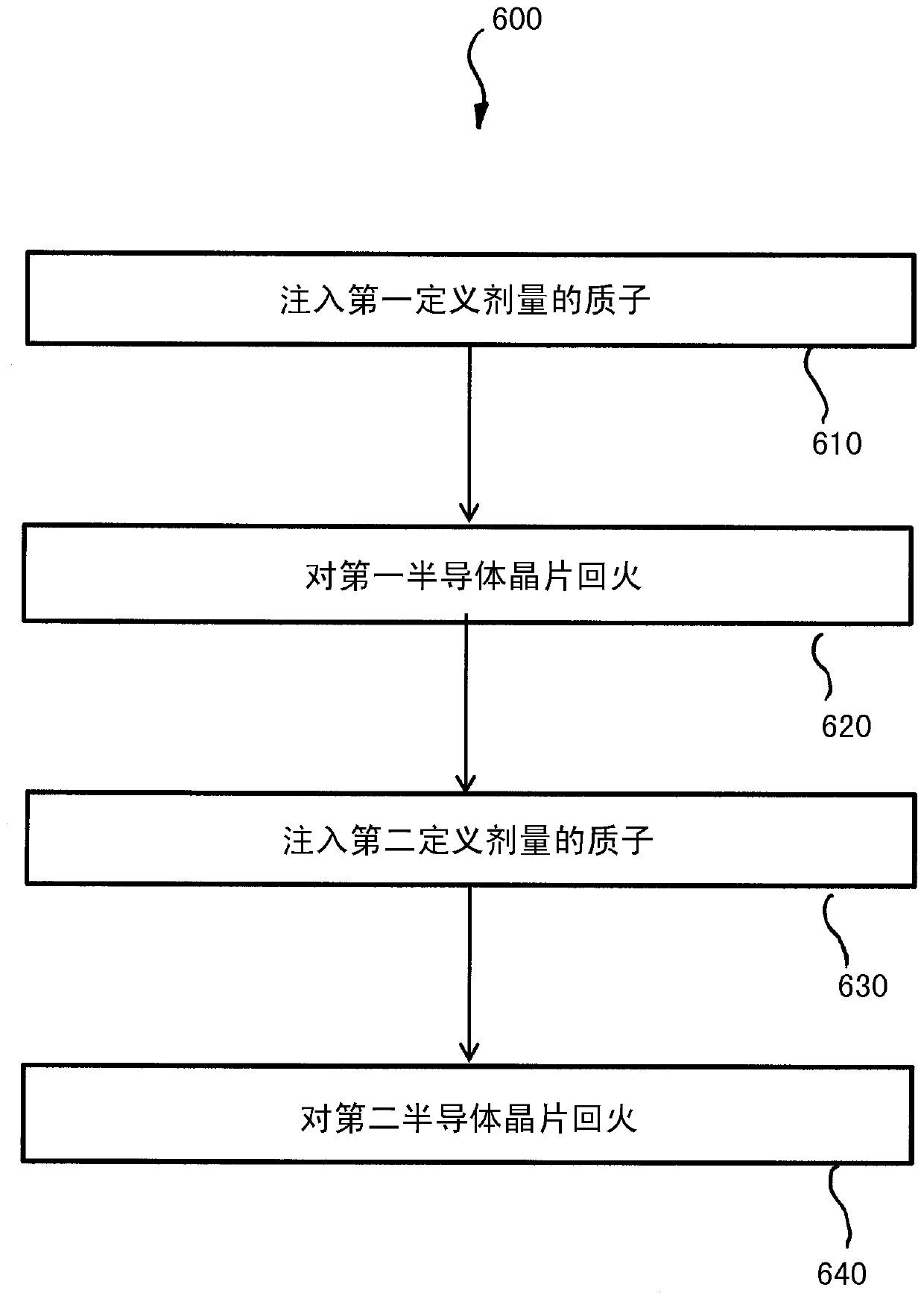

Method for forming semiconductor device and semiconductor device

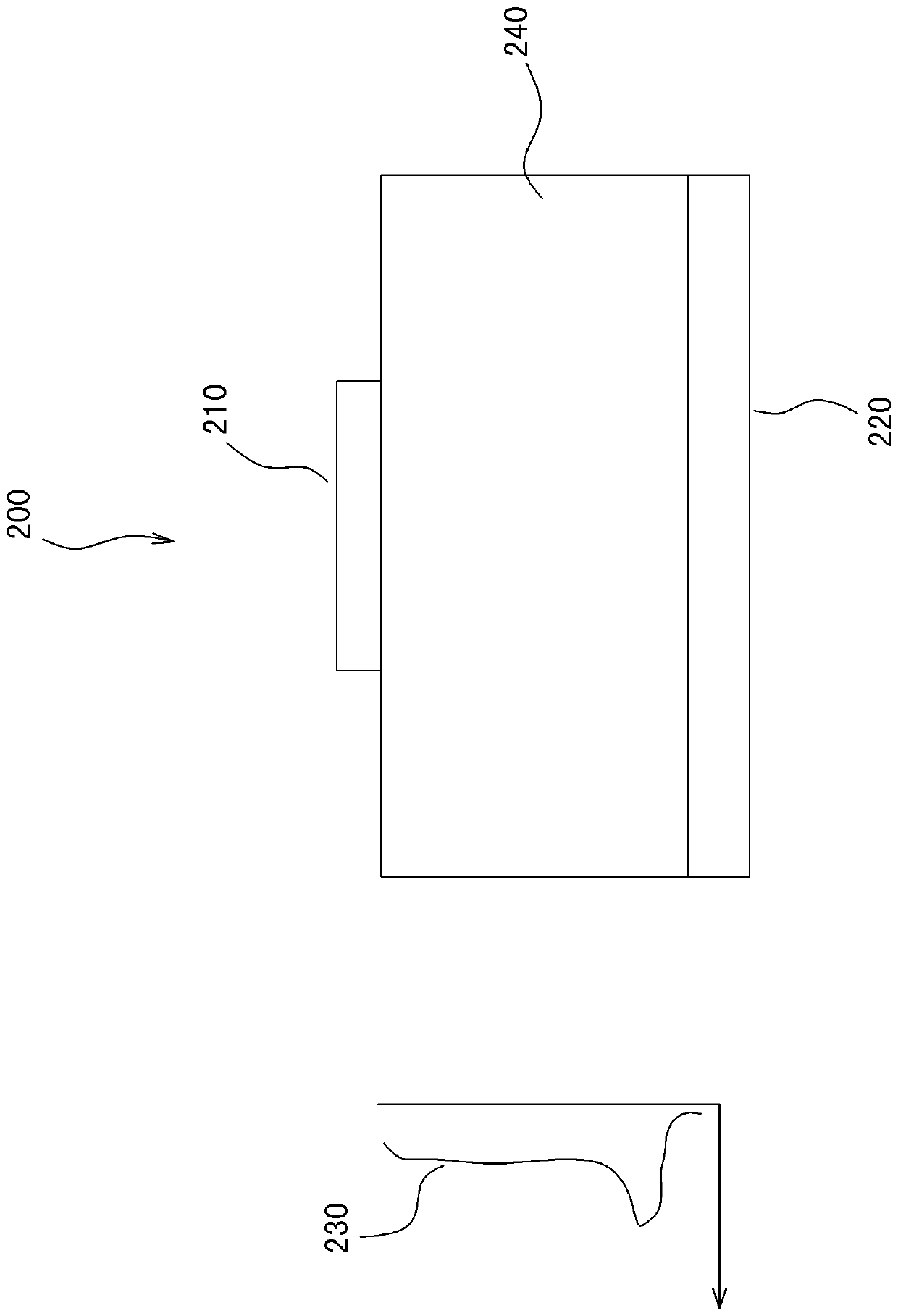

A method for forming a semiconductor device comprises implanting a defined dose of protons into a semiconductor substrate and tempering the semiconductor substrate according to a defined temperature profile. At least one of the defined dose of protons and the defined temperature profile is selected depending on a carbon-related parameter indicating information on a carbon concentration within at least a part of the semiconductor substrate.

Owner:INFINEON TECH AG

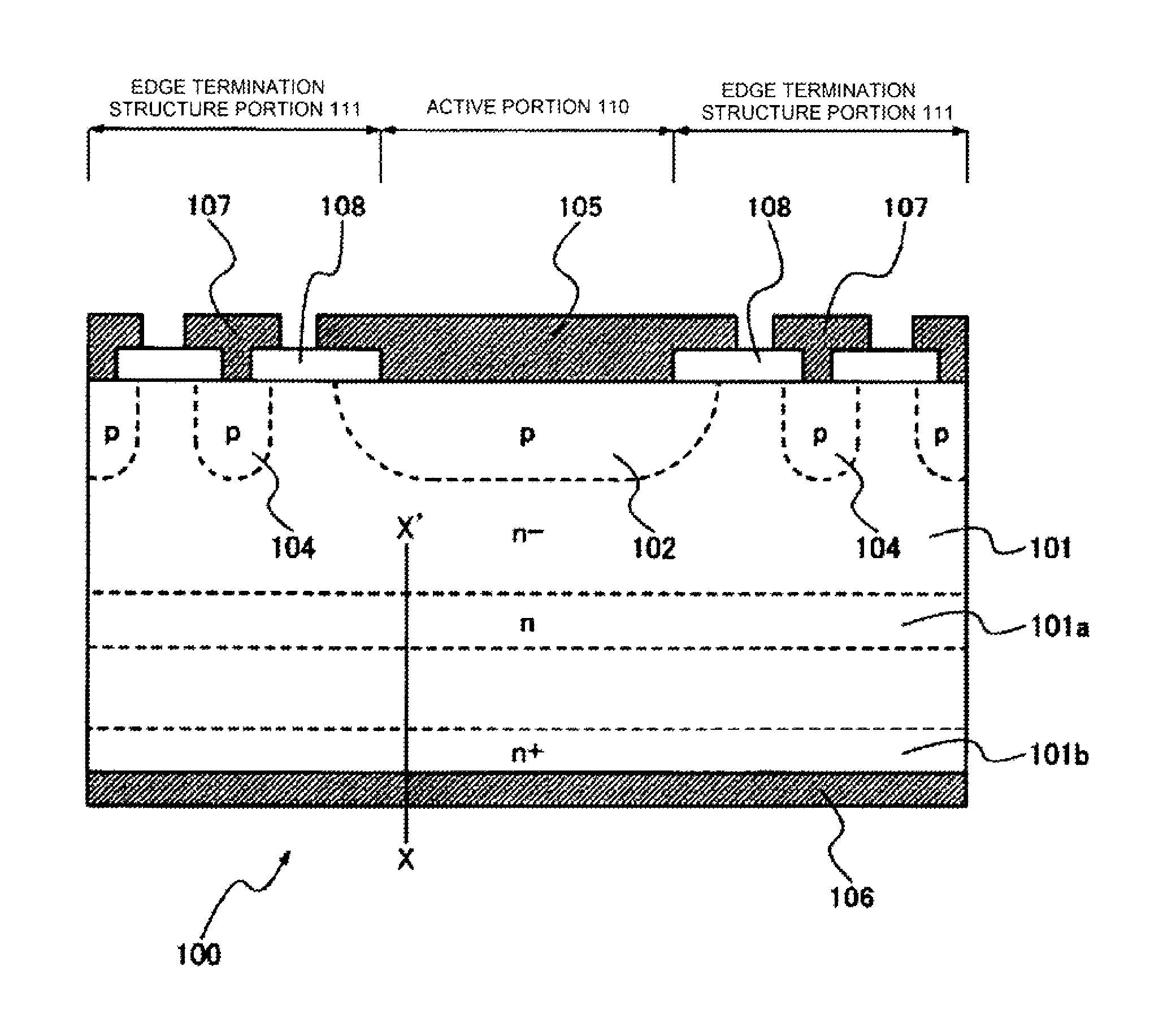

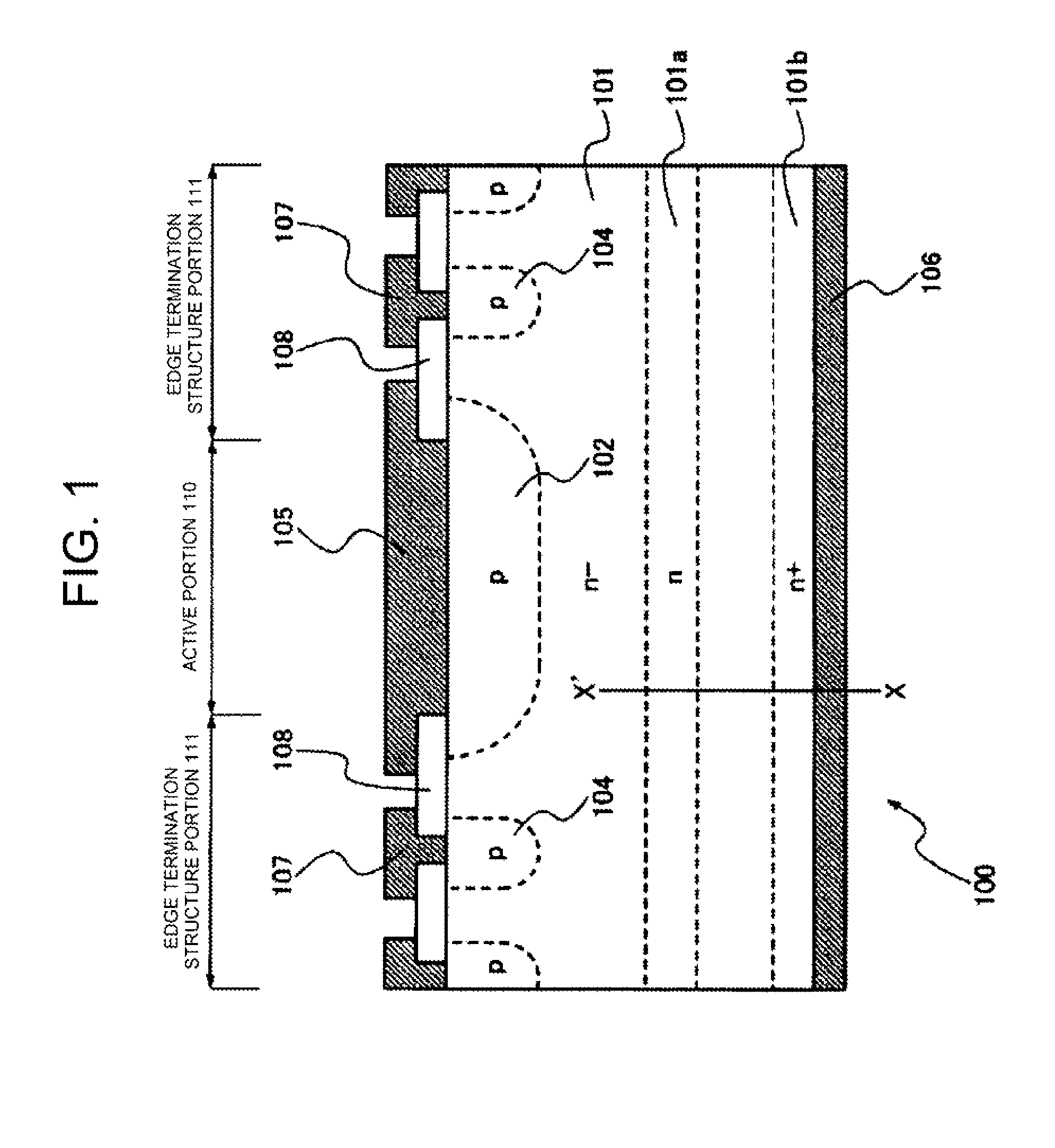

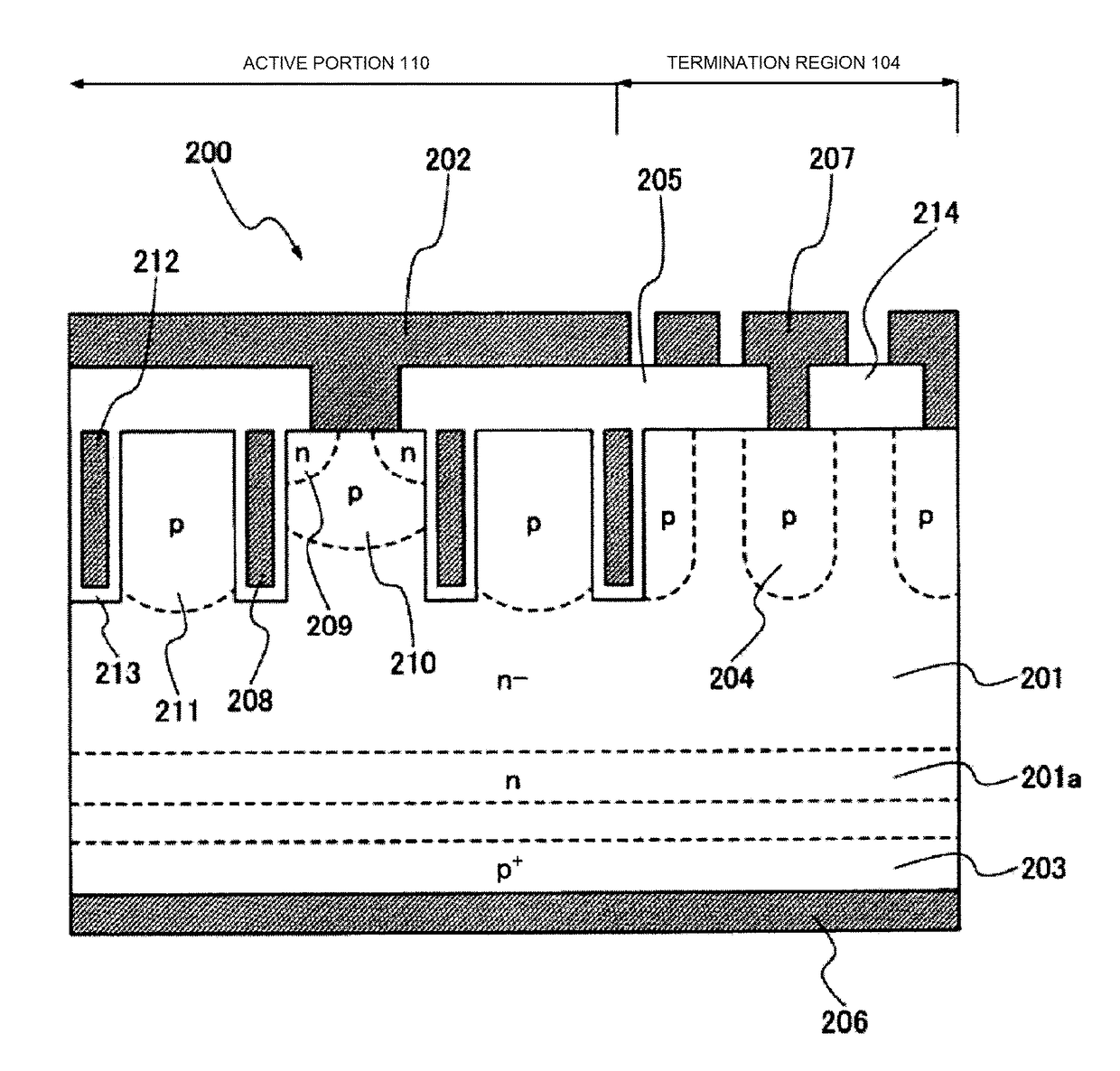

Silicon carbide semiconductor device and method of manufacturing a silicon carbide semiconductor device

ActiveUS11038020B2Semiconductor/solid-state device manufacturingDiodeProton implantationDevice material

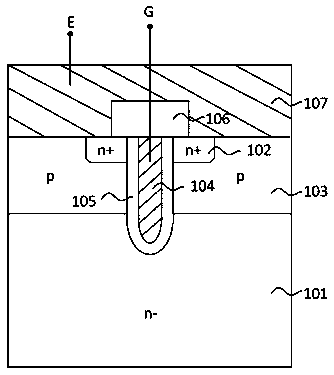

A silicon carbide semiconductor device includes a semiconductor substrate and a first semiconductor layer of the first conductivity type; a second semiconductor layer of a second conductivity type; a first semiconductor region of the first conductivity type; a gate electrode provided opposing at least a surface of the second semiconductor layer between the first semiconductor region and the first semiconductor layer, across a gate insulating film; and a first electrode provided on surfaces of the first semiconductor region and the second semiconductor layer. Protons are implanted in a first region of the semiconductor substrate, spanning at least 2 μm from a surface of the semiconductor substrate facing toward the first semiconductor layer; and in a second region of the first semiconductor layer, spanning at least 3 μm from a surface of the first semiconductor layer facing toward the semiconductor substrate. The protons having a concentration in a range from 1×1013 / cm3 to 1×1015 / cm3.

Owner:FUJI ELECTRIC CO LTD

Semiconductor device buffer layer manufacturing method

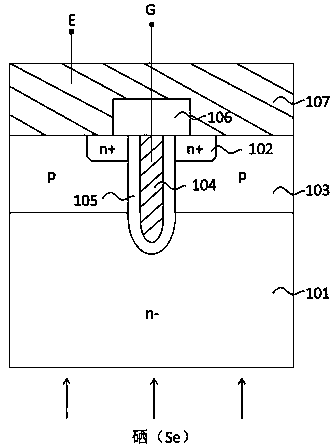

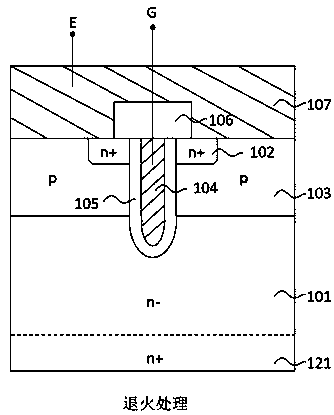

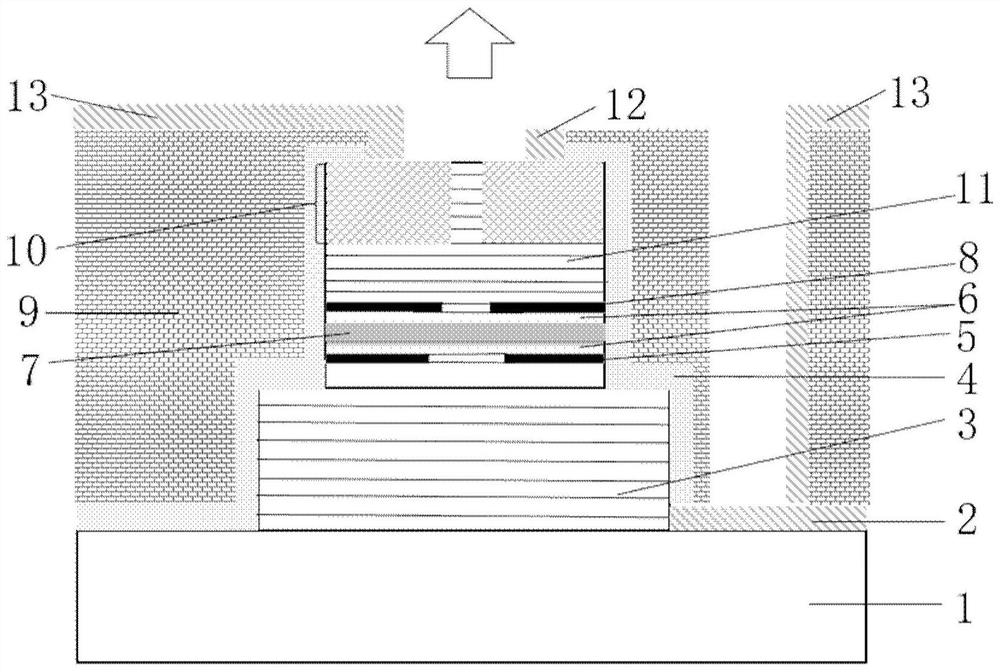

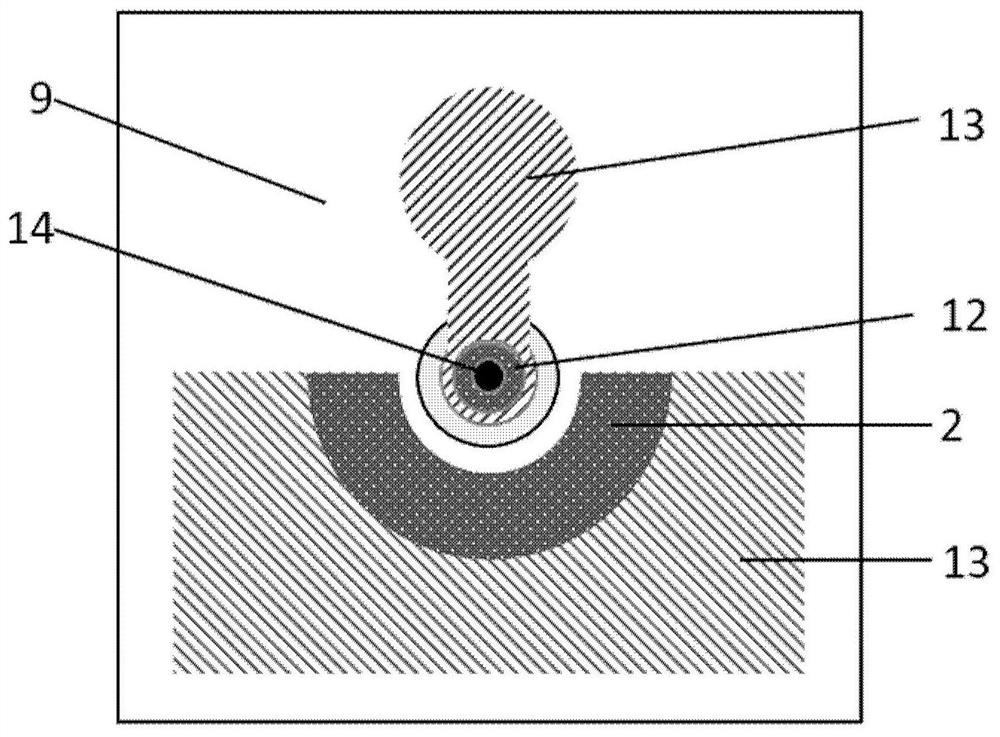

PendingCN109712885AAdd depthImprove carrier concentration distributionSemiconductor/solid-state device manufacturingSemiconductor devicesProton implantationCharge carrier

The present invention relates to the field of semiconductor device manufacture and in particular to a semiconductor device buffer layer manufacturing method. The semiconductor device comprises a semiconductor substrate, a first n-type buffer layer and a second n-type buffer layer. The first n-type buffer layer is formed by performing selenium implantation on the back surface of the semiconductor substrate and an annealing treatment after implantation. The second n-type buffer layer is formed by performing proton implantation or phosphorus implantation or a combination of proton implantation and phosphorus implantation on the back surface of the semiconductor substrate, and an annealing treatment after implantation. The method forms the first n-type buffer layer by implanting selenium elements capable of forming an n-type doping and having a high diffusion coefficient into the back surface of the semiconductor substrate, and forms a second n-type buffer layer by proton implantation witha small atomic mass or a common phosphorus implantation. Under a relative low-energy ion implantation condition, by the combination of the ion implantation of the above two elements and the annealingactivation, the depth of the n-type buffer layer is increased and the carrier concentration distribution of the n-type buffer layer and the device performance of the FS-IGBT are optimized.

Owner:成都森未科技有限公司

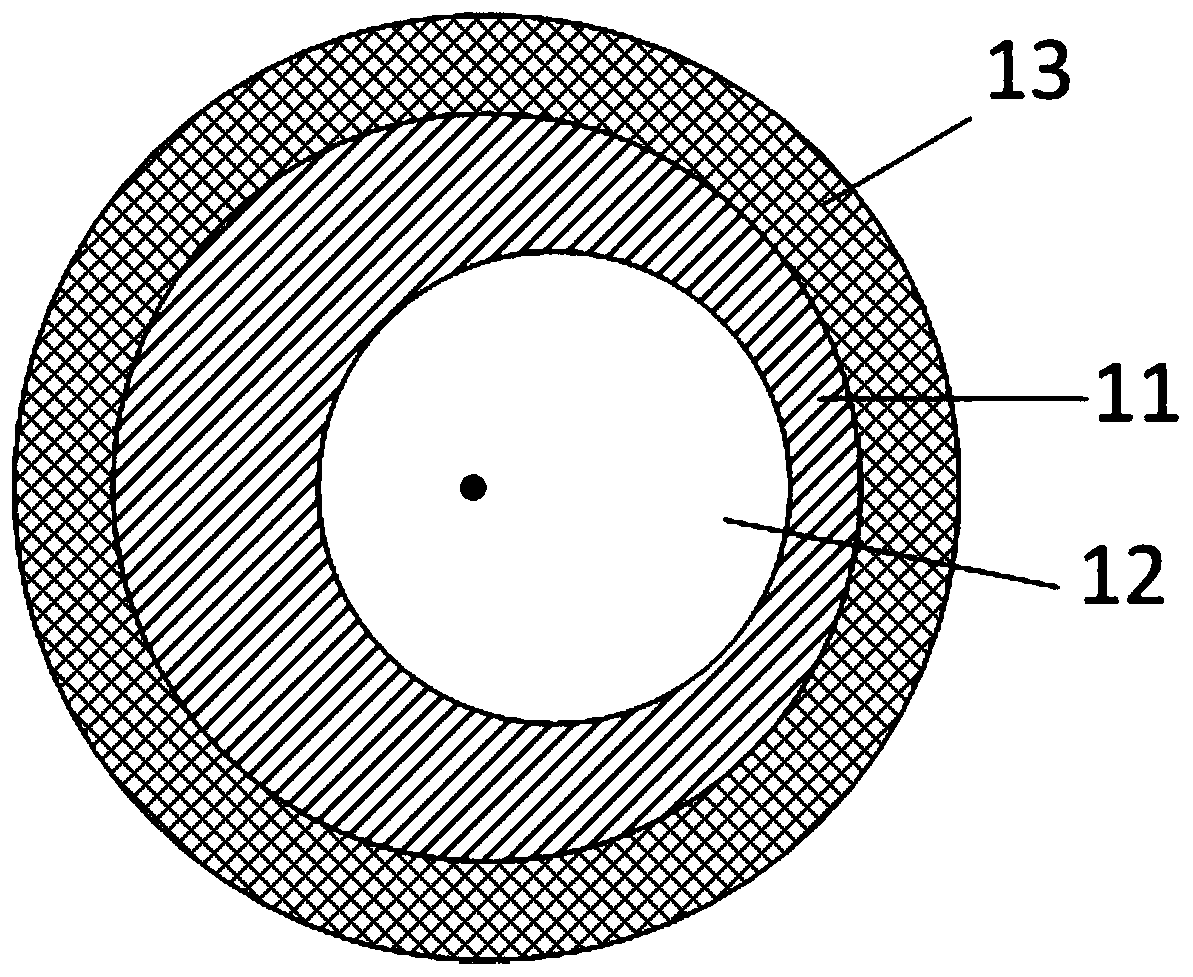

Vertical cavity surface emitting semiconductor laser structure

ActiveCN111435781BImprove uniformityImprove performanceLaser detailsSemiconductor lasersVertical-cavity surface-emitting laserParasitic capacitor

The invention discloses a vertical cavity surface emitting semiconductor laser structure, comprising: an optical oxidation confinement layer located at the antinode of the standing wave of the laser to play the role of optical confinement; an electrical oxidation confinement layer located at the node of the standing wave of the laser to play the role of optical confinement; The role of current confinement; the proton injection layer, located on the electrical oxidation confinement layer and the optical oxidation confinement layer, improves the information transmission rate of the laser; and the epitaxial growth buffer layer, N-face electrode, N-type DBR, N-type space layer, organic The source region, the P-type space layer, the P-type DBR layer and the P-surface electrode constitute the laser resonator cavity. The vertical cavity surface emitting laser adopts proton injection and separation limited oxidation structure, which improves the uniformity of current injection, reduces the parasitic capacitance of the device, has low threshold current, stable single transverse mode or multi-transverse mode output, The high-speed performance of the device is improved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

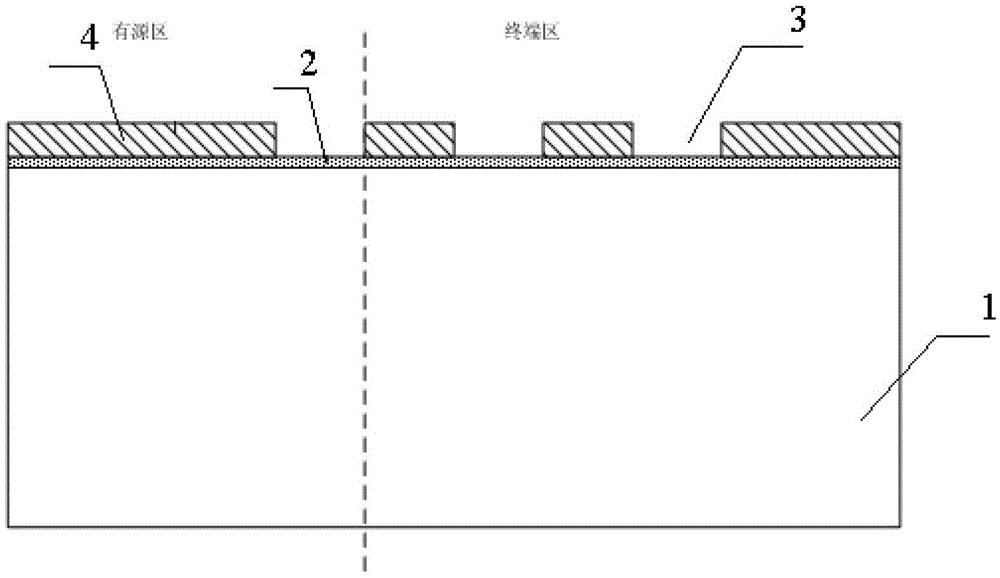

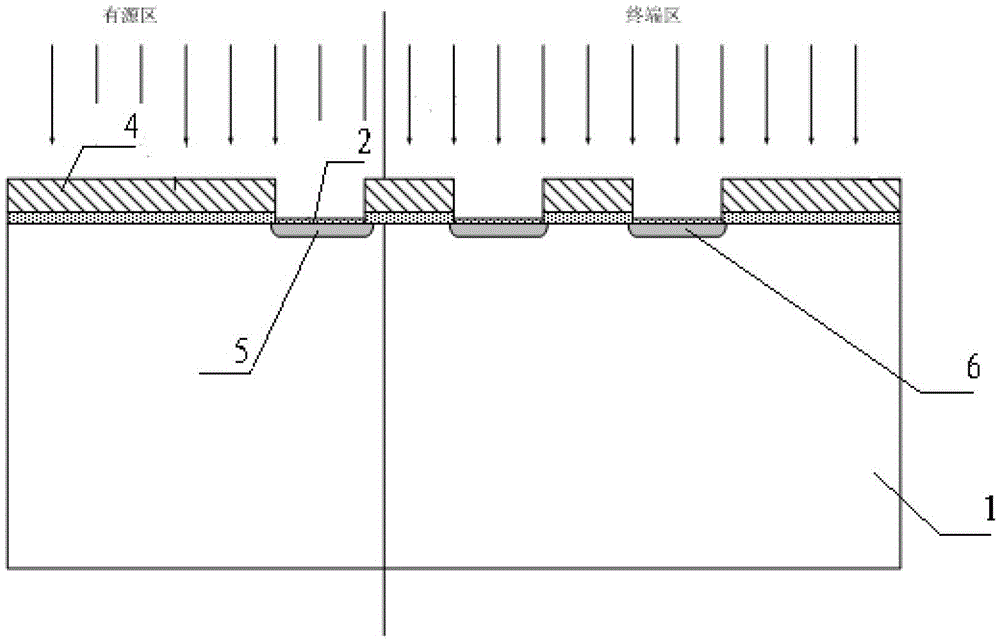

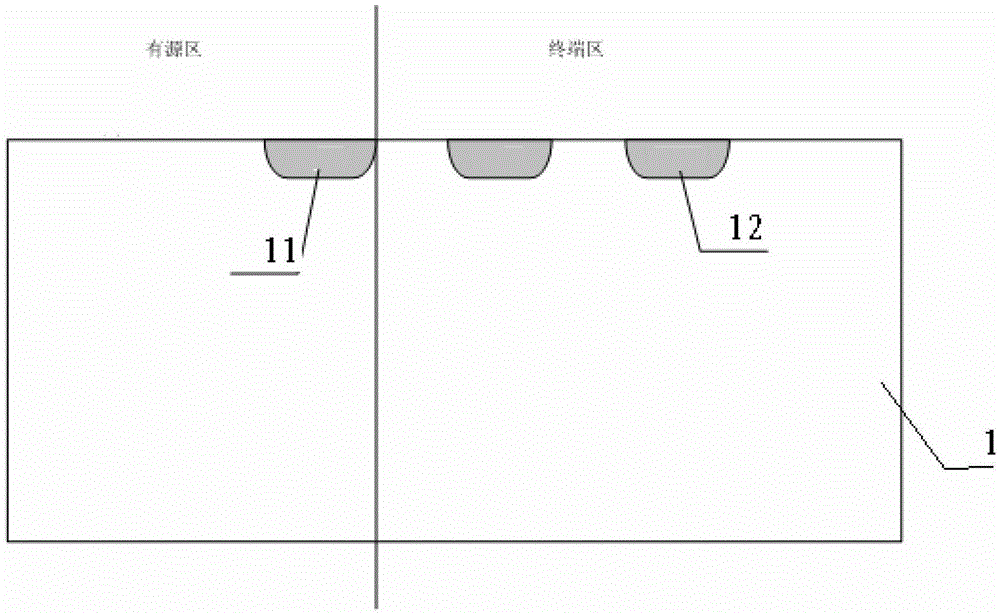

Method for preparing terminal structure by proton irradiation

ActiveCN103715074BSmall terminal areaImprove reliabilitySemiconductor/solid-state device manufacturingProton implantationProton

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +2

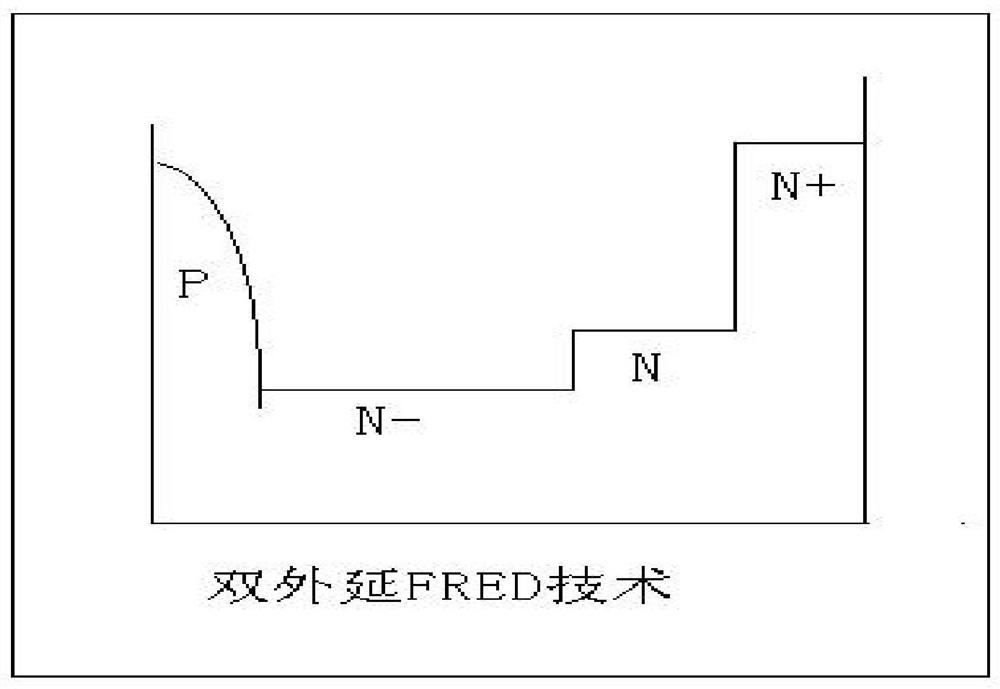

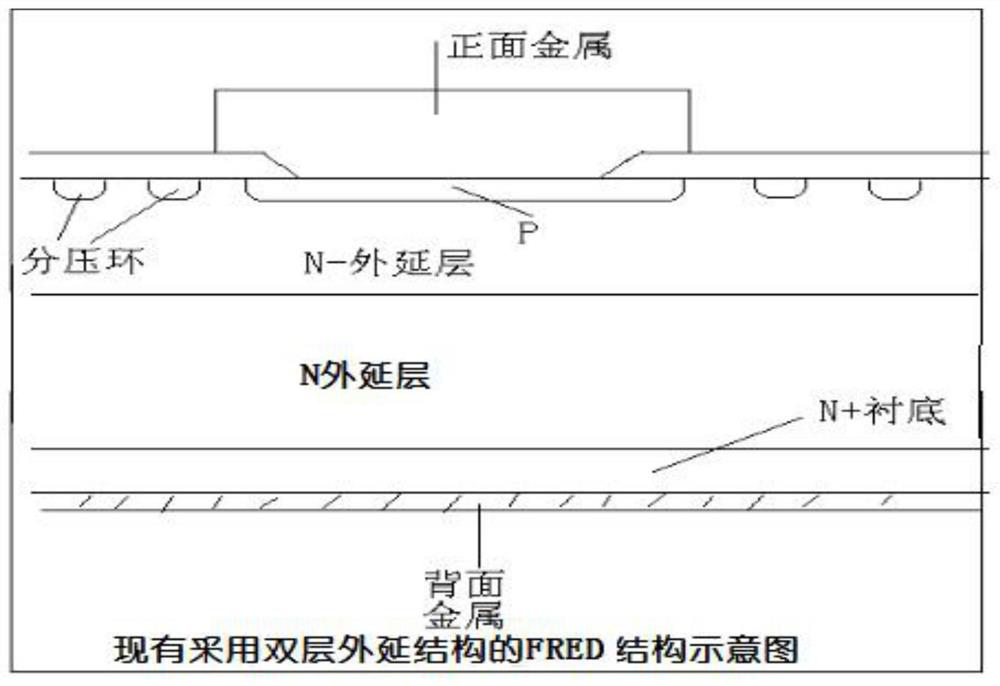

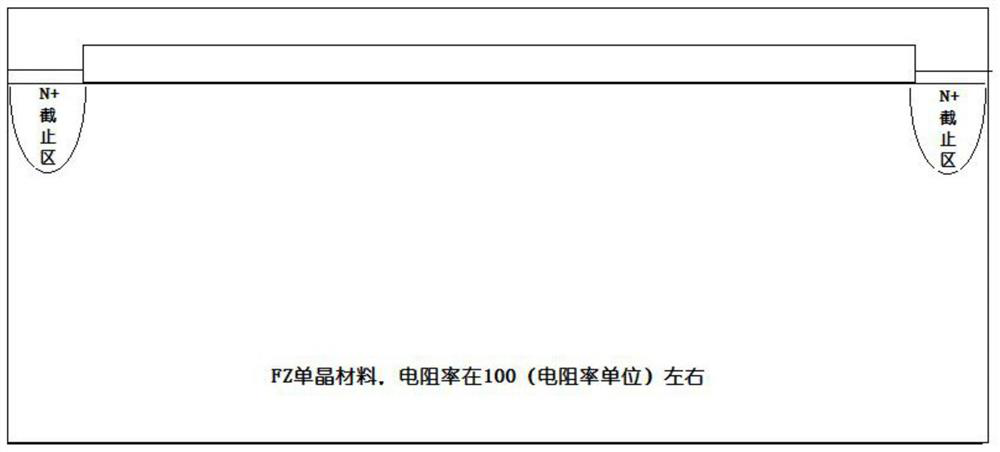

High-voltage fast recovery diode FRED manufacturing process

PendingCN114664658AReduce manufacturing costLow costSemiconductor/solid-state device manufacturingSemiconductor devicesProton implantationMetal machining

The invention provides a manufacturing process of a high-voltage fast recovery diode (FRED), which comprises the following steps of: (1) forming an N + cut-off ring region, and injecting phosphorus impurities; (2) forming an active region and injecting and annealing an N well of the active region, wherein the injected impurity of the N well is phosphorus impurity; (3) forming a P + voltage dividing ring, injecting boron impurities, and annealing; (4) forming a P well, injecting boron impurities, and annealing; (5) opening a lead hole, enriching P + on the surface of the hole, injecting boron into the P +, and annealing; (6) Pt heavy metal doping and annealing are carried out, and minority carrier lifetime is adjusted; (7) front metal is formed, aluminum-silicon-copper is adopted, and the thickness is about 4 microns; (8) forming a passivation layer; (9) thinning the back surface; (10) carrying out heavy doping injection on the back surface, wherein the injected impurities are phosphorus-based alloy; (11) performing proton injection and annealing on the back surface, wherein the thickness of the whole N-region buffer layer is 10-15 microns; and (12) processing metal on the back surface to obtain the high-voltage fast recovery diode FRED. According to the method, the FRED processing cost can be effectively reduced.

Owner:厦门中能微电子有限公司

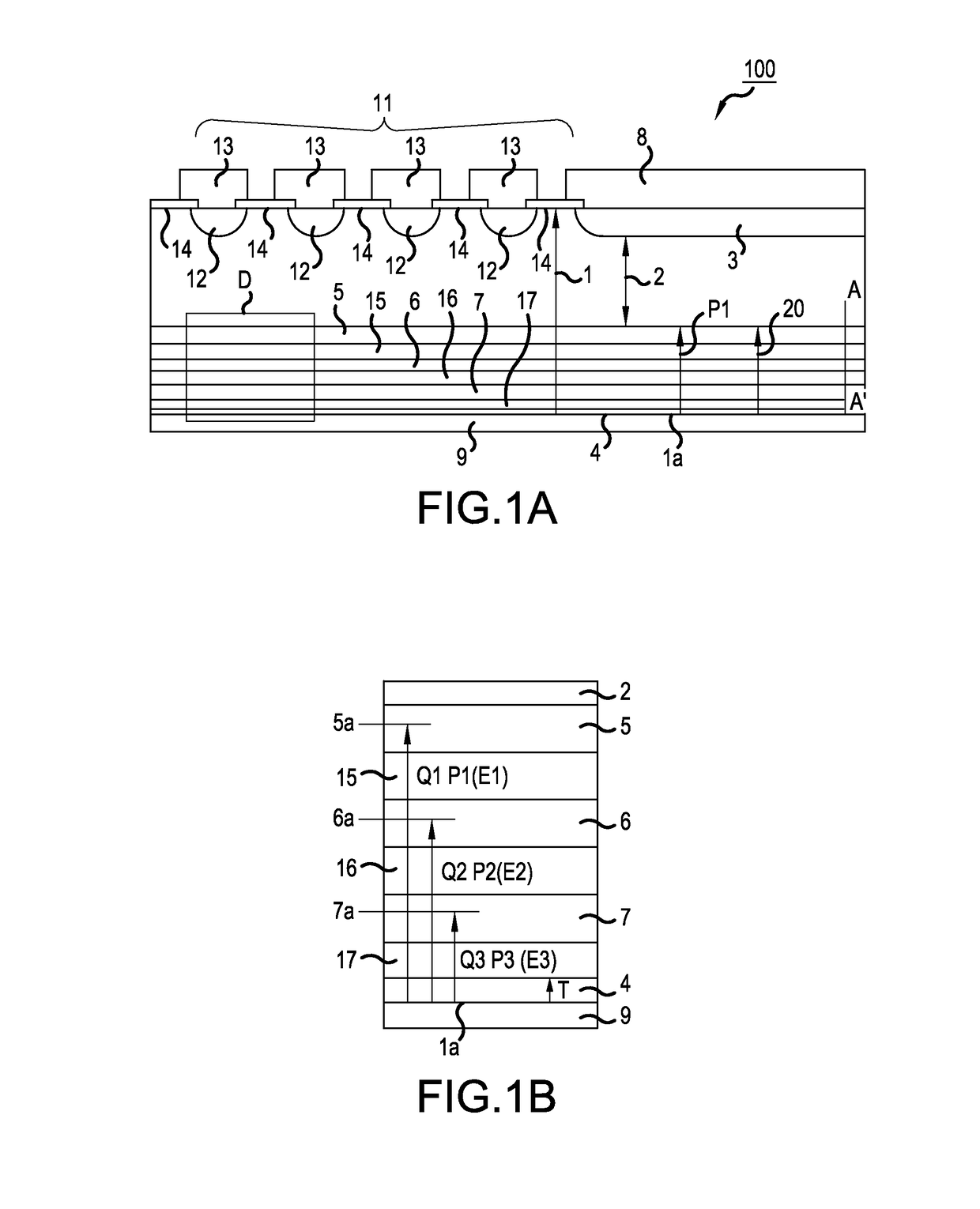

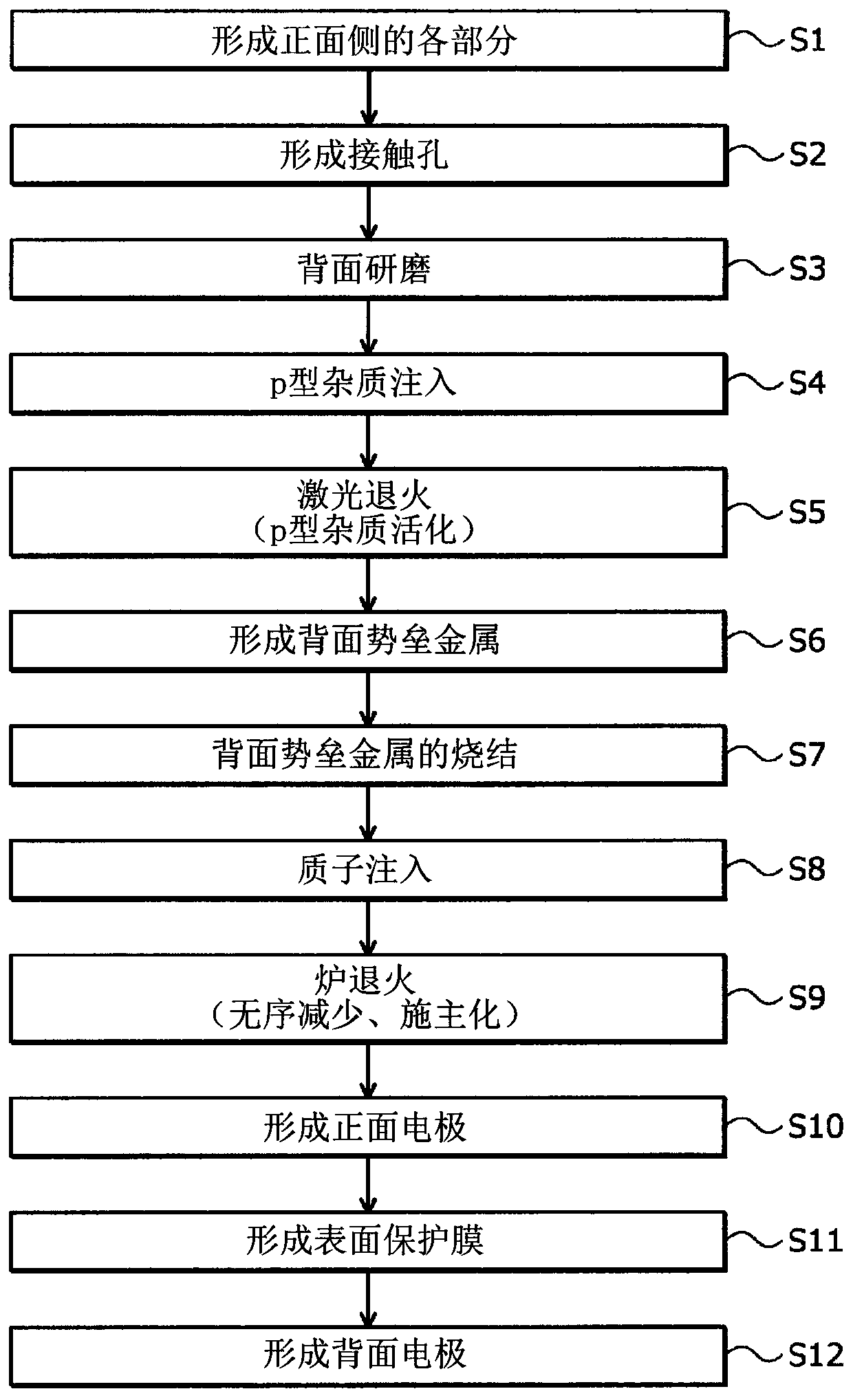

Method for manufacturing silicon carbide semiconductor device

ActiveCN106463528BImprove yieldLow mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesProton implantationMetallurgy

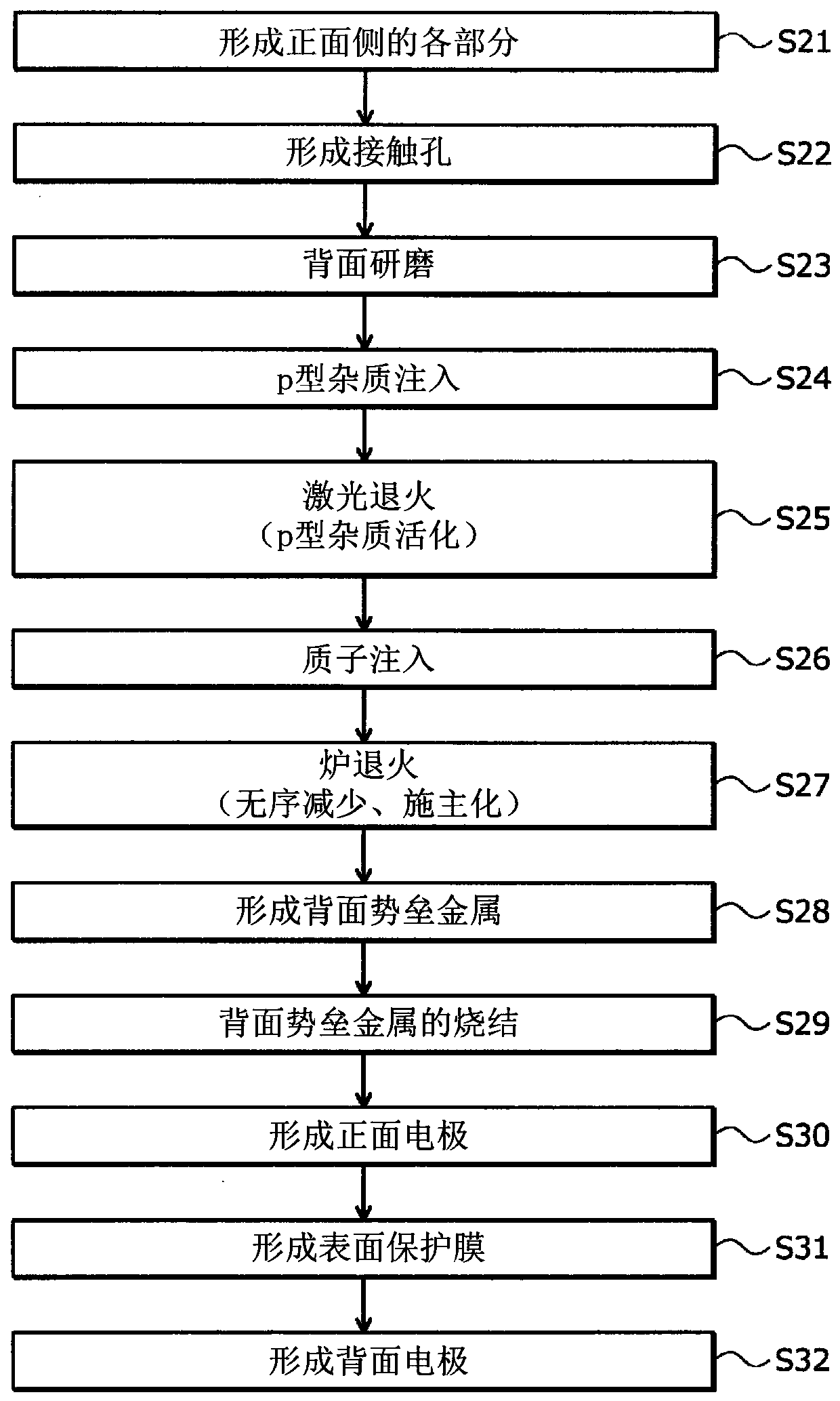

After the front component structure is formed, from n ‑ P-type impurities are ion-implanted into the back surface (11b) of the silicon carbide substrate (11). Next, from n ‑ The back surface (11b) of the silicon carbide substrate (11) is irradiated with laser light to activate the p-type impurities to form a p-type collector layer (4). Next, in n ‑ A barrier metal layer is formed on the back surface (11b) of the silicon carbide substrate (11), and the barrier metal layer is sintered. Next, from n ‑ Proton implantation (16) with a range (17) at a position deeper than the p-type collector layer (4) is performed on the back surface (11b) side of the type silicon carbide substrate (11). Next, n is subjected to furnace annealing ‑ The entire silicon carbide substrate (11) is heated to convert protons into donors to form n-type silicon carbide substrates (11). + type field cutoff layer (3). At this time, n is reduced by reducing the disorder remaining in the proton passage region (14). ‑ Crystal state recovery of type silicon carbide substrate (11). This makes it possible to stably avoid electrical characteristic defects.

Owner:FUJI ELECTRIC CO LTD

Method for forming semiconductor device and semiconductor device

ActiveCN105609407BTransistorSemiconductor/solid-state device testing/measurementProton implantationDevice material

The present invention relates to methods for forming semiconductor devices and semiconductor devices. A method for forming a semiconductor device includes implanting a defined dose of protons into a semiconductor substrate and tempering the semiconductor substrate according to a defined temperature profile. At least one of a defined dose of protons and a defined temperature profile is selected depending on a carbon-related parameter indicative of information about a carbon concentration within at least a portion of the semiconductor substrate.

Owner:INFINEON TECH AG

Semiconductor device with a cz semiconductor body and method for producing a semiconductor device with a cz semiconductor body

PendingCN109411344ATransistorSemiconductor/solid-state device manufacturingProton implantationDevice material

A method of manufacturing a semiconductor device includes reducing an oxygen concentration in a first part of a CZ semiconductor body by a thermal treatment. The first part adjoins a first surface ofthe semiconductor body. The semiconductor body is processed on the first surface. A thickness of the semiconductor body is reduced by thinning the semiconductor body at a second surface relative to the first surface. Thereafter, in the semiconductor body, a field stop zone is formed by proton implantations through the second surface and annealing of the semiconductor body. The field stop zone extends into the first part of the CZ semiconductor body.

Owner:INFINEON TECH AG

Back side processing method of power semiconductor device

InactiveCN109712886AIncrease the carrier concentrationImprove hole injection efficiencySemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceProton implantation

The present invention relates to the field of semiconductor device manufacture and in particular to a back side processing method of a power semiconductor device. The method comprises a first step ofperforming a second conductive type of collector region manufacturing process: implanting a first type of ions into the back side of the first conductive type of semiconductor substrate; performing alaser annealing treatment on the semiconductor substrate to form a second conductive type of first region having a higher carrier concentration than the first conductive type of semiconductor substrate on the back side of the semiconductor substrate; and a step of performing a buffer layer manufacturing process: performing proton implantation on the back side of the first conductive type of semiconductor substrate; and performing a annealing treatment on the semiconductor substrate. On the basis of performing proton implantation to form a buffer layer, the method performs an activation treatment after the ion implantation in the collector region in combination with a laser annealing method. Compared with the thermal annealing activation by implanting ions such as boron ions into the collector region, the laser annealing has a greatly increased activation rate, so that a higher collector region carrier concentration can be obtained while forming the buffer layer by proton implantation.

Owner:成都森未科技有限公司

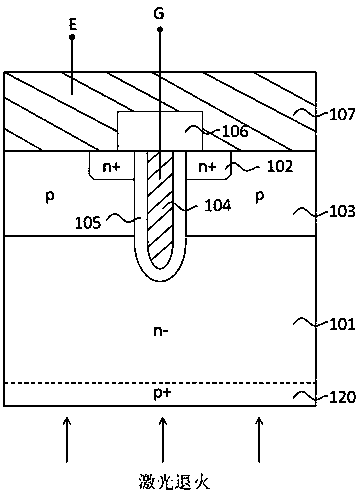

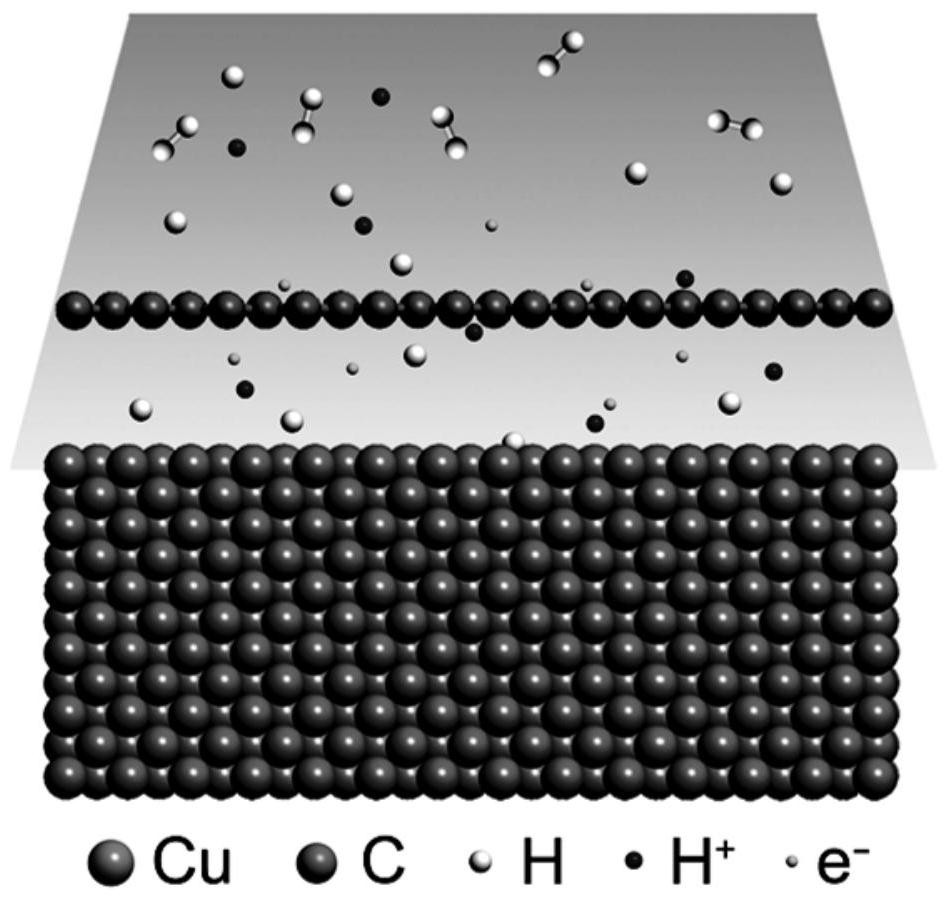

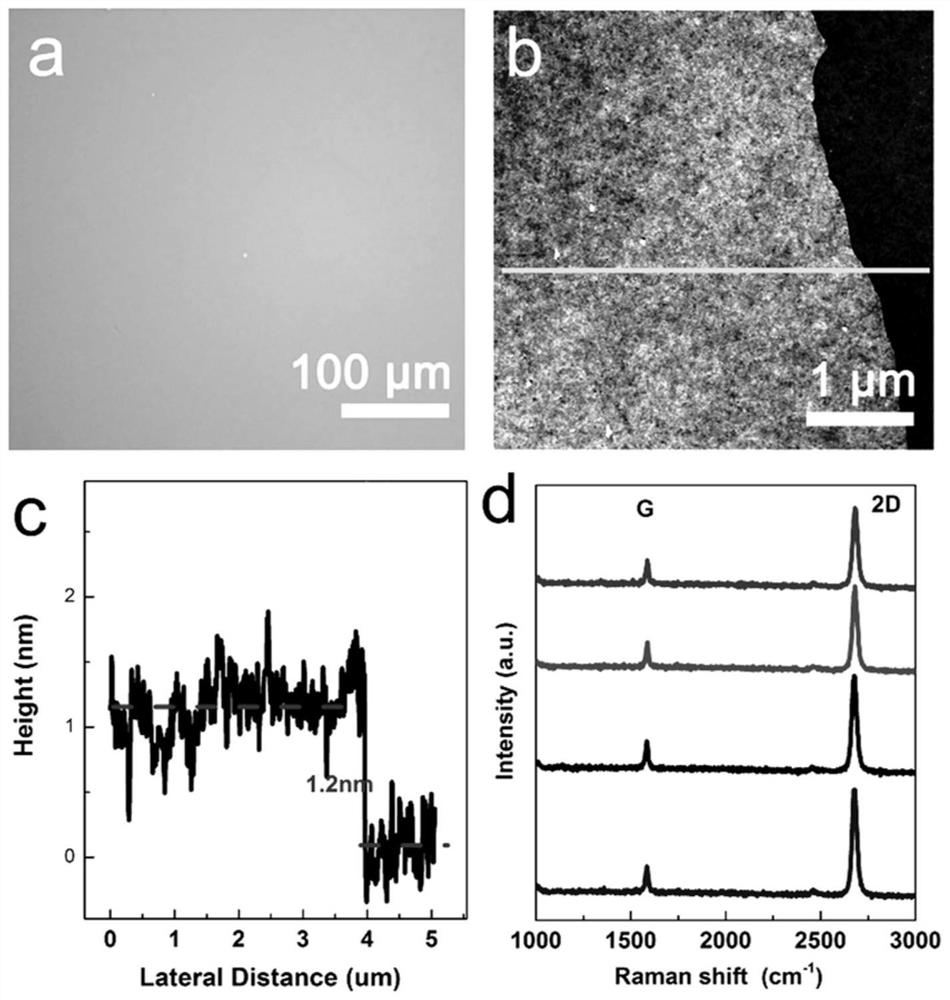

A method for efficiently eliminating the wrinkles of graphene by chemical vapor deposition

ActiveCN109824038BImprove qualityReduce defectsElectric discharge tubesGrapheneProton implantationPlasma generator

A method for efficiently eliminating the wrinkles of graphene by chemical vapor deposition, using controllable proton injection in a high-temperature environment, through precise control of the temperature environment and the hydrogen plasma power and time for generating protons, on various metals such as copper and nickel and Its alloys, on various non-metal substrates such as silicon oxide and silicon carbide, directly grow wrinkle-free ultra-flat graphene films, or eliminate wrinkles on wrinkled graphene; the plasma-assisted chemical vapor deposition system includes Plasma generator, vacuum system, and heating system; among them, the power of the plasma generator is 5-1000W, and the vacuum system is 10 ‑5 ~10 5 Pa, the controllable heating temperature range of the system is 25-1000°C; protons are injected into various substrates at the same time, and ultra-smooth non-wrinkled graphene is directly grown, including proton injection of wrinkled graphene grown by traditional methods Post-processing to reduce and eliminate wrinkles.

Owner:NANJING UNIV

Current guidance VCSEL and preparation method thereof

InactiveCN108539577AEasy to precisely control the depth of injectionPrecisely control the depth of injectionLaser detailsSemiconductor lasersMaserProton implantation

The present invention provides a current guidance VCSEL and a preparation method thereof, belonging to the technical field of semiconductors. The VCSEL comprises a conductive GaAs substrate, an n-typeGaAs buffer layer, an n-type AlGaAs / AlAs DBR, an AlGaAs lower limitation layer, a multi-quantum well luminous area, an AlGaAs upper limitation layer, a primary epitaxial p-type AlGaAs / AlAs DBR, a proton implantation lattice structure, a secondary epitaxial p-type AlGaAs / AlAs DBR, a p-type GaAs Ohmic contact layer, an n-face electrode and a p-face electrode. The proton implantation lattice structure comprises 3-5 pairs of thicknesses of the DBR to provide effective current and gain limitation and conttrol the proton injection depth; and moreover, the proton implantation lattice width is reduced from the center to two sides, the whole light gain distribution is matched with the single transverse mode Gaussian distribution to achieve stable single transverse mode maser.

Owner:BEIJING UNIV OF TECH