Patents

Literature

31results about How to "Adjust the resistance value" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

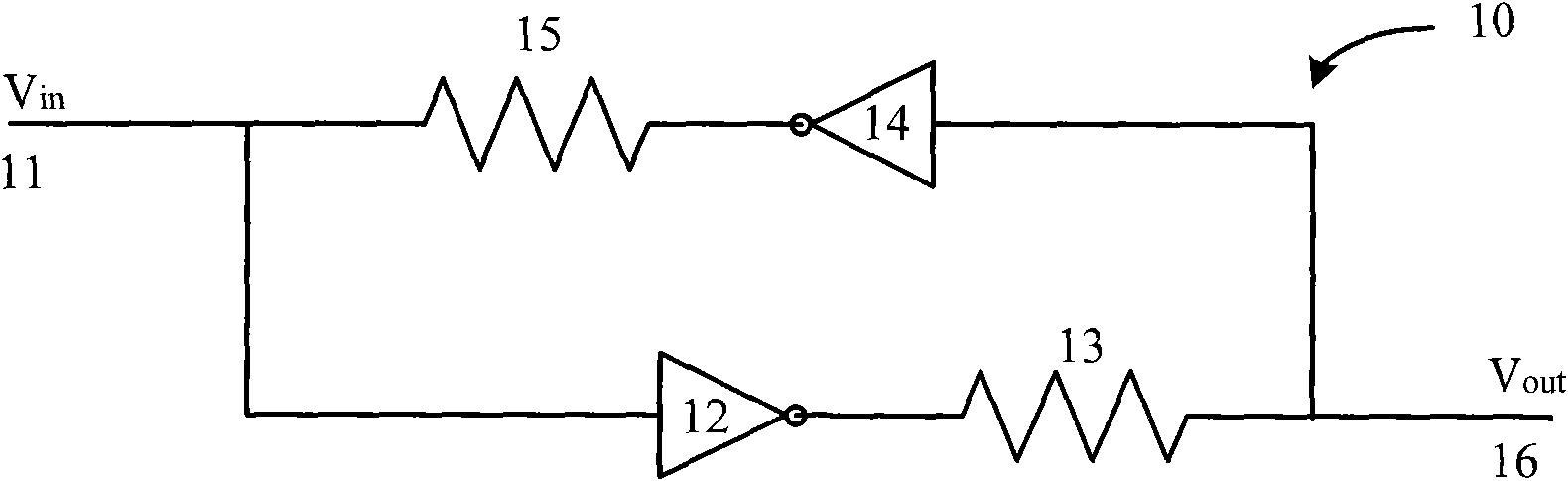

An anti-SEU storage cell circuit in an anti-radiation hardening FPGA chip

InactiveCN101552034AIncrease current pulse timeImprove Flip EffectDigital storageElectrical resistance and conductanceCross connection

The anti-SEU storage cell circuit in an anti-radiation hardening FPGA chip includes two inverters and two transistors. The two inverters are cross connected and realize the adjustment to the resistance values at the source terminals and drain terminals of the two transistors through controlling the grid voltage and substrate potential of the two transistors. The resistance values are not greater than 50 omega or not smaller than 1,000 omega. With respect to inverter design, a resistor is added to the existing circuit consisting of PMOS tube and NMOS tube. The resistor is connected between the drain terminals of PMOS transistor and NMOS transistor. Through adding a resistor into the inverter, the present invention realizes anti-SEU (single event upset) of the storage cell. Moreover, the storage circuit of the present invention has the following advantages: small noise, low power consumption, small area occupied, and easy realization of layout and process in the design of anti-radiation hardening FPGA chip.

Owner:BEIJING MXTRONICS CORP +1

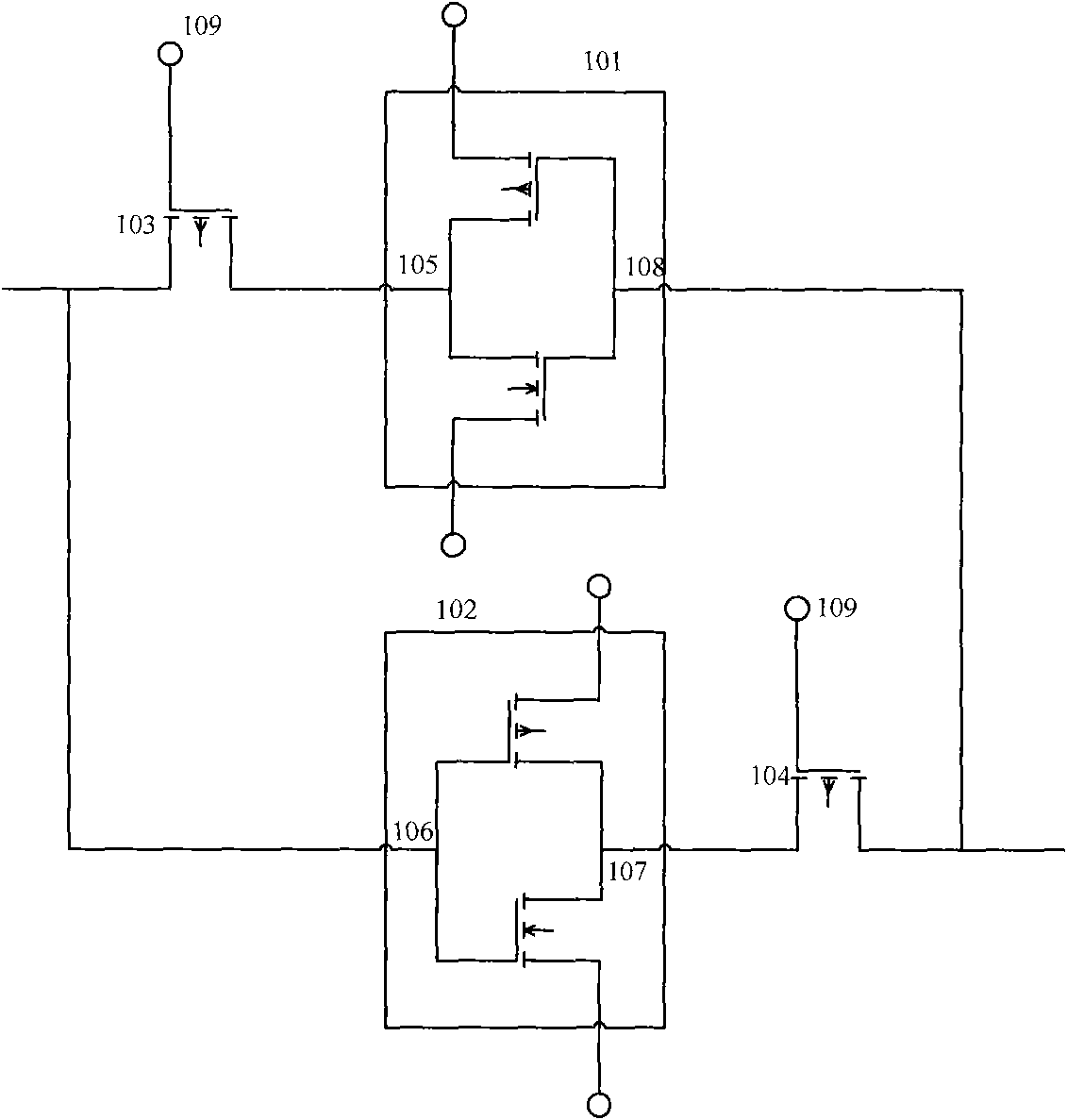

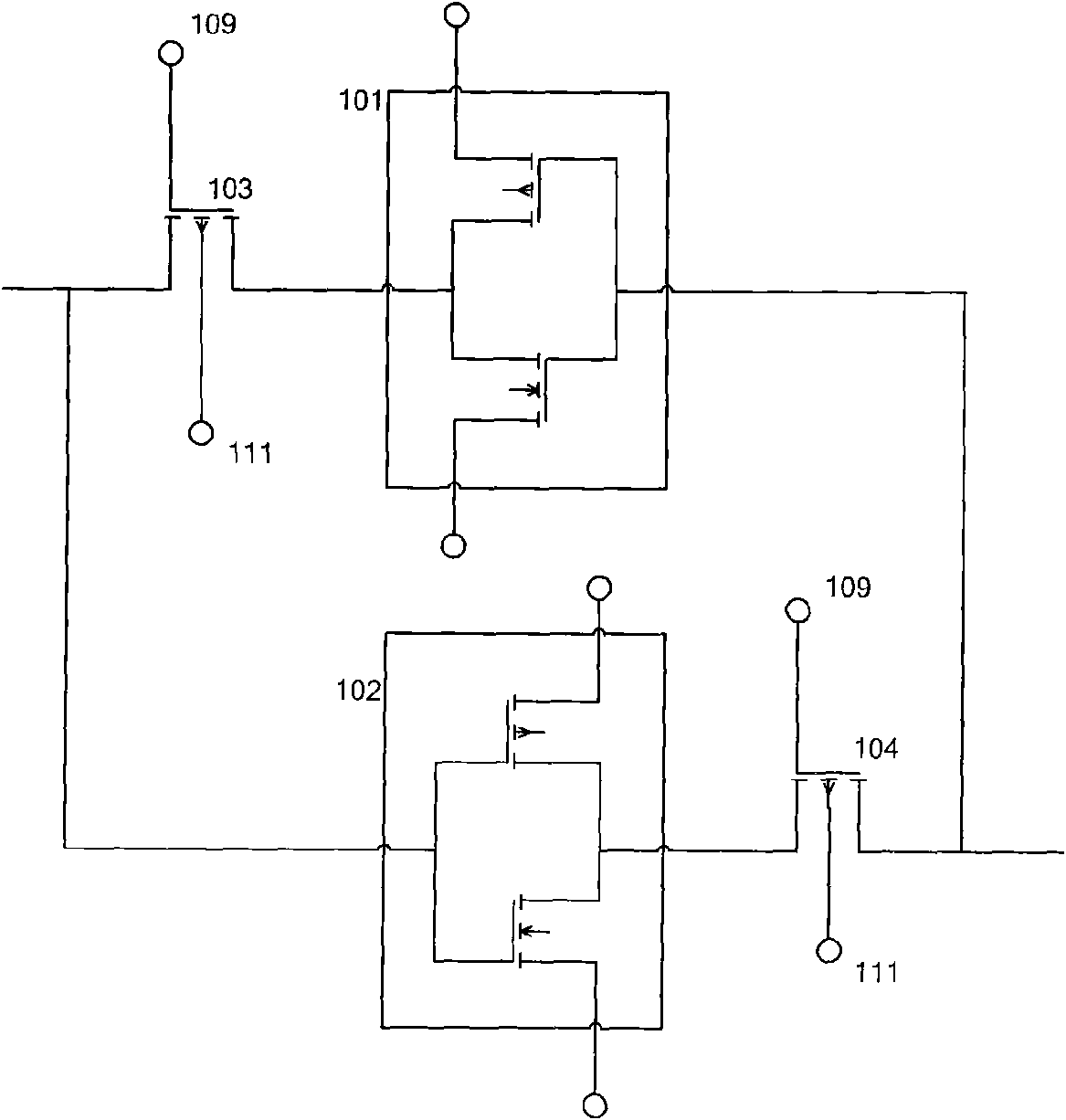

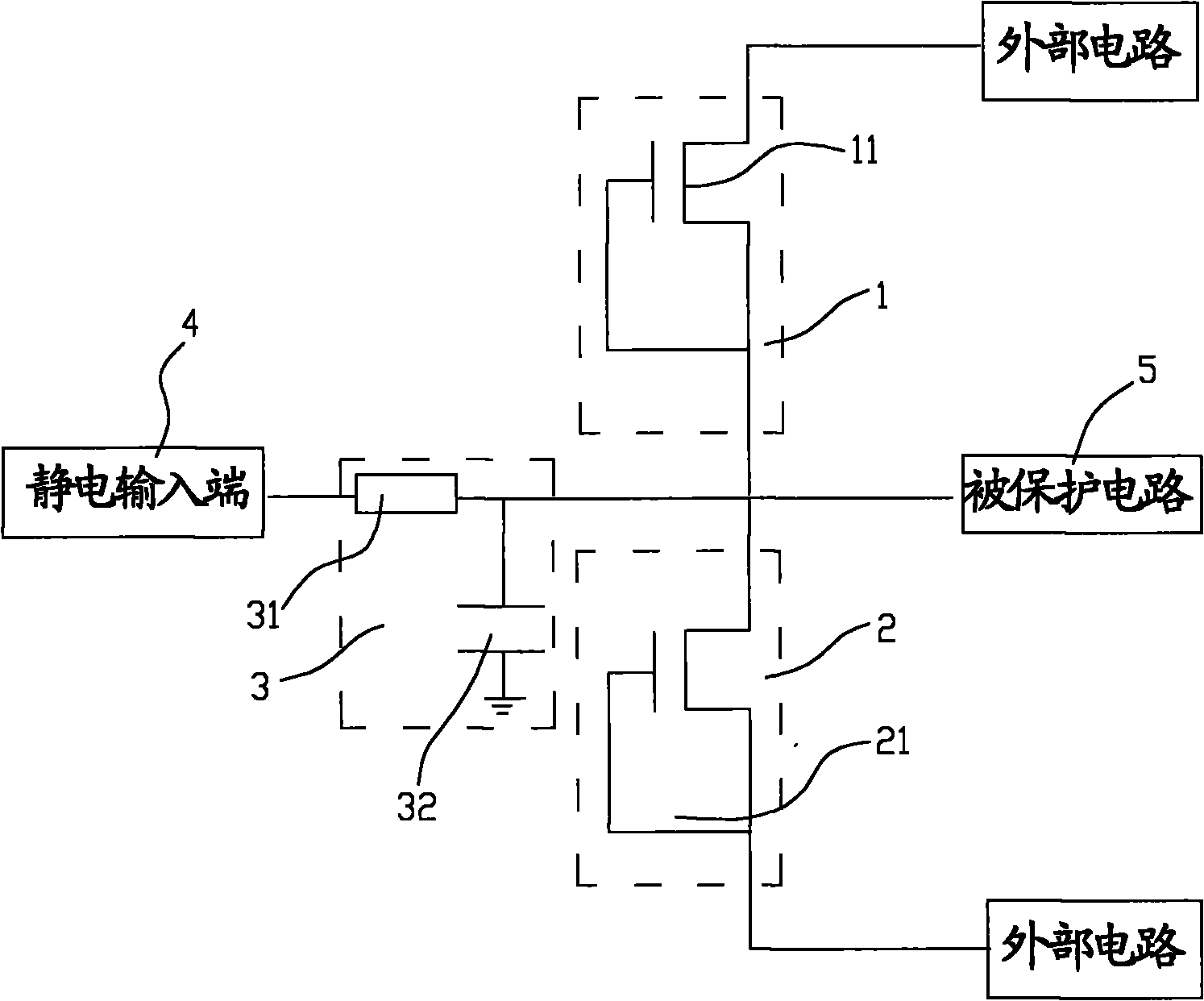

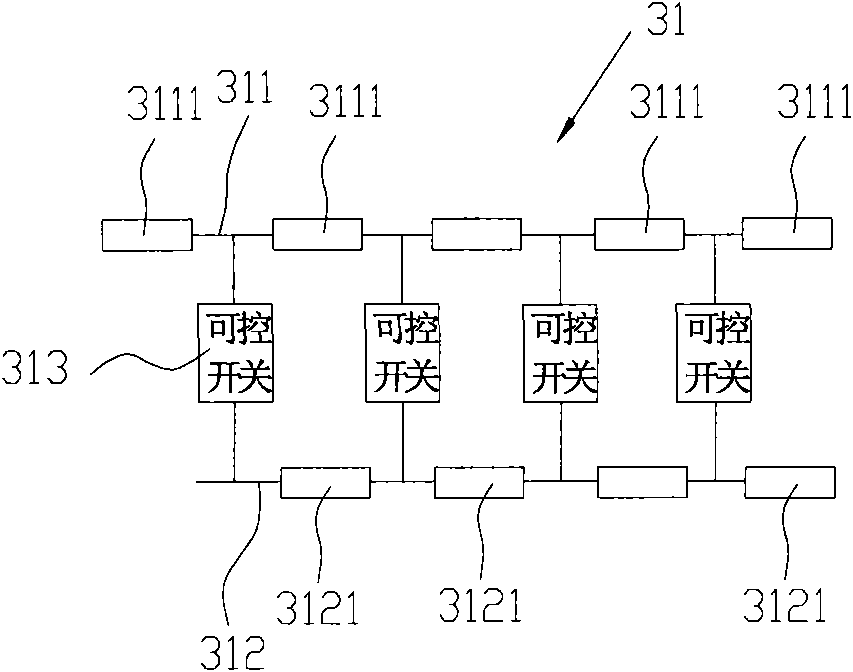

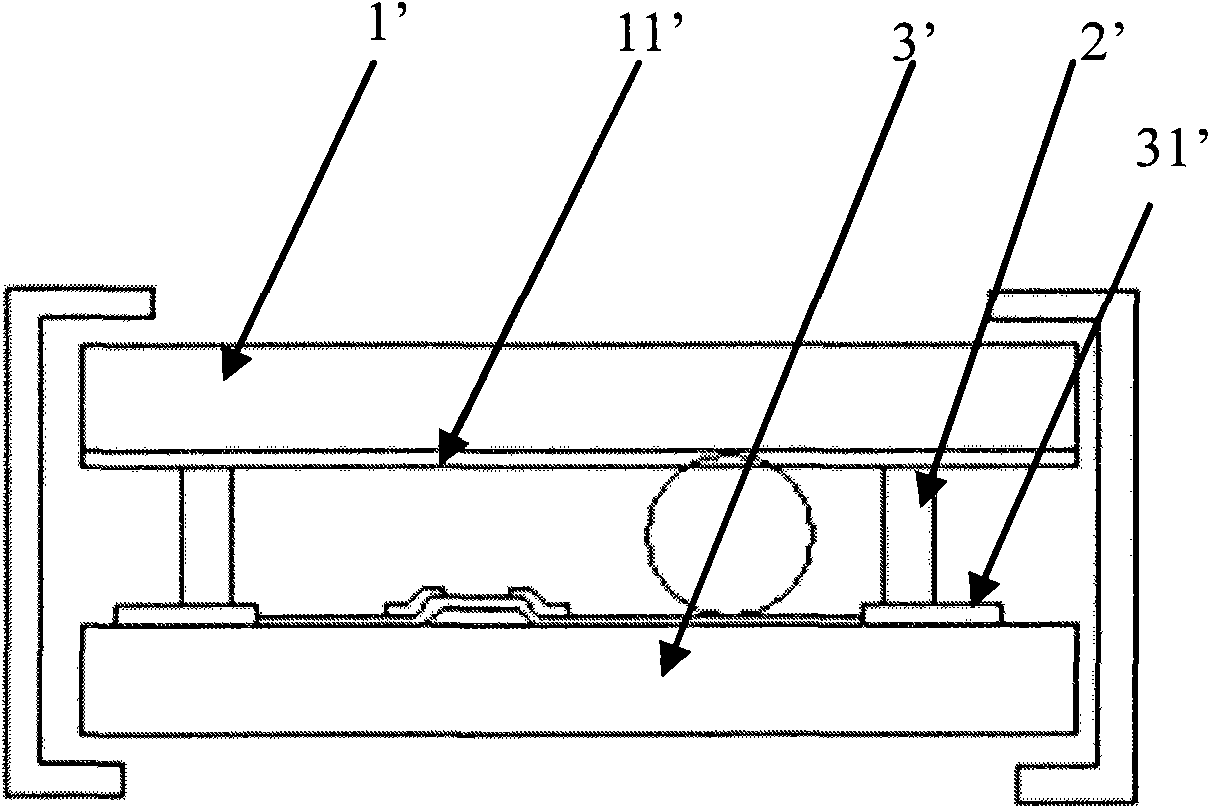

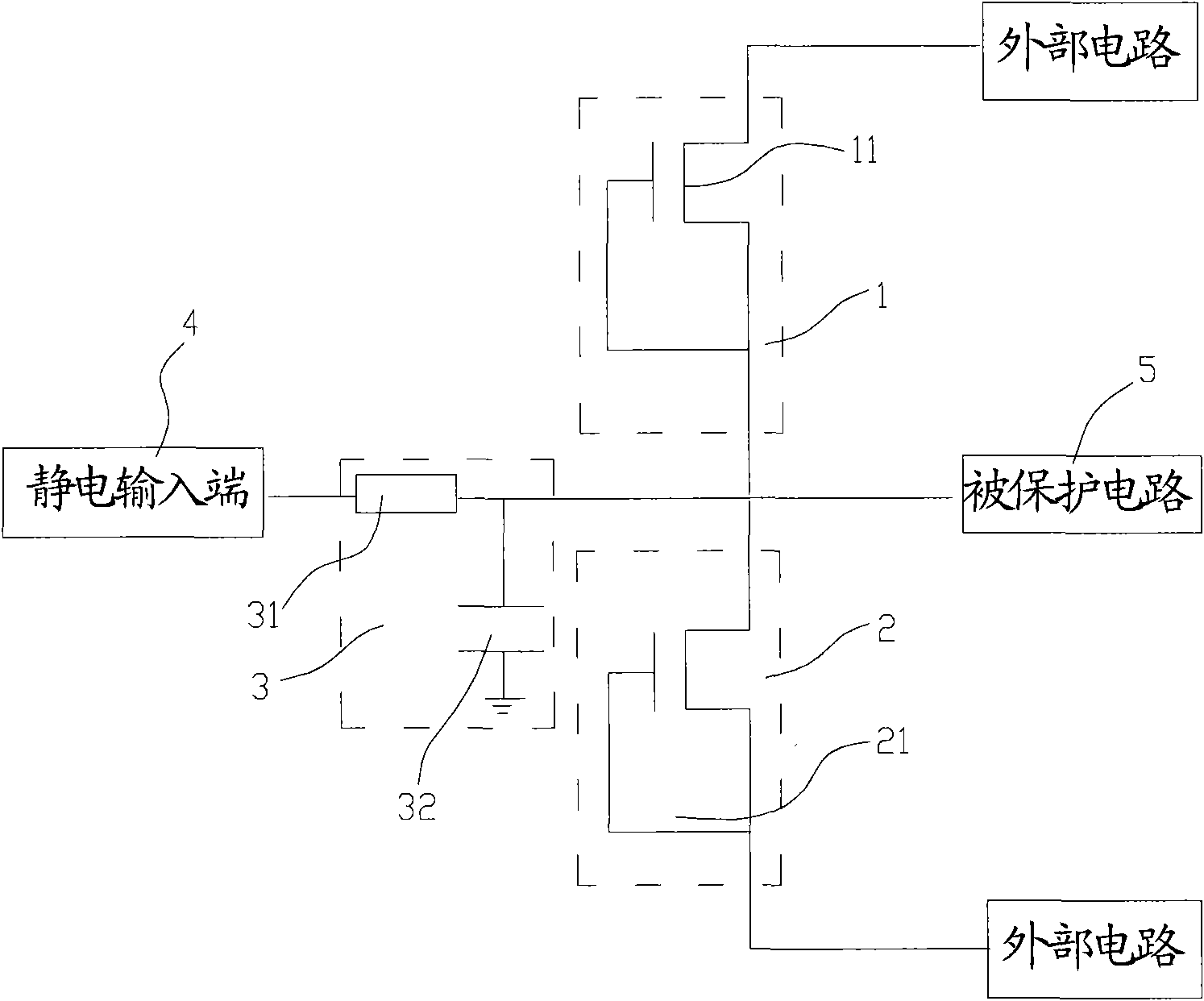

Static protection circuit, in particular static protection circuit of liquid crystal display panel and static protection circuit array of liquid crystal display panel

ActiveCN102118024AImprove the ability to resist positive and negative high voltage static electricityShow normalyStatic indicating devicesEmergency protective arrangements for limiting excess voltage/currentLiquid-crystal displayEngineering

The invention relates to a static protection circuit, in particular to a static protection circuit of a liquid crystal display panel and a static protection circuit array of the liquid crystal display panel. The static protection circuit comprises a discharging unit and a delay circuit, wherein the output end of the delay circuit is connected with the input end of the discharging unit; and by means of the delay circuit, a static pulse is delayed and the pulse width of the static pulse is increased to ensure that the pulse width of the static pulse is greater than the response time of the discharging unit so that static electricity is released through the discharging unit. Through the static protection circuit, the static pulse is prevented from entering a protected circuit.

Owner:BEIHAI HKC OPTOELECTRONICS TECH CO LTD

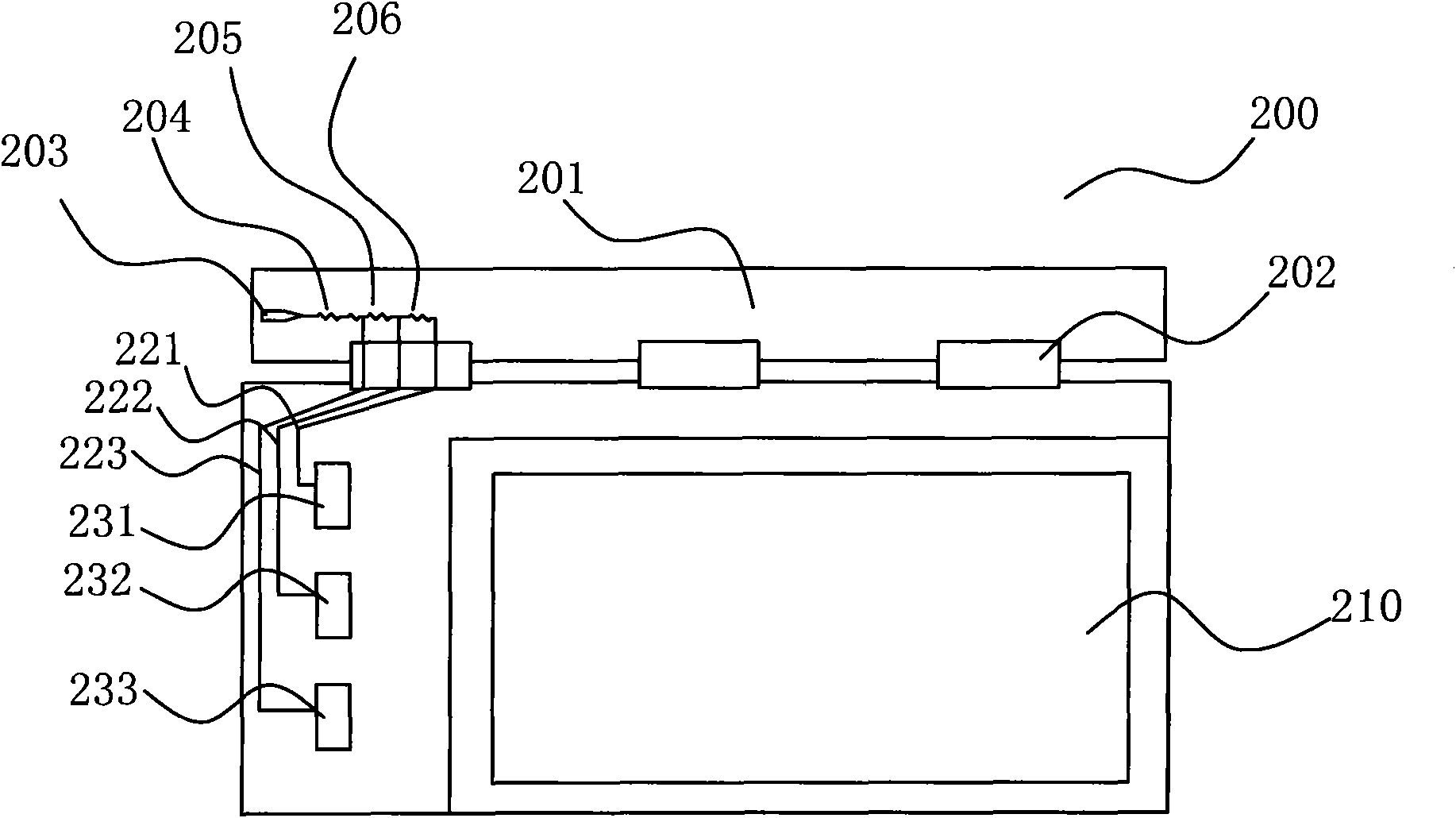

Liquid crystal display device

InactiveCN101872093AImprove qualityAdjust the resistance valueNon-linear opticsElectrical resistance and conductanceLiquid-crystal display

The invention relates to a liquid crystal display device, which comprises a liquid crystal panel, wherein the liquid crystal panel is provided with a plurality of grid drivers, a plurality of running cables is connected with one grid driver, and each running cable has identical resistance value. Through the above liquid crystal display device, the traditional serial-connection grid driver connection mode is changed to the parallel-connection mode, so the loss of the control signal in the running cable and the driver can be effectively controlled, each driver can receive the consistent voltage control signal, and the unfavorable display caused by the loss of the voltage can be avoided.

Owner:AU OPTRONICS CORP

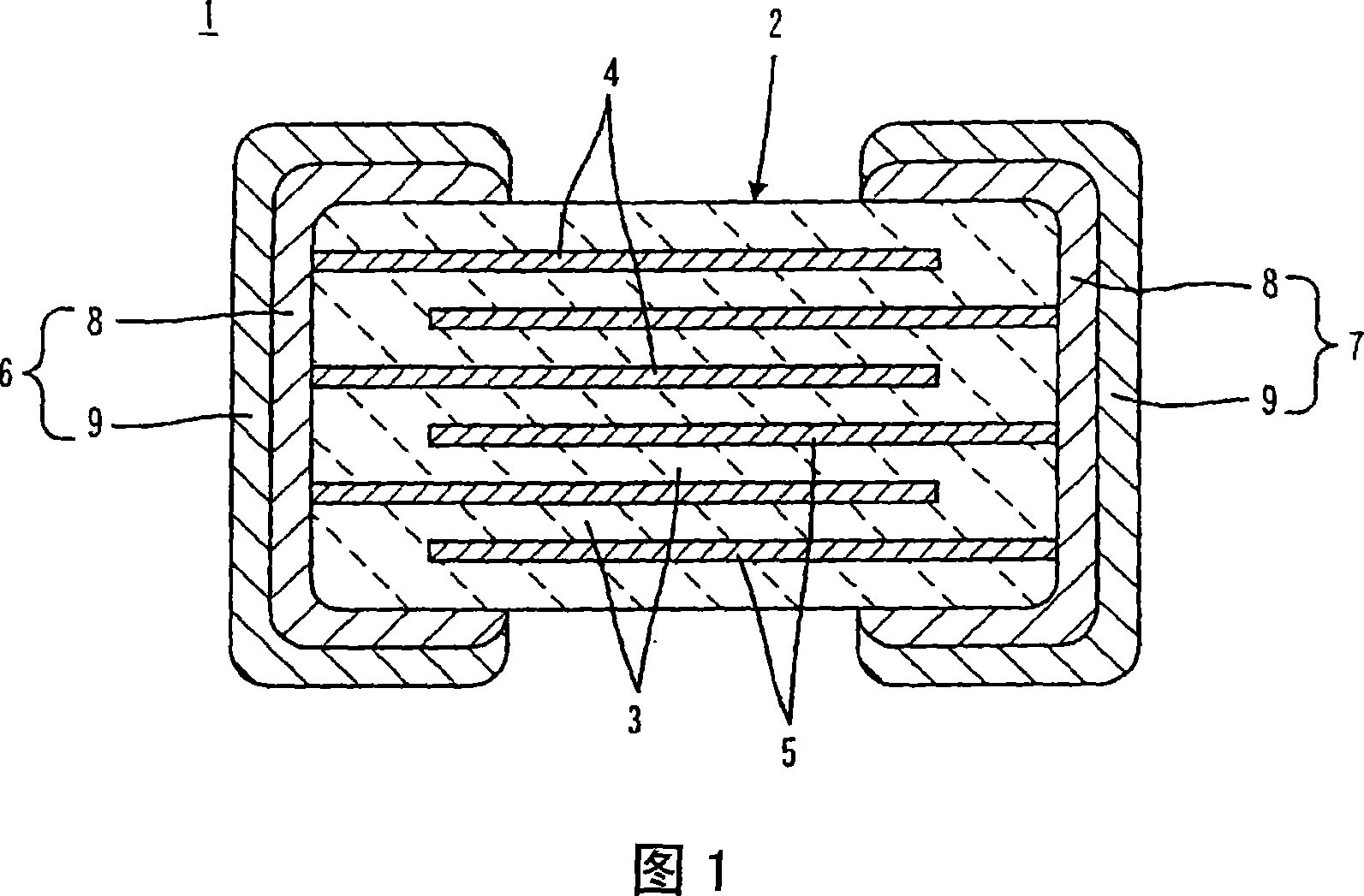

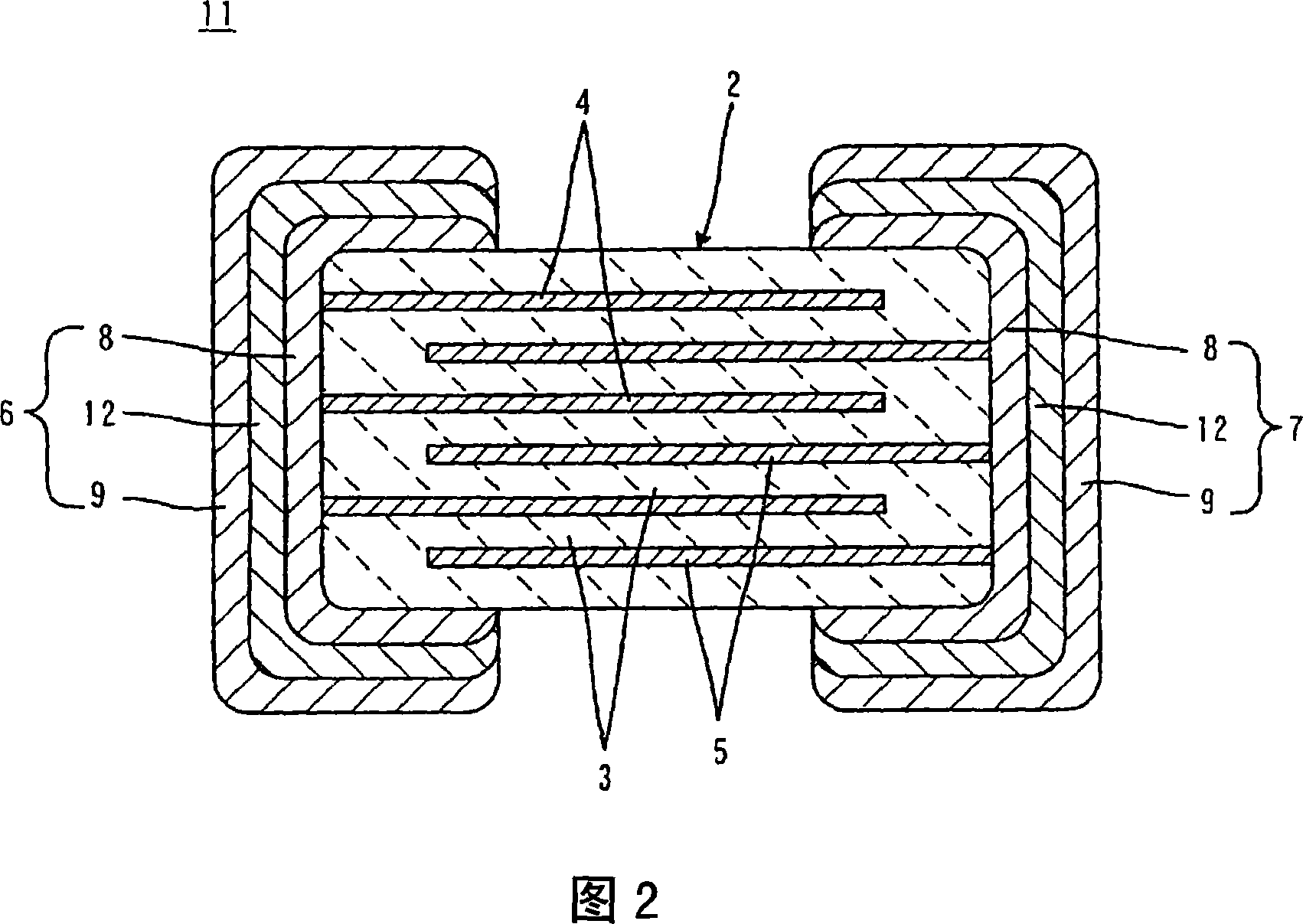

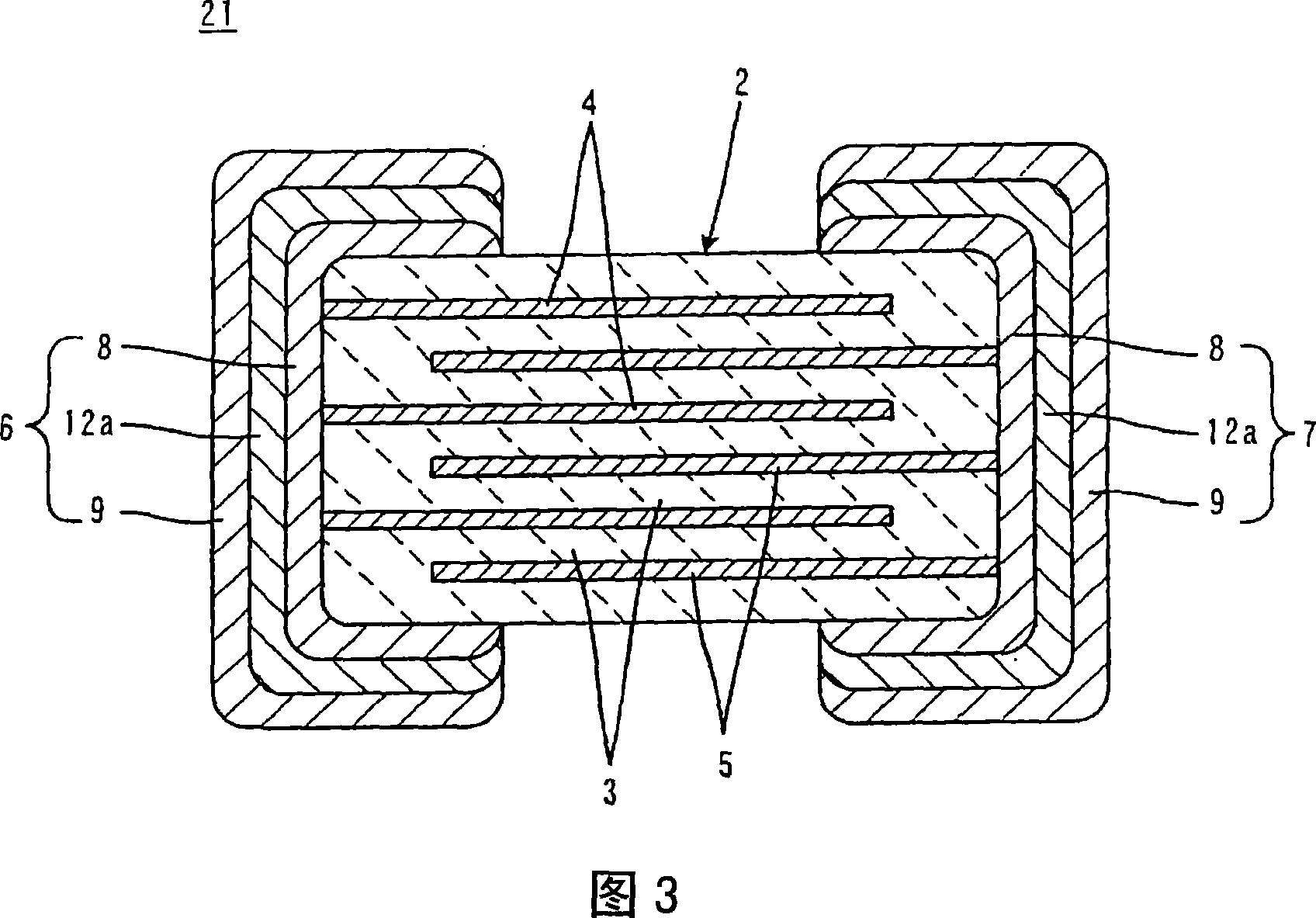

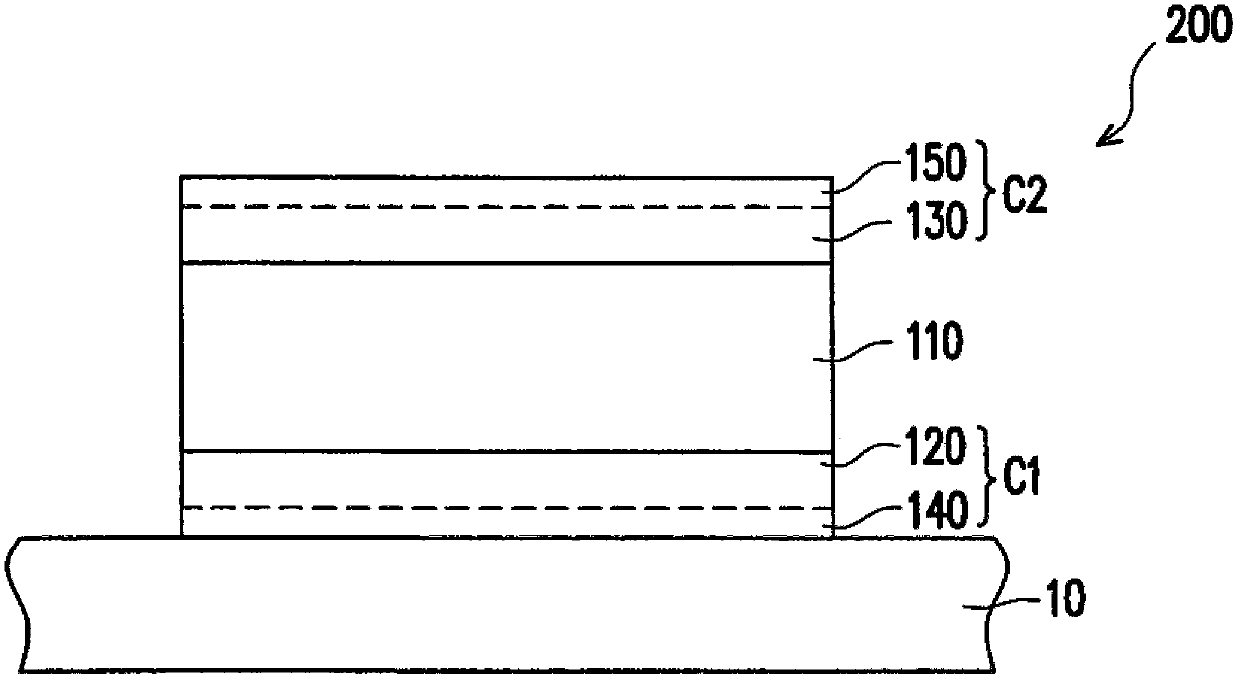

Multilayer ceramic capacitor and method for controlling equivalent series resistance

ActiveCN1993784AIncreasing the thicknessHelp miniaturizationFixed capacitor dielectricStacked capacitorsElectrical connectionCeramic capacitor

Disclosed is a preferable structure for an external electrode which is used in a multilayer ceramic capacitor and also serves as a resistor element. The external electrode having such a structure is not reduced even by firing in a reducing atmosphere, thereby allowing an internal electrode to use Ni or a Ni alloy, and realizes good electrical connection with the internal electrode. Specifically disclosed are external electrodes (6, 7) formed on the outer surface of a capacitor main body (2) which respectively have a structure comprising a conductive layer (8) and a metal plating layer (9) formed on the conductive layer (8). The conductive layer (8) has a composition containing a glass component and a complex oxide such as an In-Sn complex oxide that is reactive with Ni or a Ni alloy.

Owner:MURATA MFG CO LTD

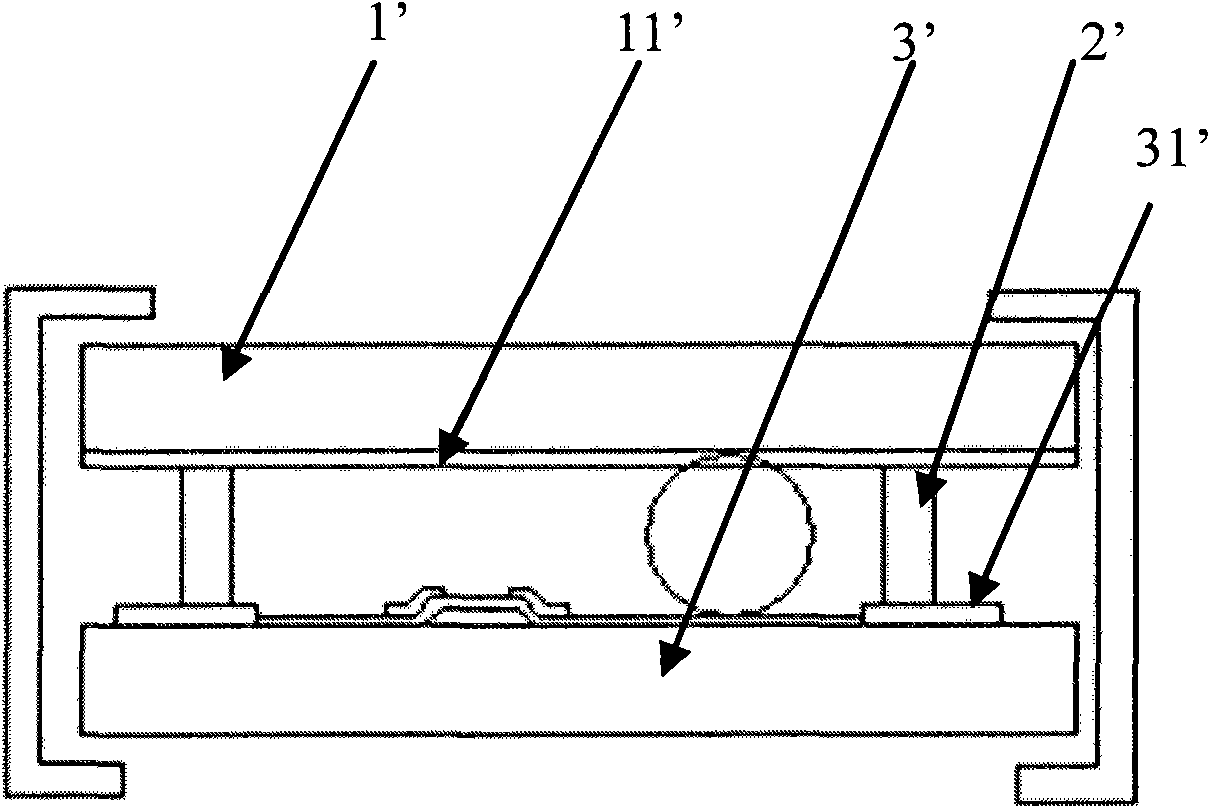

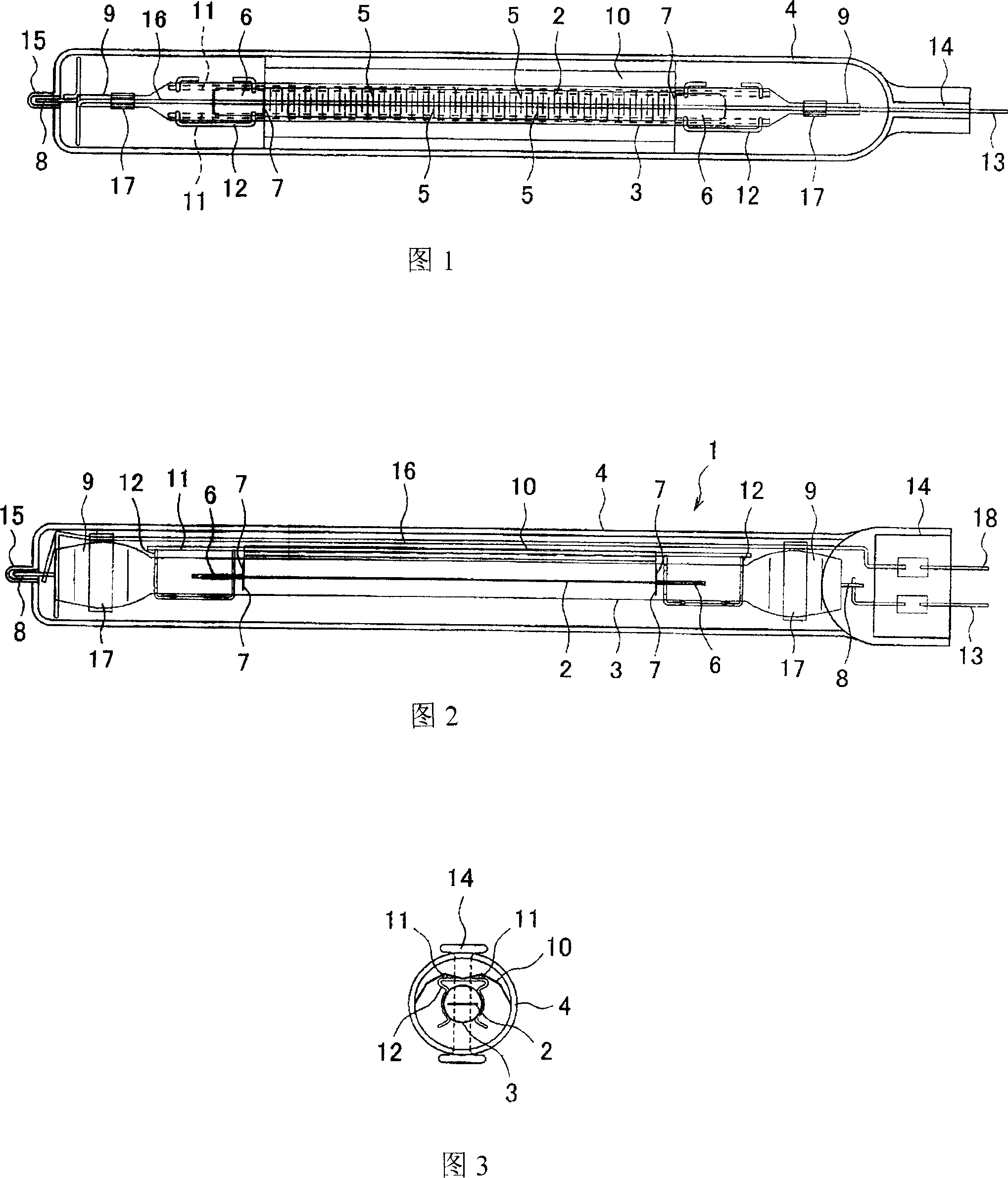

Infrared heater

InactiveCN1988739AImprove the heating effectEasy to useHeating element shapesEngineeringHeating effect

The invention relates to electric heating device, which specifically refers to an infra-red heater including the glass tube and the electrified heat body. The heat body is encased into the sealed glass tube that is a double pipe and includes the sealed inner pipe with the heat body encased and the sealed outer pipe with the inner pipe encased, and a baffle-board is set between the inside of outer pipe and the outside of inner pipe, which can make the far-infrared radiant heat generated by the heat body radiate in the regulated direction.

Owner:邹美琴

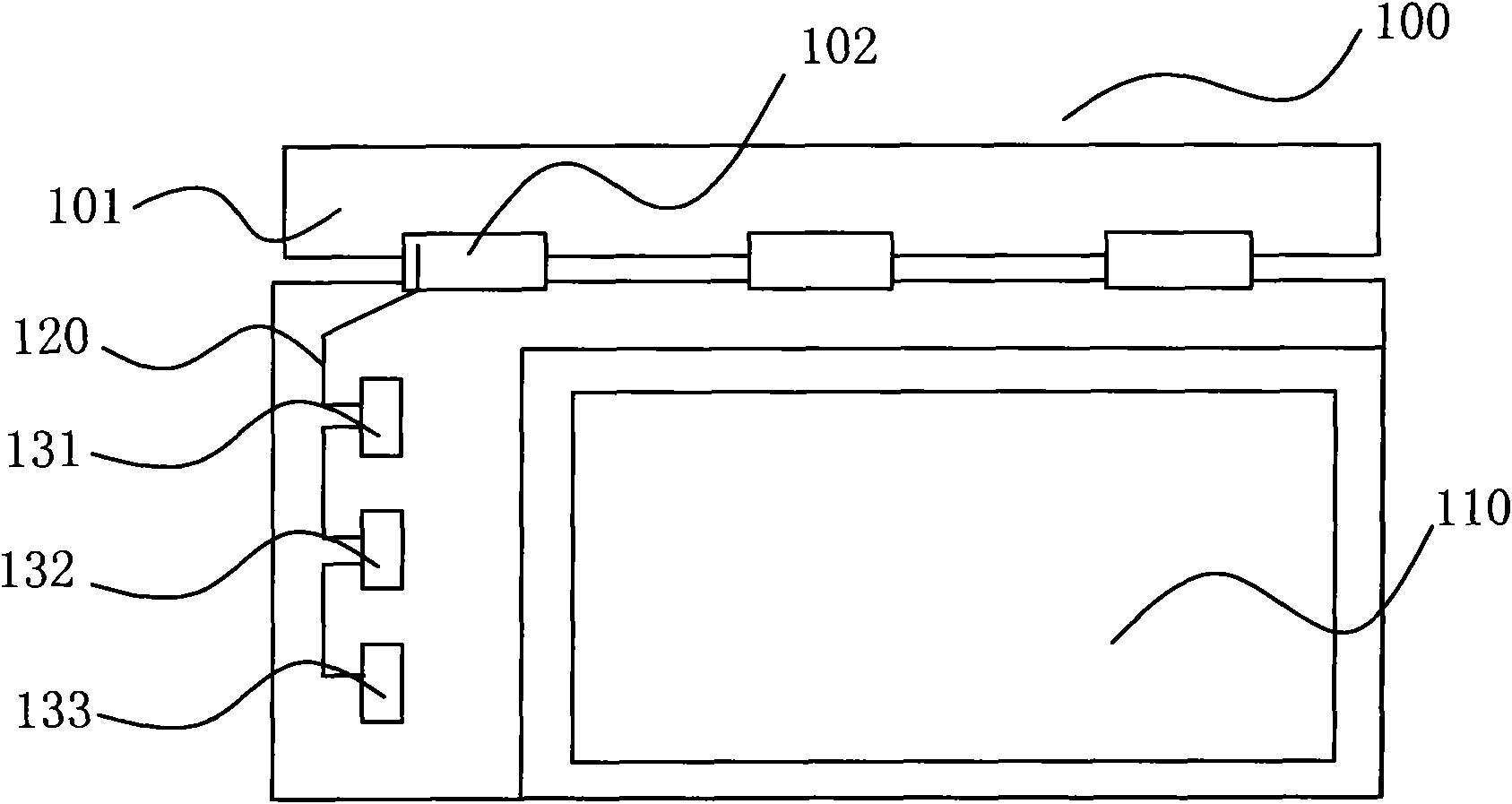

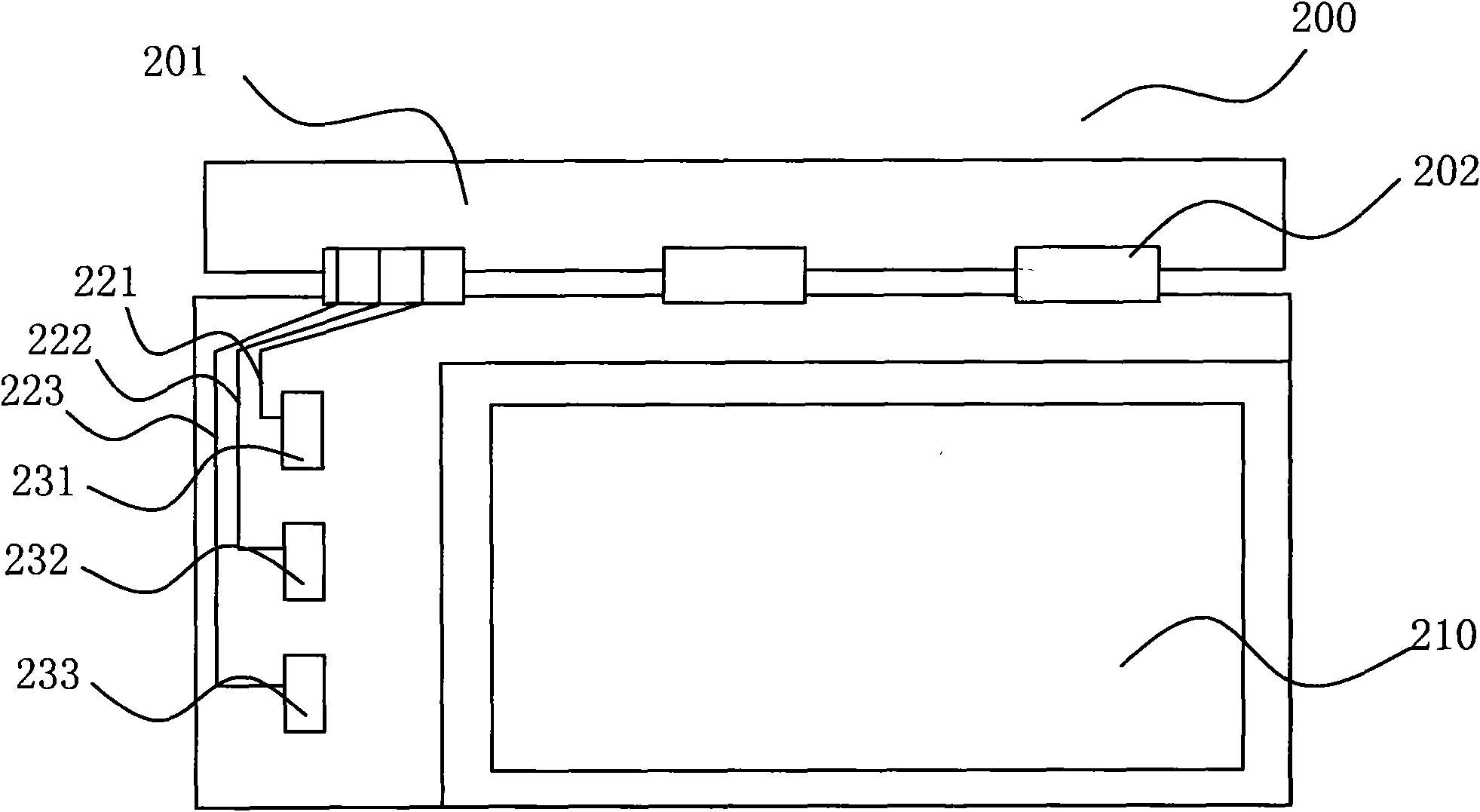

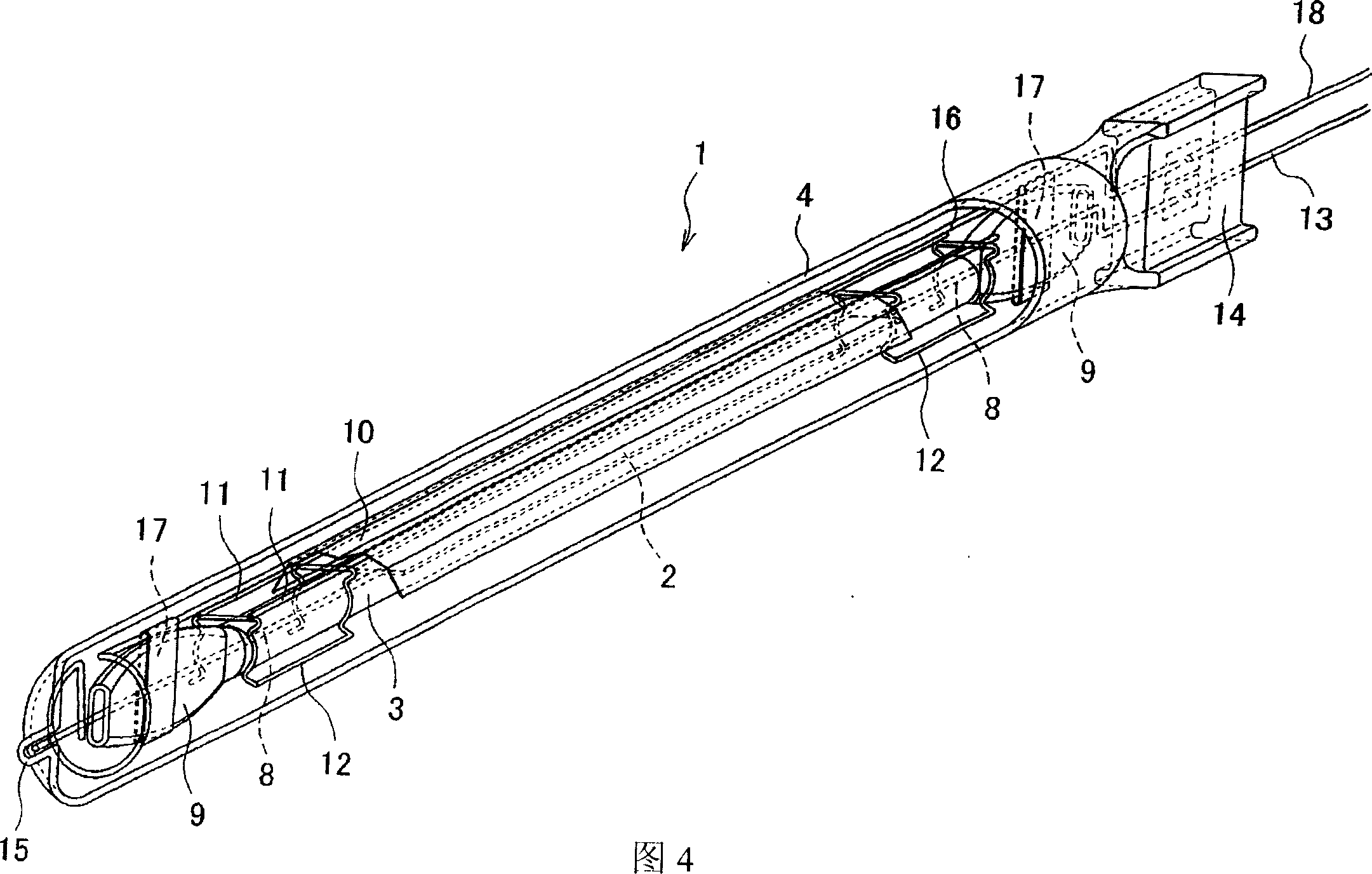

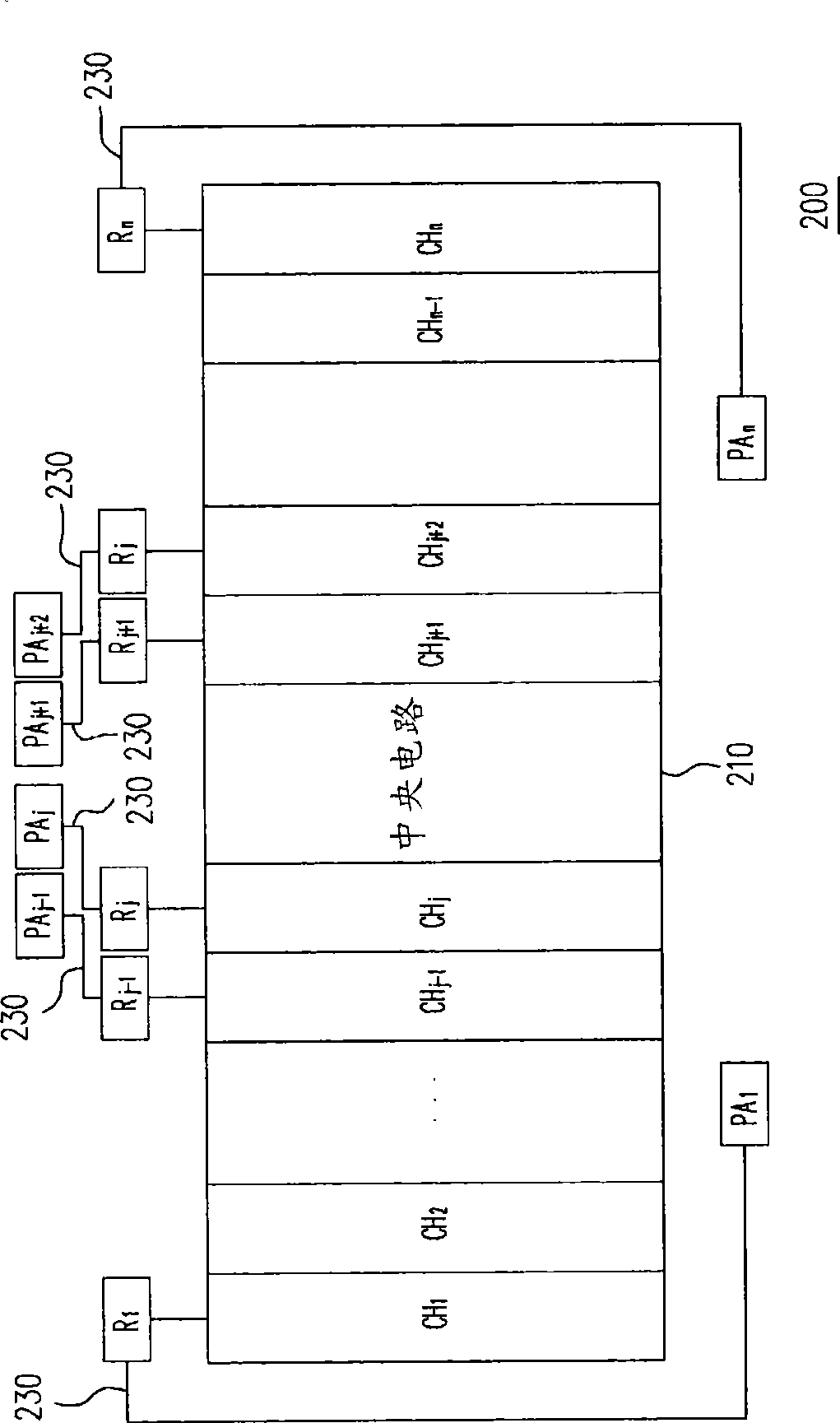

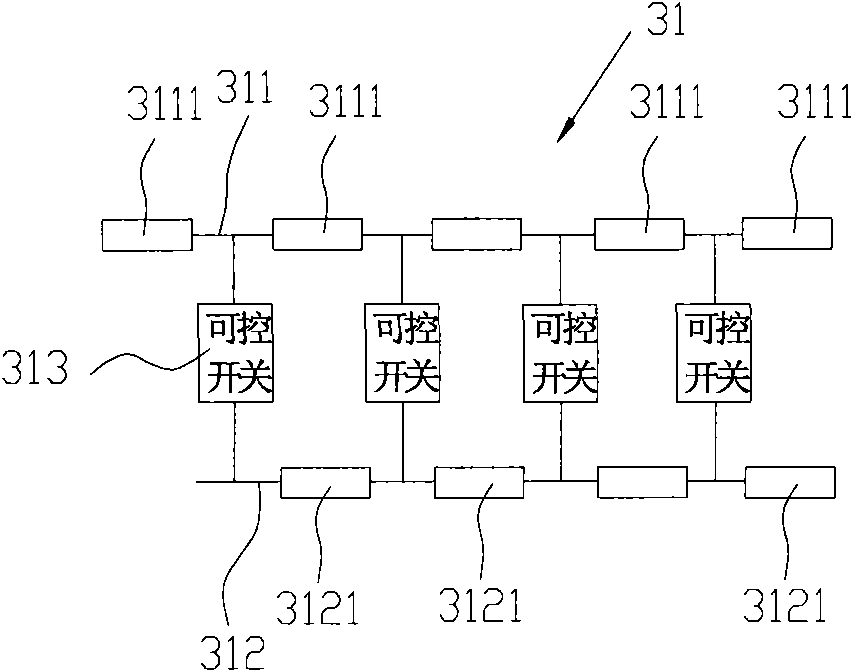

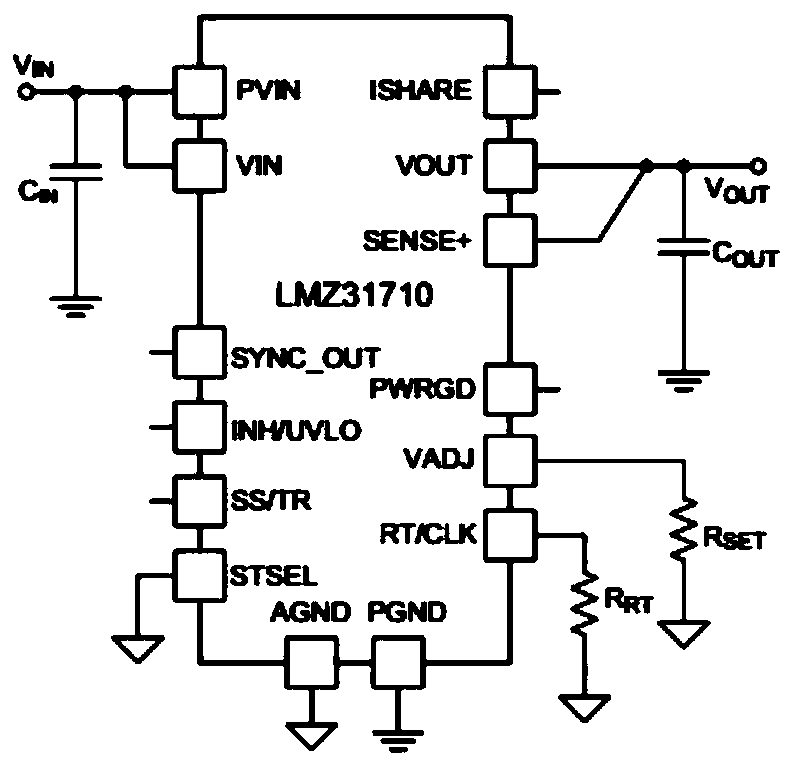

Layout structure of source driver and method thereof

InactiveCN101510017ASolve for uniformitySolve crosstalkStatic indicating devicesNon-linear opticsElectrical resistance and conductanceEngineering

A layout structure of a source driver having a plurality of driving channels, and a method thereof are provided herein. The layout structure of the source driver includes a plurality of pads and a plurality of routings. The pads are used for making electric contact between the source driver and an external circuit. The routings are respectively coupled between the driving channels and the pads for transmitting the signal. Besides, the routings respectively includes a plurality of resistance units, and each of the resistance units is used for adjusting the resistance of the respective routing so as to minimize a variation of the driving ability between the pads.

Owner:HIMAX TECH LTD

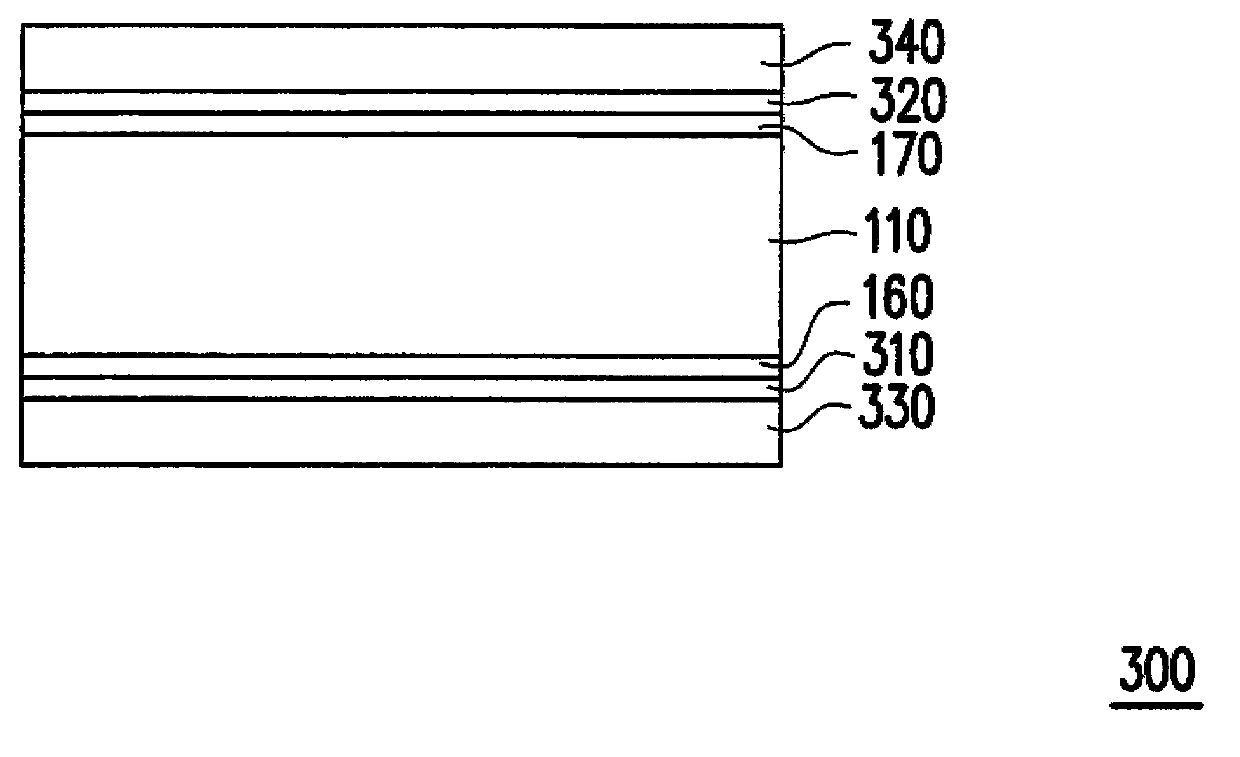

Structure of thermoelectric film

ActiveCN103872236AAdjust the resistance valueImprove thermal conductivityThermoelectric device detailsThermoelectric device junction materialsThin membraneEngineering physics

A structure of a thermoelectric film including a thermoelectric substrate and a pair of first diamond-like carbon (DLC) layers is provided. The first DLC layers are respectively located on two opposite surfaces of the thermoelectric substrate and have electrical conductivity.

Owner:IND TECH RES INST

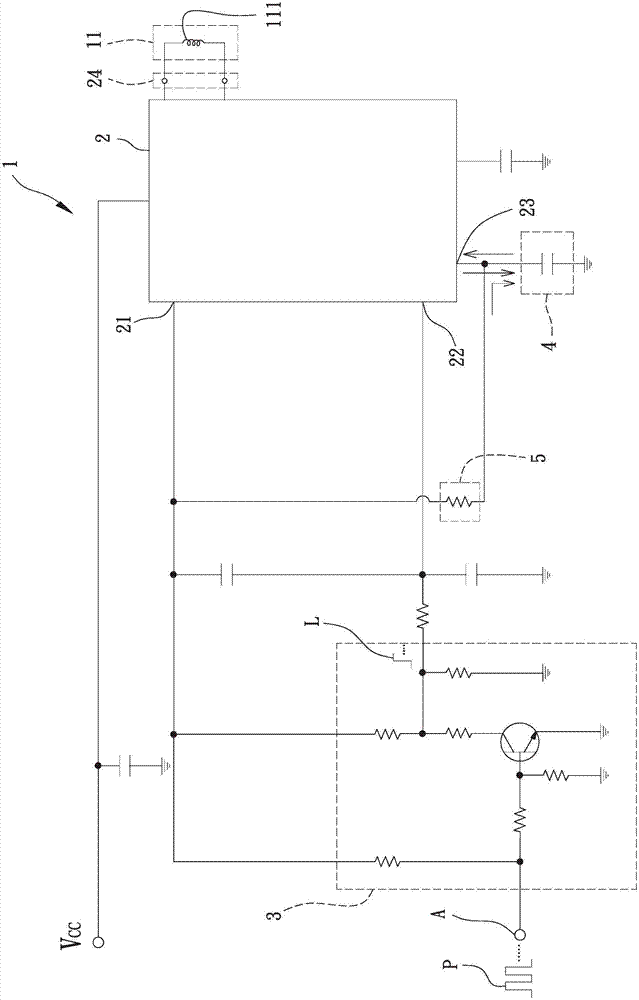

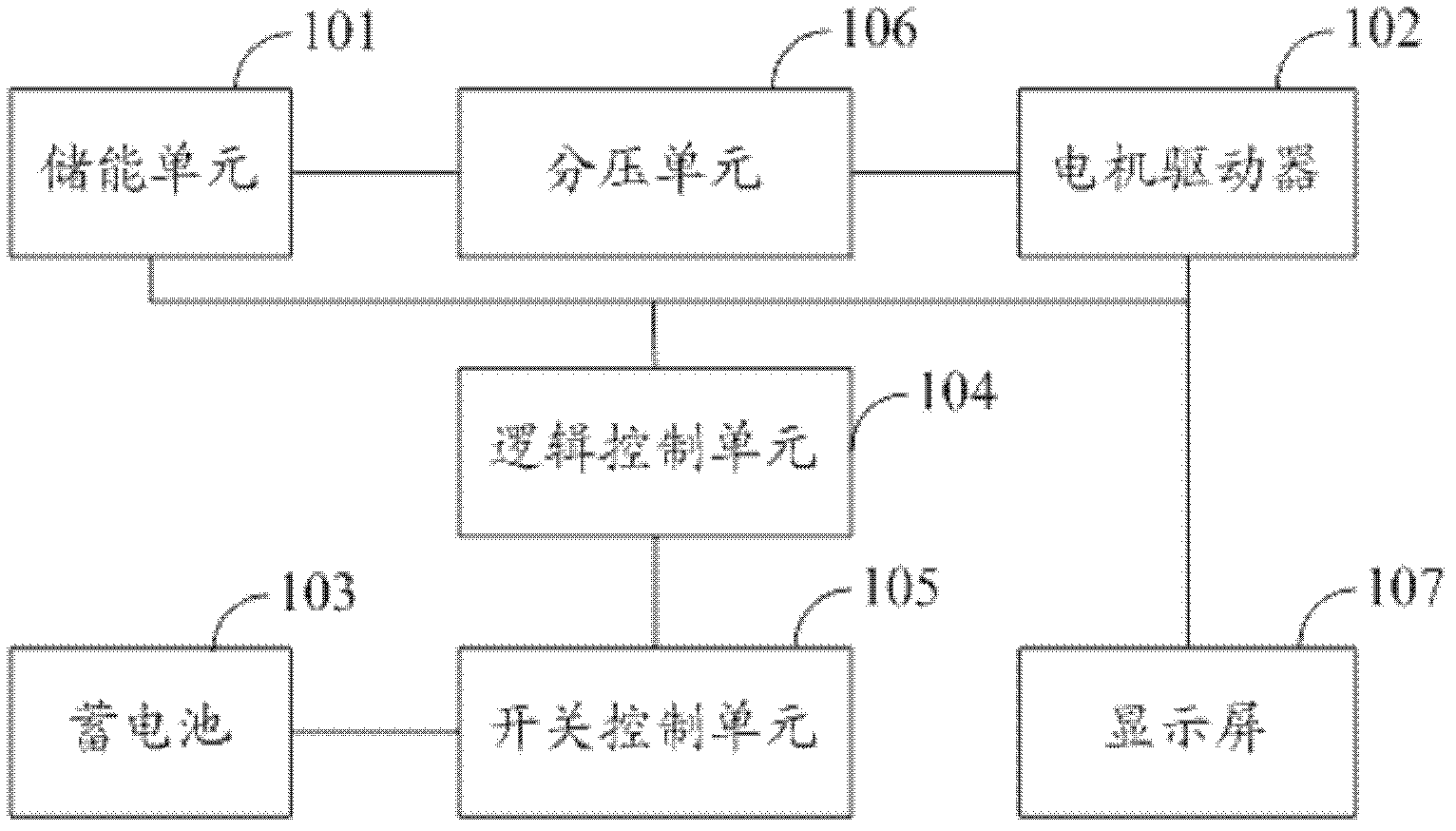

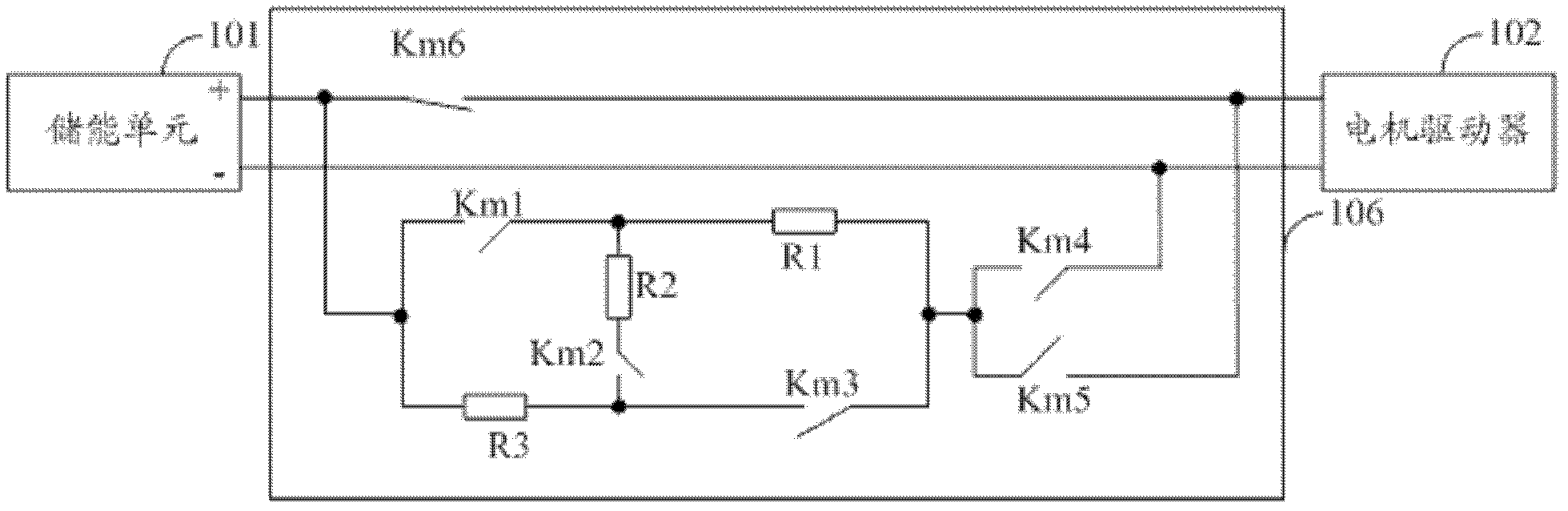

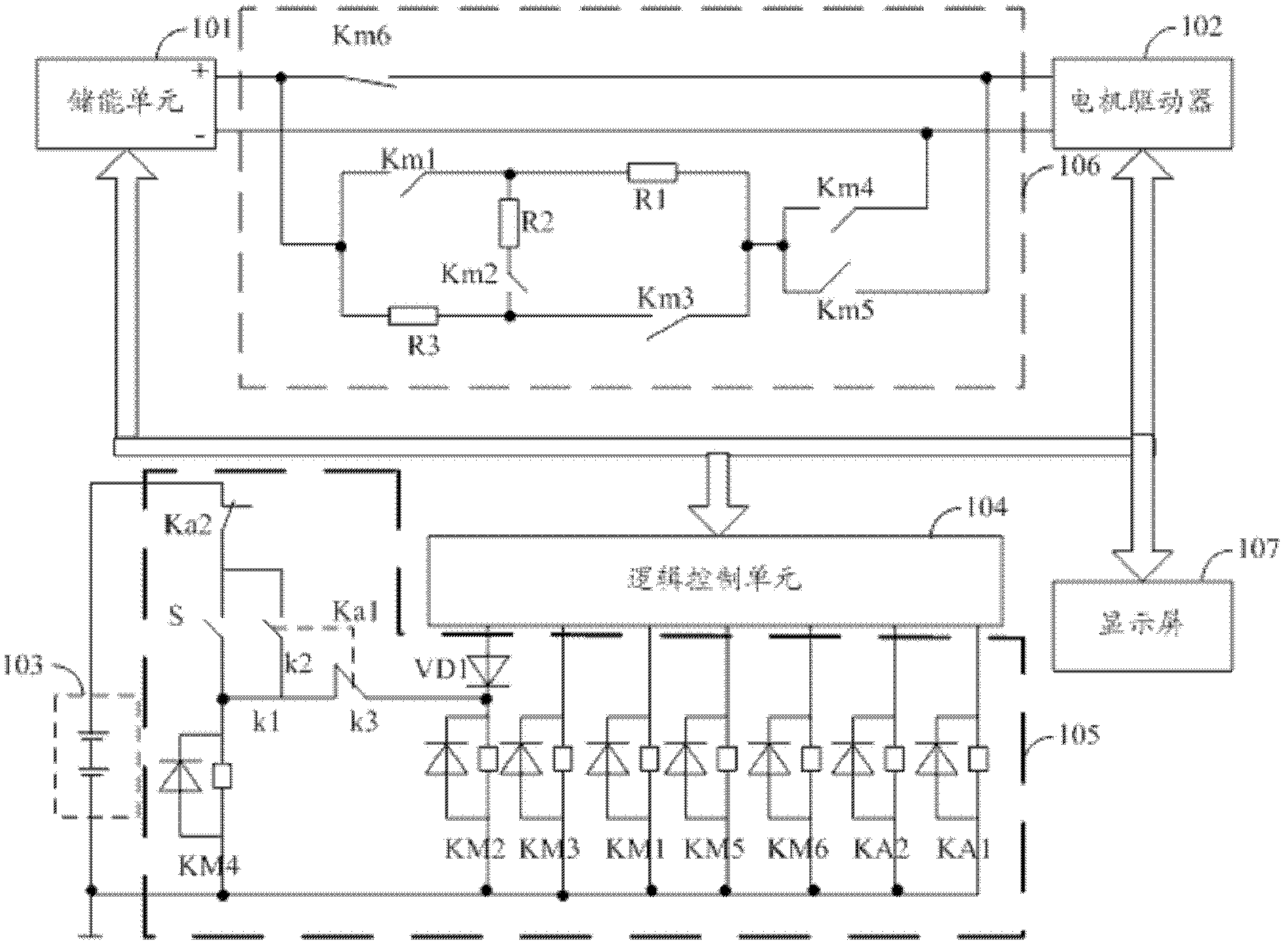

Charging and discharging circuit for electrical system

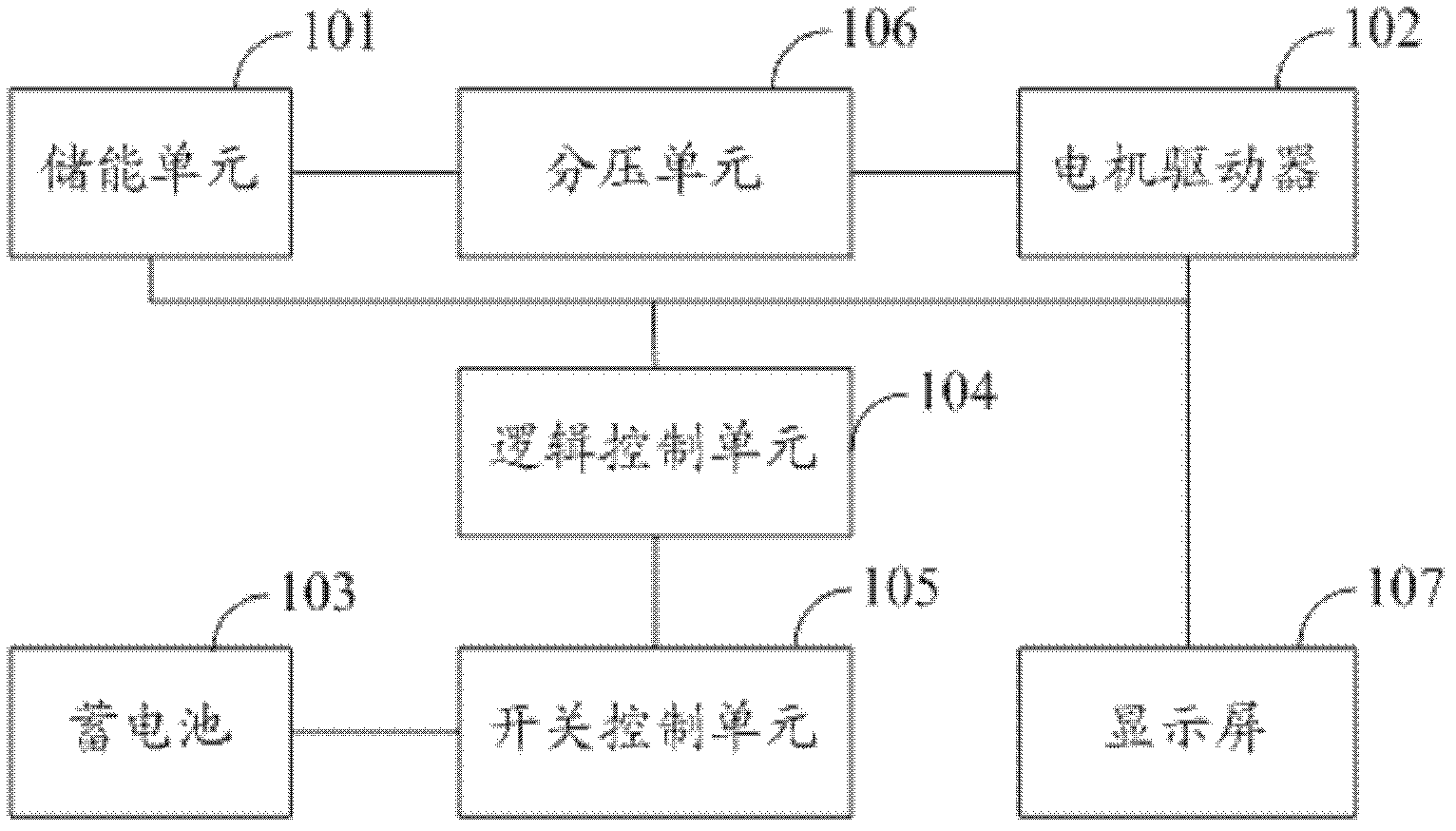

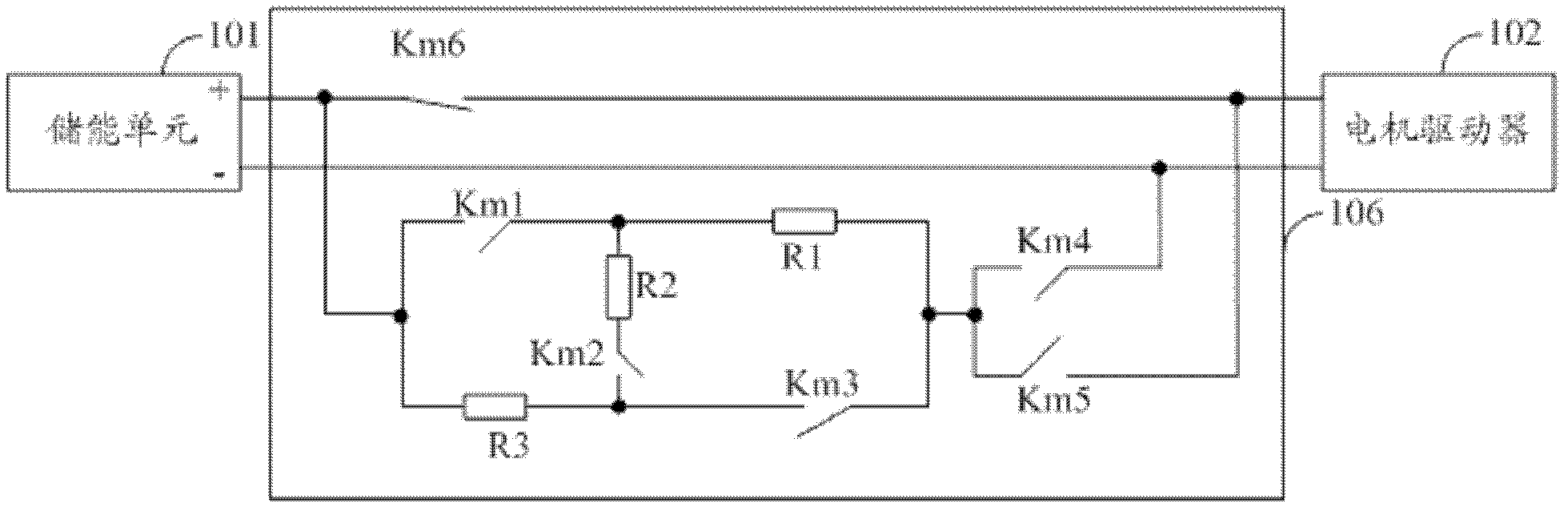

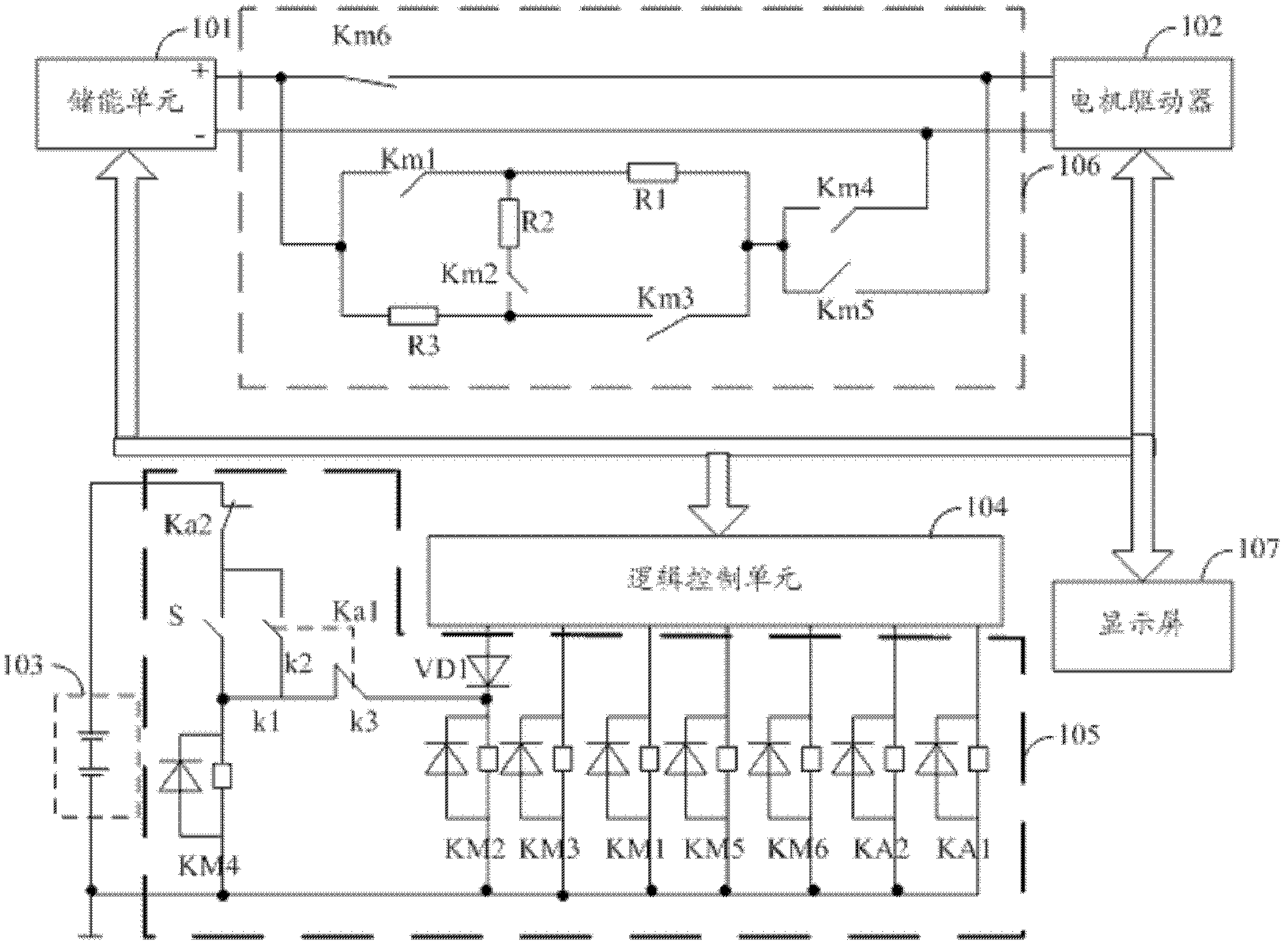

ActiveCN102412608AAdjust the resistance valueTimely adjustment of resistance valueField or armature current controlDc-dc conversionControl signalEngineering

The invention relates to a technology in the mechanical and electrical field, in particular to a charging and discharging circuit for an electrical system. The charging and discharging circuit comprises an energy storing unit, a motor driver and a storage battery, and is characterized by further comprising a logical control unit, a switch control unit and a voltage-dividing unit, wherein the logical control unit is connected with the energy storing unit and the motor driver through data buses; the switch control unit is connected with the logical control unit and the storage battery, and is used for receiving a logical control signal transmitted by the logical control unit and controlling the switch-on and switch-off of each touch control point in the voltage-dividing unit; and the voltage-dividing unit is connected with the energy storing unit and the motor driver, and is used for receiving a switch control signal transmitted by the switch control unit, switching on or off each touch control point and adjusting the resistance of a voltage-dividing resistor. Due to the adoption of the charging and discharging circuit for the electrical system provided by the embodiment of the invention, the resistance value of the voltage-dividing resistor can be adjusted appropriately, the charging and discharging efficiencies are greatly increased, and high maneuverability is achieved.

Owner:ZOOMLION HEAVY IND CO LTD

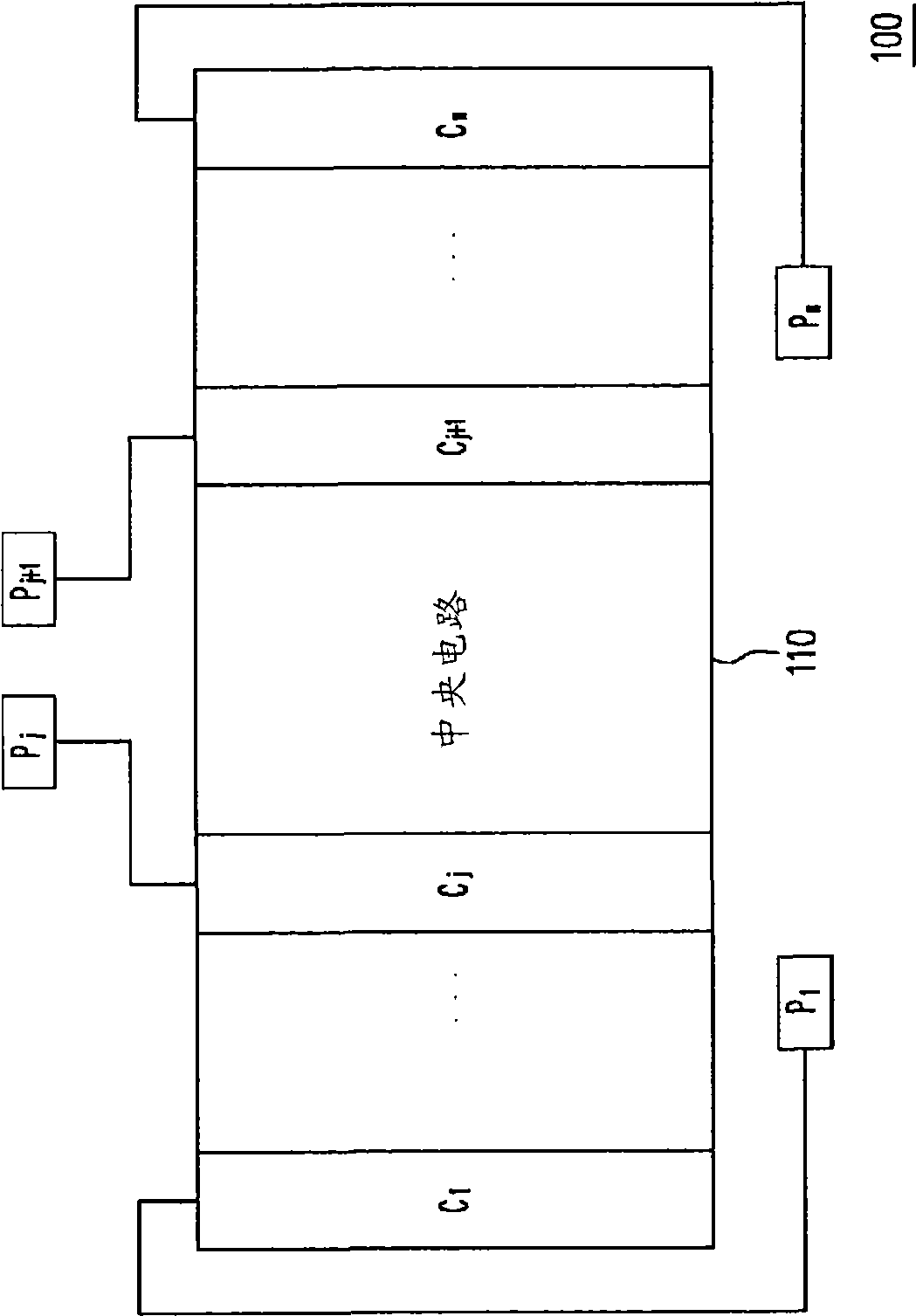

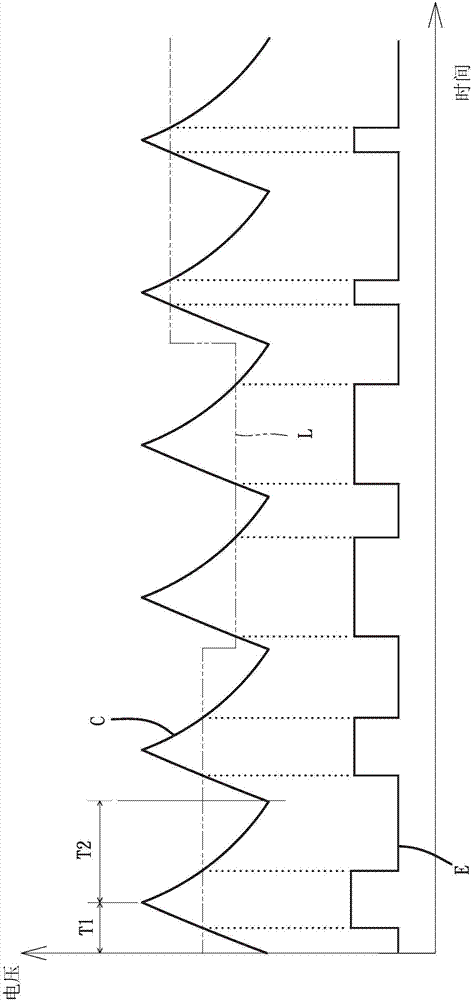

Motor and method of controlling rotation speed of same

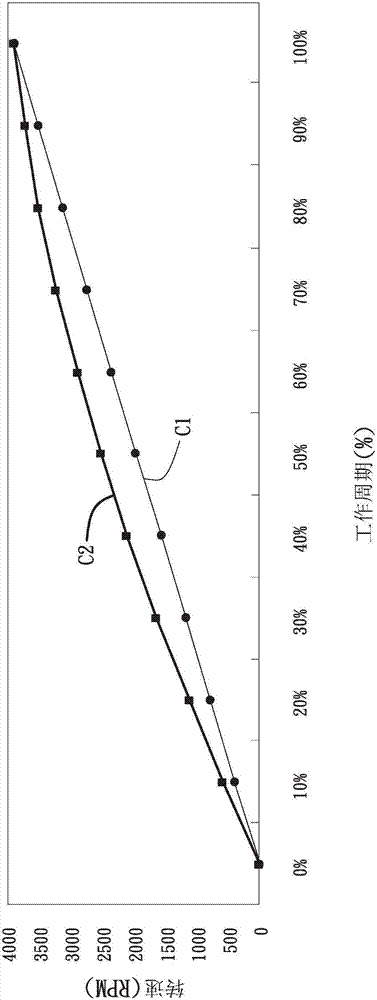

ActiveCN107404279AReduce the complexity of speed controlIncrease usage demandElectric motor controlSingle motor speed/torque controlWork periodWave shape

The invention relates to a motor and a method of controlling the rotation speed of the same, and aims to solve the problem that the rotation speed of a conventional motor is non-linear. The method can be applied to a control unit. The control unit is used to adjust the rotation speed of a motor. The method comprises the following steps: generating a logic signal by comparing the voltage value of a reference signal and the voltage value of an oscillation signal by the control unit so as to control the rotation speed of the motor; wherein the voltage value of the reference signal is generated by converting the work period of a pulse-width modulation signal, the waveform of the oscillation signal comprises a charging period and a discharging period, the time of the discharging period is longer than the time of the charging period, and the problem is solved by the abovementioned method.

Owner:SUNON ELECTRONICS (BEIHAI) CO LTD

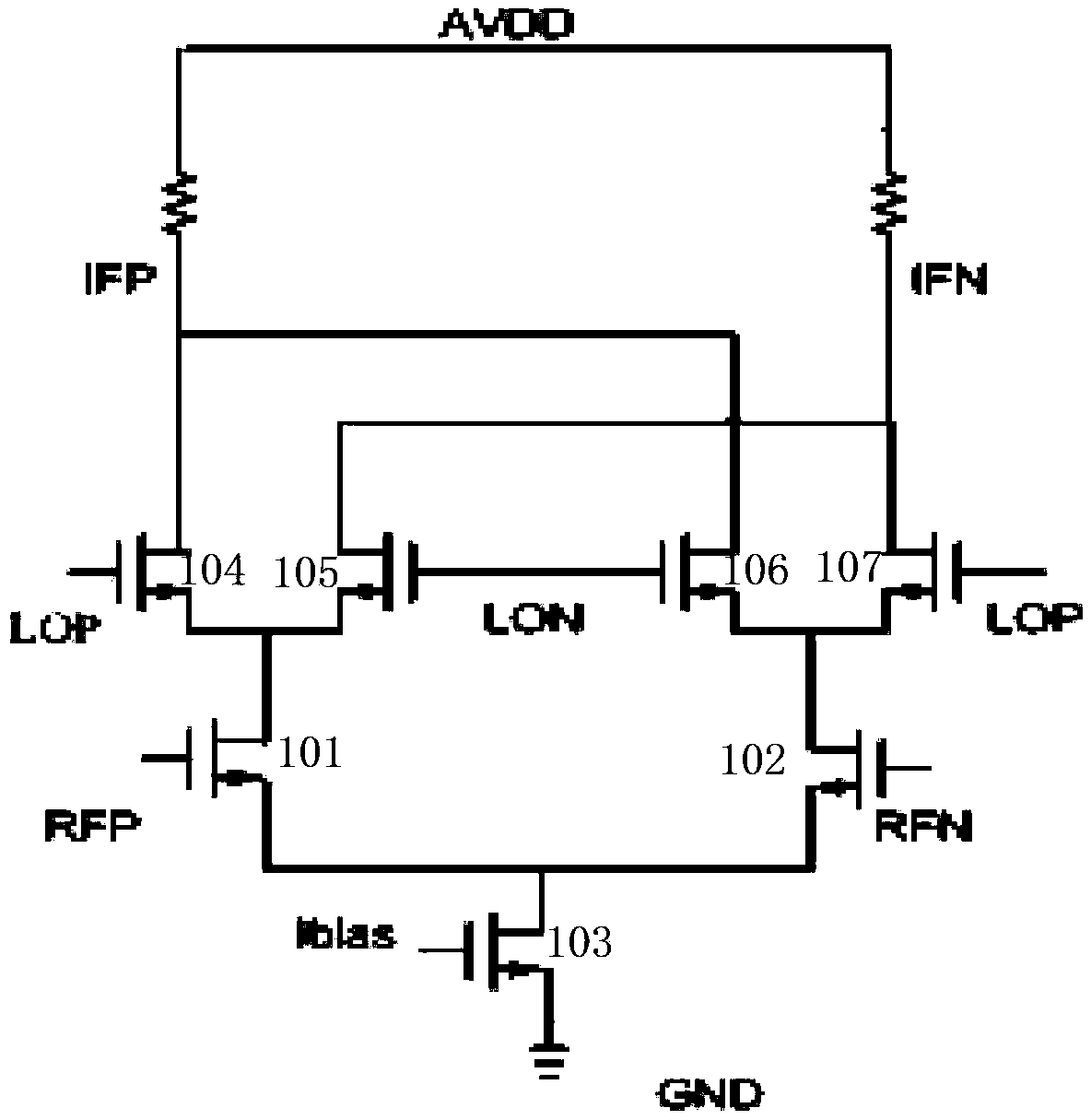

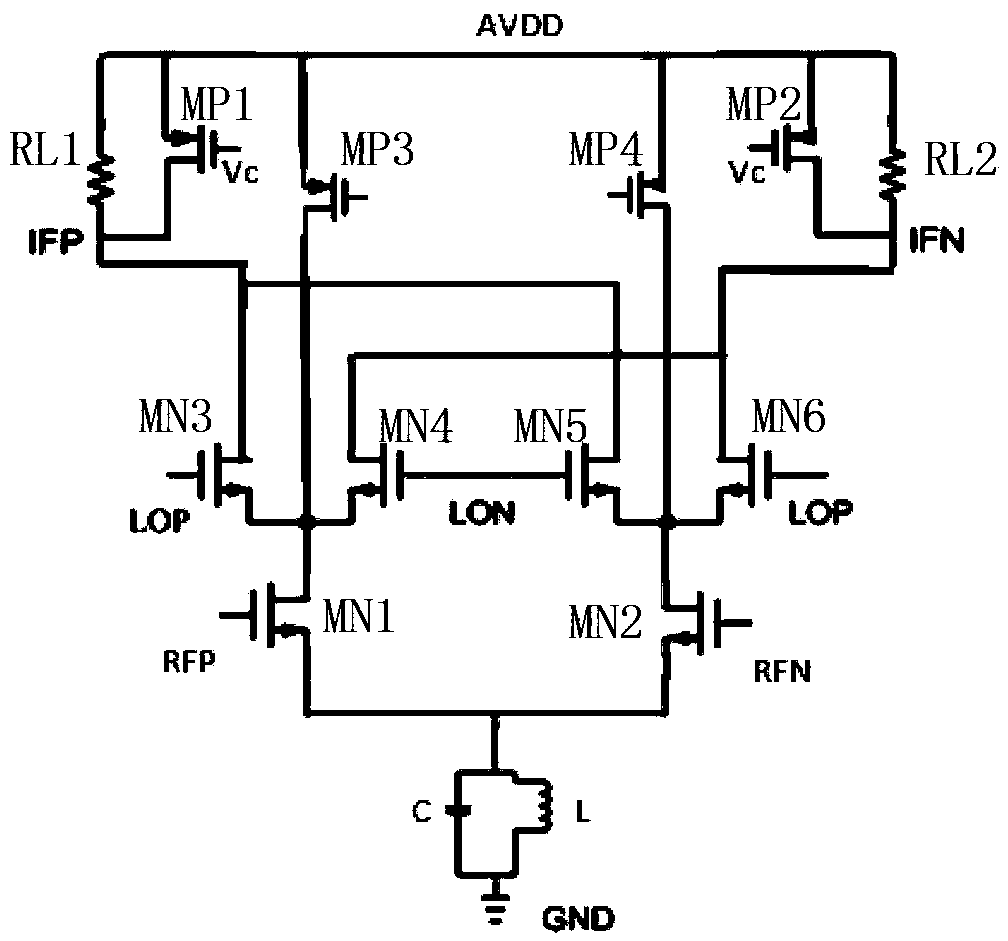

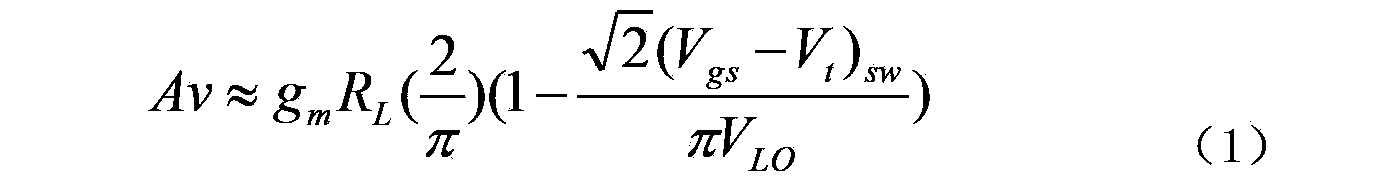

CMOS down-conversion mixer

ActiveCN104242825AAdjust working statusAdjust the resistance valueModulation transference by semiconductor devices with minimum 2 electrodesLoad circuitCMOS

The invention discloses a CMOS down-conversion mixer. The CMOS down-conversion mixer comprises a radio frequency differential input circuit and a switching circuit. Load circuits formed by connecting resistors and PMOS transistors in parallel are connected between the normal phase output end of the switching circuit and a supply voltage and between the reversal phase output end of the switching circuit and the supply voltage; grid electrodes of the PMOS transistors of the load circuits are connected with a first control voltage, and therefore load impedance of the load circuits can be adjusted. Drain electrodes of two NMOS transconductance tubes of the radio frequency differential input circuit are respectively connected with a constant current source, and source electrodes of the NMOS transconductance tubes of the radio frequency differential input circuit are jointly connected with an LC parallel circuit. According to the CMOS down-conversion mixer, gains can be improved and are adjustable, the linearity and the noise performance can be improved, and the working voltage can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

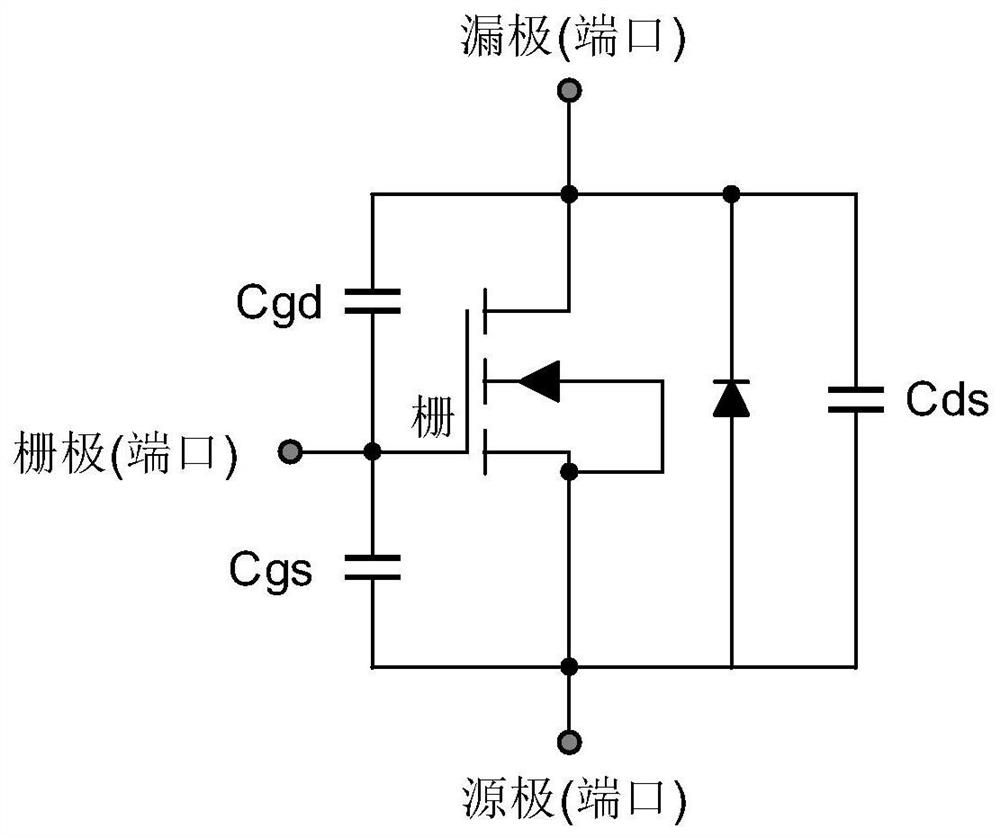

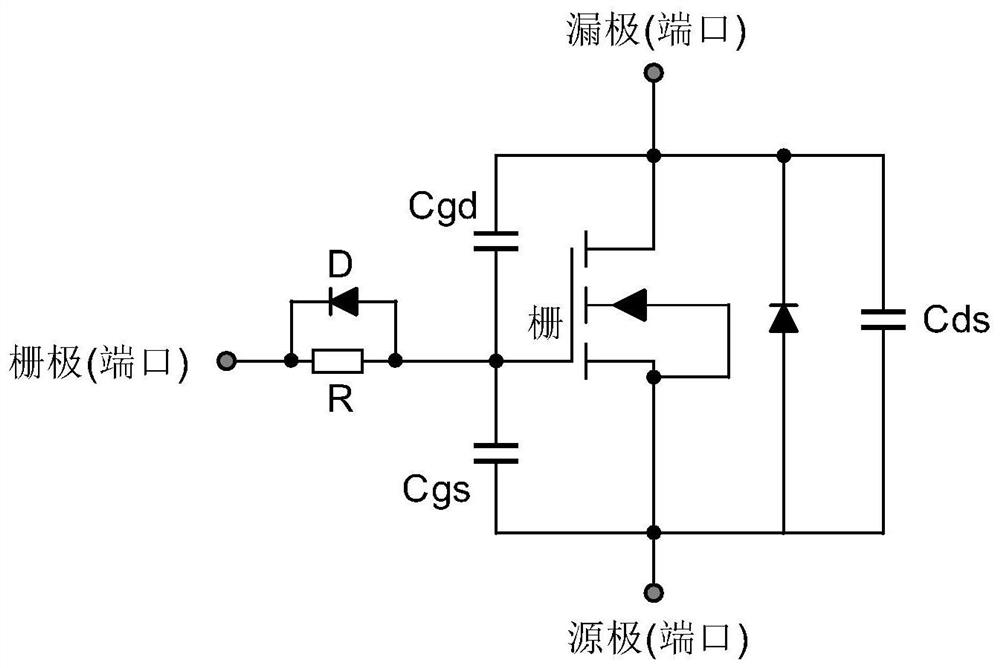

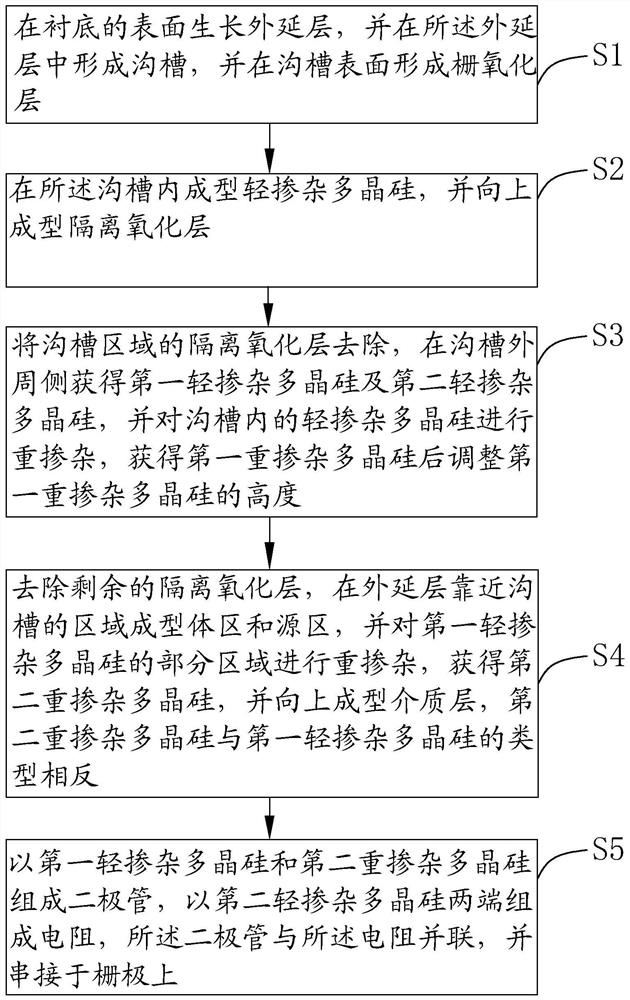

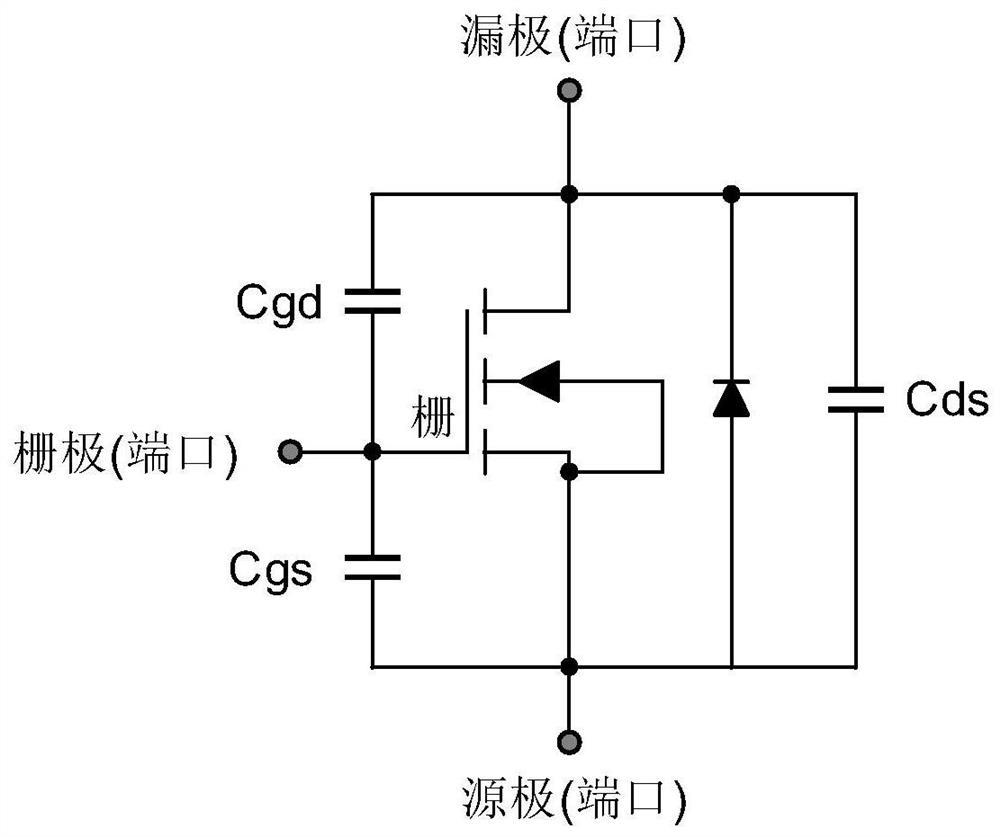

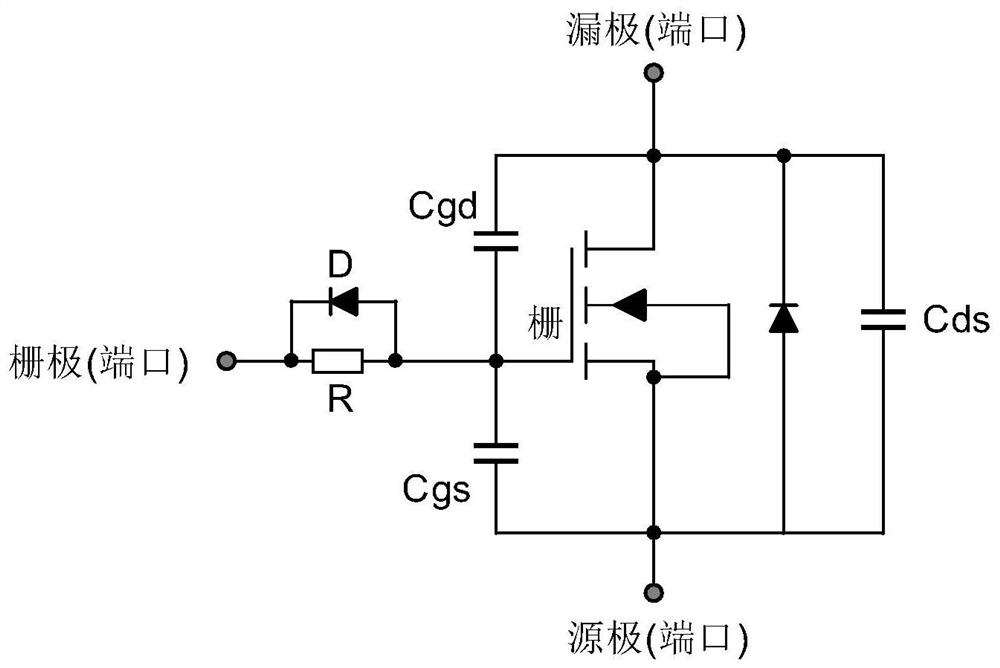

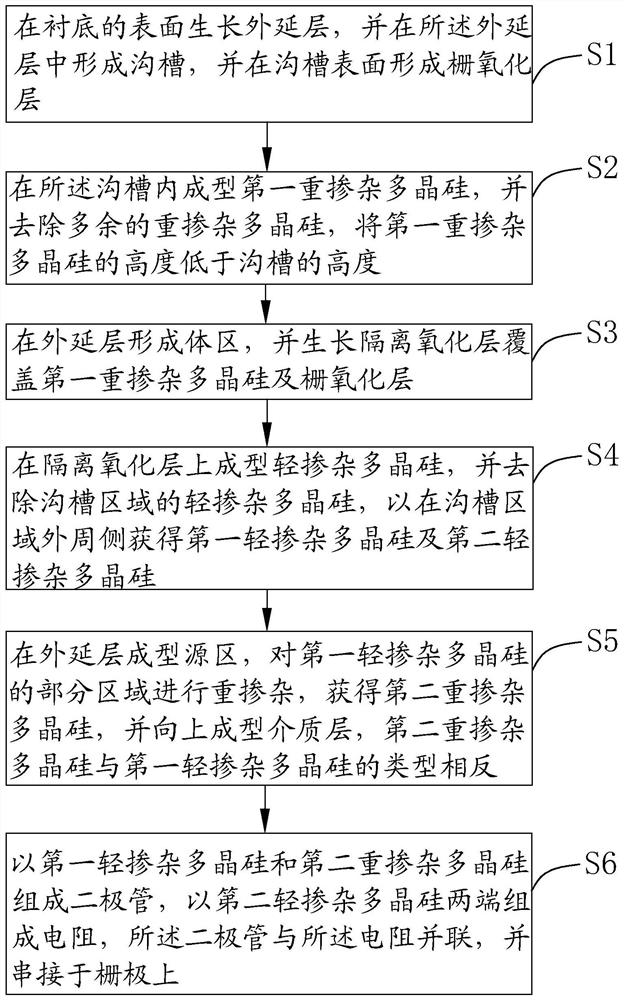

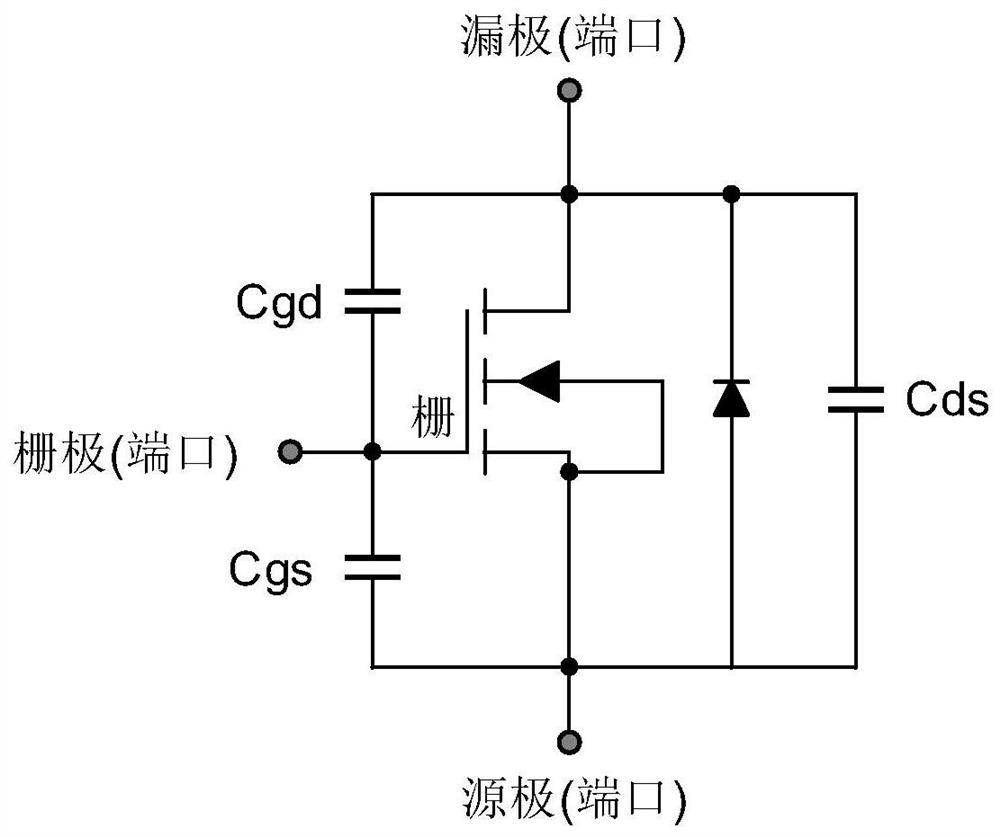

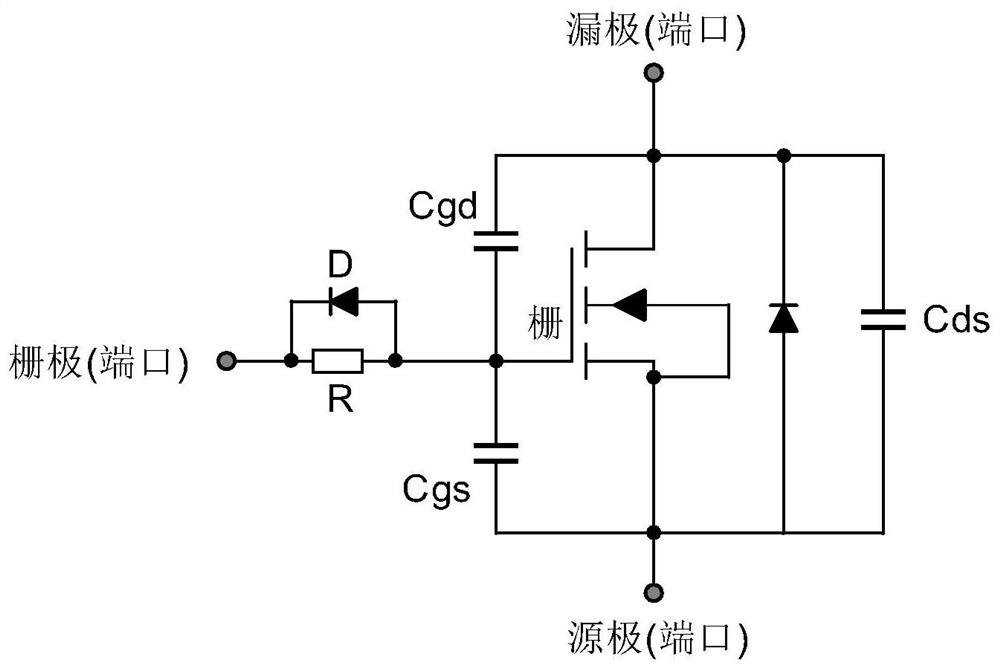

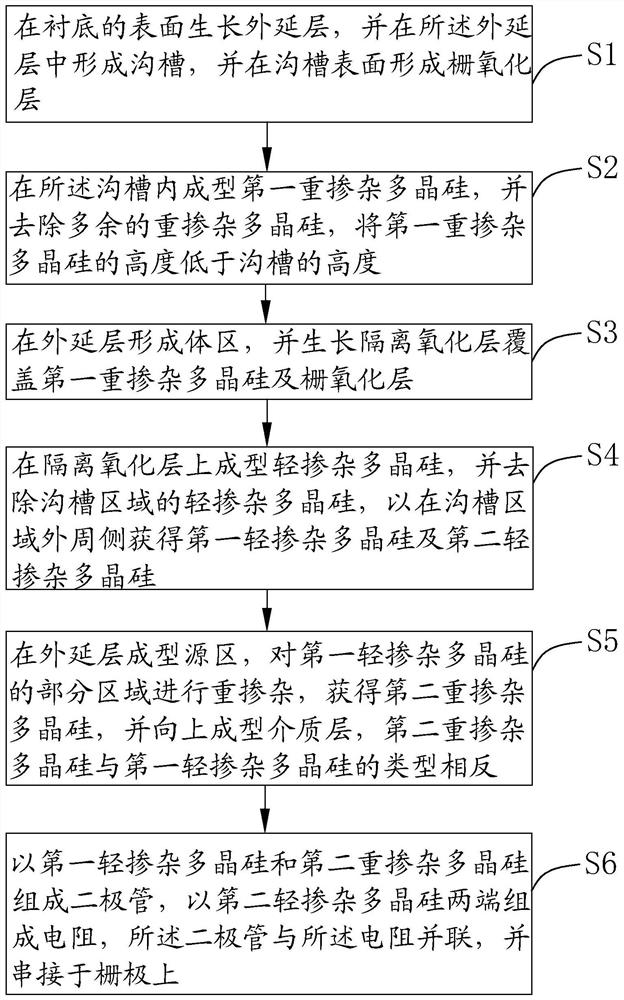

MOSFET chip manufacturing process for improving grid characteristics

PendingCN113764407AAchieve protectionImprove discharge efficiencyTransistorSolid-state devicesMOSFETEngineering

The invention discloses an MOSFET chip manufacturing process for improving grid characteristics, which comprises the following steps: removing an isolation oxide layer in a groove region, obtaining first lightly-doped polycrystalline silicon and second lightly-doped polycrystalline silicon on the peripheral side of a groove, heavily doping the lightly-doped polycrystalline silicon in the groove, obtaining first heavily-doped polycrystalline silicon, and removing the residual isolation oxide layer in a body forming region and a source region, close to the groove, of the epitaxial layer; carrying out heavy doping on part of the region of the first lightly-doped polycrystalline silicon, and obtaining second heavy-doped polycrystalline silicon; forming a dielectric layer upwards, wherein the type of the second heavy-doped polycrystalline silicon is opposite to that of the first lightly-doped polycrystalline silicon; and forming a diode by the first lightly doped polycrystalline silicon and the second heavily doped polycrystalline silicon, forming a resistor by two ends of the second lightly doped polycrystalline silicon, and connecting the diode with the resistor in parallel to be connected to the grid electrode in series. The polycrystalline silicon resistor and the polycrystalline silicon diode are integrated in the chip, so that the current flowing through the grid electrode is effectively limited, and the protection on the grid electrode is realized.

Owner:深圳市芯电元科技有限公司

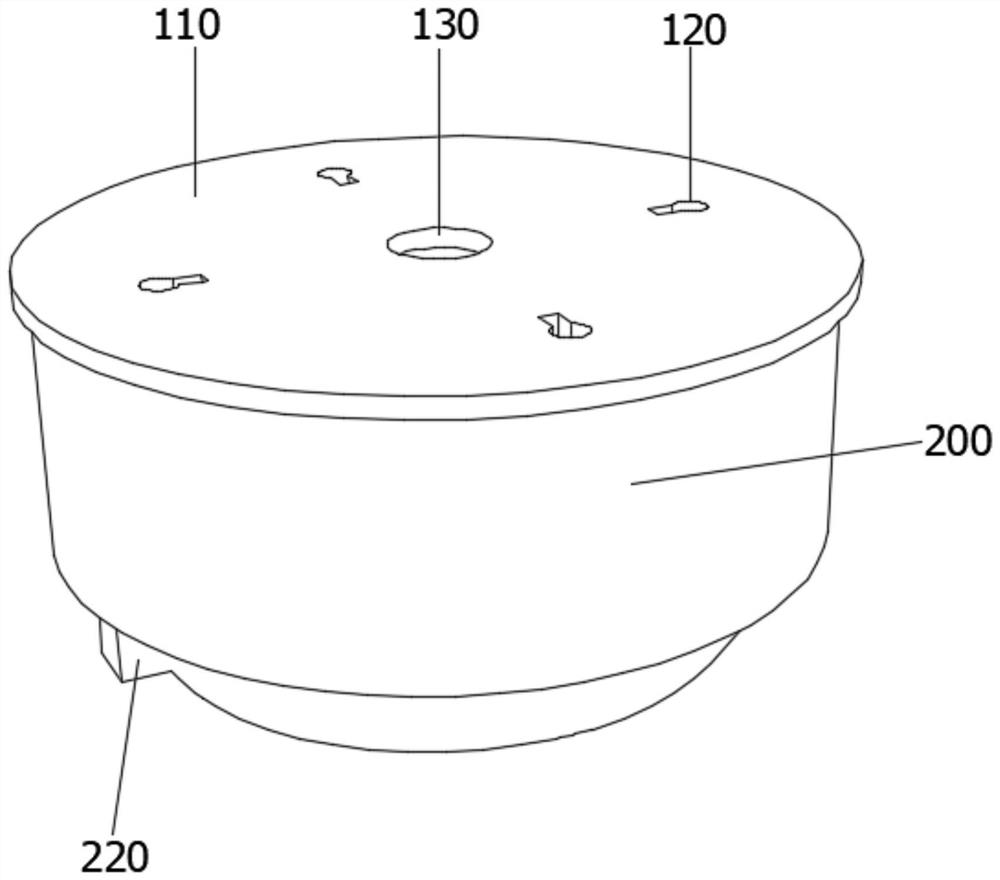

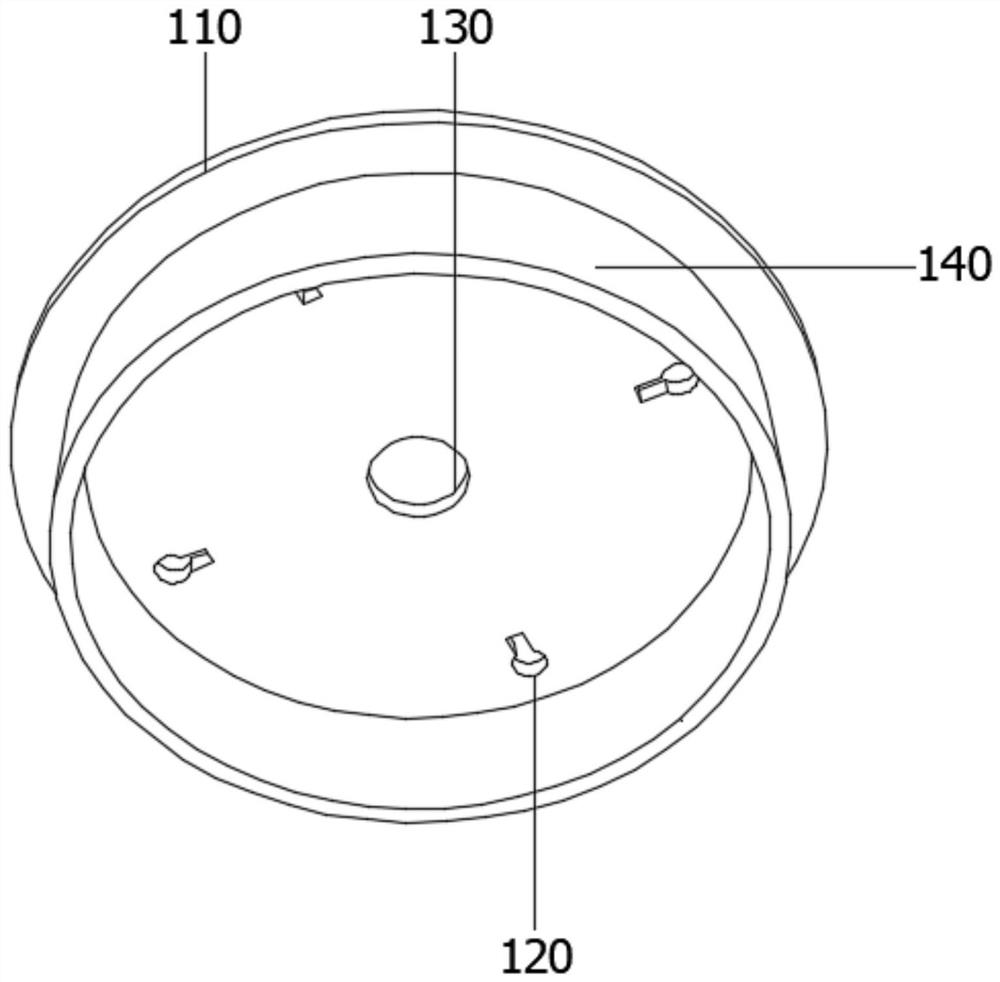

Polymer PTC thermistor and manufacturing method thereof

InactiveCN1529328ASimple production processReduce manufacturing costPositive temperature coefficient thermistorsMetallurgyHome appliance

Composite material of conduction high polymer is as main material of high polymer PTC thermistor. PTC thermistor comprises core material and metal electrodes adhibited on two surfaces of core material. Composed multiple layers of chips possessing PTC characters constitutes core material of thermistor. Method for manufacturing PTC thermistor includes steps: piling up multiple layers of chips possessing PTC characters to produce composed chip; then, metal electrodes are adhibited on two surfaces of core material; cutting PTC thermistor according to required size. In the invention, major types of PTC thermistor are made from lesser PTC material formula under fixed outline size of product relatively. The invented PTC thermistor is applicable to areas of communication, computer, industrial control and household electrical appliances.

Owner:SHANGHAI CHANGYUAN WAYON CIRCUIT PROTECTION CO LTD

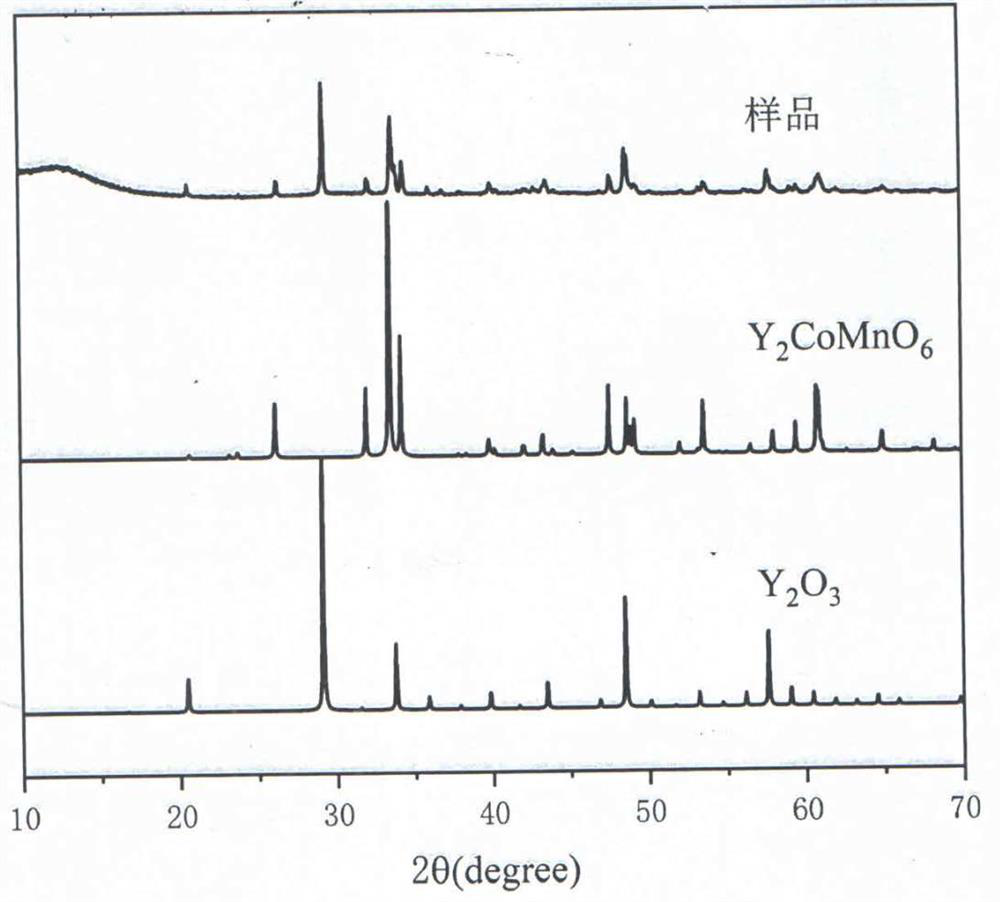

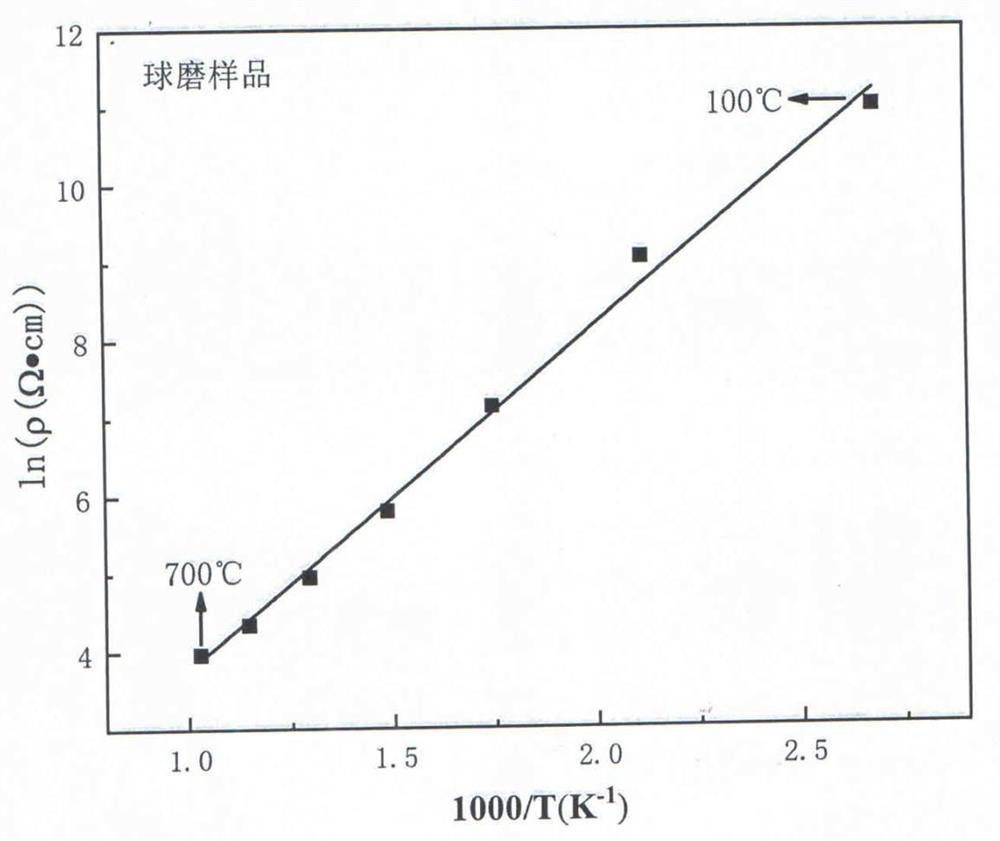

Preparation method of double perovskite type and yttrium oxide compounded negative temperature coefficient thermistor material

PendingCN113979728AAdjust the resistance valueB value has little effectNegative temperature coefficient thermistorsResistor manufactureThermistorYttrium(III) oxide

The invention relates to a preparation method of a double perovskite type and yttrium oxide compounded negative temperature coefficient thermistor material. According to the method, composite powder is formed by taking MnO2, Ni2O3, Co2O3 and Y2O3 as raw materials through high-energy ball milling and adding different dispersing agents. The novel double perovskite type and yttrium oxide compounded negative temperature coefficient thermistor material with the material constant B100-600 DEG C = 3900-4580 K, the temperature of 100 DEG C and the electrical resistivity of 32820-77460 omega.cm is obtained by mixing and ball milling, pre-sintering, re-mixing and ball milling, cold isostatic pressing molding, high-temperature sintering and electrode coating and burning. The composite thermistor material prepared by the method is stable in performance and high in consistency. The thermistor material has obvious negative temperature coefficient characteristics in a range of 100-700 DEG C, and is suitable for manufacturing high-temperature thermistors.

Owner:XINJIANG TECHN INST OF PHYSICS & CHEM CHINESE ACAD OF SCI

Method of converting non-conducting fiber felt into electrothermal active carbon fiber felt

InactiveCN1152603CGood physical propertiesQuality improvementSpecial paperPaper/cardboardActivated carbonFiber

The invention relates to the method for preparing the felt of the activated carbon fiber. The method incldues the four steps. (1) Selecting the material and medicine treatment. (2) Passing several times of the carbonizing treatment. (3) Passing several times of the activating treatment. (4) Cleaning up and clipping. The method selects the specific material and special treatment. The invented felt of the activated carbon fiber possesses the advantagesof high percent of yield, even electric density, simple manufacturing technique, large heating area, not burning, long service life and oxidation resistance.

Owner:张建春 +1

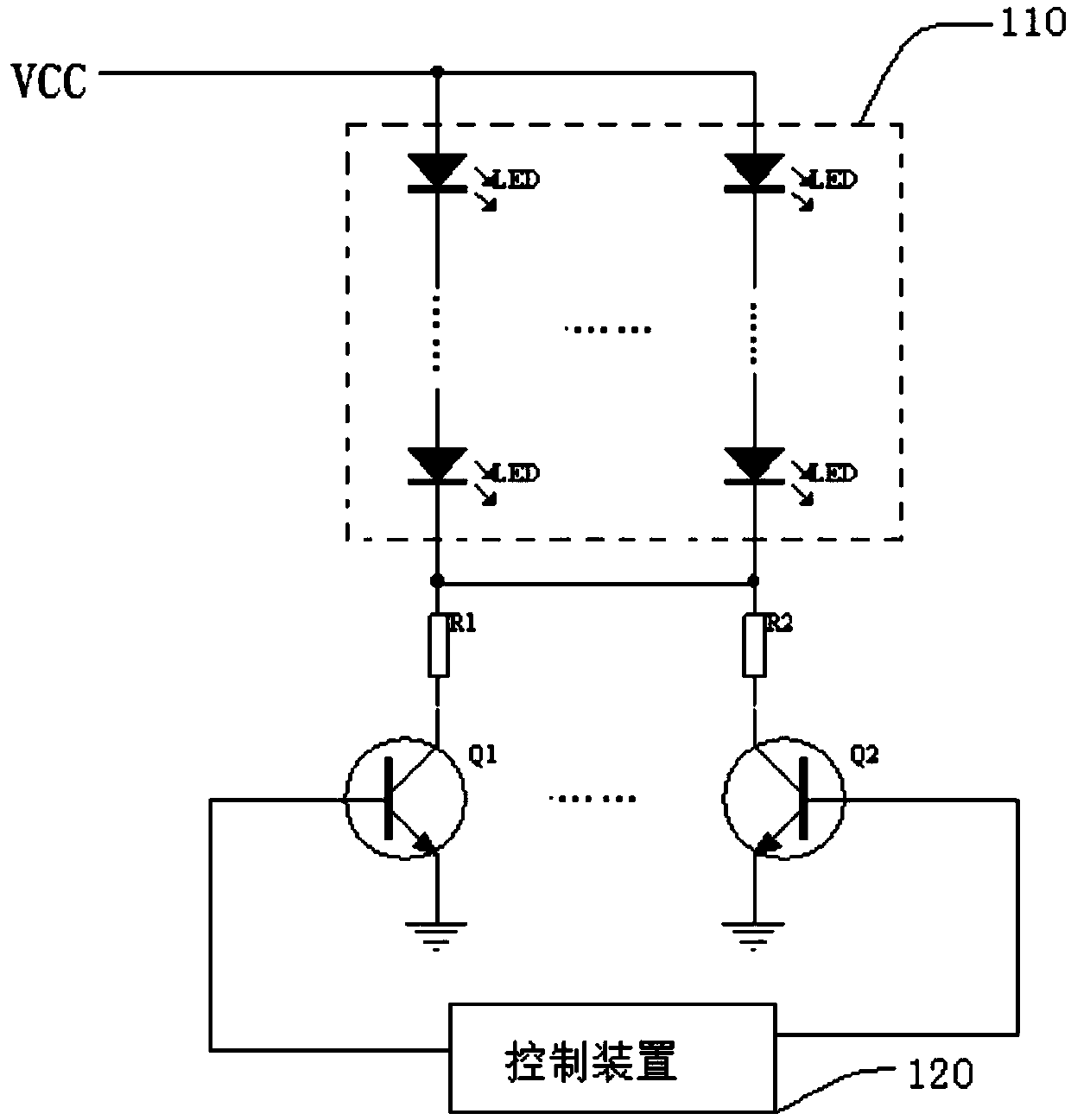

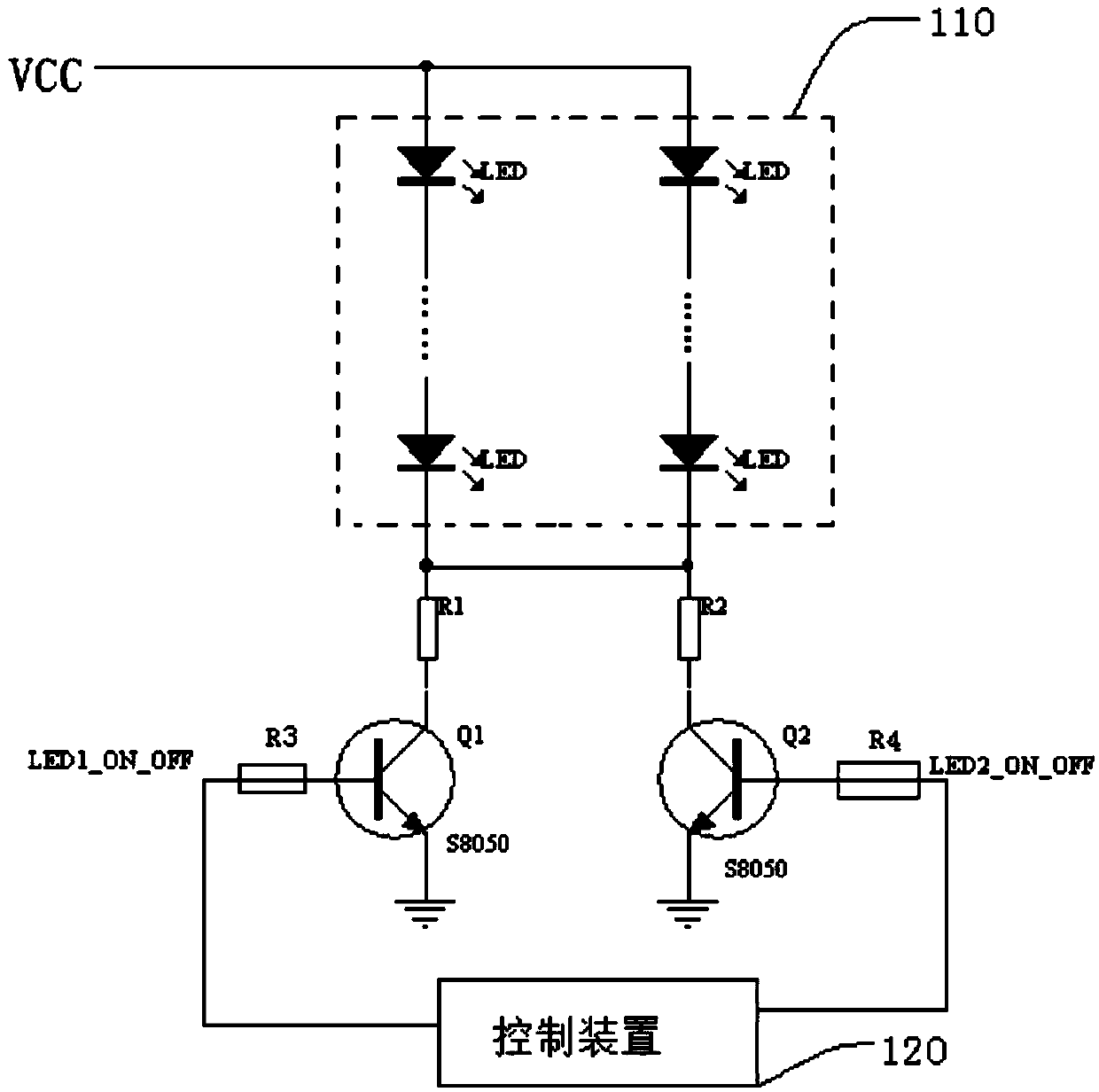

Emergency marker lamp and lamp management system

PendingCN111436176ABrightness adjustableAdjust the resistance valueElectrical apparatusEmbedded systemResistor

The invention relates to an emergency marker lamp and a lamp management system. The emergency marker lamp comprises a light-emitting unit, a control device, a plurality of resistor units and a plurality of switching circuits, the number of the resistor units and the number of the switching circuits are equal, and each resistor unit corresponds to one switching circuit. One end of the light-emitting unit is connected with power supply voltage, the other end of the light-emitting unit is connected with one end of each resistor unit, the other end of each resistor unit is connected with the inputend of the corresponding switching circuit, and the control end of each switching circuit is connected with the control device. The control device outputs a first level signal to the control end of each switching circuit in a first working mode; and the control device outputs a first level signal to the control end of the switching circuit of the first part in a second working mode, outputs a second level signal to the control end of the switching circuit of the second part except the first part, and controls the switching circuit of the first part to be switched on and the switching circuitof the second part to be switched off. According to the invention, the emergency indication effect is good.

Owner:HUNAN HUIBO ELECTRONICS TECH

Static protection circuit, in particular static protection circuit of liquid crystal display panel and static protection circuit array of liquid crystal display panel

ActiveCN102118024BImprove the ability to resist positive and negative high voltage static electricityShow normalyStatic indicating devicesSemiconductor/solid-state device detailsLiquid-crystal displayEngineering

The invention relates to a static protection circuit, in particular to a static protection circuit of a liquid crystal display panel and a static protection circuit array of the liquid crystal display panel. The static protection circuit comprises a discharging unit and a delay circuit, wherein the output end of the delay circuit is connected with the input end of the discharging unit; and by means of the delay circuit, a static pulse is delayed and the pulse width of the static pulse is increased to ensure that the pulse width of the static pulse is greater than the response time of the discharging unit so that static electricity is released through the discharging unit. Through the static protection circuit, the static pulse is prevented from entering a protected circuit.

Owner:BEIHAI HKC OPTOELECTRONICS TECH CO LTD

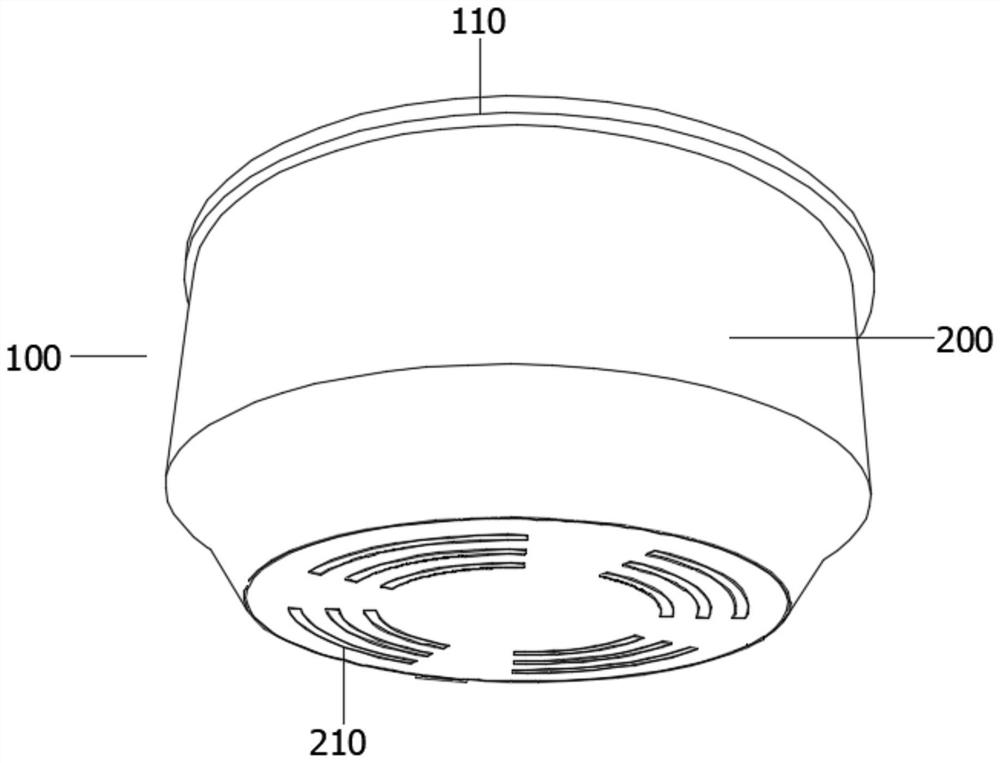

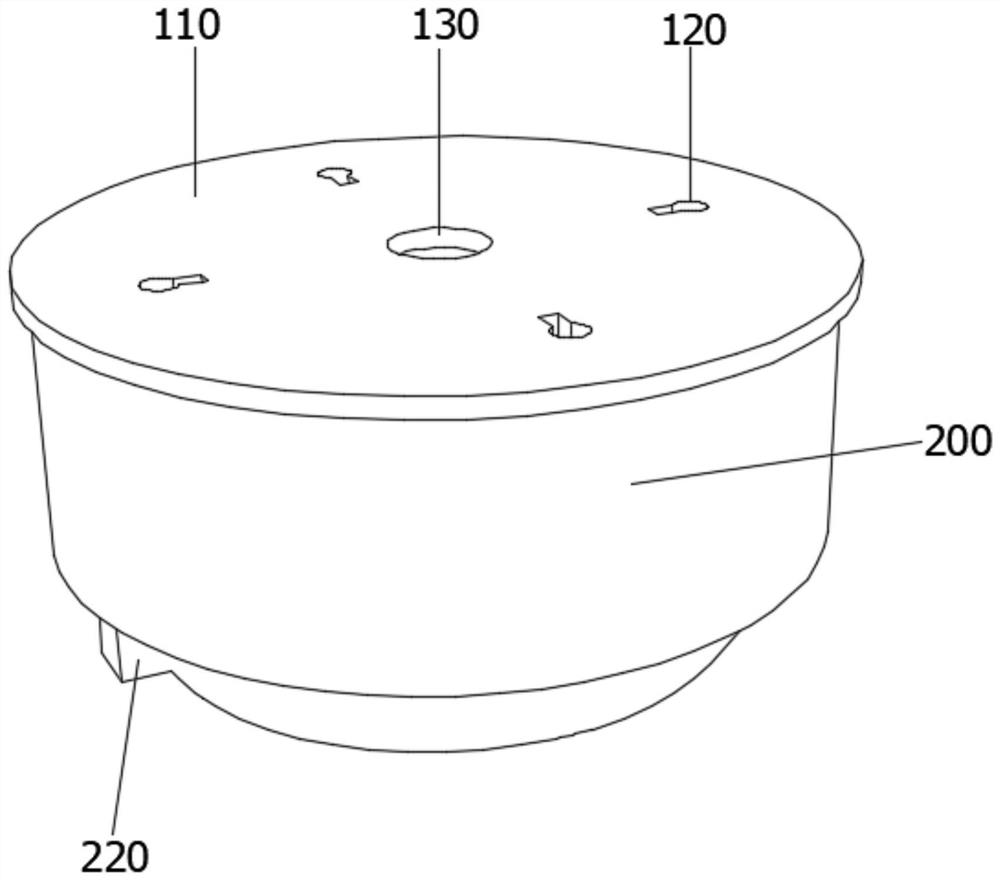

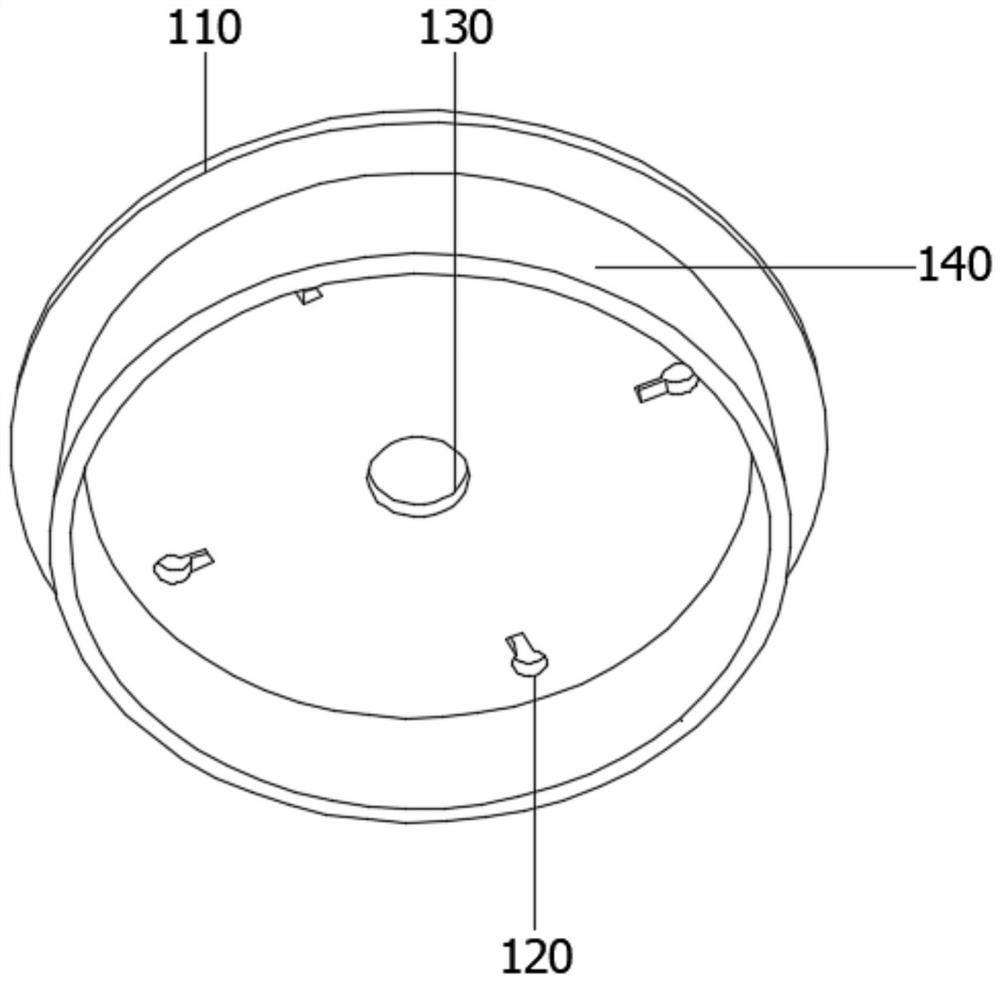

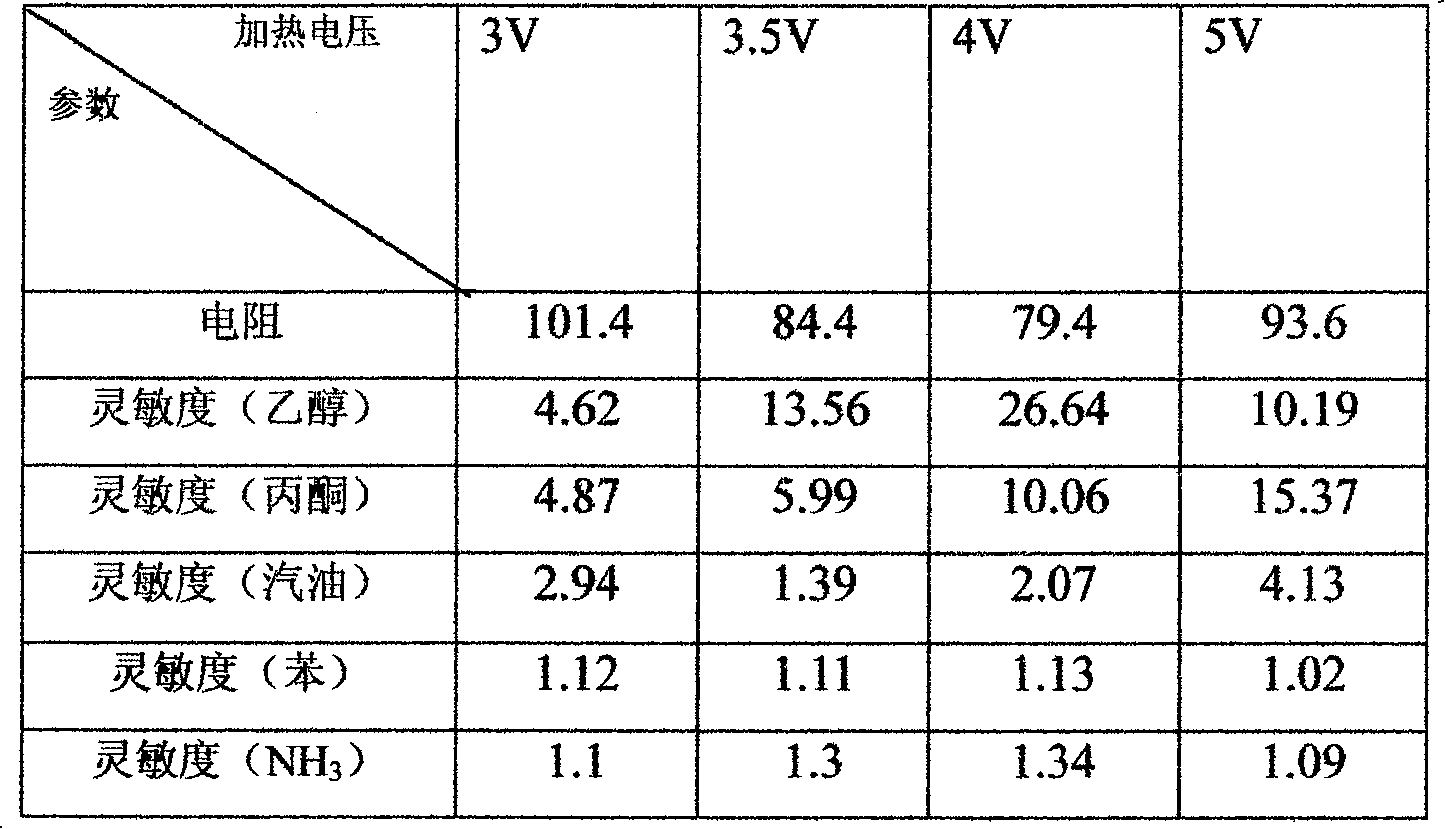

A Modular Integrated Smart Electrical IoT Sensor

ActiveCN113760008BImprove the heating effectIncrease temperatureTemperatue controlCombustible gasHemt circuits

Owner:深圳市骏嘉科技发展有限公司

A mosfet chip manufacturing method for improving gate characteristics

ActiveCN113643982BAchieve protectionImprove discharge efficiencyTransistorSemiconductor/solid-state device manufacturingMOSFETEngineering

The invention discloses a MOSFET chip manufacturing method for improving gate characteristics, including forming lightly doped polysilicon on the isolation oxide layer, and removing the lightly doped polysilicon in the groove area, so as to obtain the first light Doped polysilicon and the second lightly doped polysilicon, in the source region of the epitaxial layer, heavily doped a part of the first lightly doped polysilicon to obtain the second heavily doped polysilicon, and formed a dielectric layer upwards, the second heavily doped polysilicon The type of doped polysilicon is opposite to that of the first lightly doped polysilicon, and the first lightly doped polysilicon and the second heavily doped polysilicon form a diode, and the two ends of the second lightly doped polysilicon form a resistor, the diode and the The resistors are connected in parallel and connected in series with the grid. The polysilicon resistor and polysilicon diode are integrated inside the chip, which can effectively limit the current flowing through the gate, so as to realize the protection of the gate.

Owner:深圳市芯电元科技有限公司

MOSFET chip manufacturing method for improving grid characteristics

ActiveCN113643982AAchieve protectionImprove discharge efficiencyTransistorSemiconductor/solid-state device manufacturingMOSFETEngineering

The invention discloses an MOSFET chip manufacturing method for improving grid characteristics. The method comprises the following steps: forming lightly-doped polycrystalline silicon on an isolation oxide layer, removing the lightly-doped polycrystalline silicon in a groove region so as to obtain first lightly-doped polycrystalline silicon and second lightly-doped polycrystalline silicon on the peripheral side of the groove region, forming a source region on an epitaxial layer, carrying out heavy doping on a partial region of the first lightly-doped polycrystalline silicon to obtain second heavily-doped polycrystalline silicon, upwards forming a dielectric layer, enabling the type of the second heavily-doped polycrystalline silicon to be opposite to that of the first lightly-doped polycrystalline silicon, forming a diode by the first lightly-doped polycrystalline silicon and the second heavily-doped polycrystalline silicon, forming a resistor is formed by two ends of the second lightly-doped polycrystalline silicon, connecting the diode in parallel with the resistor, and connecting in series with the grid electrode. The polycrystalline silicon resistor and the polycrystalline silicon diode are integrated in the chip, so that the current flowing through the grid electrode can be effectively limited, and the grid electrode can be protected.

Owner:深圳市芯电元科技有限公司

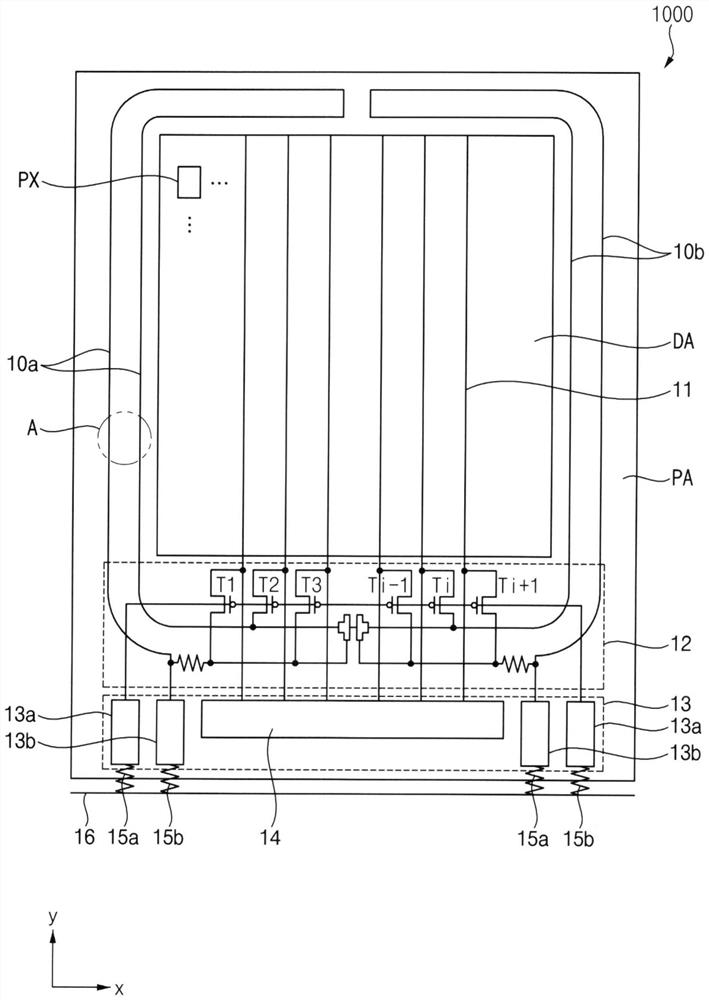

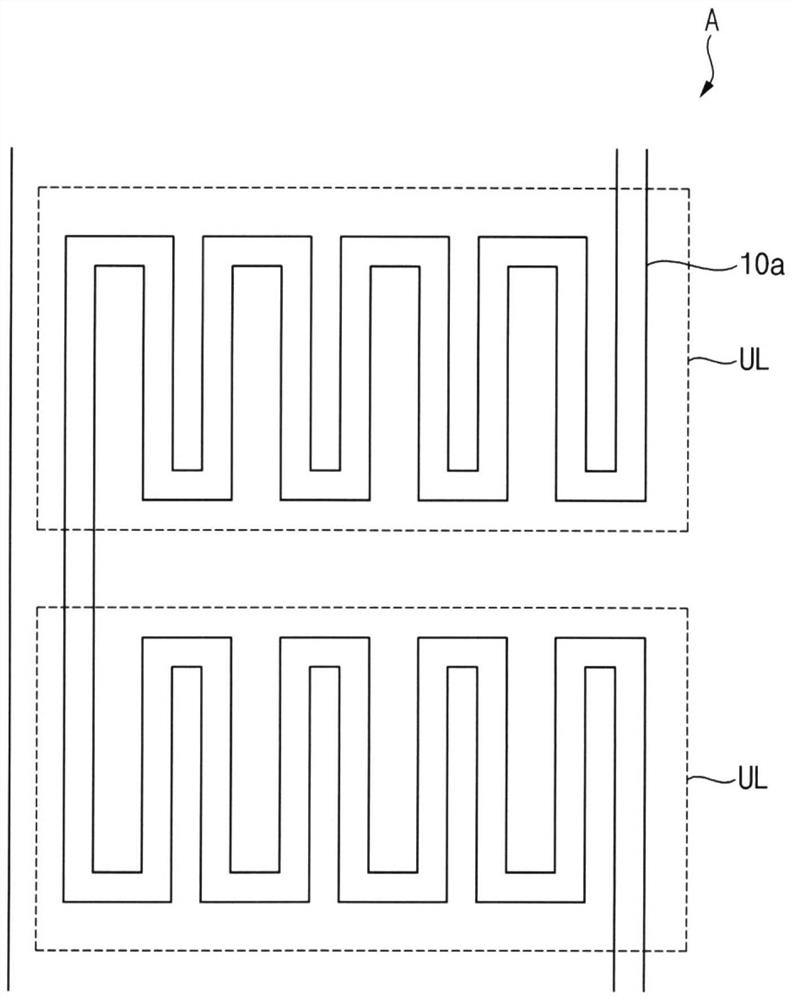

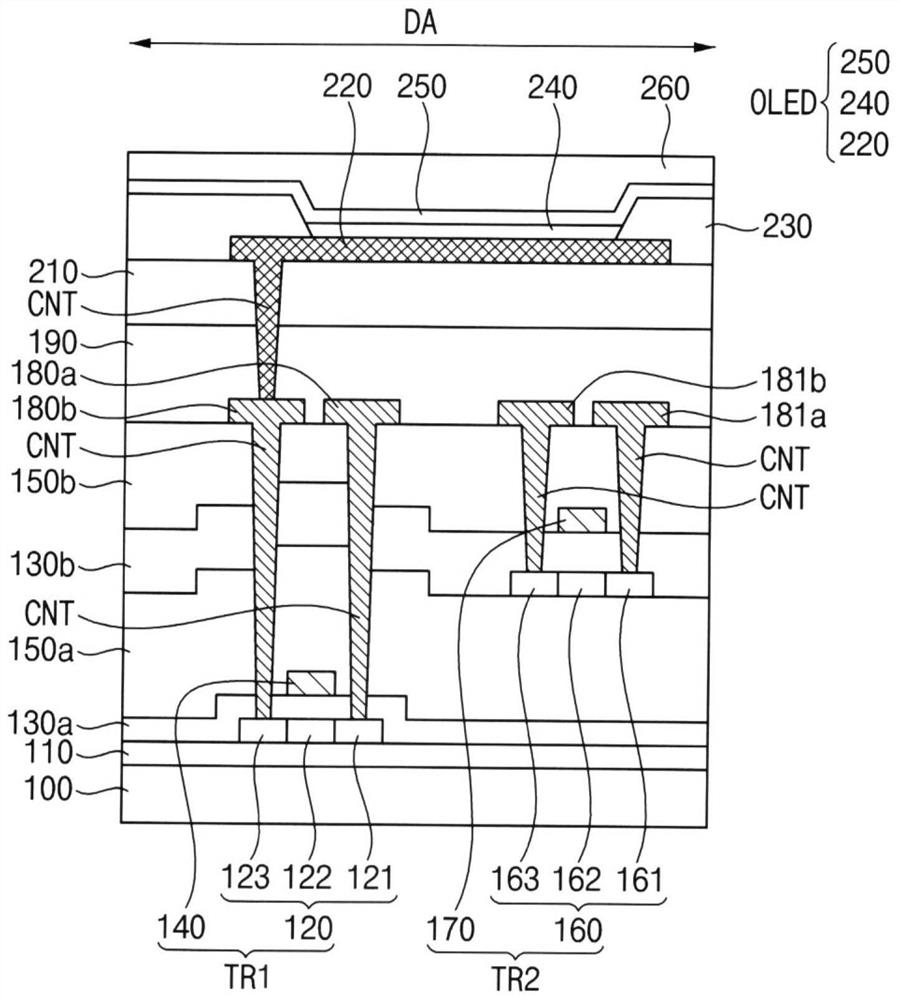

Display device and manufacturing method thereof

PendingCN114520252AHas resistance valueAdjust the resistance valueStatic indicating devicesSolid-state devicesDisplay deviceMaterials science

Disclosed are a display device and a method of manufacturing the same. The display device may include a driving transistor disposed in a display area, a test transistor disposed in a peripheral area adjacent to the display area, and a resistance line disposed in the peripheral area, electrically connected to the test transistor, and including a metal oxide.

Owner:SAMSUNG DISPLAY CO LTD

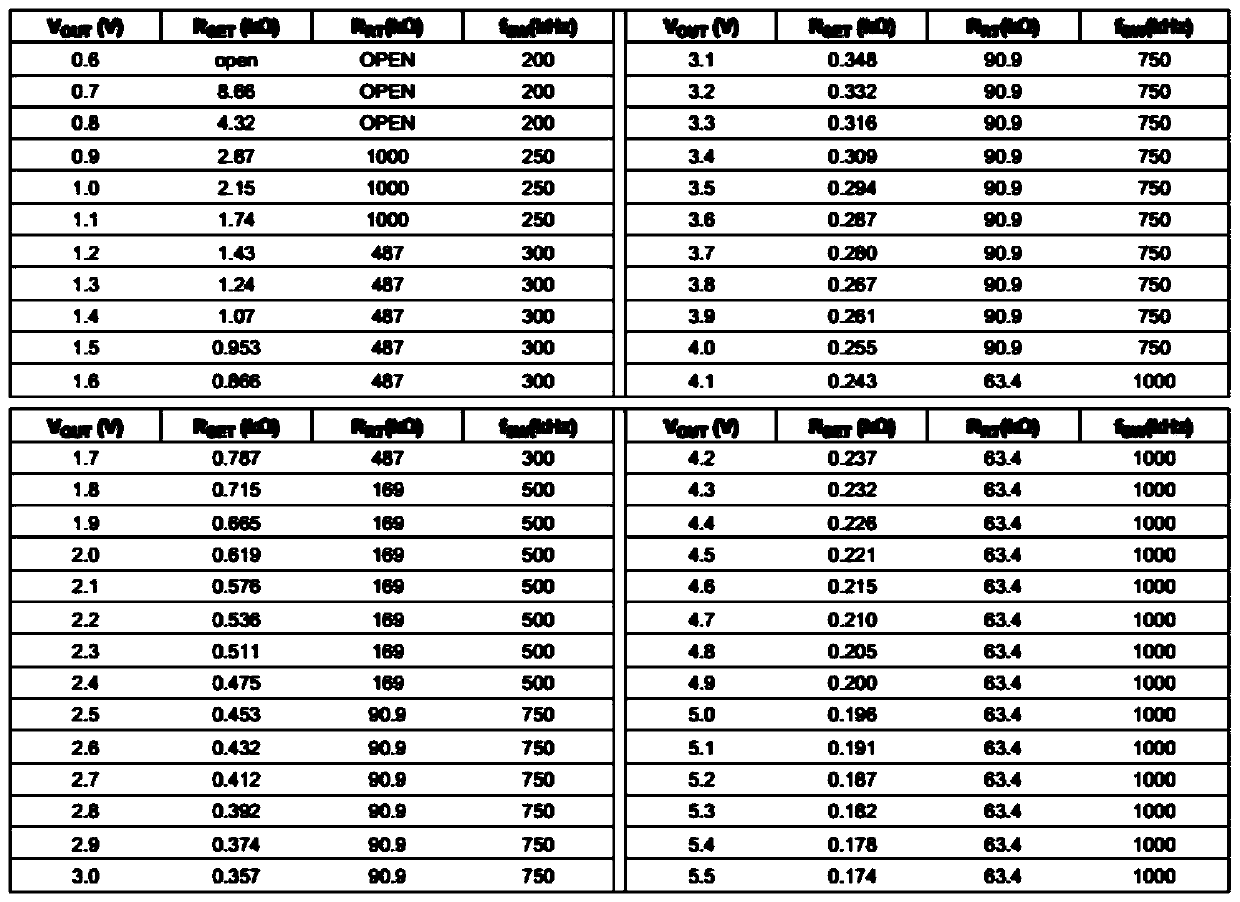

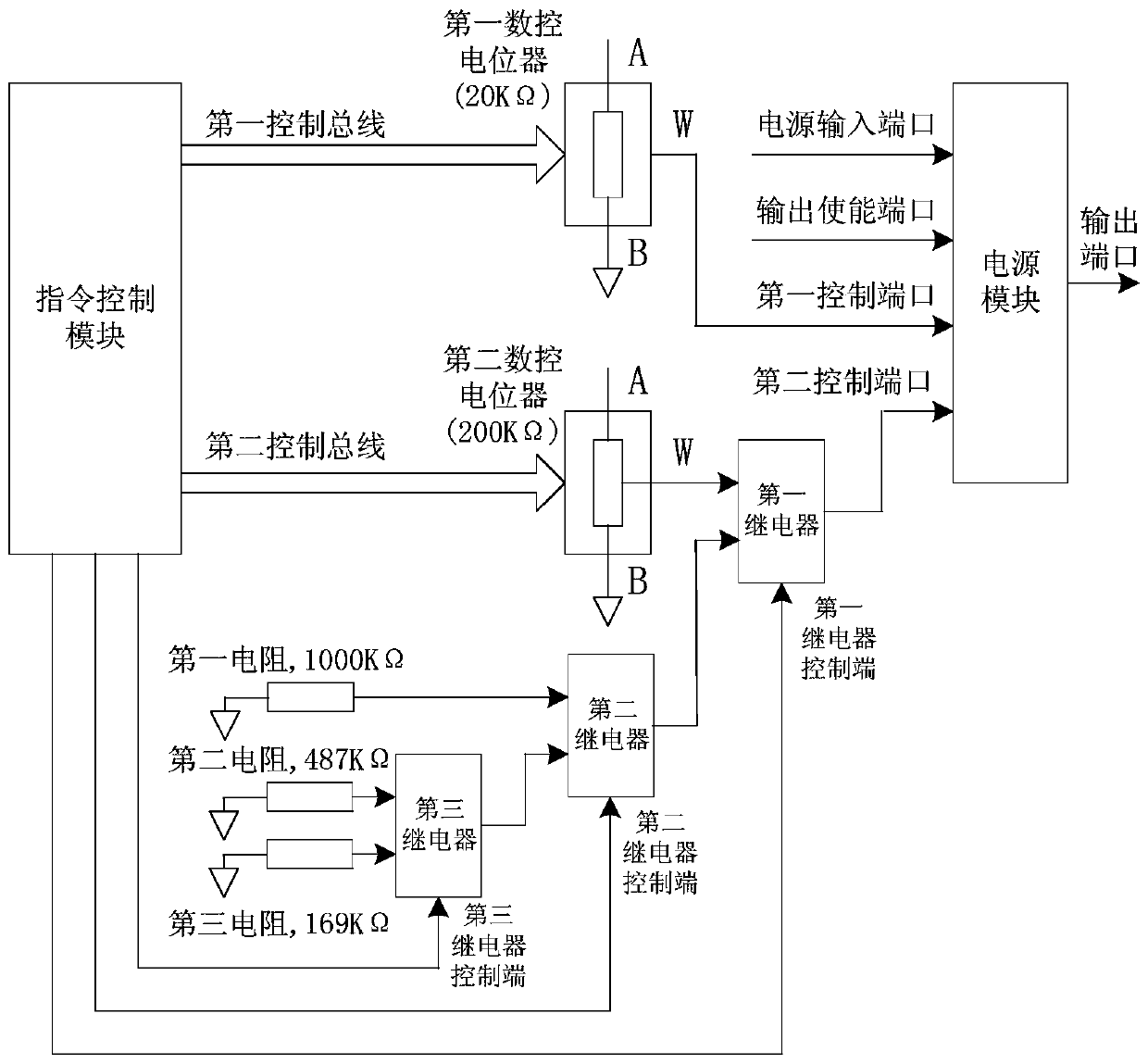

Board-mode program-controlled voltage bias test circuit of large-scale digital integrated circuit

PendingCN110907809ARealize automatic controlImprove portabilityDigital circuit testingMarginal circuit testingNumerical controlAutomatic control

The invention relates to a board-mode program-controlled voltage bias test circuit of a large-scale digital integrated circuit. The program-controlled voltage bias test circuit comprises a power supply module, a first numerical control potentiometer, a second numerical control potentiometer, a first relay, a second relay, a third relay, a first resistor, a second resistor, a third resistor and aninstruction control module, wherein a first control end of the power supply module is connected with an adjustable resistor end of the first numerical control potentiometer, a second control end of the power supply module is connected with an output end of the first relay, a first input end of the first relay is connected with an adjustable resistor end of the second numerical control potentiometer, and a first input end of the first relay is connected with an output end of the second relay. According to the invention, through cooperation of the power supply module, the numerical control potentiometer, the relay, the resistor and the instruction control module, automatic control of bias voltage in a large-scale digital circuit board mode bias test is realized, a large-size special instrument does not need to be carried, and thus the portability is better.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

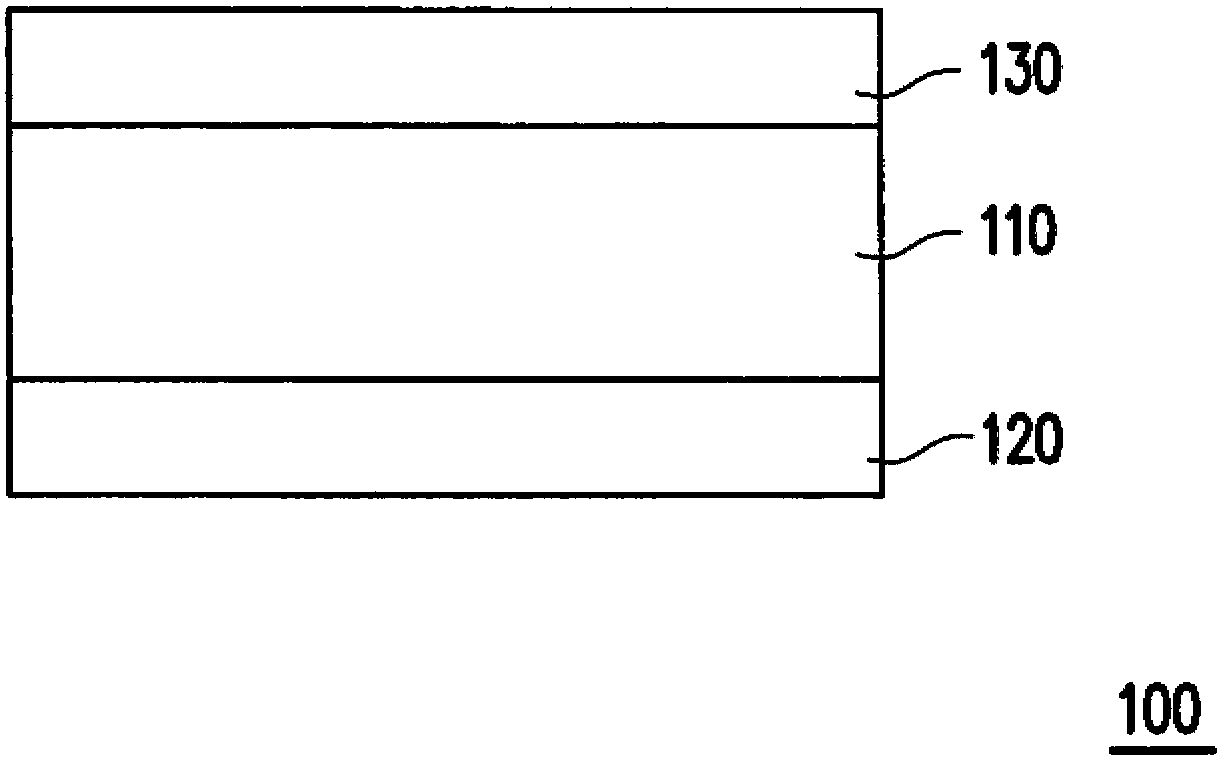

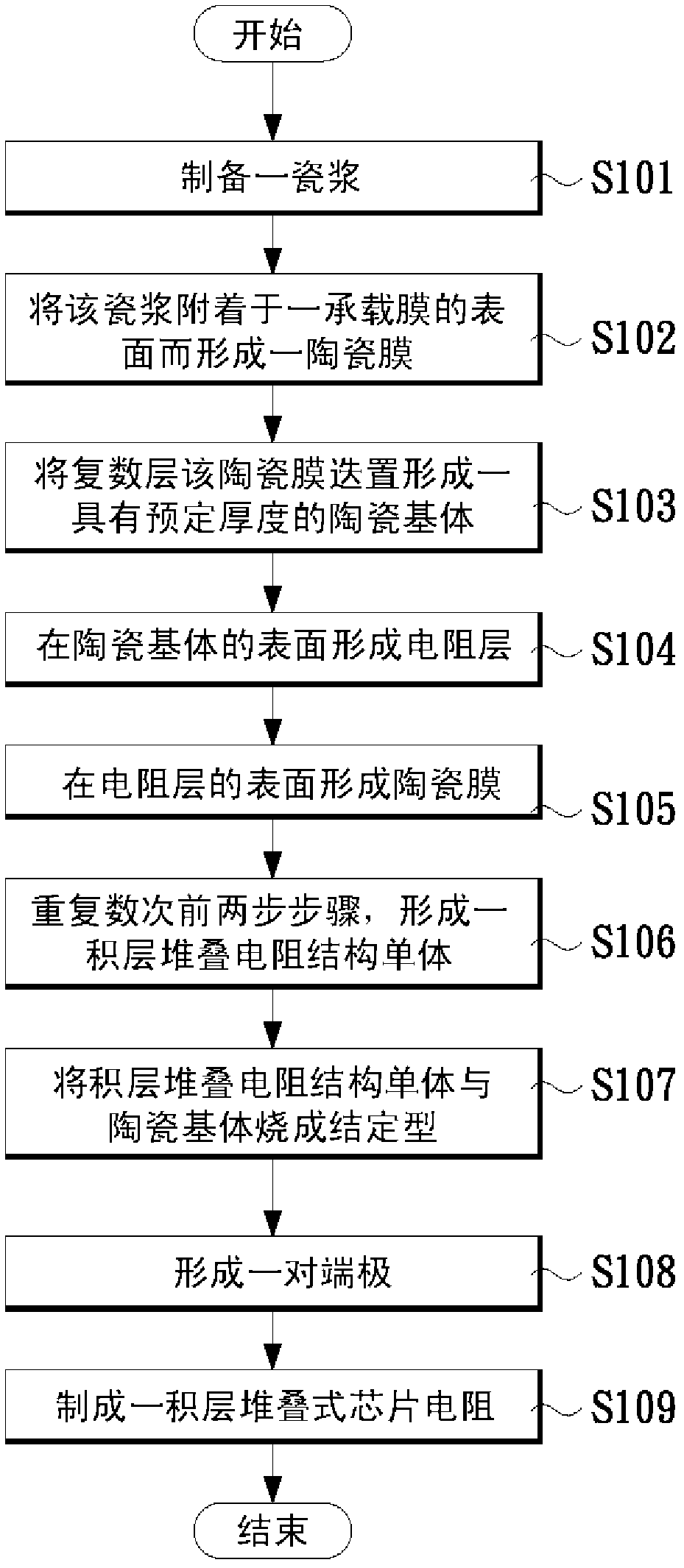

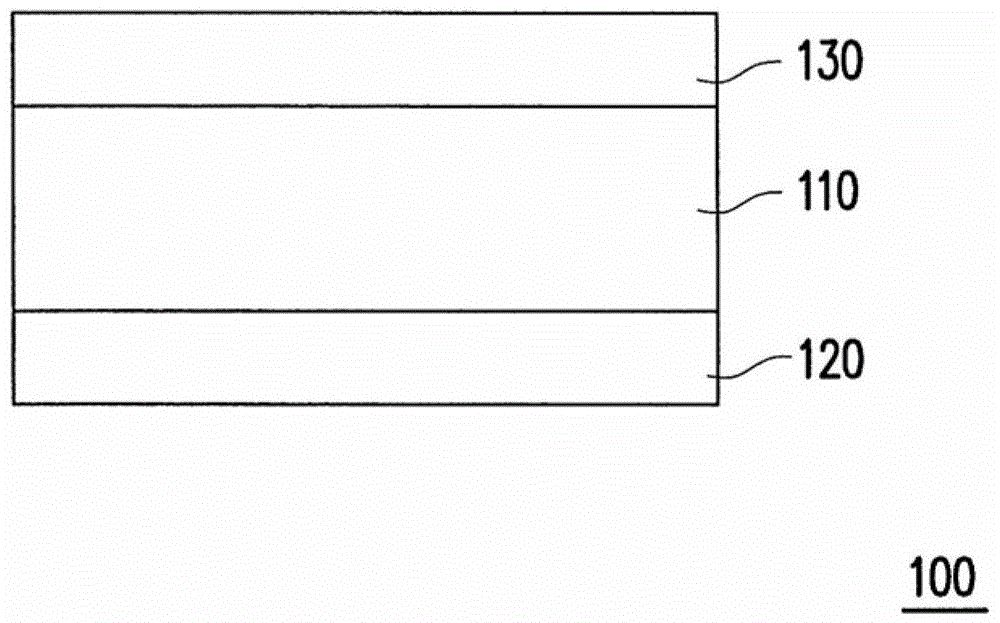

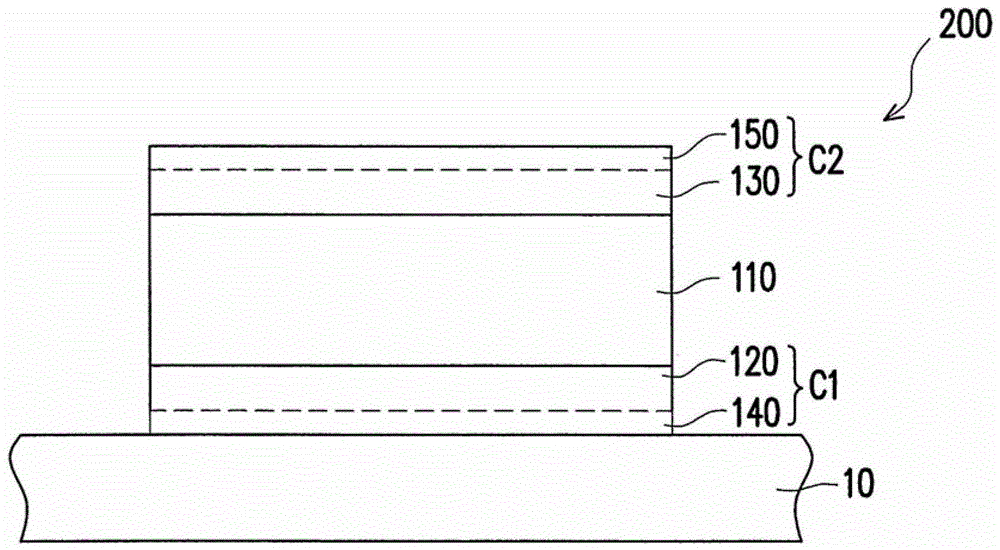

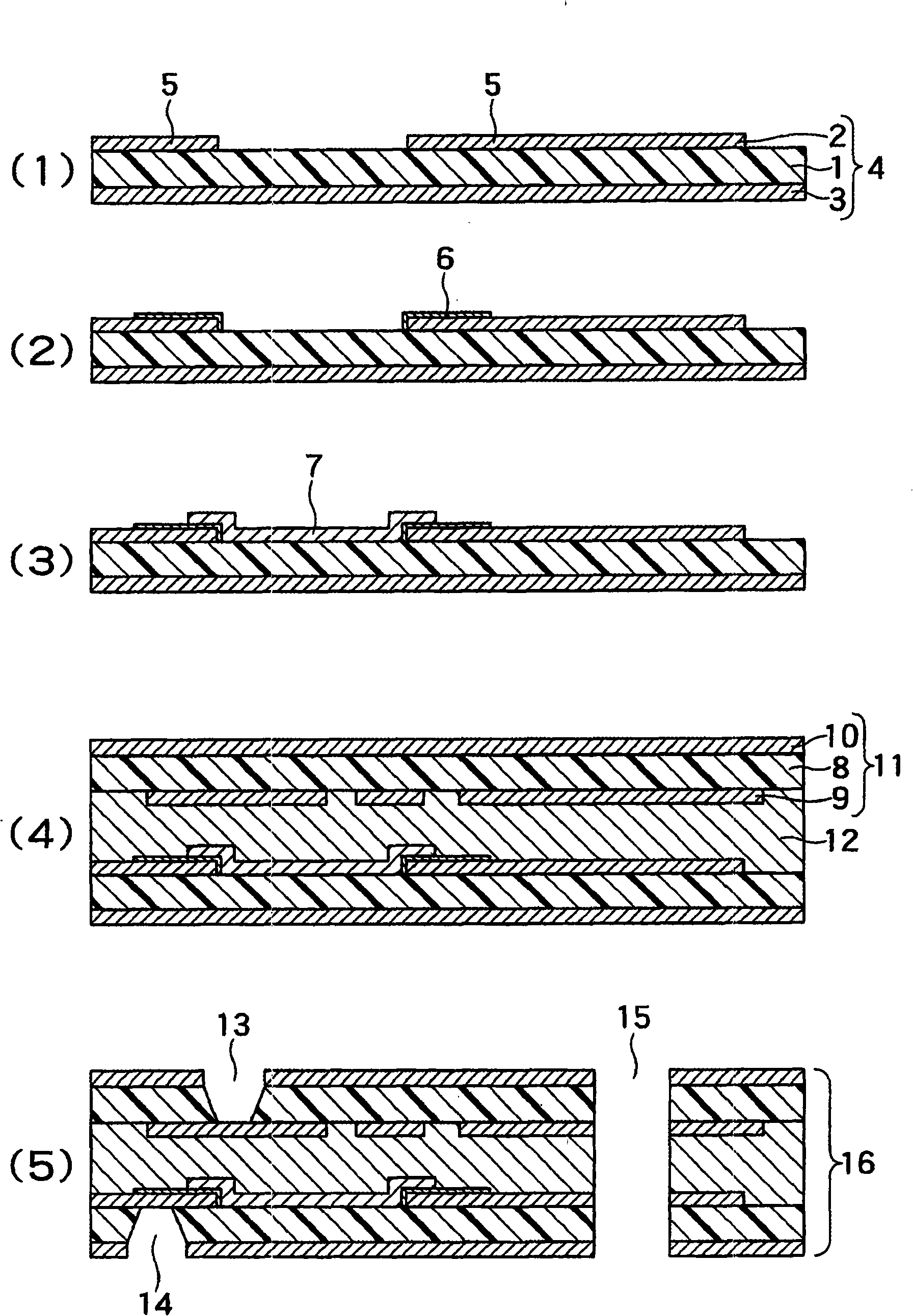

Multi-layer co-sintered lamination stackable chip resistor and manufacturing method thereof

InactiveCN103123835AExempt from stacking proceduresShorten the timeResistor trimmingNon-adjustable resistorsAdhesiveSlurry

The invention relates to a multi-layer co-sintered lamination stackable chip resistor and a manufacturing method of the multi-layer co-sintered lamination stackable chip resistor. The multi-layer co-sintered lamination stackable chip resistor comprises a ceramic substrate, a lamination stackable resistor structure body, a first terminal pole and a second terminal pole, wherein the ceramic substrate has a predetermined thickness and is formed by superposing a plurality of layers of ceramic membranes and attaching ceramic slurry containing a solvent, an adhesive and a dispersant to the surface of a bearing membrane, the lamination stackable resistor structure body is superposed on the ceramic substrate and comprises a plurality of layers of bearing membranes and a plurality of layers of resistive layers which are formed on the surfaces of the bearing membranes one by one, the resistive layers are parallel to one another and superposed in the vertical direction to separate a predetermined spacing, and the lamination stackable resistor structure body and the ceramic substrate are superposed and then sintered in a kiln at a predetermined sintering temperature and sintering time to finalize the design of the lamination stackable resistor structure body and the ceramic substrate by sintering.

Owner:PROSPERITY DIELECTRICS

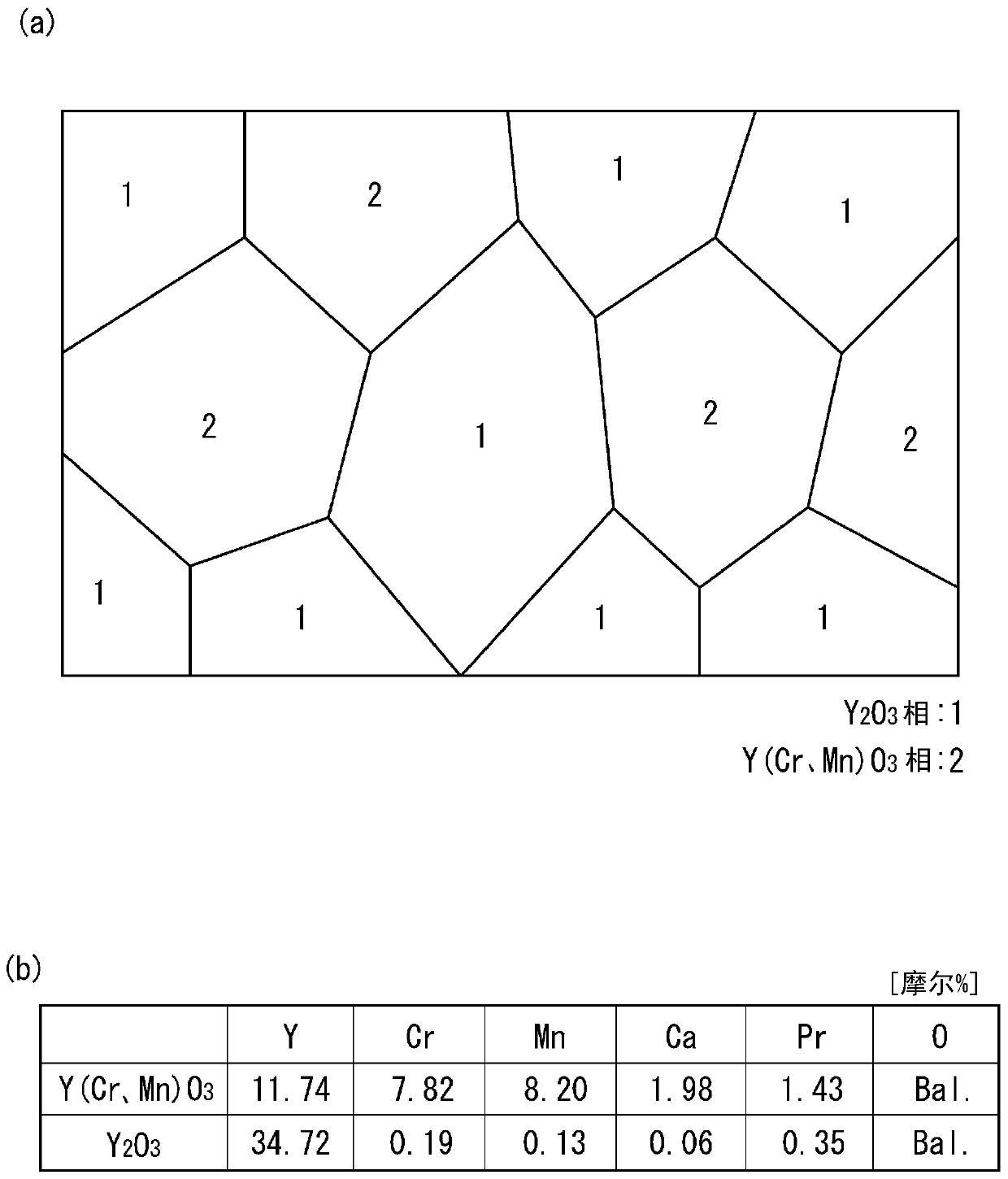

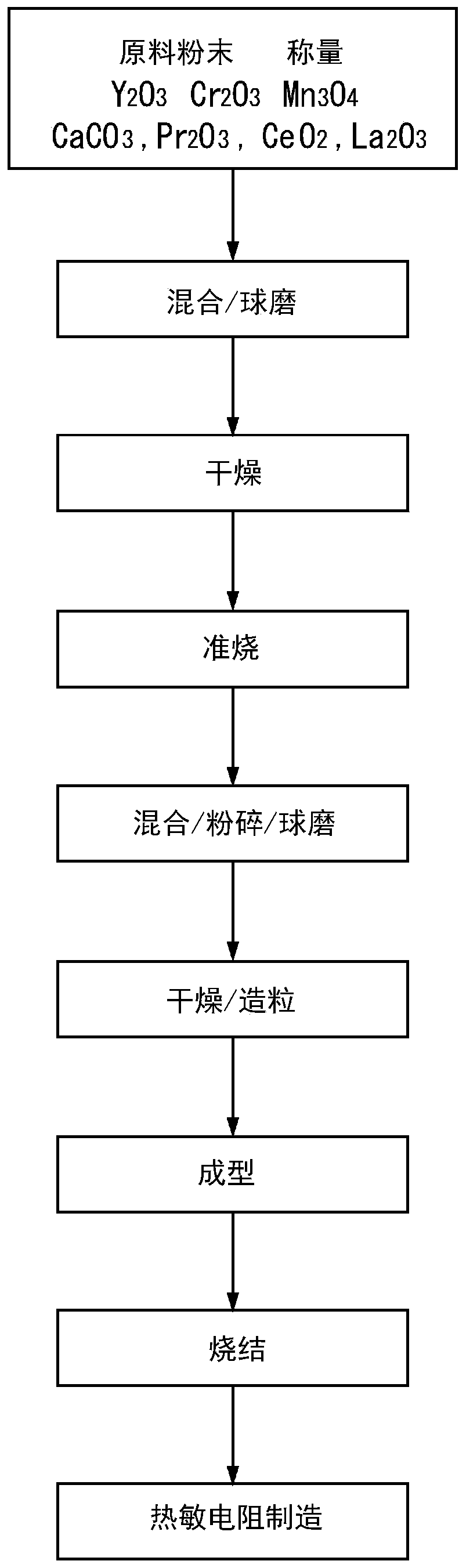

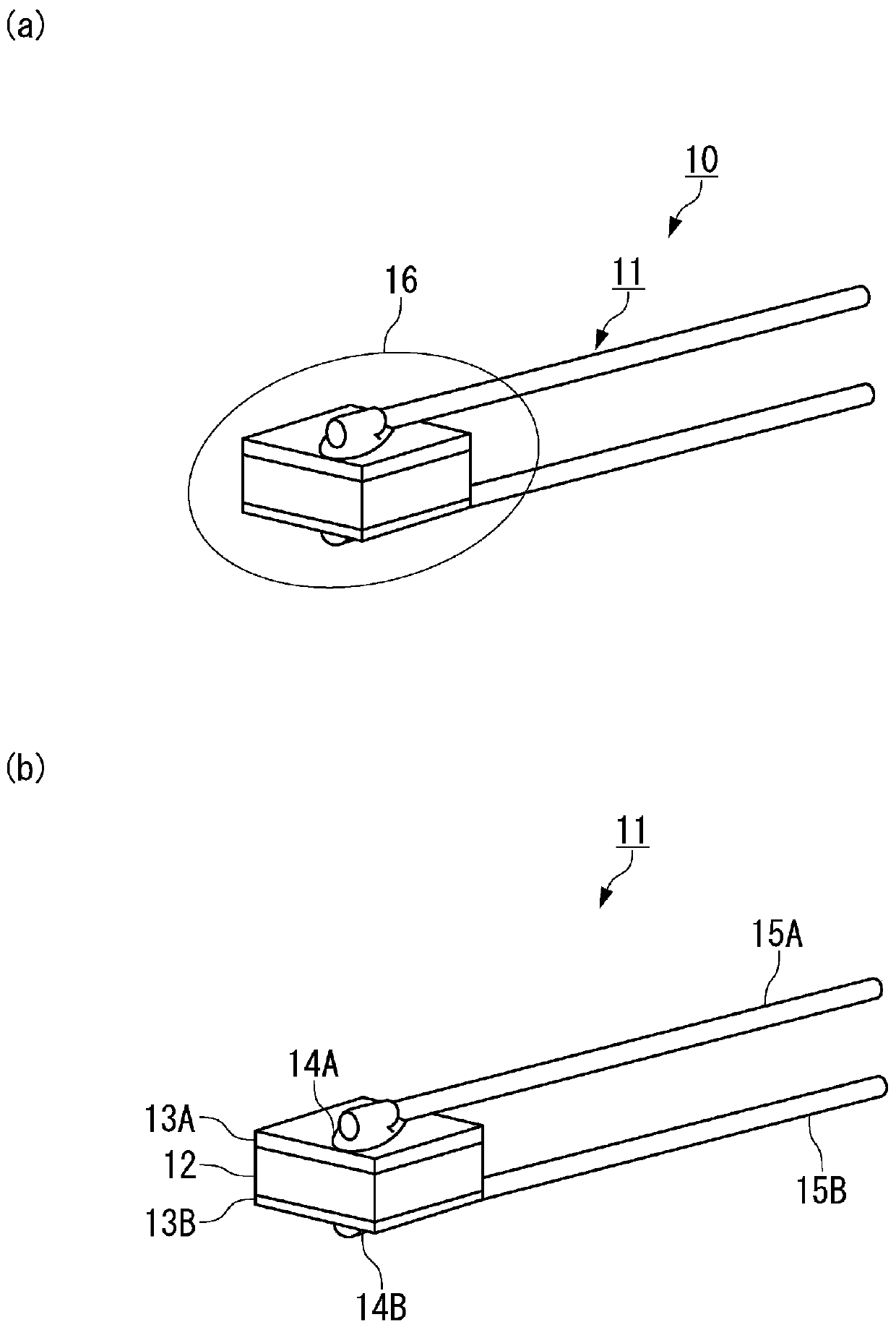

Thermistor sintered body and temperature sensor element

InactiveCN111386581AInhibition effectAdjust the resistance valueThermometers using electric/magnetic elementsUsing electrical meansChemical compositionThermistor

To provide a thermistor sintered body and a temperature sensor element such that a resistance value can be adjusted in a wider range while minimizing the effect on a B constant. [Solution] This thermistor sintered body comprises a sintered body which includes a Y2O3 phase as a main phase and a Y(Cr / Mn)O3 phase as a subphase. The chemical composition of Cr, Mn, Ca, Pr, and Y excluding oxygen comprises one or both of Cr: 20 mol% or less and Mn: 20 mol% or less, Ca: 1 to 15 mol%, and Pr: 0.5 to 30 mol%, the balance being unavoidable impurities and Y. In the present invention, preferably, the subphase is a Y(Cr,Mn)O3 phase or a YCrO3 phase, and Pr is soluble in the Y(Cr,Mn)O3 phase or the YCrO3 phase.

Owner:SHIBAURA ELECTRONICS CO LTD

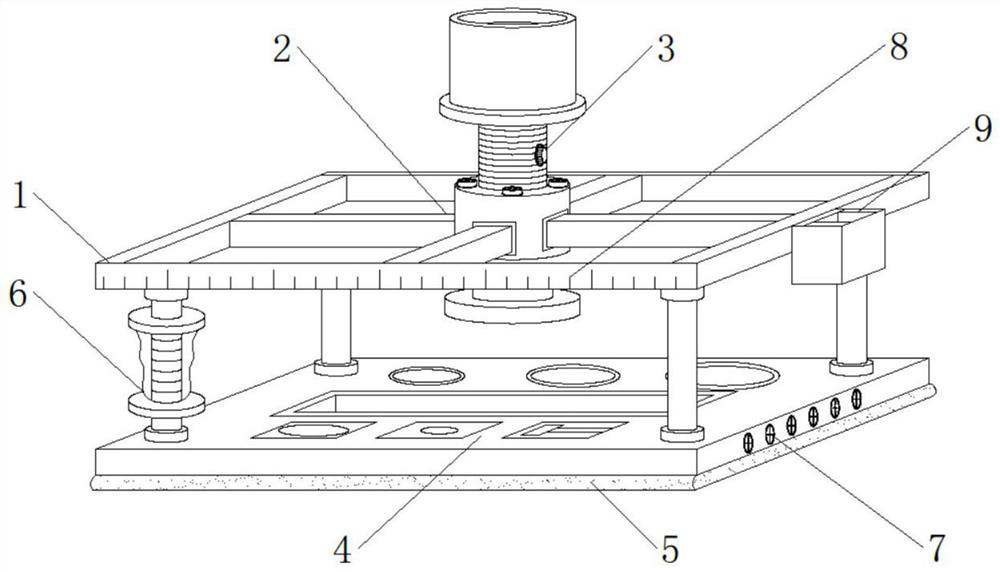

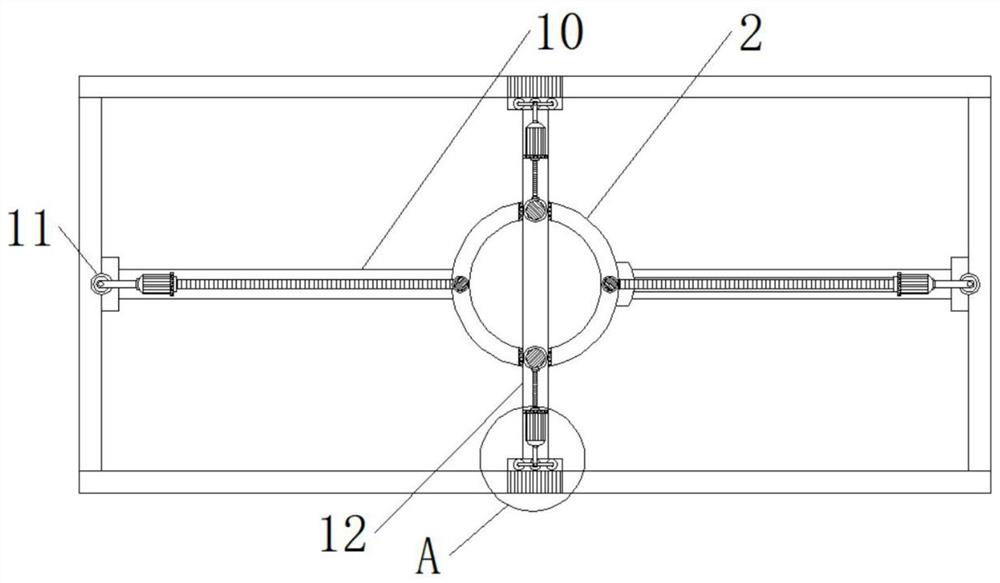

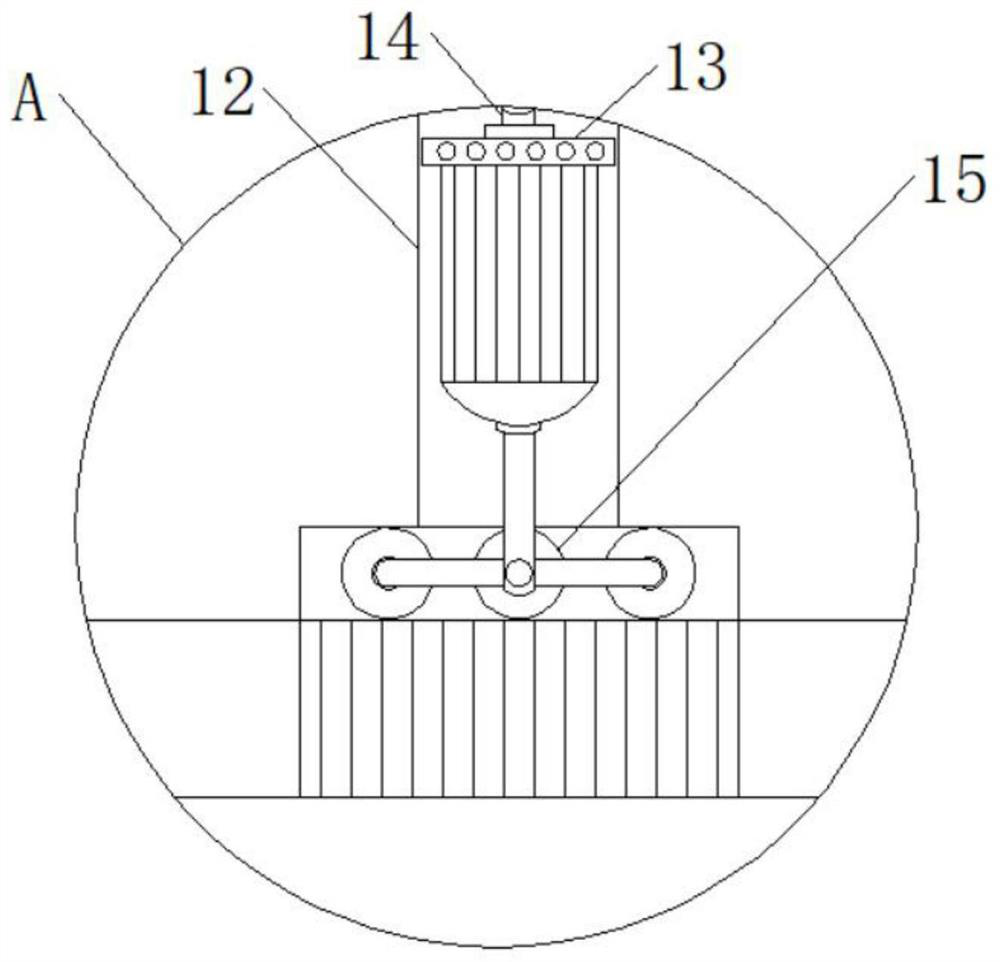

Casting combined die

InactiveCN112371916AReflect the convenience of activity controlAdjust the resistance valueCasting safety devicesFoundry mouldsEngineeringMovement control

The invention discloses a casting combined die. The casting combined die comprises a die body, a die movement control mechanism and a pouring adjusting mechanism. The inner side of the top of the diebody is movably connected with the die movement control mechanism, the top of the die movement control mechanism is fixedly connected with the pouring adjusting mechanism, the bottom of the die body is fixedly connected with a multi-type combined mechanism, and the bottom end of the multi-type combined mechanism is fixedly connected with a die buffer base pad. One side of the multi-type combined mechanism is fixedly connected with a heat dissipation side turbine, the heat dissipation side turbine well reflects the efficient heat dissipation performance of the device, movement control scales well reflect the control accuracy of the device, and the multi-type combined mechanism well reflects the multifunctional integration of the mechanism. The pouring adjusting mechanism well achieves the effect of adjusting the pouring speed, the die movement control mechanism well reflects the movement control convenience of the device, and the device is suitable for being used in the technical fieldof mechanical casting and has wide development prospects in the future.

Owner:安徽省巢湖市宏顺机械铸造有限公司

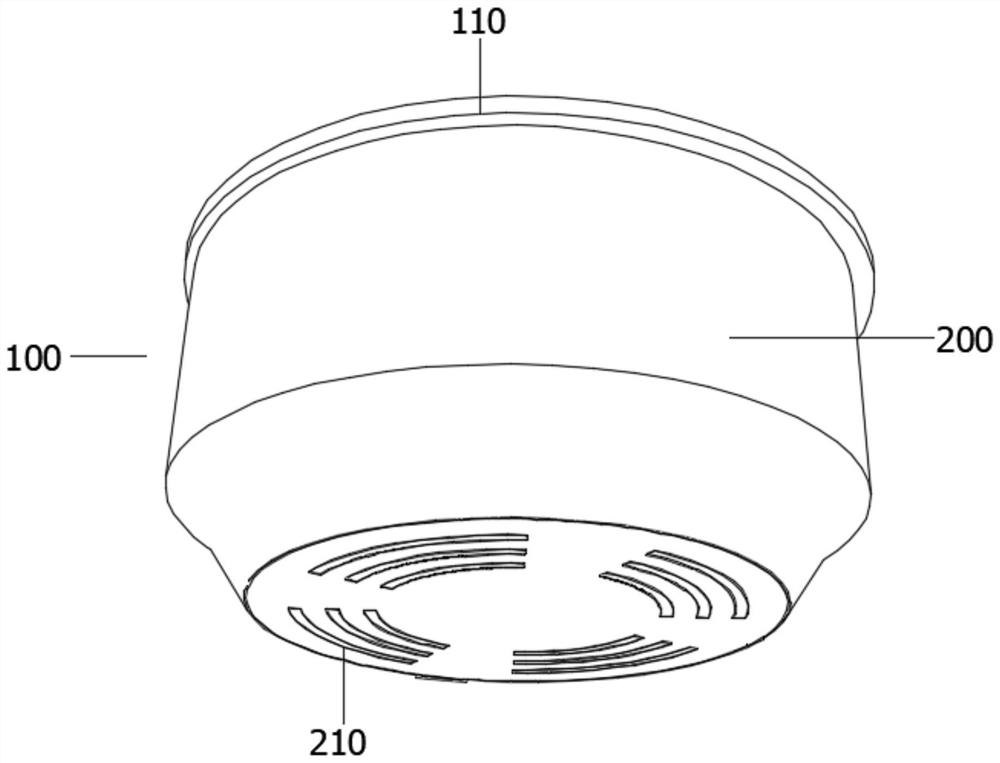

Modularized integrated intelligent electrical Internet of Things sensor

ActiveCN113760008AImprove the heating effectIncrease temperatureTemperatue controlCombustible gasBattery (electricity)

The invention discloses a modular integrated intelligent electrical Internet of Things sensor, and relates to the technical field of Internet of Things sensors; wherein the technical scheme is that the modular integrated intelligent electrical Internet of Things sensor comprises a shell, a working bin, a combustible gas detection device and an intelligent household Internet of Things control assembly, wherein the combustible gas detection device comprises an inner support, a semiconductor, a binding post, a negative electrode wire, a positive electrode wire, a first storage battery, a wire and a heating wire, and the intelligent household internet-of-things control assembly comprises a circuit board and a bath heater temperature control assembly. According to the invention, the intelligent household Internet of Things control assembly is arranged, the resistance value is changed through a semiconductor, and a relay is in signal connection with a household circuit leakage protector or an electromagnetic valve of a gas pipeline; therefore, the relay is used for controlling the disconnection of a household circuit and the closing of gas, and the safety of household electricity utilization and gas utilization is improved.

Owner:深圳市骏嘉科技发展有限公司

Thermoelectric thin film structure

ActiveCN103872236BAdjust the resistance valueImprove thermal conductivityThermoelectric device junction materialsCarbon layerThin membrane

The invention discloses a thermoelectric film structure, which includes a thermoelectric substrate and a pair of first diamond-like carbon layers. The first diamond-like carbon layer is arranged on two opposite surfaces of the thermoelectric substrate and has conductivity.

Owner:IND TECH RES INST

Charging and discharging circuit for electrical system

ActiveCN102412608BAdjust the resistance valueTimely adjustment of resistance valueField or armature current controlElectric powerControl signalEngineering

A charging and discharging circuit for an electrical system, comprising: an energy-storing unit (101), an electromotor driver (102), a battery (103), and further comprising: a logic control unit (104) connected to the energy-storing unit (101) and the electromotor driver (102) via a data bus; a switch control unit (105) connected to the logic control unit (104) and the battery (103) for receiving a logic control signal sent by the logic control unit (104) and controlling the switching on and off of individual touch points in a voltage dividing unit (106); the voltage dividing unit (106) being connected to the energy-storing unit (101) and the electromotor driver (102) for receiving a switch control signal sent by the switch control unit (105) to switch off or on the individual touch points so as to adjust the resistance values of the voltage dividing resistance. By using the charging and discharging circuit for an electrical system, the resistance value of the voltage dividing resistance can be adjusted at a proper time to improve the efficiency of charging and discharging, and a high flexibility is achieved.

Owner:ZOOMLION HEAVY IND CO LTD

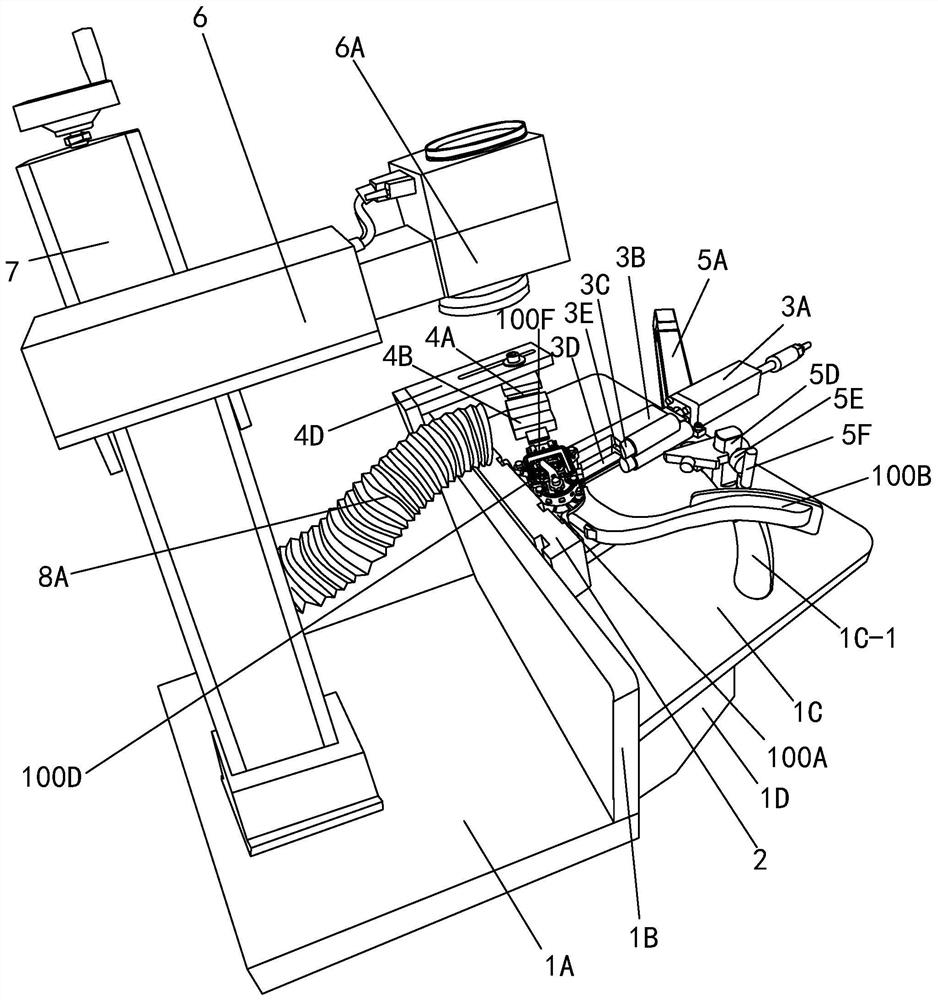

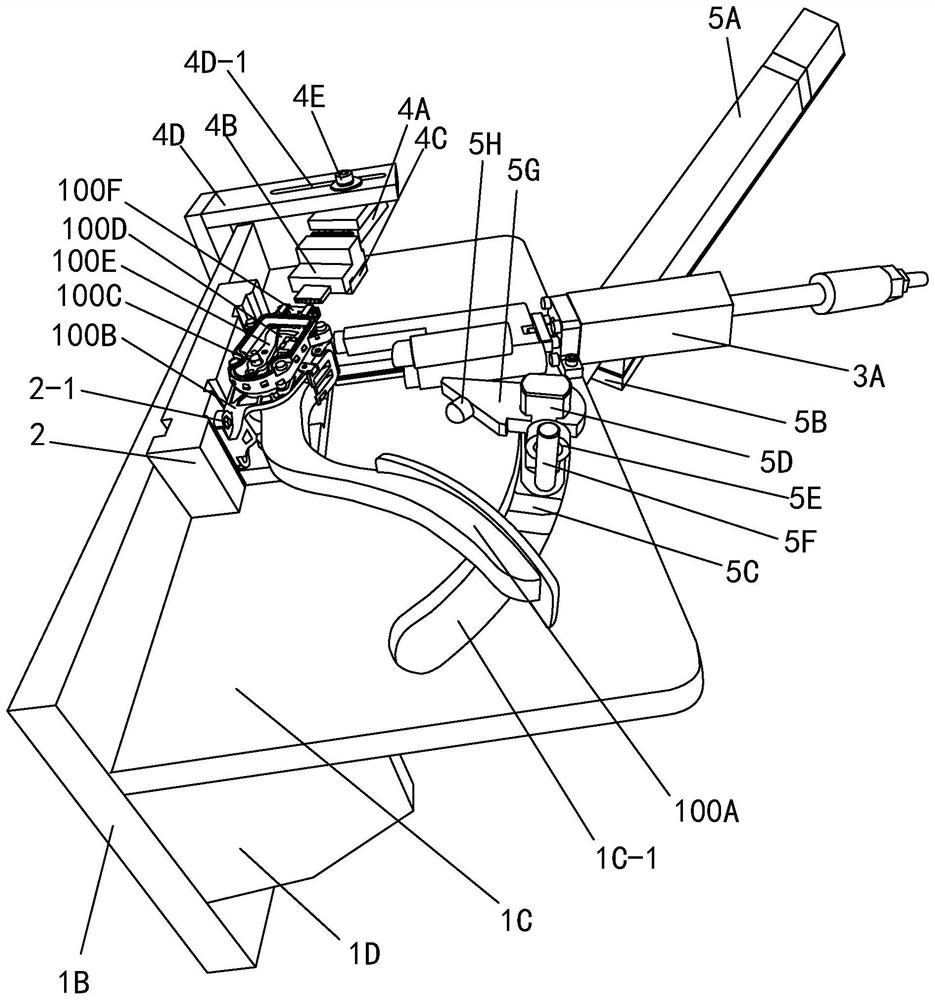

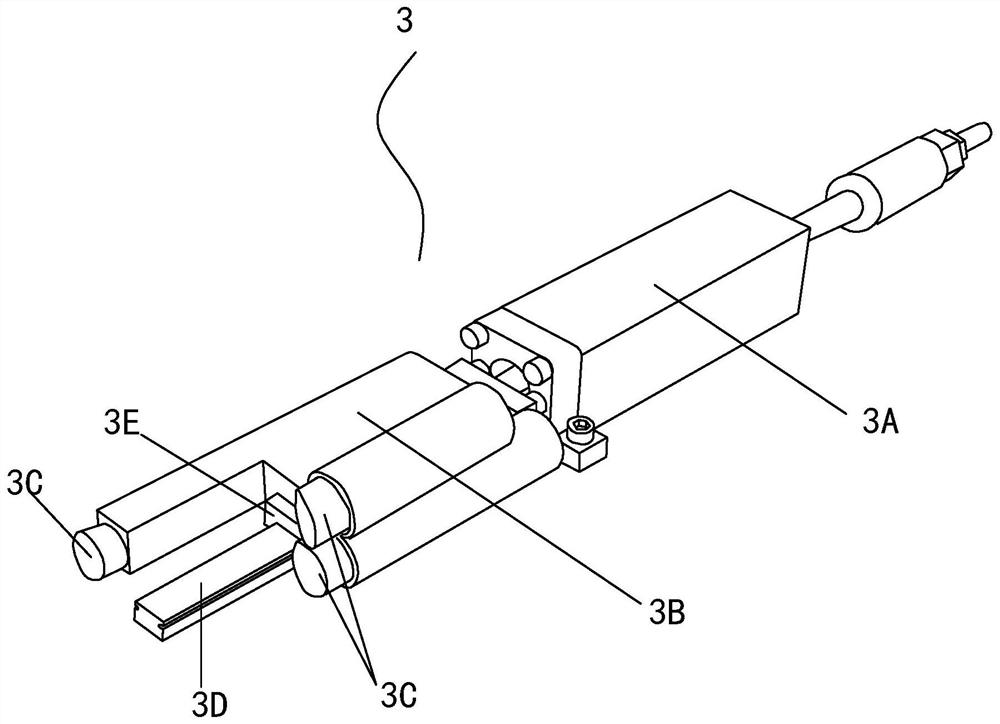

Resistance adjusting machine and resistance adjusting method for electronic accelerator pedal circuit board

ActiveCN113369707AAdjust the resistance valueVehicle componentsPrinted circuitsElectronic throttleControl engineering

The invention discloses a resistance adjusting machine and a resistance adjusting method for an electronic accelerator pedal circuit board. The resistance adjusting machine and the resistance adjusting method for the electronic accelerator pedal circuit board have the advantages that an electronic accelerator pedal component to be subjected to resistance adjusting is propped against an electronic accelerator pedal component loading plate through an electronic accelerator pedal component locking mechanism, the circuit board is electrically connected with a controller through a data connector connecting mechanism, and therefore, an electric signal generated on the circuit board when a swing arm simulation pushing mechanism pushes a swing arm to simulate the treading condition is fed back to a controller; and the electric signal is compared with a standard signal preset in the controller, the controller controls a laser machine to carry out laser cutting on a resistor disc on the circuit board, the resistance value of the resistor disc is adjusted, and therefore, output electric signals are consistent under the condition that the swing arm swings at the same angle.

Owner:NINGBO AUTO CABLE CONTROLS

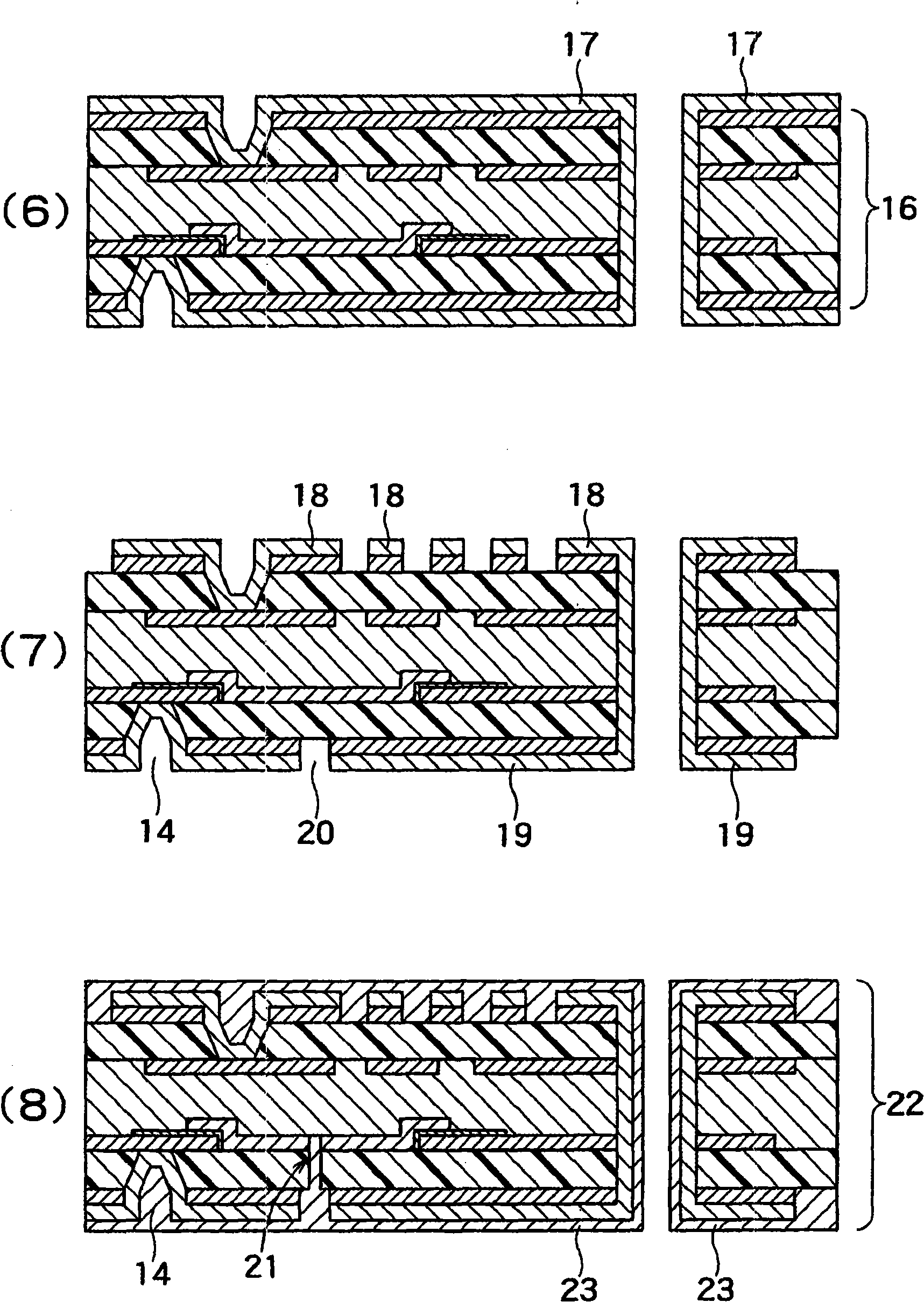

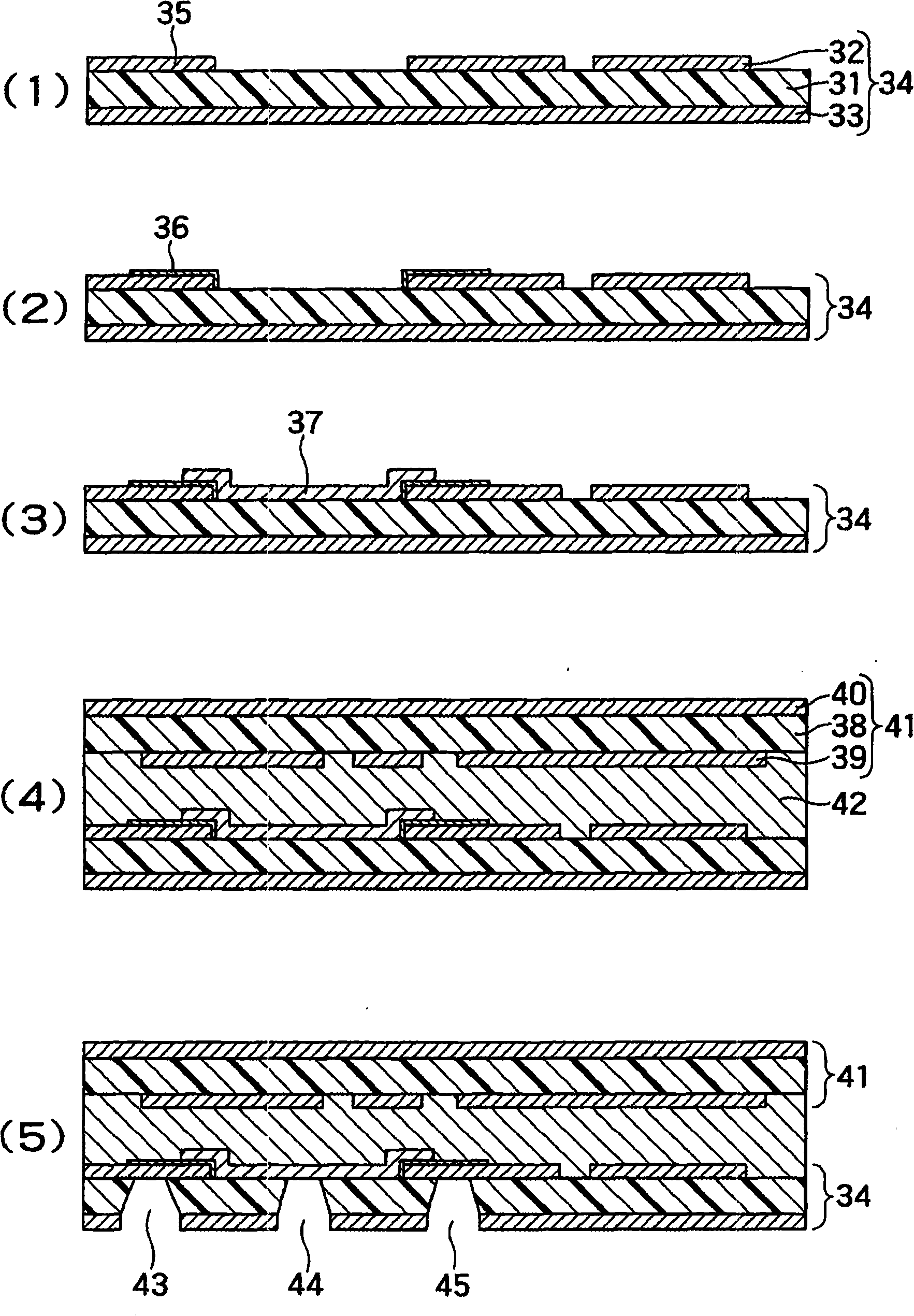

Method of producing printed circuit board incorporating resistance element

InactiveCN101321436AAdjust the resistance valueLow yieldPrinted circuit aspectsPrinted resistor incorporationMetallic foilCopper

The present invention provides a method of producing a resistance element incorporated in a printed circuit board at an accuracy of resistance value of +-1% or less, at low cost and with a good yield while the resistance element formed by a resistor paste is incorporated. A method of producing a printed circuit board incorporating a resistance element includes: preparing a double-sided copper clad board having a first metallic foil on one face of an insulating base material thereof and a second metallic foil on the other face of the insulating base material thereof; providing at least a pair of electrodes on one of the metallic foils; printing a resistor paste between the electrodes to form a resistor; preparing a circuit board having at least one wiring layer; ; causing a layer on which the resistor paste is formed to oppose the circuit board to layer the double-sided copper clad board on the circuit board; forming openings in the first and the second metallic foils; and emitting laser through the openings to partly remove the insulating base material and the resistor paste to adjust resistance value. A conformal mask for etching may be formed on the second metallic foil to form openings in the insulating base material by etching to emit laser through the openings.

Owner:NIPPON MEKTRON LTD

Tin-dioxide-base composite nano air-sensitive material and preparation method thereof

InactiveCN100410655CImprove microstructureReduce closed poresMaterial electrochemical variablesTin oxidesTin dioxideNanometre

Owner:GUANGZHOU UNIVERSITY