Patents

Literature

133results about How to "Overcome flexibility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

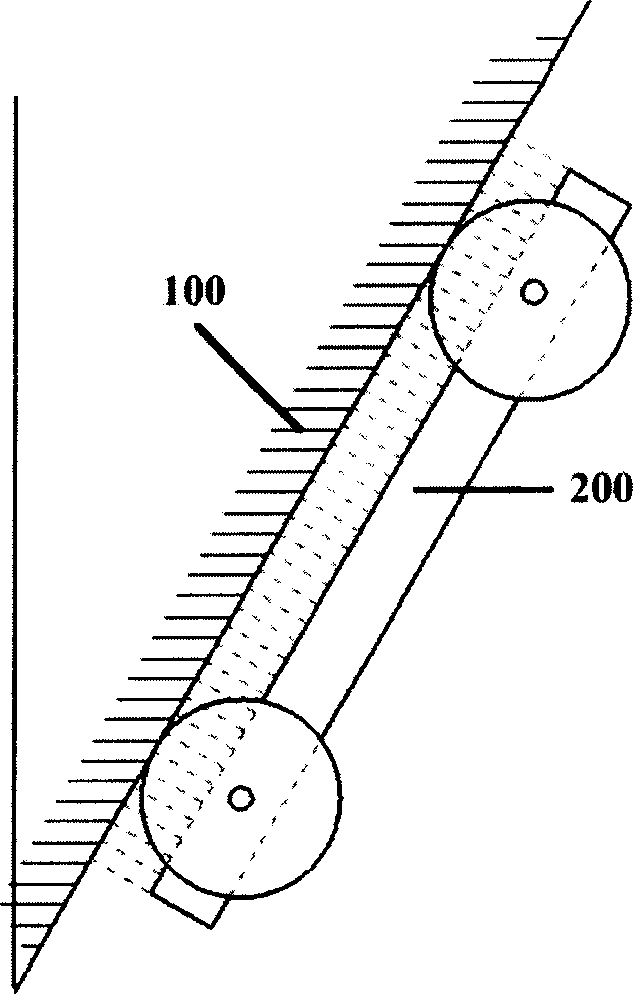

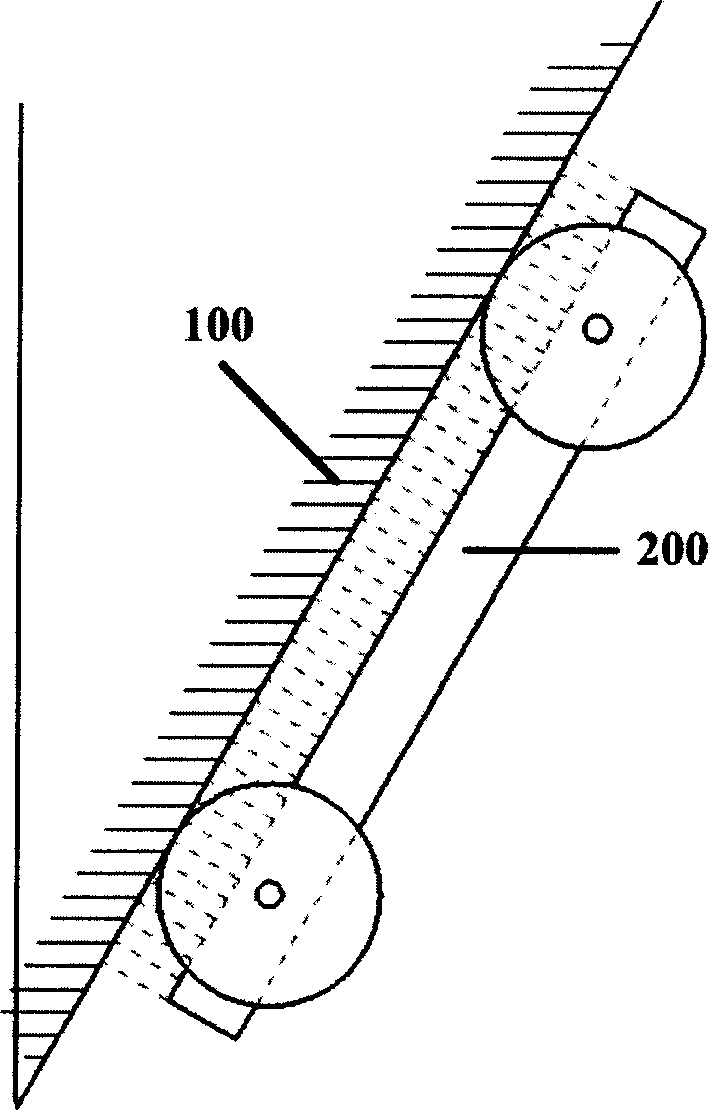

Non-contact magnetically adsorbed wall climbing robot

The present invention is non-contact magnetically adsorbed wall climbing robot, belongs to the field of robot design technology, and aims at providing robot with both high moving flexibility and great loading capacity. The non-contact magnetically adsorbed wall climbing robot includes wheeled moving mechanism and permanent adsorption mechanism. The wheeled moving mechanism includes chassis, driving mechanism and wheels, which are laid symmetrically, driven in differential mode, and turns on wall by means of the speed difference of the wheels. The permanent adsorption mechanism has no contact with the magnetically conducting wall surface, high magnetic energy utilization, and high adsorption capacity. The wall climbing robot has high loading capacity, high motion flexibility, especially high turning flexibility, and excellent application foreground.

Owner:TSINGHUA UNIV

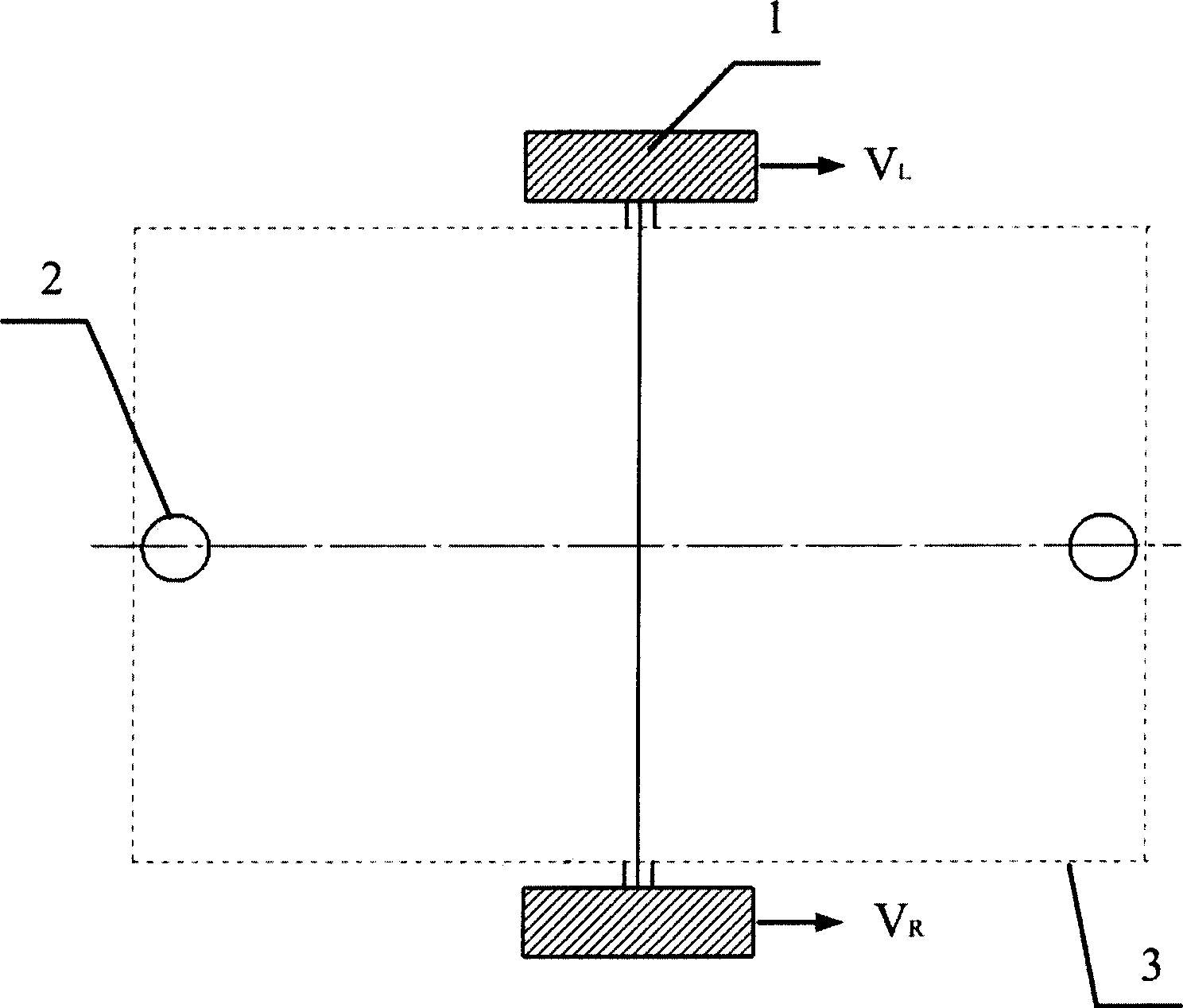

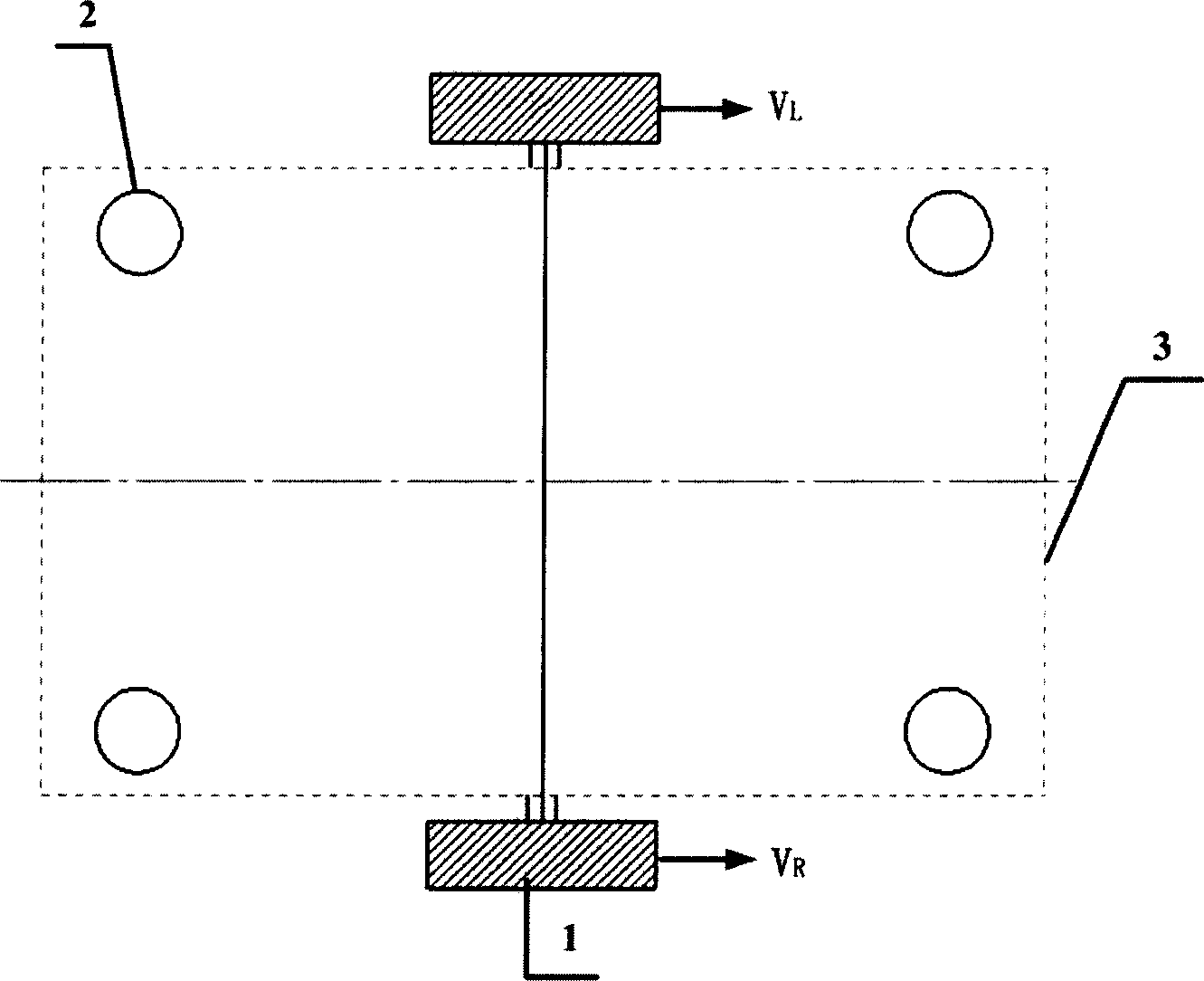

Magnetic adsorption wall climbing robot with curved surface adaptive ability

ActiveCN1736668AWith characteristicsHave made significant progressManipulatorDrive wheelRotational freedom

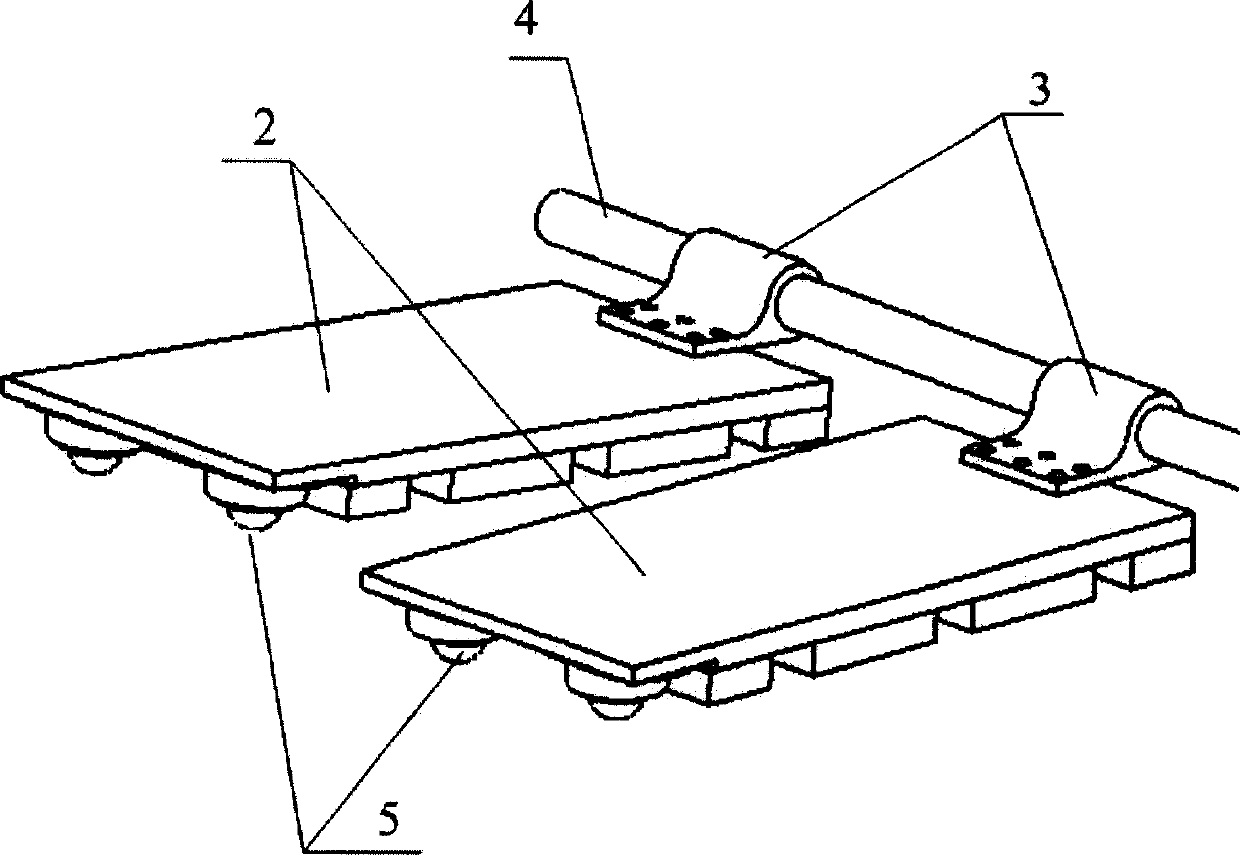

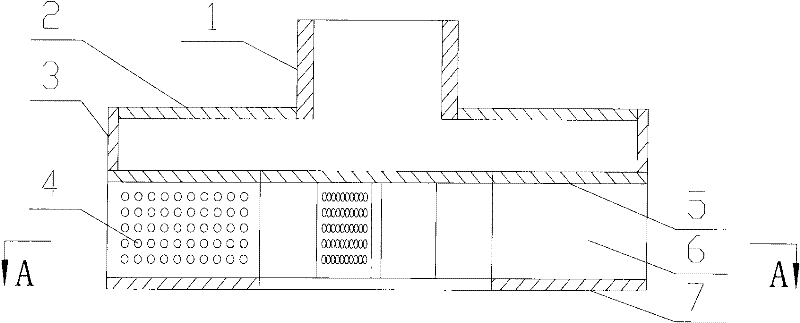

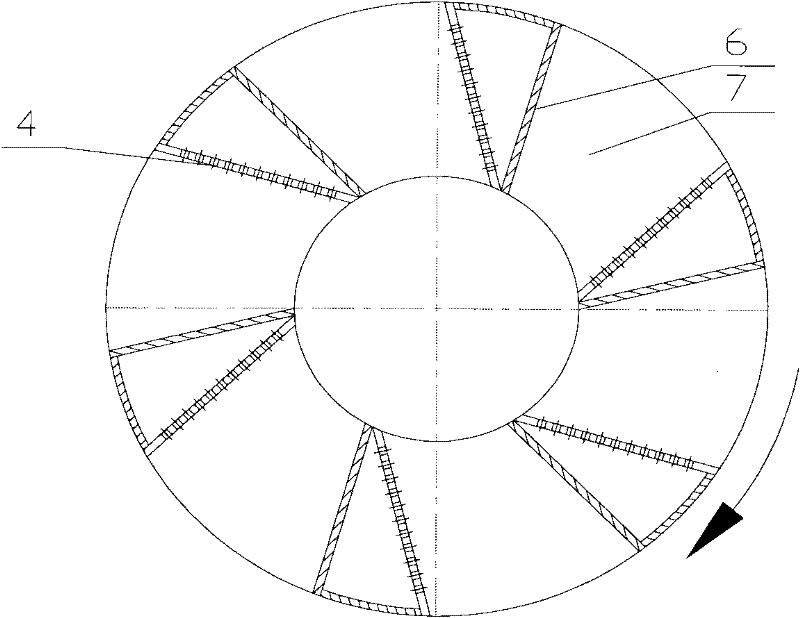

Disclosed is a magnetic-absorption wall-creeping robot with a self-adaptive capability to curved face, which belongs to the art of robot. Said robot comprises a wheeled shifter and a plural of permanent-magnet absorption devices, the wheeled shifter containing an undercarriage, a drive gear, a traction wheel and an auxiliary balancing wheel; one end of the permanent-magnet absorption device being equipped with the magnetic conduction wall surface by auxiliary balancing wheel, and the other end equipped with the undercarriage or other permanent-magnet absorption device by curved face self-adaptive device with rotational freedom degree of among one to three; the traction wheel being laid out symmetrically and driven by differential drive, and the differential of the traction wheel realizing the deflecting on the magnetic conduction wall surface. The wall-creeping robot having a strong loading power, a flexible motility and a super self-adaptive capability to curved face, has a perfect prospect.

Owner:TSINGHUA UNIV

Method and device for controlling robot simulating animal foot movement

InactiveCN1490134AImprove environmental adaptabilityOvercome flexibilityManipulatorControl layerControl signal

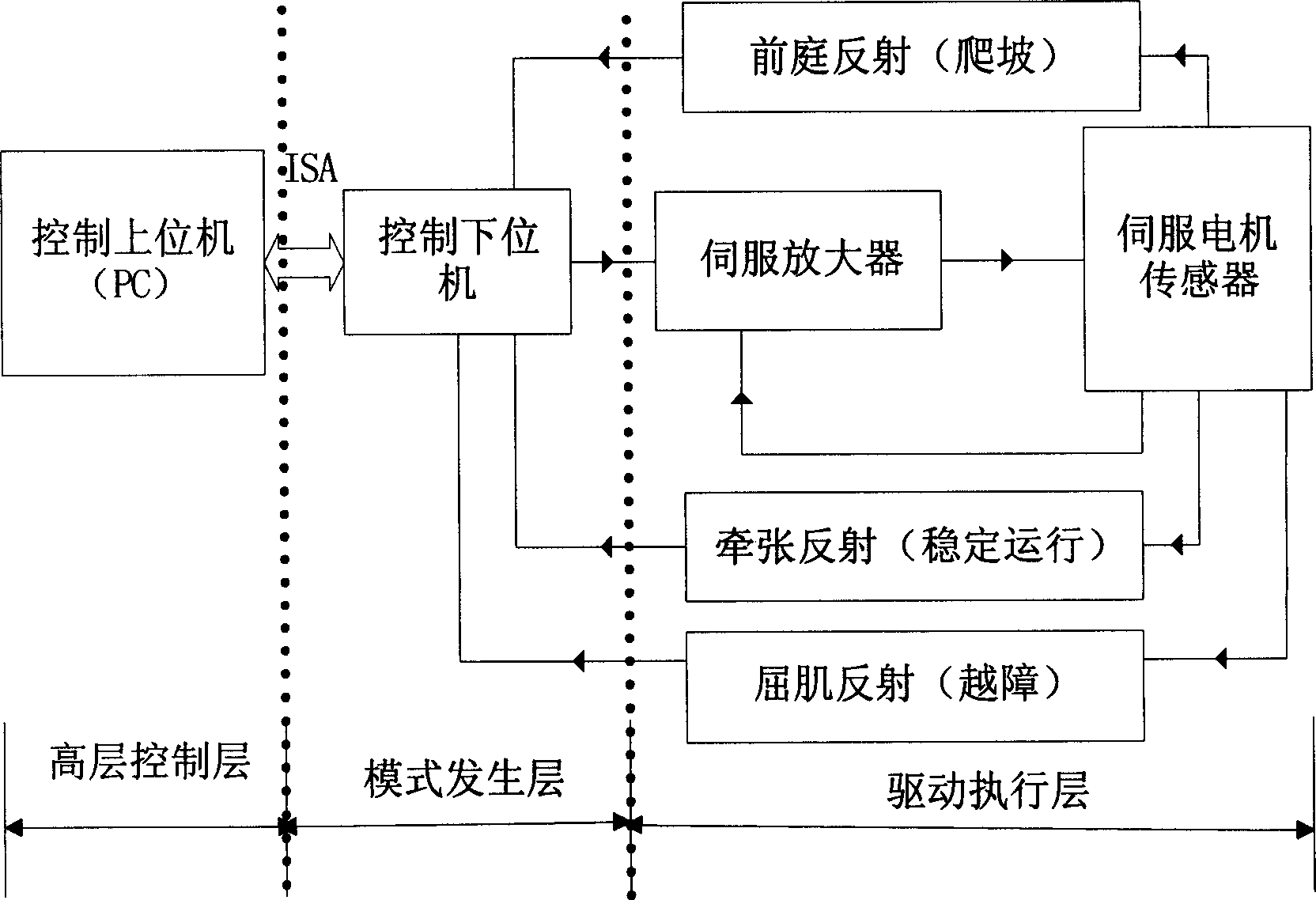

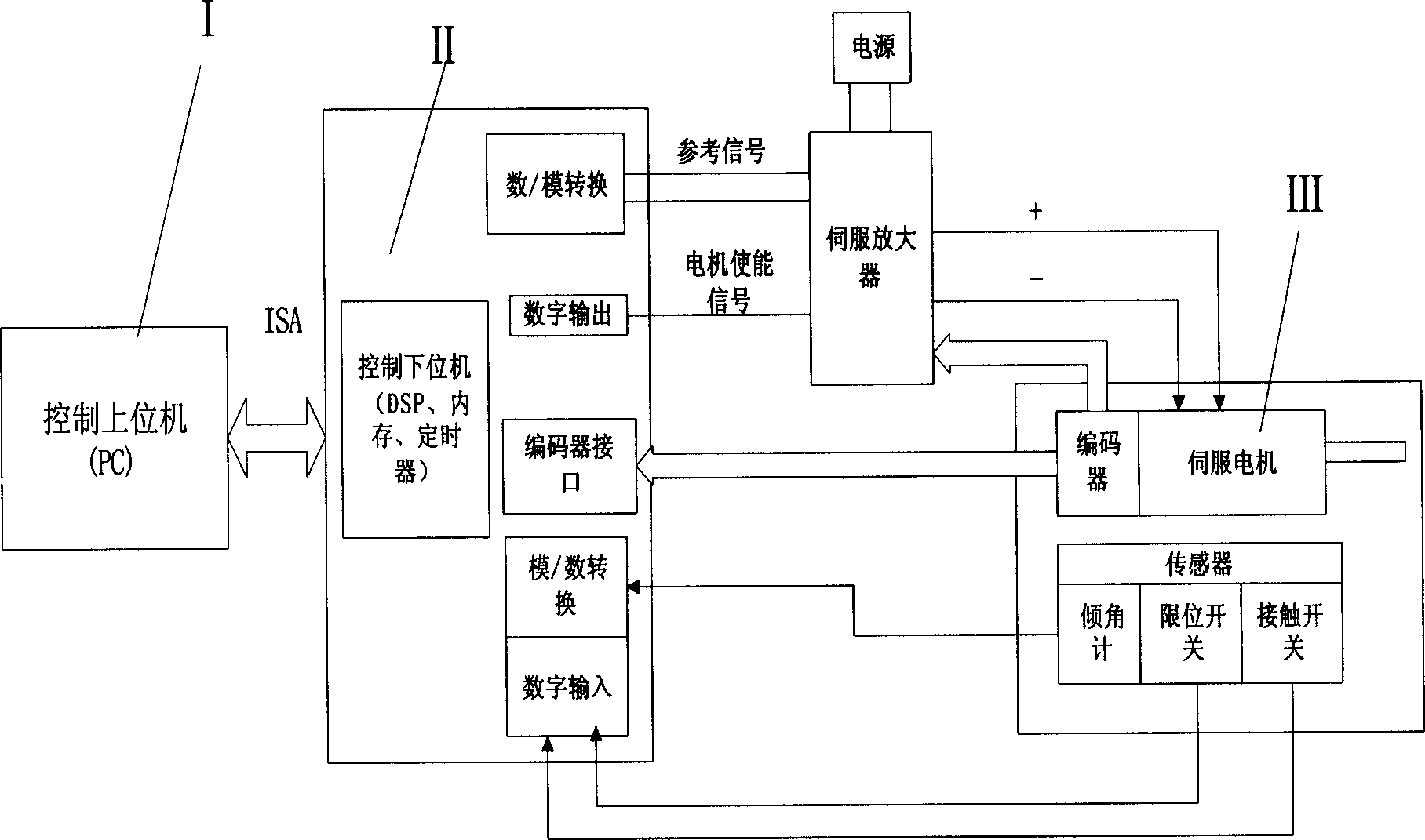

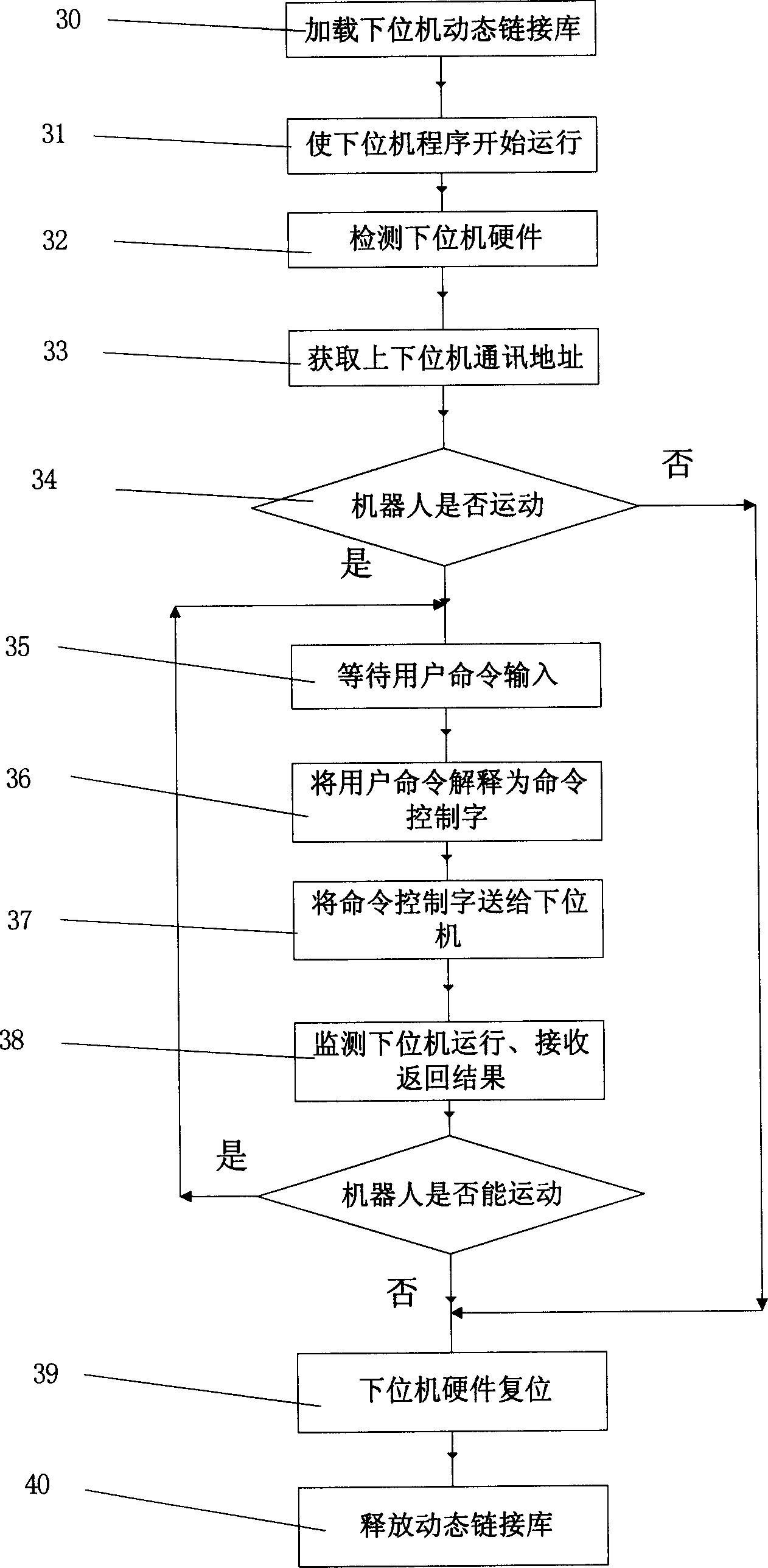

A control method and device able to realize the rhythmic movement of animal for the foot-type bionic robot feature that the rhythmic movement control mechanism smilar to that of animal is used and 3 function layers (higher-layer control layer, mode generating layer and drive executing layer) are used for control. Said mode generating layer has a mode generator to generate the rhythmic moving signals of hip joint, which are then converted to the control signals associated with the knee joint and leg, resulting in 4 running modes, free walk, stroll, slow running and fast running.

Owner:TSINGHUA UNIV

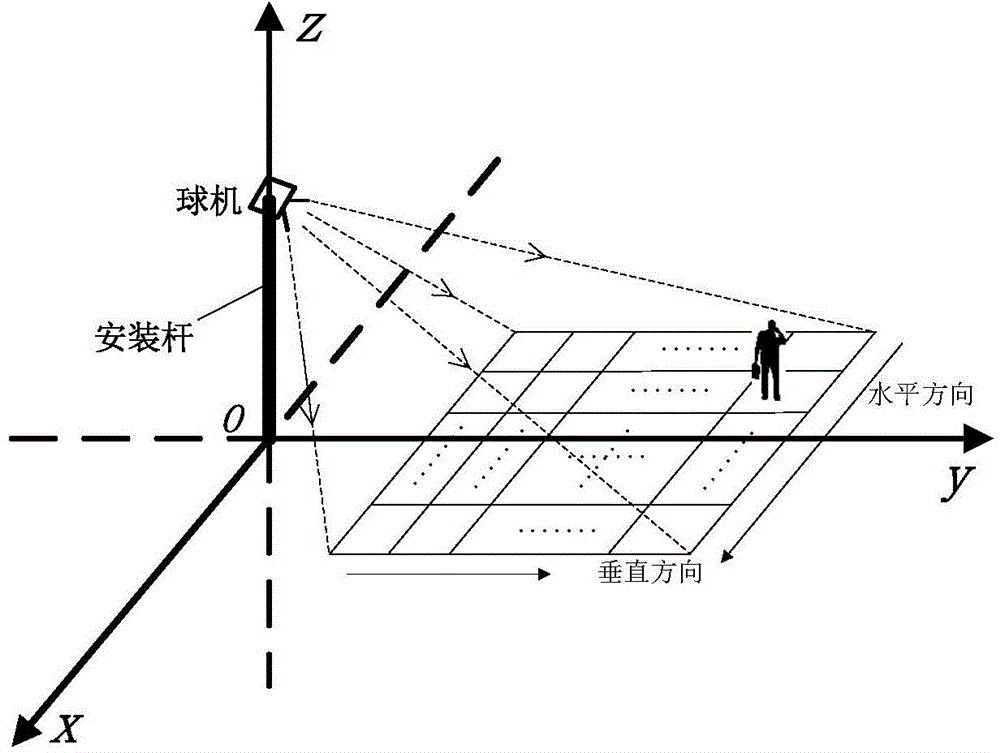

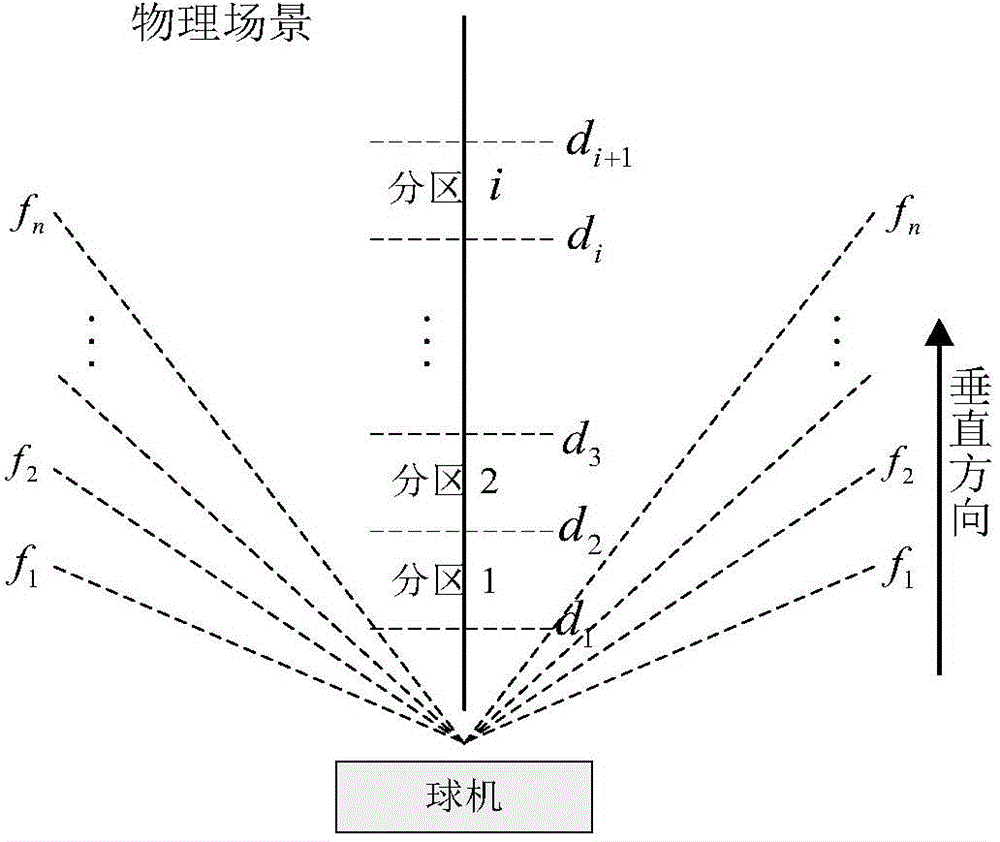

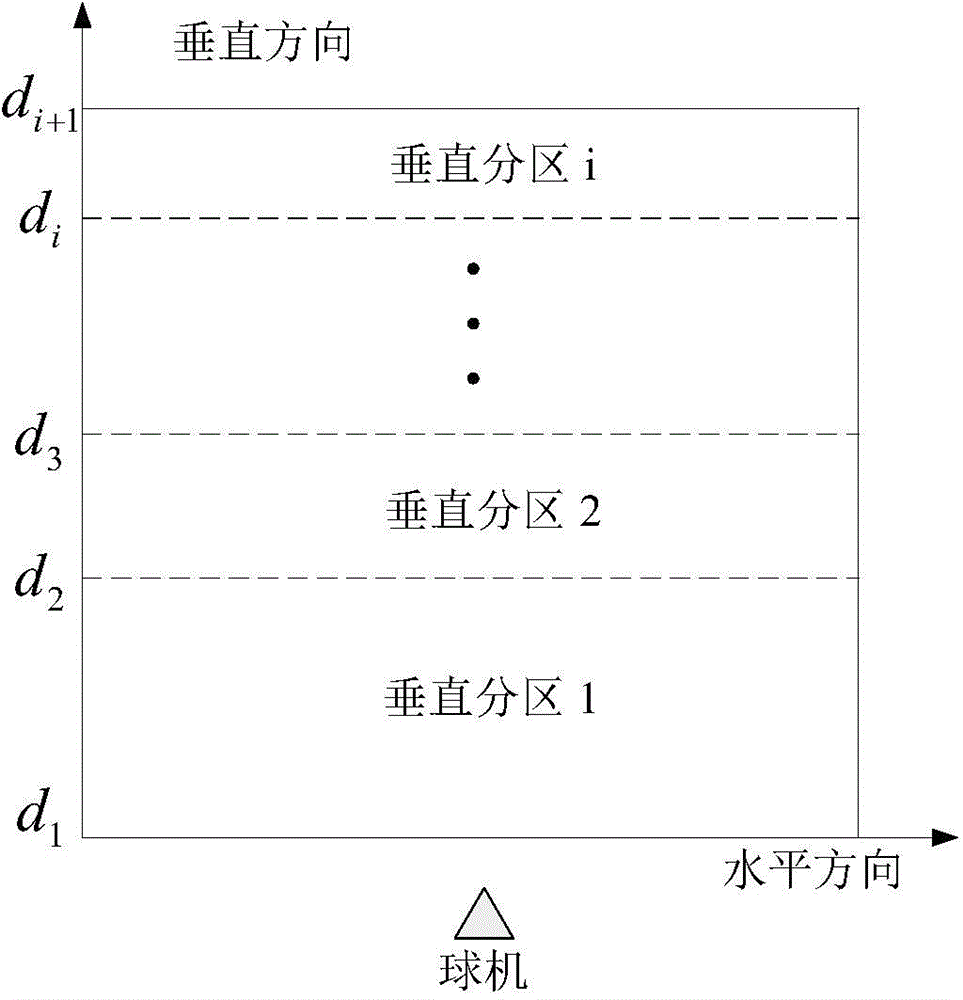

Control method of monitoring ball machine

InactiveCN104639908AFast captureGuaranteed shooting effectImage analysisClosed circuit television systemsVideo monitoringControl engineering

The invention discloses a control method of a monitoring ball machine. The method comprises the following steps of (1) vertically and horizontally dividing a to-be-monitored space into a plurality of small partitions, and setting a shooting focal distance for each small partition; (2) setting corresponding preset positions for a central point position and an edge point position of each small partition, and storing horizontal position information, vertical position information and shooting focal distance information of the ball machine; (3) reading a video frame, and performing target detection on the video frame; (4) according to direction information of a detected target in a monitoring scene, mapping the target to the corresponding preset position; (5) calling the preset position by the ball machine to acquire a monitored image. The defects that the automation degree of control is not high, the real-time property and the flexibility are not enough, and human manual interference is required in a ball machine of the traditional video monitoring system are overcome; the control method is convenient in operation, high in automation degree of control and good in instantaneity, and is particularly good in capture effect on the monitored image of a quickly moving target.

Owner:HUAZHONG UNIV OF SCI & TECH

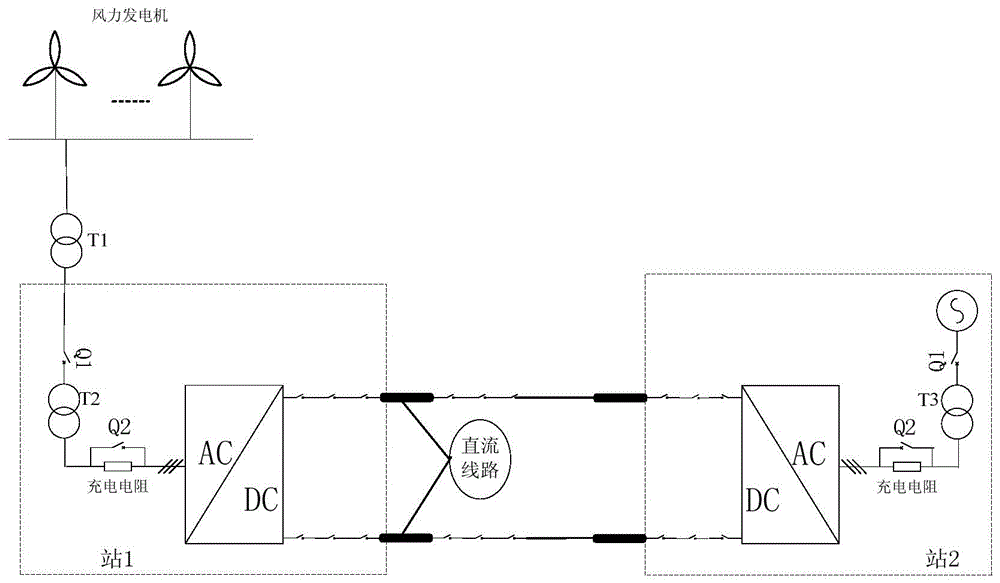

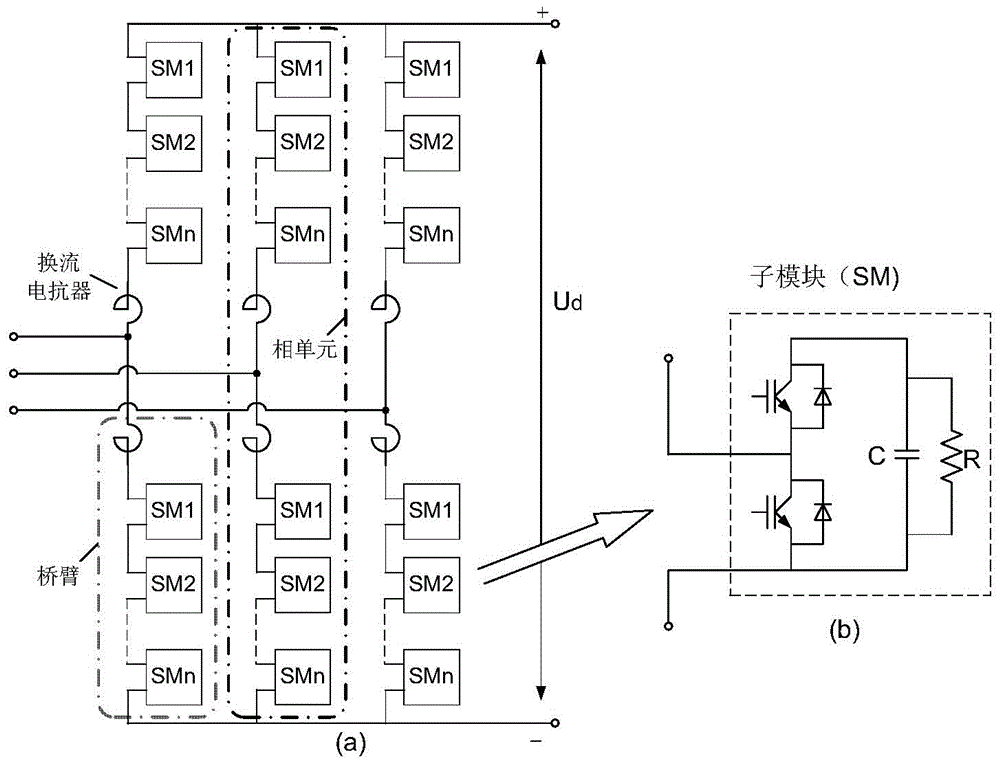

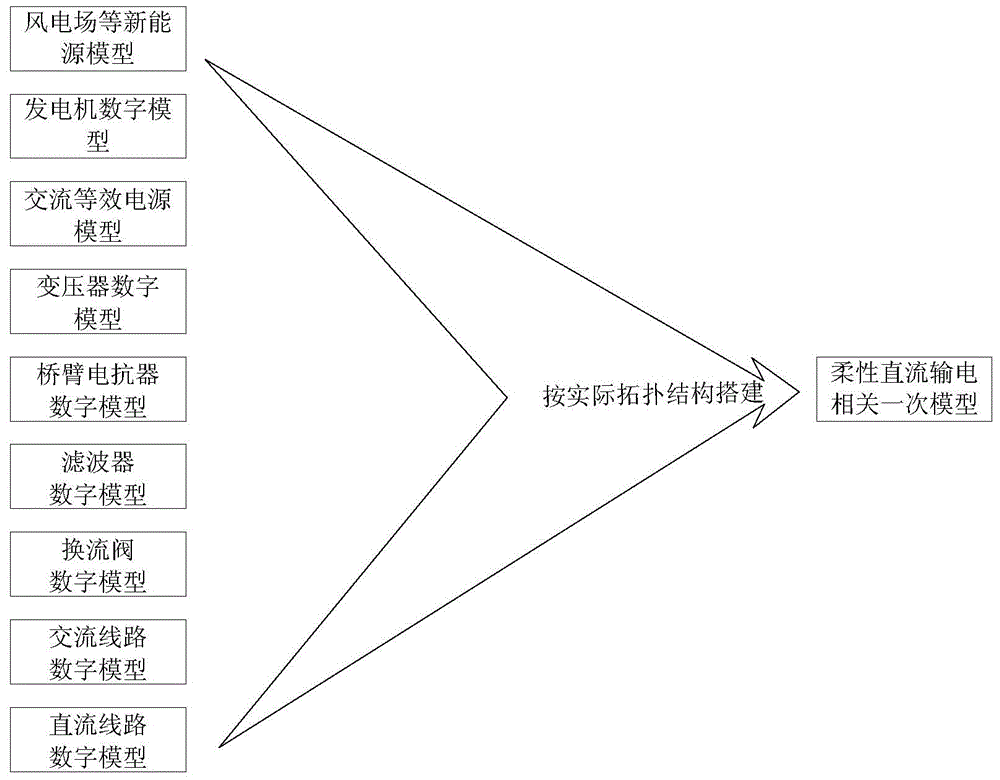

Closed-loop test system of flexible direct current transmission system control and protection system

InactiveCN104423373AShorten the development cycleShorten the design cycleElectric testing/monitoringAudio power amplifierClosed loop

The invention discloses a closed-loop test system of a flexible direct current transmission system control and protection system. The closed-loop test system includes a real-time digital simulator, interface hardware equipment and control protection equipment of a modularized multi-electric level-based flexible direct current transmission device; the interface hardware equipment includes a power amplifier, a terminal type relay and a converter valve internal analog quantity and pulse expansion plate; the real-time digital simulator is connected with the control protection equipment of the modularized multi-electric level-based flexible direct current transmission device through the interface hardware equipment; and as a result, the closed-loop test system can be formed. The closed-loop test system is simple and flexible. With the closed-loop test system adopted, an entire modularized multi-electric level-based flexible direct current transmission actual control protection system can be tested conveniently and quickly.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD +1

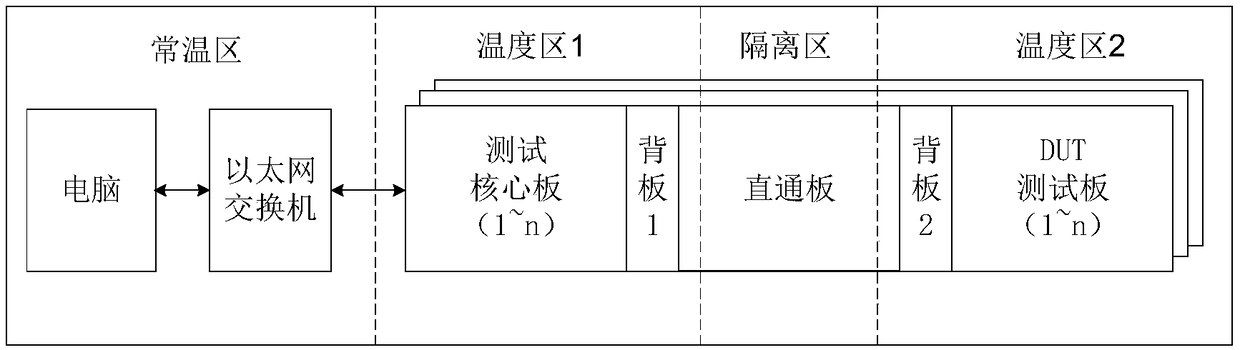

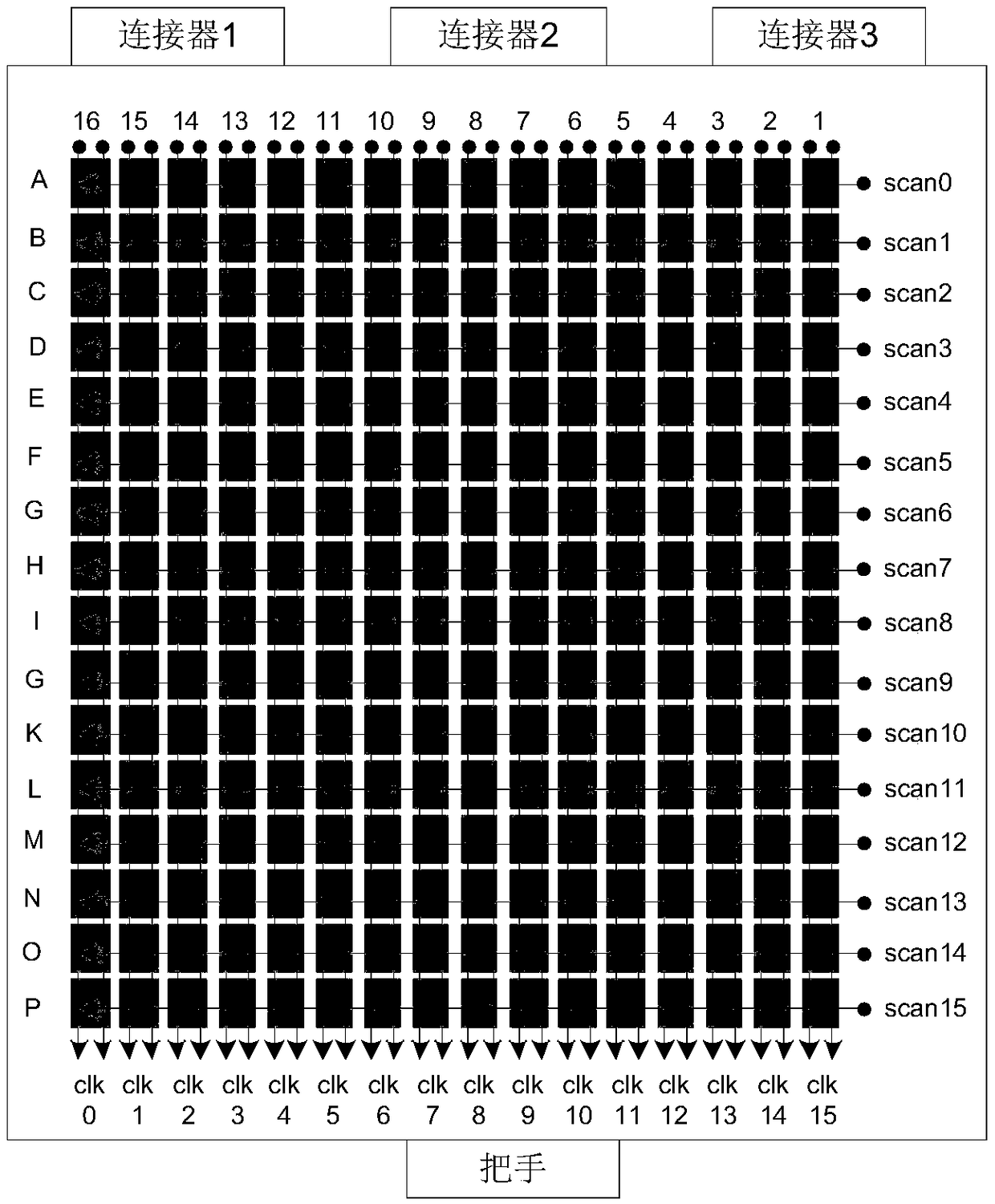

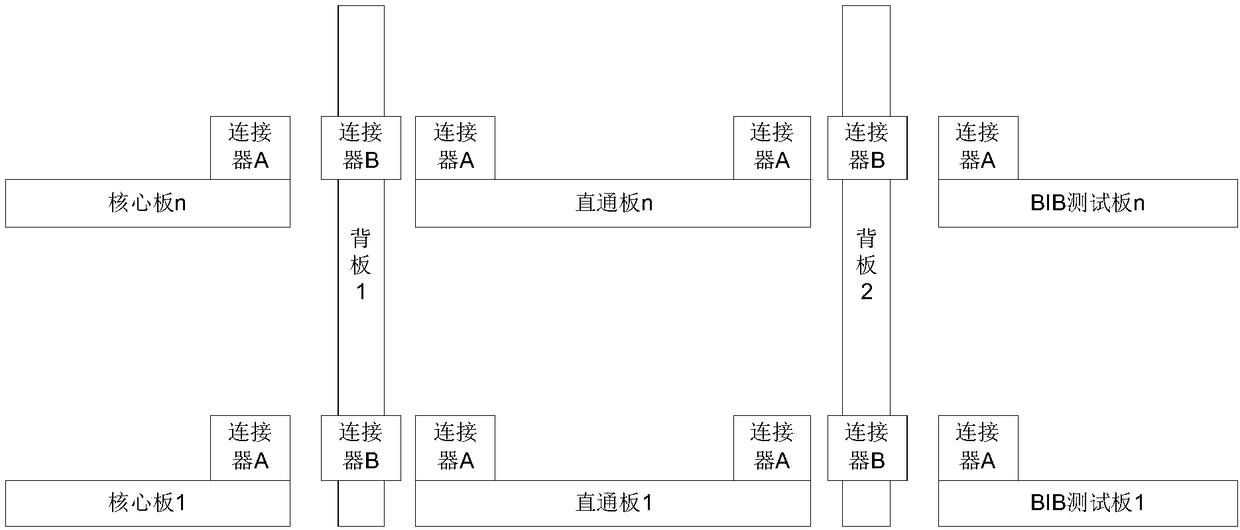

A semiconductor memory aging test system and method

The invention belongs to the technical field of semiconductor memory test and discloses a semiconductor memory aging test system and a method. The system comprises a test core board and a test board.The test core board generates a t signal and a power signal according to that instruction of the upper computer, and after the test signal and the power signal are adjusted, the test signal is provided to a DUT, and the DUT output signal is compared with a preset value to obtain a preliminary test result which is partitioned and stored, and is uploaded to the upper computer; the test board is usedfor carrying DUT, providing clock signal and chip selection signal for DUT. A single test board is provided with a plurality of t bits, and DUT aging test can be carried out by a single DUT or by multiple DUTs at the same time. By outputting various types of test signals on the test core board, and adjusting the delay time of the test signal, strengthening the processing of driving, waveform control, and compensating the power signal, and storing the test results in the partitioned storage area respectively, the functions of management of single DUT test process control and failure analysis in aging test are realized, and the same test number of DUT is increased, which reduces the test resource overhead.

Owner:武汉精鸿电子技术有限公司

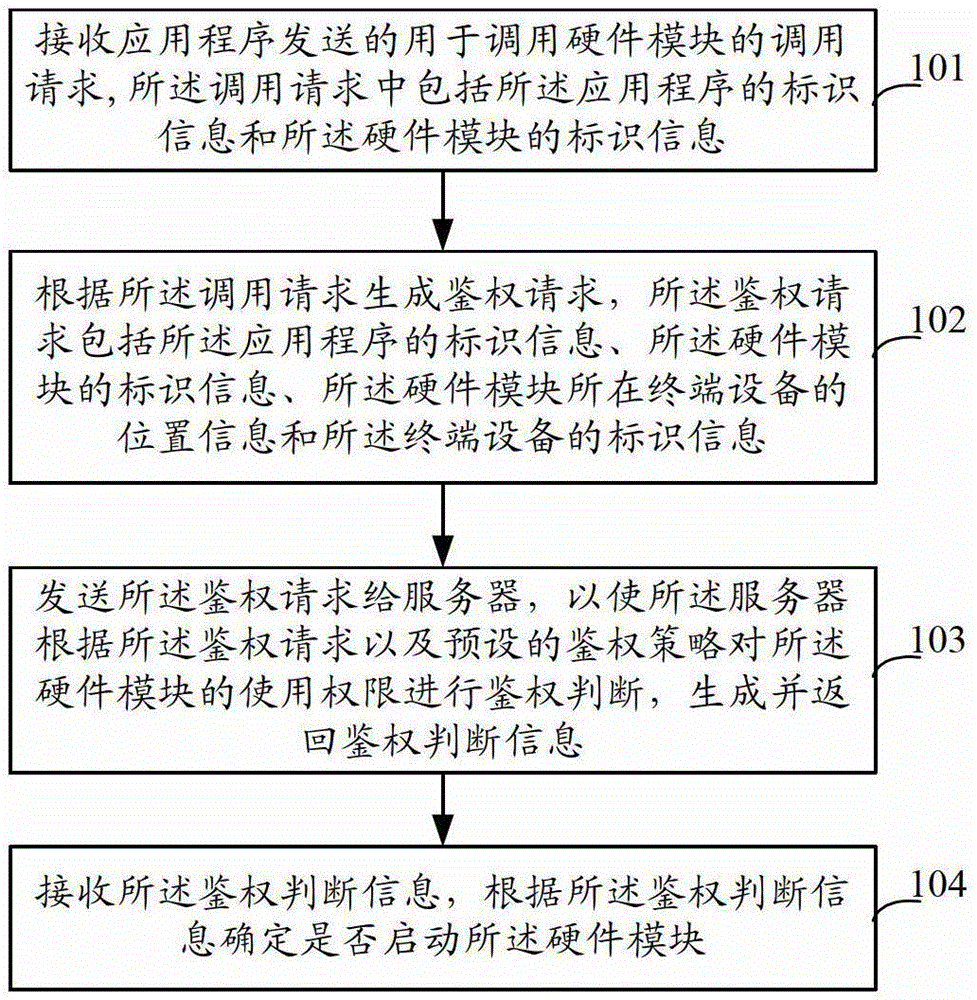

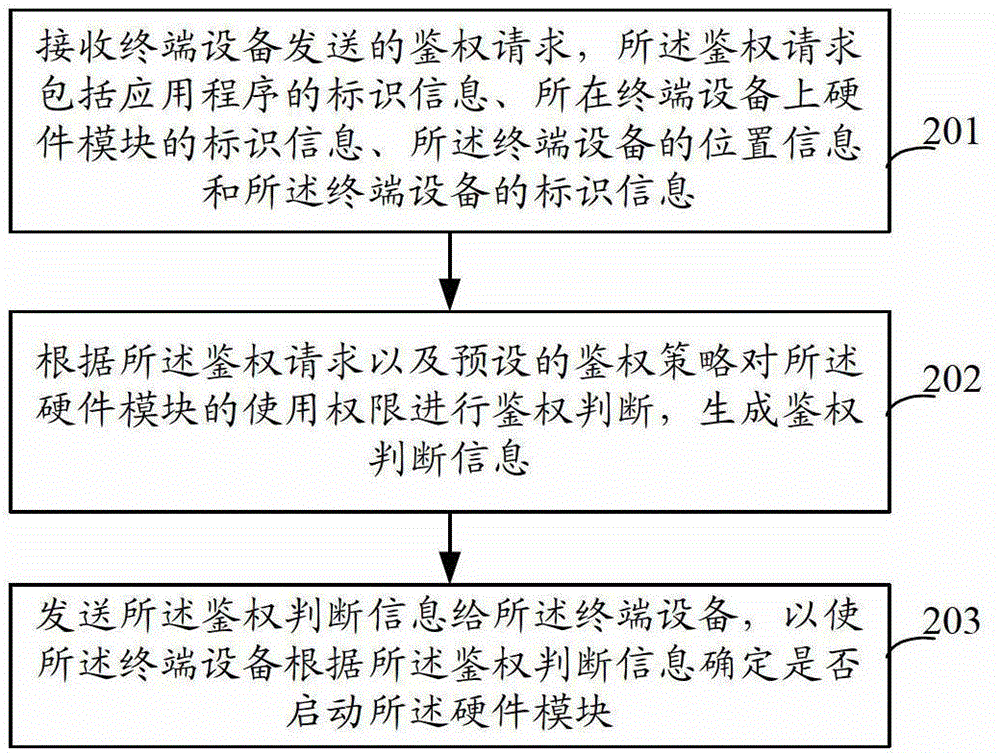

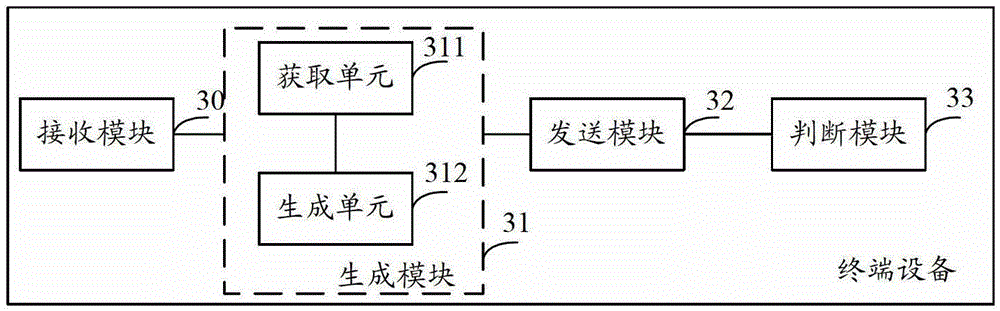

Method and equipment used for controlling hardware module

ActiveCN103067911AOvercome flexibilityIncrease flexibilityTransmissionSecurity arrangementComputer moduleTerminal equipment

The invention provided a method and equipment used for controlling a hardware module. The method comprises receiving call request sent by application program and used for calling the hardware module, packaging identification information of the application program, identification information of the hardware module, location information of a terminal of the hardware module and identification information of terminal equipment, generating authentication request, sending the authentication request to a server to ensure that the server conducts authentication judgment to use permissions of the hardware module according to the authentication request and pre-set authentication strategies, and generating authentication judgment information and returning, receiving the authentication judgment information and judging whether the hardware module is started or not according to the authentication judgment information. When the application program calls the hardware module on the terminal equipment, by conducting authentication judgment to the use permissions of the hardware module to be called, the problem that the prior art limits the use of the terminal equipment is overcome, and flexibility and convenience in the use process of the terminal equipment are improved.

Owner:CHINA UNITED NETWORK COMM GRP CO LTD

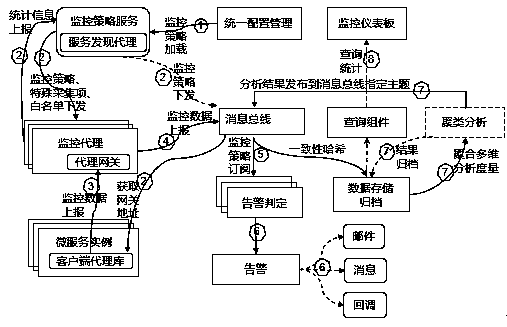

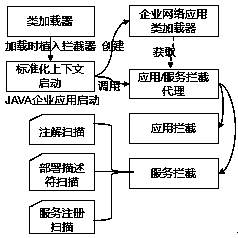

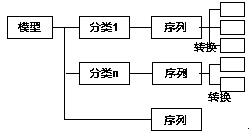

Flexible micro-service monitoring framework architecture

InactiveCN108833137AOvercome integrityOvercome flexibilityData switching networksClient agentExtensibility

The invention discloses flexible micro-service monitoring framework architecture. On the basis of combination of advantages of the traditional distributed system monitoring technology and the distributed system tracking technology based on the service invoking chain, innovation points of a configuration management center, a micro-service instance client agent, and a reusable monitoring alarm template and the like are provided, so that defects of monitoring information incompleteness, low flexibility, and low extensibility and the like are overcome. With a non-intrusive service mode, the customization capability and reliability of the collection are improved. On the basis of a warning processing strategy issued by configuration and a reusable alarm policy template, the customized extensionprocessing capacity of warning is enhanced. According to a cluster analysis algorithm, statistic analysis is carried out on real-time and historical data and intelligent alarm and determination are carried out, so that the warning accuracy is improved. The flexible micro-service monitoring framework architecture has an important practical significance in ensuring the safe and stable operation of power system application services.

Owner:NARI INFORMATION & COMM TECH

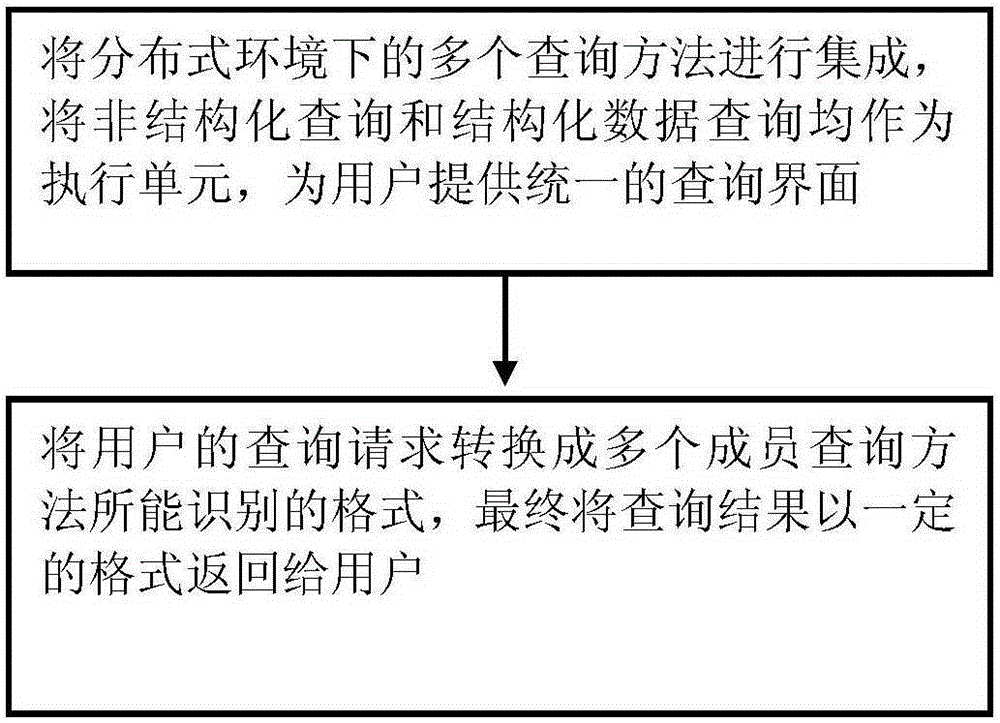

Cloud platform data acquisition method

InactiveCN105205104AOvercome flexibilityLower technical barriersOther databases indexingSpecial data processing applicationsData acquisitionExecution unit

The invention provides a cloud platform data acquisition method. The method comprises the steps of integrating multiple query methods in a distributed environment, and providing a unified query interface for a user by taking non-structured query and structured data query as execution units; converting the query requests of the user into formats which can be recognized by the multiple member query methods; and finally returning the query results to the user according to a certain format. The cloud platform financial data query method provided by the invention can be used for overcoming the defects of the conventional structured data query in the aspect of flexibility and practicability, lowering the technical difficulty that non-specialized persons query a database, and can well utilize the value of business data.

Owner:成都布林特信息技术有限公司

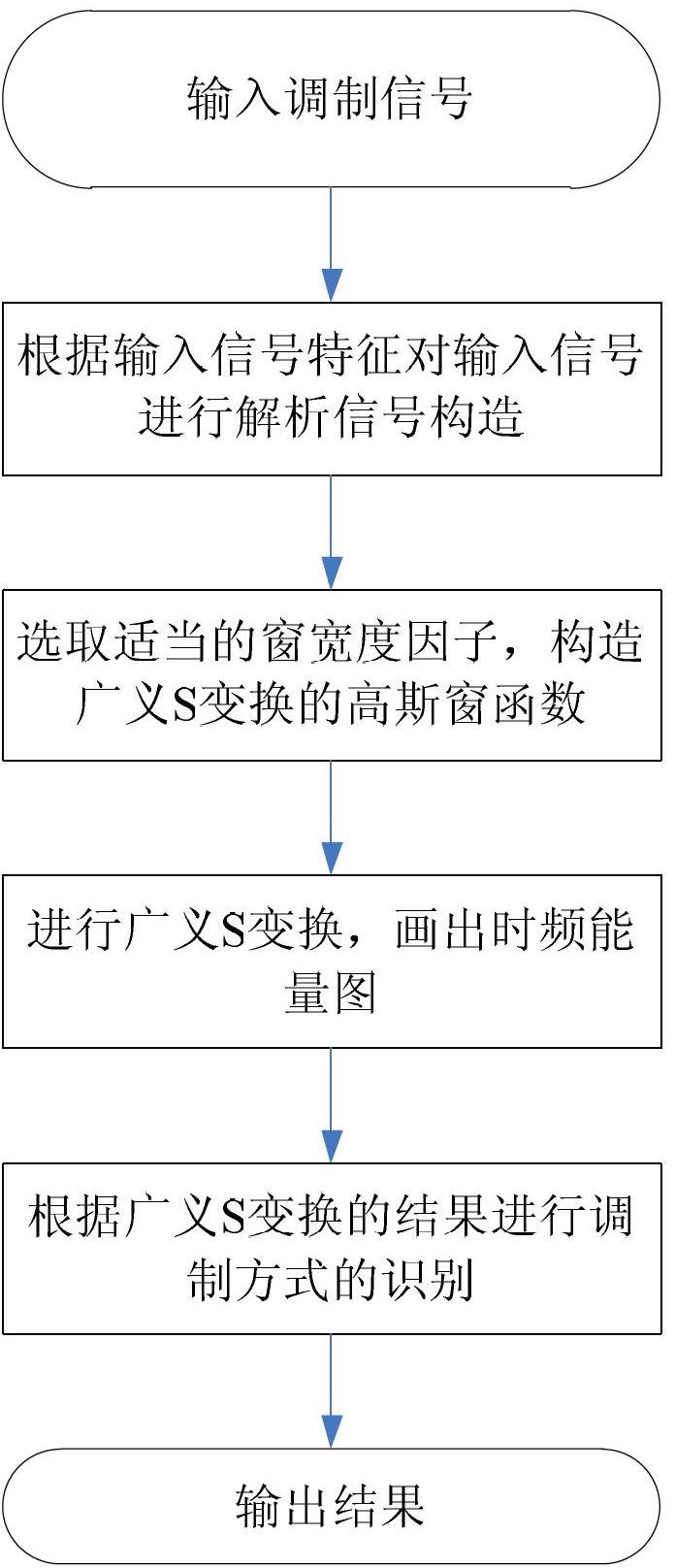

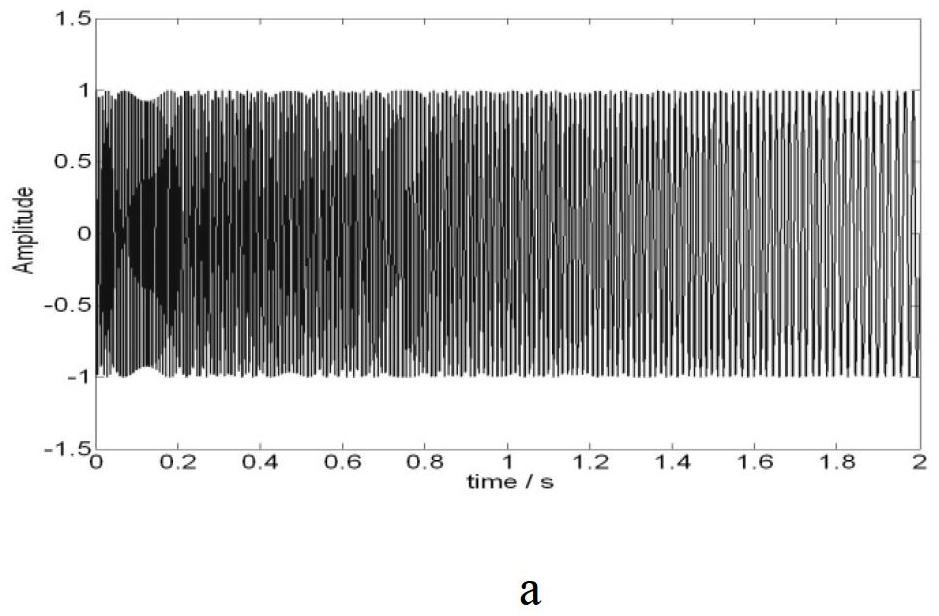

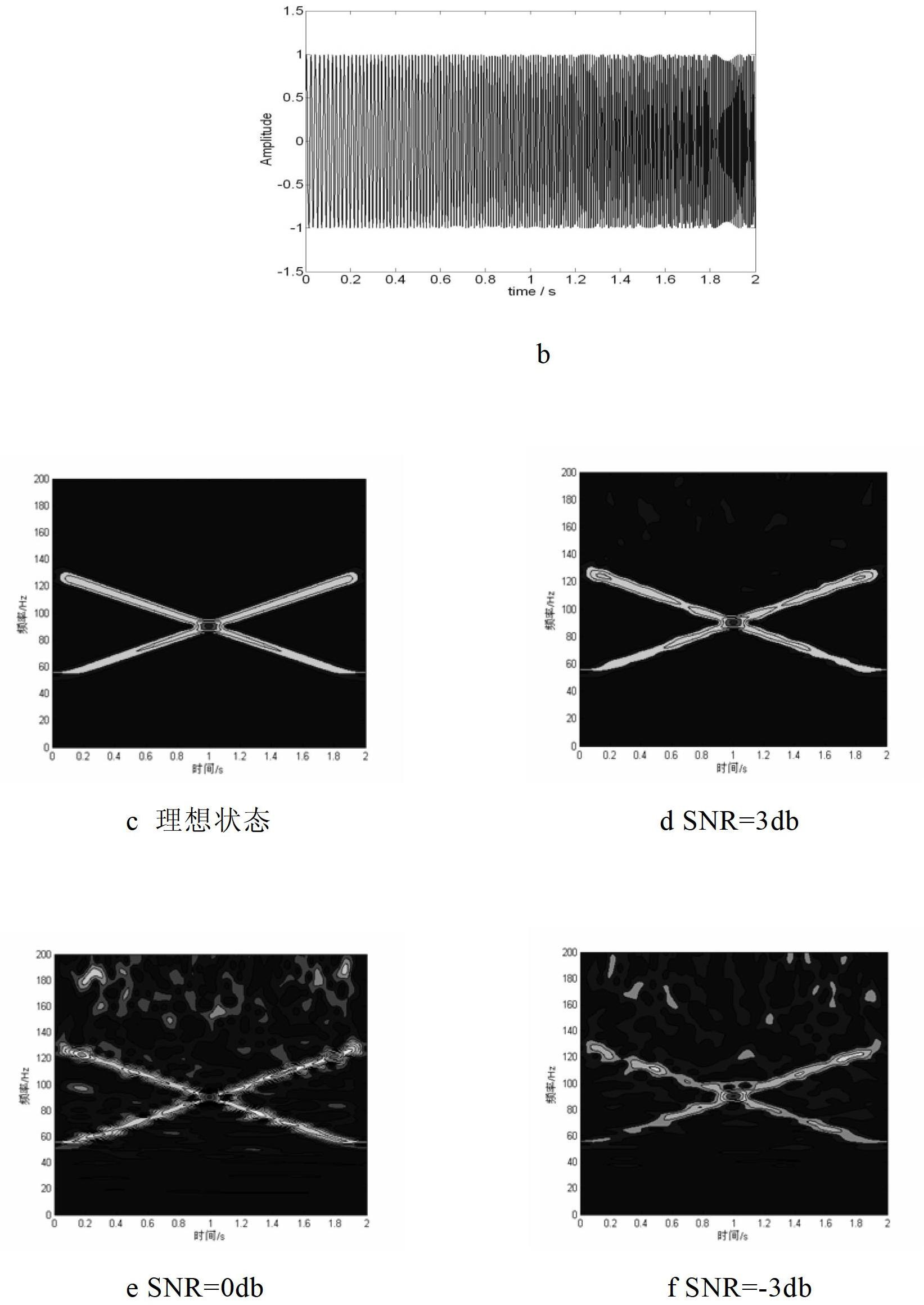

Communication signal modulating and identifying method based on generalized S transformation

InactiveCN102685053AOvercome the lack of fixed resolutionOvercome flexibilityModulated-carrier systemsShort time fourier transformationSignal-to-quantization-noise ratio

The invention provides a communication signal modulating and identifying method based on generalized S transformation. The communication signal modulating and identifying method comprises the following steps of: (1) carrying out analytic signal configuration on an input modulating signal according to the characteristic of an input signal to noise ratio modulating signal to obtain an analytic signal to be used as a signal for carrying out generalized S transformation; (2) configuring a Gaussian window function needed by the generalized S transformation; (3) determining a Gaussian window width factor sigma according to an expression formula of the generalized S transformation; carrying out the generalized S transformation on an input modulation signal by combining short-time Fourier transformation and the Gaussian window function to obtain time-frequency energy distribution images of the modulation signal; and (4) comparing energy images of all modulation signals according to the time-frequency energy distribution images obtained by the step (3) to find out a difference between the time-frequency energy distribution images of all modulation signals which are subjected to the generalized S transformation; selecting a frequency strip quantity with concentrated energy, a maximum value ratio of high-frequency component energy to low-frequency component energy, energy time domain distribution, high-frequency and low-frequency component extreme value time domain distribution and high-frequency component extreme value distribution so as to identify all modulation signals. According to the invention, a high identification rate is achieved under the condition of a low signal to noise ratio, and the method is suitable for modulating and identifying communication signals under a heavy clutter environment.

Owner:BEIHANG UNIV

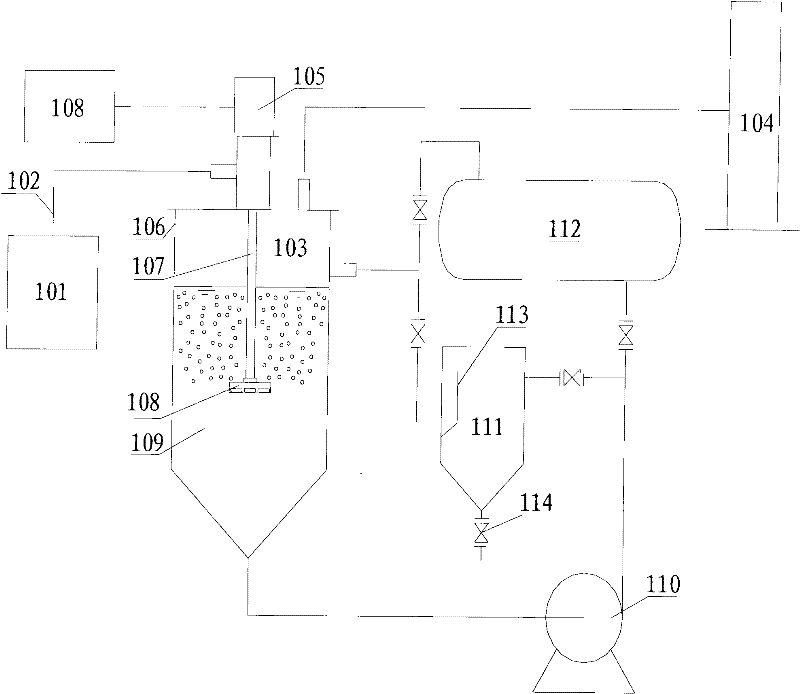

Treatment method for nitrogen oxide tail gas discharged from industrial production furnace, and apparatus thereof

ActiveCN102451610AImprove removal efficiencyNo clogging problemUsing liquid separation agentNitrogen oxidesLiquid cooling system

The present invention discloses a treatment method for nitrogen oxide tail gas discharged from an industrial production furnace, and an apparatus thereof. According to the present invention, gas generated from the furnace is connected to a self-sucking type gas-liquid mixing device through a pipeline to carry out a treatment on the furnace tail gas; the treated gas is discharged by using a gas exhaust tube with the pressure provided by the self-sucking type gas-liquid mixing device. The apparatus of the present invention comprises the self-sucking type gas-liquid mixing device, an absorption liquid cooling system and an absorption liquid settlement system. Compared to the prior art, with the method and the apparatus of the present invention, the nitrogen oxide tail gas discharged from the industrial production furnace can be effectively treated, the cost is low, the process is simple, and the operation can be stably performed for a long period.

Owner:CHINA PETROLEUM & CHEM CORP +1

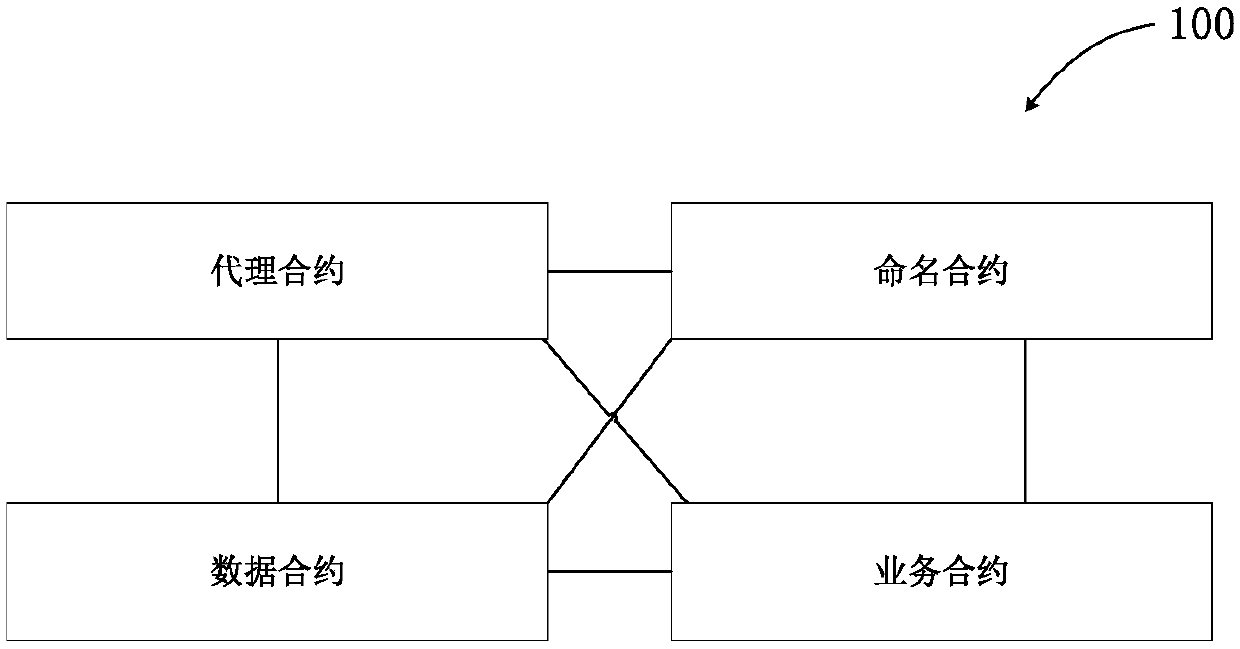

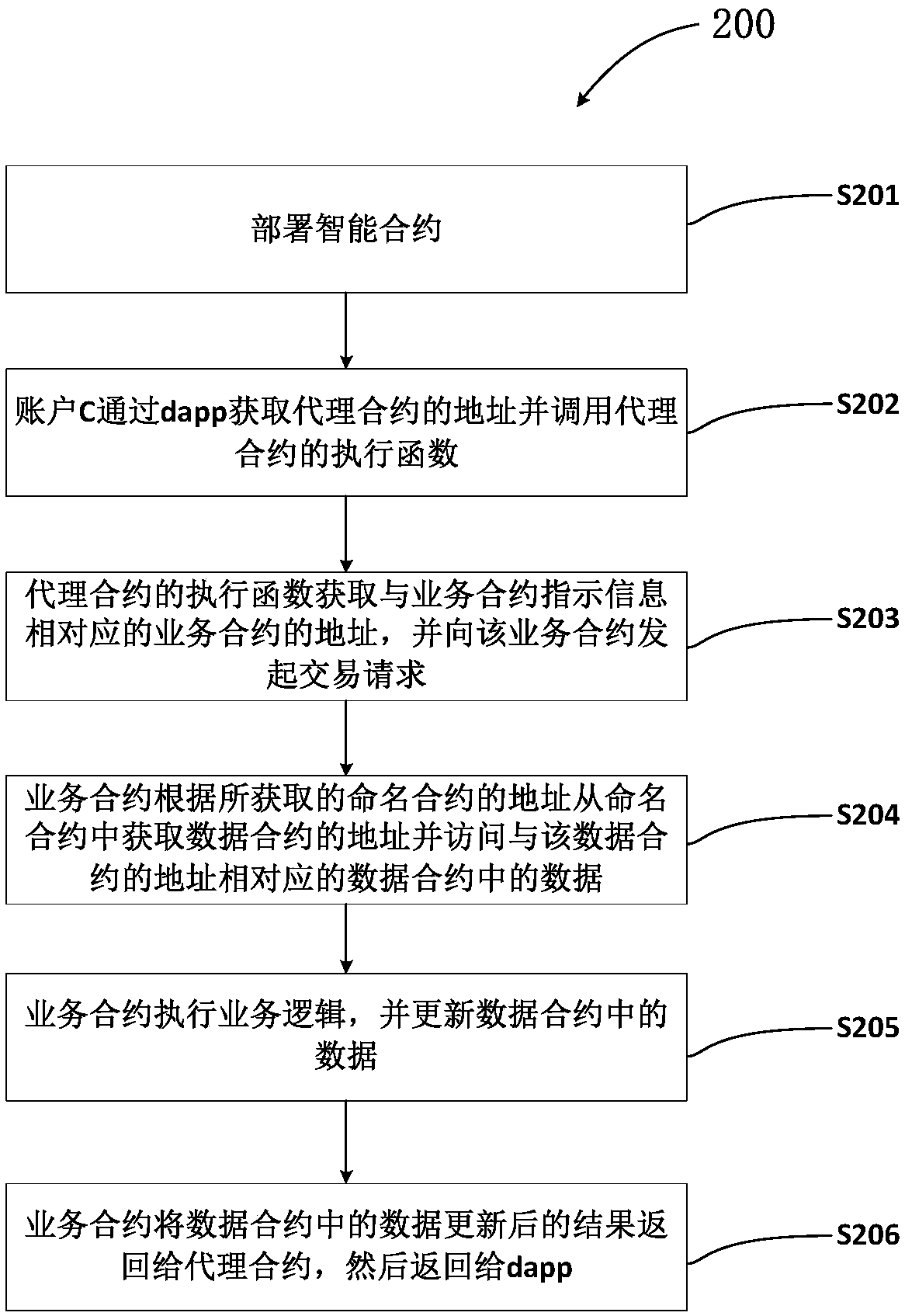

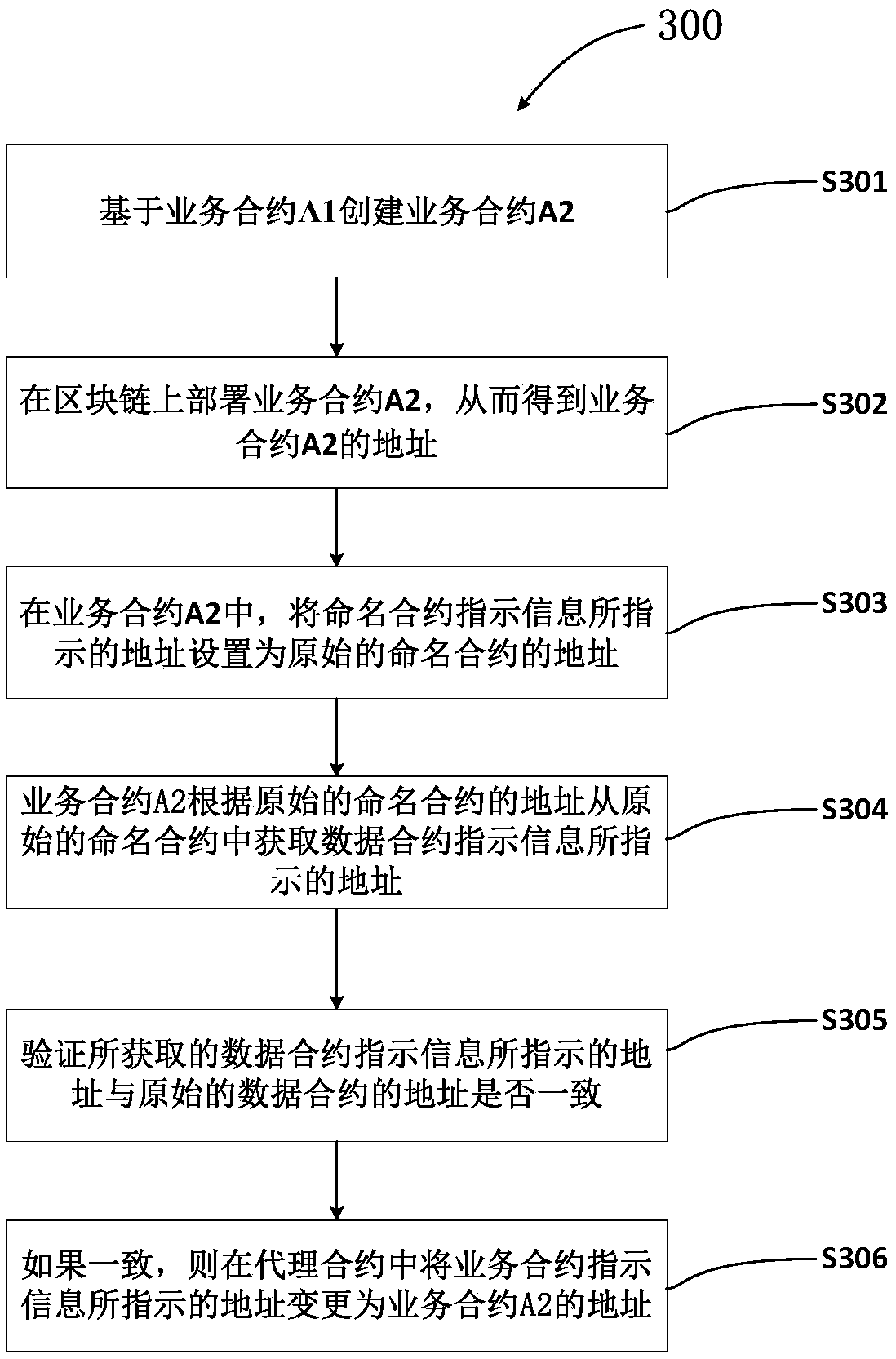

A method for updating an intelligent contract group based on a block chain

InactiveCN109559229AOvercome flexibilityOvercome the data problemFinancePayment protocolsOriginal dataSmart contract

The invention relates to a method for updating an intelligent contract group based on a block chain, the intelligent contract group comprises a proxy contract, a named contract, a service contract anda data contract, and the method comprises the following steps: creating a new version of service contract based on an original service contract; Deploying a new version of service contract on the block chain so as to obtain an address of the new version of service contract; Setting an address indicated by the named contract indication information in the service contract of the new version as theaddress of the original named contract; obtaining an address indicated by the data contract indication information from the original named contract according to the address of the original named contract; and if the address indicated by the obtained service contract indication information is consistent with the address of the original data contract, changing the address indicated by the service contract indication information into the address of the service contract of a new version in the original agency contract. According to the invention, the problem that the service and data cannot be flexibly modified on the block chain when the smart contract needs to be modified or optimized is solved.

Owner:ZHONGAN INFORMATION TECH SERVICES CO LTD

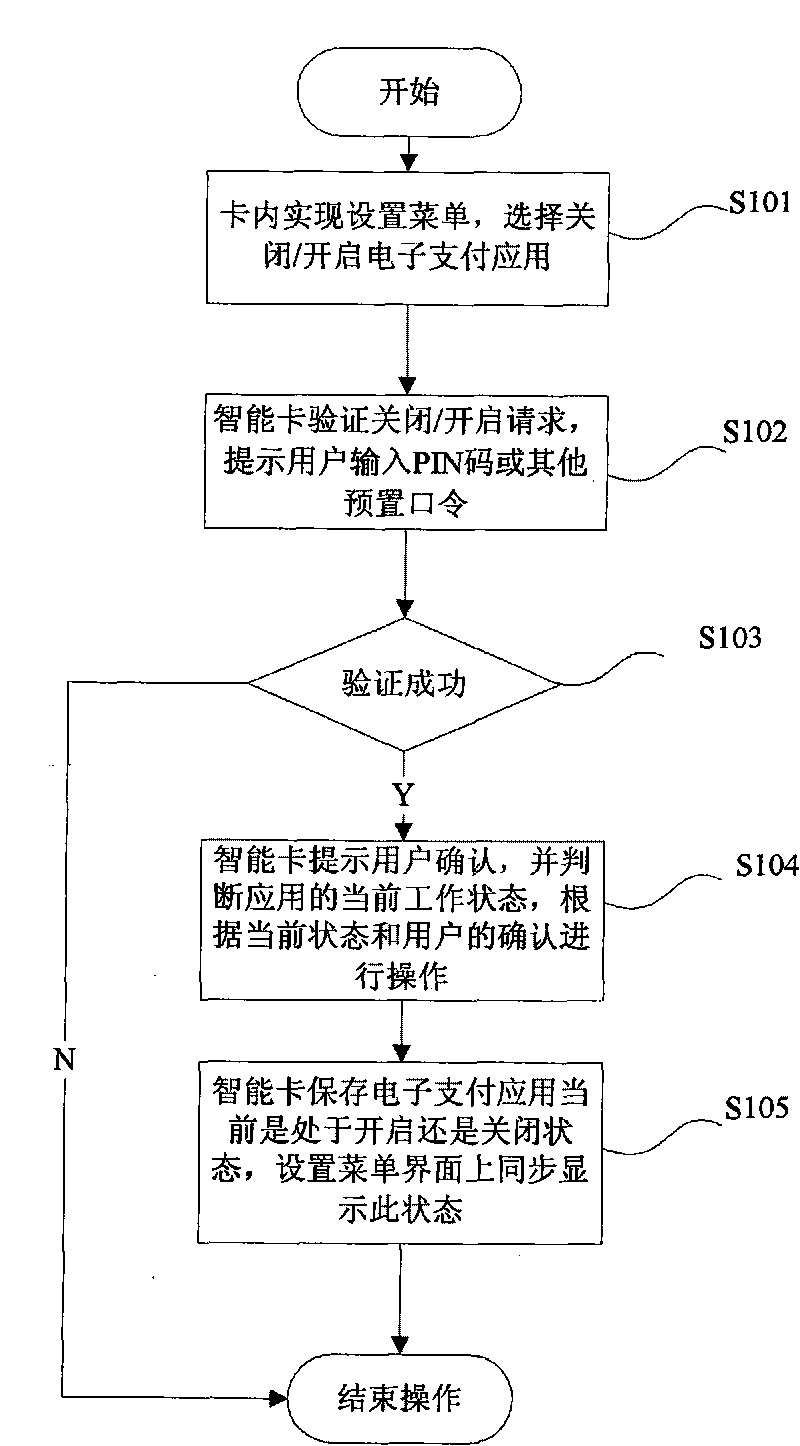

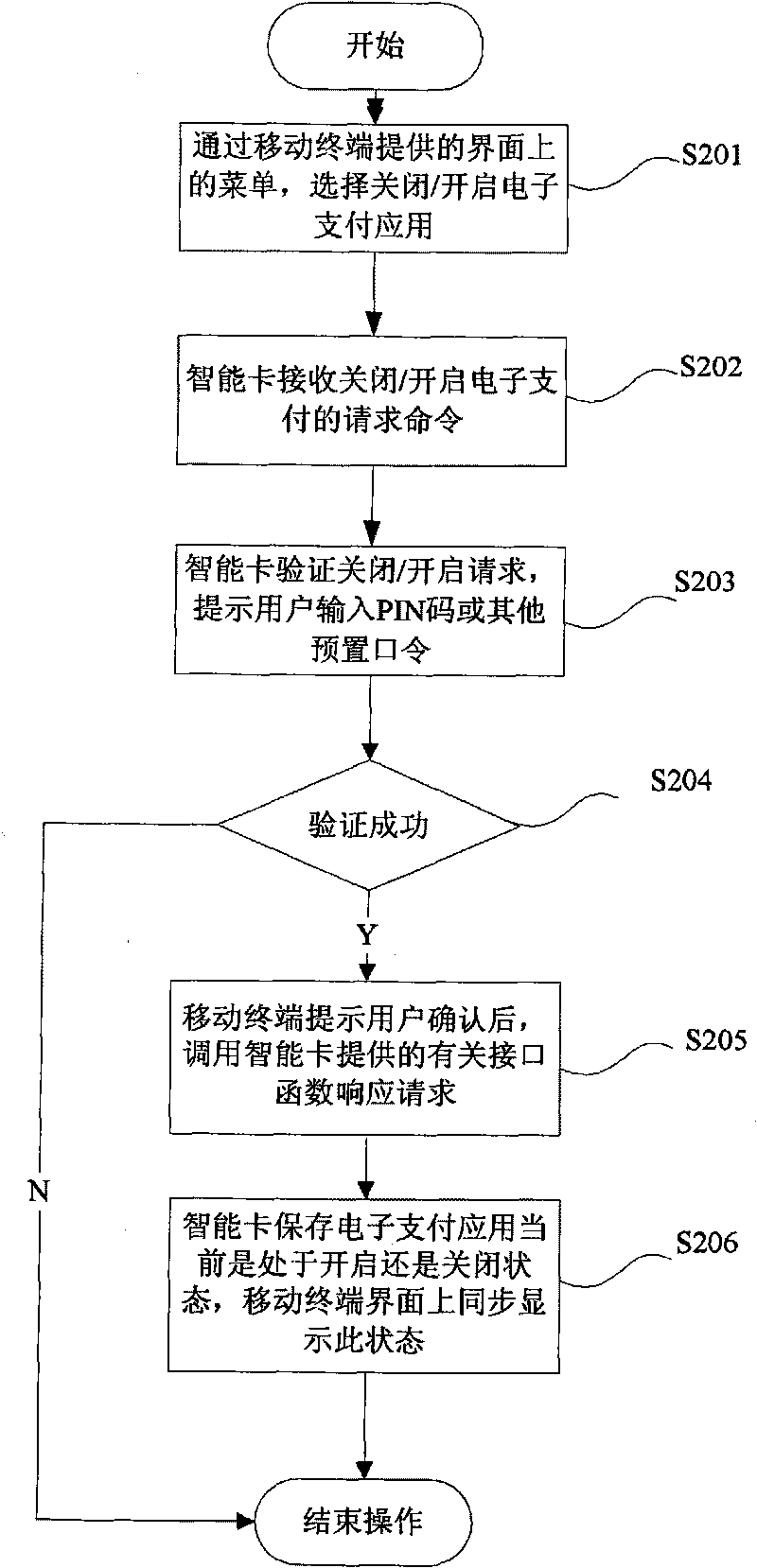

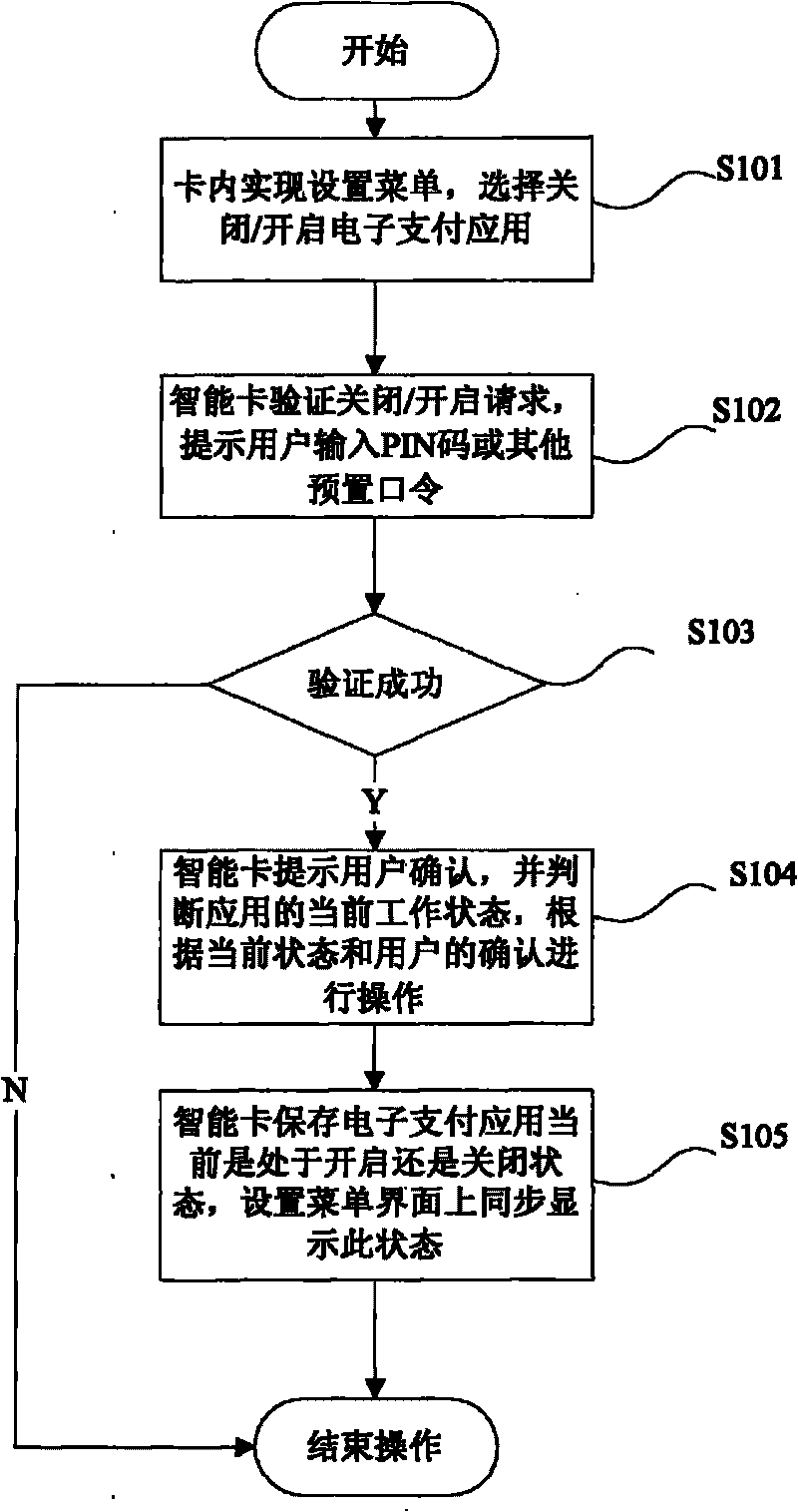

Method for closing and opening electronic payment application

InactiveCN101727705AOvercome flexibilityOvercome securityPayment architectureCoded identity card or credit card actuationPaymentUser needs

The invention discloses a method for closing and opening electronic payment application, comprising the following steps of: providing a setting for closing and opening the electronic payment application to an intelligent card on a mobile terminal; and carrying out corresponding setting on the mobile terminal when a user needs to close or open the electronic payment application. The invention solves the problems of the tradition electronic payment of the mobile terminal lacks of flexibility and has poor safety, and ensures that the user can close the functions of the electronic payment application during not using the electronic payment application, thereby preventing the electronic payment from being stolen and enhancing the safety of the electronic payment application; and when in needed use, the electronic payment application can be reopened and the user can use the functions of the electronic payment more flexibly and conveniently.

Owner:ZTE CORP

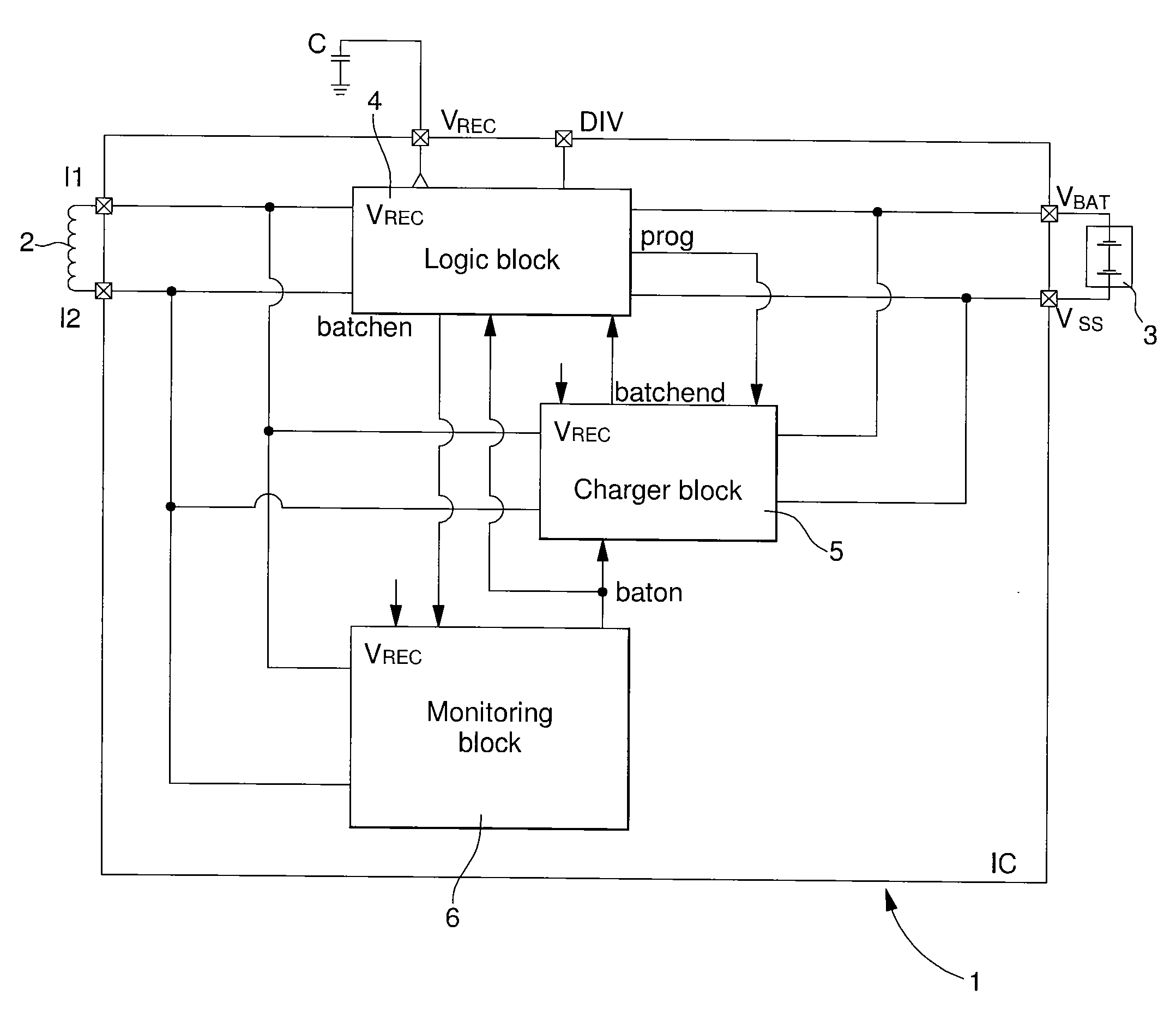

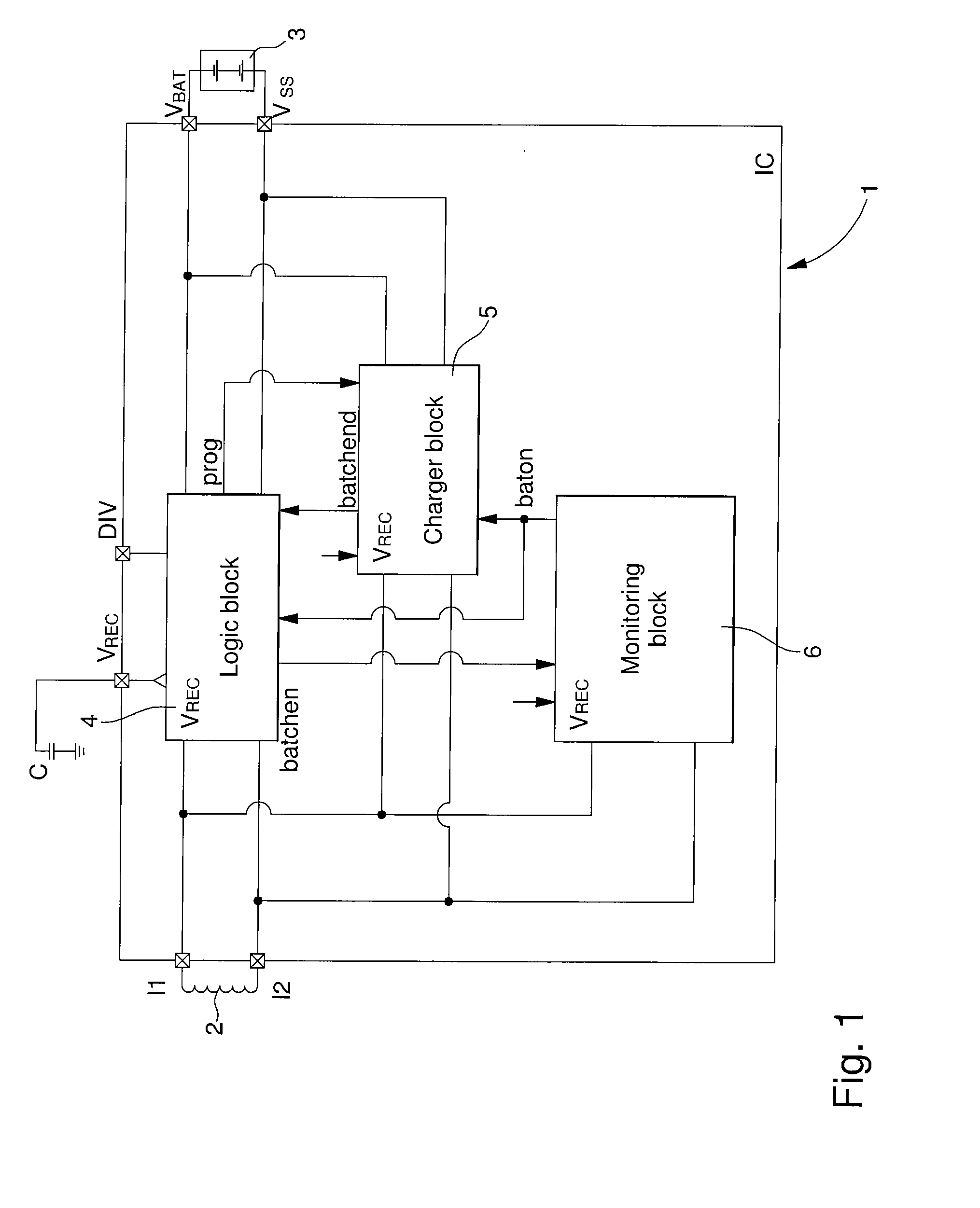

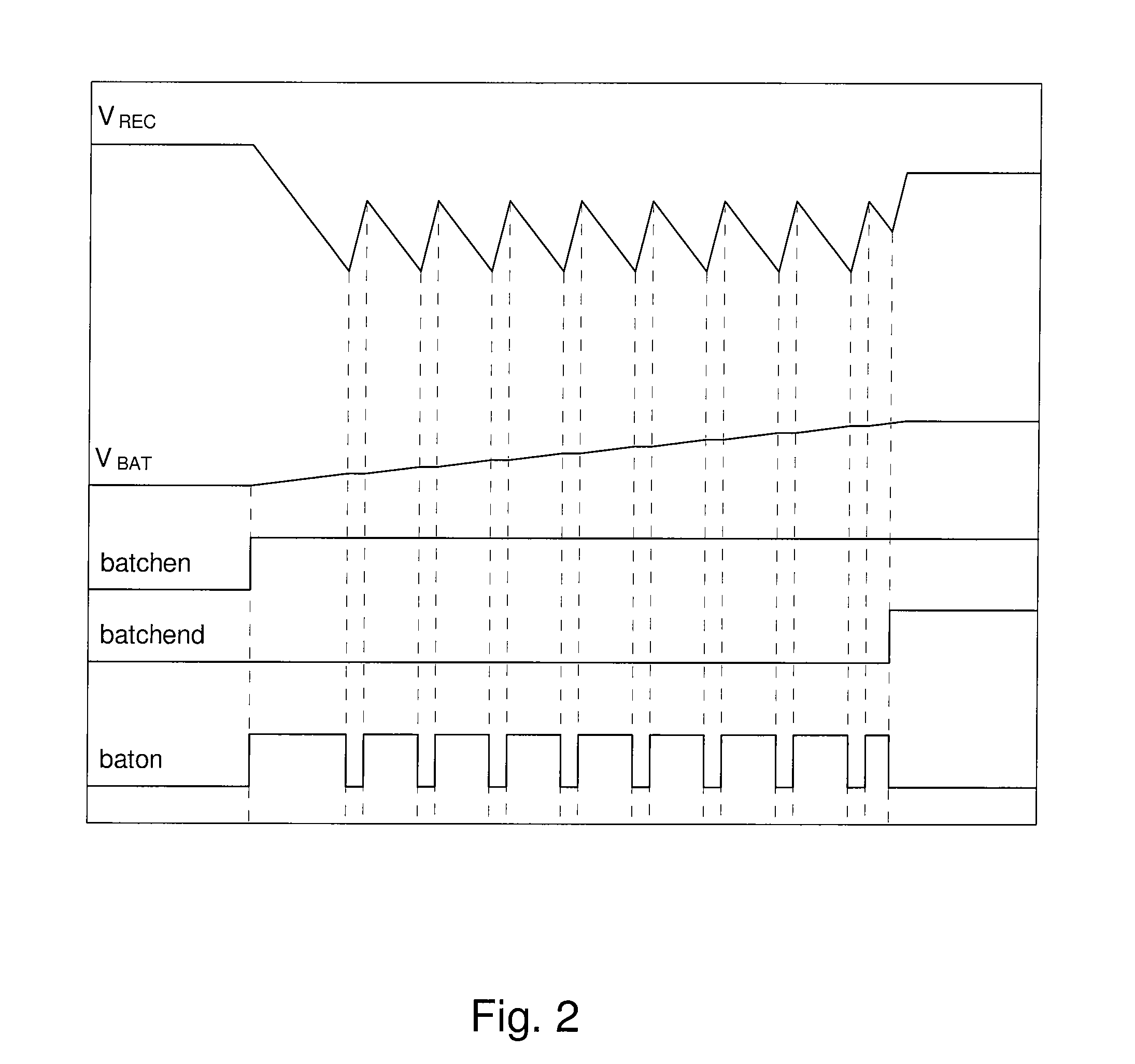

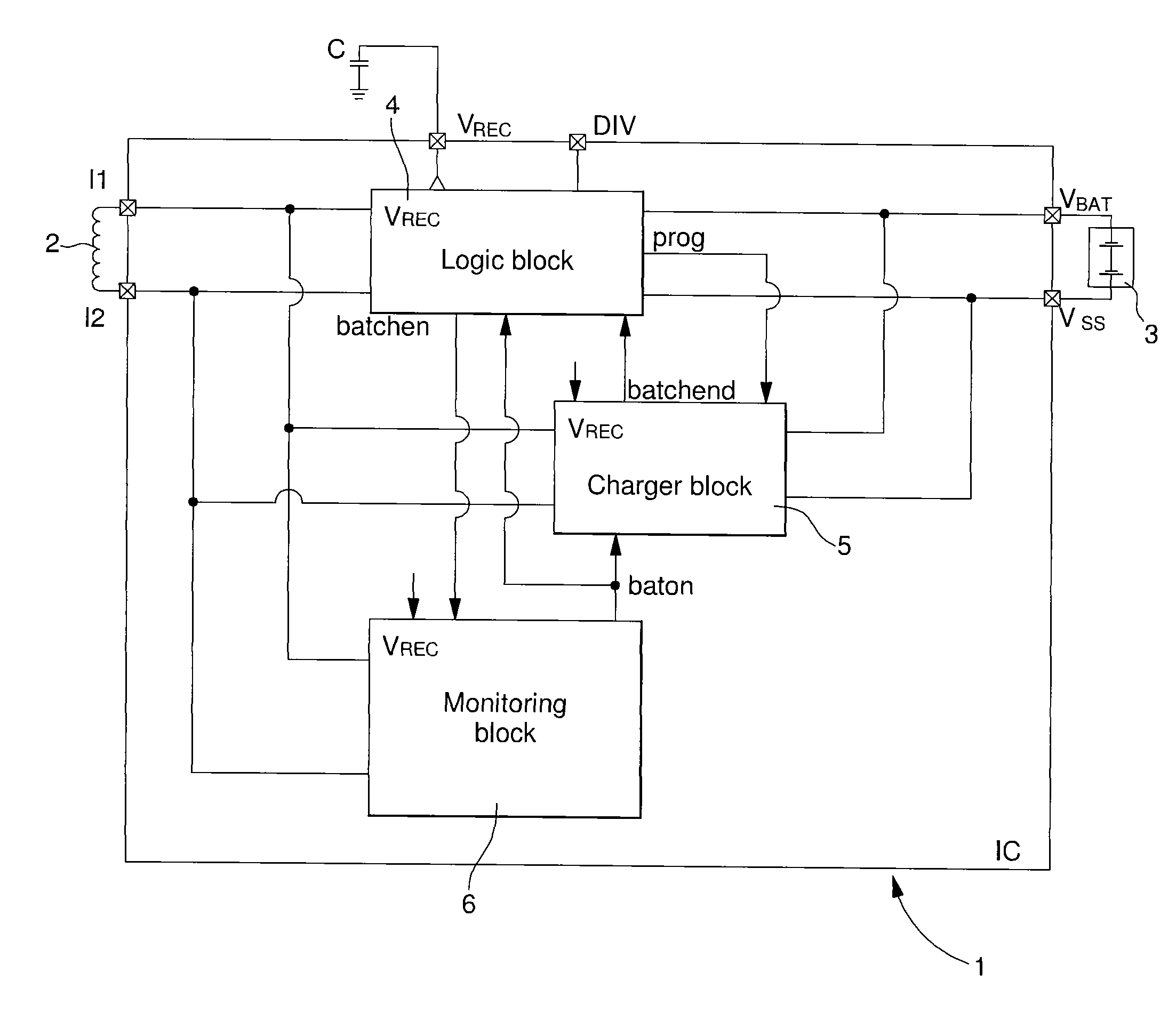

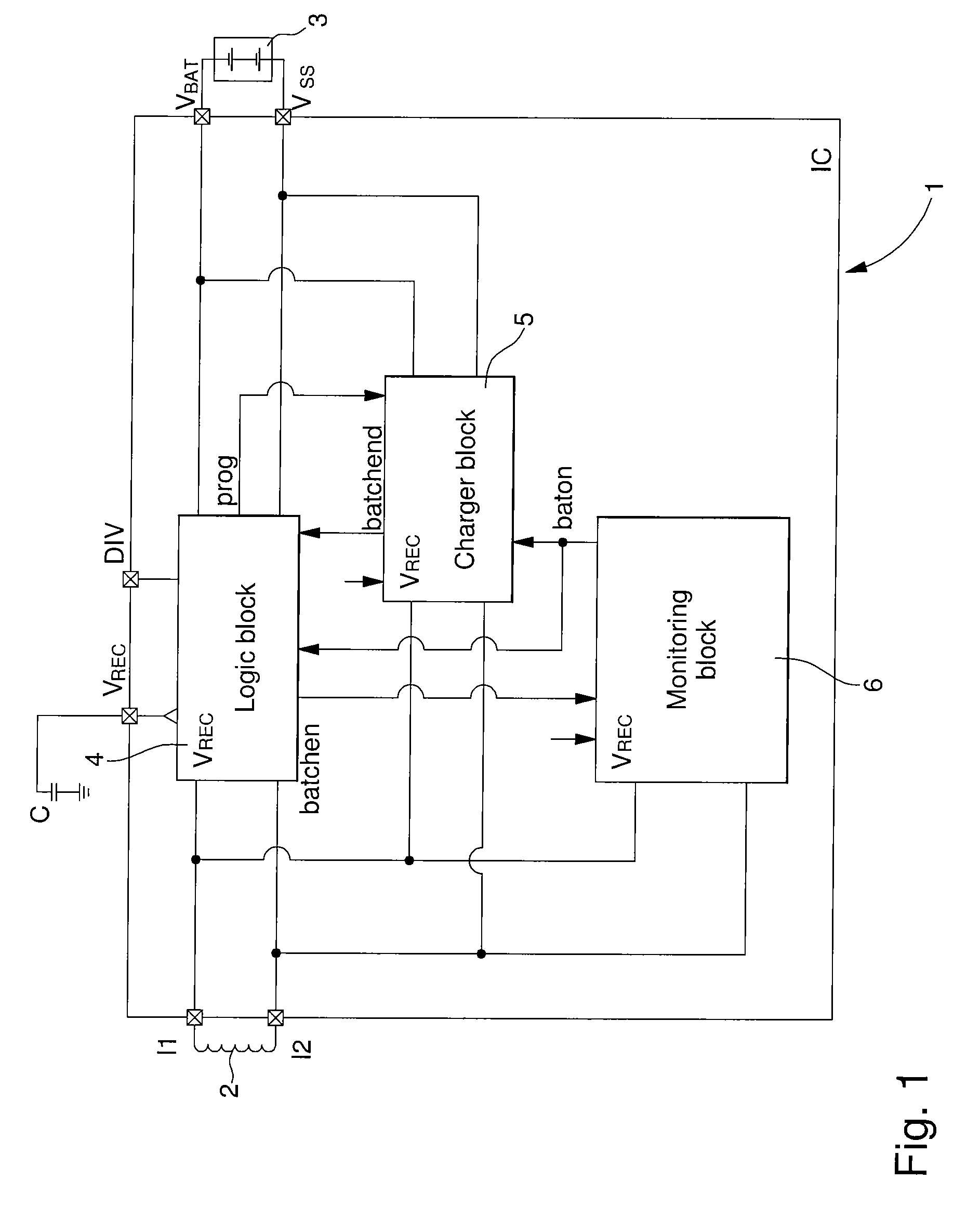

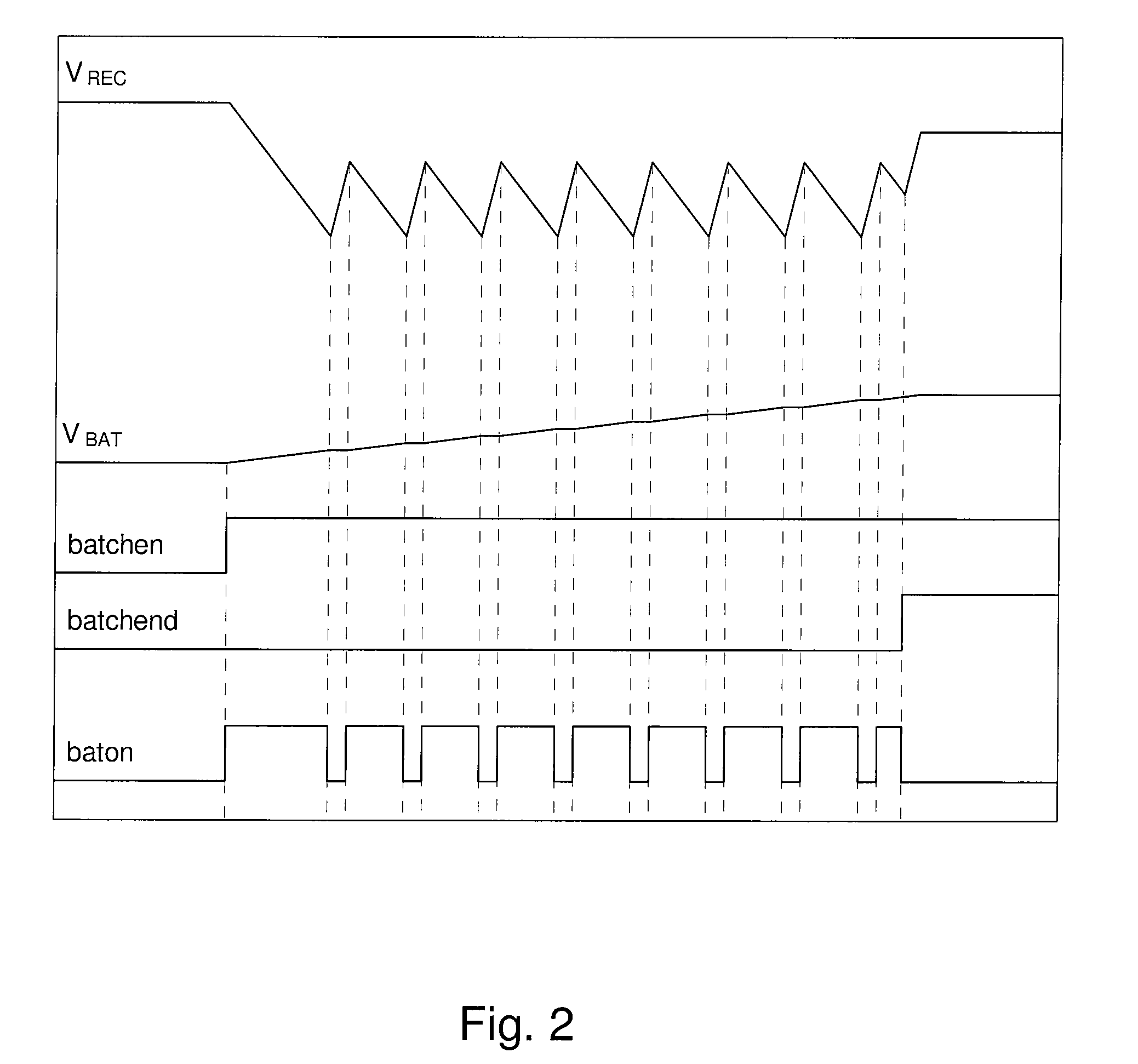

Battery charger operating "all or nothing" with a protective power supply circuit for monolithic integrated circuits using the antenna energy

ActiveUS20080150476A1Avoid operating efficiencyStart fastBatteries circuit arrangementsElectromagnetic wave systemControl signalElectrical battery

The invention concerns an integrated radiofrequency circuit (1) including an antenna (2) for receiving radiofrequency signals, a rechargeable battery (3) and a battery charger (5) using said radiofrequency signals to charge said battery. The circuit is characterized in that said battery charger is integrated in the same substrate as the integrated radiofrequency circuit and in that said battery charger includes calibrating means, a current source calibrated by said calibrating means and delivering a charge current of constant maximum intensity drawn from the received radiofrequency signals and a comparator between a reference quantity representative of the end of battery charge level and a variable quantity representative of the battery charge level supplying at output a control signal (batchend) for charging or not charging the battery.

Owner:EM MICROELECTRONIC-MARIN

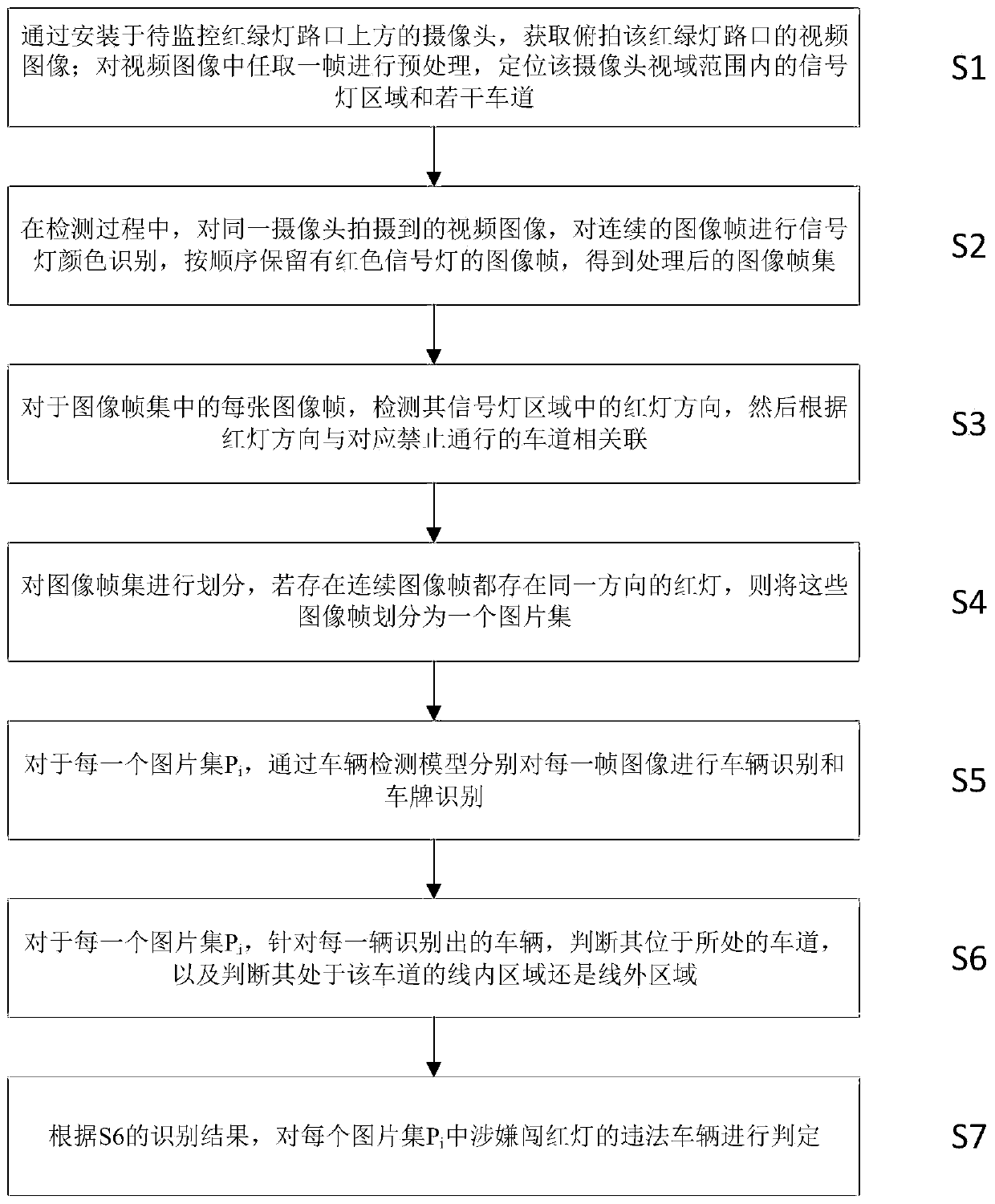

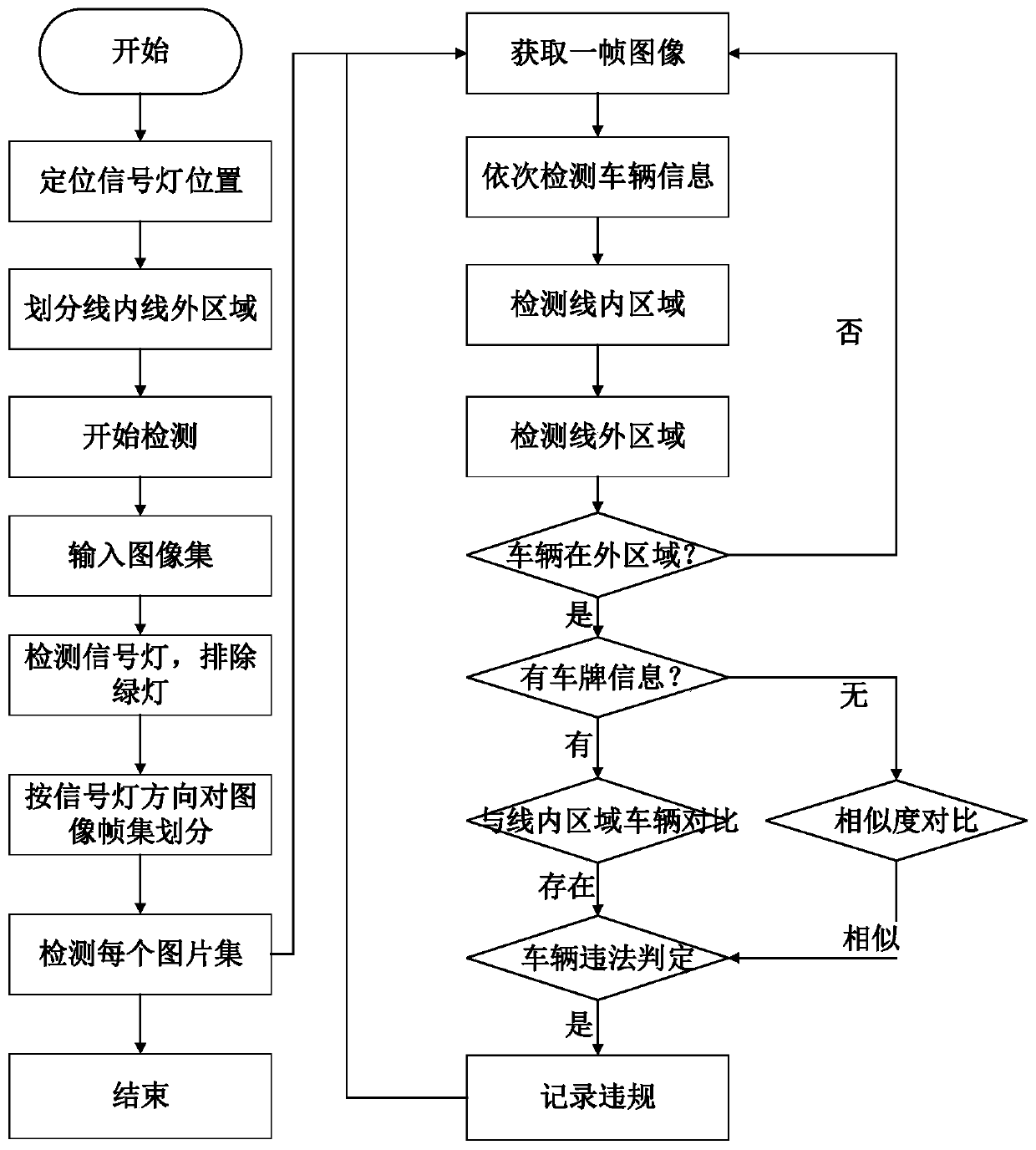

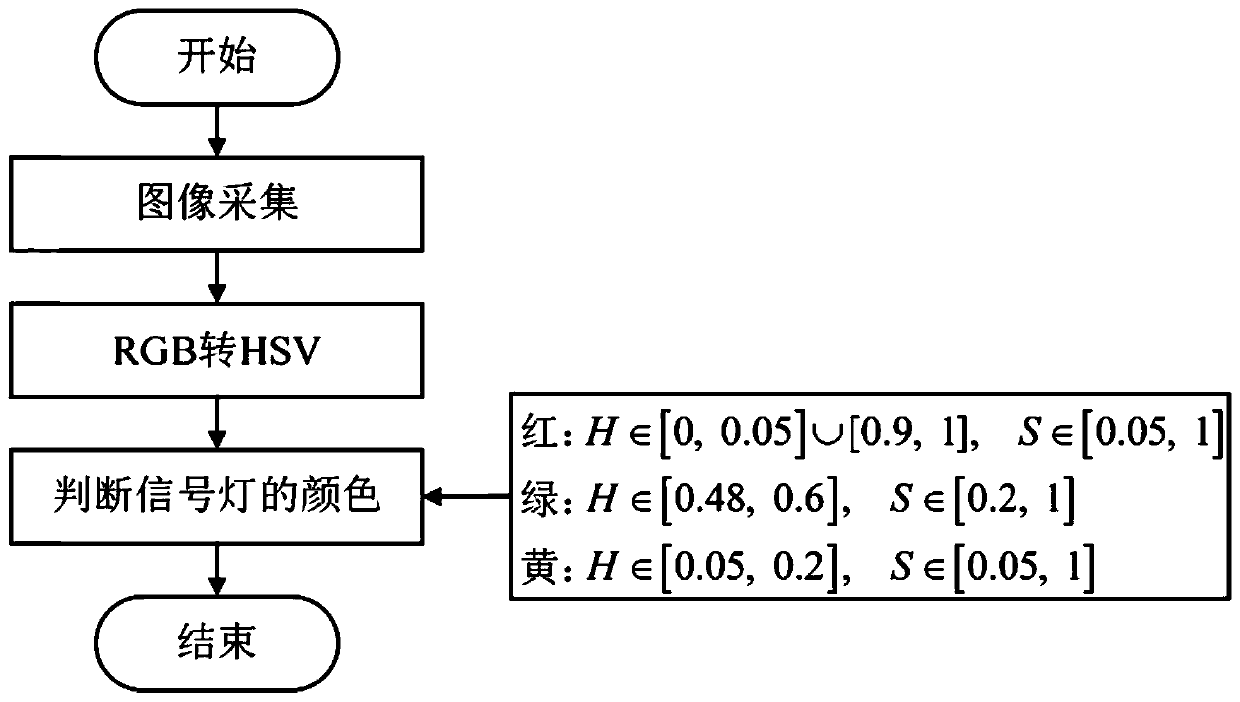

Deep learning-based red light violation detection method

ActiveCN110197589AOvercome costsOvercome efficiencyDetection of traffic movementCharacter and pattern recognitionTraffic violationComputer science

The invention discloses a deep learning-based red light violation detection method, which relates to the field of traffic violation detection. The positions of lanes and traffic lights at a traffic light intersection are determined in advance, and the traffic lights are matched with the corresponding lanes. The condition at the traffic light intersection is photographed and recorded through a camera, a photo set transmitted by the camera later is processed centrally, and whether a vehicle has a red light violation behavior is judged based on the positions of the same vehicle under the same traffic light on different photo frames. Besides, as for an off-line vehicle that is unrecognizable due to a long distance, whether to be a known vehicle is recognized in a vehicle similarity comparisonmethod. Various algorithms and models are combined, and the novel traffic violation detection method meets the requirements of violation detection accuracy and flexibility by urban road traffic management.

Owner:HANGZHOU TRUSTWAY TECH

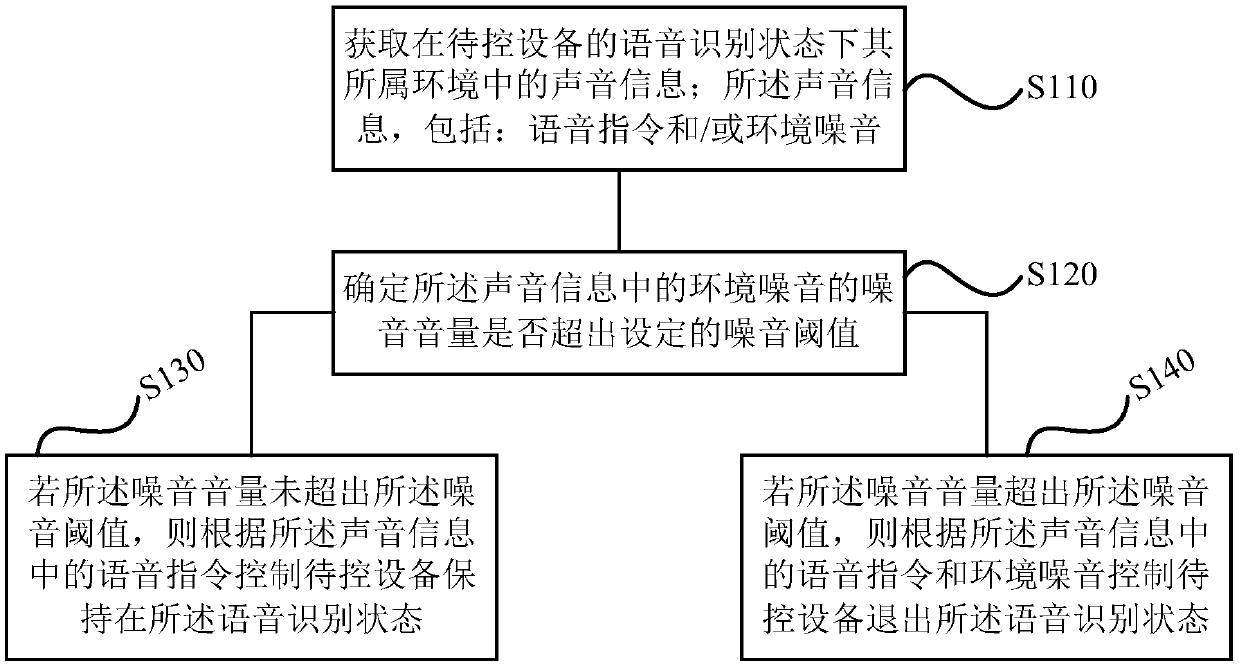

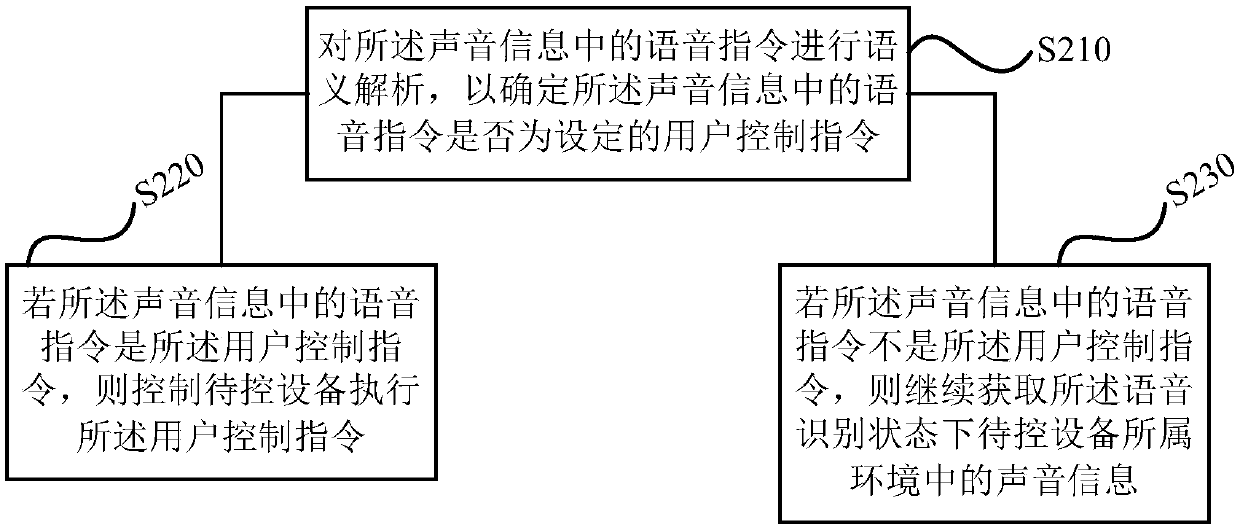

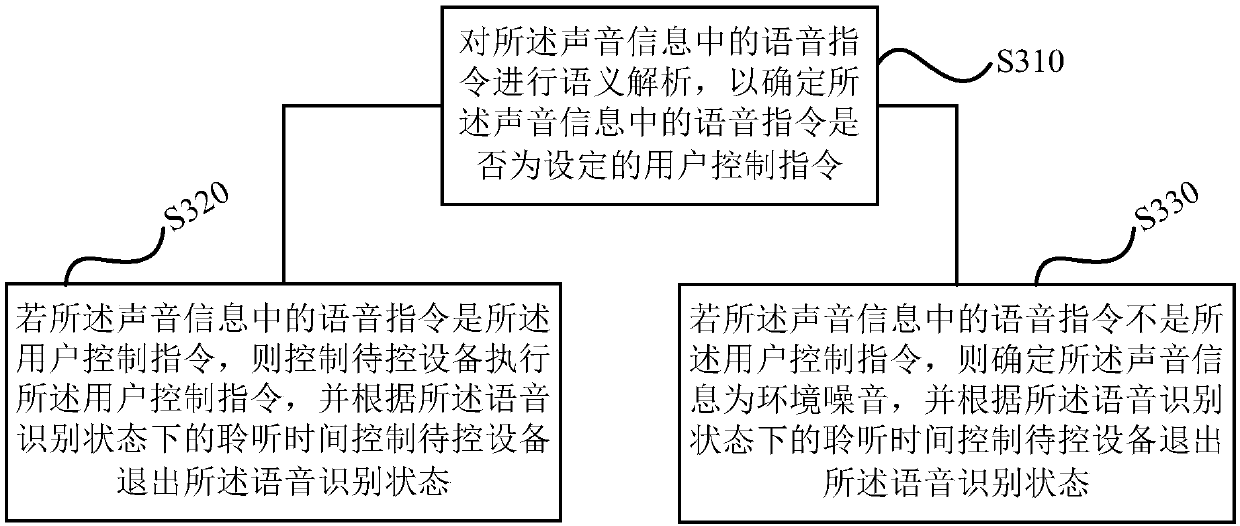

Speech control method and device, storage medium and air conditioner

ActiveCN109671426AImprove experienceInteractive friendly intelligenceMechanical apparatusSpace heating and ventilation safety systemsEnvironmental noiseSpeech sound

The invention discloses a speech control method and device, a storage medium and an air conditioner. The speech control method comprises the steps that sound information of the environment where to-be-controlled equipment belongs is obtained under a speech recognition state of the to-be-controlled equipment, wherein the sound information includes speech instructions and / or environmental noise; whether the volume of the environmental noise in the sound information exceeds a preset noise threshold or not is determined; if not, the to-be-controlled equipment is controlled to be kept in the speechrecognition state according to the speech instructions in the sound information; if yes, the to-be-controlled equipment is controlled to quit the speech recognition state according to the speech instructions and the environmental noise in the sound information. According to the scheme, the problem that due to misoperation, the behavior of controlling awakening words is repeated and accordingly the user experience is affected is solved, and the effect of improving the user experience is achieved.

Owner:GREE ELECTRIC APPLIANCES INC

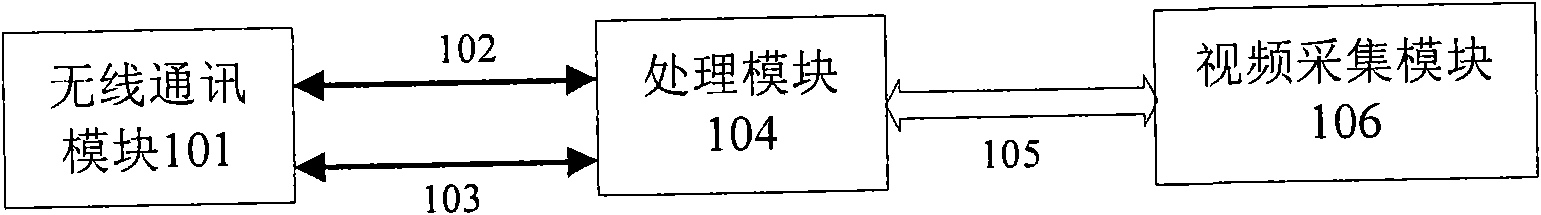

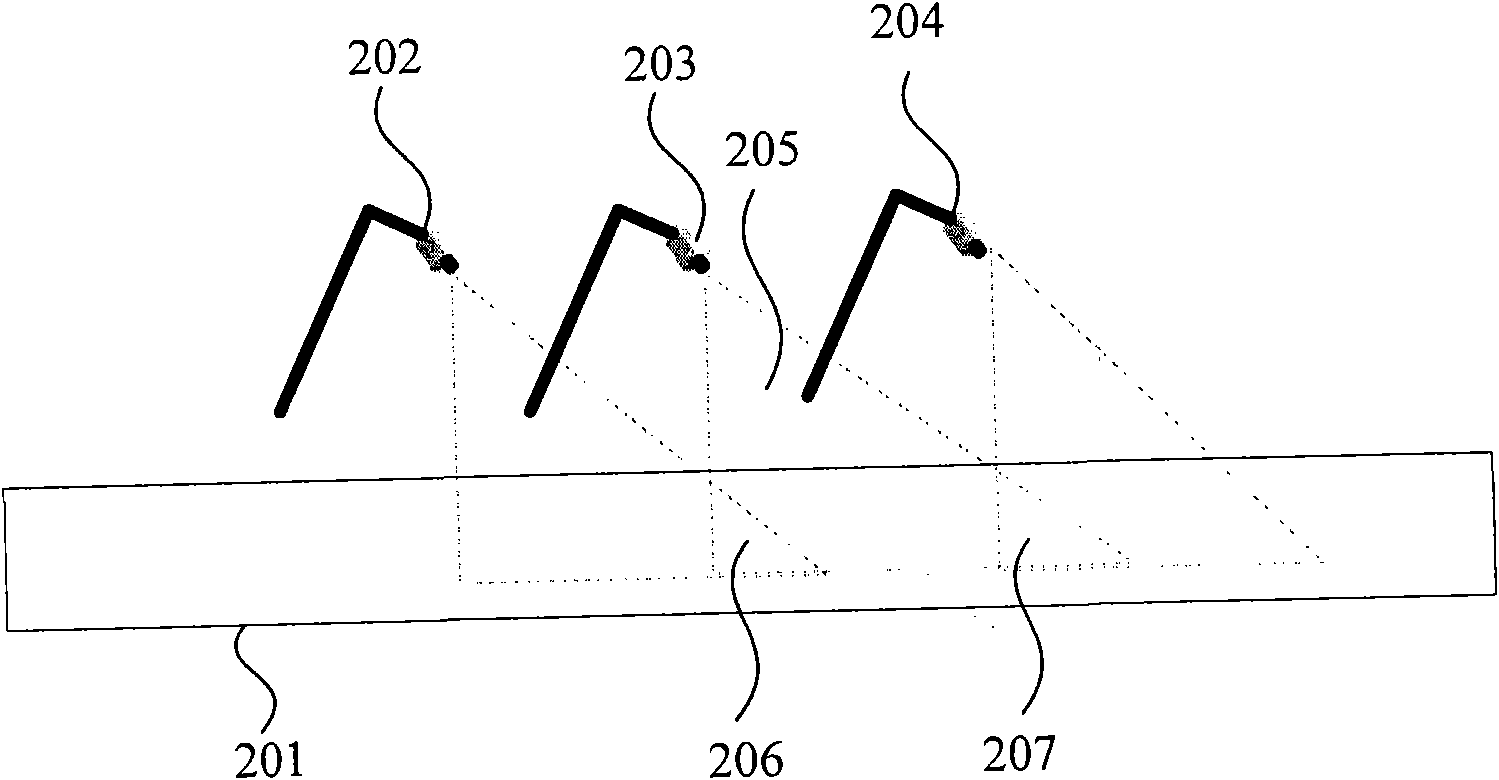

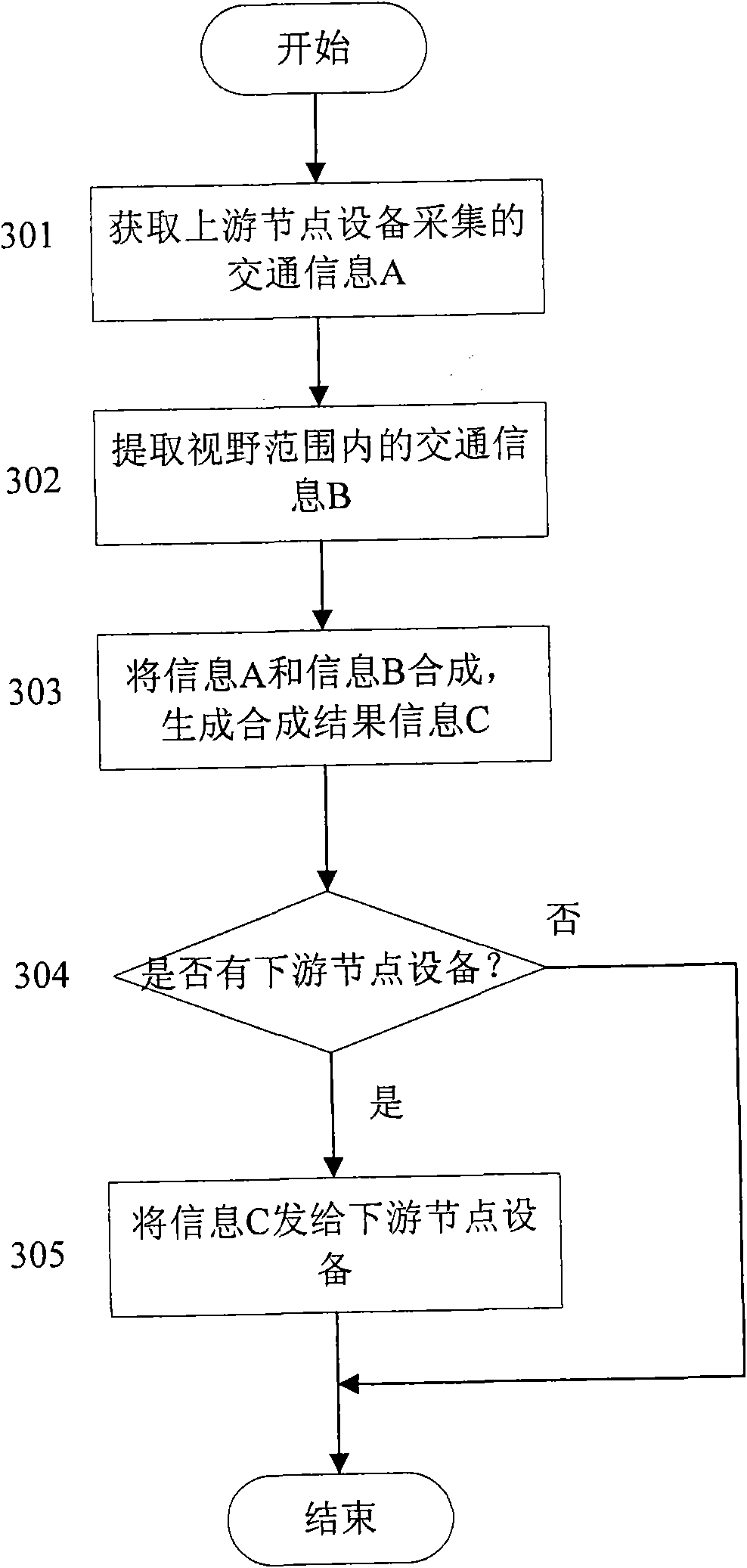

Device and method for acquiring traffic information

InactiveCN101540104AImprove collection qualityImprove real-time performanceDetection of traffic movementVisual field lossTraffic capacity

The invention discloses a device and a method for acquiring traffic information. A plurality of node devices for traffic information acquisition based on video are arranged on one side of a road one by one, and are used for acquiring the information of two-way traffic flow on the road. The adjacent node devices communicate with each other in a wireless mode so as to form a wireless sensor network. Visual fields of adjacent node devices have a covered overlap region used for providing the adjacent node devices with cooperation time and space. Through the traffic information synthesis of the adjacent node devices, a lowest-reaches node obtains the traffic information in a whole range. The node devices communicate through a Zigbee protocol, and the synthesis of overall information from the traffic information acquired by the node devices is realized through the cooperation of the adjacent node devices. The acquired traffic information comprises road flow rate, occupancy, average velocity and motion tracks of vehicles. The invention has the characteristics of flexible network structure, as well as the wide range and high real-time property of the acquired traffic information.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

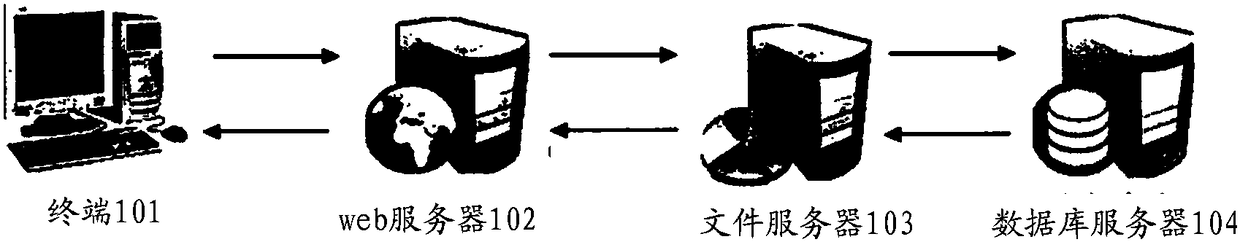

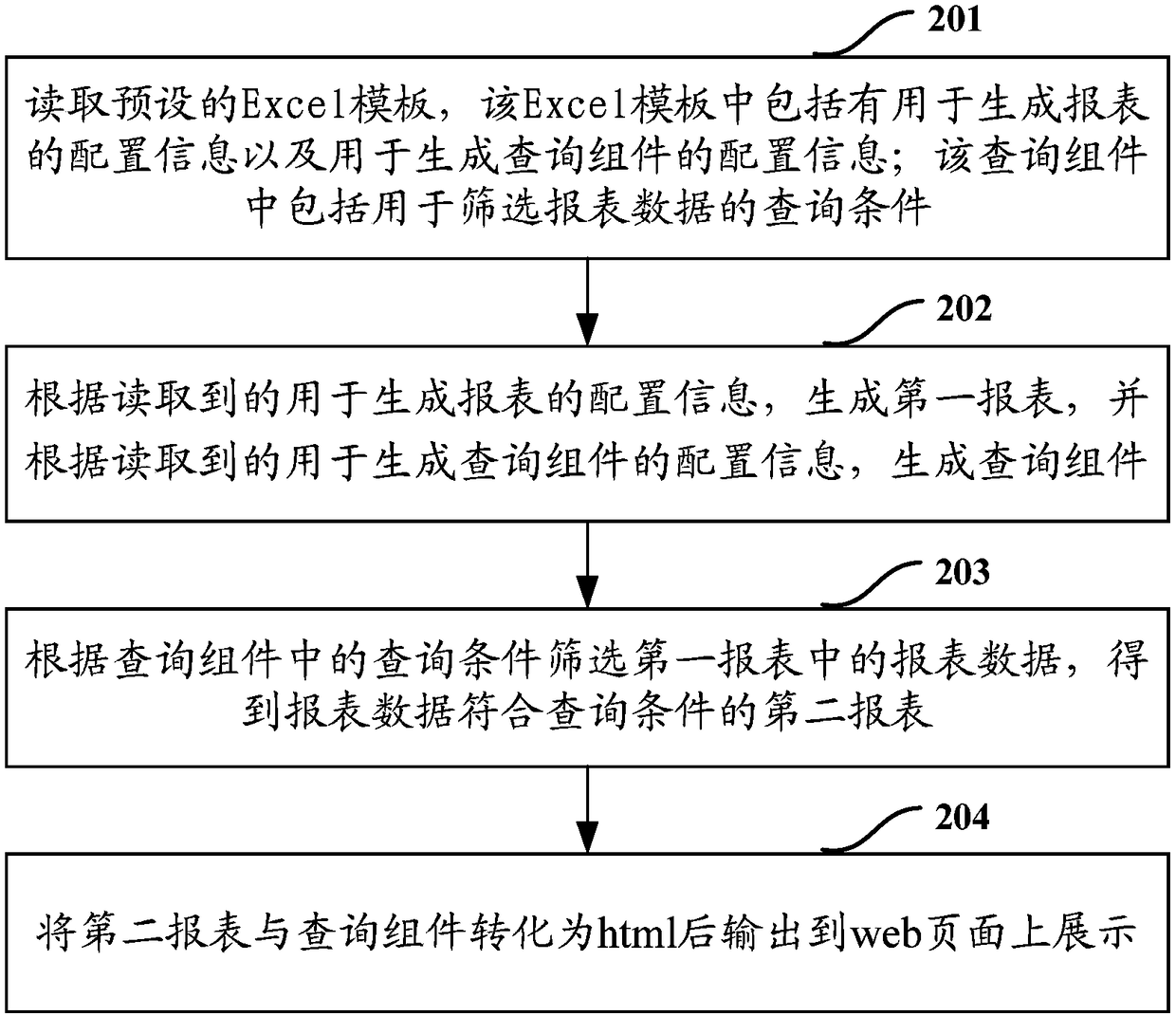

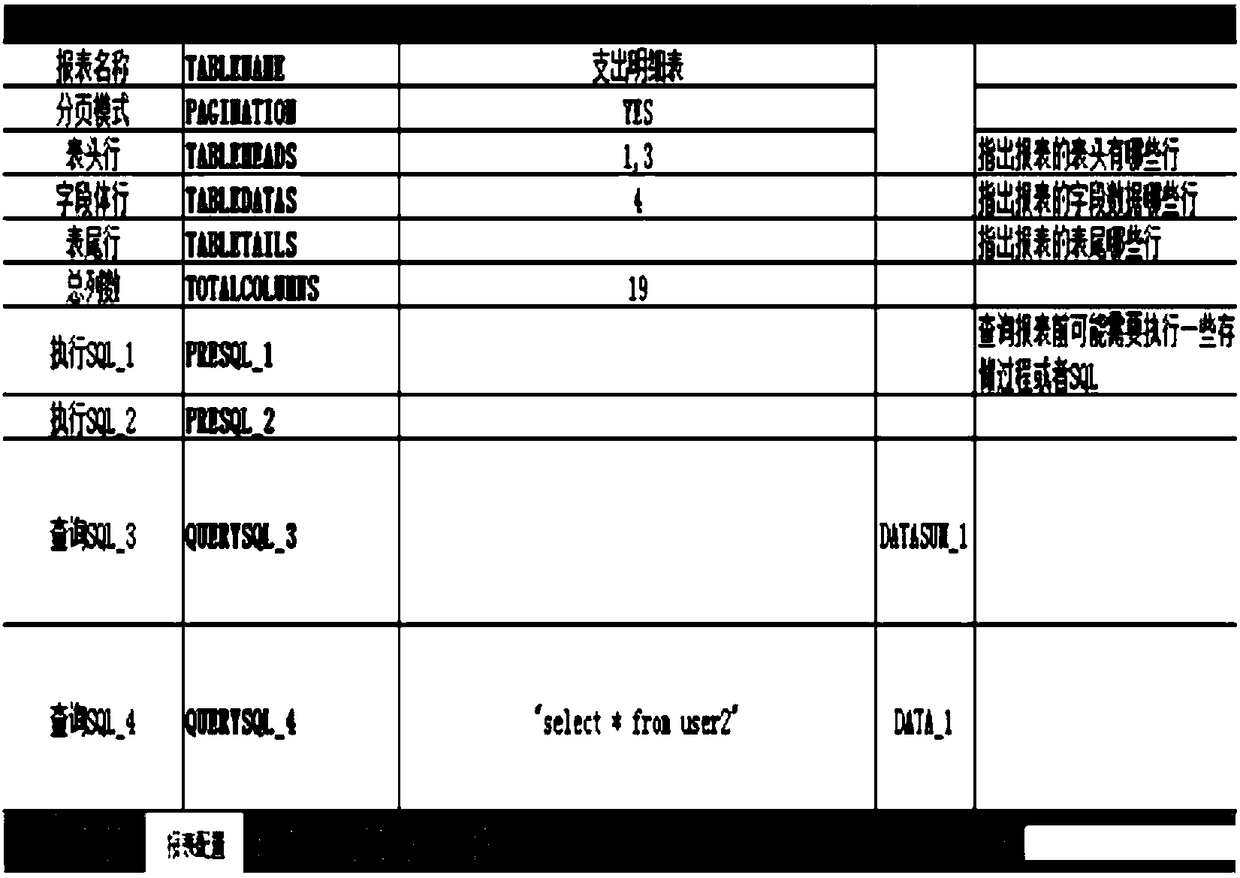

Report form realization method and device based on Excel template

InactiveCN108268525AOvercome flexibilityOvercome workloadSpecial data processing applicationsWeb pageDatabase

The invention discloses a report form realization method and device based on an Excel template. The method of the invention includes: reading the preset Excel template, wherein the Excel template includes configuration information used for generating a report form and configuration information used for generating a query component, and the query component includes query conditions used for screening report form data; generating the first report form according to the read configuration information used for generating the report form, and generating the query component according to the read configuration information used for generating the query component; screening the report form data in the first report form according to the query conditions in the query component to obtain a second report form of which report form data meet the query conditions; and converting the second report form and the query component into contents of a hypertext markup language, and then outputting the same onto a web page for display. The invention provides a report form realization scheme capable of flexibly generating the report form, and displaying and querying the report form on the same web page.

Owner:深圳市优朋普乐传媒发展有限公司

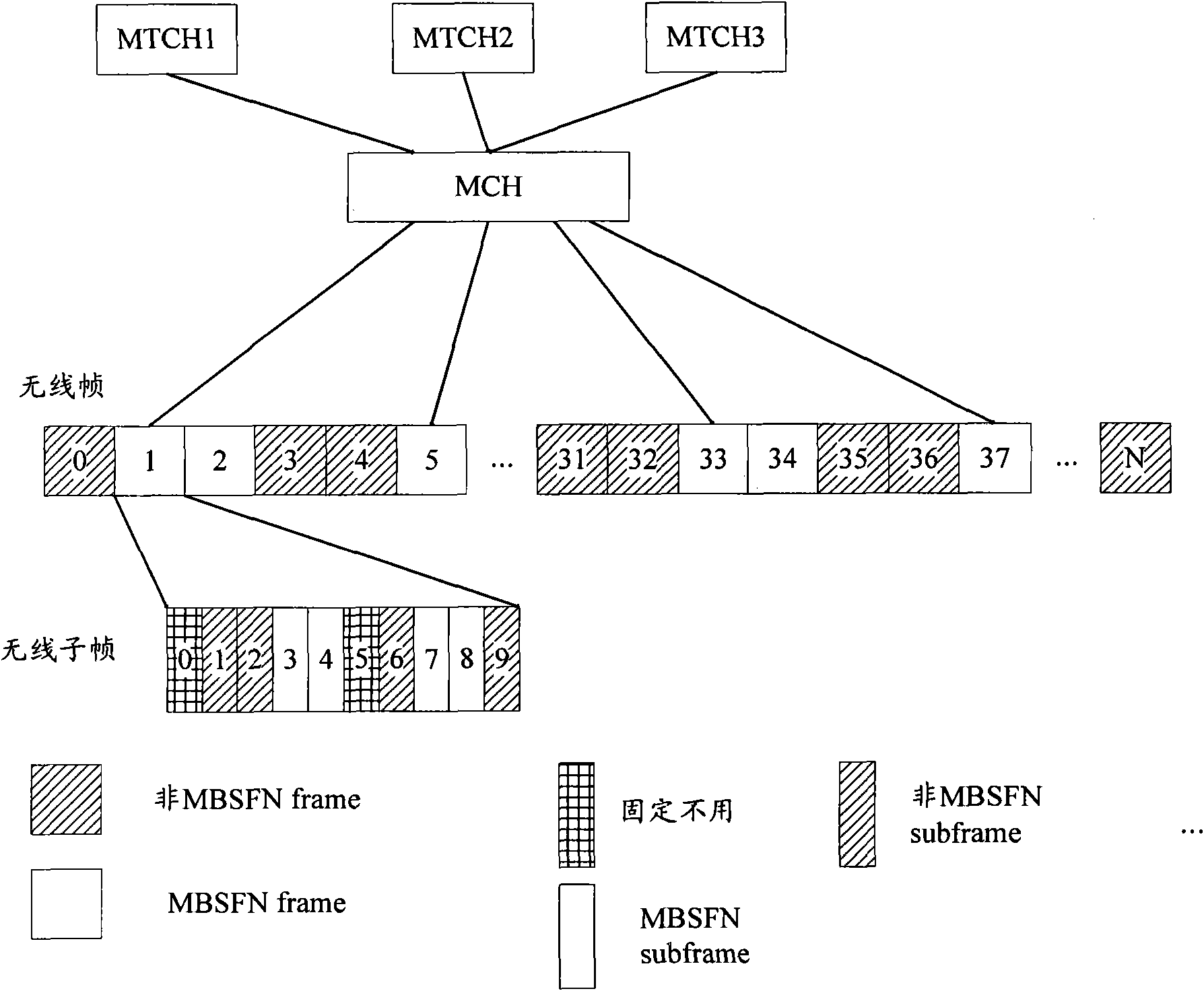

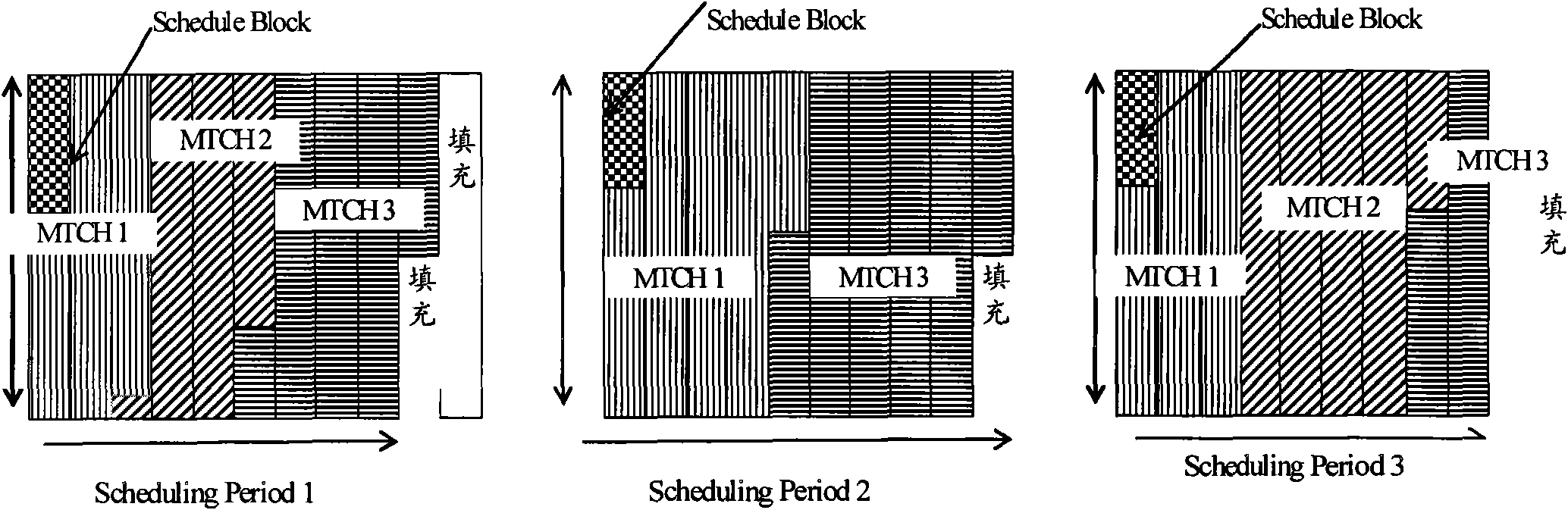

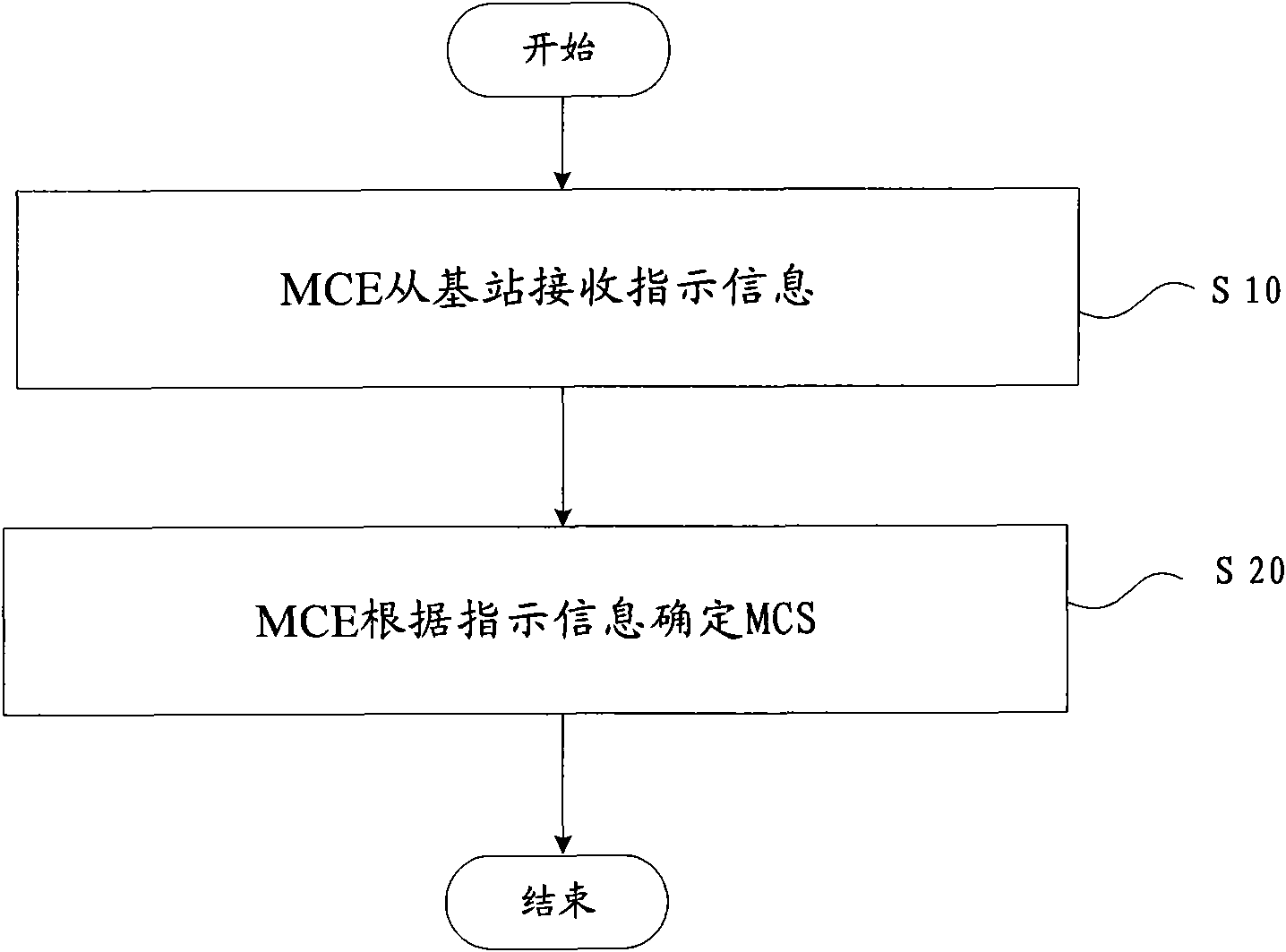

MBMS demodulating and coding solution (MCS) determining method and MCE

InactiveCN101925006AFlexible adjustmentOvercome flexibilityBroadcast service distributionMessaging/mailboxes/announcementsBroadcast multicastMultimedia broadcasting

The invention provides a method for determining the MCS of an MBMS, which comprises the following steps that: an MCE receives indication information from a base station; and the MCE determines the MCS according to the indication information. The invention also provides the MCE, which comprises a receiving module for receiving the indication information from the base station and a determination module for determining the MCS according to the indication information. In the invention, as the MCE is notified of the MCS auxiliary determination information of the MBMS through the indication information, the MCS can be adjusted flexibly by sending the indication information dynamically; therefore, the drawback that the corresponding MCS of a certain multimedia broadcast multicast service cannot be set and regulated flexibly in the application of the conventional multimedia broadcast multicast technology is overcome.

Owner:ZTE CORP

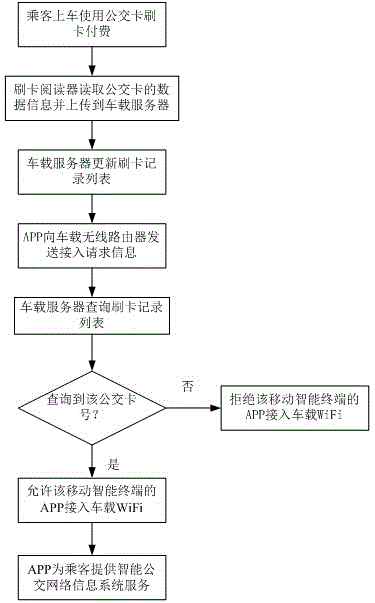

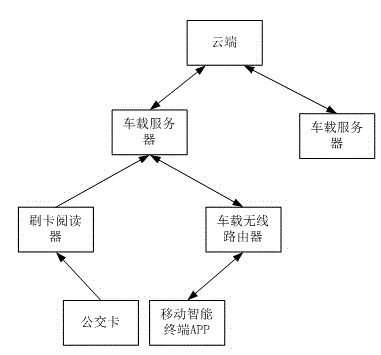

Achievement method of intelligent public transportation network information service system

ActiveCN104468770AOvercome flexibilityOvercoming real-timeAssess restrictionNetwork topologiesComputer hardwareWireless router

The invention discloses an achievement method of an intelligent public transportation network information service system. A card swiping reader reads data information including bus card number of a bus card and uploads the data information to a vehicle-mounted server. The vehicle-mounted server receives the bus card data information uploaded by the card swiping reader and updates a card swiping record list. An APP of a mobile intelligent terminal sends access request information carrying the bus card number to a vehicle-mounted wireless router and queries whether the bus card number exists in the card swiping record list or not so as to decide whether the APP of the mobile intelligent terminal is permitted to be connected to vehicle-mounted WiFi. By means of the achievement method of the intelligent public transportation network information service system, the defect that existing vehicle-mounted WiFi access modes including paper verification codes, short message verification codes and the like are not flexible and intelligent and are poor in real-timeliness and the like is overcome, and the vehicle-mounted WiFi can be quickly and intelligently accessed for a passenger who swiped the card. In addition, abundant information service can be provided for passengers by means of the achievement method.

Owner:GUANGDONG UNIV OF TECH

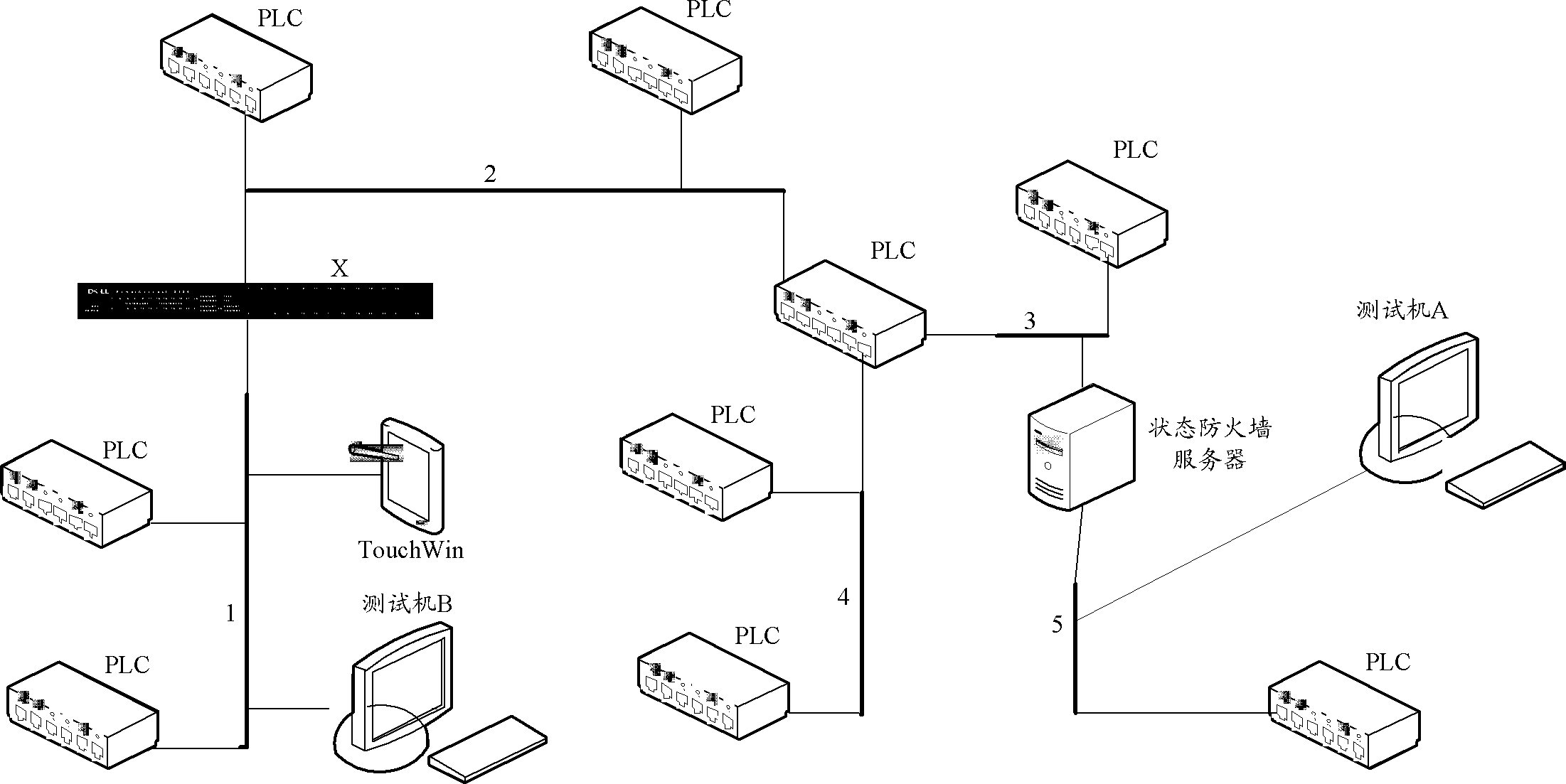

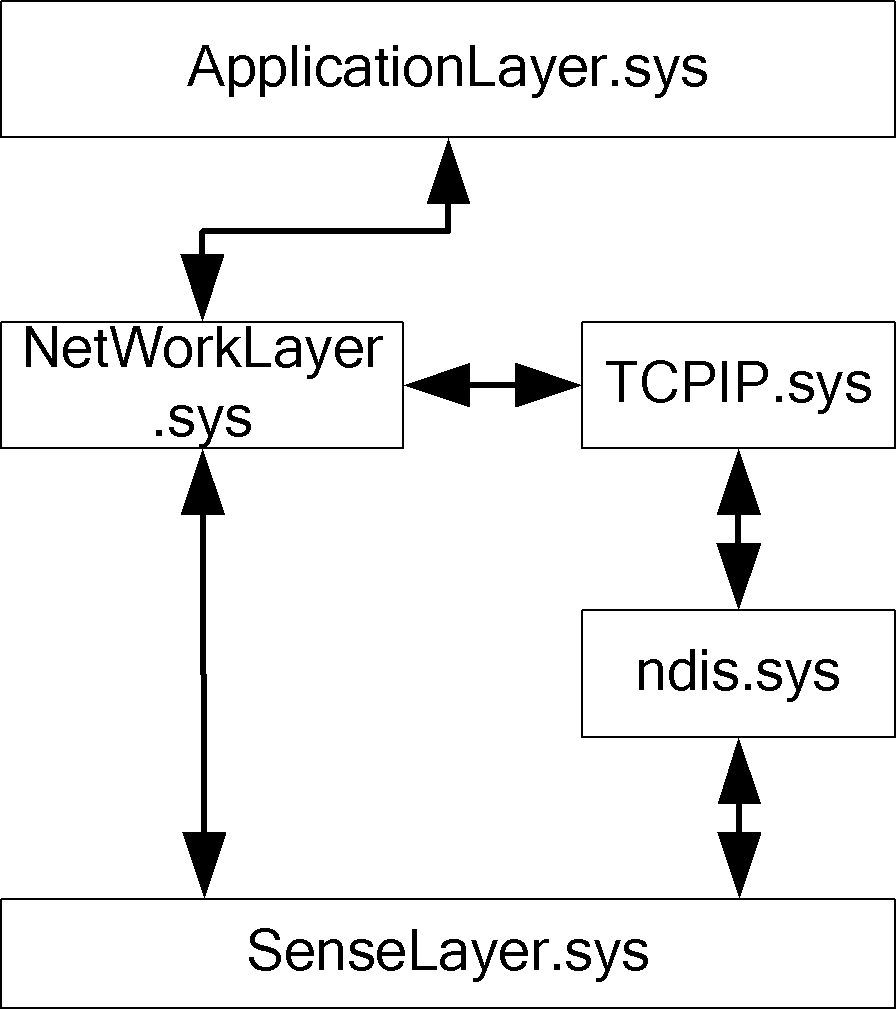

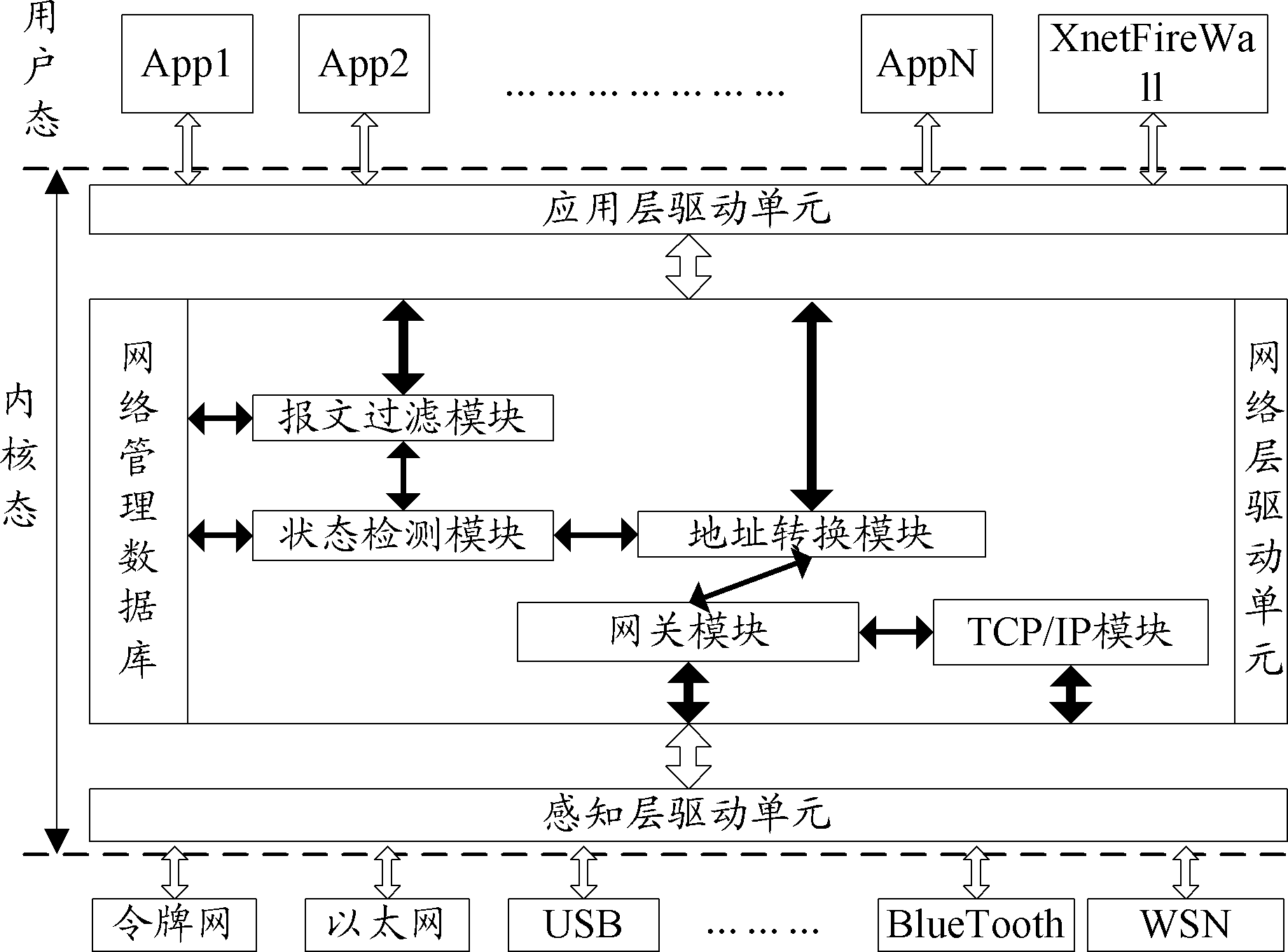

State firewall state detection system and method based on industrial Internet of Things

InactiveCN103607316AOvercome strengthOvercome speedData switching networksState of artNetwork management

The invention discloses a state firewall state detection system and a method based on the industrial Internet of Things. The system comprises an application layer drive unit used for driving user side application layer programs and / or files, a sensing layer drive unit used for driving information interaction ports, a network state detection unit used for detecting and processing the network state of the industrial Internet of Things, and a network management database used for serving the network state detection unit and matched therewith and a network layer drive unit, wherein the application layer drive unit, the network state detection unit and the sensing layer drive unit are in communication connection in sequence. The state firewall state detection system and the method based on the industrial Internet of Things in the invention can overcome the defects of weak protocol stack architecture support force, slow detection speed, and poor flexibility in the prior art, so as to realize the advantages of strong protocol stack architecture support force, fast detection speed and good flexibility.

Owner:WUXI XINJIE ELECTRICAL

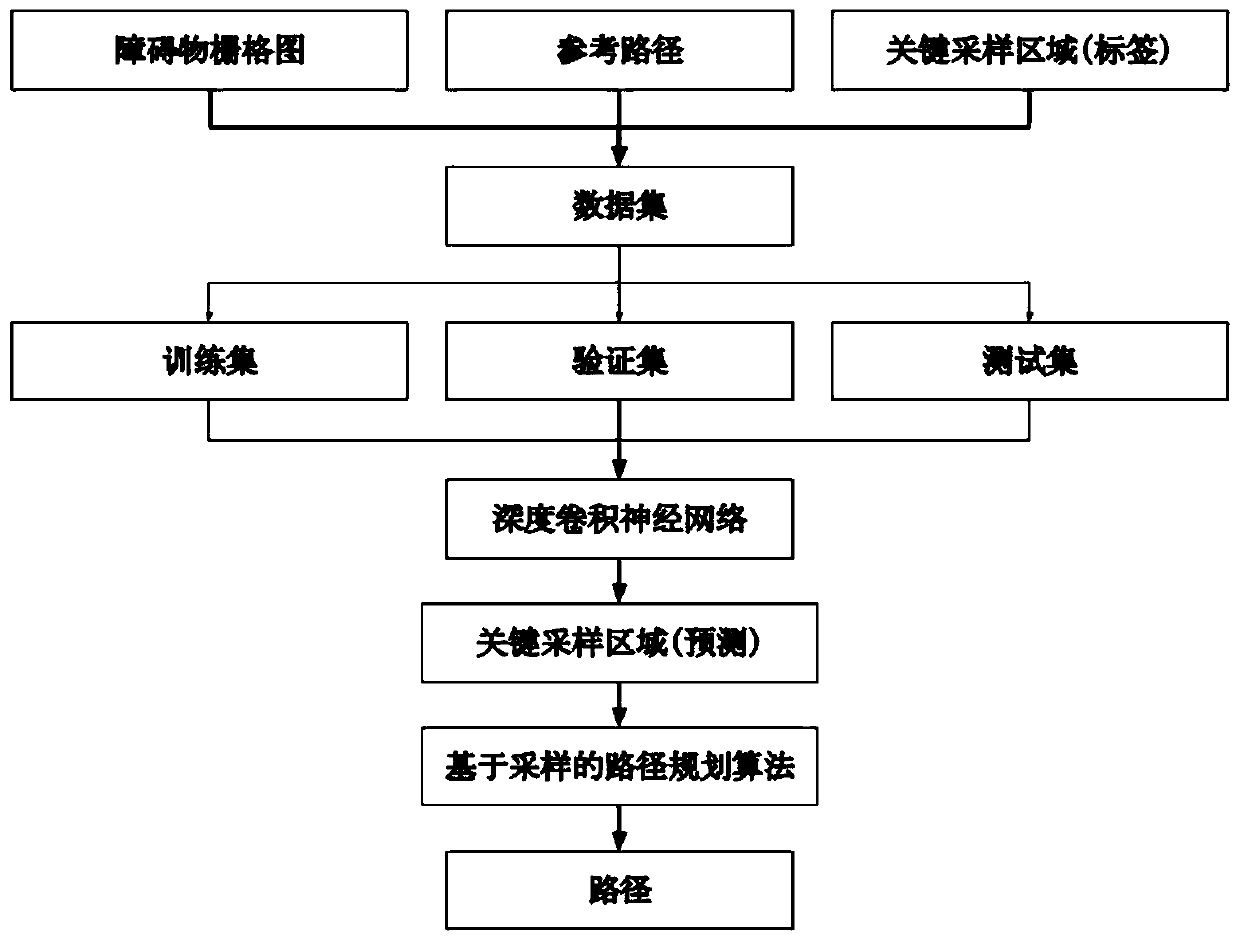

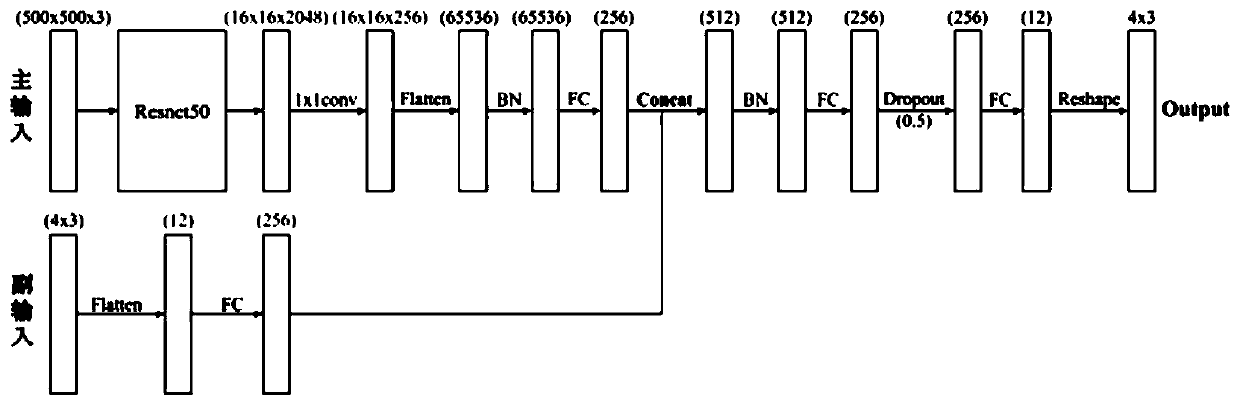

Autonomous vehicle path planning method based on deep convolutional neural network

ActiveCN110244734AAchieving safe cruisingIncrease flexibilityPosition/course control in two dimensionsVehiclesNerve networkSimulation

The invention relates to an autonomous vehicle path planning method based on a deep convolutional neural network. The method comprises the following steps: firstly, building a deep convolutional neural network model; secondly, acquiring a barrier grid map of a vehicle under different driving environments, and a corresponding reference path for building a sample database for the training, verification and testing of the deep convolutional neural network model; and finally, applying the trained and tested deep convolutional neural network model to the autonomous vehicle, inputting the barrier grid map and the reference path into the neural network in real time, generating a key sampling area, and sampling, planning and generating a path from the key sampling area by using a sampling-based path planning algorithm. Through adoption of the autonomous vehicle path planning method, the problem that the prediction error cannot be avoided in an end-to-end method is solved; the running track of an autonomous vehicle is more stable and controllable; the defect of lack in sensitivity and adaptivity of a method for selecting a path from a preset path set is overcome; the path planning flexibility is improved; and meanwhile the path quality is ensured.

Owner:SUN YAT SEN UNIV

Battery charger operating “all or nothing” with a protective power supply circuit for monolithic integrated circuits using the antenna energy

ActiveUS7952323B2Accurate chargesOvercome flexibilityBatteries circuit arrangementsElectric powerControl signalElectrical battery

An integrated radiofrequency circuit (1) is provided that includes an antenna (2) for receiving radiofrequency signals, a rechargeable battery (3) and a battery charger (5) using the radiofrequency signals to charge said battery. The circuit is characterized in that the battery charger is integrated in the same substrate as the integrated radiofrequency circuit and in that the battery charger includes a calibrating mechanism, a current source calibrated by the calibrating mechanism and delivering a charge current of constant maximum intensity drawn from the received radiofrequency signals, and a comparator between a reference quantity representative of the end of battery charge level and a variable quantity representative of the battery charge level supplying at output a control signal (batchend) for charging or not charging the battery.

Owner:EM MICROELECTRONIC-MARIN

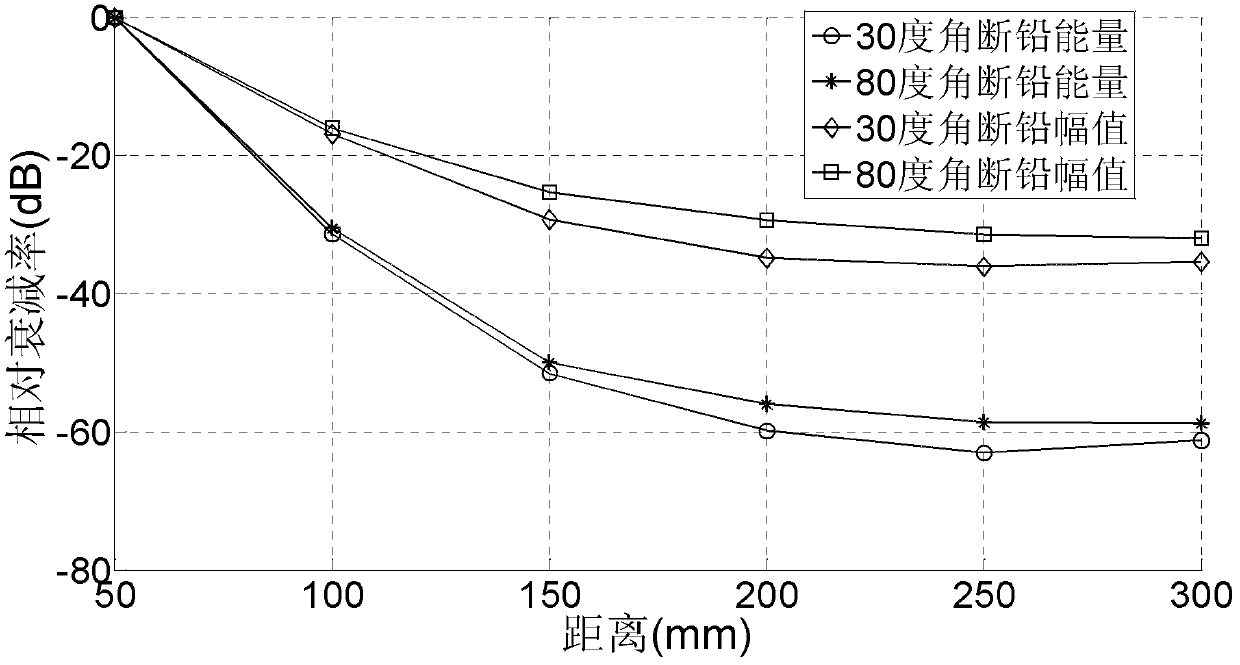

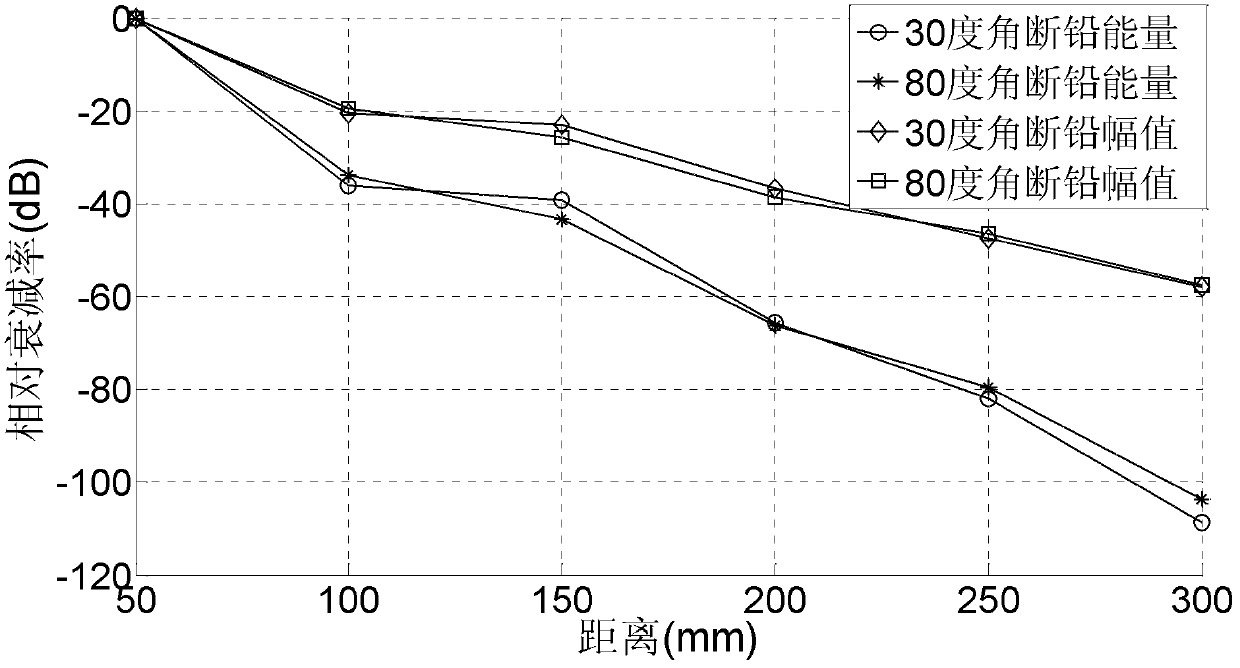

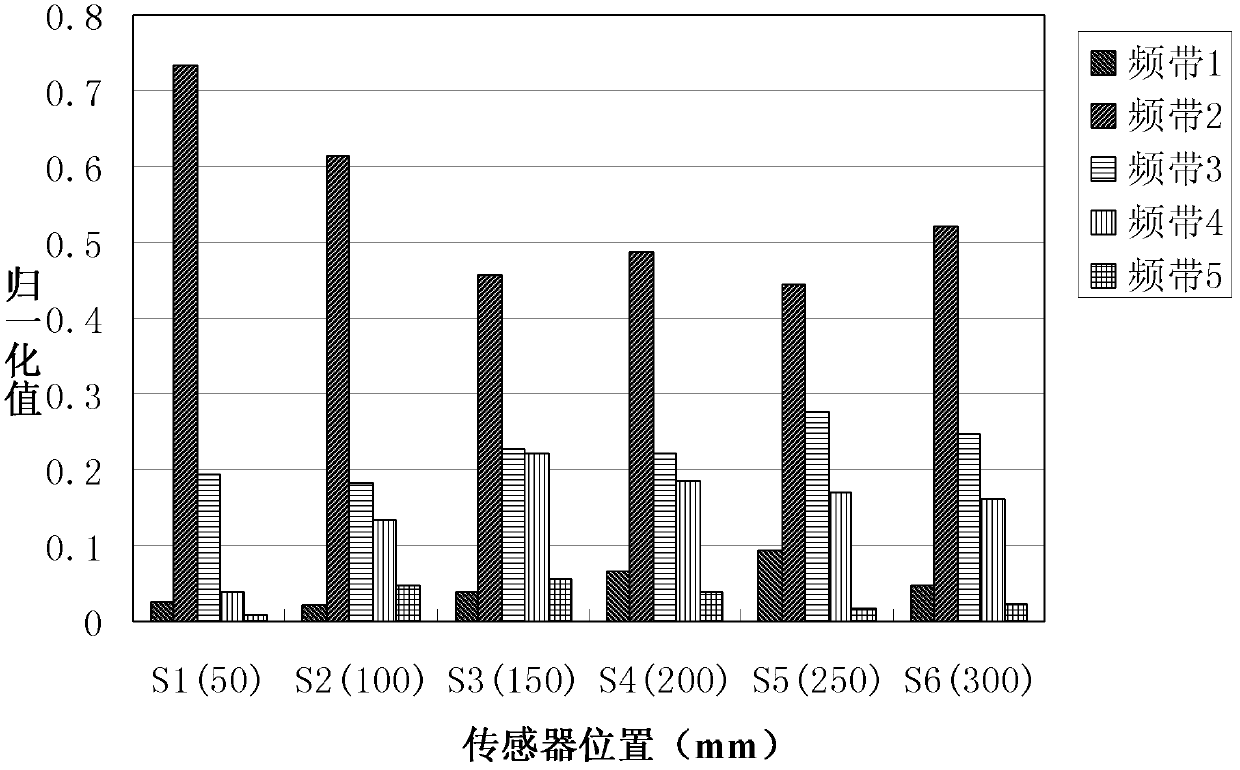

Method for testing acoustic emission signal transmission characteristics of helicopter component based on harmonic wavelet packet

InactiveCN102520075AOvercoming the Shortcomings of AnalysisOvercome Analysis Energy LeakageMaterial analysis using acoustic emission techniquesProcessing detected response signalHarmonic waveletsDecomposition

A method for testing acoustic emission signal transmission characteristics of a helicopter component based on a harmonic wavelet packet belongs to the technical field of acoustic emission detection for mechanical helicopter components, and solves the problems of energy leakage and inflexibility of frequency band selection when the acoustic emission signal transmission characteristics are analyzed by a traditional wavelet packet. The method includes: acquiring testing signals obtained by an acoustic emission sensor; determining a decomposition layer number j and a frequency bandwidth B and computing an upper limiting frequency m and a lower limiting frequency n; computing frequency domain and frequency band values of harmonic wavelets; transforming the testing signals by means of FFT (fast Fourier transform) algorithm to obtain frequency domain discrete values; computing wavelet transform of the frequency domain and frequency band values; computing time-domain signals xl (r); obtaining energy E1 by means of transforming; and normalizing the energy E1 to obtain average energy and an energy diagram of the testing signals of the helicopter component to be tested, thereby obtaining the acoustic emission signal transmission characteristics of the helicopter component to be tested. The method is applicable to testing of the acoustic emission signal transmission characteristics of the helicopter component.

Owner:HARBIN UNIV OF COMMERCE

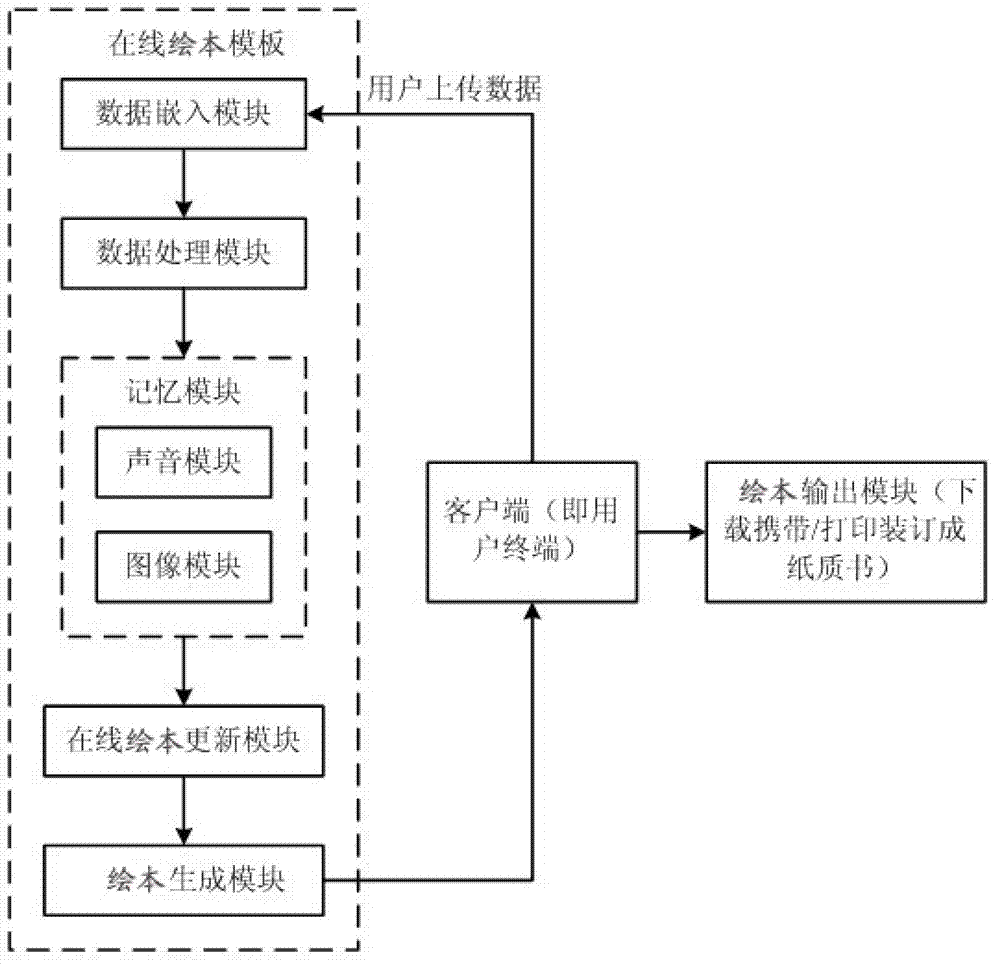

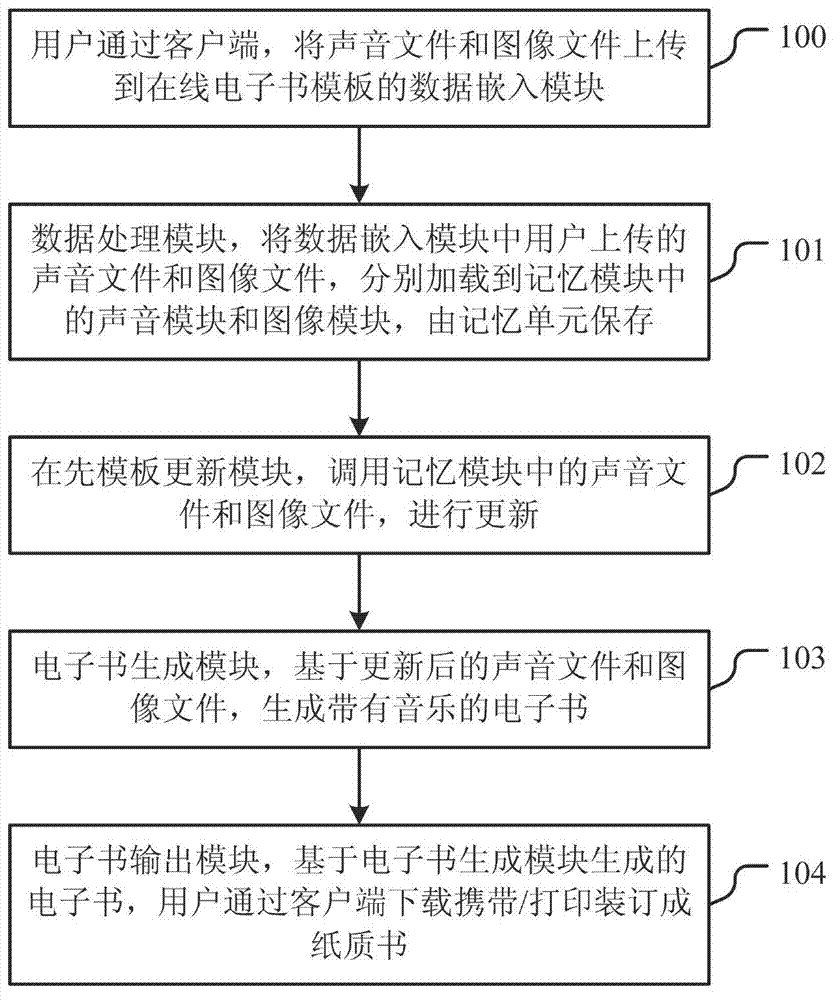

System and method for customizing and publishing picture books in online manner

InactiveCN103399898AEasy to useOvercome flexibilitySpecial data processing applicationsComputer graphics (images)Client-side

The invention discloses a system and a method for customizing and publishing picture books in an online manner. The system comprises an online picture book template, a picture book output module and a client side; the online picture book template is used for manufacturing the picture books in an online manner, the picture book output module is used for outputting the picture books manufactured by the online picture book template, and clients can respectively exchange information with the online picture book template and the picture book output module on the client side; the client side is respectively connected with the online picture book template and the picture book output module. The system and the method for manufacturing the picture books in the online manner have the advantages that shortcomings of poor flexibility and interactivity and the like in the prior art can be overcome, and the system and the method are good in flexibility and interactivity.

Owner:HOENIX EVERGREEN BEIJING OF DIGITAL SCI ANDTECH CO LTD

PTC thermosensitive resistor based on conducting polymer and application of PTC thermosensitive resistor

InactiveCN106280444AImprove stabilityHigh temperature sensitivityPositive temperature coefficient thermistorsEpoxyTemperature control

The invention discloses a PTC thermosensitive resistor based on a conducting polymer and application of the PTC thermosensitive resistor. The PTC thermosensitive resistor based on the conducting polymer is prepared from polyimide, polyacetylene, phenolic epoxy resin, conductive filler, thermal conducting filler, silicon dioxide, calcium oxide and talcum powder. The PTC thermosensitive resistor based on the conducting polymer has the advantages of being high in temperature sensibility, short in response time, low in residual current and high in stability, has the excellent winding property and fracture resistance, can be widely applied to automatic temperature-control heaters such as a plate-type automatic temperature-control heater, an automatic temperature-control heating band, a tubular automatic temperature-control heater and an automatic temperature-control heating cable which have various shapes and is long in service life.

Owner:ANHUI NINGGUO TIANCHENG ELECTRICAL APPLIANCES

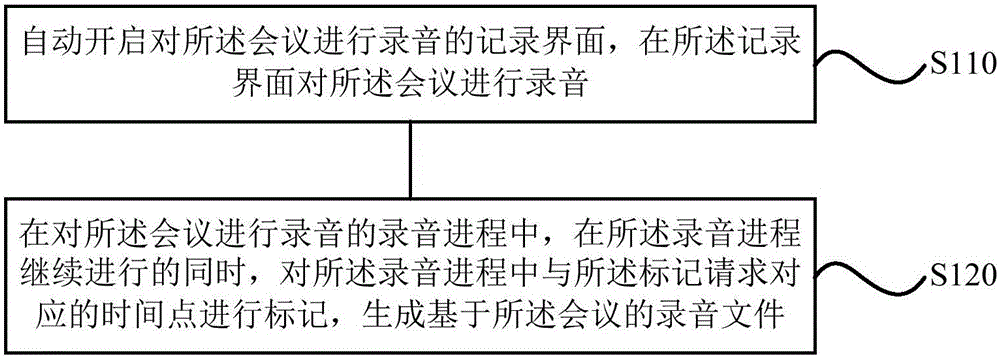

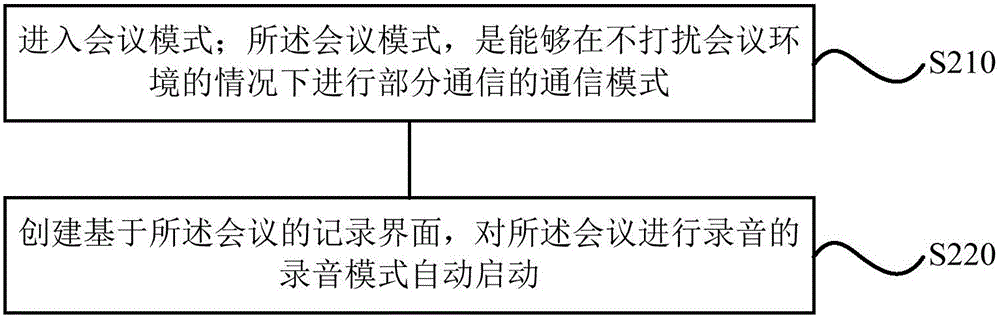

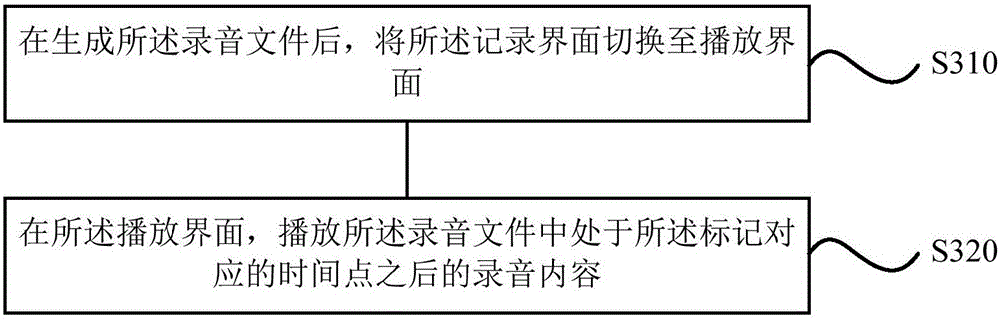

Method, device and terminal for recording sound of conferences

PendingCN105702278AFlexible dot modeEasy way to manageSpecial service provision for substationDigital storageComputer terminalService efficiency

The invention discloses a method, a device and a terminal for recording sound of conferences. The method includes automatically opening recording interfaces for recording the sound of the conferences and recording the sound of the conferences in the recording interfaces; stamping time points corresponding to stamping requests in sound recording procedures while the sound recording procedures for recording the sound of the conferences are carried out, and generating sound recording files based on the conferences. According to the scheme, the method, the device and the terminal have the advantages that shortcomings of poor flexibility and user experience, low service efficiency and the like in the prior art can be overcome by the aid of the method, the device and the terminal, and the method, the device and the terminal are good in flexibility and user experience and high in service efficiency.

Owner:GREE ELECTRIC APPLIANCES INC

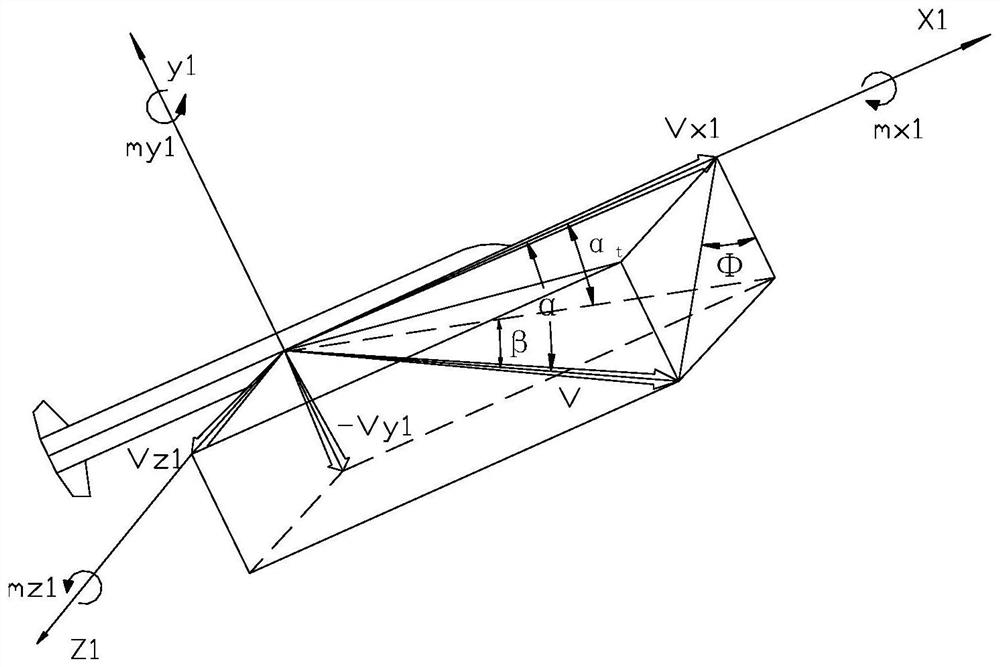

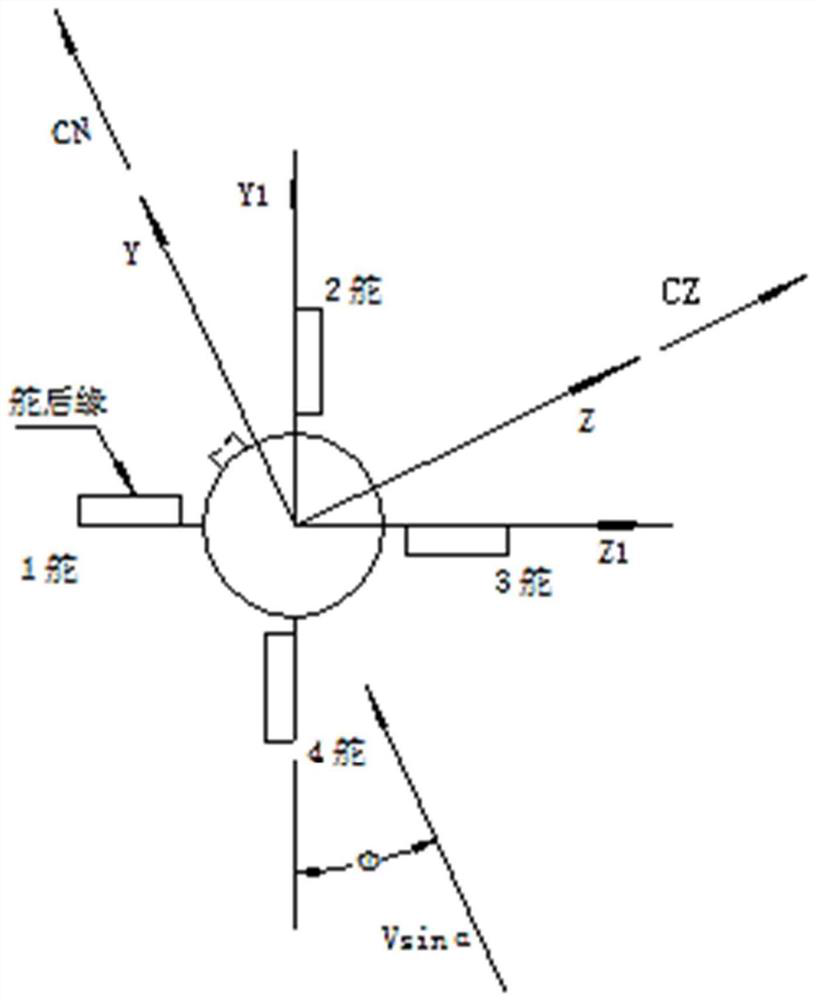

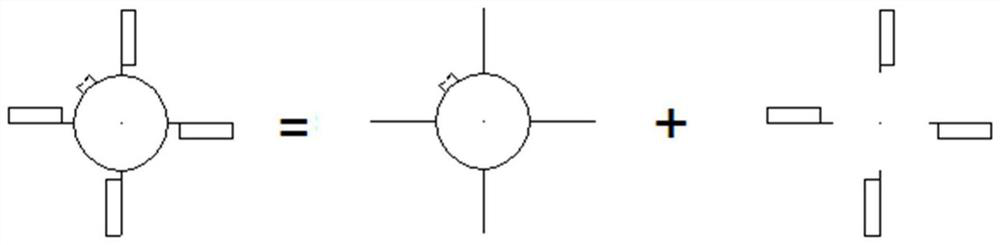

Aircraft designing and manufacturing method based on aerodynamic force mathematical model and aircraft thereof

ActiveCN113505434AFlexible useSupporting status points are fewGeometric CADSustainable transportationMathematical modelFlight vehicle

The invention provides an axial symmetry aircraft manufacturing method based on an aerodynamic force mathematical model, which is characterized by comprising the following steps: 1, establishing an aerodynamic force mathematical model; and 2, performing construction simulation on flight mechanics, a control system, a structural system and an electrical system of the aircraft according to the aerodynamic force mathematical model, and manufacturing the aircraft according to a construction simulation result. The method is suitable for an axisymmetric aircraft or an approximately axisymmetric aircraft with any number of control surfaces, the aerodynamic mathematical model starts from rudder deflection of each control surface instead of controlling rudder deflection channel combination, the model expression is simplified, the limitation of a control strategy is got rid of, the defects of an existing linear mathematical model and an existing nonlinear mathematical model in the aspects of workload, data accuracy, use flexibility and the like are overcome, the advantages of the linear mathematical model and the advantages of the nonlinear mathematical model are considered, and efficiency is improved.

Owner:SHANGHAI INST OF ELECTROMECHANICAL ENG

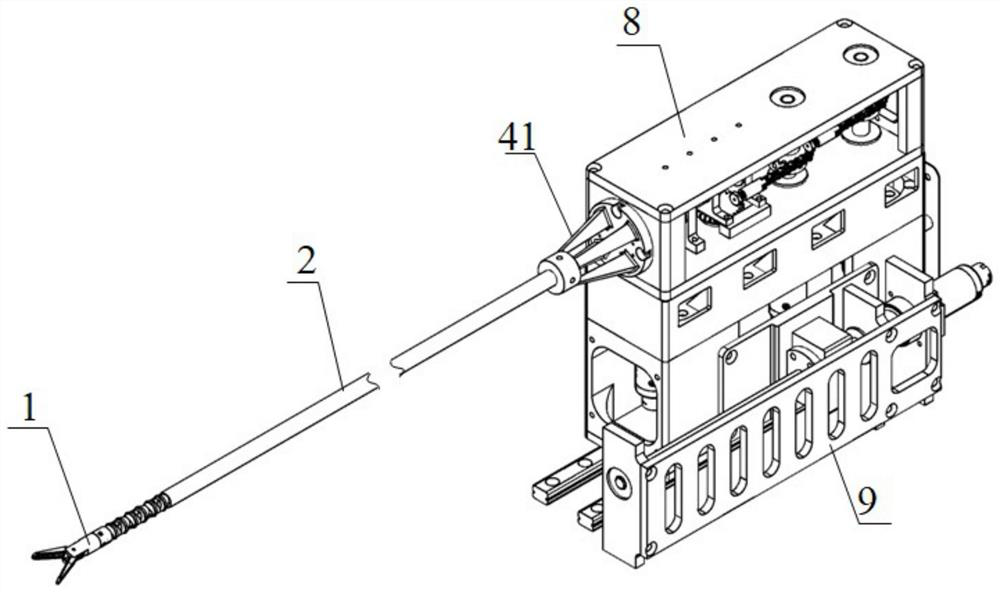

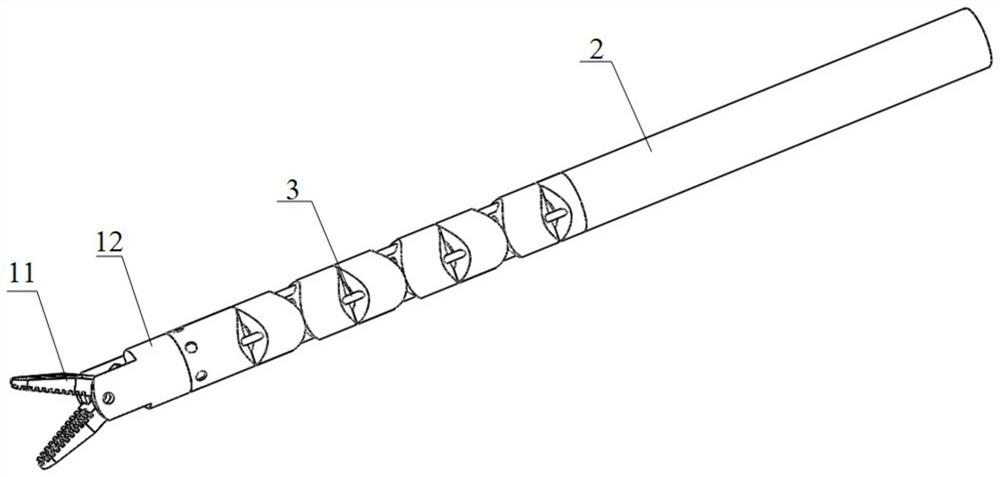

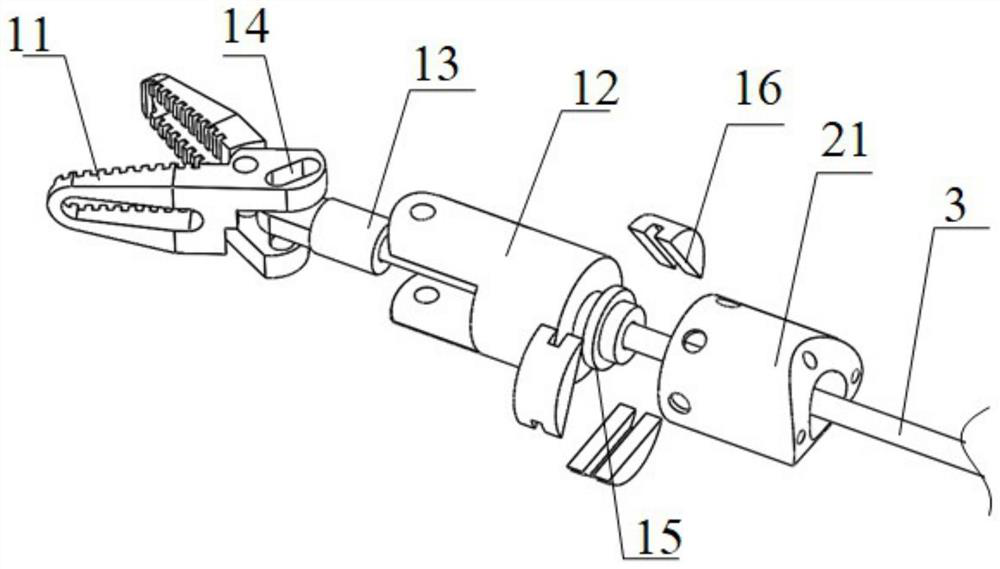

Flexible endoscope minimally invasive surgery instrument arm

PendingCN114748167AHigh surgical flexibilityMeet adjustment needsSurgical robotsSurgical forcepsLess invasive surgerySurgical operation

The invention relates to a flexible endoscopic minimally invasive surgery instrument arm which comprises a front end executing device, a continuum sleeve, a steel wire flexible shaft and a steel wire flexible shaft driving device, the front end executing device is connected with one end of the steel wire flexible shaft, and the other end of the steel wire flexible shaft penetrates through the continuum sleeve to be connected with the steel wire flexible shaft driving device. The steel wire flexible shaft driving device can drive the steel wire flexible shaft to rotate and drive the front-end executing device to rotate around the axis of the front-end executing device. The steel wire flexible shaft connected with the front-end execution device is arranged in the continuum cannula, and the steel wire flexible shaft can be driven by the driving device to drive the front-end execution device to rotate around the shaft by 360 degrees, so that the front-end execution device has high surgical operation flexibility and can meet the adjustment requirements of various postures.

Owner:TIANJIN UNIV

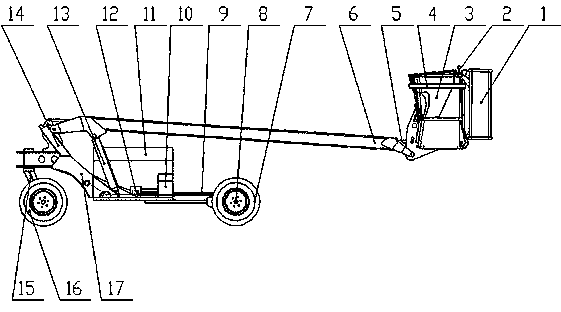

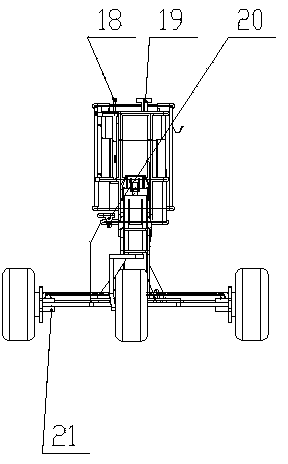

Multifunctional work platform

InactiveCN103964347AOvercome stabilityOvercome flexibilityLifting devicesSteering wheelVehicle frame

The invention relates to a multifunctional work platform which is used for high-place operation such as pruning, picking, plant protection and other agricultural production links. The multifunctional work platform is characterized in that the multifunctional work platform is mainly composed of a vehicle frame, a lifting arm, a lifting oil cylinder, a hydraulic oil tank, a hydraulic pump, a gasoline engine, walking wheels, a steering wheel, an operating deck, a collecting box and a hydraulic walking motor. The vehicle frame is integrally in a triangular shape, the two walking wheels and the one steering wheel are located on the three vertexes of the vehicle frame, and the steering wheel is connected with the vehicle frame through a steering wheel support. The lifting oil cylinder, the hydraulic pump, the gasoline engine and a protection cover are arranged in the middle of the vehicle frame, and the lifting arm is hinged to the upper portion of the vehicle frame. When the multifunctional work platform works, an operator stands on the operating platform, operates a walking wheel control rod to enable a machine to move forwards and backwards, and operates a lifting control rod to control the lifting arm to go up and down.

Owner:INST OF AGRI MECHANIZATION XINJIANG AGRI INST