Patents

Literature

34results about How to "Improve parasitic effects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

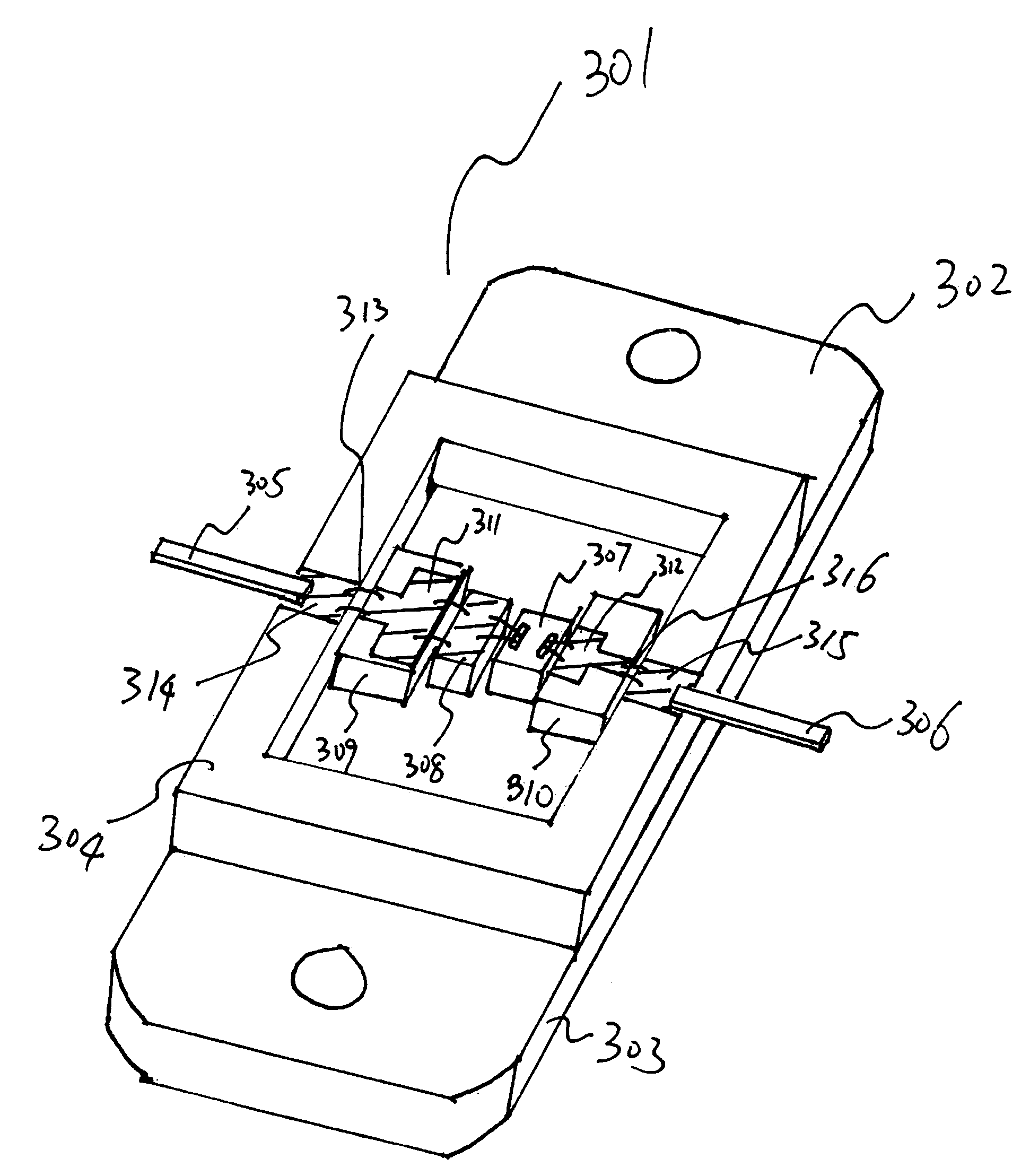

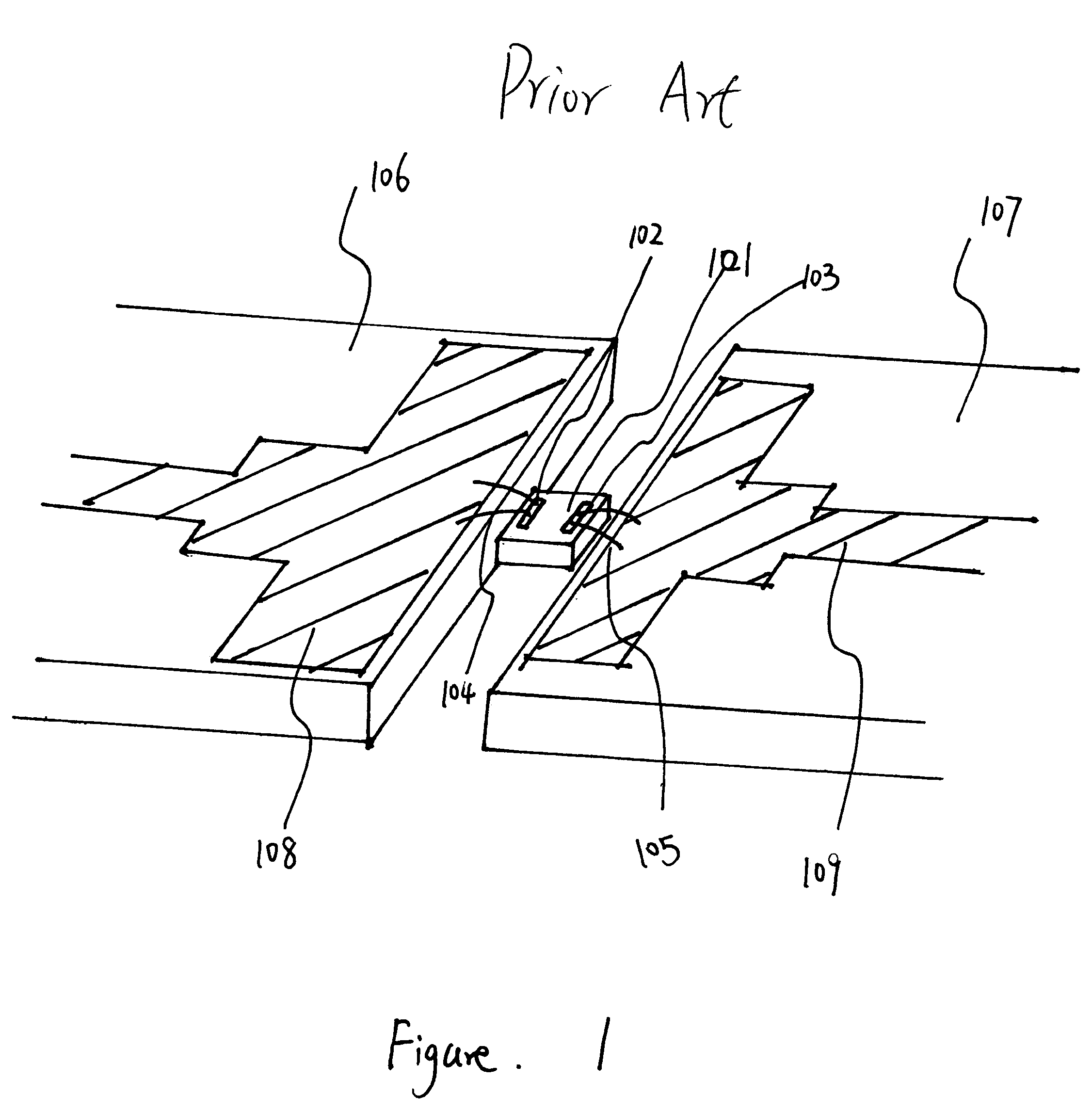

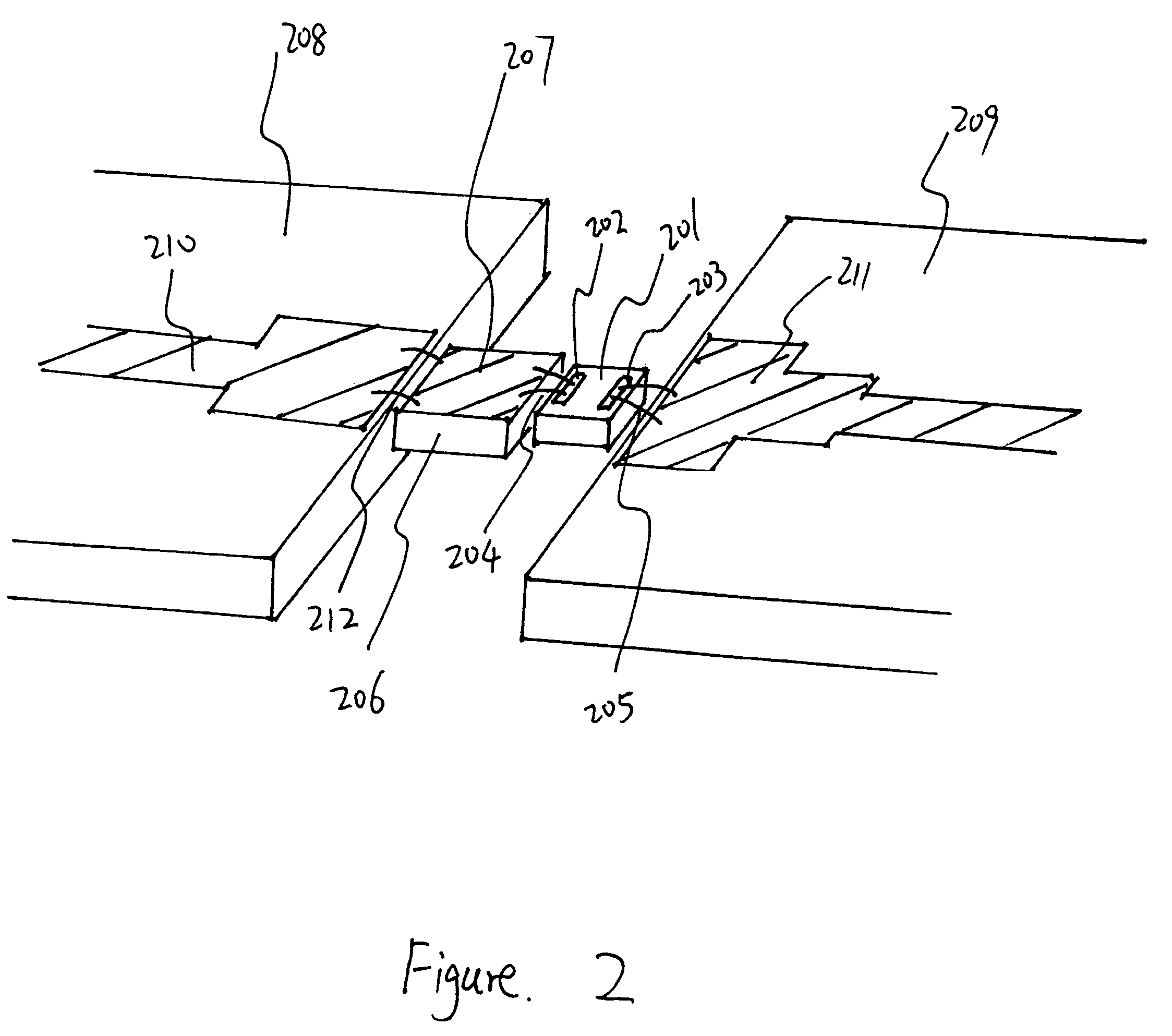

Hybrid broadband power amplifier with capacitor matching network

ActiveUS7911271B1Limited bandwidthLow impedanceMultiple-port networksSemiconductor/solid-state device detailsCapacitanceTransmission line

A hybrid broadband power amplifier module design is disclosed. In a power amplifier design, low impedance transmission lines are typically needed at the input and output of the transistor to match for its optimum source and load impedance. The peripheral of the GaN (Gallium Nitride) transistor is very small due to the high power density of the GaN transistor. The transmission line, for example a microstrip line, needs to be very wide to achieve low impedance on ceramic substrates such as Alumina. The dimensional mismatch from the low impedance transmission line to the transistor causes additional parasitic effect to the matching networks and limits the bandwidth of the amplifier. Capacitor materials are typically very high in dielectric constant; hence a single layer capacitor with small dimensions equalizes to a low impedance transmission line. Selected capacitors with proper dimensions can be used as the low impedance transmission lines in the matching networks. They will have comparable width to the GaN transistor and minimize the parasitic effect. The wavelength inside the capacitor will also be very short due to the high dielectric constant; hence the matching network can be much shorter. A compact hybrid amplifier module has been built in a small package with the GaN transistor, capacitor matching networks and other necessary circuits inside. More than an octave bandwidth can be achieved with this new scheme.

Owner:CW ACQUISITION

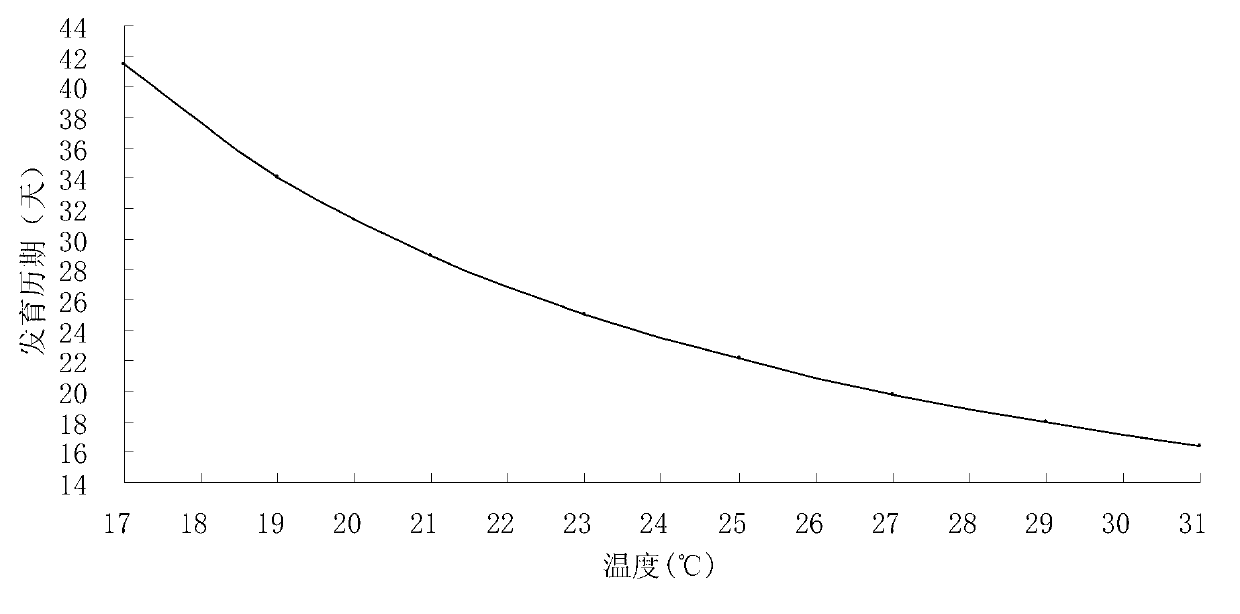

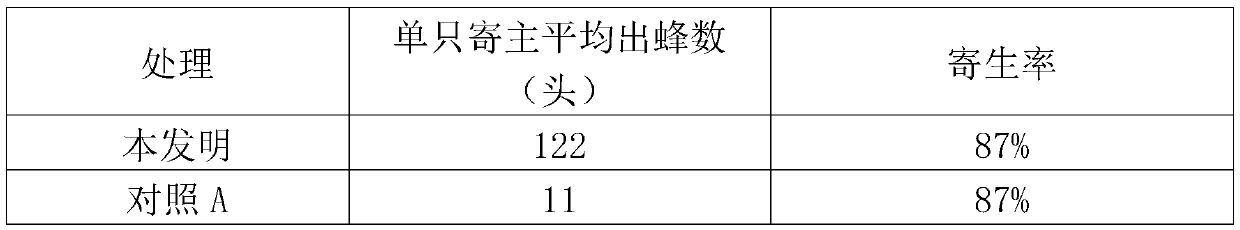

Method for biologically preventing and controlling micromelalopha troglodyte by using tetrastichus nigricoxae yang

InactiveCN102986600AGood parasitic effectBasic Control HazardsPlant protectionAnimal husbandryForest protectionTetrastichus

The invention discloses a method for biologically preventing and controlling micromelalopha troglodyte by using tetrastichus nigricoxae yang and belongs to the technical field of forest conservation and biological prevention and control. The method comprises the following technical steps of (1) collecting and preserving bees; (2) selecting and preserving substitutive hosts; (3) breeding the tetrastichus nigricoxae yang; (4) rejuvenating the bees; (5) releasing the tetrastichus nigricoxae yang; and (6) continuously controlling the micromelalopha troglodyte. The method is simple and convenient to operate and efficient in system, excellent bred bees are selected to substitute the hosts, the technical problem of artificial scale bee breeding is solved, an appropriate bee releasing technology is researched, and the preventing and controlling effect is remarkable. The bees are ordinarily released for three times in a low micromelalopha troglodyte population period to prevent and control a next generation of micromelalopha troglodyte pupas, injurious insects can be basically controlled, and a full-year disaster-free and insect-existing control target is achieved.

Owner:XUZHOU FORESTRY TECHNICAL GUIDANCE STATION

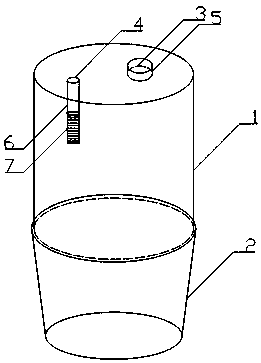

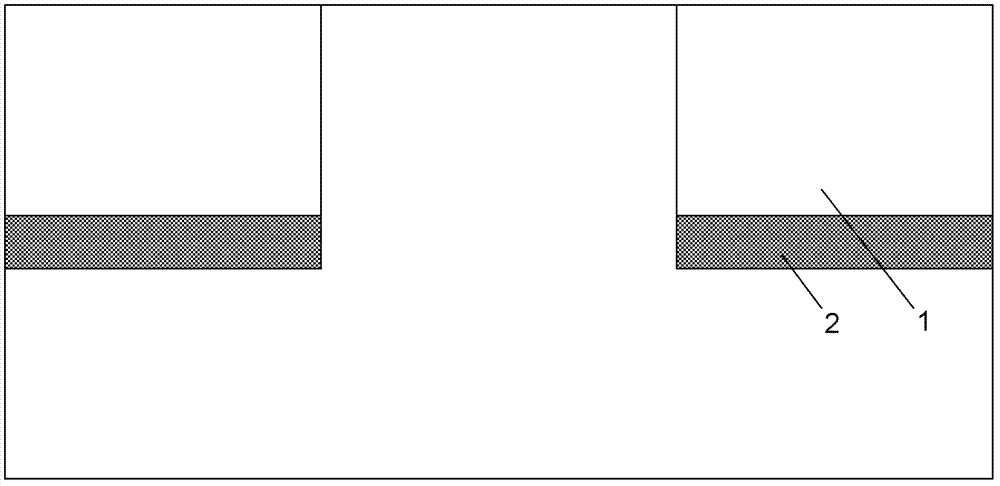

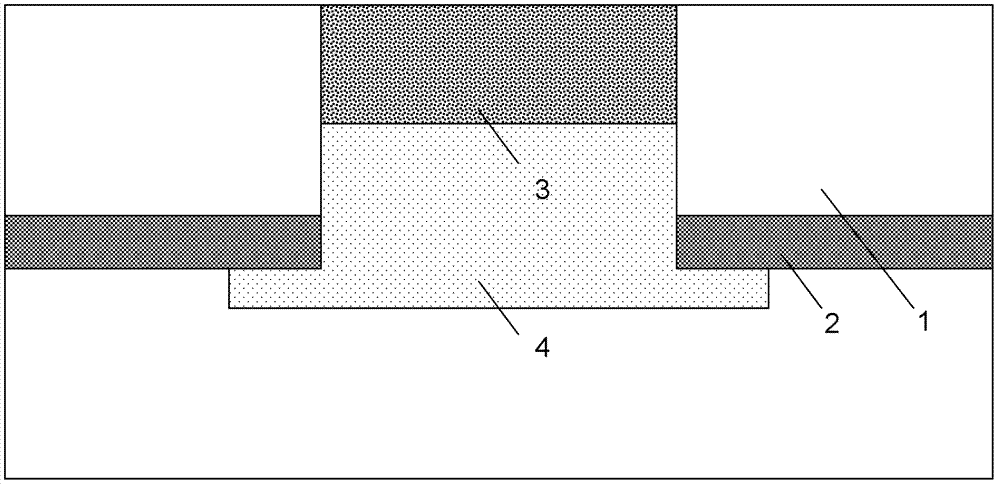

Device for detecting parasitic ability of parasitic wasps and method for evaluating parasitic ability

The invention belongs to the technical field of biology, and particularly relates to a device for detecting the parasitic ability of parasitic wasps and a method for evaluating the parasitic ability.The device for detecting the parasitic ability of the parasitic wasps comprises a parasitic wasp hive and a host tank. The parasitic wasp hive and the host tank are combined and connected with each other; a ventilation hole and a feed hole are formed in the top of the parasitic wasp hive; the host tank is matched with the parasitic wasp hive, face plates on at least one surface of the host tank are ventilated, and a top plate of the host tank can be detached. The device for detecting the parasitic ability of the parasitic wasps and the method for evaluating the parasitic ability have the advantages that the combined device is convenient to assemble, detach and operate, simple in structure and low in manufacturing cost; the device is applicable to detecting the parasitic ability and parasitic effects of diversified parasitic wasps and is high in applicability; the method for evaluating the parasitic ability of the parasitic wasps can be implemented by the aid of the device, the parasitic ability of the parasitic wasps can be quickly and accurately tested by the aid of the method, accordingly, bases and technical support can be provided to realizing pest control effects by the aid ofthe parasitic wasps, and the technical problem of difficulty in monitoring and detecting the wasp breeding quality can be solved by the aid of the device and the method.

Owner:HENAN AGRICULTURAL UNIVERSITY

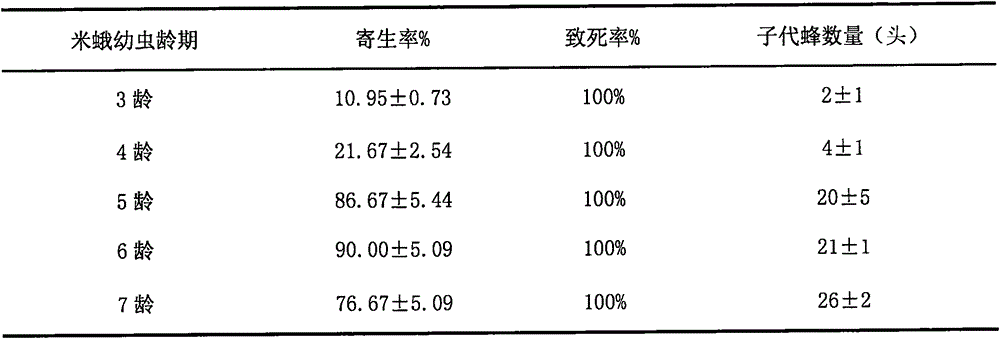

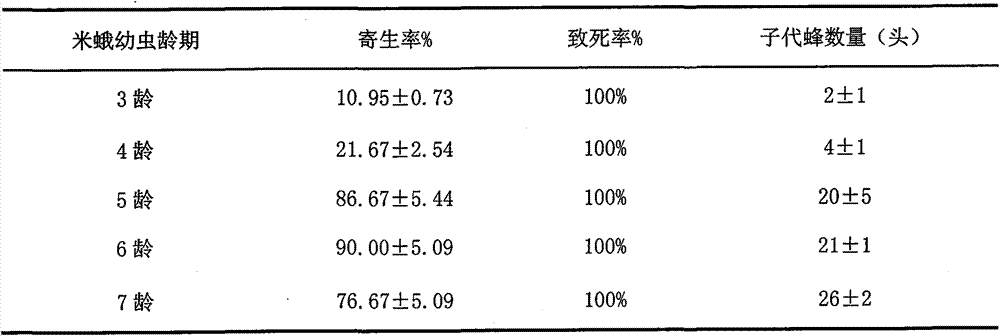

Method for mass reproduction of Bracon adoxophyesi Mimanikawa

The invention discloses a method for reproducing Bracon adoxophyesi Mimanikawa indoor. Under the conditions that the temperature is 25 DEG C, and the ratio of light to darkness is 14 h to 10 h, the Bracon adoxophyesi Mimanikawa is placed into an insect rearing cage with a sleeve, wherein the specification is 55 cm*55 cm*55 cm, the Bracon adoxophyesi Mimanikawa is fed by 15% of hydromel, fodder with insects is taken out from a feeding plate with 5-6-instar rice moth larvae every 3 days to be smoothly laid at the bottom of a plastic box to enable the height of the fodder with the insects to be approximately 1.5 cm, the plastic box without a cover is placed in a parasitoid wasp insect rearing cage, and the parasitoid wasp utilizes the rice moth as the host. The plastic box is taken out 3 days later, and the plastic box is covered by the cover, the emergence of the parasitoid wasp of the next generation begins to occur after 12 days, and the emergence time lasts more than 7 days. The method is simple in operation and high in efficiency, and the mass reproduction of the Bracon adoxophyesi Mimanikawa can be achieved easily.

Owner:ENVIRONMENT & PLANT PROTECTION INST CHINESE ACADEMY OF TROPICAL AGRI SCI

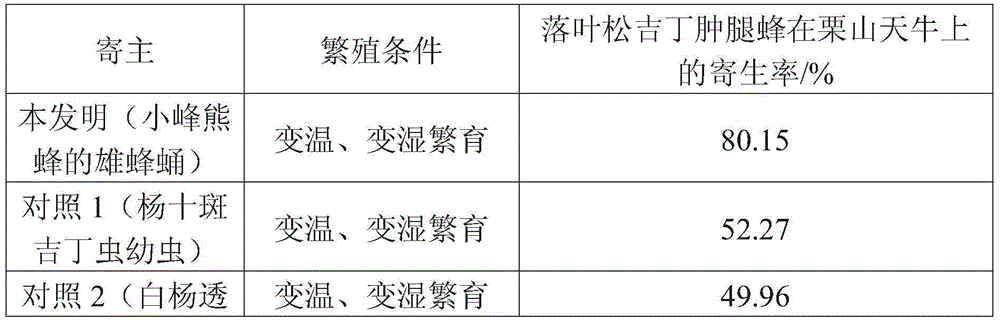

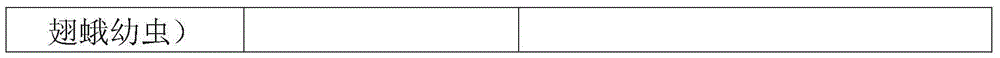

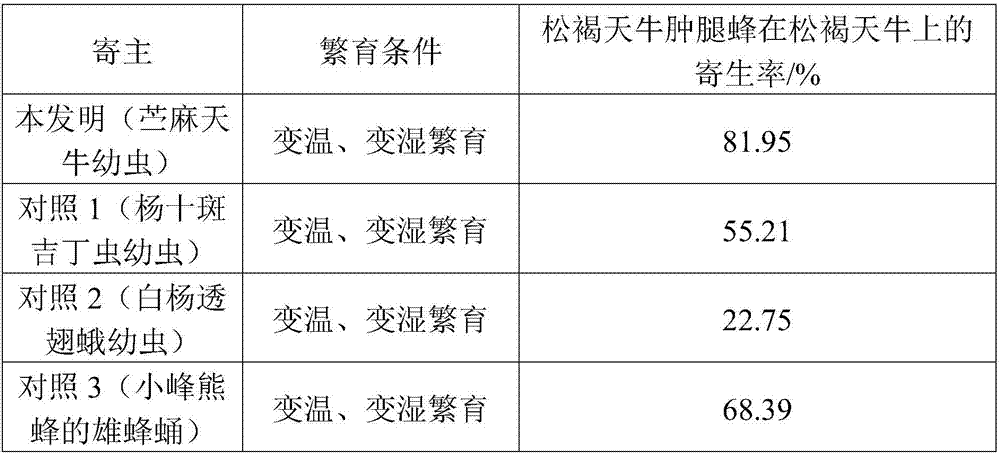

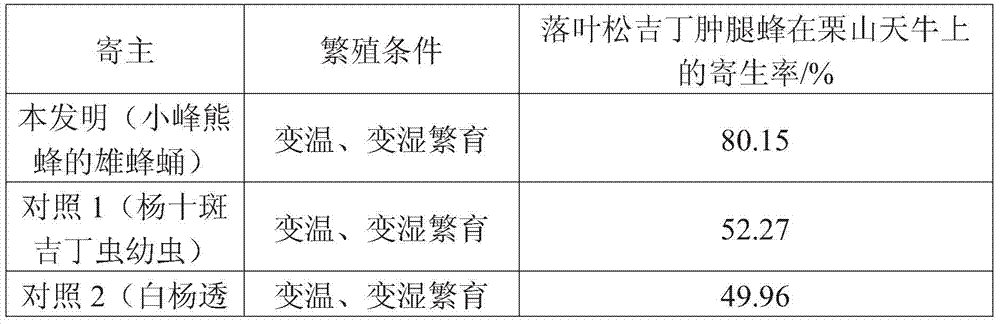

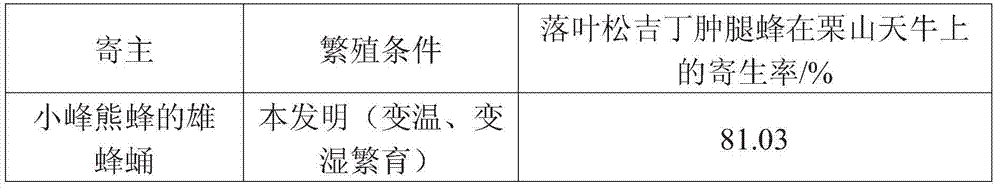

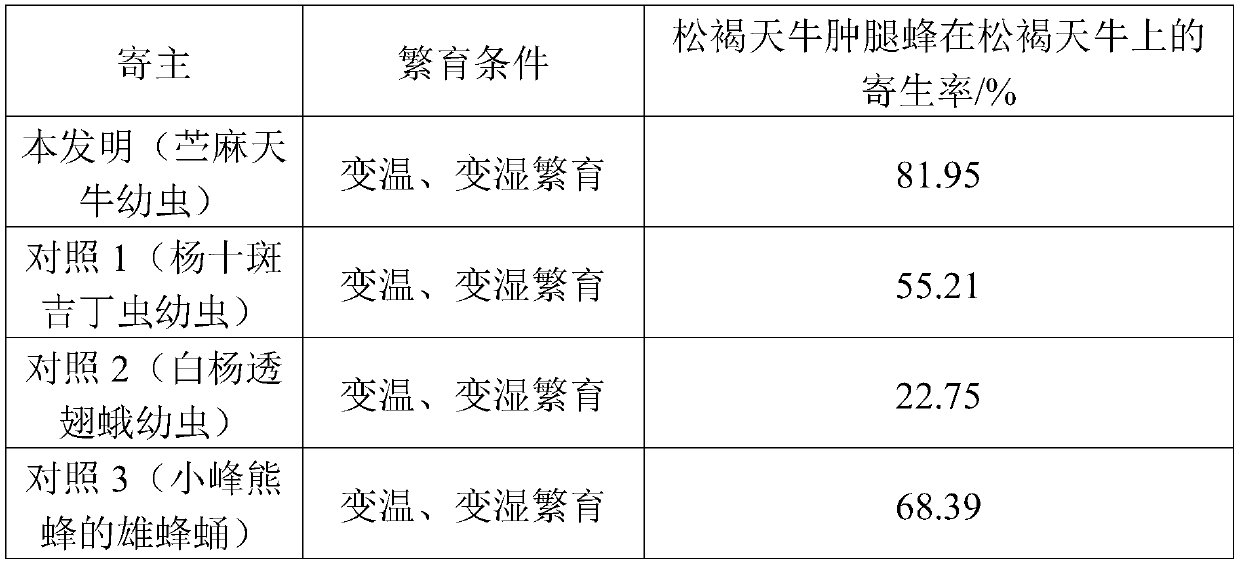

Method for artificial breeding of larch sclerodermus sp. and application of larch sclerodermus sp. for prevention of massicus raddei

InactiveCN104920308AIncreased parasitic abilityImprove parasitic effectsAnimal huntingPlant protectionLarchFishery

The invention discloses a method for artificial breeding of larch sclerodermus sp. and application of larch sclerodermus sp. for prevention of massicus raddei. Drone pupae of Bombus hypocrita are selected as substitute hosts of the larch sclerodermus sp., meanwhile, the breeding conditions are regulated and controlled, and thus the parasitic ability of the bred larch sclerodermus sp. is obviously improved. The larch sclerodermus sp. is applied to prevention of the massicus raddei in the Northeast China region, and the parasitic effect of the indoor larch sclerodermus sp. in the massicus raddei larvae of 1-3 years old is good.

Owner:INST OF FOREST ECOLOGY ENVIRONMENT & PROTECTION CHINESE ACAD OF FORESTRY

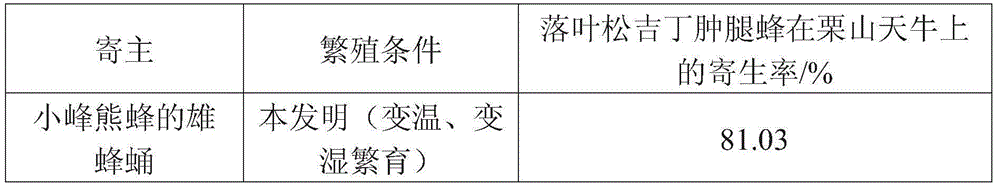

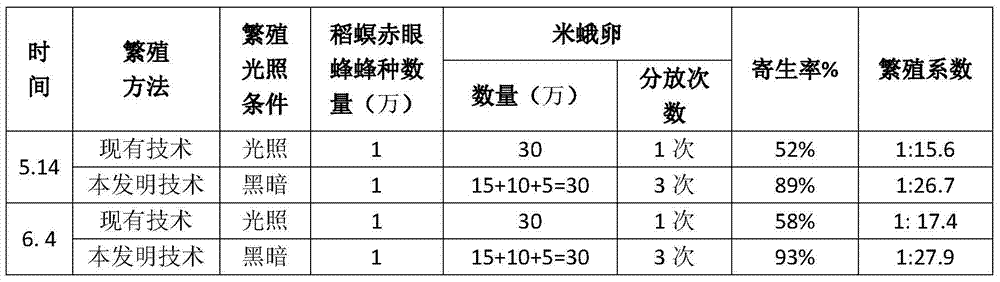

Trichogramma japonicum high-efficiency reproduction method

ActiveCN104996366AExtend the life cycleImprove reproductive performanceAnimal husbandryNutrient solutionSugar

Provided is a trichogramma japonicum high-efficiency reproduction method. The method comprises: collecting eggs of rice moths, and sticking the eggs on paper boards to make egg cards; putting trichogramma japonicum species and eggs of rice moths in a darkroom in proportion of 1:10 to 1:4, adjusting bee species emergence parasitic environment temperature to 23 to 25 DEG C, adjusting humidity to 70% to 80%; after 90% of the egg cards have parasitic bee species, adding fresh rice moth egg cards according to 1:6-10 of proportion of the bee species and the egg cards again, properly increasing temperature of the darkroom to 25 to 28 DEG C, and maintaining the humidity; after more than 90% of the egg cards have parasitic bee species, adding fresh rice moth egg cards according to 1:3-7 of proportion of the bee species and the egg cards for the third time, the egg cards this time being sprayed with cane sugar nutrient solution, the bee species continuing to reproduce. The method can realize using the trichogramma japonicum to prevent rice leaf folders and striped rice borers, and pesticide dose is greatly reduced. The method promotes agriculture to develop towards green, organic, and ecological agriculture.

Owner:HUNAN RICE RES INST +1

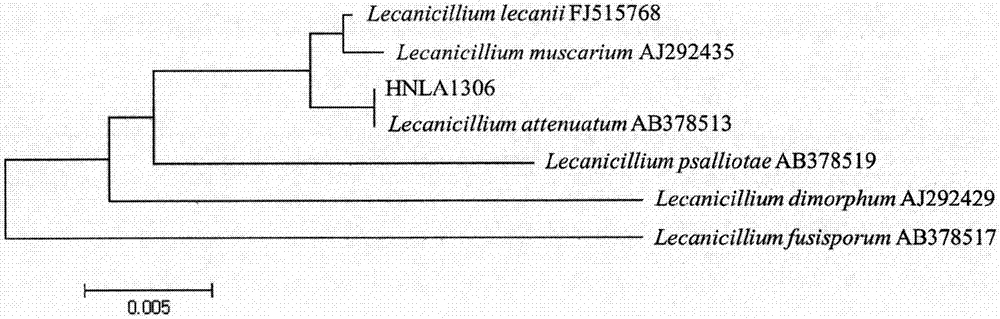

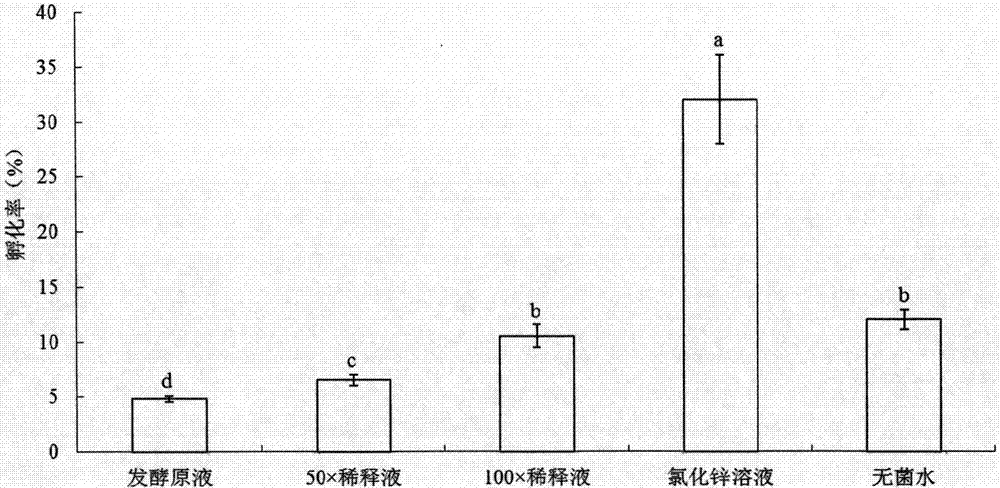

Lecanicillium attenuatum and application of lecanicillium attenuatum to control of crop nematodes and bemisia tabaci

The invention discloses lecanicillium attenuatum and application of the lecanicillium attenuatum to controlling heterodera glycines. The lecanicillium attenuatum is lecanicillium attenuatum HNLA1306, which is preserved in CGMCC (China General Microbiological Culture Collection Center) with the preservation number of CGMCC No.9220. A fermentation liquor of the lecanicillium attenuatum can remarkably restrain incubation of eggs of heterodera glycines and has a strong killing effect on J2 larvas; the conidia of the lecanicillium attenuatum have a good parasitic effect on second-stage juveniles of bemisia tabaci; the lecanicillium attenuatum can be used for biological control of crop nematodes and bemisia tabaci.

Owner:张艳军 +1

Large-scale production method of tamarixia radiate

The invention discloses a large-scale production method of tamarixia radiate. The method comprises the steps that s1, carrier plants are managed, tender shoots are cultivated, and the carrier plants are calamondin; s2, diaphorina citri is inoculated to the carrier plants in a diaphorina citri breeding cage, and nymphs are bred; s3, the carrier plants with the 4-5-age diaphorina citri nymphs are moved into a parasitic wasp breeding cage, tamarixia radiate adults are put into the parasitic wasp breeding cage, the inoculation quantity ratio of tamarixia radiate to the diaphorina citri nymphs is 1: 10-20, and the tamarixia radiate adults are bred and collected; and s4, the carrier plants are cleaned and recovered. The carrier plants developed by the method are calamondin, the carrier plants shorten the growth cycle, the breeding capacity of the diaphorina citri and the production capacity of parasitic wasps are greatly improved, and the net yield and the female ratio of the tamarixia radiate are effectively improved according to the inoculation proportion of calamondin+tamarixia radiate to the diaphorina citri nymphs.

Owner:INST OF ZOOLOGY GUANGDONG ACAD OF SCI

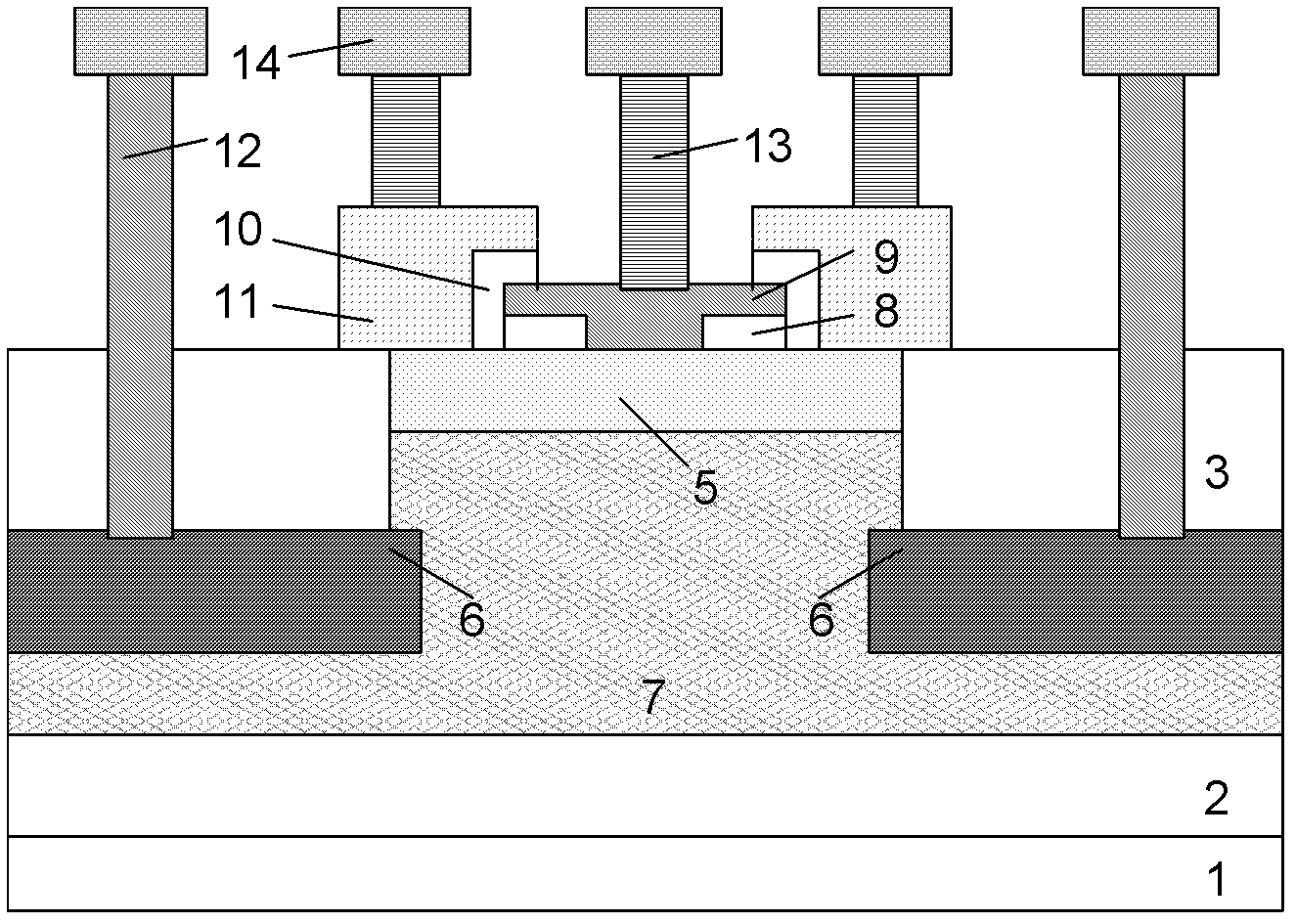

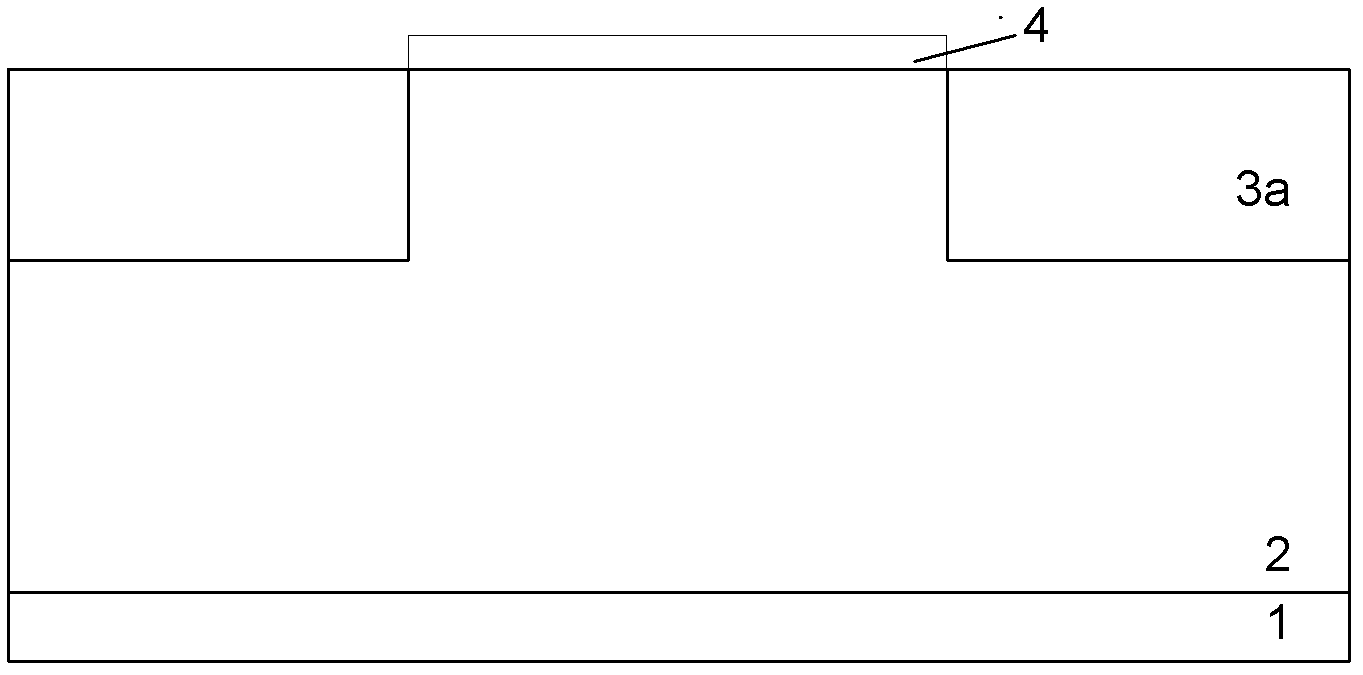

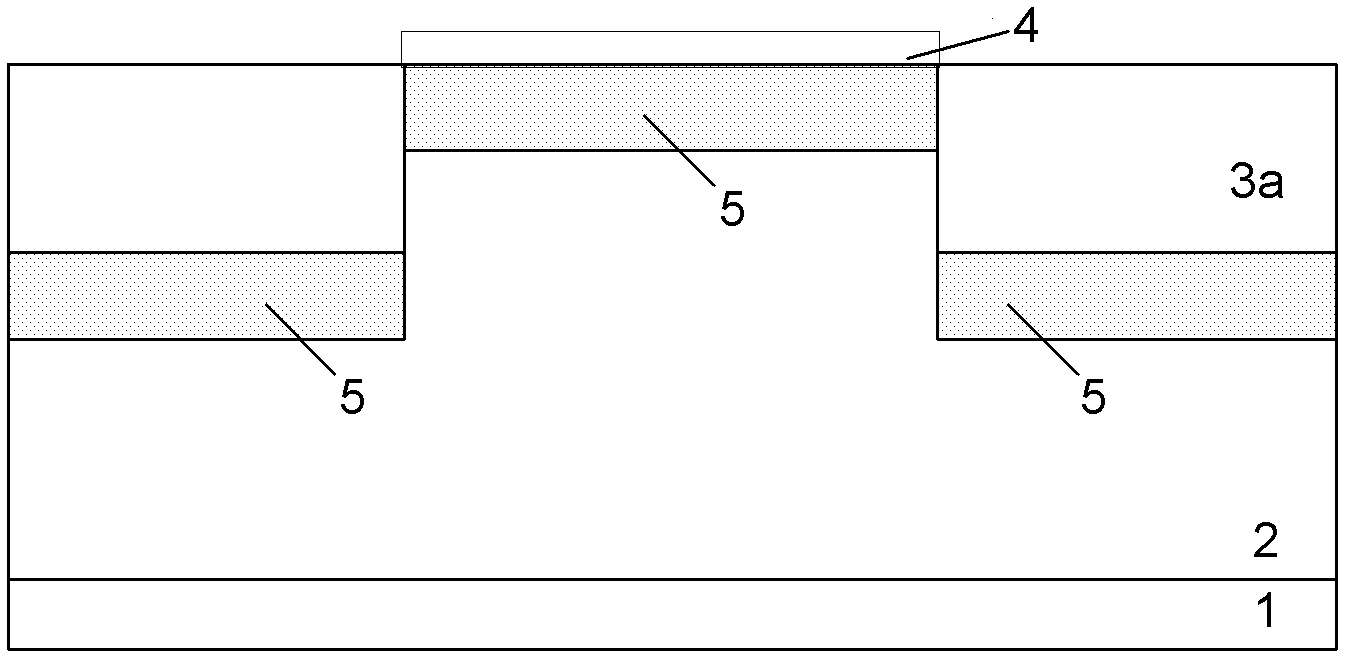

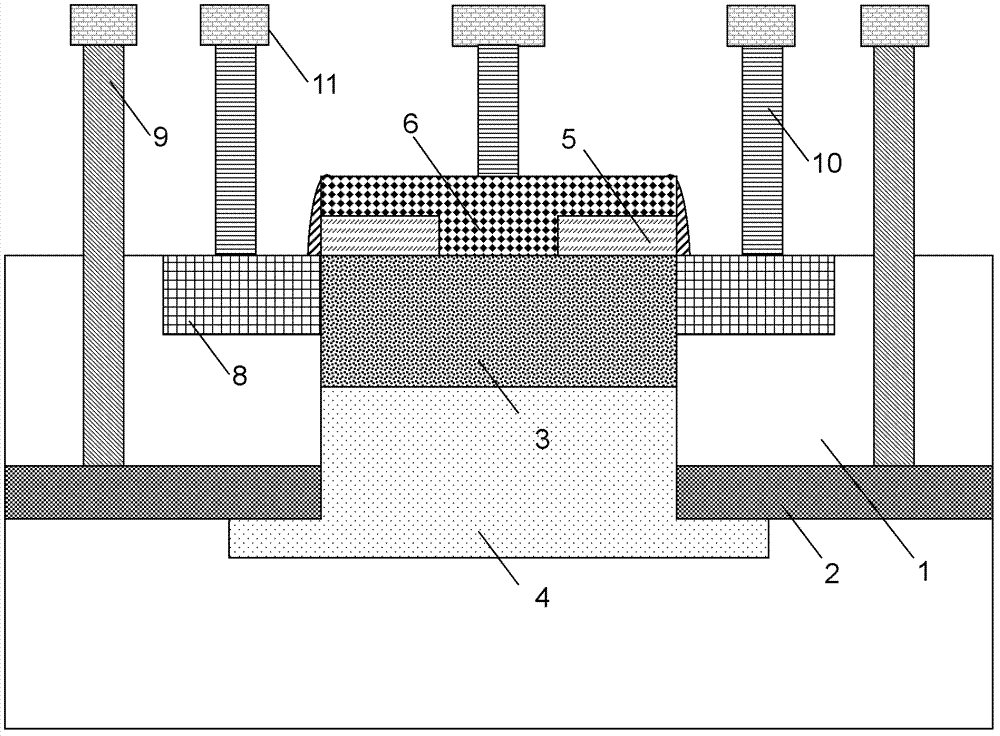

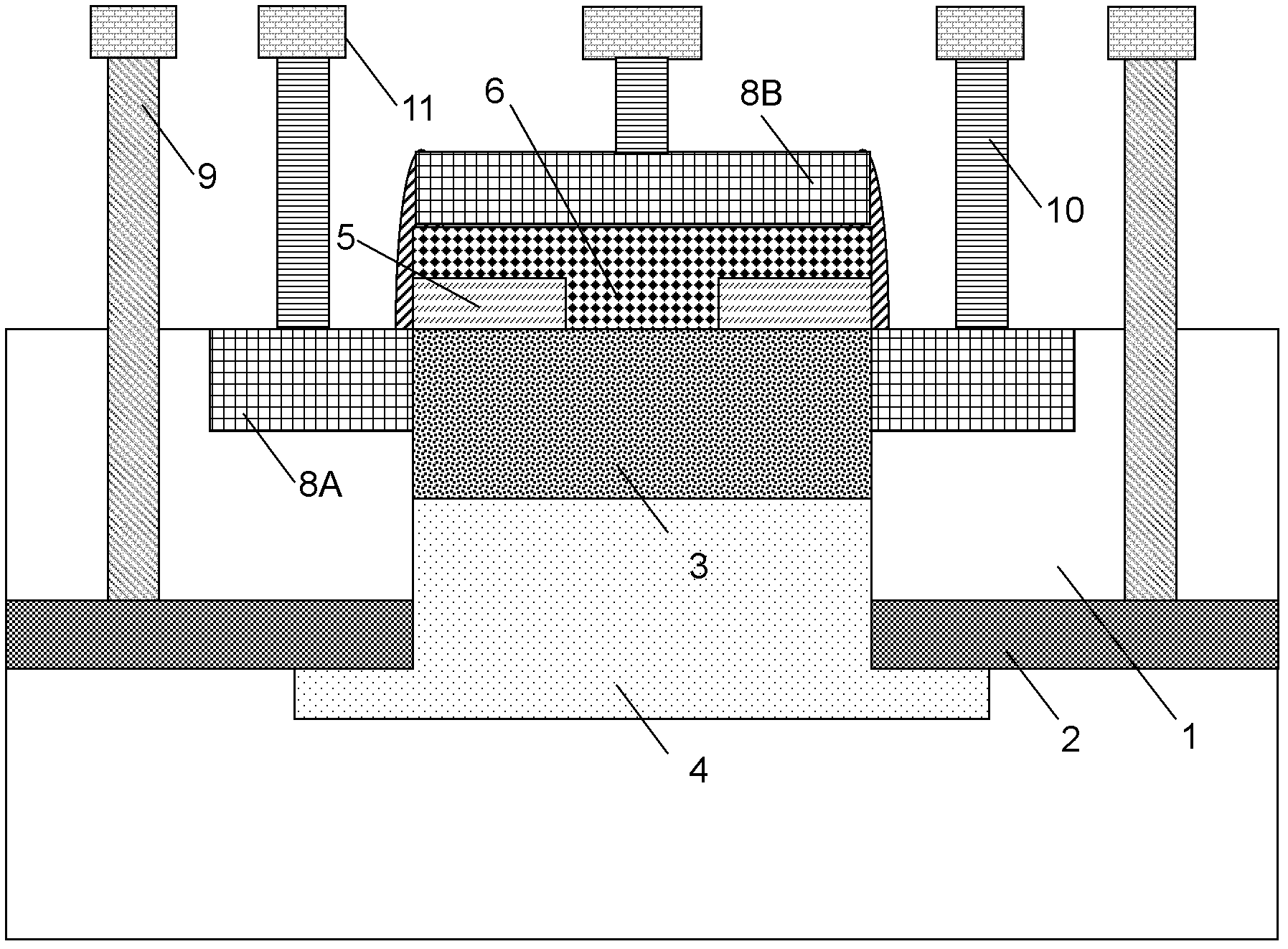

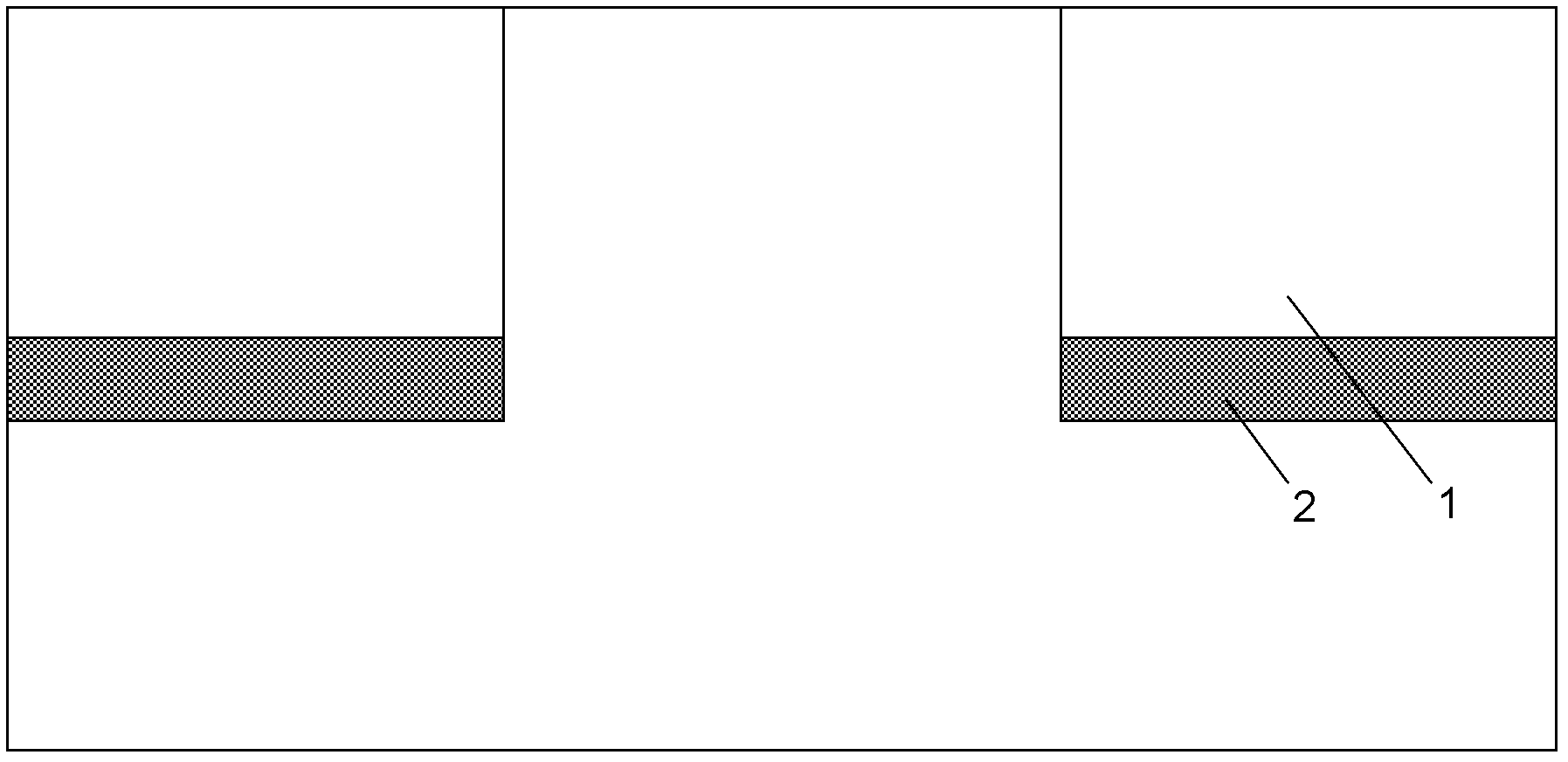

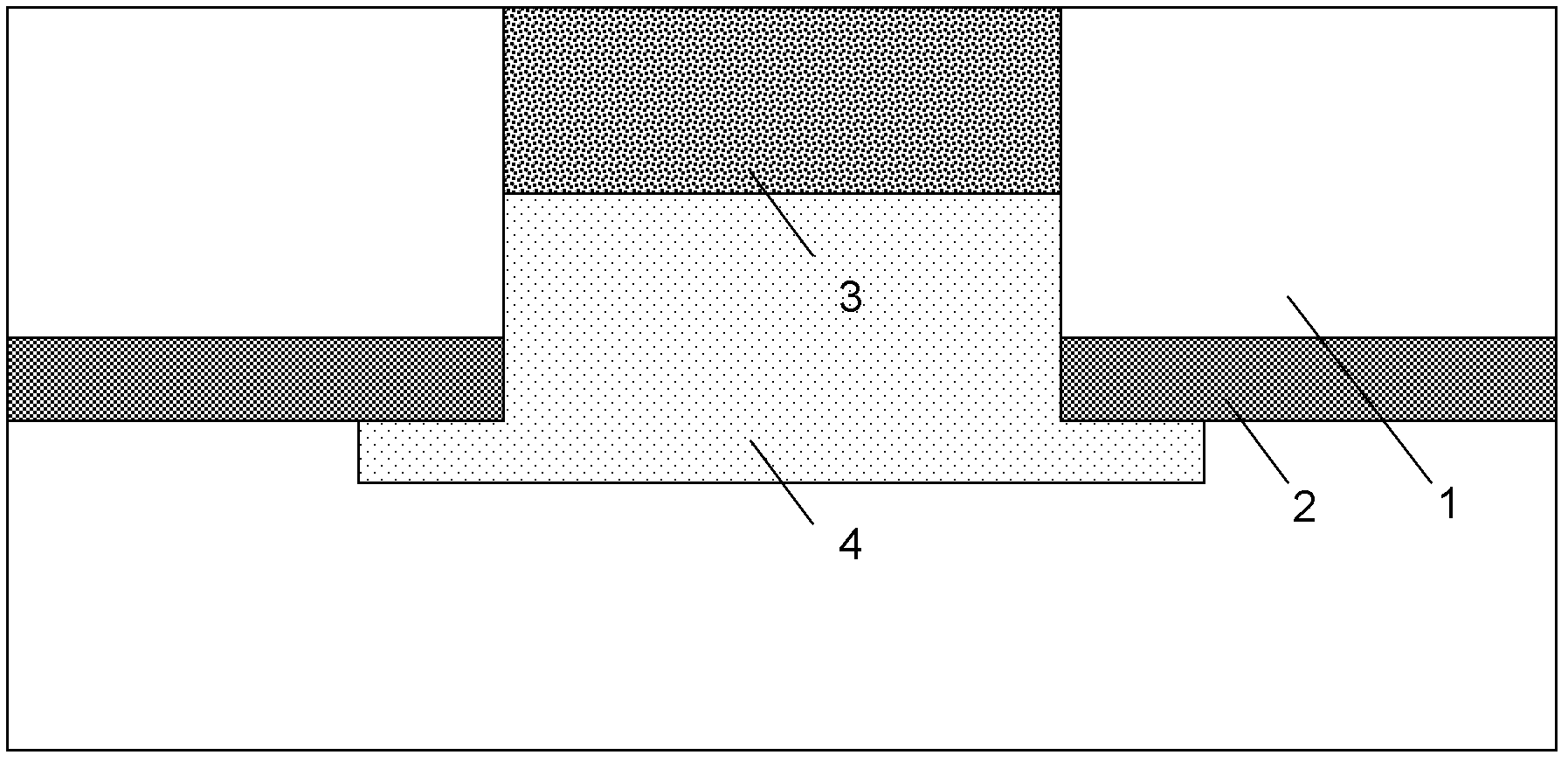

Vertical parasitic type plug-and-play (PNP) audion in germanium silicon heterojunction bipolar transistor (HBT) technology and manufacture method

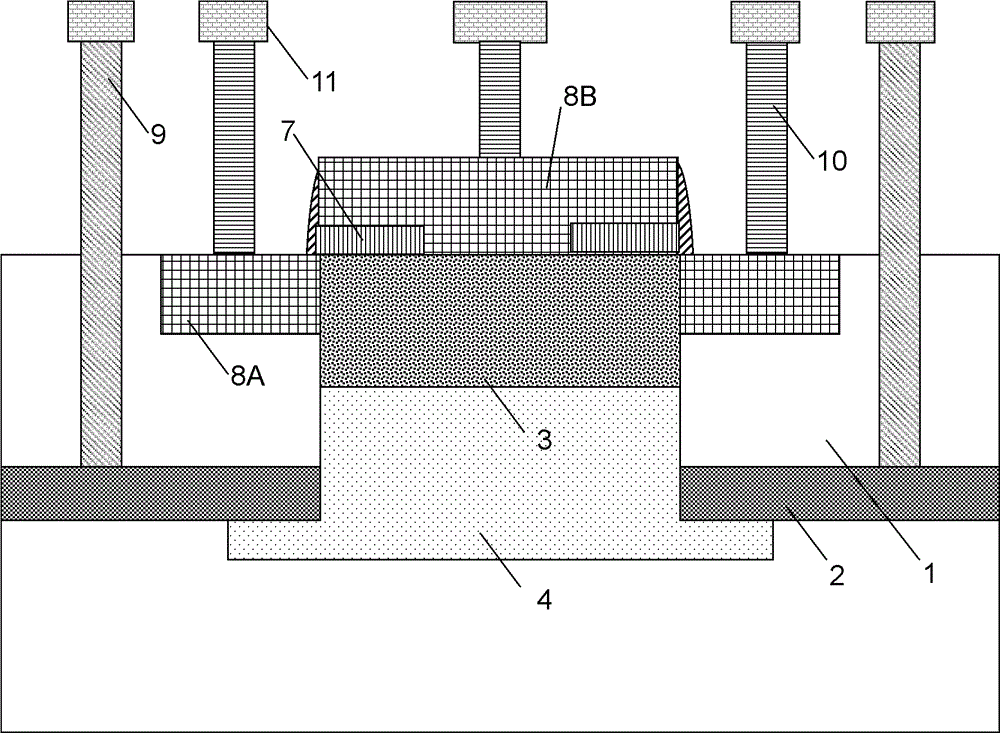

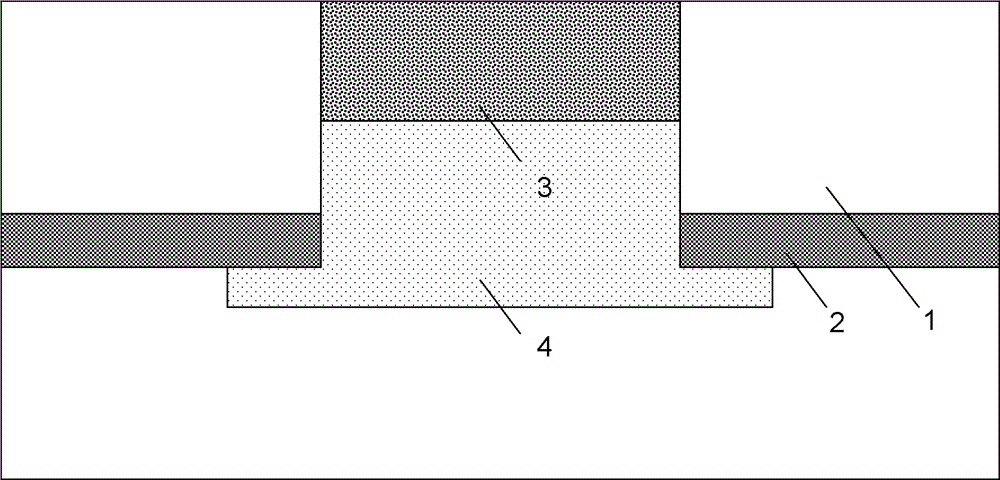

ActiveCN103165667AImprove emission efficiencyImprove parasitic effectsSemiconductor/solid-state device manufacturingSemiconductor devicesSilicon heterojunctionTransistor

The invention discloses a vertical parasitic type plug-and-play (PNP) audion in a germanium silicon heterojunction bipolar transistor (HBT) technology. A window defining germanium before growth in a trapezoid shape is adopted and germanium silicon layers in an emitter region can be in a polycrystalline structure, and therefore dosage concentration in the emitter region can be improved, emitting efficiency and amplification coefficient of a device is improved, and cut-off frequency of the device is increased. Due to the fact that the advanced deep hole contact technology and the P-type buried layer technology are adopted, area of an active region can be greatly saved, parasitic effect of the device is improved, collector resistance of the device is reduced, and performance of the device is improved. The invention further discloses a manufacture method of the vertical parasitic type PNP audion in the germanium silicon HBT technology. The manufacture method can be integrated with the technology of the PNP audion in the germanium silicon HBT technology and reduce production cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

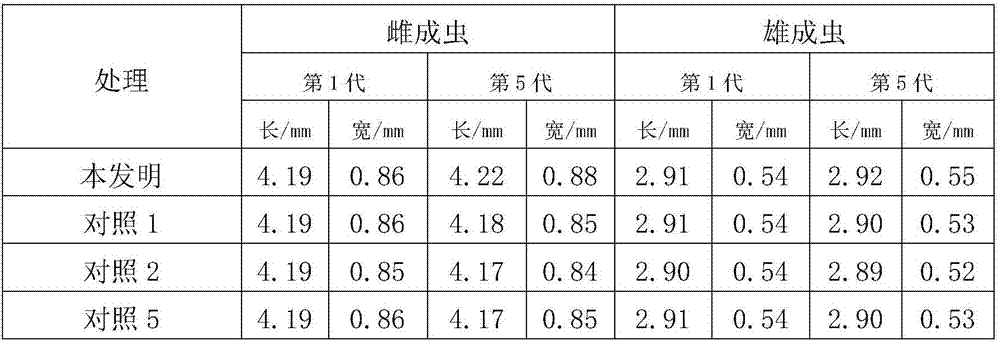

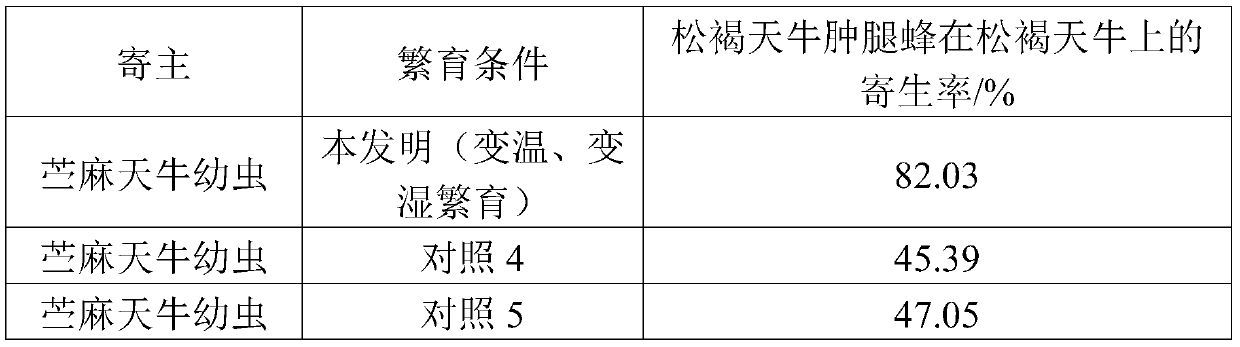

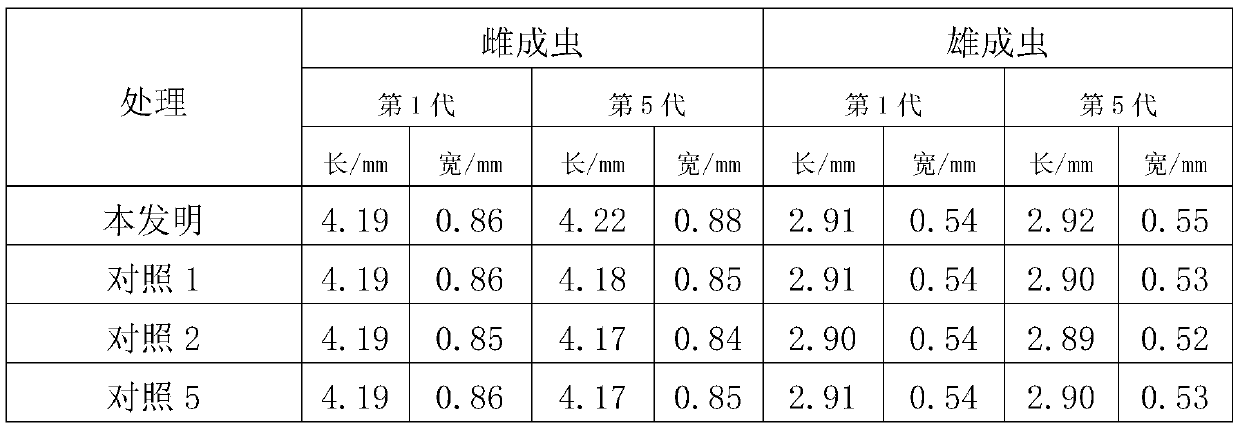

Method for artificially breeding sclerodermus and application of sclerodermus in prevention and control of trunk-boring insect pests on forest trees

InactiveCN107114326AIncreased parasitic abilityVitality is not weakenedPlant protectionAnimal husbandryInsect pestMonochamus alternatus

The invention discloses a method for artificially breeding sclerodermus and application of the sclerodermus in prevention and control of trunk-boring insect pests on forest trees. According to the method, larvae of paraglenea fortunei are selected as substitute hosts of sclerodermus, and the breeding condition is regulated, so that the parasitizing capability of the sclerodermus obtained in breeding is remarkably improved, and the viability of the slerodermus is not weakened even the sclerodermus is continuously bred indoors for five generations; and the sclerodermus is applied to prevent and control monochamus alternatus hope, and has a good parasitizing effect for larvae of paraglenea fortunei in 1-3 ages.

Owner:INST OF FOREST ECOLOGY ENVIRONMENT & PROTECTION CHINESE ACAD OF FORESTRY

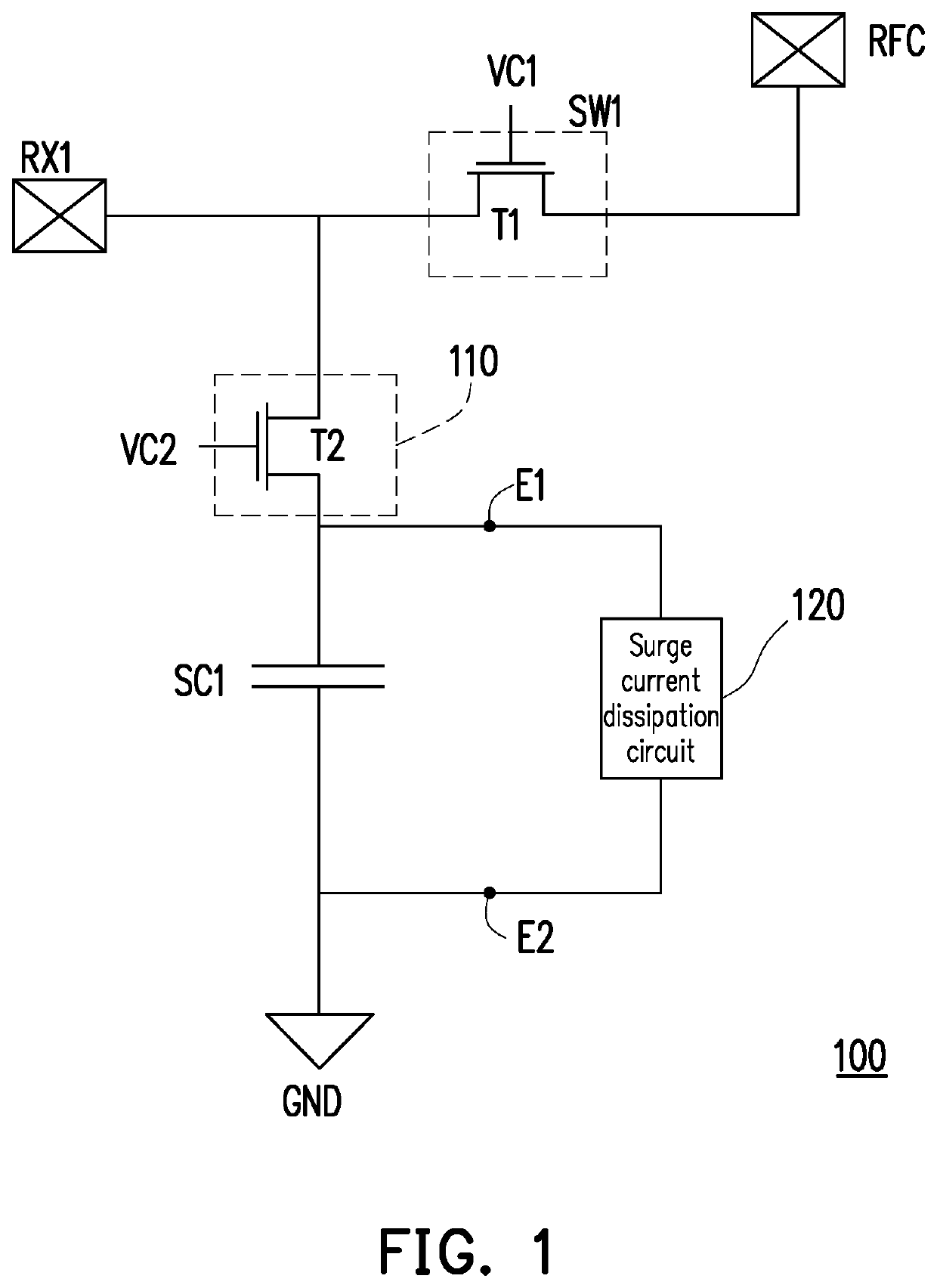

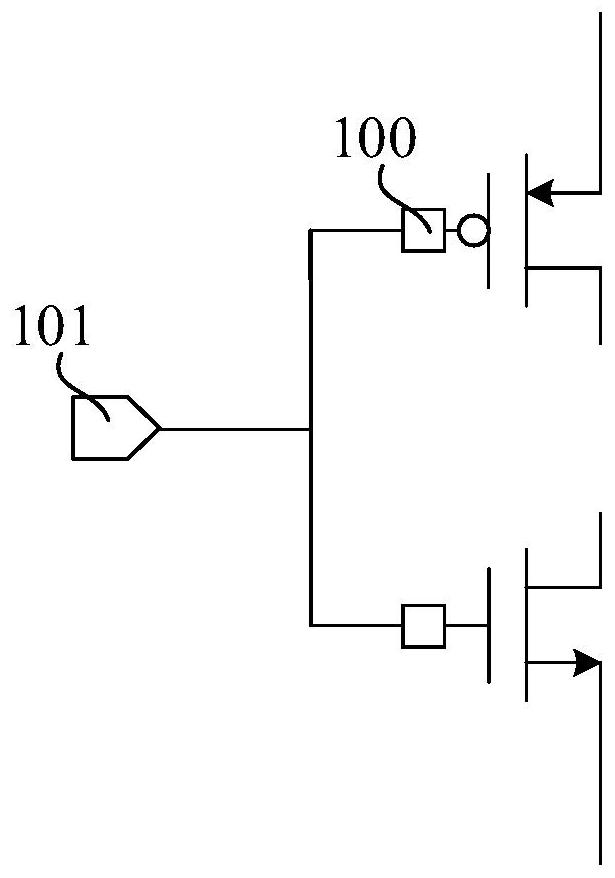

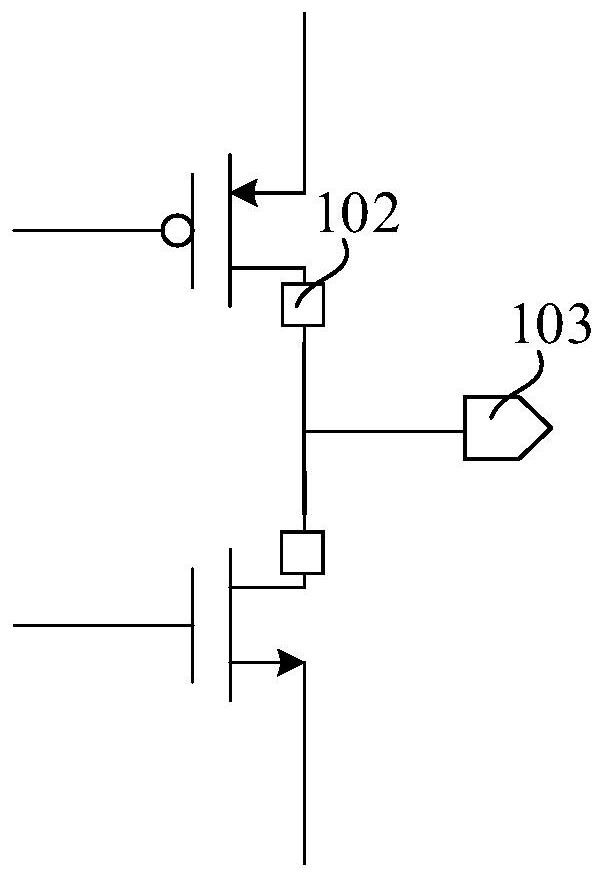

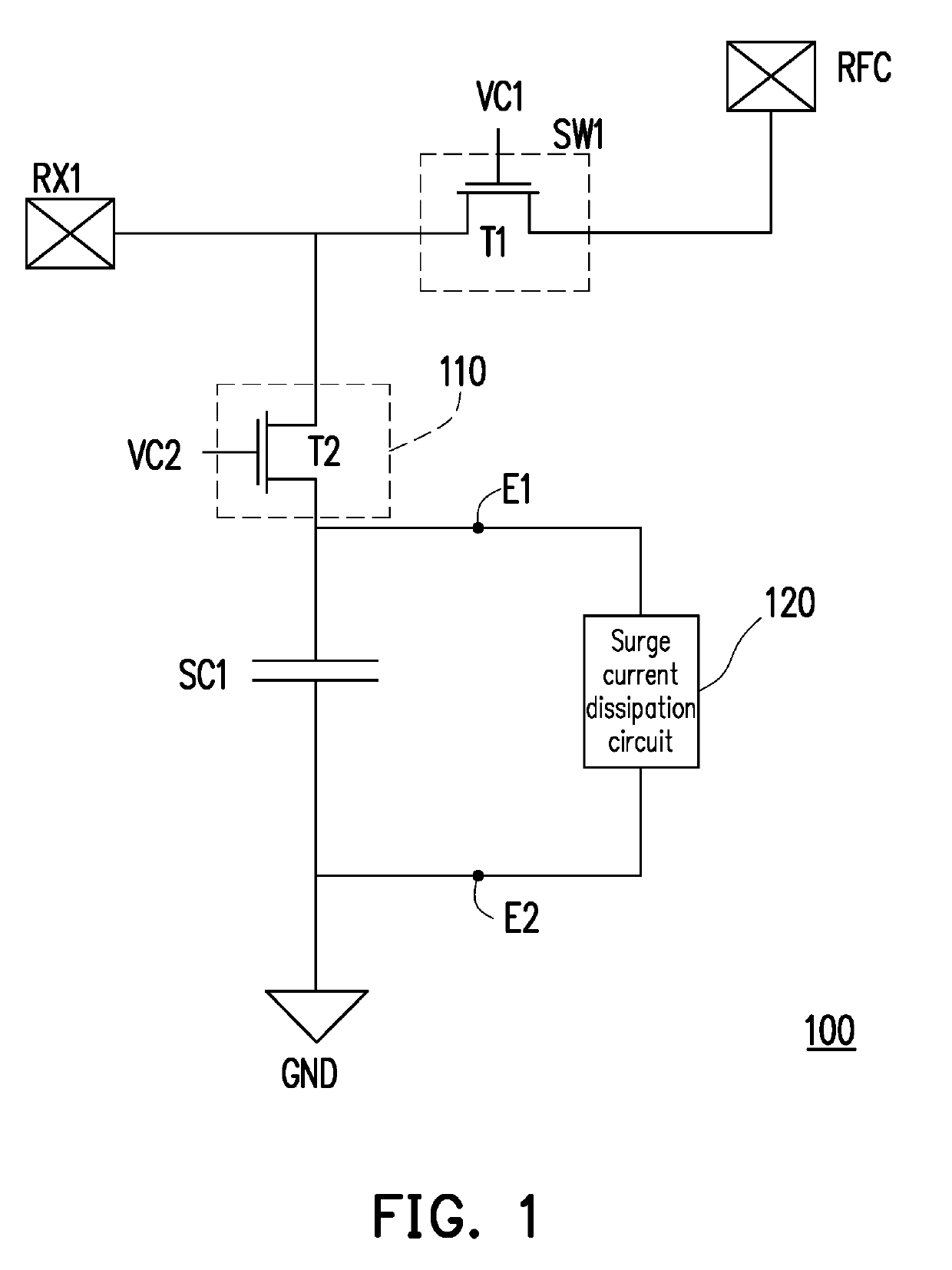

Switch apparatus

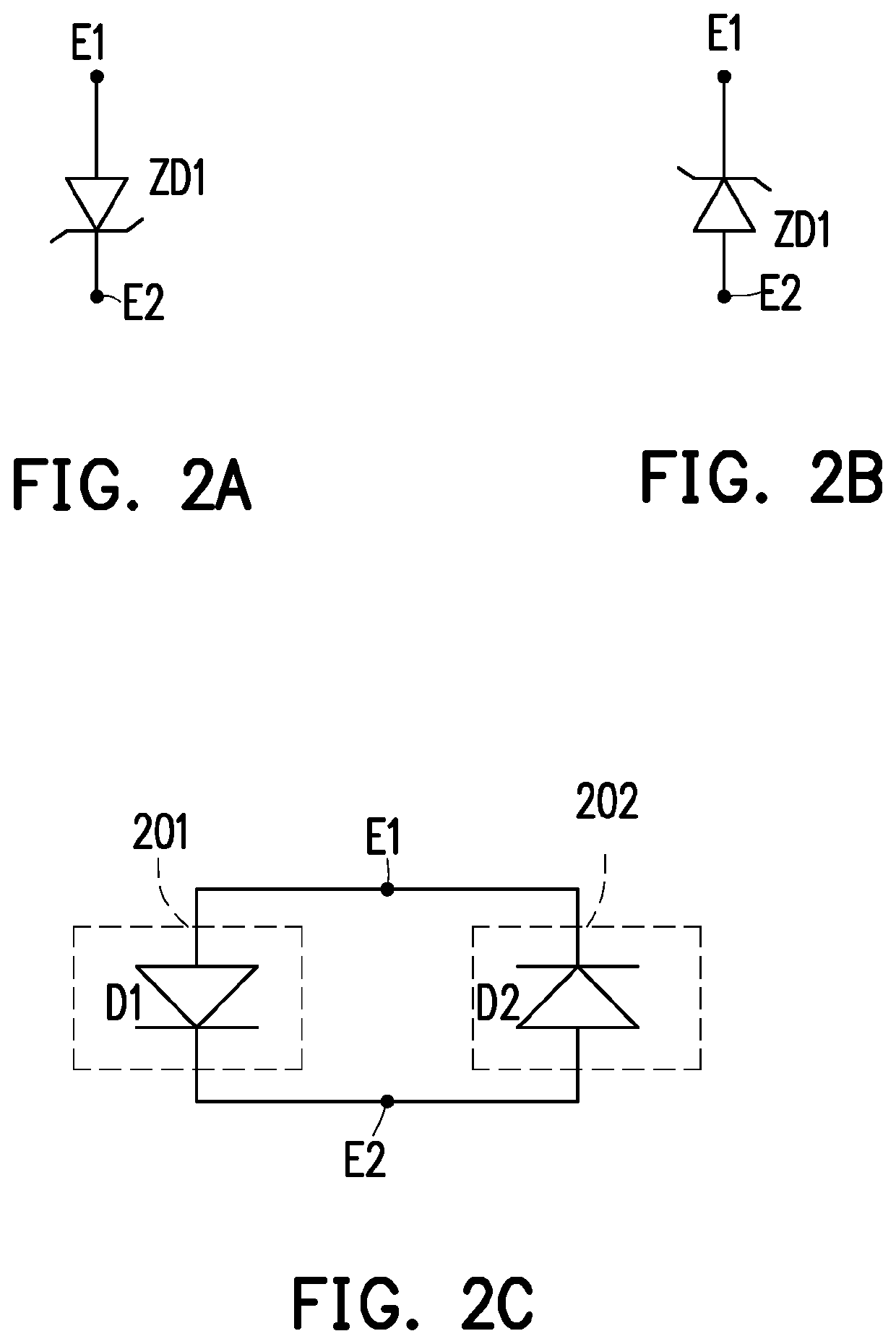

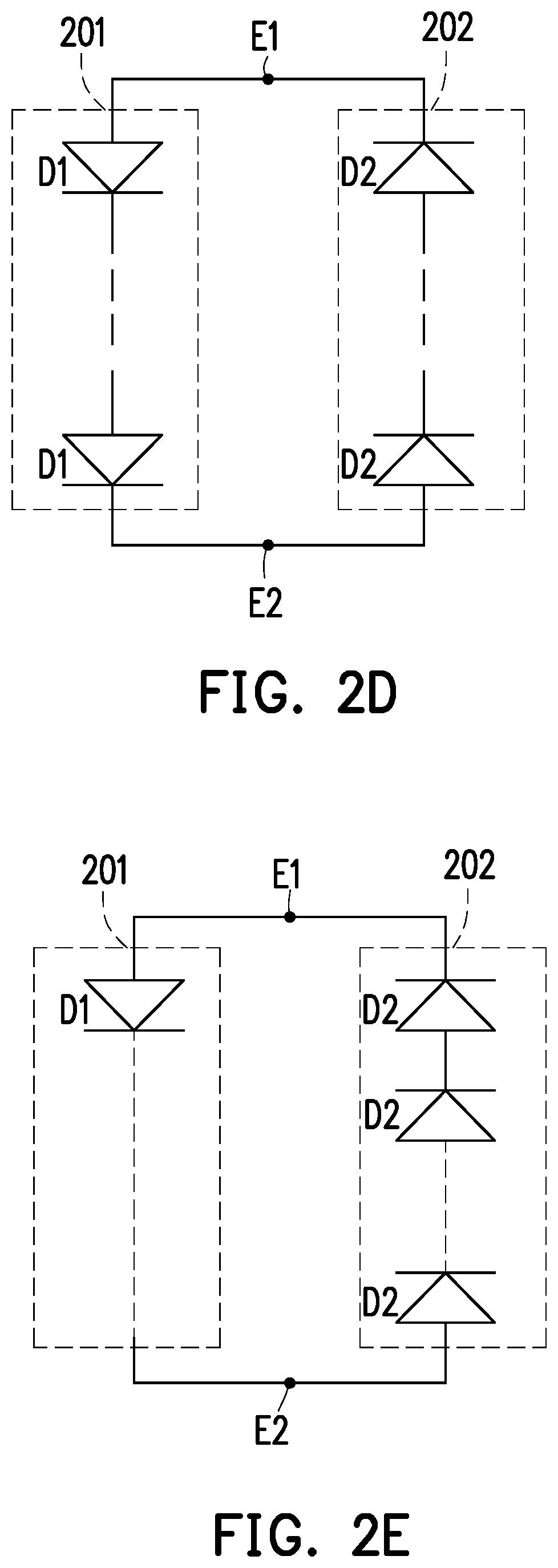

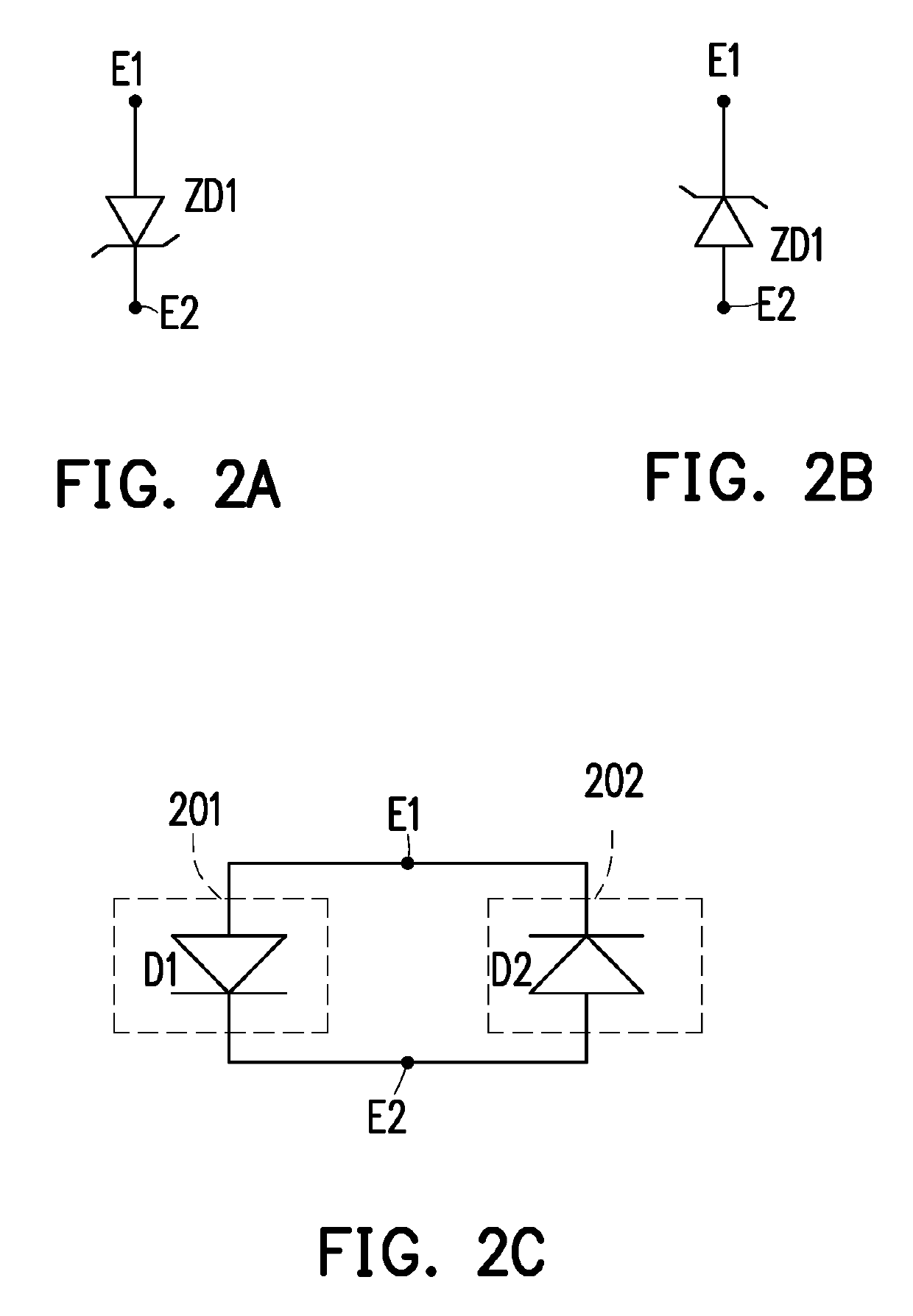

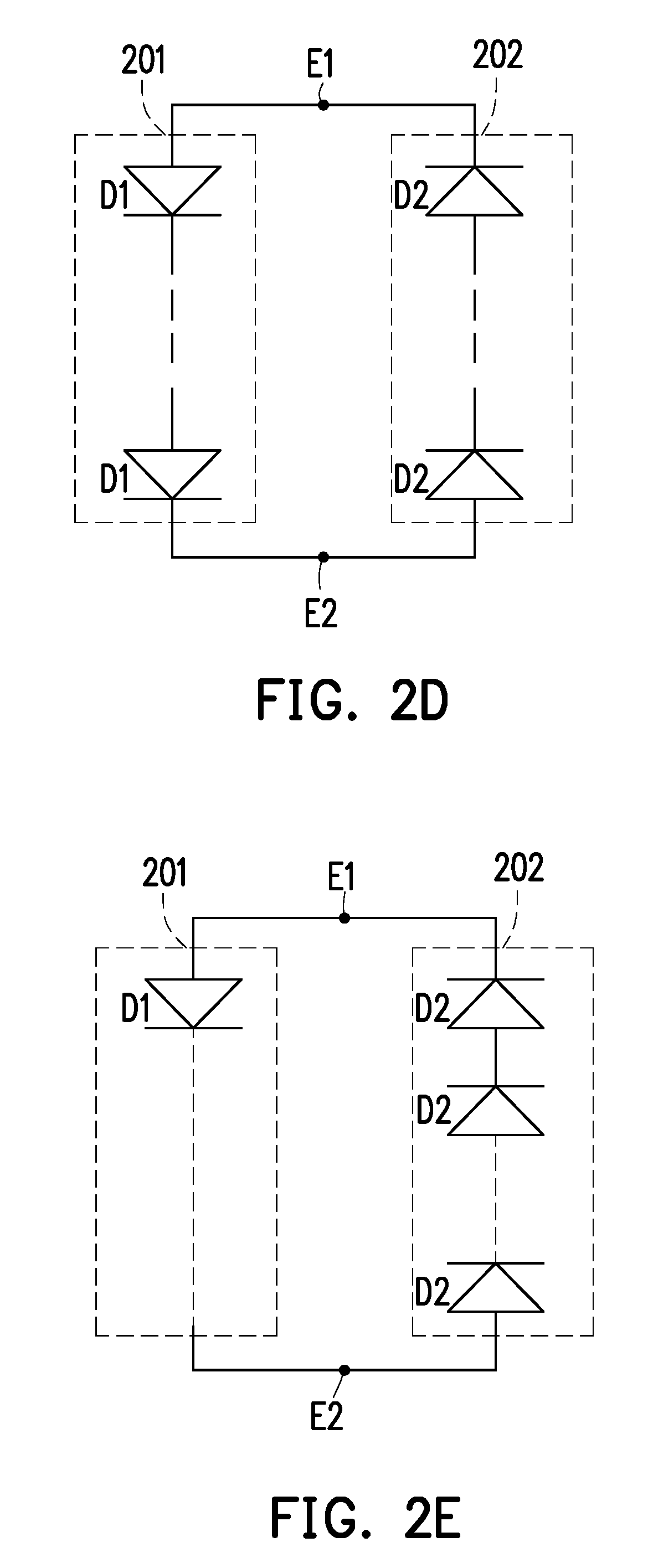

ActiveUS11050245B2Quality improvementCost difficultyElectronic switchingLine-transmission monitoring/testingCapacitanceControl signal

A switch apparatus is provided. The switch apparatus includes a signal control switch, a switch circuit, a blocking capacitor and a surge current dissipation circuit. The signal control switch and the switch circuit are respectively controlled by a first control signal and a second control signal to be turned on or off. The blocking capacitor is serially coupled between the switch circuit and a reference voltage end. The surge current dissipation circuit includes a Zener diode circuit or at least one diode circuit, and the at least one diode circuit has one or more diodes coupled in series. The one or more diodes coupled in series are coupled between two ends of the surge current dissipation circuit according to a first polarity direction.

Owner:RICHWAVE TECH CORP

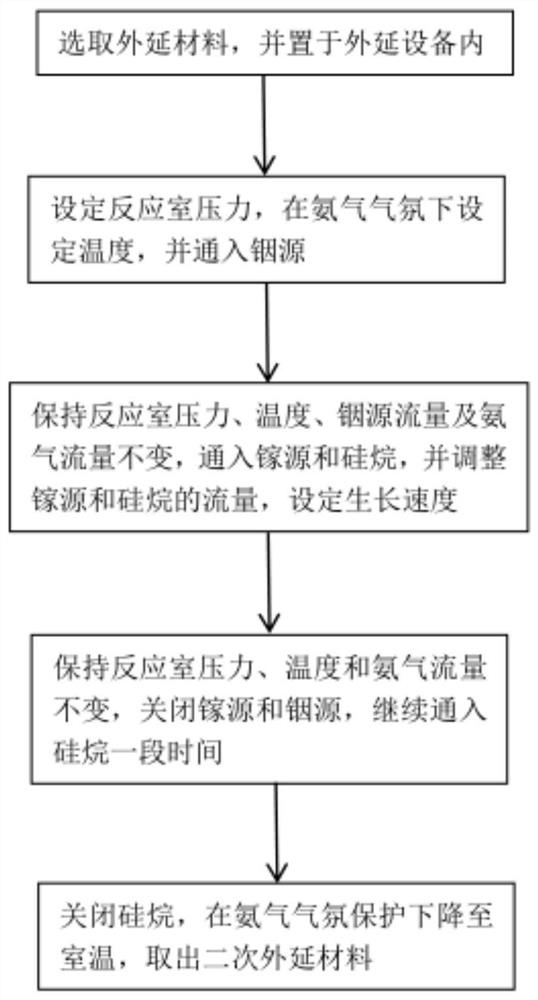

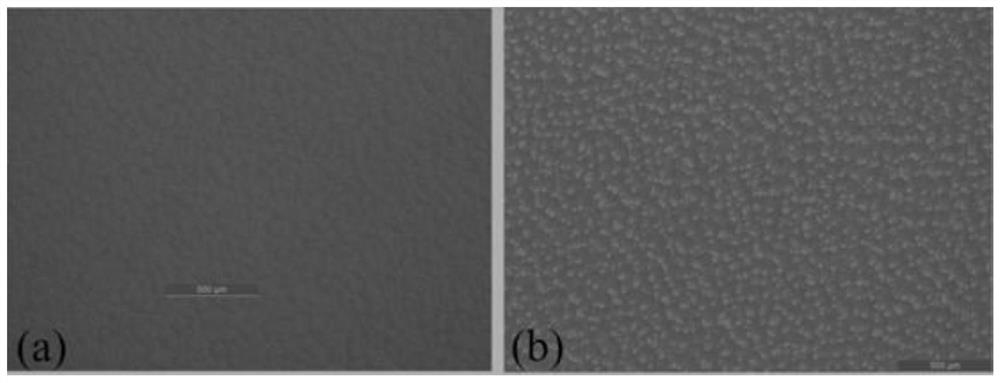

Secondary epitaxy method of N-type heavily-doped thin-layer gallium nitride material

PendingCN113808916AIncreased efficiency of GaN lattice incorporationLow resistivityPolycrystalline material growthSemiconductor/solid-state device manufacturingHigh frequency powerIndium

The invention discloses a secondary epitaxy method of an N-type heavily-doped thin-layer gallium nitride material. The method comprises the following steps: (1) selecting an epitaxial material, and placing the epitaxial material on a base in MOCVD epitaxial growth equipment; (2) setting the pressure of a reaction chamber, heating the reaction chamber to a preset temperature in an ammonia gas atmosphere, and then continuously introducing an indium source; (3) keeping the pressure, the temperature, the indium source flow and the ammonia gas flow of the reaction chamber unchanged, and introducing a gallium source and silane; adjusting the flow of the gallium source and the indium source, setting the growth rate, and starting secondary epitaxy of the N-type heavily doped thin layer GaN material; (4) keeping the pressure, the temperature and the ammonia gas flow of the reaction chamber unchanged, closing the gallium source and the indium source, and continuously introducing silane for a period of time; and (5) closing the silane, cooling to room temperature under the protection of ammonia gas atmosphere, and taking out the secondary epitaxial material. The N-type heavily-doped thin-layer GaN material is good in surface appearance and high in crystallization quality, and ohmic contact resistance of a high-frequency GaN power device can be reduced.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

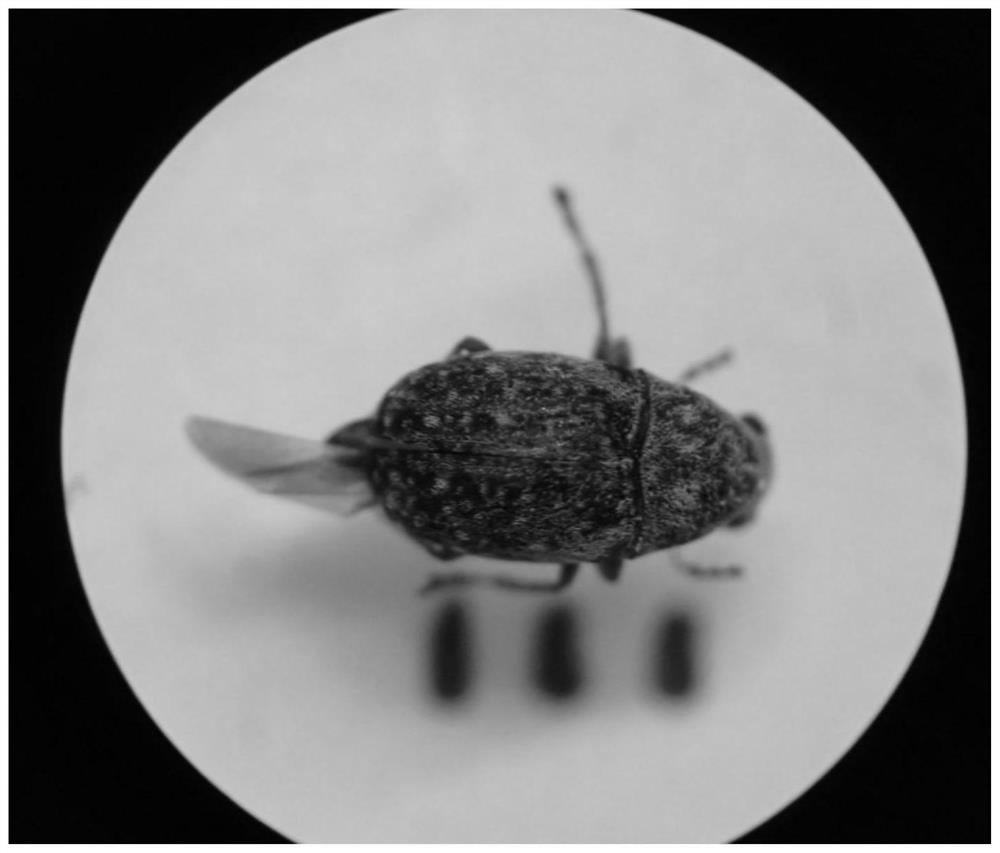

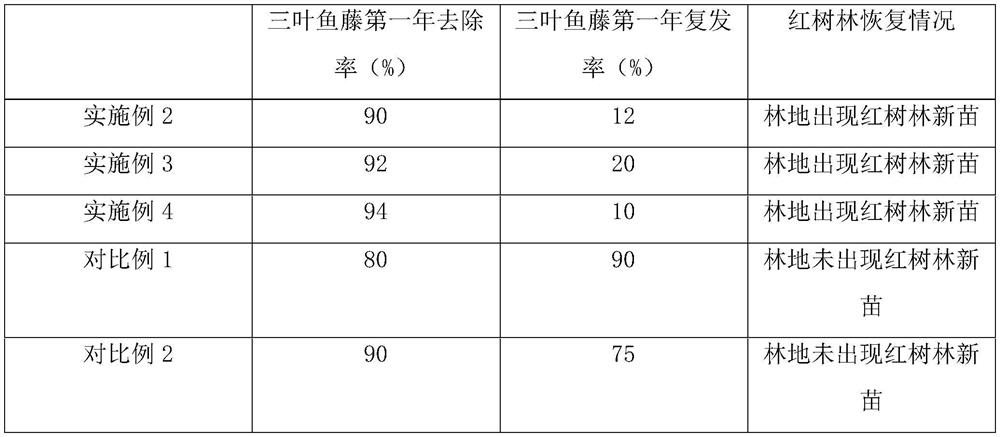

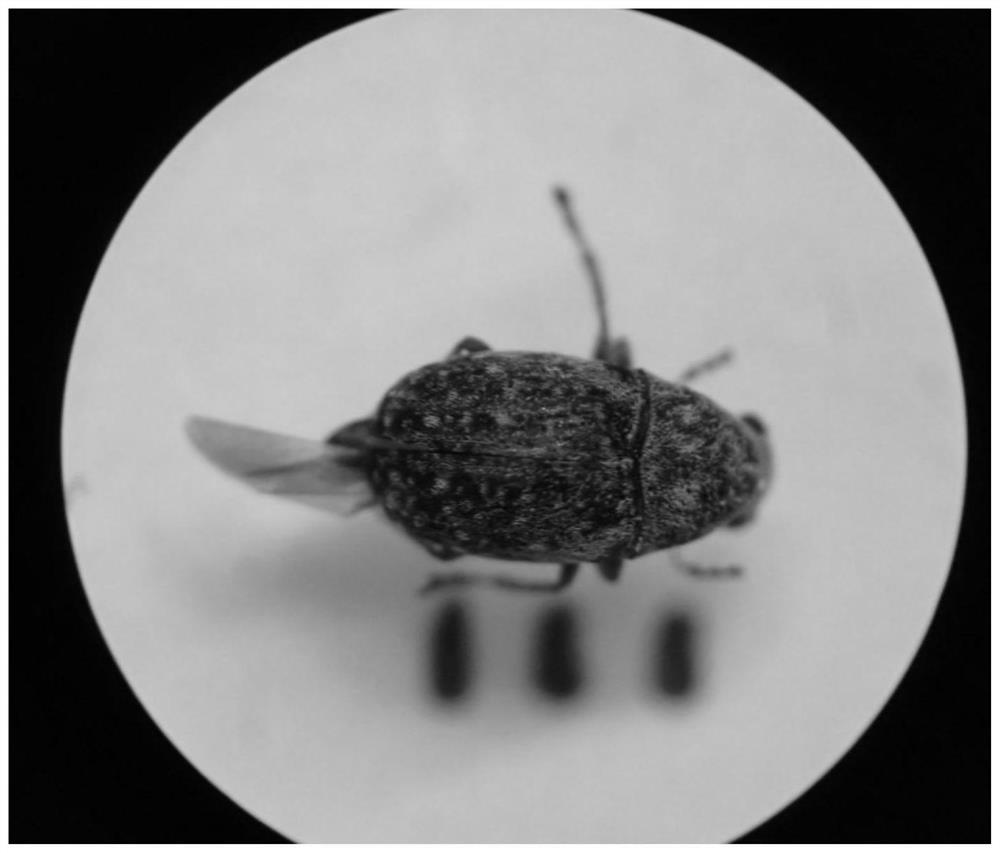

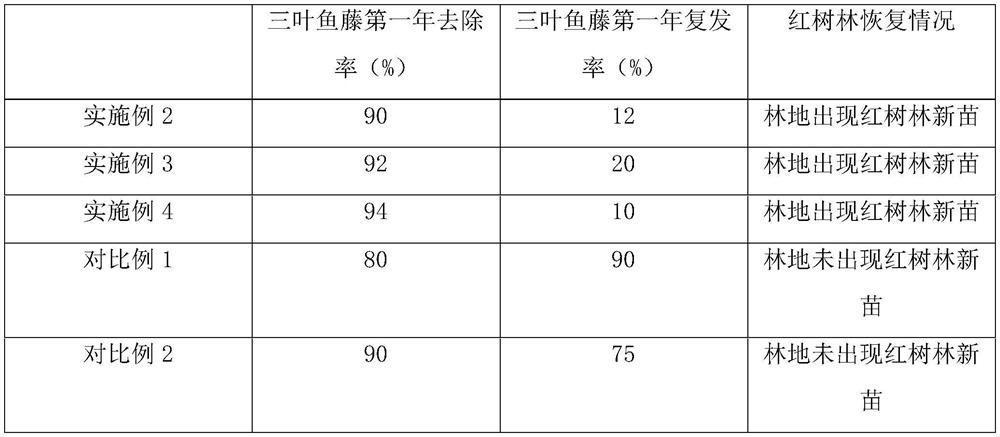

Method for preventing derris trifoliata in mangrove forest

ActiveCN112119815AEasy to collectEasy to trainPlant cultivationCultivating equipmentsForest protectionAcetic acid solution

The invention provides a method for preventing derris trifoliata in a mangrove forest, and belongs to the technical field of mangrove forest protection. The parts being 10-20 cm above rhizomes of thederris trifoliata are cut off at the lowest tide level all day long in the mangrove forest, then an acetic acid solution is sprayed to the rhizomes of the derris trifoliata once, and artificially-bredcoleopteran weevils insects are placed on the derris trifoliata; and semen cuscutae stems are placed at the canopy positions, on the water surface, of the derris trifoliata, and after semen cuscutaeis successfully parasitized on the derris trifoliata, an acetic acid solution is sprayed to the rhizomes of the derris trifoliata again. Semen cuscutae and coleopteran weevils insects are introduced and cooperate with acetic acid root spraying, prevention of the derris trifoliata is effectively achieved, operation is easy, environment friendliness is achieved, and the derris trifoliata is thoroughly eradicated from the source.

Owner:GUANGXI MANGROVE RES CENT

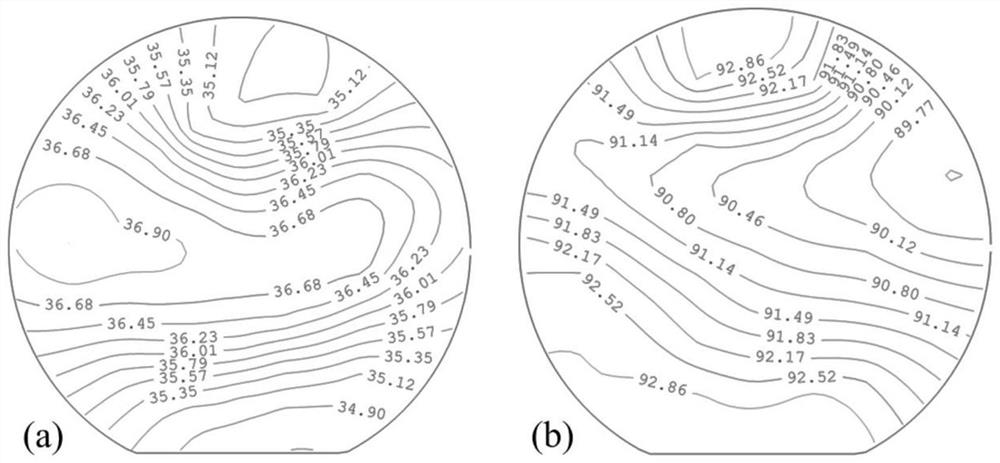

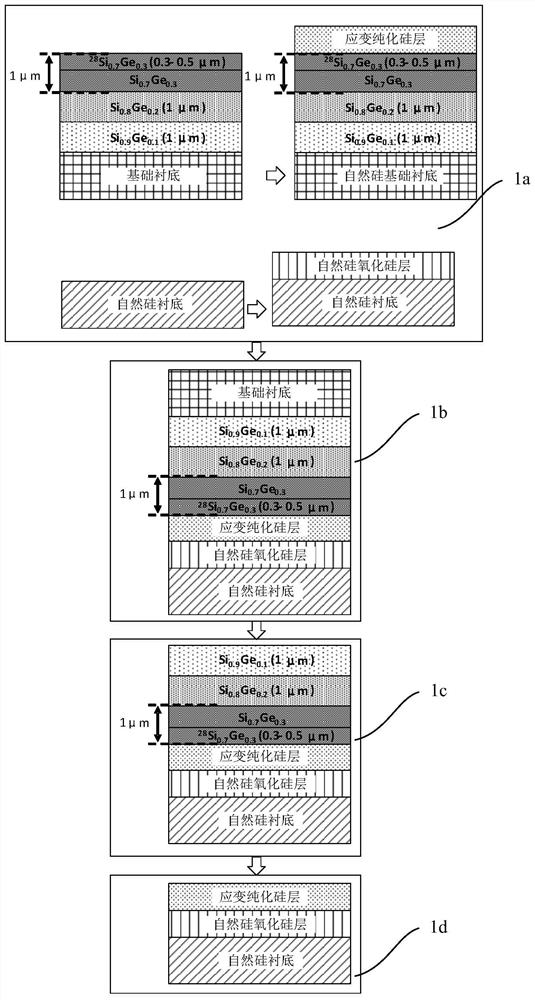

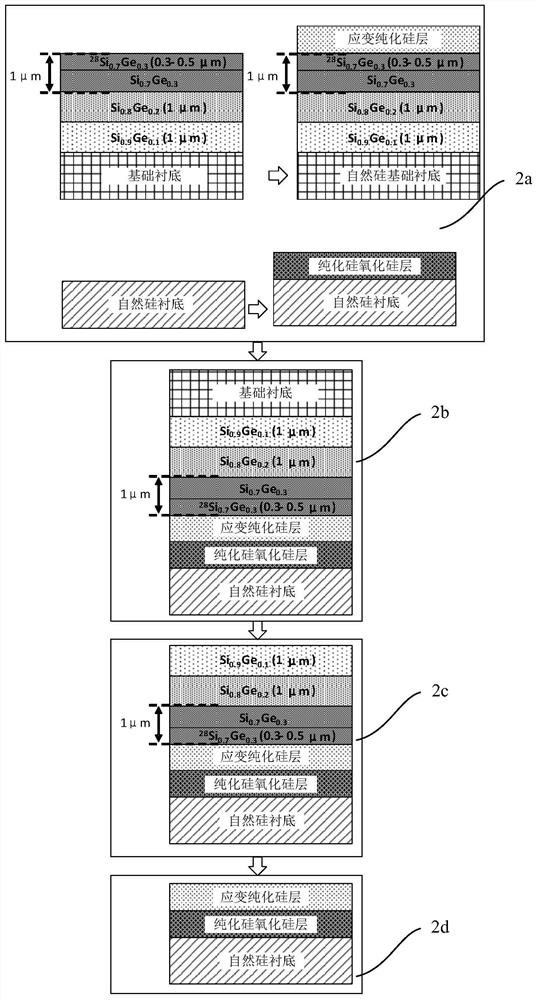

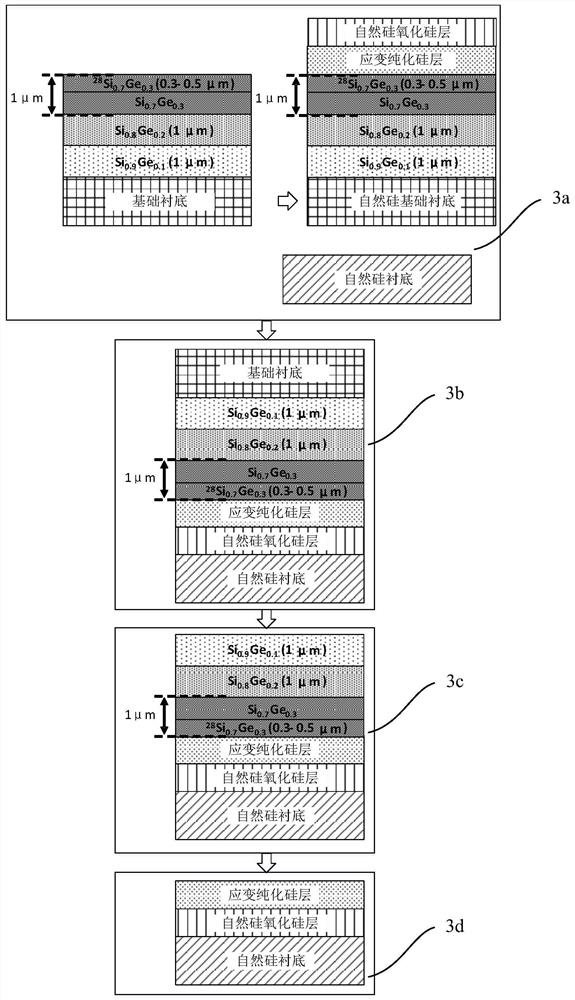

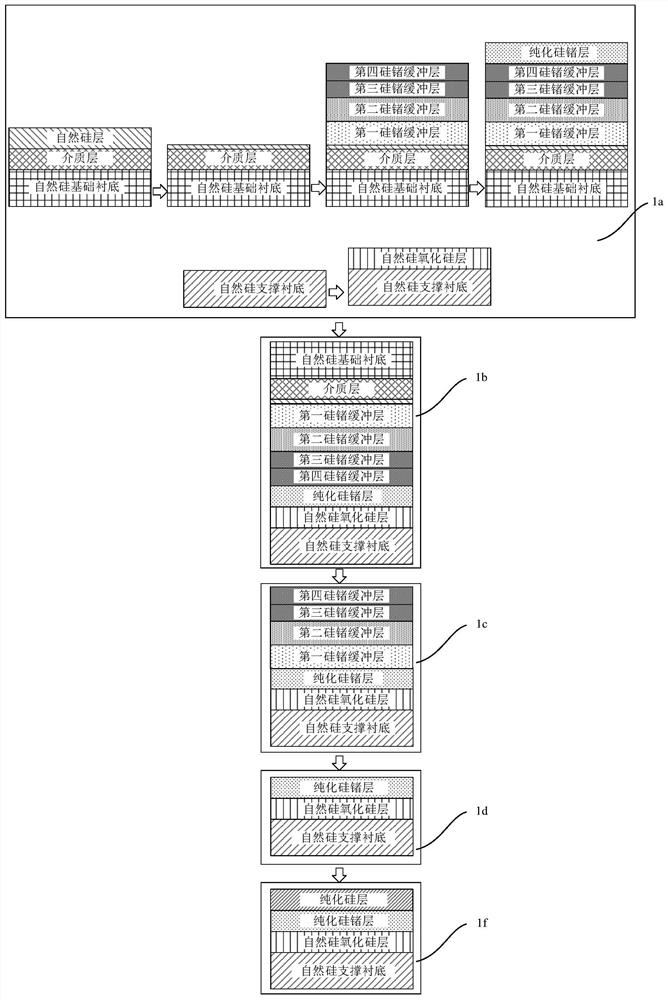

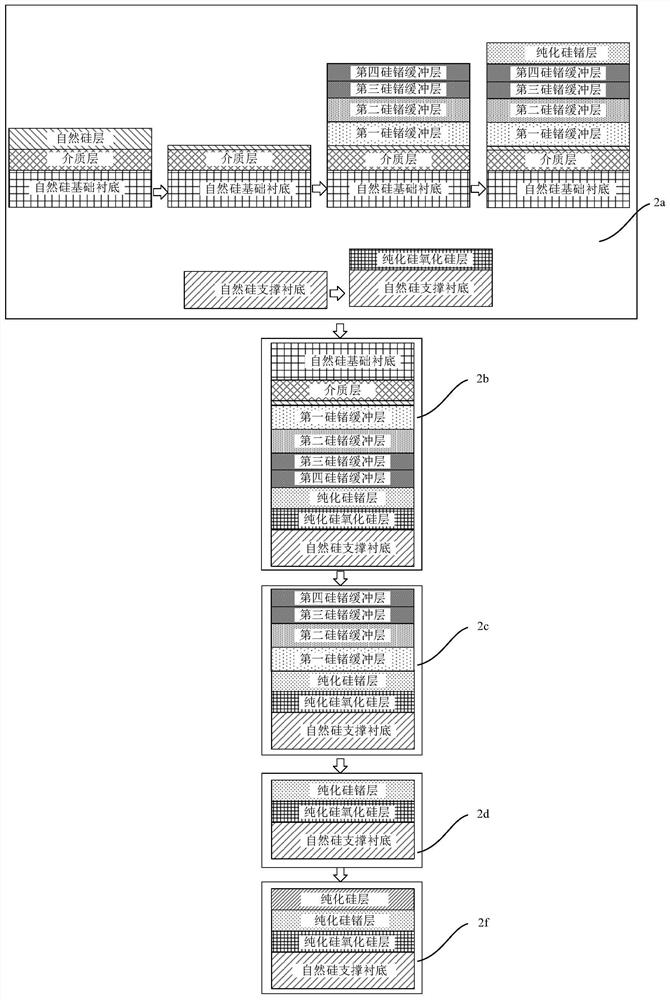

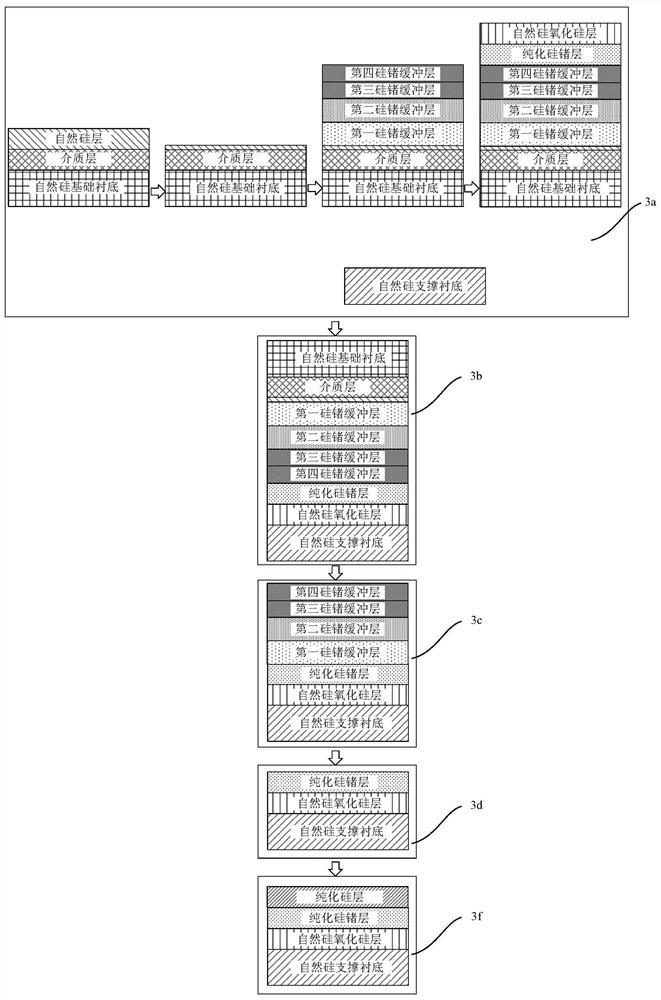

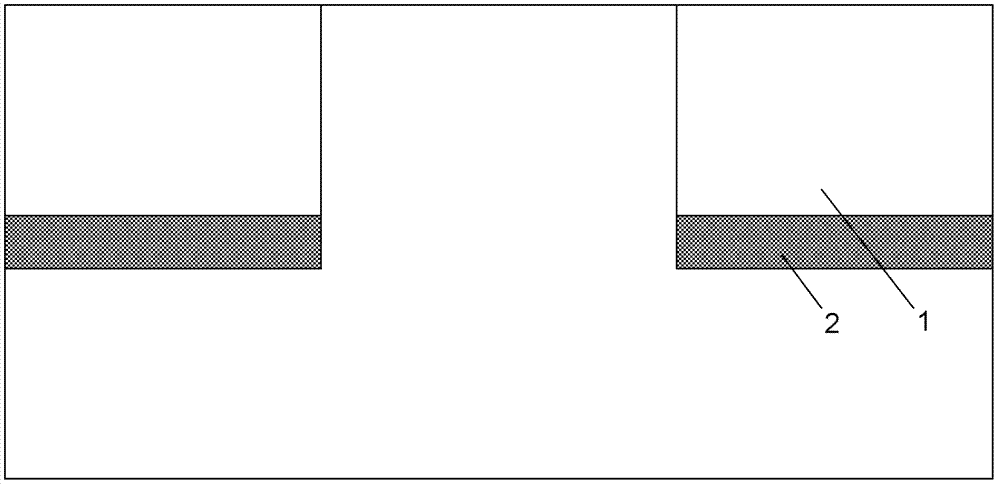

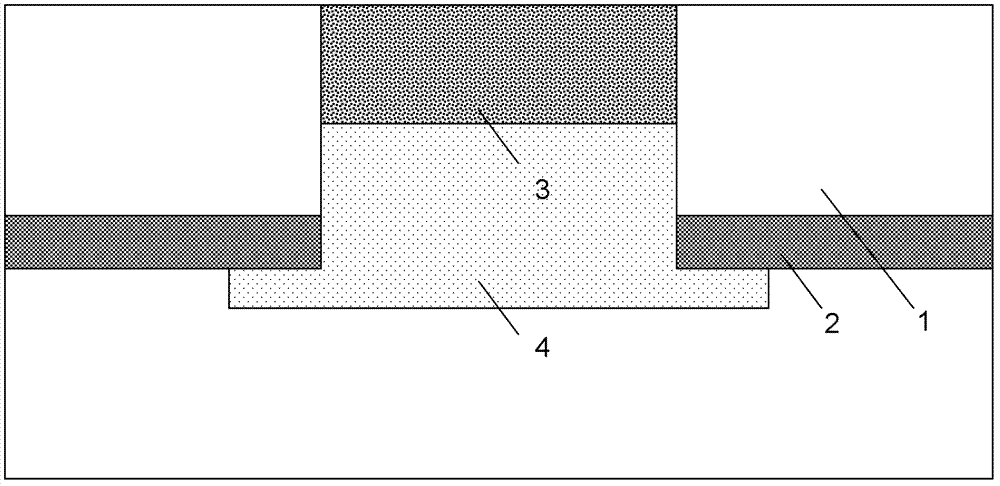

A strain purified silicon substrate for semiconductor quantum computation and method of forming same

PendingCN112582256AReduce the impactImprove decoherence timeNanoinformaticsSemiconductor/solid-state device manufacturingElectron mobilitySemiconductor

The invention discloses a strain purified silicon substrate for semiconductor quantum calculation and a forming method thereof, belongs to the technical field of semiconductors, and aims to solve theproblems that epitaxial purified silicon is greatly influenced by natural silicon isotope components of a substrate and the electron mobility of a purified silicon layer is low in the prior art. The strain purified silicon substrate comprises a natural silicon substrate, an insulating layer and a strain purification silicon layer, and tensile stress is introduced into the strain purification silicon layer. The forming method comprises the following steps: epitaxially forming a plurality of silicon-germanium buffer layers on a base substrate, gradually increasing the germanium doping concentration in the plurality of silicon-germanium buffer layers, and forming a strain purification silicon layer on the silicon-germanium buffer layers to obtain a donor substrate; providing a natural siliconsubstrate; forming an insulating layer on the donor substrate and / or the natural silicon substrate; and bonding the donor substrate with a natural silicon substrate, and removing the silicon-germanium buffer layer and the base substrate to obtain the strain purified silicon substrate. The strain purified silicon substrate and the forming method can be used for semiconductor quantum calculation.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

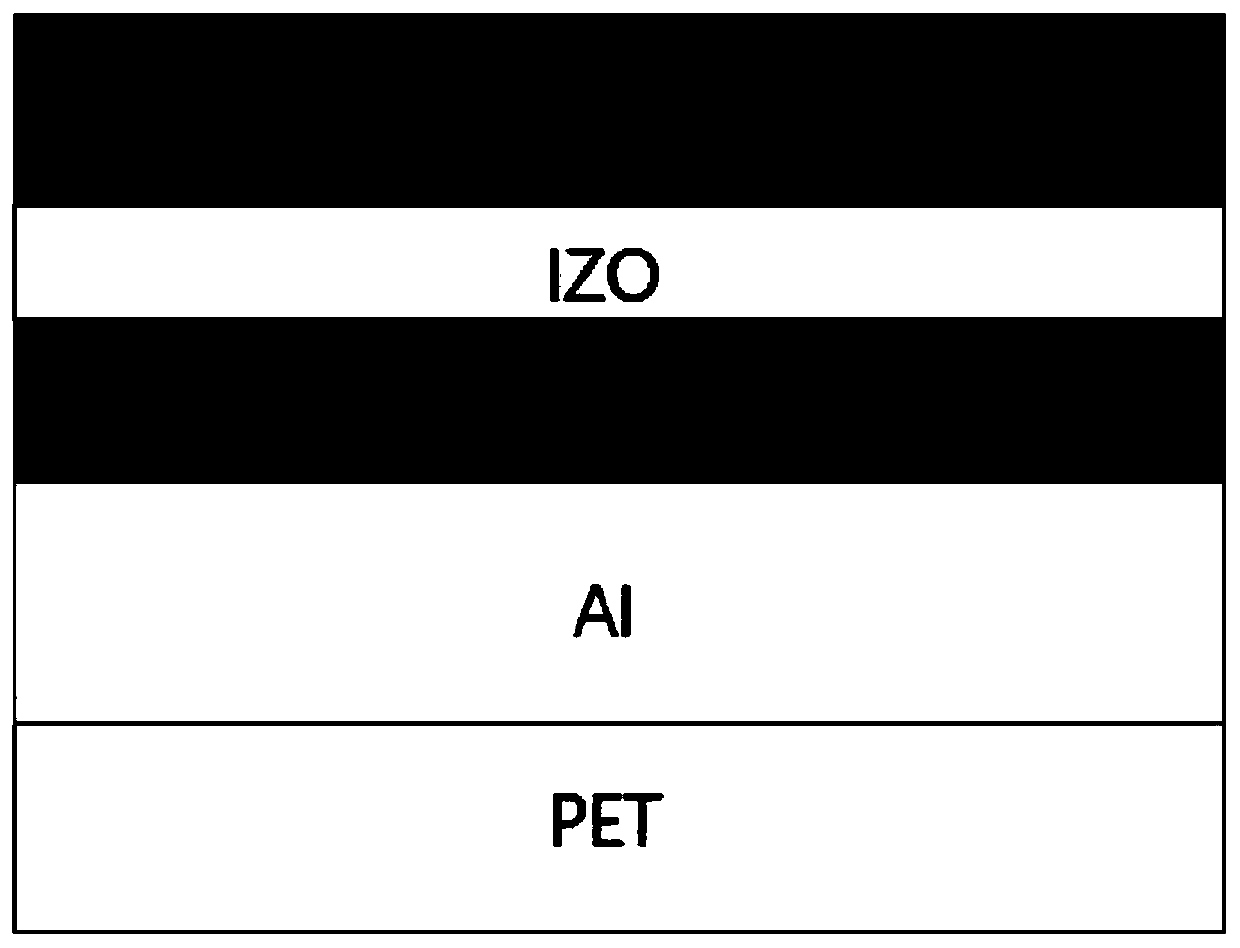

Flexible indium zinc oxide thin film transistor and manufacturing method thereof

InactiveCN110571277AAchieve normal workAchieving bending propertiesTransistorSemiconductor/solid-state device manufacturingMechanical impactIndium zinc oxide

The invention discloses a flexible metal oxide thin film transistor and a manufacturing method thereof. A PET substrate is plated with an aluminum thin film and an aluminum oxide thin film formed through anodic oxidation, the aluminum thin film and the aluminum oxide thin film serve as a gate electrode and a gate electrode insulating layer respectively, an indium zinc oxide thin film is deposited,an indium tin oxide (ITO) source-drain electrode is prepared through a lift-off method, and finally silicon dioxide is deposited to serve as a device passivation layer. The flexible metal oxide thinfilm transistor is suitable for a flexible integrated circuit, and the transistor has good performance and high working frequency. Moreover, the device has the advantages of light and thin structure,bendability and foldability, strong mechanical shock resistance and the like, and has a wide application prospect in the fields of flexible display equipment, intelligent wearing and photoelectric devices.

Owner:TIANJIN UNIV

Artificial breeding method of piliferocallus hezhangensis yang et zhan,sp.n.

ActiveCN109874750AReduce the cost of captive breedingMature reproductive technologyPlant protectionAnimal husbandryPupaInstar

Owner:ZUNYI INST OF FORESTRY

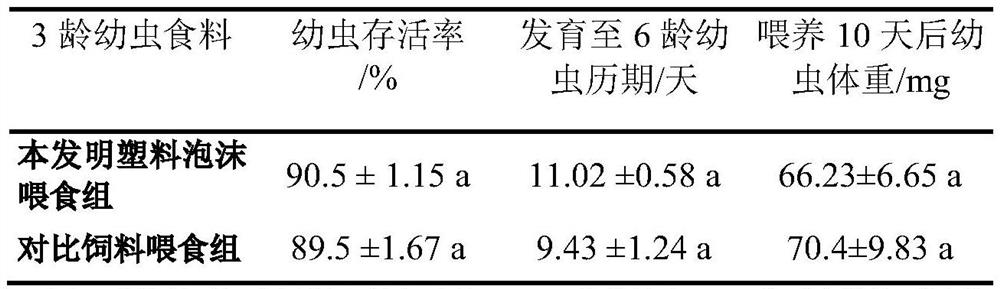

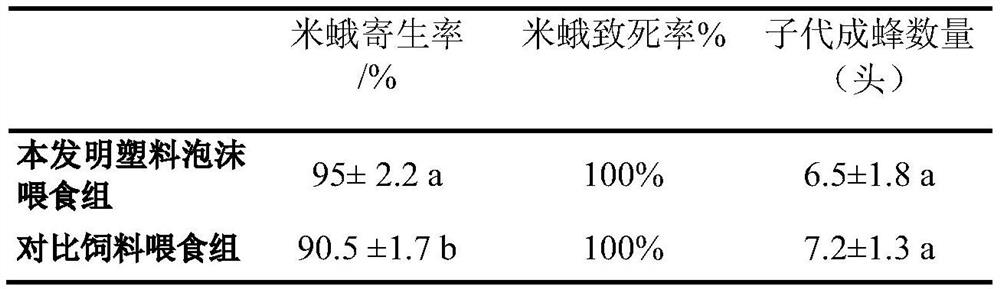

Feeding rice moth larvae with plastic foam as host breeding method

The invention discloses a method for breeding corcyra cephalonica larvae with plastic foam as hosts to breed bracon adoxophyesi mimankawa. The corcyra cephalonica larvae can be fed on the plastic foamto complete growth and development, the foam texture is light, the corcyra cephalonica larvae are easy to be separated from the foam, the foam can be better supplied to allow the bracon adoxophyesi mimankawa to search for parasitism, the parasitic effect is very good, and the reproduction efficiency is high. The plastic foam further has anti-mites and bacteriostatic effect, maintains the stability of the growth and development environment of the bracon adoxophyesi mimankawa, and further has a very good effect. In addition, a large number of plastic foam is used for replacing grain feed as a feed source and a feeding medium for the corcyra cephalonica larvae, the environmental pollutants are reduced, meanwhile, the plastic foam of environmental waste is turned into treasure, and a way to degrade the pollution of the plastic foam in the future is provided. A large number of parasitic bee sources are provided for the control of palm plant pests coconut woven moths and tirathaba rufivenawalker and the other prevention and control technology application by making further use of corcyra cephalonica larvae to breed the bracon adoxophyesi mimankawa.

Owner:ENVIRONMENT & PLANT PROTECTION INST CHINESE ACADEMY OF TROPICAL AGRI SCI

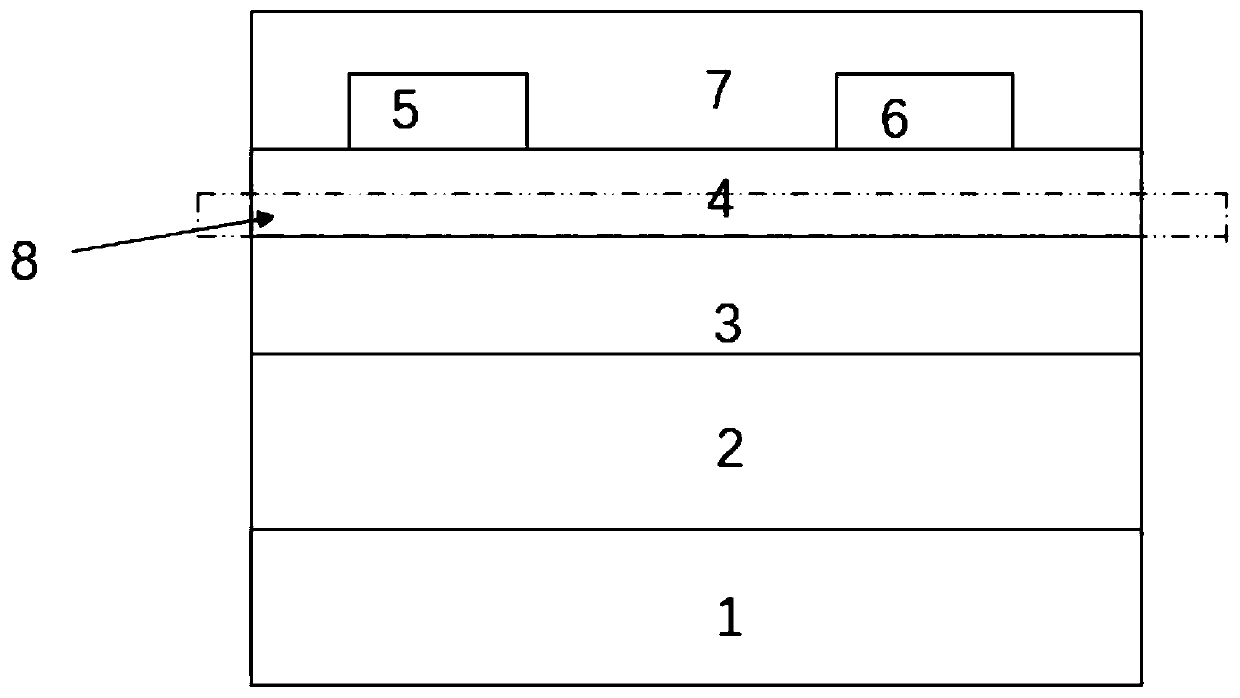

Vertical parasitic PNP transistor in silicon-germanium BICMOS (Bipolar Complementary Metal Oxide Semiconductor) technique and fabrication method

ActiveCN102412279BImprove parasitic effectsReduce collector resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesDopantEngineering

The invention discloses a vertical parasitic PNP transistor in the silicon-germanium BICMOS technique. A groove which is in contact with a base region is formed in a shallow trench field oxide around the base region, the depth of the groove is smaller than or equal to the depth of the base region, polycrystalline silicon is filled in the groove and doped with N-type dopant, the polycrystalline silicon doped with the N-type dopant is formed into an outer base region, which is in contact with the side of the base region, and a metal contact is formed on the outer base region, and leads out a base. The invention also discloses a fabrication method for the vertical parasitic PNP transistor in the silicon-germanium BICMOS technique. The vertical parasitic PNP transistor can be used as an output device in a high-speed, high-gain HBT (heterojunction bipolar transistor) circuit, so that one more type of device is provided as an option for the circuit, the area of the device can be effectively reduced, the parasitic effect of the device can be effectively decreased, the collector resistance of the PNP transistor can be effectively decreased, and the performance of the device can be effectively enhanced; and the method does not need additional process conditions, and can reduce the production cost.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A kind of artificial breeding of Larix gidinosa and method applied to control Lishan longhorn beetle

InactiveCN104920308BIncreased parasitic abilityImprove parasitic effectsAnimal huntingPlant protectionBiotechnologyDrone

The invention discloses a method for artificial breeding of larch sclerodermus sp. and application of larch sclerodermus sp. for prevention of massicus raddei. Drone pupae of Bombus hypocrita are selected as substitute hosts of the larch sclerodermus sp., meanwhile, the breeding conditions are regulated and controlled, and thus the parasitic ability of the bred larch sclerodermus sp. is obviously improved. The larch sclerodermus sp. is applied to prevention of the massicus raddei in the Northeast China region, and the parasitic effect of the indoor larch sclerodermus sp. in the massicus raddei larvae of 1-3 years old is good.

Owner:INST OF FOREST ECOLOGY ENVIRONMENT & PROTECTION CHINESE ACAD OF FORESTRY

A strain purified silicon substrate for semiconductor quantum computation and forming method thereof

PendingCN112582257AReduce the impactImprove decoherence timeSemiconductor/solid-state device manufacturingCrystallographyElectron mobility

The invention discloses a strain purified silicon substrate for semiconductor quantum calculation and a forming method thereof, belongs to the technical field of semiconductors, and aims to solve theproblems that epitaxial purified silicon is greatly influenced by natural silicon isotope components of a substrate and the electron mobility of the purified silicon is low in the prior art. The purified silicon germanium substrate comprises a natural silicon supporting substrate, an insulating layer, a purified silicon germanium layer and a purified silicon layer which are stacked in sequence. The forming method comprises the following steps: epitaxially forming a plurality of silicon-germanium buffer layers and purified silicon-germanium layers on a base substrate to obtain a donor substrate; providing a natural silicon support substrate; forming at least one insulating layer on the donor substrate and / or the natural silicon support substrate; bonding the donor substrate with a natural silicon support substrate, and removing the base substrate and the multiple silicon-germanium buffer layers or removing the base substrate, the multiple silicon-germanium buffer layers and part of thepurified silicon-germanium layer to obtain a purified silicon-germanium substrate; and epitaxially forming a purified silicon layer on the purified silicon germanium substrate to obtain the strain purified silicon substrate. The purified silicon germanium substrate and the forming method thereof can be used for semiconductor quantum calculation.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Vertical parasitic PNP transistor and manufacturing method thereof in germanium silicon heterojunction bipolar transistor (HBT) technology

ActiveCN103066118BImprove parasitic effectsReduce collector resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOxygenSilicon heterojunction

The invention discloses a vertical parasitic PNP transistor in a germanium silicon heterojunction bipolar transistor (HBT) technology. A groove contacted with a base region is formed in shallow groove field oxygen in the circumference of the base region, the depth of the groove is smaller than or equal to that of the base region, polycrystalline silicon mixed with N type impurities is filled in the groove, a outer base region is formed by the polycrystalline silicon mixed with N type impurities, the outer base region are contacted with the base region on the sides of the base region, metal is arranged on the outer base region, and the metal is contacted with a base electrode and leads the base electrode out. The invention further discloses a manufacturing method of the vertical PNP transistor in the germanium silicon HBT technology. The vertical PNP transistor in the germanium silicon HBT technology can be used as an output component in a high speed and high gain HBT circuit, and thus one more component choice is supplied for the circuit, the size of a component, the parasitic effect of the component and the collector resistance of the PNP transistor are effectively reduced, the performance of the component is improved, and production lost can be reduced due to the fact that according to the manufacturing method of the vertical PNP transistor in the germanium silicon HBT technology, no extra technological conditions are needed.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

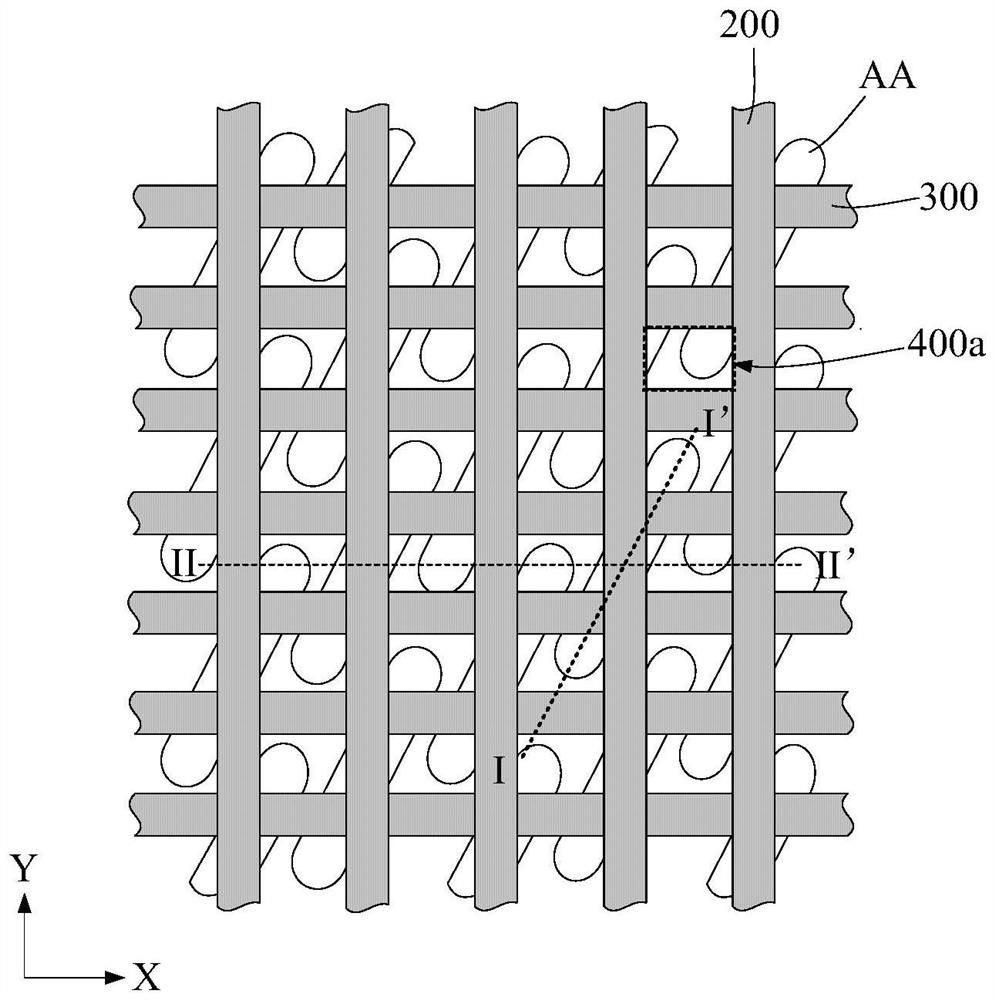

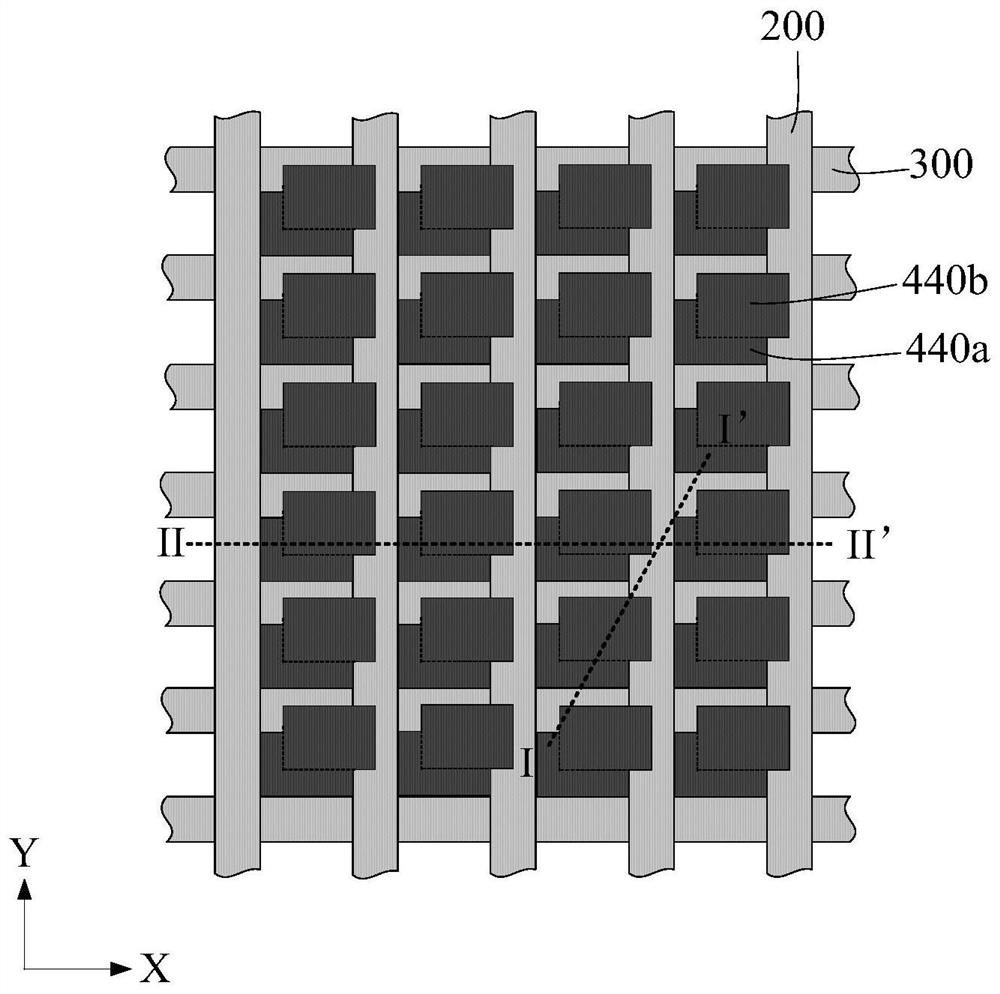

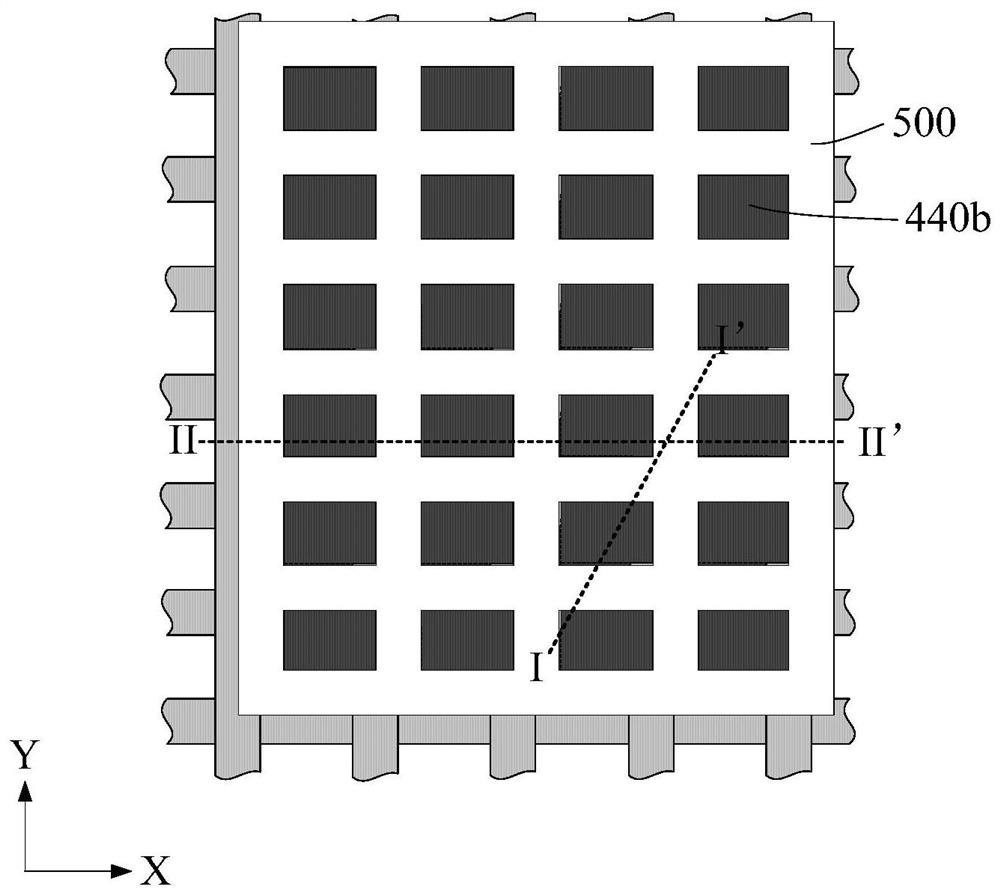

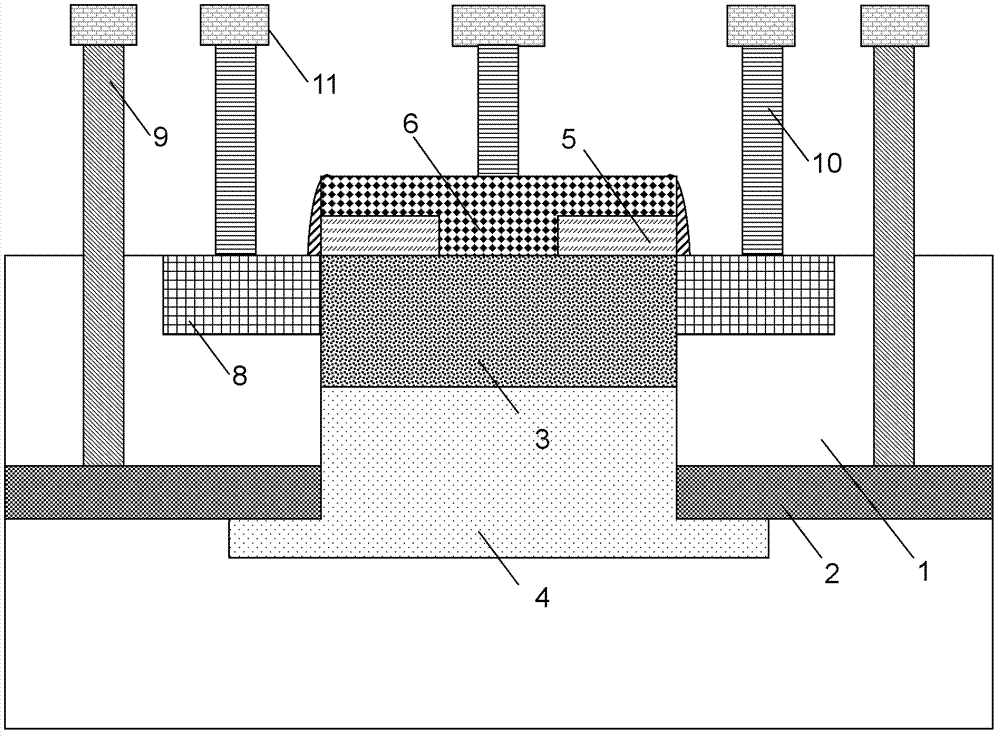

Memory and method of forming the same

ActiveCN112382632BIncreased top surface contact areaLow dielectric constantTransistorSemiconductor/solid-state device manufacturingBit lineDielectric permittivity

Owner:FUJIAN JINHUA INTEGRATED CIRCUIT CO LTD

Vertical parasitic pnp transistor in silicon germanium hbt process and its manufacturing method

ActiveCN103117301BImprove emission efficiencyIncrease the magnification factorSemiconductor/solid-state device manufacturingSemiconductor devicesMicrometerSemiconductor

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

A kind of method of large-scale reproduction of the brown banded moth Braconis

The invention discloses a method for indoor breeding of the brown-banded moth wasps. At 25°C of temperature, light: under the condition of darkness=14h:10h, put into the insect cage with sleeves of 55cm * 55cm * 55cm by the brown scalloped wasp, feed with 15% honey water, every 3 Every day, take out the feed with worms from the breeding tray with 5-6 instar rice moth larvae and spread it on the bottom of the plastic box, so that the height of the feed with worms is about 1.5cm, and put the plastic box without a cover into the parasitic bee insect cage Among them, the parasitic wasps take the rice moth in the feed as their host. After 3 days, the plastic box was taken out, and the lid was covered. After 12 days, the next generation of parasitoids began to emerge, and the emergence time continued for more than 7 days. The invention has the advantages of simple operation and high efficiency, and is easy to realize the large-scale reproduction of the coronis.

Owner:ENVIRONMENT & PLANT PROTECTION INST CHINESE ACADEMY OF TROPICAL AGRI SCI

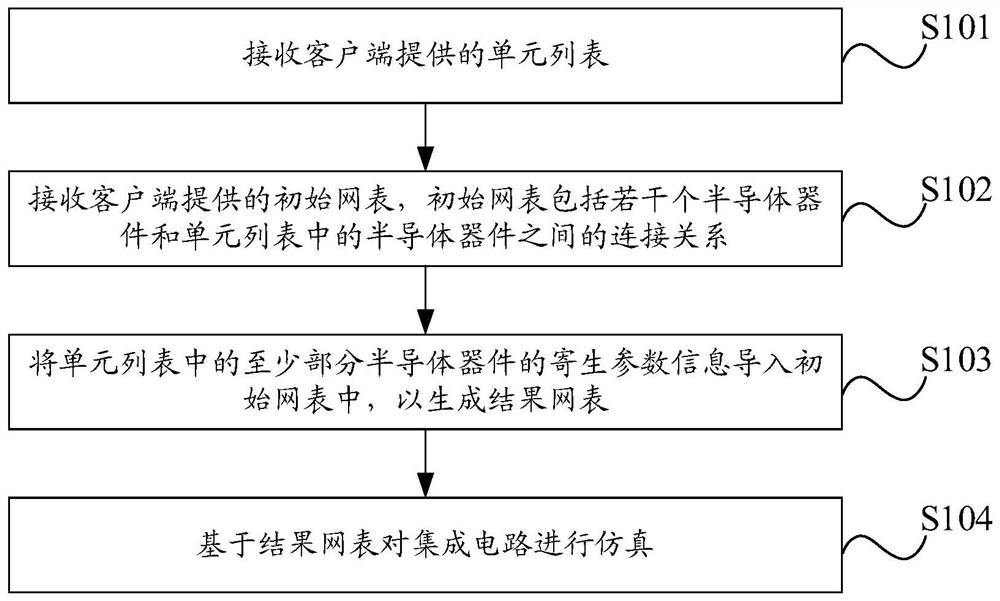

Simulation method and simulation system of integrated circuit

PendingCN114741994AImprove simulation accuracyImprove parasitic effectsComputer aided designSpecial data processing applicationsDevice materialSoftware engineering

The embodiment of the invention relates to the technical field of semiconductors, and provides a simulation method of an integrated circuit and a simulation system thereof, the simulation method is applied to a server, and the method comprises the following steps: receiving a unit list provided by a client; receiving an initial netlist provided by the client, wherein the initial netlist comprises a plurality of semiconductor devices and a connection relationship between the semiconductor devices in the unit list; importing parasitic parameter information of at least part of semiconductor devices in the unit list into the initial netlist to generate a result netlist; and simulating the integrated circuit based on the result netlist. The embodiment of the invention is at least beneficial to improving the simulation precision of simulating the integrated circuit.

Owner:CHANGXIN MEMORY TECH INC

A kind of control method of trefoil in mangrove

ActiveCN112119815BEasy to collectEasy to trainPlant cultivationCultivating equipmentsBiotechnologyMangrove

The invention provides a method for preventing and treating cloverleaf in mangroves, belonging to the technical field of mangrove protection. At the lowest tide level in the mangroves, 10-20 cm above the rhizome of cloverleaf is cut, and then the The rhizome is drenched with acetic acid solution once, and after 3 to 5 days, artificially raised Coleopteran weevil insects are placed on the clover vine; After the dodder successfully parasitized on the clover vine, the rhizome of the clover vine was drenched with acetic acid solution again. By introducing dodder and coleopteran weevil, and dipping roots with acetic acid, the control of clover vine is effectively realized, and the operation is simple and environmentally friendly, and the clover vine is completely eliminated from the root.

Owner:GUANGXI MANGROVE RES CENT

A kind of high-efficiency propagation method of Trichogramma rice borer

ActiveCN104996366BExtend the life cycleImprove reproductive performanceAnimal husbandryNutrient solutionSugar

Provided is a trichogramma japonicum high-efficiency reproduction method. The method comprises: collecting eggs of rice moths, and sticking the eggs on paper boards to make egg cards; putting trichogramma japonicum species and eggs of rice moths in a darkroom in proportion of 1:10 to 1:4, adjusting bee species emergence parasitic environment temperature to 23 to 25 DEG C, adjusting humidity to 70% to 80%; after 90% of the egg cards have parasitic bee species, adding fresh rice moth egg cards according to 1:6-10 of proportion of the bee species and the egg cards again, properly increasing temperature of the darkroom to 25 to 28 DEG C, and maintaining the humidity; after more than 90% of the egg cards have parasitic bee species, adding fresh rice moth egg cards according to 1:3-7 of proportion of the bee species and the egg cards for the third time, the egg cards this time being sprayed with cane sugar nutrient solution, the bee species continuing to reproduce. The method can realize using the trichogramma japonicum to prevent rice leaf folders and striped rice borers, and pesticide dose is greatly reduced. The method promotes agriculture to develop towards green, organic, and ecological agriculture.

Owner:HUNAN RICE RES INST +1

A method of artificial breeding of Scleroderma pine brown beetle and its application in the prevention and control of tree borer pests

InactiveCN107114326BIncreased parasitic abilityVitality is not weakenedPlant protectionAnimal husbandryVerminInsect pest

The invention discloses a method for artificially breeding sclerodermus and application of the sclerodermus in prevention and control of trunk-boring insect pests on forest trees. According to the method, larvae of paraglenea fortunei are selected as substitute hosts of sclerodermus, and the breeding condition is regulated, so that the parasitizing capability of the sclerodermus obtained in breeding is remarkably improved, and the viability of the slerodermus is not weakened even the sclerodermus is continuously bred indoors for five generations; and the sclerodermus is applied to prevent and control monochamus alternatus hope, and has a good parasitizing effect for larvae of paraglenea fortunei in 1-3 ages.

Owner:INST OF FOREST ECOLOGY ENVIRONMENT & PROTECTION CHINESE ACAD OF FORESTRY

Vertical parasitic pnp transistor in silicon germanium hbt process and manufacturing method thereof

ActiveCN102412284BImprove parasitic effectsReduce collector resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOutput deviceProcess conditions

The invention discloses a vertical parasitic positive-negative-positive (PNP) triode in a SiGe heterojunction bipolar transistor (HBT) process. A slot which is contacted with a base region is formed in shallow slot field oxides around the base region, and the depth of the slot is less than or equal to that of the base region; polycrystalline silicon which is doped with N-type impurities is filled in the slot and forms an external base region; the external base region and the base region are contacted on the side of the base region; and metal contact is formed on the external base region and a base is led out. The invention also discloses a manufacturing method for the vertical parasitic PNP triode in the SiGe HBT process. The vertical parasitic PNP triode can be used as an output device in a high-speed and high-gain HBT circuit, one more device choice is provided for a circuit, the device area can be effectively reduced, the parasitic effect of the device can be reduced, the collector resistance of a PNP tube is reduced and the performance of the device is improved; and in the method, extra process conditions are not needed and production cost can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Switch apparatus

ActiveUS20190229532A1Quality improvementCost difficultyElectronic switchingLine-transmission monitoring/testingPower flowControl signal

A switch apparatus is provided. The switch apparatus includes a signal control switch, a switch circuit, a blocking capacitor and a surge current dissipation circuit. The signal control switch and the switch circuit are respectively controlled by a first control signal and a second control signal to be turned on or off. The blocking capacitor is serially coupled between the switch circuit and a reference voltage end. The surge current dissipation circuit includes a Zener diode circuit or at least one diode circuit, and the at least one diode circuit has one or more diodes coupled in series. The one or more diodes coupled in series are coupled between two ends of the surge current dissipation circuit according to a first polarity direction.

Owner:RICHWAVE TECH CORP