Patents

Literature

92results about How to "Equipment is cheap" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

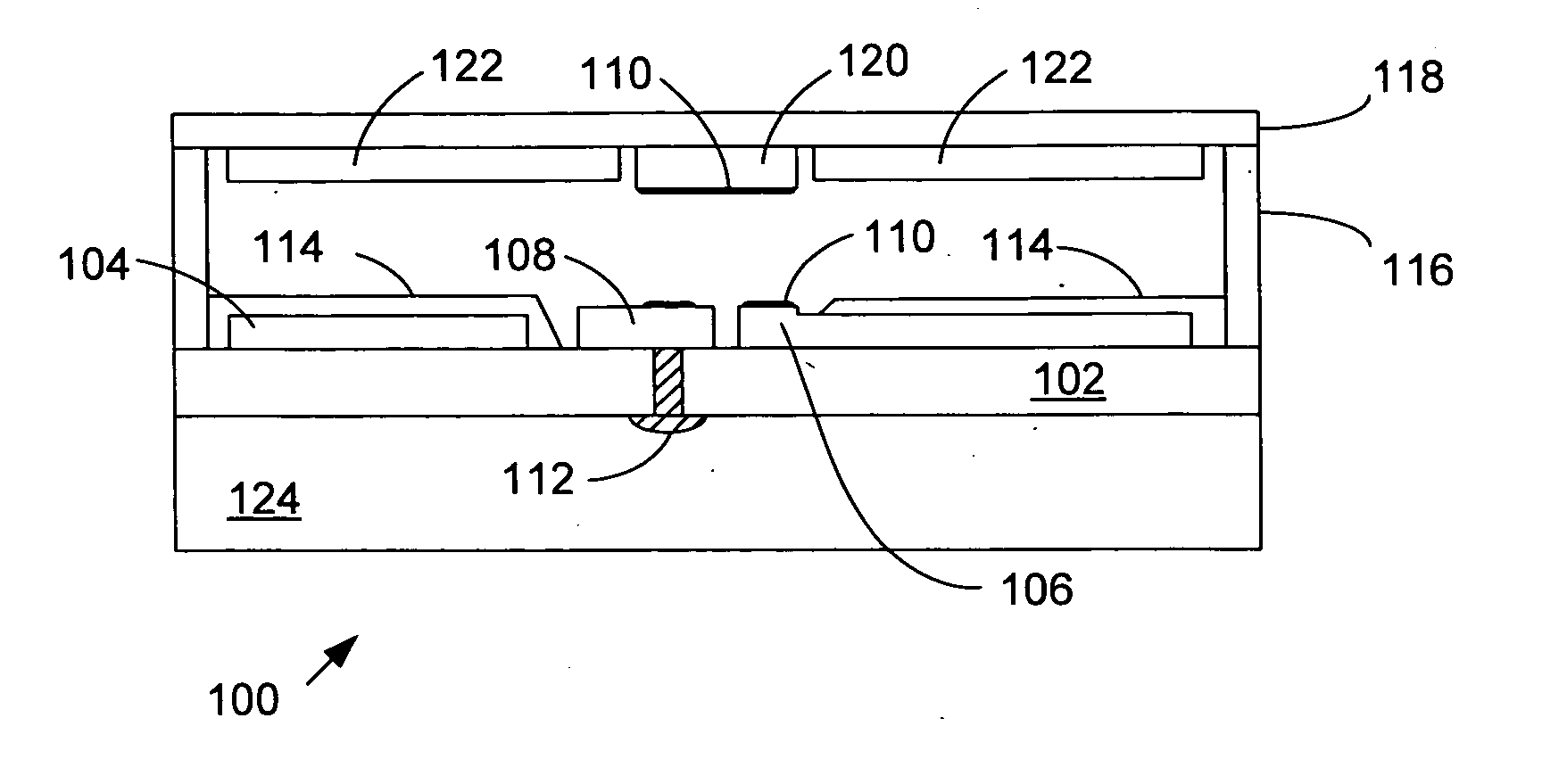

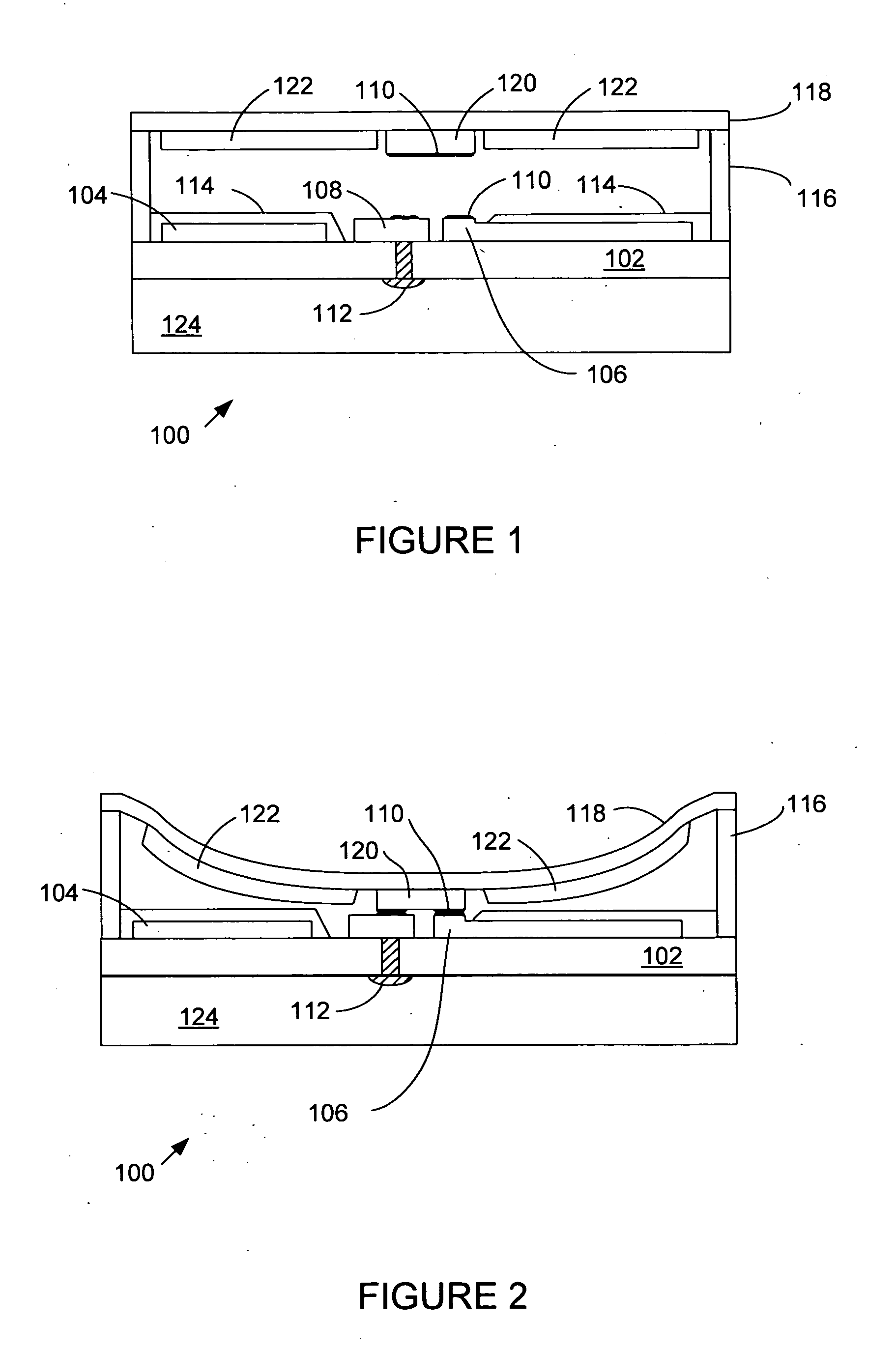

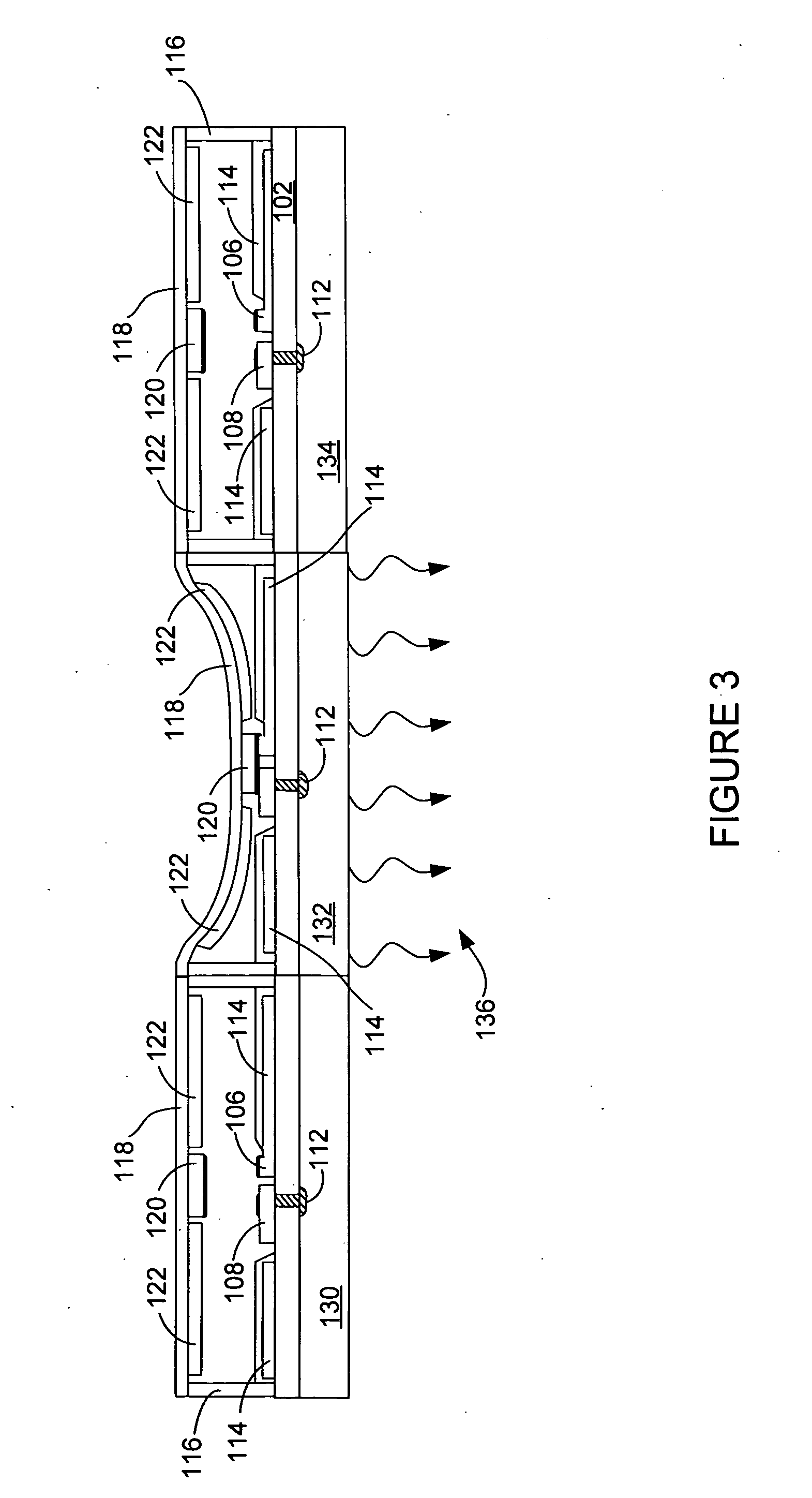

Micro-electromechanical switching backplane

InactiveUS20050116924A1Low costLow-cost techniqueElectrostatic/electro-adhesion relaysStatic indicating devicesDisplay deviceEngineering

A low cost, scalable backplane for black and white or color optical displays comprises a multi-membrane plastic structure on which is printed or deposited row and column drivers to form a matrix of micro electromechanical (MEM) switches. Each switch controls the state of a pixel in the optical display device. Critical to successful long-term operation, the backplane includes the controlled application of voltages to each switch so that the display functions correctly and display life is maximized. The MEM switches include a substantially non-pliable membrane and a substantially flexible membrane both of which include electrodes that when energized will create electrostatic forces that attracts the flexible membrane to the non-pliable membrane. The MEM switches are manufactured in an array with a pitch that provides a sufficient number of switches to drive an optical display device and each switch may be latched to eliminate the need to constantly refresh the device.

Owner:SEERTECH CORP

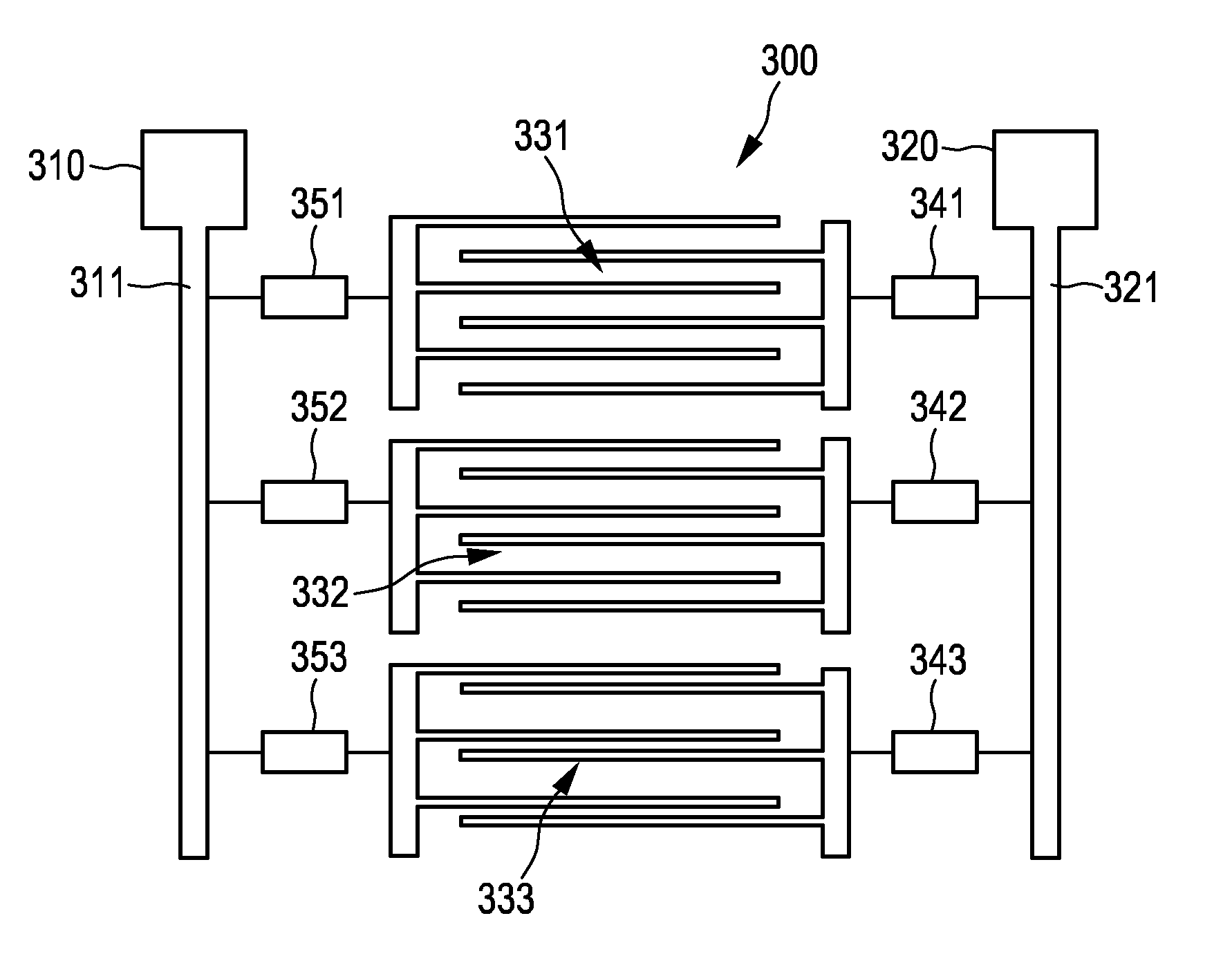

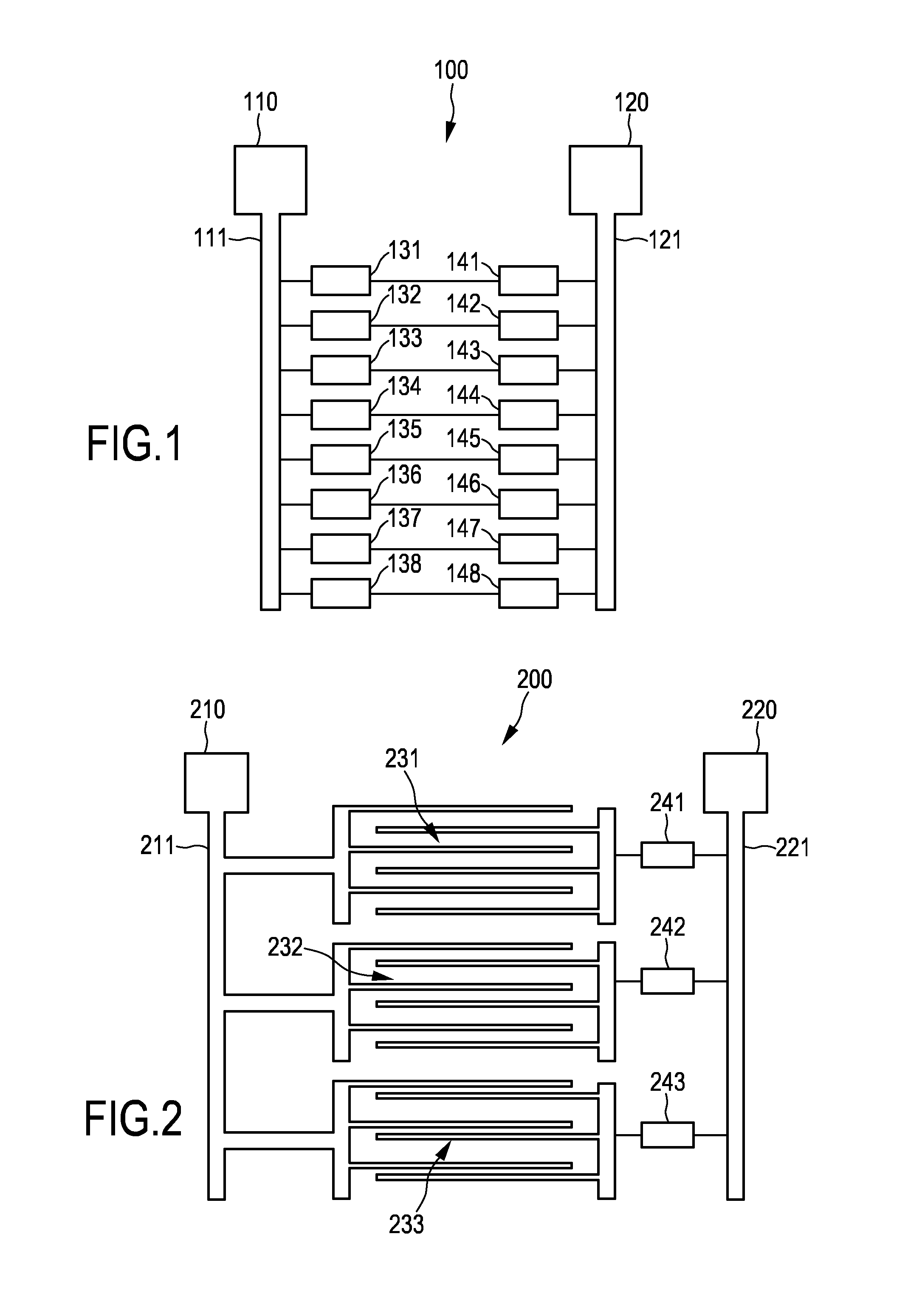

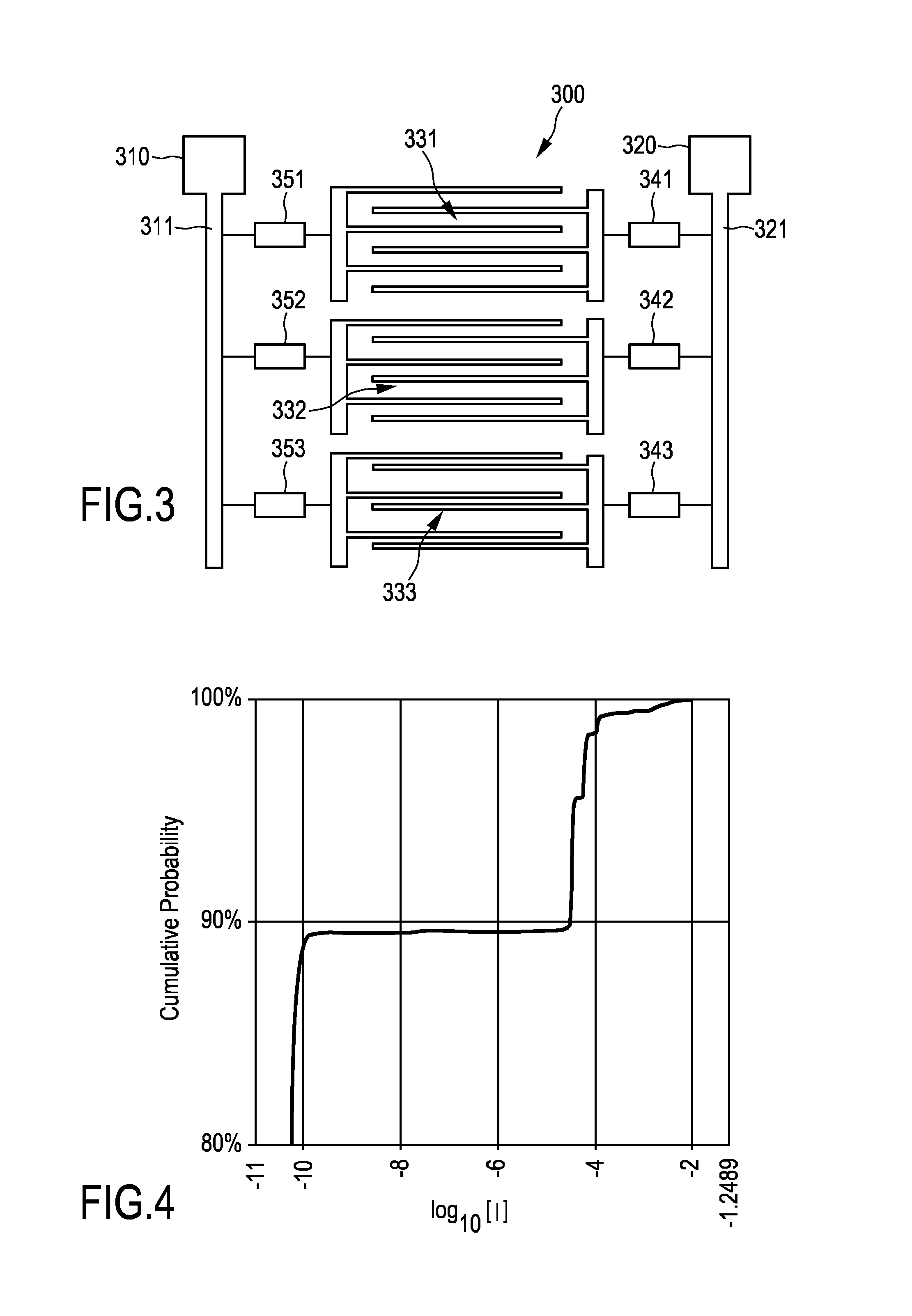

Electric connection of electrochemical and photoelectrochemical cells

InactiveUS6657119B2Equipment is cheapReduce needLight-sensitive devicesPV power plantsPhotoelectrochemical cellEngineering

Owner:FORSKARPATENT I UPPSALA

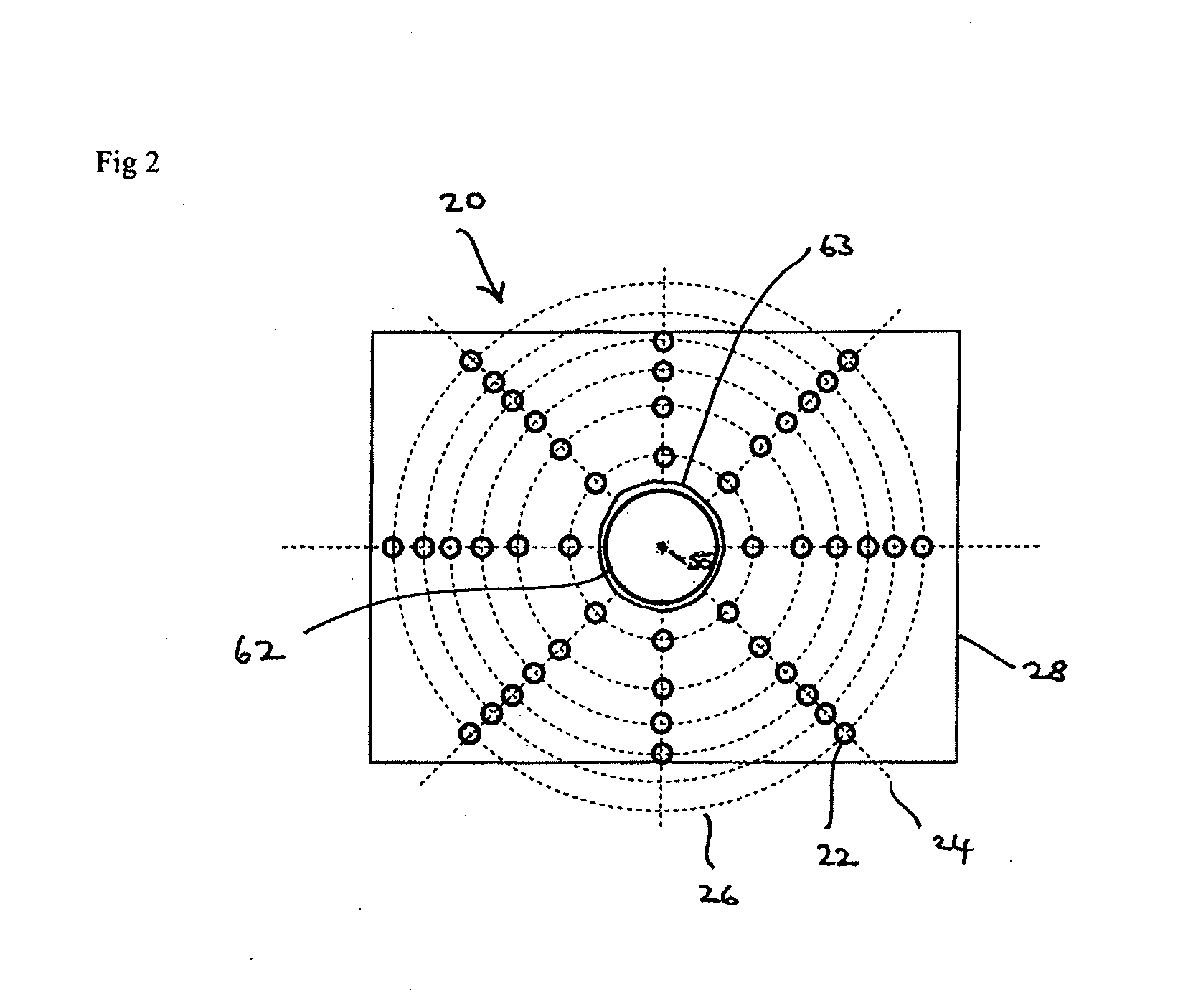

Biometric authentication using the eye

InactiveUS20100310133A1Great rapiditySmall amountPerson identificationAcquiring/recognising eyesImage captureSoftware

Owner:YUKATA INVESTMENT MARKETING PTY LTD

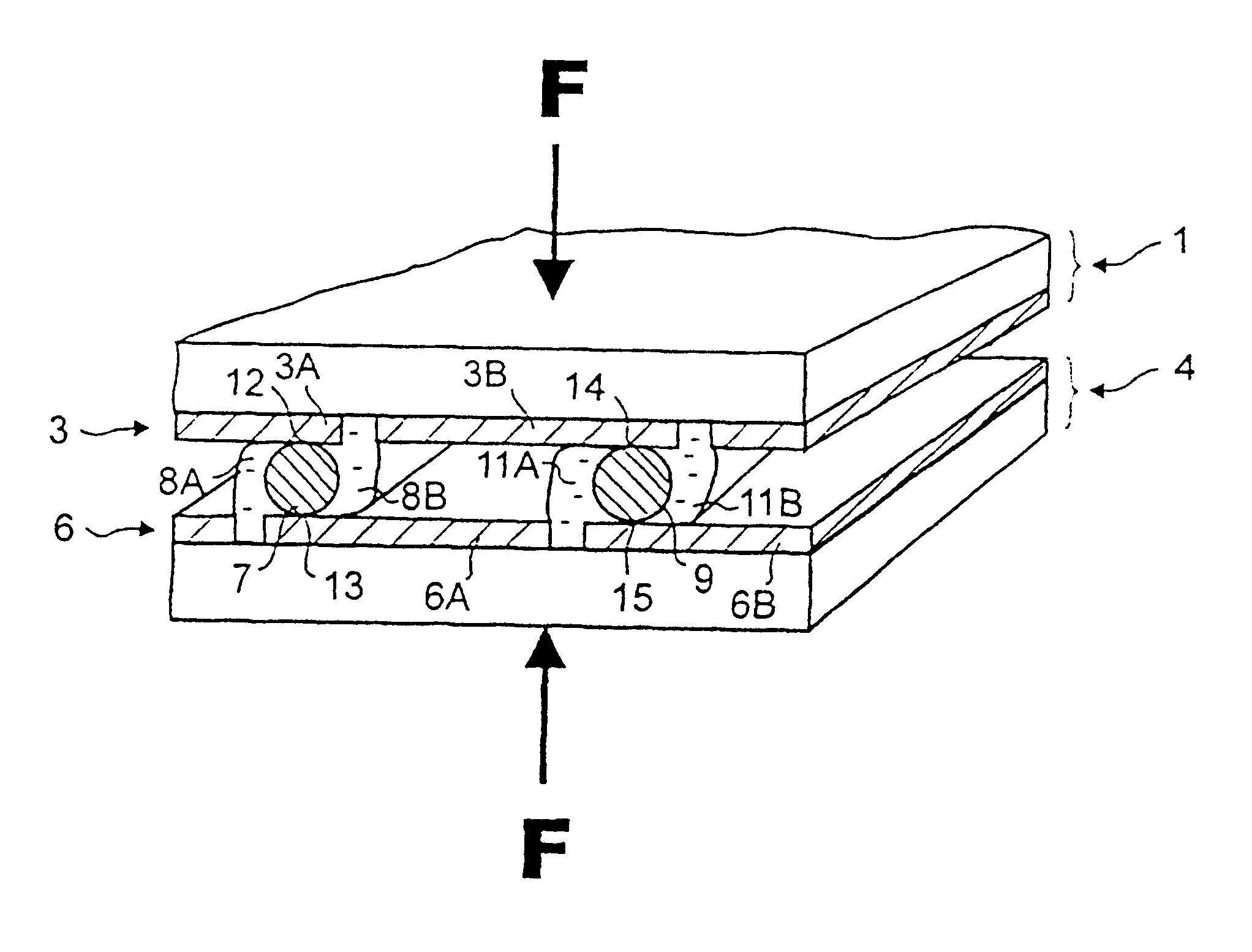

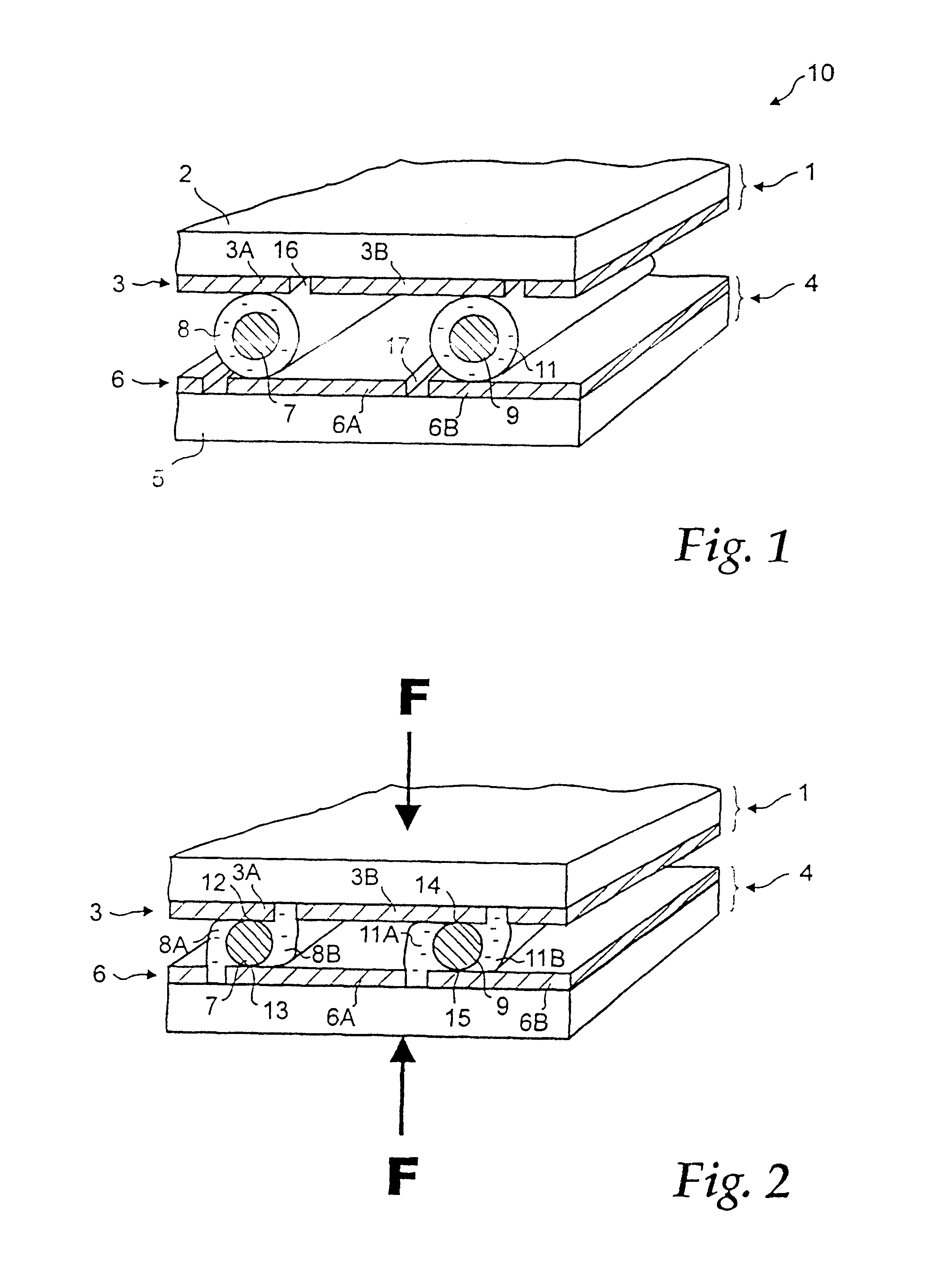

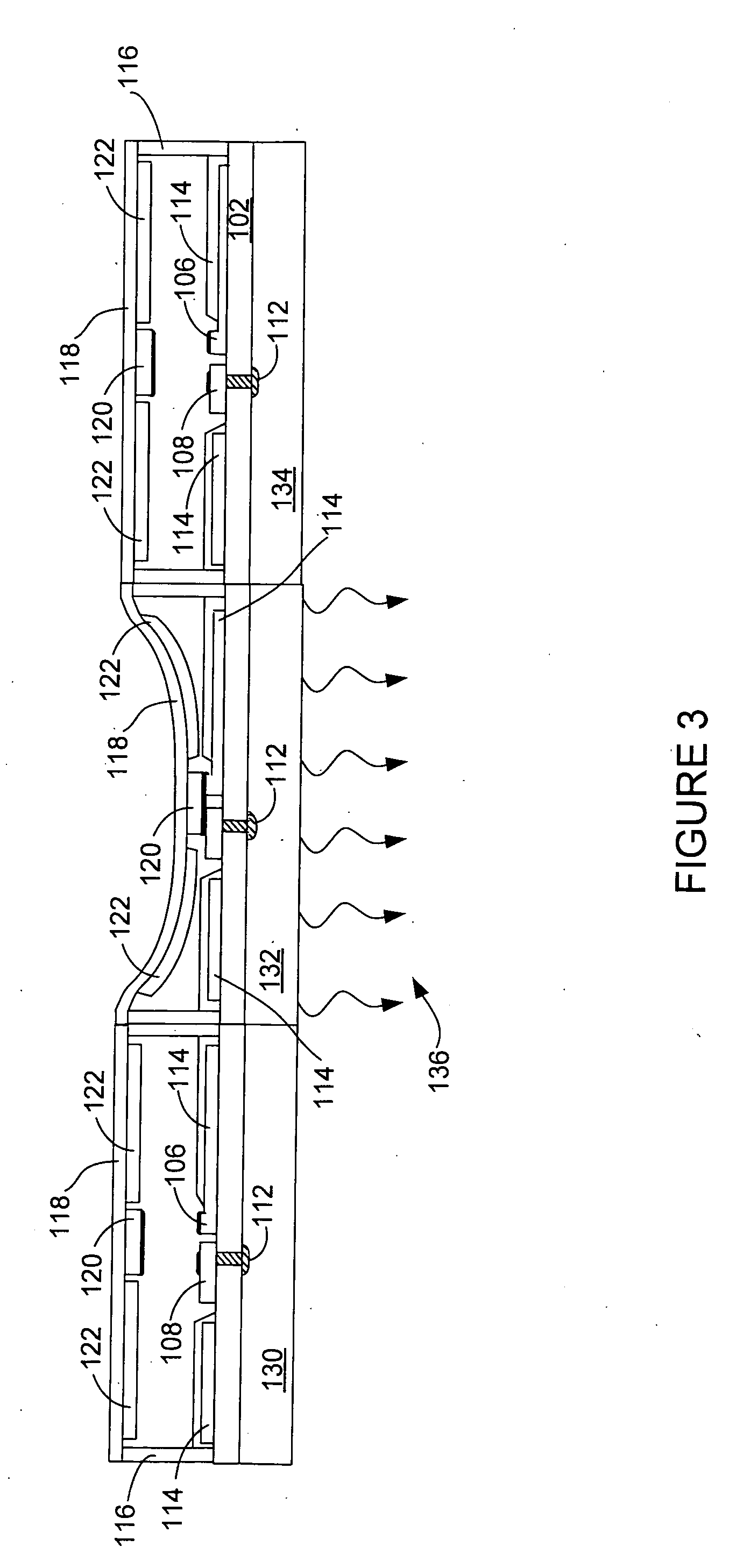

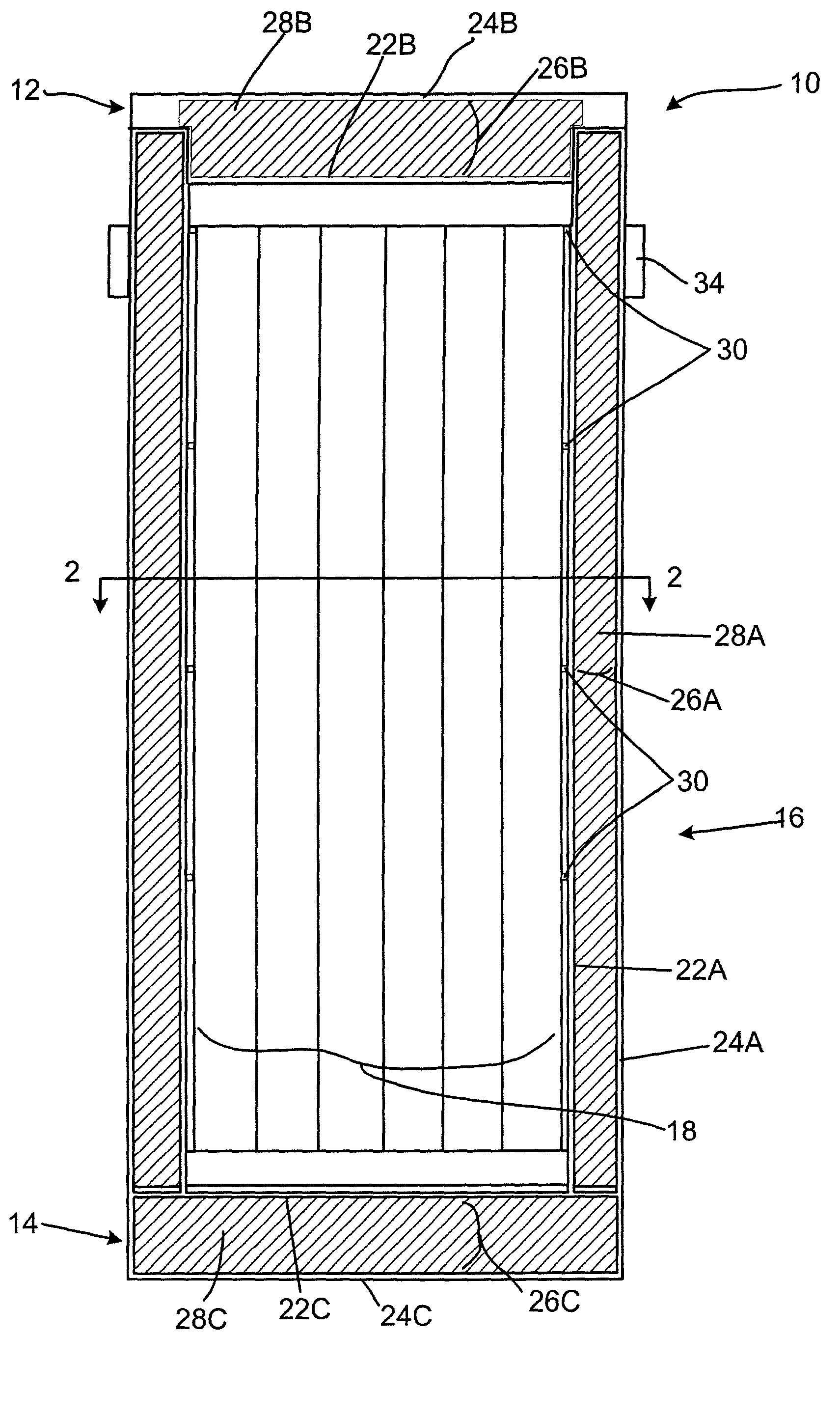

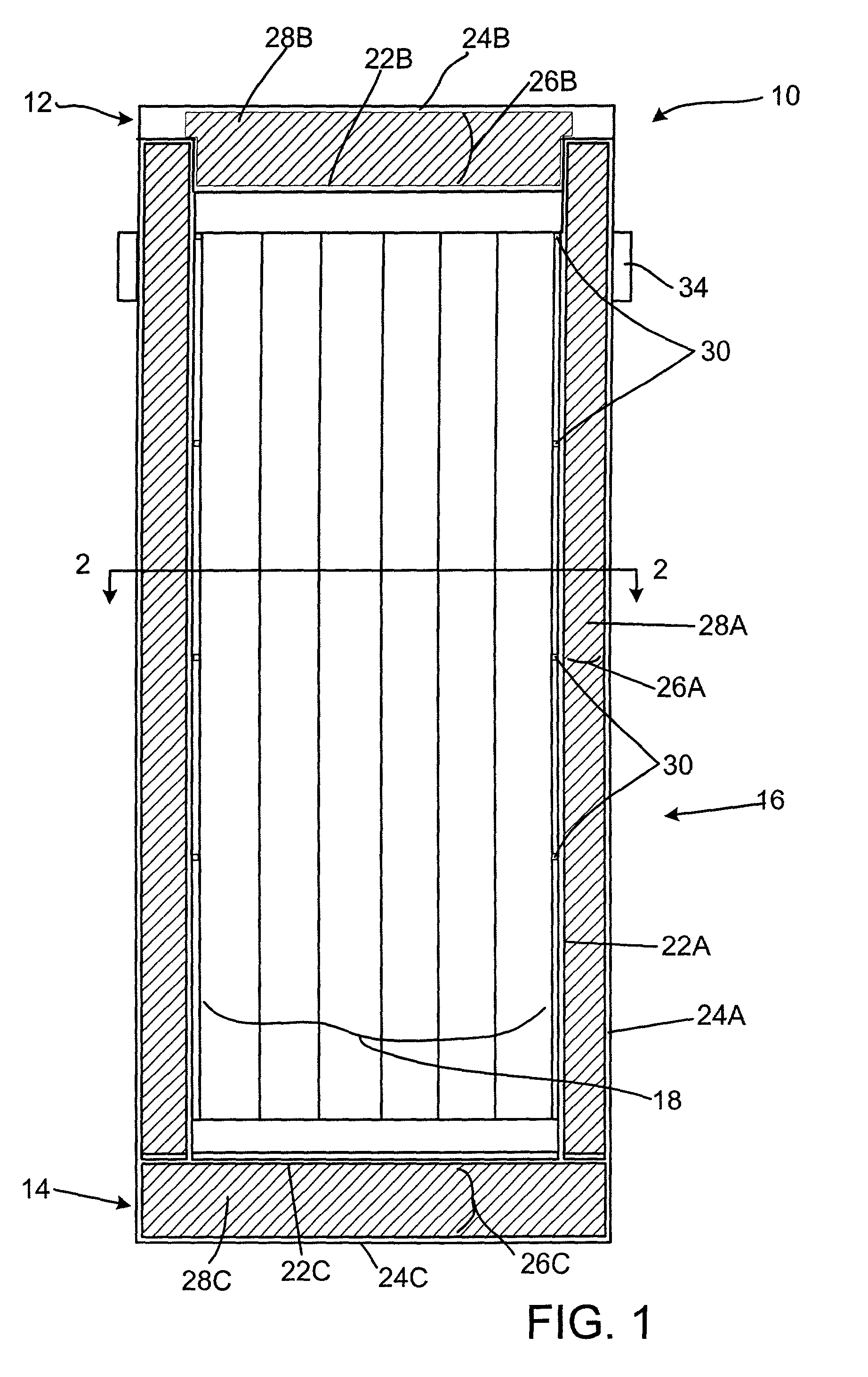

Micro-electromechanical display backplane and improvements thereof

InactiveUS20070002009A1Low costLow-cost techniqueElectrostatic/electro-adhesion relaysStatic indicating devicesDisplay deviceEngineering

A low cost, scalable backplane for electrophoretic displays comprising a multi-membrane plastic array of micro electromechanical (MEM) switches. Each switch controls the state of a pixel in the electrophoretic display device. Each switch may be latched to eliminate the need to constantly refresh the device and each switch may function as an enunciator

Owner:SEERTECH CORP

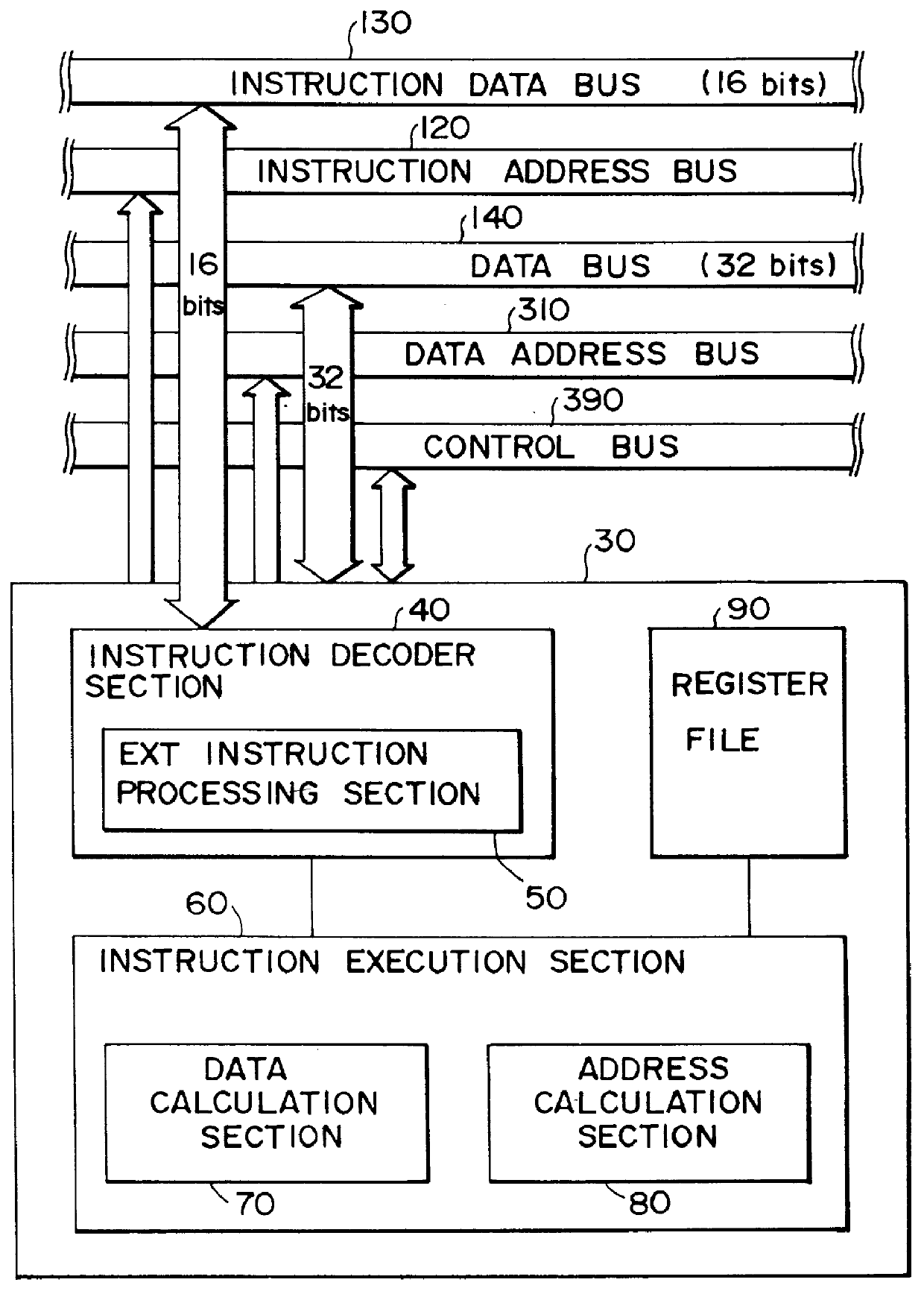

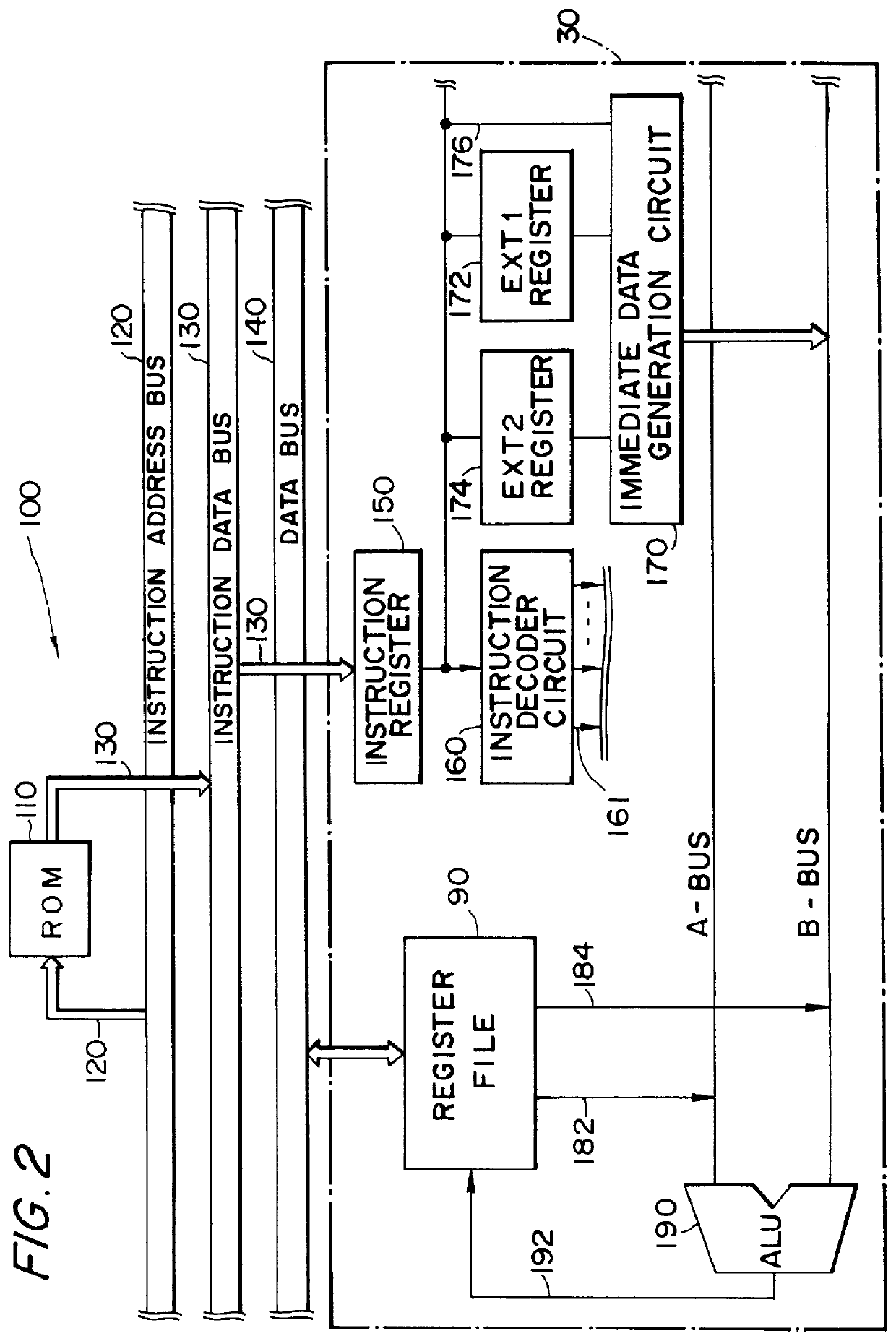

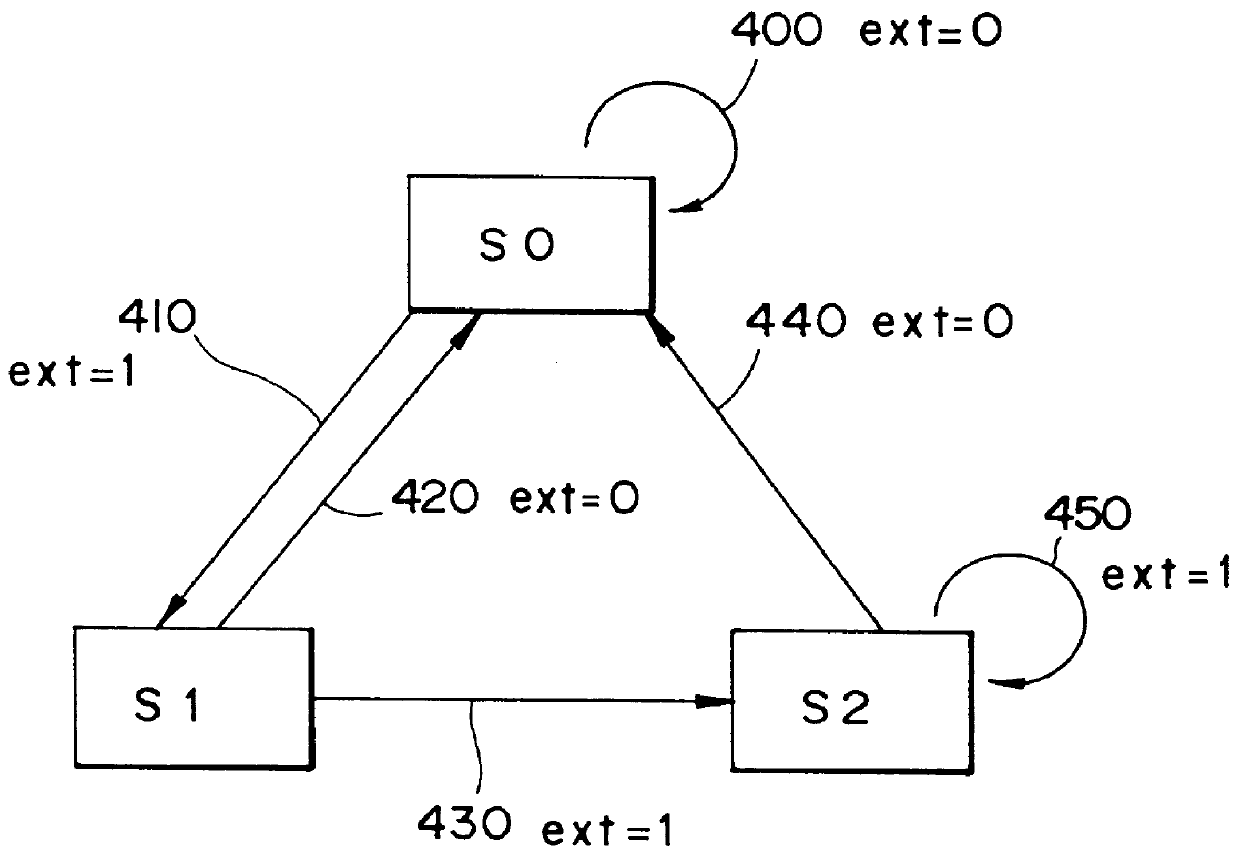

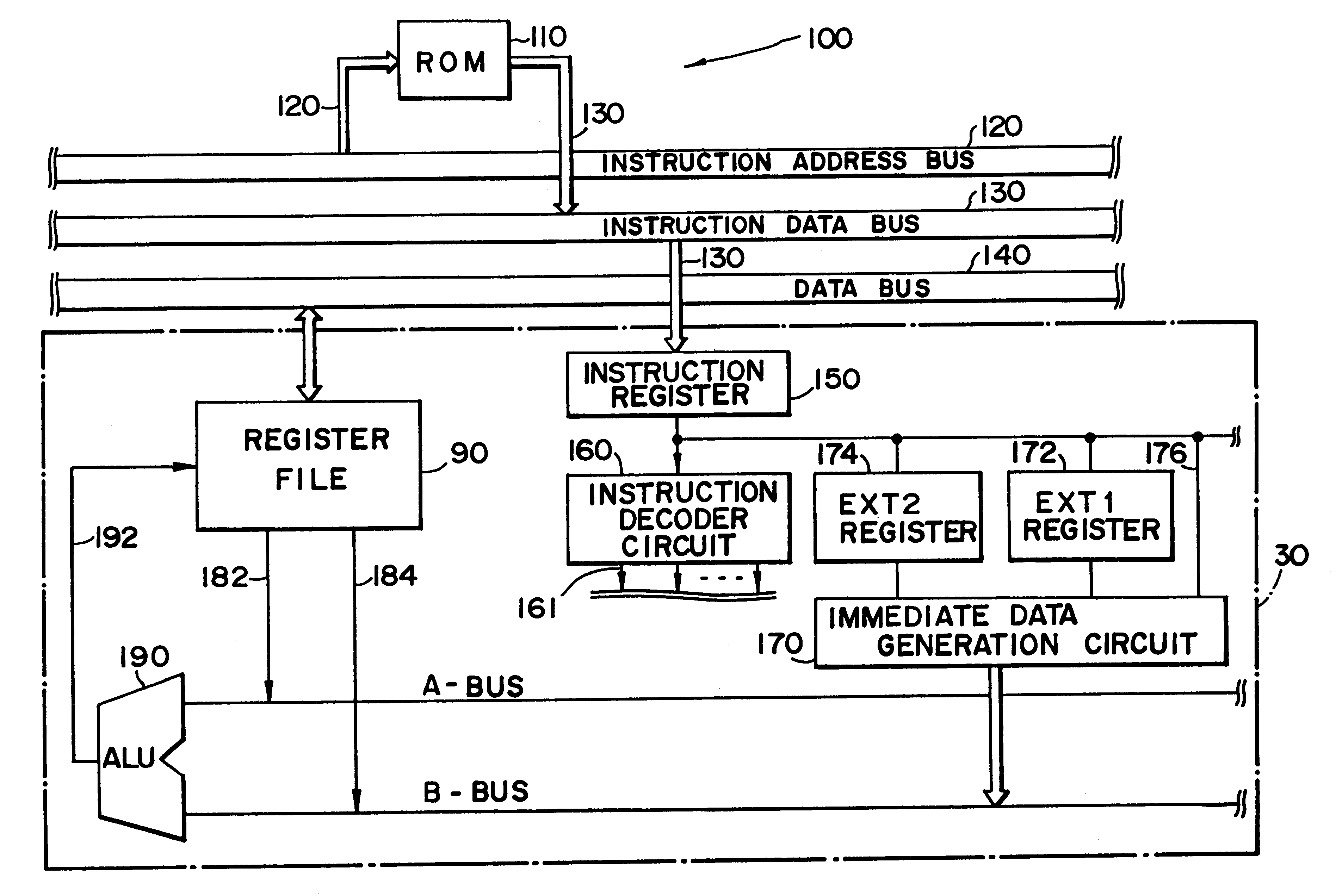

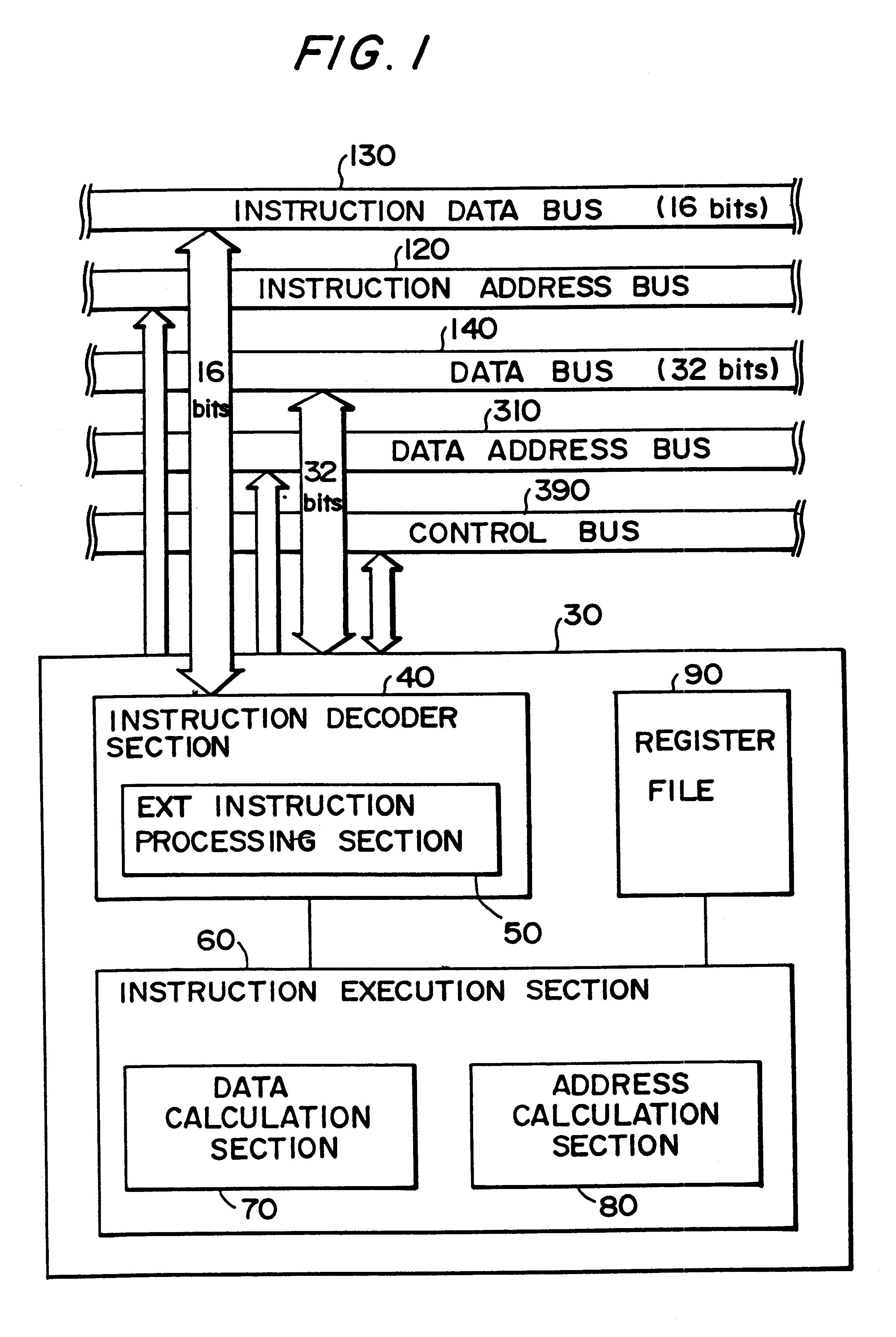

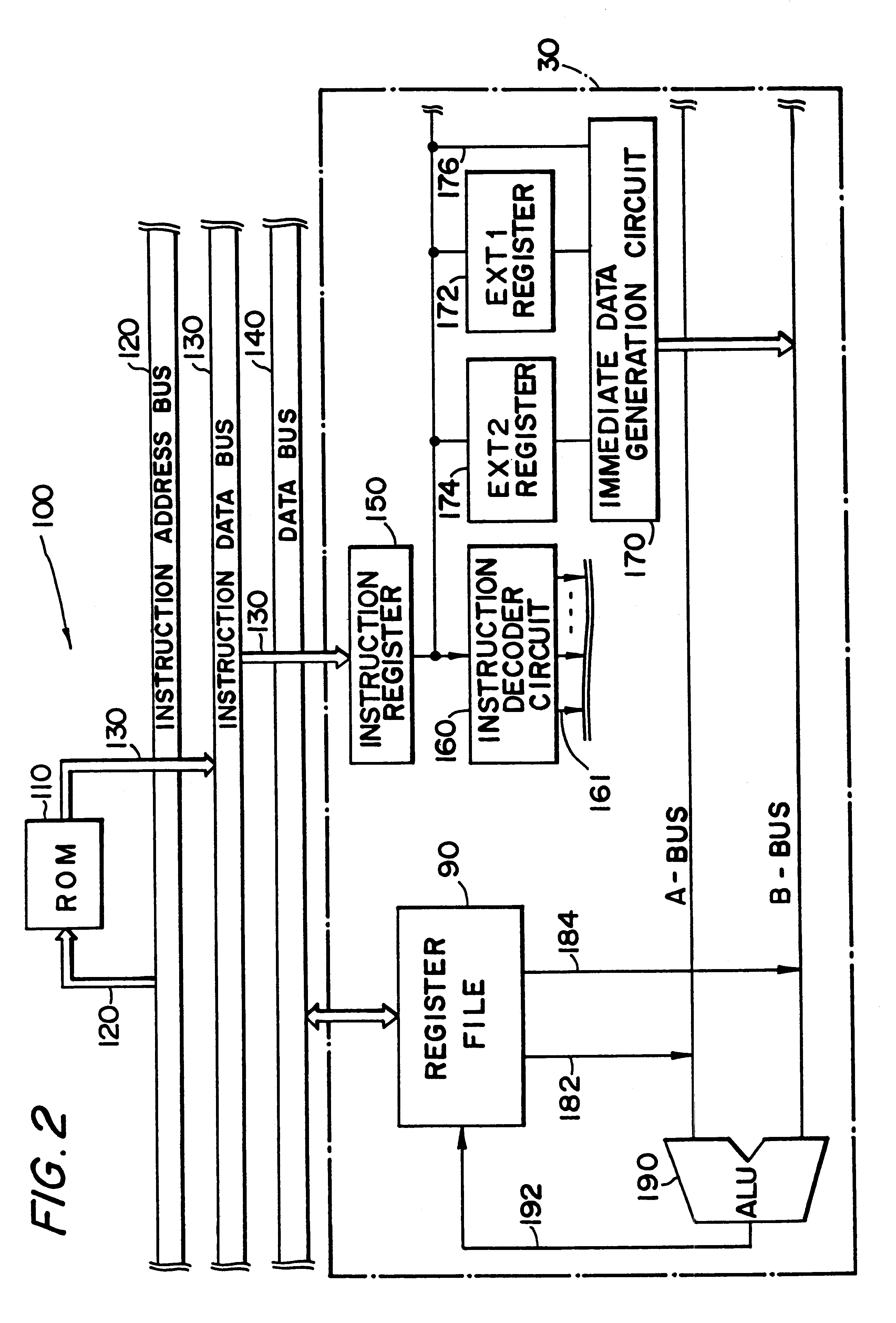

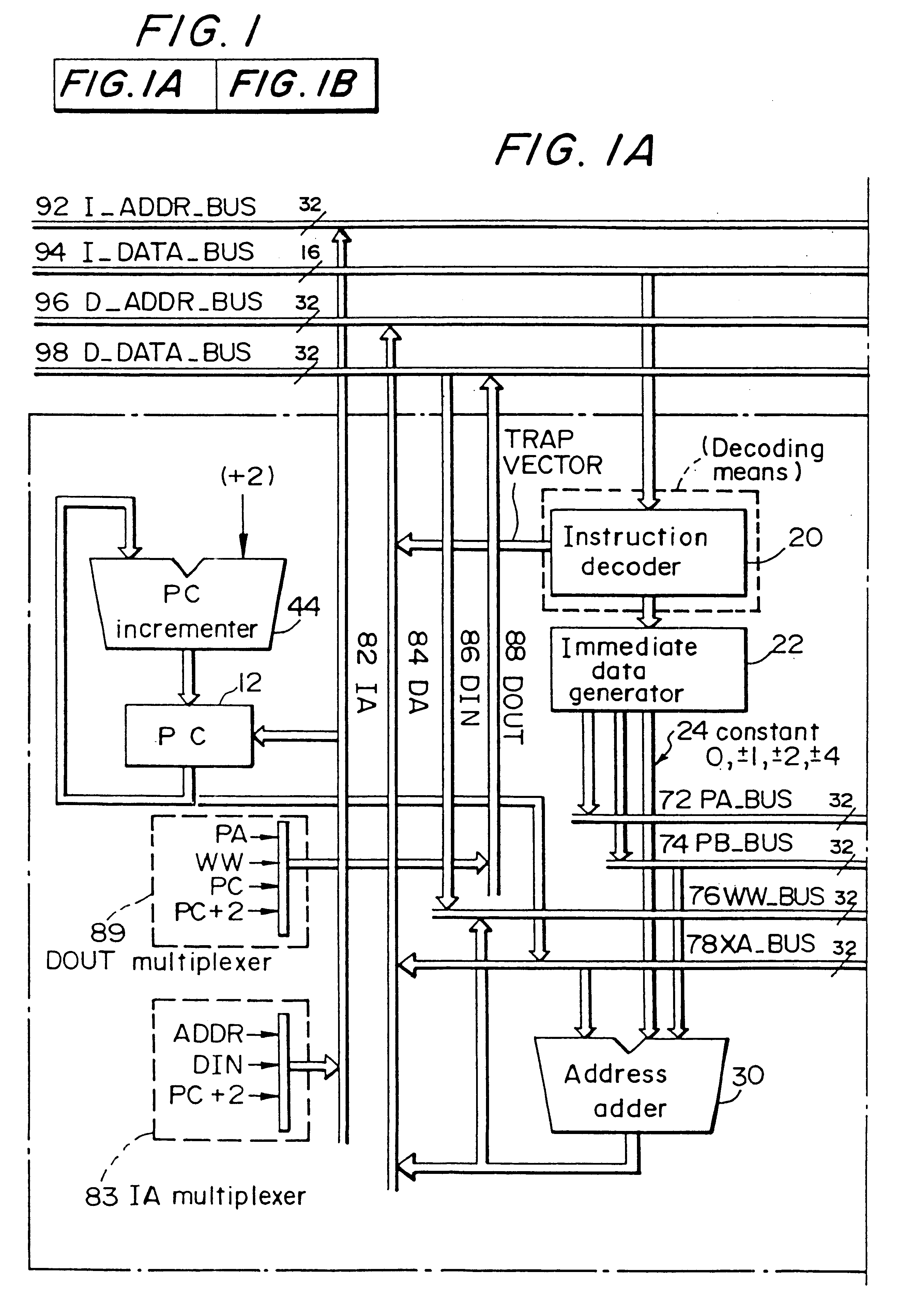

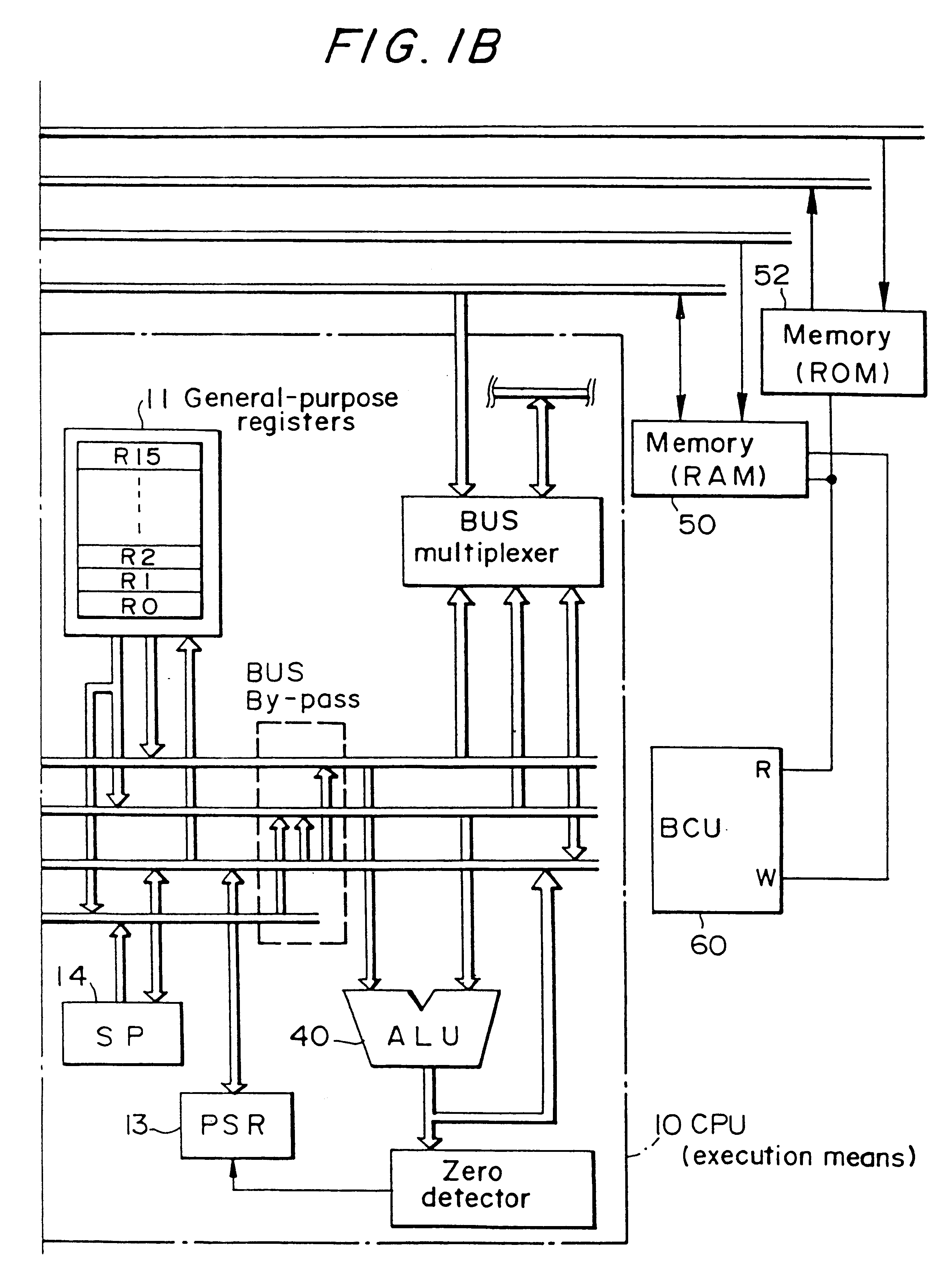

Data processing circuit with target instruction and prefix instruction

InactiveUS6167505AEasy to operateSimple structureInstruction analysisDigital computer detailsRegister fileInstruction code

A certain target instruction and a prefix instruction for expanding the function of that target instruction are input to the present data processing circuit. The data processing circuit analyzes the thus-input instruction code and performs the processing necessary for the execution of that instruction. The data processing circuit comprises an instruction decoder section, a register file, and an instruction execution section that executes the instruction based on operational details of the instruction analyzed by the instruction decoder section. The instruction decoder section comprises an ext instruction processing section that processed the expansion of immediate data from the prefix instruction.

Owner:SEIKO EPSON CORP

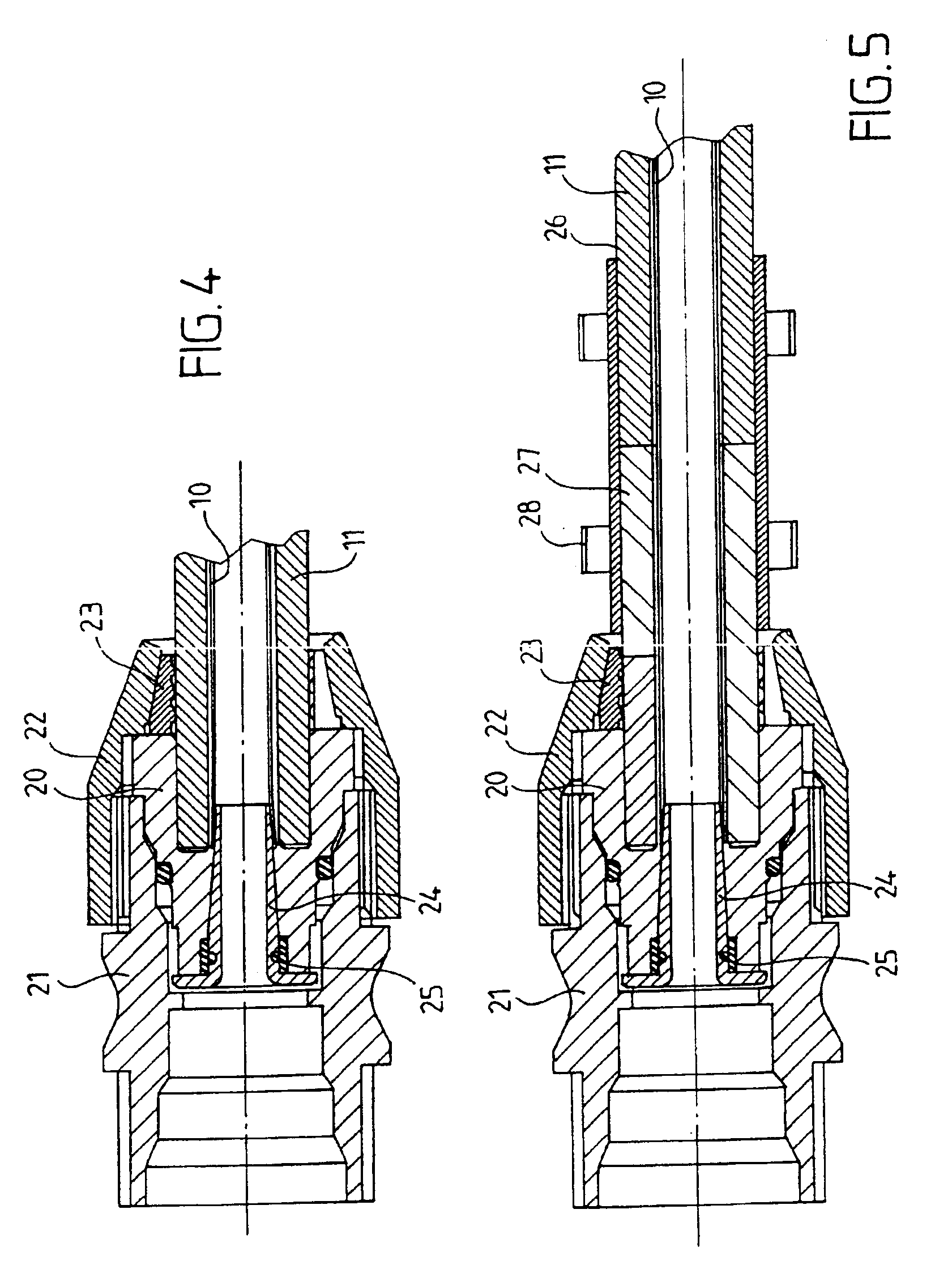

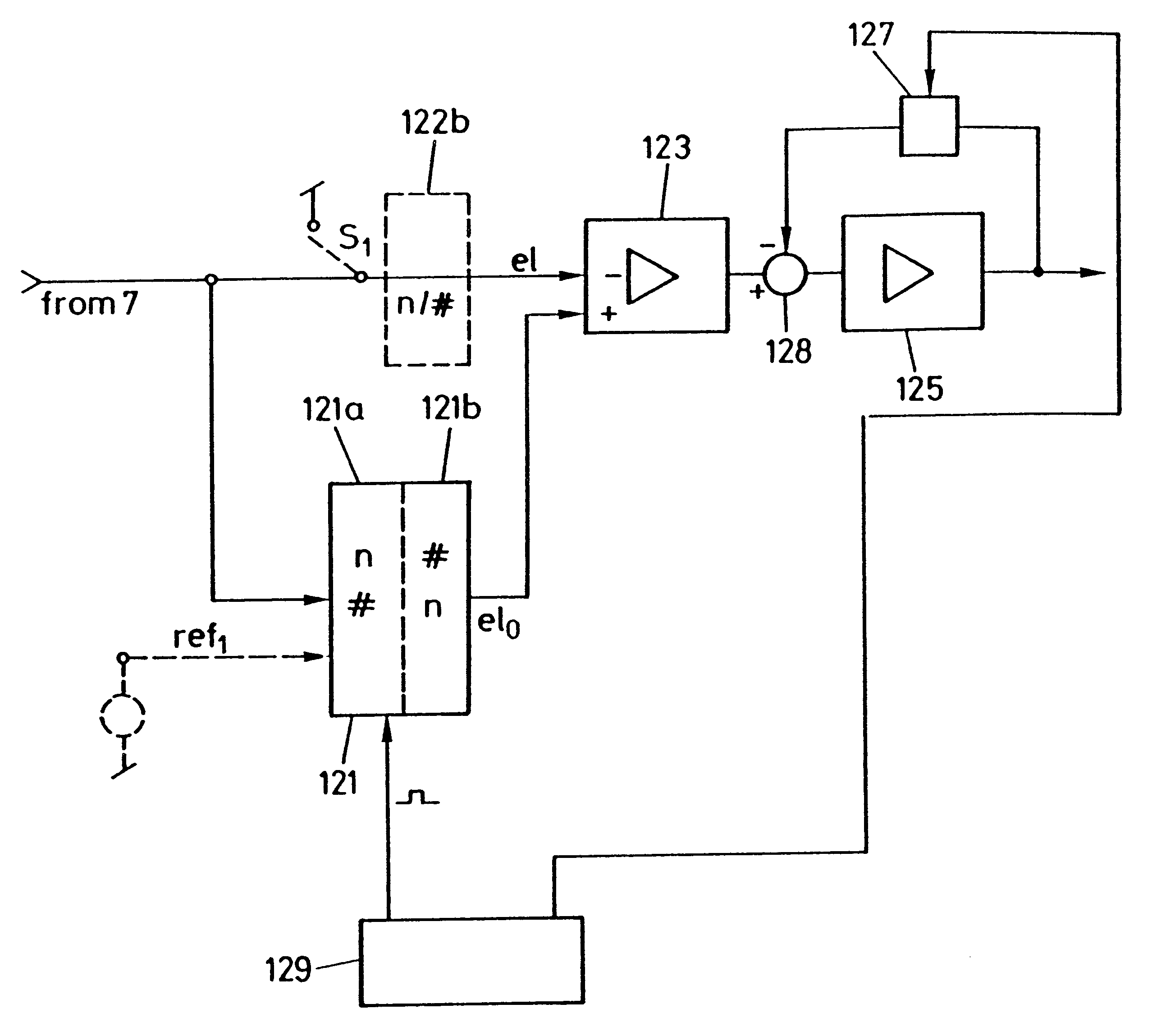

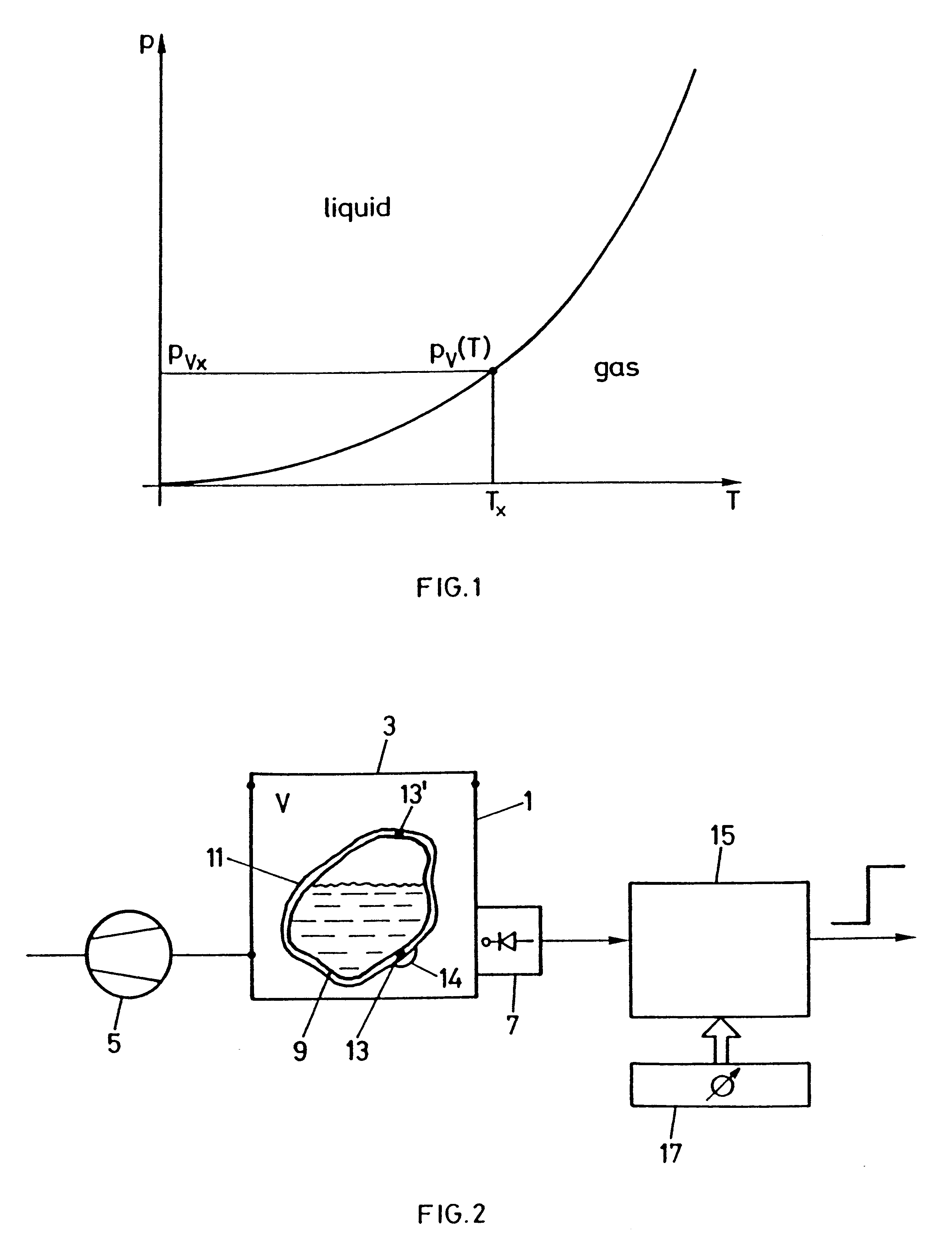

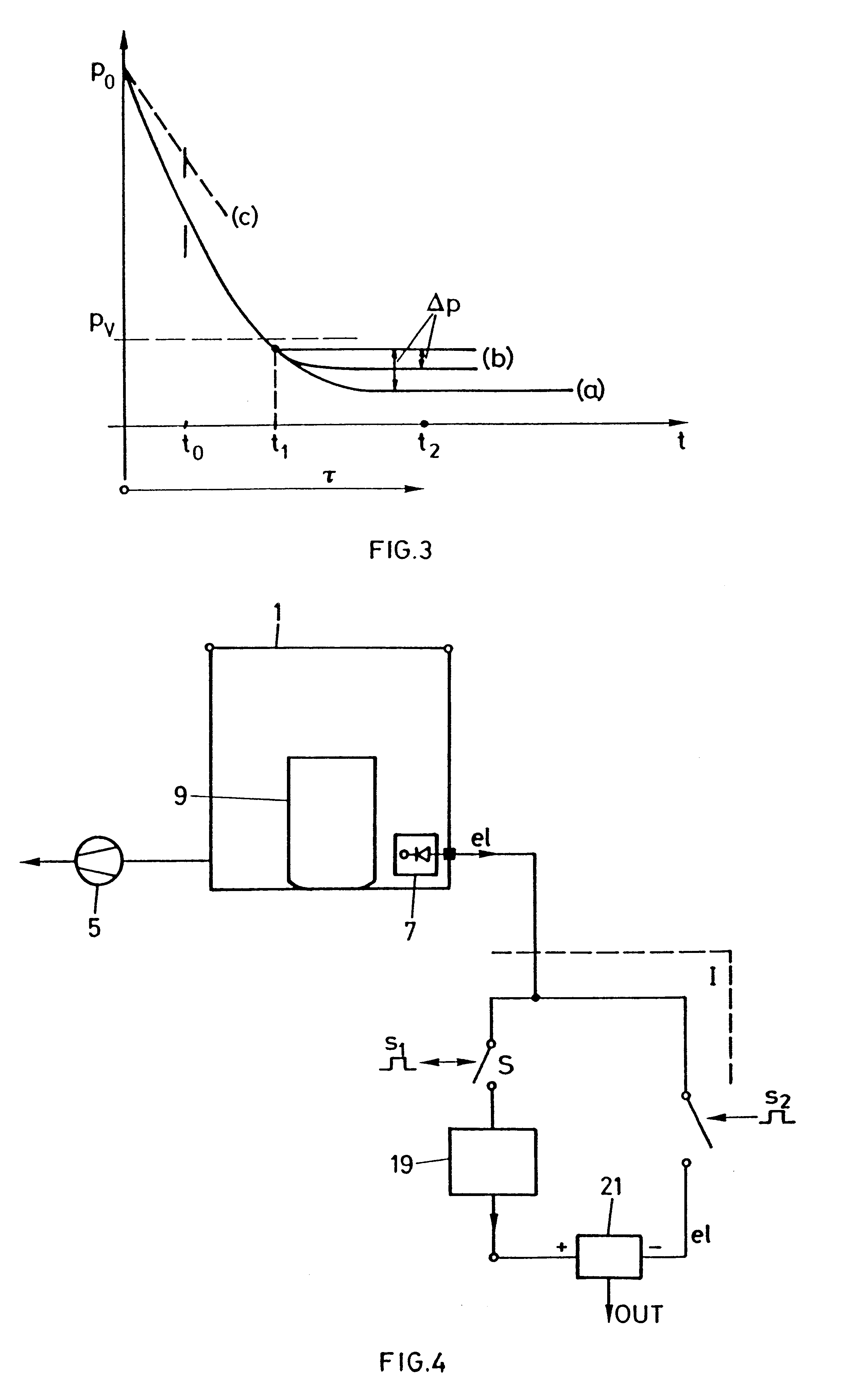

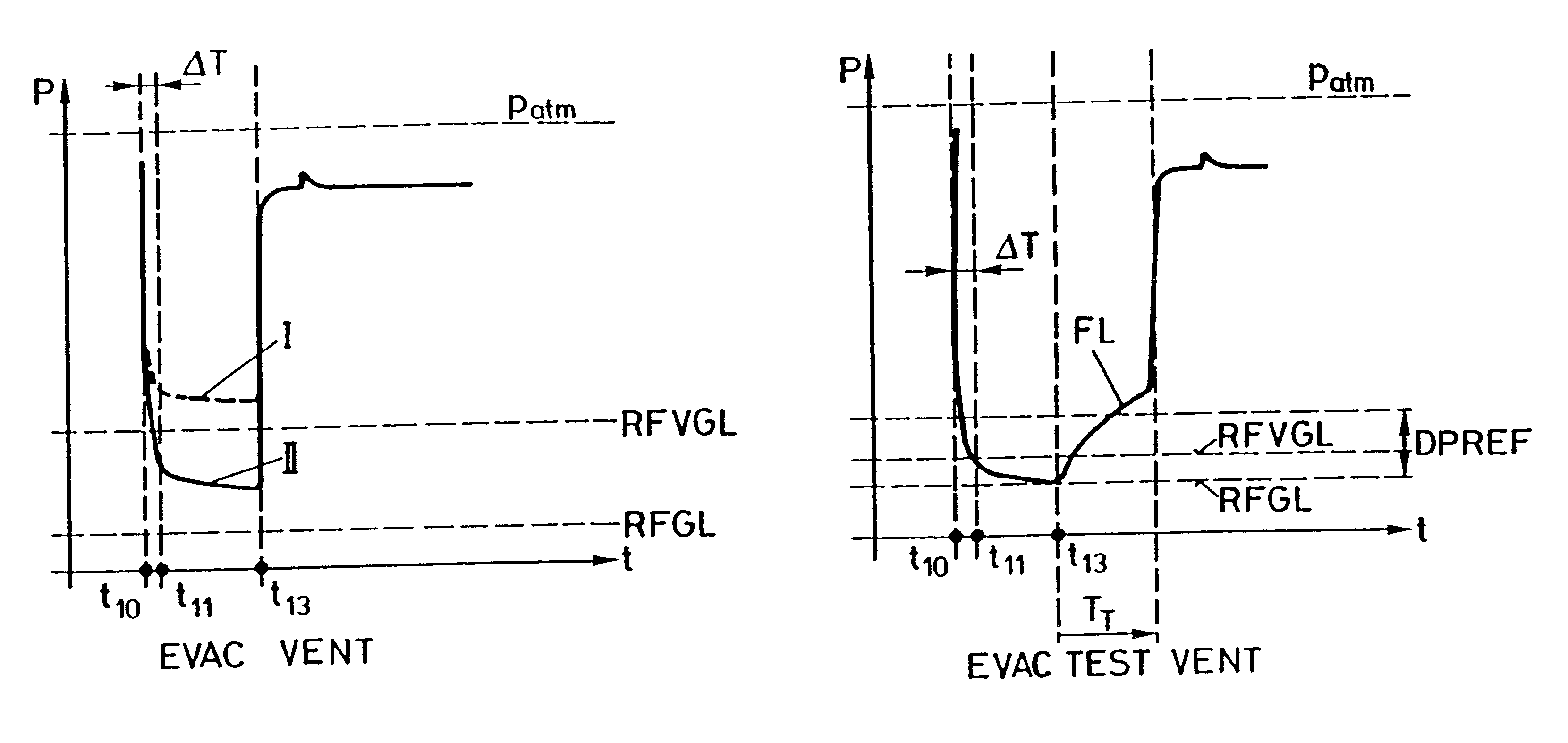

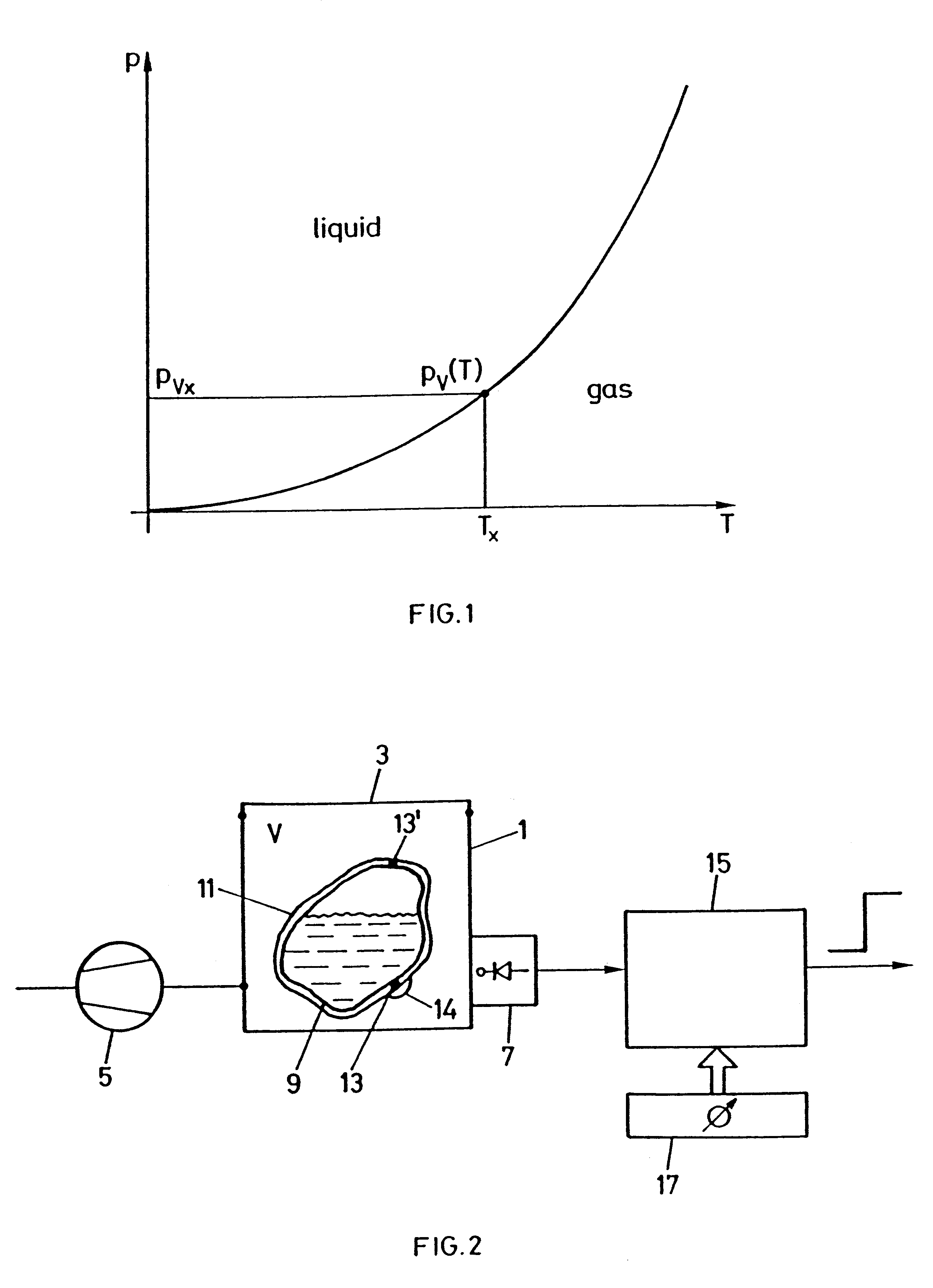

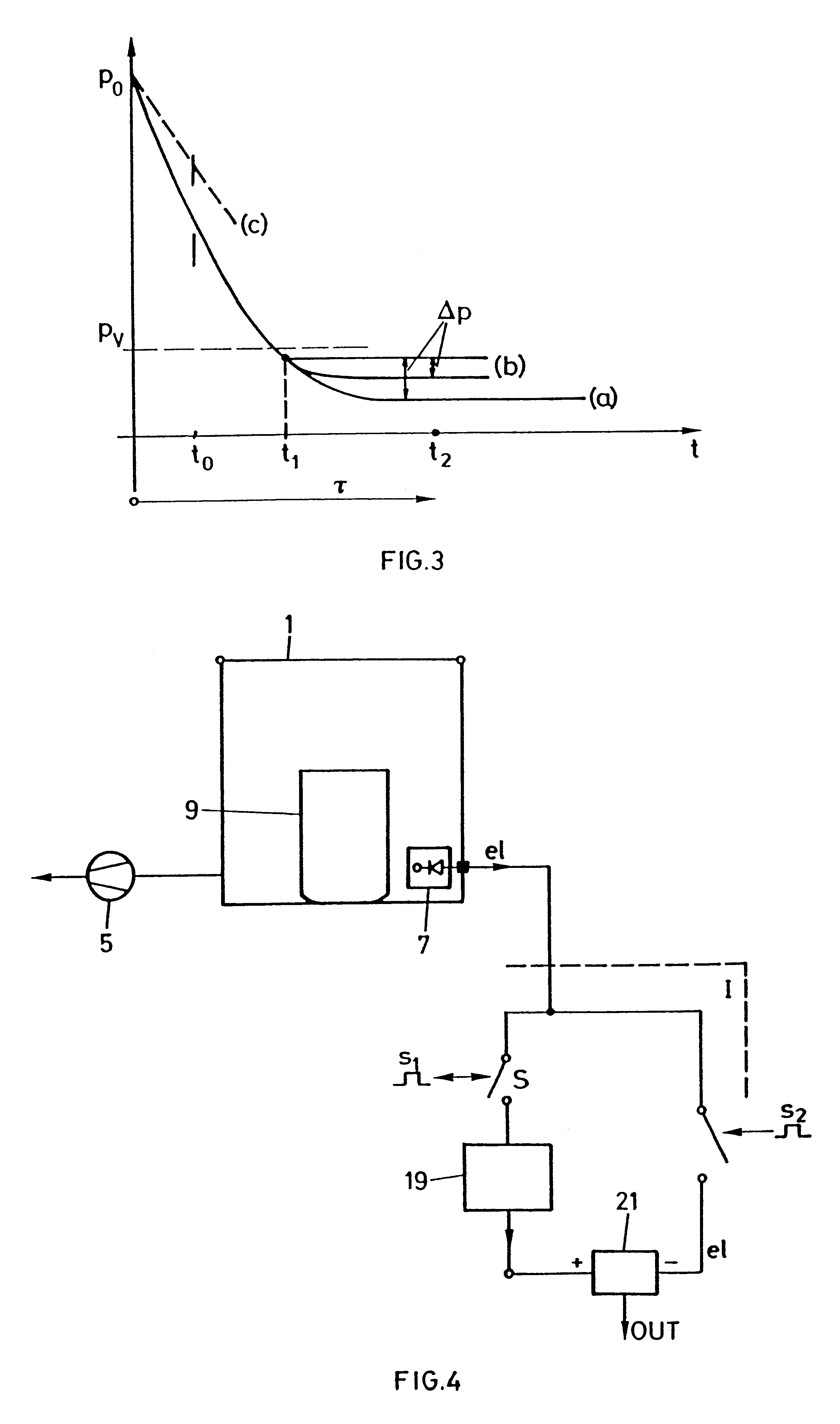

Method for leak testing and leak testing apparatus

InactiveUS6202477B1Equipment is cheapDetection of fluid at leakage pointMeasurement of fluid loss/gain rateVacuum pressureEvaporation

For leak testing closed containers (9) which are filled with a filling product containing at least one liquid component the container is introduced in a test cavity (1) which is evacuated at least down to vapour pressure of that liquid component. The pressure in the surrounding of the container (9) and thus within test cavity (1) is monitored. Monitoring is performed by a vacuum pressure sensor (7), whereas lowering pressure surrounding the container (9) is performed by a vacuum pump (5). Leakage is detected by monitoring a pressure change in the surrounding of the container which is due to evaporation of liquid emerging from a leak and being evaporated in the low pressure surrounding.

Owner:WILCO AG

Method for leak testing and leak testing apparatus

InactiveUS6305215B2Equipment is cheapDetection of fluid at leakage pointMeasurement of fluid loss/gain rateVacuum pressureEvaporation

For leak testing closed containers (9) which are filled with a filling product containing at least one liquid component the container is introduced in a test cavity (1) which is evacuated at least down to vapor pressure of that liquid component. The pressure in the surrounding of the container (9) and thus within test cavity (1) is monitored. Monitoring is performed by a vacuum pressure sensor (7), whereas lowering pressure surrounding the container (9) is performed by a vacuum pump (5). Leakage is detected by monitoring a pressure change in the surrounding of the container which is due to evaporation of liquid emerging from a leak and being evaporated in the low pressure surrounding.

Owner:WILCO AG

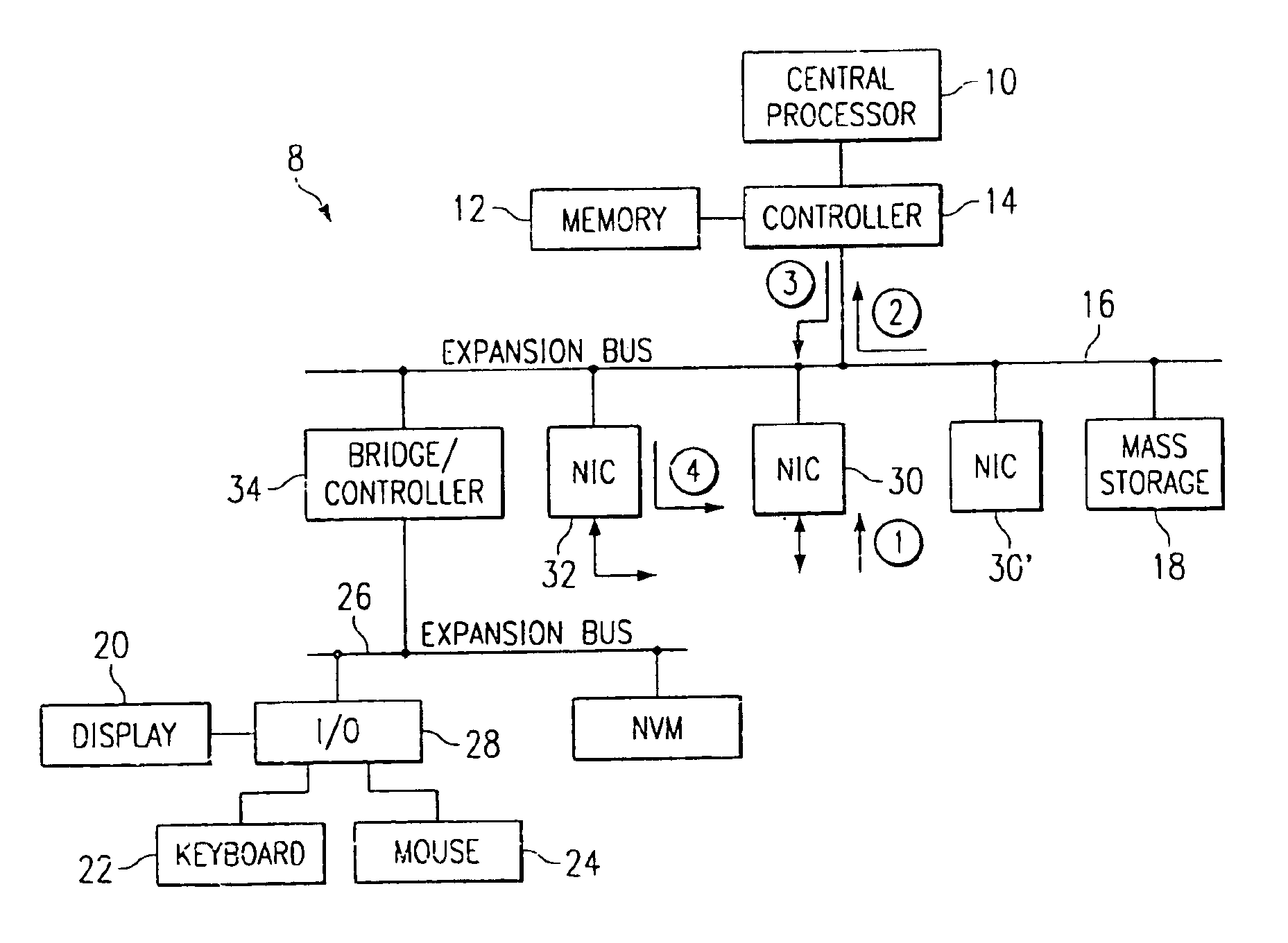

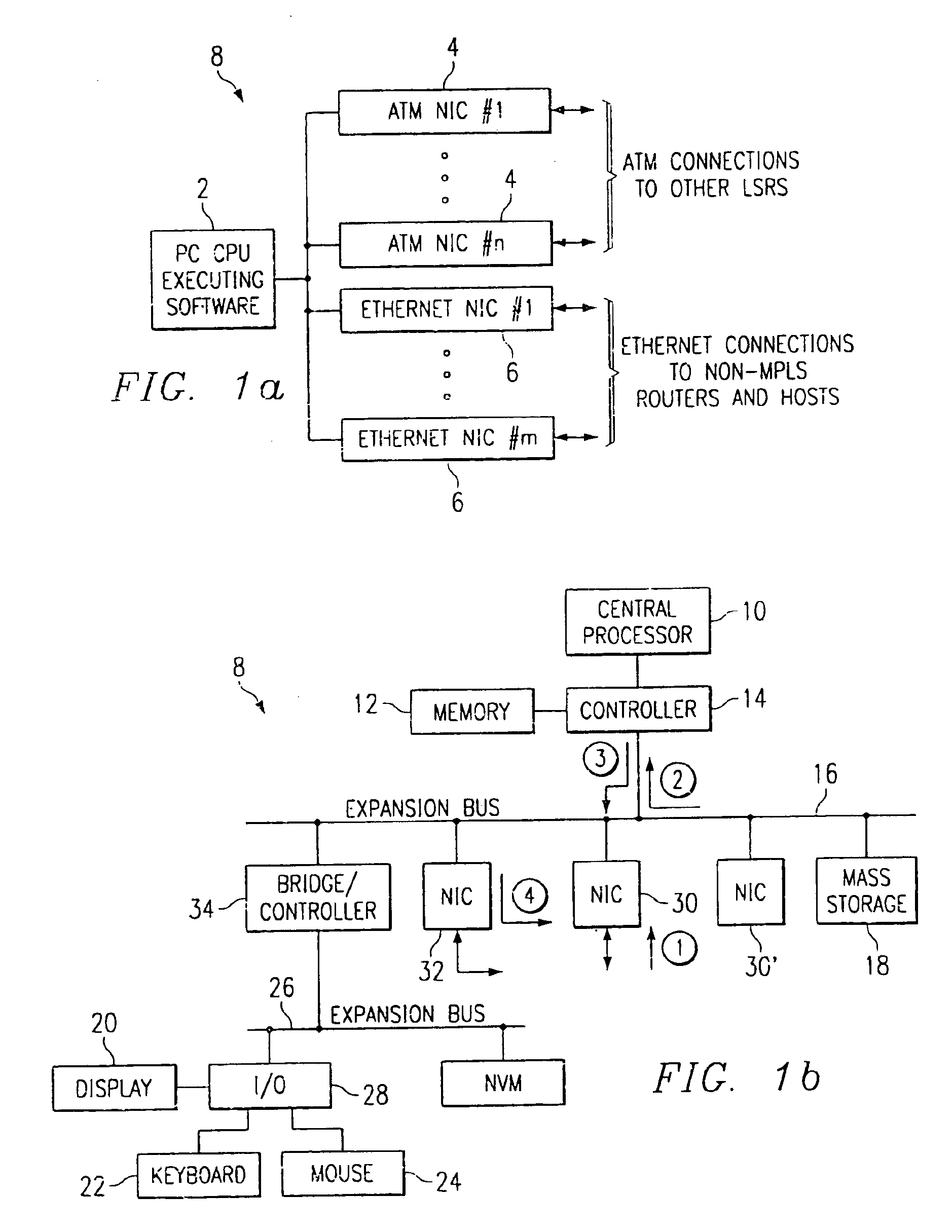

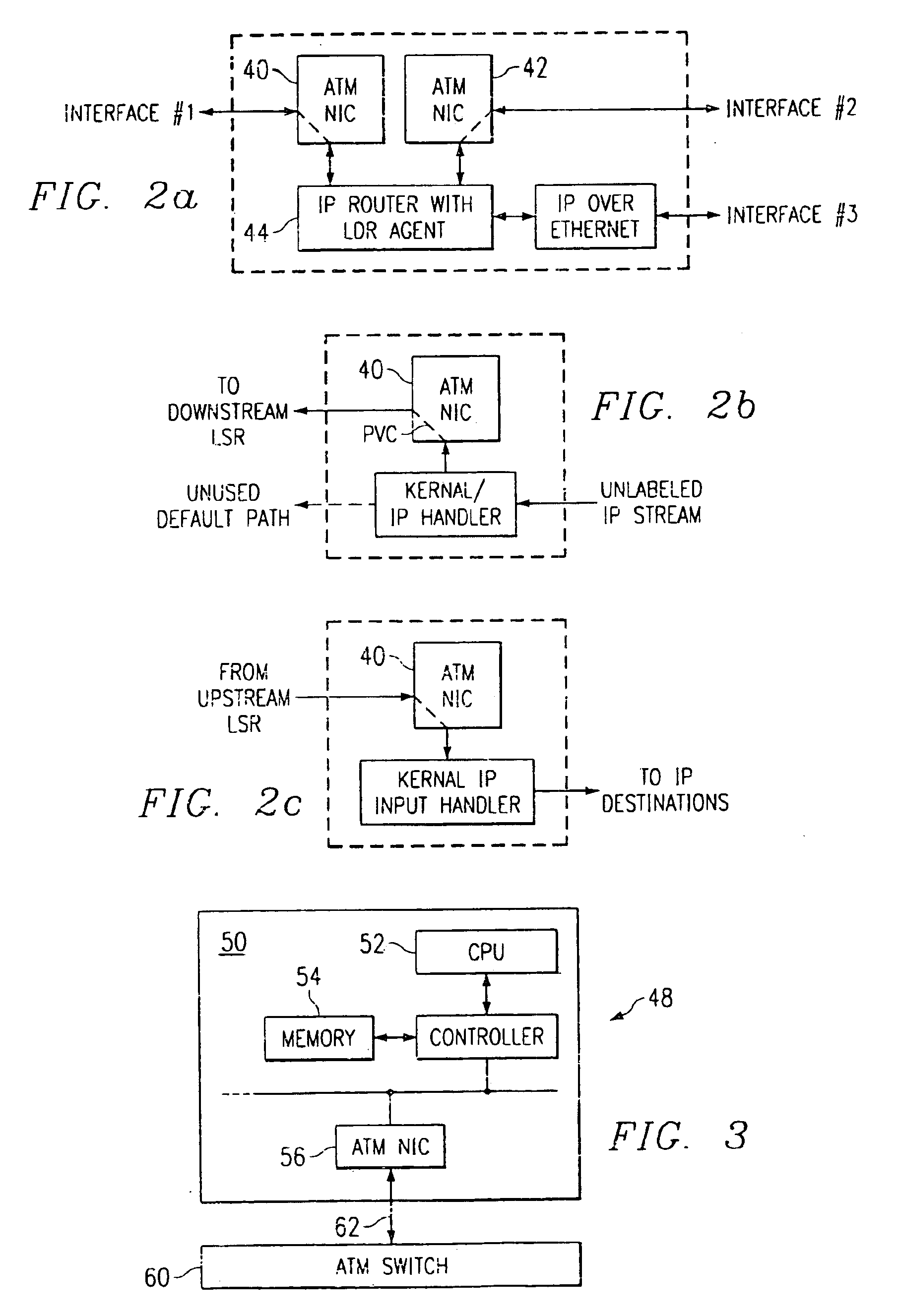

Multiprotocol label switching routers

InactiveUS6885677B1Equipment is cheapMinimize complexityTime-division multiplexData switching networksMultiprotocol Label SwitchingGeneral purpose computer

In one aspect, a method of using a general purpose computer 8 as an MPLS-enabled label switched router includes executing software on the general purpose computer 8 that allows it to communicate with other label switched routers using label distribution protocol. The general purpose computer 8 includes a central processor 10, a memory 12, network interface cards 30 and 32 and also typically includes local I / O such as a keyboard 22, a mouse 24 and a display device 20 for communicating with a local user.

Owner:FUJITSU LTD

Data processing circuit with target instruction and prefix instruction

InactiveUS6308258B1Simple structureUses memory efficientlyInstruction analysisDigital computer detailsRegister fileInstruction decoder

A certain target instruction and a prefix instruction for expanding the function of that target instruction are input to the present data processing circuit. The data processing circuit analyses the thus-input instruction code and performs the processing necessary for the execution of that instruction. The data processing circuit comprises an instruction decoder section, a register file, and an instruction execution section that executes the instruction based on operational details of the instruction analyzed by the instruction decoder section. The instruction decoder section comprises an ext instruction processing section that processed the expansion of immediate data from the prefix instruction.

Owner:SEIKO EPSON CORP

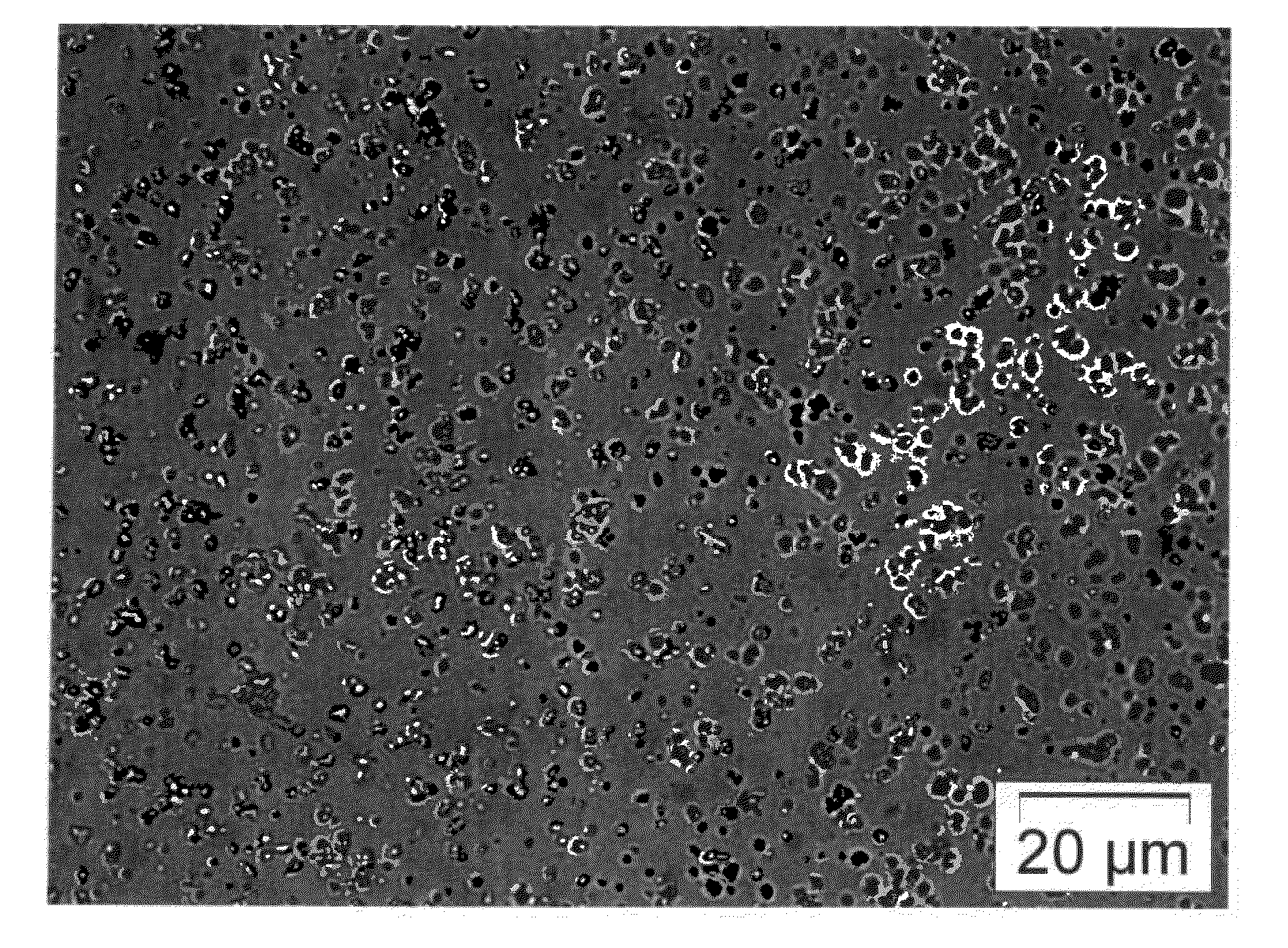

Crystalline active ingredient microparticles, method for producing the same and use thereof in drugs

InactiveUS20110144071A1Narrow particle size distributionQuick releaseOrganic active ingredientsSteroidsDrugChemistry

A method for producing highly crystalline and stable microparticles of an active substance with a very narrow size distribution. The microparticles being crystallized out of a suspension made of primary particles of the active substance, a solution of the active substance, a non-solvent for the active substance and inert formed pieces. The resulting microparticles hare highly stable largely independent of the physiochemical properties of the active substance and can be especially suitable for fast release dosage forms of pharmaceuticals.

Owner:JESALIS PHARMA

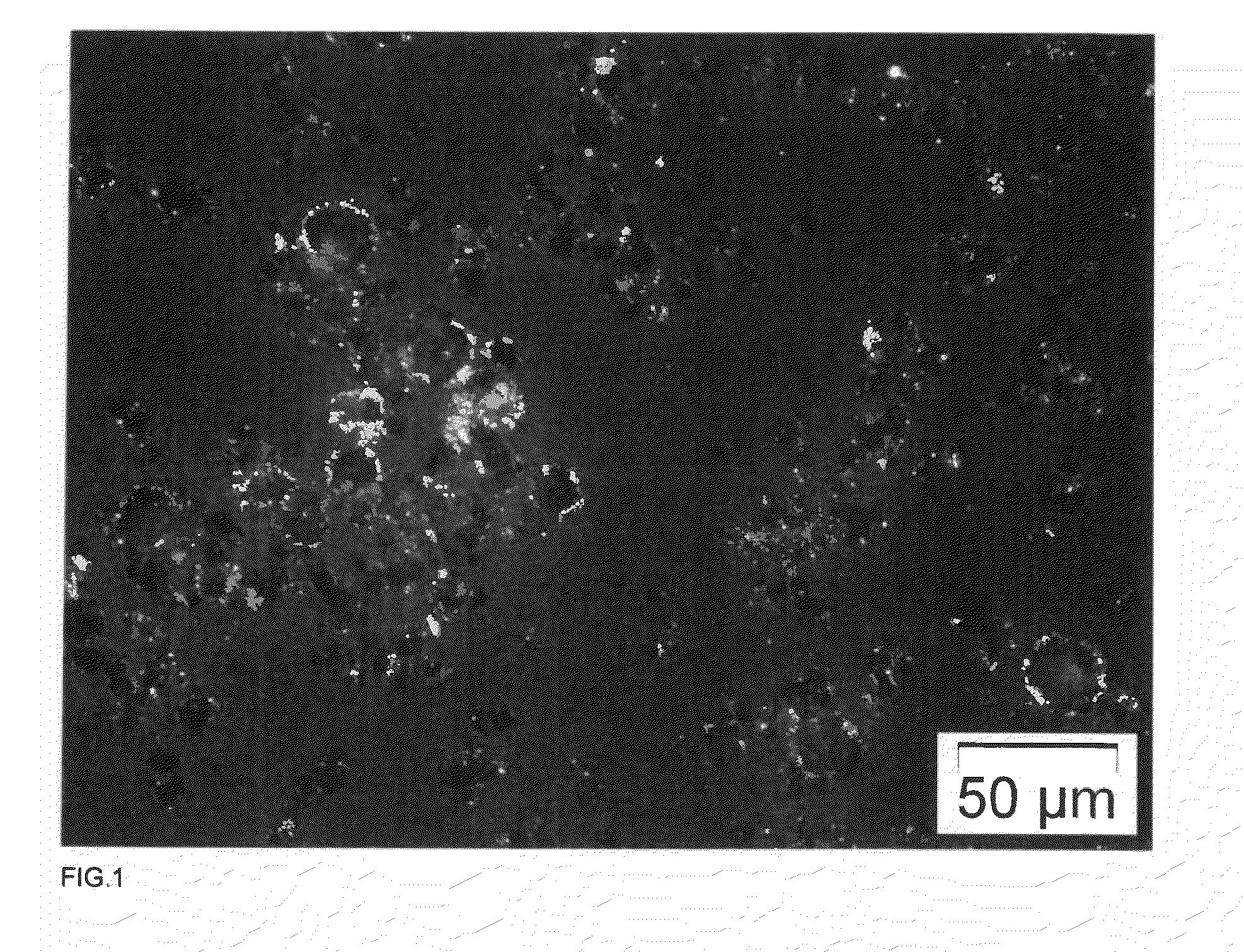

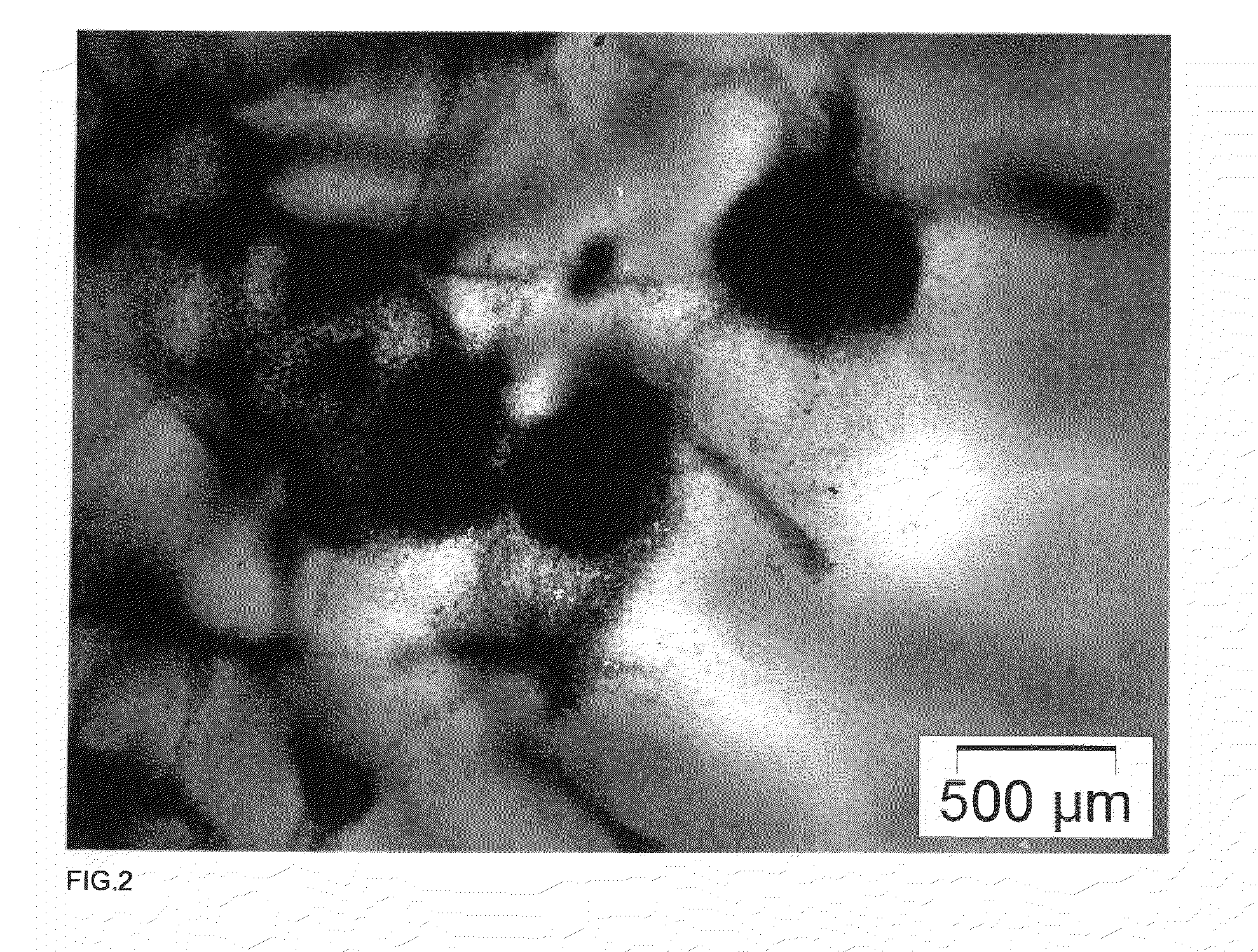

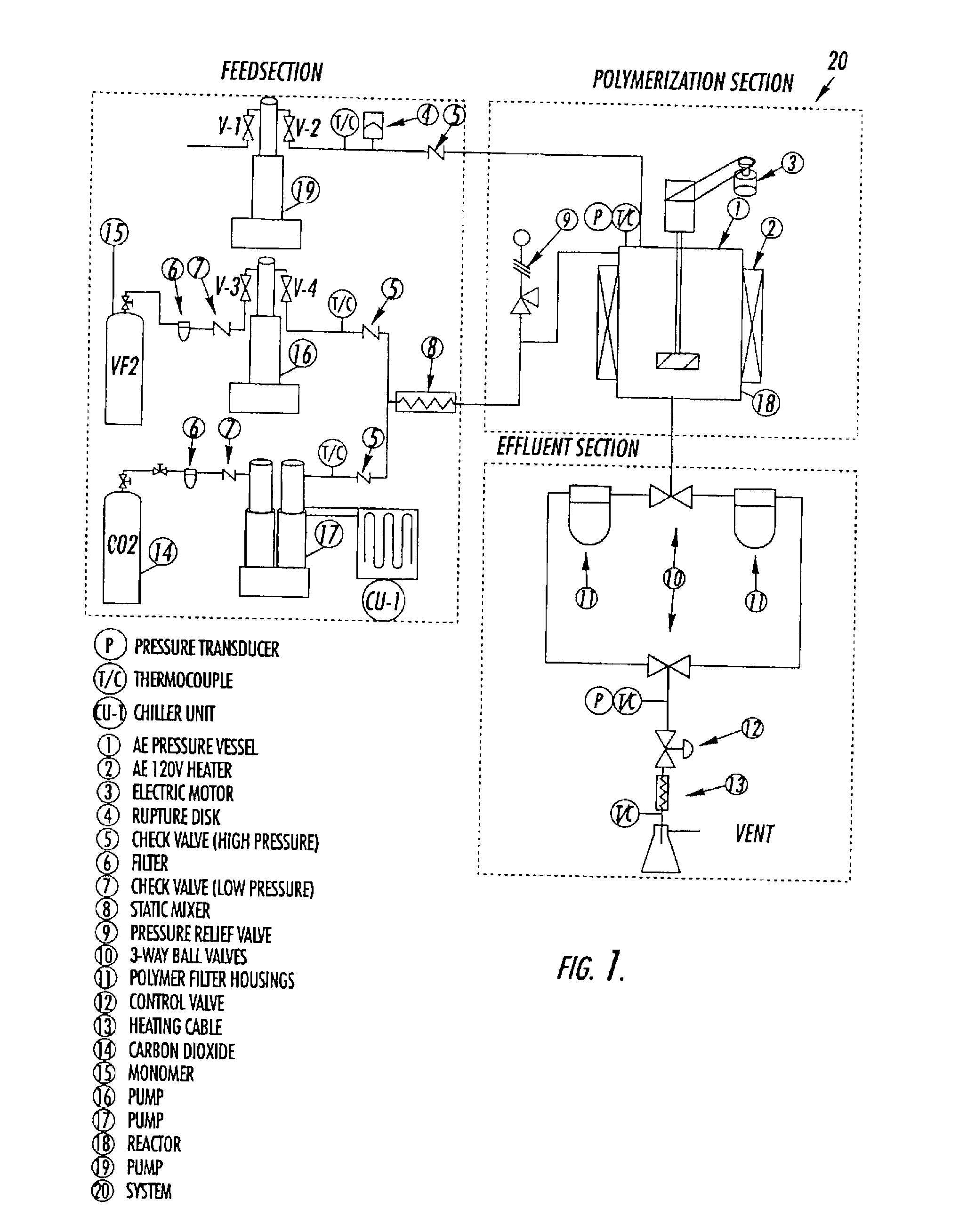

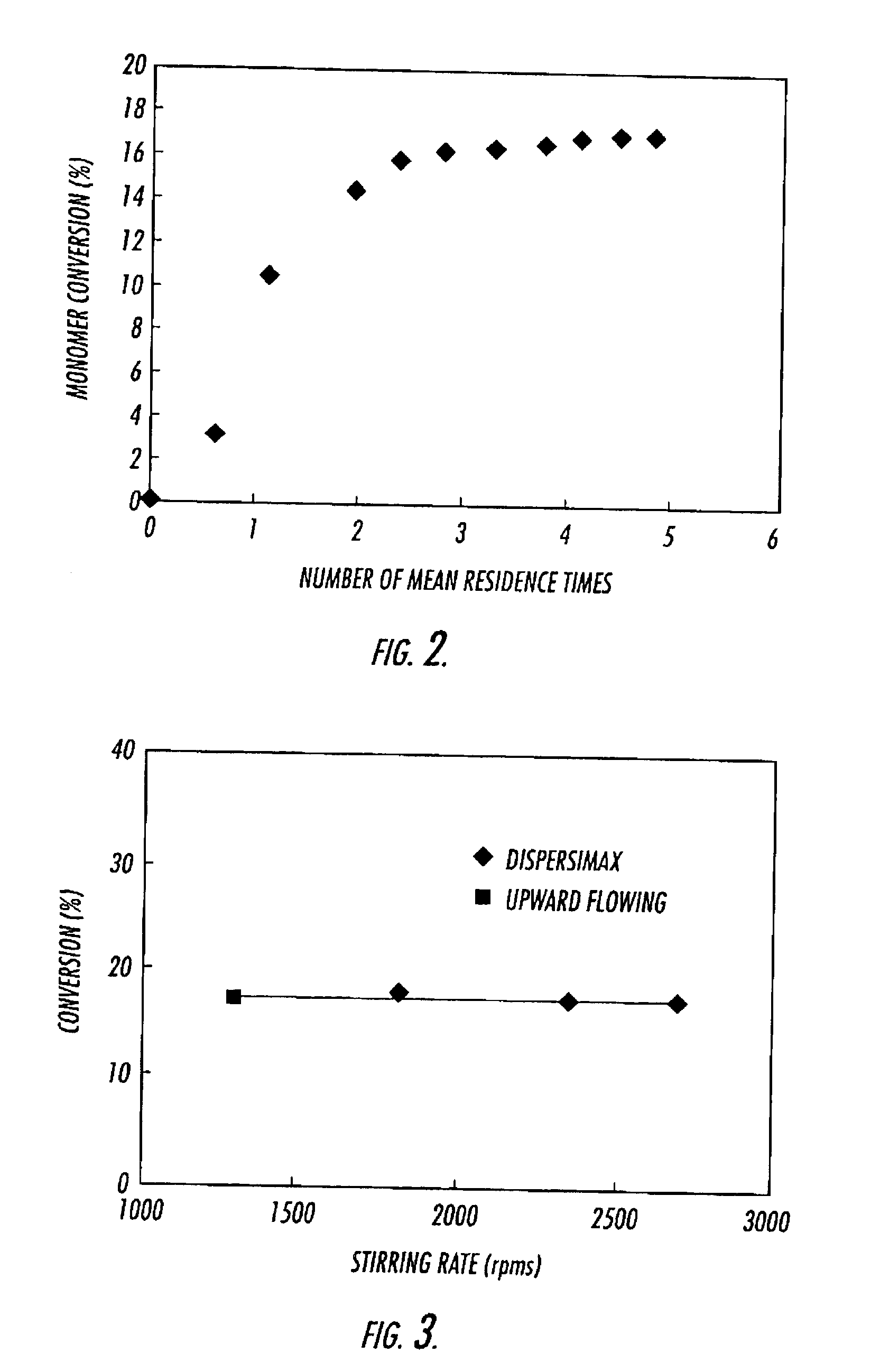

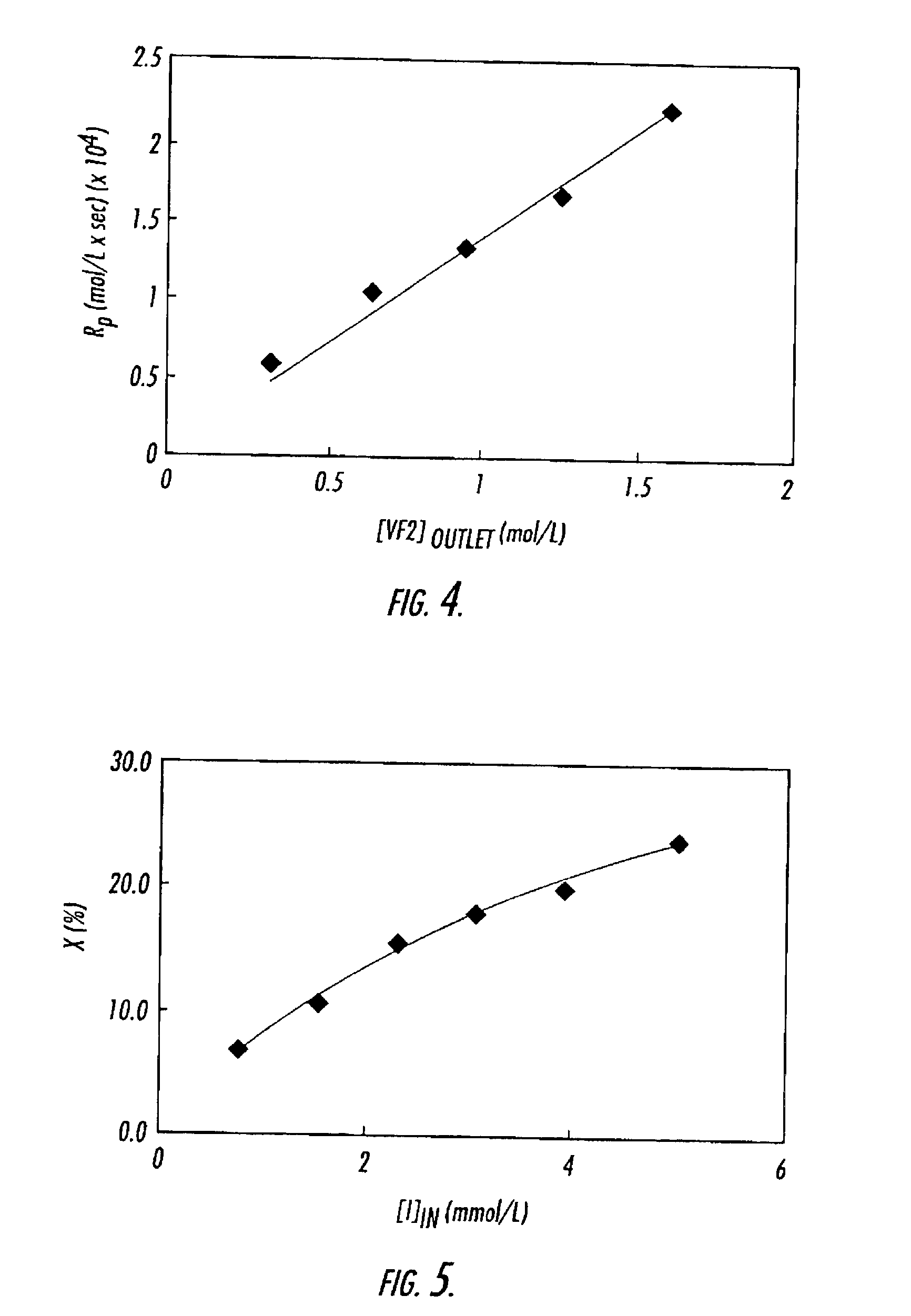

Continuous process for making polymers in carbon dioxide

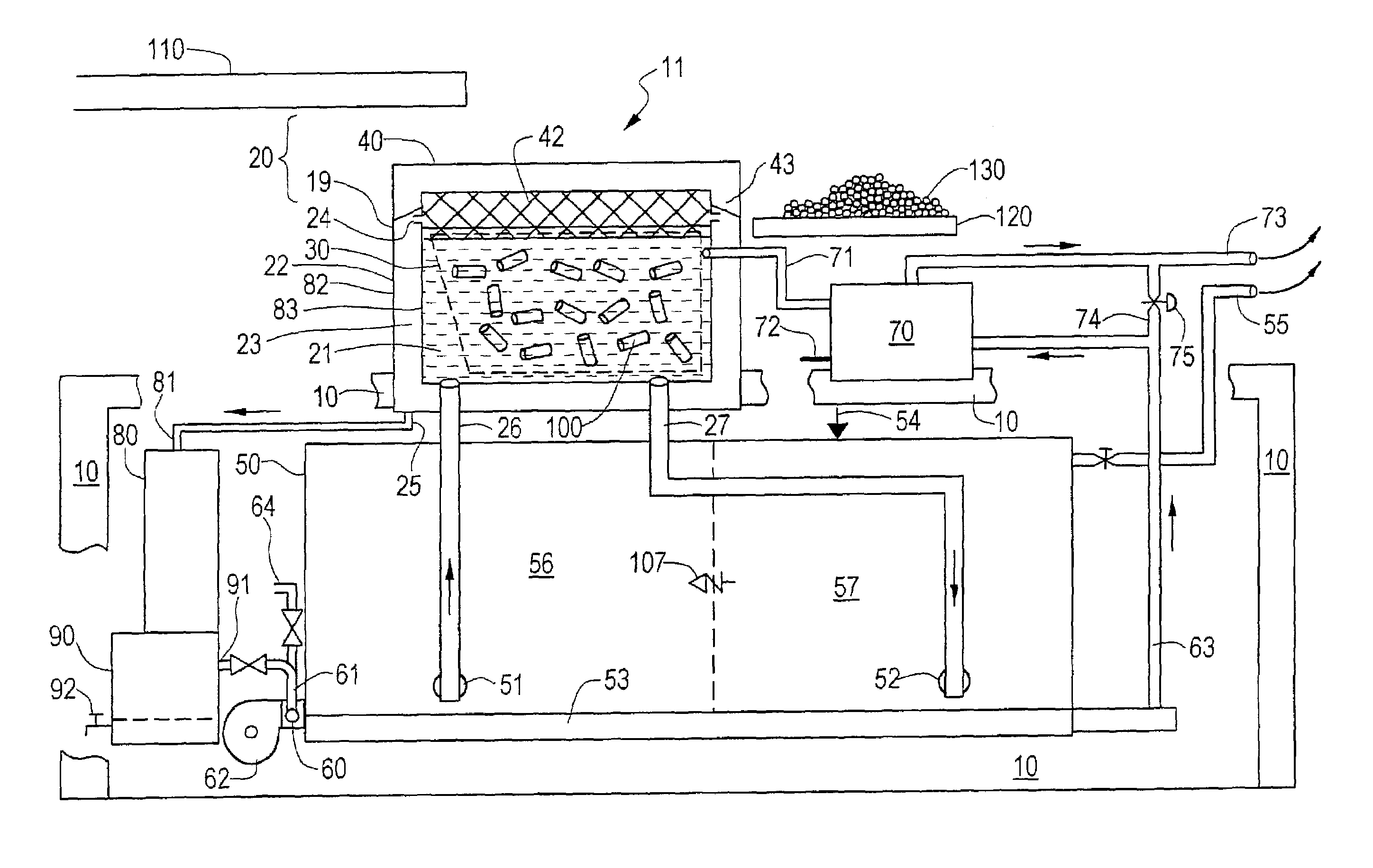

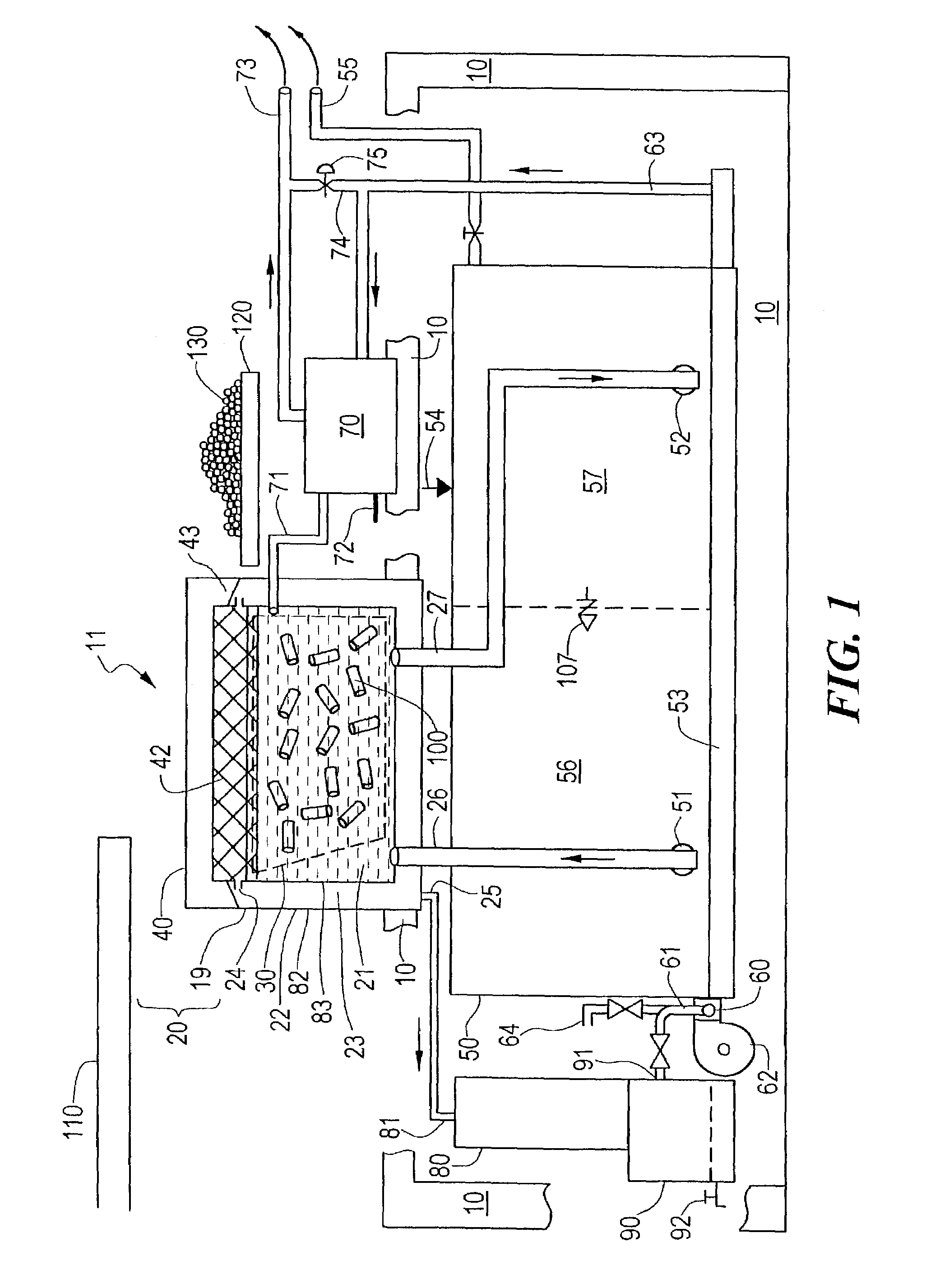

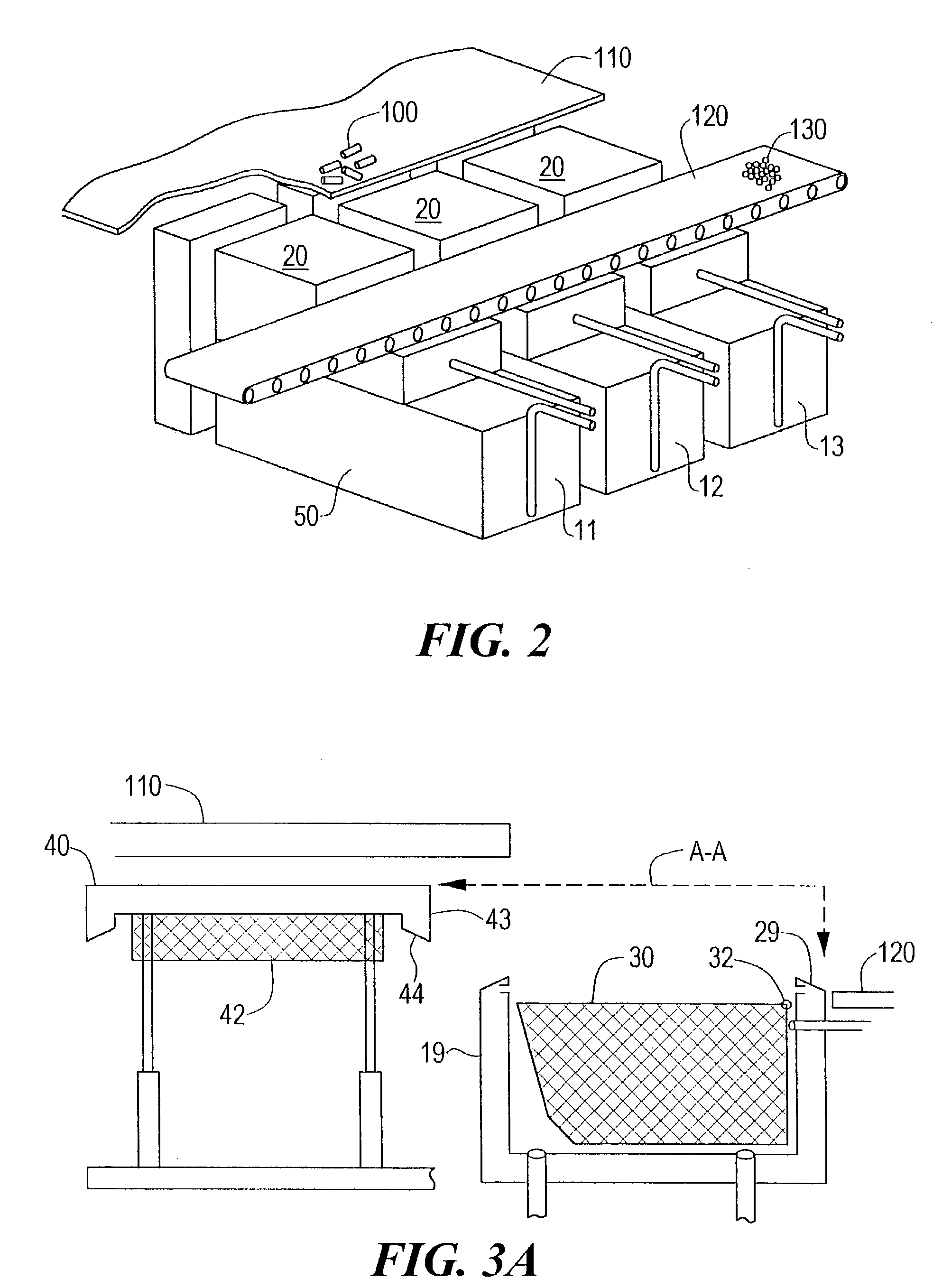

InactiveUS6914105B1Smaller andEquipment is cheapChemical/physical/physico-chemical stationary reactorsBulk chemical productionMonomerContinuous reaction

A method for carrying out the continuous polymerization of a monomer in a carbon dioxide reaction medium comprises the steps of: (a) providing an apparatus including a continuous reaction vessel and a separator; (b) carrying out a polymerization reaction in the reaction vessel by combining a monomer and a carbon dioxide reaction medium therein (and preferably by also combining an initiator therein), wherein the reaction medium is a liquid or supercritical fluid, and wherein the reaction produces a solid polymer product in the reaction vessel; then (c) withdrawing a continuous effluent stream from the reaction vessel during the polymerization reaction, wherein the effluent stream is maintained as a liquid or supercritical fluid; then (d) passing the continuous effluent stream through the separator and separating the solid polymer therefrom while maintaining at least a portion of the effluent stream as a liquid or supercritical fluid; and then (e) returning at least a portion of the continuous effluent stream to the reaction vessel while maintaining the effluent stream as a liquid or supercritical fluid. The need for significant recompression of the continuous effluent stream prior to return to the reaction vessel is thereby minimized. Apparatus for carrying out such methods is also disclosed.

Owner:THE UNIV OF NORTH CAROLINA AT CHAPEL HILL +1

Radiation shielding materials and containers incorporating same

InactiveUS6960311B1Improve shielding effectMaximum flexibilityOther chemical processesTransuranic element compoundsMicrosphereUranium carbide

An improved radiation shielding material and storage systems for radioactive materials incorporating the same. The PYRolytic Uranium Compound (“PYRUC”) shielding material is preferably formed by heat and / or pressure treatment of a precursor material comprising microspheres of a uranium compound, such as uranium dioxide or uranium carbide, and a suitable binder. The PYRUC shielding material provides improved radiation shielding, thermal characteristic, cost and ease of use in comparison with other shielding materials. The shielding material can be used to form containment systems, container vessels, shielding structures, and containment storage areas, all of which can be used to house radioactive waste. The preferred shielding system is in the form of a container for storage, transportation, and disposal of radioactive waste. In addition, improved methods for preparing uranium dioxide and uranium carbide microspheres for use in the radiation shielding materials are also provided.

Owner:THE UNITED STATES AS REPRESENTED BY THE DEPARTMENT OF ENERGY

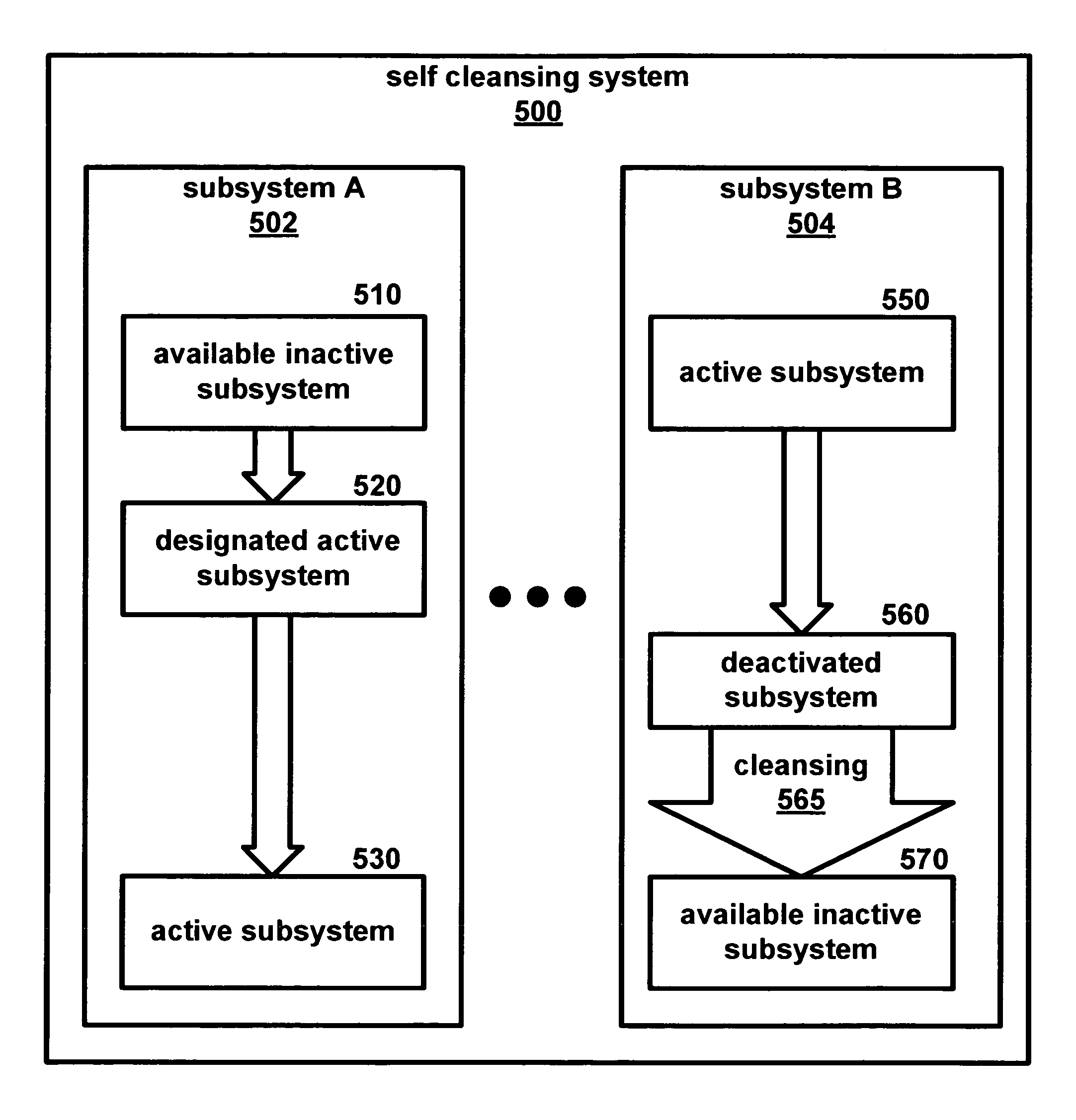

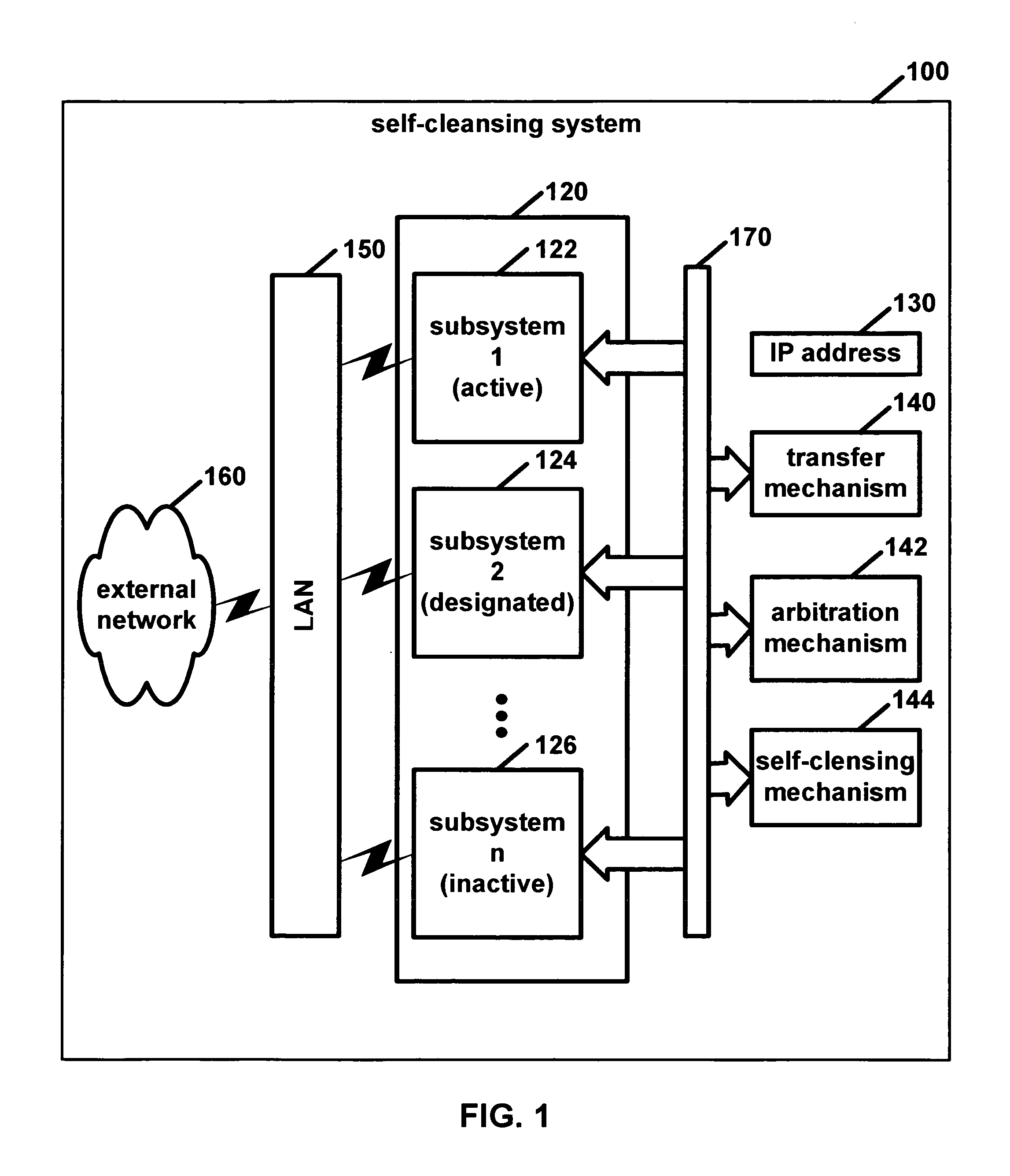

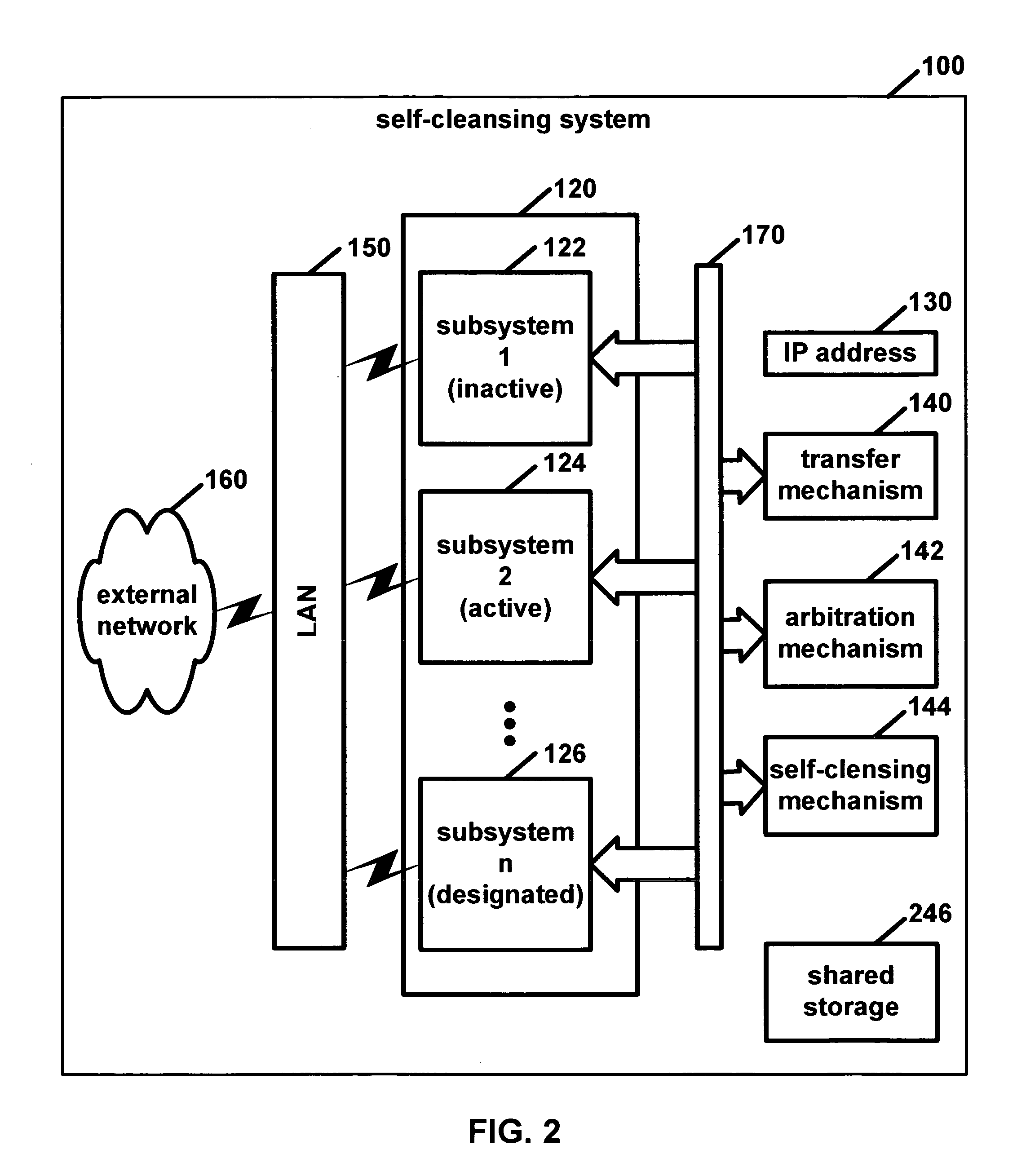

Self-cleansing system

ActiveUS7549167B1Highly-available and inexpensiveEquipment is cheapMemory loss protectionError detection/correctionComputer hardwareTelecommunications link

Disclosed is a self-cleansing system comprising at least two subsystems including an active subsystem and at least one available inactive subsystem. At least two of the subsystems may be connected to each other by a communications link and connected to an external network through a local network. An arbitration mechanism is capable of designating one of the at least one available inactive subsystem to be a designated active system. An active subsystem and a designated active subsystem may share an IP address, but only the active subsystem utilizes the IP address to output information to the external network. A transfer mechanism capable of deactivating the active subsystem and then activating a designated active system may be initiated by a transfer criterion. A self-cleansing mechanism may then cleanse the deactivated subsystem.

Owner:GEORGE MASON INTPROP INC

Batch thermolytic distillation of carbonaceous material

InactiveUS7056422B2Minimizes disposal problemMinimizing substantially exposure to riskCharging-discharging device combinationsDirect heating destructive distillationDistillationTin

A distillation system is provided for batch thermolytic distillation of lump carbonaceous material, such as lump wood and shredded rubber tires. The system preferably includes multiple distillation units mounted side-by-side. Each unit includes a reactor bath for holding molten tin at approximately 455° C., a two-compartment reservoir for storing molten tin, and a porous basket pivotally mounted within the reactor bath for tipping motion. A process for batch thermolytic distillation of lump carbonaceous material includes rotating the porous basket into a reactor bath by rotating the basket about an axis passing through the reactor bath; putting a charge of wood into the basket; closing a retractable lid onto the reactor bath; filling the reactor bath with molten material to produce gas and char by thermolytic conversion of the charge, draining the reactor bath of molten material while the lid is closed; quenching the char in the reactor bath with steam; opening the lid; and tipping the char from the basket.

Owner:SECTOR CAPITAL CORP

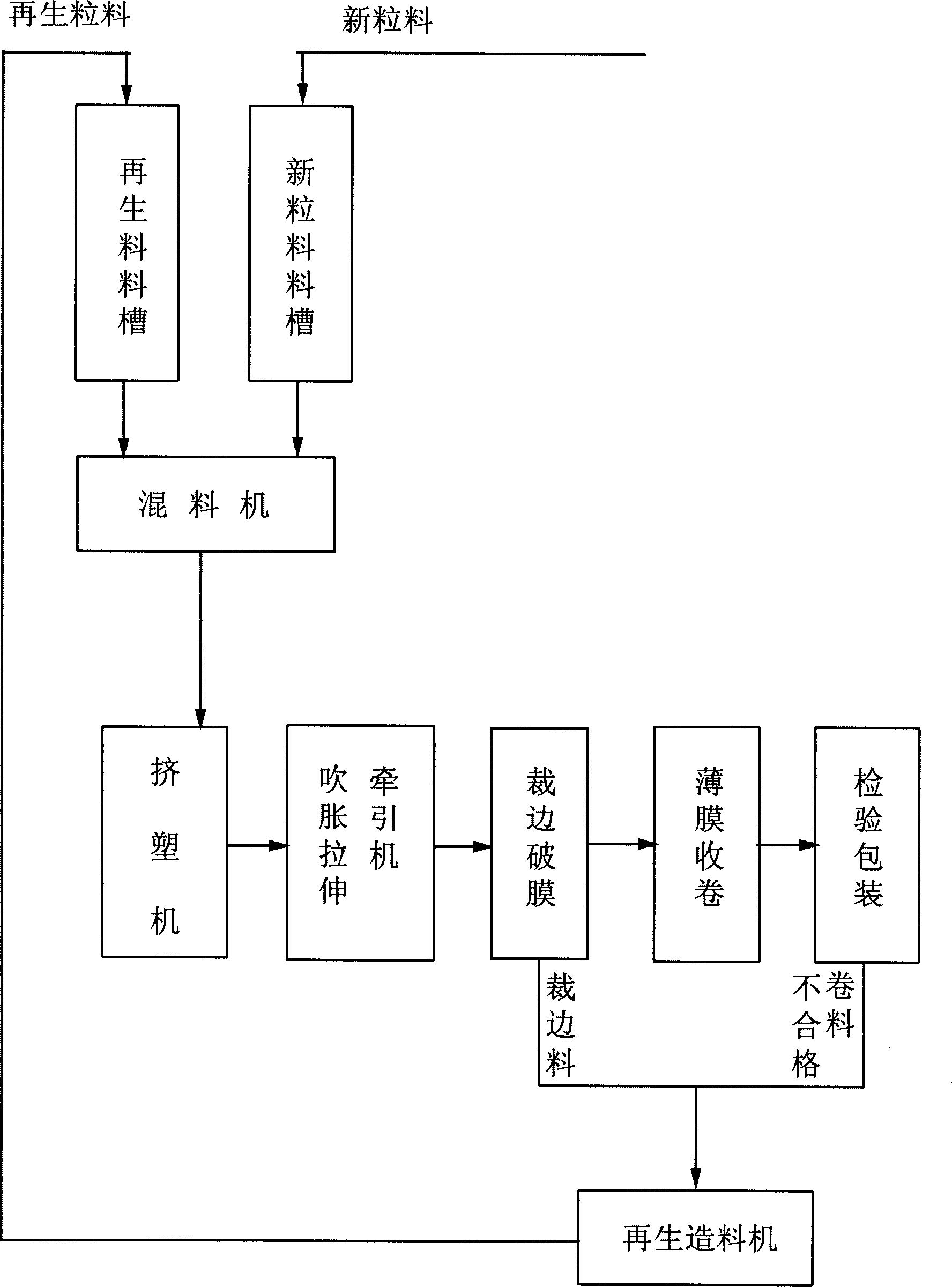

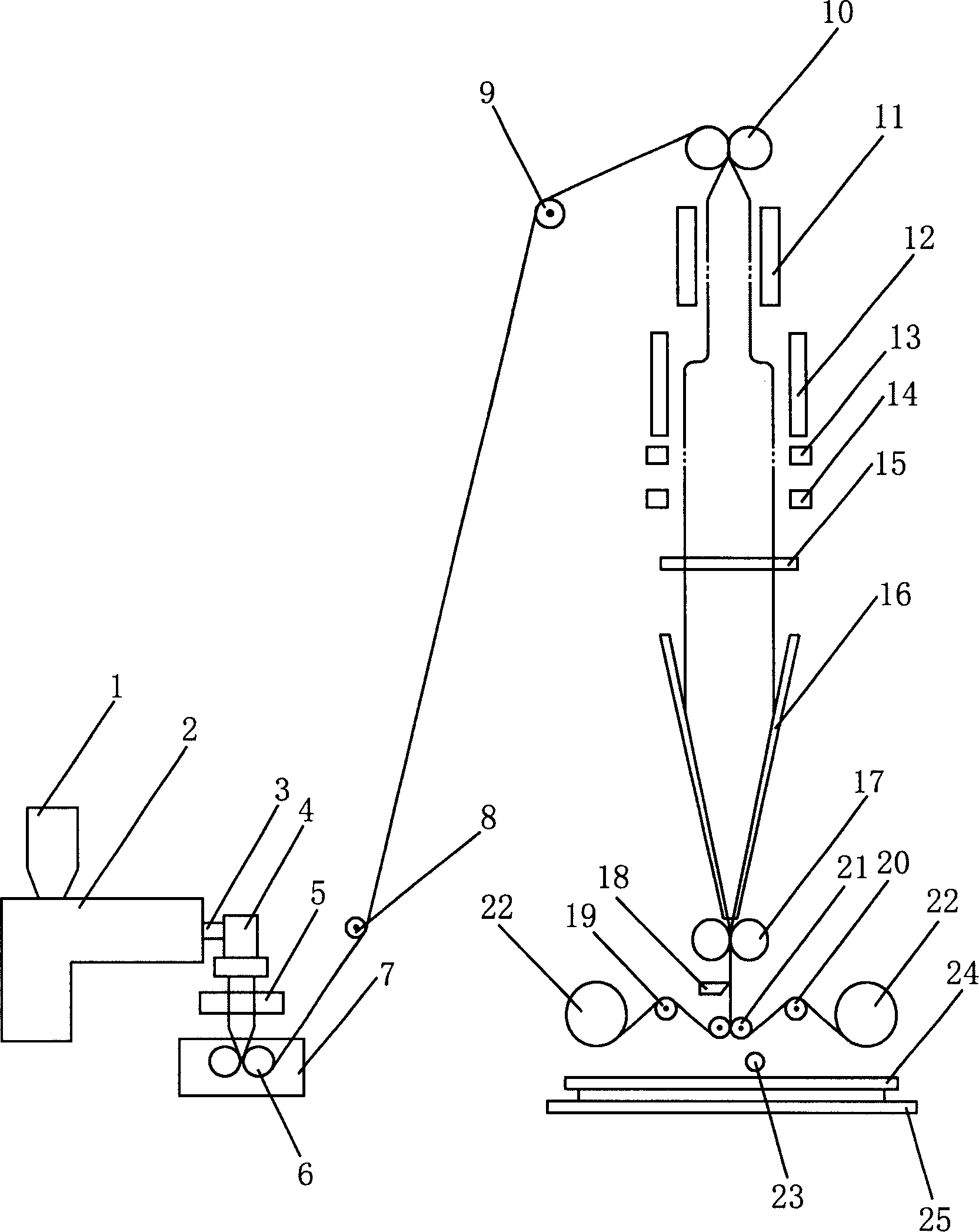

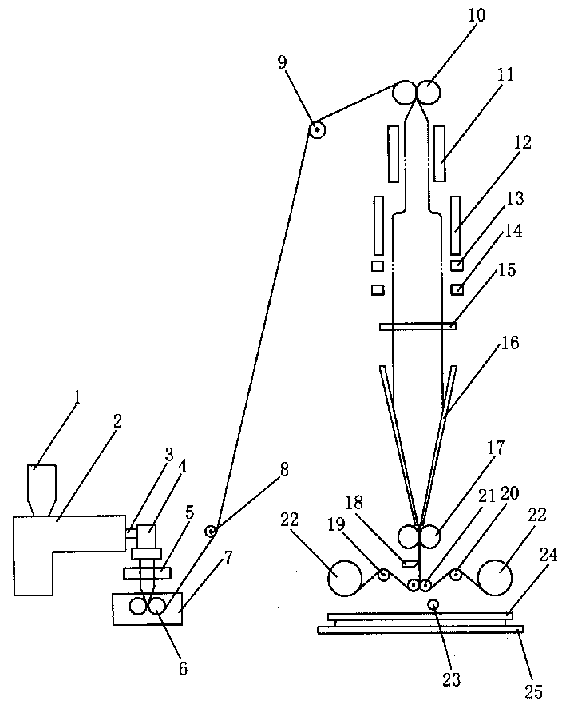

Method and equipment for producing bidirectional stretching plastic film

The present invention discloses a method for producing two-way stretched plastic film and equipment, including the procedures of extrusion, blowing-up and drawing, edge-cutting and film-breaking and film-rolling. It is characterized by that in the blowing-up and drawing procedure the plastic film tube discharged from extrusion procedure can be pulled to the upper portion of tower frame, reheated to high-elastic drawable temp.,and the proper qantity of air can be charged into the tube film, then the tube film is longitudinally progressively and quickly drawn and laterally stretched toward bothsides, then heat-set. Said invention simplifies production process, and reduces cost of equipment.

Owner:汕头市江鸿塑胶设备有限公司

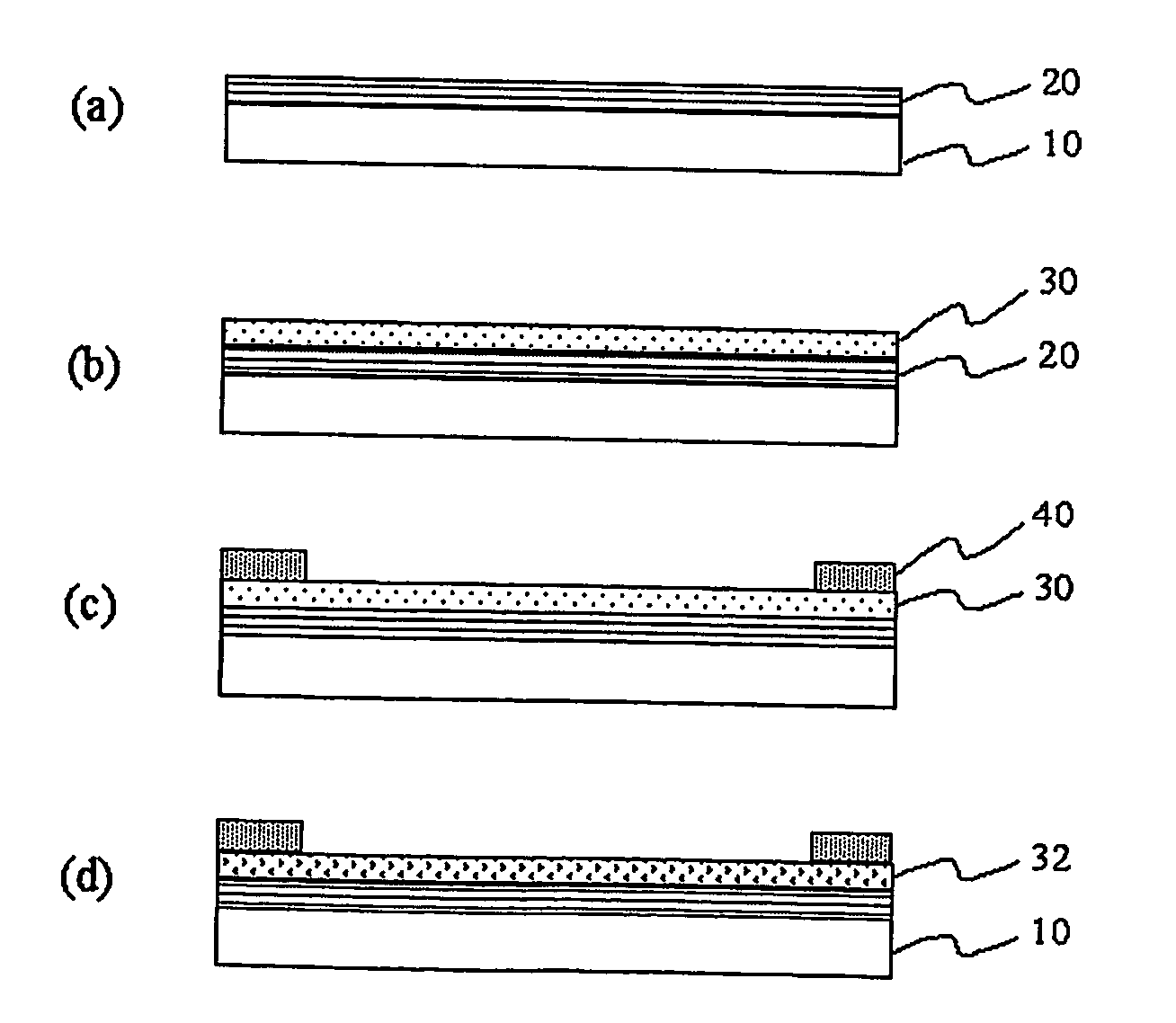

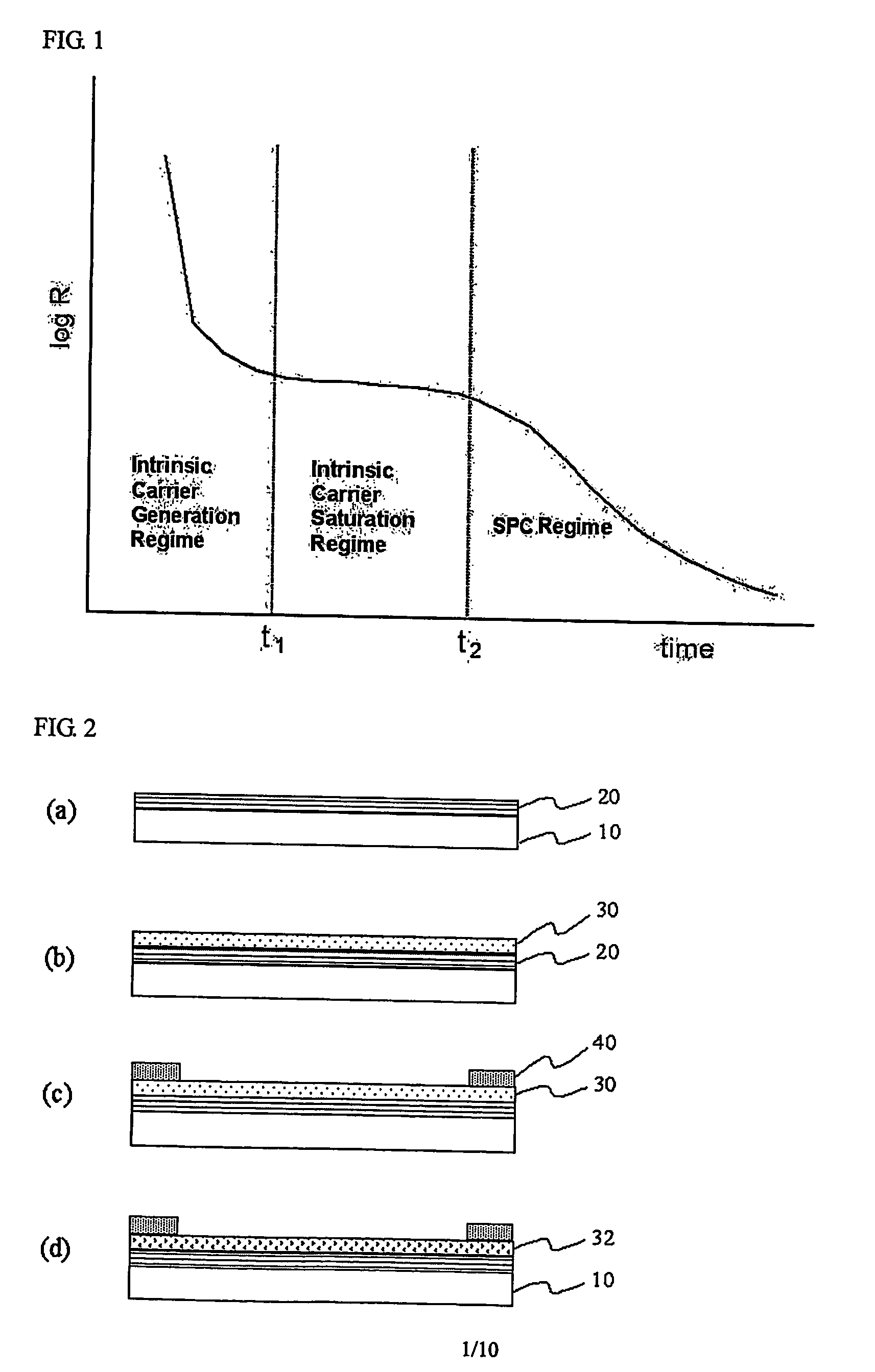

Method for annealing silicon thin films and polycrystalline silicon thin films prepared therefrom

InactiveUS20070099352A1Simple processReduce defectsTransistorSolid-state devicesInsulation layerCrystallographic defect

Disclosed is a method for annealing a silicon thin film in a substrate in which an insulation layer and the silicon thin film are subsequently formed. The method includes heating or preheating the silicon thin film within a temperature range at which the substrate is not transformed during the process so as to generate an intrinsic carrier therein, thereby lowering a resistance to a value at which Joule heating is possible; and applying an electric field to the preheated silicon thin film so as to induce Joule heating by means of movement of the carrier, thereby conducting crystallization, eliminating crystal defects, and ensuring crystal growth. When using the method, Joule heating is selectively induced to a-Si thin film, a-Si / Poly-Si thin film or a Poly-Si thin film according to the preheating condition, thereby making a Poly-Si thin film of good quality within a very short time without damaging the substrate.

Owner:ENSIL TECH CO LTD

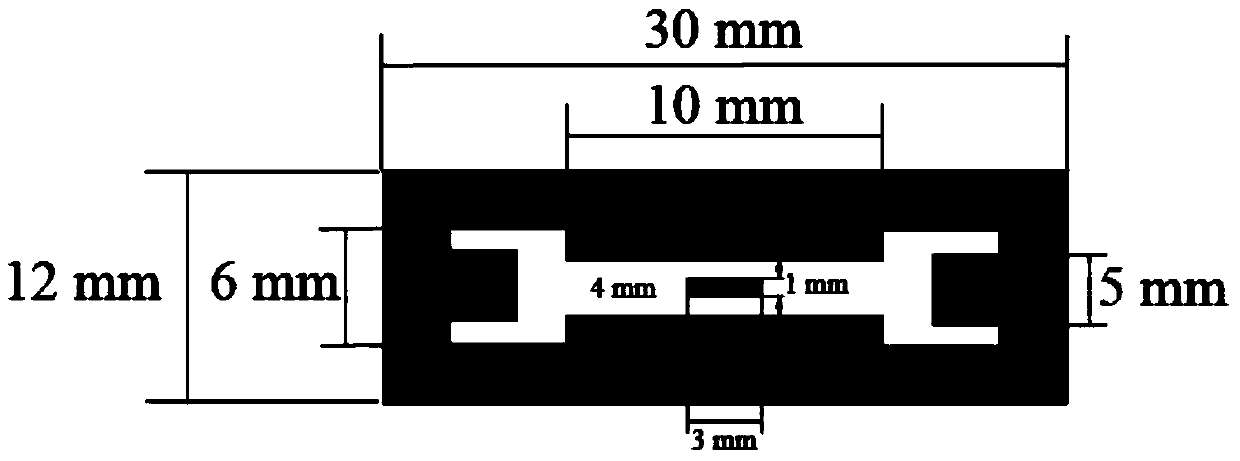

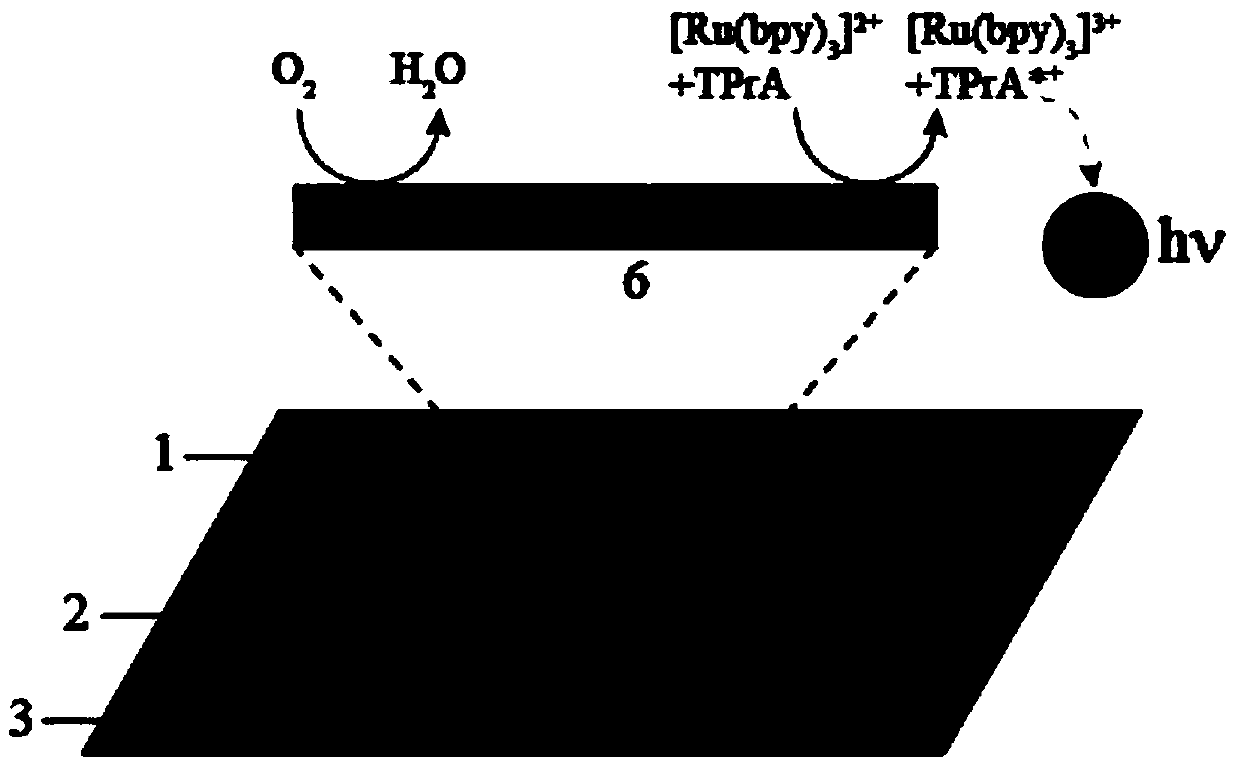

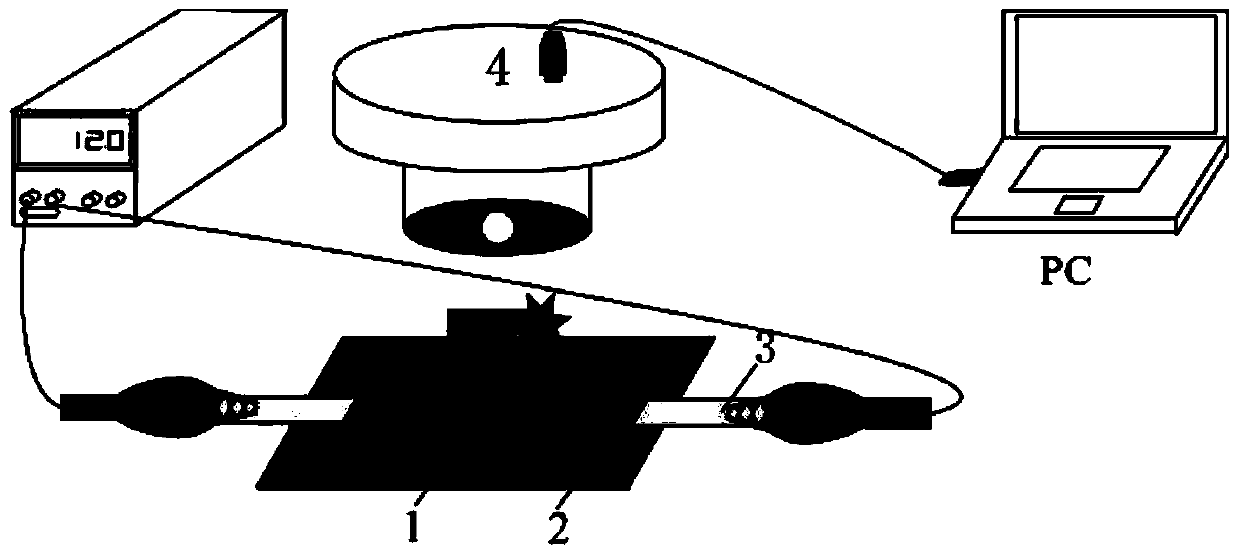

Bipolar electrode electrogenerated chemiluminescence paper based micro-fluidic chip and imaging sensing application thereof

ActiveCN104198469ASimple processing technologyEquipment is cheapChemiluminescene/bioluminescenceLaboratory glasswaresMicrofluidic chipMicro fluidic

The invention discloses a bipolar electrode electrogenerated chemiluminescence paper based micro-fluidic chip and the application thereof to imaging sensing. The preparation method of the chip comprises the following steps: designing patterns of a micro-fluidic channel and an electrode through software and then manufacturing screens, clinging the electrode screen onto filter paper, printing the shape and the size of the electrode on the filter paper by brushing conductive carbon paste on the electrode screen, taking the filter paper on which the electrode is printed, clinging the channel screen onto filter paper, performing grinding and brushing on the channel screen through a wax pencil, then performing heating, so as to ensure that wax penetrates through the filter paper to form the micro-fluidic channel and a solution storage tank, and obtaining the bipolar electrode electrogenerated chemiluminescence paper based micro-fluidic chip. The chip takes the carbon paste as bipolar electrode material on paper for the first time, an electrogenerated chemiluminescence chip manufactured by taking the chip as a basis performs imaging sensing detection on tripropylamine, and the chip has the advantages of bipolar electrode electrochemistry and paper based microfluidics.

Owner:SOUTH CHINA NORMAL UNIVERSITY

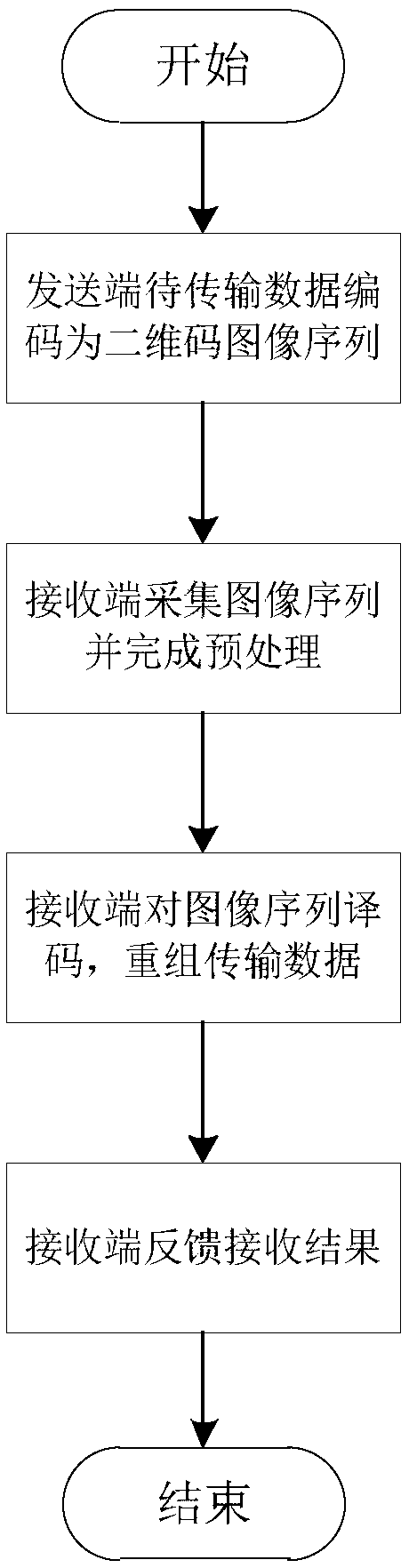

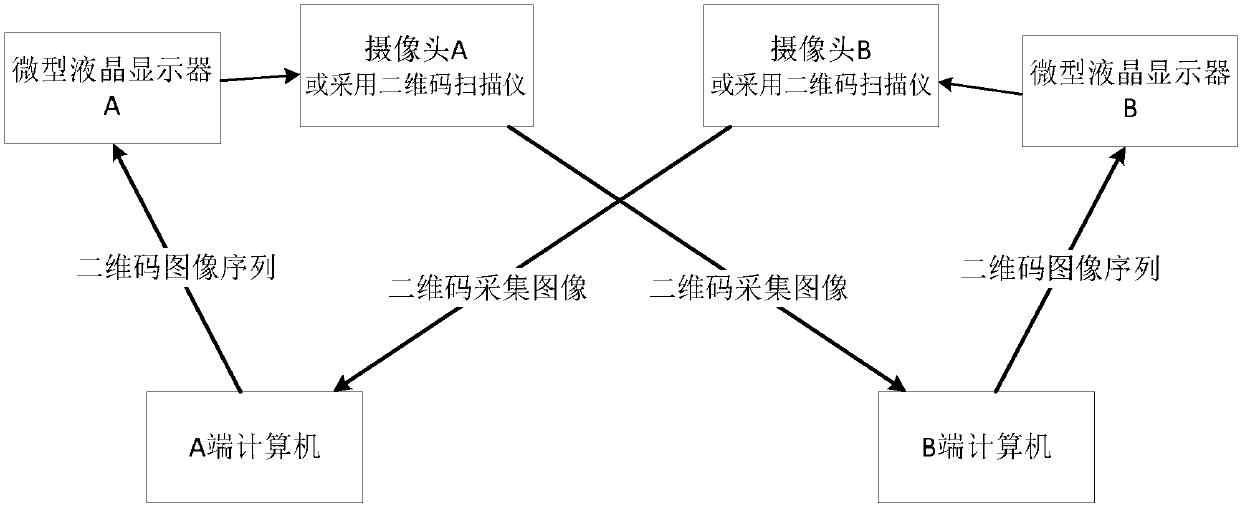

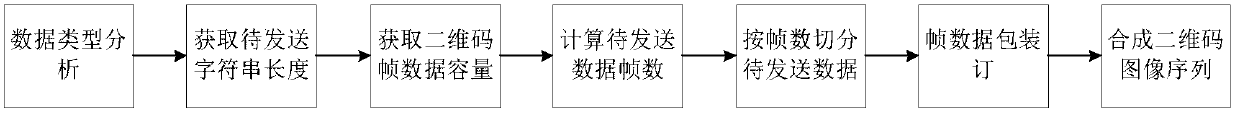

Two-dimensional bar code duplex communication method

InactiveCN108055116AEquipment is cheapLow priceRecord carriers used with machinesDuplex signal operationData transmissionLiquid-crystal display

The invention discloses a two-dimensional bar code duplex communication method and aims at providing the duplex communication method based on two-dimensional bar codes. According to the duplex communication method, the communication security is high and the data transmission efficiency and reliability are high in a scene with a relatively high confidentiality demand. The method is realized throughutilization of the following technical scheme that a sending end codes to-be-transmitted data into a two-dimensional bar code image sequence and displays the two-dimensional bar code image sequence in sequence through utilization of a miniature liquid crystal display; a receiving end collects the two-dimensional bar code image sequence through utilization of a vision camera or a two-dimensional bar code scanner, carries out repeated frame elimination, image graying, median filtering and binarization preprocessing on collection results and decodes the collection results according to a two-dimensional bar code coding format, thereby acquiring decoding results; the receiving end integrates the decoding results according to frame serial numbers and the frame number, thereby acquiring a sending end source transmission file; and the receiving end carries out real-time feedback or delayed feedback on a receiving result according to system transmission configuration. According to the method,the defect of a data transmission security hinge is solved.

Owner:10TH RES INST OF CETC

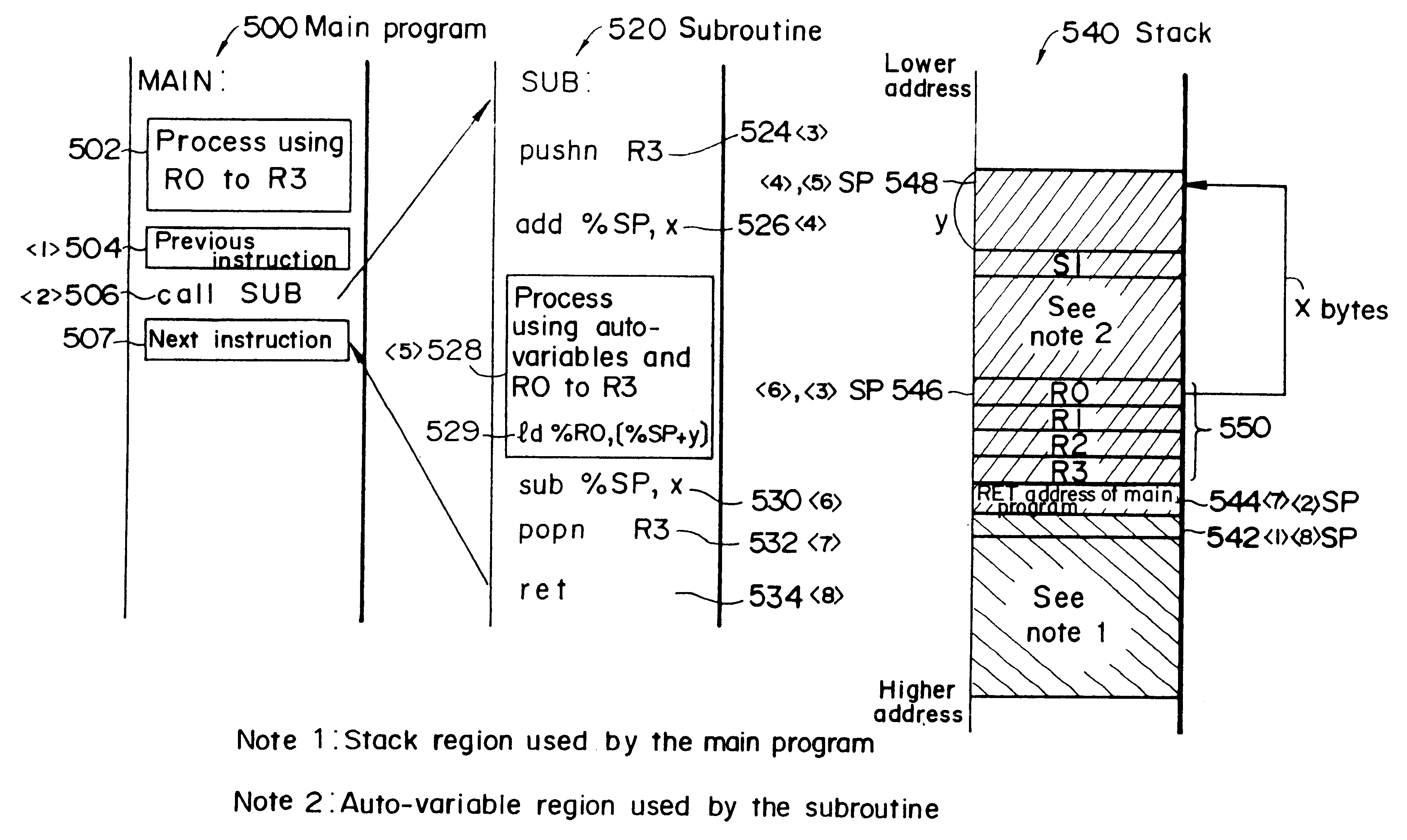

Data processing circuit, microcomputer, and electronic equipment

InactiveUS6560692B1Easy to handleValid encodingProgram initiation/switchingGeneral purpose stored program computerGeneral purposeMicrocomputer

The data processing circuit of this invention enables efficient description and execution of processes that act upon the stack pointer, using short instructions. It also enables efficient description of processes that save and restore the contents of registers, increasing the speed of processing of interrupts and subroutine calls and returns. A CPU that uses this data processing circuit comprises a dedicated stack pointer register SP and uses an instruction decoder to decode a group of dedicated stack pointer instructions that specify the SP as an implicit operand. This group of dedicated stack pointer instructions are implemented in hardware by using general-purpose registers, the PC, the SP, an address adder, an ALU, a PC incrementer, internal buses, internal signal lines, and external buses. This group of dedicated stack pointer instructions comprises SP-relative load instructions, stack pointer move instructions, a call instruction, a ret instruction, a sequential push instruction, and a sequential pop instruction.

Owner:SEIKO EPSON CORP

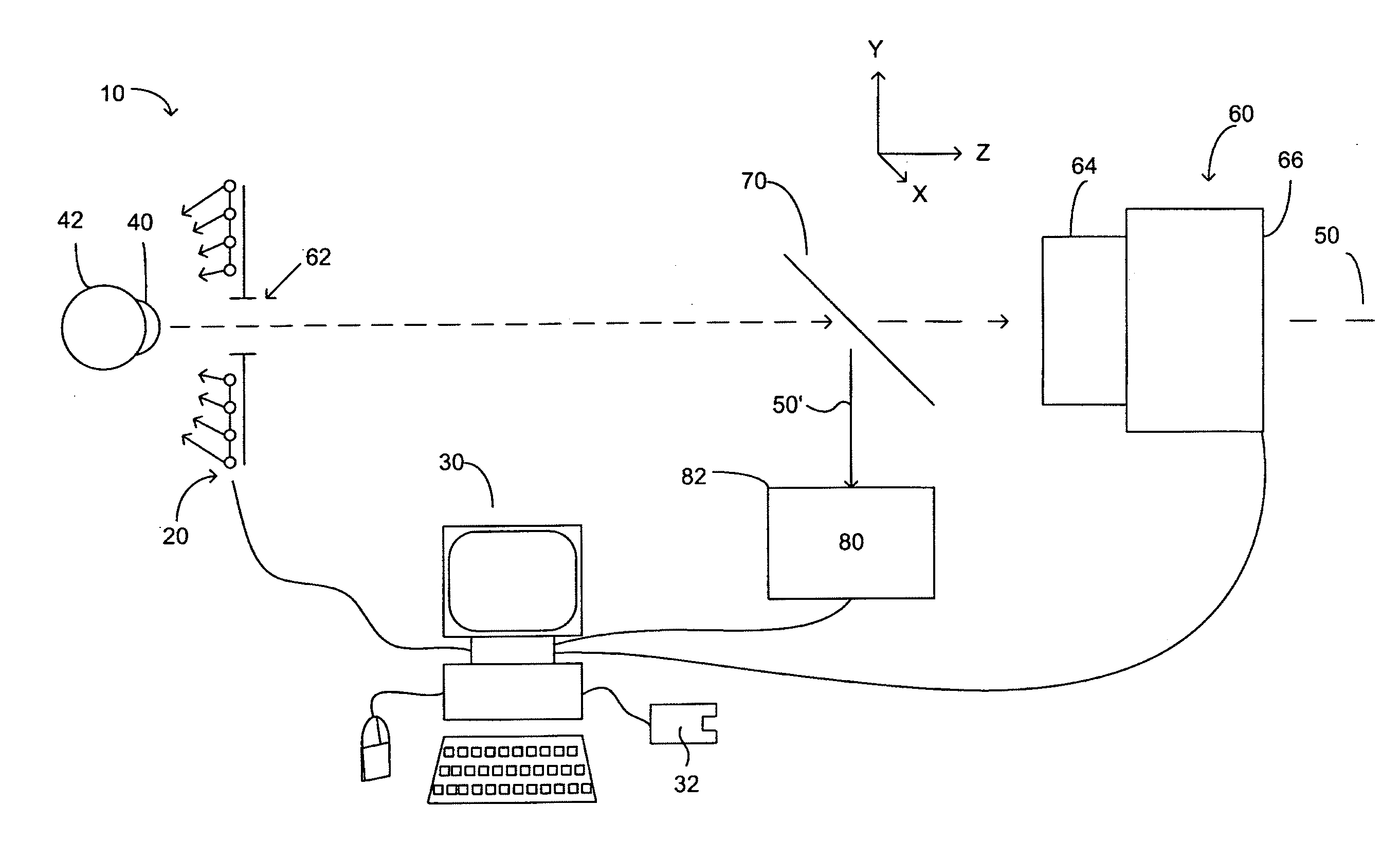

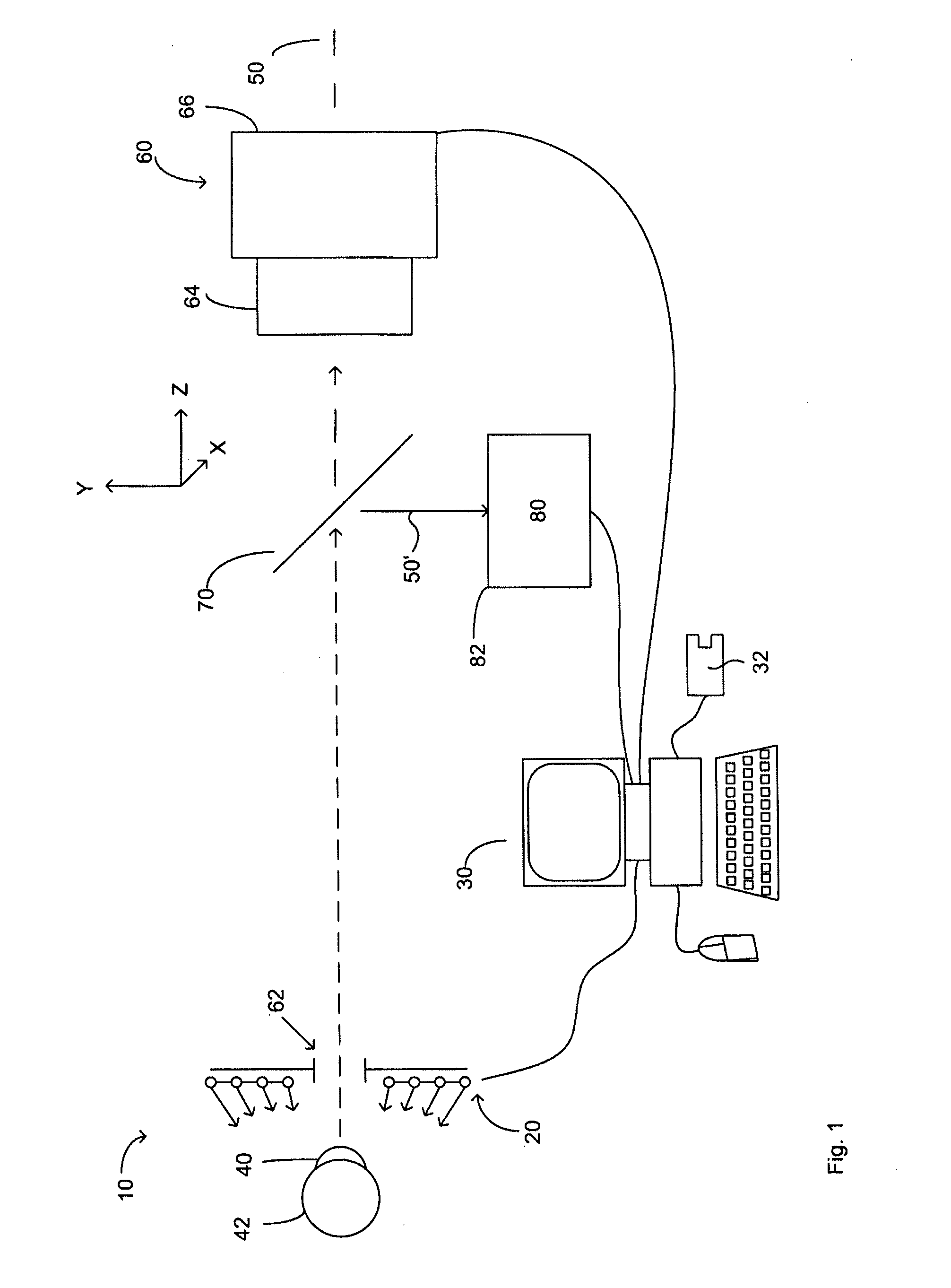

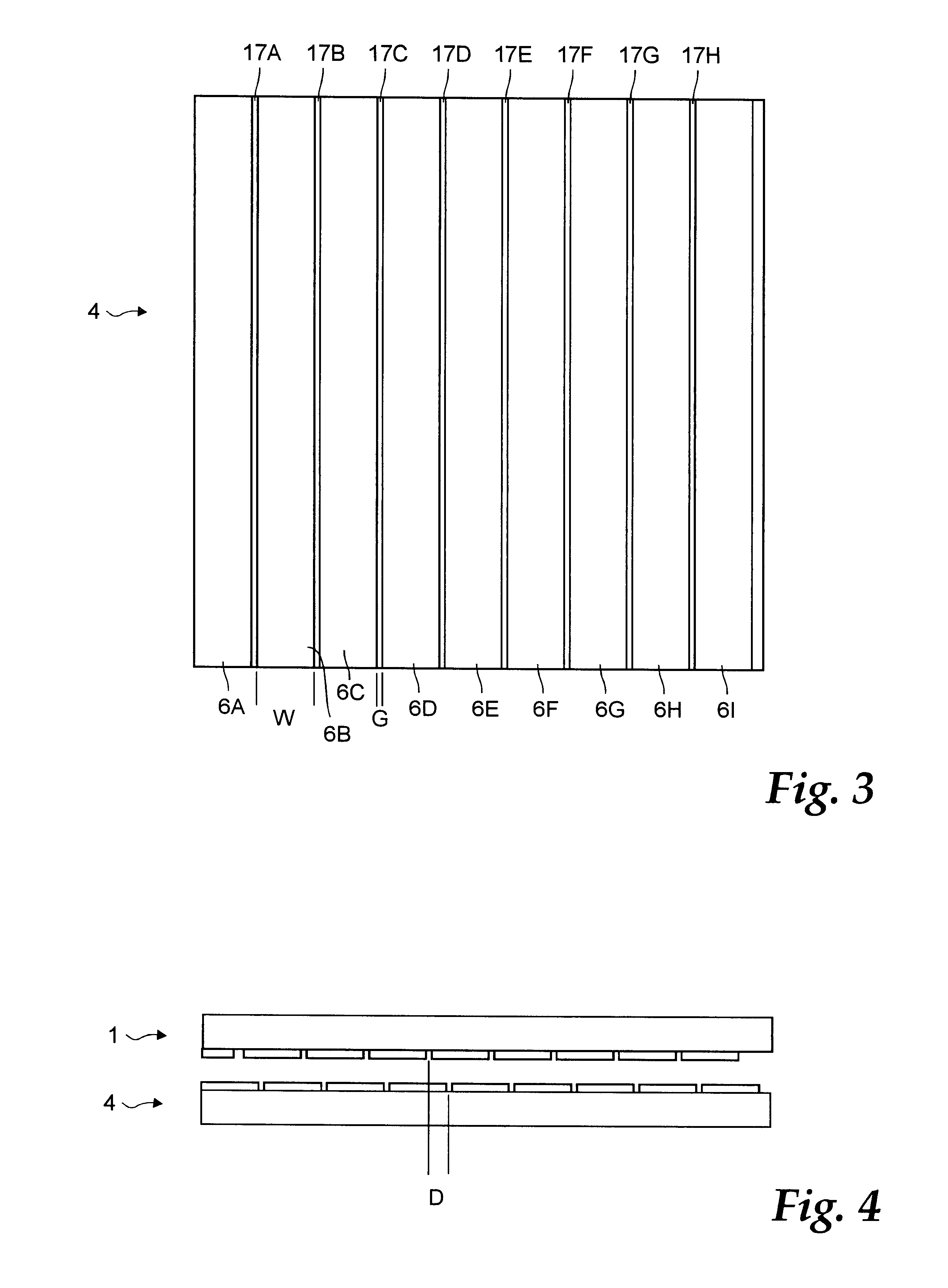

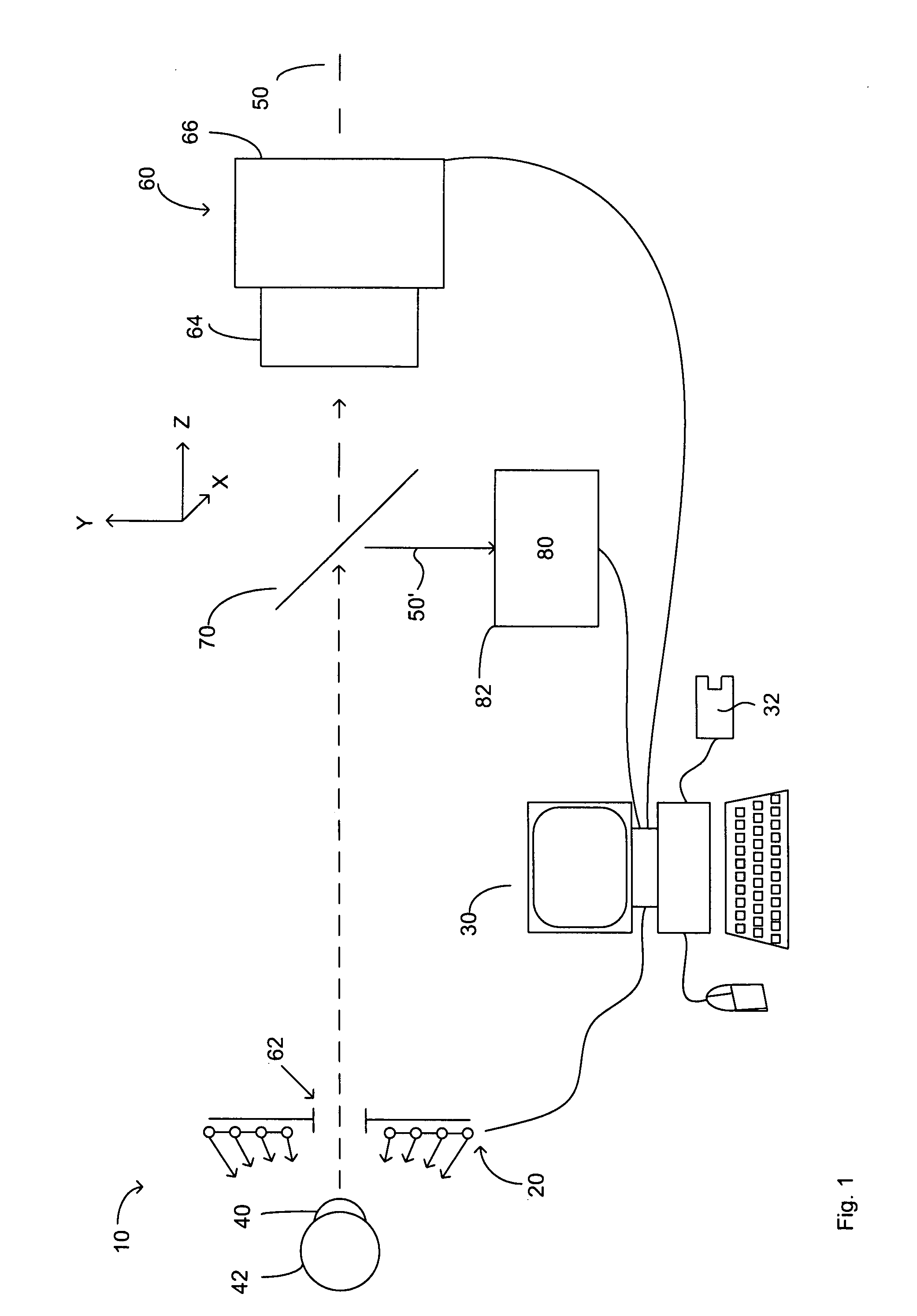

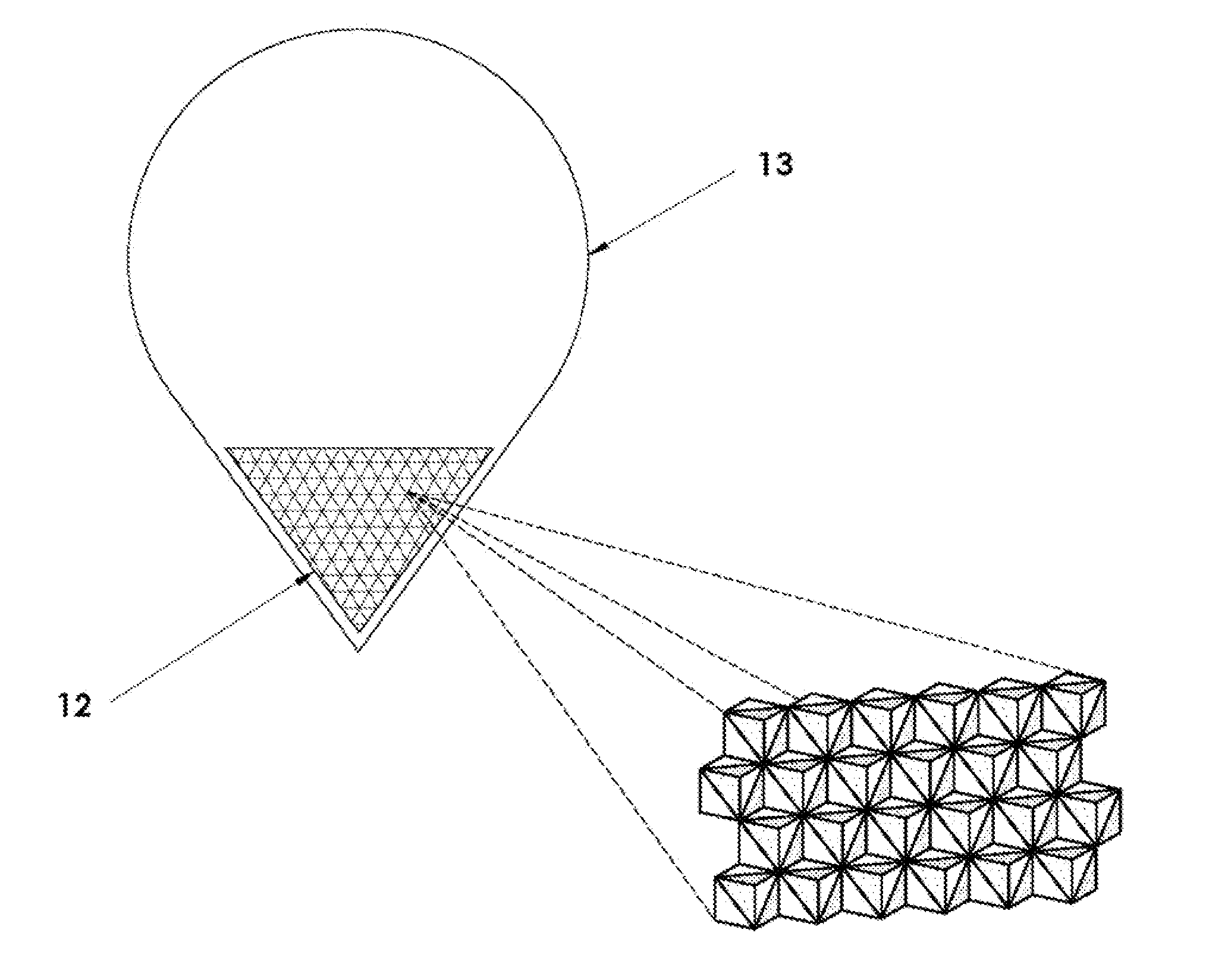

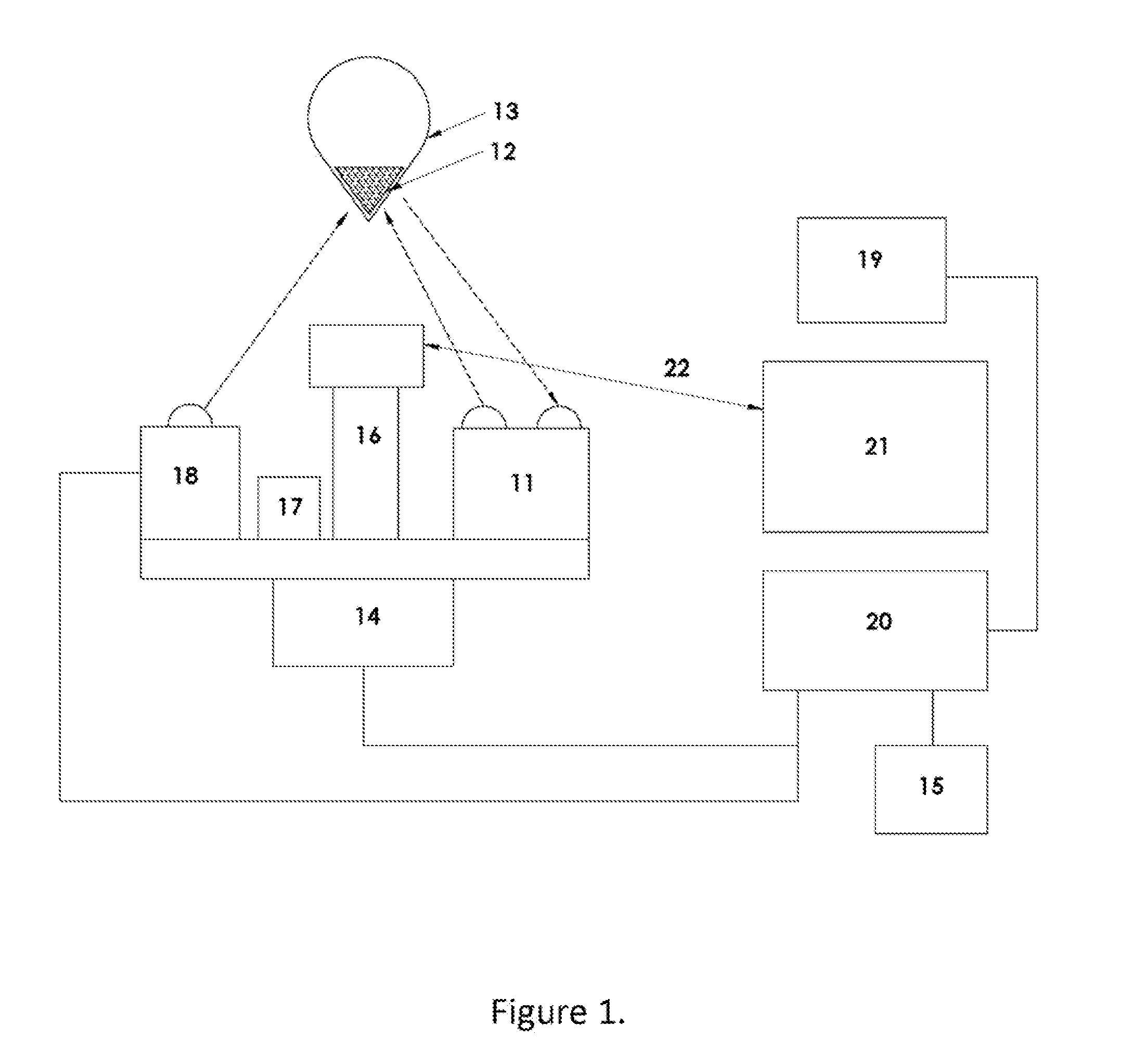

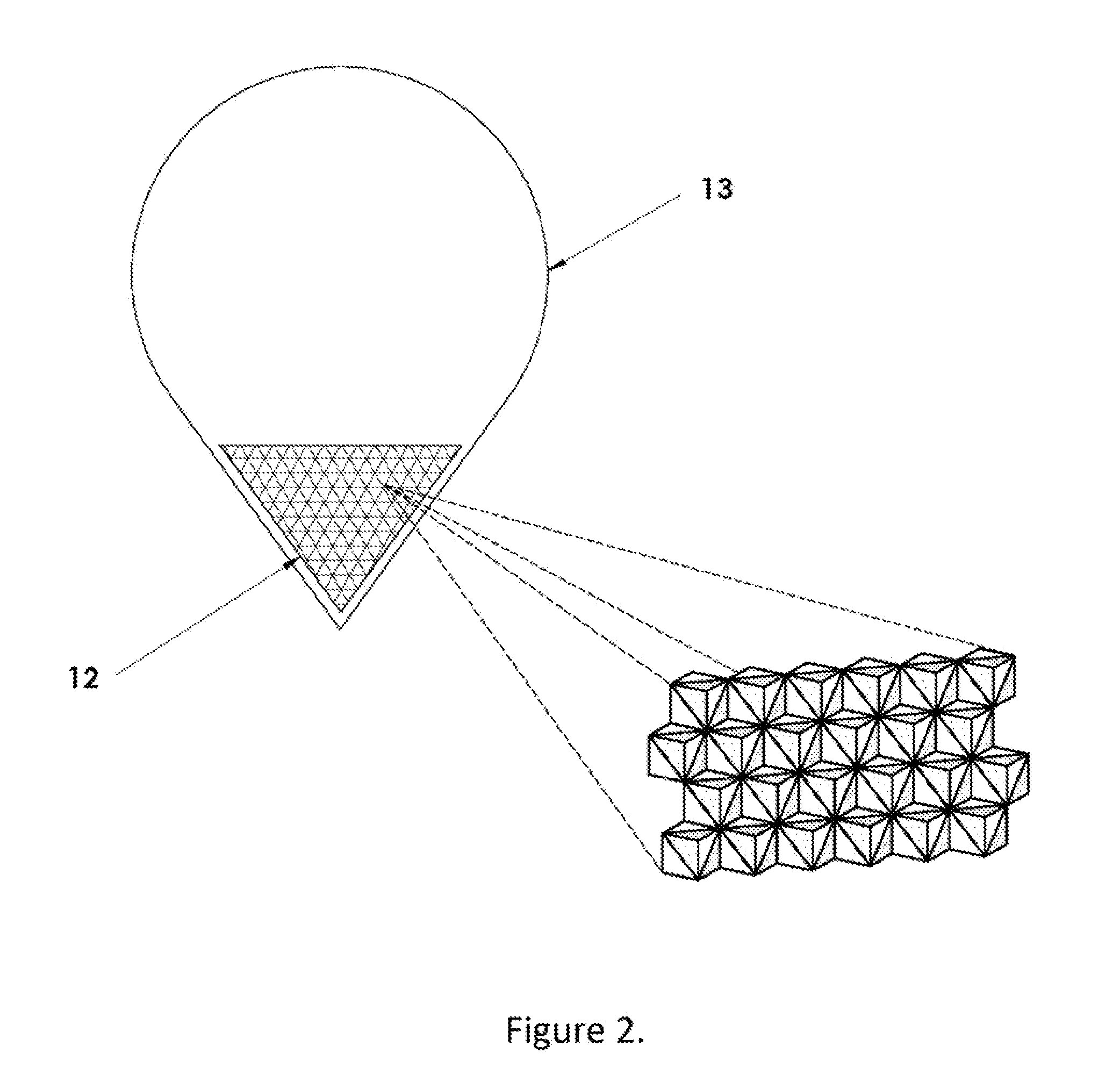

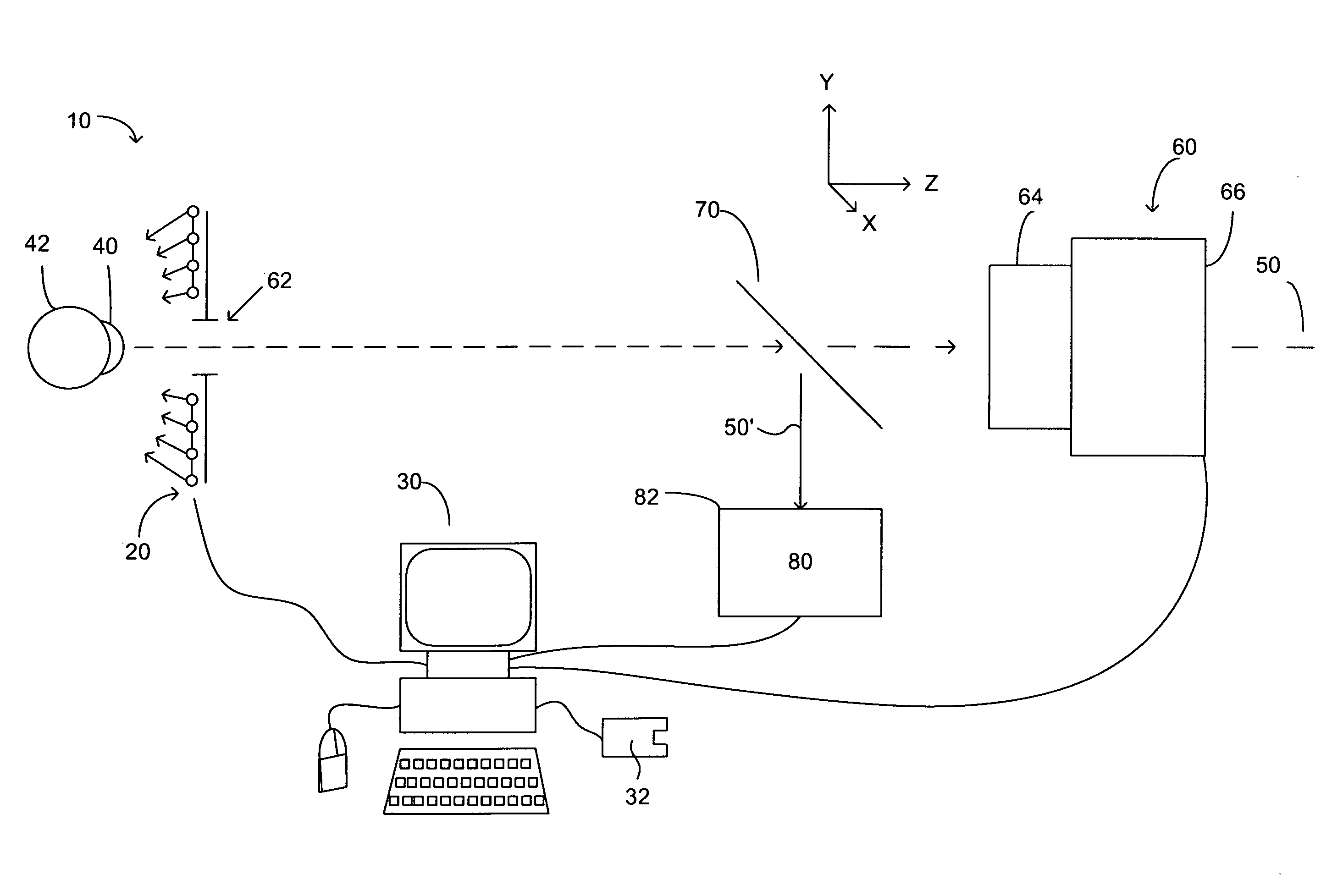

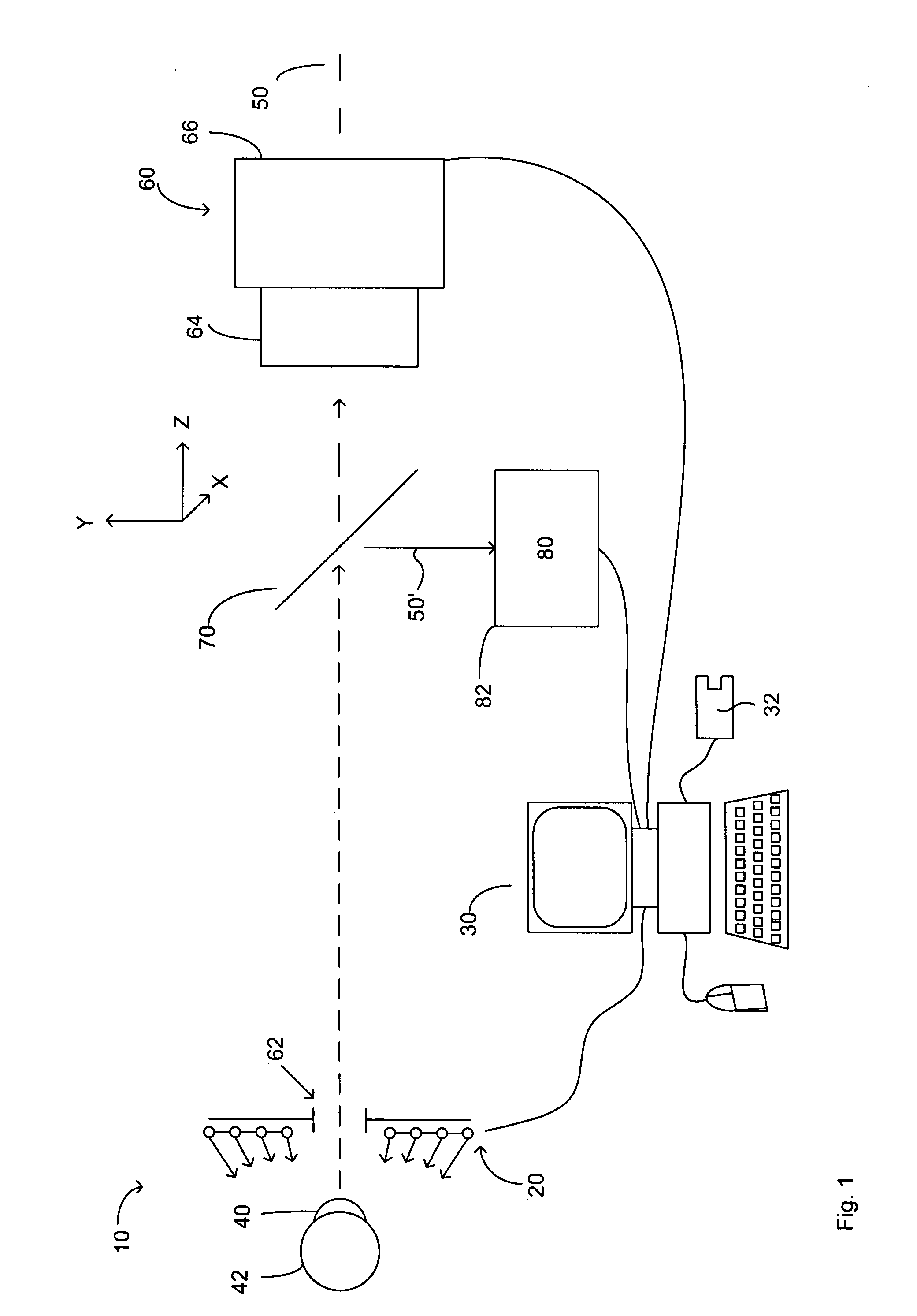

Apparatus and Method for Small Scale Wind Mapping

InactiveUS20120120230A1Easily deployableEnhancement of the sensorOptical rangefindersCharacter and pattern recognitionWind forceAirflow

An apparatus and method for wind profiling using a lighter than air tracer balloon moving under the influence of air currents. A retroreflective target is attached to the tracer balloon to improve the intensity of a return signal reflected back to the rangefinder. After the balloon is released, the rangefinder and attitude sensor are used to measure the range and direction angles of the retroreflective target on the tracer balloon at periodic time intervals. The recorded trajectory data are processed by a computer program using data smoothing and filtering techniques to calculate the wind velocity components, horizontal wind speed and direction, and an estimate of wind shear,

Owner:UTAH STATE UNIVERSITY

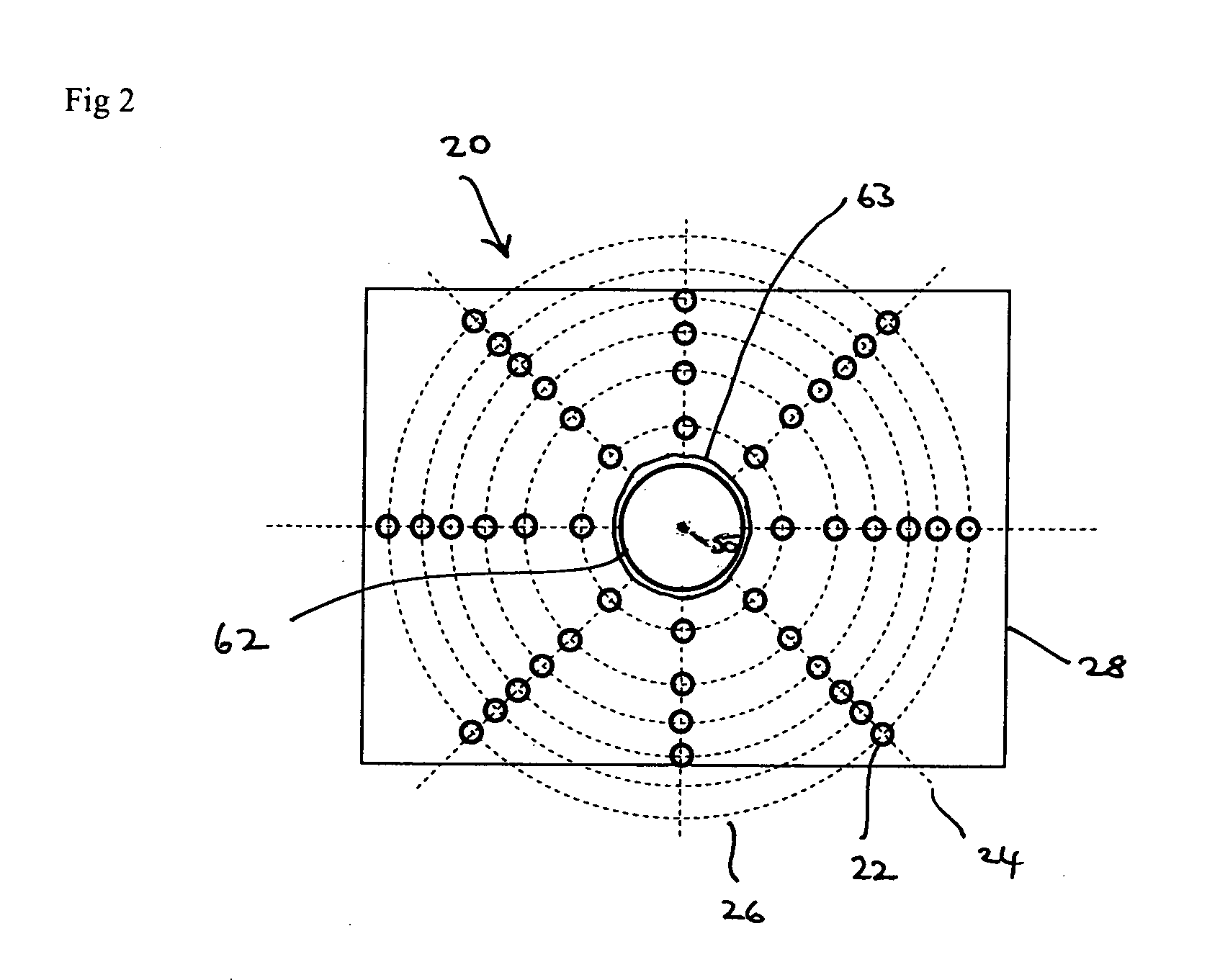

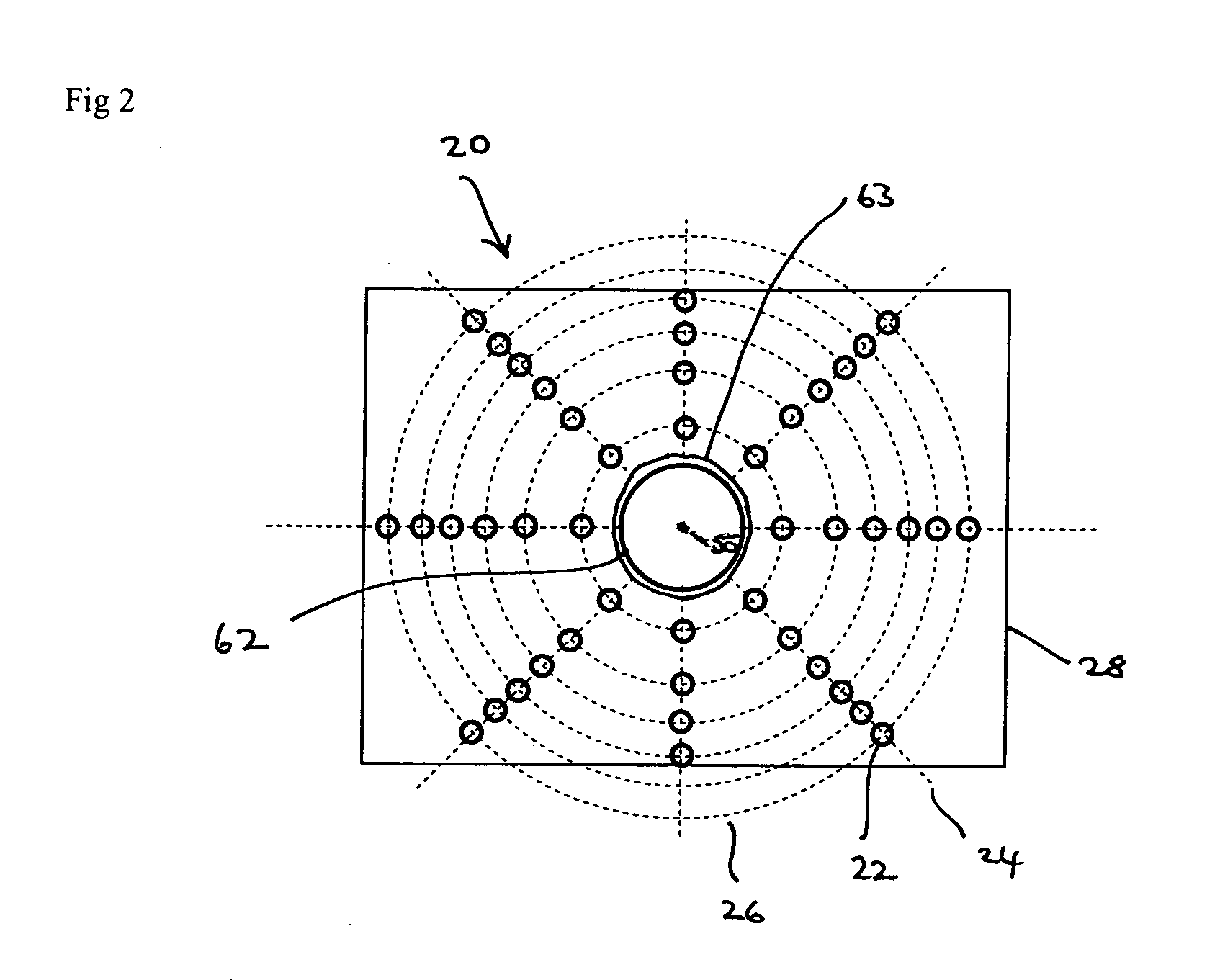

Biometric authentication using the eye

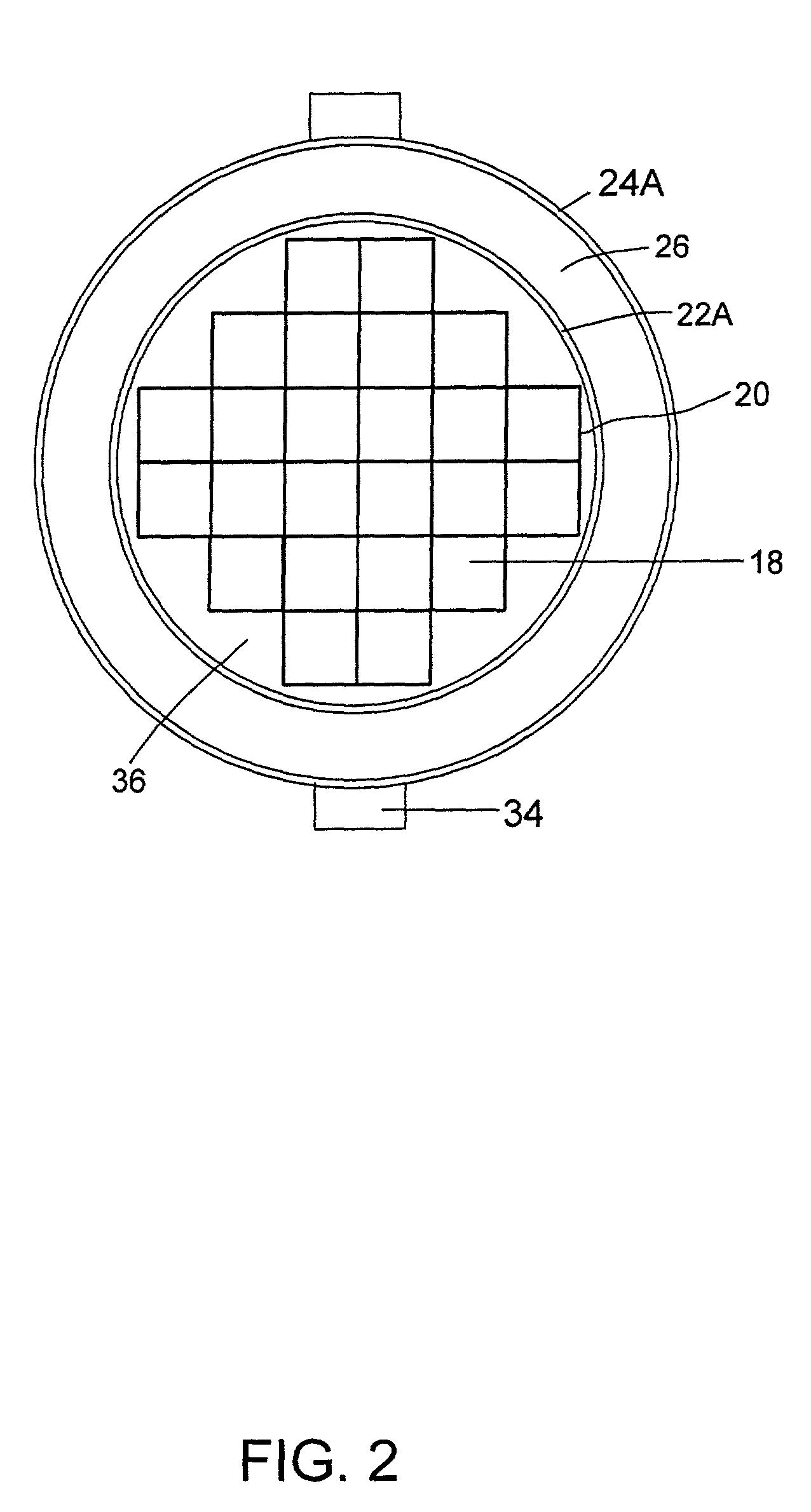

InactiveUS8718335B2Harder to subvertRobust processing resultPerson identificationAcquiring/recognising eyesData setSubject matter

This invention concerns apparatus and a method for authenticating a subject using their eye as an identifying biometric, in particular the shape of their cornea. The apparatus comprises an image projection device to generate and project an image of a pattern, made up of plural discrete points, onto at least a part of the cornea of an eye of the person. An image capture device to capture an image of the pattern of plural discrete points, after reflection in at least a part of the cornea of an eye of the person. And, a computer processor to extract a data set defining the locations of the discrete points in the captured image. The method comprises capturing an image of an illuminated pattern, made up of plural discrete points, after reflection in at least a part of the cornea of an eye of the subject. Comparing the locations of the discrete points in the pattern of the captured image against the locations of the discrete points in the pattern of a reference image. And, authenticating the identity of the subject depending on the similarity of comparison. In a further aspect the invention is software for performing the method.

Owner:YUKATA INVESTMENT MARKETING PTY LTD

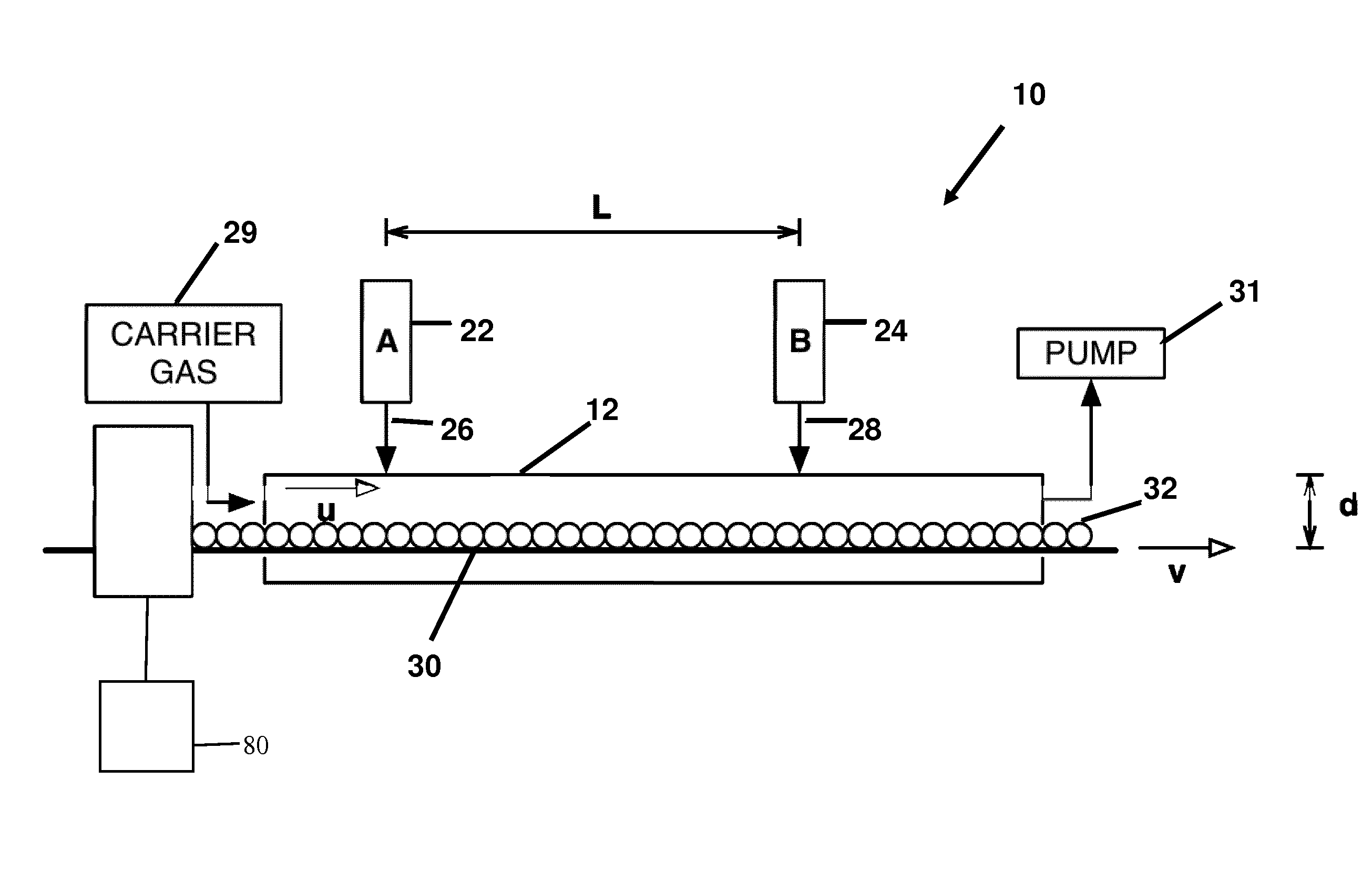

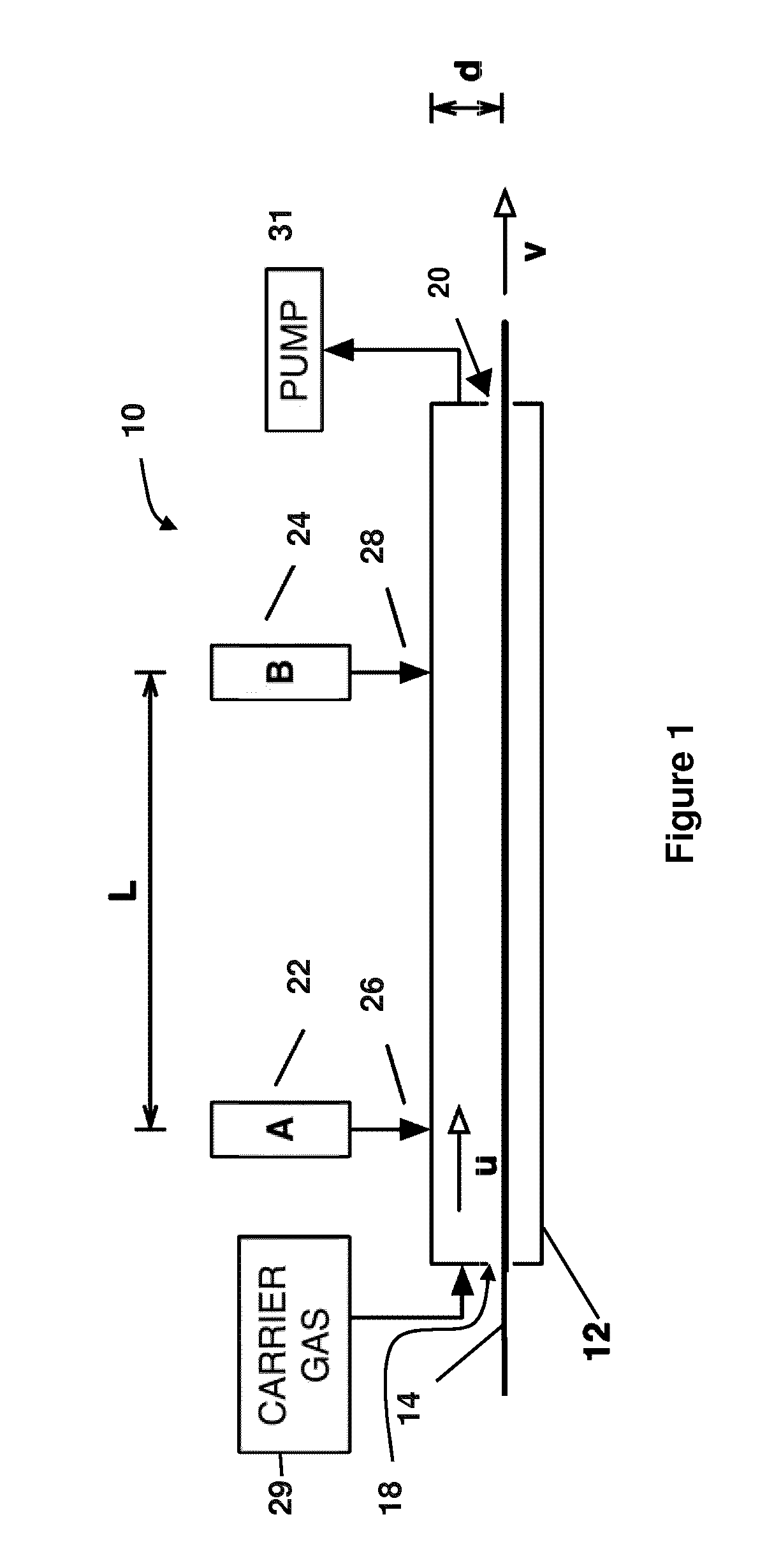

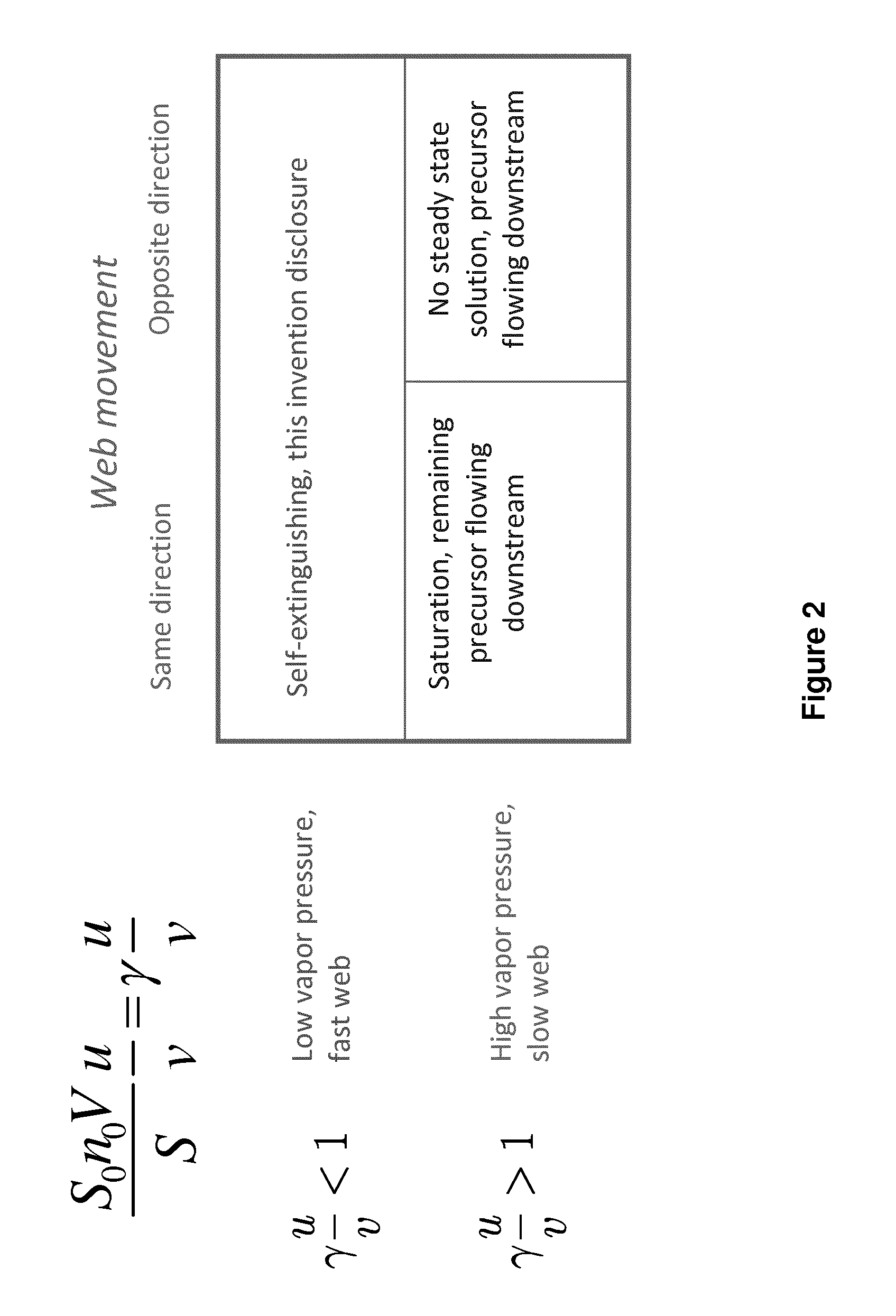

Method and system for continuous atomic layer deposition

ActiveUS20150031157A1Less amountSolve the lack of spaceMolecular sieve catalystsFinal product manufactureProduct gasEngineering

A system and method for continuous atomic layer deposition. The system and method includes a housing, a moving bed which passes through the housing, a plurality of precursor gases and associated input ports and the amount of precursor gases, position of the input ports, and relative velocity of the moving bed and carrier gases enabling exhaustion of the precursor gases at available reaction sites.

Owner:UCHICAGO ARGONNE LLC

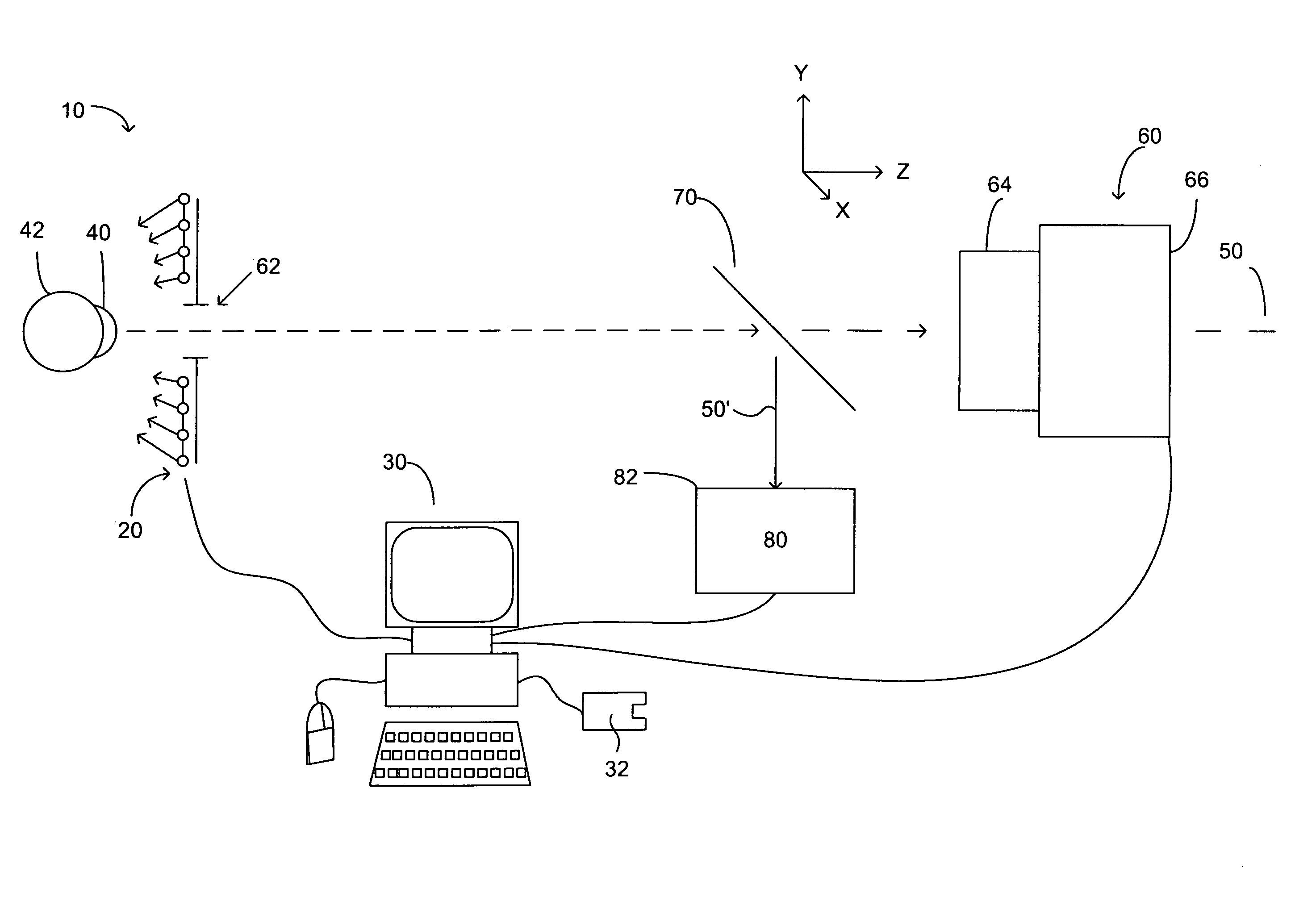

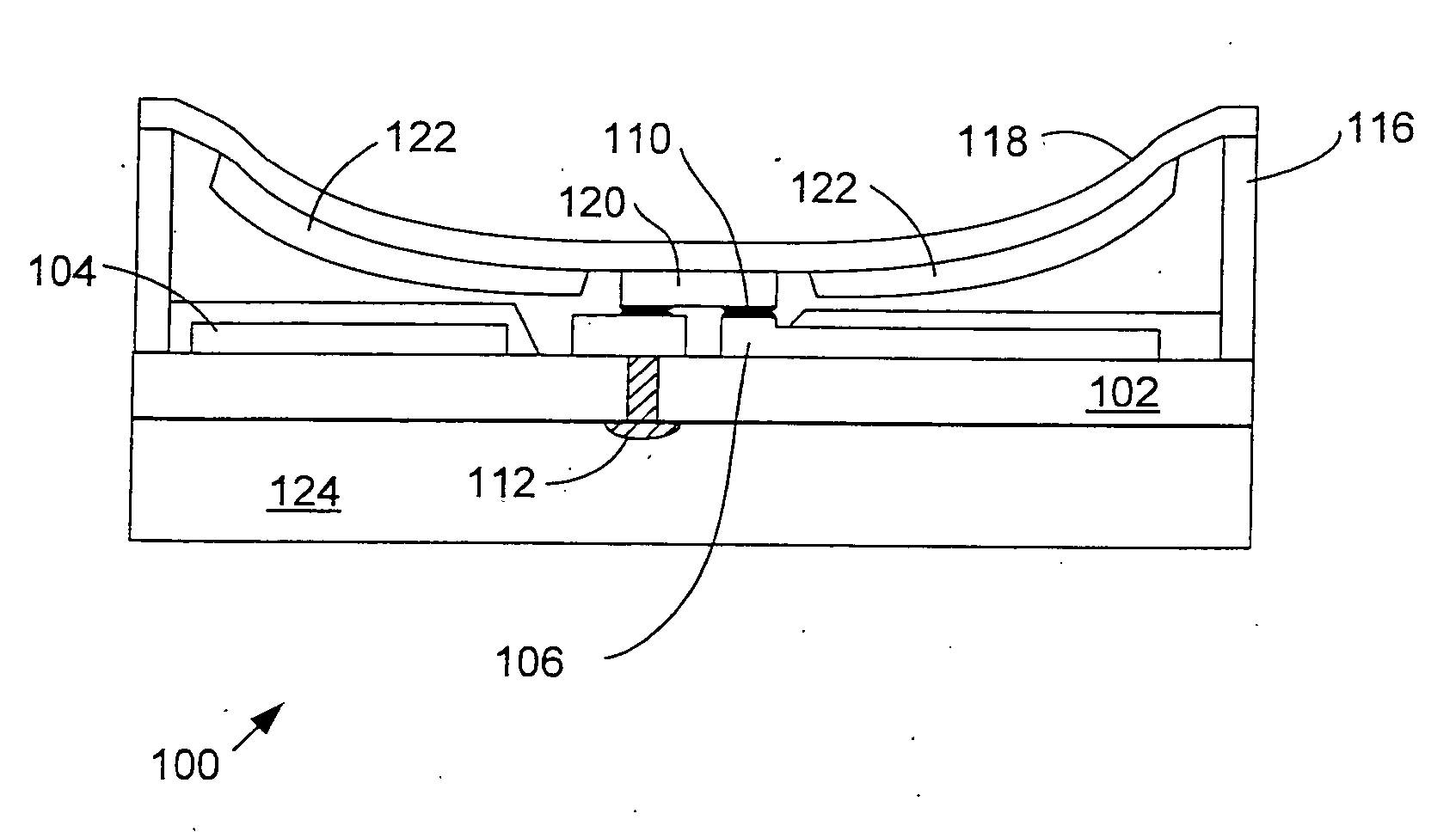

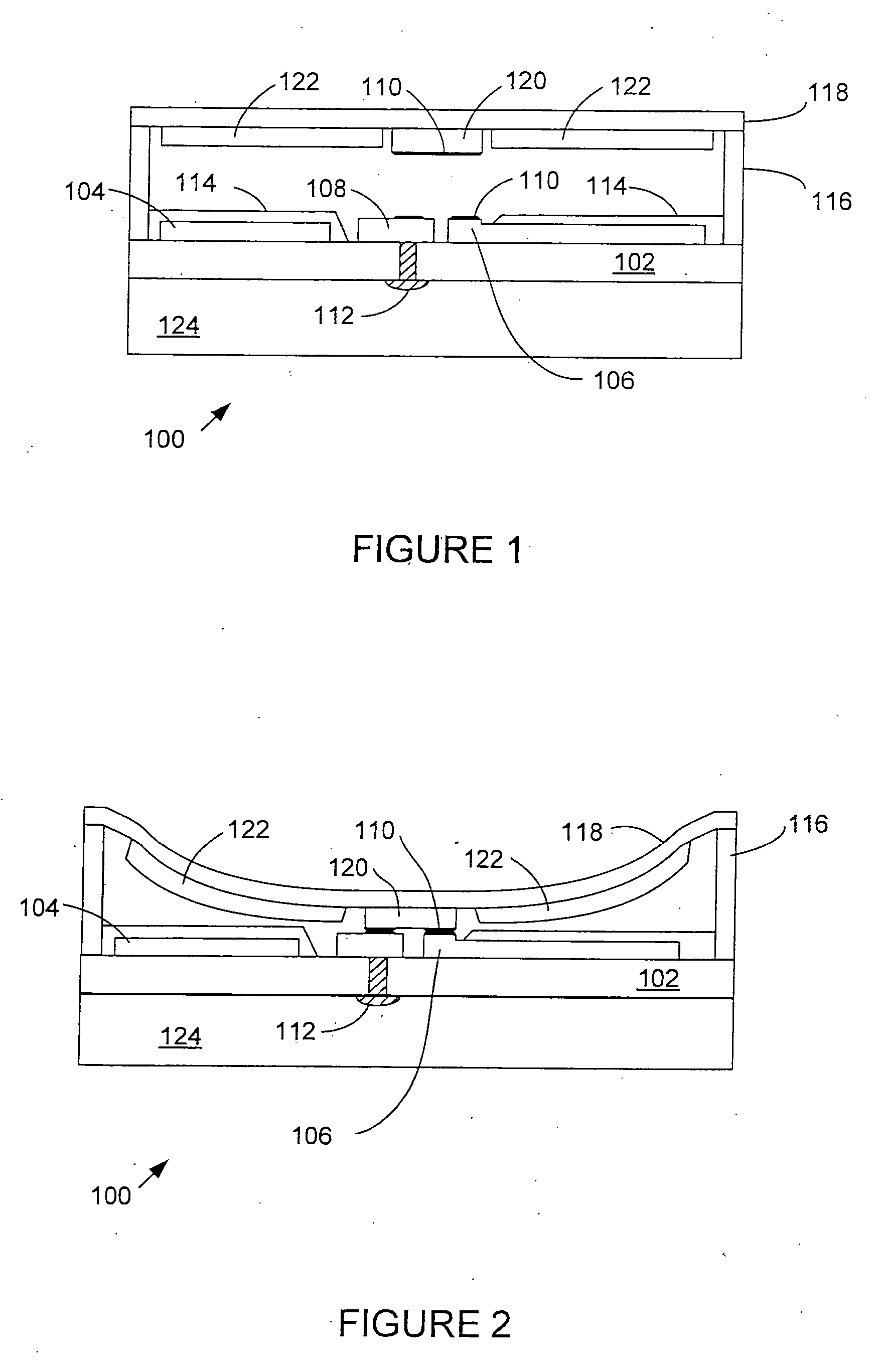

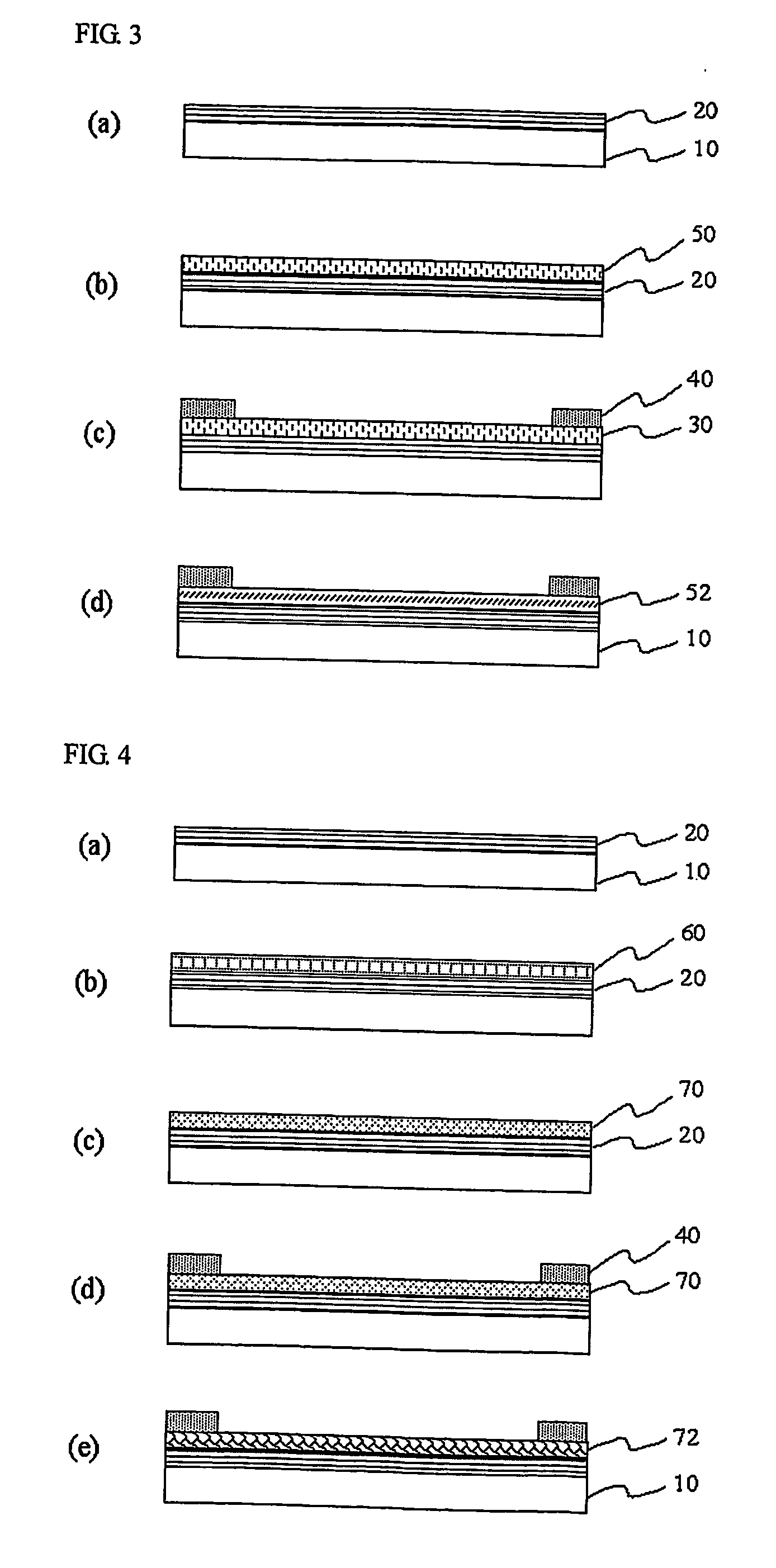

[method of manufacturing non-volatile memory cell]

ActiveUS20050227434A1Simple processReduced dimensionTransistorSolid-state devicesDielectric layerNon-volatile memory

A method of manufacturing a non-volatile memory cell is described. The method includes forming a first dielectric layer on a substrate and then forming a patterned mask layer with a trench on the first dielectric layer. A pair of charge storage spacers is formed on the sidewalls of the trench. The patterned mask layer is removed and then a second dielectric is formed on the substrate covering the pair of charge storage spacers. A conductive layer is formed on the second dielectric layer and subsequently patterned to form a gate structure on the pair of charge storage spacers. Portions of the second and first dielectric layers outside the gate structure are removed and then a source / drain region is formed in the substrate on each side of the conductive gate structure.

Owner:POWERCHIP SEMICON MFG CORP

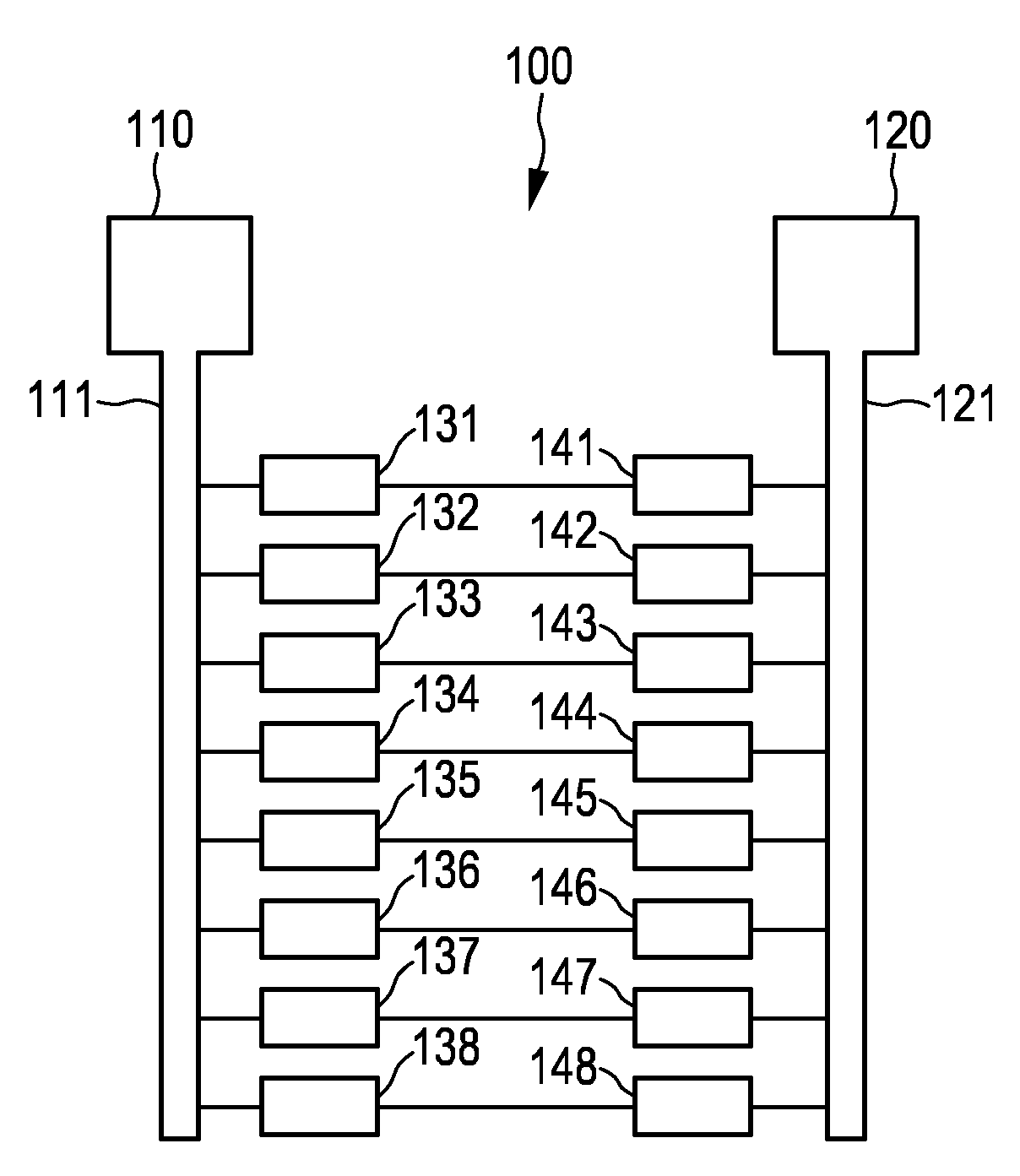

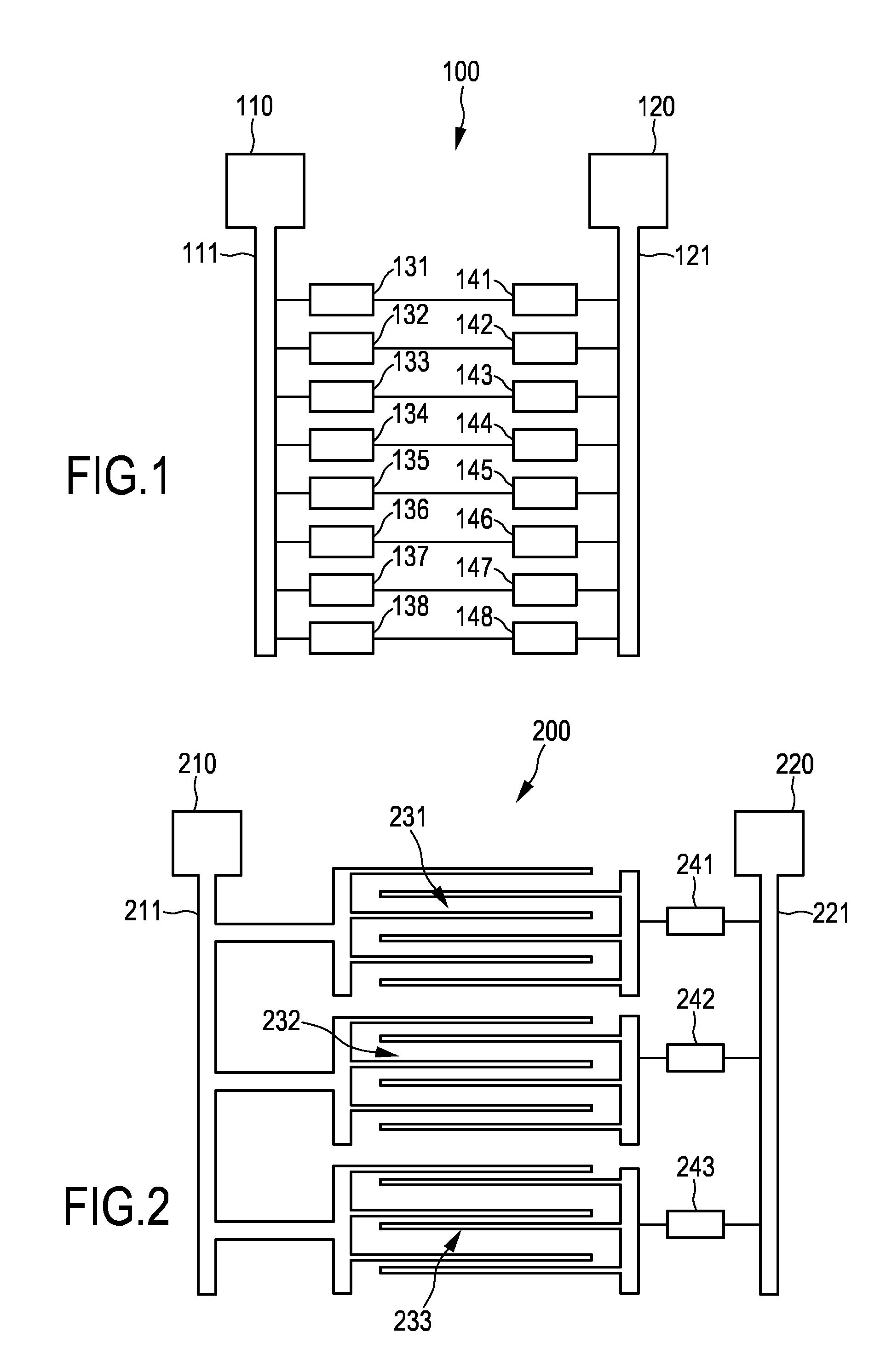

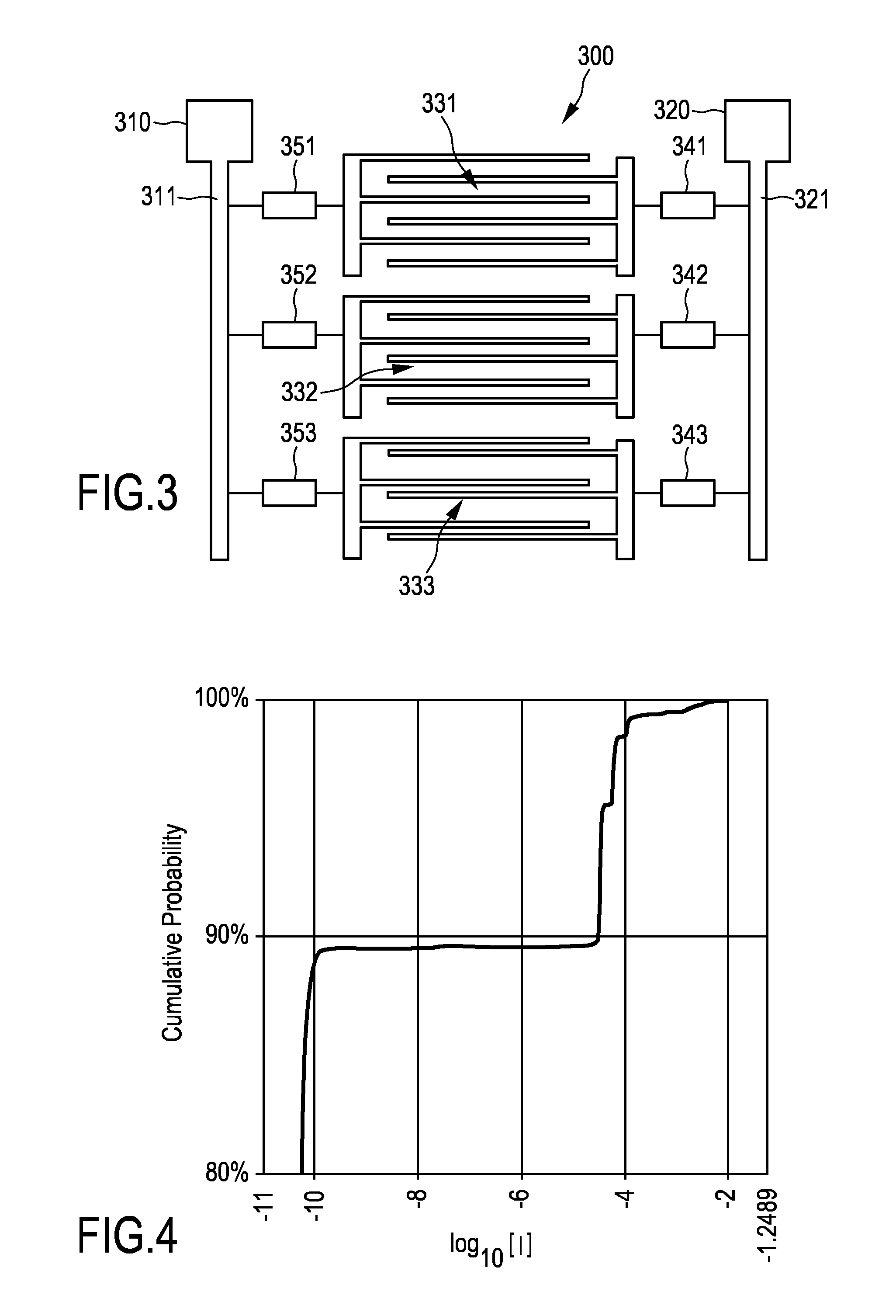

Test structure for detection of defect devices with lowered resistance

ActiveUS8264235B2Easy and fast measurementEquipment is cheapSemiconductor/solid-state device testing/measurementSolid-state devicesElectrical resistance and conductanceContact pad

Owner:NXP BV

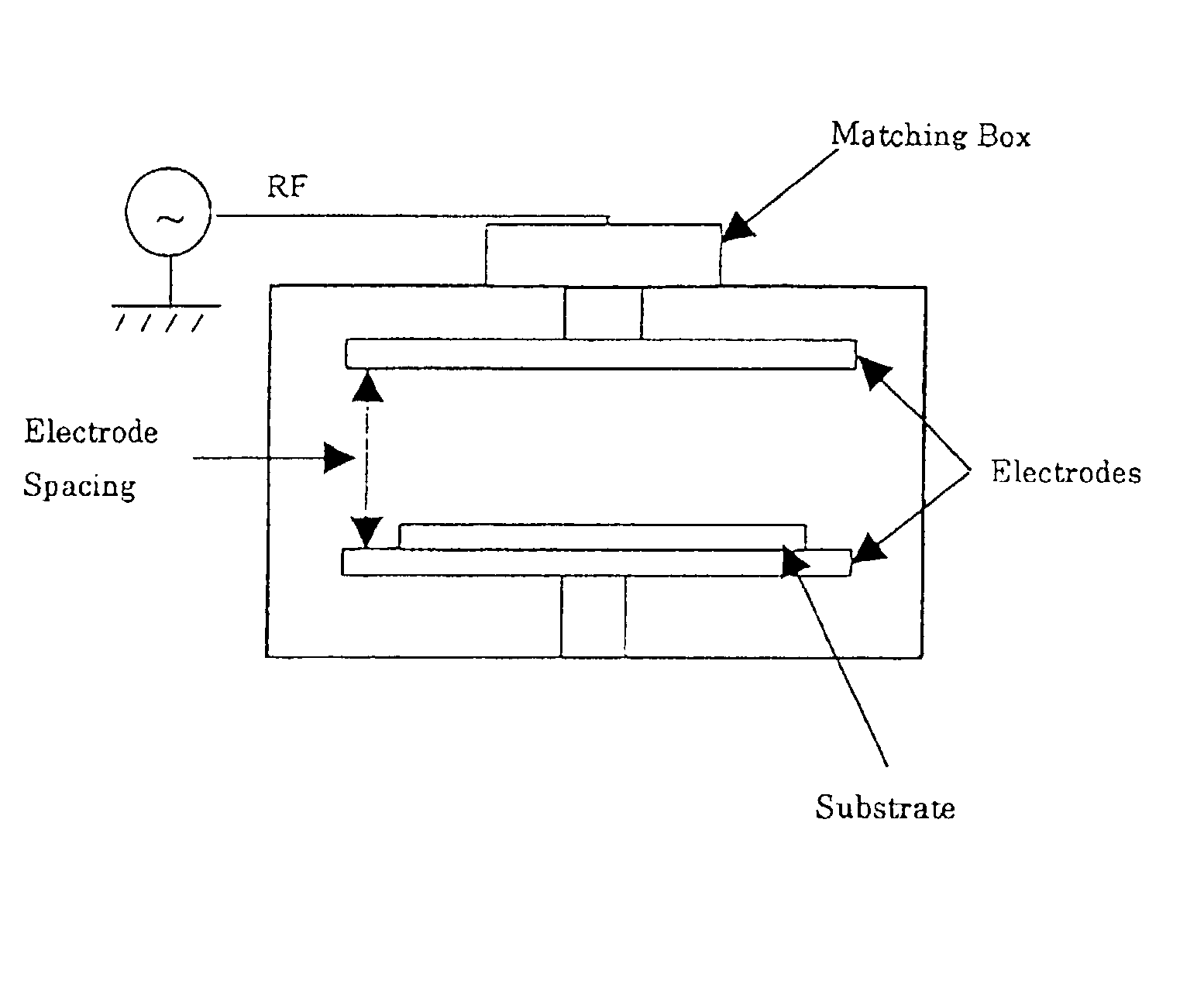

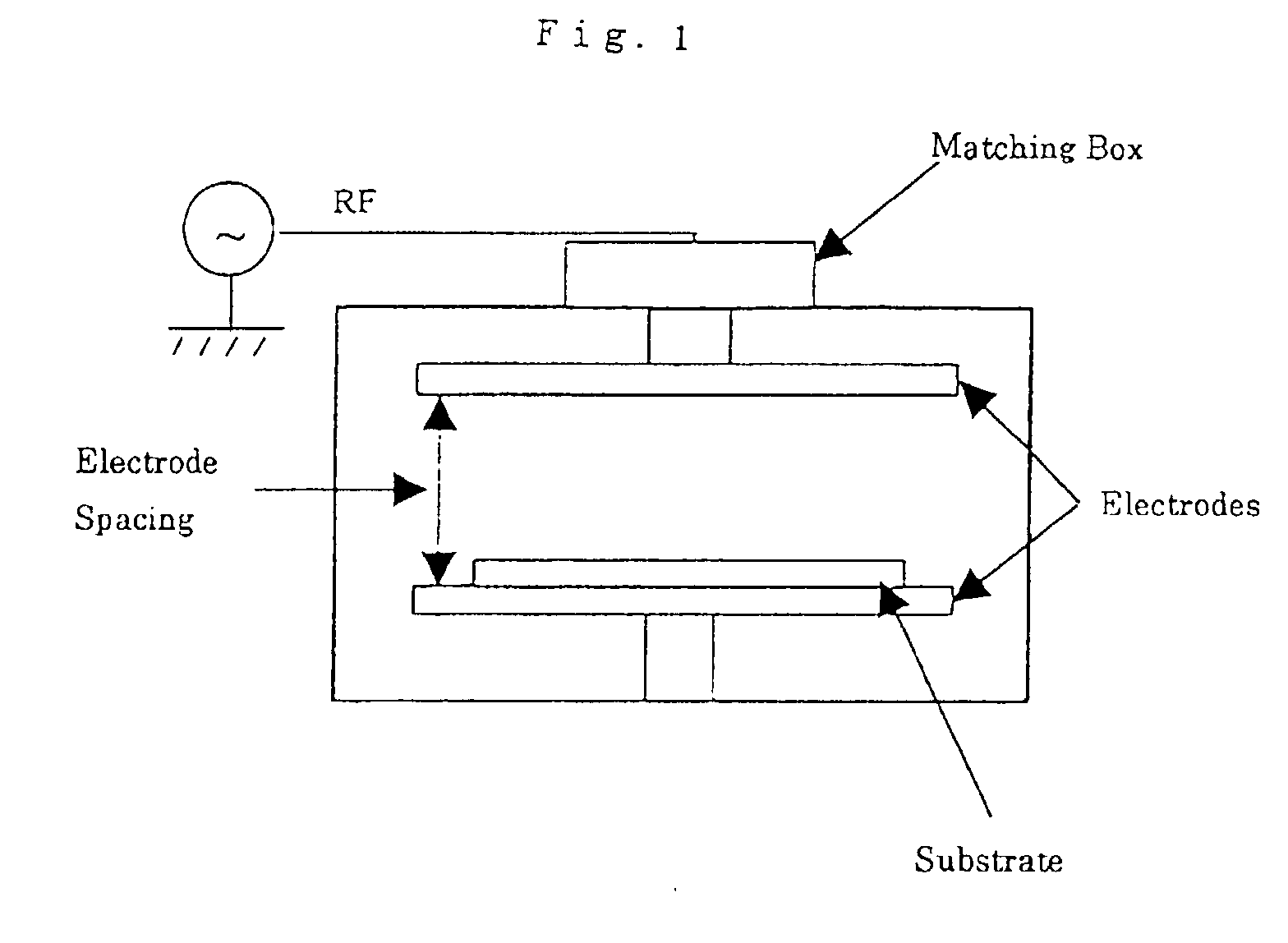

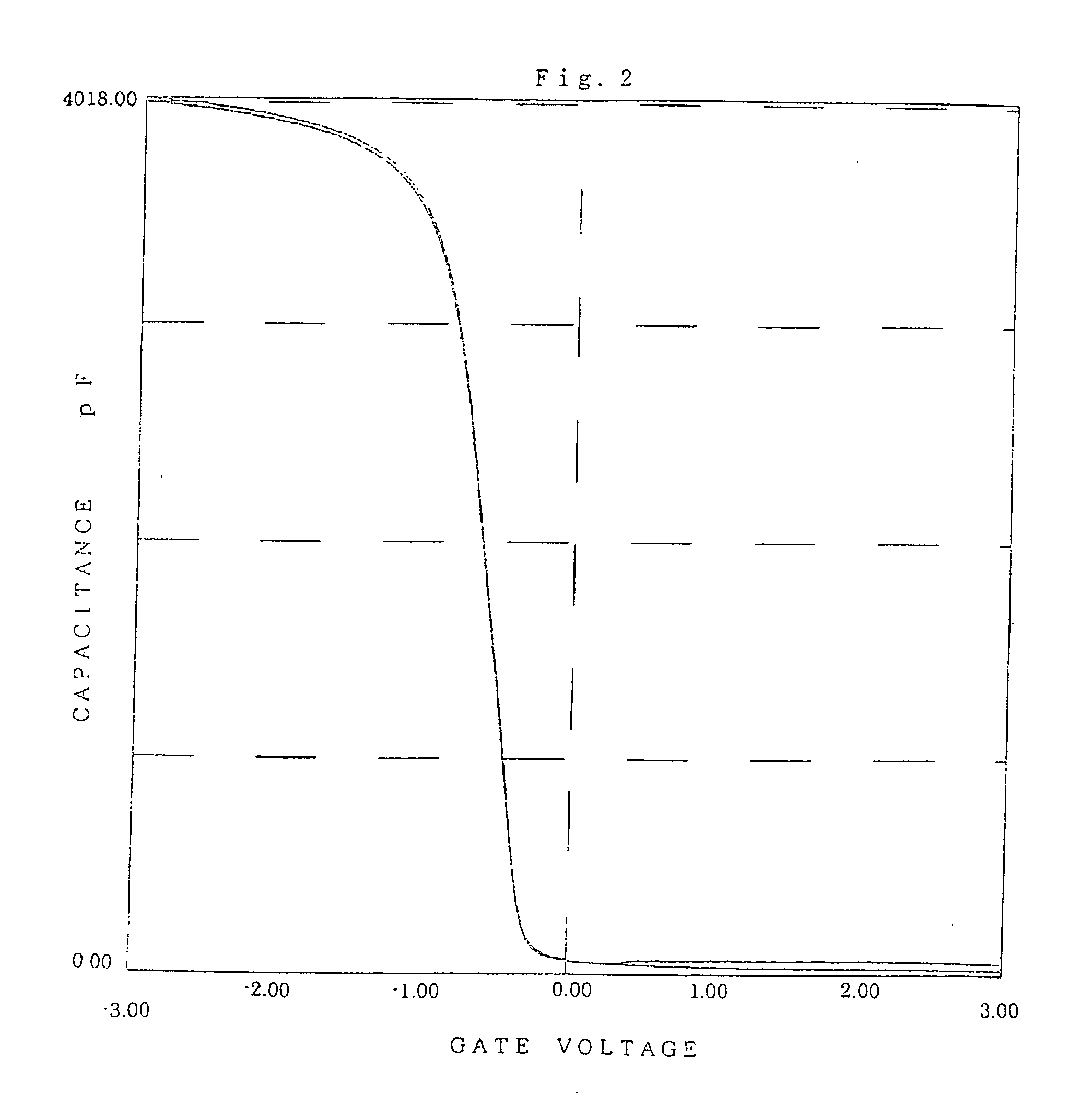

Method to fabricate thin insulating film

InactiveUS20020160623A1Quality improvementInexpensive to fabricateTransistorVacuum evaporation coatingNoble gasNitrogen

In this disclosure, we present processes of growing SiO2 films over silicon at temperatures as low as room temperature and at pressures as high as 1 atmosphere. The lower temperature oxidation was made possible by creation of oxygen atoms and radicals by adding noble gas(es) along with oxidizing gas(es) and applying RF power to create plasma. It was also possible to fabricate silicon nitride films by flowing nitrogen containing gas(es) with noble gas(es) and applying RF power to create plasma at pressures as high as one atmosphere. In addition, the above processes could also be carried out using microwave power instead of RF power to create plasma.

Owner:SEIKO EPSON CORP

Biometric authentication using the eye

InactiveUS20140193046A1Achieve rapiditySmall amountAcquiring/recognising eyesPattern recognitionComputer science

An apparatus and method for authenticating a subject using the eye as an identifying biometric, in particular the shape of the cornea. An image projection device generates and projects an image of a pattern, of plural discrete points, onto at least a part of the cornea of the eye. An image capture device captures an image of the pattern of plural discrete points, after reflection from the cornea of the eye. A computer processor extracts data defining the locations of the discrete points in the captured image. The method steps are capturing an image of a pattern, made up of plural discrete points, after reflection from of the cornea of a subject; comparing the locations of the discrete points in the captured image against the locations of discrete points in a pattern of a reference image; and, authenticating the identity of the subject depending on the similarity of the comparison.

Owner:YUKATA INVESTMENT MARKETING PTY LTD

Test structure for detection of defect devices with lowered resistance

ActiveUS20100060292A1Increase resistanceIdentification is simpleSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceContact padTest structure

The present invention relates to a test structure that comprises at least two devices under test DUT, which respectively have a first electrical device resistance in a non-defect state and a second electrical device resistance in defect state, the first being higher than the second electrical device resistance. In the test structure the DUTs are connected in parallel to a first test contact pad via a first conducting line and connected in parallel to a second test contact pad via a second conducting line, and respectively connected to the first conducting line via respective first test resistors, which have known respective electrical test resistances, such that a total electrical resistance between the first an second test contact pads is indicative of the number of DUTs, which have the second electrical device resistance. The test structure allows testing a larger number of DUTs in parallel in a single measurement.

Owner:NXP BV

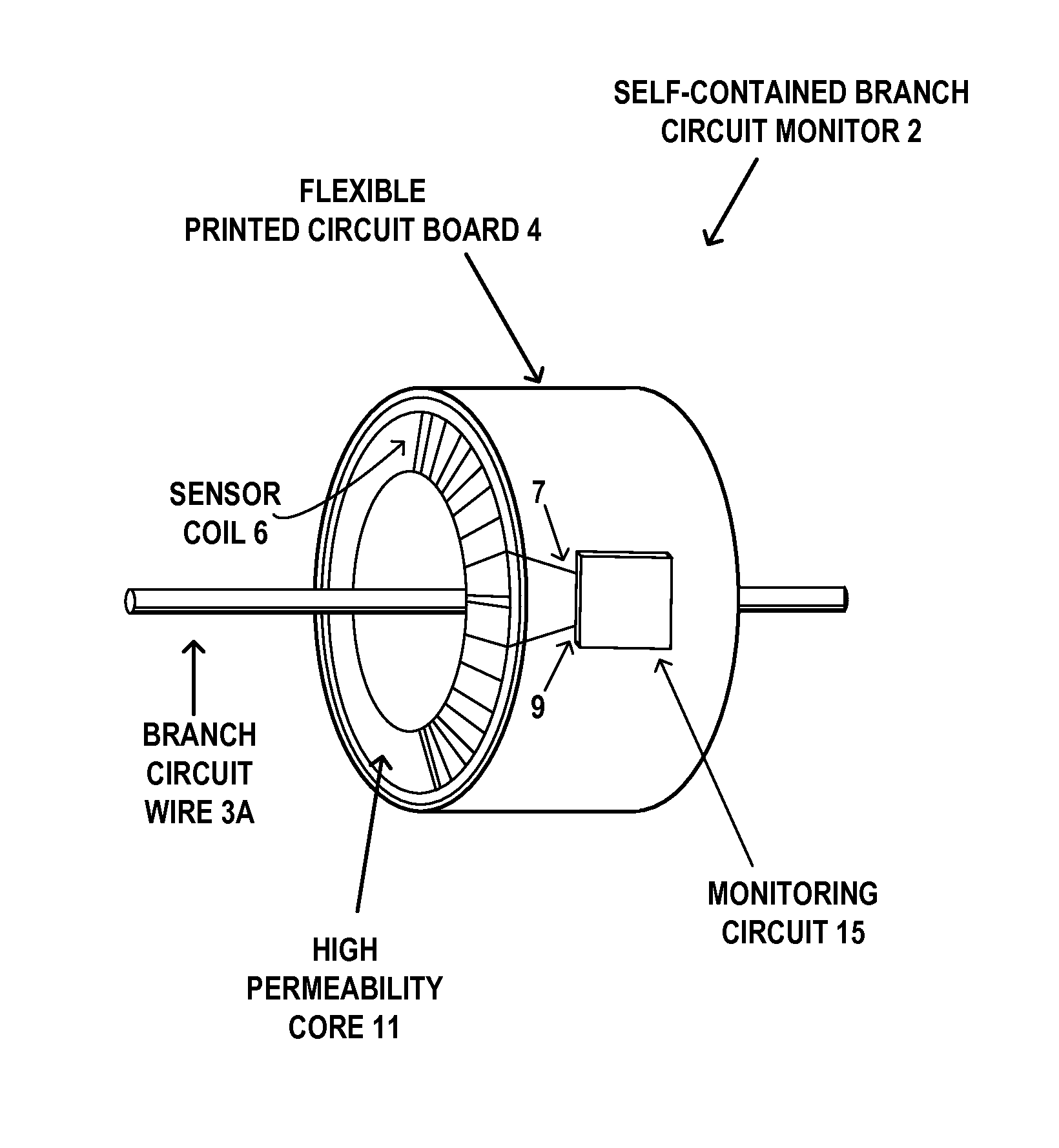

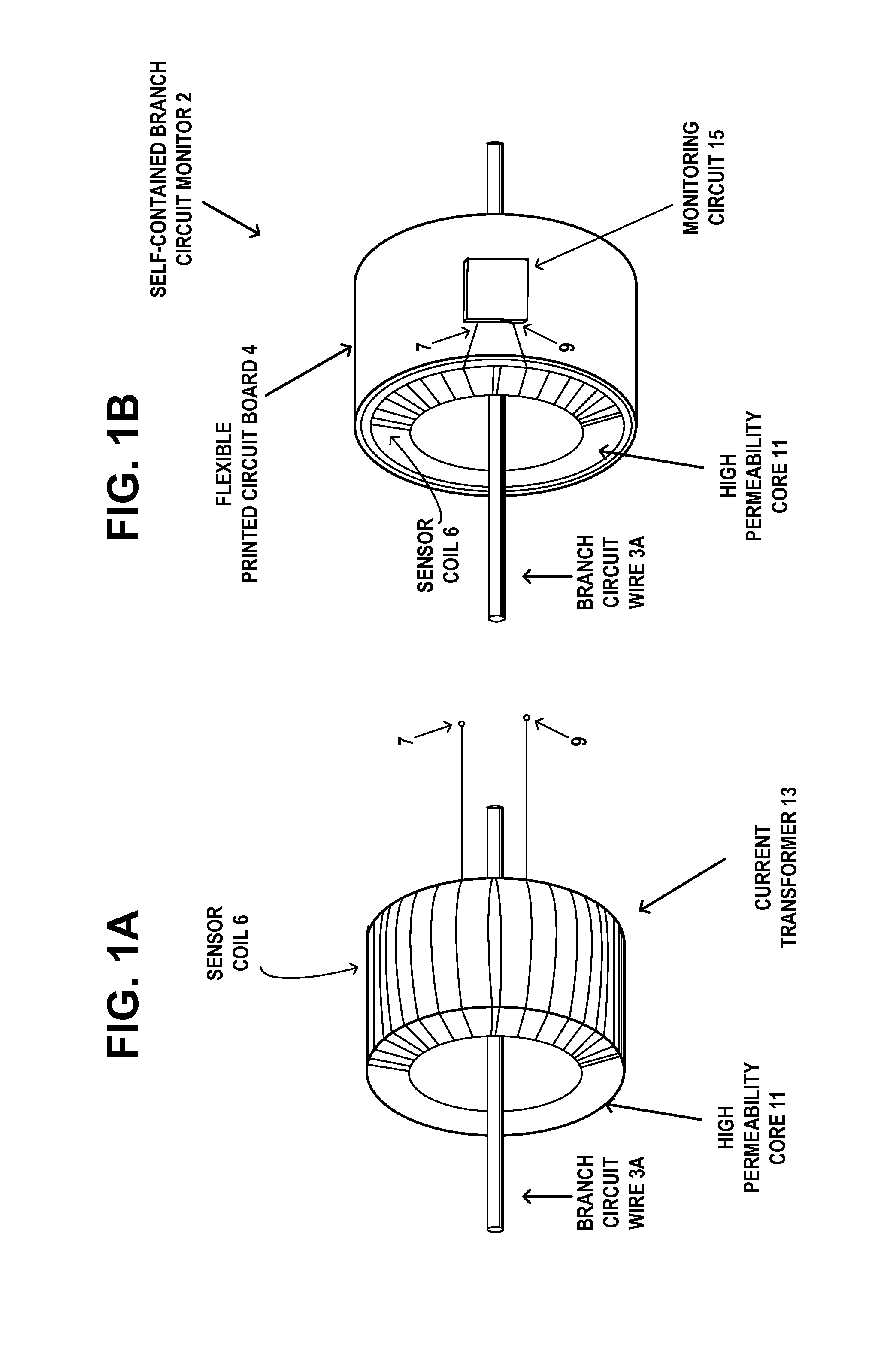

Self-contained branch circuit monitor

ActiveUS20160258984A1Minimal installation costImmunePower distribution line transmissionRemote meteringSmall form factorEngineering

A self-contained branch circuit monitor 2 is has a small form factor configured to fit in the limited space available in a load center 1, in association with a branch circuit breaker 10A occupying a branch location slot 45 in the load center 1. A flexible printed circuit board 4 is wrapped around an outside circumference of a toroidal sensor coil 6 of a current transformer. A current monitoring circuit 15 is formed on the flexible printed circuit board. The monitoring circuit is electrically connected to leads 7, 9 from the sensor coil and is powered by current 17 induced in the sensor coil from current 5 in the branch circuit wire. A branch circuit wire 3A is threaded through the current transformer's center. A transmitter 22 is part of the flexible printed circuit board, to transfer the monitored current data to other locations.

Owner:SCHNEIDER ELECTRIC USA INC

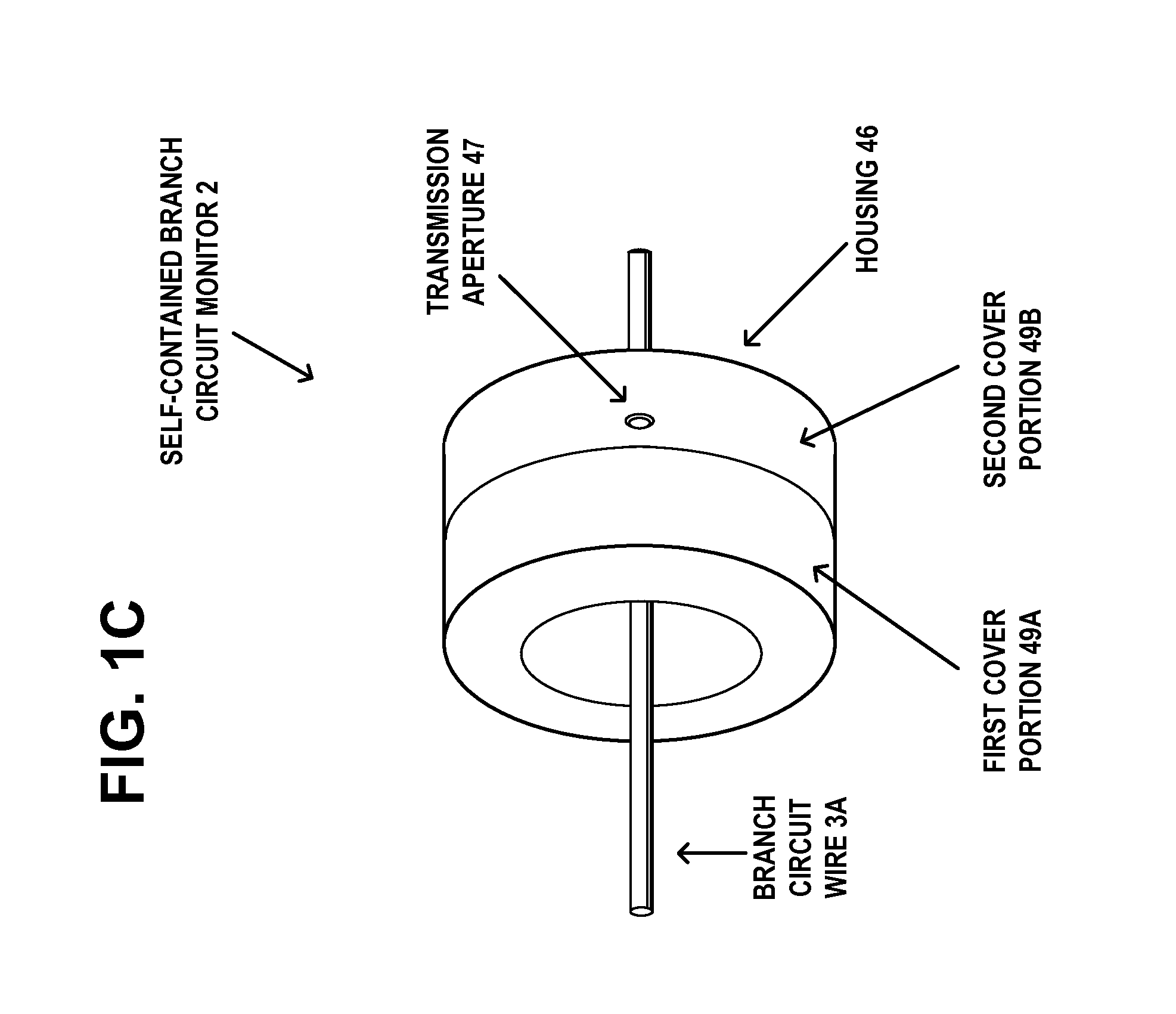

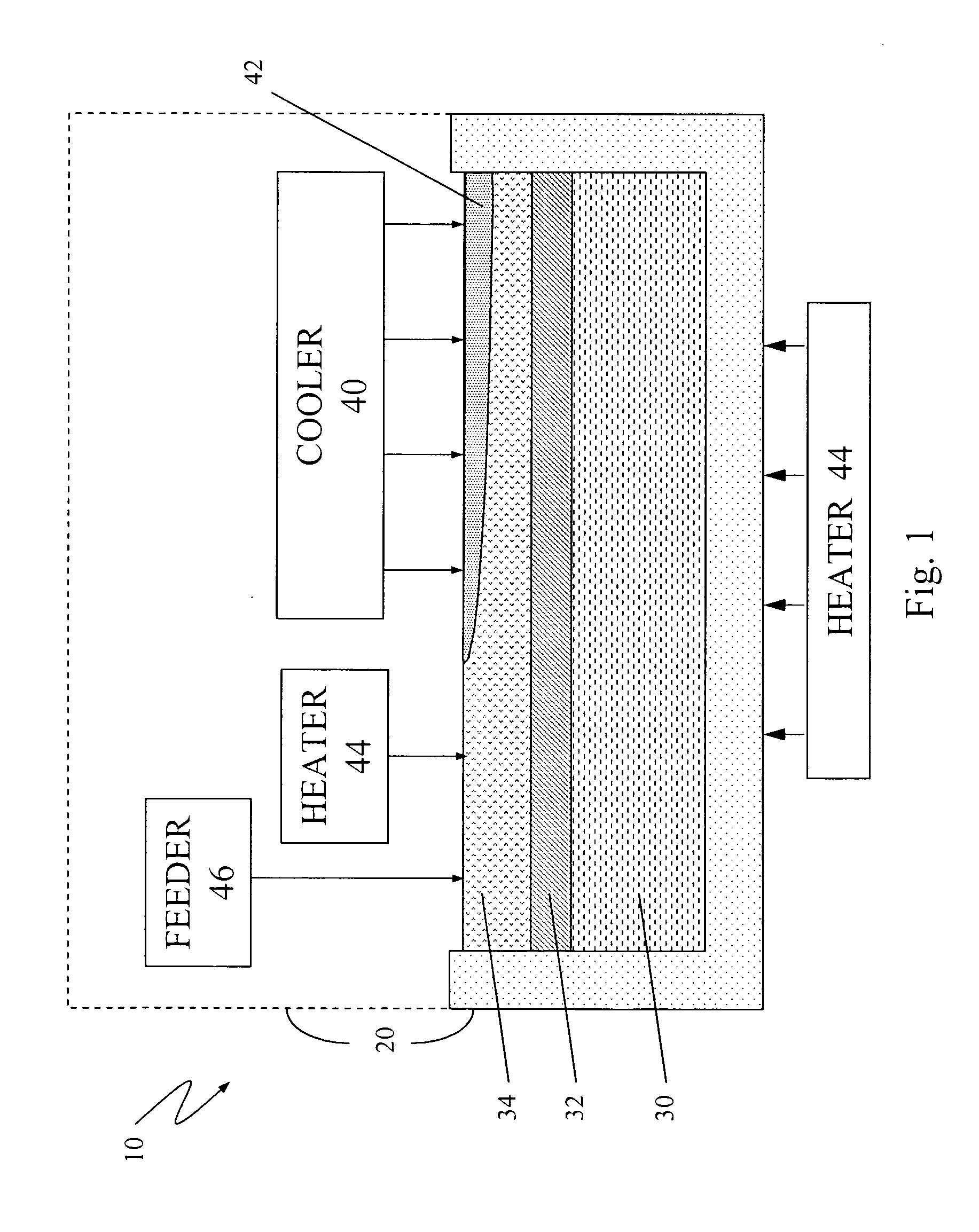

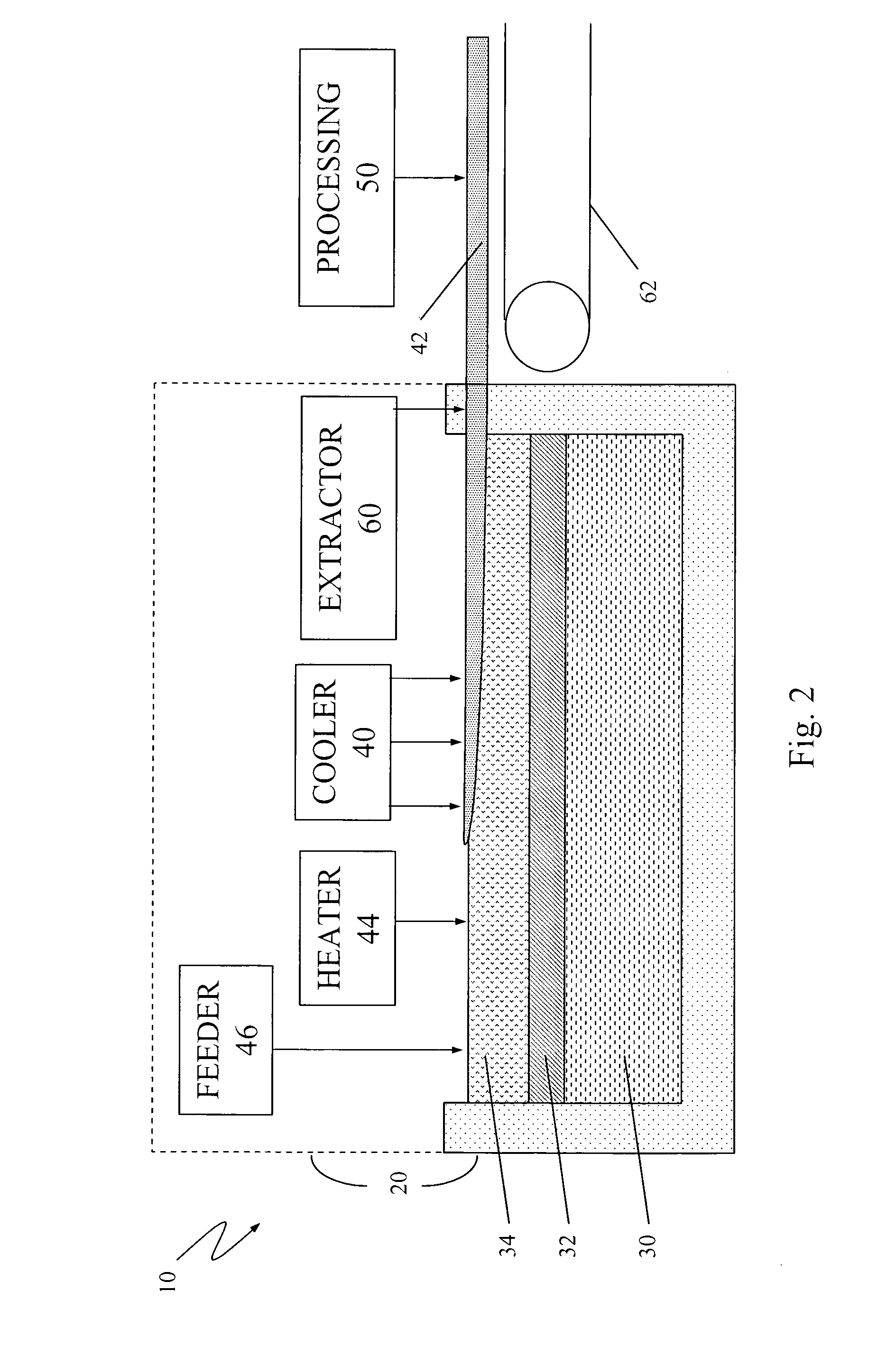

Methods for Casting By a Float Process and Associated Apparatuses

InactiveUS20110280784A1Equipment is cheapRapid scale-upFinal product manufactureBy pulling from meltLiquid layerOptoelectronics

A method for producing a solid layer material (42), comprising providing (70) a first layer (30); providing (72) a second liquid layer (32) on the first layer (30); providing (74) a third liquid layer (34) on the second liquid layer (32), wherein the third liquid layer has a melting point that is higher than a melting point of the second liquid layer, and wherein the second liquid layer is between the first and third layers; cooling (76) a surface of the third liquid layer to a temperature less than the melting point of the third liquid layer; forming (78) the solid layer from the third liquid layer while cooling the third layer liquid; and removing (80) the solid layer.

Owner:CARNEGIE MELLON UNIV

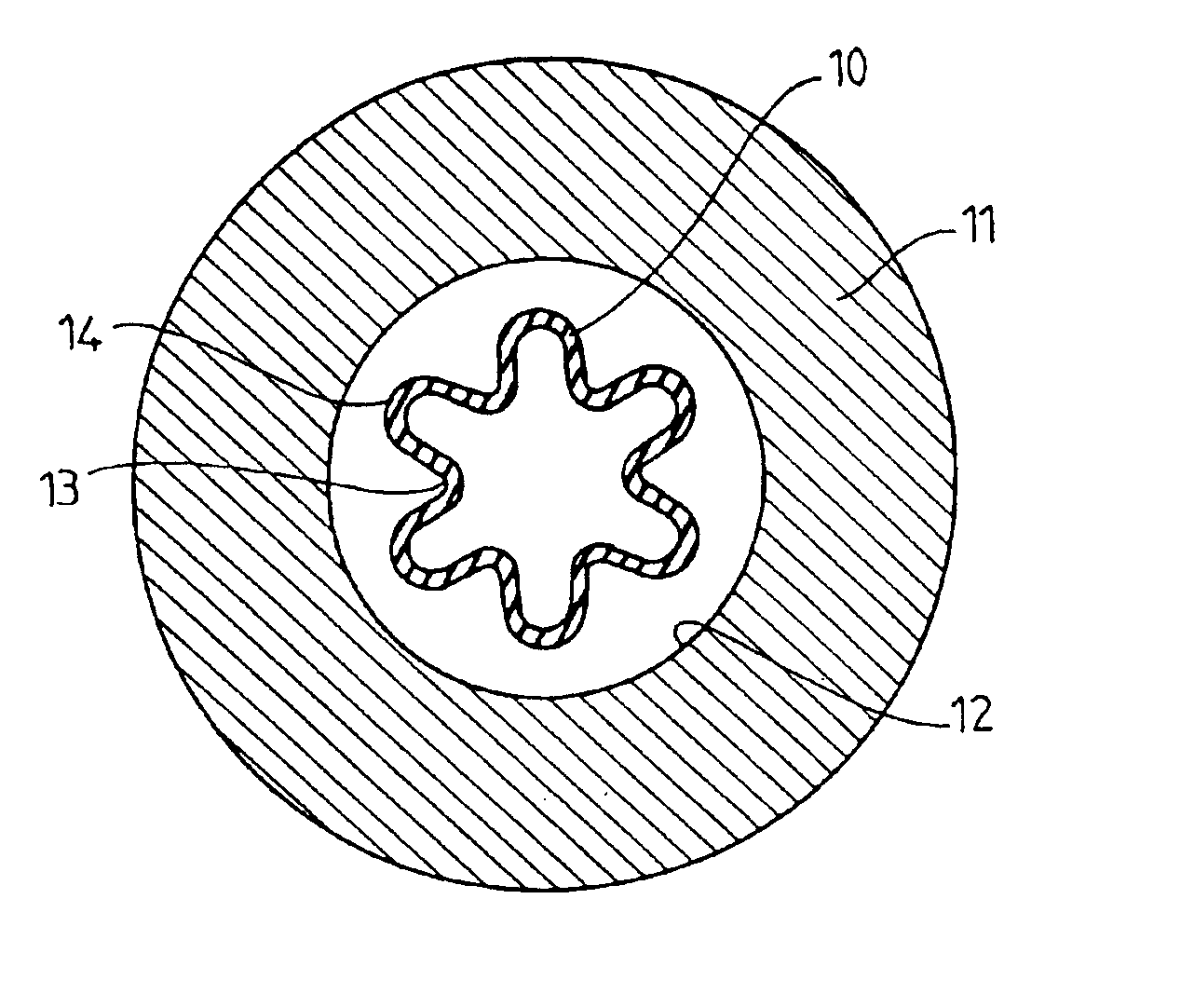

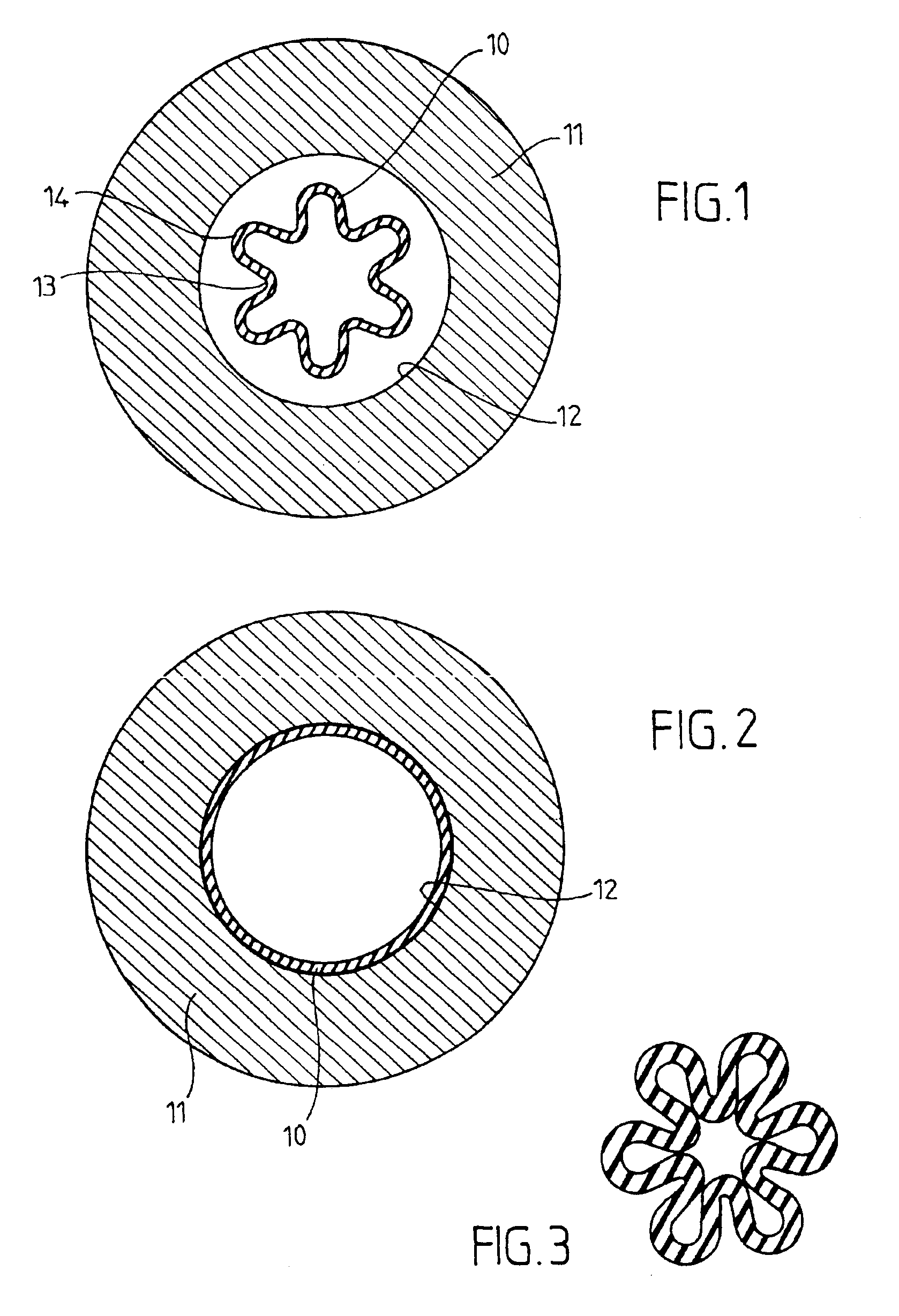

Rehabilitation of water supply pipes

A water supply pipe has a tubular liner of a polyolefin elastomer / plastomer installed therein. To install it, a messenger pig is attached to a line that pulls the liner through the pipe. The liner is produced by extrusion and die drawing during extrusion.

Owner:SUEZ LYONNAISE DES EAUX

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com

![[method of manufacturing non-volatile memory cell] [method of manufacturing non-volatile memory cell]](https://images-eureka.patsnap.com/patent_img/39c5838e-e4a1-459d-9a58-eafb9204ec04/US20050227434A1-20051013-D00000.png)

![[method of manufacturing non-volatile memory cell] [method of manufacturing non-volatile memory cell]](https://images-eureka.patsnap.com/patent_img/39c5838e-e4a1-459d-9a58-eafb9204ec04/US20050227434A1-20051013-D00001.png)

![[method of manufacturing non-volatile memory cell] [method of manufacturing non-volatile memory cell]](https://images-eureka.patsnap.com/patent_img/39c5838e-e4a1-459d-9a58-eafb9204ec04/US20050227434A1-20051013-D00002.png)