Patents

Literature

77results about How to "High equipment integration" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

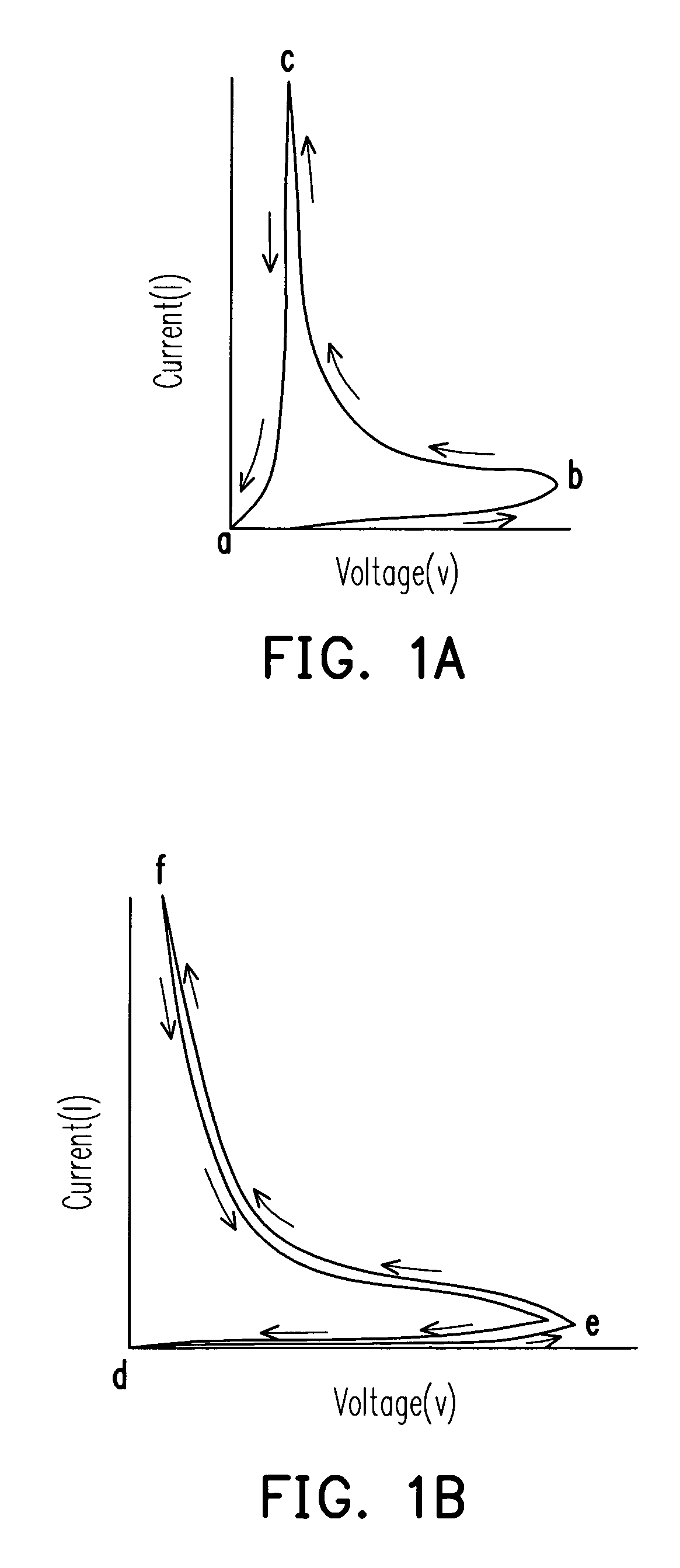

Non-volatile memory cell and operating method thereof

InactiveUS20060126395A1High equipment integrationReduced dimensionRead-only memoriesDigital storageEngineeringThreshold voltage

A non-volatile memory cell is provided. The non-volatile memory cell includes of a threshold switch material thin film and a memory switch material thin film, and the phases of the memory switch material layer is capable of changing. In addition, the memory switch material layer serves as a memory unit; the threshold switch material serves as a steering unit. Furthermore, the steering unit will breakdown when a voltage larger than its threshold voltage is provided, and the phase restores to the original state when the voltage is off.

Owner:MACRONIX INT CO LTD

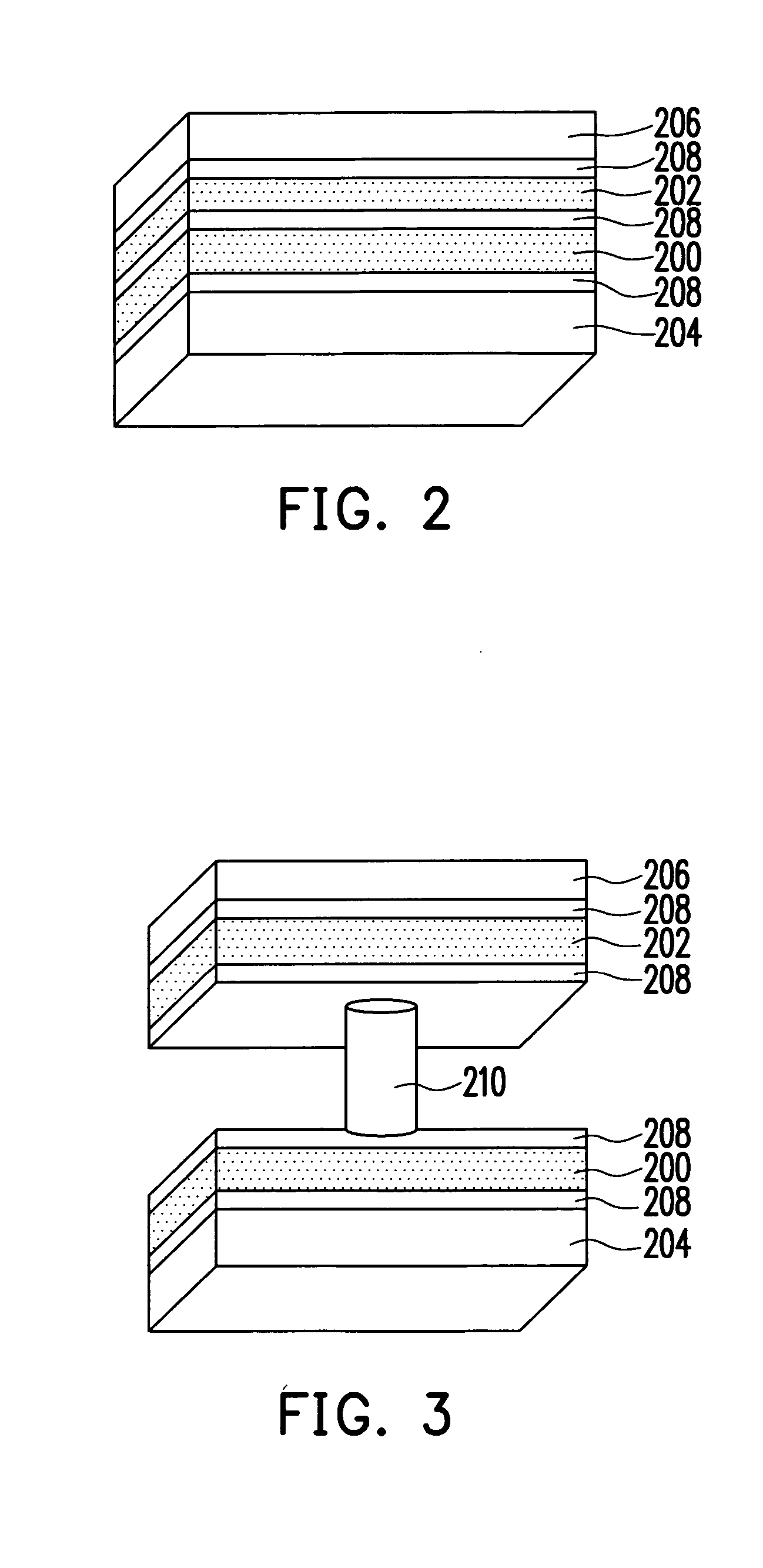

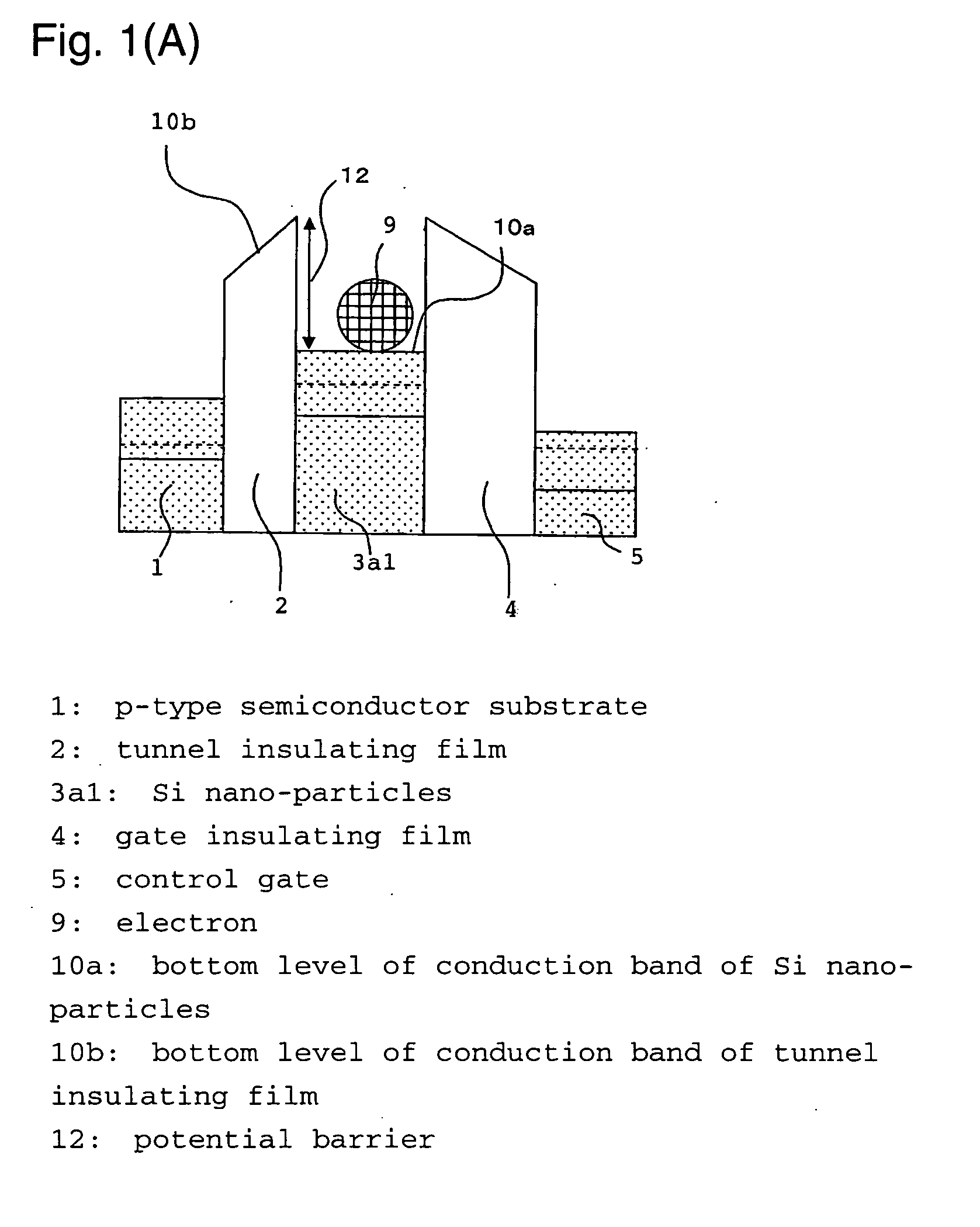

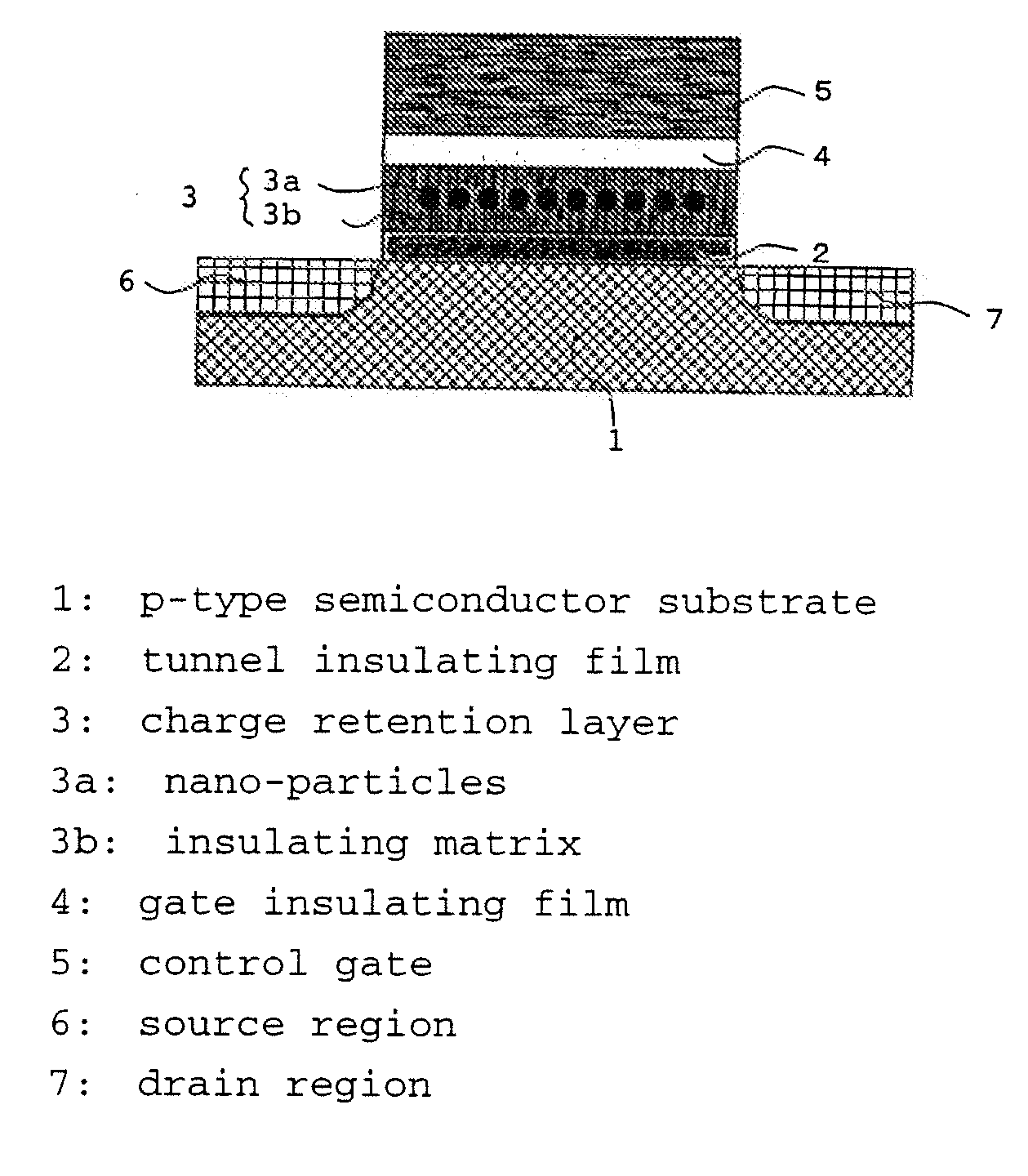

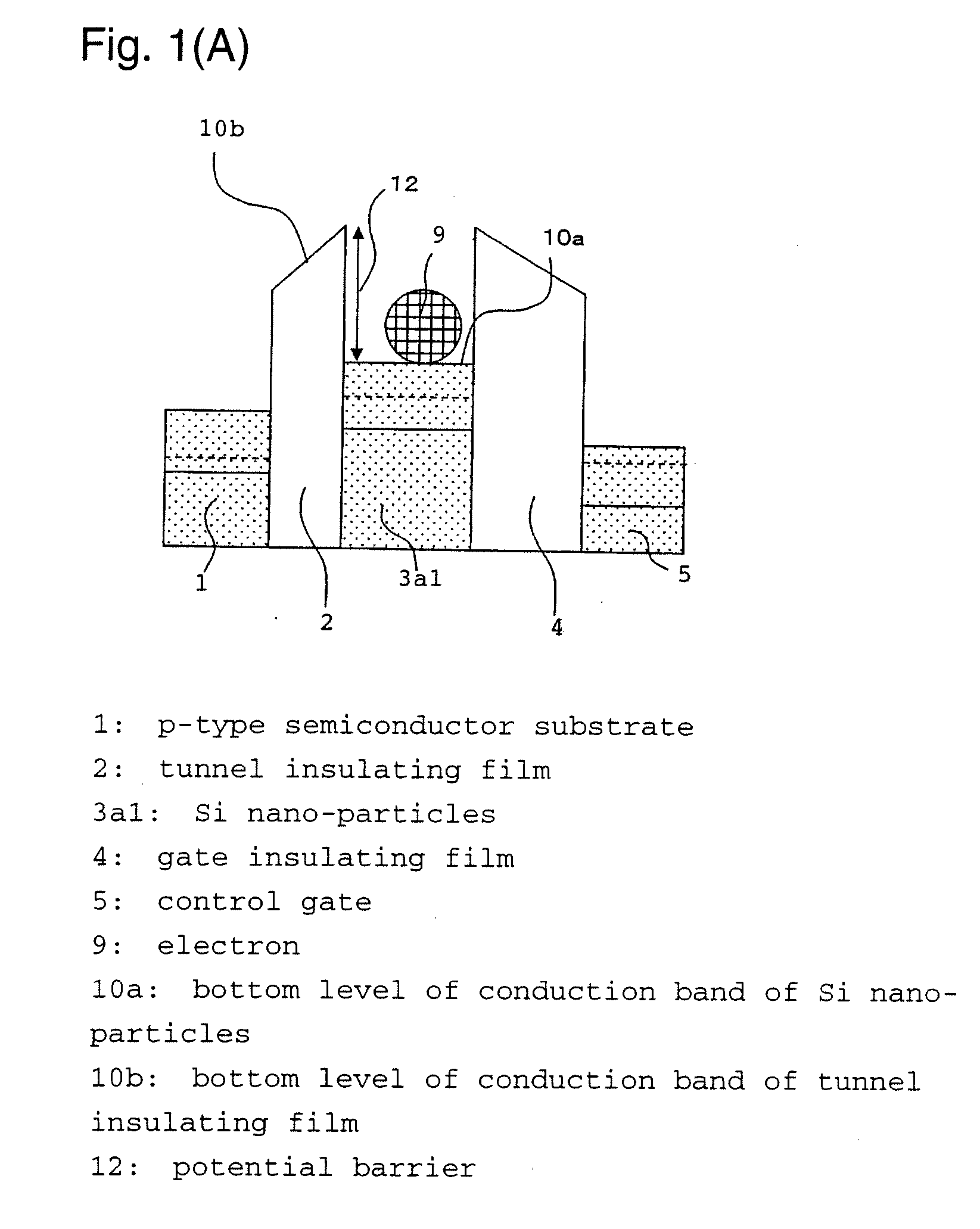

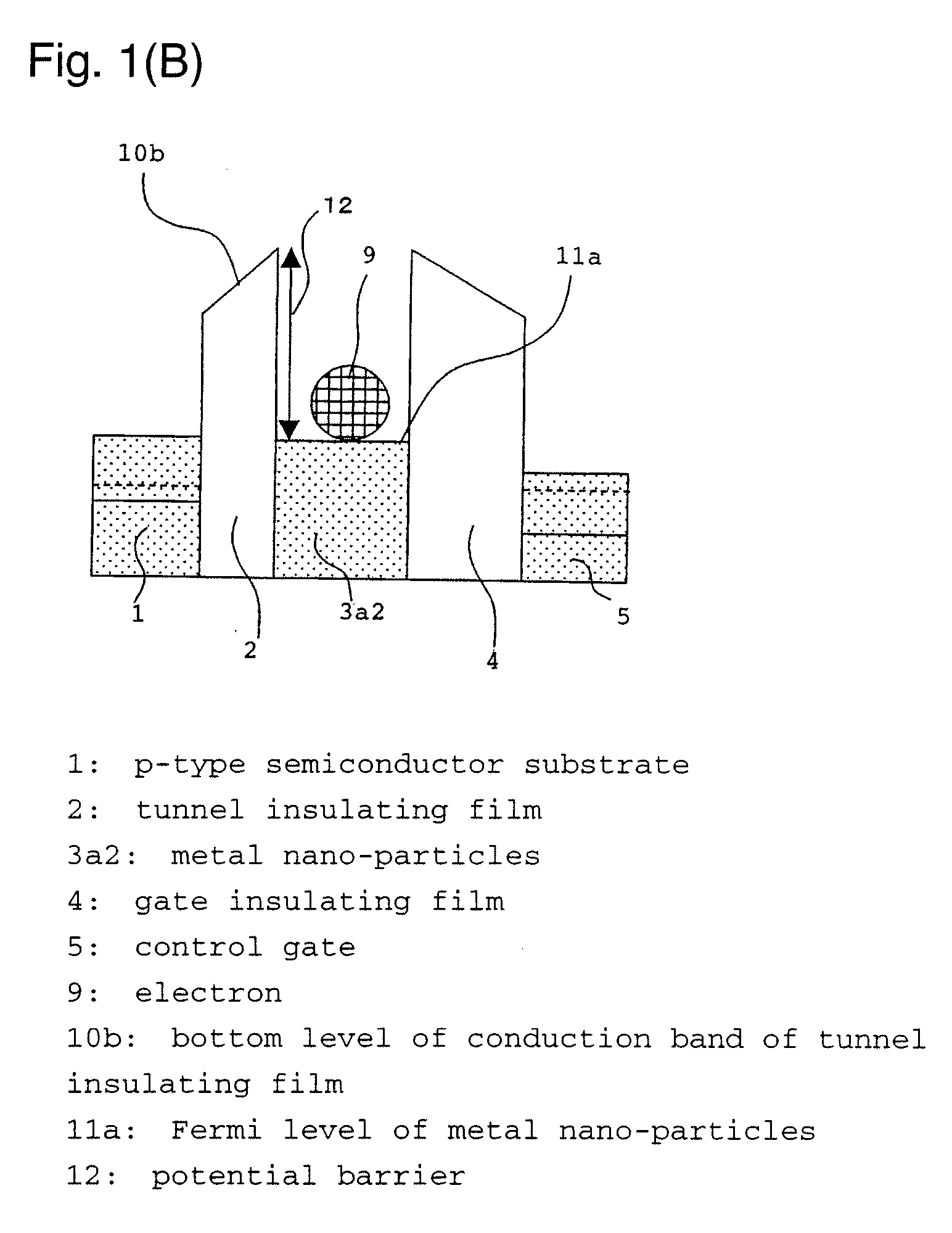

Nonvolatile semiconductor memory device having excellent charge retention and manufacturing process of the same

InactiveUS20060118853A1Improve adhesionIncrease production capacityNanotechRead-only memoriesCharge retentionManufacturing technology

There has been a problem in conventional Si-type floating-gate type nonvolatile semiconductor memory devices that the charge retention characteristic is low due to insufficiently large electron affinity of Si, therefore improvement of the memory performances, such as scaling down of a memory cell and increasing operation speed, have been difficult to be achieved due to the essential problem. In order to solve the above problem, in the nonvolatile semiconductor memory device of the present invention, a material having large work function or large electron affinity or a material having a work function close to that of semiconductor substrate or of a control gate, is employed for a floating gate retaining charges. Further, an amorphous material having small electron affinity for an insulating matrix is used. Further, at a time of deposition of charge retention layer, the supply ratio of the nano-particle material and the insulating matrix material, such as the mixture ratio of materials of both phases in a target in a sputtering method, is adjusted. By these methods, the charge retention characteristic of the floating-gate type nonvolatile semiconductor memory device can be improved, and the above-mentioned problem of the nonvolatile semiconductor memory device can be solved.

Owner:ASAHI GLASS CO LTD +1

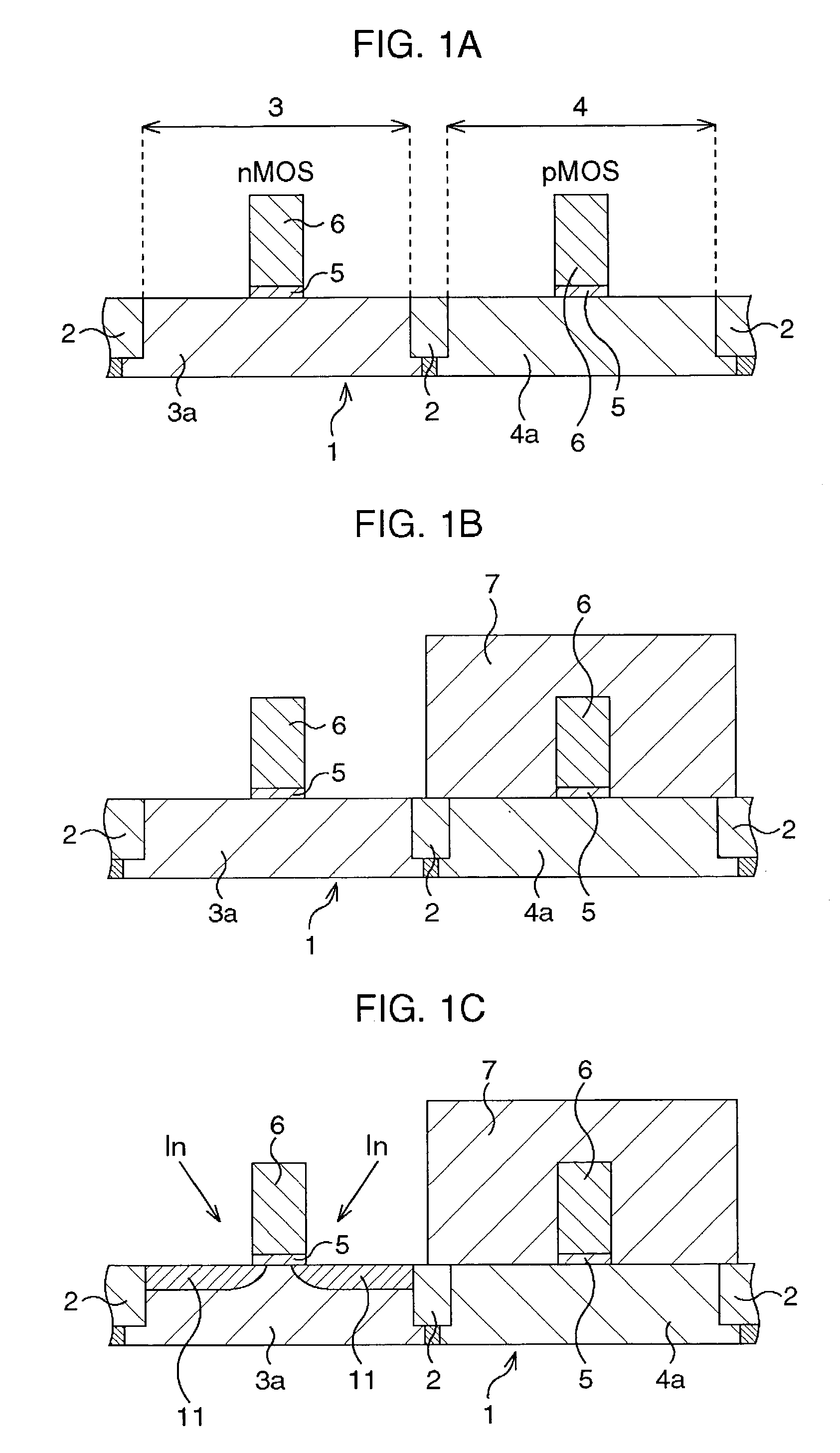

Transistor of semiconductor device, and method for manufacturing the same

InactiveUS20050104055A1Increase speedHigh equipment integrationSemiconductor/solid-state device manufacturingBulk negative resistance effect devicesDevice materialEngineering

A semiconductor device and a method for forming the same are disclosed. The semiconductor device includes an epitaxial source / drain junction layer having an insulating film thereunder. The method comprises the step of forming a under-cut under an epitaxial source / drain junction layer so that an insulating film filling the under-cut can be formed.

Owner:SK HYNIX INC

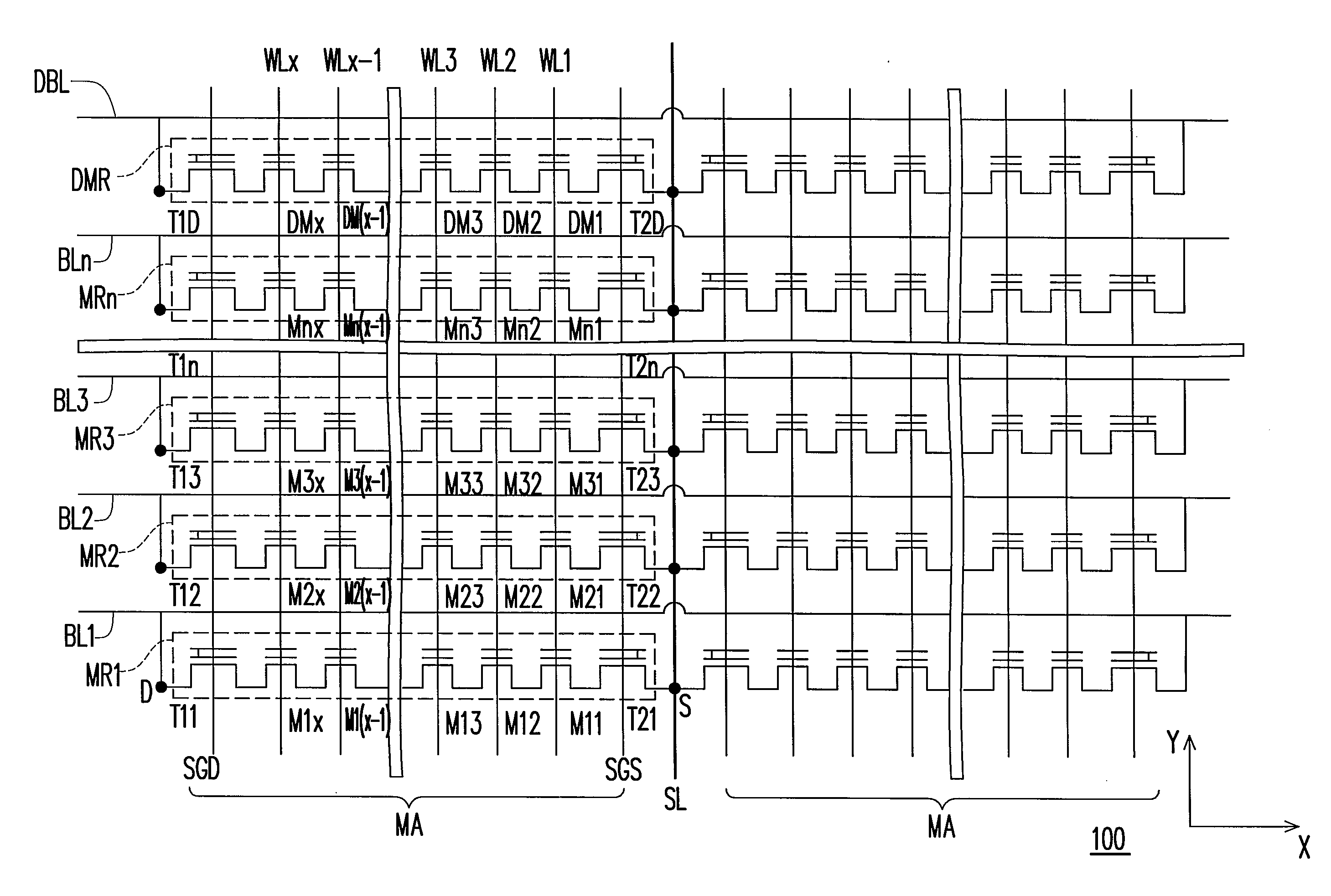

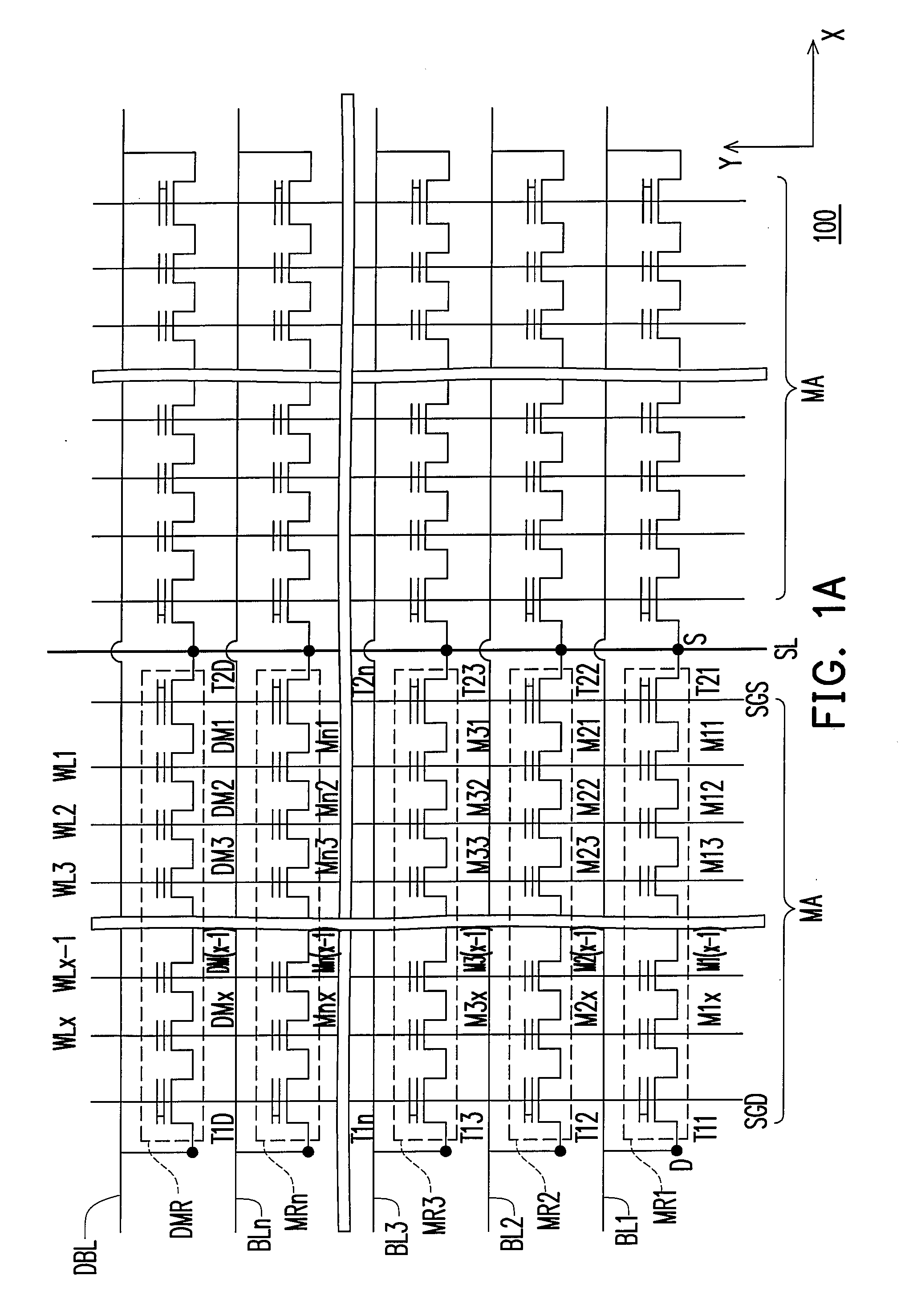

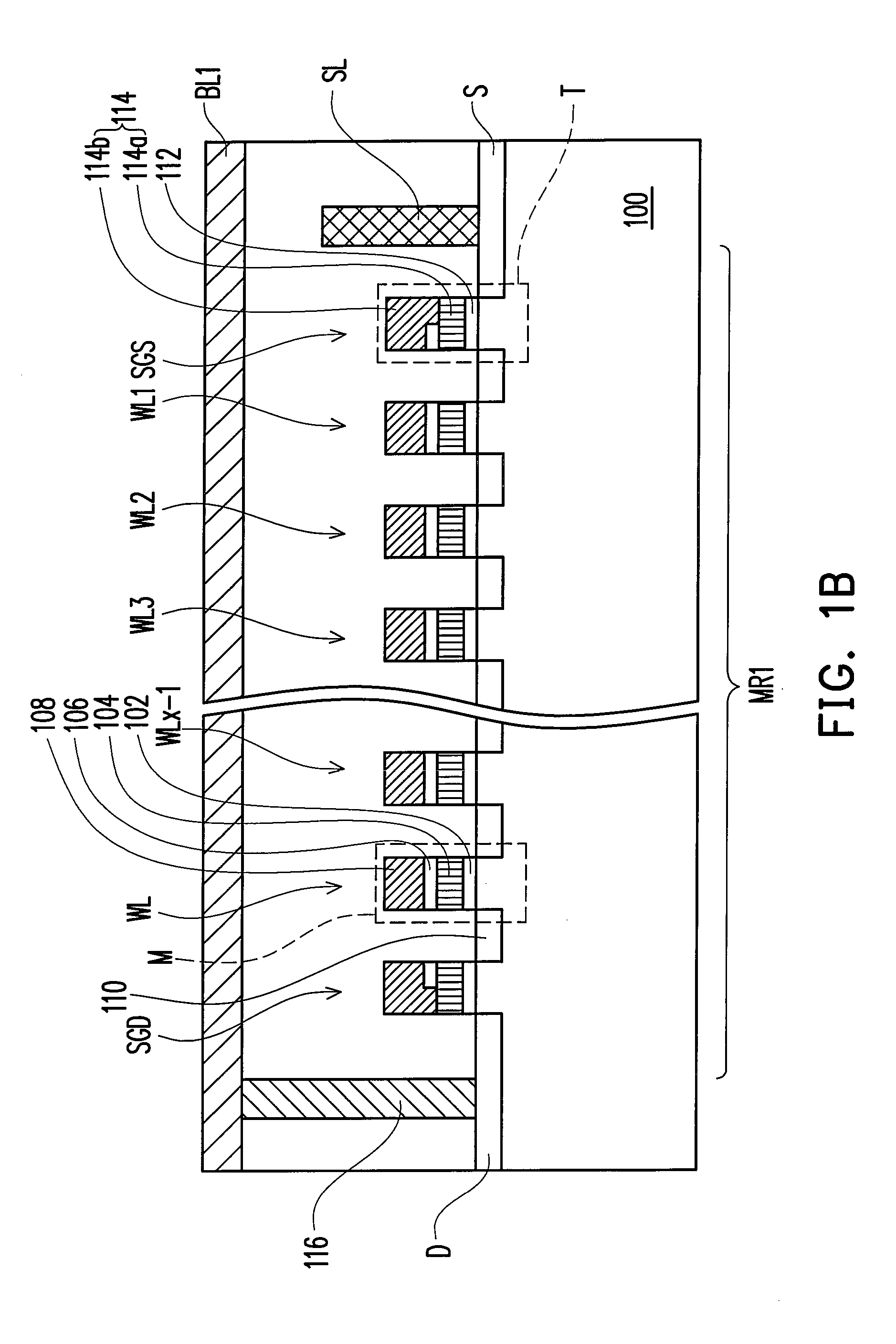

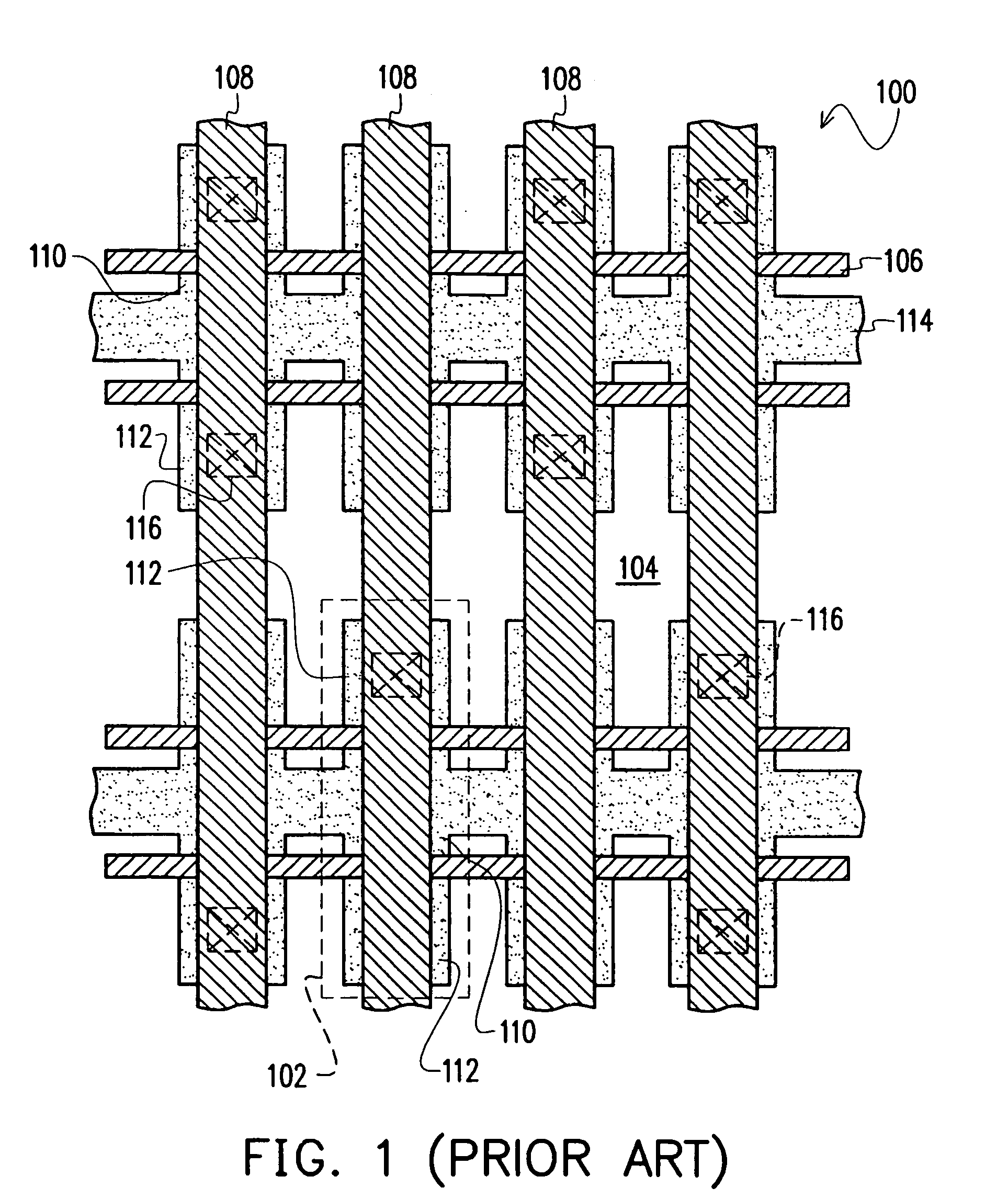

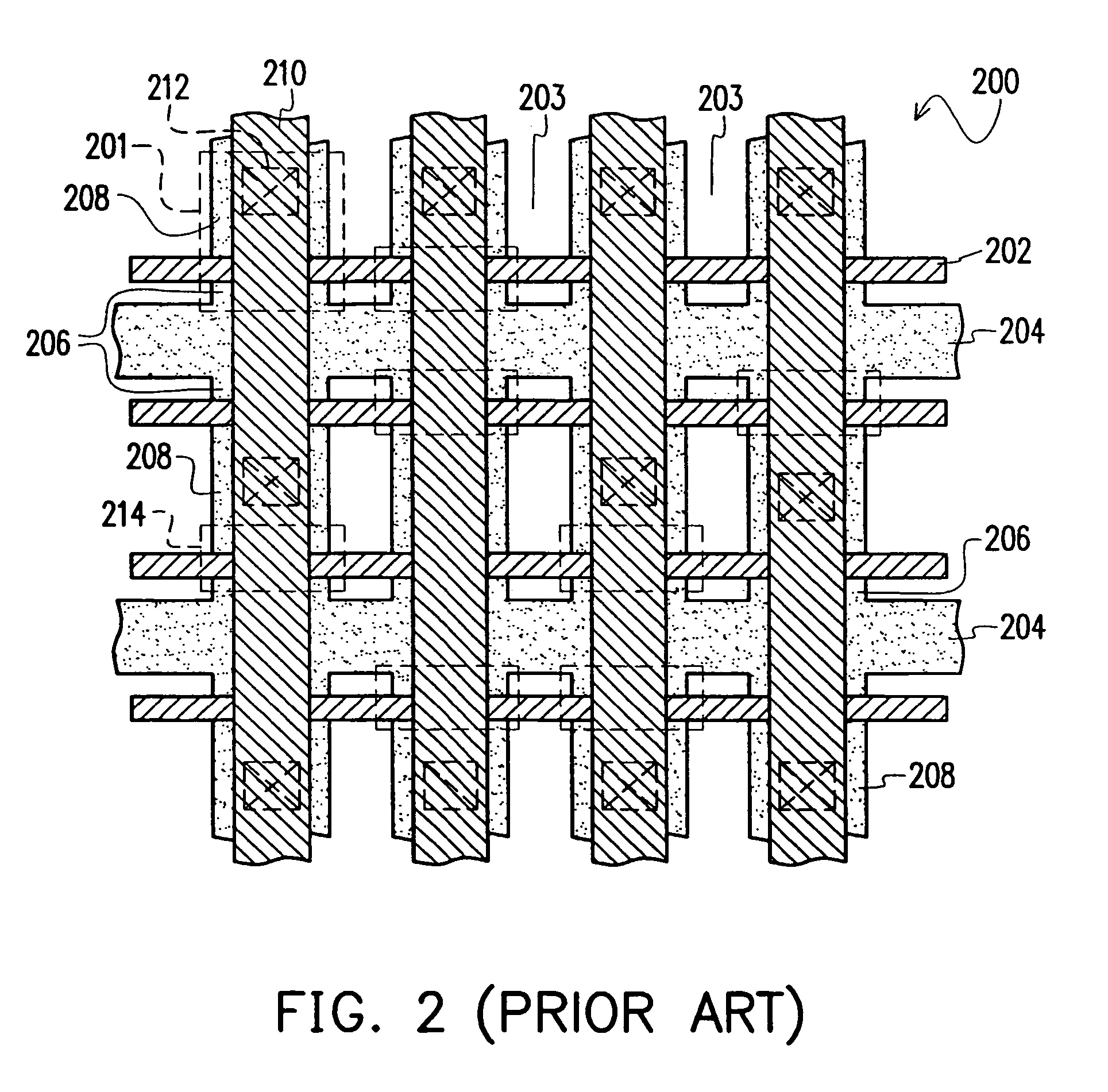

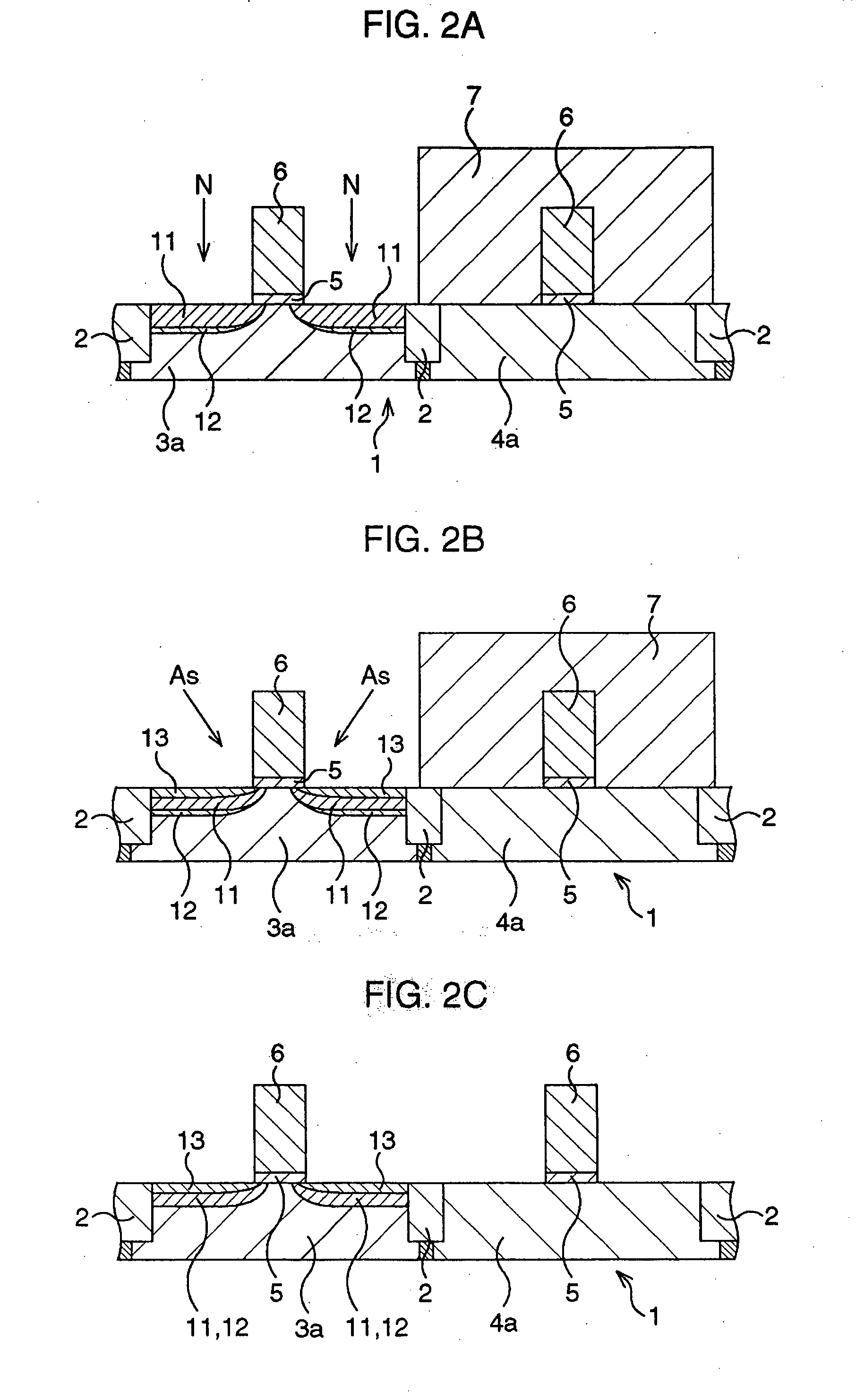

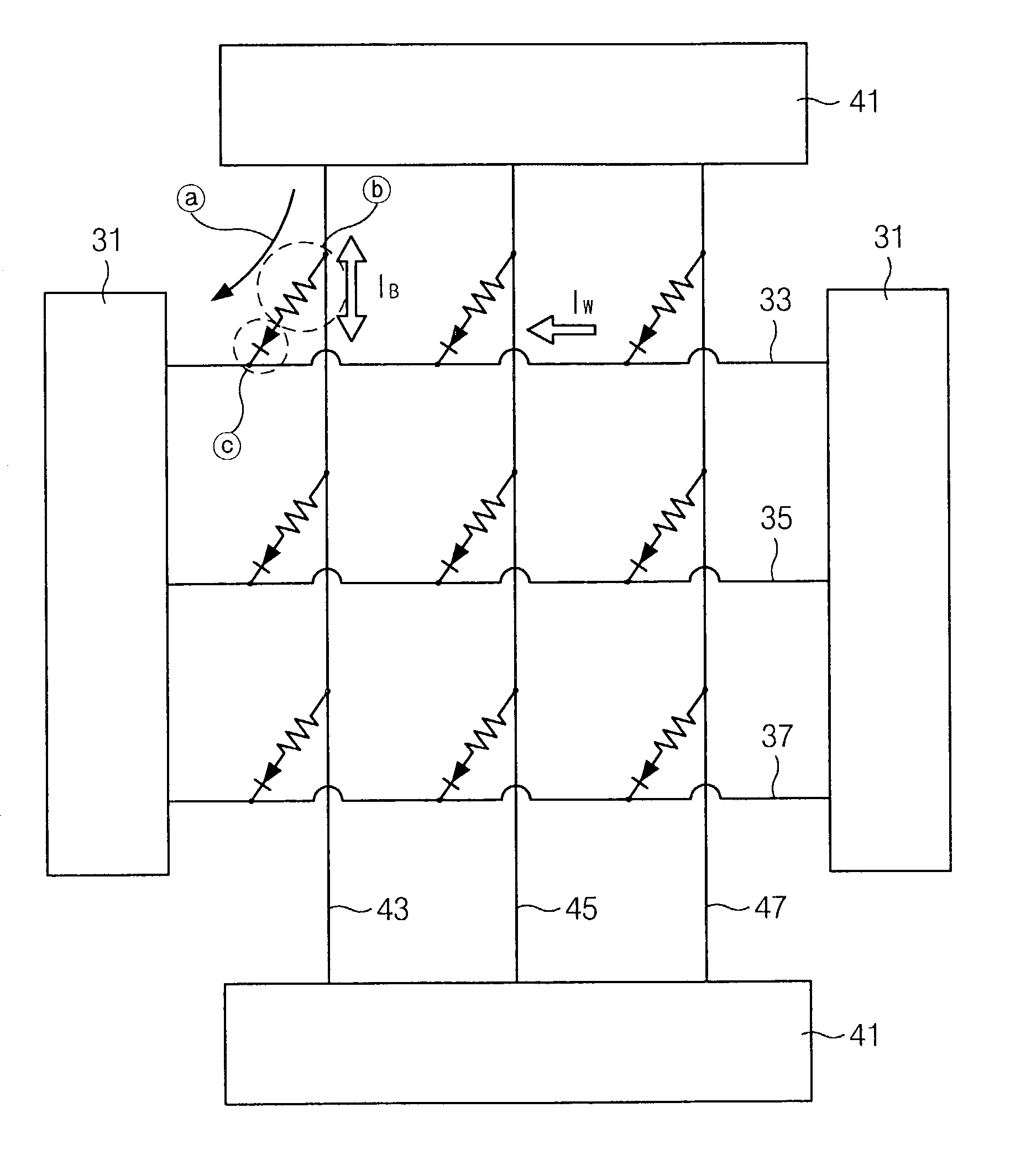

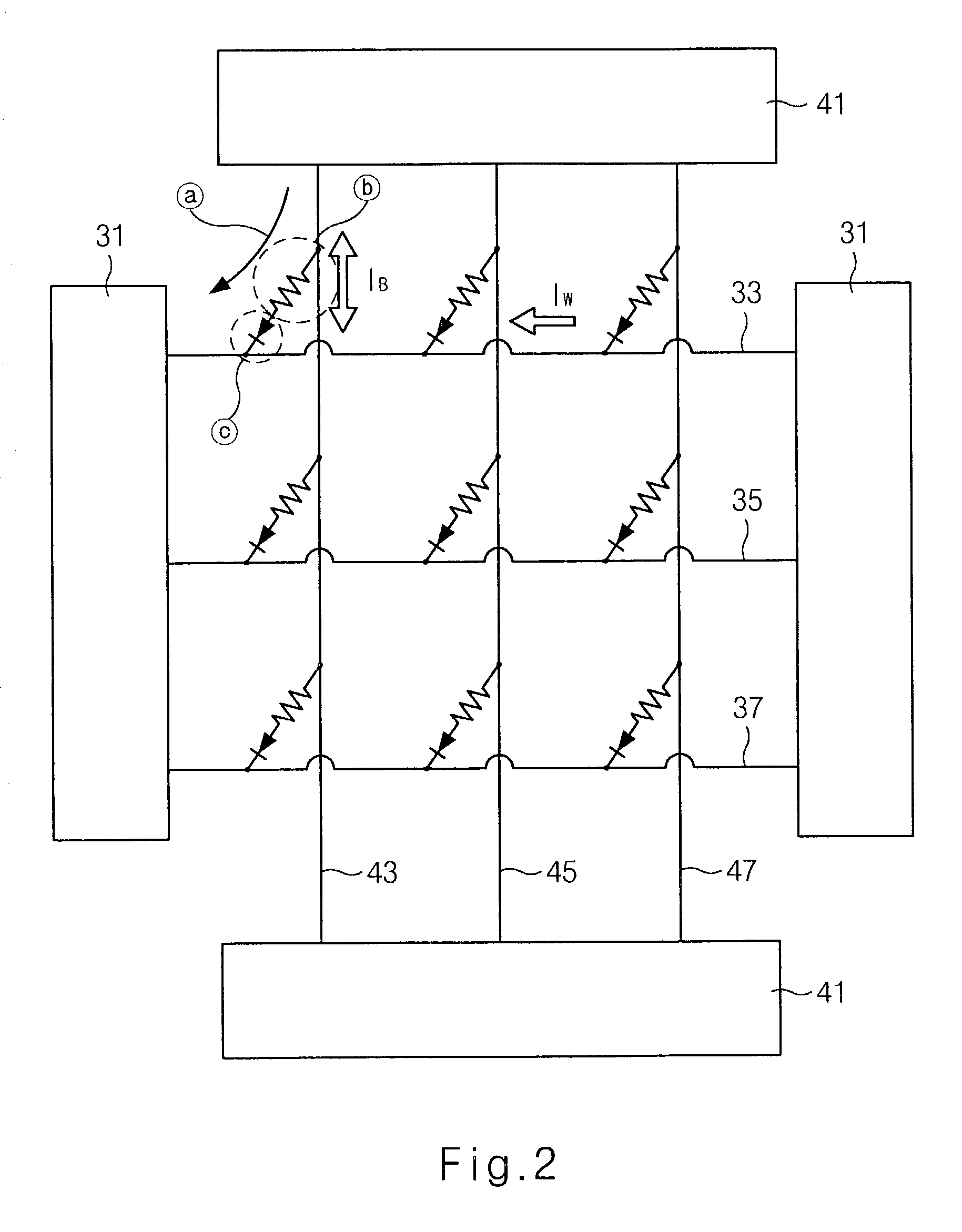

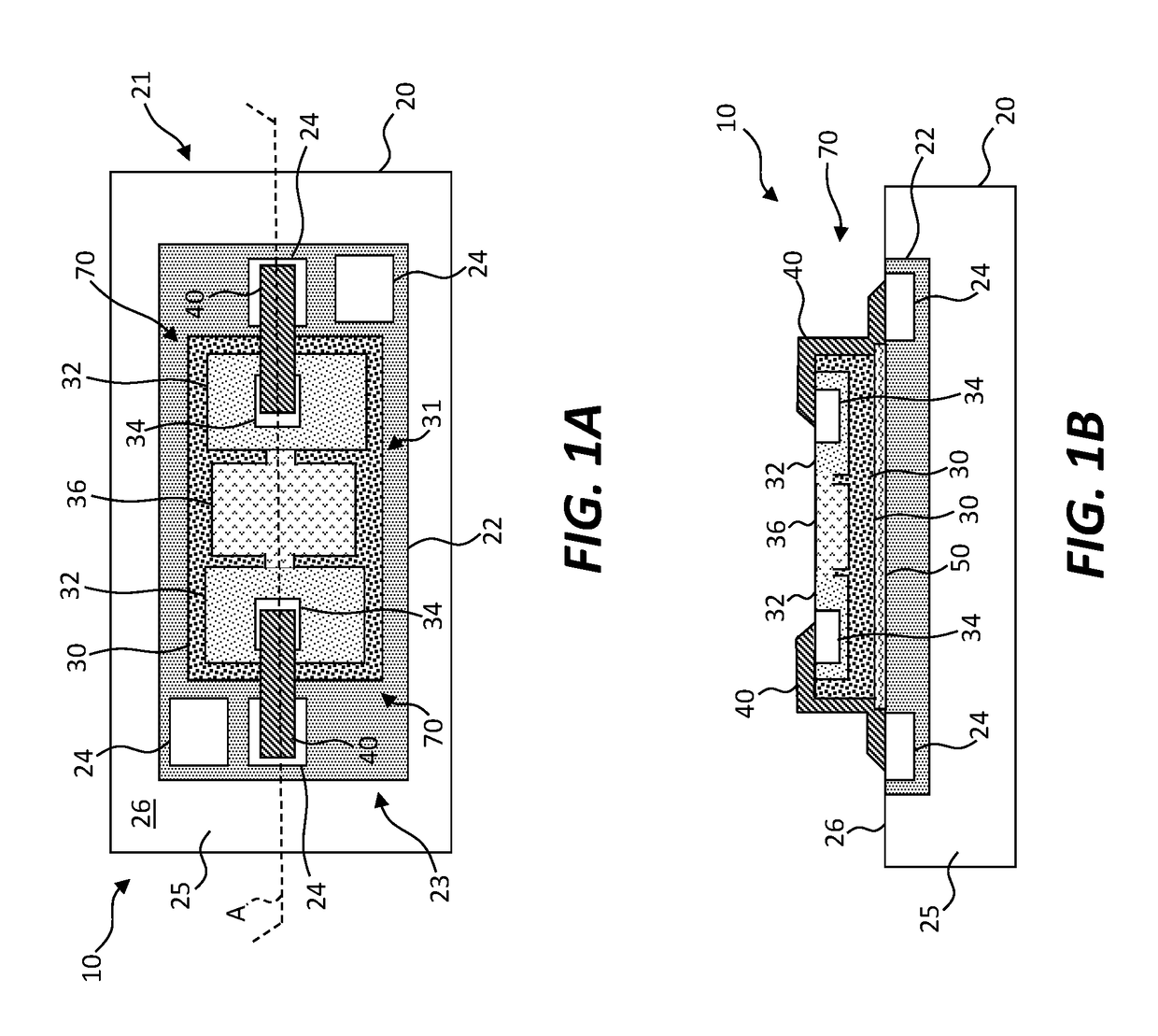

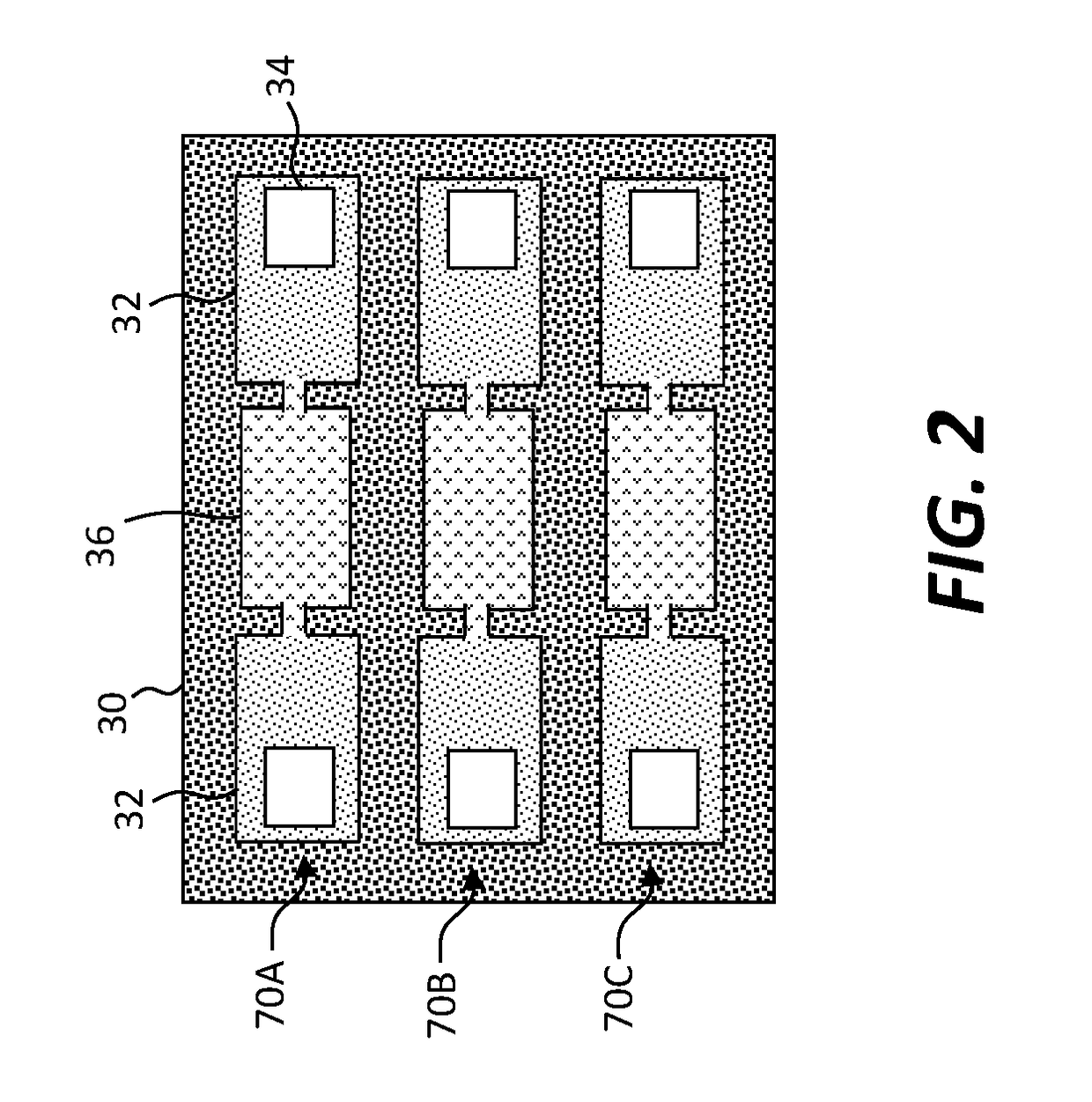

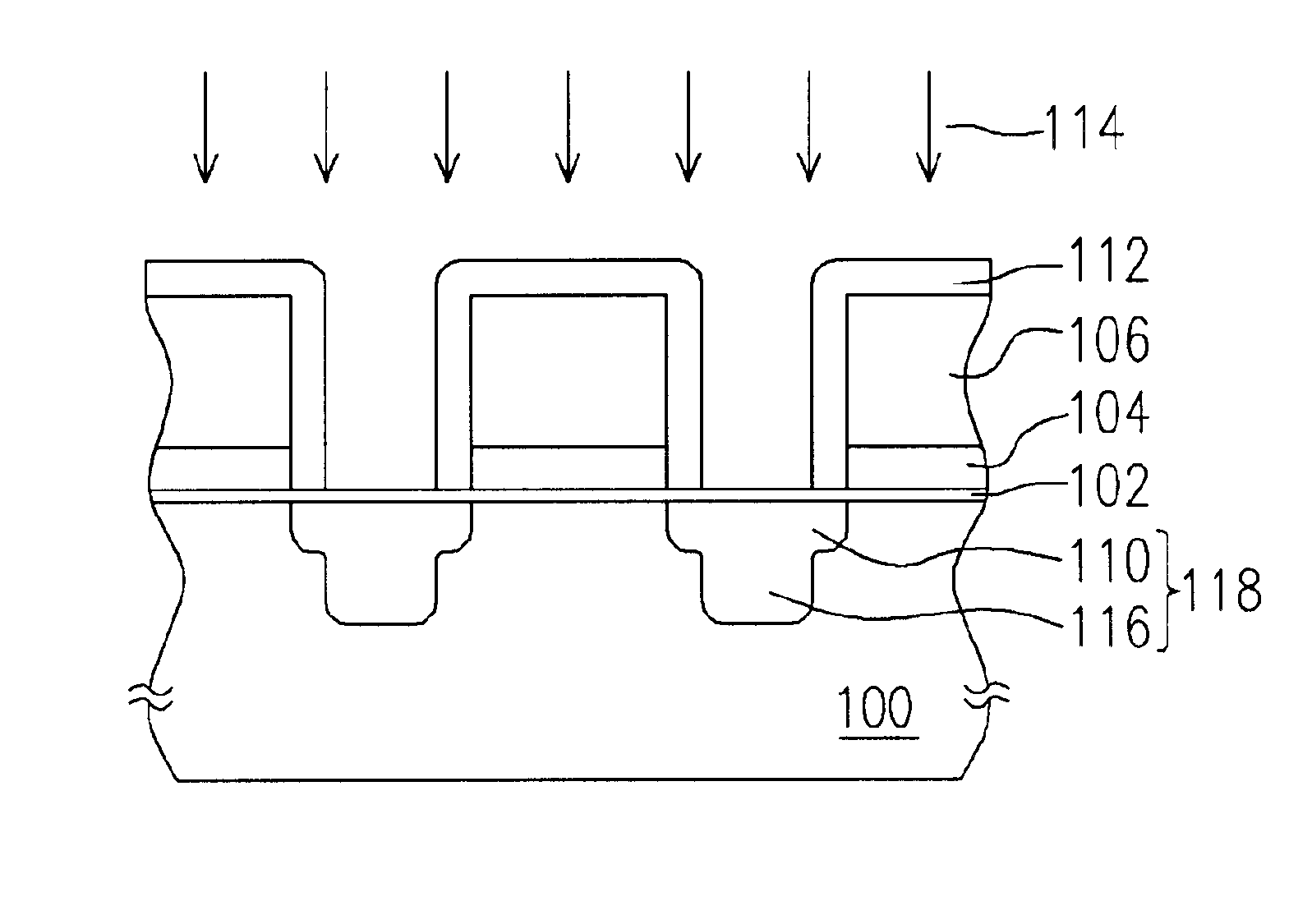

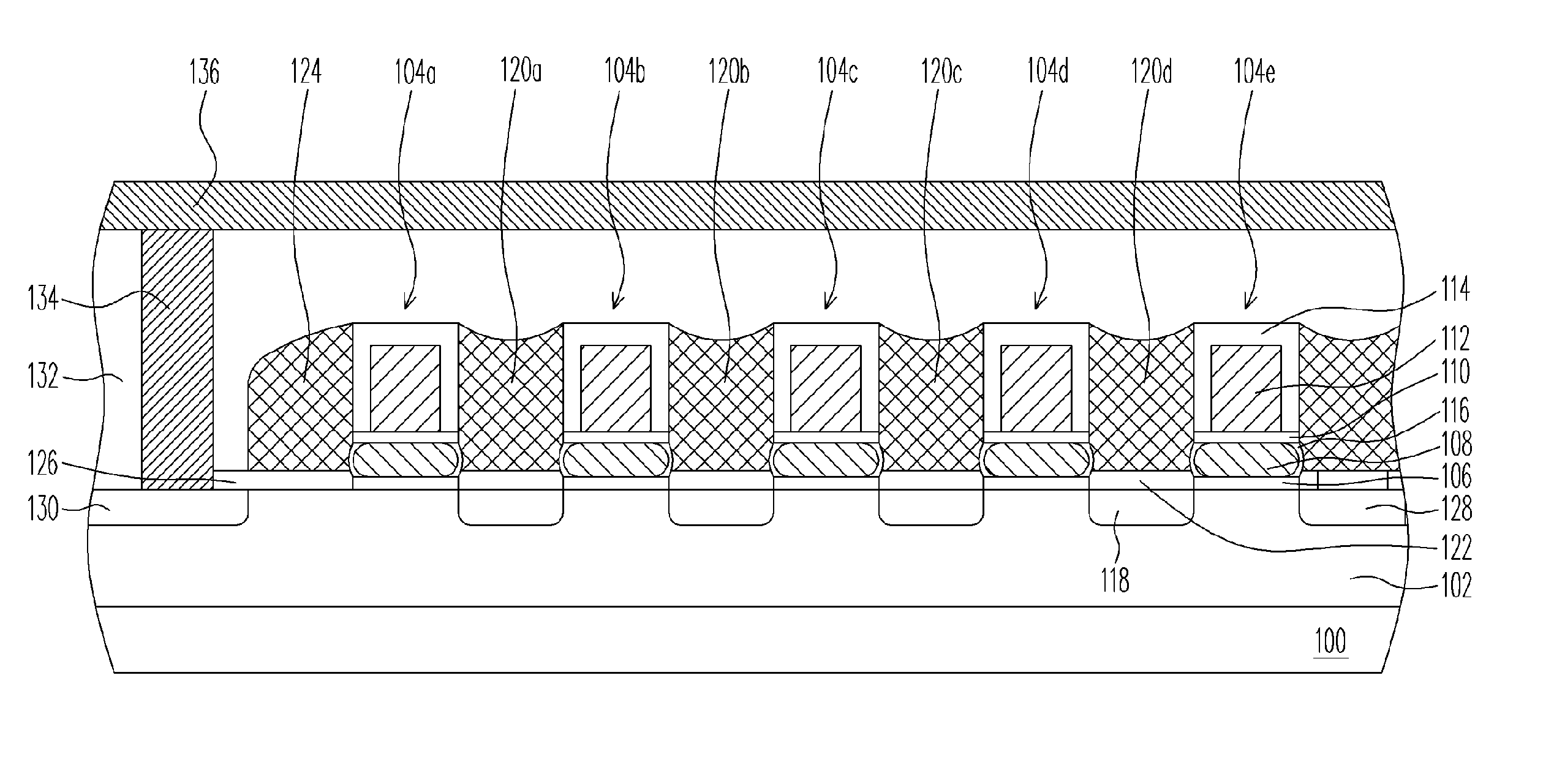

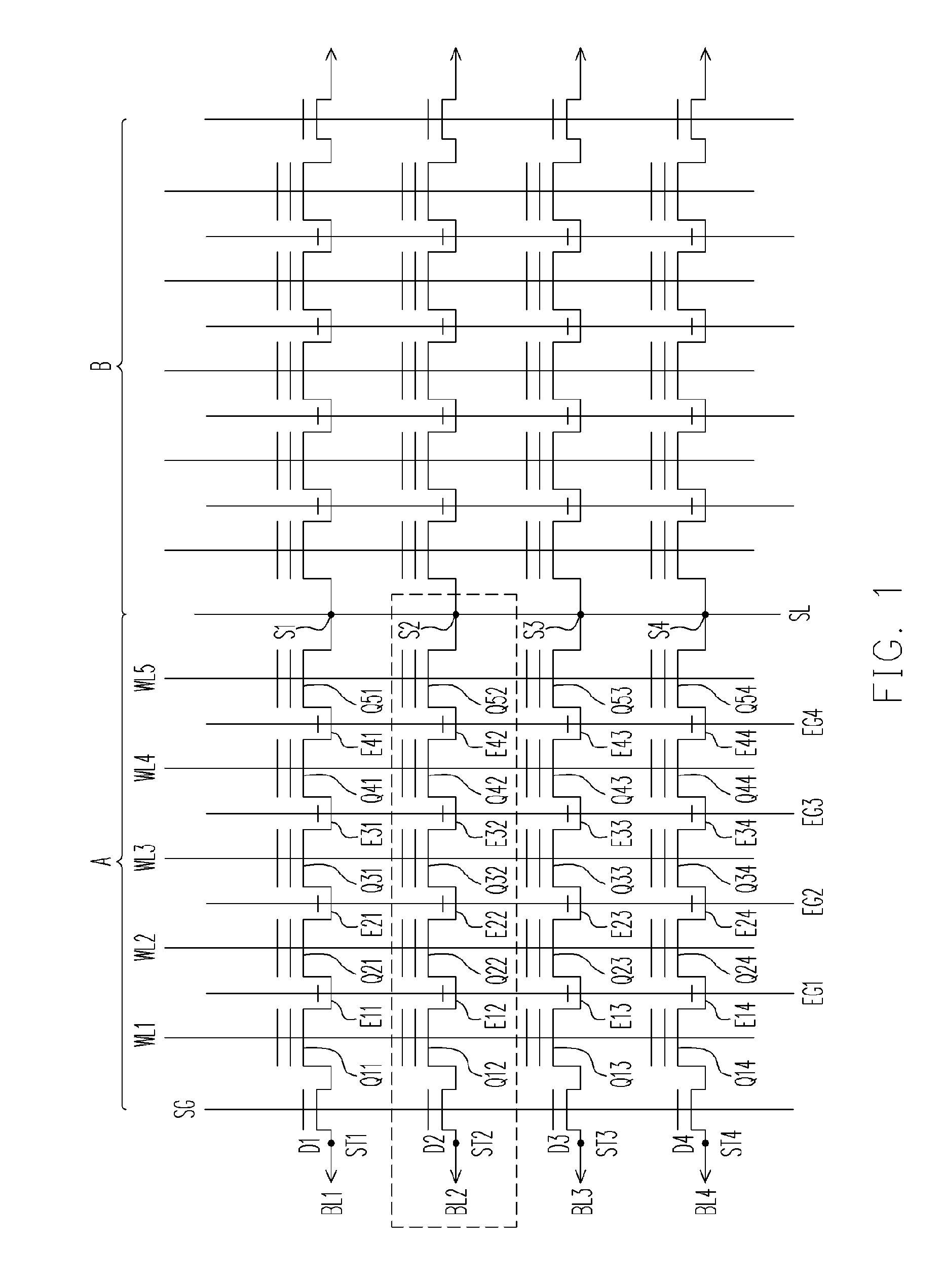

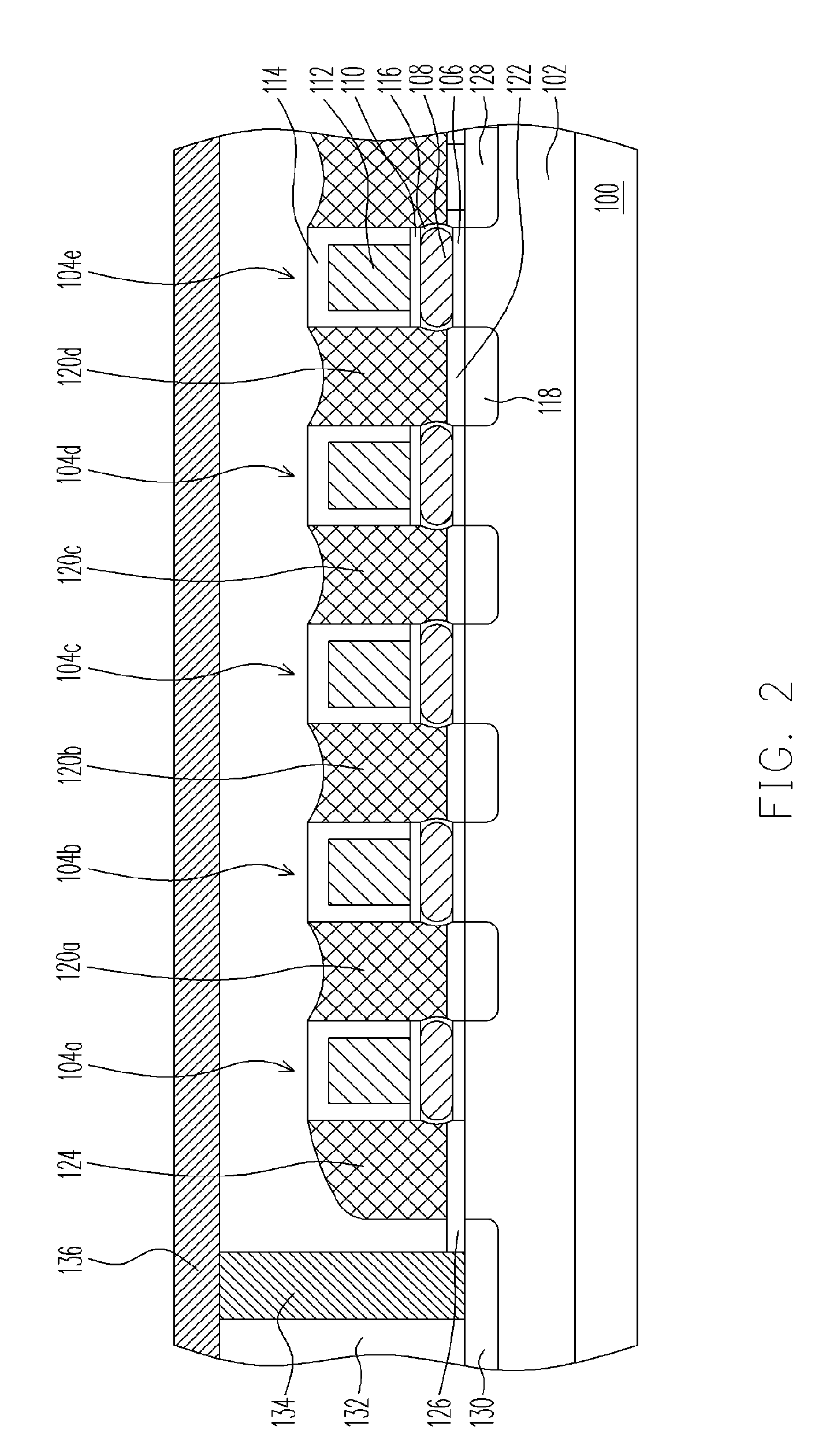

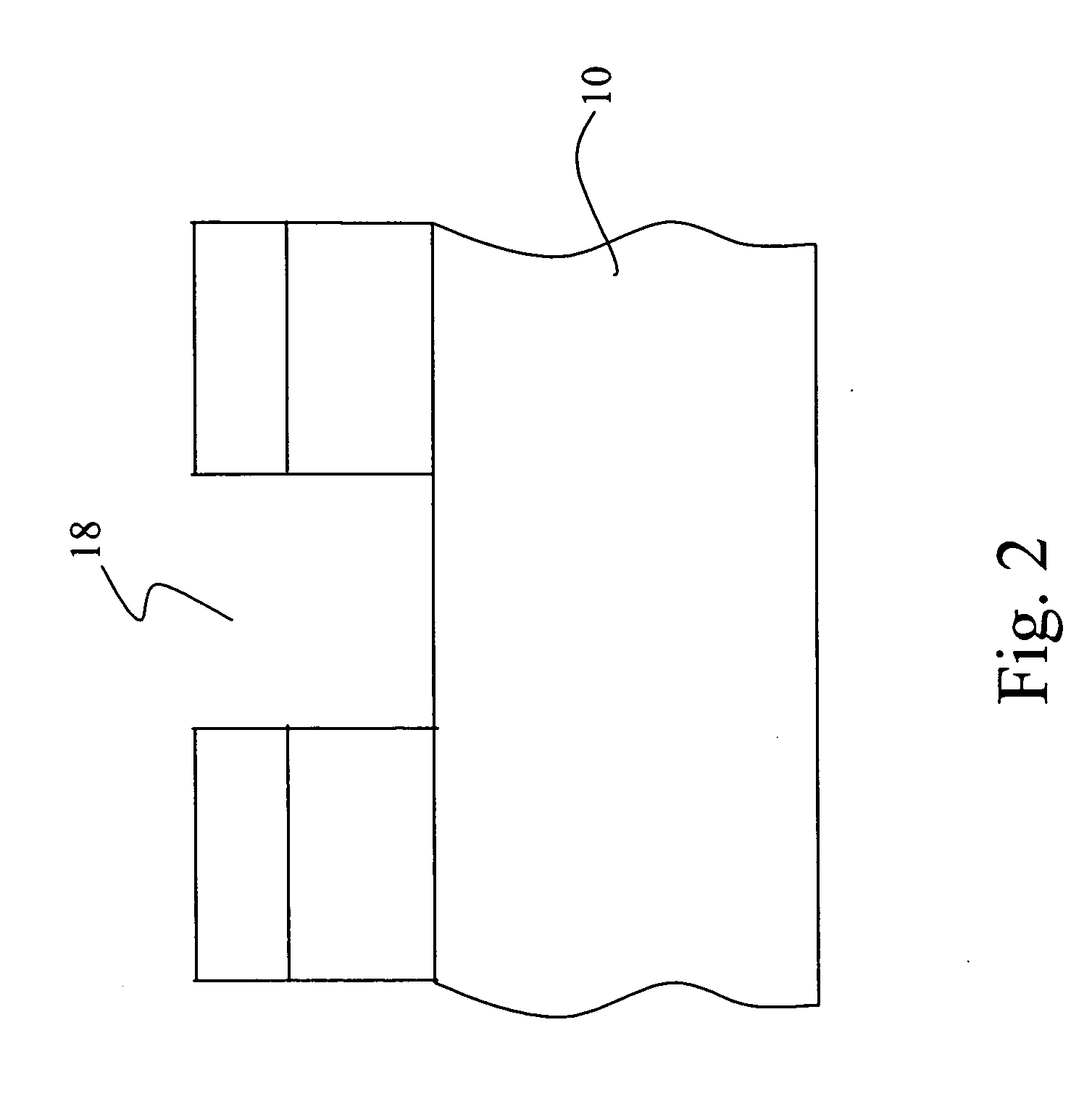

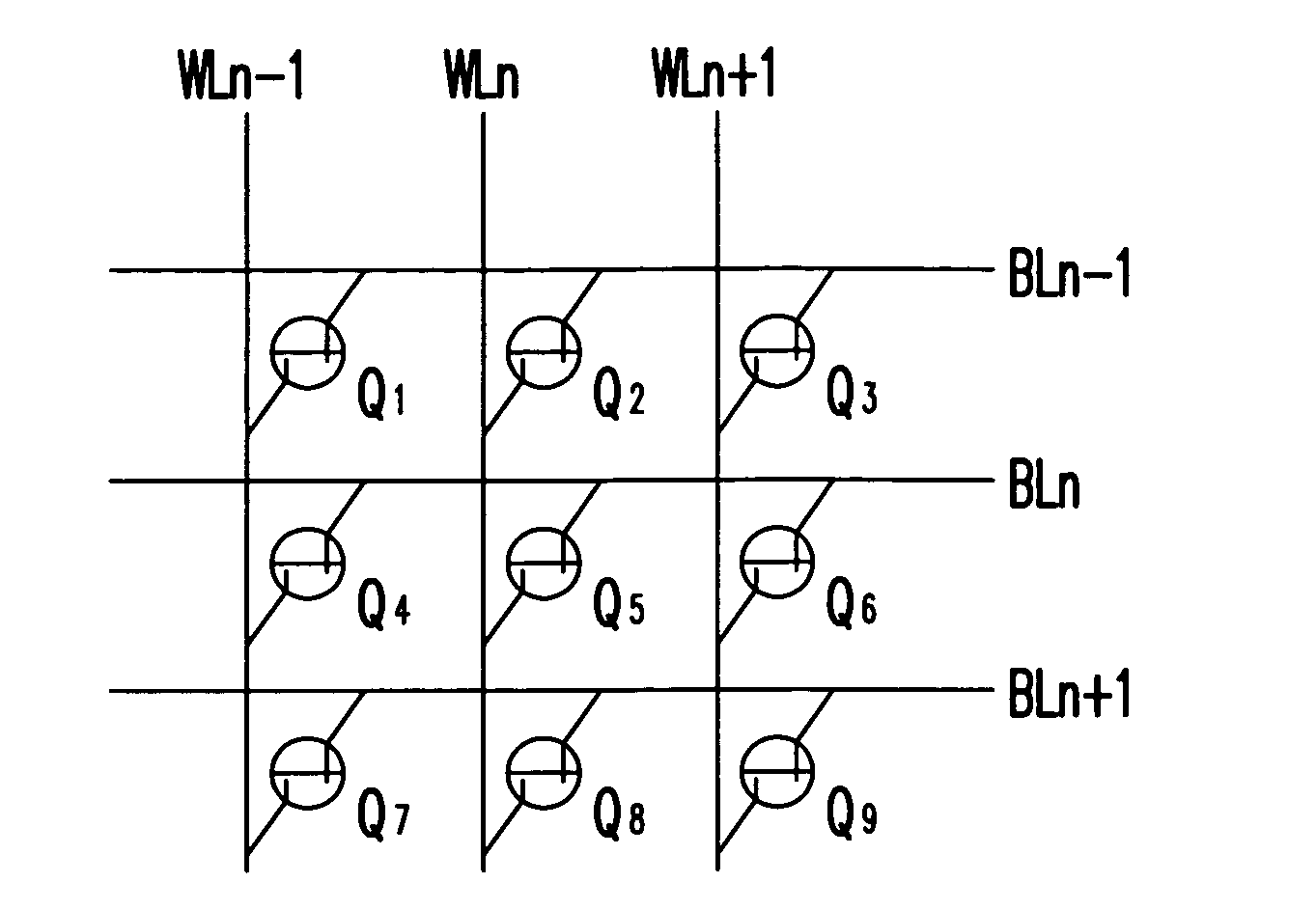

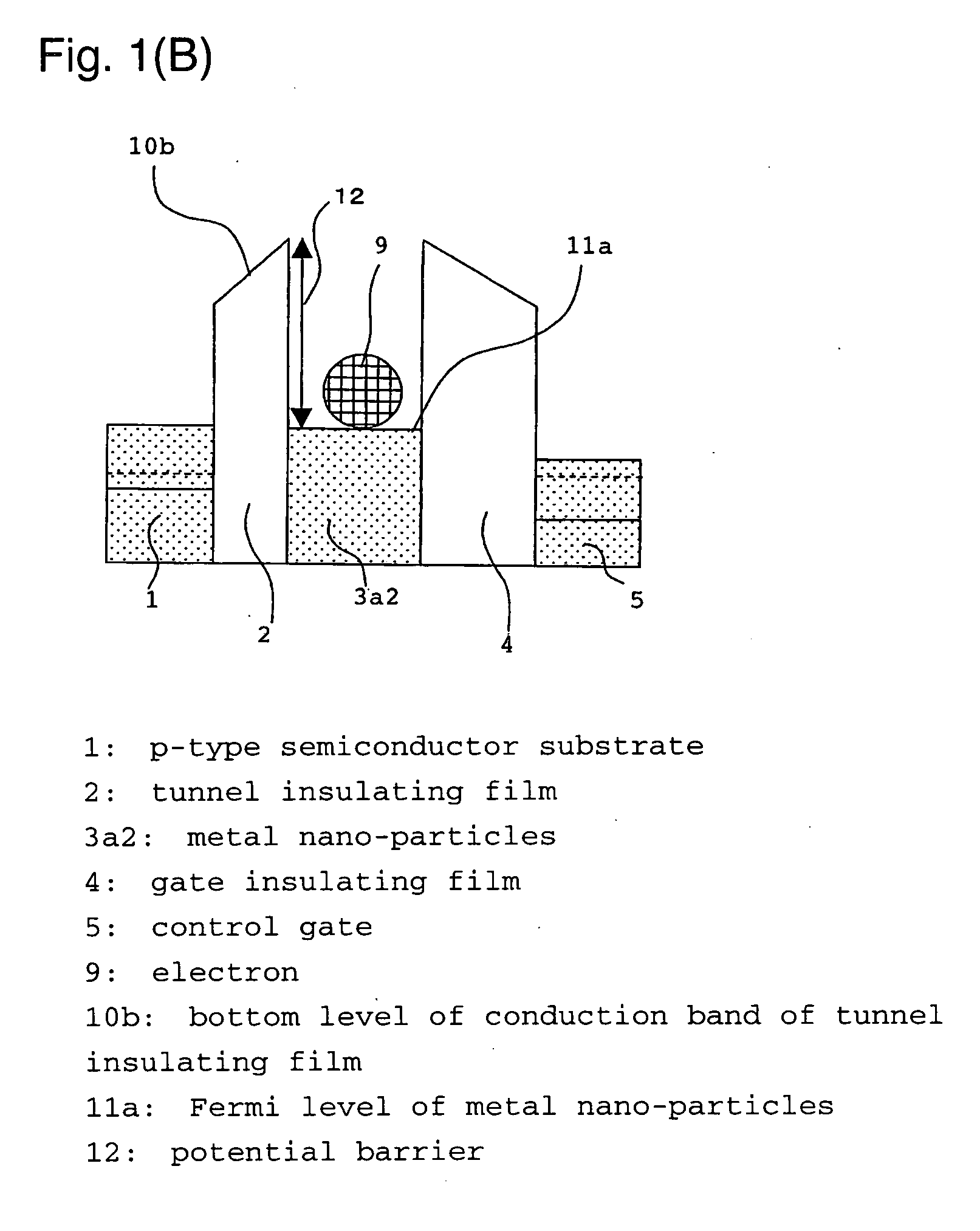

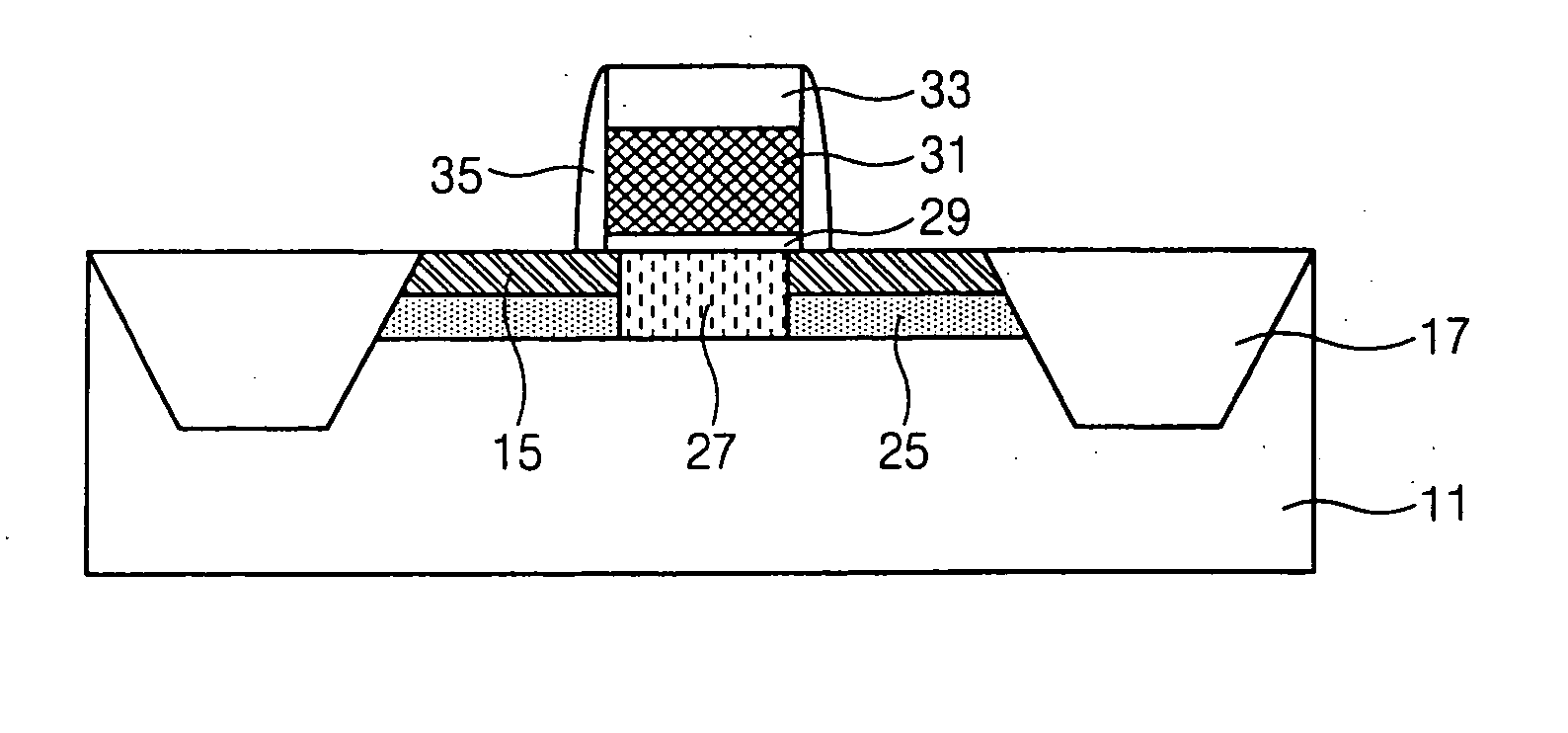

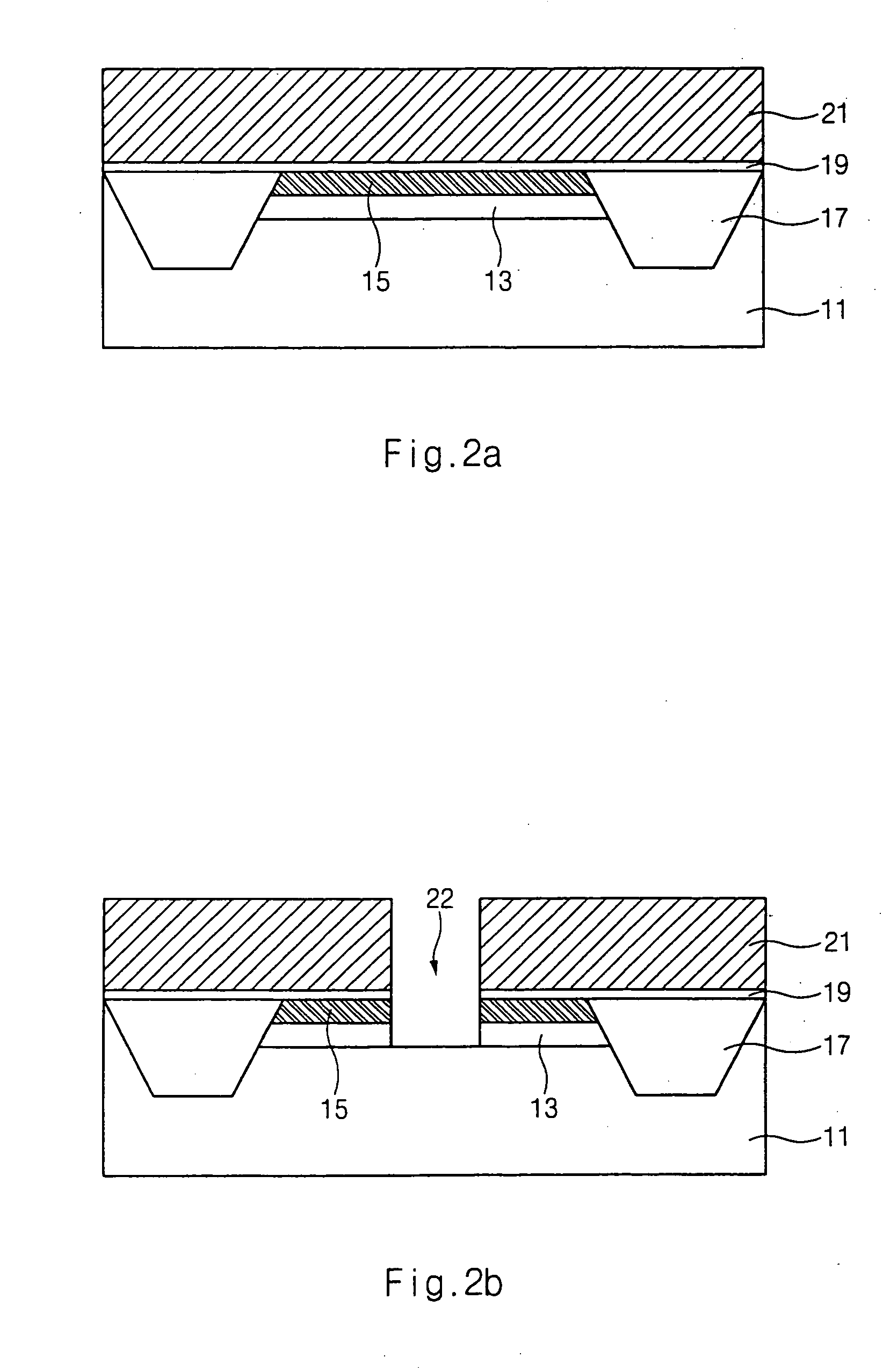

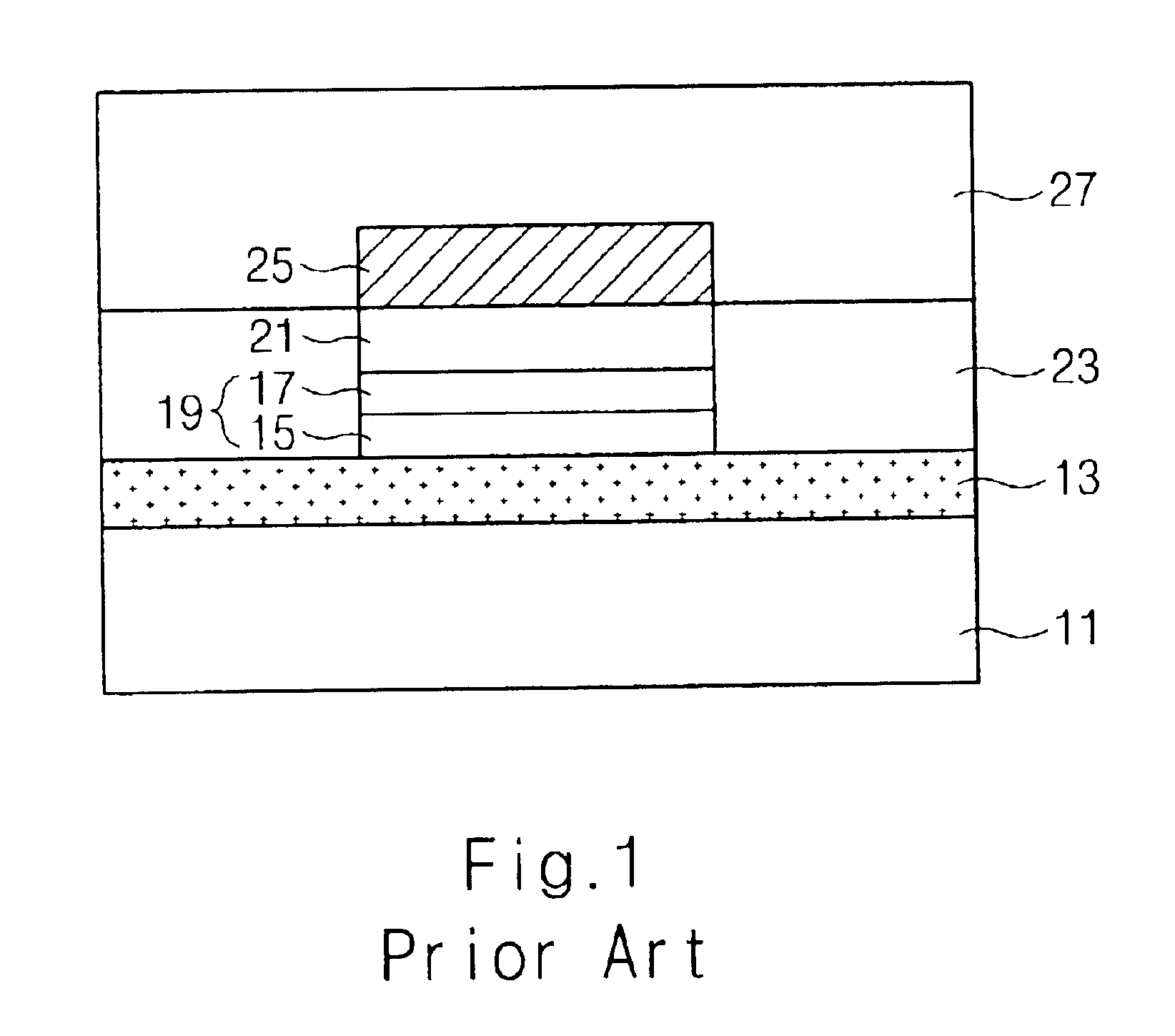

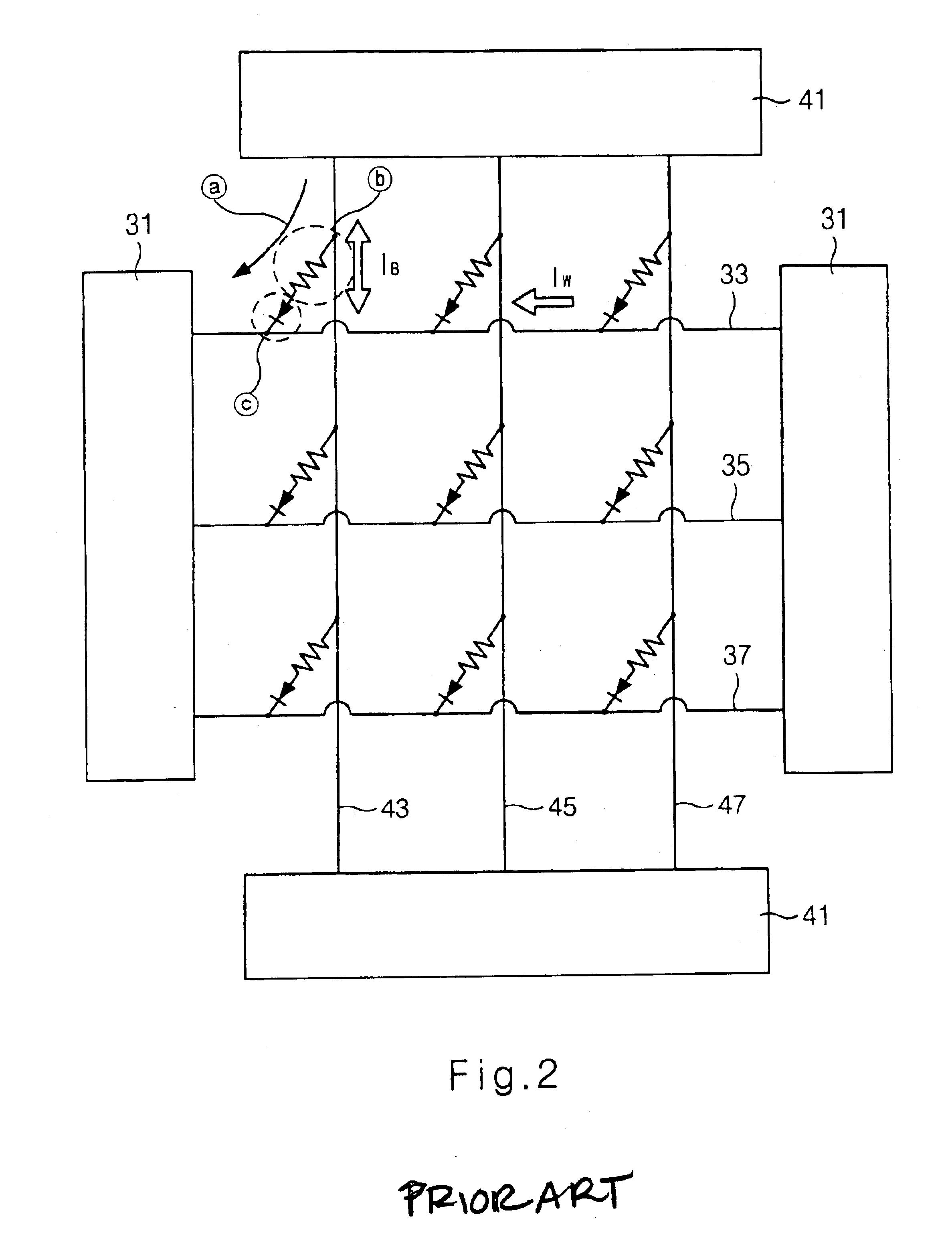

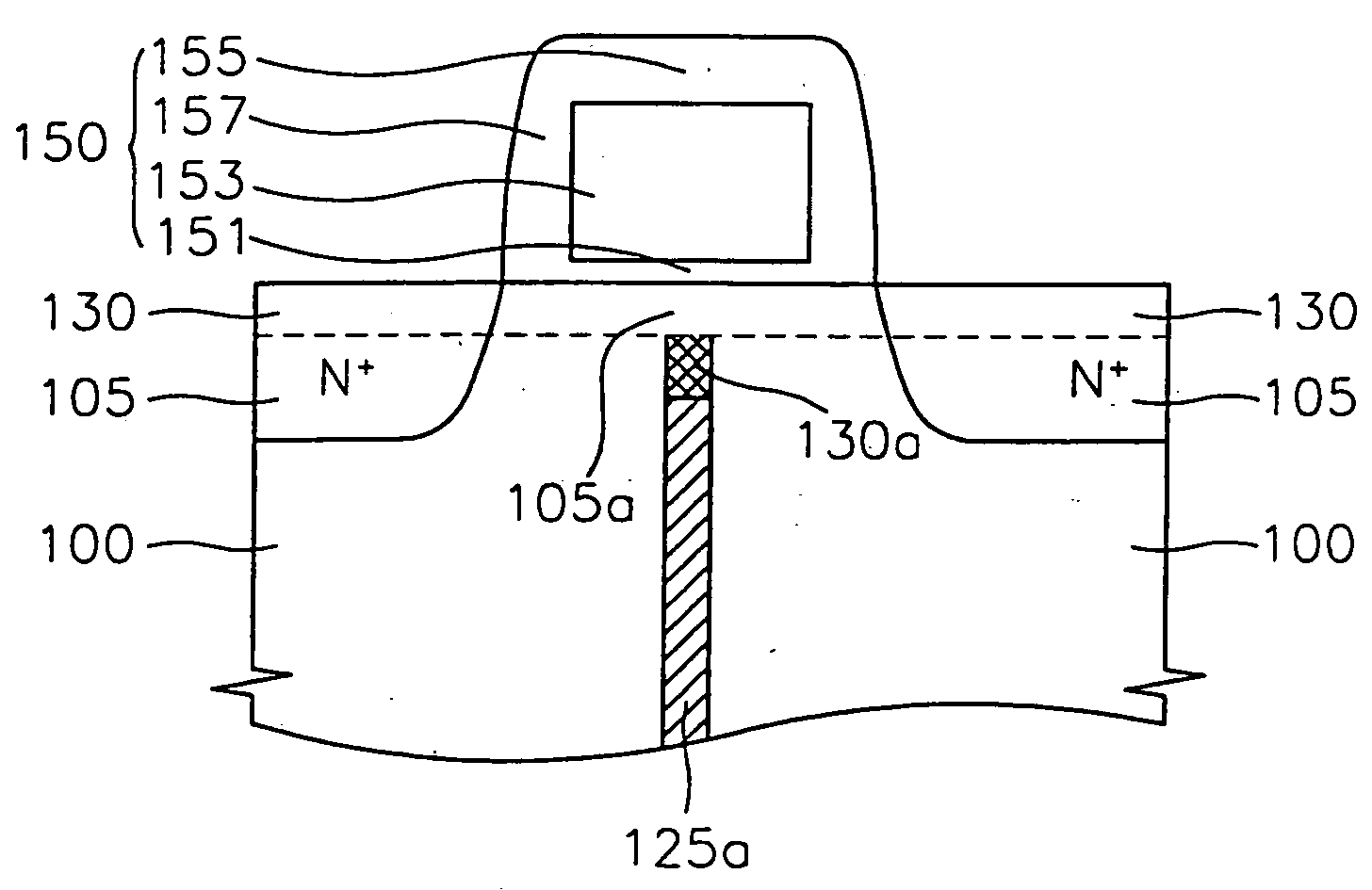

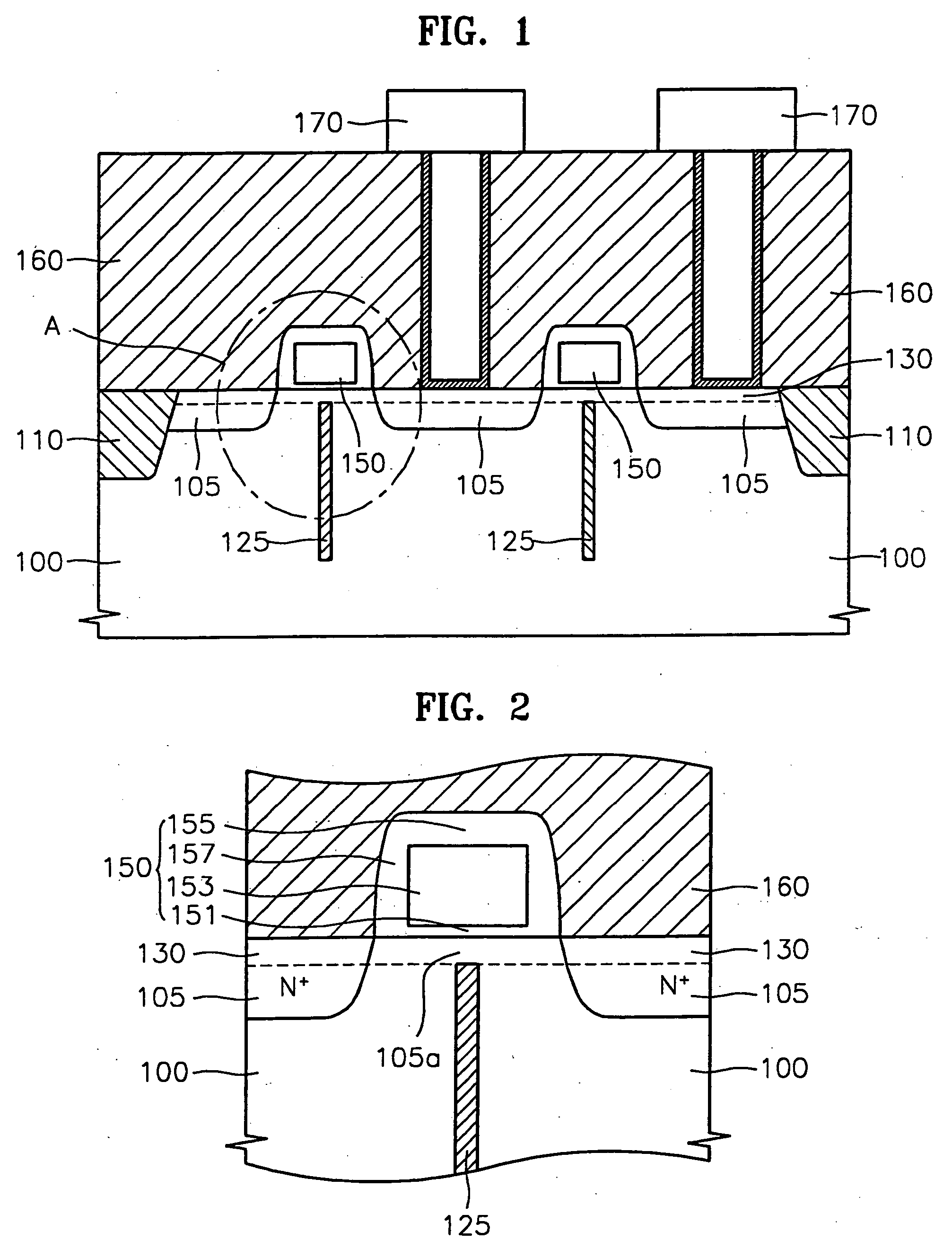

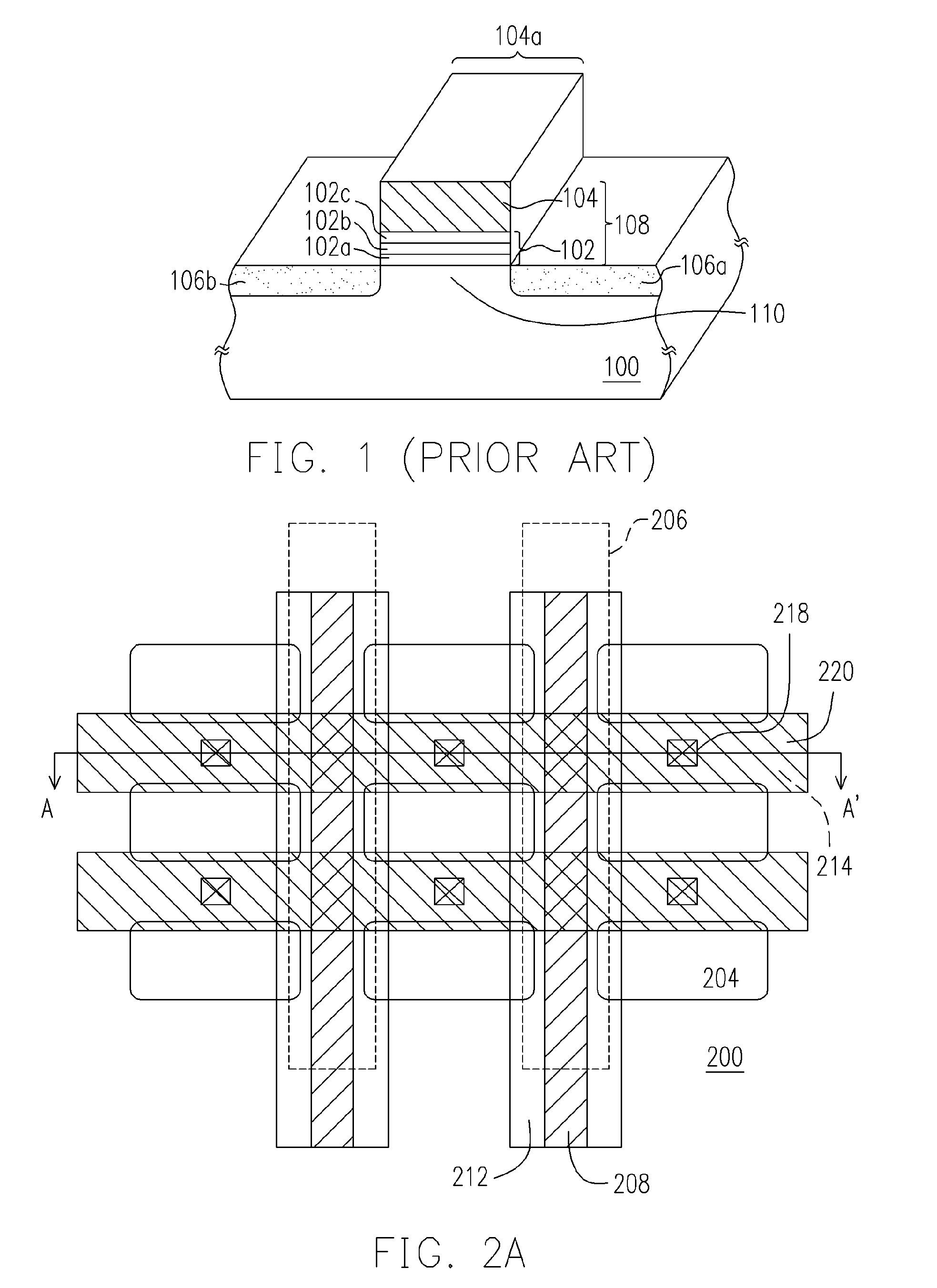

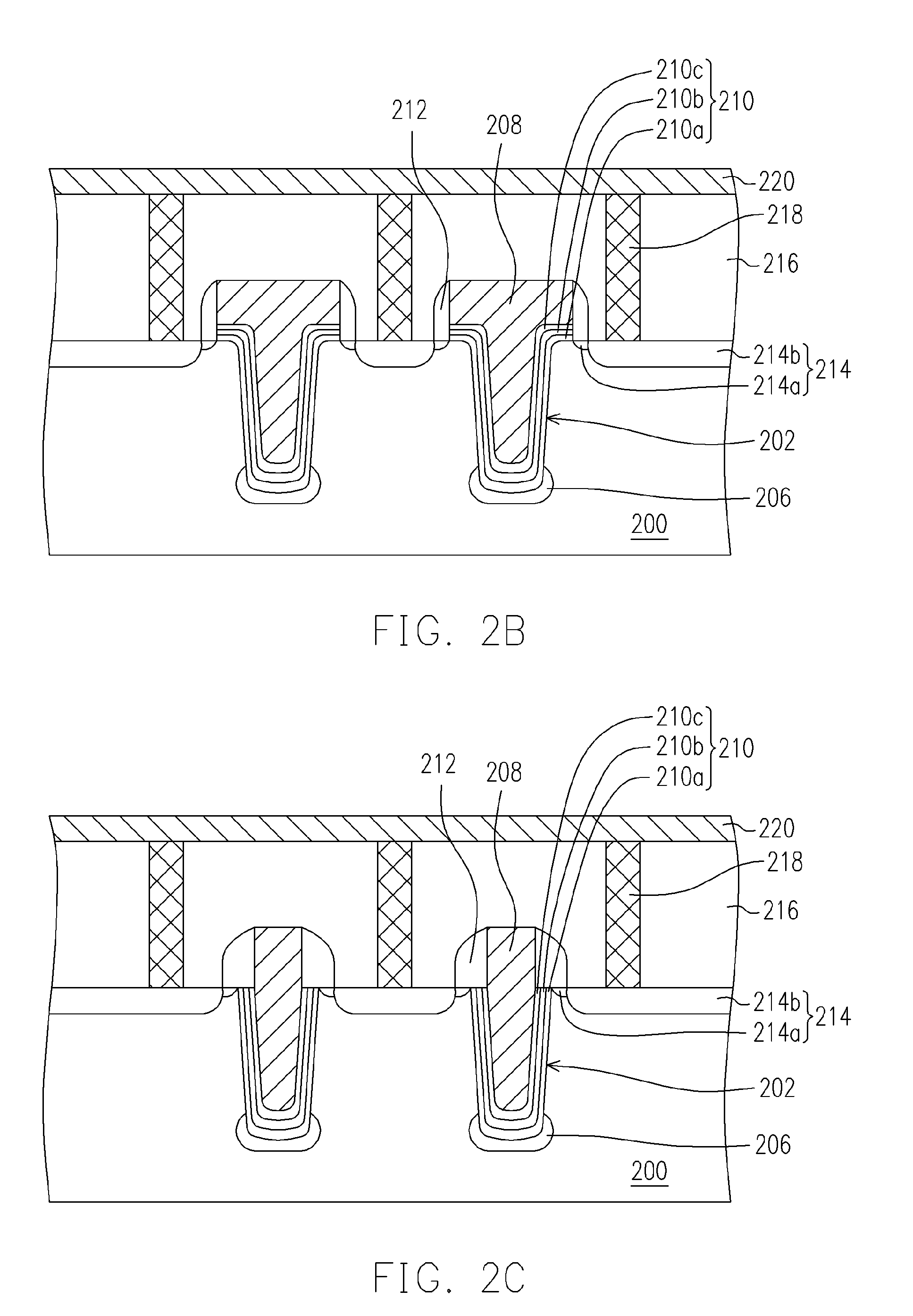

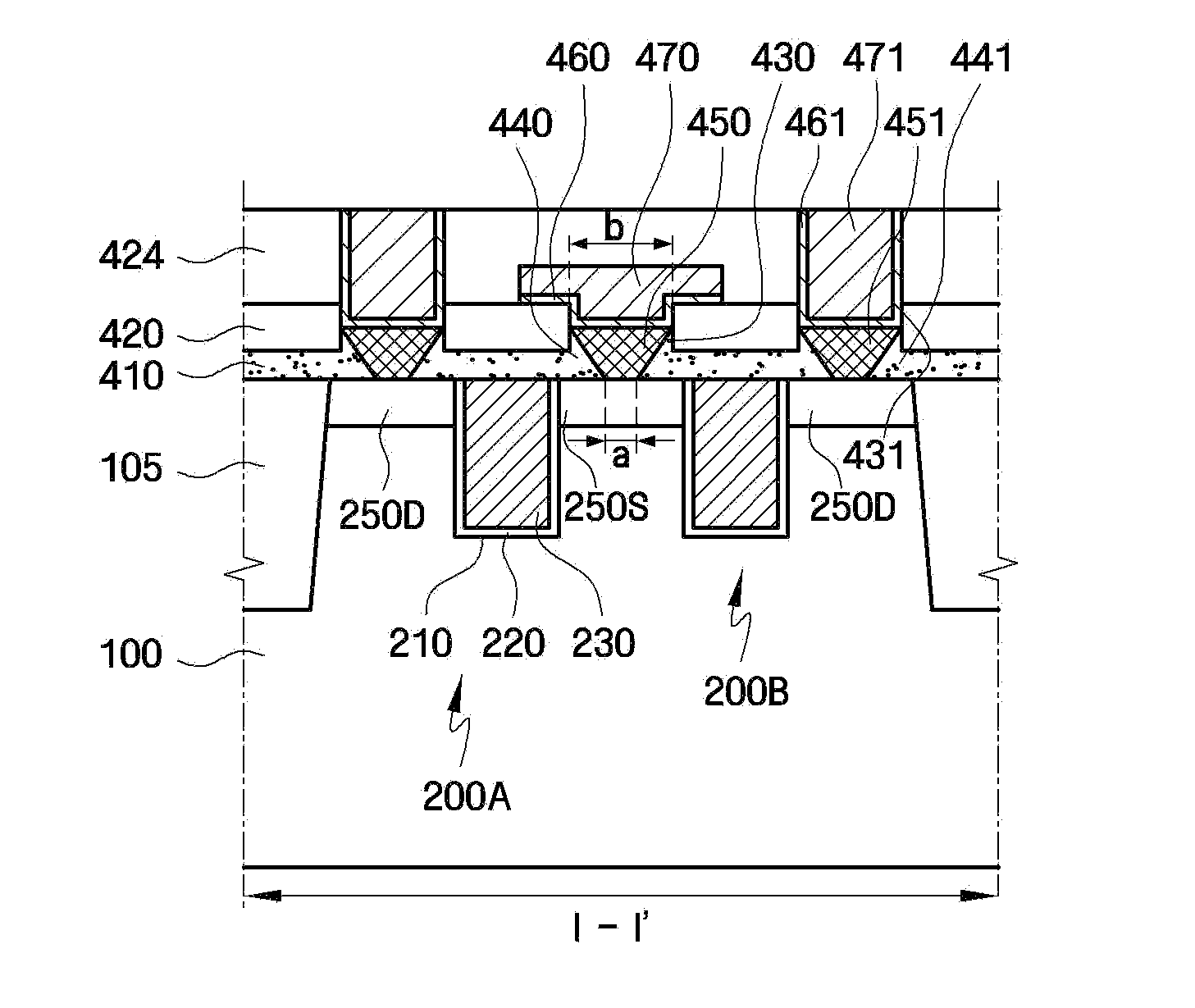

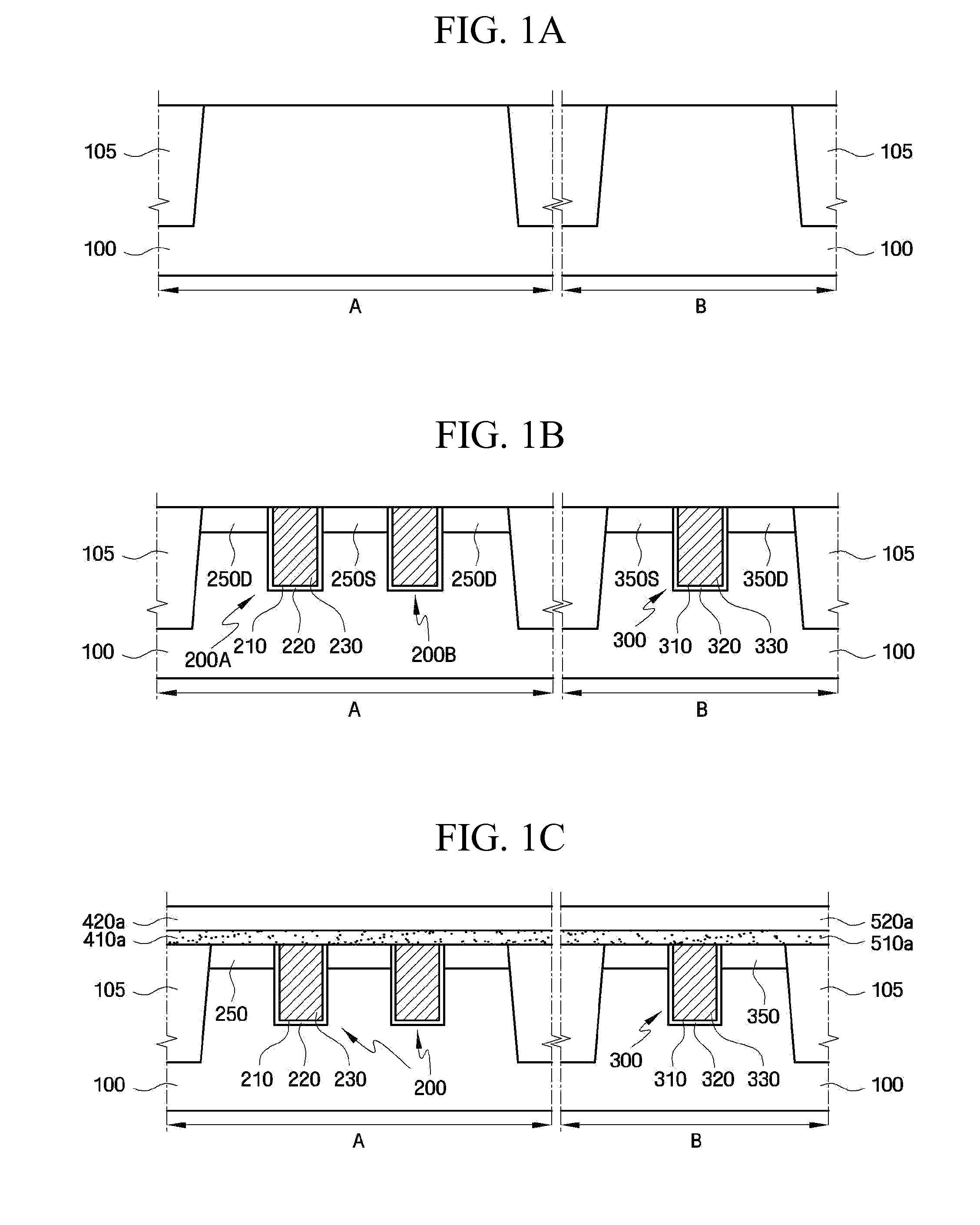

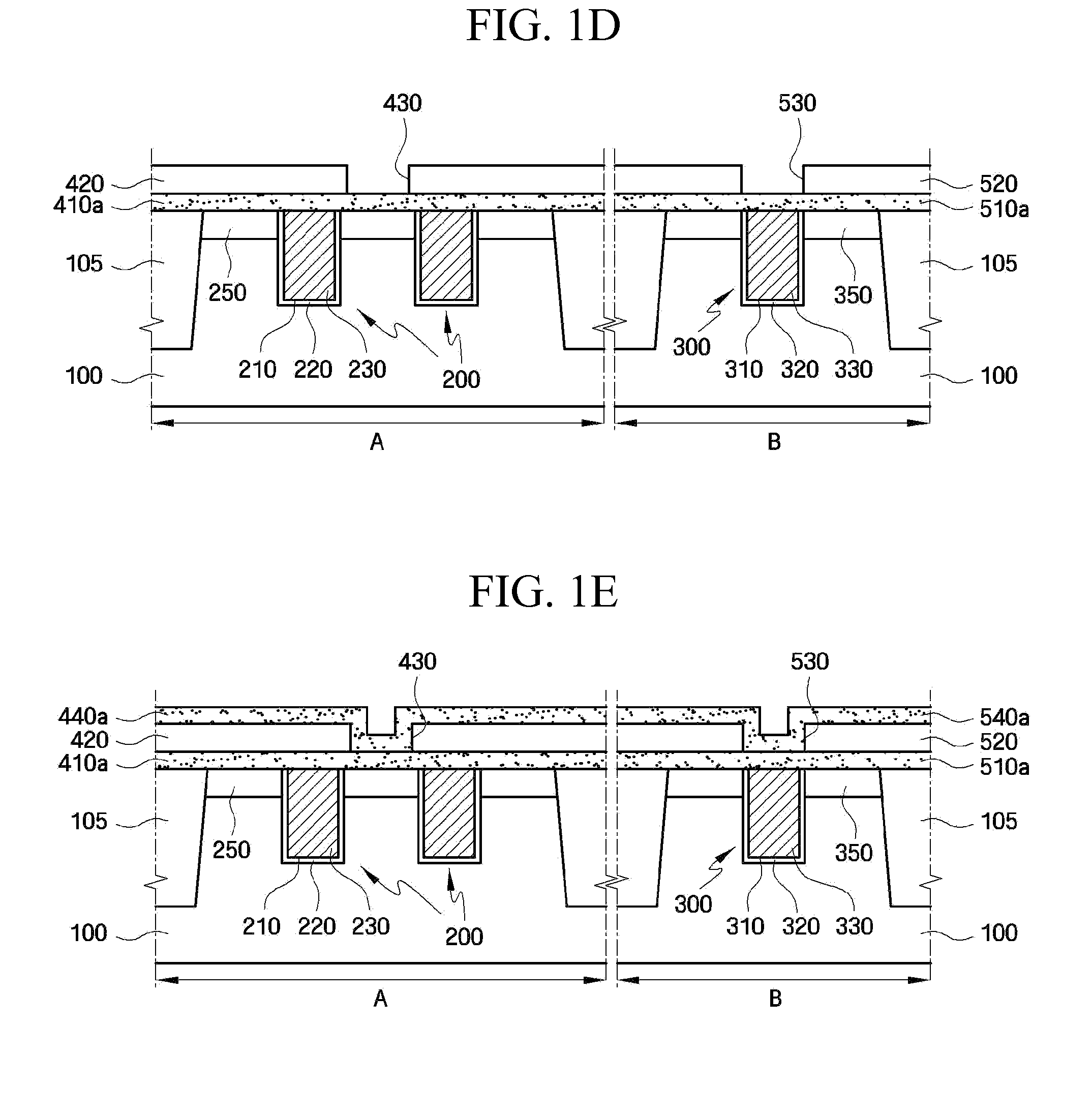

[NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof]

InactiveUS20050087892A1Simplify the manufacturing processIncrease speedTransistorSolid-state devicesBit lineComputer architecture

A NAND flash memory cell array including a plurality of memory cell row is provided. Each of memory cell row includes a plurality of memory cells disposed between first selecting transistor and second selecting transistor connected in series. Each memory cell has a tunneling dielectric layer, a floating gate, an inter-gate dielectric, a control gate and source / drain regions. An erase gate is disposed between two adjacent memory cells. A plurality of word lines serve to connect the memory cells in rows. A source line serves to connect the source region of the first transistor in a row, whereas a plurality of bit lines serve to connect the drain region of second transistor in a row. A first selecting gate line and a second selecting gate line serve to connect the gate of the first transistor in a row and the gate of second transistor in a row respectively. A plurality of erase gate lines is connected to the erase gates in a row.

Owner:POWERCHIP SEMICON CORP

Magnetic random access memory using schottky diode

InactiveUS6750540B2High equipment integrationTransistorSemiconductor/solid-state device detailsBit lineStatic random-access memory

Owner:SK HYNIX INC

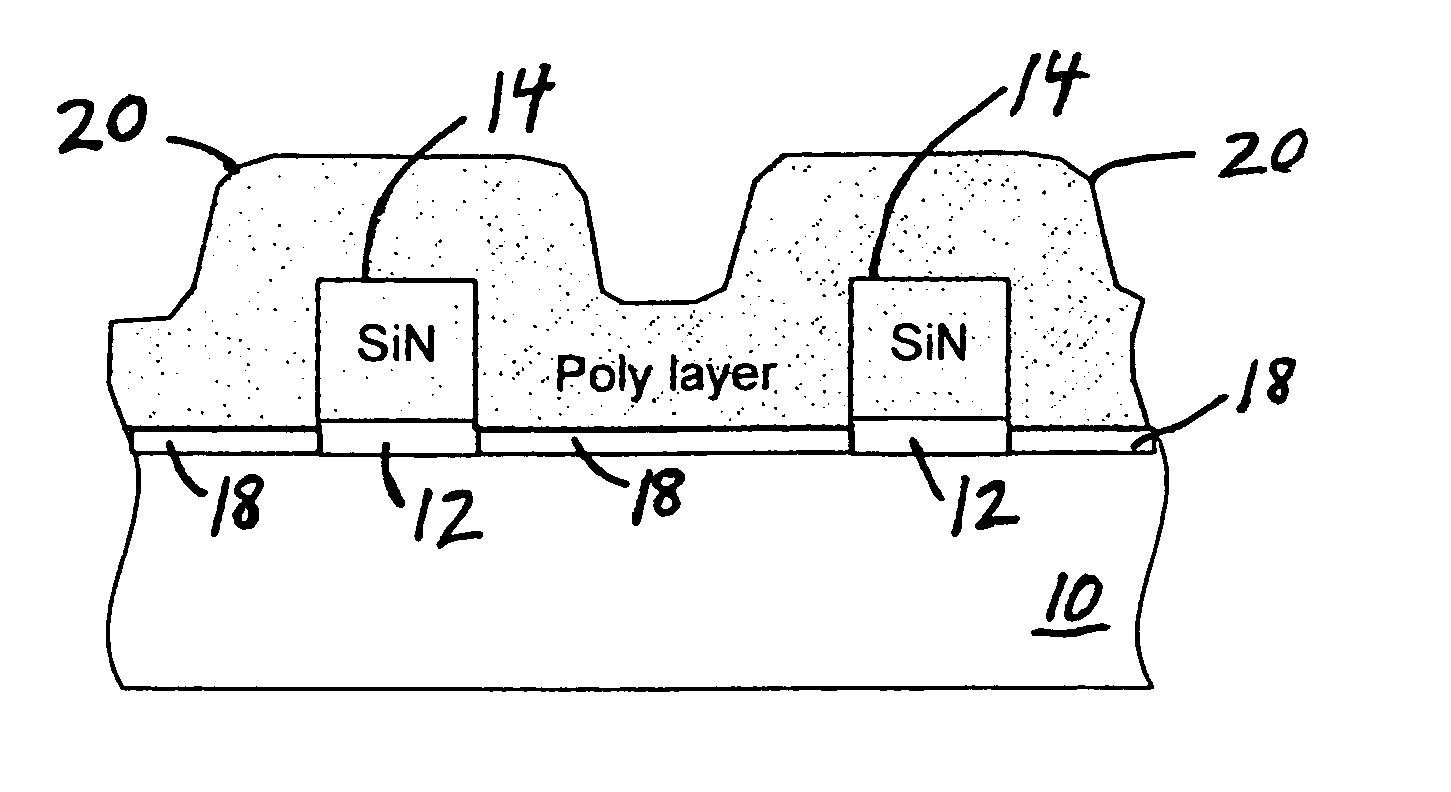

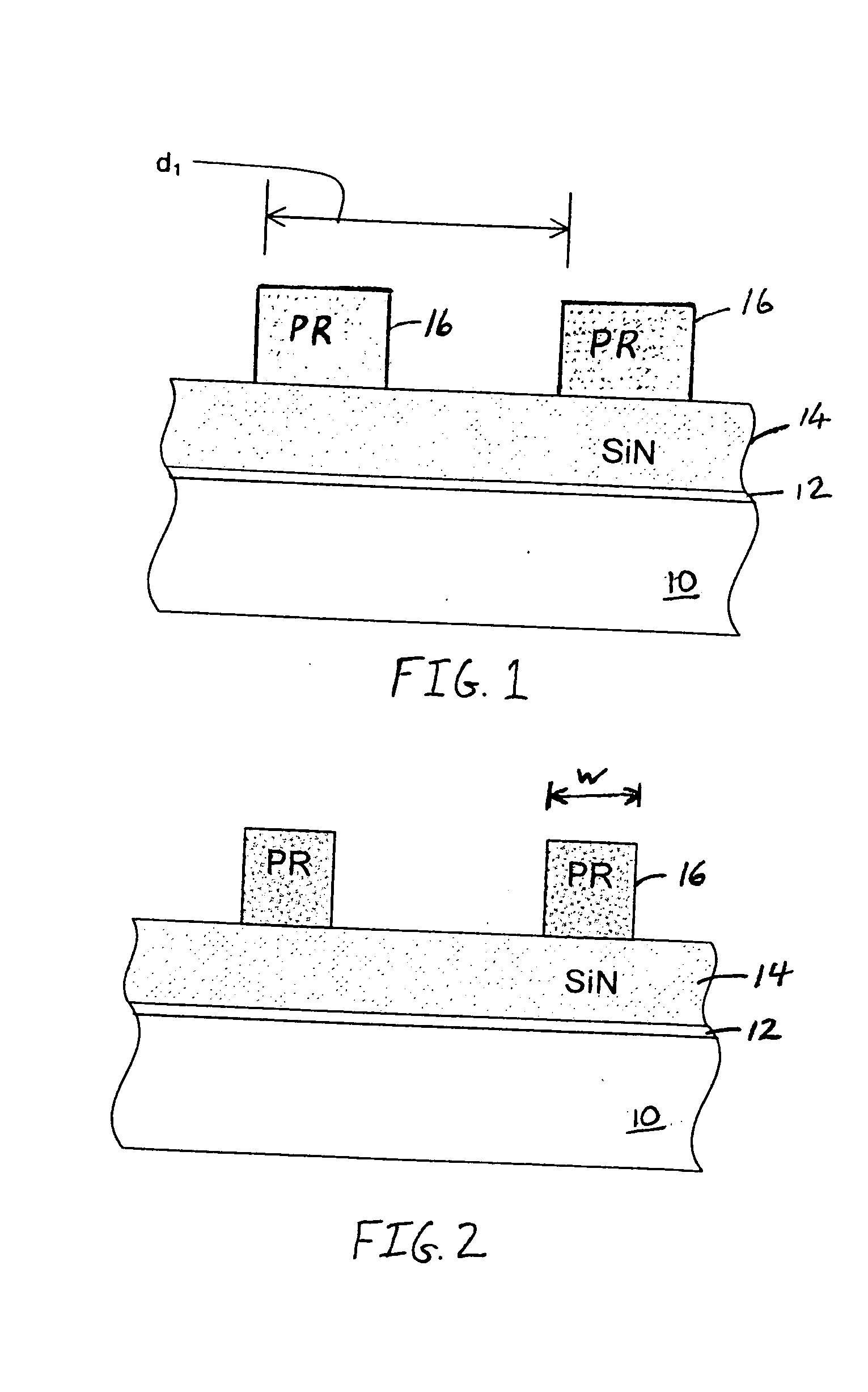

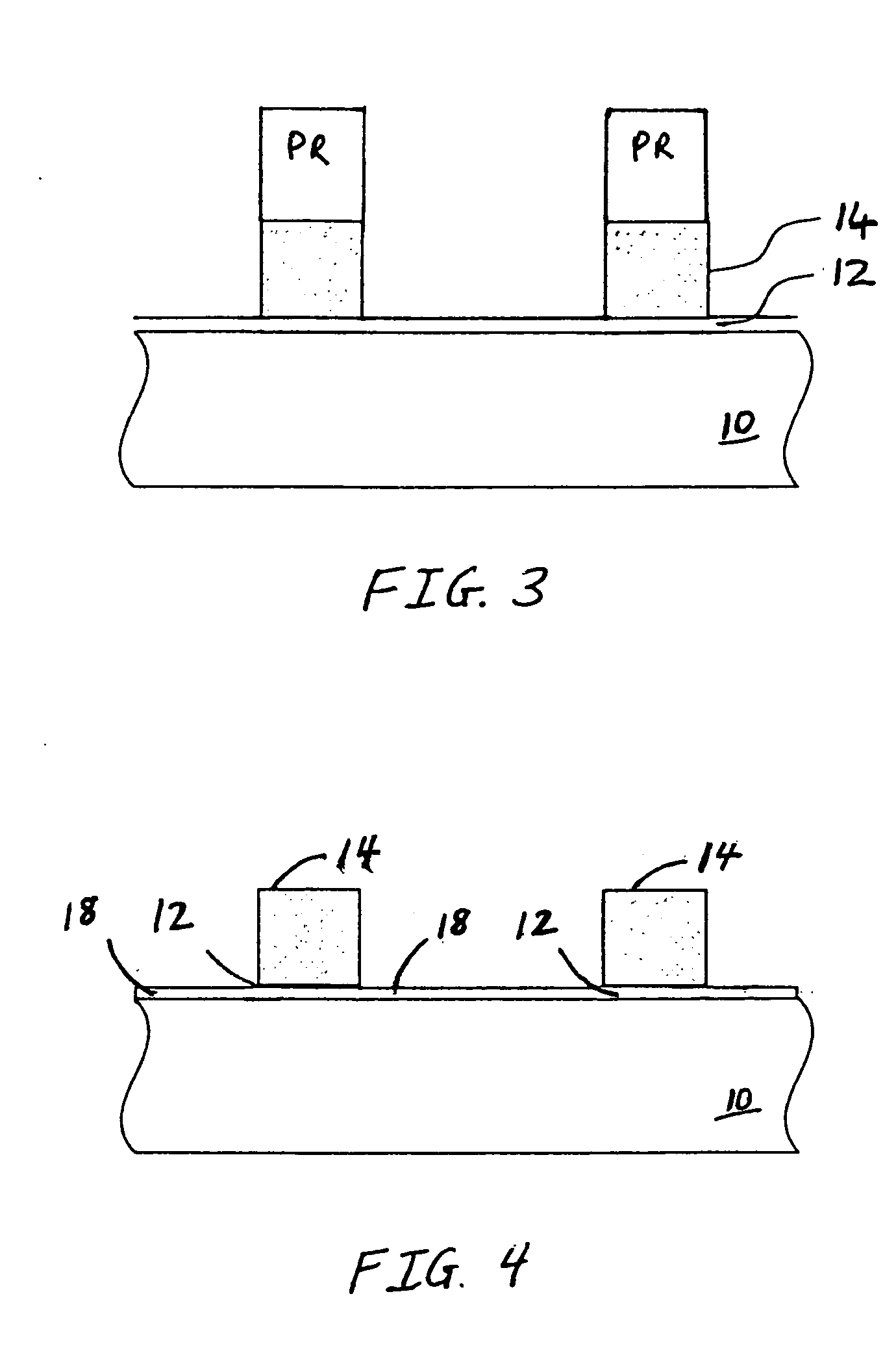

Methods for reducing cell pitch in semiconductor devices

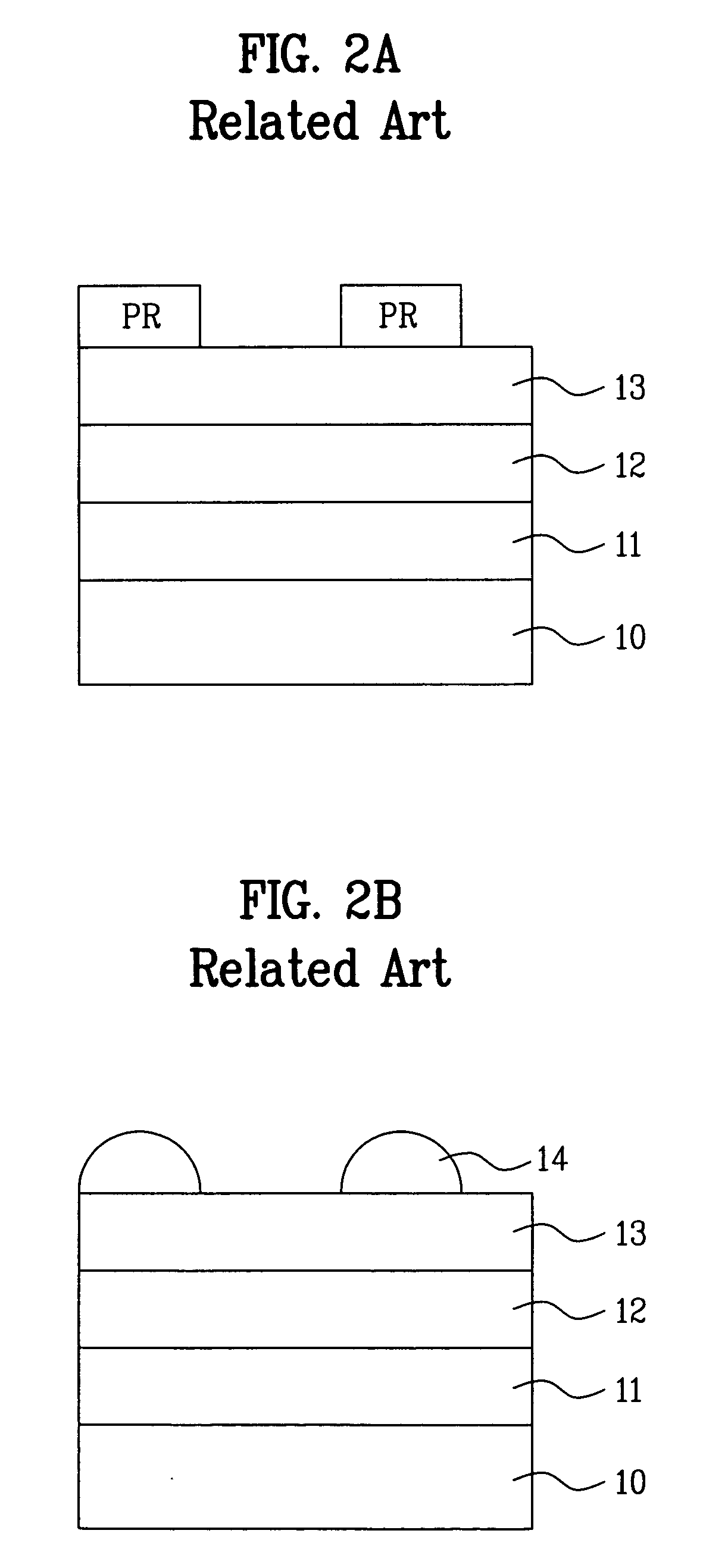

InactiveUS20050020043A1Reducing cell pitchReduced form requirementsSolid-state devicesSemiconductor/solid-state device manufacturingGate oxidePhotoresist

A method for forming a semiconductor device having a reduced pitch is provided. A pad oxide layer is formed on a substrate, and a silicon nitride layer is formed on the pad oxide layer. A trimmed photoresist layer is formed on the silicon nitride layer, and the silicon nitride layer is etched using the trimmed photoresist layer as an etch mask. The trimmed photoresist layer is removed until the silicon nitride layer is completely exposed, and an exposed portion of the pad oxide layer is removed until a portion of the substrate is exposed. A gate oxide layer is formed on the exposed portion of the substrate. A poly layer is deposited on the silicon nitride layer, and the poly layer is etched back to form a plurality of poly gates. Then, the silicon nitride layer is removed.

Owner:MACRONIX INT CO LTD

Semiconductor device and method of fabricating the same

ActiveUS6977417B2Improve roll-off characteristicReduce drain leakage currentTransistorAccounting/billing servicesSemiconductorCrystal

An impurity-diffused layer having an extension structure is formed first by implanting Sb ion as an impurity for forming a pocket region; then by implanting N as a diffusion-suppressive substance so as to produce two peaks in the vicinity of the interface with a gate electrode and at an amorphous / crystal interface which serves as an defect interface generated by the impurity in the pocket region; and by carrying out ion implantations for forming an extension region and deep source and drain regions.

Owner:FUJITSU SEMICON LTD

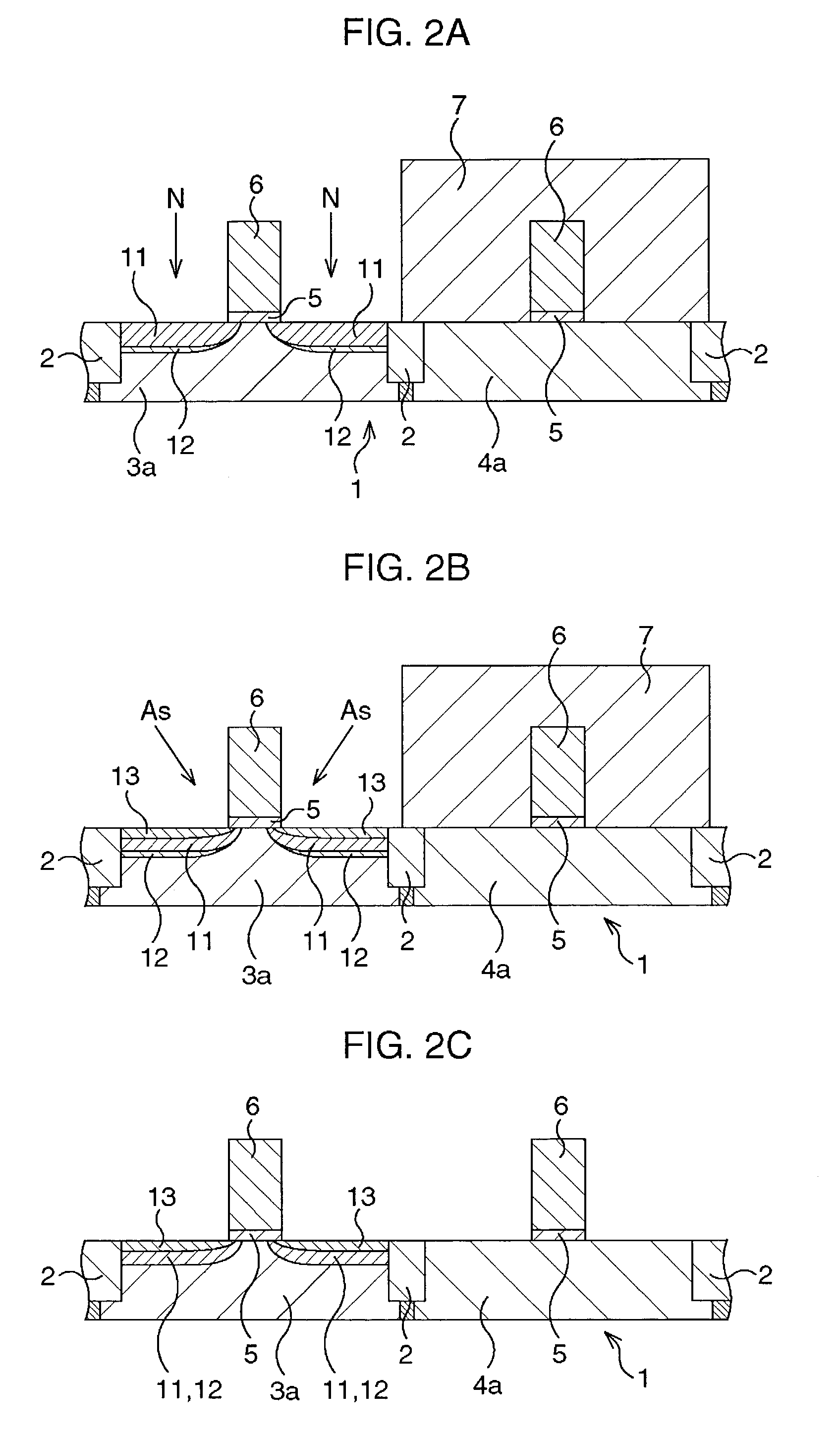

Dynamic performance testing system for fuel cell automobile power system

InactiveCN103207084AHigh equipment integrationGood versatilityVehicle testingEngine testingElectric driveAutomotive engineering

The invention relates to a dynamic performance testing system for a fuel cell automobile power system. The dynamic performance testing system comprises an environment simulation module, a noise vibration and harshness (NVH) test matching module, an engine hardware-in-loop test matching module for testing, an electric driving system hardware-in-loop test matching module for testing, an automobile power system hardware-in-loop test matching module for testing, an analogue simulation module, a power load parameter observe and control module and a master control management module. The environment simulation module and the NVH test matching module are used for providing actual working conditions. The analogue simulation module is used for simulating operation environment parameters of the actual working conditions under the software environment. The power load parameter observe and control module is used for testing and controlling the power parameters of the engine hardware-in-loop test matching module and load parameters of the electric driving system hardware-in-loop test matching module. The master control management module is connected with the other modules and used for controlling and saving the testing data in real time. Compared with the prior art, the dynamic performance testing system is high in integrity and good in generality, can simulate the actual working conditions, and can comprehensively take the influence of the hot environment and the vibration noise environment on the fuel cell automobile power system into account.

Owner:TONGJI UNIV

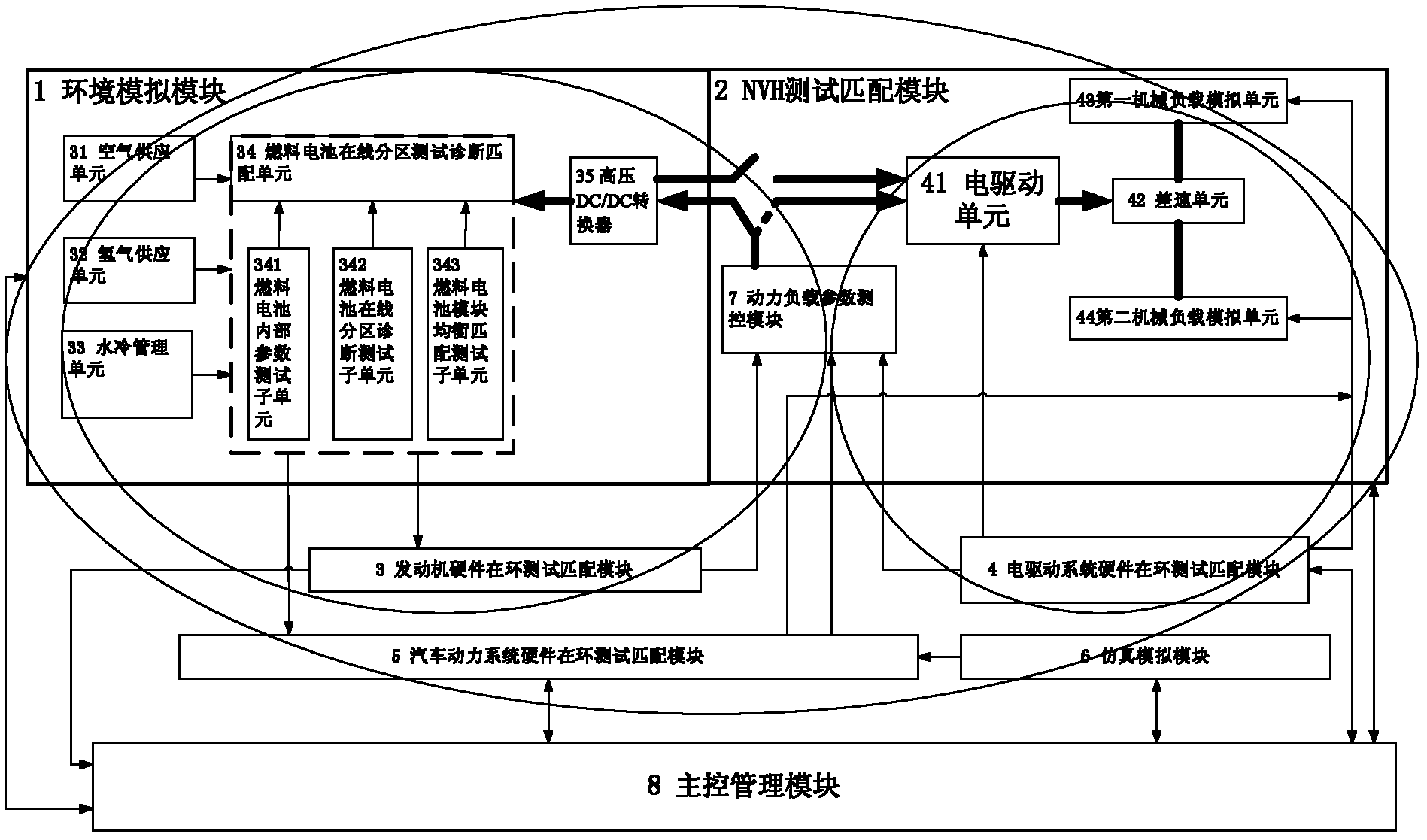

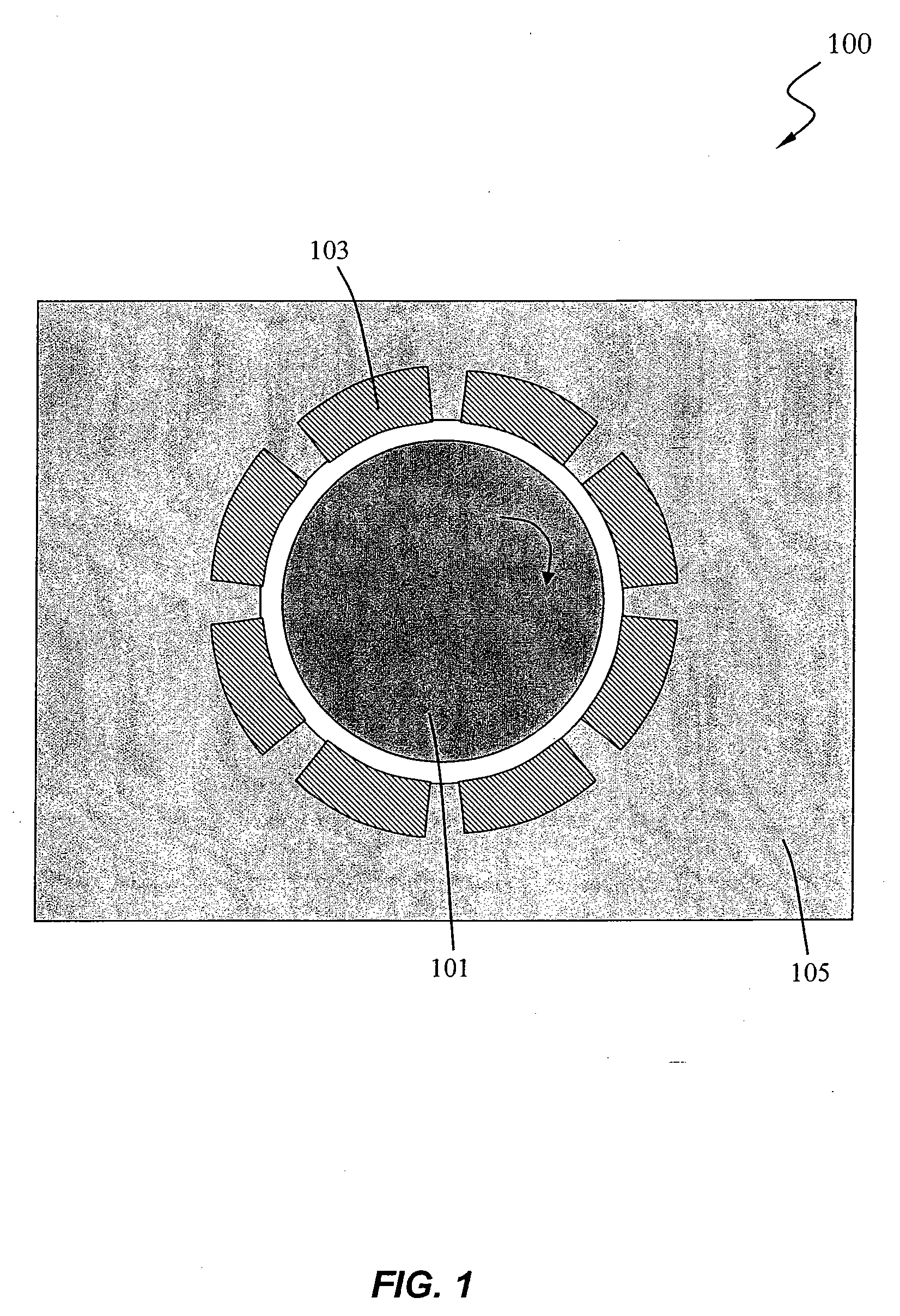

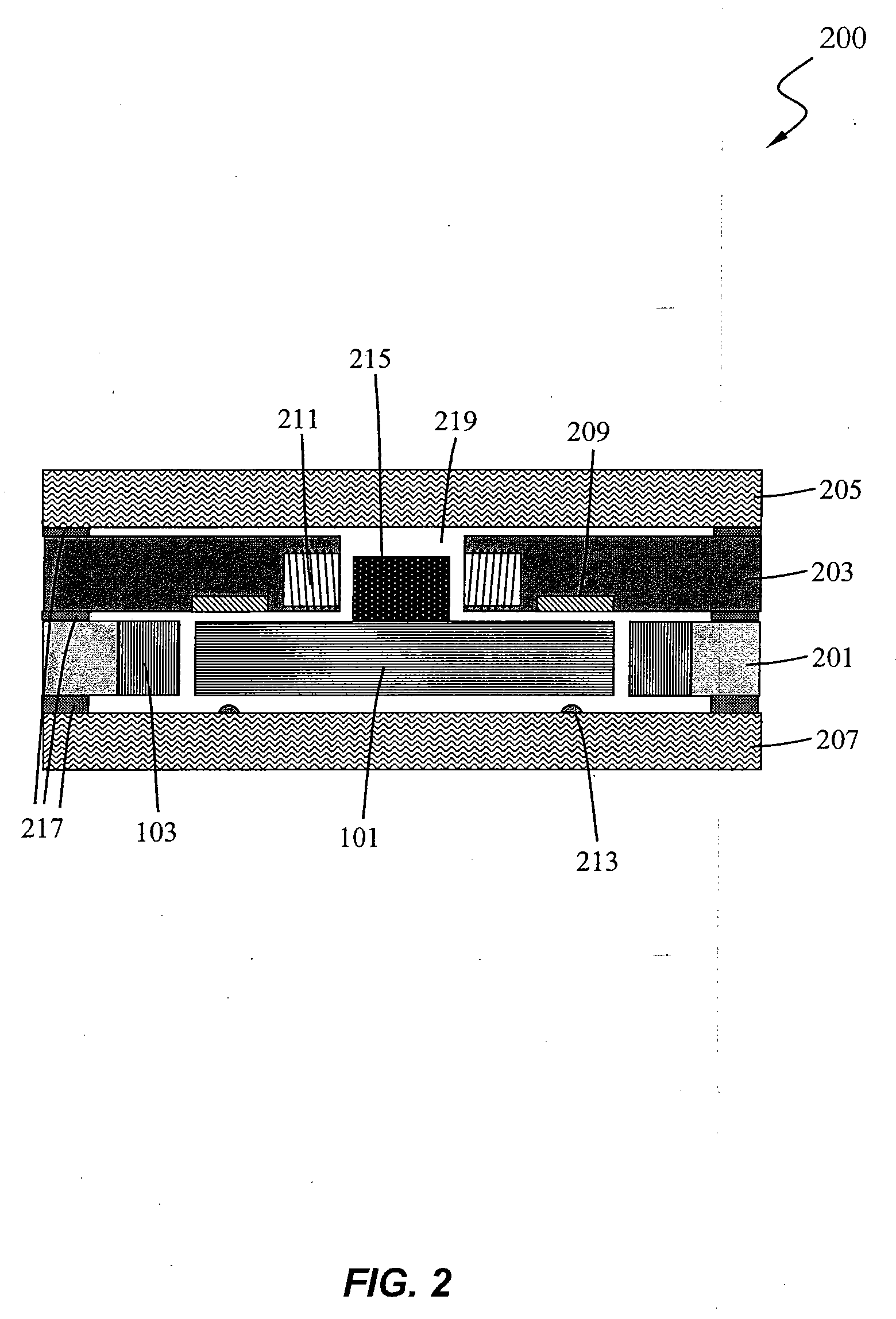

Method and Structure for Integrated Energy Storage Device

InactiveUS20070103009A1High tensile strengthHigh tensile stressMechanical energy handlingElectrostatic motorsFlywheel energy storage systemHigh energy

The present invention relates to a method and device for fabricating an integrated flywheel device using semiconductor materials and IC / MEMS processes. Single crystal silicon has high energy storage / weight ratio and no defects. Single crystal silicon flywheel can operate at much higher speed than conventional flywheel. The integrated silicon flywheel is operated by electrostatic motor and supported by electrostatic bearings, which consume much less power than magnetic actuation in conventional flywheel energy storage systems. The silicon flywheel device is fabricated by IC and MEMS processes to achieve high device integration and low manufacturing cost. For the integrated silicon flywheel, high vacuum can be achieved using hermetic bonding methods such as eutectic, fusion, glass frit, SOG, anodic, covalent, etc. To achieve larger energy capacity, an array of silicon flywheels is fabricated on one substrate. Multiple layers of flywheel energy storage devices are stacked.

Owner:YANG XIAO CHARLES

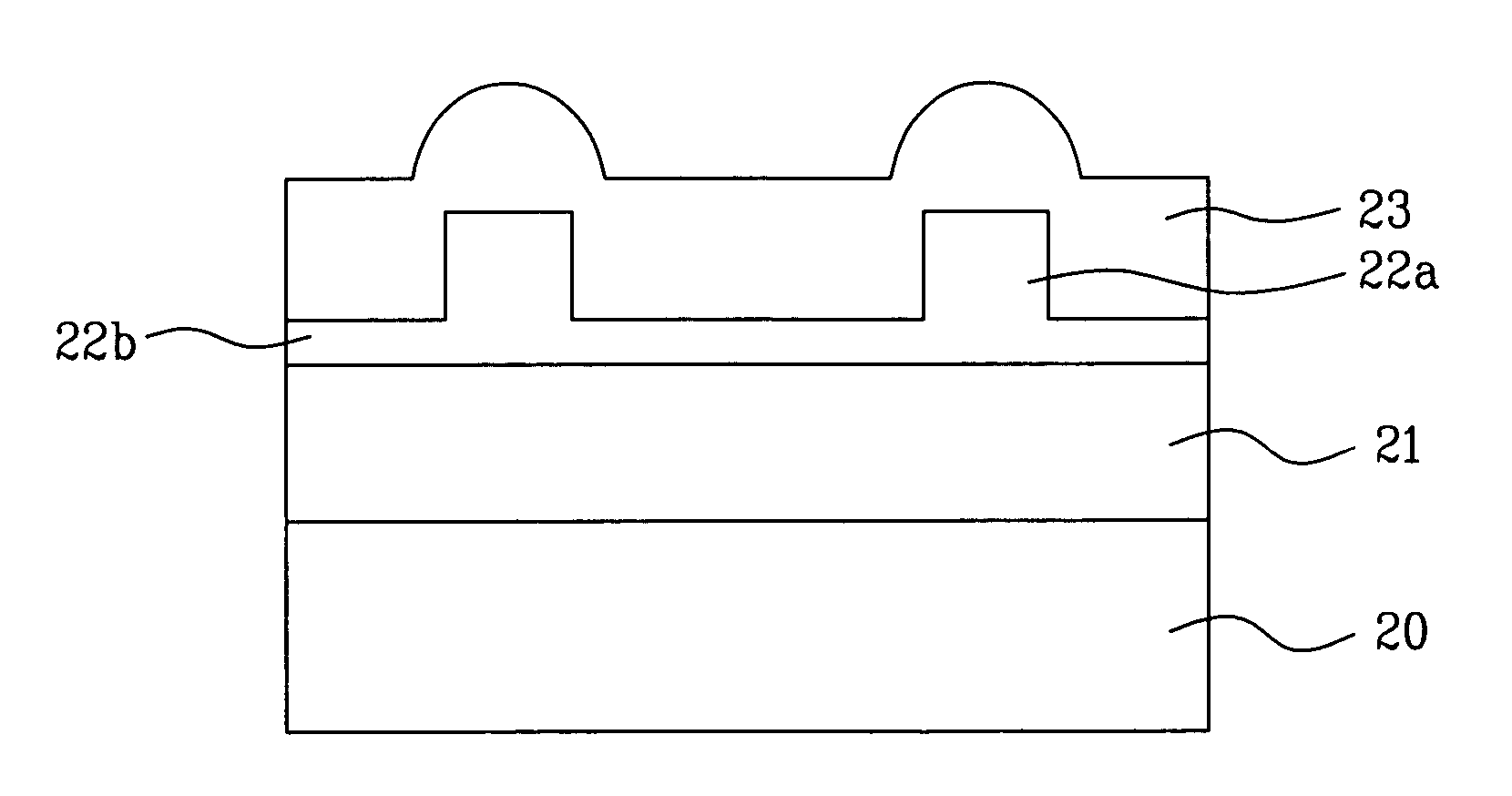

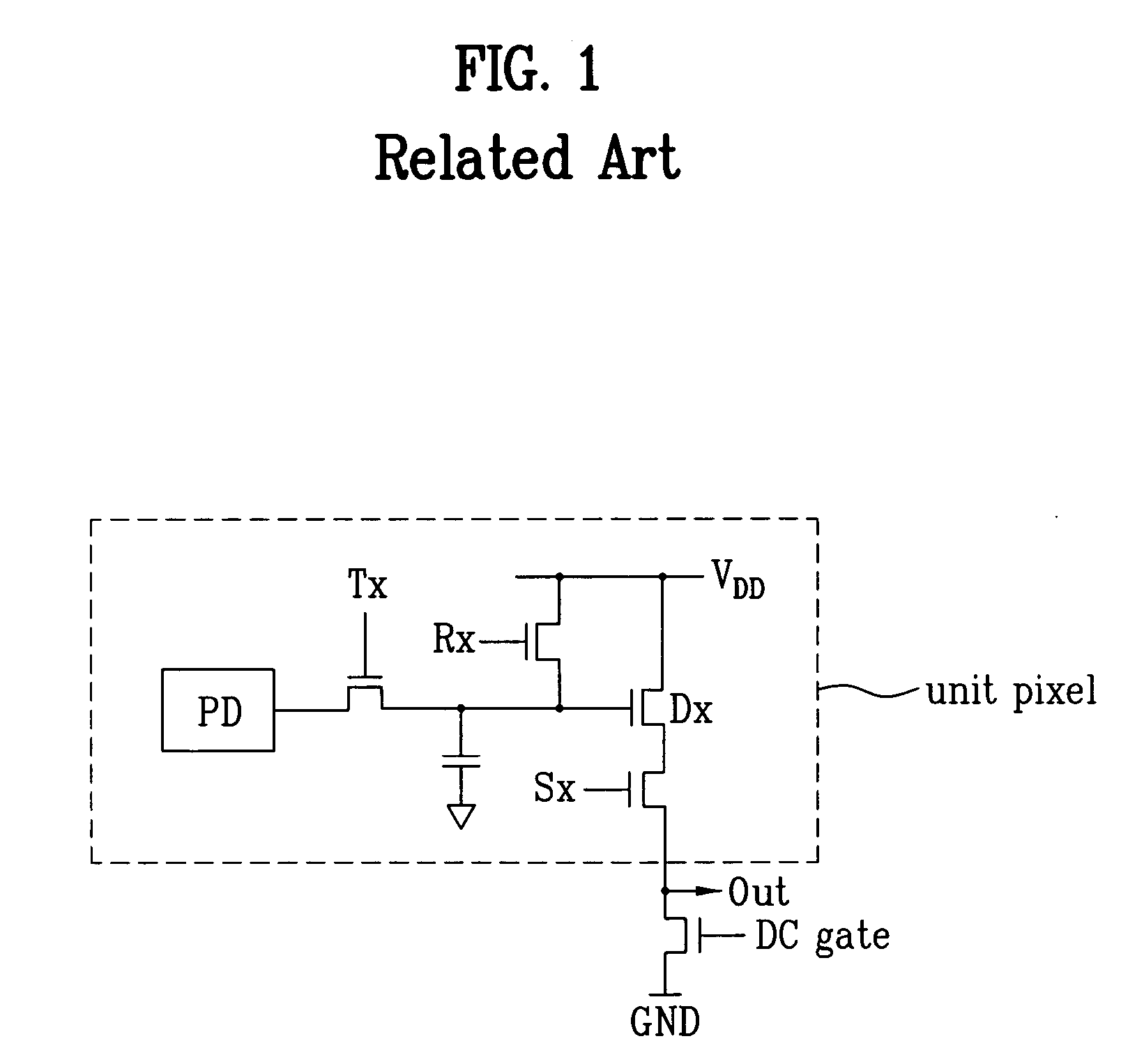

CMOS image sensor and method for fabricating the same

InactiveUS20060012001A1Reduce radius of curvatureHigh equipment integrationSolid-state devicesSemiconductor/solid-state device manufacturingCMOSPhotodiode

A complementary metal-oxide semiconductor (CMOS) image sensor and a method for fabricating the same are disclosed. The image sensor includes a sub-layer having a photodiode and a plurality of transistors formed thereon, a pad insulating layer formed on the sub-layer, a micro-lens formed on the pad insulating layer, the micro-lens including a first insulating layer having an uneven surface and a second insulating layer covering upper and side surfaces of a projected portion of the first insulating layer to form a dome shape, and a planarization layer formed on the micro-lens, and a color filter formed on the planarization layer.

Owner:DONGBU ELECTRONICS CO LTD

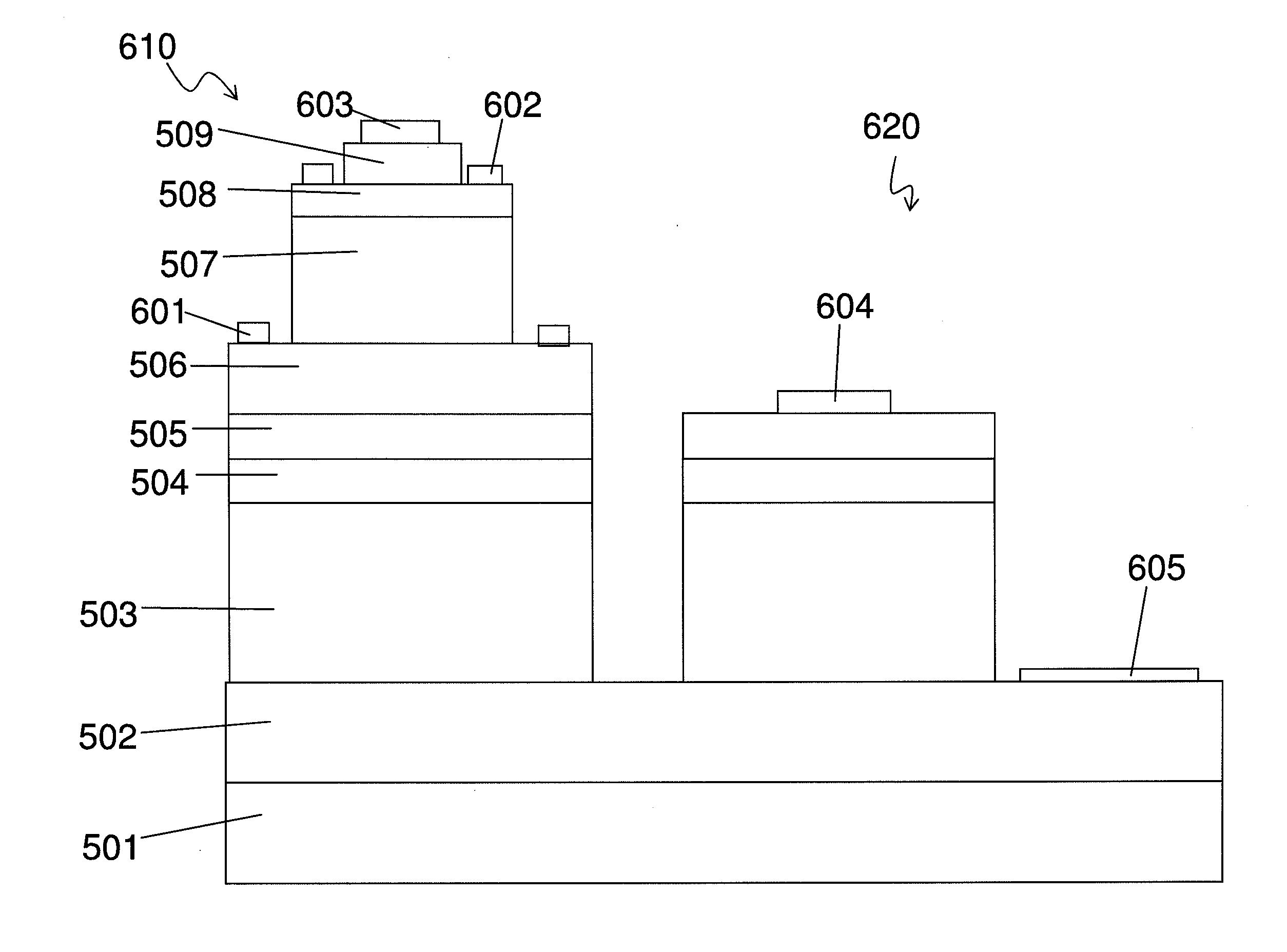

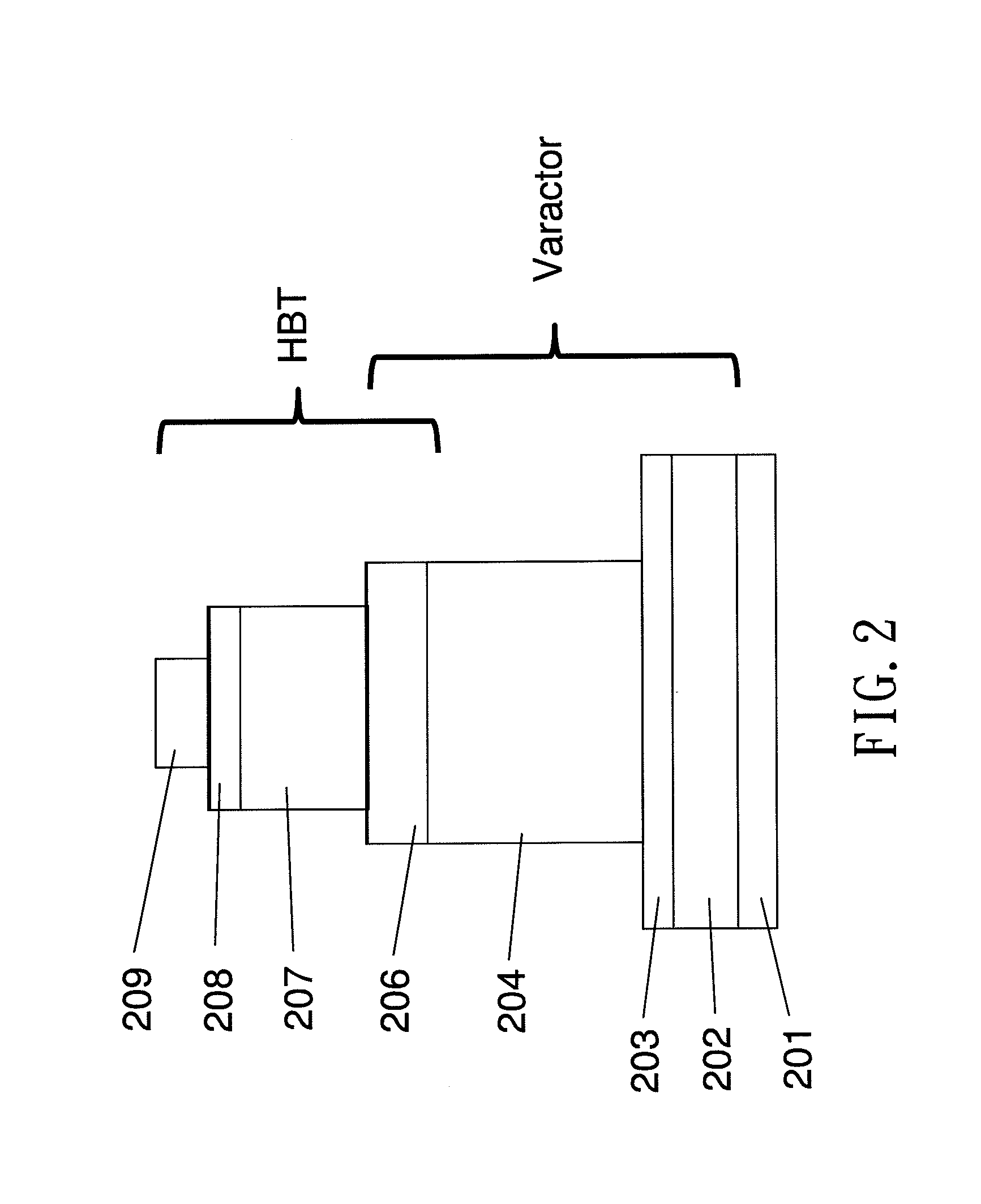

Integrated structure of compound semiconductor devices

ActiveUS20130334570A1High breakdown voltageLow leakage currentSolid-state devicesSemiconductor devicesVaricapPower semiconductor device

An integrated structure of compound semiconductor devices is disclosed. The integrated structure comprises from bottom to top a substrate, a first epitaxial layer, an etching-stop layer, a second epitaxial layer, a sub-collector layer, a collector layer, a base layer, and an emitter layer, in which the first epitaxial layer is a p-type doped layer, the second epitaxial layer is an n-type graded doping layer with a gradually increased or decreased doping concentration, and the sub-collector layer is an n-type doped layer. The integrated structure can be used to form an HBT, a varactor, or an MESFET.

Owner:WIN SEMICON

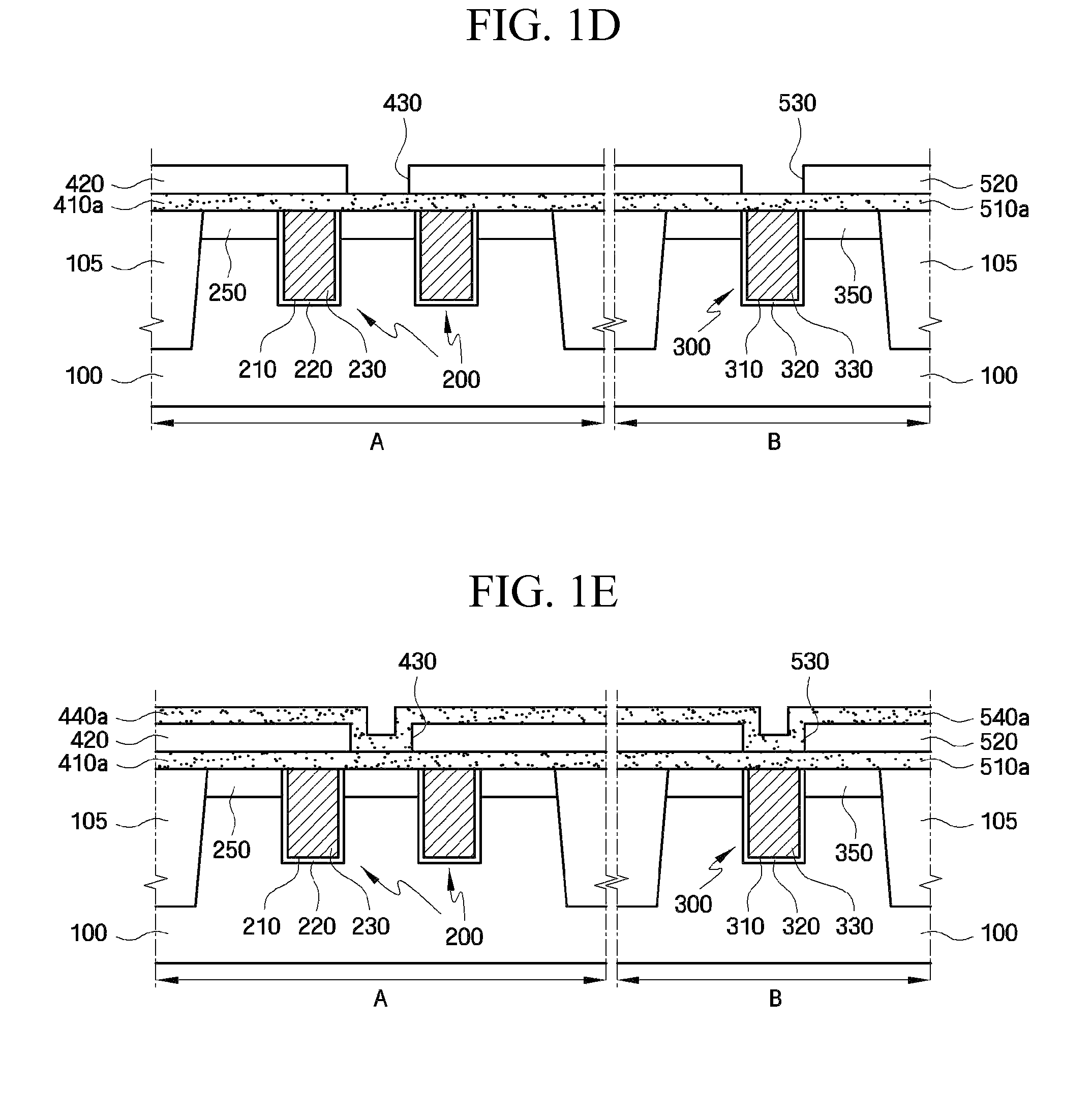

Semiconductor device and method for fabricating the same

InactiveUS20060160295A1Excellent electrical propertiesEffective preventionTransistorSemiconductor/solid-state device detailsDevice materialSemiconductor

A semiconductor device and a method for fabricating the same are provided. The provided semiconductor device includes a field oxide layer formed in a semiconductor substrate to define an active region; gate structures formed on the active region; source / drain junctions formed on either side of the gate structures on the semiconductor substrate; a channel silicon layer arranged under the gate insulating layer to operate as a channel for connecting sources and drains; and buried junction isolation insulating layers under the channel silicon layer. The buried junction isolation insulating layers isolate source / drain junction regions of a MOS transistor, so that a short circuit in a bulk region under the channel of a transistor due to the high-integration of the device can be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

Non-volatile memory cell and manufacturing method thereof

ActiveUS7038267B2Highly integratedImprove the coupling ratioTransistorSolid-state devicesTrappingDielectric layer

Owner:POWERCHIP SEMICON MFG CORP

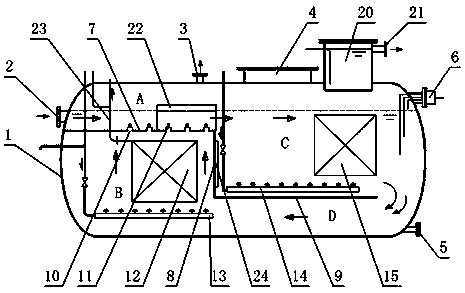

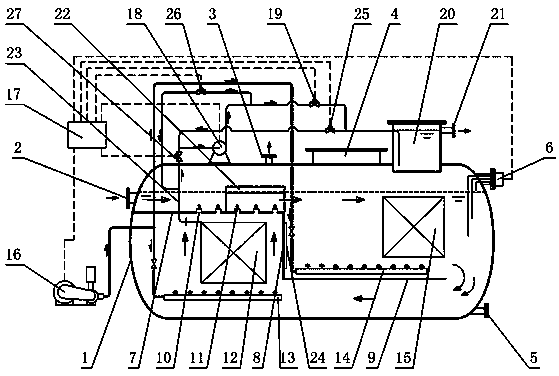

Sewage treatment device

ActiveCN104016474AGood effectHigh equipment integrationTreatment using aerobic processesSustainable biological treatmentPipingSmall footprint

The invention discloses a sewage treatment device, comprising a fan, a water pump and a tank body. The upper part of the tank body is provided with a sewage inlet and an exhaust port; a Z shape separator is fixed inside the tank below the sewage inlet; the Z shape separator comprises an upper baffle plate, a vertical baffle plate, a lower baffle plate, and divides the tank body into four regions; the upper baffle plate is provided with a plurality of reflux holes, the reflux holes are equipped with anti-reflux nozzles for preventing the water above the upper baffle plate from flowing to the lower position; a membrane module is fixed below the upper baffle plate, and a hanging membrane packing assembly is fixed above the lower baffle plate; a left aeration device is fixed below the membrane assembly, and is connected with a fan outside the tank body through a gas supply pipeline; a water inlet of the water pump outside the tank body is connected with a membrane assembly water outlet duct through a water pipes; and the gas supply pipeline and the water pipe are equipped with installation valves. The device integrates two sewage treatment technology and equipment of biological membrane method and a membrane bioreactor, and has the advantages of small land occupation, and low investment and operating cost.

Owner:宁波中车时代电气设备有限公司

Nonvolatile semiconductor memory device having excellent charge retention and manufacturing process of the same

InactiveUS20070155099A1Improve charge retention characteristicsHigh speedNanotechSemiconductor/solid-state device manufacturingCharge retentionManufacturing technology

There has been a problem in conventional Si-type floating-gate type nonvolatile semiconductor memory devices that the charge retention characteristic is low due to insufficiently large electron affinity of Si, therefore improvement of the memory performances, such as scaling down of a memory cell and increasing operation speed, have been difficult to be achieved due to the essential problem. In order to solve the above problem, in the nonvolatile semiconductor memory device of the present invention, a material having large work function or large electron affinity or a material having a work function close to that of semiconductor substrate or of a control gate, is employed for a floating gate retaining charges. Further, an amorphous material having small electron affinity for an insulating matrix is used. Further, at a time of deposition of charge retention layer, the supply ratio of the nano-particle material and the insulating matrix material, such as the mixture ratio of materials of both phases in a target in a sputtering method, is adjusted. By these methods, the charge retention characteristic of the floating-gate type nonvolatile semiconductor memory device can be improved, and the above-mentioned problem of the nonvolatile semiconductor memory device can be solved.

Owner:ASAHI GLASS CO LTD +1

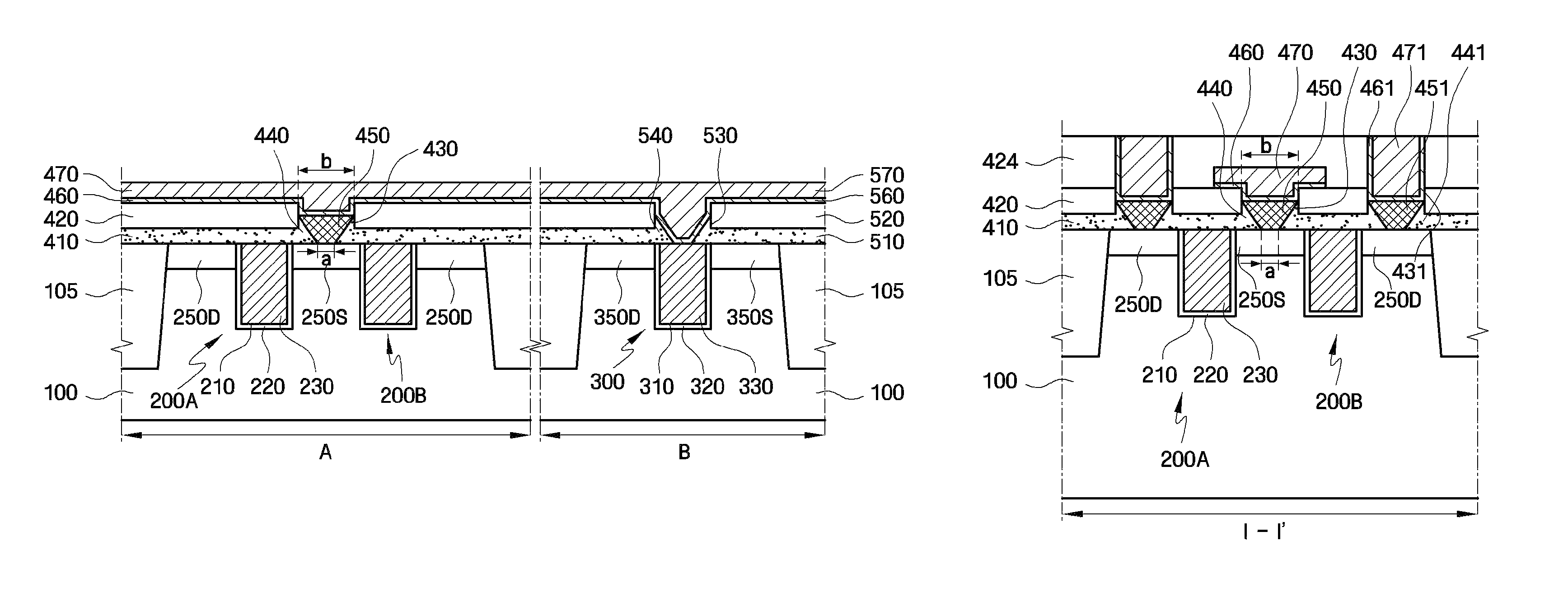

Semiconductor integrated circuit devices and fabrication methods thereof

ActiveUS20090020808A1Easy to separateImprove critical dimensionsTransistorSolid-state devicesInsulation layerEngineering

A memory cell of memory device, comprises an active region of a memory cell defined in a semiconductor substrate, and a conductive gate electrode in a trench of the active region. The gate electrode is isolated from the semiconductor substrate. An insulation layer is on the active region and on the conductive gate electrode. A conductive contact is in the insulation layer on the active region at a side of the gate electrode and isolated from the gate electrode. The contact has a first width at a top portion thereof and a second width at a bottom portion thereof, the first width being greater than the second width. The contact is formed of a single-crystal material.

Owner:IMBERATEK LLC

Semiconductor device and method for fabricating the same

InactiveUS7416937B2Minimized in sizeHigh equipment integrationTransistorSolid-state devicesProper functionEngineering

A method creates semiconductor device in which a storage dielectric film and a storage electrode included in the capacitor is transferred from an inactive region of a semiconductor substrate to the active region thereof, i.e., into a device isolating trench such that the capacitor is prevented from unnecessarily occupying an active region of a semiconductor substrate while maintaining its proper function. In contrast to a conventional device where a capacitor is formed in the active region of the semiconductor substrate, to the capacitor is formed in the inactive region according to this process. Accordingly, the capacitor is able to maintain a trench structure without needing to perform a step of removal of a step height difference, and the active region is minimized in size. Therefore, without having a problem of a step height increase, a finished semiconductor device is able to accommodate modern demands for increased device interpretation.

Owner:DONGBU ELECTRONICS CO LTD

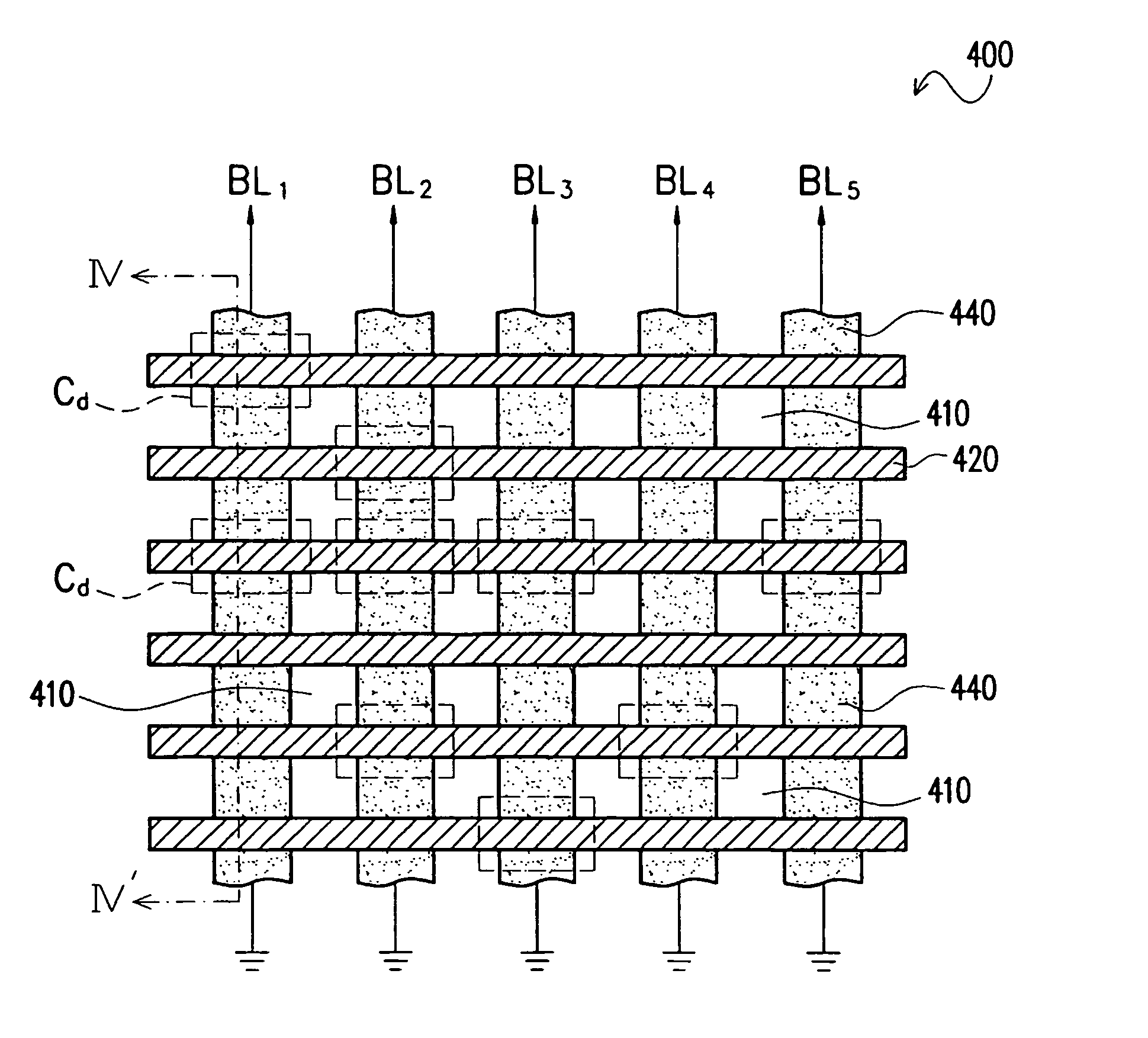

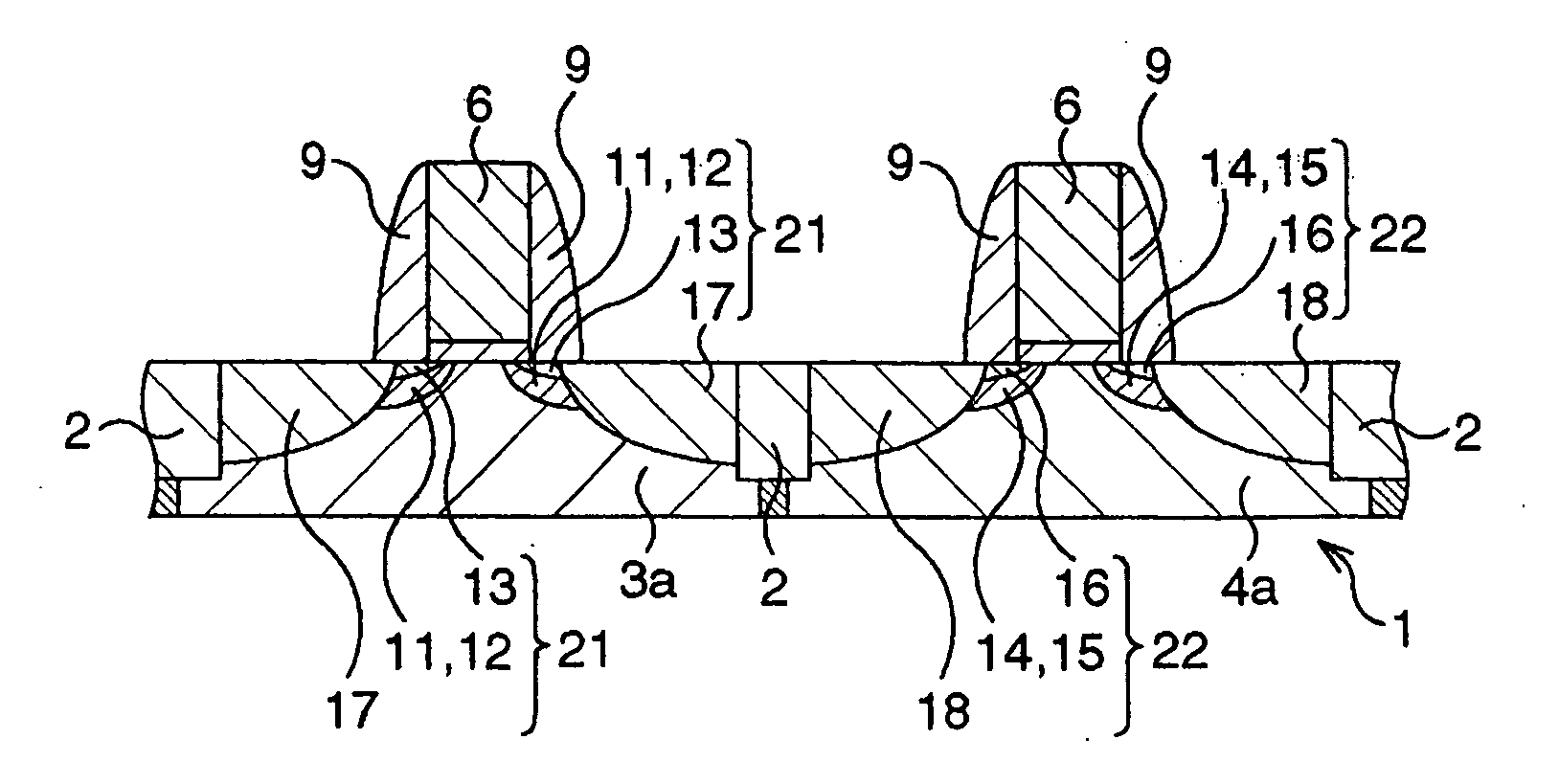

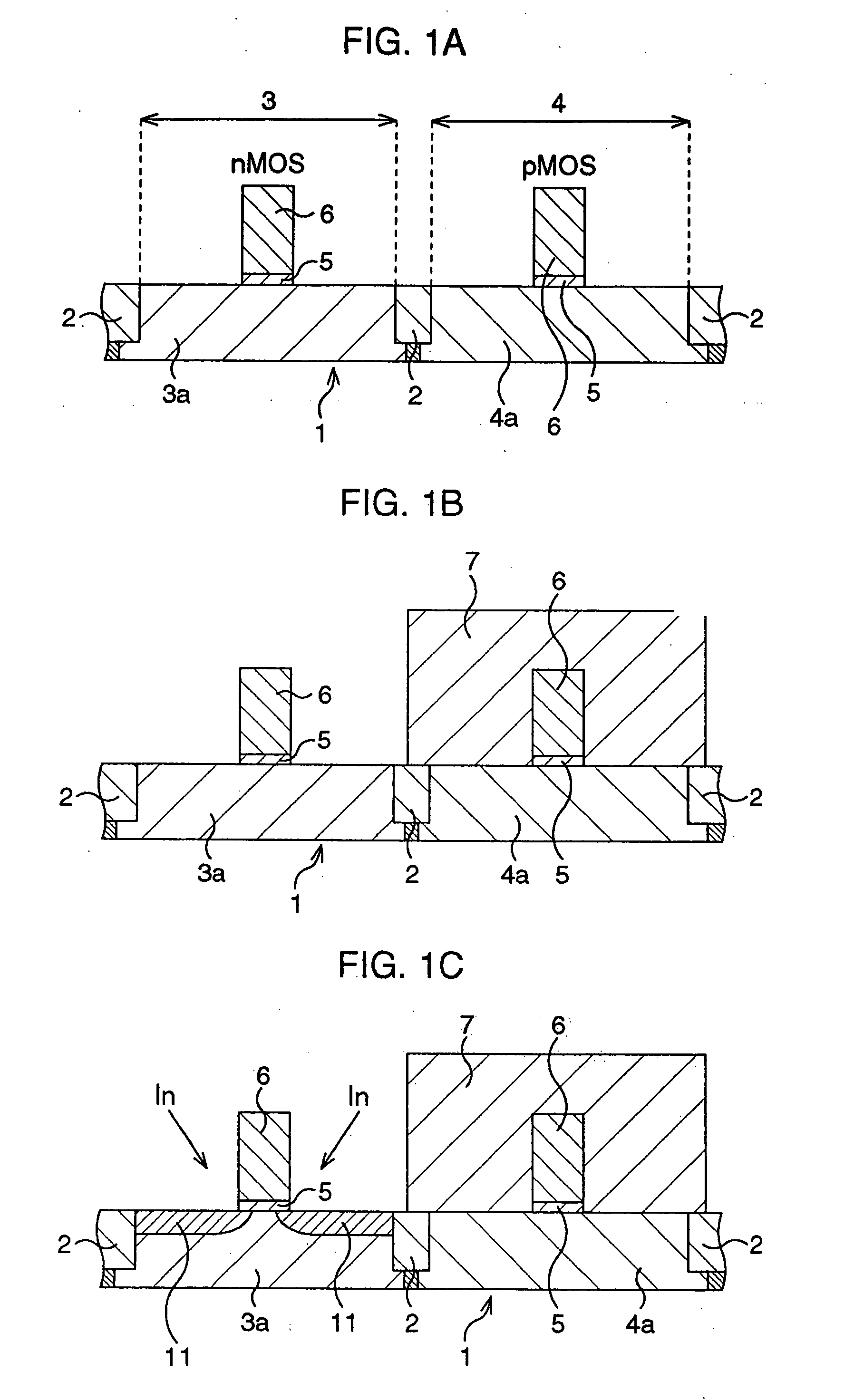

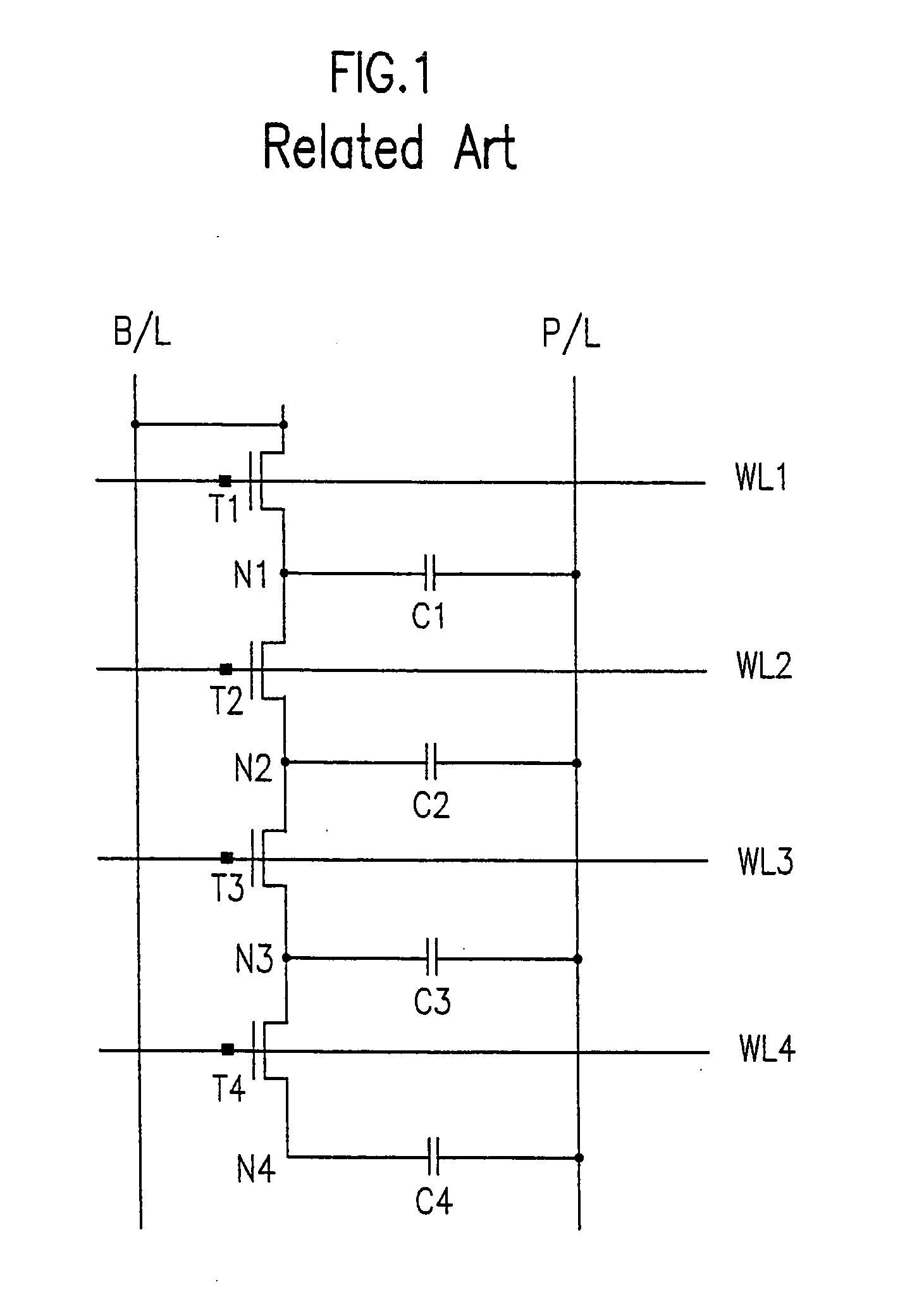

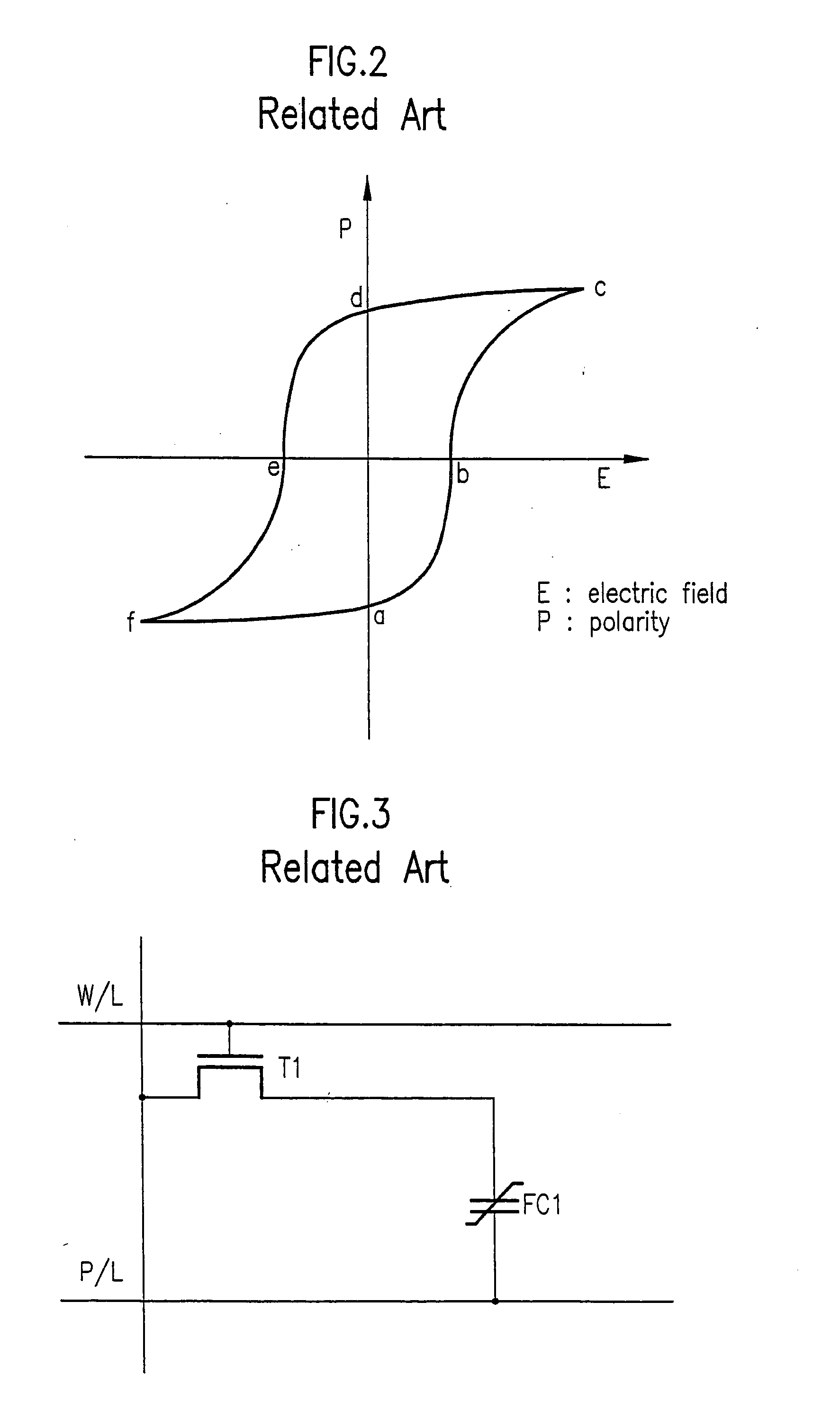

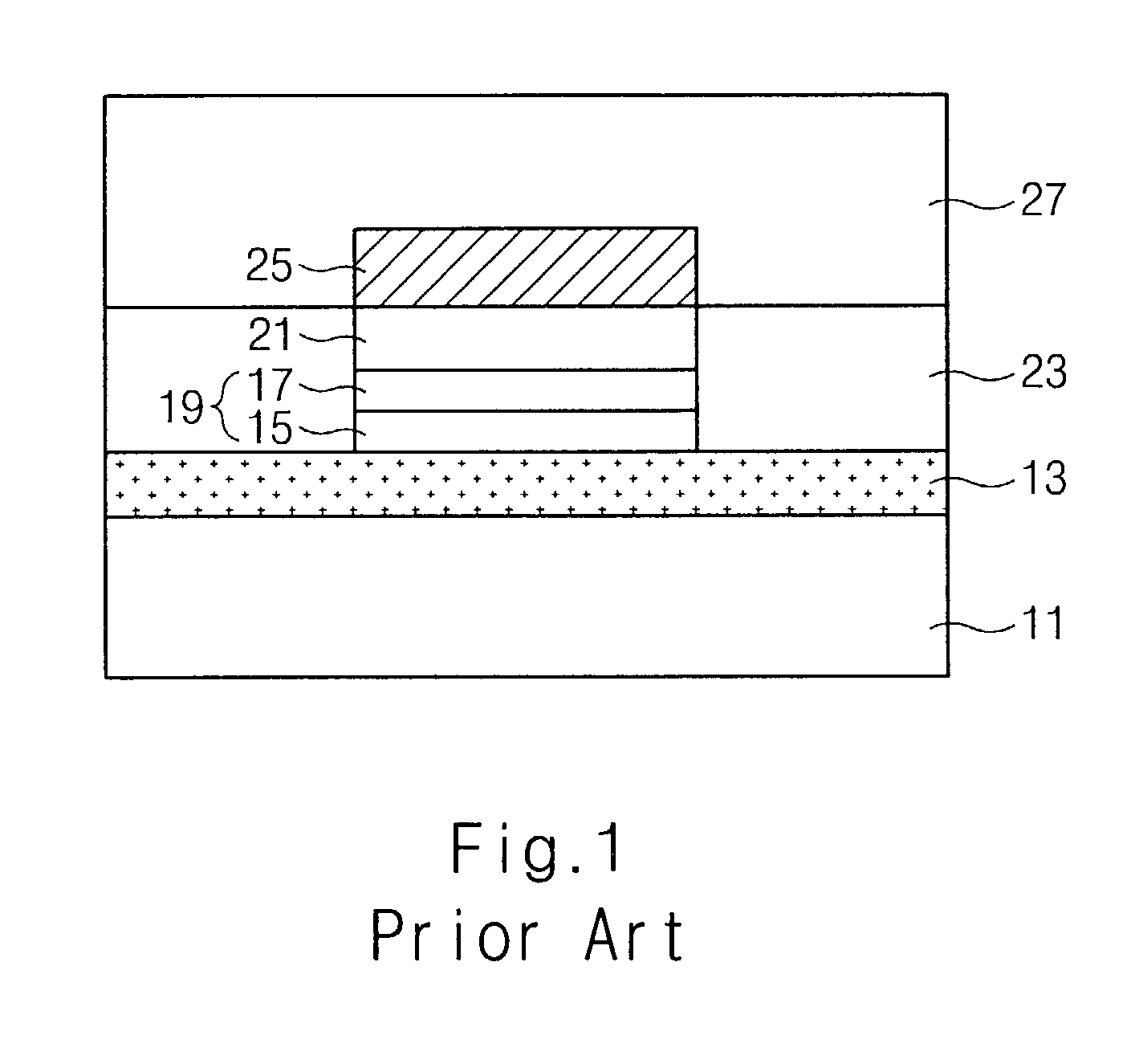

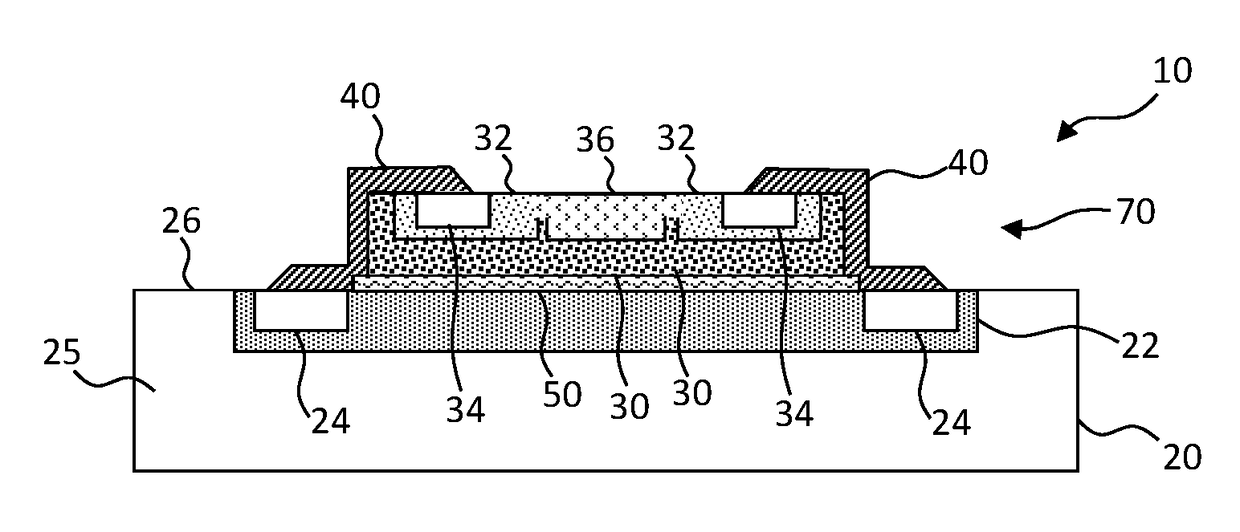

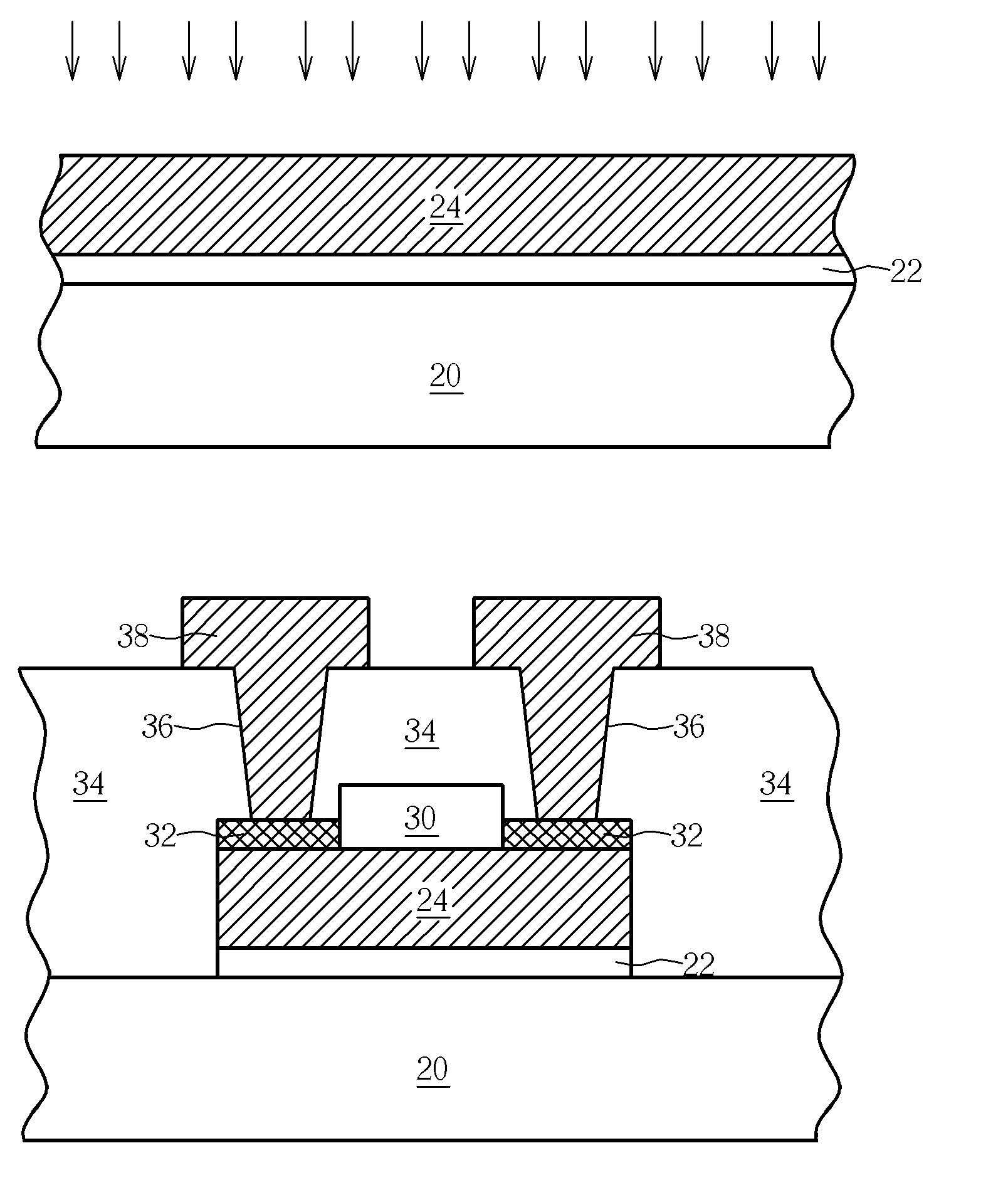

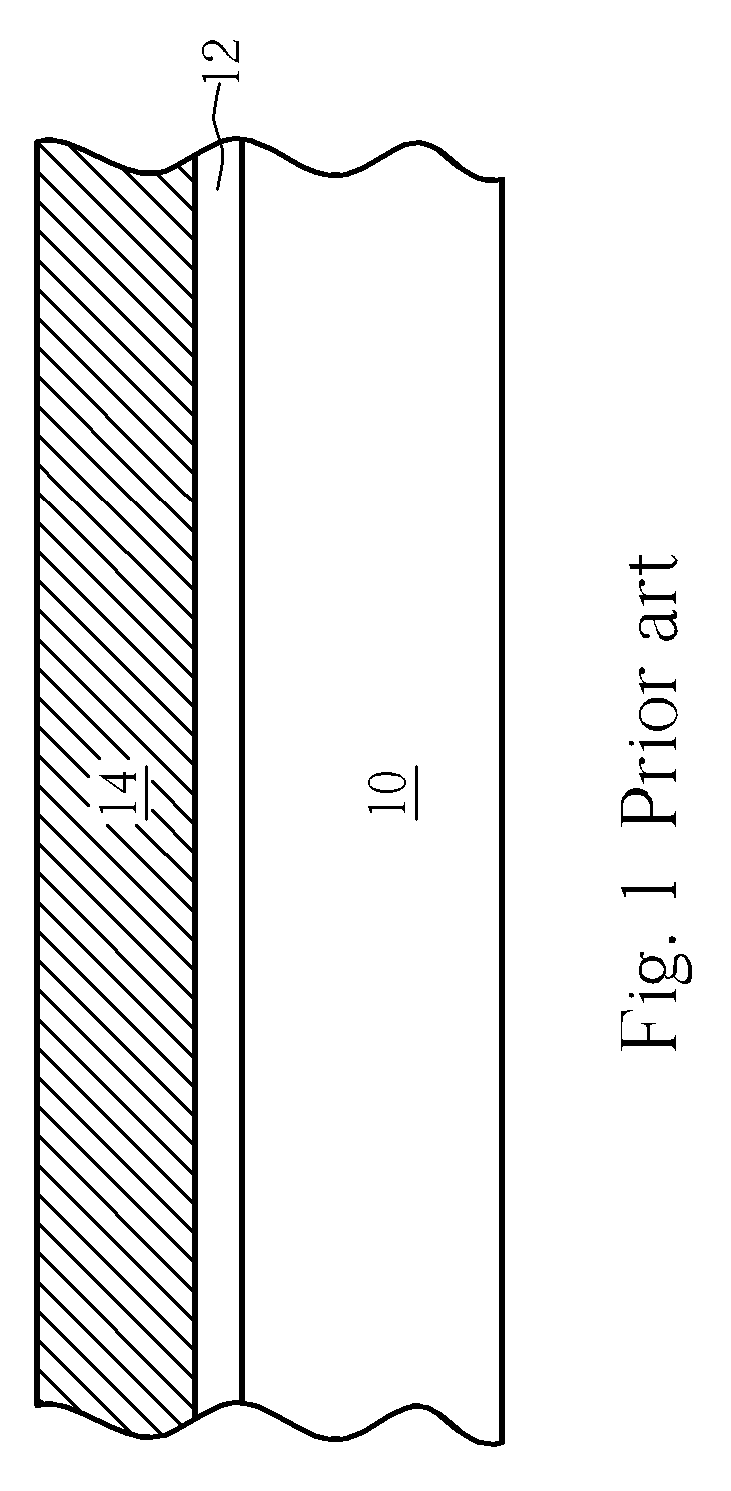

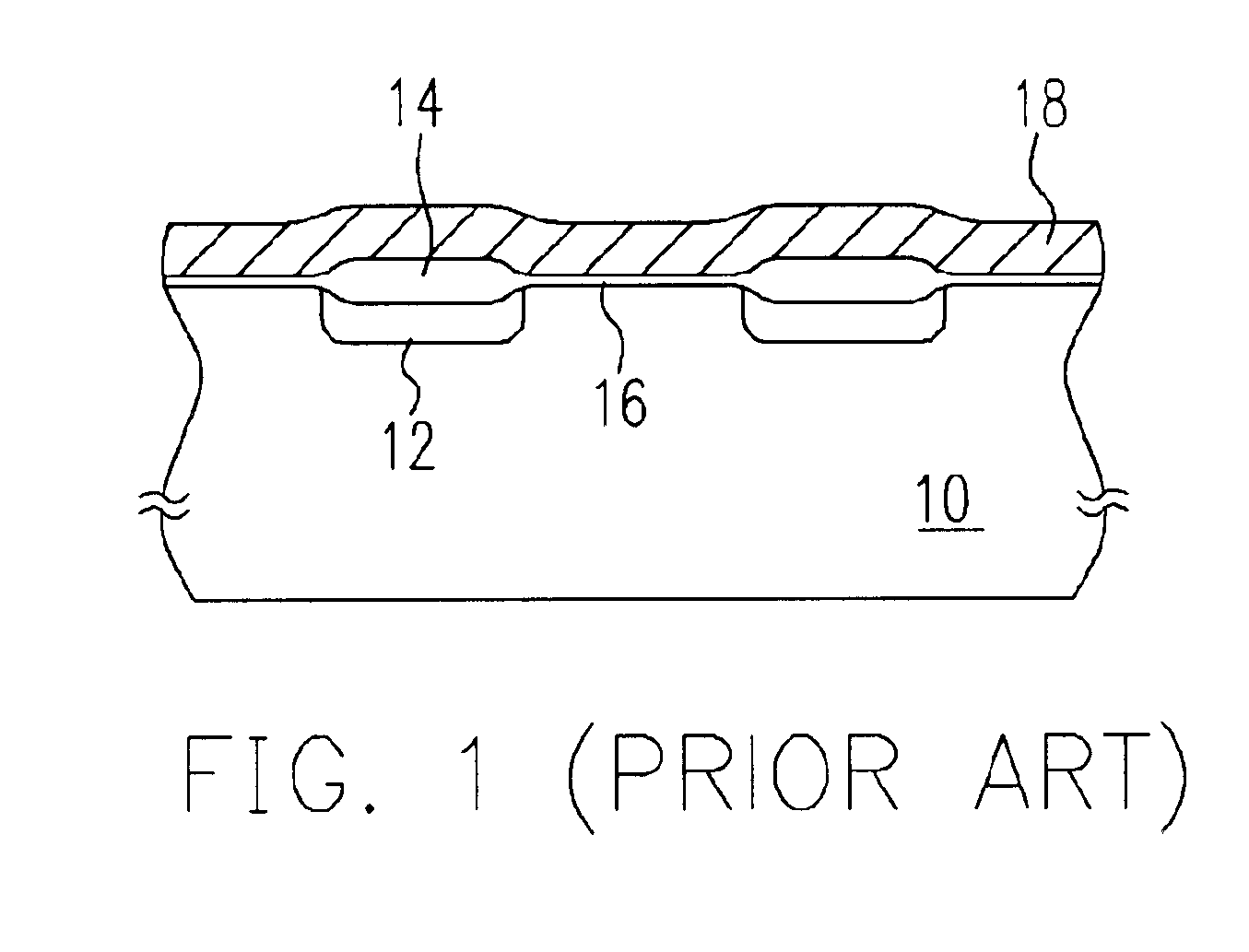

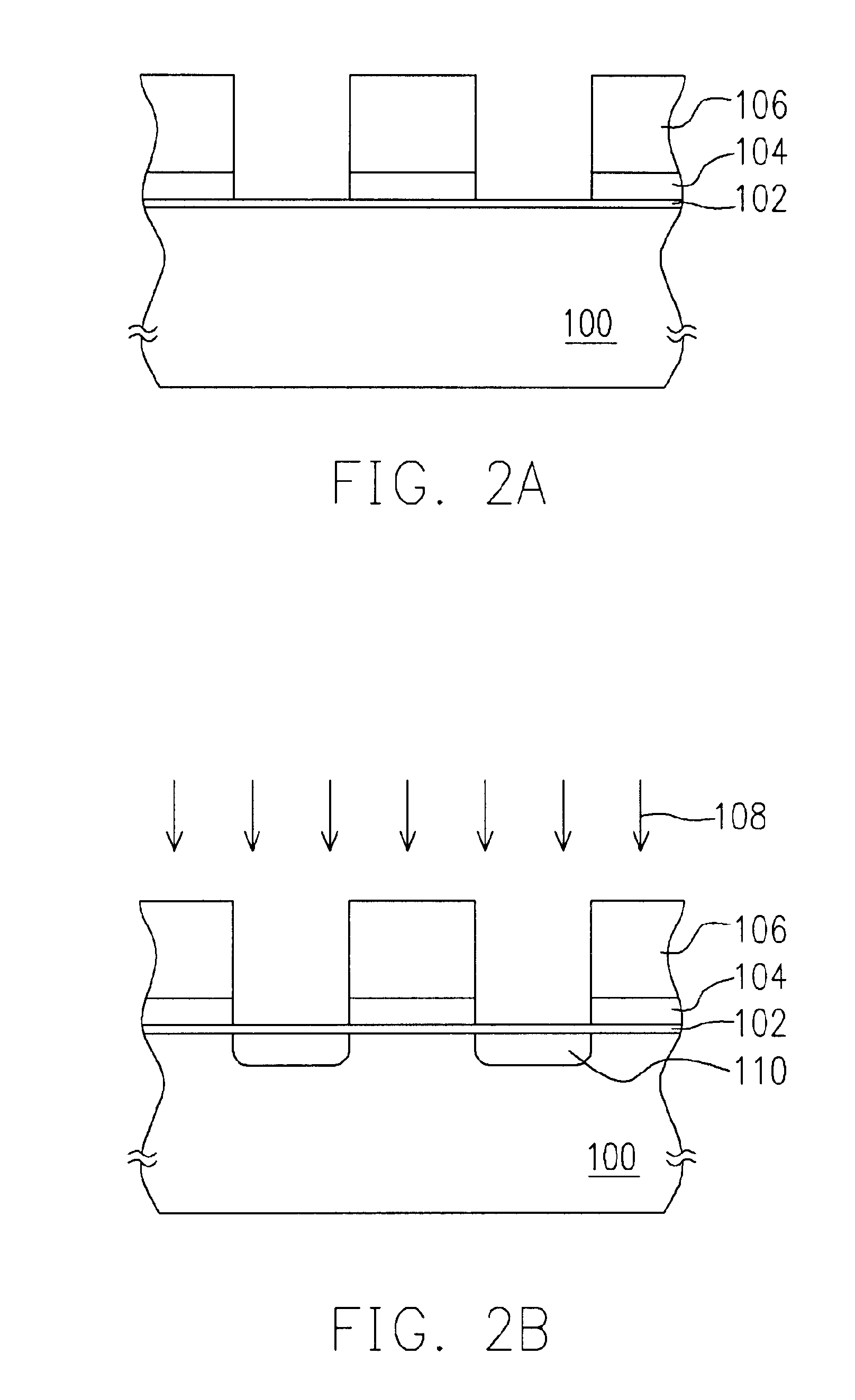

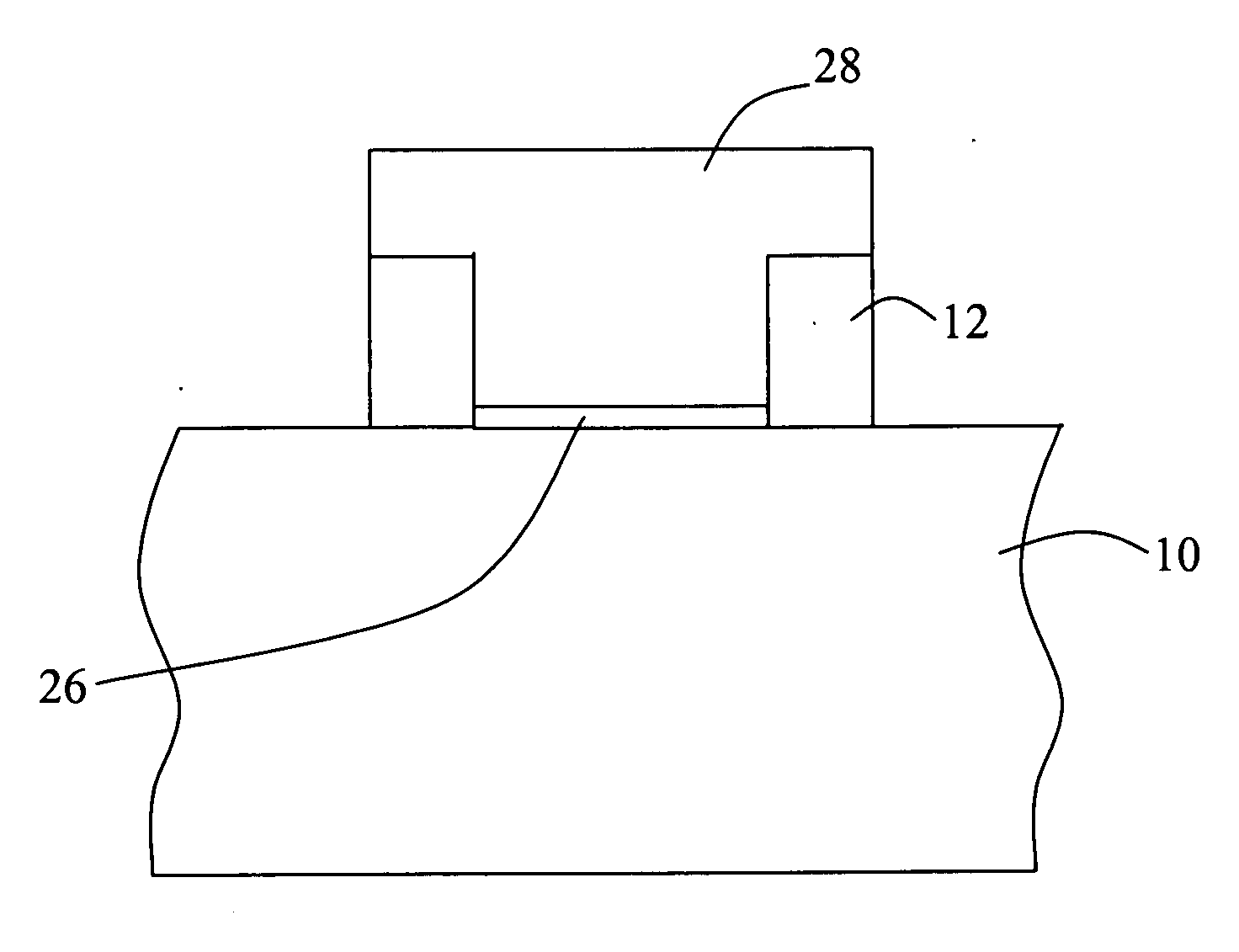

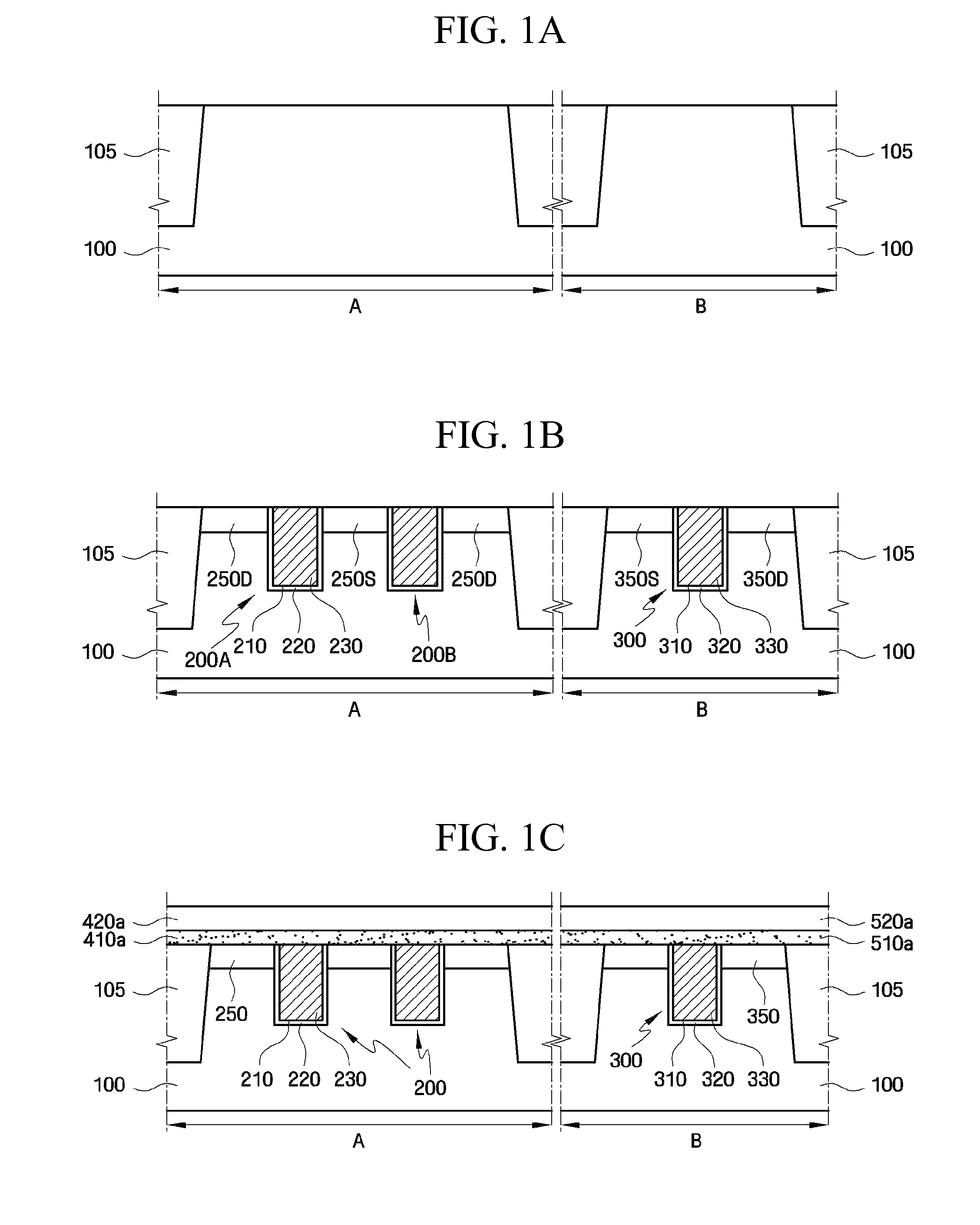

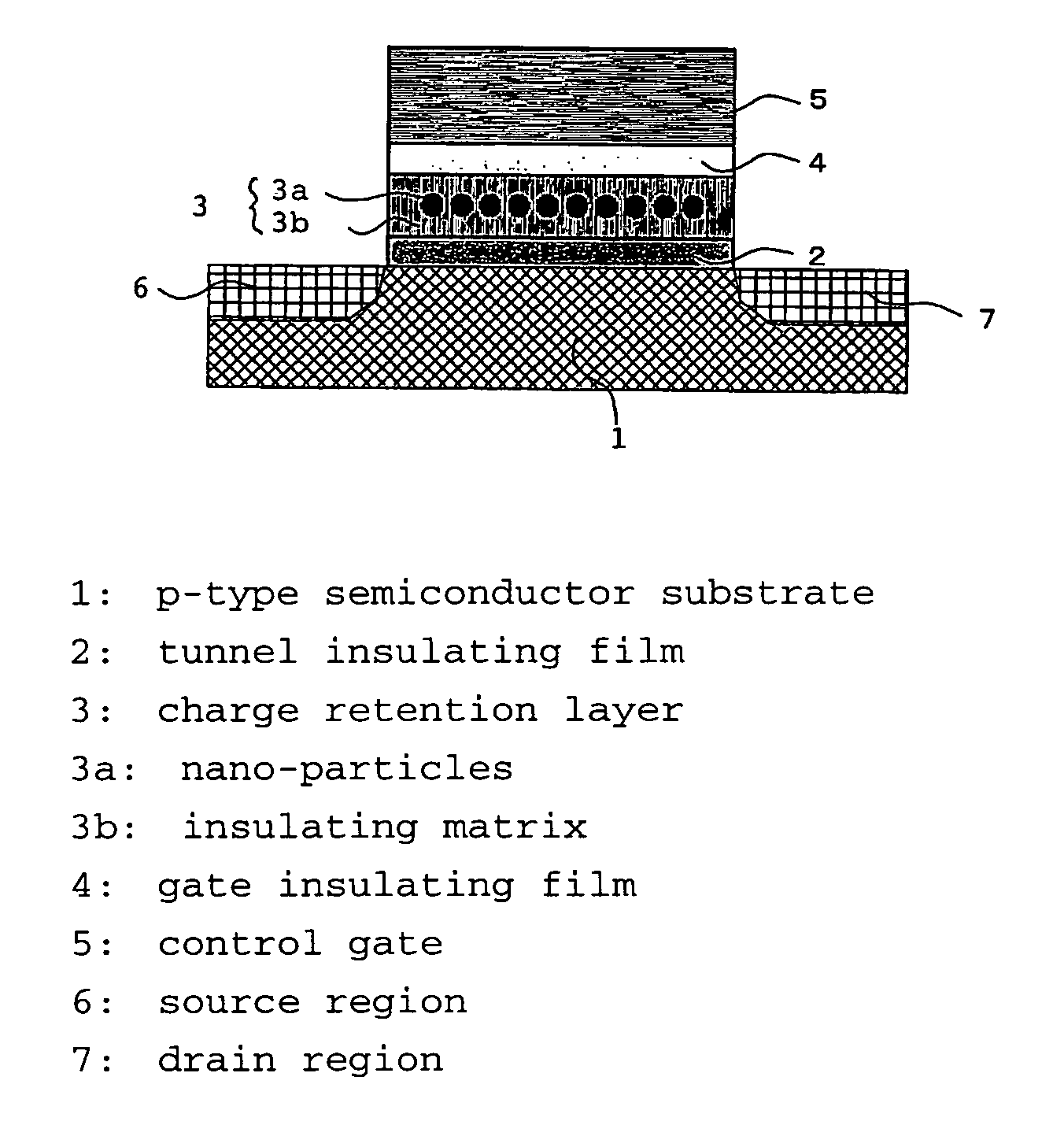

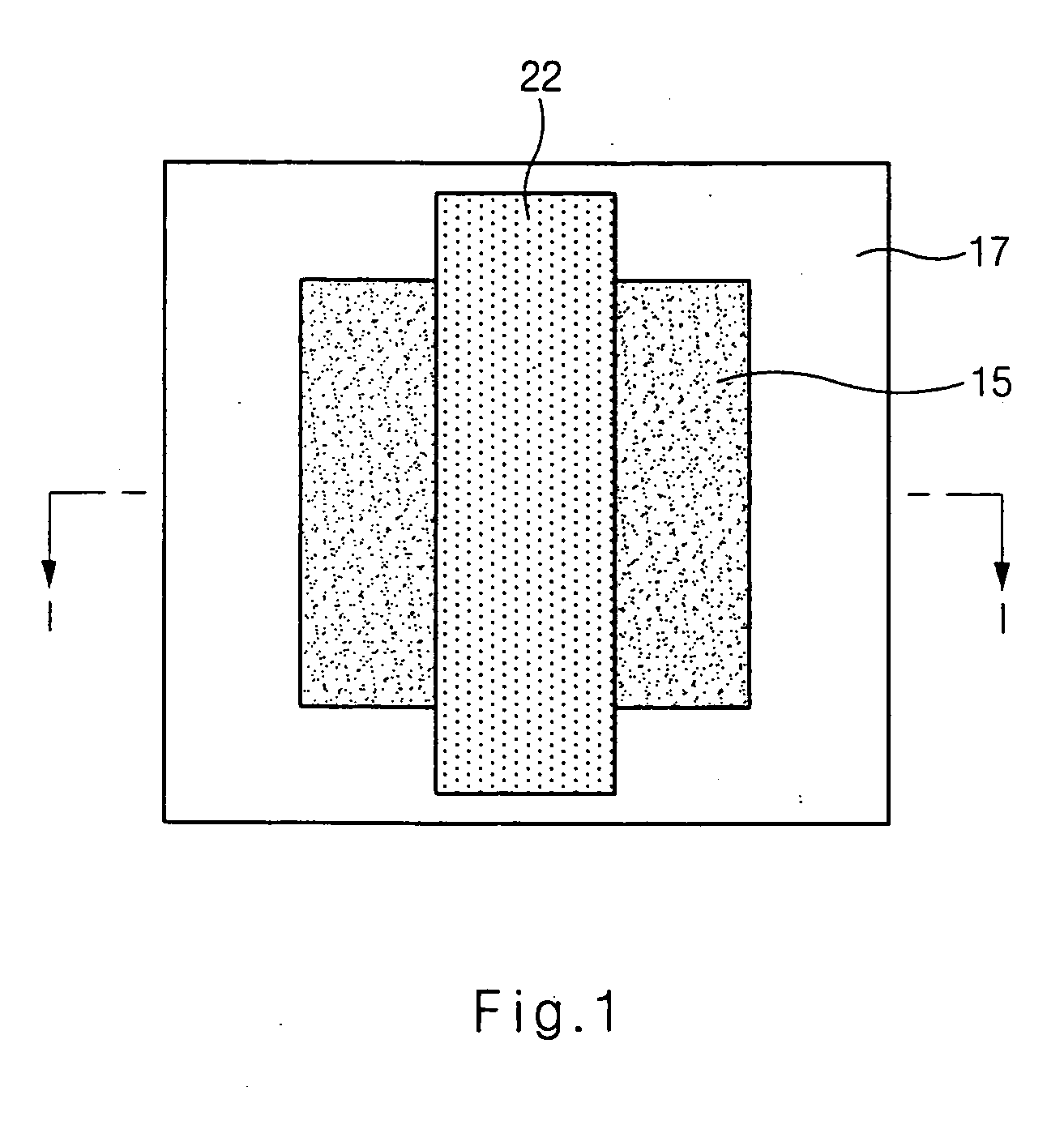

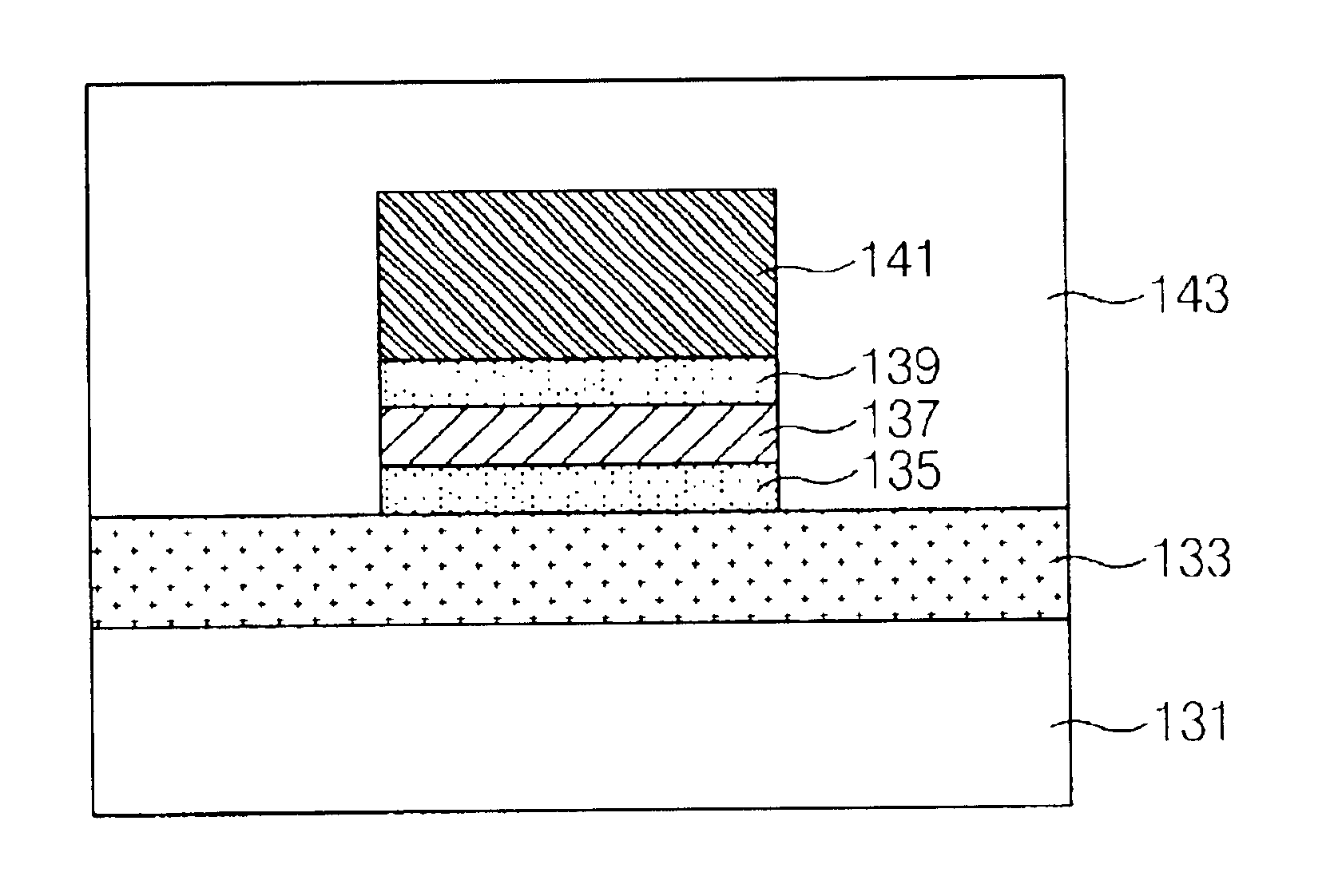

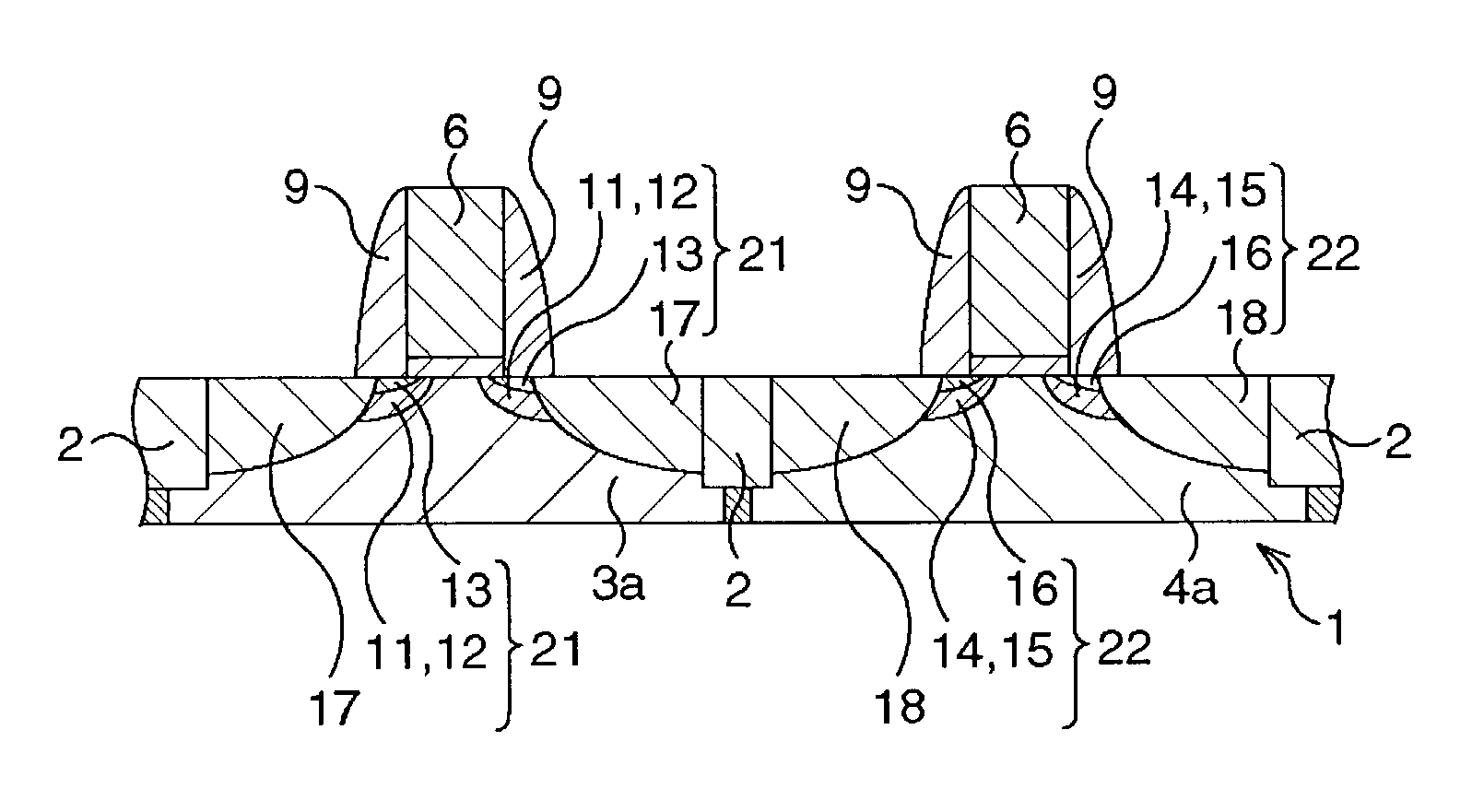

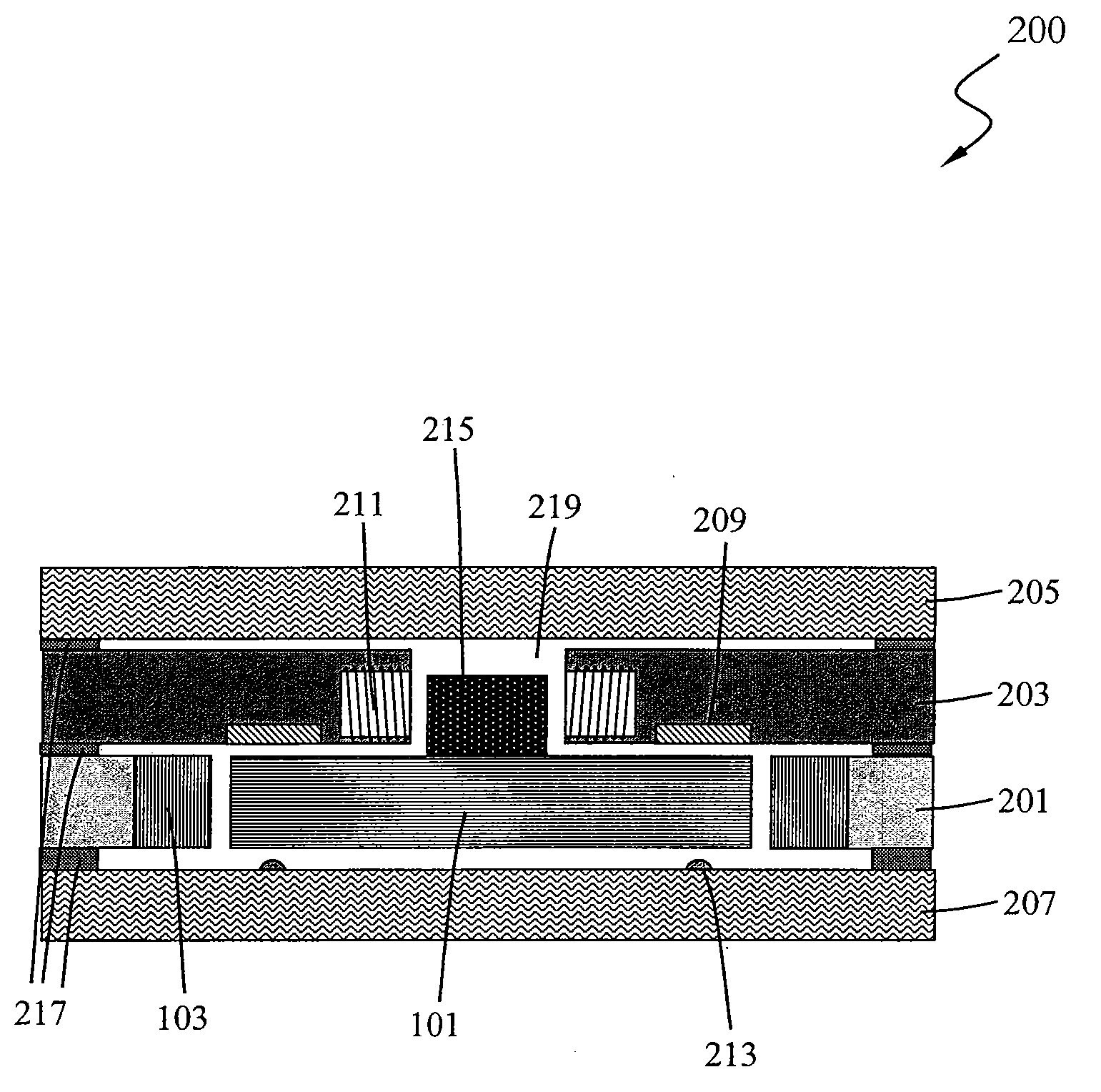

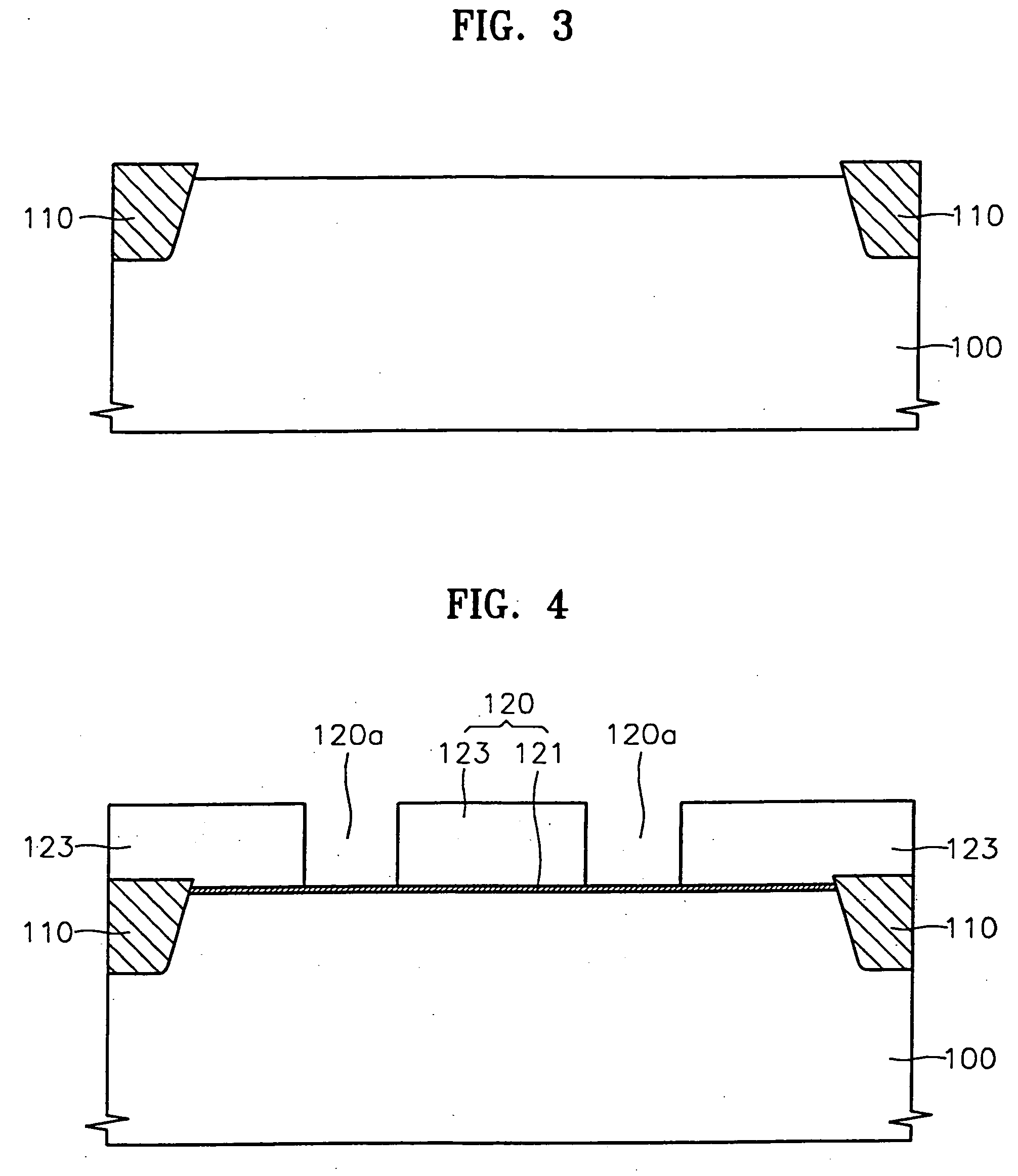

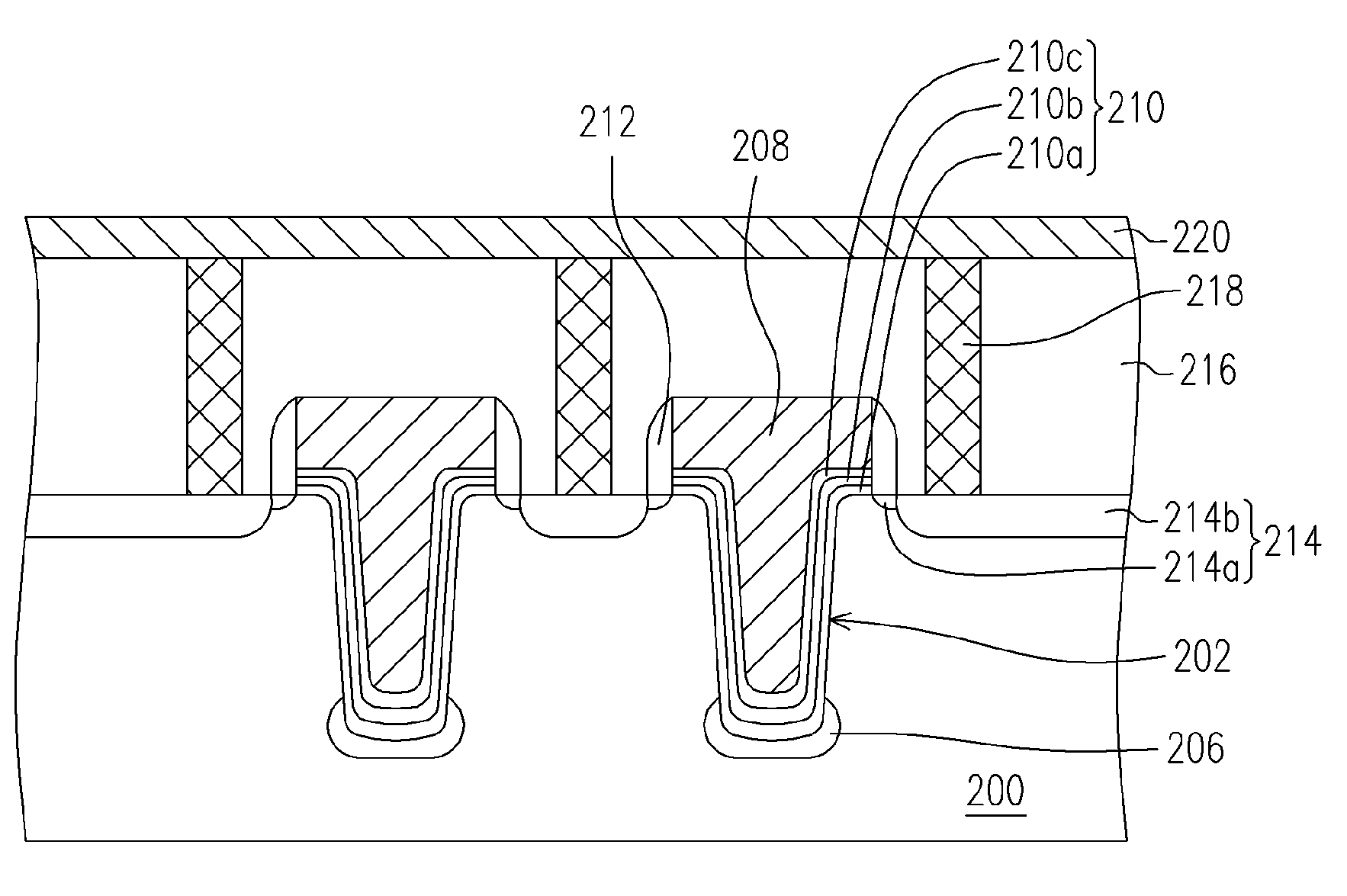

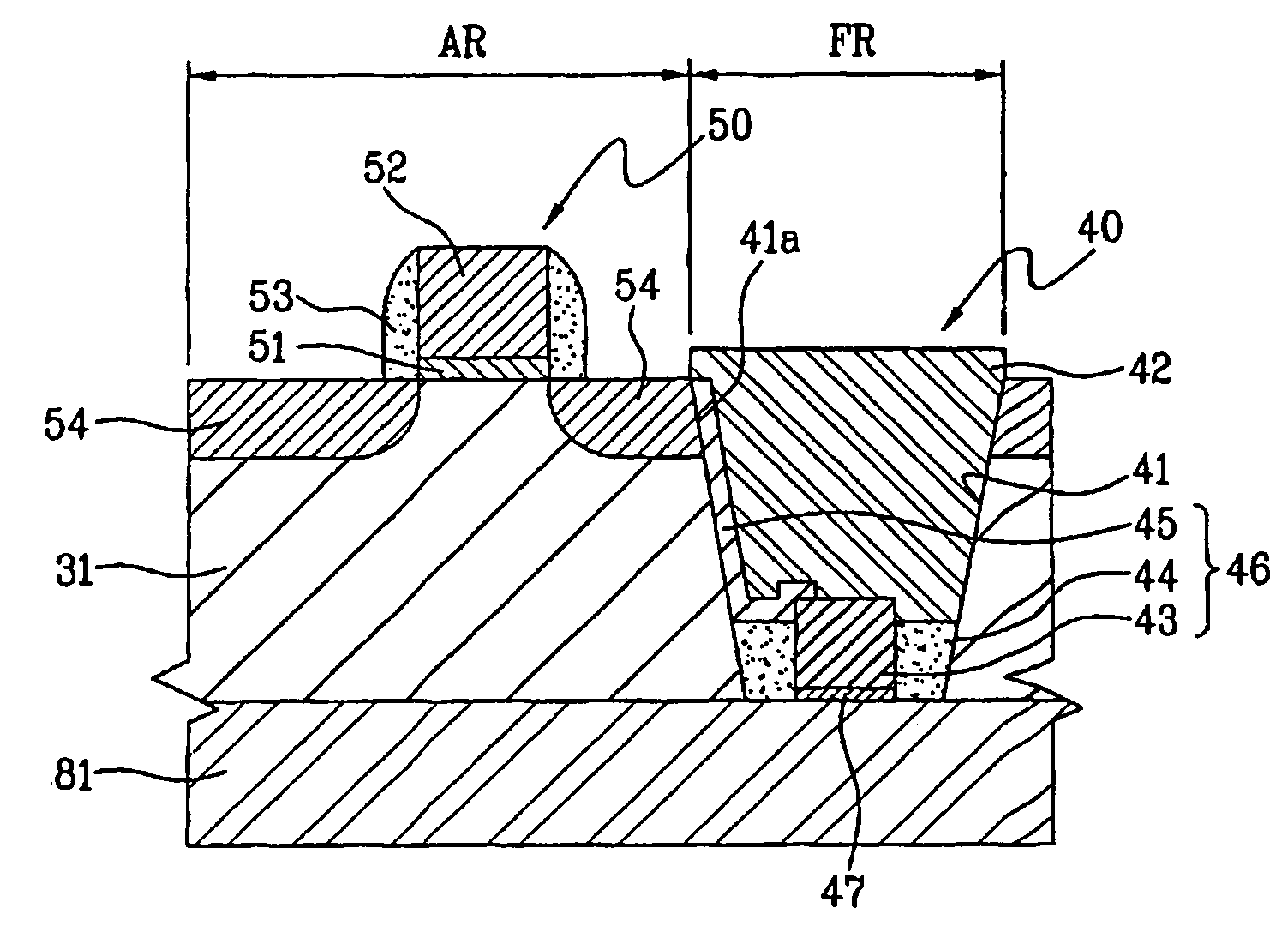

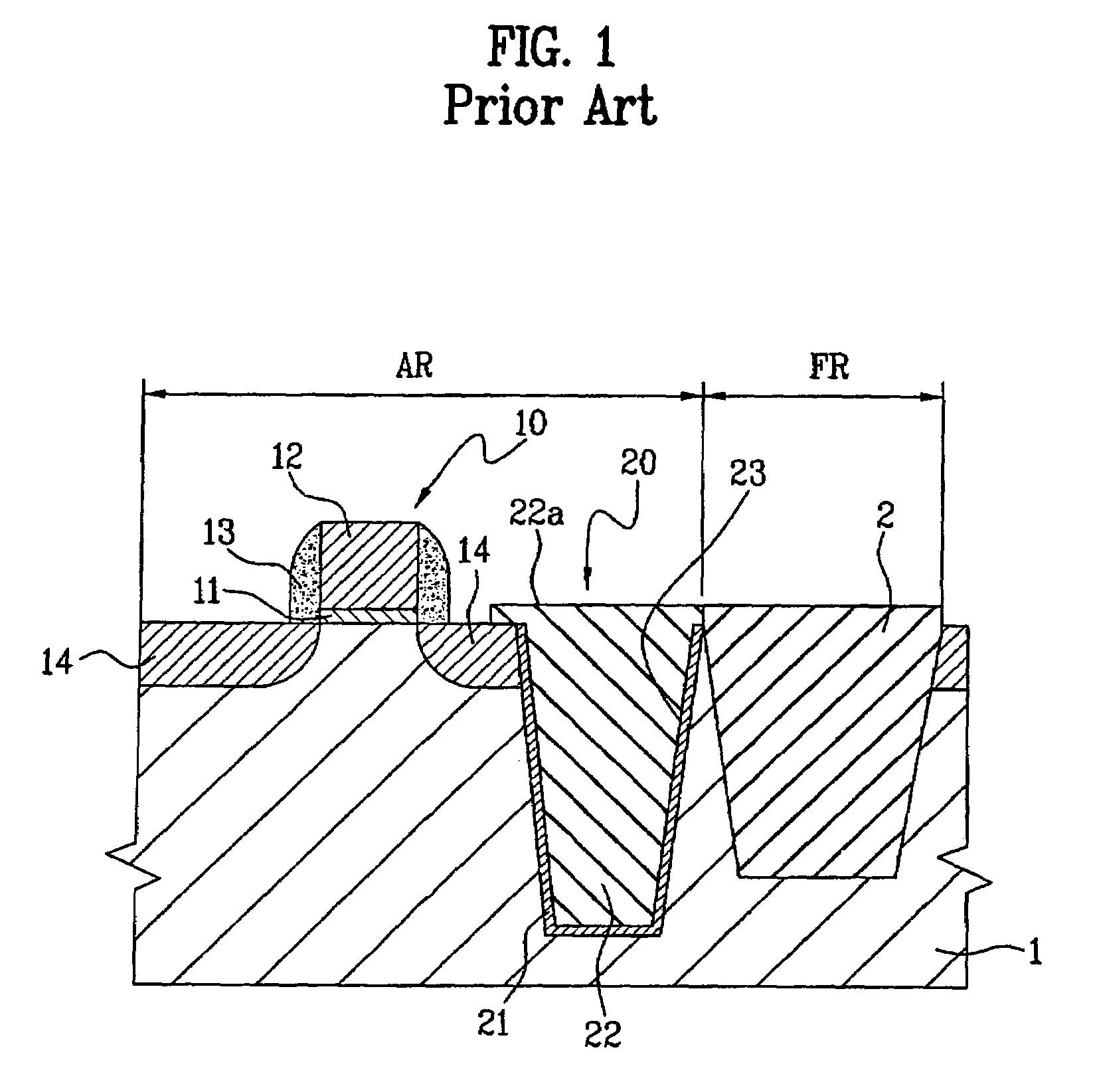

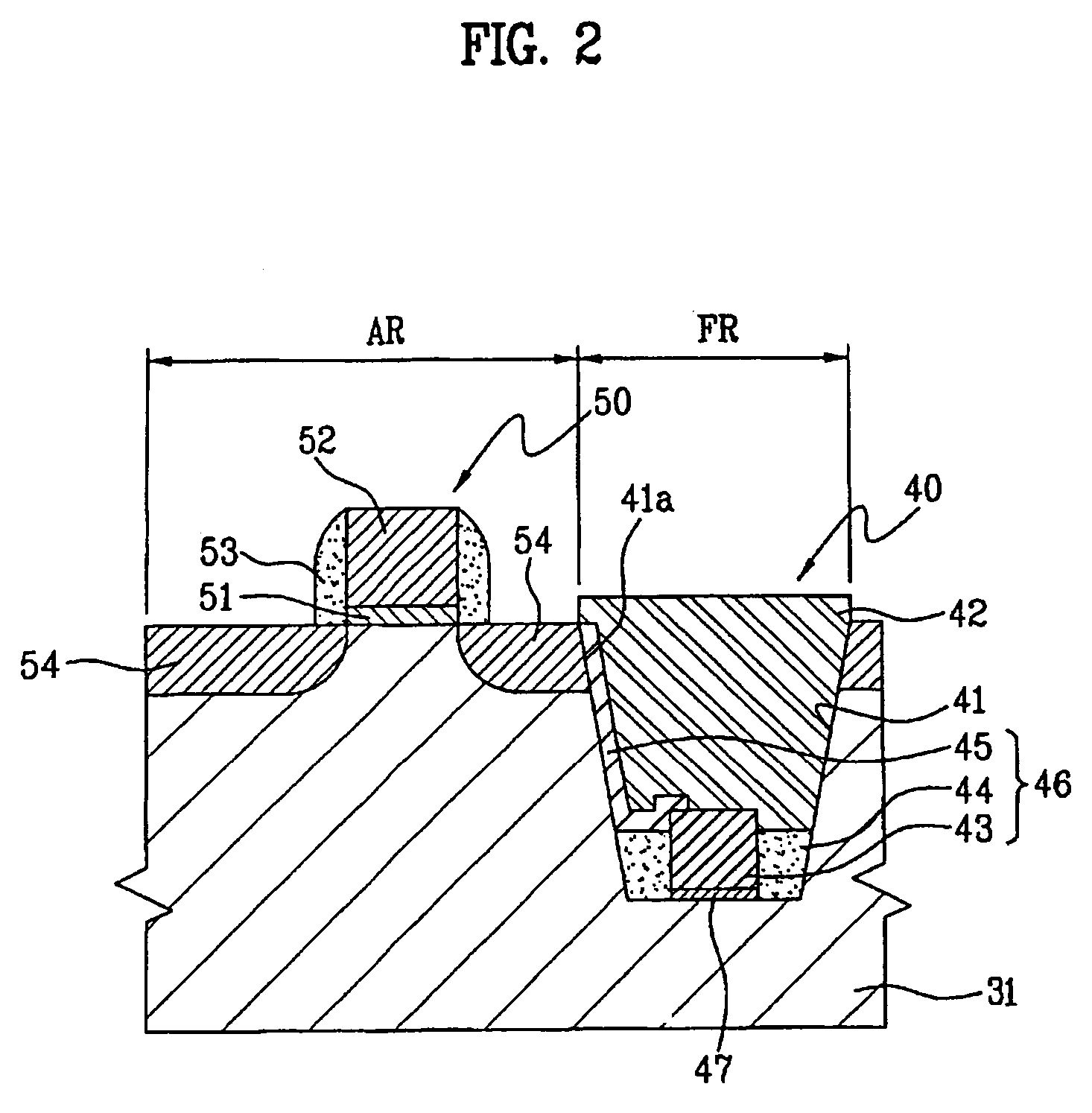

[non-volatile memory cell and manufacturing method thereof]

ActiveUS20050145921A1Easy to distinguishEasy to integrateTransistorSolid-state devicesTrappingDielectric layer

A non-volatile memory cell is provided. The non-volatile memory at least includes a substrate, a gate, a first source / drain region, a composite dielectric layer and a second source / drain region. A trench is formed in a substrate and a gate is formed inside the trench. The first source / drain region is formed at the bottom of the trench. The composite dielectric layer is formed between the gate and the surface of the trench. The composite dielectric layer includes at least a charge-trapping layer. The second source / drain region is formed in the substrate next to the sides of the gate.

Owner:POWERCHIP SEMICON MFG CORP

NAND type non-volatile memory and operating method thereof

InactiveUS20090238002A1Improve process windowReduce surface areaSolid-state devicesRead-only memoriesNon-volatile memoryBit line

A NAND type non-volatile memory having a plurality of bit lines and a dummy bit line is provided. The intersections of each of the bit lines with a first select gate line, a plurality of word lines, and a second select gate line are corresponding to a memory cell row. The intersections of the dummy bit line with the first select gate line, the word lines, and the second select gate line are corresponding to a dummy memory cell row. A source line is disposed on the substrate at one side of the memory cell rows, wherein the dummy memory cell row and the dummy bit line are served as a current path for connecting the source line.

Owner:POWERCHIP SEMICON CORP

Contactless mask programmable ROM

InactiveUS7227232B2High equipment integrationTransistorSolid-state devicesMask ROMChannel conductivity

A contactless Mask ROM is described, comprising a plurality of MOS-type memory cells. The memory cells include a plurality of first memory cells and a plurality of second memory cells. The first memory cells have a first channel conductivity so that they are depletion-mode MOS transistors, and the second memory cells have a second channel conductivity so that they are enhanced-mode MOS transistors. In the contactless Mask ROM, a memory cell shares two diffusions with two adjacent memory cells that are aligned with the memory cell along a first direction.

Owner:SOLID STATE SYST

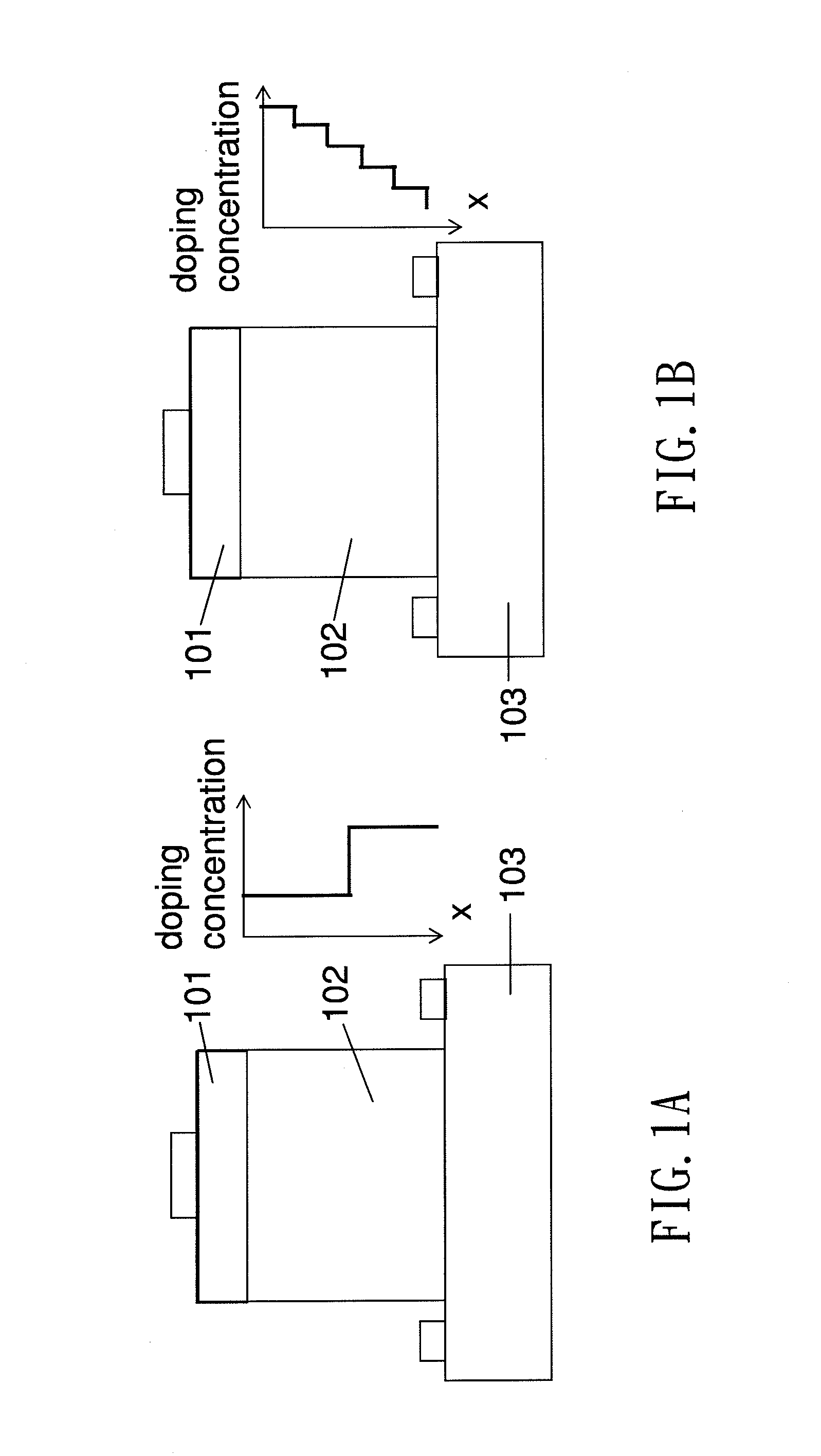

Method of fabricating semiconductor a device

InactiveUS20060046372A1Improve roll-off characteristicHigh equipment integrationTransistorAccounting/billing servicesIon implantationImpurity

An impurity-diffused layer having an extension structure is formed first by implanting Sb ion as an impurity for forming a pocket region; then by implanting N as a diffusion-suppressive substance so as to produce two peaks in the vicinity of the interface with a gate electrode and at an amorphous / crystal interface which serves as an defect interface generated by the impurity in the pocket region; and by carrying out ion implantations for forming an extension region and deep source and drain regions.

Owner:FUJITSU SEMICON LTD

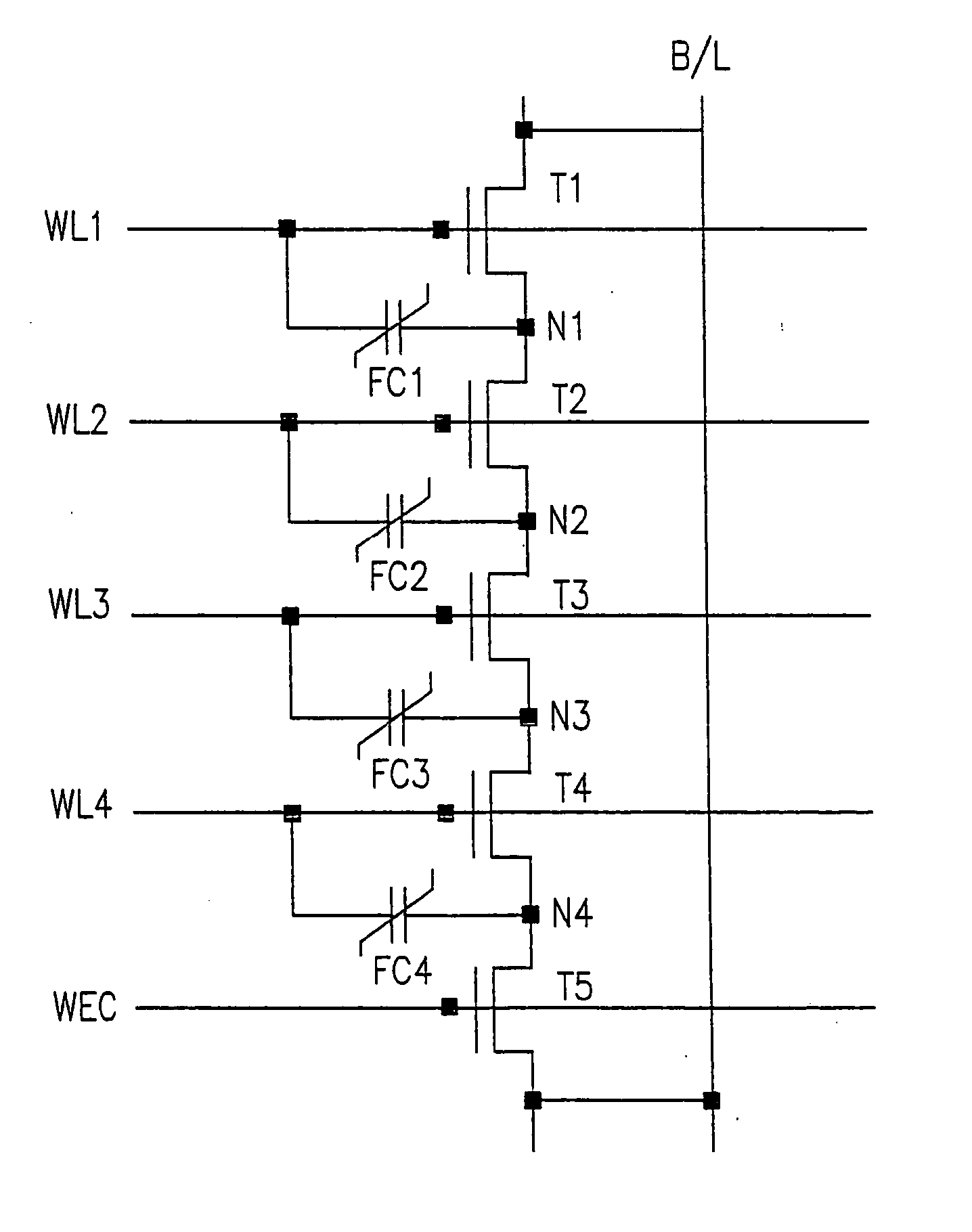

Method for manufacturing NAND type nonvolatile ferroelectric memory cell

InactiveUS20050141259A1Improve running characteristicsArea minimizationTransistorSolid-state devicesHigh densityComputer science

NAND type non-volatile ferroelectric memory cell and non-volatile ferroelectric memory of the same, in which numbers of access to a main cell and a reference cell are made the same, to maintain bitline induced voltages by the reference cell and by the main cell constant, for improving operation characteristics, minimizing a layout area, and permits a high density device integration, the memory cell including an N number of transistors connected in series, a bitline having an input terminal of a first transistor and an output terminal of (N)th transistor among the N number of transistors connected thereto, wordlines respectively connected to gates of the transistors except the (N)th transistor, a WEC signal line connected to a gate of the (N)th transistor and adapted to have an enable signal applied thereto only in a write or re-store mode, and ferroelectric capacitors respectively connected both to the wordlines and output terminals of the transistors.

Owner:HYUNDAI ELECTRONICS IND CO LTD

Magnetic random access memory using schottky diode

InactiveUS20030116847A1High integrationHigh equipment integrationTransistorSemiconductor/solid-state device detailsPhysicsSemiconductor

A magnetic random access memory (MRAM) using a schottky diode is disclosed. In order to achieve high integration of the memory device, a word line is formed on a semiconductor substrate without using a connection layer and a stacked structure including an MTJ cell, a semiconductor layer and a bit line is formed on the word line, thereby forming the schottky diode between the MTJ cell and the bit line. As a result, a structure of the device is simplified, and the device may be highly integrated due to repeated stacking.

Owner:SK HYNIX INC

Micro-transfer-printed compound sensor device

ActiveUS20170225945A1Easy to integrateImprove performancePrecision positioning equipmentSoldering apparatusElectrical conductorActuator

A compound sensor device includes a semiconductor substrate having an active electronic circuit formed in or on the semiconductor substrate. A sensor comprising a sensor substrate including a sensor circuit having an environmental sensor or actuator formed in or on the sensor substrate is micro-transfer printed onto the semiconductor substrate. One or more electrical conductors electrically connects the active electronic circuit to the sensor circuit. The semiconductor substrate comprises a first material and the sensor substrate comprises a second material different from the first material.

Owner:X CELEPRINT LIMITED

Method of forming a polysilicon resistor

InactiveUS20060121684A1Resistance regionIncrease resistanceSolid-state devicesSemiconductor/solid-state device manufacturingDopantSalicide

A method of forming a polysilicon resistor includes: providing a substrate, the substrate comprising a dielectric layer; forming a polysilicon layer on the dielectric layer; doping the entire polysilicon layer evenly with first type dopants; doping said polysilicon layer containing the first type dopants with second type dopants; defining a polysilicon resistor pattern on the polysilicon layer and removing the polysilicon layer and the dielectric layer outside the polysilicon resistor pattern down to the surface of the substrate, the remainder of the polysilicon layer comprising at least a high resistance region and a low resistance region; and forming a salicide layer on the remainder of the polysilicon layer within the low resistance region.

Owner:UNITED MICROELECTRONICS CORP

Method of improving device resistance

InactiveUS6849526B2Low line resistanceAvoid it happening againSolid-state devicesSemiconductor/solid-state device manufacturingBit lineEngineering

A buried bit line and a fabrication method thereof, wherein the device includes a substrate, a shallow doped region disposed in the substrate, a deep doped region disposed in the substrate below a part of the shallow doped region, wherein the shallow doped region and the deep dope region together form a bit line of the memory device.

Owner:MACRONIX INT CO LTD

P-channel NAND flash memory and operating method thereof

ActiveUS7061805B2Improve efficiencySpeed up the programming operationSolid-state devicesRead-only memoriesComputer scienceP type doping

A p-channel NAND flash memory includes a plurality of memory cells in series connection between a p-type source region and a p-type drain region. Each memory cell includes a tunneling dielectric layer, a floating gate, and a control gate. An erase gate is formed between two adjacent memory cells, and a p-type doped region is formed in the substrate between two adjacent memory cells. A select transistor is formed between the p-type drain and the cell nearest to the p-type drain. The cells in the p-channel NAND flash memory is programmed by band-to-band tunneling induced hot carrier injection, and erased via F-N tunneling.

Owner:POWERCHIP SEMICON MFG CORP

Method of fabricating T-shaped polysilicon gate by using dual damascene process

InactiveUS20050260840A1Prevents low polysilicon gate edge breakdown voltageReduce voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPhotoresistOxide

A method of fabricating a T-shaped polysilicon gate by using dual damascene process. An oxide layer, a hard mask layer, and a patterned first photoresist layer in sequence are formed on a semiconductor substrate. Using the patterned first photoresist layer as a mask, an etching process is performed on the hard mask layer to form a first trench. The patterned first photoresist layer is removed. An organic layer is then deposited in the first trench. A patterned second photresist layer is formed on the semiconductor substrate. Using the patterned second photresist layer as a mask, an etching process is performed on the hard mask layer to define a second trench dimension. The patterned second photoresist layer and the organic layer are removed. An oxide layer and a polysilicon layer are deposited in the first trench and the second trench. The residual hark mask layer is removed to obtain a T-shaped profile polysilicon gate.

Owner:GRACE SEMICON MFG CORP

Semiconductor integrated circuit devices having contacts formed of single-crystal materials

ActiveUS8053831B2Easy to separateImprove critical dimensionsTransistorSolid-state devicesInsulation layerSingle crystal

A memory cell of memory device, comprises an active region of a memory cell defined in a semiconductor substrate, and a conductive gate electrode in a trench of the active region. The gate electrode is isolated from the semiconductor substrate. An insulation layer is on the active region and on the conductive gate electrode. A conductive contact is in the insulation layer on the active region at a side of the gate electrode and isolated from the gate electrode. The contact has a first width at a top portion thereof and a second width at a bottom portion thereof, the first width being greater than the second width. The contact is formed of a single-crystal material.

Owner:IMBERATEK LLC

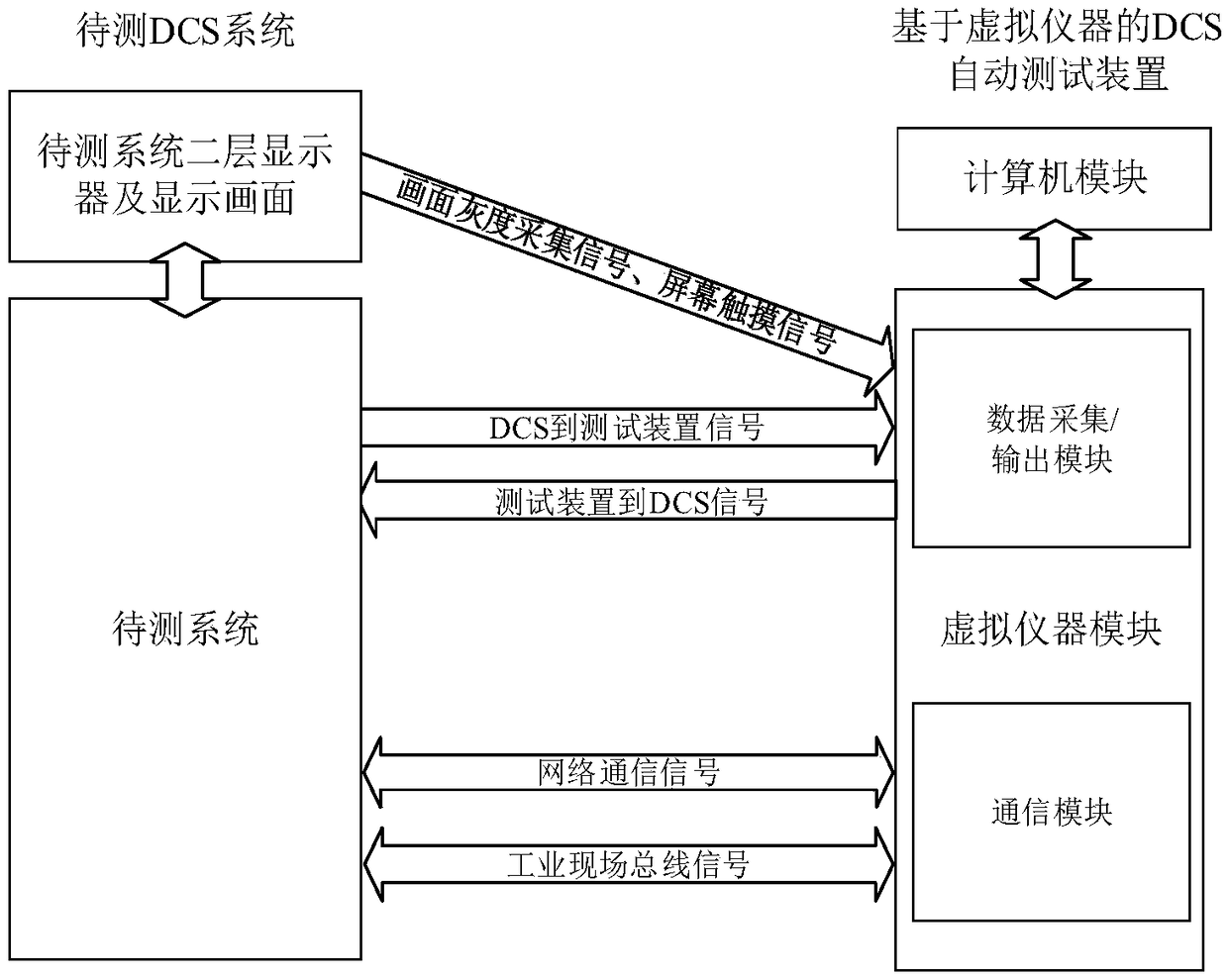

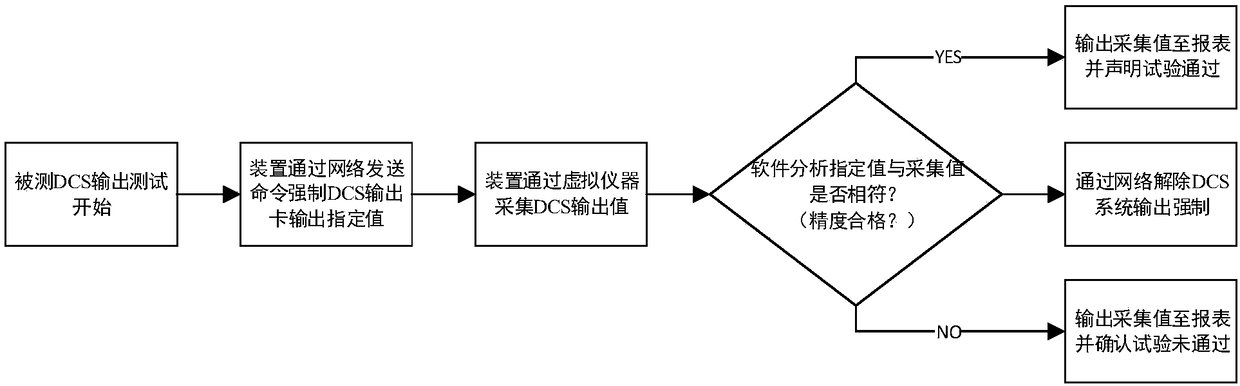

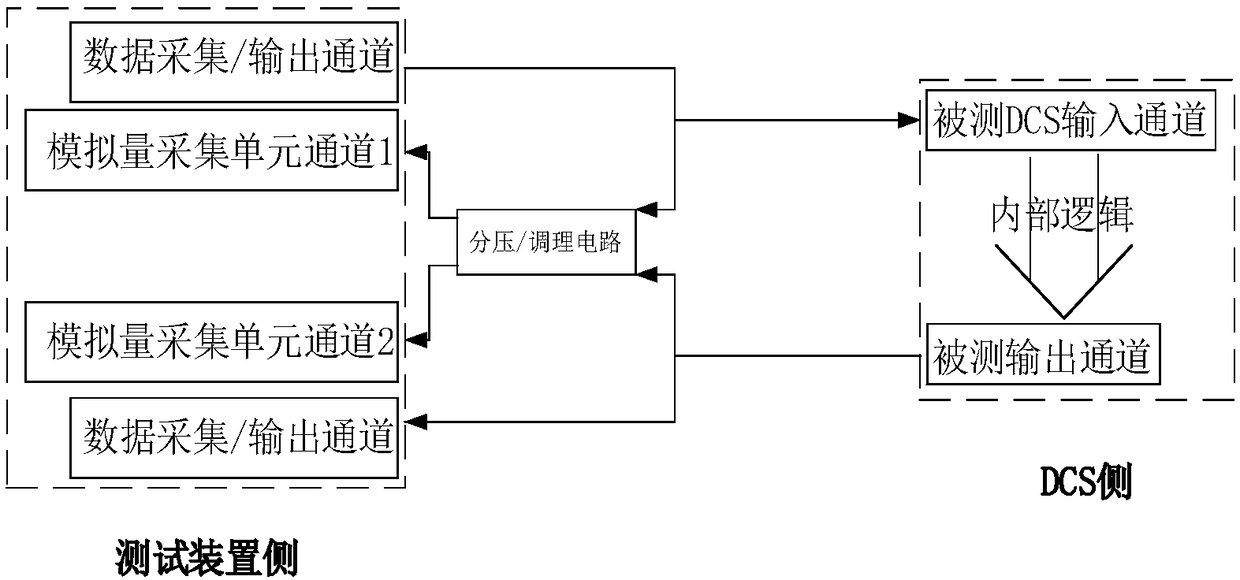

DCS automation test device based on virtual instrument

InactiveCN108181890AHigh equipment integrationFlexible configurationElectric testing/monitoringInstrumentationCommunication unit

The invention belongs to the technical field of nuclear power automation tests, and relates to a DCS automation test device based on a virtual instrument. The device comprises a computer module as a control device and a virtual instrument module as an execution device of the test, the virtual instrument module comprises a data acquisition / output module and a communication module, the data acquisition / output module processes three kinds of signals including signals output to the test device by a DCS, signals output to the DCS by the test device, and DCS two-layer display image grayscale acquisition / screen touch signals, and the communication module comprises a network communication unit and an industrial field bus communication unit. According to the device, the one-layer logic function andthe two-layer display function of the DCS system and the communication function between DCS devices can be tested, and defects of insufficient test tool resources and single function of the conventional nuclear power station DCS are overcome.

Owner:CHINA NUCLEAR CONTROL SYST ENG

![[NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof] [NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof]](https://images-eureka.patsnap.com/patent_img/fd24ad20-241c-499a-ae01-18d1c3524bcb/US20050087892A1-20050428-D00000.png)

![[NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof] [NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof]](https://images-eureka.patsnap.com/patent_img/fd24ad20-241c-499a-ae01-18d1c3524bcb/US20050087892A1-20050428-D00001.png)

![[NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof] [NAND flash memory cell row, NAND flash memory cell array, operation and fabrication method thereof]](https://images-eureka.patsnap.com/patent_img/fd24ad20-241c-499a-ae01-18d1c3524bcb/US20050087892A1-20050428-D00002.png)

![[non-volatile memory cell and manufacturing method thereof] [non-volatile memory cell and manufacturing method thereof]](https://images-eureka.patsnap.com/patent_img/142d6a62-38e6-4178-a5e3-4784f18a0782/US20050145921A1-20050707-D00000.png)

![[non-volatile memory cell and manufacturing method thereof] [non-volatile memory cell and manufacturing method thereof]](https://images-eureka.patsnap.com/patent_img/142d6a62-38e6-4178-a5e3-4784f18a0782/US20050145921A1-20050707-D00001.png)

![[non-volatile memory cell and manufacturing method thereof] [non-volatile memory cell and manufacturing method thereof]](https://images-eureka.patsnap.com/patent_img/142d6a62-38e6-4178-a5e3-4784f18a0782/US20050145921A1-20050707-D00002.png)