Patents

Literature

45results about How to "Layer can be damaged" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

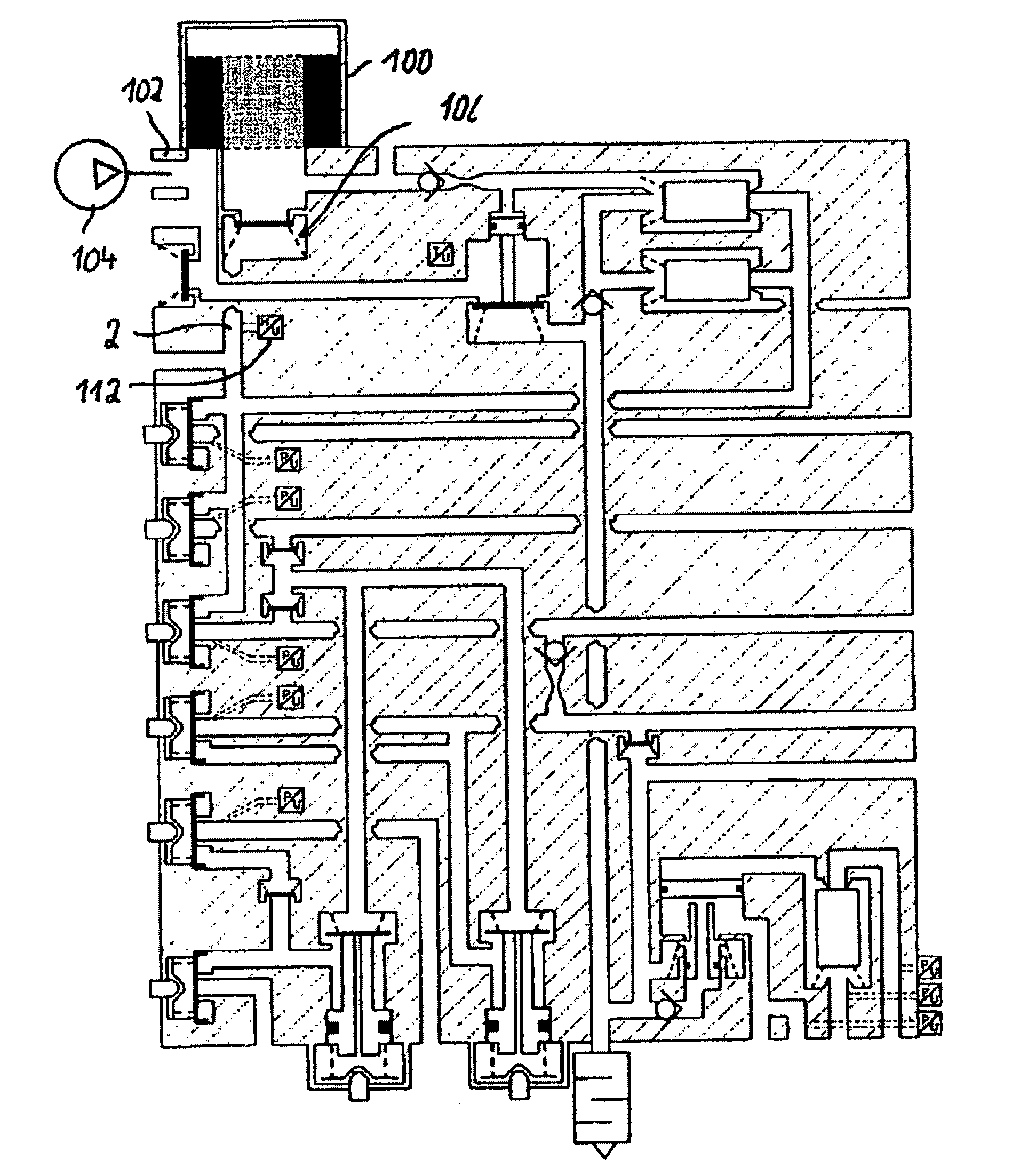

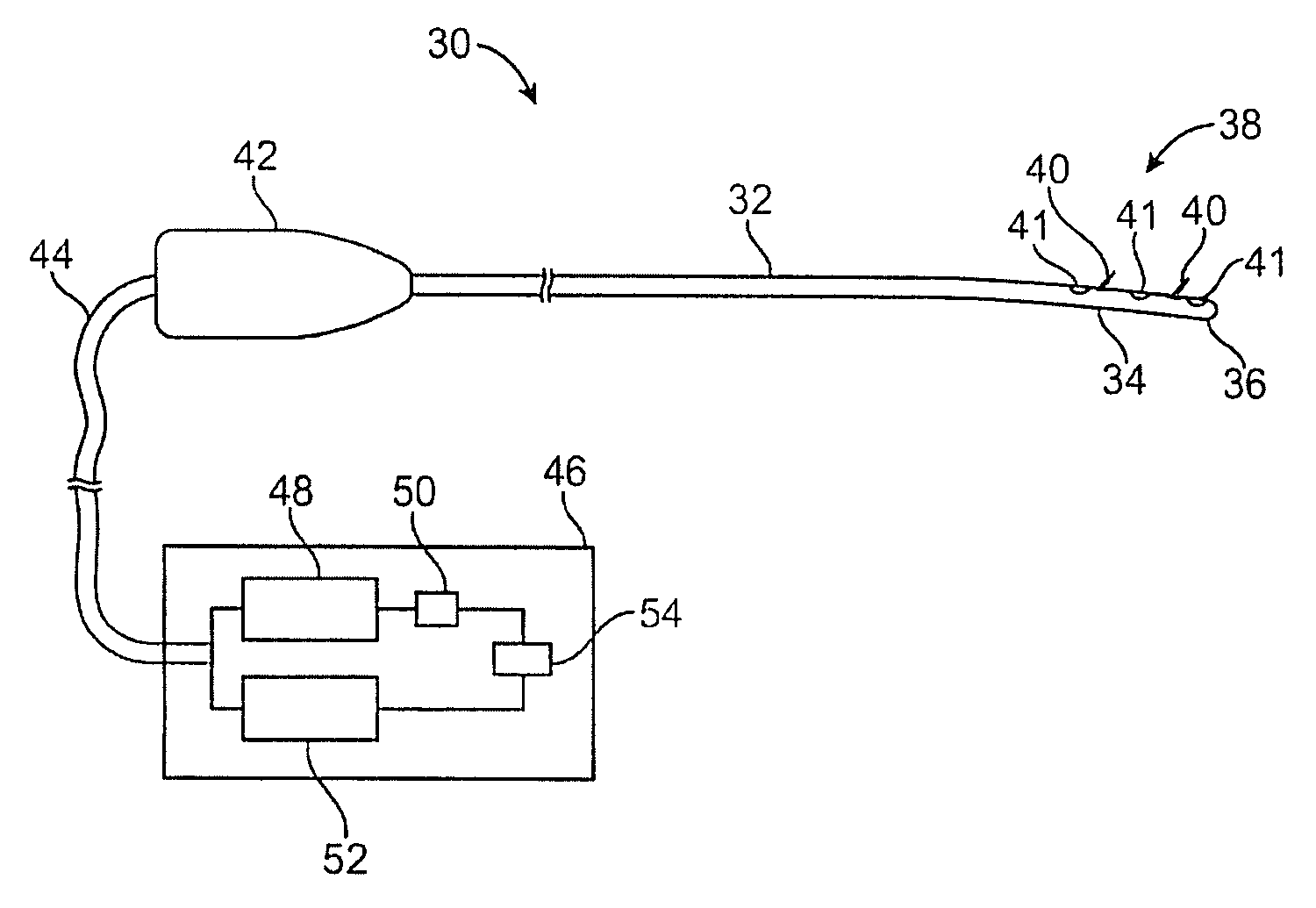

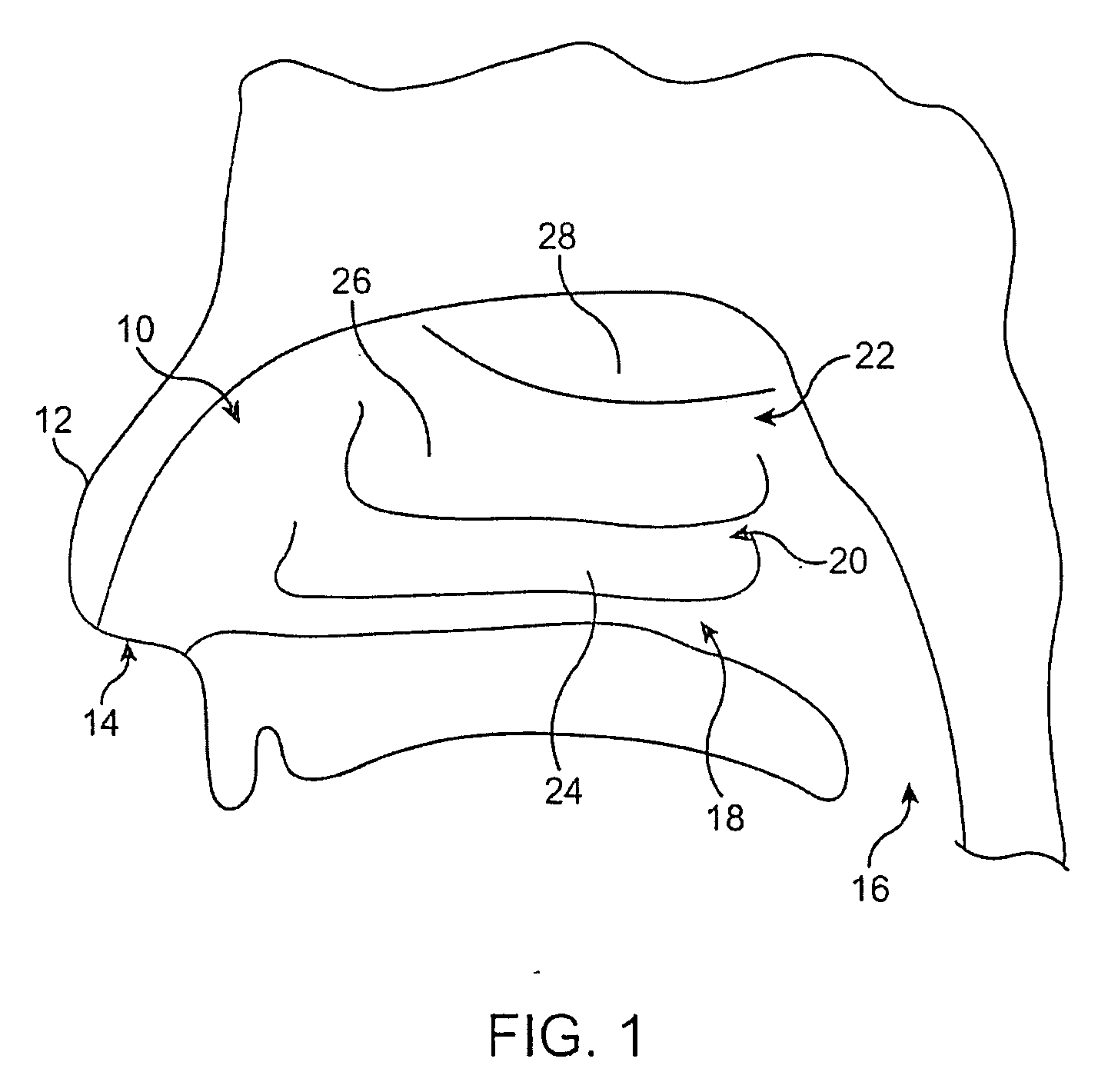

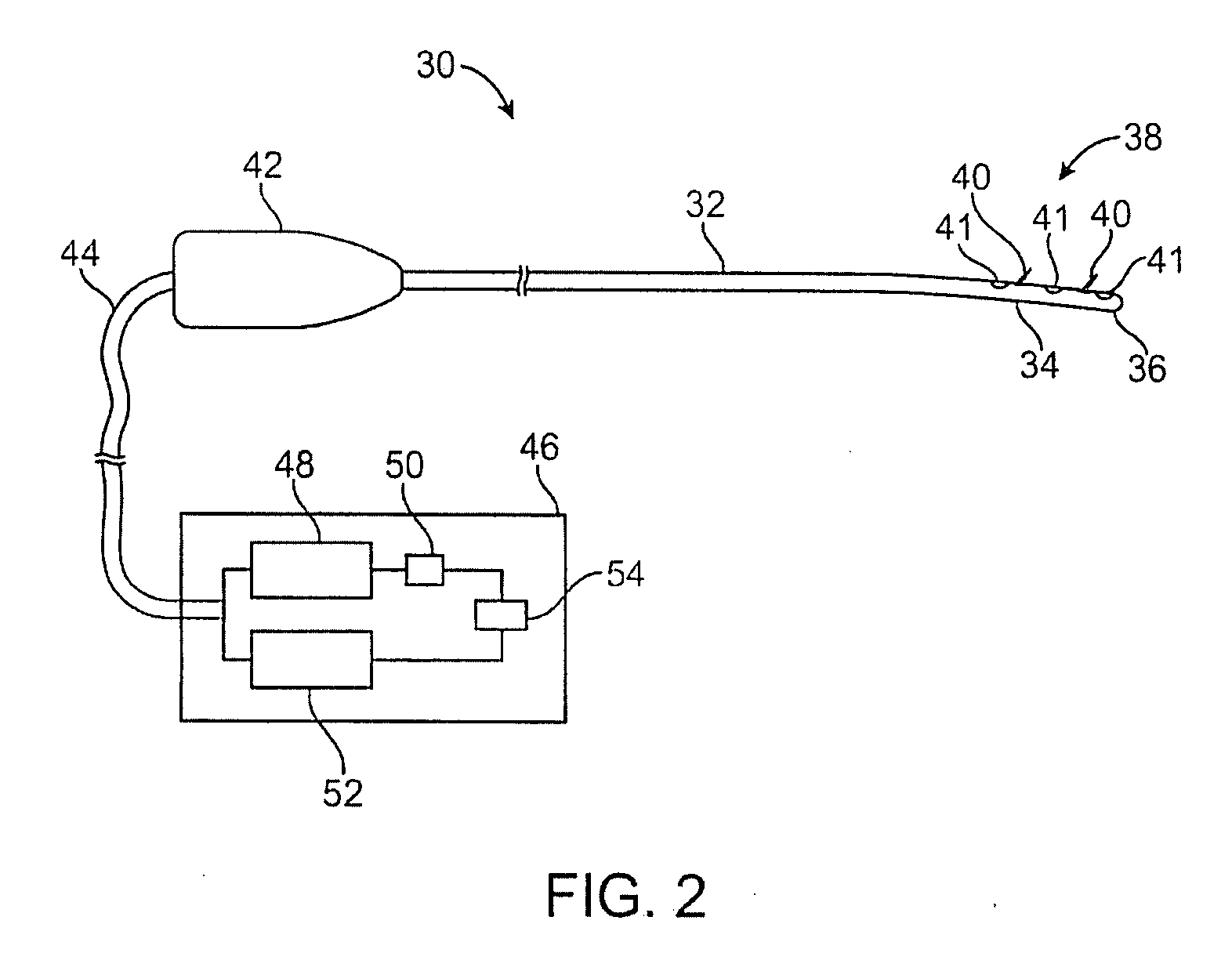

Systems for treatment of nasal tissue

InactiveUS20080027423A1Small sizeIncrease airflowUltrasound therapySurgical instrument detailsPain managementAnalgesic agents

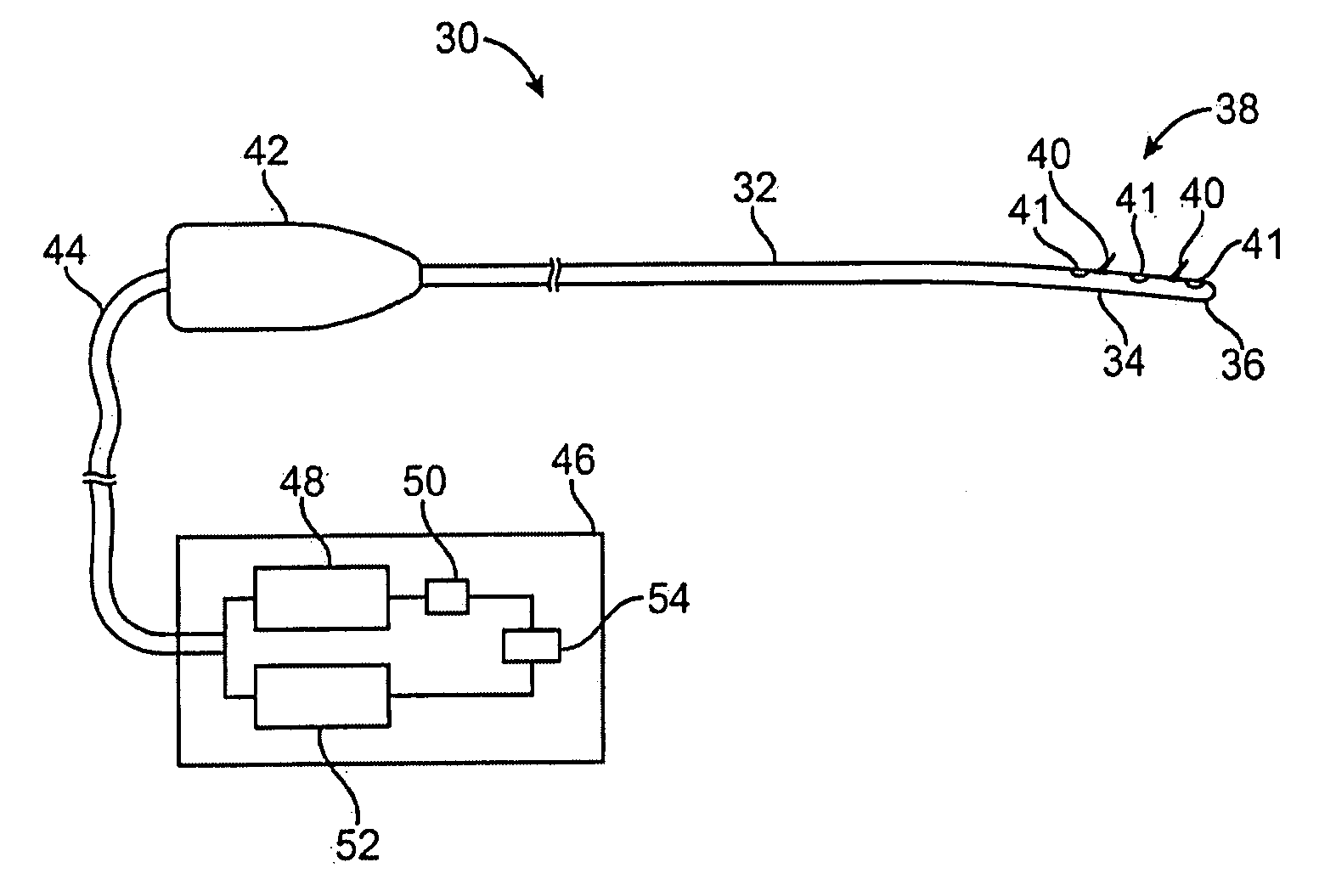

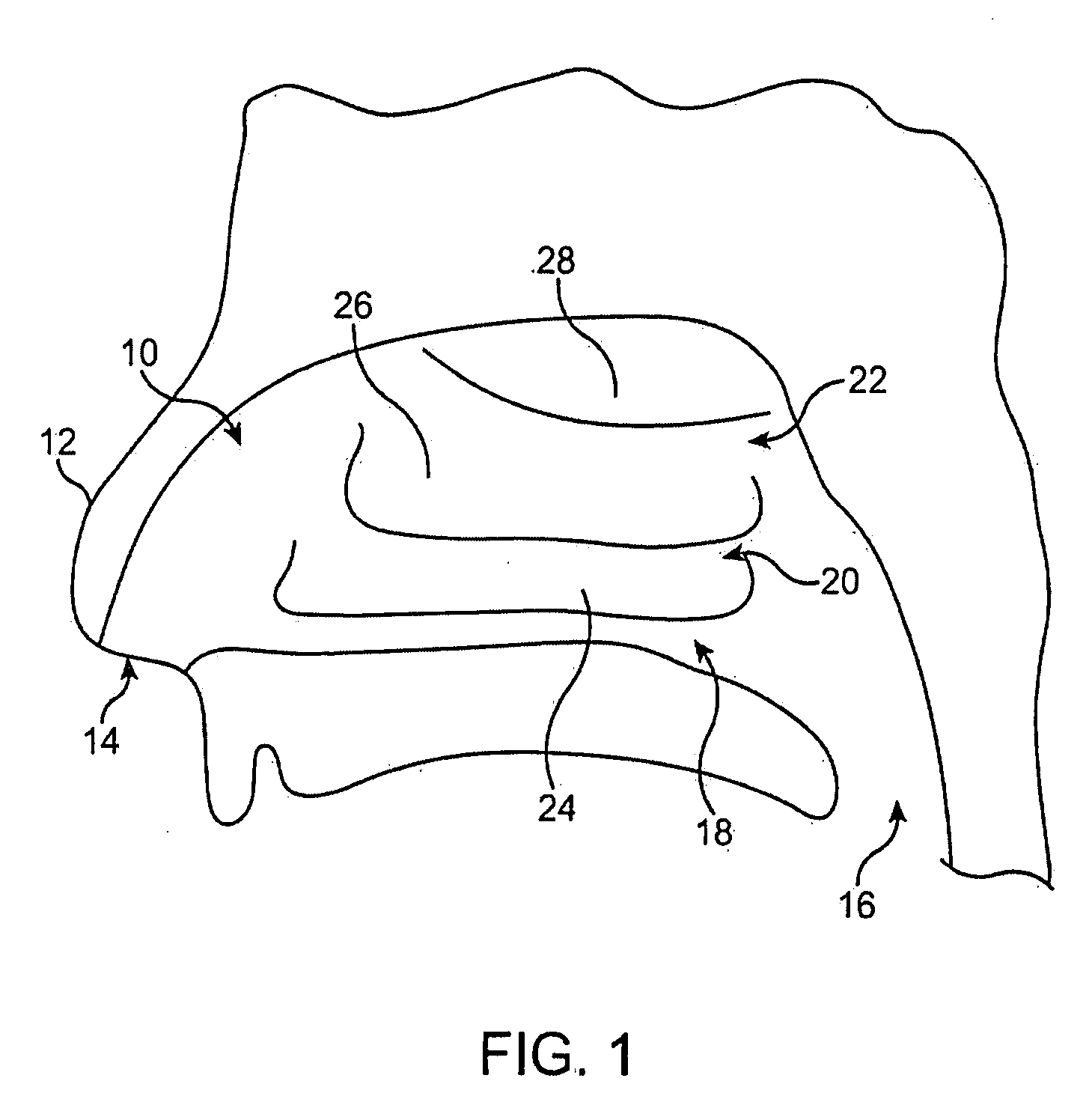

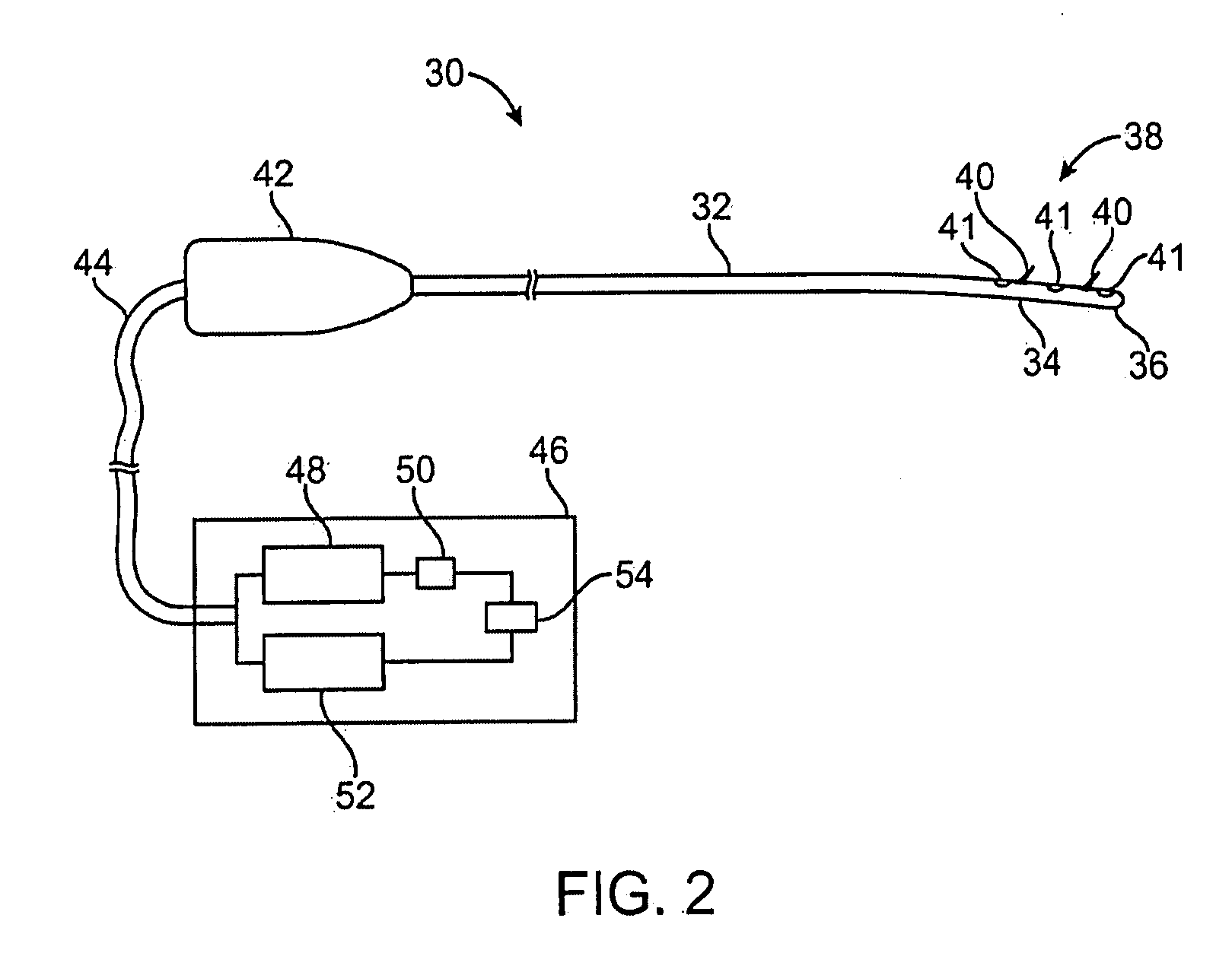

Systems for the treatment of nasal tissue, particularly the nasal turbinates, are described. One method for reducing the size of the inferior nasal turbinate is to apply ultrasound energy to the tissue regions beneath the surface of the turbinate tissue. One instrument may be used to deliver ultrasound energy and provide an infusion or injection of a fluid directly into the turbinate being treated, e.g., to bulk up the size of the turbinate to ensure that the ultrasound energy is properly delivered directly into the intended turbinate tissue. Fluids containing anesthetics, fluids infused with analgesics, etc. may be used for pain management while other medications, such as non-steroidal drugs, steroidal drugs, anti-inflammatory drugs, anti-histamines, anti-bacterial drugs, etc., can also be used. Such assemblies can also be utilized with other instruments as a system. For example, such a probe can be used with nasal speculums or imaging instrument in treating tissue.

Owner:CHOI GEORGE Y

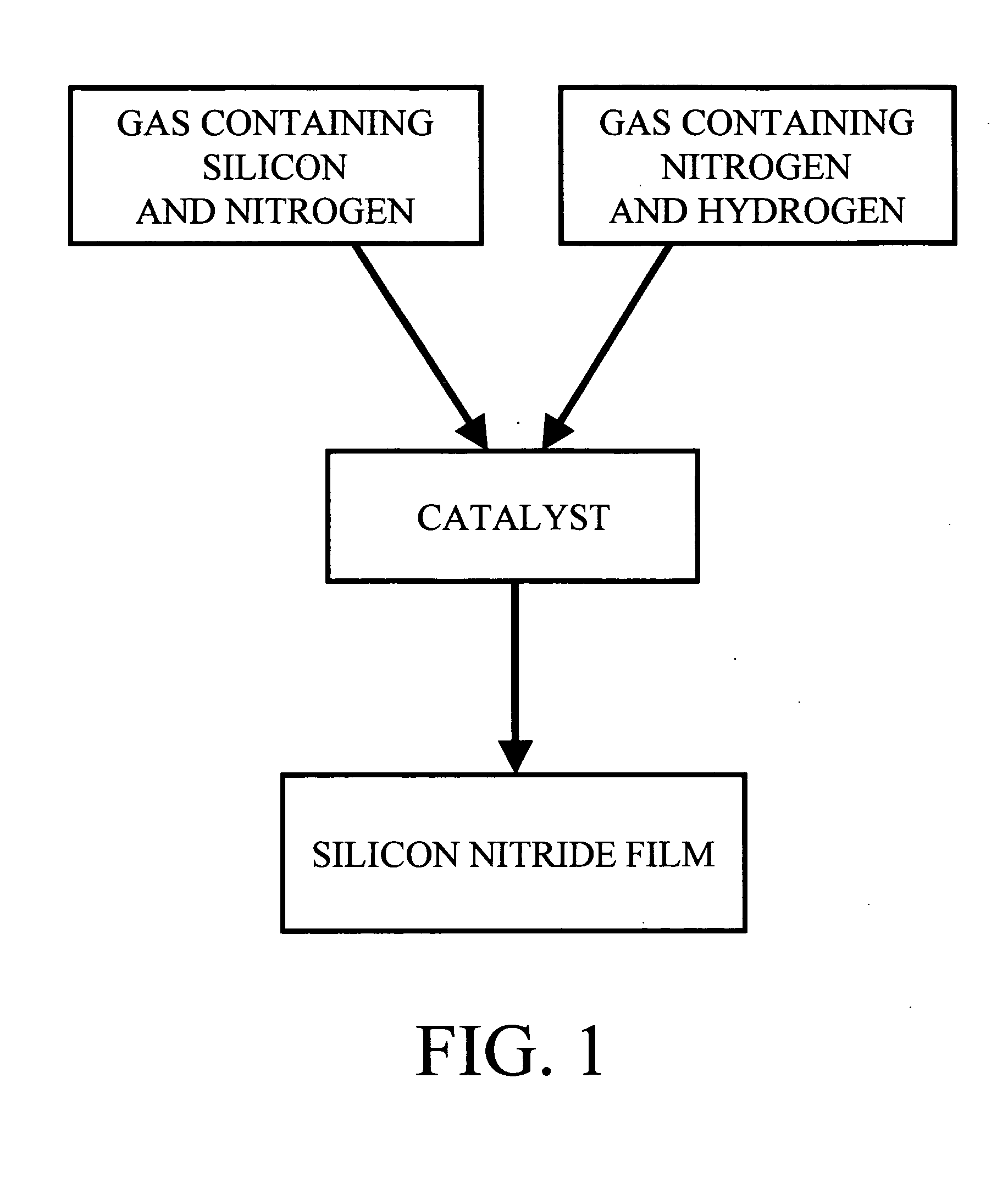

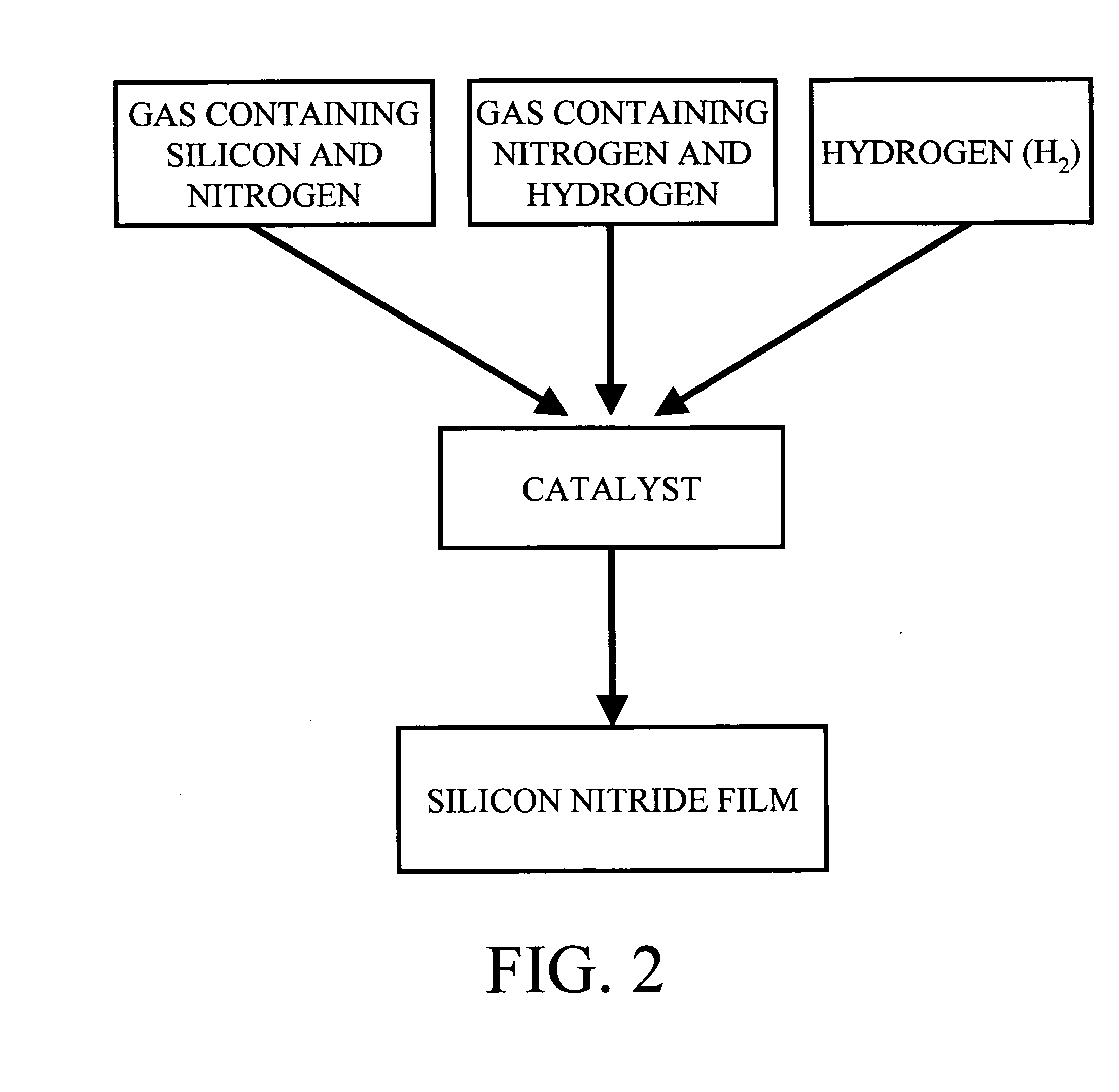

Method of forming silicon nitride film and method of manufacturing semiconductor device

ActiveUS20050196977A1Good step coverageIdeal balanceSemiconductor/solid-state device manufacturingChemical vapor deposition coatingInsulation layerHydrogen

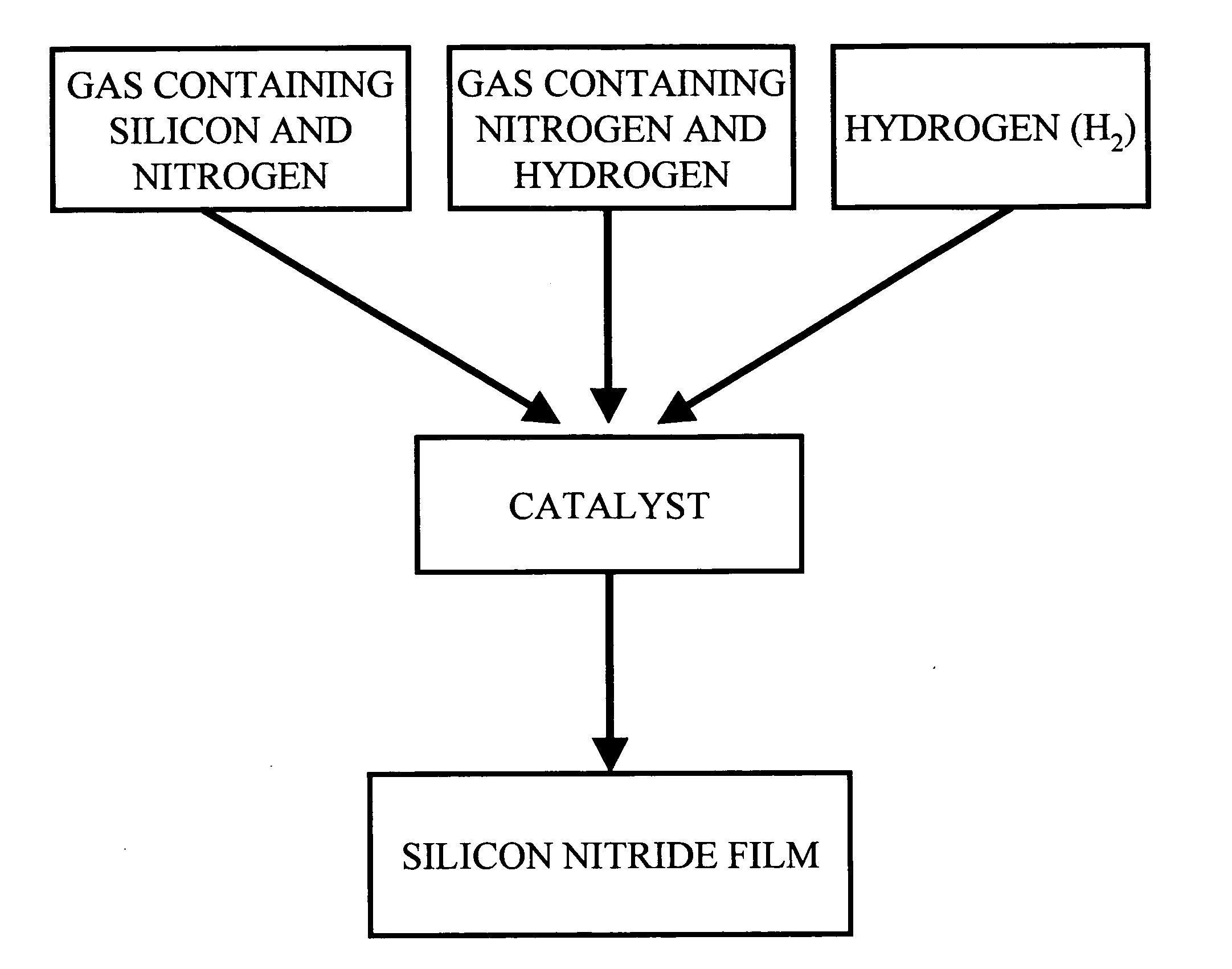

A method of forming a silicon nitride film comprises: forming a silicon nitride film by applying first gas containing silicon and nitrogen and second gas containing nitrogen and hydrogen to catalyst heated in a reduced pressure atmosphere. A method of manufacturing a semiconductor device comprising the steps of: forming a silicon nitride film by the method as claimed in claim 1 on a substrate having the semiconductor layer, a gate insulation film selectively provided on a principal surface of the semiconductor layer, and a gate electrode provided on the gate insulation film; and removing the silicon nitride film on the semiconductor layer and the gate electrode and leaving a sidewall comprising the silicon nitride film on a side surface of the gate insulation film and the gate electrode by etching the silicon nitride film in a direction generally normal to the principal surface of the semiconductor layer. A method of manufacturing a semiconductor device comprising the steps of: forming a silicon nitride film by the method as claimed in claim 1 on a substrate including a semiconductor layer; forming an interlayer insulation layer on the silicon nitride film; forming a layer having an opening on the interlayer insulation layer; and etching the interlayer insulation layer via the opening in a condition where an etching rate for the silicon nitride film is greater than an etching rate for the interlayer insulation layer.

Owner:ULVAC INC

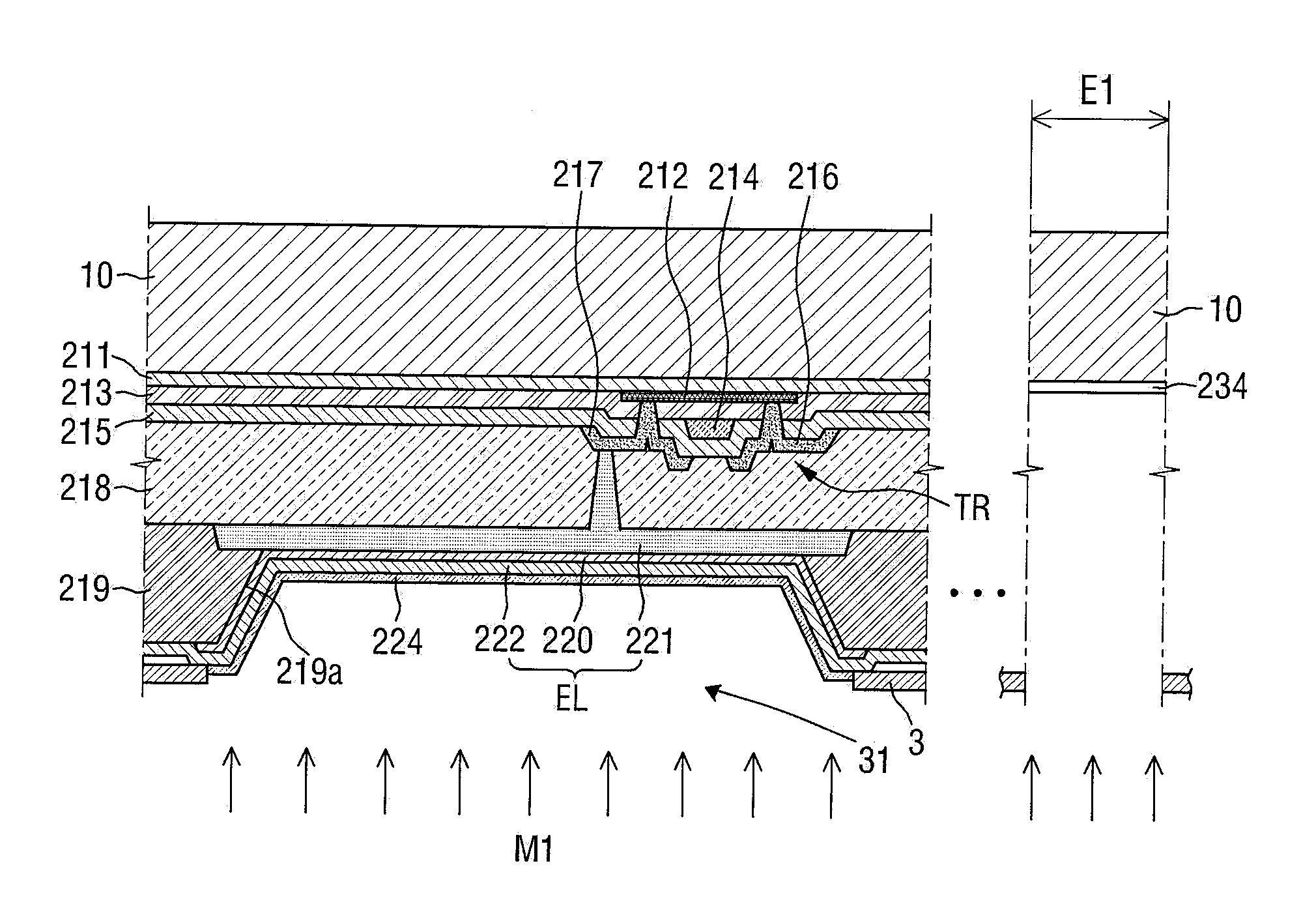

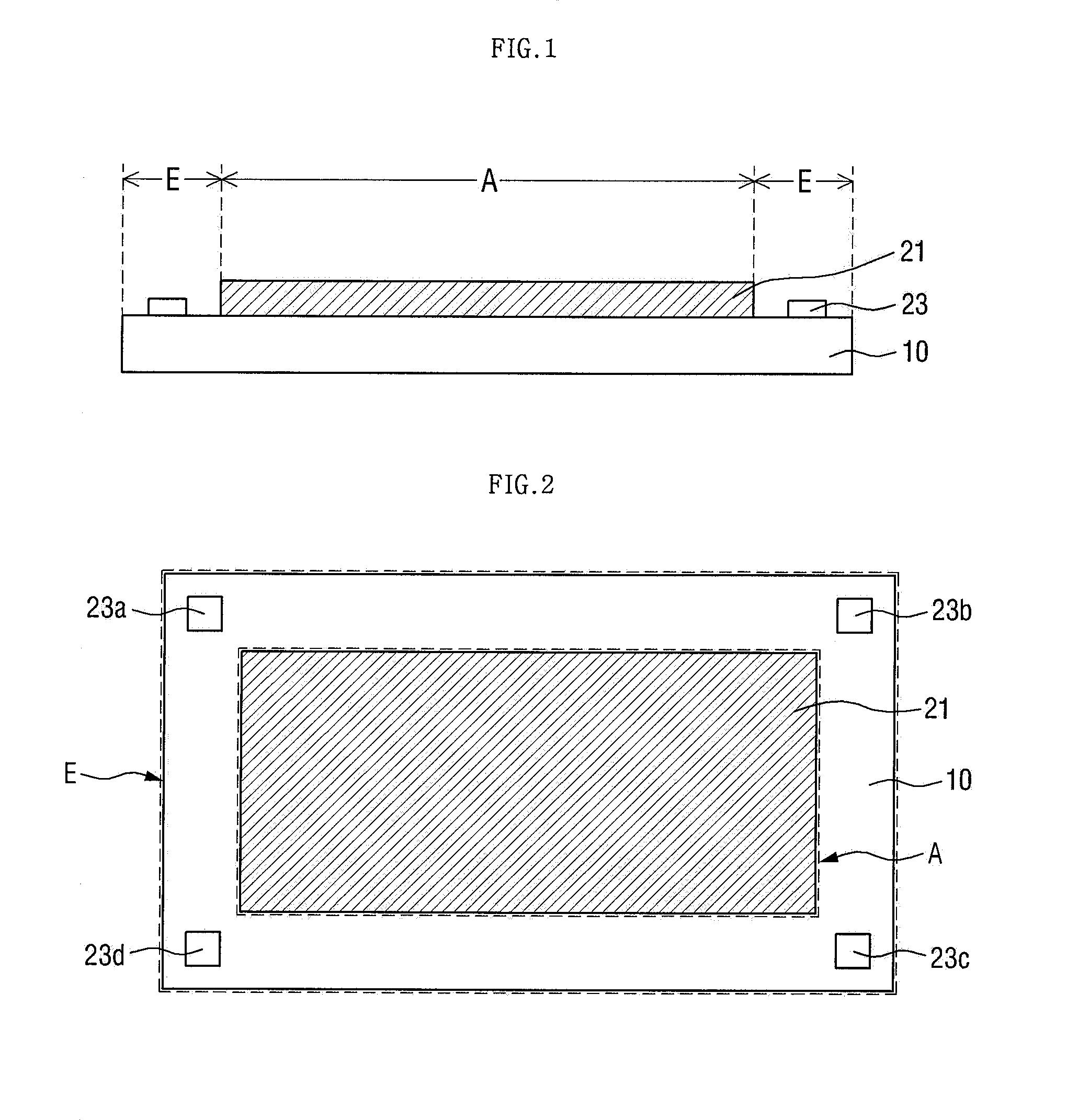

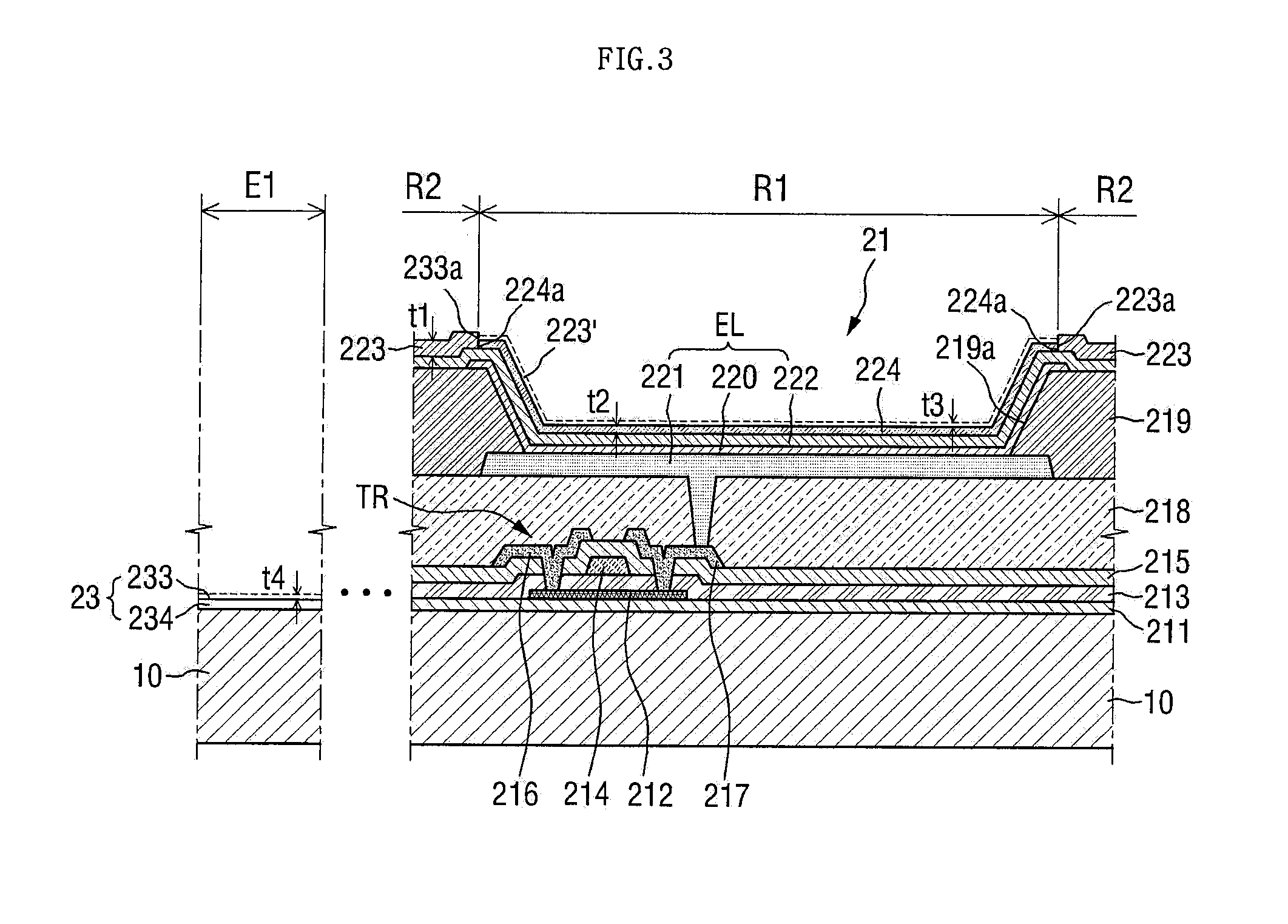

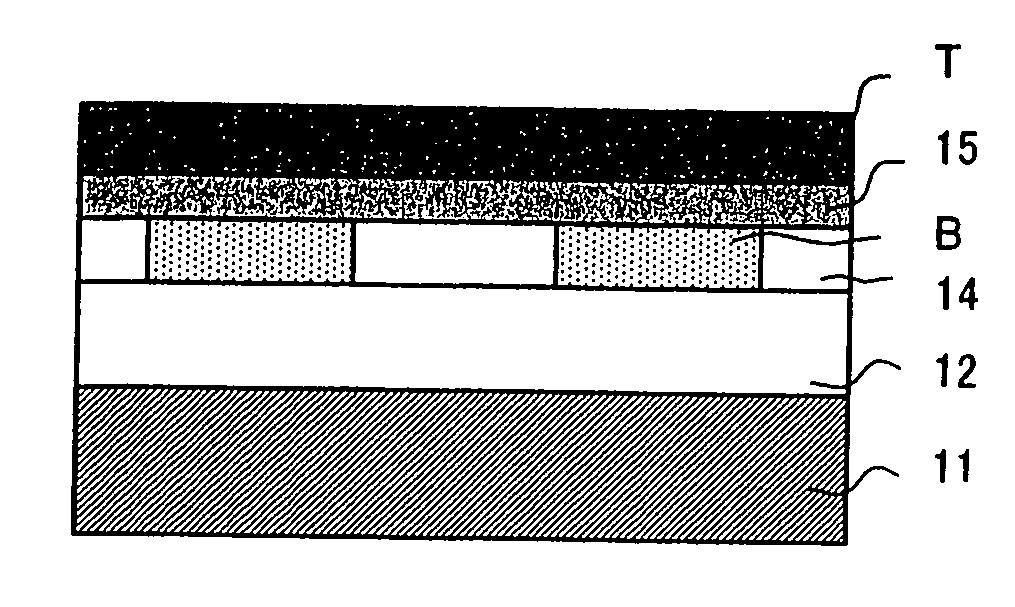

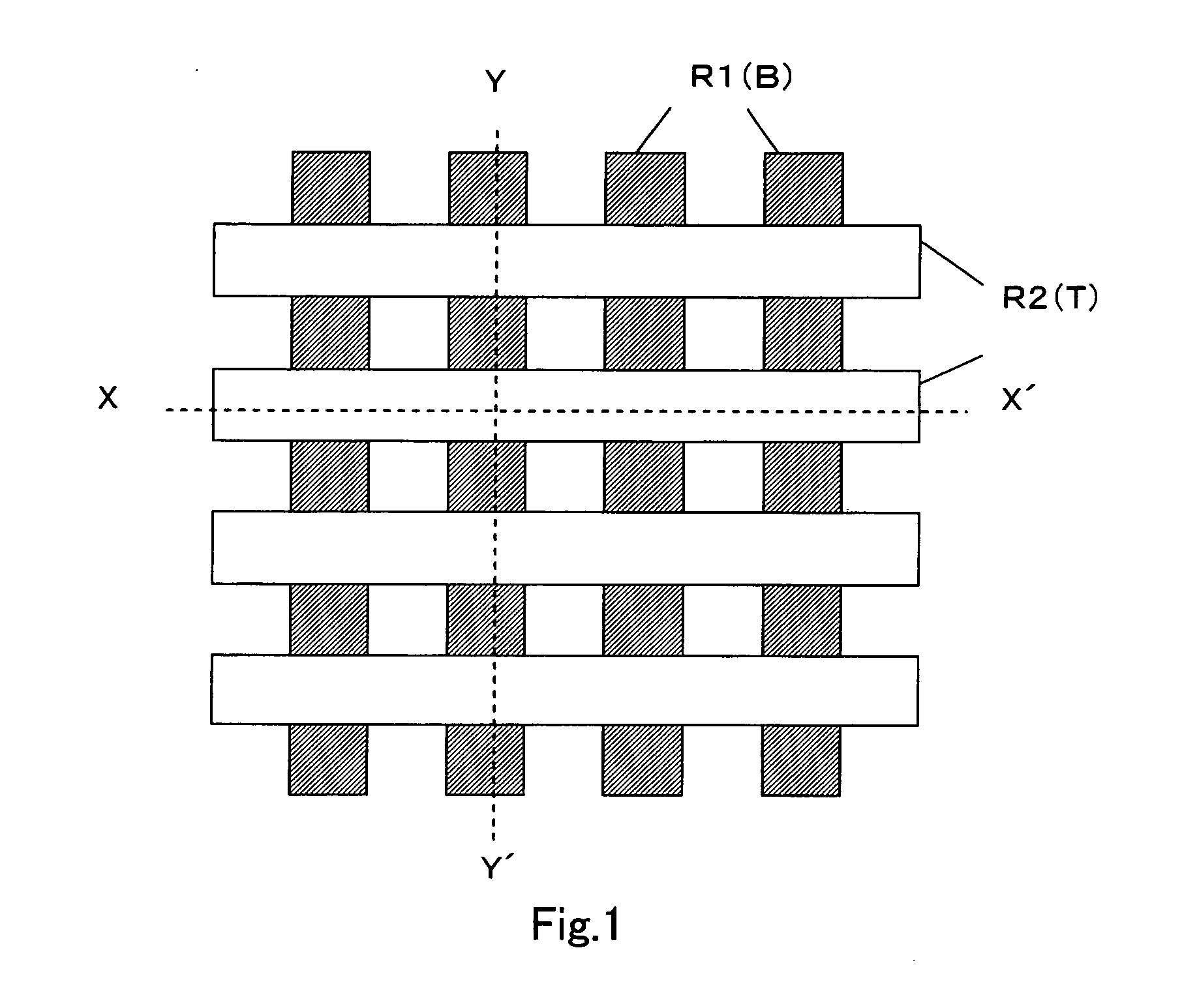

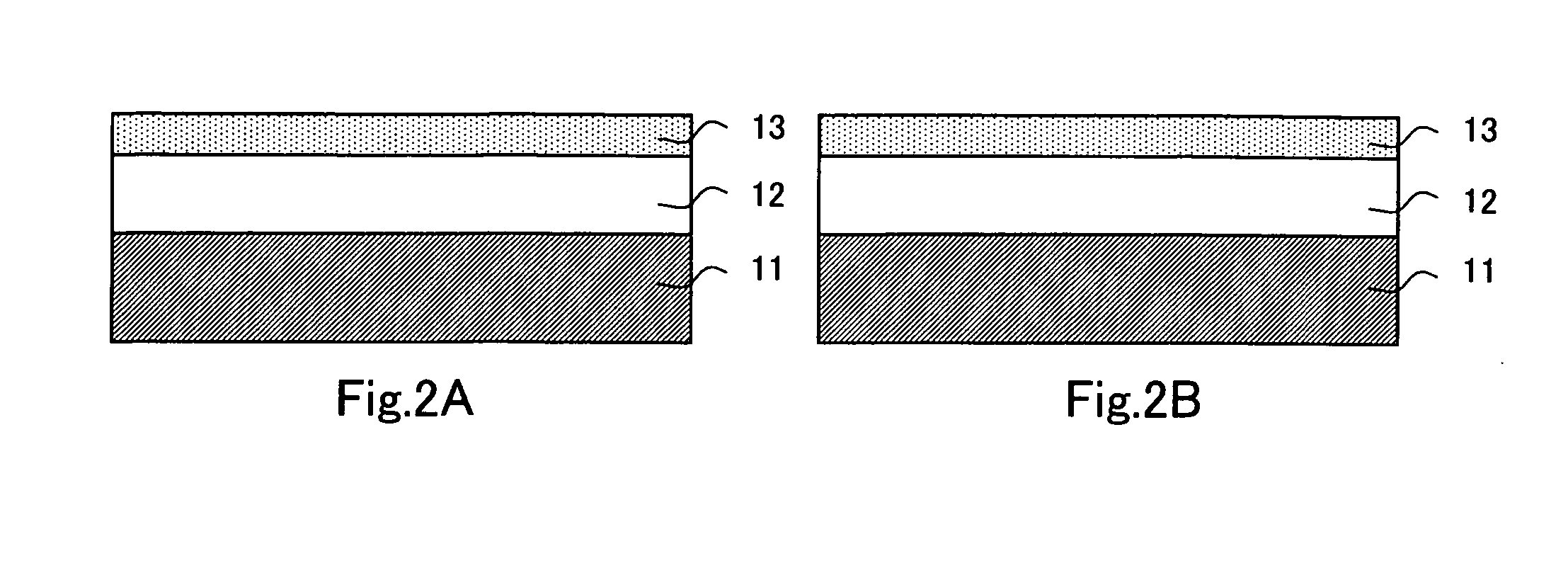

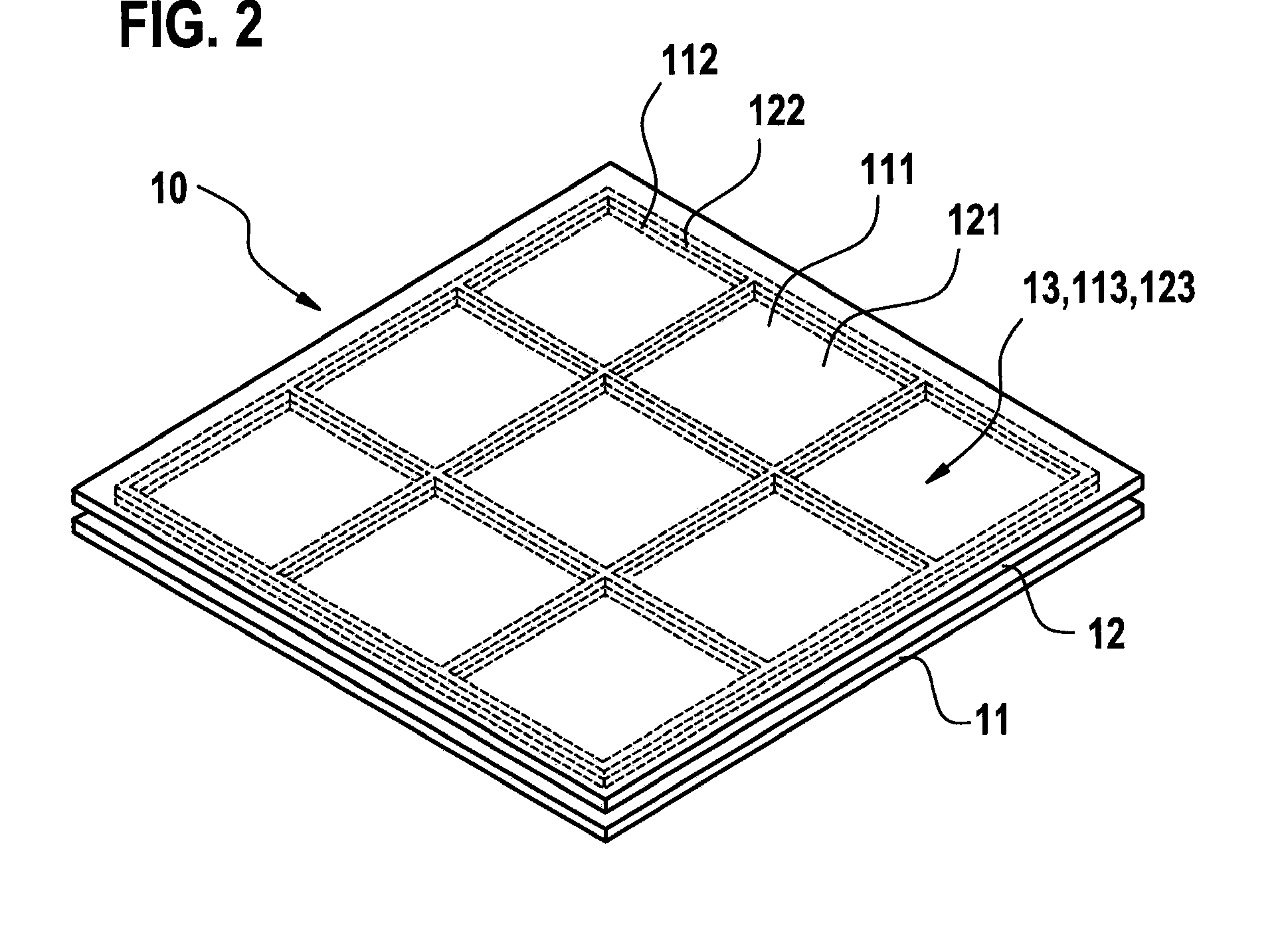

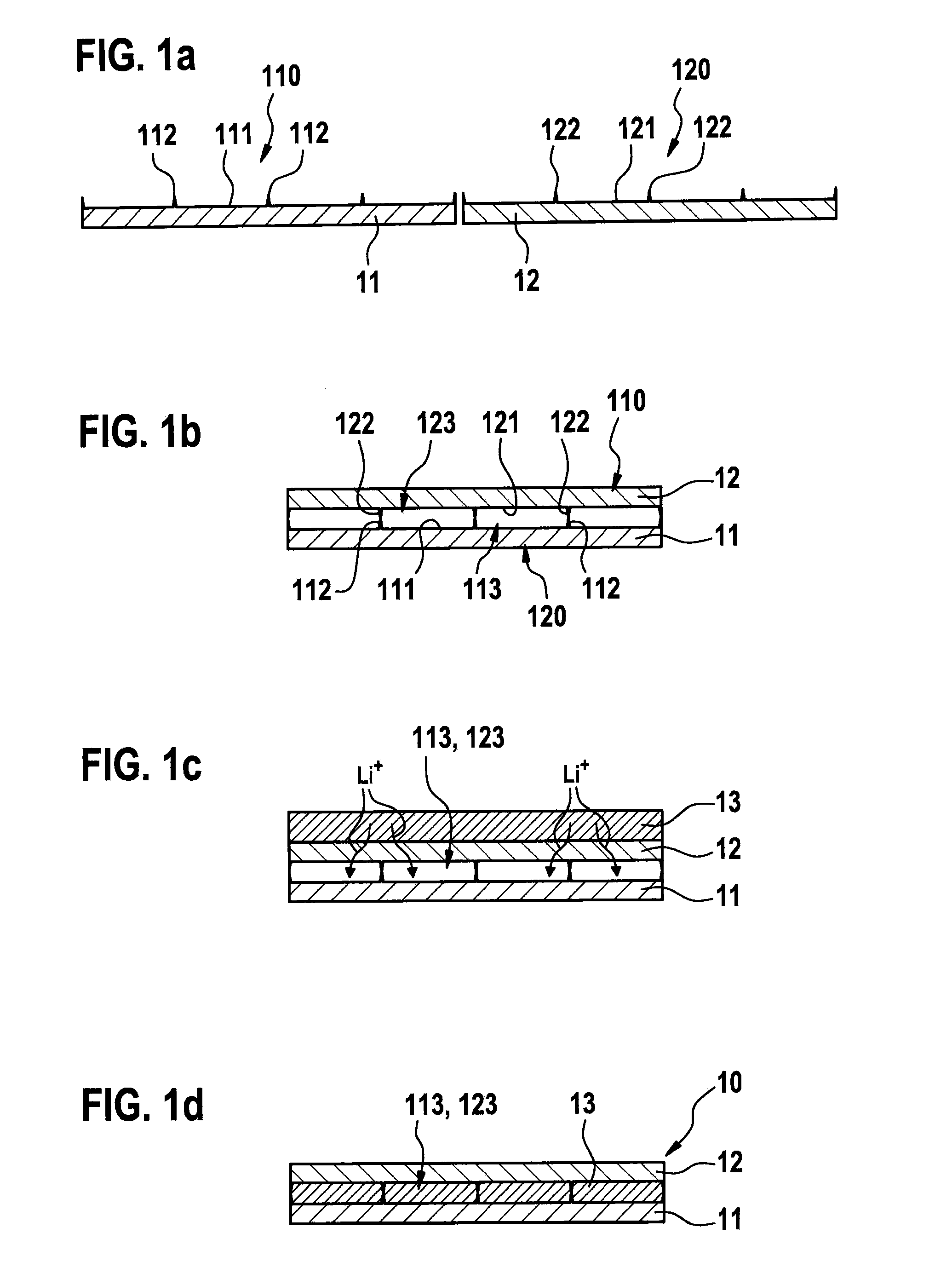

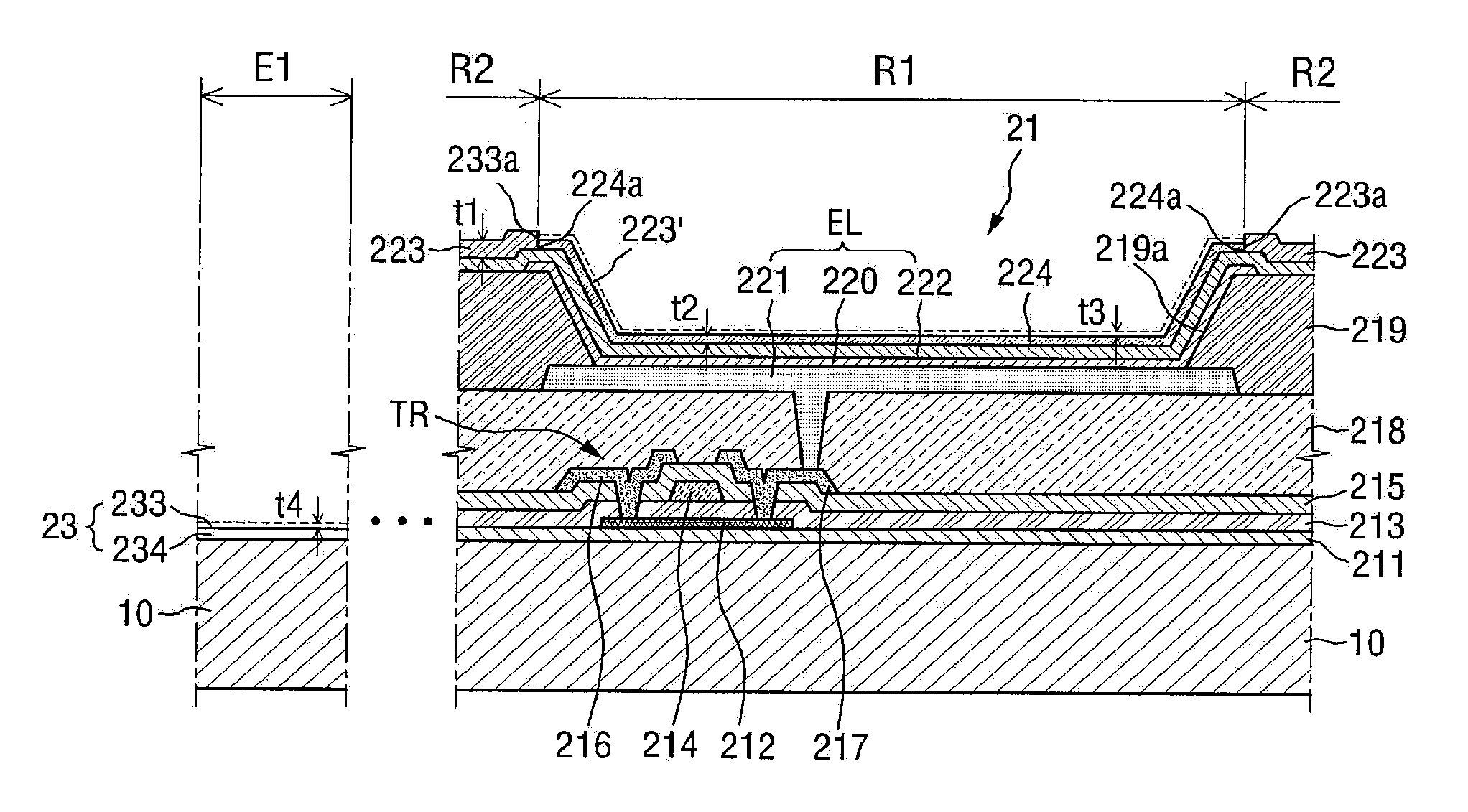

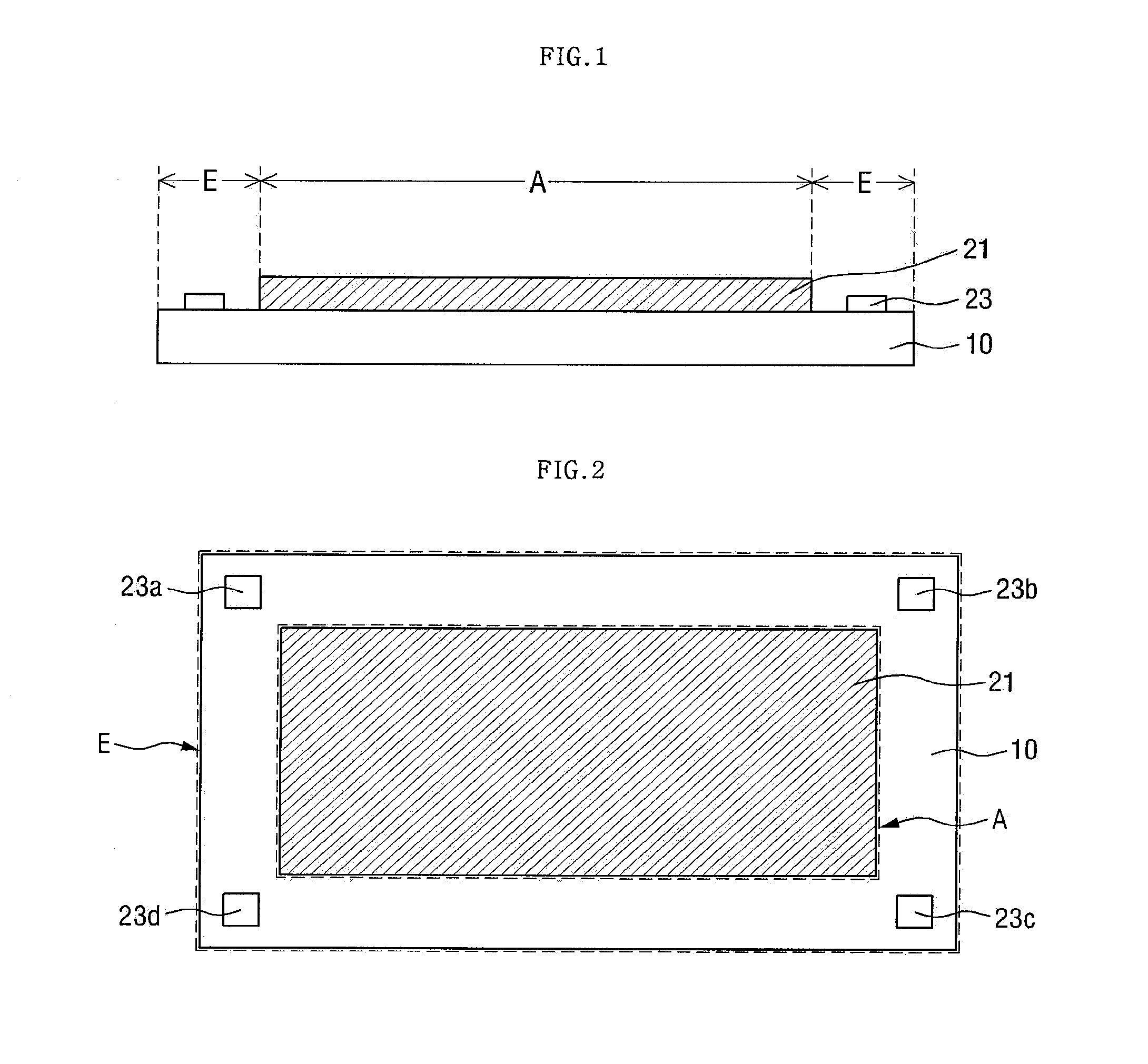

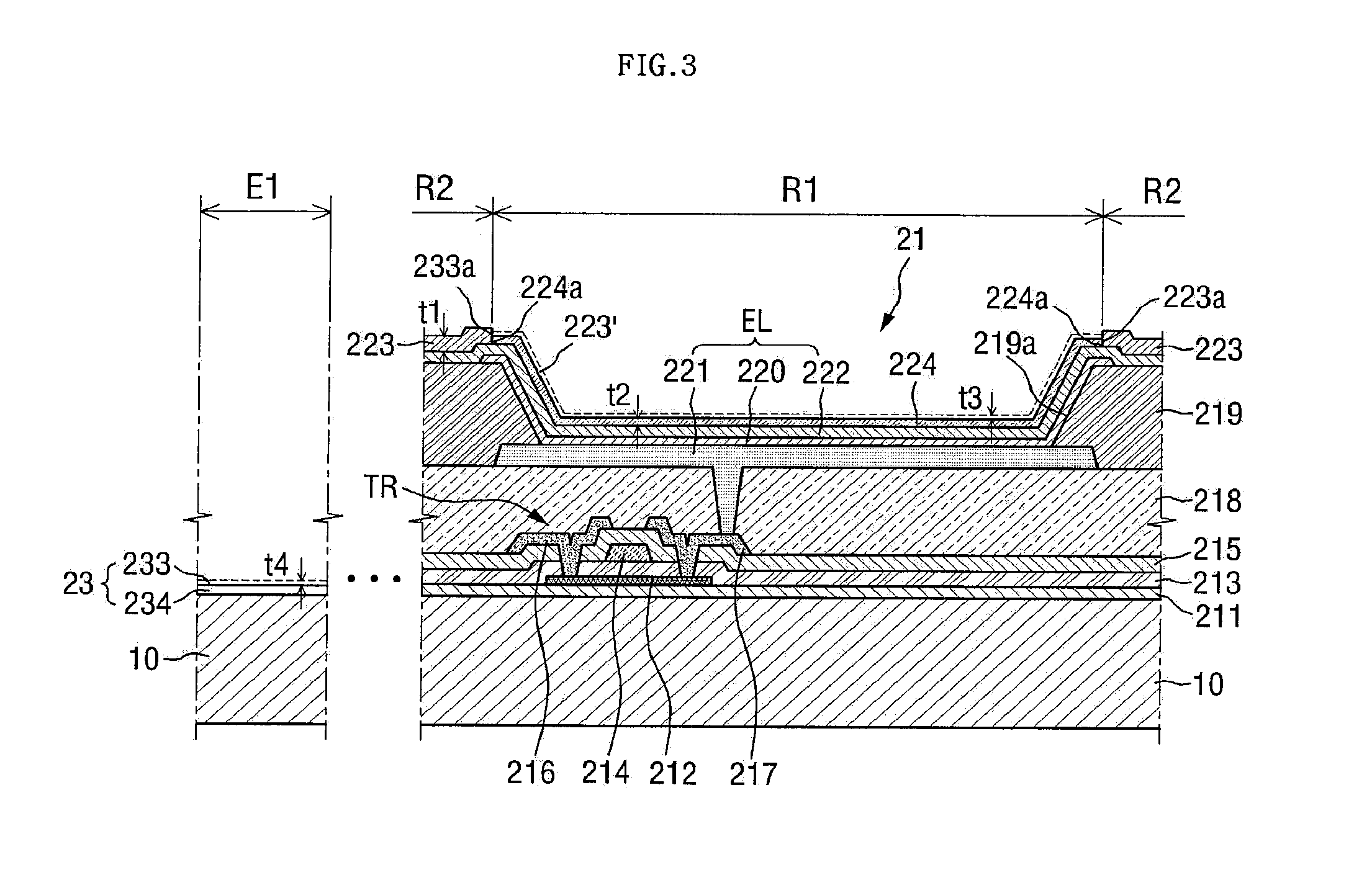

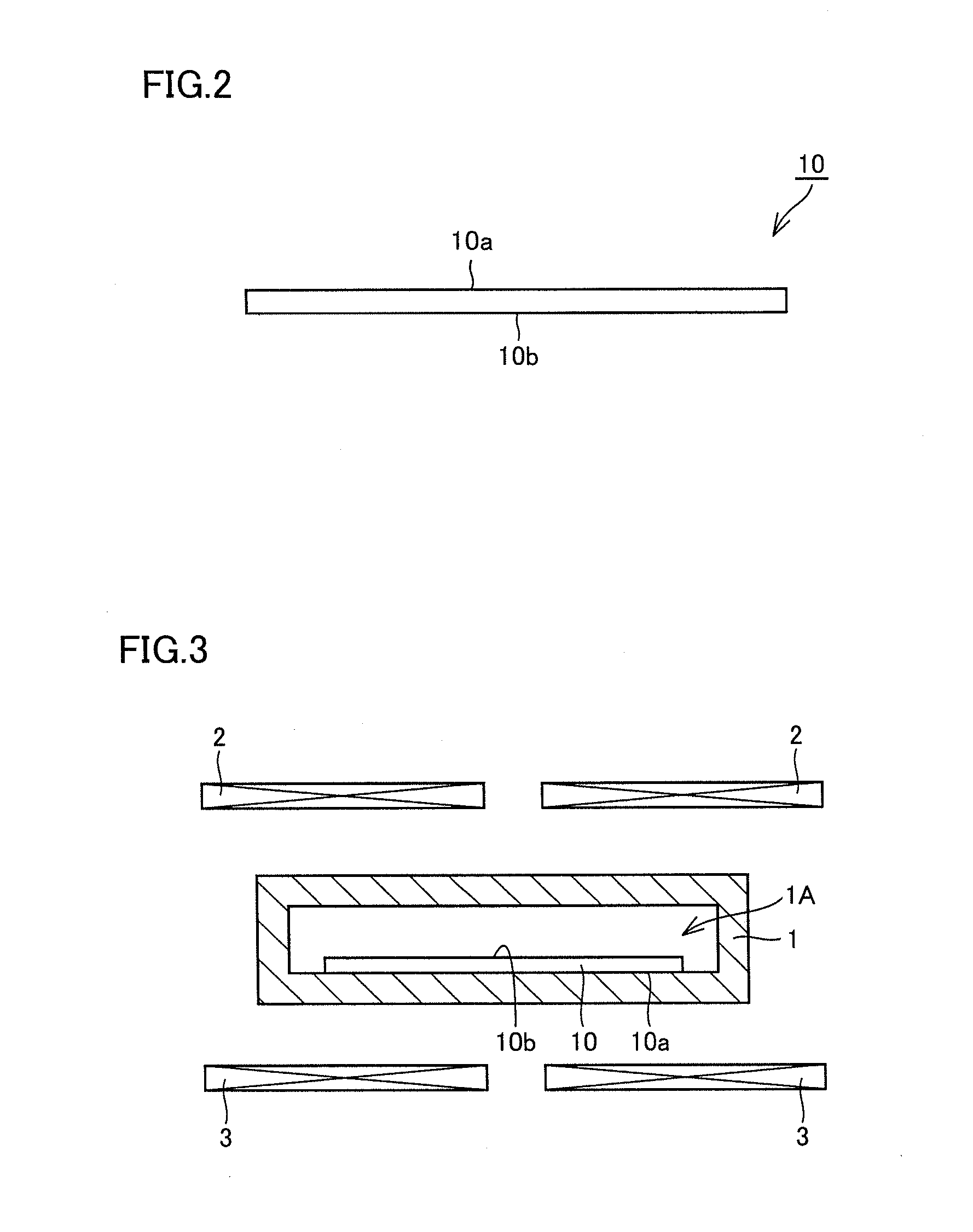

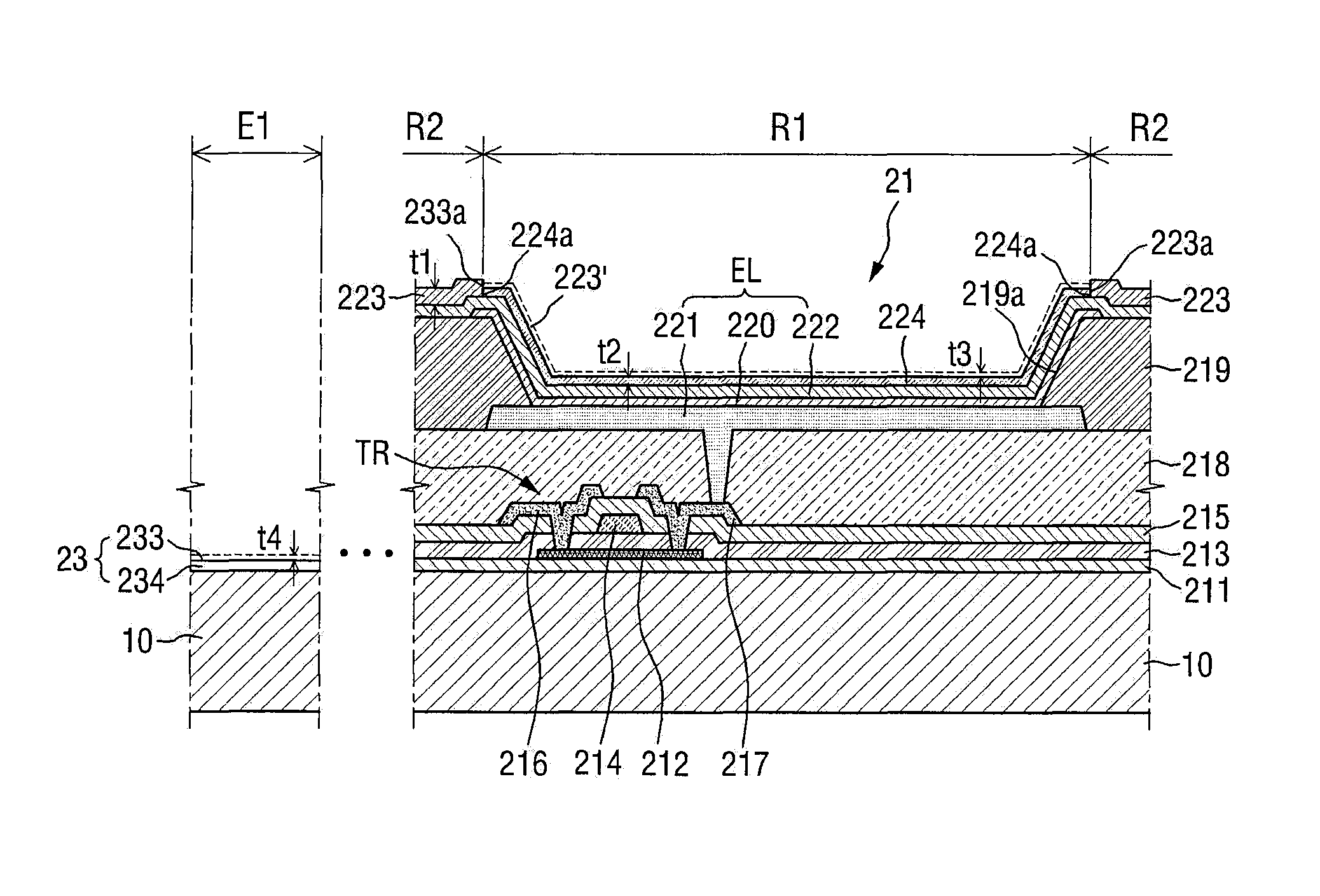

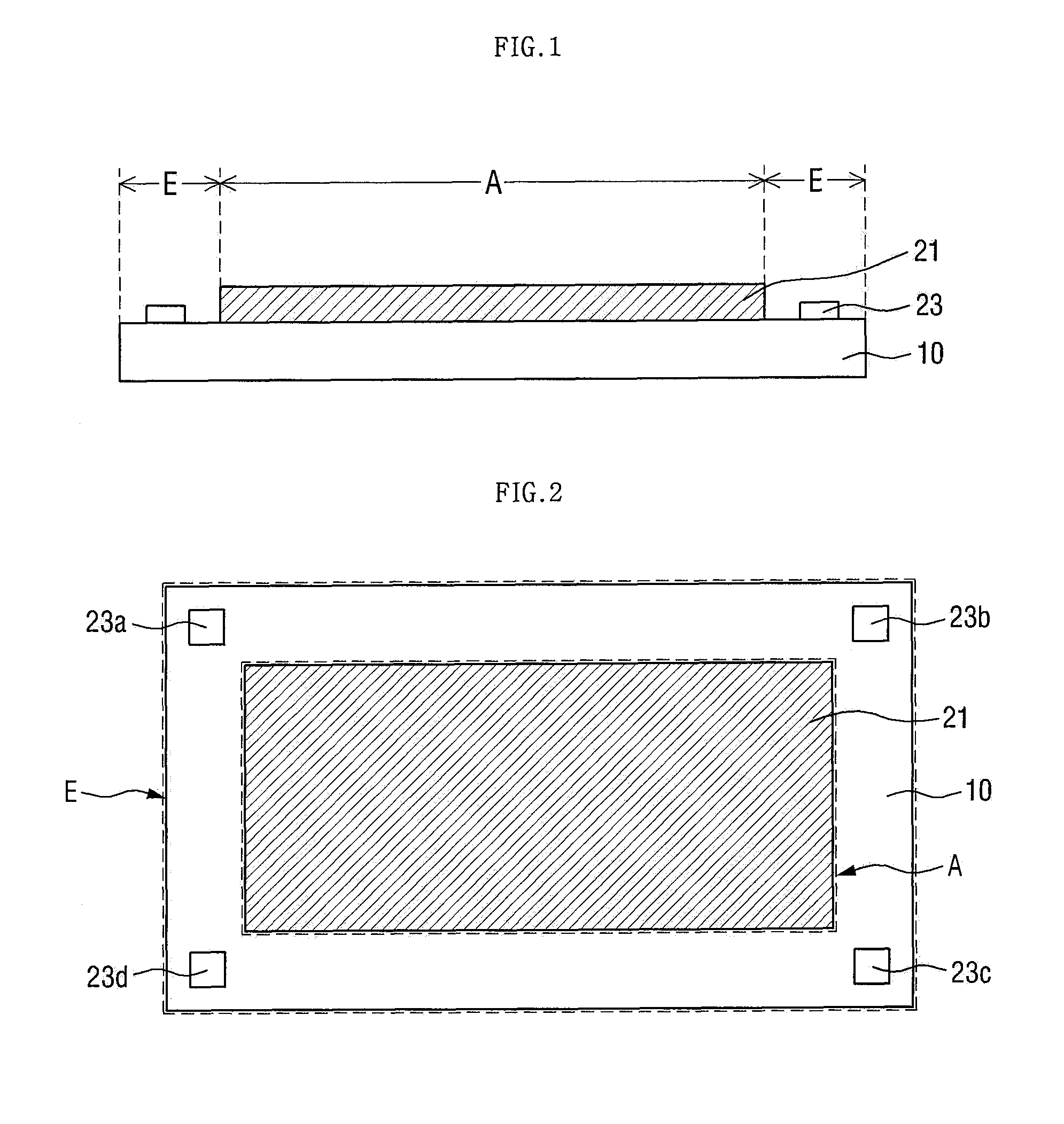

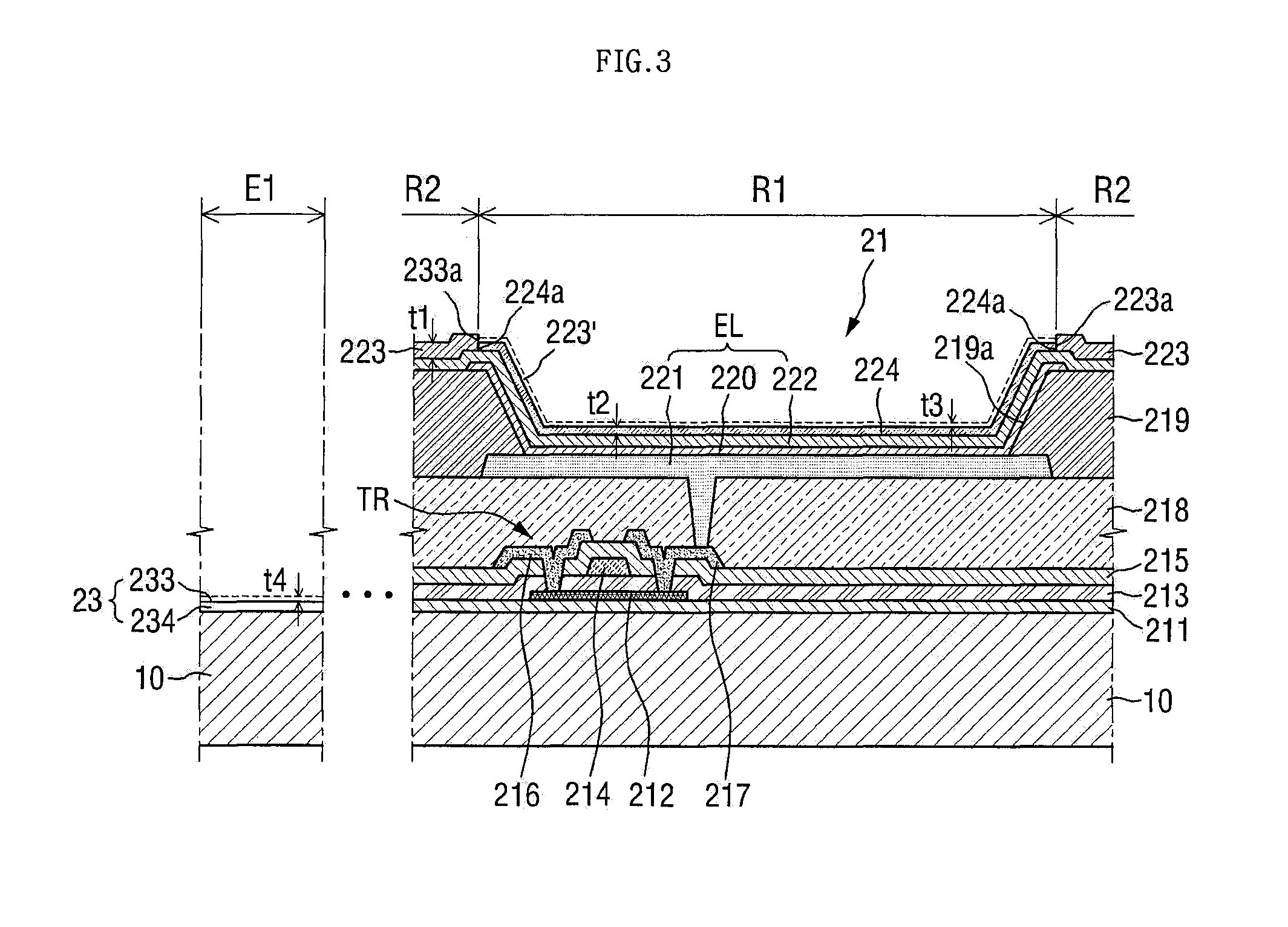

Display substrate and method of manufacturing the same

ActiveUS20140231761A1Prevent and reduce voltage dropLayer can be damagedSemiconductor/solid-state device testing/measurementElectroluminescent light sourcesTransmittanceEngineering

A display substrate and a method of manufacturing the same. The display substrate includes a substrate including an active area and an inactive area, an organic light-emitting diode (OLED) unit disposed on the active area of the substrate, and a transmittance measurement pattern unit disposed on the inactive area of the substrate. The transmittance measurement pattern unit includes a deposition assistant layer pattern disposed on the substrate.

Owner:SAMSUNG DISPLAY CO LTD

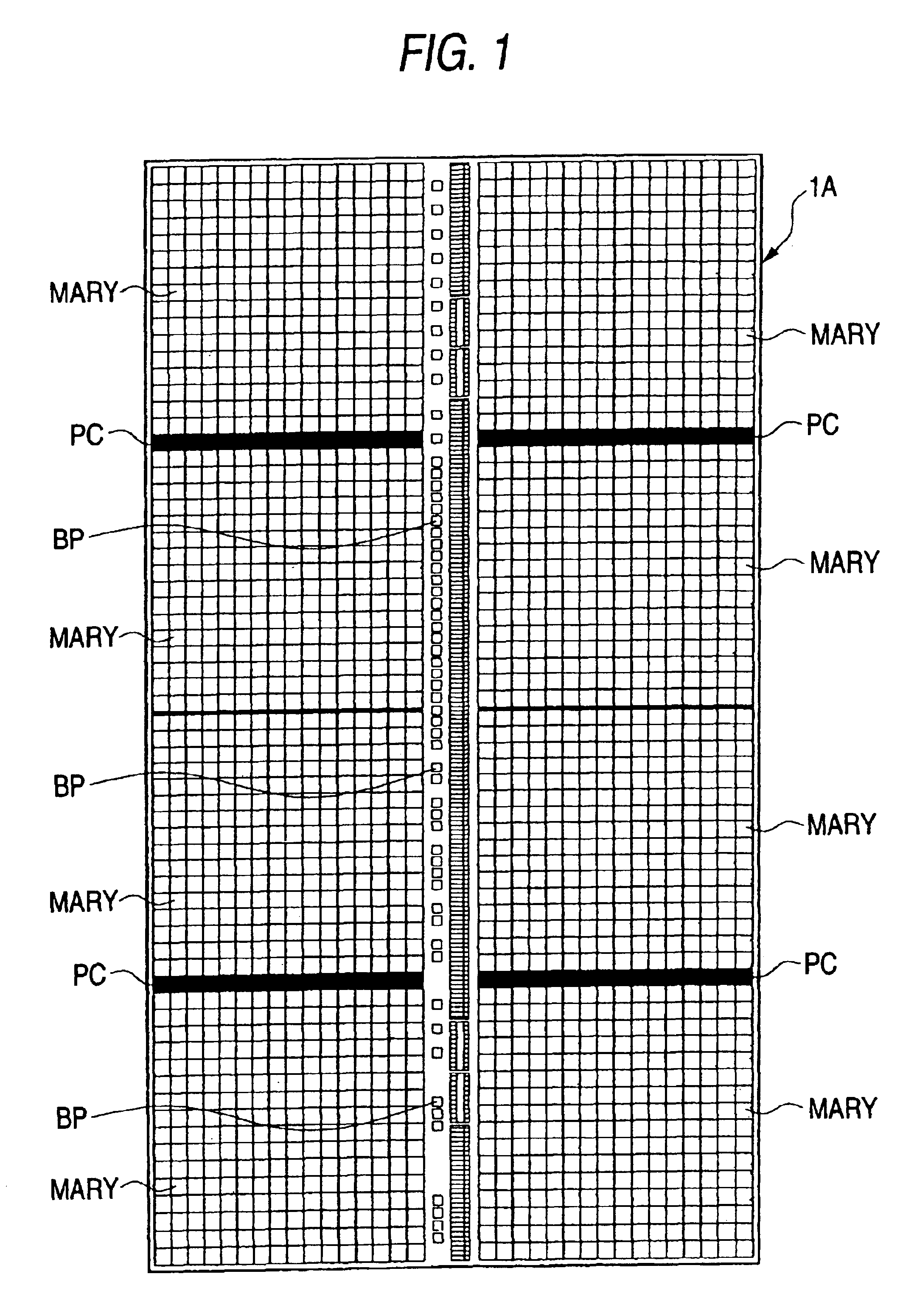

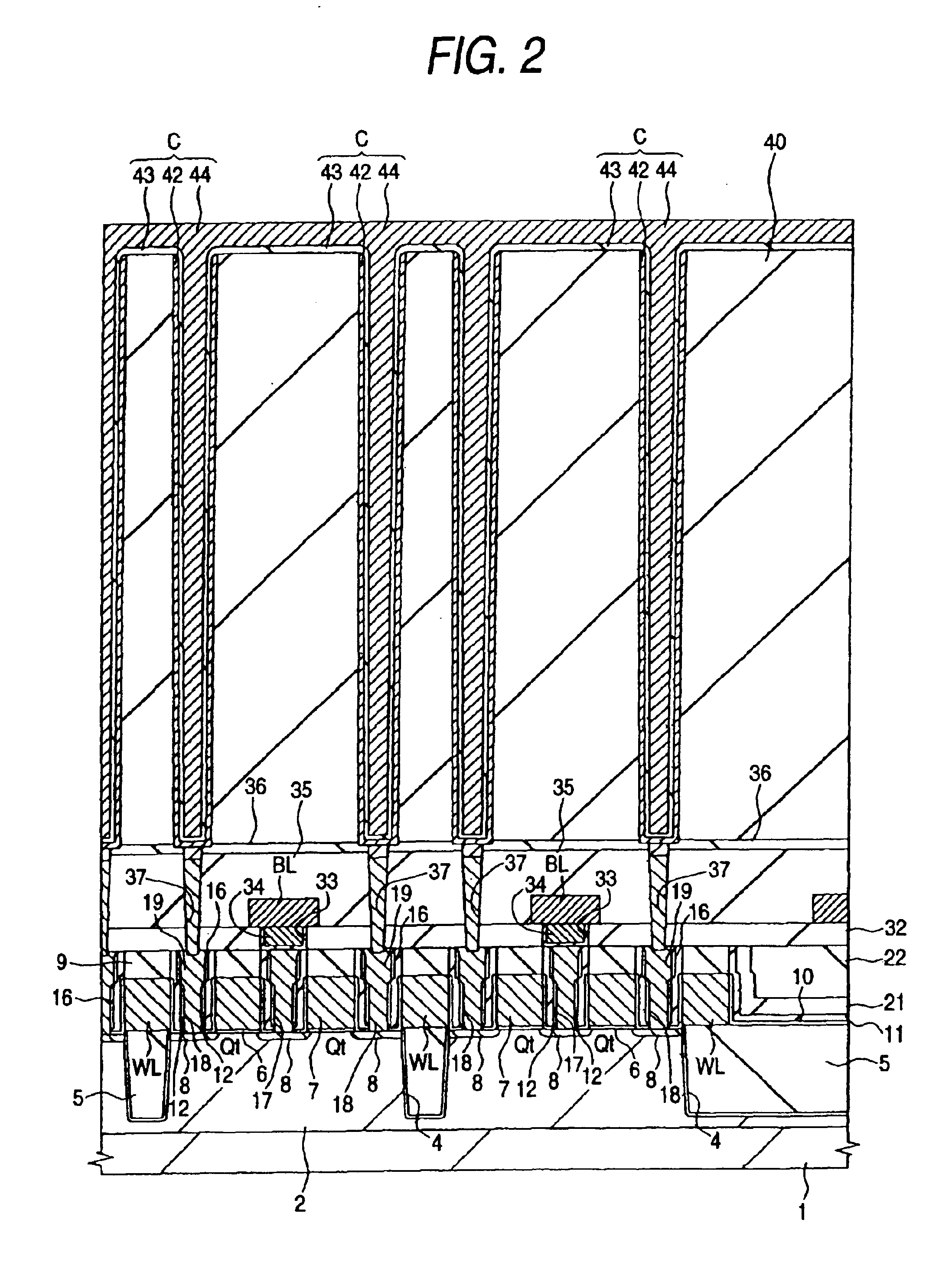

Semiconductor memory device

InactiveUS20060154417A1Minimize changesUnwanted variation can be minimizedSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

The present invention is directed towards a method of manufacturing a semiconductor memory device arranged of a cross point memory array having memory elements provided between upper and lower electrodes for storage of data. The present invention comprises a lower electrode lines forming step of planarizing each of the lower electrode lines and insulating layers provided on both sides of the lower electrode line so as to be substantially uniform in the height thus for patterning the lower electrode lines, a memory element layer depositing step of depositing on the lower electrode lines a memory element layer for the memory elements, and an annealing step of annealing with heat treatment either between the lower electrode lines forming step and the memory element layer depositing step or after the memory element layer depositing step so that any damages caused by the polishing of the surface of the lower electrode lines can be eliminated.

Owner:SHARP KK

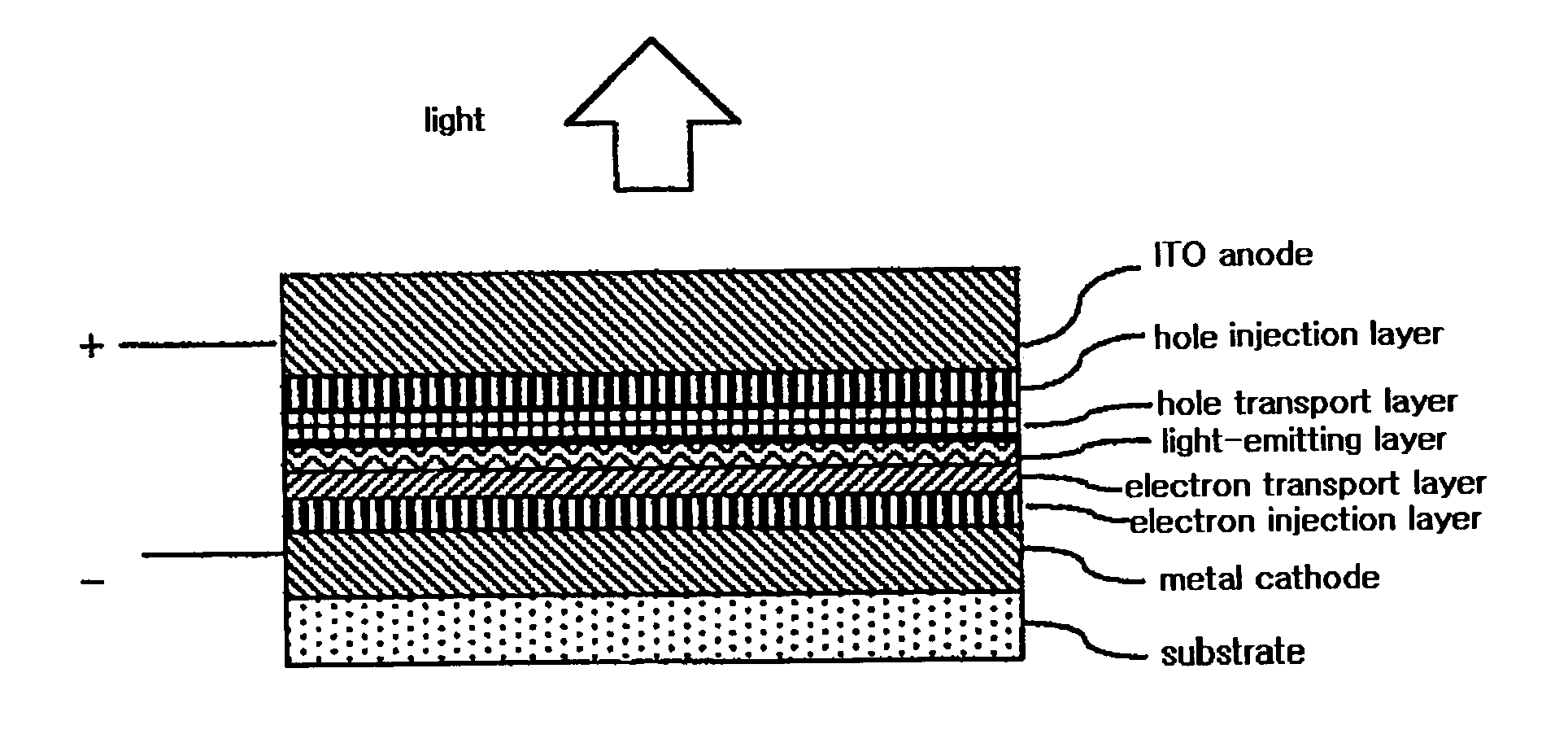

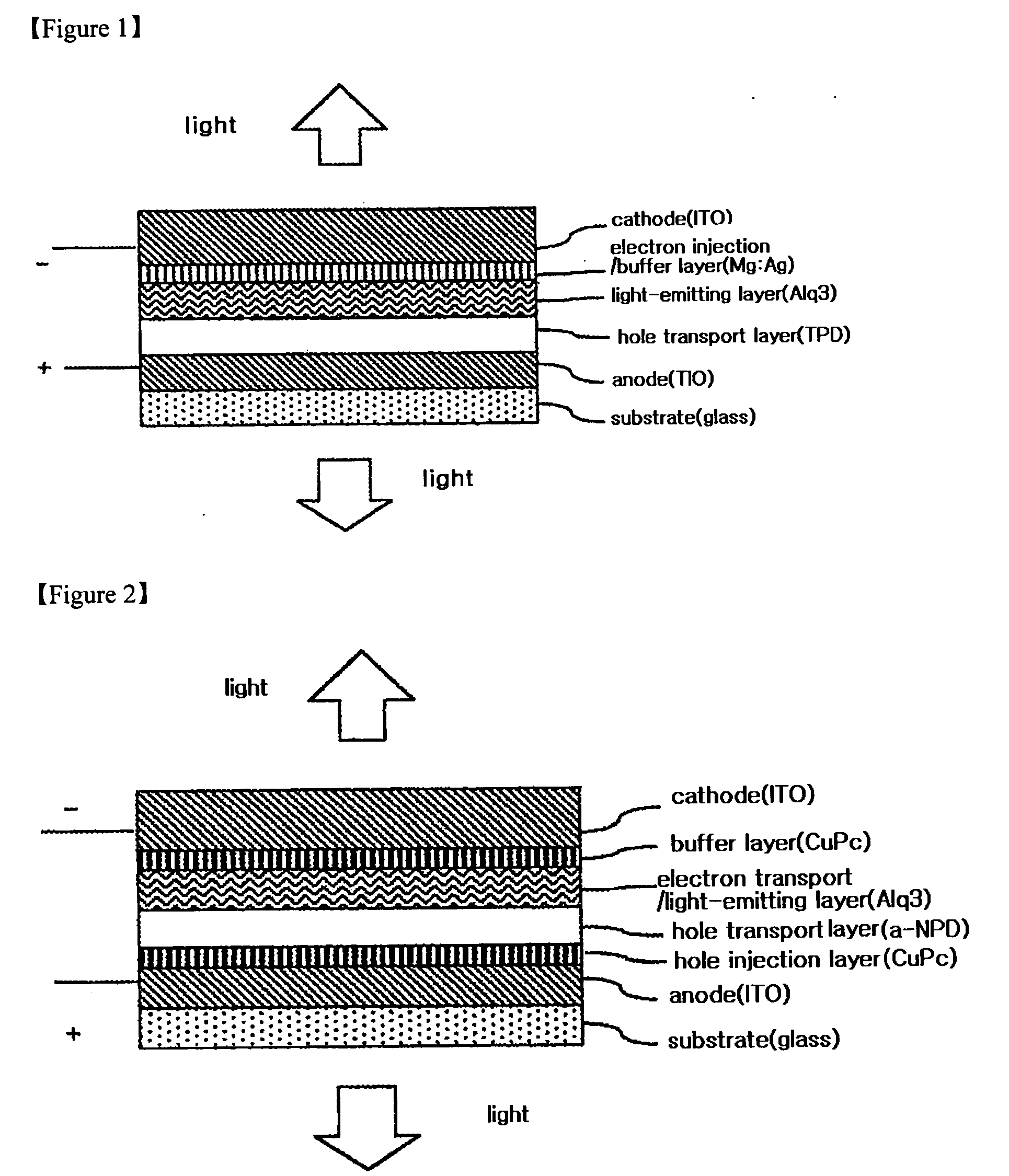

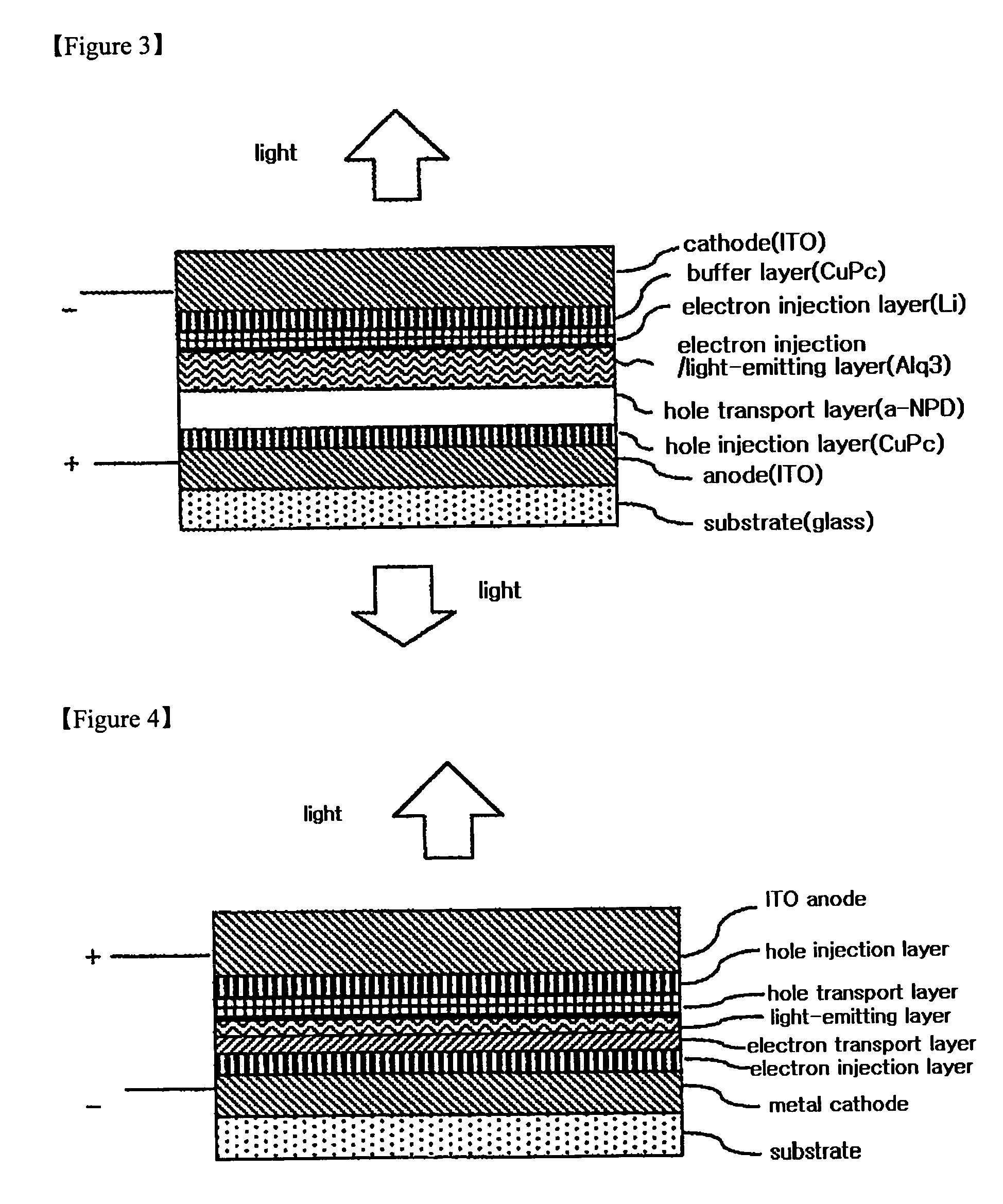

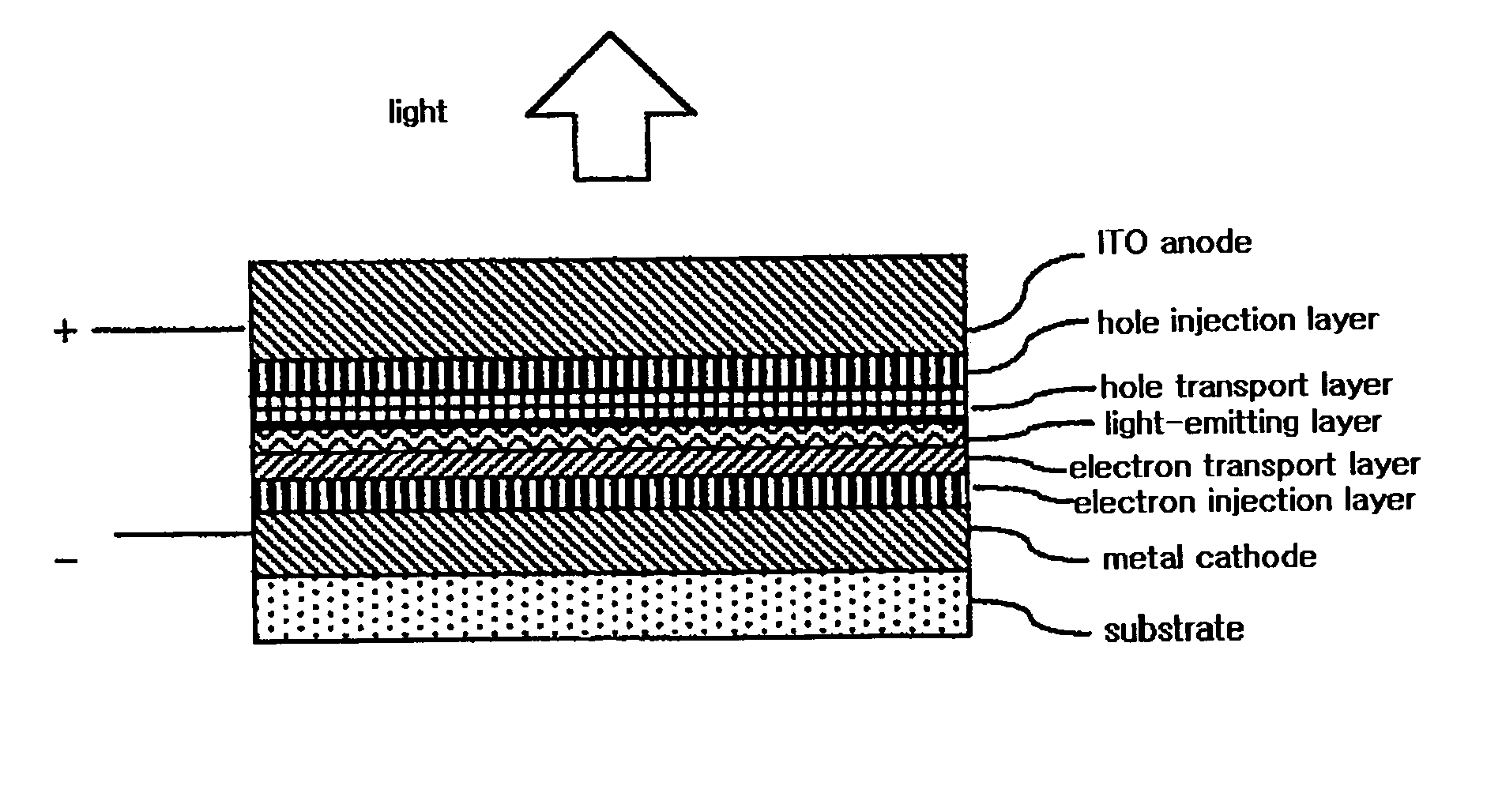

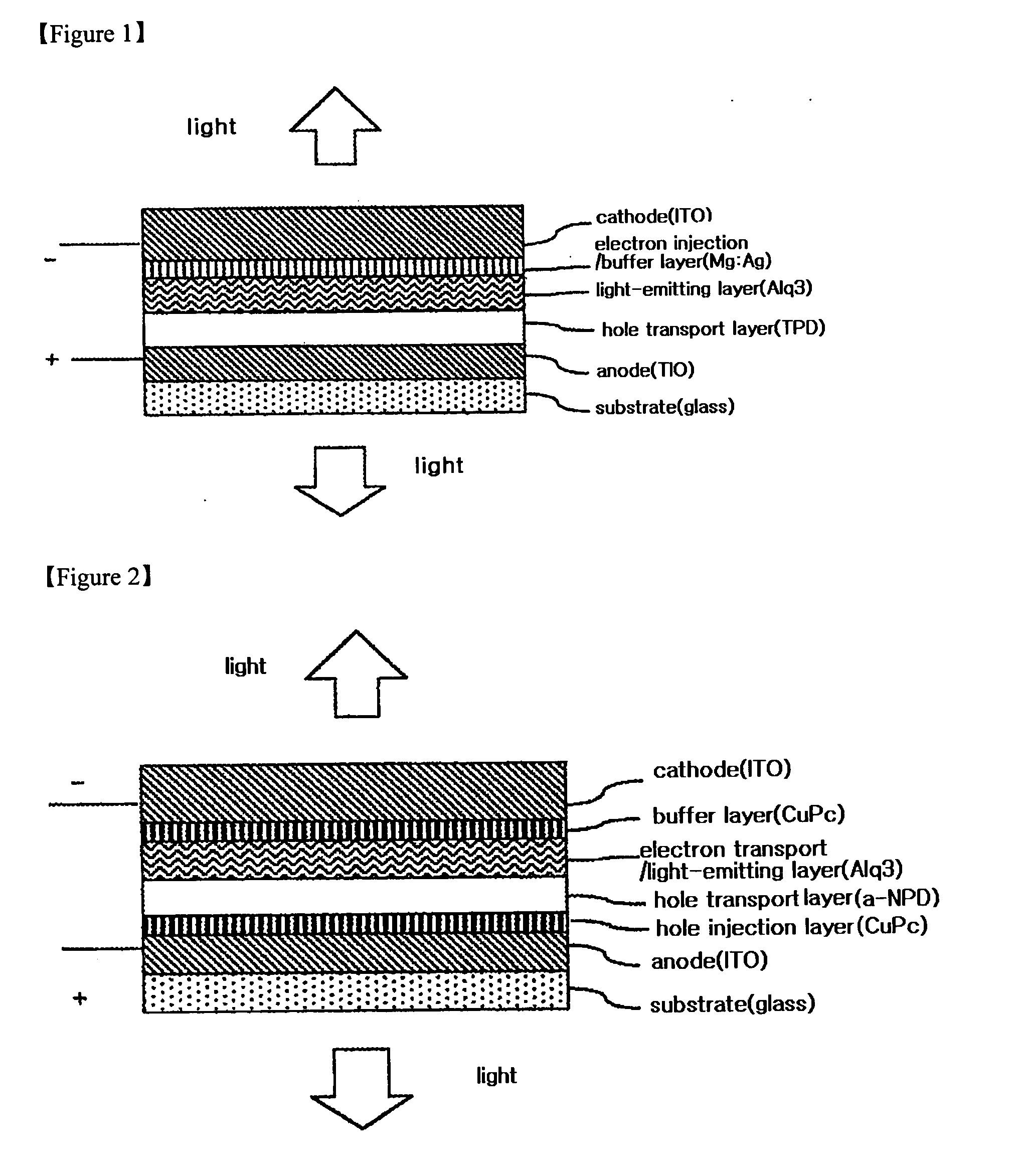

Organic light-emitting device comprising buffer layer and method for fabricating the same

InactiveUS20060038484A1Layer can be damagedAvoid damageOrganic chemistryDischarge tube luminescnet screensSequential depositionPhotochemistry

Disclosed herein are an organic light-emitting device having a structure formed by the sequential deposition of a substrate, a first electrode, at least two organic layers and a second electrode, in which the organic layers include a light-emitting layer, and one of the organic layers, which is in contact with the second electrode, is a buffer layer comprising a compound represented by the following formula 1, as well as a fabrication method thereof: wherein R1 to R6 have the same meanings as defined in the specification. The buffer layer makes it possible to minimize or prevent damage to the organic layer, which can occur when forming the second electrode on the organic layer.

Owner:LG CHEM LTD

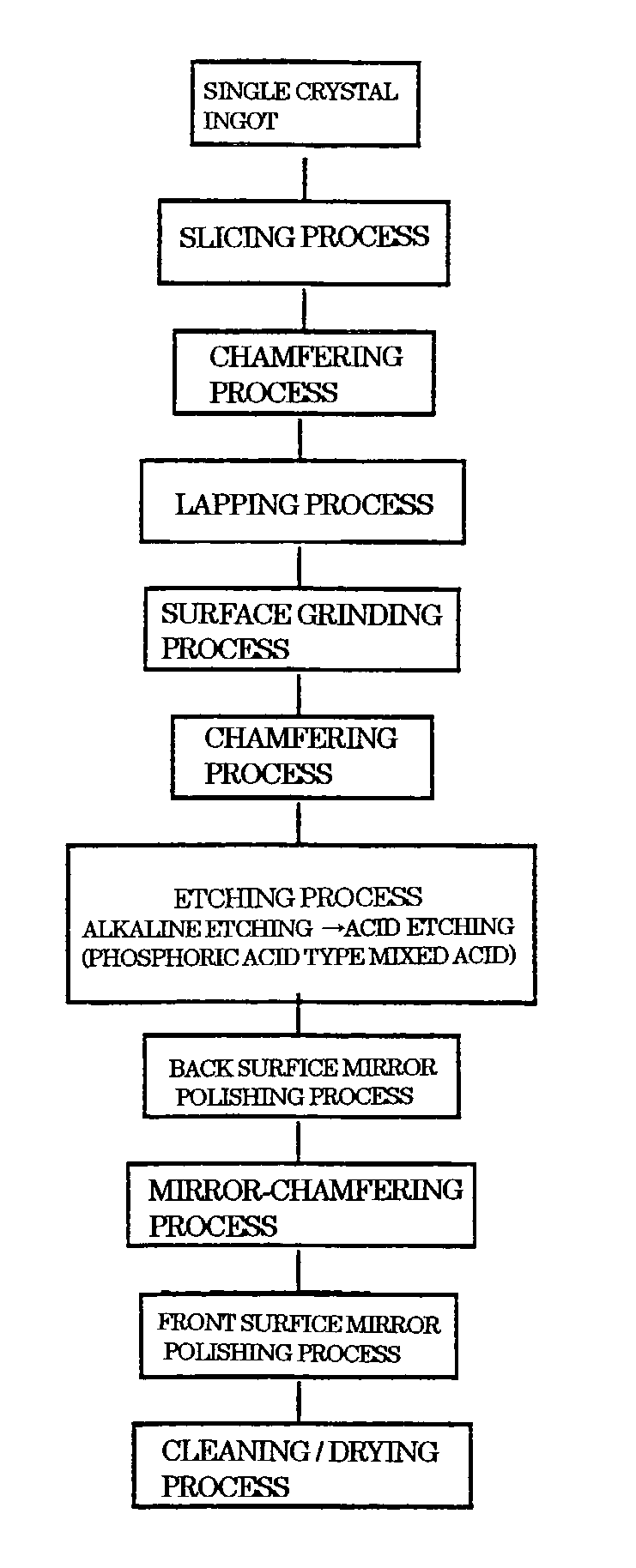

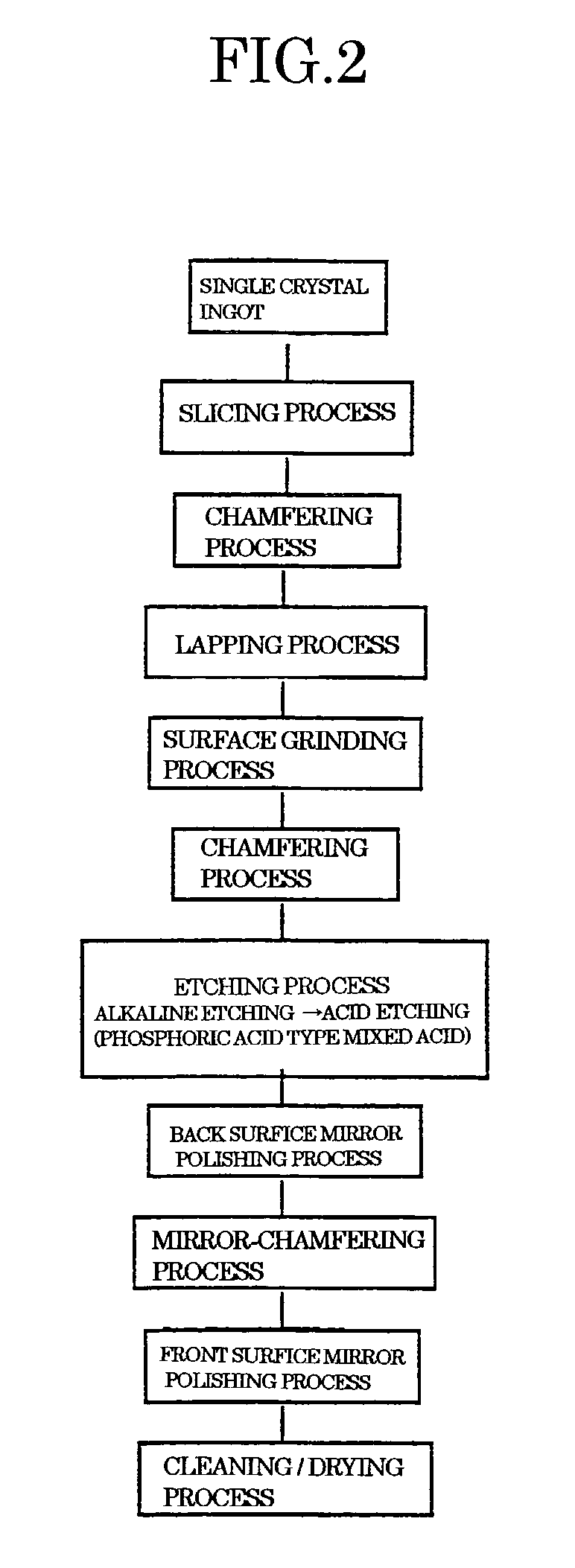

Semiconductor wafer and method for fabrication thereof

InactiveUS6352927B2Easily causedImprove flatnessSemiconductor/solid-state device manufacturingEngineeringSurface grinding

There is disclosed a semiconductor wafer obtained, at least, by removing a mechanical damage layer by etching both surfaces of the wafer, flattening one of the surfaces by a surface-grinding means, polishing both of the surfaces, and then subjecting a front surface of the wafer to a finishing mirror-polishing when defining the surface subjected to surface-grinding as a back surface of the wafer, and a method for fabricating it. There can be provided a method for fabricating a semiconductor wafer wherein grinding striations which remain on a semiconductor wafer even when double side polishing and finishing mirror-polishing are conducted after a conventional step of surface-grinding of the front surface or the both surfaces, are eliminated to improve quality of the front surface of the wafer, and the back surface having a quality suitable for the device process can be obtained, and a semiconductor wafer obtained thereby.

Owner:SHIN-ETSU HANDOTAI CO LTD

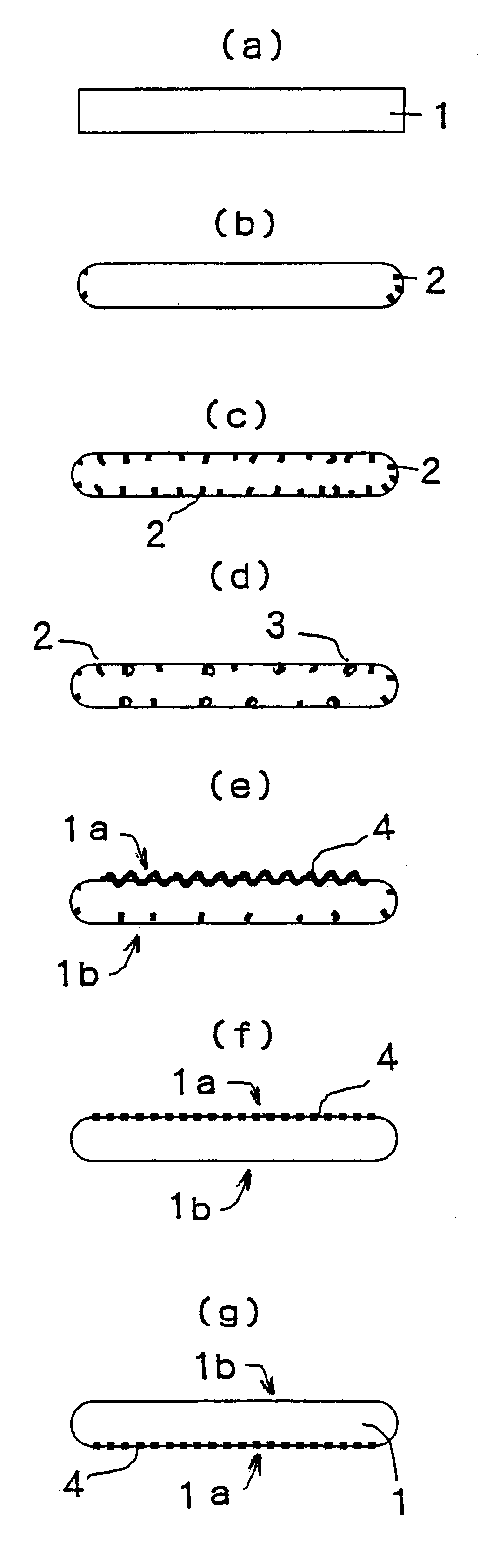

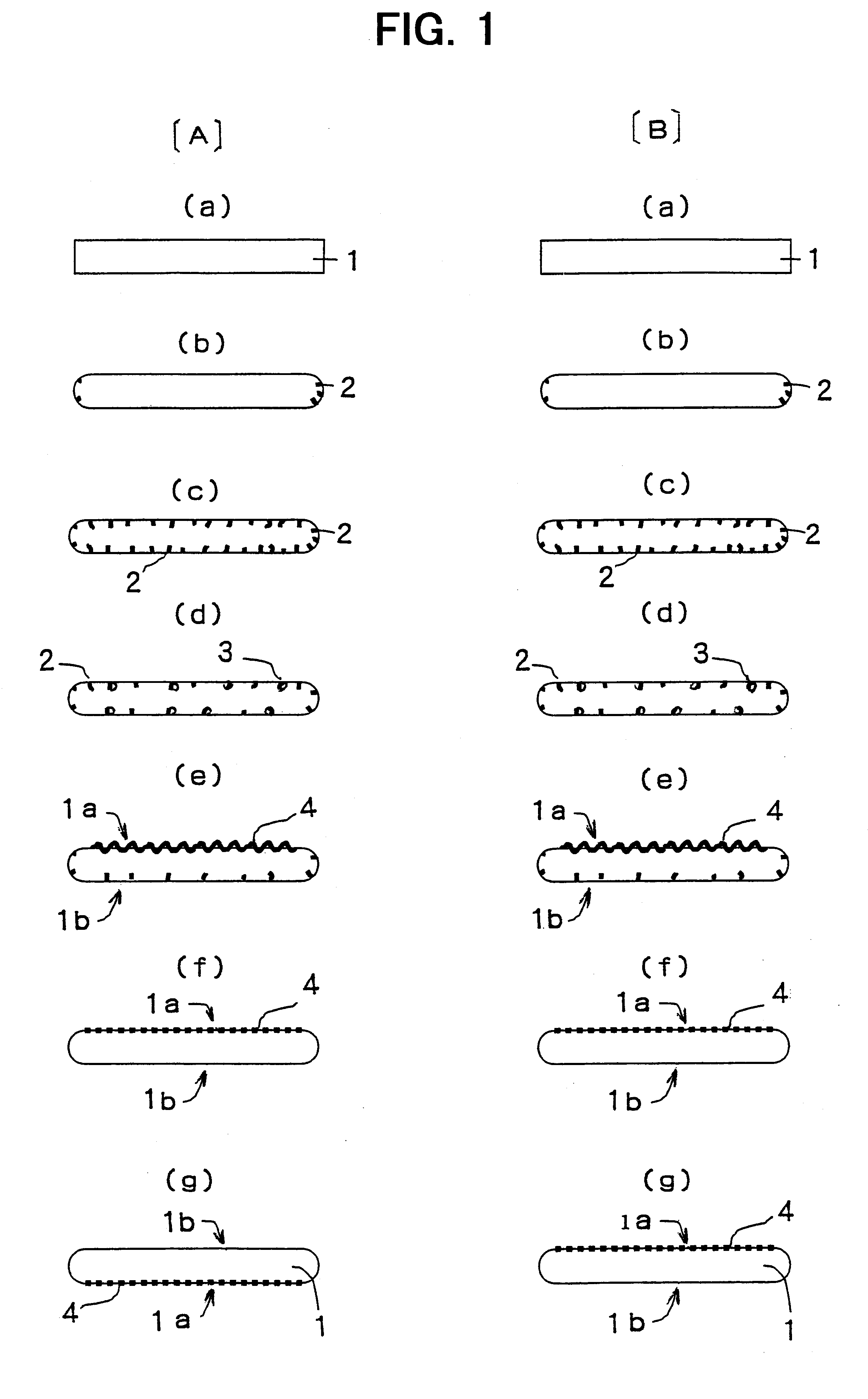

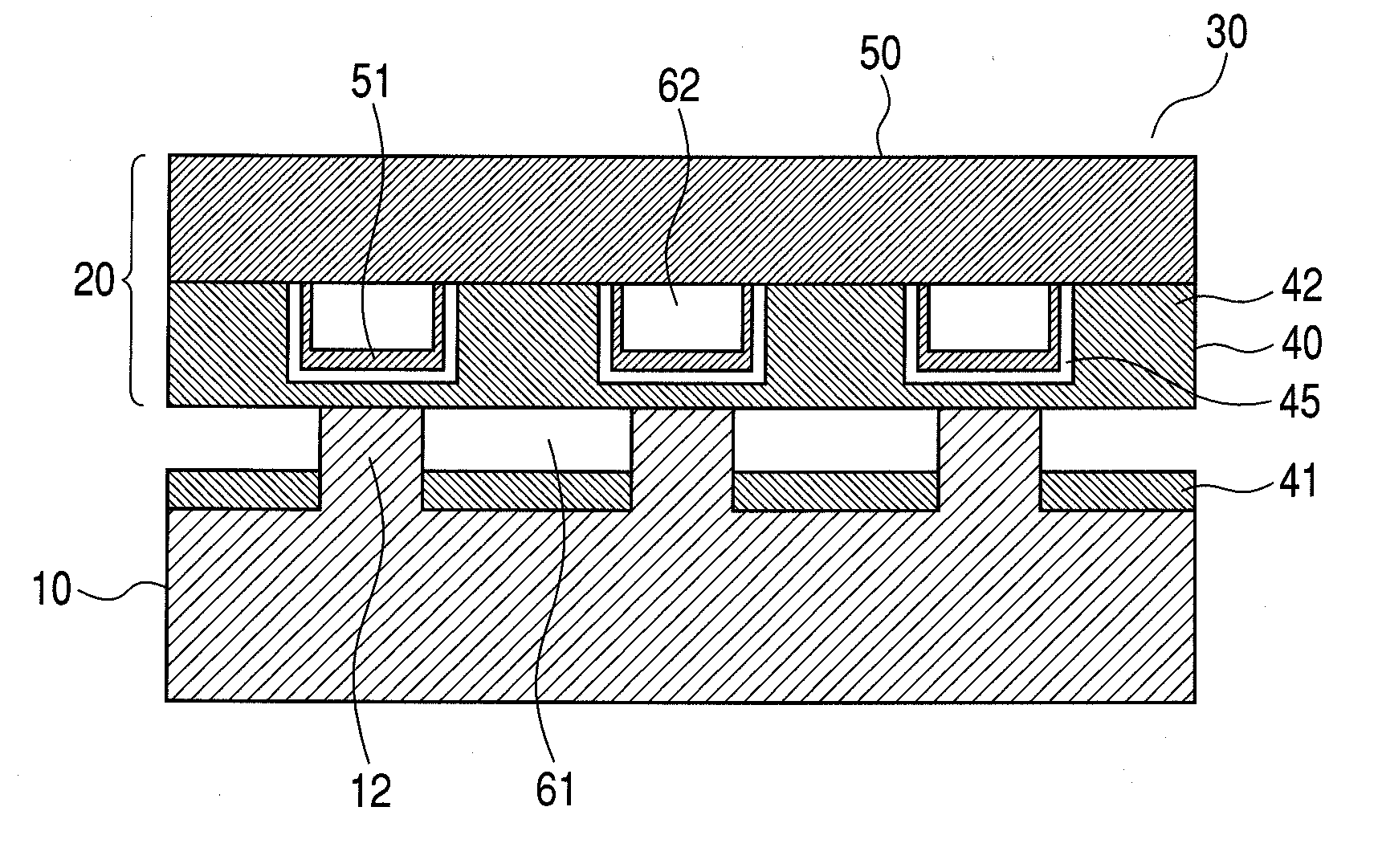

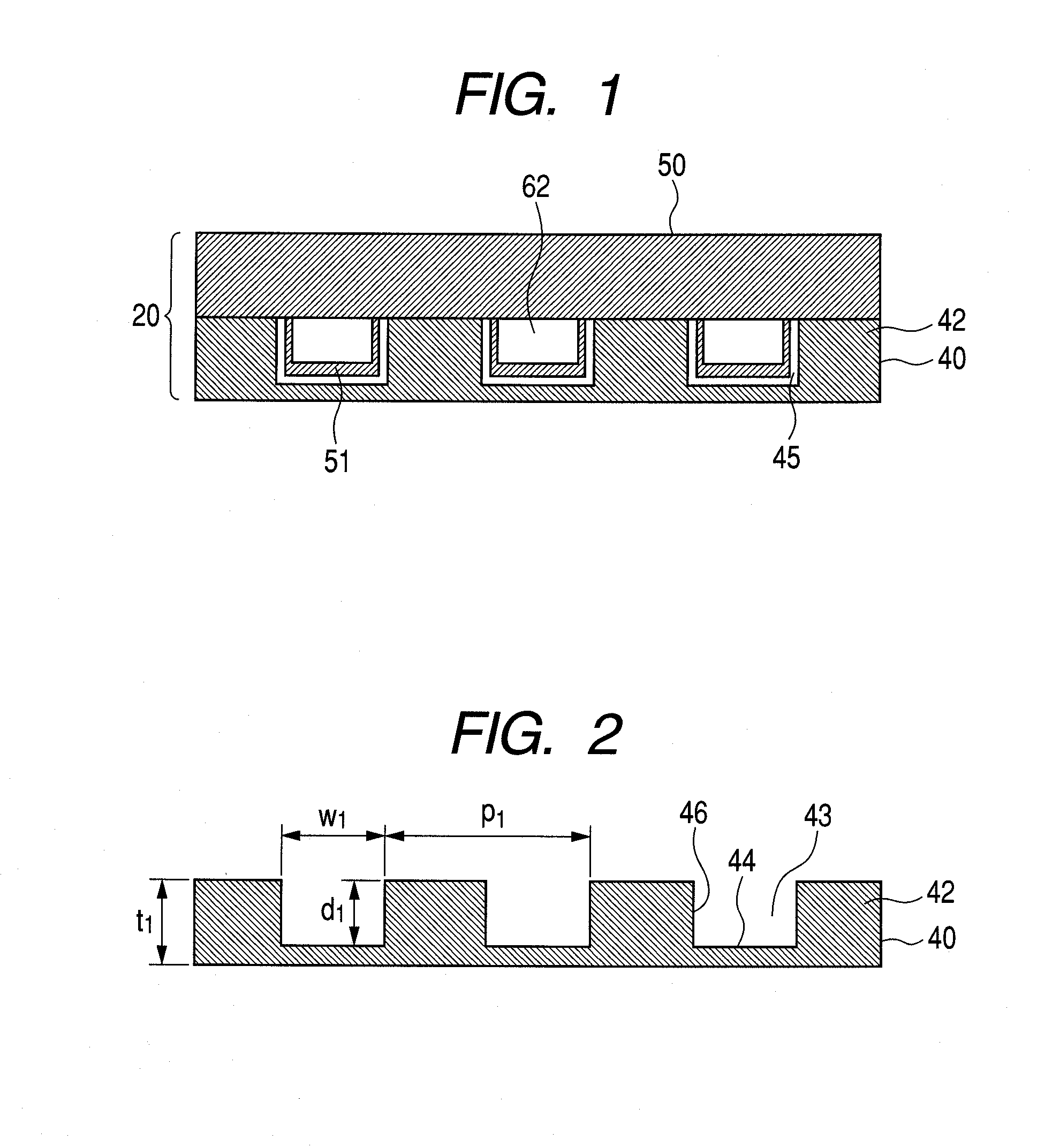

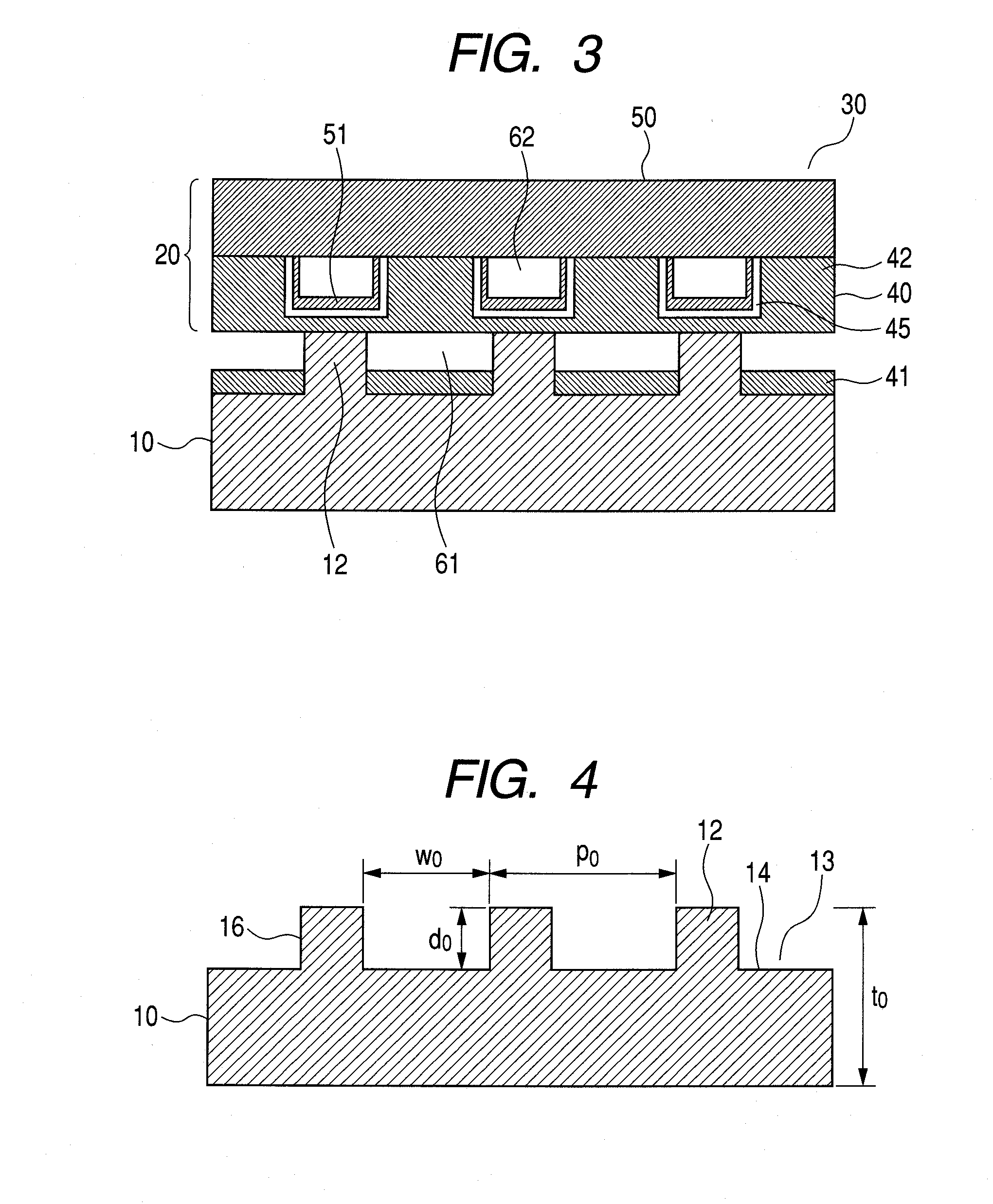

Three-dimensionally structured lithium anode

InactiveUS20150311501A1Inhibit side effectsImprove adhesionFuel and secondary cellsElectrode carriers/collectorsElectrical conductorLithium-ion battery

A method is provide for manufacturing a lithium anode and to a lithium anode for a lithium cell and / or a lithium battery. In order to improve the service life, performance capability and safety of a lithium cell and / or a lithium battery equipped with the lithium anode, the lithium anode includes a surface-structured current conductor and / or a surface-structured protective layer having at least one surface section circumscribed by a raised surface section, the surface structuring / structurings forming at least one cavity, and the at least one cavity being, in particular electrochemically, filled with anode active material. Also provided are a lithium cell and a lithium battery equipped with a lithium anode.

Owner:ROBERT BOSCH GMBH

Nitride semiconductor layer-containing structure, nitride semiconductor layer-containing composite substrate and production methods of these

InactiveUS20110042718A1Layer can be damagedReduce damageSemiconductor/solid-state device manufacturingSemiconductor devicesComposite substrateCrystallinity

A nitride semiconductor layer-containing structure having a configuration in which: the structure includes a laminated structure based on at least two nitride semiconductor layers; the structure includes between the two nitride semiconductor layers in the laminated structure a plurality of voids surrounded by the faces of the walls inclusive of the inner walls of the recessed portions of the asperity pattern formed on the nitride semiconductor layer that is the lower layer of the two nitride semiconductor layers; and crystallinity defect-containing portions to suppress the lateral growth of the nitride semiconductor layer are formed on at least part of the inner walls of the recessed portions to form the voids.

Owner:CANON KK

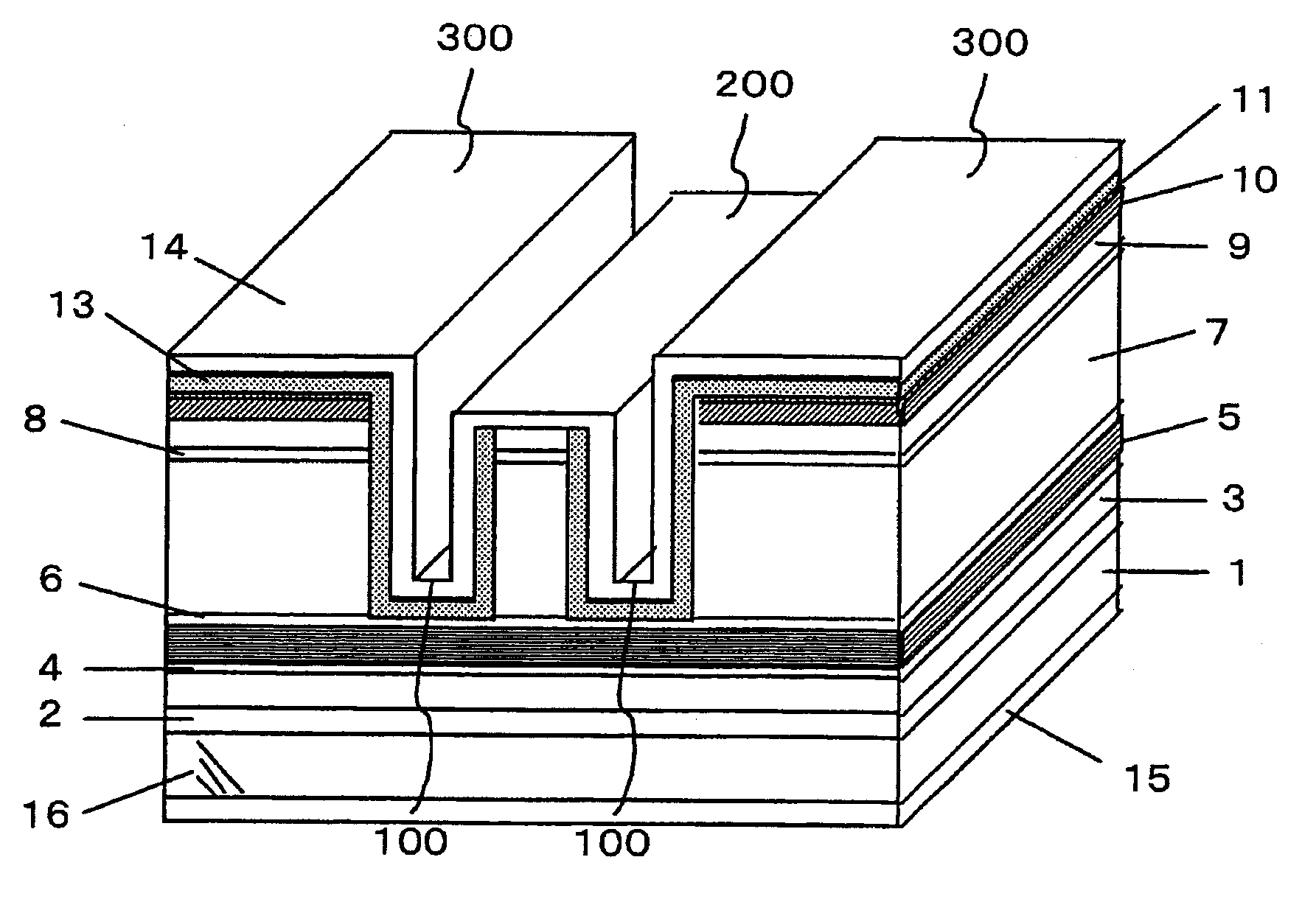

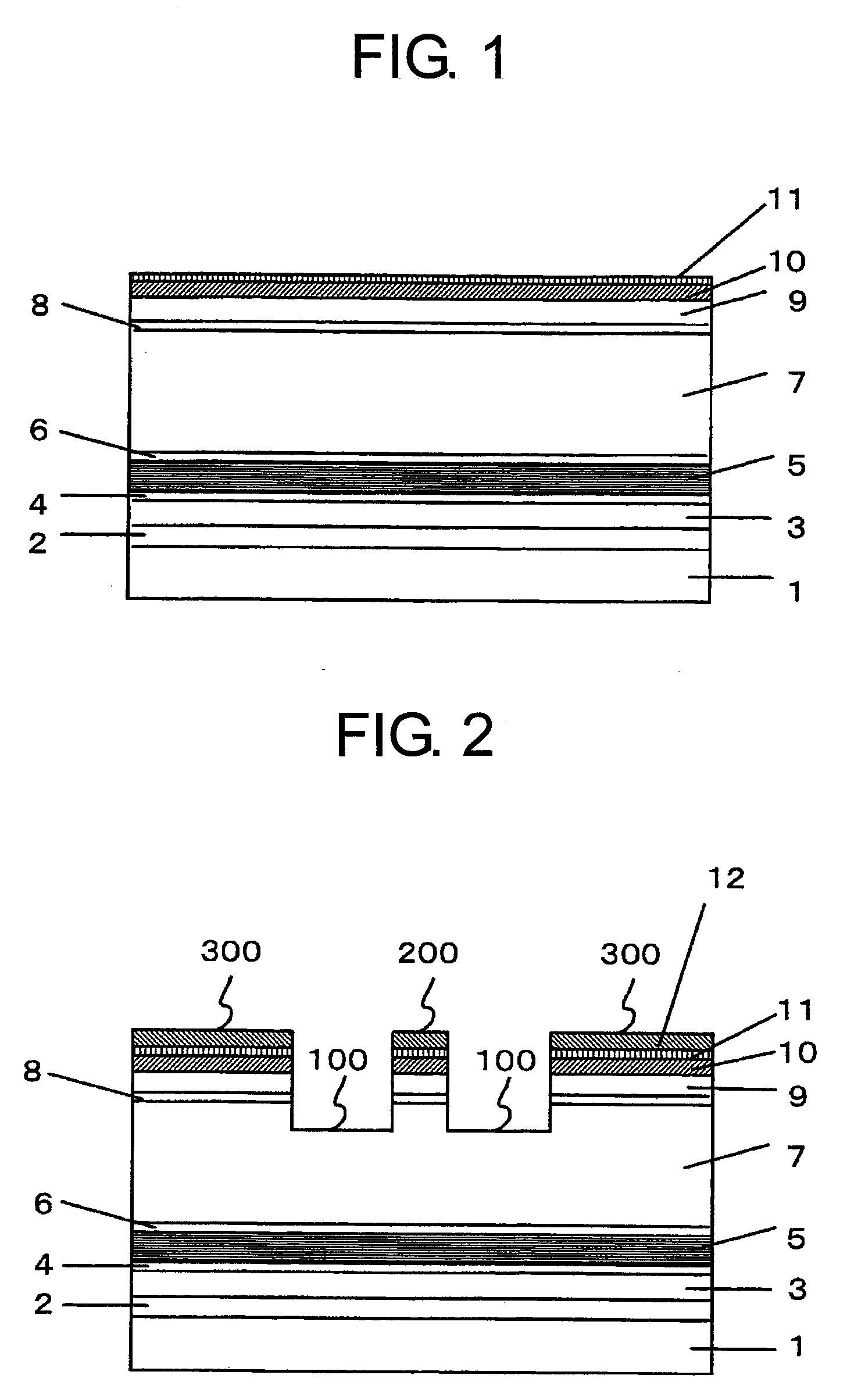

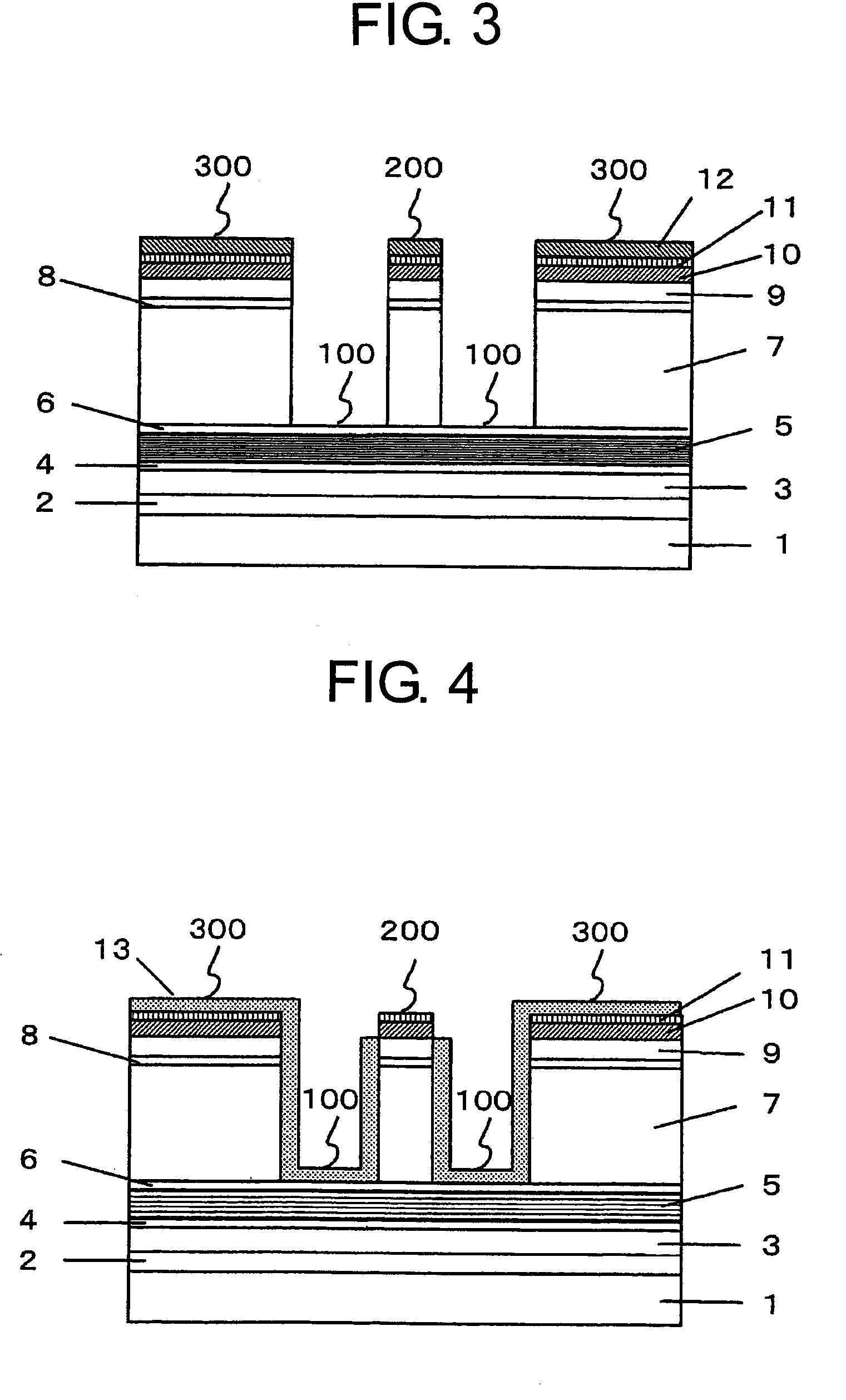

Semiconductor optical device and manufacturing method therefor

InactiveUS20080036044A1Inhibition formationPrevent damaged layerOptical wave guidanceLaser detailsContact layerEngineering

To eliminate generation of a damaged layer caused by dry etching of a contact layer, occurring in a manufacturing process of a ridge waveguide type semiconductor laser, and to improve reliability and yield thereof, a method is provided involving forming a spacer layer and a damage receptor layer on the contact layer, making the two layer absorb damage caused by dry etching a passivation film in an upper portion of the ridge waveguide structure, and thereafter removing the damaged layer by the dry etching, by selective removal by wet etching.

Owner:OPNEXT JAPAN INC

Organic light-emitting device comprising buffer layer and method for fabricating the same

InactiveUS20090058260A9Layer can be damagedAvoid damageOrganic chemistryDischarge tube luminescnet screensOrganic light emitting deviceOrganic layer

Disclosed herein are an organic light-emitting device having a structure formed by the sequential deposition of a substrate, a first electrode, at least two organic layers and a second electrode, in which the organic layers include a light-emitting layer, and one of the organic layers, which is in contact with the second electrode, is a buffer layer comprising a compound represented by the following formula 1, as well as a fabrication method thereof: wherein R1 to R6 have the same meanings as defined in the specification. The buffer layer makes it possible to minimize or prevent damage to the organic layer, which can occur when forming the second electrode on the organic layer.

Owner:LG CHEM LTD

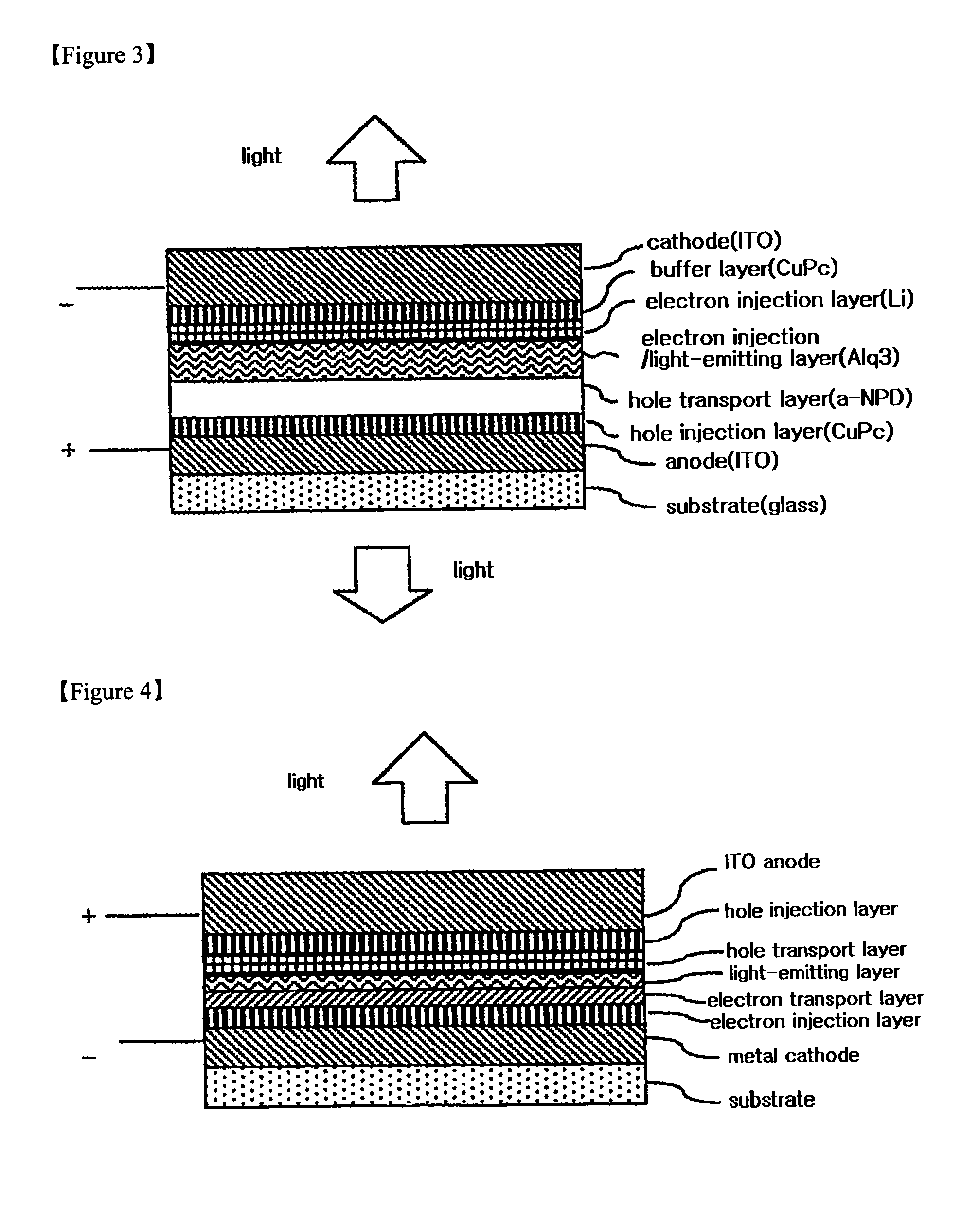

Method for processing semiconductor wafer and semiconductor wafer

InactiveUS7332437B2Promote generationEasy to produceDecorative surface effectsSemiconductor/solid-state device manufacturingAcid etchingHydrofluoric acid

There is provided a method for processing a semiconductor wafer subjected to a chamfering process, a lapping process, an etching process, and a mirror-polishing process, wherein acid etching is performed after alkaline etching as the etching process, and the acid etching is performed with an acid etchant composed of hydrofluoric acid, nitric acid, phosphoric acid, and water, a method for processing a semiconductor wafer subjected to a chamfering process, a surface grinding process, an etching process, and a mirror-polishing process, wherein the etching process is performed as described above, and a method for processing a semiconductor wafer subjected to a flattening process, an etching process, and a mirror-polishing process, wherein the etching process is performed as described above, a back surface polishing process is performed after the acid etching as the mirror-polishing process, and then a front surface polishing process is performed. According to this, there can be provided a method for processing a semiconductor wafer to have good flatness, good surface roughness, and good condition on a back surface thereof.

Owner:SHIN-ETSU HANDOTAI CO LTD

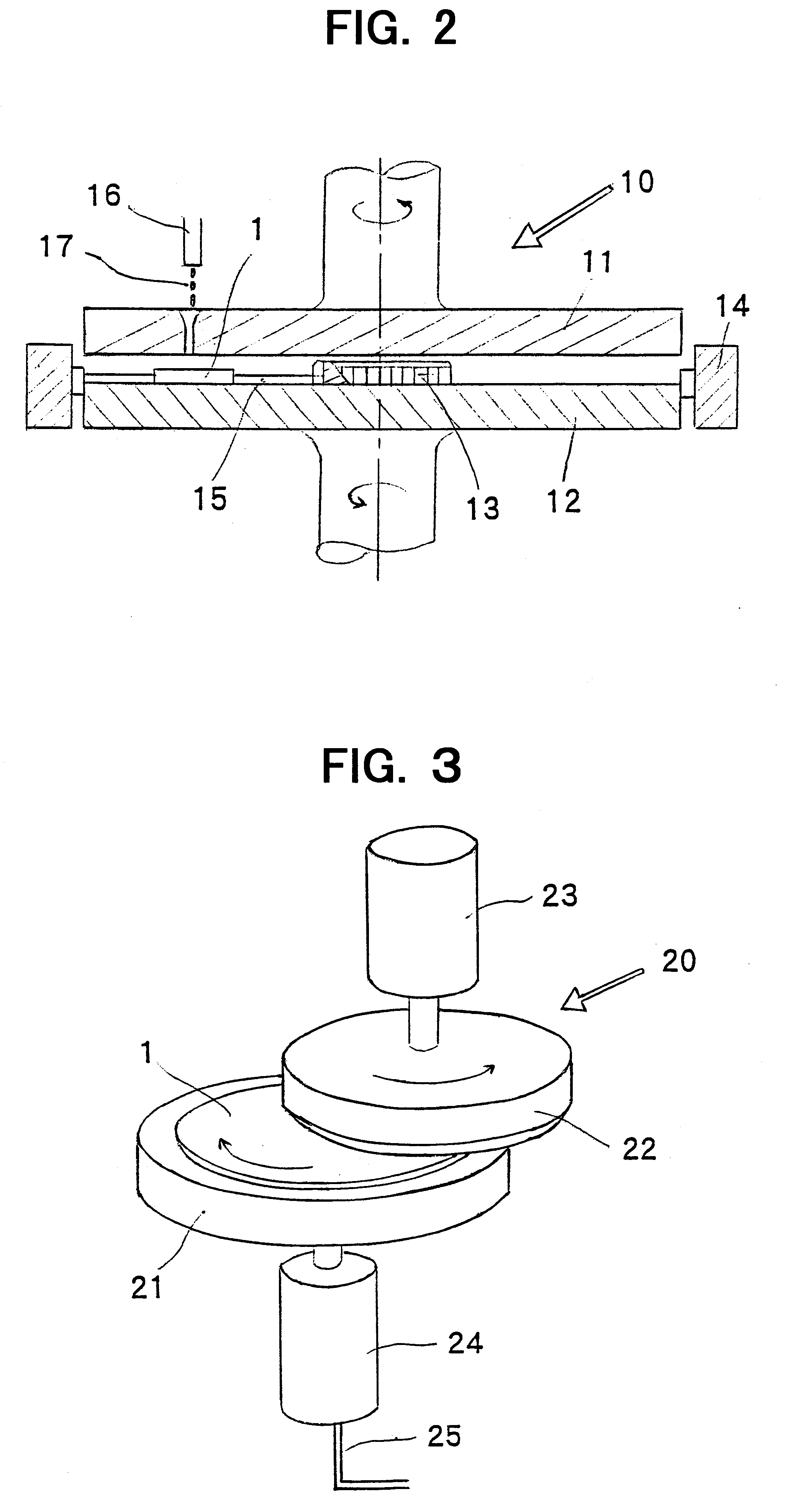

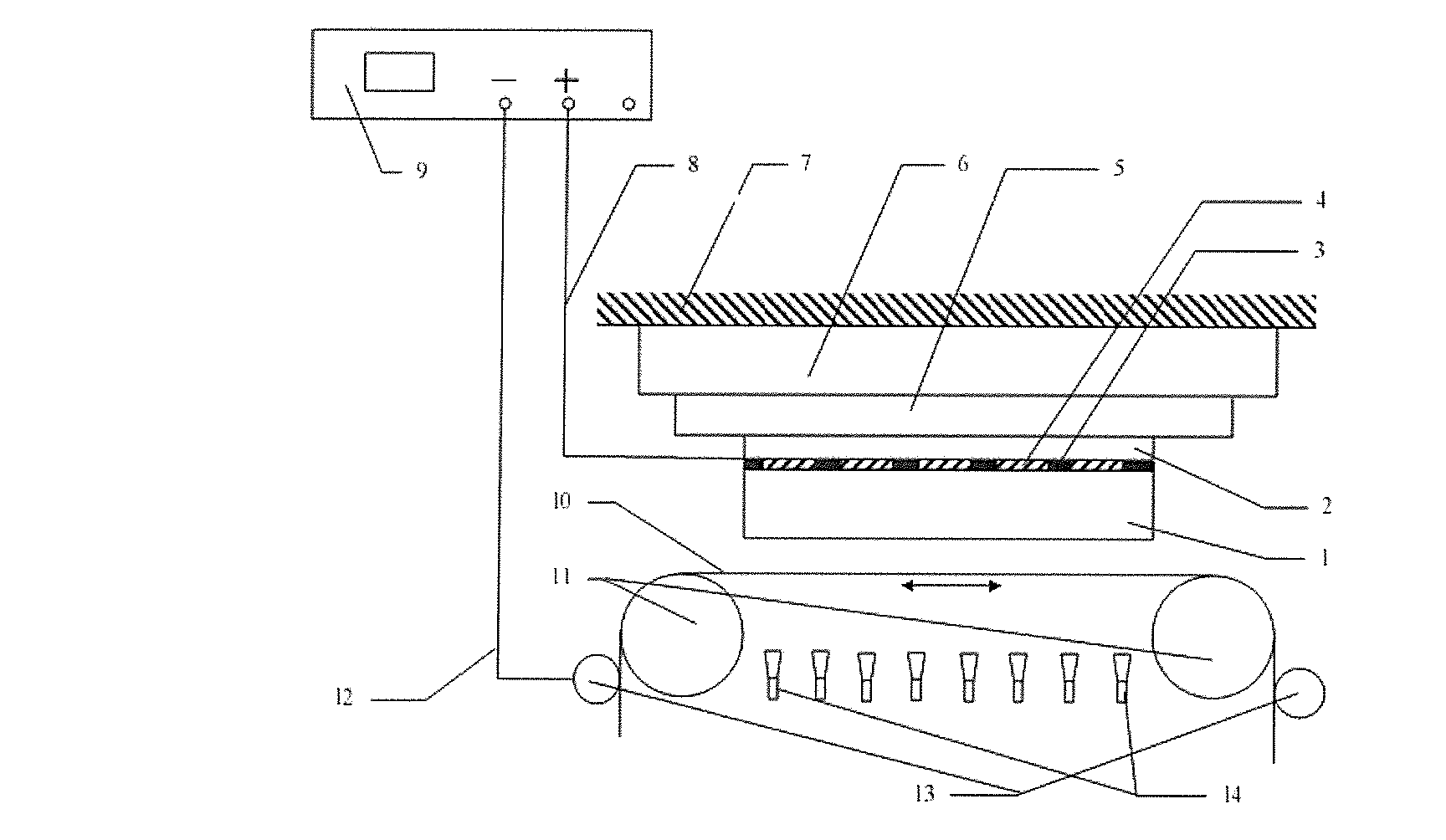

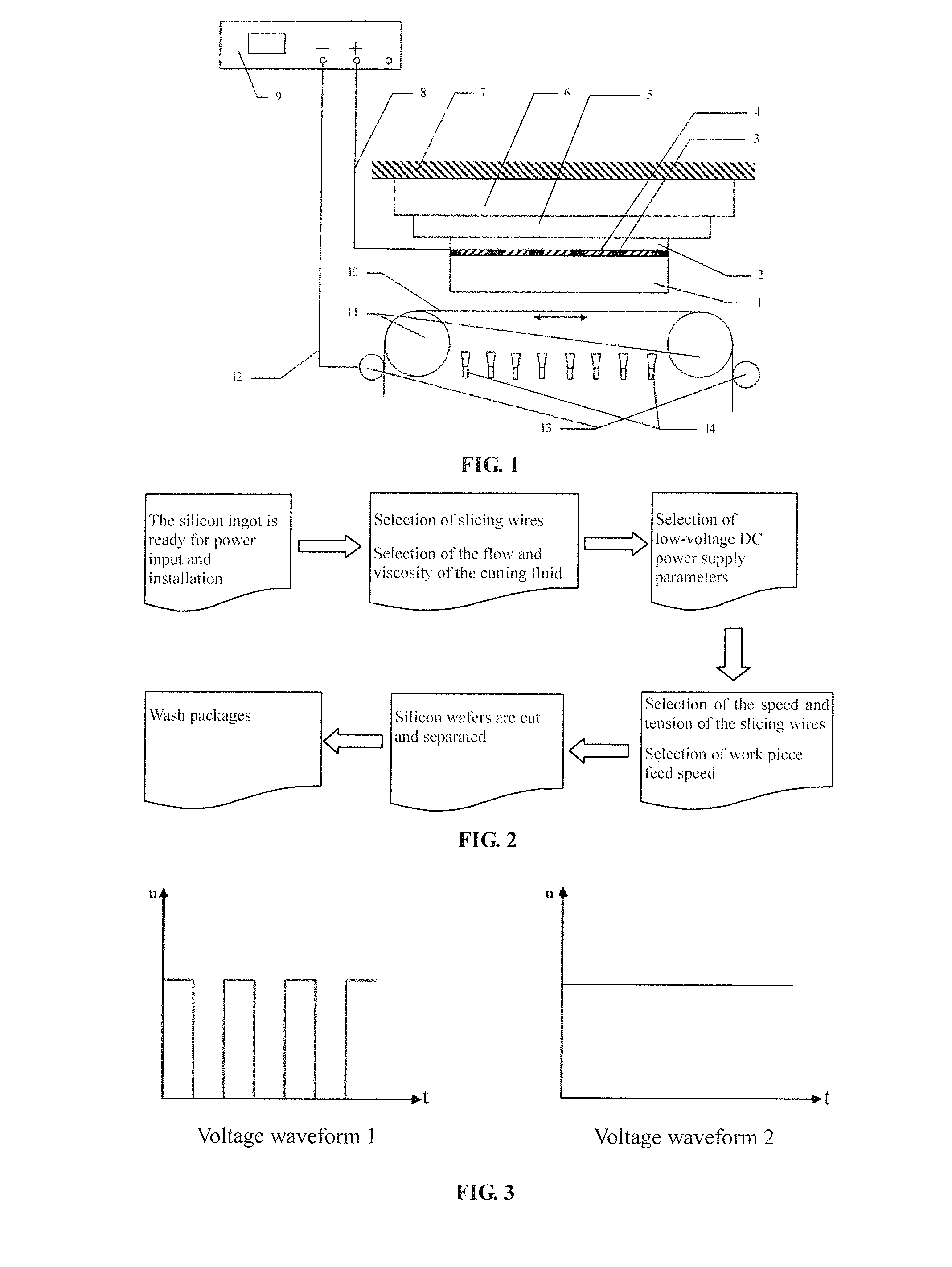

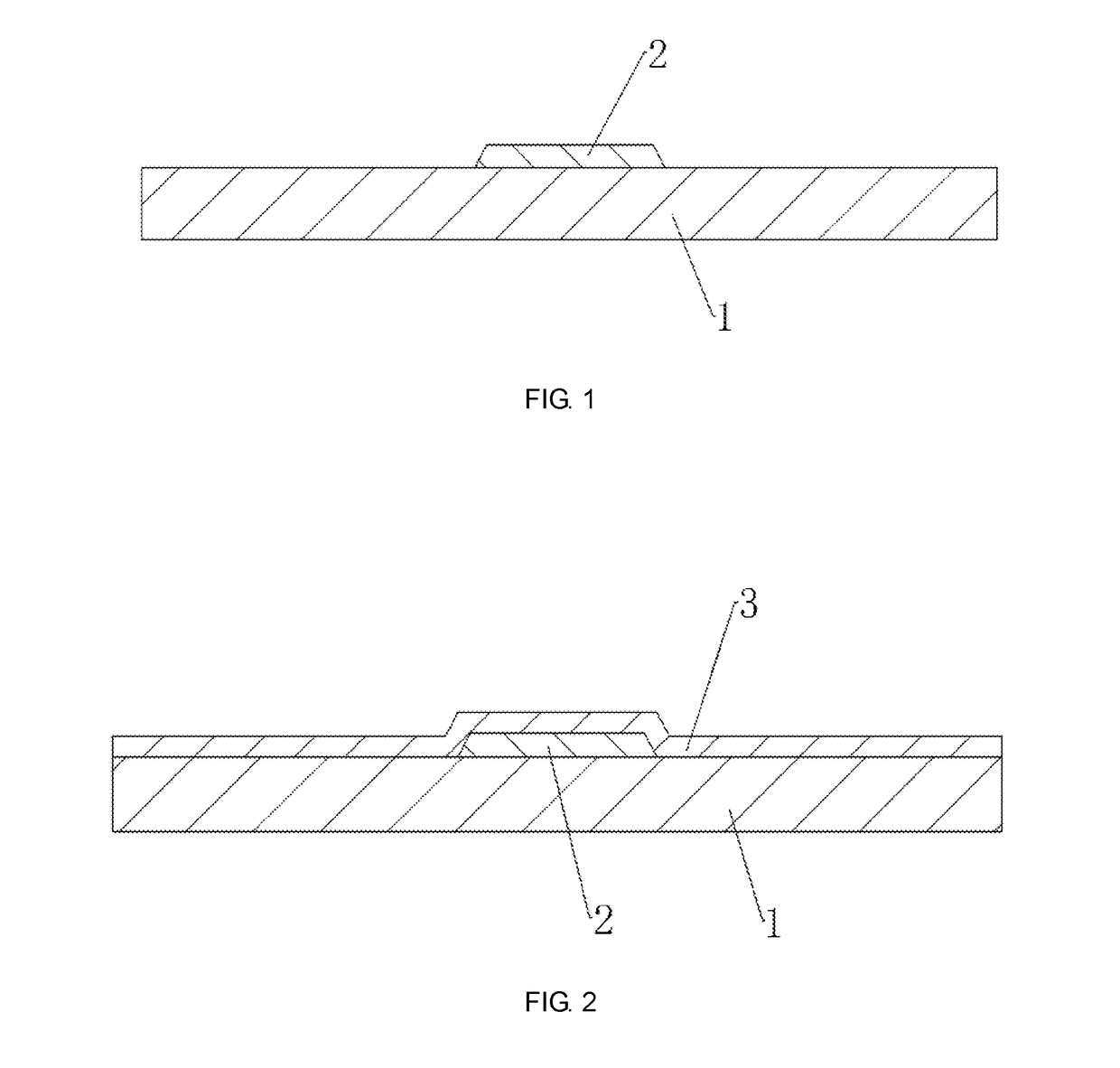

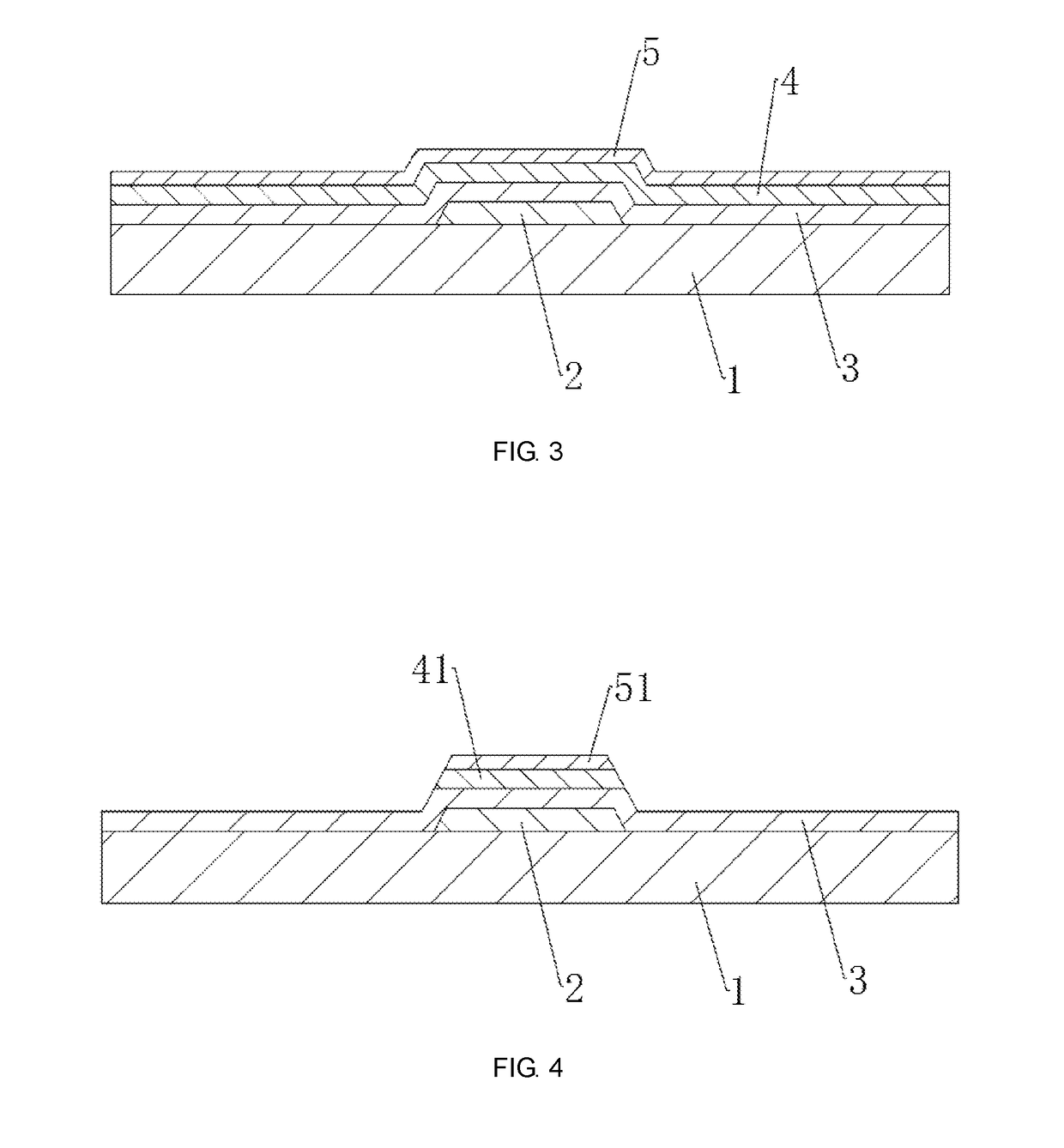

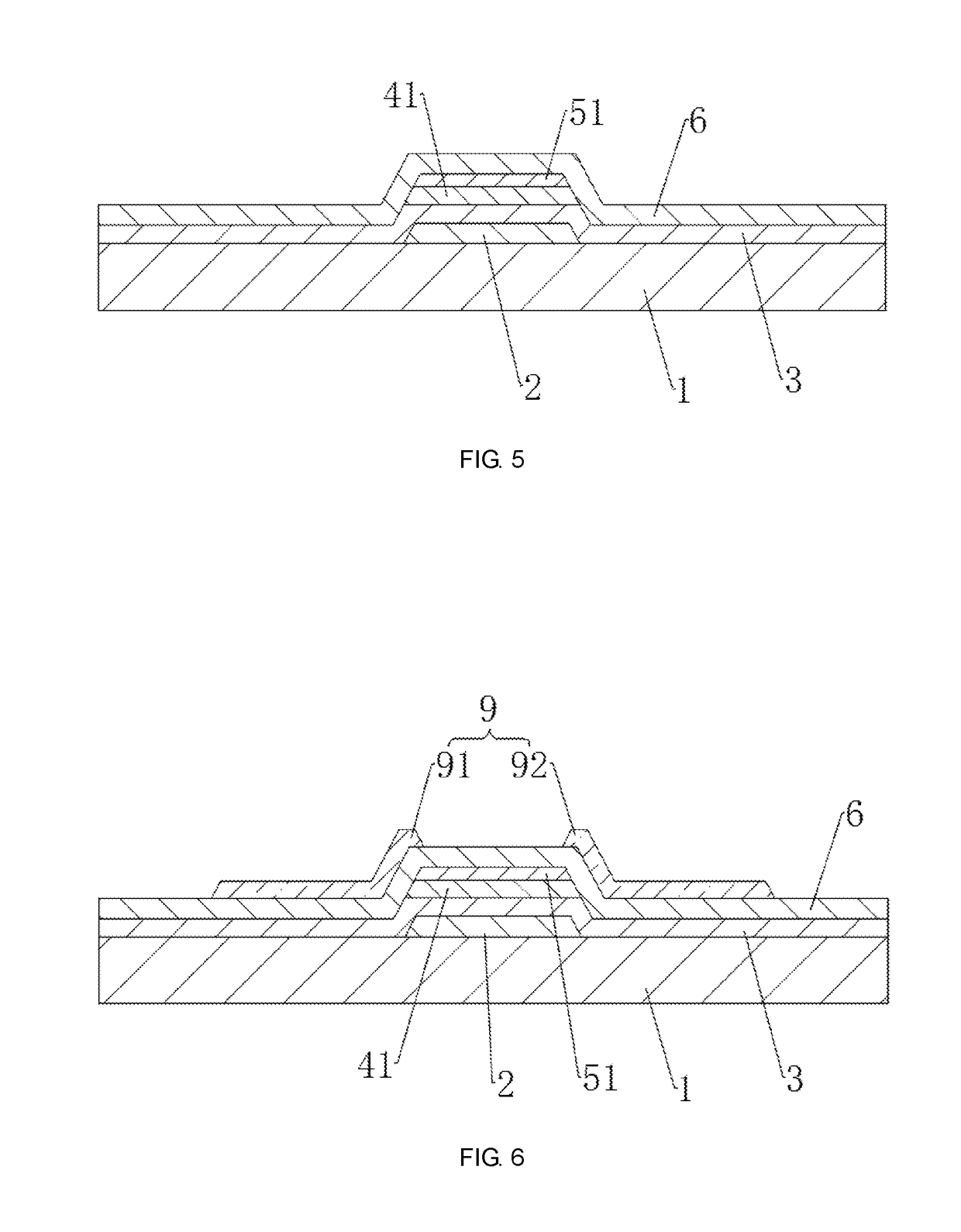

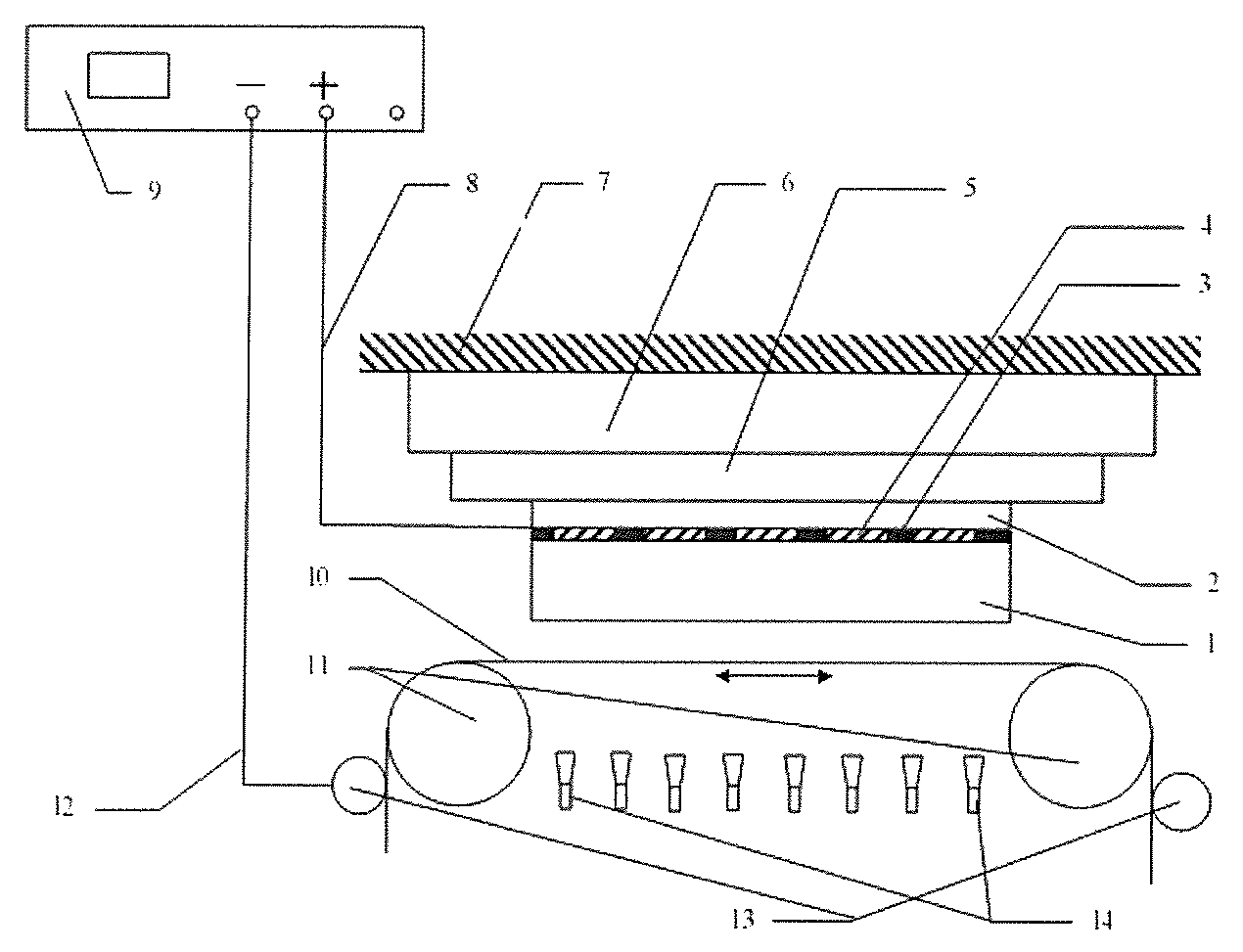

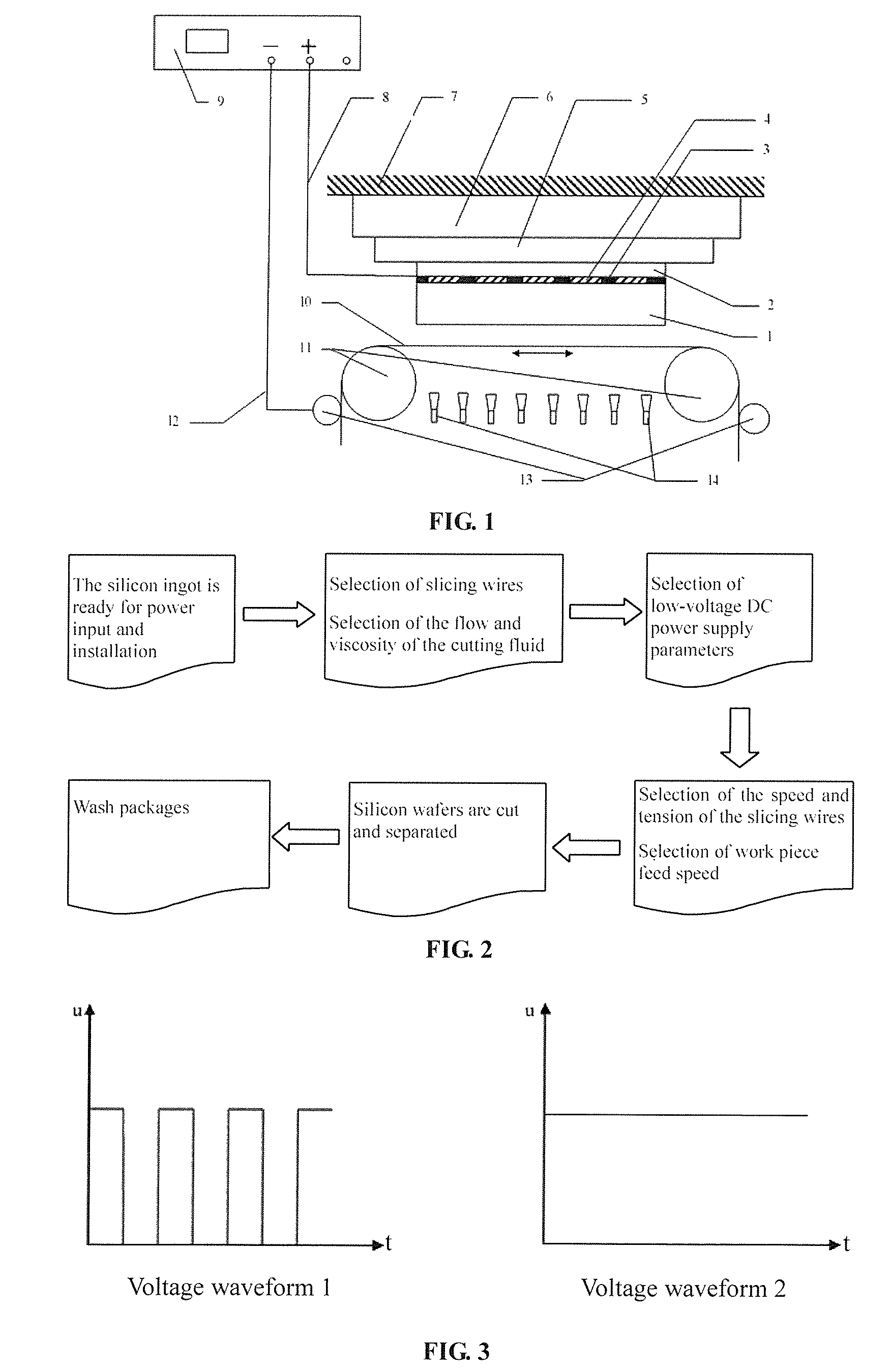

Grinding/electrolysis combined multi-wire-slicing processing method for silicon wafers

InactiveUS20130075274A1Reduce probabilityImprove slicing efficiencyElectrolysis componentsSemiconductor/solid-state device manufacturingElectrolytic agentLow voltage

A grinding / electrolysis combined multi-wire-slicing processing method for silicon wafers includes the following steps: first, with a metal slicing wire(10) provided on a multi-wire-slicing machine serving as cathode, a silicon rod or a silicon ingot(1)(anode) is processed by grinding / electrolysis combined multi-wire-slicing through application of a voltage; second, during said processing, the metal slicing wire(10) and the silicon rod or a silicon ingot(1) are connected with a low-voltage continuous or pulsed direct current power supply(9); third, an electrolytic liquid is sprayed into the cutting area to ensure cooling and anode erosion. The method reduces macroscopic cutting force and enables a grinding / electrolysis combined multi-wire-slicing processing method for large size ultra-thin silicon wafers.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

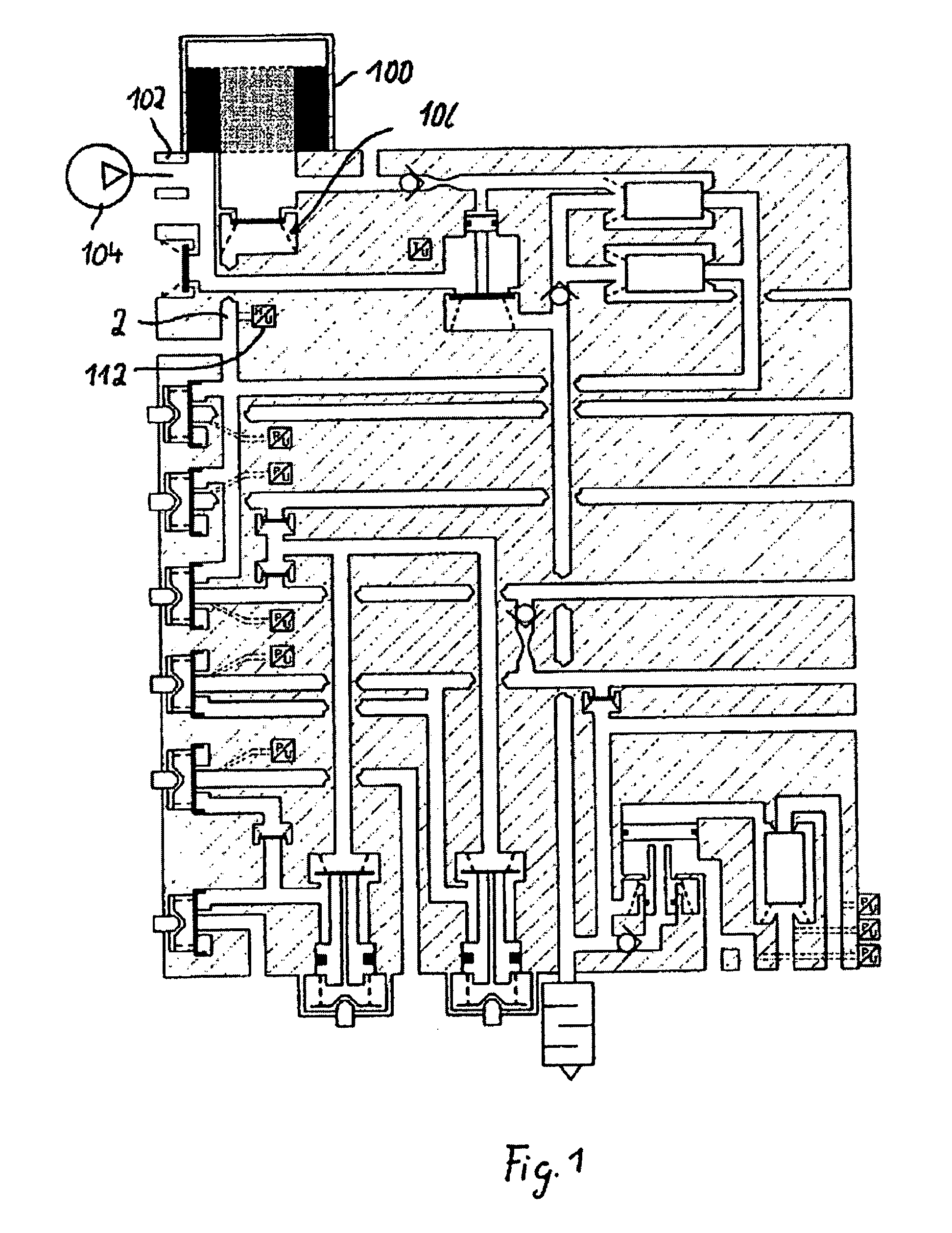

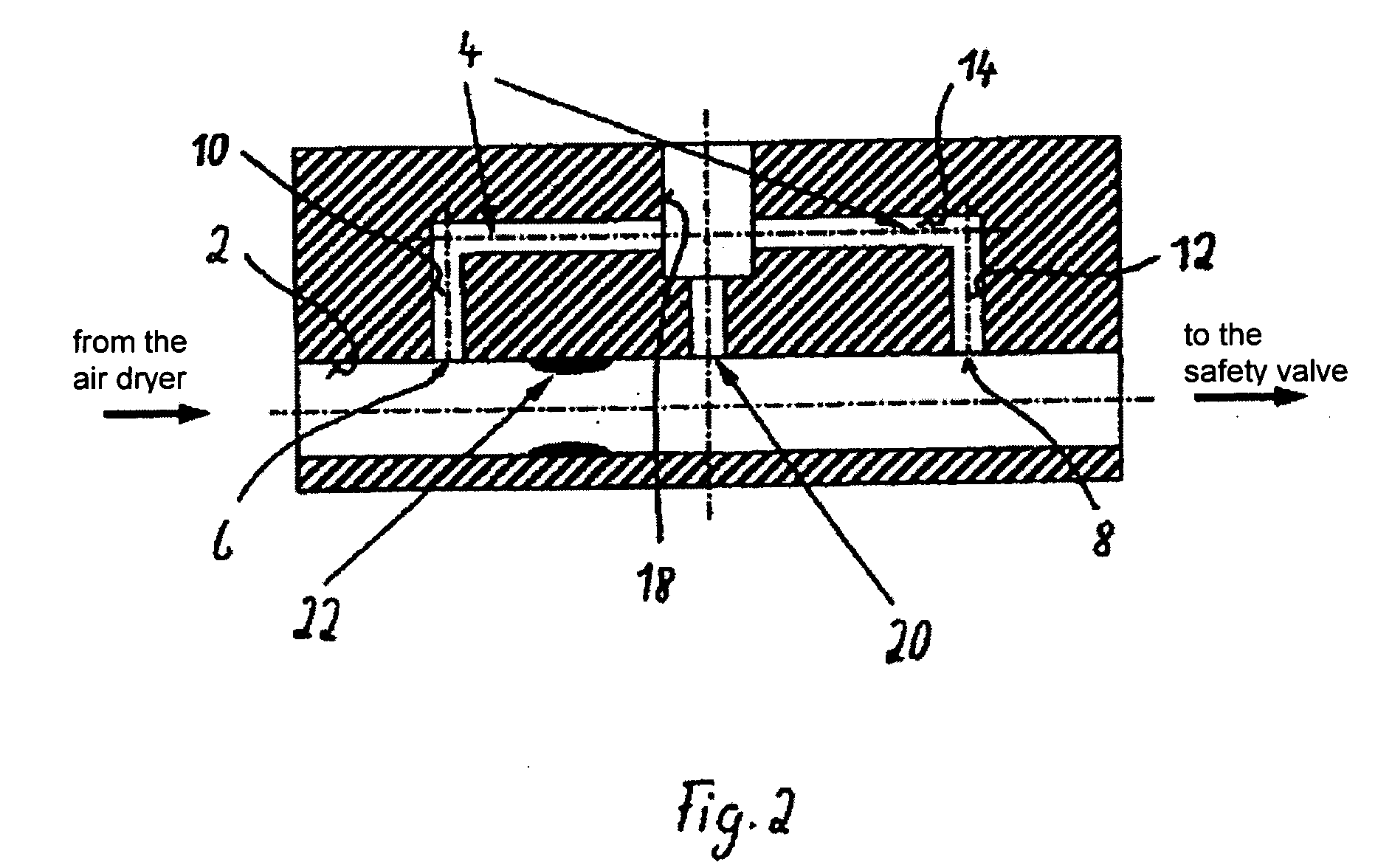

Compressed air supply device for motor vehicles

ActiveUS20100059126A1AmountLayer can be damagedWithdrawing sample devicesPump controlControl electronicsEnvironmental engineering

A compressed air supply system for motor vehicles includes a compressor, control electronics, an air dryer having an inlet channel for non-dried compressed air, an outlet channel for the dried compressed air, and a dehumidification device through which the compressed air to be dried can flow, a pressure regulator having an outlet valve for controlling the compressor between an idle phase and a load phase, a multi-circuit safety valve that is connected to the outlet channel of the air dryer via a compressed air line, and over-flow valves for the individual circuits, a regeneration valve and a moisture sensor for detecting the atmospheric moisture in the compressed air flowing in the compressed air line. To reduce the detrimental effects of admixtures and components of the compressed air on the moisture sensor, the moisture sensor is located in a bypass channel of the compressed air line.

Owner:ZF CV SYST EURO BV

Laser treatment of tissue

InactiveUS20080027520A1Facilitate turbinate tissue reductionMinimizing tissue injuryUltrasound therapySurgical needlesNasal cavityMedicine

Laser treatment of tissue, particularly the tissues in or around the nasal and oral cavities, are described herein. One method for reducing the size of the tissue being treated is to apply laser energy to the underlying tissue. One instrument may be used to deliver laser energy and to optionally provide an infusion or injection of a fluid directly into the tissue as well as optionally provide for ultrasound energy application as well. One or more optical fibers which may extend through needles inserted into the tissue may be utilized to deliver the laser energy.

Owner:CHOI GEORGE Y

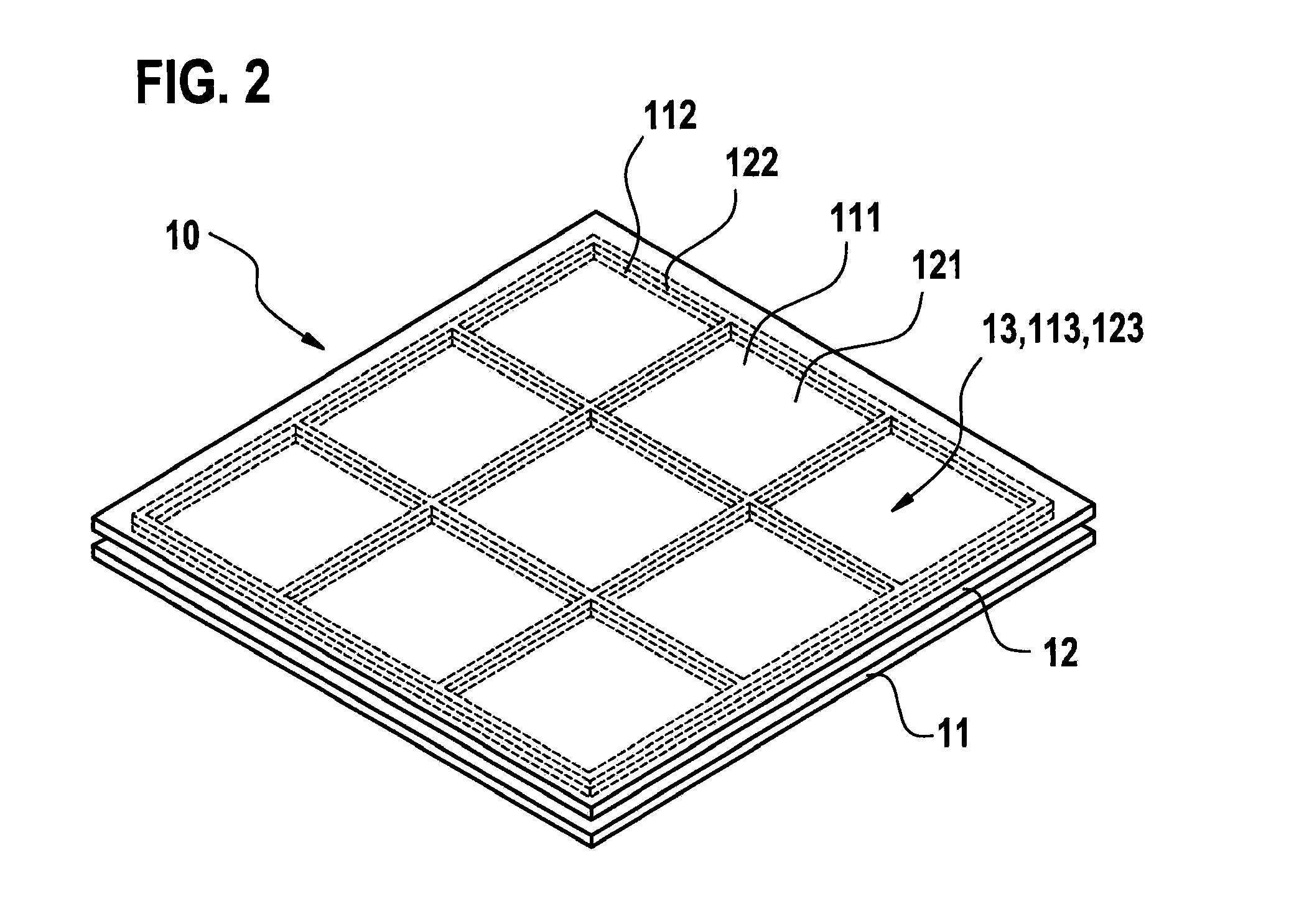

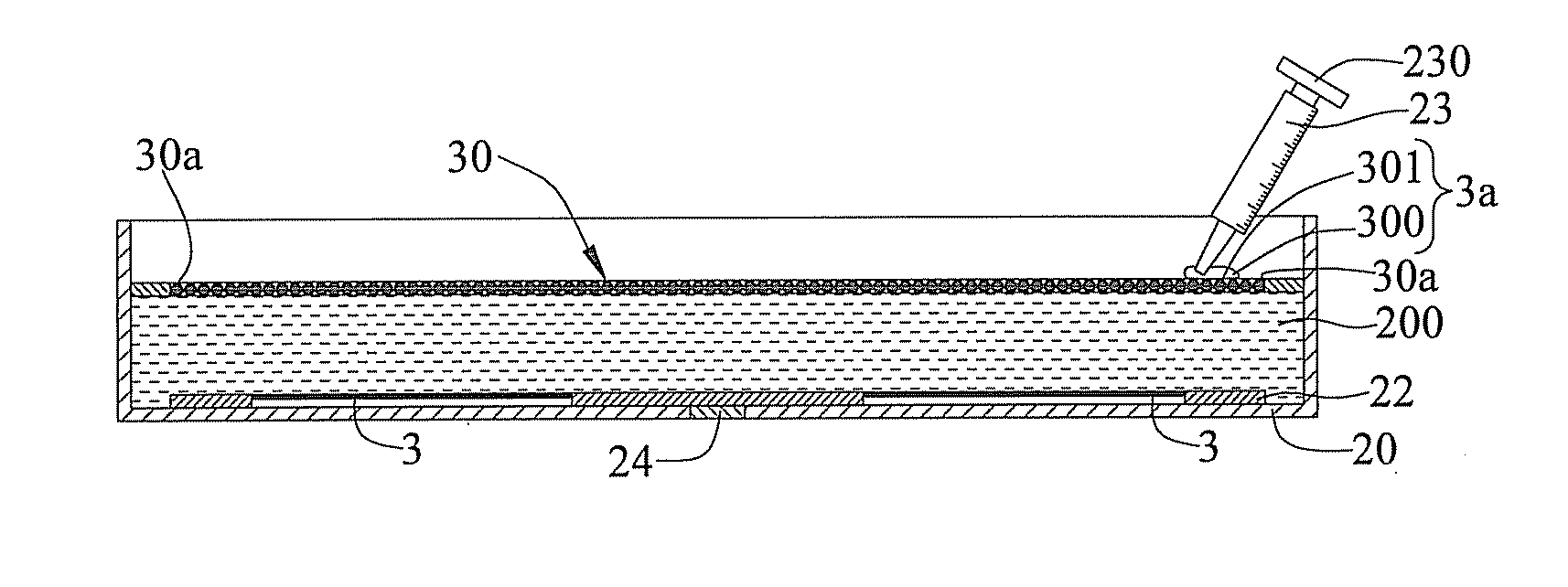

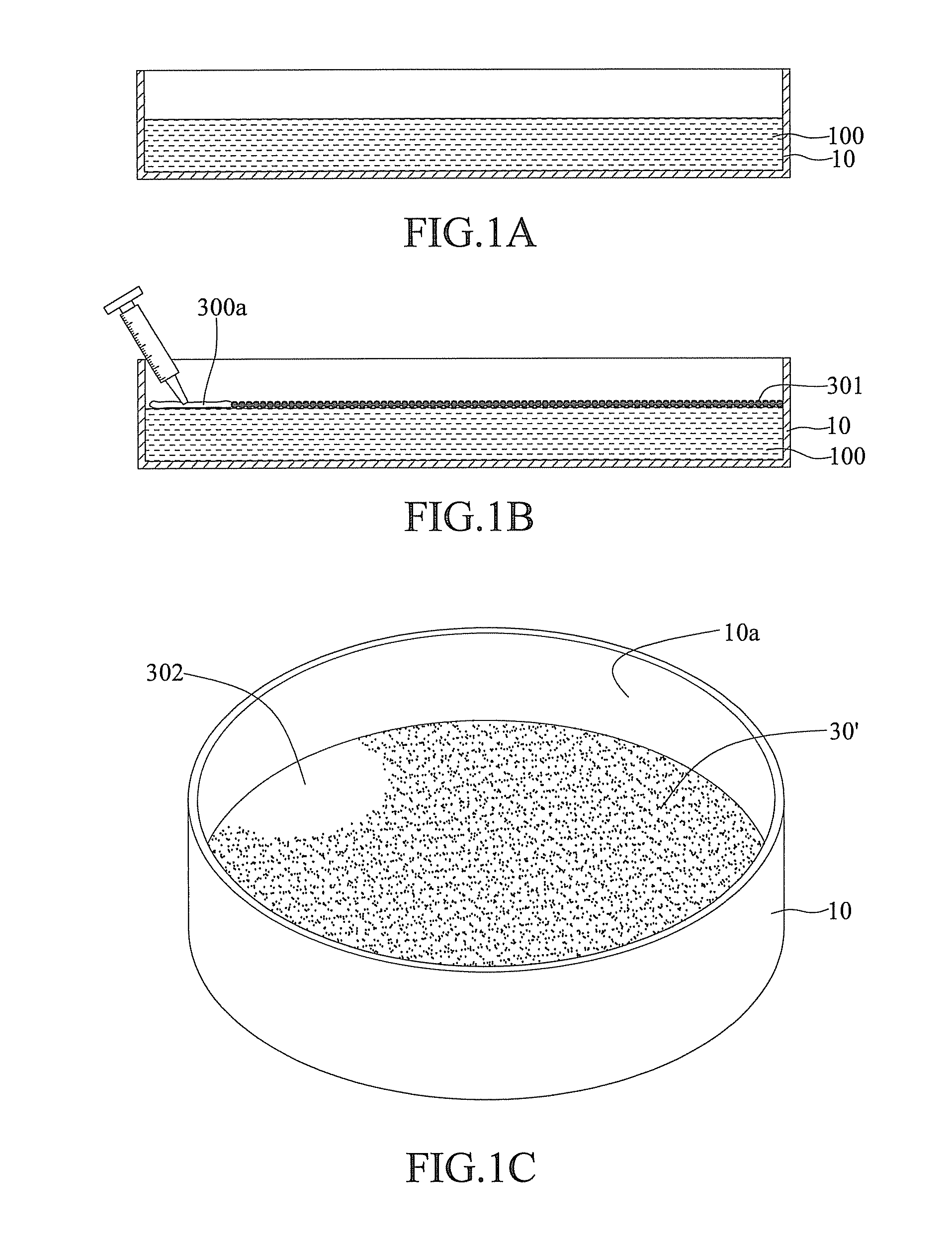

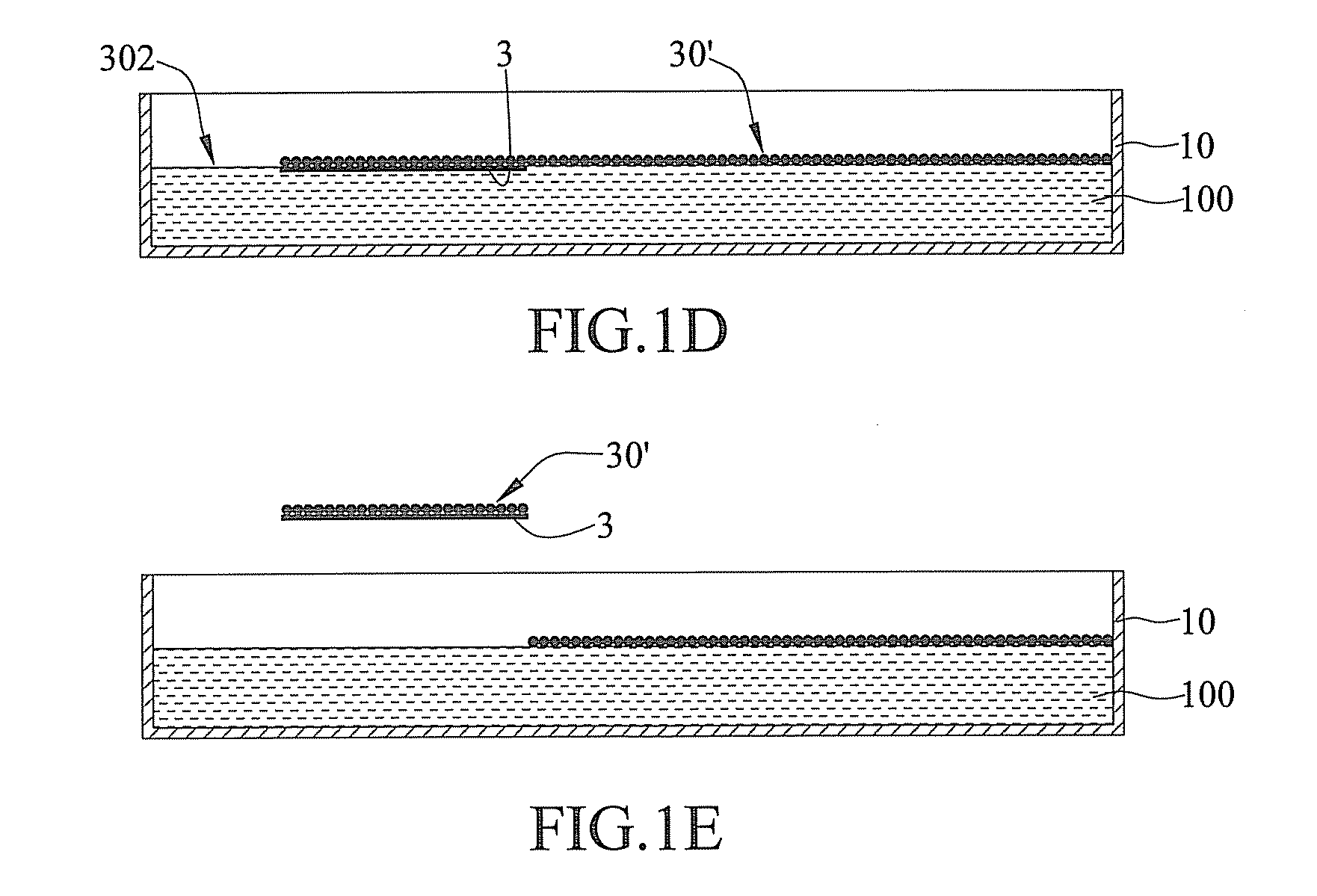

Film formation system and film formation method

InactiveUS20110159700A1Large areaLarge disposition areaMaterial nanotechnologyLiquid surface applicatorsElectrical and Electronics engineering

Owner:AUROTEK CORP

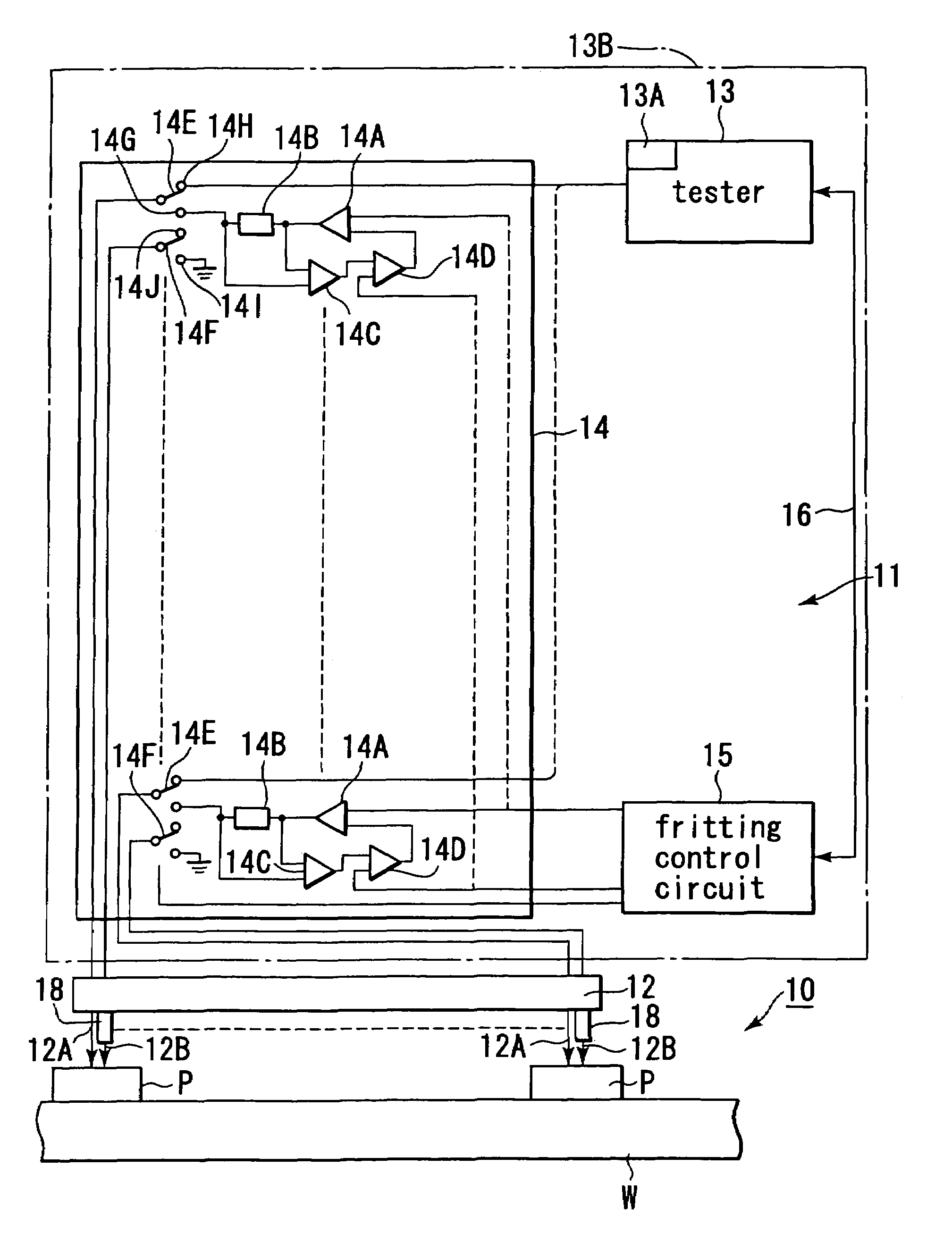

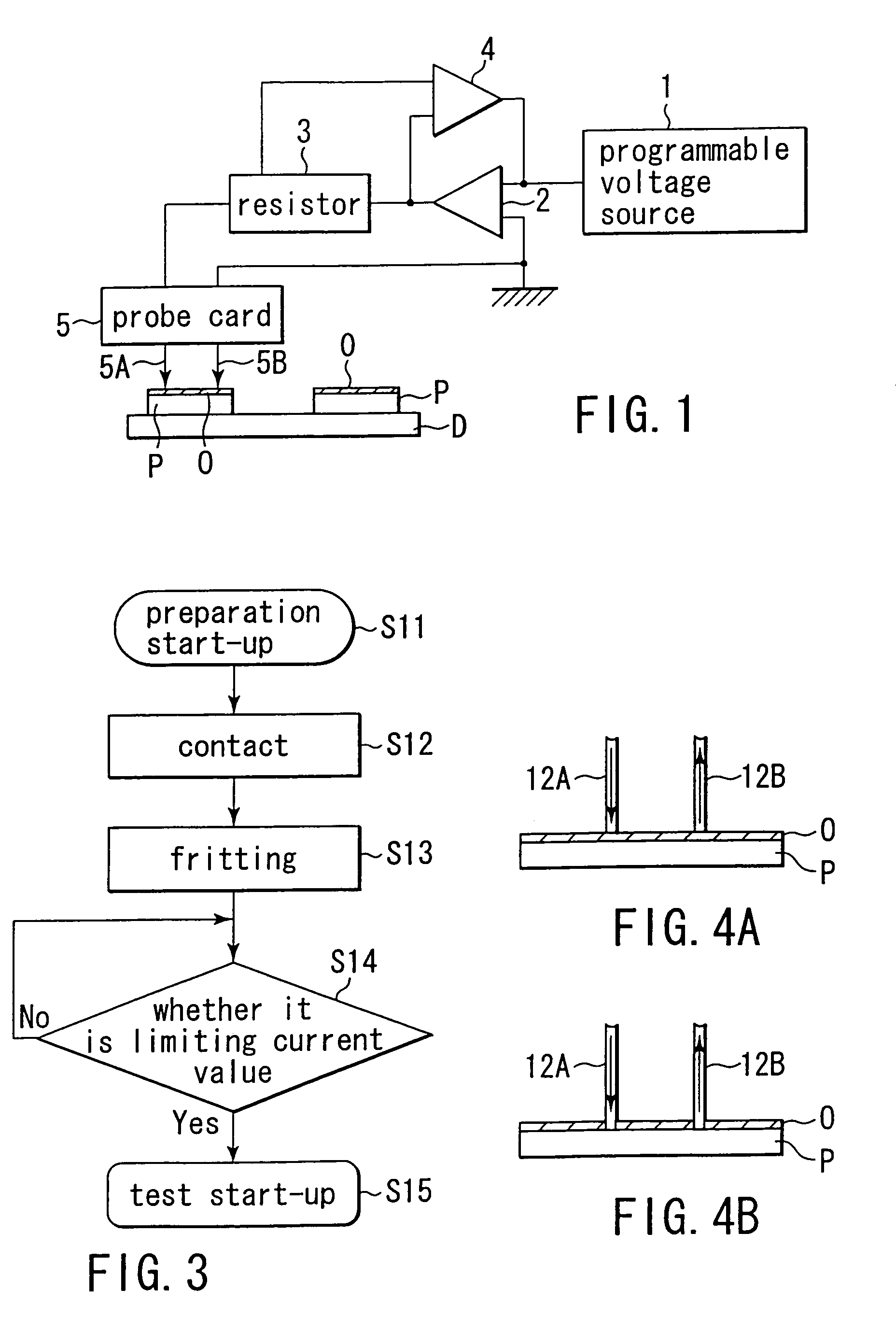

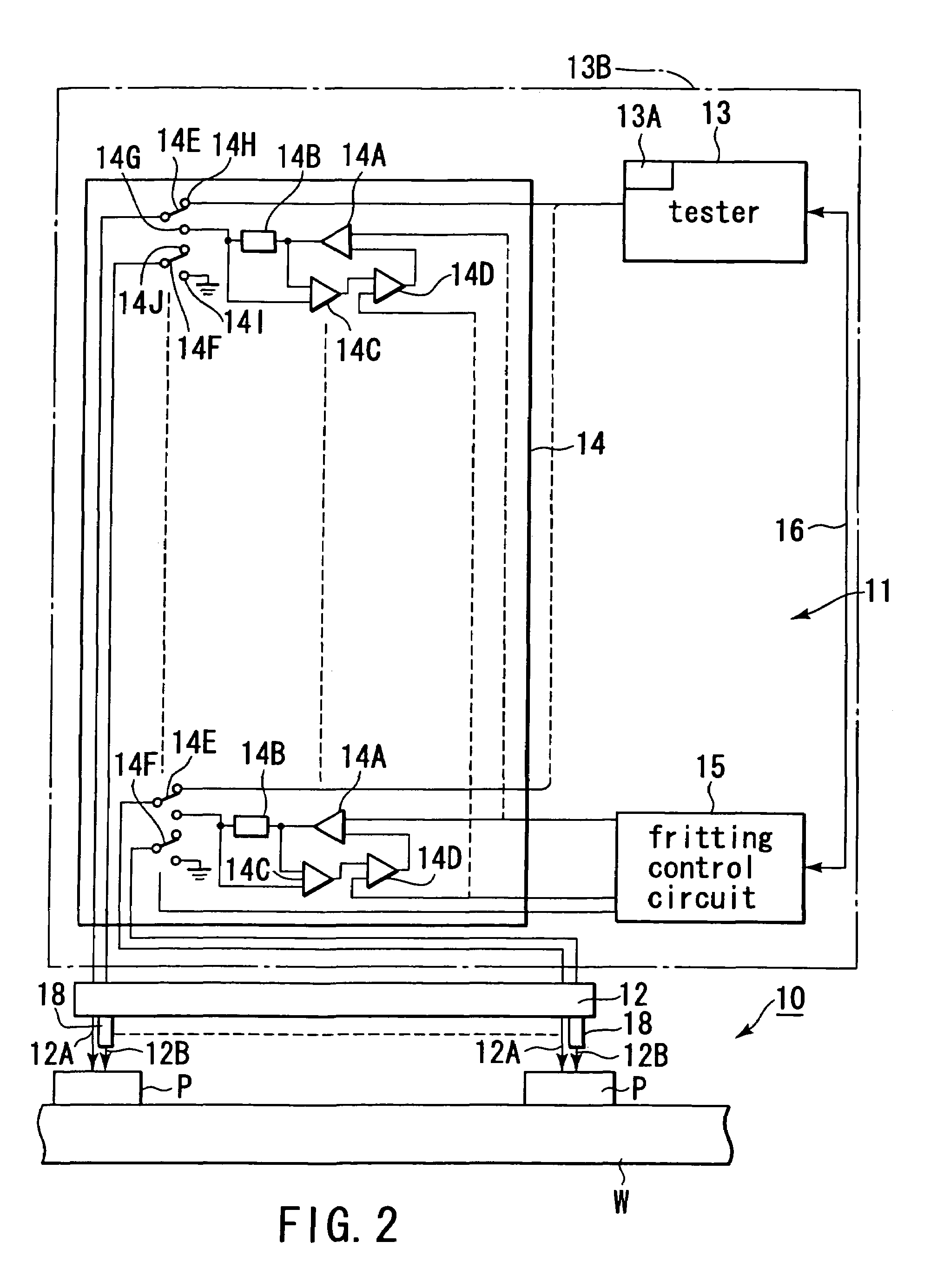

Inspection method and inspection apparatus

InactiveUS7061259B2Damage suppressionProlong lifeSemiconductor/solid-state device testing/measurementElectronic circuit testingElectricityEngineering

Disclosed is an inspection method for inspecting the electrical characteristics of a device by bringing an inspecting probe into electrical contact with an inspection electrode. An insulating film formed on the surface of the inspection electrode is broken by utilizing a fritting phenomenon so as to bring the inspection electrode into electrical contact with the inspection electrode.

Owner:TOKYO ELECTRON LTD +2

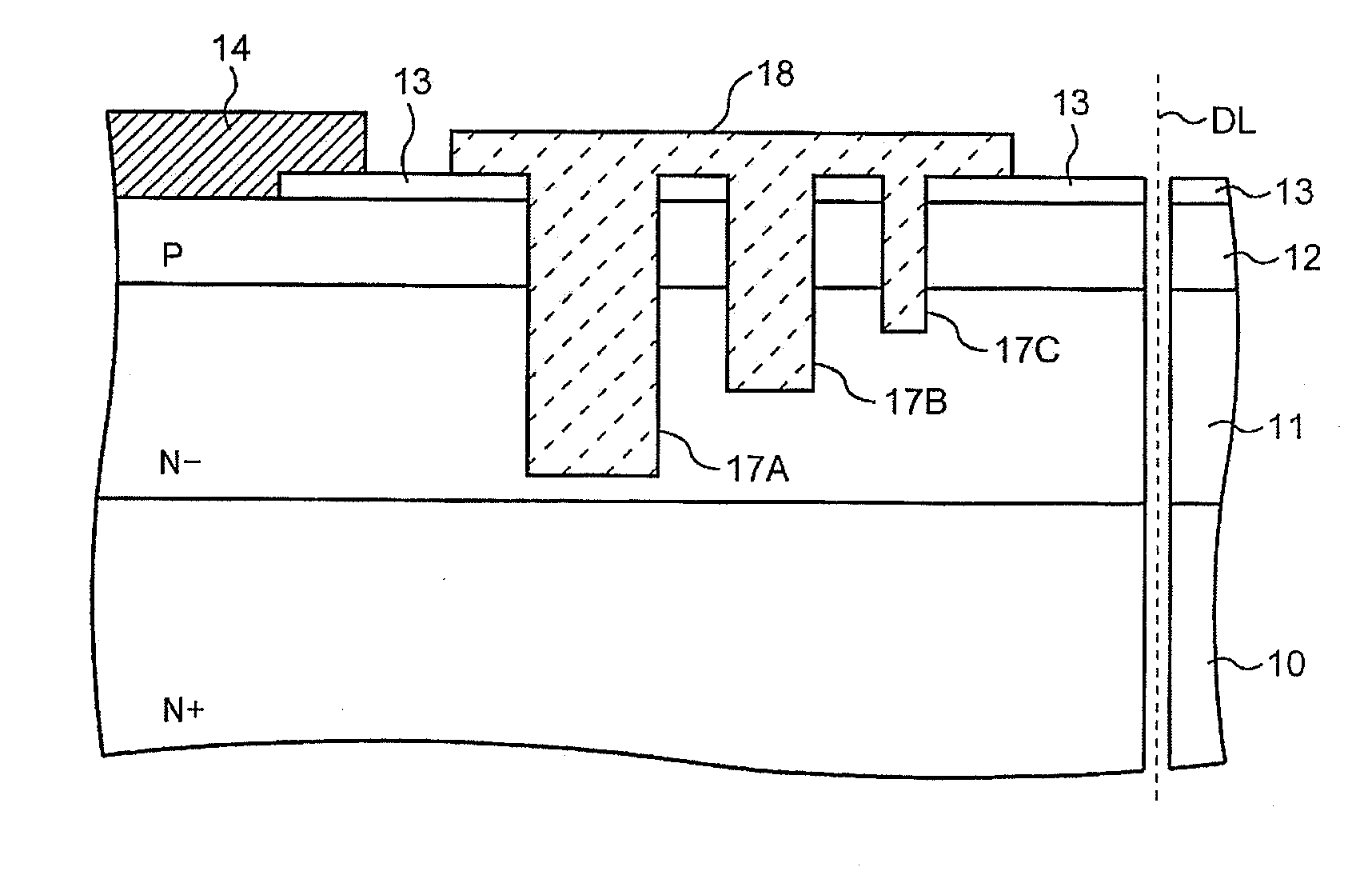

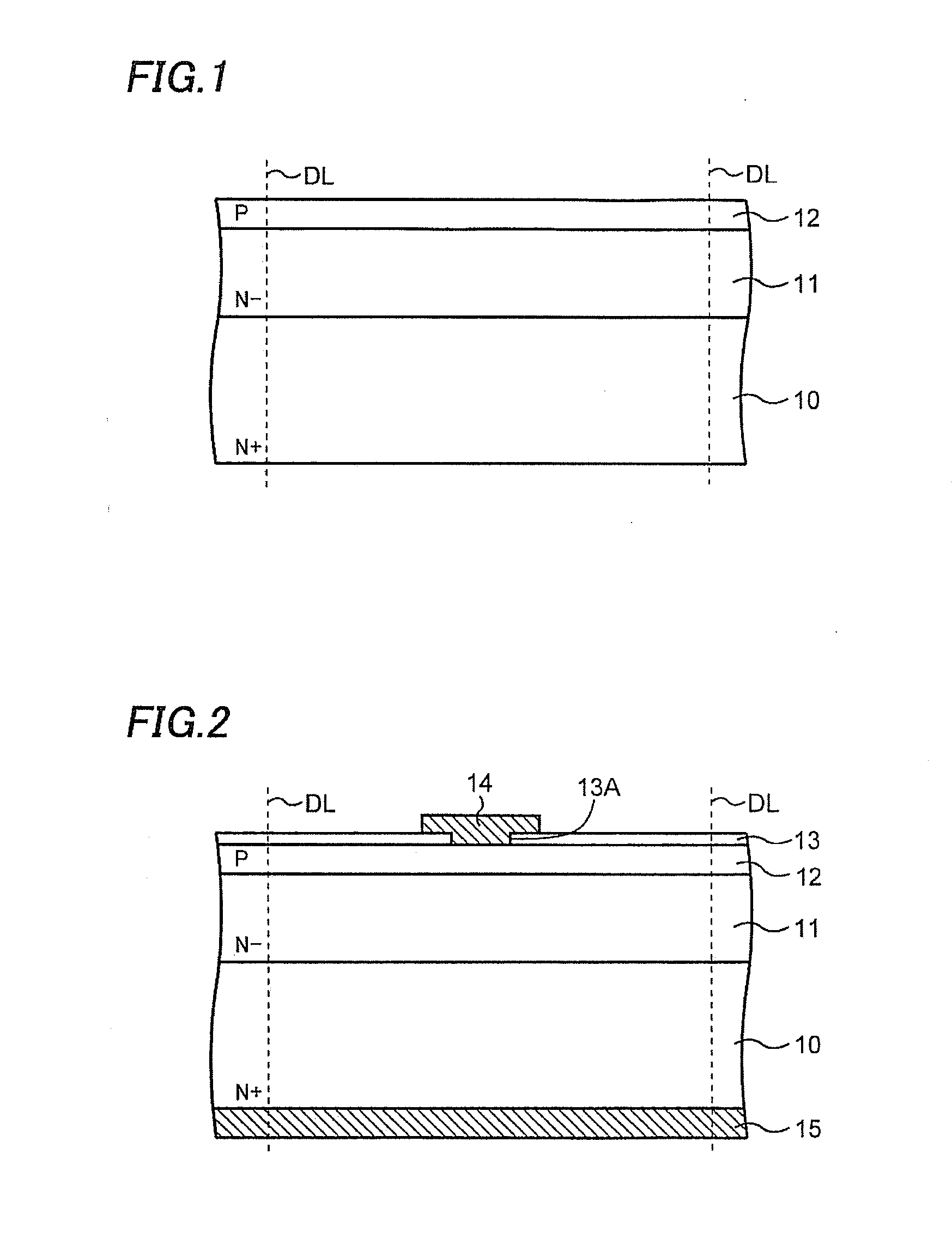

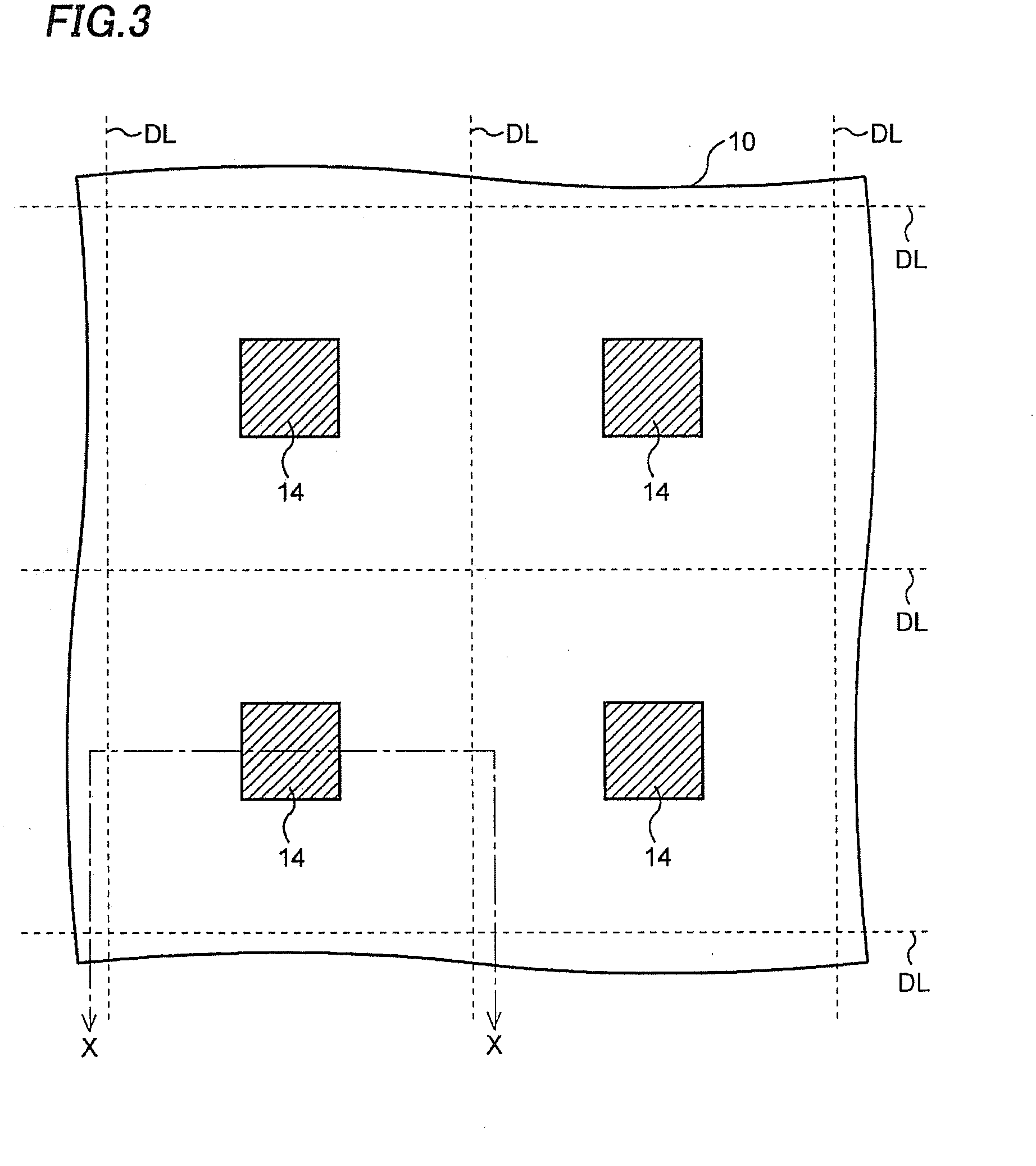

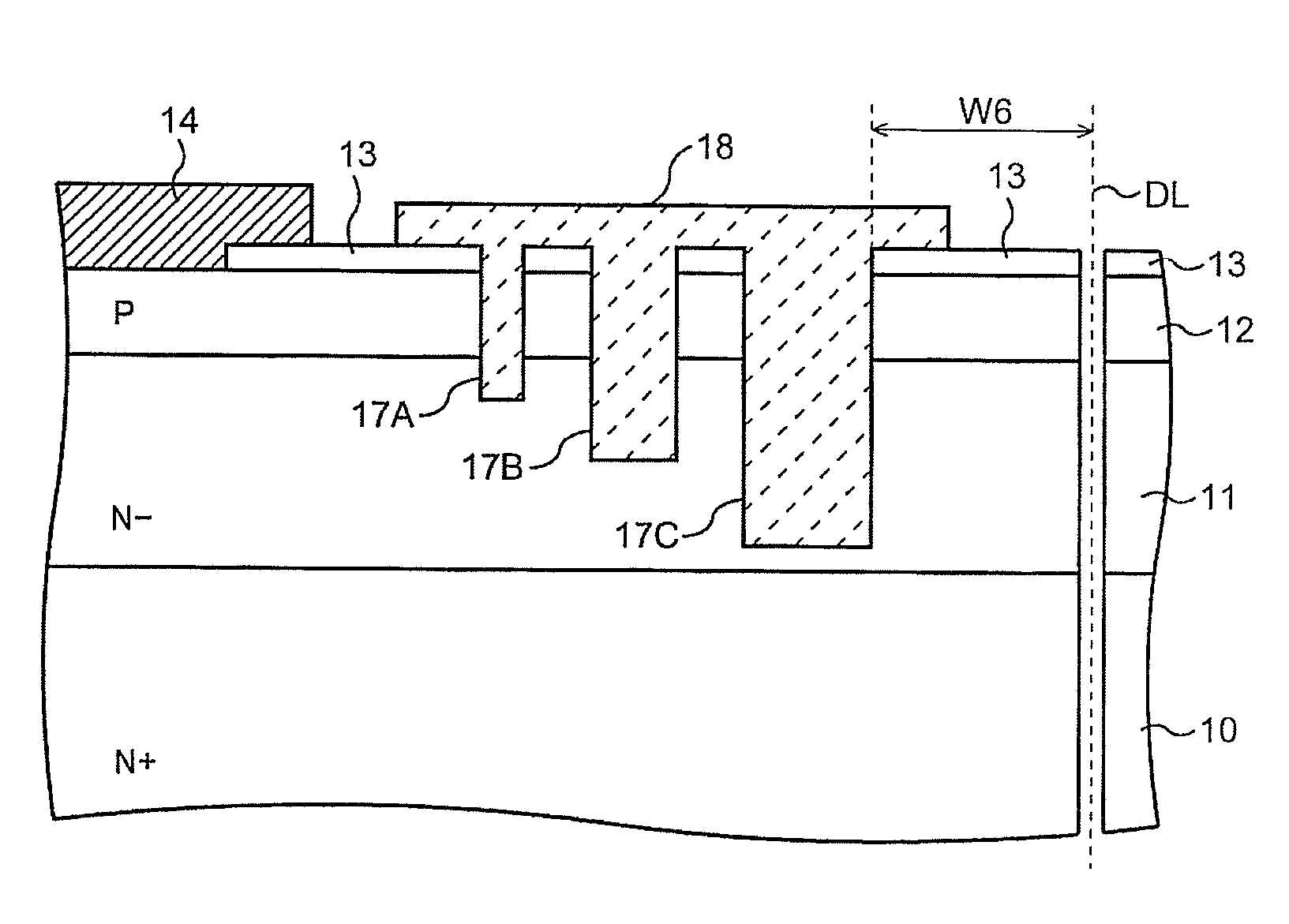

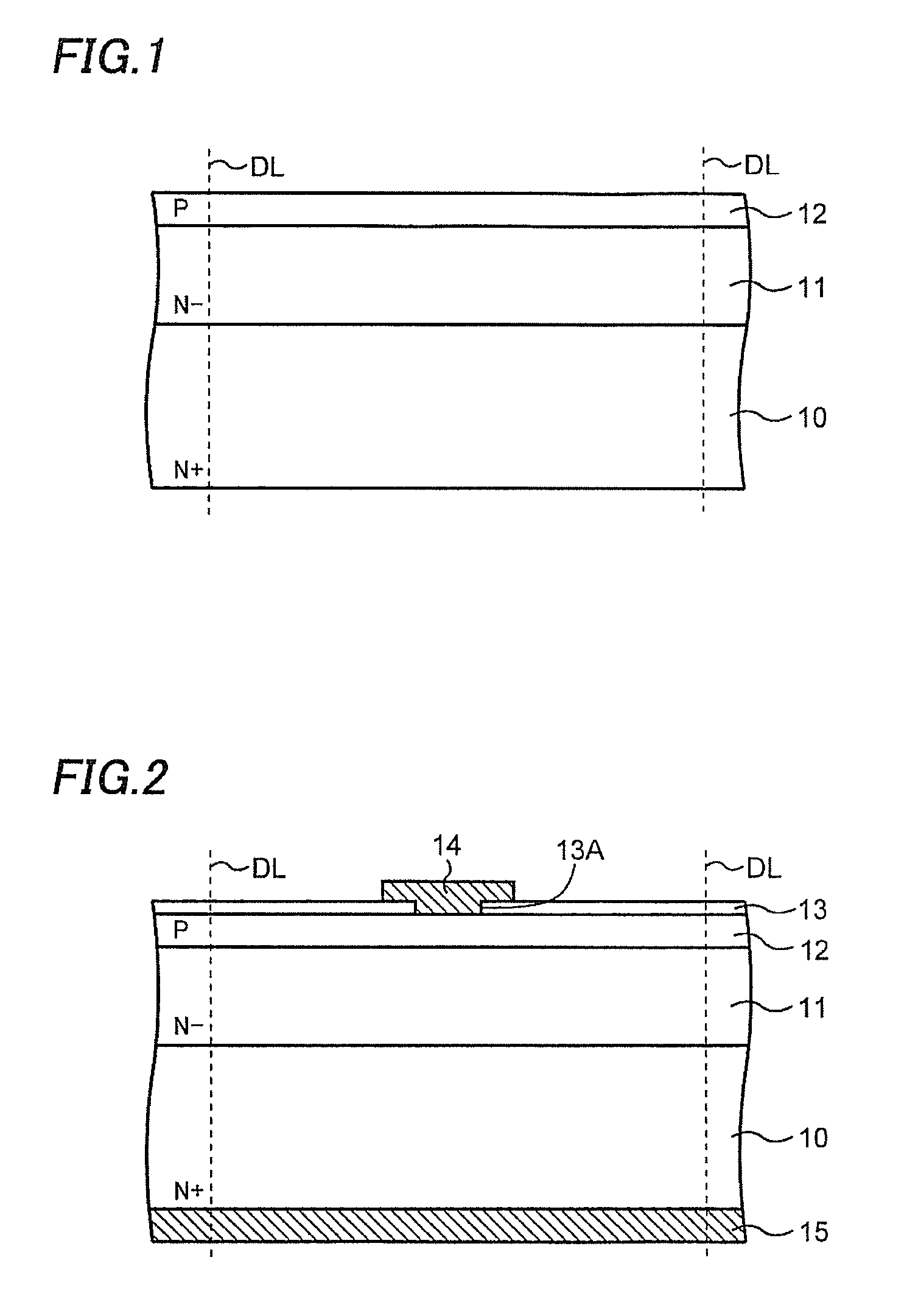

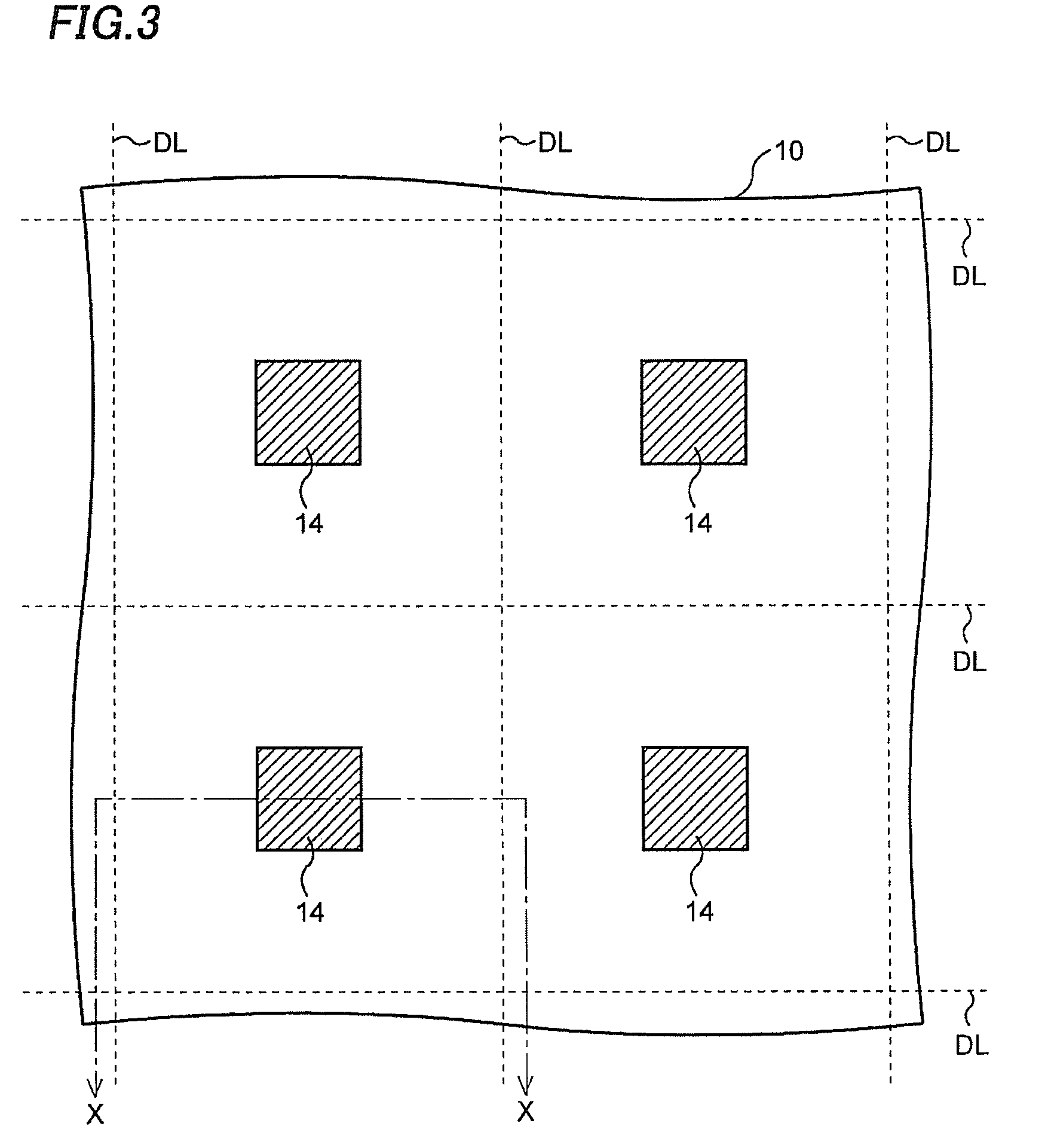

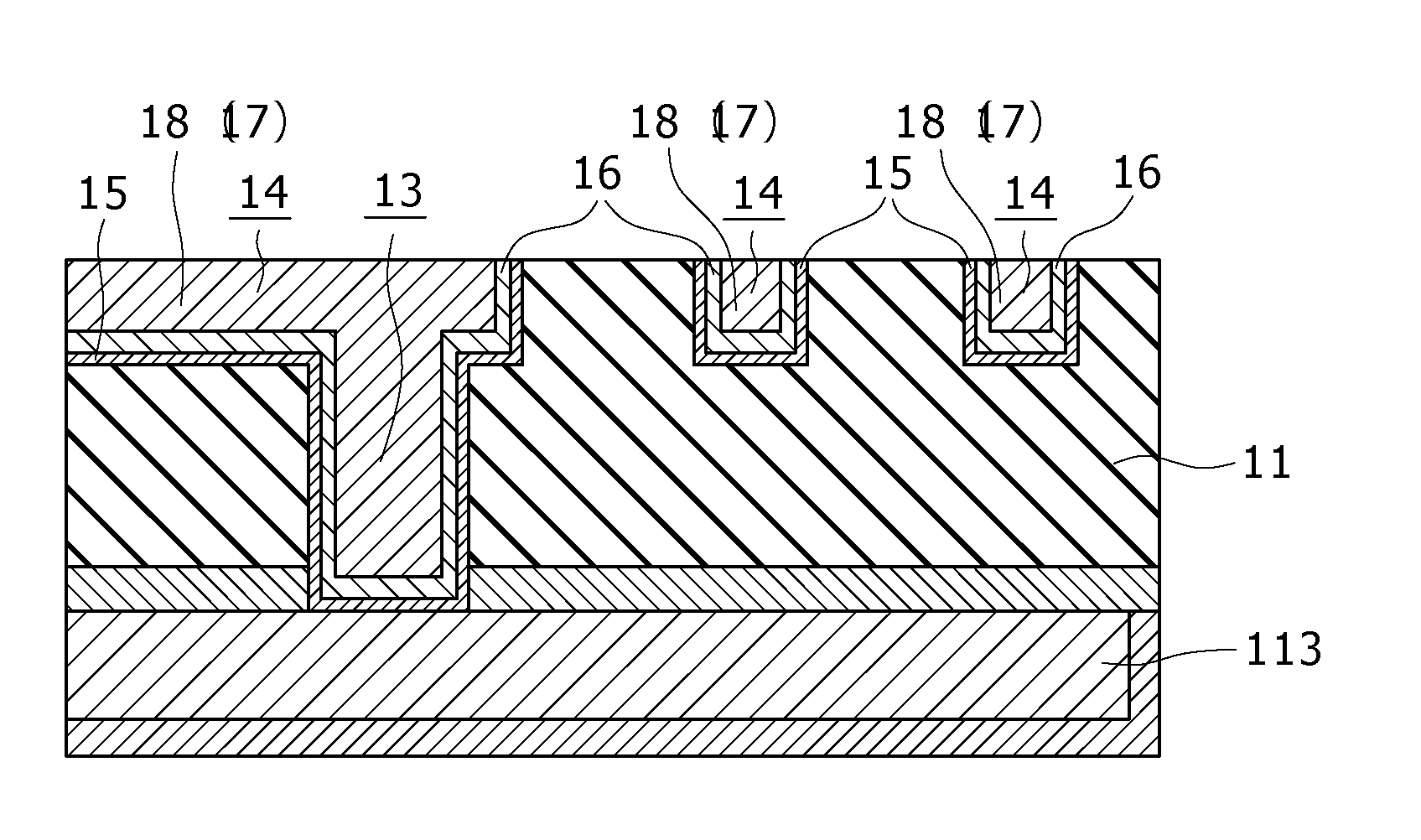

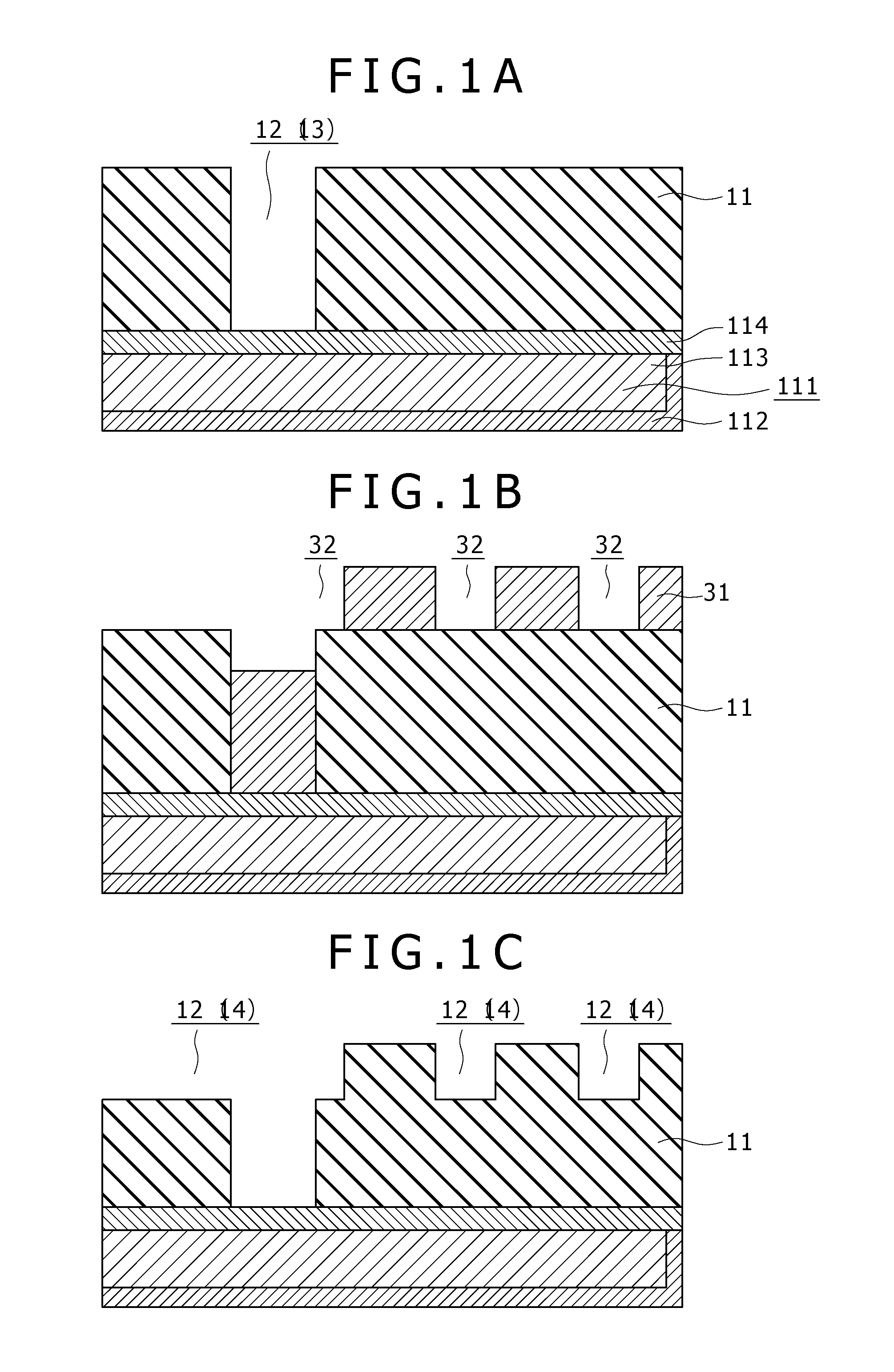

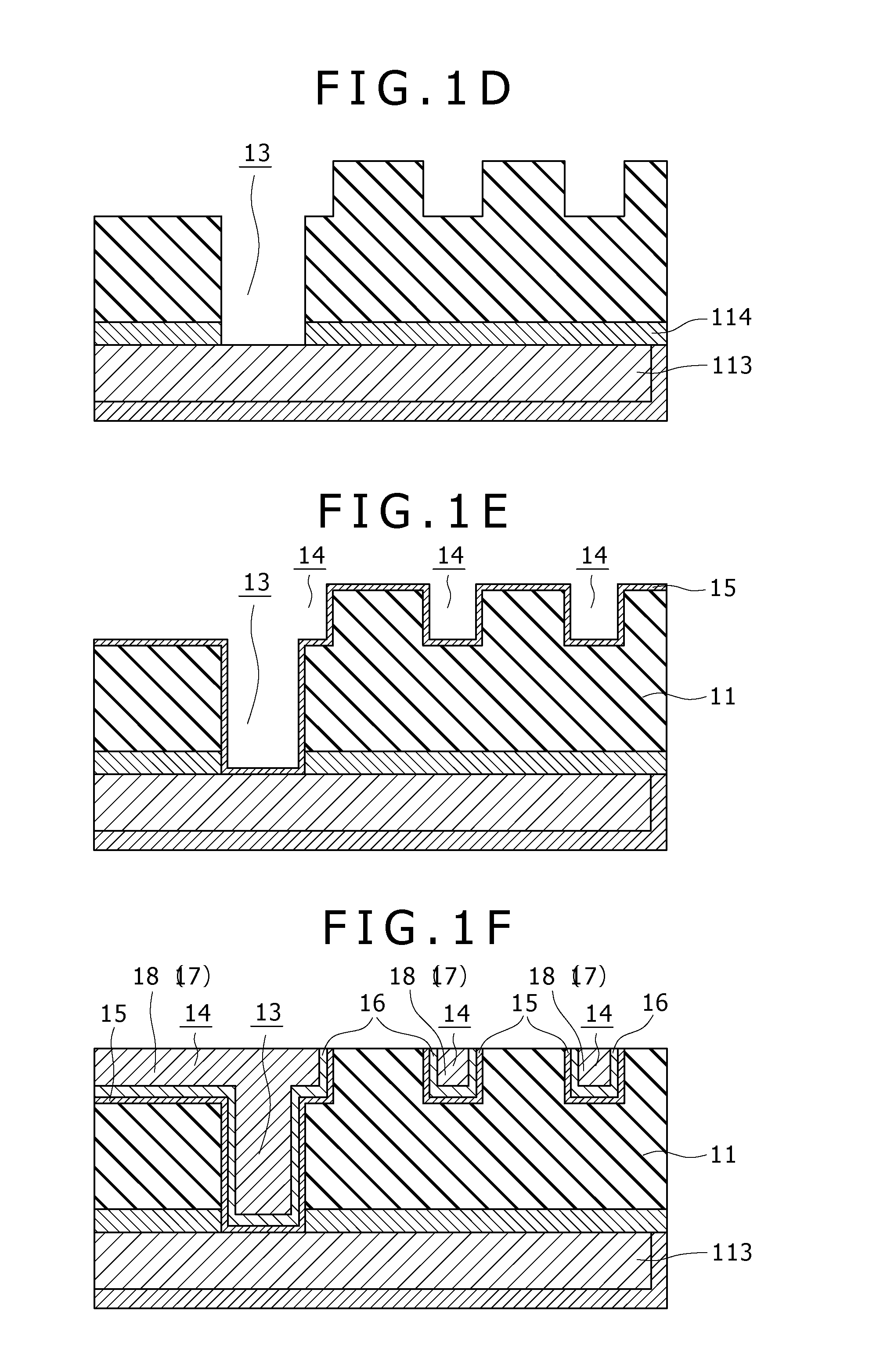

Semiconductor device and method of manufacturing the same

ActiveUS20100052090A1Reduce manufacturing costLayeredSemiconductor/solid-state device manufacturingDiodeManufacturing cost reductionEngineering

The invention is directed to reduction of a manufacturing cost and enhancement of a breakdown voltage of a PN junction portion abutting on a guard ring. An N− type semiconductor layer is formed on a front surface of a semiconductor substrate, and a P type semiconductor layer is formed thereon. An insulation film is formed on the P type semiconductor layer. Then, a plurality of grooves, i.e., a first groove, a second groove and a third groove are formed from the insulation film to the middle of the N− type semiconductor layer in the thickness direction thereof. The plurality of grooves is formed so that one of the two grooves next to each other among these, that is closer to an electronic device, i.e., to an anode electrode, is formed shallower than the other located on the outside of the one. Then, an insulating material is deposited in the first groove, the second groove and the third groove. The lamination body of the semiconductor substrate and the layers laminated thereon is then diced along dicing lines.

Owner:SEMICON COMPONENTS IND LLC

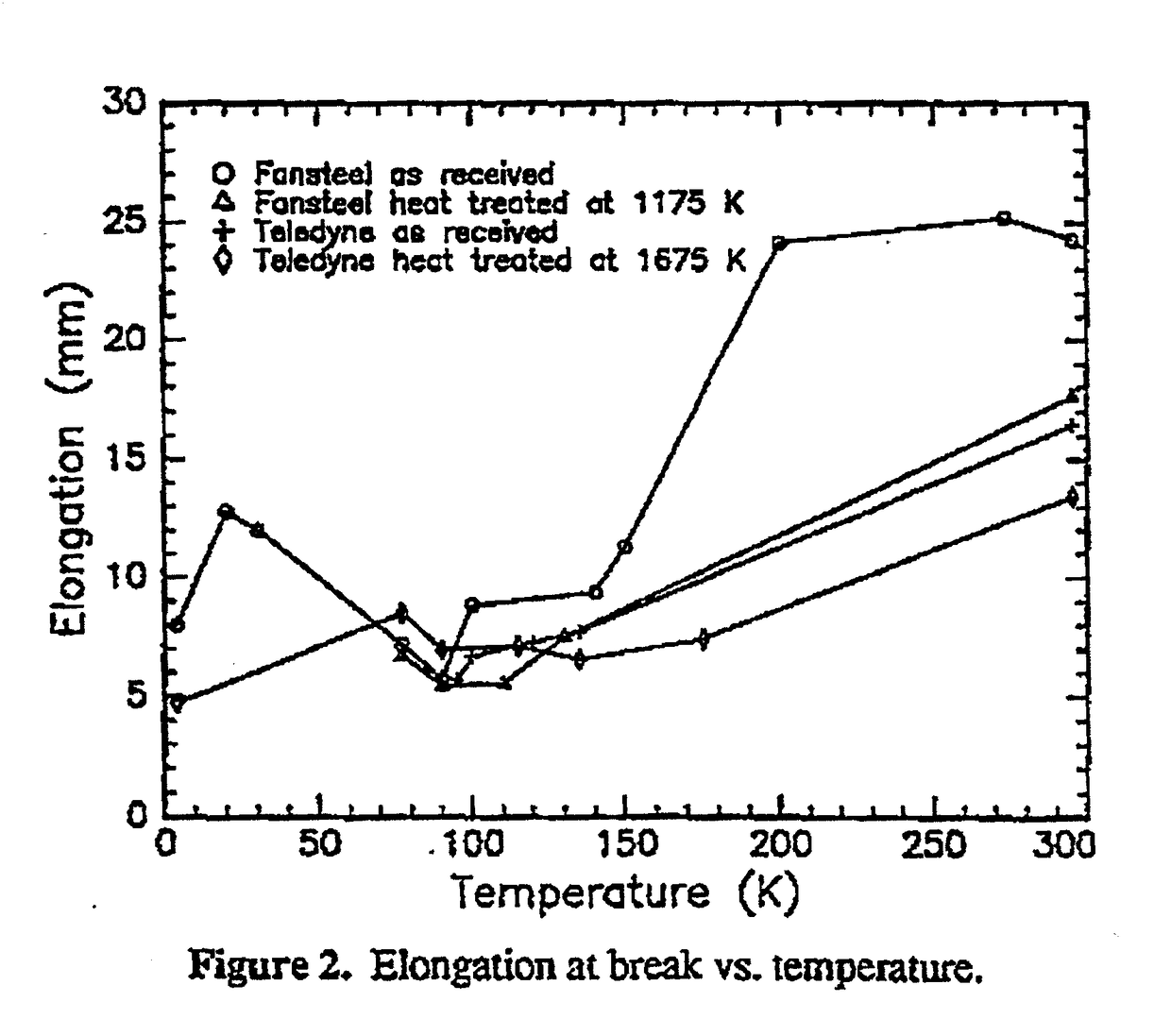

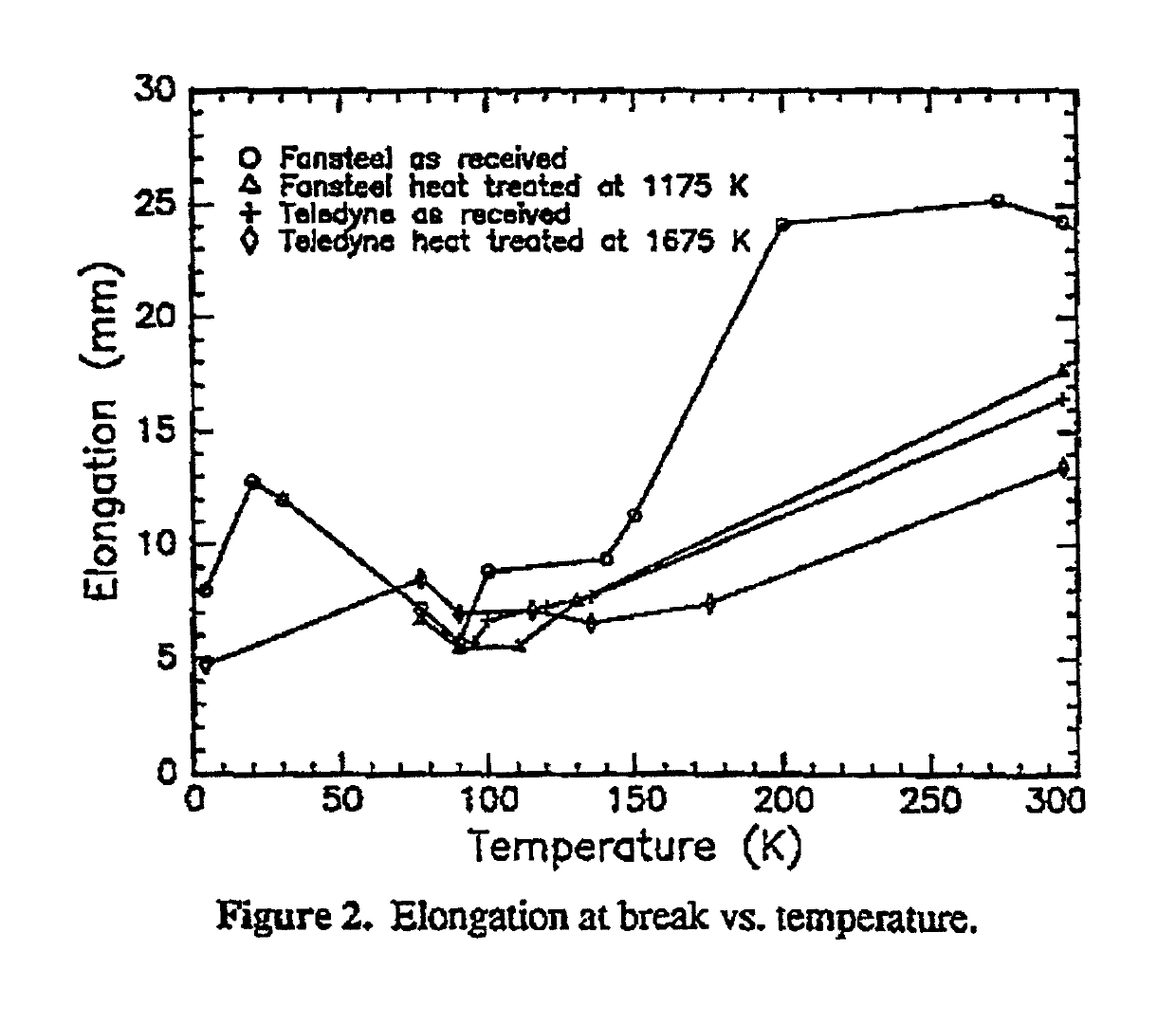

High performance srf accelerator structure and method

A high performance accelerator structure and method of production. The method includes precision machining the inner surfaces of a pair of half-cells that are maintained in an inert atmosphere and at a temperature of 100 K or less. The method includes removing thin layers of the inner surfaces of the half-cells after which the roughness of the inner surfaces in measured with a profilimeter. Additional thin layers are removed until the inner surfaces of the half-cell measure less than 2 nm root mean square (RMS) roughness over a 1 mm2 area on the profilimeter. The two half-cells are welded together in an inert atmosphere to form an SRF cavity. The resultant SRF cavity includes a high accelerating gradient (Eacc) and a high quality factor (Q0).

Owner:JEFFERSON SCI ASSOCS LLC

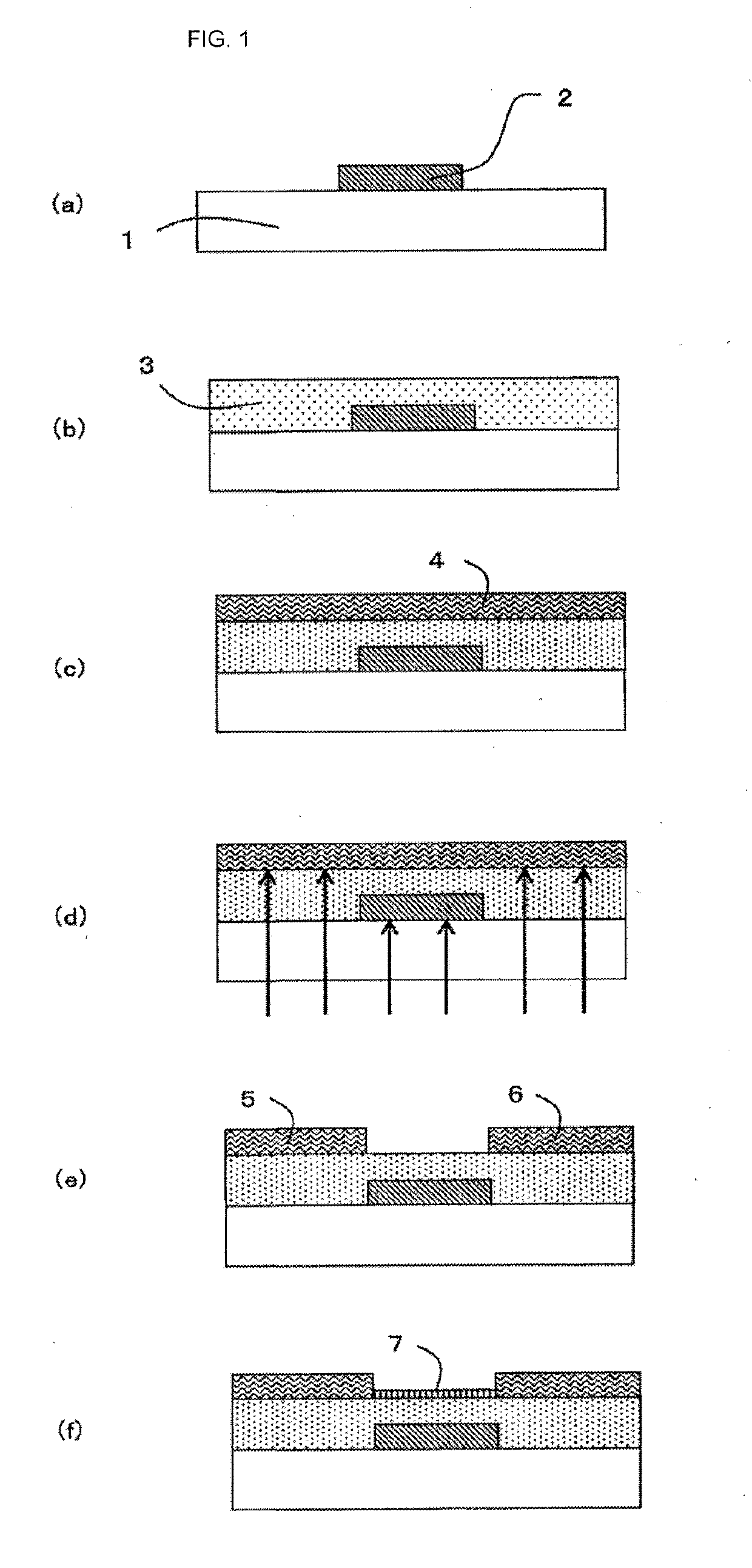

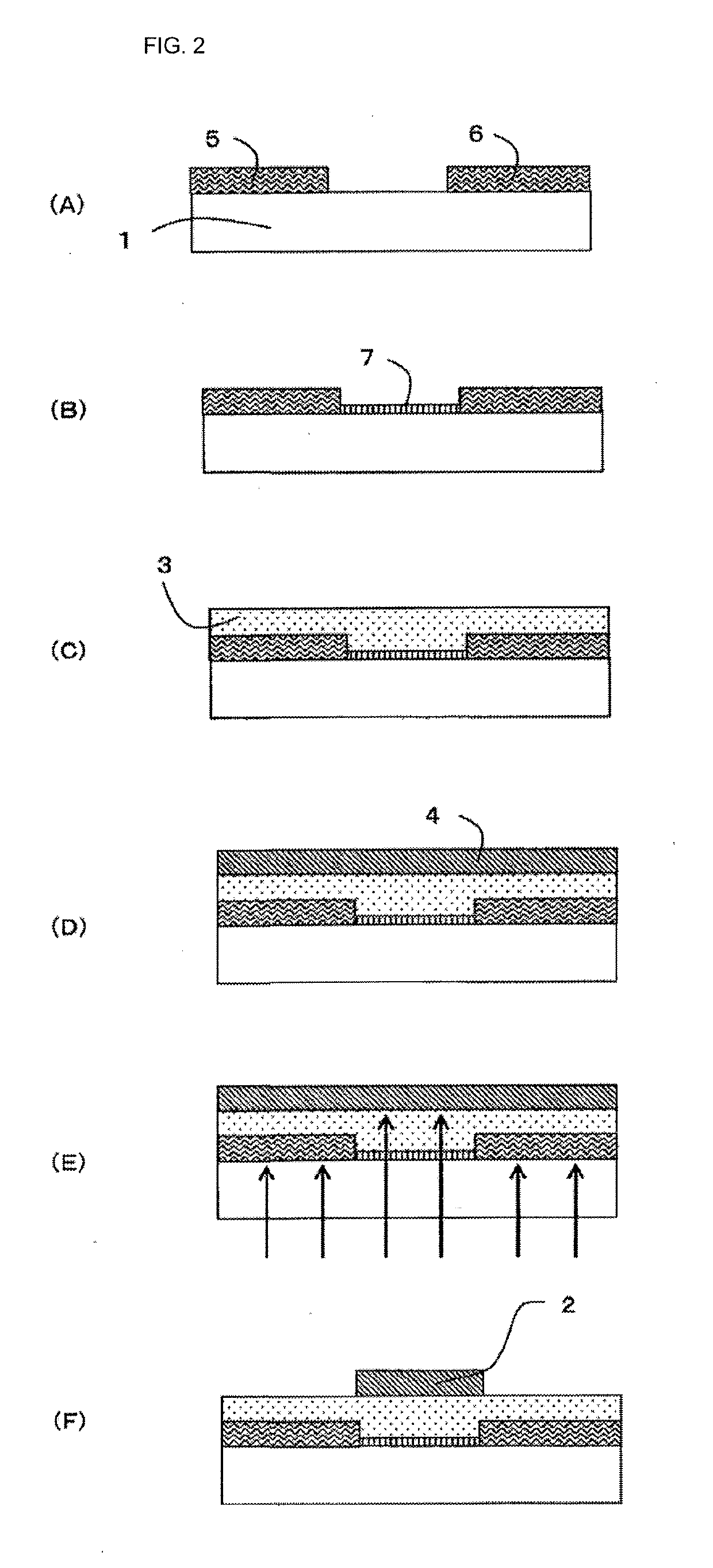

Method for manufacturing field effect transistor and method for manufacturing wireless communication device

ActiveUS20190198786A1Reduce manufacturing costImprove accuracyTransistorFinal product manufactureElectrical conductorEngineering

Provided is a method for manufacturing a field-effect transistor, the method including the steps of: forming a gate electrode on the surface of a substrate; forming a gate insulating layer on the gate electrode; forming a conductive film containing a conductor and a photosensitive organic component by a coating method on the gate insulating layer; exposing the conductive film from the rear surface side of the substrate with the gate electrode as a mask; developing the exposed conductive film to form a source electrode and a drain electrode; and forming a semiconductor layer by a coating method between the source electrode and the drain electrode. This method makes it possible to provide an FET, a semiconductor device, and an RFID which can be prepared by a simple process, and which have a high mobility, and have a gate electrode and source / drain electrodes aligned with a high degree of accuracy.

Owner:TORAY IND INC

Semiconductor device and method of manufacturing the same

ActiveUS8148788B2Reduce manufacturing costLayeredSemiconductor/solid-state device manufacturingDiodeManufacturing cost reductionEngineering

The invention is directed to reduction of a manufacturing cost and enhancement of a breakdown voltage of a PN junction portion abutting on a guard ring. An N− type semiconductor layer is formed on a front surface of a semiconductor substrate, and a P type semiconductor layer is formed thereon. An insulation film is formed on the P type semiconductor layer. Then, a plurality of grooves, i.e., a first groove, a second groove and a third groove are formed from the insulation film to the middle of the N− type semiconductor layer in the thickness direction thereof. The plurality of grooves is formed so that one of the two grooves next to each other among these, that is closer to an electronic device, i.e., to an anode electrode, is formed shallower than the other located on the outside of the one. Then, an insulating material is deposited in the first groove, the second groove and the third groove. The lamination body of the semiconductor substrate and the layers laminated thereon is then diced along dicing lines.

Owner:SEMICON COMPONENTS IND LLC

Display substrate and method of manufacturing the same

ActiveUS20150295177A1Prevent and reduce voltage dropLayer can be damagedSemiconductor/solid-state device testing/measurementElectroluminescent light sourcesTransmittanceEngineering

A display substrate and a method of manufacturing the same. The display substrate includes a substrate including an active area and an inactive area, an organic light-emitting diode (OLED) unit disposed on the active area of the substrate, and a transmittance measurement pattern unit disposed on the inactive area of the substrate. The transmittance measurement pattern unit includes a deposition assistant layer pattern disposed on the substrate.

Owner:SAMSUNG DISPLAY CO LTD

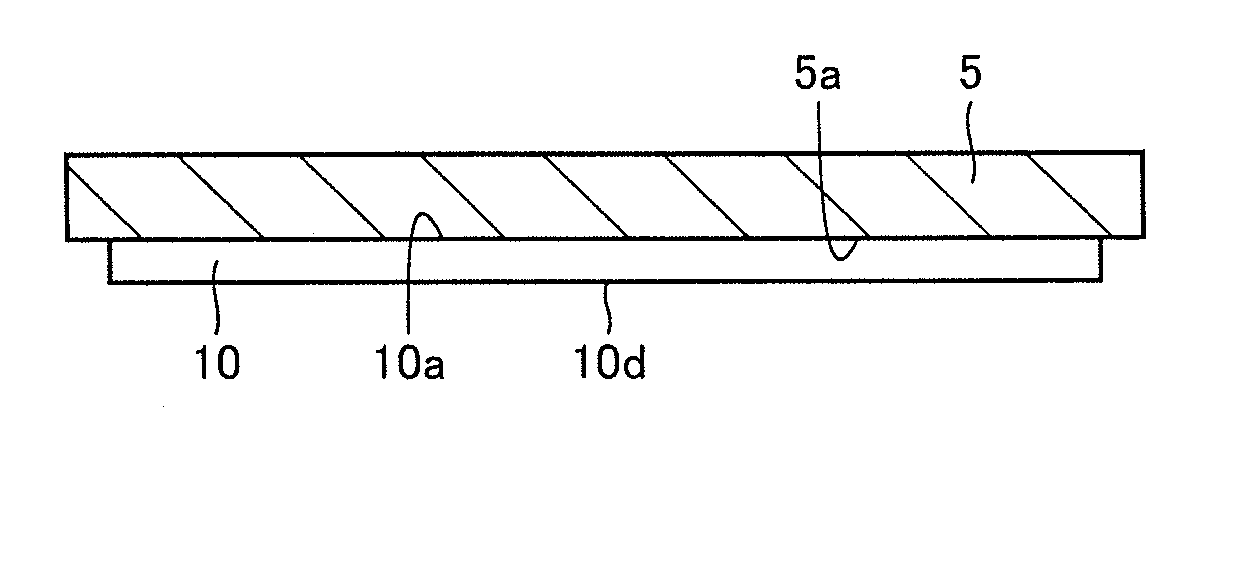

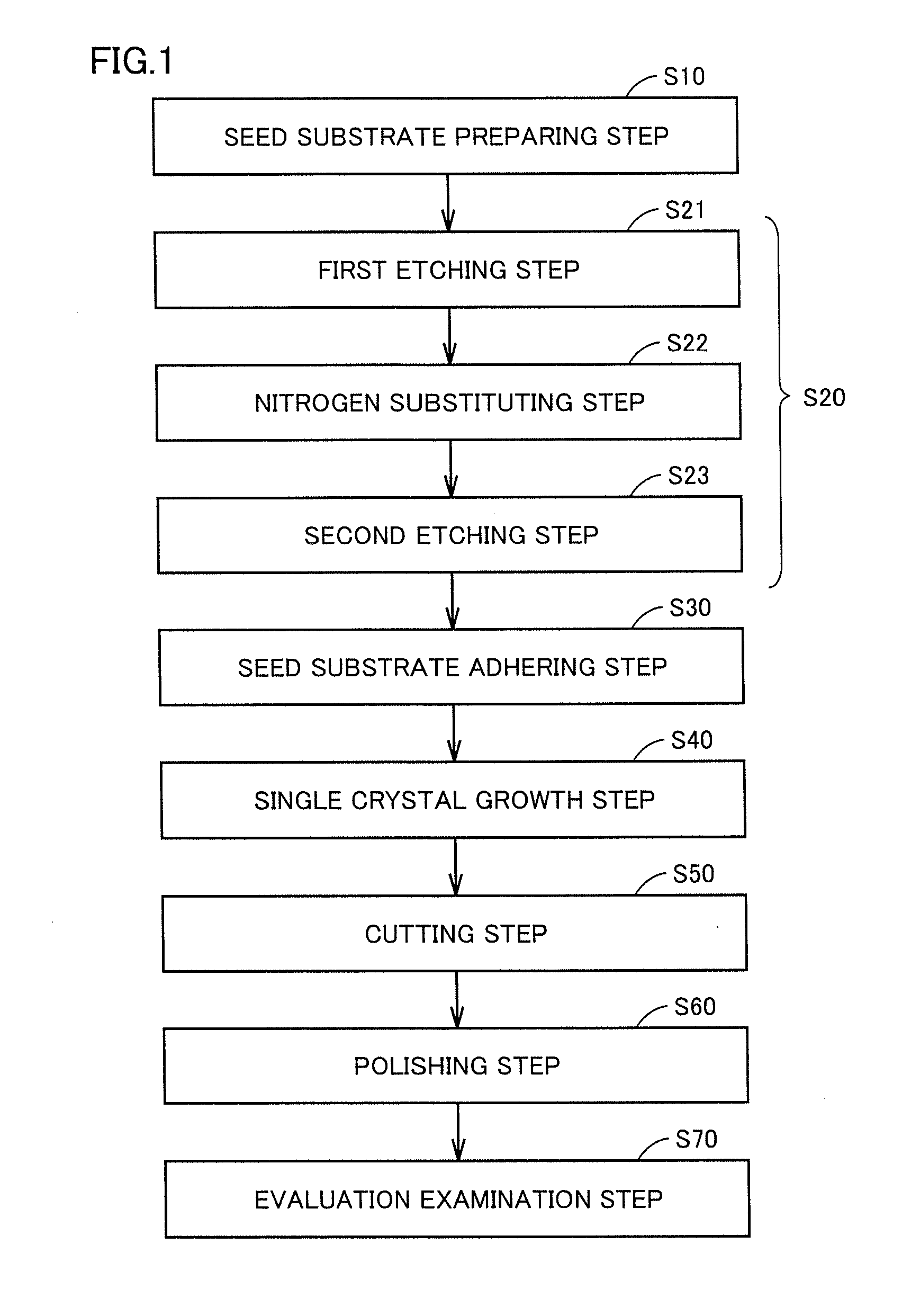

Method for manufacturing silicon carbide substrate

InactiveUS20140030874A1High qualityIncrease the amount of etchingPolycrystalline material growthSemiconductor/solid-state device manufacturingSingle crystalCarbon atom

A method for manufacturing a silicon carbide substrate includes the steps of: preparing a seed substrate made of silicon carbide; etching a main surface of the seed substrate prepared; obtaining an ingot by growing a silicon carbide single crystal film on a crystal growth surface formed by etching the main surface of the seed substrate;and obtaining a silicon carbide substrate by cutting the ingot. The step of etching the seed substrate includes: a first etching step of removing silicon atoms, which form the silicon carbide, from an etching region using chlorine gas, the etching region being a region including the main surface of the seed substrate; and a second etching step of removing carbon atoms, which form the silicon carbide, from the etching region from which the silicon atoms have been removed, using oxygen gas.

Owner:SUMITOMO ELECTRIC IND LTD

High performance SRF accelerator structure and method

A high performance accelerator structure and method of production. The method includes precision machining the inner surfaces of a pair of half-cells that are maintained in an inert atmosphere and at a temperature of 100 K or less. The method includes removing thin layers of the inner surfaces of the half-cells after which the roughness of the inner surfaces in measured with a profilimeter. Additional thin layers are removed until the inner surfaces of the half-cell measure less than 2 nm root mean square (RMS) roughness over a 1 mm2 area on the profilimeter. The two half-cells are welded together in an inert atmosphere to form an SRF cavity. The resultant SRF cavity includes a high accelerating gradient (Eacc) and a high quality factor (Q0).

Owner:JEFFERSON SCI ASSOCS LLC

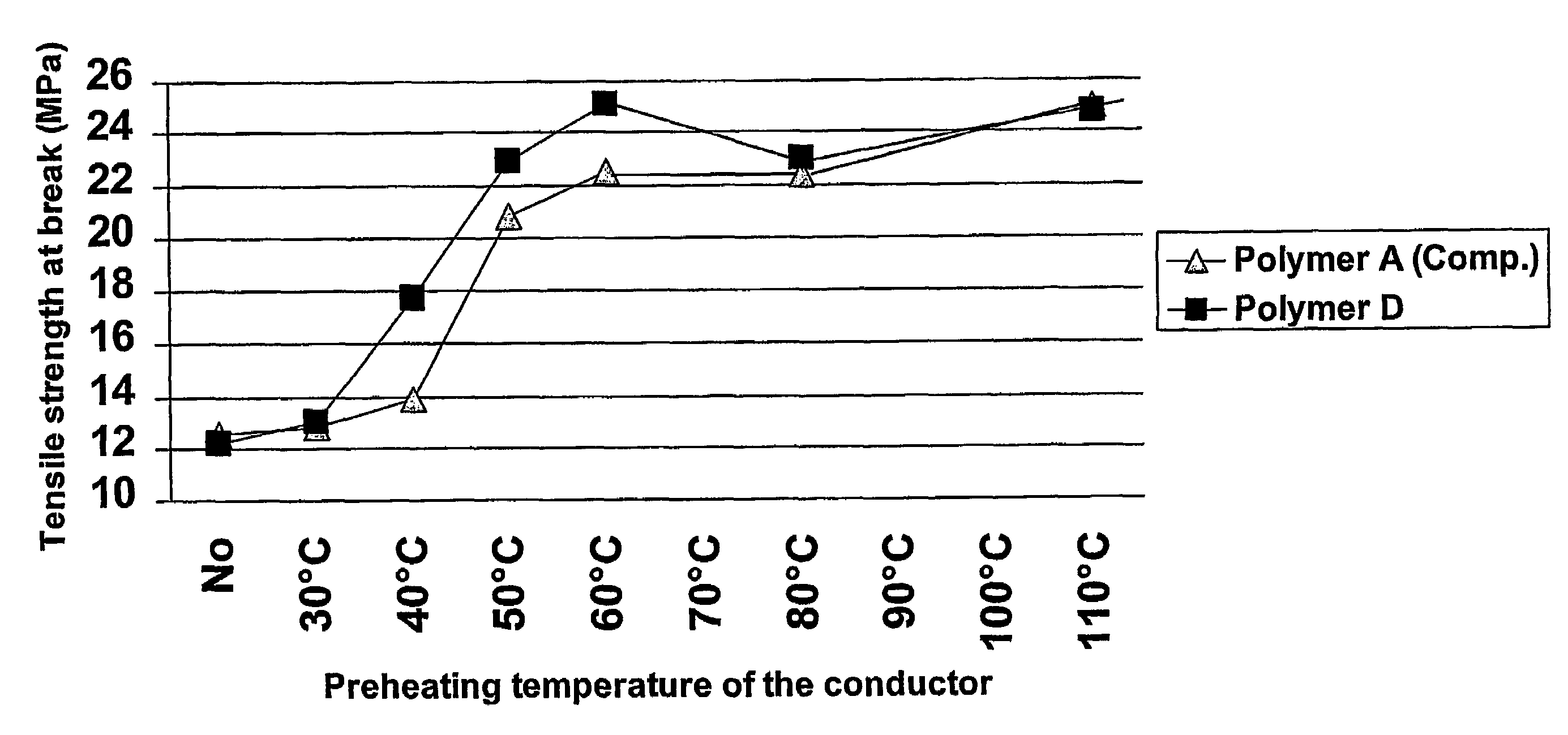

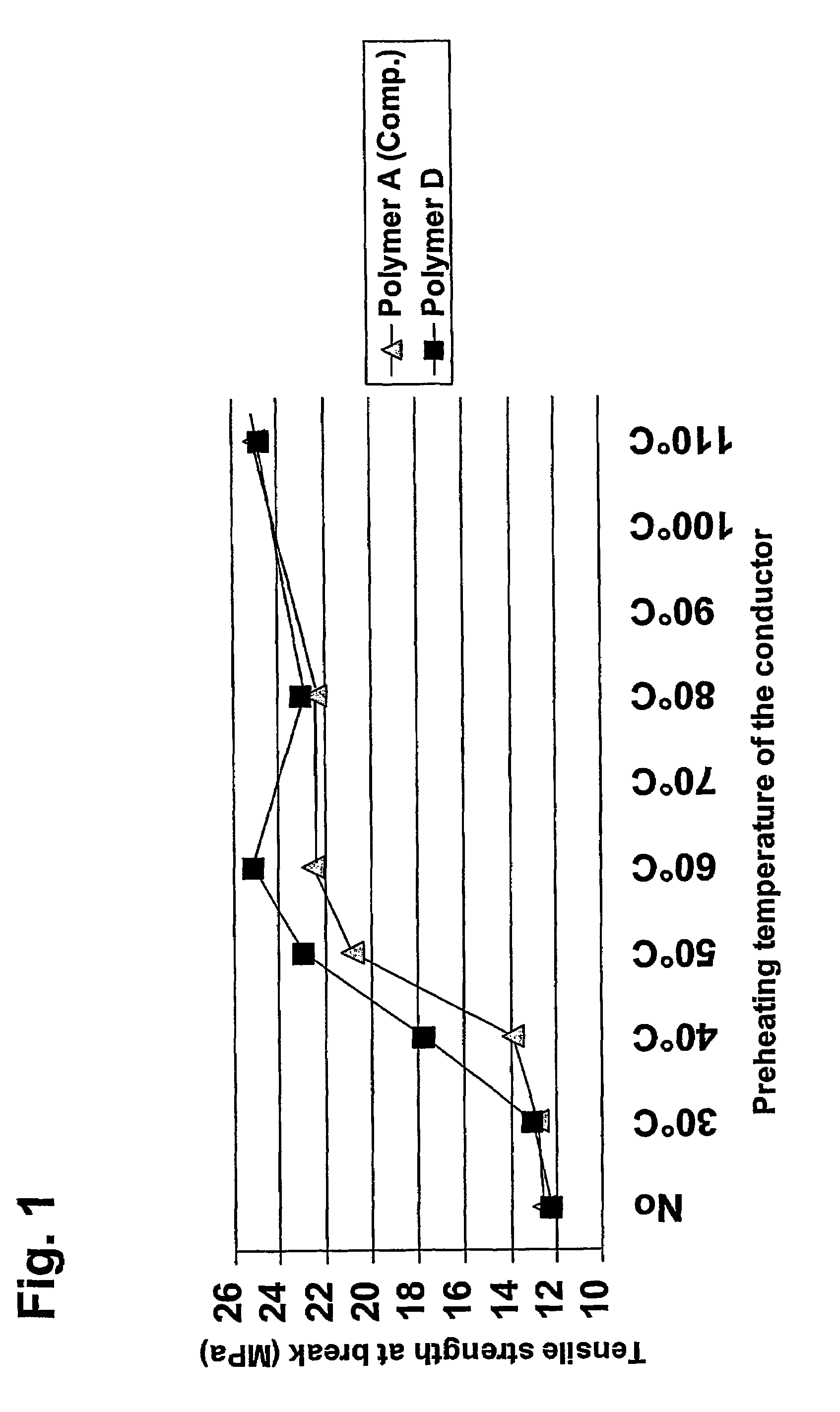

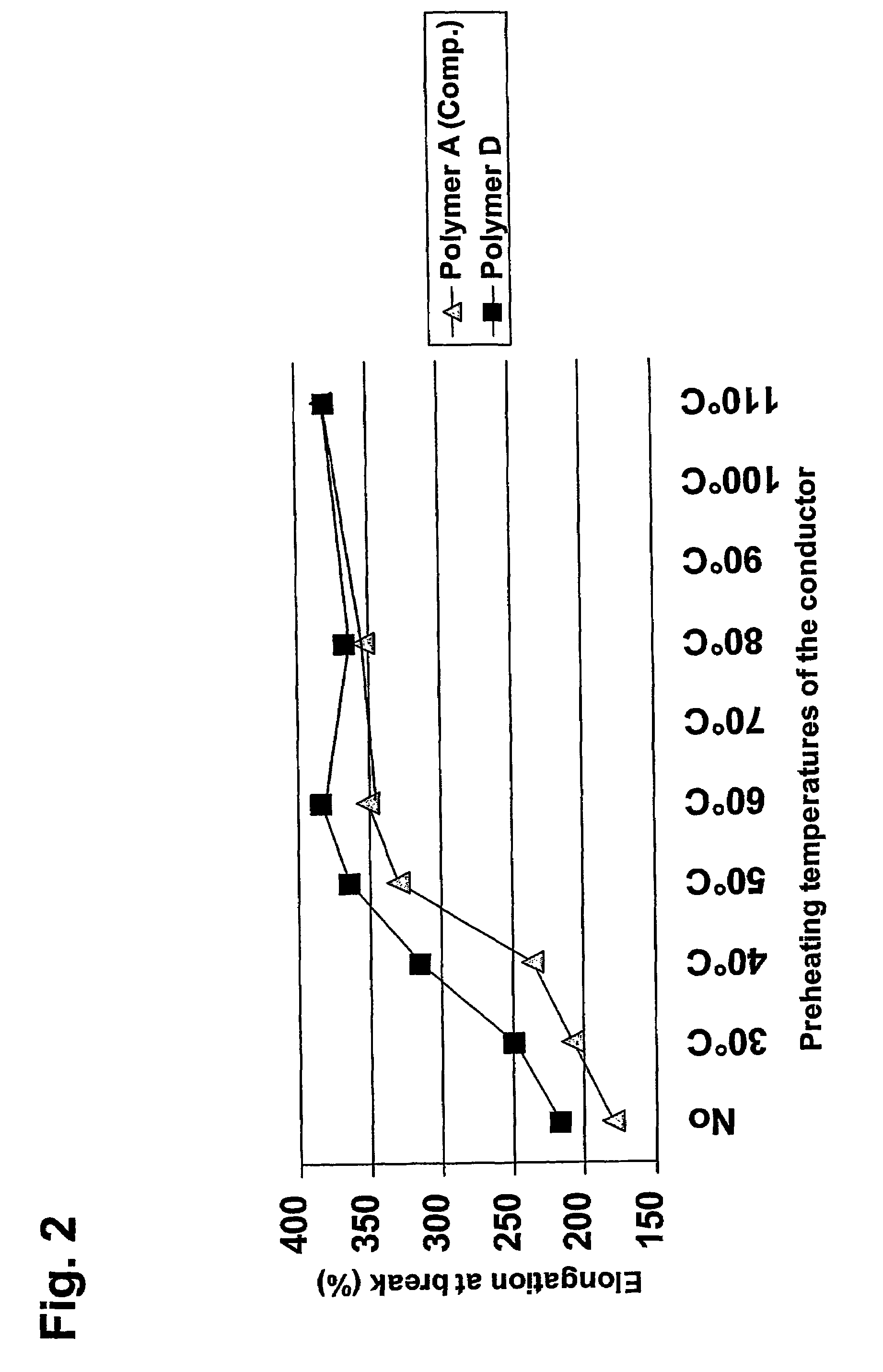

Low voltage power cable with insulation layer comprising polyolefin having polar groups, hydrolysable silane groups, and including a silanol condensation catalyst

ActiveUS7435908B2Improve adhesionAvoid breakingPlastic/resin/waxes insulatorsInsulated cablesPower cableInsulation layer

A low voltage power cable having an insulation layer with a density below 1100 kg / m3, which has a polyolefin having 0.002-4% mol of a compound that has polar groups and further having a compound that has hydrolysable silane groups and includes 0.0001-3% weight of a silanol condensation catalyst and a process of manufacturing such a cable.

Owner:BOREALIS TECH OY

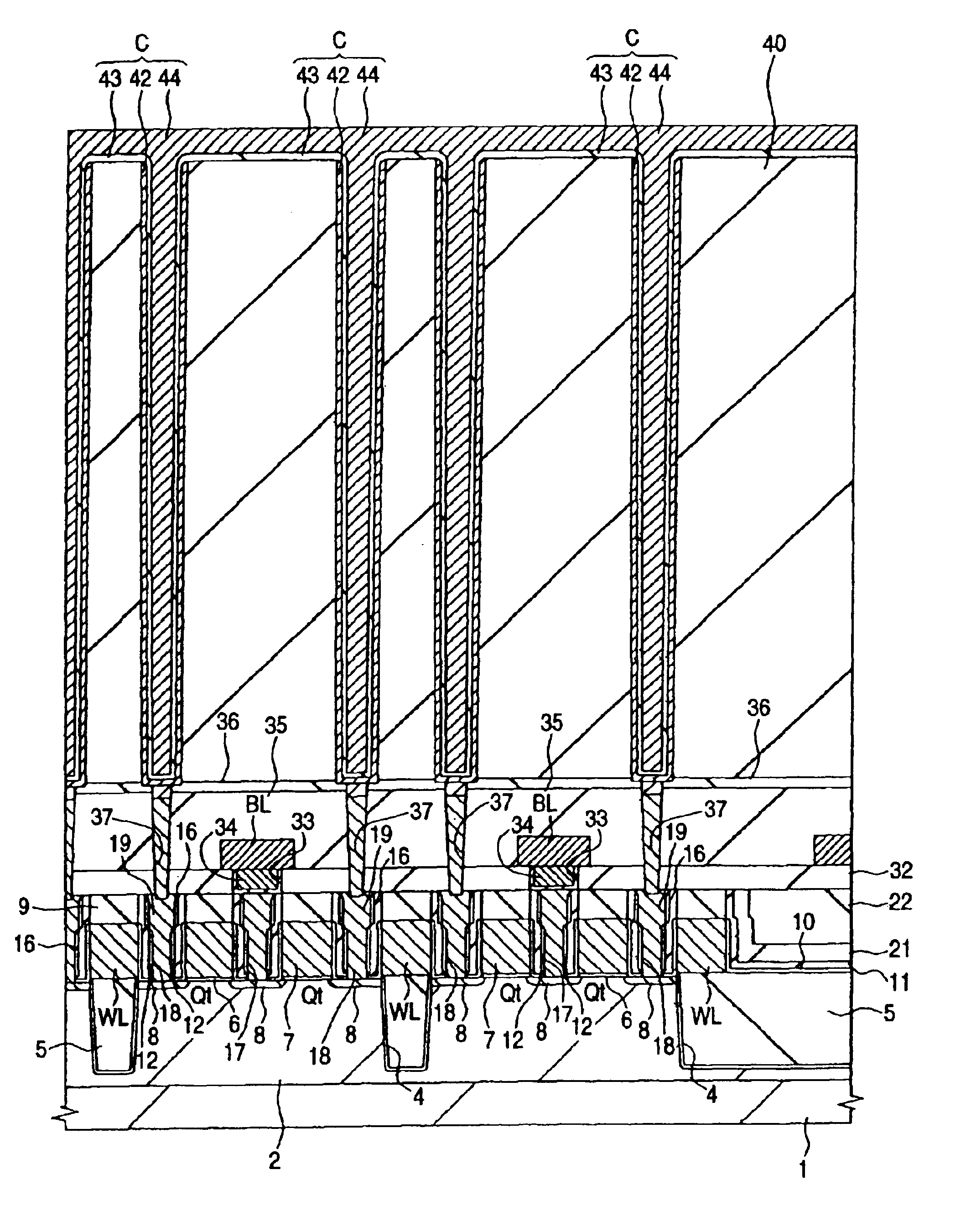

Method of producing a semiconductor integrated circuit device and the semiconductor integrated circuit device

InactiveUS6849885B2Layer can be damagedPrevent short-circuitingTransistorSemiconductor/solid-state device detailsSilicon oxideSemiconductor

An amount of a semiconductor substrate cut due to etching in the bottom of a contact hole formed by the SAC technique is reduced. Silicon oxide films are dry etched under the conditions of increasing the etching selective ratio of the silicon oxide films to an insulating film. Then, the conditions are changed to those increasing the etching selective ratio of the insulating film to the silicon oxide films and the insulating film is etched by a predetermined amount.

Owner:RENESAS ELECTRONICS CORP

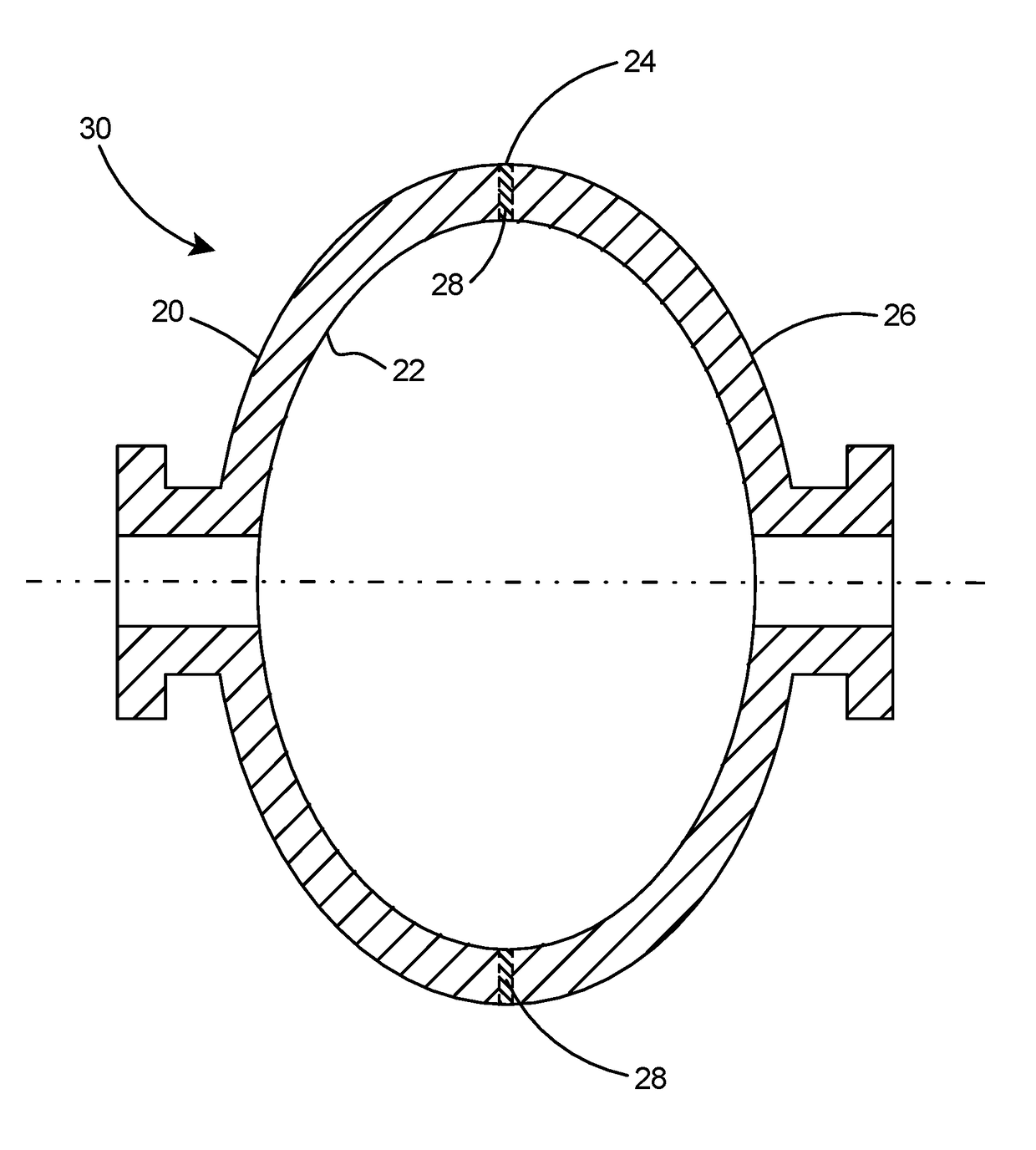

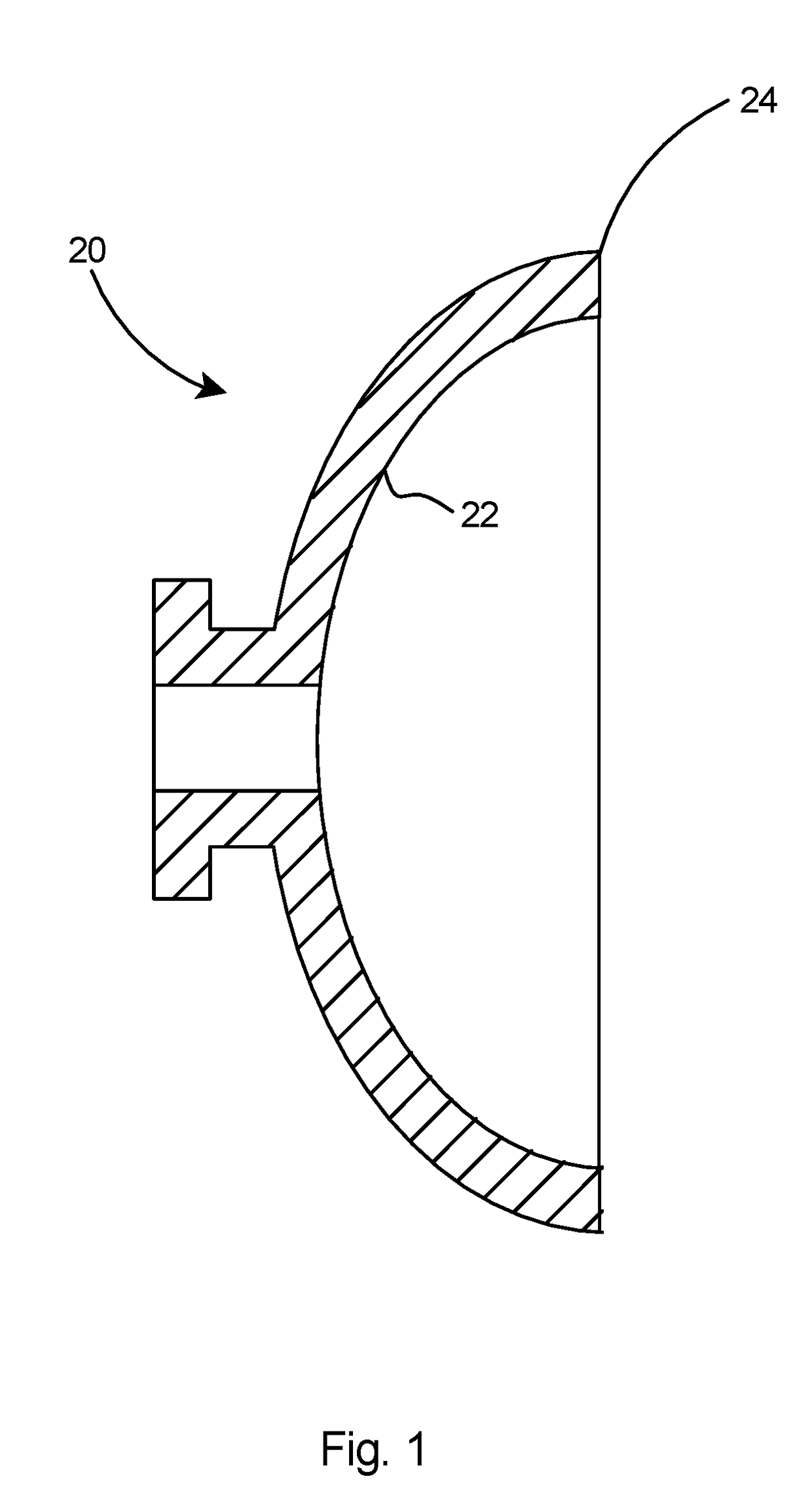

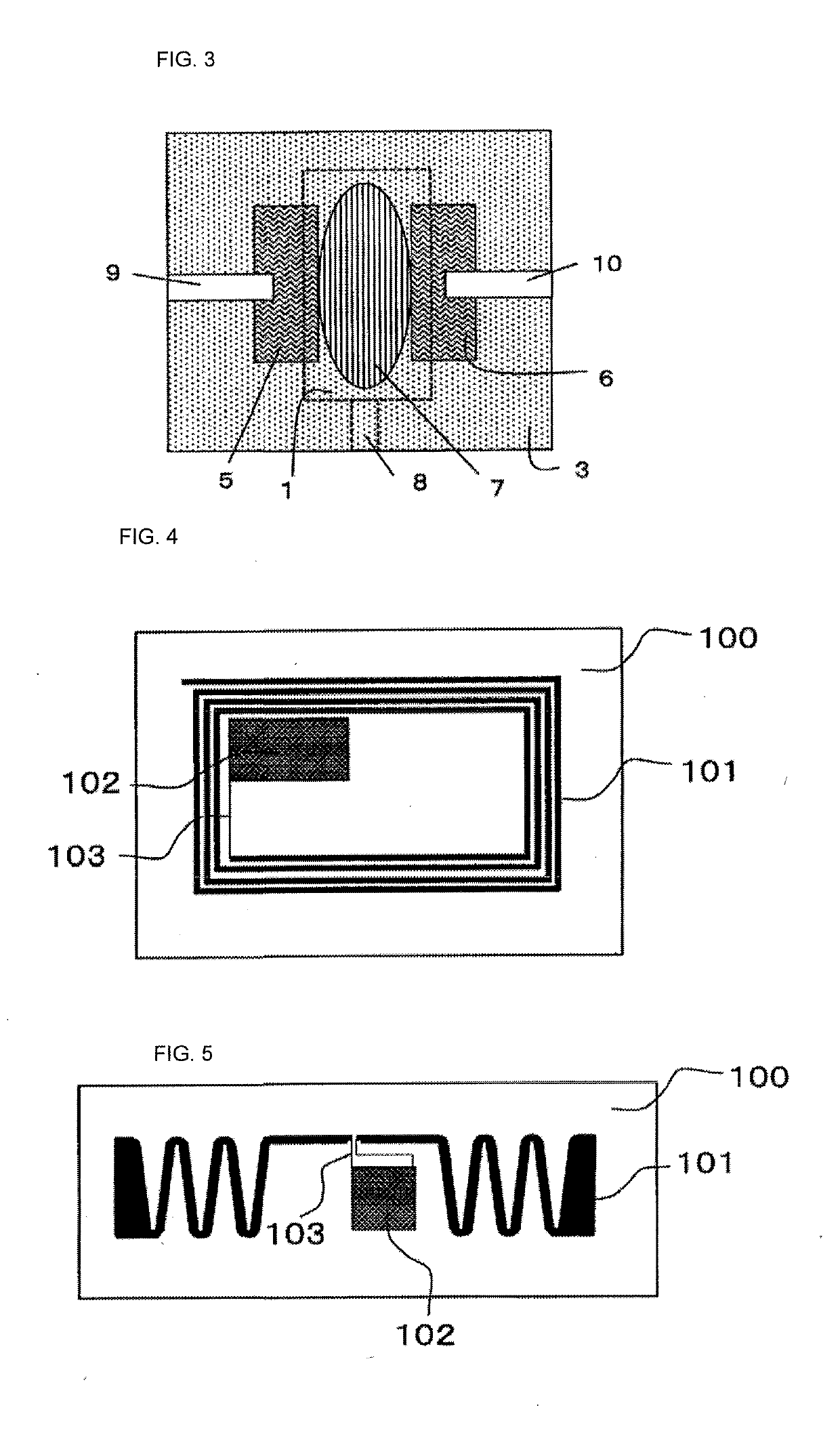

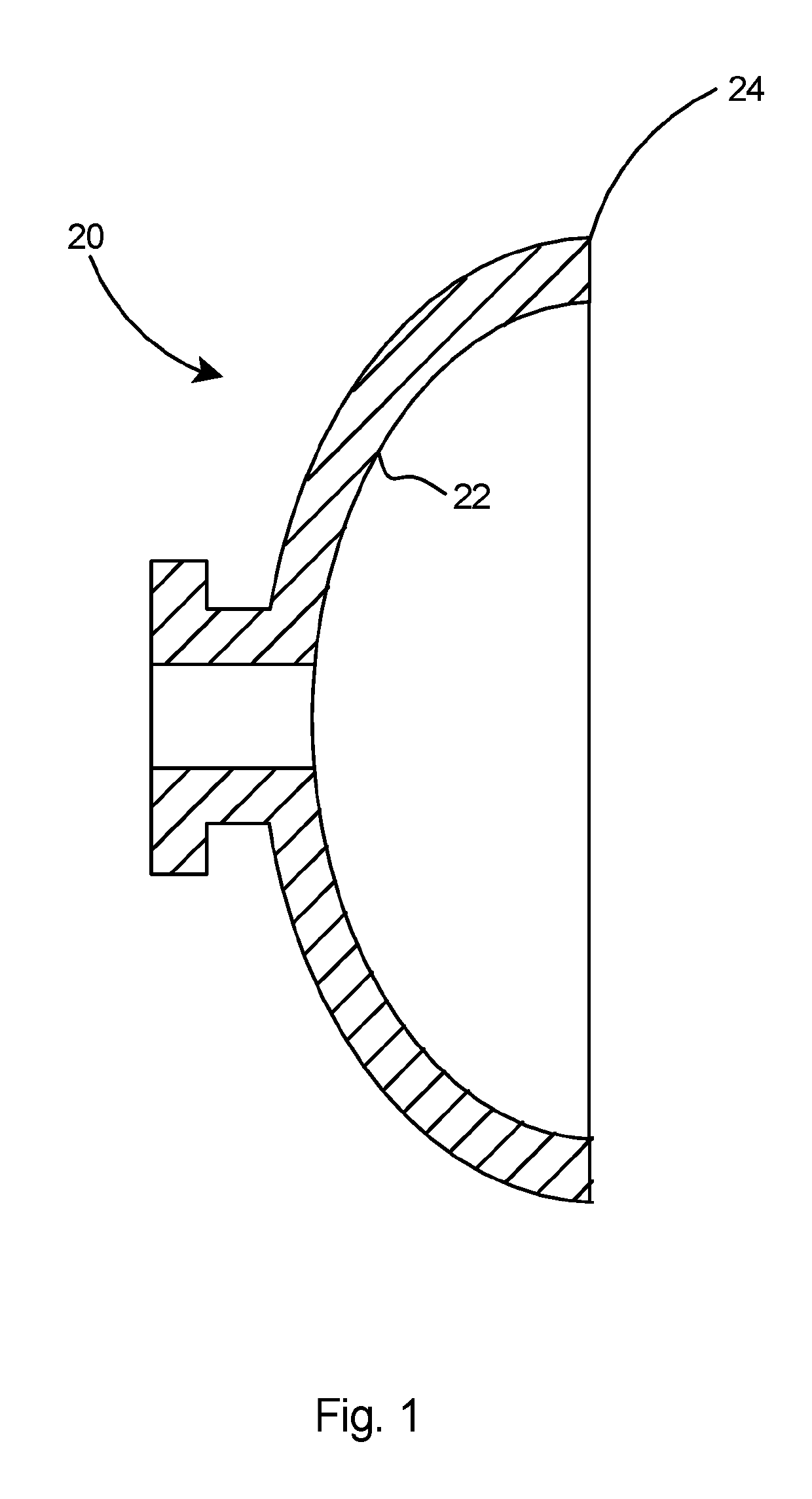

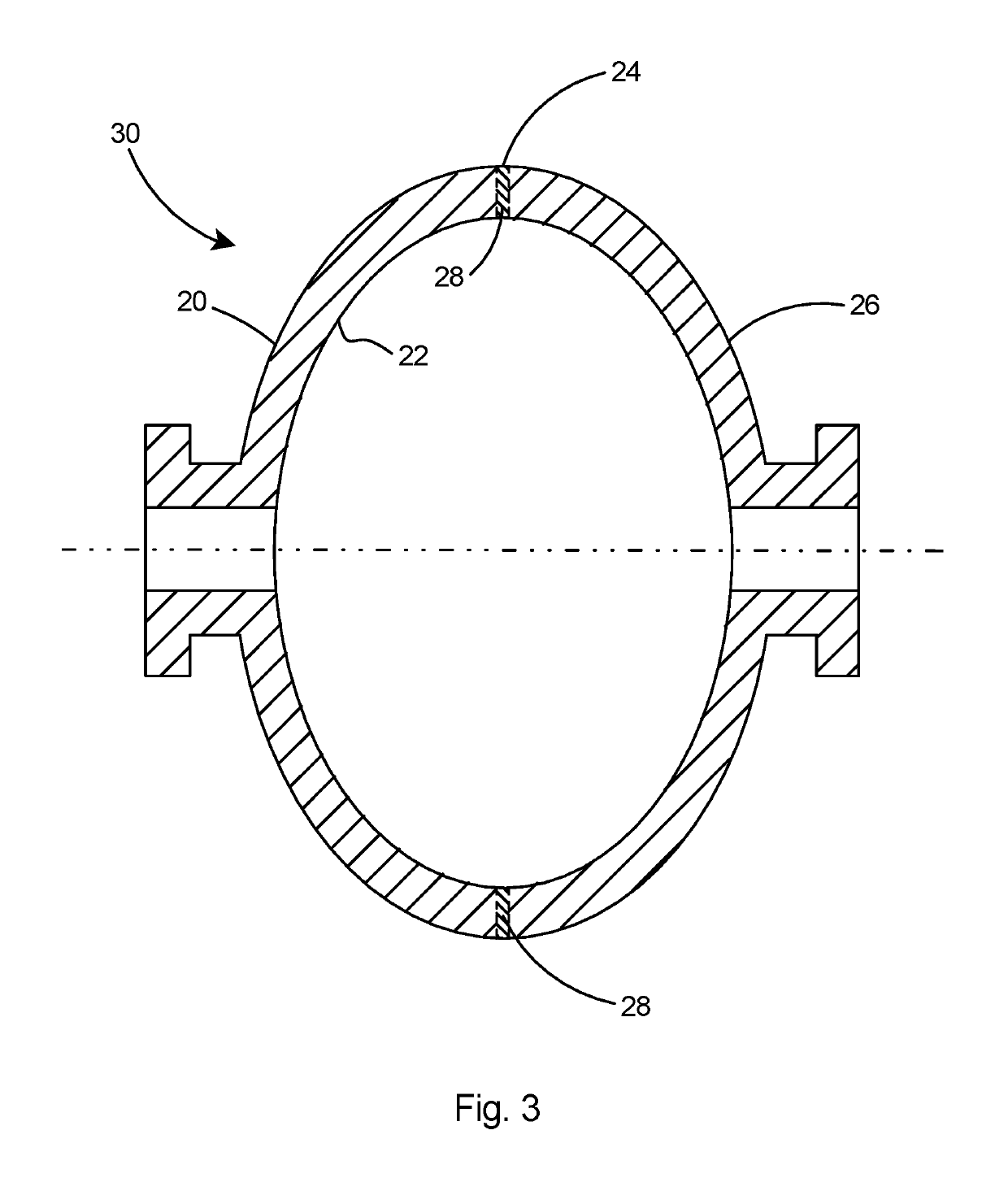

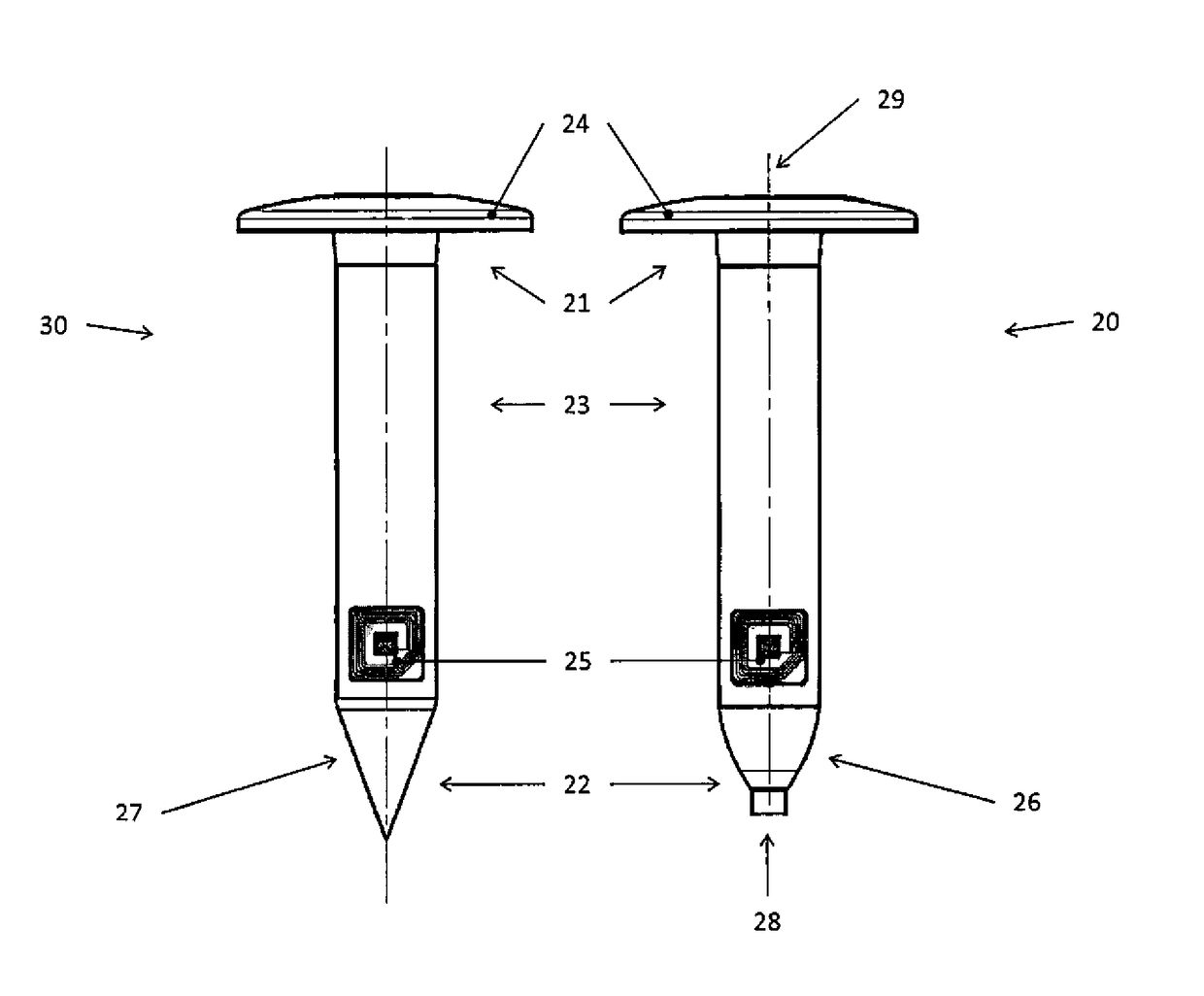

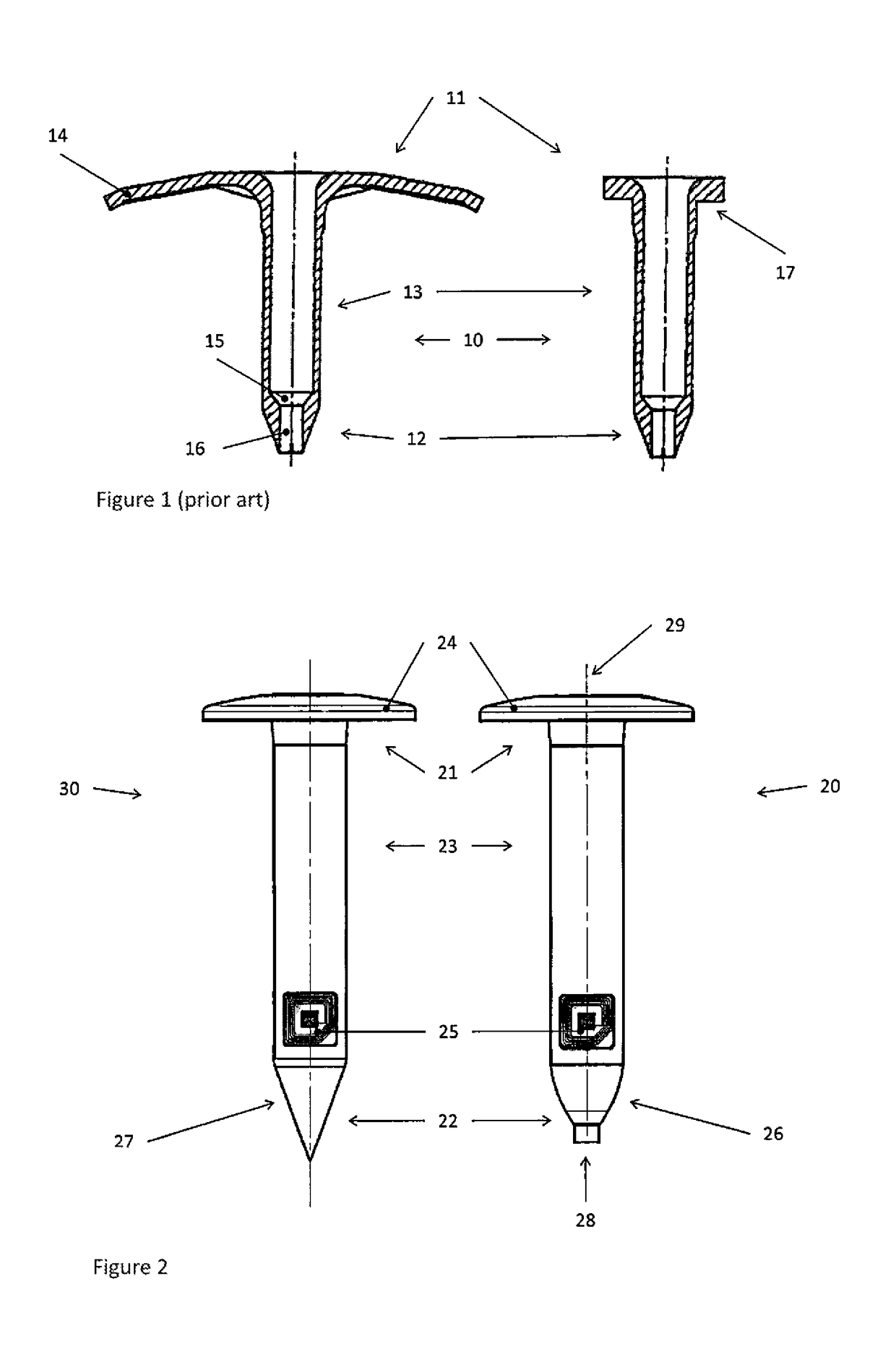

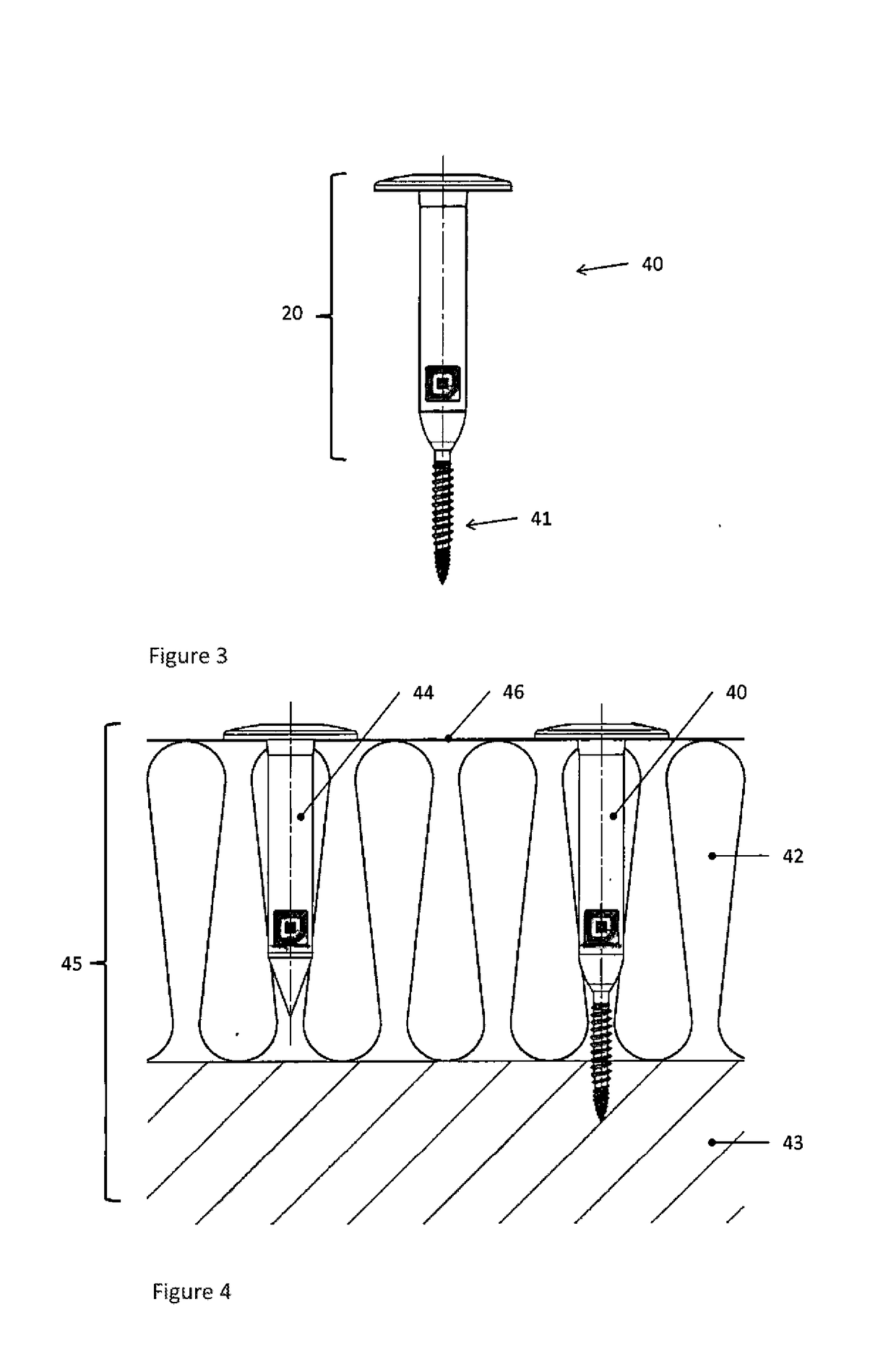

Sensor arrangement with RFID

ActiveUS20180240004A1Easy to receiveImprove transmission conditionsBuilding constructionsMeasurement apparatus housingsBiomedical engineeringBuilding envelope

A grommet (20, 30) as part of a fastening element for a building envelope essentially comprises a head (21), a tip (22) and a sleeve (23) therebetween, wherein the head (21) is essentially constructed as an extensive washer (24), the central hole of which is adjoined by the tubular sleeve (23). The tip (22) narrows essentially in a conical or tapered manner to a smaller diameter. The grommet (20, 30) has a sensor arrangement (25), with at least one RFID transponder with antenna and a sensor operatively connected to the transponder.

Owner:SFS GRP INT AG

Display substrate and method of manufacturing the same

ActiveUS9099413B2Prevent and reduce voltage dropLayer can be damagedSemiconductor/solid-state device testing/measurementElectroluminescent light sourcesTransmittanceEngineering

Owner:SAMSUNG DISPLAY CO LTD

Manufacturing method for array substrate

InactiveUS20190013334A1Improve device performanceImprove performanceTransistorSolid-state devicesIndiumZinc tin oxide

The present disclosure discloses a method for manufacturing an array substrate comprising: forming a gate electrode on a substrate; forming a gate insulating layer on one side of the substrate facing the gate electrode, the gate insulating layer covering the gate electrode; depositing an indium gallium zinc tin oxide layer and an indium gallium zinc oxide layer on one side of the gate insulating layer away from the gate electrode; patterning the indium gallium zinc oxide layer and the indium gallium zinc tin oxide layer by a first yellow light process to form a protective layer and an active layer, the protective layer covering the active layer; depositing a metal layer on one side of the protective layer away from the active layer; and patterning the metal layer and the protective layer by a second yellow light process to form a source electrode, a drain electrode, and a separation region.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Grinding/electrolysis combined multi-wire-slicing processing method for silicon wafers

InactiveUS8747625B2Reduce probabilityImprove slicing efficiencyElectrolysis componentsSemiconductor/solid-state device manufacturingElectrolysisPulsed DC

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Method of manufacturing semiconductor device

InactiveUS7648920B2Low reliabilityAdhesionSemiconductor/solid-state device manufacturingElectrical conductorSilanes

A method of manufacturing a semiconductor device includes the steps of: forming recesses (a via hole and wiring grooves) in a insulation film; forming a seal layer on inside surfaces of the recesses by using a gas based on a silane having an alkyl group as a precursor; applying EB-cure or UV-cure to the seal layer; and filling up the recesses with a conductor.

Owner:SONY CORP