Patents

Literature

83results about How to "Inhibits the formation of defects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

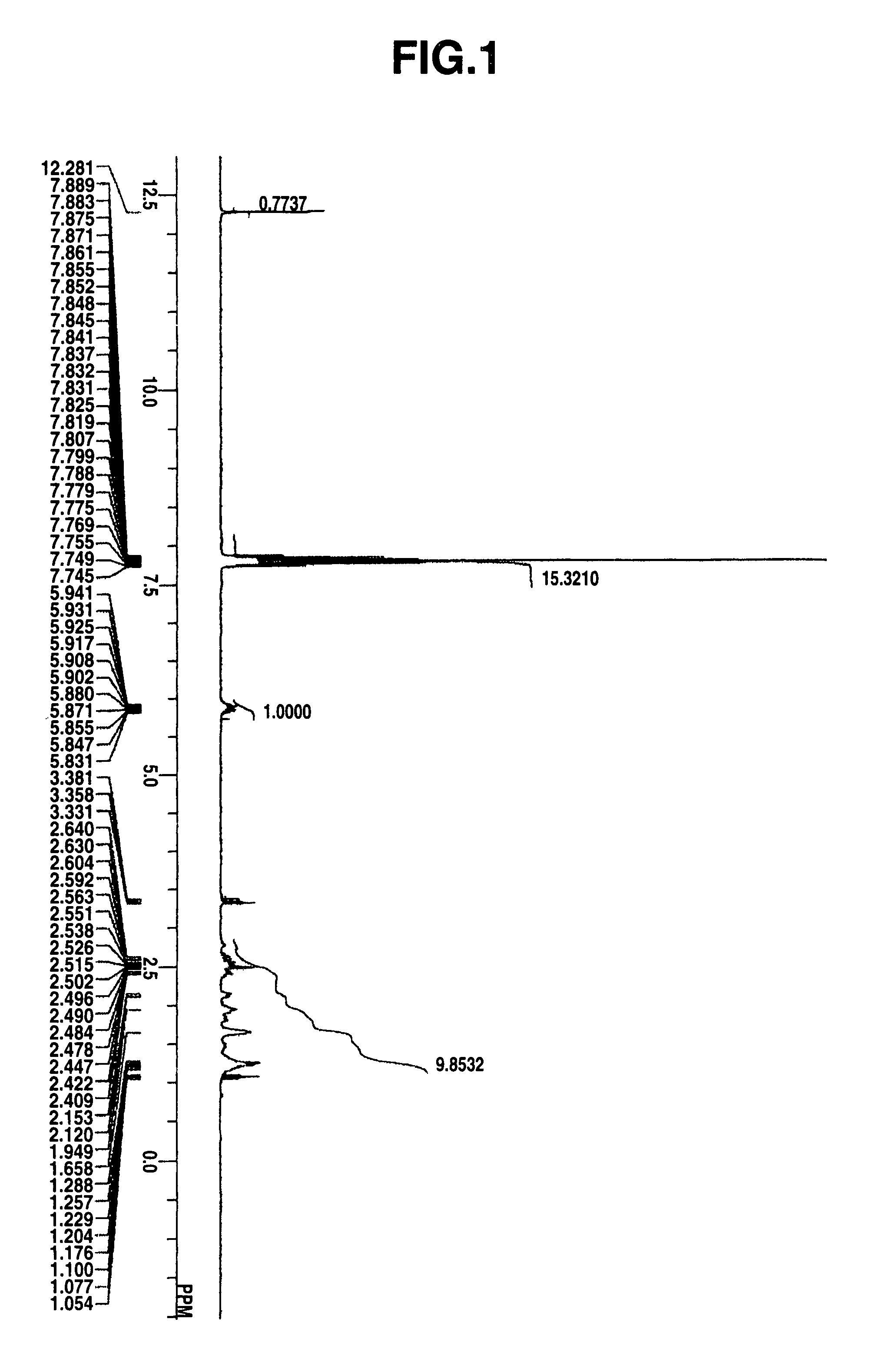

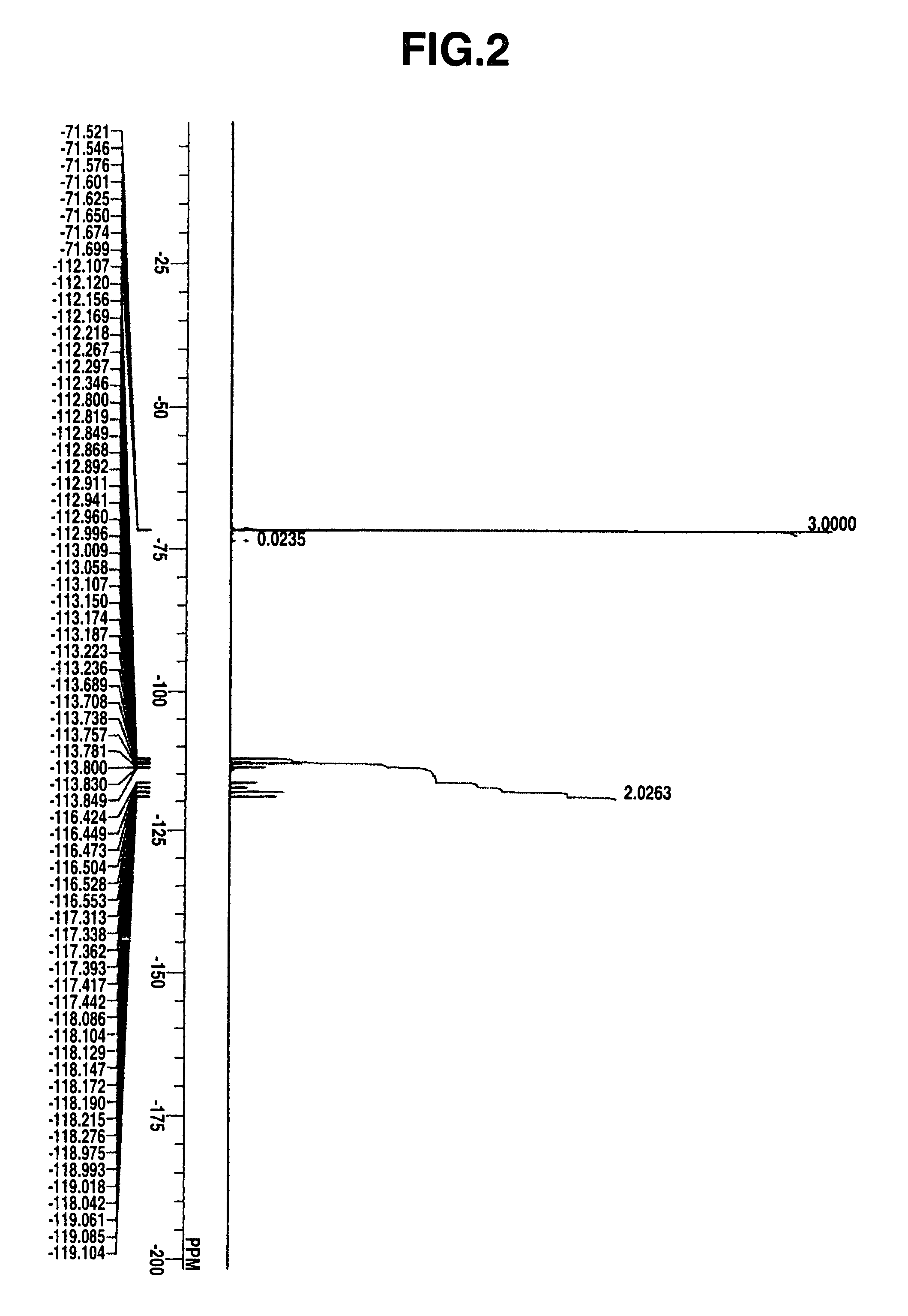

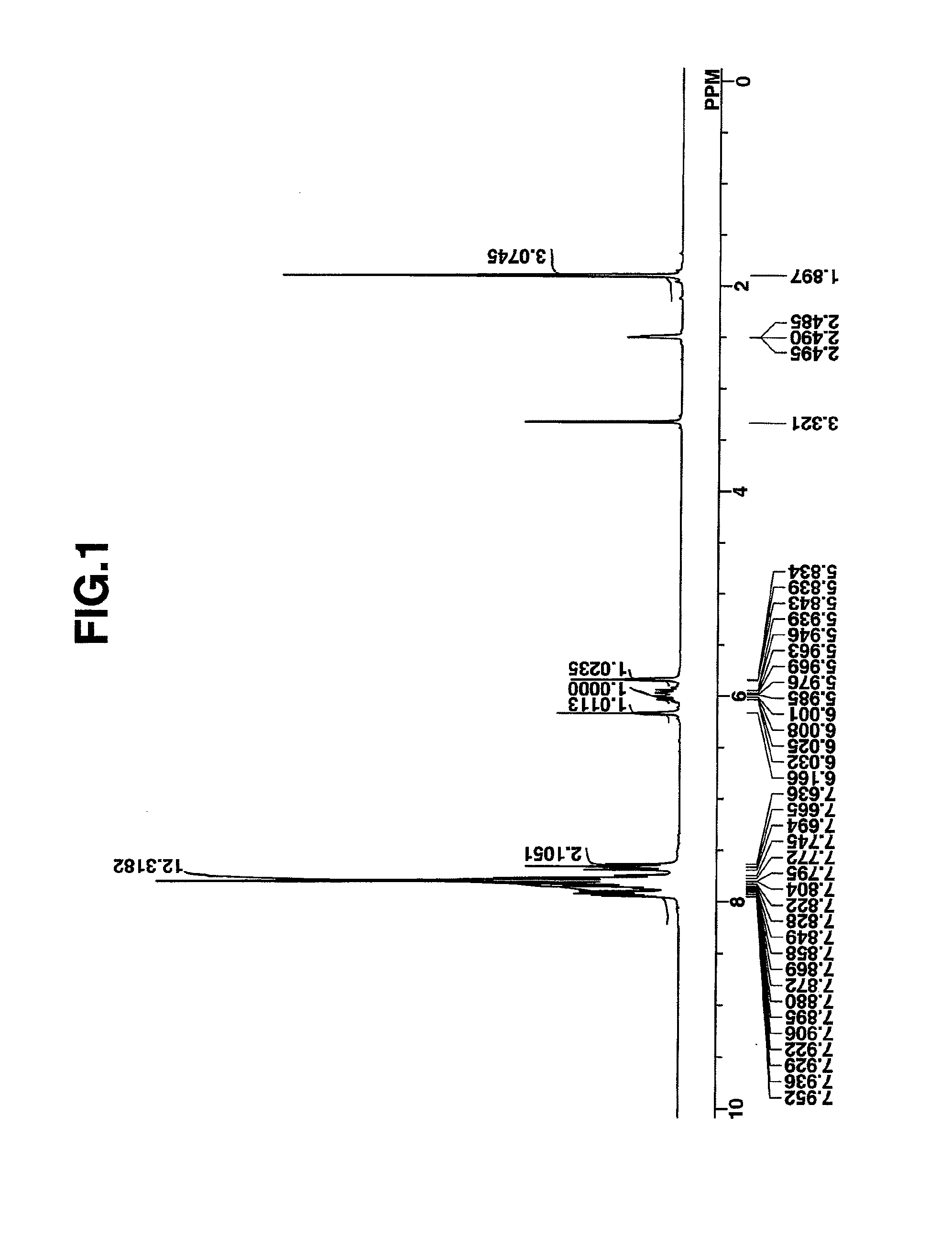

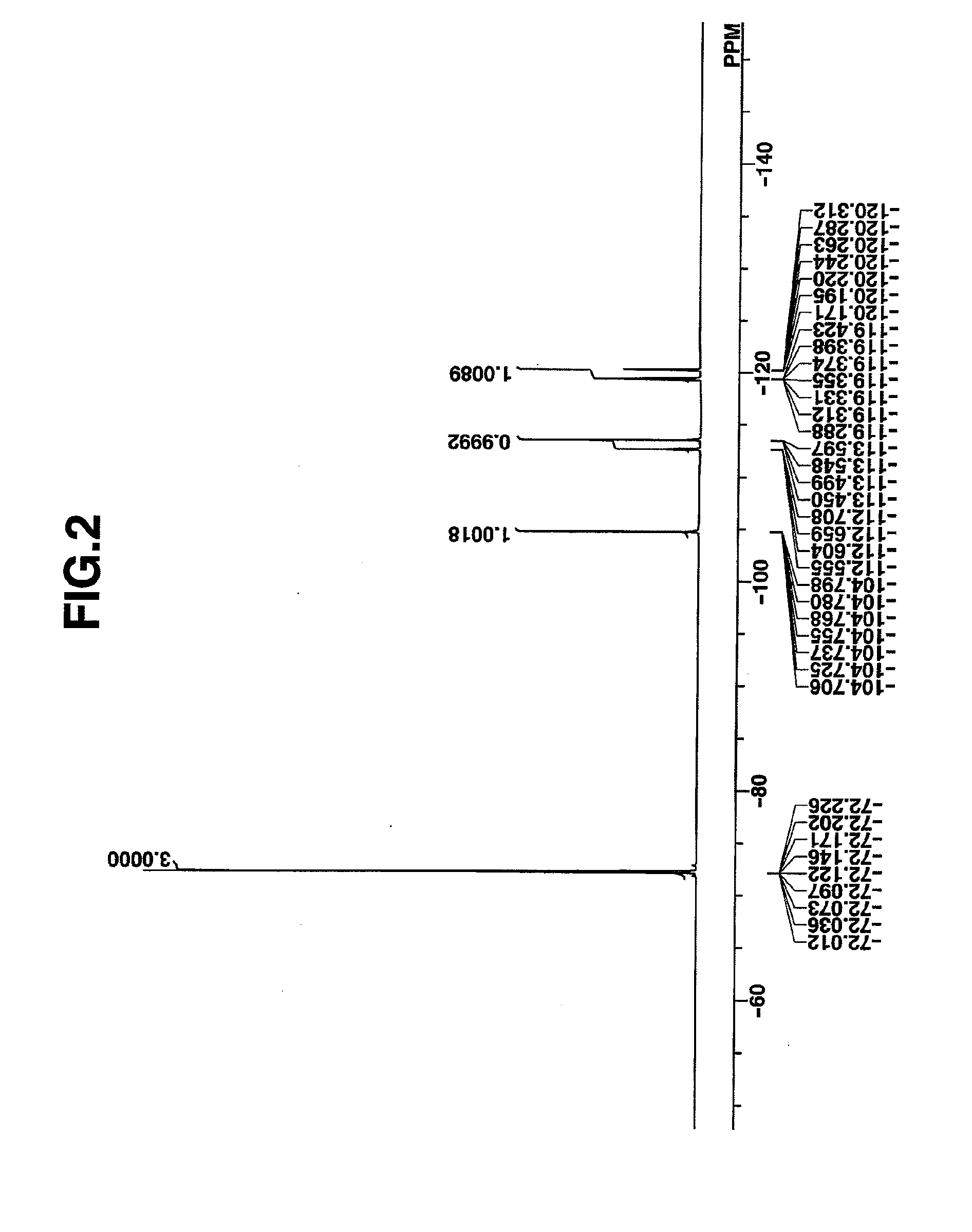

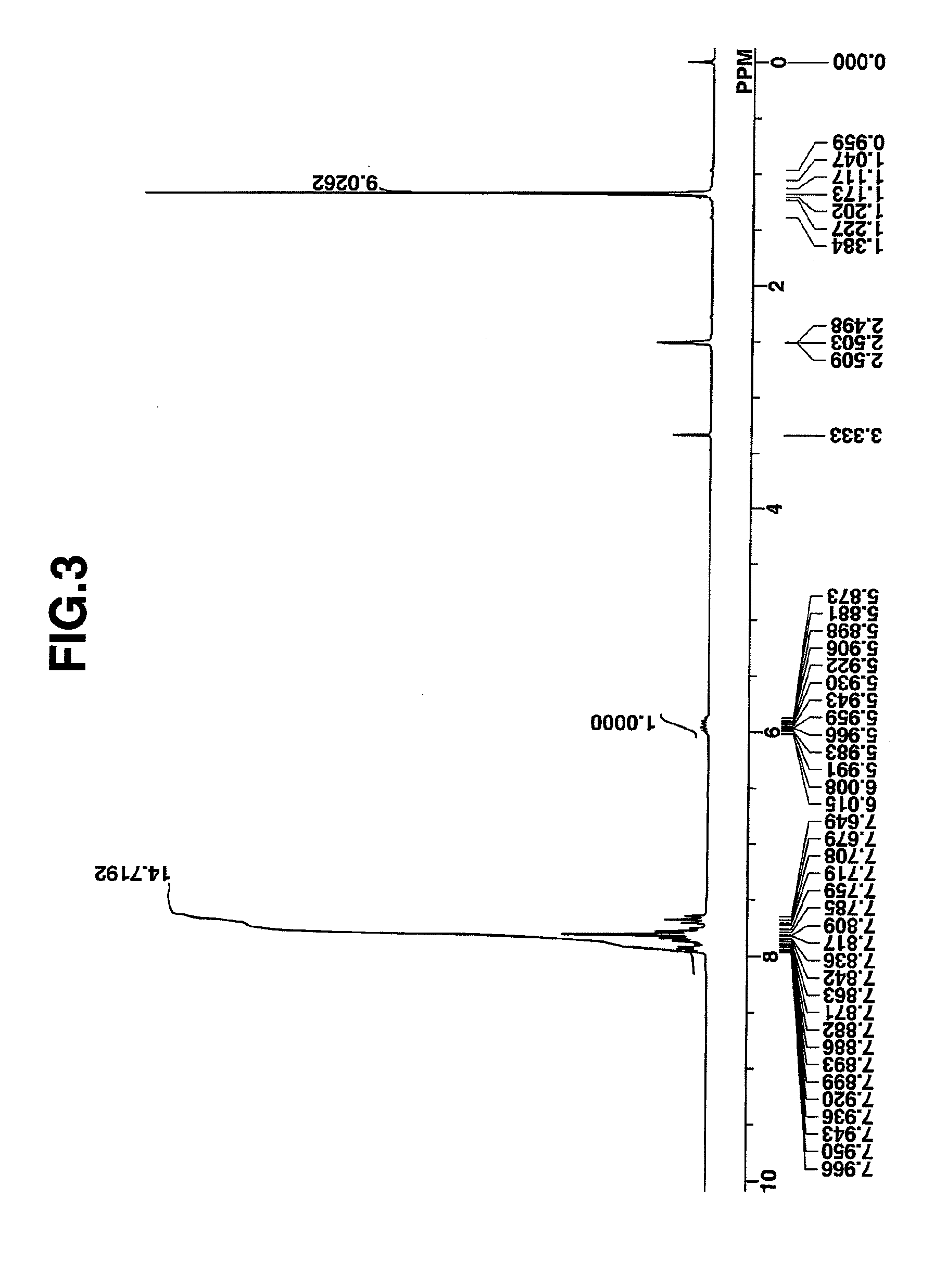

Sulfonium salt having polymerizable anion, polymer, resist composition, and patterning process

ActiveUS20080102407A1Feature size of to decreaseSmall feature sizeOrganic chemistryPhotosensitive materialsResistHigh energy

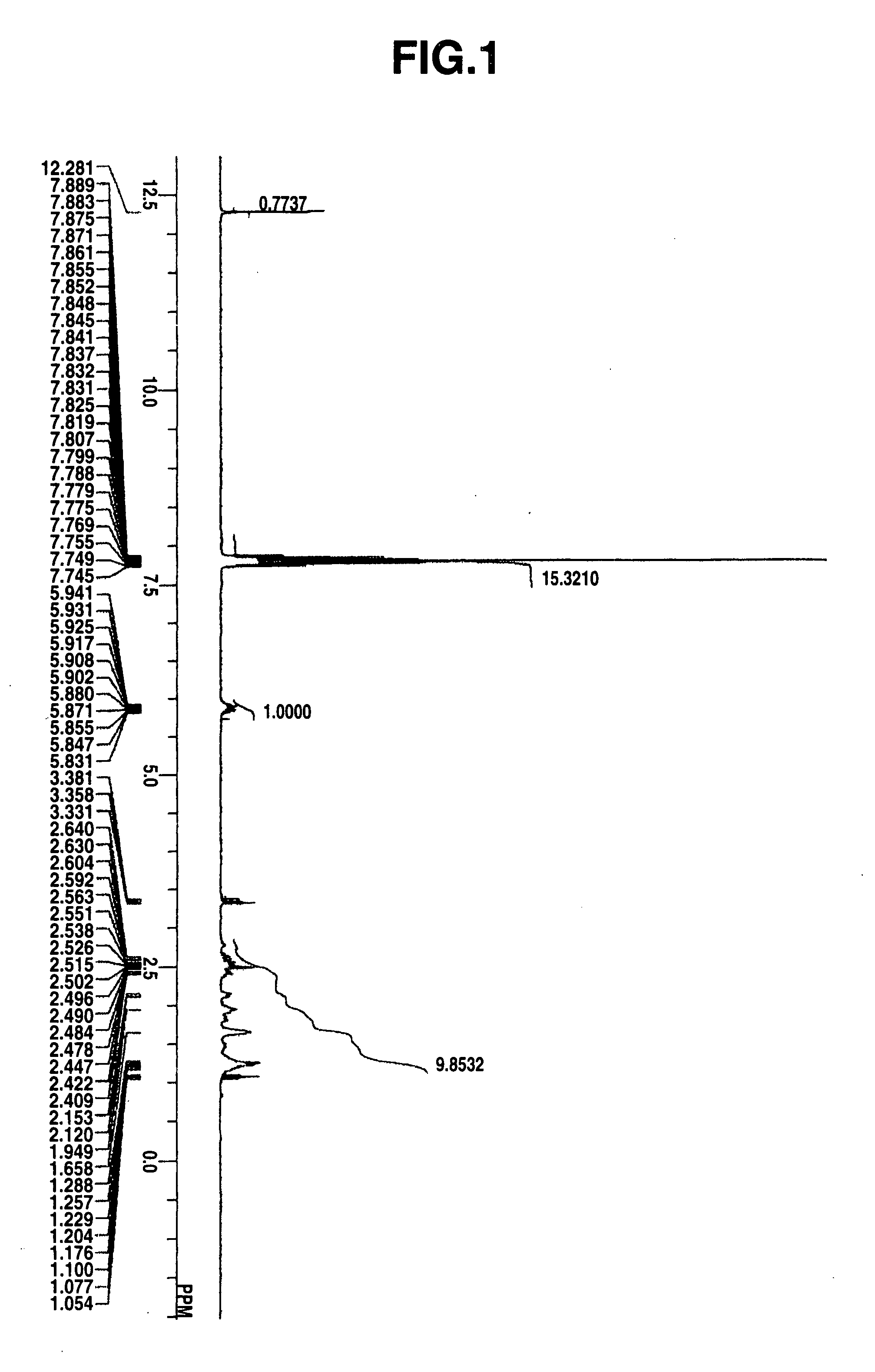

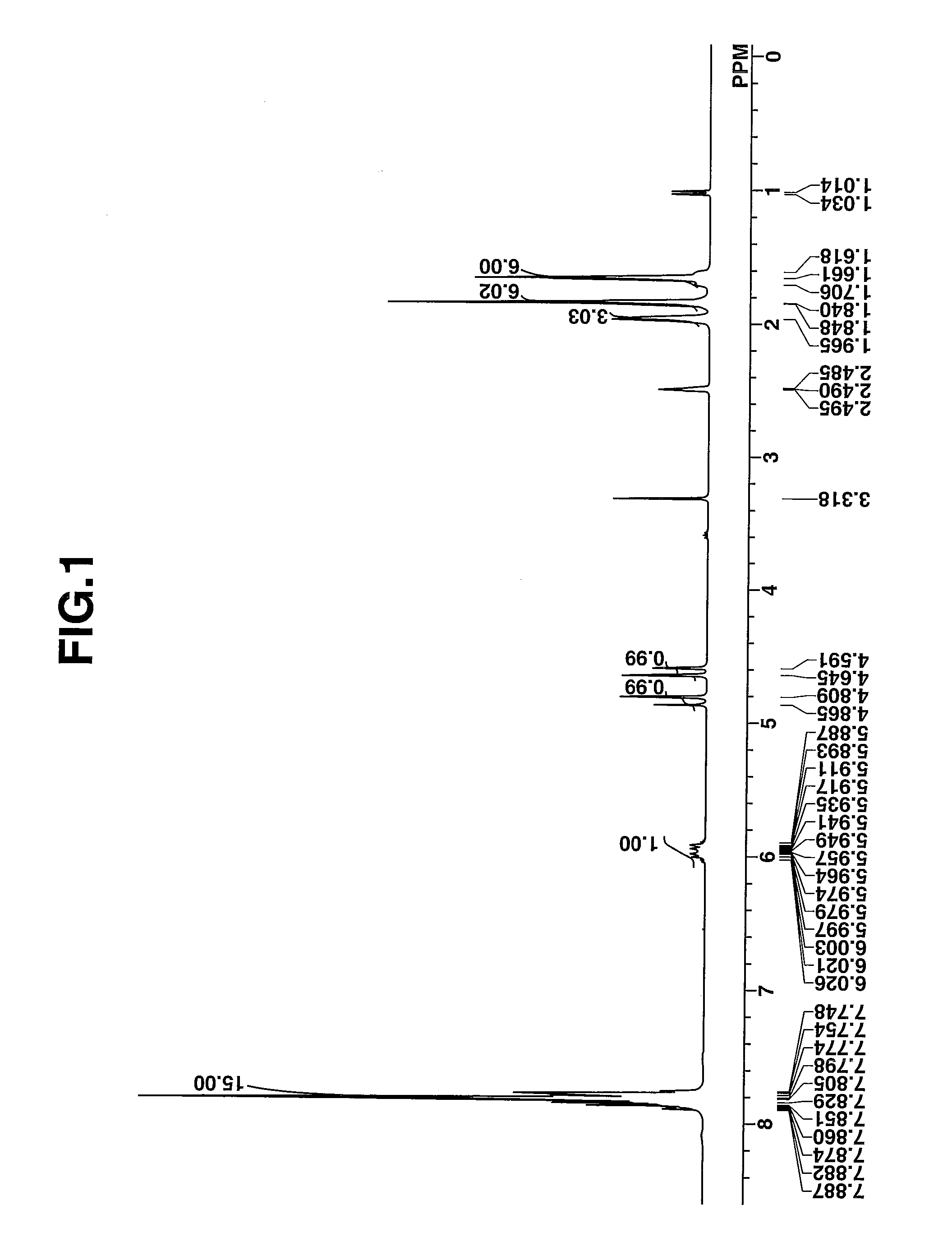

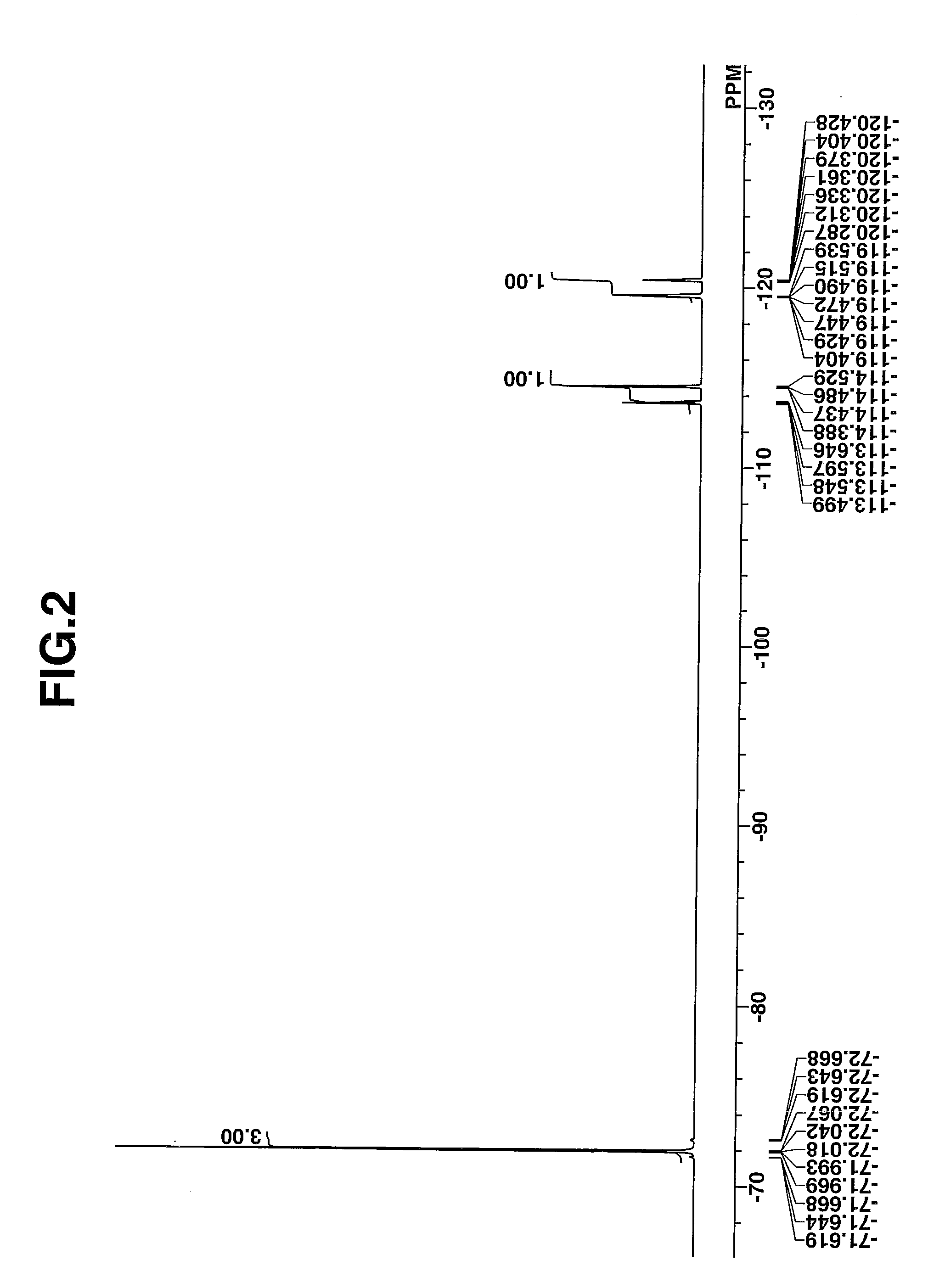

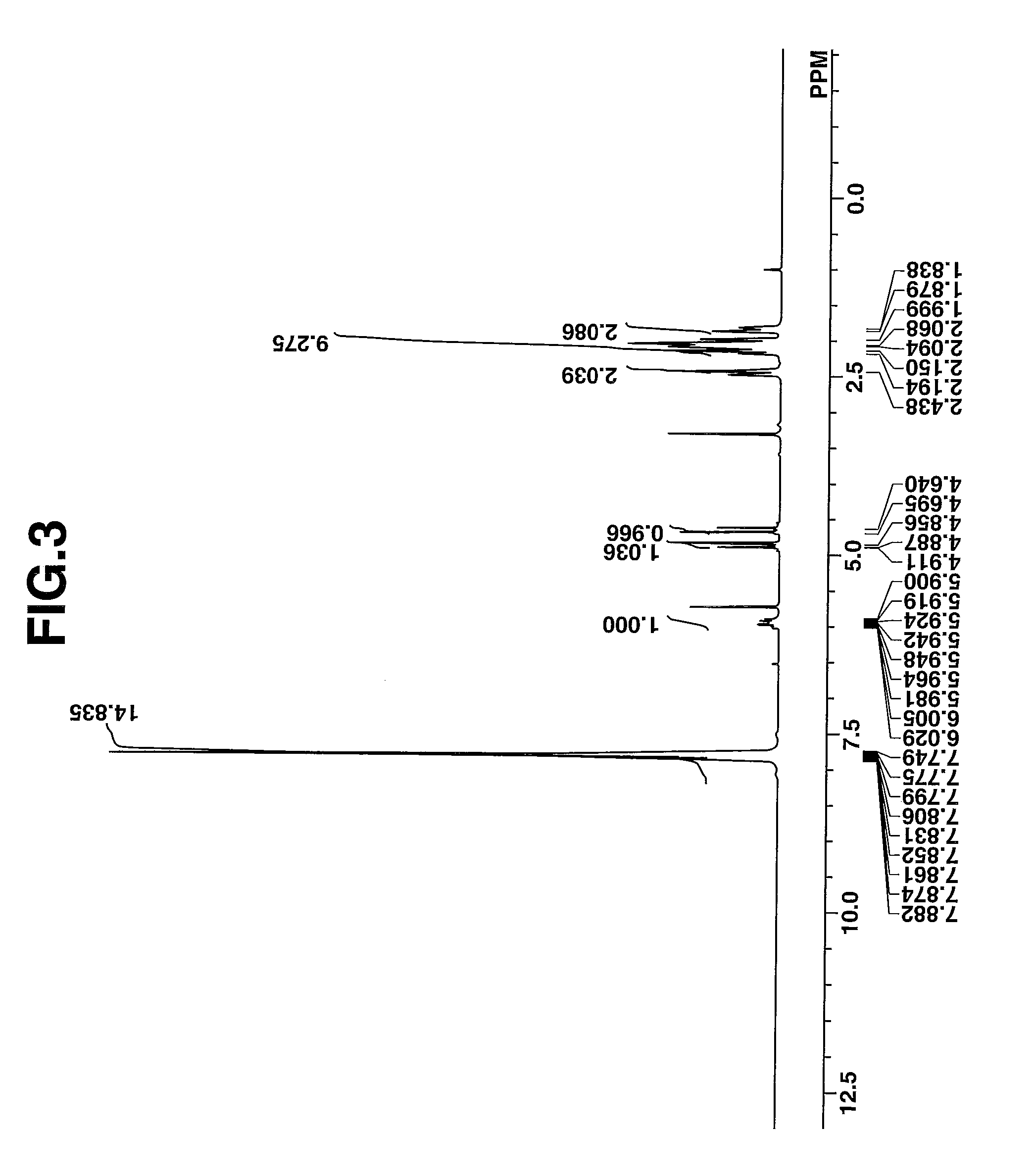

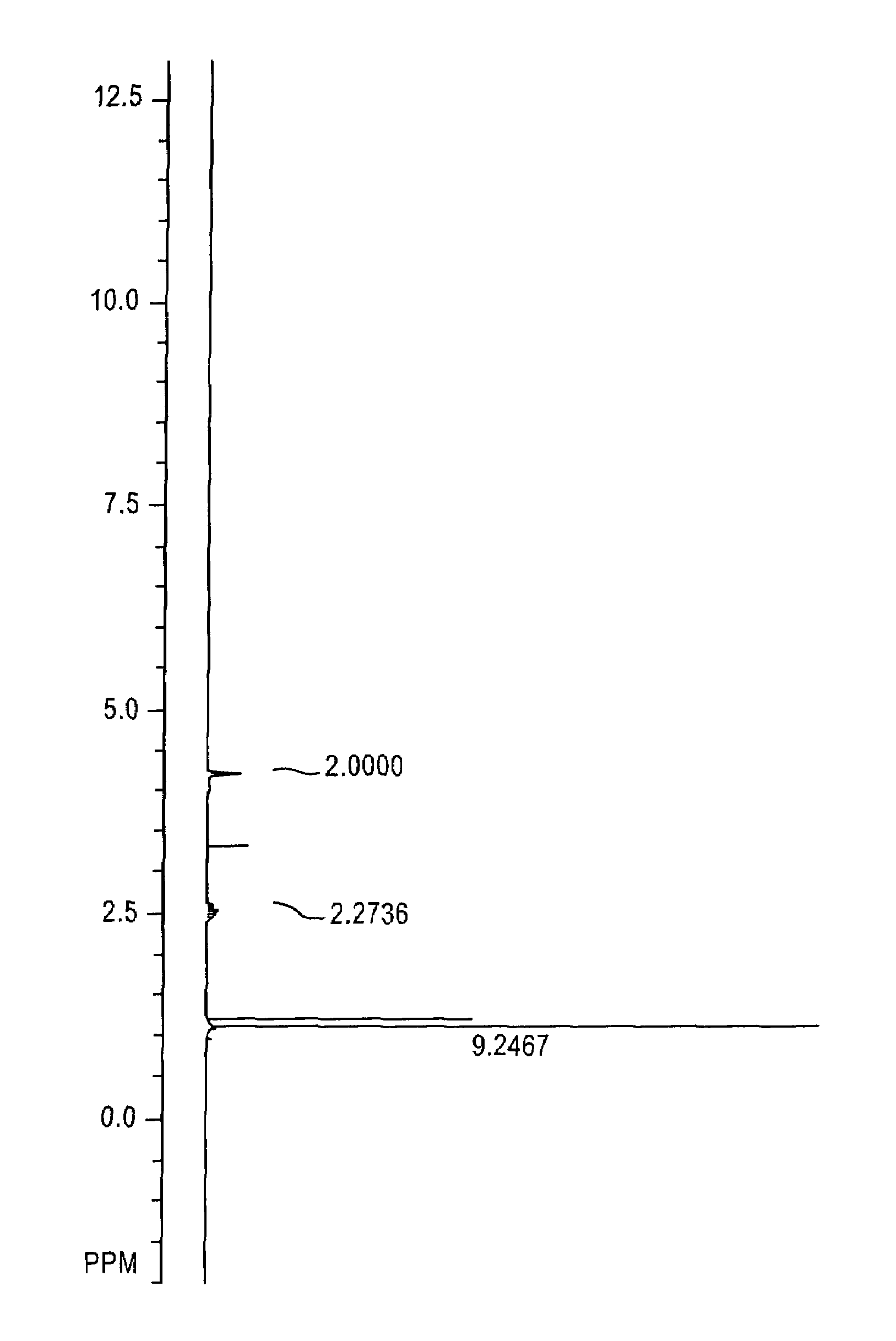

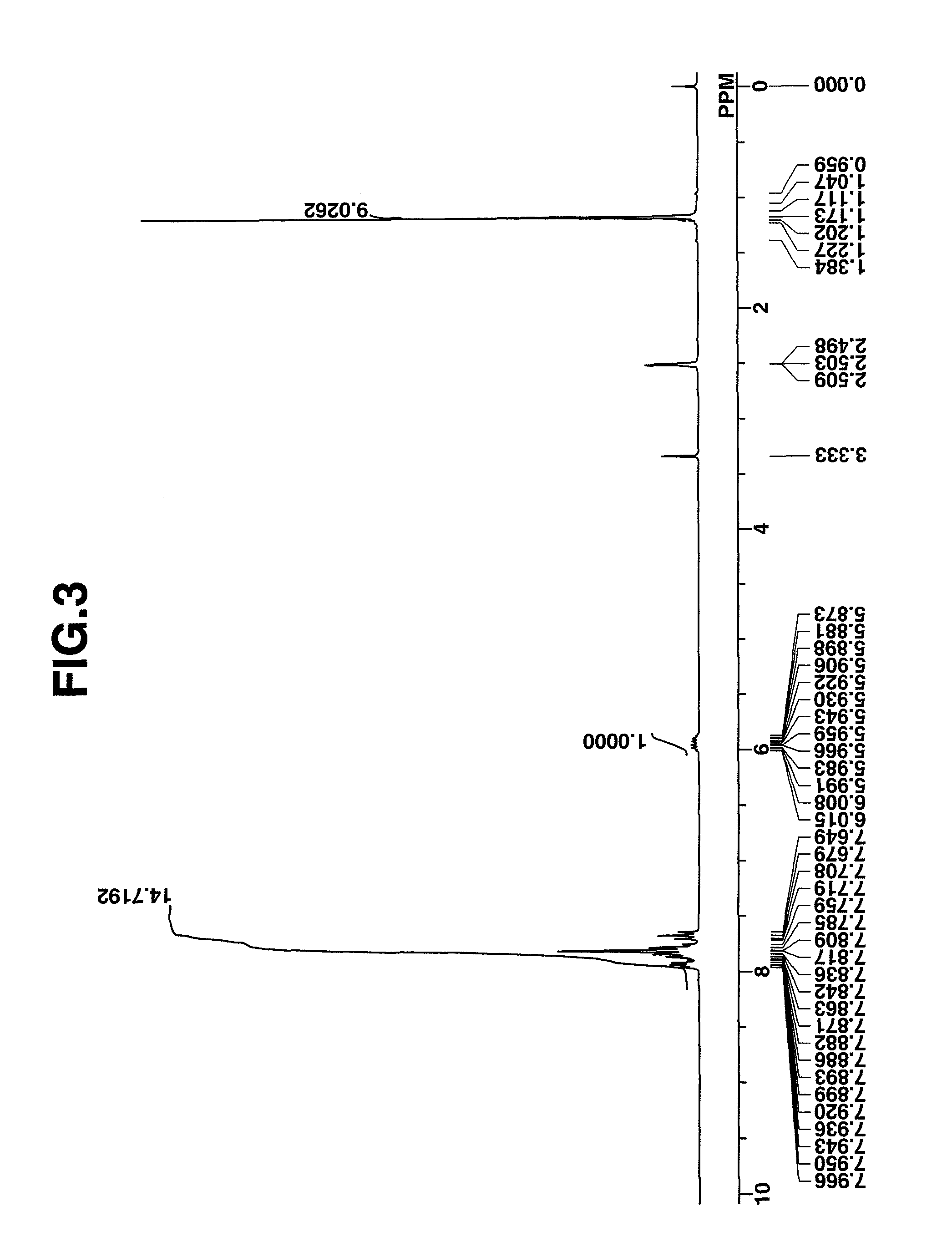

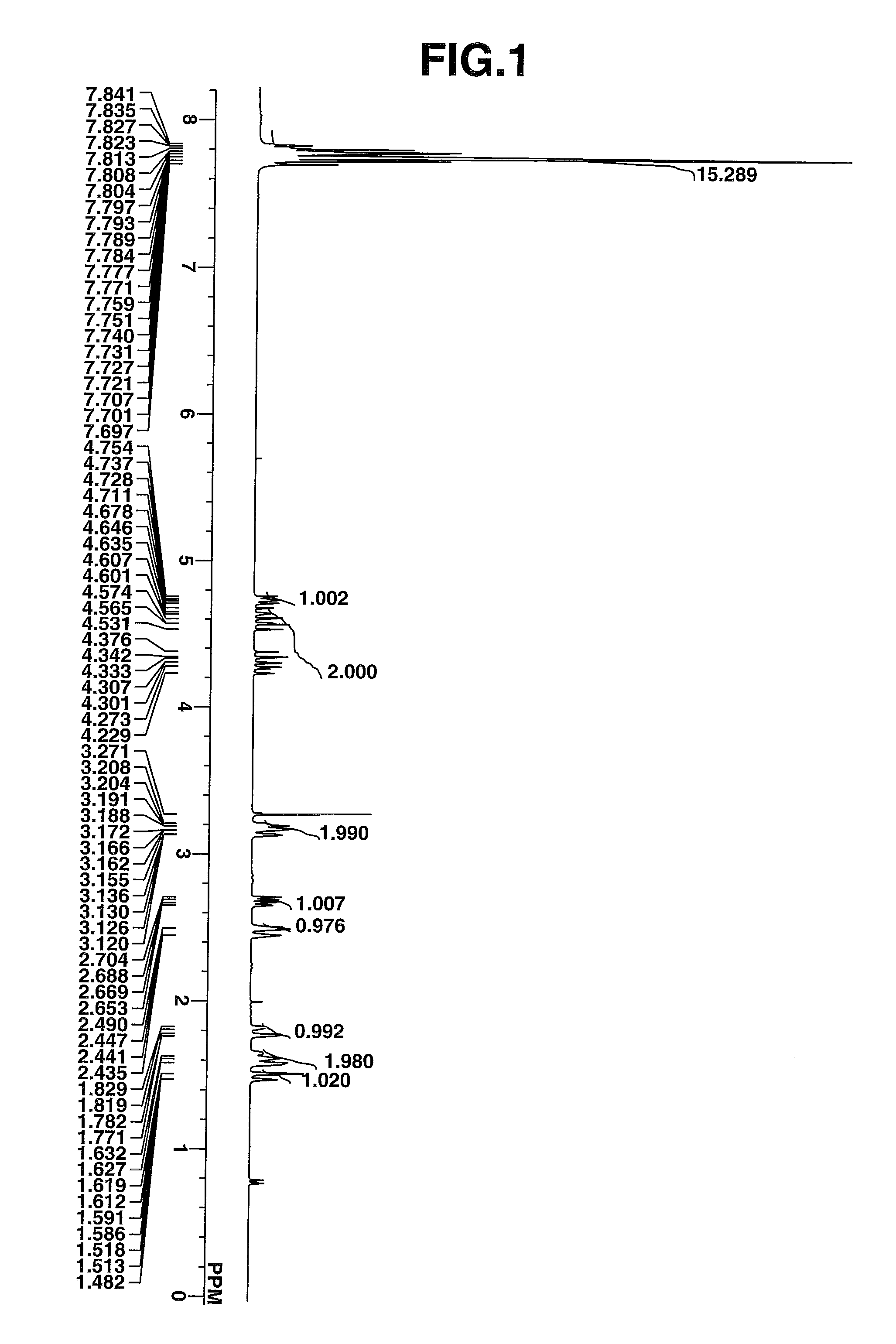

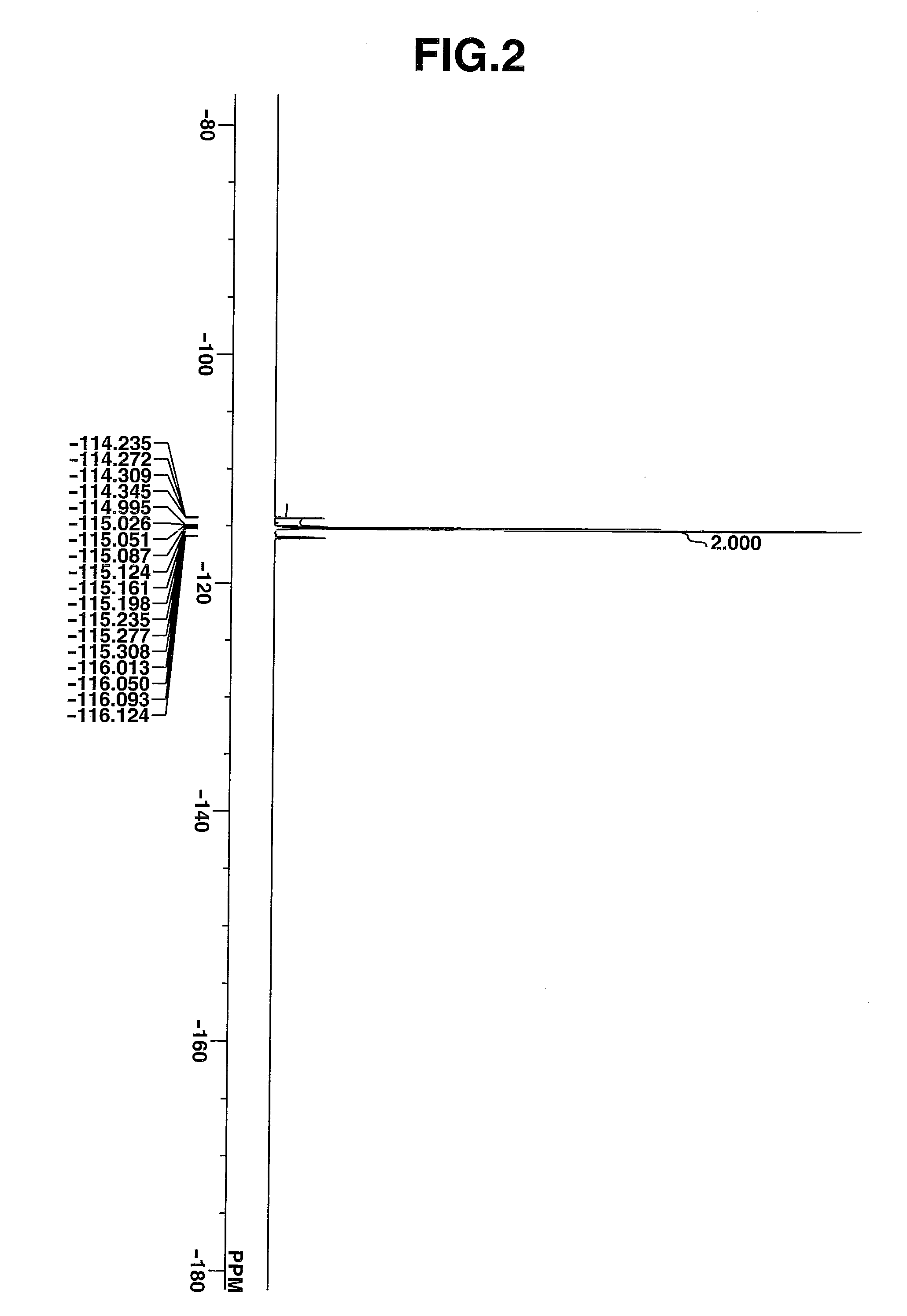

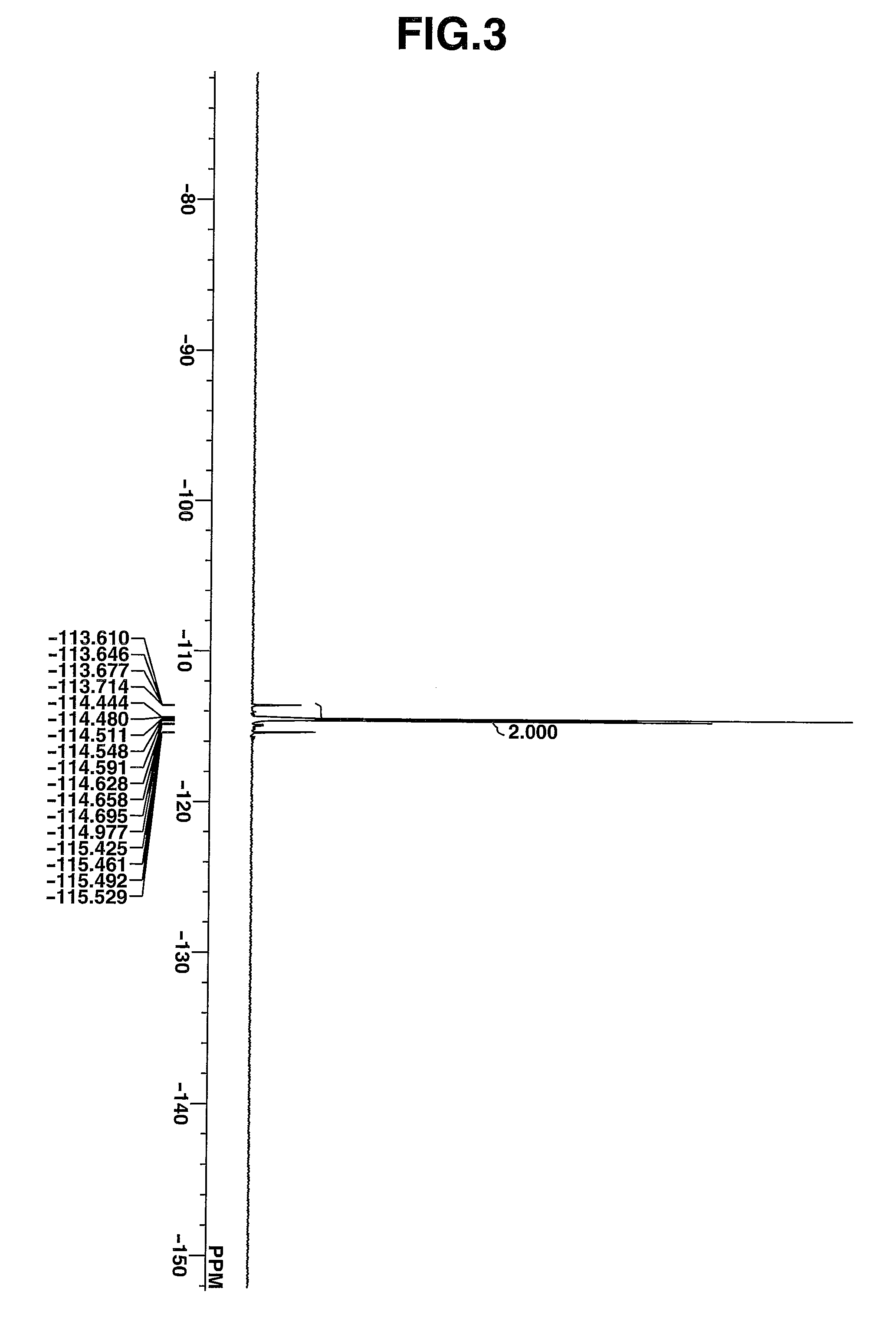

A sulfonium salt having a polymerizable anion generates a strong sulfonic acid upon exposure to high-energy radiation so that it facilitates effective scission of acid labile groups in chemically amplified resist compositions. It is useful as a monomer from which a base resin for use in radiation-sensitive resist compositions is derived.

Owner:SHIN ETSU CHEM IND CO LTD

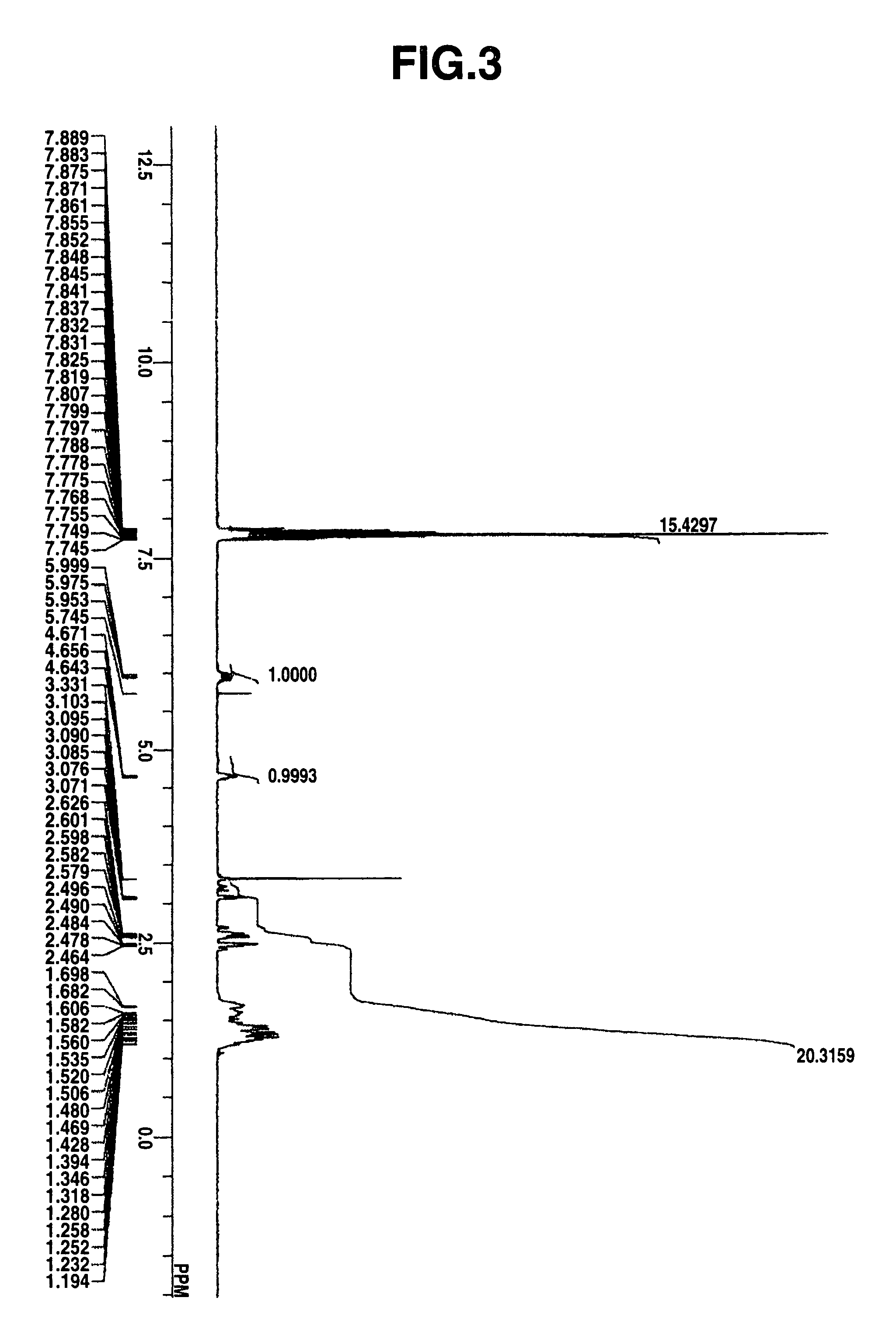

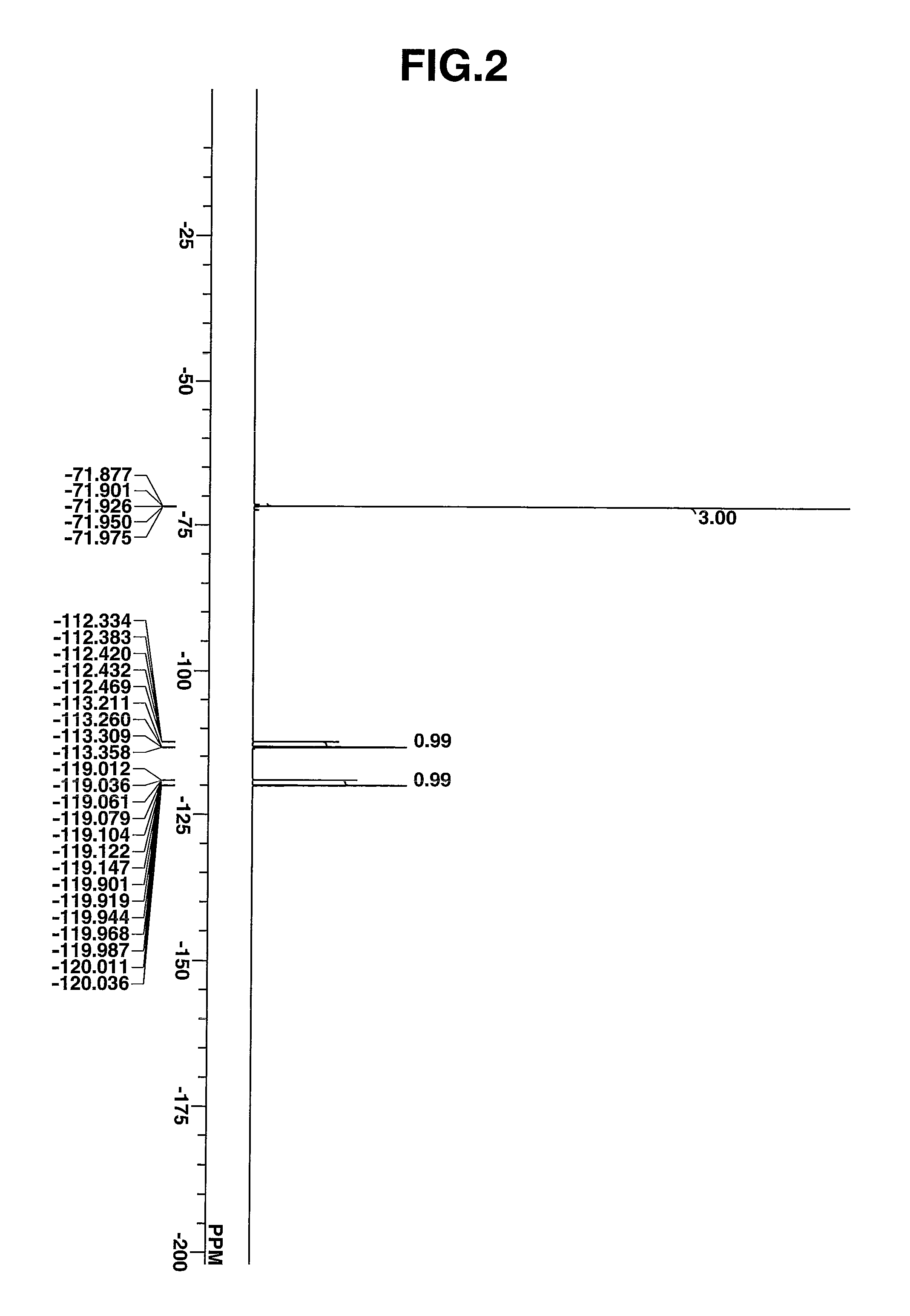

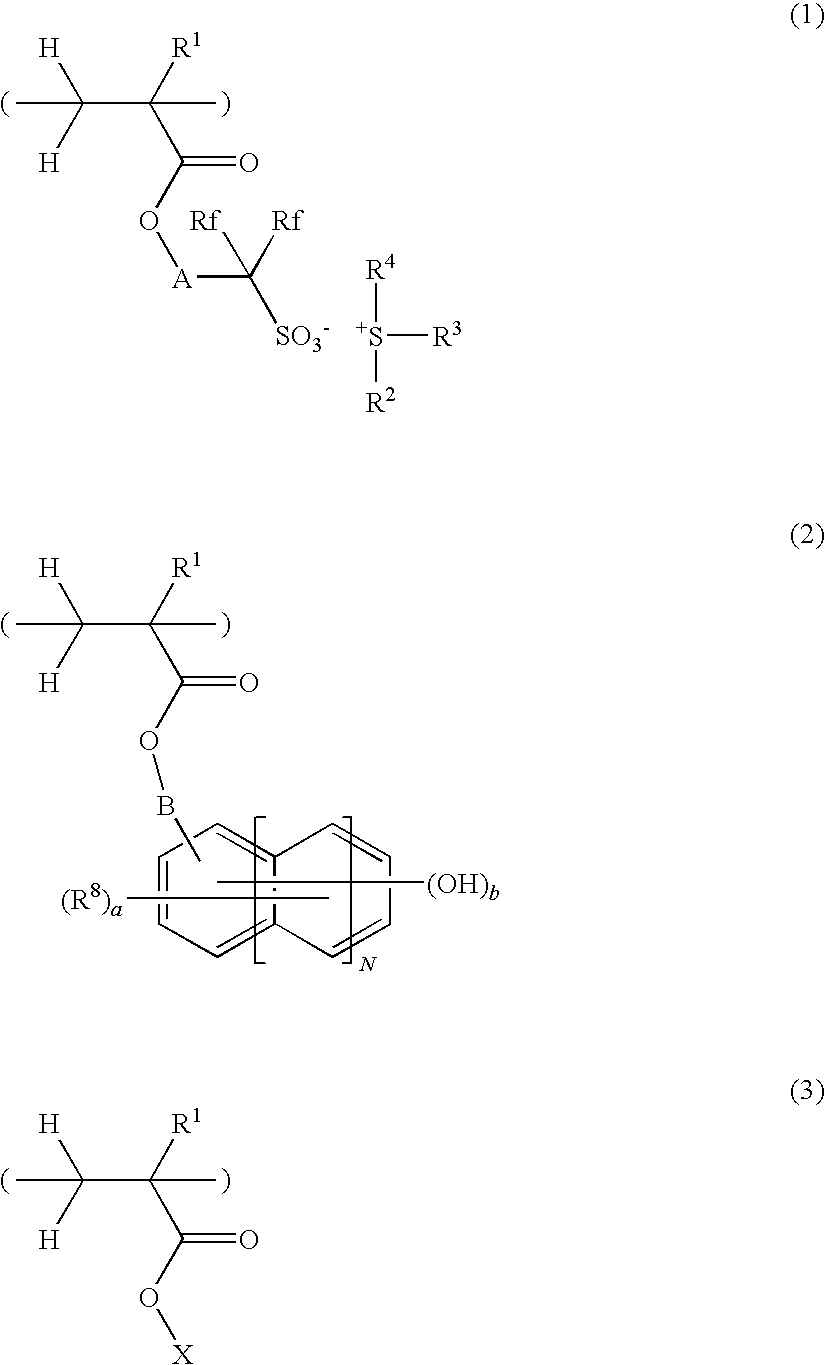

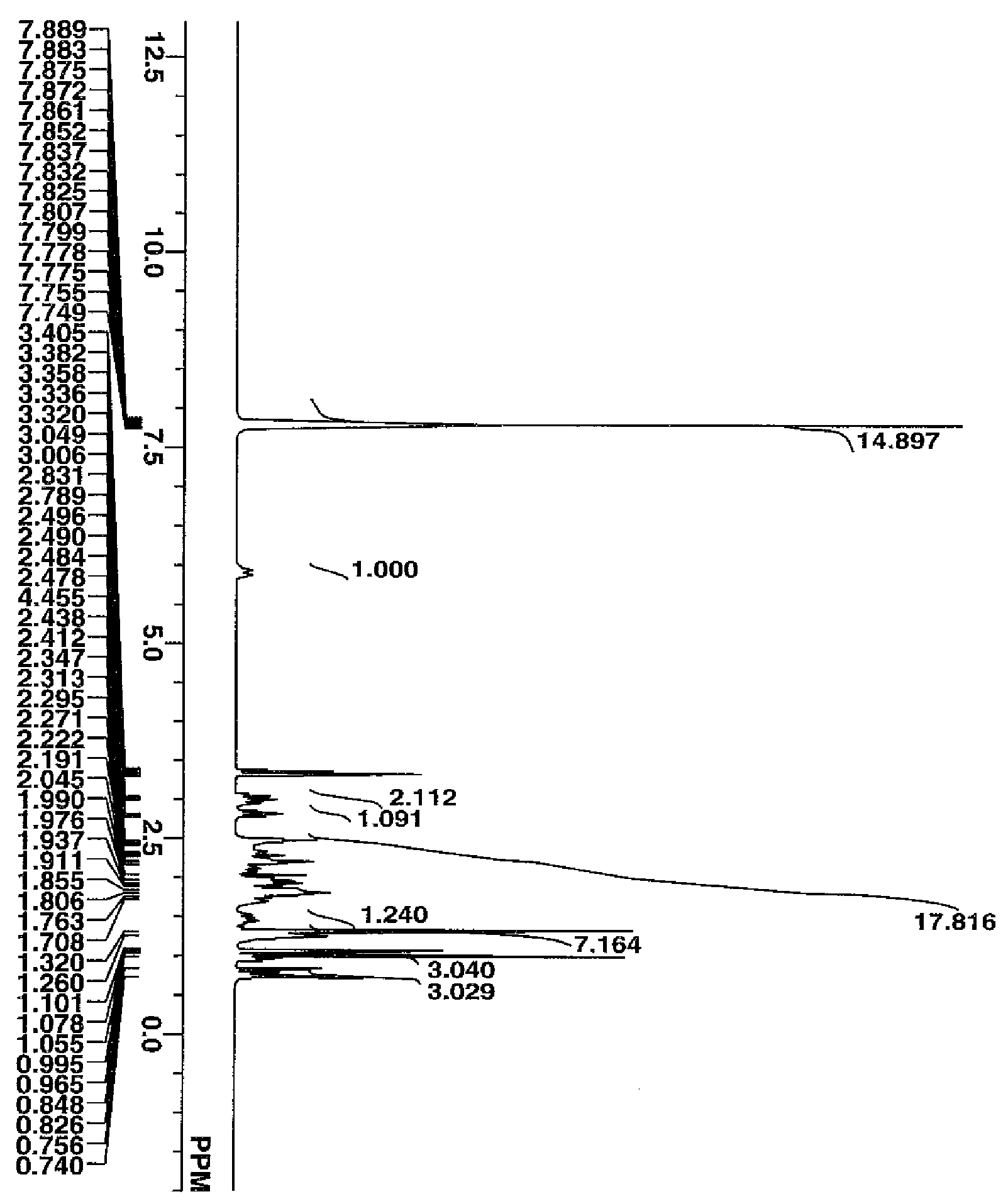

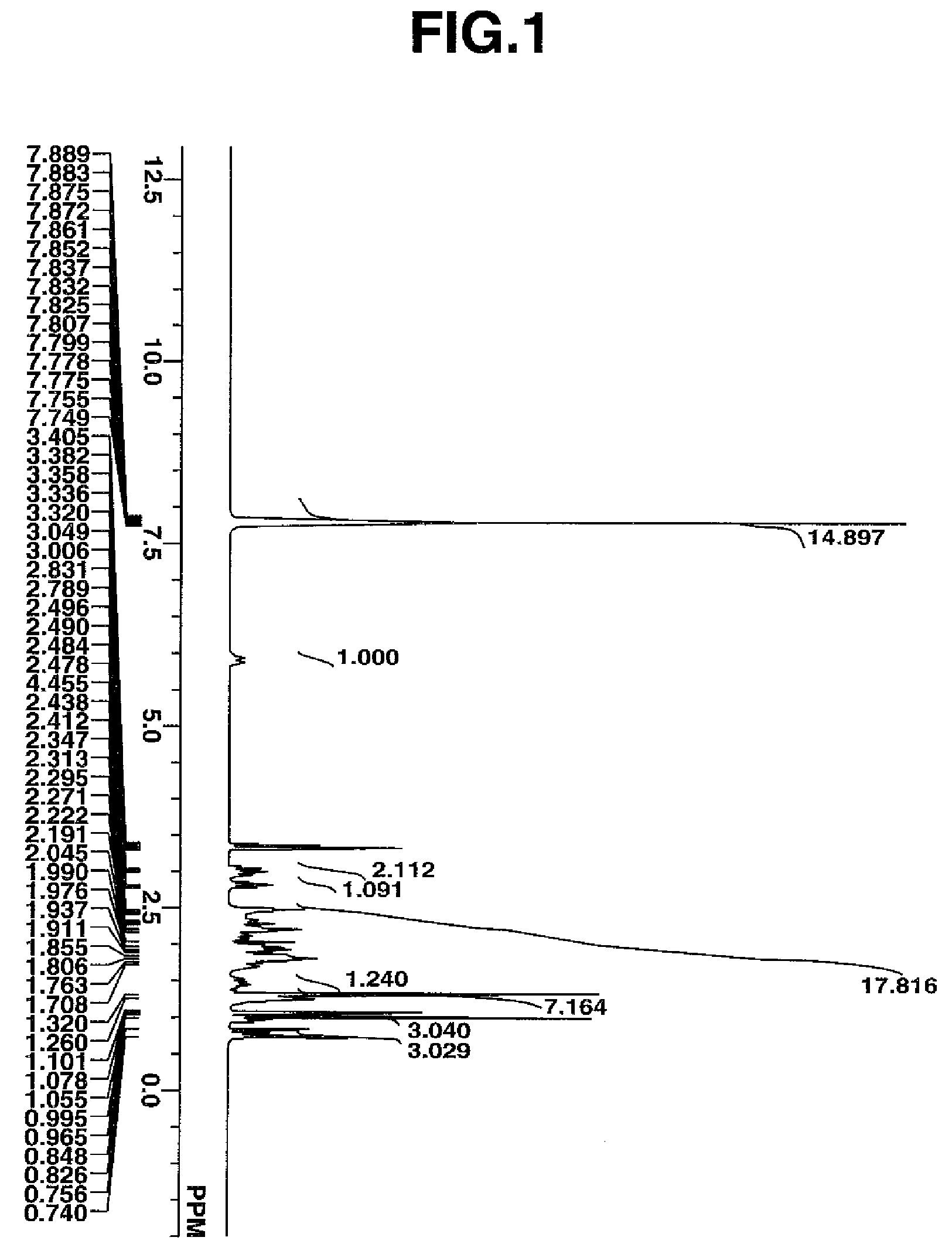

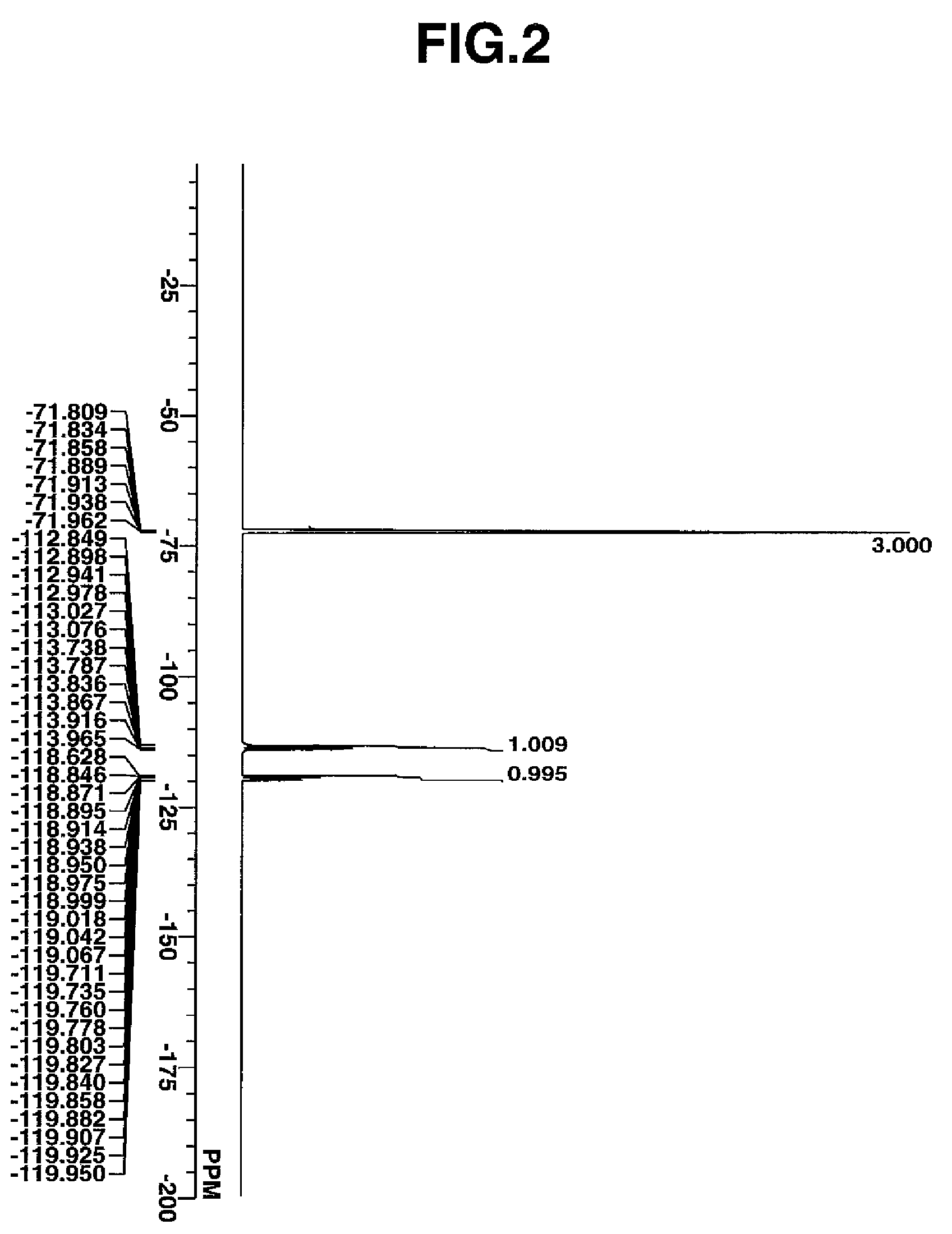

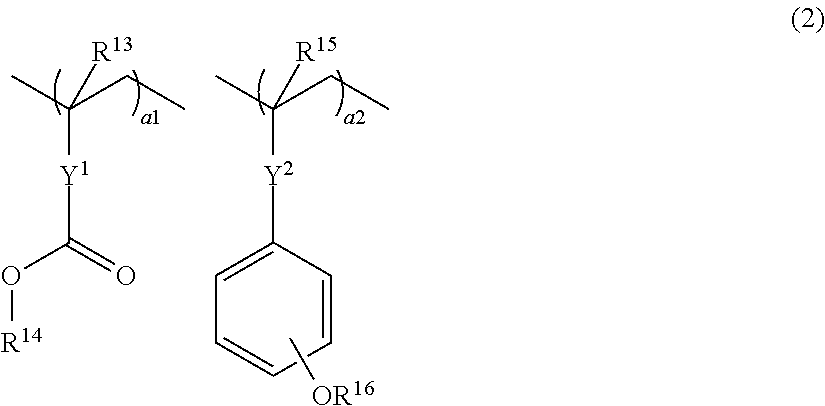

Sulfonium salt-containing polymer, resist composition, and patterning process

ActiveUS20090269696A1Promote divisionHigh sensitivity and resolutionPhotosensitive materialsRadiation applicationsResistAryl

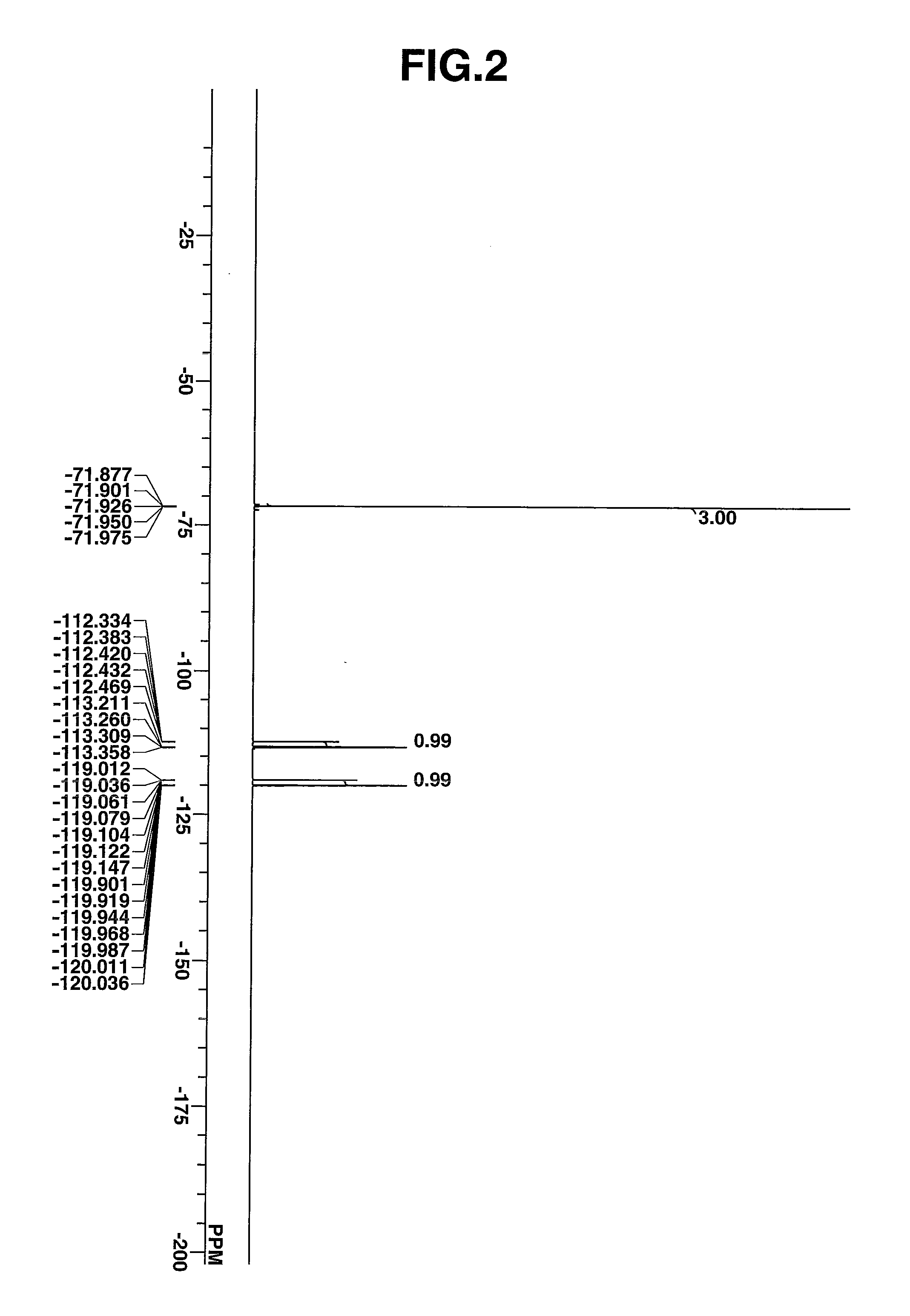

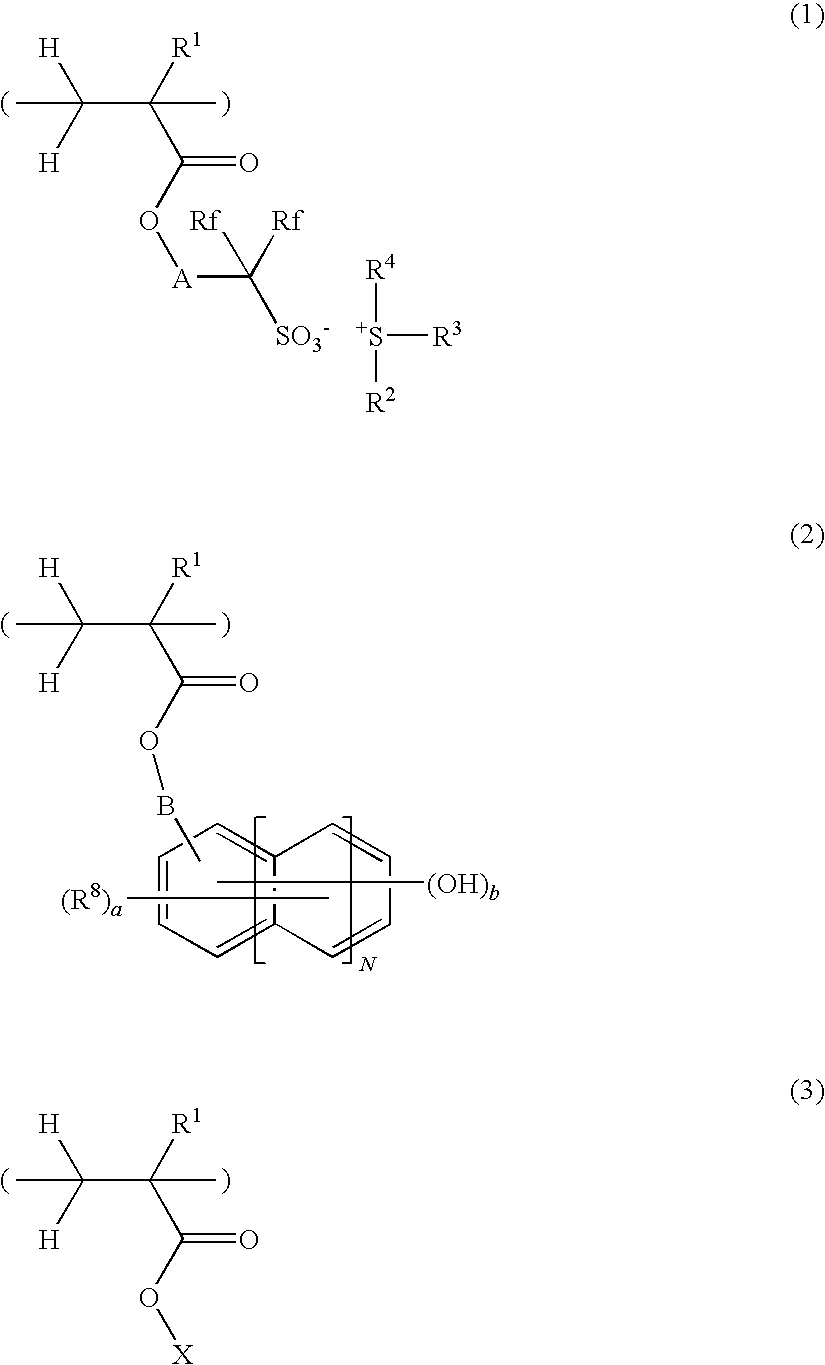

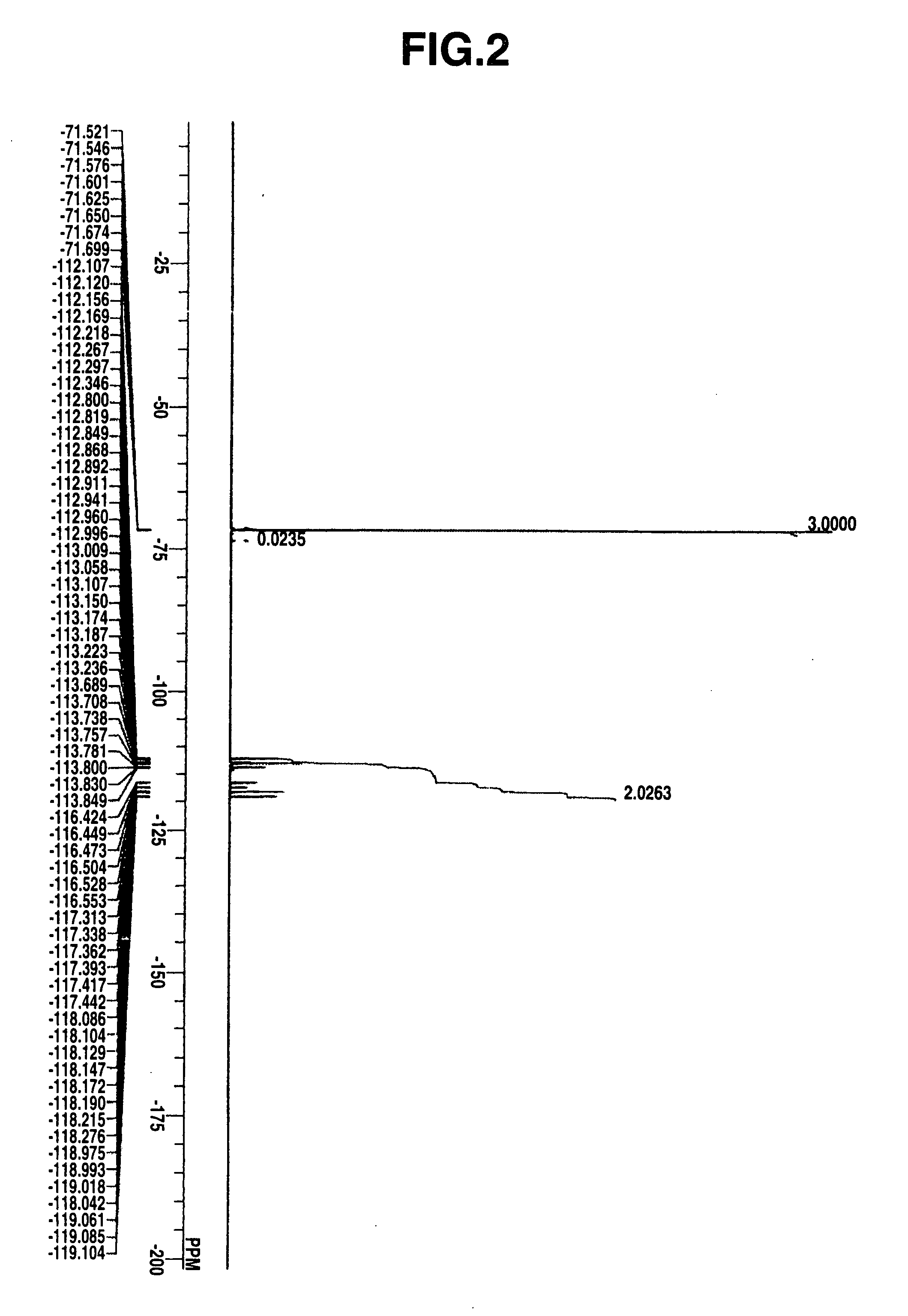

A polymer comprising recurring units having formulae (1), (2) and (3) is provided as well as a chemically amplified resist composition comprising the same. R1 is H, F, CH3 or CF3, Rf is H, F, CF3 or C2F5, A is an optionally fluorine or oxygen-substituted divalent organic group, R2, R3 and R4 are alkyl, alkenyl, oxoalkyl, aryl, aralkyl or aryloxoalkyl, or may form a ring with the sulfur atom, N=0-2, R8 is H or alkyl, B is a single bond or optionally oxygen-substituted divalent organic group, a=0-3, b=1-3, and X is an acid labile group. The polymer generates a strong sulfonic acid which provides for effective cleavage of acid labile groups in a chemically amplified resist composition.

Owner:SHIN ETSU CHEM IND CO LTD

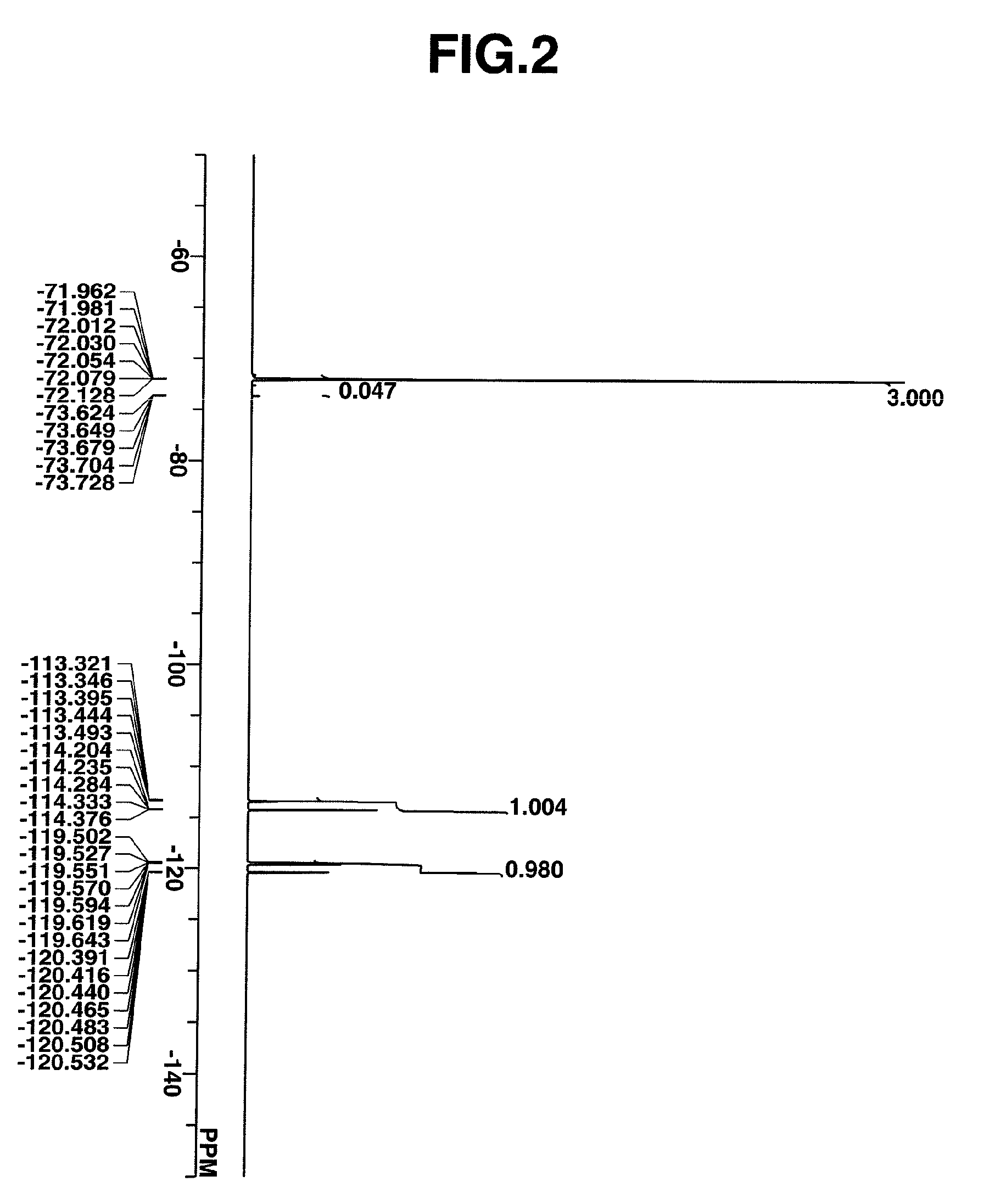

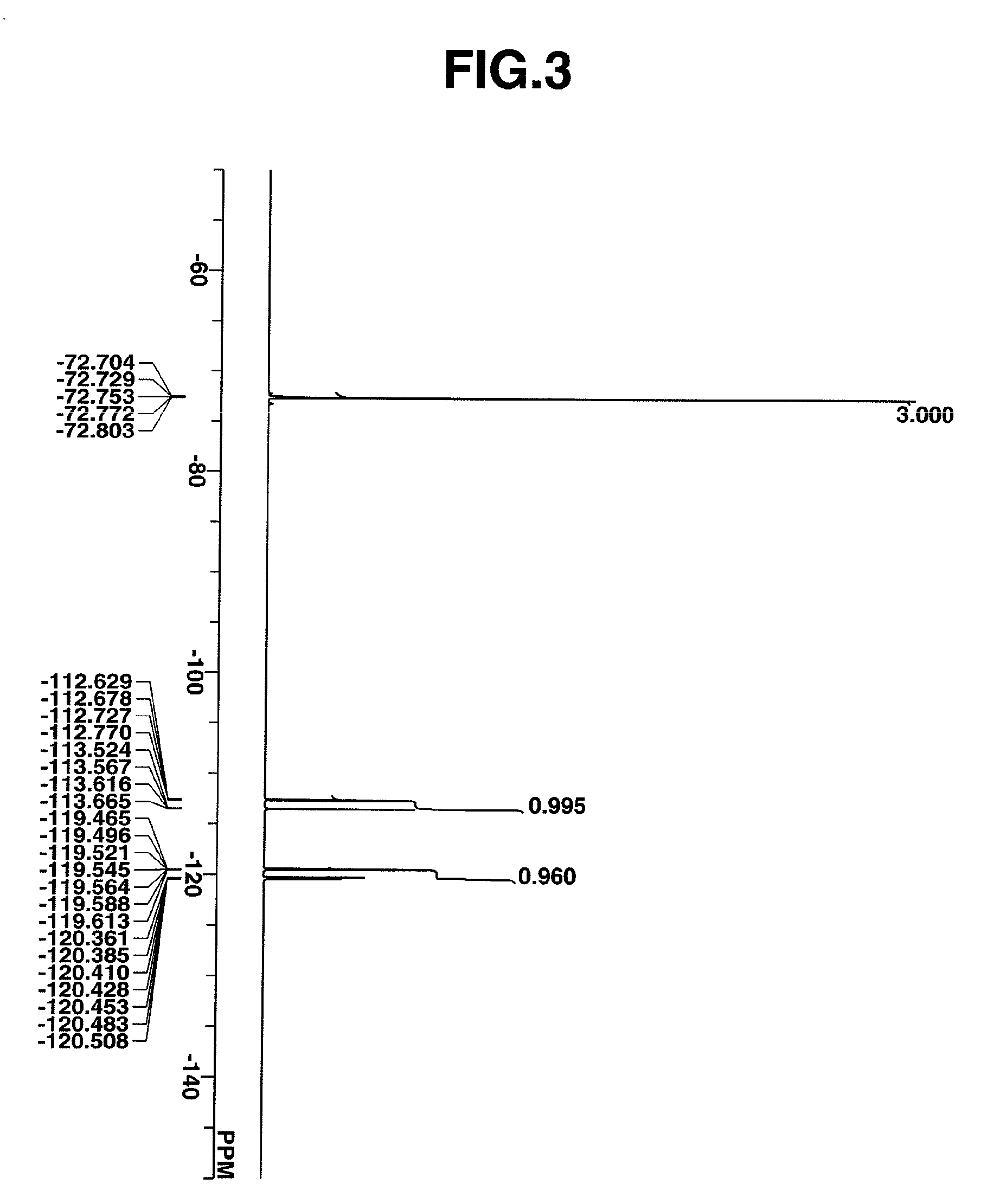

Polymerizable anion-containing sulfonium salt and polymer, resist composition, and patterning process

A polymerizable anion-containing sulfonium salt having formula (1) is provided wherein R1 is H, F, methyl or trifluoromethyl, R2, R3 and R4 are C1-C10 alkyl, alkenyl or oxoalkyl or C6-C18 aryl, aralkyl or aryloxoalkyl, or two of R2, R3 and R4 may bond together to form a ring with S, A is a C2-C20 hydrocarbon group having cyclic structure, and n is 0 or 1. The sulfonium salt generates a very strong sulfonic acid upon exposure to high-energy radiation. A resist composition comprising a polymer derived from the sulfonium salt is also provided.

Owner:SHIN ETSU CHEM CO LTD

Polymerizable anion-containing sulfonium salt and polymer, resist composition, and patterning process

ActiveUS20100099042A1Promote divisionImproved in pattern density dependencyOrganic chemistryPhotosensitive materialsResistAryl

A polymerizable anion-containing sulfonium salt having formula (1) is provided wherein R1 is H, F, methyl or trifluoromethyl, R2, R3 and R4 are C1-C10 alkyl, alkenyl or oxoalkyl or C6-C18 aryl, aralkyl or aryloxoalkyl, or two of R2, R3 and R4 may bond together to form a ring with S, A is a C2-C20 hydrocarbon group having cyclic structure, and n is 0 or 1. The sulfonium salt generates a very strong sulfonic acid upon exposure to high-energy radiation. A resist composition comprising a polymer derived from the sulfonium salt is also provided.

Owner:SHIN ETSU CHEM IND CO LTD

Novel photoacid generators, resist compositions, and patterning process

ActiveUS20080085469A1Minimize dissolutionResist formationOrganic chemistryPhotosensitive materialsResistAryl

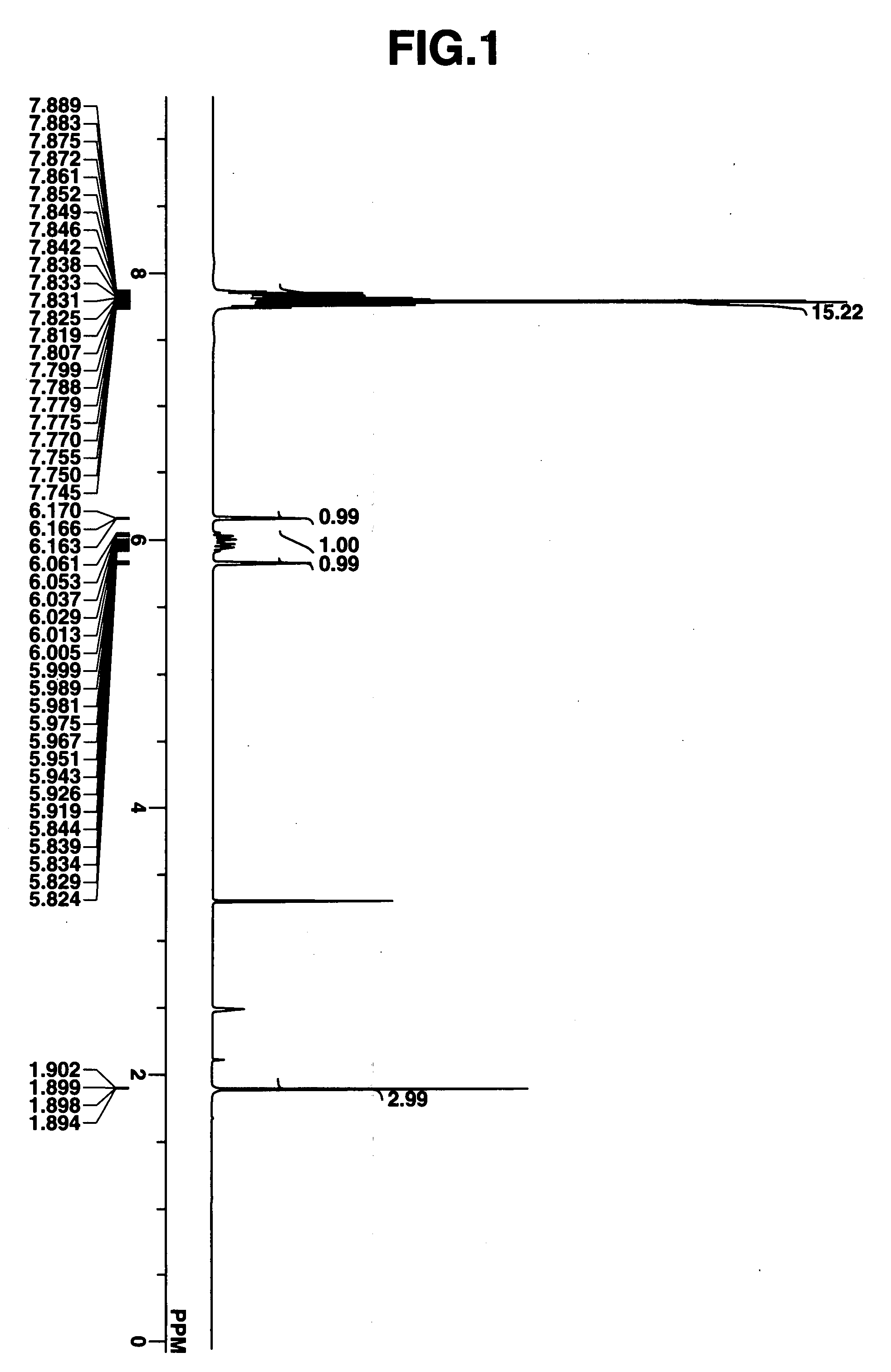

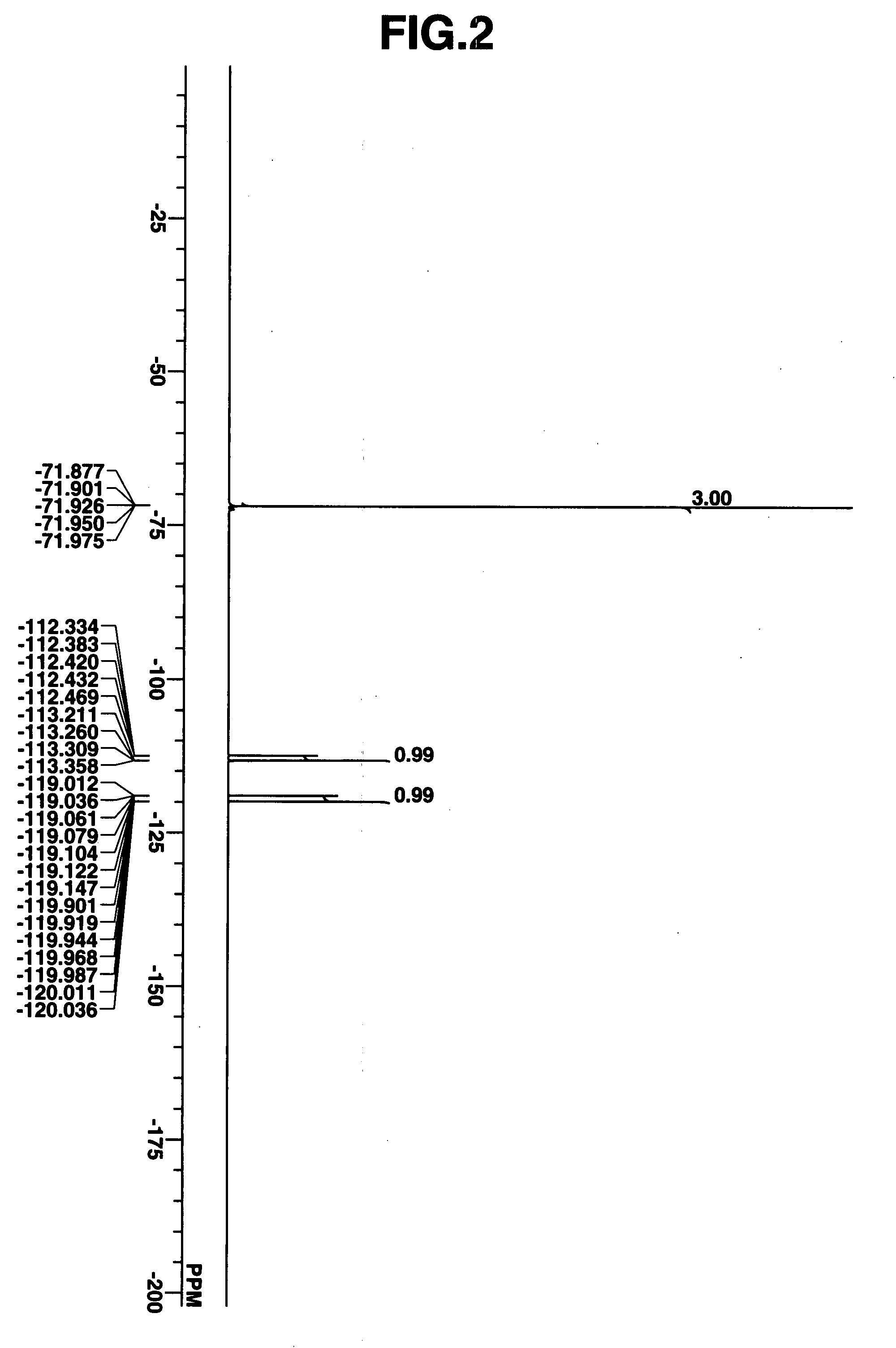

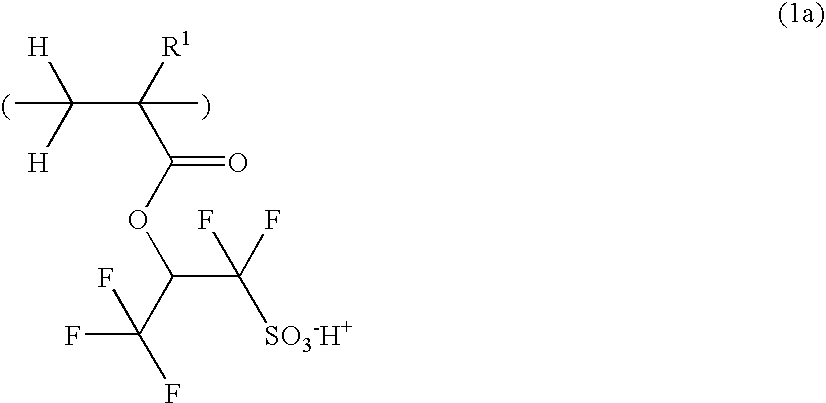

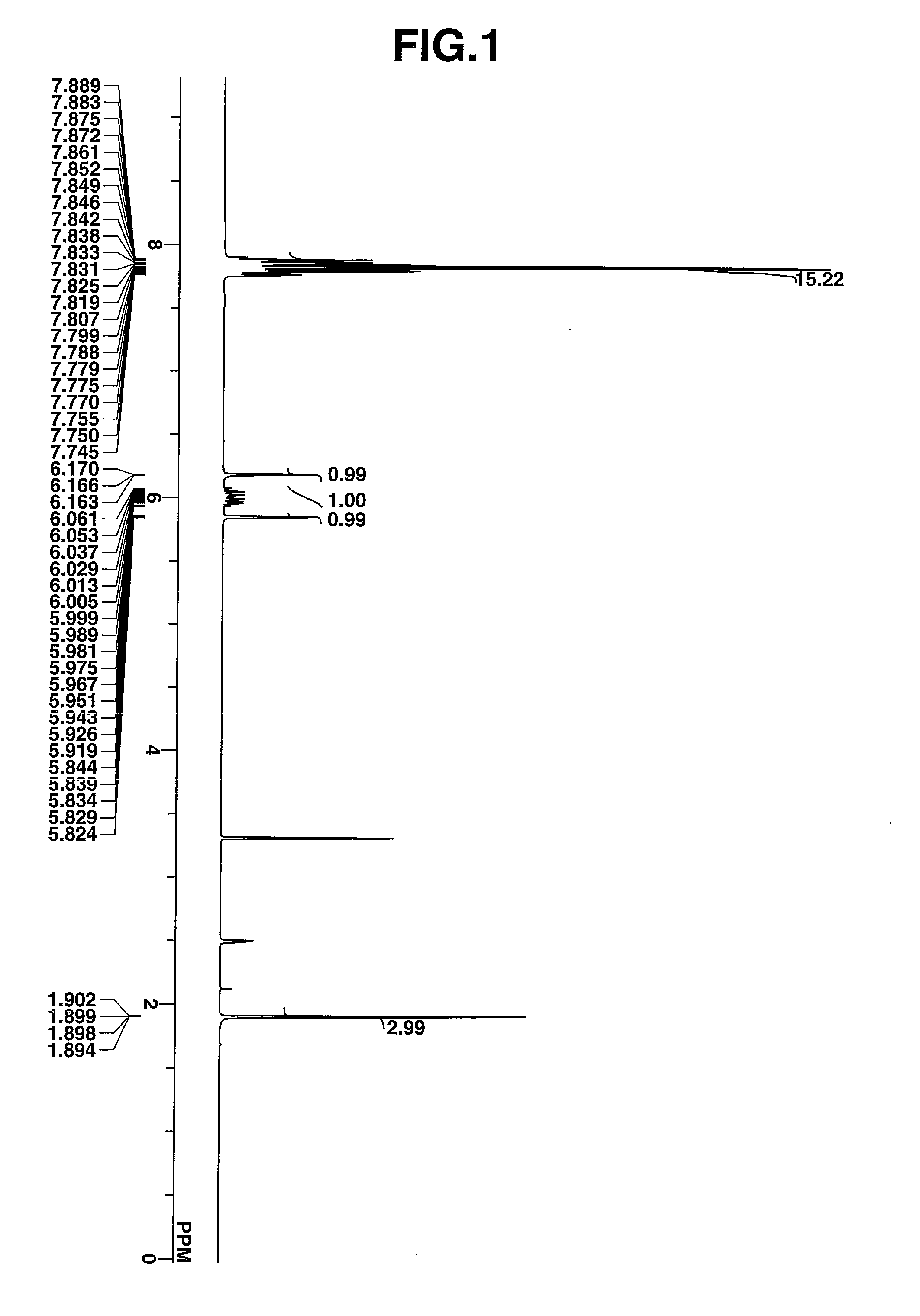

Photoacid generators generate sulfonic acids of formula (1a) upon exposure to high-energy radiation. RC(═O)R1—COOCH(CF3)CF2SO3−H+ (1a) R is hydroxyl, alkyl, aryl, hetero-aryl, alkoxy, aryloxy or hetero-aryloxy, R1 is a divalent organic group which may have a heteroatom (O, N or S) containing substituent, or R1 may form a cyclic structure with R. The photoacid generators are compatible with resins and can control acid diffusion and are thus suited for use in chemically amplified resist compositions.

Owner:SHIN ETSU CHEM IND CO LTD

Polymerizable anion-containing sulfonium salt and polymer, resist composition, and patterning process

ActiveUS8057985B2Promote divisionHigh resolutionOrganic chemistryOrganic compound preparationArylResist

A polymerizable anion-containing sulfonium salt having formula (1) is provided wherein R1 is H, F, methyl or trifluoromethyl, R2, R3 and R4 are C1-C10 alkyl, alkenyl or oxoalkyl or C6-C18 aryl, aralkyl or aryloxoalkyl, or two of R2, R3 and R4 may bond together to form a ring with S, A is a C1-C20 organic group, and n is 0 or 1. The sulfonium salt generates a very strong sulfonic acid upon exposure to high-energy radiation. A resist composition comprising a polymer derived from the sulfonium salt is also provided.

Owner:SHIN ETSU CHEM IND CO LTD

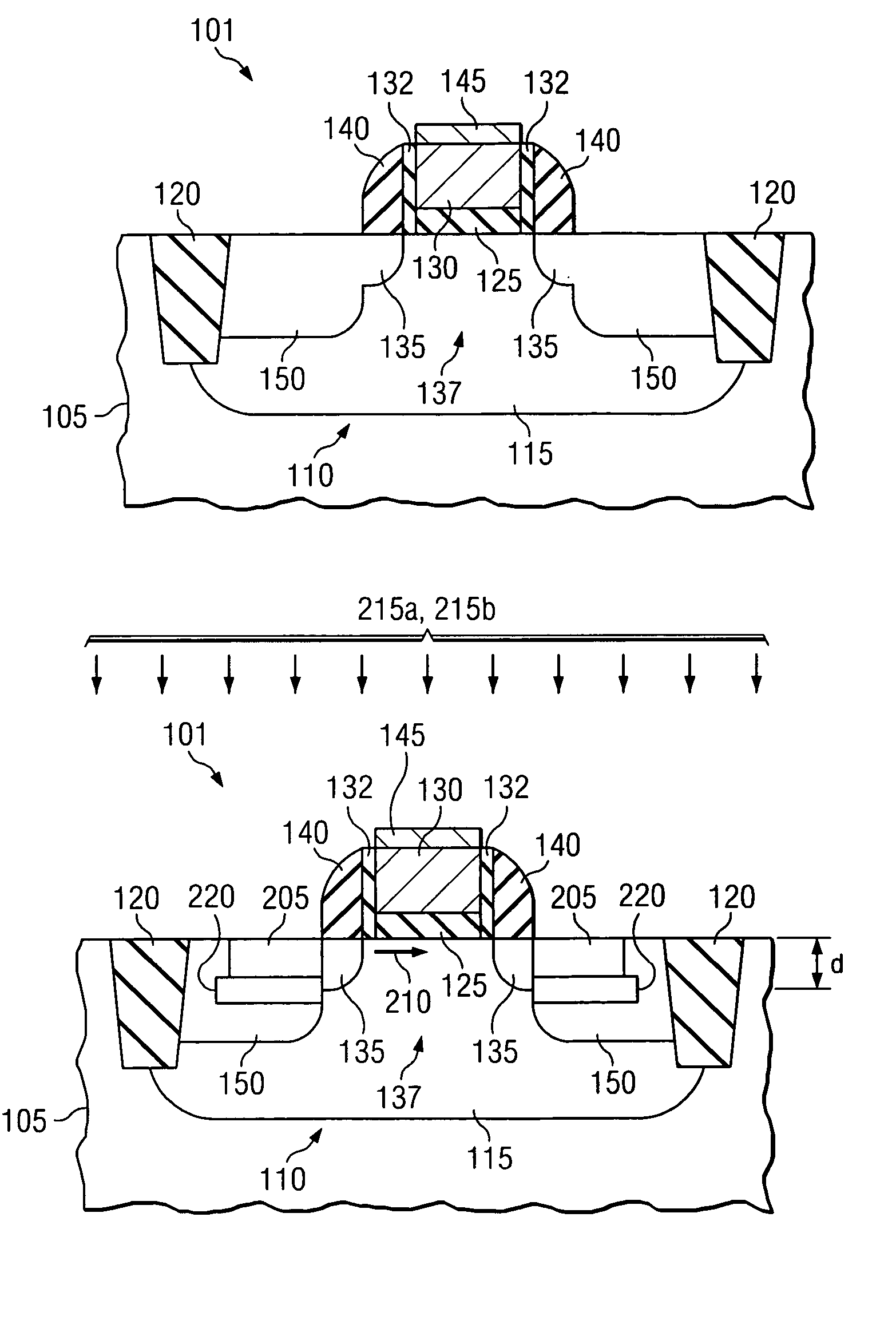

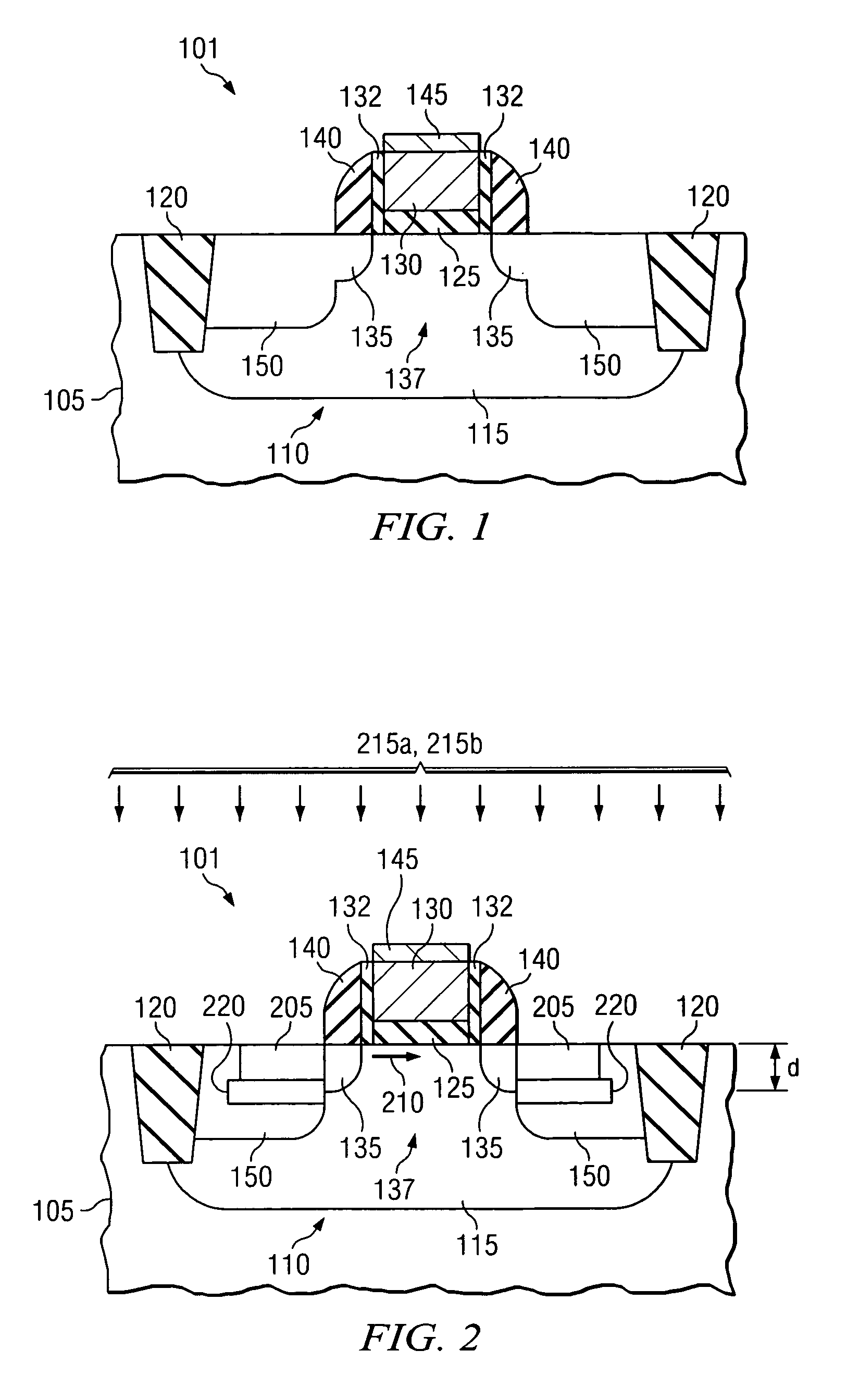

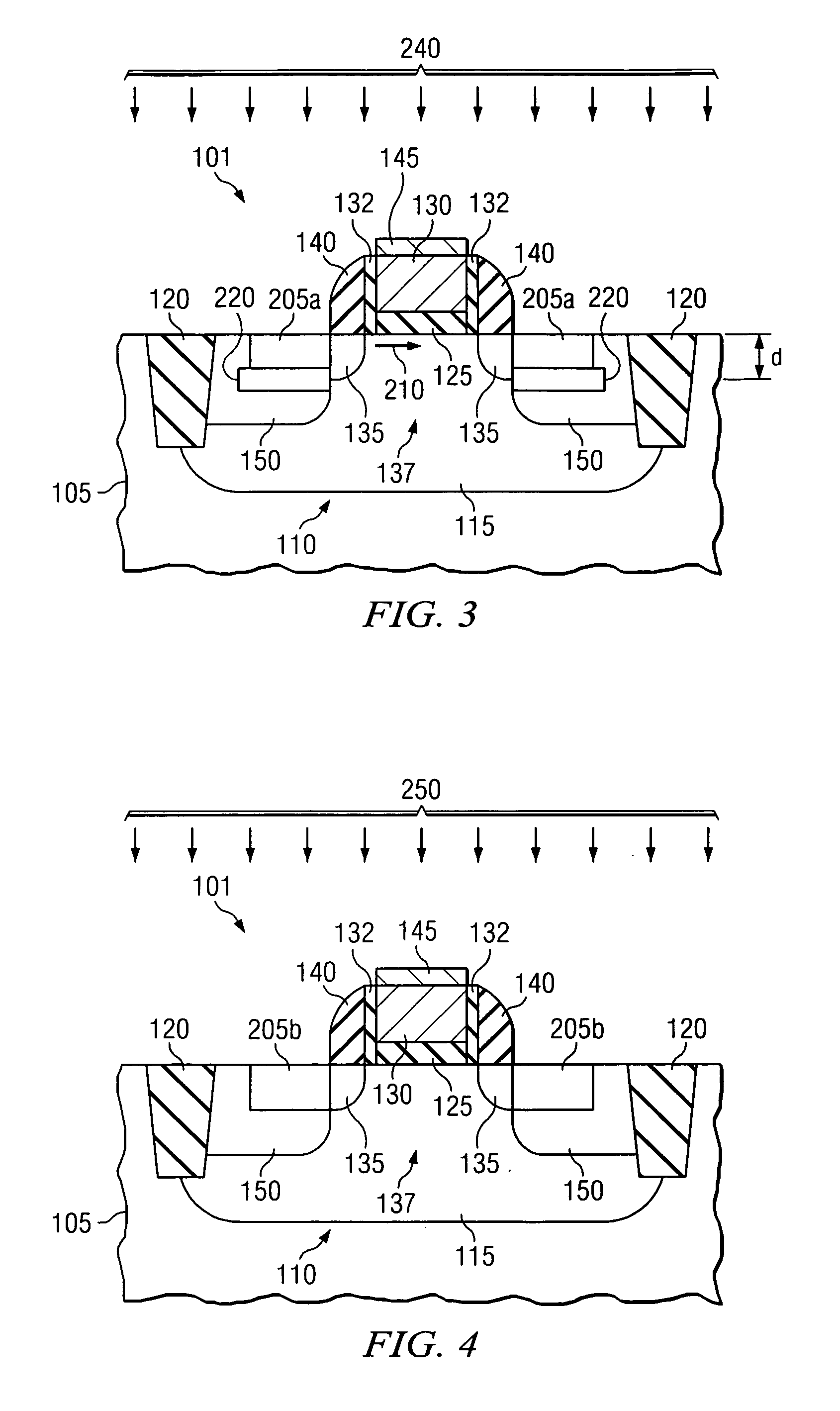

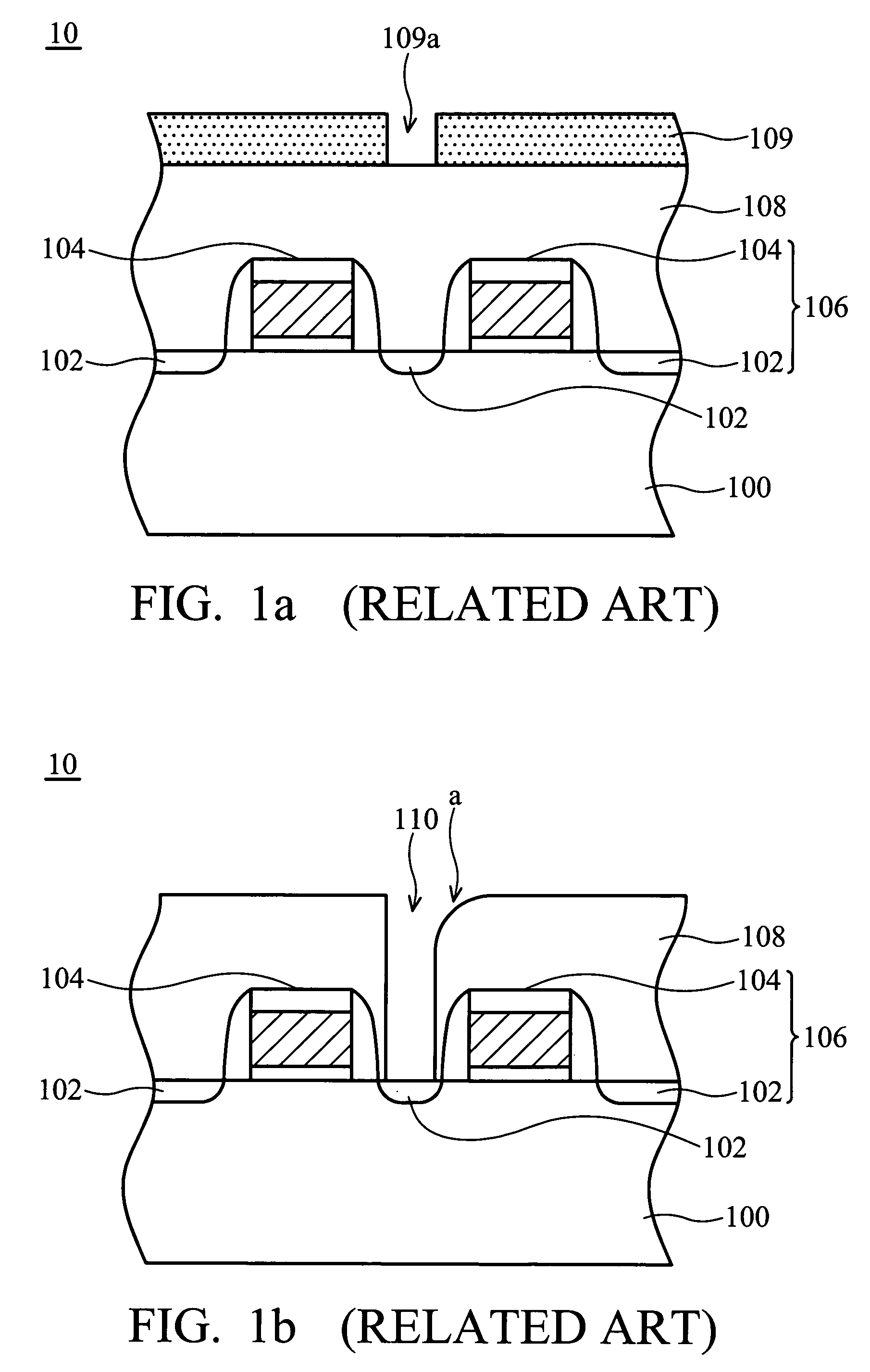

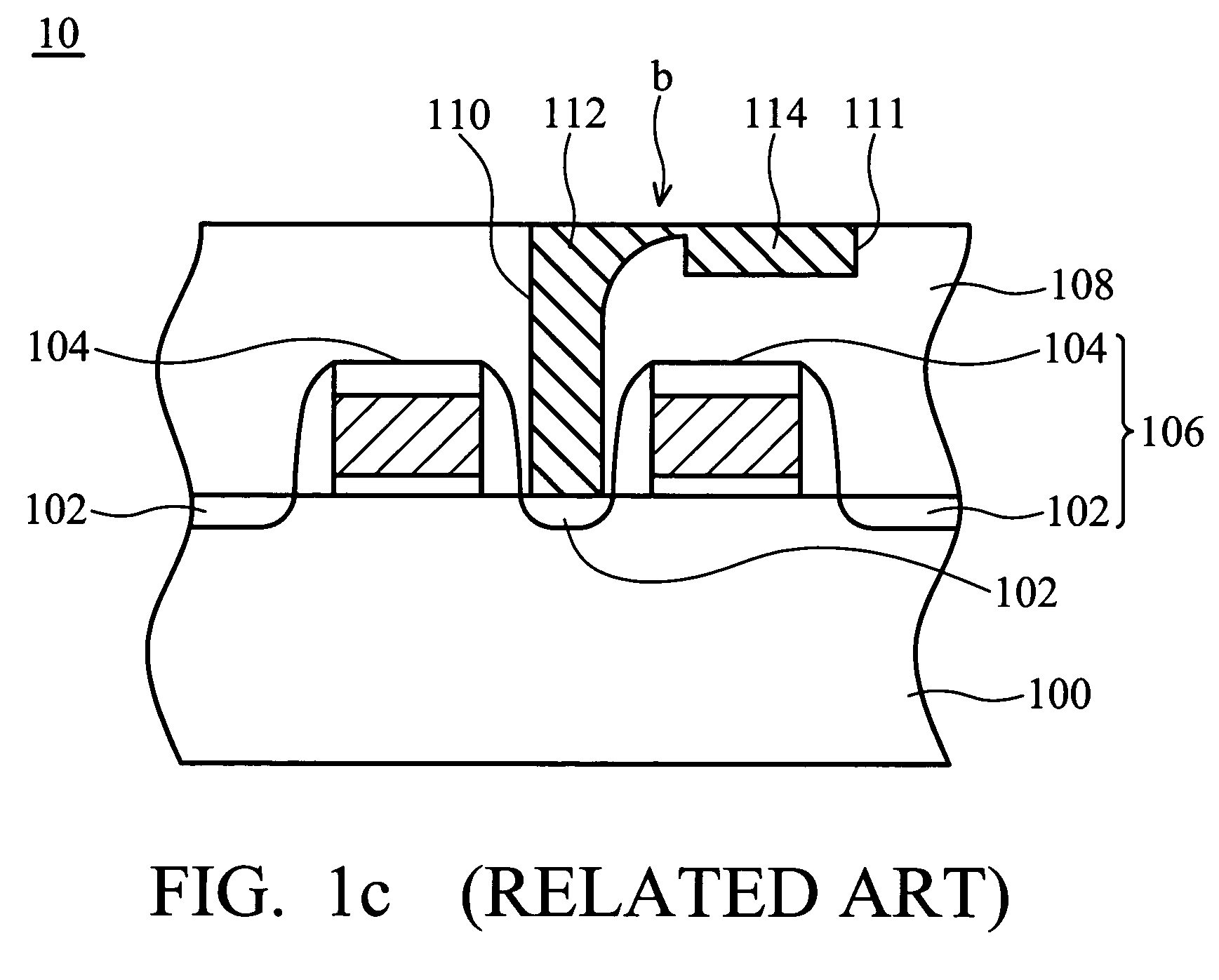

Defect-free SiGe source/drain formation by epitaxy-free process

InactiveUS20070173022A1Low costReduce throughputTransistorSemiconductor/solid-state device manufacturingMOSFETCharge carrier mobility

MOSFET transistors having localized stressors for improving carrier mobility are provided. Embodiments of the invention comprise a gate electrode formed over a substrate, a carrier channel region in the substrate under the gate electrode, and source / drain regions on either side of the carrier channel region. The source / drain regions include an embedded stressor having a lattice constant different from the substrate. In a preferred embodiment, the substrate is silicon and the embedded stressor is SiGe. Implanting a portion of the source / drain regions with Ge forms the embedded stressor. Implanting carbon into the source / drain regions and annealing the substrate after implanting the carbon suppresses dislocation formation, thereby improving device performance.

Owner:TAIWAN SEMICON MFG CO LTD

Photoacid generators, resist compositions, and patterning process

ActiveUS7527912B2Minimize dissolutionResist formationOrganic chemistryPhotosensitive materialsResistHigh energy

Photoacid generators generate sulfonic acids of formula (1a) upon exposure to high-energy radiation.RC(═O)R1—COOCH(CF3)CF2SO3−H+ (1a)R is hydroxyl, alkyl, aryl, hetero-aryl, alkoxy, aryloxy or hetero-aryloxy, R1 is a divalent organic group which may have a heteroatom (O, N or S) containing substituent, or R1 may form a cyclic structure with R. The photoacid generators are compatible with resins and can control acid diffusion and are thus suited for use in chemically amplified resist compositions.

Owner:SHIN ETSU CHEM IND CO LTD

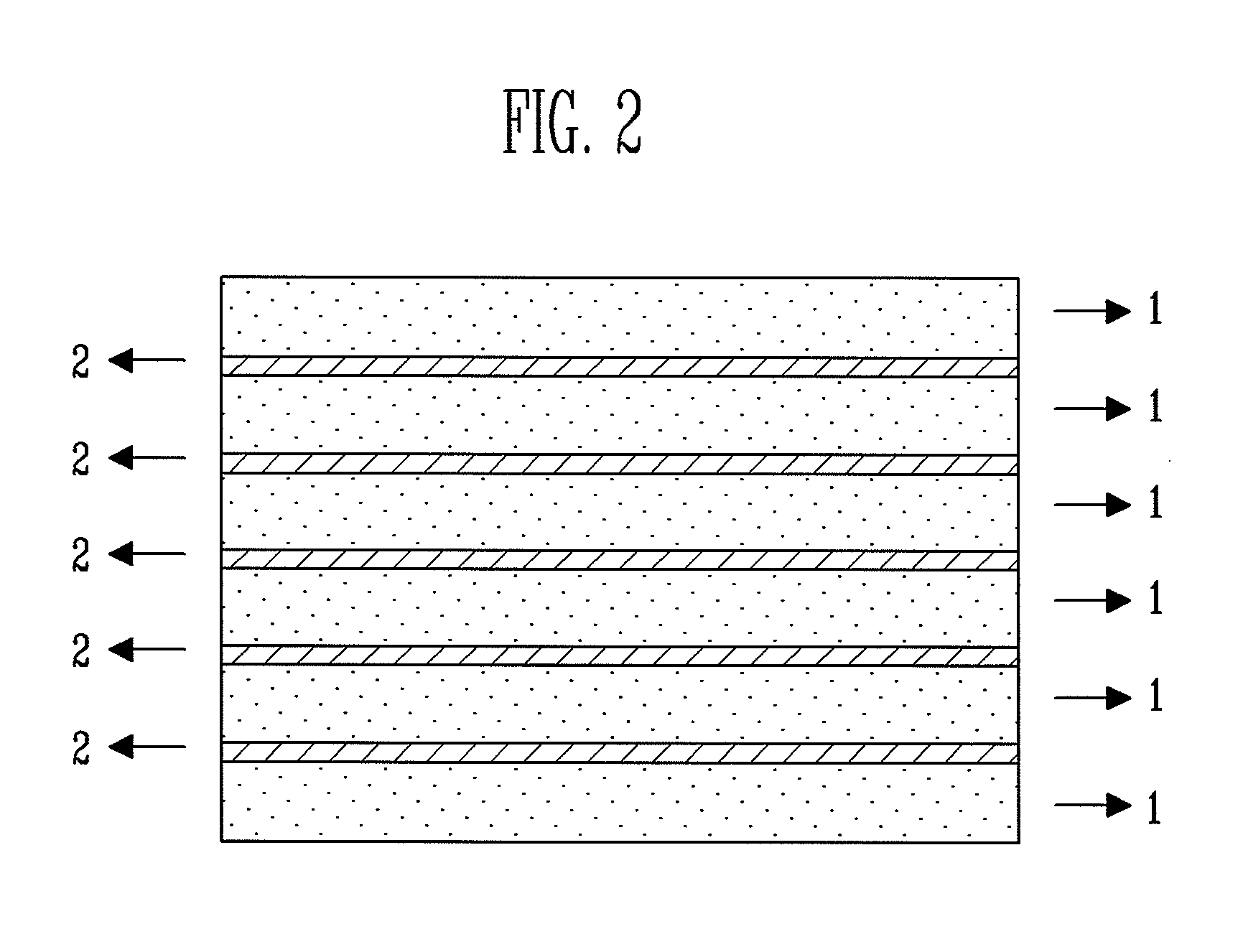

Glass substrate with protective glass, and process for producing display device using glass substrate with protective glass

InactiveUS20090321005A1Improve productivityEasy to separateLamination ancillary operationsSynthetic resin layered productsDisplay deviceProtective glasses

To provide a glass substrate with protective glass which suppresses formation of microscopic scratches on the back surface of the glass substrate in the production process for a display device, and which prevents a strength decrease in the process or formation of etch pits after a chemical etching treatment; a process for producing a display device by using the glass substrate with protective glass; and a double-sided removable resin sheet for the glass substrate with protective glass.A glass substrate with protective glass, which comprises a glass substrate and a protective glass plate laminated on each other, and which is characterized in that the glass substrate and the protective glass plate are laminated by a double-sided removal resin sheet.

Owner:ASAHI GLASS CO LTD

Sulfonium salt-containing polymer, resist composition, and patterning process

ActiveUS8048610B2Promote divisionHigh sensitivity and resolutionPhotosensitive materialsRadiation applicationsArylPolymer science

Owner:SHIN ETSU CHEM CO LTD

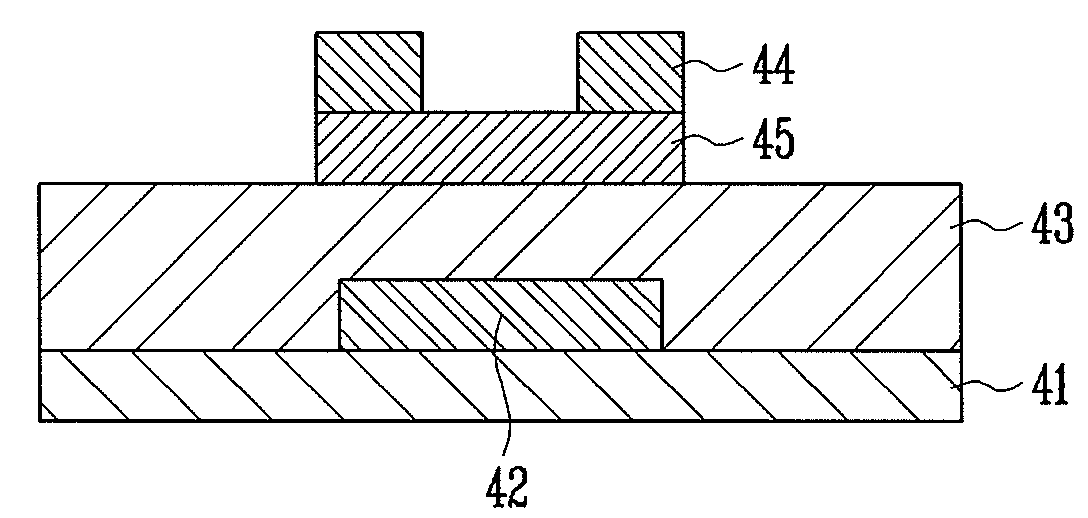

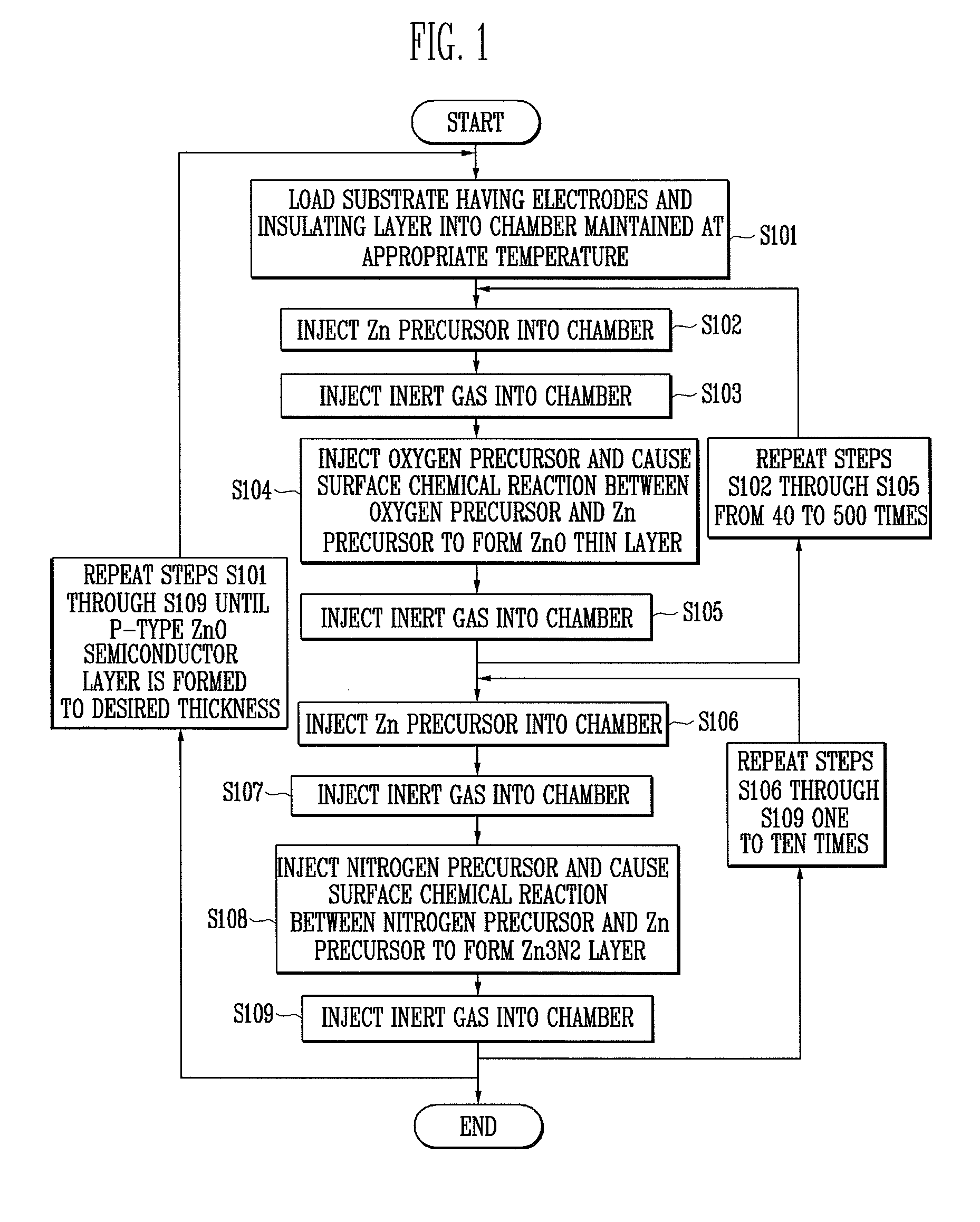

METHOD OF MANUFACTURING P-TYPE ZnO SEMICONDUCTOR LAYER USING ATOMIC LAYER DEPOSITION AND THIN FILM TRANSISTOR INCLUDING THE P-TYPE ZnO SEMICONDUCTOR LAYER

InactiveUS20080164476A1Improve featuresSimple processPolycrystalline material growthSemiconductor/solid-state device manufacturingChemical reactionNitrogen

Provided are a method of manufacturing a transparent N-doped p-type ZnO semiconductor layer using a surface chemical reaction between precursors containing elements constituting thin layers, and a thin film transistor (TFT) including the p-type ZnO semiconductor layer. The method includes the steps of: preparing a substrate and loading the substrate into a chamber; injecting a Zn precursor and an oxygen precursor into the chamber, and causing a surface chemical reaction between the Zn precursor and the oxygen precursor using an atomic layer deposition (ALD) technique to form a ZnO thin layer on the substrate; and injecting a Zn precursor and an nitrogen precursor into the chamber, and causing a surface chemical reaction between the Zn precursor and the nitrogen precursor to form a doping layer on the ZnO thin layer.

Owner:ELECTRONICS & TELECOMM RES INST

Photoacid generator, resist composition, and patterning process

ActiveUS7670751B2Minimized leach-out in waterResist formationPhotosensitive materialsRadiation applicationsResistHigh energy

Owner:SHIN ETSU CHEM CO LTD +1

Photoacid generator, resist composition, and patterning process

ActiveUS20110003247A1Reduce molecular weightPromote adequate diffusionOrganic chemistryOrganic compound preparationImage resolutionExposure latitude

The photoacid generator produces a sulfonic acid which has a bulky cyclic structure in the sulfonate moiety and a straight-chain hydrocarbon group and thus shows a controlled acid diffusion behavior and an adequate mobility. The PAG is fully compatible with a resin to form a resist composition which performs well during the device fabrication process and solves the problems of resolution, LWR, and exposure latitude.

Owner:SHIN ETSU CHEM IND CO LTD

Sulfonate salts and derivatives, photoacid generators, resist compositions, and patterning process

ActiveUS7569324B2Minimize dissolutionResist formationLithium organic compoundsOrganic compound preparationResistAryl

Owner:SHIN ETSU CHEM IND CO LTD

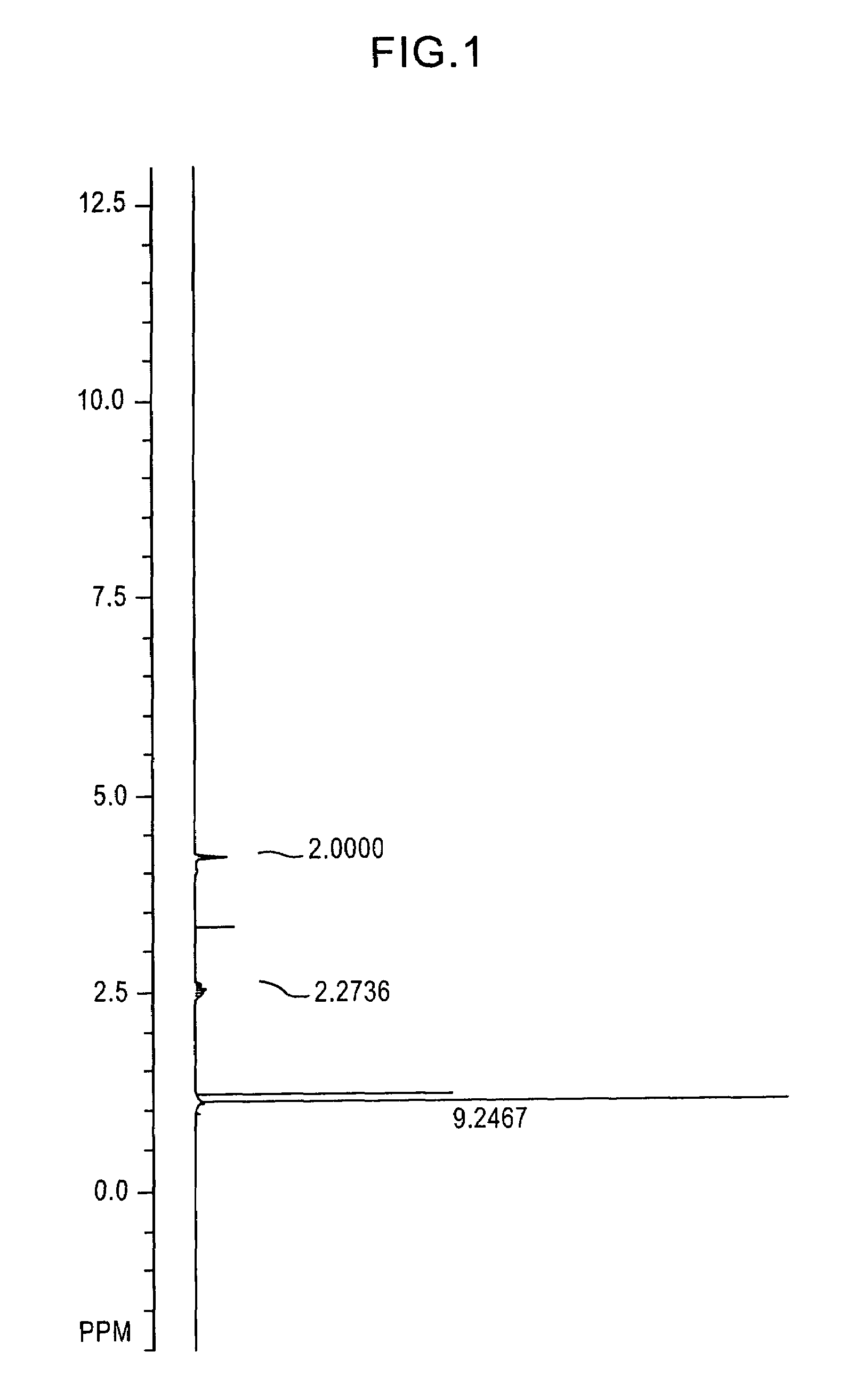

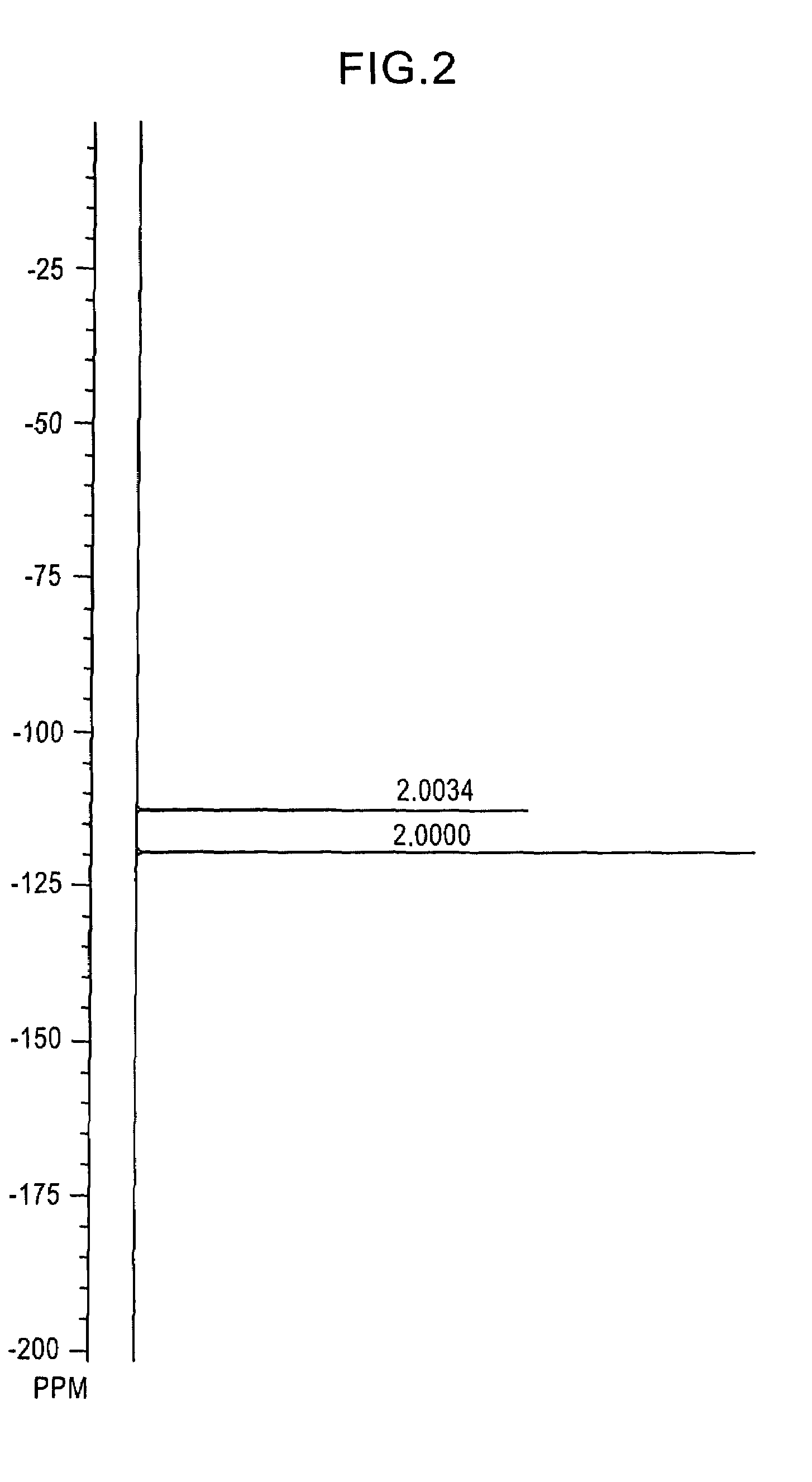

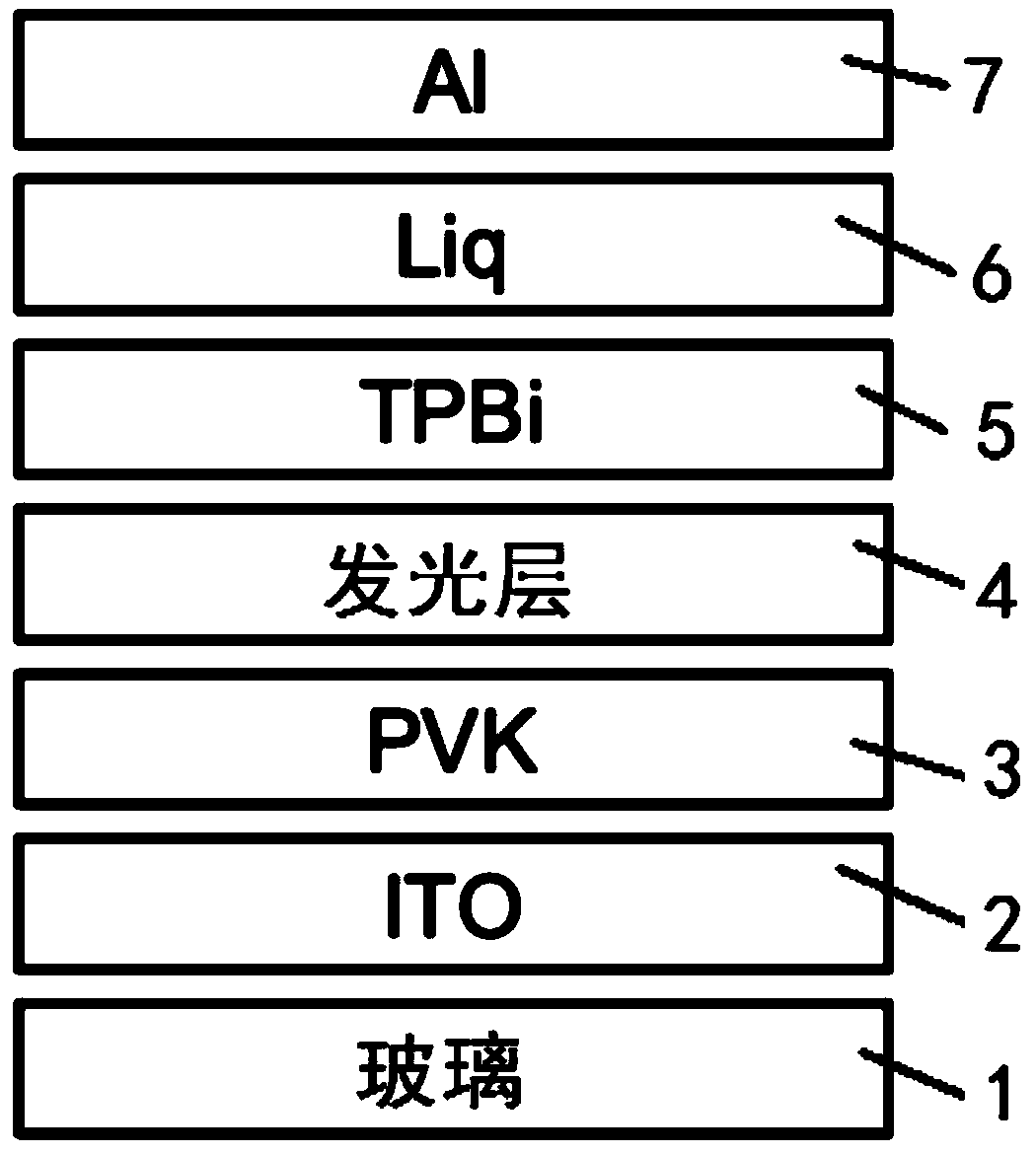

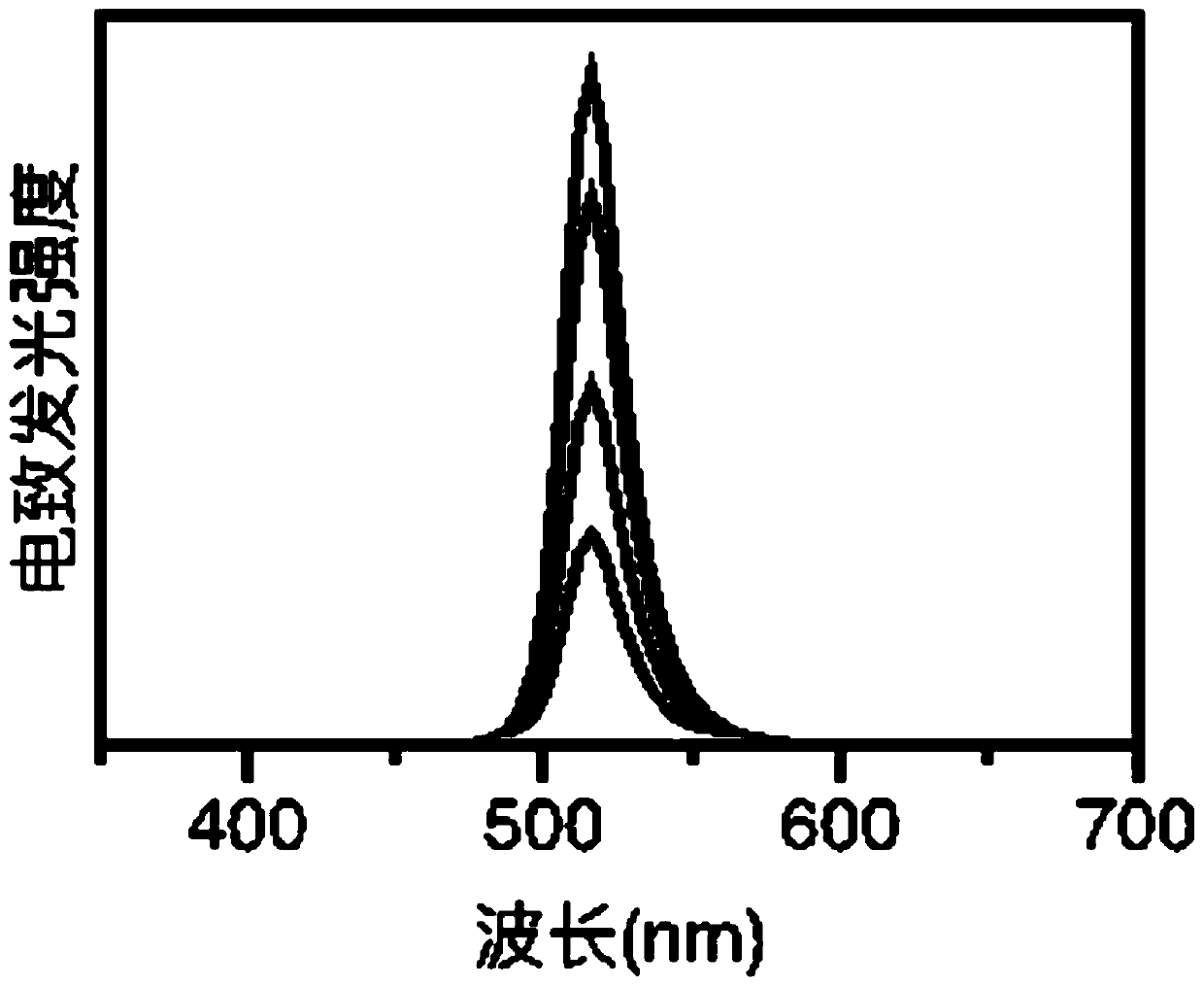

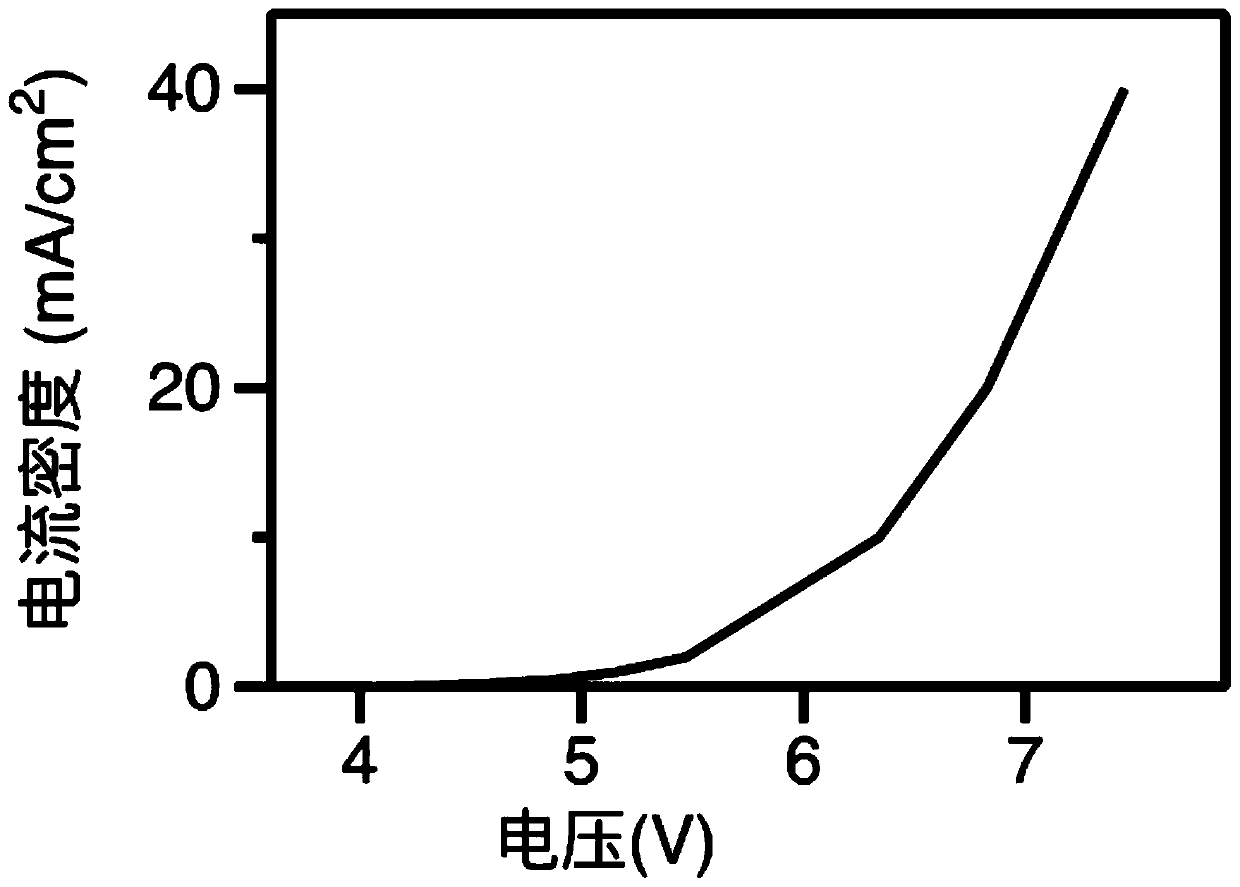

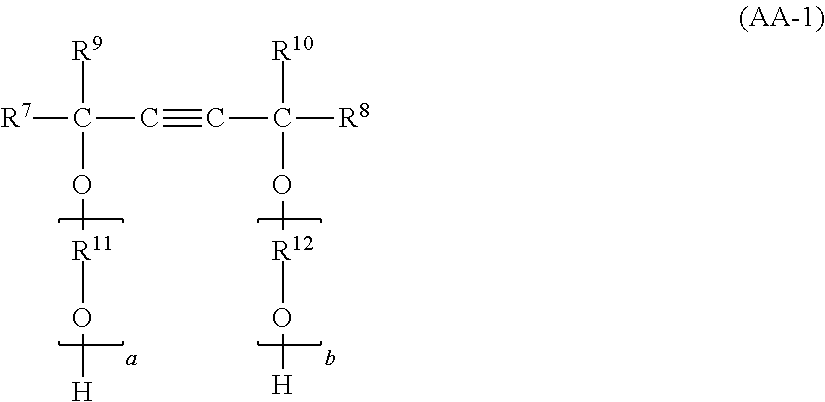

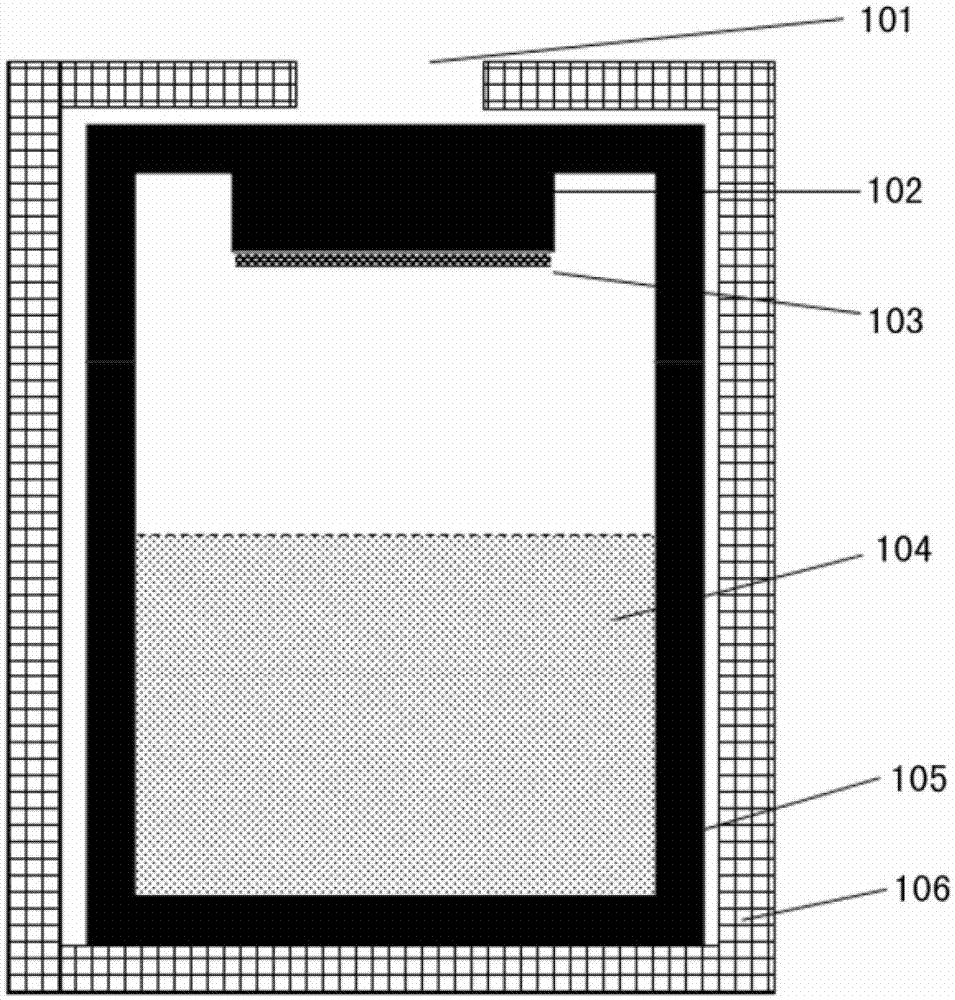

Perovskite LED device based on surface ligand control and preparation method thereof

InactiveCN110867532ALong luminous lifeImprove luminous efficiencySolid-state devicesSemiconductor/solid-state device manufacturingActive agentSurface-active agents

The invention relates to a method for preparing a perovskite LED device based on surface ligand control, including the following steps: applying an organic solution of a hole injection layer materialto the surface of a conductive substrate, and forming a hole injection layer after annealing; dissolving cesium bromide, lead bromide and phenethylamine bromide in an organic solvent under the effectof a 3-(decyl dimethyl ammonium) propane-1-sulfonic acid inner salt surfactant to obtain a perovskite precursor solution, applying the perovskite precursor solution to the surface of the hole injection layer and obtaining a perovskite film after annealing; treating the surface of the perovskite film with an alkylamine organic solution to form a light-emitting layer; and successively preparing an electron transport layer, an electron injection layer and a metal cathode electrode on the surface of the light-emitting layer. The method of the invention is simple and convenient, has a wide range ofmaterials and good repeatability, and can achieve the device performance. Through surface ligand exchange, the flatness and uniformity of the perovskite film are improved, the formation of defects iseffectively suppressed, and the overall performance of the device is significantly improved.

Owner:SUZHOU UNIV

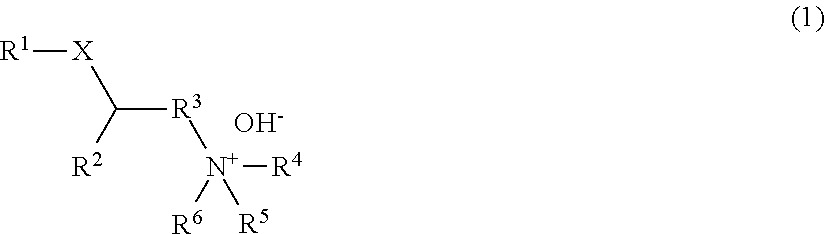

Developer for photosensitive resist material and patterning process

ActiveUS20140377706A1Minimal edge roughnessPreventing pattern collapseCarbamic acid derivatives preparationOrganic compound preparationResistHigh energy

An aqueous solution containing 0.1-20 wt % of a substituted choline or thiocholine hydroxide is a useful developer for photosensitive resist materials. A resist pattern is formed by applying a chemically amplified positive resist composition onto a substrate to form a resist film, exposing the resist film to high-energy radiation, and developing the exposed resist film in an ammonium hydroxide-containing aqueous solution.

Owner:SHIN ETSU CHEM IND CO LTD

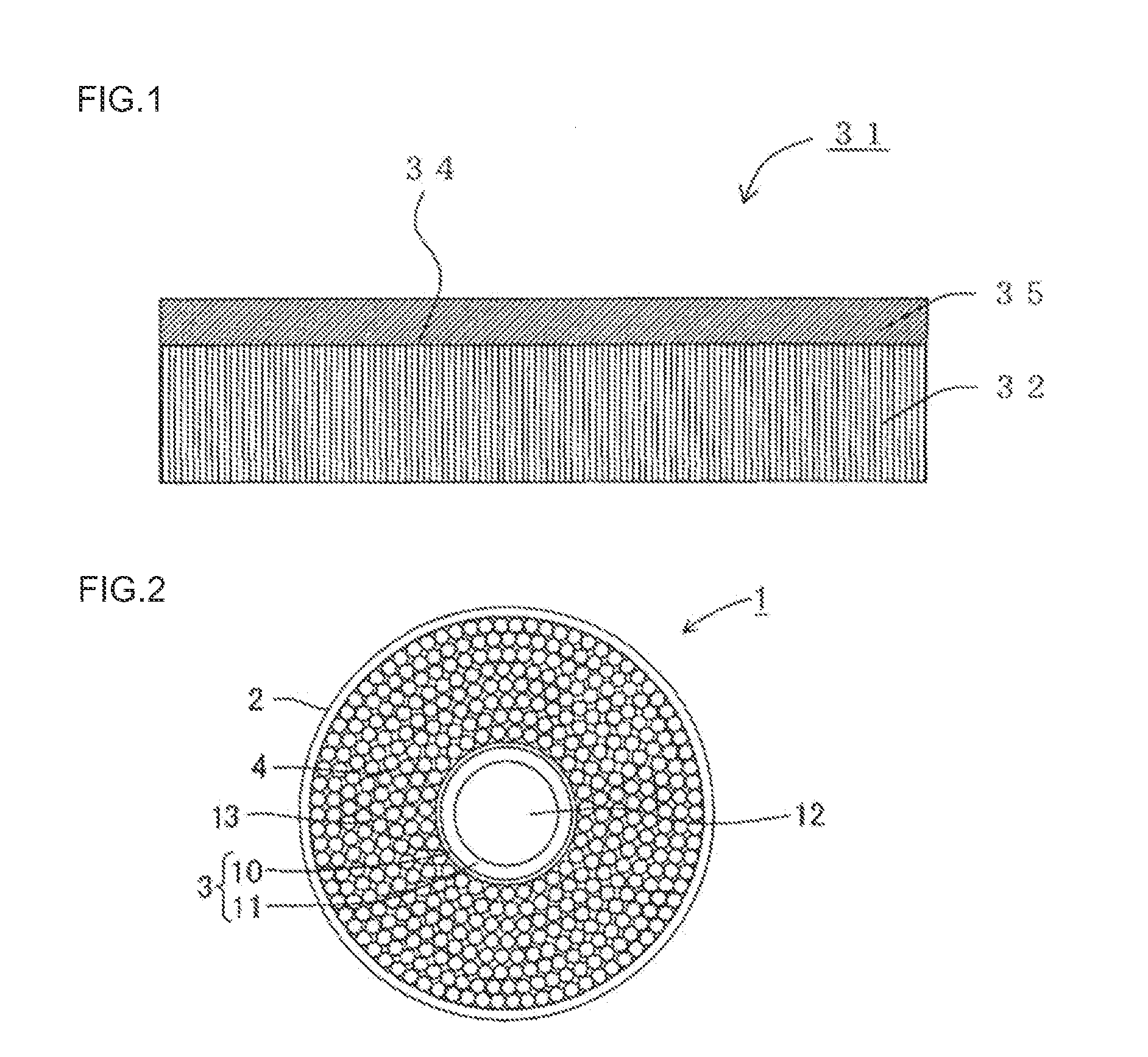

Seed crystal laying method and single crystal growth method through ingotting

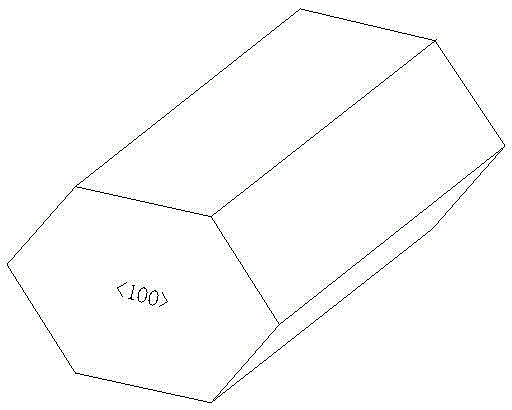

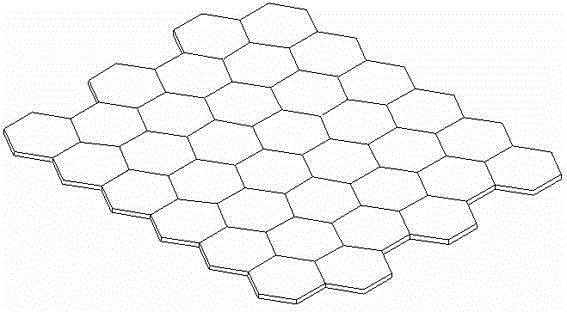

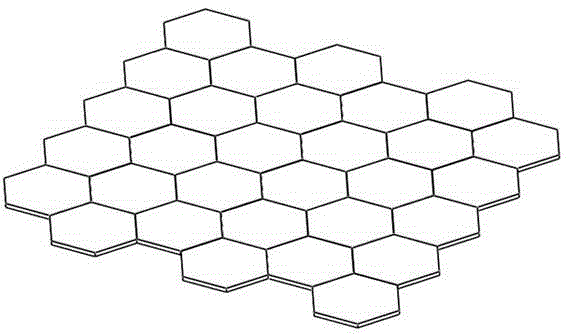

InactiveCN105316758AImprove life expectancyImprove conversion efficiencyPolycrystalline material growthFrom frozen solutionsCrystal orientationSingle crystal growth

The invention relates to a seed crystal laying method which comprises the following steps: A, manufacturing monocrystalline silicon columnar seed crystals with orthohexagonal sections, wherein the section normal direction of the monocrystalline silicon columnar seed crystals is <100> crystal orientation and the crystal orientation of the side surface normal direction is not required specifically; B, laying the side surfaces of the seed crystals on the bottom surface of a crucible fully in a close fit manner, wherein that the side surfaces of the seed crystals are in close fit is taken as a standard. According to the invention, the vertex angle seam of each monocrystalline silicon columnar seed crystal with the orthohexagonal section is reduced to three from four in comparison with that of the traditional quadrilateral seed crystal and is reduced by 25%, so that the probability of defects at the vertex angle is reduced greatly. In addition, the orthohexagonal seed crystals can splice into regular triple-junction crystal boundaries (the inclined angles are 120 degrees), so that greater heat stress can be borne, defect formation and increase caused by heat stress in a growth process can be restrained, the minor carrier lifetime of silicon wafer bodies is prolonged and the conversion efficiency of preparing the silicon wafers into battery pieces is improved. On the other hand, the invention provides a single crystal growth method through ingotting.

Owner:TRINA SOLAR CO LTD

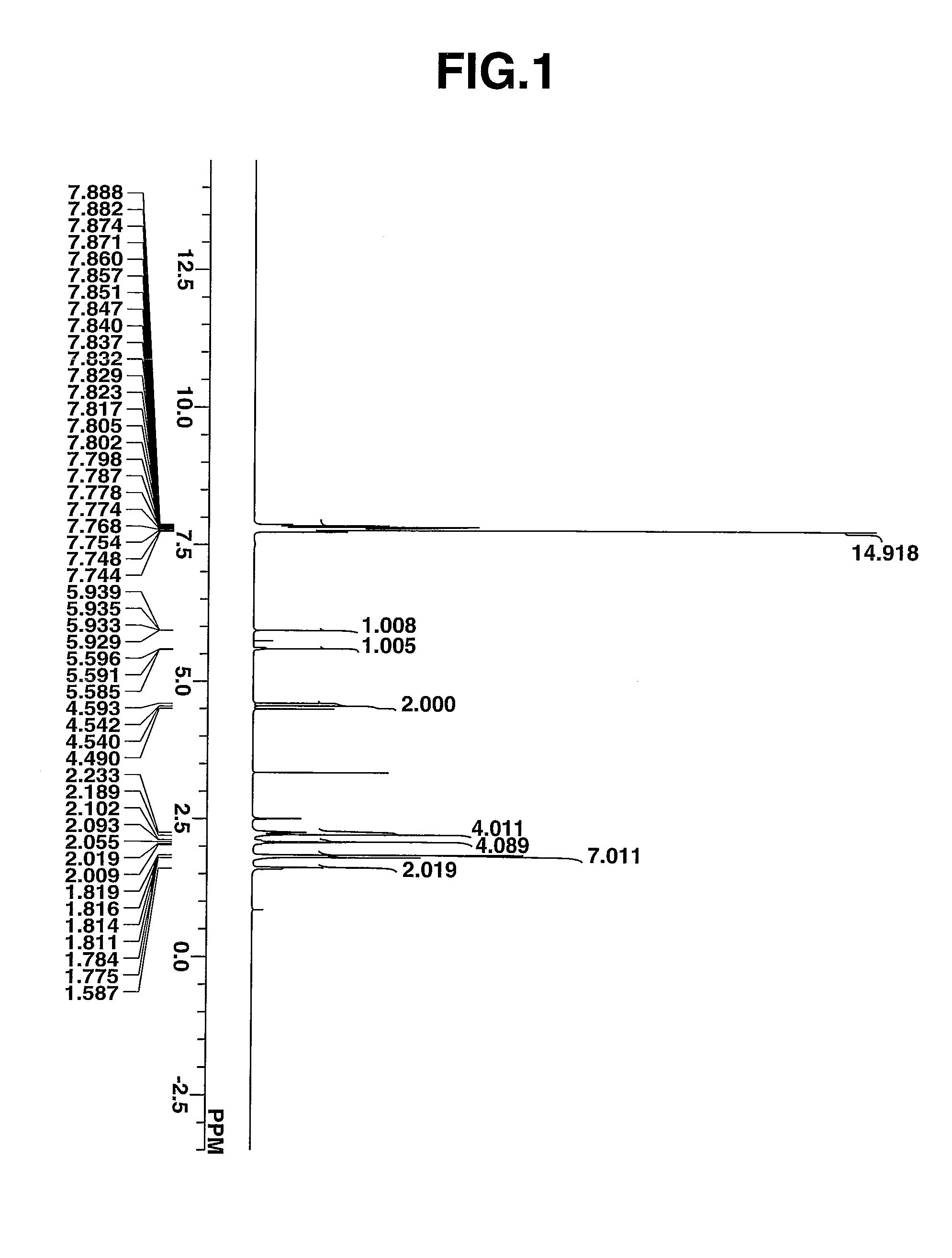

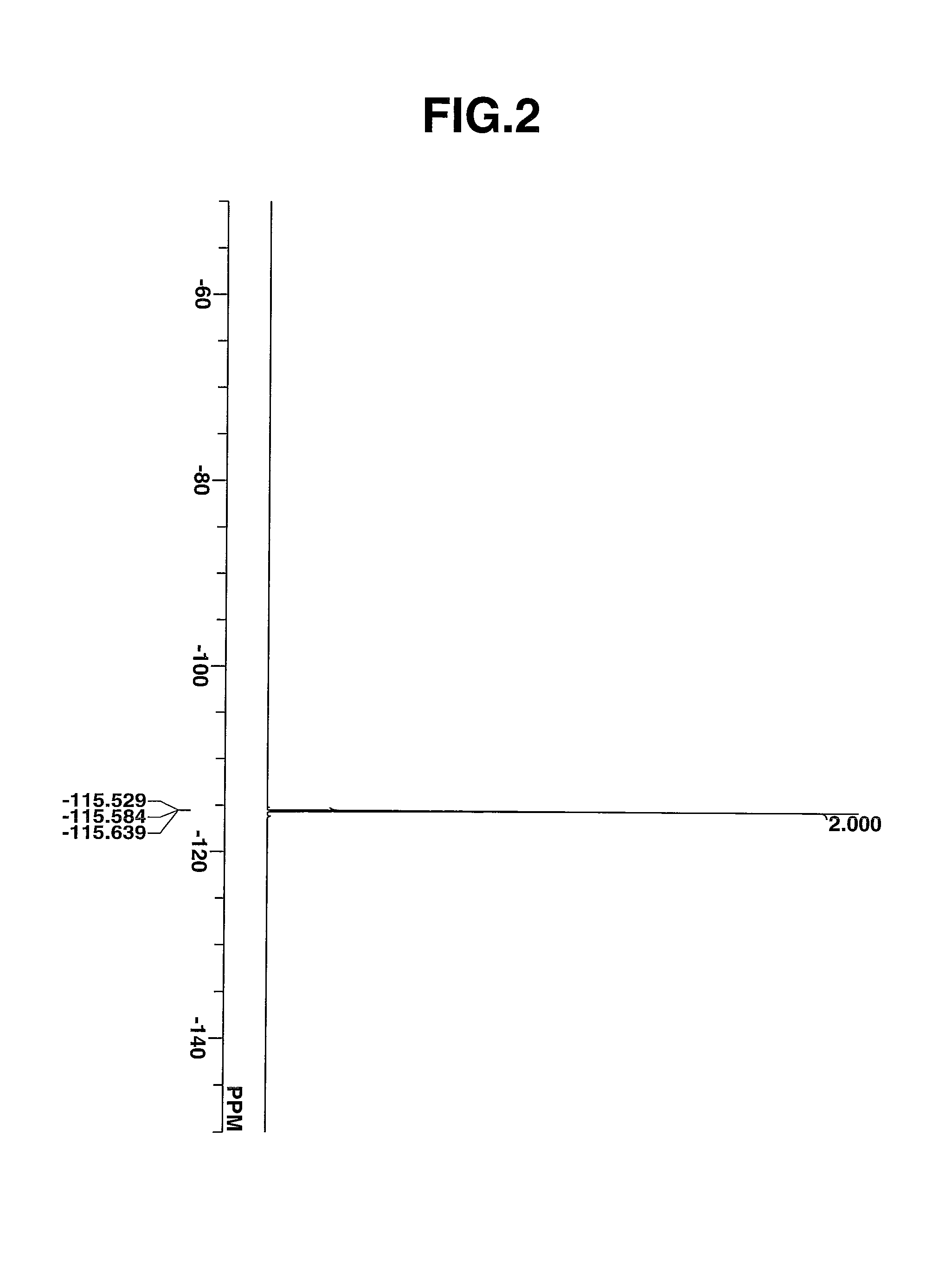

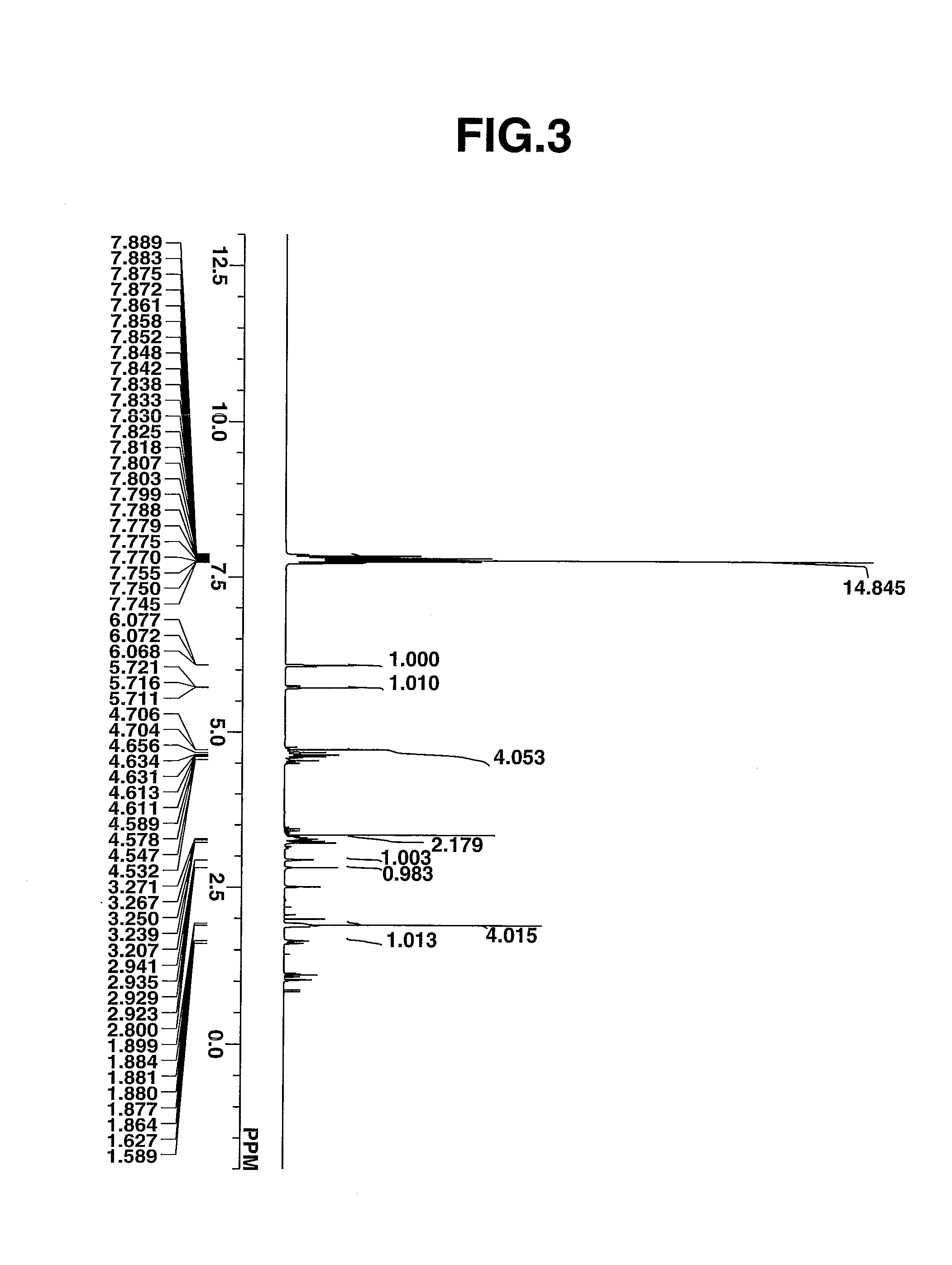

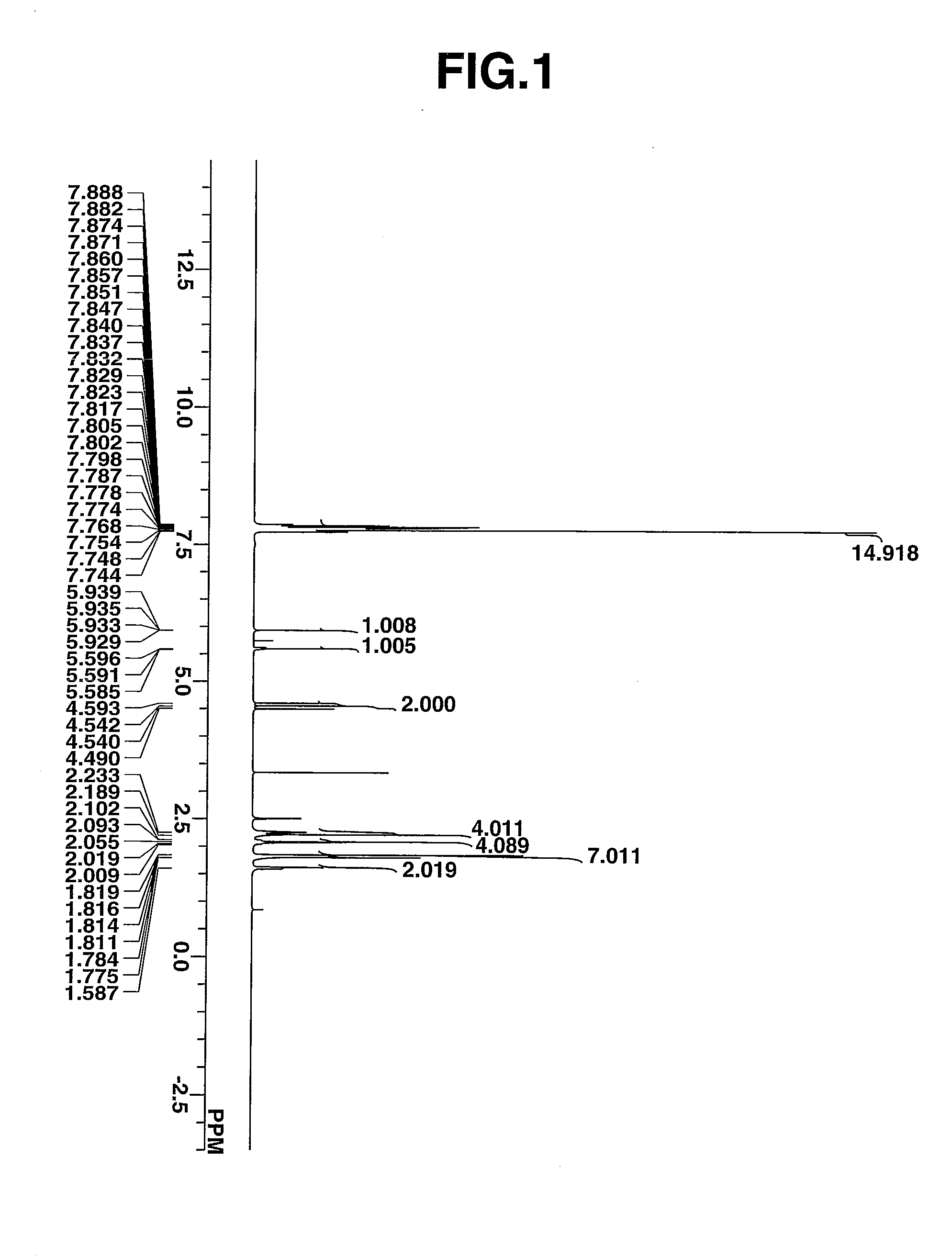

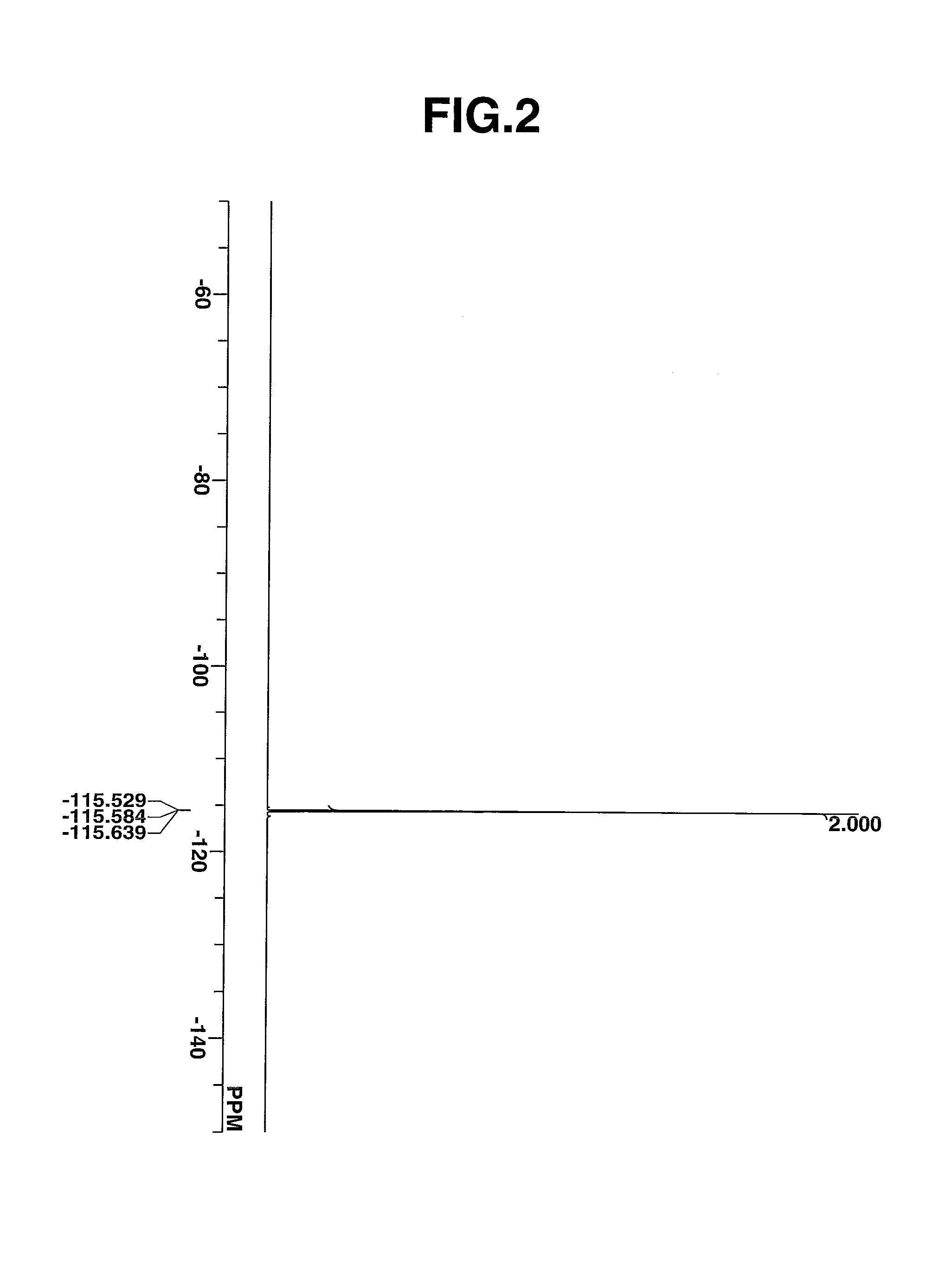

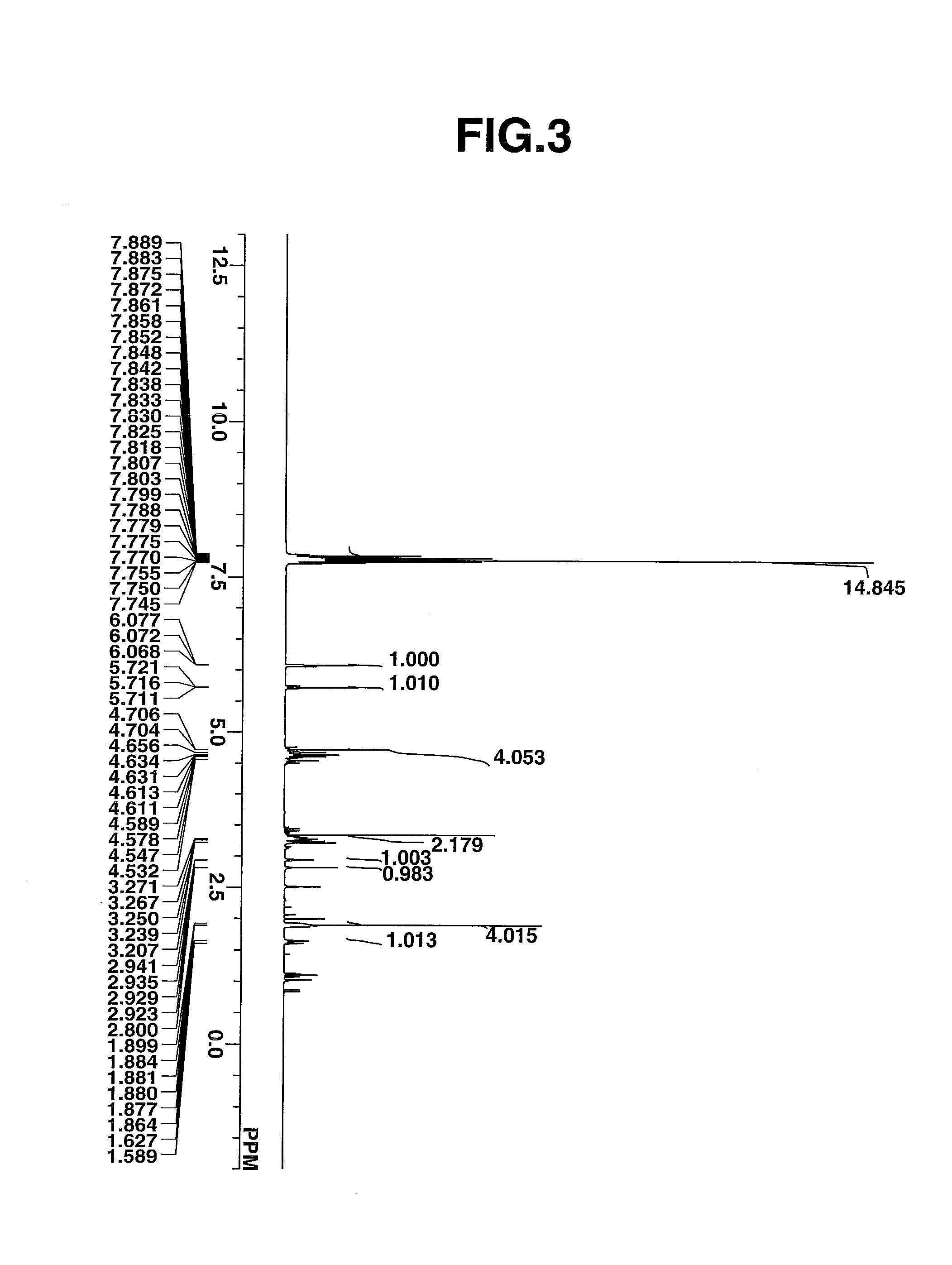

Sulfonium salt-containing polymer, resist composition, patterning process, and sulfonium salt monomer and making method

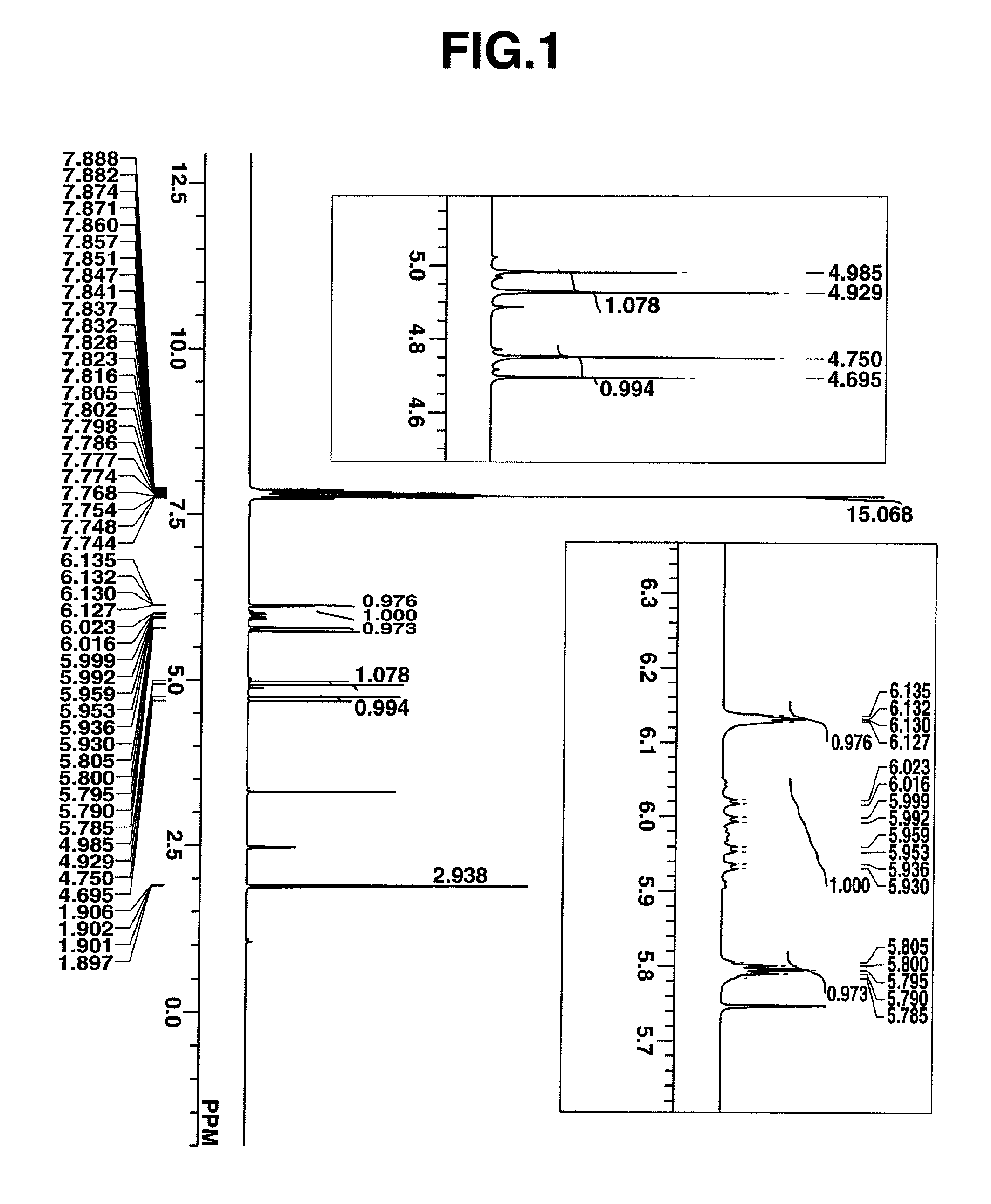

ActiveUS8785105B2High sensitivityPrevent seepagePhotosensitive materialsElectric discharge tubesResistMeth-

A sulfonium salt having a 4-fluorophenyl group is introduced as recurring units into a polymer comprising hydroxyphenyl (meth)acrylate units and acid labile group-containing (meth)acrylate units to form a polymer which is useful as a base resin in a resist composition. The resist composition has a high sensitivity, high resolution and minimized LER.

Owner:SHIN ETSU CHEM IND CO LTD

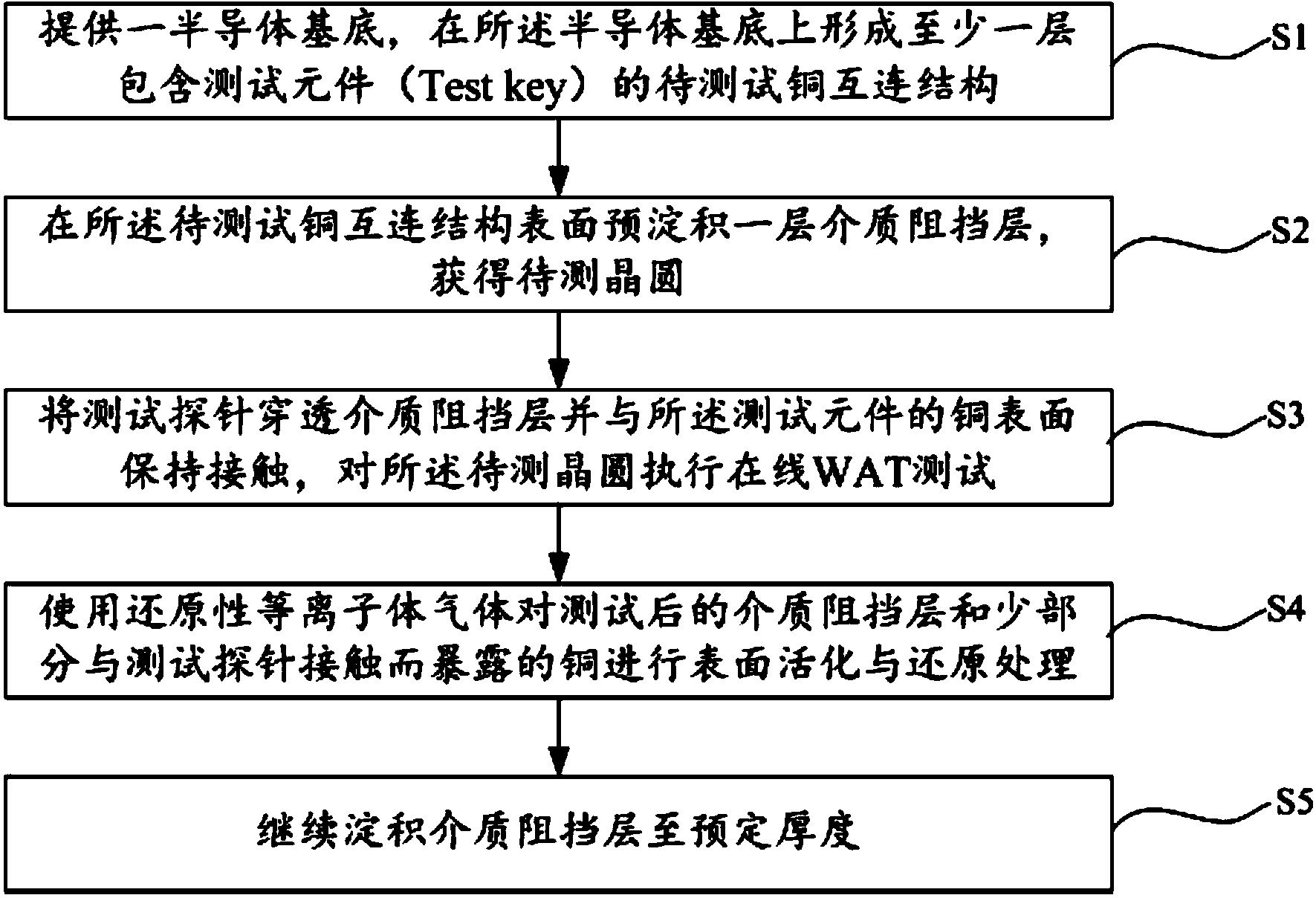

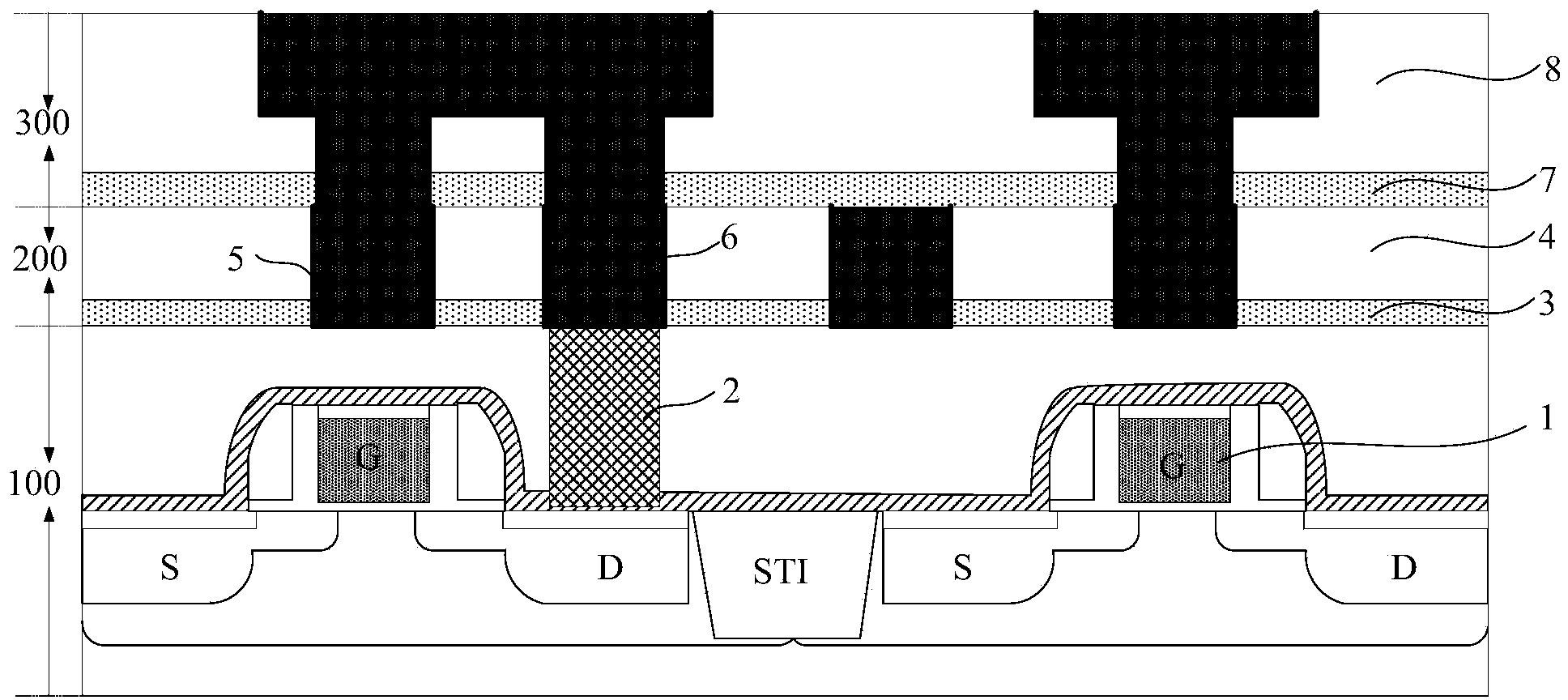

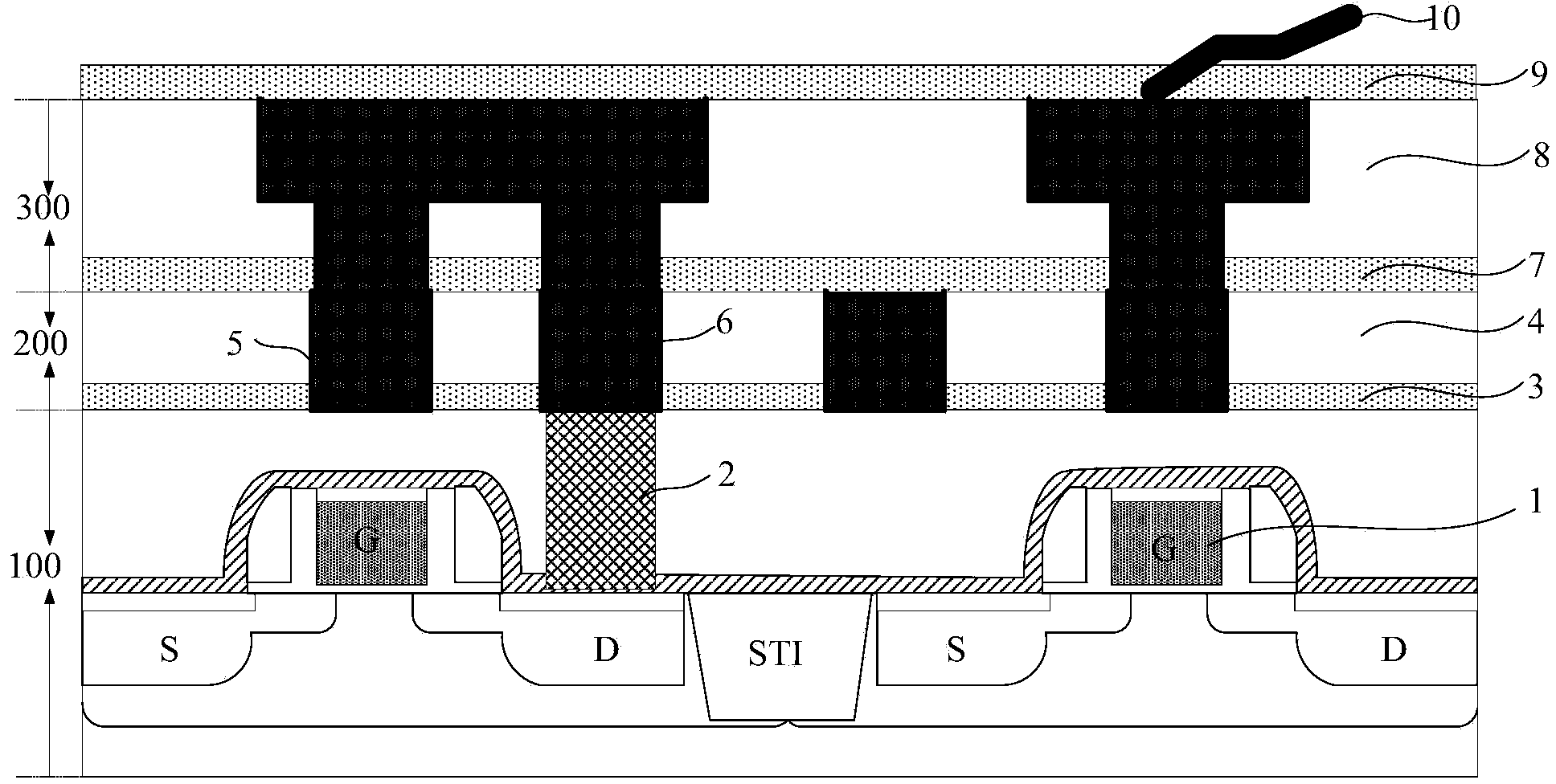

Method for lowering influence on copper interconnection reliability from online WAT testing

ActiveCN103972160AConvenient thermal protectionEfficient removalSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingReduction treatmentSurface plasmon

The invention provides a method for lowering the influence on the copper interconnection reliability from the online WAT testing. The method comprises the steps that at least one layer of to-be-tested copper interconnection structure comprising a testing component is formed on a semiconductor substrate; a dielectric barrier layer is deposited on the surface of the to-be-tested copper interconnection structure in advance, and a wafer to be tested is obtained; a testing probe penetrates through the dielectric barrier layer and keeps contact with the copper surface of the testing component, and online WAT testing is carried out on the wafer to be tested; surface activation and reduction treatment are carried out on the tested dielectric barrier layer and a small part of copper exposed after making contact with the testing probe through reducing plasma gas; the dielectric barrier layer continues to be deposited to be at the preset thickness. Through the method for combining the pre-deposited dielectric barrier layer serving as an isolation protection layer before the testing with the surface plasma activation and reduction treatment after the testing, defects in copper and dielectric materials are effectively restrained from being generated in the online WAT testing process, and the influence on the copper interconnection reliability from the online WAT testing is lowered significantly.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Photoacid generator, resist composition, and patterning process

ActiveUS8114570B2Controlled diffusionMinimize impactOrganic chemistryOrganic compound preparationResistHigh energy

Photoacid generators generate sulfonic acids of formula (1a) upon exposure to high-energy radiation.ROC(═O)R1—COOCH2CF2SO3−H+ (1a)RO is OH or C1-C20 organoxy, R1 is a divalent C1-C20 aliphatic group or forms a cyclic structure with RO. The photoacid generators are compatible with resins and can control acid diffusion and are thus suited for use in chemically amplified resist compositions.

Owner:SHIN ETSU CHEM IND CO LTD

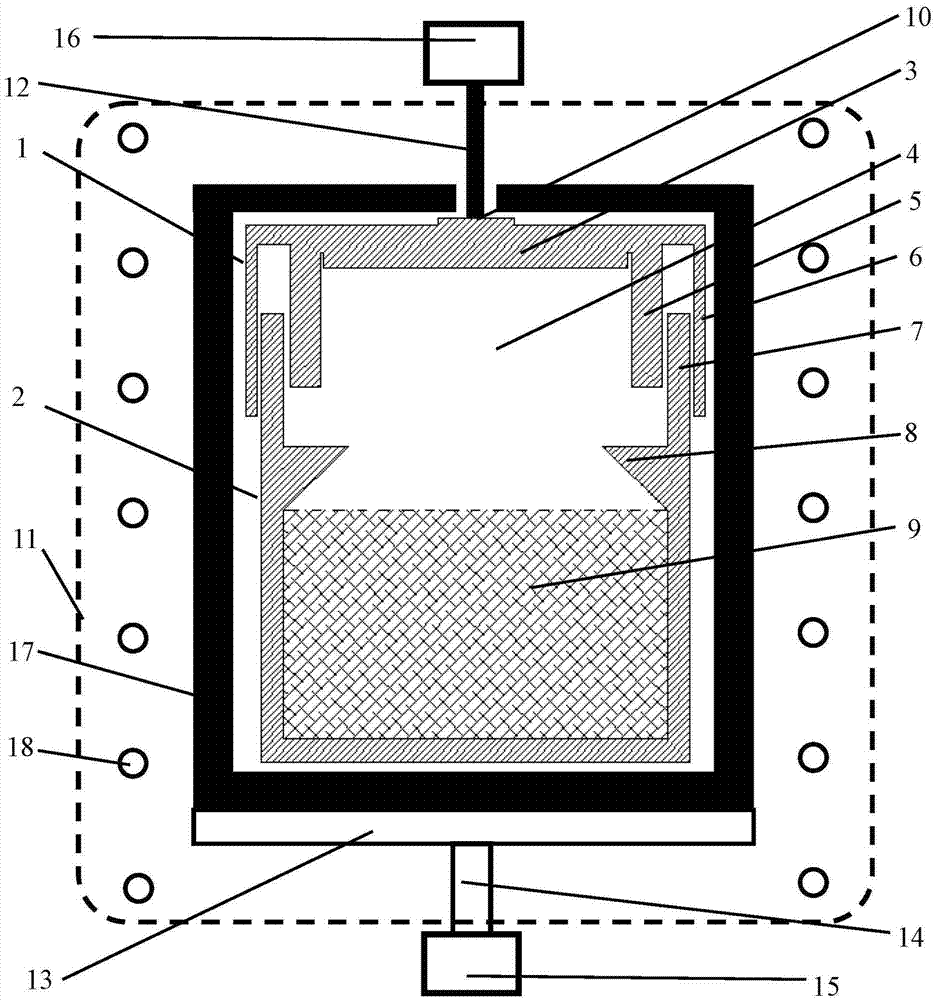

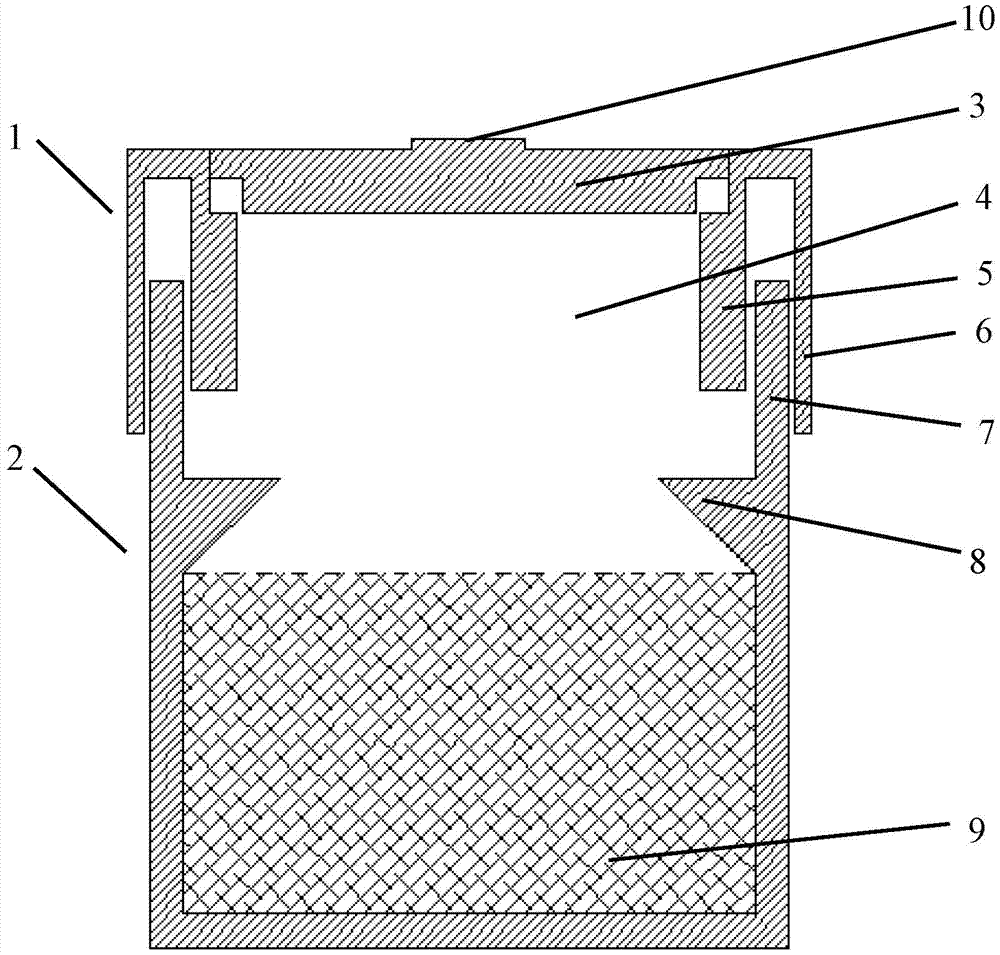

Split type crucible for crystal growth of silicon carbide

InactiveCN106929913AQuality improvementAvoid destructionPolycrystalline material growthFrom condensed vaporsCrucibleEngineering

The invention provides a split type crucible for crystal growth of silicon carbide. The crucible comprises the following components: a raw material chamber for containing raw materials for crystal growth of SiC; a growth chamber which is nested on the upper part of the raw material chamber in relative movement mode in order to form a crystallization area of crystal, wherein the growth chamber comprises a growth chamber, and a seed crystal holder which is arranged on a upper wall of the growth chamber; and a double layer structure which is formed by sidewalls of the growth chamber and comprises an inner cylinder and an outer cylinder. The crucible can be used for adjusting distance between the crystal surface and the raw material surface in a process of growth, and the stability of a temperature field is kept.

Owner:SHANGHAI INST OF CERAMIC CHEM & TECH CHINESE ACAD OF SCI

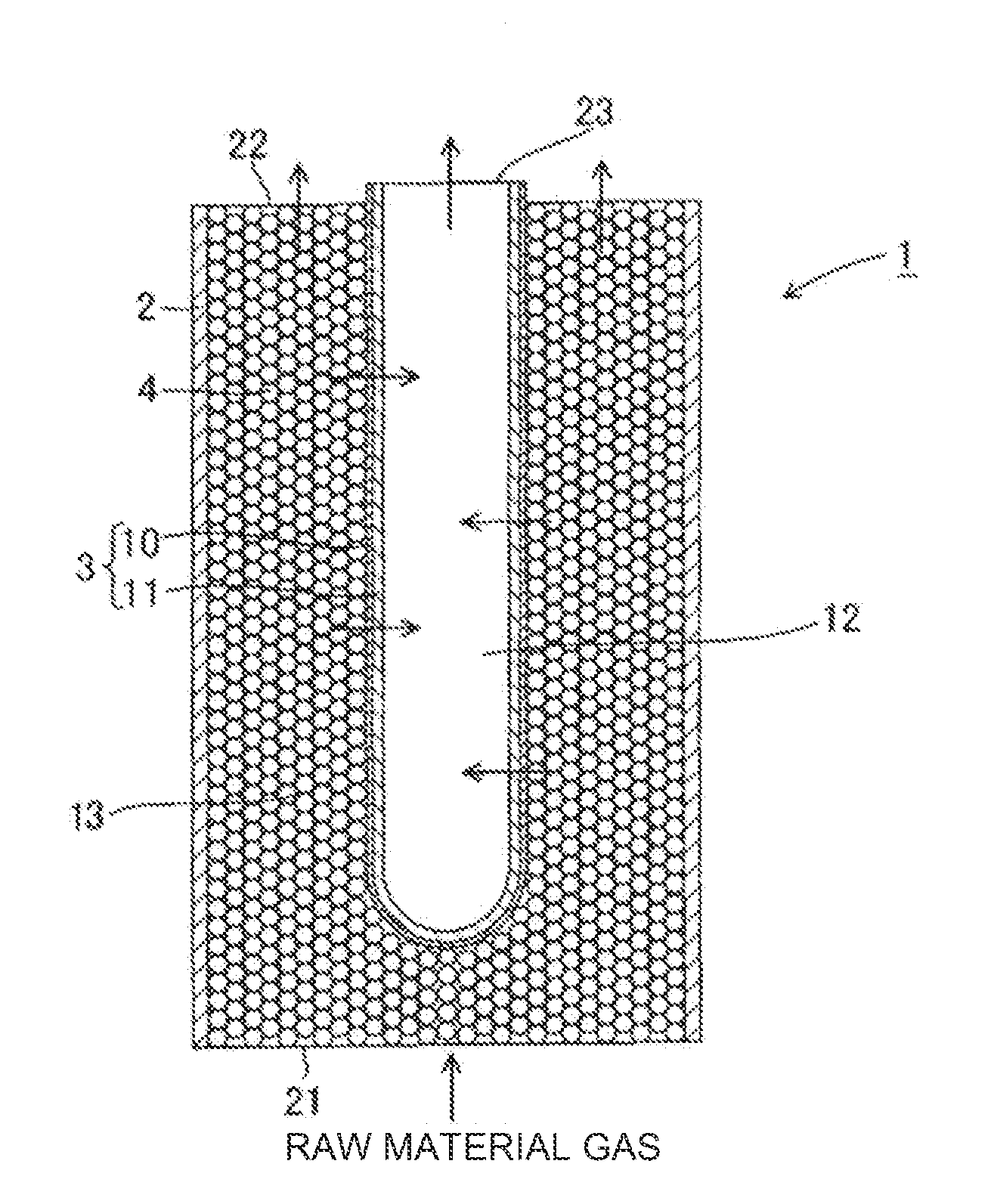

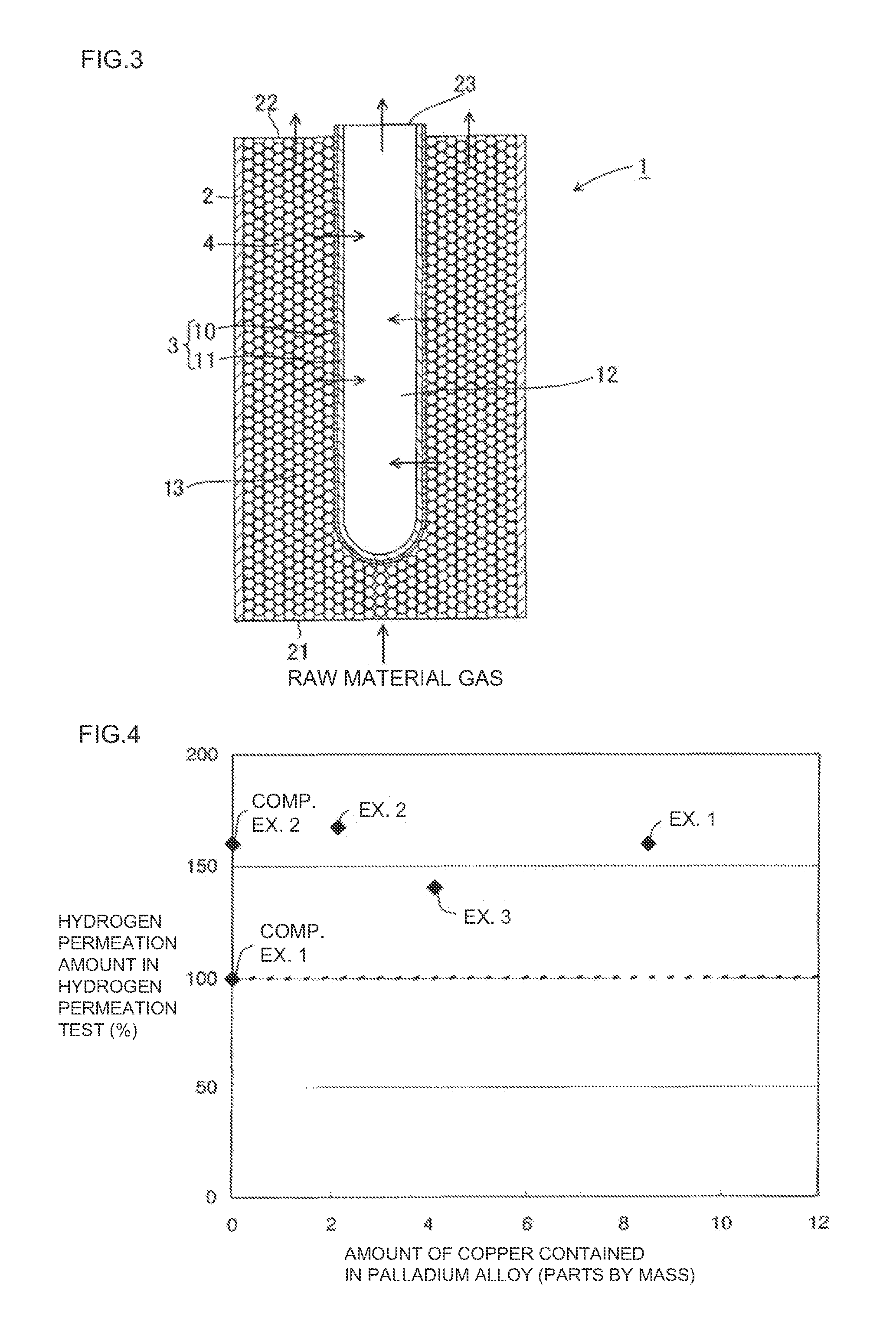

Hydrogen separation membrane and permselective membrane reactor

InactiveUS20100092353A1Inhibits the formation of defectsReduce penetrationSemi-permeable membranesMembranesTriple pointHydrogen

Owner:NGK INSULATORS LTD

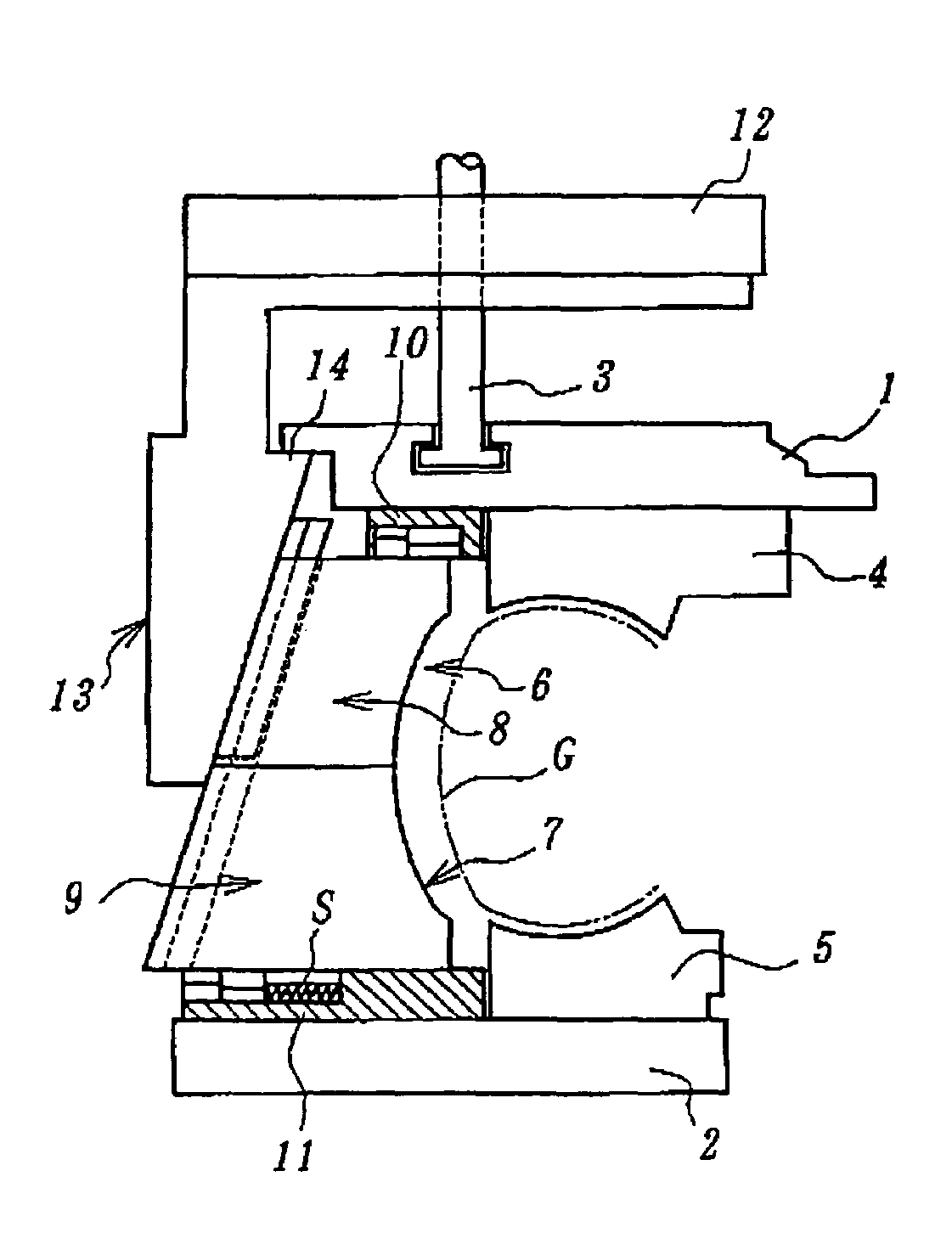

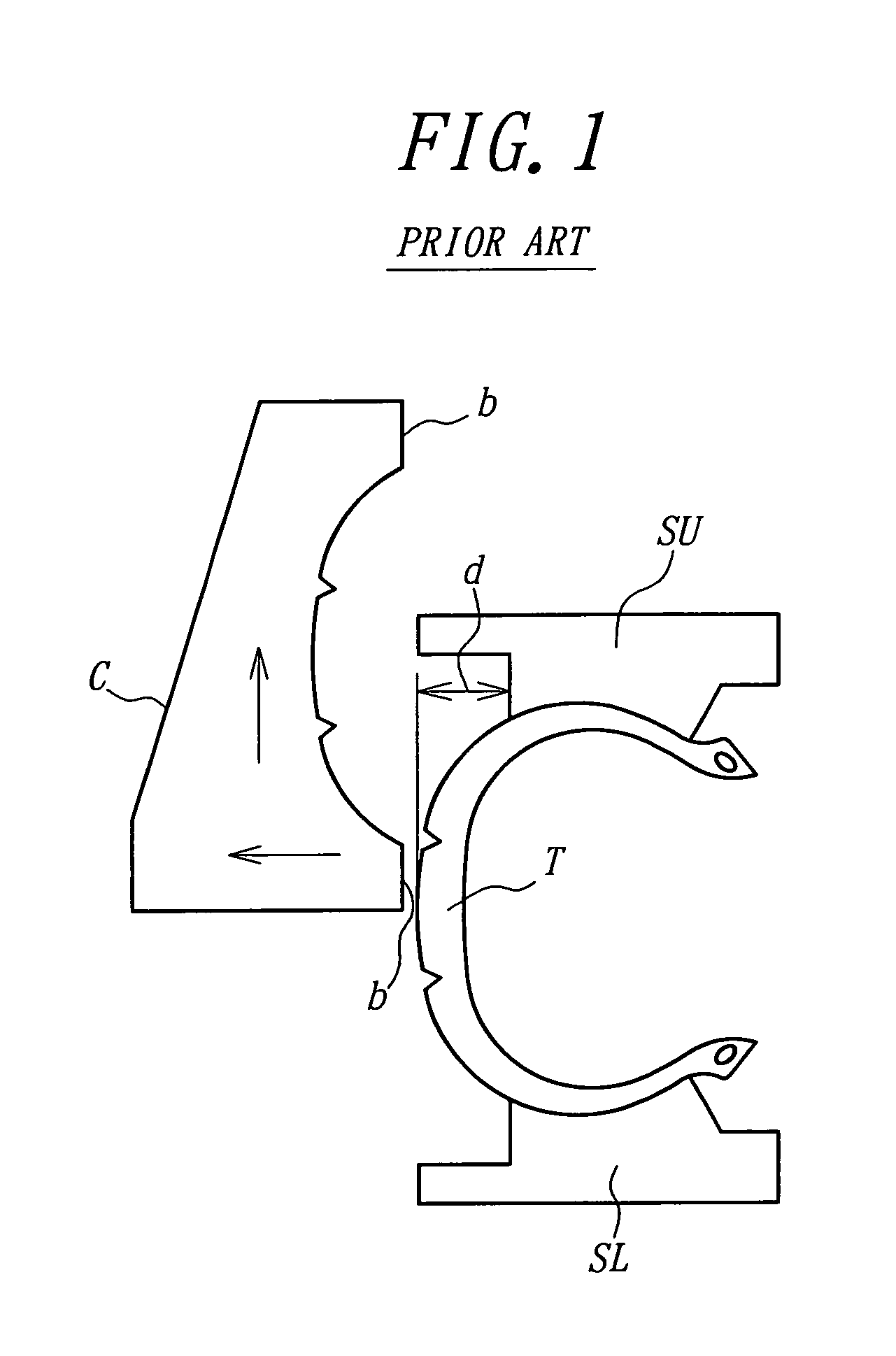

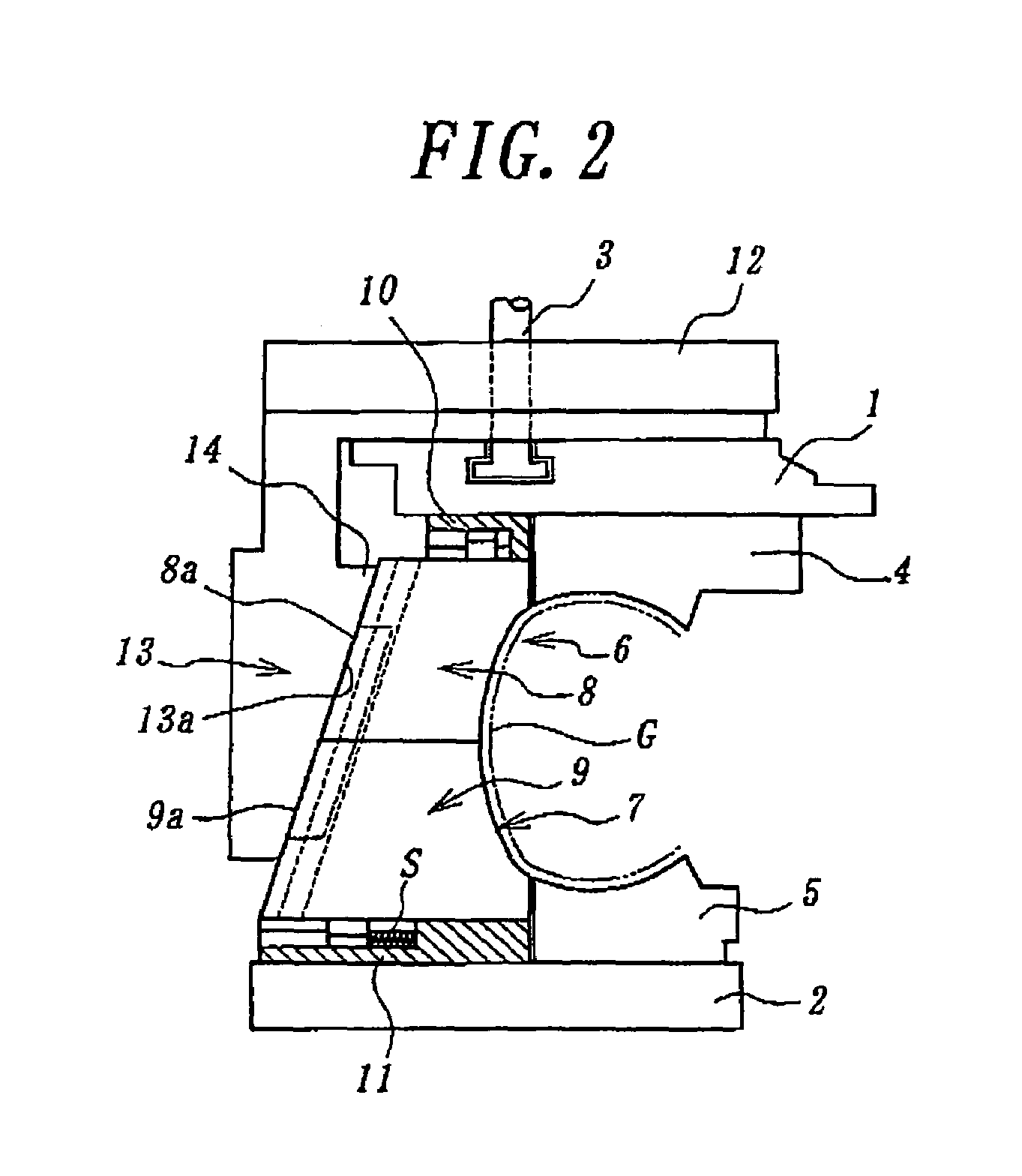

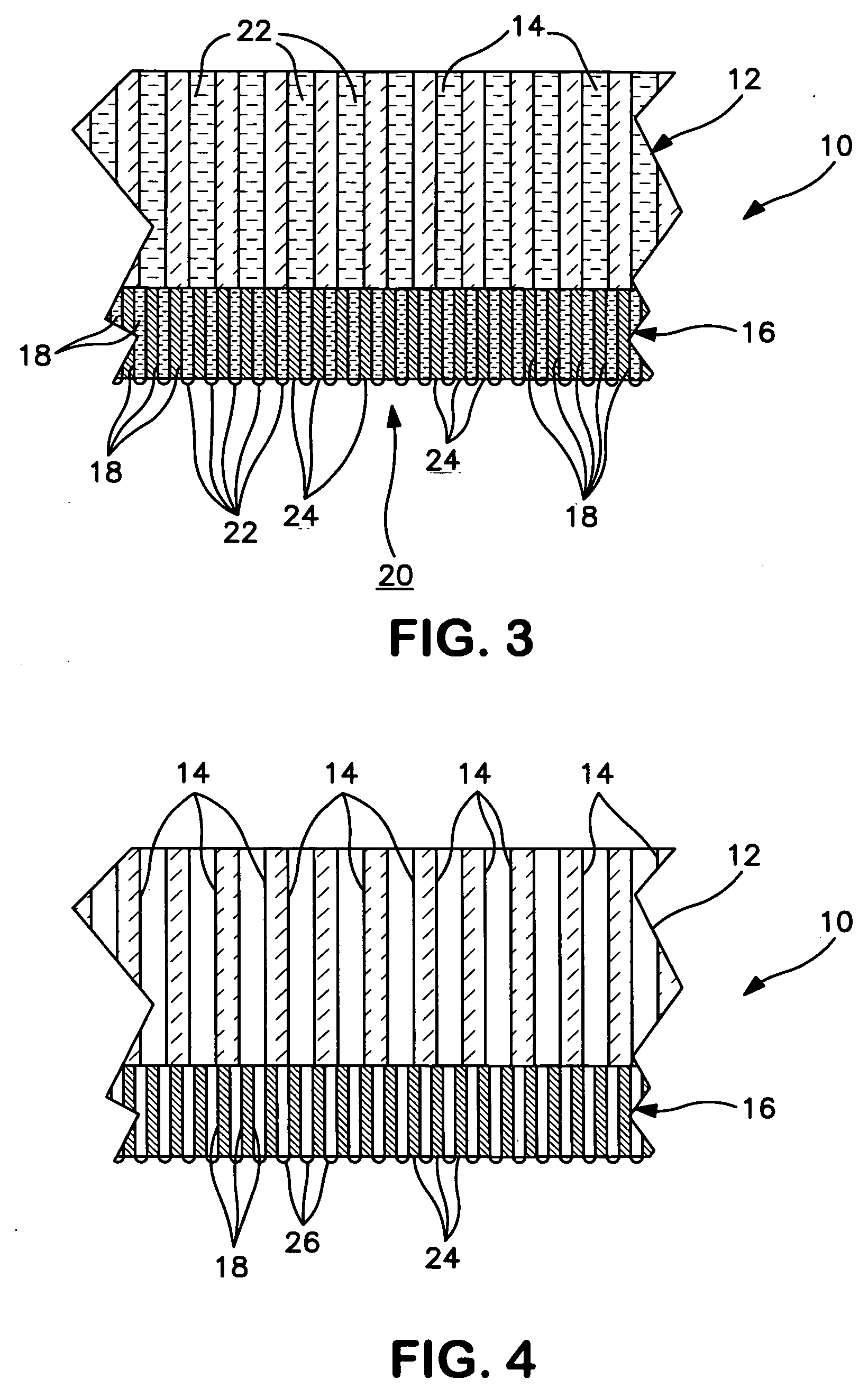

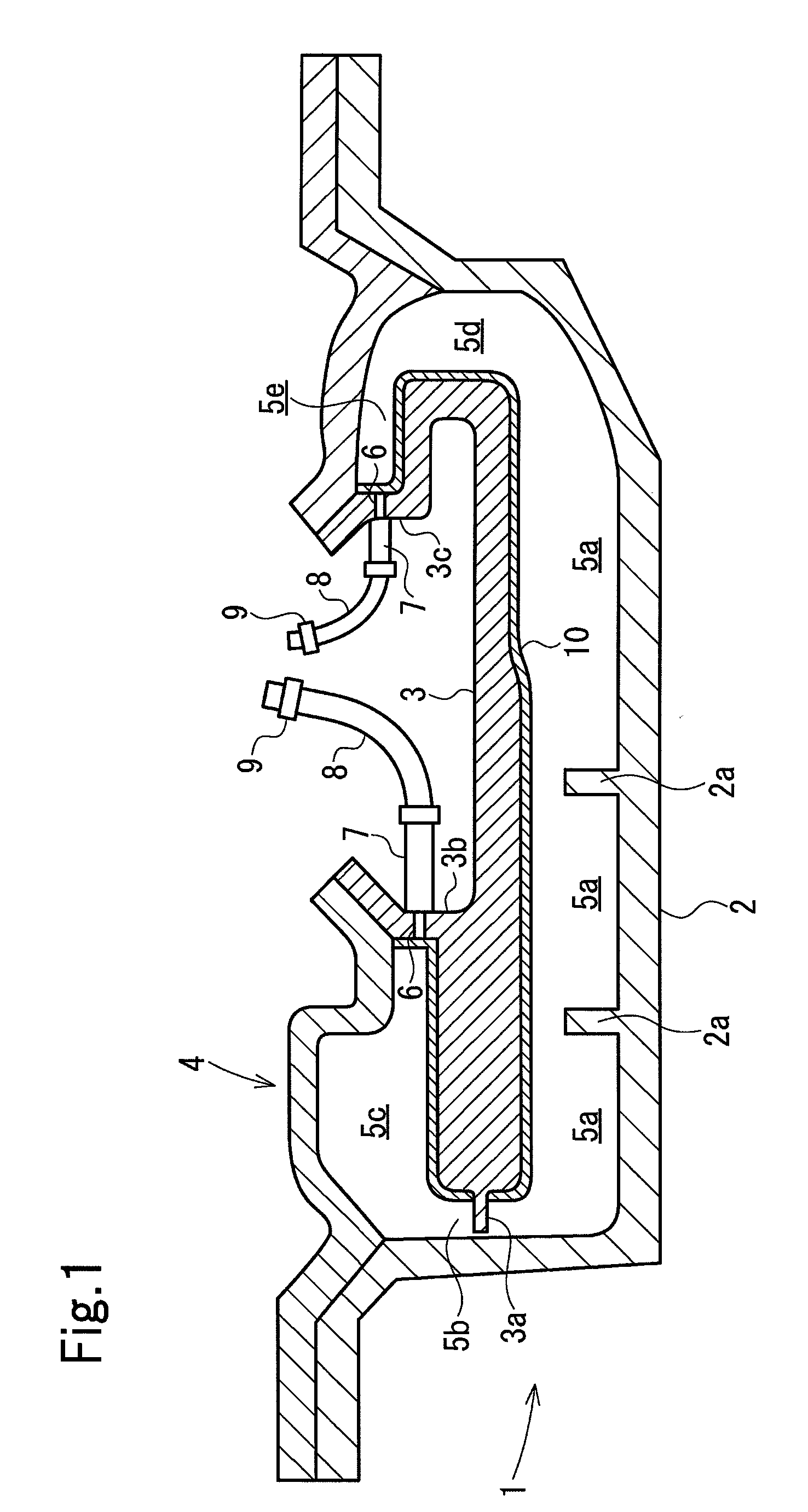

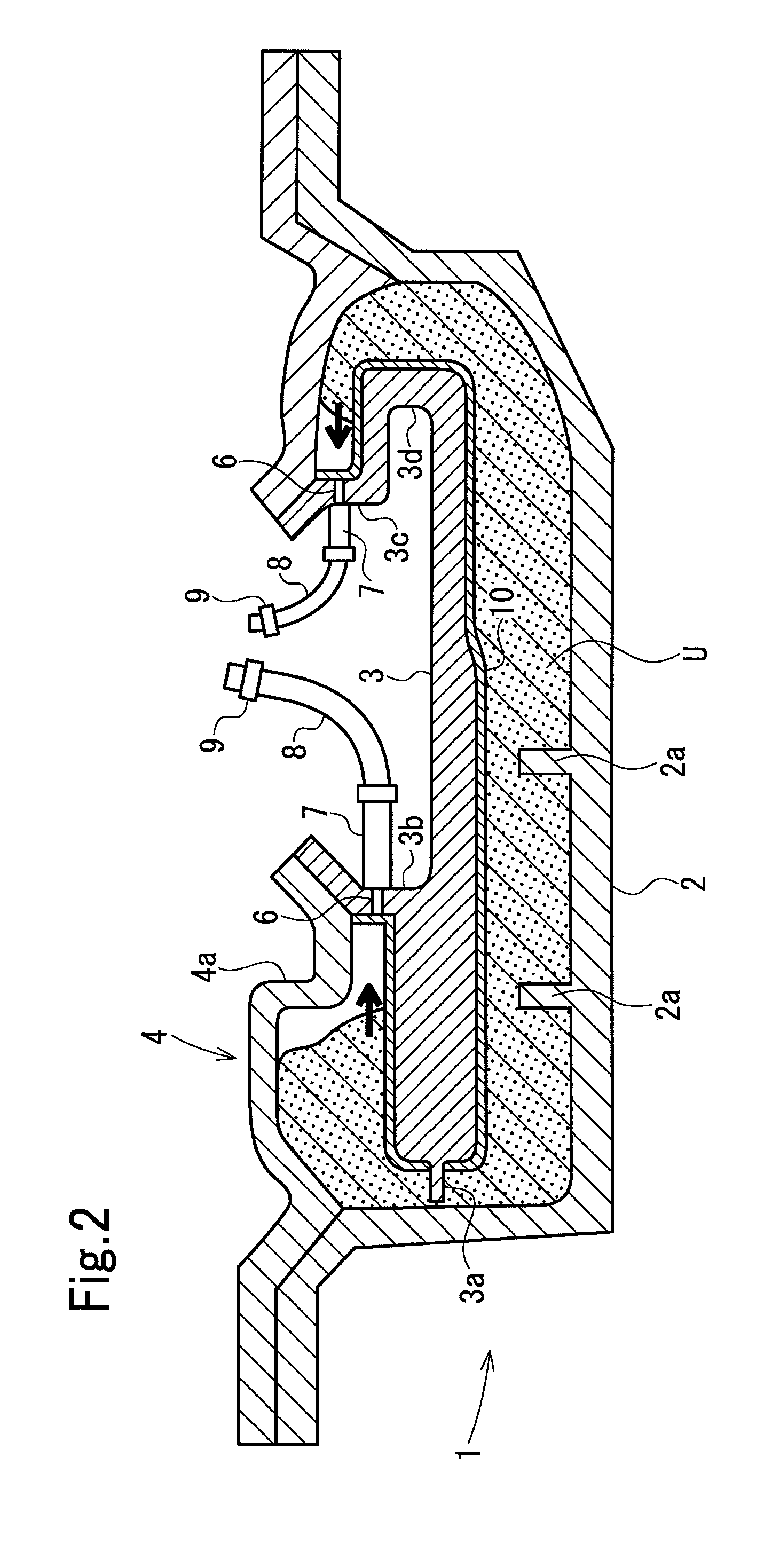

Vulcanizing mold for pneumatic tires

InactiveUS6949213B1Inhibits the formation of defectsFree from unevennessTyresBeltsAbutmentEngineering

A vulcanizing mold for pneumatic tires includes upper and lower base plates, upper and lower sidewall mold members attached to the upper and lower base plates, respectively; and upper and lower tread mold members attached to the upper and lower base plates, respectively. The upper and lower tread mold members are constituted of upper segments and lower segments, respectively. The upper and lower segments can be radially expanded and contracted relative to the upper and lower sidewall mold members, respectively. In operation, the upper and lower sidewall mold members are displaced toward each other so that the upper and lower segments are brought into abutment with each other. Then, a single cam ring is operated to cause all of the segments to be simultaneously displaced radially inwards and relative to the upper and lower sidewall mold members, with the upper segments in abutment with the lower segments.

Owner:BRIDGESTONE CORP

Metal gasket and a material for its manufacture and a method for their manufacture

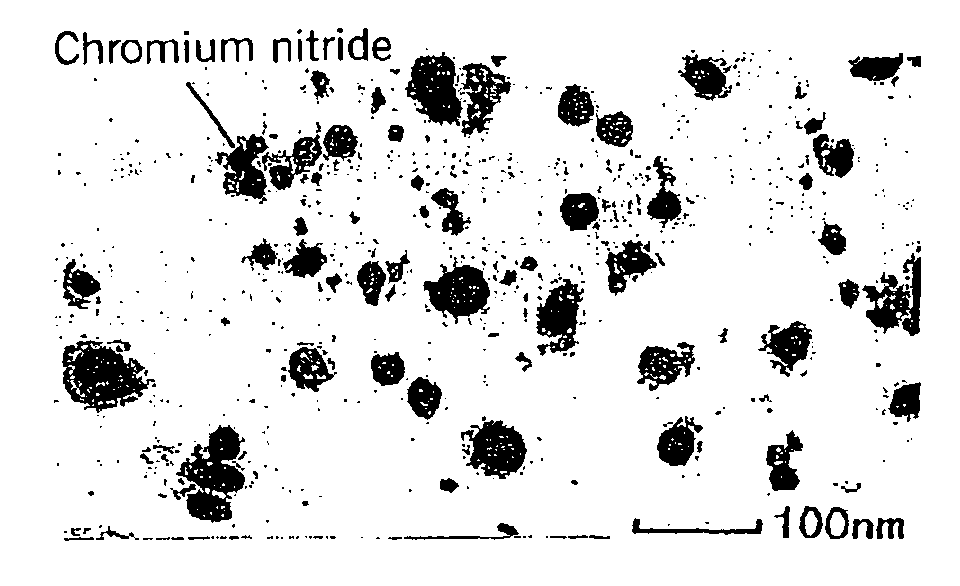

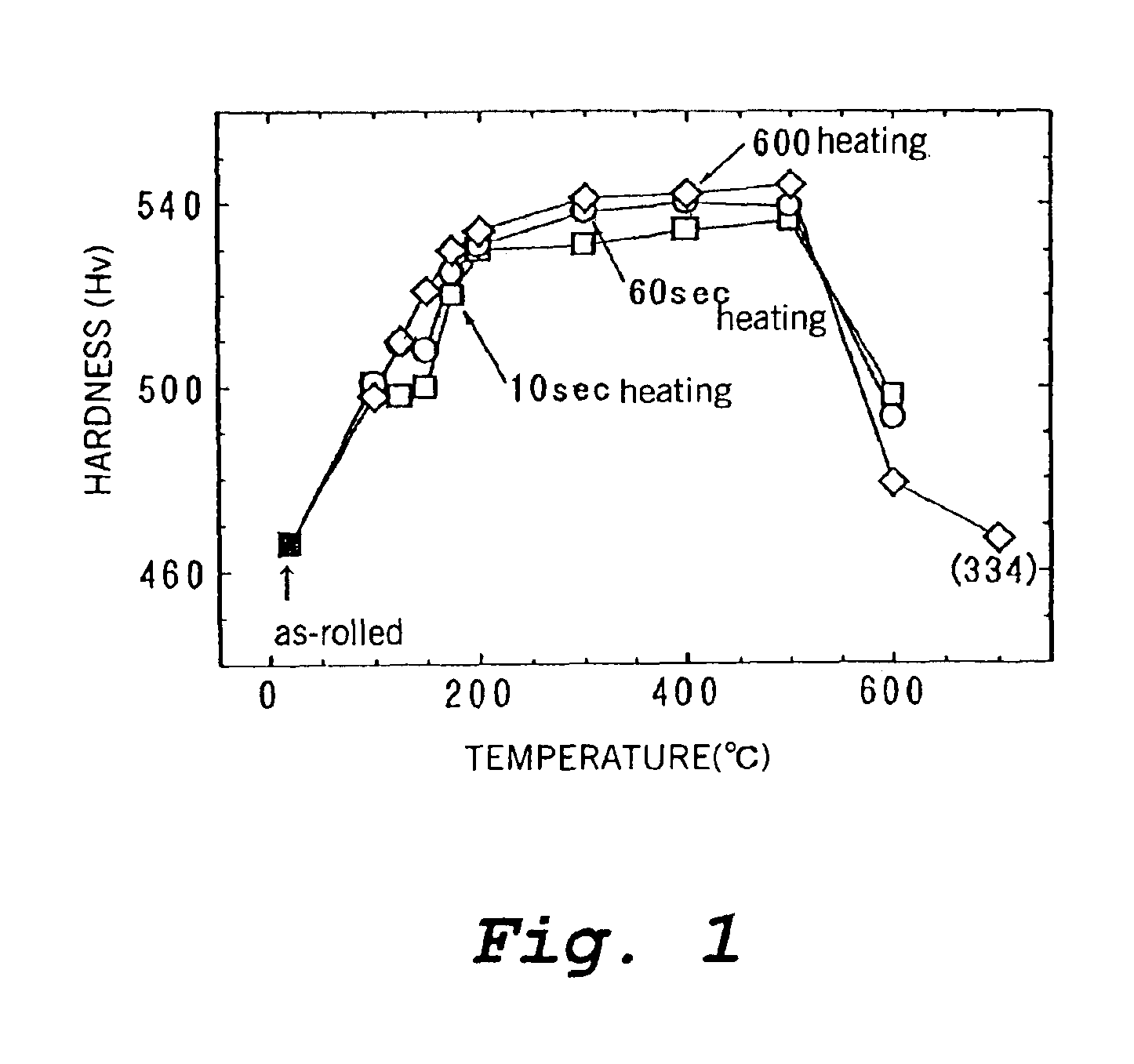

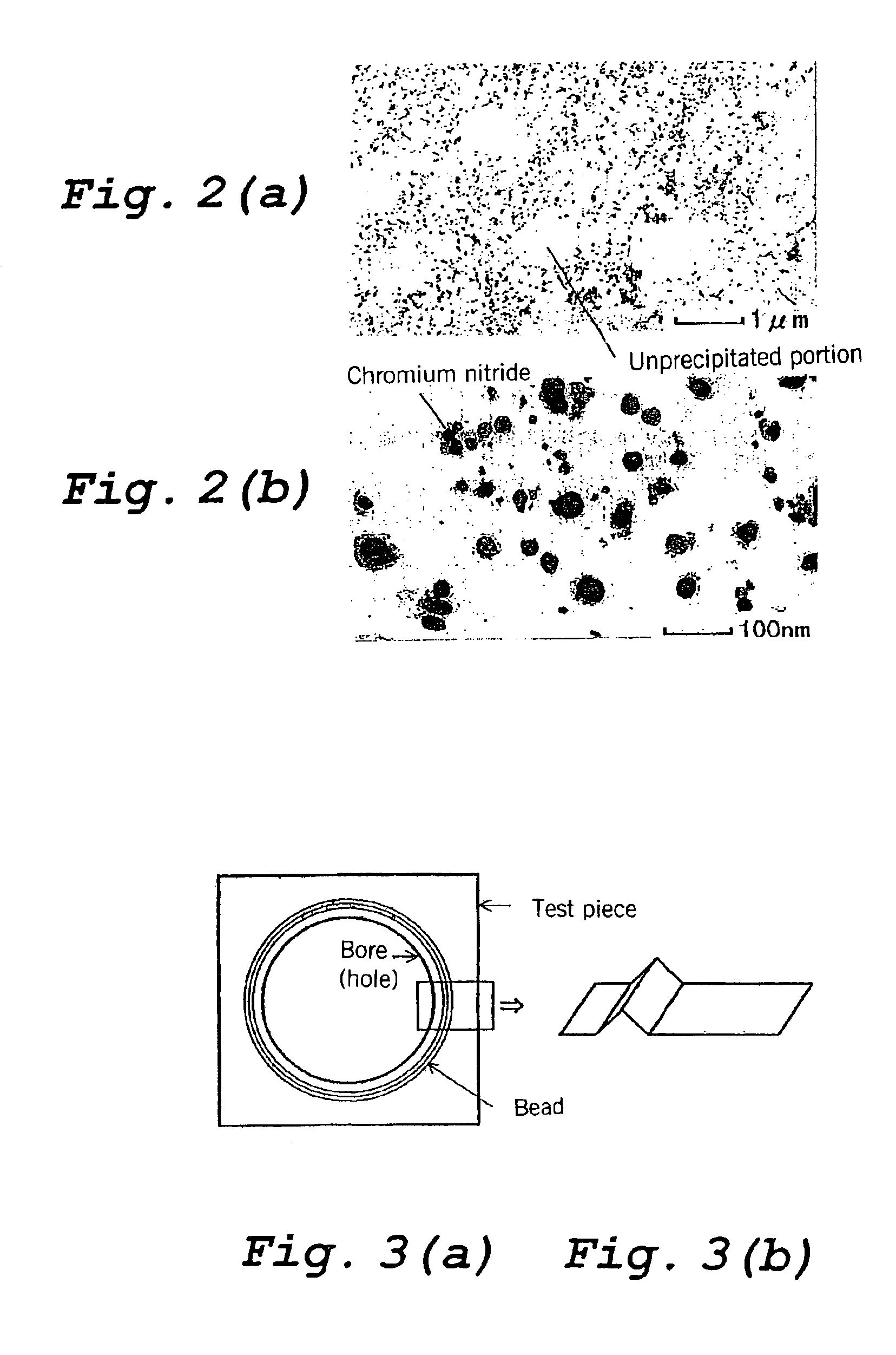

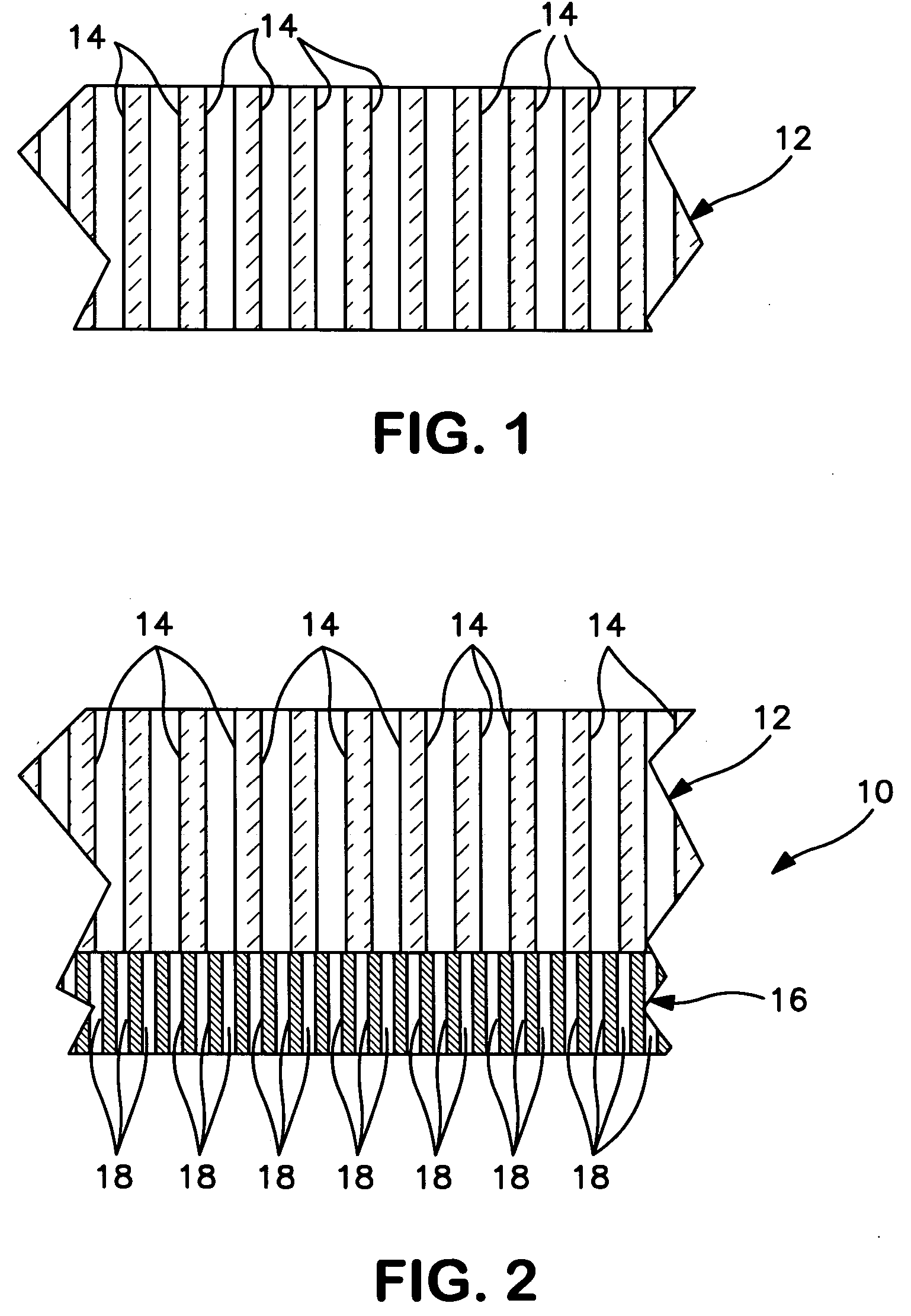

InactiveUS6893727B2Improve machinabilityComplex shapeEngine sealsPiston ringsStrain induced martensiteChromium nitride

This invention relates to a stainless steel gasket having markedly improved strength and fatigue properties due to precipitation strengthening. Its composition comprises C: at most 0.03%, Si: at most 1.0%, Mn: at most 2%, Cr: 16.0%-18.0%, Ni: 6.0%-8.0%, N: at most 0.25%, if necessary Nb: at most 0.30%, and a remainder of Fe and unavoidable impurities. After cold rolling, final annealing is carried out, and after a structure is formed of recrystallized grains with an average grain diameter of at most 5 μm having an area ratio of 50-100% and an unrecrystallized portion having an area ratio of 0-50%, a metal gasket is formed by steps including temper rolling with a reduction of at least 30% to make the area ratio of a strain induced martensite phase at least 40%, and forming and heat treatment at 200-350° C. The metal gasket has a duplex phase structure of at least 40% martensite in which chromium nitride is precipitated and a remainder of austenite, or it has a single phase structure of martensite in which chromium nitride is precipitated, and it has Hv of at least 500.

Owner:HONDA MOTOR CO LTD +1

Hydrogen transport membrane fabrication method

InactiveUS20070110991A1Inhibits the formation of defectsMembranesSemi-permeable membranesAlloySalt solution

A method of forming a hydrogen transport membrane to separate hydrogen from a hydrogen containing feed in which a porous ceramic support is formed to support a dense layer of palladium or an alloy of palladium serving as a hydrogen transport material. Isolated deposits of palladium, a palladium alloy or a component of such alloy are produced on a surface of the porous ceramic support that bridge pores within the porous ceramic support without penetrating the pores and without bridging regions of the surface defined between the pores. The isolated deposits of the metal are produced by an electroless plating process that involves contacting the porous ceramic support with a precipitating agent so that the precipitating agent fills the pores but does not seep out of the pores onto the regions of the surfaces defined between the pores. The surface is then contacted with a salt solution containing a salt of the metal so that said metal precipitates and produces the isolated deposits of the metal. Thereafter, the dense layer is formed on the surface having the isolated deposits.

Owner:PRAXAIR TECH INC

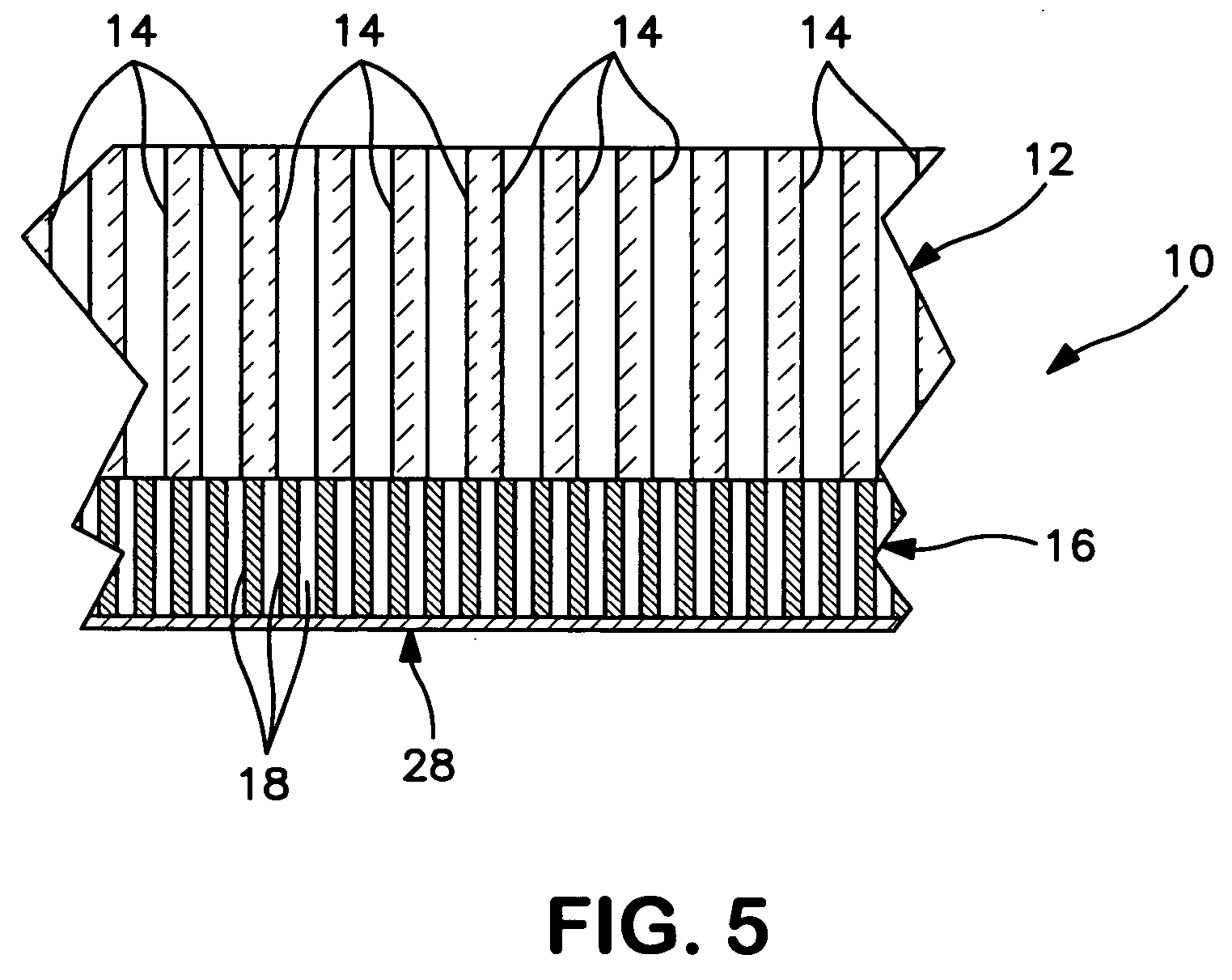

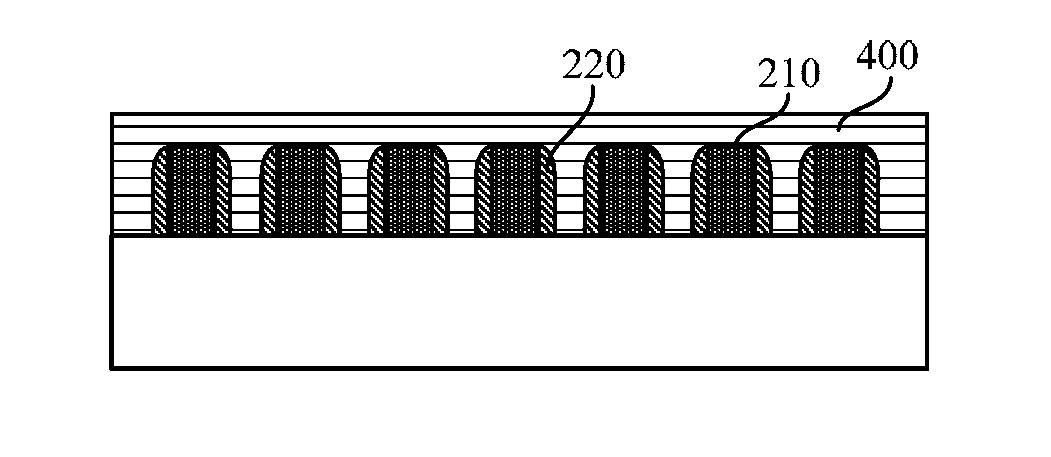

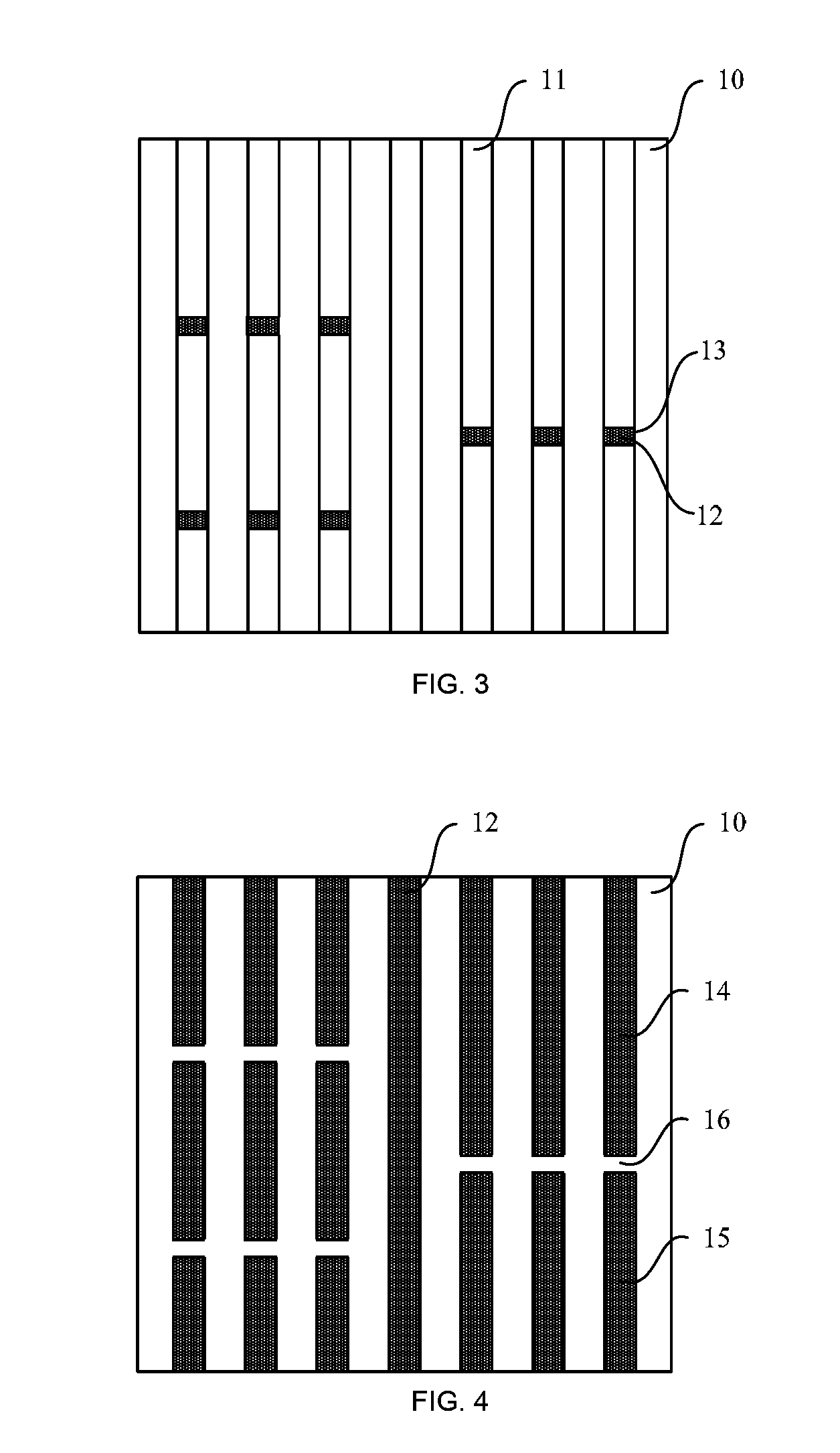

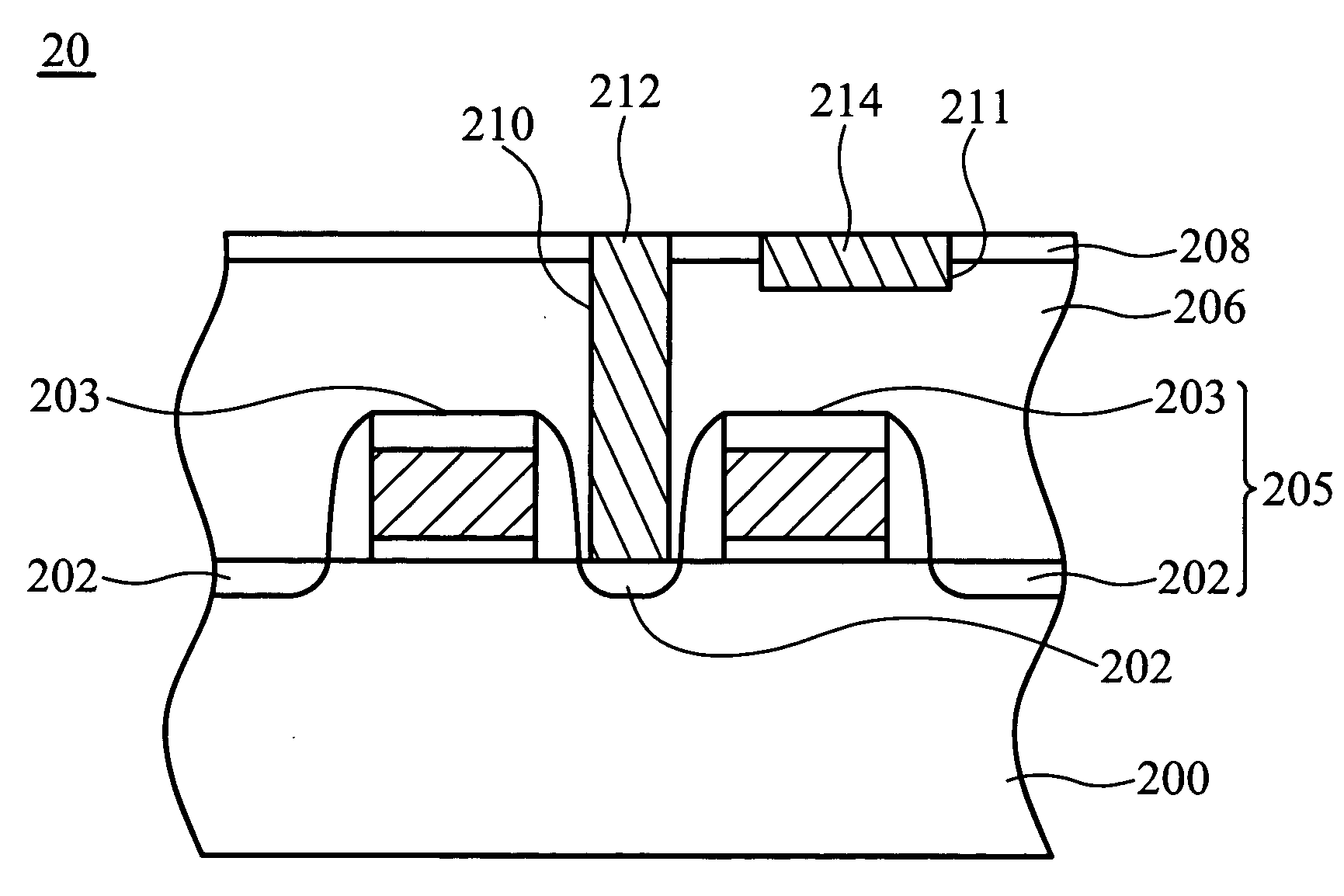

Semiconductor structure and method for manufacturing the same

InactiveUS20150243654A1Guaranteed performanceInhibits the formation of defectsTransistorSolid-state devicesState of artSemiconductor structure

The present invention provides a method for manufacturing a semiconductor structure, which comprises: a) forming gate lines extending along one direction on a substrate; b) forming a photoresist layer that covers the semiconductor structure; patterning the photoresist layer to form openings that span over the gate lines: c) implanting ions into the gate lines, such that the gate lines are insulated at the openings. The present invention enables the gate lines to maintain complete shape at formation of electrically isolated gates, which will not cause defects that exist in the prior art when forming a dielectric layers at subsequent steps, thereby guaranteeing performance of semiconductor devices. Additionally, the present invention further provides a semiconductor structure manufactured according to the method provided by the present invention.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

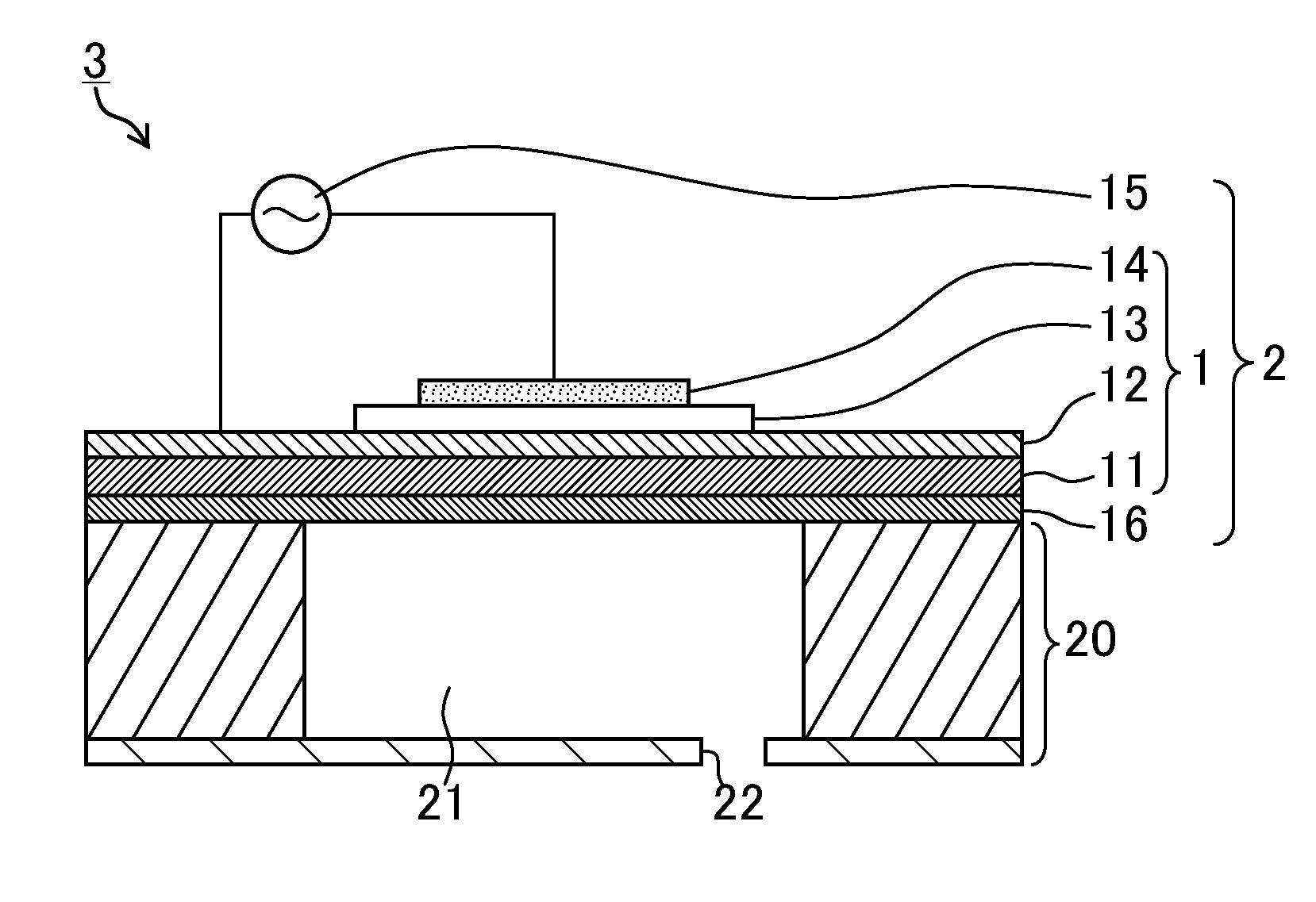

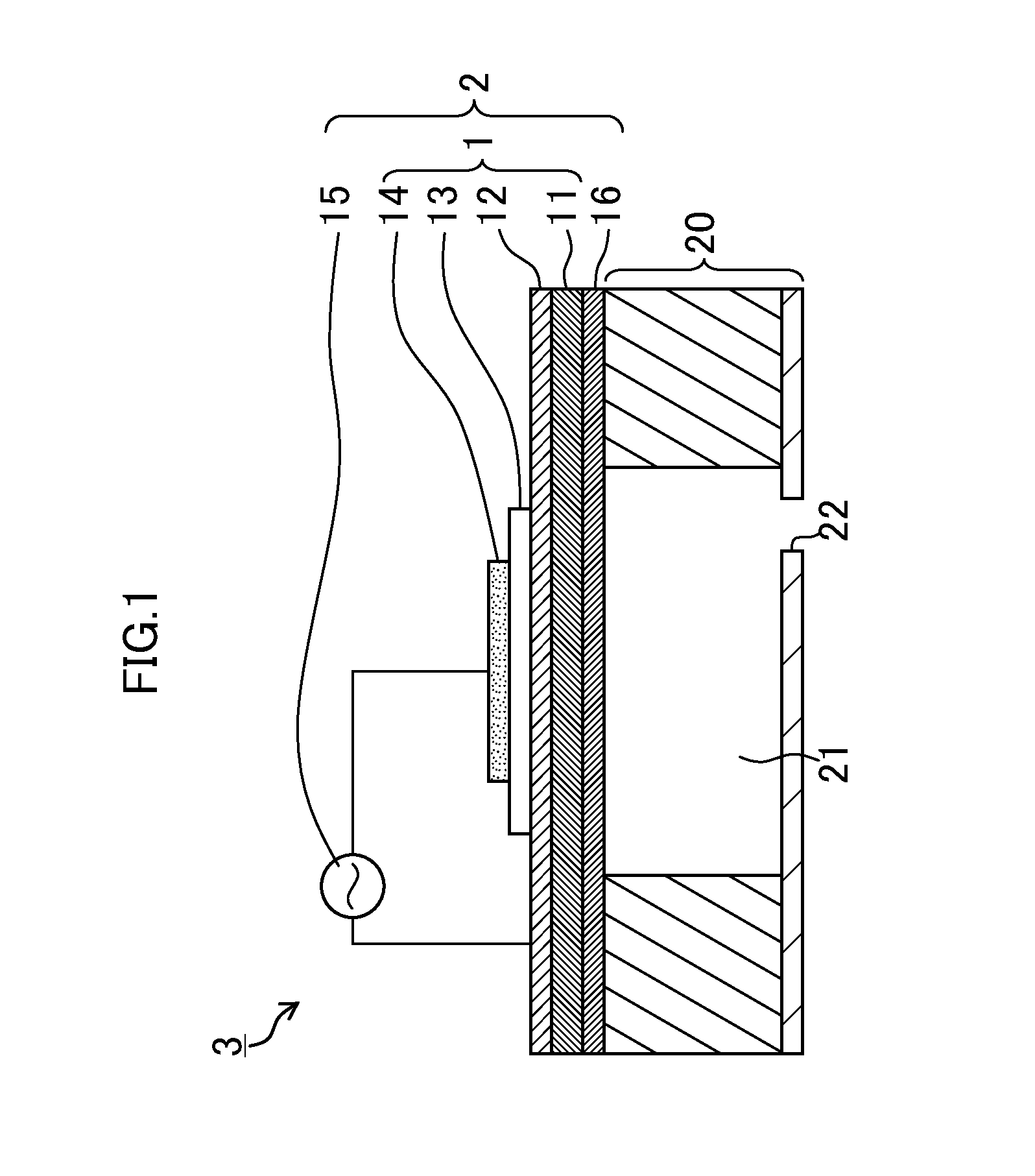

Piezoelectric film, piezoelectric device, liquid ejection apparatus, and method of producing piezoelectric film

InactiveUS20110215679A1Inhibition formationImprove driving durabilityPiezoelectric/electrostriction/magnetostriction machinesSynthetic resin layered productsGas phaseDeposition process

A piezoelectric film is formed on a surface of a substrate by a vapor deposition process without generating grain boundaries which are substantially parallel to the surface of the substrate and are caused by lamination. A normal of a (100) plane of each of crystals constituting the piezoelectric film is inclined from a normal of the surface of the substrate by an angle of not smaller than 6° and not larger than 36°.

Owner:FUJIFILM CORP

Method for preventing contact defects in interlayer dielectric layer

ActiveUS20050048763A1Good hygroscopicityImprove thermal stabilitySemiconductor/solid-state device manufacturingNitrogenNitrogen gas

A method of forming an interlayer dielectric (ILD) layer. A dielectric layer containing boron and phosphorous is formed overlying a substrate. A plasma treatment is subsequently performed on the dielectric layer using argon or nitrogen as a process gas. A capping layer is formed in-situ overlying the dielectric layer to serve as the ILD layer with the dielectric layer. A reflow process is subsequently performed on the ILD layer. A method for preventing formation of etching defects in a contact is also disclosed.

Owner:NAN YA TECH

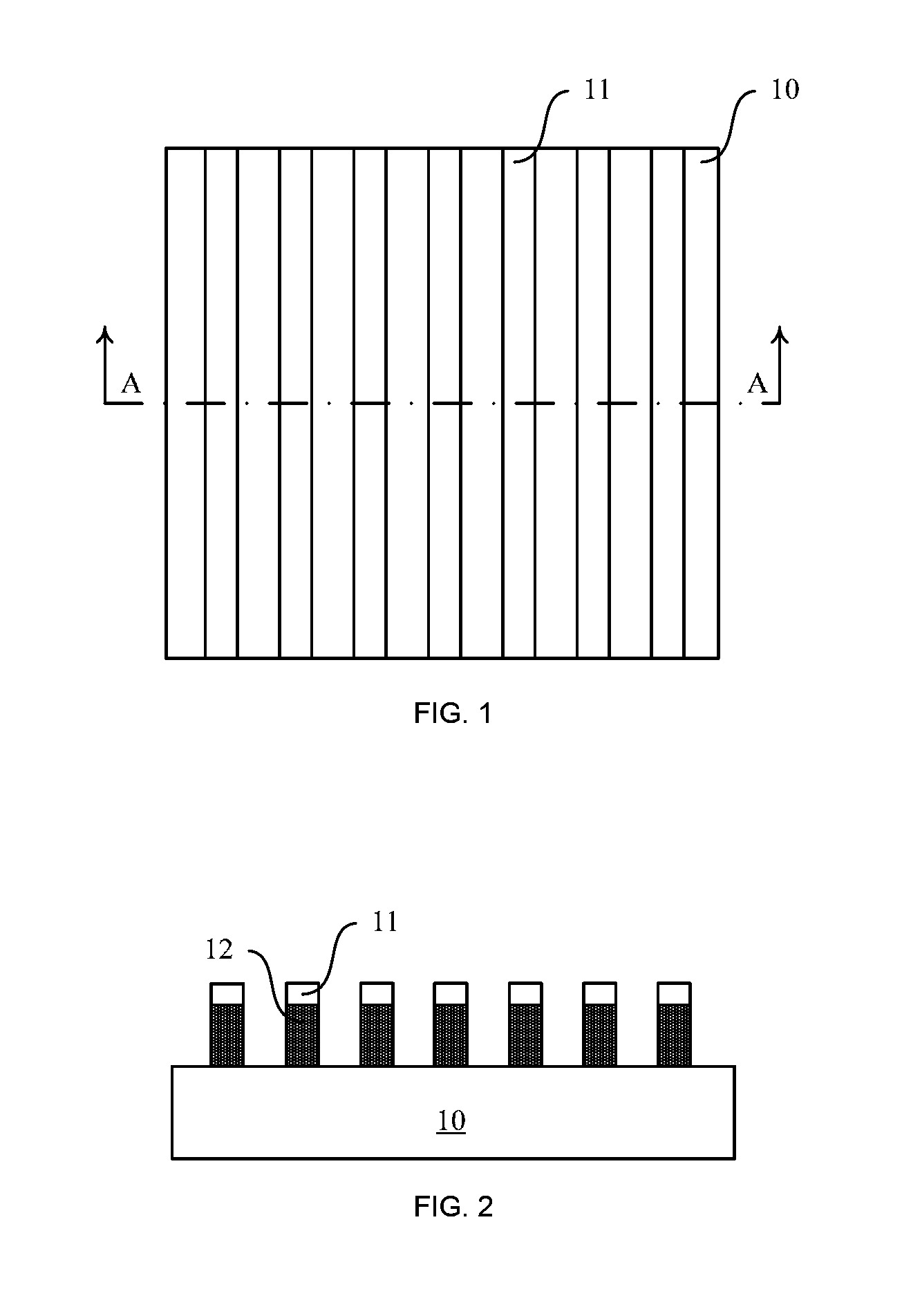

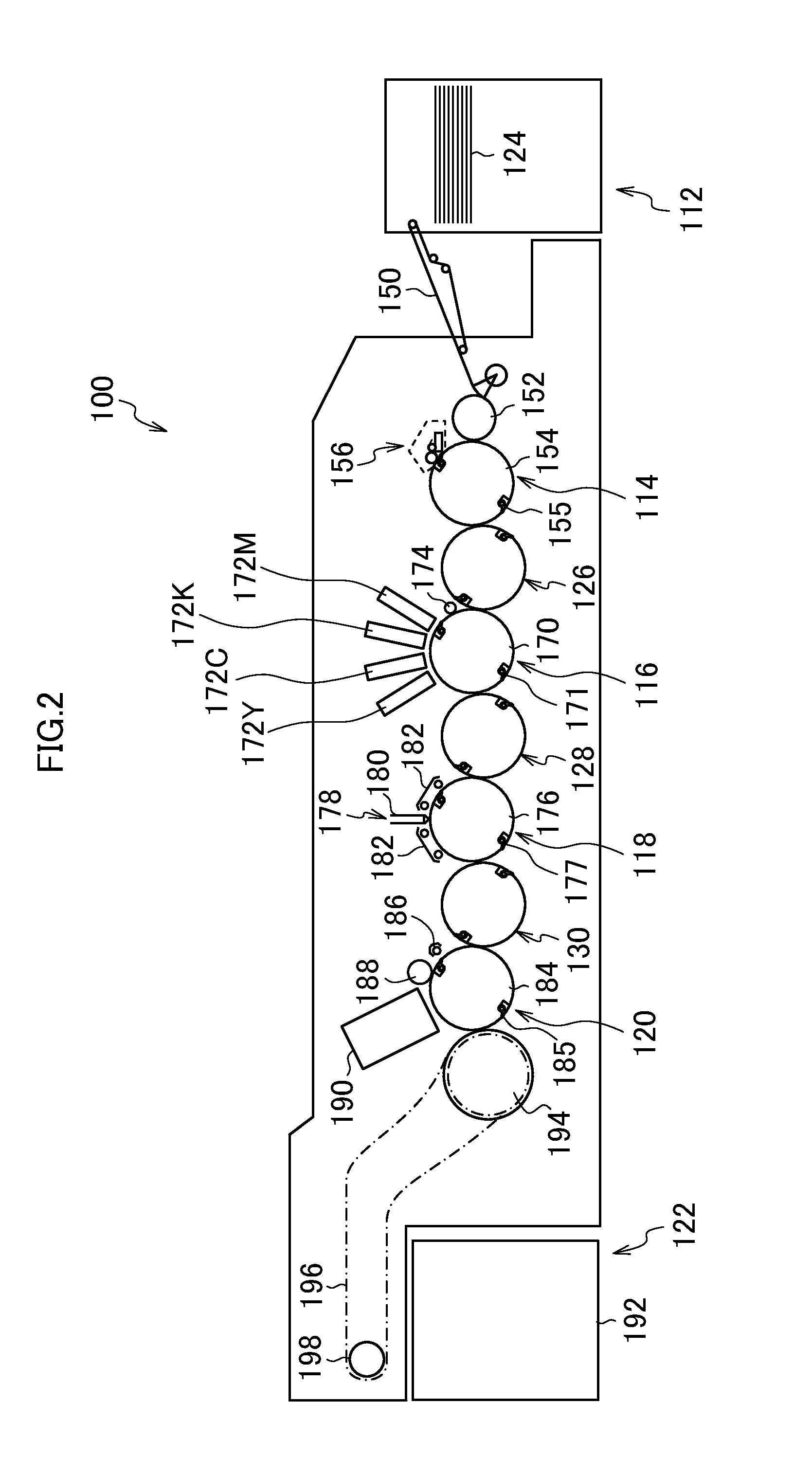

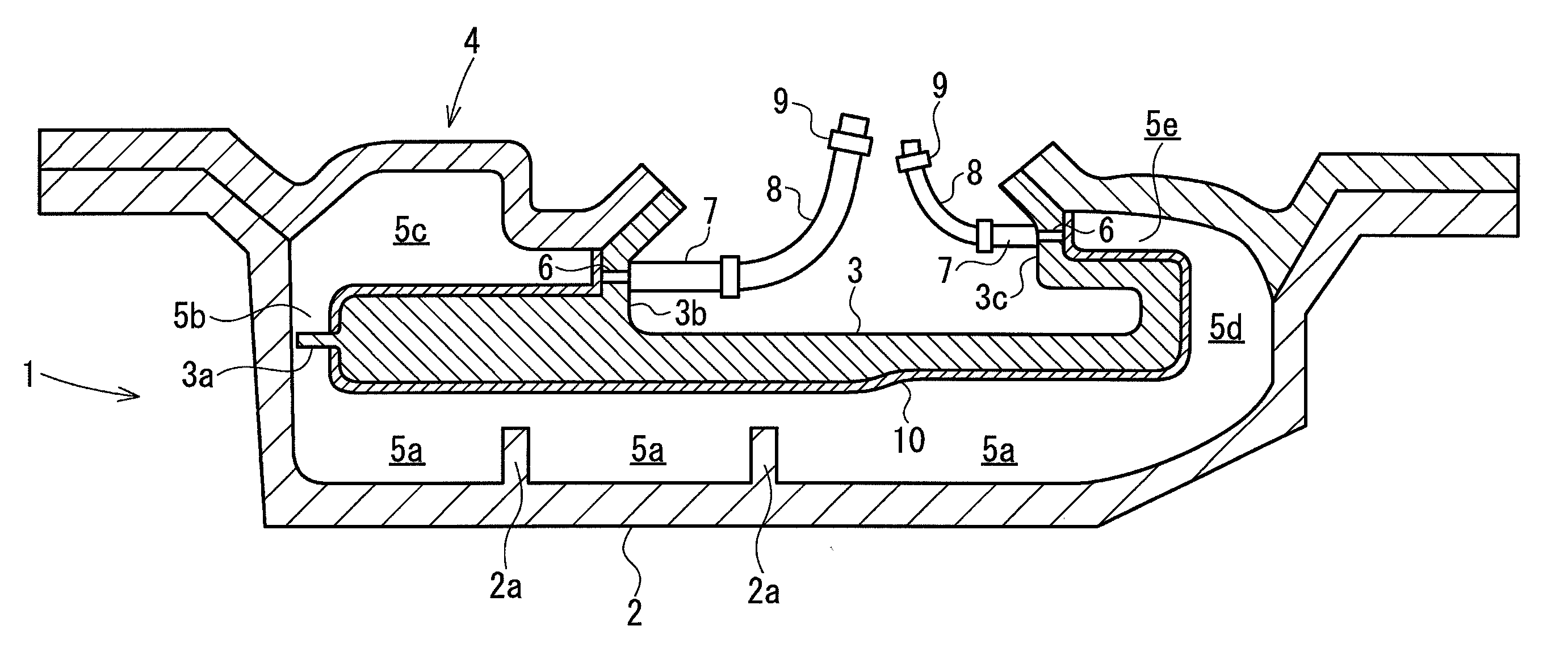

Mold and method for molding resin foamed molding

ActiveUS20110062614A1Simplify configurationInhibits the formation of defectsConfectionerySweetmeatsExhaust gasMaterials science

Provided is a mold which can be configured to be able to properly exhaust gas from a cavity and to prevent resin from entering into a vent hole, and a method for molding resin foamed molding using the mold. The mold 1 includes a lower mold 2, an upper mold 4, and a core mold 3 mounted directly under the upper mold 4. The core mold 3 is provided at wall portions 3b, 3c thereof with respective vent holes 6. Annexed members 7 are detachably attached to the outer surface sides of the wall portions 3b, 3c. Each of the annexed members 7 has a tubular shape having an air passage with a shape of a small passage which is in communication with the vent hole, and the sectional dimension of the passage of at least a part of the air passage is smaller than that of the vent hole 6. A nonwoven cloth 10 is attached to the core mold 3 so as to cover each surface thereof facing the cavity. The end portions of the nonwoven cloth 10 also cover the wall portions 3b, 3c, thereby covering the vent hole 6 from the cavity side.

Owner:ARCHEM INC

Sulfonium salt-containing polymer, resist composition, patterning process, and sulfonium salt monomer and making method

ActiveUS20140296561A1High sensitivityPrevent seepageRadiation applicationsSulfonic acids salts preparationResistSulfonium

A sulfonium salt having a 4-fluorophenyl group is introduced as recurring units into a polymer comprising hydroxyphenyl(meth)acrylate units and acid labile group-containing (meth)acrylate units to form a polymer which is useful as a base resin in a resist composition. The resist composition has a high sensitivity, high resolution and minimized LER.

Owner:SHIN ETSU CHEM CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com