Patents

Literature

92results about How to "High thermal expansion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

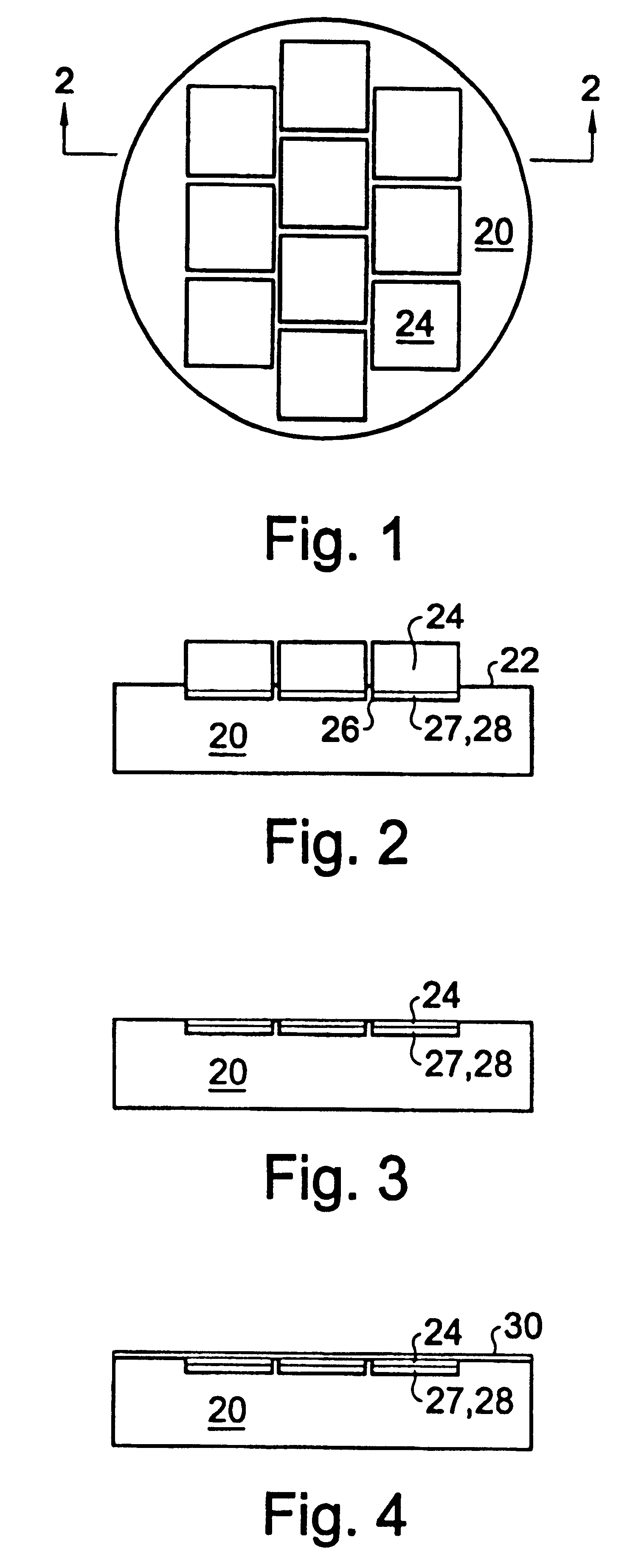

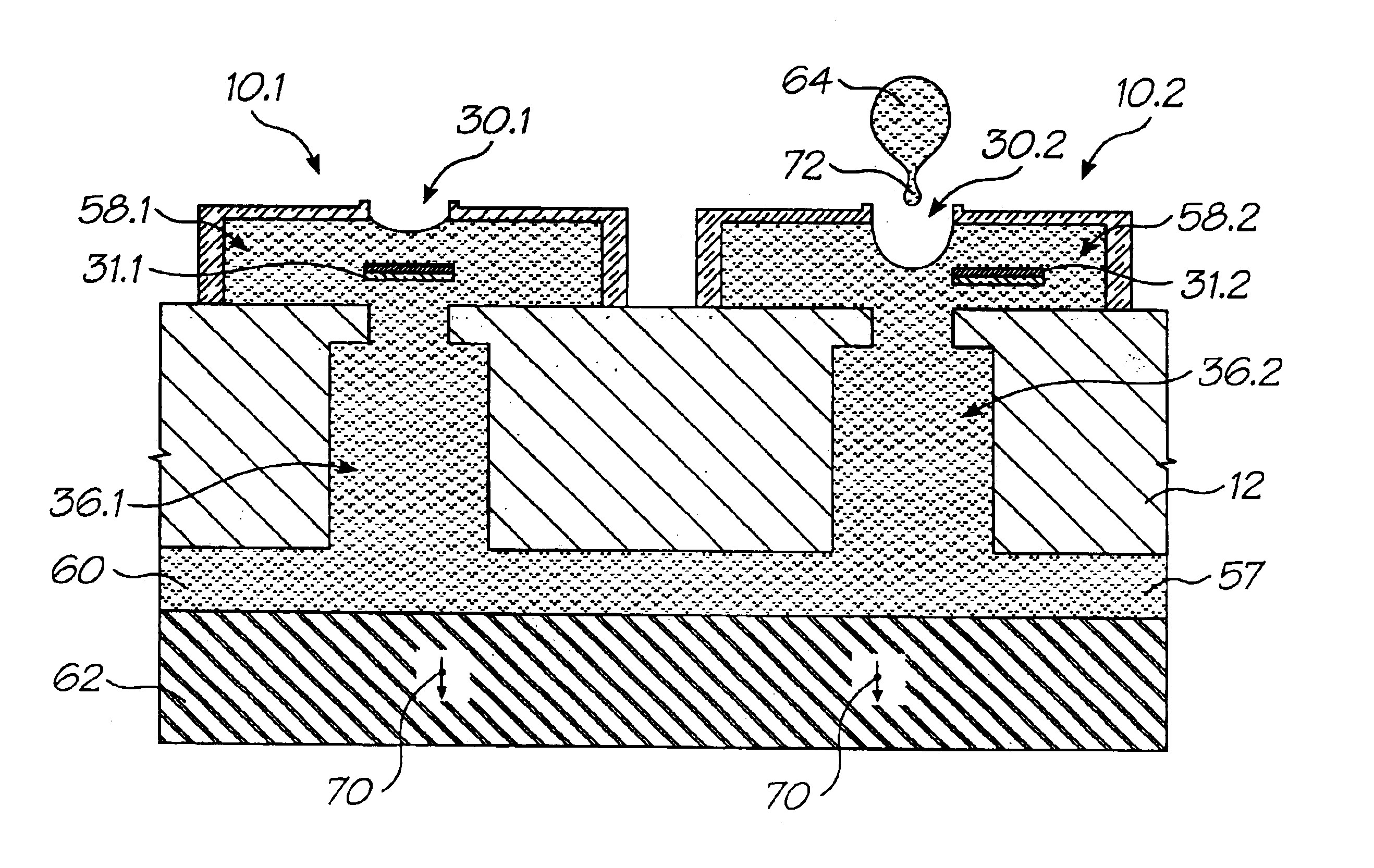

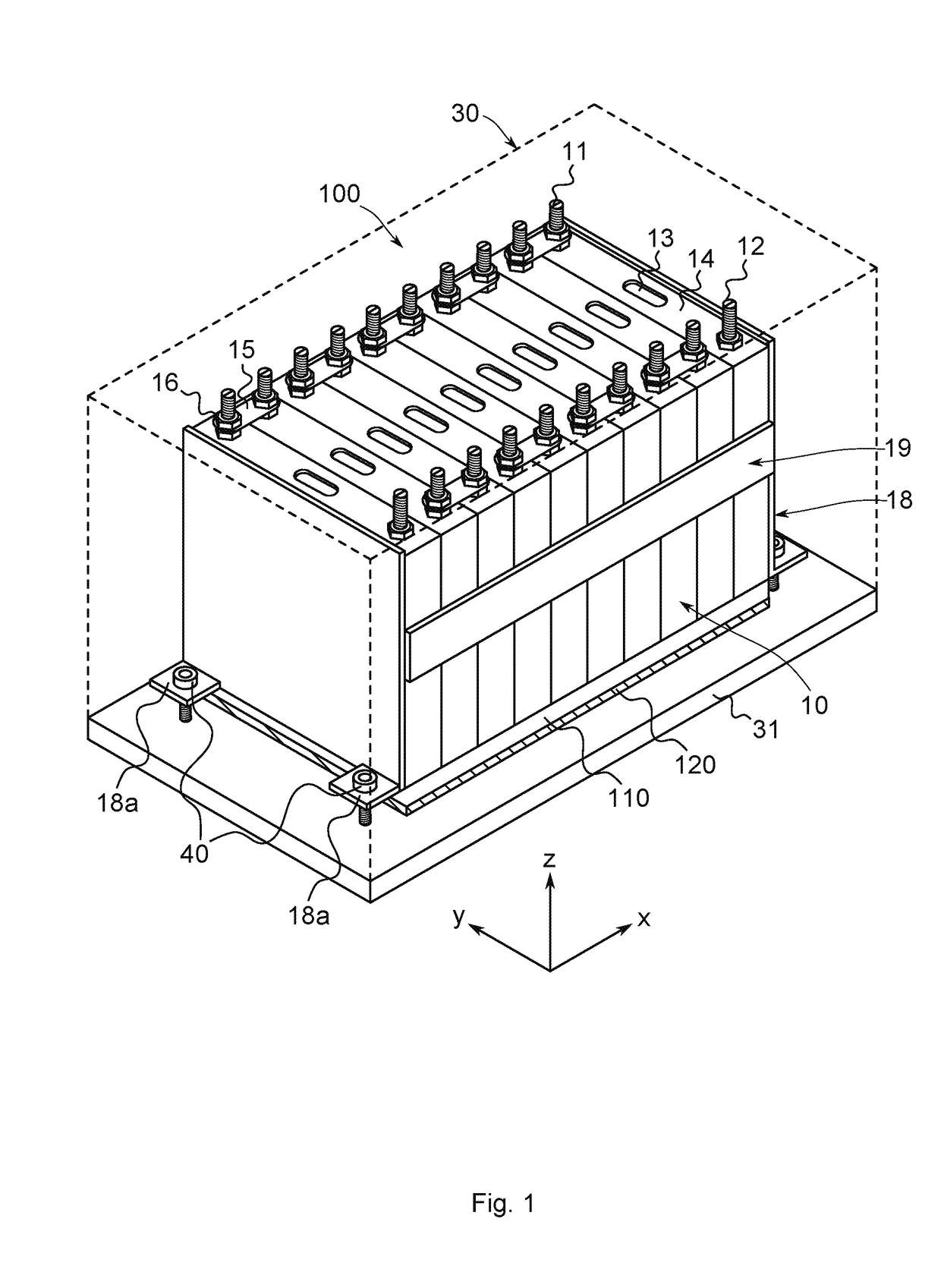

Wafer level packaging process

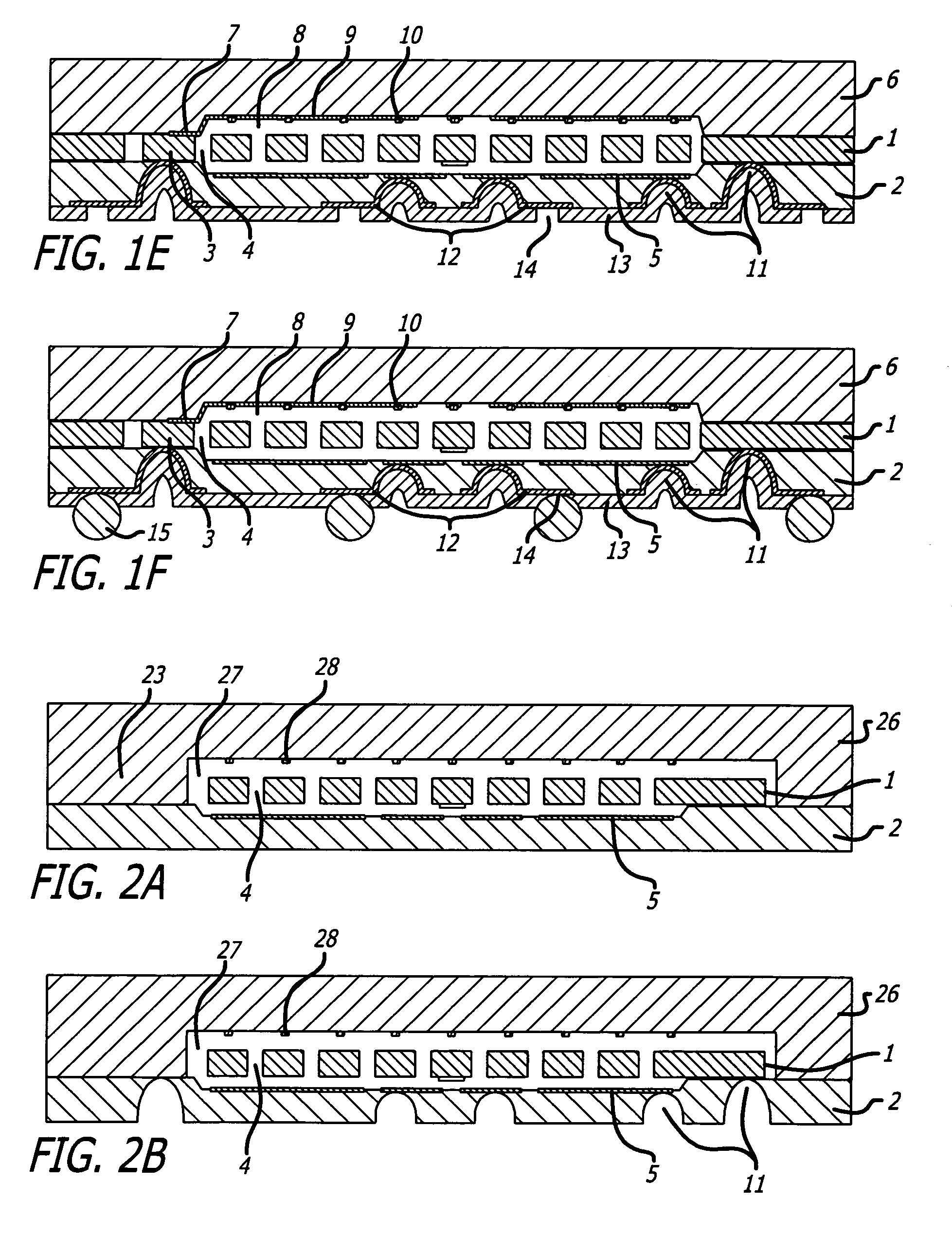

ActiveUS20070099395A1Improve performanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesThinningWafer-level packaging

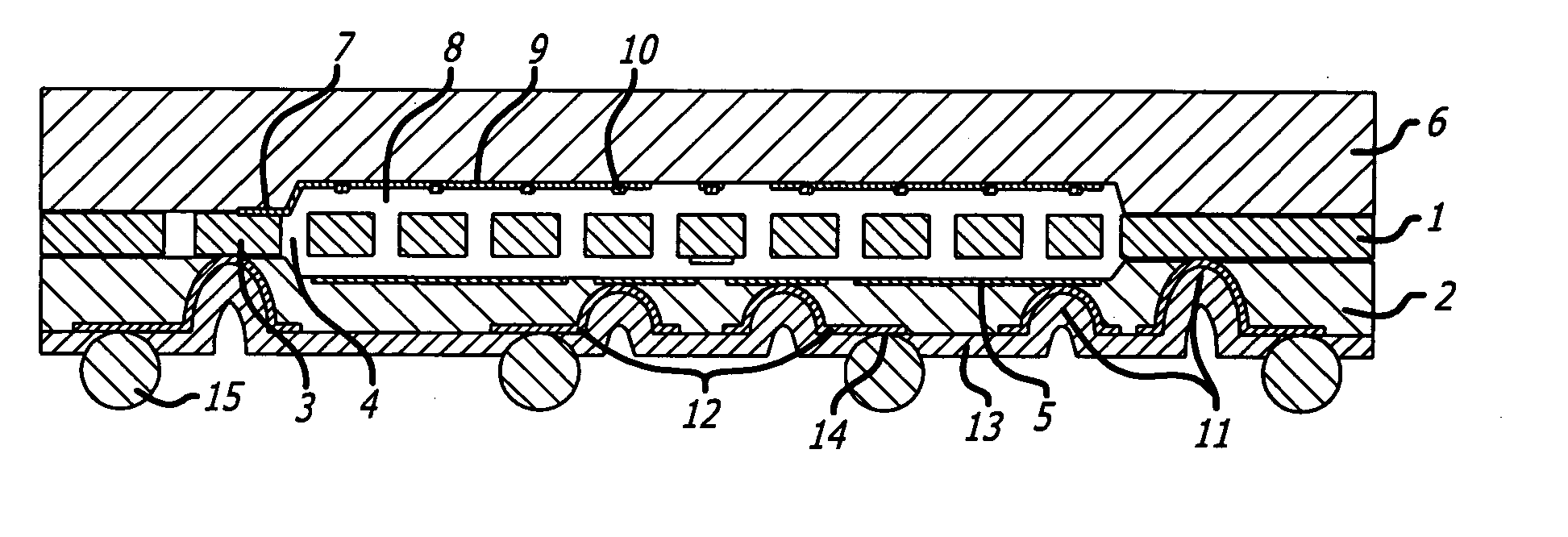

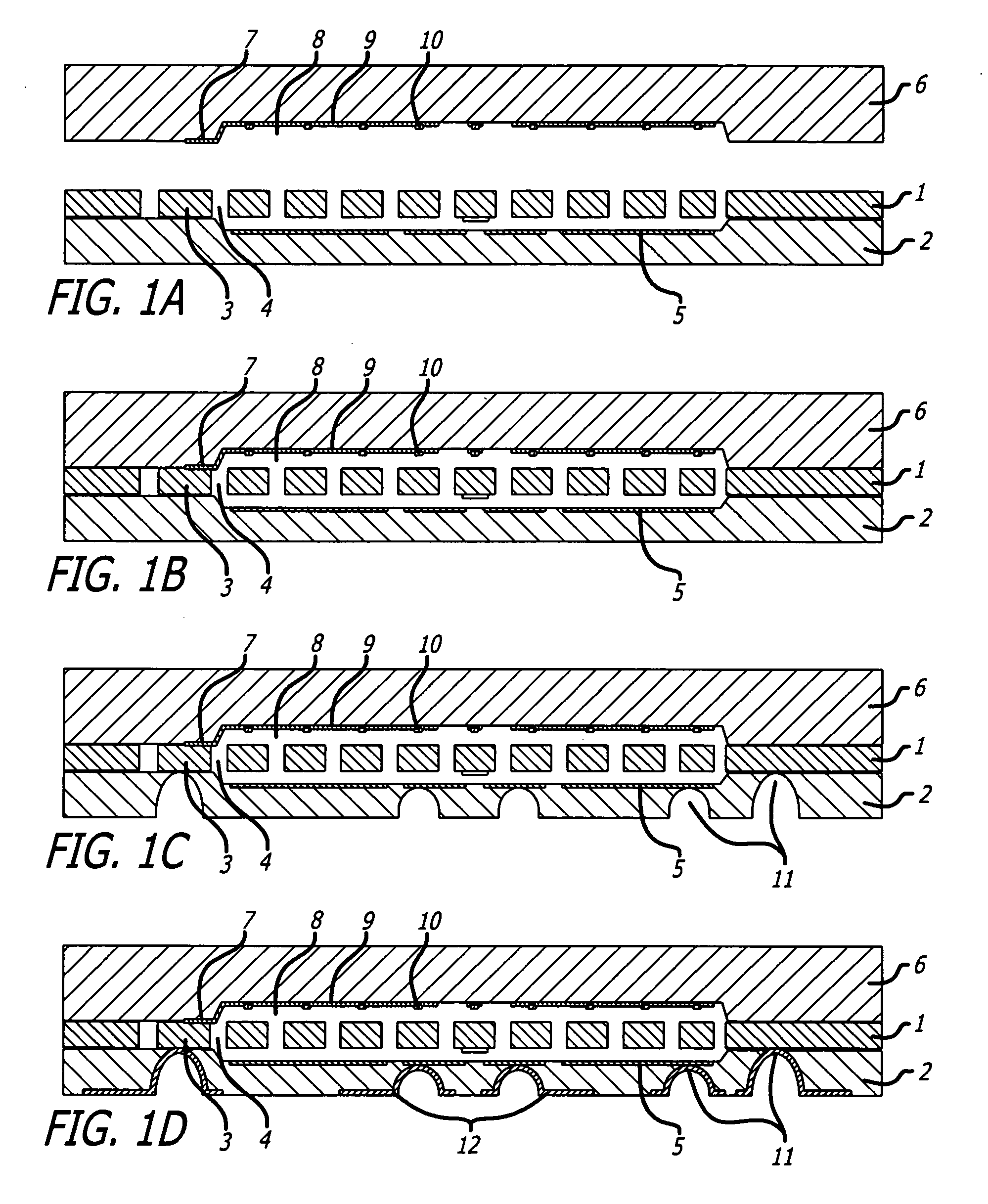

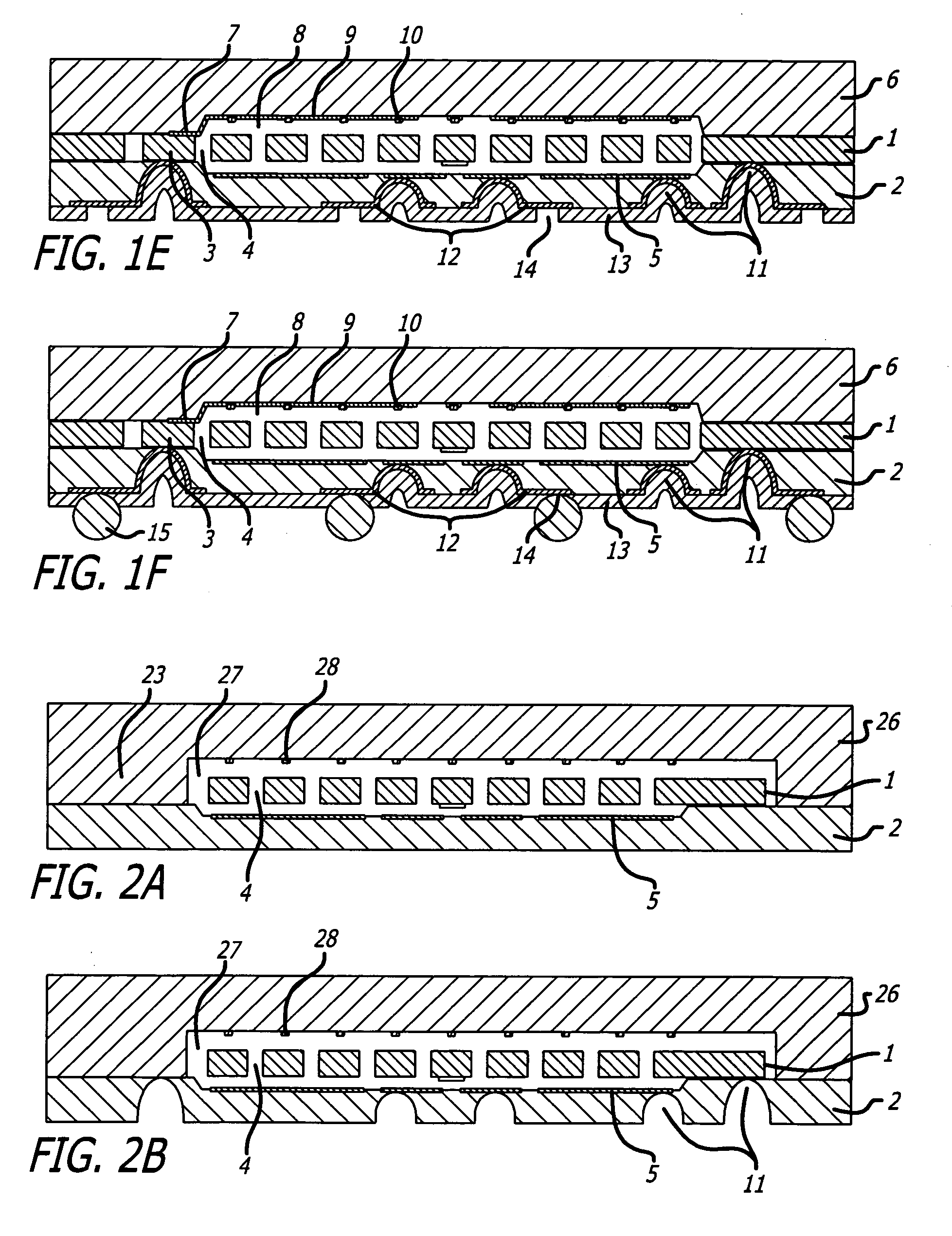

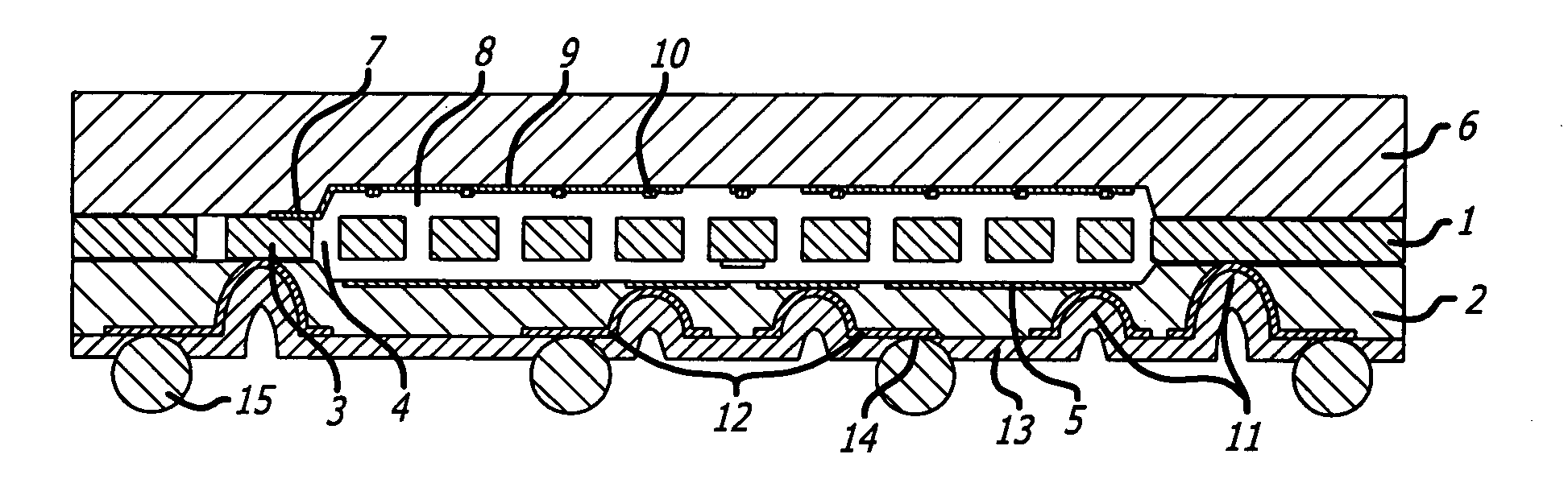

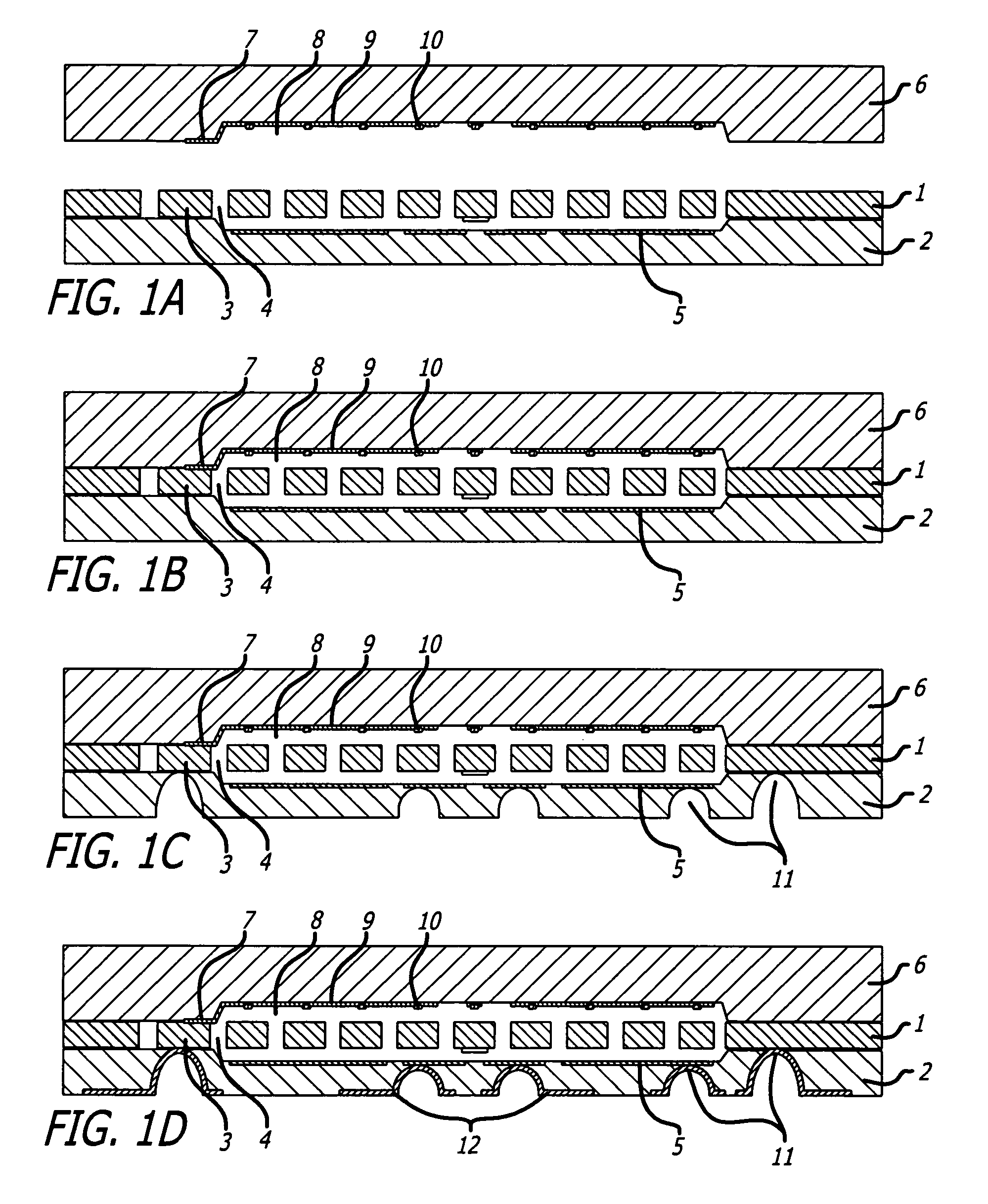

Wafer level packaging process for packaging MEMS or other devices. In some embodiments, a MEMS wafer with normal thickness is firstly bonded to a cap wafer of normal thickness, followed by a thinning on the backside of the MEMS wafer. After this, the bonded wafer stack and the capping of the hermetically packaged MEMS devices are still rigid enough to do further processing. On this basis, through vias on the thinned substrate can be easily formed and stopped on the regions to be led out (e.g., metal pads / electrodes, highly doped silicon, etc.). Vias can be partially filled as this is the final surface of process. Even thick metal coated / patterned vias have much more space to relax possible thermal stress, as long as the vias are not completely filled with hard metal(s). Various embodiments are disclosed.

Owner:MAXIM INTEGRATED PROD INC

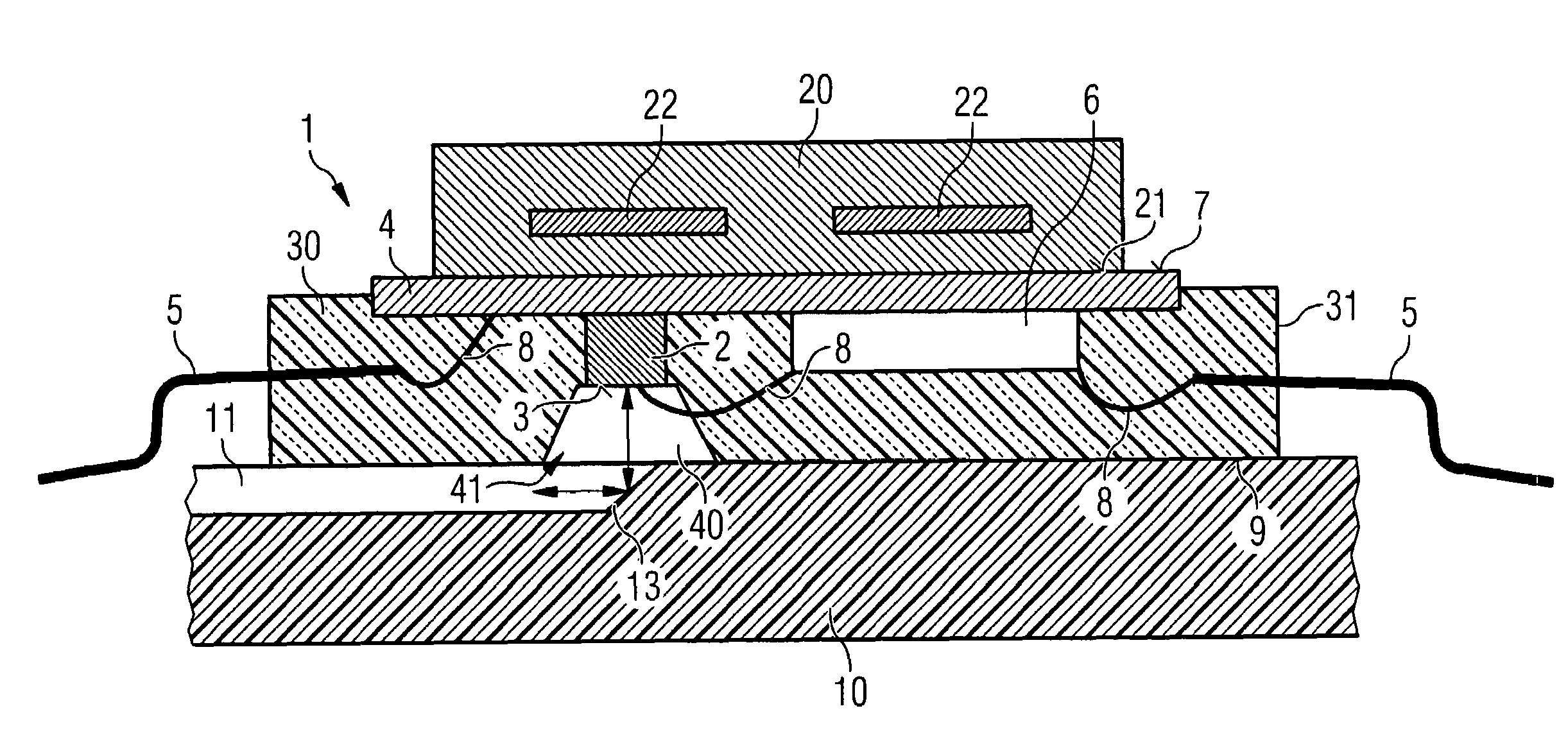

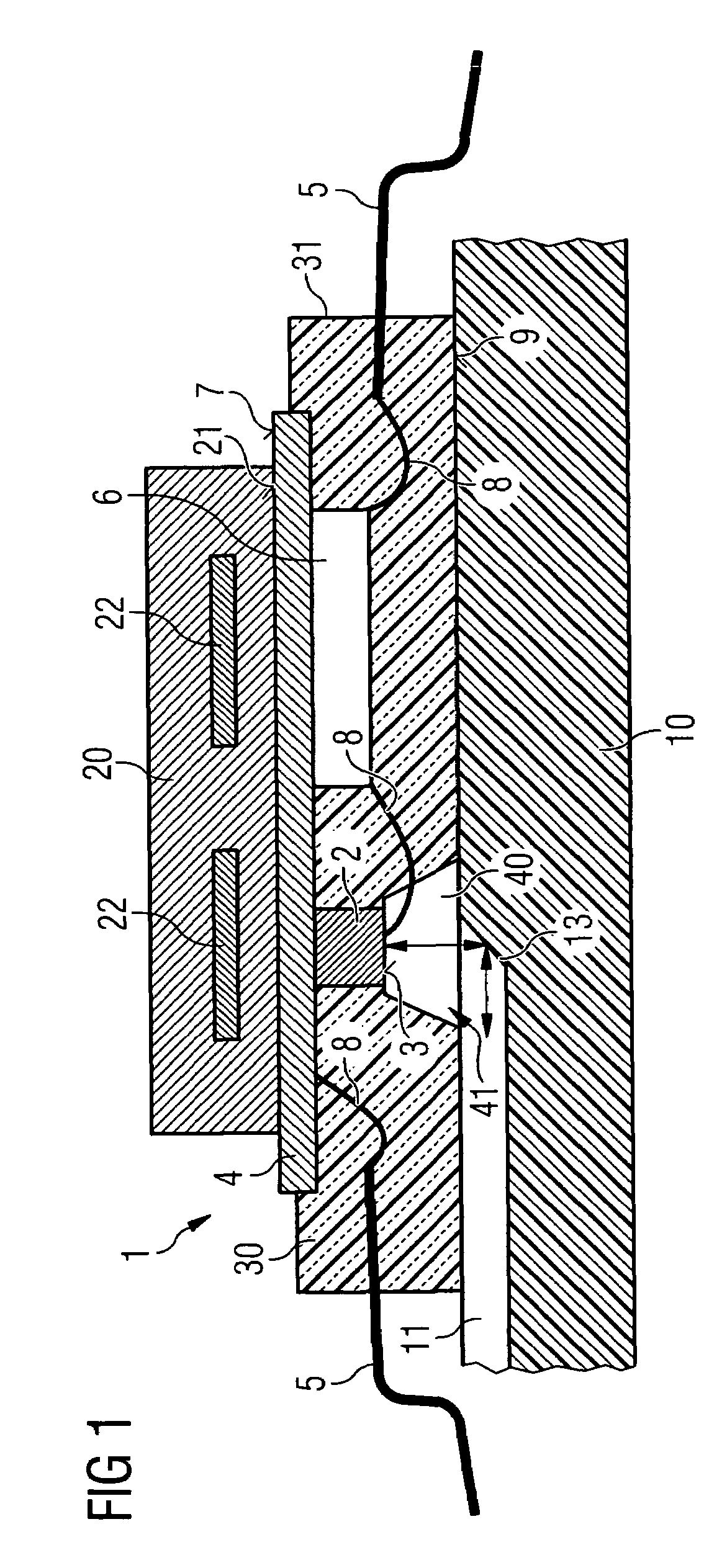

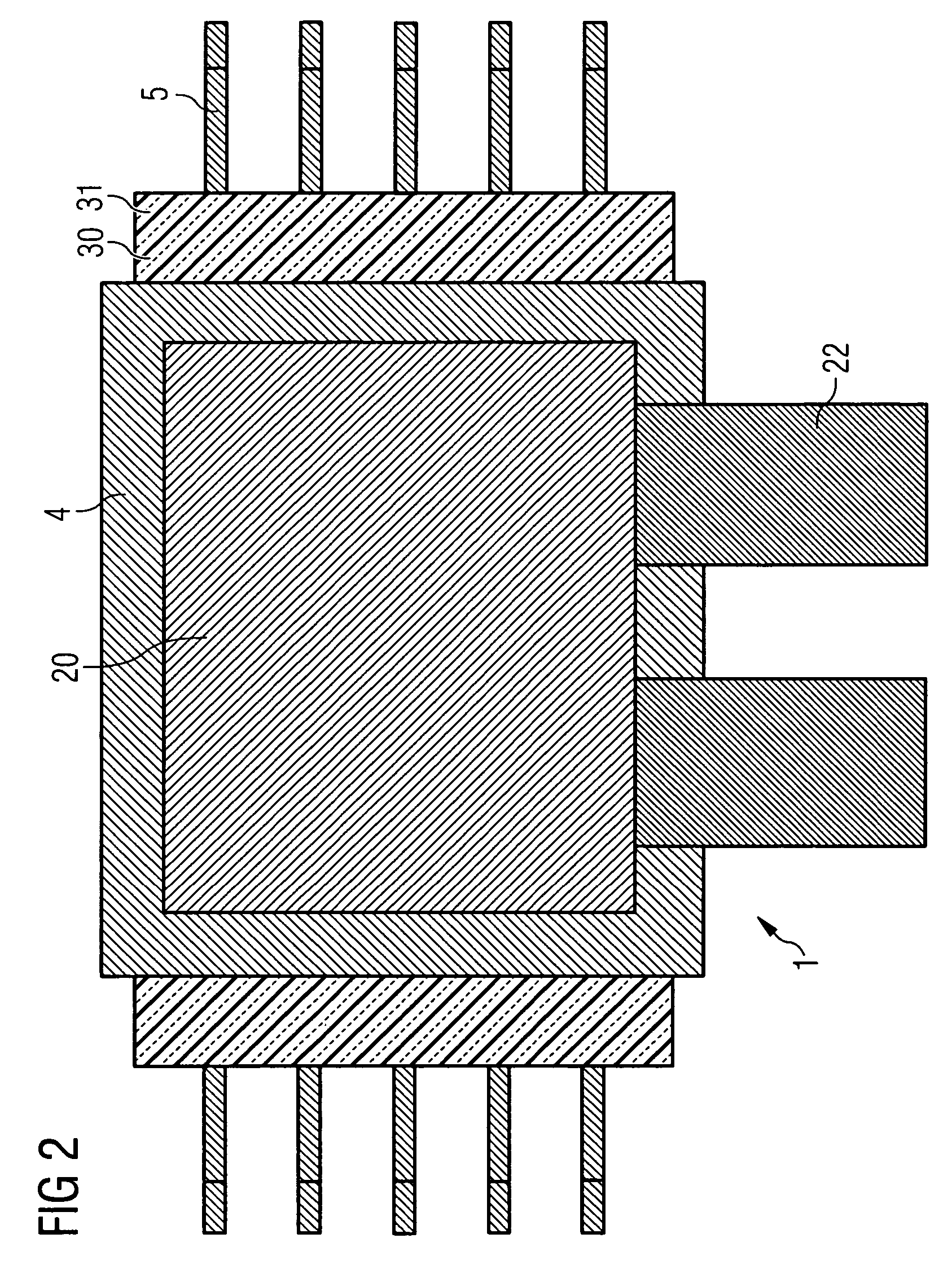

Optical structure with ridges arranged at the same and method for producing the same

ActiveUS20160154202A1Small structure sizeLow production costPrismsContact member assembly/disassemblyElectrostatic actuatorEngineering

An apparatus having an optical structure, ridges and an electrostatic actuator with a cantilever electrode is described, wherein the ridges connect the optical structure to a supporting structure and the electrostatic drive is implemented to deflect the optical structure.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

Wafer level packaging process

ActiveUS7393758B2Improve performanceImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesHard metalWafer stacking

Owner:MAXIM INTEGRATED PROD INC

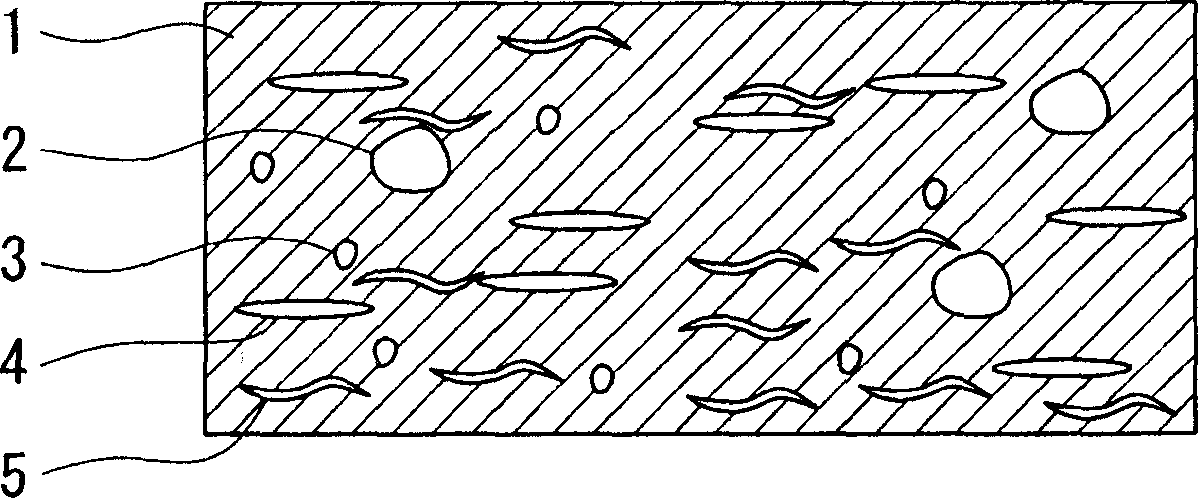

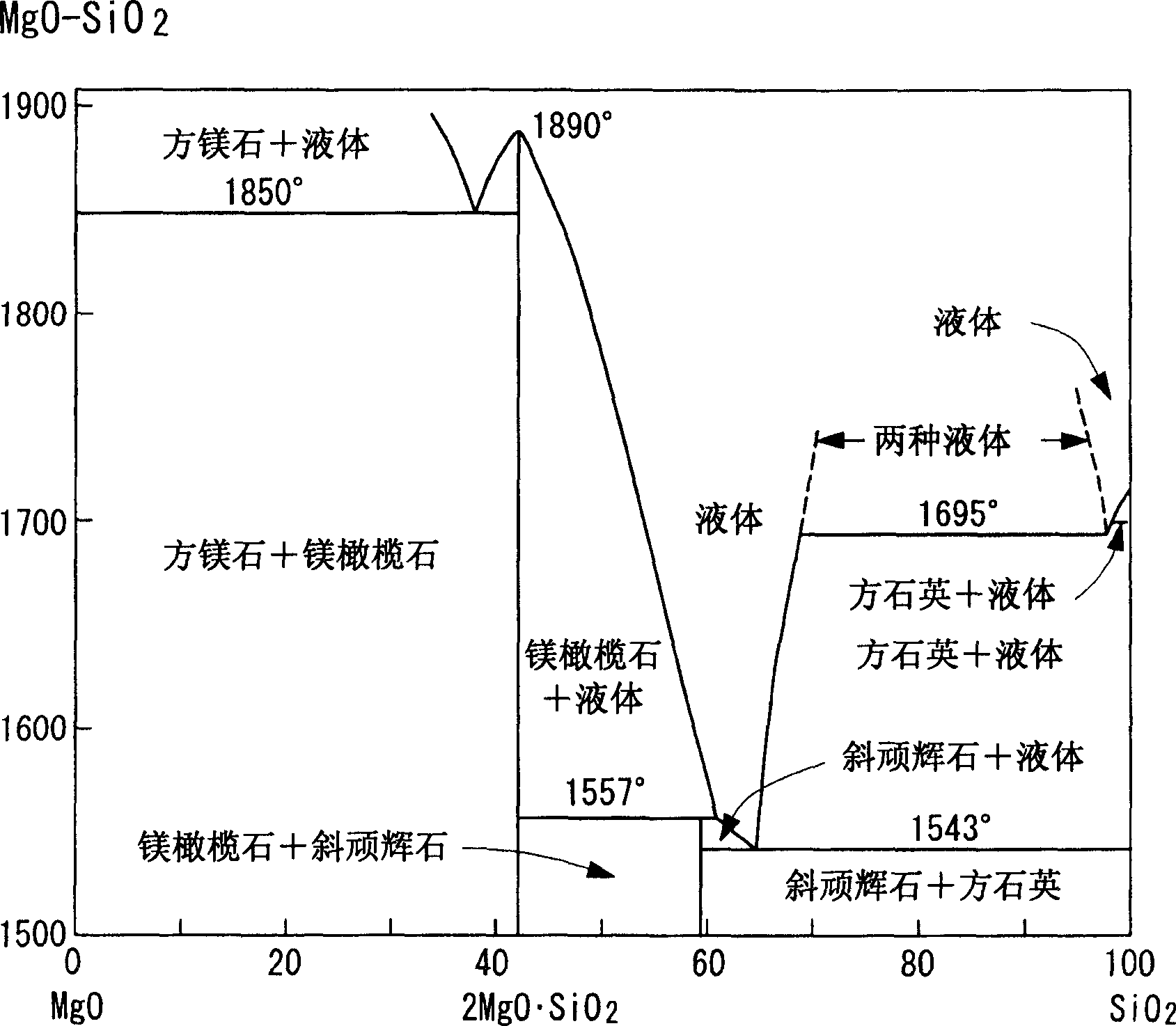

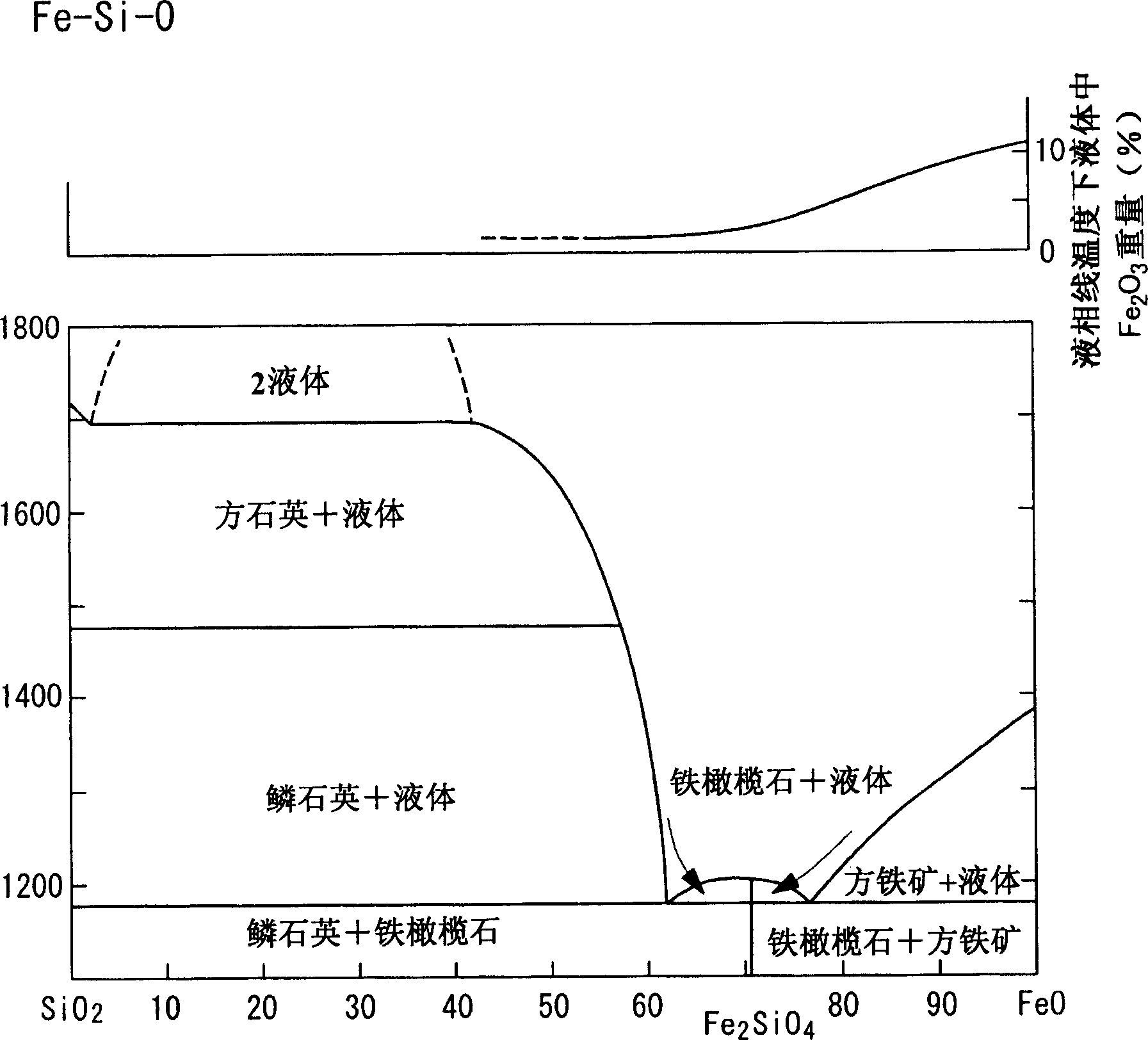

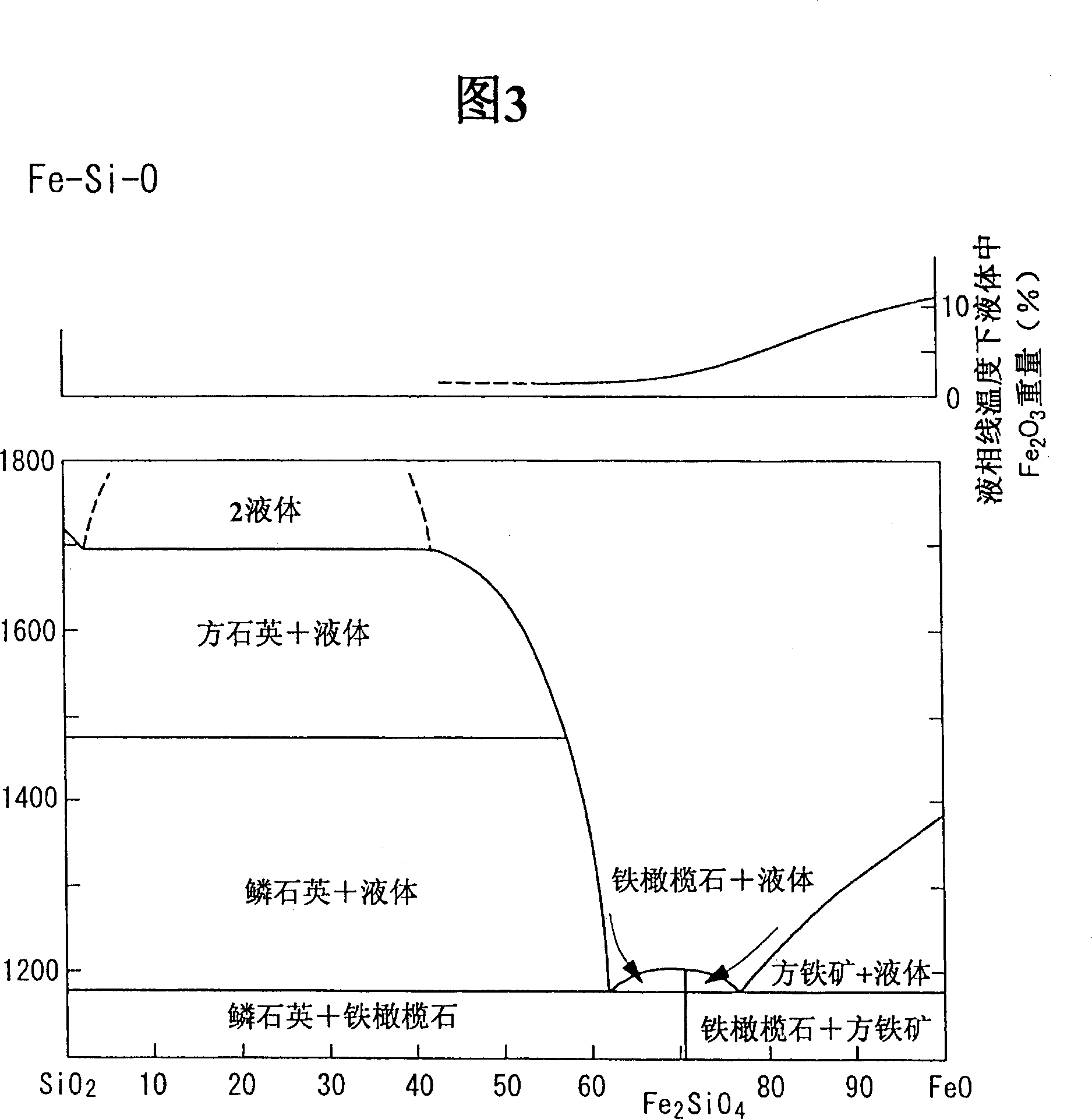

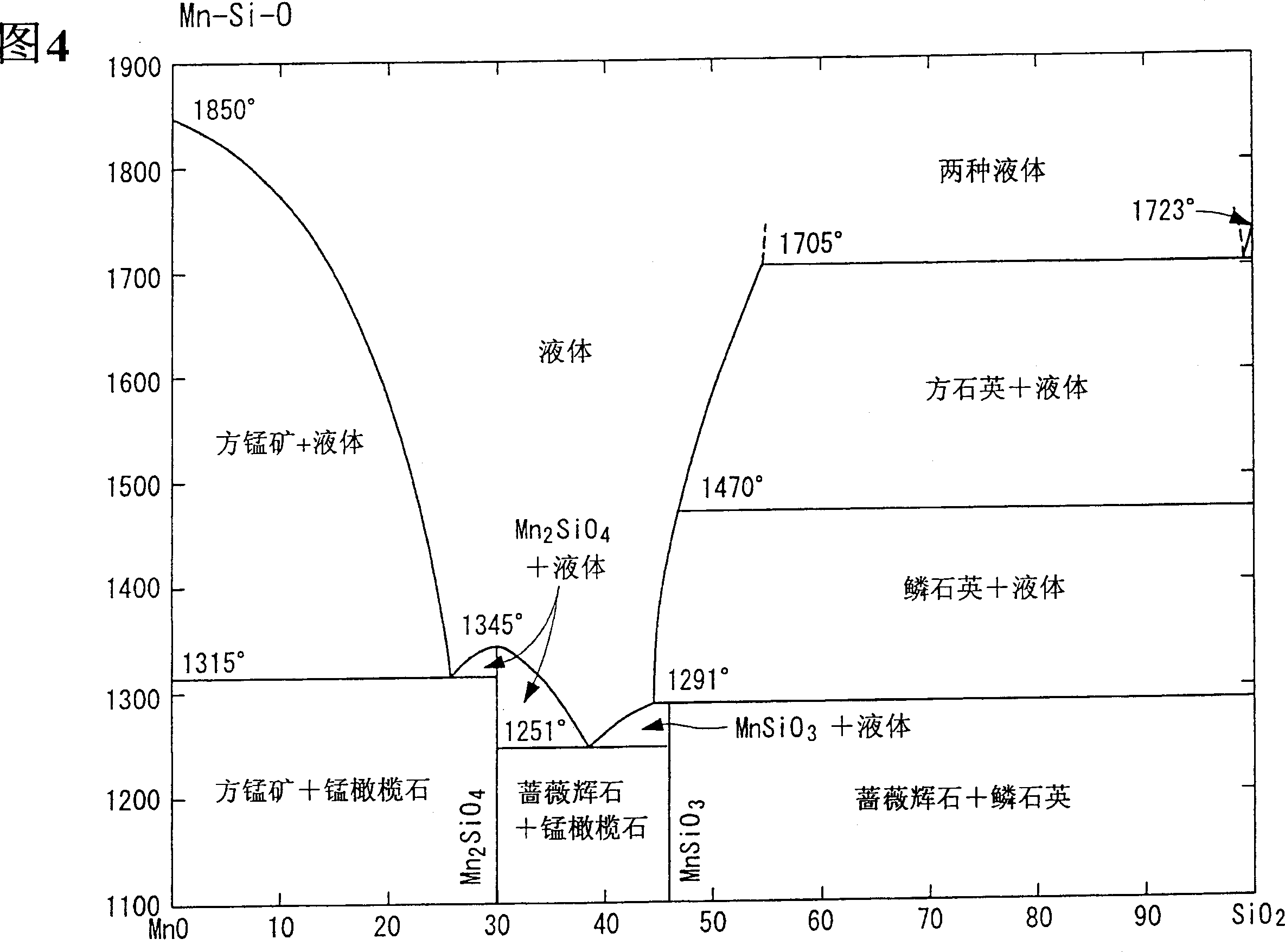

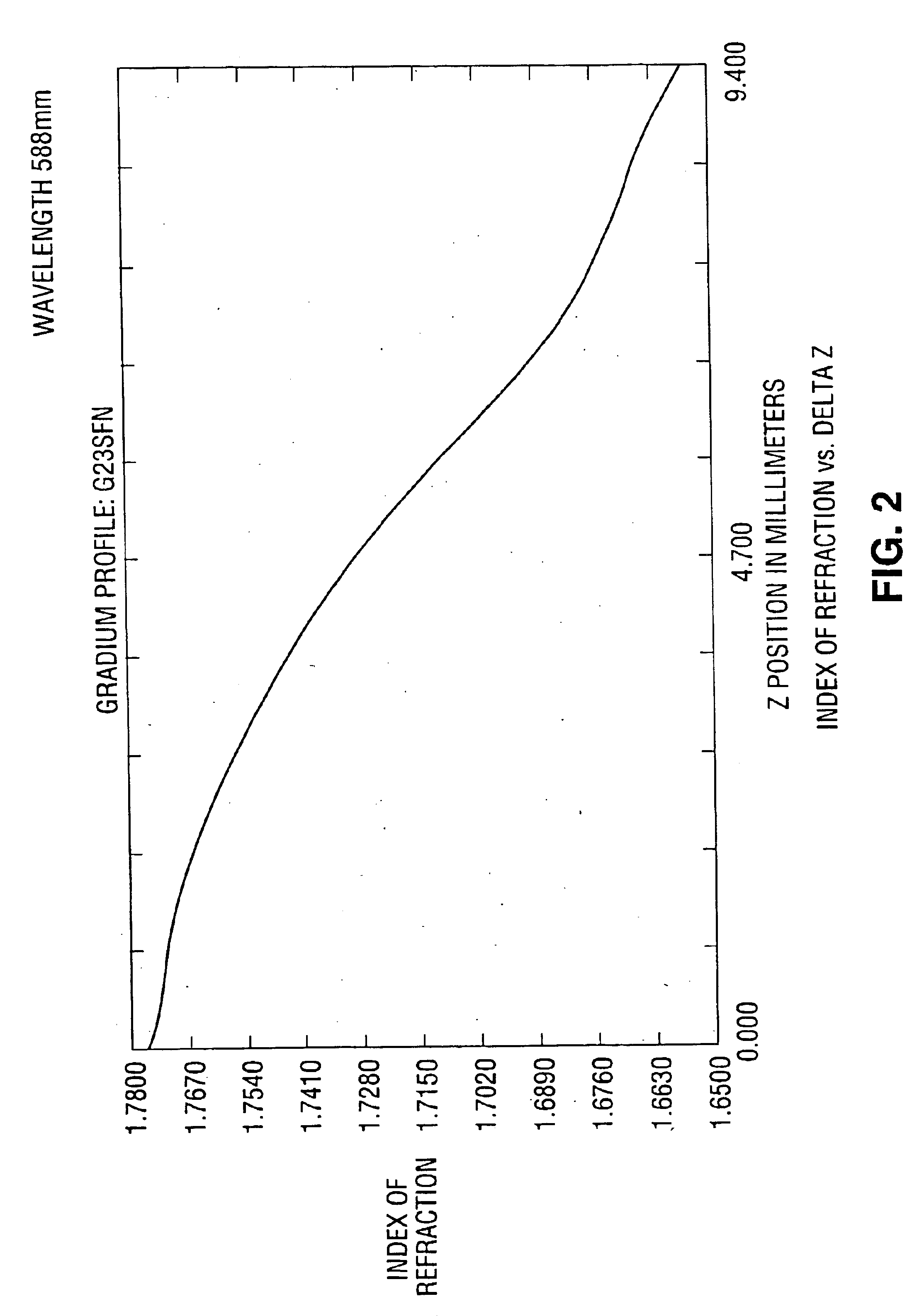

Material for thermal barrier coating

InactiveCN1764613AImprove efficiencyReduce weightMolten spray coatingEfficient propulsion technologiesCrystal structureThermal expansion

The invention provides a novel thermal insulation coating material with no phase transfer problem, a melting point higher than the working temperature range, a thermal conductivity lower than that of zirconia, and a thermal expansion rate higher than that of zirconia. The thermal barrier coating material has an orthorhombic or monoclinic crystal structure derived from perovskite (for example, a platy perovskite structure represented by the composition formula A2B2O7), or a c-axis / a-axis ratio of 3 or more The composition of the tetragonal layered structure (such as K2NiF4 structure and Sr3Ti2O7 structure, Sr4Ti3O10 structure), and the composition represented by the composition formula LaTaO4, and the composition with the composition formula M2SiO4 or (MM') 2SiO4 (wherein M, M 'is a divalent metal element) composition of the olivine structure represented as the main body.

Owner:MITSUBISHI HEAVY IND LTD

Optoelectronic arrangement having a surface-mountable semiconductor module and a cooling element

ActiveUS7228020B2Constricted between semiconductor module and printed circuit board is avoidedEfficient thermal energySolid-state devicesCoupling light guidesSurface mountingComputer module

An optoelectronic arrangement having a surface-mountable semiconductor module having at least one optoelectronic transmitting and / or receiving unit, a housing, in which the optoelectronic transmitting and / or receiving unit is arranged, and a mounting side of the housing, which, in the case of surface mounting of the semiconductor module on a printed circuit board, faces the printed circuit board. The arrangement furthermore has a cooling element, which is thermally coupled to the semiconductor module for the purpose of cooling the optoelectronic transmitting and / or receiving unit. The cooling element is arranged on a side of the housing that is remote from the mounting side.

Owner:II VI DELAWARE INC

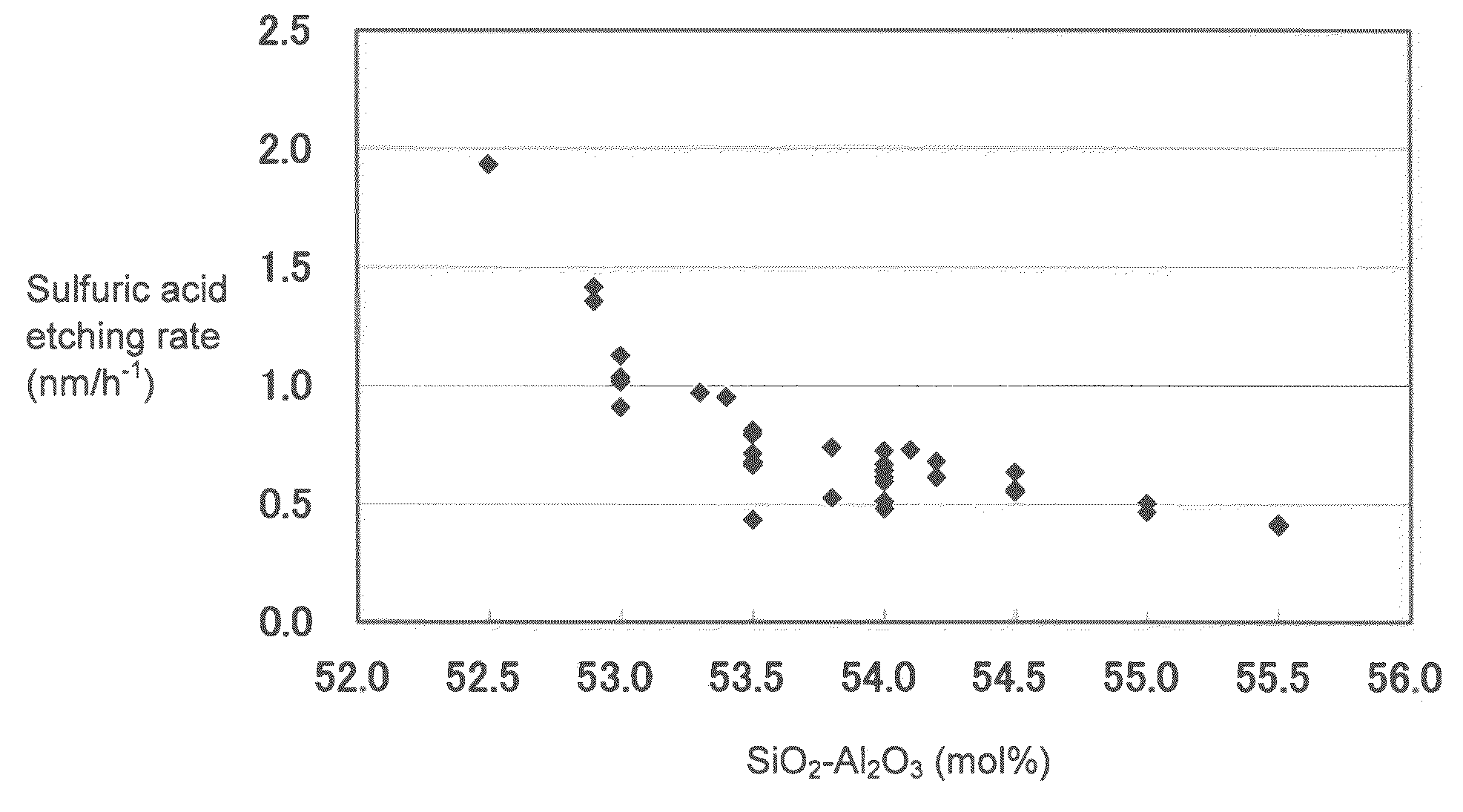

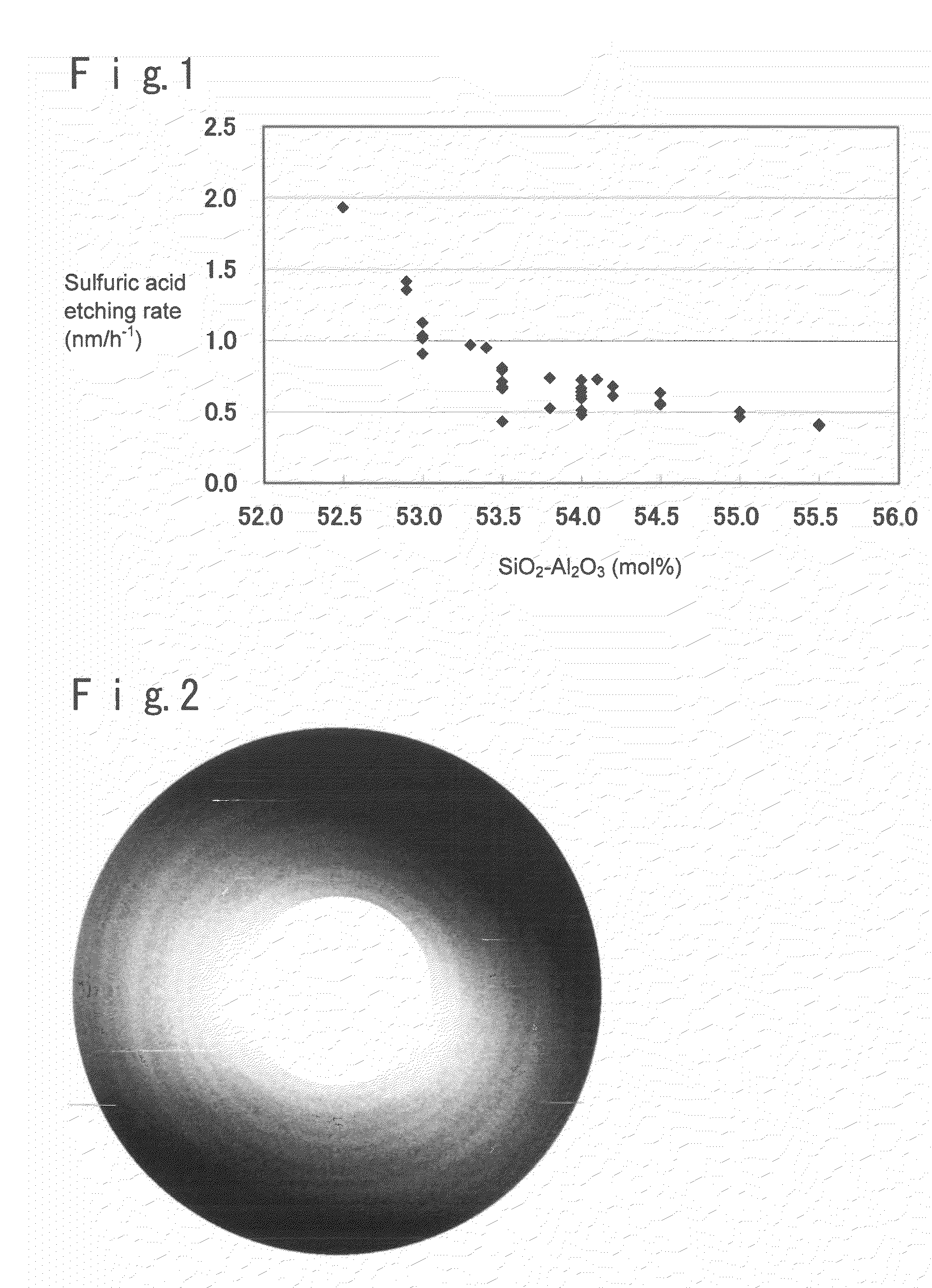

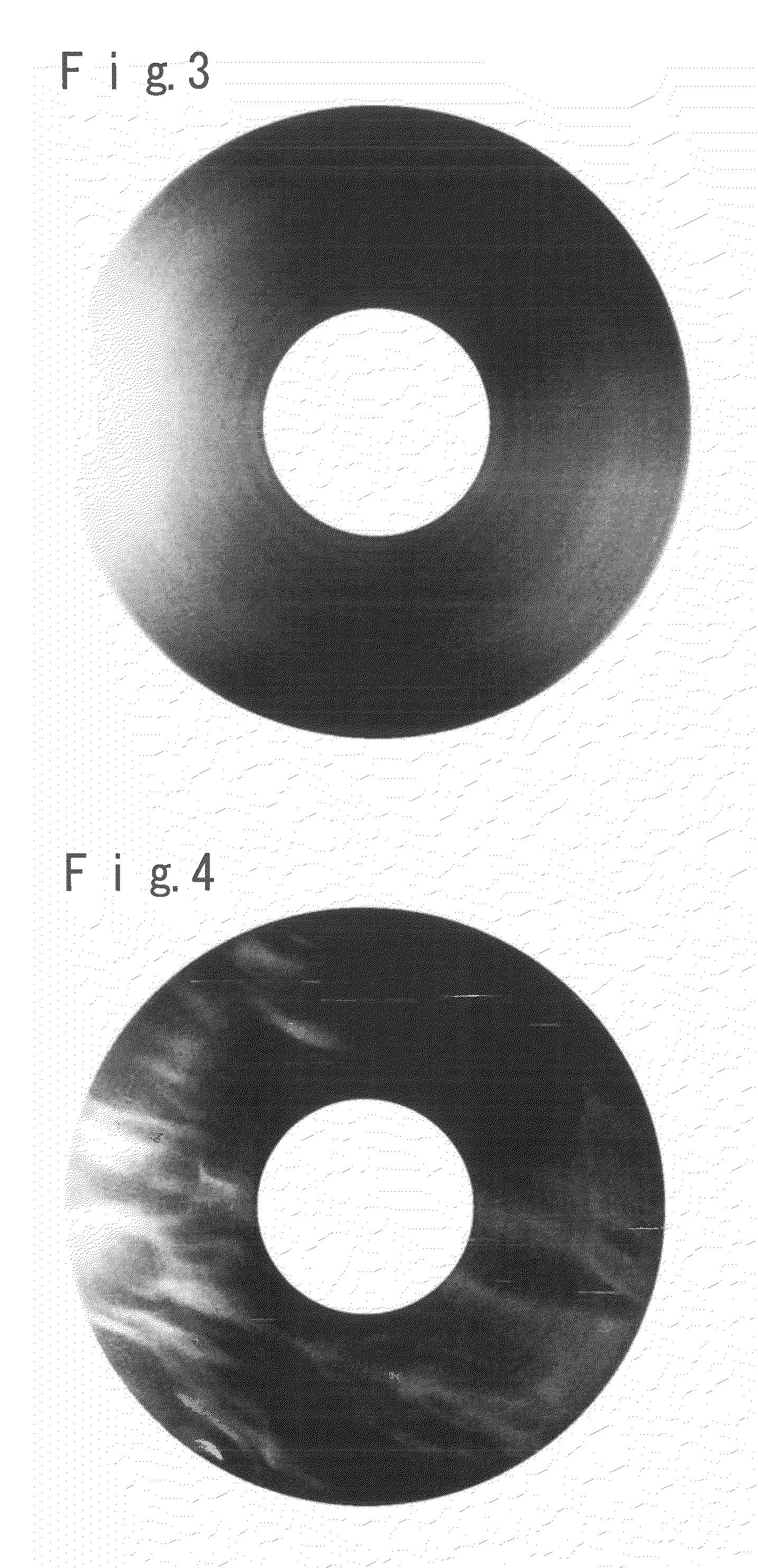

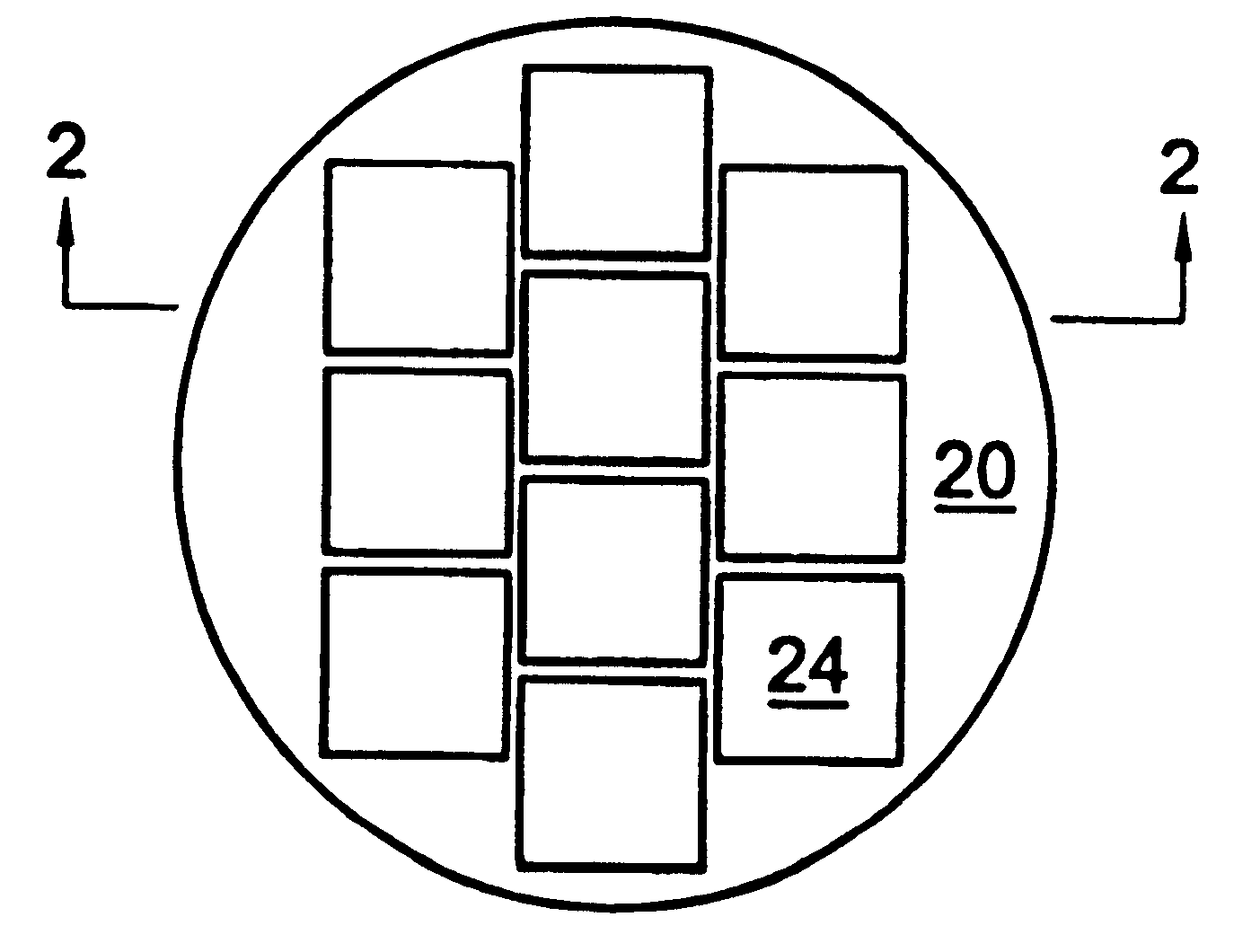

Glass for substrate, and glass substrate

ActiveUS8580411B2Improve acid resistanceEfficient removalMagnetic materials for record carriersBase layers for recording layersPhotochemistrySurface roughening

To provide glass to be used for a substrate which is, as a substrate, less susceptible to surface roughening even if subjected to cleaning by means of a strongly acidic solution.Glass for a substrate, which comprises, as represented by mol % based on the following oxides, from 62.5 to 69% of SiO2, from 9 to 15.5% of Al2O3, from 8 to 16 of Li2O, from 0 to 8% of Na2O, from 0 to 7% of K2O and from 0 to 3.5% of ZrO2, provided that SiO2—Al2O3 is at least 53.3%, Li2O+Na2O+K2O is from 17 to 24%, and the total of contents of the above six components is at least 97%.

Owner:ASAHI GLASS CO LTD

Discrete wafer array process

InactiveUS6248646B1High temperature resistanceGreat ruggednessSolid-state devicesSemiconductor/solid-state device manufacturingWaferingCompound (substance)

A method of preparing small wafers for compatibility with conventional large wafer fabrication equipment comprising the following steps: indenting a face of a large wafer to form an array of depressions thereon, each depression sized to matingly accept a lower portion of a small wafer; applying a bonding medium to an exterior side of the depressions on the indented face of the large wafer; matingly fitting the small wafers into the depressions so that the small wafers are positioned in an array on the large wafer; and, removing the top portion of the small wafers standing out of the depressions by chemical mechanical polishing so that the remaining portions of the small wafers then have a uniform thickness generally equal to the depth of the indentations in the large wafer. A preferred aspect of this invention provides for a method as above wherein the small wafer is SiC and the large wafer is made from an amorphous substance which comprises SiC or aluminum nitride.

Owner:OKOJIE ROBERT S

Material for thermal barrier coating

InactiveCN100376505CHigh thermal expansionLow thermal conductivityMolten spray coatingEfficient propulsion technologiesDivalent metalOperating temperature range

Owner:MITSUBISHI HEAVY IND LTD

Two-Part Dental Implant

A two-part dental implant includes distal and proximal implant portions which in an interconnected condition at least indirectly adjoin each other at a connecting location and have mutually facing surfaces in the region of the connecting location. A sealing body is provided between the mutually facing surfaces of the distal and proximal implant portions. The sealing body has sealing surfaces which face towards the mutually facing surfaces and which in the interconnected condition of the two implant portions bear sealingly against the mutually facing surfaces thereof. In addition, mutually facing abutment surfaces are provided between the distal and proximal implant portions. These mutually facing abutment surfaces bear against each other in the final assembled dental implant and limit the degree of approach of the two mutually facing surfaces of the implant portions between which the sealing body is arranged. The abutment surfaces define a minimum spacing of the two mutually facing surfaces of the implant portions, which is bridged over by the sealing body. The sealing body is at least partially comprised of an elastic material.

Owner:MEHROF IMPLANT TECH GMBH

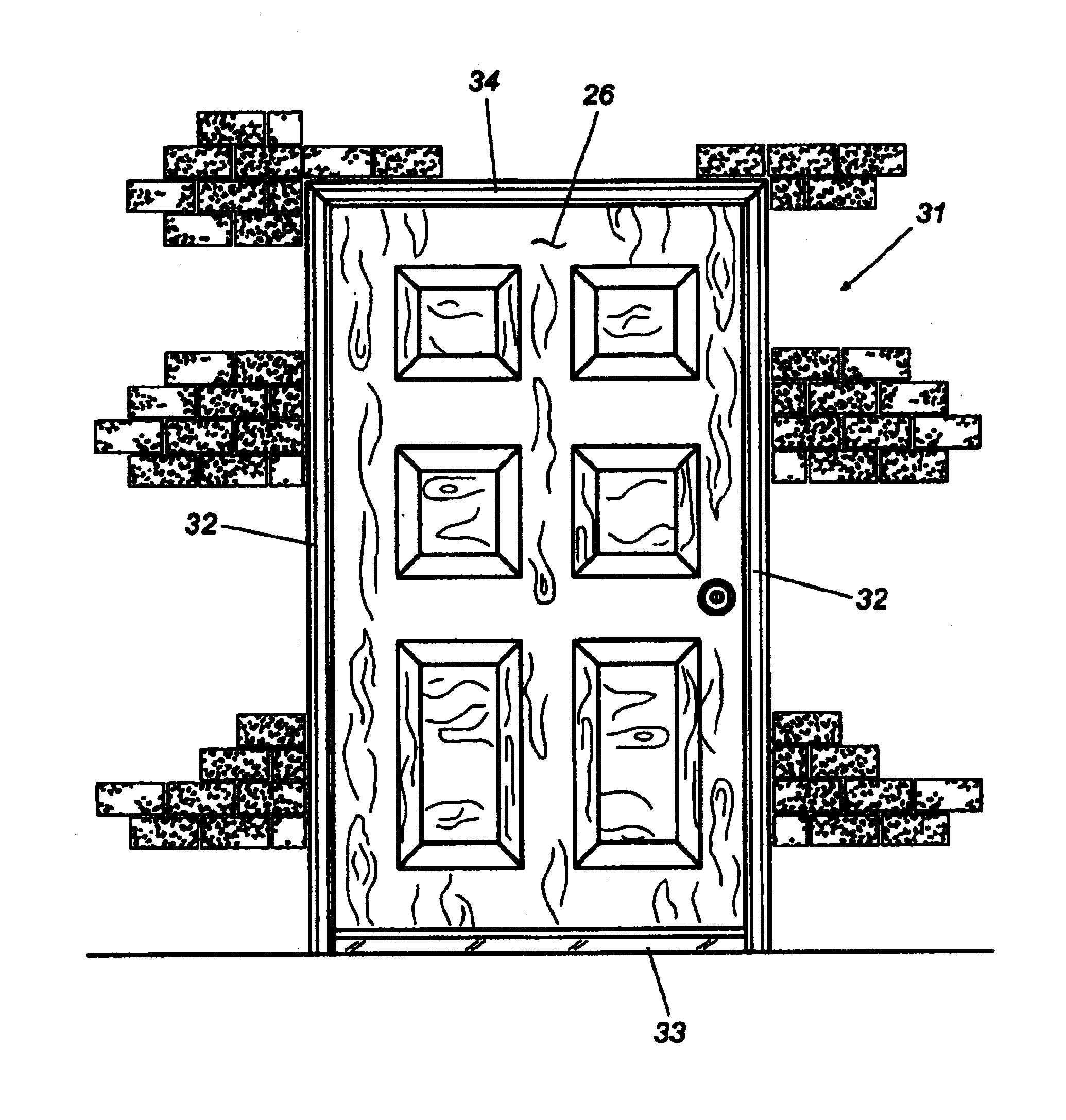

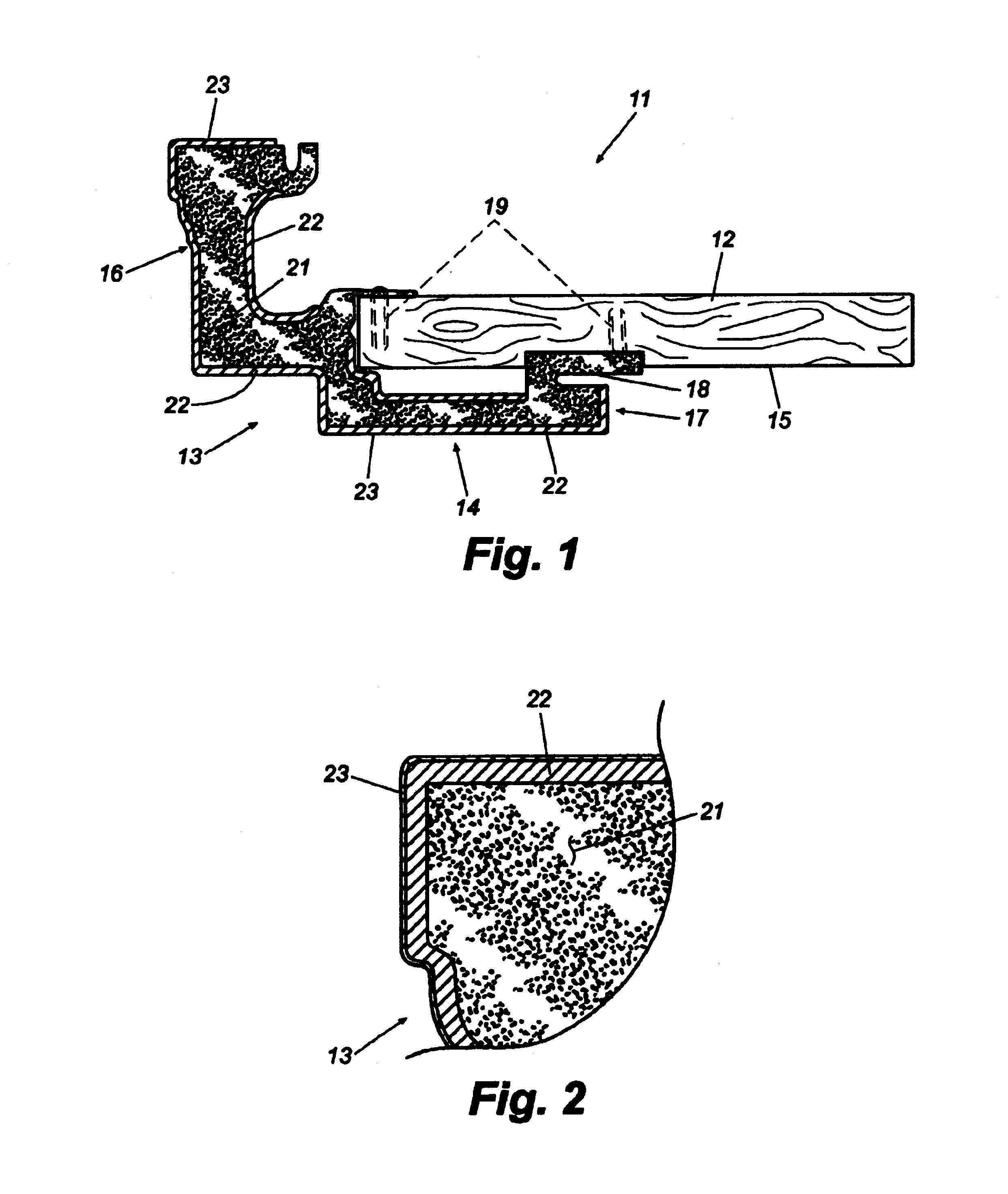

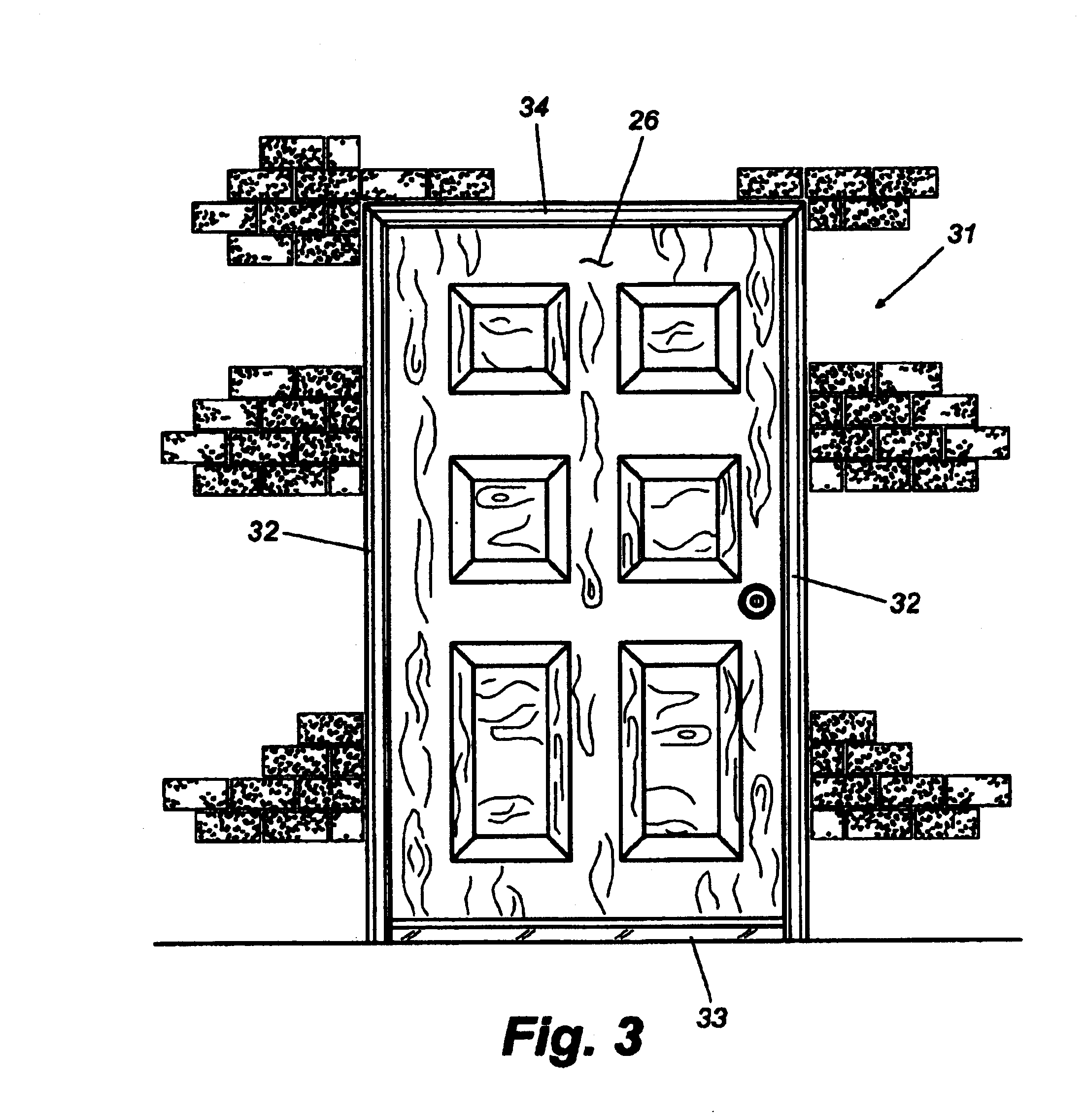

Entryway with dimensionally stable plastic components

InactiveUS7160601B2High thermal expansionLow costScaffold connectionsPicture framesHeat deflection temperatureEntryway

A door jamb assembly for an entryway has a wooden jamb plate to which an extruded plastic brick mold and stop member is attached. The brick mold and stop member forms the raised stop of the jamb assembly also may form the brick mold thereof. The extruded plastic brick mold and stop member has a core made of economical cellular PVC plastic at least partially encased in a stabilizing layer of a plastic material, such as SAN, having a heat distortion temperature greater than that of the PVC plastic of the core. The stabilizing layer holds the core material in place and restrains it against distortion and shrinkage due to extreme temperatures, such as those found between a storm door and a door exposed to direct sunlight.

Owner:REESE ENTERPRISES

High-heat-conductance electronic packaging material and its preparing method

InactiveCN1935926AHigh thermal conductivityLow thermal conductivityOther chemical processesSemiconductor/solid-state device detailsEpoxyBeta phase

The invention relates to high thermal conduction electronic package material. Its components are as follows filling powder 10-80%, epoxy resin 5-30%, curing agent 10-65%, curing accelerating agent 0.1-2.5%, release agent 0.5-3%, colorant 0.5-3%, and proper flame retardant and thixotropic agent. The filling powder can be beta phase silicon nitride powder, or the mixture of the beta phase silicon nitride powder and the silicon dioxide whose adding proportion is 5-95% of the filling total weight. The invention uses beta phase silicon nitride powder as the filling to increase material electrical thermal, property, and mechanical properties, optimize filling powder size distribution to increase package material thermal conductivity and high temperature fluidity, mixes the beta phase silicon nitride powder and silicon dioxide to use as filling to make the package material thermal conductivity and expansion coefficient controllable, and greatly shorten industrialization production transformation period.

Owner:TSINGHUA UNIV +1

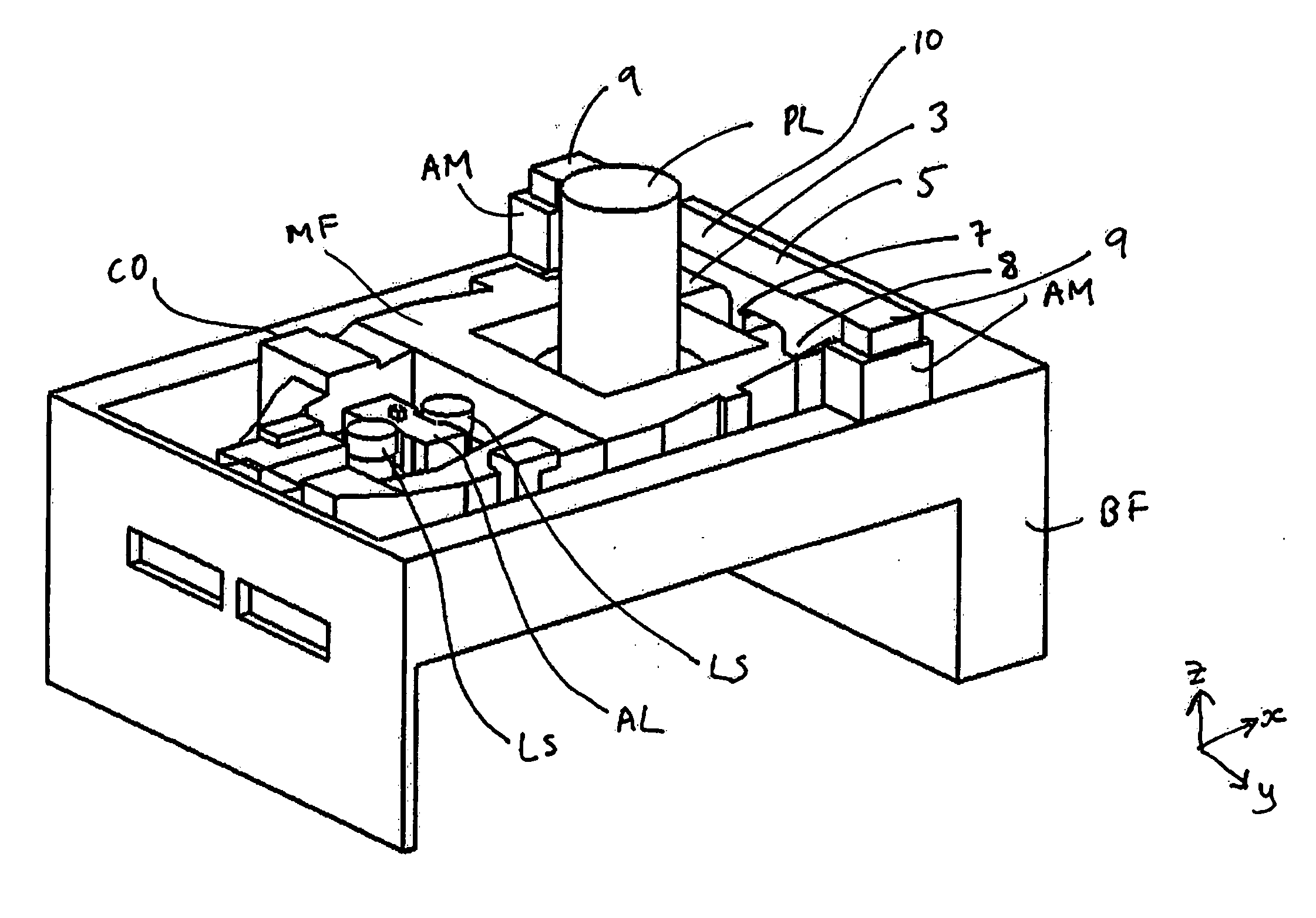

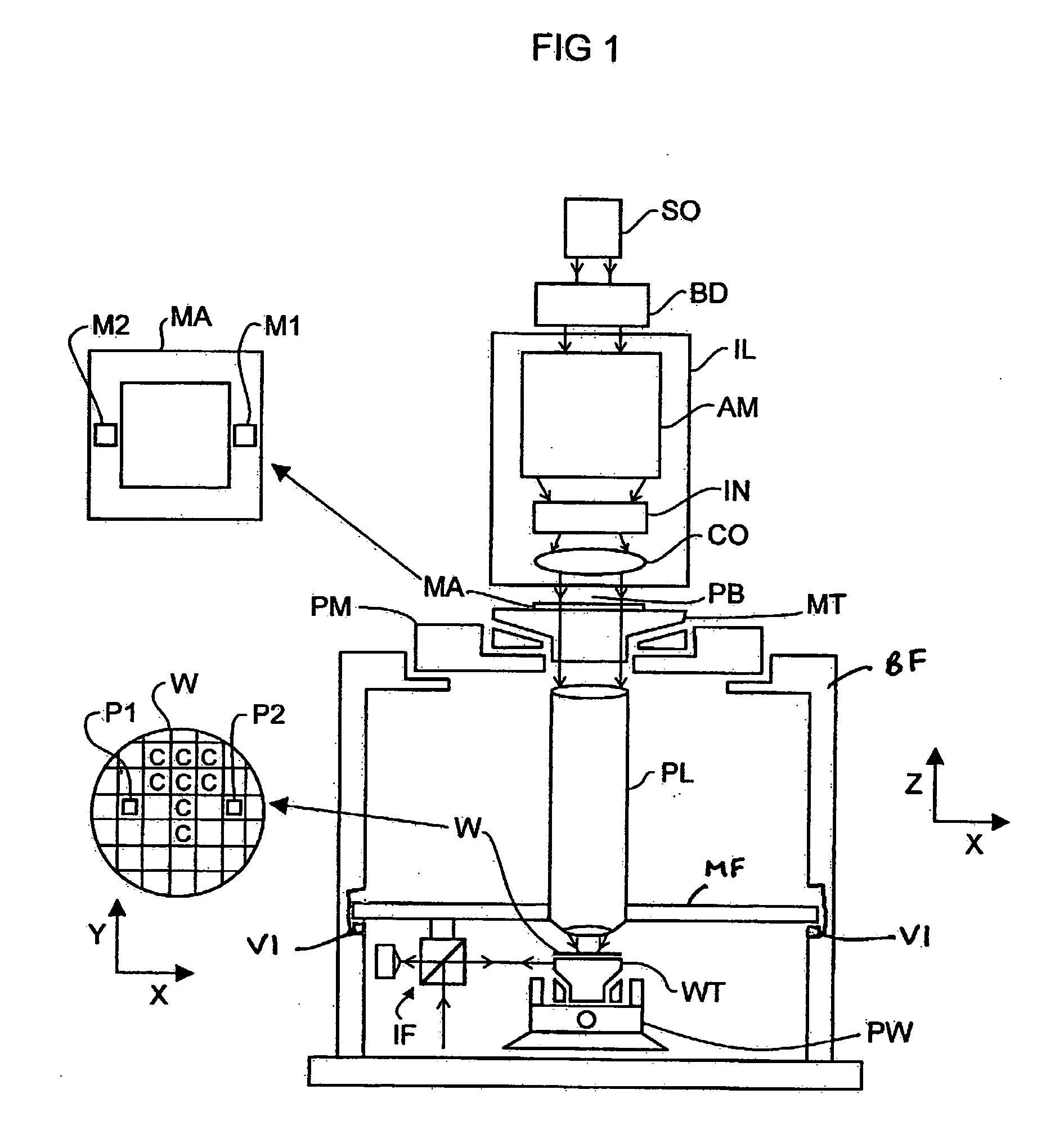

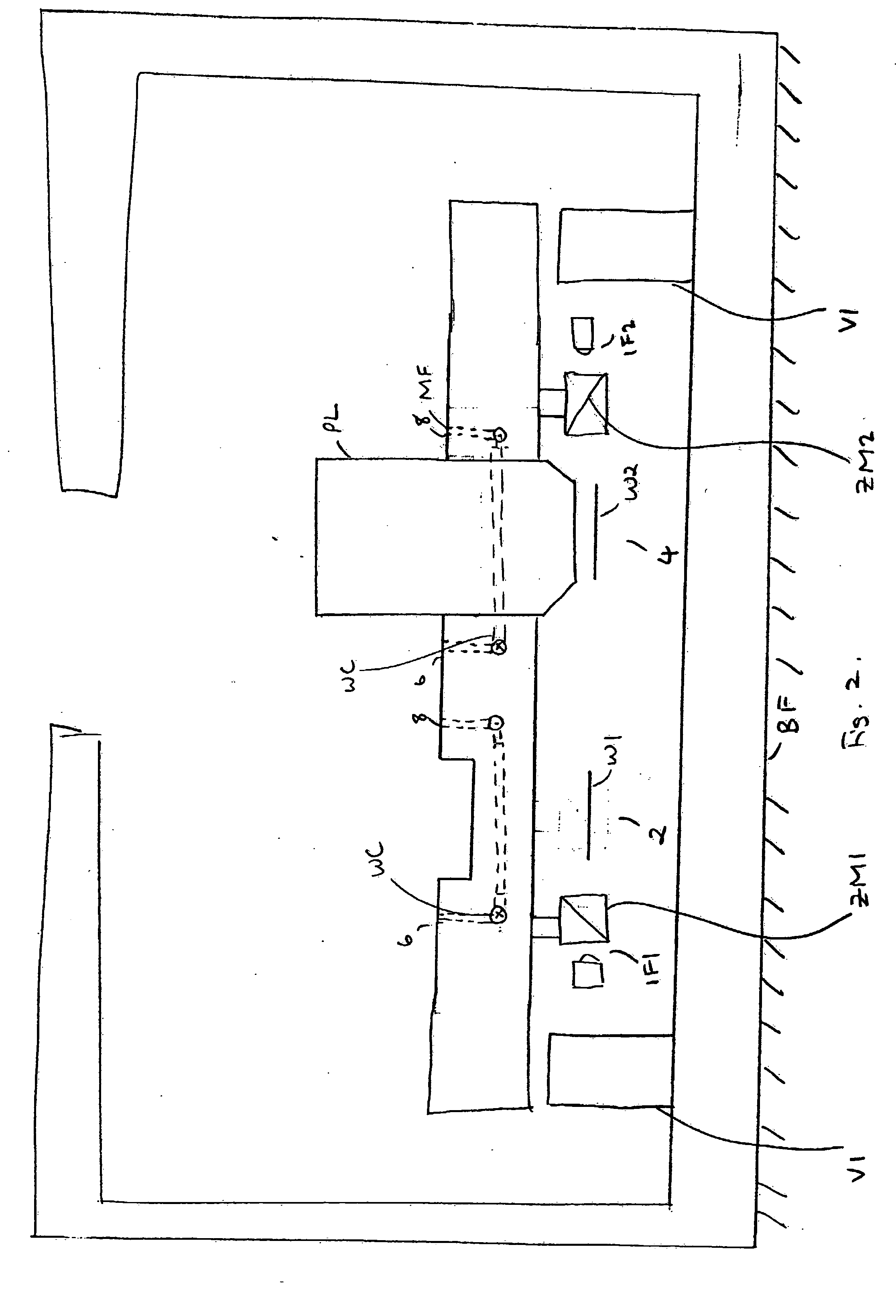

Lithographic apparatus and device manufacturing method

ActiveUS20050105070A1Increased Design FreedomLow production costSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusPhysicsProjection system

A lithographic apparatus is disclosed. The apparatus includes an illumination system that provides a beam of radiation, and a support structure that supports a patterning structure. The patterning structure is configured to impart the beam of radiation with a pattern in its cross-section. The apparatus also includes a substrate support that supports a substrate, a projection system that projects the patterned beam onto a target portion of the substrate, and a reference frame that provides a reference surface with respect to which a position of at least one of the substrate and the patterning structure is measured. The reference frame includes a material that has a coefficient of thermal expansion of greater than about 2.9×10−6 / K.

Owner:ASML NETHERLANDS BV

Ceramsite sand for casting and preparation method thereof

ActiveCN107298584AImprove thermal conductivityHigh thermal expansionFoundry mouldsFoundry coresExpanded clay aggregateSilicon dioxide

The invention relates to a ceramsite sand for casting and a preparation method thereof. The ceramsite sand comprises the following chemical components in parts by weight: 35-65 parts of silicon dioxide, 30-50 parts of aluminum oxide, 1-10 parts of iron oxide, 1-4 parts of manganese dioxide and 2-8 parts of chromic oxide. The method comprises the following steps: performing grinding, and detecting the chemical composition and contents of the raw materials; and sequentially performing proportioning, ball making, screening, sintering and grading to obtain the finished product. The ceramsite sand prepared by the invention is high in thermal conductivity and refractoriness, conforms to the requirements for casting sand, can be used for casting and casting mold production instead of silica sand, chromite sand and the like, reduces the discharge amount of solid waste in the casting industry, and improves the quality of cast products.

Owner:NINGXIA KOCEL MOLD

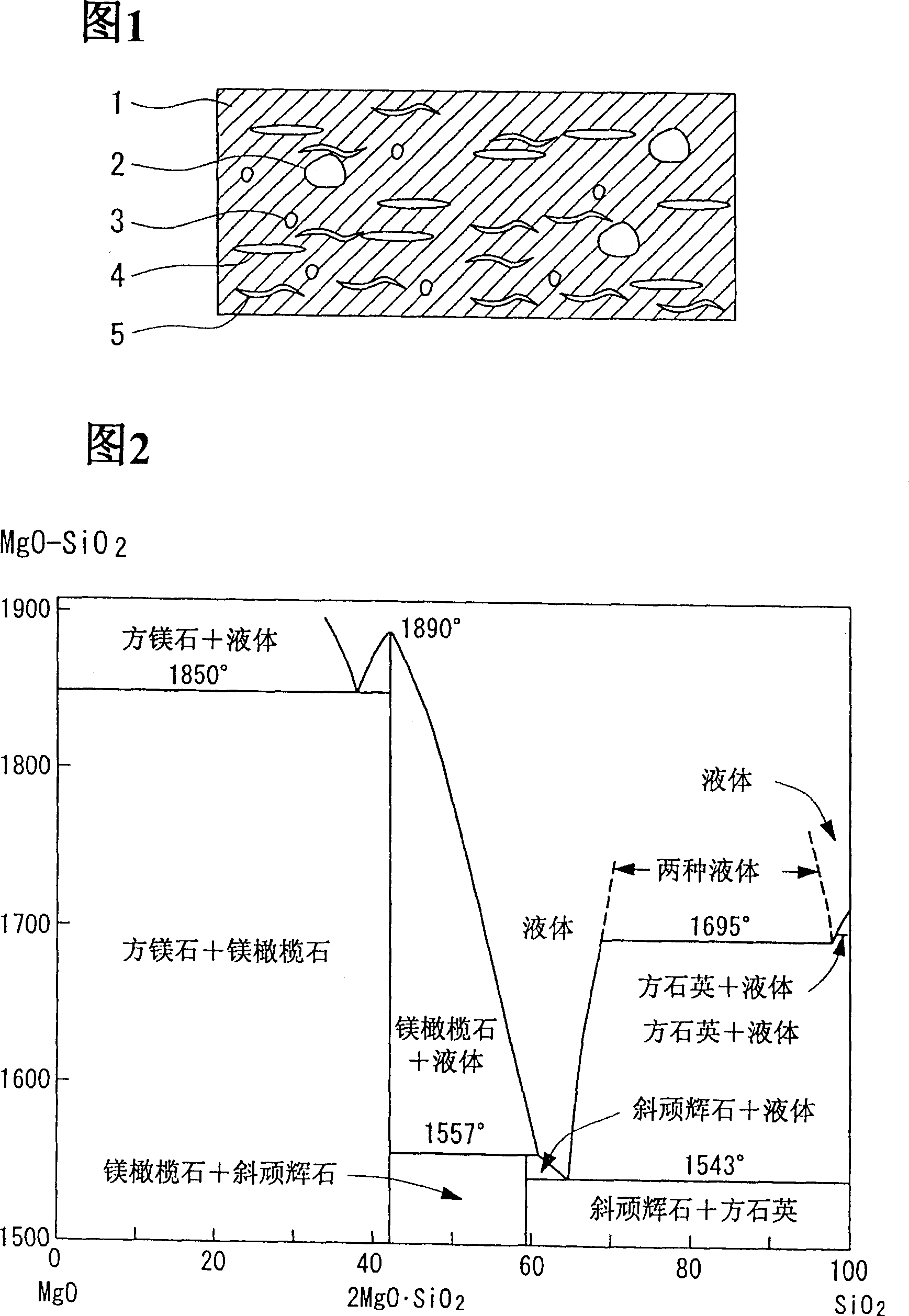

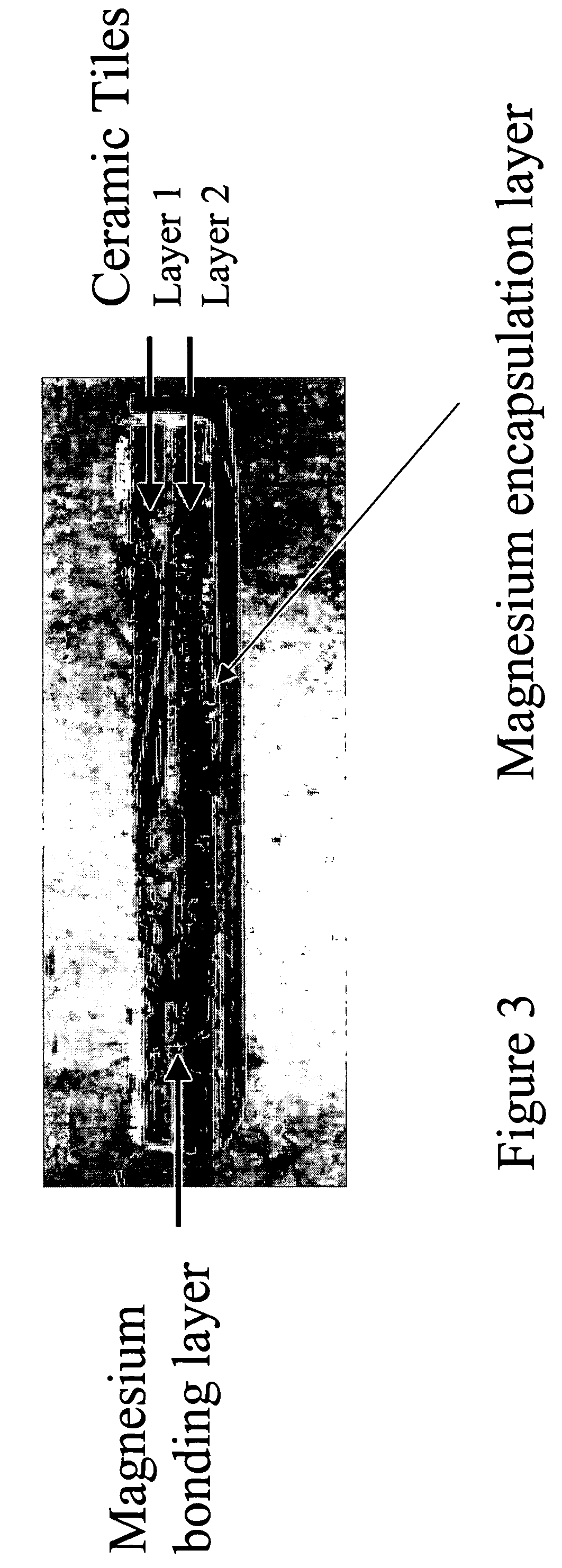

Metal-ceramic materials

InactiveUS20060141237A1Increase stiffnessReduce and internal tensile stressProtective equipmentConstructions elementsFiberMetal

A composite material that includes a ceramic with or without a fiber and a metal with the metal being magnesium, wherein the magnesium infiltrates the ceramic to form a continuous matrix, encapsulates the ceramic, or both infiltrates and encapsulates the ceramic or encapsulates the ceramic and fiber.

Owner:DYNAMIC DEFENSE MATERIALS

Sealant for high strength carbon foam

InactiveUS20060159905A1Efficient fillingImprove wettabilityOther chemical processesSynthetic resin layered productsPolymer scienceSealant

A sealant useful for sealing the surfaces of carbon foams to provide a surface useful for, inter alia, composite tooling or other high temperature applications or for bonding of carbon foams together to form larger blocks.

Owner:GRAFTECH INT HLDG INC

Inkjet printhead chip for use with a pulsating pressure ink supply

InactiveUS6929352B2High thermal expansionTelevision system detailsMaterial nanotechnologyActuatorInkjet printing

An ink jet printhead chip includes a substrate that incorporates drive circuitry. A plurality of nozzle arrangements is positioned on the substrate. Each nozzle arrangement includes nozzle chamber walls that define a nozzle chamber and an ink ejection port in fluid communication with the nozzle chamber. The nozzle chamber is in fluid communication with an ink supply channel through the substrate for supplying the nozzle chamber with ink. A closure is operatively positioned with respect to the ink supply channel. The closure is displaceable between a closed position in which the closure closes the ink supply channel and an open position in which ink is permitted to flow into the nozzle chamber. An actuator is connected to the drive circuitry and the closure so that, on receipt of an electrical signal from the drive circuitry, the actuator can act to displace the closure between the closed and open positions. An ink reservoir is in fluid communication with each ink supply channel. A source of oscillating pressure imparts an oscillating pressure to ink in the reservoir, so that, when the closure is displaced into the open position, a drop of ink can be ejected from the ink ejection port.

Owner:SILVERBROOK RES PTY LTD +1

Calcium aluminosilicate glasses for use as information recording medium substrates

InactiveUS20080130171A1Low densityHigh modulusDifferent record carrier formsRecord information storageCalcium silicateAlkali metal oxide

A glass substrate, and a information recording medium comprised of a glass substrate, comprising an a alkali-containing calcium aluminosilicate glass comprising SiO2, Al2O3, CaO, and alkali oxides (Li2O+Na2O+K2O) as essential components, specifically comprising the following components, expressed in terms of mole percent (mol %): 55-70% SiO2, 4-15% Al2O3, 0-8% B2O3, 8-20% CaO, 3-12% Na2O+K2O+Li2O, 0-5% MgO, up to 5% BaO and 13-35% MgO+CaO+BaO.

Owner:CORNING INC

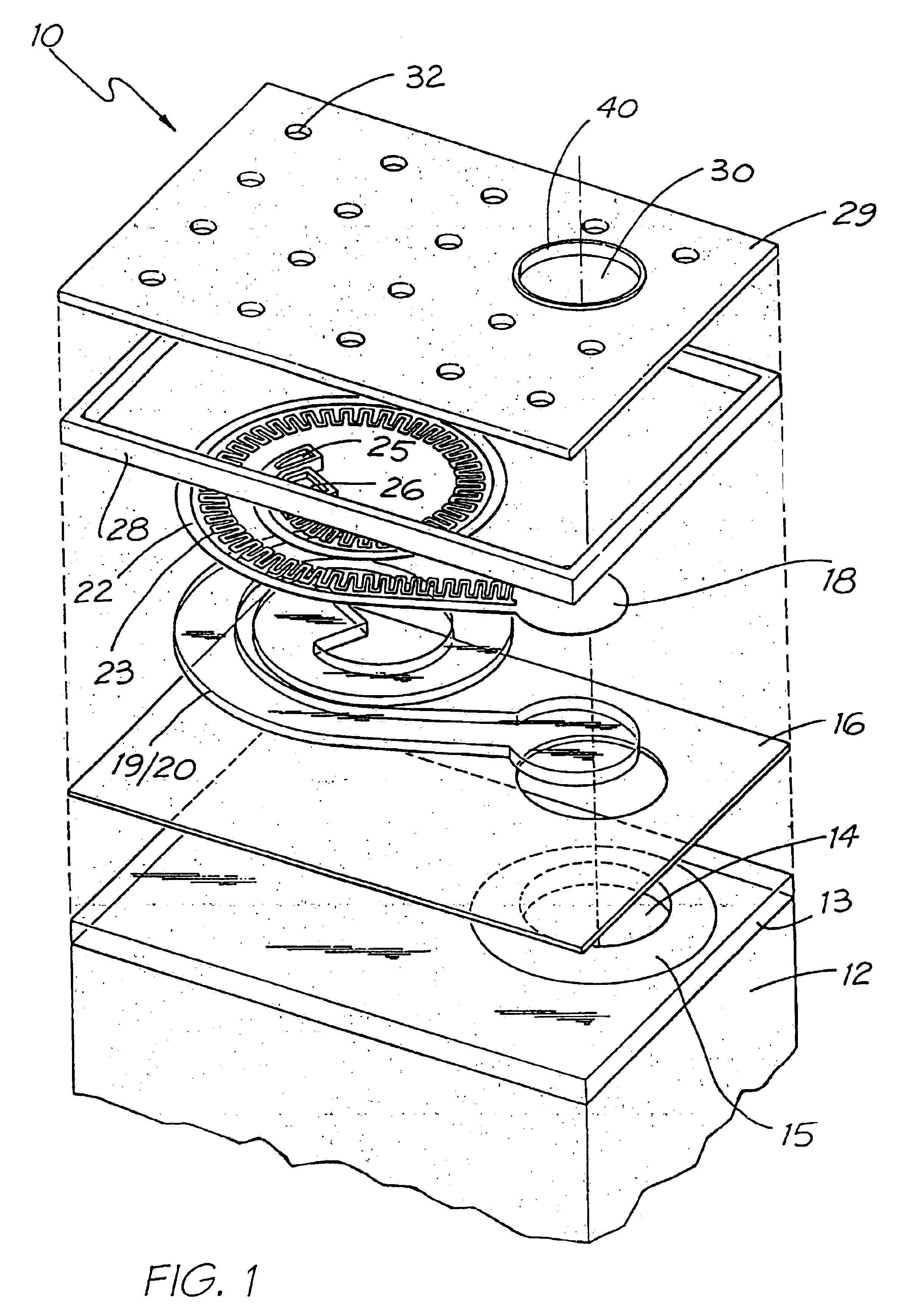

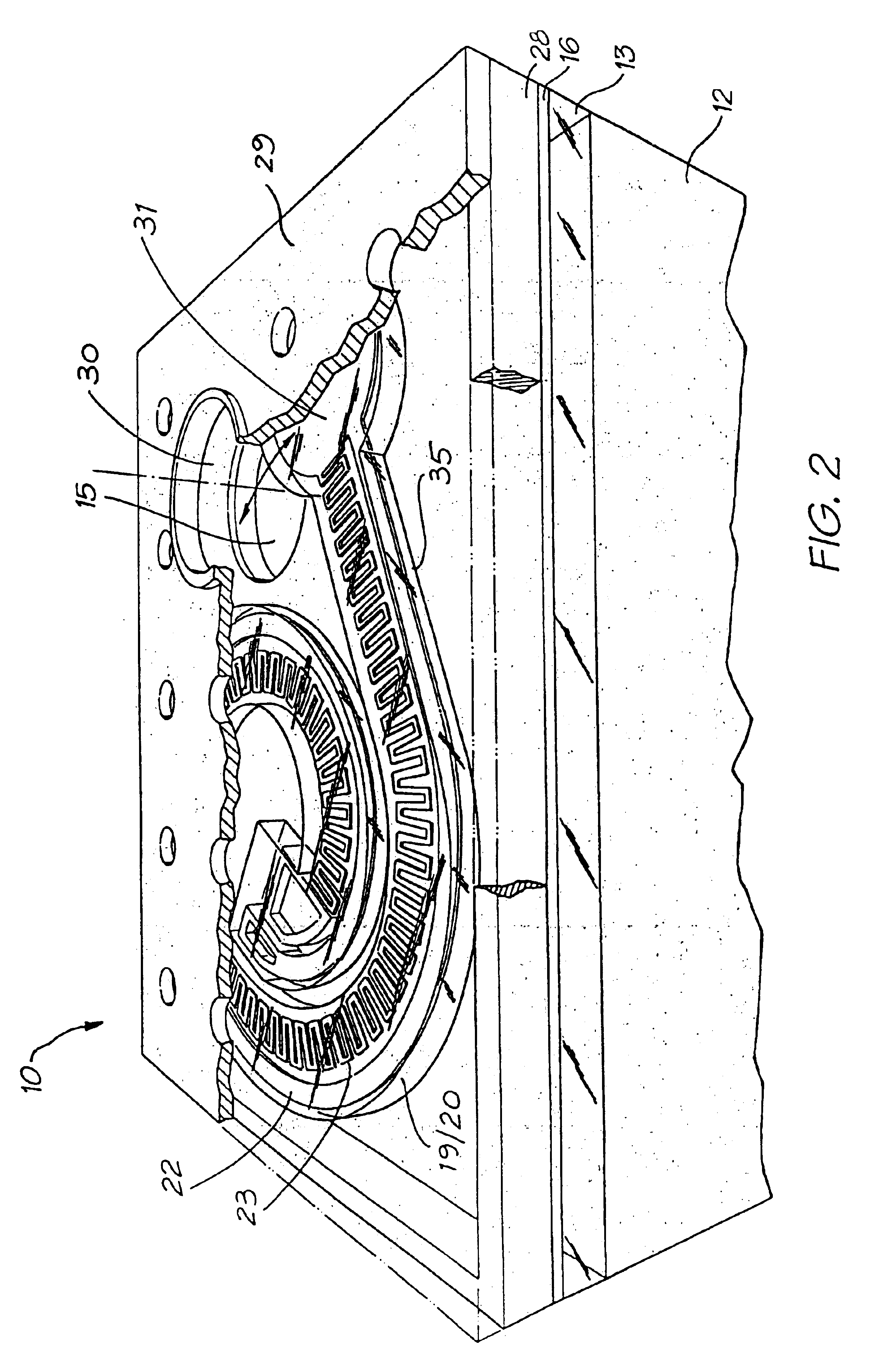

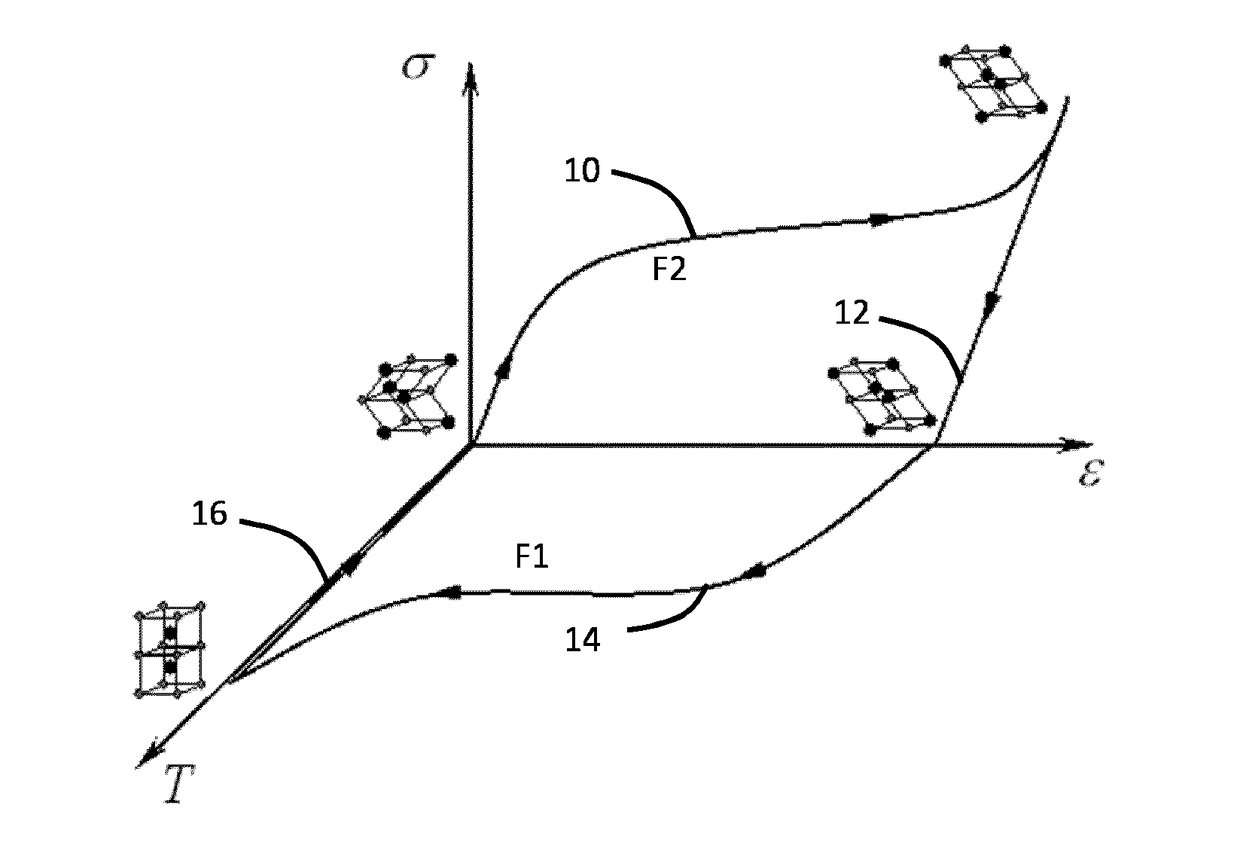

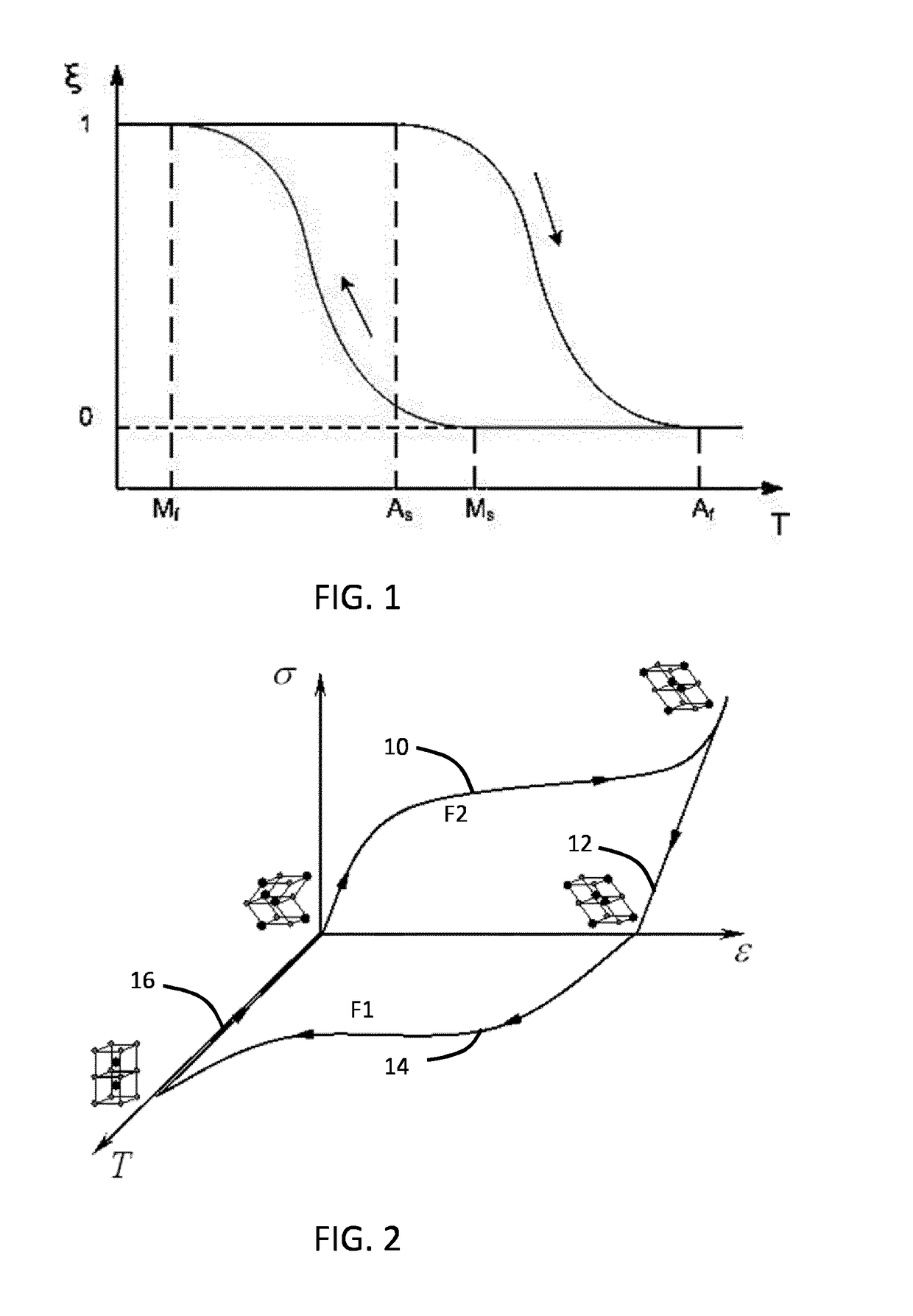

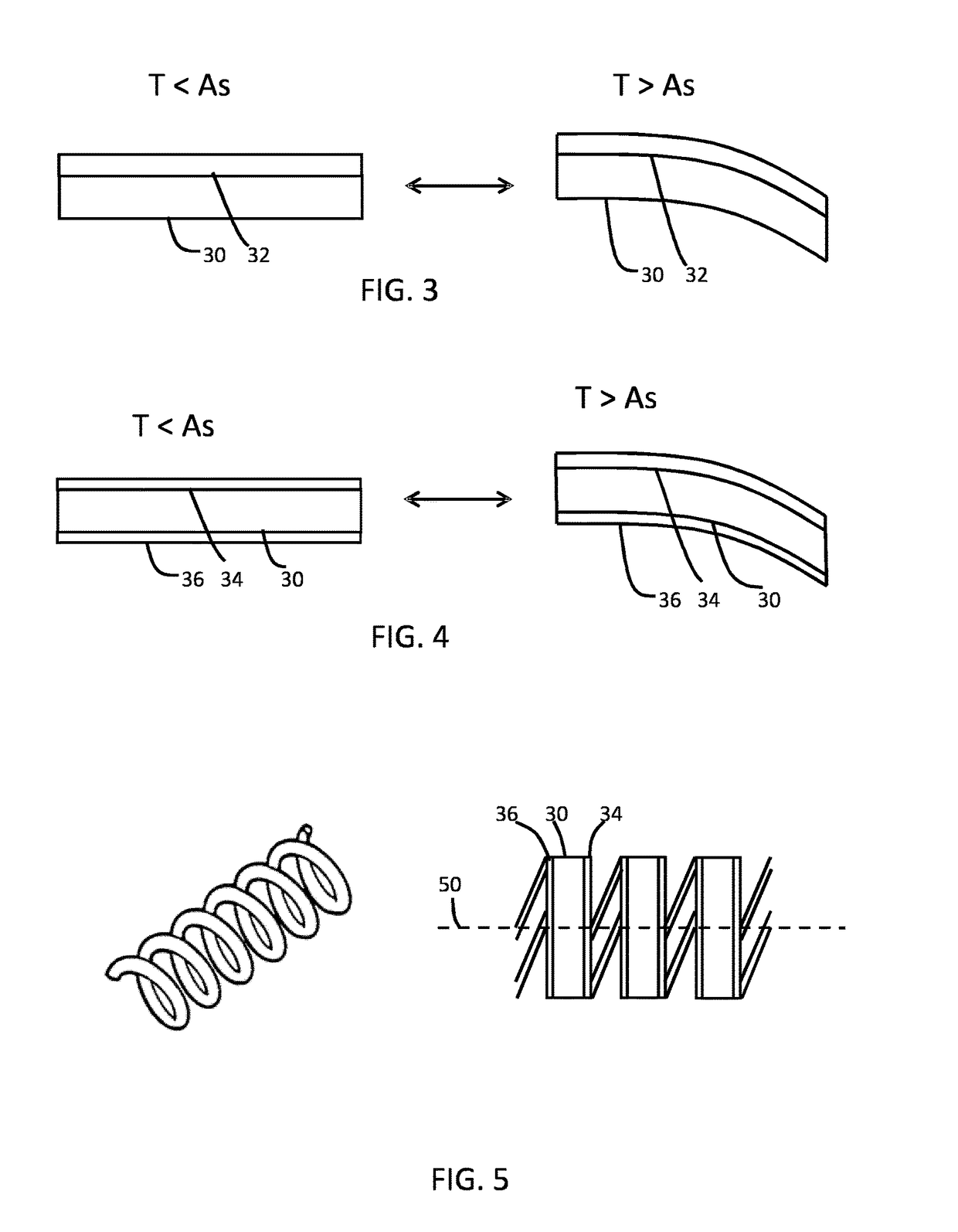

Heat sensitive actuator device

ActiveUS20170276122A1Avoid the needRelieve stressMachines/enginesMechanical power devicesHeat sensitiveEngineering

A heat sensitive actuator uses a shape memory material layer which is thermally stimulated to change shape, in response to a rise in temperature, from a first shape at a first temperature to a second shape at a second temperature. A layer stack is associated with the shape memory material layer, and it can adopt the first shape at the first temperature. In this way, the layer stack is used to return the shape memory material to its original shape after cooling.

Owner:KONINKLJIJKE PHILIPS NV

Sealant for high strength carbon foam

InactiveUS7232606B2Efficient fillingImprove wettabilityOther chemical processesSynthetic resin layered productsMetallurgyHigh intensity

A sealant useful for sealing the surfaces of carbon foams to provide a surface useful for, inter alia, composite tooling or other high temperature applications or for bonding of carbon foams together to form larger blocks.

Owner:GRAFTECH INT HLDG INC

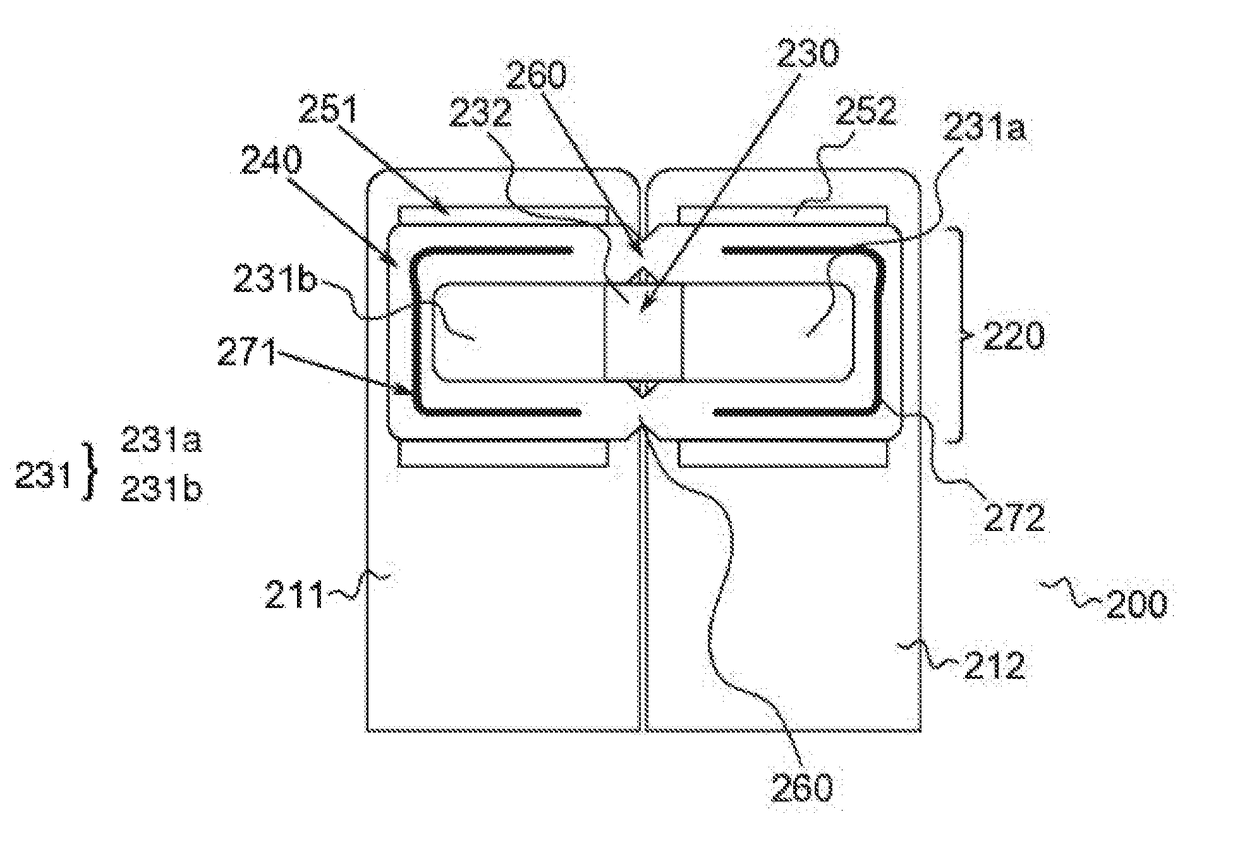

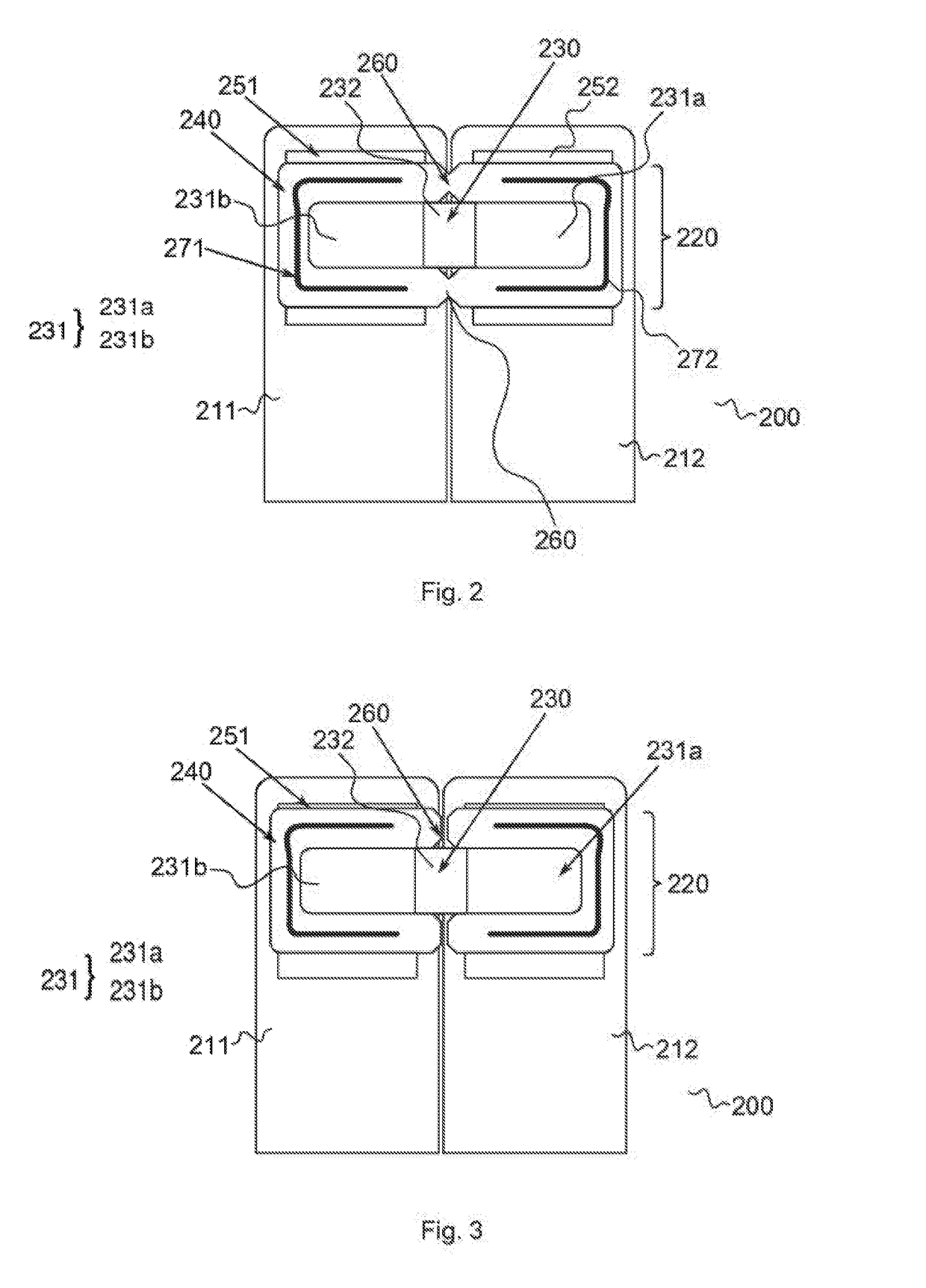

Busbar

ActiveUS20170098814A1High thermal expansionFinal product manufactureCoupling device detailsThermal runawayBusbar

The present invention refers to a busbar for electrically connecting a plurality of cells of a battery module. In order to electrically disconnect the battery cells from each other upon thermal runaway of at least one of the cells or short circuit, the busbar includes a core and a shell at least partially made of a first material, said first material being an electrically conducting material, wherein the core is at least partially made of a second material having a coefficient of thermal expansion which is significantly higher than the coefficient of thermal expansion of the first material.

Owner:SAMSUNG SDI CO LTD

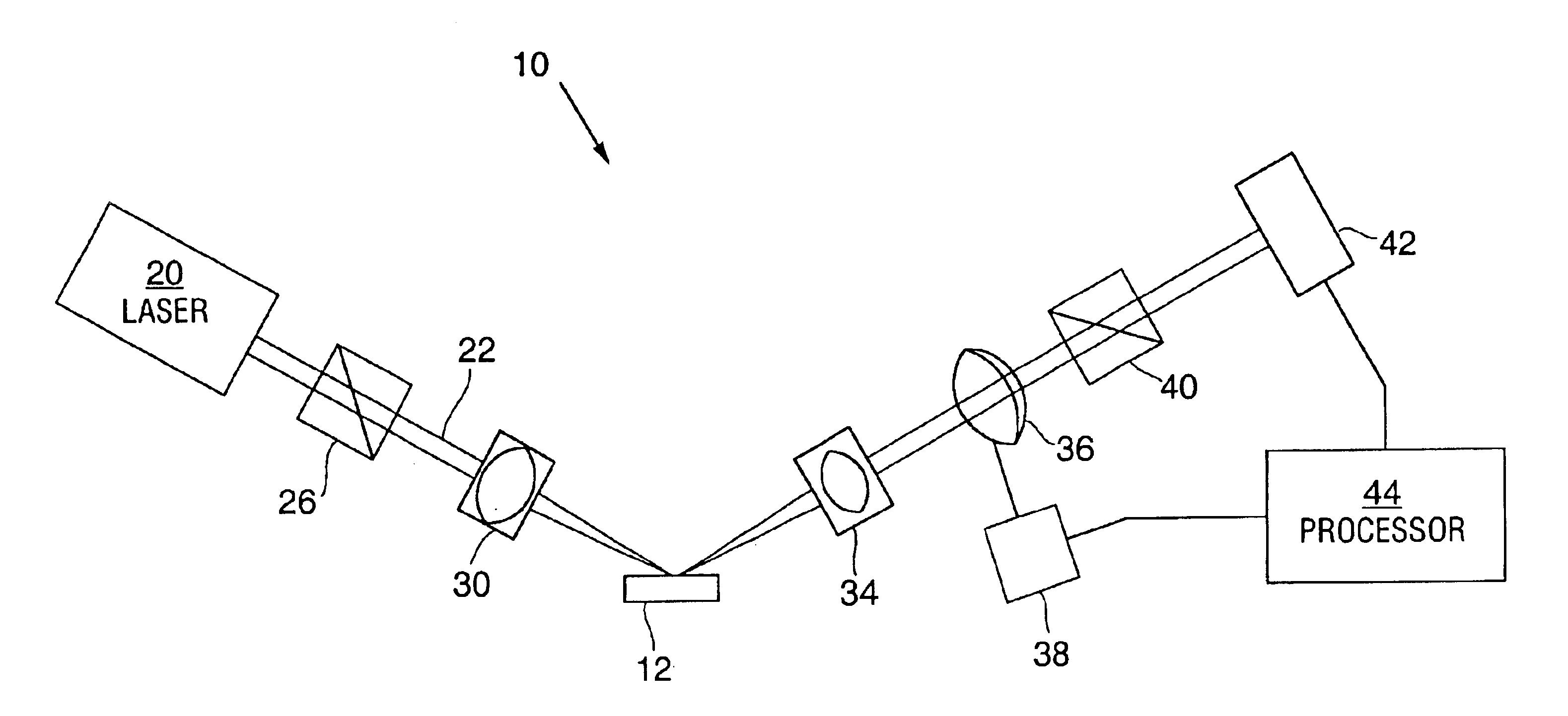

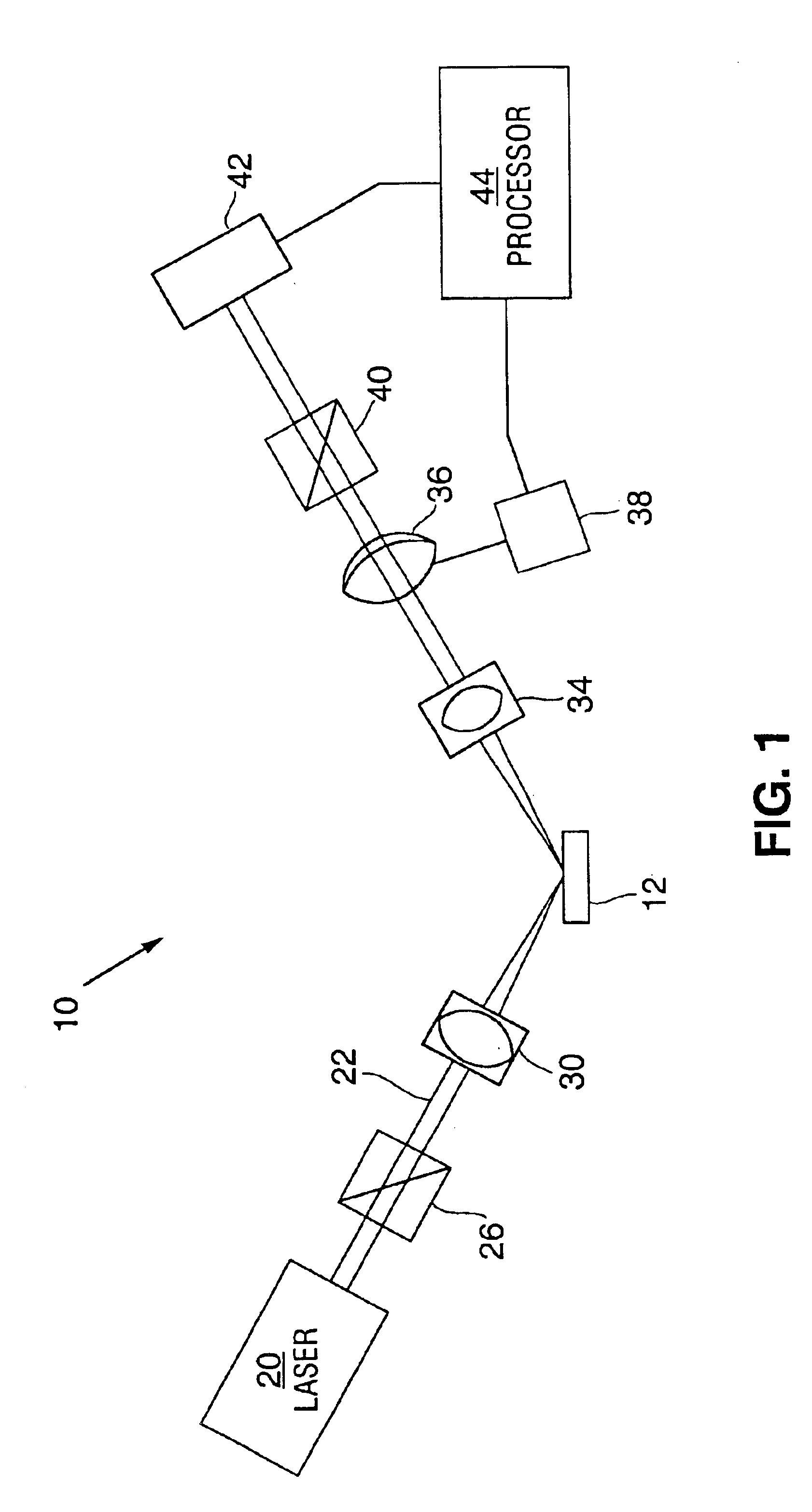

Small spot ellipsometer

InactiveUS6870621B2Reduce accuracyHigh coefficientLight polarisation measurementLight sourceRefractive index

An ellipsometer capable of generating a small beam spot is disclosed. The ellipsometer includes a light source for generating a narrow bandwidth probe beam. An analyzer is provided for determining the change in polarization state of the probe beam after interaction with the sample. A lens is provided having a numerical aperture and focal length sufficient to focus the beam to a diameter of less than 20 microns on the sample surface. The lens is formed from a graded index glass wherein the index of refraction varies along its optical axis. The lens is held in a relatively stress free mount to reduce stress birefringence created in the lens due to changes in ambient temperature. The ellipsometer is capable of measuring features on semiconductors having a dimensions as small as 50×50 microns.

Owner:THERMA WAVE INC

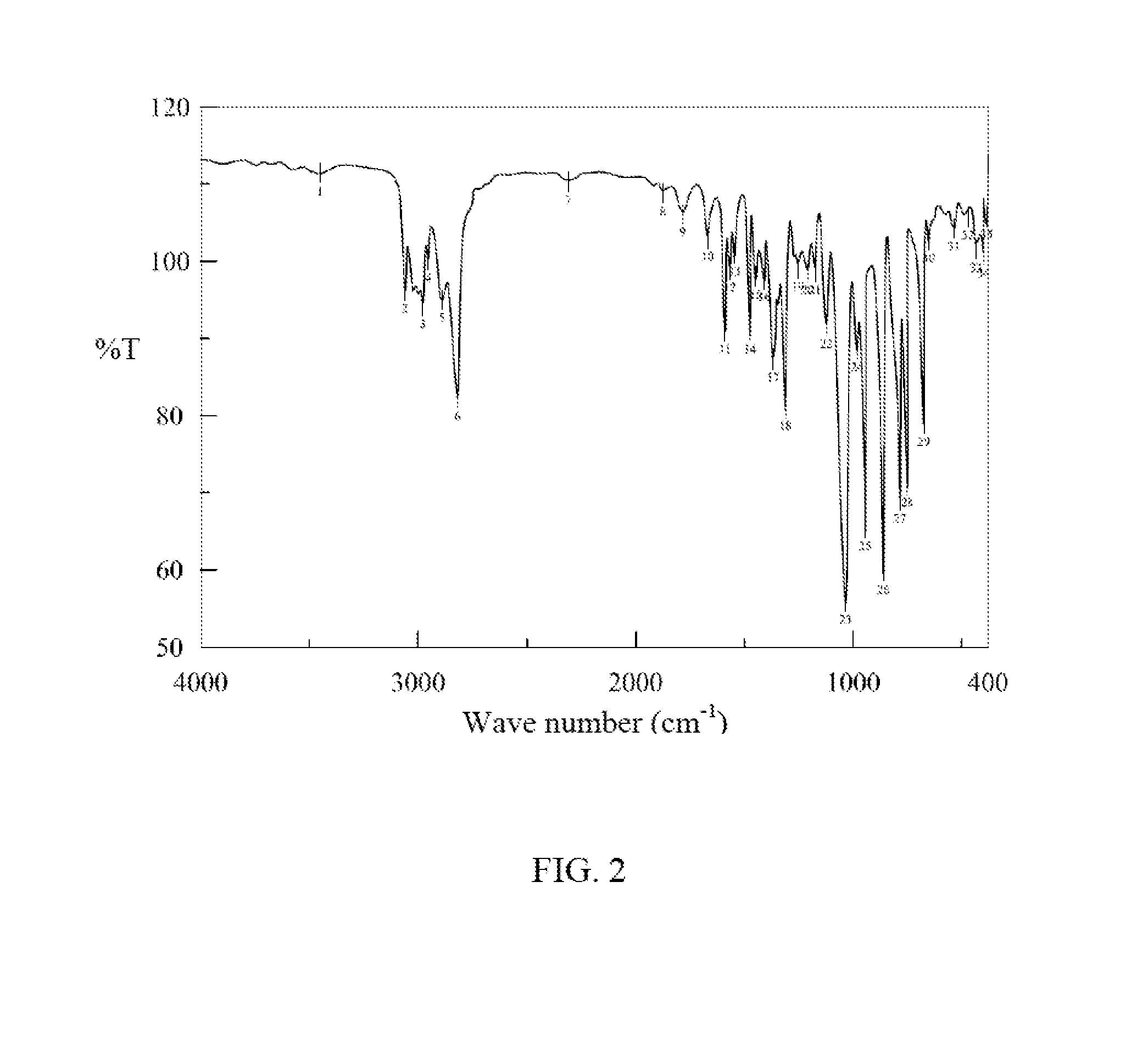

Low dissipation factor resin composition and product made thereby

A low dissipation factor resin composition comprises: (A) 100 to 150 parts by weight of a vinyl-containing compound or a polymer thereof; (B) 0 to 75 parts by weight of styrene-butadiene-divinylbenzene terpolymer, styrene-butadiene-maleic anhydride terpolymer, vinyl functional polybutadiene urethane oligomer or a combination thereof; (C) 30 to 150 parts by weight of flame retardant; and (D) 0.1 to 10 parts by weight of peroxide. The resin composition and a product made thereby are applicable to a copper-clad laminate and a printed circuit board, characterized by having low dissipation factor at high frequency and satisfactory thermal resistance and thermal expansion.

Owner:ELITE ELECTRONICS MATERIAL KUNSHAN

Bubble cap assembly

InactiveUS6868795B2Low costHigh thermal expansionFluidized bed combustionDrying solid materials with heatFluidized bedEngineering

A bubble cap assembly for use in fluidized bed boilers, furnaces, or reactors, has a bubble cap, a stem, and at least one pin. One end of the stem is inserted into the bubble cap. The bubble cap has outlet holes for delivering a fluidizing medium, typically into a bed of granulated material, but which prevent backsifting of the granulated material into the bubble cap. The bubble cap also has at least one insertion hole, through which a pin may be inserted. When the pin is inserted through the bubble cap insertion hole, it also occupies a groove or indentation on the stem thereby preventing separation or disassembly of the bubble cap and stem combination. An elastic gasket may be provided between the bubble cap and stem to form a fluid tight connection.

Owner:THE BABCOCK & WILCOX CO +1

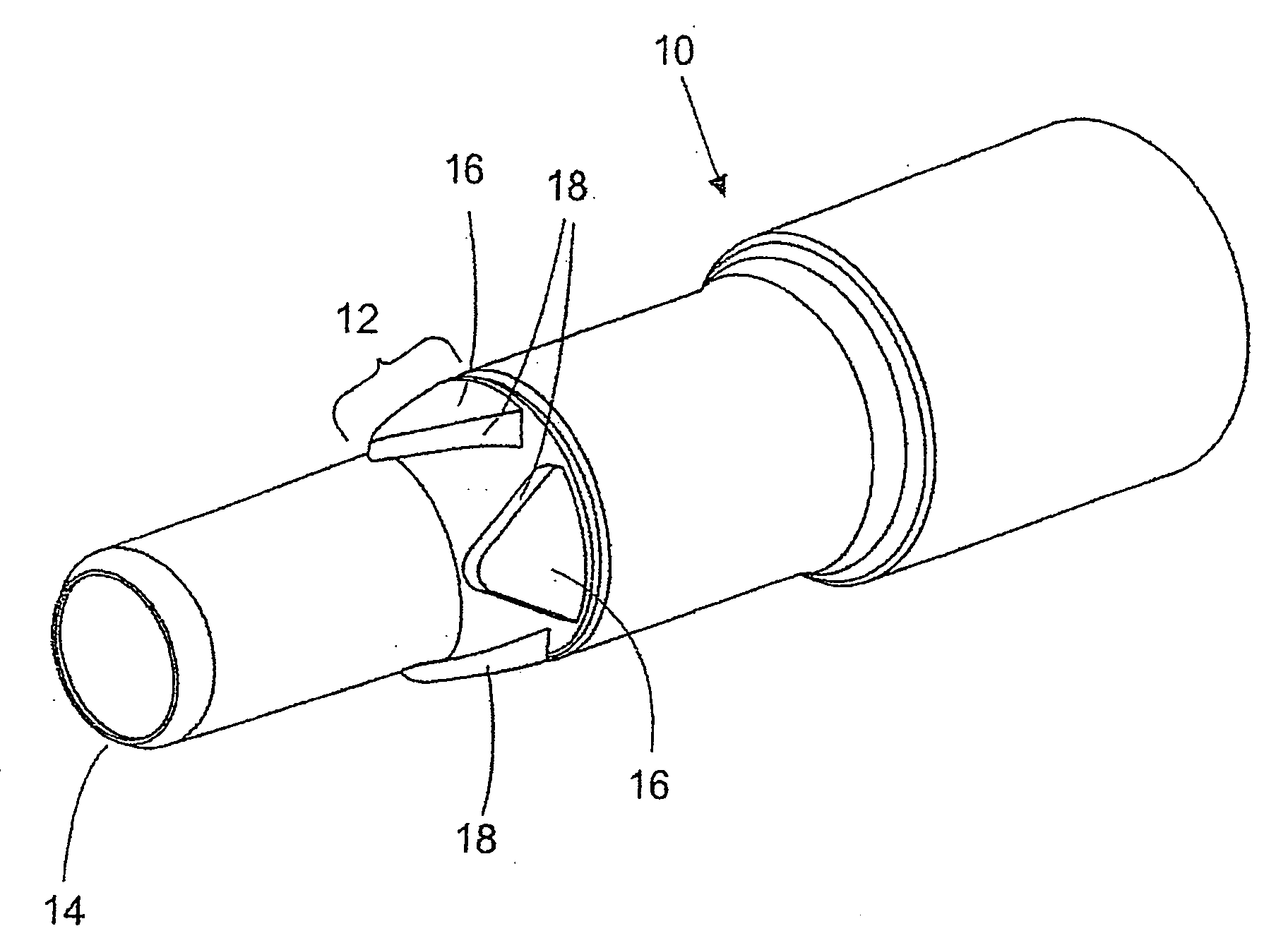

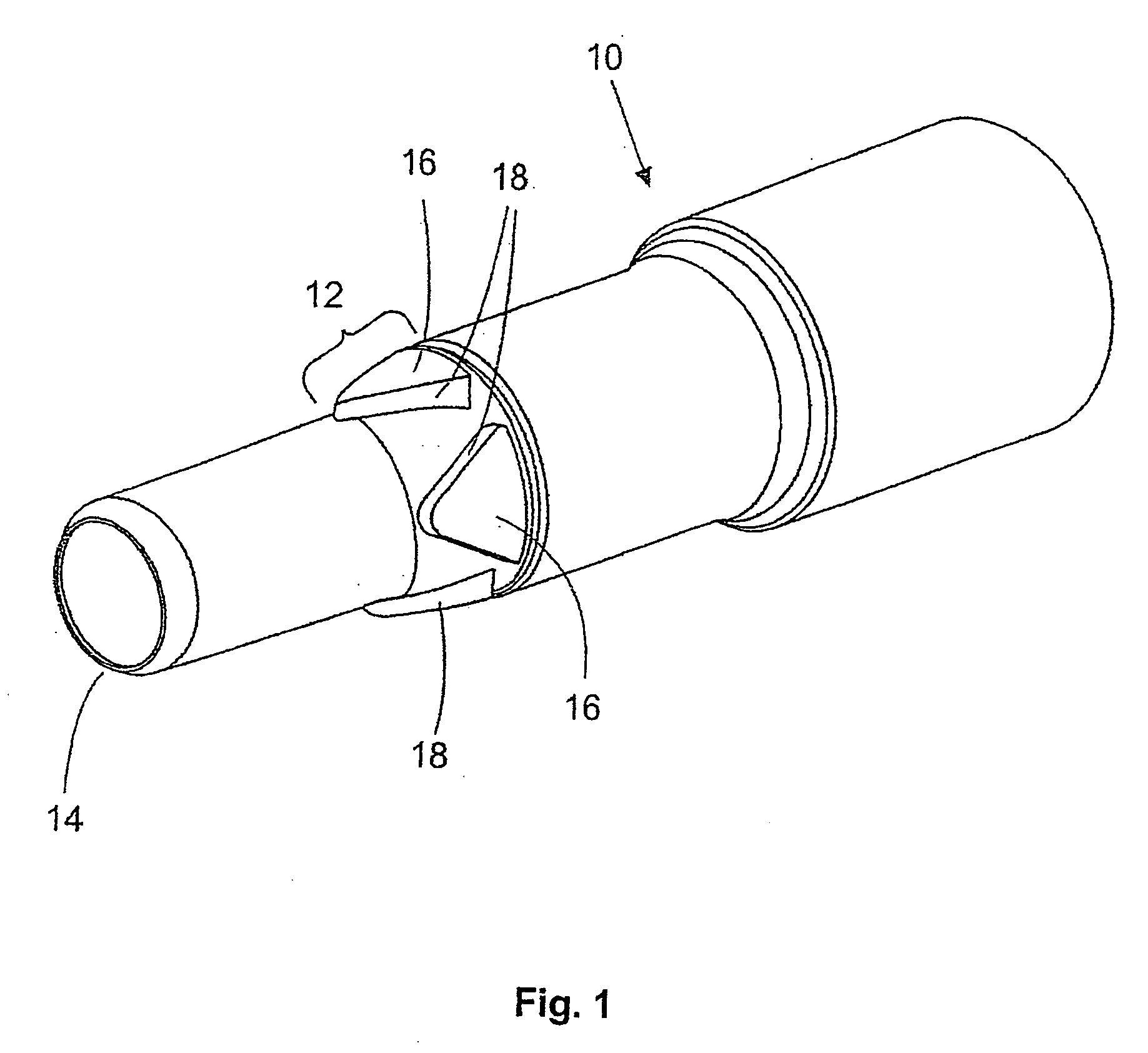

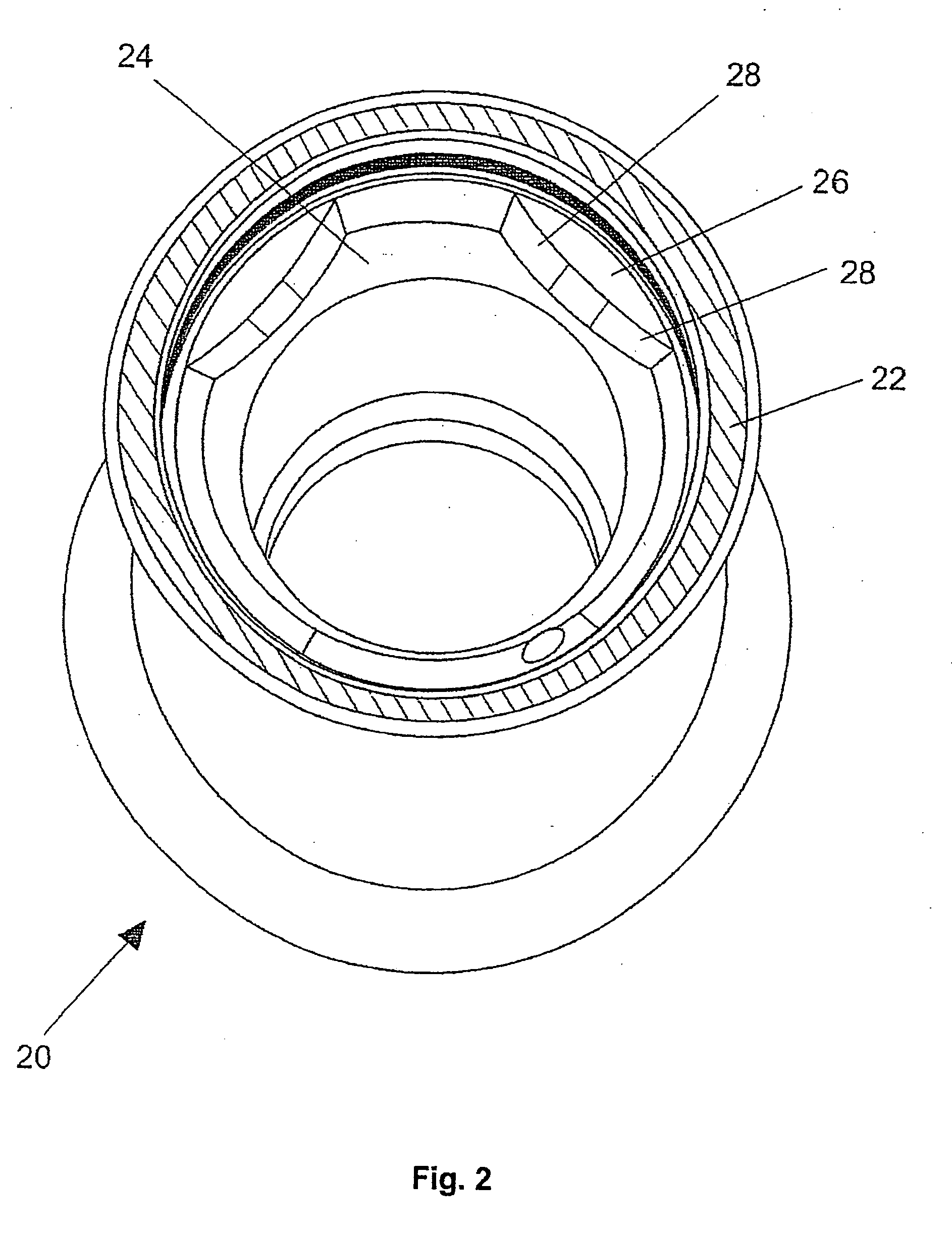

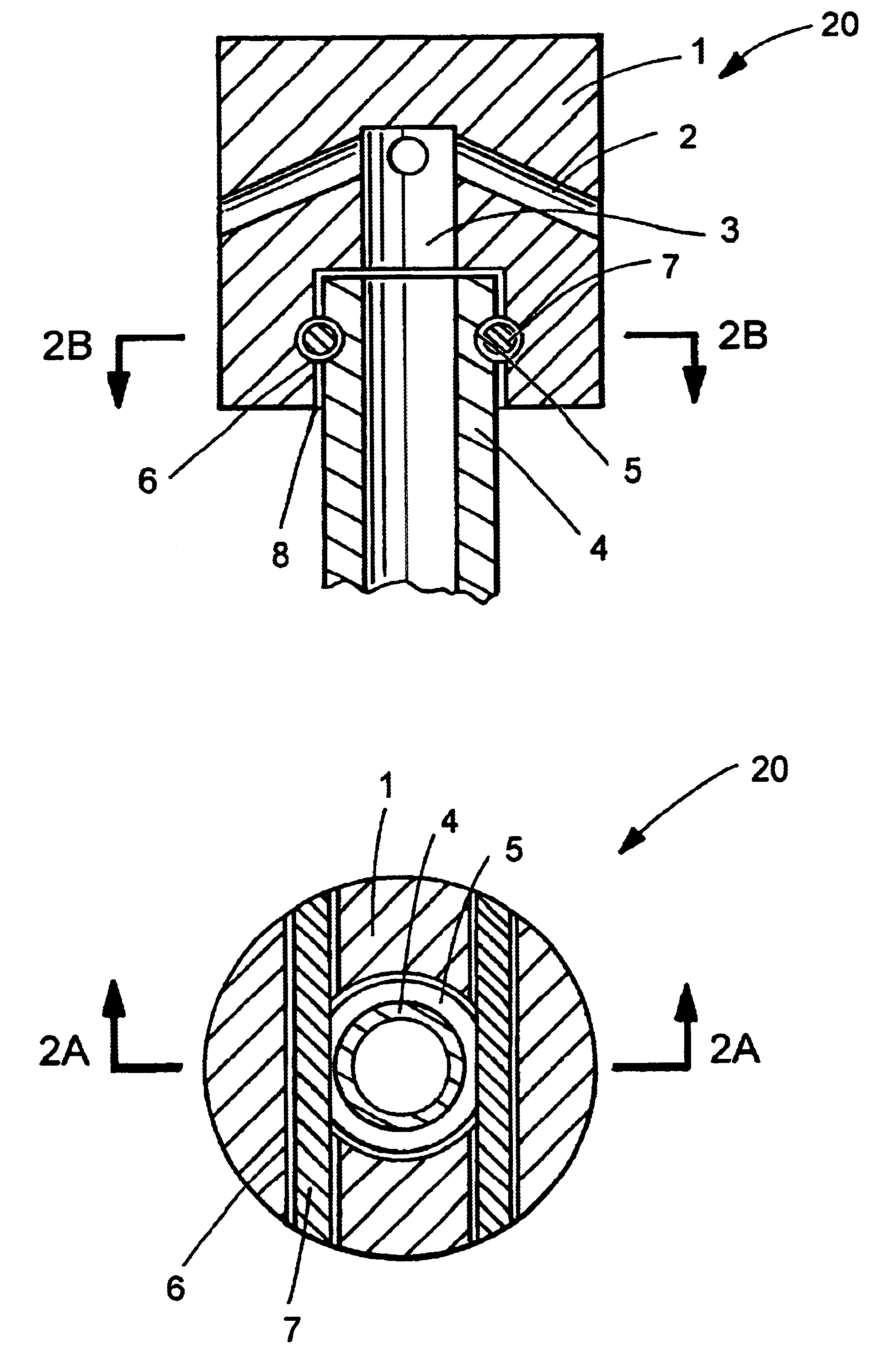

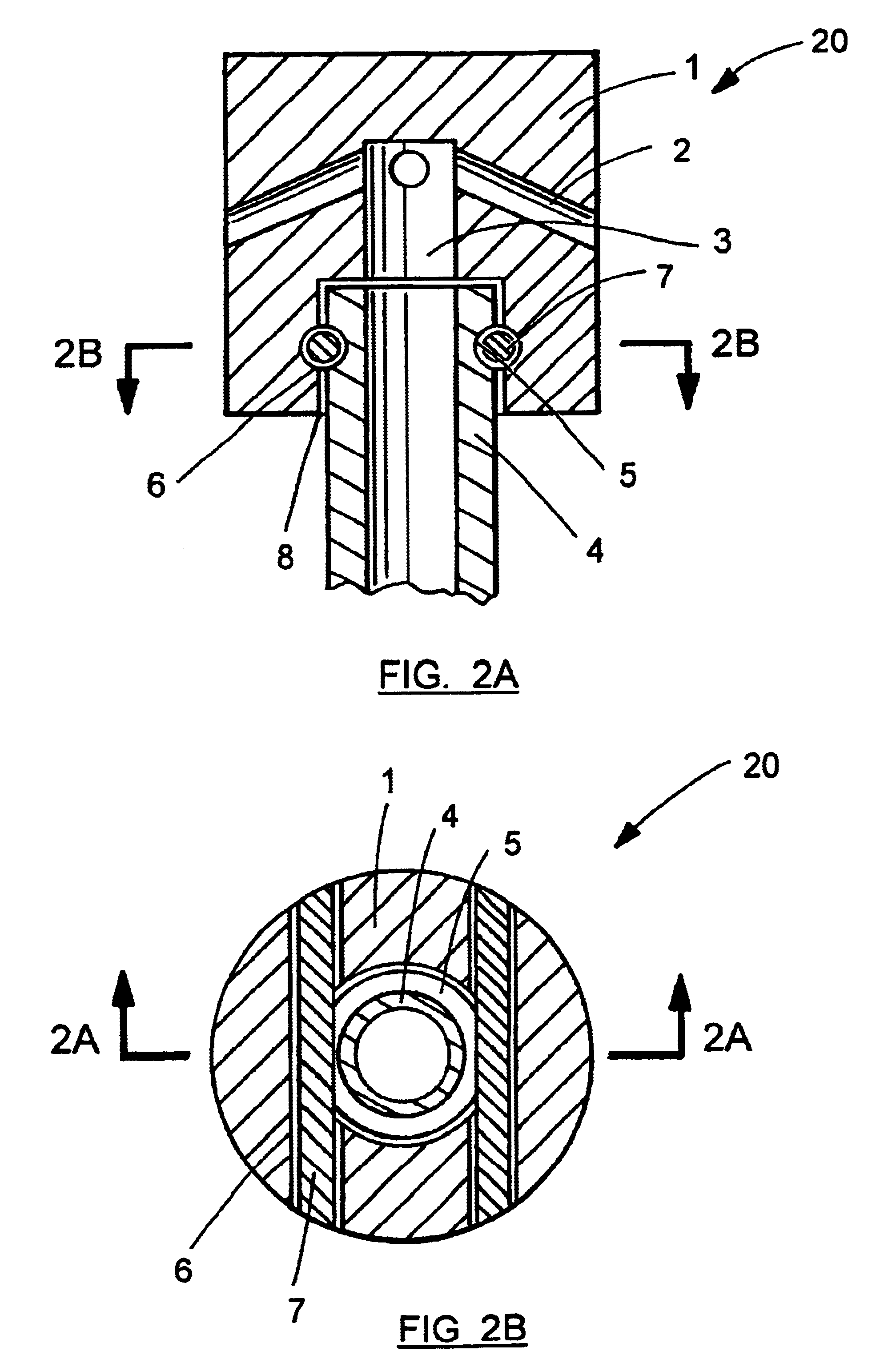

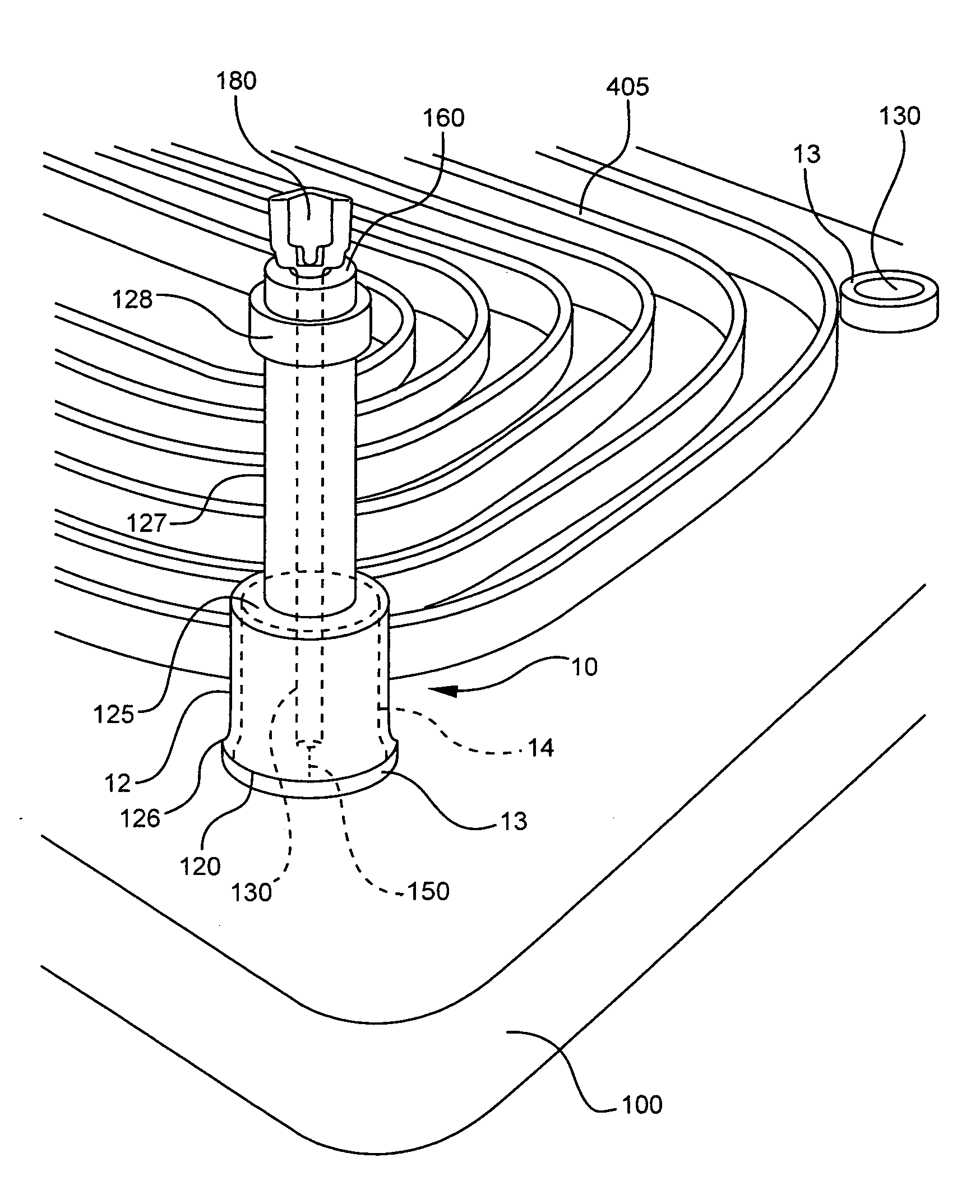

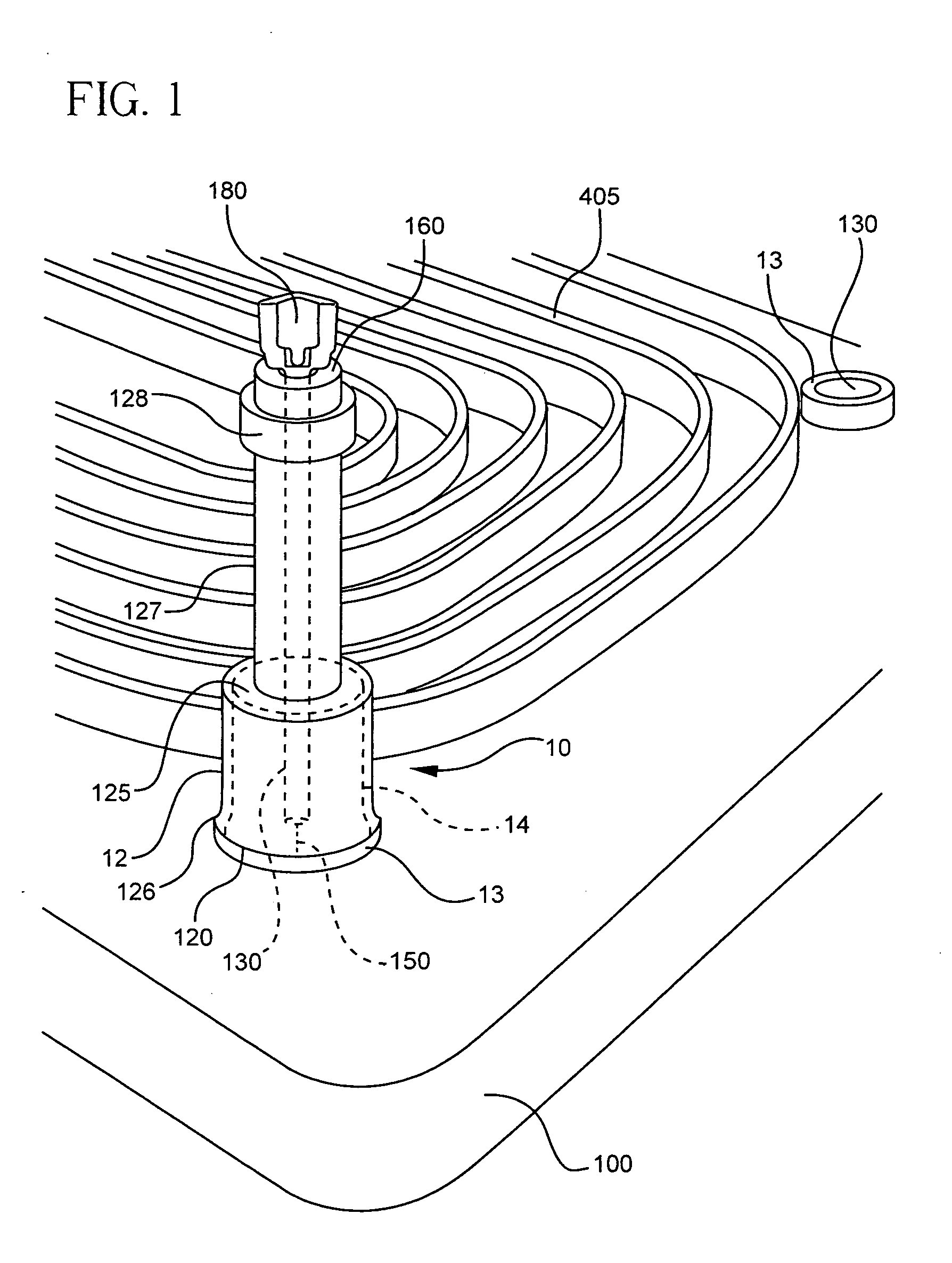

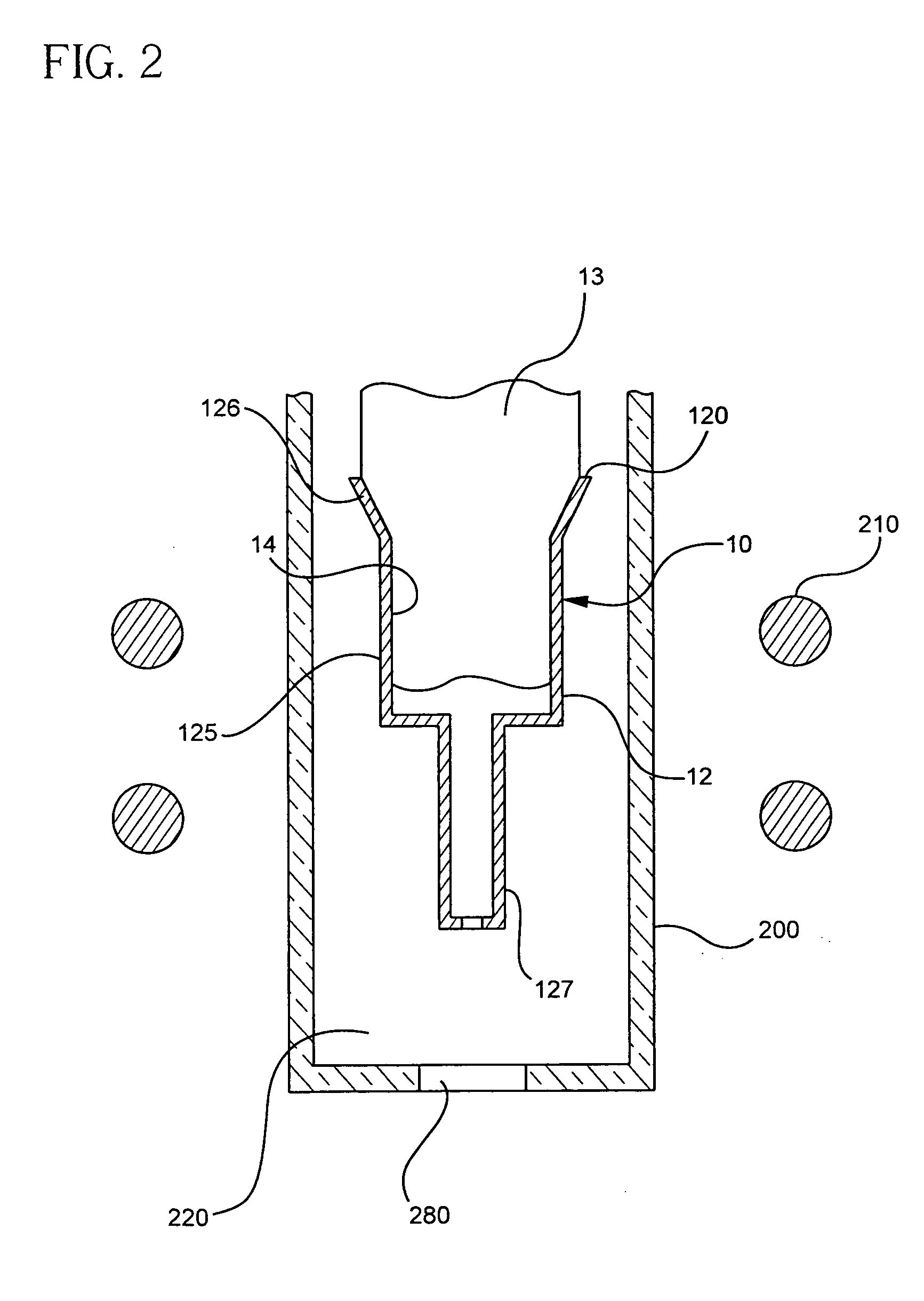

Hermetic glass micro reactor porting

InactiveUS20050276730A1High thermal expansionAnalysis using chemical indicatorsChemical/physical/physico-chemical microreactorsMetalMaterials science

A hermetic porting assembly (10) for a glass or glass ceramic reactor (100) includes a metallic connector member (12) having a metal aperture (120), and a glass member (13) having a glass aperture (130). The glass member (13) is positioned within the metal aperture (120), wherein the metallic connector member (12) has a higher coefficient of thermal expansion than the glass member (13) and wherein at least a portion of the glass member (13) is held within the metallic aperture of the metallic member by a fused glass-to-metal hermetic compression seal (14).

Owner:CORNING INC

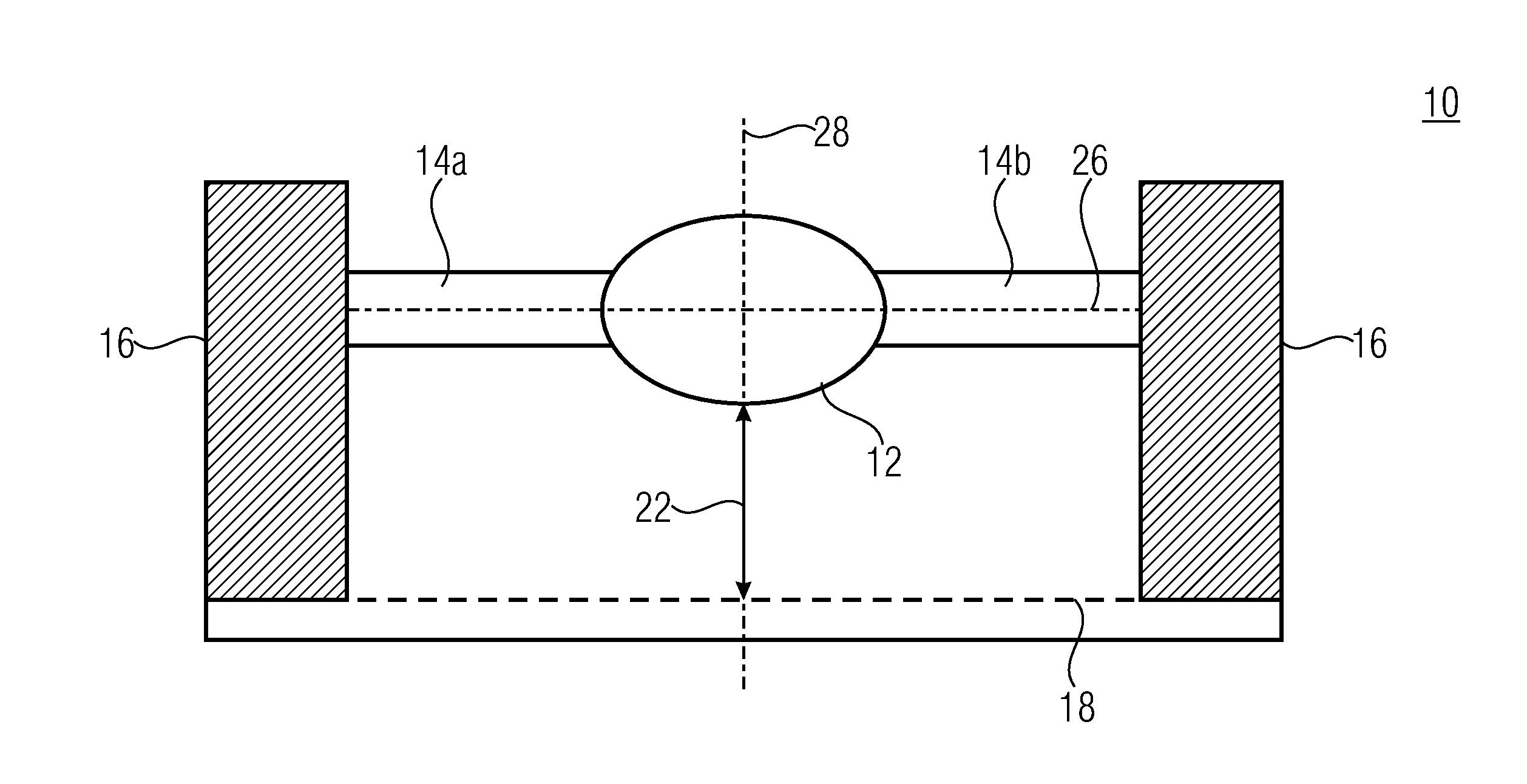

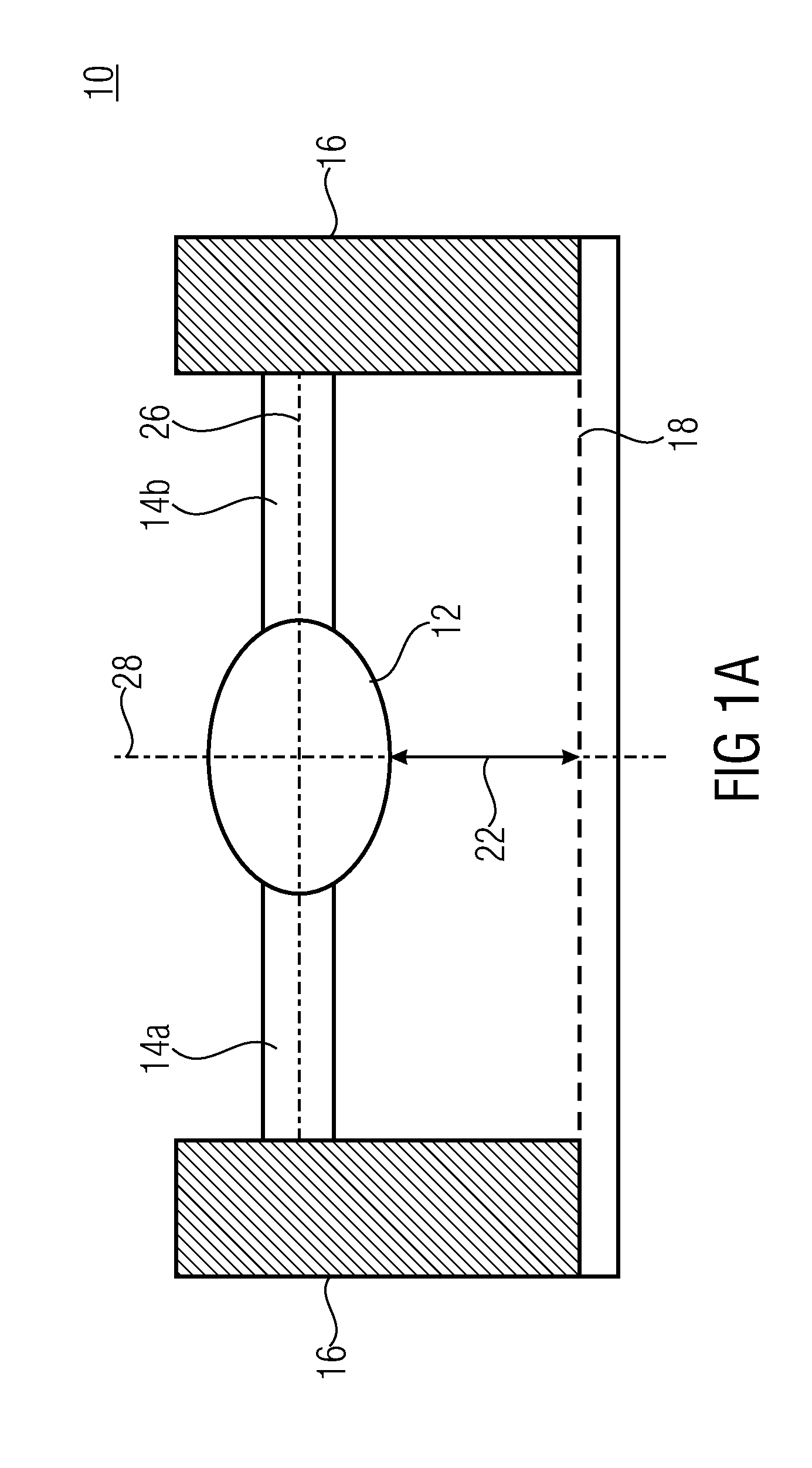

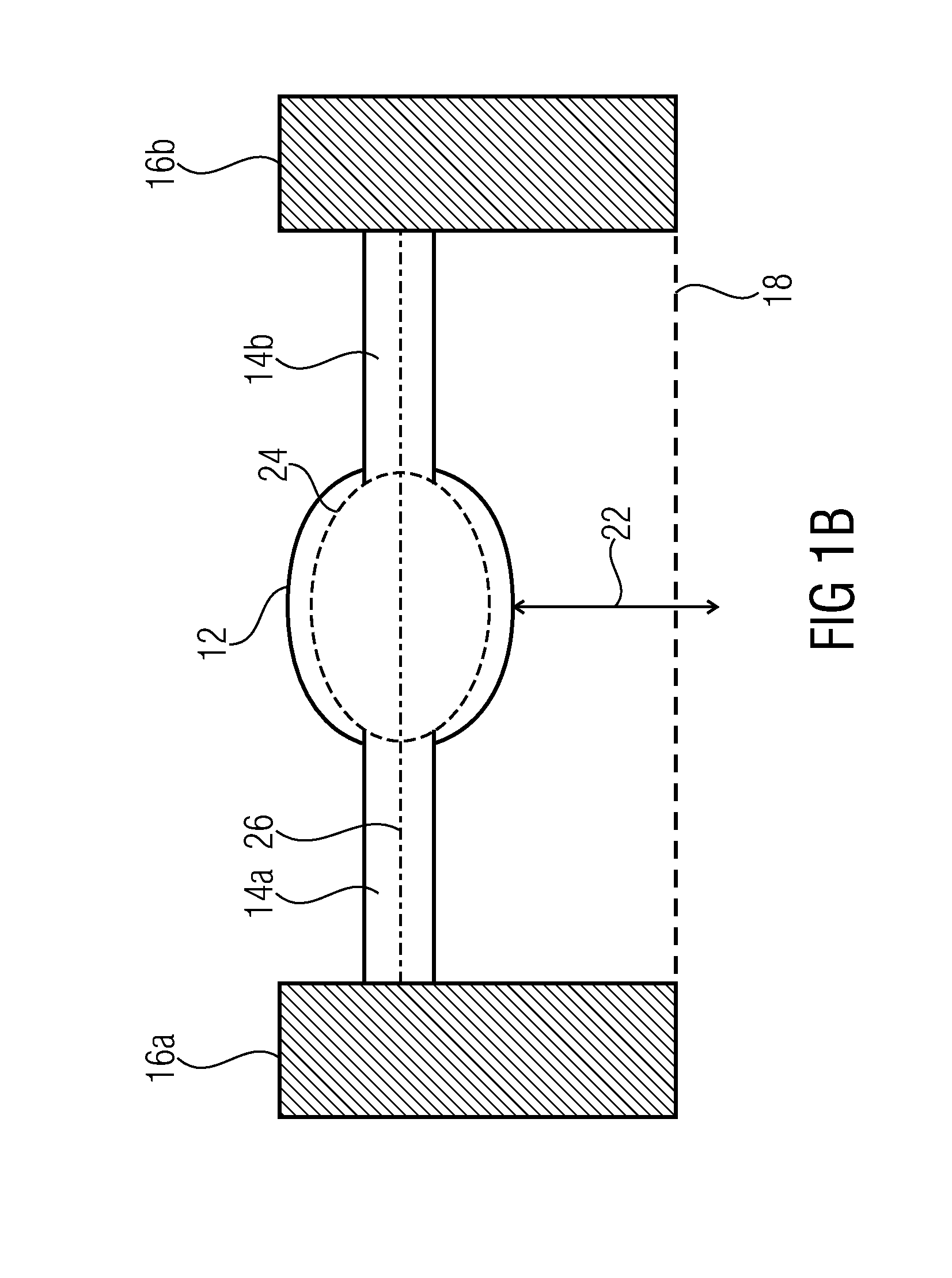

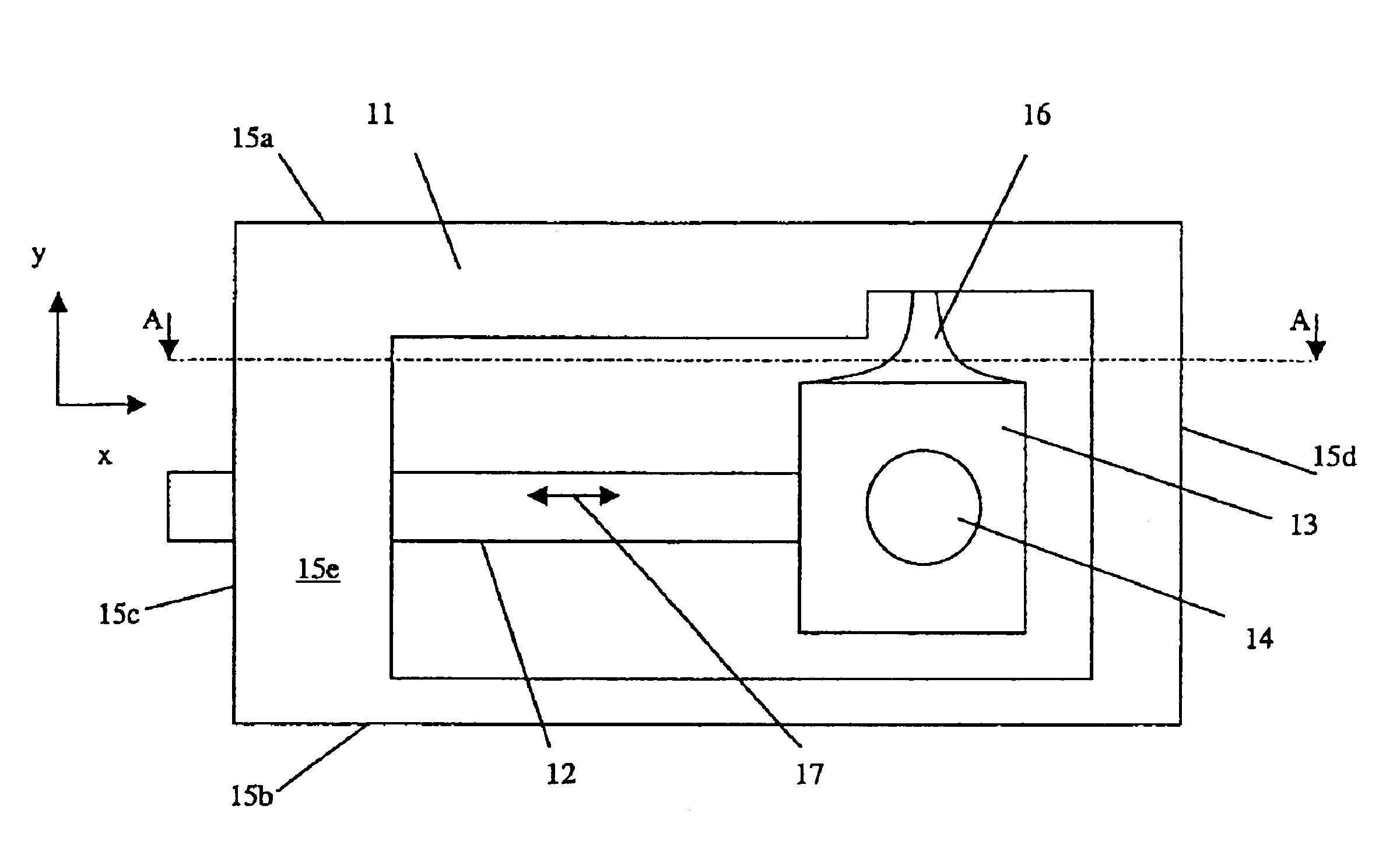

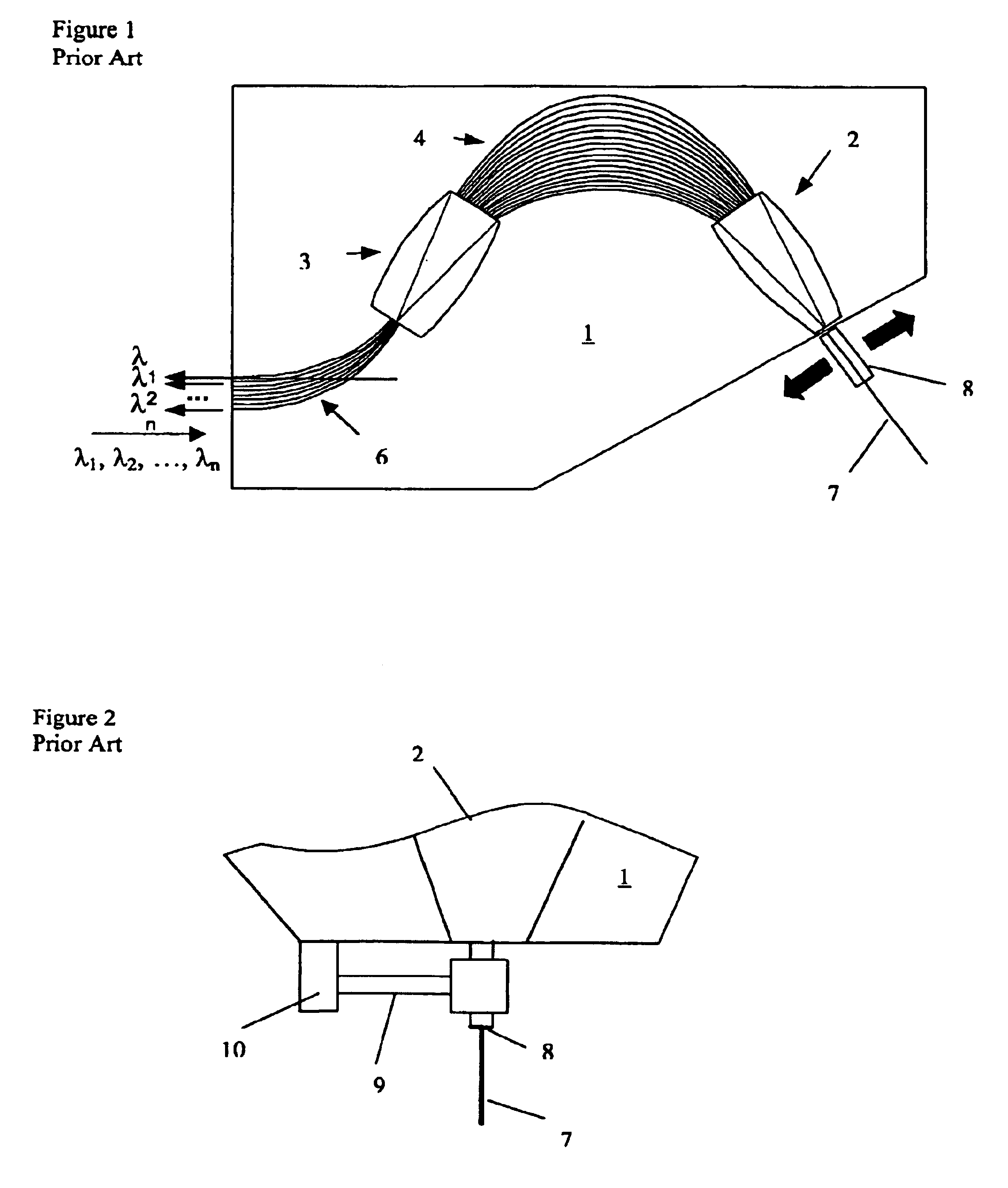

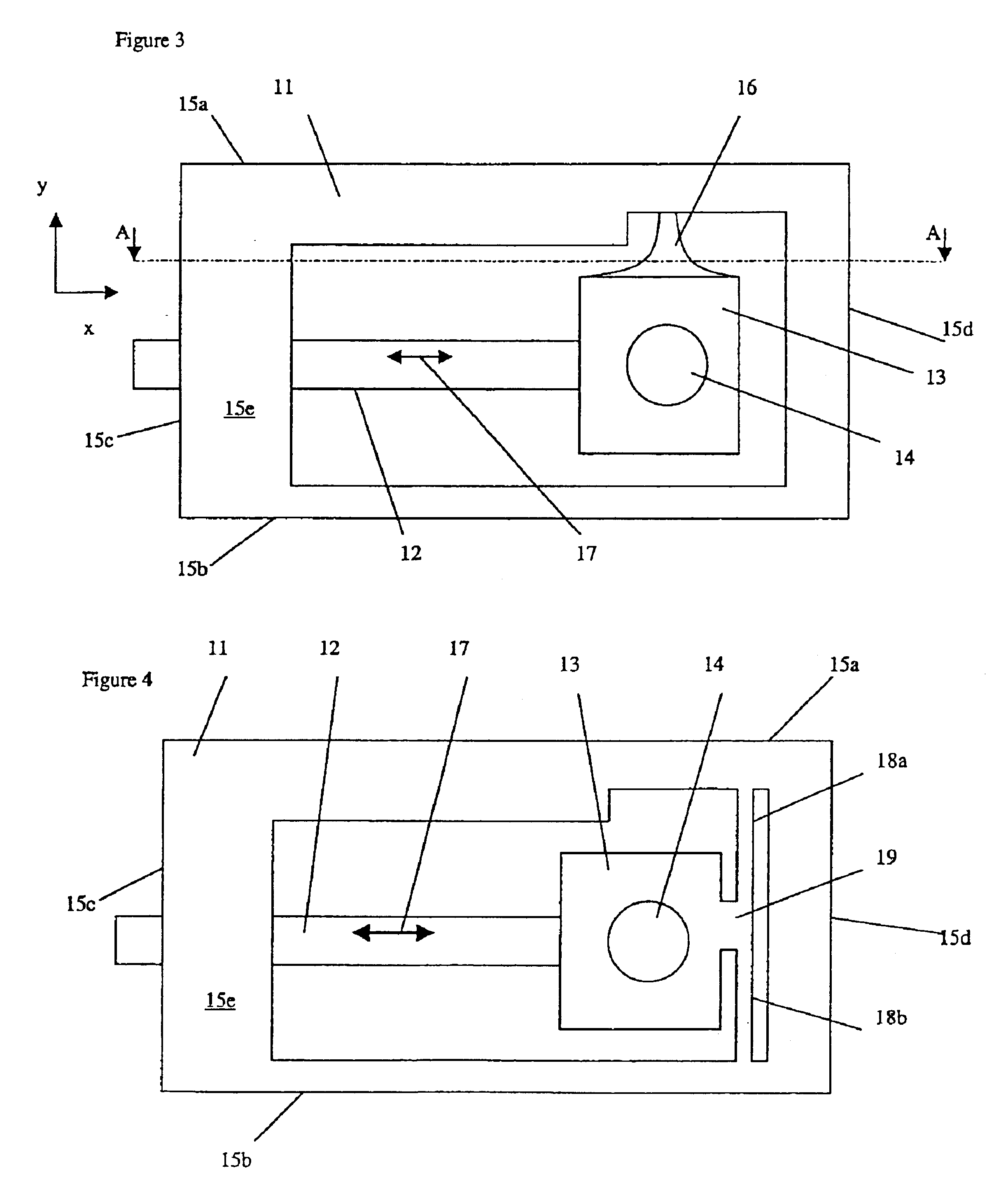

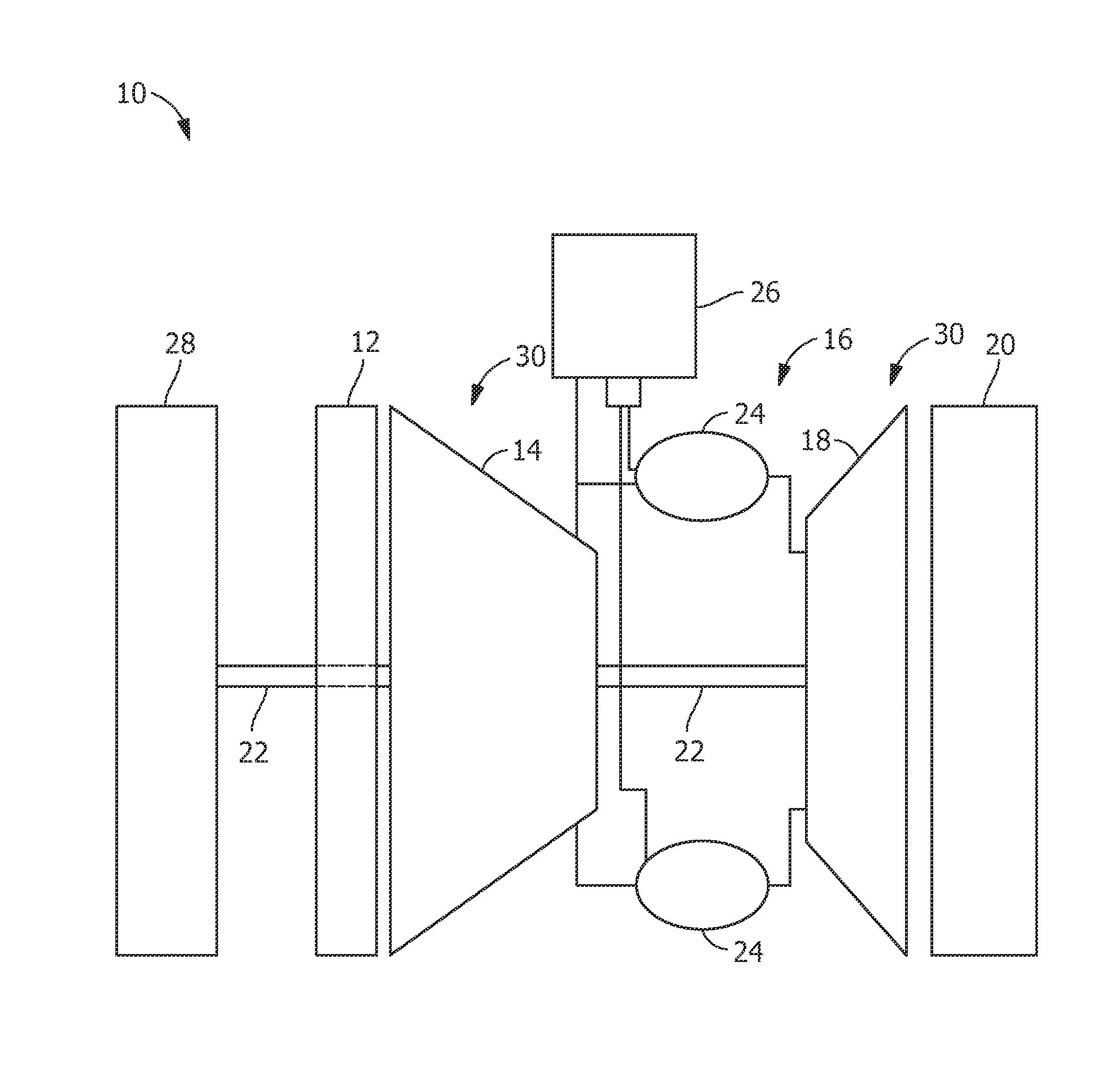

Athermal optical coupler

The invention relates to an optical coupling device that provides passive compensation for a shift in center wavelength due to a change in ambient temperature. A conventional solution is to mount one of the elements to be coupled on a pedestal or cantilevered arm, which has a coefficient of thermal expansion (CTE) different from a frame fixed relative to the other of the elements to be coupled. Unfortunately, these devices do not provide consistent results over long periods of time, due to uncontrolled movement of the outer free end of the cantilevered arm or pedestal. The present invention provides an expansion arm fixed on one end to a frame, a holder on the other end of the expansion arm, and a pair of flexible arms connecting the holder to the frame. This arrangement enables the expansion arm to freely expand in a first direction, while greatly restricting movement in any other direction. The present invention also relates to a optical coupling device that includes a expansion arm with an adjustable effective length. Furthermore, optical coupling devices are disclosed that include an expansion arm for moving a lens relative to one or more waveguides providing thermal compensation.

Owner:LUMENTUM OPERATIONS LLC

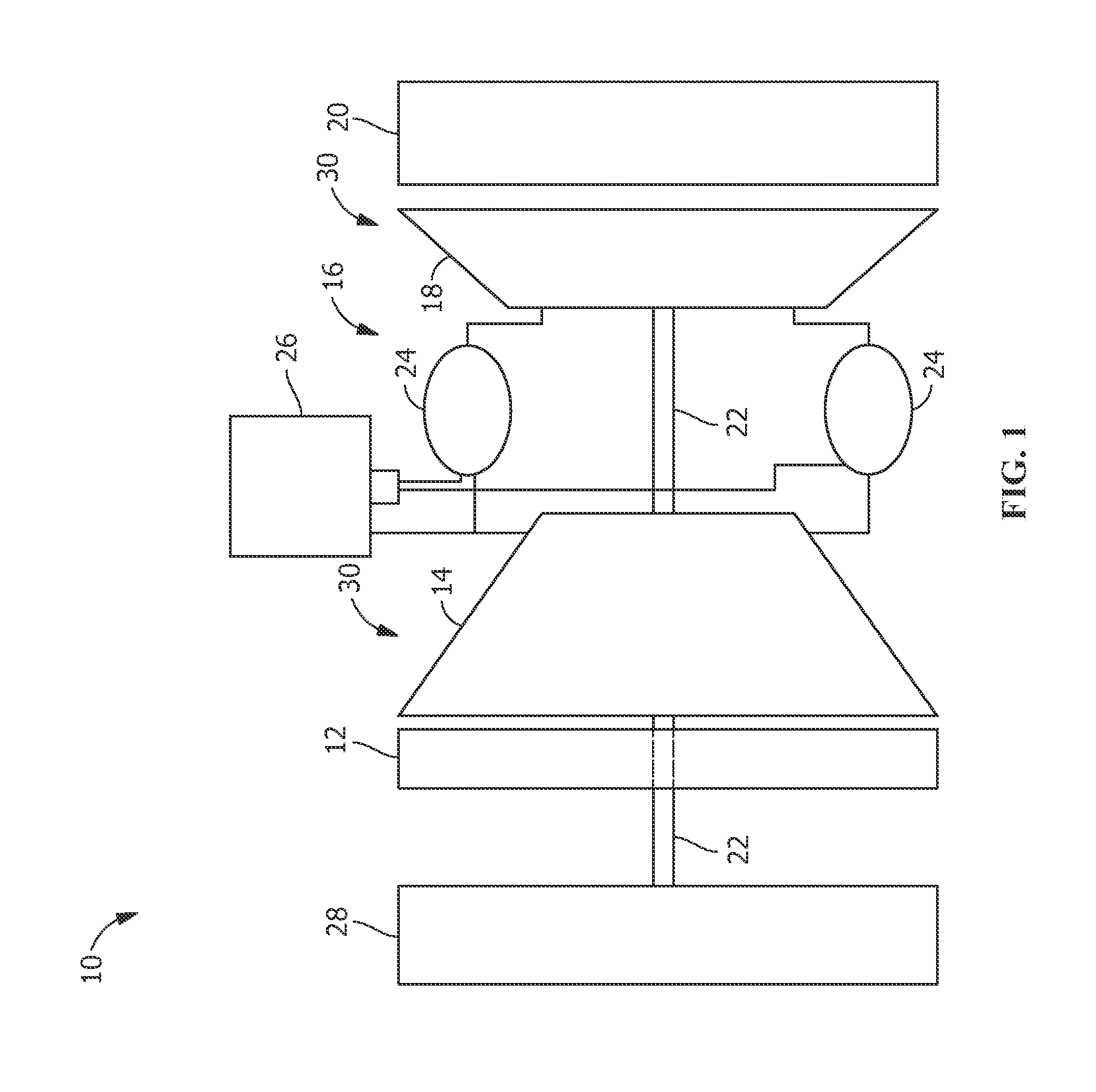

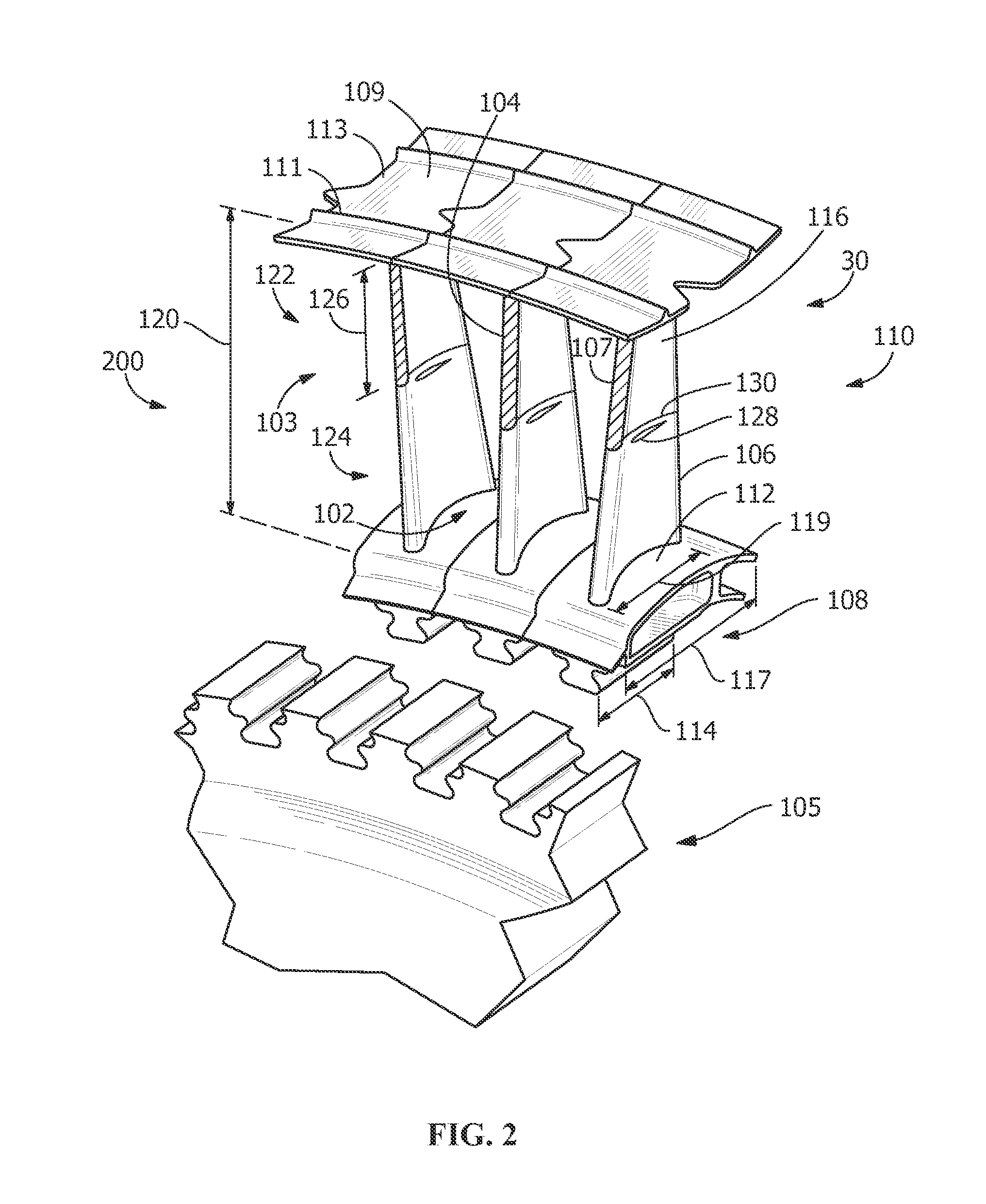

Turbine bucket assembly and turbine system

InactiveUS20150345307A1Reduce heat resistance requirementsHigh thermal expansionPropellersPump componentsImpellerTurbine blade

A turbine bucket assembly and turbine system are disclosed. The assembly includes a multi-lobe joint having an integral platform, the joint having a first axial length; a segmented airfoil having a root segment extending radially outward from the platform and a tip segment coupled to the root segment, the tip segment having a second axial length less than the first axial length; and a turbine wheel defining a receptacle with a geometry corresponding to the multi-lobe joint and being coupled to the multi-lobe joint. A tip segment material, a root segment material, and a turbine wheel material are selected, such that the turbine wheel material and the root segment material have a lower heat resistance and a higher thermal expansion than the tip segment material.

Owner:GENERAL ELECTRIC CO

Glass substrate for magnetic recording medium and its use

ActiveUS20120188663A1High thermal expansionImprove impact resistanceDriving/moving recording headsMagnetic materials for record carriersYoung's modulusSpecific modulus

An aspect of the present invention relates to a glass substrate for a magnetic recording medium, which is comprised of glass with a glass transition temperature of equal to or greater than 600° C., an average coefficient of linear expansion at 100 to 300° C. of equal to or greater than 70×10−7 / ° C., a Young's modulus of equal to or greater than 81 GPa, a specific modulus of elasticity of equal to or greater than 30 MNm / kg, and a fracture toughness value of equal to or greater than 0.9 MPa·m1 / 2.

Owner:HOYA CORP

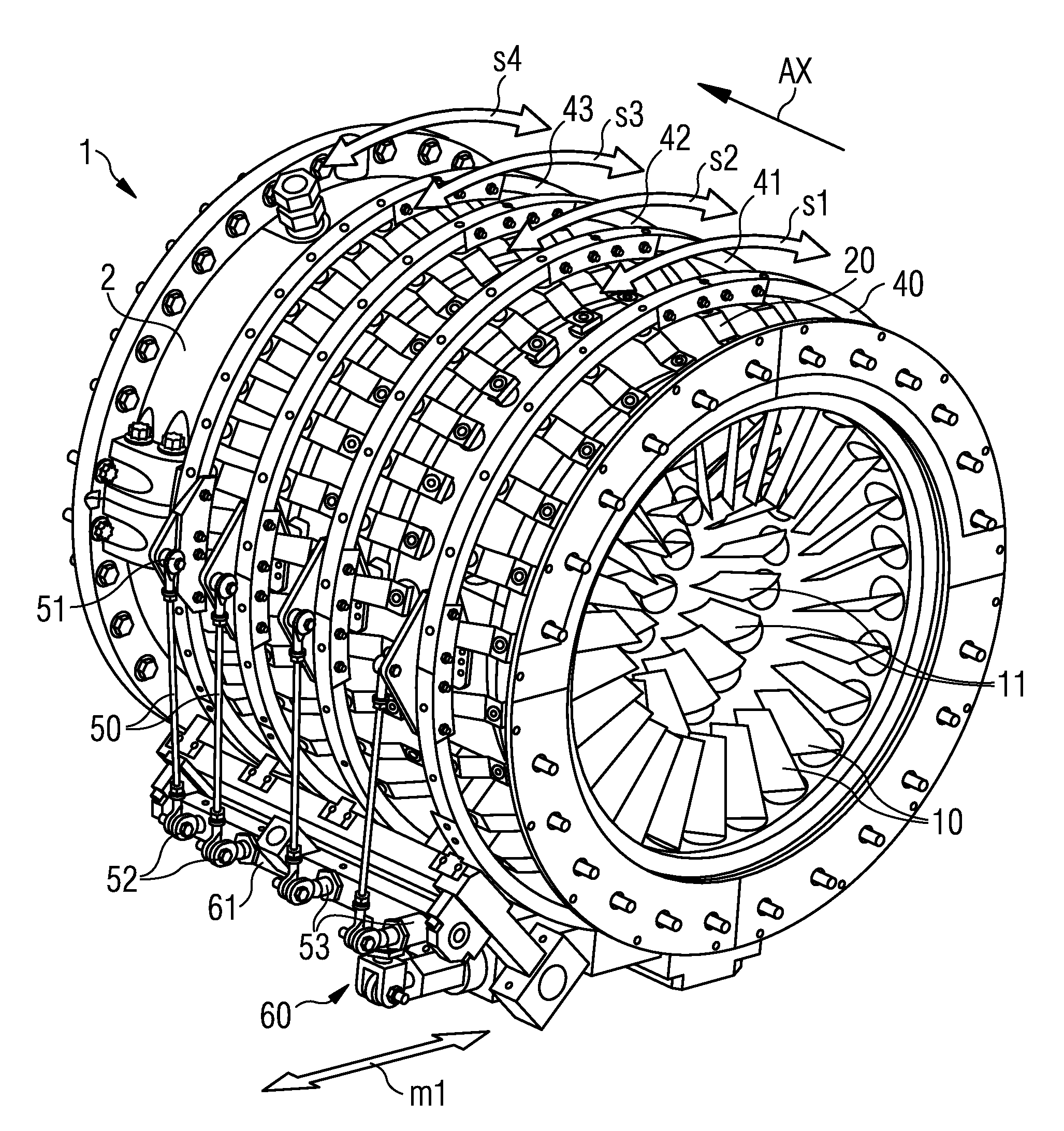

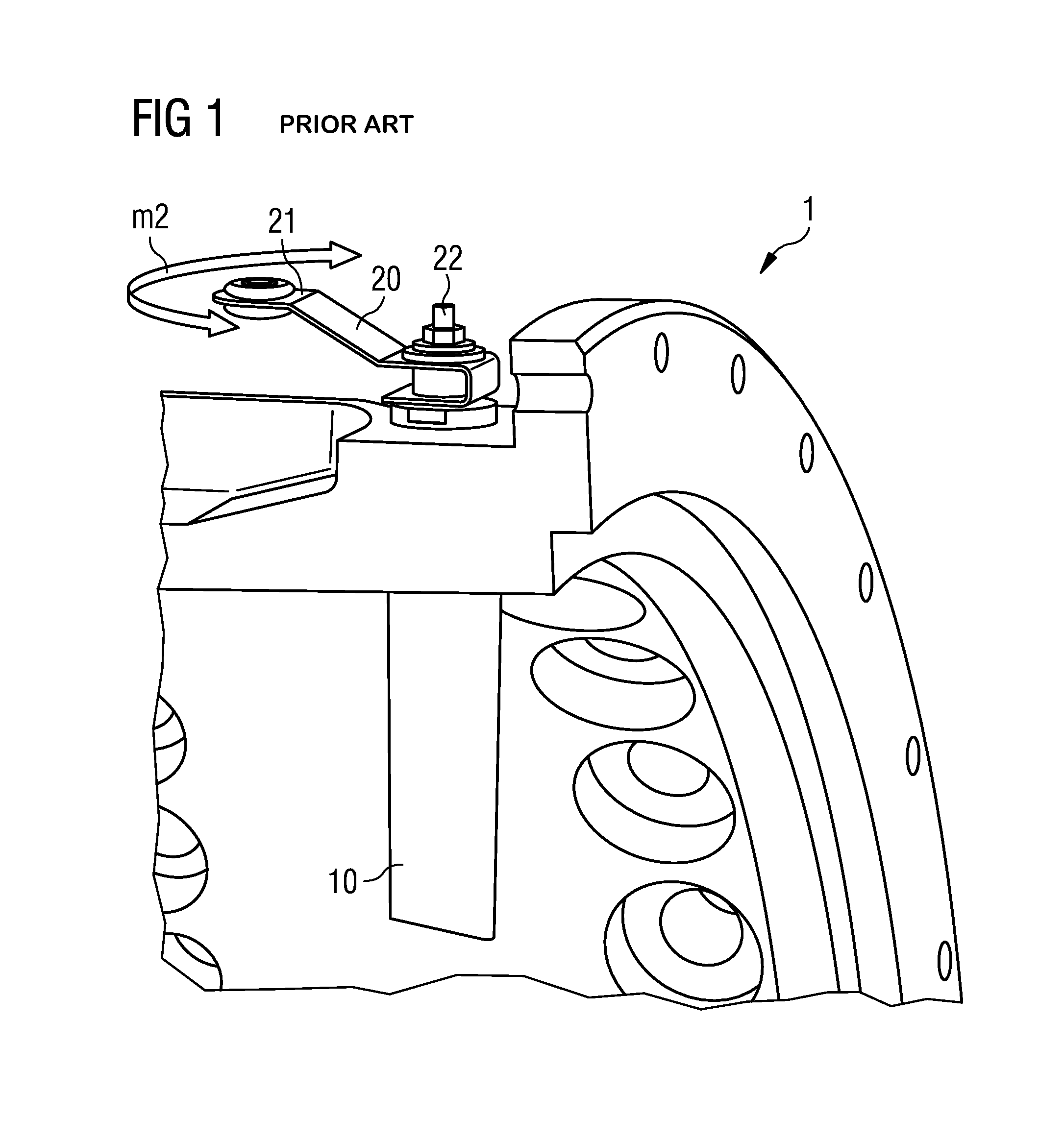

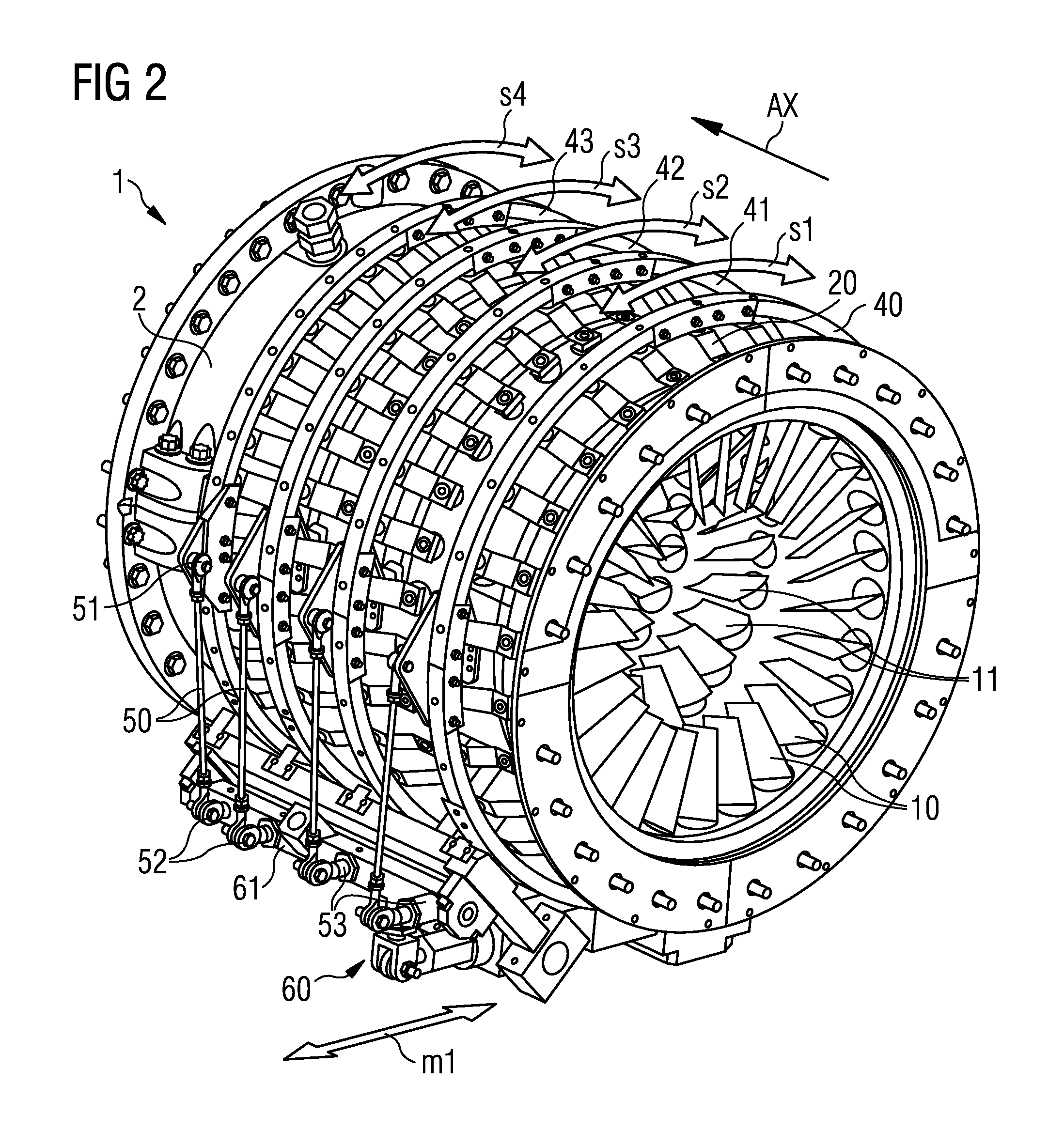

Device for adjusting variable guide vanes

ActiveUS9188138B2Convenient distanceHigh thermal expansionWind motor controlPump componentsEngineeringControl rod

A device for adjusting variable guide vanes of an axial-flow machine includes a control rod that adjusts an angular position of the variable guide vanes and is pivotably connected to a shaft. Each of a first and a second bracket has a first end connectable to a casing of the machine. A first joint is fixed to a second end of the first bracket and provides adjustable positioning of a first end of the shaft. A second joint is fixed to a second end of the second bracket and provides adjustable positioning of a second end of the shaft. The two joints are spatially positioned to each other solely via a first fixed connection between the first end of the first bracket to the casing and via a second fixed connection between the first end of the second bracket to the casing.

Owner:SIEMENS ENERGY GLOBAL GMBH & CO KG

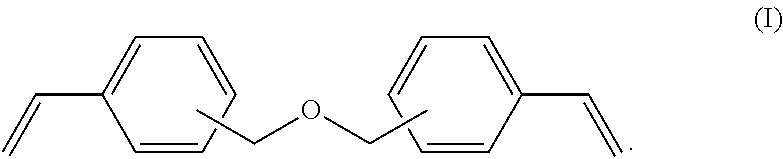

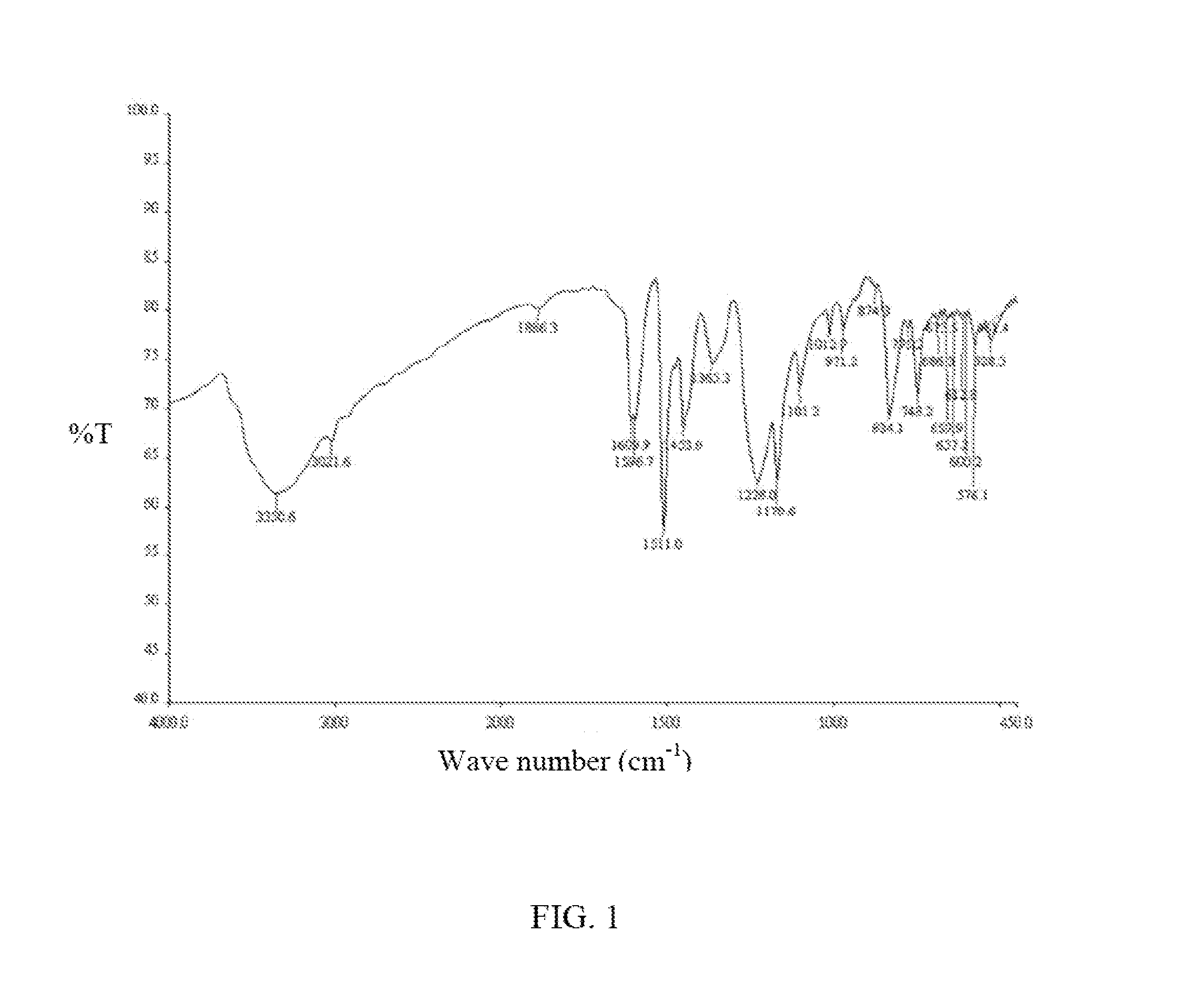

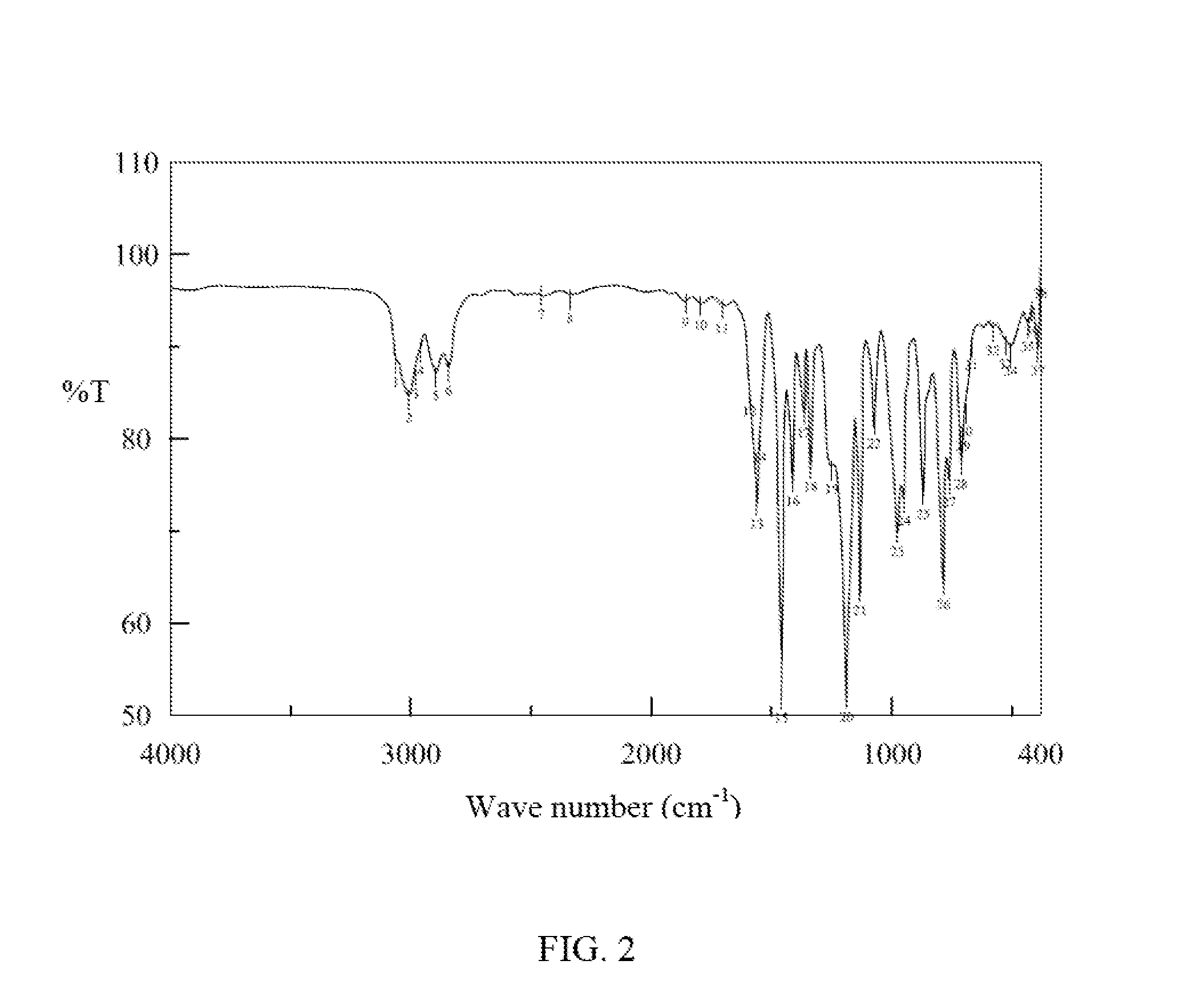

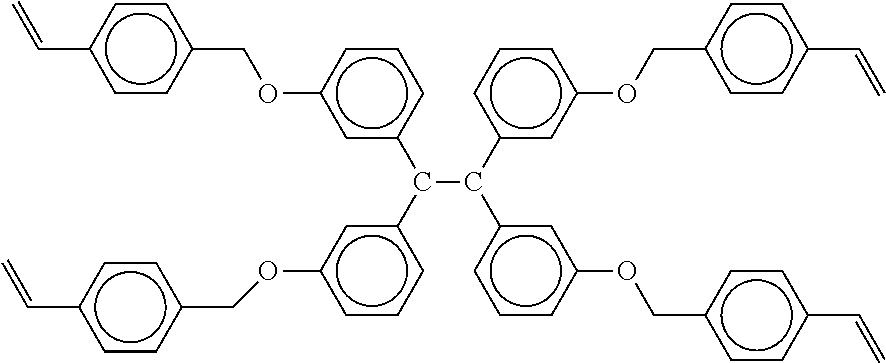

Aromatic tetrafunctional vinylbenzyl resin composition and use thereof

ActiveUS20160160008A1Low dissipation factorHigh thermal expansionPrinted circuit aspectsLow dissipationFire retardant

A low dissipation factor resin composition comprises the following components: (A) an aromatic tetrafunctional vinylbenzyl monomer, its prepolymer or a combination thereof, the aromatic tetrafunctional vinylbenzyl monomer having a structure shown below; (B) flame retardant; and (C) peroxide.

Owner:ELITE ELECTRONICS MATERIAL KUNSHAN

Glue solution for producing thermal expansive glass web and method for producinb thermal expansive glass web with the glue solution

ActiveCN101294051ANo pollution in the processWill not polluteGlass making apparatusUnsaturated alcohol polymer adhesivesGlass fiberPulp and paper industry

The invention discloses a glue liquid for manufacturing a thermally-expandable glass mat and the method for manufacturing the thermally-expandable glass mat by using the glue liquid. The glue liquid comprises polyvinyl alcohol 1 to 2 parts, acrylic ester 10 to 14 parts and water 85 to 89 parts. The method for manufacturing the thermally-expandable glass mat by using the glue liquid comprises the following steps: (a) preparing a glue; (b) starting a gluing machine, heating to 100 DEG C, and filling a glue groove with the glue liquid; (c) loading a glass mat made from continuous glass fibers on the gluing machine and connecting with a guide cloth; (d) starting gluing; (e) cutting the glass mat and orderly arranging; (f) pre-heating an oil pressure machine to 60 to 70 DEG C for later use; (g) orderly arranging the glass mats according to a required thickness to obtain glass mat blanks, and arranging a separator between each two glass mat blanks; (h) pressing and cooling; and (i) trimming and packaging. The glass mat manufactured by using the glue liquid of the invention has the advantages of high thermal expansion efficiency, environmental protection and no pollution.

Owner:浙江博菲电气股份有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com