Patents

Literature

70 results about "Nanomanufacturing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Nanomanufacturing is both the production of nanoscaled materials, which can be powders or fluids, and the manufacturing of parts "bottom up" from nanoscaled materials or "top down" in smallest steps for high precision, used in several technologies such as laser ablation, etching and others. Nanomanufacturing differs from molecular manufacturing, which is the manufacture of complex, nanoscale structures by means of nonbiological mechanosynthesis (and subsequent assembly).

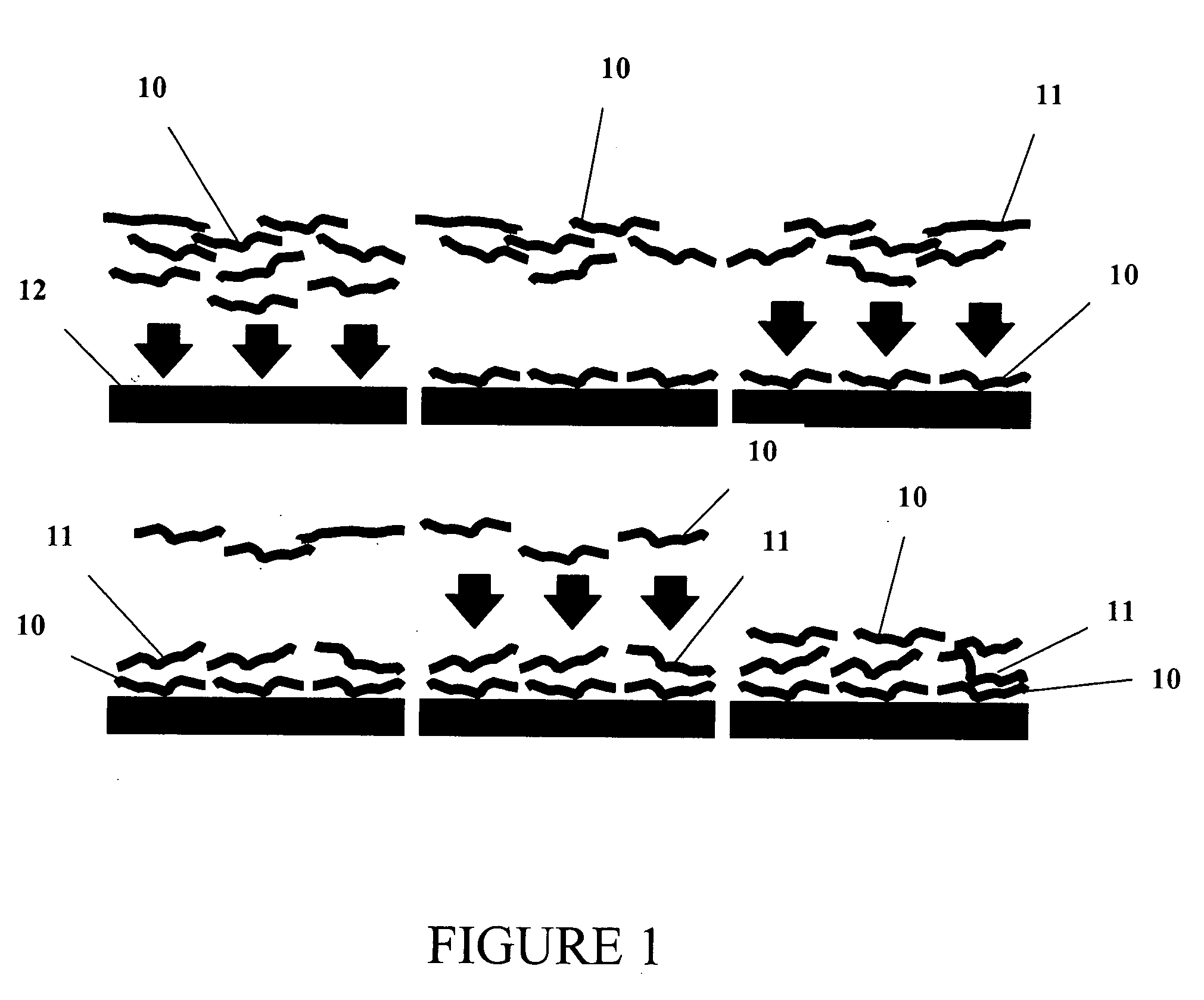

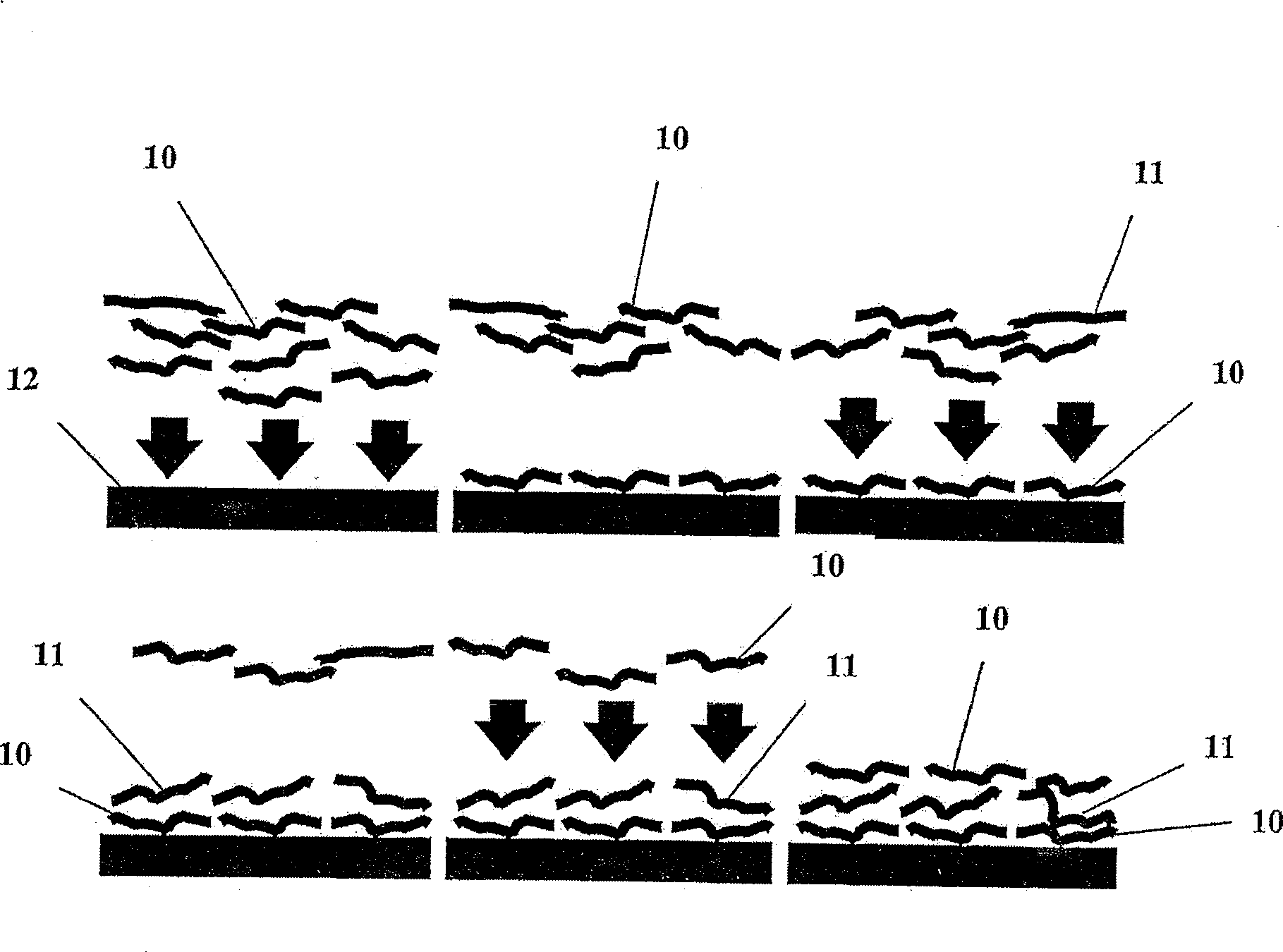

Method for Fabricating a Long-Range Ordered Periodic Array of Nano-Features, and Articles Comprising Same

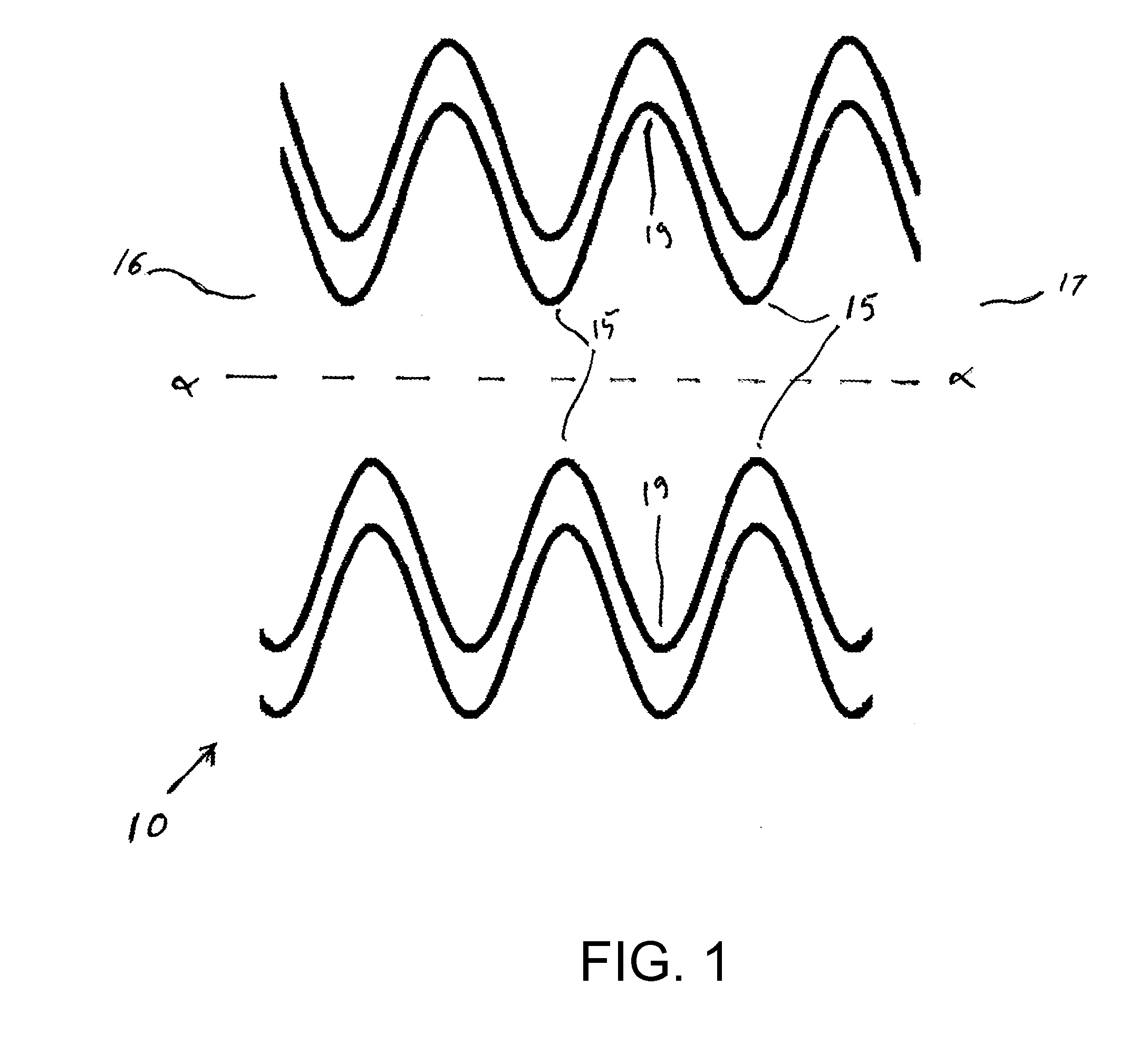

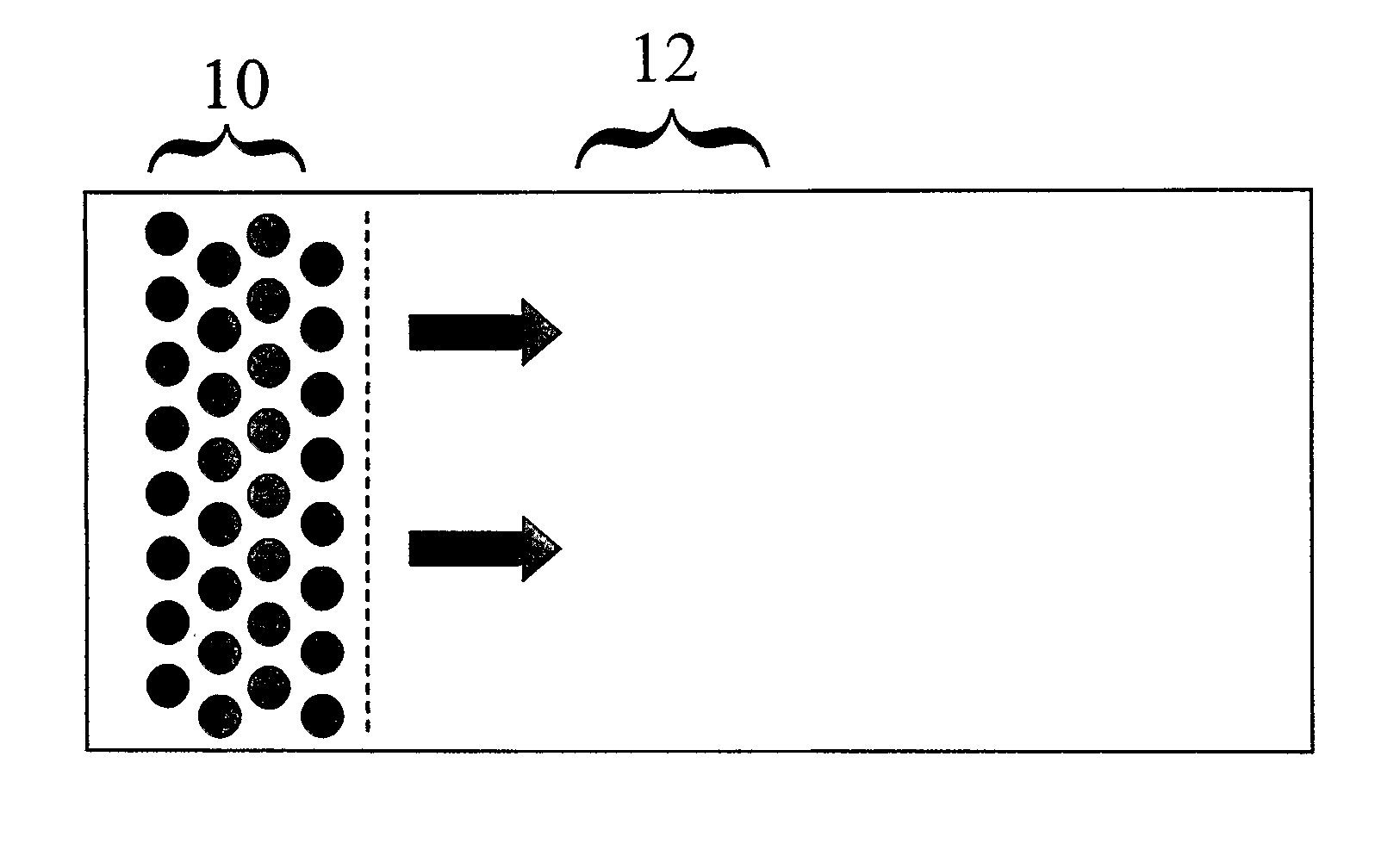

A long range, periodically ordered array of discrete nano-features (10), such as nano-islands, nano-particles, nano-wires, non-tubes, nano-pores, nano-composition-variations, and nano-device-components, are fabricated by propagation of a self-assembling array or nucleation and growth of periodically aligned nano-features. The propagation may be induced by a laterally or circularly moving heat source, a stationary heat source arranged at an edge of the material to be patterned (12), or a series of sequentially activated heaters or electrodes. Advantageously, the long-range periodic array of nano-features (10) may be utilized as a nano-mask or nano-implant master pattern for nano-fabrication of other nano-structures. In addition, the inventive long-range, periodically ordered arrays of nano-features are useful in a variety of nanoscale applications such as addressable memories or logic devices, ultra-high-density magnetic recording media, magnetic sensors, photonic devices, quantum computing devices, quantum luminescent devices, and efficient catalytic devices.

Owner:RGT UNIV OF CALIFORNIA

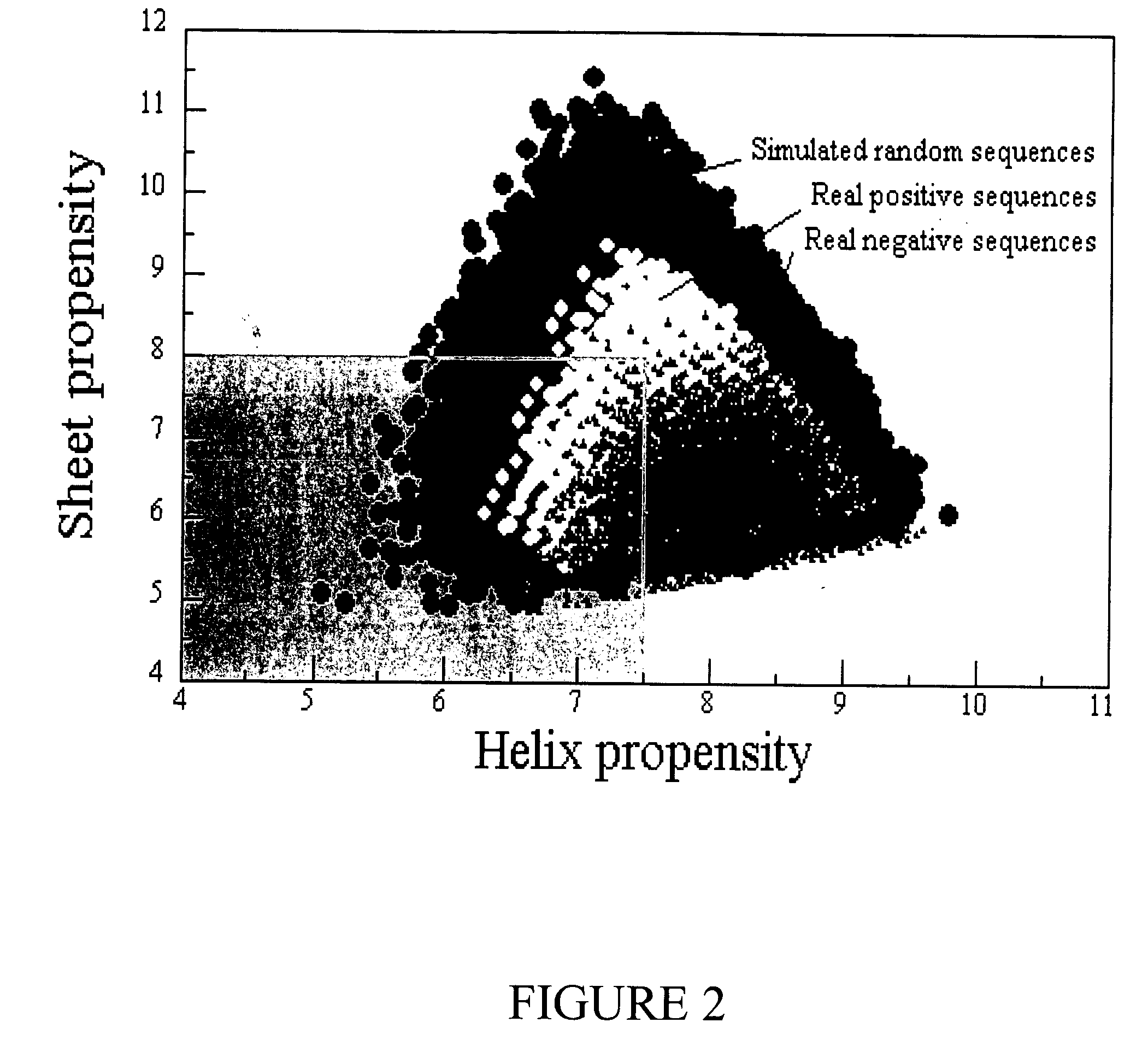

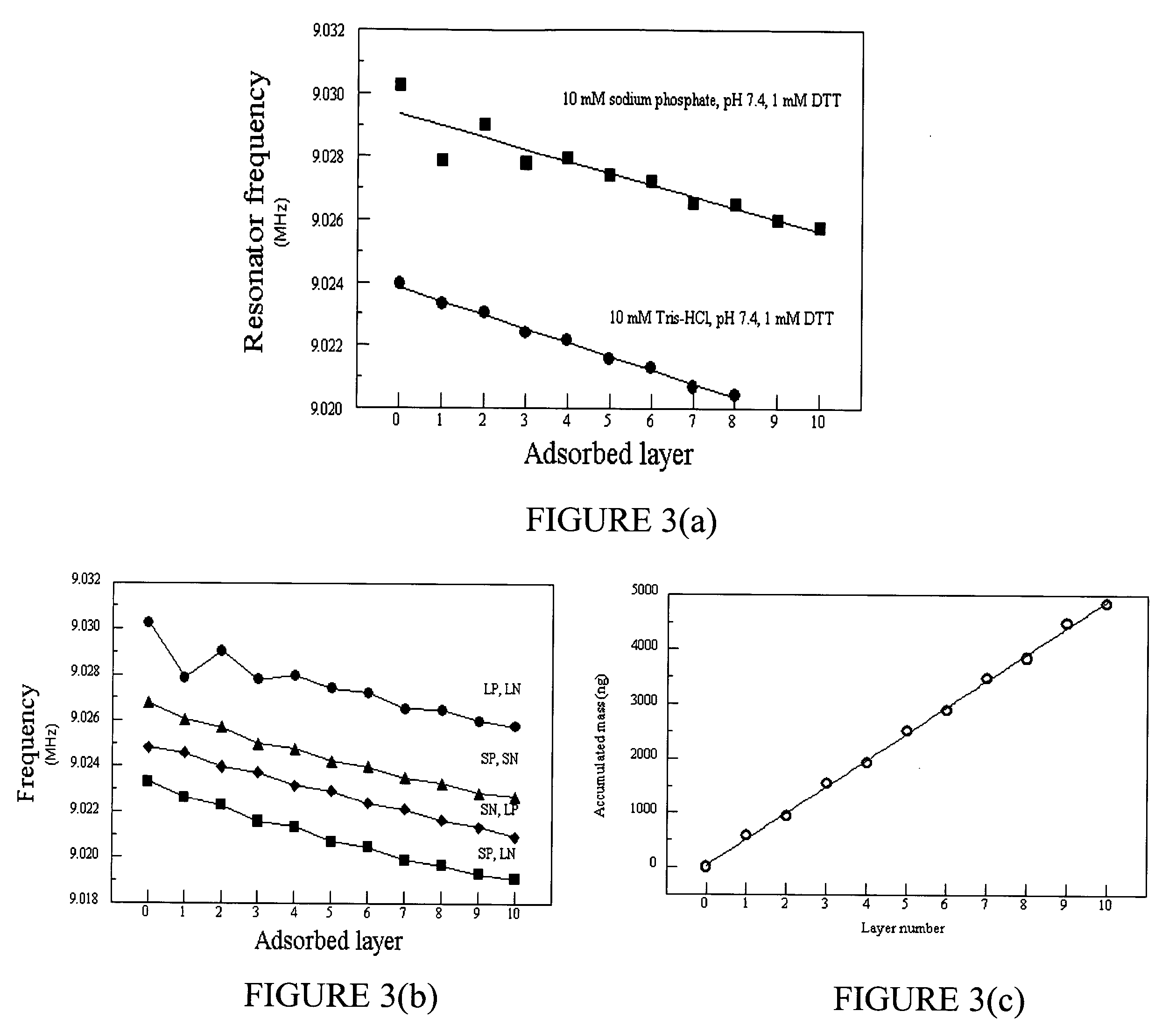

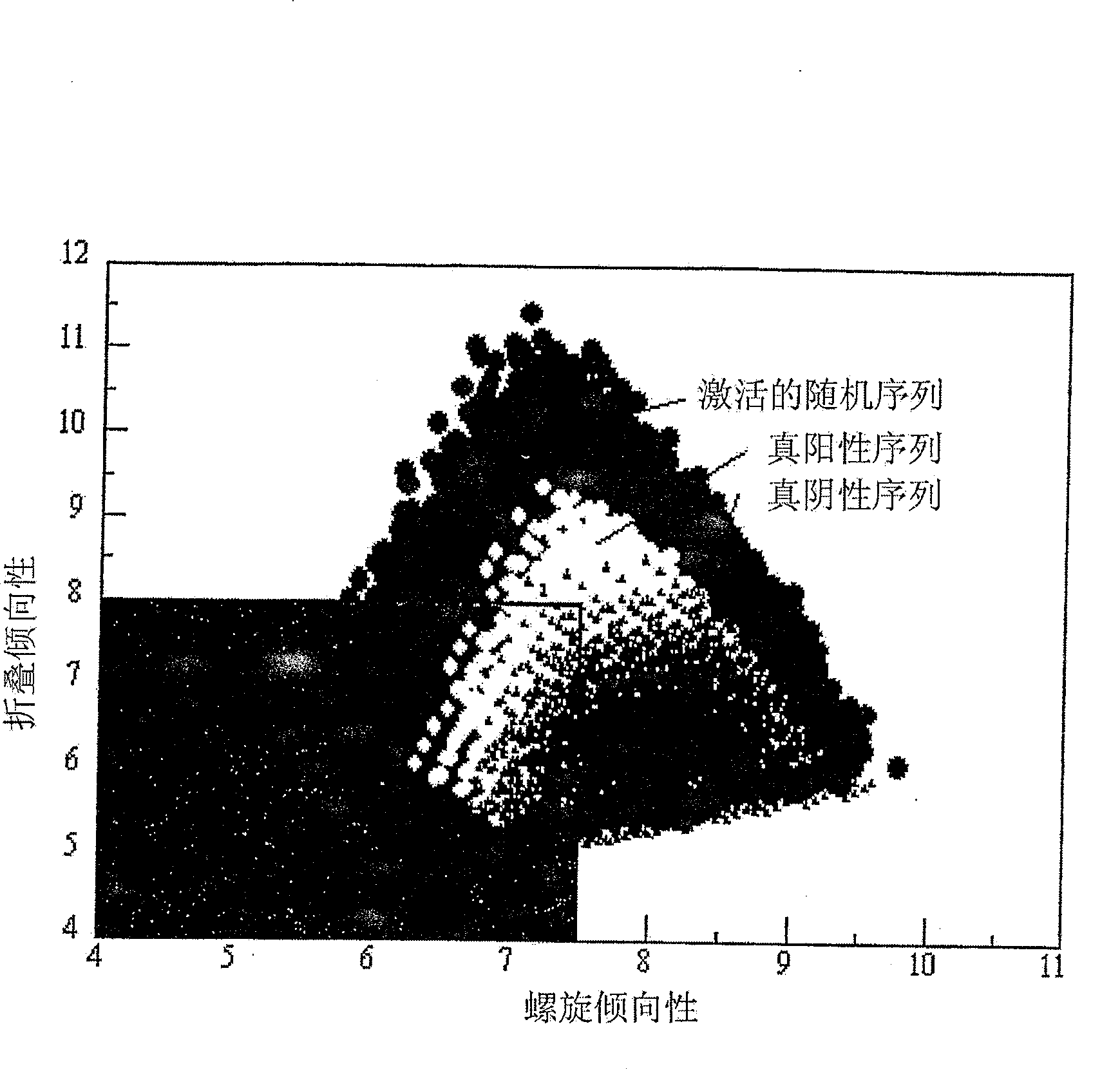

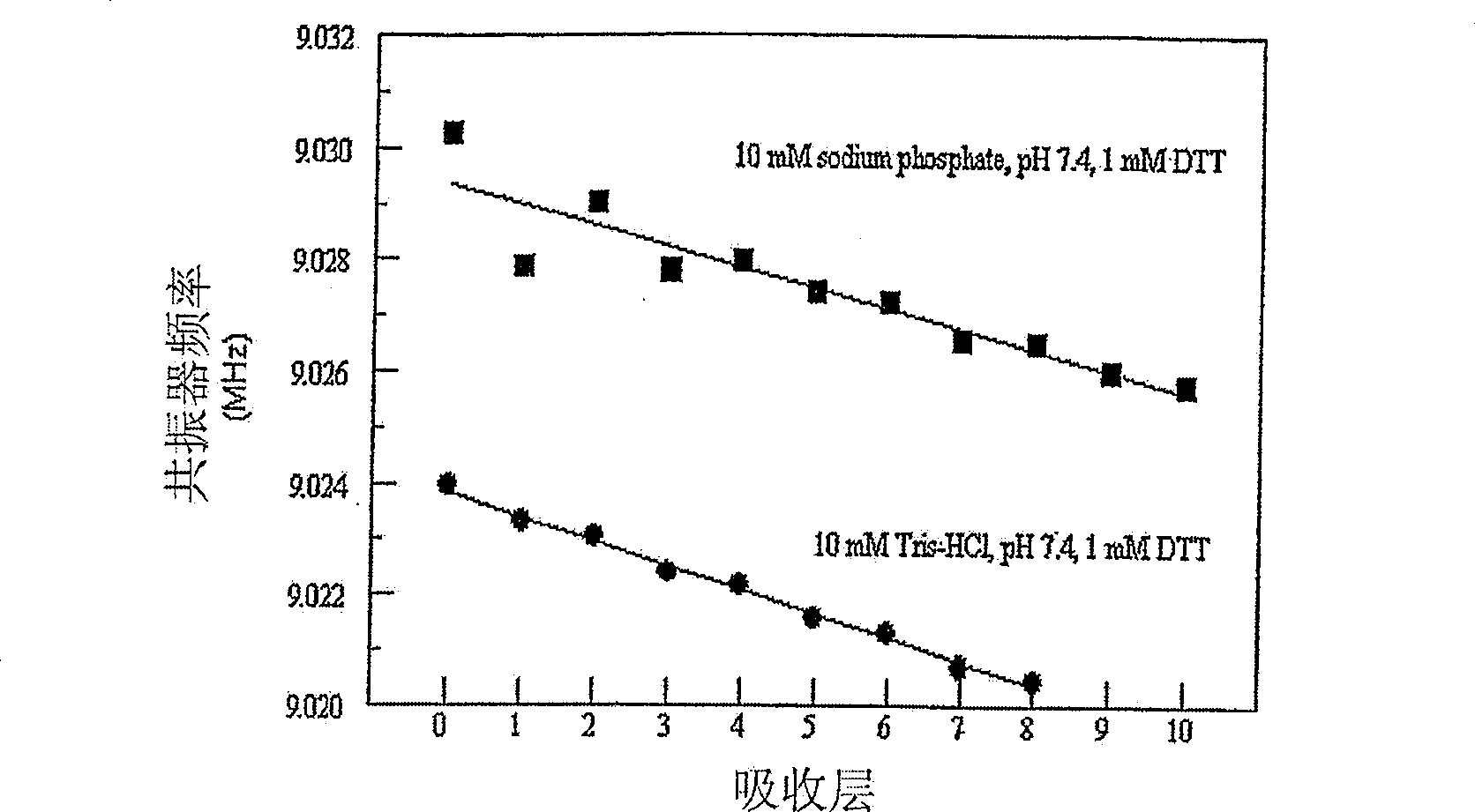

Method for designing polypeptides for the nanofabrication of thin films, coatings, and microcapsules by electrostatic layer-by-layer self assembly

ActiveUS20050069950A1Great control over mechanical stability and diffusive propertyIncrease profitPeptide/protein ingredientsPeptide sourcesThin membraneNanomanufacturing

A method for designing polypeptides for the nanofabrication of thin films, coatings, and microcapsules by ELBL for applications in biomedicine and other fields.

Owner:LOUISIANA TECH UNIV RES FOUND A DIV OF LOUISIANA TECH UNIV FOUND

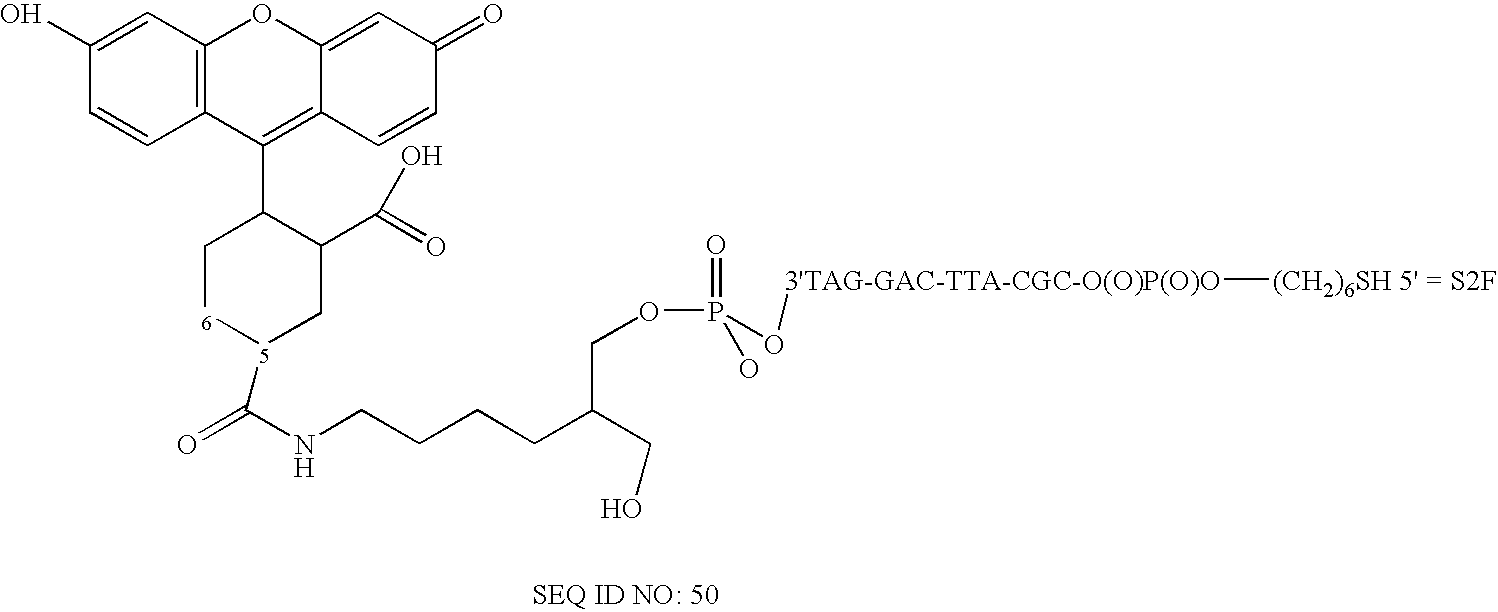

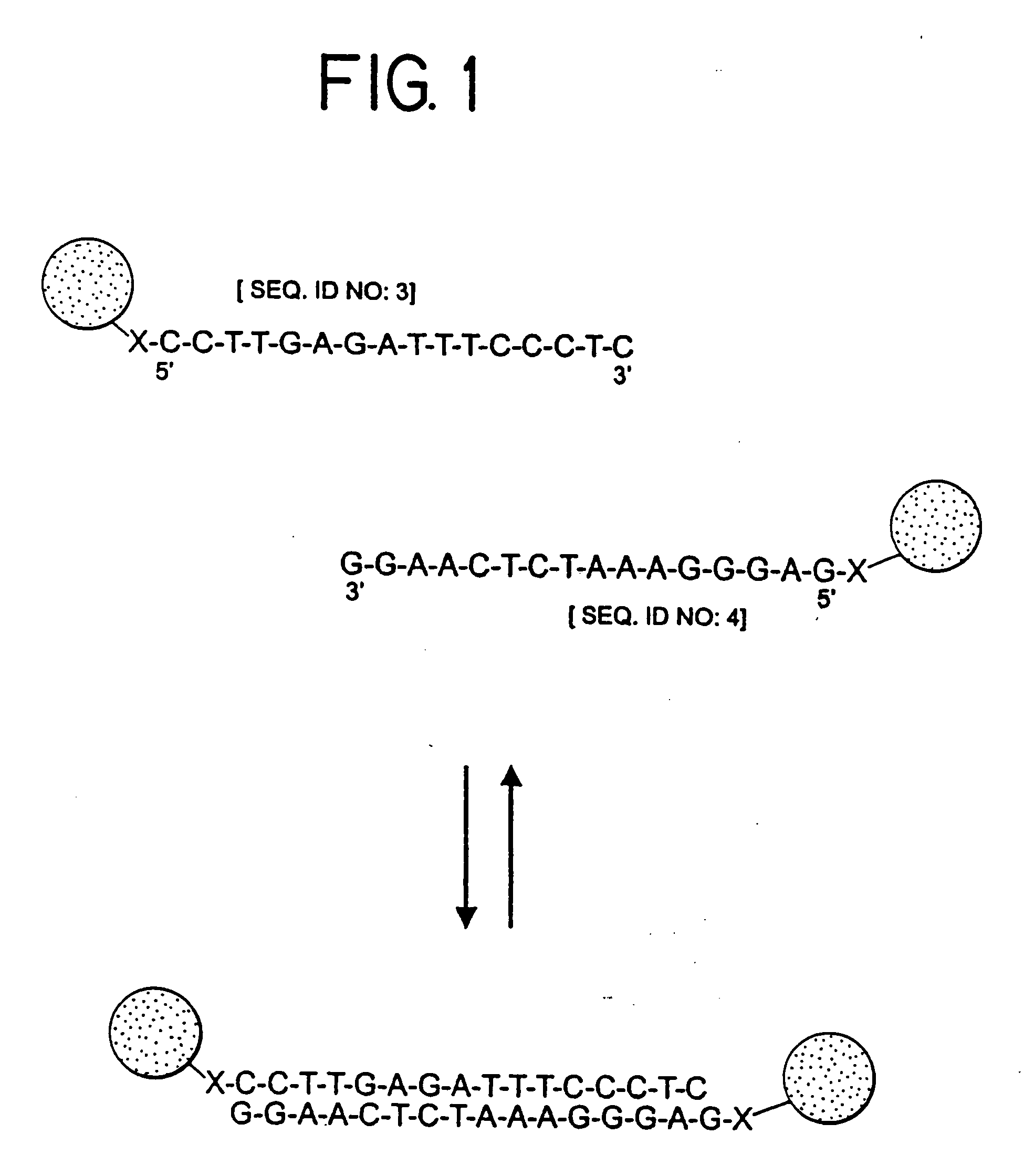

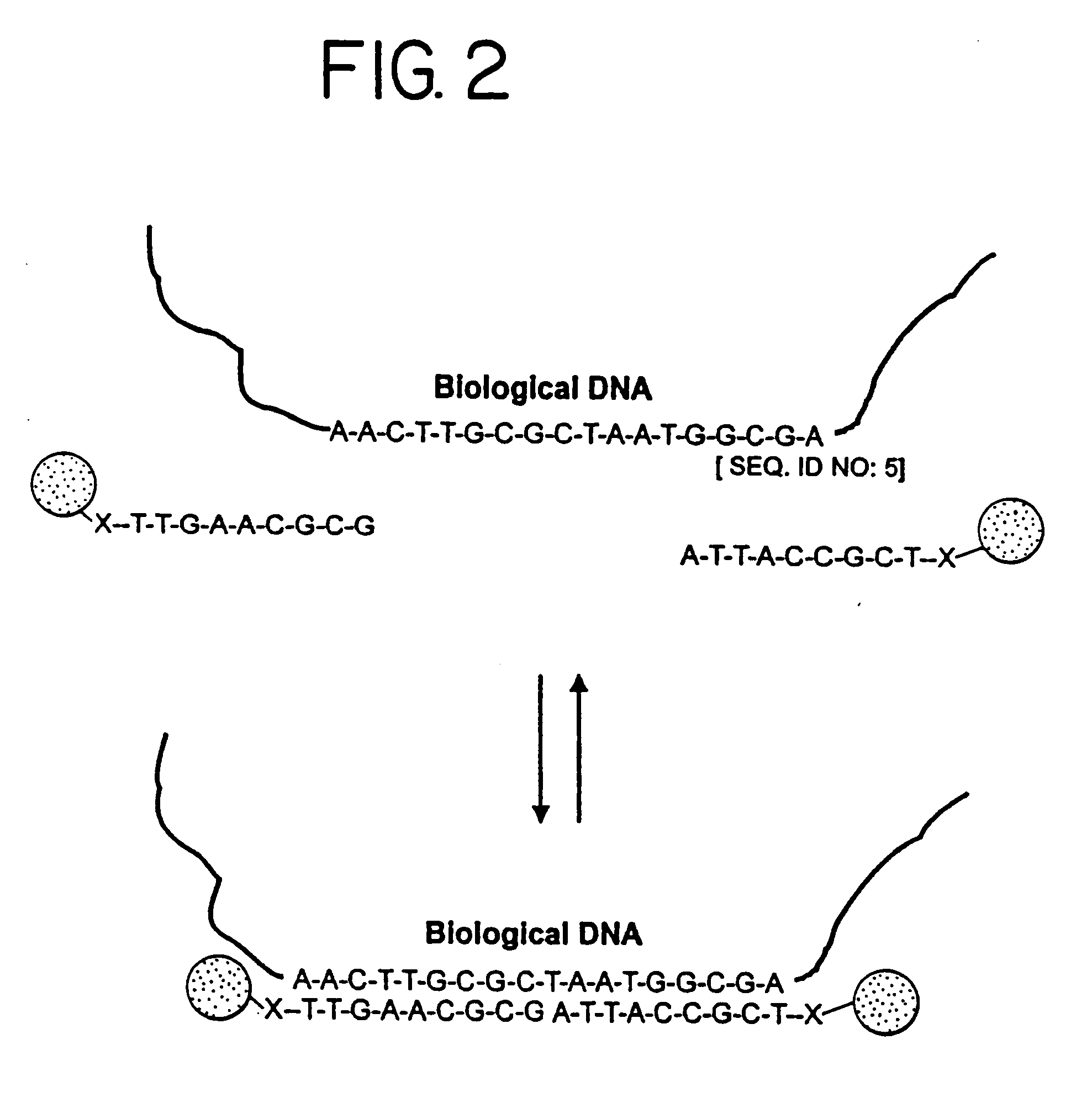

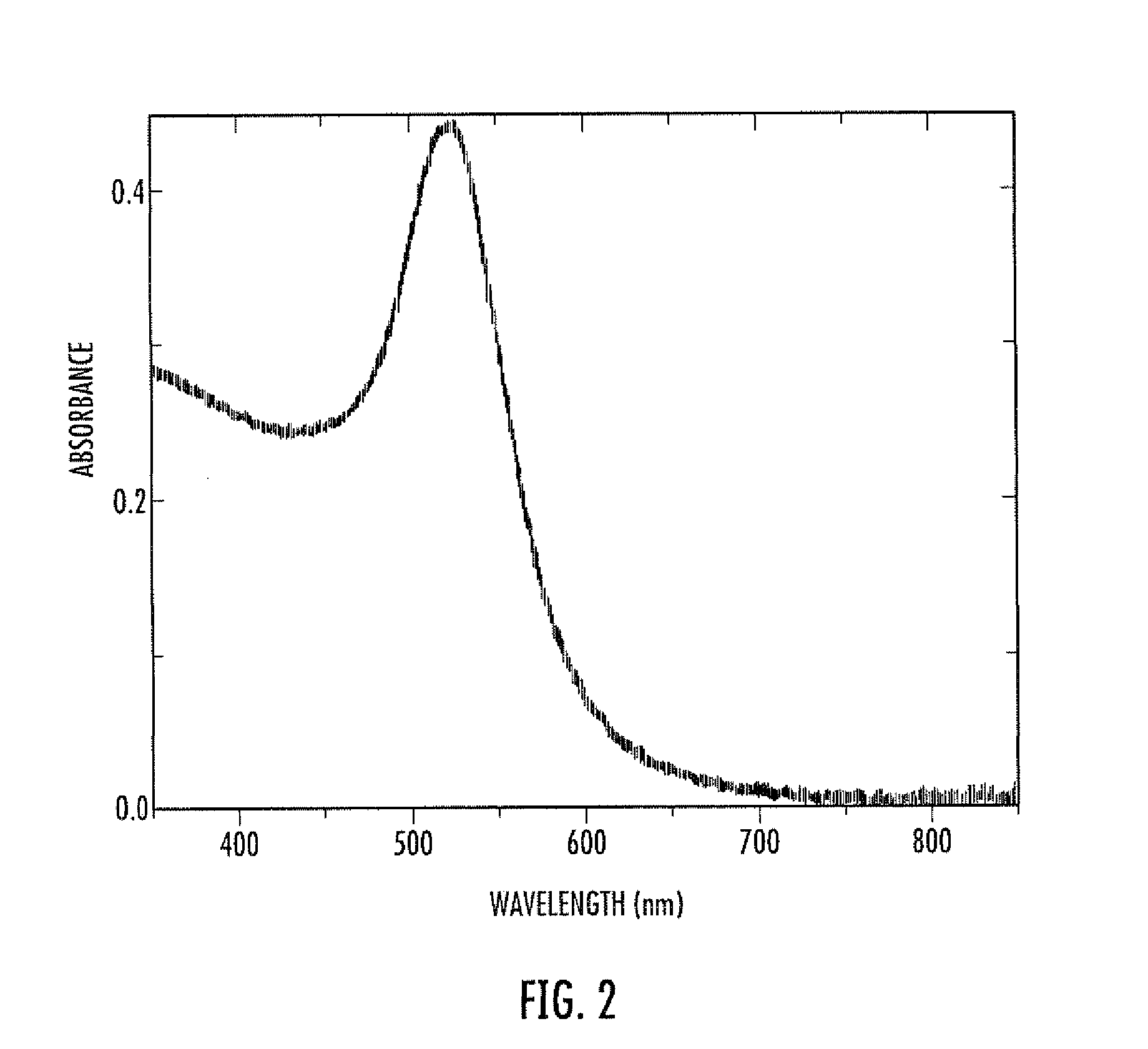

Nanoparticles having oligonucleotides attached thereto and uses therefor

InactiveUS20060068378A1Additional movementImprove bindingMaterial nanotechnologySugar derivativesNanoparticleColor changes

The invention provides methods of detecting a nucleic acid. The methods comprise contacting the nucleic acid with one or more types of particles having oligonucleotides attached thereto. In one embodiment of the method, the oligonucleotides are attached to nanoparticles and have sequences complementary to portions of the sequence of the nucleic acid. A detectable change (preferably a color change) is brought about as a result of the hybridization of the oligonucleotides on the nanoparticles to the nucleic acid. The invention also provides compositions and kits comprising particles. The invention further provides methods of synthesizing unique nanoparticle-oligonucleotide conjugates, the conjugates produced by the methods, and methods of using the conjugates. In addition, the invention provides nanomaterials and nanostructures comprising nanoparticles and methods of nanofabrication utilizing nanoparticles. Finally, the invention provides a method of separating a selected nucleic acid from other nucleic acids.

Owner:NORTHWESTERN UNIV +1

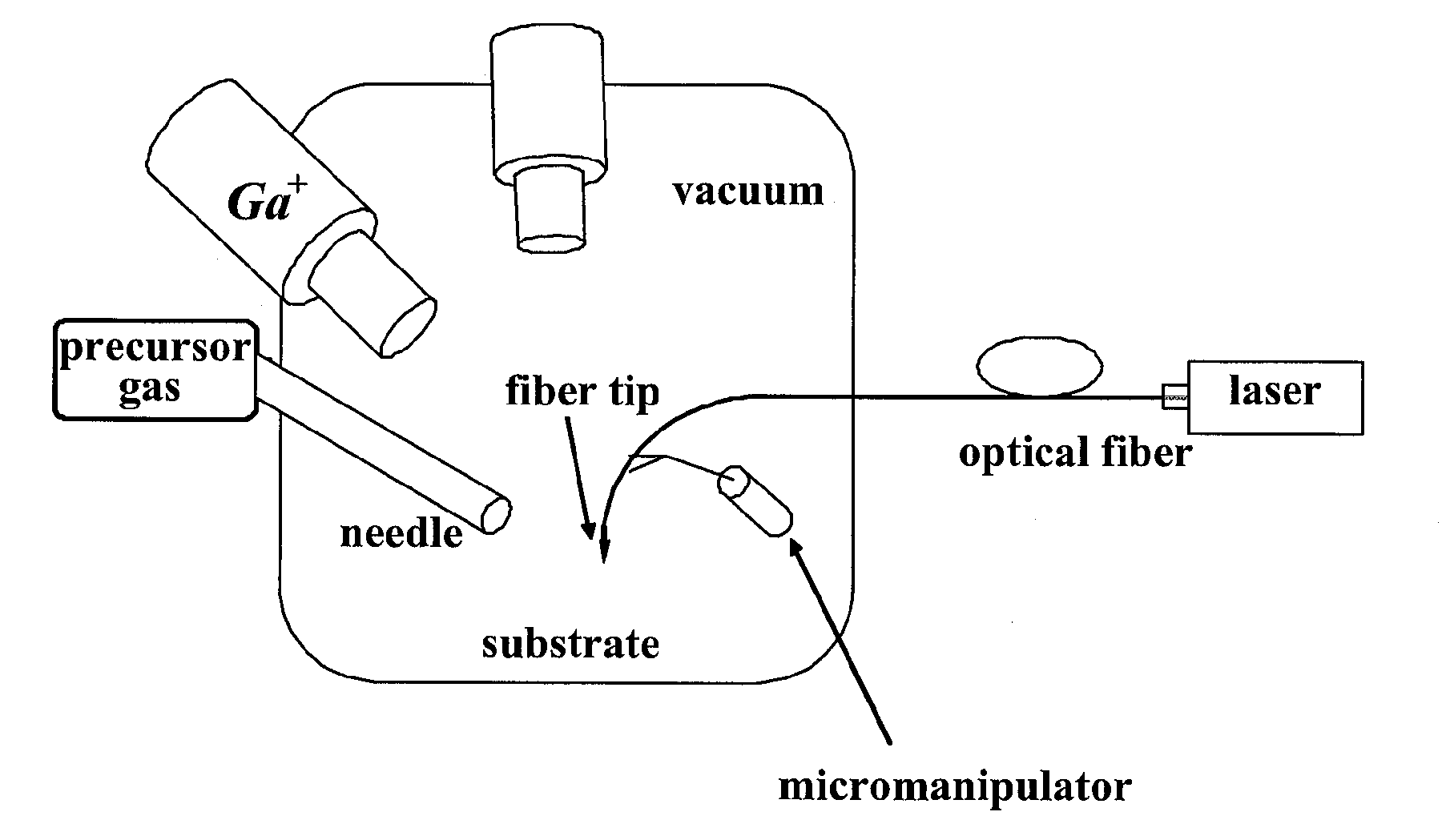

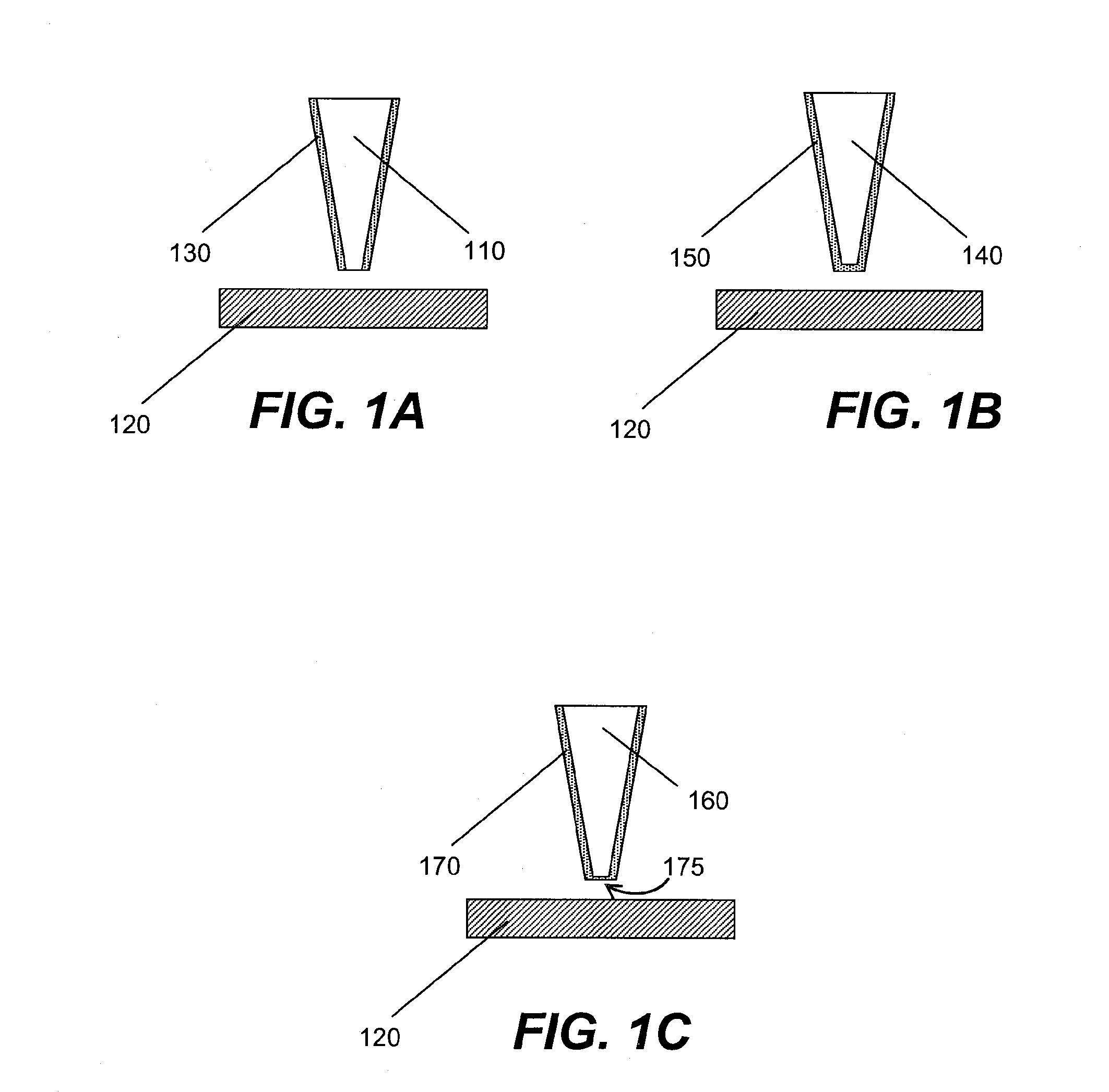

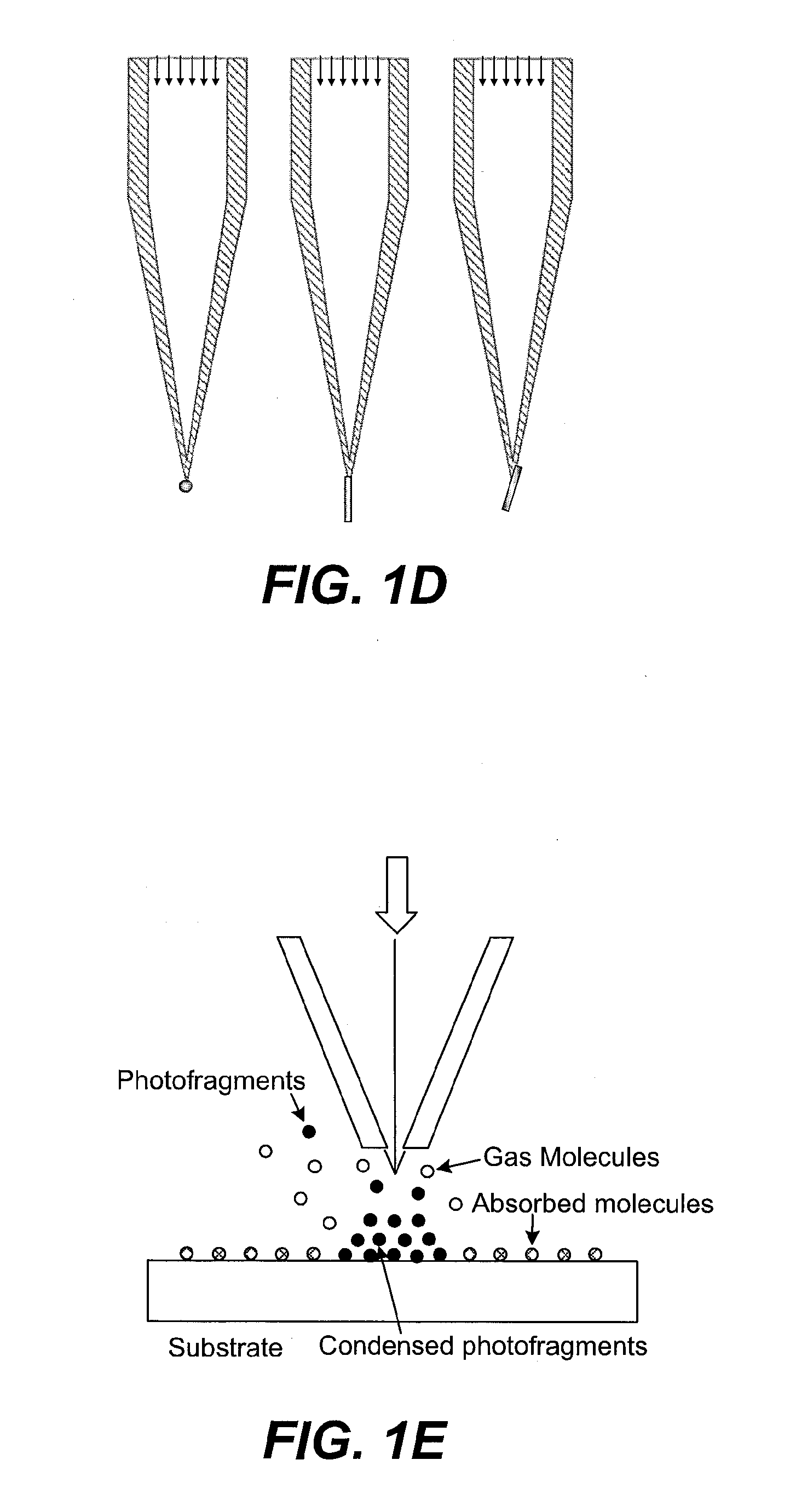

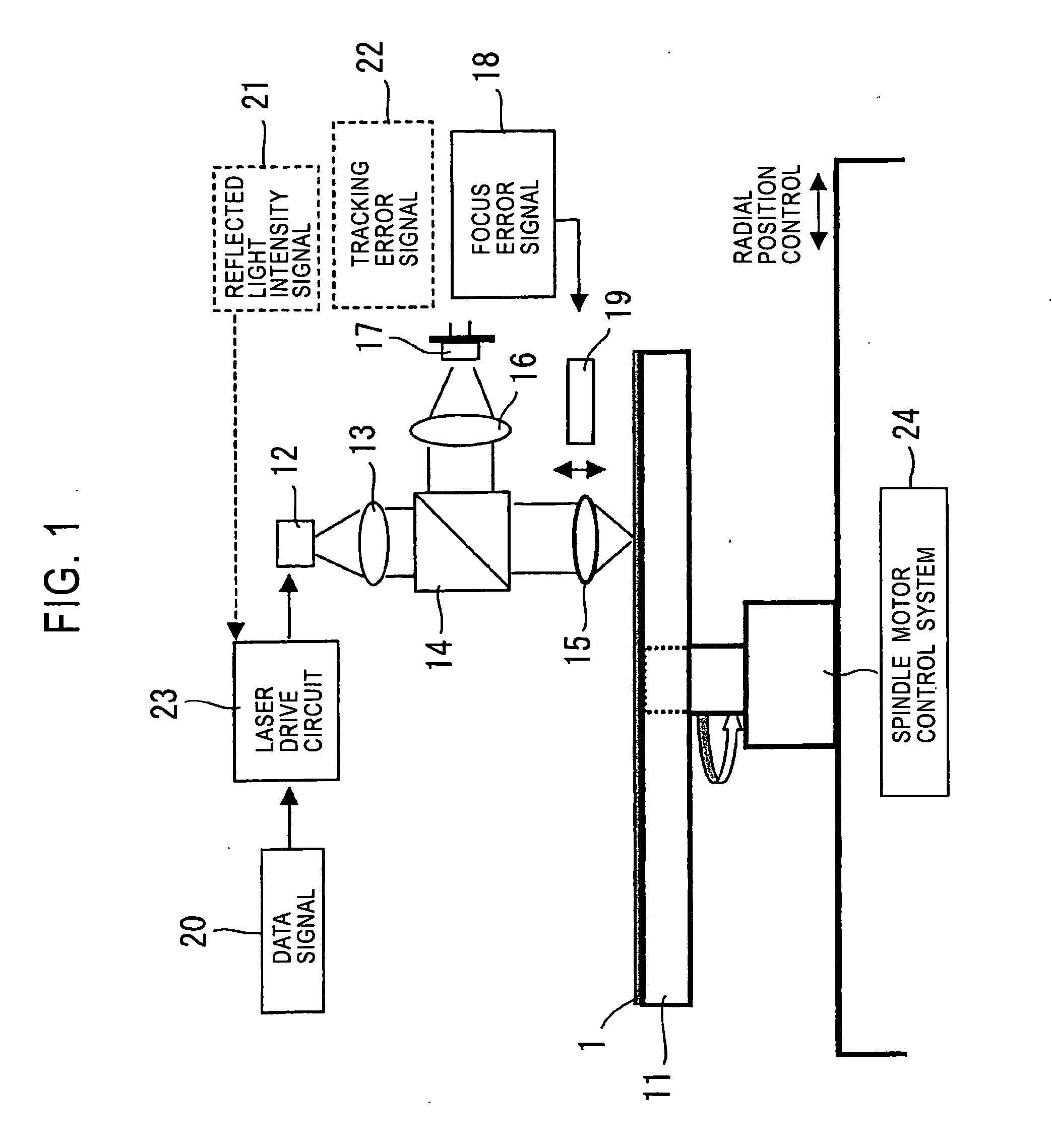

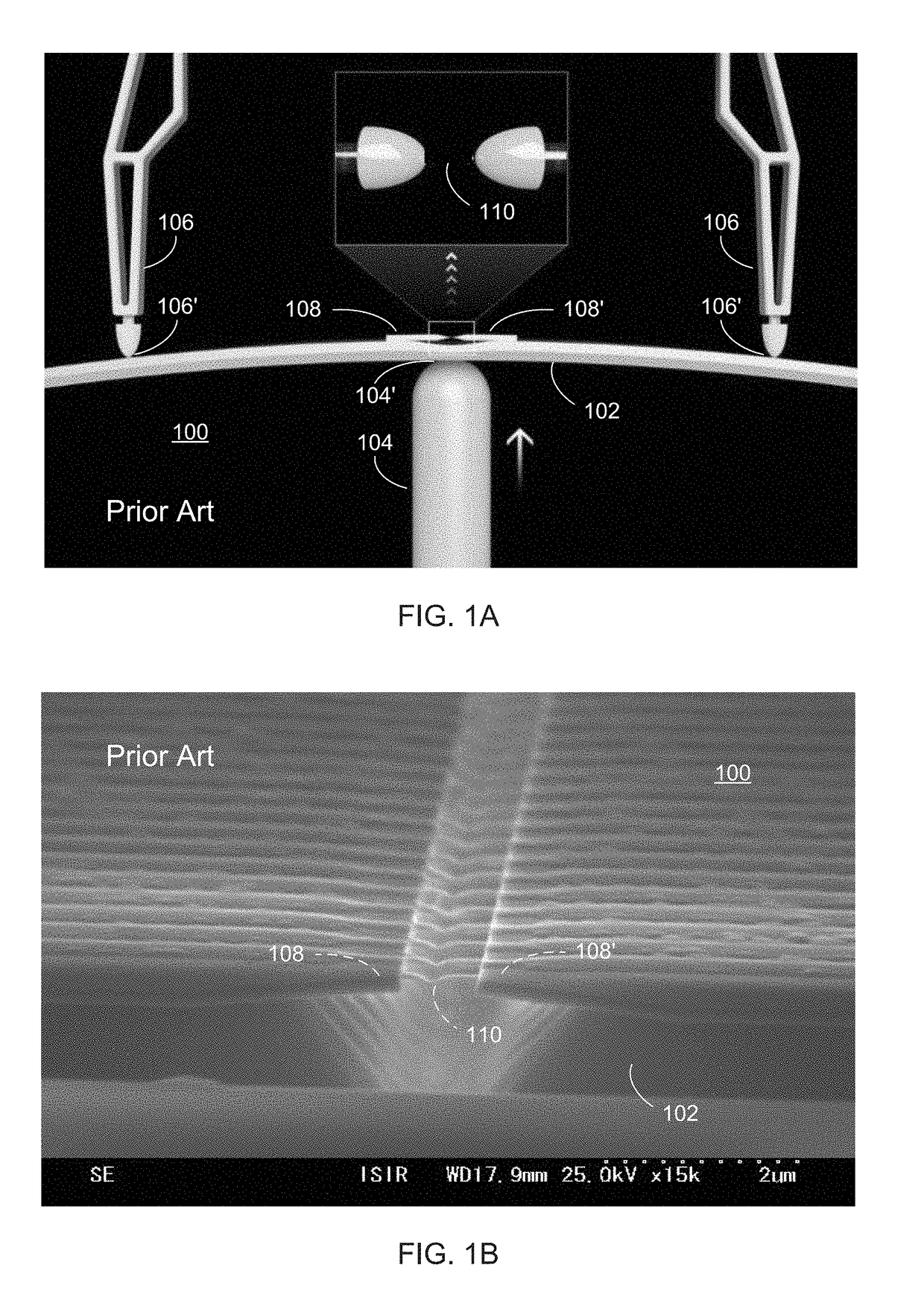

Laser-assisted nanomaterial deposition, nanomanufacturing, in situ monitoring and associated apparatus

Laser-assisted apparatus and methods for performing nanoscale material processing, including nanodeposition of materials, can be controlled very precisely to yield both simple and complex structures with sizes less than 100 nm. Optical or thermal energy in the near field of a photon (laser) pulse is used to fabricate submicron and nanometer structures on a substrate. A wide variety of laser material processing techniques can be adapted for use including, subtractive (e.g., ablation, machining or chemical etching), additive (e.g., chemical vapor deposition, selective self-assembly), and modification (e.g., phase transformation, doping) processes. Additionally, the apparatus can be integrated into imaging instruments, such as SEM and TEM, to allow for real-time imaging of the material processing.

Owner:RGT UNIV OF CALIFORNIA

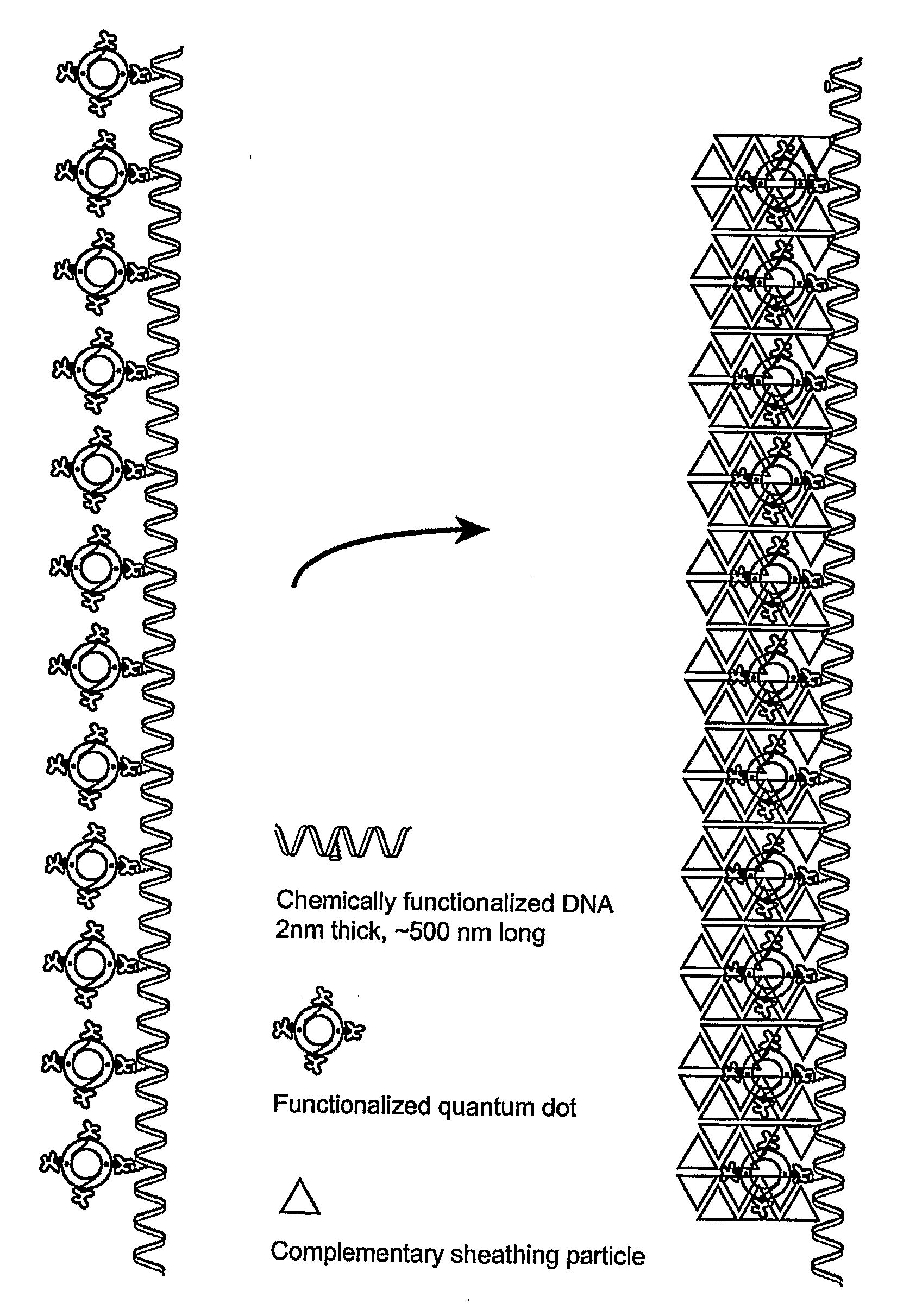

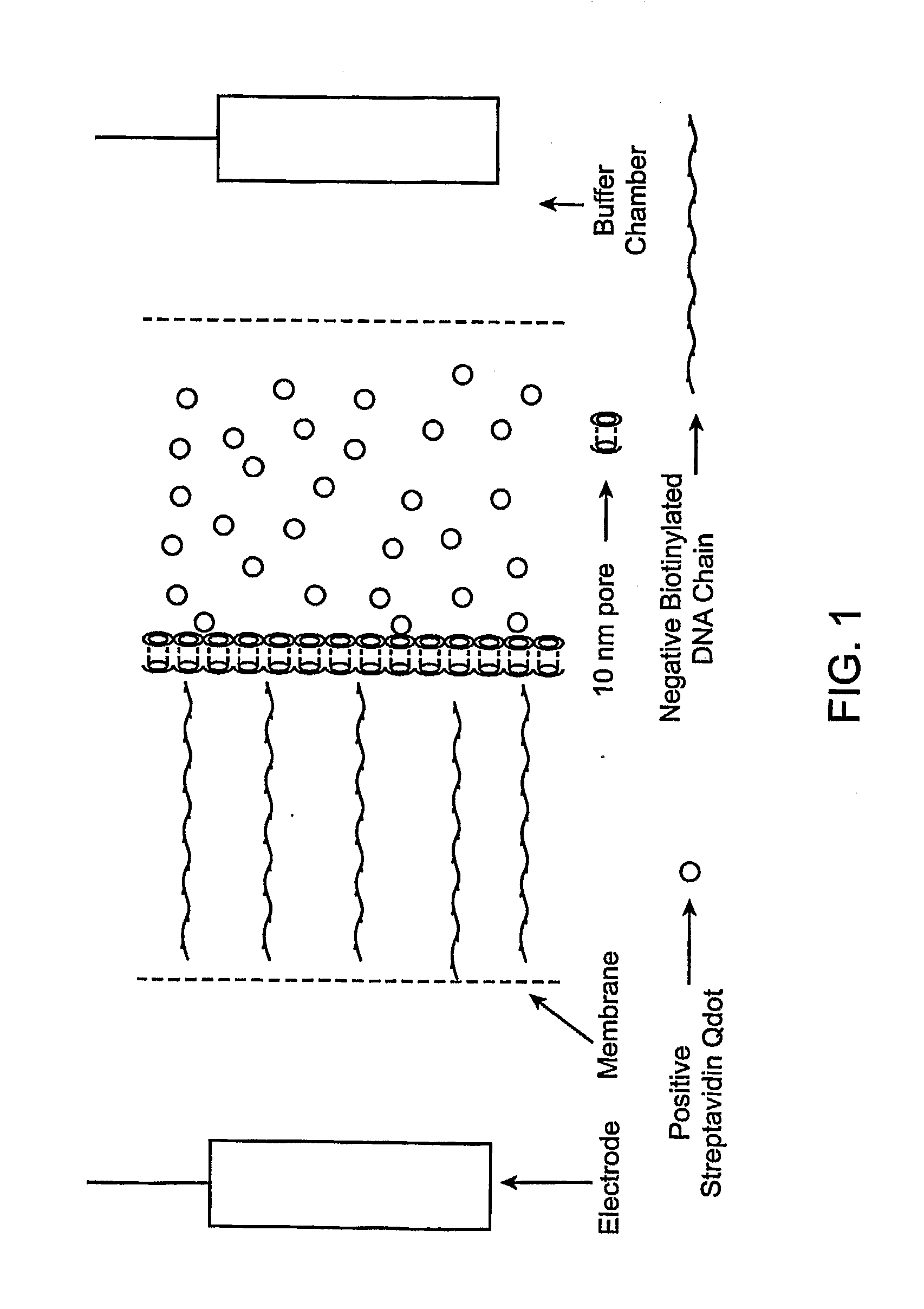

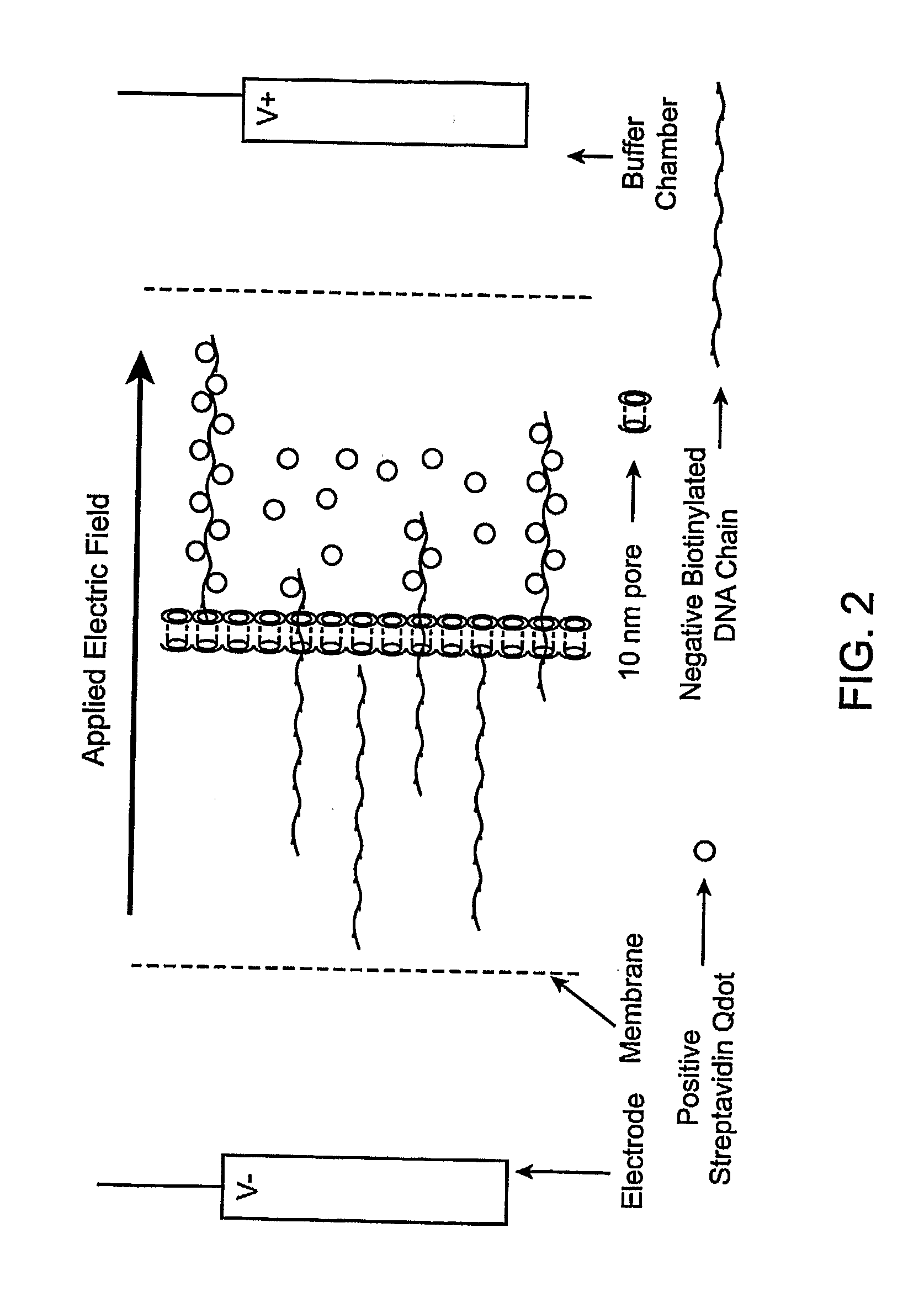

Nanofabrication processes and devices for the controlled assembly of functionalized nanostructures

InactiveUS20090221443A1Improve propertiesImprove transportMaterial nanotechnologyNucleotide librariesNanostructureNanomanufacturing

The invention relates to processes and devices for the controlled fabrication of nanostructures from starting components that have high fidelity recognition properties and multiple binding groups. In one embodiment, the invention relates to the formation of nanostructures using controlled sequential addition of nanocomponents at regular intervials via sequential formation of binding pairs or other chemical binding reactions.

Owner:RGT UNIV OF CALIFORNIA

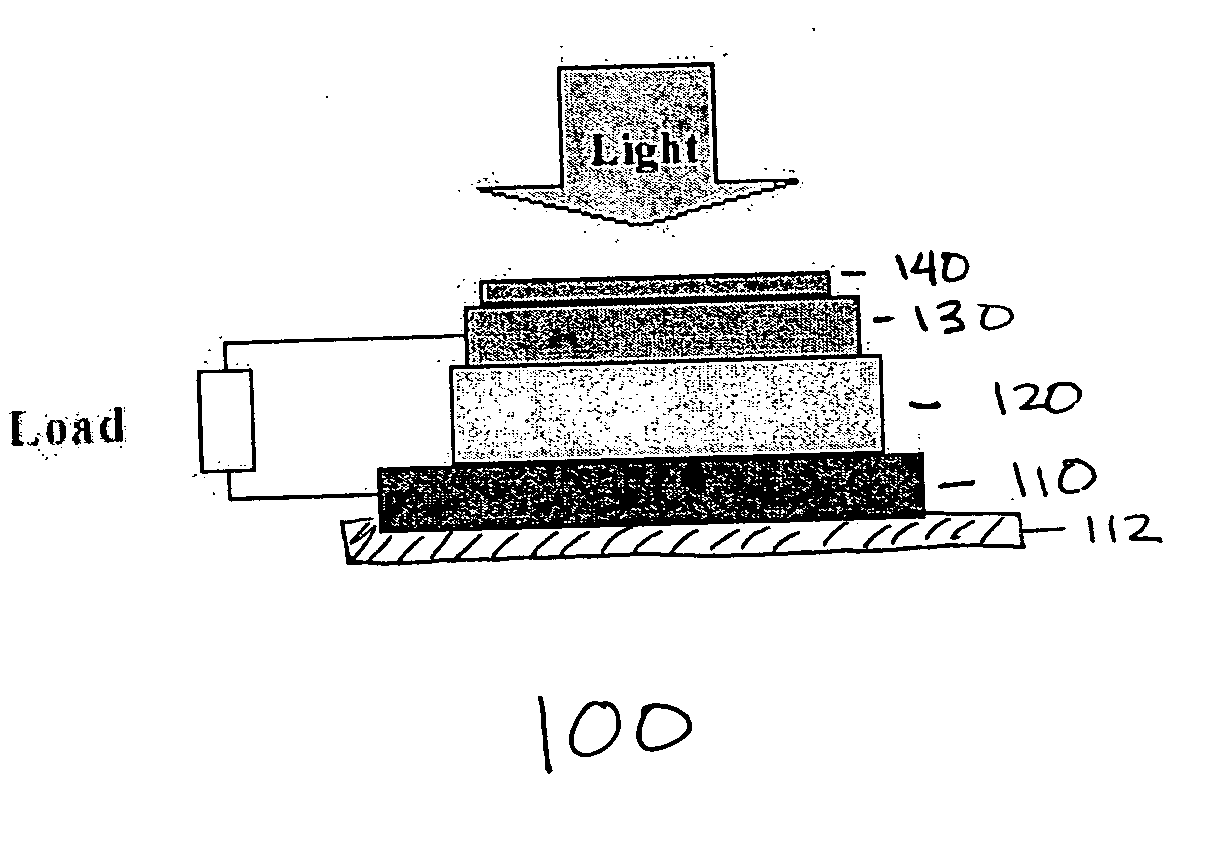

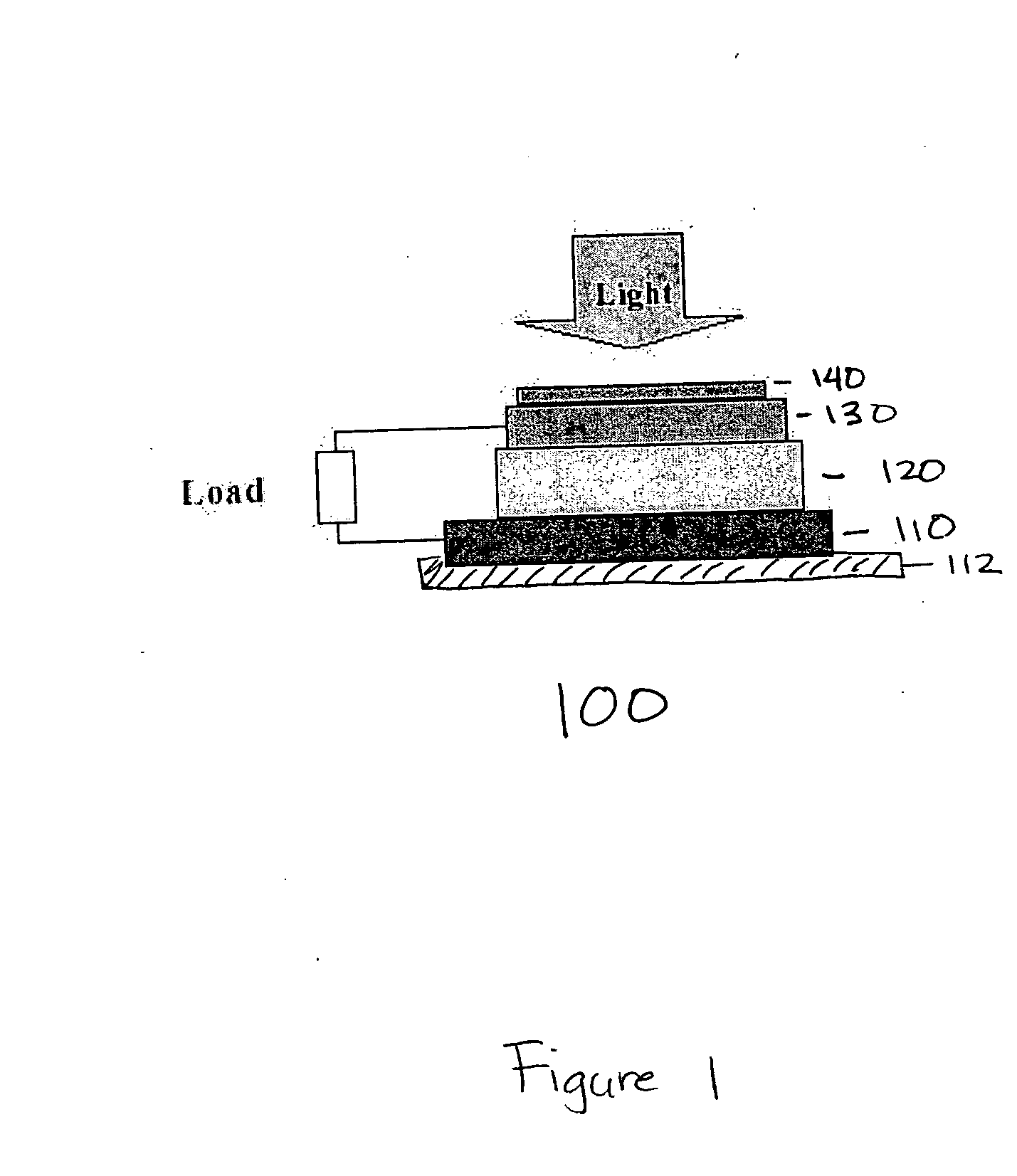

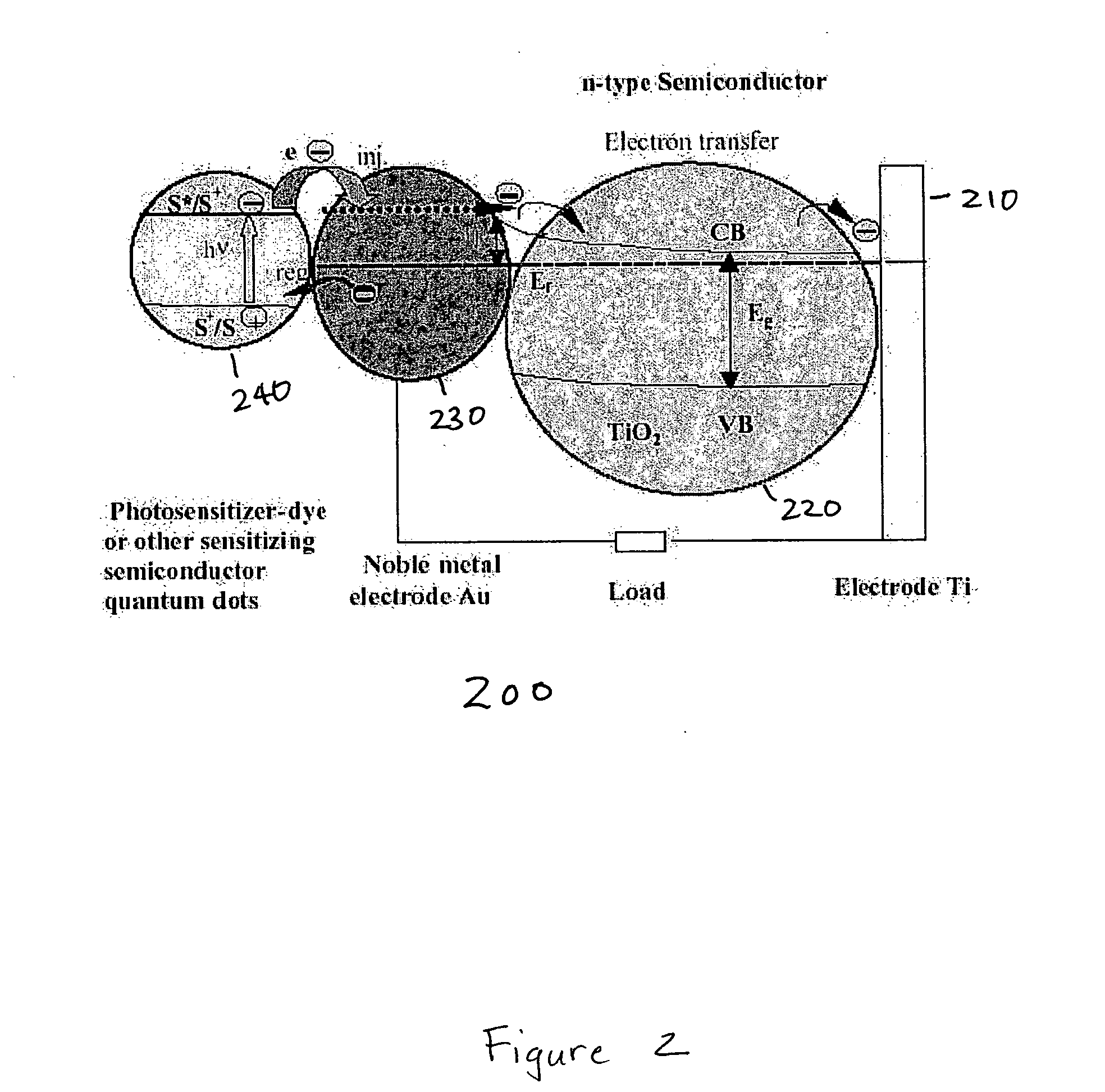

Self-assembly methods for the fabrication of McFarland-Tang photovoltaic devices

InactiveUS20050000565A1Material nanotechnologyElectrolytic capacitorsPhotovoltaic detectorsPhotosensitizer

The present invention relates to self-assembly methodologies, such as electrostatic self-assembly, layer by layer covalent self-assembly, nuclear induced self-assembly, regular ink jet printing and self-assembly inkjet printing methodologies for the fabrication of McFarland-Tang multilayer structured photovoltaic devices, photo-detectors and sensors. The methodology of the present invention allows for the flexibility to nanofabricate the thin layer of the semiconductor layer, the ultra-thin noble metal layer, and the ultra-thin photosensitizer layers to form the desired multilayer photovoltaic devices. Extending the self-assembly processes by ink-jet printing allows for the up-scaled nano-manufacture of McFarland-Tang photovoltaic devices on any type of substrate, including light-weight flexible photovoltaic fabrics and paper.

Owner:NANOSCALE MATERIALS

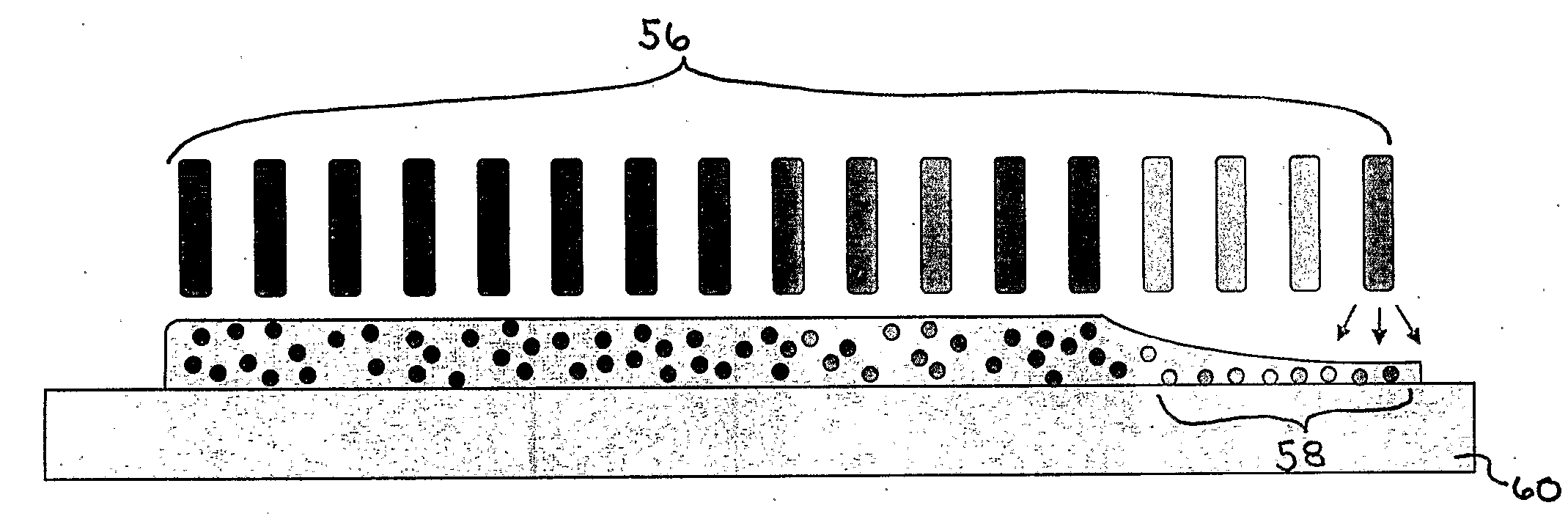

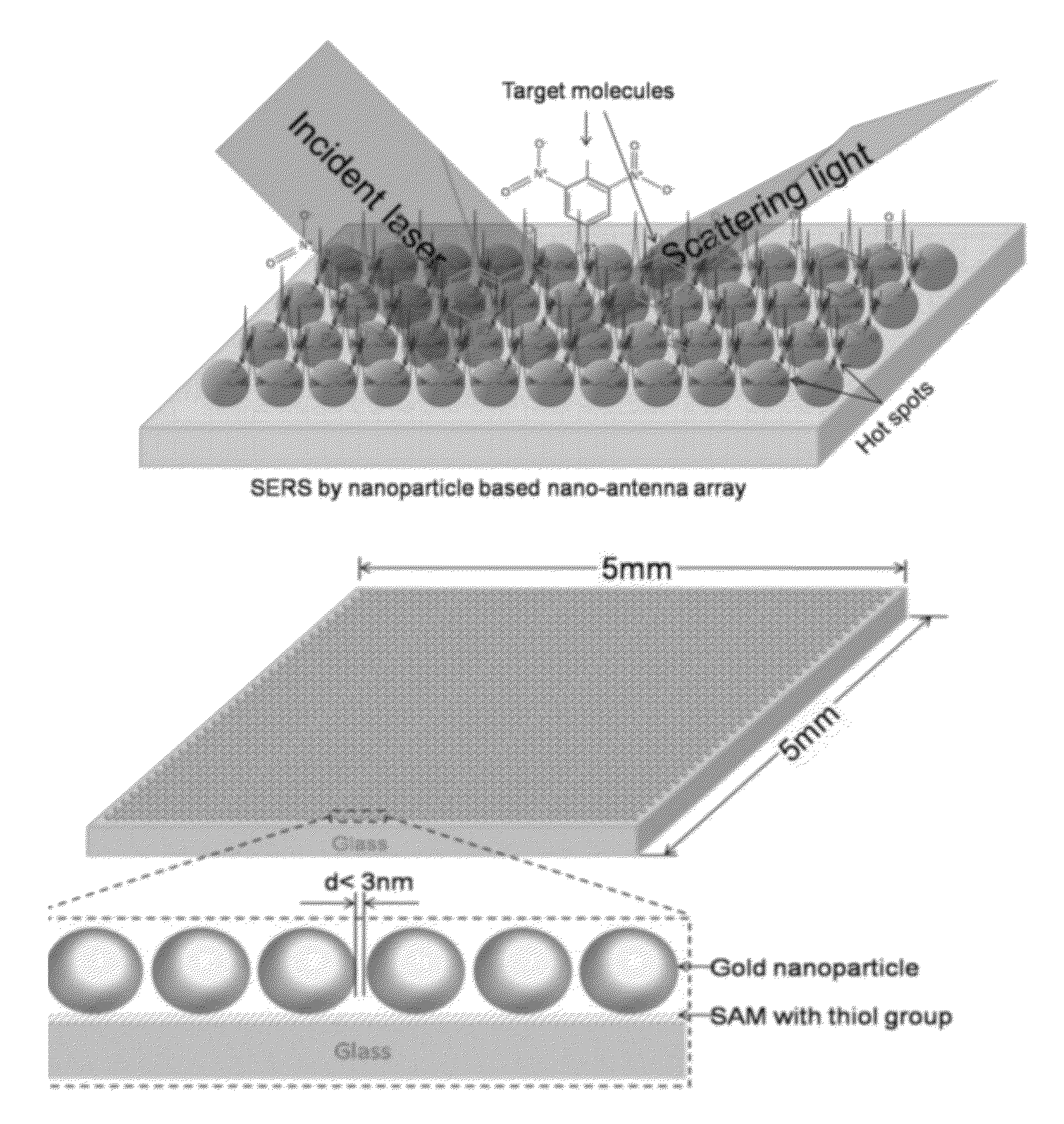

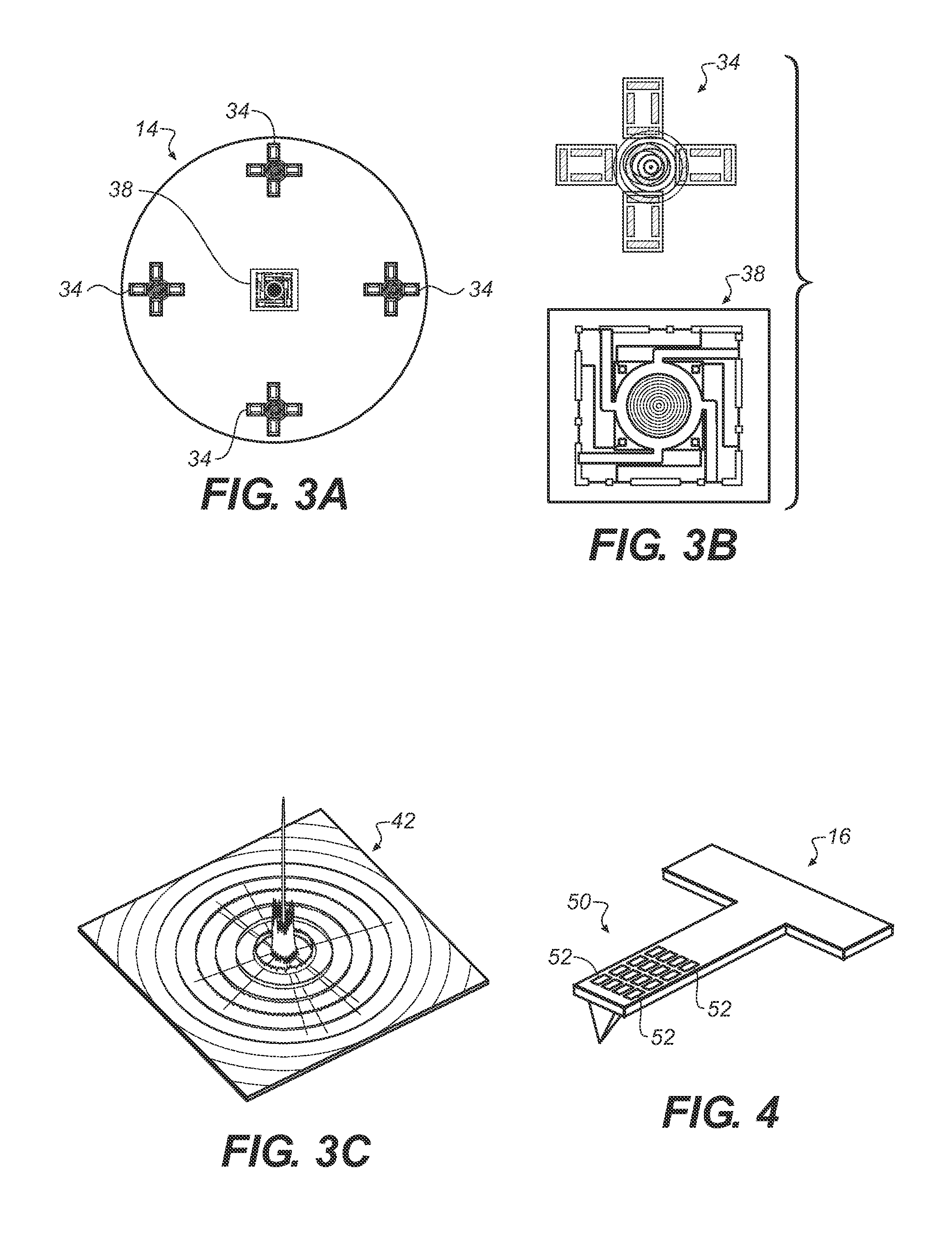

Sensor system with plasmonic nano-antenna array

ActiveUS20120050732A1Increase heightRapid and sensitive chemical/biological agent detectionMaterial nanotechnologyRadiation pyrometrySystems designEngineering

In order to provide the high sensitivity SERS active substrates needed for rapid and sensitive chemical / biological agent detection, the present invention provides a Plasmonic Nano-antenna Array (PNA) substrate with large local electromagnetic field enhancements; a controllable and repeatable nano-fabrication process for creating the PNA surface; and a system design for a compact, portable device capable of using the PNA technology to acquire and analyze target molecular samples. Both 2D and 3D systems are provided.

Owner:LU WEIXING +1

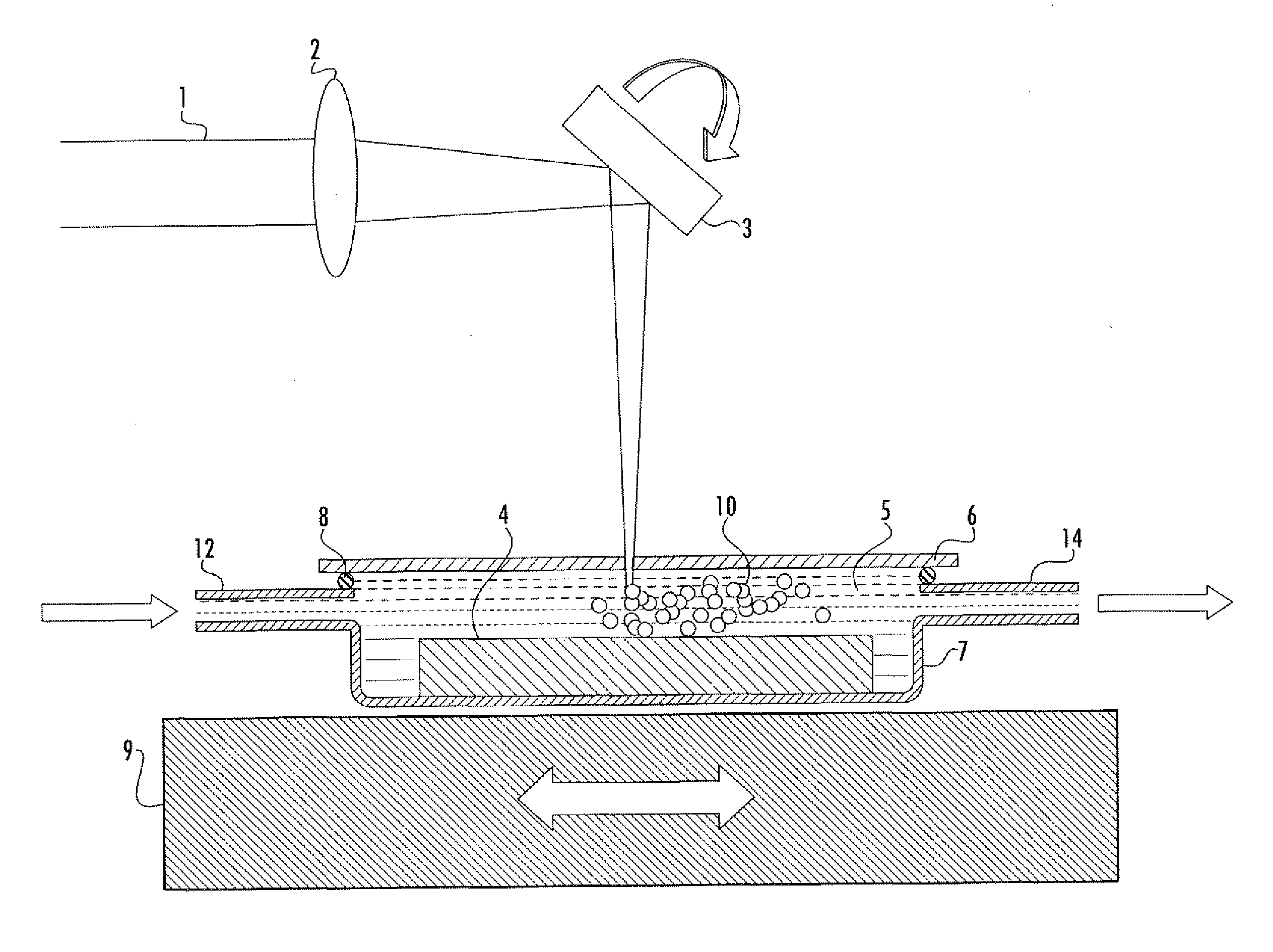

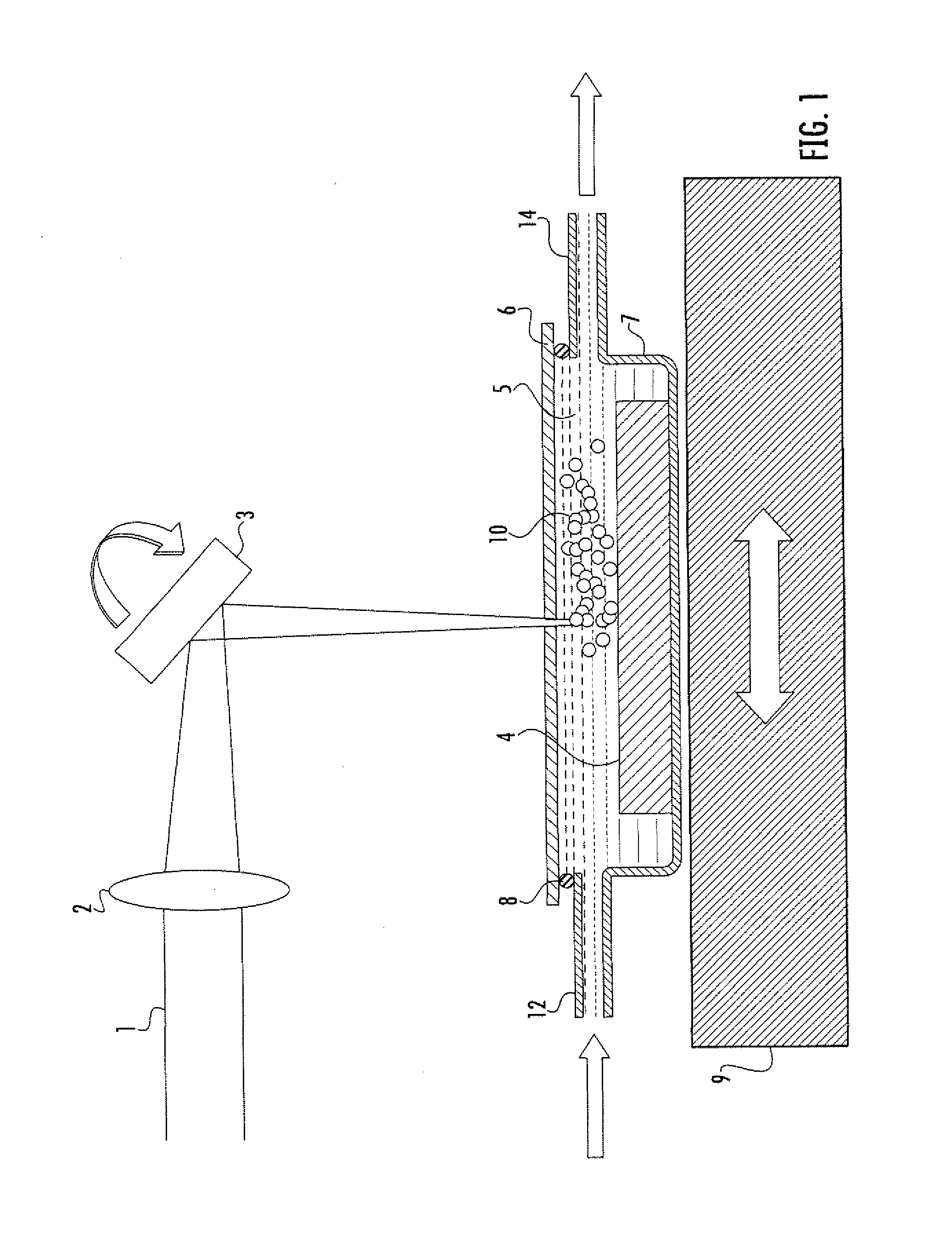

Stable colloidal gold nanoparticles with controllable surface modification and functionalization

ActiveUS20120225021A1Ultrasonic/sonic/infrasonic diagnosticsMaterial nanotechnologySource materialColloid

In the present invention, a method of producing stable bare colloidal gold nanoparticles is disclosed. The nanoparticles can subsequently be subjected to partial or full surface modification. The method comprises preparation of colloidal gold nanoparticles in a liquid by employing a top-down nanofabrication method using bulk gold as a source material. The surface modification of these nanoparticles is carried out by adding one or multiple types of ligands each containing functional groups which exhibit affinity for gold nanoparticle surfaces to produce the conjugates. Because of the high efficiency and excellent stability of the nanoparticles produced by this method, the fabricated gold nanoparticle conjugates can have surface coverage with functional ligands which can be tuned to be any percent value between 0 and 100%.

Owner:IMRA AMERICA

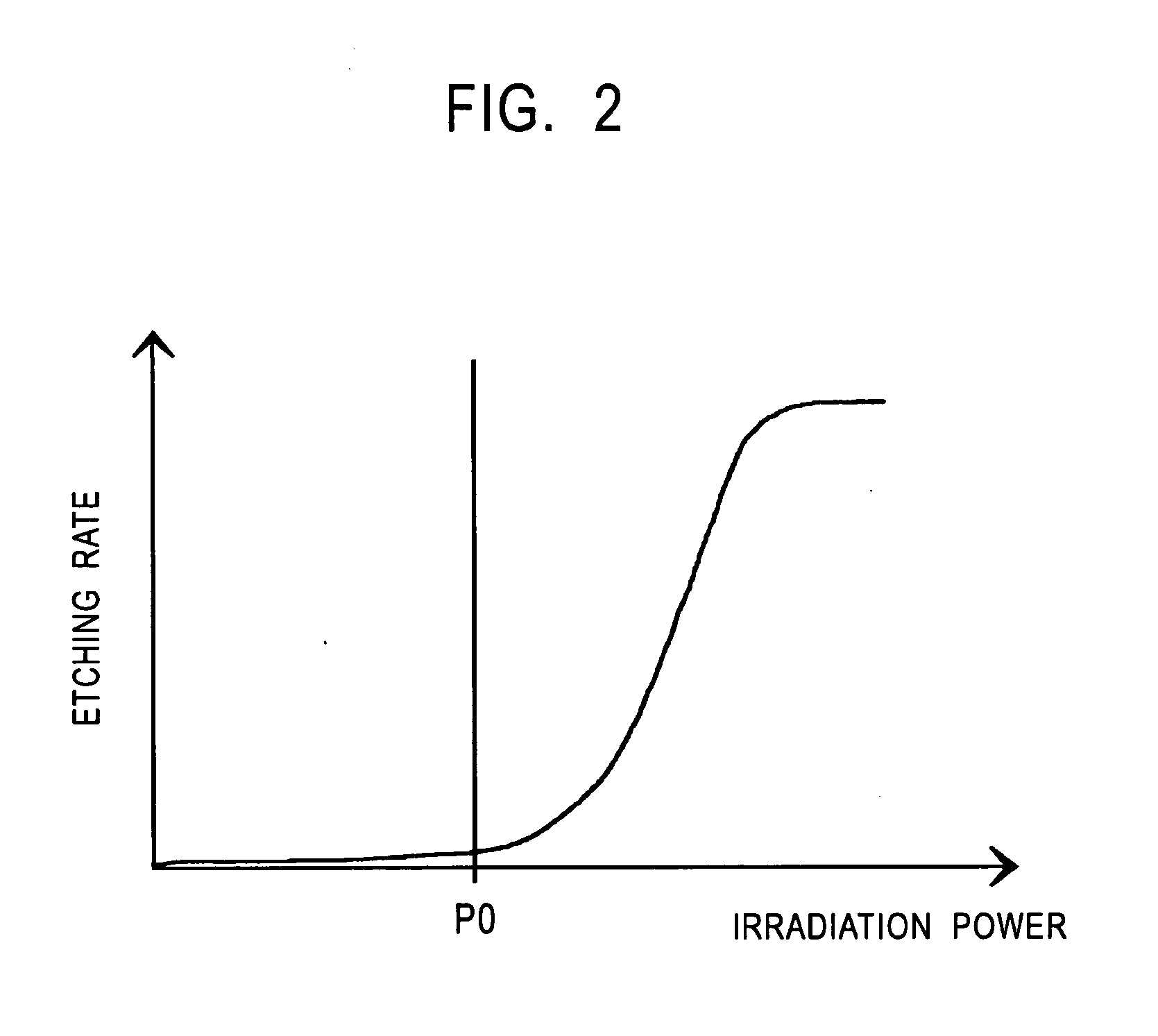

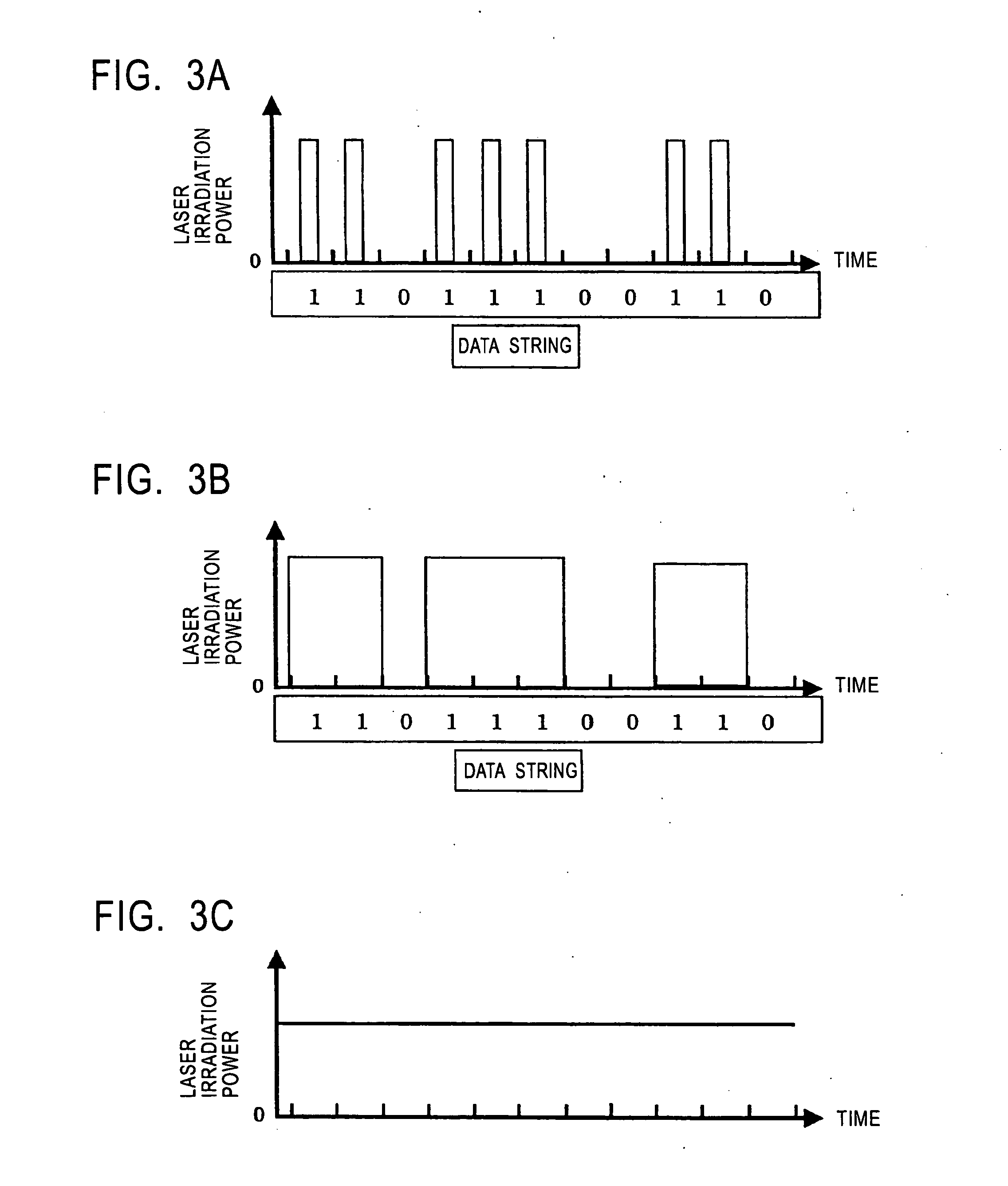

Resist material and nanofabrication method

InactiveUS20040170916A1Reduce exposure timeImprove drawing speedNanoinformaticsSemiconductor/solid-state device manufacturingResistChemical compound

A resist material and a nanofabrication method provide high-resolution nanofabrication without an expensive irradiation apparatus using, for example, electron beams or ion beams. That is, the resist material and the nanofabrication method provide finer processing using exposure apparatuses currently in use. A resist layer of an incompletely oxidized transition metal such as W and Mo is selectively exposed and developed to be patterned in a predetermined form. The incompletely oxidized transition metal herein is a compound having an oxygen content slightly deviated to a lower content from the stoichiometric oxygen content corresponding to a possible valence of the transition metal. In other words, the compound has an oxygen content lower than the stoichiometric oxygen content corresponding to a possible valence of the transition metal.

Owner:SONY CORP

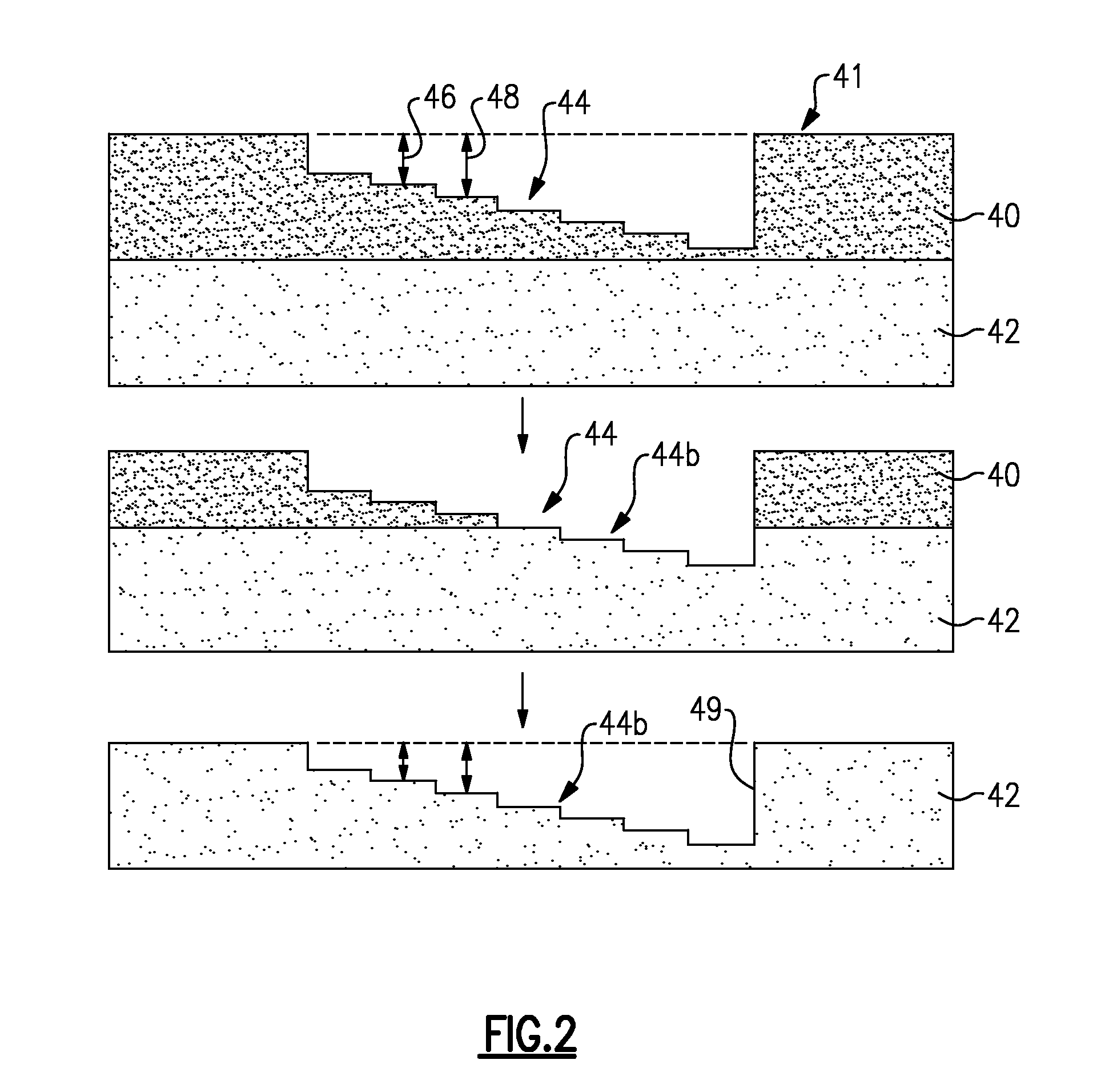

Method for fabricating dual damascene profiles using sub pixel-voting lithography and devices made by same

ActiveUS20090023098A1Reduce complexityLow costElectric discharge tubesSolid-state devicesScale structureIntegrated electronics

This invention provides processing steps, methods and materials strategies for making patterns of structures for integrated electronic devices and systems. Processing methods of the present invention are capable of making micro-and nano-scale structures, such as Dual Damascene profiles, recessed features and interconnect structures, having non-uniform cross-sectional geometries useful for establishing electrical contact between device components of an electronic device. The present invention provides device fabrication methods and processing strategies using sub pixel-voting lithographic patterning of a single layer of photoresist useful for fabricating and integrating multilevel interconnect structures for high performance electronic or opto-electronic devices, particularly useful for Very Large Scale Integrated (VLSI) and Ultra large Scale Integrated (ULSI) devices. Processing methods of the present invention are complementary to conventional microfabrication and nanofabrication methods for making integrated electronics, and can be effectively integrated into existing photolithographic, etching, and thin film deposition patterning systems, processes and infrastructure.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ILLINOIS

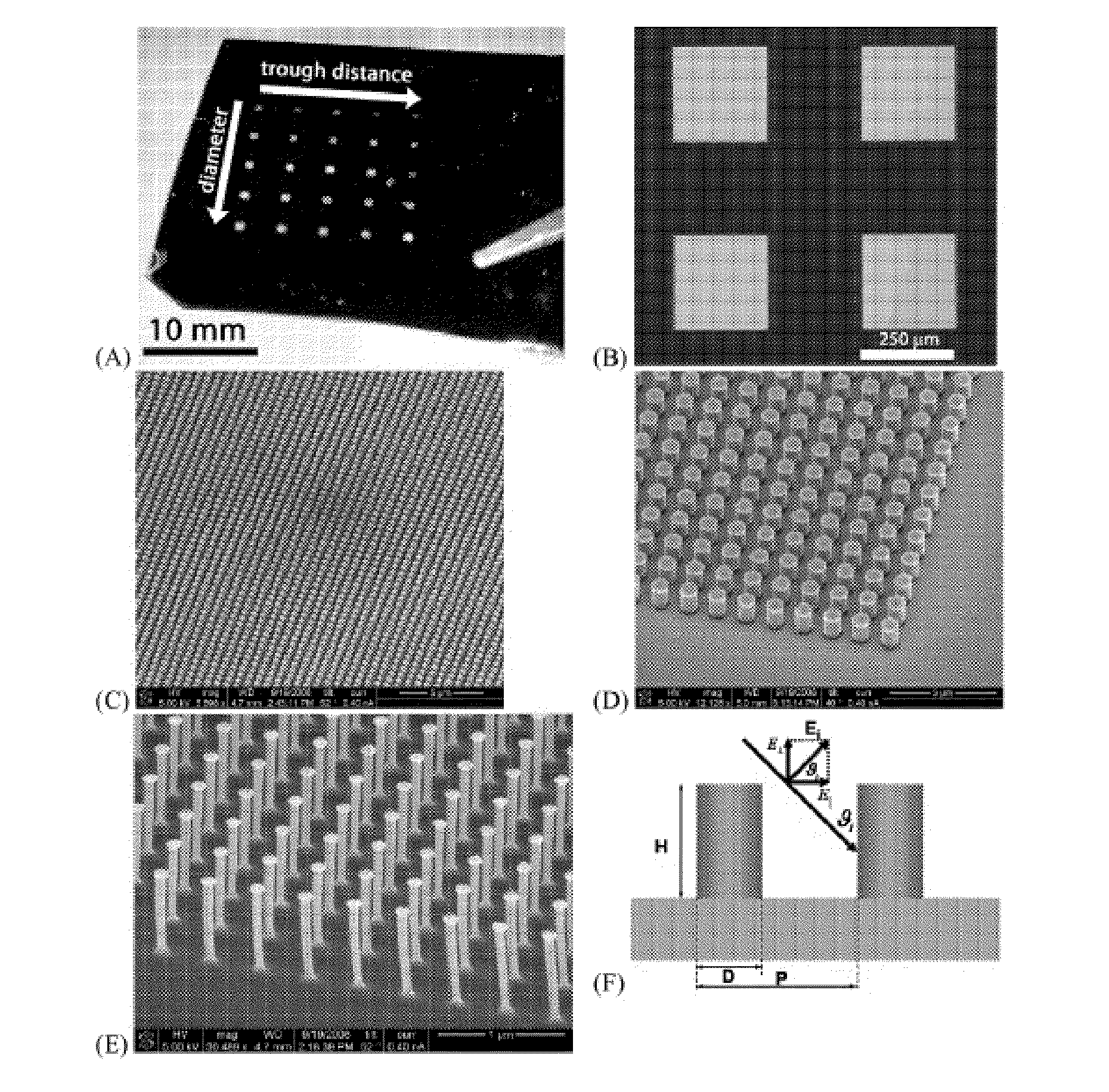

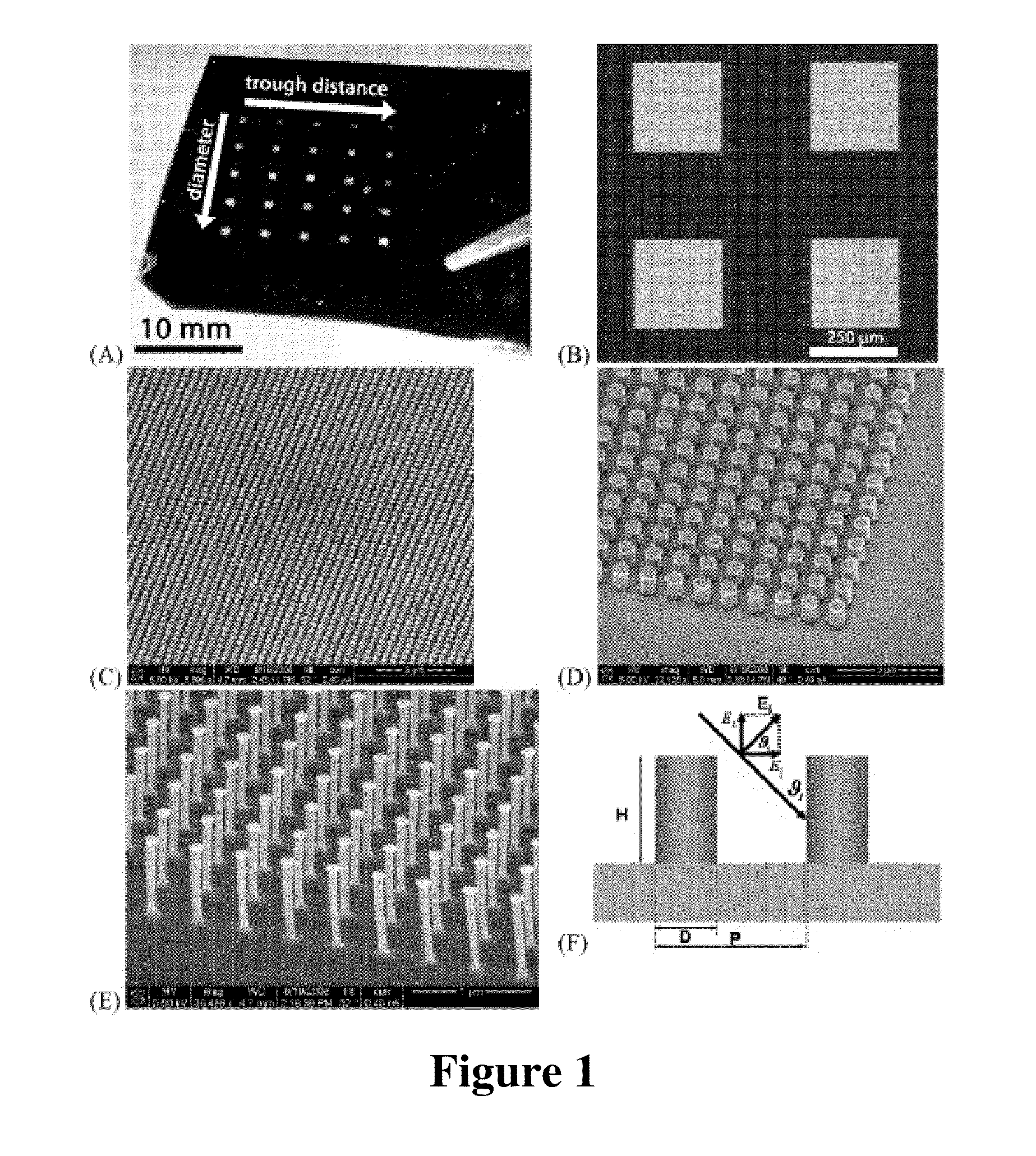

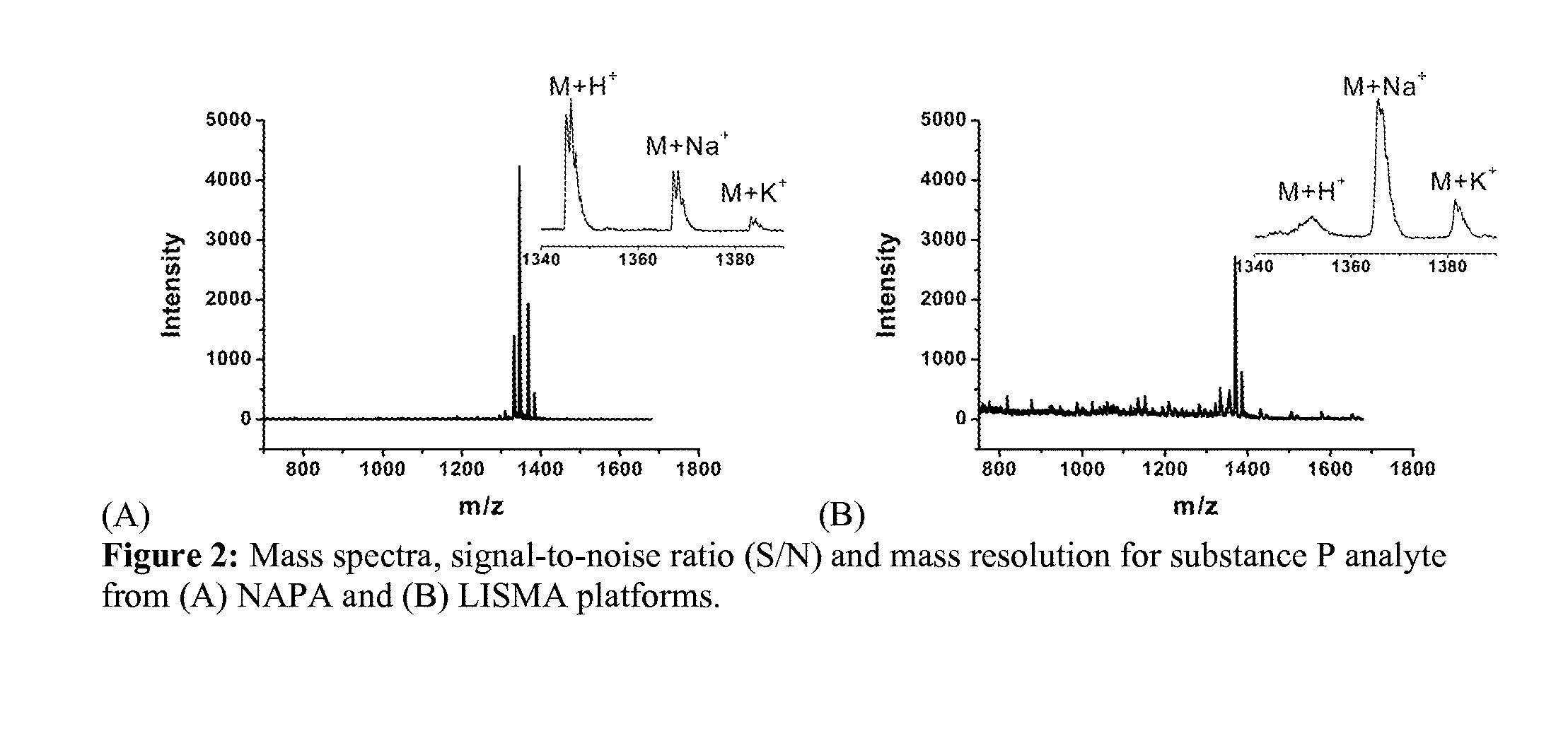

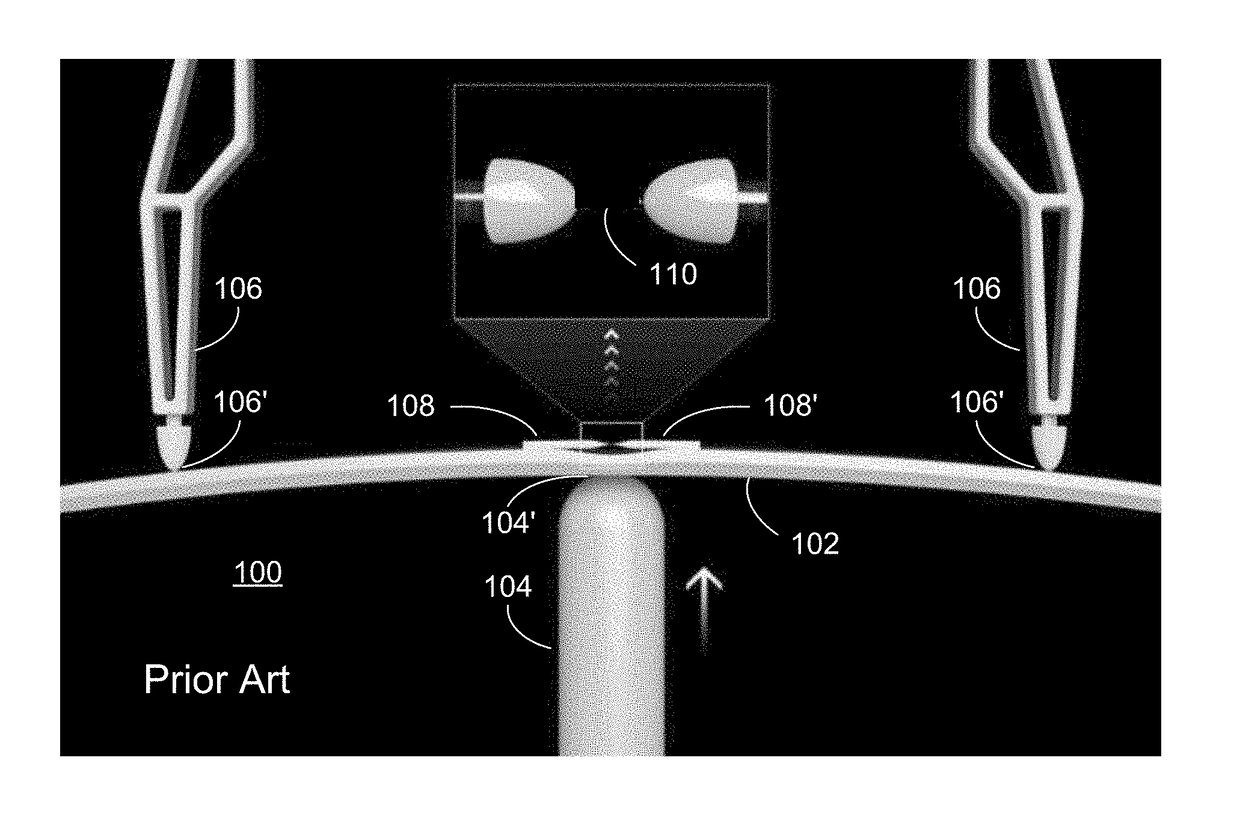

Tailored nanopost arrays (NAPA) for laser desorption ionization in mass spectrometry

ActiveUS20100323917A1Increased ion productionIncreased molecular fragmentationParticle separator tubesPV power plantsMass Spectrometry-Mass SpectrometryMass spectrometry imaging

The production and use of semiconducting nanopost arrays made by nanofabrication is described herein. These nanopost arrays (NAPA) provide improved laser ionization yields and controllable fragmentation with switching or modulation capabilities for mass spectrometric detection and identification of samples deposited on them.

Owner:UT BATTELLE LLC +1

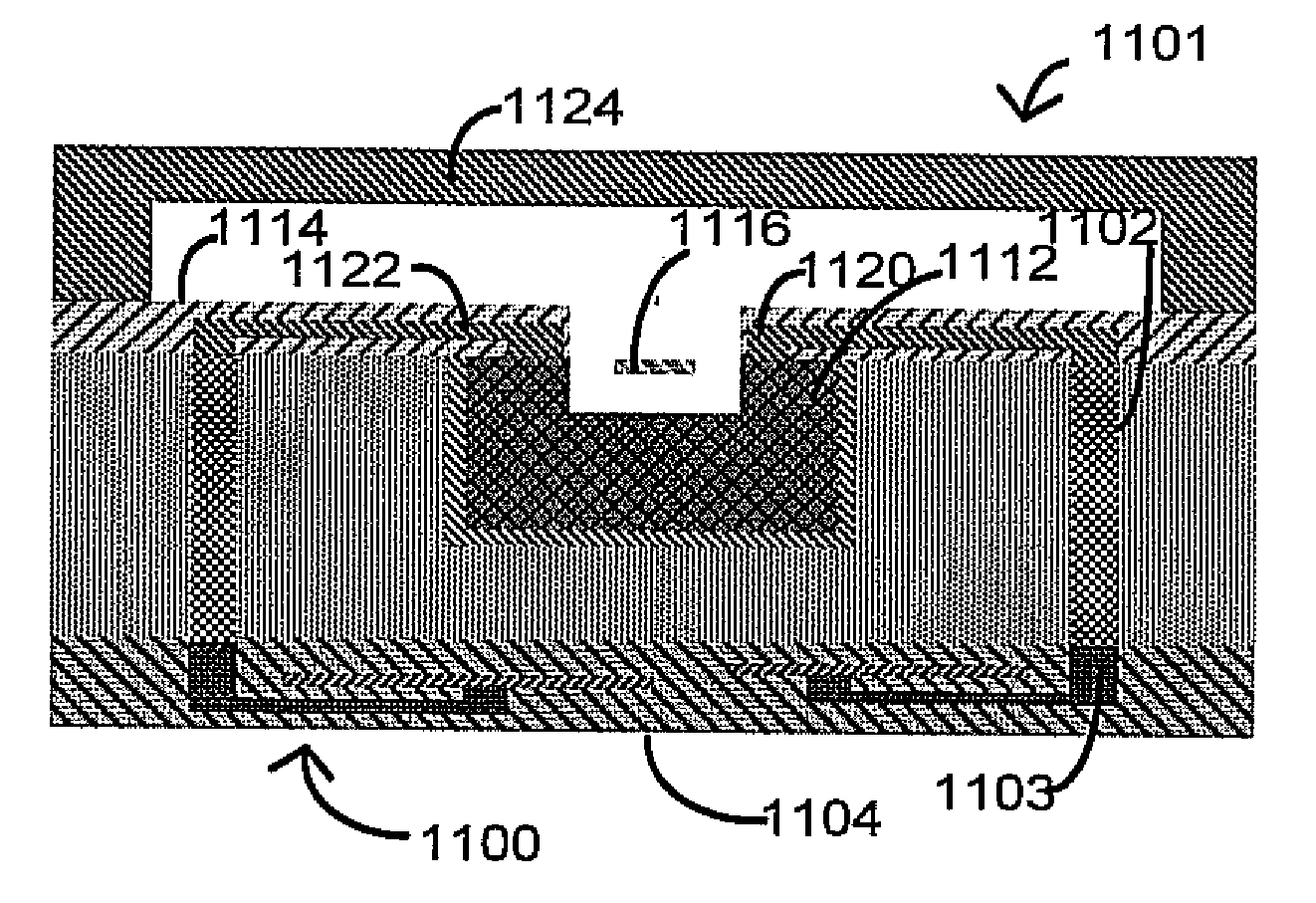

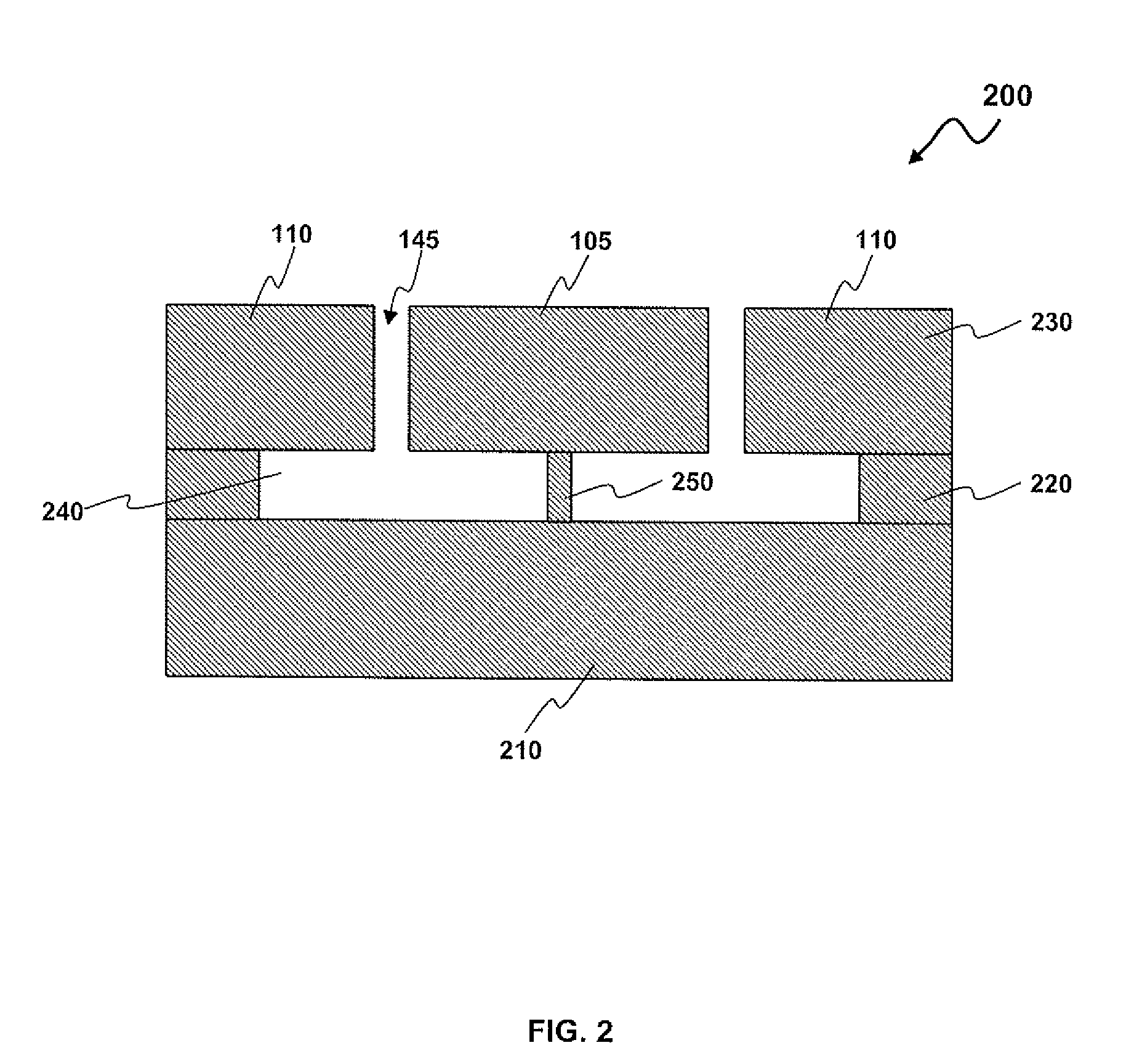

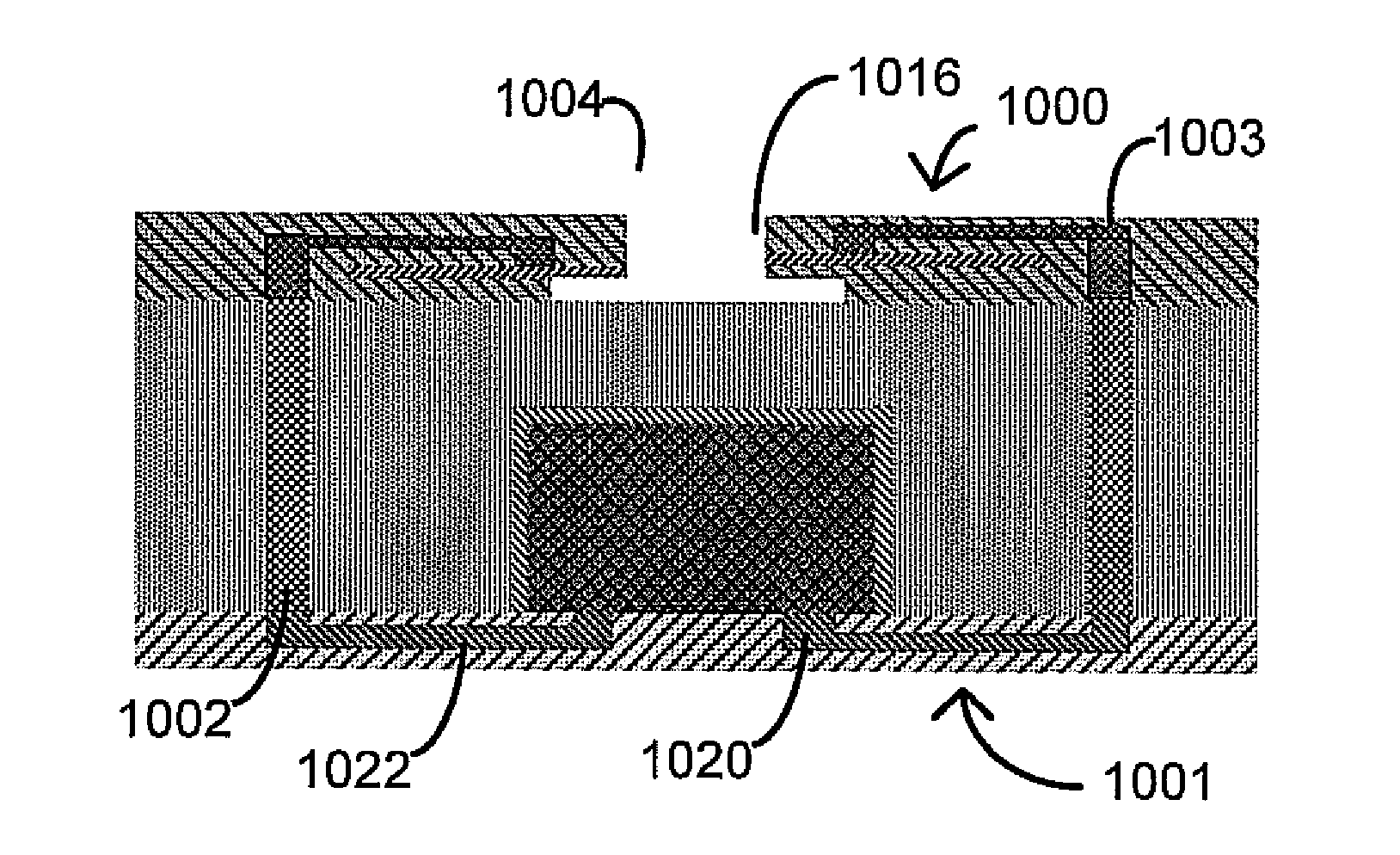

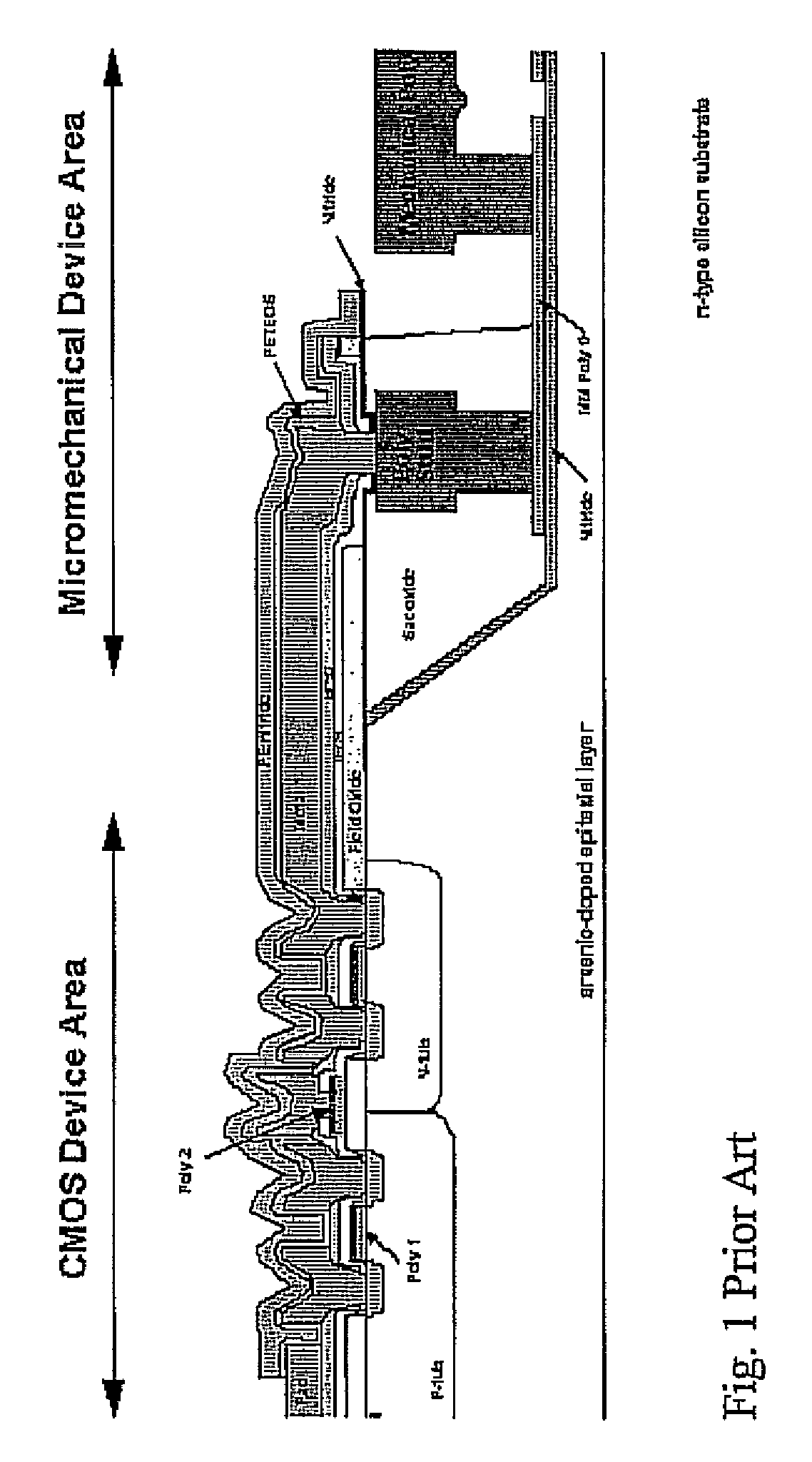

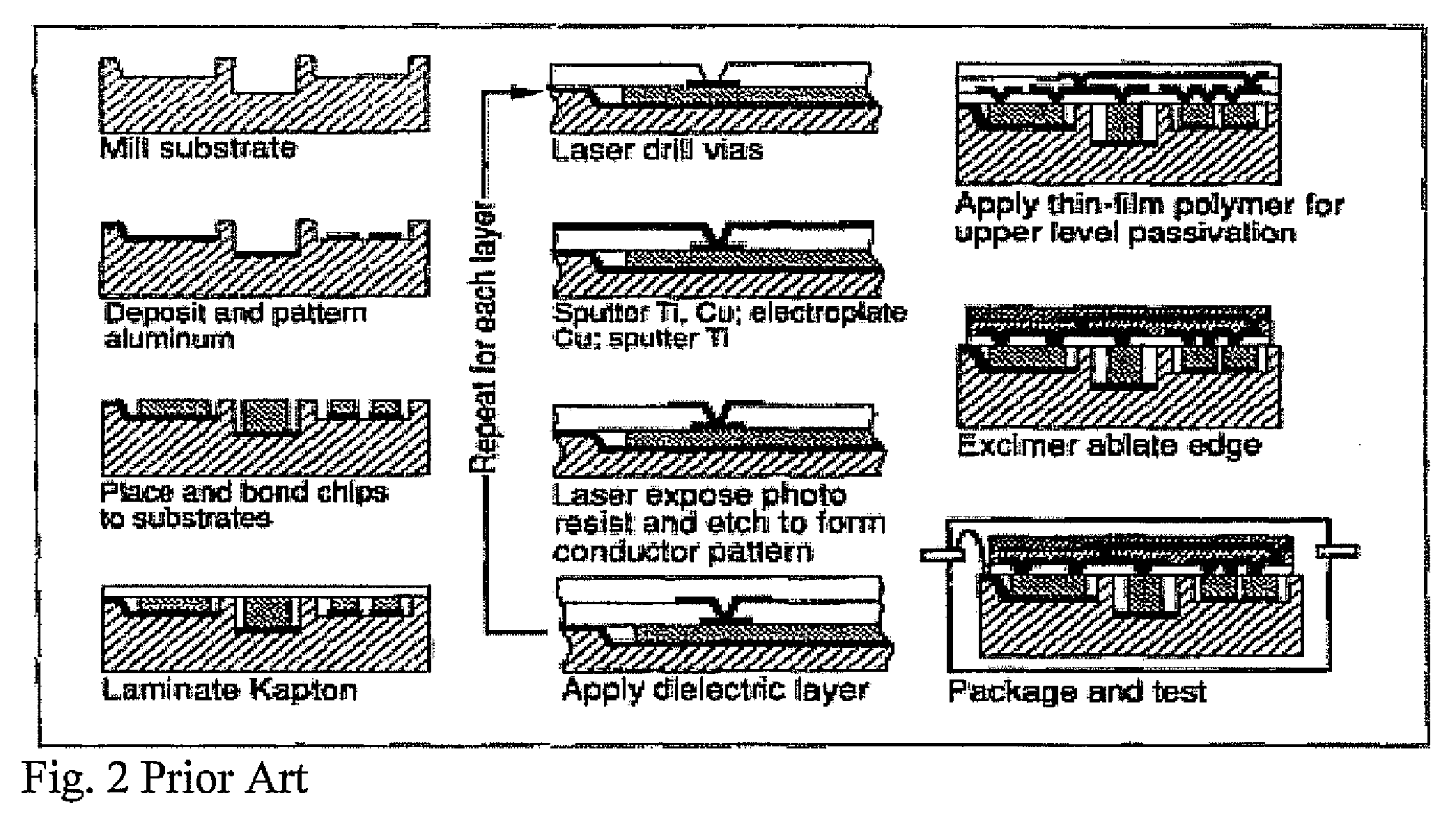

Method of forming monolithic cmos-mems hybrid integrated, packaged structures

InactiveUS20110027941A1Solid-state devicesSemiconductor/solid-state device manufacturingLayer interfaceFilling materials

A method of forming Monolithic CMOS-MEMS hybrid integrated, packaged structures includes the steps of providing: providing a semiconductor substrate with pre-fabricated cmos circuits on the front side and a polished back-side with through substrate conductive vias; forming at least one opening in the polished backside of the semiconductor substrate by appropriately protecting the front-side; applying at least one filler material in the at least one opening on the semiconductor substrate; positioning at least one prefabricated mems, nems or cmos chip on the filler material, the chip including a front face and a bare back face with the prefabricated mems / nems chips containing mechanical and dielectric layers; applying at least one planarization layer overlying the substrate, filler material and the chip; forming at least one via opening on a portion of the planarization layer interfacing pads on the chip and the through substrate conductive vias; applying at least one metallization layer overlying the planarization layer on the substrate and the chip connecting the through substrate conductive vias to the at least one chip; applying at least one second insulating layer overlying the metallization layer; performing at least one micro / nano fabrication etching step to release the mechanical layer on the prefabricated mems / nems chips; positioning protective cap to package the integrated device over the mems / nems device area on the pre-fabricated chips.

Owner:AMF NANO

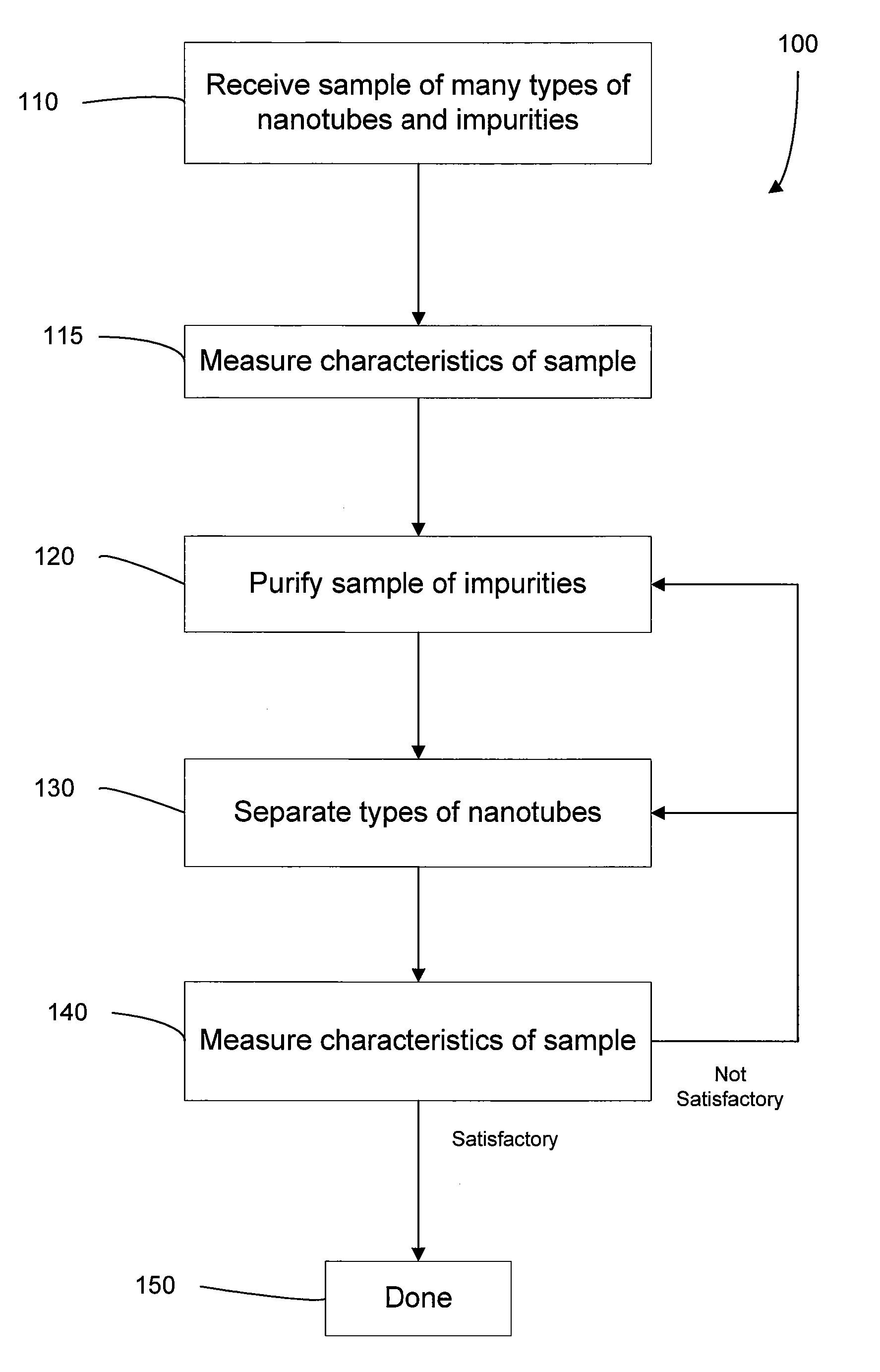

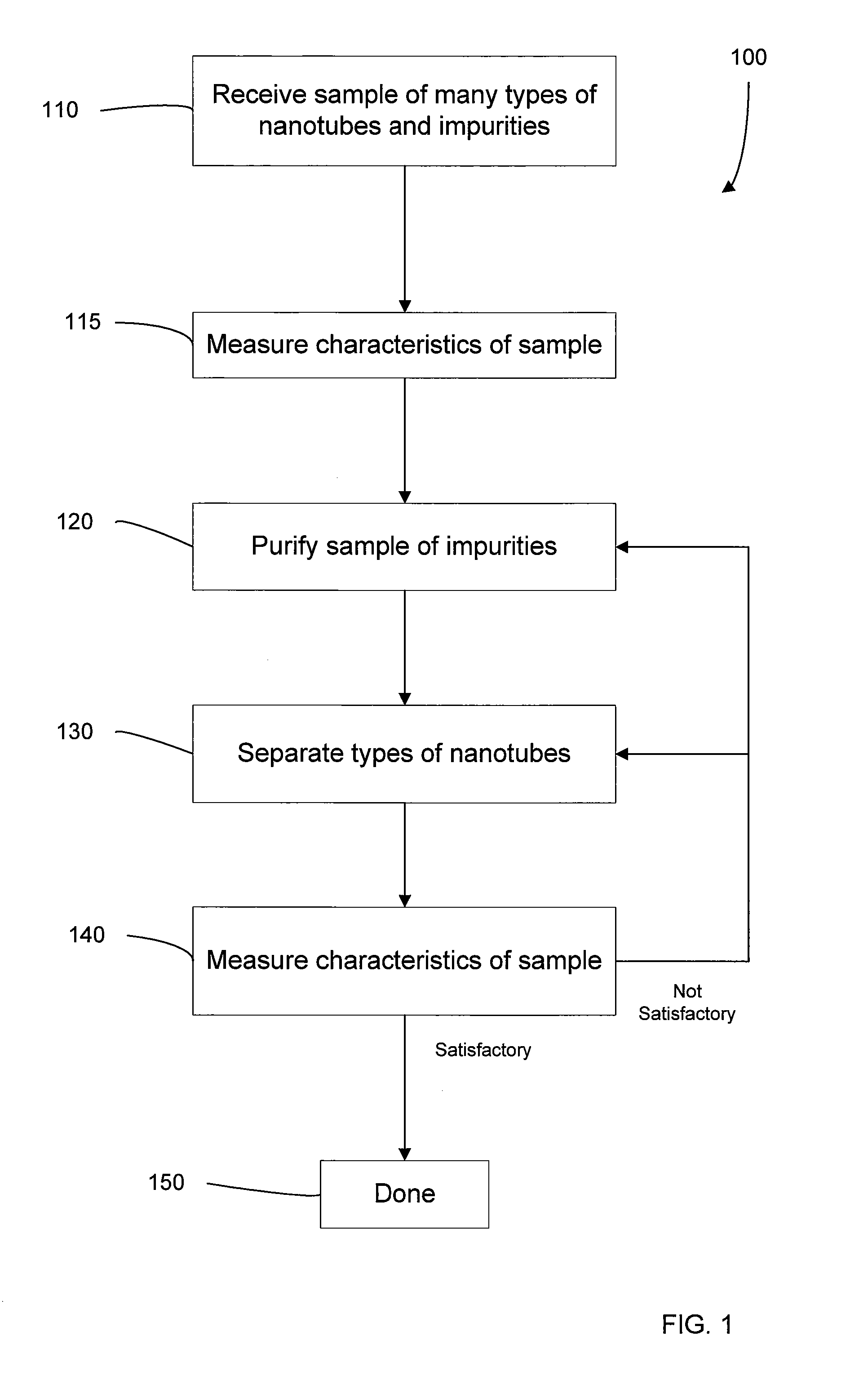

Carbon Nanotube Purification and Separation System

InactiveUS20080069758A1Large rangeConvenient amountPigmenting treatmentMaterial nanotechnologyPyroelectric detectorsCarbon nanotube

The present invention provides systems and methods for quantifying, purifying and separating fullerenes, such as single wall carbon nanotubes (SWNTs). The purification / separation combination provides nearly 100% carbonaceous impurity-free SWNT content from a given impure sample and provides a desired chirality and diameter from a given non-separated sample. Nanometrological validation of the success of purification and separation uses a pyroelectric detector and Raman spectroscopy in a single system, thus providing a critical aspect for the nanomanufacturing environment. The purification / separation and nanometrological validations may be performed in a feedback loop to provide a satisfactorily refined sample and optimized purification / separation settings.

Owner:ADA TECH

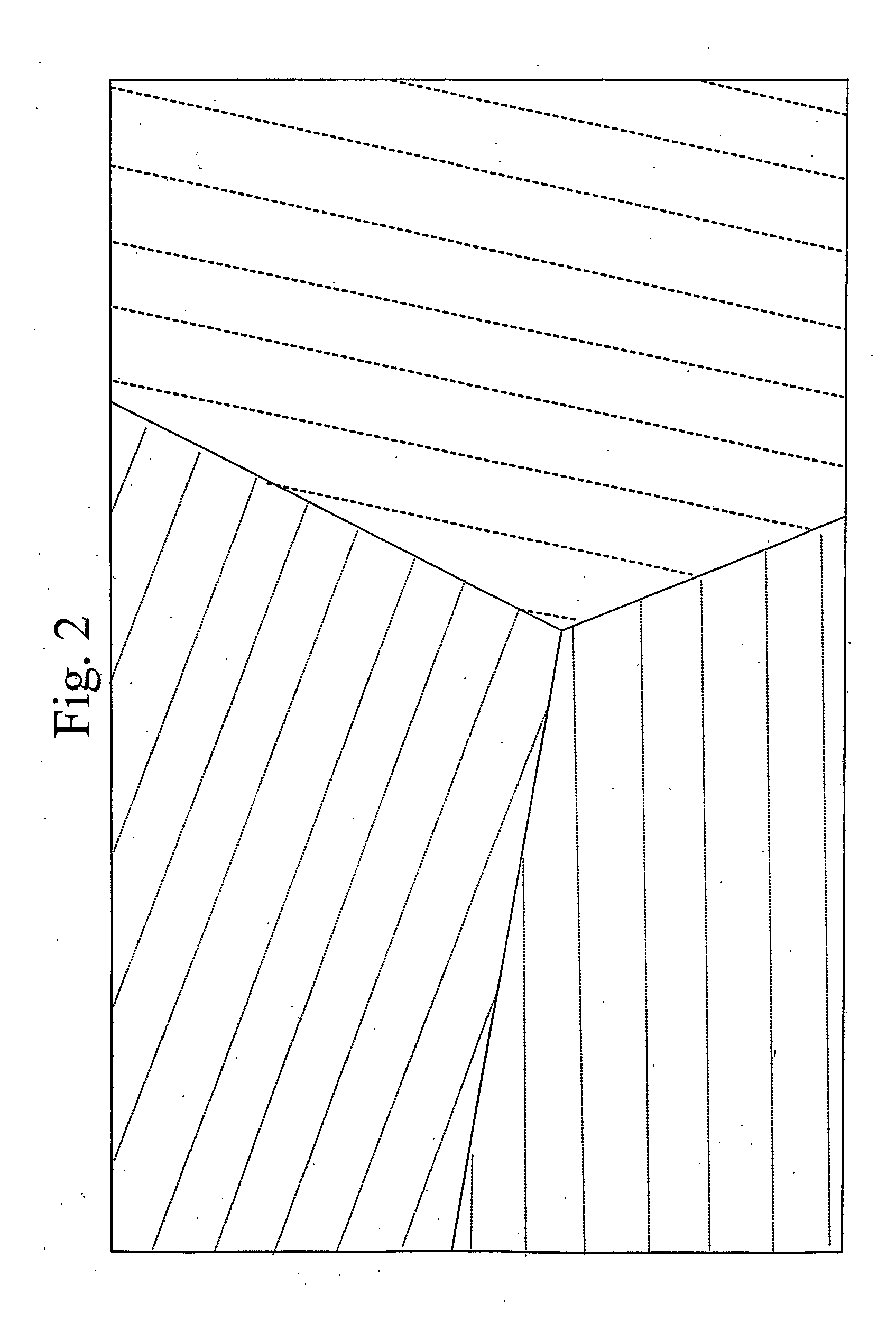

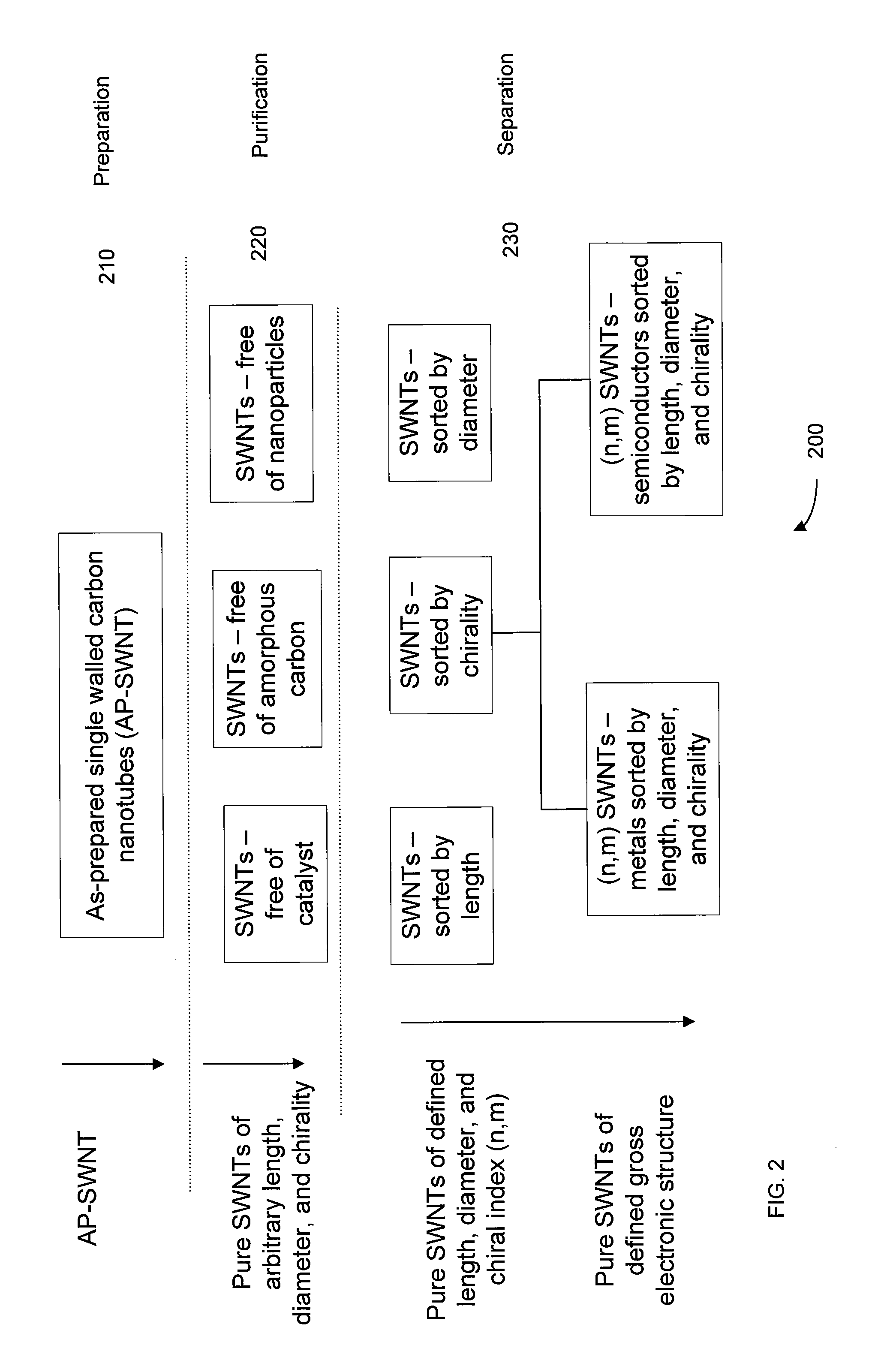

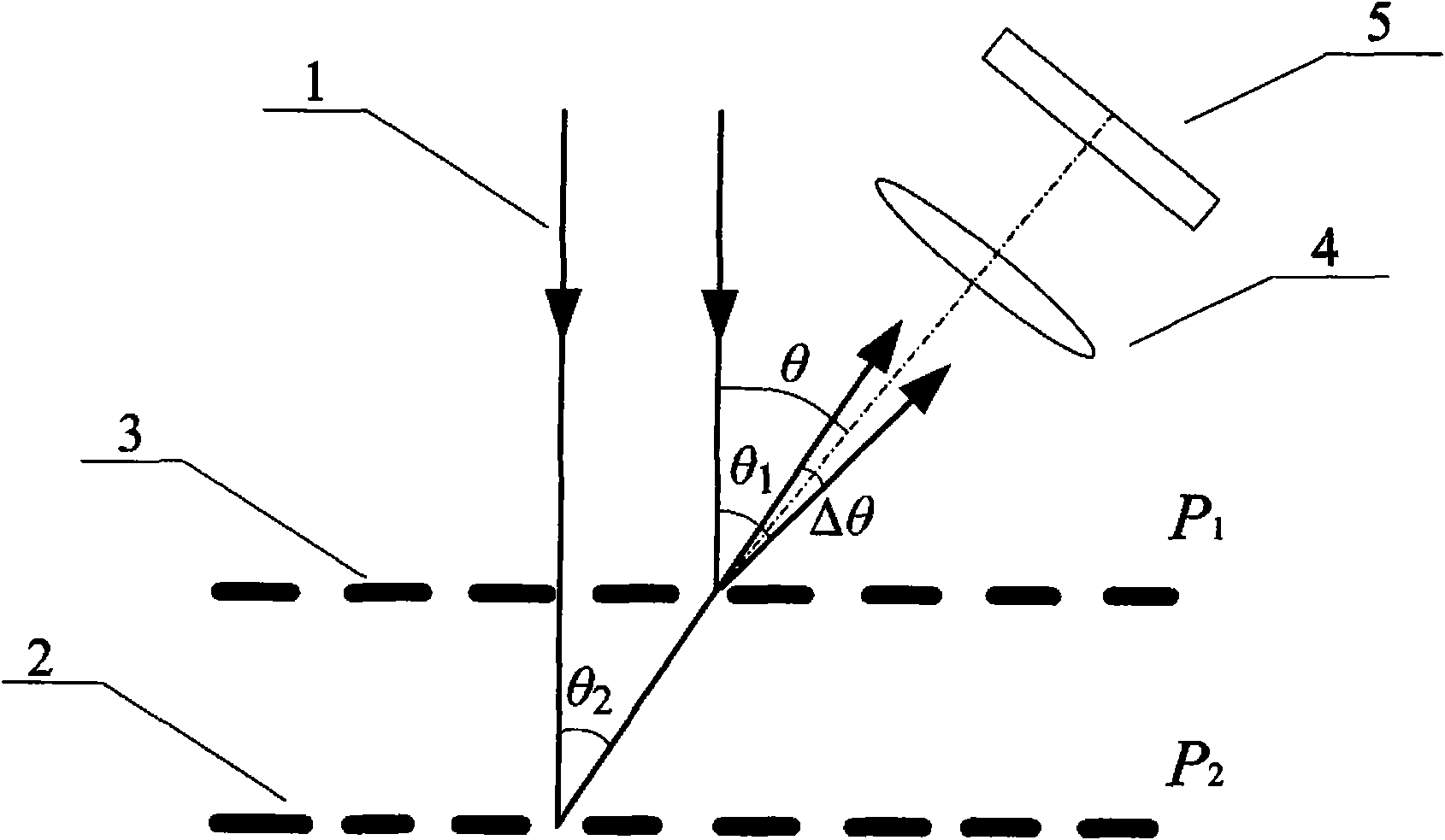

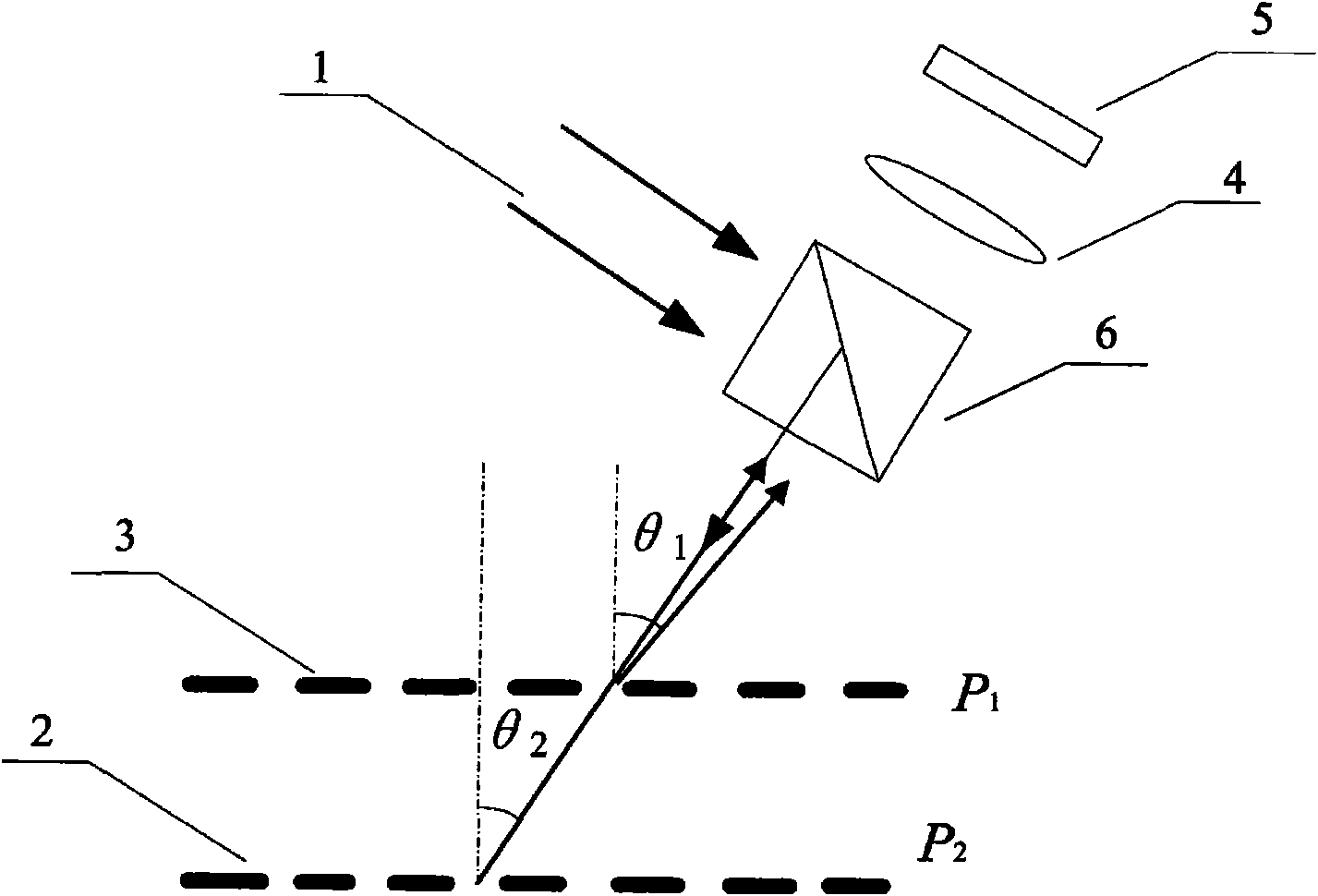

Method for measuring clearance in proximity nanometer lithography

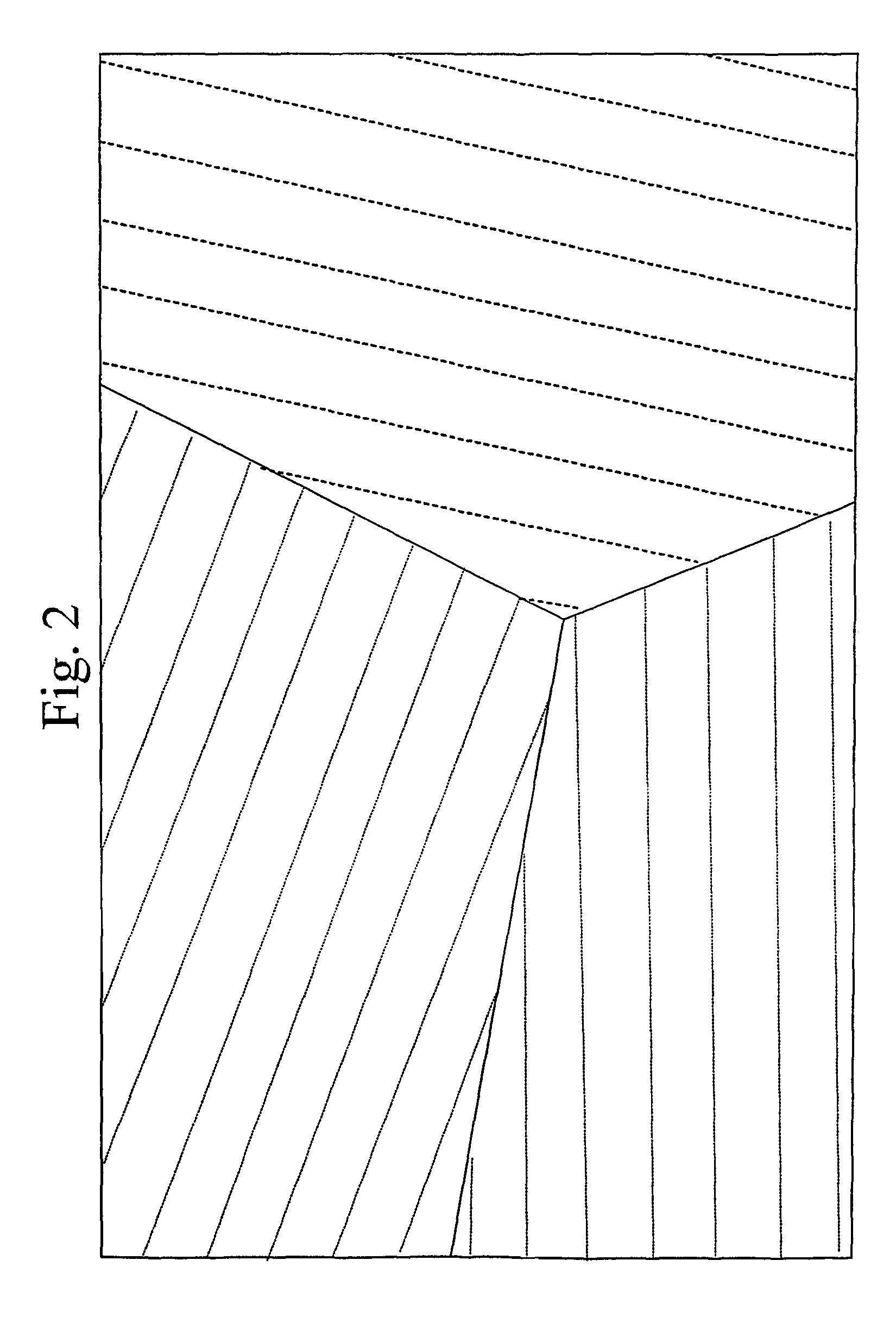

InactiveCN101876538AHigh Sensitivity DetectionHigh measurement accuracyUsing optical meansNanolithographyGrating

The invention discloses a method for measuring clearance in proximity nanometer lithography and mainly aims at the controlling of the clearance of a masking silicon wafer in nanometer manufacturing technology, such as nano-imprint, wave zone plate array imaging and the like. The basic process of the method can be simply explained in the picture 1 that: incident plane waves pass through a silicon wafer gratings and a mask grating and diffract for multiple times, wherein the two periods of the gratings are approximate and the two gratings are overlapped with a certain gap; two beams of lateral diffracted light from the two gratings interfere with each other and are superposed, and form Moire interference fringes of which the period is amplified relative to the conventional gratings on the surfaces of the silicon wafer grating; and the fringes are imaged on a CCD image detector through an objective lens with certain multiplying power. The change of the gap between the two gratings causes the change of optical path difference of the two beams and then causes the change of the movement or phases of the interference fringes so that the aim of measuring the gap is fulfilled; the more approximate the period is, the higher the sensitivity of the measurement is; and, at the same time, because the periods of the two gratings are approximate, the included angle between the lateral diffracted light is very small, the frequency of the interference fringes is very low (namely, the period is long), and the requirement on the numerical aperture of the objective lens is low. With the development of microfabrication technology, the machining accuracy of the grafting is higher and the method has great significance for gap measurement in proximity nanometer lithography and the related field.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

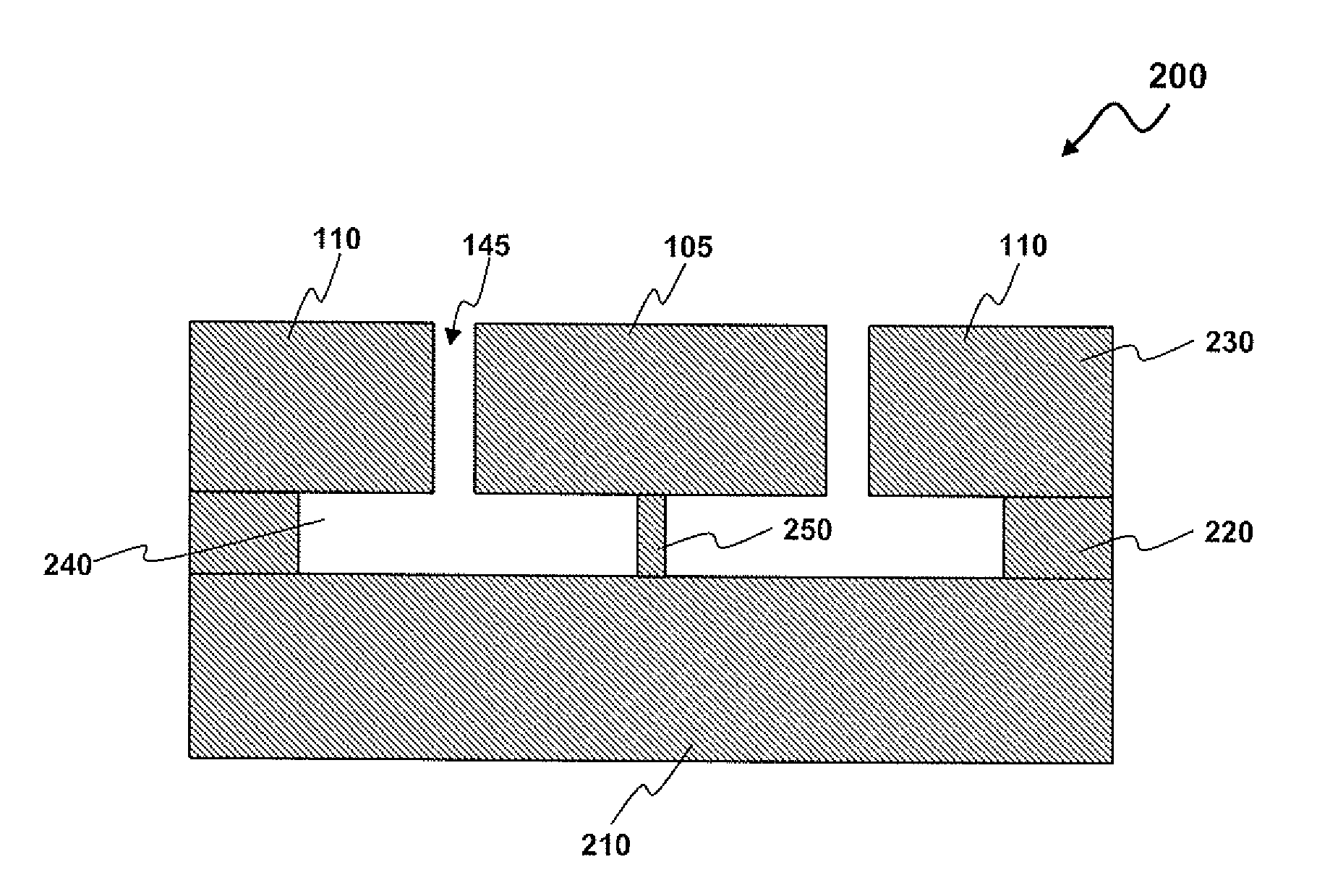

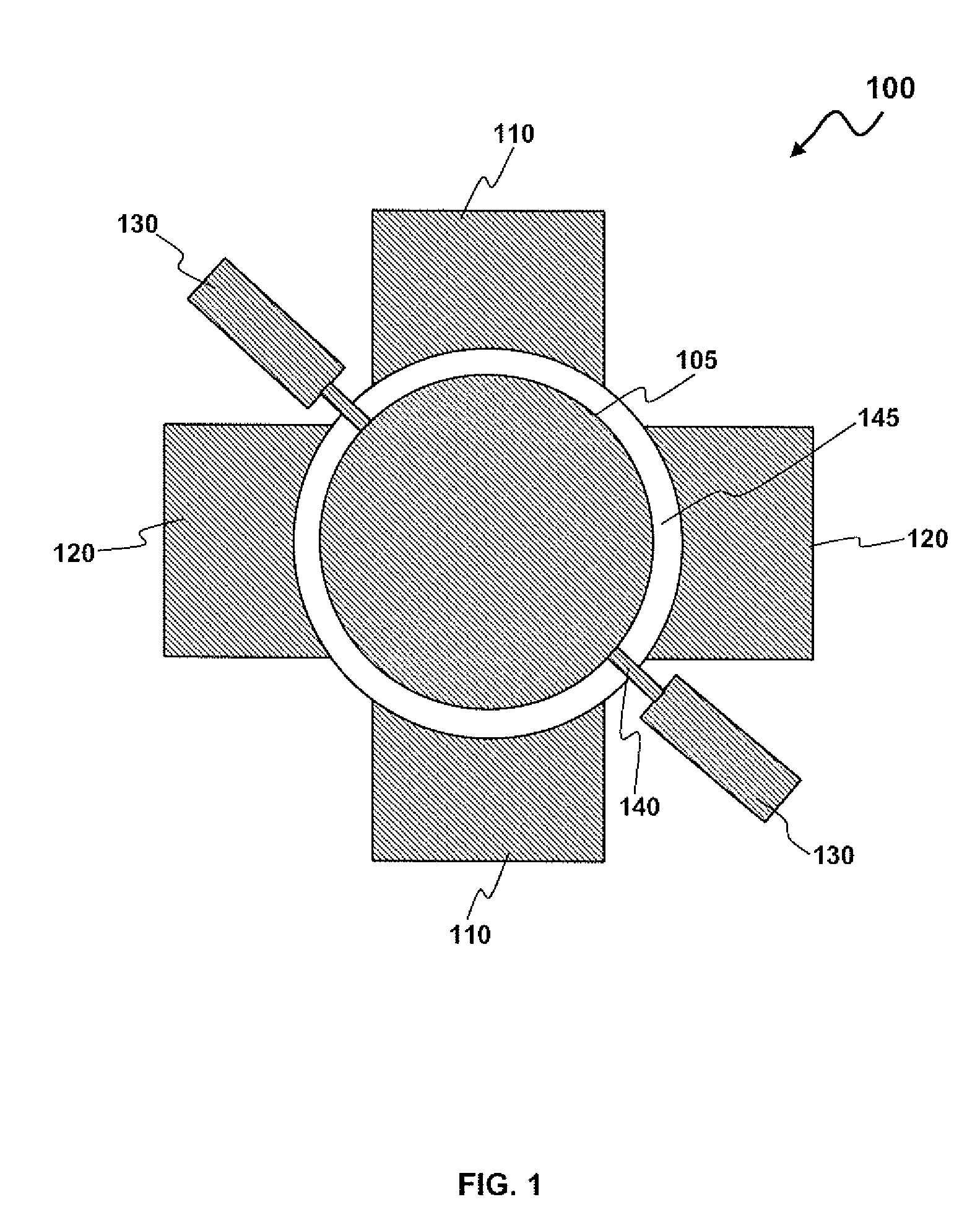

High-q disk NANO resonator device and method of fabricating the same

InactiveUS20090315644A1High quality factorReduce air dampingImpedence networksSemiconductor/solid-state device manufacturingResonanceNanomanufacturing

A nanoresonator device with high quality factor and method for fabricating the same is disclosed herein. The nanoresonator device generally includes an input electrode, an output electrode, a nanoresonator anchored at its motionless nodal points of its resonance modes by support beam(s) and / or anchor. The nanoresonator device can be fabricated on various wafers including a silicon on insulator (SOI) wafer, which includes an insulating layer and a heavily doped silicon layer. The nano structures with high quality factor can be patterned on a film utilizing nano fabrication tools and the patterned structures can be utilized as a mask to form permanent nano structures on the silicon layer by reactive ion etching (RIE). The insulating layer can be removed to form the anchor beams and a cavity by wet etching utilizing an etching solution.

Owner:HONEYWELL INT INC

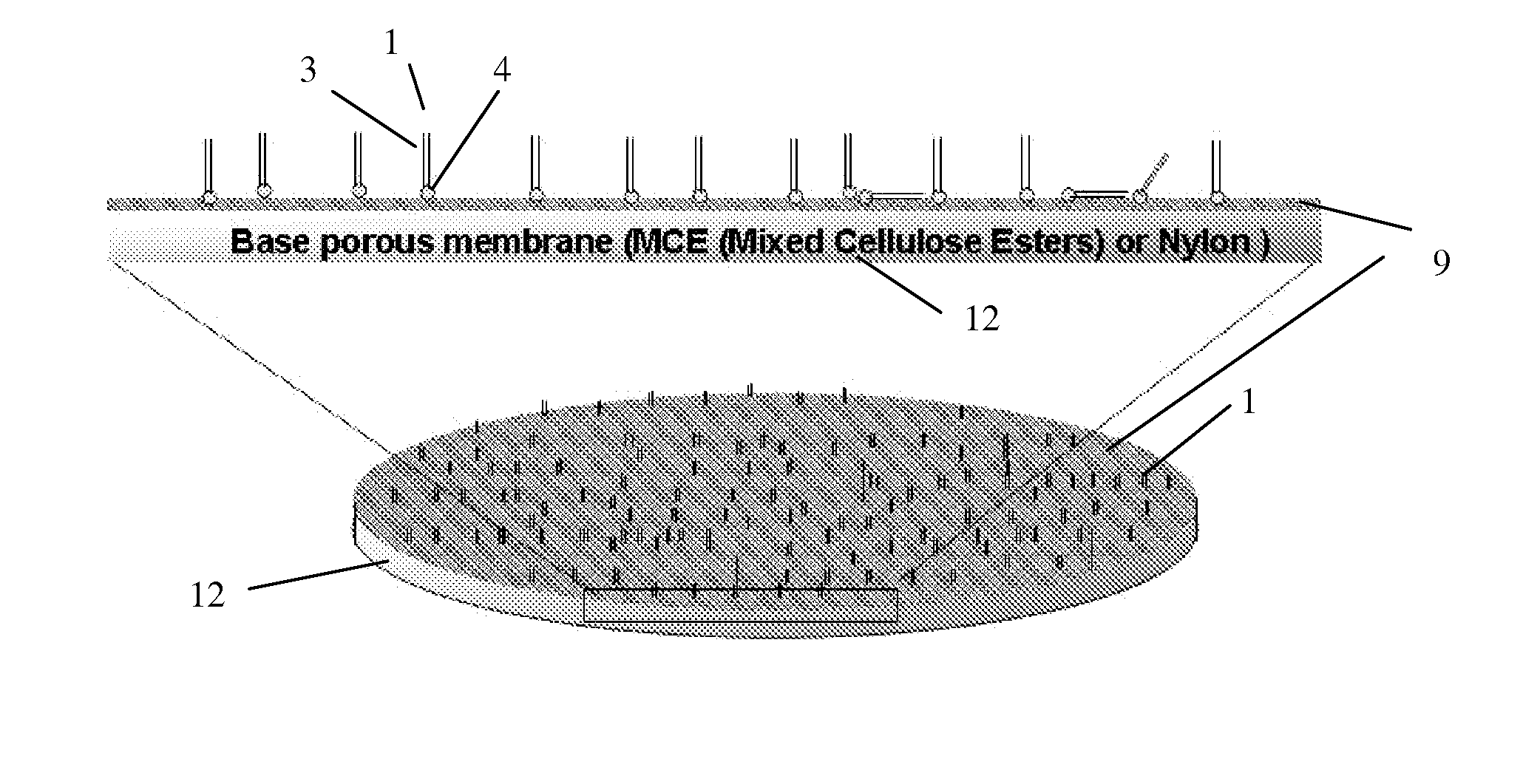

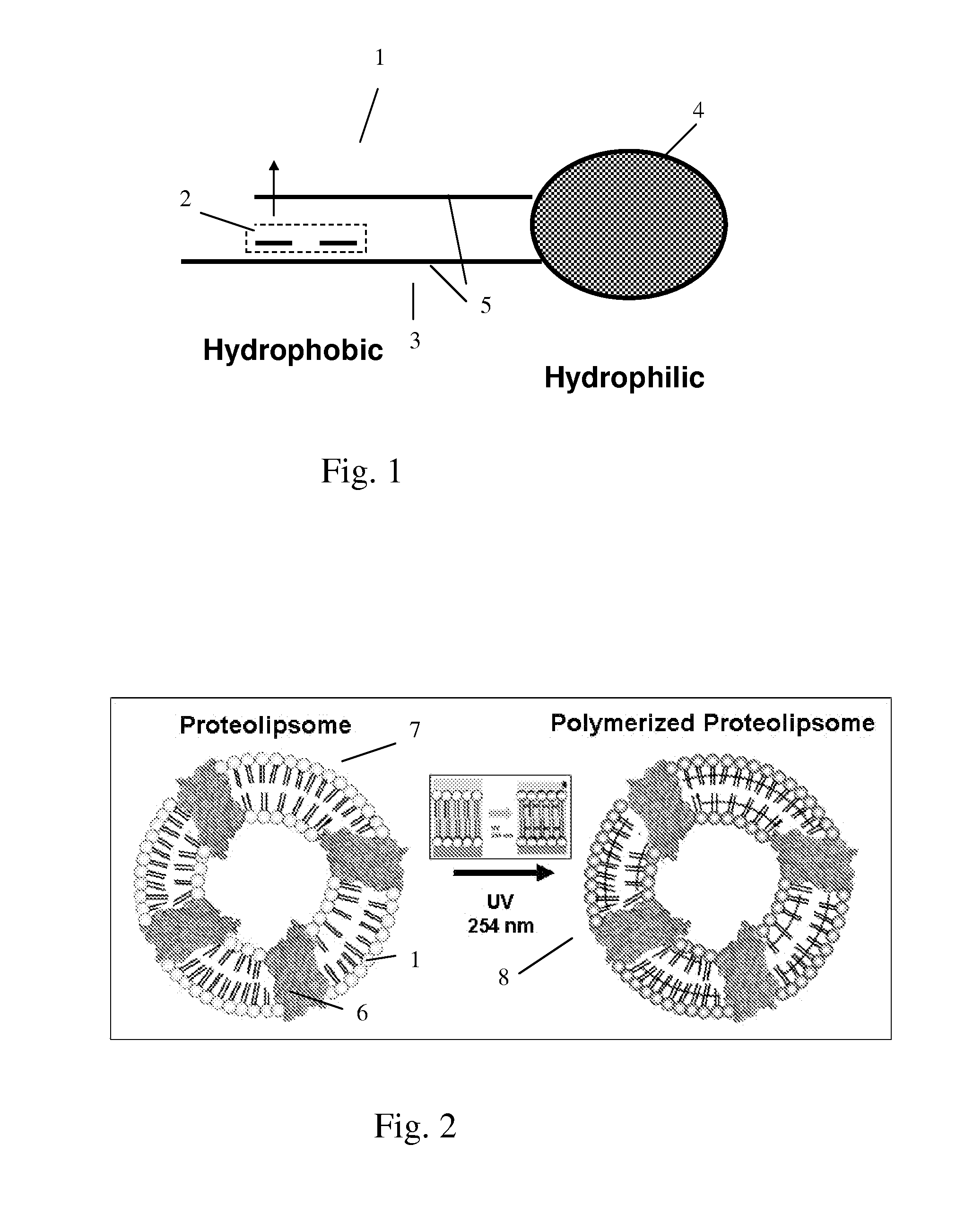

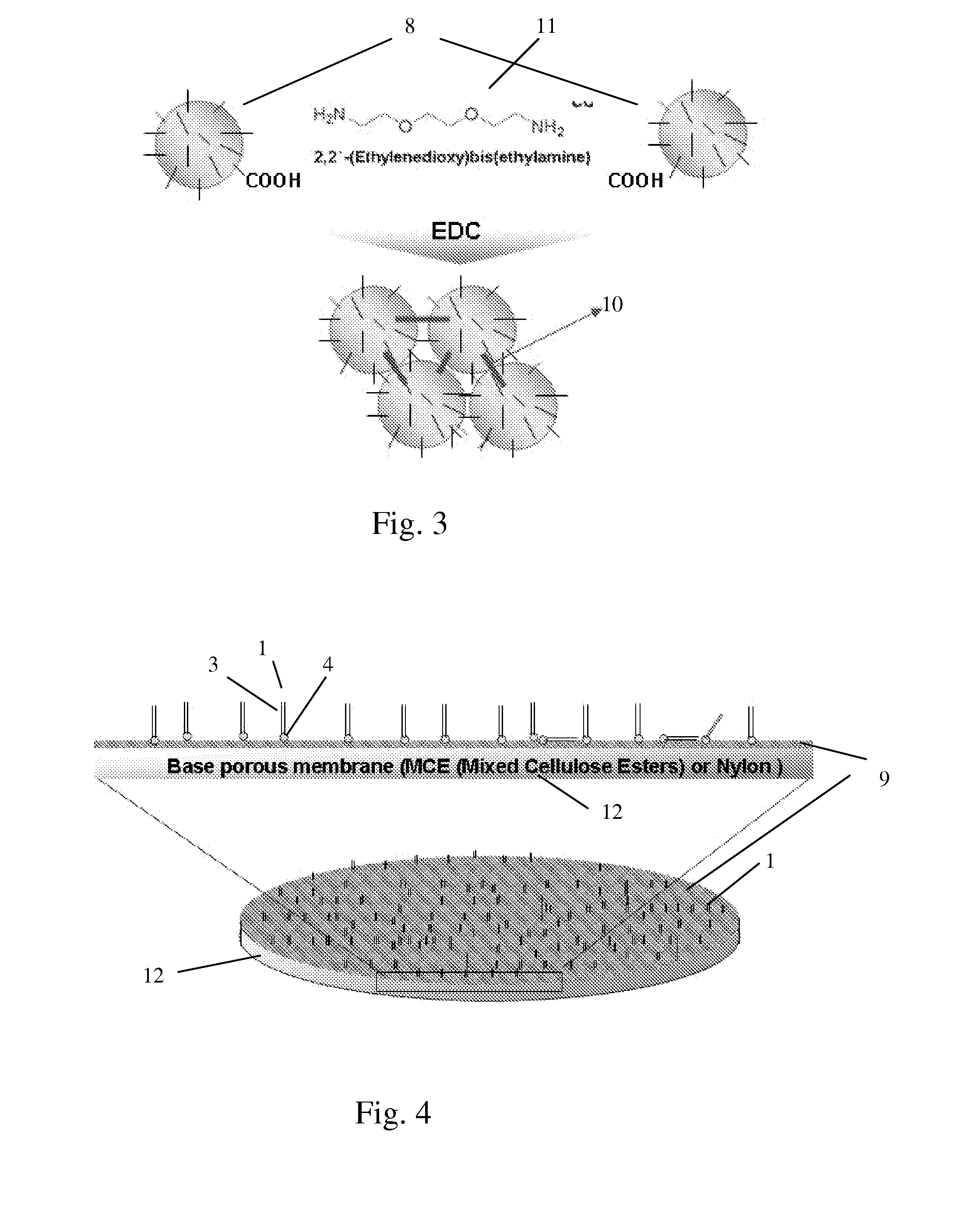

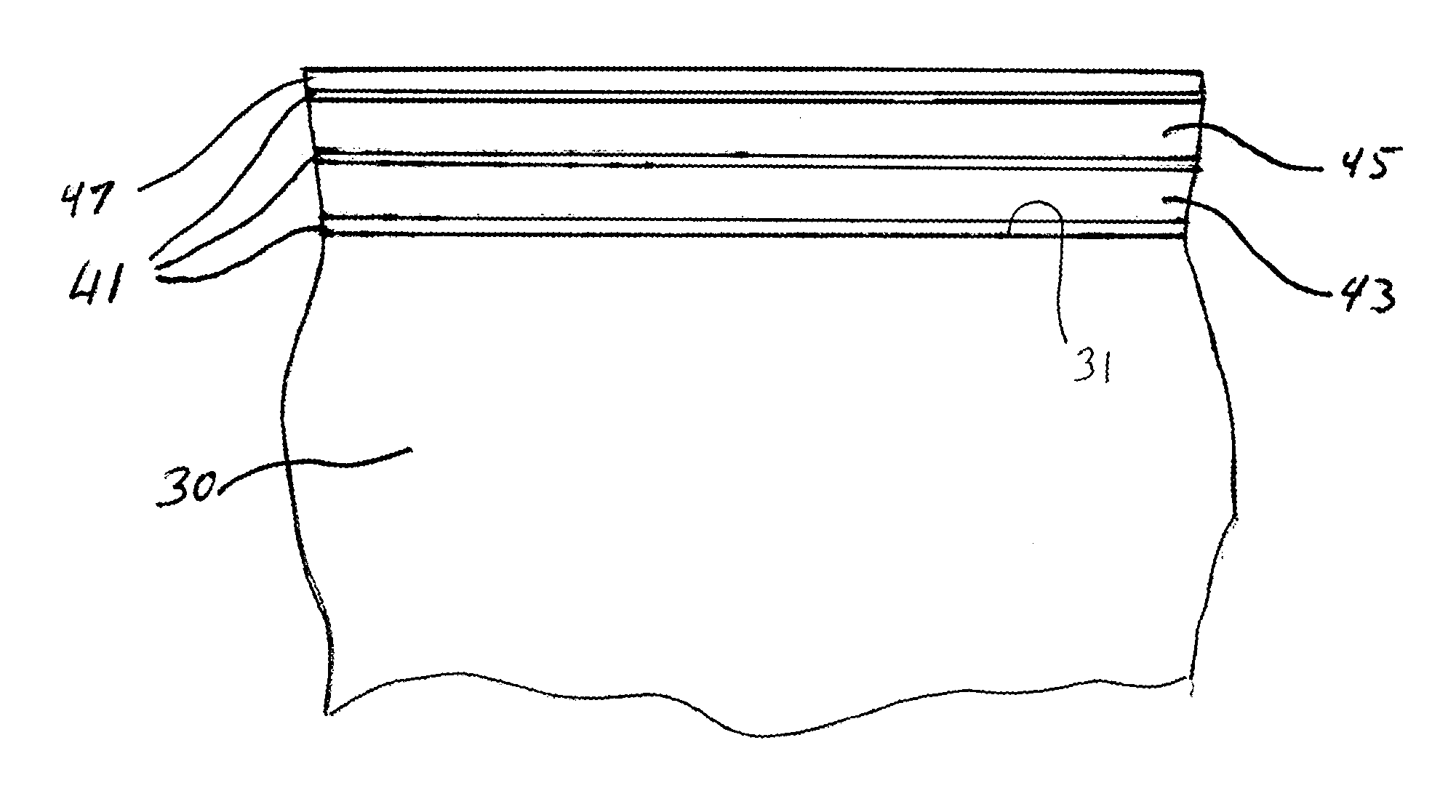

Nanofabricated Membrane Using Polymerized Proteoliposomes

ActiveUS20120043275A1Short lifeReduce resistanceSemi-permeable membranesMembranesChemical reactionUltraviolet

The present invention generally related to a nanofabricated membrane including polymerized proteoliposomes. The nanofabricated membrane is a bio-nano fused selective membrane using protein-incorporated uv-crosslinkable liposomes with a chemical reactive biocompatible interstitial matrix. In the present invention, internally UV-crosslinked protein-incorporated proteolipsomes are used because the proteoliposomes made by natural lipids have a short life time and a weak resistance to the circumstantial stresses such as a high and low temperature, pressure, ionic strength etc. Furthermore, the proteo-vesicles made by amphiphilic block copolymers provide less consistency in accomplishing proper functionality batch to batch because of the inevitable polydiversity of the polymer.

Owner:APPL BIOMIMETIC AS

Nanocontact printing

InactiveUS7862849B2Constant production of mastersMaterial nanotechnologySugar derivativesNanomanufacturingSelf-assembly

A method of stamping of molecular patterns and / or devices based on the reversible self-assembly of molecules, particularly organic molecules is disclosed. This method is suitable for the stamping of almost any nanofabricated device and can be used to transferring a large amount of pattern information from one substrate to another at the same time.

Owner:MASSACHUSETTS INST OF TECH

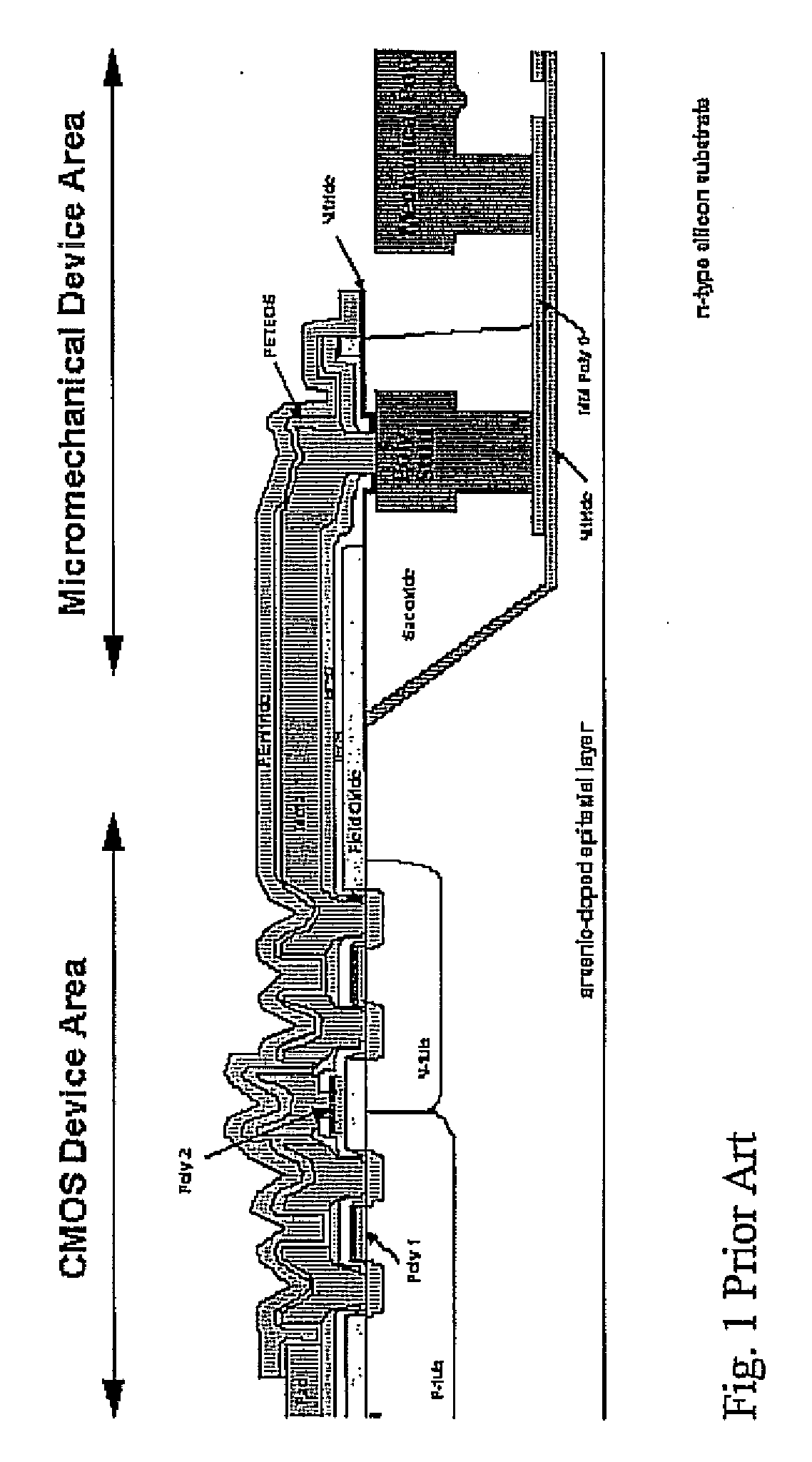

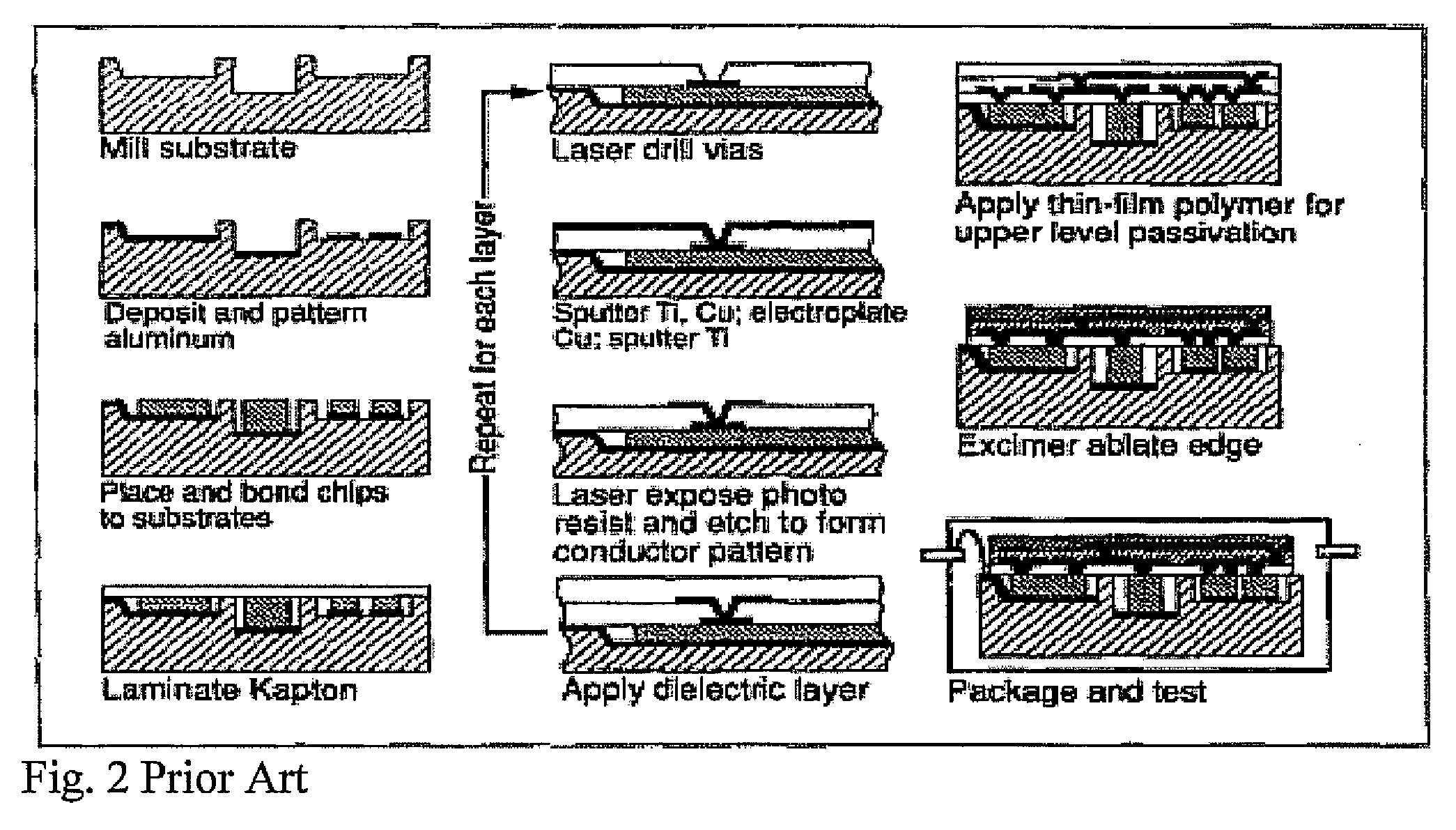

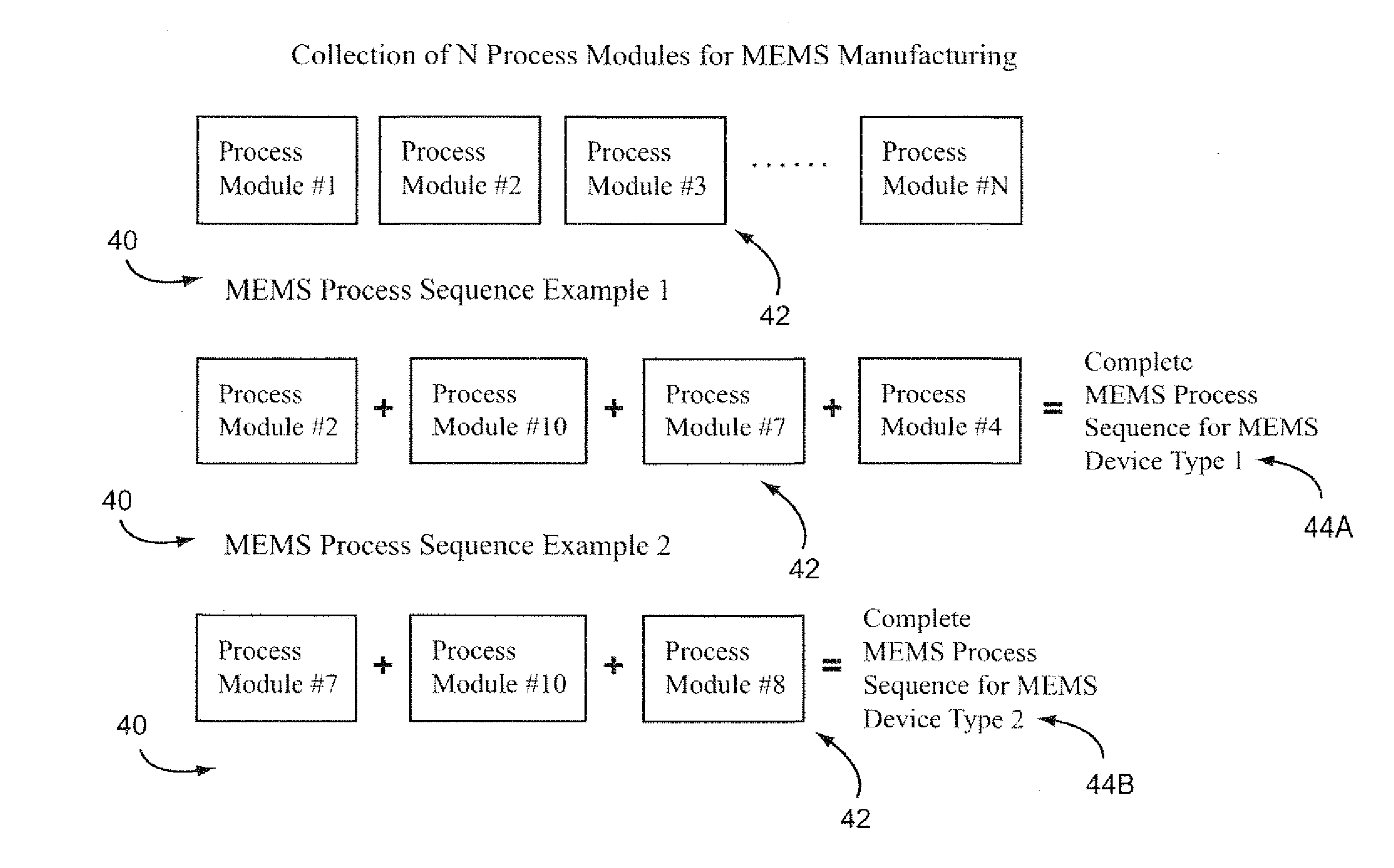

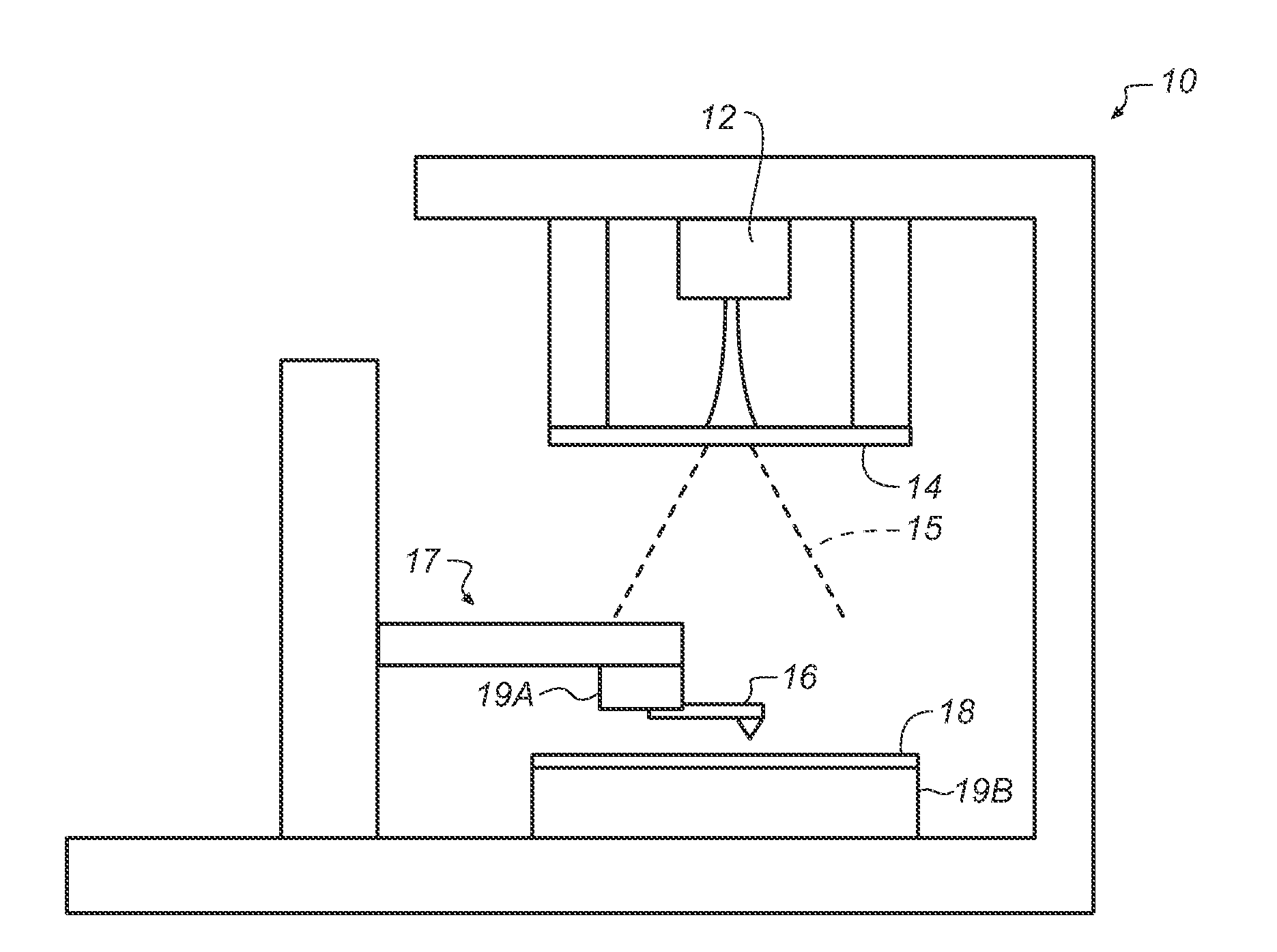

Method of fabricating mems, nems, photonic, micro- and nano-fabricated devices and systems

ActiveUS20110250706A1Low costFaster rateSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingProcess moduleComputer module

An improved method for the fabrication of Micro-Electro-Mechanical Systems (MEMS), Nano-Electro-Mechanical Systems (NEMS), Photonics, Nanotechnology, 3-Dimensional Integration, Micro- and Nano-Fabricated Devices and Systems for both rapid prototyping development and manufacturing is disclosed. The method includes providing a plurality of different standardized and repeatable process modules usable in fabricating the devices and systems, defining a process sequence for fabricating a predefined one of the devices or systems, and identifying a series of the process modules that are usable in performing the defined process sequence and thus in fabricating the predefined device or system.

Owner:FOR NAT RES INITIATIVES

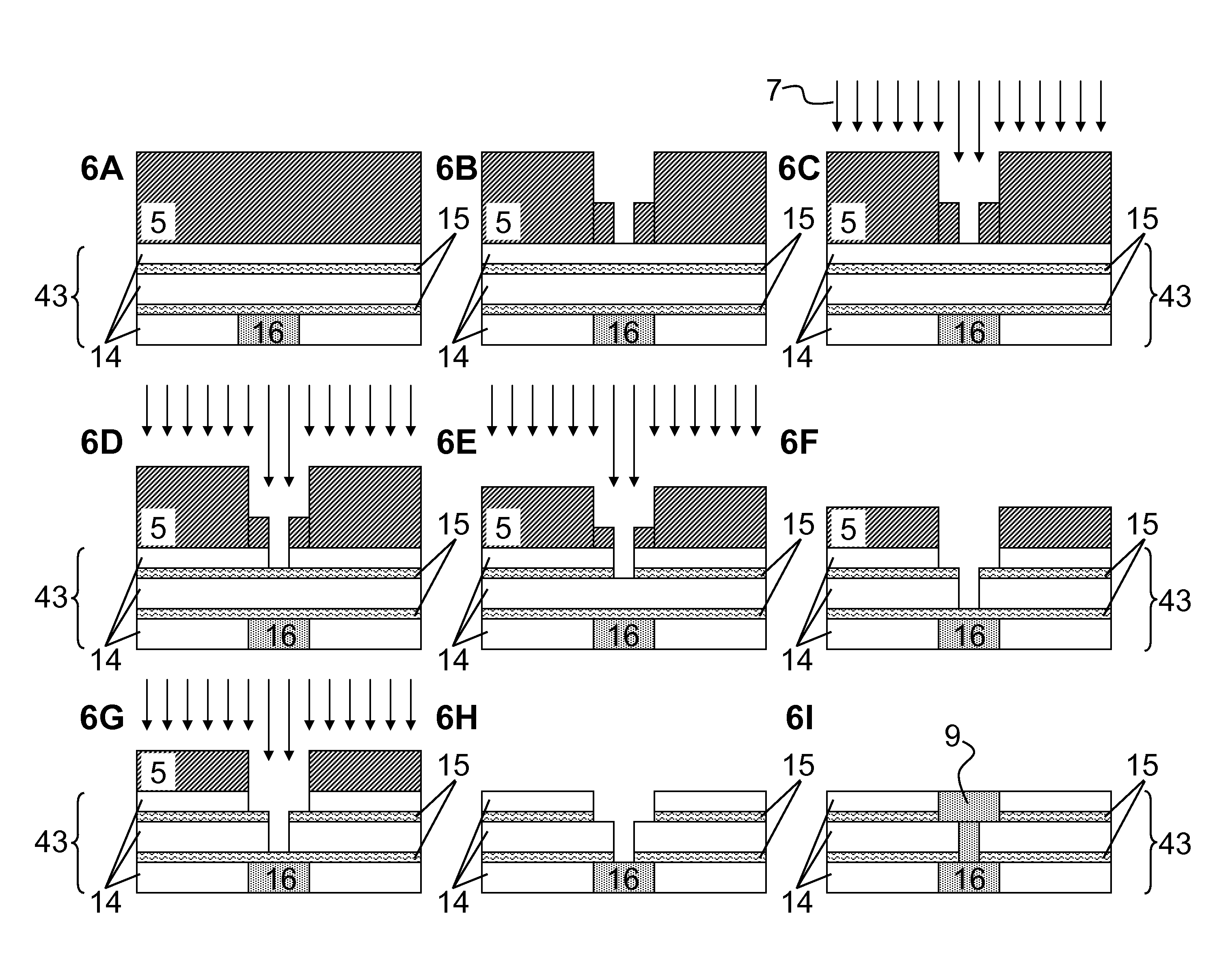

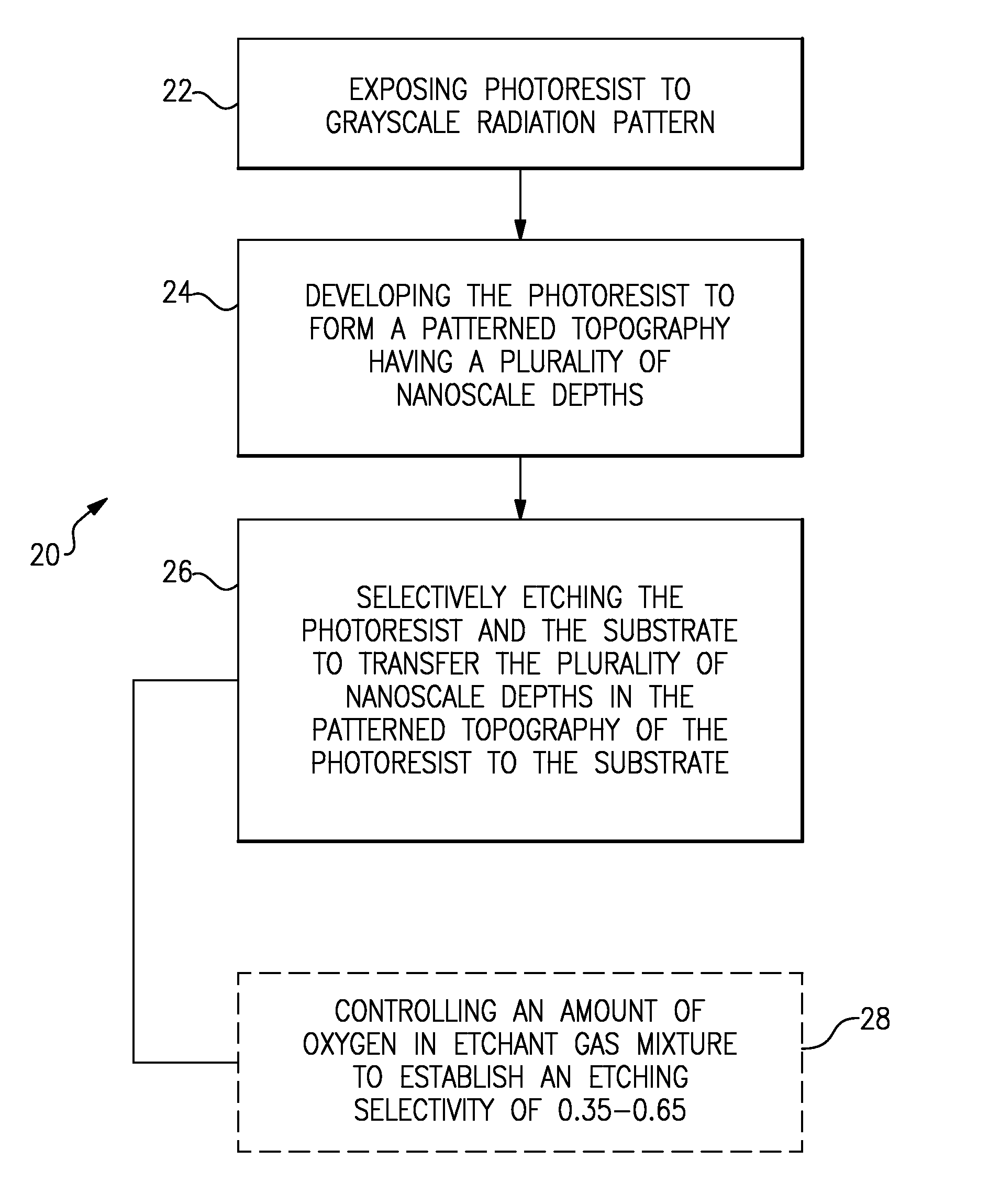

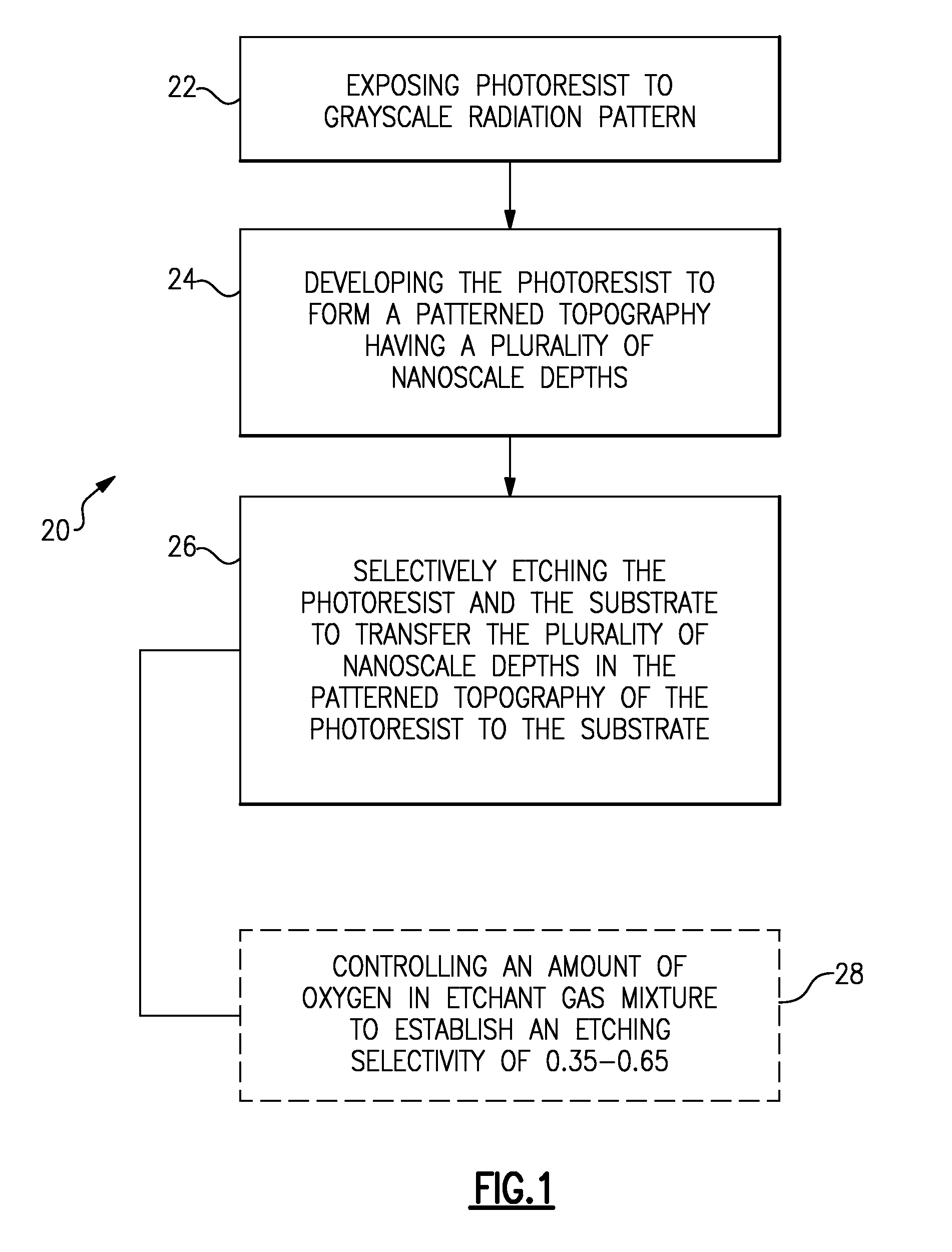

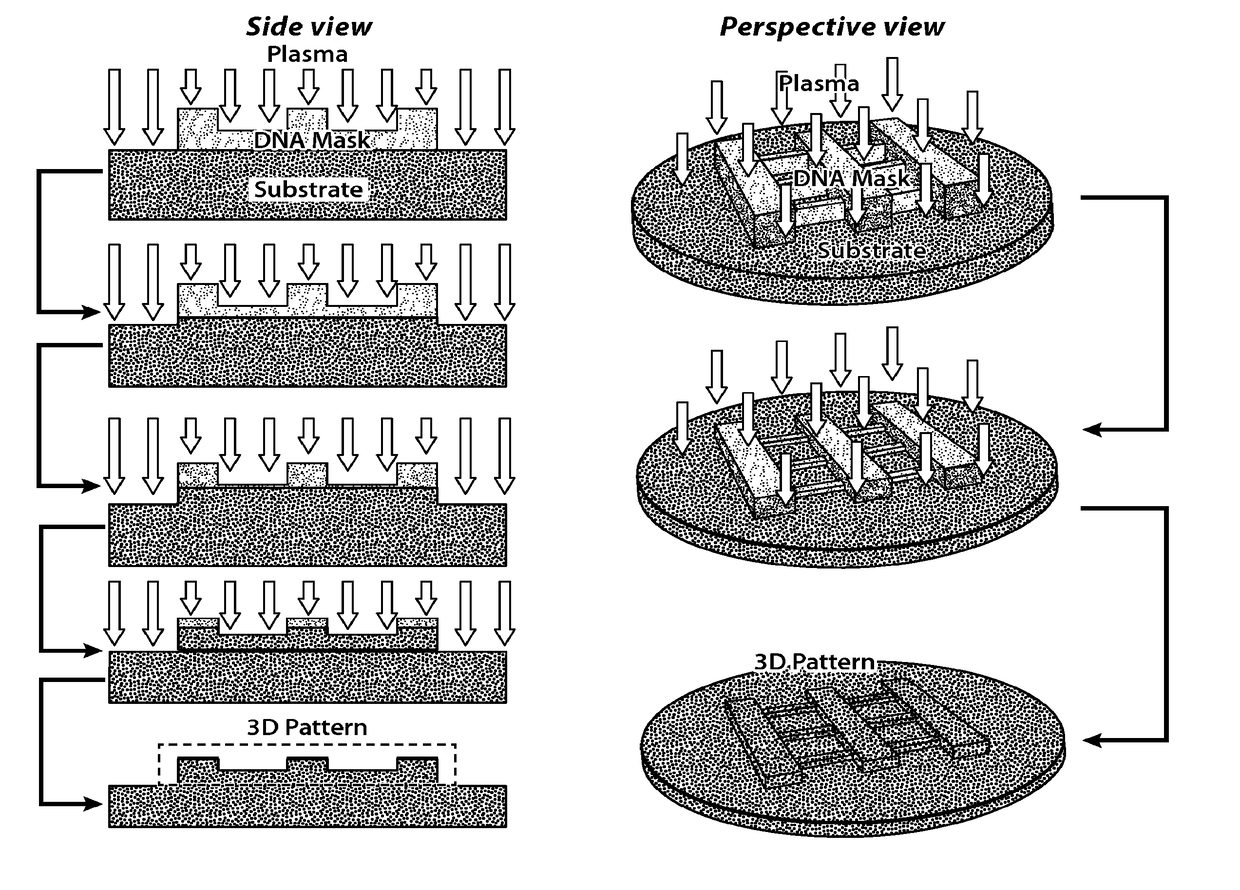

Nanofabrication process and nanodevice

ActiveUS20110123771A1Material nanotechnologyFixed microstructural devicesResistComputational physics

A nanofabrication process for use with a photoresist that is disposed on a substrate includes the steps of exposing the photoresist to a grayscale radiation pattern, developing the photoresist to remove a irradiated portions and form a patterned topography having a plurality of nanoscale critical dimensions, and selectively etching the photoresist and the substrate to transfer a corresponding topography having a plurality of nanoscale critical dimensions into the substrate.

Owner:CORNELL UNIV CORNELL CENT FOR TECH ENTERPRISE & COMMLIZATION CCTEC

Method for designing polypeptides for the nanofabrication of thin films, coatings and microcapsules by electrostatic layer-by-layer self assembly

ActiveCN101421416AReliable controlImprove utilizationPeptide-nucleic acidsMaterial nanotechnologyLayer by layer self assemblyNanomanufacturing

A method for designing polypeptides for the nanofabrication of thin films, coatings, and microcapsules by ELBL for applications in biomedicine and other fields.

Owner:路易斯安那科技大学基金会

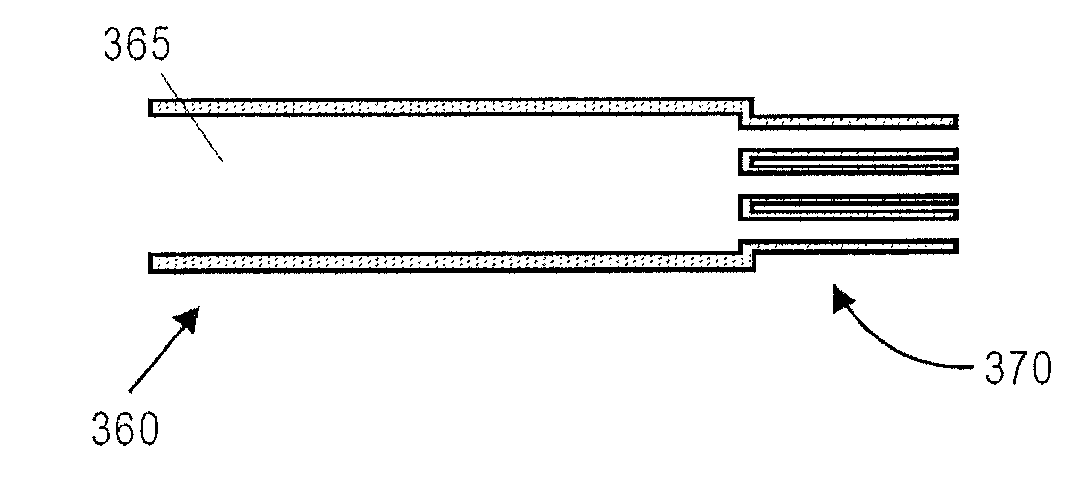

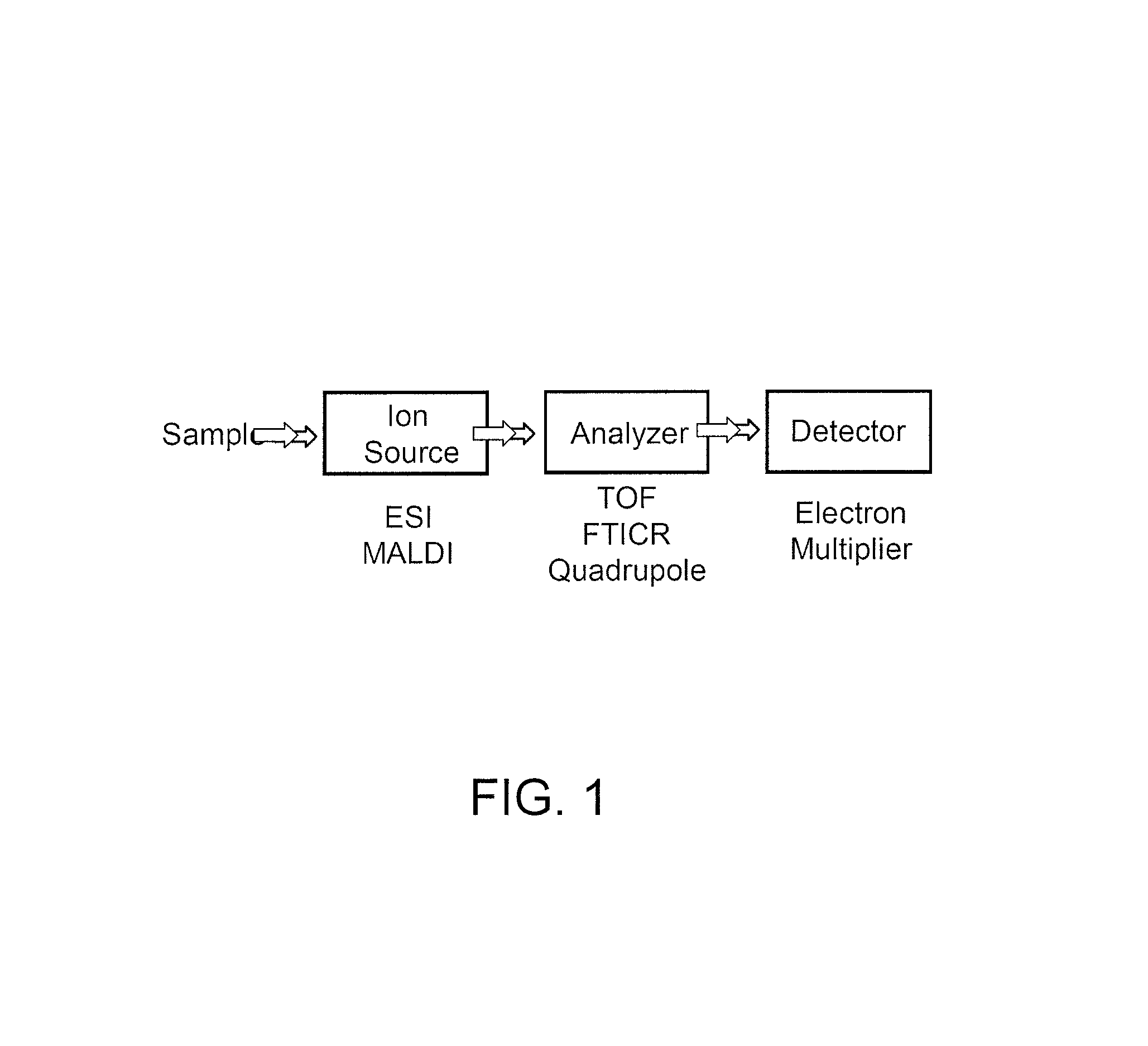

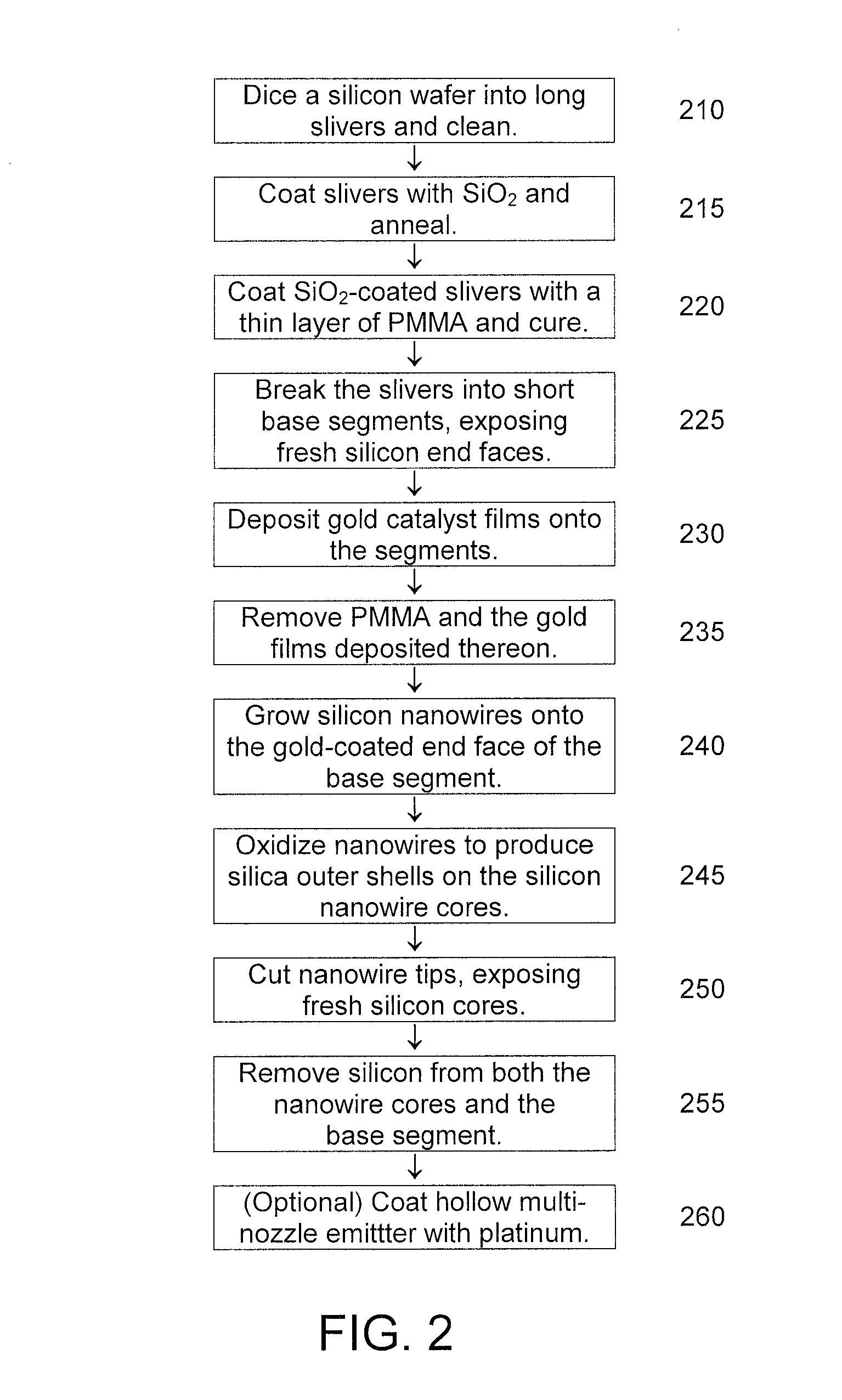

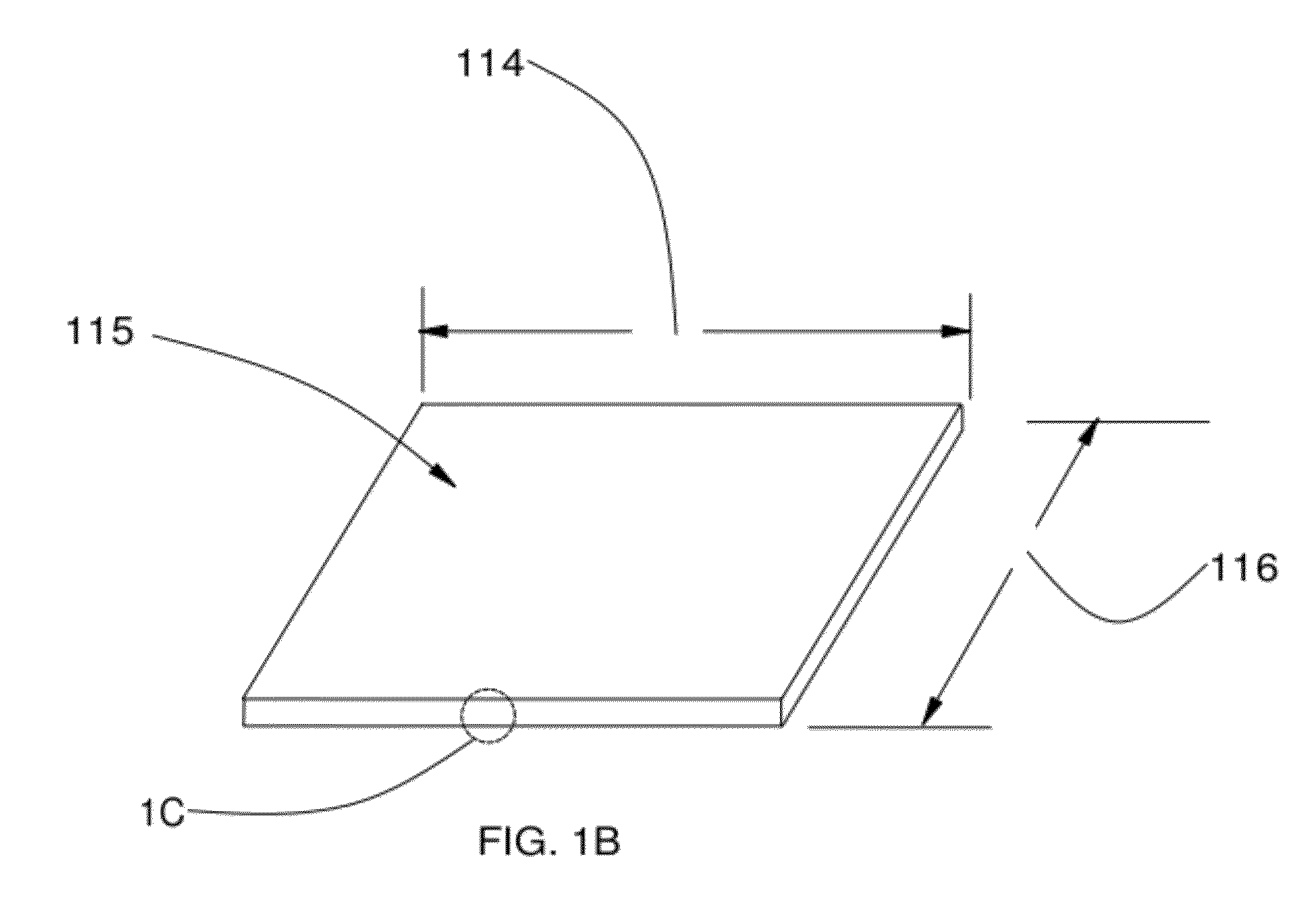

Monolithic multinozzle emitters for nanoelectrospray mass spectrometry

ActiveUS8022361B2Promote formationPossibility for surface functionalizationBurnersParticle separator tubesMass Spectrometry-Mass SpectrometrySilicon nanowires

Novel and significantly simplified procedures for fabrication of fully integrated nanoelectrospray emitters have been described. For nanofabricated monolithic multinozzle emitters (NM2 emitters), a bottom up approach using silicon nanowires on a silicon sliver is used. For microfabricated monolithic multinozzle emitters (M3 emitters), a top down approach using MEMS techniques on silicon wafers is used. The emitters have performance comparable to that of commercially-available silica capillary emitters for nanoelectrospray mass spectrometry.

Owner:RGT UNIV OF CALIFORNIA

Design and methods for measuring analytes using nanofabricated device

ActiveUS20180120287A1Microbiological testing/measurementMaterial analysis by electric/magnetic meansNucleobaseNanomanufacturing

Devices for sequencing linear biomolecules (e.g., DNA, RNA, polypeptides, proteins, and the like) using quantum tunneling effects, and methods of making and using such devices, are provided. A nanofabricated device can include a small gap formed by depositing a thin film between two electrodes, and subsequently removing the film using an etching process. The width of the resulting gap can correspond with the size of a linear biomolecule such that when a part of the biomolecule (e.g., a nucleobase or amino acid) is present in the gap, a change in tunneling current, voltage, or impedance can be measured and the part of the biomolecule identified. The gap dimensions can be precisely controlled at the atomic-scale by, for example, atomic layer deposition (ALD) of the sacrificial film. The device can be made using existing integrated circuit fabrication equipment and facilities, and multiple devices can be formed on a single chip.

Owner:ROCHE MOLECULAR SYST INC

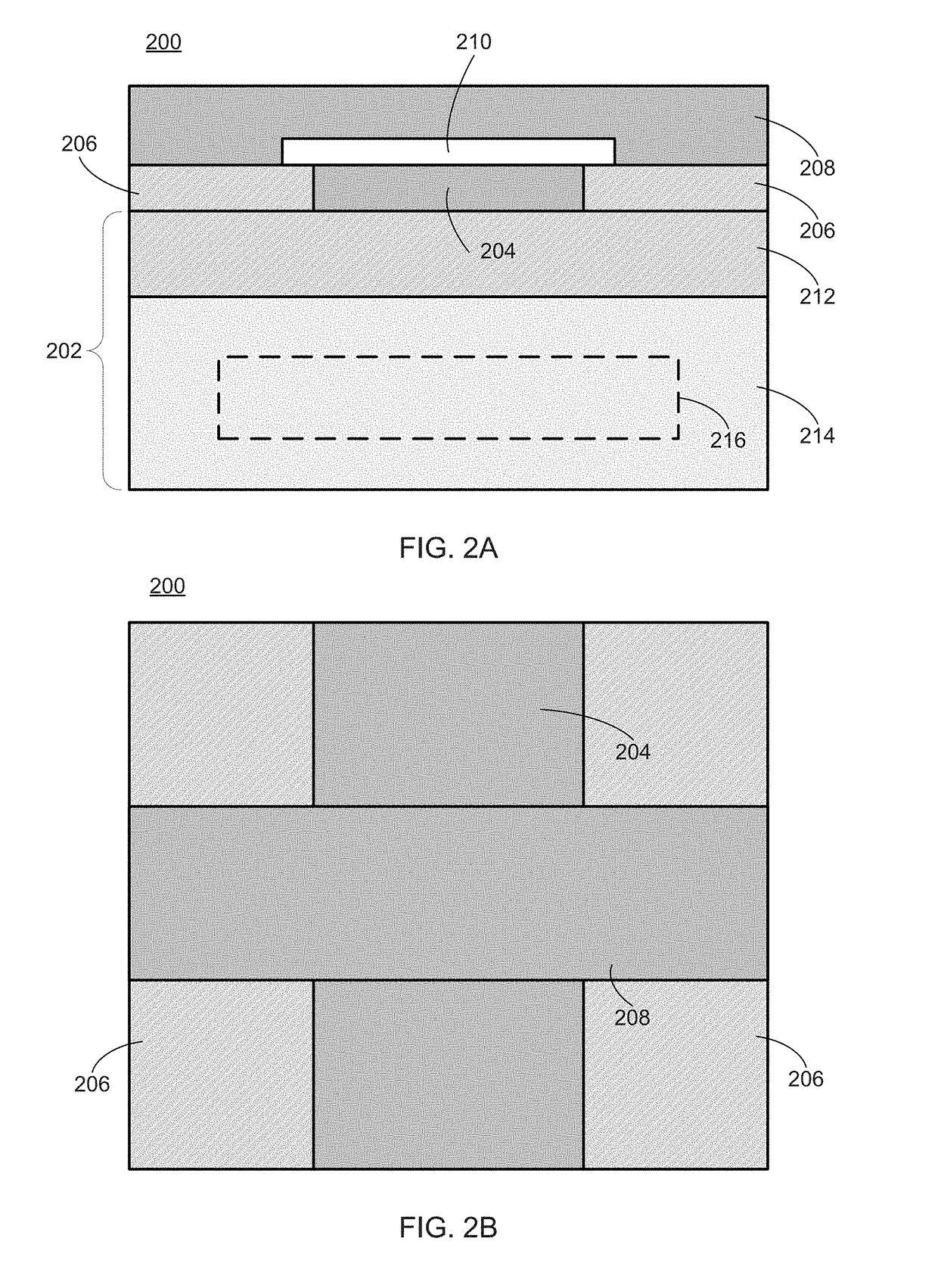

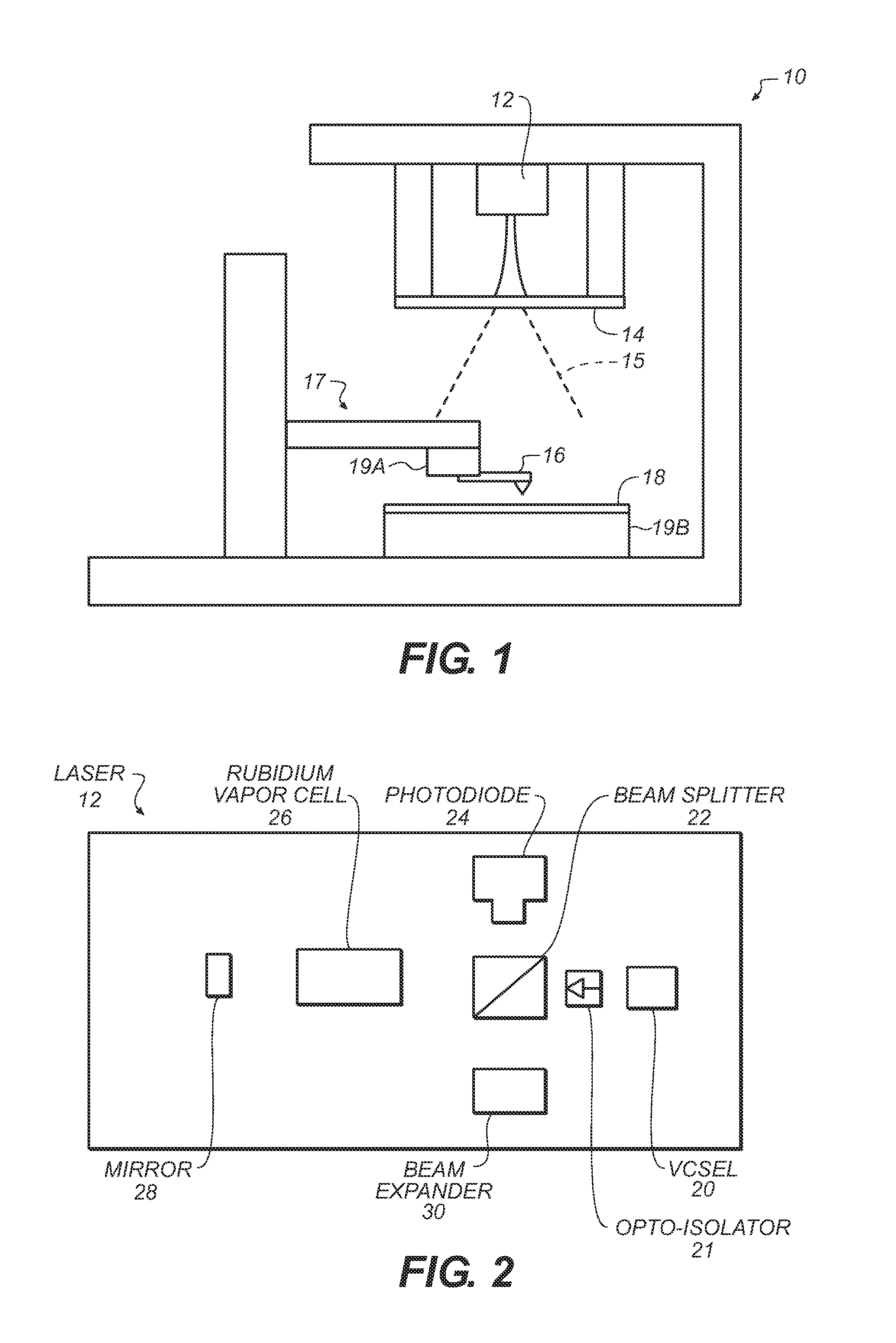

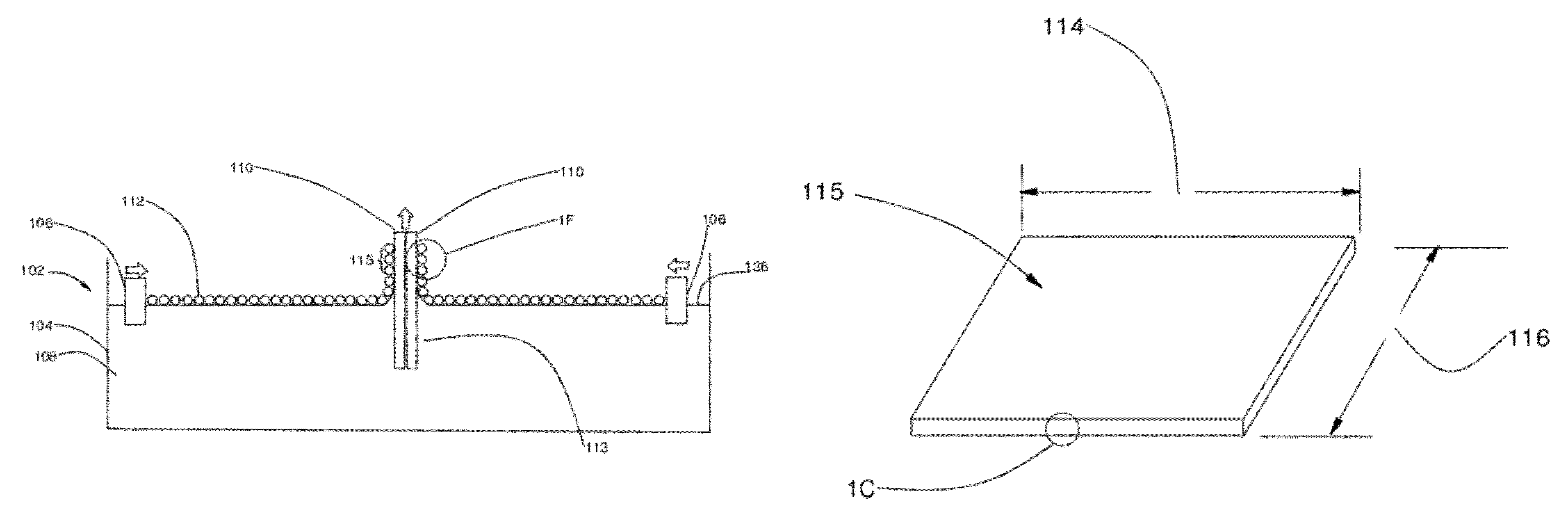

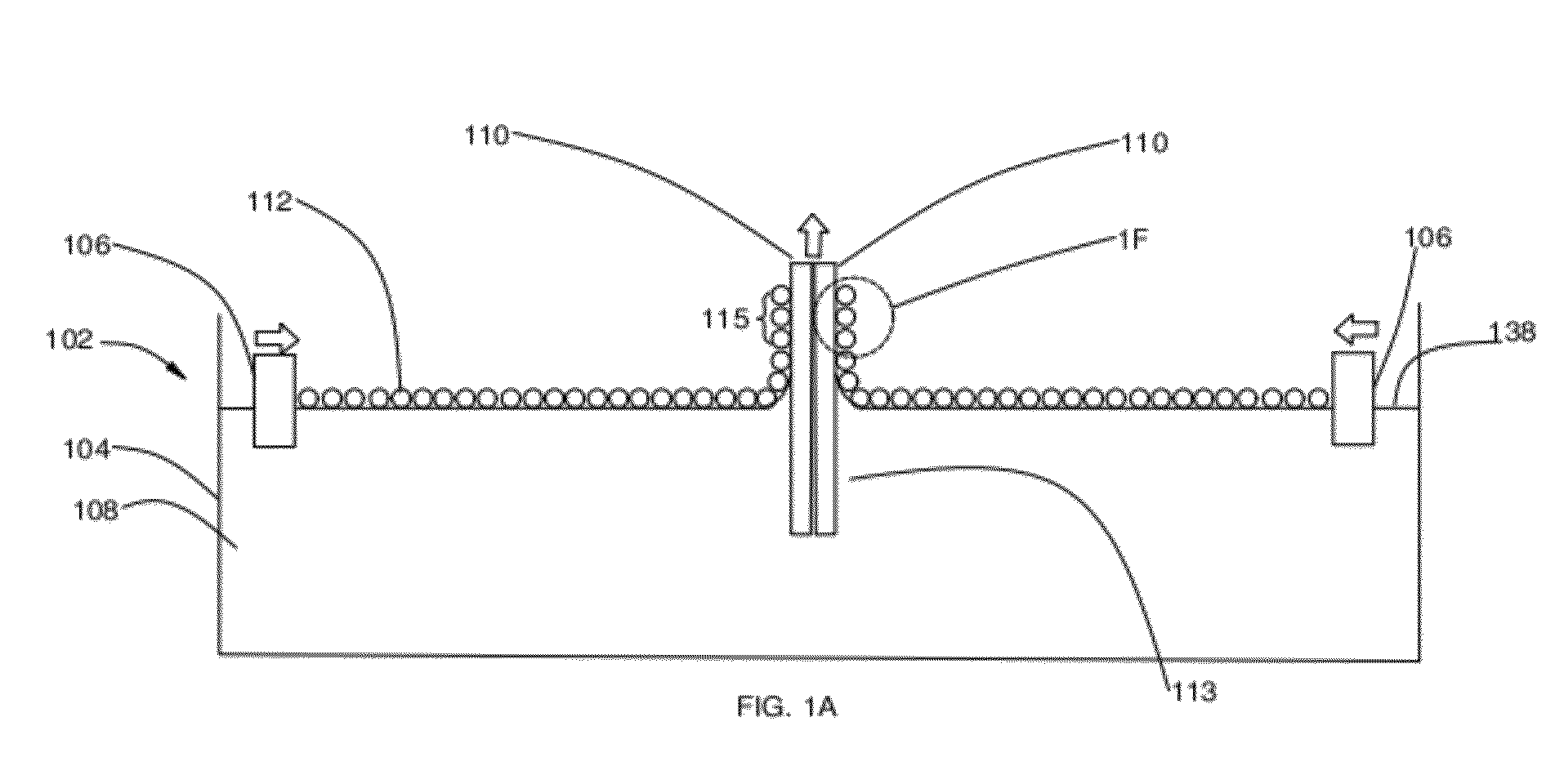

Optical grid for high precision and high resolution method of wafer-scale nanofabrication

ActiveUS20110249275A1Improve accuracyHigh resolutionNanoinformaticsPhotomechanical apparatusSensor arrayLaser transmitter

A wafer-scale nano-metrology system (10) for sensing position of a nanofabrication element (16) when illuminated by a patterned optical projection defining a grid or position measuring gauge includes a frequency stabilized laser emitter (12) configured to generate a laser emission at a selected frequency, where the laser emission forms a diverging beam configured to illuminate a selected area occupied by a target fabrication object (18) having a proximal surface. An optical pattern generator (14) is illuminated by laser (12) and generates a patterned optical projection grid or gauge for projection upon the target fabrication object (18). A movable tool or nanofabrication element (16) carries an optical sensor array (50), and the sensor array detect at least a portion of the optical projection grid, and, in response to that detection, generates grid position data for use in controlling the position of the tool (16).

Owner:CORNELL UNIVERSITY

Sensor system with plasmonic nano-antenna array

ActiveUS8462334B2Increase heightRapid and sensitive chemical/biological agent detectionMaterial nanotechnologyLiquid surface applicatorsSystems designEngineering

In order to provide the high sensitivity SERS active substrates needed for rapid and sensitive chemical / biological agent detection, the present invention provides a Plasmonic Nano-antenna Array (PNA) substrate with large local electromagnetic field enhancements; a controllable and repeatable nano-fabrication process for creating the PNA surface; and a system design for a compact, portable device capable of using the PNA technology to acquire and analyze target molecular samples. Both 2D and 3D systems are provided.

Owner:LU WEIXING +1

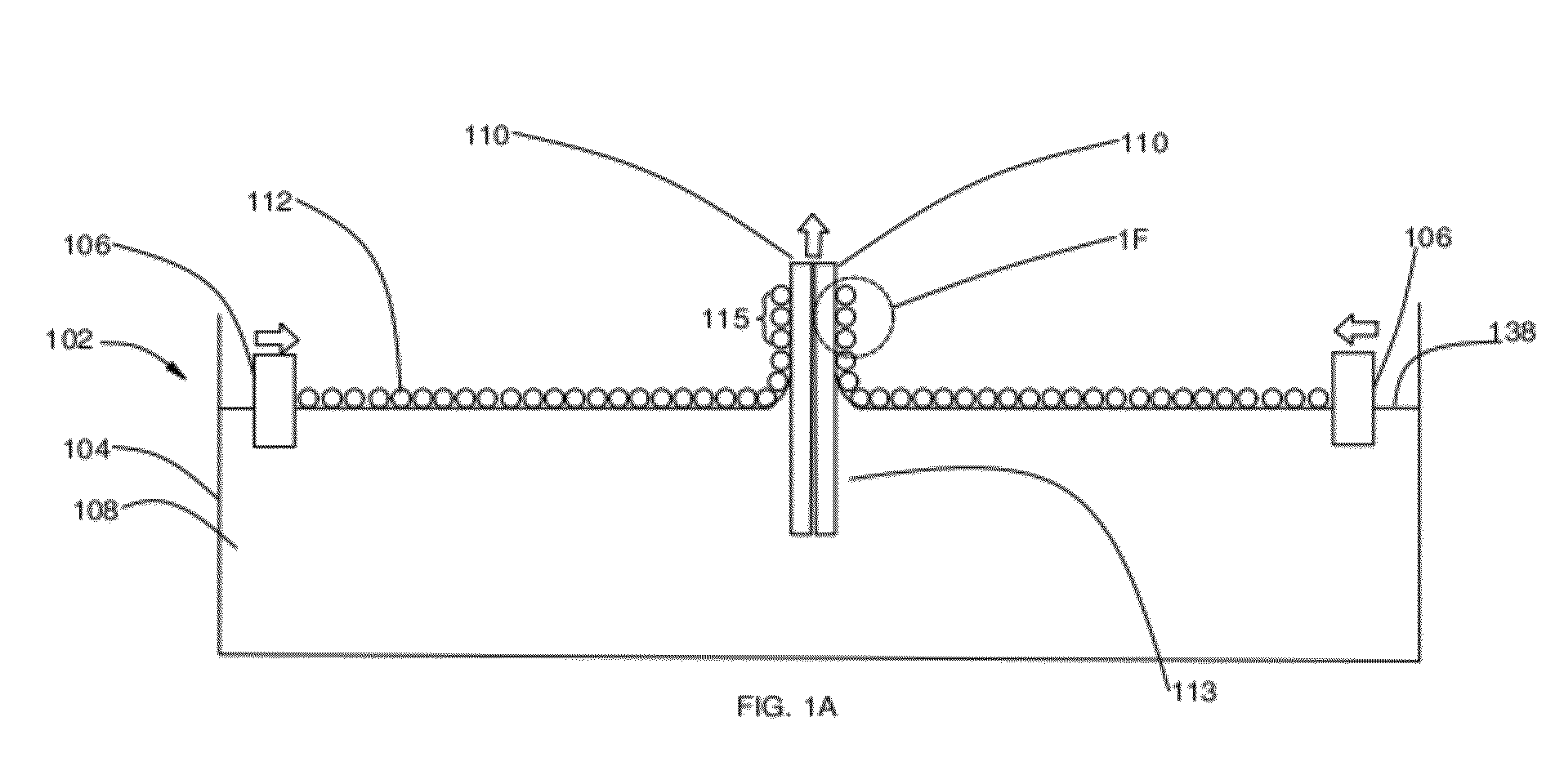

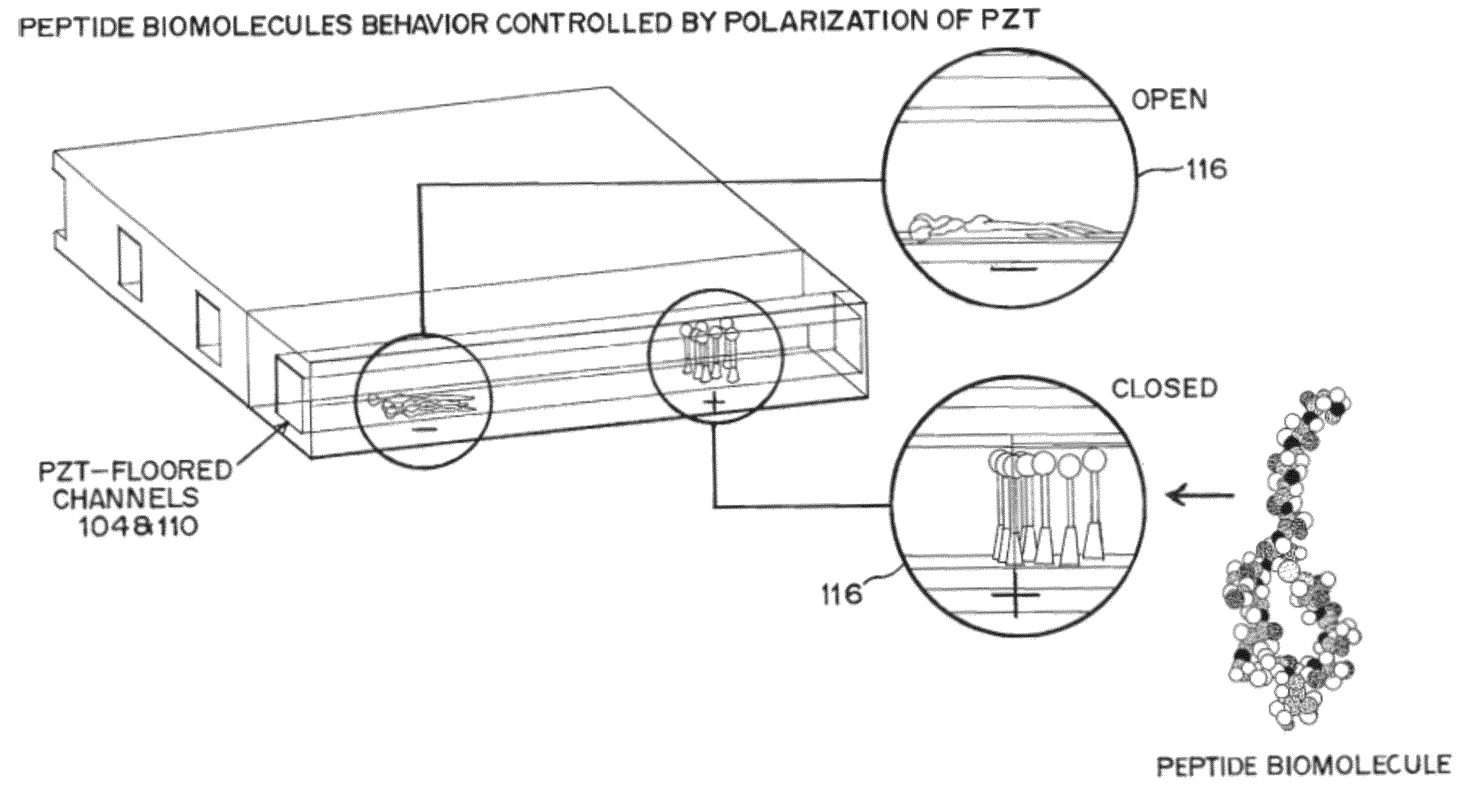

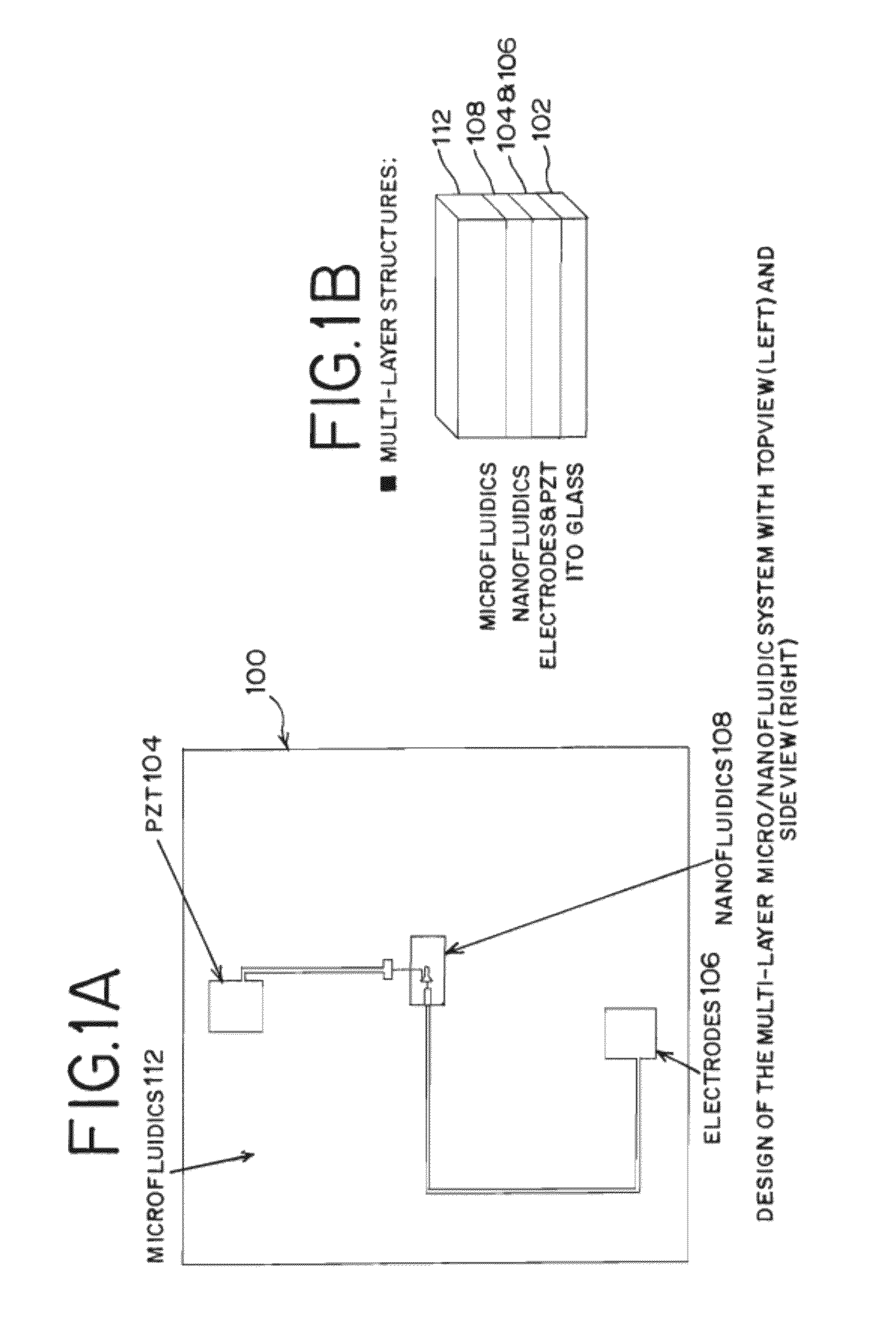

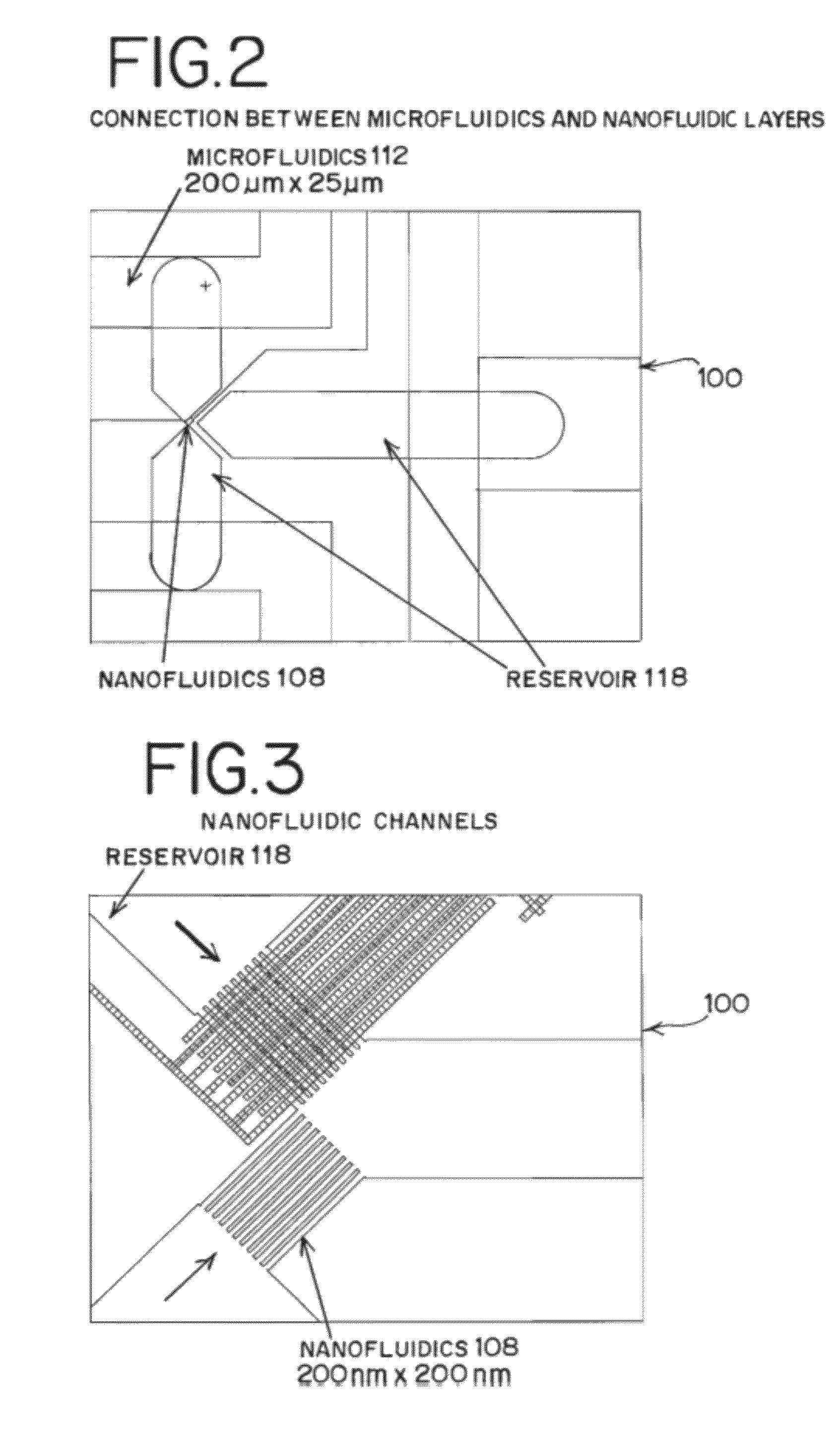

Multi-layer micro/nanofluid devices with bio-nanovalves

InactiveUS8343425B1Economical and effective and efficientPromote resultsRadiation applicationsCircuit elementsLead zirconate titanateMicrofluidics

A user-friendly multi-layer micro / nanofluidic flow device and micro / nano fabrication process are provided for numerous uses. The multi-layer micro / nanofluidic flow device can comprise: a substrate, such as indium tin oxide coated glass (ITO glass); a conductive layer of ferroelectric material, preferably comprising a PZT layer of lead zirconate titanate (PZT) positioned on the substrate; electrodes connected to the conductive layer; a nanofluidics layer positioned on the conductive layer and defining nanochannels; a microfluidics layer positioned upon the nanofluidics layer and defining microchannels; and biomolecular nanovalves providing bio-nanovalves which are moveable from a closed position to an open position to control fluid flow at a nanoscale.

Owner:UCHICAGO ARGONNE LLC

Nano-fabricated superconducting radio-frequency composites, method for producing nano-fabricated superconducting RF composites

ActiveUS20090312186A1Increase the areaElimination of elaborate cleaning and etching processSuperconductor device manufacture/treatmentCoatingsNanometreNanomanufacturing

Superconducting rf is limited by a wide range of failure mechanisms inherent in the typical manufacture methods. This invention provides a method for fabricating superconducting rf structures comprising coating the structures with single atomic-layer thick films of alternating chemical composition. Also provided is a cavity defining the invented laminate structure.

Owner:UCHICAGO ARGONNE LLC

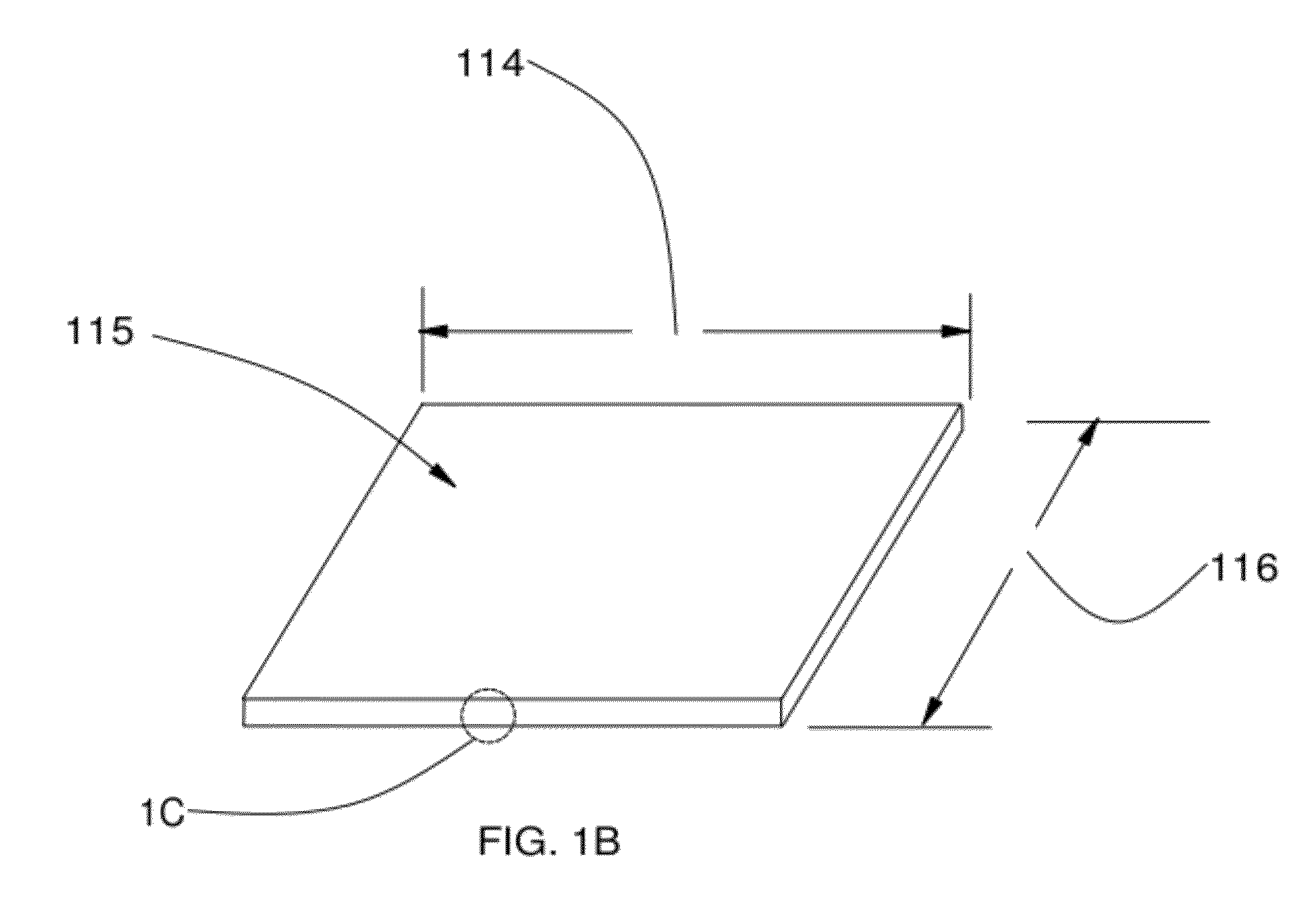

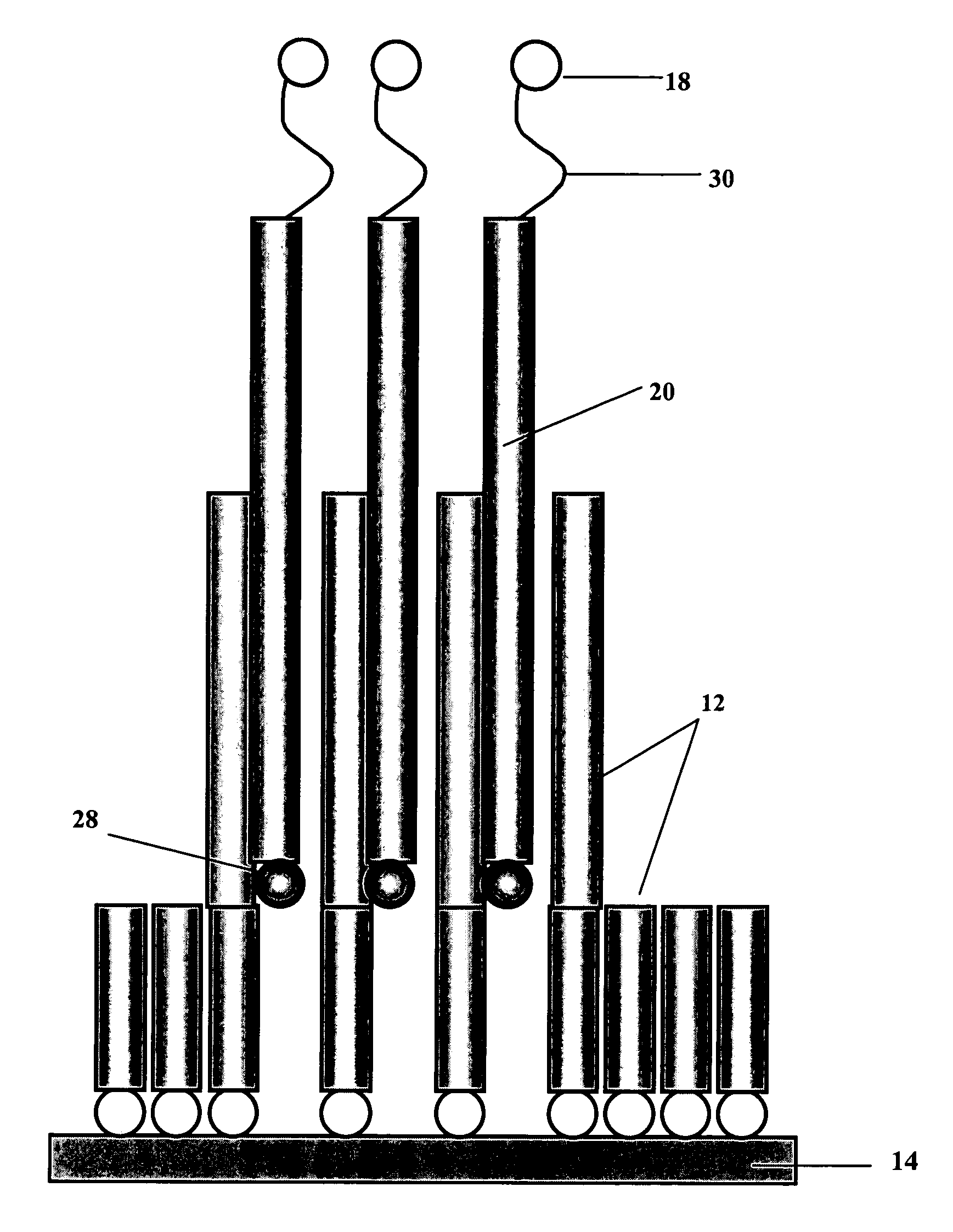

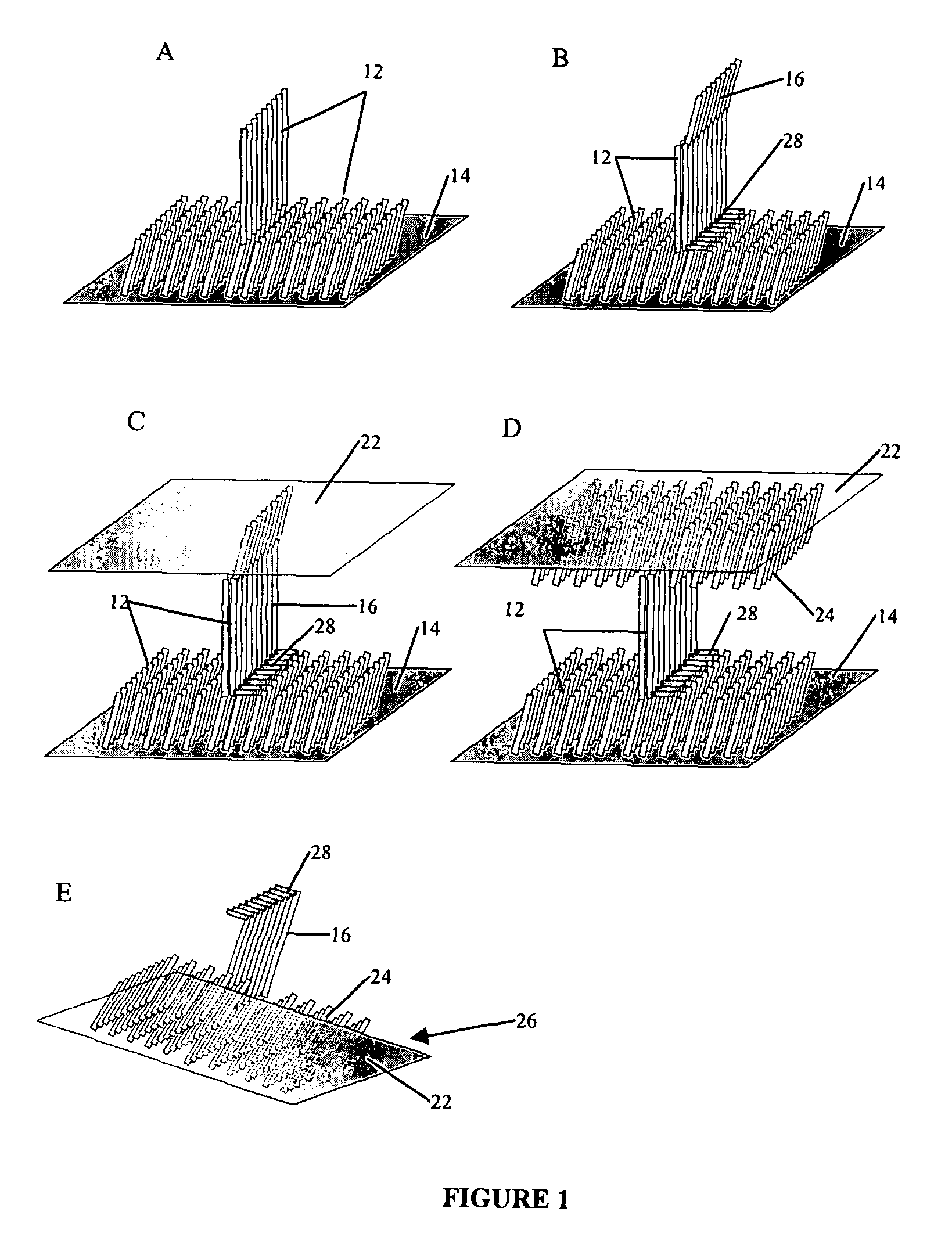

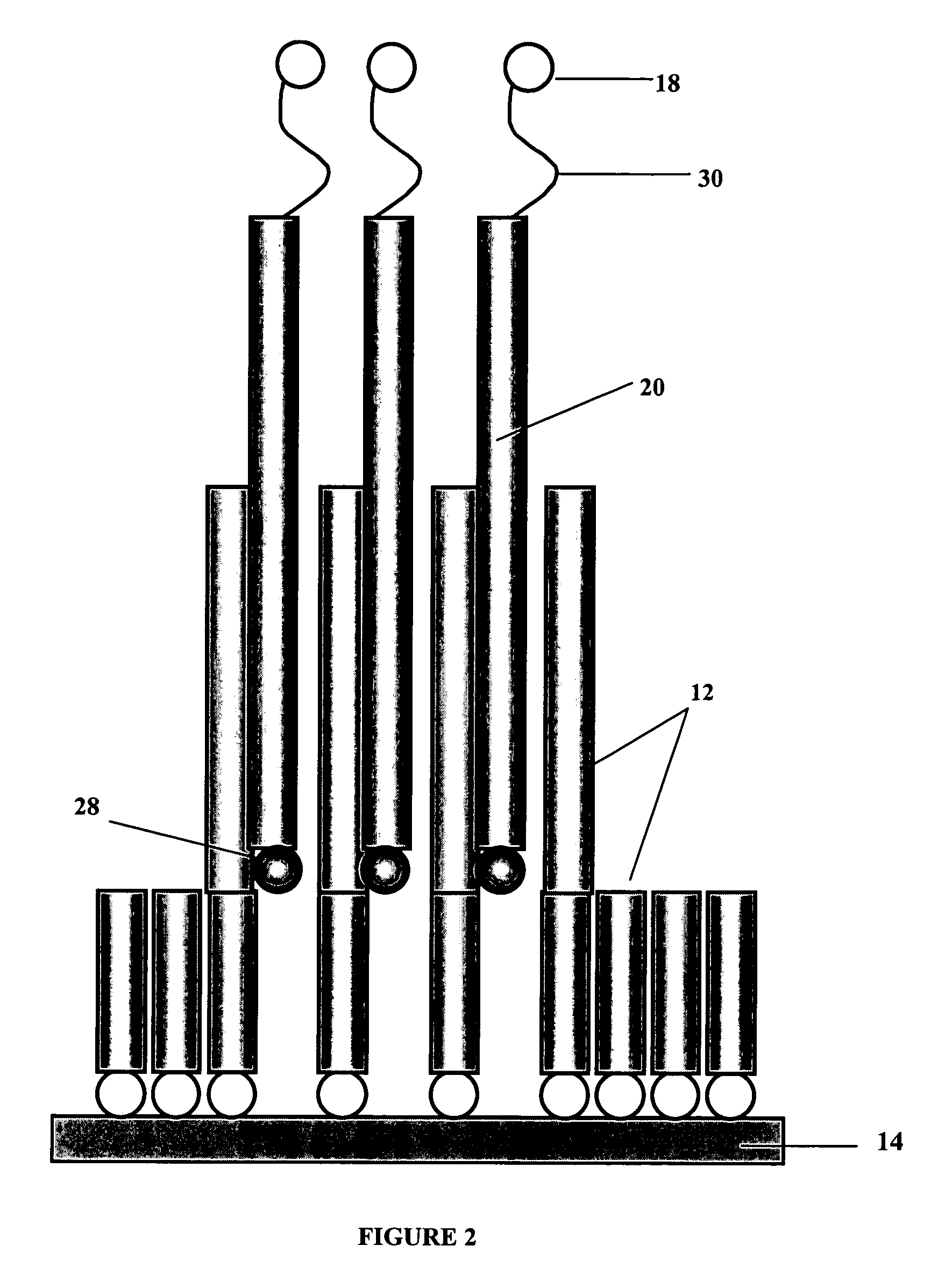

Method for fabricating a long-range ordered periodic array of nano-features, and articles comprising same

A long range, periodically ordered array of discrete nano-features (10), such as nano-islands, nano-particles, nano-wires, non-tubes, nano-pores, nano-composition-variations, and nano-device-components, are fabricated by propagation of a self-assembling array or nucleation and growth of periodically aligned nano-features. The propagation may be induced by a laterally or circularly moving heat source, a stationary heat source arranged at an edge of the material to be patterned (12), or a series of sequentially activated heaters or electrodes. Advantageously, the long-range periodic array of nano-features (10) may be utilized as a nano-mask or nano-implant master pattern for nano-fabrication of other nano-structures. In addition, the inventive long-range, periodically ordered arrays of nano-features are useful in a variety of nanoscale applications such as addressable memories or logic devices, ultra-high-density magnetic recording media, magnetic sensors, photonic devices, quantum computing devices, quantum luminescent devices, and efficient catalytic devices.

Owner:RGT UNIV OF CALIFORNIA

Method of forming monolithic CMOS-MEMS hybrid integrated, packaged structures

InactiveUS8101458B2Solid-state devicesSemiconductor/solid-state device manufacturingFilling materialsLayer interface

A method of forming Monolithic CMOS-MEMS hybrid integrated, packaged structures includes the steps of providing: providing a semiconductor substrate with pre-fabricated cmos circuits on the front side and a polished back-side with through substrate conductive vias; forming at least one opening in the polished backside of the semiconductor substrate by appropriately protecting the front-side; applying at least one filler material in the at least one opening on the semiconductor substrate; positioning at least one prefabricated mems, nems or cmos chip on the filler material, the chip including a front face and a bare back face with the prefabricated mems / nems chips containing mechanical and dielectric layers; applying at least one planarization layer overlying the substrate, filler material and the chip; forming at least one via opening on a portion of the planarization layer interfacing pads on the chip and the through substrate conductive vias; applying at least one metallization layer overlying the planarization layer on the substrate and the chip connecting the through substrate conductive vias to the at least one chip; applying at least one second insulating layer overlying the metallization layer; performing at least one micro / nano fabrication etching step to release the mechanical layer on the prefabricated mems / nems chips; positioning protective cap to package the integrated device over the mems / nems device area on the pre-fabricated chips.

Owner:AMF NANO

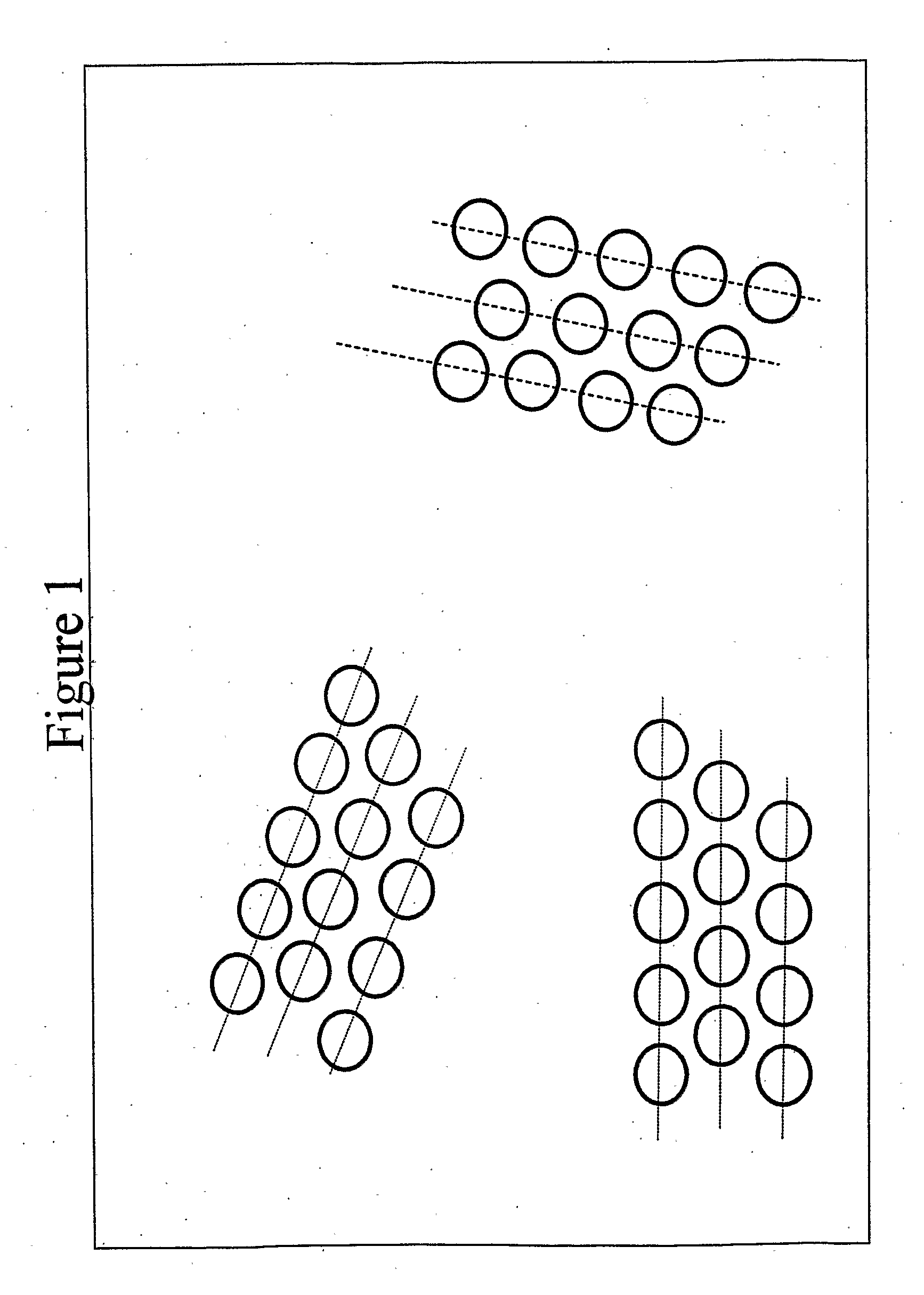

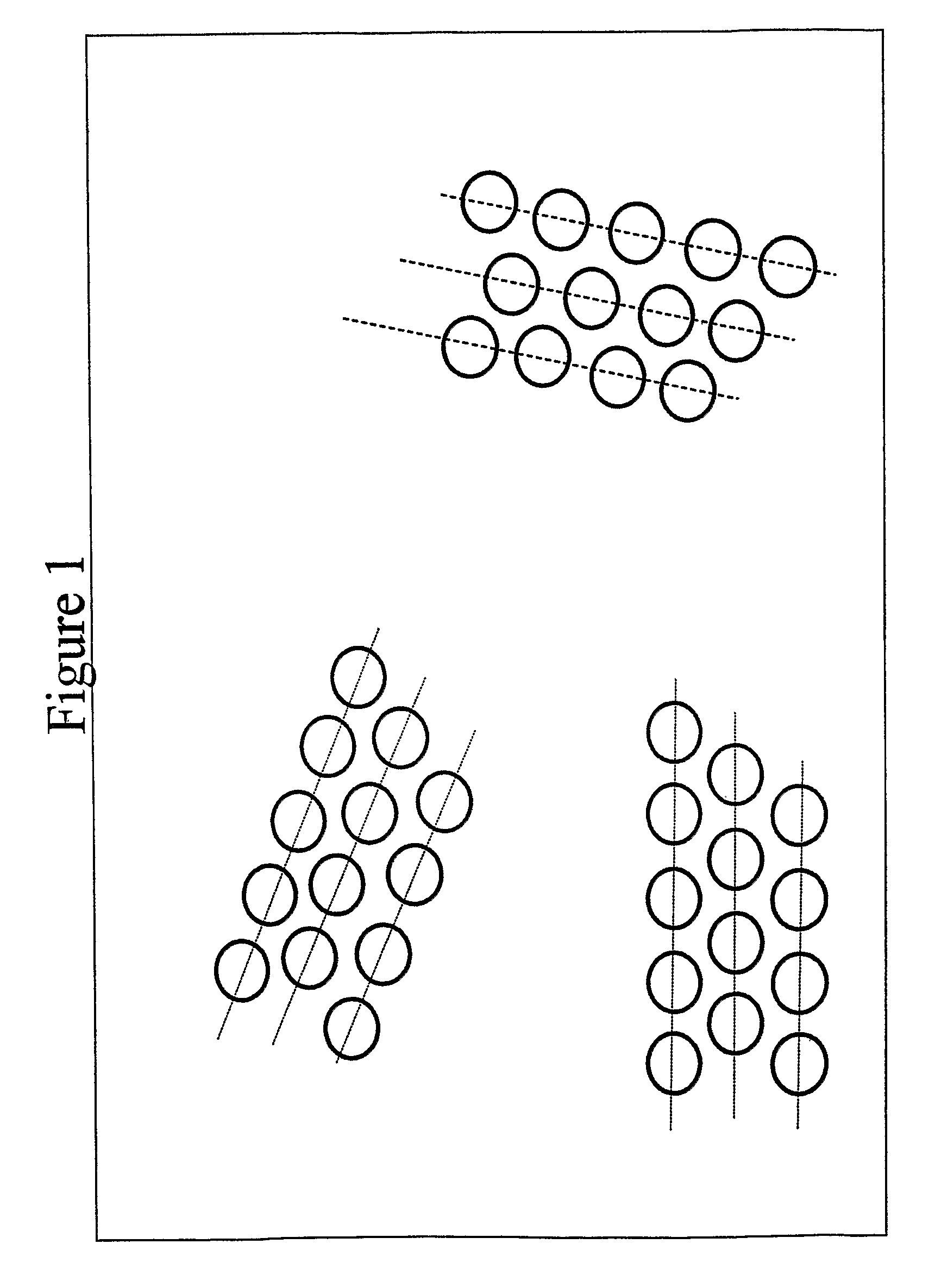

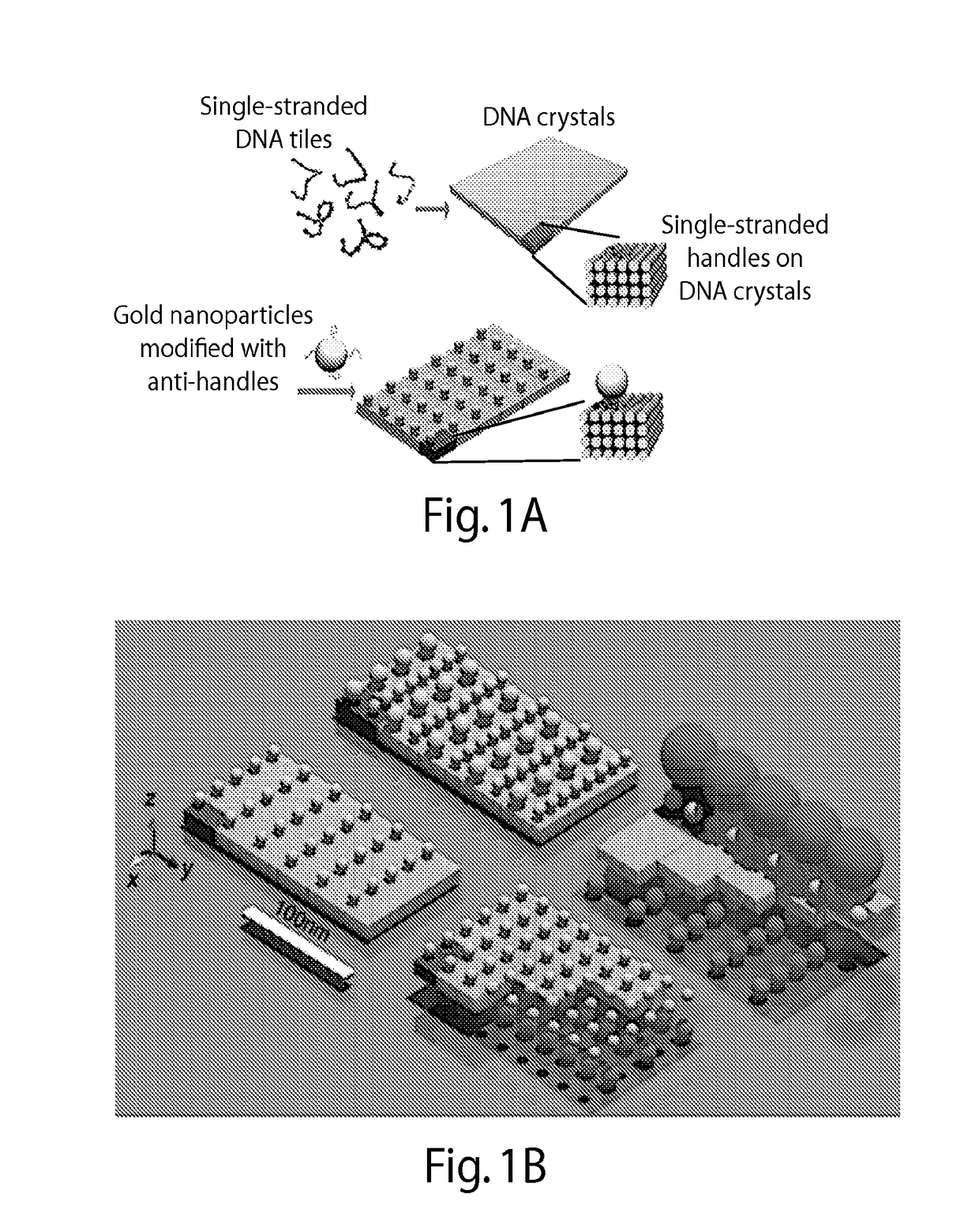

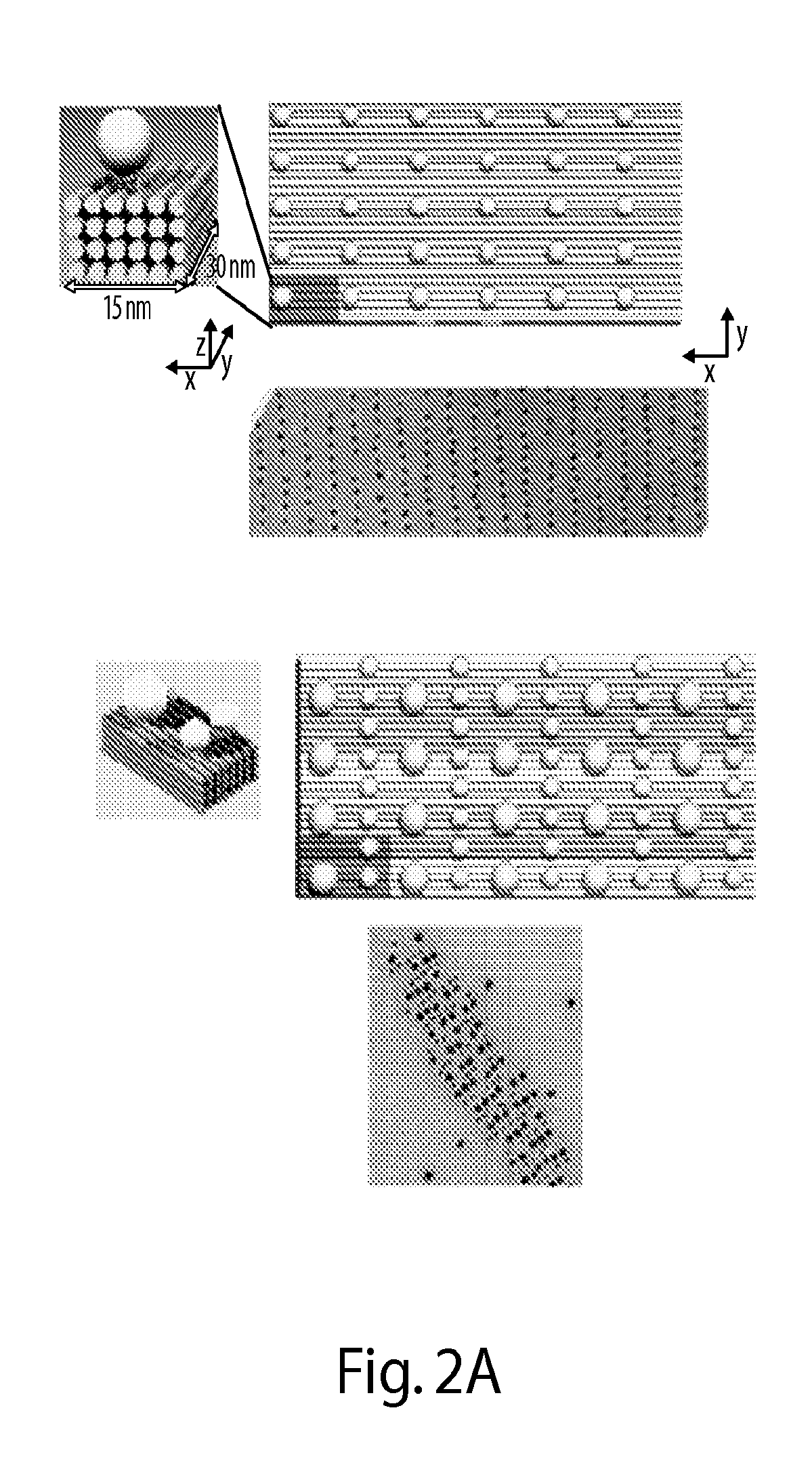

Scalable nucleic acid-based nanofabrication

ActiveUS10099920B2Minimal feature defectPattern can be very complexMaterial nanotechnologyNanostructure assemblyLithographic artistNanoparticle

The present disclosure relates to the alignment of moieties (e.g., nanoparticles and / or nanowires) into prescribed architectures on two- and / or three-dimensional substrates (e.g., nucleic acid nanostructures / crystals). The present disclosure also relates to a nucleic acid (e.g., DNA) lithography method that includes, in some embodiments, adsorbing a bare nucleic acid nanostructure onto a surface of a substrate, and etching the surface of the substrate containing the bare nucleic acid nanostructure, thereby producing a patterned substrate.

Owner:PRESIDENT & FELLOWS OF HARVARD COLLEGE

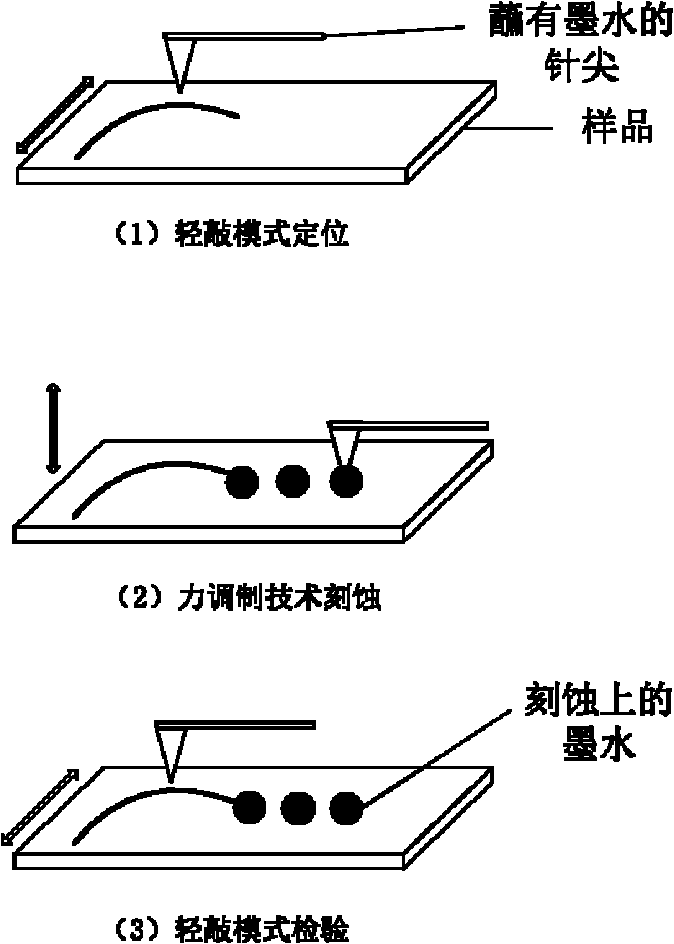

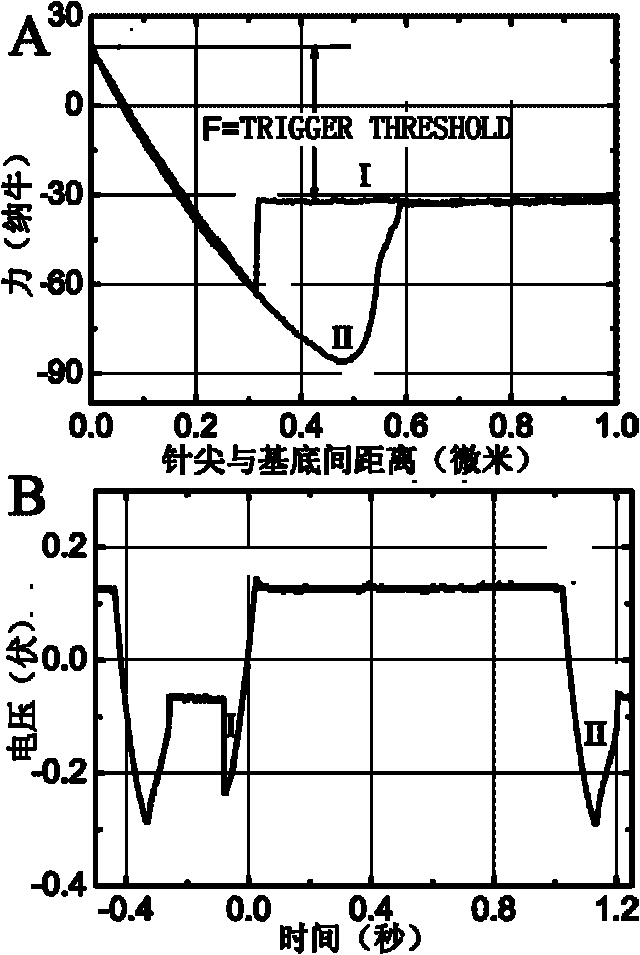

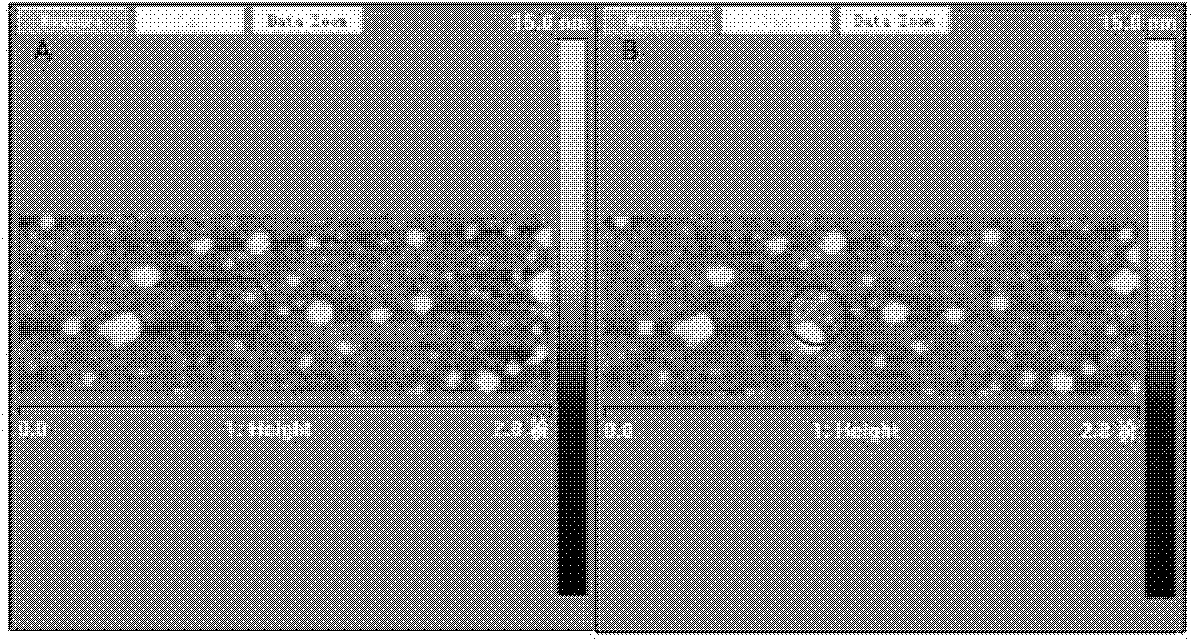

Force modulation mode-based dip-pen nanolithography method

The invention provides a force modulation mode-based dip-pen nanolithography method in the technical field of nanometer manufacture, which is realized by combining a tapping mode and the force modulation technology, imaging by the tapping mode and lithographing on a setpoint by the force modulation technology. The method can accurately control the acting force and the acting time between a tip and a substrate, so the lithographing effect can be better controller, and the repeatability of lithographing operation is improved; and furthermore, the method can perform multi-point automatic location and dip-pen lithography operation once, is convenient and practical, and is advantageous to industrialization.

Owner:SHANGHAI JIAO TONG UNIV