Patents

Literature

33results about How to "Reduced packaging requirements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

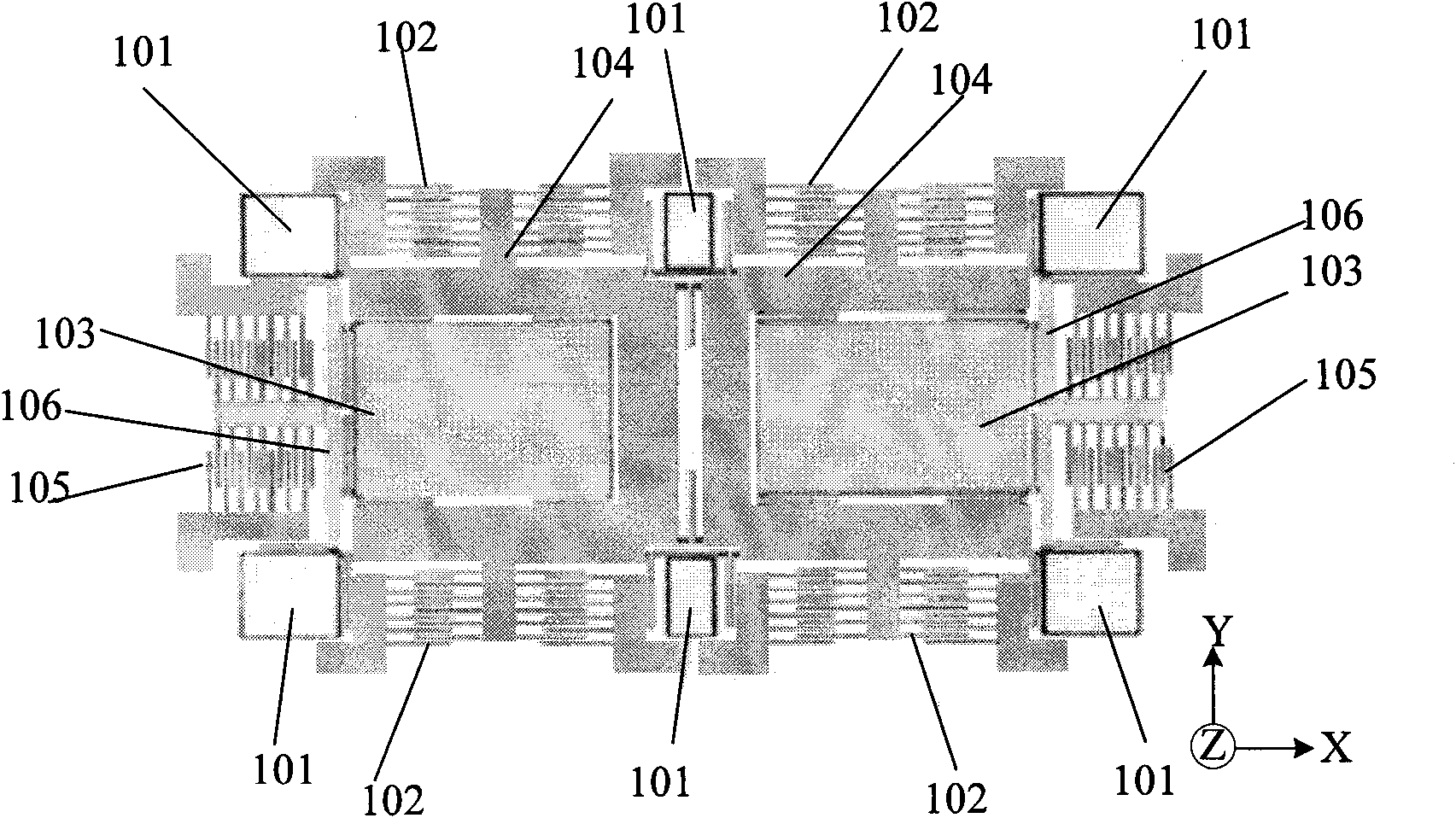

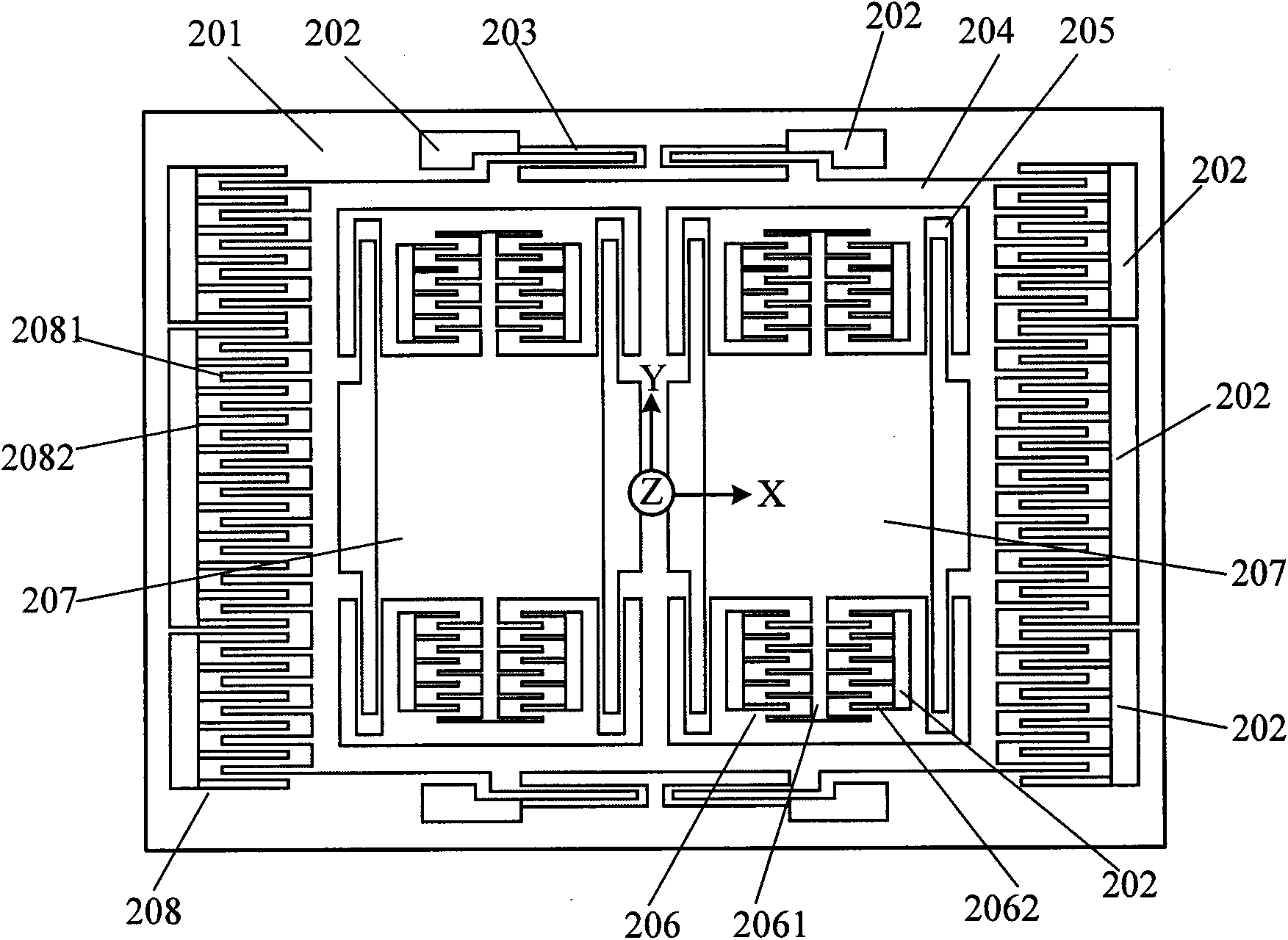

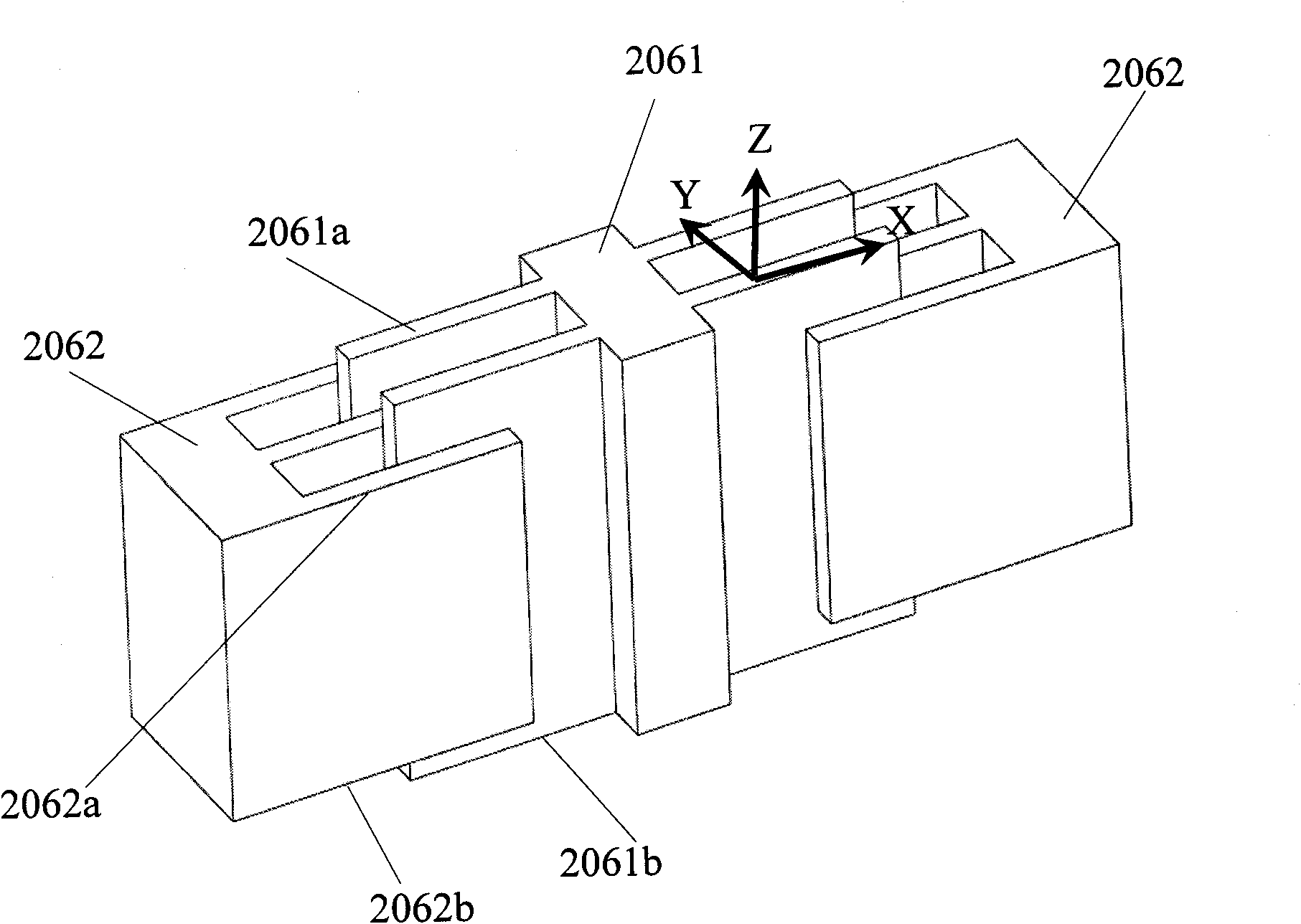

Capacitive micromachined tuning fork gyroscope

InactiveCN102062604ASuppress couplingNo changeTelevision system detailsImpedence networksCapacitanceTuning fork

The invention provides a capacitive micromachined tuning fork gyroscope. The gyroscope is the symmetrical dual-mass structural gyroscope, comprising a substrate and a framework arranged in the centre of the substrate, wherein the middle of the framework is provided with a framework beam perpendicular to the framework; two detection mass blocks are symmetrically arranged in the framework with the framework beam as a symmetry axis, and four corners of each detection mass block are connected with the framework and the framework beam through at least four drive beams; decoupling drive comb capacitors are respectively arranged at both ends of each detection mass block in the direction of a vertical axis; detection comb capacitors are symmetrically arranged on both outer sides of the framework in the direction of a horizontal axis; at least four detection beams are arranged on both outer sides of the framework in the direction of the vertical axis; and the detection beams are distributed symmetrically relative to the vertical axis and the horizontal axis and are fixed on the substrate through corresponding anchor points. According to the capacitive horizontal-axis micromachined tuning fork gyroscope provided by the invention, the mechanical coupling between the detection mode and the driving mode of the micromachined tuning fork gyroscope can be solved easily and effectively.

Owner:PEKING UNIV

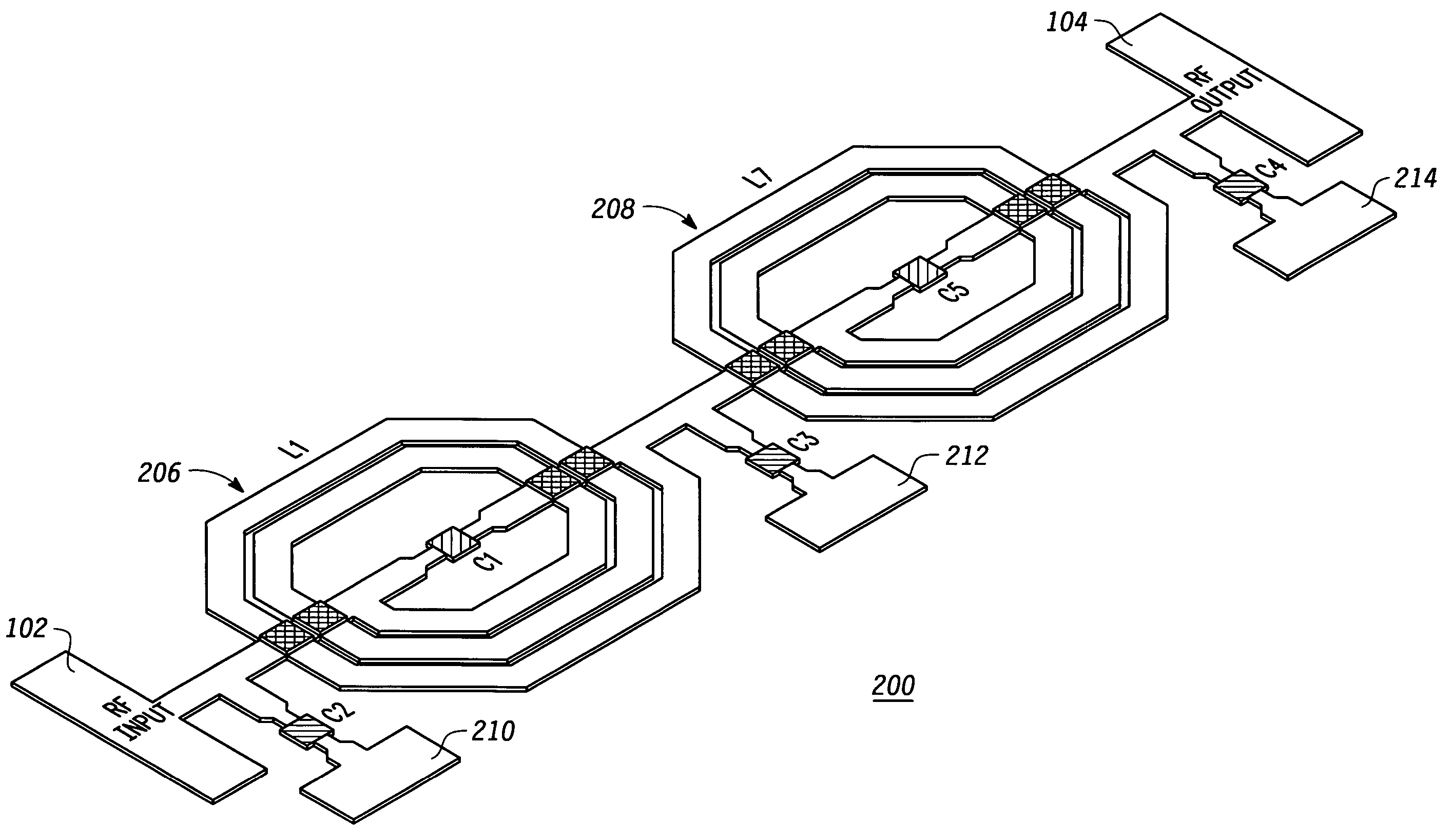

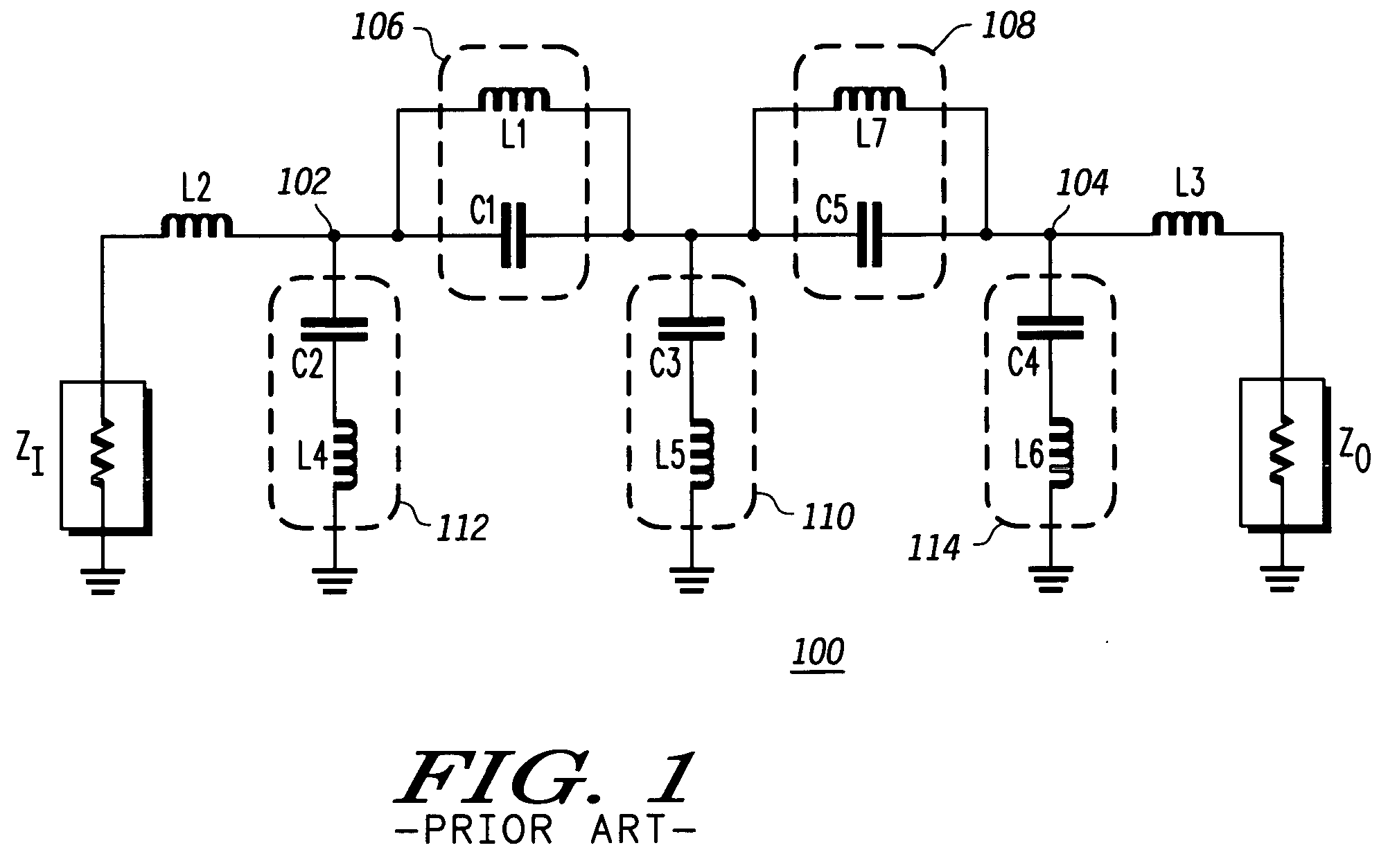

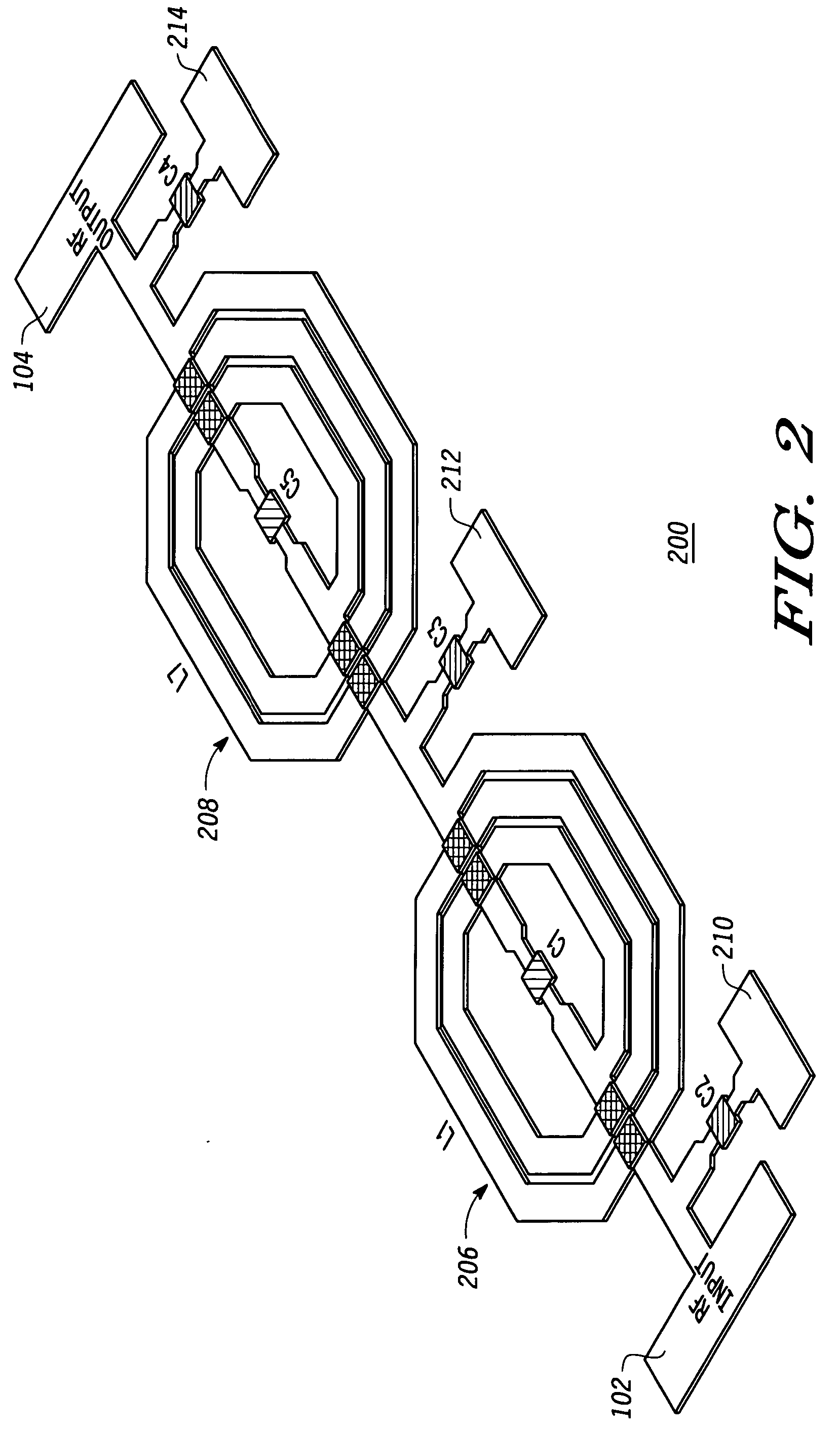

Compact radio frequency harmonic filter using integrated passive device technology

ActiveUS20060141978A1Small sizeReduced packaging requirementsMultiple-port networksTransmissionFourth harmonicThird harmonic

A radio frequency (“RF”) harmonic filter circuit as disclosed herein is fabricated using integrated passive device (“IPD”) technology. The RF harmonic filter circuit is configured to provide second, third, and fourth harmonic rejection while providing good input and output impedance matching. The RF harmonic filter circuit employs only one IPD loop inductance (preferably used for a second harmonic resonance circuit), which results in a significant die / package size reduction. The RF harmonic filter circuit also employs a combined circuit that performs input and / or output impedance matching and third harmonic rejection.

Owner:NXP USA INC

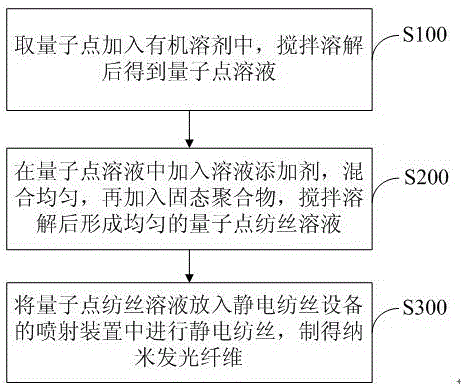

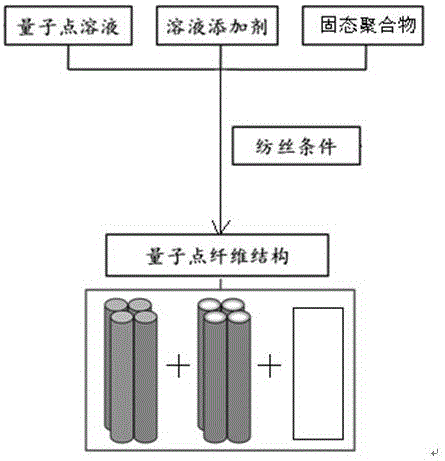

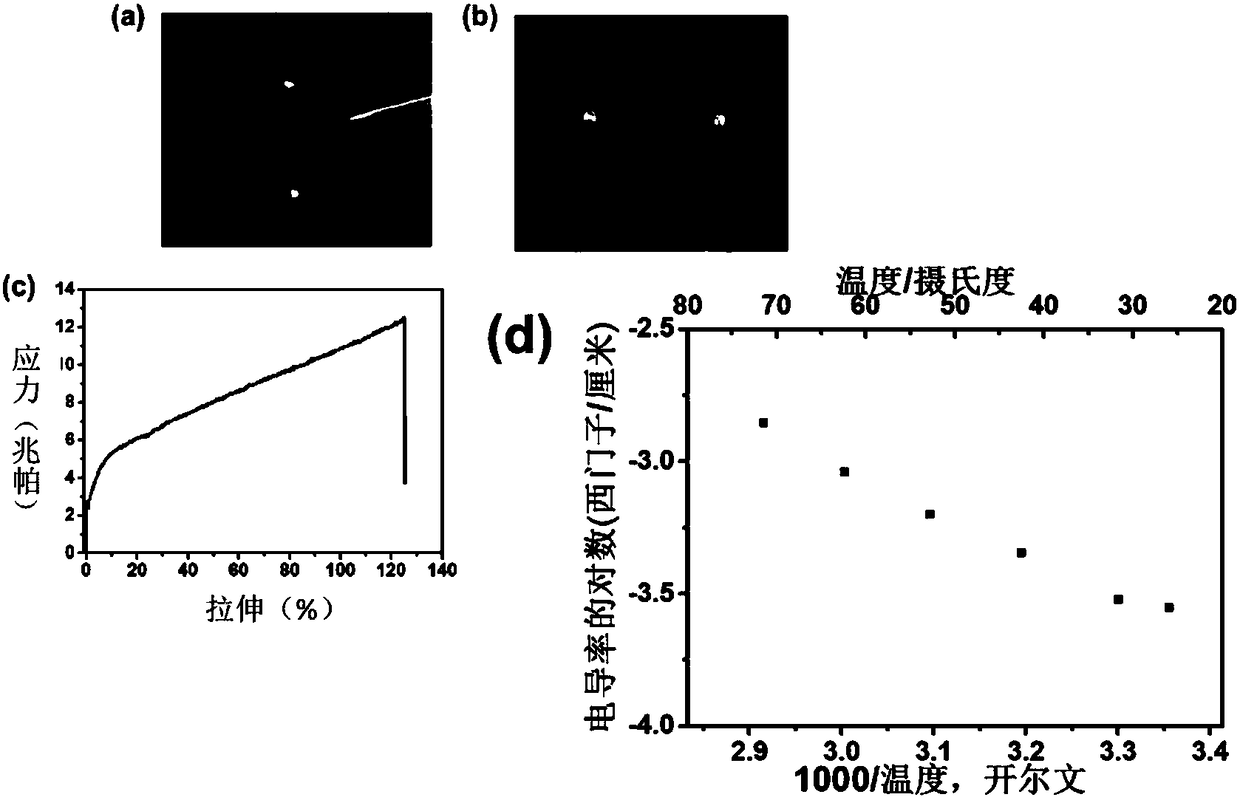

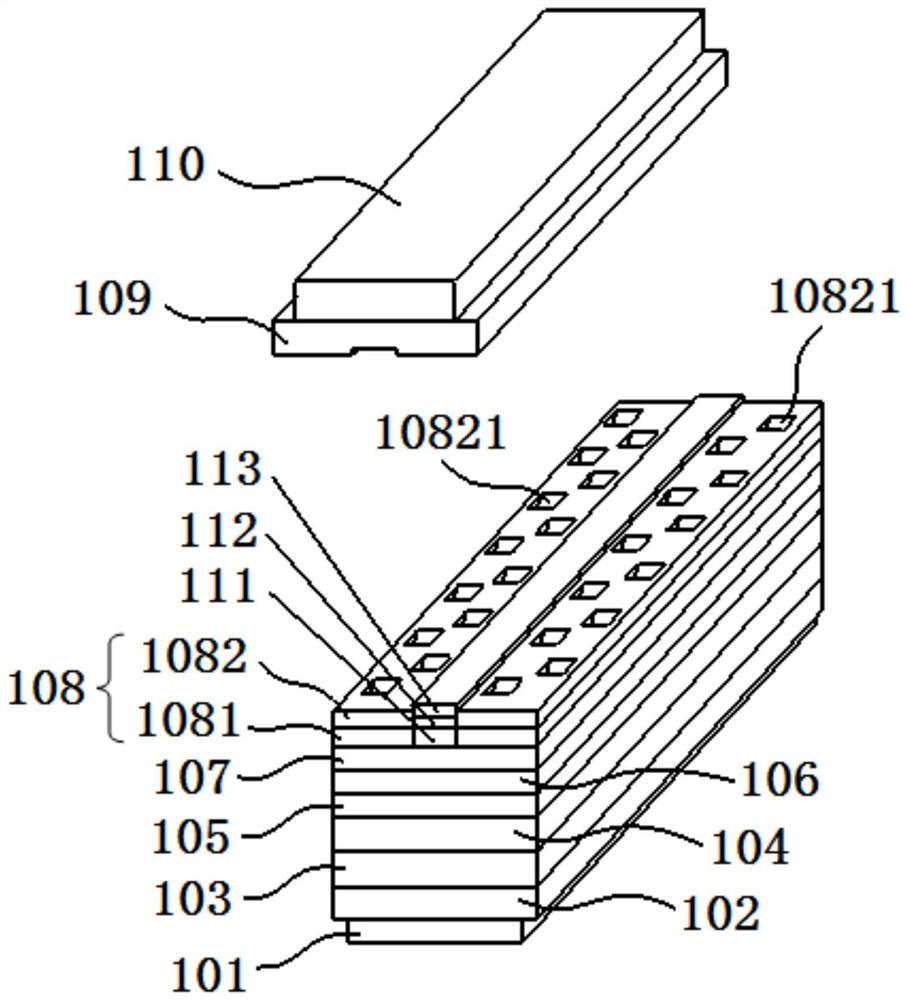

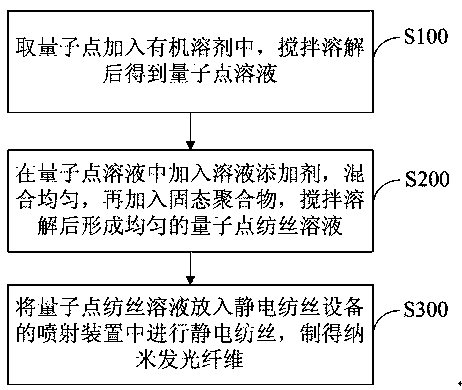

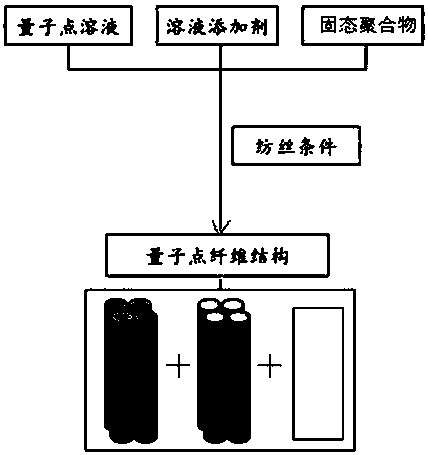

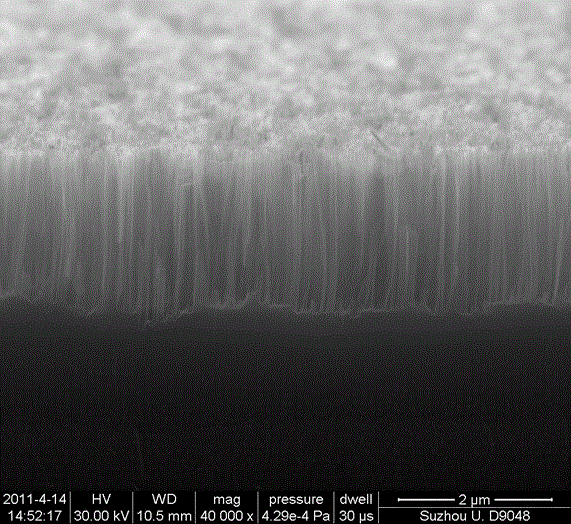

Nanometer luminescent fiber and preparation method thereof

ActiveCN106245129AReduce aggregationAvoid Fluorescence Intensity DecayElectro-spinningMonocomponent synthetic polymer artificial filamentFiberOrganic solvent

The invention discloses a nanometer luminescent fiber and a preparation method thereof. The method comprises the steps that quantum dots are taken to be added into an organic solvent, stirring dissolution is performed to obtain a quantum dot solution; a solution additive is added into the quantum dot solution, mixing is performed to be uniform, then, solid polymer is added, stirring dissolution is performed to obtain an uniform quantum dot spinning solution; the quantum dot spinning solution is placed into a jet apparatus device of electrostatic spinning equipment for performing electrostatic spinning, and nanometer luminescent fiber is obtained. The method is simple, controllable and easy to repeat, the oil soluble quantum dot solution of any kind can be adopted for spinning, in the electrostatic spinning process, and the nanometer luminescent fiber of different shapes such as solid nanometer fiber, tubular nanometer fiber and strap nanometer fiber is obtained by adjusting the conditions such as the mass percentage of the components in the electrostatic spinning solution, electrostatic spinning voltage, the solution injection rate, the solution injection distance and the spun nanometer luminescent fiber drying temperature.

Owner:TCL CORPORATION

Low-expansion composite electrodes for all-solid-state batteries

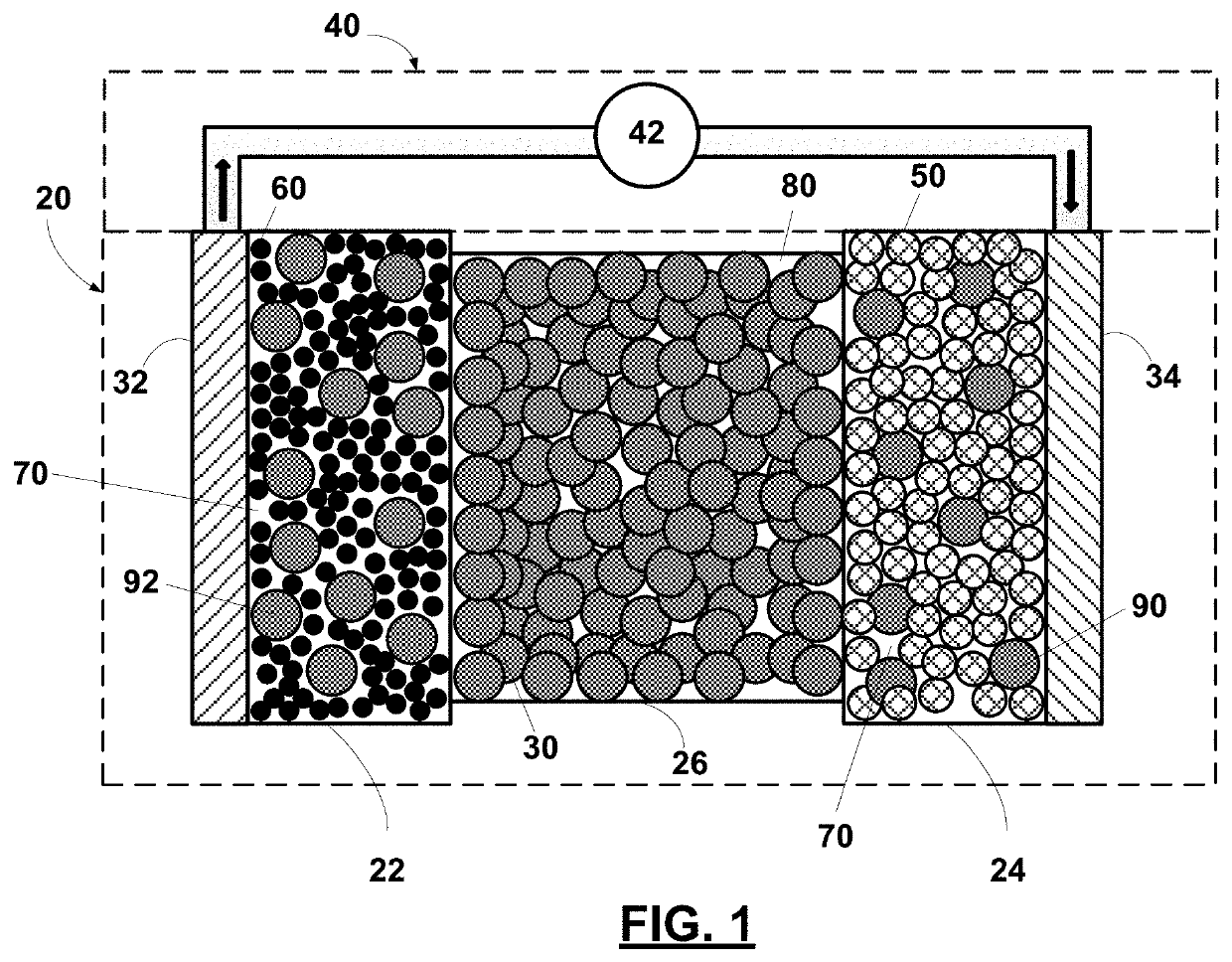

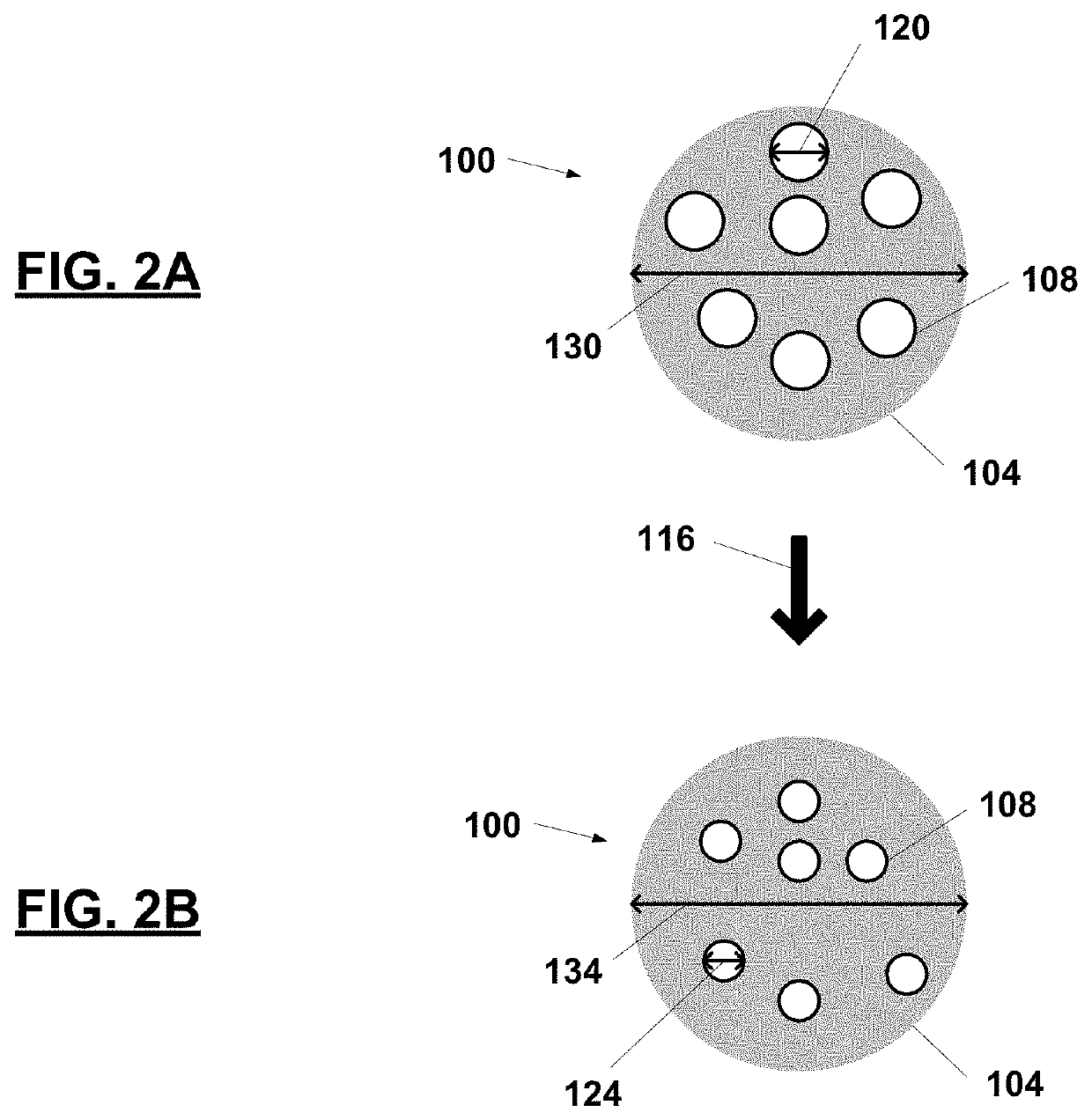

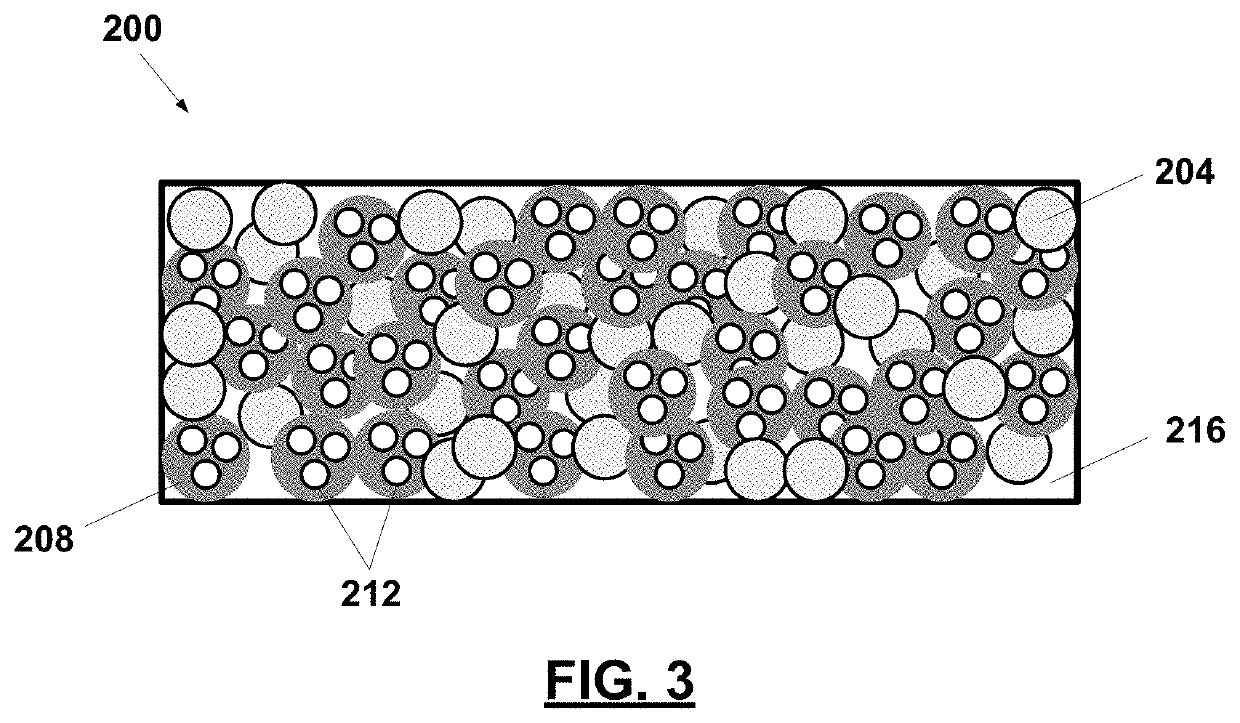

ActiveUS20200127282A1Extended shelf lifeMinimal to no self-dischargeSolid electrolytesSecondary cellsSolid state electrolyteAll solid state

A composite electrode for use in an all-solid-state electrochemical cell that cycles lithium ions is provided. The composite electrode comprises a solid-state electroactive material that undergoes volumetric expansion and contraction during cycling of the electrochemical cell and a solid-state electrolyte. The solid-state electroactive material is in the form of a plurality of particles and each particle has a plurality of internal pores formed therewithin. Each particle has an average porosity ranging from about 10% to about 75%, and the composite electrode has an interparticle porosity between the solid-state electroactive material and solid-state electrolyte particles ranging from about 5% to about 40%. The intraparticle pores and the interparticle porosity accommodate the volumetric expansion and contraction of the solid-state electroactive material so to minimize outward expansion of the electroactive particles, micro-cracking of the solid-state electrolyte, and delamination within the electrochemical cell.

Owner:GM GLOBAL TECH OPERATIONS LLC

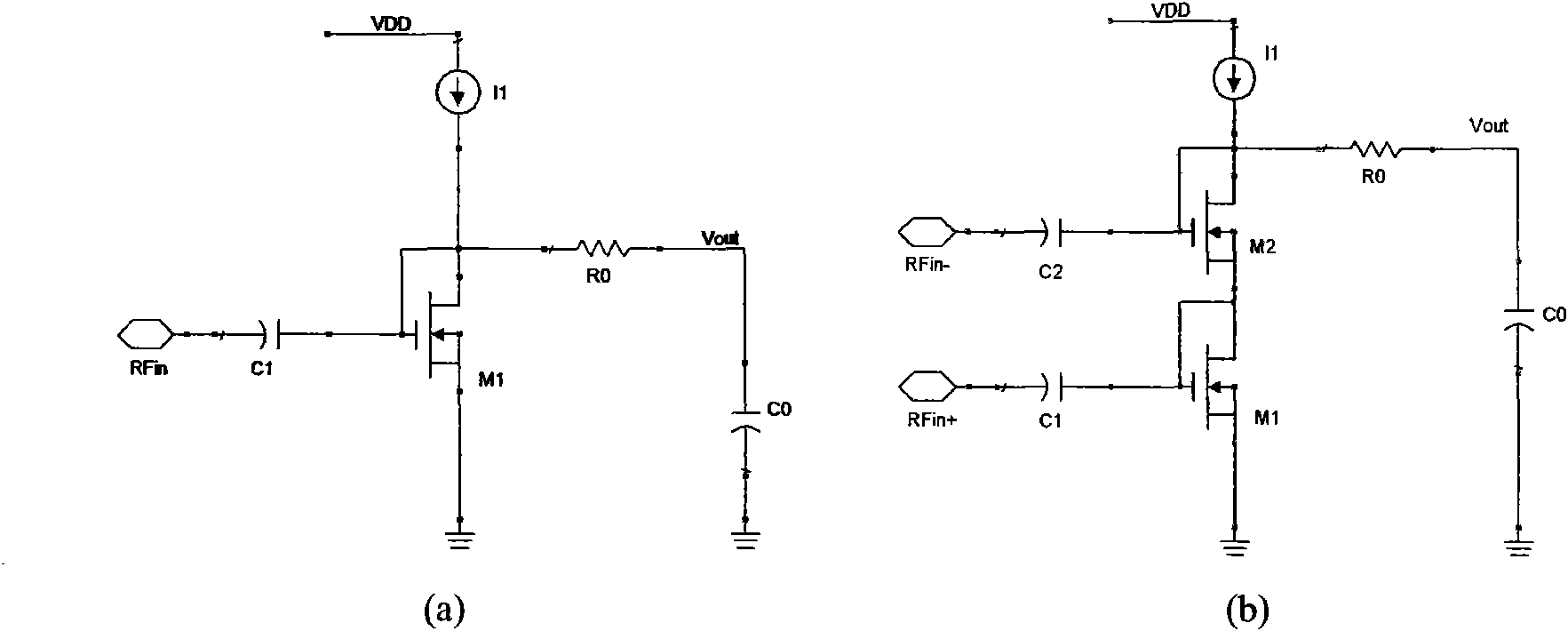

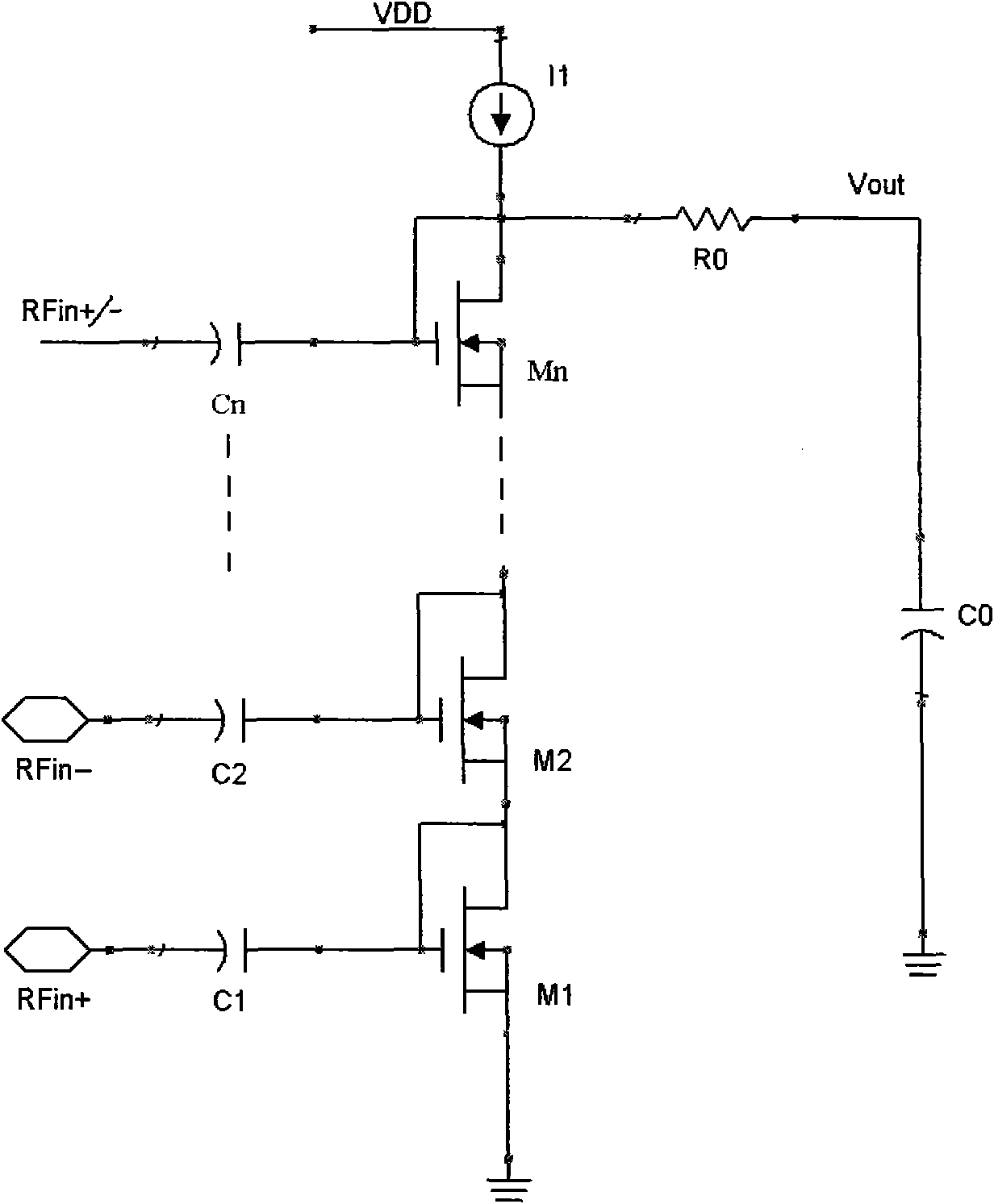

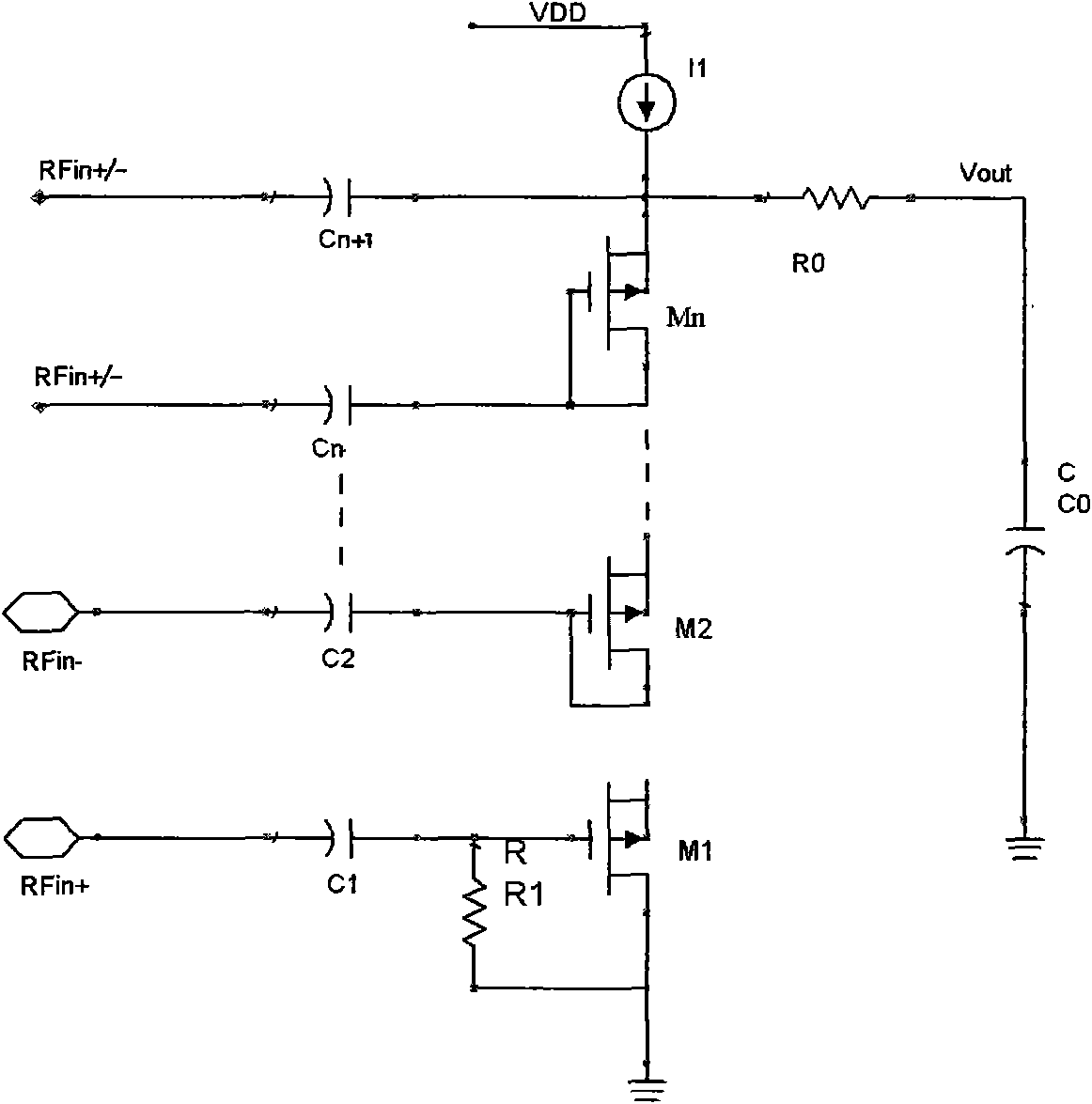

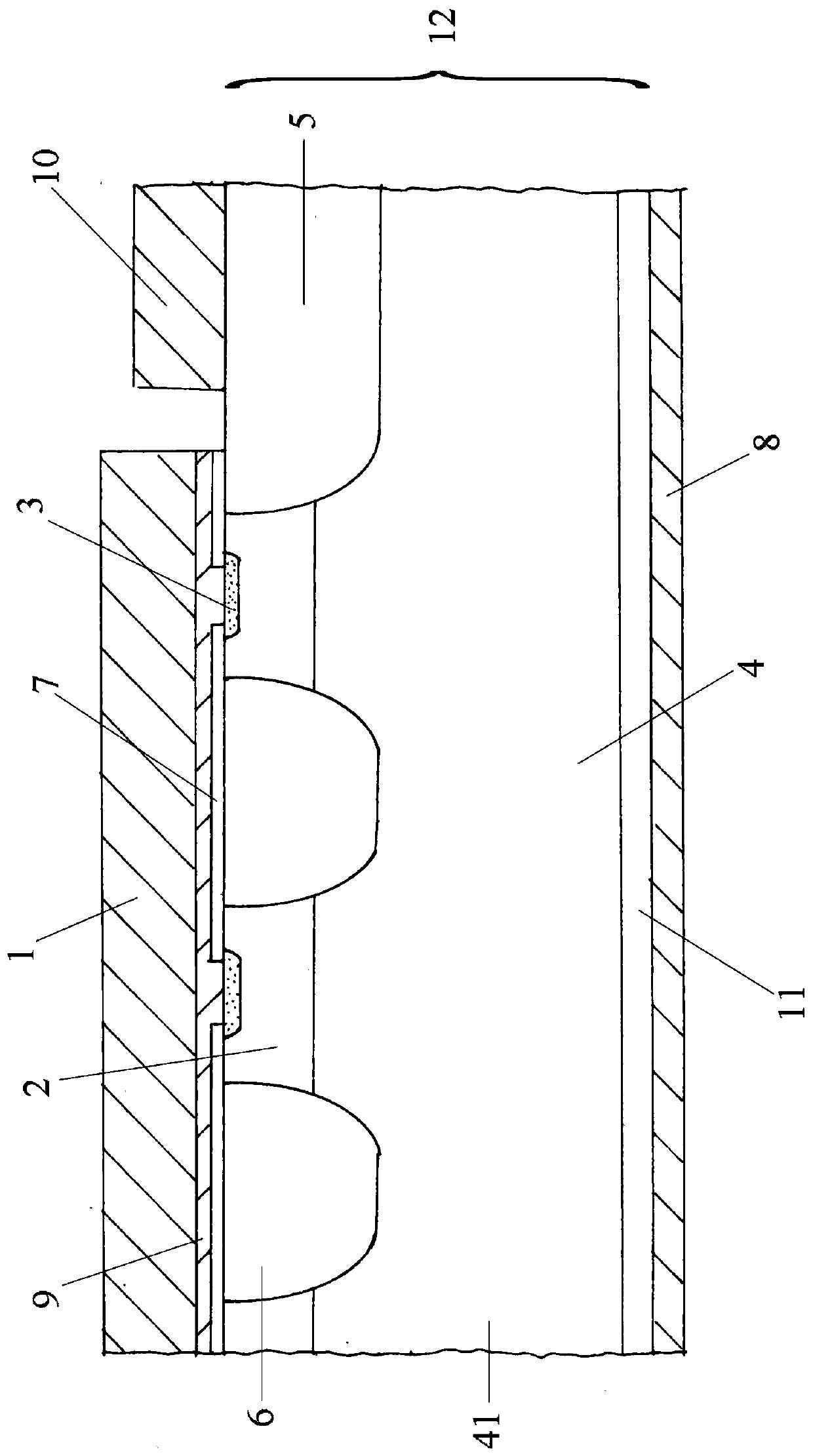

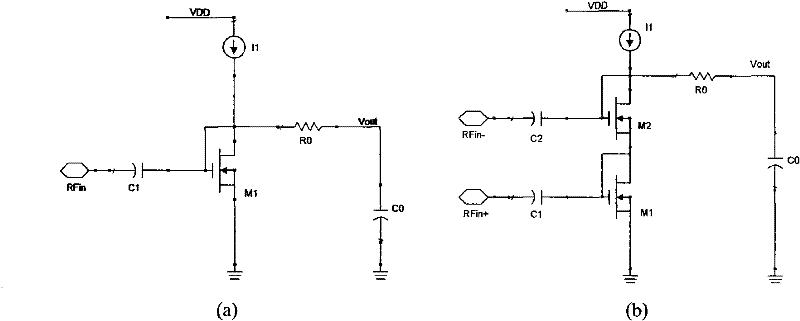

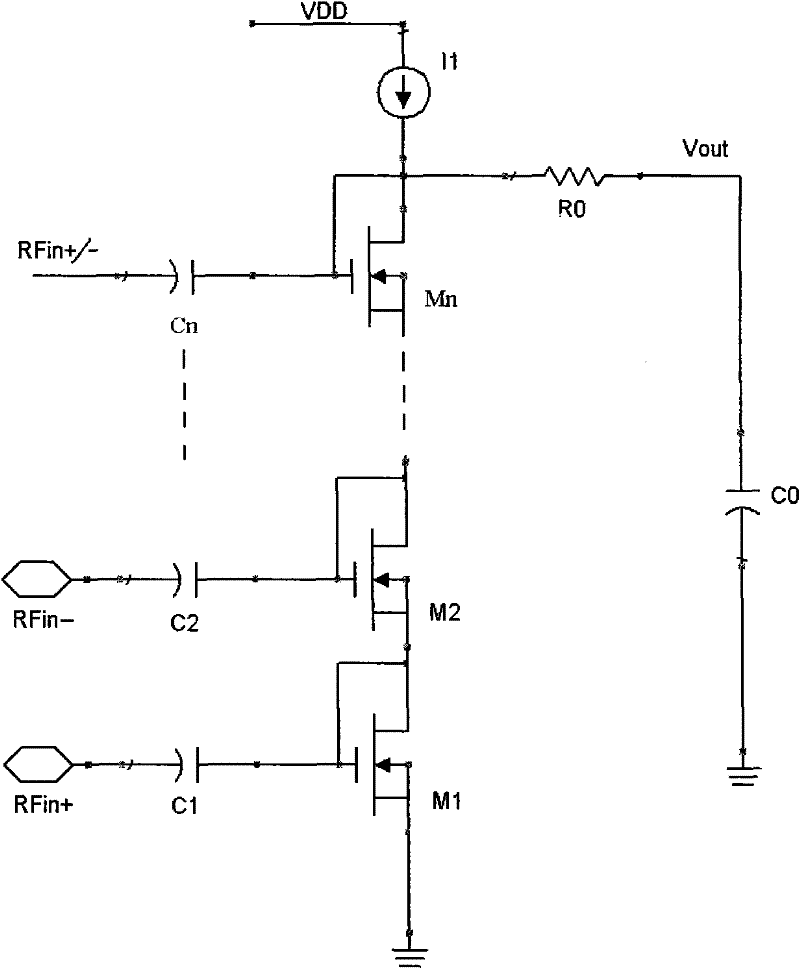

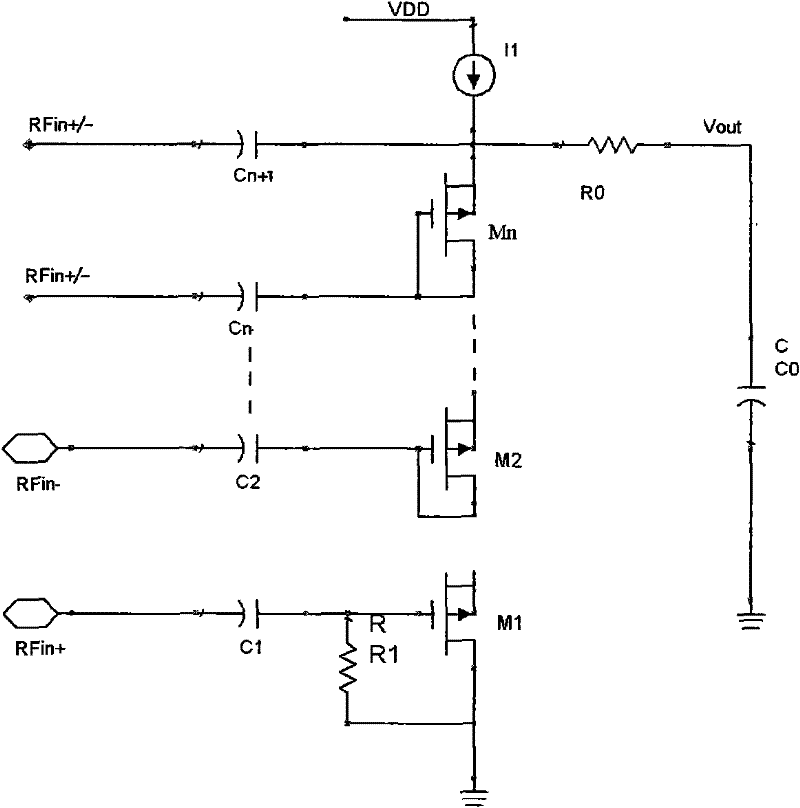

CMOS difference radio-frequency signal amplitude detection circuit

ActiveCN101666833AHigh Amplitude Detection GainReduce power consumptionEnergy efficient ICTNoise figure or signal-to-noise ratio measurementCapacitanceDifferential signaling

The invention discloses a CMOS difference radio-frequency signal amplitude detection circuit, being composed of MOS transistors from M1 to Mn which work under the weak inversion polarization and a filter resistance R0 and a capacitance C0; the MOS transistors from M1 to Mn are serially connected, and the polarization is provided by a current source I1, the grids or drains of the transistors from M1 to Mn are respectively connected with the input positive end Rfin+ of a radio-frequency signal or the input negative end Rfin- of the radio-frequency signal through the capacitances from C1 to Cn, and an amplitude detection result is output by the filter resistance R0 and the capacitance C0, the current change of the MOS transistors under the weak inversion polarization submits to index property, and higher amplitude detection gain is obtained compared with square frequency characteristics, particularly for the weak signal detection, the gain is obvious, and the power consumption is low andis approximate to zero consumption; a plurality of the MOS transistors are serially connected to lead amplitude detection output of each MOS transistor to be serially added, thereby obtaining n timesof detection gain; meanwhile, input impedances of radio-frequency inputs of all MOS transistors are connected in parallel, the whole input impedance value is reduced by n times, the requirements of Qvalue that a high-frequency signal is input to a matching circuit is reduced, so as to realize to be directly connected with a radio-frequency antenna; the differential signal input is adopted, so asto be easy for chip integration and reduce the requirements of chip encapsulation. The circuit is particularly suitable for being applied to wake-up signal detection in a short range communication system and weak radio-frequency signal detection in an RFID system.

Owner:斯凯瑞利(北京)科技有限公司

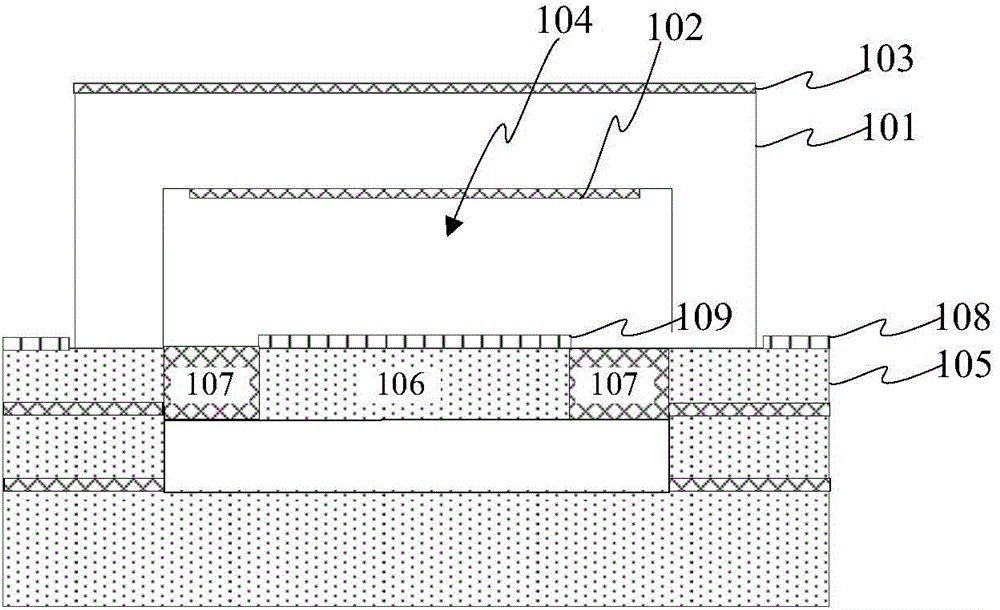

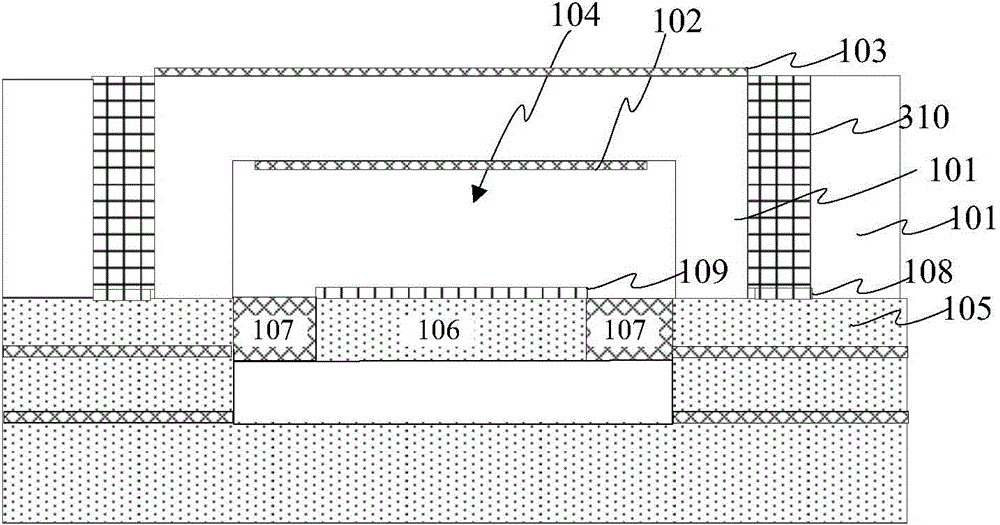

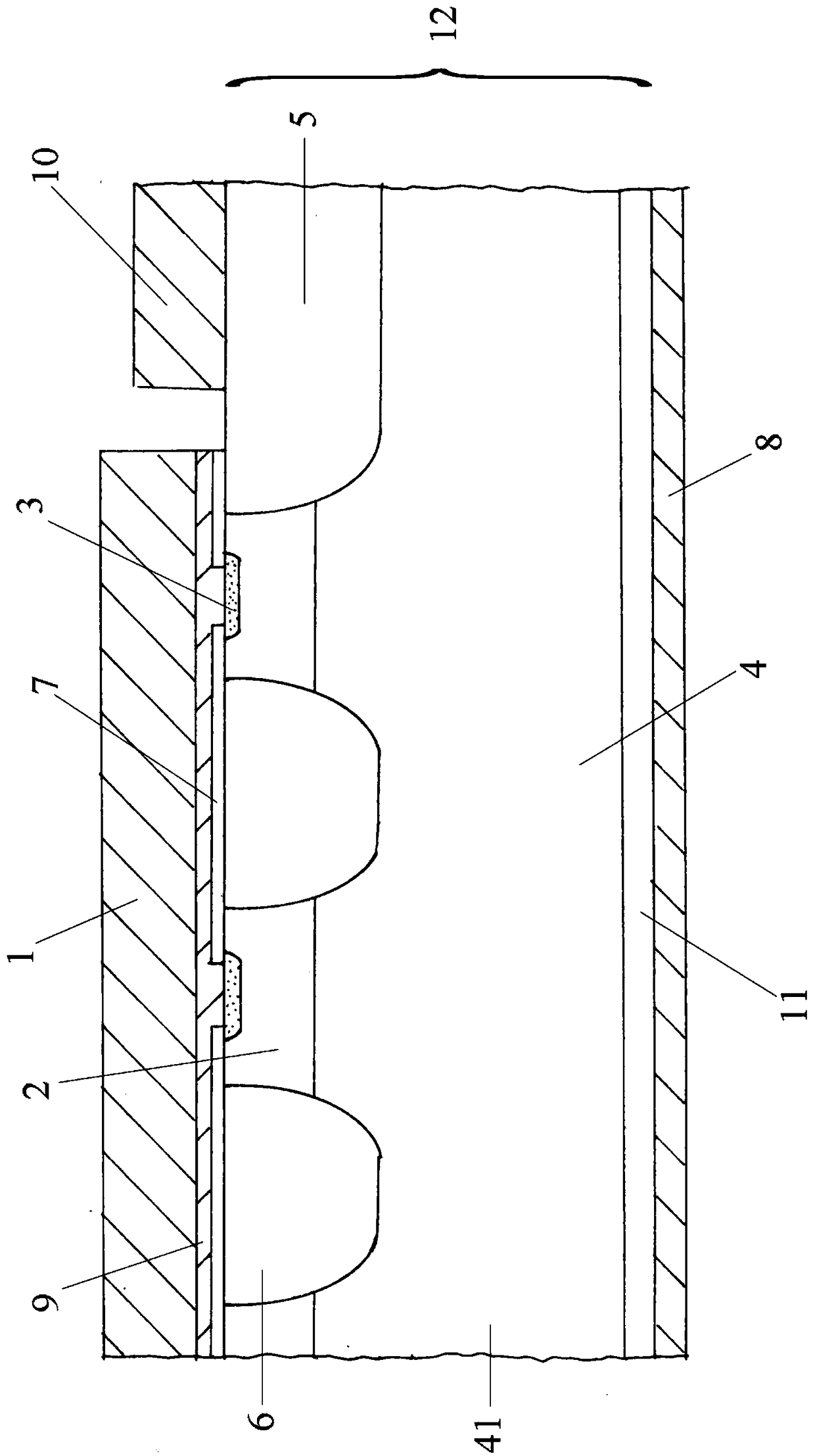

Packaging structure and method of MEMS optical chip based on silicon-glass bonding

ActiveCN104803340AImprove reliabilityImprove stabilityTelevision system detailsPrecision positioning equipmentElectricityGlass frit bonding

The invention provides a packaging structure and method of an MEMS optical chip based on silicon-glass bonding. The packaging structure comprises a first part and a second part, wherein the first part comprises optical glass of which the upper surface is coated with an upper optical antireflection film and while the lower surface is provided with a cavity; the upper surface of the cavity meets the requirement on smoothness of an optical surface, and a lower optical antireflection film is plated; the second part comprises the MEMS optical chips; the first part and the second part are subjected to silicon-glass bonding to achieve chip-stage bonding, and an independent sealing cavity is formed for each MEMS optical chip. With the adoption of the structure and the method, the chip-stage packaging requirement can be achieved; the reliability and stability of the chip can be improved; the electric performance, mechanical performance and optical performance for application of the optical chip can be ensured; in addition, the comprehensive level superior to that of other packaging technologies is brought; the packaging cost can be reduced; the packaging efficiency can be increased; the light loss can be decreased; the structure and the method have a wide application prospect in the packaging of optical communication devices and optical sensors.

Owner:ANHUI CHINA SCI MW ELECTRONIC TECH CO LTD

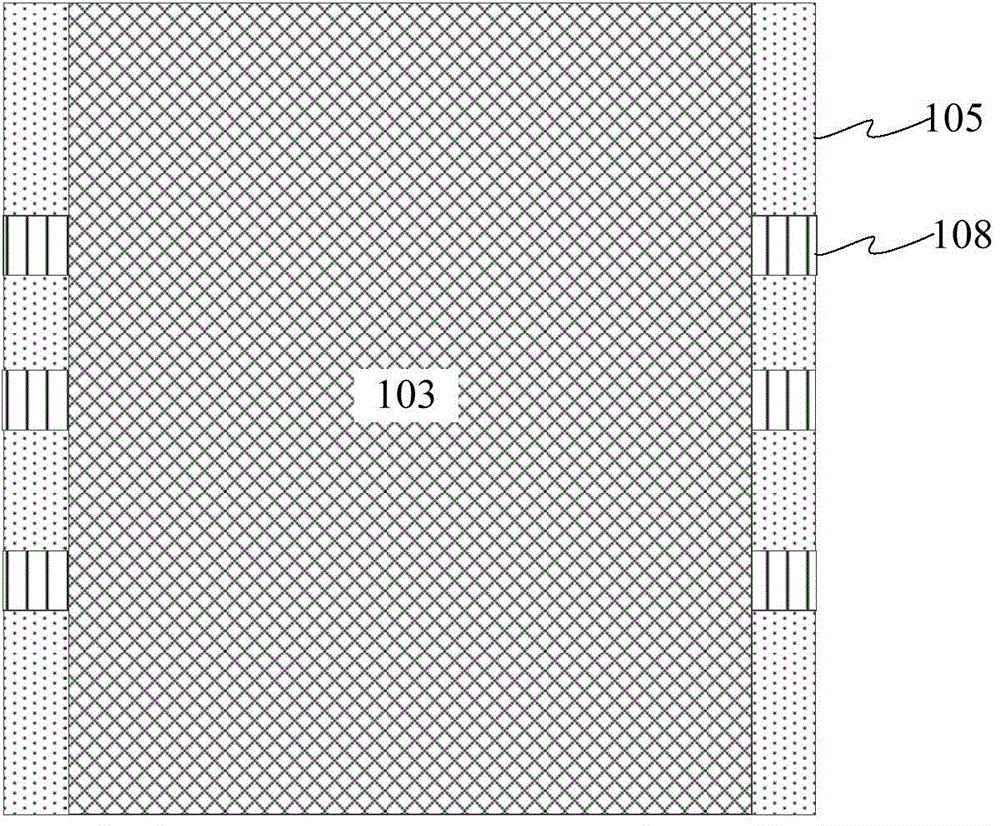

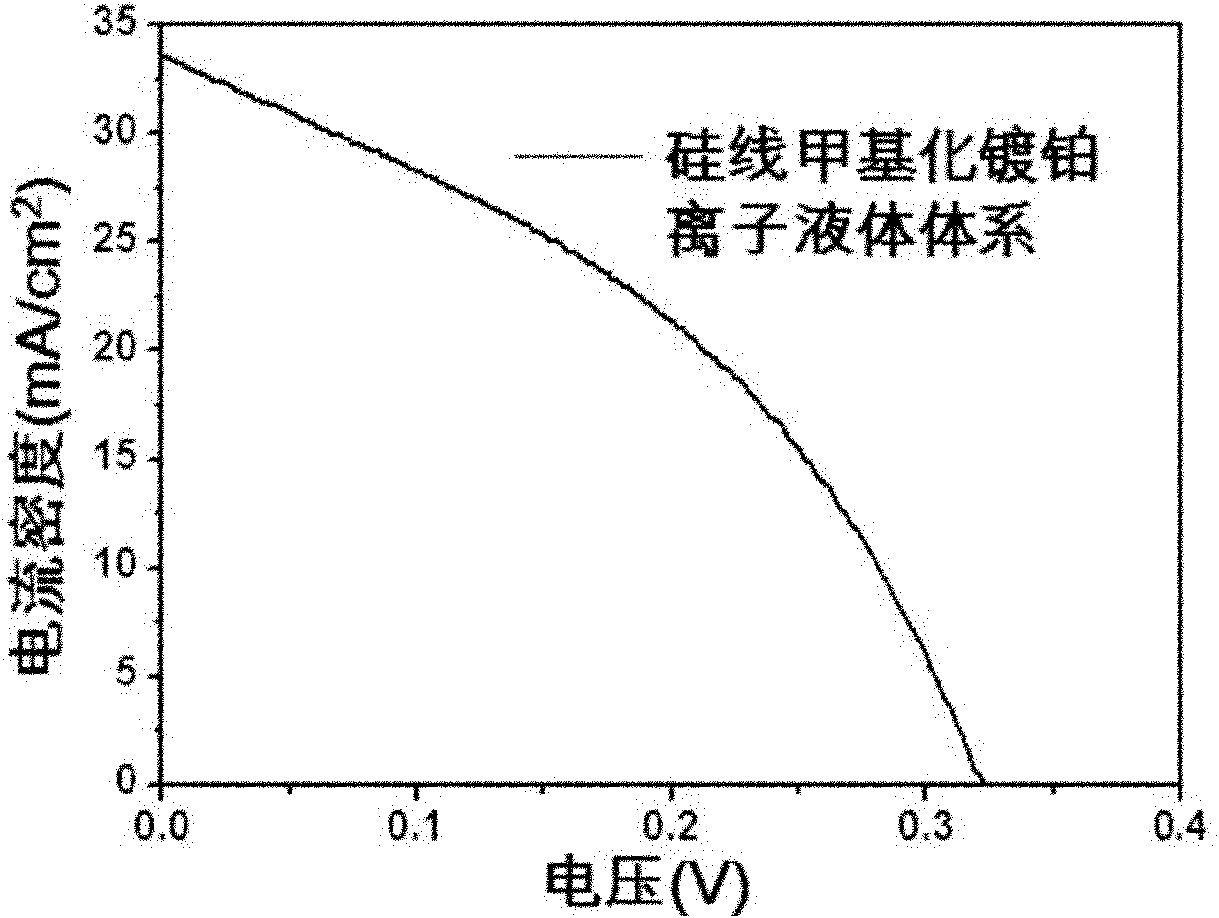

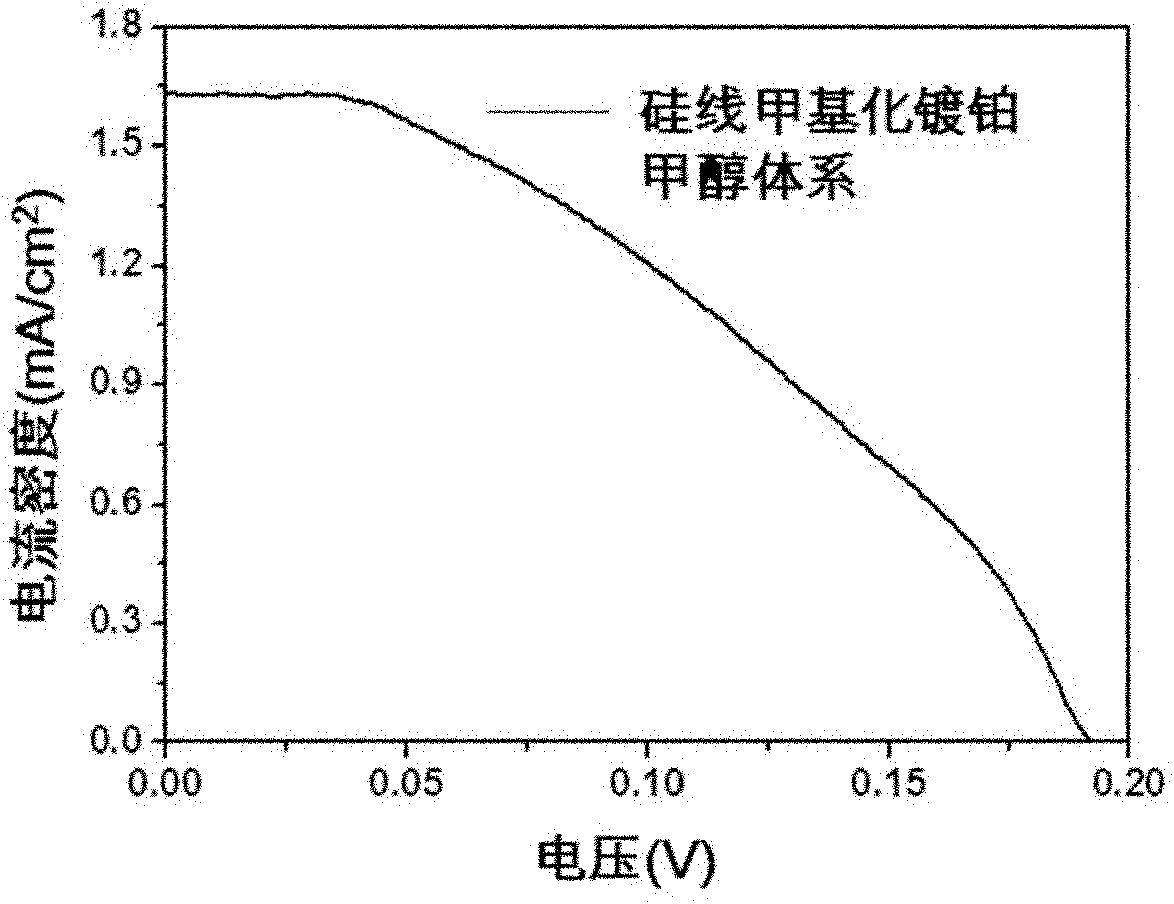

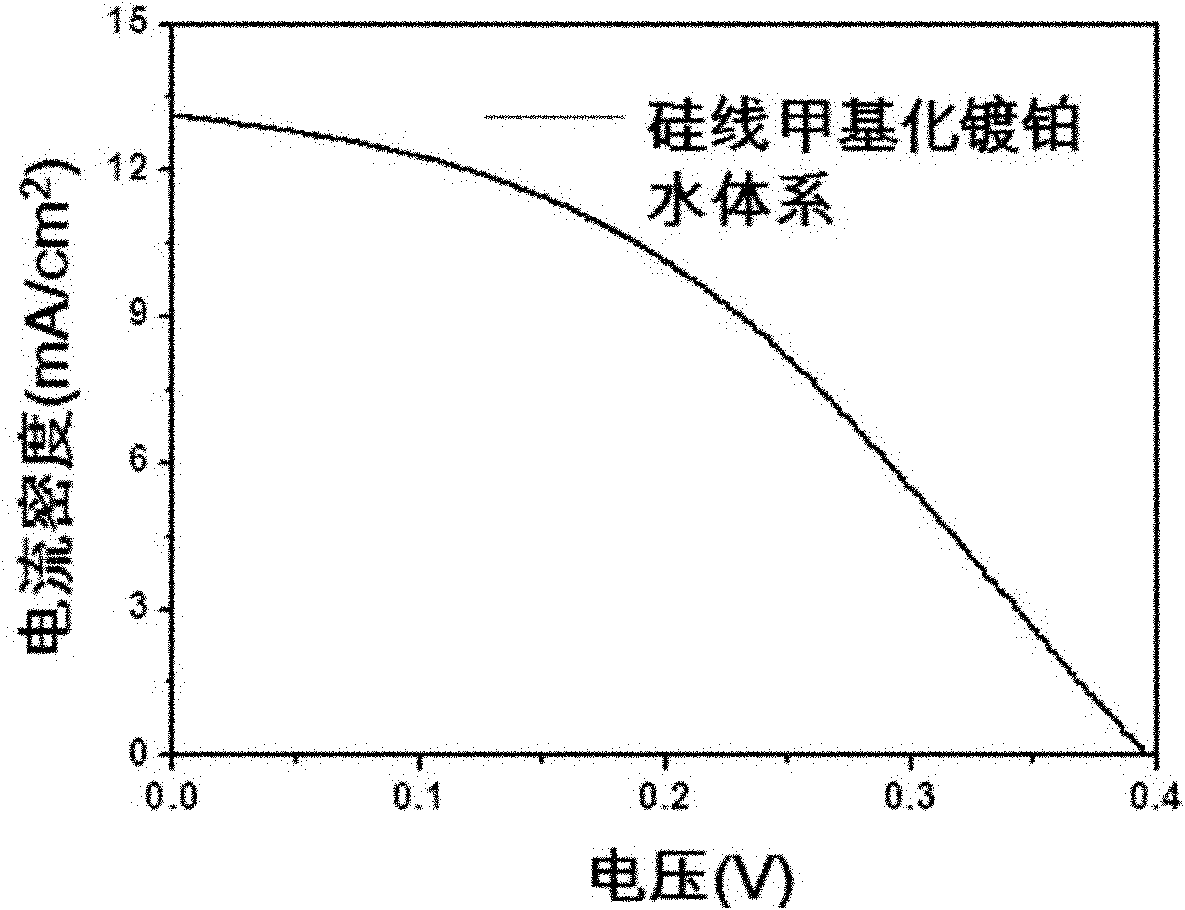

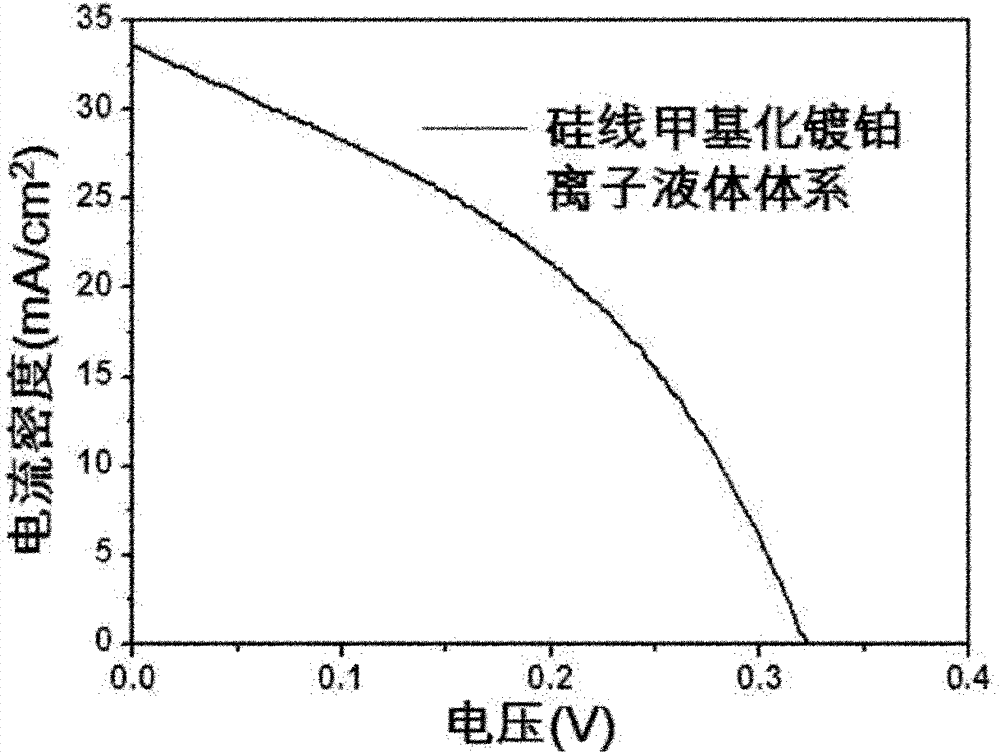

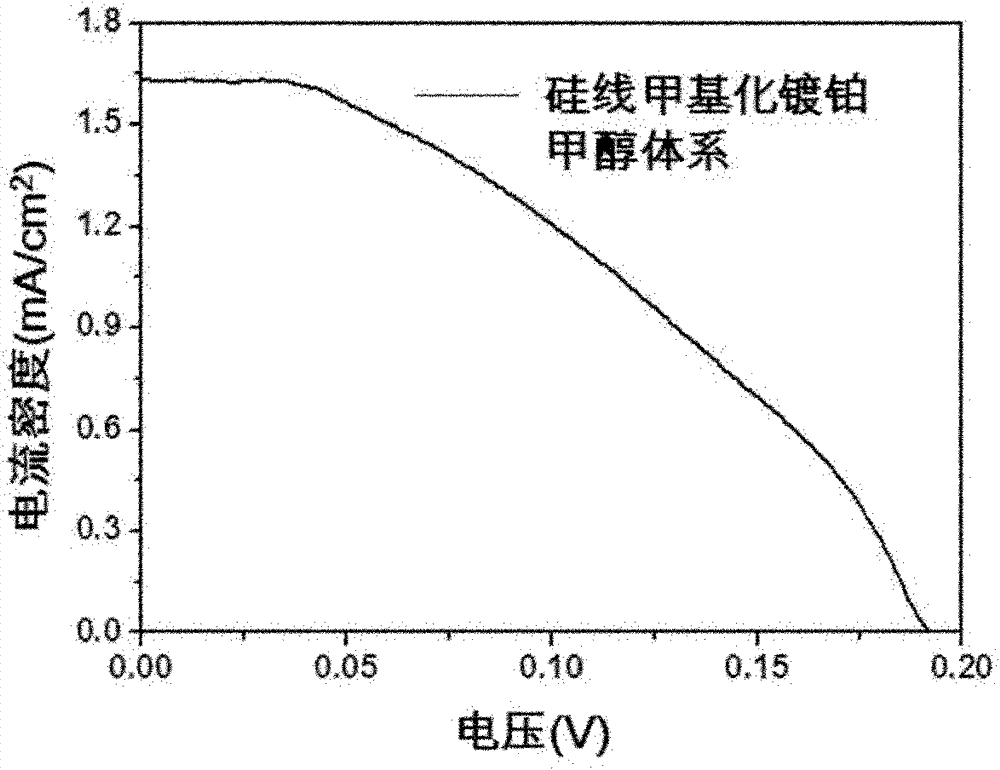

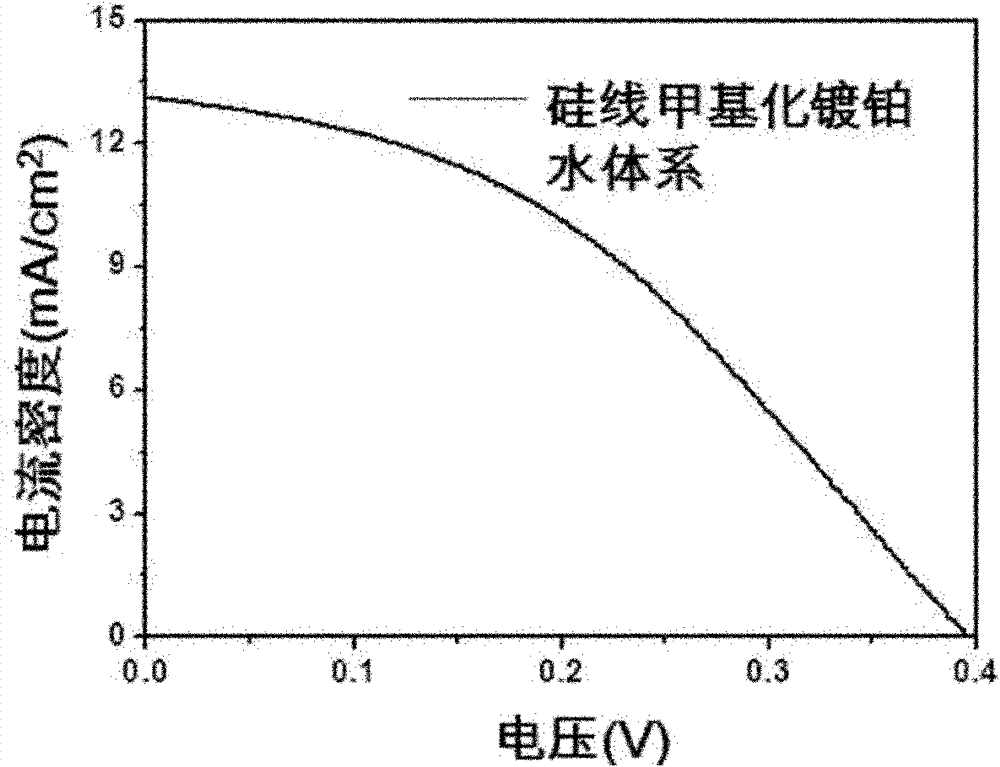

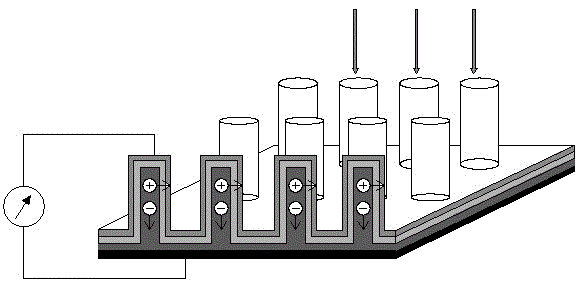

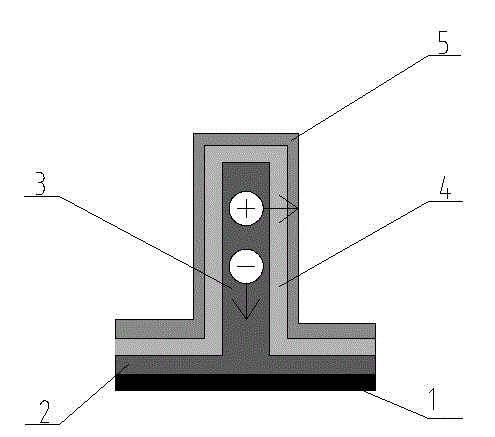

Solar battery based on silicon nano material

InactiveCN102157579ADesignableImprove conductivityLight-sensitive devicesPhotovoltaic energy generationSilicon electrodeSolar battery

The invention discloses a solar battery based on a silicon nano material. The solar battery based on the silicon nano material comprises a silicon wafer on which conductive glass is arranged; an insulation sealing layer is encircled between the conductive glass and the silicon wafer; an electrolyte chamber is formed between the conductive glass and the silicon wafer; ion liquid electrolyte is arranged in the electrolyte chamber; and lead-out electrodes are arranged on the backs of the conductive glass and the silicon wafer so as to form an ohm electrode structure. The solar battery has the characteristics of high thermal stability and chemical stability; a thinner silicon wafer can be used as a silicon electrode, the requirement for purity of the silicon is relatively low and the encapsulation requirement on the battery is reduced greatly at the same time. The invention also provides a low-cost, high-efficiency and stable technology for preparing the solar battery, which has a positive practical significance.

Owner:SUZHOU UNIV

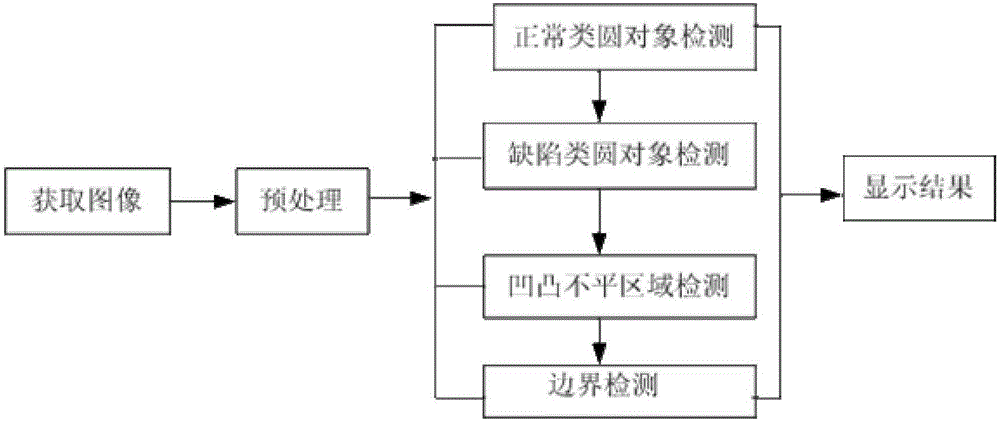

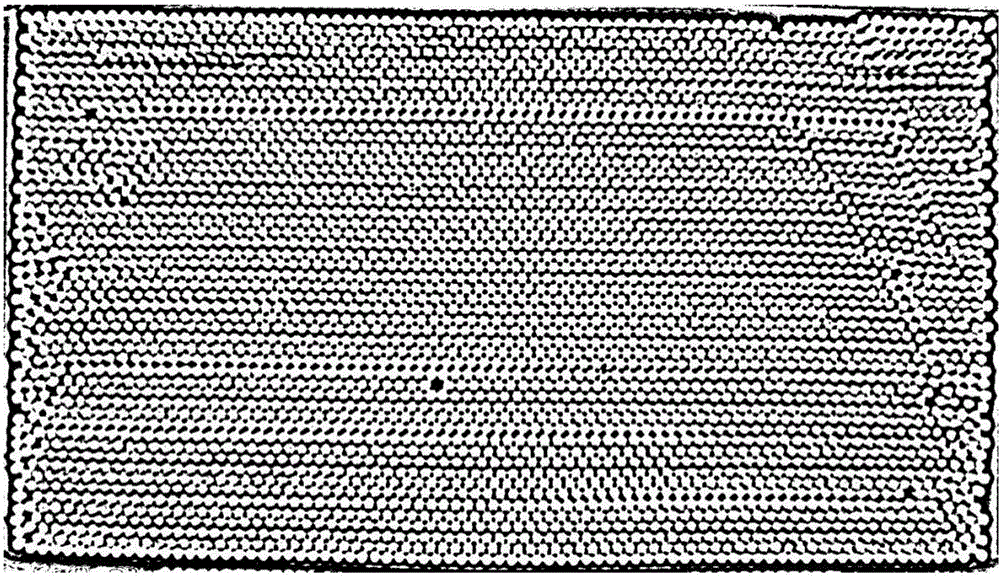

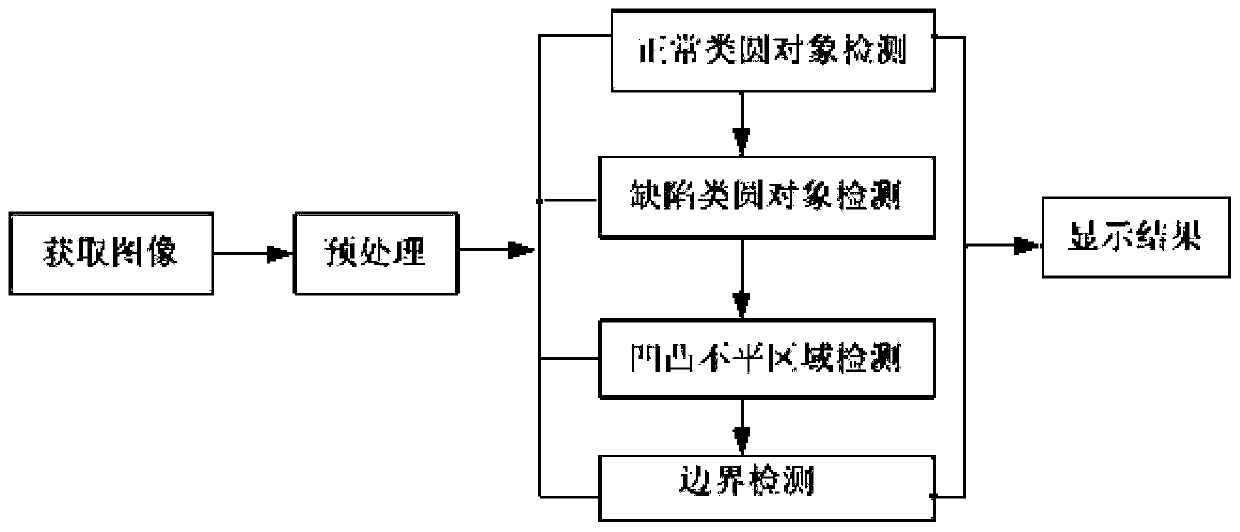

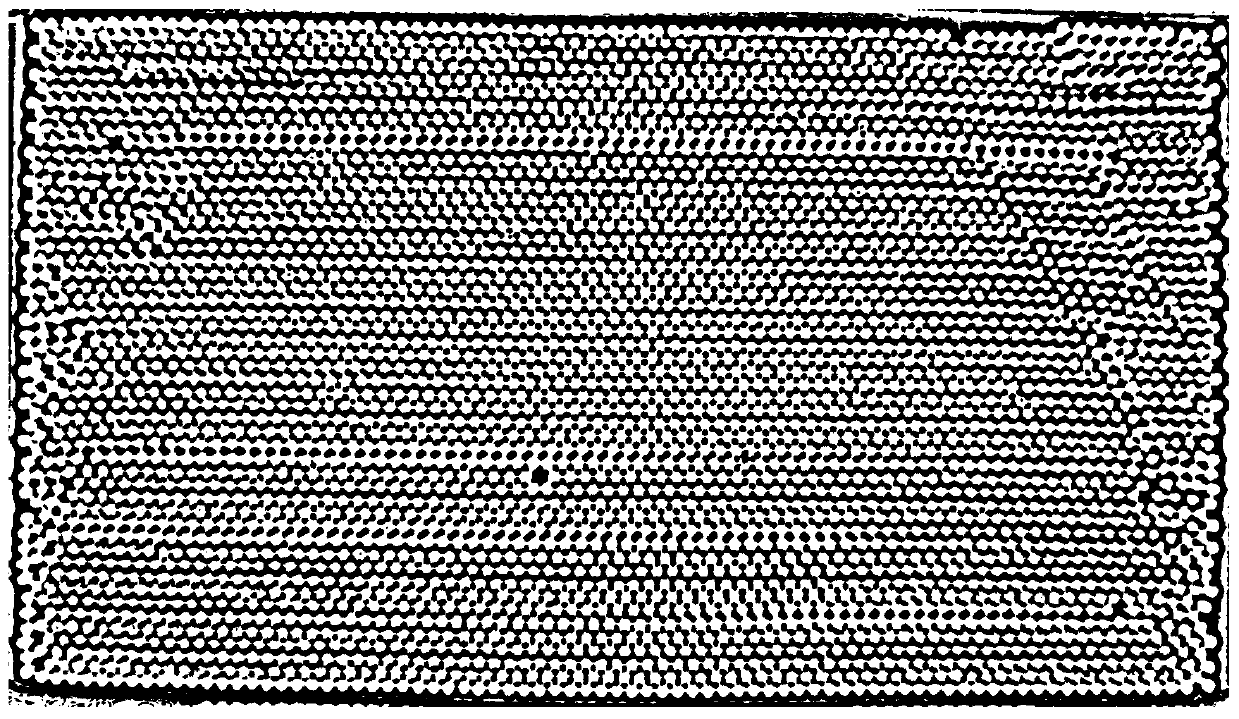

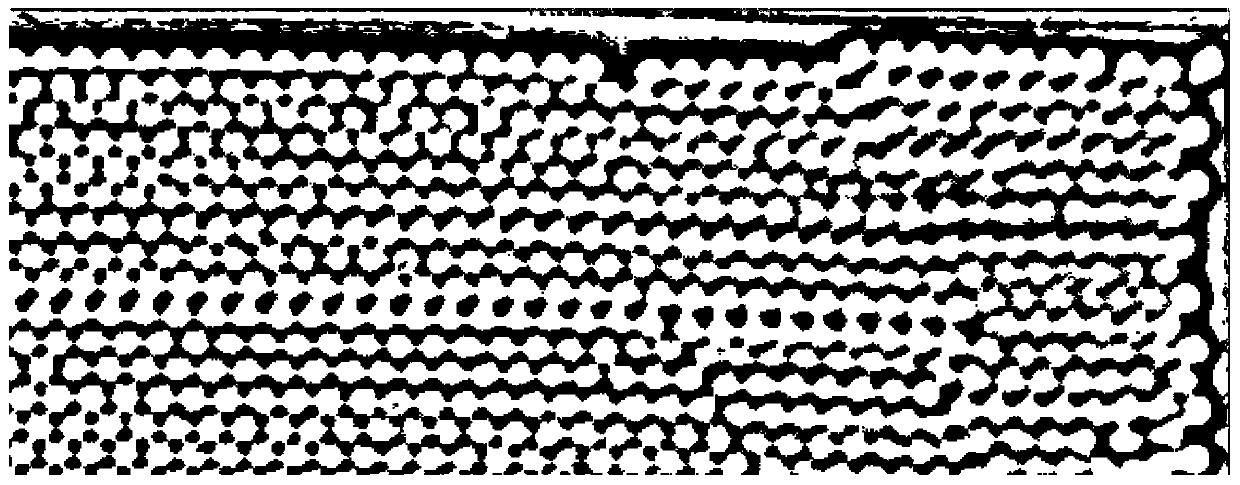

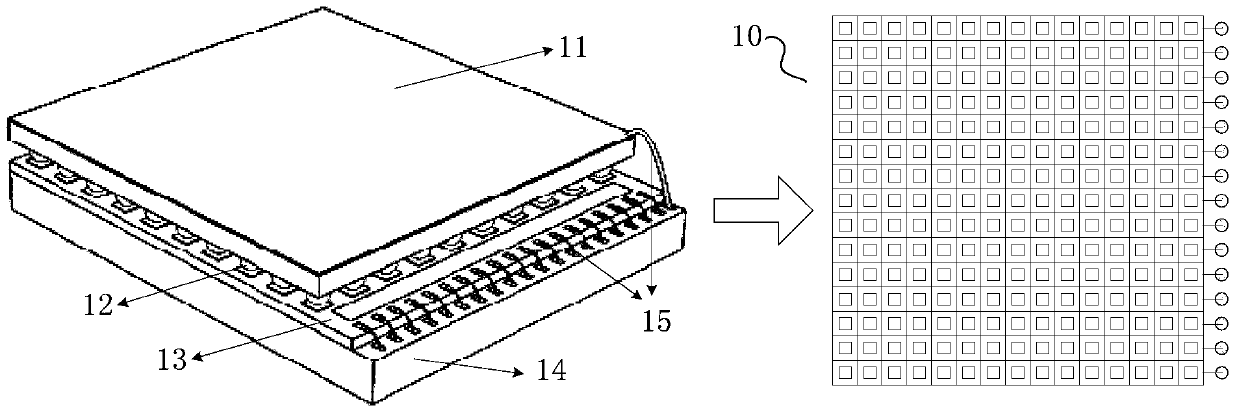

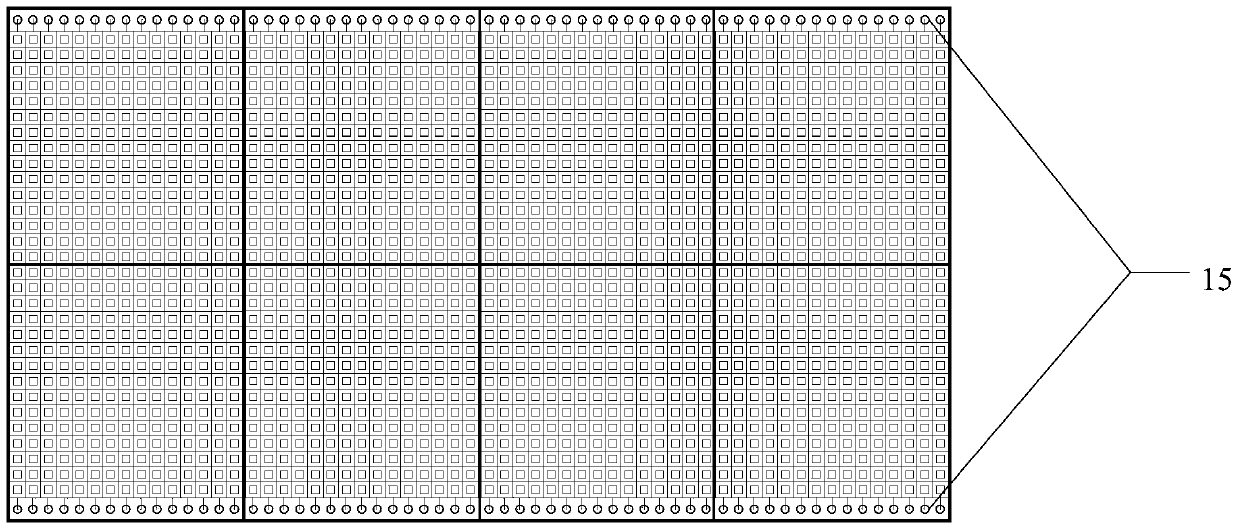

Intelligent recognition, counting, and detection algorithm for quasi-circle object facing packaging industry

ActiveCN106529551AImprove Counting AccuracyReduced packaging requirementsCharacter and pattern recognitionImage denoisingPretreatment method

The invention discloses an intelligent recognition, counting, and detection algorithm for a quasi-circle object facing a packaging industry. According to images collected by an industrial camera, effective regions where quasi-circle objects are located are obtained. An image pretreatment method includes: removing original image noises by using a median filtering algorithm and obtaining binary images after image denoising by using an adaptive local binary algorithm. Geometric feature extraction is carried out by detection for four times; to be specific, quasi-circle objects with normal areas after binaryzation are detected for first detection; the rest of quasi-circle objects with defects are detected after first detection during the second detection process; quasi-circle objects at an uneven region are detected during the third detection process; and quasi-circle objects may existing at a detection boundary are detected during the fourth detection process. Therefore, the counting accuracy of quasi-circle three-dimensional objects is improved; and the packaging requirement is low and the detection robustness is high. Meanwhile, real-time, rapid, on-line monitoring can be realized. The algorithm is applied to detection of various quasi-circle objects.

Owner:NANTONG UNIVERSITY

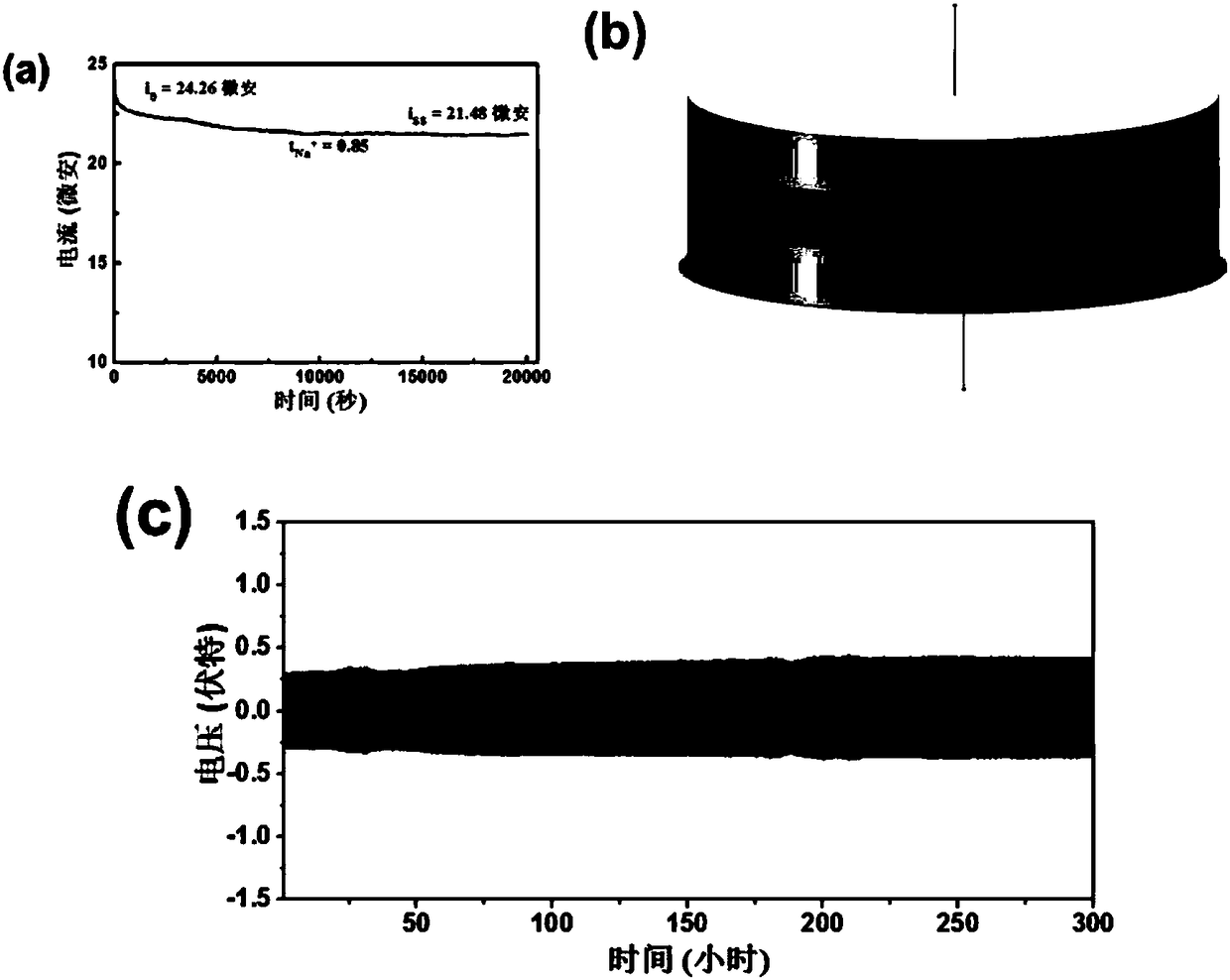

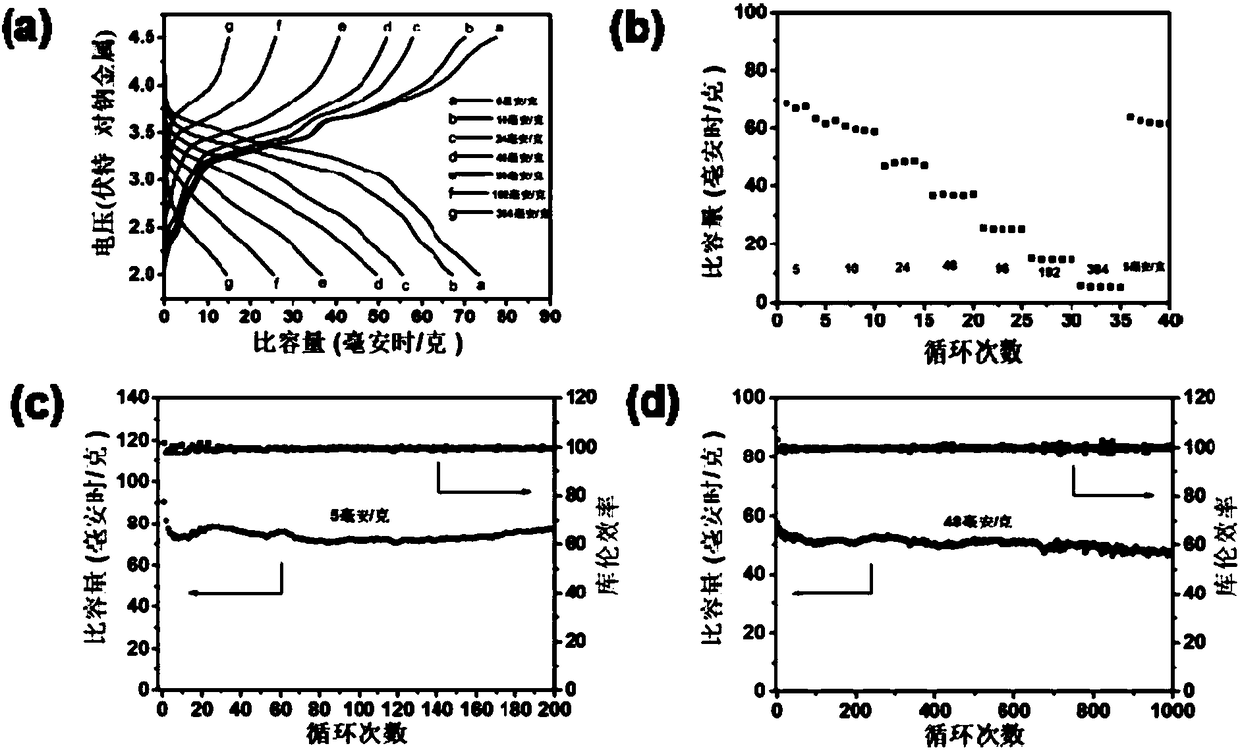

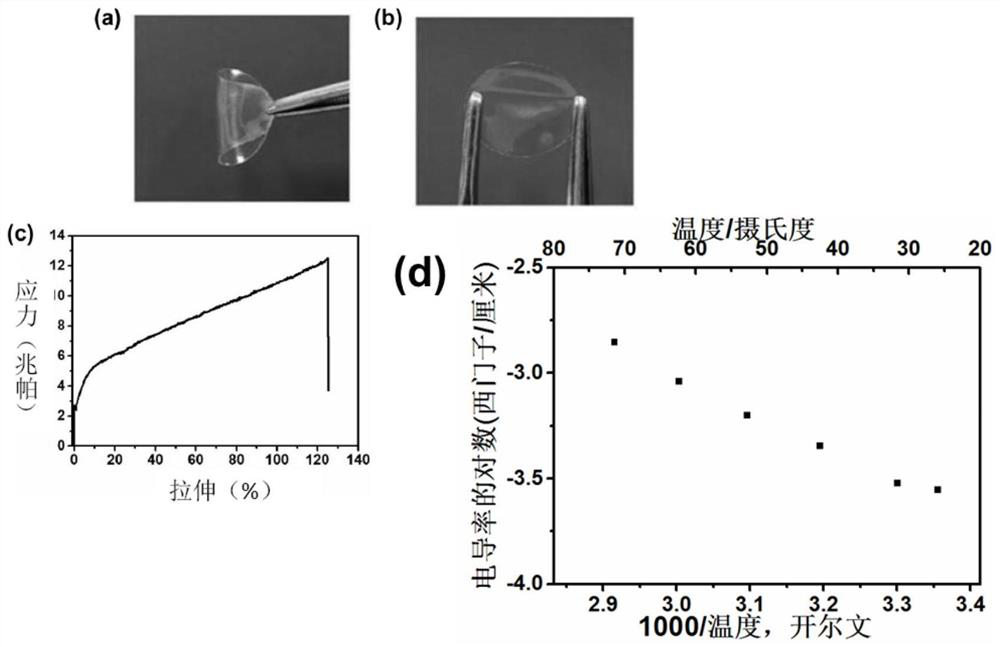

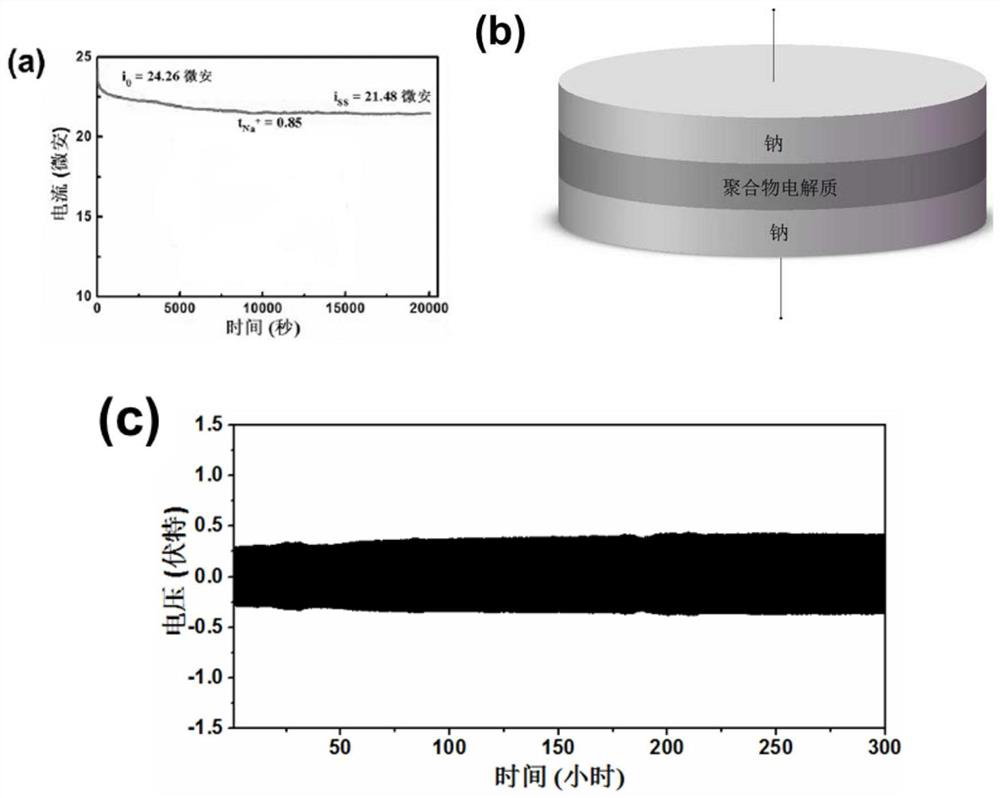

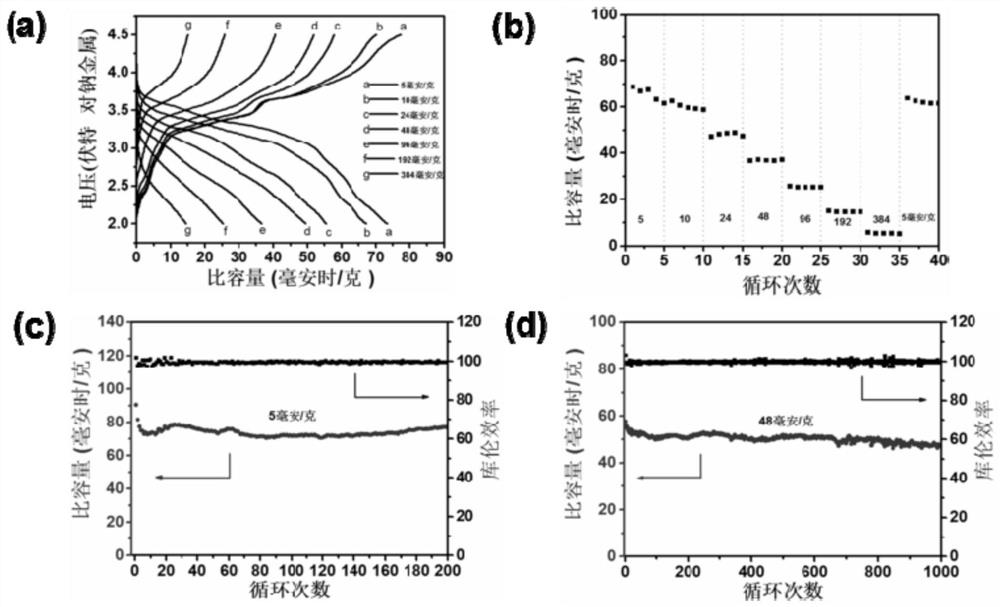

Perfluoro sodium polymer electrolyte, preparation method and application of perfluoro sodium polymer electrolyte, all-solid-state sodium-ion battery and friction nano-generator system

ActiveCN108539259AImprove securityIncrease energy densitySecondary cellsAll solid statePolymer electrolytes

The invention relates to the field of sodium-ion batteries and discloses a perfluoro sodium polymer electrolyte, a preparation method and an application of the perfluoro sodium polymer electrolyte, anall-solid-state sodium-ion battery and a friction nano-generator system; the preparation method of the perfluoro sodium polymer electrolyte comprises implementing ion exchange between perfluorinatedsulfonic acid resin and a Na+ containing solution. The provided all-solid-state sodium-ion battery comprises the above perfluoro sodium polymer electrolyte, and in addition, compared with a battery using a liquid electrolyte, the all-solid-state sodium-ion battery is excellent in safety and the energy density is higher.

Owner:BEIJING INST OF NANOENERGY & NANOSYST

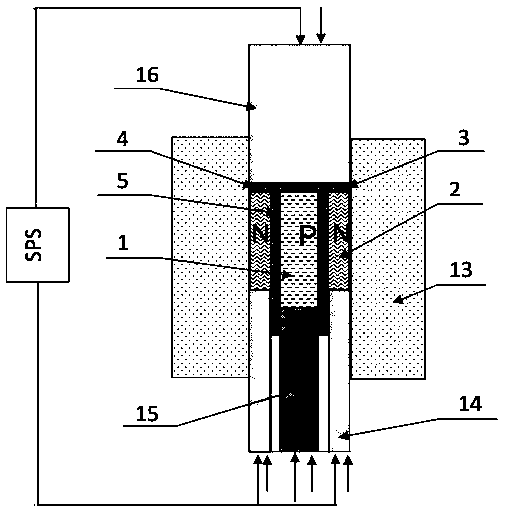

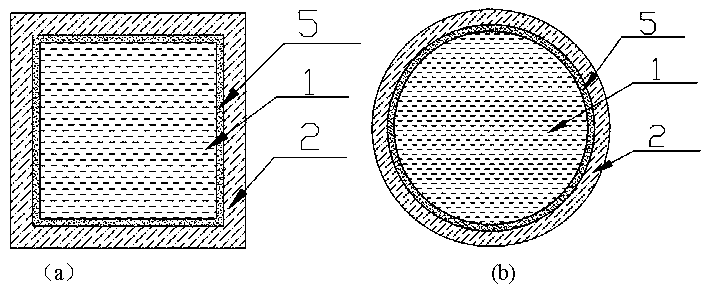

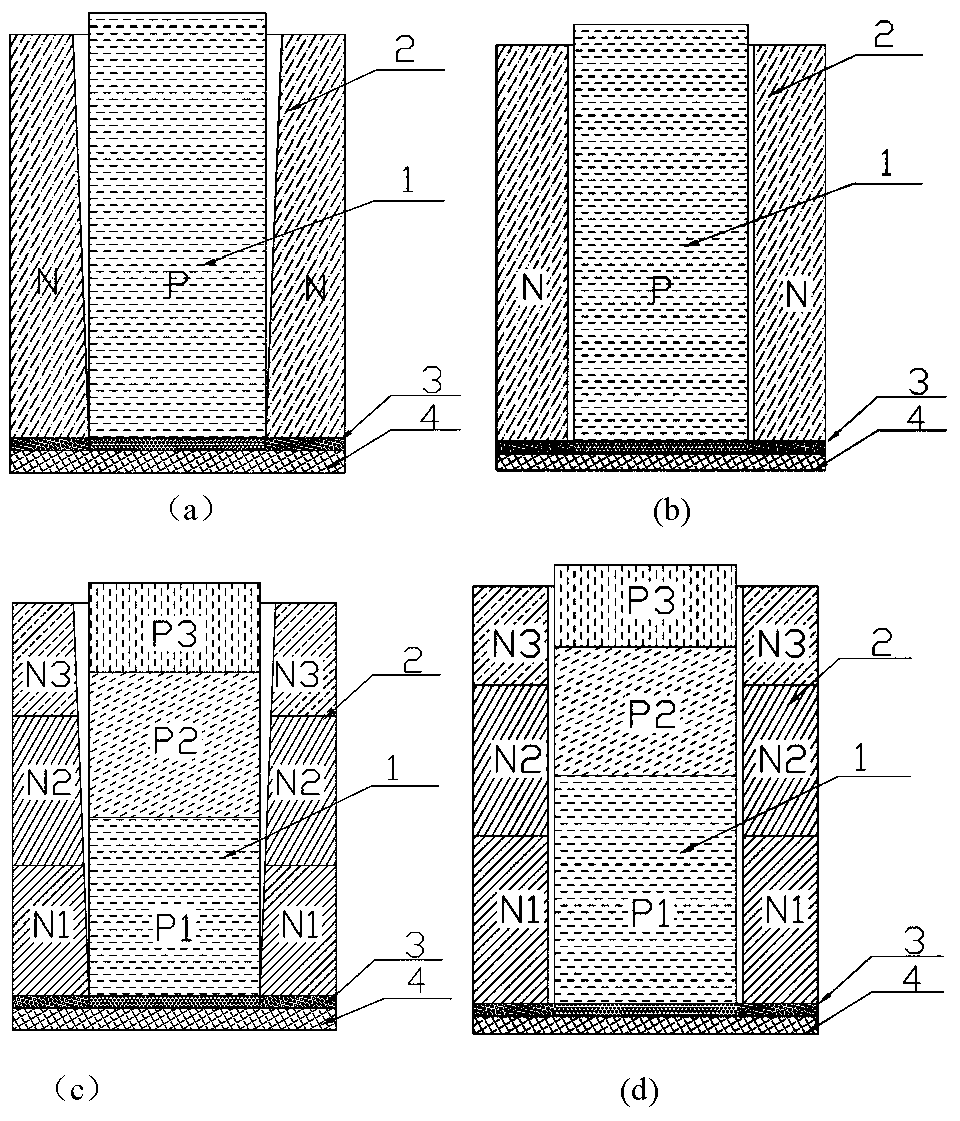

A thermoelectric component having a wrapping body structure

ActiveCN109037422AReduced packaging requirementsReduce the difficulty of packagingThermoelectric device manufacture/treatmentThermoelectric device detailsThermoelectric materialsMaterials science

The invention relates to a thermoelectric component device with a wrapping body structure, comprising: a first thermoelectric material; and a second thermoelectric material that wraps the first thermoelectric material; wherein the first thermoelectric material is one of a P-type thermoelectric material or an N-type thermoelectric material, and the second thermoelectric material is the other of theP-type thermoelectric material or the N-type thermoelectric material, and the sublimation stability or oxidation resistance of the second thermoelectric material at a high temperature in the range ofoperating temperature thereof is greater than that of the first thermoelectric material.

Owner:SHANGHAI INST OF CERAMIC CHEM & TECH CHINESE ACAD OF SCI

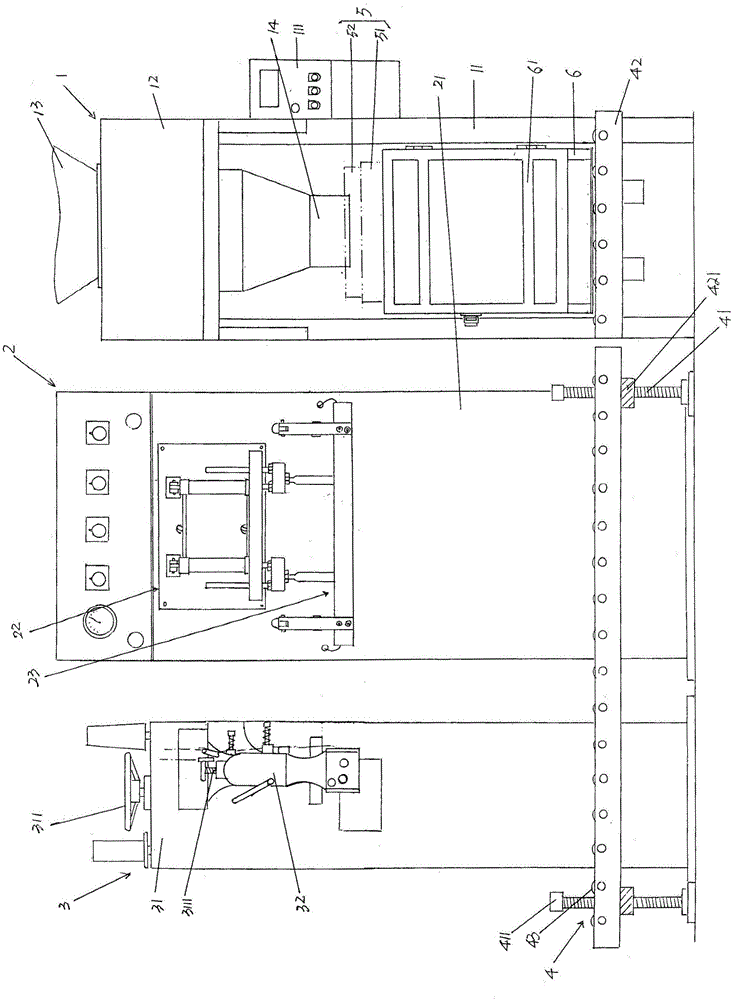

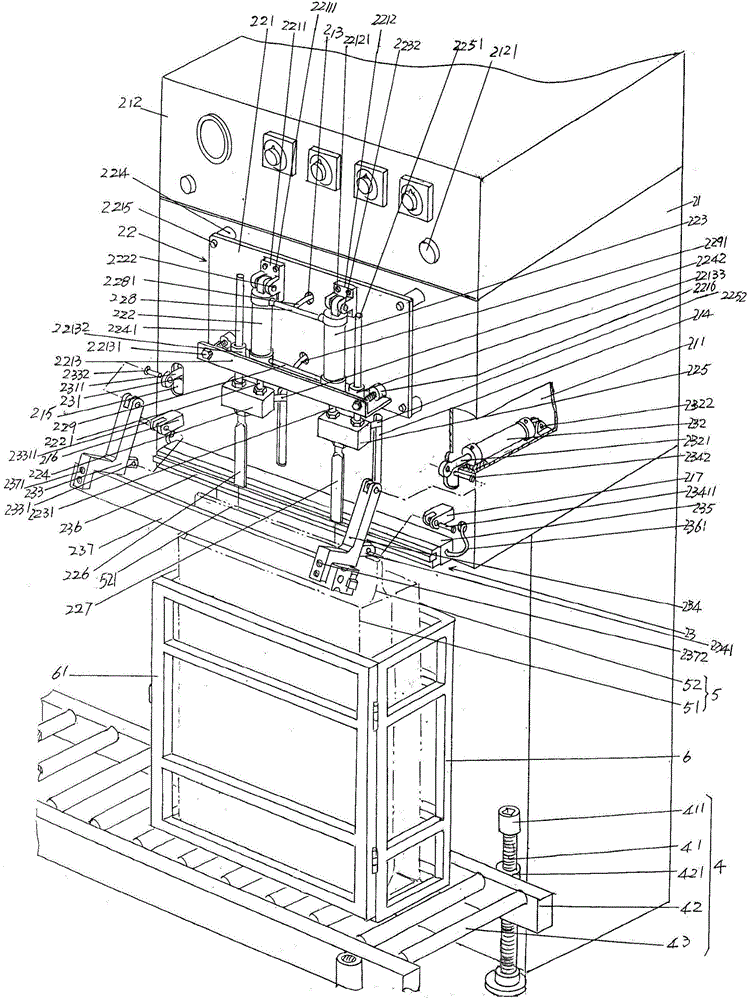

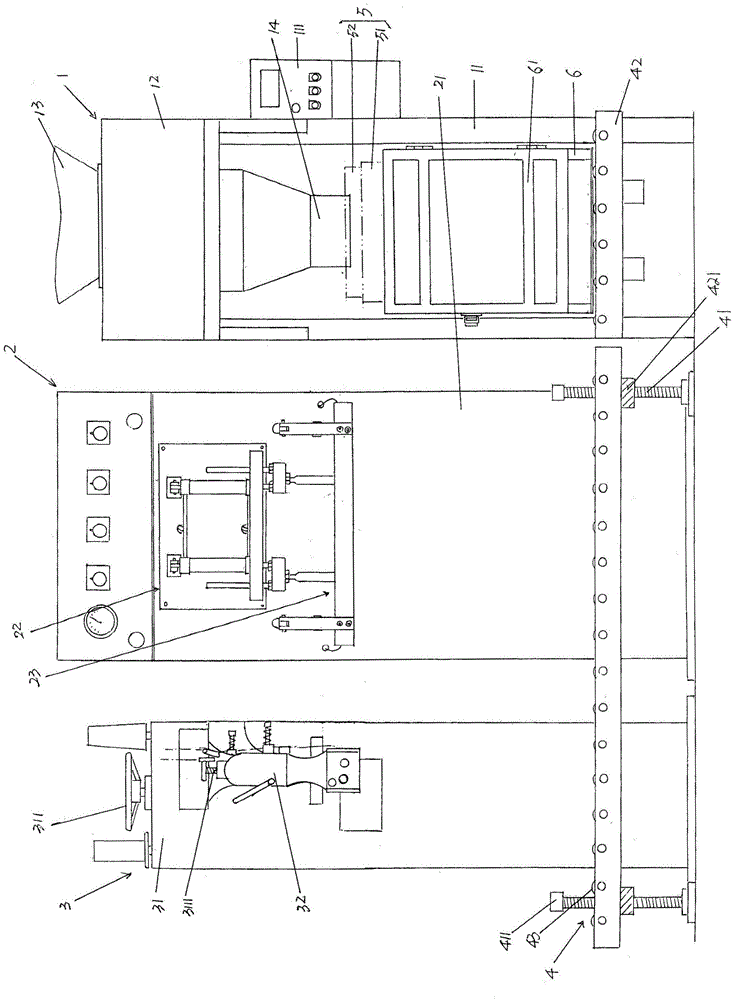

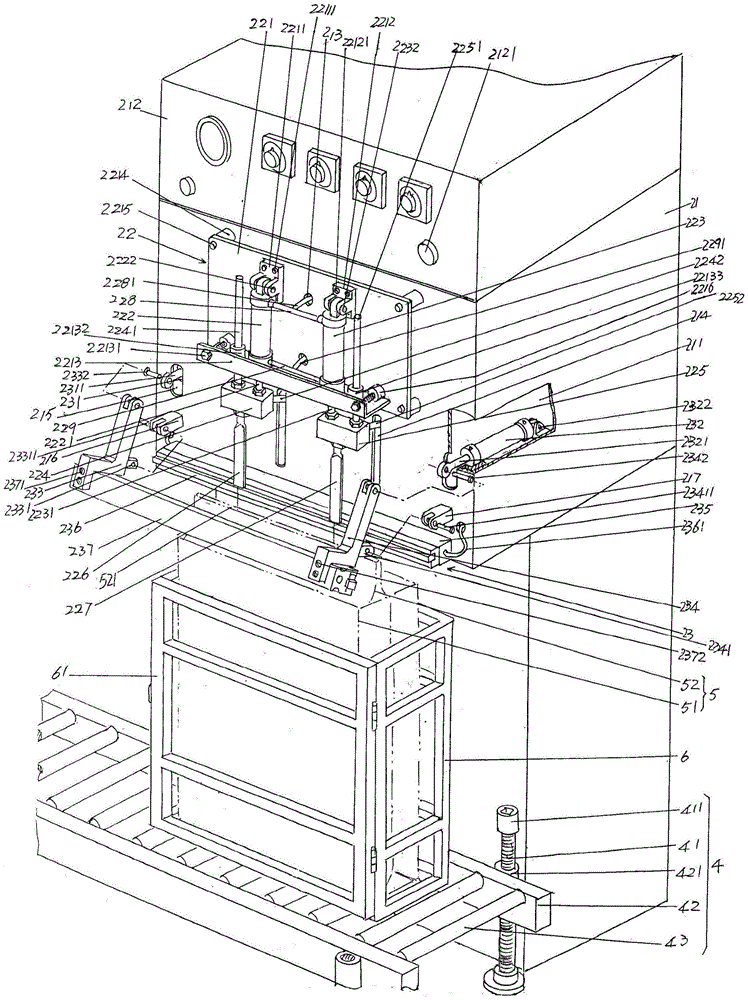

Automatic weighing, sealing and seaming device for wire and cable material

ActiveCN104670569AReduce the distanceGood coherent effectWrapper twisting/gatheringEngineeringCoherence effect

The invention discloses an automatic weighing, sealing and seaming device for a wire and cable material, and belongs to the technical field of packaging machinery for plastic particles for the wires and cables. The automatic weighing, sealing and seaming device comprises a weighing device supported on the terrace under a used state, a sealing device, a seaming device and a packaging bag supporting device, and is characterized in that the weighing device, the sealing device and the seaming device are arrayed on the same straight line in an arranging manner of left to right; the packaging bag supporting device is supported on a terrace of the use place at the position simultaneously corresponding to the lower parts of the front sides of weighing device, the sealing device and the seaming device. The automatic weighing, sealing and seaming device achieves a good coherence effect; the space is saved, and the adaptability to a packaging place is improved; the labor investment is reduced; furthermore, the sealing efficiency is improved; the labor intensity of an on-line worker is relieved, and the labor cost is reduced so as to save precious labor resources; the sealing quality is guaranteed; the packaging bag can be sealed under a vertical state; the automatic weighing, sealing and seaming device has an effect of preventing the wire and cable material in the bag from leaking from the bag opening.

Owner:CHANGSHU ZHONGLIAN PHOTOELECTRICITY NEW STUFF +1

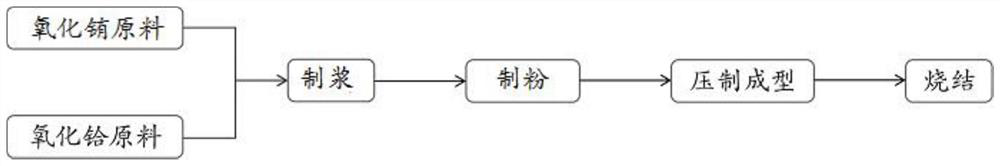

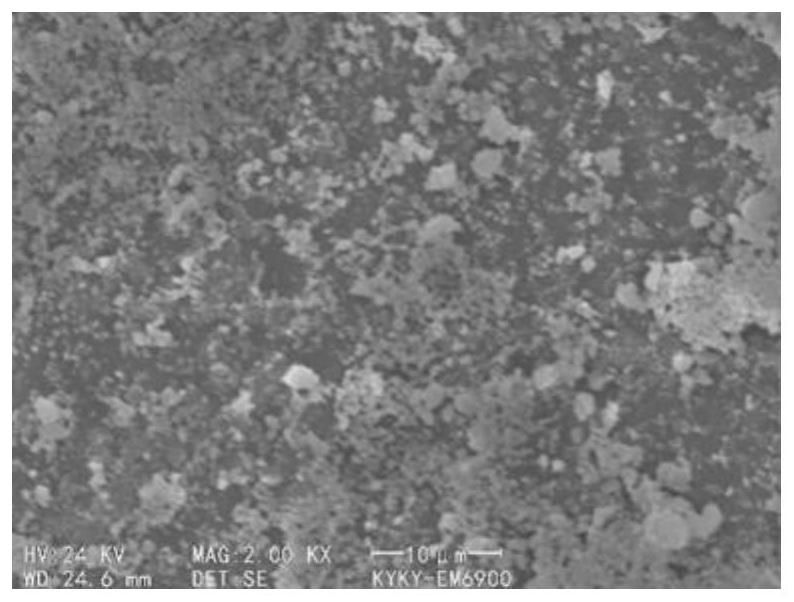

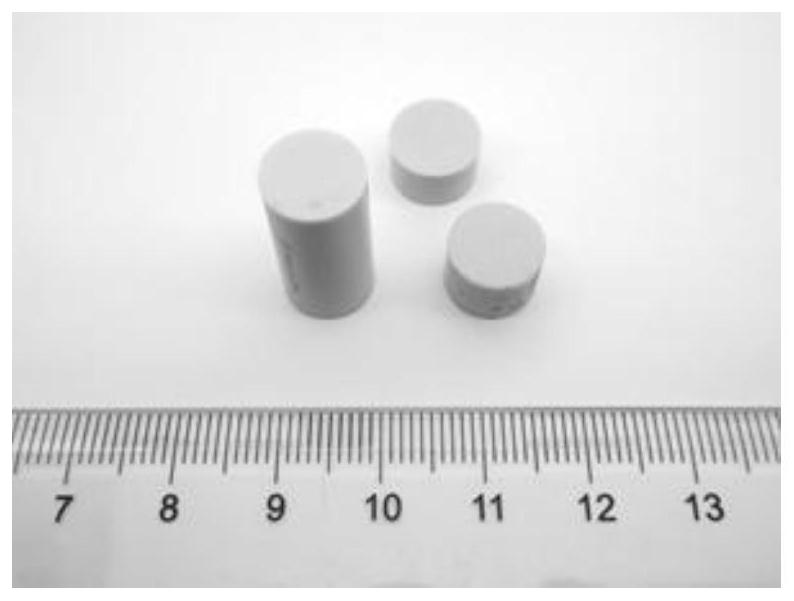

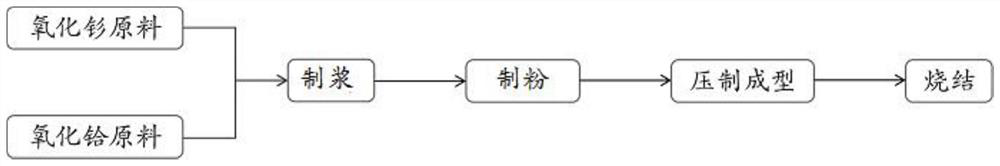

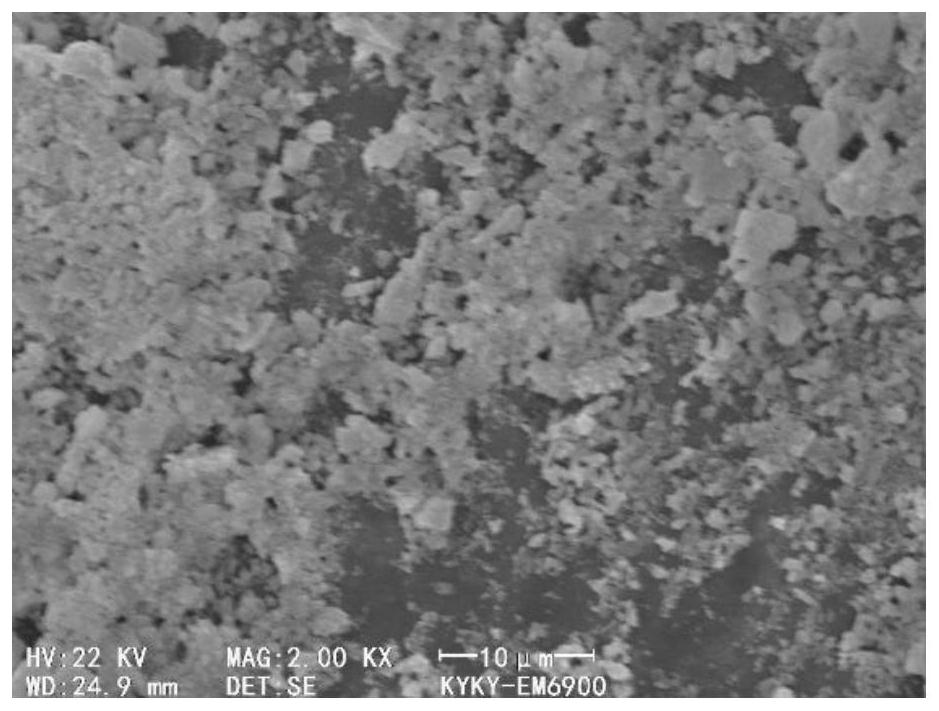

Neutron absorber material, preparation method thereof and control rod

InactiveCN111646794AExcellent resistance to radiation swellingExcellent radiation creep resistanceNuclear energy generationReactors manufactureSlurrySolid particle

The invention discloses a neutron absorber material and a preparation method thereof. The preparation method comprises the following steps: S1, preparing 30-90 parts by weight of an europium oxide rawmaterial and 10-70 parts by weight of a hafnium oxide raw material into slurry, and grinding solid particles in the slurry to be below a submicron level; s2, drying the prepared slurry below the submicron level, and then crushing and sieving the slurry to obtain powder particles with required particle sizes; s3, pressing the sieved powder particles into a biscuit; and S4, carrying out high-temperature sintering on the biscuit to obtain the neutron absorber. The invention further discloses a control rod, and an absorber of the control rod adopts a neutron absorbing material. The method is simple in process, and the prepared neutron absorbing material and the control rod are small in irradiation swelling, small in irradiation creep and long in service life.

Owner:CHINA NUCLEAR POWER ENG CO LTD +1

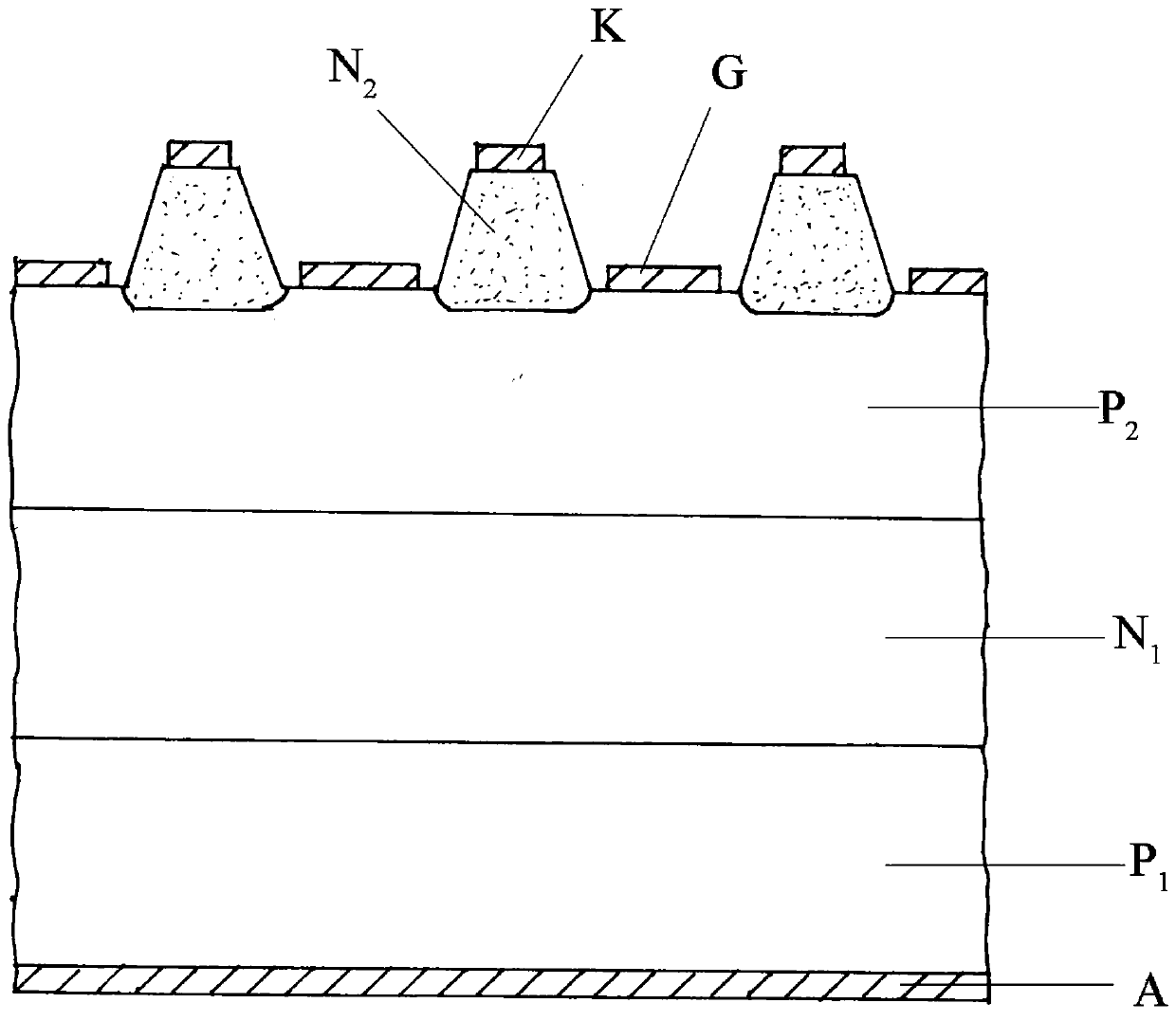

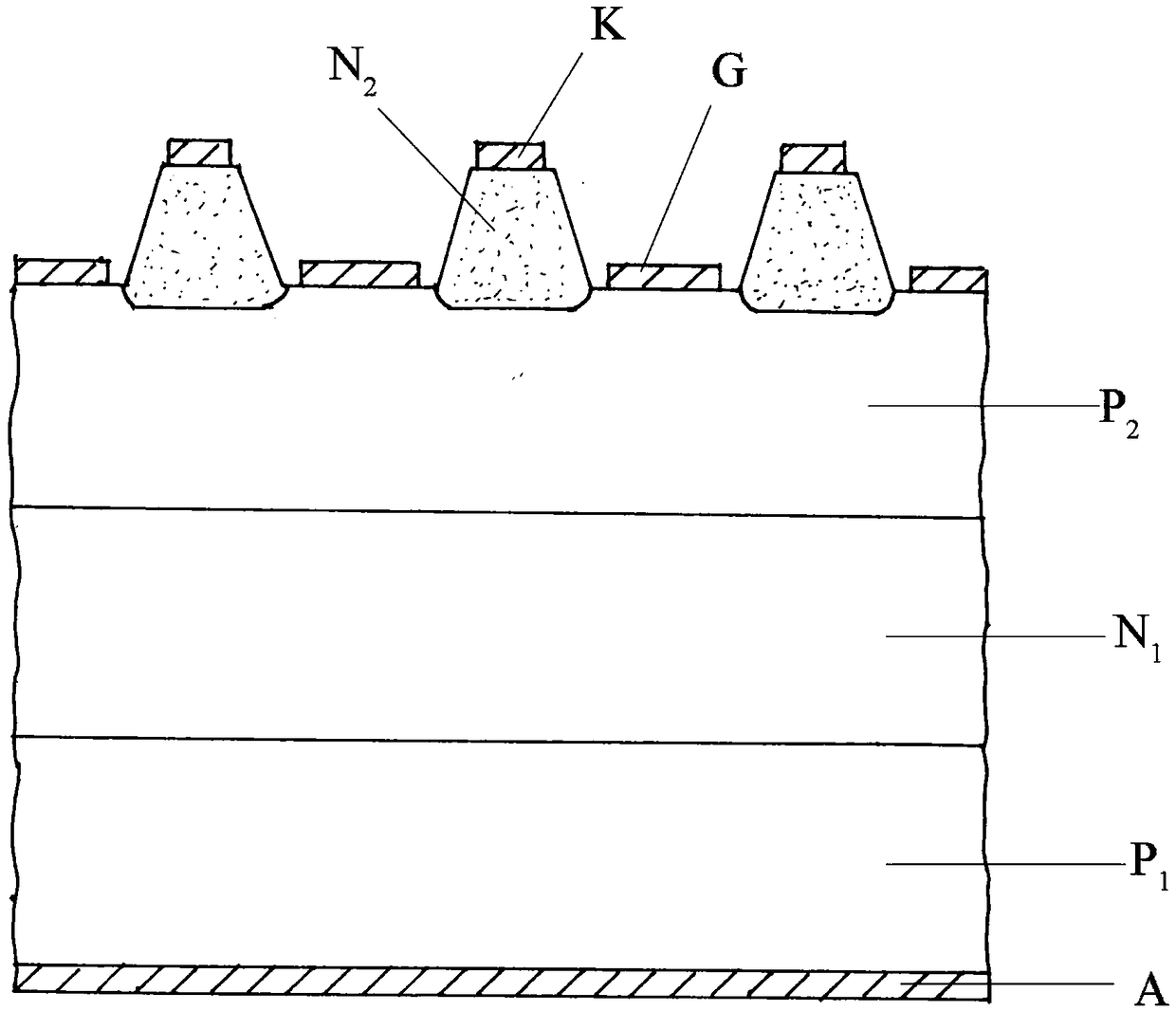

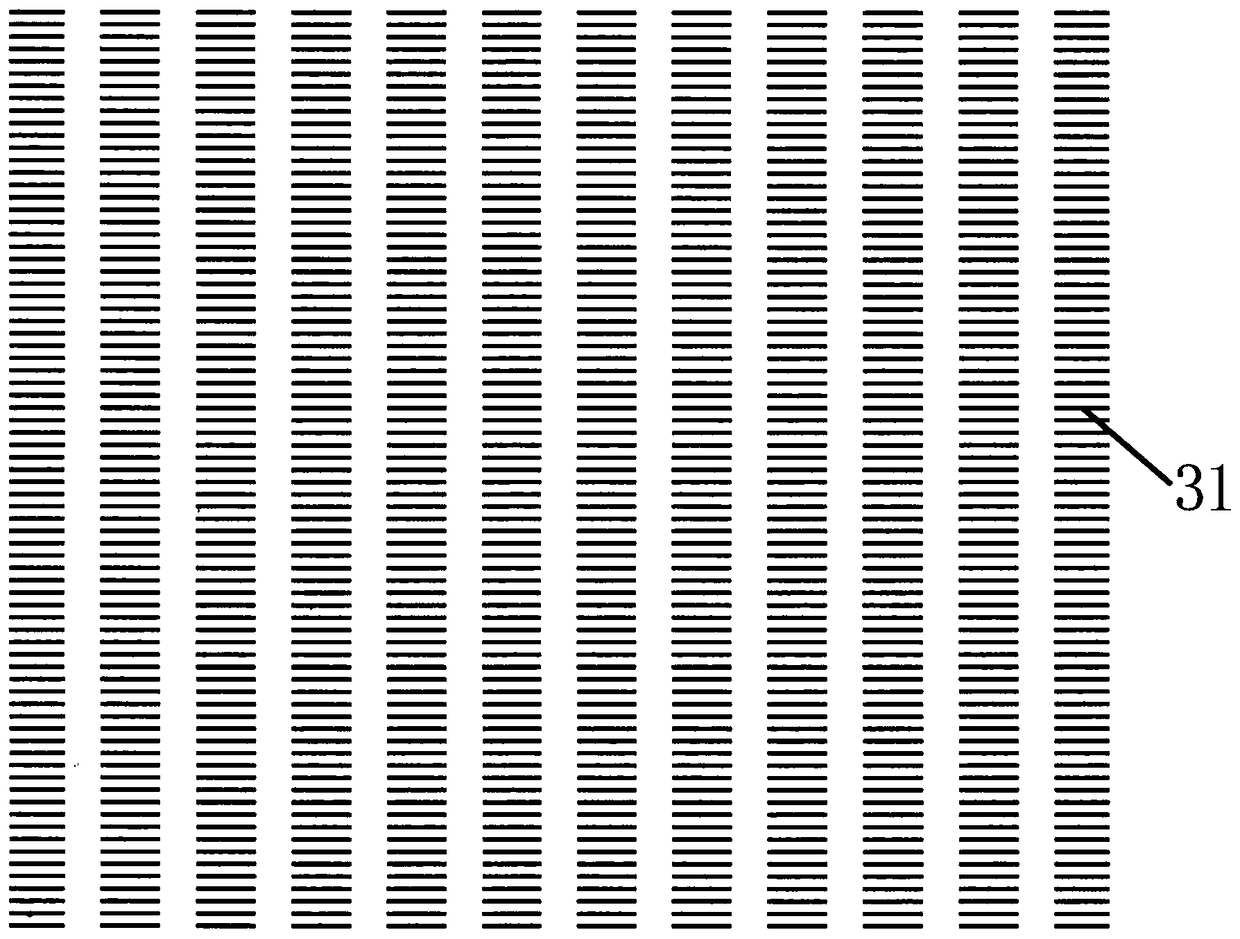

Thyristor with gate capable of being turned off and manufacturing method thereof

ActiveCN110047913AImprove reliabilityLower requirementThyristorSemiconductor/solid-state device manufacturingGate turn-off thyristorEngineering

The invention provides a thyristor with a gate capable of being turned off. A plurality of strips formed by repeatedly arranging a plurality of high-doping-concentration upper tube N-type emitting regions are arranged on the upper surface of an N-type silicon substrate sheet; an upper tube P-type concentrated base region bus bar surrounds the periphery of each strip; a cathode metal layer is arranged on the upper surface of each upper tube N-type emitting region; an upper tube P-type base region is arranged below each upper tube N-type emitting region; the side surface of each upper tube P-type base region is connected with an upper tube P-type concentrated base region or an upper tube P-type concentrated base region bus bar; an upper tube N-type collector region is arranged below the upper tube P-type base region, the upper tube P-type concentrated base region and the upper tube P-type concentrated base region bus bar; a lower tube P-type emitting region is arranged below the upper tube N-type collector region; the lower surface of the lower tube P-type emitting region is connected with an anode metal layer; and a gate metal layer is arranged above the silicon substrate sheet. According to the thyristor with the gate capable of being turned off, the dI / dt resistance and the dV / dt resistance are remarkably enhanced, and the breakdown voltage and the current capacity have a wideapplication range.

Owner:HANGZHOU UG MIN SEMICON TECH CO LTD

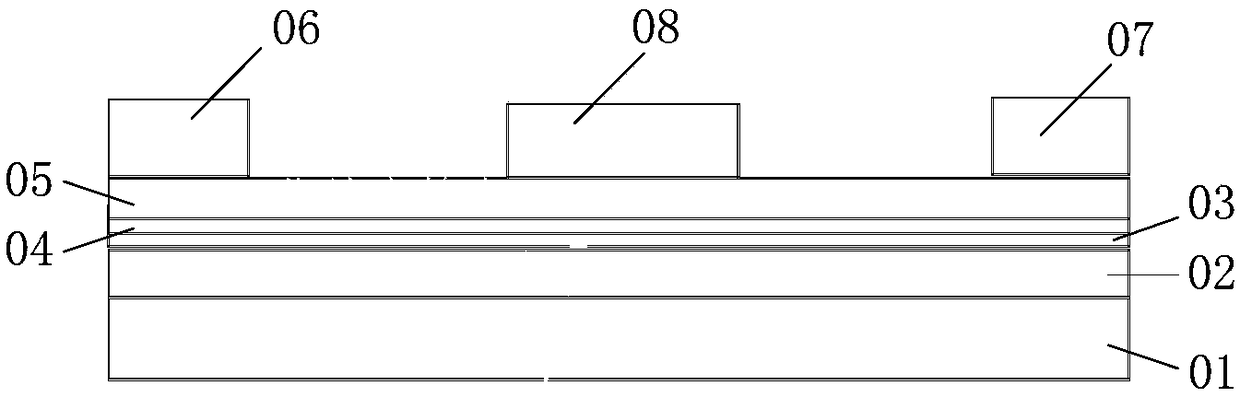

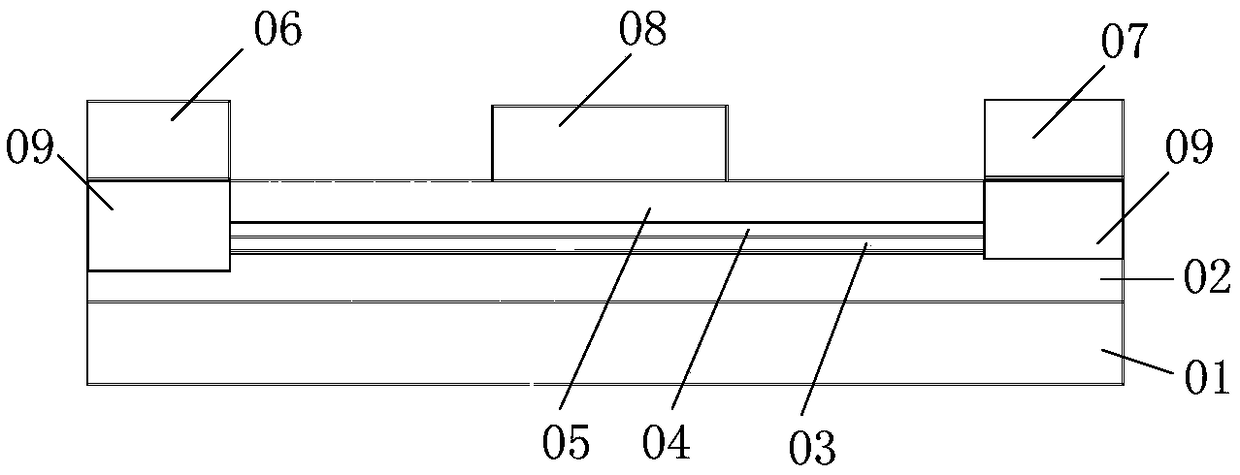

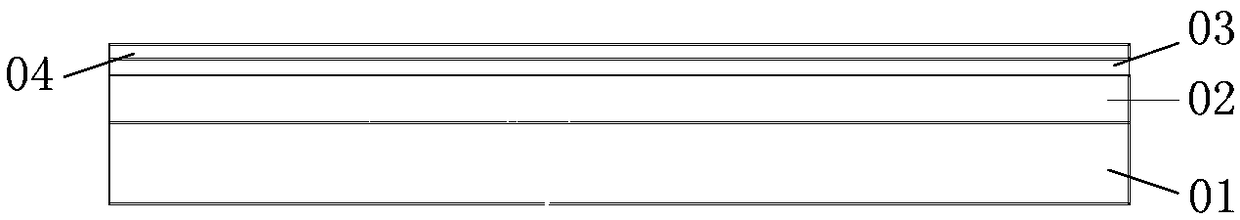

A high-speed transistor and a manufacturing method thereof

PendingCN109244131AHigh frequencyIncrease powerSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionSemiconductor materials

The invention belongs to the field of electronic technology and discloses a high-speed transistor and a manufacturing method thereof. The high-speed transistor comprises a substrate laye; a channel layer disposed on the upper surface of the substrate layer; a first undoped (AlxGa1-x) 2O3 layer disposed on the upper surface of the channel layer; a highly doped (AlxGa1-x) 2O3 layer disposed on the upper surface of the first undoped (AlxGa1-x) 2O3 layer; a voltage modulation layer disposed on the upper surface of the highly doped (AlxGa1-x) 2O3 layer; a source electrode and a drain electrode spaced apart on an upper surface of the voltage modulation layer; and a gate electrode disposed on the upper surface of the voltage modulation layer and located in a region between the source electrode and the drain electrode; As that novel high-speed and high-power transistor are fabricated by the ultra-wide band-gap semiconductor material system and the high-doping (AlxGa1-x) 2-D heterojunction electron gas is formed by the modulation of 2O 3 layer, which effectively improves the frequency and power performance of the device, improves the breakdown voltage of the device material, reduces the requirement of device packaging, and increases the market competitiveness of the device.

Owner:深圳市华讯方舟智能信息技术有限公司

CMOS difference radio-frequency signal amplitude detection circuit

ActiveCN101666833BHigh Amplitude Detection GainReduce power consumptionEnergy efficient ICTNoise figure or signal-to-noise ratio measurementCapacitanceDifferential signaling

The invention discloses a CMOS difference radio-frequency signal amplitude detection circuit, being composed of MOS transistors from M1 to Mn which work under the weak inversion polarization and a filter resistance R0 and a capacitance C0; the MOS transistors from M1 to Mn are serially connected, and the polarization is provided by a current source I1, the grids or drains of the transistors from M1 to Mn are respectively connected with the input positive end Rfin+ of a radio-frequency signal or the input negative end Rfin- of the radio-frequency signal through the capacitances from C1 to Cn, and an amplitude detection result is output by the filter resistance R0 and the capacitance C0, the current change of the MOS transistors under the weak inversion polarization submits to index property, and higher amplitude detection gain is obtained compared with square frequency characteristics, particularly for the weak signal detection, the gain is obvious, and the power consumption is low andis approximate to zero consumption; a plurality of the MOS transistors are serially connected to lead amplitude detection output of each MOS transistor to be serially added, thereby obtaining n timesof detection gain; meanwhile, input impedances of radio-frequency inputs of all MOS transistors are connected in parallel, the whole input impedance value is reduced by n times, the requirements of Qvalue that a high-frequency signal is input to a matching circuit is reduced, so as to realize to be directly connected with a radio-frequency antenna; the differential signal input is adopted, so asto be easy for chip integration and reduce the requirements of chip encapsulation. The circuit is particularly suitable for being applied to wake-up signal detection in a short range communication system and weak radio-frequency signal detection in an RFID system.

Owner:斯凯瑞利(北京)科技有限公司

Gate-turn-off thyristor and manufacturing method thereof

InactiveCN108899358AEnhanced anti-dIEnhanced dtThyristorSemiconductor/solid-state device manufacturingGate turn-off thyristorEngineering

The invention provides a gate-turn-off thyristor. A plurality of strips formed by repeatedly arraying a plurality of high-doping-concentration upper tube N type emission regions are arranged on an upper surface of an N type silicon substrate chip; an upper tube P-type concentrated basic region bus bar is arranged around the periphery of each strip; a cathode metal layer is arranged on the upper surface of one upper tube N type emission region, an upper tube P-type basic region is arranged below the upper tube N type emission region, and a side face of the upper tube P-type basic region is connected with an upper tube P-type concentrated basic region or the upper tube P-type concentrated basic region bus bar; an upper tube N-type current collection region is arranged below the upper tube P-type basic region, the upper tube P-type concentrated basic region and the upper tube P-type concentrated basic region bus bar; a lower tube P-type emission region is arranged below the upper tube N-type current collection region; a lower surface of the lower tube P-type emission region is connected with an anode metal layer; a gate metal layer is arranged above the silicon substrate chip. According to the gate-turn-off thyristor provided by the invention, anti-dI / dt ad anti-dV / dt capabilities of turn-off thyristor are remarkably enhanced, and breakdown voltage and a current capacity have a wide application range.

Owner:HANGZHOU UG MIN SEMICON TECH CO LTD

Neutron absorber material, preparation method thereof and control rod

InactiveCN111704459AExcellent resistance to radiation swellingExcellent radiation creep resistanceNuclear energy generationNuclear reaction controlSlurrySolid particle

Owner:CHINA NUCLEAR POWER ENG CO LTD +1

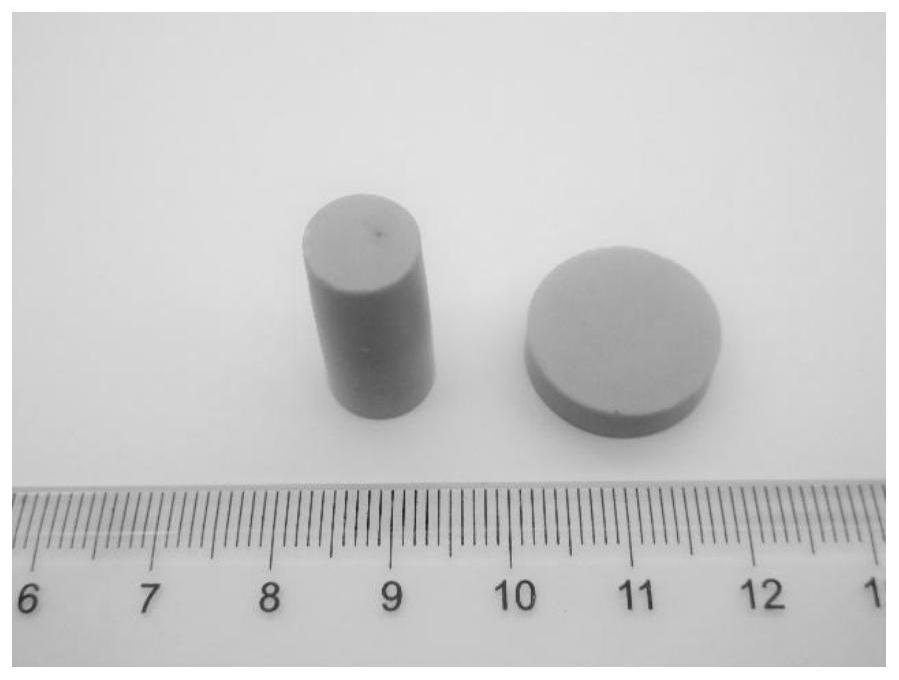

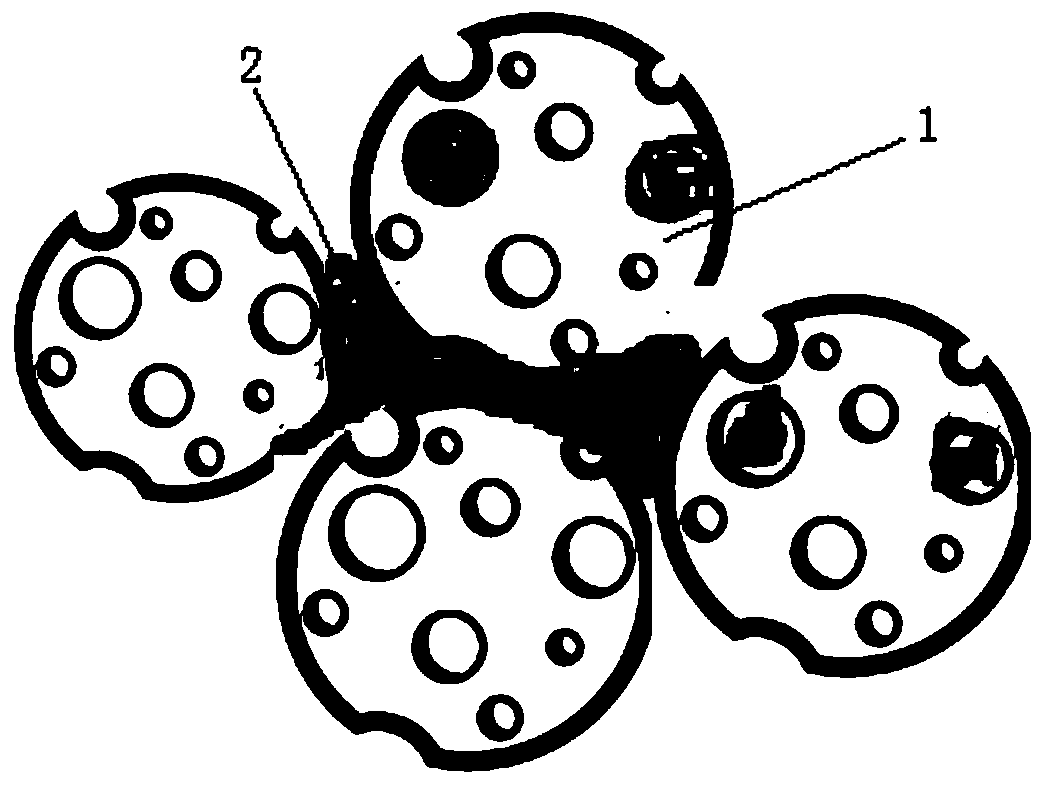

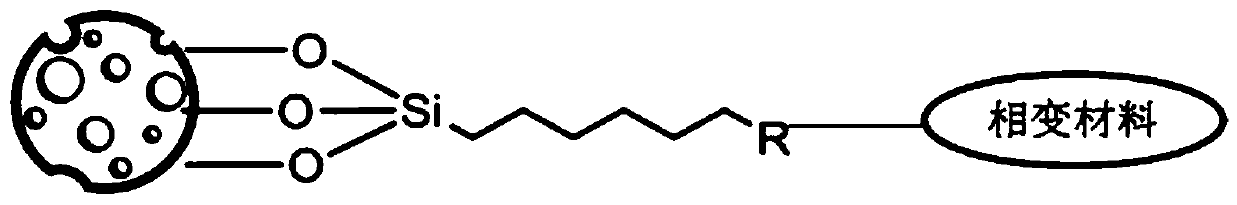

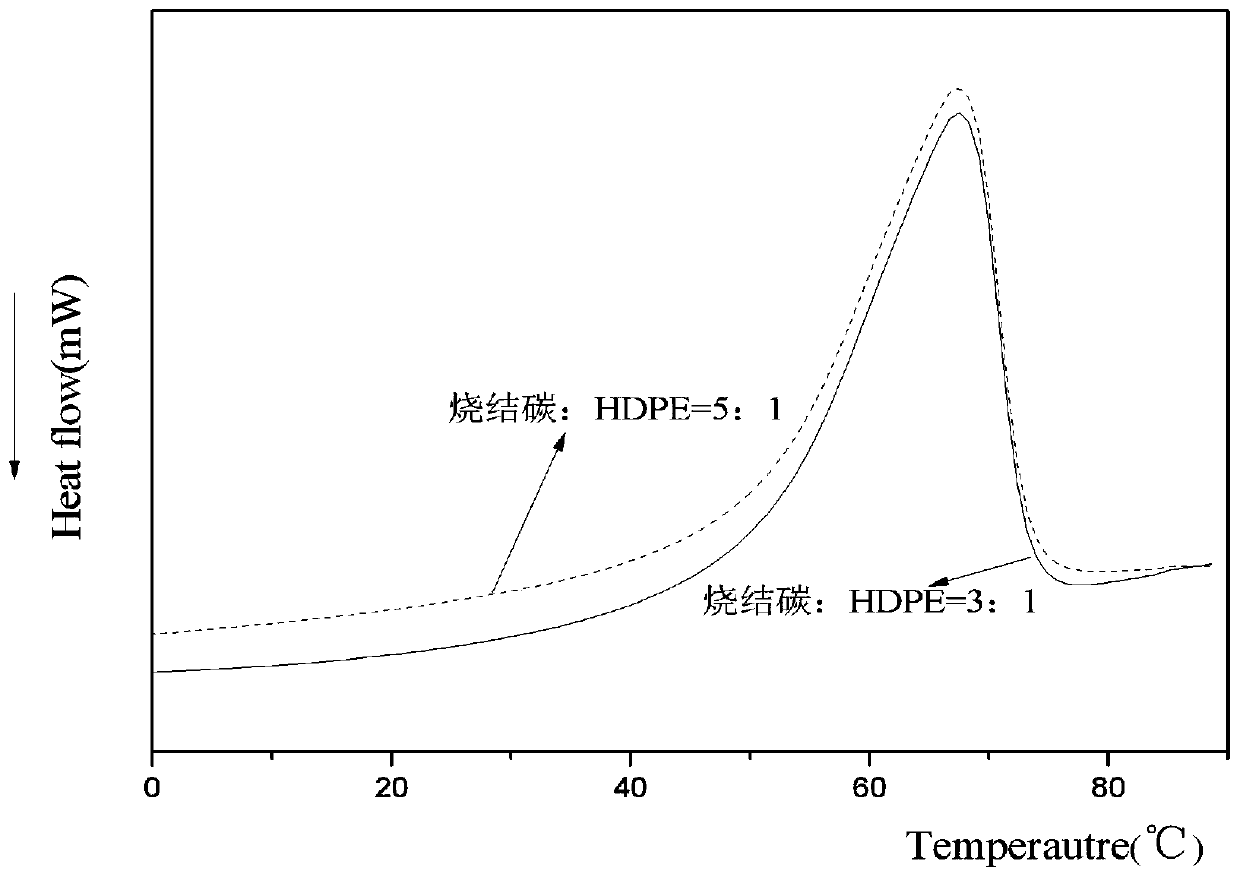

A shape-fixed phase-change material with sintered carbon as a carrier and its preparation method

ActiveCN108531139BReduce manufacturing costImprove applicabilityHeat-exchange elementsCompatibilizationPolymer

The invention discloses a shape-stabilized phase change material with shaped sintered carbon as the carrier and a preparation method thereof. The shape-stabilized phase change material with the shapedsintered carbon as the carrier and the preparation method thereof solve the technical problems easy loss of accumulated energy, low thermal conductivity, poor encapsulation properties and poor dimension and shape design of existing composite phase change materials. The shape-stabilized phase change material with the shaped sintered carbon as the carrier is composed of, by weight percentage, 85-95% of organic high-polymer phase change materials and 5-15% of the shaped sintered carbon, wherein the shaped sintered carbon is processed through surface compatibility treatment; the high-polymer phase change materials are distributed inside gaps formed among particles of the shaped sintered carbon. The preparation method of the shape-stabilized phase change material with the shaped sintered carbon as the carrier comprises preparation of the shaped sintered carbon, surface compatibility treatment, heating and melting of the phase change materials and pressurized permeation.

Owner:WUHAN XINBOMING TECH DEV

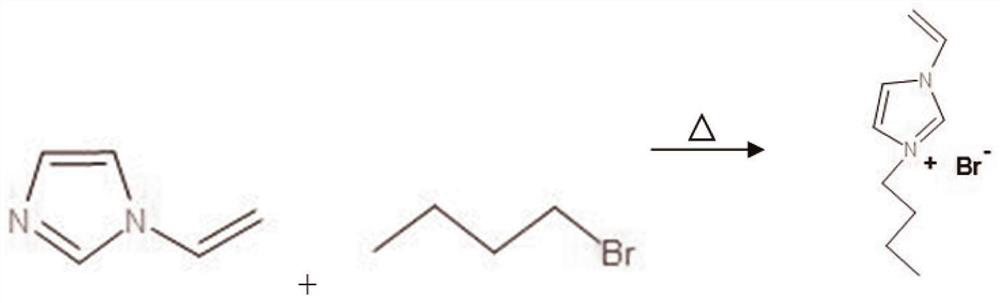

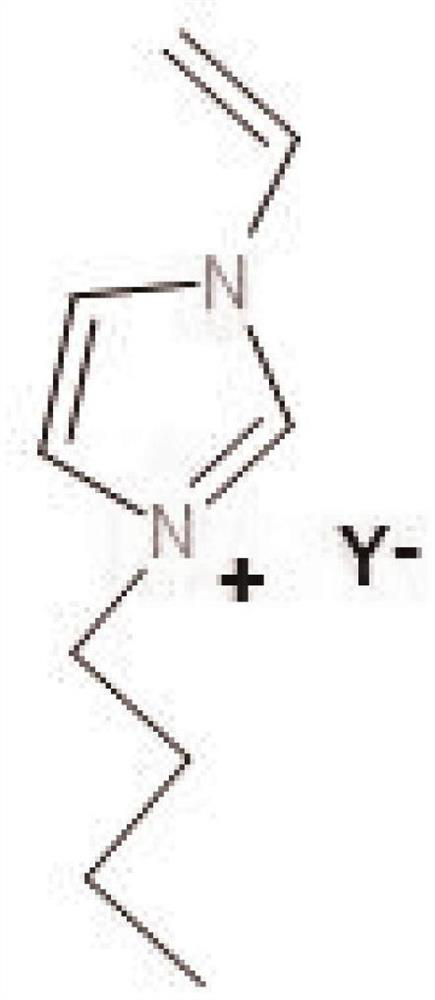

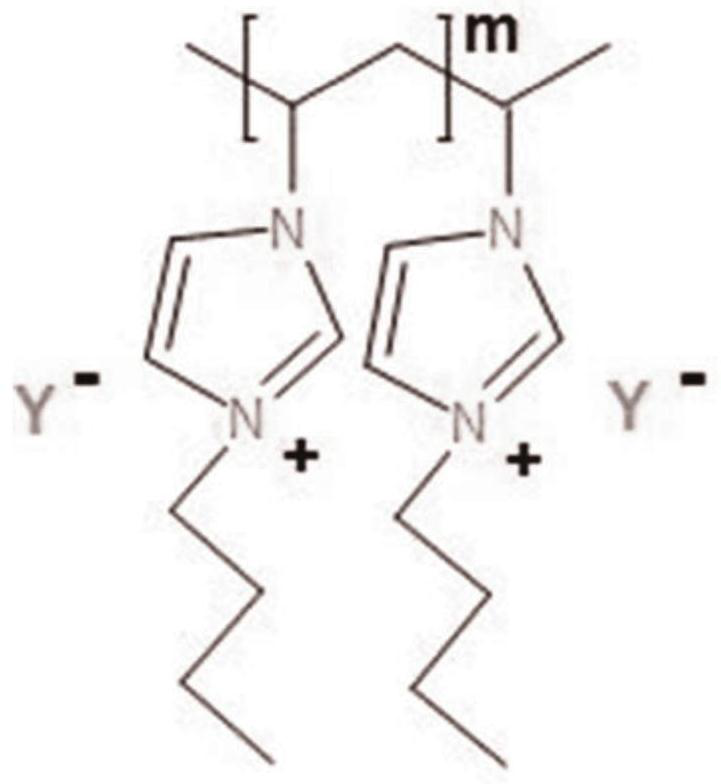

A kind of preparation method of semi-solid polyionic liquid electrolyte for lithium battery

ActiveCN113429504BImprove securityReduced packaging requirementsLi-accumulatorsElectrolyte immobilisation/gelificationElectrolytic agentPhysical chemistry

The invention relates to a preparation method of a semi-solid polyionic liquid electrolyte for lithium batteries. The traditional organic electrolyte containing lithium hexafluorophosphate is replaced with a gel-like polyionic liquid electrolyte. Specifically, based on the ionic liquid as a matrix, it is polymerized at a higher temperature using an initiator, thereby forming a colloidal non-flowable electrolyte. Therefore, while having high safety, it solves the problem of easy leakage of the electrolyte, and greatly reduces the packaging requirements of the battery.

Owner:宁波世贤科技有限公司

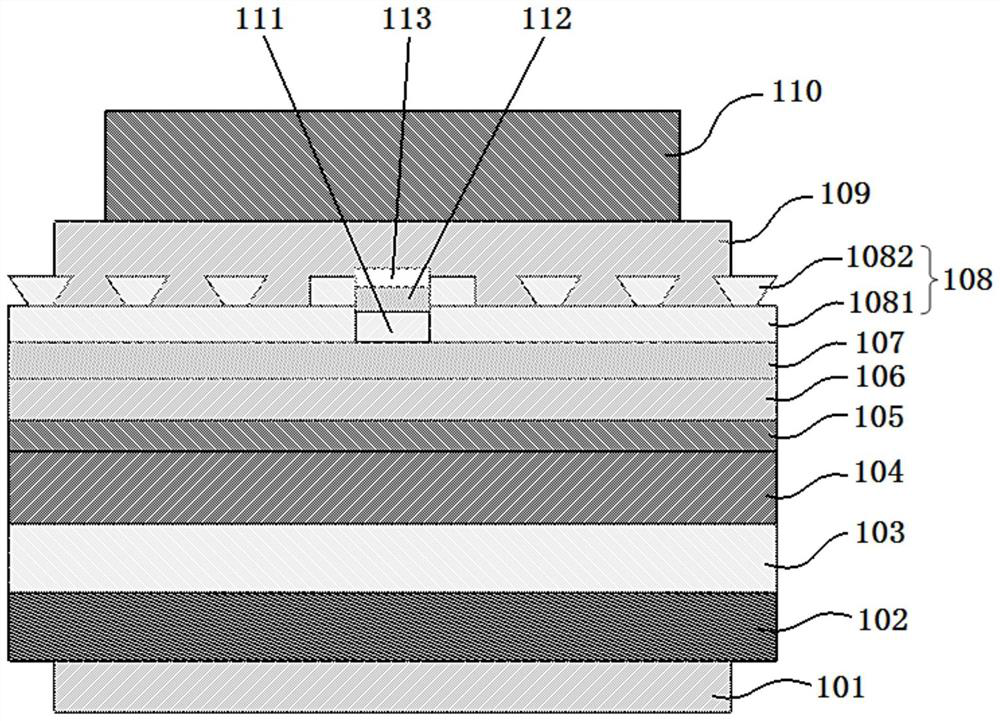

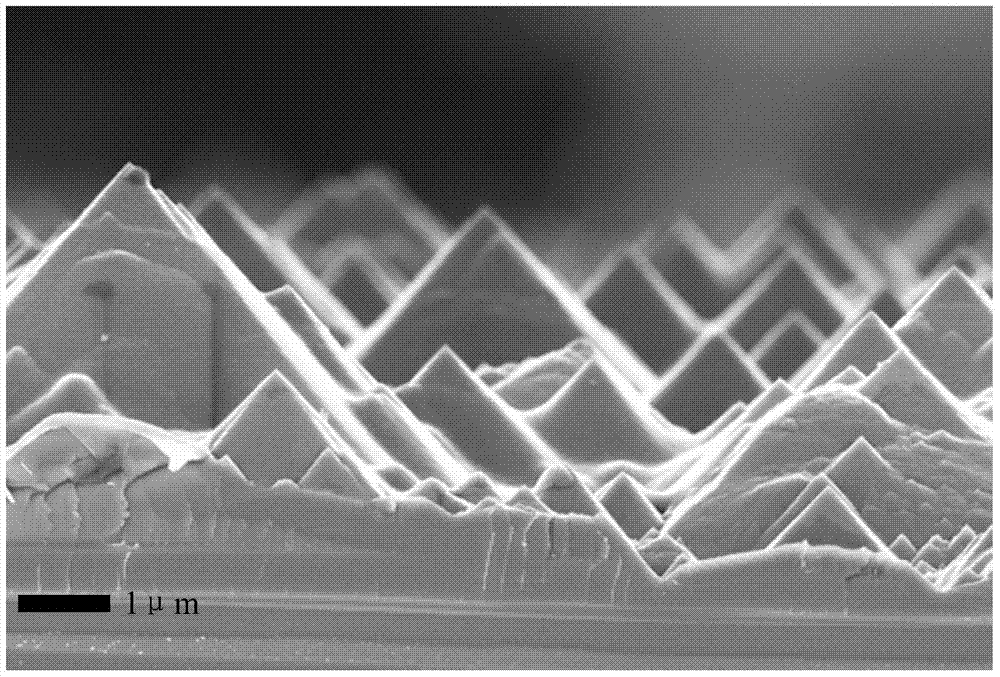

GaN-based laser diode structure and manufacturing method

PendingCN114552371AReduce stressImprove adhesionLaser detailsLaser active region structureMetallic electrodeContact layer

The invention provides a GaN-based laser diode structure and a manufacturing method. The GaN-based laser diode structure comprises an N electrode, an n-type GaN substrate, an N covering layer, an N waveguide layer, a light-emitting active layer, a P waveguide layer, an electron blocking layer and a passivation layer which are sequentially arranged in a stacked mode. A ridge strip is arranged on the upper surface of the P-type electron barrier layer and comprises a P covering layer, and a P contact layer and a P contact electrode layer which are sequentially stacked on the P covering layer; the passivation layer comprises a first passivation layer and a second passivation layer which are arranged in a stacked mode, the first passivation layer is arranged on the upper surface of the P-type electron blocking layer and located on the two sides of the ridge strip, a groove is formed in the second passivation layer, a first metal layer is arranged on the upper surface of the second passivation layer and on the ridge strip, the first metal layer is provided with a protruding part corresponding to the groove, and a second metal layer is arranged on the protruding part. And a P electrode is arranged on the upper surface of the first metal layer. The stress of the electrode structure is reduced, the adhesive force between the metal electrode and the passivation layer is improved, a thick metal electrode can be formed, the packaging requirement is reduced, the heat dissipation performance is improved, and application is expanded.

Owner:安徽格恩半导体有限公司

Nano-luminescent fiber and preparation method thereof

ActiveCN106245129BReduce aggregationAvoid Fluorescence Intensity DecayElectro-spinningMonocomponent synthetic polymer artificial filamentFiberOrganic solvent

The invention discloses a nanometer luminescent fiber and a preparation method thereof. The method comprises the steps that quantum dots are taken to be added into an organic solvent, stirring dissolution is performed to obtain a quantum dot solution; a solution additive is added into the quantum dot solution, mixing is performed to be uniform, then, solid polymer is added, stirring dissolution is performed to obtain an uniform quantum dot spinning solution; the quantum dot spinning solution is placed into a jet apparatus device of electrostatic spinning equipment for performing electrostatic spinning, and nanometer luminescent fiber is obtained. The method is simple, controllable and easy to repeat, the oil soluble quantum dot solution of any kind can be adopted for spinning, in the electrostatic spinning process, and the nanometer luminescent fiber of different shapes such as solid nanometer fiber, tubular nanometer fiber and strap nanometer fiber is obtained by adjusting the conditions such as the mass percentage of the components in the electrostatic spinning solution, electrostatic spinning voltage, the solution injection rate, the solution injection distance and the spun nanometer luminescent fiber drying temperature.

Owner:TCL CORPORATION

Solar battery based on silicon nano material

InactiveCN102157579BDesignableImprove conductivityLight-sensitive devicesPhotovoltaic energy generationSilicon electrodeSolar battery

The invention discloses a solar battery based on a silicon nano material. The solar battery based on the silicon nano material comprises a silicon wafer on which conductive glass is arranged; an insulation sealing layer is encircled between the conductive glass and the silicon wafer; an electrolyte chamber is formed between the conductive glass and the silicon wafer; ion liquid electrolyte is arranged in the electrolyte chamber; and lead-out electrodes are arranged on the backs of the conductive glass and the silicon wafer so as to form an ohm electrode structure. The solar battery has the characteristics of high thermal stability and chemical stability; a thinner silicon wafer can be used as a silicon electrode, the requirement for purity of the silicon is relatively low and the encapsulation requirement on the battery is reduced greatly at the same time. The invention also provides a low-cost, high-efficiency and stable technology for preparing the solar battery, which has a positive practical significance.

Owner:SUZHOU UNIV

Perfluorosodium polymer electrolyte, preparation method and application thereof, all-solid-state sodium-ion battery and triboelectric nanogenerator system

ActiveCN108539259BImprove securityIncrease energy densitySecondary cellsPolymer electrolytesAll solid state

The invention relates to the field of sodium-ion batteries and discloses a perfluoro sodium polymer electrolyte, a preparation method and an application of the perfluoro sodium polymer electrolyte, anall-solid-state sodium-ion battery and a friction nano-generator system; the preparation method of the perfluoro sodium polymer electrolyte comprises implementing ion exchange between perfluorinatedsulfonic acid resin and a Na+ containing solution. The provided all-solid-state sodium-ion battery comprises the above perfluoro sodium polymer electrolyte, and in addition, compared with a battery using a liquid electrolyte, the all-solid-state sodium-ion battery is excellent in safety and the energy density is higher.

Owner:BEIJING INST OF NANOENERGY & NANOSYST

Intelligent recognition and counting detection method for circle-like objects for packaging industry

ActiveCN106529551BImprove Counting AccuracyReduced packaging requirementsCharacter and pattern recognitionImage denoisingFeature extraction

The invention discloses an algorithm for intelligent recognition, counting, and detection of circle-like objects for the packaging industry. The effective area where the circle-like objects are located is obtained through images collected by industrial cameras; the image preprocessing method includes: using a median filter algorithm to remove original image noise, The binarized image after image denoising is obtained by using the adaptive local binary algorithm; the geometric feature extraction includes four detections, the first detection: detection of a circle-like object with a normal area after binarization; the second detection: detection of the second The defective circle-like objects remain after the first detection; the third detection: detect the circle-like objects in the uneven area; the fourth detection: detect the circle-like objects that may exist in the boundary. The invention can improve the counting accuracy of round-like three-dimensional objects, has low requirements on packaging conditions, and has strong detection robustness. At the same time, it can realize rapid and real-time fast online monitoring, and can be used for detection of various round-like objects.

Owner:NANTONG UNIVERSITY

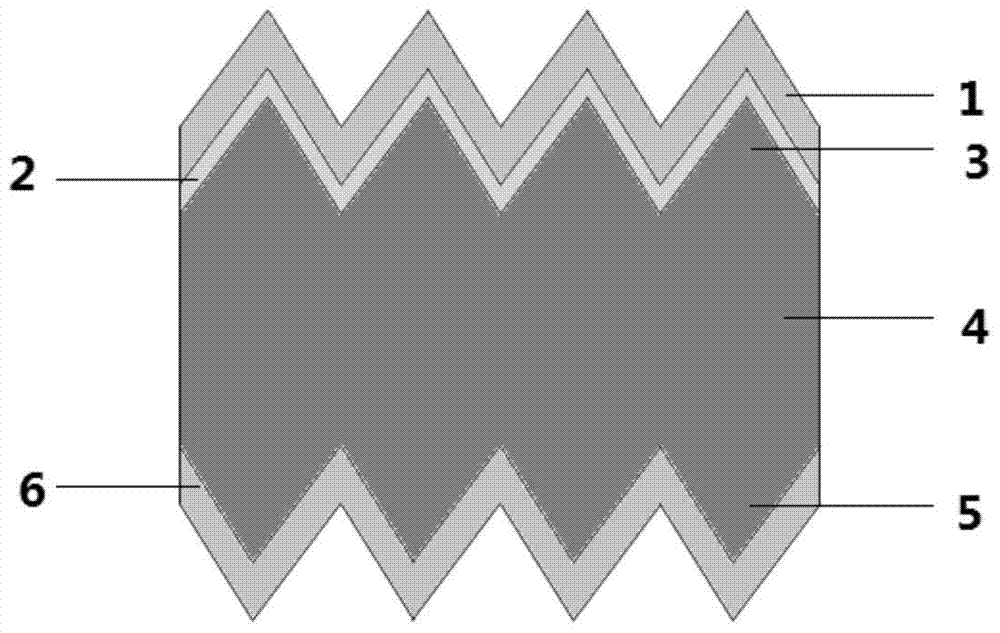

Organic-inorganic hybridization solar battery and manufacturing method thereof

InactiveCN102263204BImprove stabilityReduced packaging requirementsSolid-state devicesSemiconductor/solid-state device manufacturingCharge carrierSilicon nanowires

The invention discloses an organic-inorganic hybridization solar battery which comprises a metal backing electrode, an n-type silicon substrate layer, a silicon nanometer wire array and a battery positive electrode and also comprises a p-type cavity transmission shell layer, wherein the p-type cavity transmission shell layer is a conjugated organic matter semiconductor thin film; the metal backing electrode is arranged on the lower surface of the n-type silicon substrate layer; the silicon nanometer wire array is arranged on the upper surface of the n-type silicon substrate layer; the surfaceof a silicon nanometer wire in the silicon nanometer wire array is covered by the layer of p-type cavity transmission shell layer; and the battery positive electrode is arranged on the p-type cavity transmission shell layer. As a three-dimensional radial p-n junction hybridization structure formed by the silicon nanometer wire array and the conjugated organic matter is adopted in the organic-inorganic hybridization solar battery, on one hand, the absorption of light is increased, the usage amount of silicon is reduced, the purify requirement on the silicon is reduced, on the other hand, the transmission range of current carriers is shortened, the problem that the current carriers are easy to combine is reduced, and the photoelectric conversion efficiency is improved.

Owner:SUZHOU UNIV

Wire and cable material automatic weighing sealing and suturing device

ActiveCN104670569BImprove adaptabilityMeet packaging requirementsWrapper twisting/gatheringEngineeringElectric cables

Owner:CHANGSHU ZHONGLIAN PHOTOELECTRICITY NEW STUFF +1

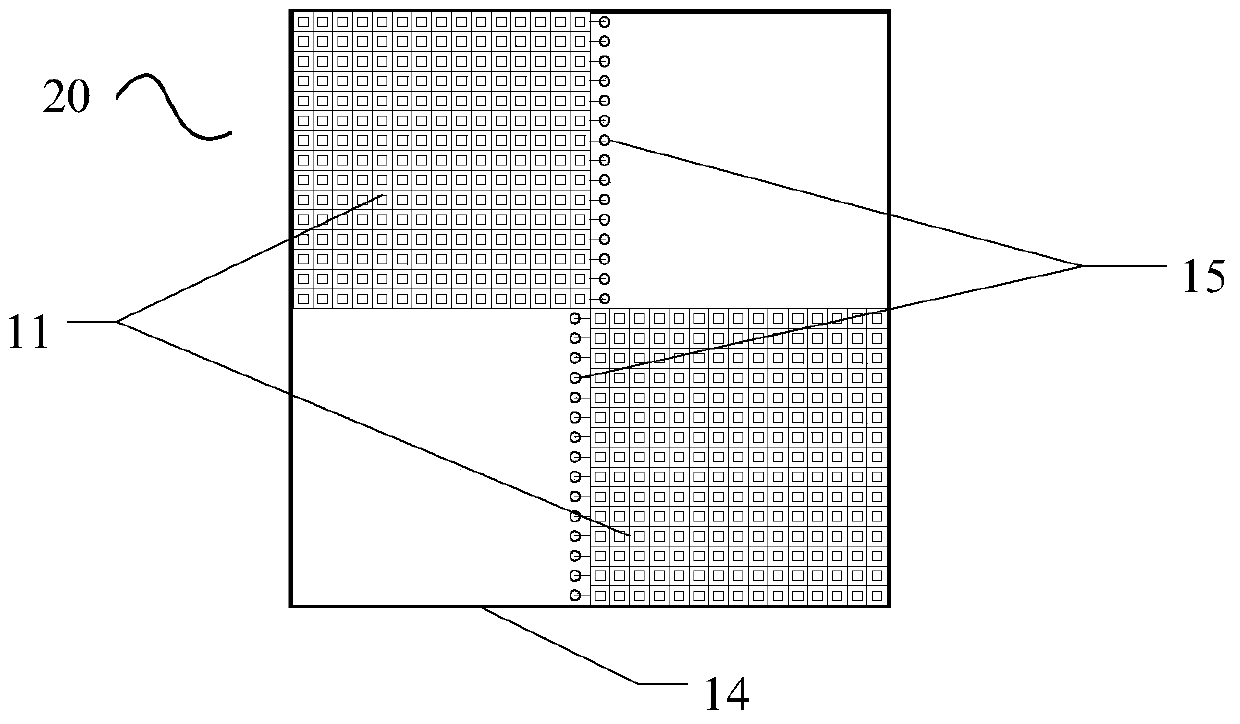

A photon counting detector array and its imaging method

ActiveCN106483548BReduced packaging requirementsLow costRadiation intensity measurementPhoton counting detectorSystems design

Owner:成都善思微科技有限公司

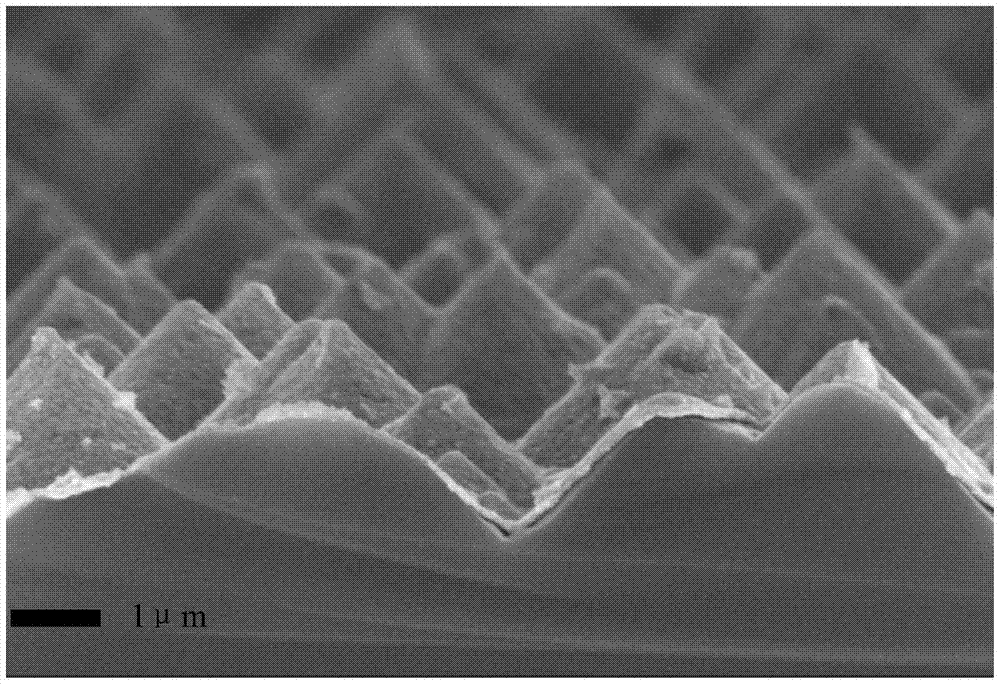

A transition metal oxide-silicon heterojunction solar cell and its preparation method

ActiveCN104993006BImprove stabilityReduced packaging requirementsFinal product manufacturePhotovoltaic energy generationSilicon solar cellHole transport layer

The invention discloses a transition metallic oxide-silicon heterojunction solar cell and a preparation method thereof. The solar cell comprises a metal back electrode, a silicon inverted pyramid array, an N-type silicon substrate, a silicon pyramid array, a hole transport layer and a positive electrode. The hole transport layer is a transition metallic oxide thin film. According to the invention, by using the transition metallic oxide thin film as the hole transport layer, so on one hand, compared with the P-type conjugated organic matters, stability of the solar cell is improved and technical requirements on encapsulation are reduced, thereby reducing manufacturing cost; and on the other hand, compared with a traditional silicon solar cell, technology of high-temperature phosphorus diffusion and diffusion layer removing are not required, so technology is simplified, and manufacturing cost is reduced. In addition, methylation processing is performed on surface of the silicon substrate, so performance of a device is improved and stability in air of the device is also improved.

Owner:JINAN UNIVERSITY

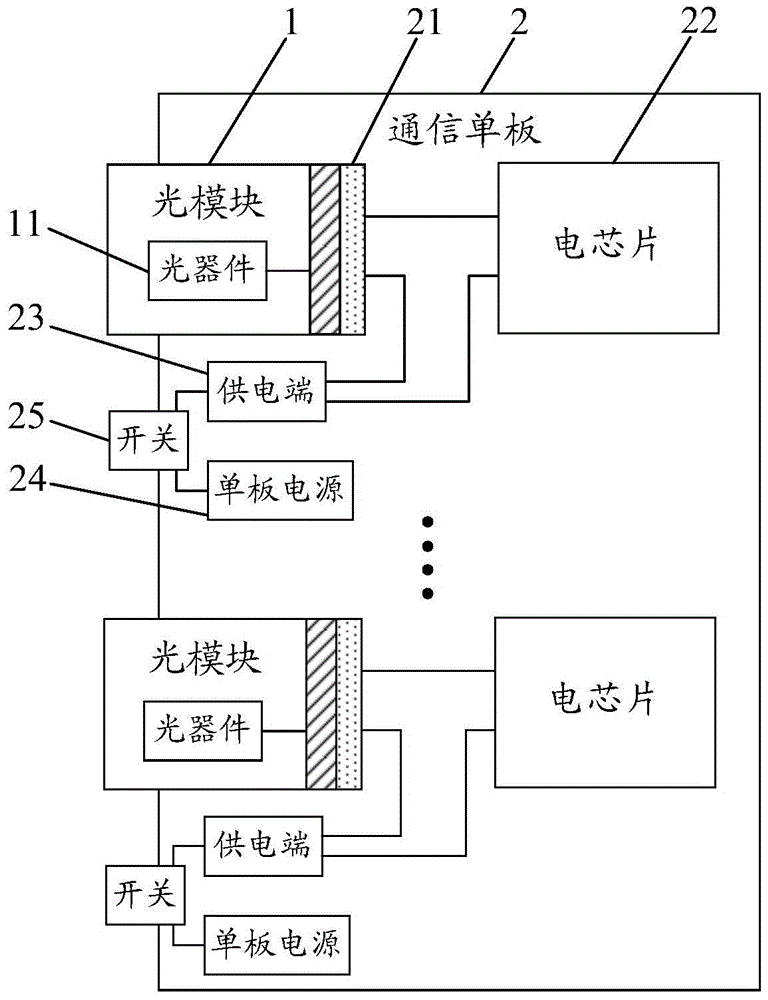

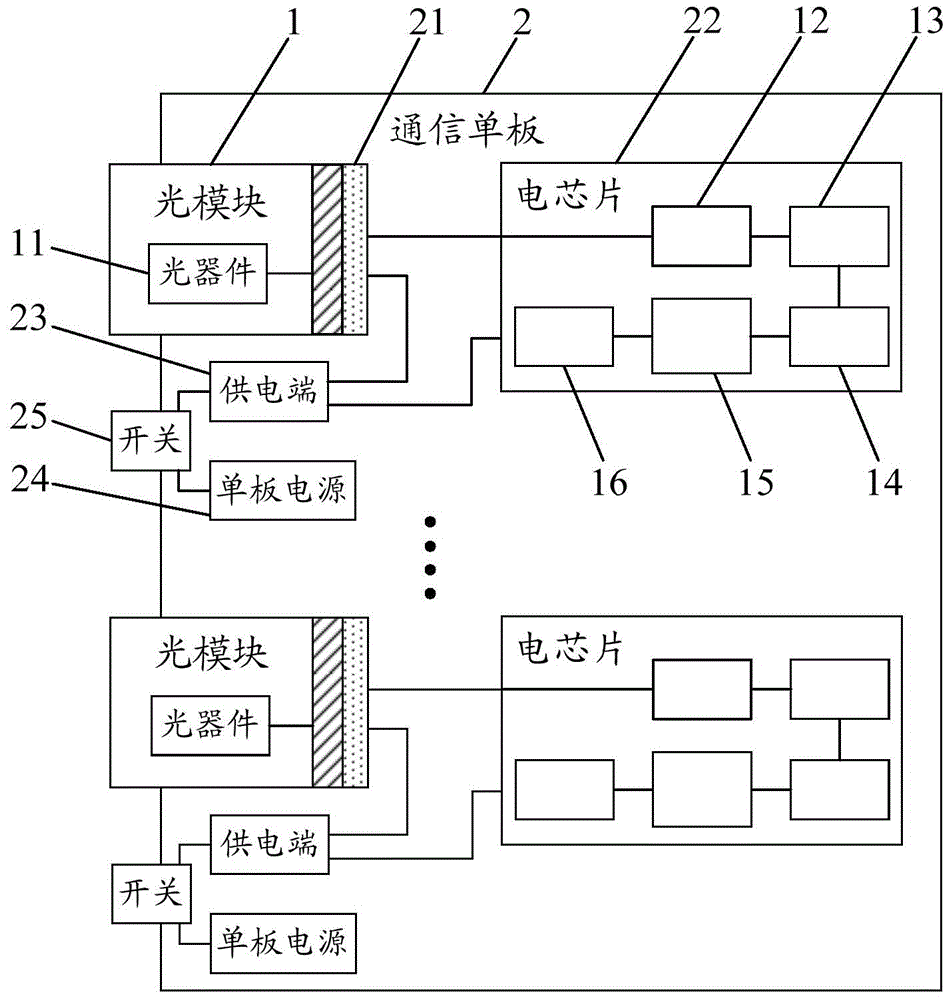

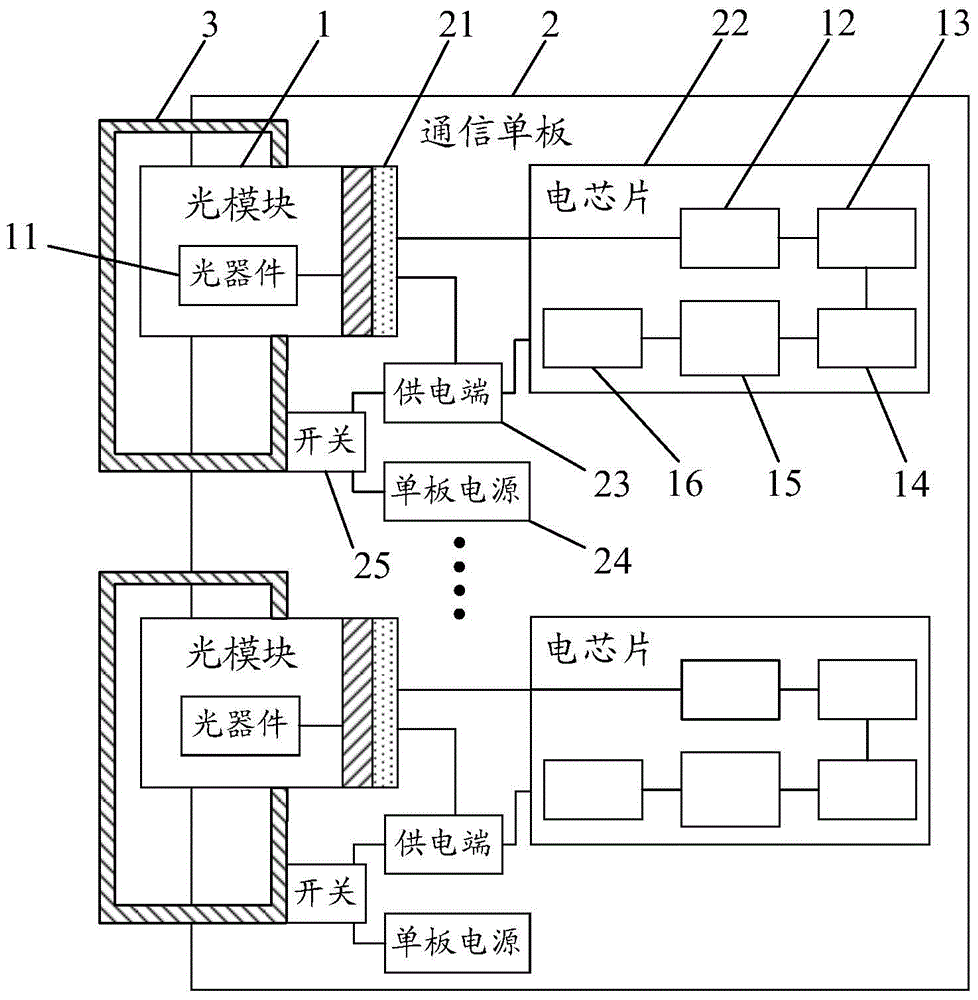

Optical components and passive optical network pon systems

ActiveCN103650388BReduce power consumptionReduced packaging requirementsMultiplex system selection arrangementsElectromagnetic transceiversOptical ModuleMonoboard

The invention discloses an optical component and a passive optical network PON system, relates to the technical field of communication, and reduces the packaging requirements of the optical module, thus reducing the cost. The optical component includes: an optical module and a communication single board; an optical module interface is arranged on the communication single board; an optical device and a golden finger connected to the optical device are arranged on the optical module, and the golden finger It is used to insert the optical module interface on the communication single board; the electrical chip corresponding to the optical module is arranged on the communication single board; the communication pin of the electrical chip is connected to the communication pin of the optical module interface. Pins; a power supply terminal connected to the power supply pin of the optical module interface and the power supply pin of the electronic chip; a single board power supply connected to the power supply terminal through a switch.

Owner:HUAWEI TECH CO LTD

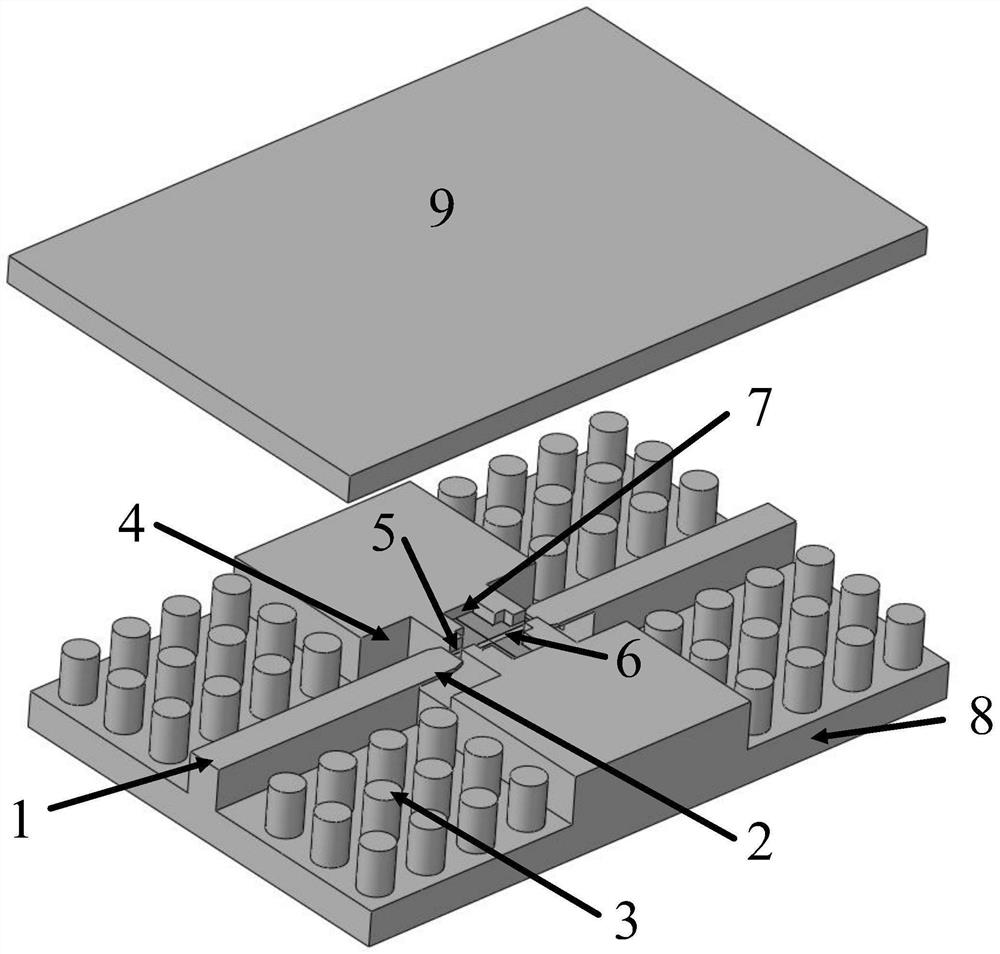

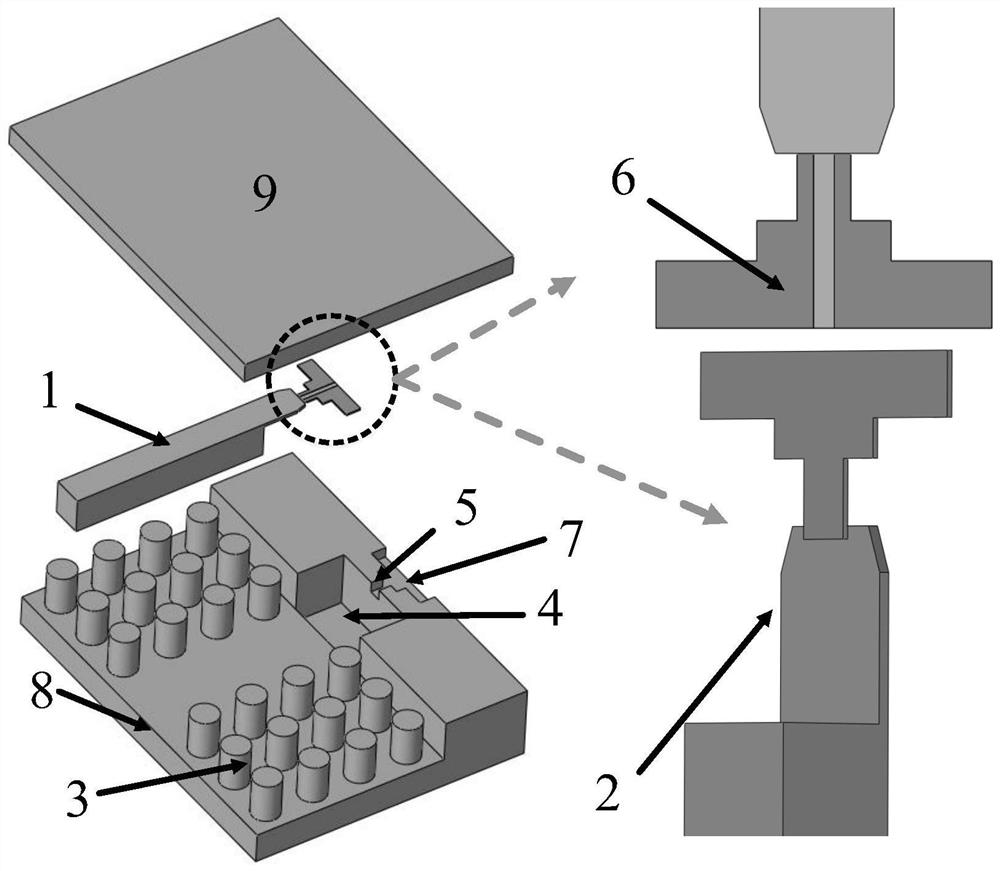

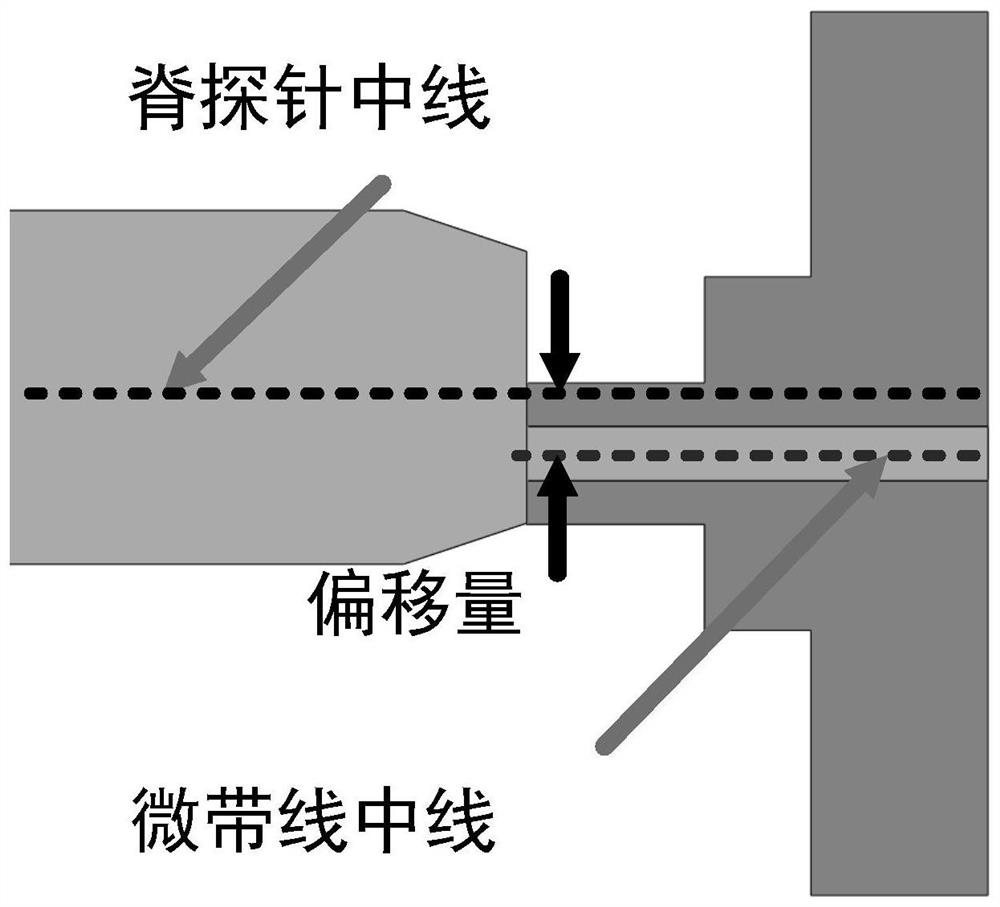

A Broadband Transition Structure from Ridge-Gap Waveguide to Microstrip Line Based on Probe Current Coupling

ActiveCN110504515BReduced packaging requirementsLow machining accuracy requirementsCoupling devicesUltra-widebandMicrowave

The invention discloses a probe current coupling based ridge gap waveguide to microstrip line broadband transition structure, which relates to the field of microwave / millimeter wave passive devices, specifically a probe current coupling based ridge gap waveguide to microstrip line Broadband transition structure. In order to solve the problems of limited bandwidth, excessive loss, and low assembly tolerance performance faced by the ridge-gap waveguide in the prior art when it is integrated with an MMIC circuit. The invention proposes a probe-current-coupled ridge-gap waveguide-to-microstrip broadband transition structure, which has the advantages of ultra-broadband, low loss, strong tolerance performance, compact structure, and easy processing and assembly.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA