Patents

Literature

116results about How to "Reduce contact resistivity" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

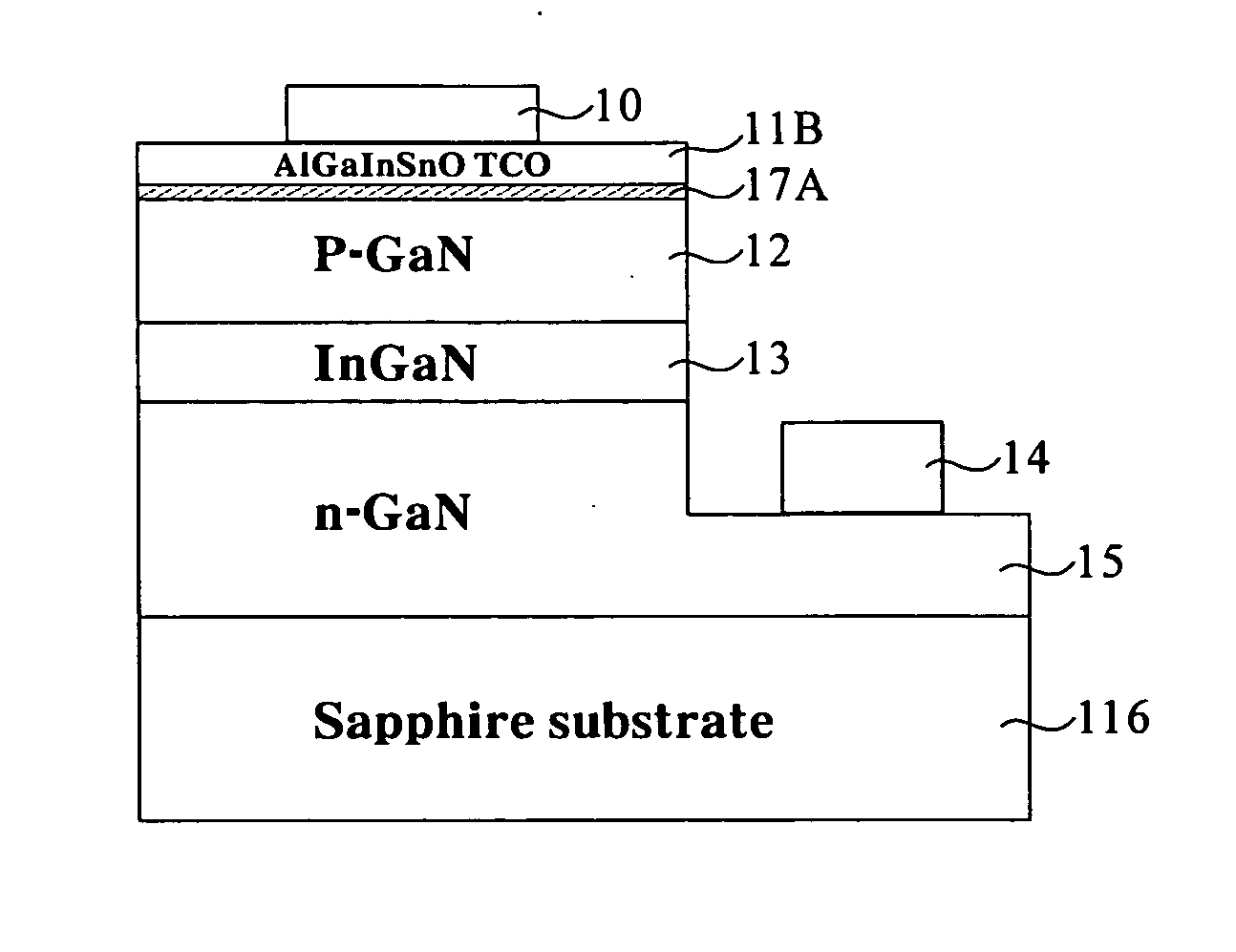

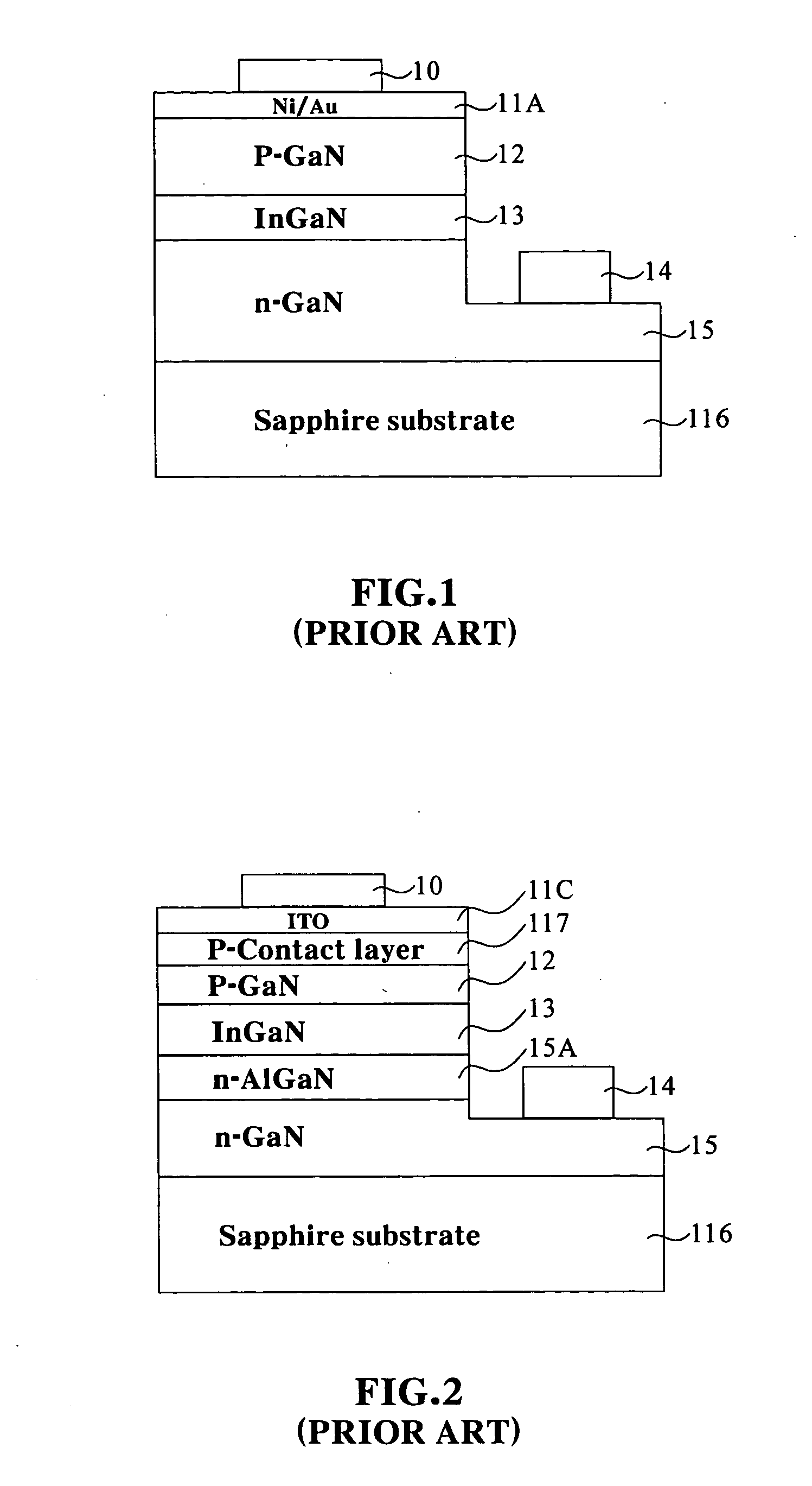

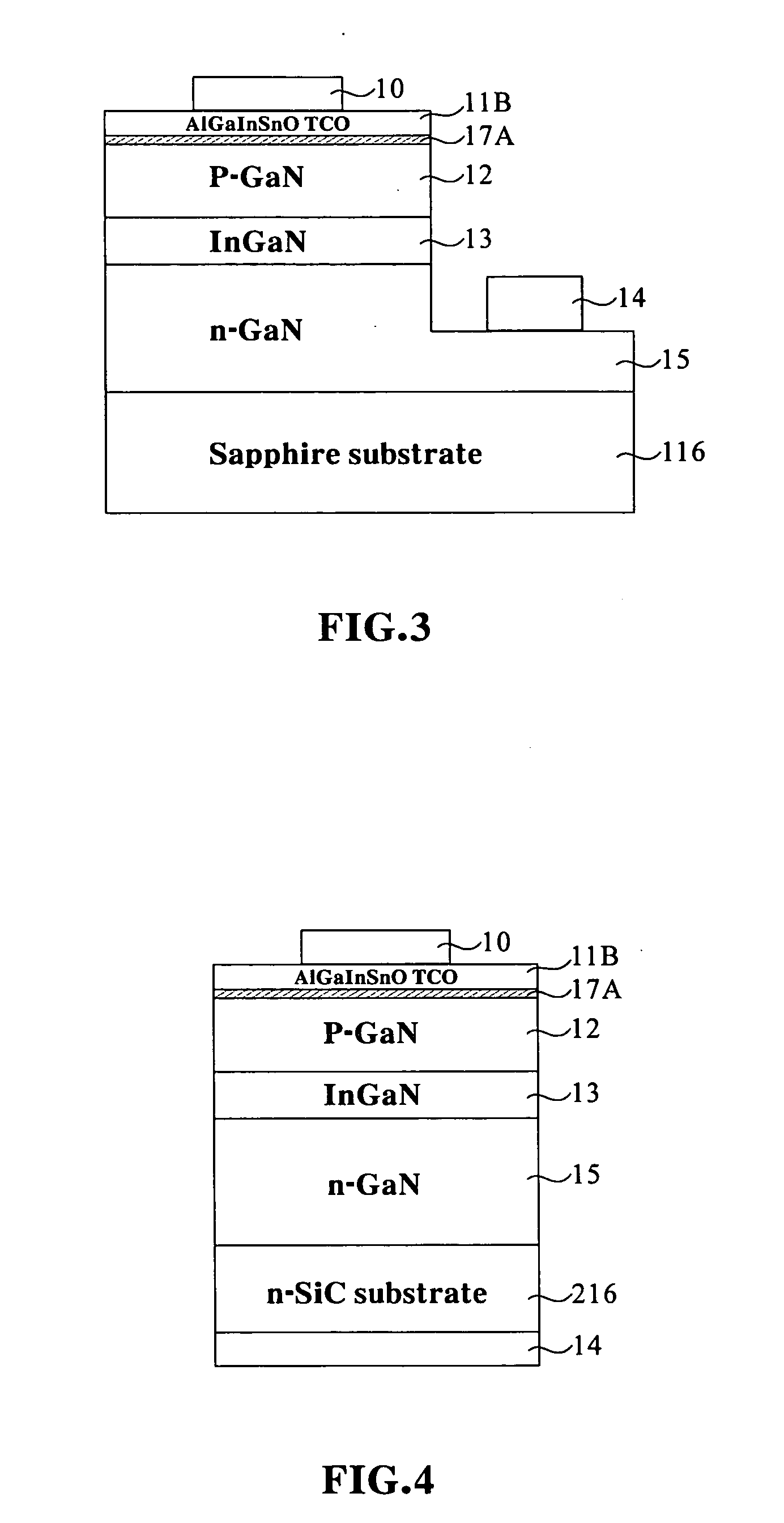

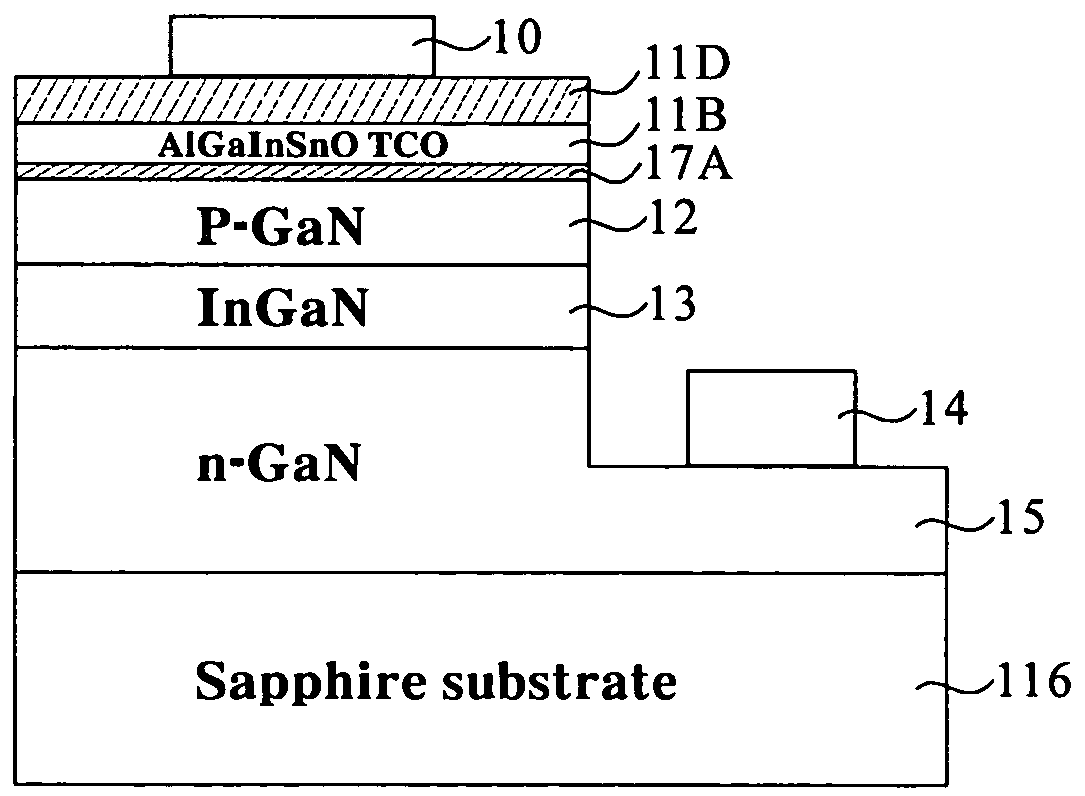

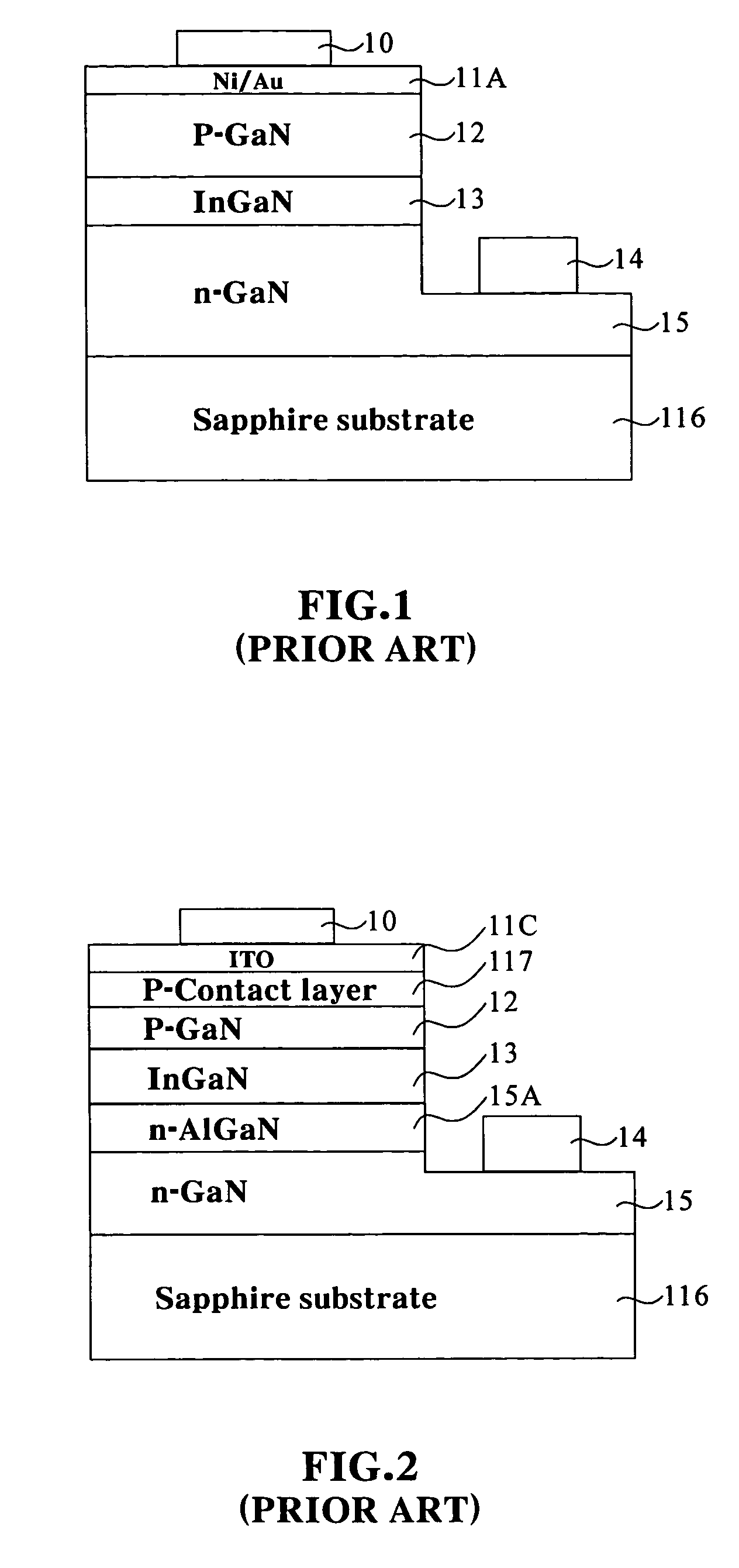

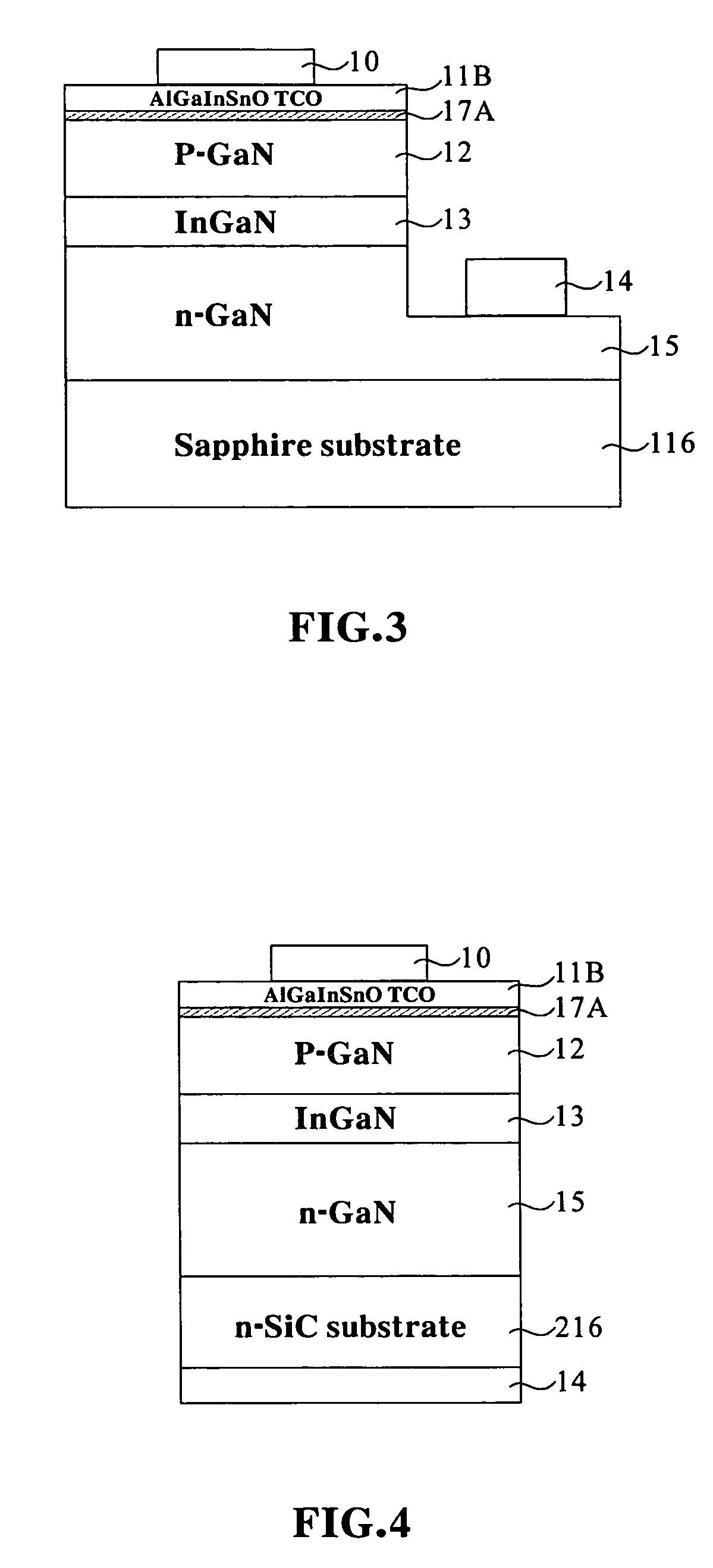

High brightness gallium nitride-based light emitting diode with transparent conducting oxide spreading layer

InactiveUS20050230701A1Reduce contact resistanceReduce the impactFibre treatmentSolid-state devicesOptical propertyGallium

A new transparent conducting oxide (TCO), which can be expressed as AlxGa3−x−yIn5+ySn2−zO16−2z; 0≦x<1, 0<y<3, 0≦z<2, has been used to improve the brightness and current spreading in GaN base LED process. The optical properties of this system are superior to regular Ni / Au transparent conducting layer in blue-green region, and the new Al2O3—Ga2O3—In2O3—SnO2 system is able to increase the brightness at 1.5˜2.5 time to compare to regular process. Furthermore, the new transparent conducting oxide thin film has the highest conductivity, which is better than the Ni / Au transparent conducting thin film.

Owner:ARIMA OPTOELECTRONICS

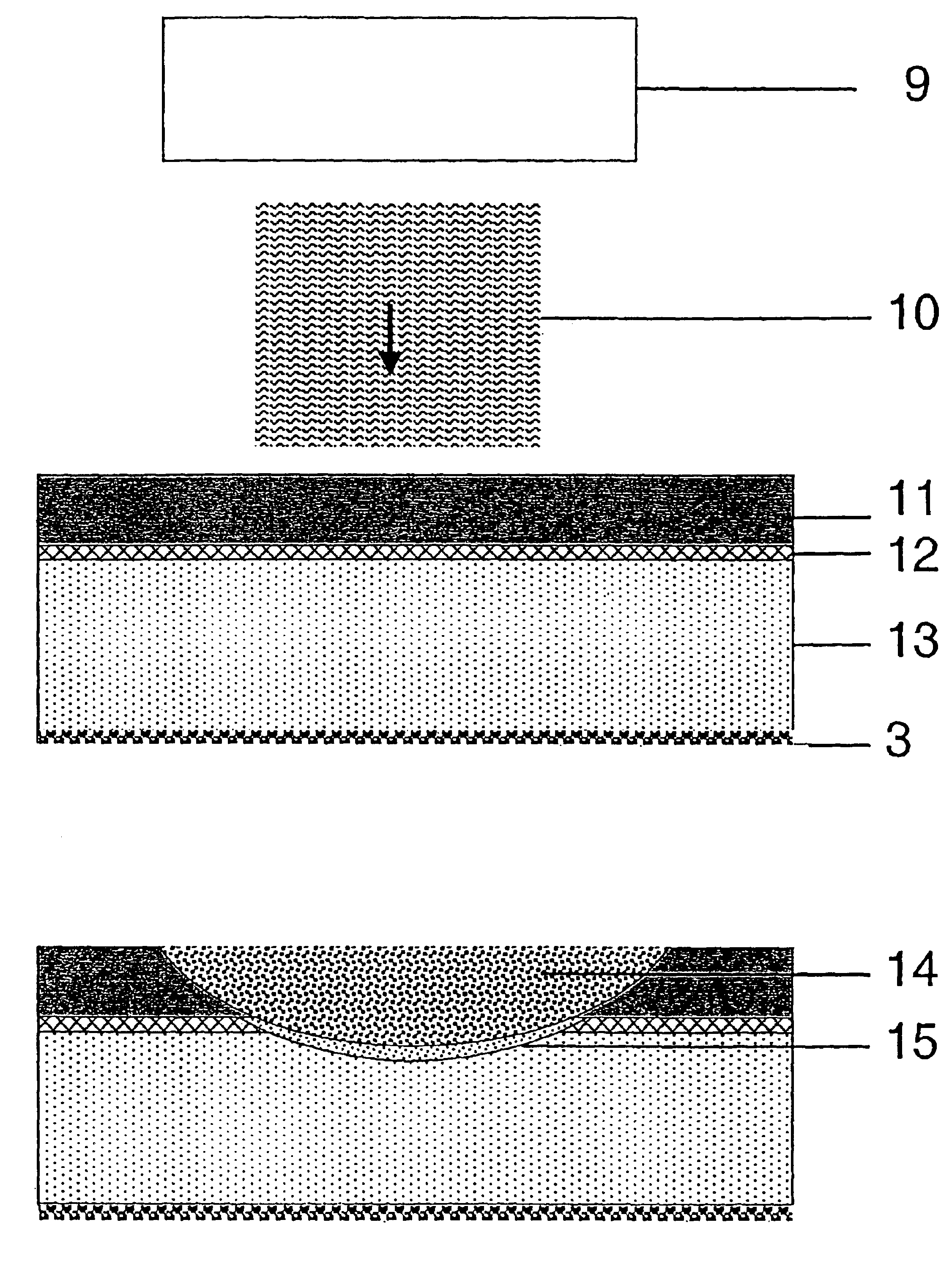

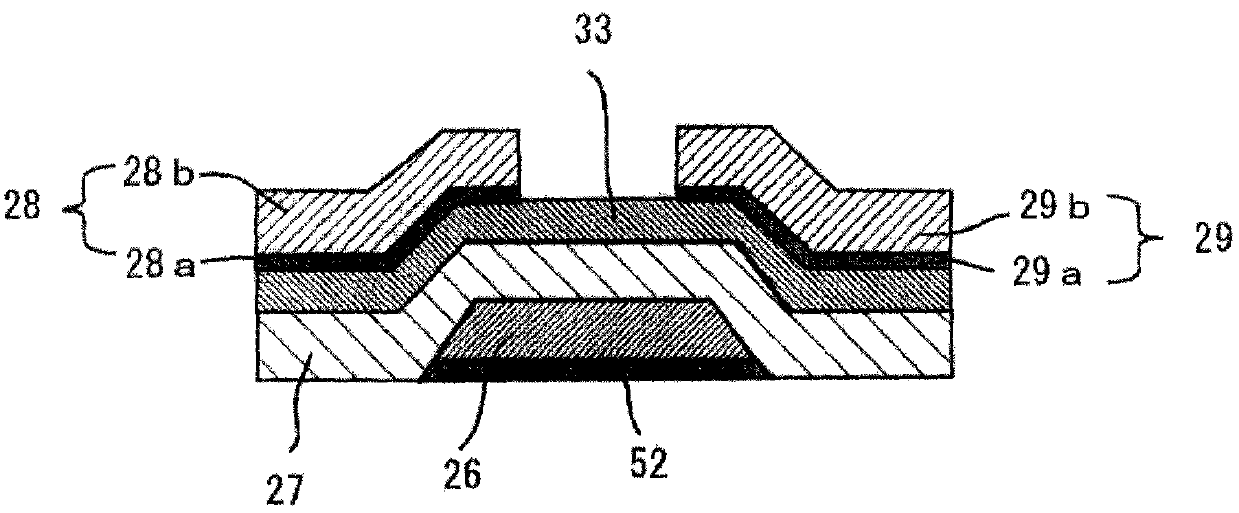

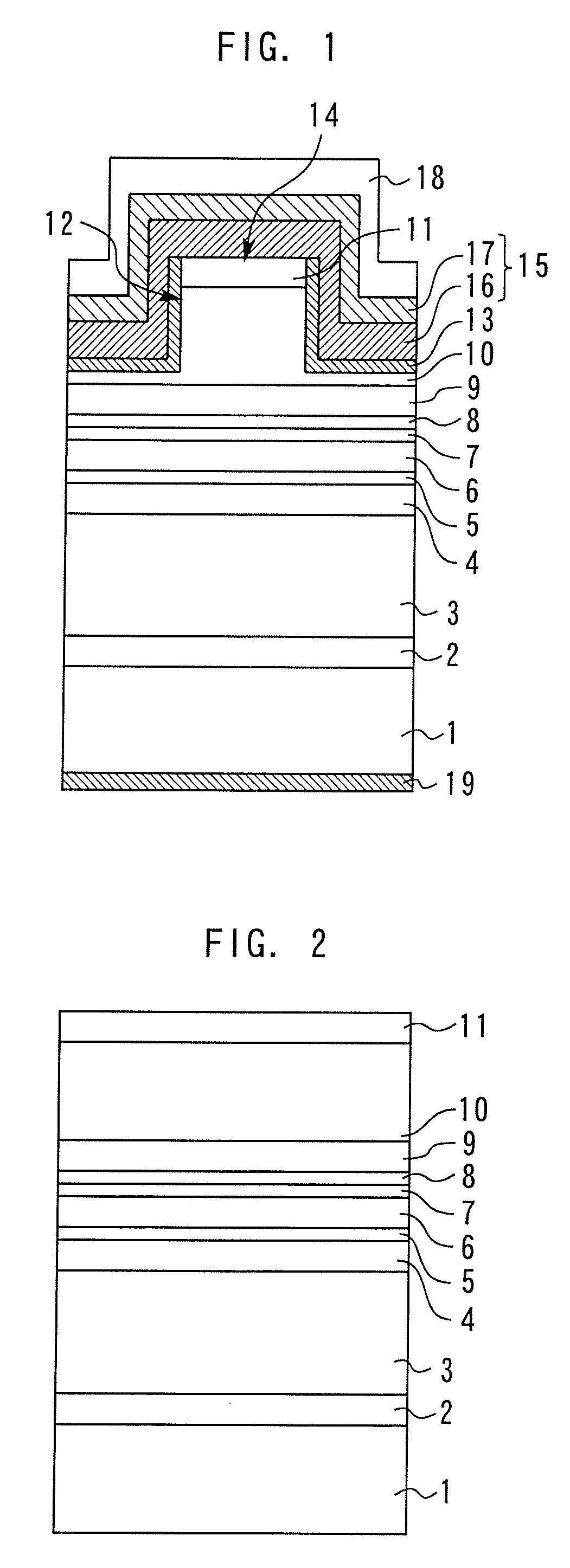

Method of producing a semiconductor-metal contact through a dielectric layer

InactiveUS6982218B2Reduce recombination rateSuitable energy densitySemiconductor/solid-state device manufacturingPhotovoltaic energy generationControl mannerDielectric layer

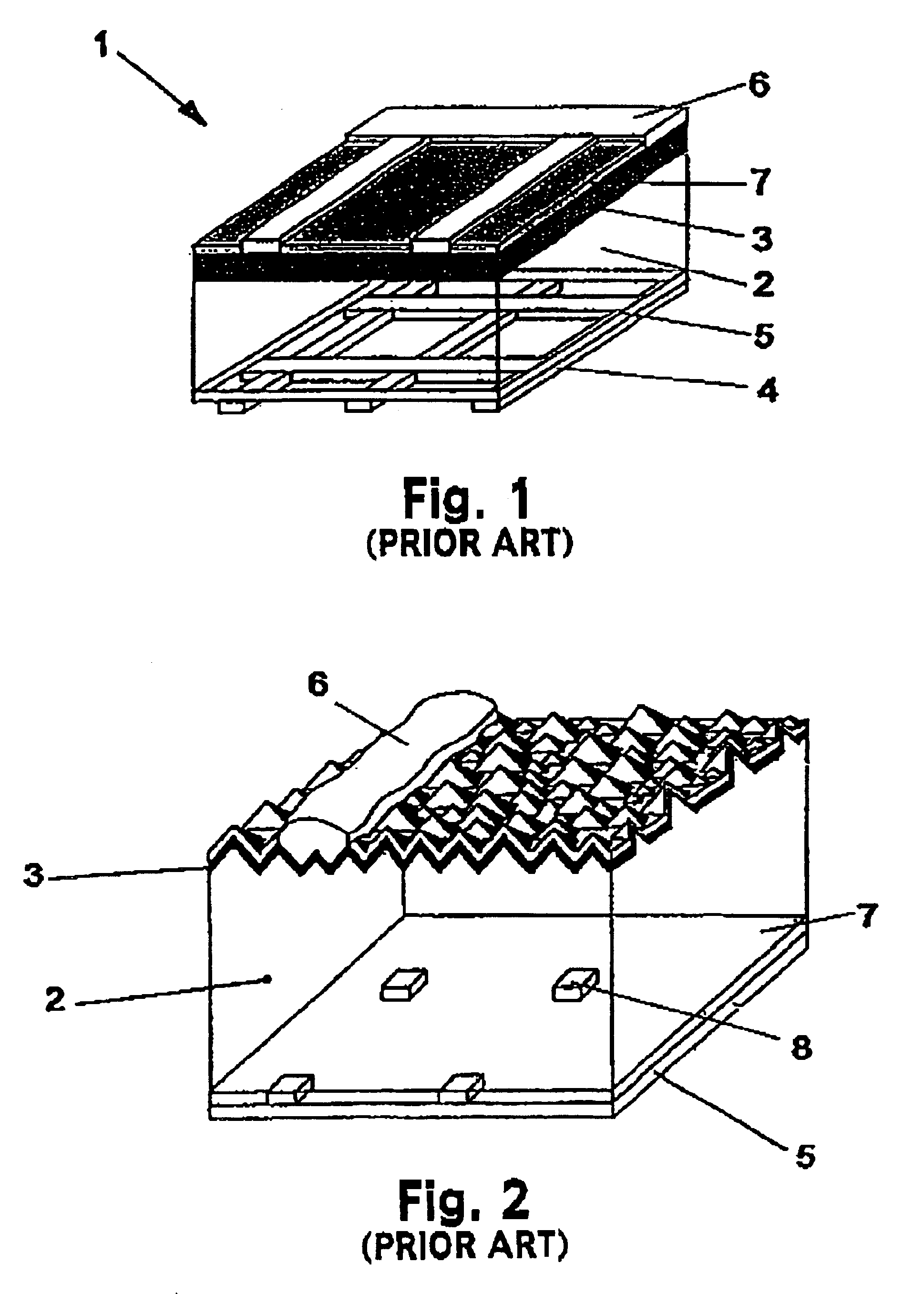

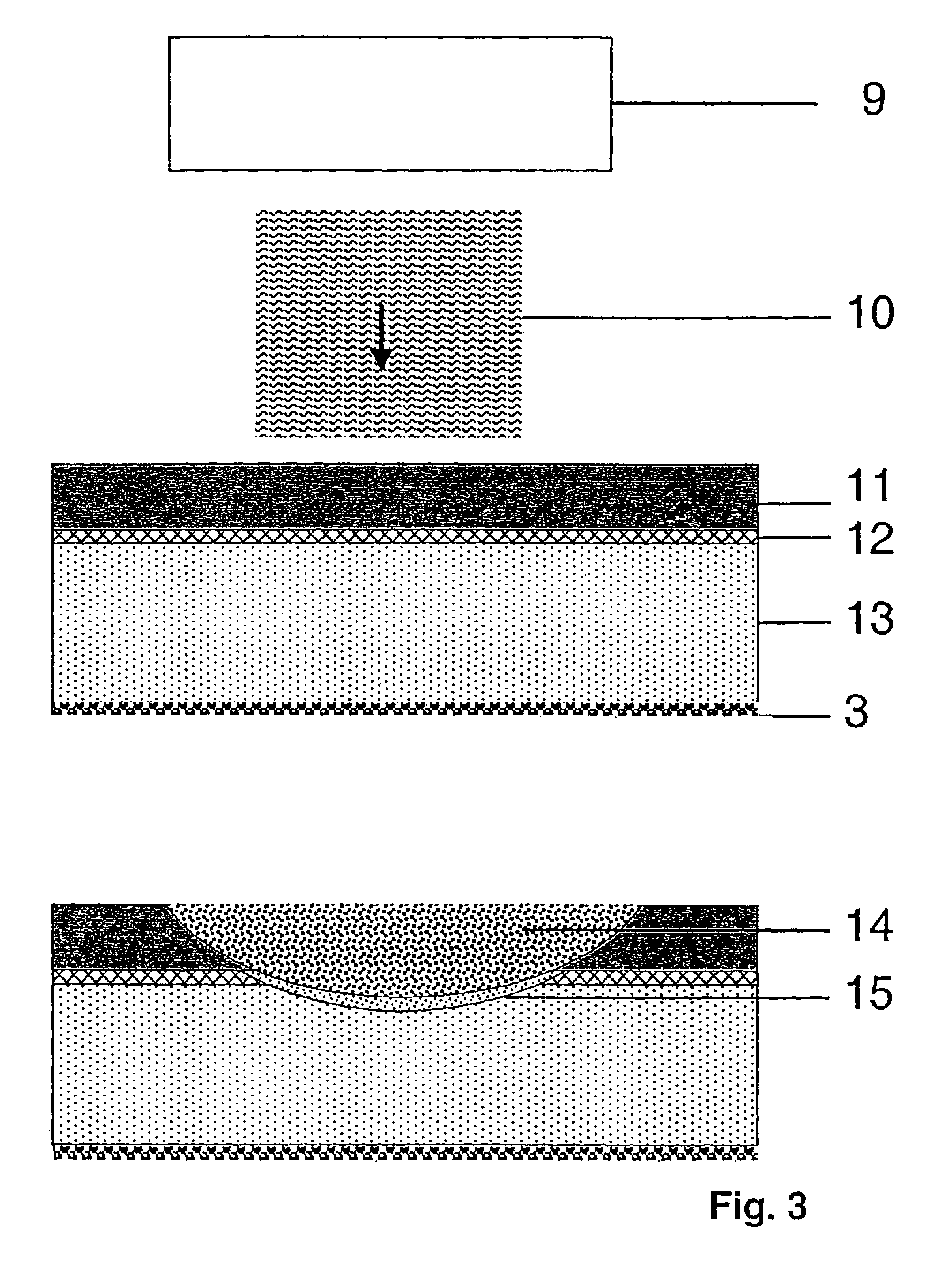

A method of electrically contacting a semiconductor layer (13) coated with at least one dielectic layer (12) which is coated with a metal layer the metal layer (11) is applied on the dielectric layer (12) and the metal layer (11) is temporarily locally heated in a line, linear or dotted pattern by means of a source of radiation (9) in a controlled manner in such a way that a local molten mixture, is formed consisting exclusively of the metal layer (11), the dielectric layer (12) and the semiconductor layer (13) are located directly underneath the metal layer (11) and upon solidification, leads to an electrical contact between the semiconductor layer (13) and the metal layer (11).

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

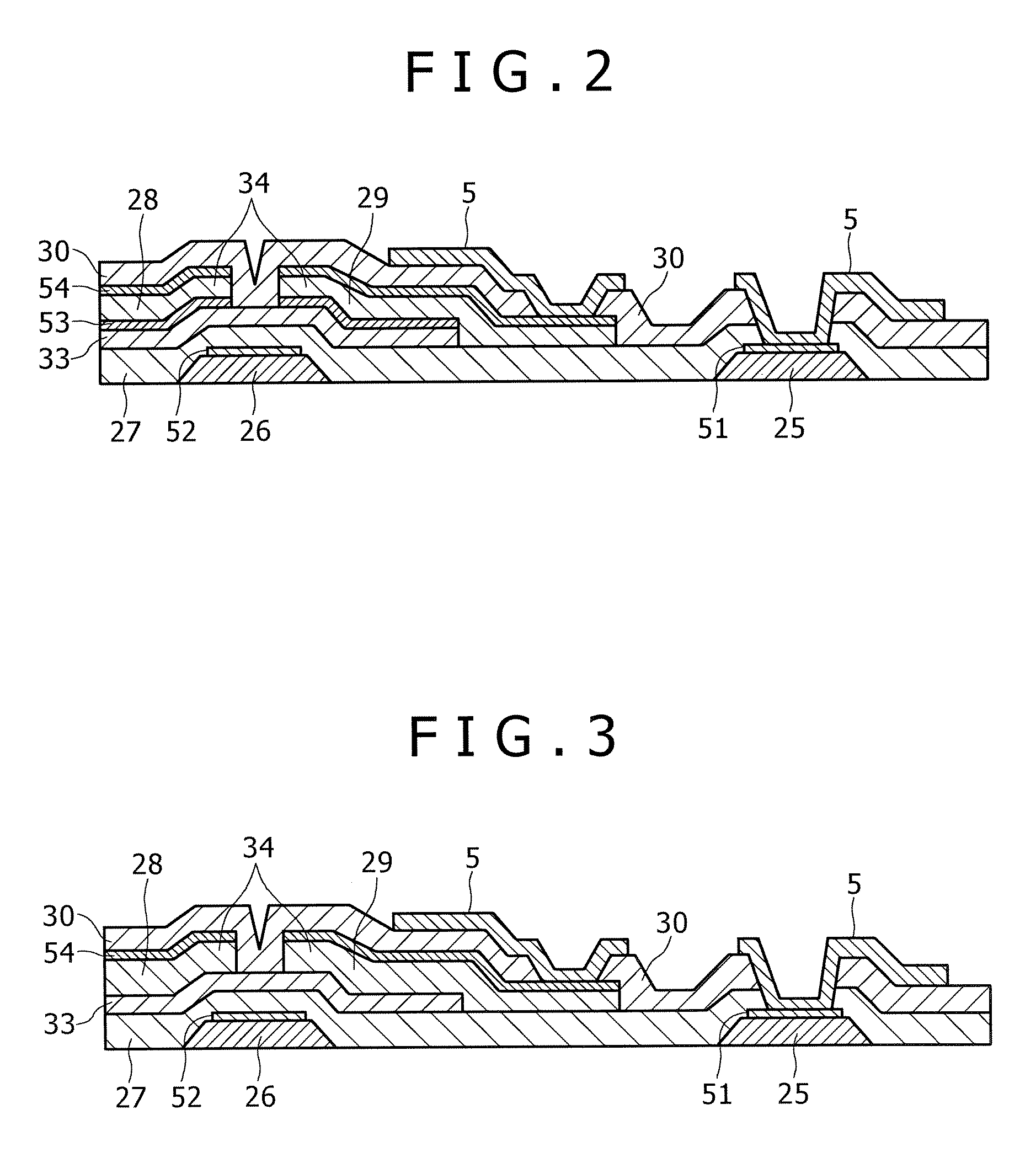

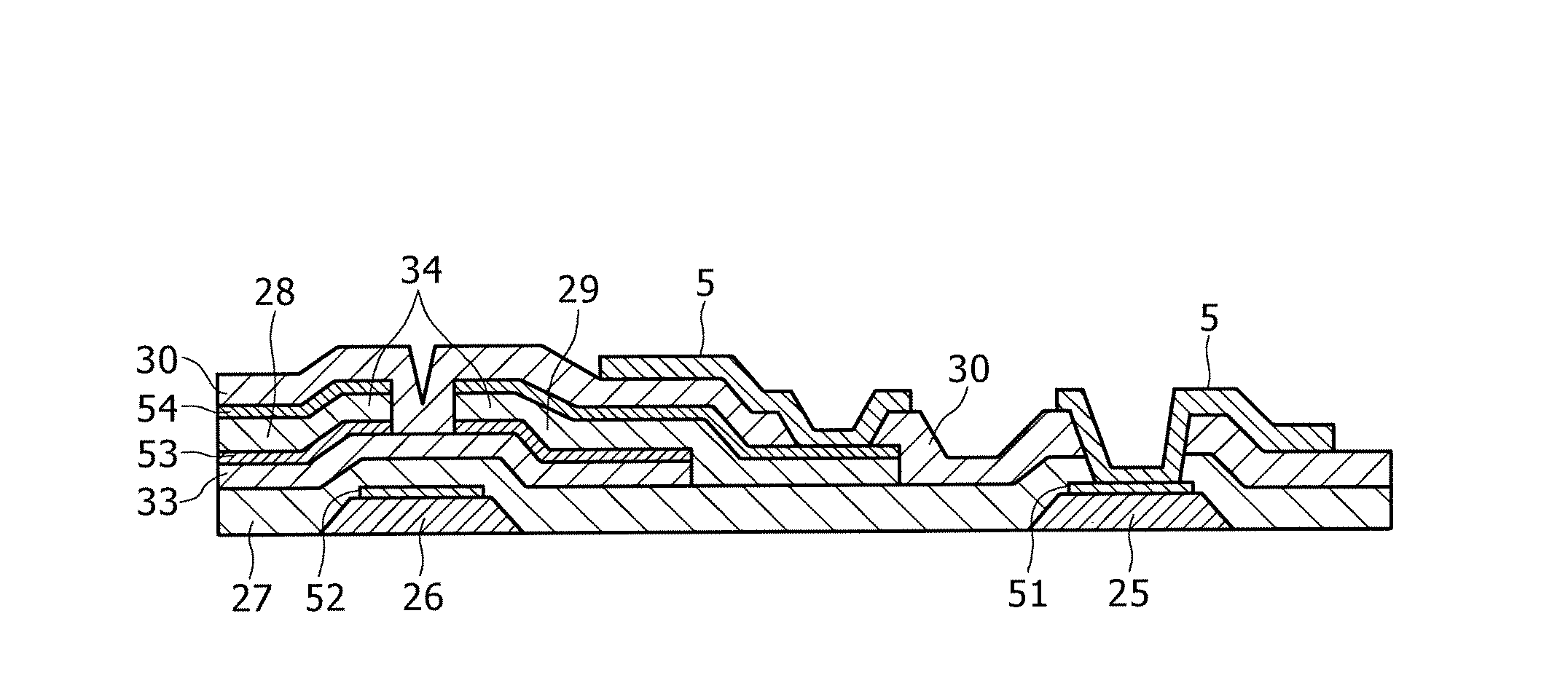

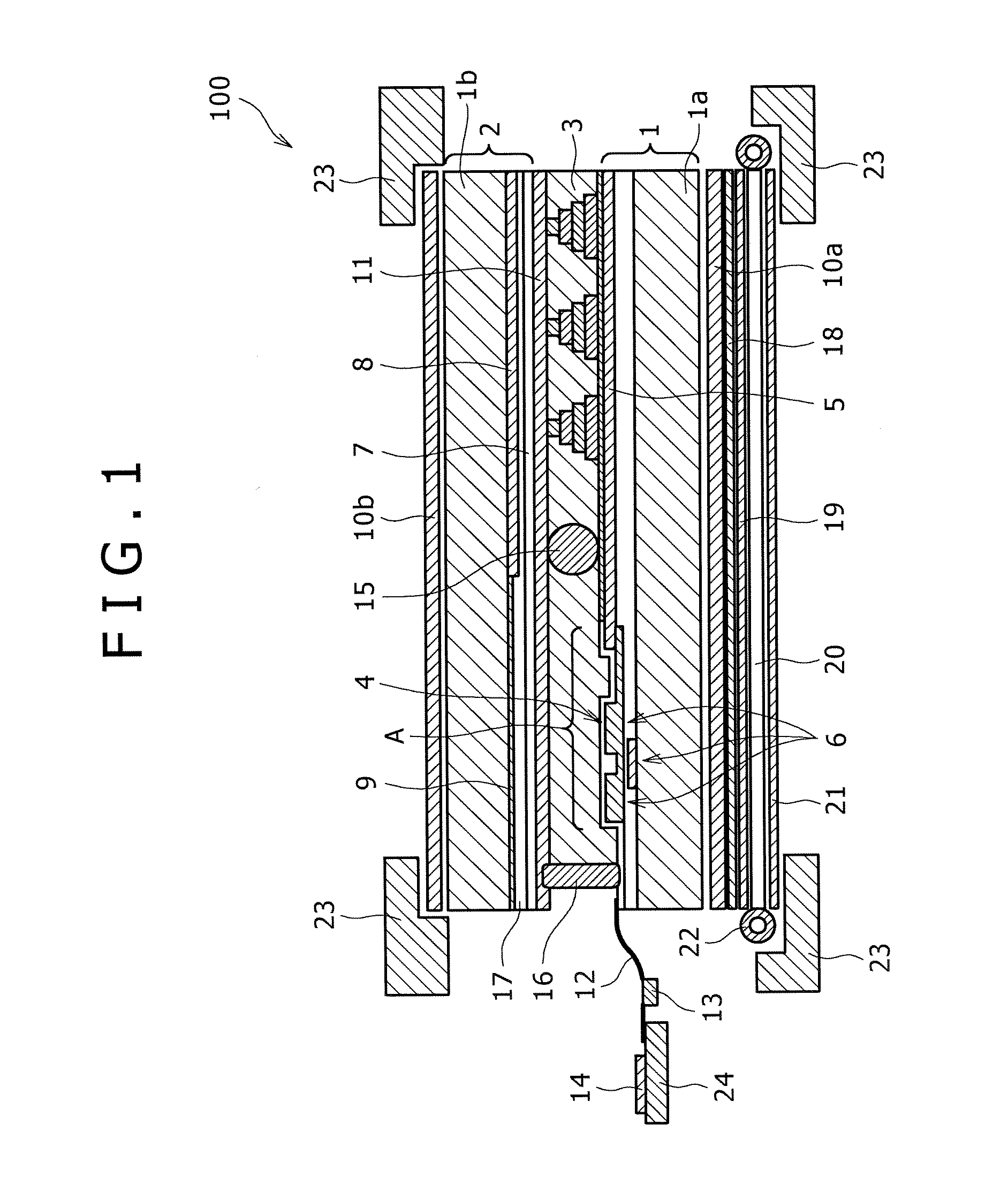

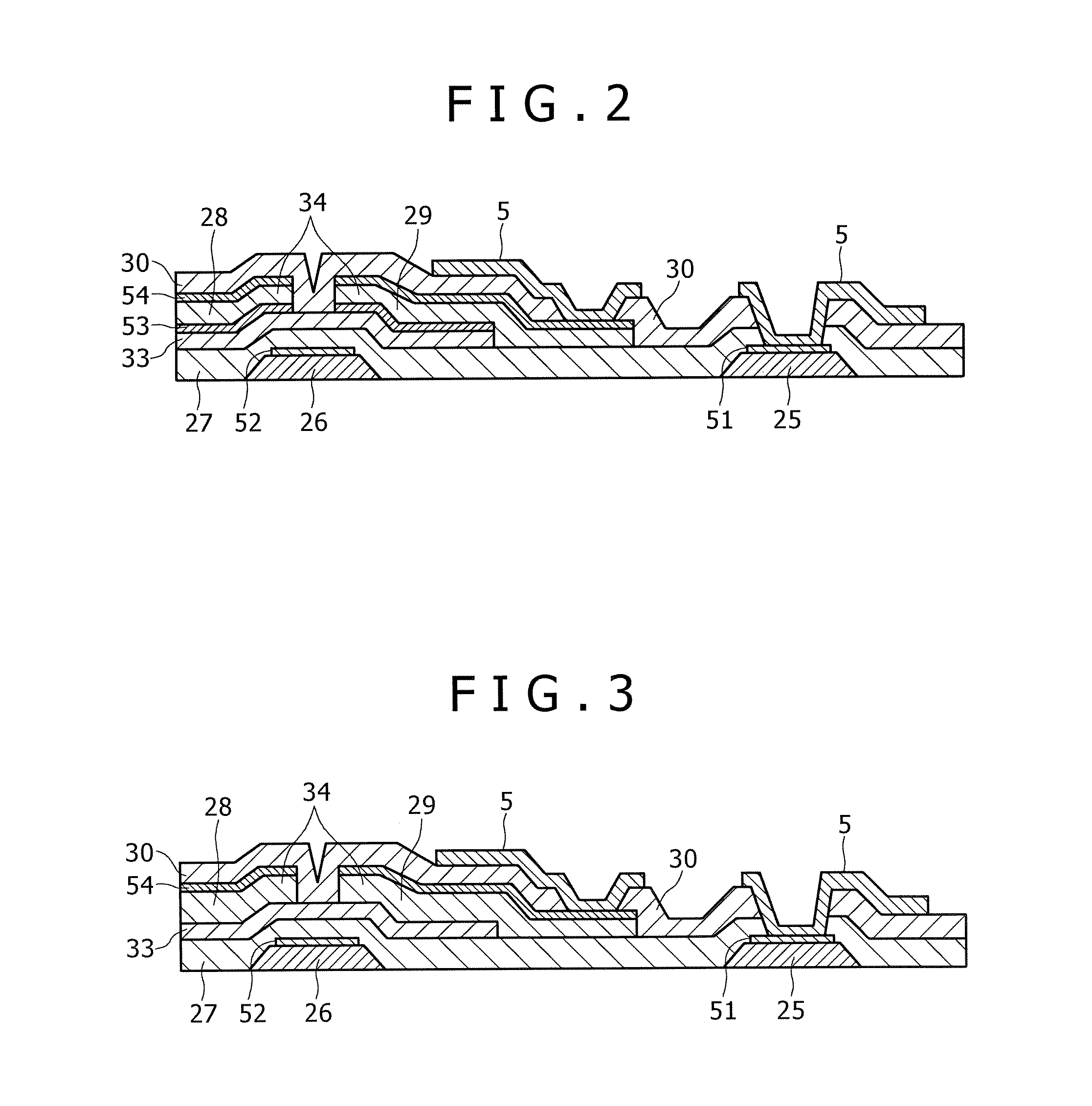

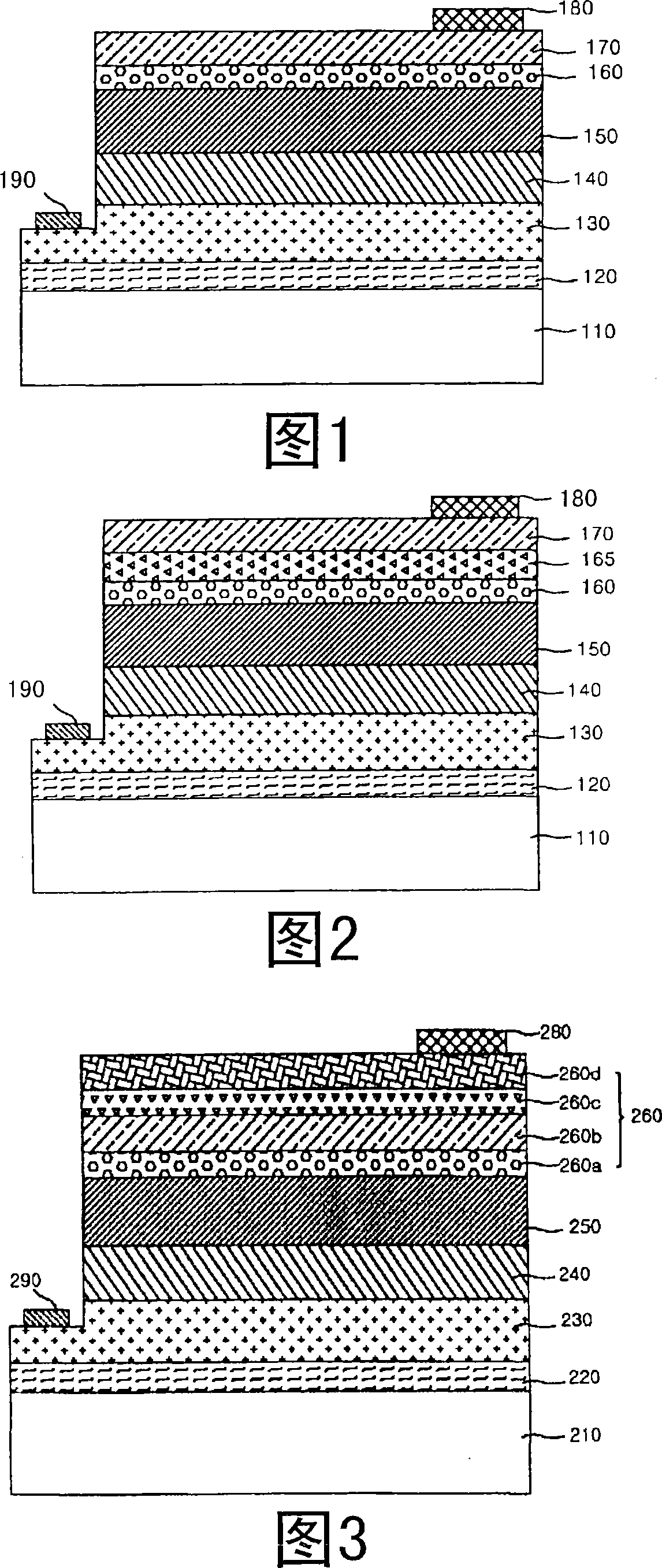

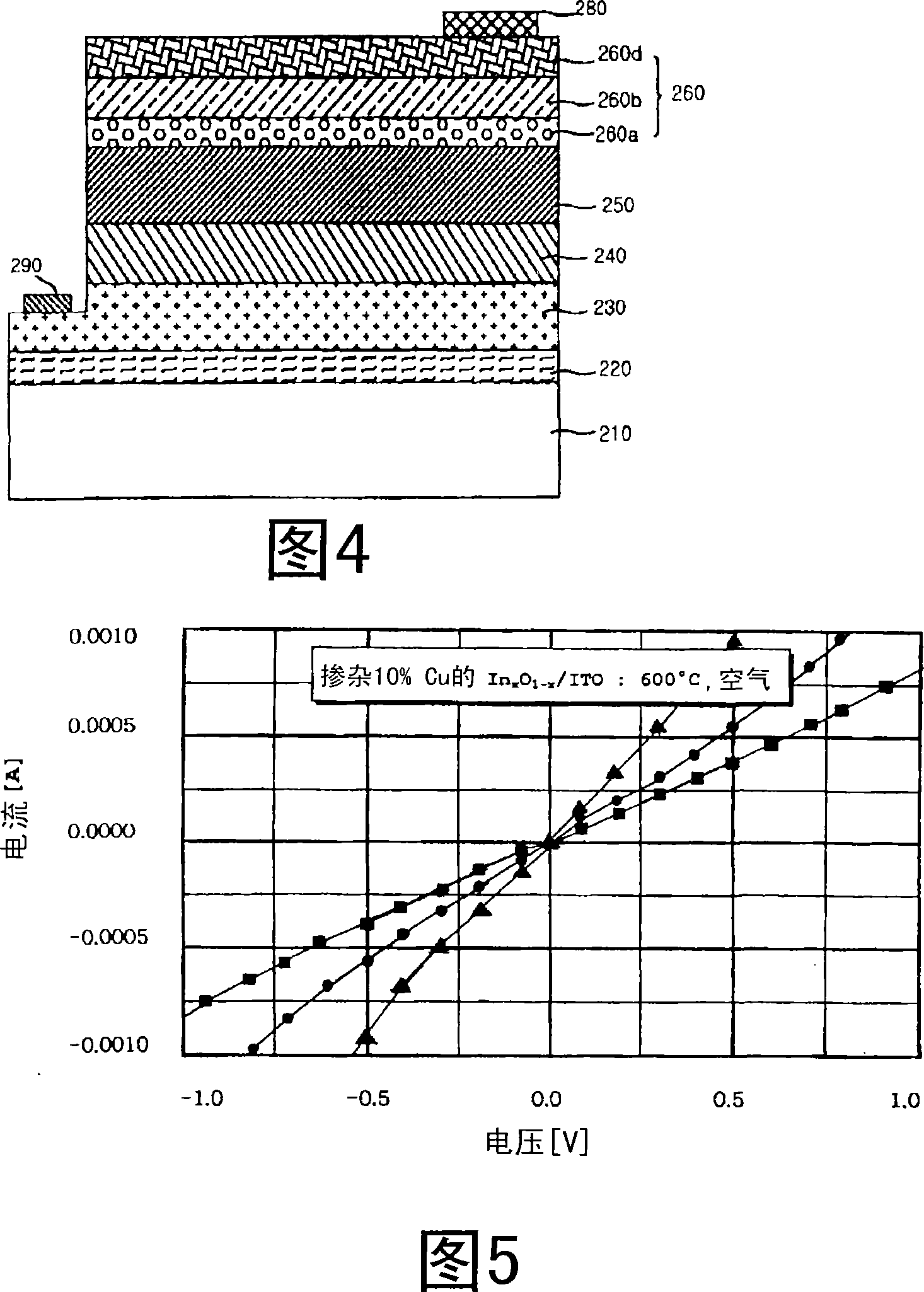

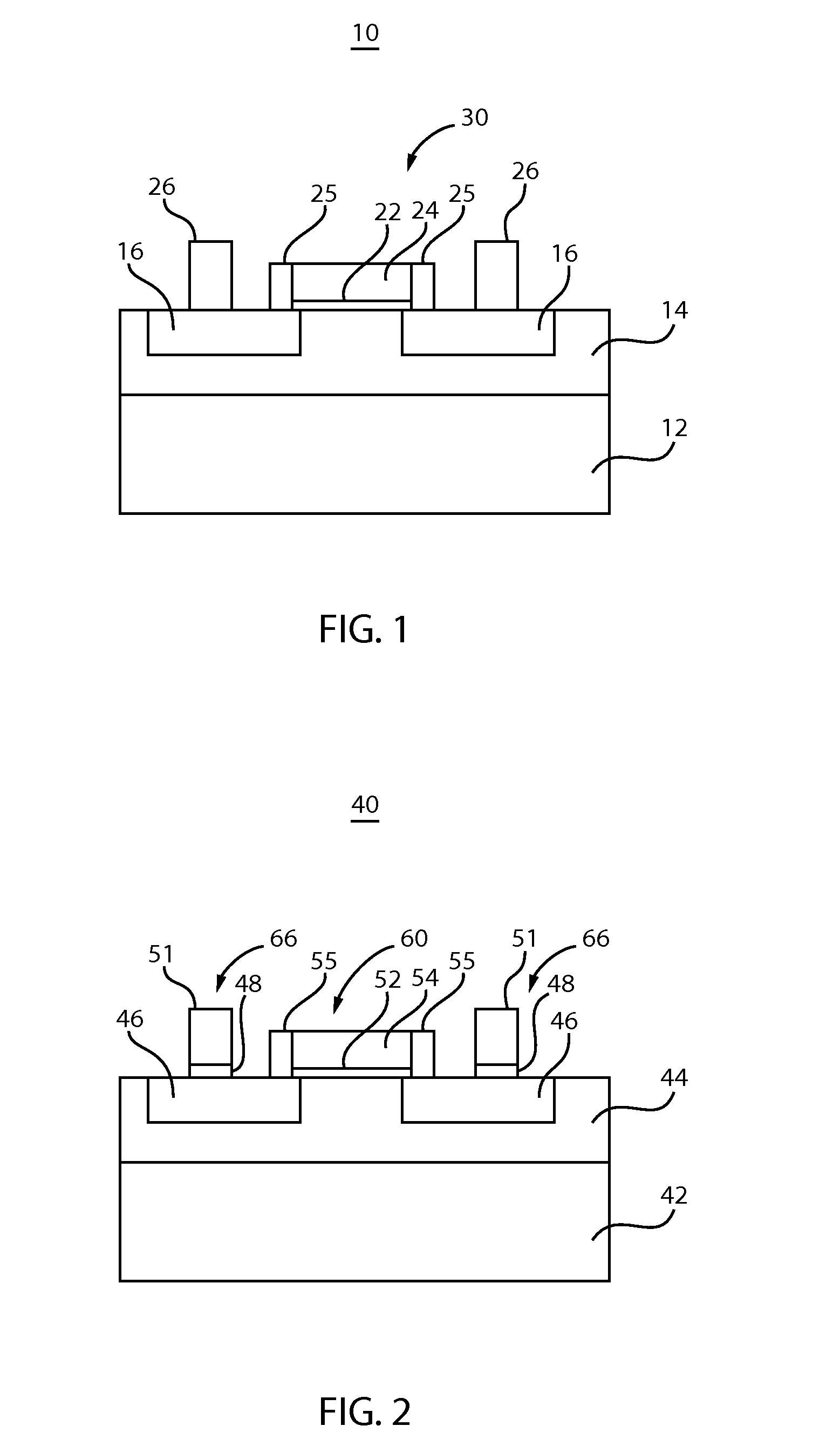

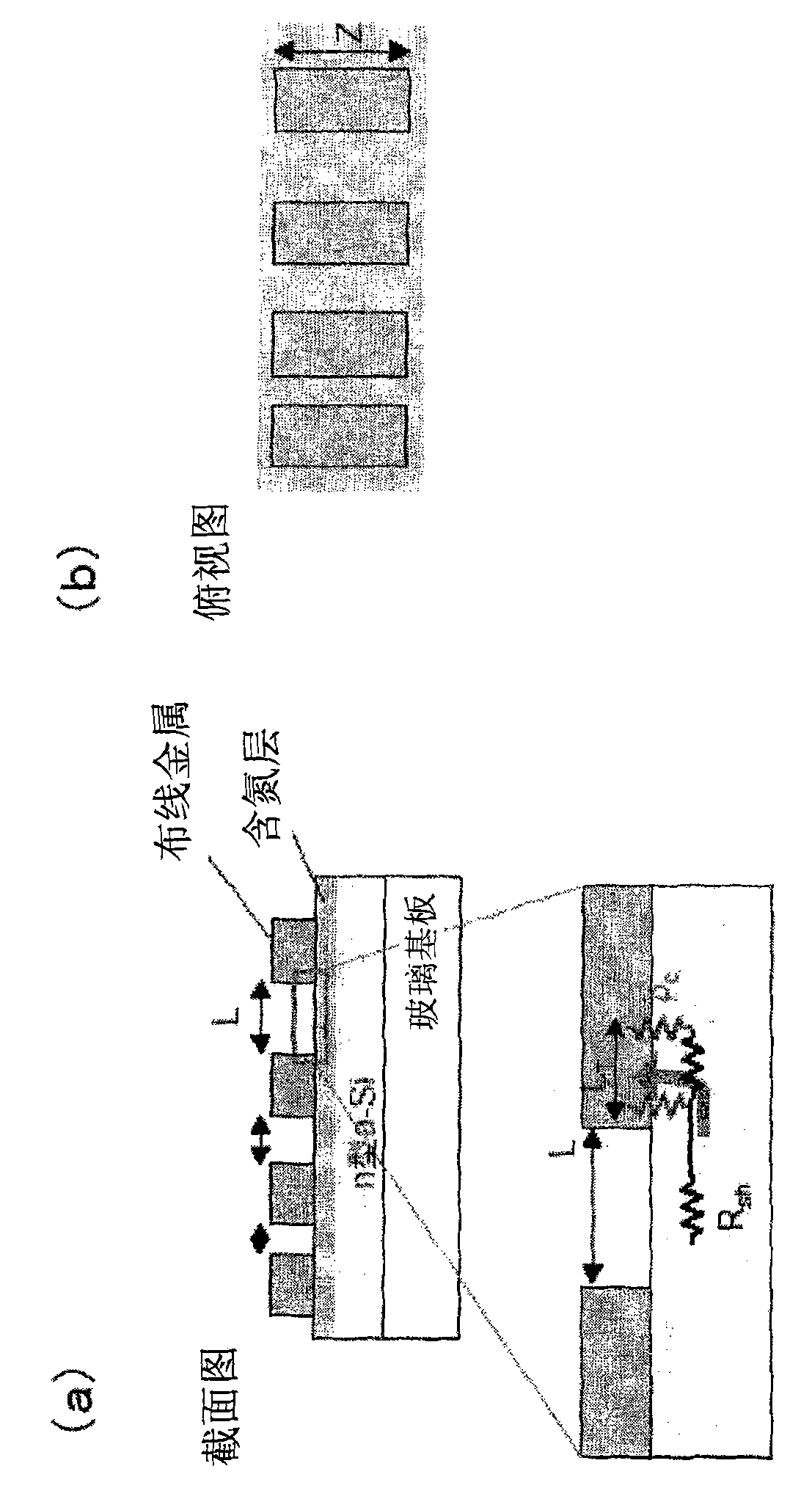

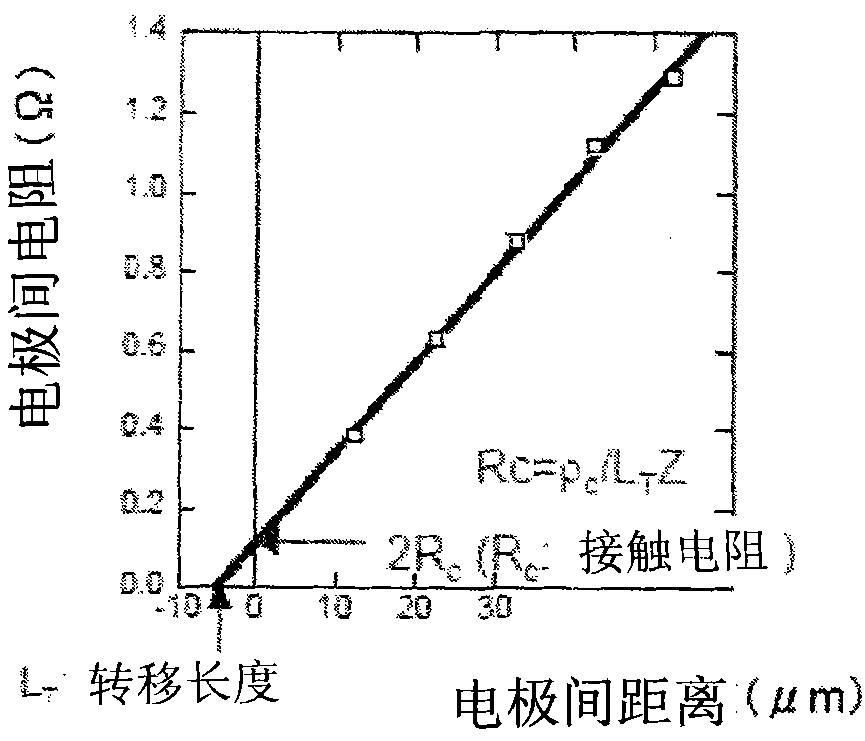

Source/drain electrodes, thin-film transistor substrates, manufacture methods thereof, and display devices

ActiveUS20070040172A1Good thin-film transistor propertyIncrease production capacitySemiconductor/solid-state device detailsSolid-state devicesDisplay deviceNitrogen

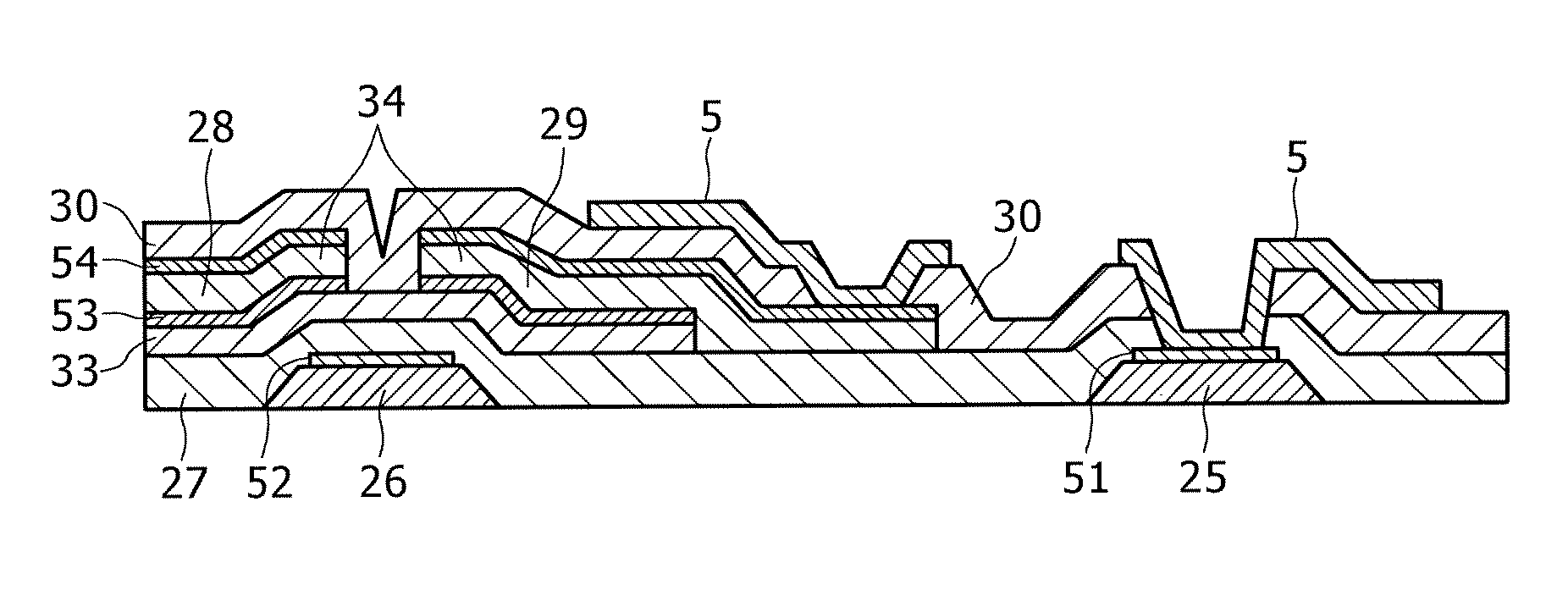

A source / drain electrode is used in a thin-film transistor substrate containing a substrate, a thin-film transistor semiconductor layer, source / drain electrodes, and a transparent picture electrode. The source / drain electrode includes a nitrogen-containing layer and a thin film of pure aluminum or an aluminum alloy. Nitrogen of the nitrogen-containing layer binds to silicon of the thin-film transistor semiconductor layer, and the thin film of pure aluminum or aluminum alloy is connected to the thin-film transistor semiconductor layer through the nitrogen-containing layer.

Owner:KOBE STEEL LTD

Source/drain electrodes, thin-film transistor substrates, manufacture methods thereof, and display devices

ActiveUS7411298B2Excellent thin-film transistor propertyMaintain good propertiesSemiconductor/solid-state device detailsSolid-state devicesNitrogenDisplay device

A source / drain electrode is used in a thin-film transistor substrate containing a substrate, a thin-film transistor semiconductor layer, source / drain electrodes, and a transparent picture electrode. The source / drain electrode includes a nitrogen-containing layer and a thin film of pure aluminum or an aluminum alloy. Nitrogen of the nitrogen-containing layer binds to silicon of the thin-film transistor semiconductor layer, and the thin film of pure aluminum or aluminum alloy is connected to the thin-film transistor semiconductor layer through the nitrogen-containing layer.

Owner:KOBE STEEL LTD

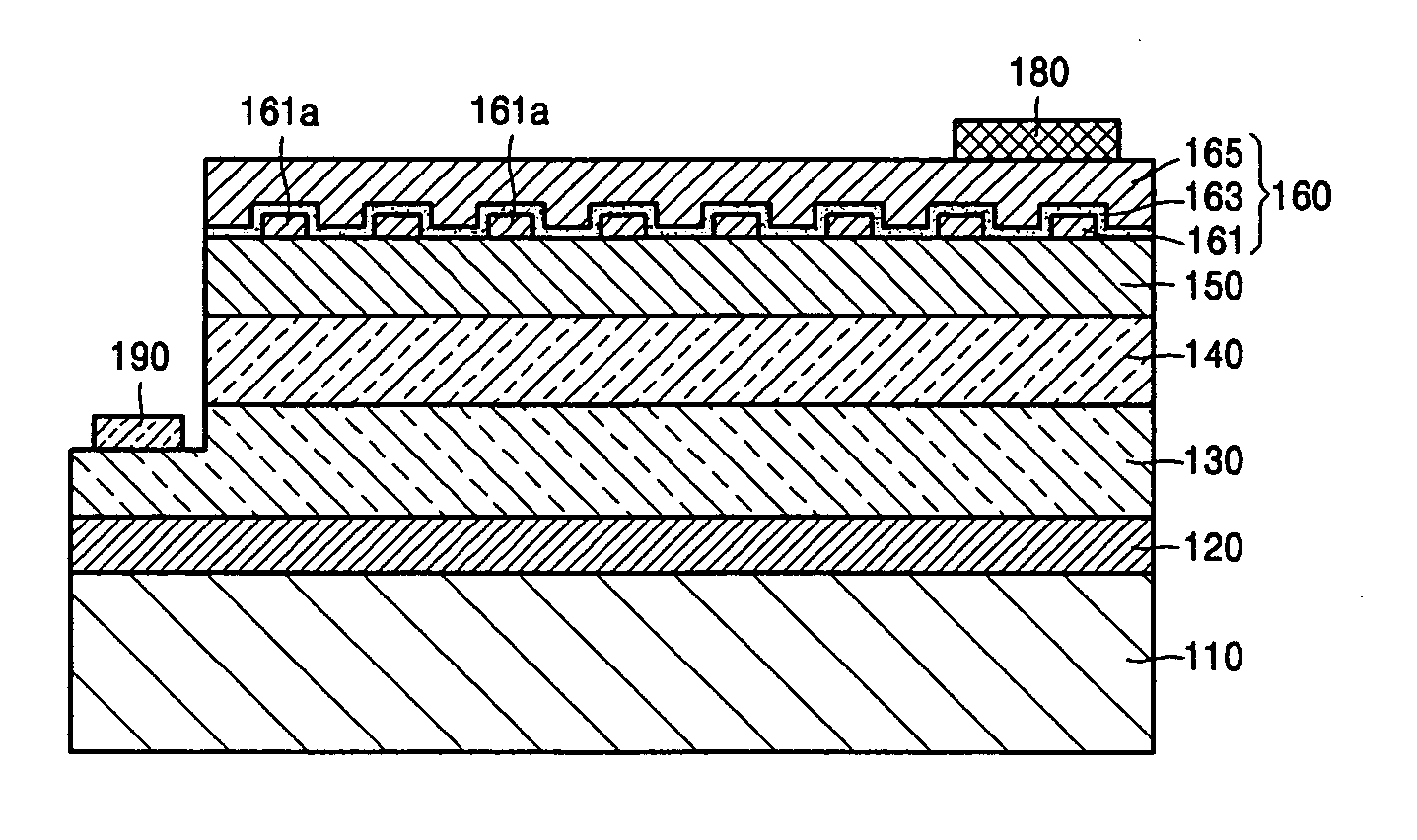

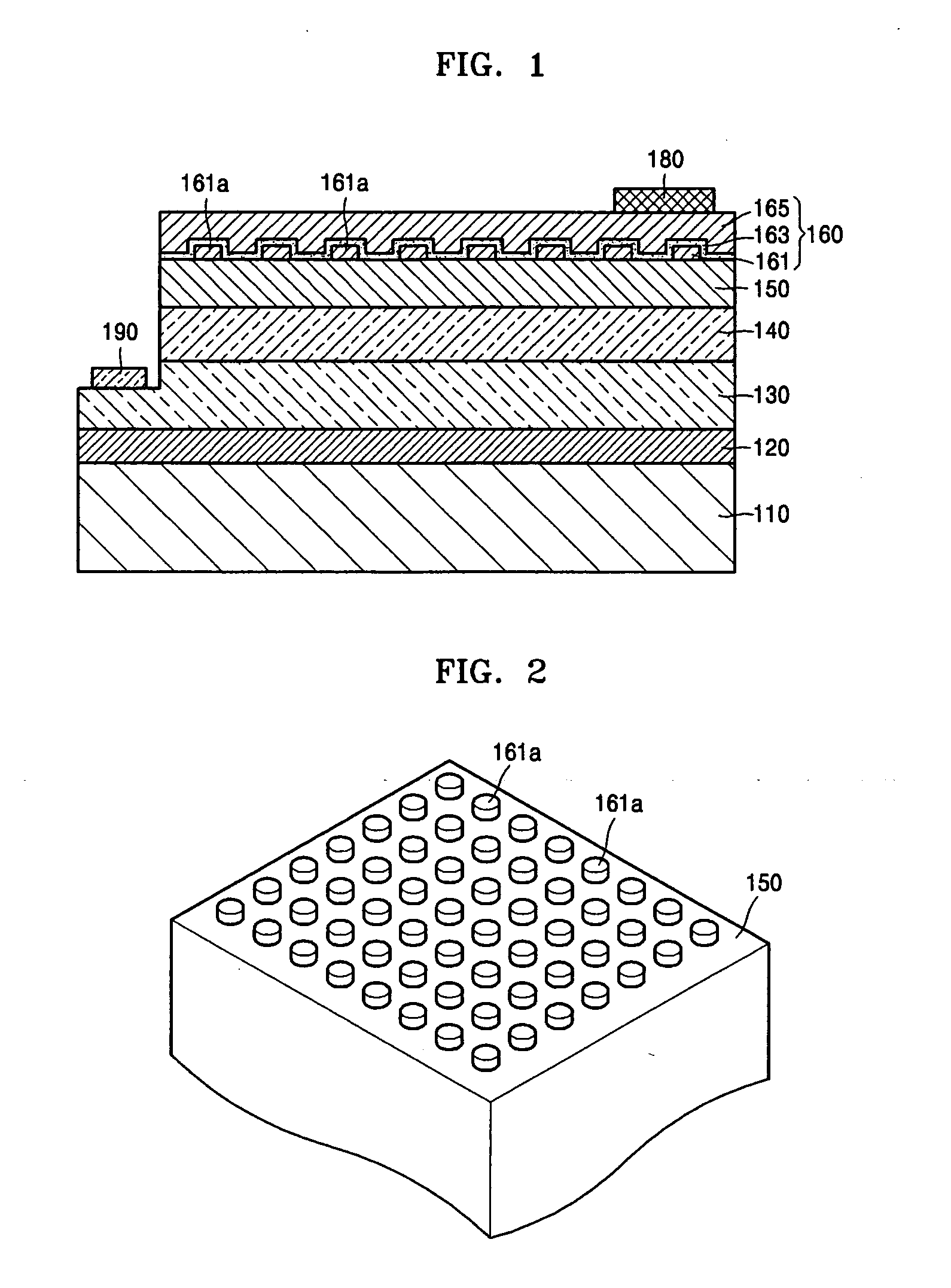

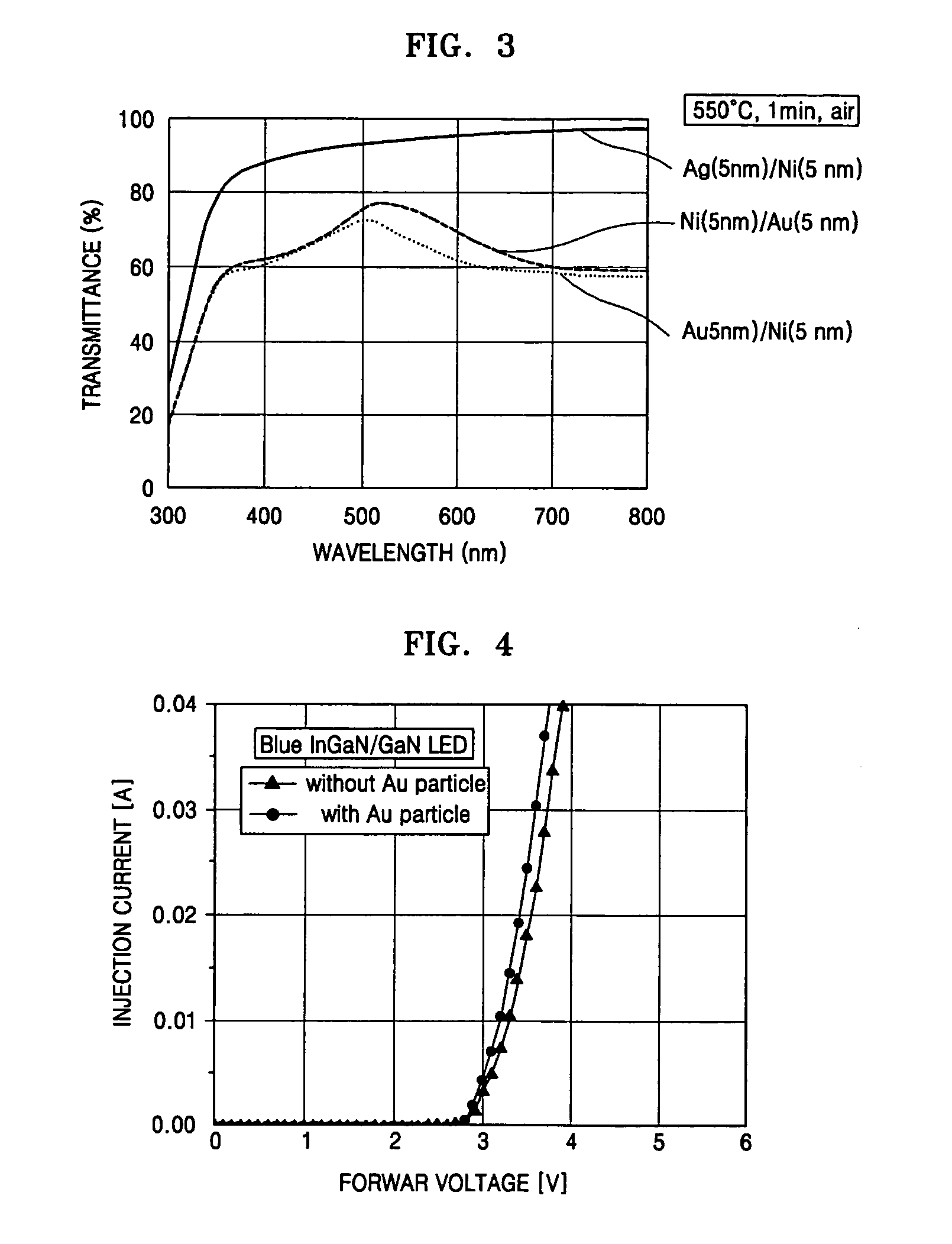

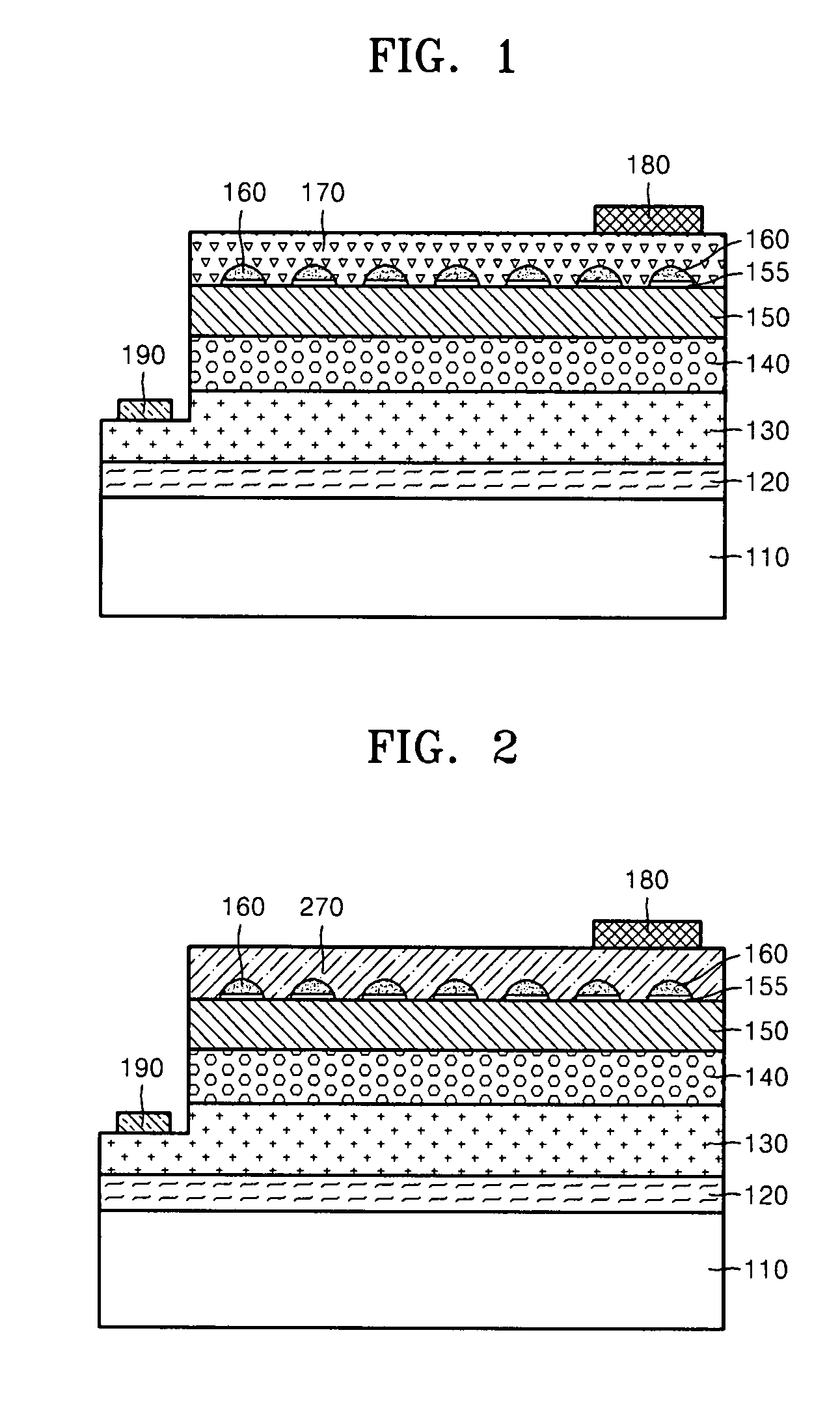

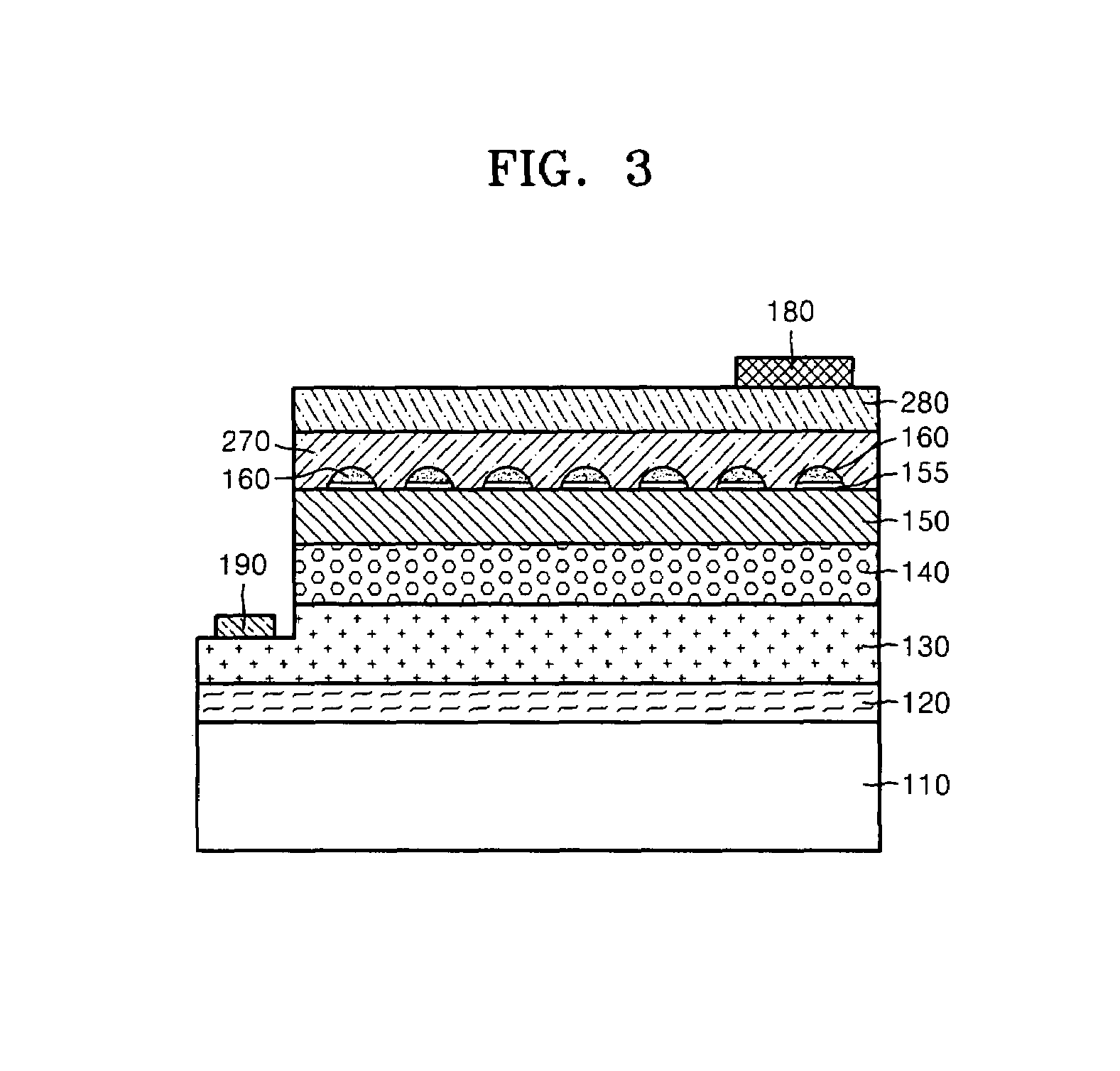

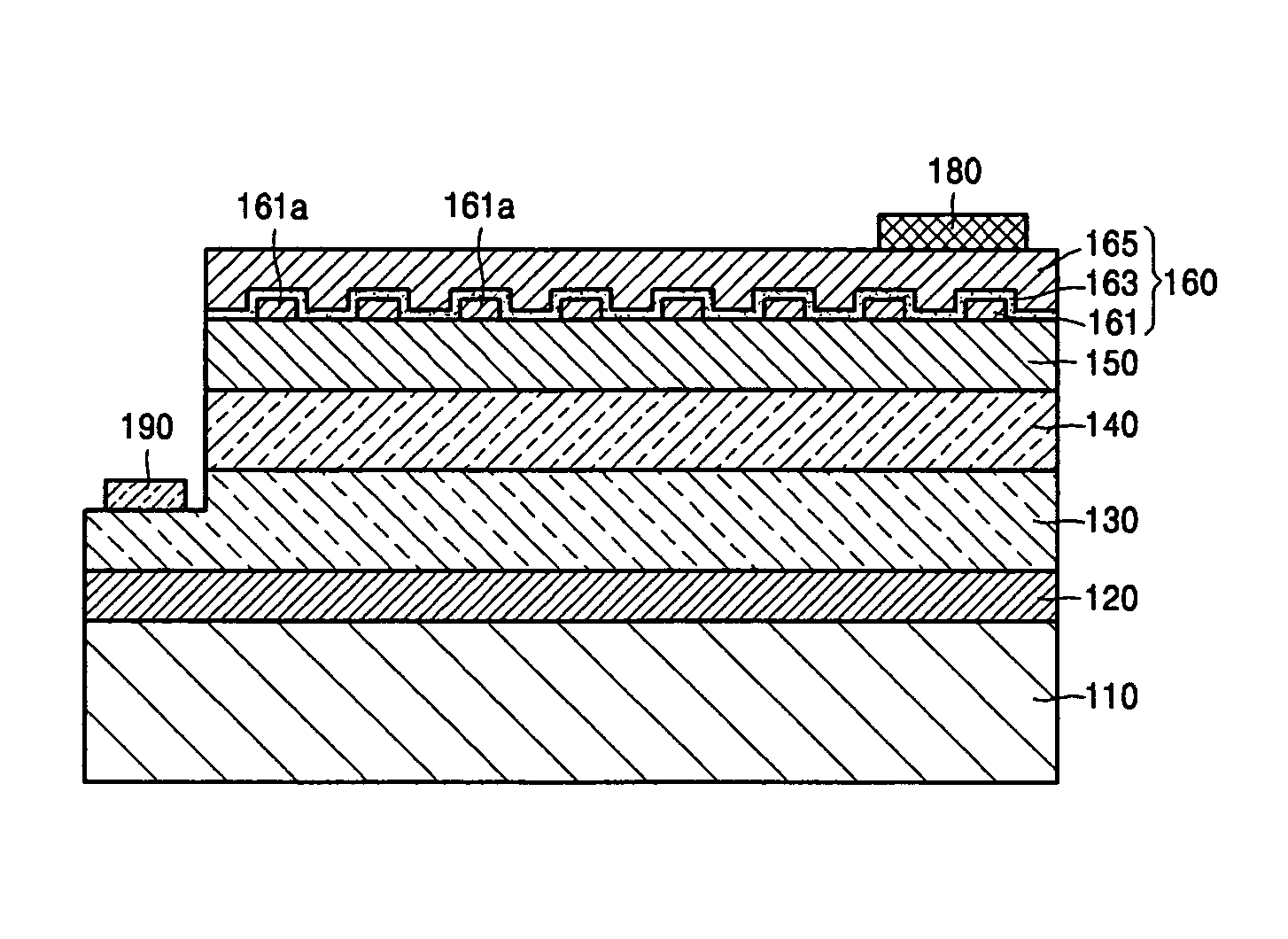

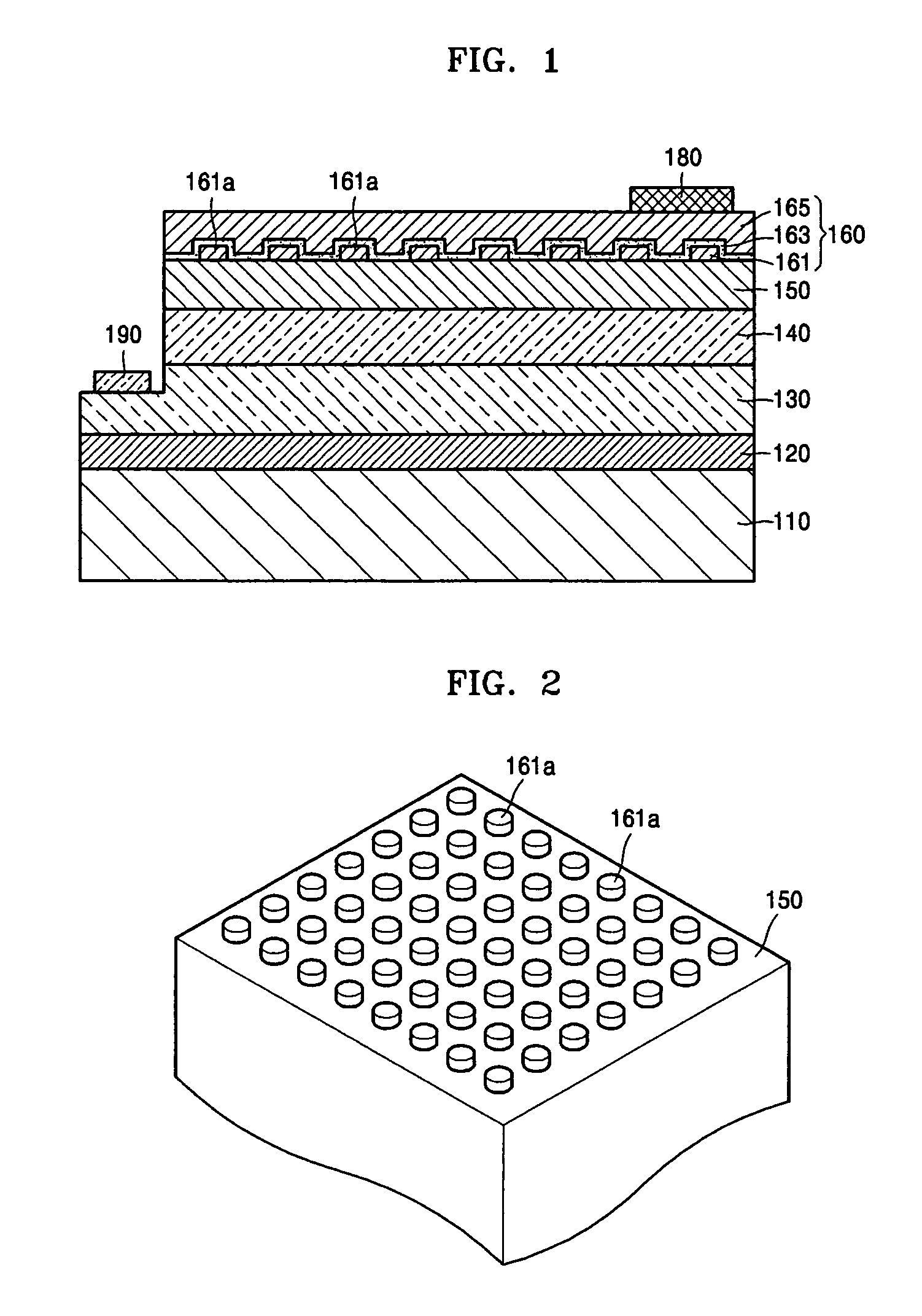

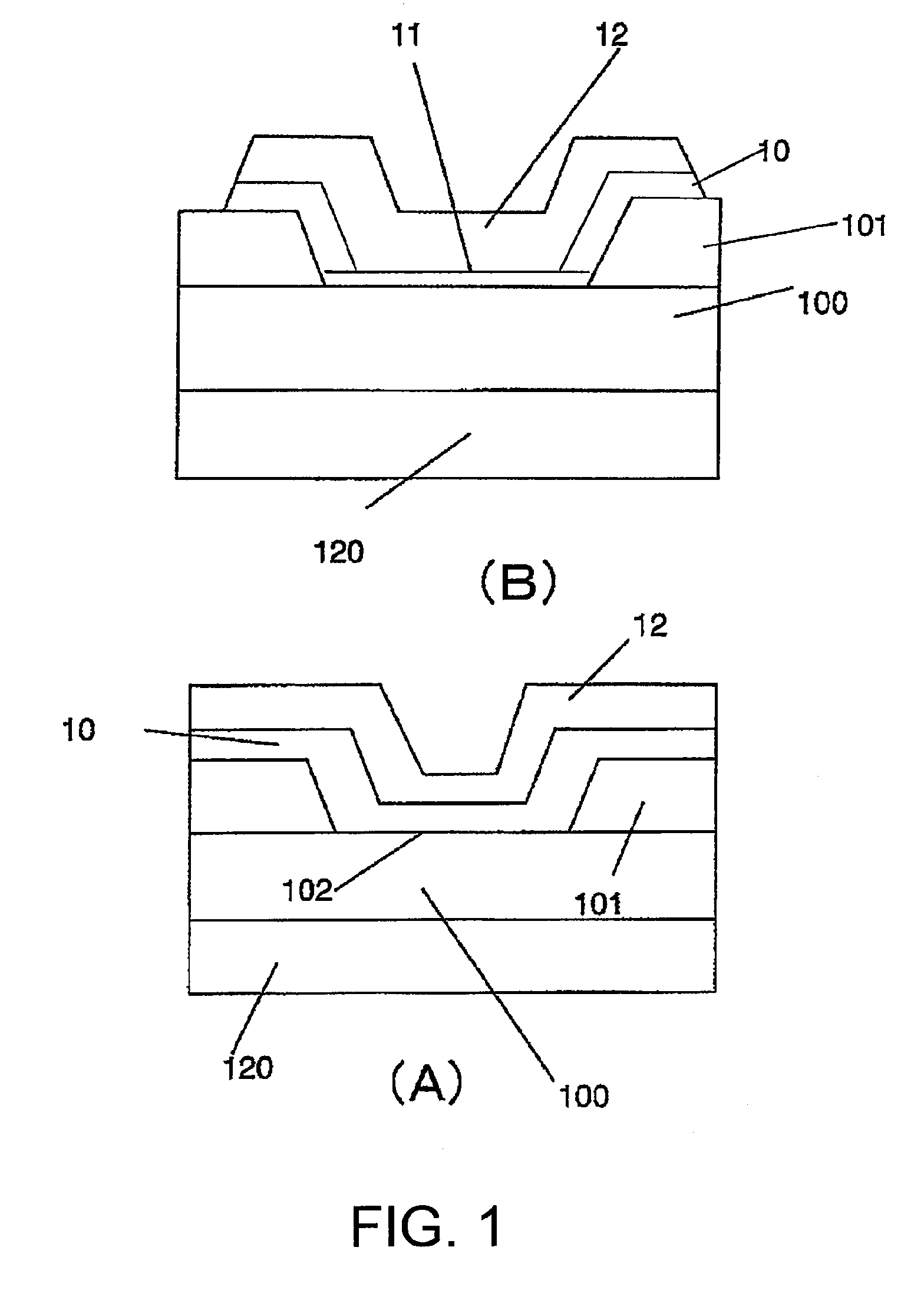

Top-emitting nitride-based light-emitting device and method of manufacturing the same

ActiveUS20050199888A1High light transmittanceReduce sheet resistanceElectroluminescent light sourcesSolid-state devicesMicrometerOhmic contact

A top-emitting nitride-based light-emitting device and a method of manufacturing the same. The top-emitting nitride-based light-emitting device having a substrate, an n-cladding layer, an active layer, and a p-cladding layer sequentially formed includes: a grid cell layer formed on the p-cladding layer by a grid array of separated cells formed from a conducting material with a width of less than 30 micrometers to improve electrical and optical characteristics; a surface protective layer that is formed on the p-cladding layer and covers at least regions between the cells to protect a surface of the p-cladding layer; and a transparent conducting layer formed on the surface protective layer and the grid cell layer using a transparent conducting material. The light-emitting device and the method of manufacturing the same provide an improved ohmic contact to the p-cladding layer, excellent I-V characteristics, and high light transmittance, thus increasing luminous efficiency of the device.

Owner:SAMSUNG ELECTRONICS CO LTD +1

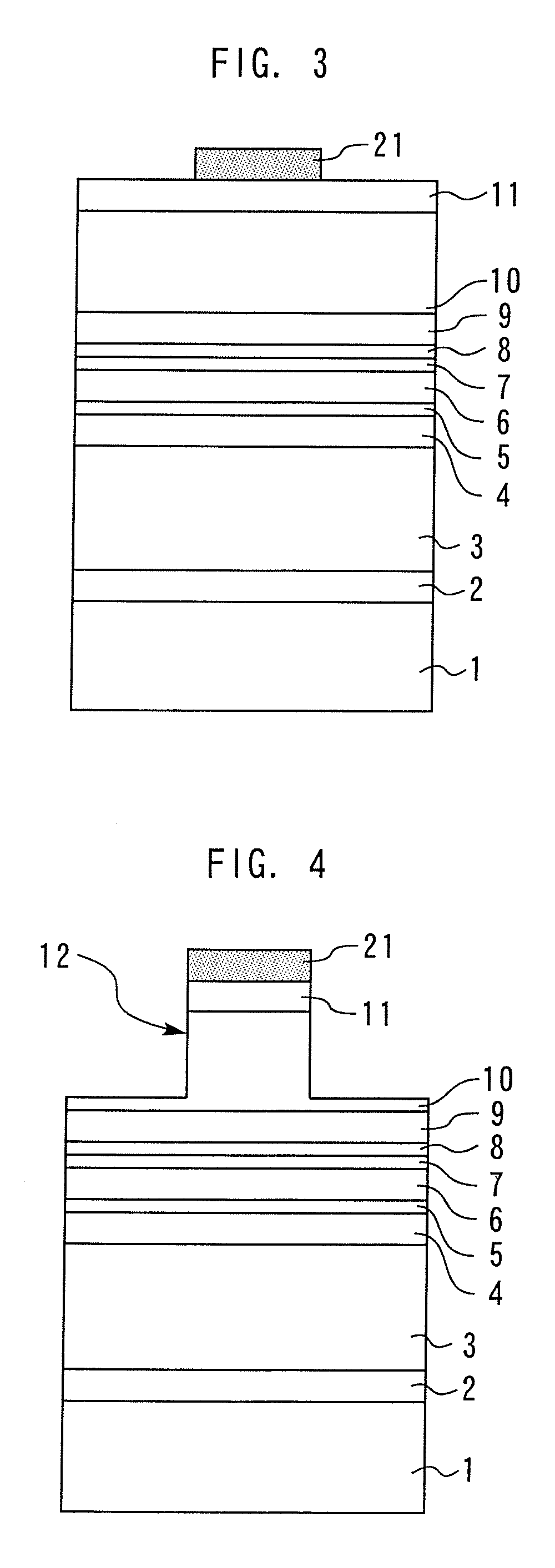

Nitride-based light-emitting device having grid cell layer

ActiveUS7485897B2Reduce contact resistivityAvoid performance degradationLaser detailsSolid-state devicesMicrometerOhmic contact

A nitride-based light-emitting device and a method of manufacturing the same. The light-emitting device includes a substrate, and an n-cladding layer, an active layer, a p-cladding layer, a grid cell layer and an ohmic contact layer sequentially formed on the substrate. The grid cell layer has separated, conducting particle type cells with a size of less than 30 micrometers buried in the ohmic contact layer. The nitride-based light-emitting device and the method of manufacturing the same improve the characteristics of ohmic contact on the p-cladding layer, thereby increasing luminous efficiency and life span of the device while simplifying a manufacturing process by omitting an activation process after wafer growth.

Owner:SAMSUNG ELECTRONICS CO LTD +1

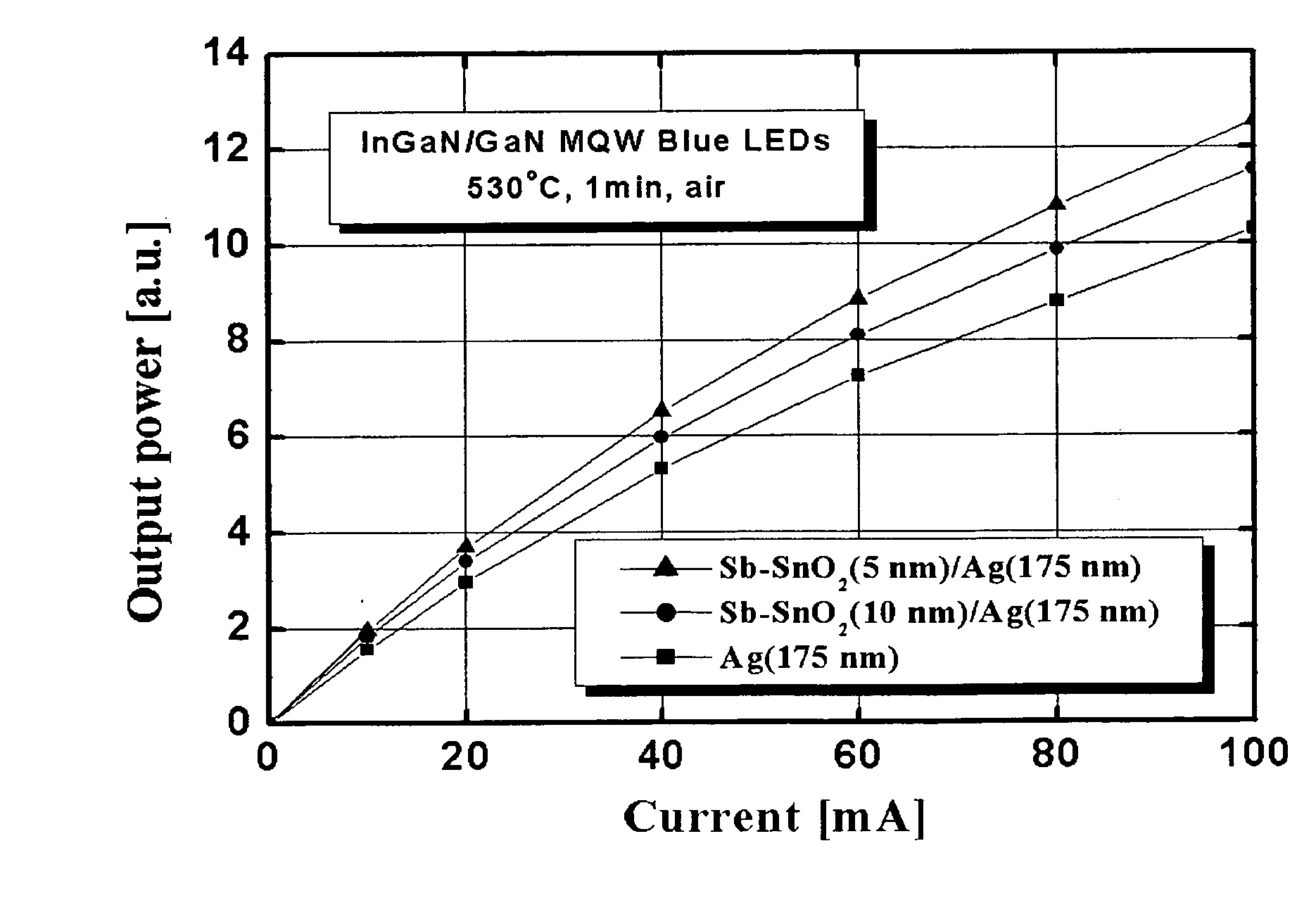

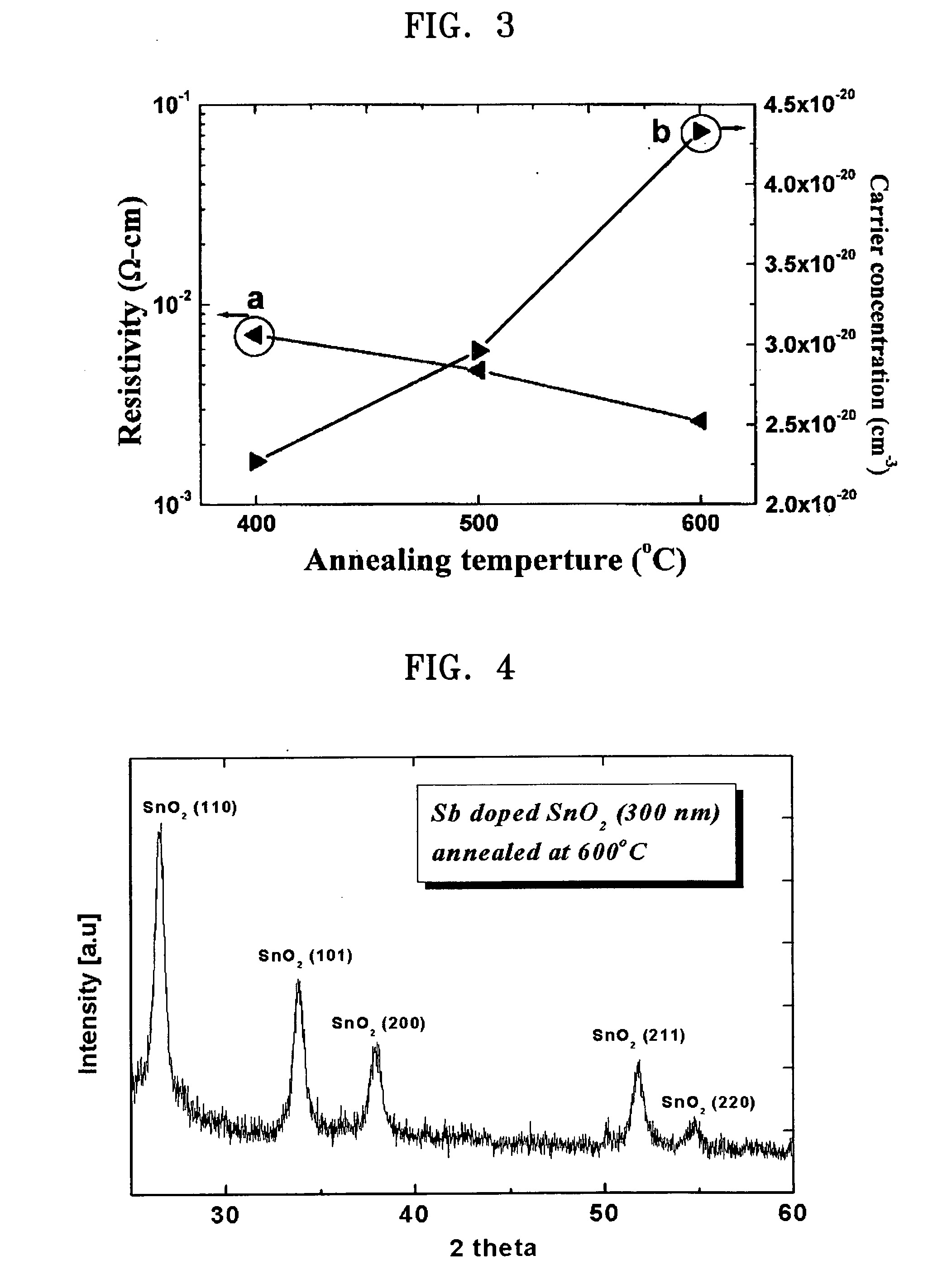

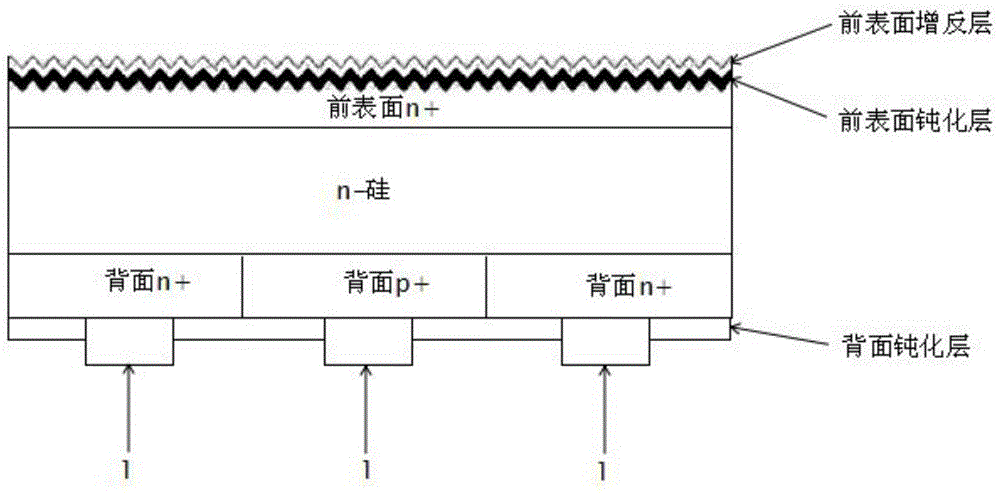

Flip-chip light emitting diode and method of manufacturing the same

InactiveUS20050121685A1Reduce contact resistivityImprove reflectivitySemiconductor devicesLight emitting deviceLight-emitting diode

Provided are a flip-chip type light emitting device and a method of manufacturing the same. The provided flip-chip type light emitting device includes a substrate, an n-type cladding layer, an active layer, a p-type cladding layer, an ohmic contact layer formed of tin oxide to which at least one of antimony, fluorine, phosphorus, and arsenic is doped, and a reflection material formed of a reflective material. According to the provided flip-chip type light emitting device and the method of manufacturing the same, a current-voltage characteristic and durability are improved by applying a conductive oxide electrode structure having low surface resistivity and high carrier concentration.

Owner:SAMSUNG ELECTRONICS CO LTD +1

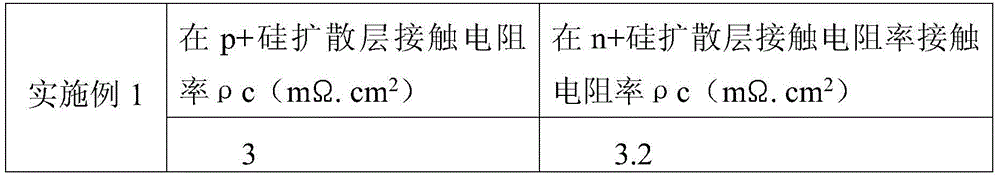

Production technology of all-back electrode solar battery

InactiveCN105489710ASimple production processReduce manufacturing costFinal product manufactureNon-conductive material with dispersed conductive materialSlurrySolar cell

The invention discloses a production technology of an all-back electrode solar battery. The production technology comprises the steps of: (1) forming a back n+ diffusion layer area and a back p+ diffusion layer area, which are arranged in a finger-crossed manner, on the back surface of a n type silicon substrate, and forming a front surface n+ diffusion layer on the front surface of the n type silicon substrate; (2) carrying out annealing oxidation treatment on the n type silicon substrate to form an oxide layer; (3) deposing passivation layers on the front surface and the back surface of the n type silicon substrate, and deposing a reflection increasing film on the passivation layer on the front surface; and (4) printing conductive slurry on the back passivation layer, after sintering, forming contact electrodes respectively on the back p+ diffusion layer area and the back n+ diffusion layer area, and finishing the preparation of the all-back electrode solar battery. According to the invention, the single conductive slurry is printed on the passivation layers of the back p+ diffusion layer and the back n+ diffusion layer at the same time, the finger-crossed conductive electrodes low in contact resistance are formed on the p+ diffusion layer and the n+ diffusion layer after the sintering, the production technology of the IBC battery is simplified, and the production cost of the IBC battery is lowered.

Owner:SICHUAN YINHE STARSOURCE TECH CO LTD

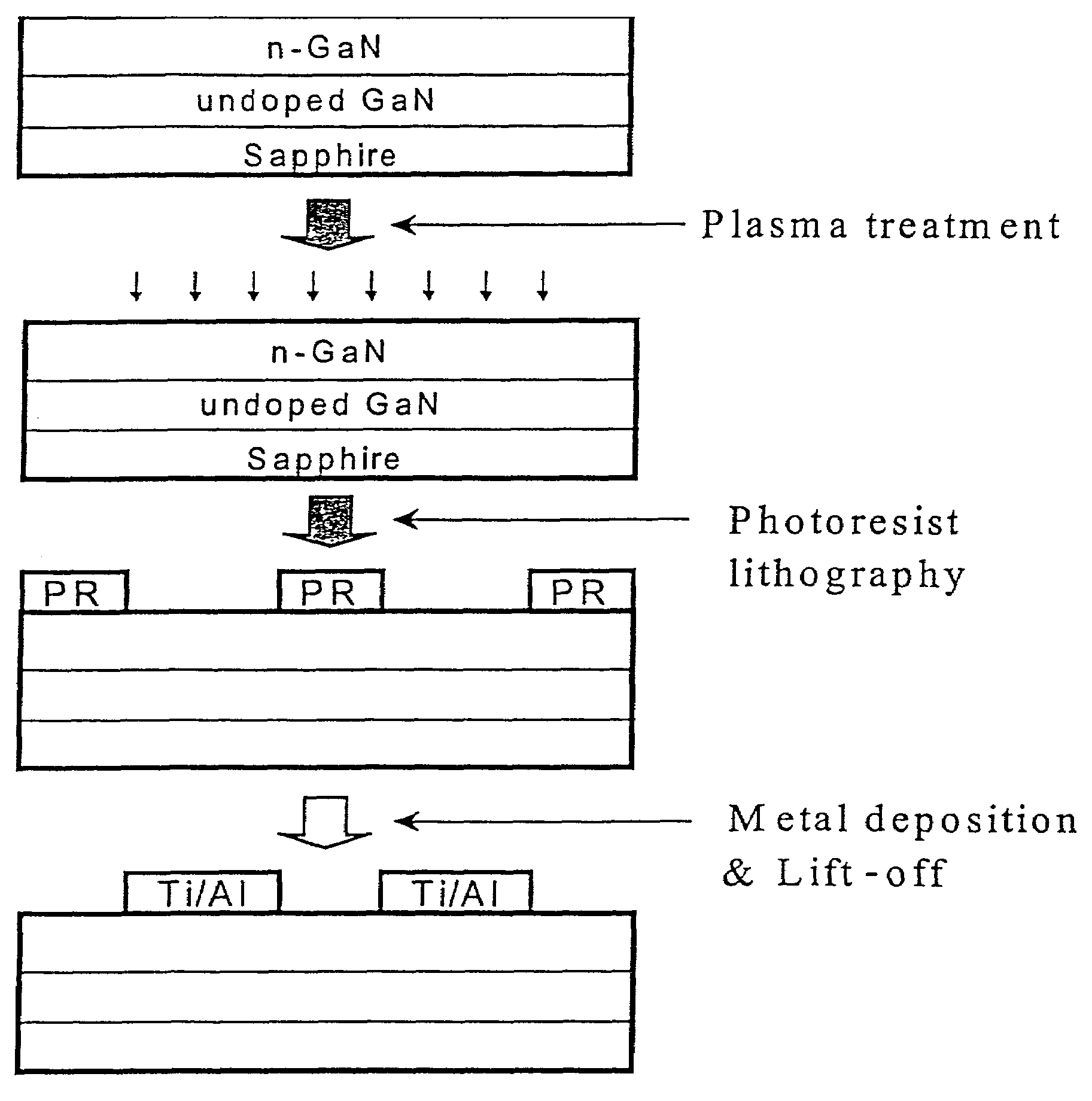

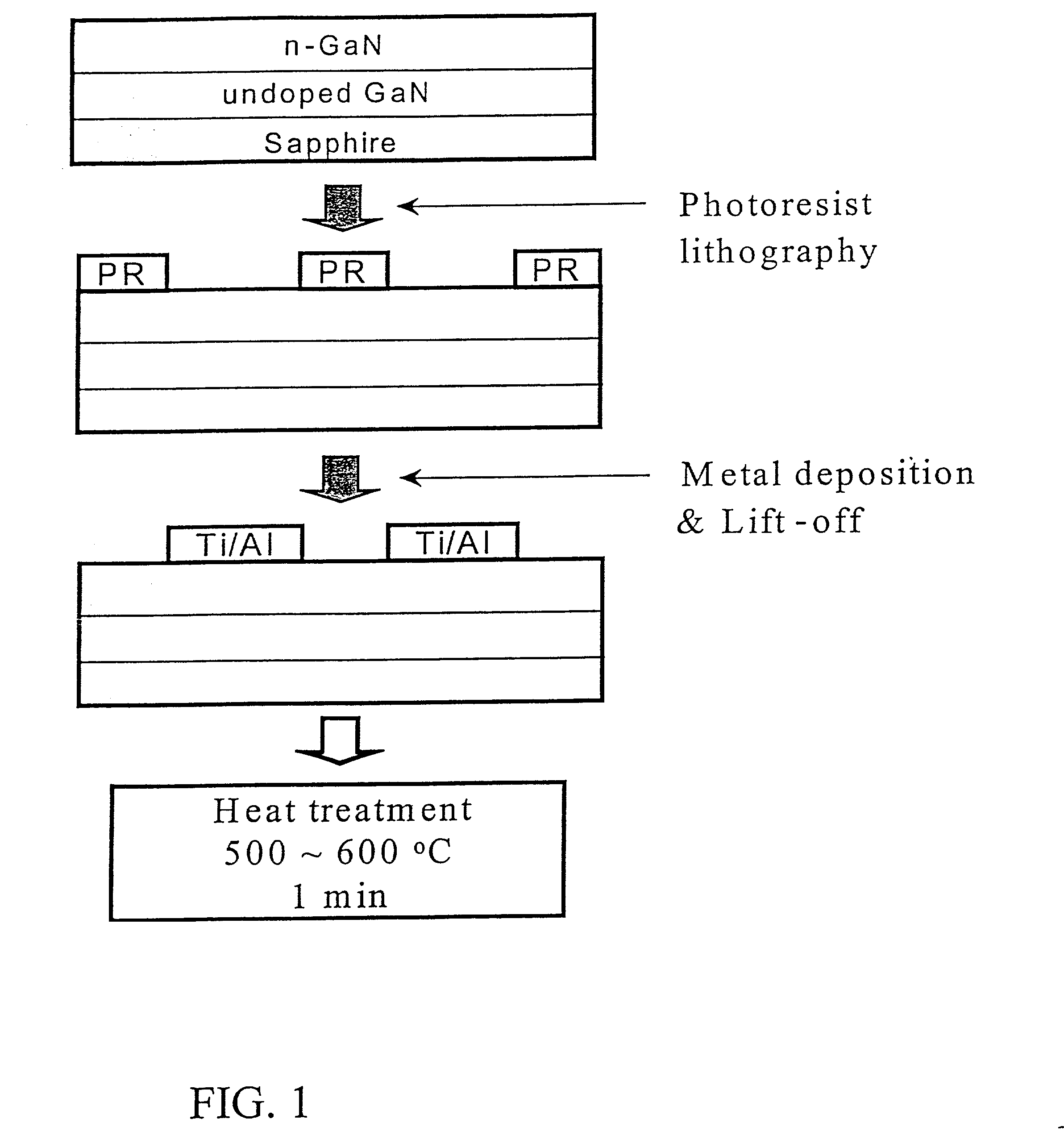

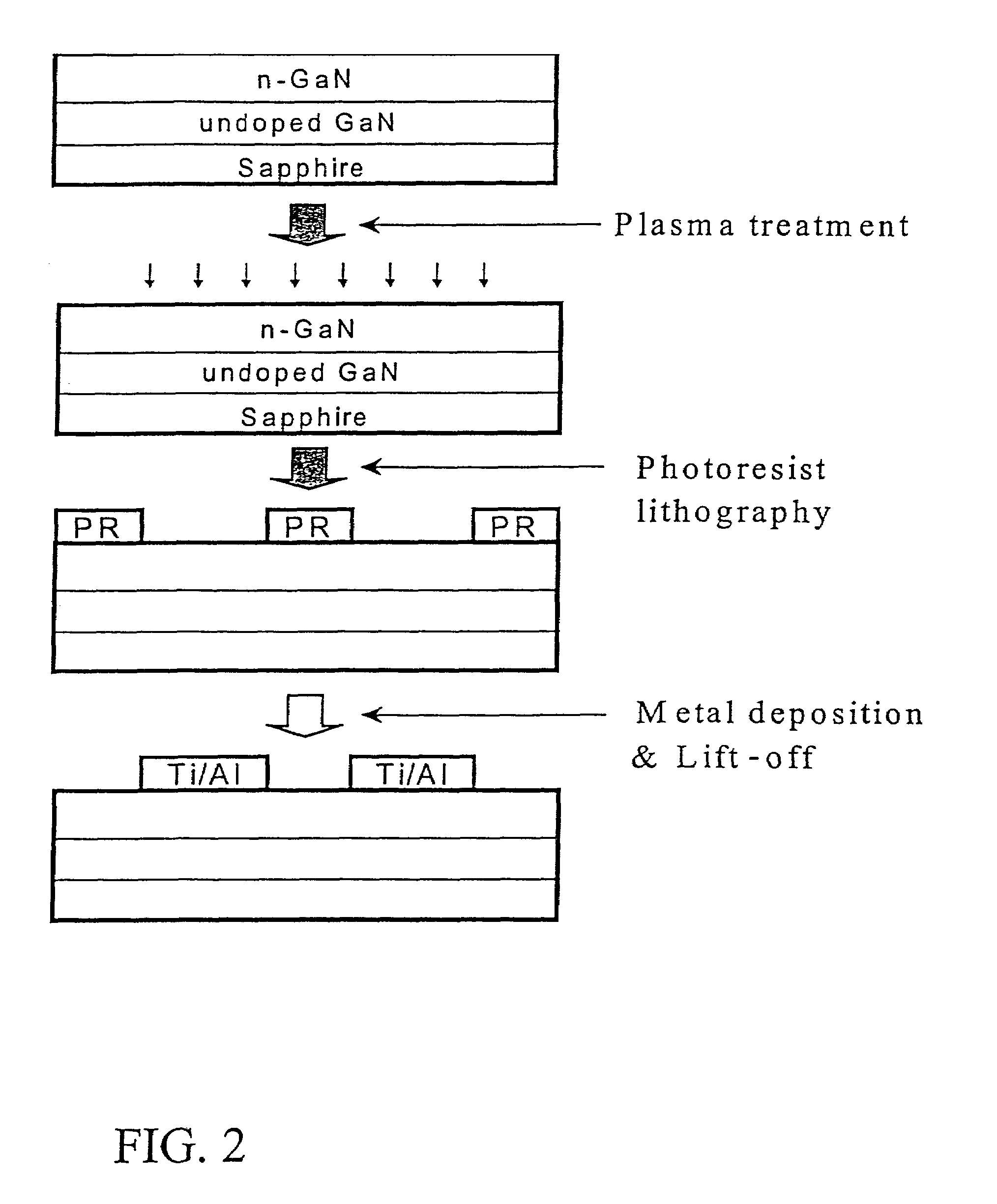

Method of fabricating ohmic contact on n-type gallium nitride (GaN) of room temperature by plasma surface treatment

InactiveUS7214325B2Increase the number ofReduce contact resistivityDecorative surface effectsSemiconductor/solid-state device manufacturingContact formationOhmic contact

Forming low contract resistance metal contacts on GaN films by treating a GaN surface using a chlorine gas Inductively Coupled Plasma (ICP) etch process before the metal contacts are formed. Beneficially, the GaN is n-type and doped with Si, while the metal contacts include alternating layers of Ti and Al. Additionally, the GaN film is dipped in a solution of HCl:H2O prior to metal contact formation.

Owner:SUZHOU LEKIN SEMICON CO LTD

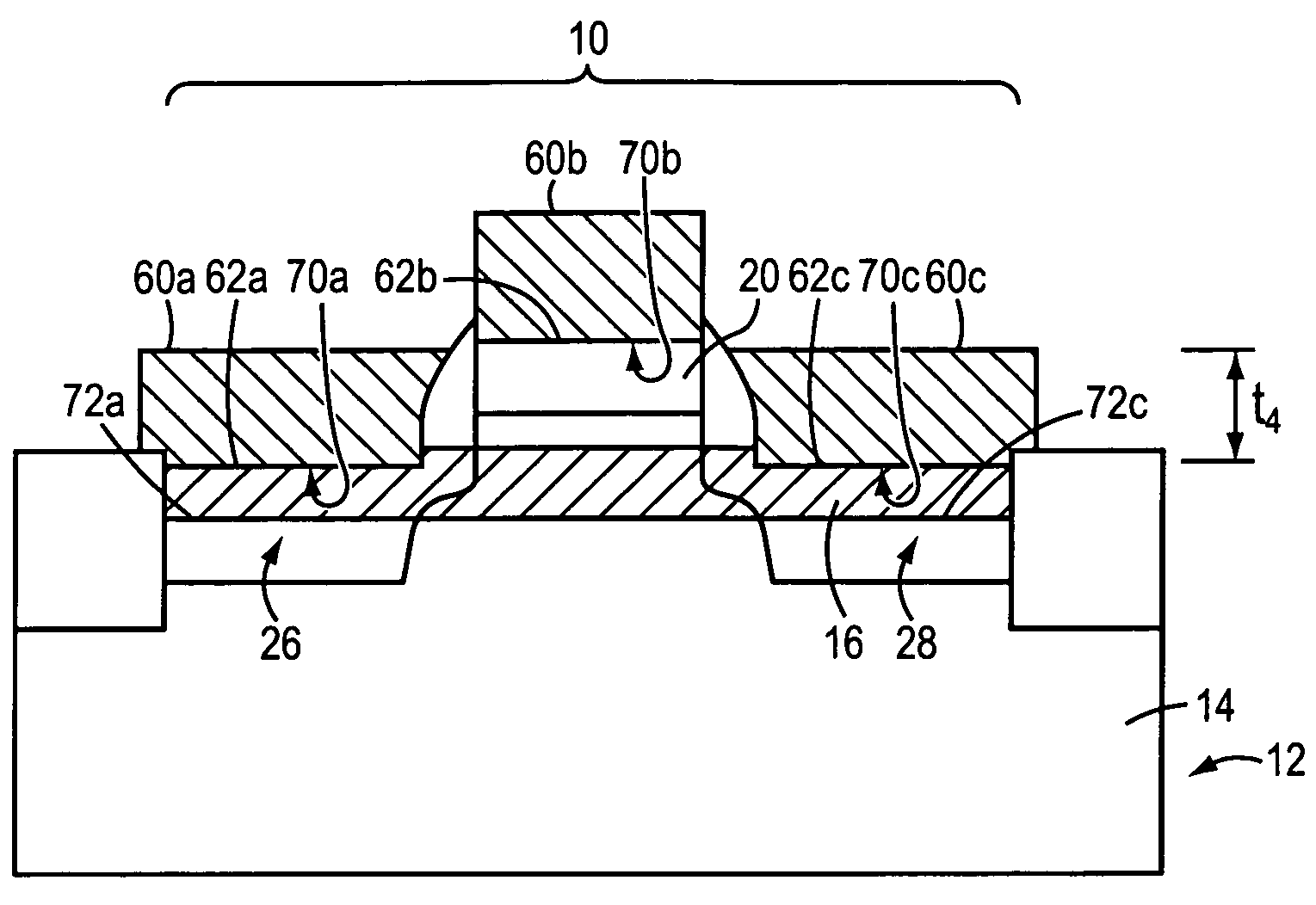

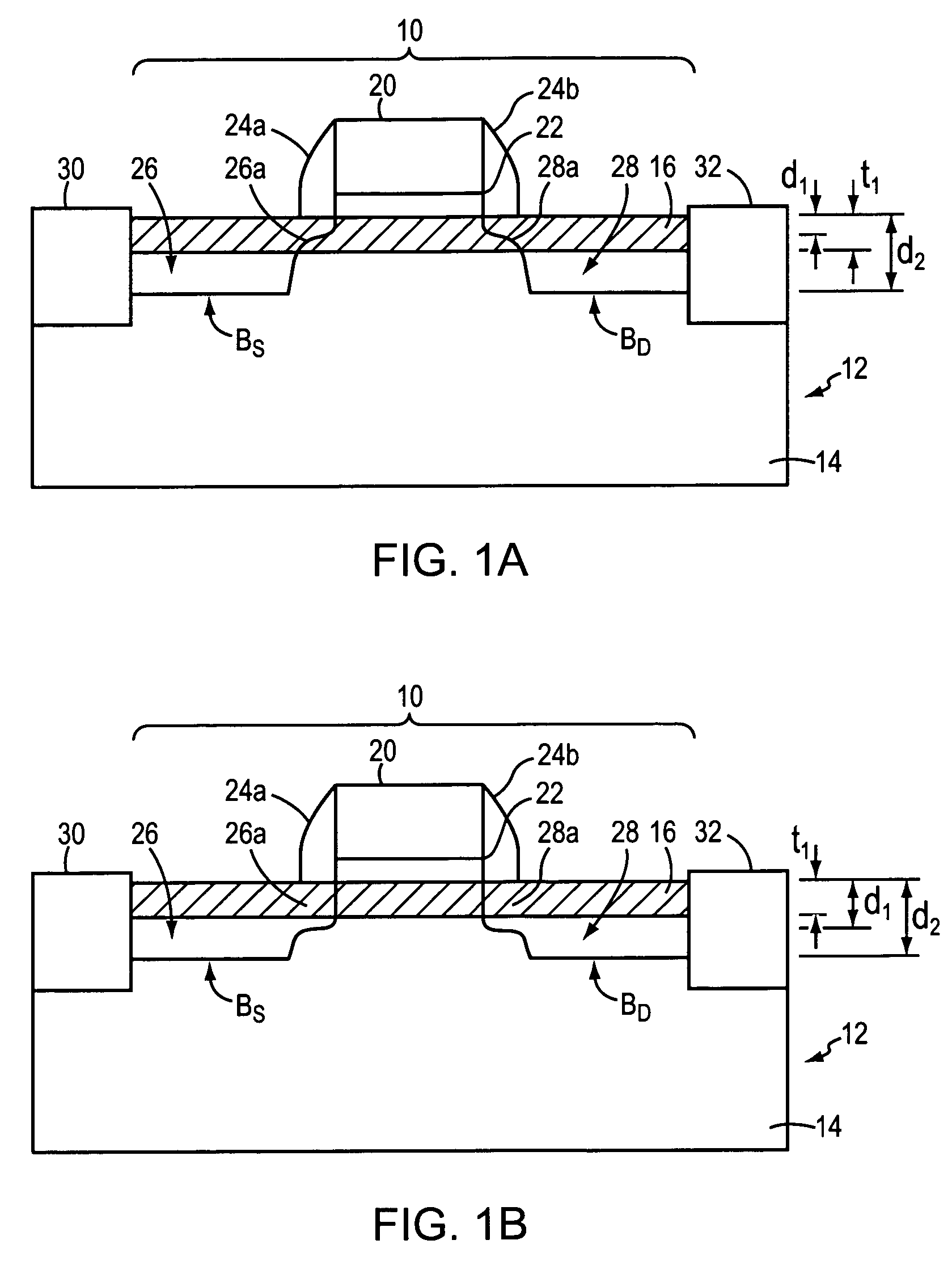

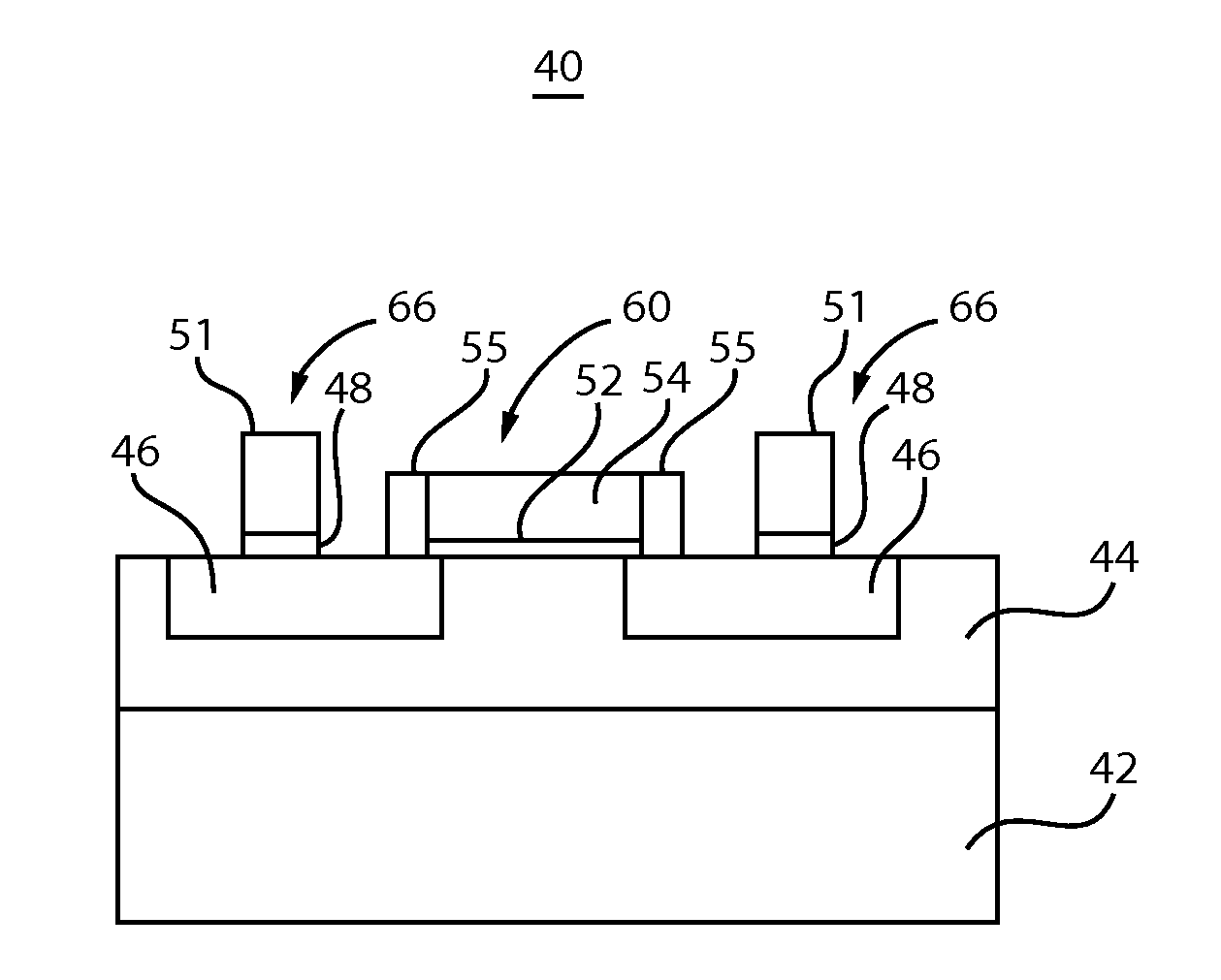

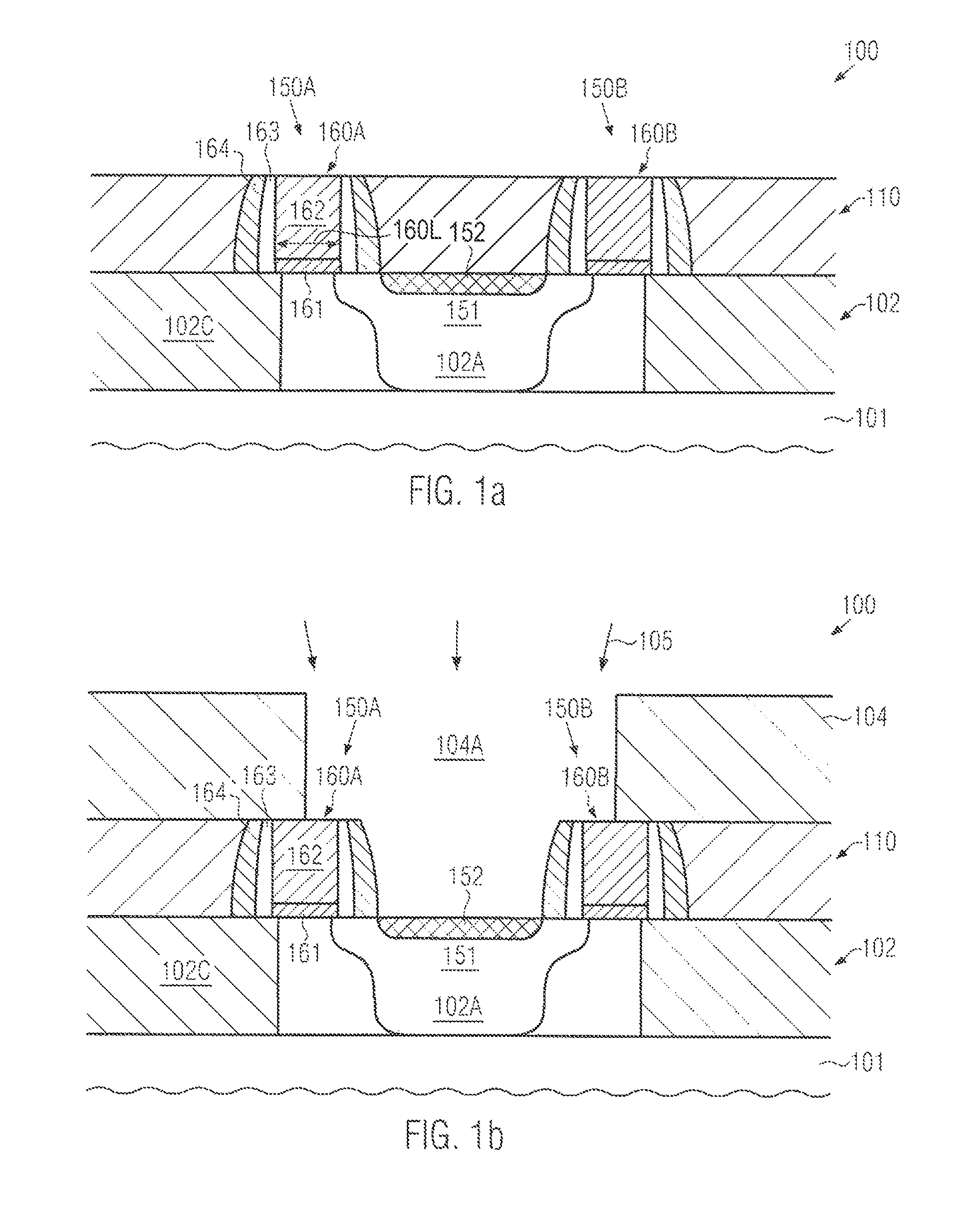

Elevated source and drain elements for strained-channel heterojuntion field-effect transistors

InactiveUS7615829B2Reduce contact resistanceInhibition formationTransistorSemiconductor/solid-state device manufacturingSurface layerSemiconductor structure

A semiconductor structure having a surface layer disposed over a substrate, the surface layer including strained silicon. A contact layer is disposed over a portion of the surface layer, the contact layer including a metal-semiconductor alloy. A bottommost boundary of the contact layer is disposed above a bottommost boundary of the surface layer.

Owner:TAIWAN SEMICON MFG CO LTD

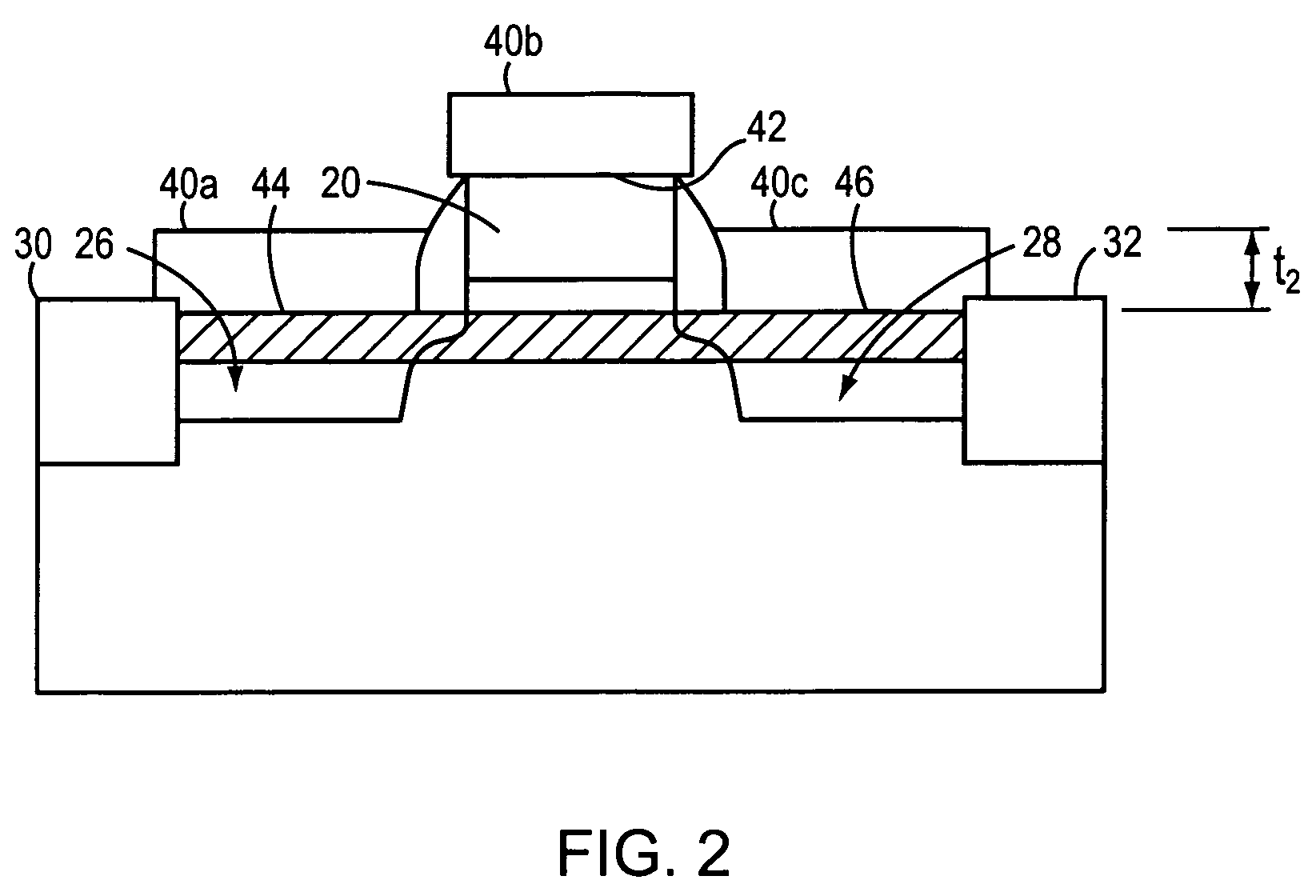

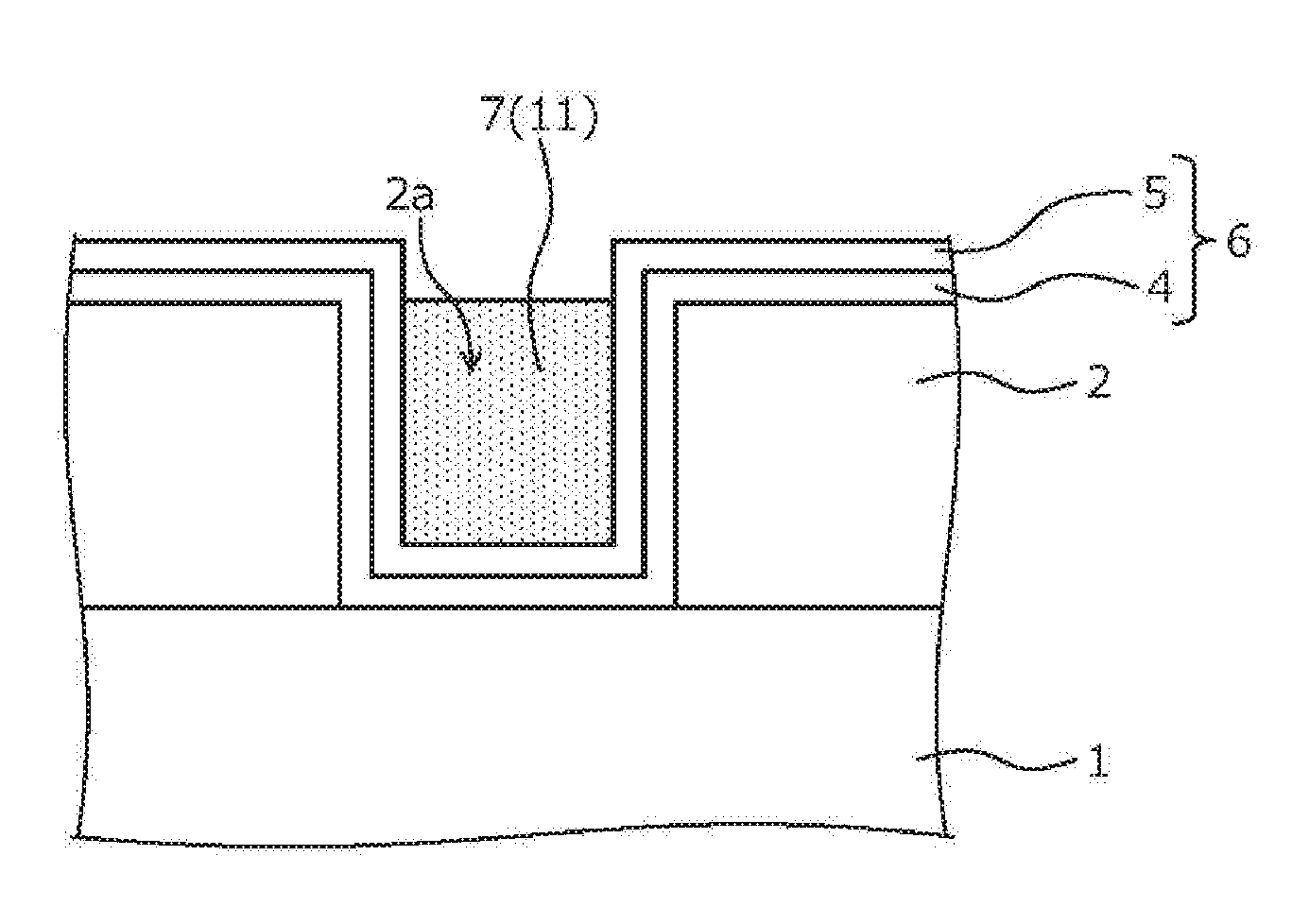

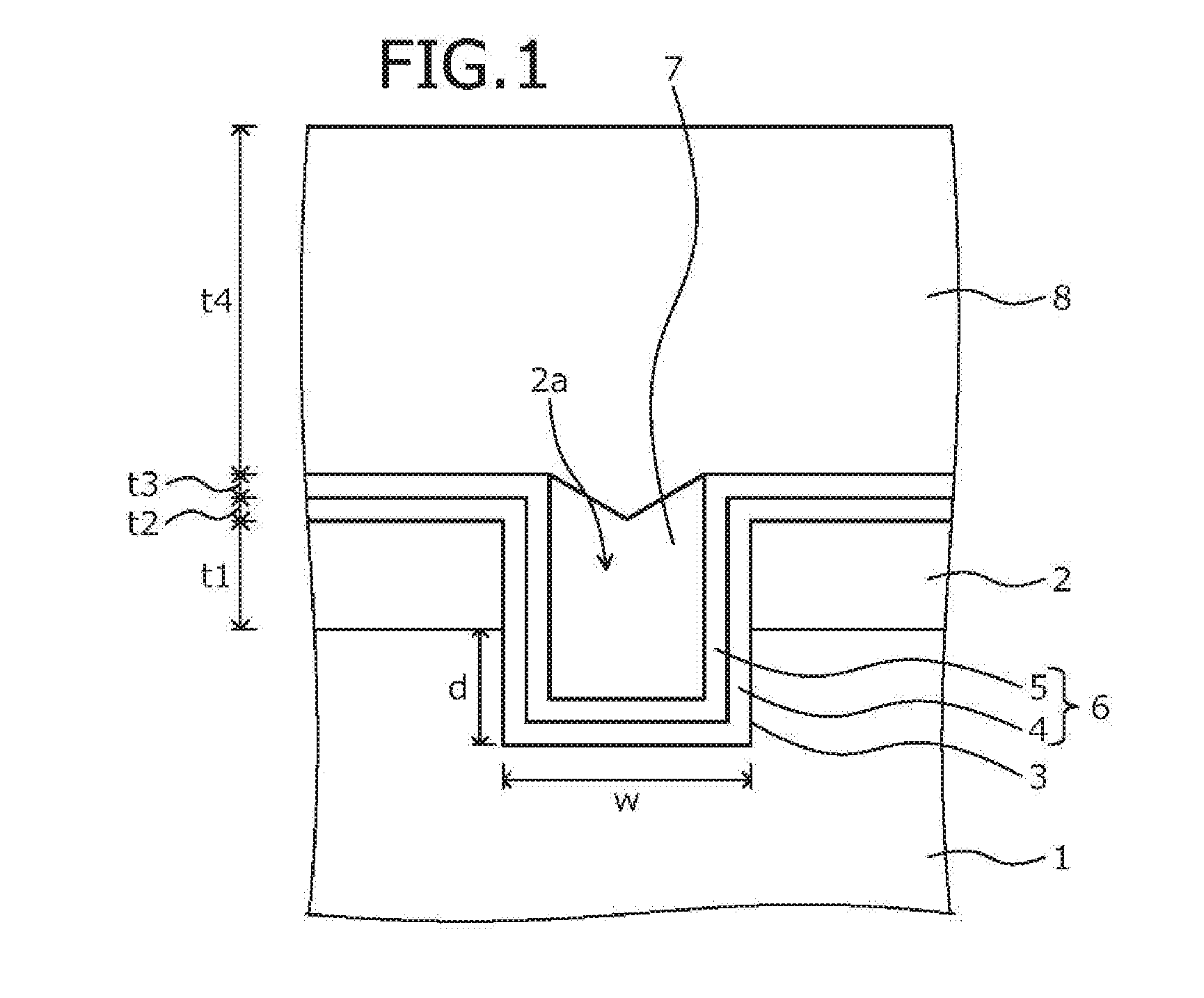

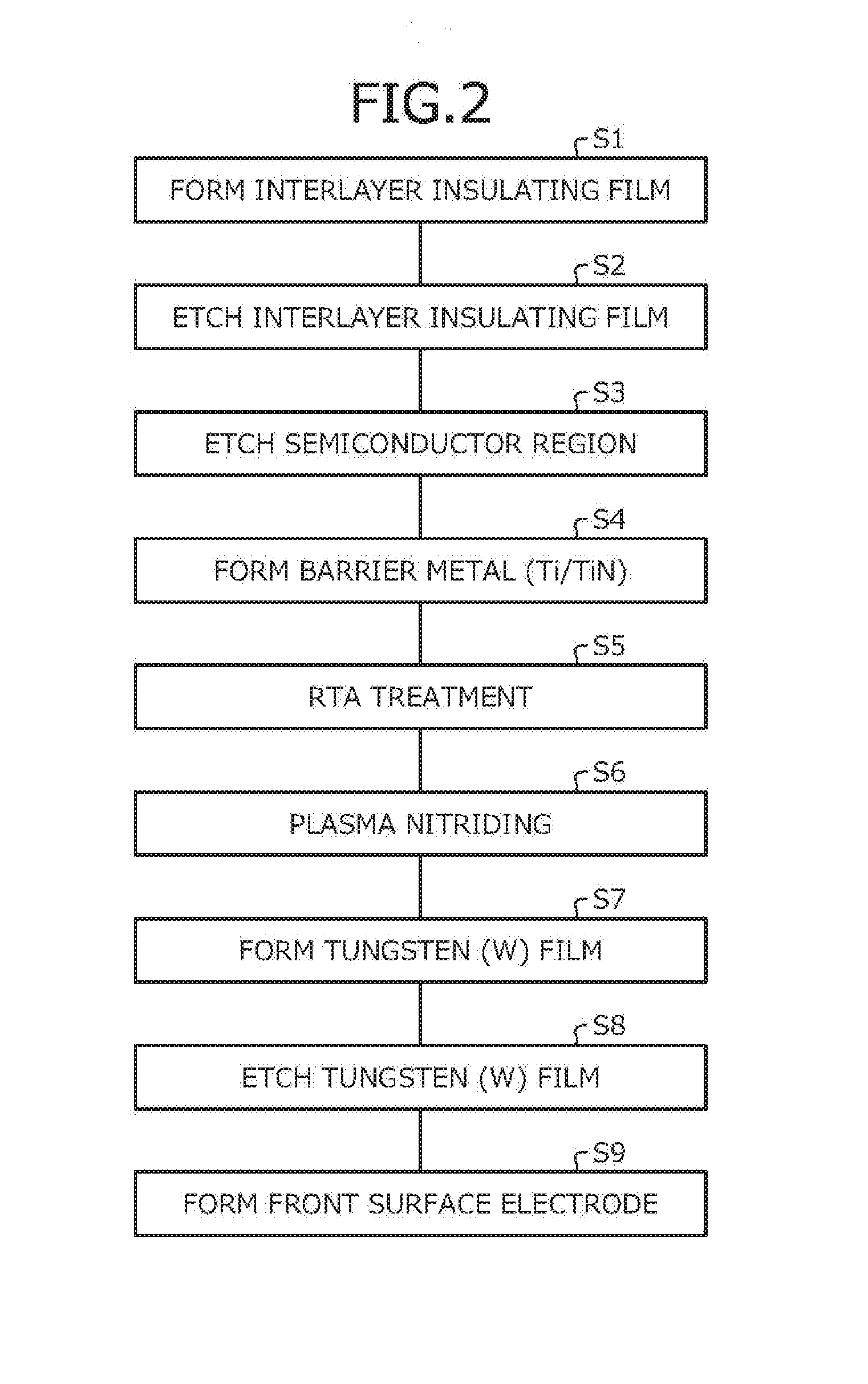

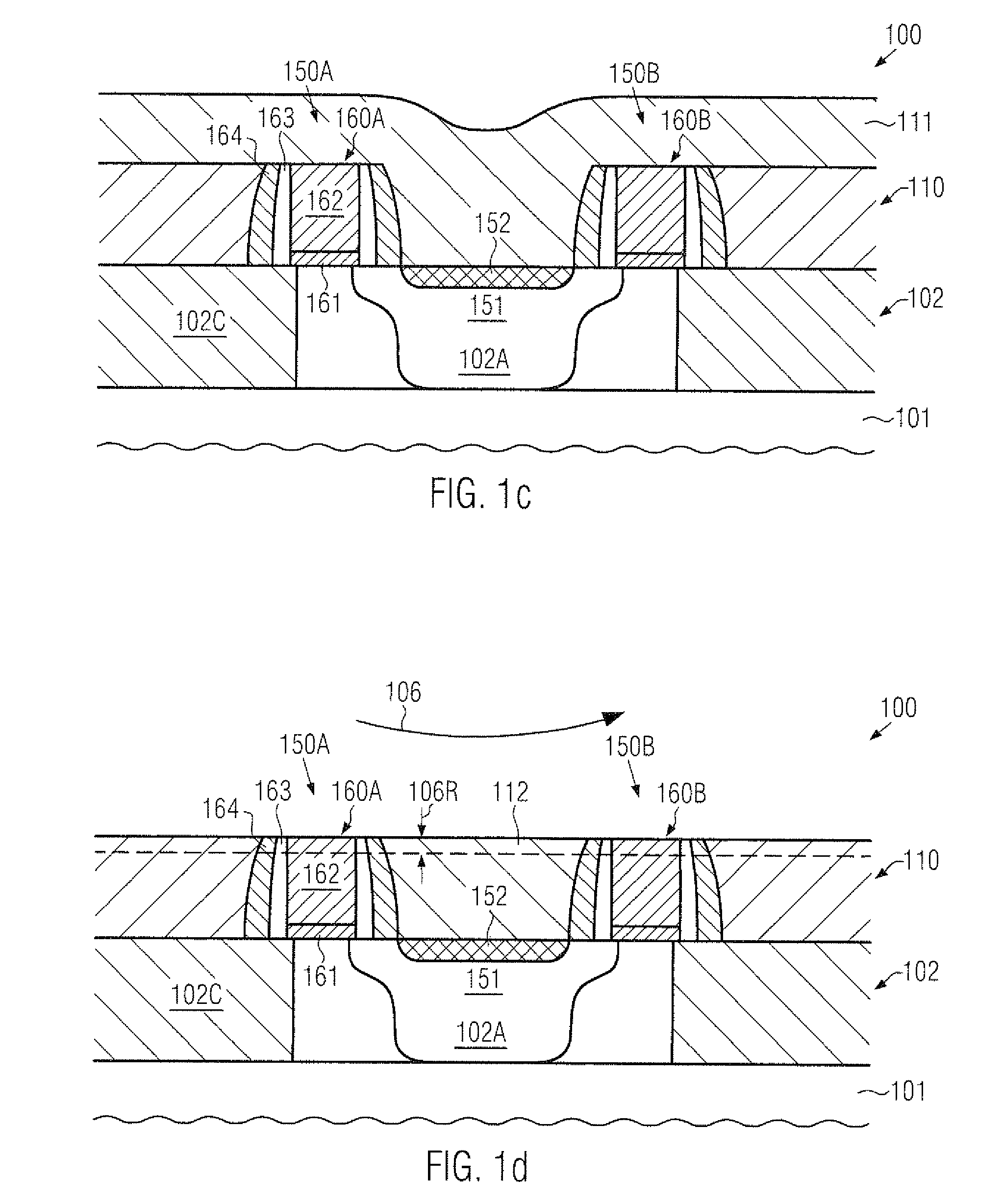

Method of manufacturing semiconductor device

ActiveUS20160351446A1Reduce contact resistivityImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceTitanium nitride

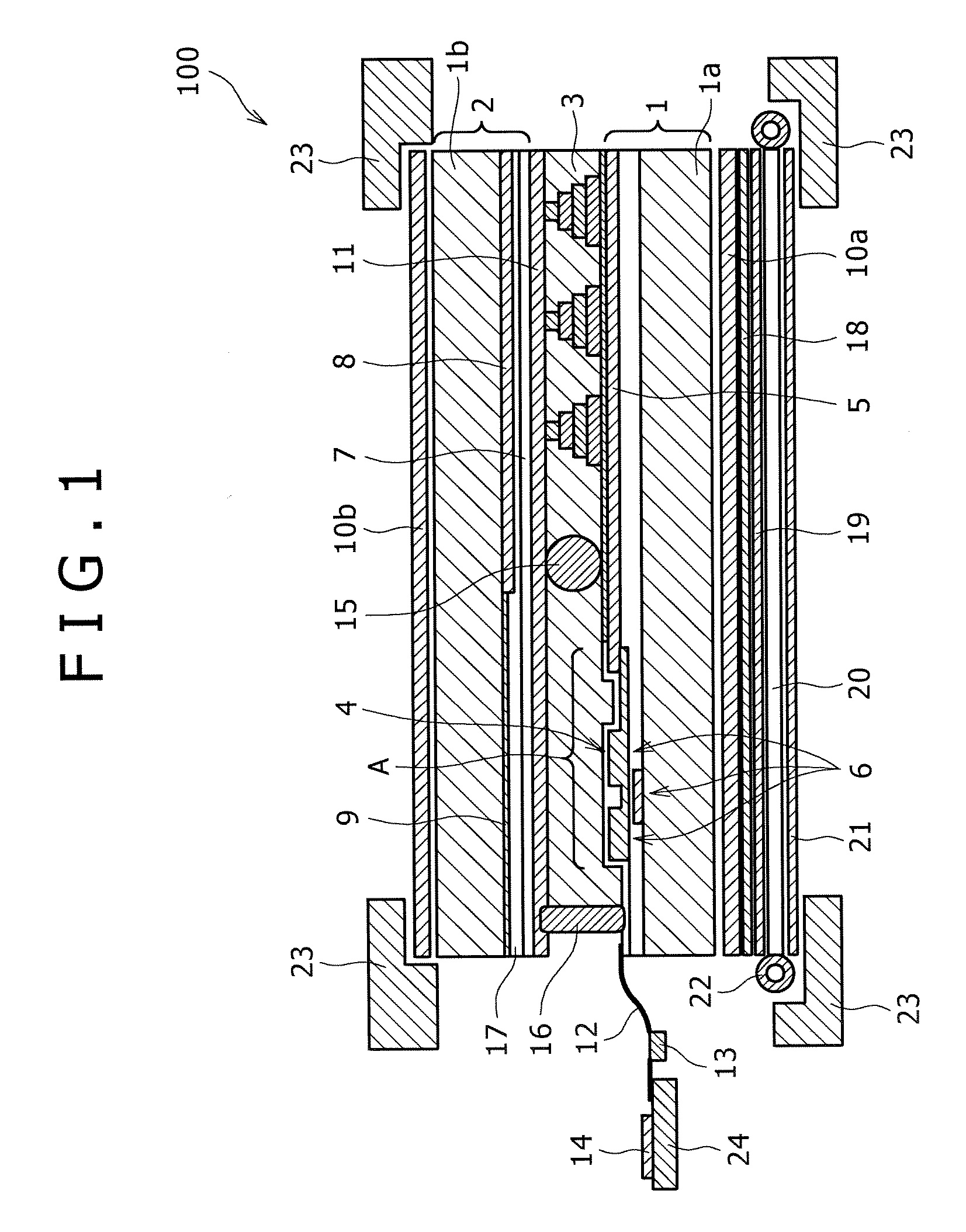

A barrier metal is formed from a surface of an interlayer insulating film 2 to a trench that is formed in a semiconductor portion exposed in a contact hole. After RTA treatment and a plasma nitriding process, a plug is embedded at an inner side of the barrier metal inside the trench and the contact hole. The RTA treatment is performed at a temperature range of about 500 degrees C. to 650 degrees C. The plasma nitriding process is performed at a temperature lower than that of the RTA treatment. The barrier metal is formed by a first metal film of titanium and a second metal film of titanium nitride sequentially stacked. The plug is formed from tungsten. A surface electrode formed of aluminum is formed from a surface of the second metal film on the interlayer insulating film to a surface of the plug.

Owner:FUJI ELECTRIC CO LTD

High brightness gallium nitride-based light emitting diode with transparent conducting oxide spreading layer

InactiveUS7061026B2Reduce contact resistanceReduce impactFibre treatmentSolid-state devicesOptical propertyGallium nitride

A new transparent conducting oxide (TCO), which can be expressed as AlxGa3-x-yIn5+ySn2-zO16-2z; 0≦x<1, 0<y<3, 0≦z<2, has been used to improve the brightness and current spreading in GaN base LED process. The optical properties of this system are superior to regular Ni / Au transparent conducting layer in blue-green region, and the new Al2O3—Ga2O3—In2O3—SnO2 system is able to increase the brightness at 1.5˜2.5 time to compare to regular process. Furthermore, the new transparent conducting oxide thin film has the highest conductivity, which is better than the Ni / Au transparent conducting thin film.

Owner:ARIMA OPTOELECTRONICS

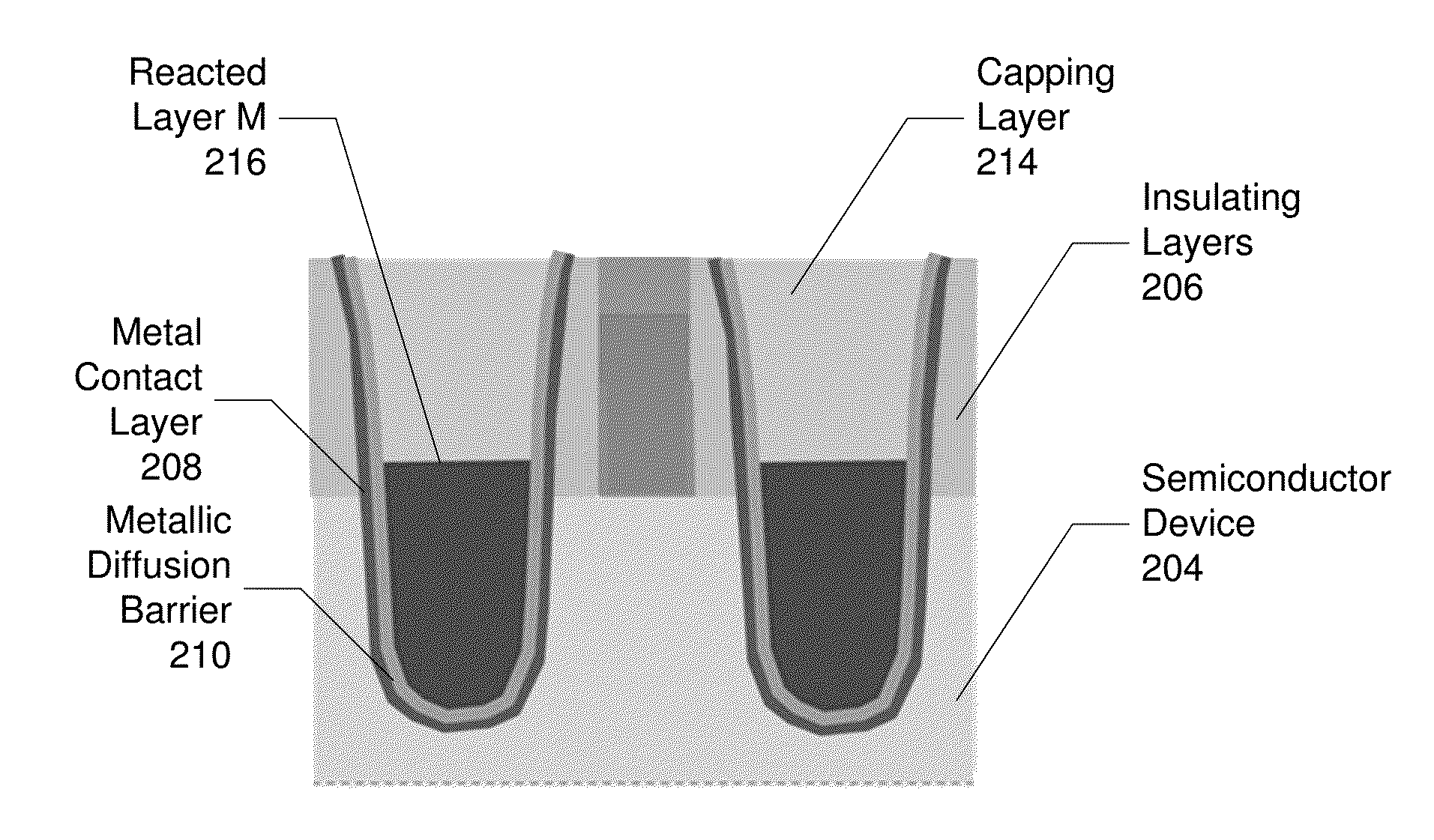

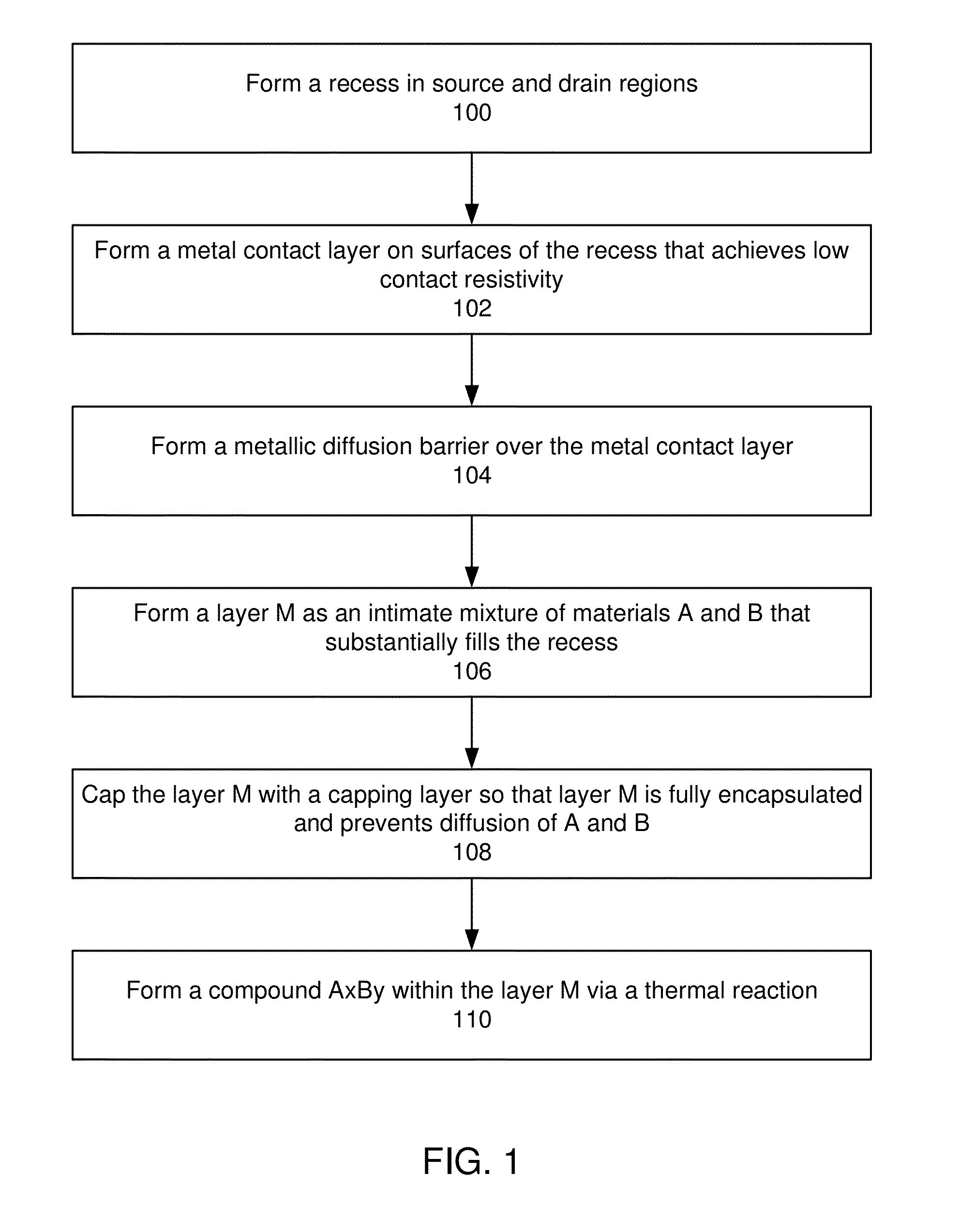

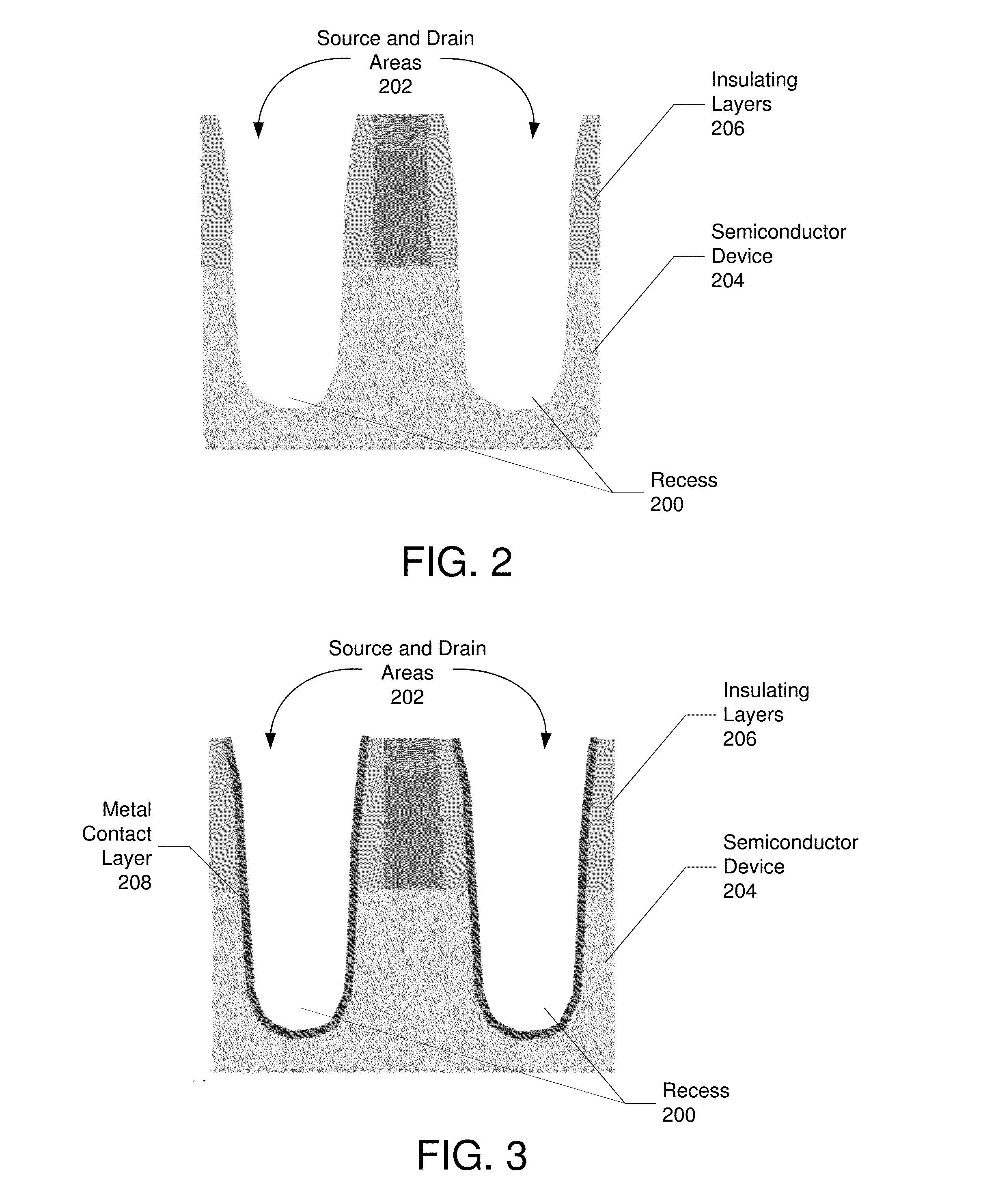

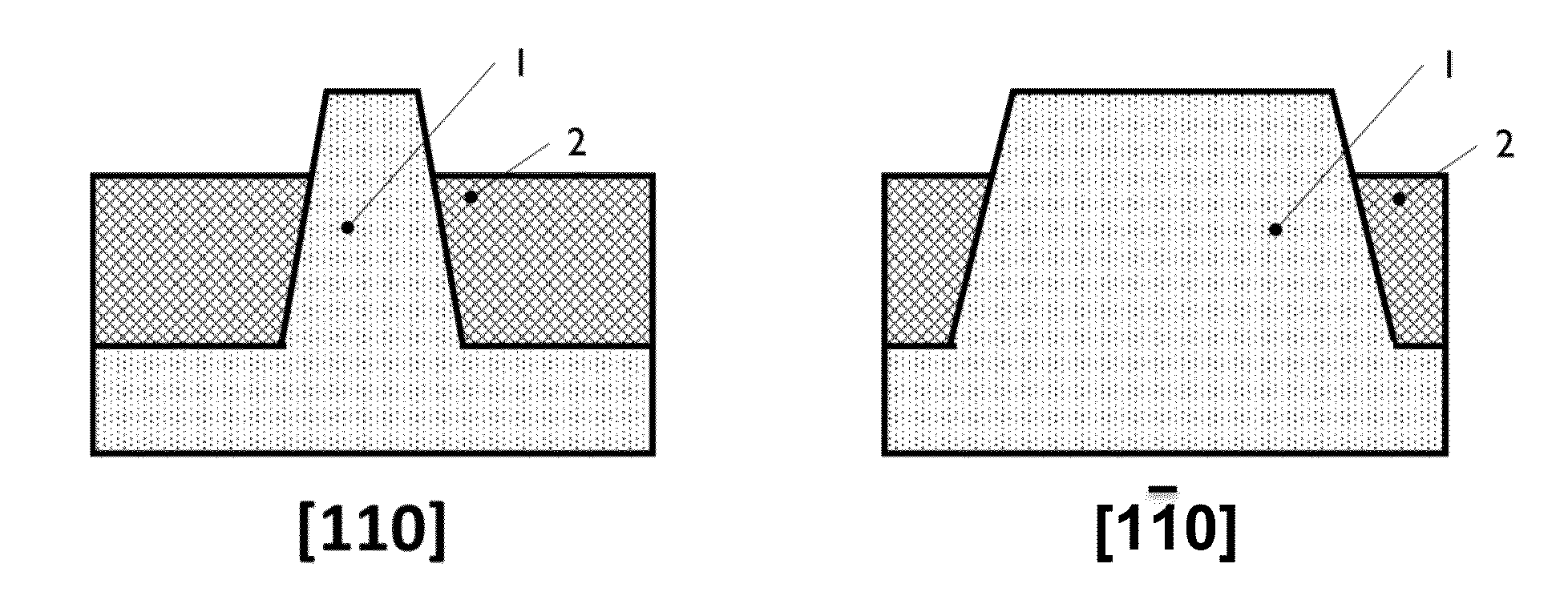

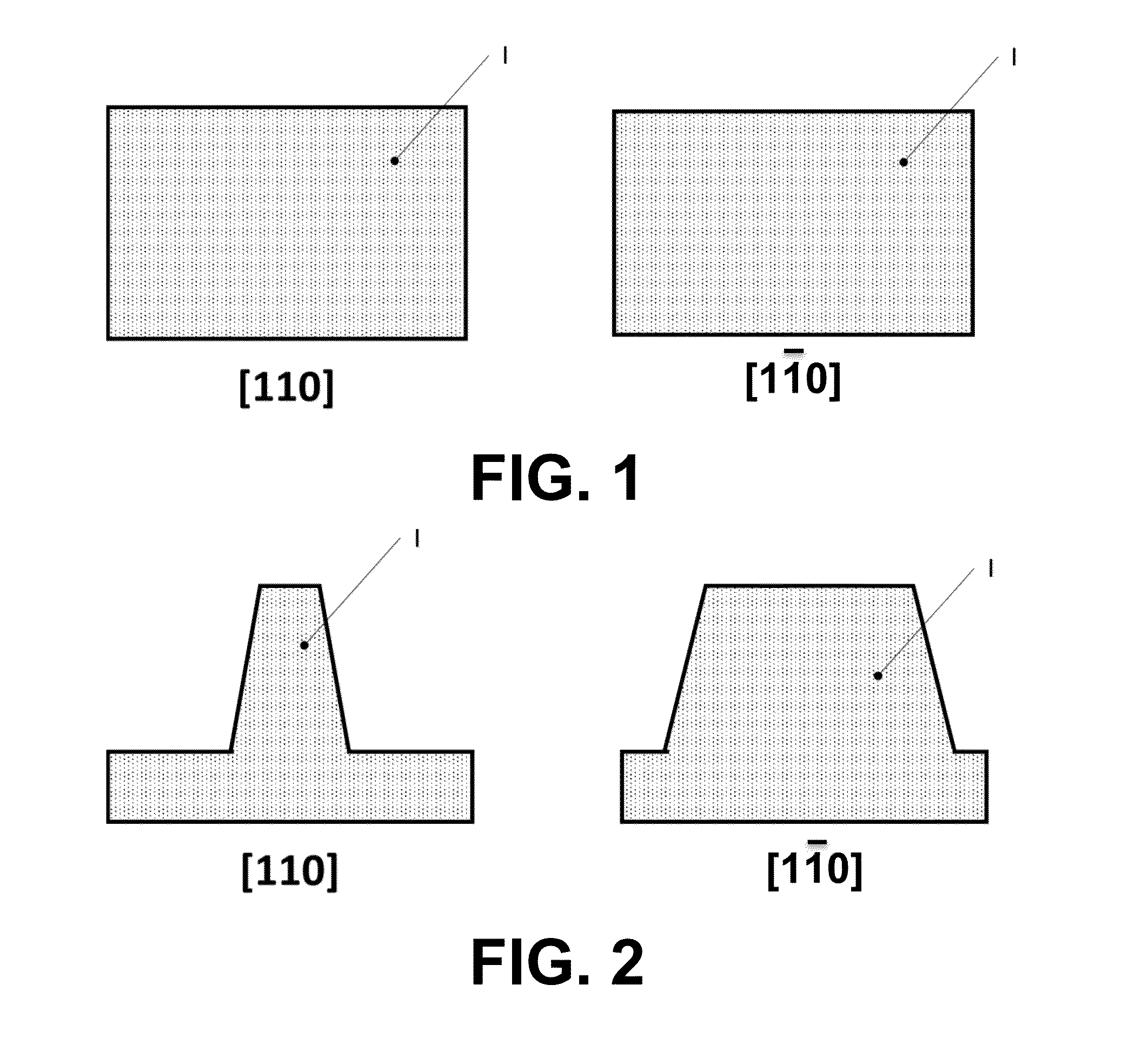

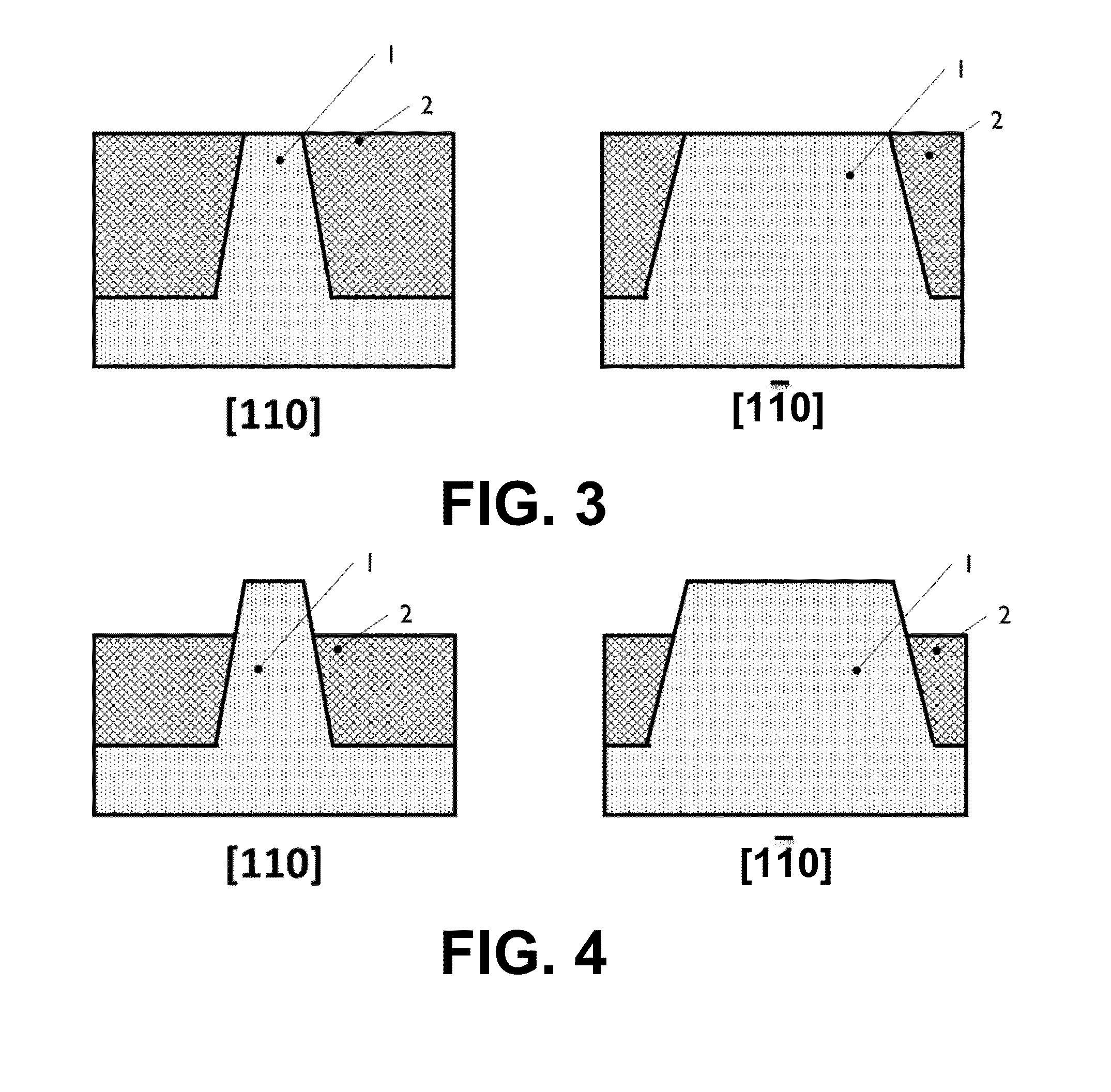

Fabricating metal source-drain stressor in a mos device channel

InactiveUS20160133745A1Increase the tensile stressReduce contact resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesCompound (substance)Contact layer

Exemplary embodiments provide methods and systems for fabricating a metal source-drain stressor in a MOS device channel having improved tensile stress. Aspects of exemplary embodiment include forming a recess in source and drain areas; forming a metal contact layer on surfaces of the recess that achieves low contact resistivity; forming a metallic diffusion barrier over the metal contact layer; forming a layer M as an intimate mixture of materials A and B that substantially fills the recess; capping the layer M with a capping layer so that layer M is fully encapsulated and the capping layer prevents diffusion of A and B; and forming a compound AxBy within the layer M via a thermal reaction resulting in a reacted layer M comprising the metal source-drain stressor.

Owner:SAMSUNG ELECTRONICS CO LTD

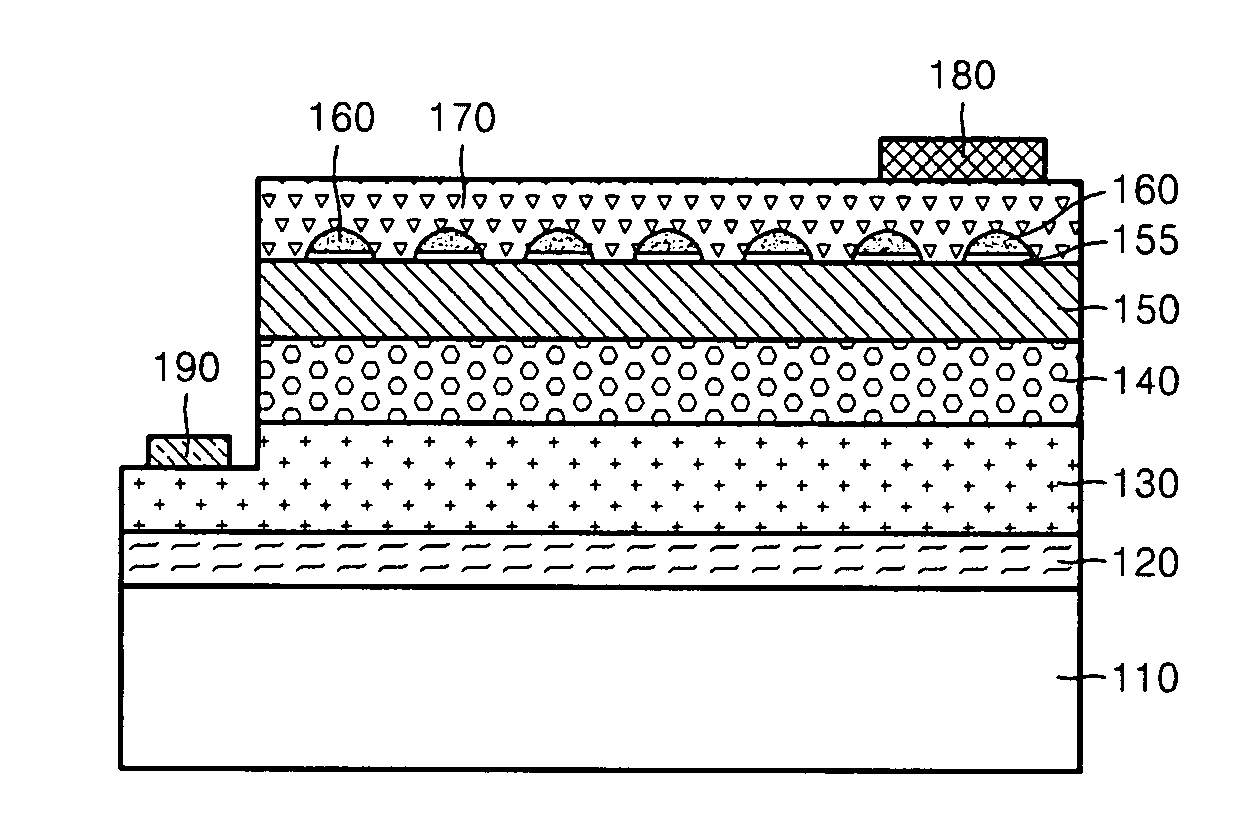

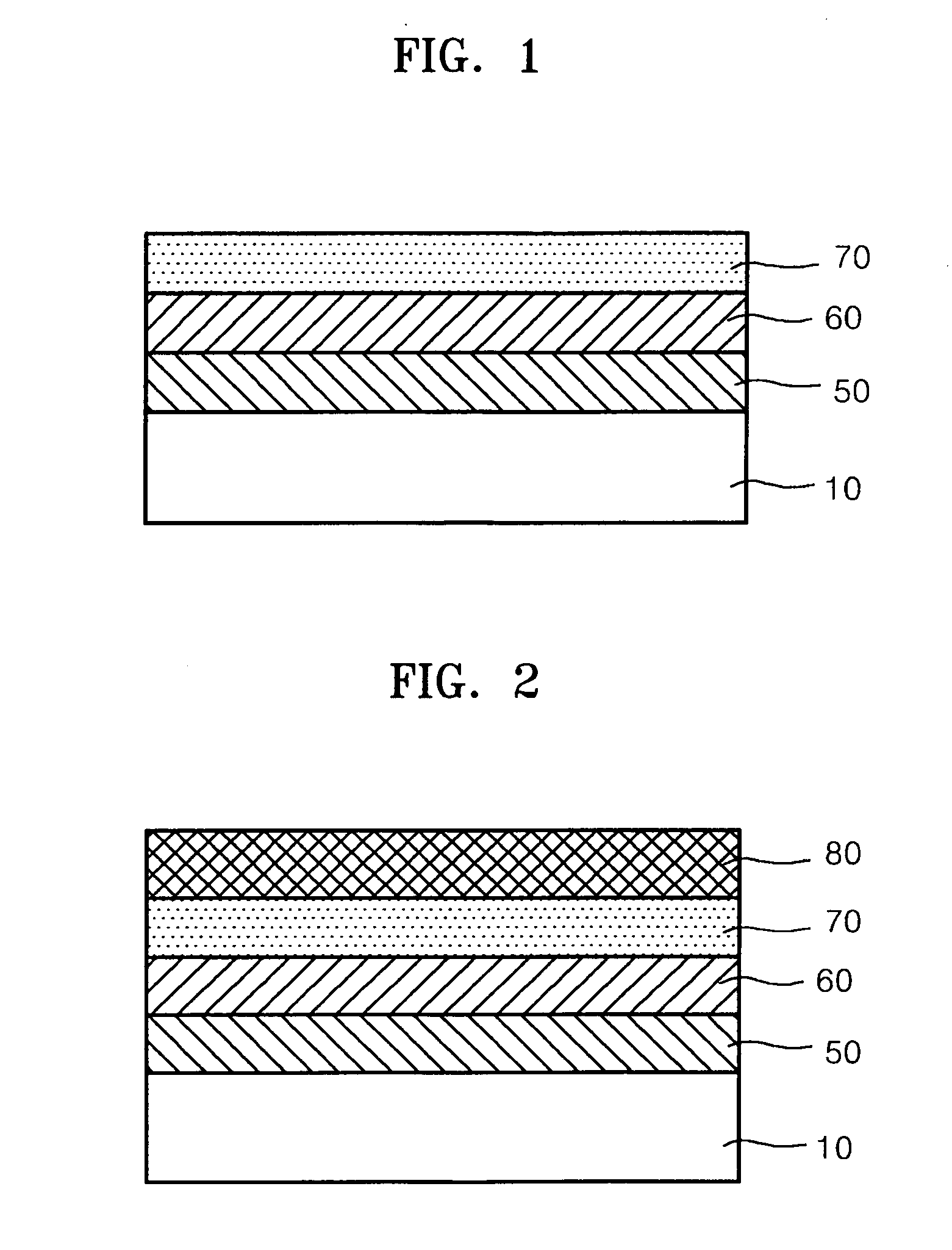

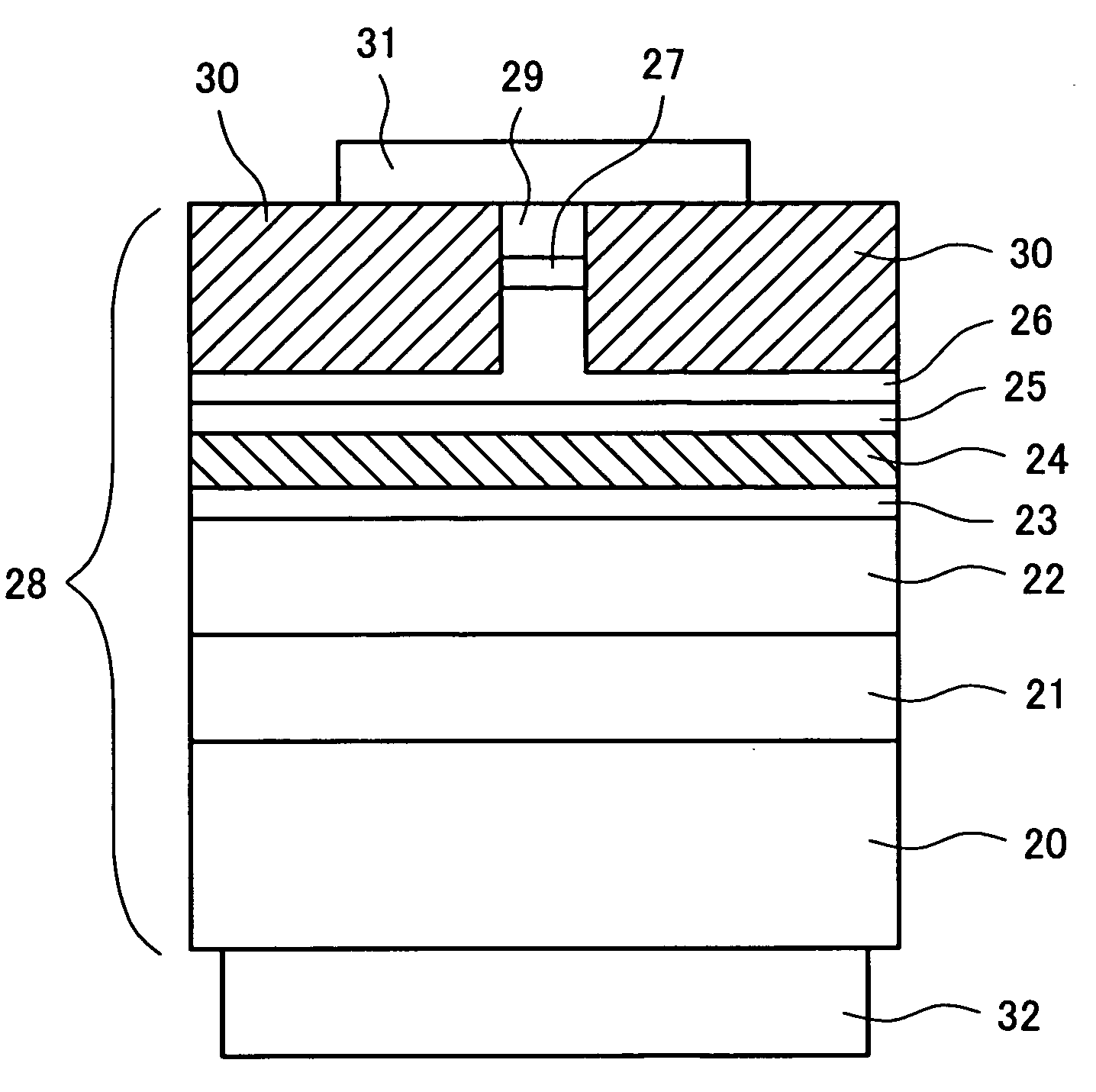

Top-emitting light emitting diodes and method of manufacturing thereof

InactiveCN101027790AImprove packaging yieldImproved ohmic contact characteristicsSemiconductor devicesOhmic contactConductive materials

Provided are a top-emitting nitride-based light emitting device having an n-type clad layer, an active layer and a p-type clad layer sequentially stacked thereon, comprising an interface modification layer formed on the p-type clad layer and a transparent conductive thin film layer made up of a transparent conductive material formed on the interface modification layer; and a process for preparing the same. In accordance with the top-emitting nitride-based light emitting device of the present invention and a process for preparing the same, there are provided advantages such as improved ohmic contact with the p-type clad layer, leading to increased wire bonding efficiency and yield upon packaging the light emitting device, capability to improve luminous efficiency and life span of the device due to low specific contact resistance and excellent current- voltage properties.

Owner:GWANGJU INST OF SCI & TECH

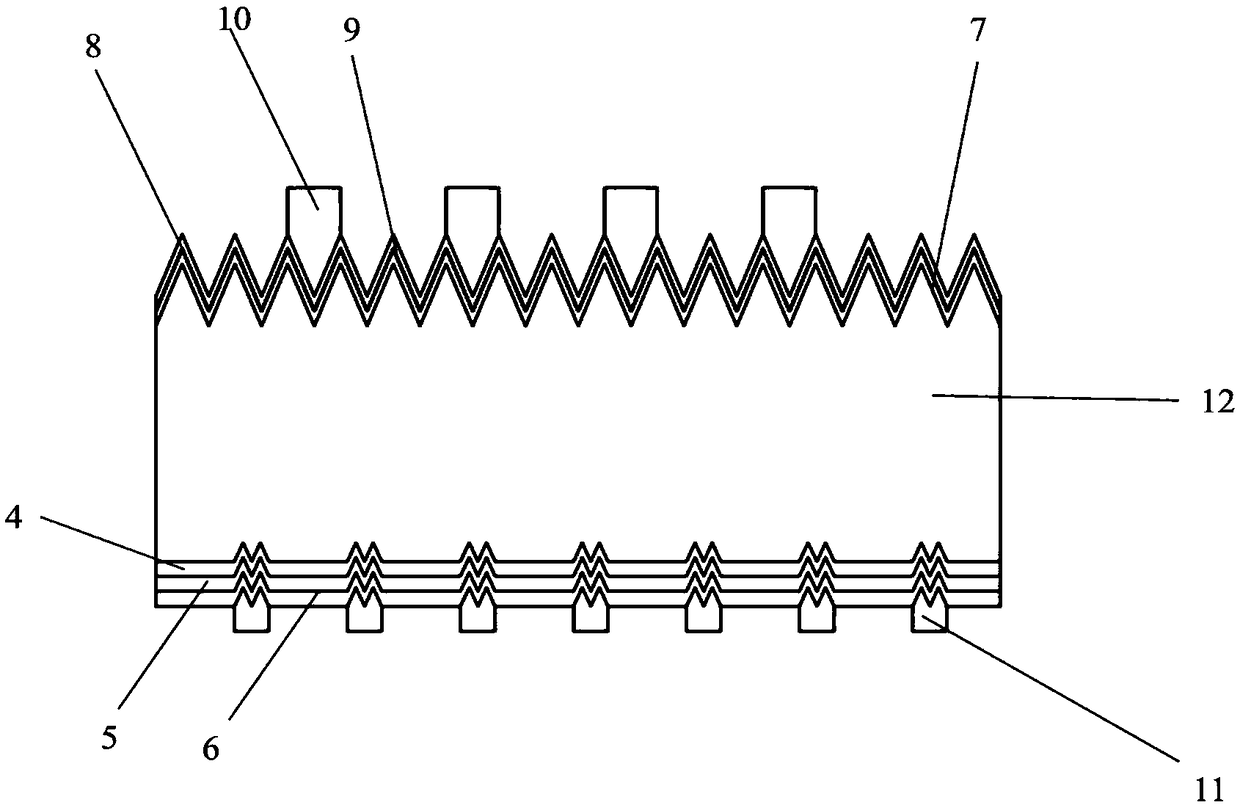

Method for fabricating selective textured surface and emitter of silicon solar cell by laser

InactiveCN109346535AReduce contact resistivityGood for compound rateFinal product manufacturePhotovoltaic energy generationRough surfaceSilicon solar cell

The invention discloses a method for fabricating a selective textured surface and an emitter of a silicon solar cell by laser. The textured surface is fabricated at a metal electrode gate line contactregion by the laser on a back surface of a polished single crystal wafer to form a rough surface, the specific area is expanded, so that low contact resistivity between a gate line and a silicon baseis ensured; and a back polishing surface is fabricated at a non-metal contact region by an alkali polishing process, the recombination rate of minority carriers at the non-metal contact region is facilitated, an open current and a filling factor are simultaneously increased, and the conversion efficiency absolute value of the cell can be improved by 0.2-0.3%.

Owner:JIANGSU LINYANG PHOTOVOLTAIC TECH

Method for Reducing Contact Resistance in MOS

ActiveUS20160141391A1Less stressLow contact resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureAnalytical chemistry

A method for growing a III-V semiconductor structure on a SinGe1-n substrate, wherein n is from 0 to 1 is provided. The method includes the steps of: (a) bringing a SinGe1-n substrate to a high temperature; (b) exposing the area to a group V precursor in a carrier gas for from 5 to 30 min, thereby forming a doped region at said area; (c) bringing the SinGe1-n substrate to a low temperature; (d) exposing the doped region to a group III precursor in a carrier gas and to a group V precursor in a carrier gas until a nucleation layer of III-V material of from 5 to 15 nm is formed on the nucleation layer; (e) bringing the SinGe1-n substrate to an intermediate temperature; and (f) exposing the nucleation layer to a group III precursor in a carrier gas and to a group V precursor in a carrier gas.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

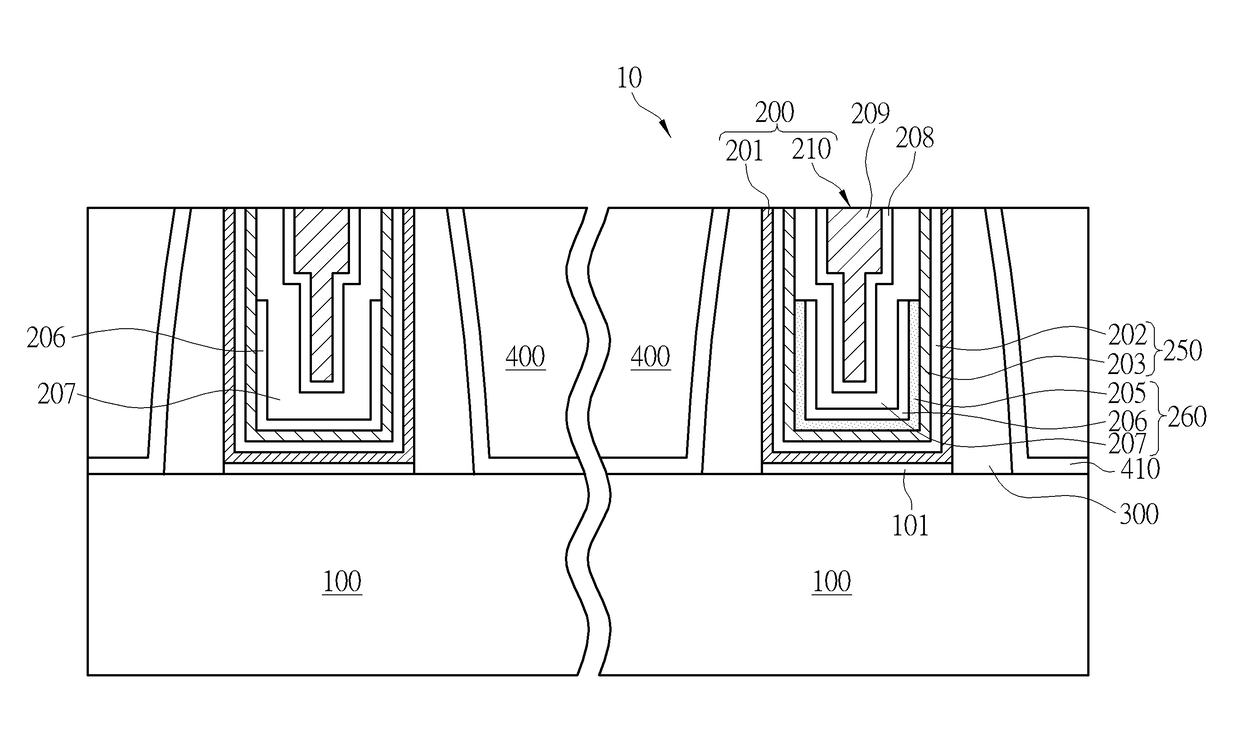

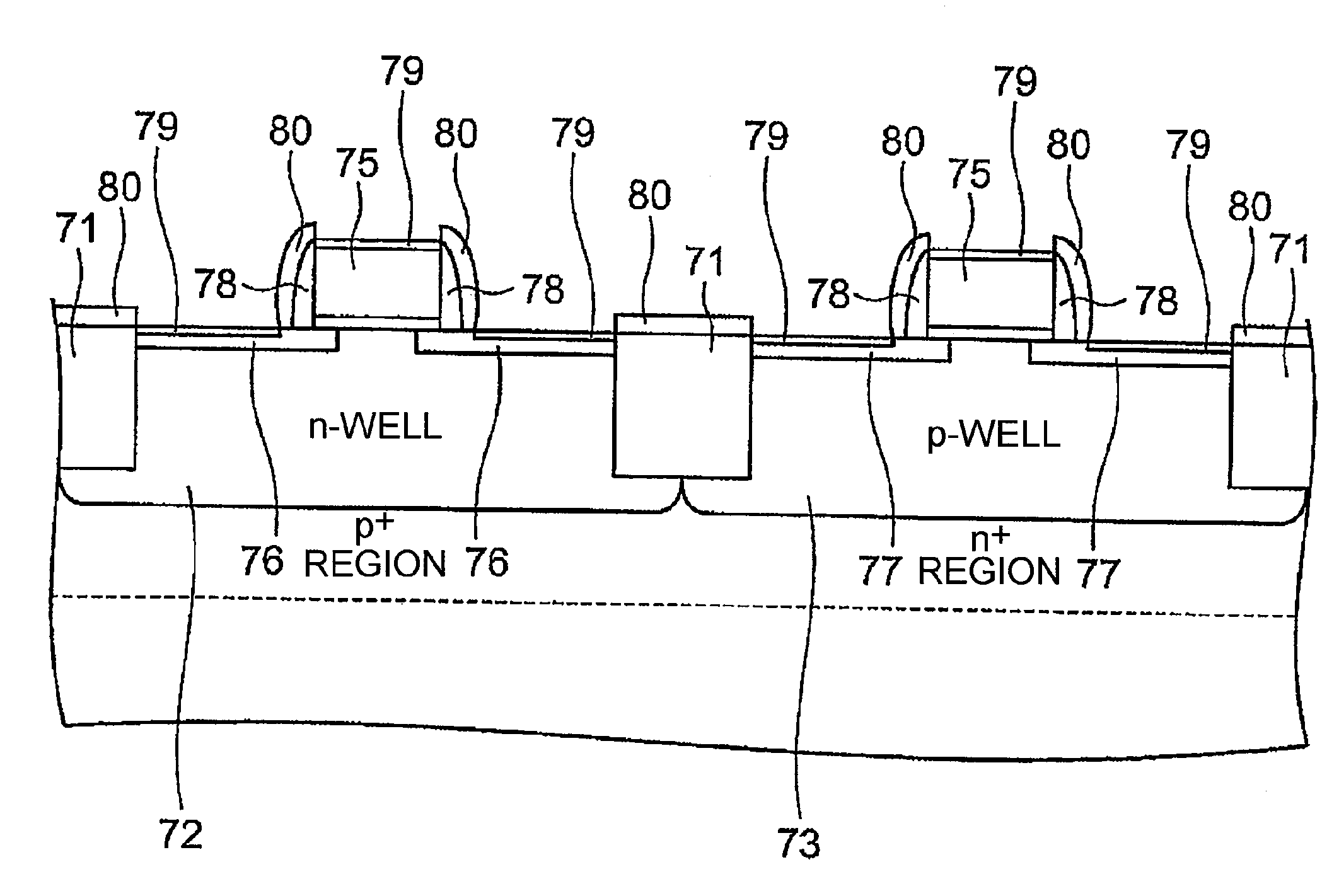

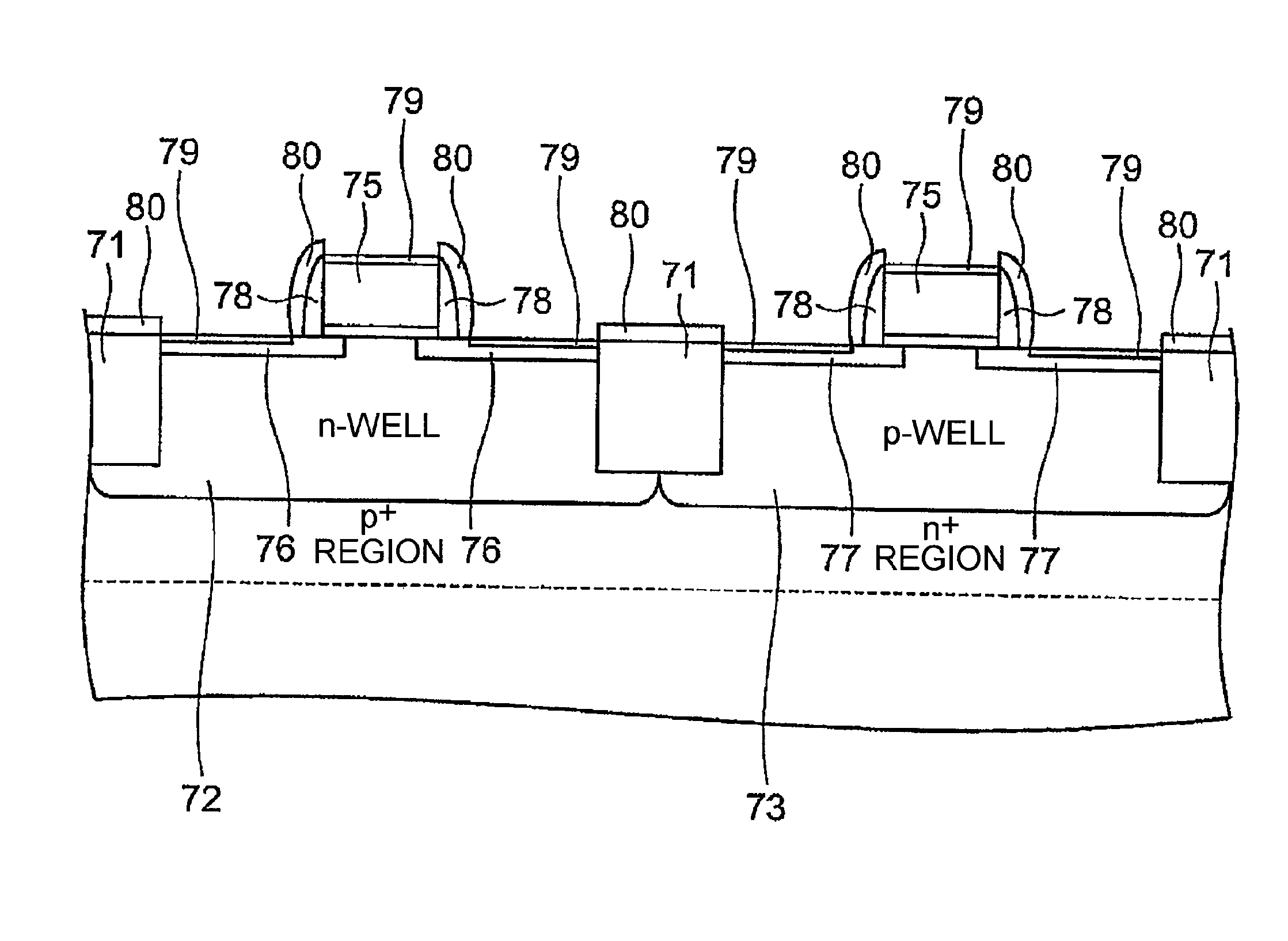

Semiconductor structure

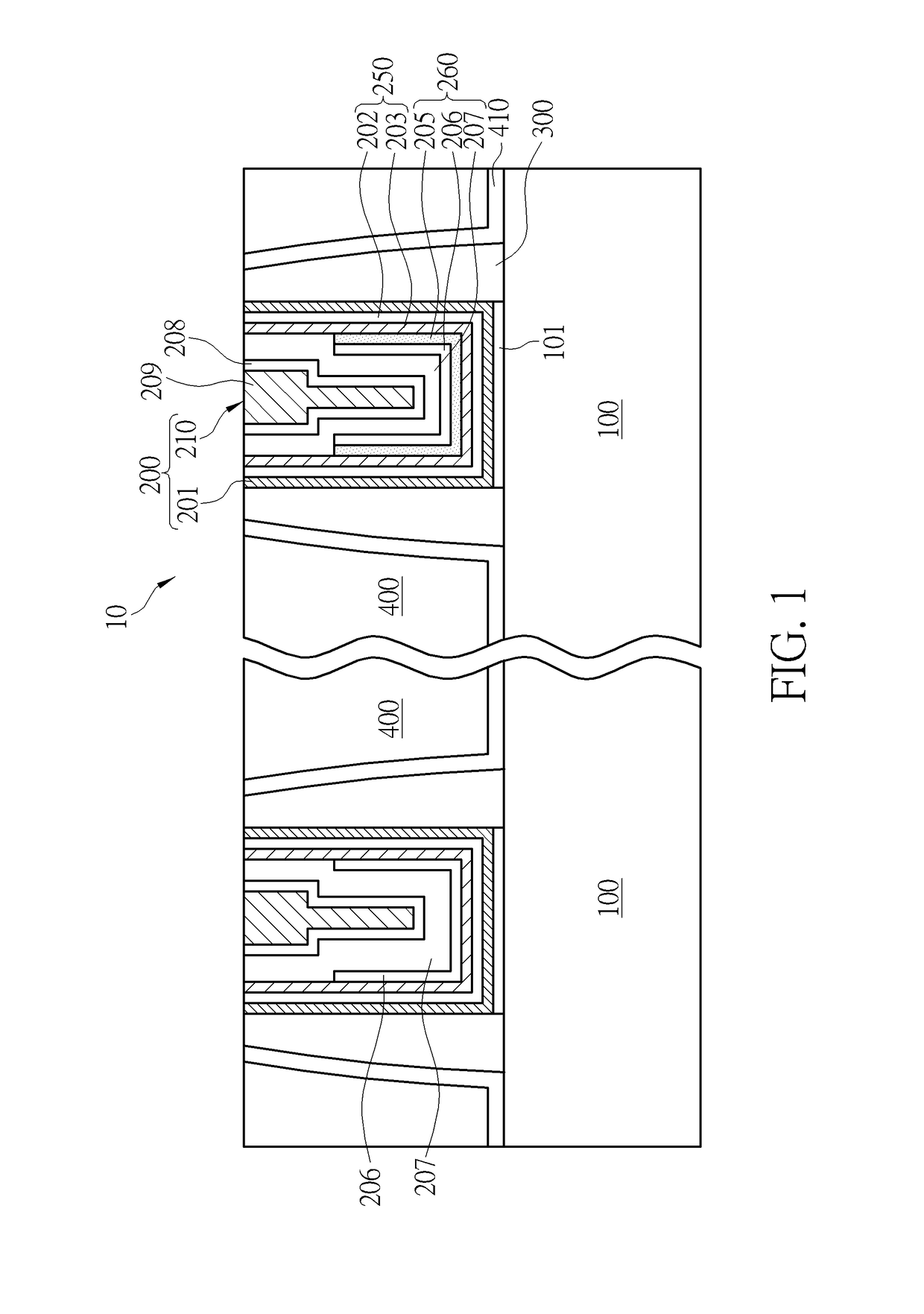

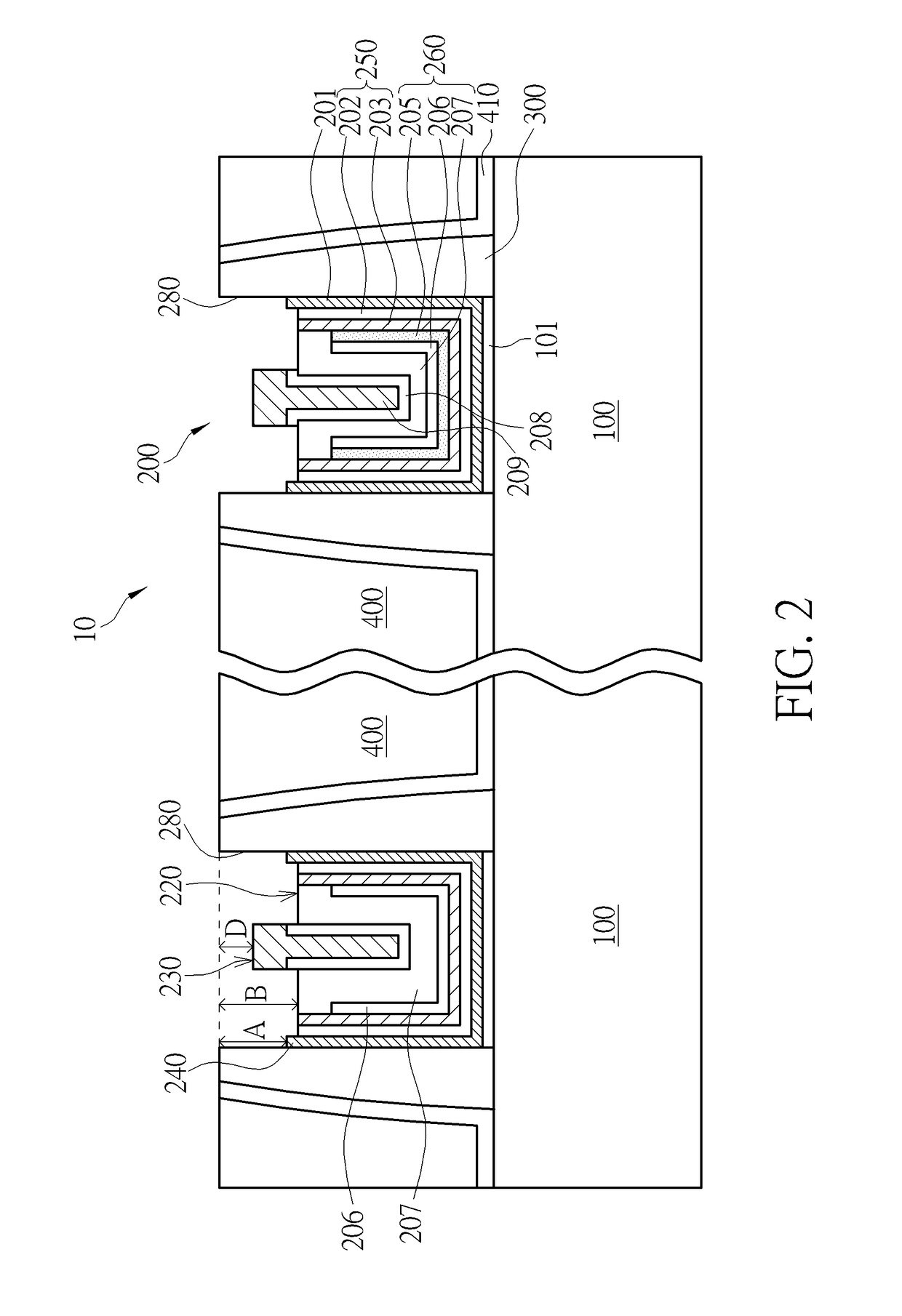

ActiveUS20170077257A1Avoid shortingReduce contact resistivitySemiconductor devicesDielectricGate dielectric

A semiconductor structure is disclosed. The semiconductor structure includes a substrate, and an interlayer dielectric disposed on the substrate which has agate structure therein. The gate structure further includes a gate electrode with a protruding portion, and a gate dielectric layer disposed between the gate electrode and the substrate. A spacer is disposed between the interlayer dielectric and the gate electrode. An insulating cap layer is disposed atop the gate electrode and encompasses the top and the sidewall of the protruding portion.

Owner:UNITED MICROELECTRONICS CORP

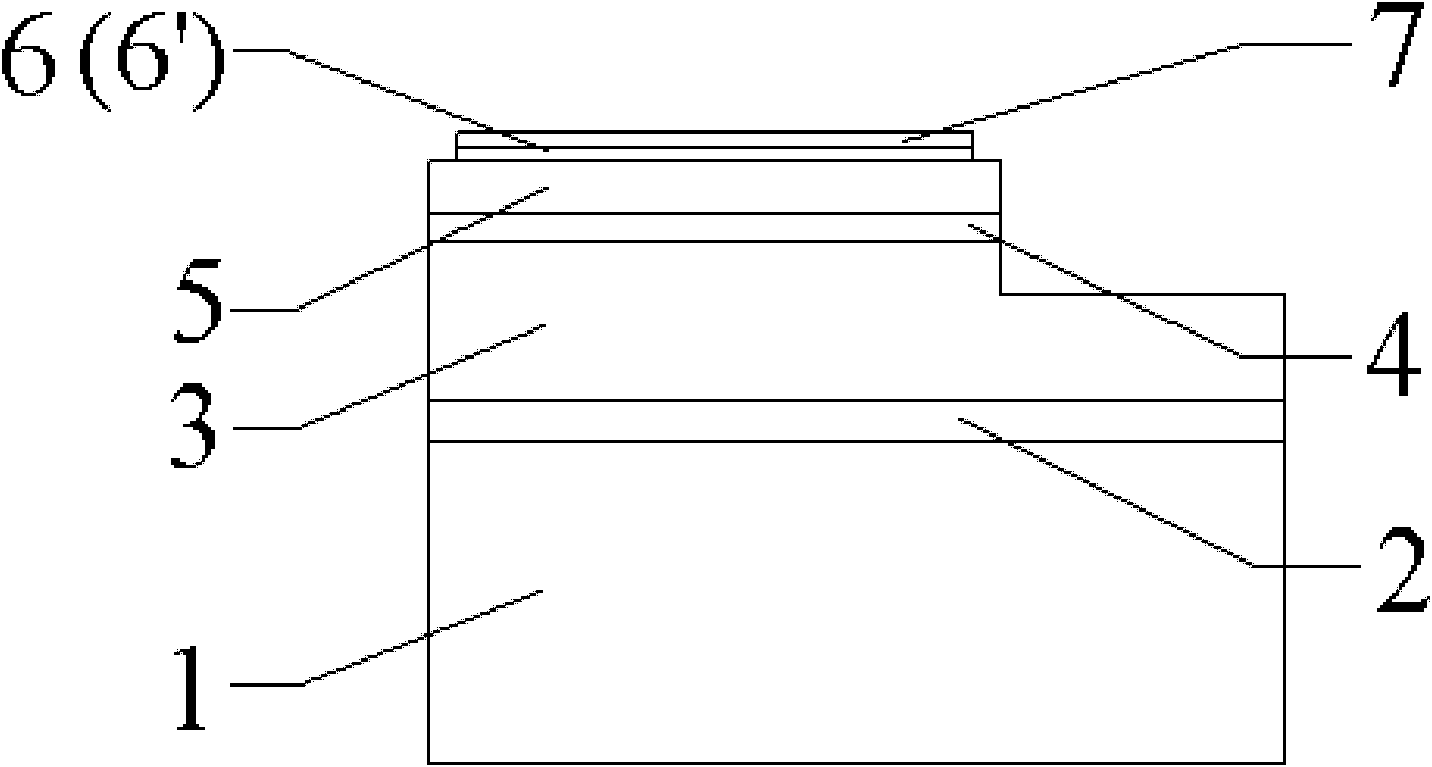

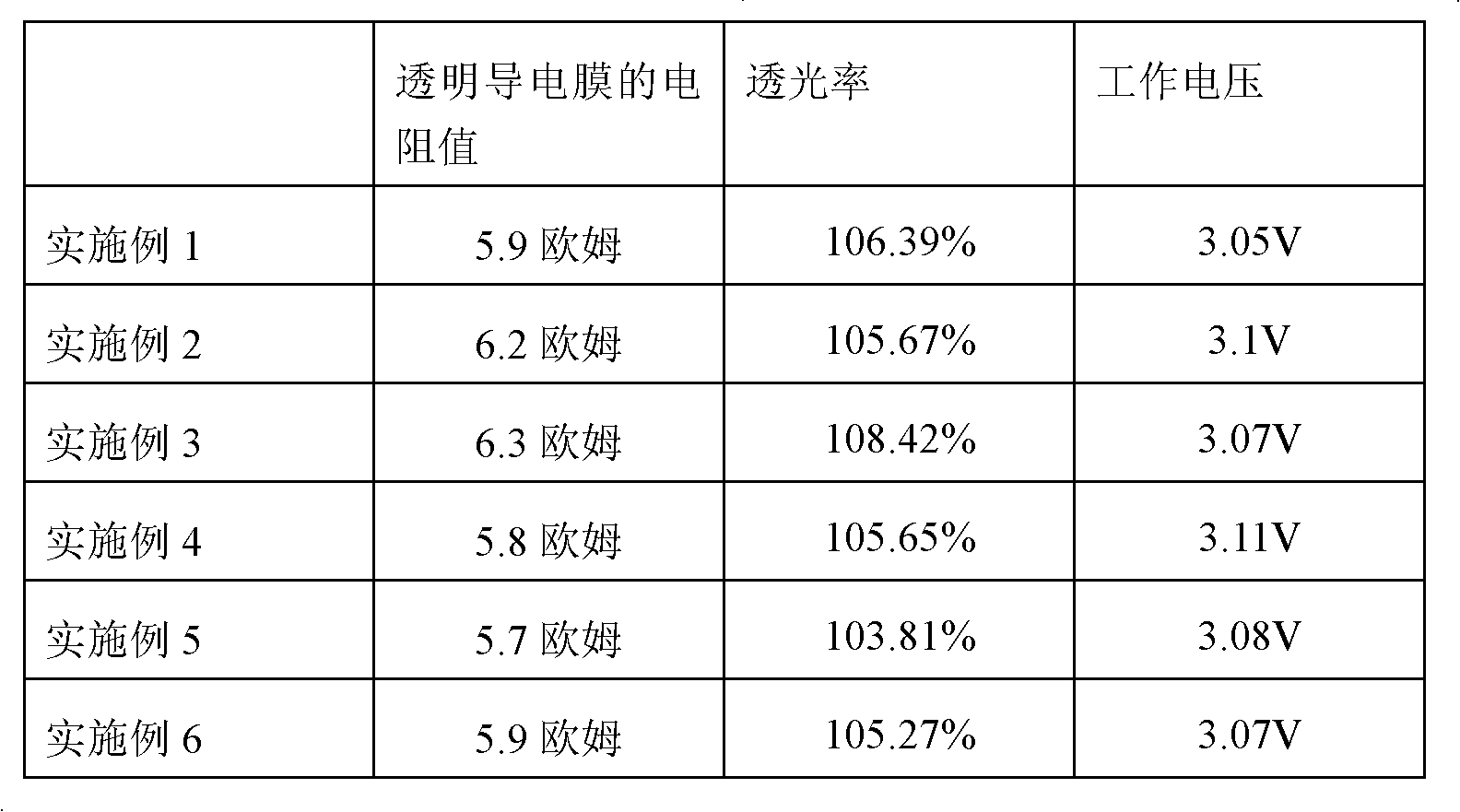

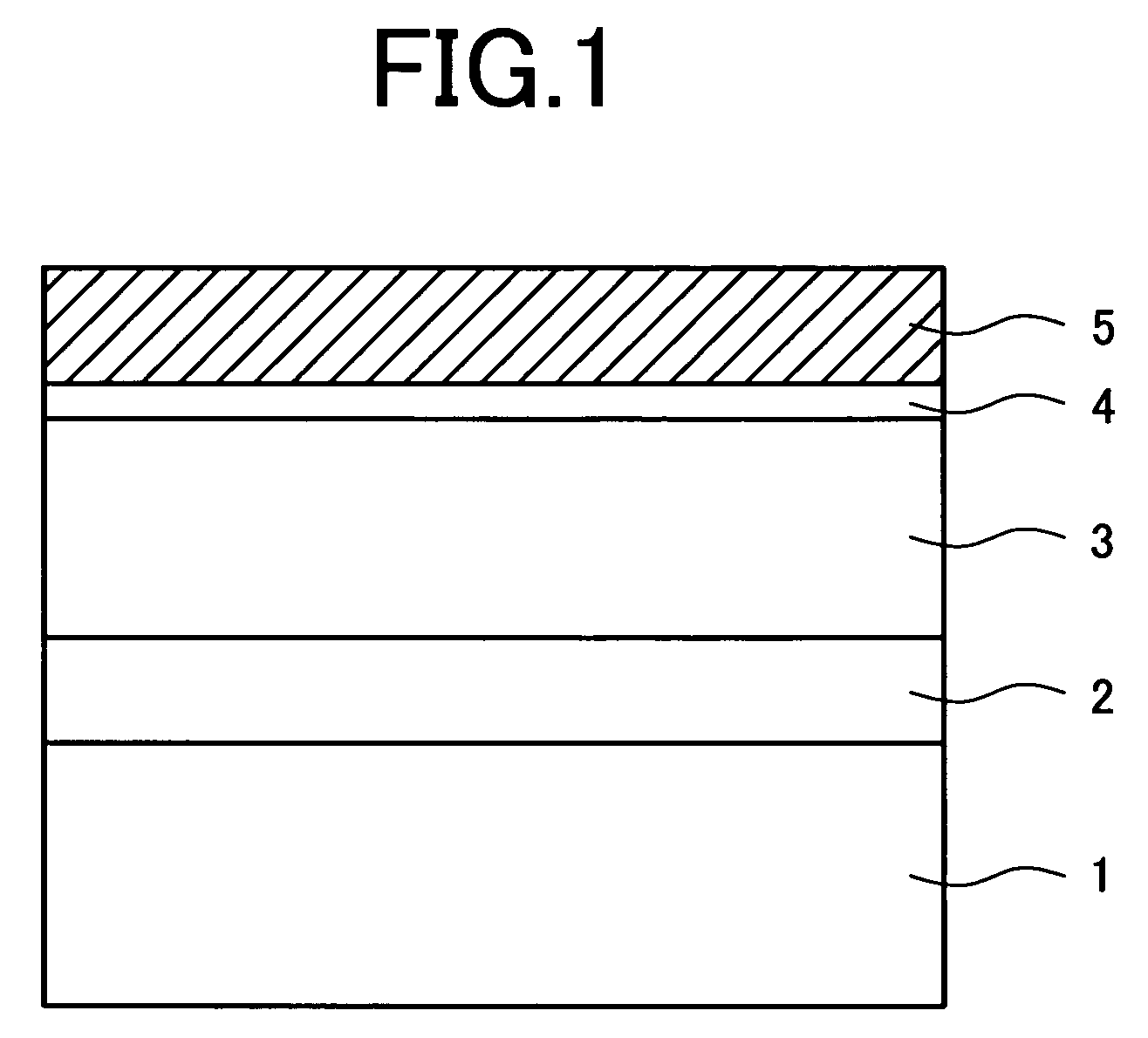

Light-emitting diode with transparent electrode and preparation method

ActiveCN102255028AImprove luminous efficiencyExtended service lifeSemiconductor devicesOxide compositeTransmittance

The invention discloses a light-emitting diode with a transparent electrode and a preparation method. The light-emitting diode with the transparent electrode comprises a gallium nitride epitaxial wafer. In the gallium nitride epitaxial wafer, a transparent conductive film layer is covered on a P-type gallium nitride layer, and is a titanium / zinc oxide or titanium oxide / zinc oxide composite transparent conductive film. The titanium / zinc oxide composite transparent conductive film comprises a titanium layer covered on the P-type gallium nitride layer and a zinc oxide layer covered on the titanium layer. The titanium oxide / zinc oxide composite transparent conductive film comprises a titanium oxide layer covered on the P-type gallium nitride layer and the zinc oxide layer covered on the titanium oxide layer. In the light-emitting diode with the transparent electrode, the material of the transparent conductive film layer on the P-type gallium nitride layer in the gallium nitride epitaxial wafer of the diode is improved to reduce the contact resistivity of the transparent conductive film layer, improve light transmittance and the luminous efficiency of the light-emitting diode with the transparent electrode and prolong the service life of the light-emitting diode with the transparent electrode.

Owner:XIANGNENG HUALEI OPTOELECTRONICS

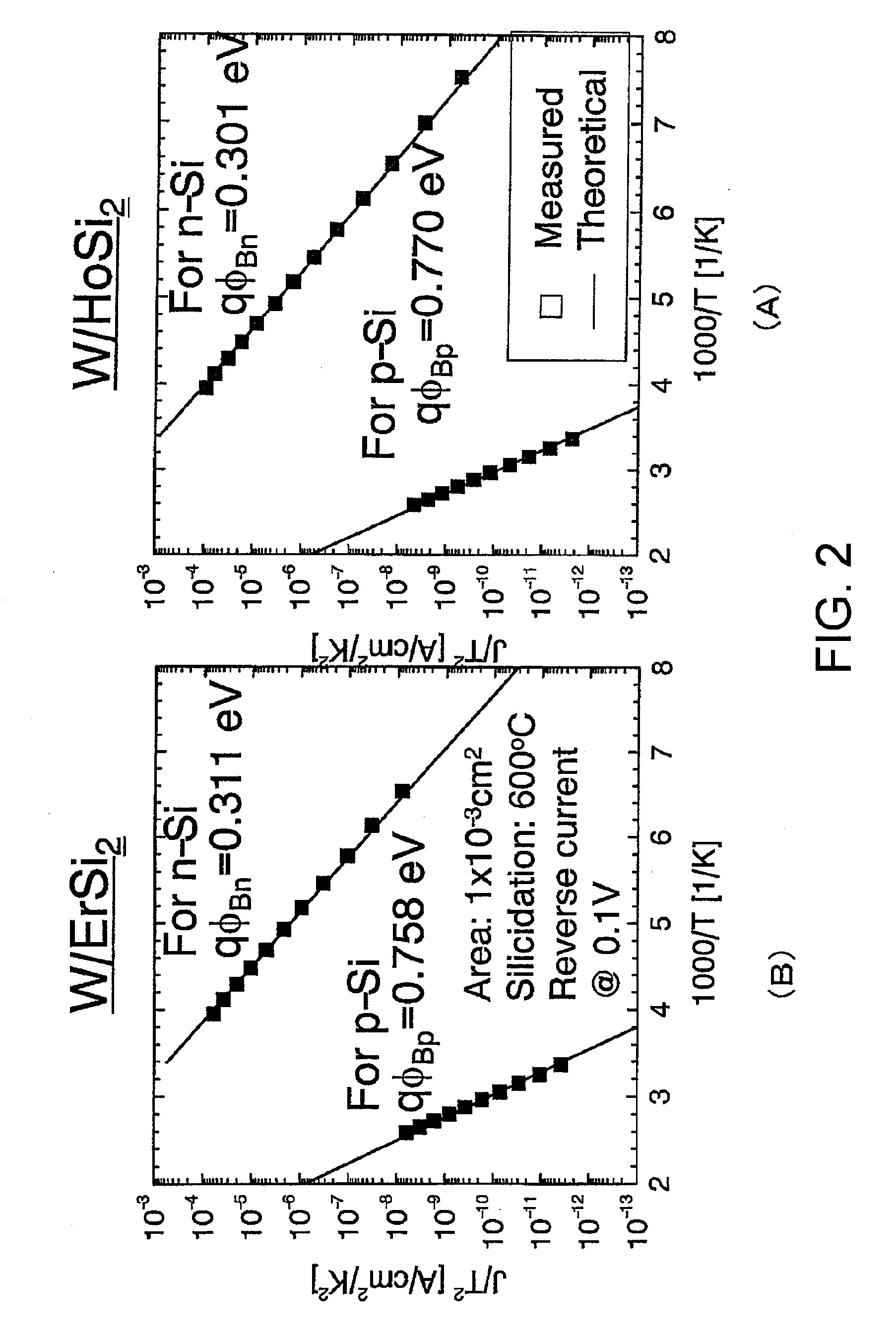

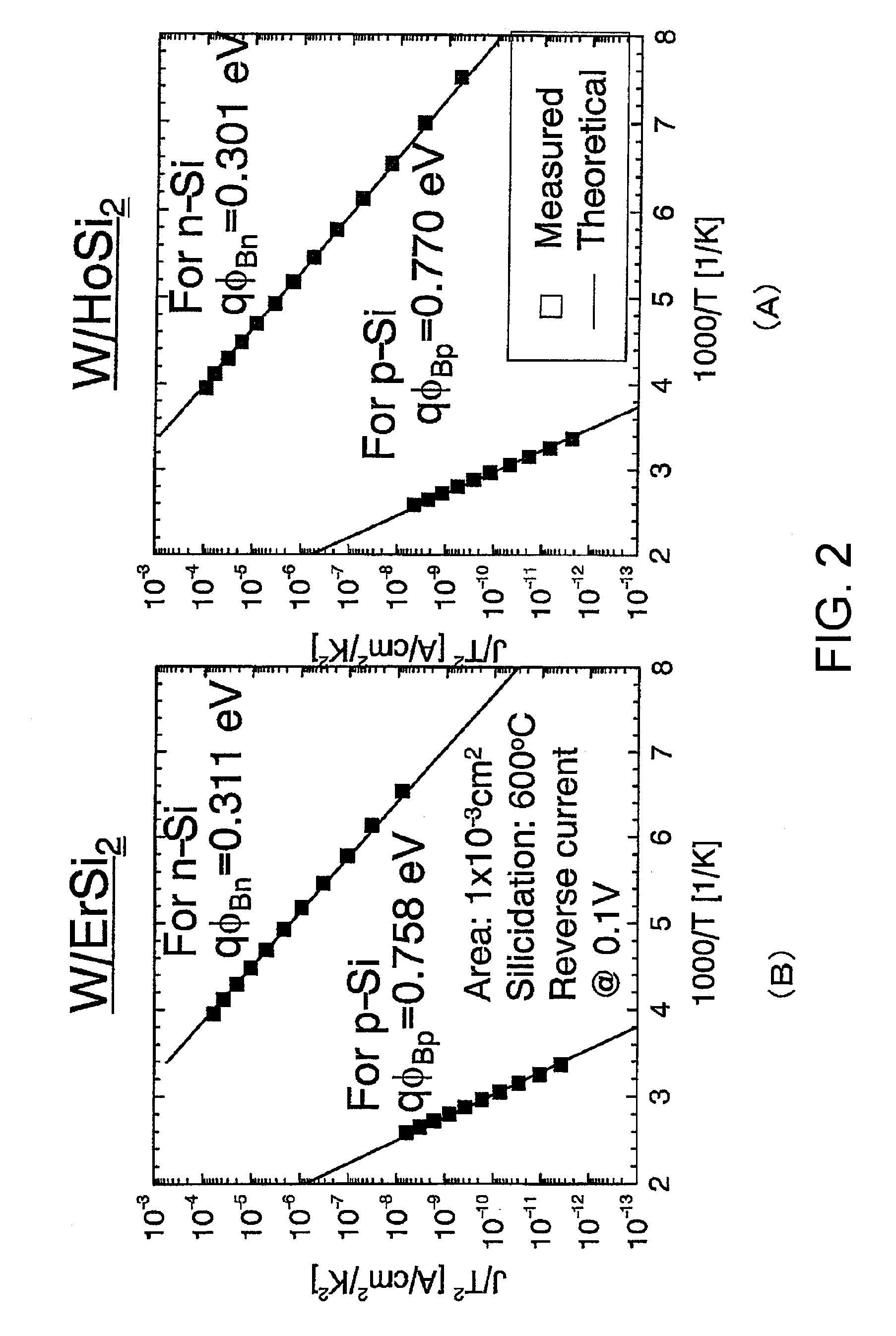

Contact Formation Method, Semiconductor Device Manufacturing Method, and Semiconductor Device

ActiveUS20110198702A1Reduce contact resistivityAvoid oxygenTransistorSemiconductor/solid-state device detailsContact formationWork function

Owner:TOHOKU UNIV +1

Graphene field effect transistor and manufacturing method thereof

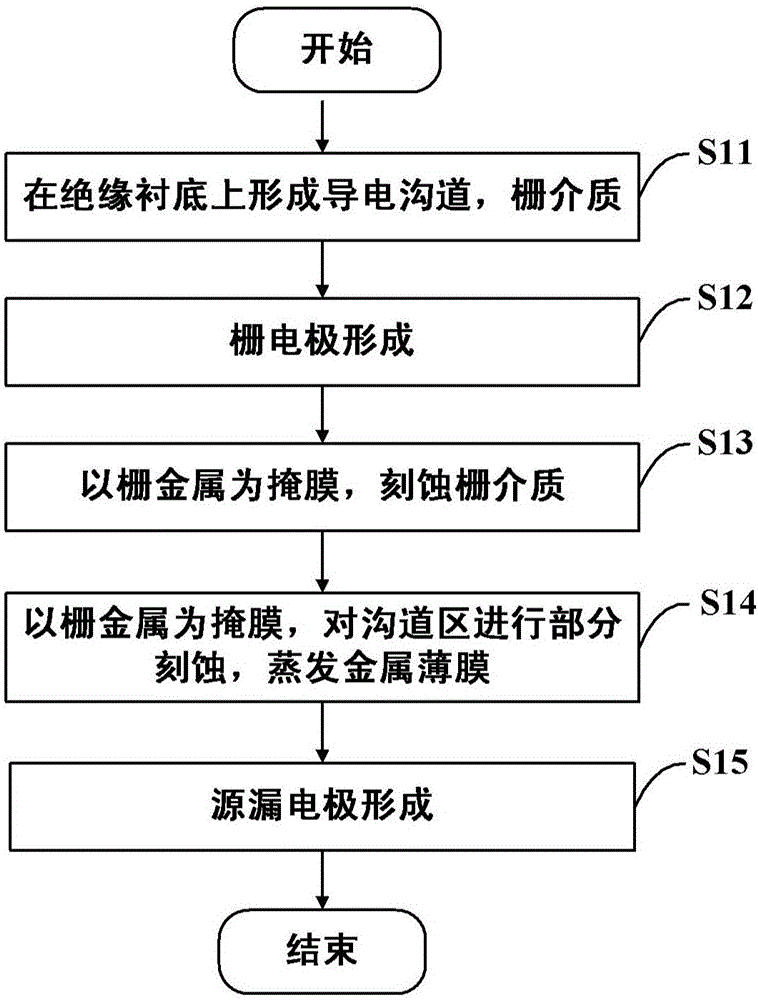

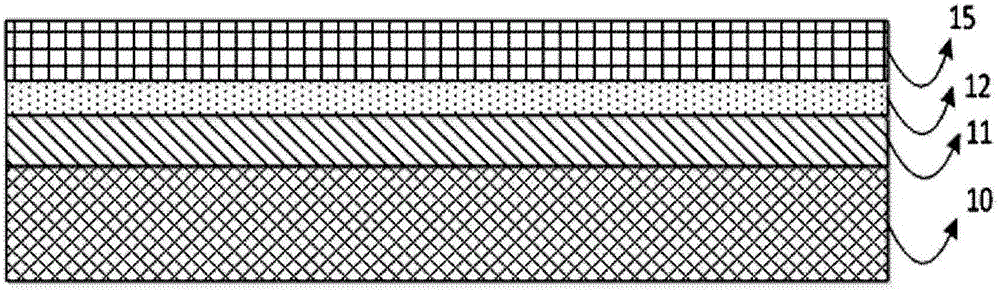

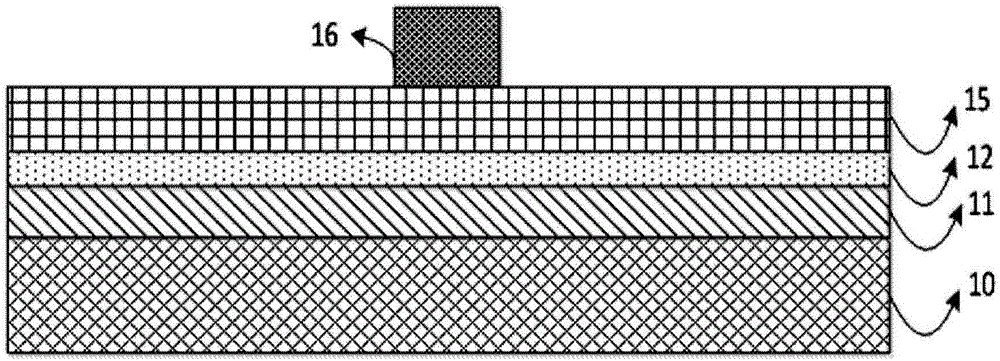

ActiveCN105762194AAvoid pollutionAvoid direct contactSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringMedia layer

Provided are a graphene field effect transistor and a manufacturing method thereof.The manufacturing method comprises the following steps that a top gate metal is used as a gate medium under a mask protecting top gate metal, and a gate medium layer is etched to remove the gate medium covering a graphene active area between a gate source and a gate drain; a top gate electrode is used as a mask to etch graphene, and a lattice structure of a graphene material is destroyed to form a defect; then, a metal film layer is formed on a formed device, and a source electrode and a drain electrode are prepared on the metal film layer; and the completed device is annealed.By the adoption of the manufacturing method, the separation distance between the gate source and the gate drain can be decreased, the graphene pollution caused by a device machining process is effectively avoided, the lower contact resistivity can be obtained by partially etching the graphene material in a contact area, and accordingly the performance of the graphene transistor can be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

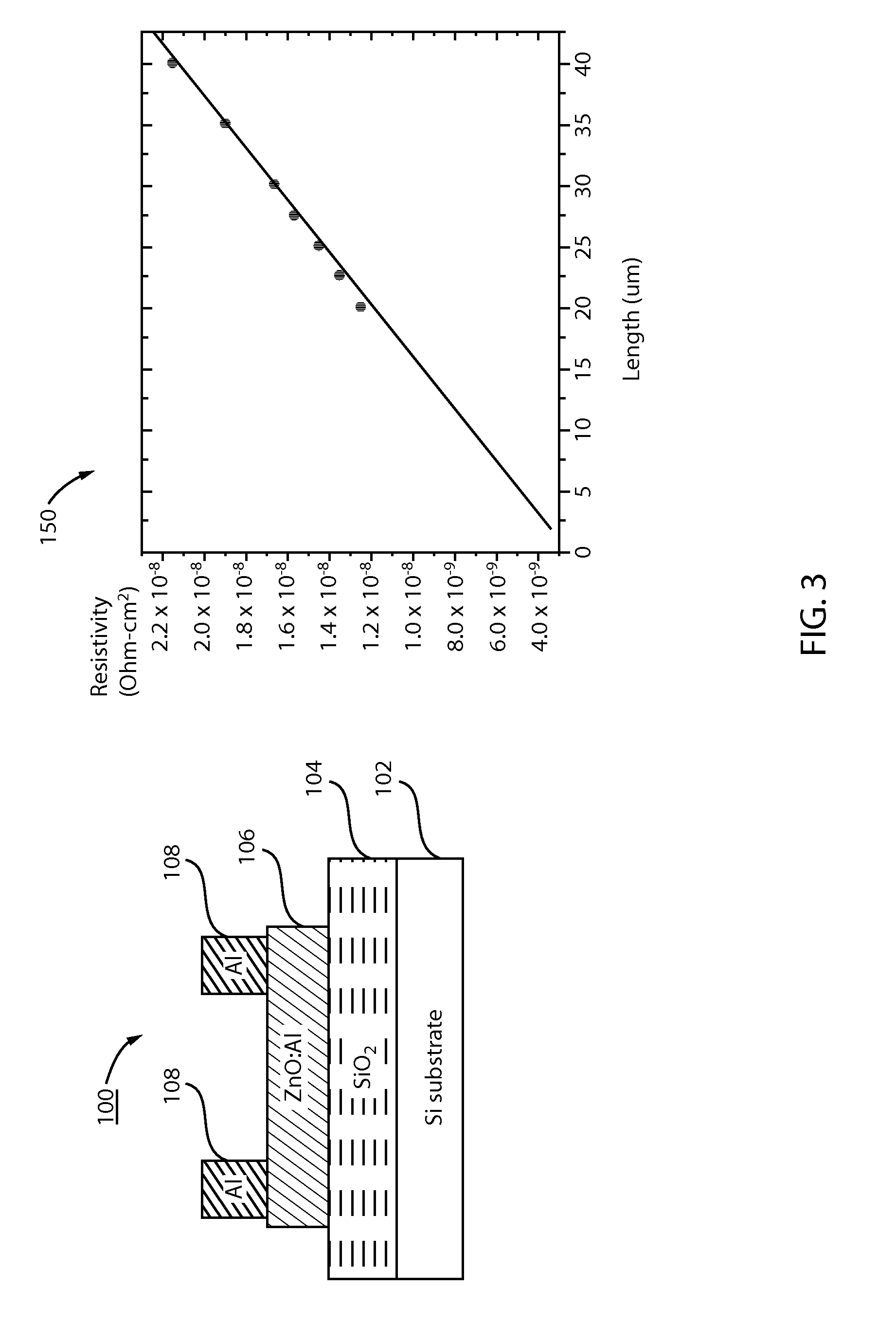

Low resistance contact for semiconductor devices

InactiveUS20160268377A1Reduce contact resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesElectronSemiconductor

A semiconductor device includes a substrate and a p-doped layer including a doped III-V material on the substrate. An n-type material is formed on or in the p-doped layer. The n-type layer includes ZnO. An aluminum contact is formed in direct contact with the ZnO of the n-type material to form an electronic device.

Owner:IBM CORP

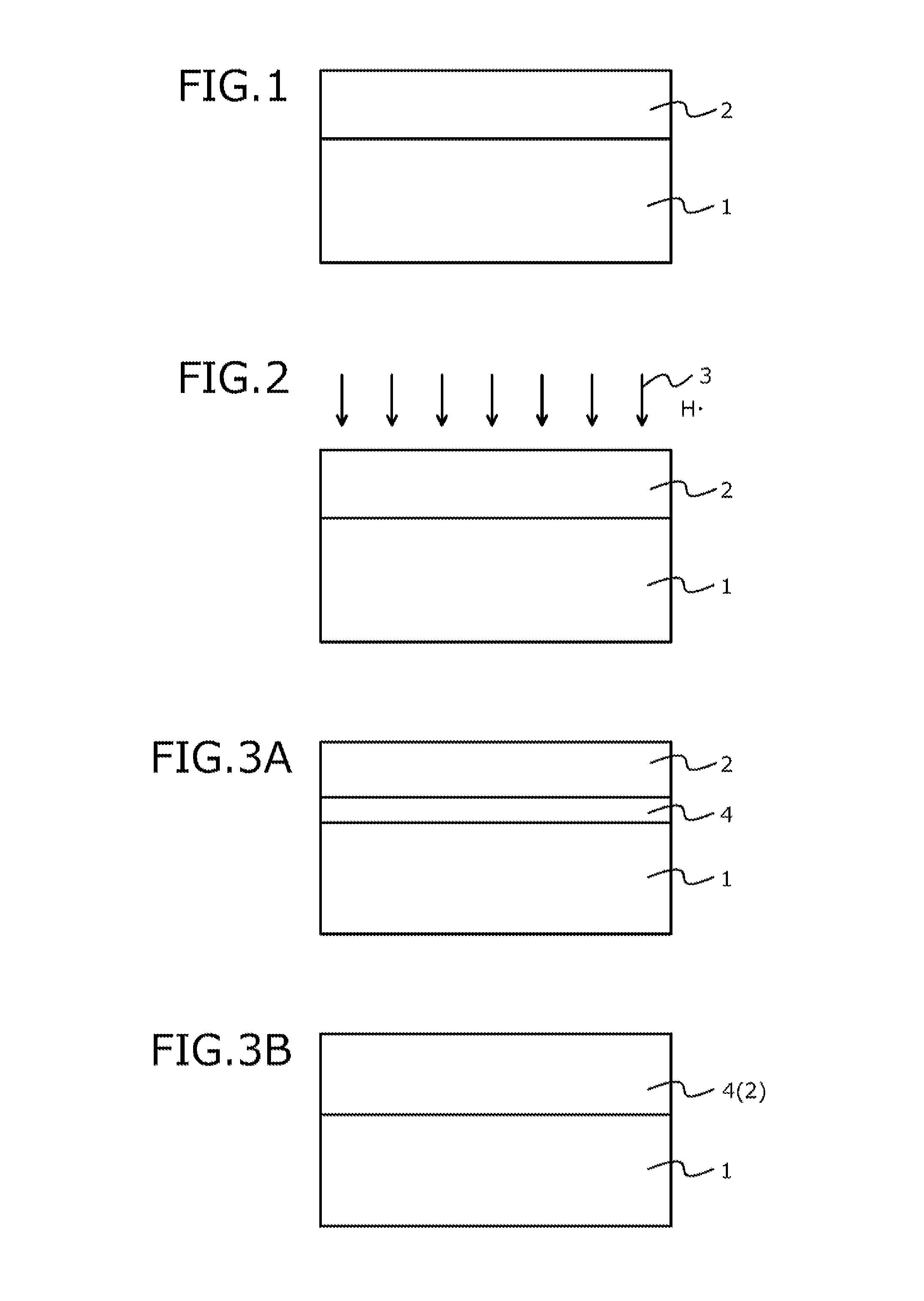

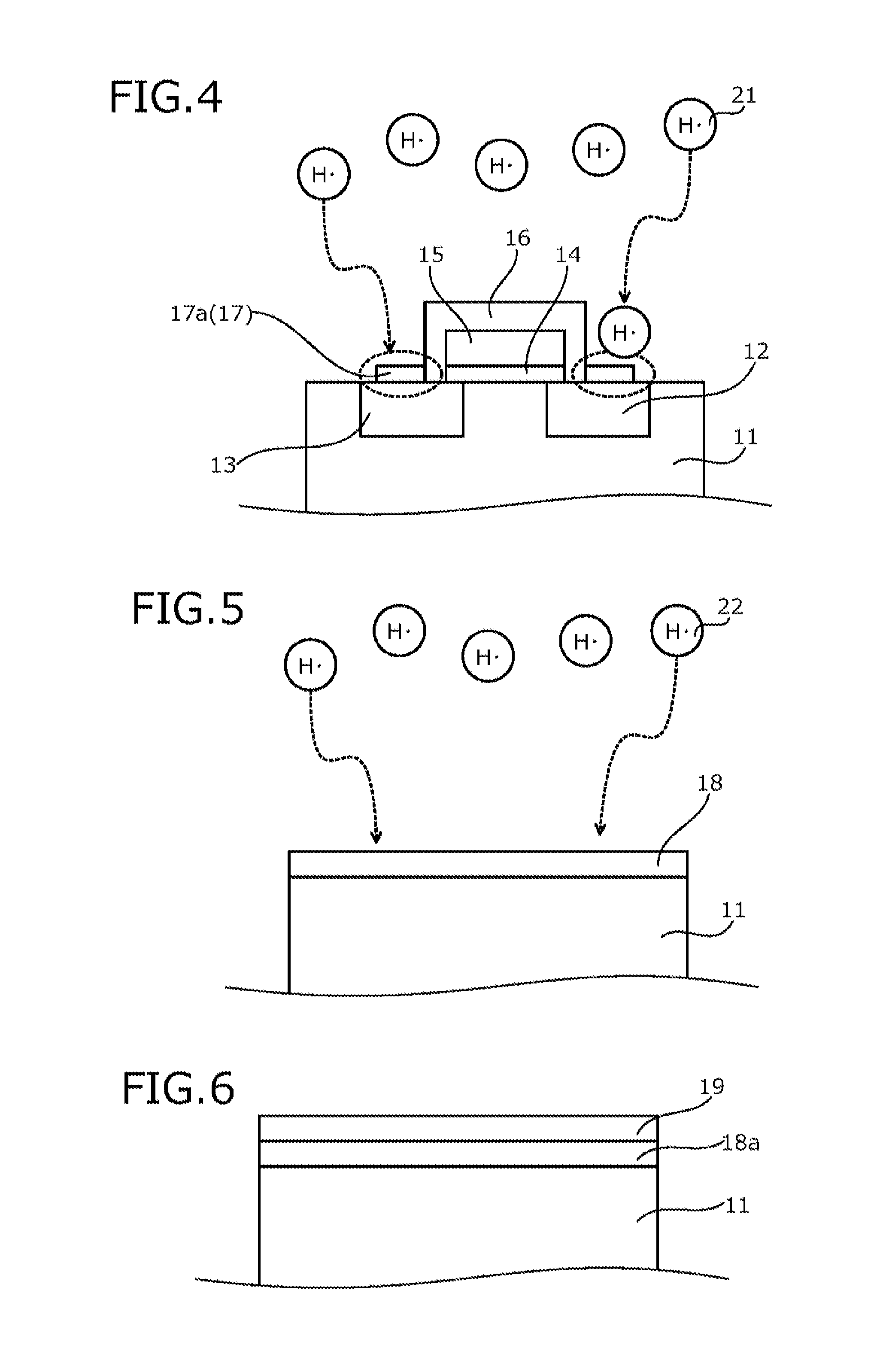

Method of manufacturing semiconductor device

ActiveUS20160189967A1Reduce contact resistivityImprove suppression propertiesSolid-state devicesSemiconductor/solid-state device manufacturingSalicideMicrowave

A method of manufacturing a semiconductor device includes providing a semiconductor substrate having a front surface and a back surface; forming a transition metal layer in a surface of the semiconductor substrate; and exposing the semiconductor substrate having the transition metal layer formed thereon to a hydrogen plasma atmosphere formed by microwaves, to cause the transition metal layer to generate heat, Thus, during the exposure of the semiconductor substrate, a portion of the semiconductor substrate contacting the transition metal layer is heated by a transfer of heat from the transition metal layer and, at an interface of the transition metal layer and the semiconductor substrate, an ohmic contact is formed by reaction of the transition metal layer and the semiconductor substrate, such as to form a transition metal silicide when the semiconductor substrate is silicon carbide. The ohmic contact provides a lower contact resistivity and device properties can be prevented from degrading.

Owner:FUJI ELECTRIC CO LTD

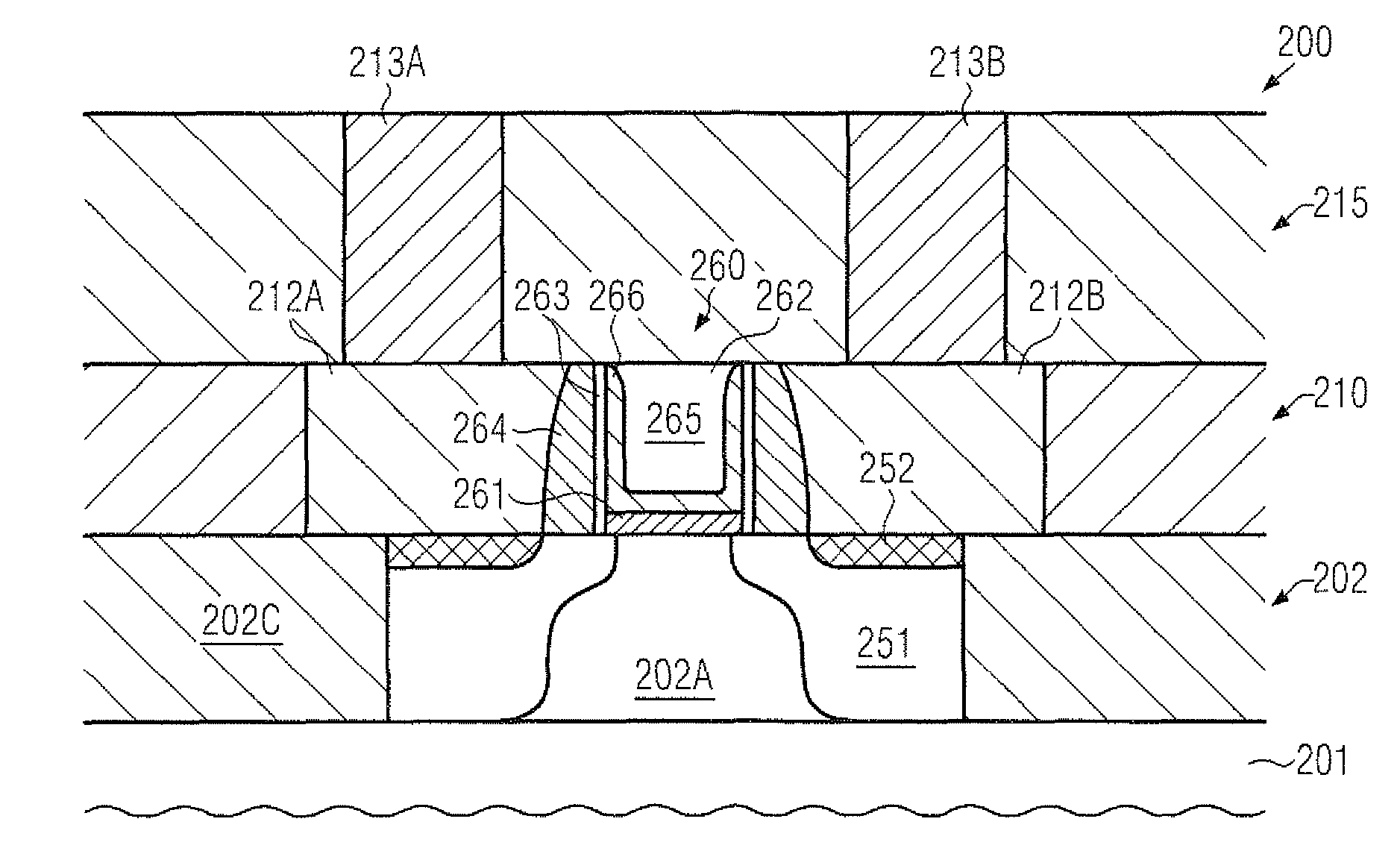

Contact bars with reduced fringing capacitance in a semiconductor device

InactiveUS9184095B2Increasing overall parasitic fringing capacitanceReduce capacitanceSemiconductor/solid-state device detailsSolid-state devicesFringing capacitanceContact element

In sophisticated semiconductor devices, the contact structure may be formed on the basis of contact bars formed in a lower portion of an interlayer dielectric material, which may then be contacted by contact elements having reduced lateral dimensions so as to preserve a desired low overall fringing capacitance. The concept of contact bars of reduced height level may be efficiently combined with sophisticated replacement gate approaches.

Owner:GLOBALFOUNDRIES INC

Film transistor substrate and display device thereof

InactiveCN102169905AExcellent adhesionReduce contact resistivityTransistorSolid-state devicesDisplay deviceThin membrane

The invention provides a film transistor substrate which has a low contact resistivity and good space continuity even a Cu series alloy wiring film directly contacts with a semiconductor. The film transistor substrate comprises a semiconductor layer and a Cu alloy layer. An oxygen-containing layer is disposed between the semiconductor layer and the Cu alloy layer. A part of or the whole oxygen of the oxygen-containing layer combines with the Si of the semiconductor layer of the film transistor. The Cu alloy layer as an alloy element has X arranged from 2 atom% to 20 atom% (X is at least one of Mn, Ni, Zn and Mg). . The Cu alloy layer is connected to the semiconductor layer of the film transistor through the oxygen-containing layer.

Owner:KOBE STEEL LTD

Top-emitting nitride-based light-emitting device with ohmic characteristics and luminous efficiency

ActiveUS8395176B2High light transmittanceReduce sheet resistanceElectroluminescent light sourcesSolid-state devicesMicrometerOhmic contact

Owner:SAMSUNG ELECTRONICS CO LTD +1

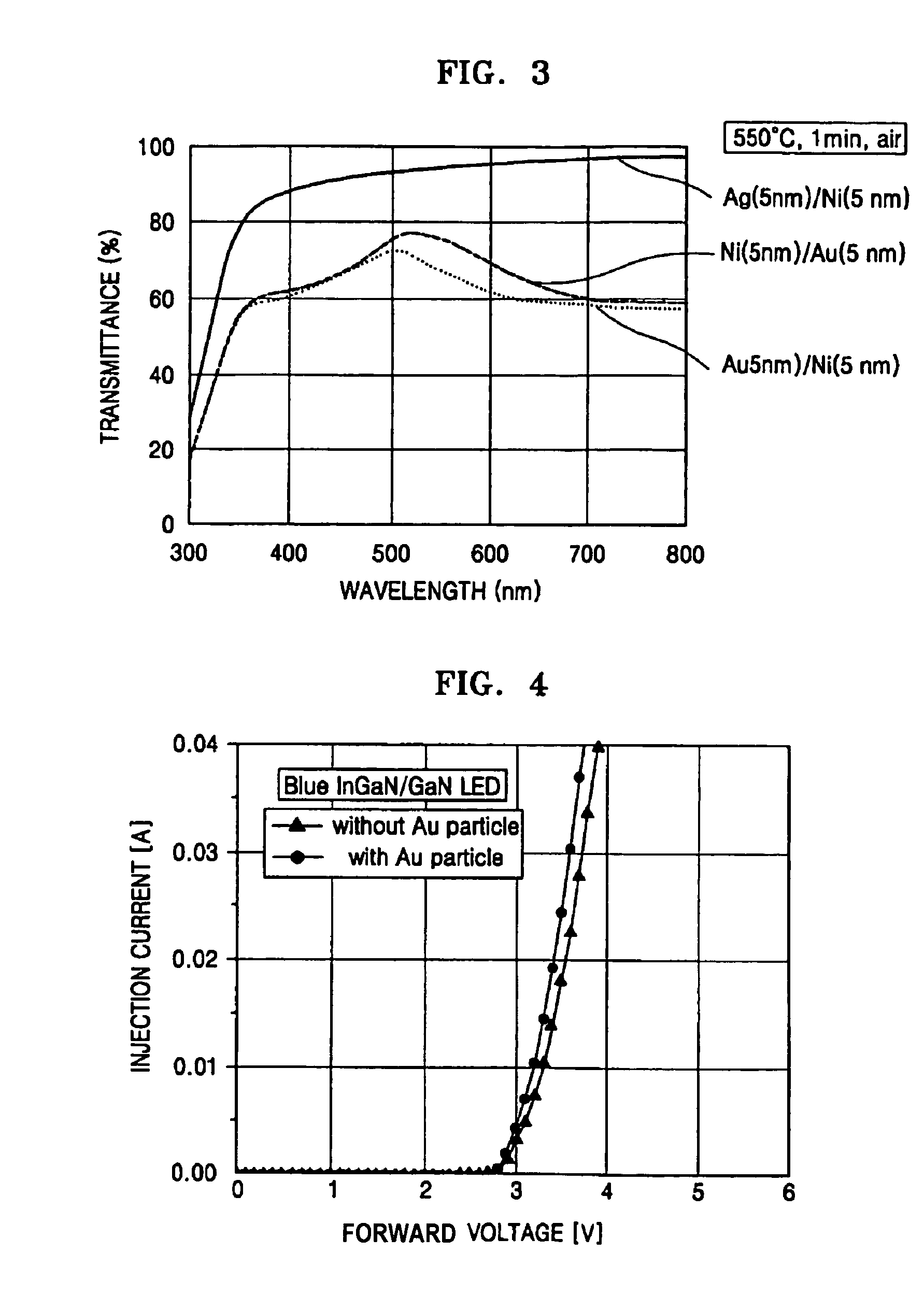

Nitride semiconductor based light-emitting device and manufacturing method thereof

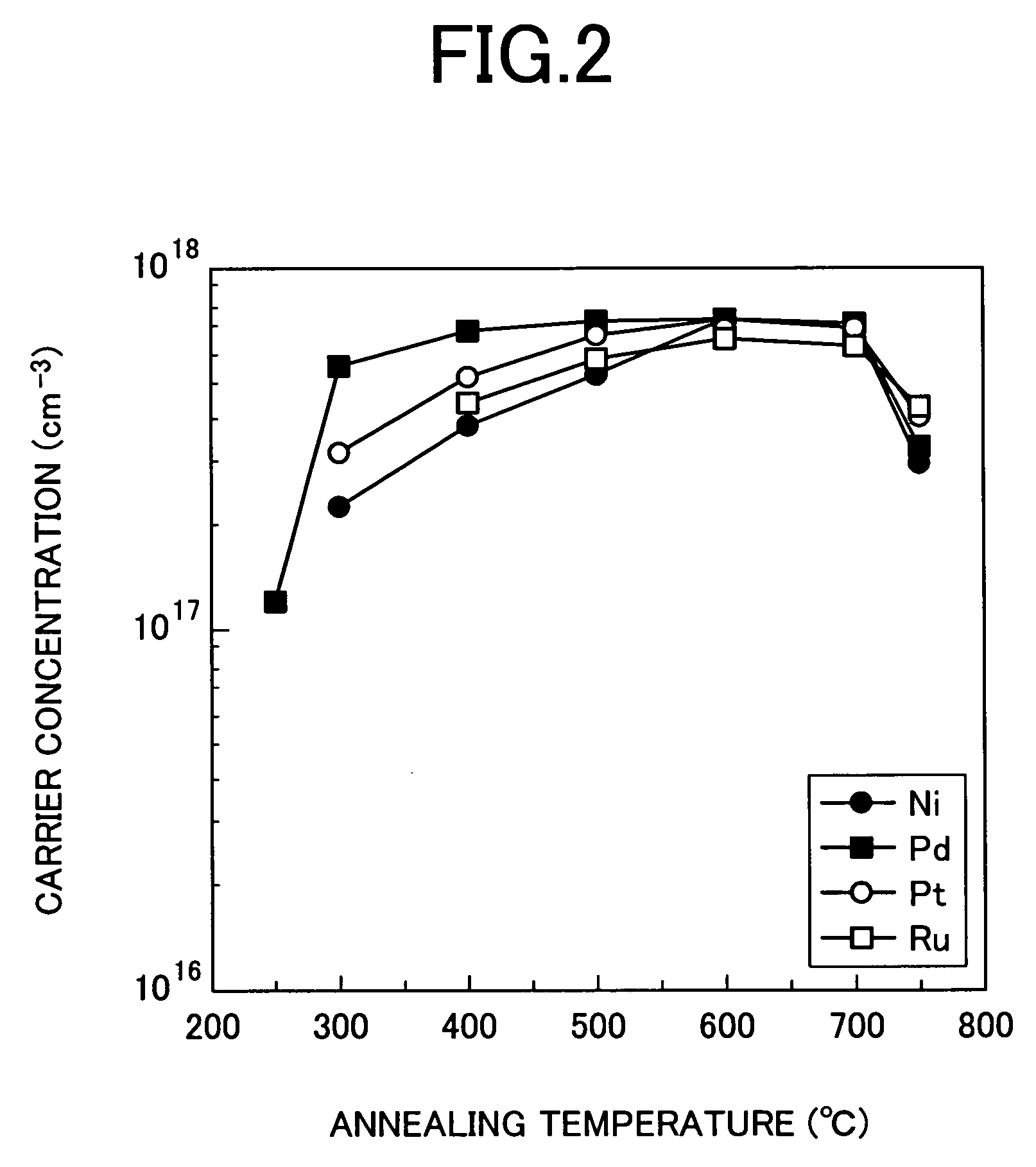

ActiveUS20070224715A1Increase the carrier concentrationReduce contact resistivitySemiconductor/solid-state device manufacturingNanoopticsMetalOperating voltage

An object of the present invention is to provide a nitride semiconductor based light-emitting device, which is low in operating voltage reduction and is high in performance, and a manufacturing method thereof.A first metal film is formed on a P-type conductive nitride semiconductor formed on a substrate, and then, a film (WOX) made of tungsten oxide is formed in superimposition, followed by annealing.

Owner:USHIO OPTO SEMICON

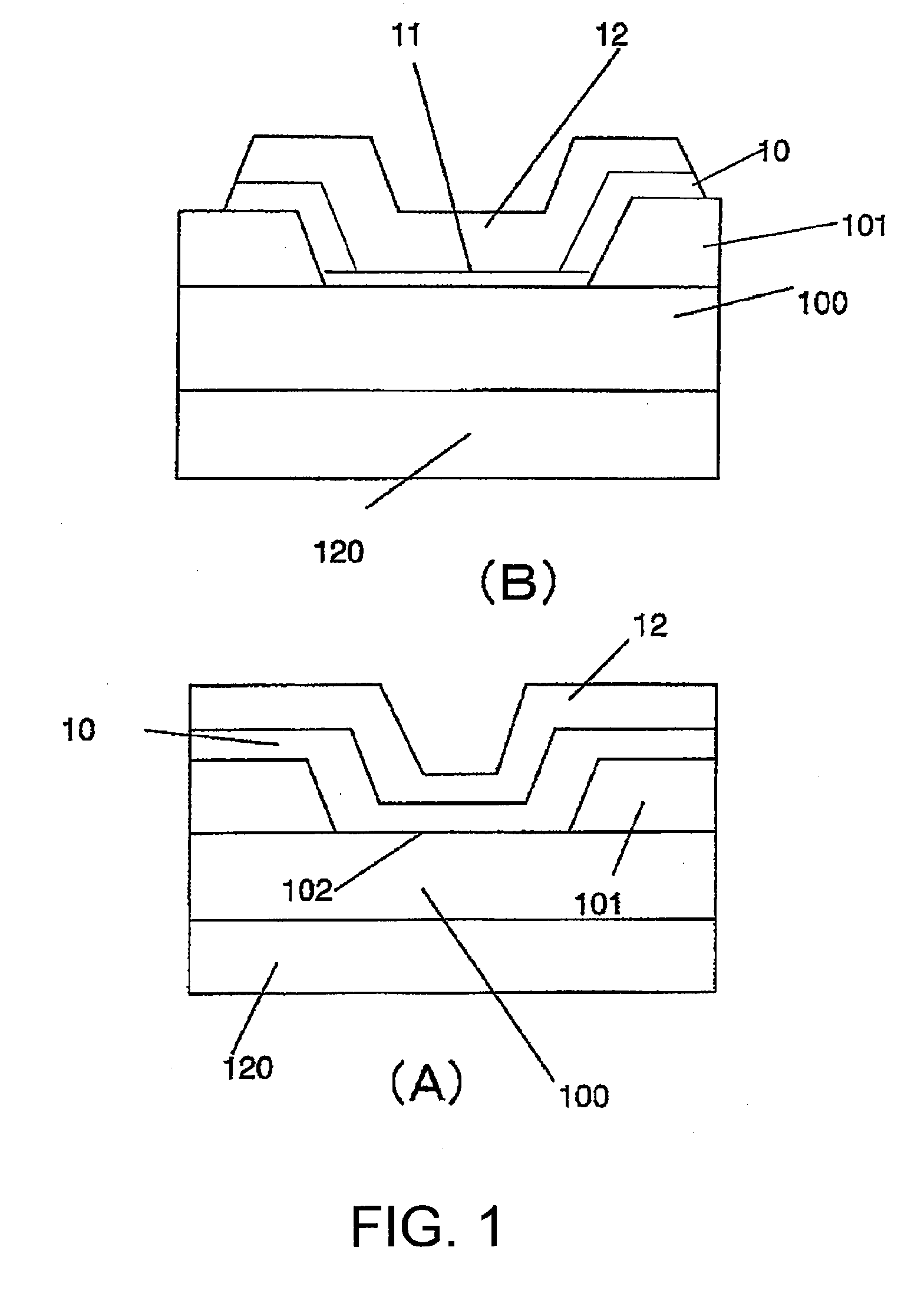

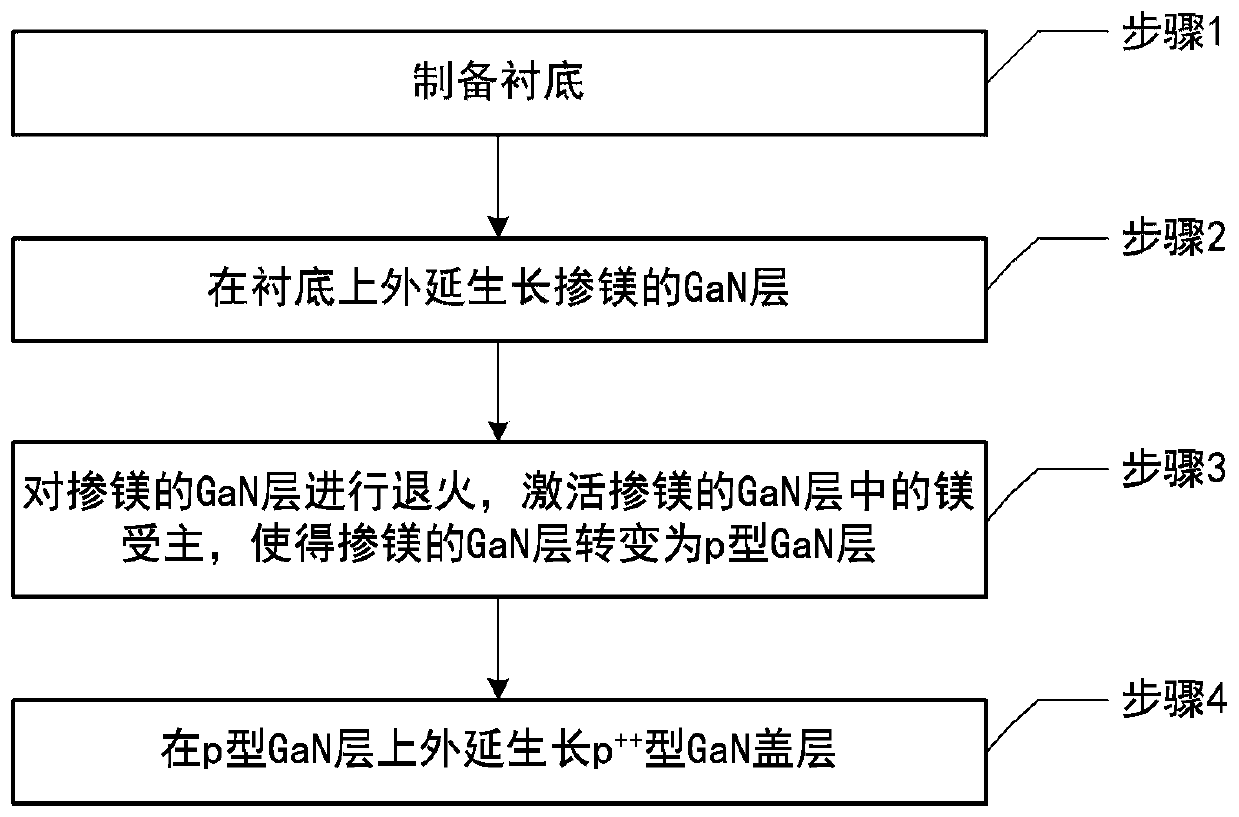

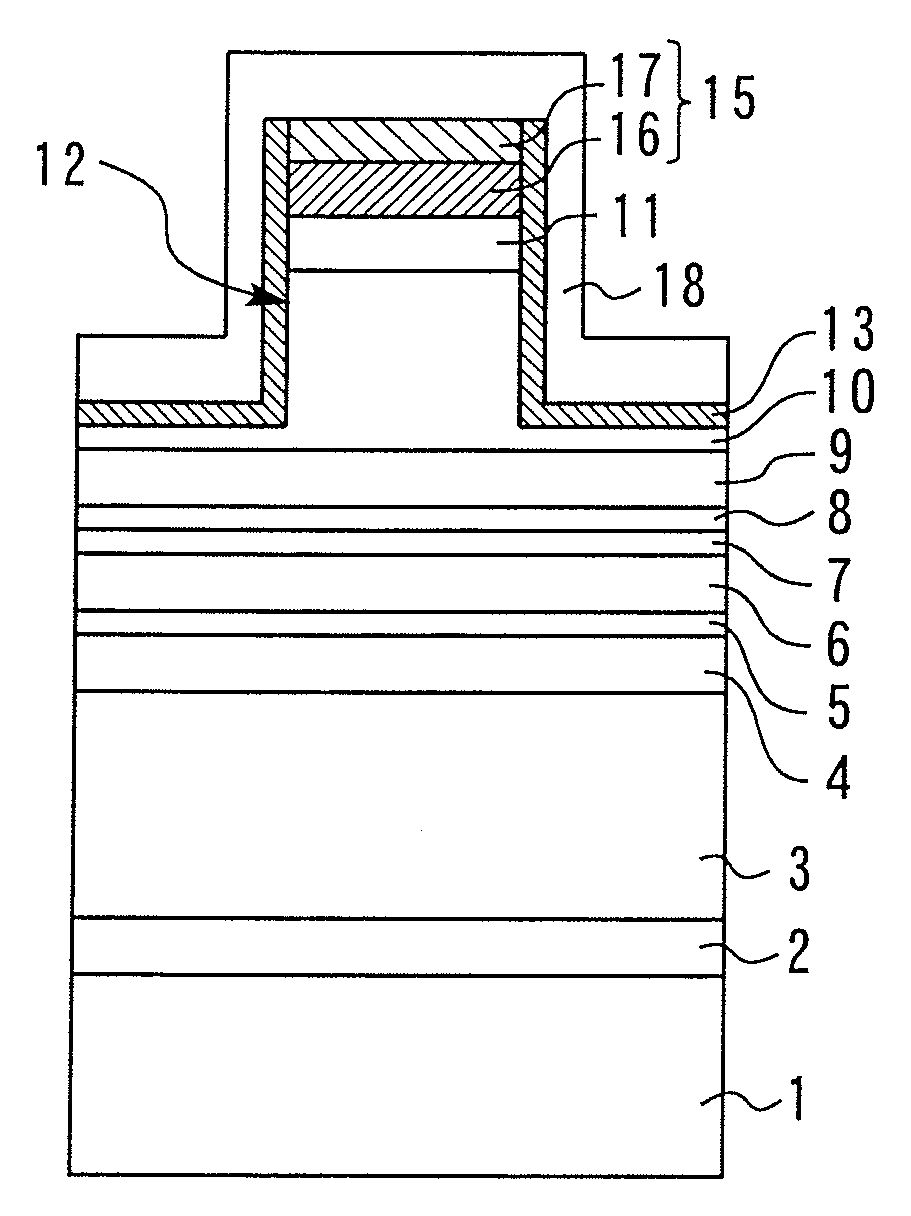

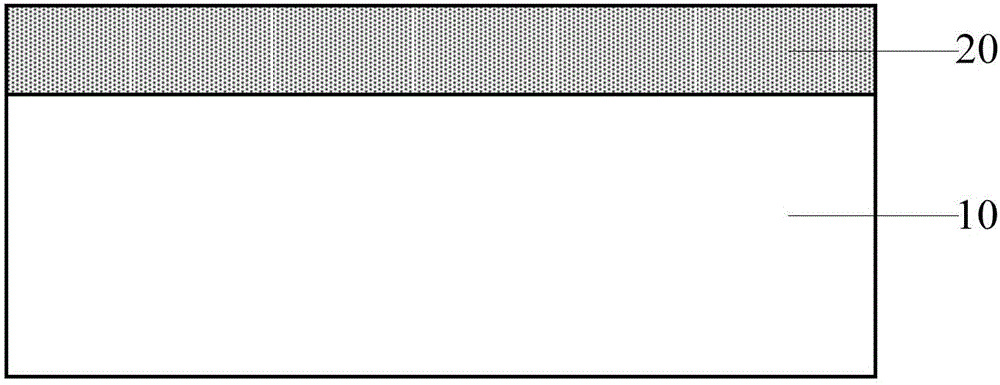

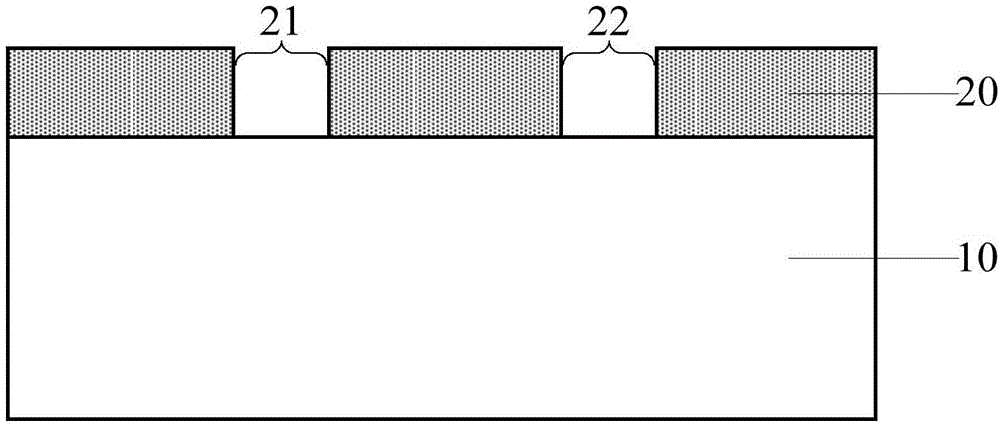

p-type GaN epitaxial wafer with high ohmic contact features and preparation method thereof

InactiveCN109860044AImprove electro-optical conversion efficiencyImprove reliabilityLaser active region structureSemiconductor/solid-state device manufacturingOhmic contactOptoelectronics

The present invention provides a p-type GaN epitaxial wafer with high ohmic contact features and a preparation method thereof. The preparation method comprises the steps of: the step 1: preparing a substrate (10); the step 2: performing epitaxial growth of an Mg-doped GaN layer on the substrate (10); the step 3: performing annealing for the Mg-doped GaN layer to activate a magnesium acceptor in the Mg-doped GaN layer to convert the Mg-doped GaN layer to a p-type GaN epitaxial layer (11); and the step (4): performing epitaxial growth of a p++-type GaN cover layer (12) on the p-type GaN epitaxial layer (11). The heavily-doped p++-type GaN cover layer is grown on the p-type GaN layer, and the heavily-doped p++-type GaN cover layer does not perform high-temperature annealing to improve the quality of the ohmic contact layer of the epitaxial wafer and reduce the specific contact resistance rate of the contact of the p-type material and the metal.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Contact formation method, semiconductor device manufacturing method, and semiconductor device

ActiveUS8575023B2Reduce contact resistivityAvoid oxygenTransistorSemiconductor/solid-state device detailsContact formationWork function

A semiconductor device manufacturing method which achieves a contact of a low resistivity is provided.In a state where a first metal layer in contact with a semiconductor is covered with a second metal layer for preventing oxidation, only the first metal layer is silicided to form a silicide layer with no oxygen mixed therein. As a material of the first metal layer, a metal having a work function difference of a predetermined value from the semiconductor is used. As a material of the second metal layer, a metal which does not react with the first metal layer at an annealing temperature is used.

Owner:TOHOKU UNIV +1

Method for manufacturing nitride semiconductor light-emitting element

InactiveUS20090130790A1High-output operationLittle time degradationOptical wave guidanceLaser detailsOxygenActive layer

A method for manufacturing a nitride semiconductor light-emitting element comprises: forming a semiconductor laminated structure wherein an n-type nitride semiconductor epitaxial layer, an active layer, and a p-type nitride semiconductor epitaxial layer are laminated on a substrate; forming a p-type electrode having a first electrode layer containing Pd and a second electrode layer containing Ta on the p-type nitride semiconductor epitaxial layer; heat treating at a temperature between 400° C. and 600° C. in an ambient containing oxygen after forming the p-type electrode; and forming a pad electrode containing Au on the p-type electrode after the heat treating.

Owner:MITSUBISHI ELECTRIC CORP

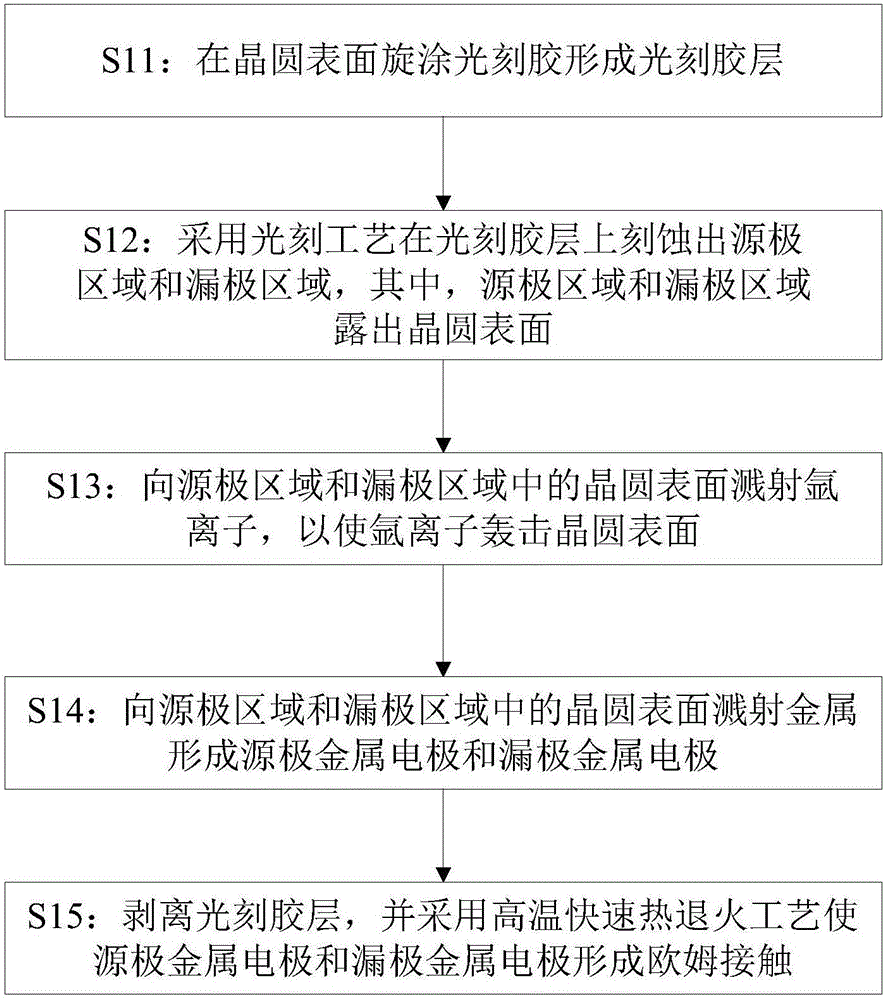

Method for reducing Ohmic contact resistivity of gallium nitride high electron mobility transistor

InactiveCN106067421AIncrease concentrationImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesAlloyGallium nitride

The invention provides a method for reducing Ohmic contact resistivity of a gallium nitride high electron mobility transistor. The method comprises the following steps: a photoresist layer is formed by coating photoresist on a wafer surface via spin coating operation, a source electrode area and a drain electrode area are etched on the photoresist layer via photoetching processes, and the source electrode area and the drain electrode area are exposed on the wafer surface; argon ions are sputtered on parts, positioned in the source electrode area and the drain electrode area, of the wafer surface; the argon ions are enabled to bombard the wafer surface; a source metal electrode and a drain metal electrode are formed by sputtering metal on the parts, positioned in the source electrode area and the drain electrode area, of the wafer surface; the photoresist layer is peeled off, and the source metal electrode and the drain metal electrode are enable to be in Ohmic contact with each other via adoption of high temperature rapid thermal annealing processes. Via the above mode, the method for reducing Ohmic contact resistivity of the gallium nitride high electron mobility transistor can help increase concentration of N vacancy in a semiconductor, and low Ohmic contact resistivity can be obtained via high temperature thermal annealing alloying technologies.

Owner:CHENGDU HIWAFER SEMICON CO LTD