Patents

Literature

77results about How to "Yield minimization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

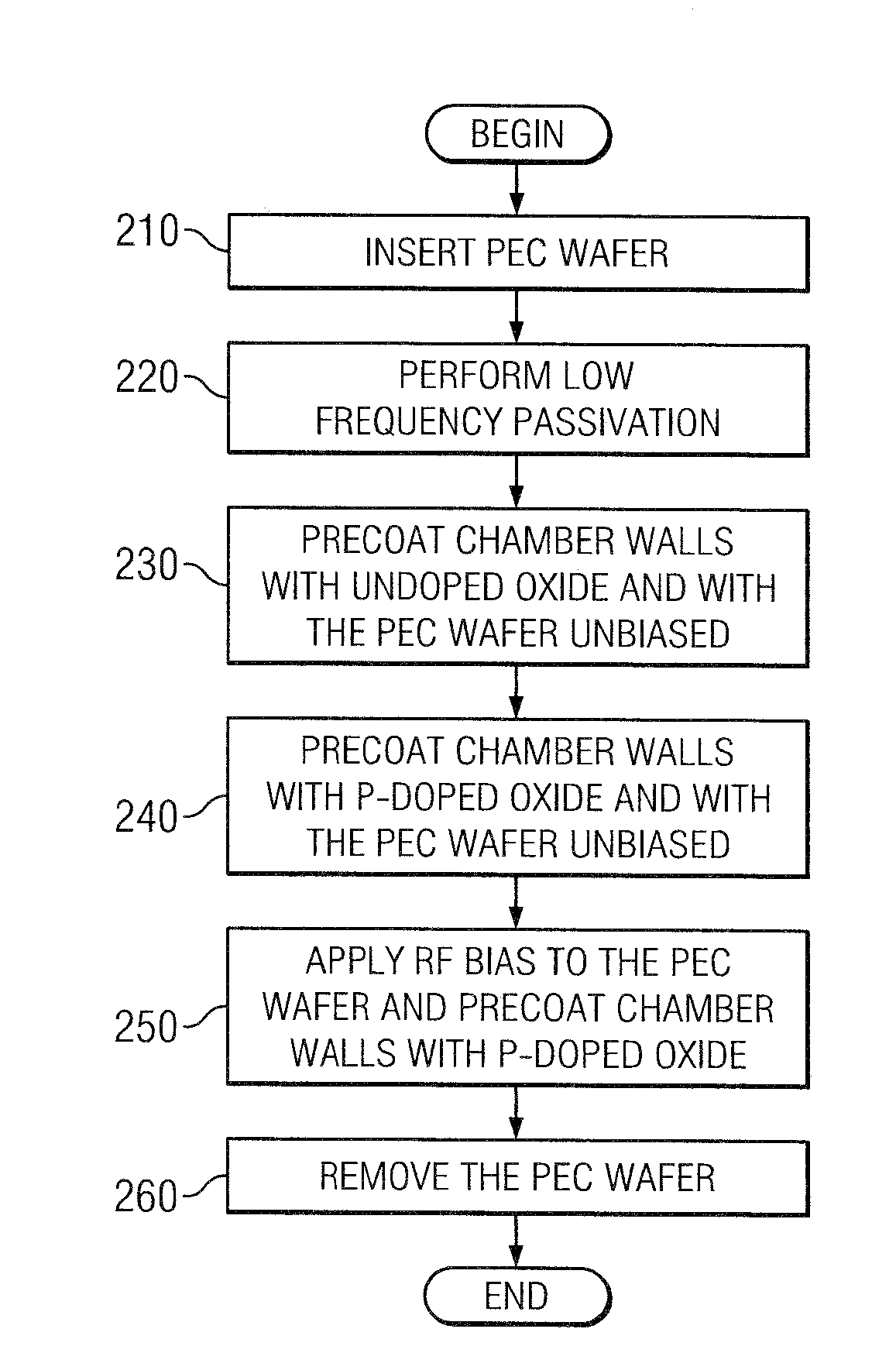

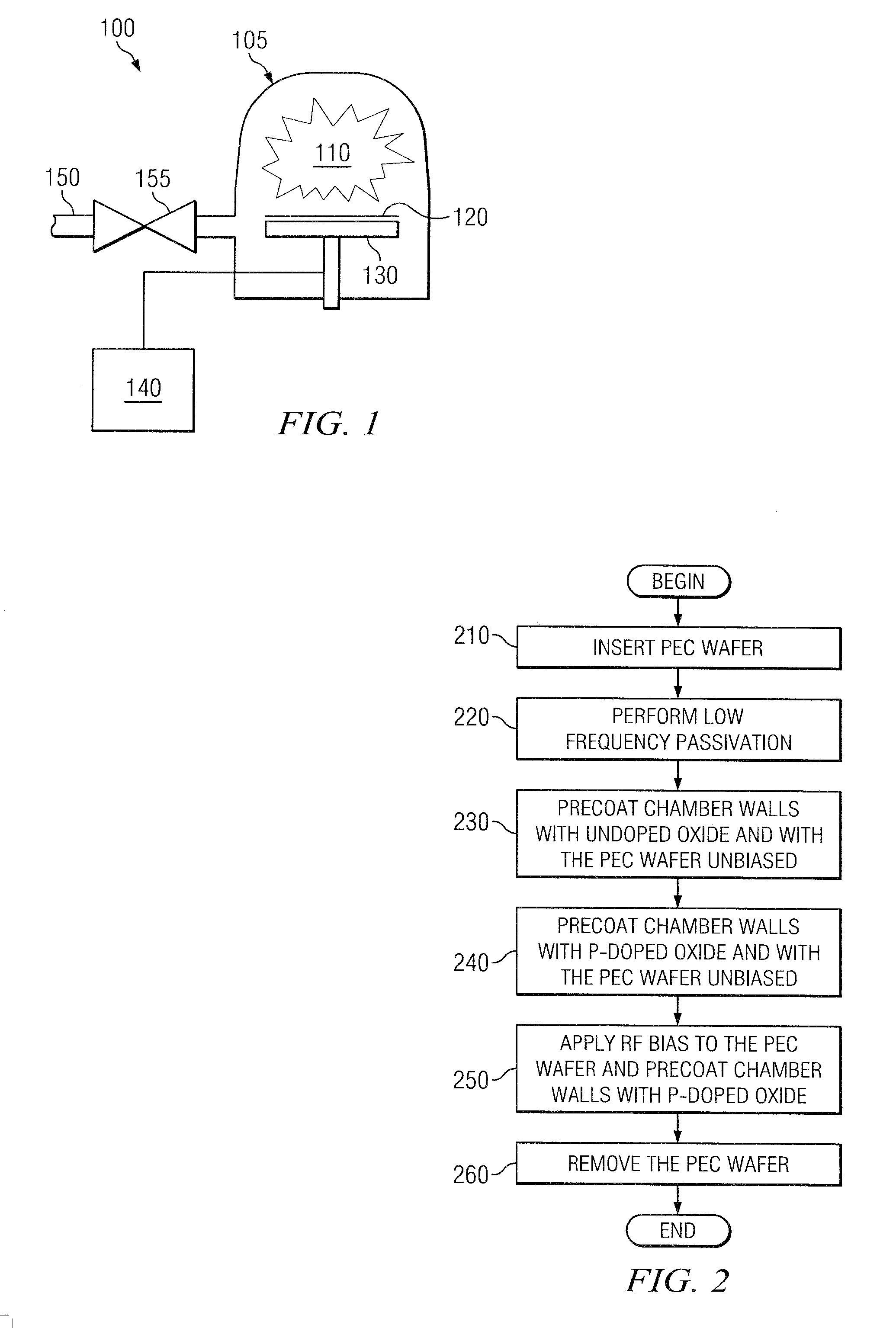

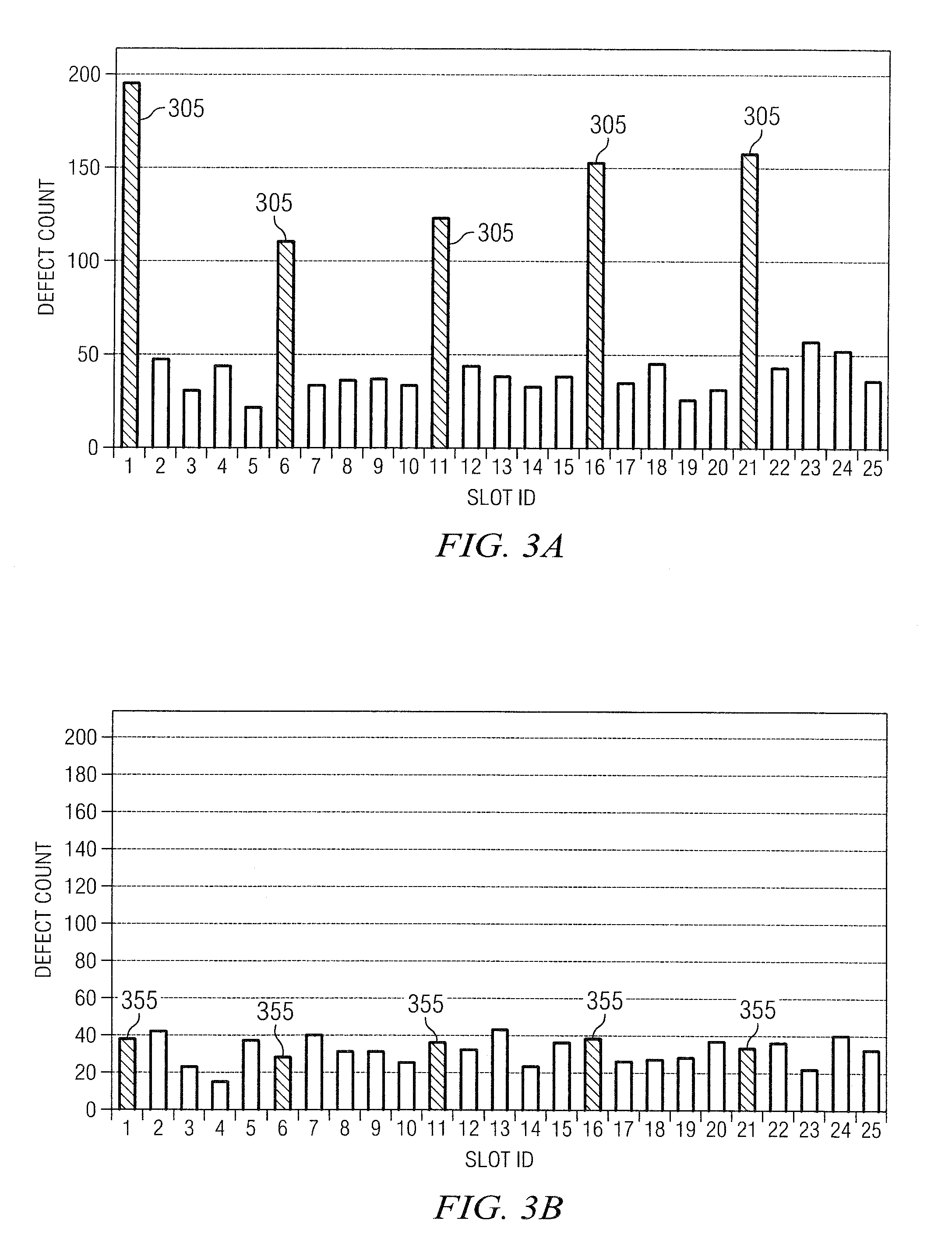

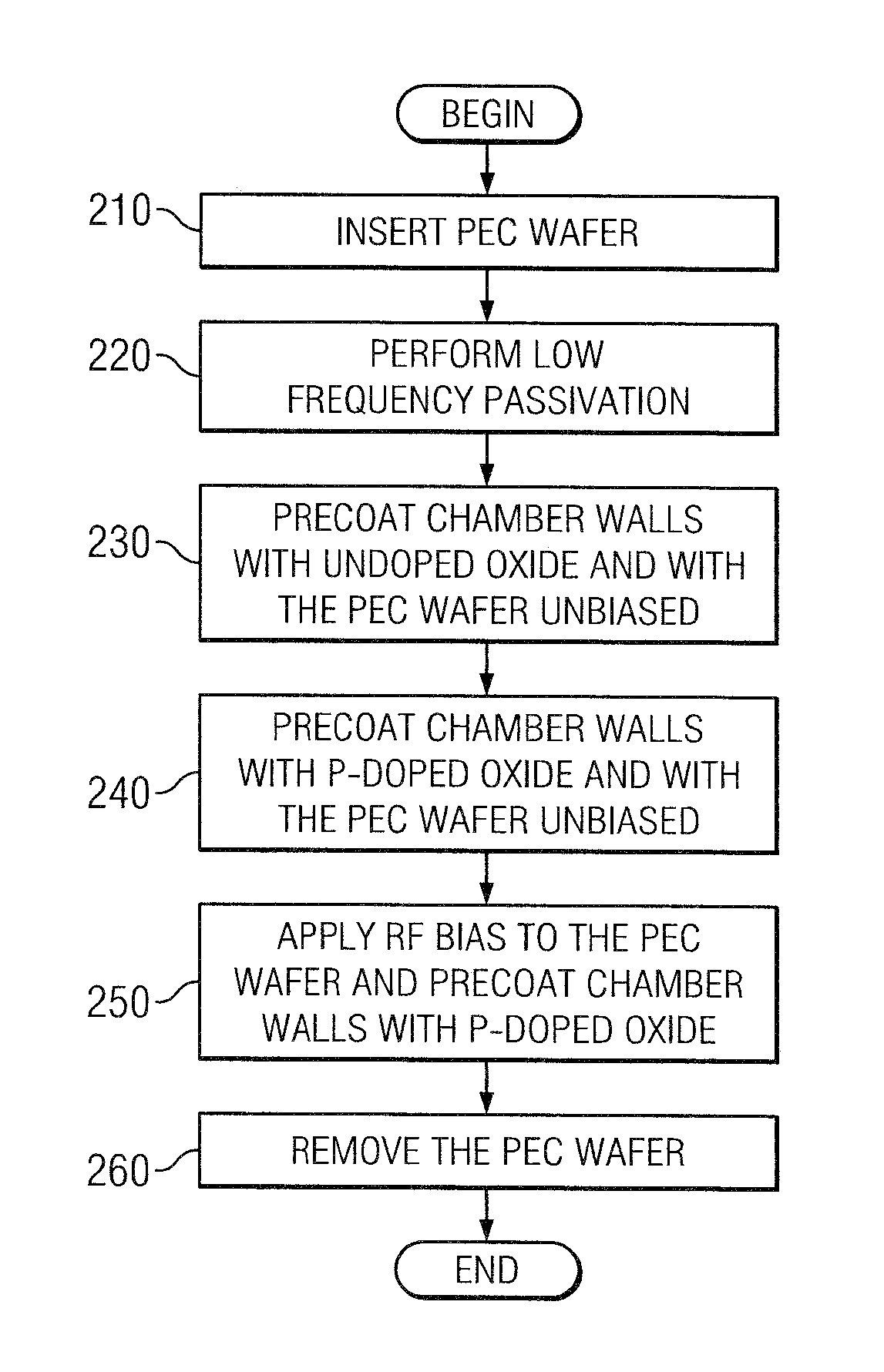

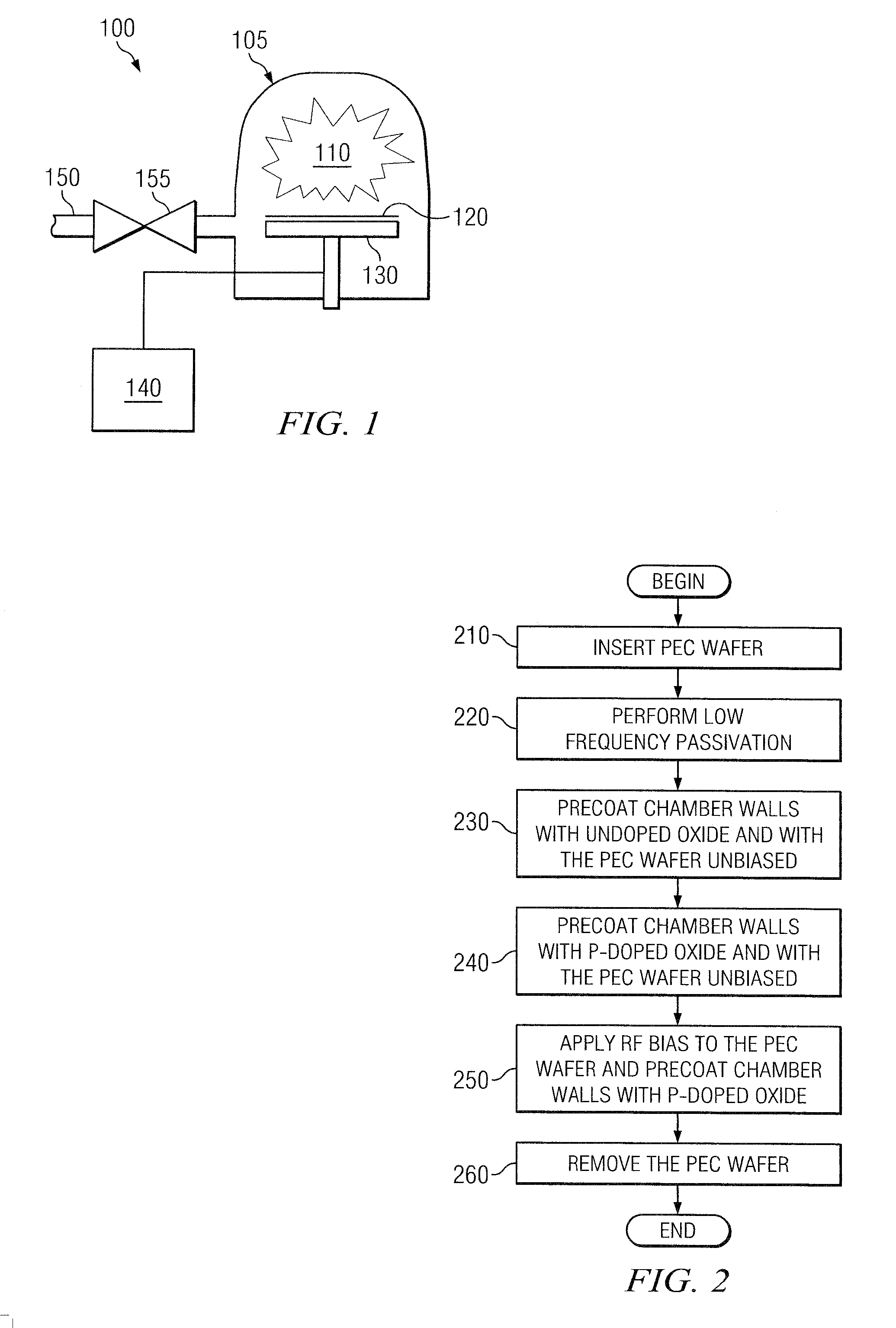

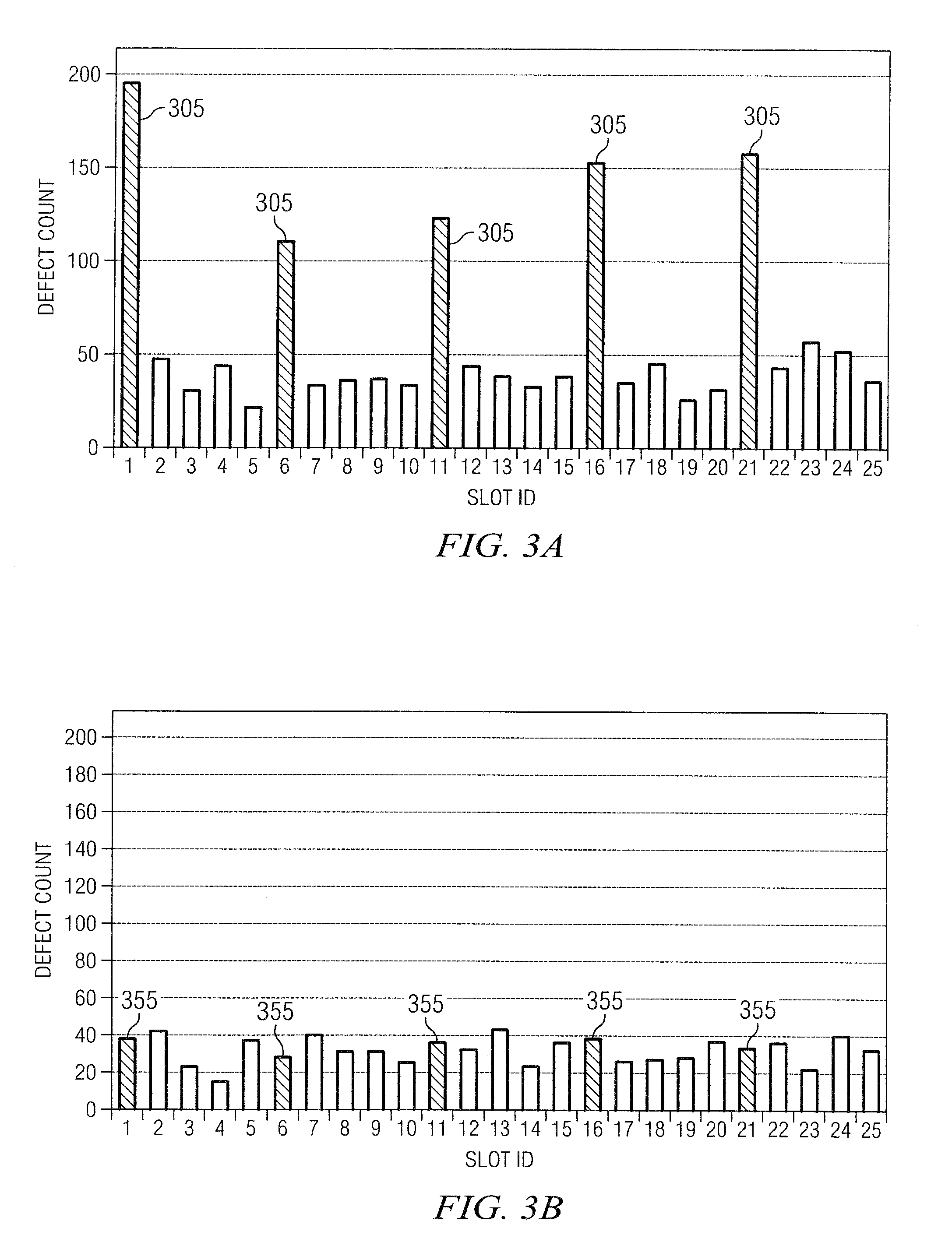

Use of a biased precoat for reduced first wafer defects in high-density plasma process

ActiveUS20100190352A1Minimizing yield lossReducing first wafer defectRadiation applicationsPretreated surfacesHigh densityGas phase

According to various embodiments, the present teachings include methods for reducing first wafer defects in a high-density plasma chemical vapor deposition process. In an exemplary embodiment, the method can include running a deposition chamber for deposition of film on a first batch of silicon wafers and then cleaning interior surfaces of the deposition chamber. The method can further include inserting a protective electrostatic chuck cover (PEC) wafer on an electrostatic chuck in the deposition chamber and applying power to bias the PEC wafer while simultaneously precoating the deposition chamber with an oxide. The exemplary method can also include re-starting the deposition chamber for deposition of film on a second batch of silicon wafers.

Owner:TEXAS INSTR INC

Seed coatings, coating compositions and methods for use

InactiveUS20120220454A1Promote seedling establishmentEasy to keepBiocideDead plant preservationCoatingFood science

Coating compositions and methods of use, allowing for improved water and / or nutrient usage by seeds, plants, shrubs, and vegetation, among others, are disclosed.

Owner:RHODIA OPERATIONS SAS

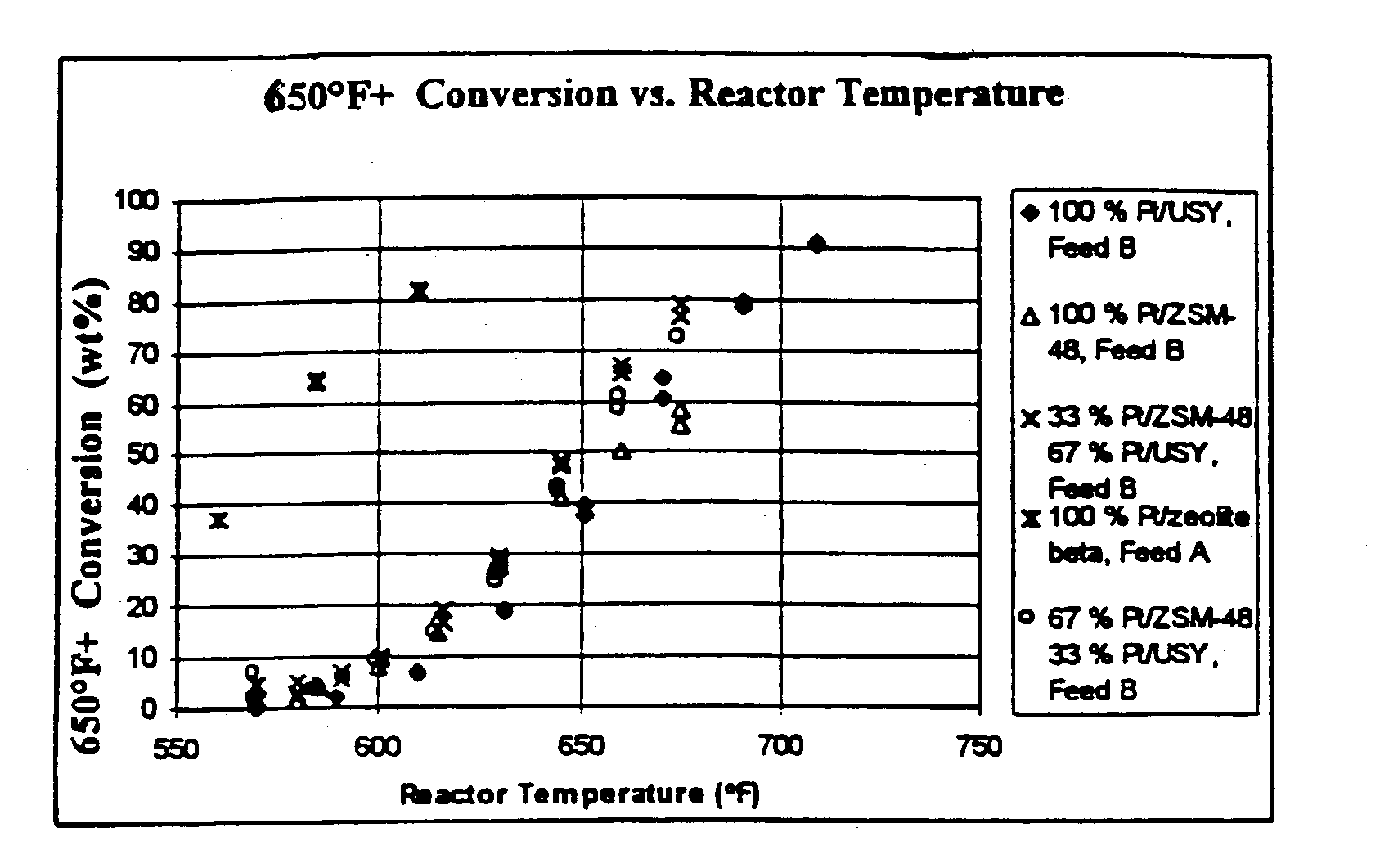

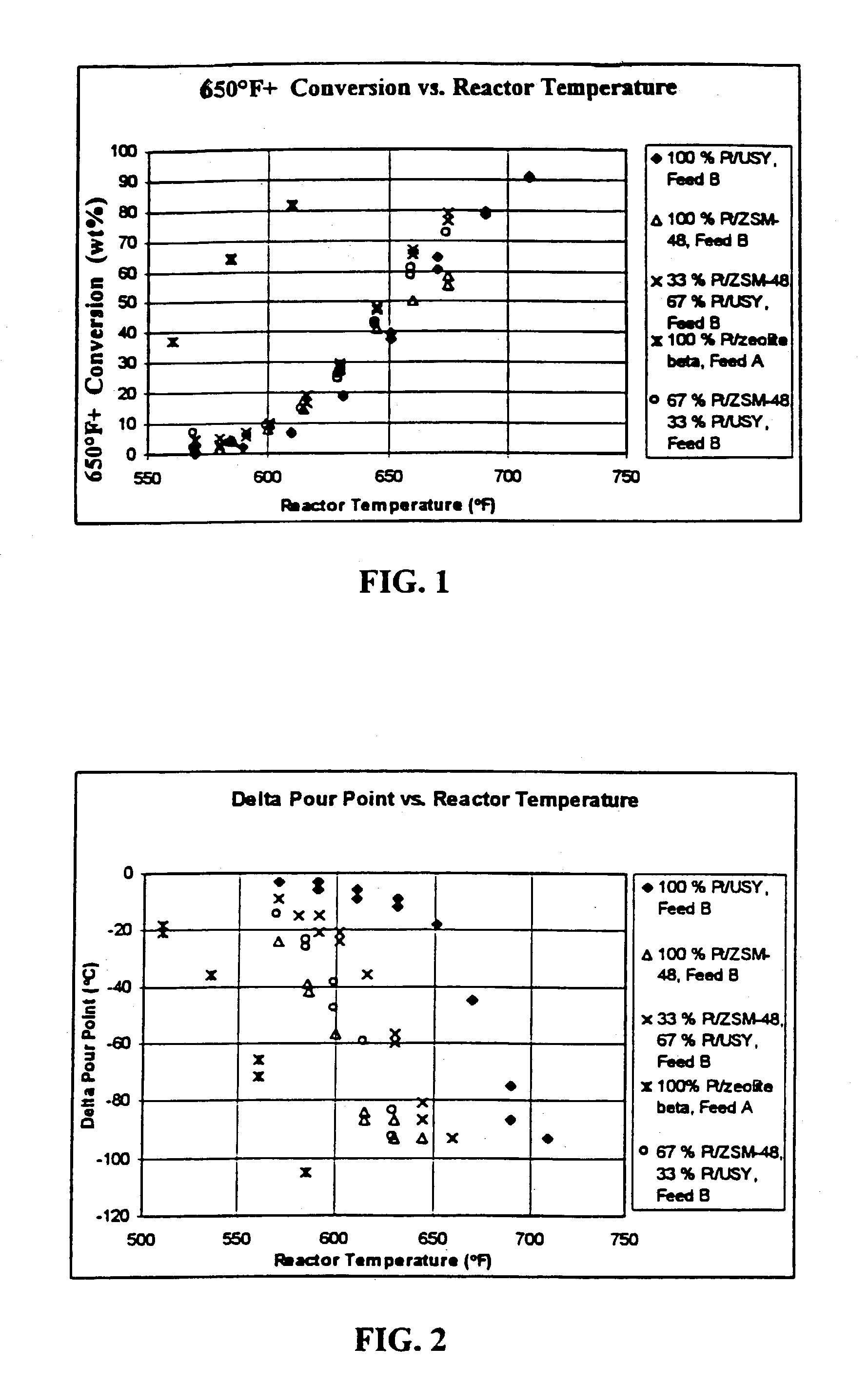

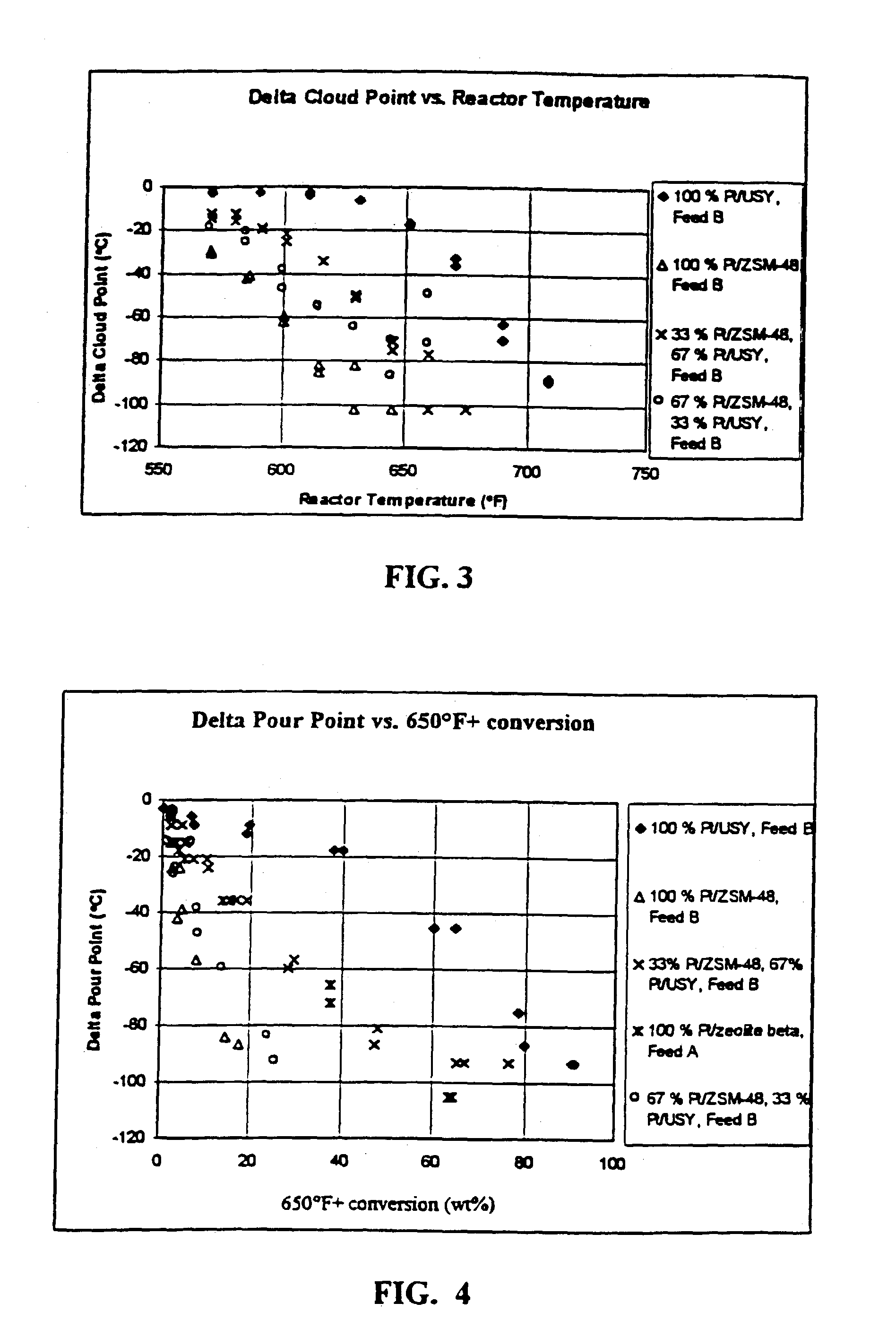

Process for isomerization dewaxing of hydrocarbon streams

InactiveUS20030168379A1Yield maximizationReduce pointsMolecular sieve catalystsHydrocarbon by hydrogenationMolecular sieveIsomerization

A process for isomerization dewaxing of a hydrocarbon feed which includes contacting the hydrocarbon feed with a large pore size, small crystal size, crystalline molecular sieve and an intermediate pore size, small crystal size, crystalline molecular sieve to produce a dewaxed product with a reduced pour point and a reduced cloud point. In a preferred embodiment, the feed is contacted with the molecular sieves sequentially, first with the large pore sieve followed by the intermediate pore sieve.

Owner:EXXON RES & ENG CO

Process for catalytic dewaxing and catalytic cracking of hydrocarbon streams

InactiveUS7261805B2Reducing pour point pointReducing point cloud pointTreatment with plural serial cracking stages onlyCoke ovensWaxIsomerization

A process for upgrading a hydrocarbon feedstock containing waxy components and having an end boiling point exceeding 650° F., which includes contacting the feedstock at superatmospheric hydrogen partial pressure with an isomerization dewaxing catalyst that includes ZSM-48 and contacting the feedstock with a hydrocracking catalyst to produce an upgraded product with a reduced wax content. Each catalyst is present in an amount sufficient to reduce the cloud point and the pour point of the feedstock at a conversion of greater than about 10%, and an overall distillate yield of greater than about 10% results from the process.

Owner:EXXON RES & ENG CO

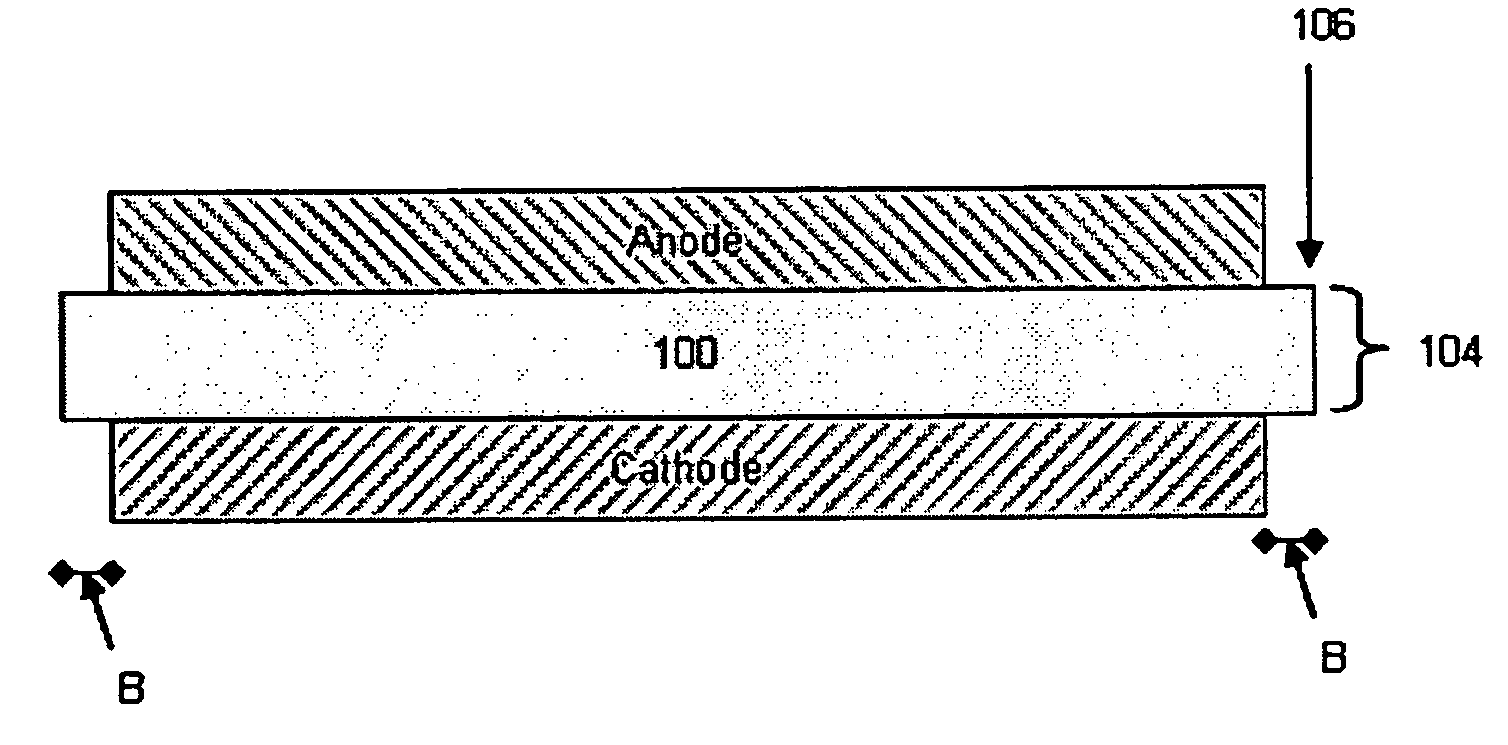

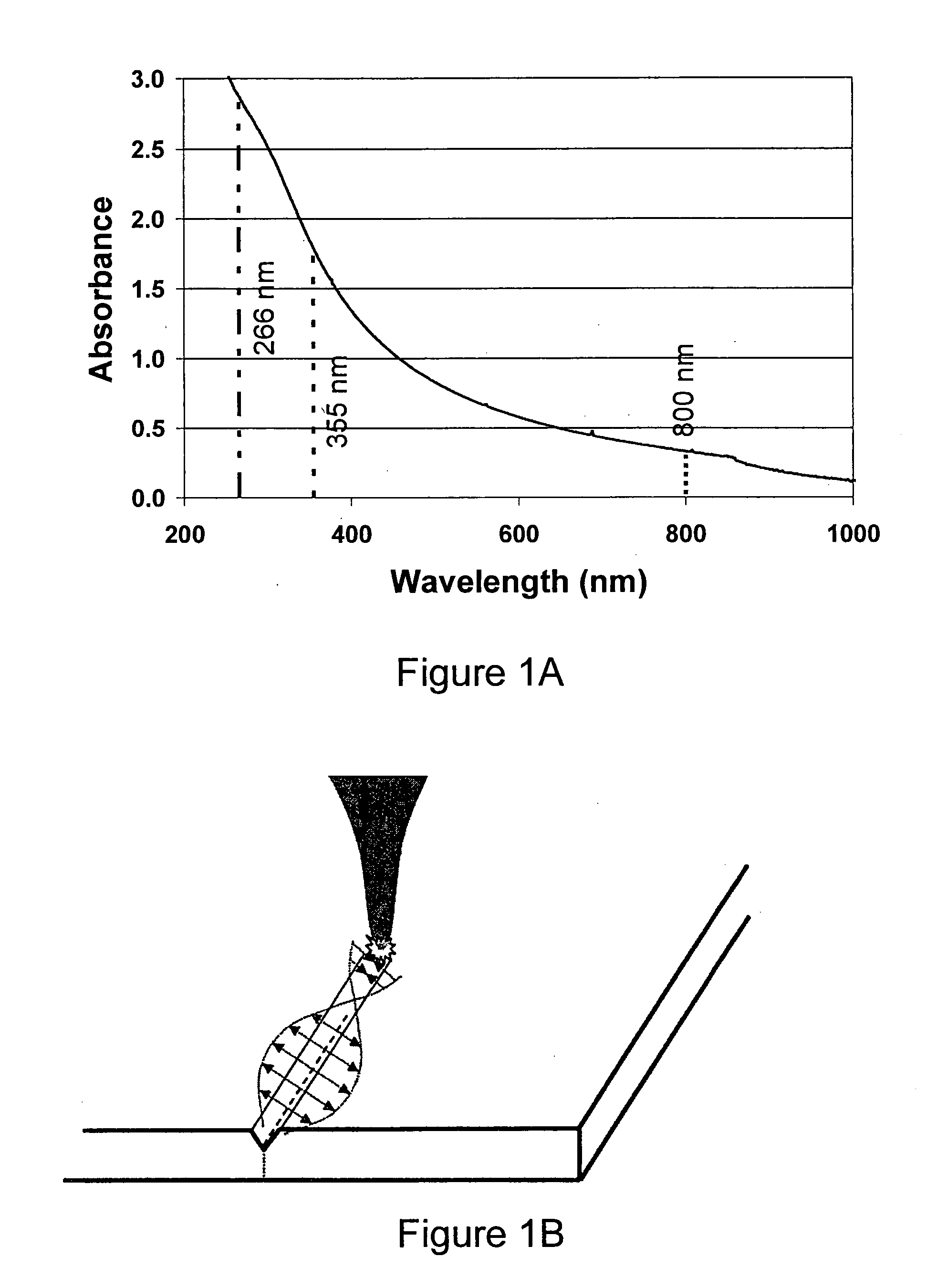

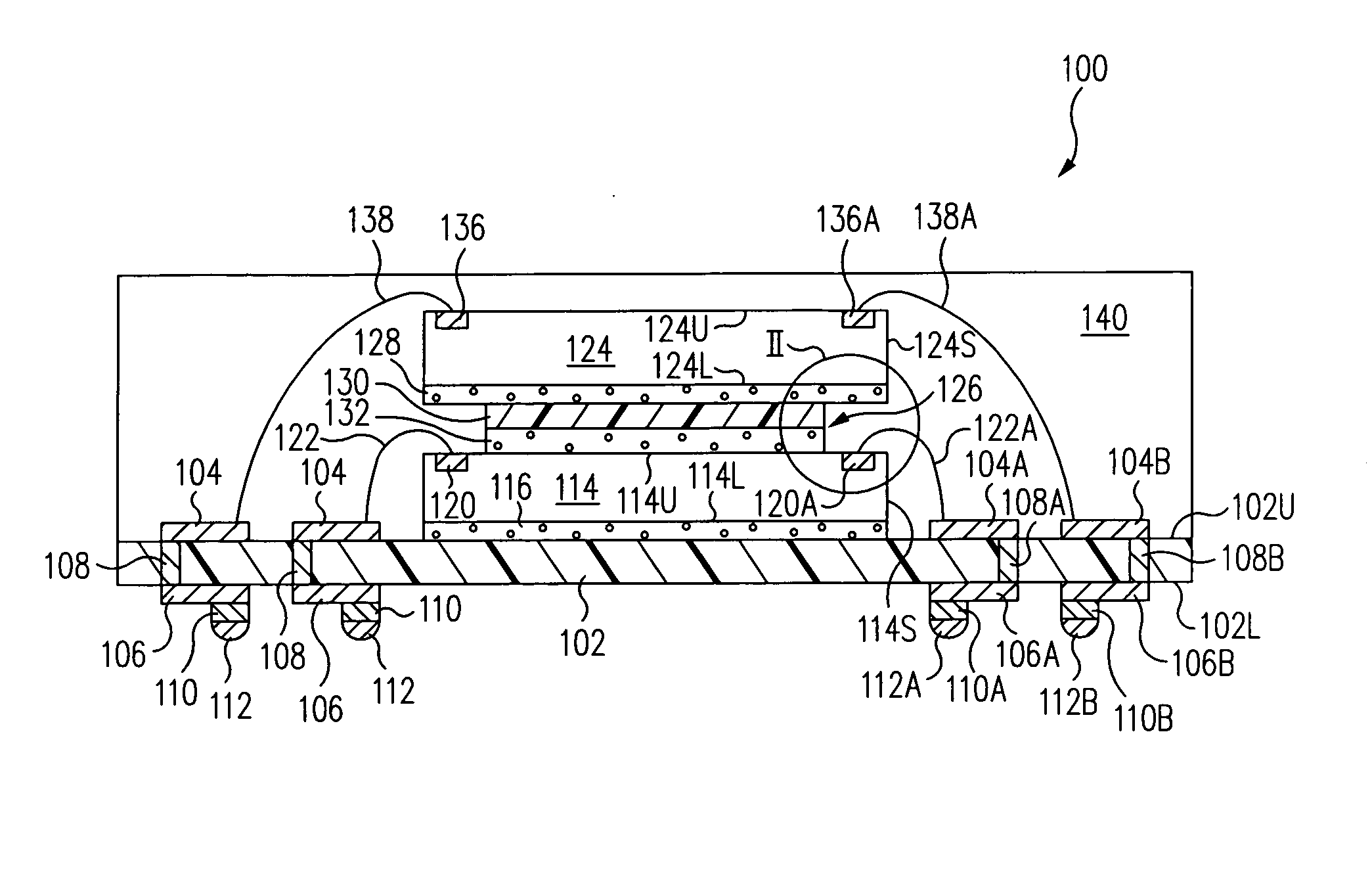

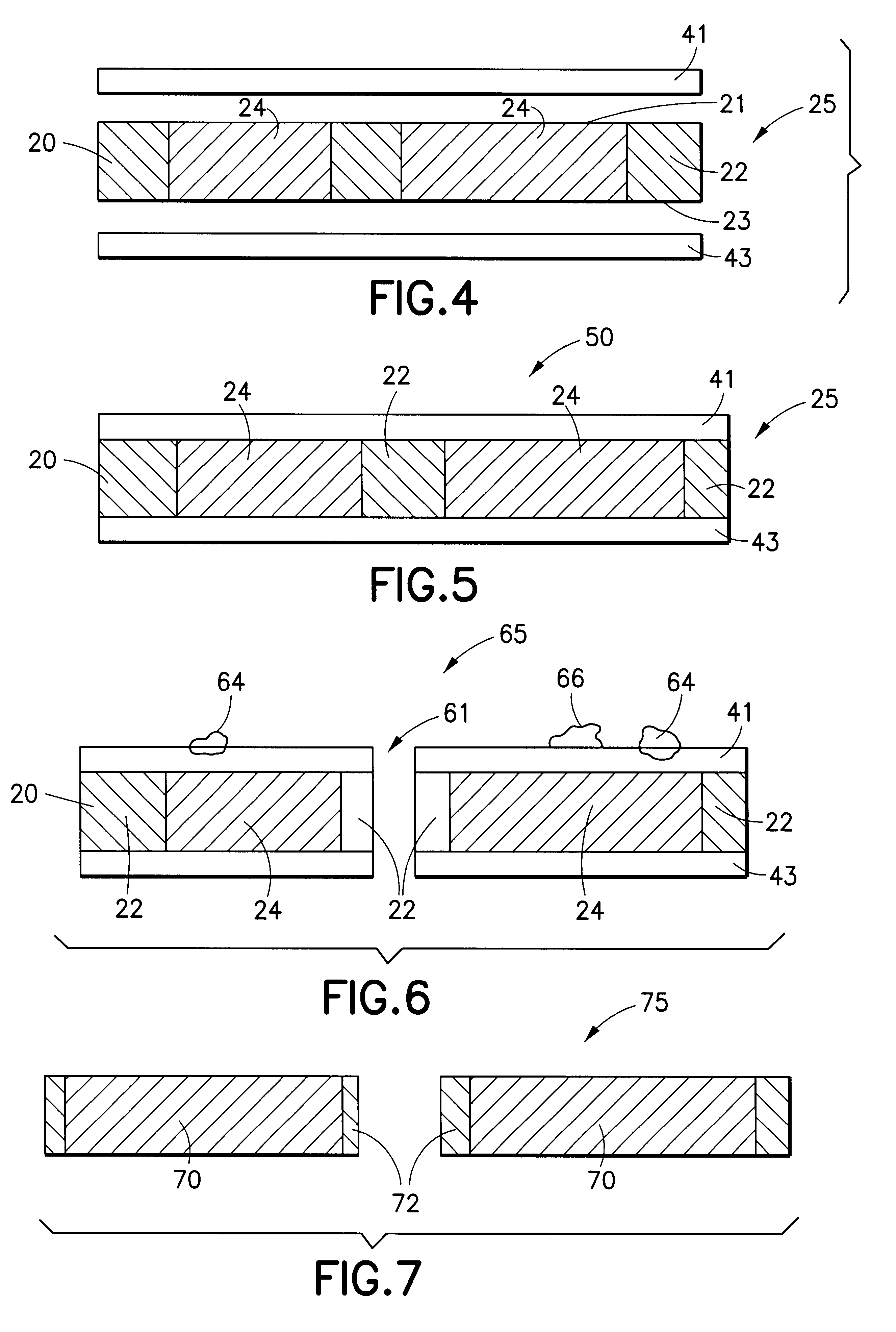

Micromachined electrolyte sheet, fuel cell devices utilizing such, and micromachining method for making fuel cell devices

InactiveUS20090081512A1Increases fabrication yieldHigh strengthFinal product manufactureDecorative surface effectsFuel cellsElectrolysis

A sintered electrolyte sheet comprising: a body of no more than 45 μm thick and laser machined features with at least one edge surface having at least 10% ablation. A method of micromachining the electrolyte sheet includes the steps of: (i) supporting a sintered electrolyte sheet; (ii) micromachining said sheet with a laser, wherein said laser has a wavelength of less than 2 μm, fluence of less than 200 Joules / cm2, repetition rate (RR) of between 30 Hz and 1 MHz, and cutting speed of preferably over 30 mm / sec.

Owner:CORNING INC

Process for isomerization dewaxing of hydrocarbon streams

InactiveUS6652735B2Yield maximizationReduce pointsHydrocarbon by isomerisationRefining to change hydrocarbon structural skeletonMolecular sieveIsomerization

A process for isomerization dewaxing of a hydrocarbon feed which includes contacting the hydrocarbon feed with a large pore size, small crystal size, crystalline molecular sieve and an intermediate pore size, small crystal size, crystalline molecular sieve to produce a dewaxed product with a reduced pour point and a reduced cloud point. In a preferred embodiment, the feed is contacted with the molecular sieves sequentially, first with the large pore sieve followed by the intermediate pore sieve.

Owner:EXXON RES & ENG CO

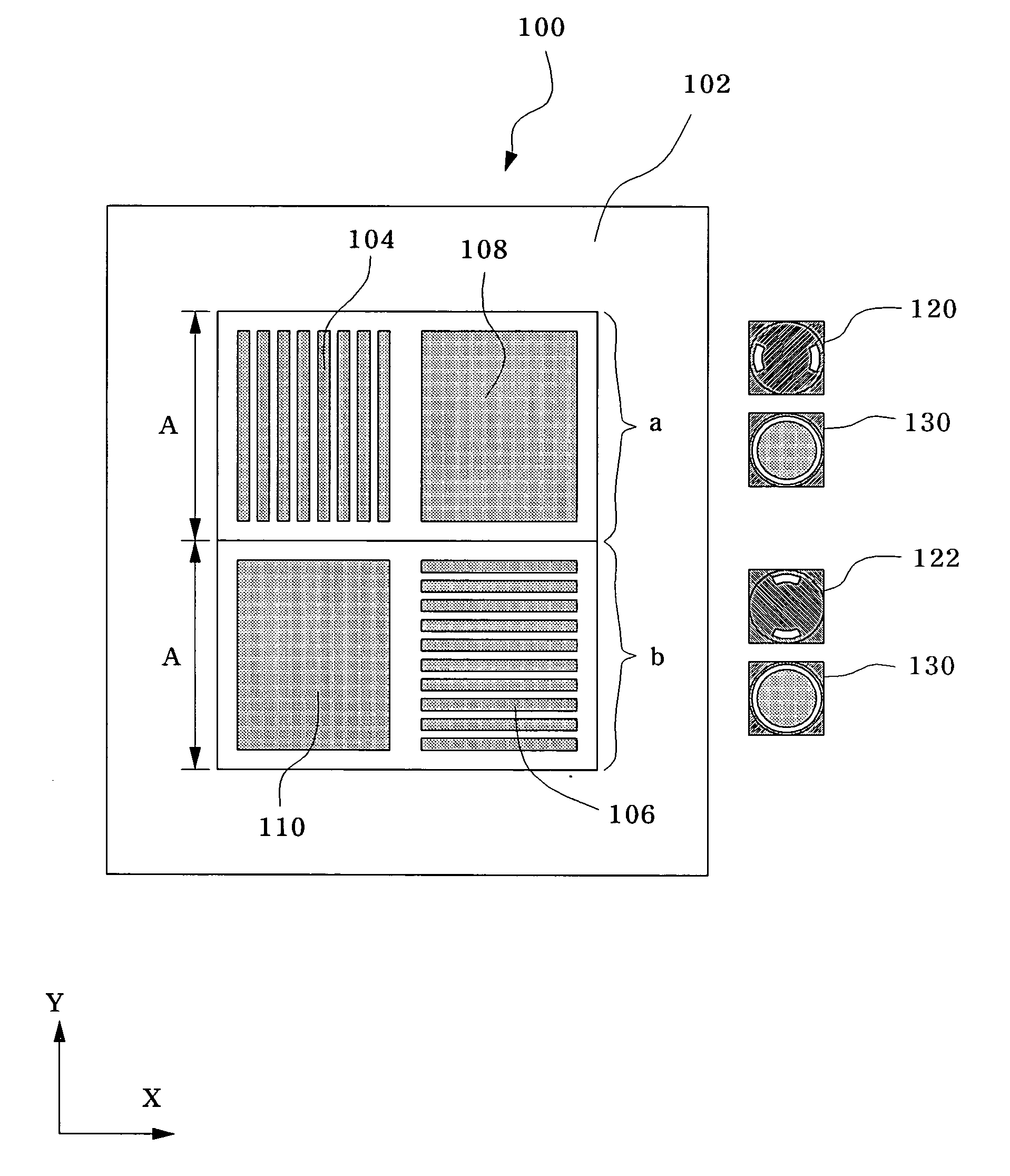

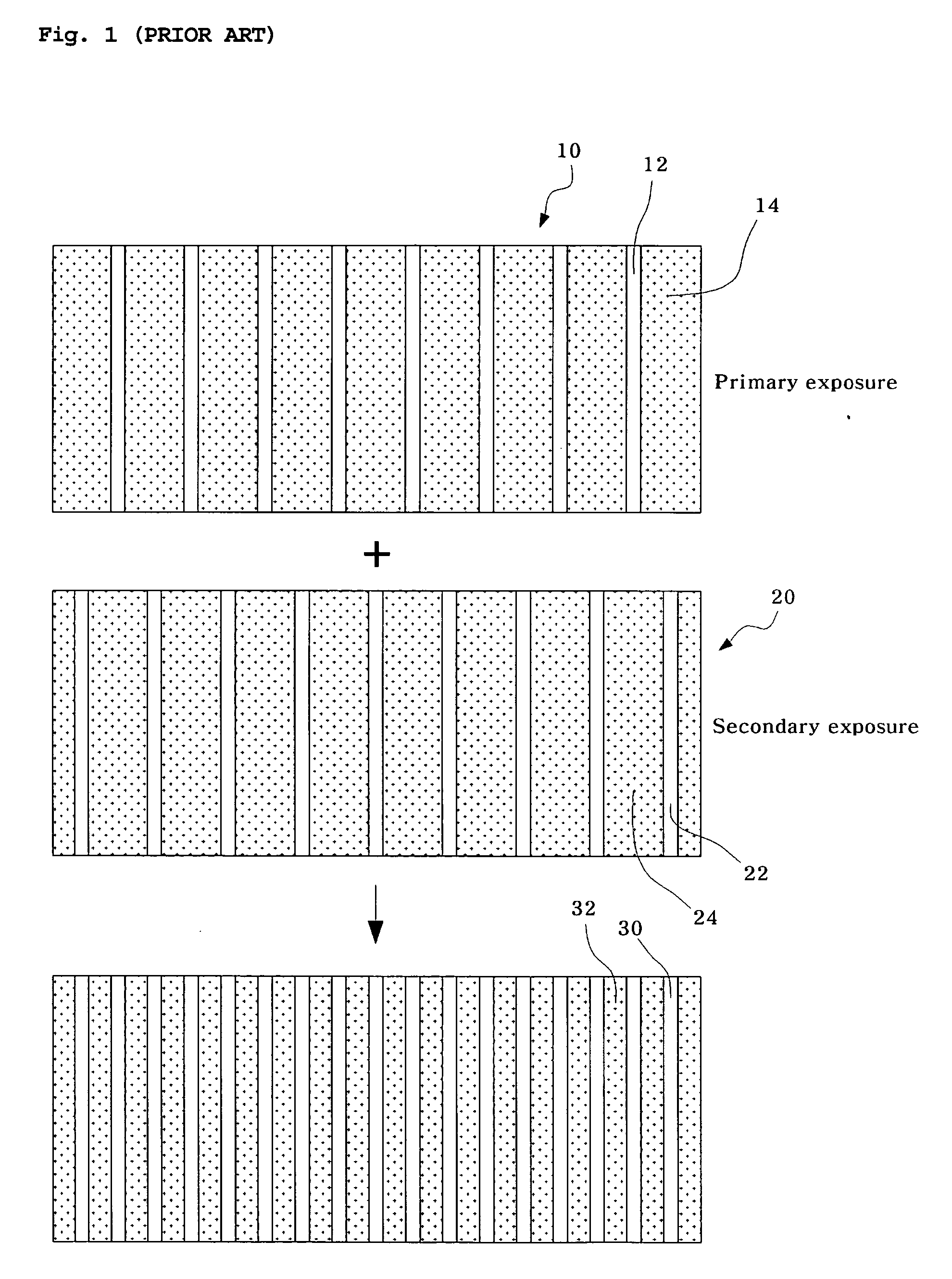

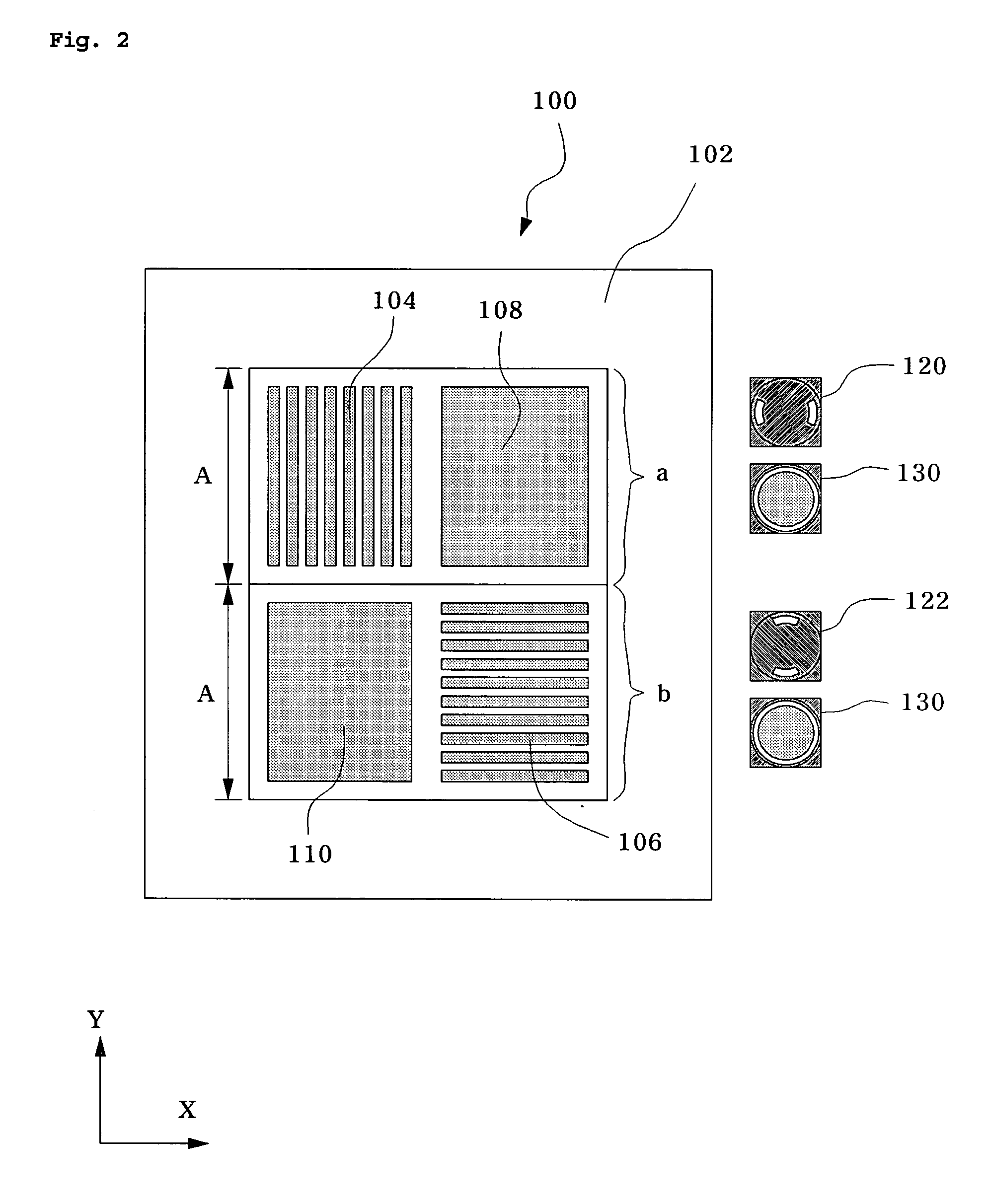

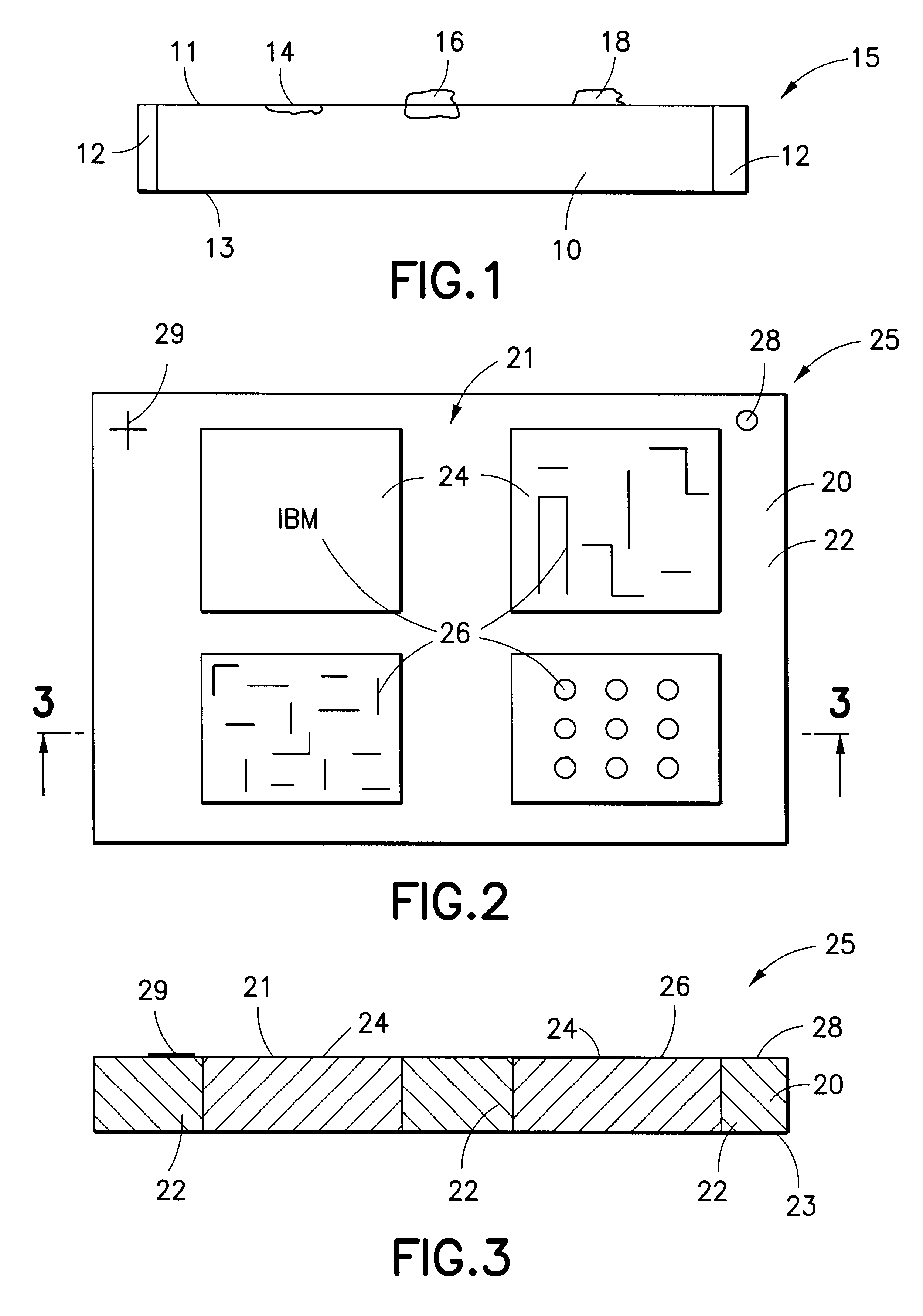

Photomask for double exposure and double exposure method using the same

InactiveUS20070054198A1Finer photoresist patternMinimizing yield reductionPhotomechanical apparatusSemiconductor/solid-state device manufacturingResistProduction rate

A photomask for double exposure, and a double exposure method using the same are disclosed. The photomask for double exposure comprises a mask substrate divided into first and second regions equally arranged to upper and lower sideson different sides, respectively, a first mask pattern formed on the first region of the mask substrate, and a second mask pattern formed on the second region of the mask substrate. The photomask and the double exposure method using the same enable a finer photoresist pattern to be formed on a semiconductor wafer, while minimizing reduction in yield and productivity due to misalignment and replacement.

Owner:SK HYNIX INC

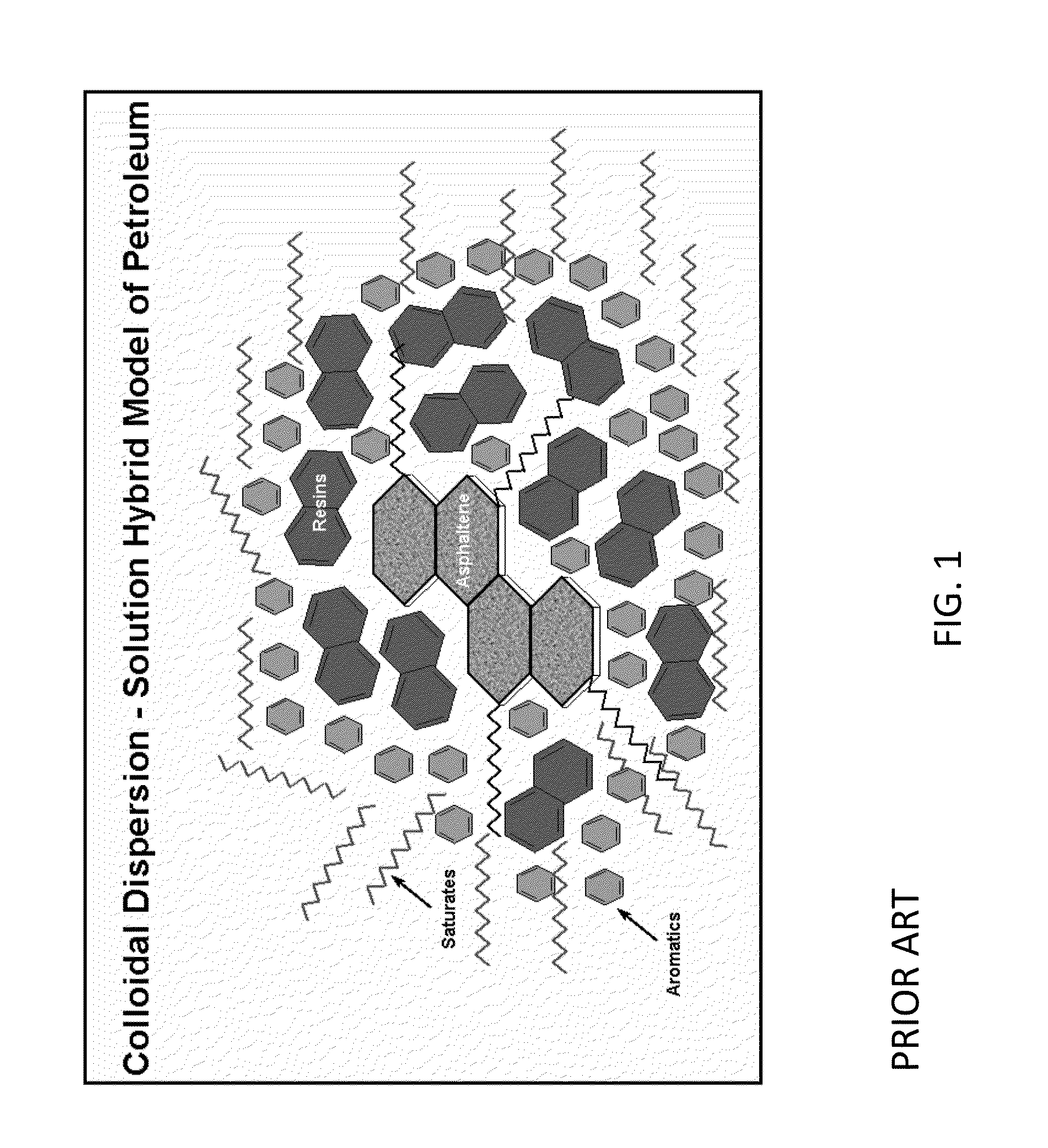

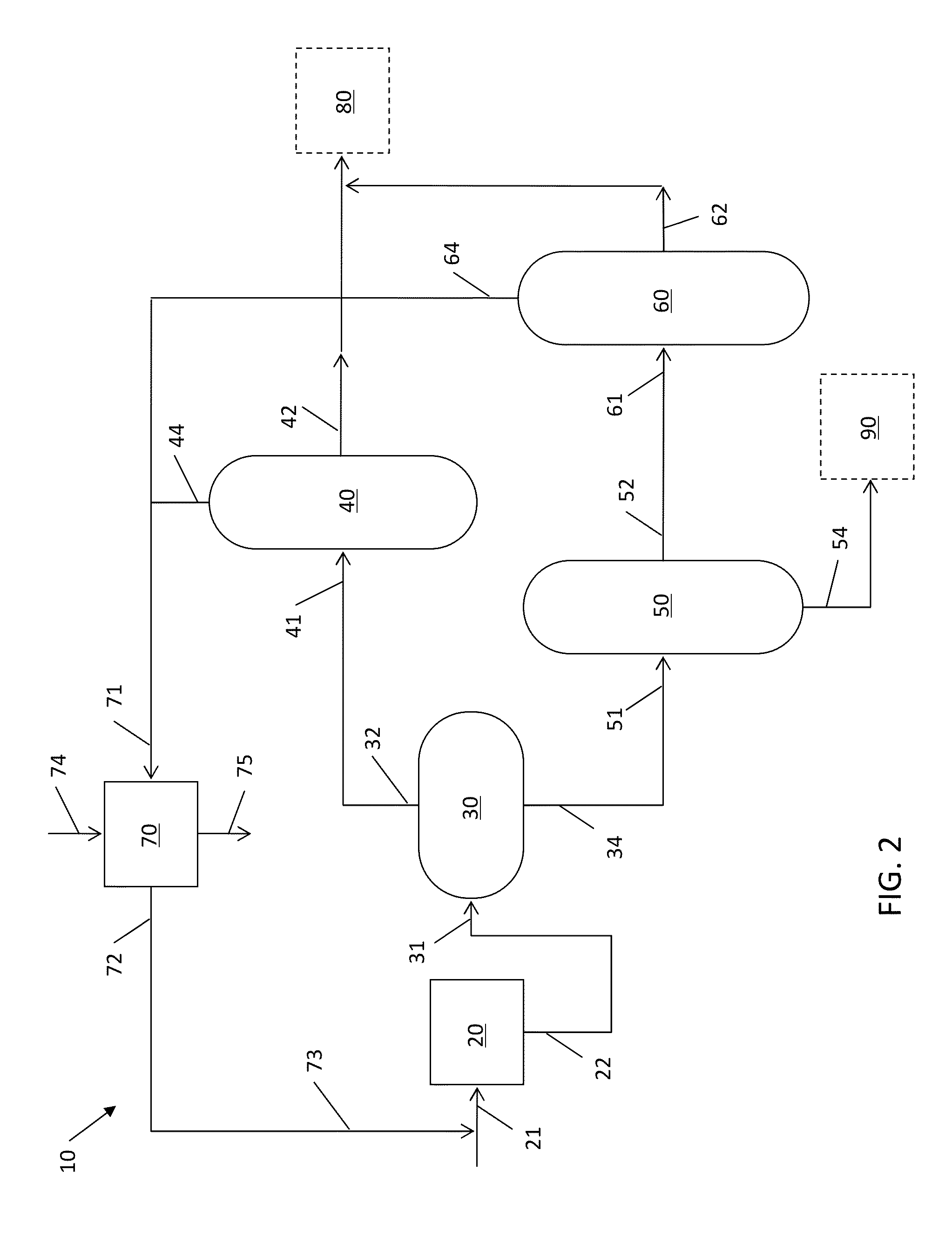

Process for stabilization of heavy hydrocarbons

ActiveUS20130026074A1Prevent further sediment formationReduces sludge formationWorking-up pitch/asphalt/bitumen by selective extractionRefining by heating/coolingCarbon numberAlkane

A process for stabilization of heavy hydrocarbons to reduce sludge formation in storage tanks and / or transportation lines and to enhance the hydrocarbon yield includes mixing a paraffinic or heavy naphtha solvent having carbon numbers in the range 10 to 20 with the feedstock to solvent-flocculate a relatively small, predetermined portion of asphaltenes present in the feedstock, separating and flashing the sediment to recover a light hydrocarbon fraction, flashing the heavy hydrocarbon / solvent phase and recycling the solvent to stabilize the heavy hydrocarbons without significantly affecting the yield of valuable products.

Owner:SAUDI ARABIAN OIL CO

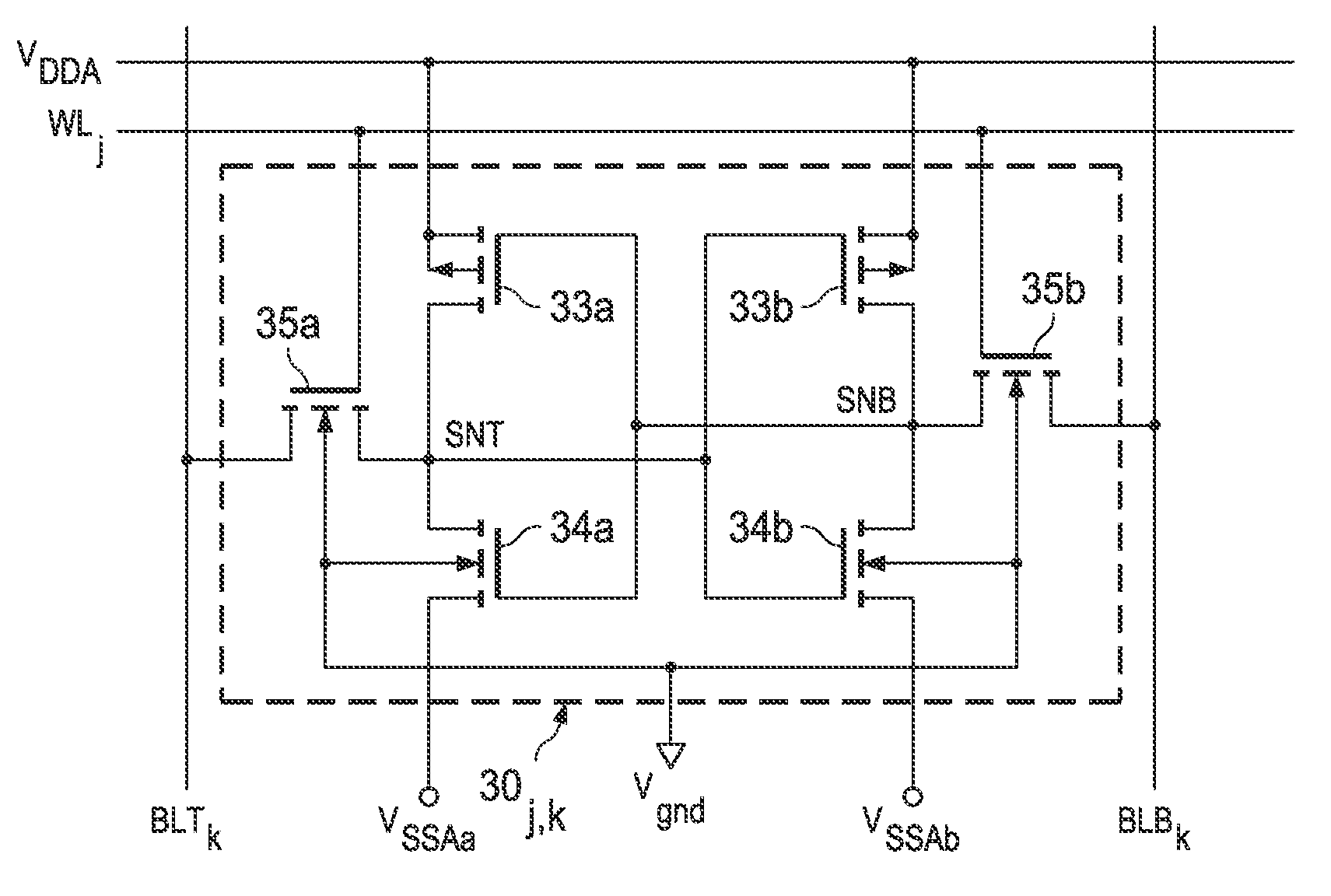

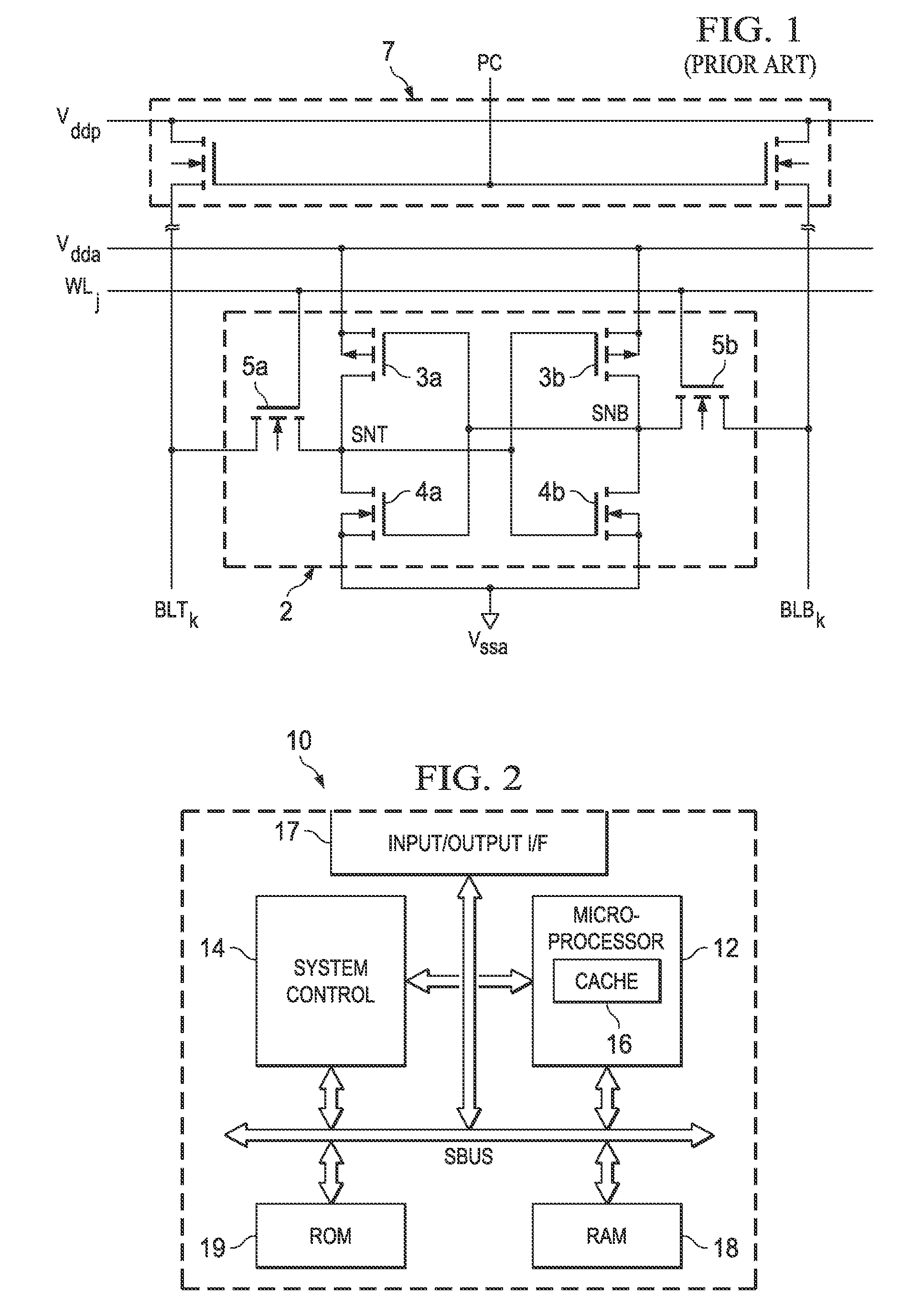

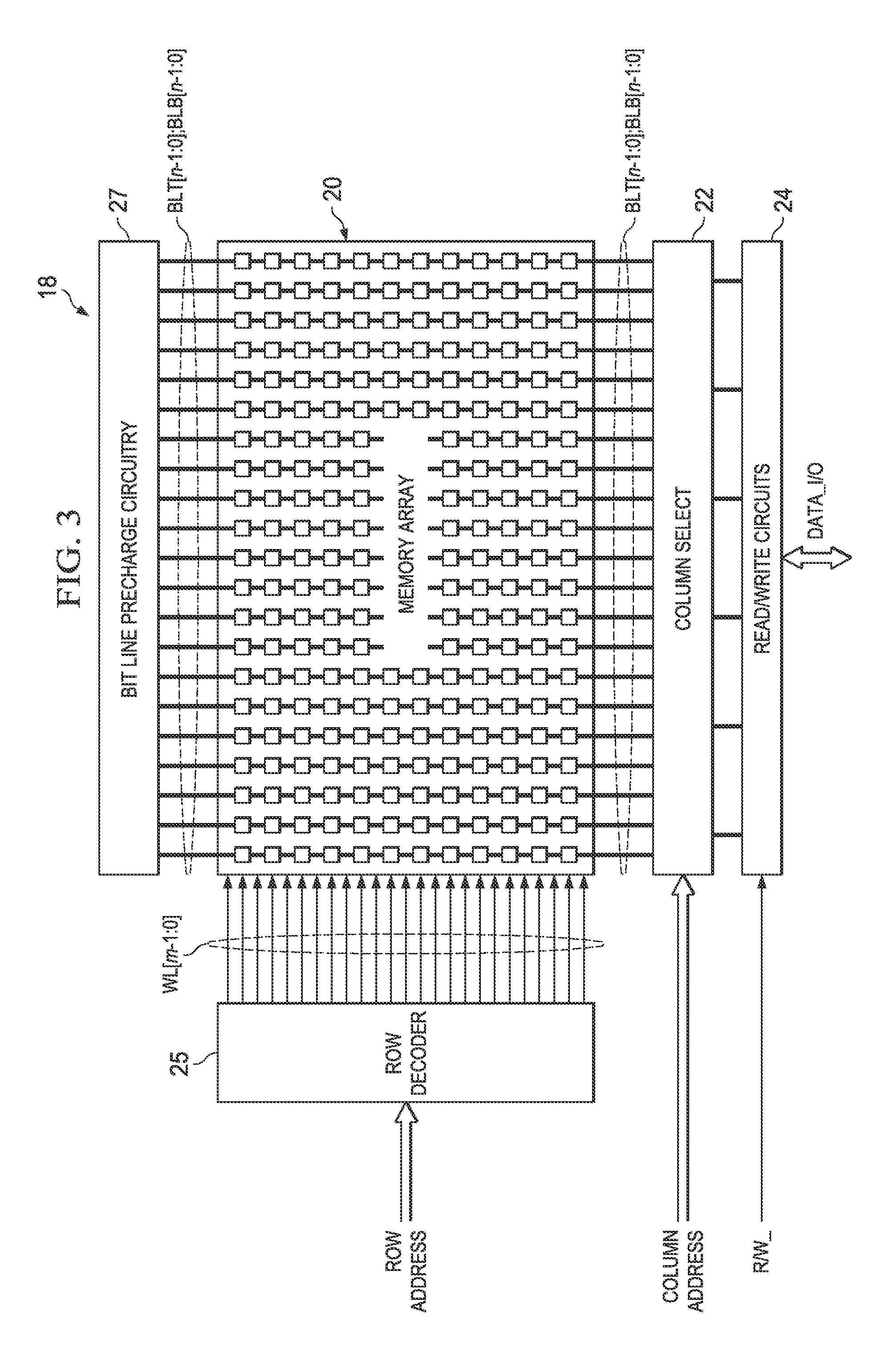

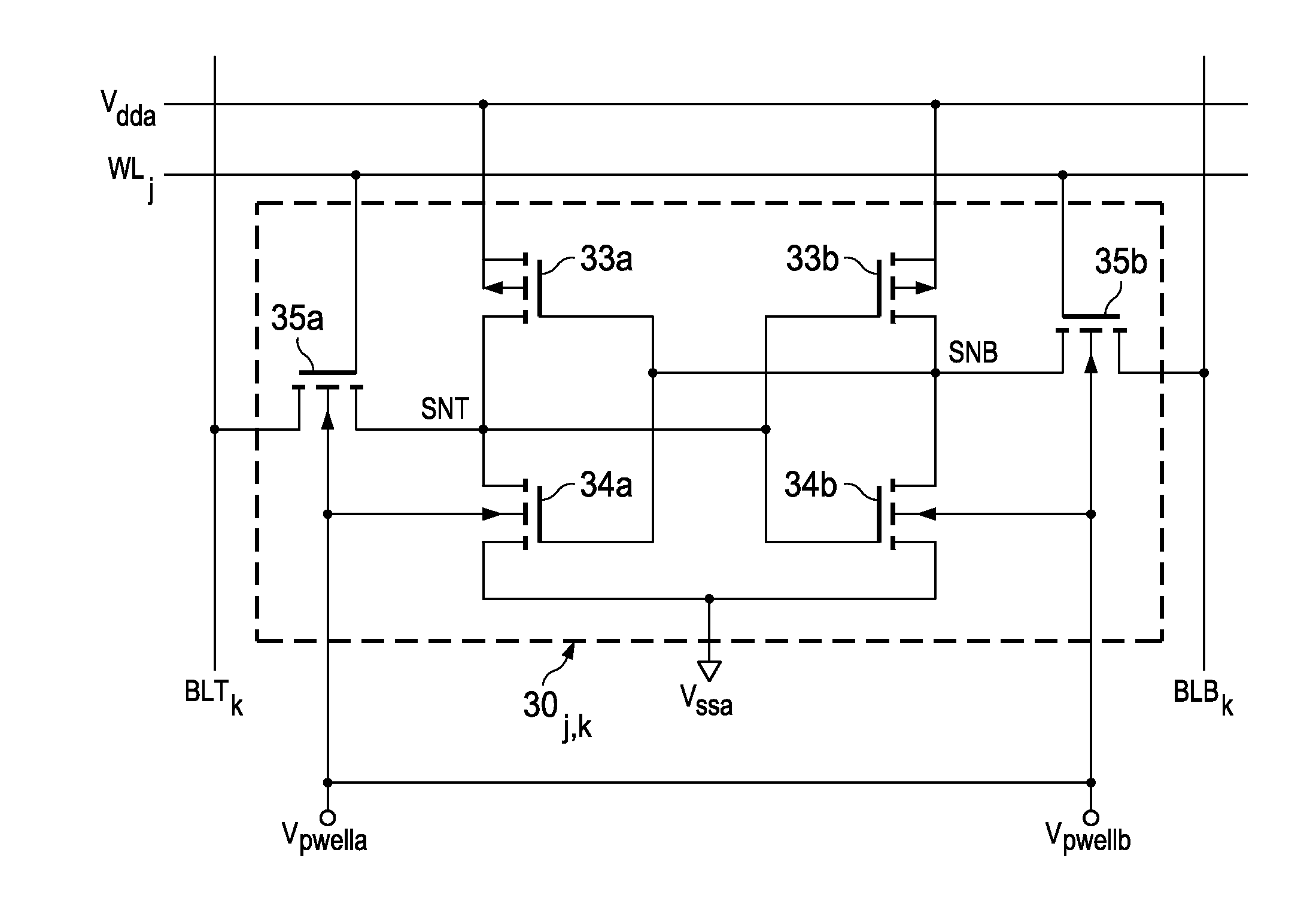

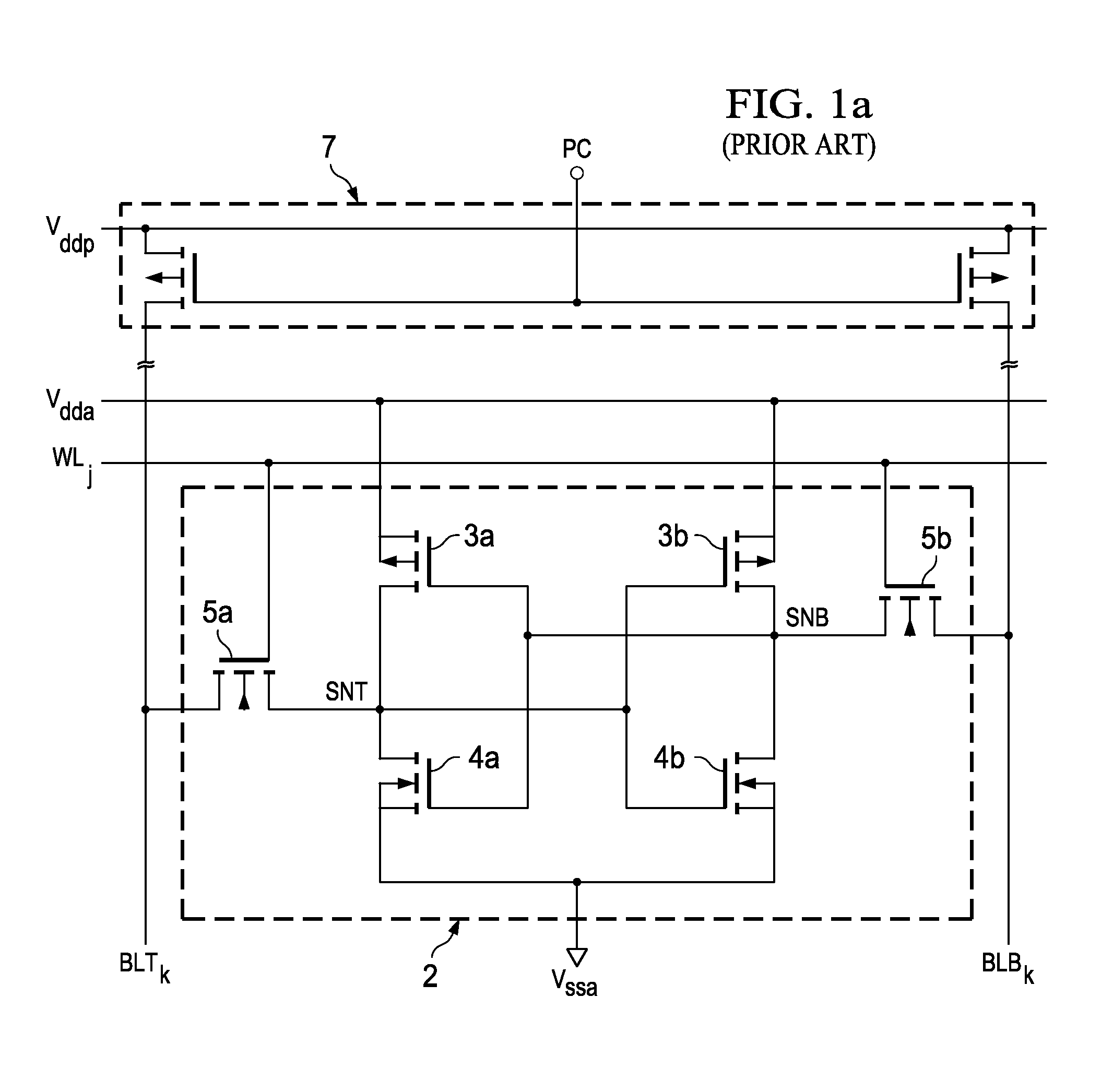

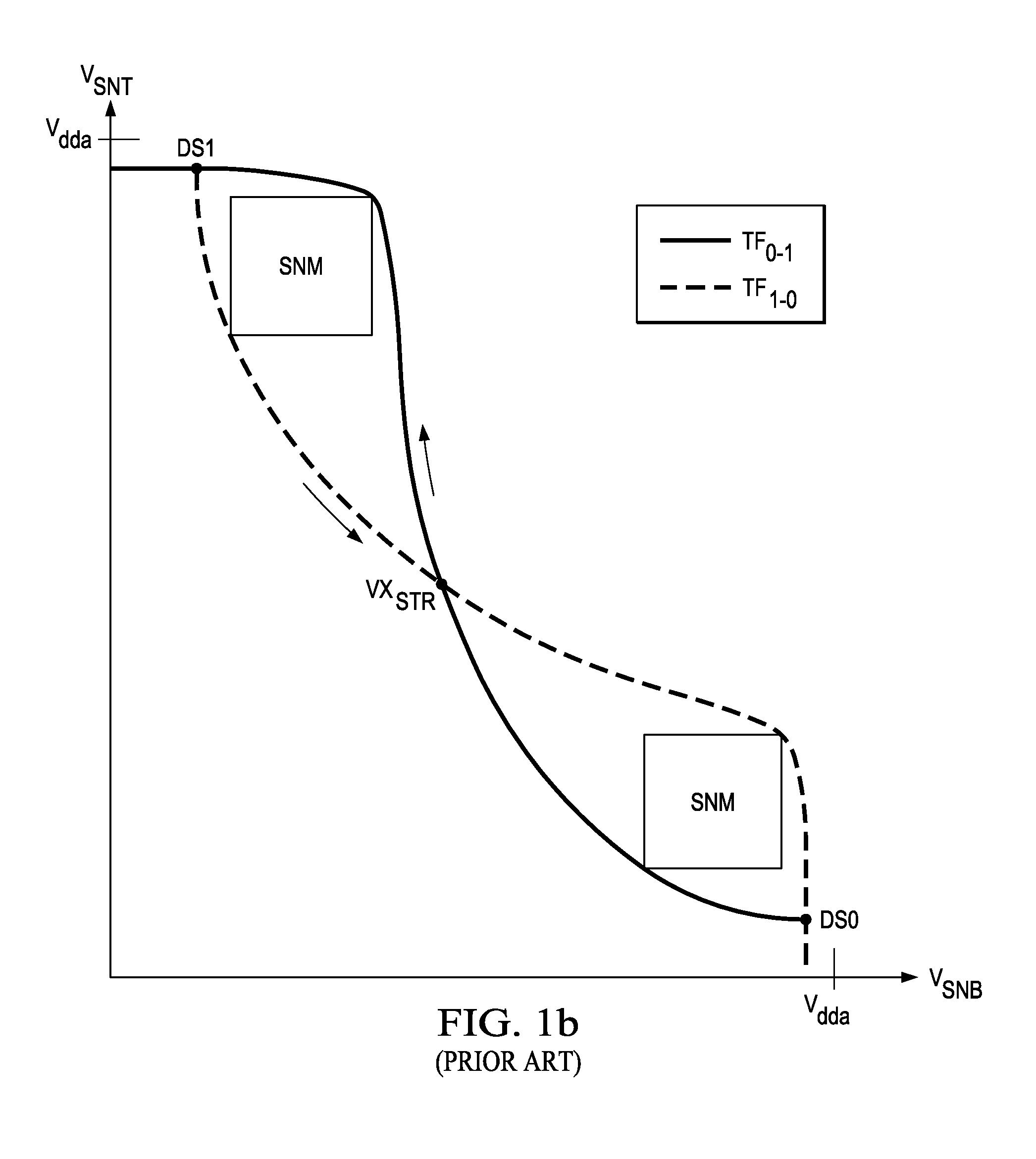

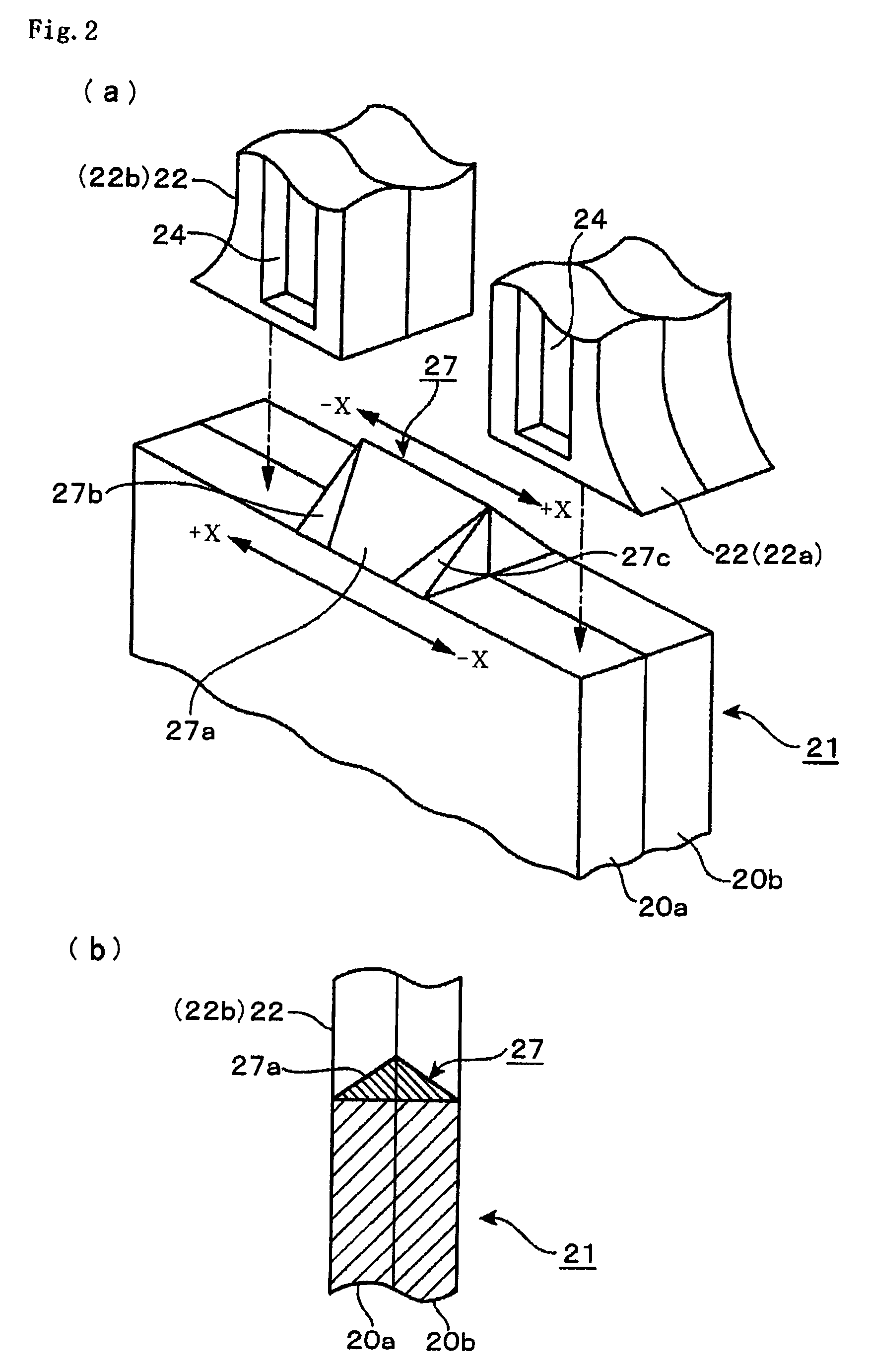

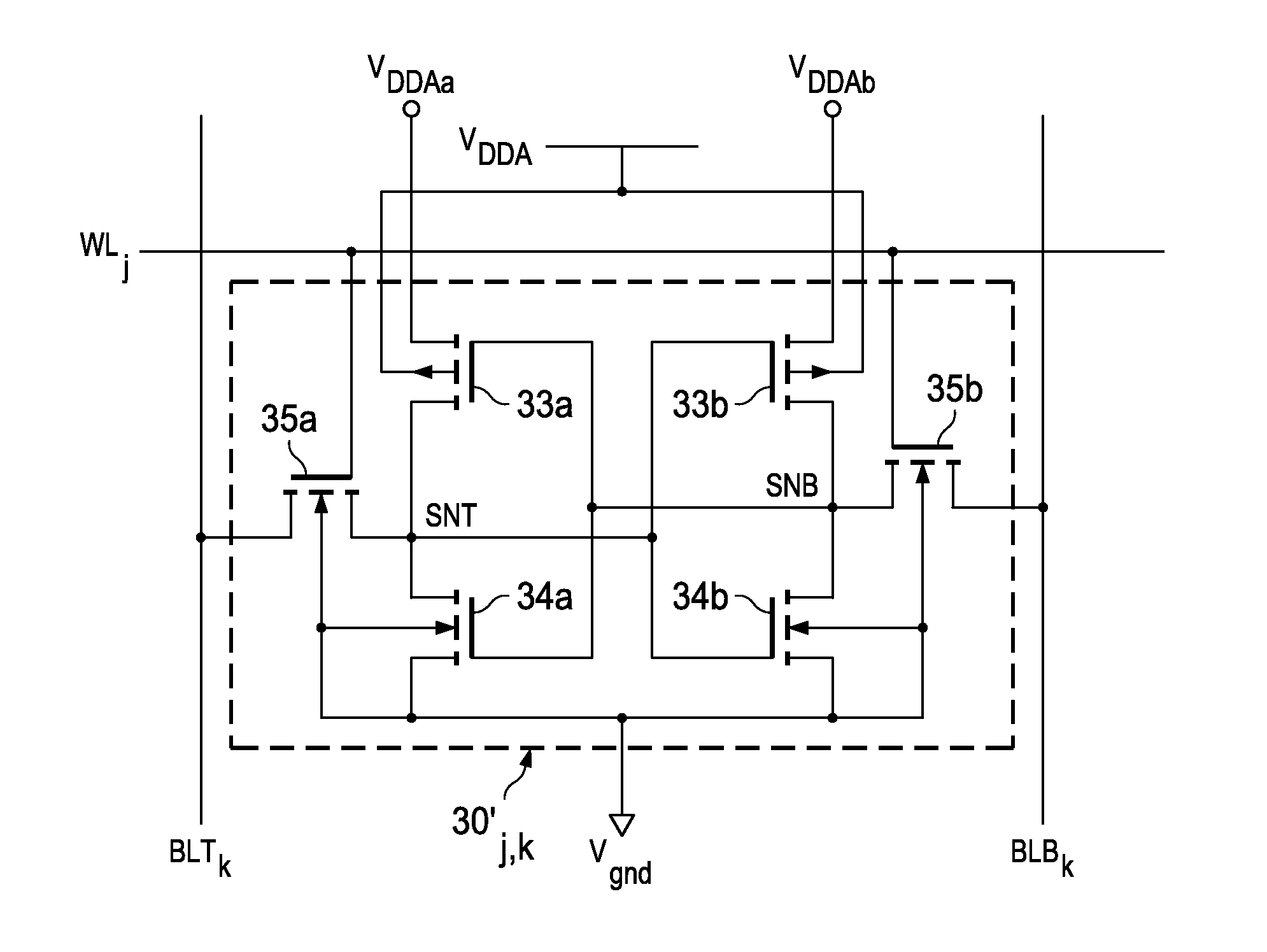

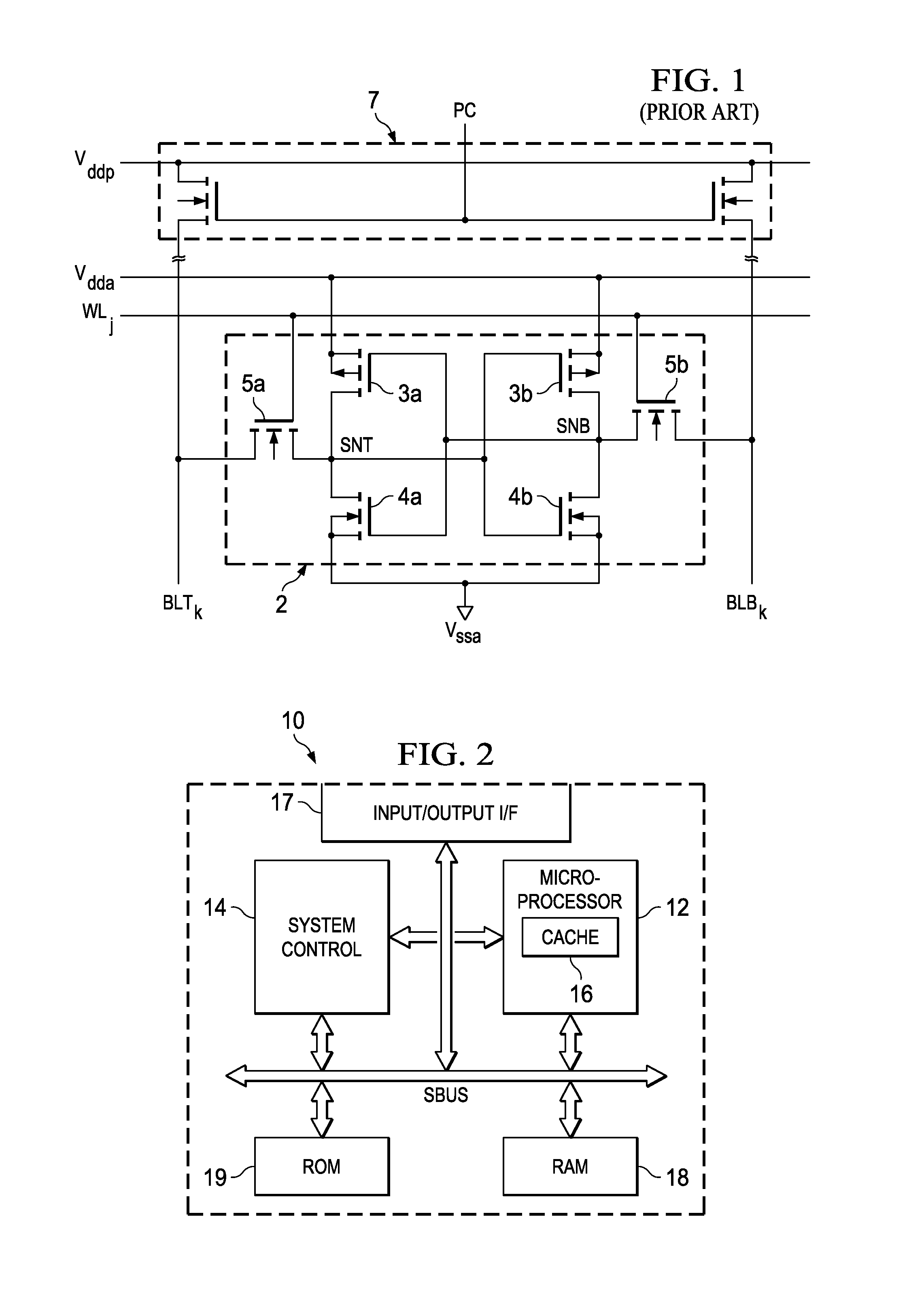

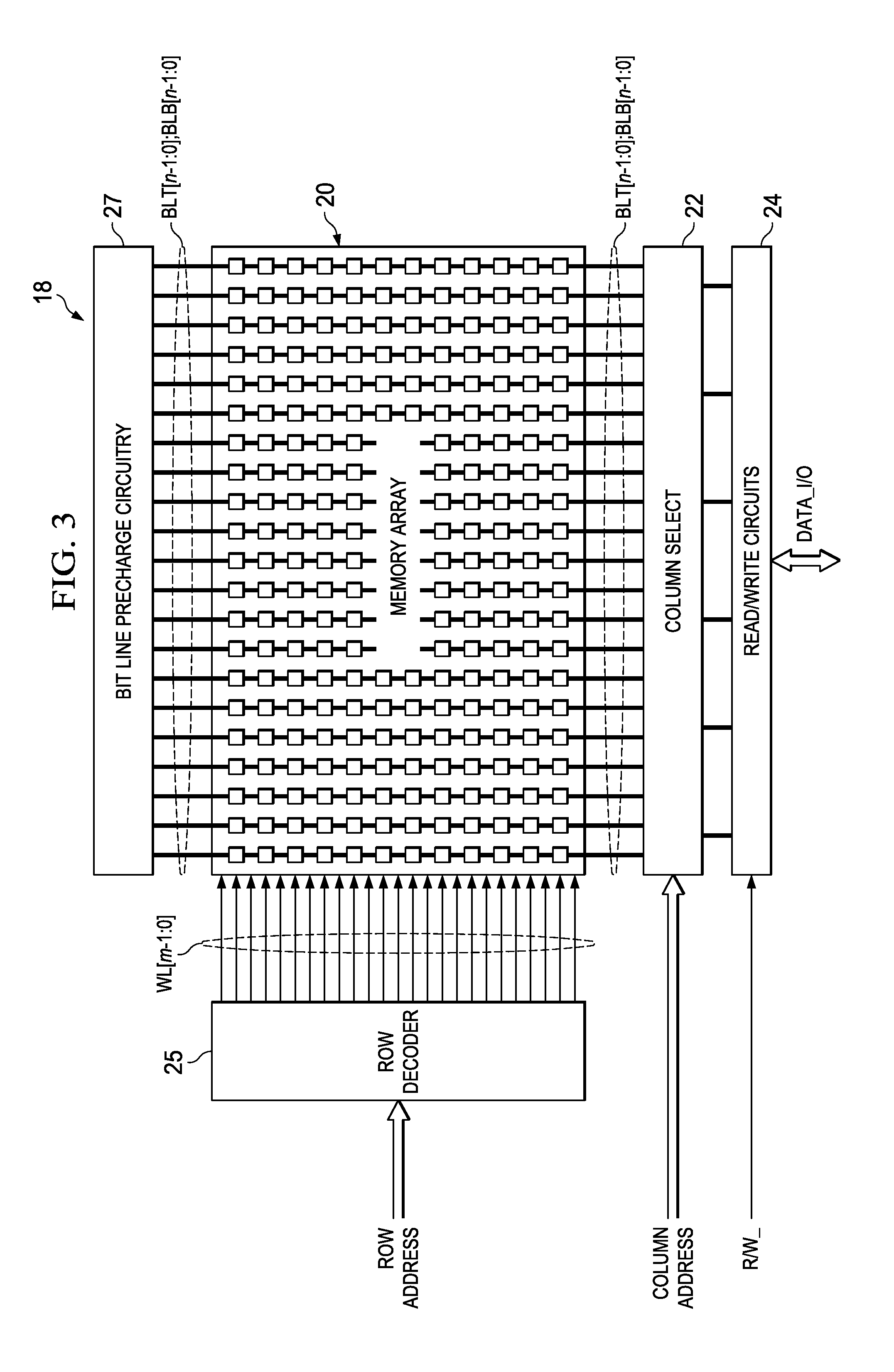

Array Power Supply-Based Screening of Static Random Access Memory Cells for Bias Temperature Instability

ActiveUS20130021864A1Reduce biasIncreased ground voltageDigital storageStatic random-access memoryNon symmetric

A method of screening complementary metal-oxide-semiconductor CMOS integrated circuits, such as integrated circuits including CMOS static random access memory (SRAM) cells, for transistors susceptible to transistor characteristic shifts over operating time. For the example of SRAM cells formed of cross-coupled CMOS inverters, separate ground voltage levels can be applied to the source nodes of the driver transistors, or separate power supply voltage levels can be applied to the source nodes of the load transistors (or both). Asymmetric bias voltages applied to the transistors in this manner will reduce the transistor drive current, and can thus mimic the effects of bias temperature instability (BTI). Cells that are vulnerable to threshold voltage shift over time can thus be identified.

Owner:TEXAS INSTR INC

Use of a biased precoat for reduced first wafer defects in high-density plasma process

ActiveUS7964517B2Yield minimizationReducing first wafer defectsRadiation applicationsSemiconductor/solid-state device manufacturingHigh densityGas phase

According to various embodiments, the present teachings include methods for reducing first wafer defects in a high-density plasma chemical vapor deposition process. In an exemplary embodiment, the method can include running a deposition chamber for deposition of film on a first batch of silicon wafers and then cleaning interior surfaces of the deposition chamber. The method can further include inserting a protective electrostatic chuck cover (PEC) wafer on an electrostatic chuck in the deposition chamber and applying power to bias the PEC wafer while simultaneously precoating the deposition chamber with an oxide. The exemplary method can also include re-starting the deposition chamber for deposition of film on a second batch of silicon wafers.

Owner:TEXAS INSTR INC

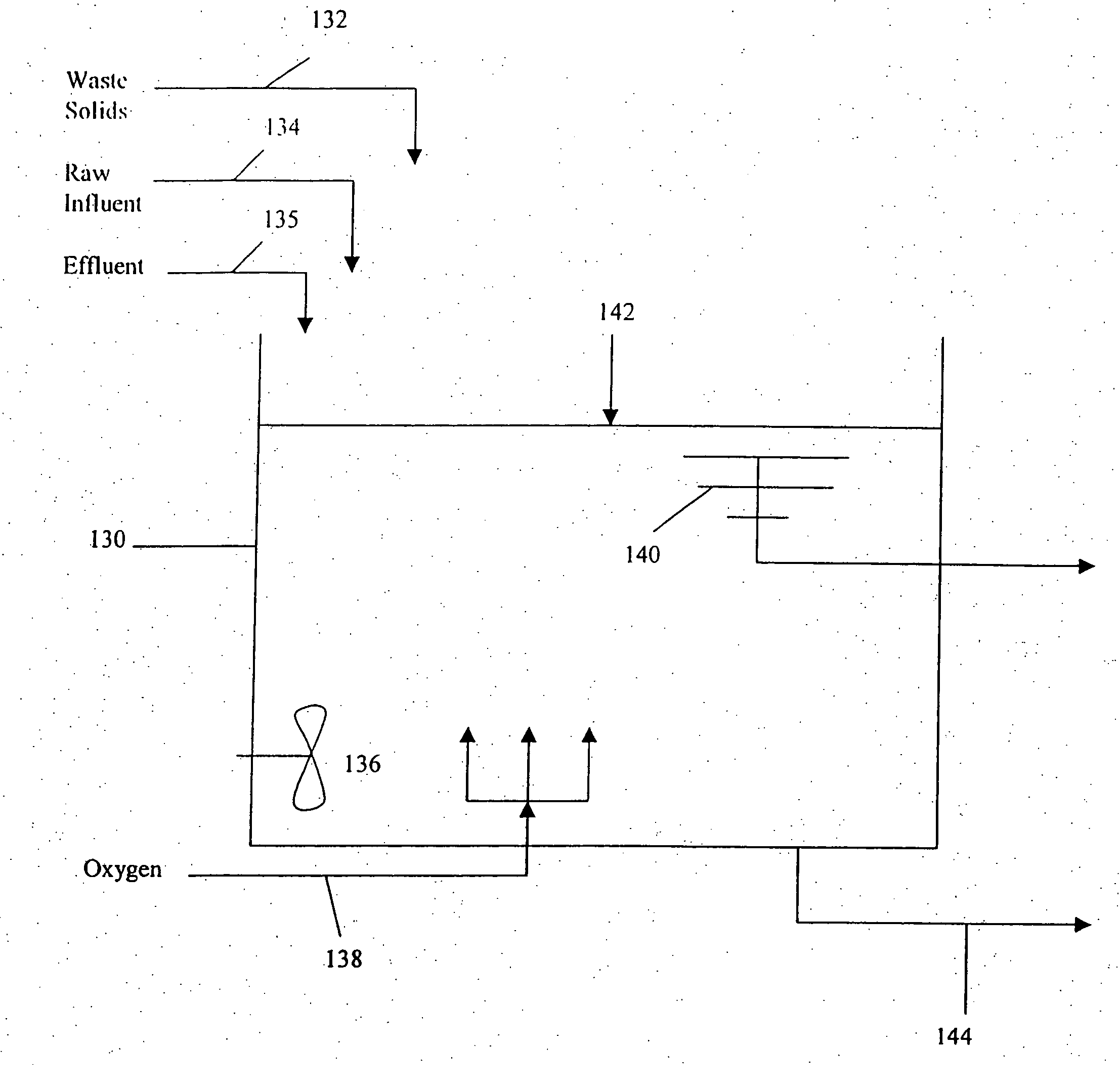

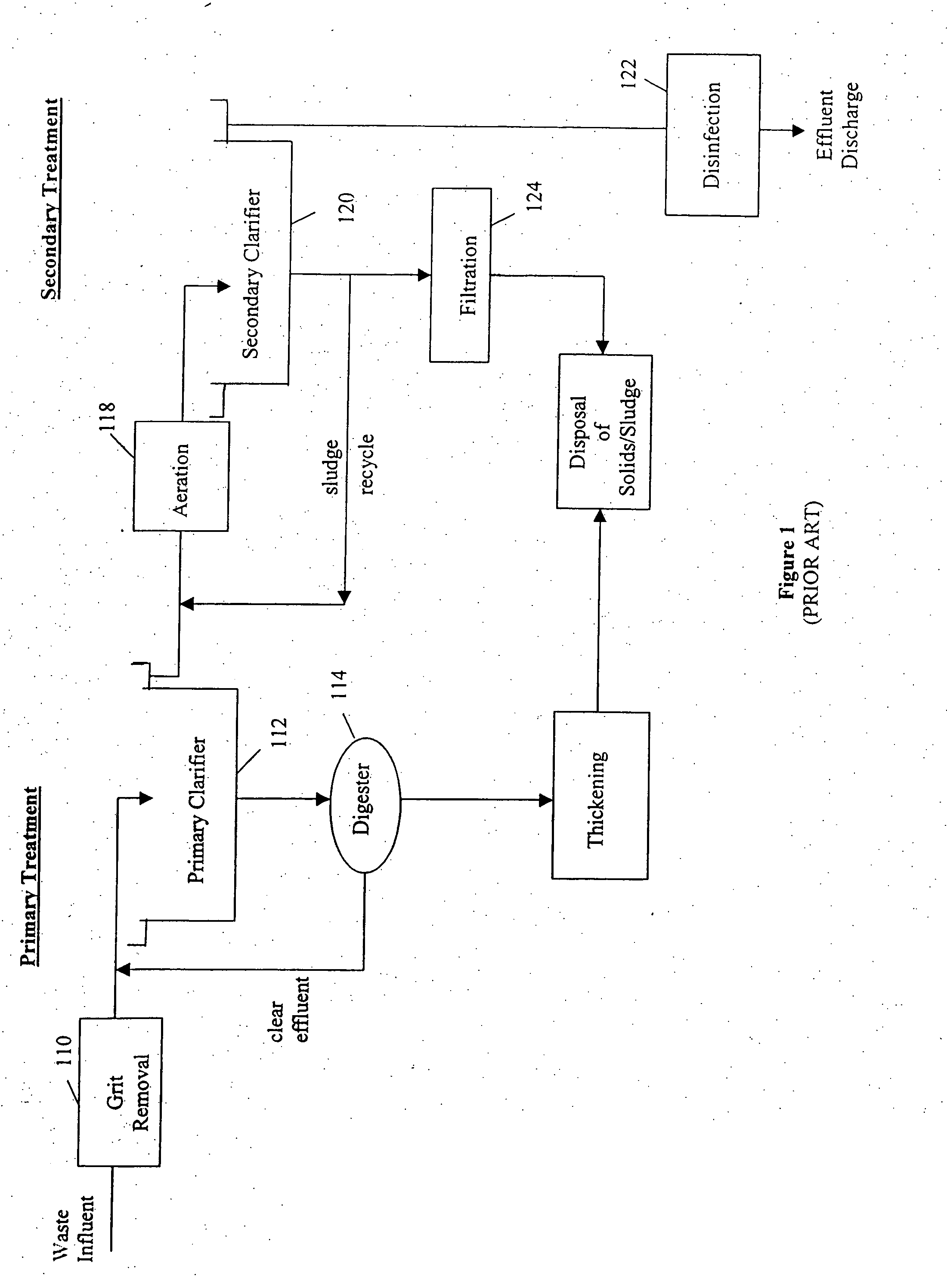

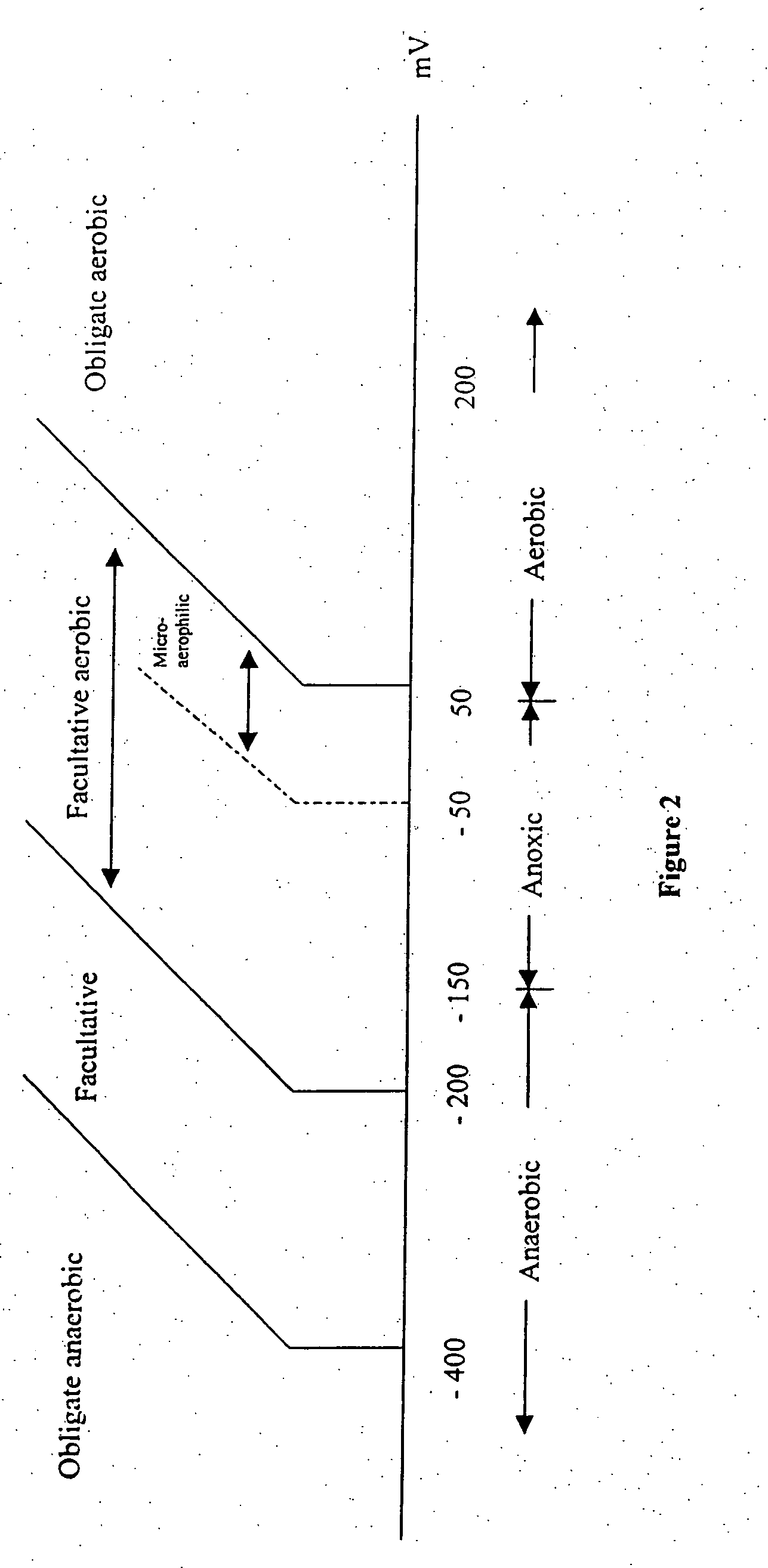

Apparatus and methods for control of waste treatment processes

InactiveUS20060000768A1Prevent significant sulfate reductionLower Level RequirementsWater treatment parameter controlTreatment using aerobic processesActivated sludgeParticulates

Waste-treatment processes are enhanced through generation and introduction of specific biological populations customized to perform or favor specific tasks either during the main process, for the formation or precipitation of certain biological nutrients, or to accomplish solids formation reduction in a post-treatment process. These bacteria may be grown from specialized mixes of activated sludge and waste influent by exposing these materials to controlled environments (e.g., in an off-line treatment area). They may then be returned to the main process to perform certain tasks such as converting particulate cBOD into soluble cBOD for utilization, to reduce high solids yield organisms by supplementing the population characteristics with low yield organism characteristics, to provide biological nutrients or oxygenation assistance, to improve nitrification / denitrification efficiency, or to disfavor filamentous biology such as Norcardia sp.

Owner:MIKLOS DANIEL ROBERT

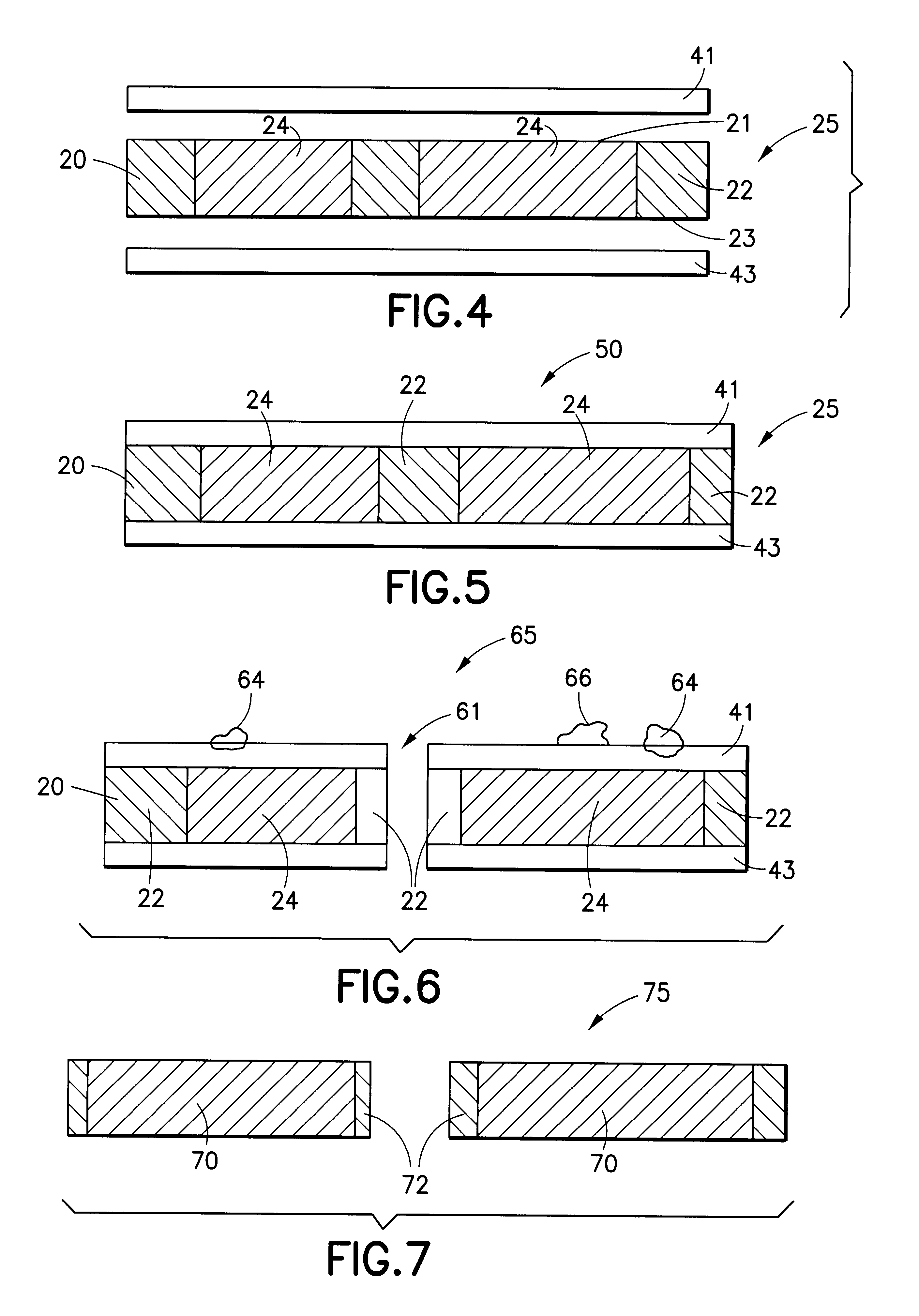

Stacked electronic component package having single-sided film spacer

InactiveUS20080237824A1Minimal costMinimizing yield lossSemiconductor/solid-state device detailsSolid-state devicesOrganic filmEngineering

A method of fabricating a stacked electronic component package includes placing a single-sided film spacer on an upper surface of a lower electronic component inward of bond pad with a pickup tool. After being adhered to the upper surface of the lower electronic component, the pickup tool is retracted from the single-sided film spacer. An upper surface of a film, e.g., an organic film, of the single-sided film spacer is nonadhesive. Accordingly, the single-sided film spacer does not stick to the pickup tool during retraction of the pickup tool from the single-sided film spacer.

Owner:AMKOR TECH INC DW US

Method of Screening Static Random Access Memory Cells for Positive Bias Temperature Instability

ActiveUS20130058177A1Efficient and accurate identificationYield minimizationDigital storageStatic random-access memorySemiconductor materials

A method of screening complementary metal-oxide-semiconductor CMOS integrated circuits, such as integrated circuits including CMOS static random access memory (SRAM) cells, for n-channel transistors susceptible to transistor characteristic shifts over operating time. For the example of SRAM cells formed of cross-coupled CMOS inverters, static noise margin and writeability (Vtrip) screens are provided. Each of the n-channel transistors in the CMOS SRAM cells are formed within p-wells that are isolated from p-type semiconductor material in peripheral circuitry of the memory and other functions in the integrated circuit. Forward and reverse body node bias voltages are applied to the isolated p-wells of the SRAM cells under test to determine whether such operations as read disturb, or write cycles, disrupt the cells under such bias. Cells that are vulnerable to threshold voltage shift over time can thus be identified.

Owner:TEXAS INSTR INC

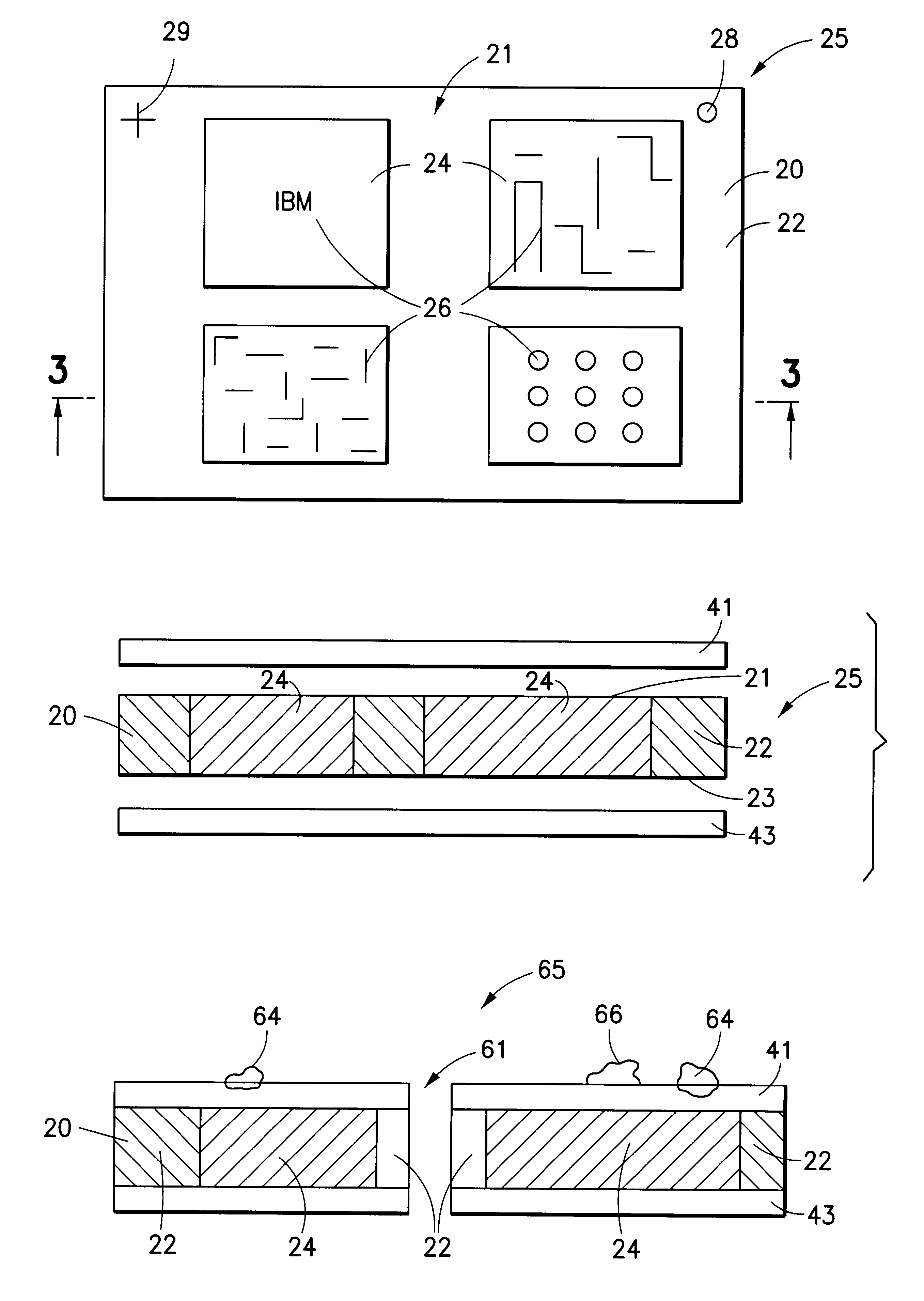

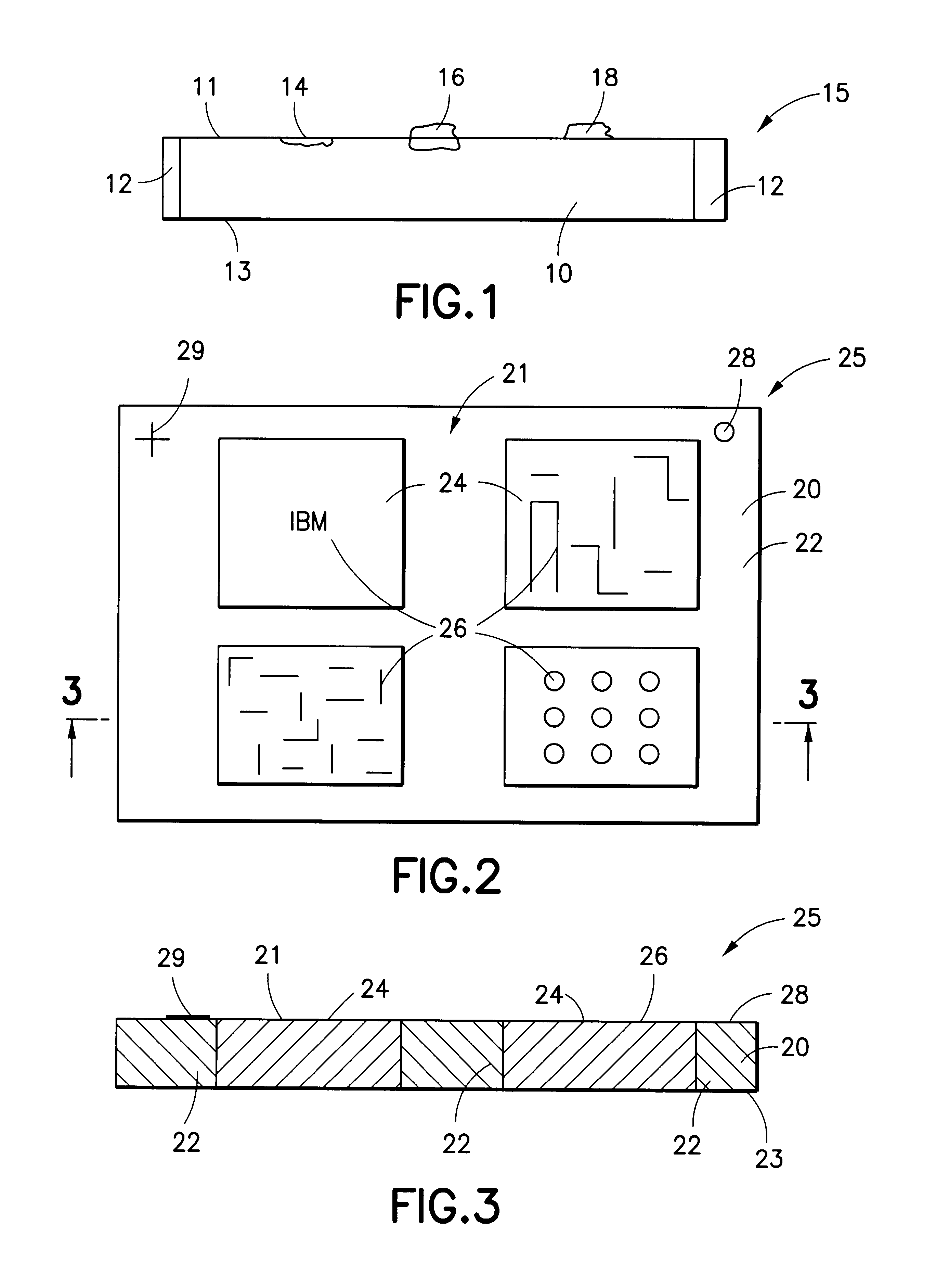

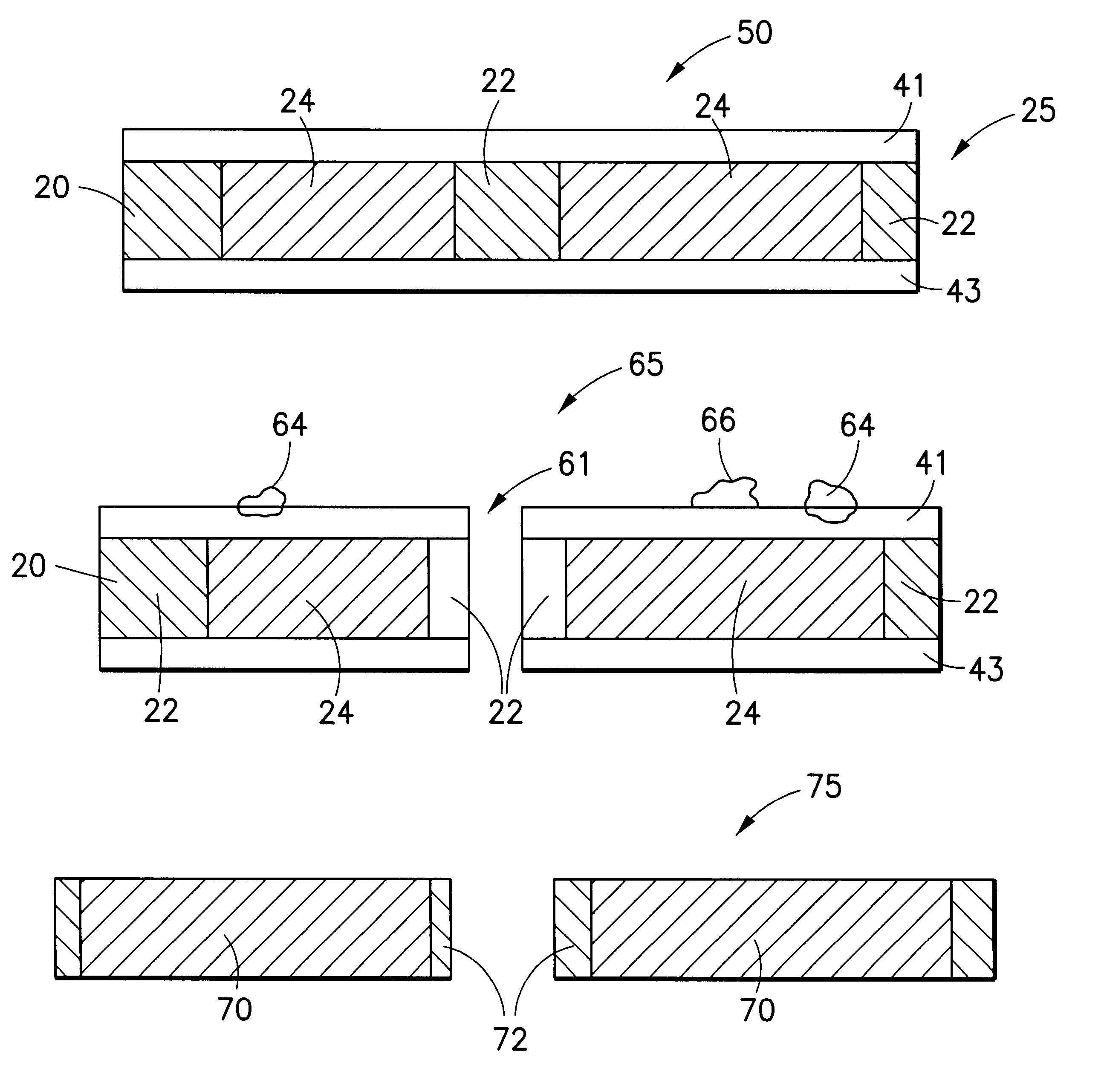

Method of forming defect-free ceramic structures using thermally depolymerizable surface layer

InactiveUS6261927B1Minimize and eliminate processing defectImprove protectionSemiconductor/solid-state device detailsSolid-state devicesSurface layerTopography

This invention relates generally to a new method of forming semiconductor substrates with defect-free surface metallurgical features. In particular, the invention related to a method for providing surface protected ceramic green sheet laminates using at least one thermally depolymerizable surface layer. More particularly, the invention encompasses a method for fabricating semiconductor substrates wherein a thermally depolymerizable / decomposable surface film is placed over a ceramic green sheet stack or assembly prior to lamination and caused to conform to the surface topography of the green sheet during lamination. The invention also encompasses a method for fabricating surface protected green sheet laminates which can be sized or diced without causing process related defects on the ceramic surface. After lamination the thermally depolymerizable / decomposable film is conveniently and cleanly removed due to thermal depolymerization and burn-off of volatile species during the sintering process, thus providing surface defect-free ceramic substrates.

Owner:IBM CORP

Seed coatings, coating compositions and methods for use

ActiveUS20180251654A1Promote seedling establishmentEasy to grow plantsBiocideCellulose coatingsPolyethylene oxidePotato starch

A seed or seedling is coated with underivatized guar, cationic hydroxypropyl guar, polyacrylamide, poly(methacrylic acid), poly(acrylic acid), polyacrylate, polyethylene glycol), polyethyleneoxide, poly(vinyl alcohol), polyglycerol, polytetrahydrofuran, polyamide, hydroxypropyl guar, carboxymethyl guar, carboxymethylhydroxypropyl guar, underivatized starch, cationic starch, corn starch, wheat starch, rice starch, potato starch, tapioca, waxy maize, sorghum, waxy sorghum, sago, dextrin, chitin, chitosan, xanthan gum, carageenan gum, gum karaya, gum arabic, pectin, cellulose, hydroxycellulose, hydroxyalkyl cellulose, hydroxyethyl cellulose, carboxymethylhydroxyethyl cellulose, or hydroxypropyl cellulose, the coated seed or seedling having a shelf-life at room temperature in ambient conditions in an unsealed container to at least two months.

Owner:RHODIA OPERATIONS SAS

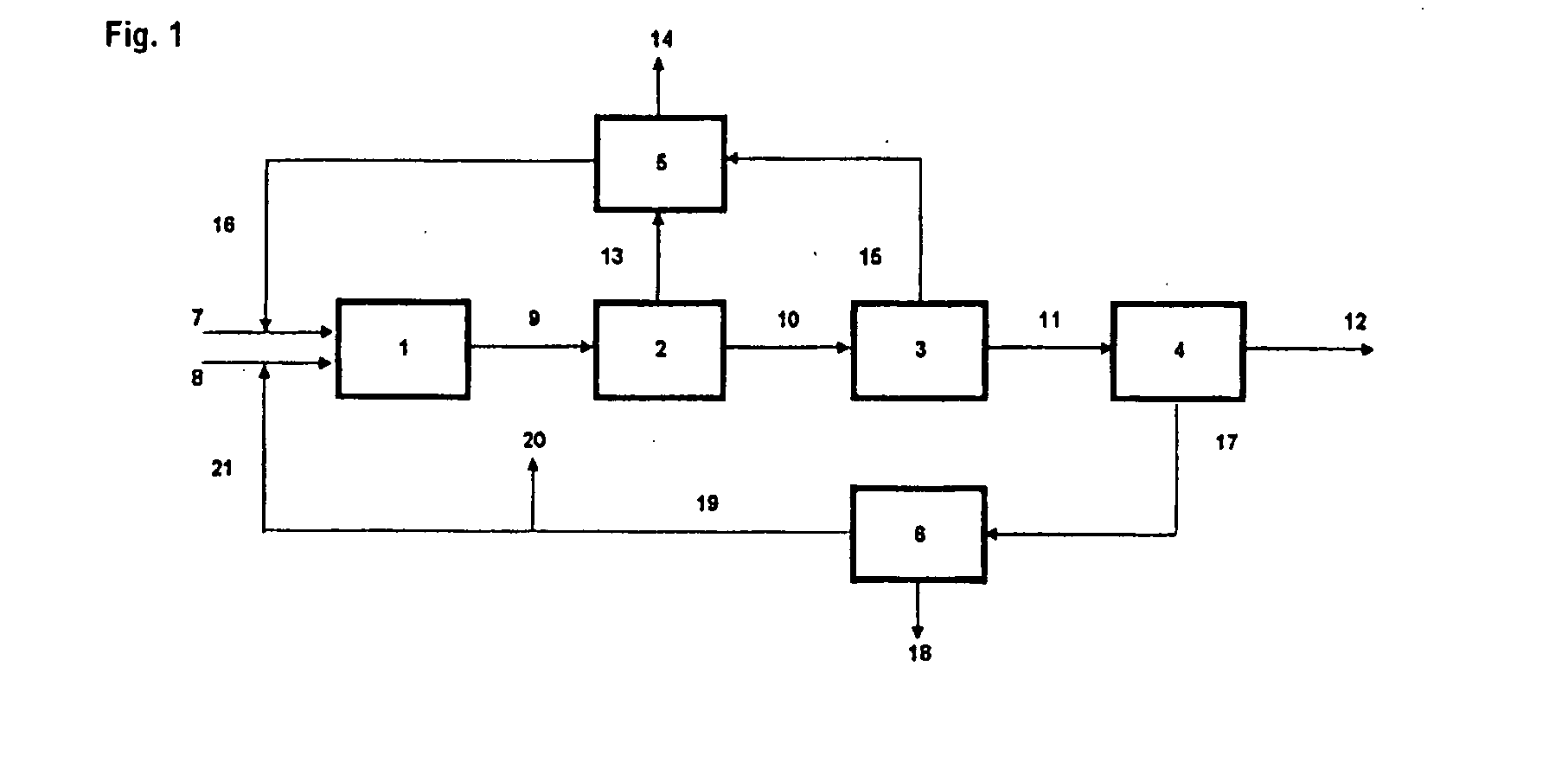

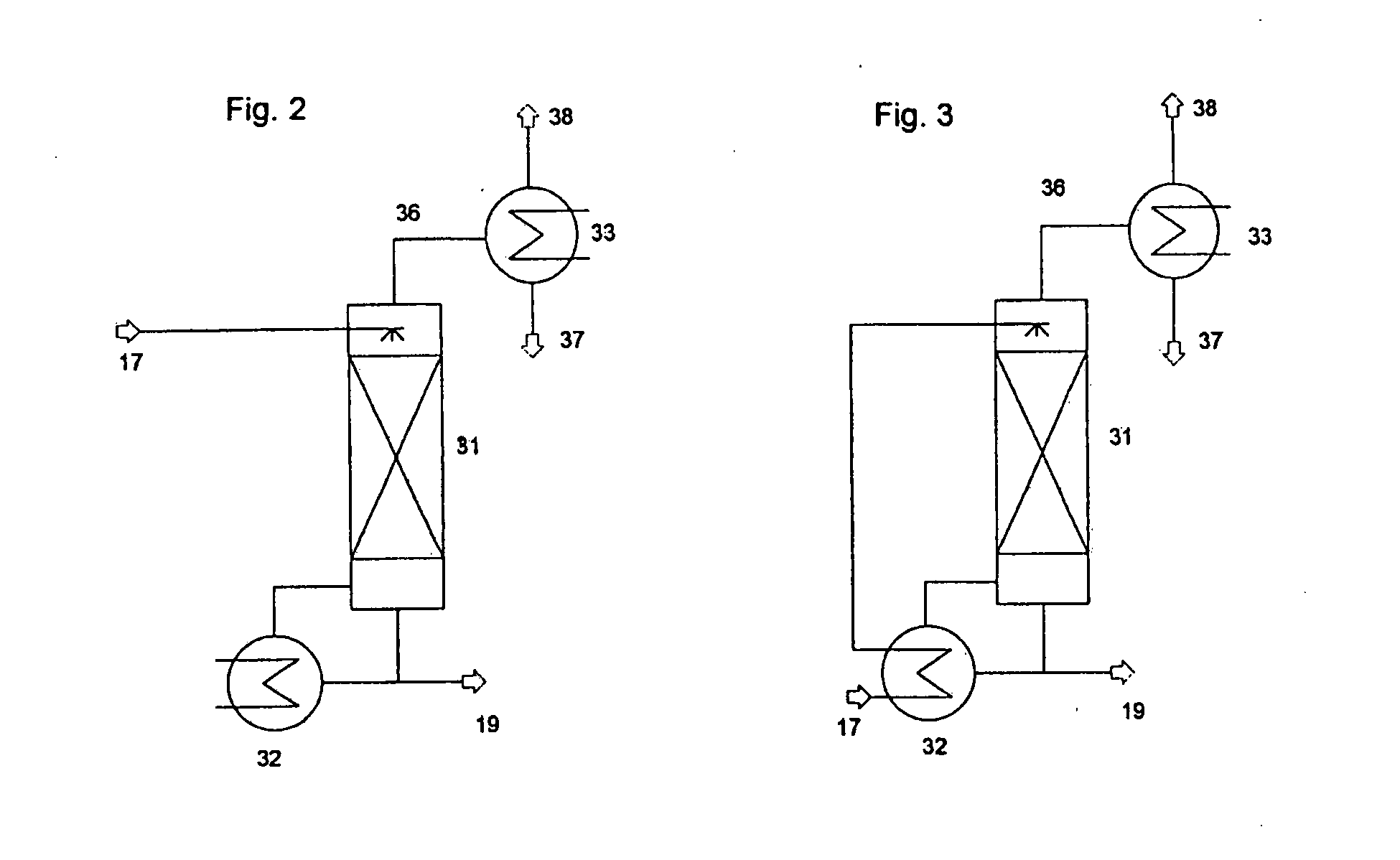

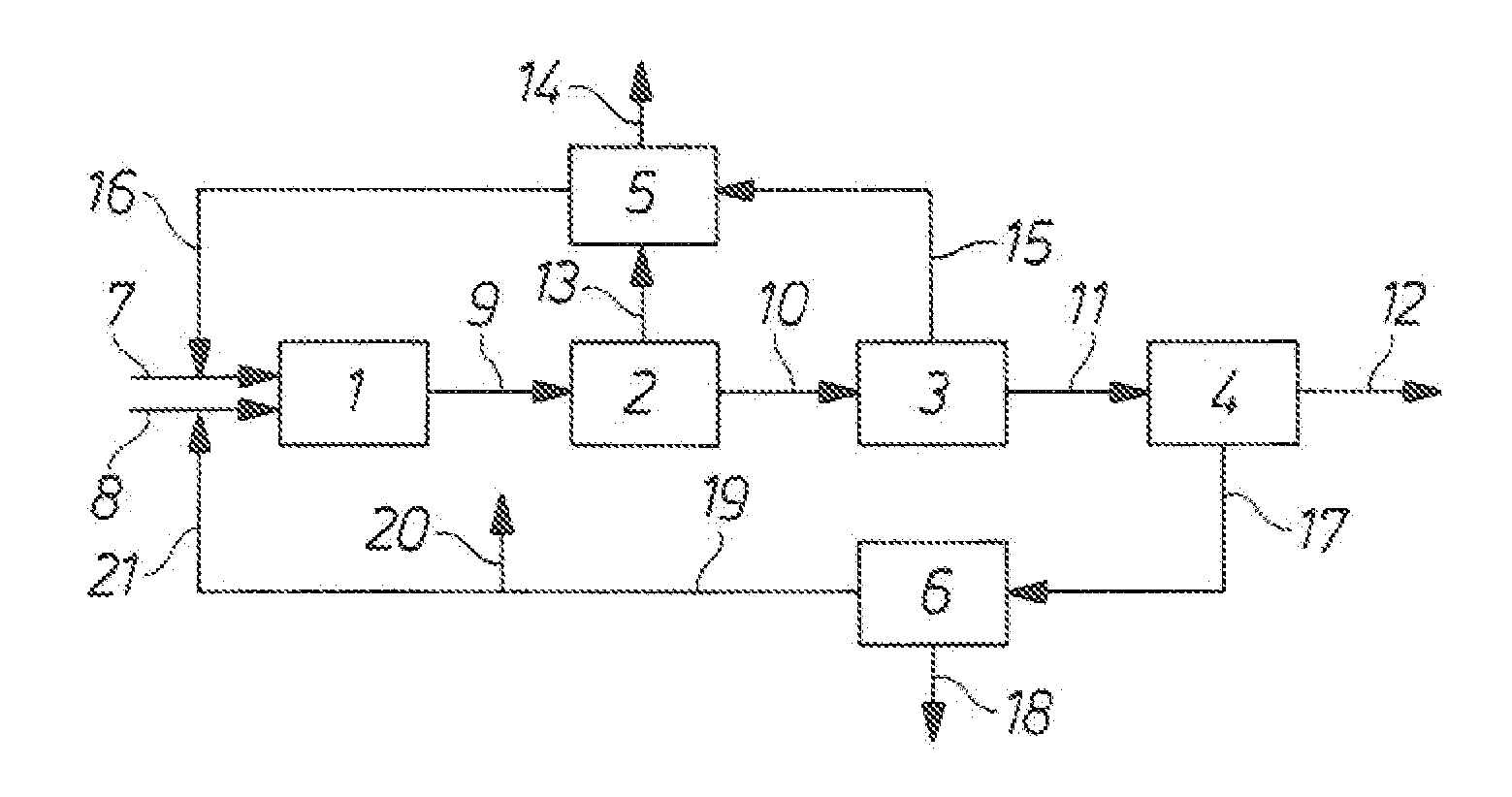

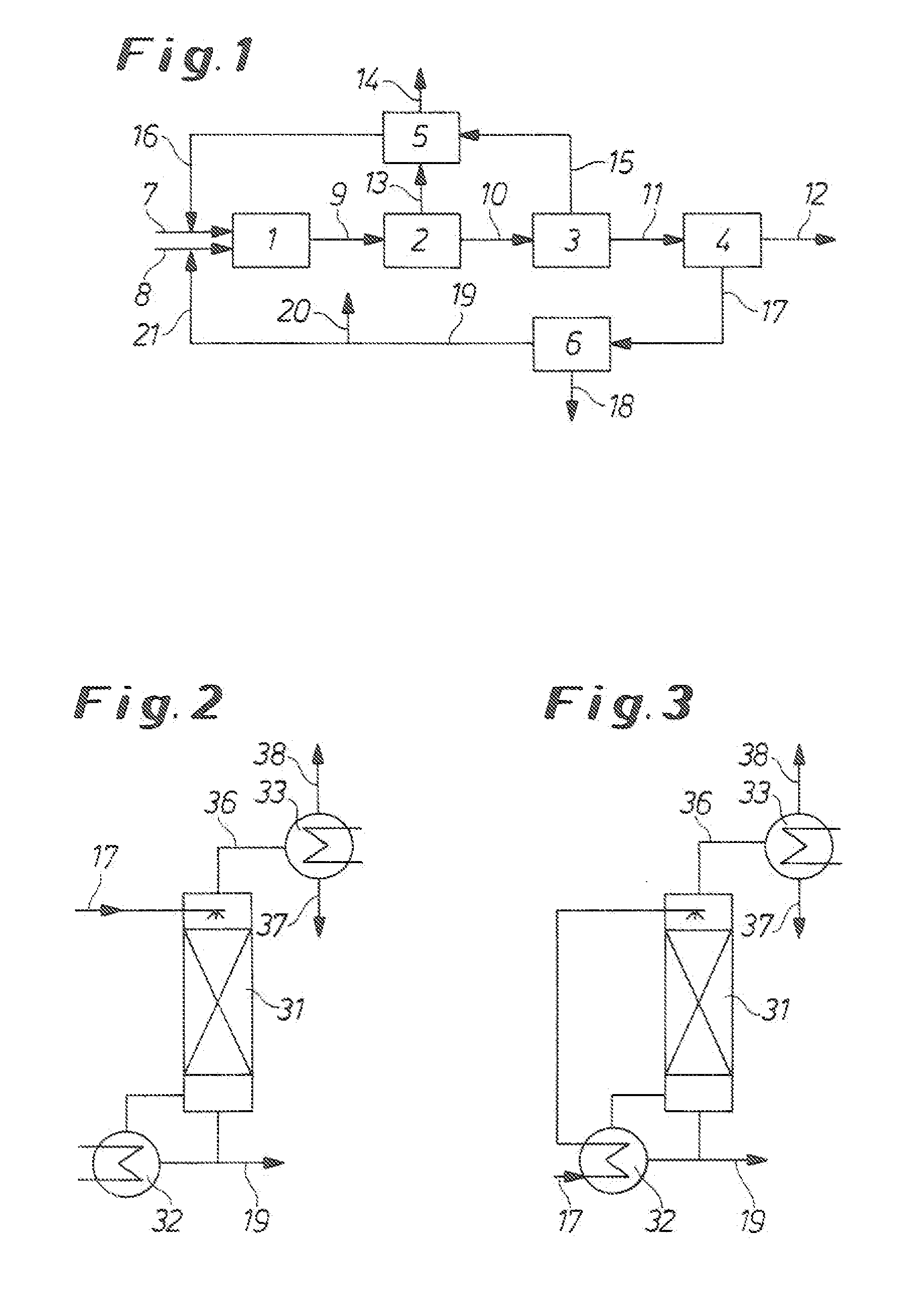

Process for the production of isocyanates

InactiveUS20070265465A1Quality of minimizedYield minimizationOrganic compound preparationIsocyanic acid derivatives purification/separationDiphenylmethaneDistillation

Isocyanates, preferably diisocyanates and polyisocyanates of the diphenylmethane series (MDI), are produced by reaction of amines dissolved in a solvent with phosgene in the same solvent to form the corresponding isocyanates. Hydrogen chloride and excess phosgene are subsequently removed from the reaction mixture to obtain a crude isocyanate-containing solution. Subsequently, the crude isocyanate-containing solution is separated by distillation into isocyanates and solvent. The solvent is recycled and used for the production of solutions of the amines and of phosgene. The solvent being recycled is treated to reduce the phosgene and diisocyanate contents before being used for the production of the solution of the amine.

Owner:BAYER MATERIALSCIENCE AG

Method of forming defect-free ceramic structures using thermally depolymerizable surface layer

InactiveUS6597058B1Minimize and eliminate processing defectImprove protectionSemiconductor/solid-state device detailsSolid-state devicesSurface layerTopography

Owner:INT BUSINESS MASCH CORP

Process for the production of isocyanates

InactiveUS20100298596A1Quality of minimizedYield minimizationOrganic compound preparationIsocyanic acid derivatives purification/separationDiphenylmethaneDistillation

Isocyanates, preferably diisocyanates and polyisocyanates of the diphenylmethane series (MDI), are produced by reaction of amines dissolved in a solvent with phosgene in the same solvent to form the corresponding isocyanates. Hydrogen chloride and excess phosgene are subsequently removed from the reaction mixture to obtain a crude isocyanate-containing solution. Subsequently, the crude isocyanate-containing solution is separated by distillation into isocyanates and solvent. The solvent is recycled and used for the production of solutions of the amines and of phosgene. The solvent being recycled is treated to reduce the phosgene and diisocyanate contents before being used for the production of the solution of the amine.

Owner:BAYER MATERIALSCIENCE AG

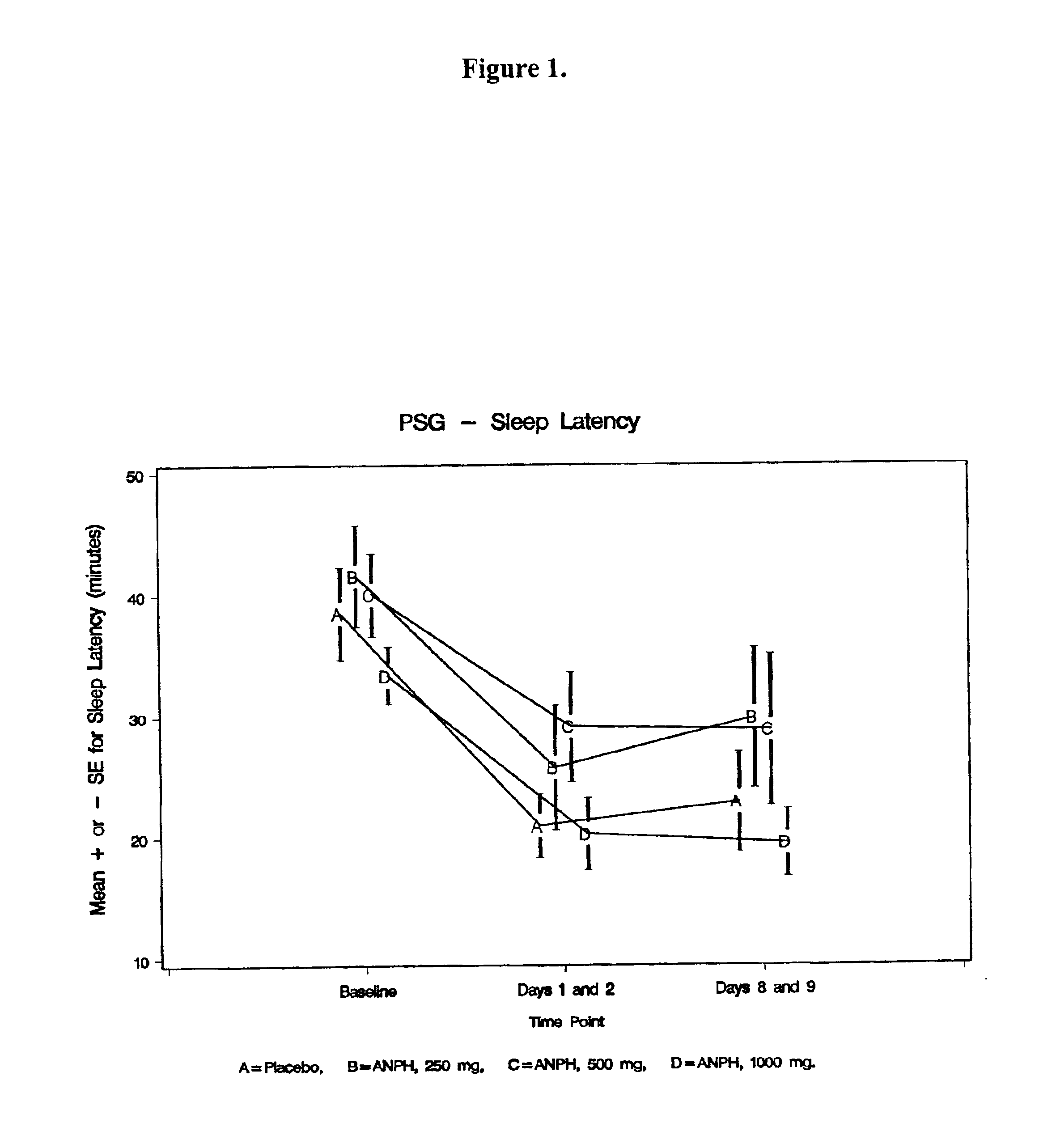

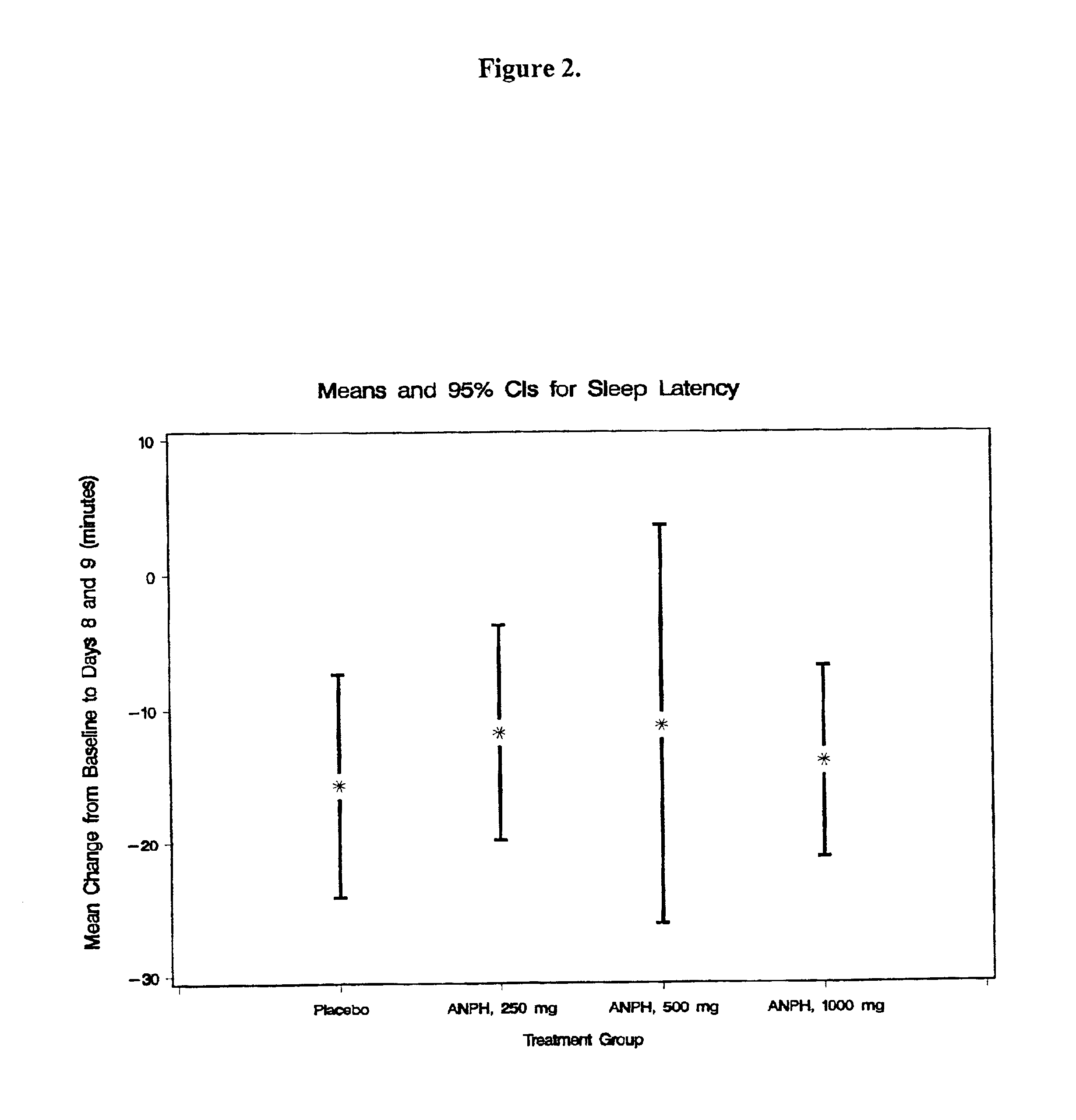

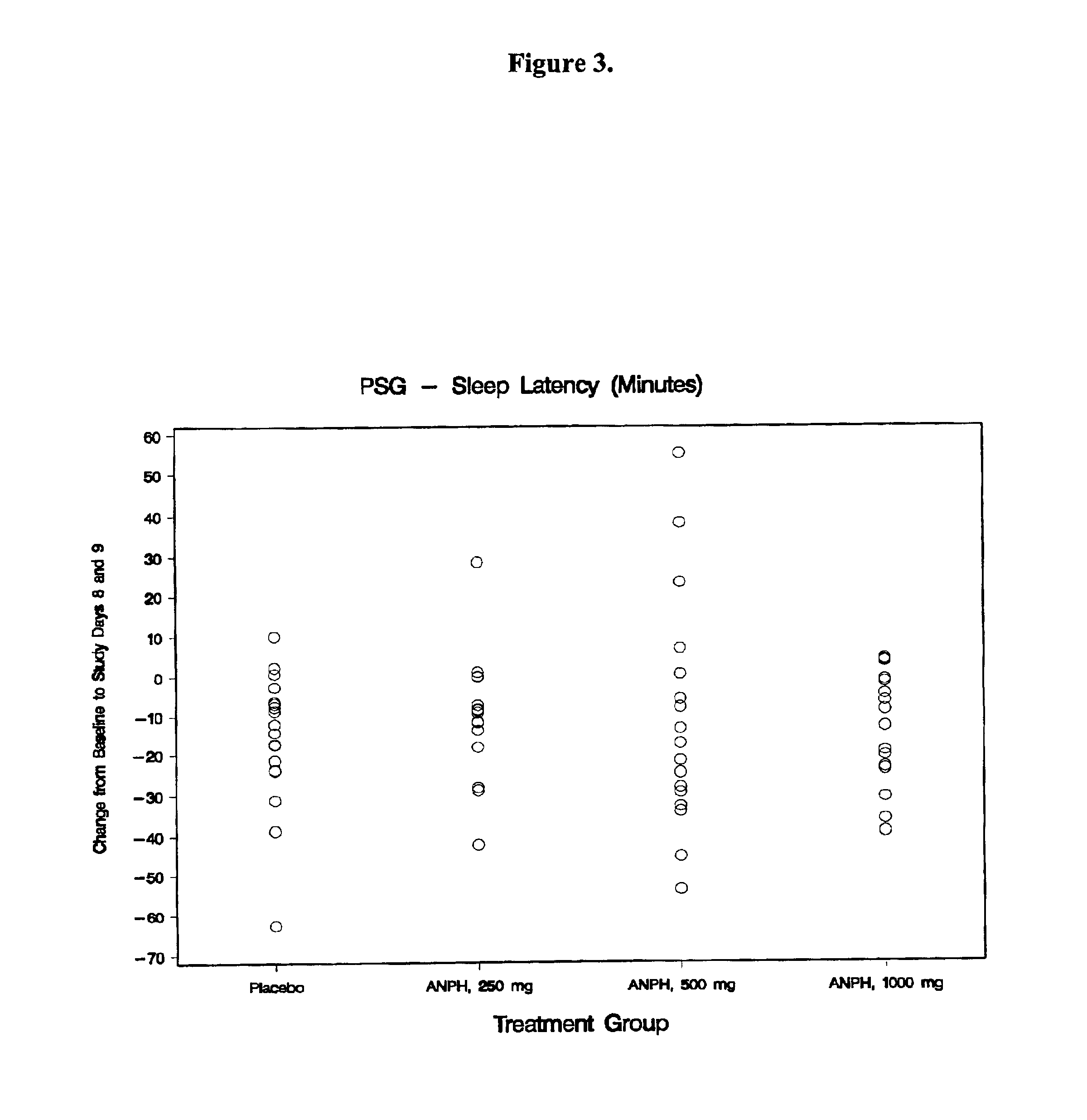

Composition for improving sleep quality and efficiency, and methods of preparing and using the composition

InactiveUS6869622B2Yield minimizationReduces wake after sleep onsetBiocideNervous disorderSleep architecturePhysiology

A pharmaceutical composition comprising extracts of the root of a plant of the family Valerianacae, and methods of using such composition and / or extracts of the root of a plant of the family Valerianacae to improve sleep quality and sleep efficiency and to improve sleep structure and sleep architecture, are described. Sleep quality, sleep efficiency, sleep structure and sleep architecture may be in the context of various criteria or parameters, as described herein. Specifically, a pharmaceutical composition that reduces wake after sleep onset, increases total sleep time, increases sleep efficiency, and / or increases sleep time spent in sleep stages three and four, in a normal adult is described, the composition comprising therapeutically effective amounts of valerenic acid and its derivatives, kessane derivatives, valeranone, valerenal, and amino acids. The composition may be prepared by the steps of (i) adding the roots to an alcoholic extraction solvent to form a mixture, wherein the alcoholic extraction solvent comprises between approximately 50% (v / v) to approximately 100% (v / v) ethanol in a remainder of water, and (ii) heating the mixture to a temperature of between approximately 70° C. to approximately 80° C. for a period of at least two hours; wherein valerenic acid is present in the extract, the content of valepotriates in the extract is substantially reduced with respect to its content in the root, and the content of valerenic acids in the extract is not substantially reduced with respect to its content in the root; and minimizing the yield of unstable valepotriates. The valerenic acid derivative, where present, is preferably selected from acetoxyvalerenic acid, hydroxyvalerenic acid, valerenal, valerenol.

Owner:KNOBBE MARTENS OLSON & BEAR

Process for the production of needle coke

ActiveUS7604731B2Yield minimizationPromote formationThermal non-catalytic crackingTreatment with plural serial cracking stages onlyGraphite electrodeDistillation

A process is disclosed for producing needle coke from heavy atmospheric distillation residues having sulfur no more than 0.7 wt %, which process involves the steps of heating the feedstock to a temperature in the range of 440 to 520° C. for thermal cracking in a soaking column under pressure in the range of 1 to 10 kg / cm2 to separate the easily cokable material, separating the cracked products in a quench column and a distillation column and then subjecting the hydrocarbon fraction from the bottom of the quench column and a hydrocarbon fraction having a boiling point in the range of 380 to 480° C. from the distillation column and / or any other suitable heavier hydrocarbon streams in a definite ratio depending on certain characteristic parameters to thermal cracking in a second soaking column at a temperature of 460 to 540° C., pressure in the range of 2 to 20 kg / cm2 in presence of added quantity of steam for formation of a mesophase carbonaceous structure which on steam stripping and cooling forms a solid crystalline coke suitable for manufacturing of graphite electrode of large diameter having co-efficient of thermal expansion lower than 1.1×10−6 / ° C. measured on graphite artifact in the temperature range of 25 to 525° C.

Owner:INDIAN OIL CORPORATION

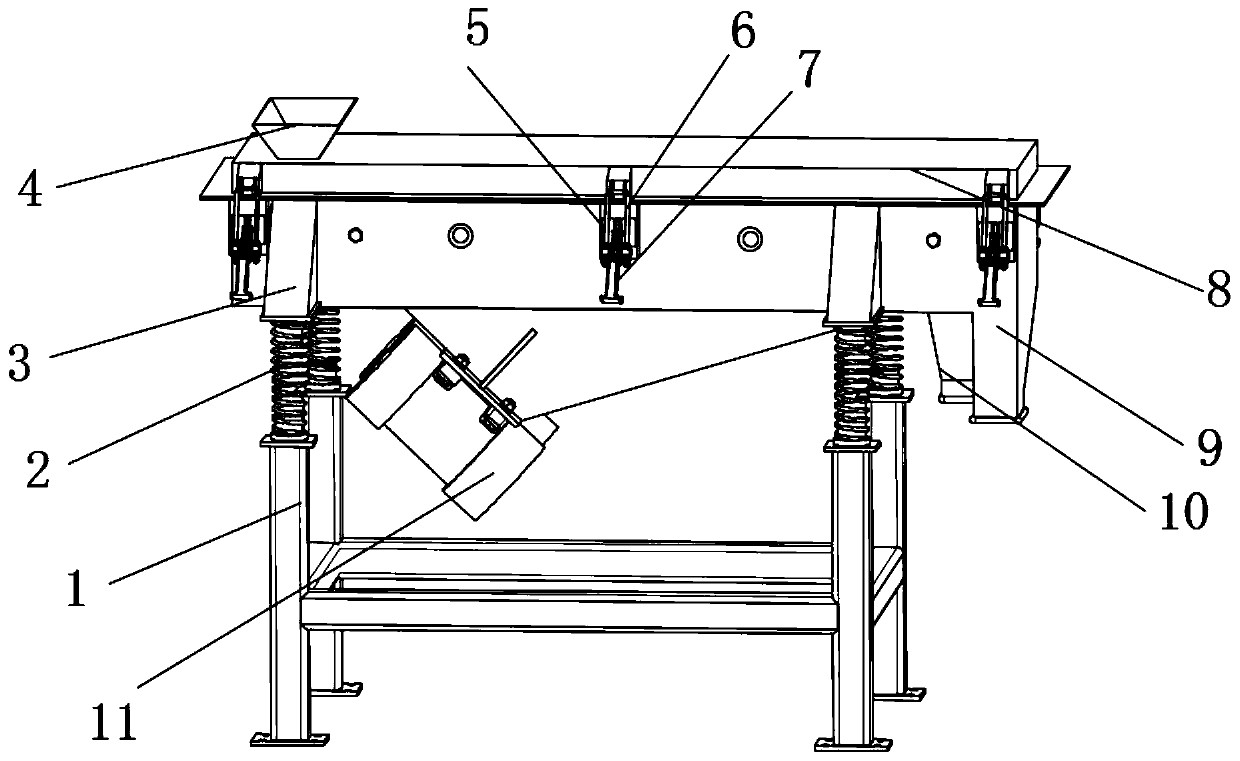

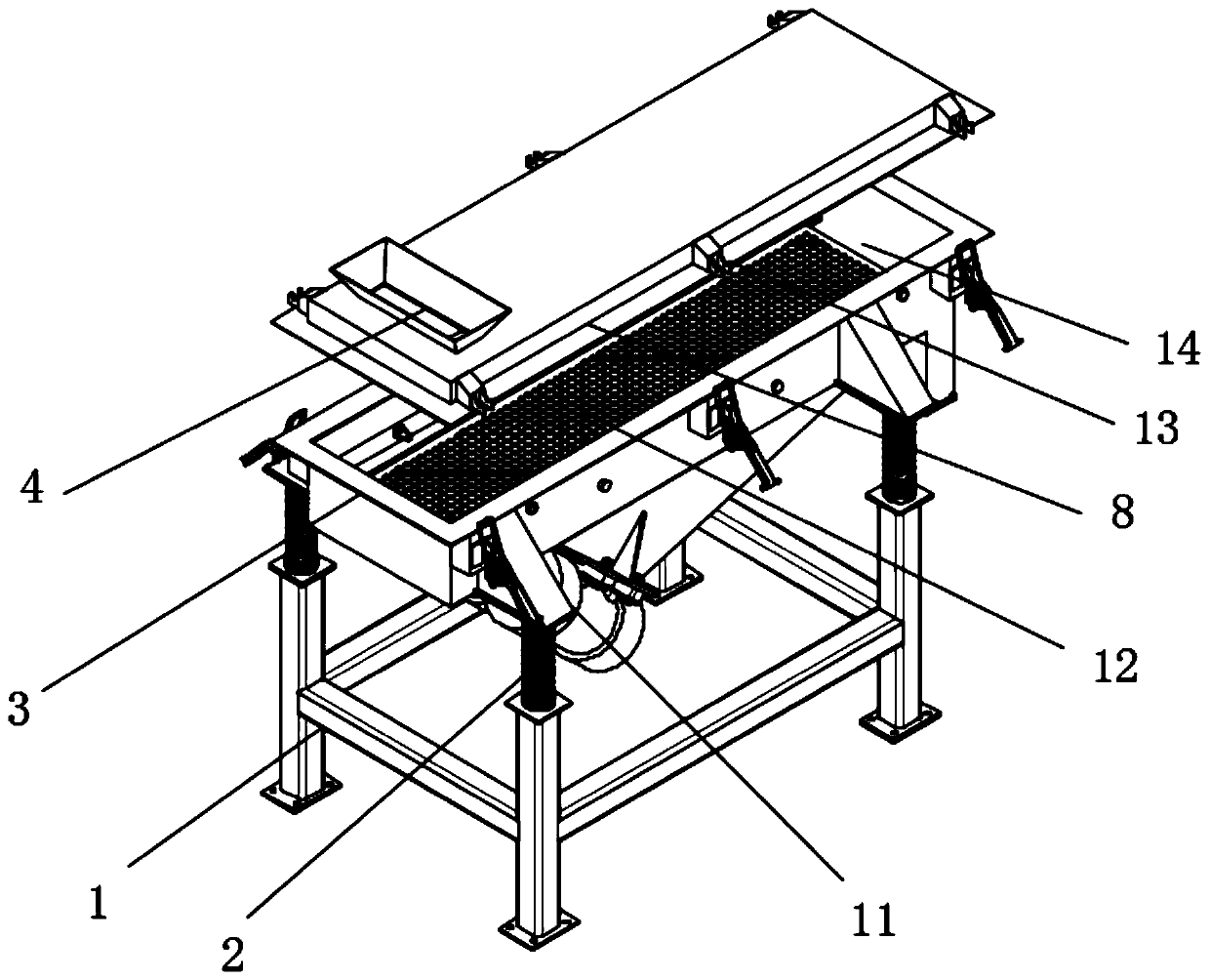

Harmless low-temperature carbonization treatment process of sludge

The invention discloses a harmless low-temperature carbonization treatment process of sludge. The treatment process comprises the following steps: selecting garbage rich in plant fibers, putting the garbage into a crushing machine, performing crushing, adding the crushed plant fiber garbage into a screening box from a material inlet hopper of a screening machine, and driving a first motor to driveoverall vibration of the screening box under the action of first springs. According to the process provided by the invention, second teeth are matched with first teeth for use, so that a filter screen is convenient to install and disassemble, and the filter screen is convenient to replace and repair and convenient to use; a conveyor belt and an inclined plate are arranged, so that particle impactforce caused by falling of a pressing mechanism can be reduced, particles can be prevented from being splashed in the falling process to cause loss, the resources can be saved, and waste can be avoided; through conveying of the conveyor belt, manpower can be saved, and the working efficiency can be improved; and a fire grate rotates, so that residues can be eliminated, the air flow can be accelerated, the particle combustion is more full, and the carbonization rate is high.

Owner:克拉玛依顺通环保科技有限责任公司

Method for enhancing organoleptic properties of protein for inclusion in consumer food products and products produced thereby

The present invention relates a method for improving the organoleptic properties of protein used in the production of frozen and retort consumer food applications. More specifically, the present invention is directed to the addition of a liquid fat during the step of marinating the protein to enhance the flavor and texture of the meat products.

Owner:GEN MILLS CEREALS

Method for infusing meat products with a starch binder solution

InactiveUS6869631B2Stabilizing ultimate yieldMinimizing yield lossMeat/fish preservationFood preparationFlavorWater holding

The present invention relates to an improved binder system to stabilize and improve yield for thermally processed meat products such as those that are used in canning or retort operations. More specifically, the present invention pertains to the novel starch / binder matrix that produces a meat product having enhanced moisture flavor and texture over those treated using currently available techniques. The novel matrix uses a combination of starches that provide differential water holding and moisture control for the meat products treated therewith.

Owner:GENERAL MILLS INC

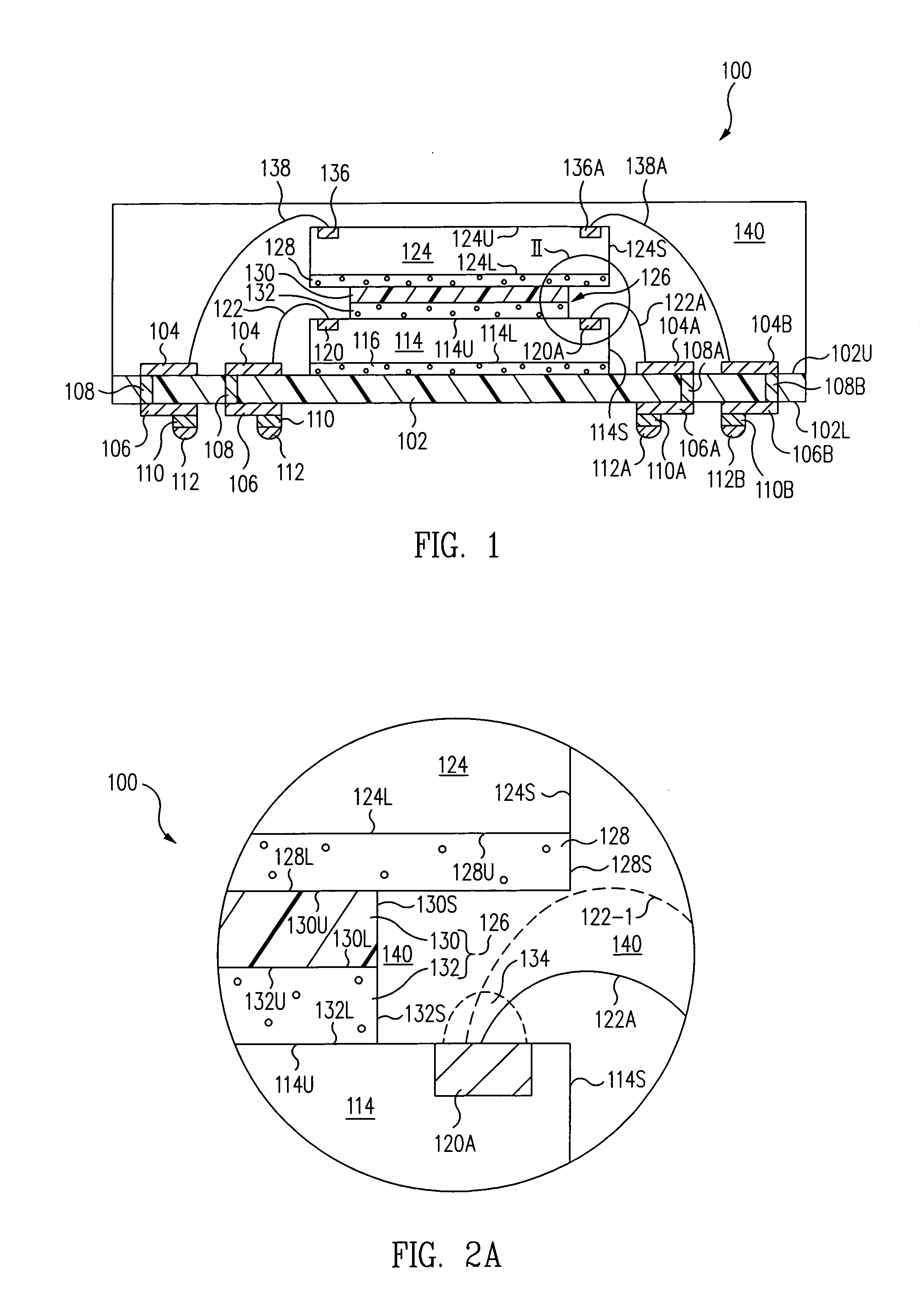

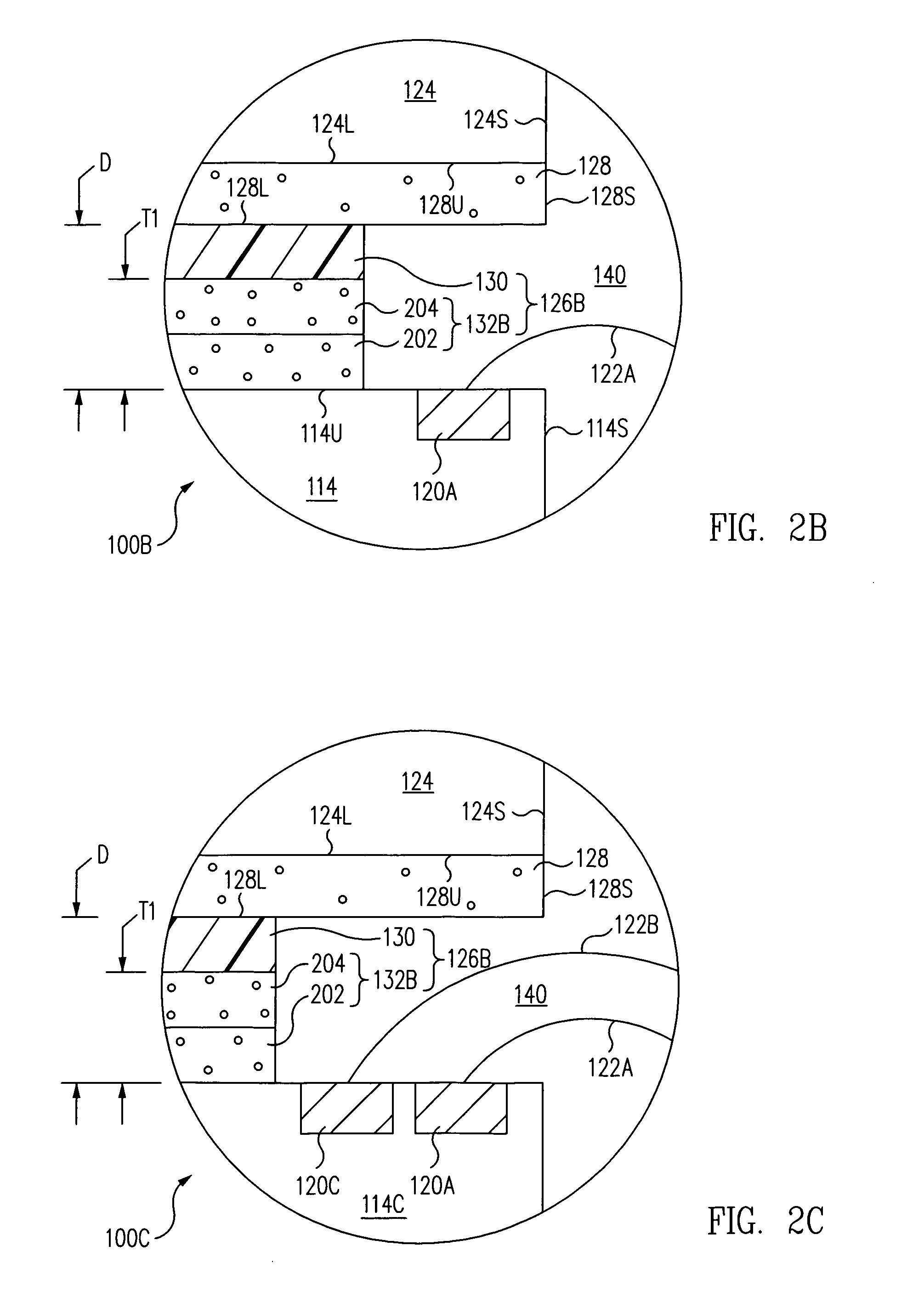

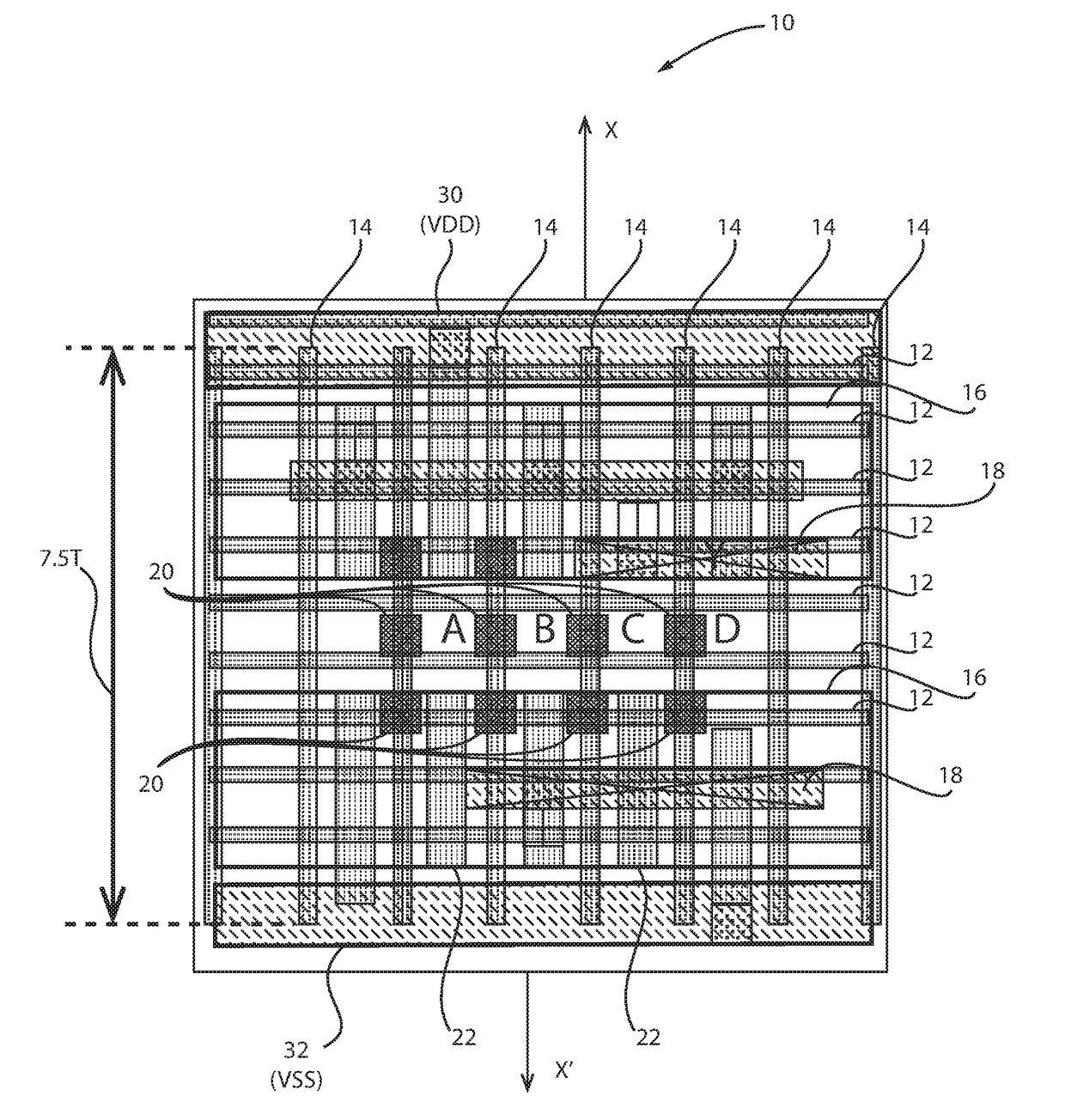

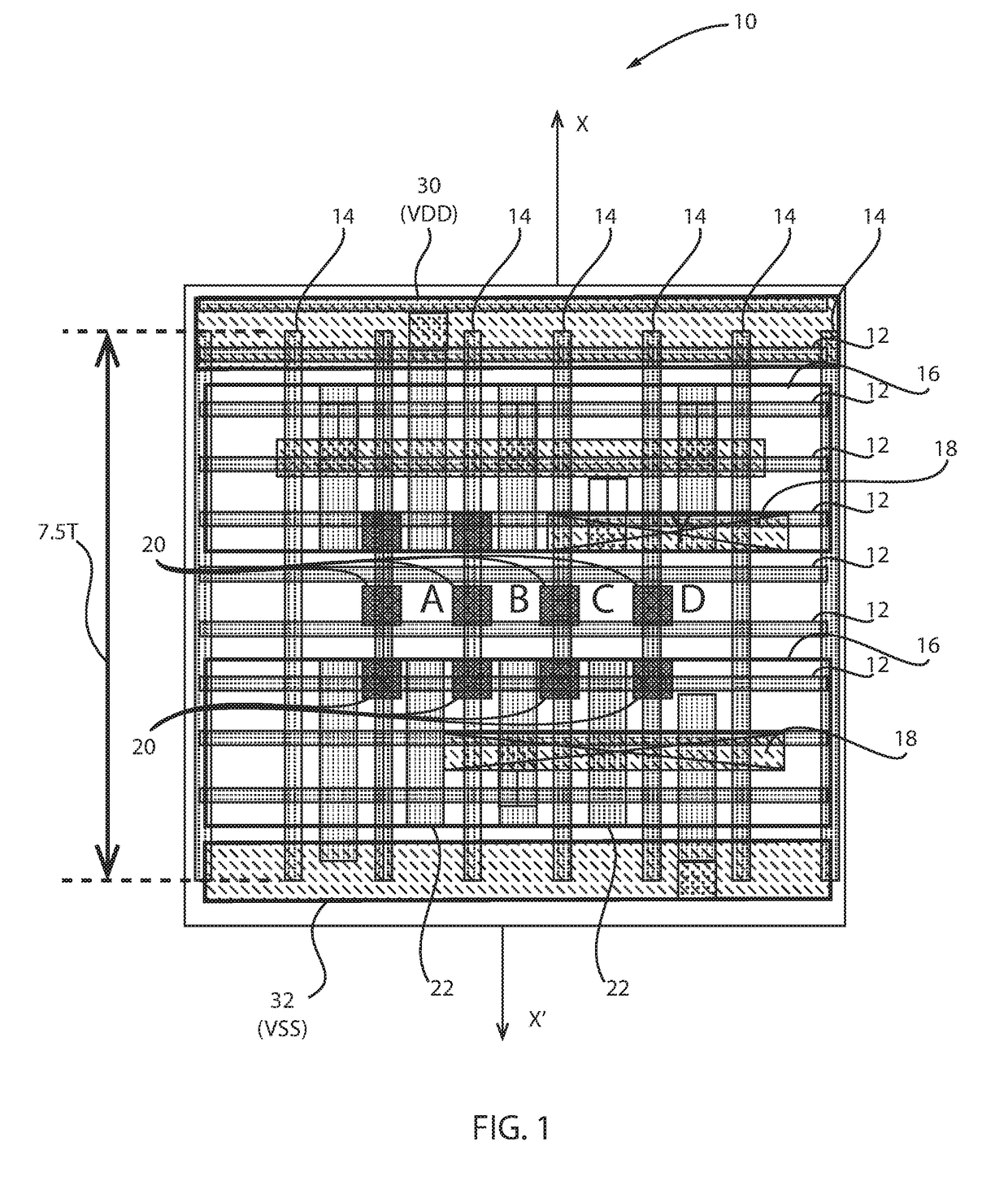

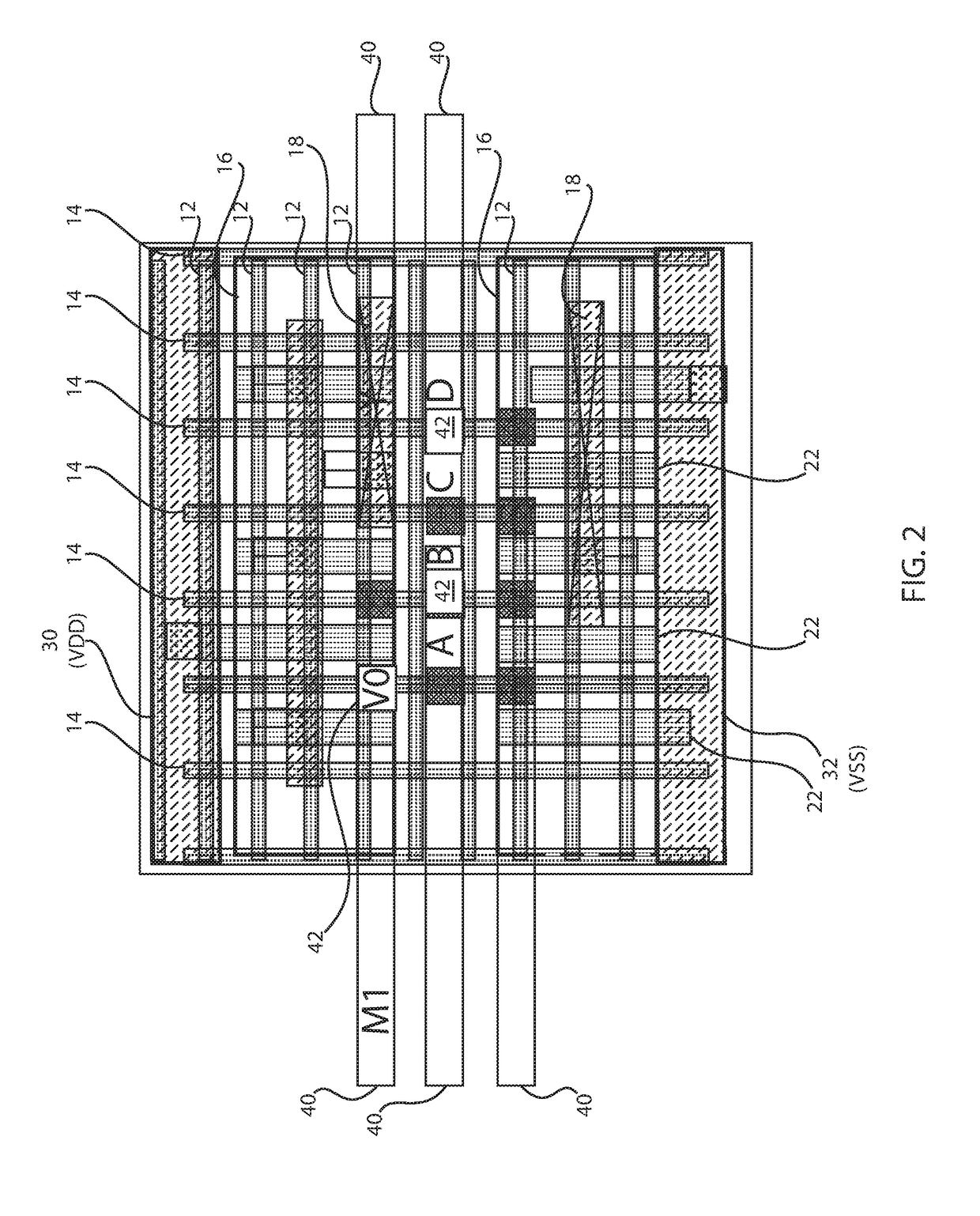

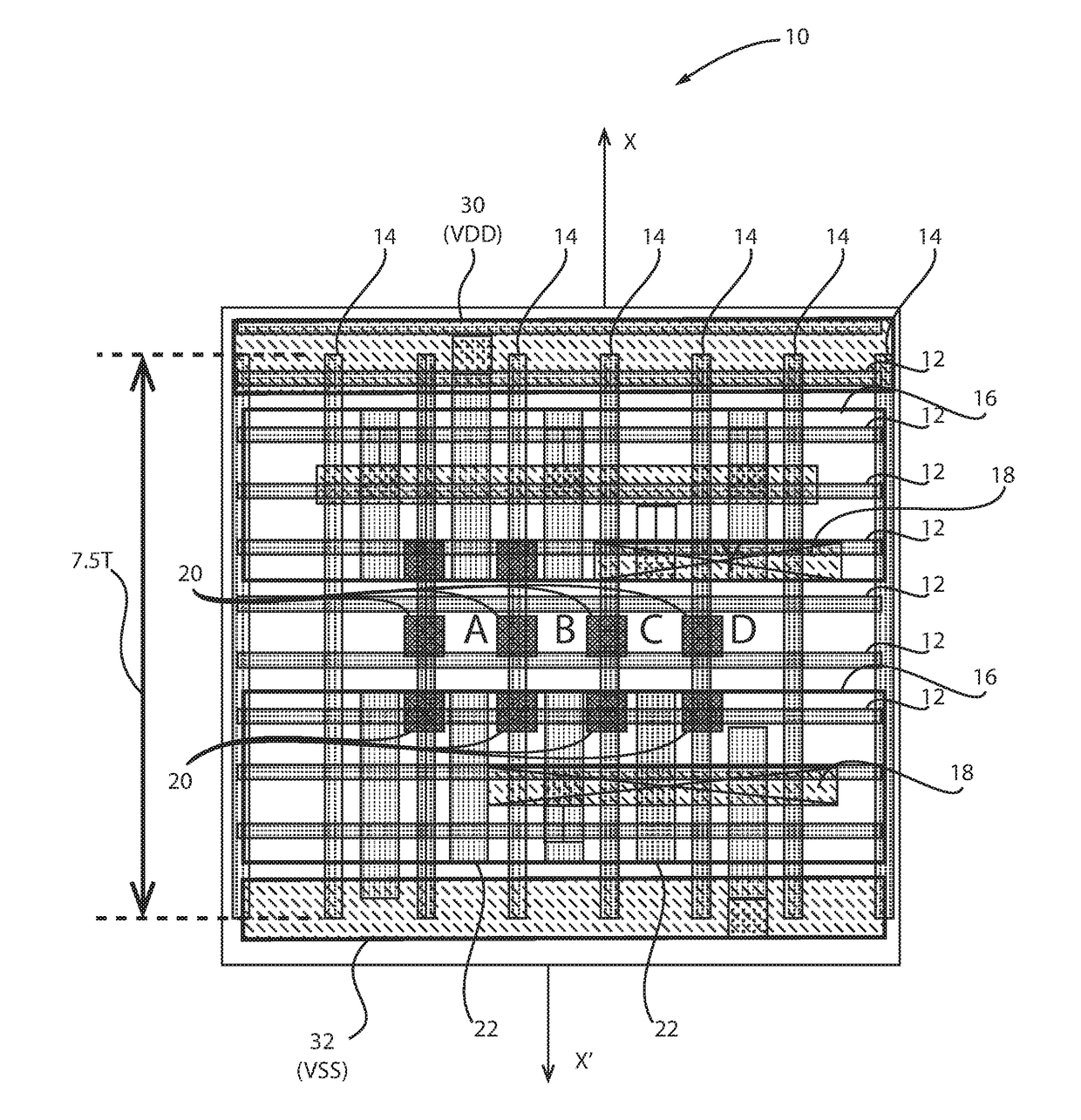

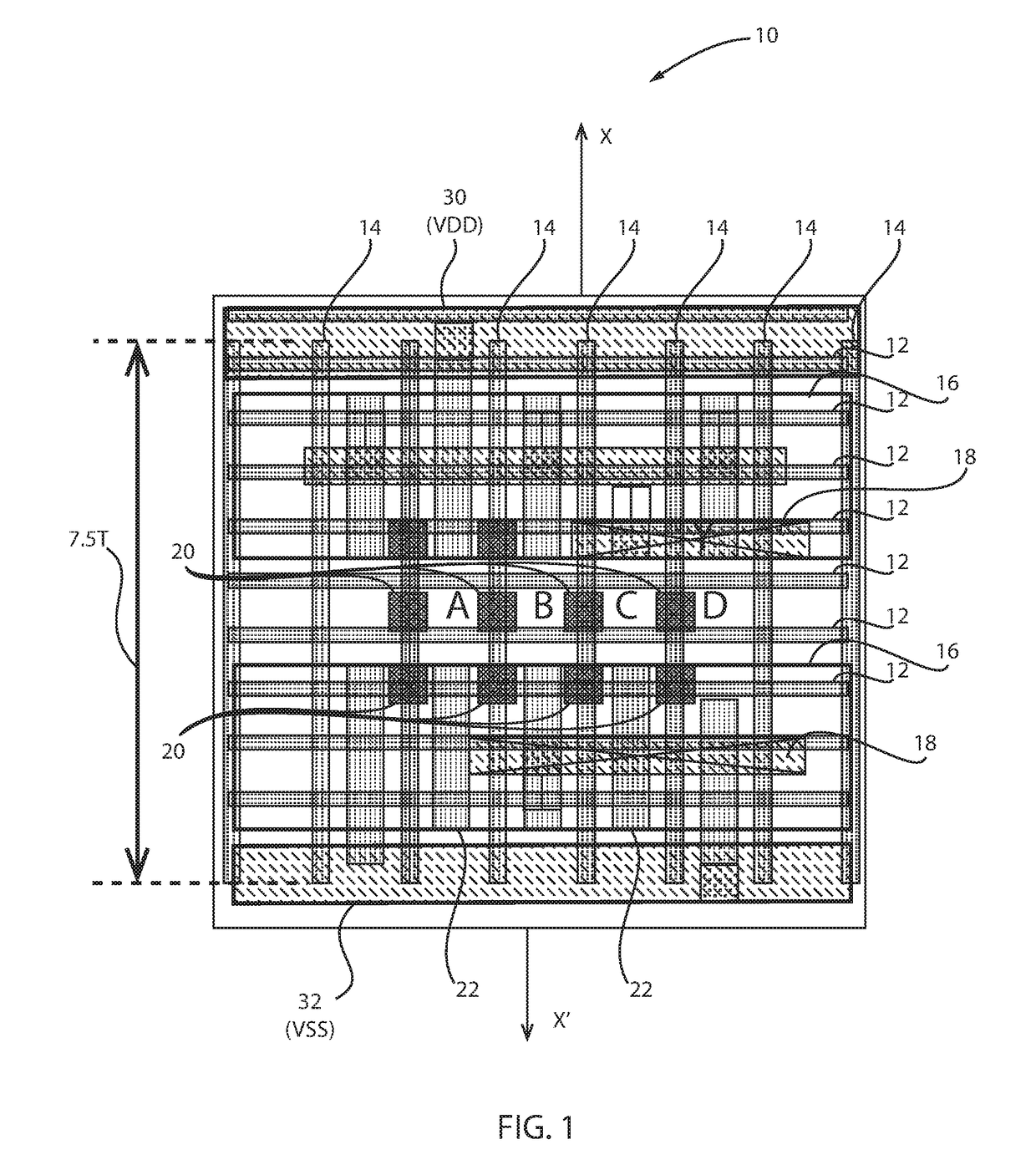

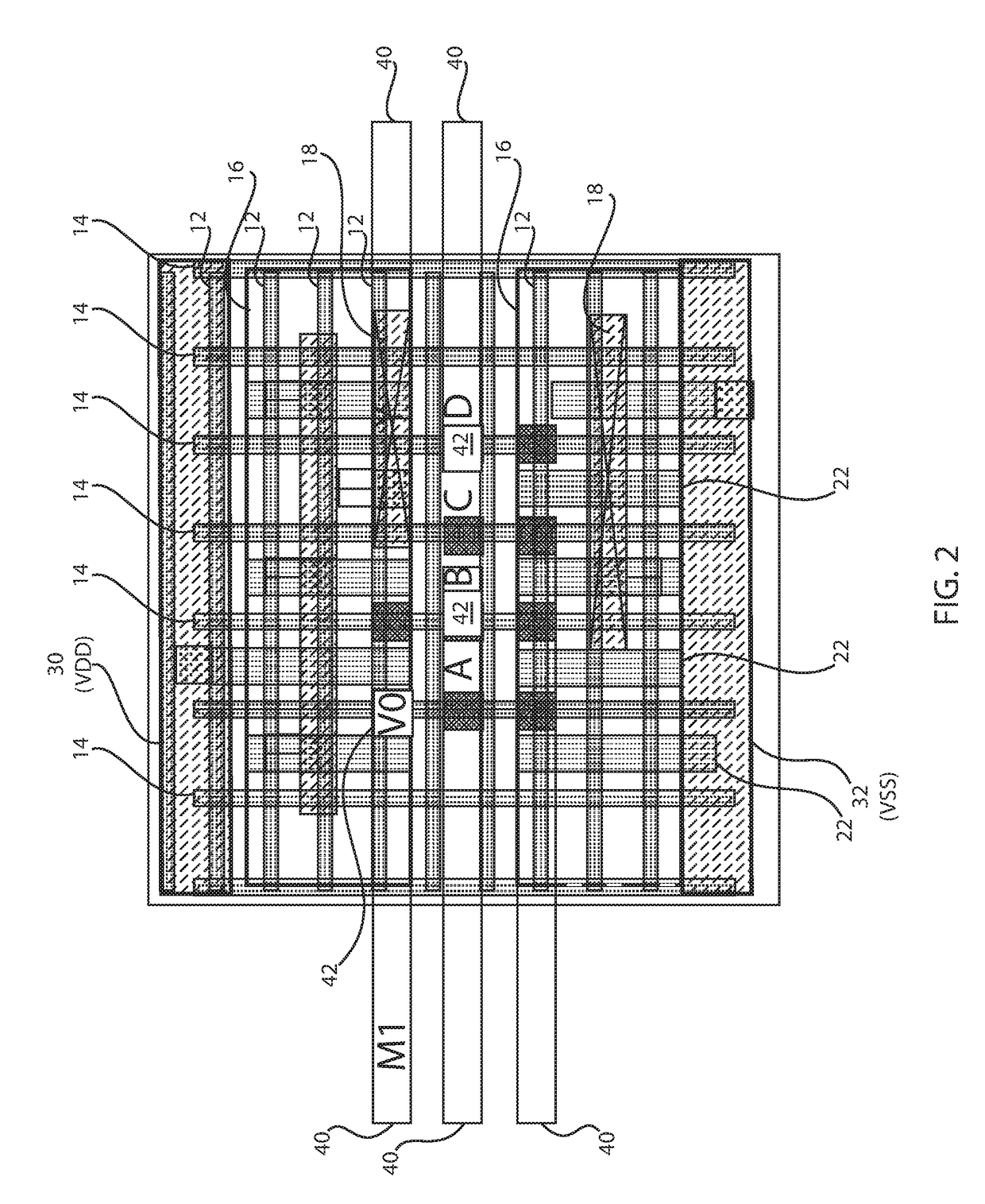

Standard cell architecture with at least one gate contact over an active area

ActiveUS20180211948A1Reduce in quantityImproving pin accessSolid-state devicesCAD circuit designMOSFETElectrical conductor

A method is presented for forming a layout of a MOSFET (metal oxide semiconductor field effect transistor) circuit. The method includes forming a plurality of gate conductors, forming a plurality of active areas, and forming at least one gate contact (CB contact) within an active region of the plurality of active regions. The method further includes placing a marker over the at least one gate contact to identify a location of the at least one gate contact. Additionally, a distance between the at least one gate contact and at least one TS contact is optimized based on device specifications.

Owner:IBM CORP

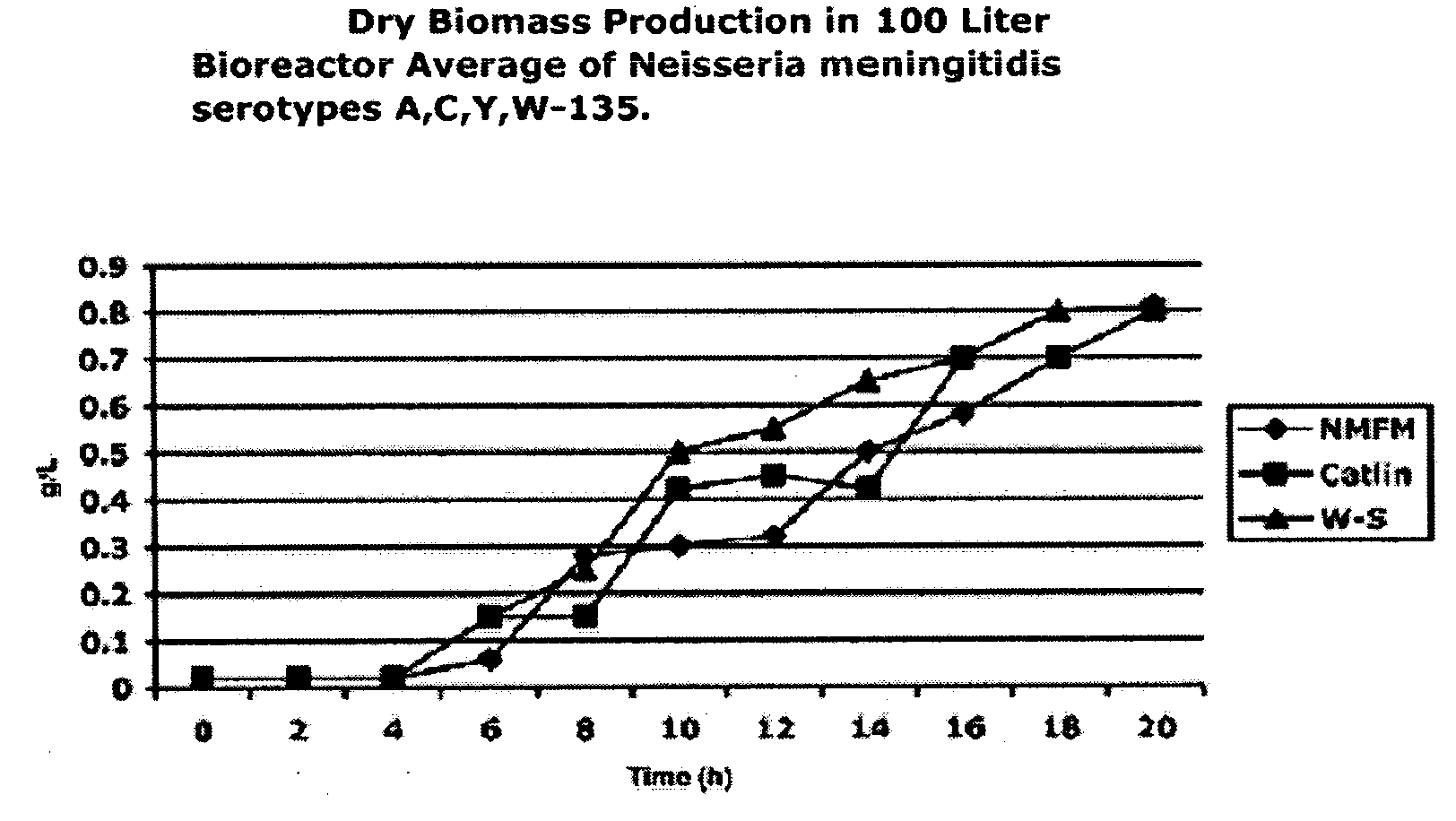

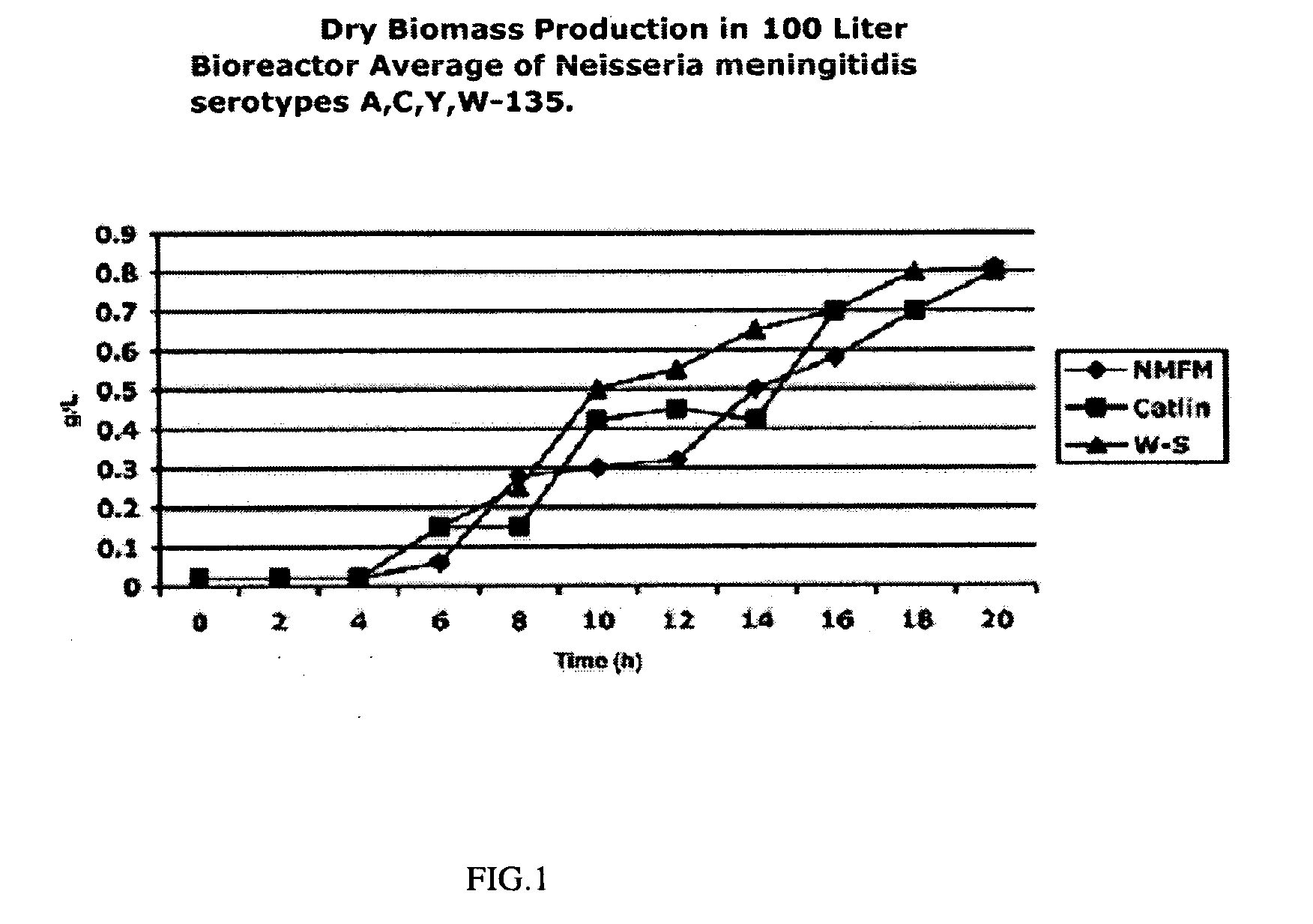

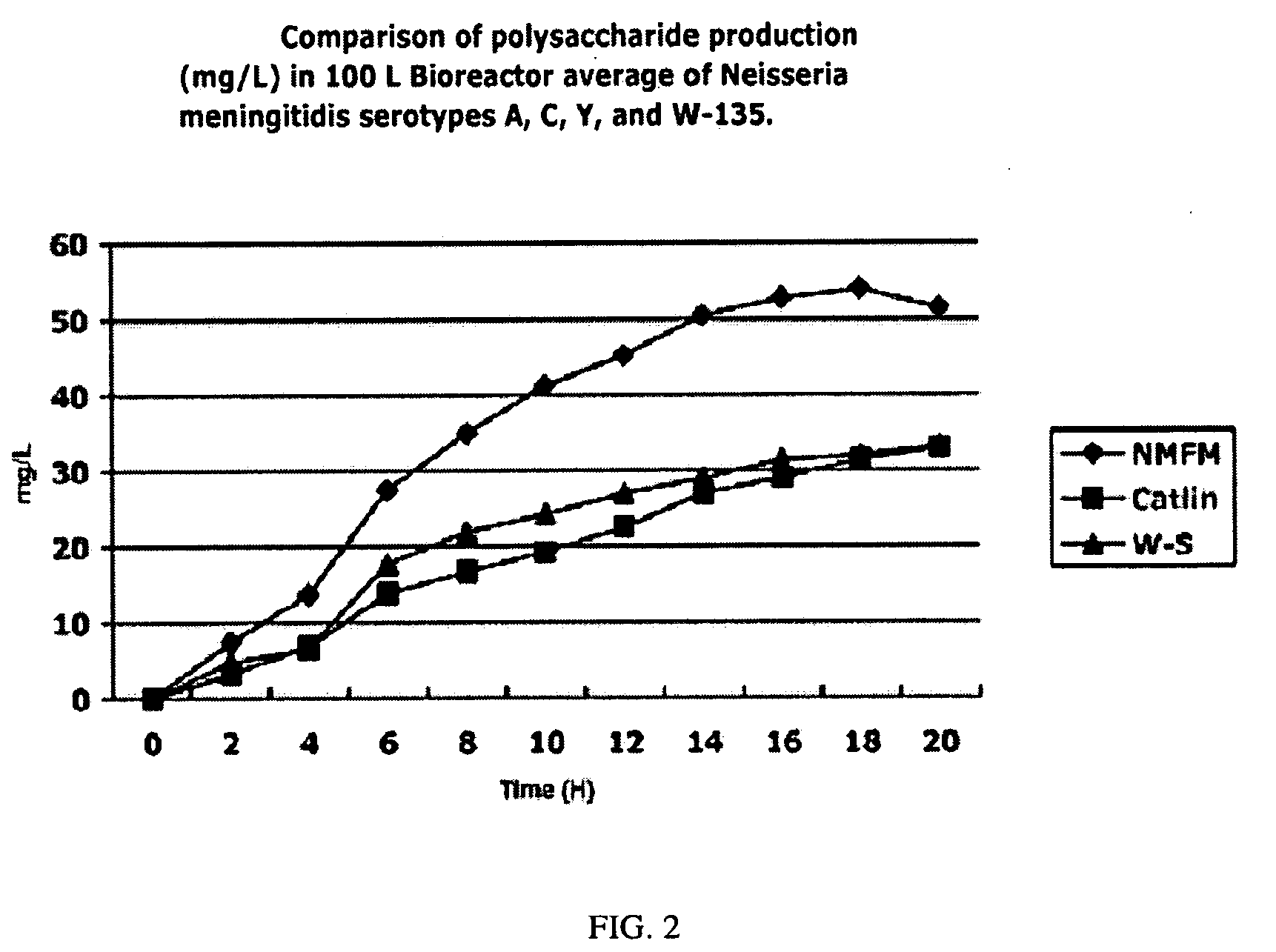

METHOD OF PRODUCING MENINGOCOCCAL MENINGITIS VACCINE FOR NEISSERIA MENINGITIDIS SEROTYPES A, C, Y, and W-135

InactiveUS20080318285A1Yield maximizationYield minimizationAntibacterial agentsBacteriaDiseaseSynechococcus

Owner:REDDY JEERI R

Standard cell architecture with at least one gate contact over an active area

ActiveUS20180211947A1Reduce numberImproving pin accessSolid-state devicesCAD circuit designMOSFETOxide semiconductor

A method is presented for forming a layout of a MOSFET (metal oxide semiconductor field effect transistor) circuit. The method includes forming a plurality of gate conductors, forming a plurality of active areas, and forming at least one gate contact (CB contact) within an active region of the plurality of active regions. The method further includes placing a marker over the at least one gate contact to identify a location of the at least one gate contact. Additionally, a distance between the at least one gate contact and at least one TS contact is optimized based on device specifications.

Owner:IBM CORP

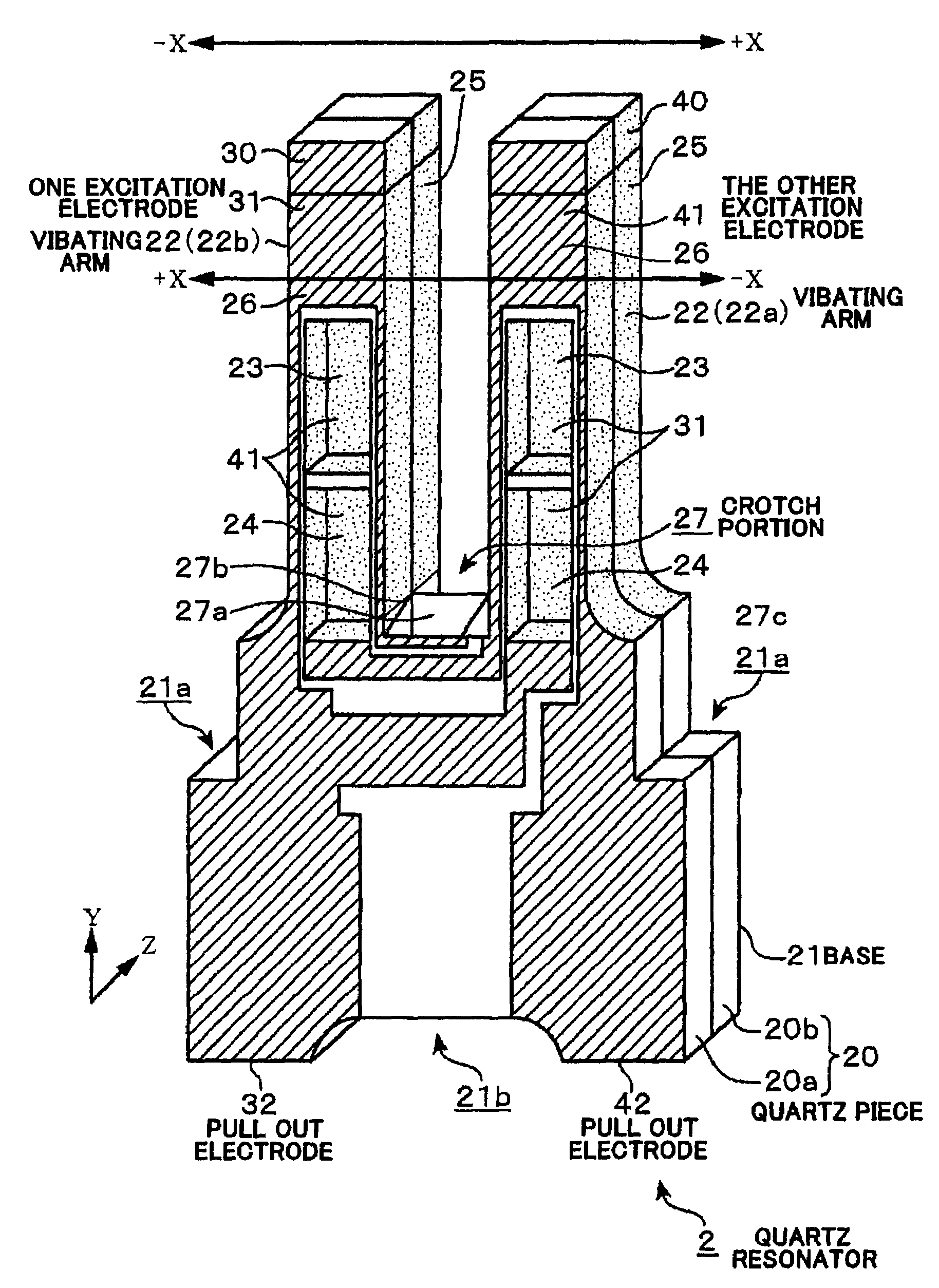

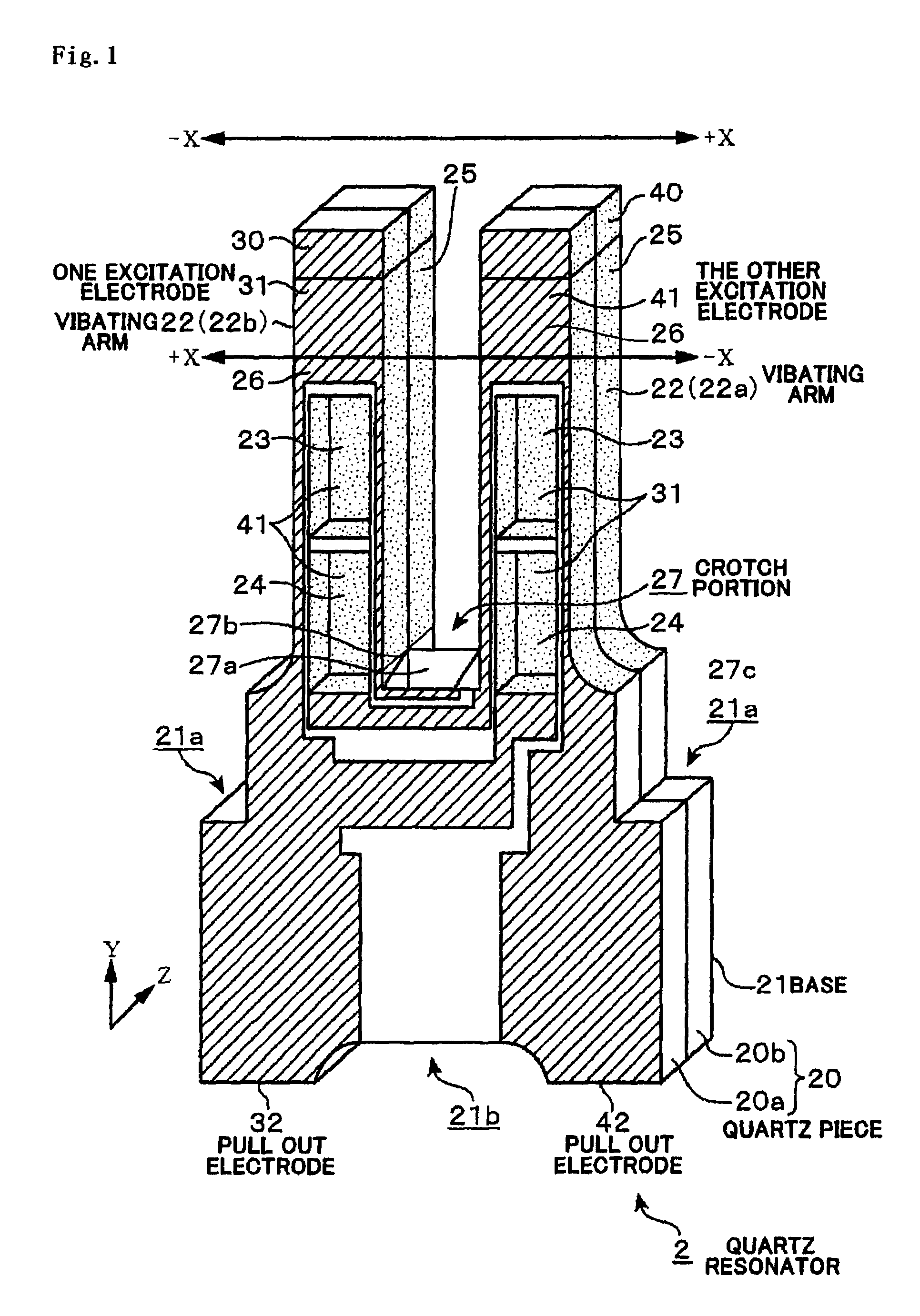

Method of manufacturing a quartz resonator

InactiveUS7596851B2Suppressing short circuitingAvoid stayingPrinted circuit assemblingPiezoelectric/electrostrictive device manufacture/assemblyTuning forkEngineering

Owner:NIHON DEMPA KOGYO CO LTD

Array Power Supply-Based Screening of Static Random Access Memory Cells for Bias Temperature Instability

ActiveUS20150340084A1Efficient and accurate identificationYield minimizationDigital storageStatic random-access memoryNon symmetric

A method of screening complementary metal-oxide-semiconductor CMOS integrated circuits, such as integrated circuits including CMOS static random access memory (SRAM) cells, for transistors susceptible to transistor characteristic shifts over operating time. For the example of SRAM cells formed of cross-coupled CMOS inverters, separate ground voltage levels can be applied to the source nodes of the driver transistors, or separate power supply voltage levels can be applied to the source nodes of the load transistors (or both). Asymmetric bias voltages applied to the transistors in this manner will reduce the transistor drive current, and can thus mimic the effects of bias temperature instability (BTI). Cells that are vulnerable to threshold voltage shift over time can thus be identified.

Owner:TEXAS INSTR INC

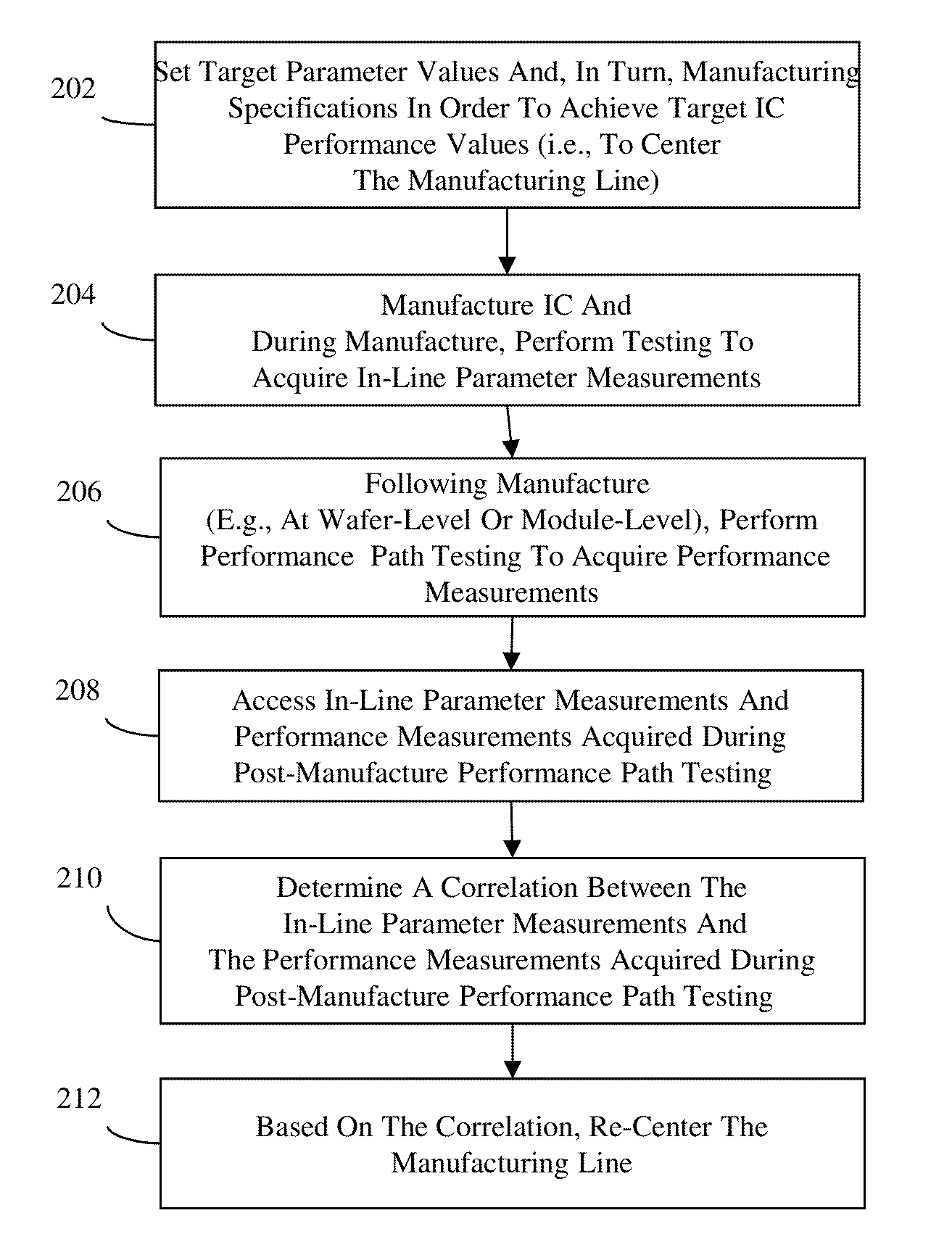

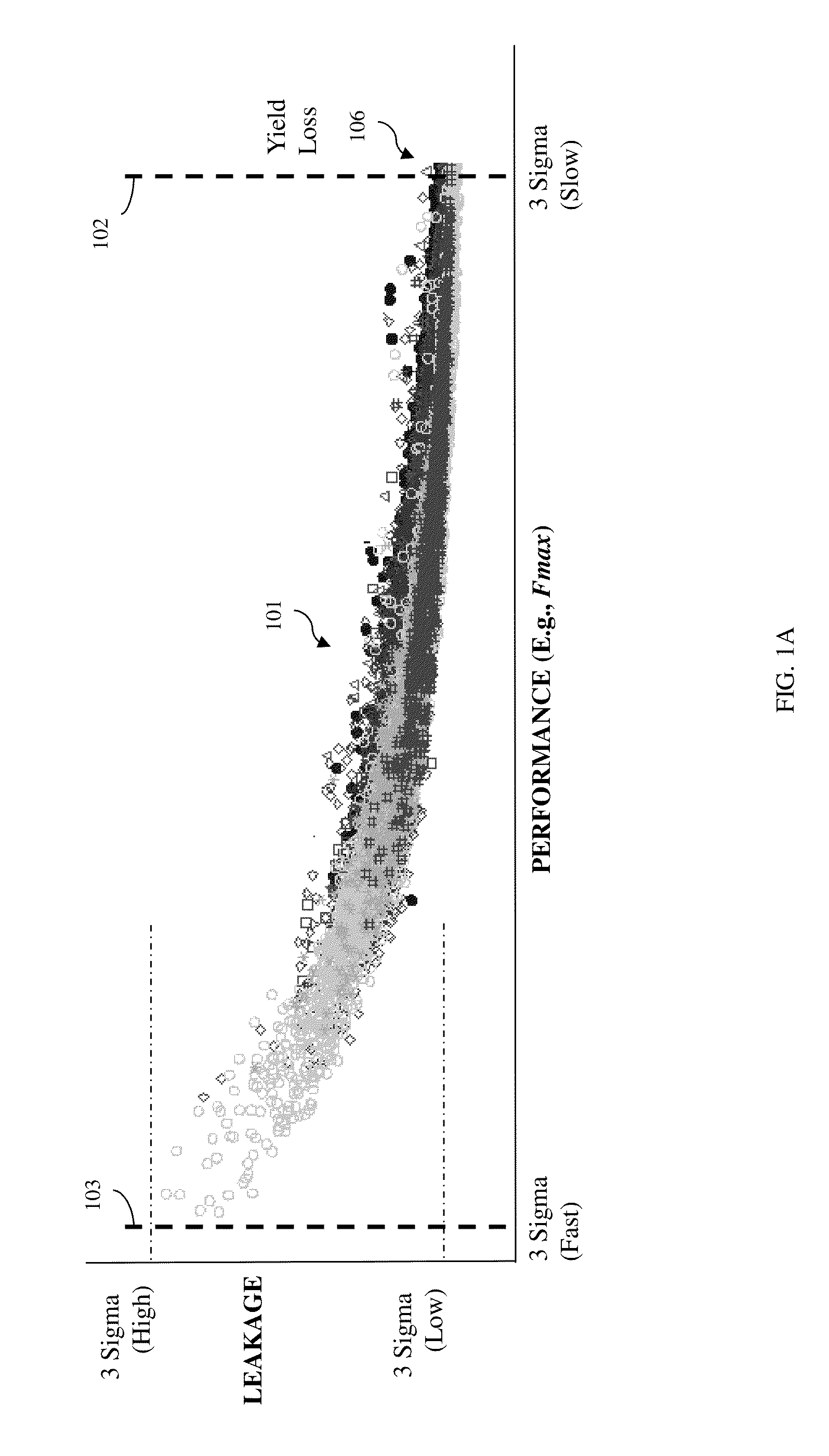

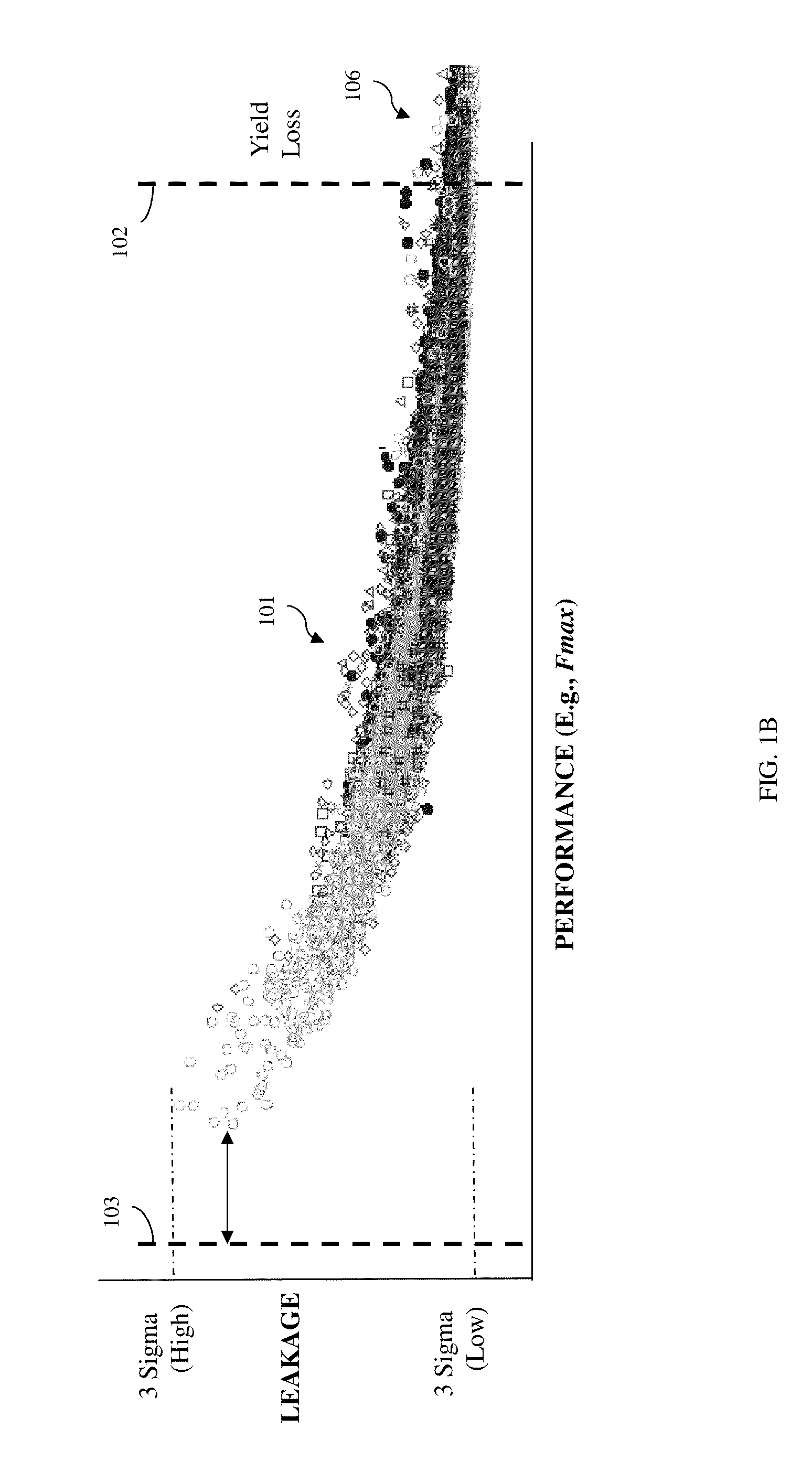

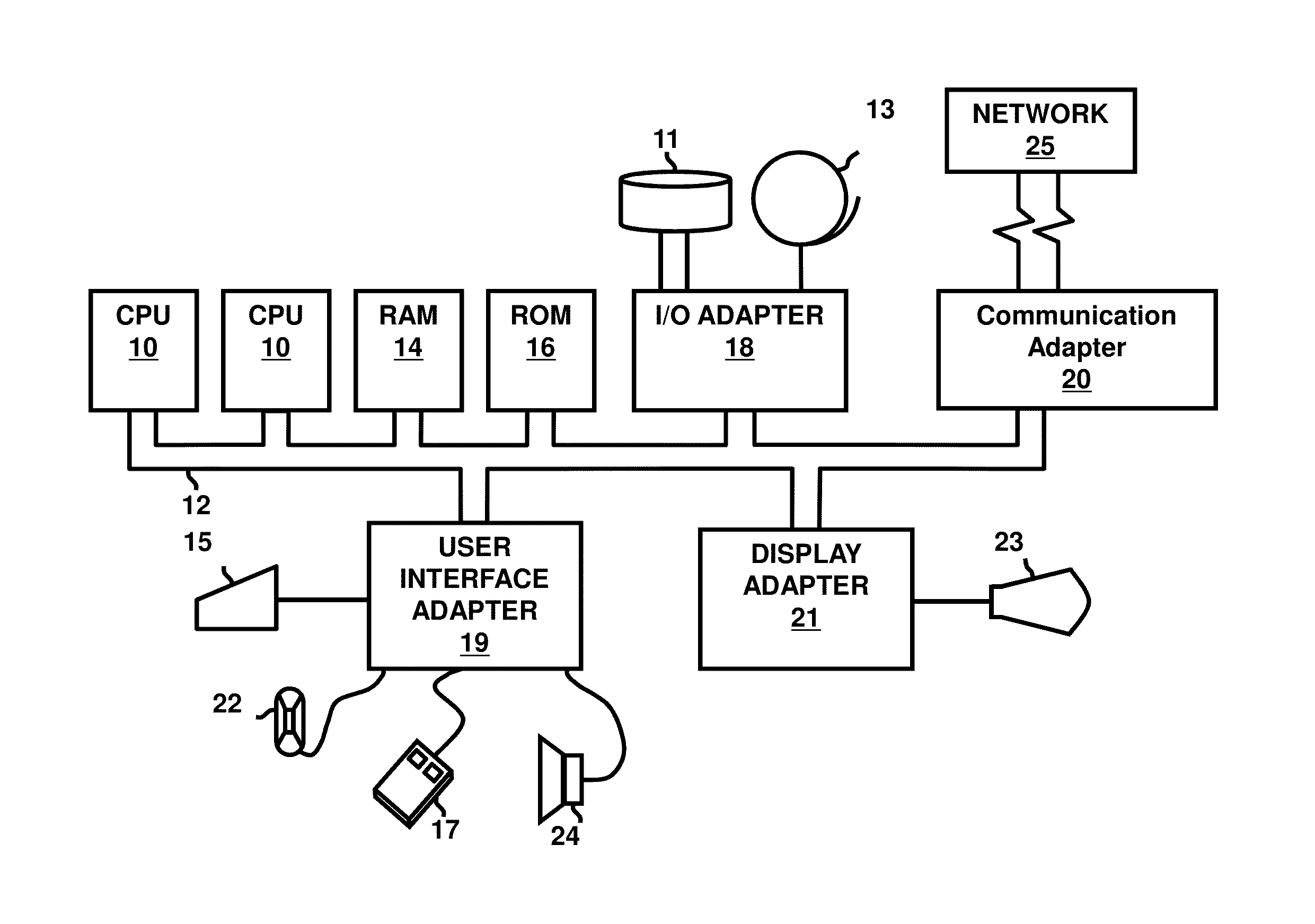

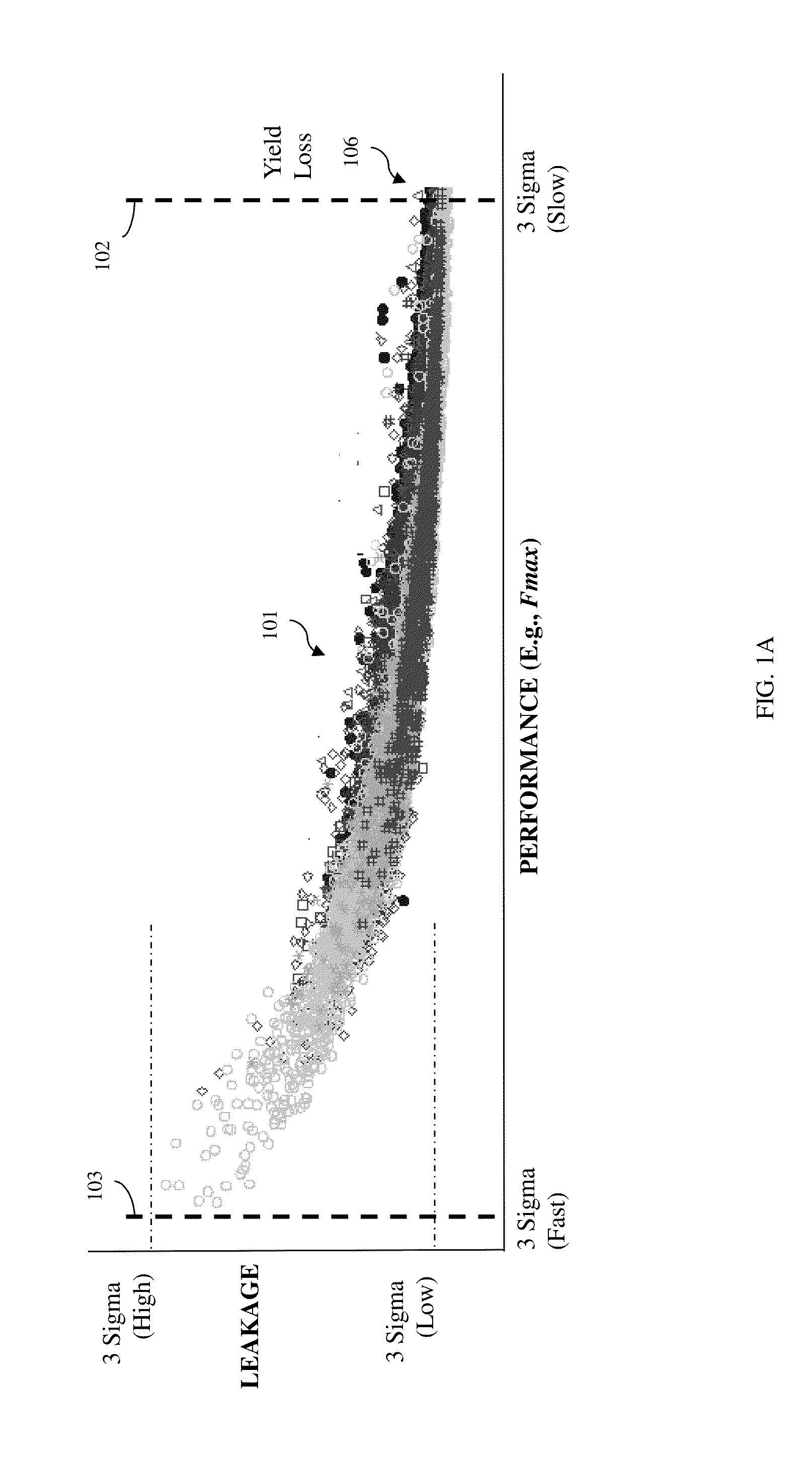

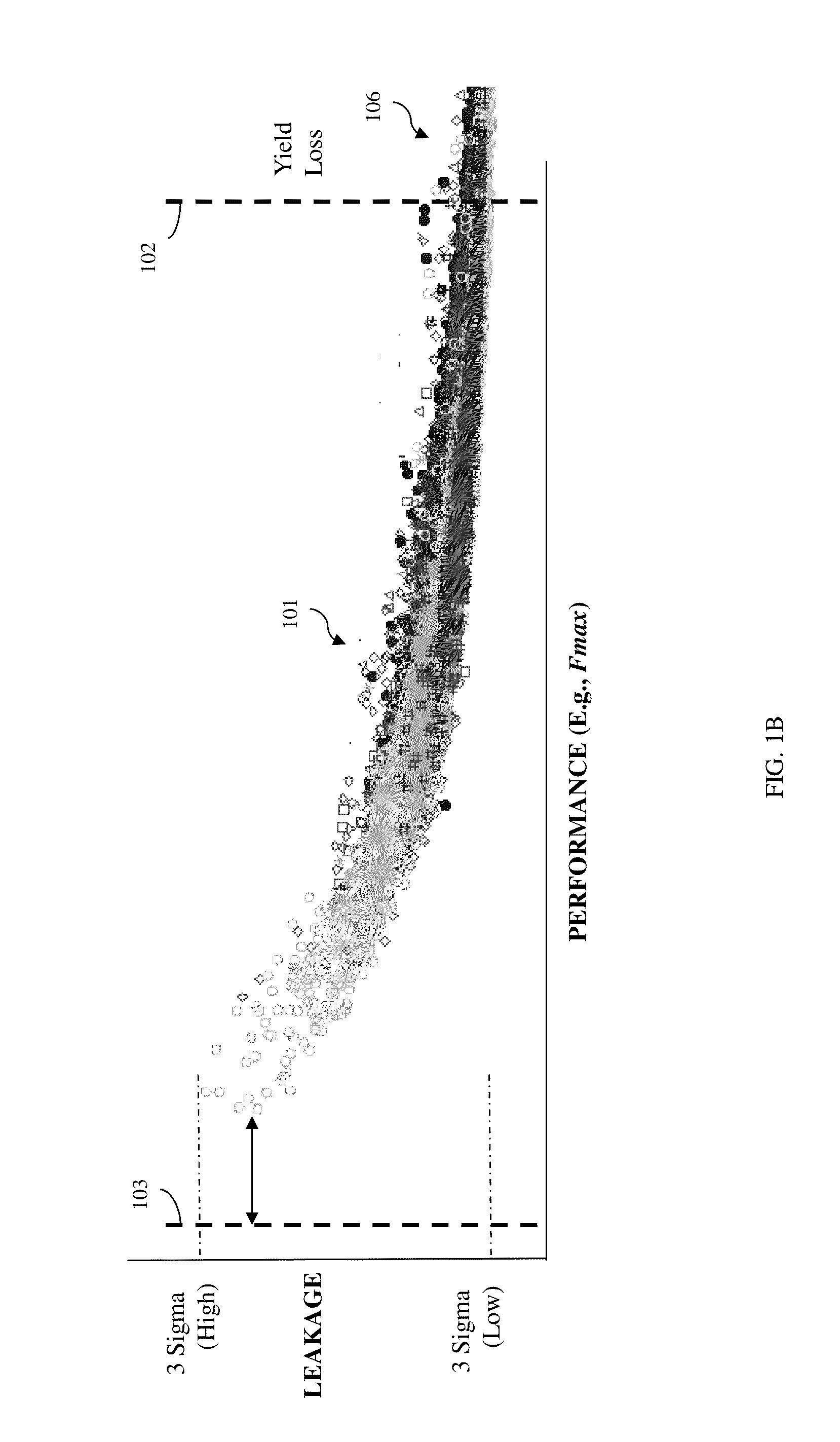

Integrated circuit product yield optimization using the results of performance path testing

InactiveUS9058034B2High yieldYield minimizationTotal factory controlSpecial data processing applicationsEngineeringManufacturing line

Disclosed are embodiments of a method, system and computer program product for optimizing integrated circuit product yield by re-centering the manufacturing line and, optionally, adjusting wafer-level chip dispositioning rules based on the results of post-manufacture (e.g., wafer-level or module-level) performance path testing. In the embodiments, a correlation is made between in-line parameter measurements and performance measurements acquired during the post-manufacture performance path testing. Then, based on this correlation, the manufacturing line can be re-centered. Optionally, an additional correlation is made between performance measurements acquired during wafer-level performance testing and performance measurements acquired particularly during module-level performance path testing and, based on this additional correlation, adjustments can be made to the wafer-level chip dispositioning rules to further minimize yield loss.

Owner:GLOBALFOUNDRIES INC

Integrated circuit product yield optimization using the results of performance path testing

InactiveUS20140046466A1Optimizing integrated circuit product yieldMinimizing yield lossTotal factory controlSpecial data processing applicationsEngineeringManufacturing line

Disclosed are embodiments of a method, system and computer program product for optimizing integrated circuit product yield by re-centering the manufacturing line and, optionally, adjusting wafer-level chip dispositioning rules based on the results of post-manufacture (e.g., wafer-level or module-level) performance path testing. In the embodiments, a correlation is made between in-line parameter measurements and performance measurements acquired during the post-manufacture performance path testing. Then, based on this correlation, the manufacturing line can be re-centered. Optionally, an additional correlation is made between performance measurements acquired during wafer-level performance testing and performance measurements acquired particularly during module-level performance path testing and, based on this additional correlation, adjustments can be made to the wafer-level chip dispositioning rules to further minimize yield loss.

Owner:GLOBALFOUNDRIES INC