Patents

Literature

70results about How to "Avoid contact resistance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

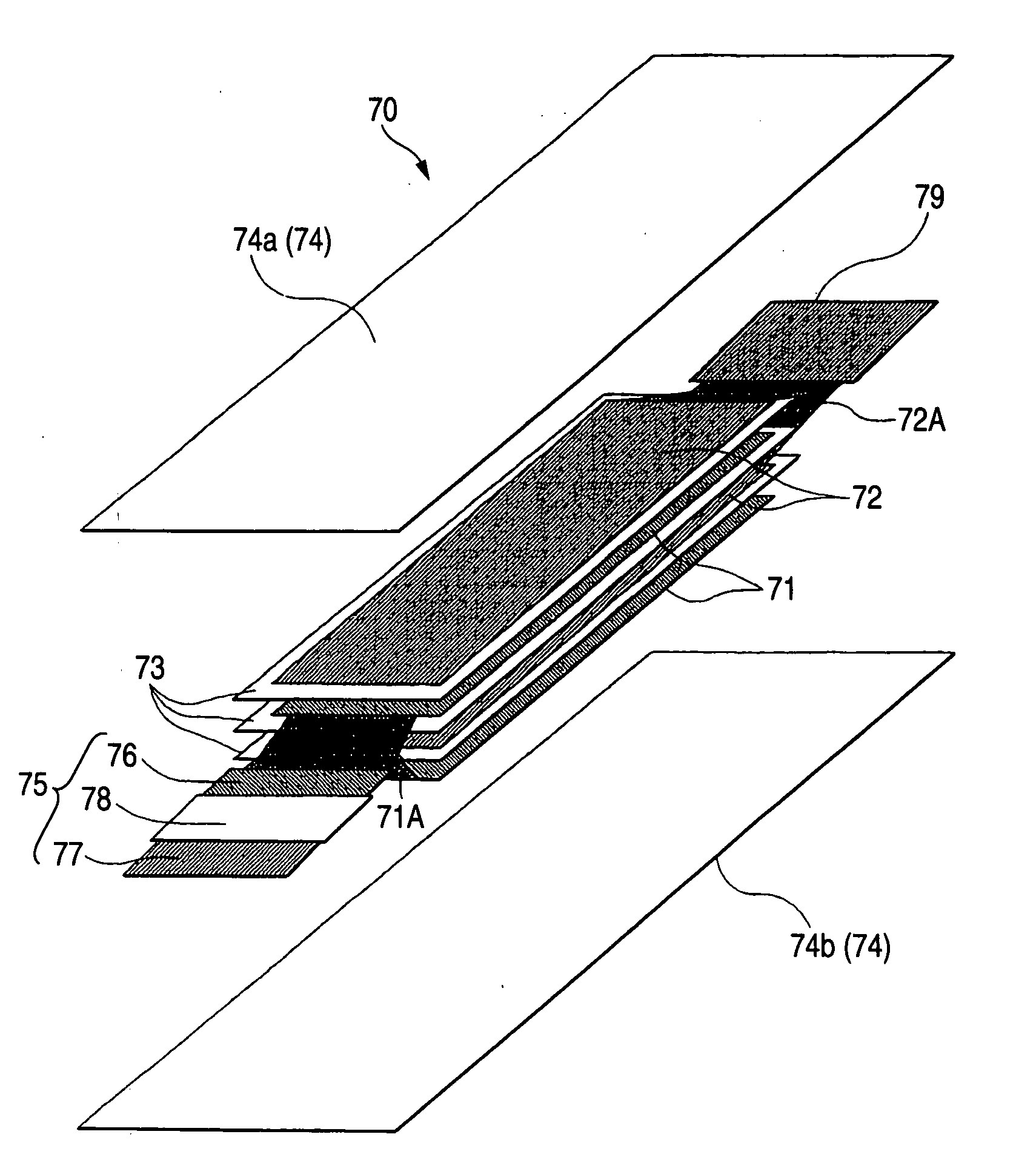

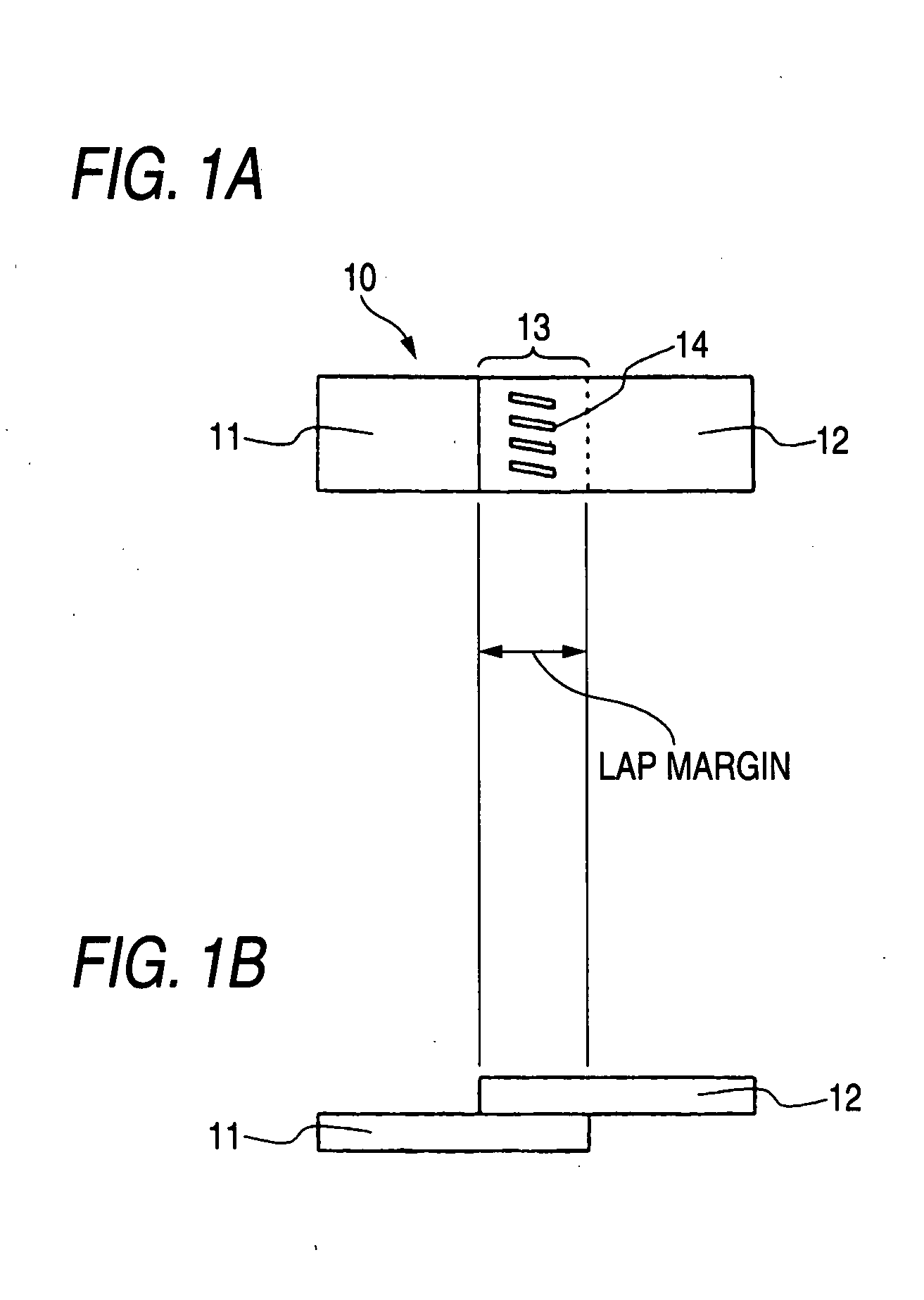

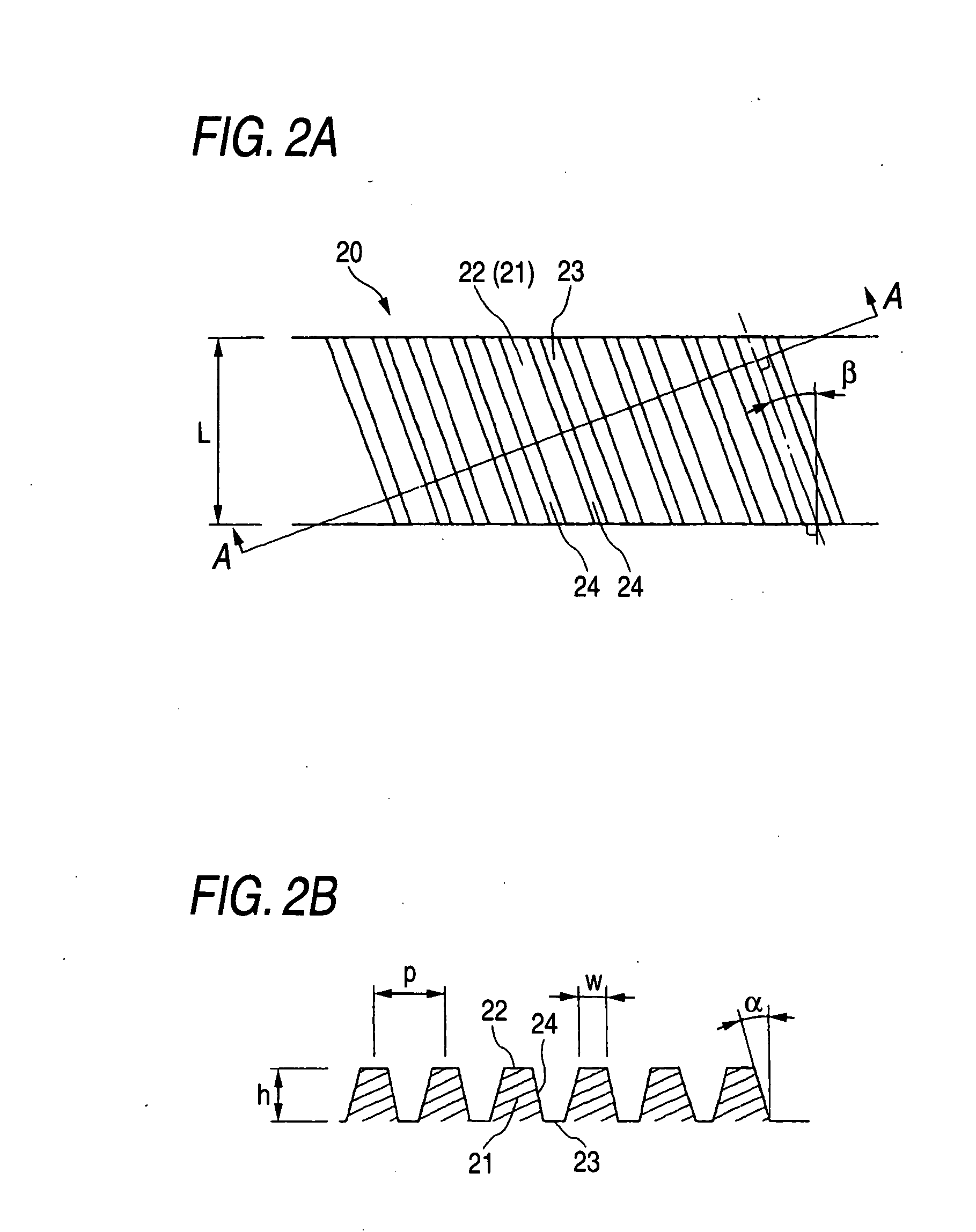

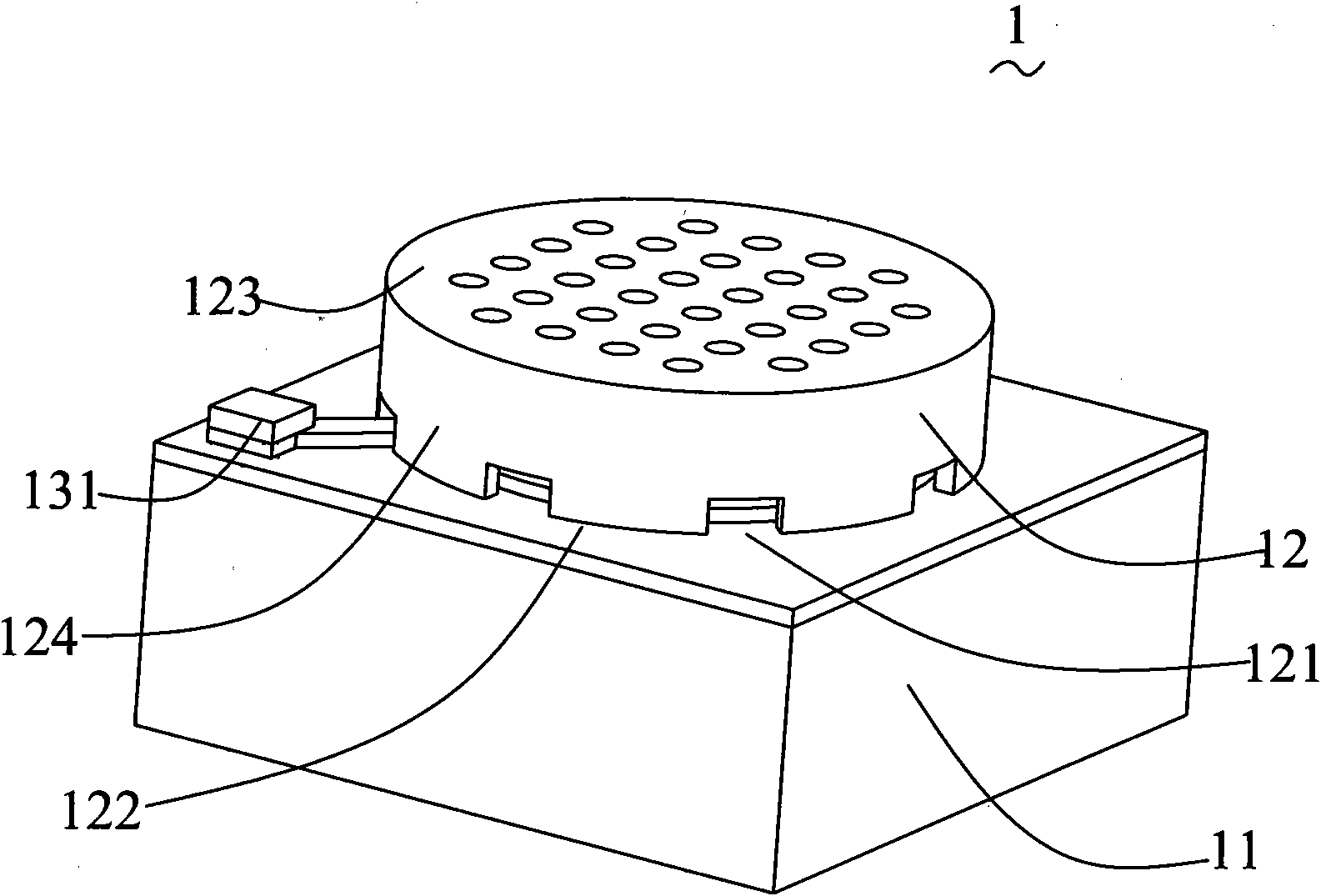

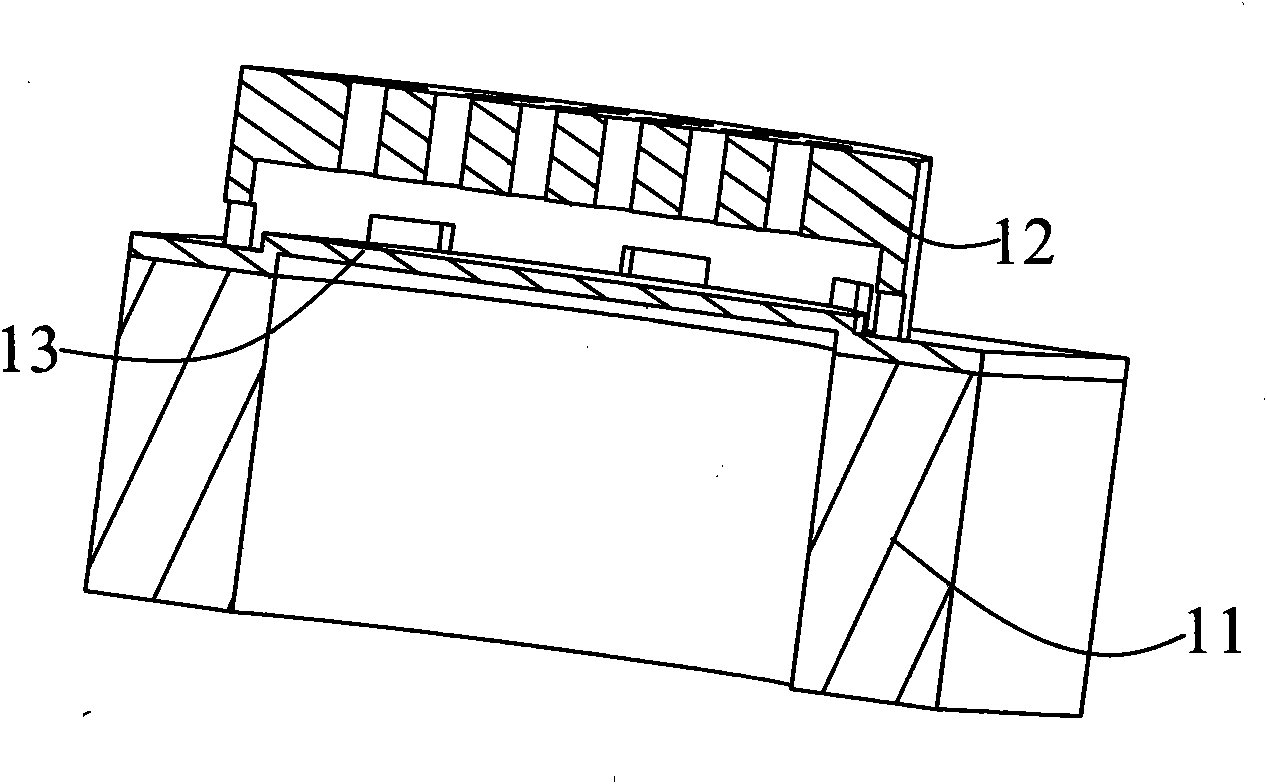

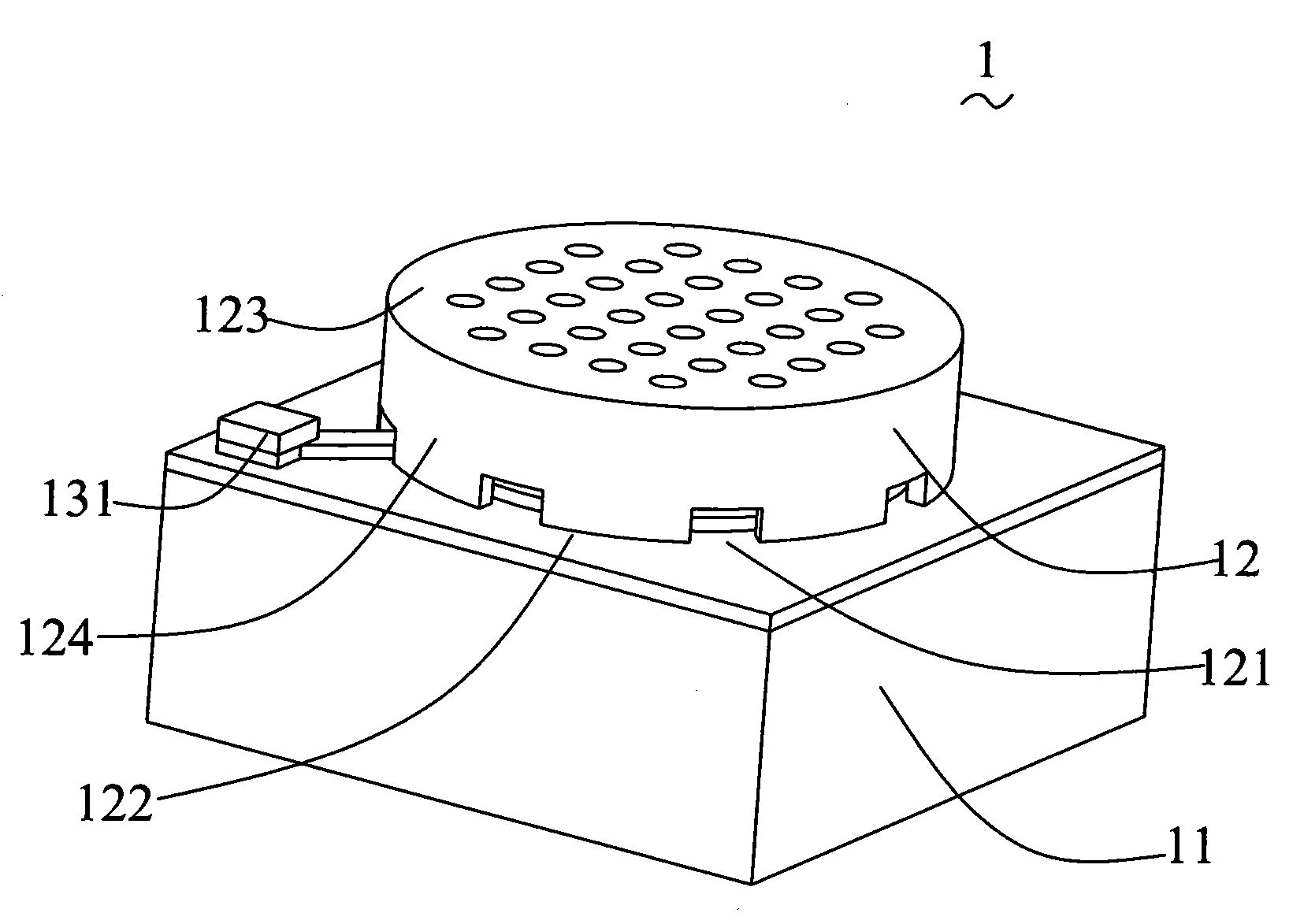

Lead member and boding method thereof and nonaqueous electrolyte electricity storing device

InactiveUS20080102362A1Easy to carryPrevent leakageHybrid capacitor electrolytesHybrid capacitor electrodesElectricityMechanical engineering

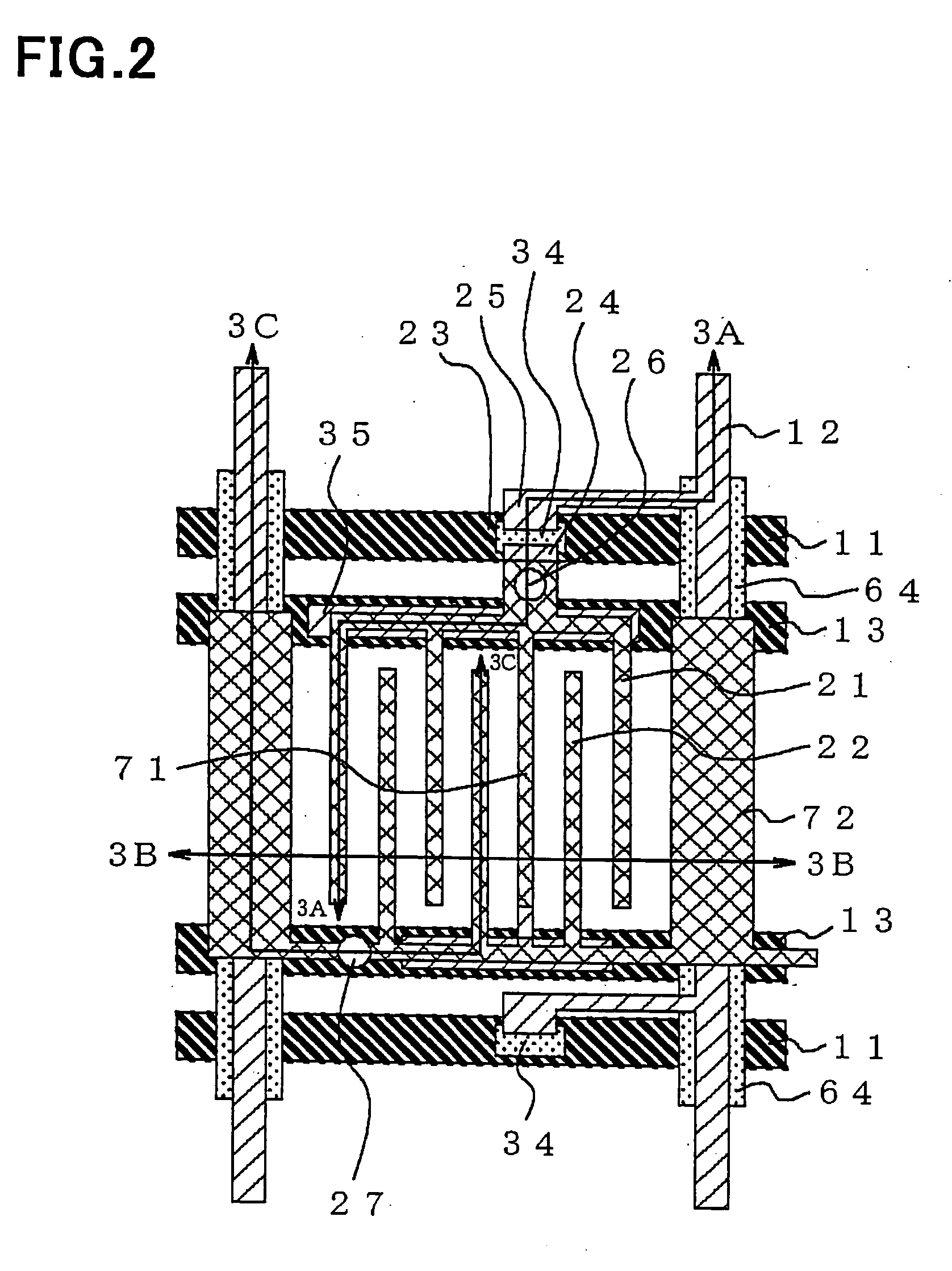

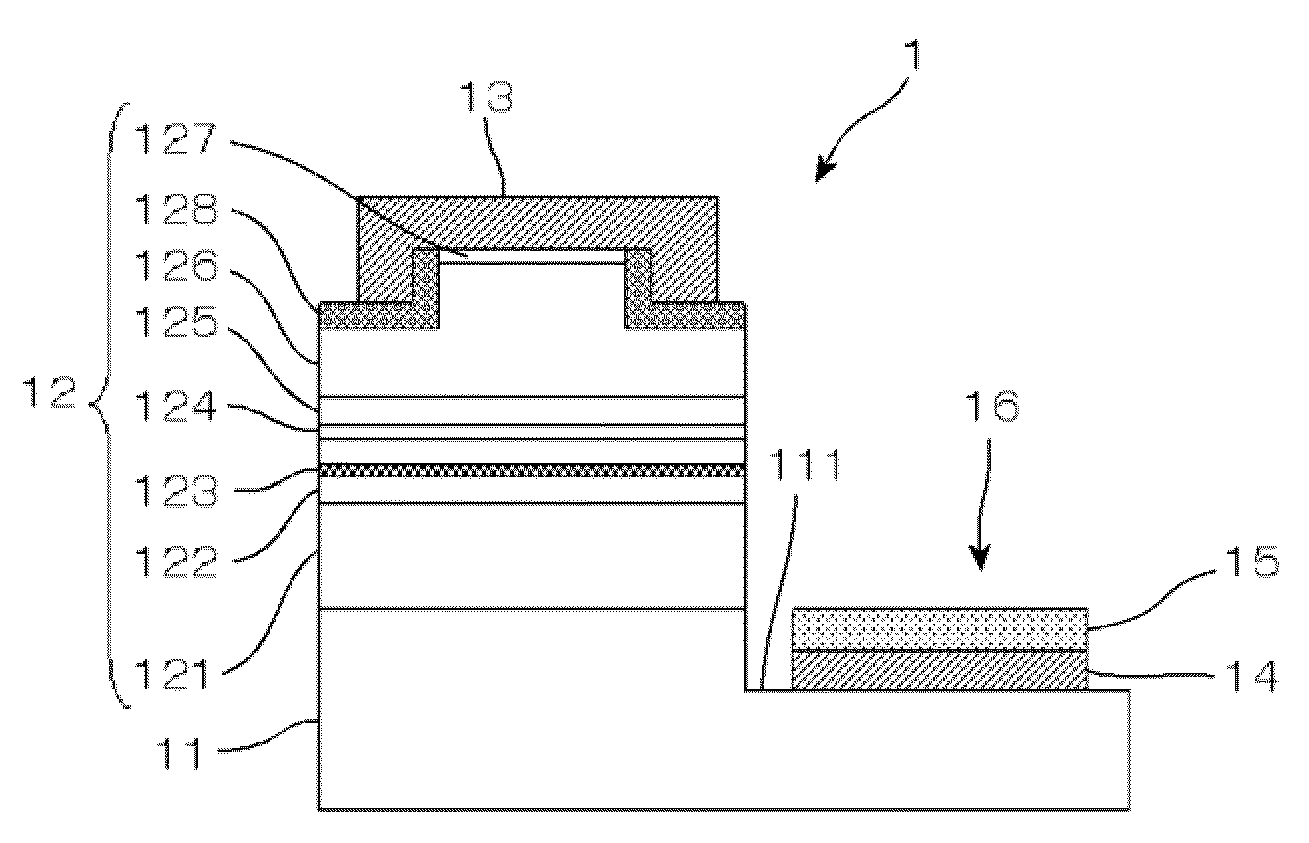

A first member 11 and a second member 12 connected to each other are provided. The first member 11 is electrically connected to an electrode. The second member 12 is bonded to a position of the first member 11 remote from the electrode and is constituted by a material of a kind different from that of the first member 11. An overlapped portion 13 is formed at the first member 11 and the second member 12 and the overlapped portion 13 is bonded by cold welding. By the cold welding, the overlapped portion 13 is formed with a plurality of pressure marks 14 in a recess shape. Each cold pressure welded mark 14 is formed with a deformation mark reducing a depth of the cold pressure welded mark of the recess shape before plastic working by plastically working the overlapped portion 13 in a thickness direction thereof.

Owner:SUMIDEN ASAHI IND LTD +1

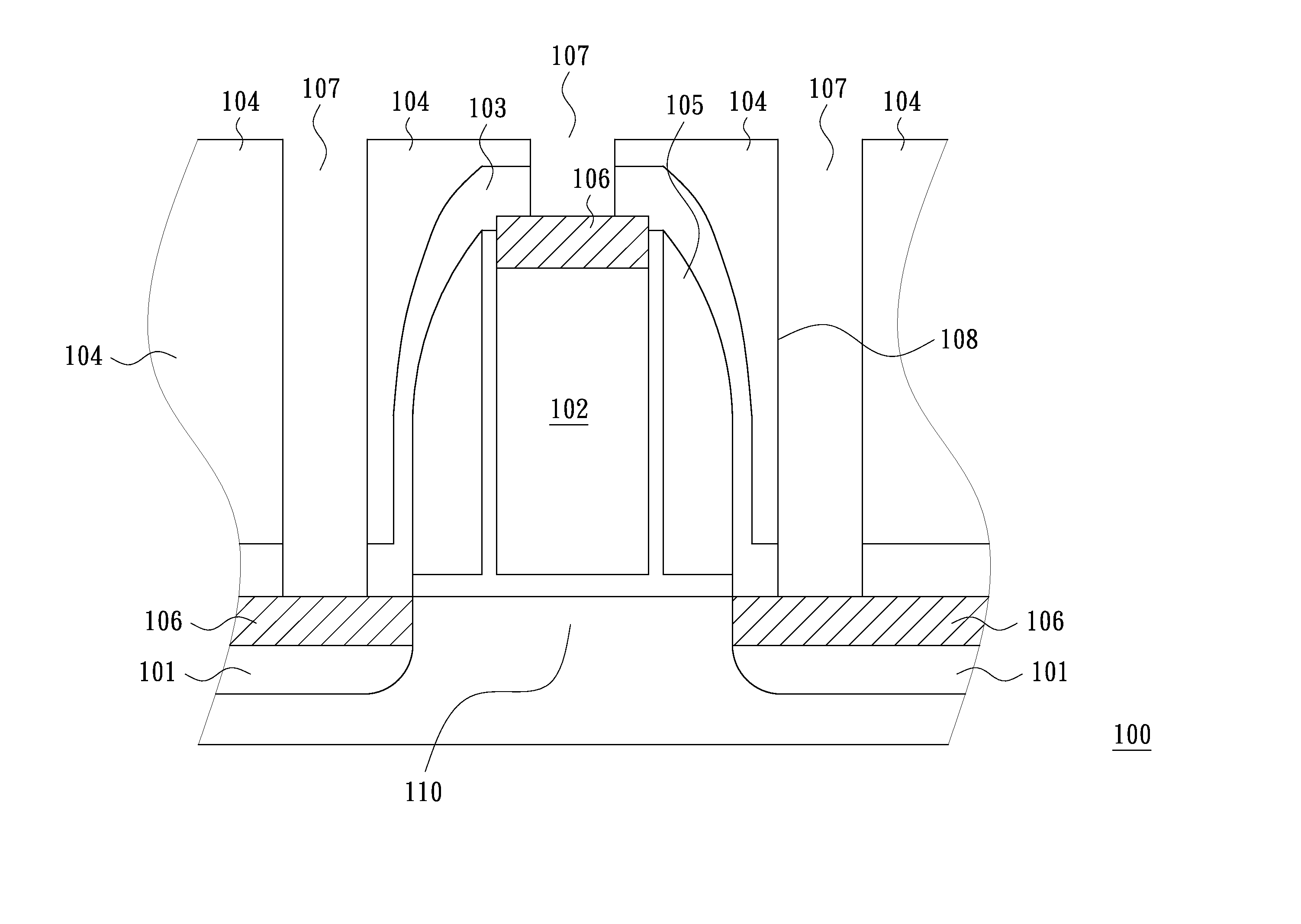

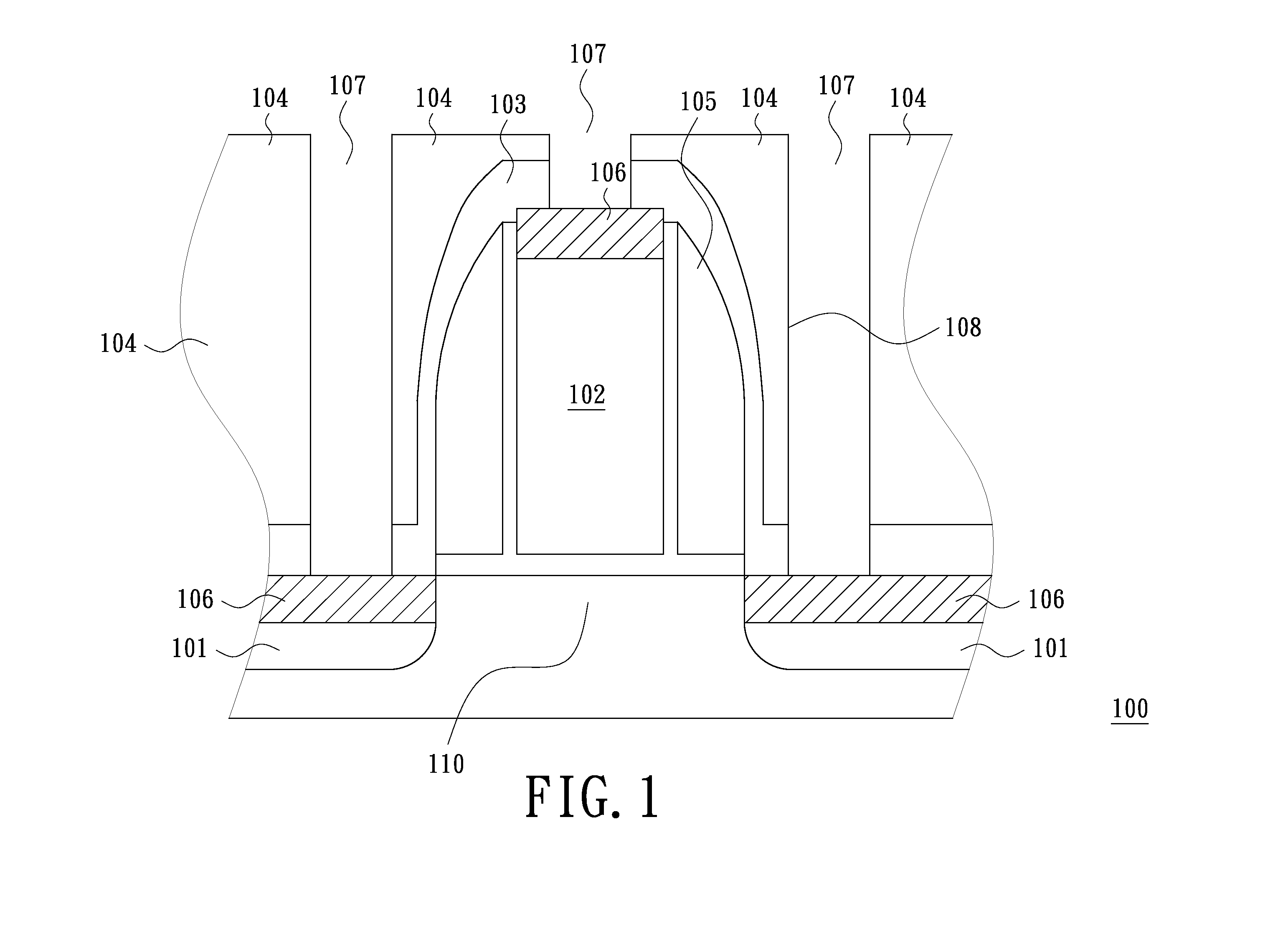

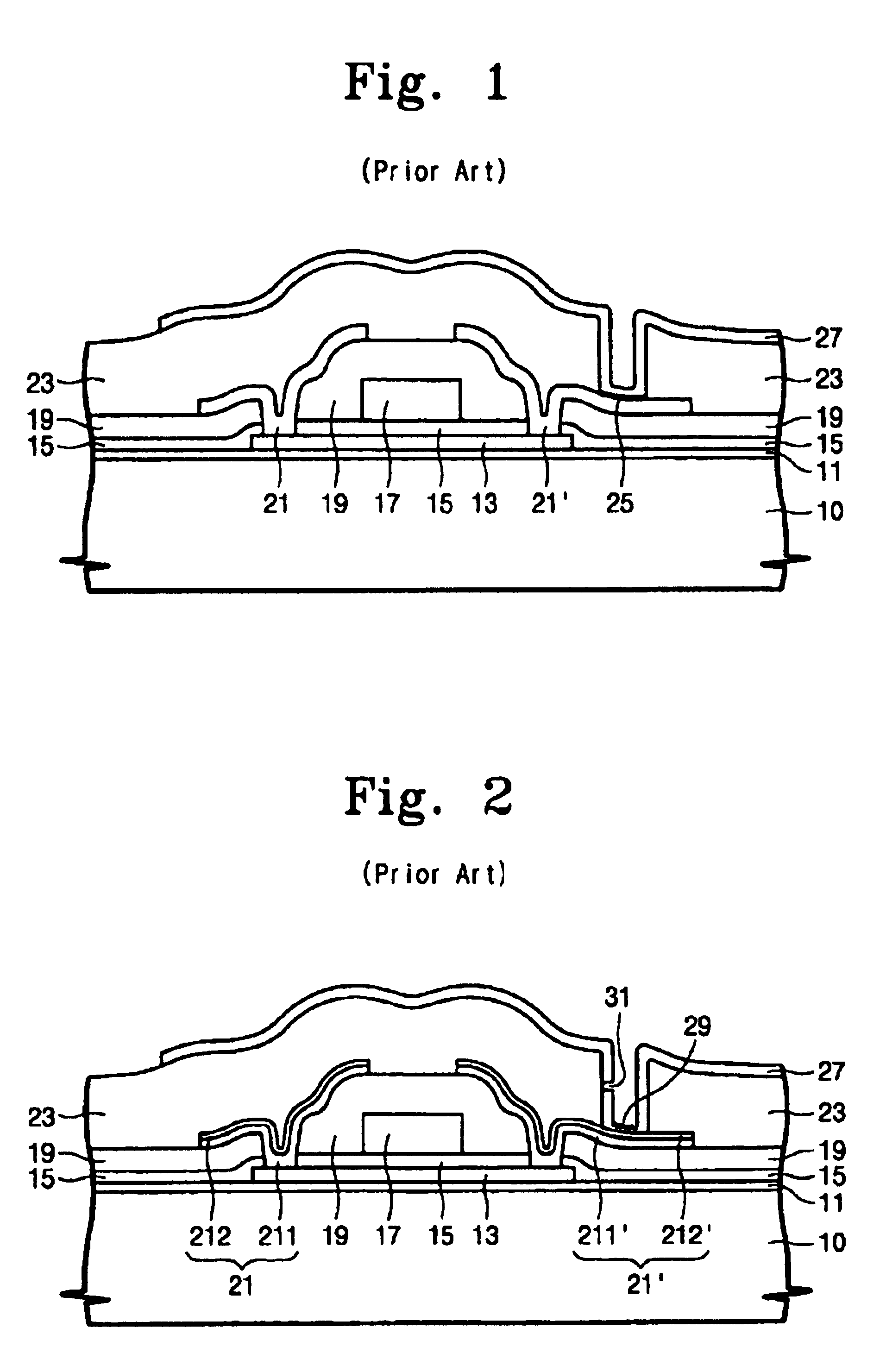

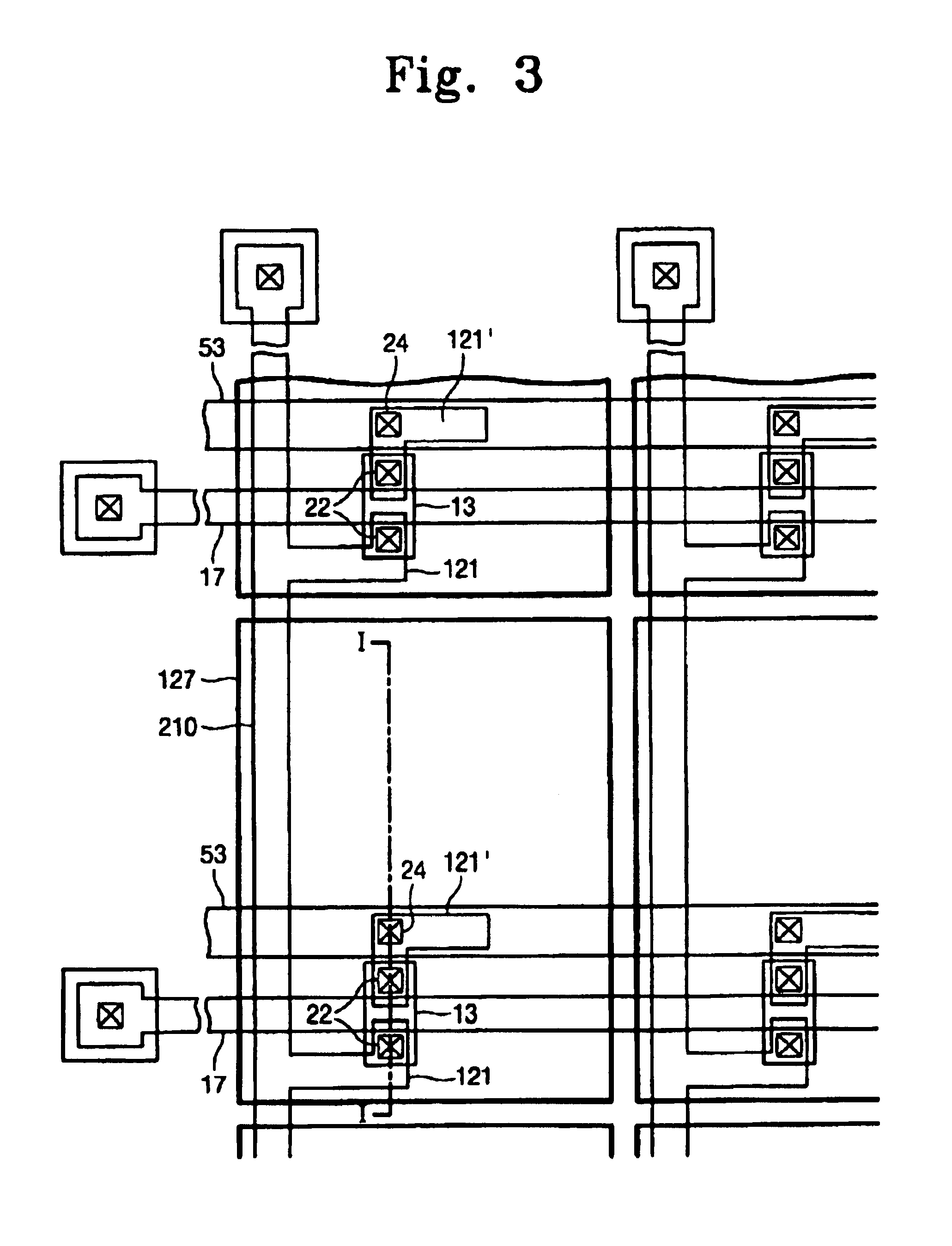

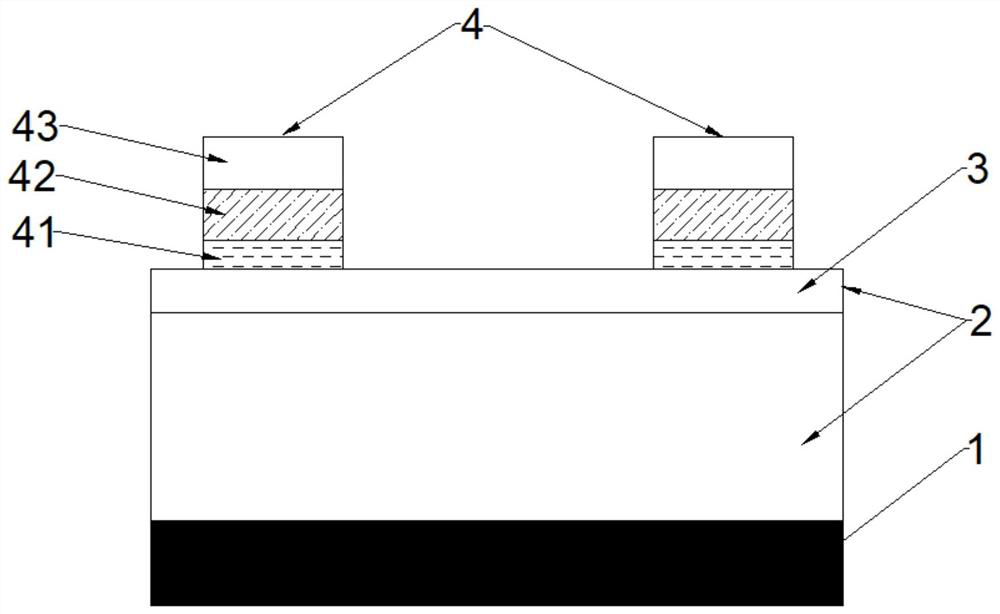

World line structure with single-sided partially recessed gate structure

A word line structure with a single-sided partially recessed gate structure. The word line structure includes a gate structure, a first gate spacer, and a second gate spacer. The gate structure includes a gate dielectric layer, a first gate layer, a second gate layer, and a gate capping layer and has a recess region adjacent to one of opposing sidewalls of the second gate layer. The first gate spacer is disposed over opposing sidewalls of the gate dielectric layer and the first gate layer. The second gate spacer is disposed over opposing sidewalls of the gate structure and covers the first gate spacer. A method for forming a word line structure with a single-sided partially recessed gate structure is also disclosed.

Owner:NAN YA TECH

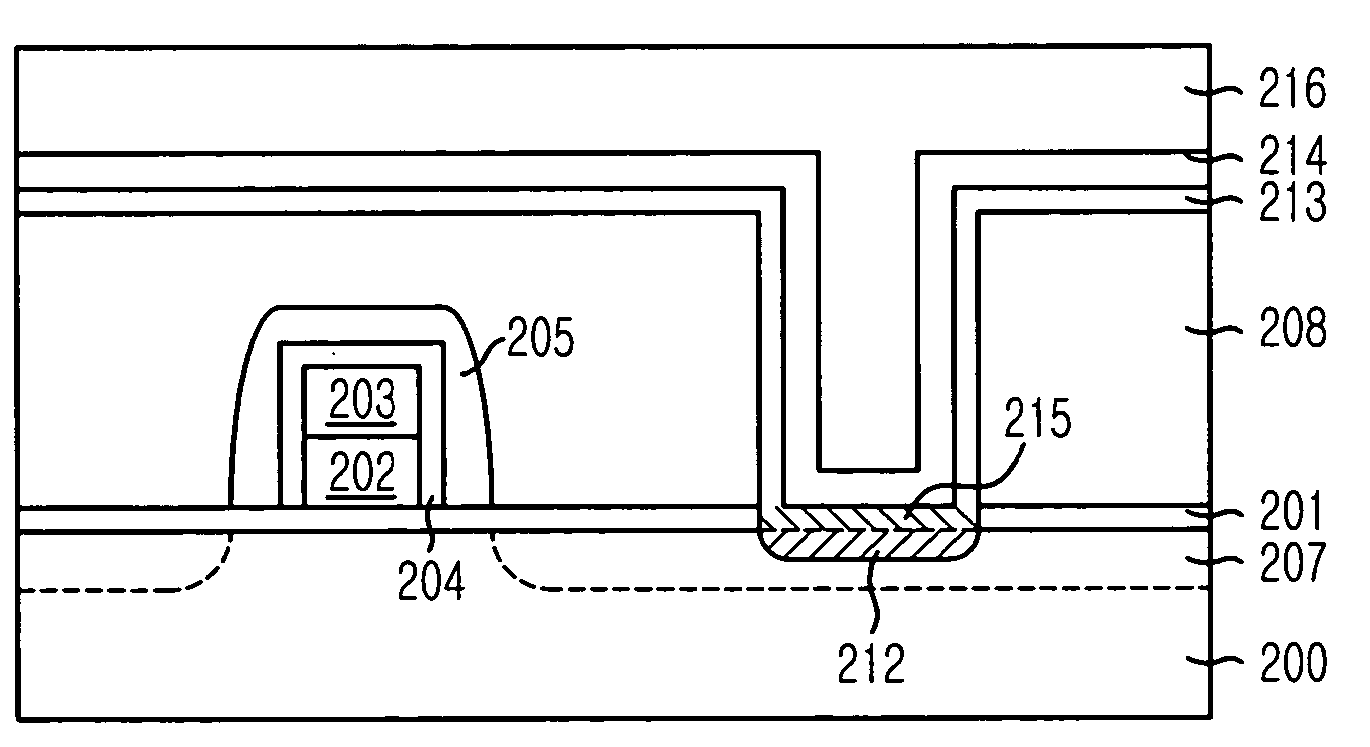

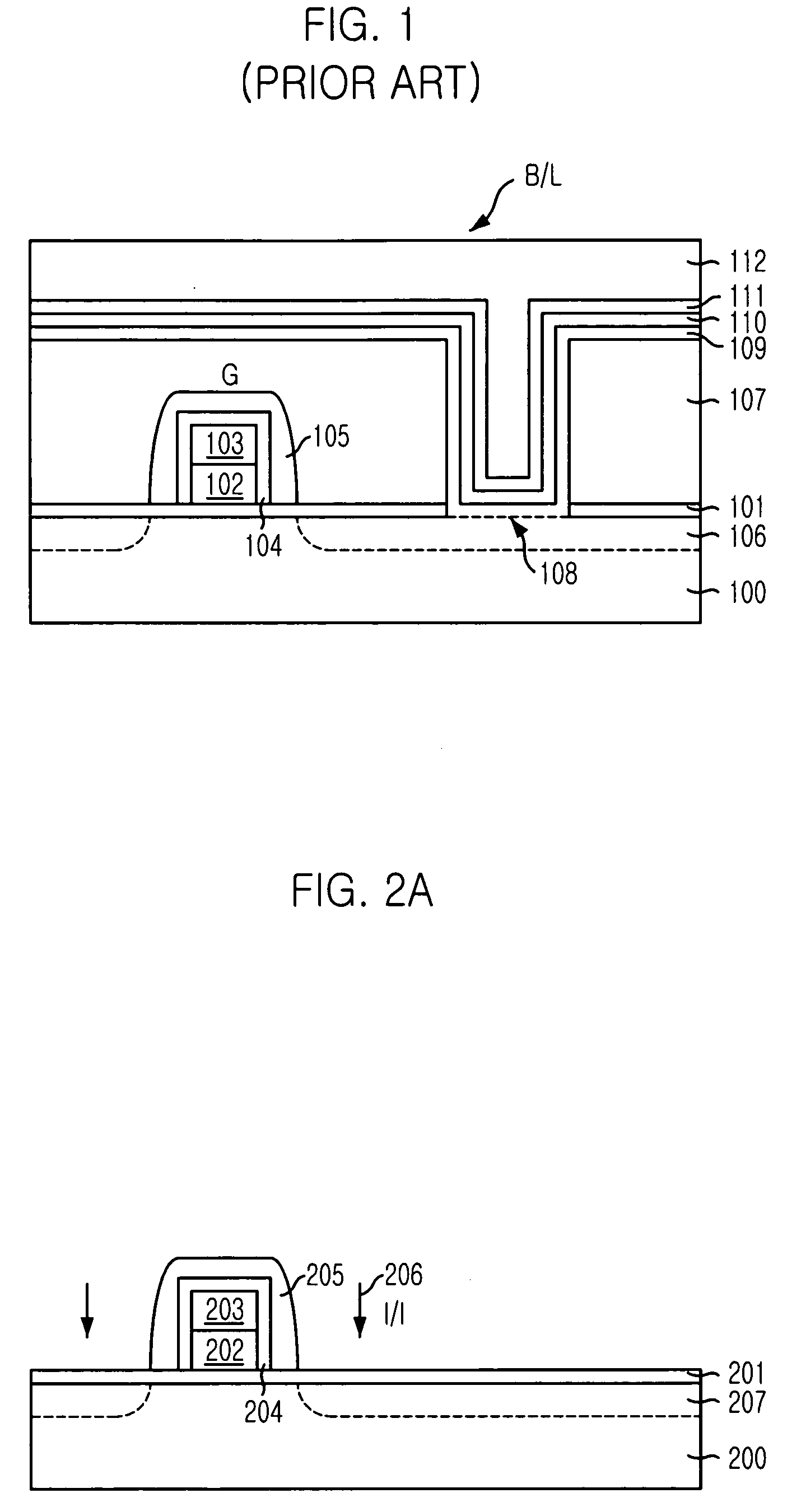

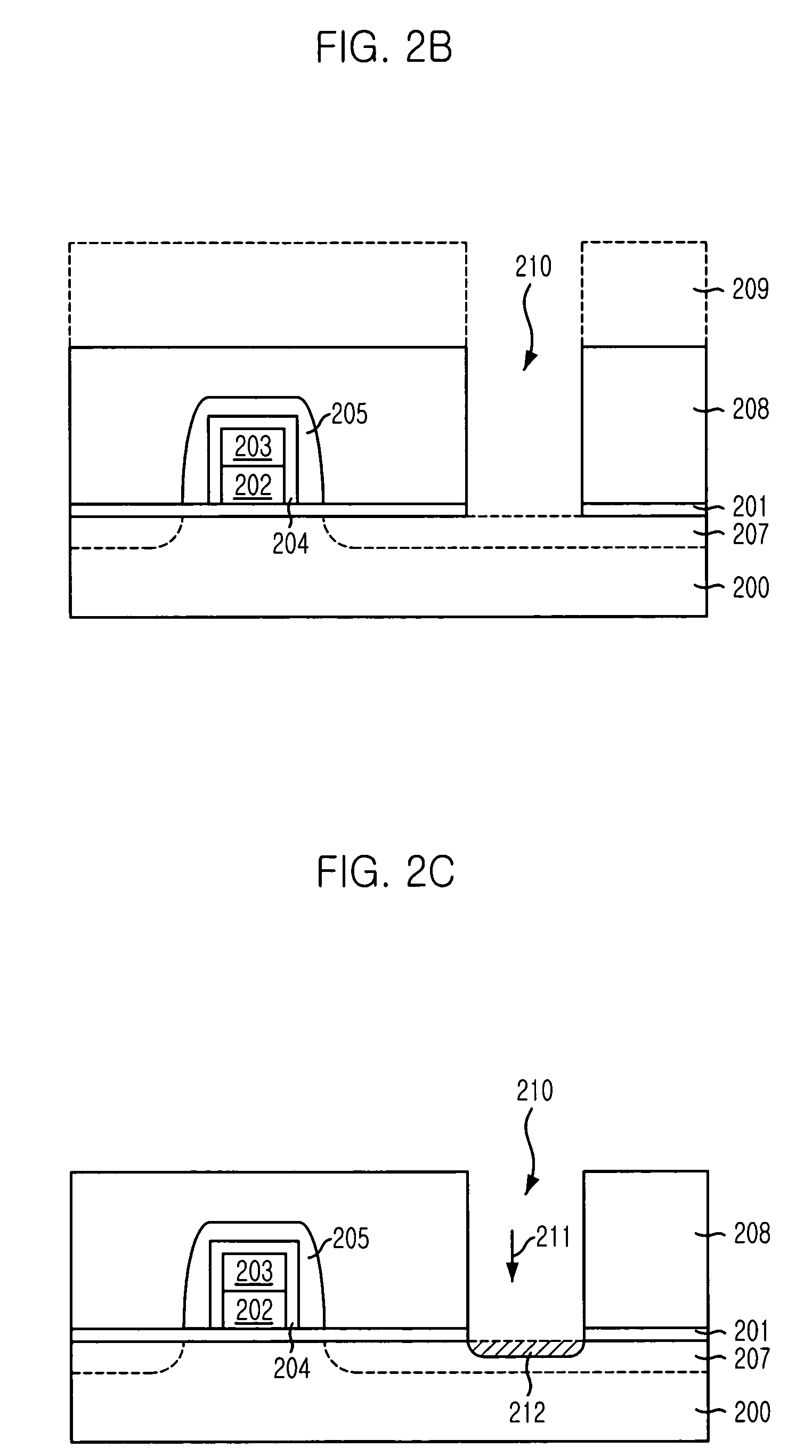

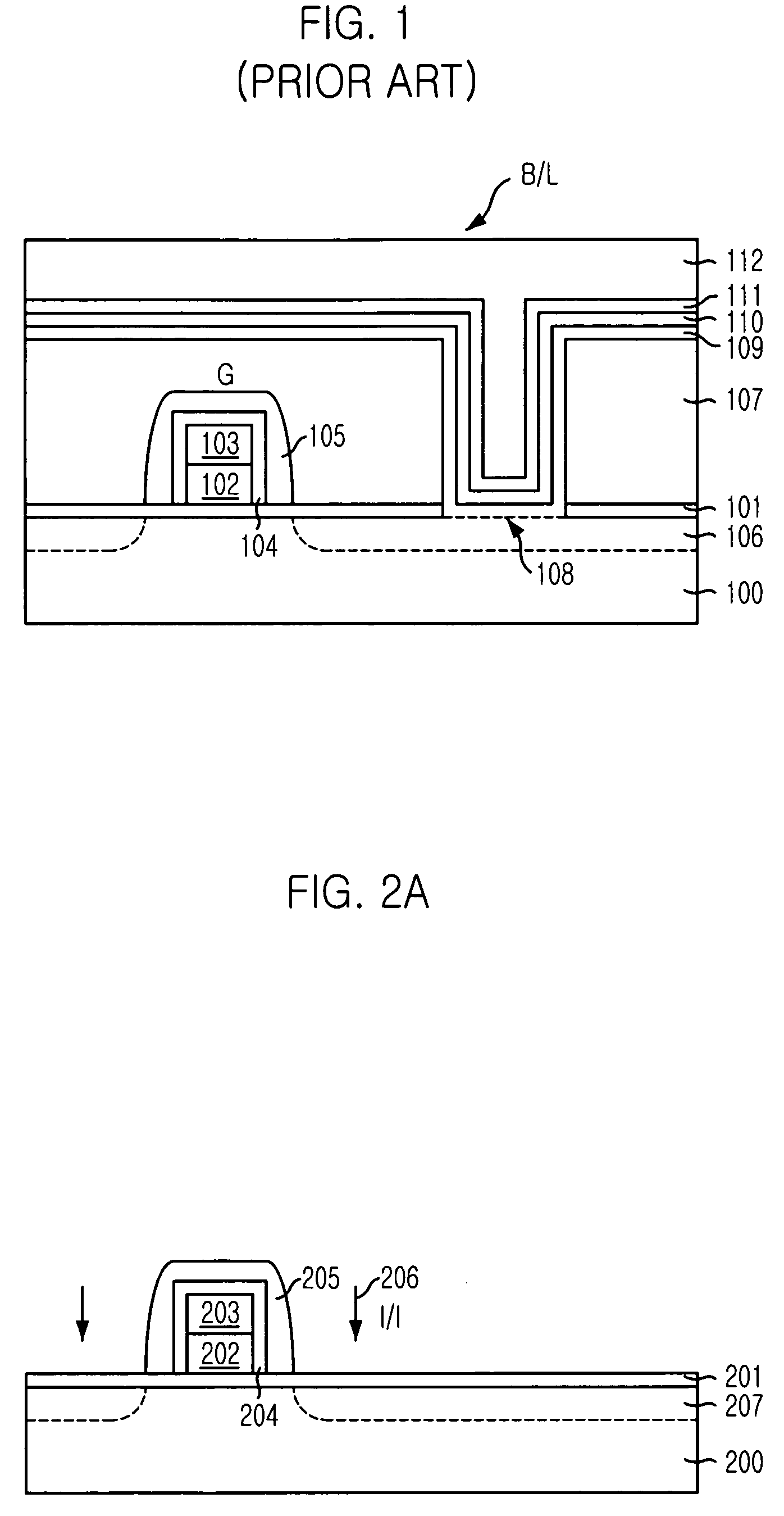

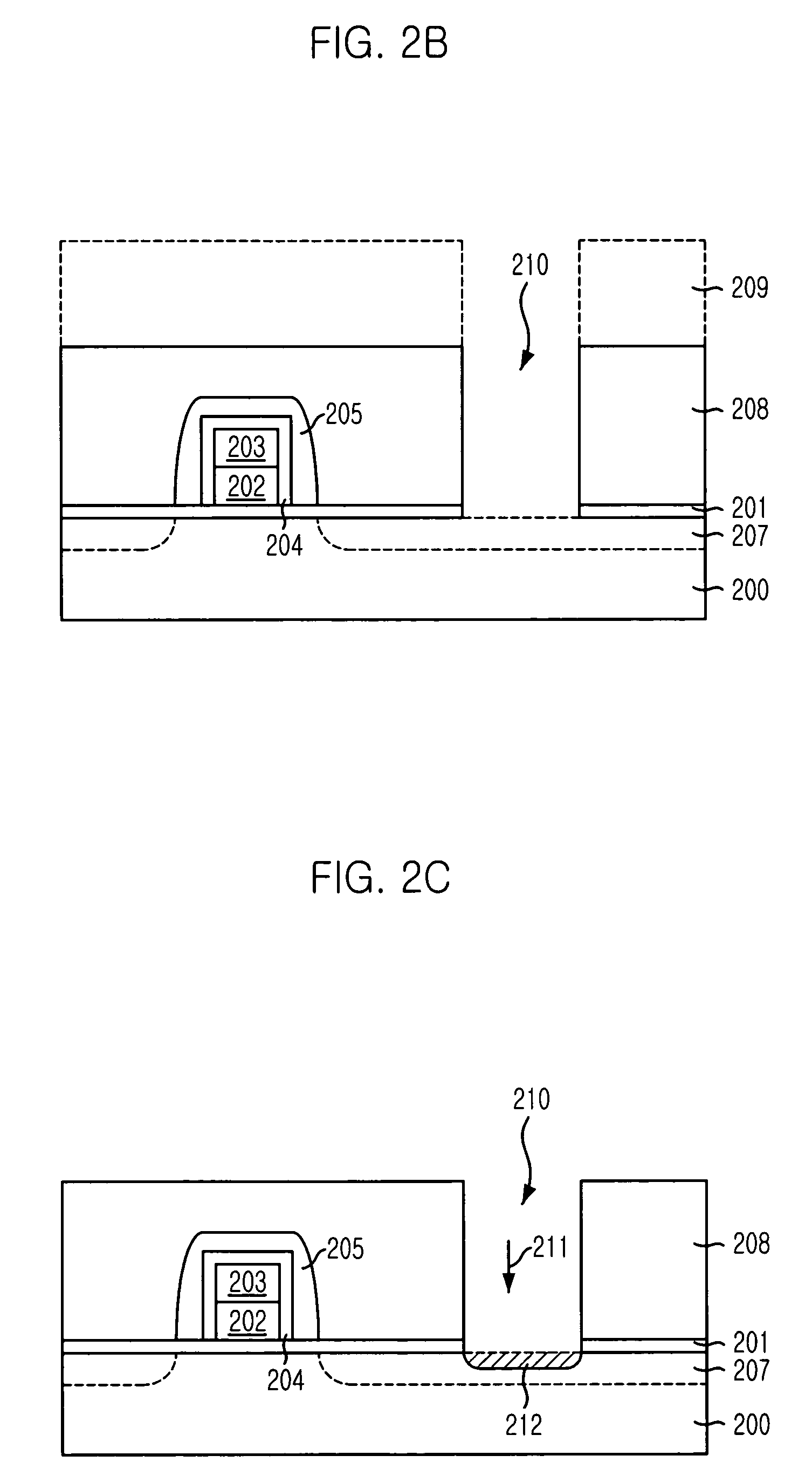

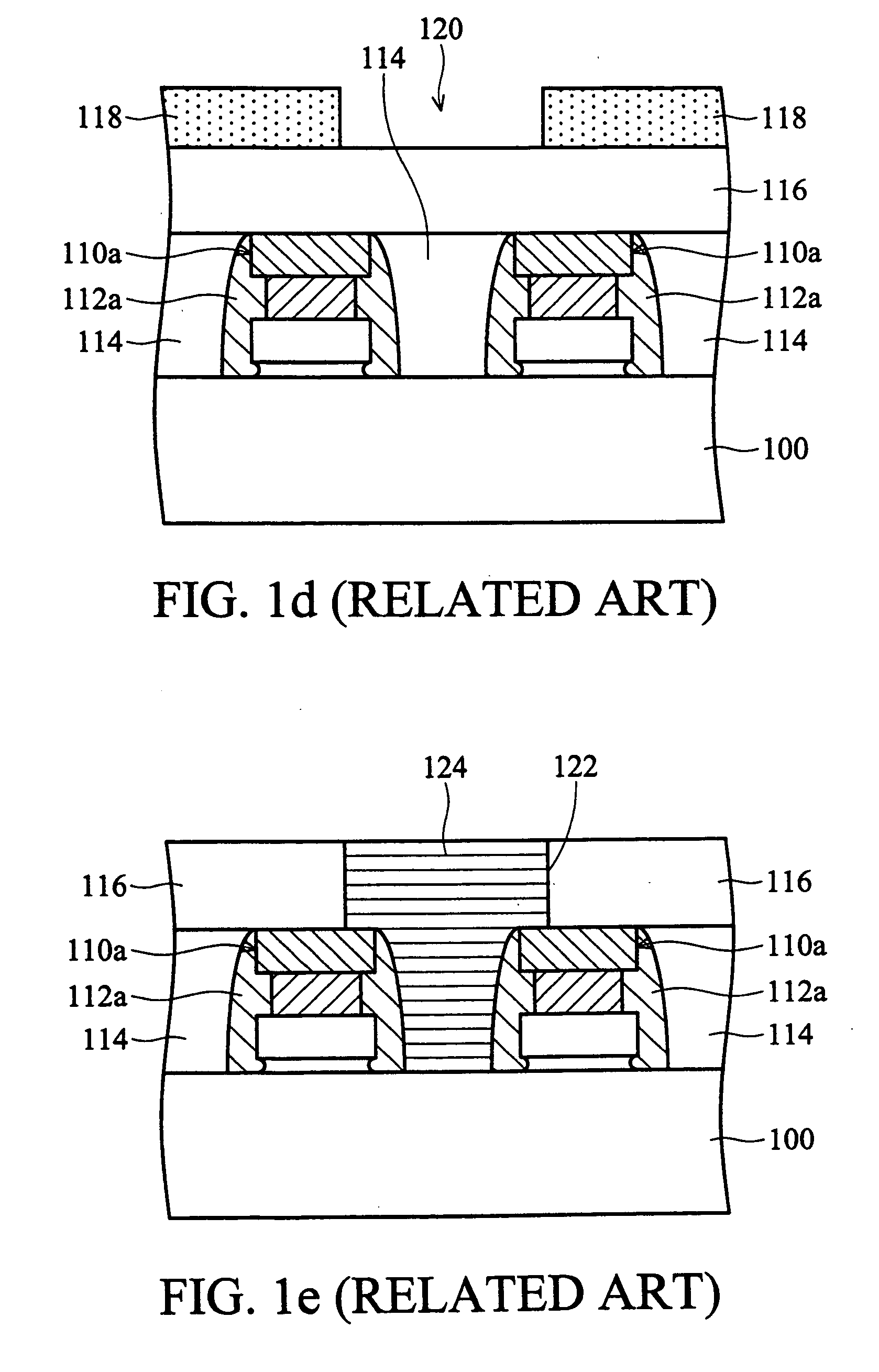

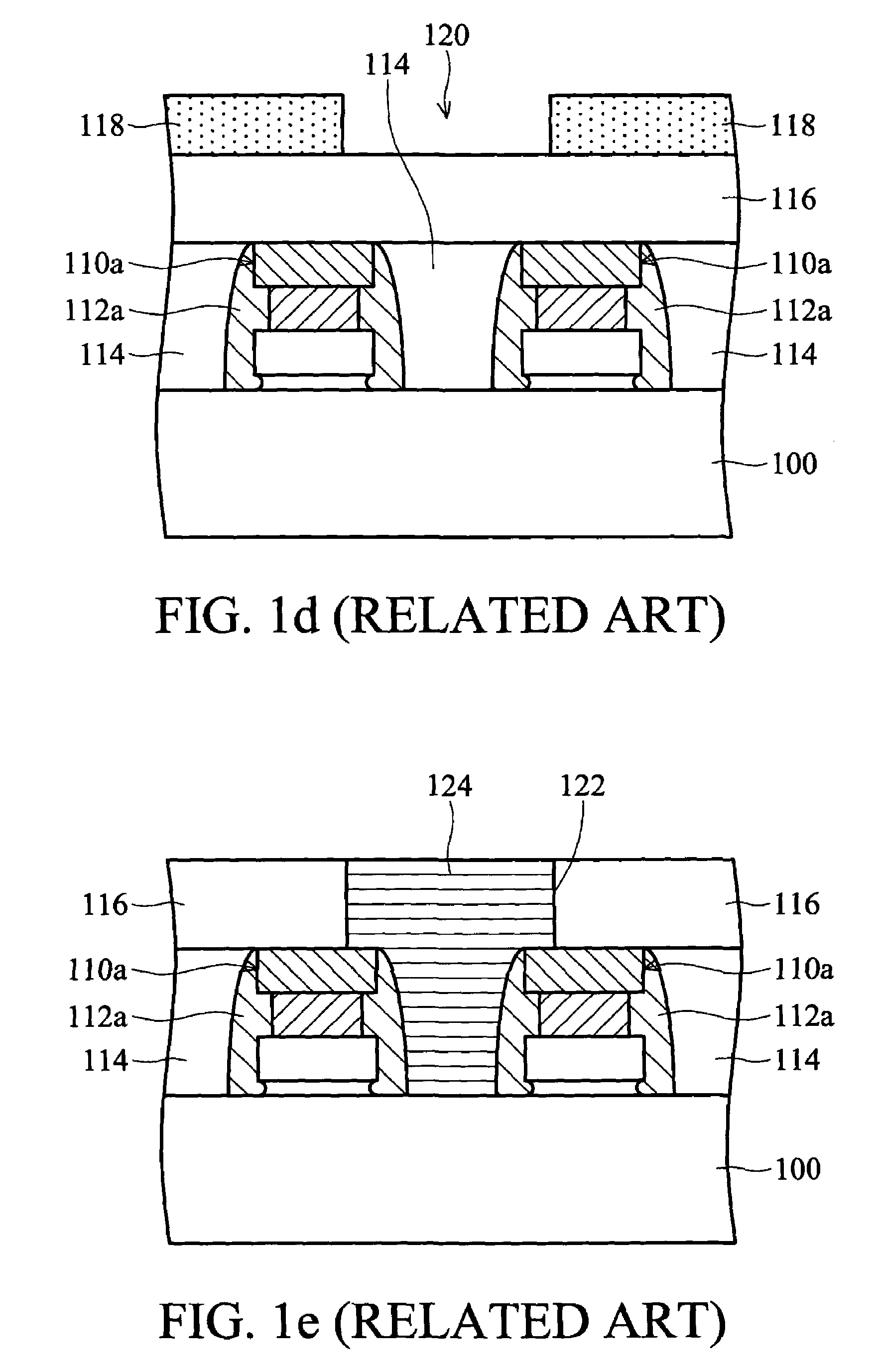

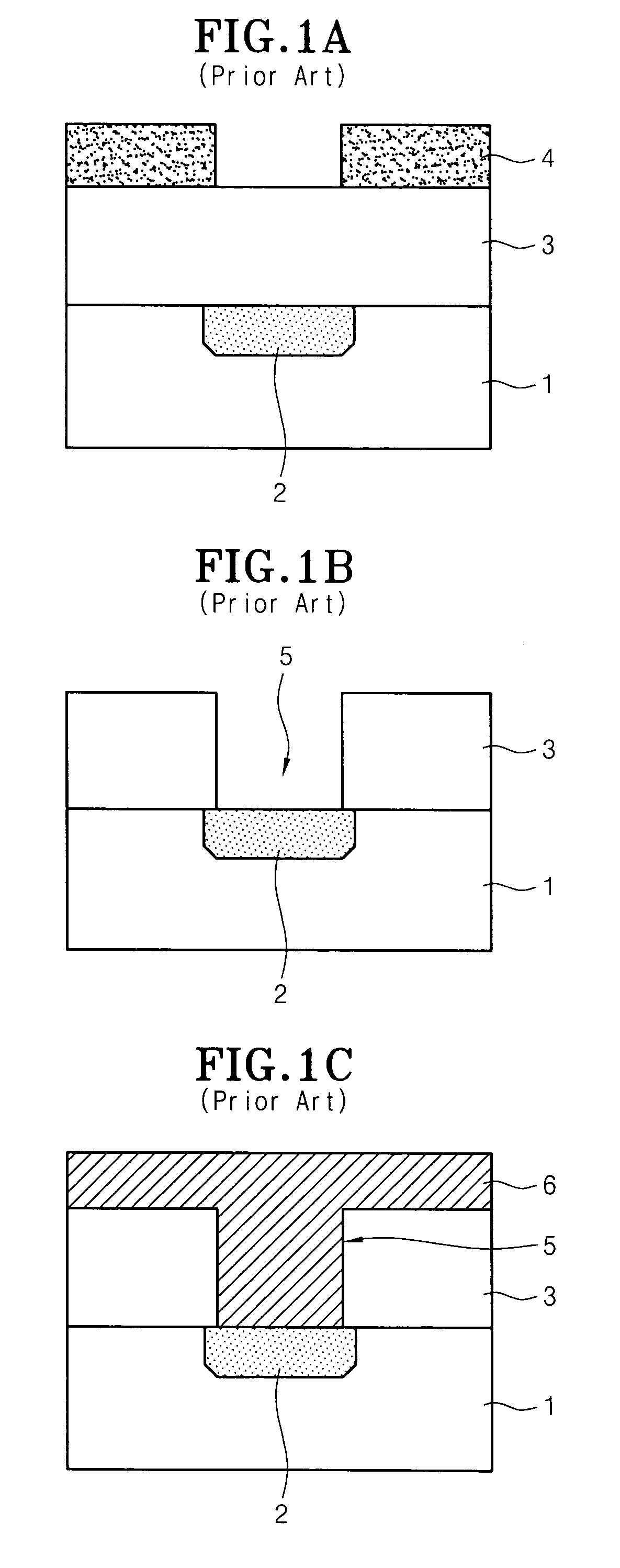

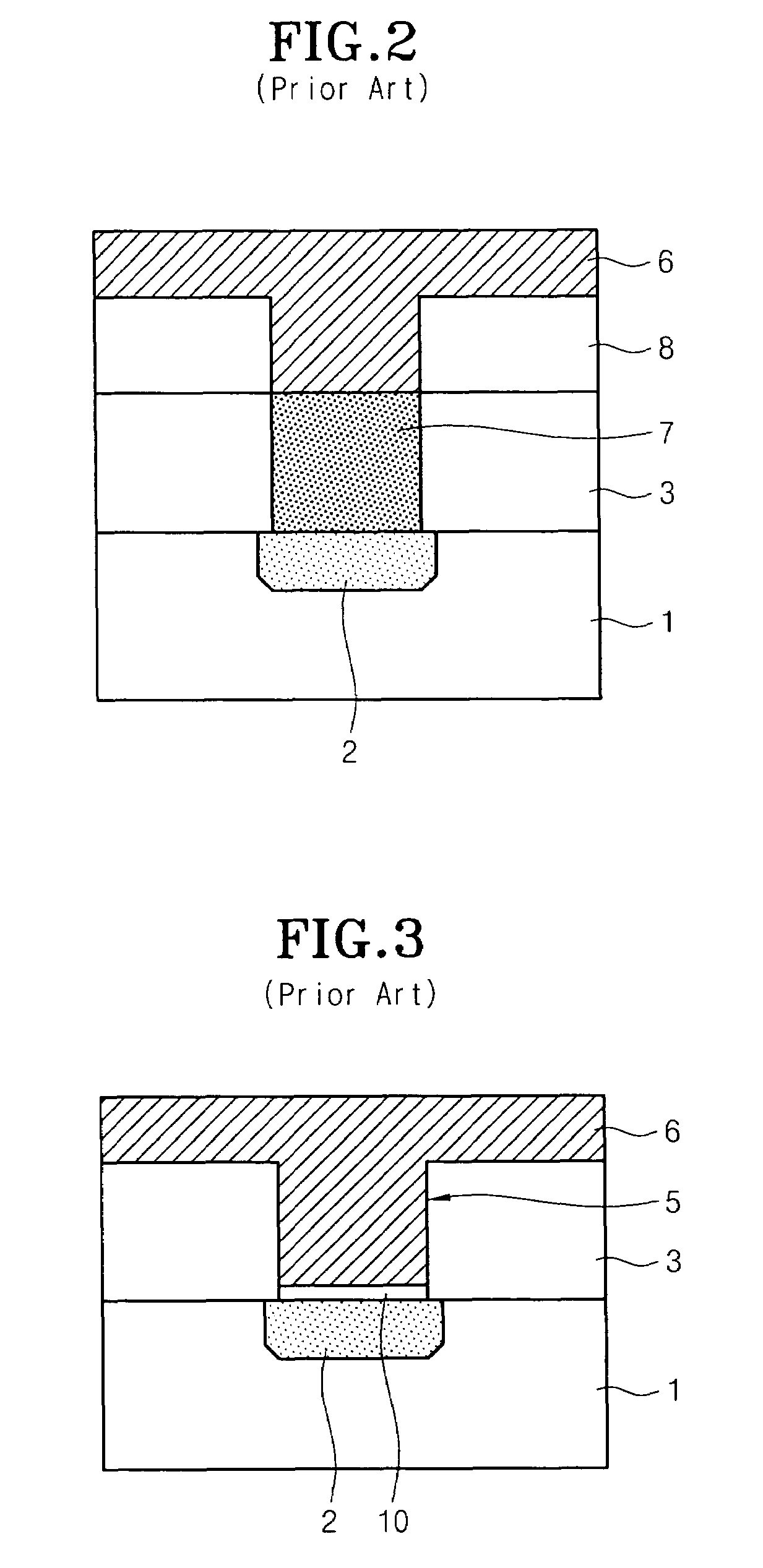

Method for fabricating semiconductor device

ActiveUS20050287799A1Increase in parasitic capacityAvoid contact resistanceTransistorSolid-state devicesElectrical resistance and conductanceDevice material

The present invention provides a method for fabricating a semiconductor device capable of preventing a contact resistance from increasing in a region contacted to an N-type conductive region during forming a conductive pattern directly contacted to the N-type conductive region including a conductive pattern and silicon, and preventing an increase in a parasitic capacity of the conductive pattern according to an increase in a thickness of a barrier layer.

Owner:SK HYNIX INC

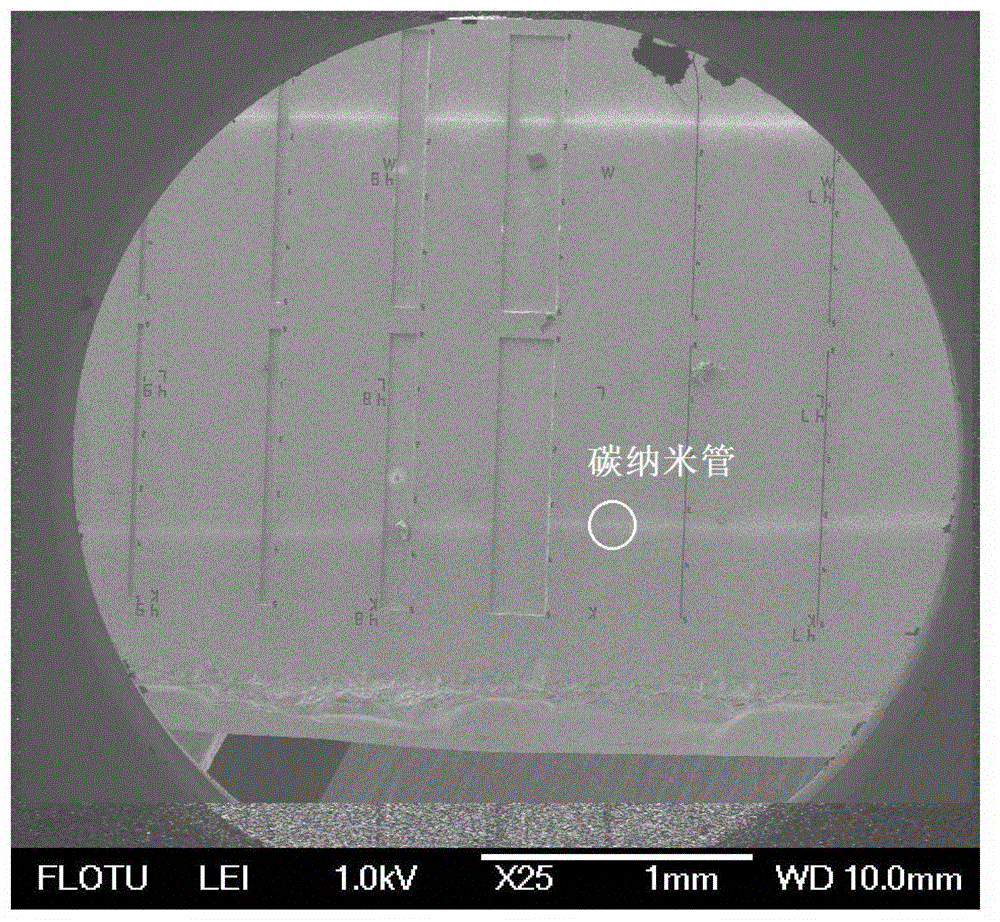

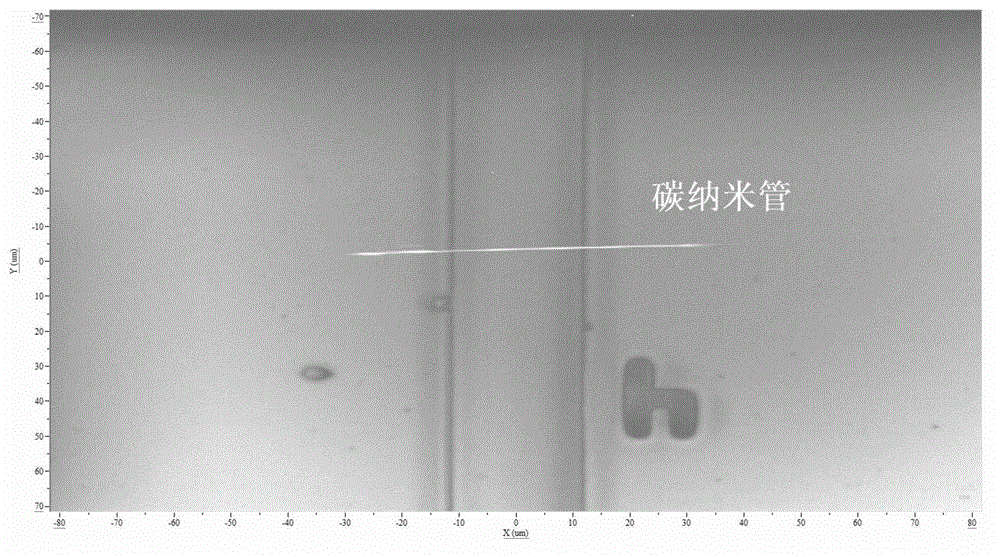

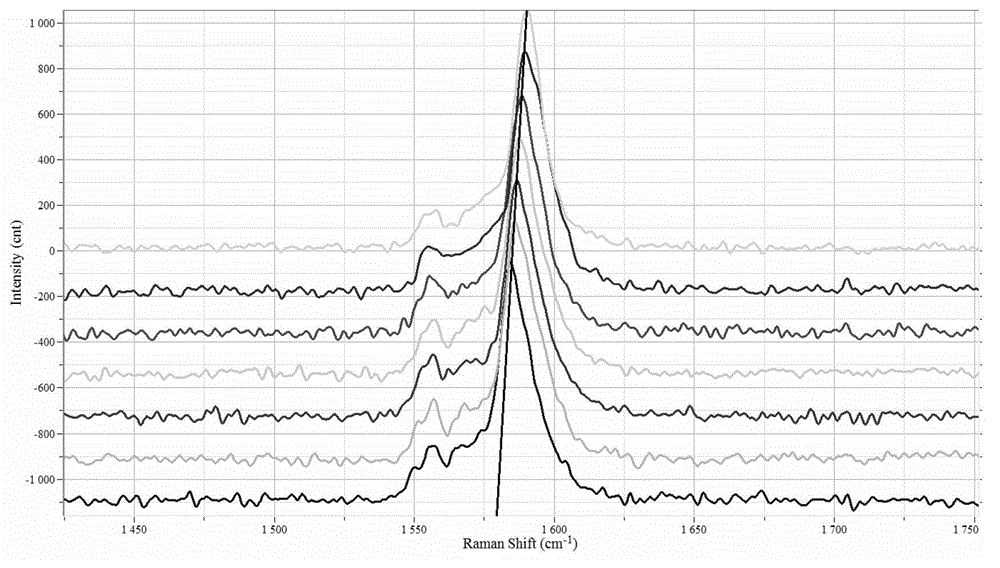

Method for simultaneously measuring laser absorptivity and thermal conductivity of single micro-nano wire rod

ActiveCN102944573AFilling the technology gap of laser absorption rateEffective experimental methodMaterial heat developmentThermometers using physical/chemical changesMicro nanoCarbon nanotube

The invention provides a method for simultaneously measuring the laser absorptivity and thermal conductivity of a single micro-nano wire rod, belonging to the technical field of characterization of property of nano-materials. The method disclosed herein is characterized by using contactless laser Raman measurement technology to position and carry out temperature calibration on the single micro-nano wire rod; then respectively using laser heating and electric heating methods in a vacuum environment to reach equal core temperature of samples to be measured and measure respective heating power; substituting the geometry size, core temperature and heating power of the micro-nano wire rod in a theoretical formula to simultaneously calculate the laser absorptivity and thermal conductivity of the samples to be measured. According to the invention, the method has the advantages of wide range of application, simple principle and convenient operation, is suitable for various micro-nano wire rods which have characteristic Raman spectrum and have different materials, diameters and lengths, fills the technical gap of measuring the laser absorptivity of the single micro-nano wire rod, and provides valuable basic physical property data for practical engineering application.

Owner:TSINGHUA UNIV

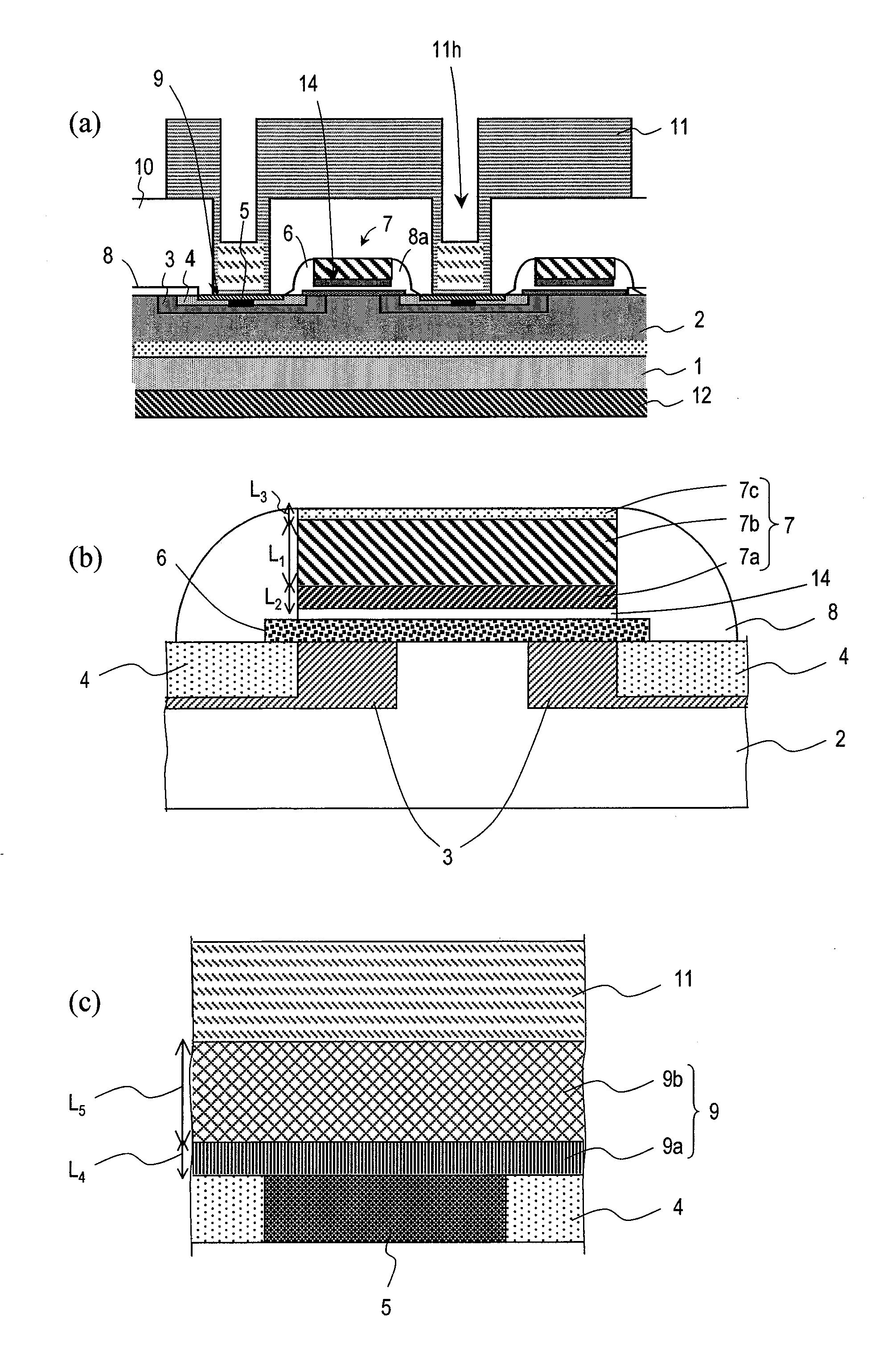

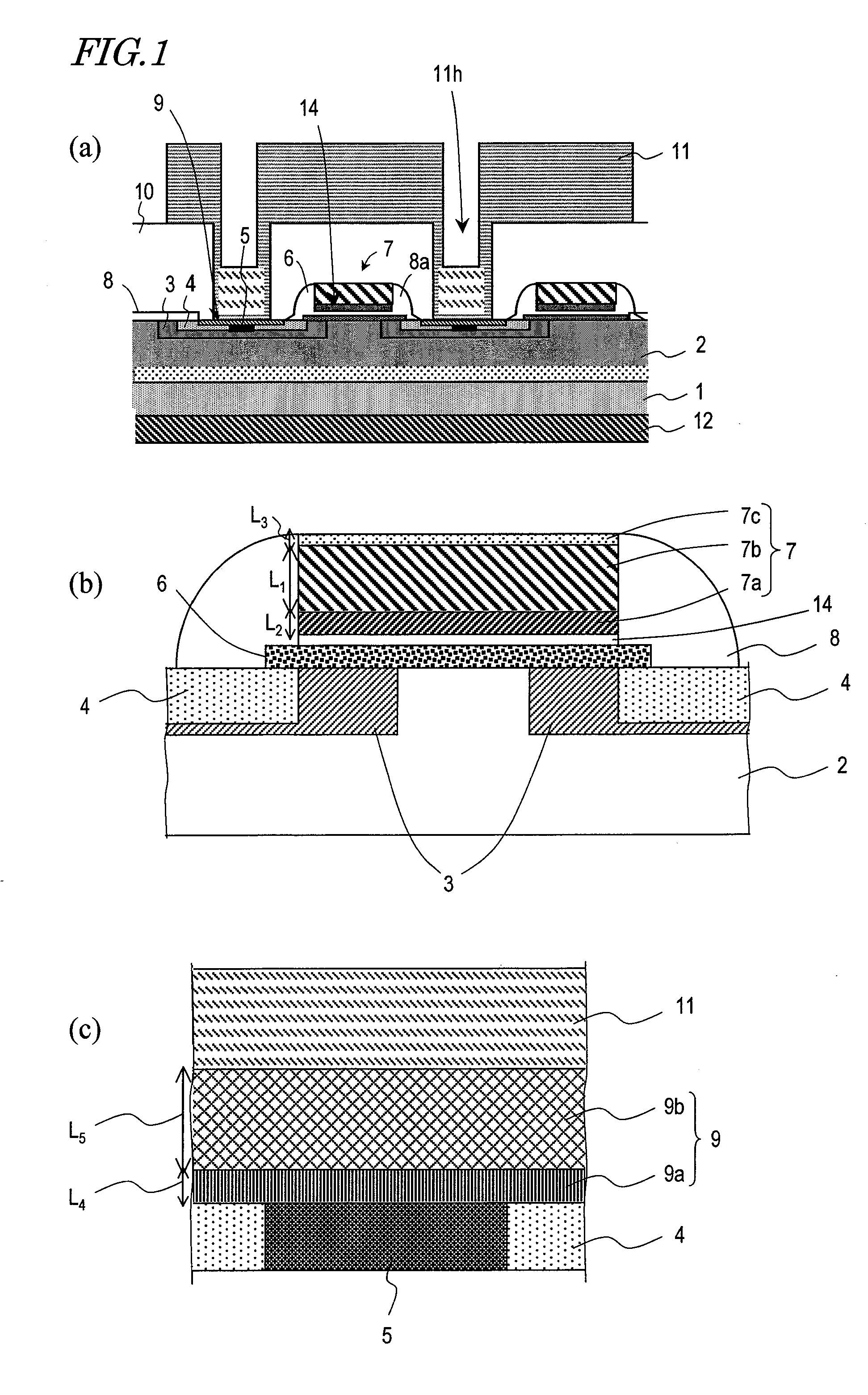

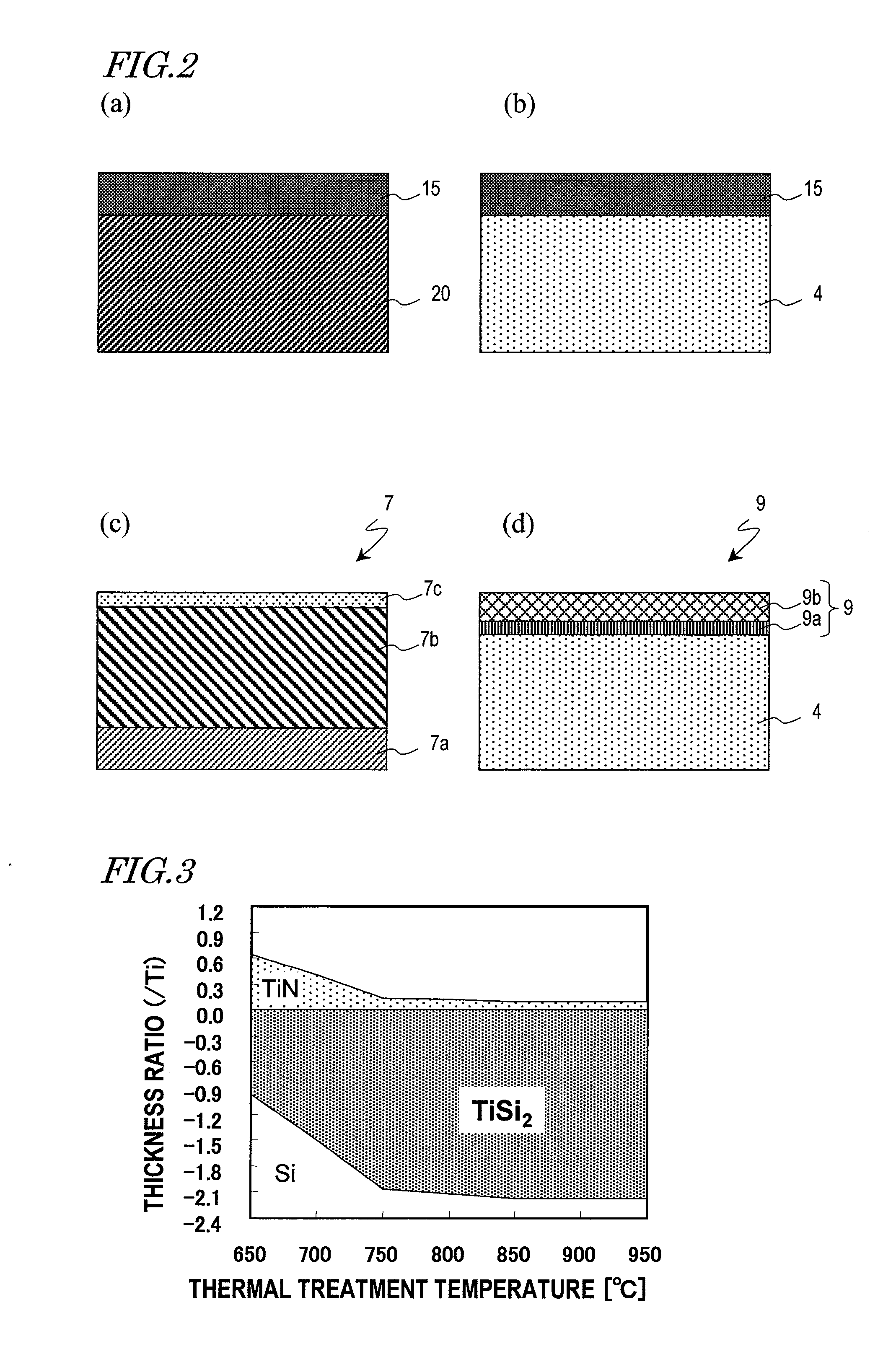

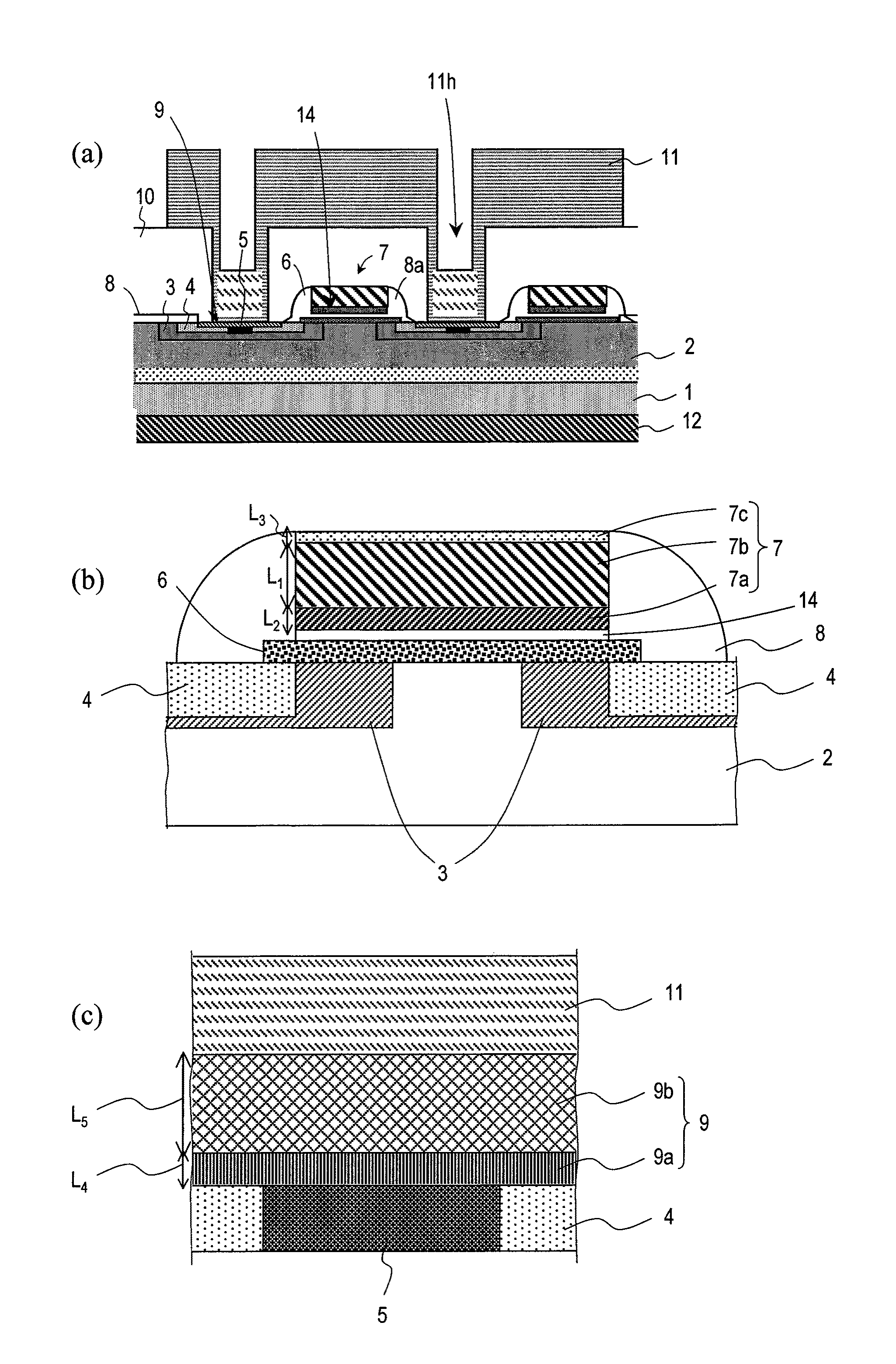

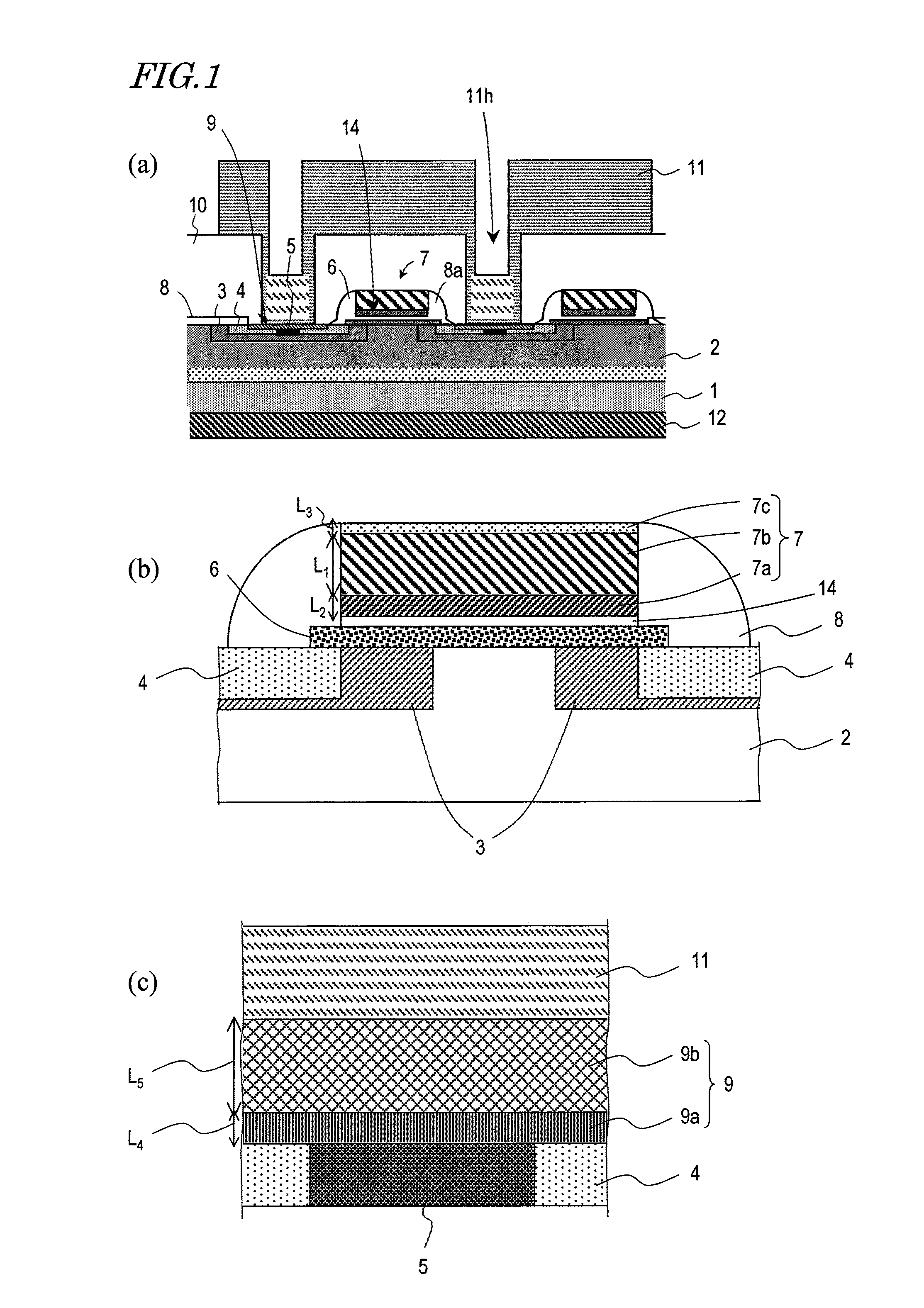

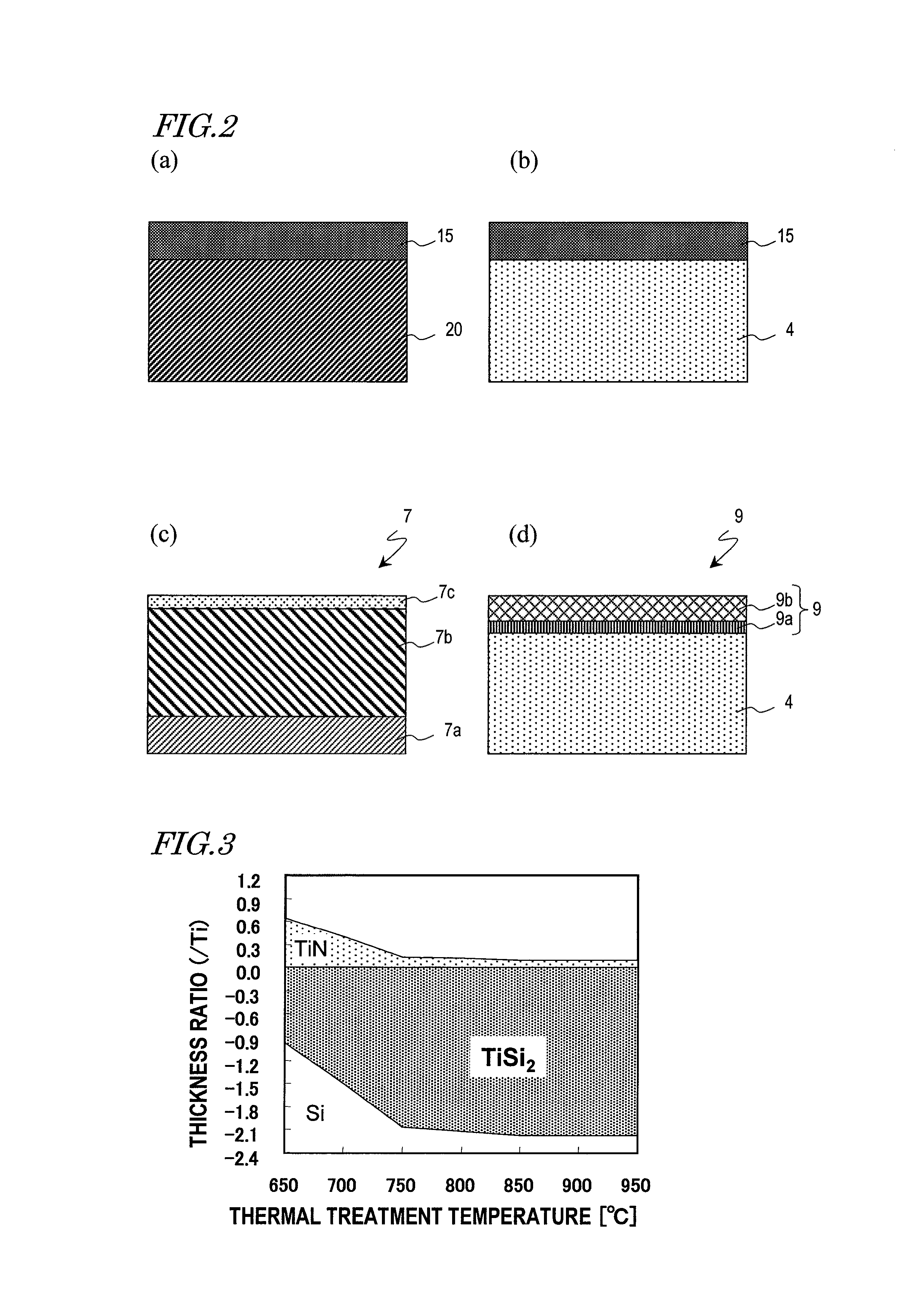

Semiconductor device and method for manufacturing the same

ActiveUS20100244048A1Adhesiveness decreaseDecrease gate resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesTitaniumHigh concentration

A semiconductor device according to the present invention comprises a silicon carbide semiconductor substrate (1) including a silicon carbide layer (2); a high-concentration impurity region (4) provided in the silicon carbide layer (2); an ohmic electrode (9) electrically connected with the high-concentration impurity region (4); a channel region electrically connected with the high-concentration impurity region; a gate insulating layer (14) provided on the channel region; and a gate electrode (7) provided on the gate insulating layer (14). The ohmic electrode (9) contains an alloy of titanium, silicon and carbon, and the gate electrode (7) contains titanium silicide.

Owner:PANASONIC CORP

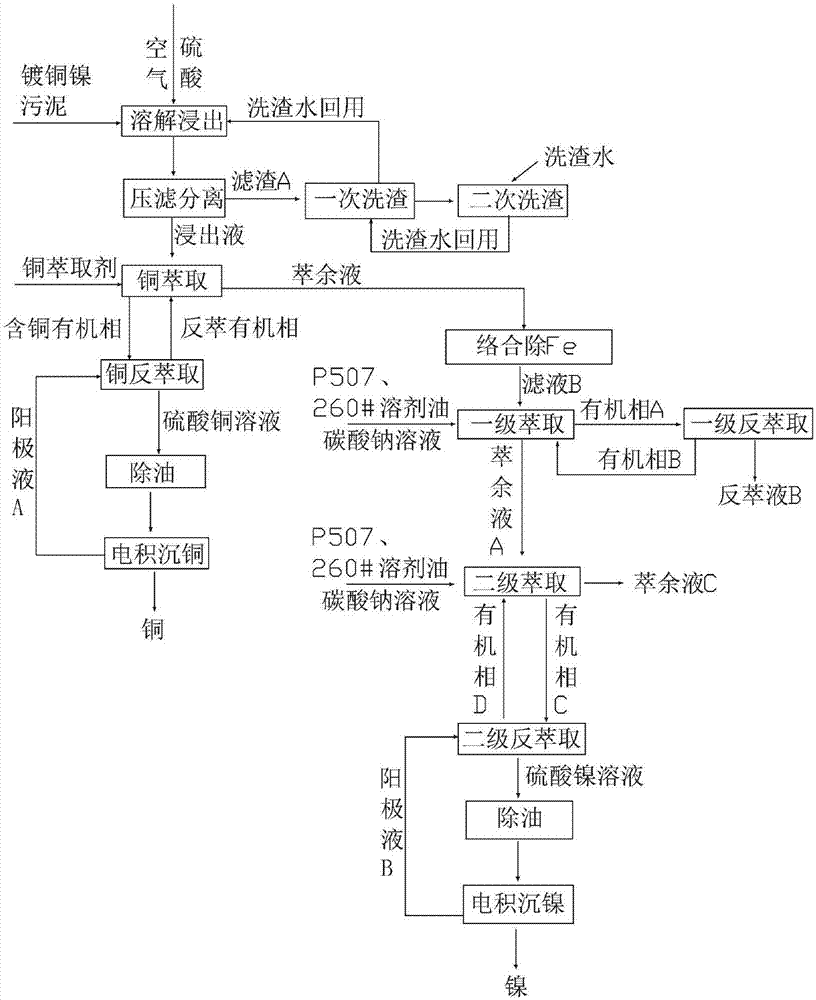

Method for recycling copper and nickel by treating copper and nickel plating sludge through rotational flow electrolysis

ActiveCN107385219APromote leachingHigh recovery ratePhotography auxillary processesProcess efficiency improvementElectrolysisCopper plating

The invention relates to the technical field of recycling of scrap metal, in particular to a method for recycling copper and nickel by treating copper and nickel plating sludge through rotational flow electrolysis. The method comprises the following steps: taking the copper and nickel plating sludge as a raw material, adding sulfuric acid in the copper and nickel plating sludge for leaching, adding a copper extracting agent in leachate obtained by filter pressing for extracting to obtain a copper-containing organic phase and raffinate, carrying out copper reextraction on the copper-containing organic phase to remove oil, and then carrying out copper electrodeposition by a rotational flow electrolysis device to obtain copper with the purity greater than 99.95% on a cathode; carrying out complexing on the raffinate to remove iron from the raffinate, then carrying out continuous saponification and counter-current extraction on the raffinate, removing oil from the raffinate, and then carrying out nickel electrodeposition by the rotational flow electrolysis device to obtain nickel with the purity greater than 99.95% on the cathode. The method for recycling copper and nickel by treating the copper and nickel plating sludge through rotational flow electrolysis is efficient, reliable, clean and pollution-free; a technological process is simple; copper and nickel recycling rate is high; and regenerated copper and nickel products are high in purity.

Owner:俞振元

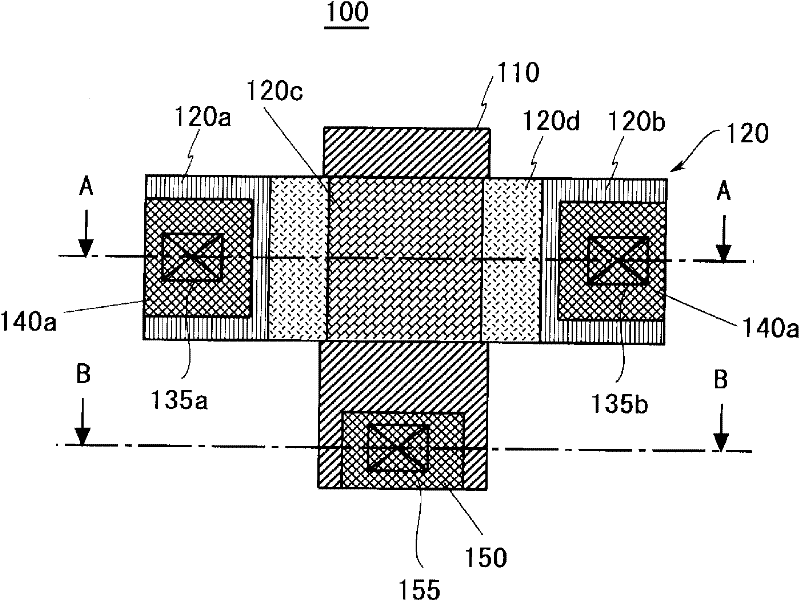

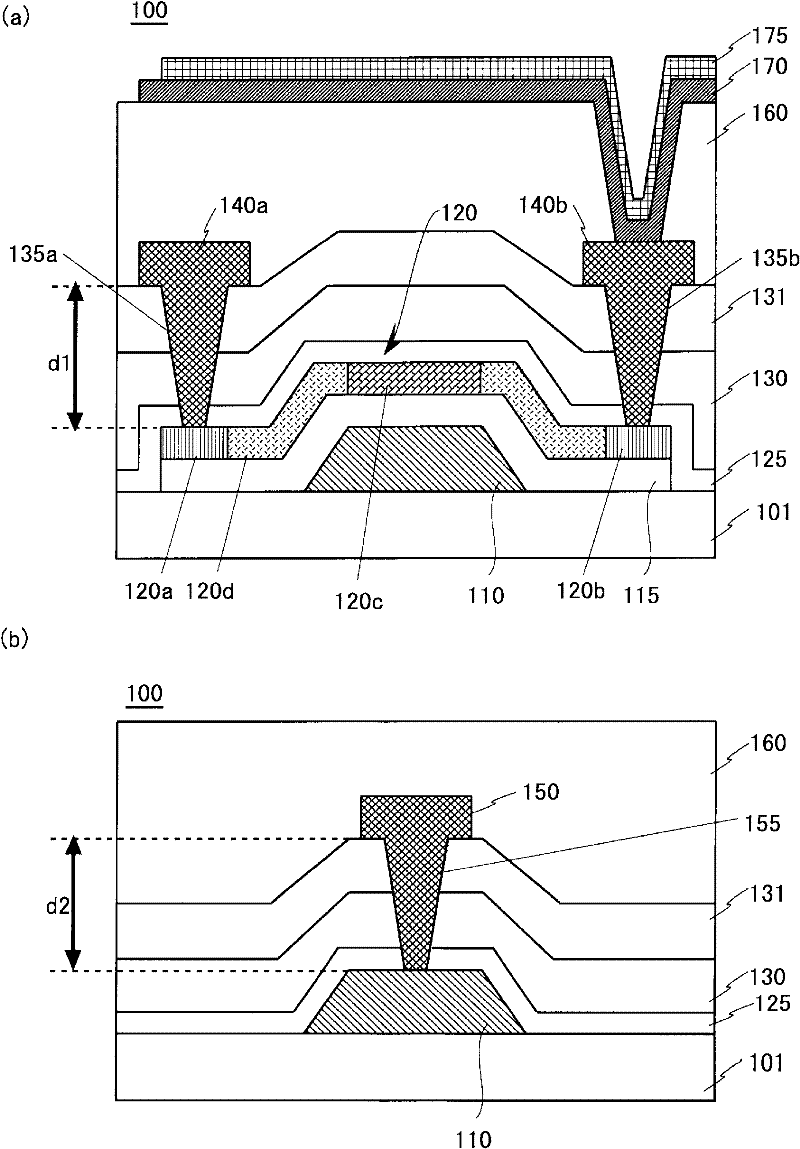

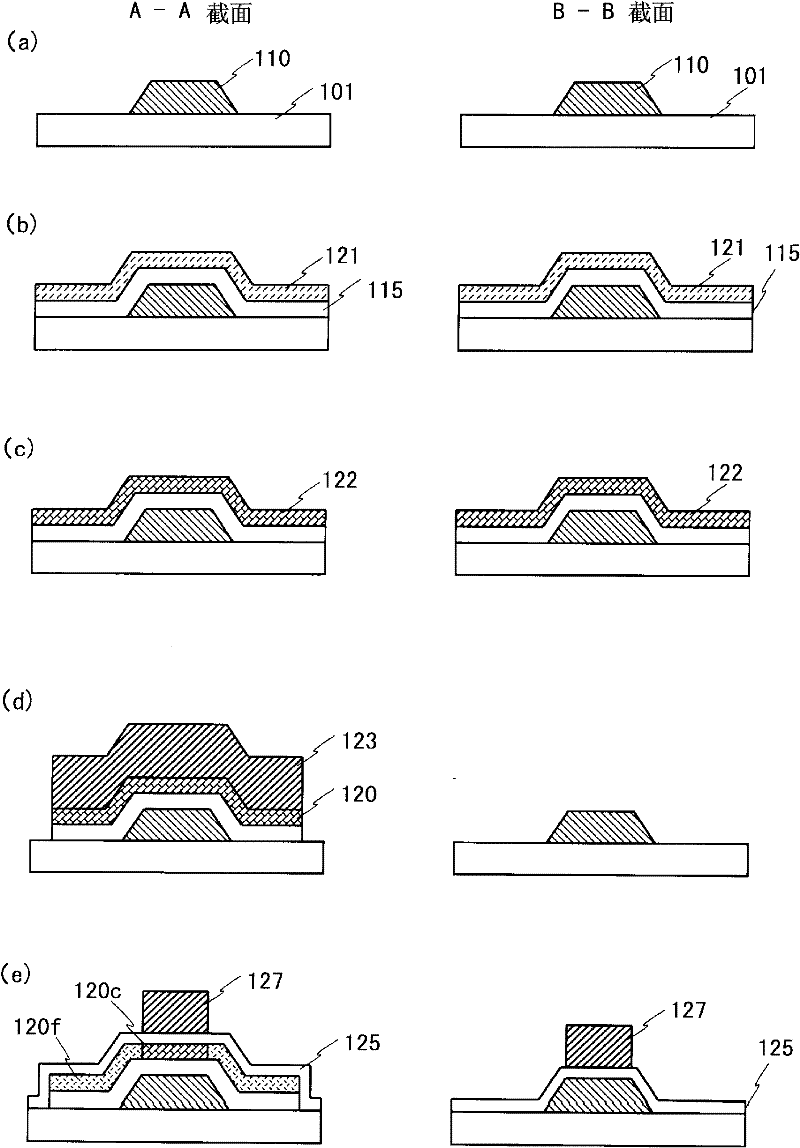

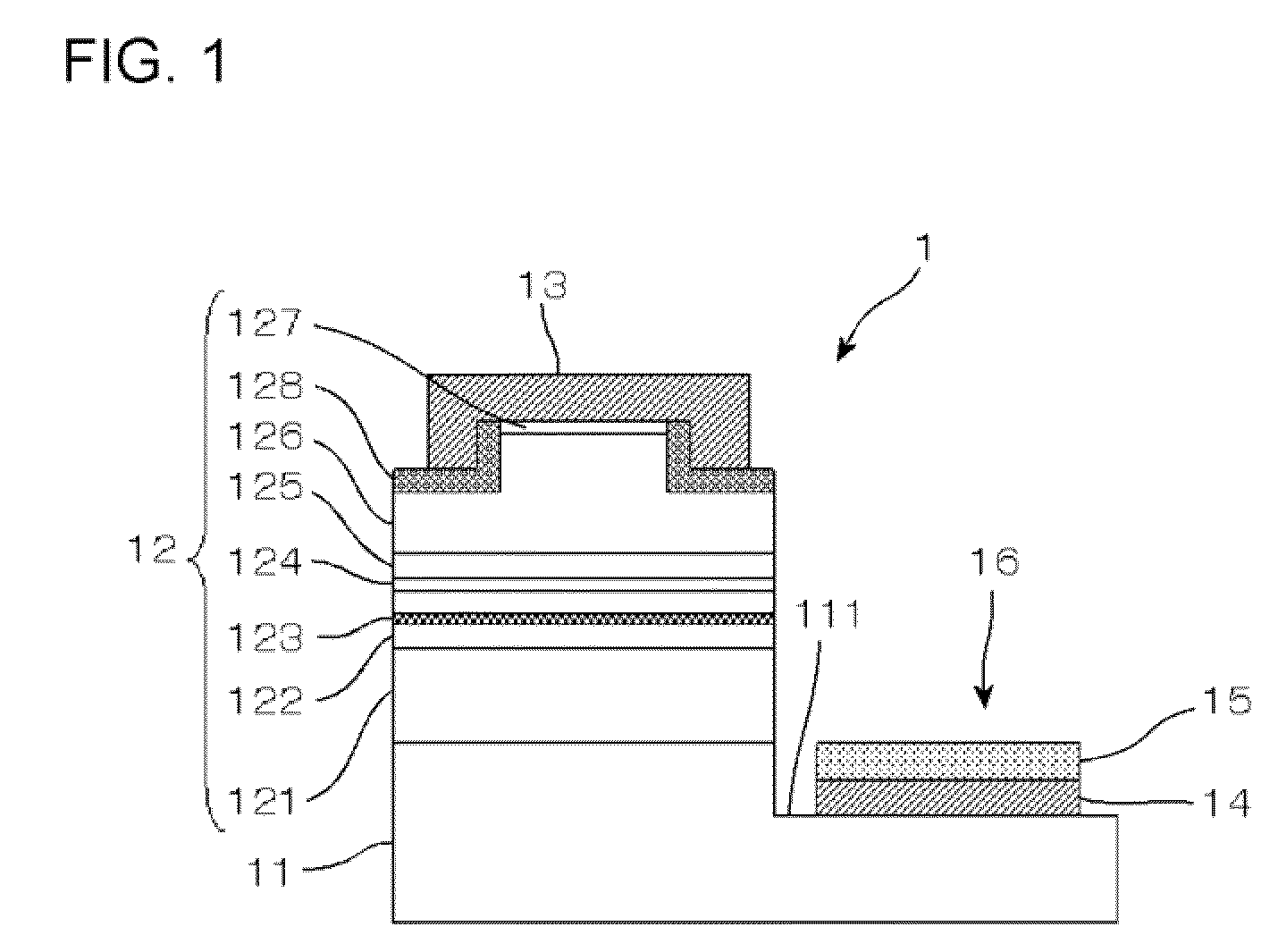

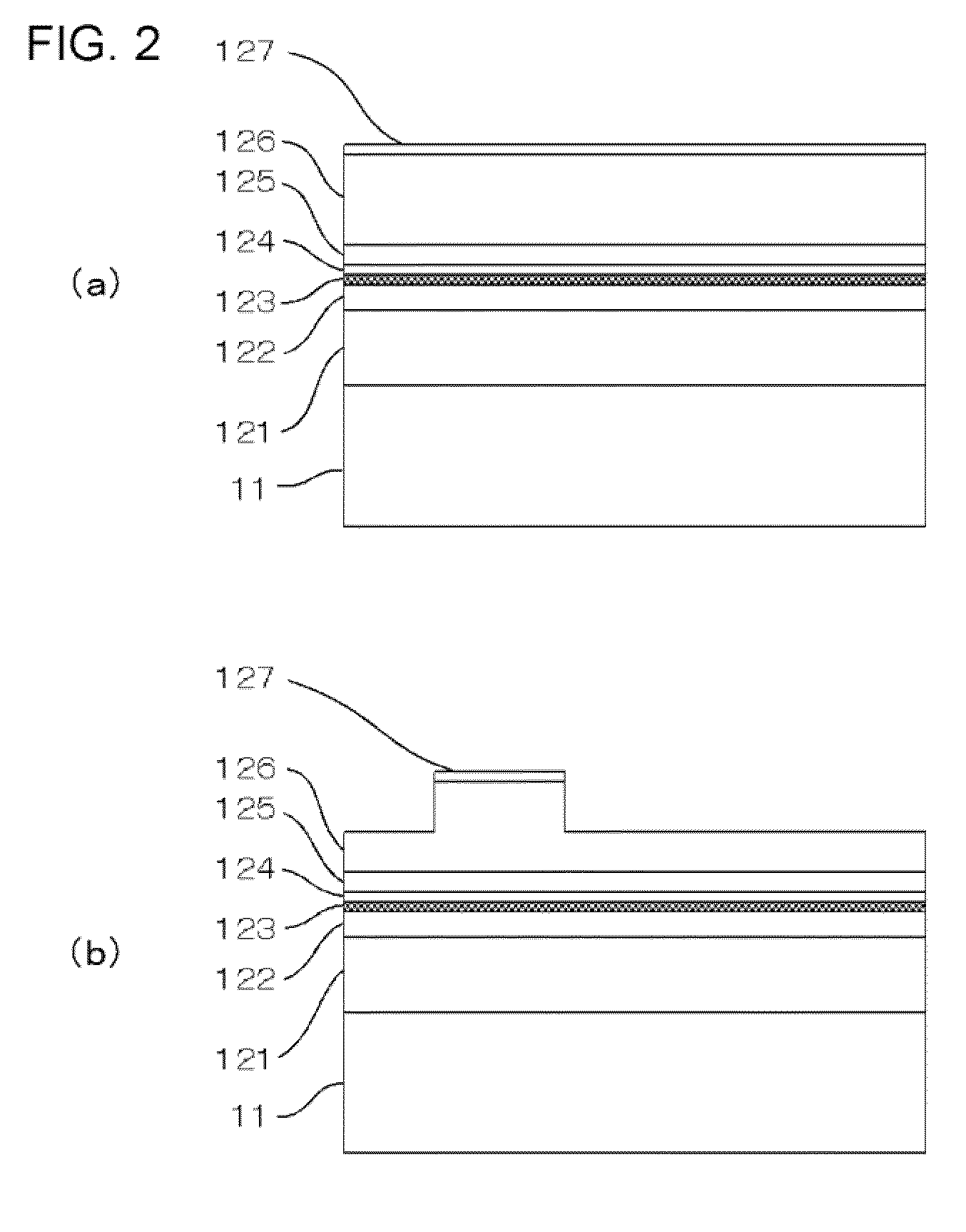

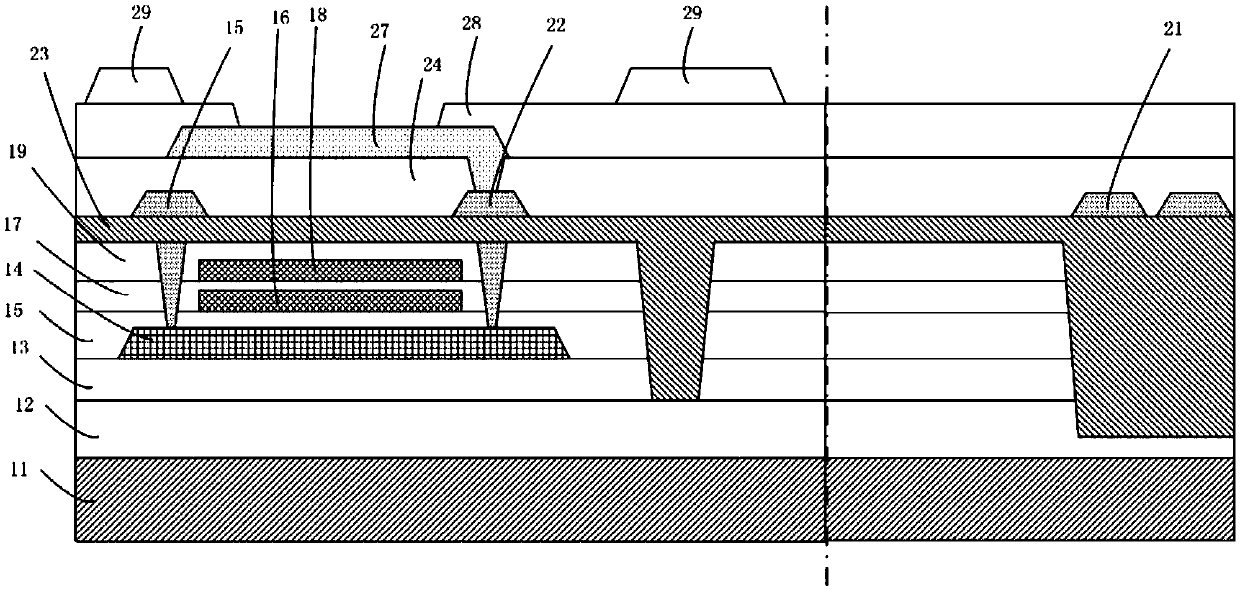

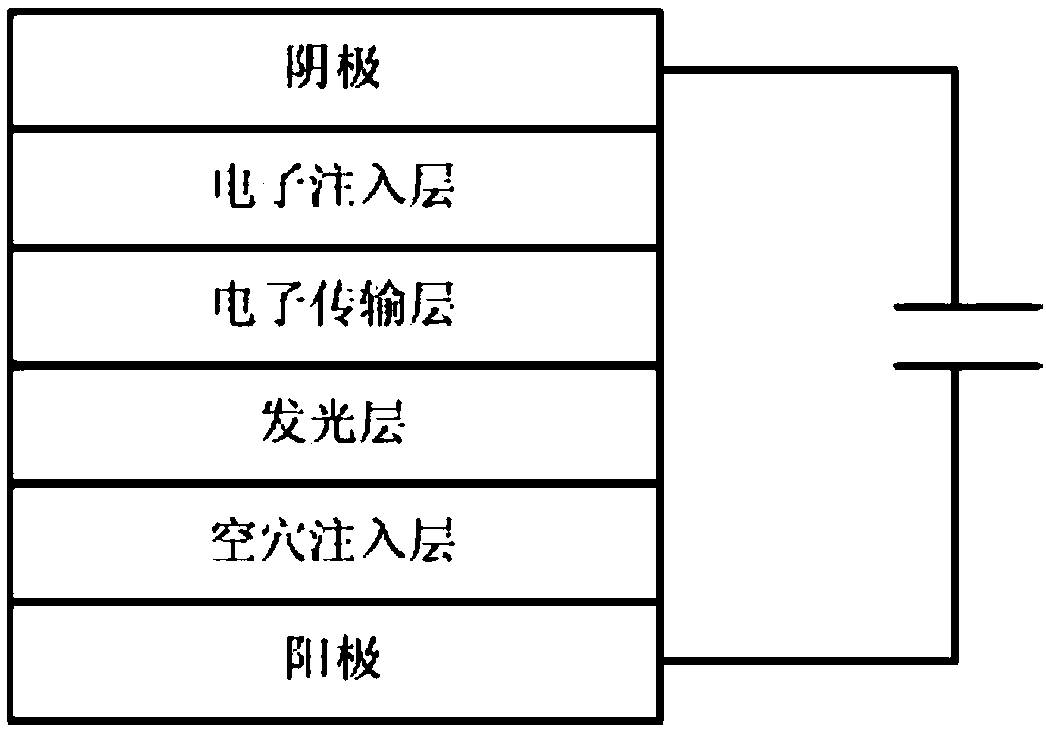

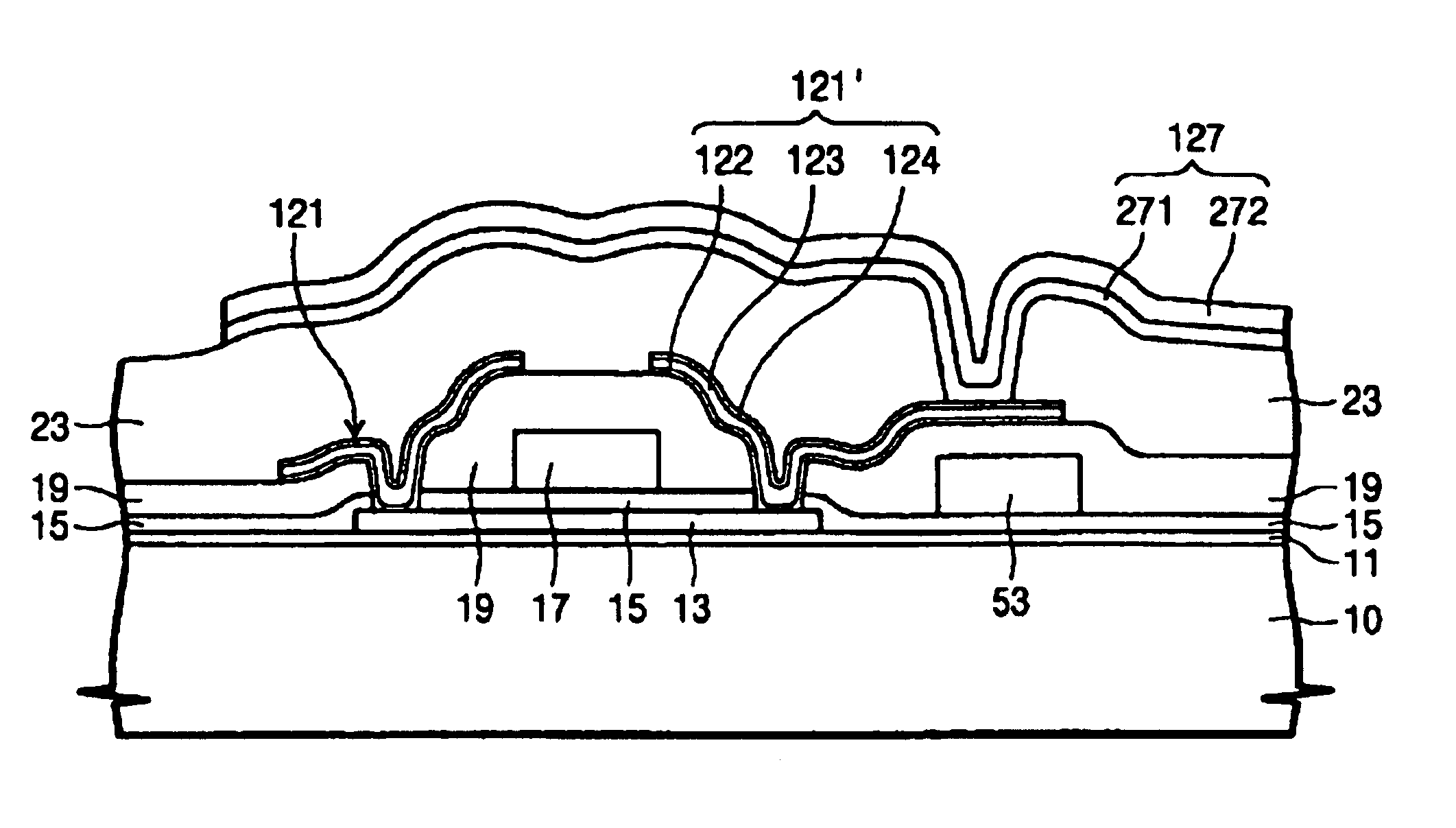

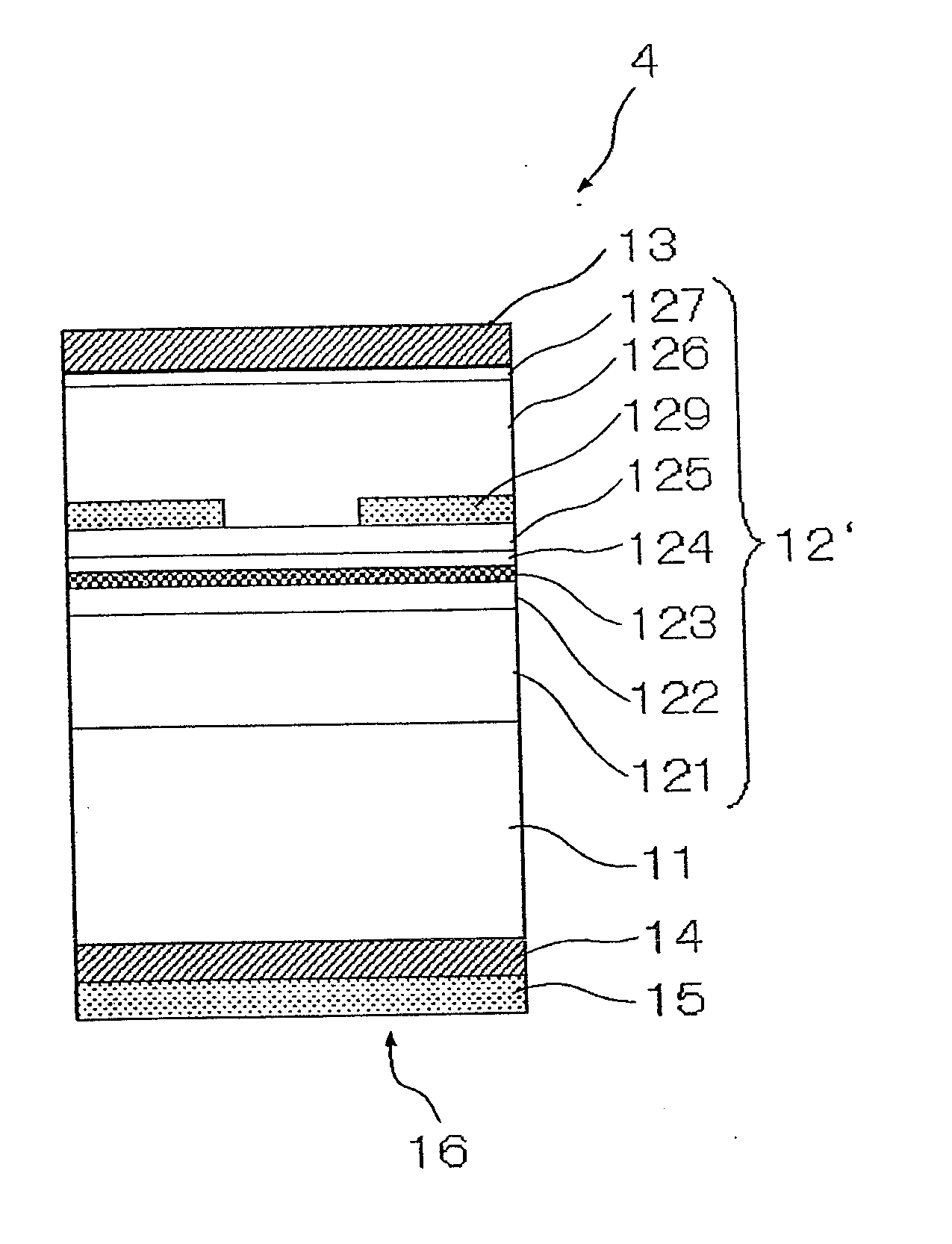

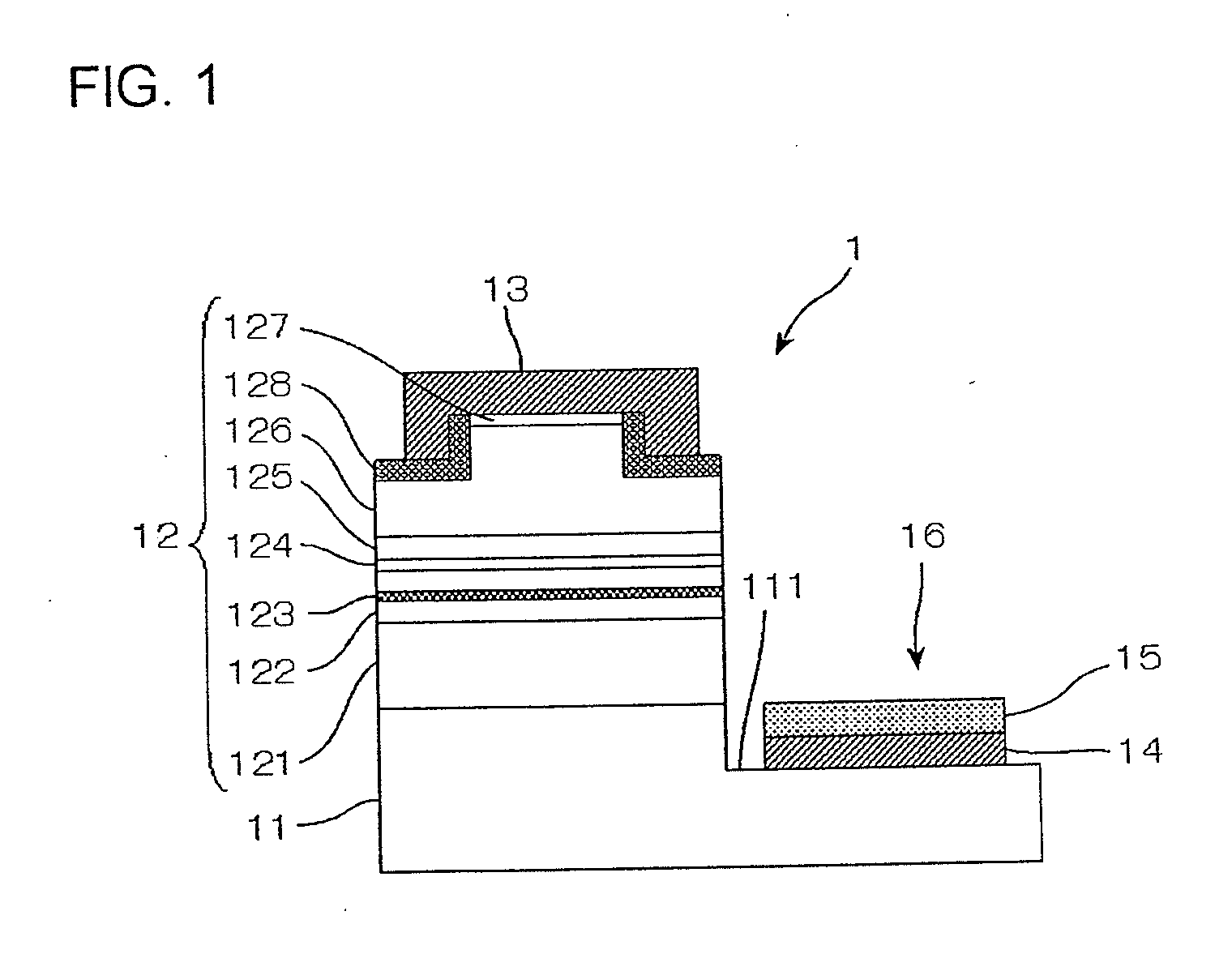

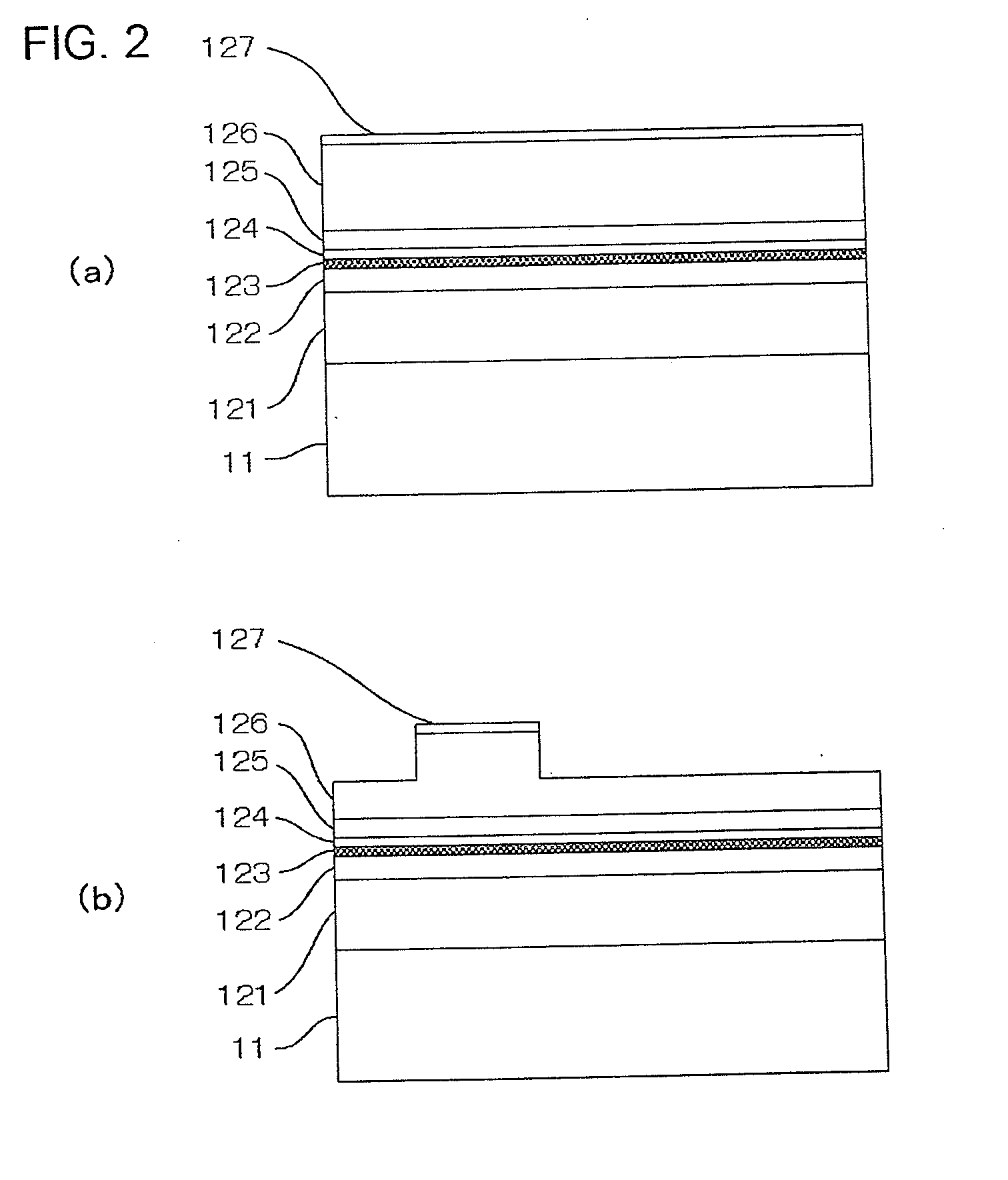

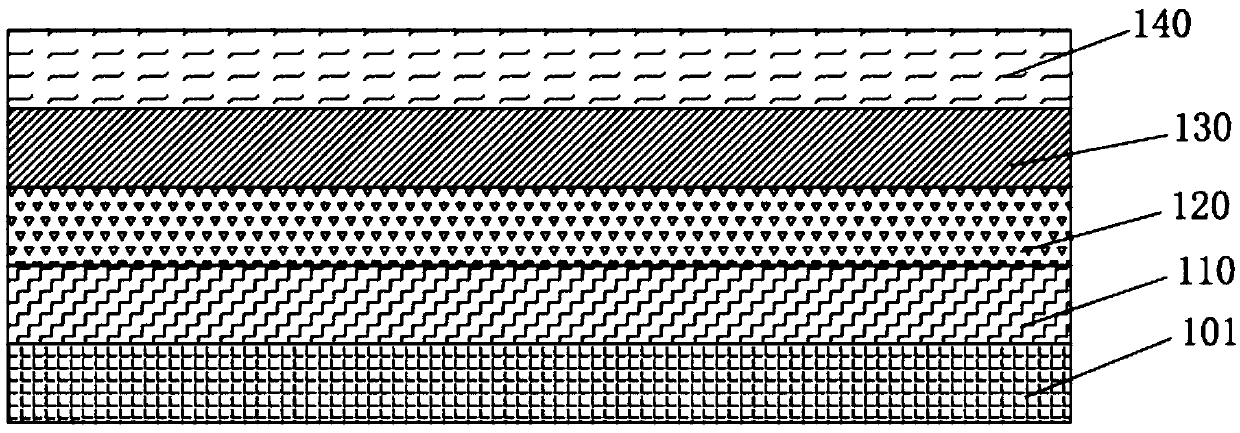

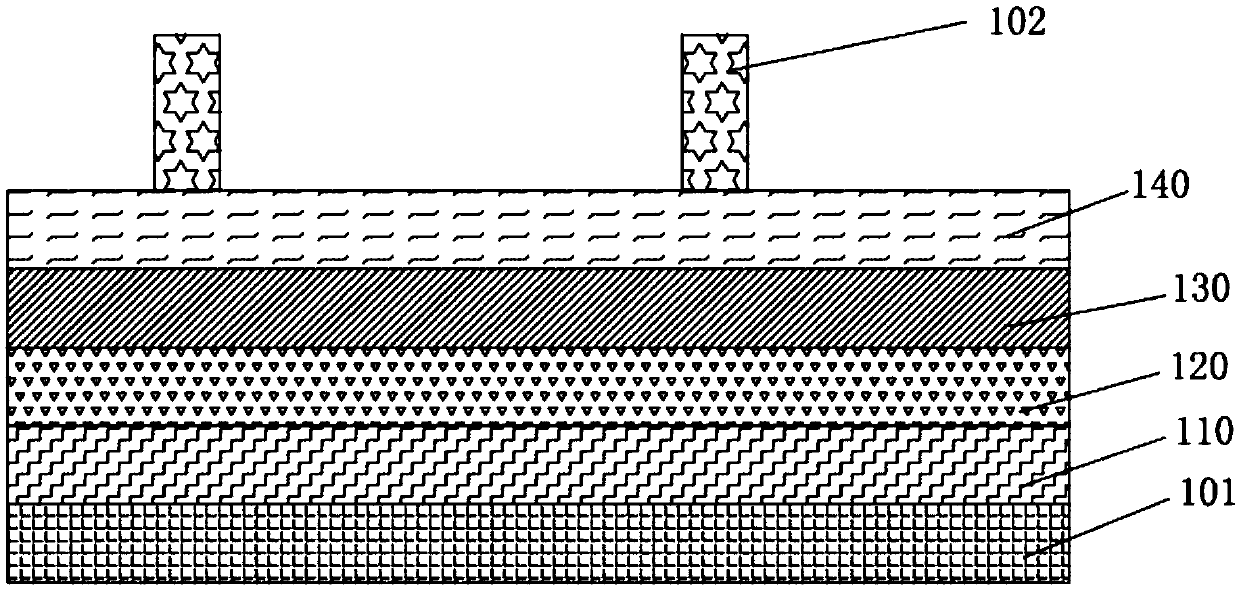

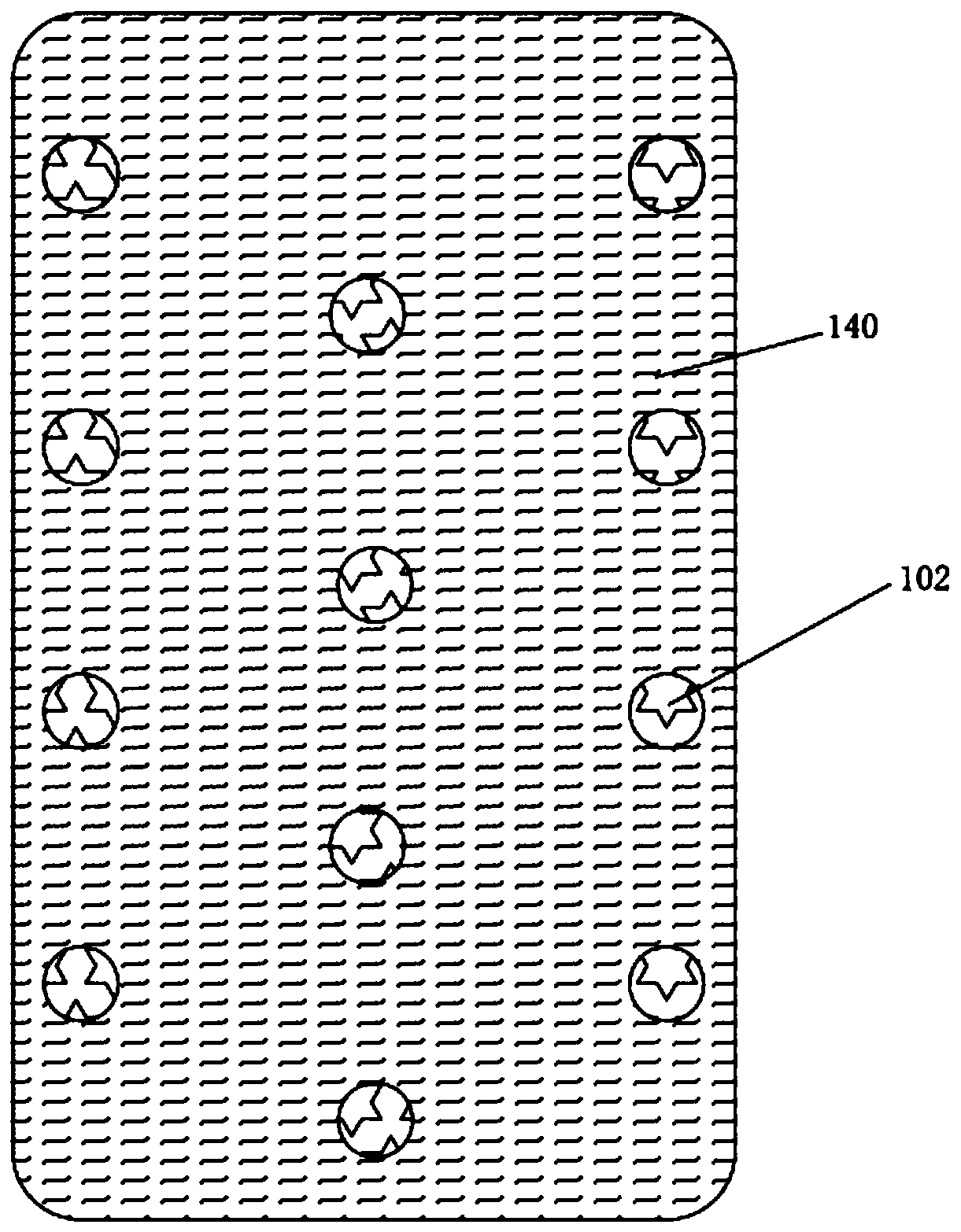

Thin film transistor and manufacturing method for same, semiconductor device and manufacturing method for same, and display device

InactiveCN102576739AAvoid contact resistanceIncrease contact resistanceTransistorSolid-state devicesDisplay deviceEngineering

Disclosed is a thin film transistor manufacturing method in which the process for opening contact holes has been simplified. Due to the removal in advance of a gate insulating film (115) which is formed on a gate electrode (110) not covered by a channel layer (120) of a TFT (100), the film thickness of the insulating film formed on the gate electrode (110) which is not covered by the channel layer (120) is the same as the film thickness of the insulating film formed on the source region (120a) and the drain region (120b). Therefore, it is possible to simultaneously open a contact hole (155) which reaches the surface of the gate electrode (110), a contact hole (135a) which reaches the surface of the source region (120a), and a contact hole (135b) which reaches the surface of the drain region (120b).

Owner:SHARP KK

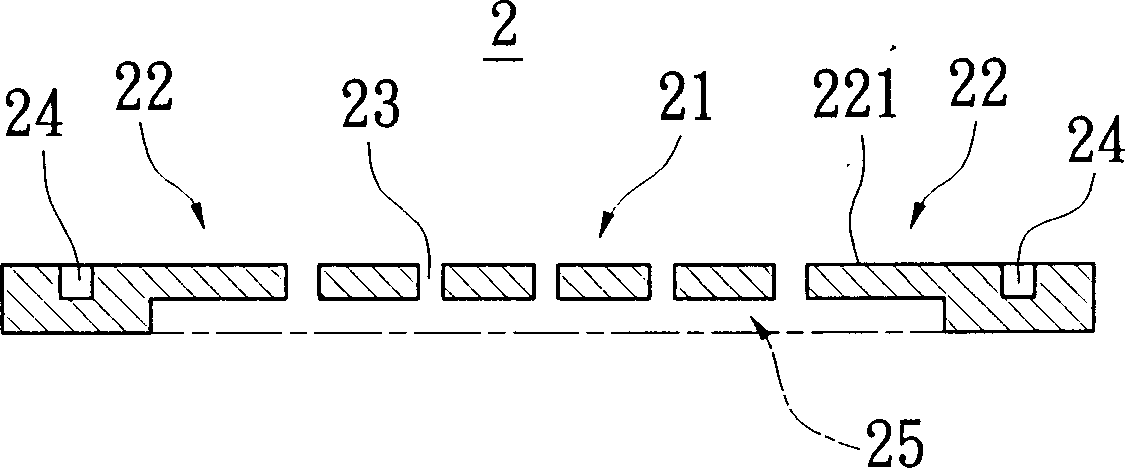

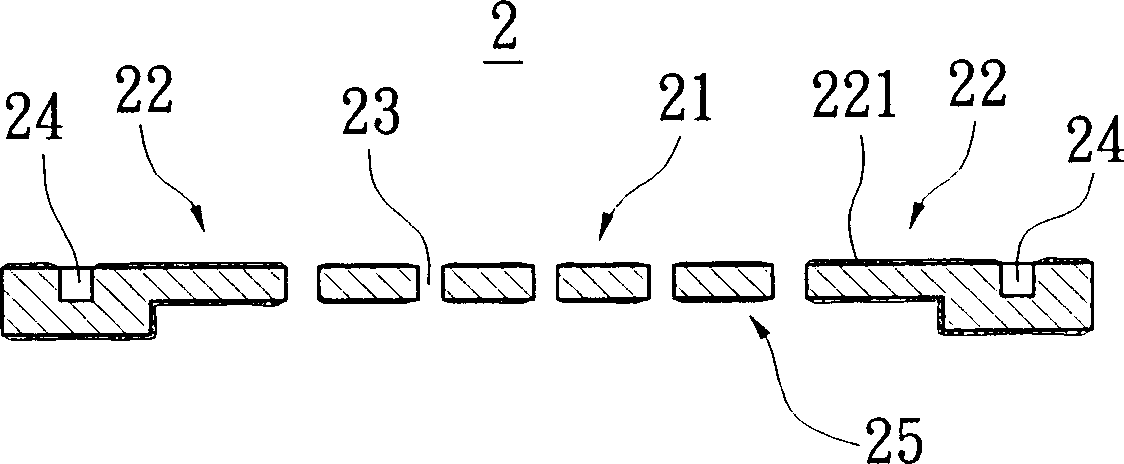

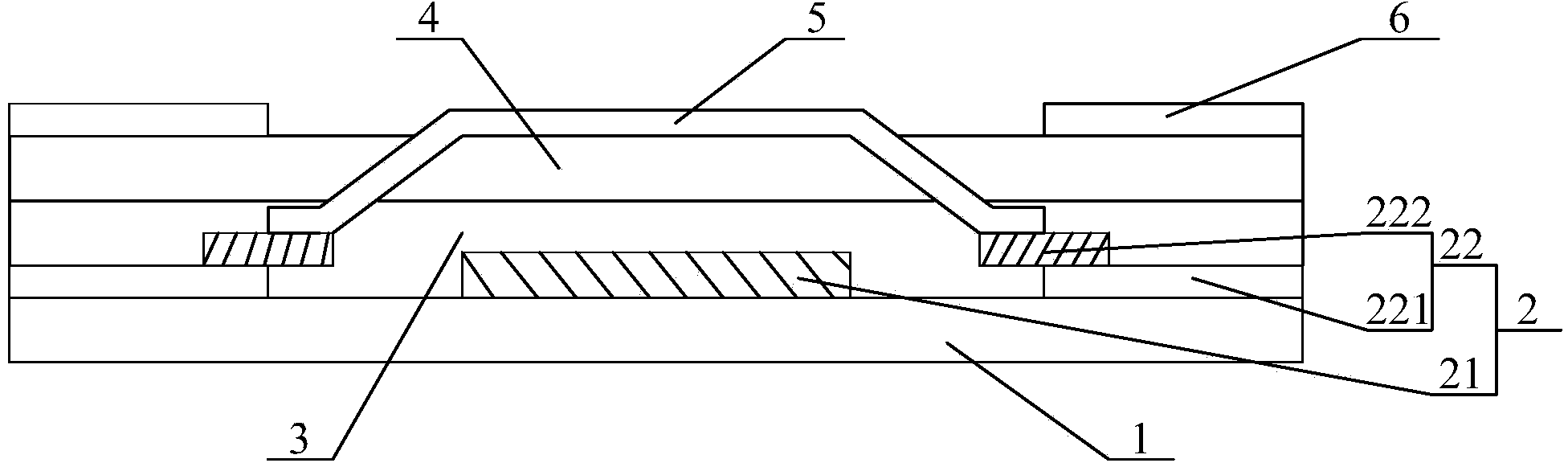

Image sensor single-layer conductor rest secondary semi-etching mfg. method and packaging structure thereof

InactiveCN1452229ASolve the problem of contact resistanceAvoid contact resistanceTelevision system detailsSemiconductor/solid-state device detailsGlass coverElectrical conductor

A package of image sensor is composed of sensor chip, single-layer wiring body with chip holder and pins, glass cover plate, and plastics for sealing. Its preparing process includes semi-etching on top surface of plate substrate to form chip holder and pins, semi-etching recess structure, inlay plastics by moulding for electric isolating, electroplating the etched wiring body, inlaying it in premould, adhering sensor chip to its holder, soldering leading wires of pins, and adhering glass cover plate.

Owner:谢志鸿

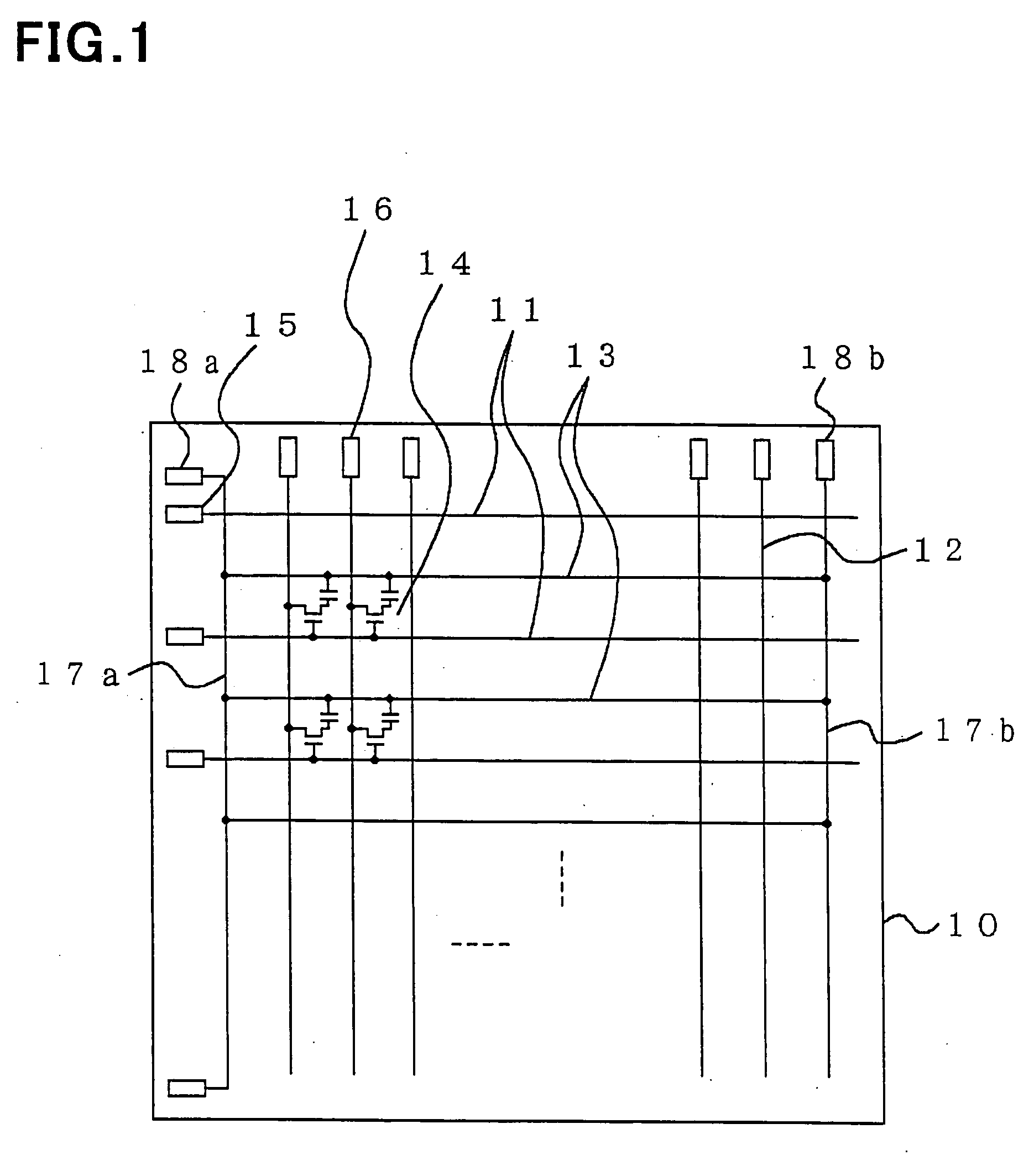

Method of fabricating liquid crystal display device

InactiveUS20050250260A1Avoid contact resistanceIncrease resistanceSolid-state devicesSemiconductor/solid-state device manufacturingLiquid-crystal displayPolycrystalline silicon

The method of fabricating a liquid crystal display device includes the steps of (a) fabricating a switching device on a substrate, (b) forming an interlayer insulating film on the substrate such that the switching device is covered with the interlayer insulating film, and (c) forming a transparent electrode on the interlayer insulating film, the transparent electrode being electrically connected to the switching device through the interlayer insulating film, the step (c) including (c1) depositing electrically conductive, transparent and amorphous material on the interlayer insulating film, (c2) patterning the material into the transparent electrode, and (c3) turning the transparent electrode into polysilicon by thermal annealing carried out after formation of an alignment film.

Owner:NEC LCD TECH CORP

Loosening-preventing and automatic-fastening device of connection bolts for combination and fixation of storage batteries

The invention discloses a loosening-preventing and automatic-fastening device of connection bolts for combination and fixation of storage batteries. According to the loosening-preventing and automatic-fastening device, a ratchet sleeve is arranged on the front side of a fixed connection handle, a ratchet is arranged inside the ratchet sleeve, fixed inner teeth are arranged on the inner side of the ratchet, ratchet teeth are arranged on the outer circumference of the ratchet, receding stopping grooves are formed in the inner side of the ratchet sleeve, receding stopping springs are arranged in the receding stopping grooves, a receding stopping pin is arranged on the front side of each receding stopping spring, a fixed clamping base is arranged on the rear side of the fixed connection handle, and a tension spring is arranged on the upper side of the fixed clamping base. When copper connection bars of a storage battery pack are twisted slightly, and alternatively vibration is produced due to environmental factors, the ratchet teeth prevent the bolts from moving in the loosening direction under the action of the receding stopping pins, the bolts are pushed to rotate in the fastening direction, and the function of automatically fastening the bolts is achieved.

Owner:桑永礼

Electrode structure, semiconductor element, and methods of manufacturing the same

InactiveUS20100032839A1Reduce contact resistanceContact resistanceOptical wave guidanceSemiconductor/solid-state device detailsTectorial membraneNitride semiconductors

According to the present invention, there is provided an electrode structure which includes: a nitride semiconductor layer; an electrode provided over the nitride semiconductor layer; and an electrode protective film provided over the electrode, wherein the nitride semiconductor layer contains a metal nitride containing Hb, Hf or Zr as a constitutive element, the electrode has a portion having a metal oxide containing Ti or V as a constitutive element formed therein, and the electrode protective film covers at least a portion of the electrode, and contains a protective layer having Au or Pt as a constitutive element.

Owner:RENESAS ELECTRONICS CORP

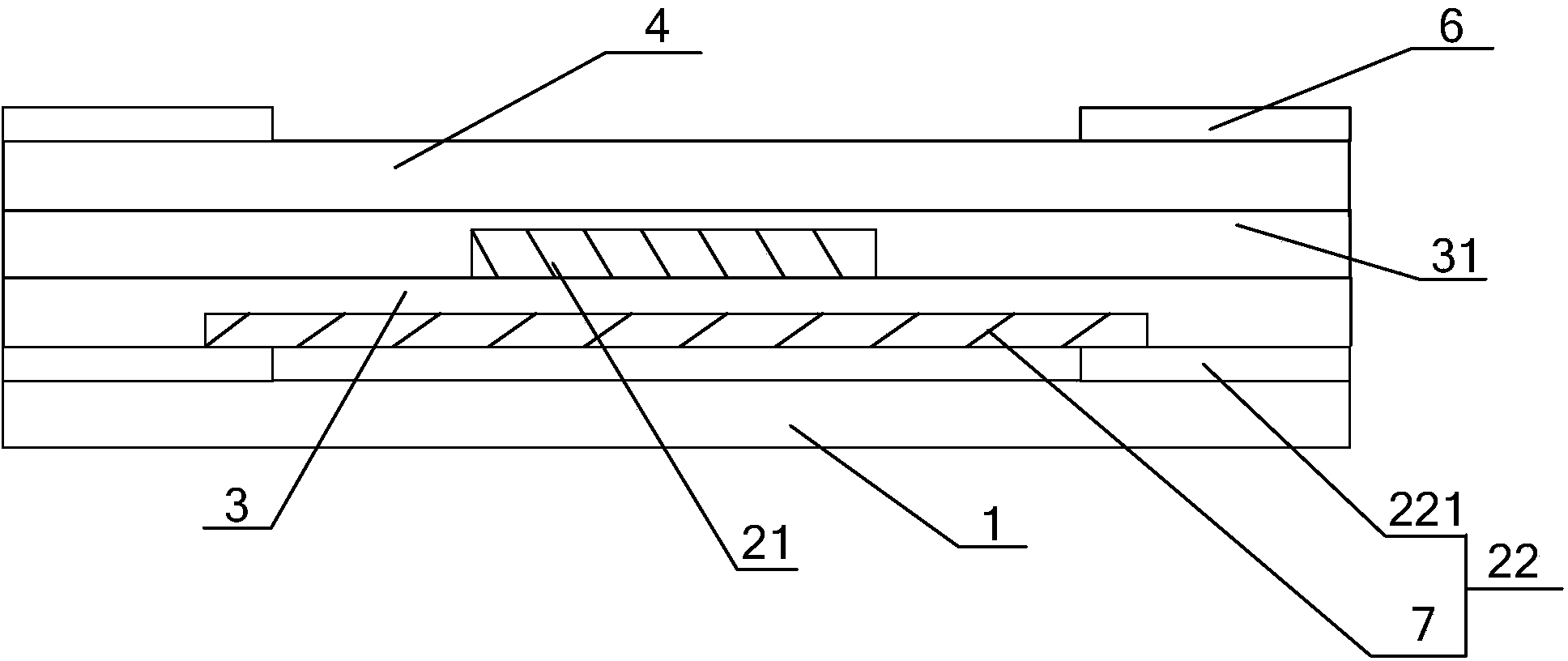

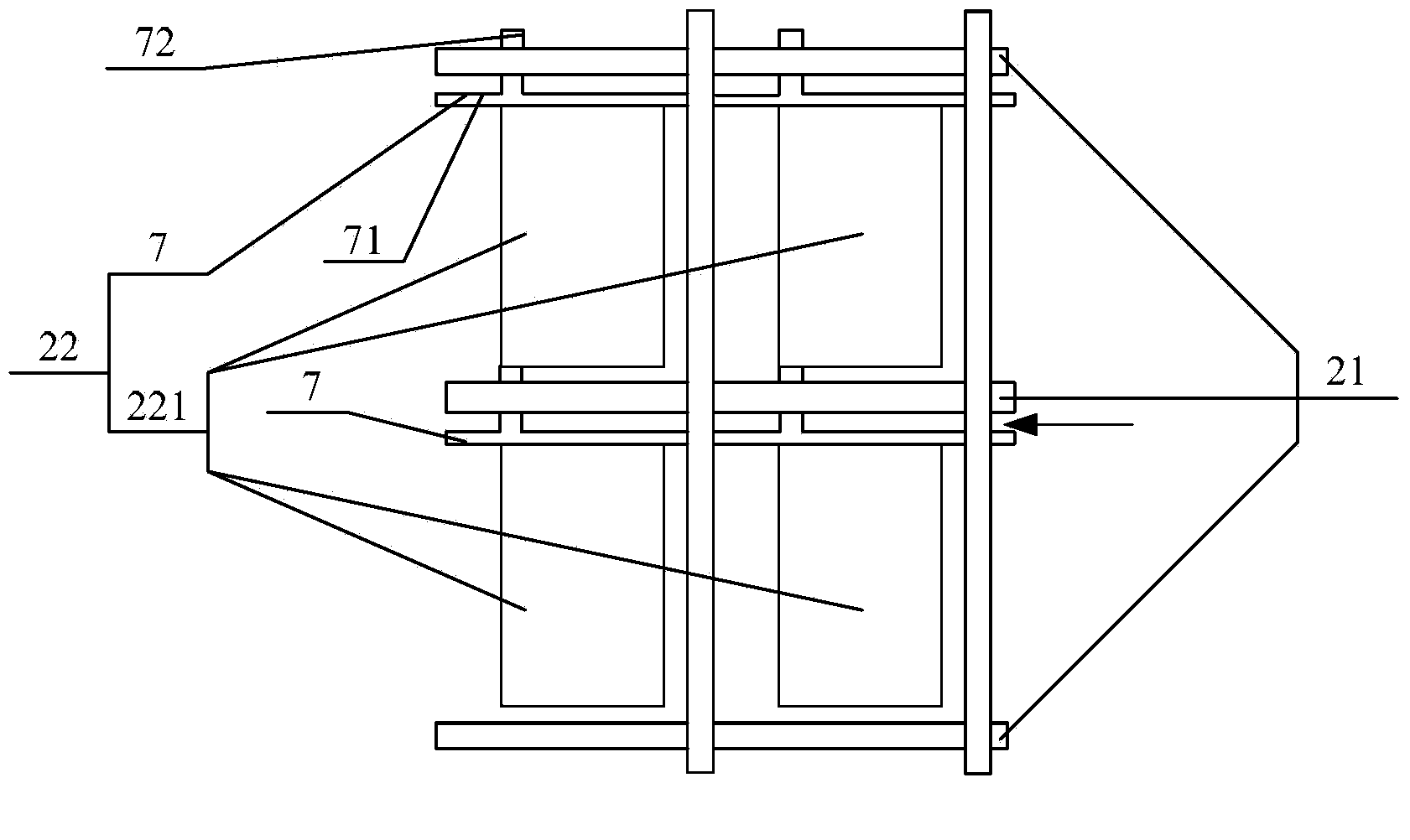

Array substrate used in ADS (adaptive damping system) display device

InactiveCN104298020AImprove the display effectImprove picture qualityNon-linear opticsElectrical resistance and conductanceDisplay device

The invention discloses an array substrate used in an ADS (adaptive damping system) display device, and relates to the technical field of display devices. The problems that the electrical resistance of a whole common electrode network of an array substrate in the prior art is quite high, so that signal delay time is prolonged, and the quality of images of the display device is high are solved. The array substrate used in the ADS display device comprises a substrate body, wherein a common electrode layer is arranged on the substrate body; a first insulating layer is paved on the common electrode layer; a grid electrode is arranged on the first insulating layer; a second insulating layer is paved on the grid electrode; a passivation layer is paved on the second insulating layer; a pixel electrode is formed on the passivation layer; the common electrode layer comprises common electrodes and metal conductive layers; the common electrodes are arranged on the substrate body at intervals; each metal conductive layer is connected between the two corresponding adjacent common electrodes; and the metal conductive layers correspond to a non-displaying region. The array substrate is mainly used in production of ADS display devices.

Owner:BOE TECH GRP CO LTD +1

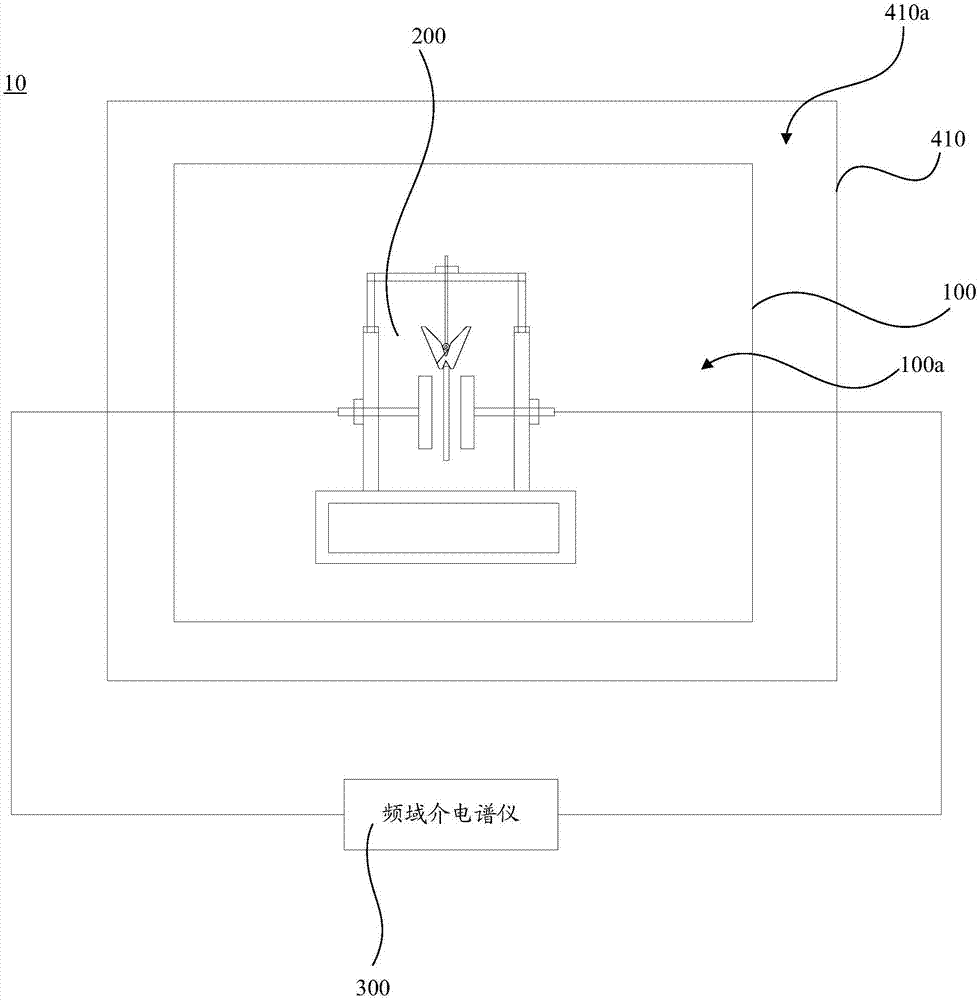

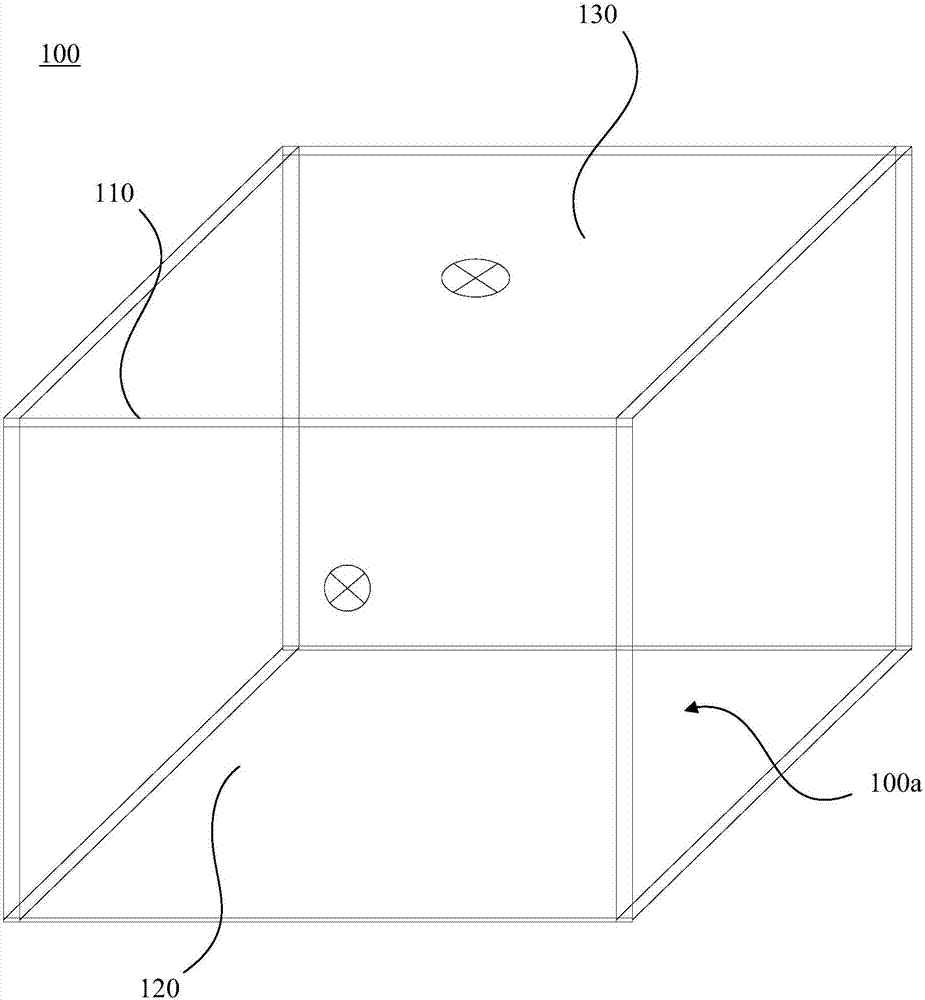

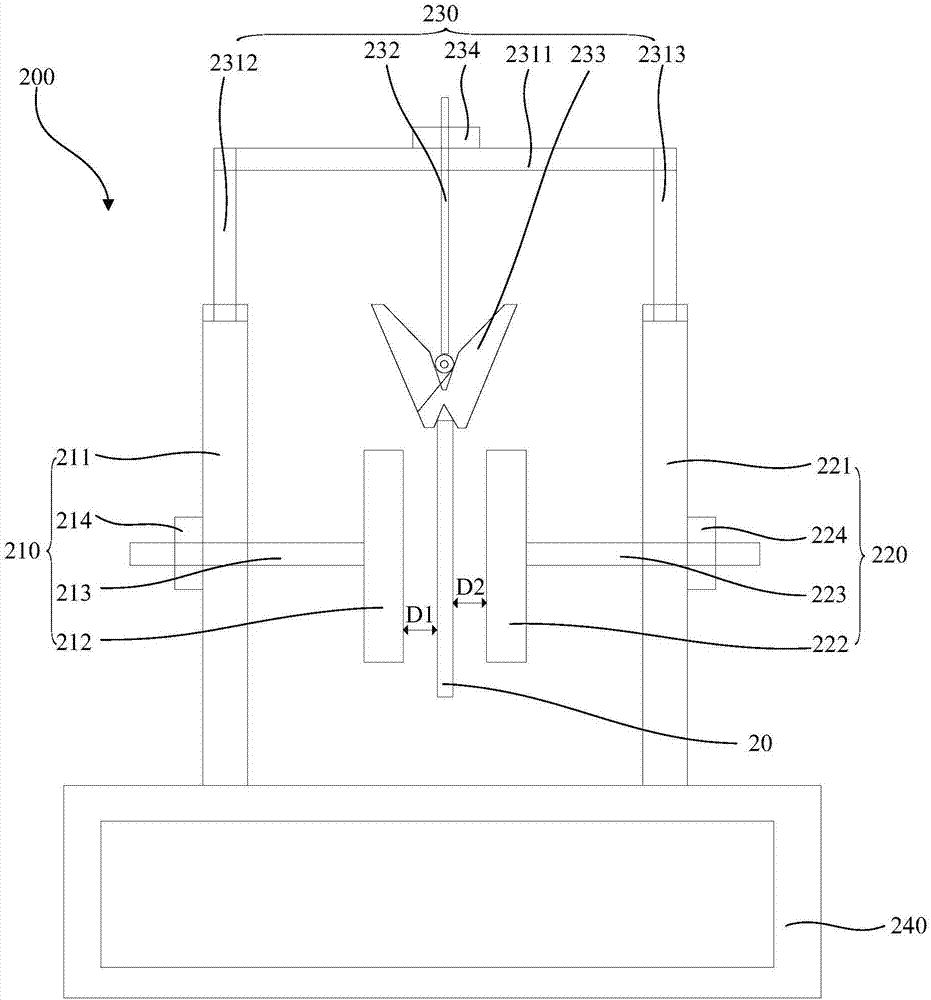

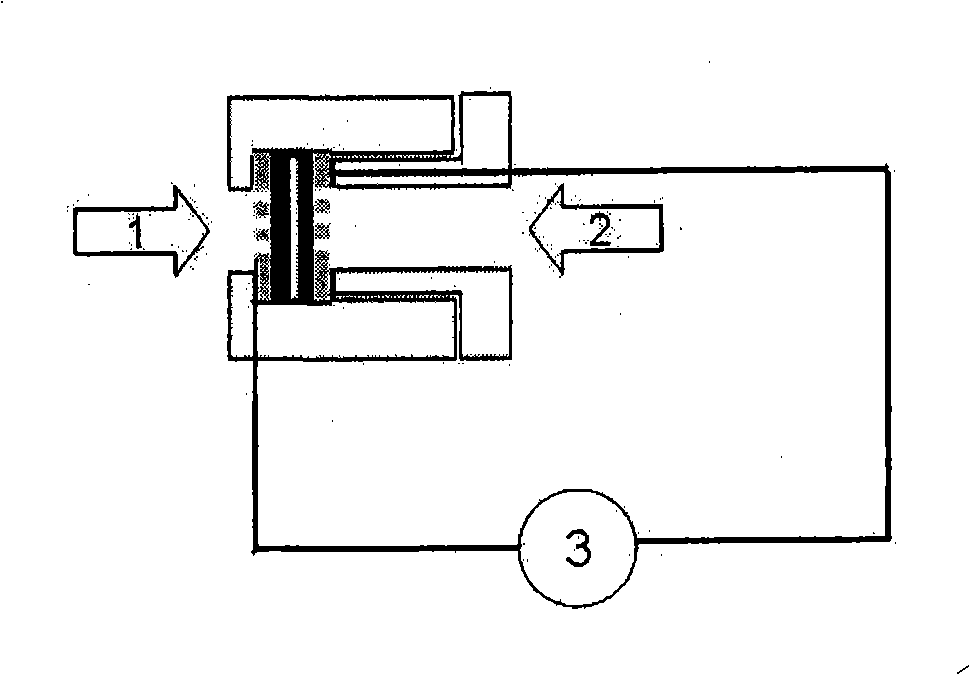

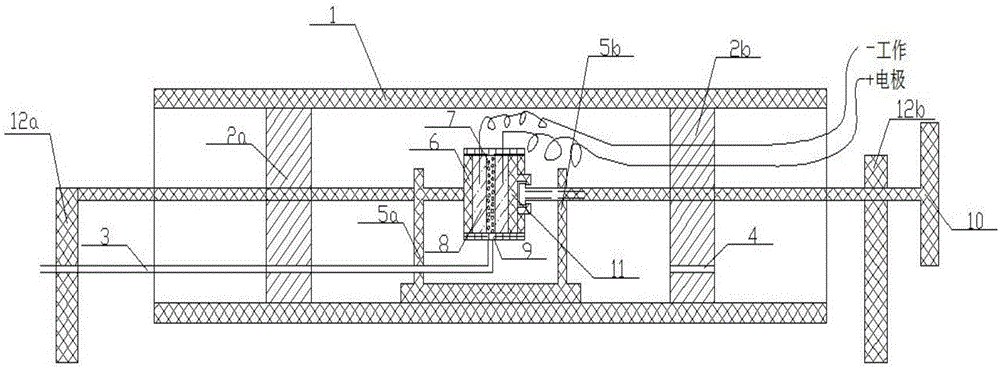

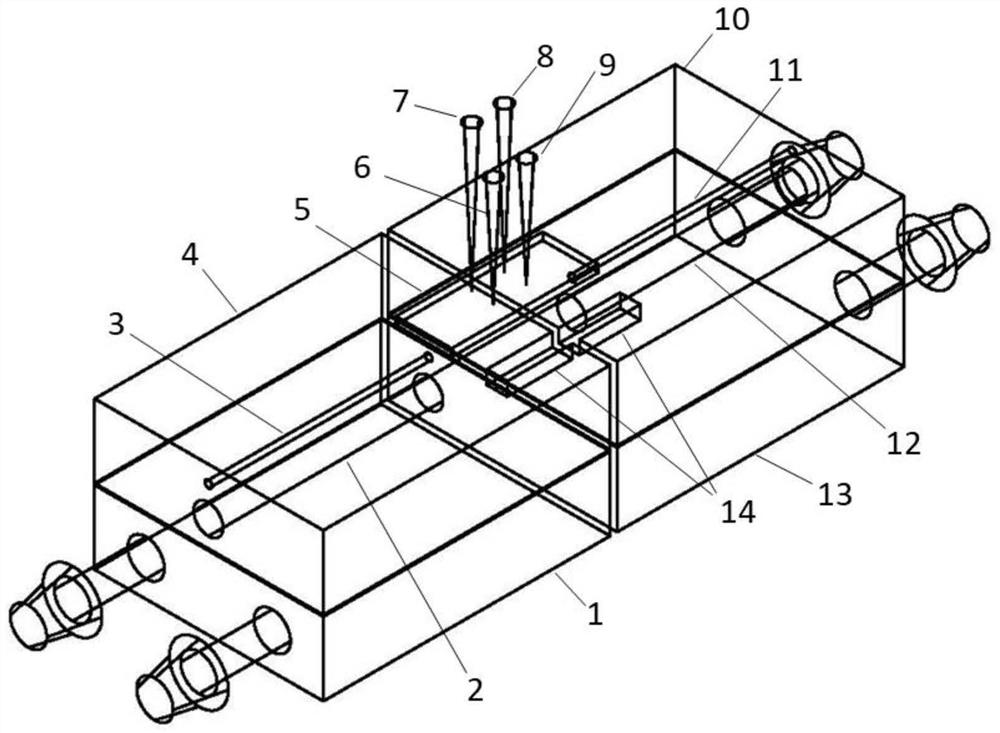

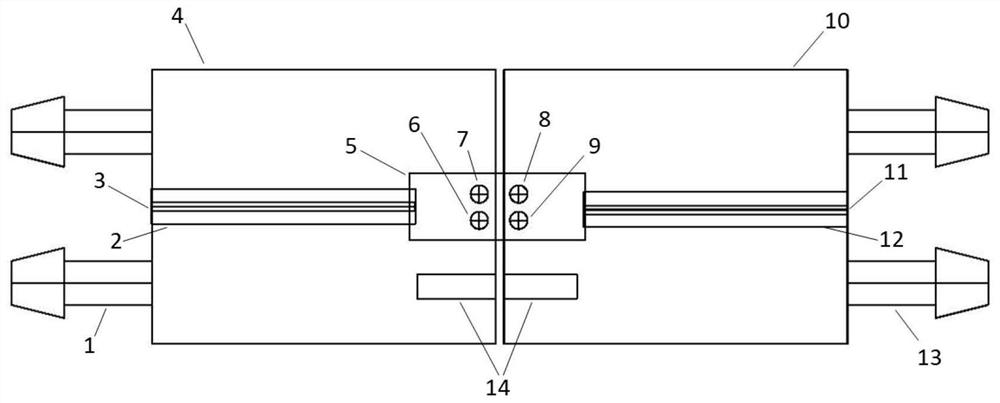

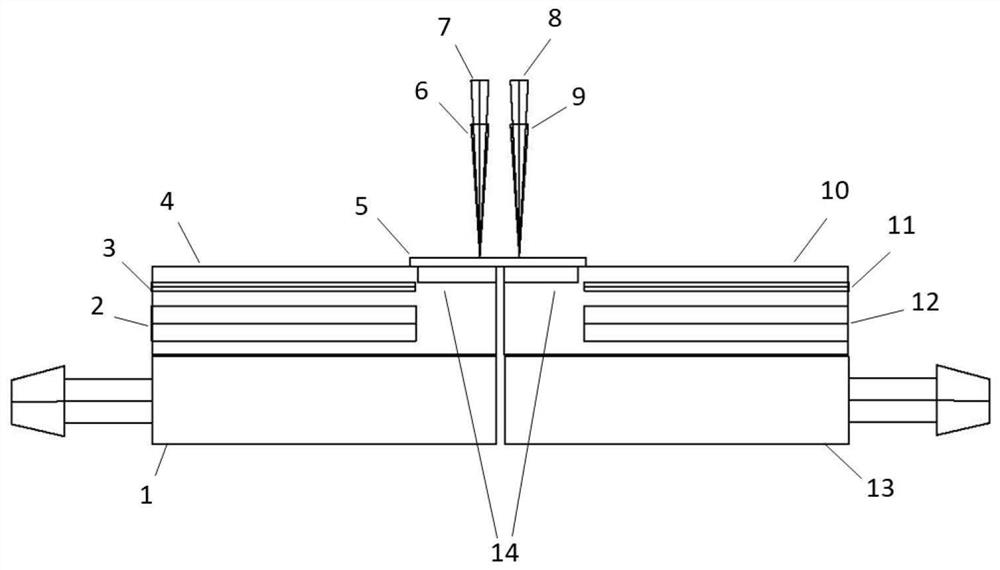

Composite-insulating-material frequency-domain dielectric spectroscopy testing apparatus

ActiveCN107390033AAvoid deformationAvoid direct contactResistance/reactance/impedenceTesting vessel constructionDielectricElectrical resistance and conductance

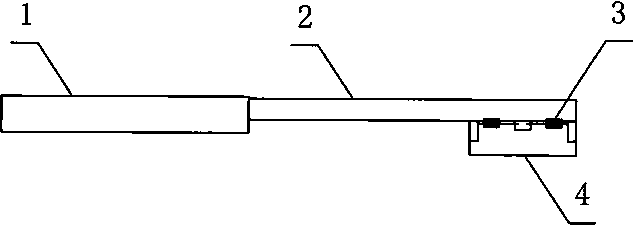

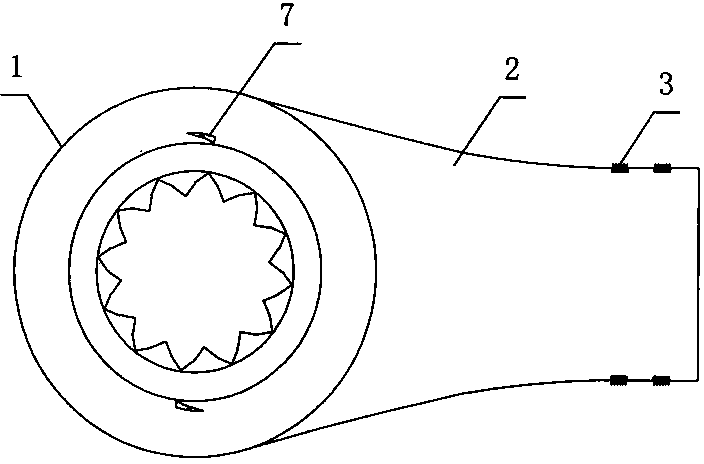

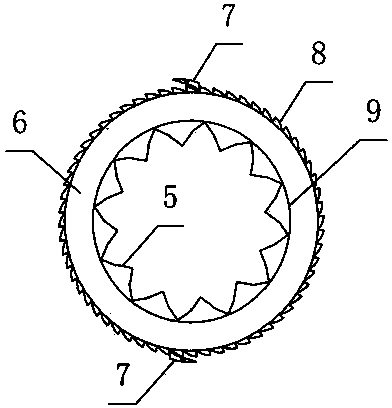

The invention relates to a composite-insulating-material frequency-domain dielectric spectroscopy testing apparatus comprising a shielding box, an electrode system and a frequency-domain dielectric spectroscopy instrument. The electrode system consists of a high-voltage electrode assembly, a measuring electrode assembly and a supporting assembly. When being tested, a sample is clamped and installed at one end of a support rod. The sample is arranged between a first electrode and a second electrode, wherein the first electrode, the second electrode, and the sample are spaced; the space among the first electrode, the second electrode, and the sample is filled with air dielectrics. The frequency-domain dielectric spectroscopy instrument applies voltages signals with different frequencies on the sample by the first electrode; and the second electrode is used for measuring a current signal flowing through the sample. Because the direct contact between the sample and surfaces of the first electrode and the second electrode is avoided, the contact resistance is avoided, so that the measurement error is reduced. The first electrode and the second electrode do not need to apply pressures on the surface of the sample, so that the sample deformation during measurement is avoided and thus the measurement accuracy of the complex dielectric constant of the sample is improved. With the shielding box, the interference signal from the electrode system is shielded to guarantee the high accuracy of the measurement result.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD

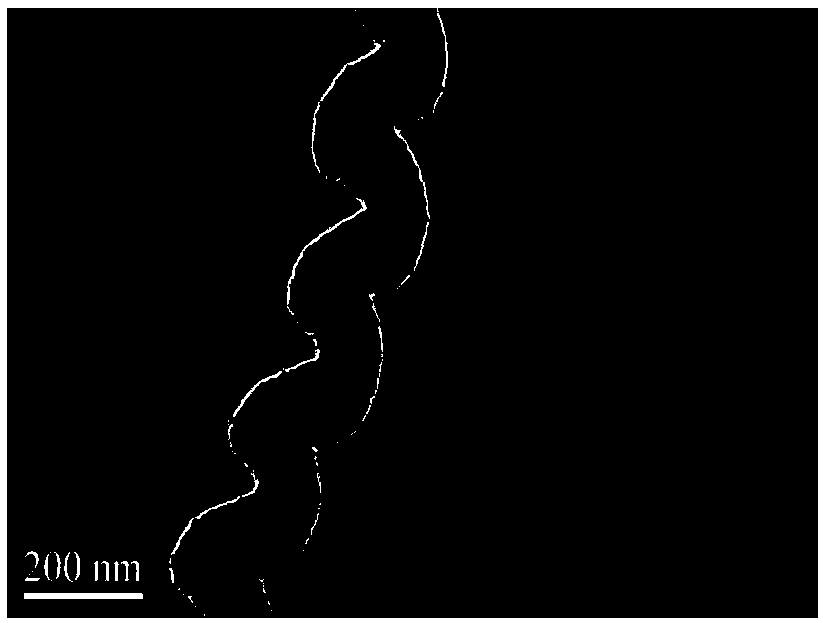

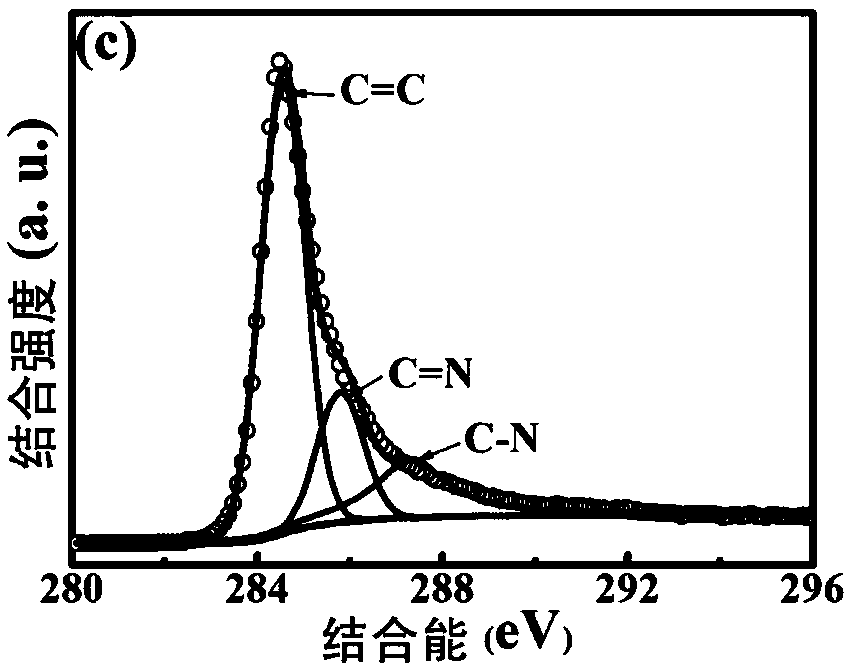

Preparation method of graphene oxide-clad spiral carbon pipe three-dimensional composite materials and photochemical reduction nitrogen doping

ActiveCN108711519AIncrease contact areaImprove conductivityHybrid capacitor electrodesHybrid/EDL manufactureCross-linkDoped graphene

The invention discloses a preparation method of graphene oxide-clad spiral carbon pipe three-dimensional composite materials and photochemical reduction nitrogen doping. The method comprises steps oftaking graphene oxide prepared through chemical oxidation and spiral carbon pipes prepared through combustion chemical vapor deposition method as raw materials; mixing the graphene oxide and the spiral carbon pipes and coating foamed nickel with the mixer through a knife, thereby achieving high nitrogen doped graphene method through illumination; and carrying out illumination on the foamed nickelcoated with the mixer of the graphene oxide and the spiral carbon pipes through knife under the atmosphere of ammonia gas by use of laser with 100-120 mJ / cm<2> energy or a mercury lamp in a selectableregion position, wherein the illumination time is 1-30 minutes so as to obtain the high nitrogen-doped photo-reduction graphene oxide and the spiral carbon pipe three-dimensional composite materials.According to the invention, the operation is convenient; the cost is low; the large-scale preparation is achieved; through the special cross linking function of the illumination time, the intensity and the mixed spiral carbon pipes, modulation and control of the nitrogen doping contents and conductivity of graphene and machinery performance are achieved.

Owner:GUILIN UNIVERSITY OF TECHNOLOGY

Method for fabricating semiconductor device

ActiveUS7338871B2Increase capacityAvoid contact resistanceTransistorSolid-state devicesElectrical resistance and conductanceParasitic capacitance

Owner:SK HYNIX INC

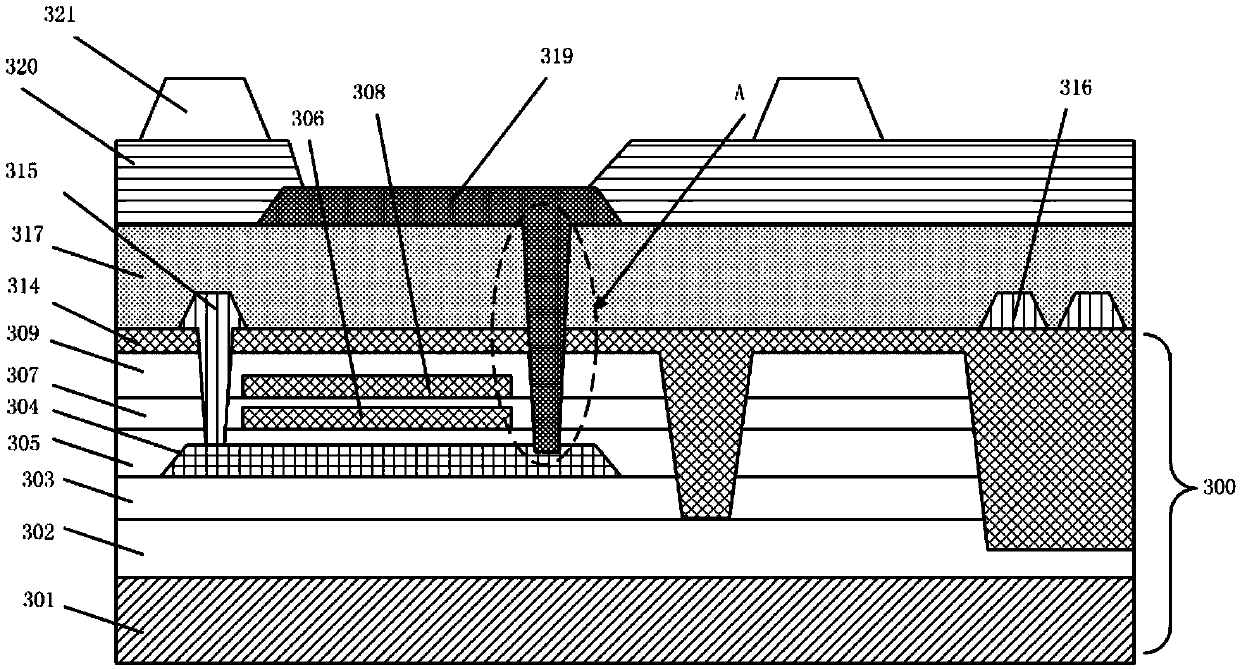

Display panel and manufacturing method thereof

ActiveCN109638050ALower resistanceHigh light transmittanceSolid-state devicesSemiconductor devicesLight reflectionTransmittance

The invention discloses a display panel and a manufacturing method thereof. In the display panel, an anode and a drain are integrated so as to avoid contact resistance between the anode and the drain,thereby reducing a metal annealing process. Moreover, the anode is made of a zinc oxide material superior to ITO in resistivity and light transmittance and easy to be subsequently etched, thereby reducing the on-resistance of the display panel and increasing the light reflection of the anode.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Turnbuckle type edge leakage proof hydrogen sensor outer housing structure

InactiveCN101261243AAvoid destructionEven by forceMaterial electrochemical variablesEngineeringHydrogen sensor

The invention discloses a turnbuckle type anti-side leakage hydrogen sensor outer shell structure which belongs to the air sensor field. The outer shell of the invention uses the turnbuckle type structure. The outer shell of the sensor and a flow combine plate are separately designed. The sandwich structure of a membrane electrode of two flow combine plates is positioned in the concave groove of the anode end of the outer shell, the cathode end of the outer shell is screwed in the concave groove of the anode end to close the shell body of the outer shell, and the flow combine plates and the membrane electrode are correspondingly clamped tightly. The structure of the sensor is screwed tightly and closed with each point stressed evenly, prevents the membrane electrode from being damaged and reduces contact resistance; furthermore the structure effectively prevents the tested air from side leaking without using two side sealing rings of the membrane electrode, simplifies the structure of the sensor, reduces production cost and improves the test precision. Moreover, the different materials of the outer shell and the flow combine plate can avoid a short circuit and the use of an independent flow combine plate facilitates the maintenance and replacement of components.

Owner:UNIV OF SCI & TECH BEIJING

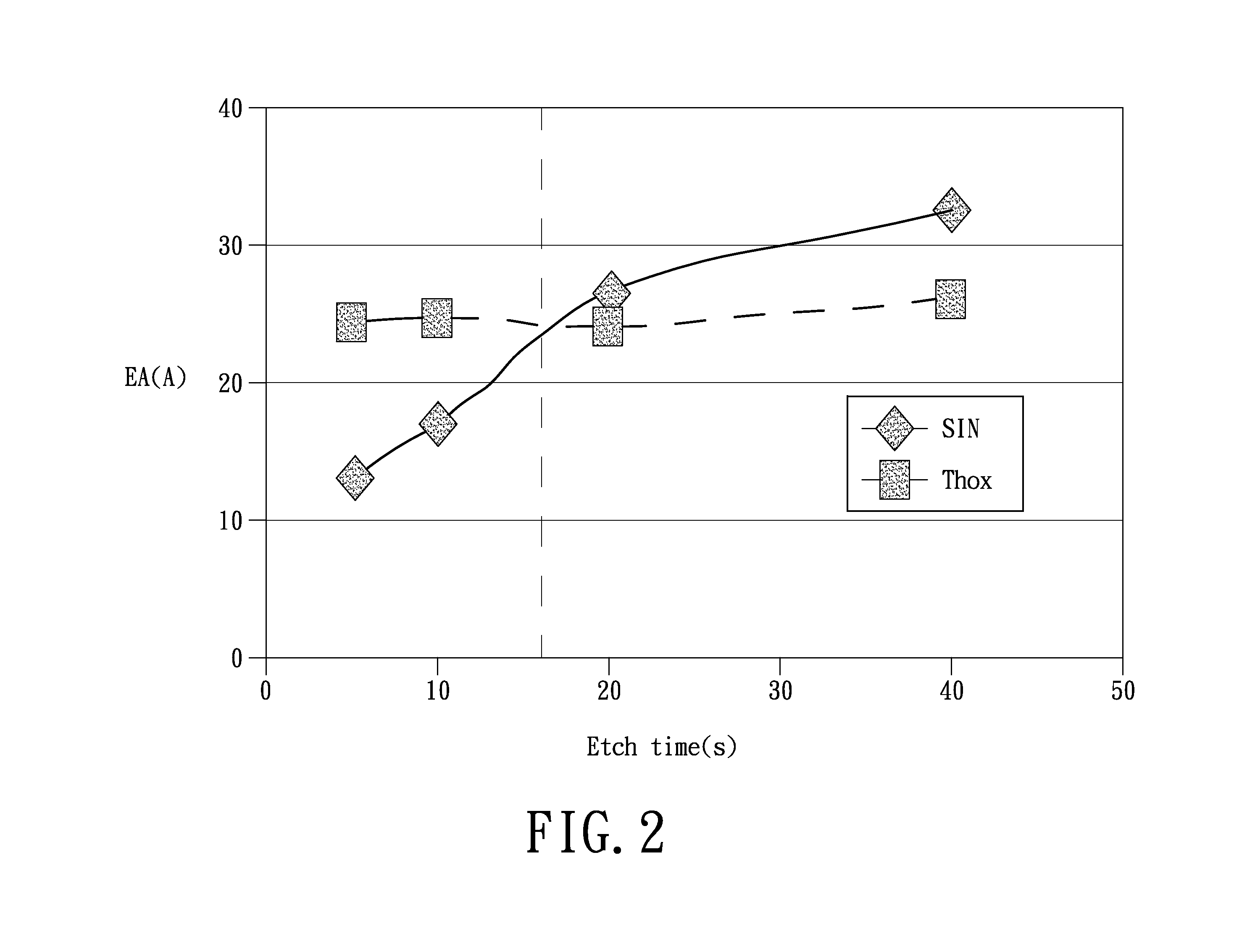

Cleaning method of semiconductor manufacturing process

ActiveUS20130014779A1Increase in contact resistanceAvoid enlarge sizeSemiconductor/solid-state device manufacturingCleaning using gasesEngineeringSemiconductor components

A cleaning method of a semiconductor manufacturing process is provided. The cleaning method is applied to a semiconductor component including a plurality of material layers formed thereon. An opening is defined in the material layers, and a side wall is exposed from the opening The side wall at least includes a first material layer and a second material layer. At first, a first cleaning process is performed till a lateral etched thickness of the first material layer is equal to a lateral etched thickness of the second material layer. Then, a byproduct formed in the first cleaning process is removed.

Owner:UNITED MICROELECTRONICS CORP

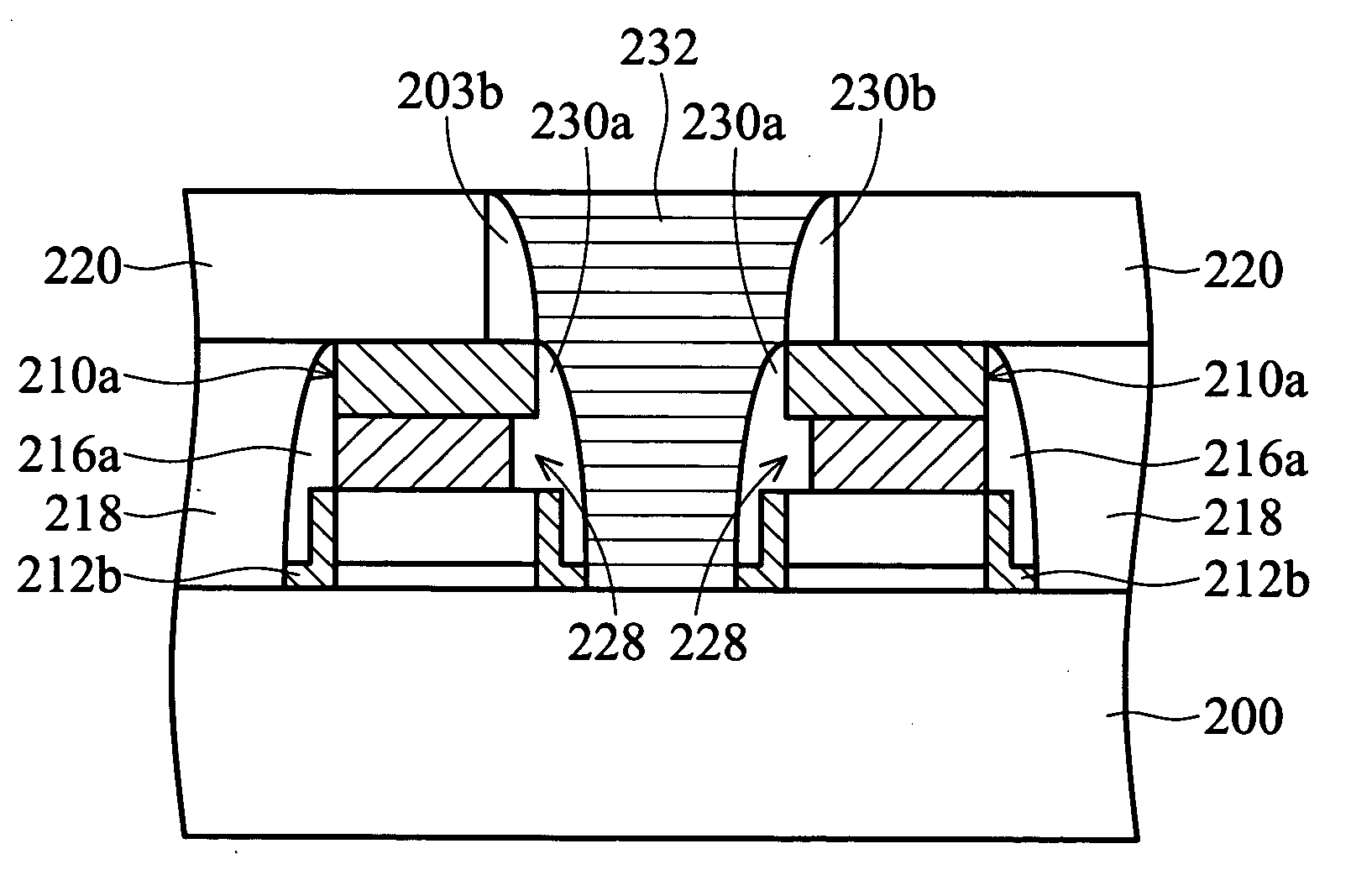

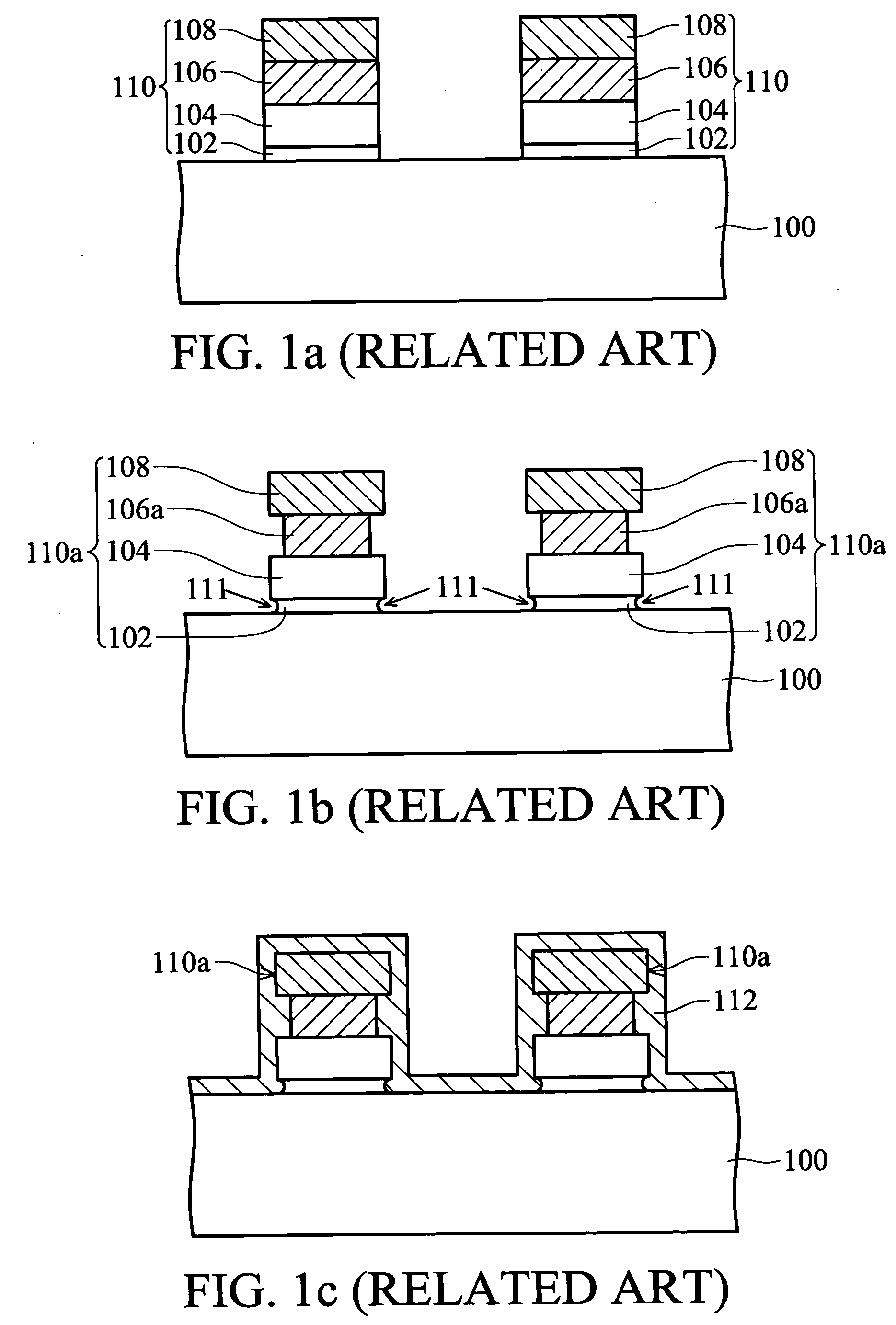

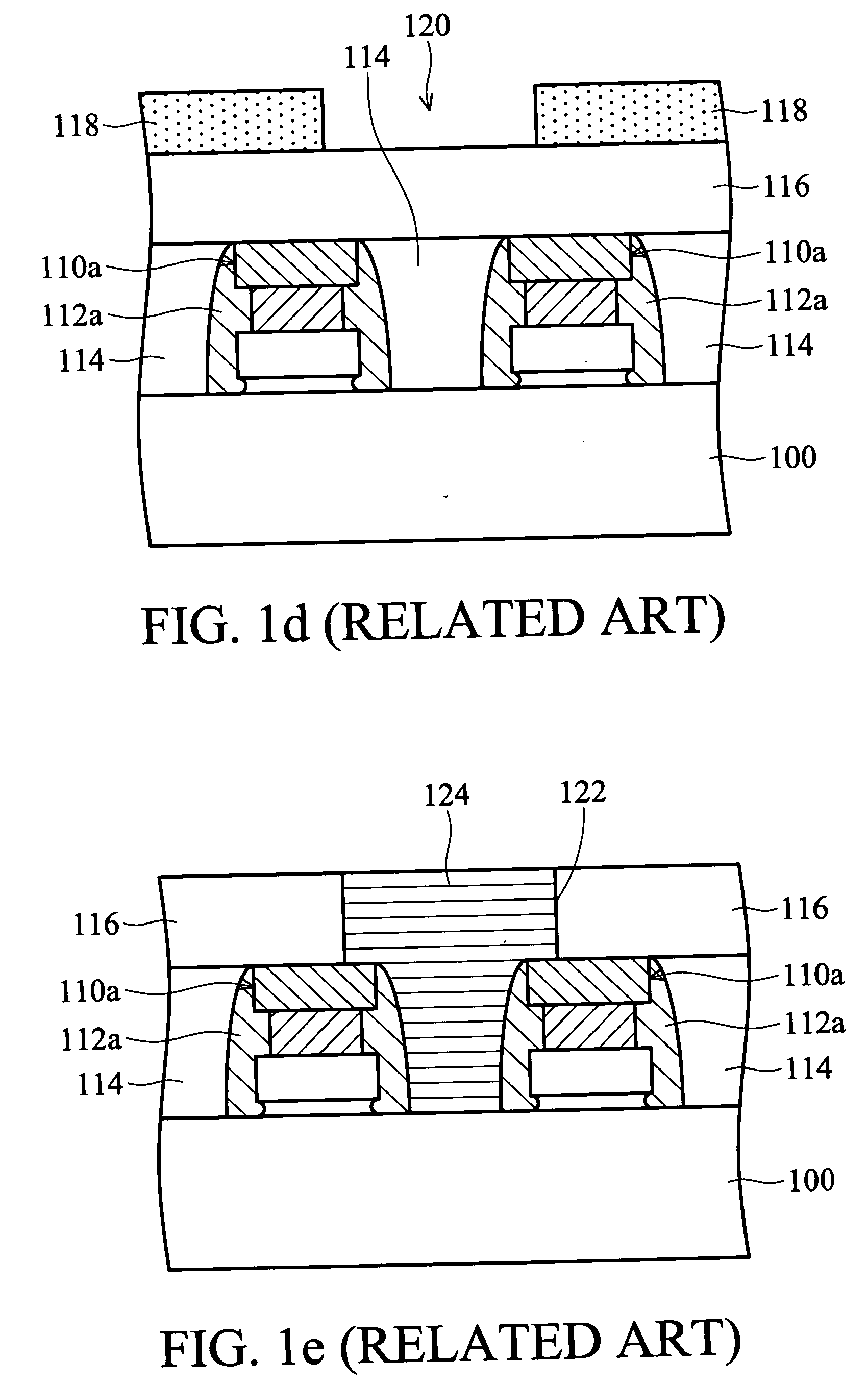

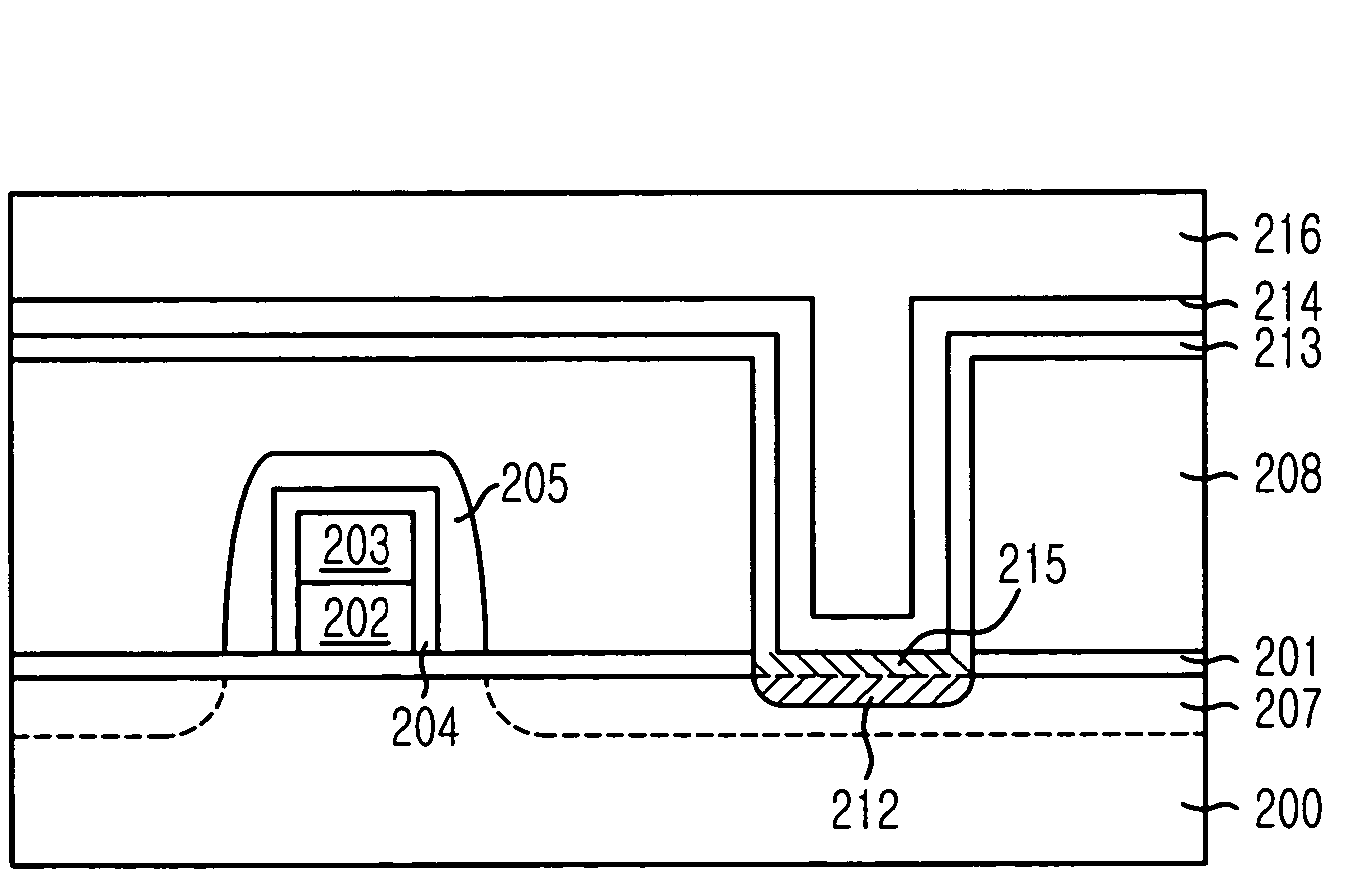

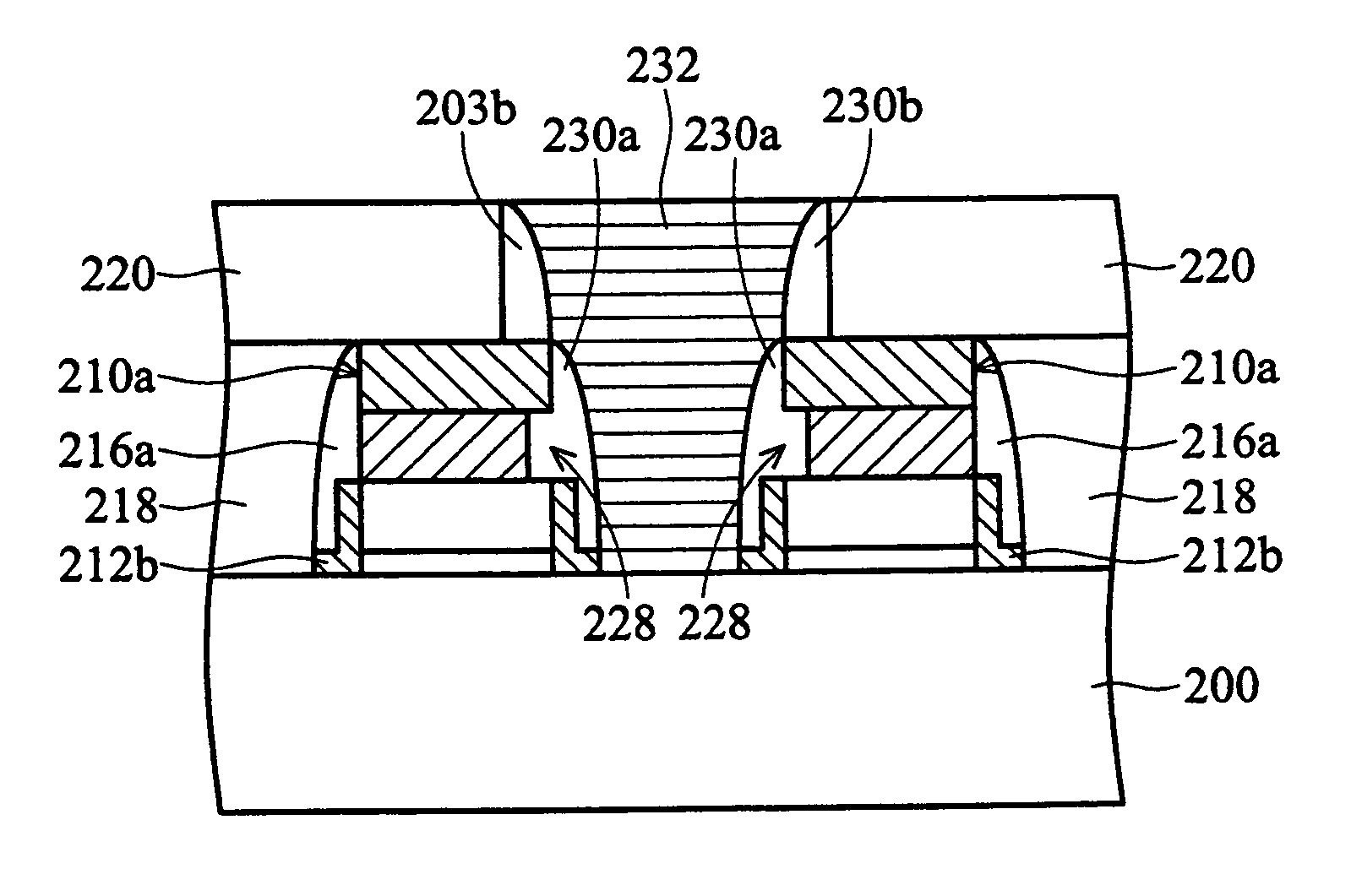

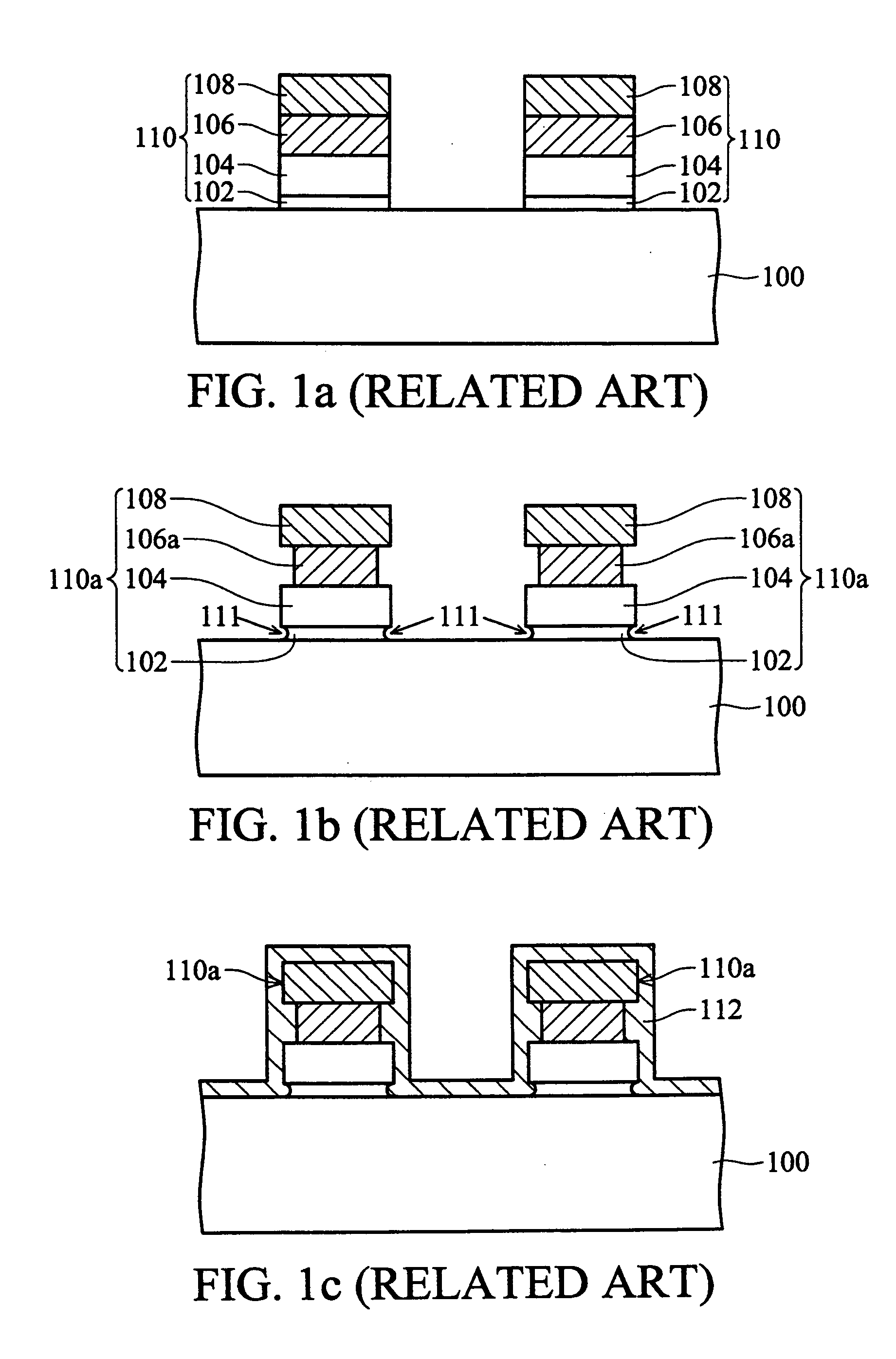

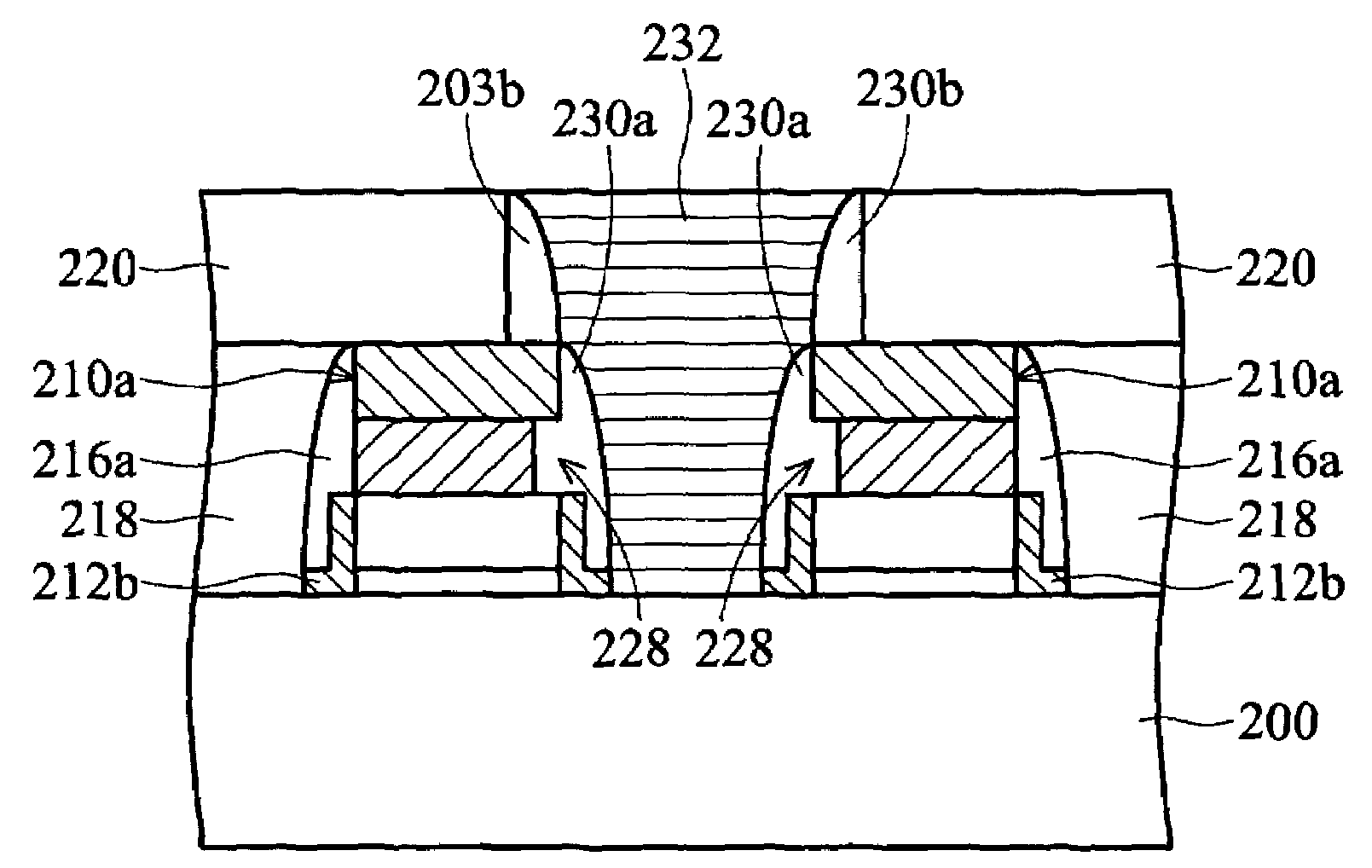

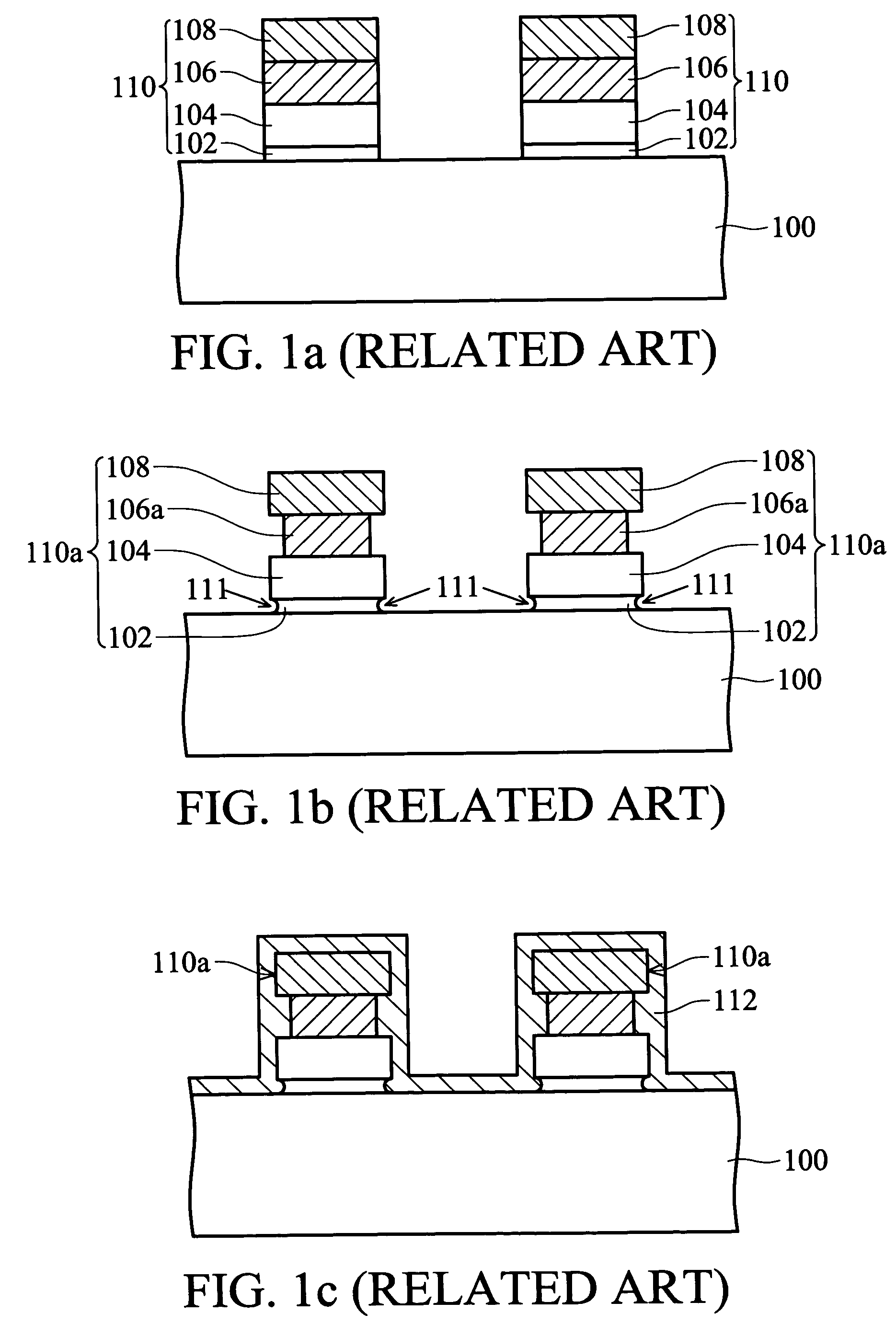

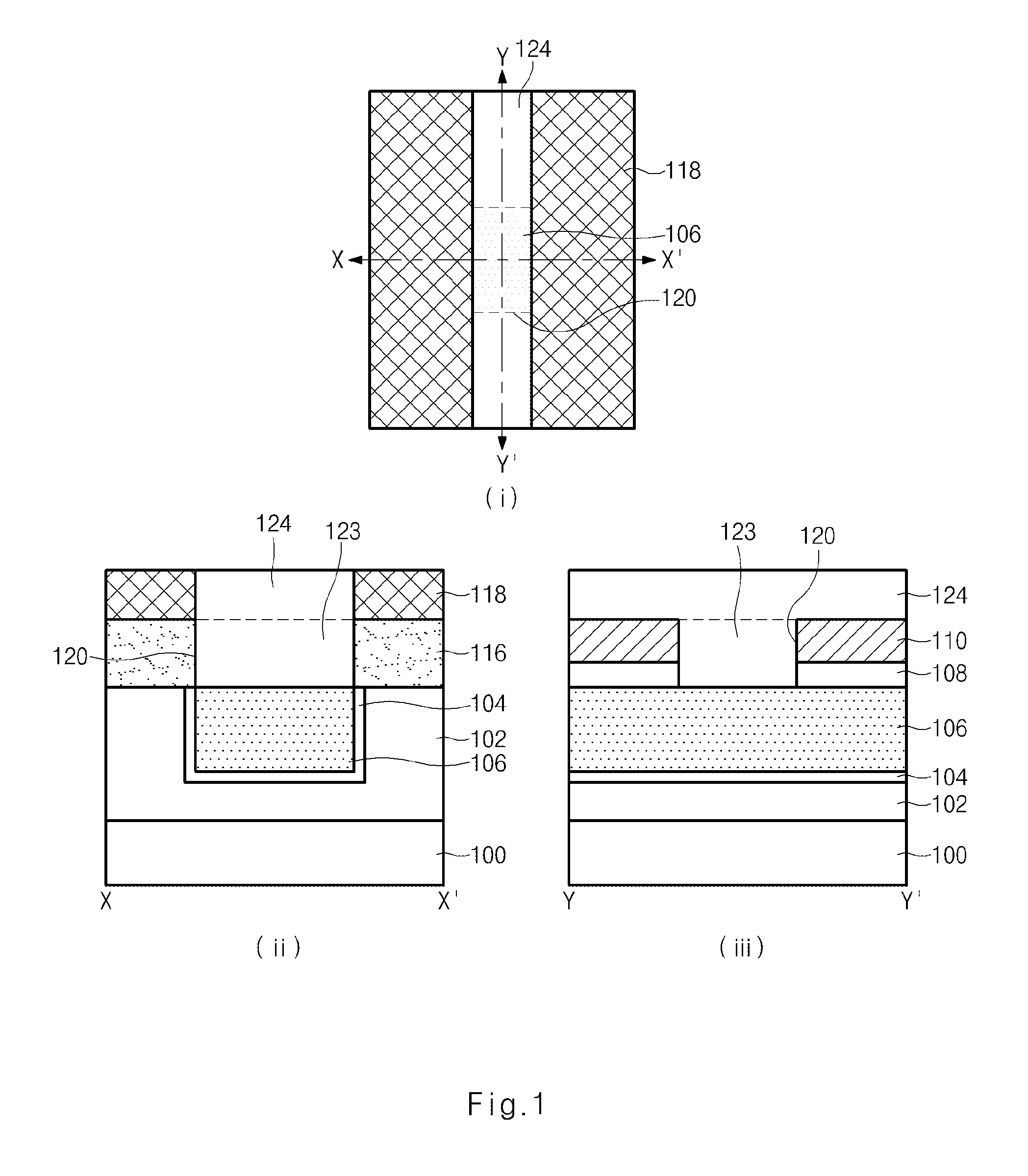

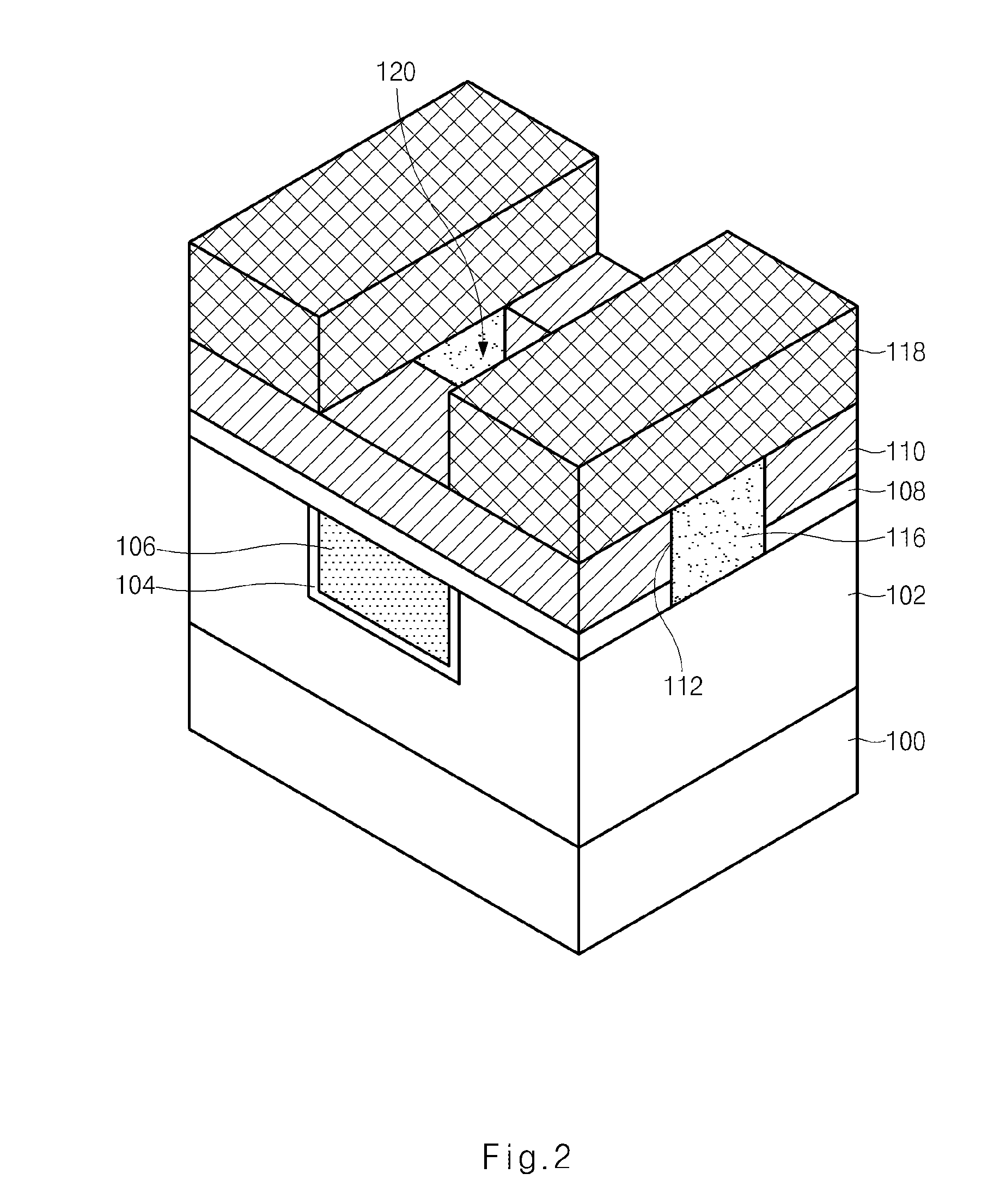

Word line structure with single-sided partially recessed gate structure

InactiveUS20060030091A1Prevent openingAvoid contact resistanceSolid-state devicesSemiconductor/solid-state device manufacturingGate dielectricLine structure

A word line structure with a single-sided partially recessed gate structure. The word line structure includes a gate structure, a first gate spacer, and a second gate spacer. The gate structure includes a gate dielectric layer, a first gate layer, a second gate layer, and a gate capping layer and has a recess region adjacent to one of opposing sidewalls of the second gate layer. The first gate spacer is disposed over opposing sidewalls of the gate dielectric layer and the first gate layer. The second gate spacer is disposed over opposing sidewalls of the gate structure and covers the first gate spacer. A method for forming a word line structure with a single-sided partially recessed gate structure is also disclosed.

Owner:NAN YA TECH

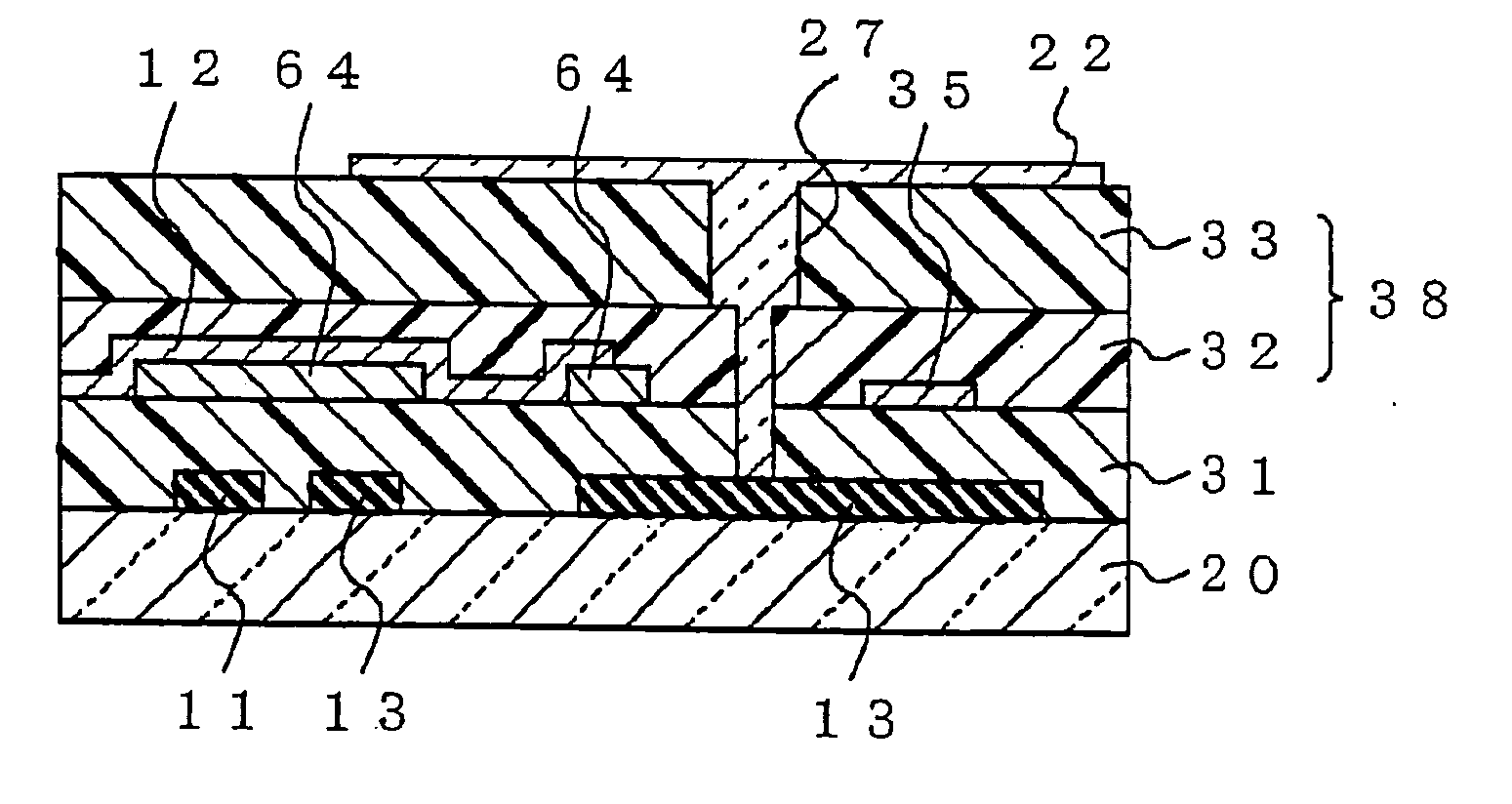

TFT LCD device having multi-layered pixel electrodes

InactiveUSRE41927E1Reduce the impactImprove conductivityTransistorSemiconductor/solid-state device detailsOptoelectronicsReflective layer

In a TFT LCD device comprising a substrate, at least one thin film transistor formed on the substrate, having a source electrode and a drain electrode, an insulating layer formed over the whole surface of the substrate on which the thin film transistor is formed, having at least one contact hole exposing a portion of the drain electrode, and reflective layer pixel electrode corresponding to the thin film transistor, formed on the insulating layer to be connected with the drain electrode through the contact hole, the pixel electrode is formed of a multi-layered conductive layer. The drain electrode is composed of multiple layers, and the most upper layer of the multiple layers is one selected from a Cr layer and a MoW layer. Preferably, the multi-layered conductive layer is composed of two-layered conductive layer having a lower layer of the same material as that of the most upper layer and an upper layer of Al-containing metal.

Owner:SAMSUNG DISPLAY CO LTD

Semiconductor device and method for manufacturing the same

ActiveUS8076736B2Avoid depositionAvoid contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationPower semiconductor device

A semiconductor device according to the present invention comprises a silicon carbide semiconductor substrate (1) including a silicon carbide layer (2); a high-concentration impurity region (4) provided in the silicon carbide layer (2); an ohmic electrode (9) electrically connected with the high-concentration impurity region (4); a channel region electrically connected with the high-concentration impurity region; a gate insulating layer (14) provided on the channel region; and a gate electrode (7) provided on the gate insulating layer (14). The ohmic electrode (9) contains an alloy of titanium, silicon and carbon, and the gate electrode (7) contains titanium silicide.

Owner:PANASONIC CORP

Silica-based condenser microphone and production method thereof

InactiveCN101848411AIncrease resistanceImprove electrical performanceElectrostatic transducer microphonesCapacitanceOhmic contact

The invention relates to a method for producing a silica-based condenser microphone. The method comprises the following steps of: A. providing a silicon substrate, and depositing an etching barrier layer on the silicon substrate; B. depositing a stress balancing layer on the etching barrier layer; C. depositing a vibrating diaphragm on the stress balancing layer; D. depositing a sacrificial layer on the silicon substrate, and etching latent images; E. depositing a backplate; F. caying out doping on the backplate to form a conductor; G. etching the backplate; and H. depositing an electrode, and performing ohmic contact.

Owner:AAC ACOUSTIC TECH (SHENZHEN) CO LTD +1

World line structure with single-sided partially recessed gate structure

ActiveUS6991978B2Prevent openingAvoid contact resistanceTransistorSolid-state devicesGate dielectricEngineering

A word line structure with a single-sided partially recessed gate structure. The word line structure includes a gate structure, a first gate spacer, and a second gate spacer. The gate structure includes a gate dielectric layer, a first gate layer, a second gate layer, and a gate capping layer and has a recess region adjacent to one of opposing sidewalls of the second gate layer. The first gate spacer is disposed over opposing sidewalls of the gate dielectric layer and the first gate layer. The second gate spacer is disposed over opposing sidewalls of the gate structure and covers the first gate spacer. A method for forming a word line structure with a single-sided partially recessed gate structure is also disclosed.

Owner:NAN YA TECH

Semiconductor device and method for forming the same

ActiveUS20120013014A1Easy to integrateAvoid contact resistanceSemiconductor/solid-state device detailsSolid-state devicesElectrical resistance and conductanceInsulation layer

The semiconductor device comprises a metal line configured to be buried in an interlayer insulation layer formed over a semiconductor substrate, a first insulating pattern configured to be formed over the interlayer insulating layer and the first metal line so that the first metal line is exposed, a second insulating pattern configured to be buried between the first insulating patterns so that the first metal line is exposed, and a third insulating pattern configured to be formed over the first insulating pattern and the second insulating pattern so that the first metal line is exposed, thereby reducing the resistance of a contact plug, such that it operates at high speed and requires low power consumption.

Owner:SK HYNIX INC

Electrode stucture, semiconductor element, and methods of manufacturing the same

ActiveUS20120028456A1Reduce contact resistanceAvoid contact resistanceOptical wave guidanceSemiconductor/solid-state device manufacturingTectorial membraneNitride semiconductors

According to the present invention, there is provided an electrode structure which includes: a nitride semiconductor layer; an electrode provided over the nitride semiconductor layer; and an electrode protective film provided over the electrode, wherein the nitride semiconductor layer contains a metal nitride containing Nb, Hf or Zr as a constitutive element, the electrode has a portion having a metal oxide containing Ti or V as a constitutive element formed therein, and the electrode protective film covers at least a portion of the electrode, and contains a protective layer having Au or Pt as a constitutive element.

Owner:RENESAS ELECTRONICS CORP

Resistivity testing device capable of regulating temperature, atmosphere and density of powder material

ActiveCN106353372ASolve the pressure unchangedAvoid contact resistanceMaterial resistanceElectrical resistance and conductanceTube furnace

The invention discloses a resistivity testing device capable of regulating the temperature, atmosphere and density of a powder material. Firstly, the equipment is small in volume and convenient, temperature regulation is performed through a constant-temperature zone of a tubular furnace, different electrodes are changed for connection at different temperatures and in different atmospheres, and direct contact resistance between the powder and a wire as well as the redox of an electrode at different temperatures and in different atmospheres is reduced, so that the accuracy of the test data is high; secondly, by adopting a straight-blowing gas supply way at the sealed bottom, direct contact between the gas and the powder as well as uniform gas distribution can be guaranteed, and uniform gas distribution is guaranteed and the problem of powder particle loss is solved through different numbers of gas guide plates; and finally, by adopting a screw type central pressurizing way and increasing the length of a pressurizing screw, uniform pressure distribution between the powder and the electrode can be guaranteed, the fixing stability is high, and the pressure is kept unchanged in the case of material expansion at a high temperature; and moreover, with the same powder mass, the resistivity of the powder of the same material and at different compaction densities is measured according to the rotation number of turns of the screw.

Owner:BEIJING UNIV OF TECH

Electrode of p-type gallium nitride-based device as well as preparation method and application thereof

PendingCN113488530ASolving the Schottky Barrier Height ElevationReduced ohmic contact resistanceSemiconductor devicesPhysicsCMOS

The invention provides an electrode of a p-type gallium nitride-based device as well as a preparation method and application thereof. The electrode comprises a nickel oxide layer, a platinum layer and a gold layer which are sequentially stacked, wherein the nickel oxide layer is of a P-type structure, the platinum layer is located between the P-type nickel oxide layer and the gold layer, and the nickel oxide layer is an ohmic contact layer of the p-type gallium nitride-based device. The electrode of the p-type gallium nitride-based device is used for a source electrode and a drain electrode of the p-type gallium nitride-based device, more carriers flow between metal and a semiconductor by introducing a Schottky barrier height of the P-type NiO layer, the transition metal and the semiconductor interface, and meanwhile, by means of ultrahigh vacuum heat treatment, the problem that the height of the Schottky barrier is increased due to a Ga2O3 pollution layer is solved, the ohmic contact resistance of the source electrode and the drain electrode of the device is reduced, the performance of a p-type gallium nitride-based transistor is improved, the p-type gallium nitride-based device can play a greater role in a CMOS circuit, and the defect is changed into the advantage.

Owner:SOUTH UNIVERSITY OF SCIENCE AND TECHNOLOGY OF CHINA +1

Horizontal test device and method for Seebeck coefficient and conductivity of thermoelectric material

PendingCN113758961AEasy to testQuick testResistance/reactance/impedenceMaterial heat developmentThermoelectric materialsEngineering

The invention discloses a horizontal test device and method for Seebeck coefficient and conductivity of a thermoelectric material. The equipment provided by the invention is provided with two cooling systems, so that the Seebeck coefficient of a material when the temperature is lower than room temperature can be tested, and meanwhile, after the previous test is completed, the heater can be quickly recovered to a relatively low temperature, so that the test of a next sample can be quickly started, the sample test is simpler and more convenient, and the efficiency of testing a plurality of temperatures of a plurality of samples is improved. According to the invention, a contact heating mode is adopted, and a double-heating table mode is adopted, so that any temperature difference can be accurately and quickly provided for a test sample. The distance between the two heating blocks can be adjusted and controlled, the surface is provided with the groove, and a block sample can be placed in the groove, so that the purpose of testing the block sample and a film sample can be simultaneously met.

Owner:XIAMEN INST OF RARE EARTH MATERIALS

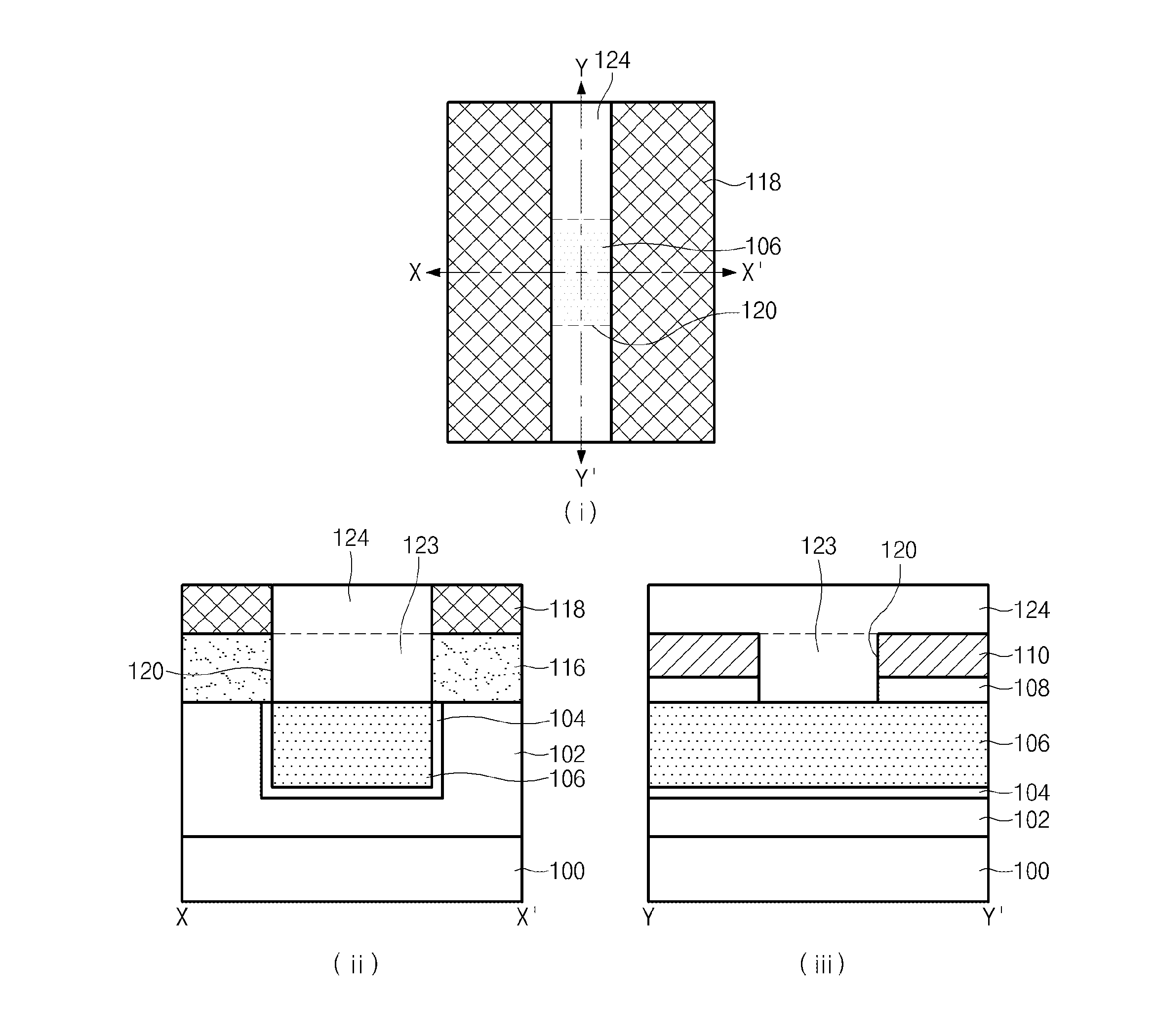

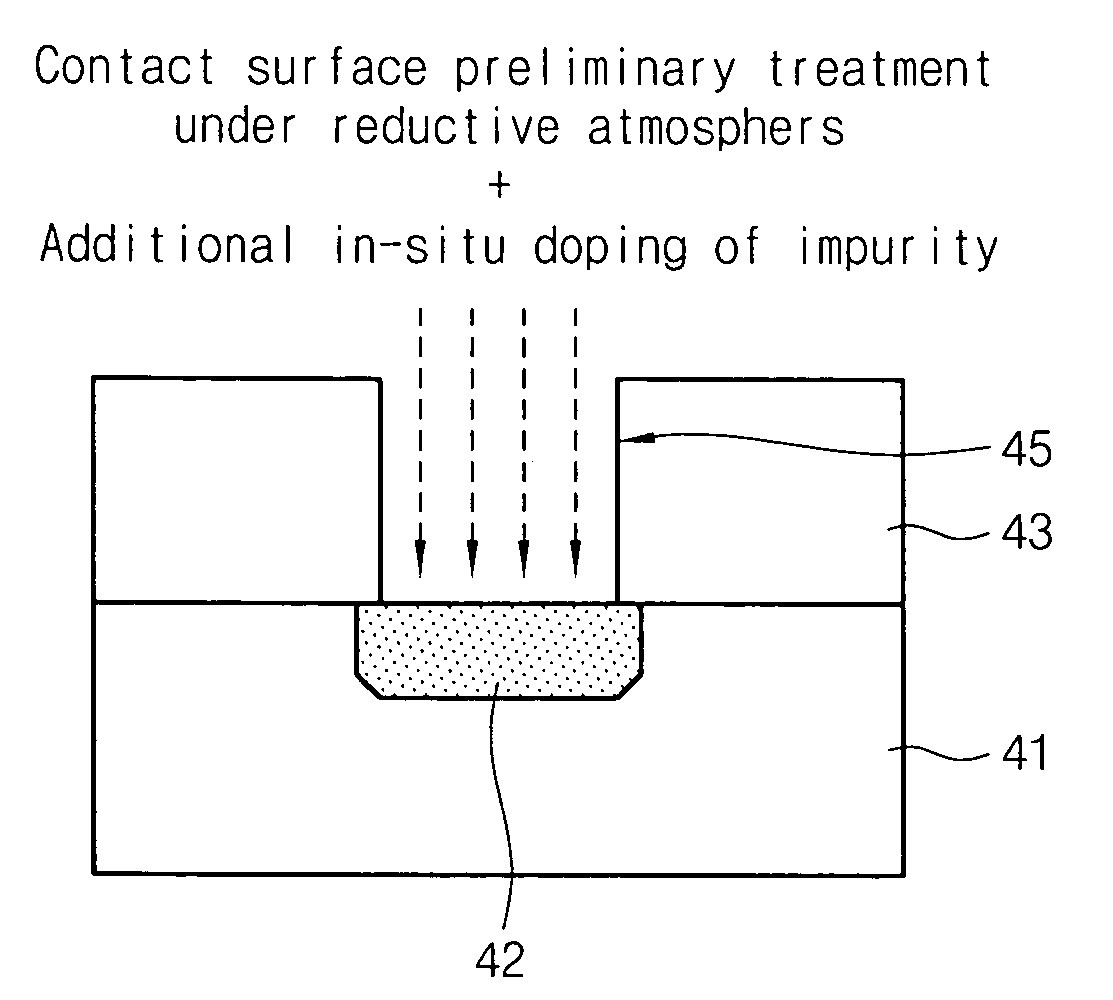

Method of manufacturing semiconductor device

InactiveUS6979633B2Increase impurity concentrationAvoid contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesOxideDielectric

Disclosed is a method of manufacturing a semiconductor device, which prevents a contact resistance due to a native oxide film from being increased. Semiconductor substrate on which a lower structure having a junction region is formed is prepared. Interlayer dielectric film is formed over a whole surface of semiconductor substrate. Contact hole exposing the junction region is formed by etching interlayer dielectric film. Dry-cleaning and wet-cleaning for a substrate surface exposed by the contact hole are sequentially performed. Washed contact surface is preliminarily treated under reducing gas atmosphere to remove a native oxide film formed on contact surface. Impurity is additionally doped to a surface of the junction region in-situ so that impurity damages on preliminary-treated contact surface are compensated for. Conductive film is deposited on the contact hole and the interlayer dielectric film in-situ.

Owner:SK HYNIX INC

A method of forming micro-pattern in semiconductor device

PendingCN110911272AImprove overlay accuracyImprove yieldSemiconductor/solid-state device manufacturingParasitic capacitorCapacitance

The invention provides a method for forming a micro-pattern in a semiconductor device. The method comprises the following steps: providing a substrate, forming a hard mask layer on the substrate, forming a first sacrificial layer on the hard mask layer, forming a second sacrificial layer on the first sacrificial layer, and forming a third sacrificial layer on the second sacrificial layer; firstly,forming a first dot pattern; forming a second dot pattern; forming a third dot pattern; and finally, etching the first sacrificial layer to form a micro-pattern. According to the method, the overlayprecision in the capacitor pattern manufacturing process is improved, the problems of contact resistance and parasitic capacitance are avoided, the product yield is greatly improved, and meanwhile themethod is simple in operation process, low in cost and short in period.

Owner:CHANGXIN MEMORY TECH INC