Patents

Literature

475results about How to "Promote stratification" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

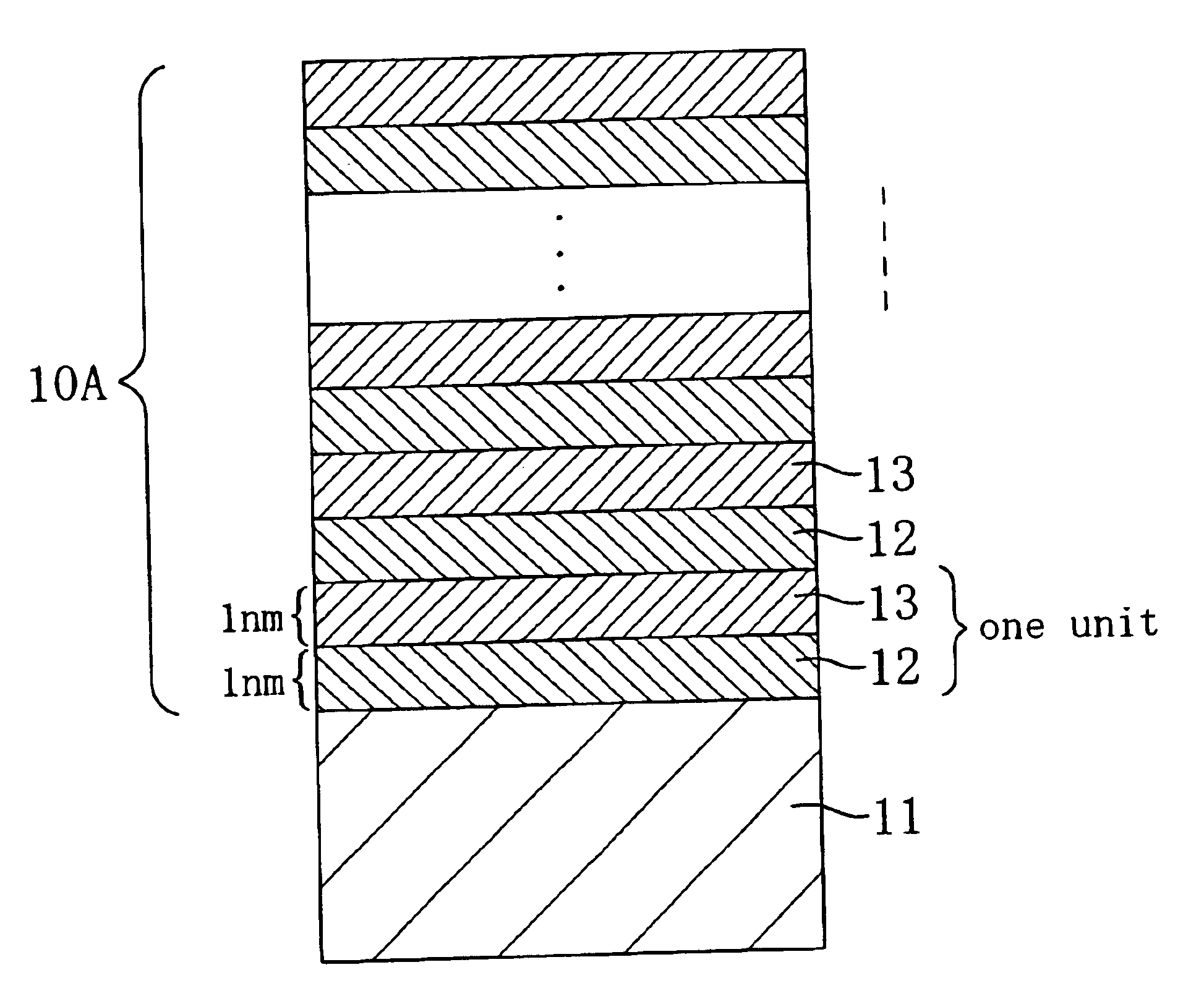

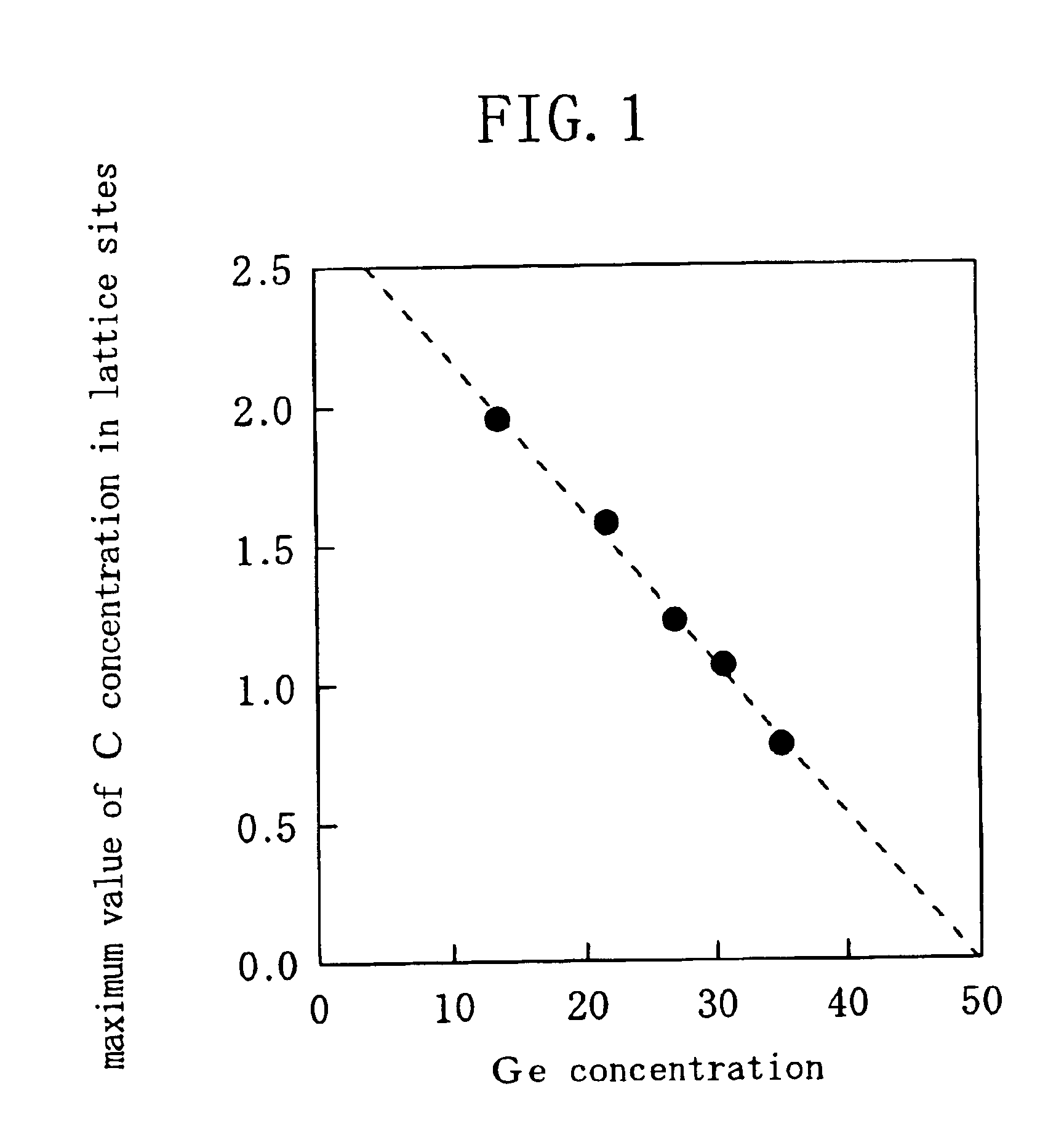

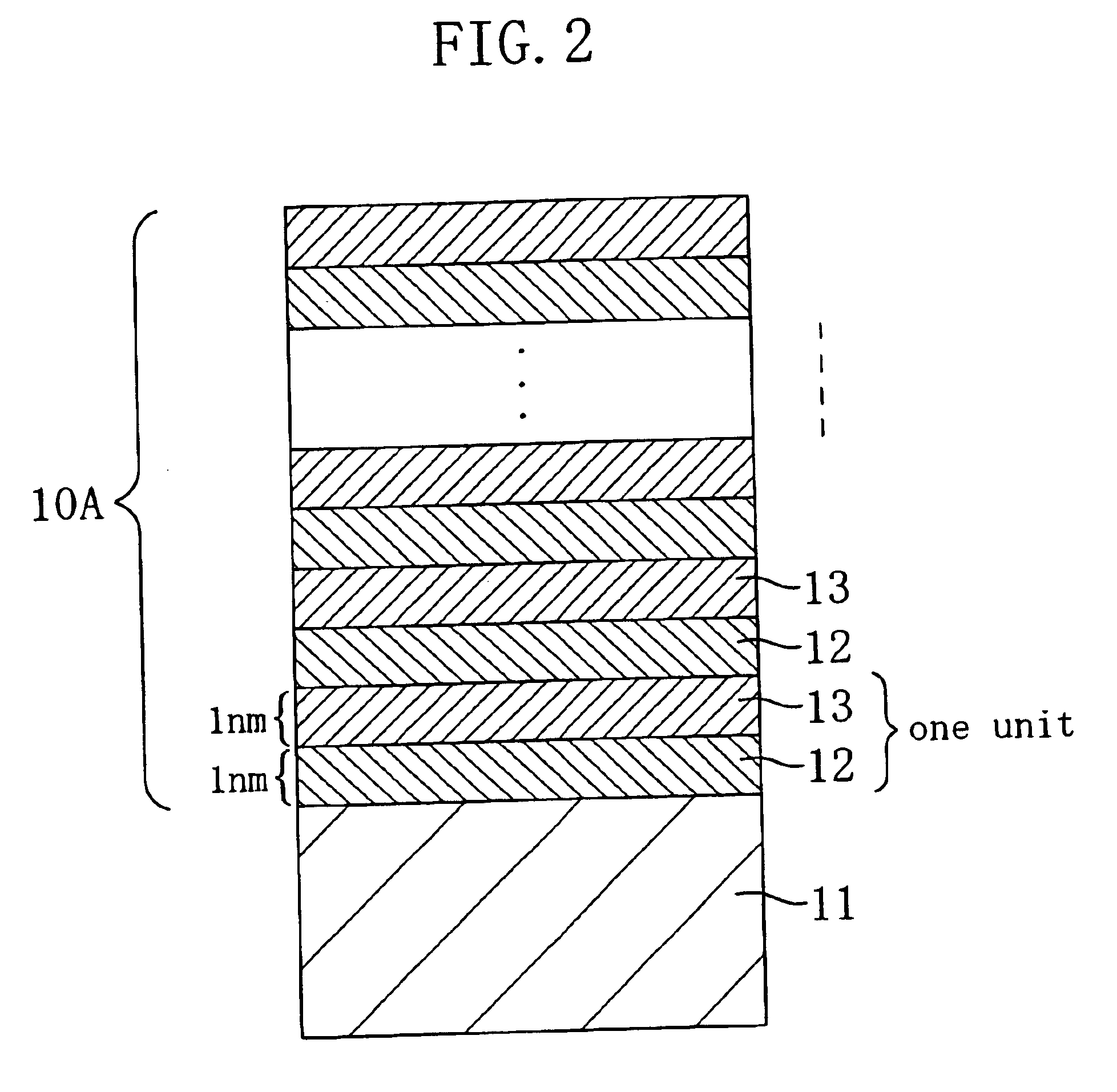

Semiconductor crystal film and method for preparation thereof

InactiveUS6852602B2Promote stratificationEasy to getTransistorSemiconductor/solid-state device manufacturingMultilayer membraneThin membrane

Owner:PANASONIC CORP

Aqueous coating compositions, methods for making same and uses thereof

InactiveUS6140386AImprove stabilityMinimum tendencyFilm/foil adhesivesOptical articlesOligomerEmulsion

An aqueous unpigmented coating and printing composition useful for gravure and flexographic printing on plastic and metal substrates is provided by preparing an aqueous emulsion of a hydrophobic UV curable oligomer and a photoinitiator and adding about 1 to 10% by weight of the composition of a water soluble or reducible polymeric thickener in an amount effective to provide a viscosity of about 10 to 50 poises and specified rheology properties whereby the composition is capable of yielding clear cured films as low as about 2 microns in thickness.

Owner:LEHIGH UNIVERSITY

Wiping sheet

InactiveUS20060009106A1Improve wiping effectPromote stratificationCarpet cleanersFloor cleanersNonwoven fabricFiber structure

A wiping sheet is provided, which presents excellent in handling during wiping, high wiping ability for greasy dirt, and less liquid remains on an object after wiping. A wiping sheet having a fiber structure (such as a woven fabric, a knitted fabric and a nonwoven) is obtained, which includes an ultrafine fiber layer containing ultrafine fibers having a fineness of at most 0.9 dtex which result from at least two types of ultrafine fiber-generating conjugate fibers, at least one conjugate fiber giving ultrafine fibers containing a modified vinyl alcohol resin, and the other conjugate fibers giving ultrafine fibers containing another resin(s). The ultrafine fibers can be obtained by a first splittable conjugate fiber including a component containing the modified vinyl alcohol resin and a second splittable conjugate fiber composed of components of other resins. In the ultrafine fiber layer, the fibers are preferably bonded by thermoadhesive resin-containing ultrafine fibers.

Owner:DAIWABO HLDG +1

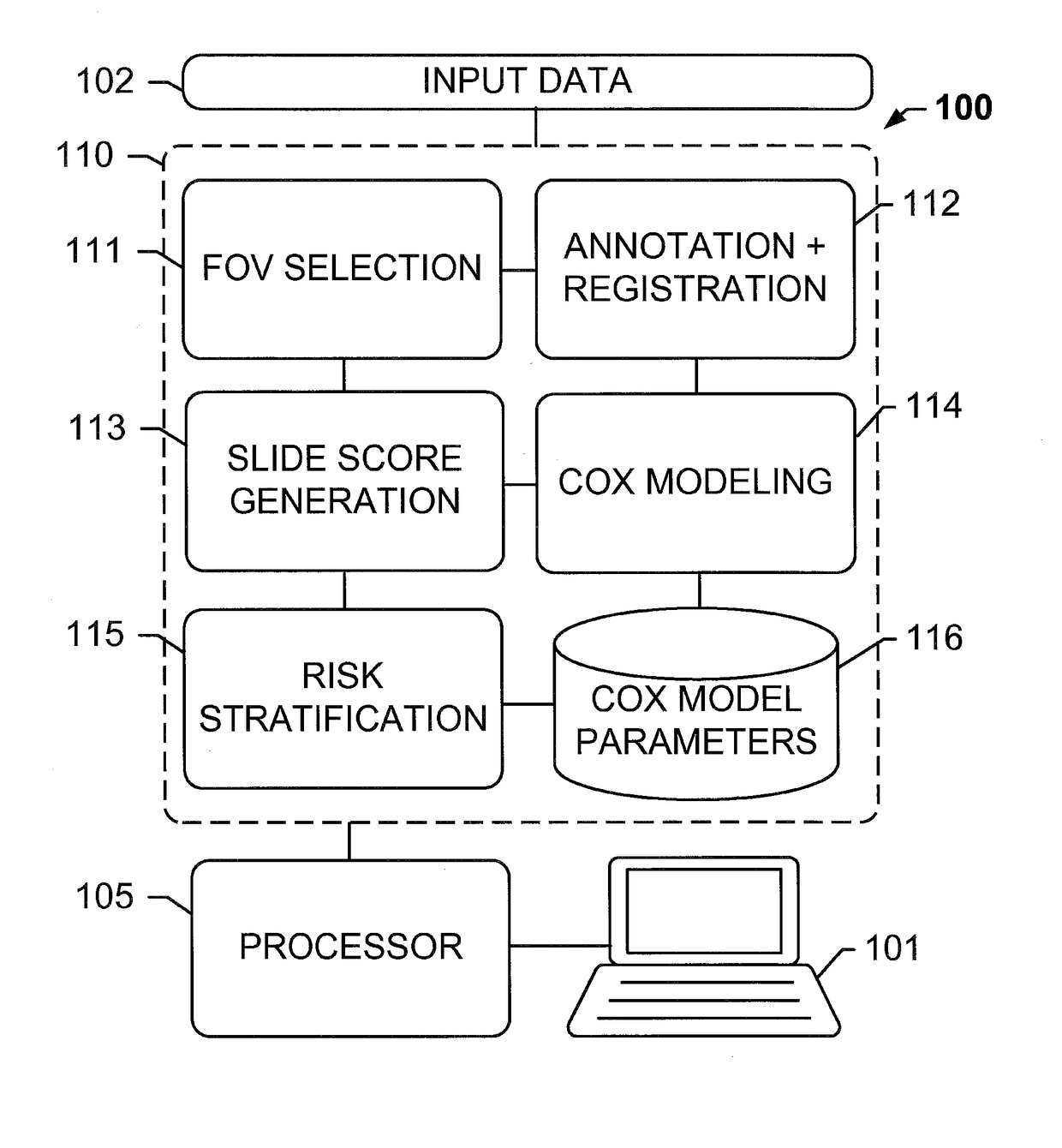

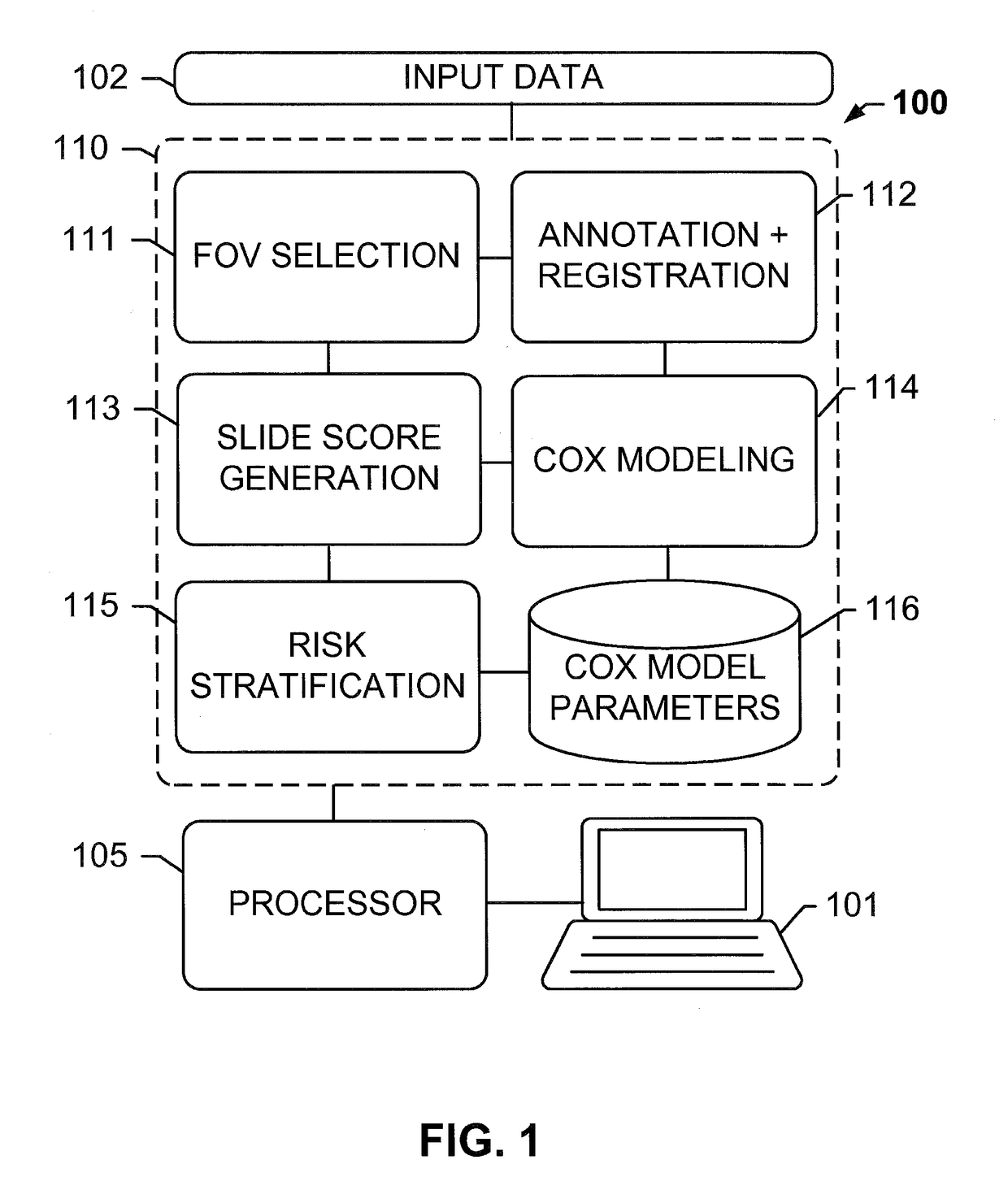

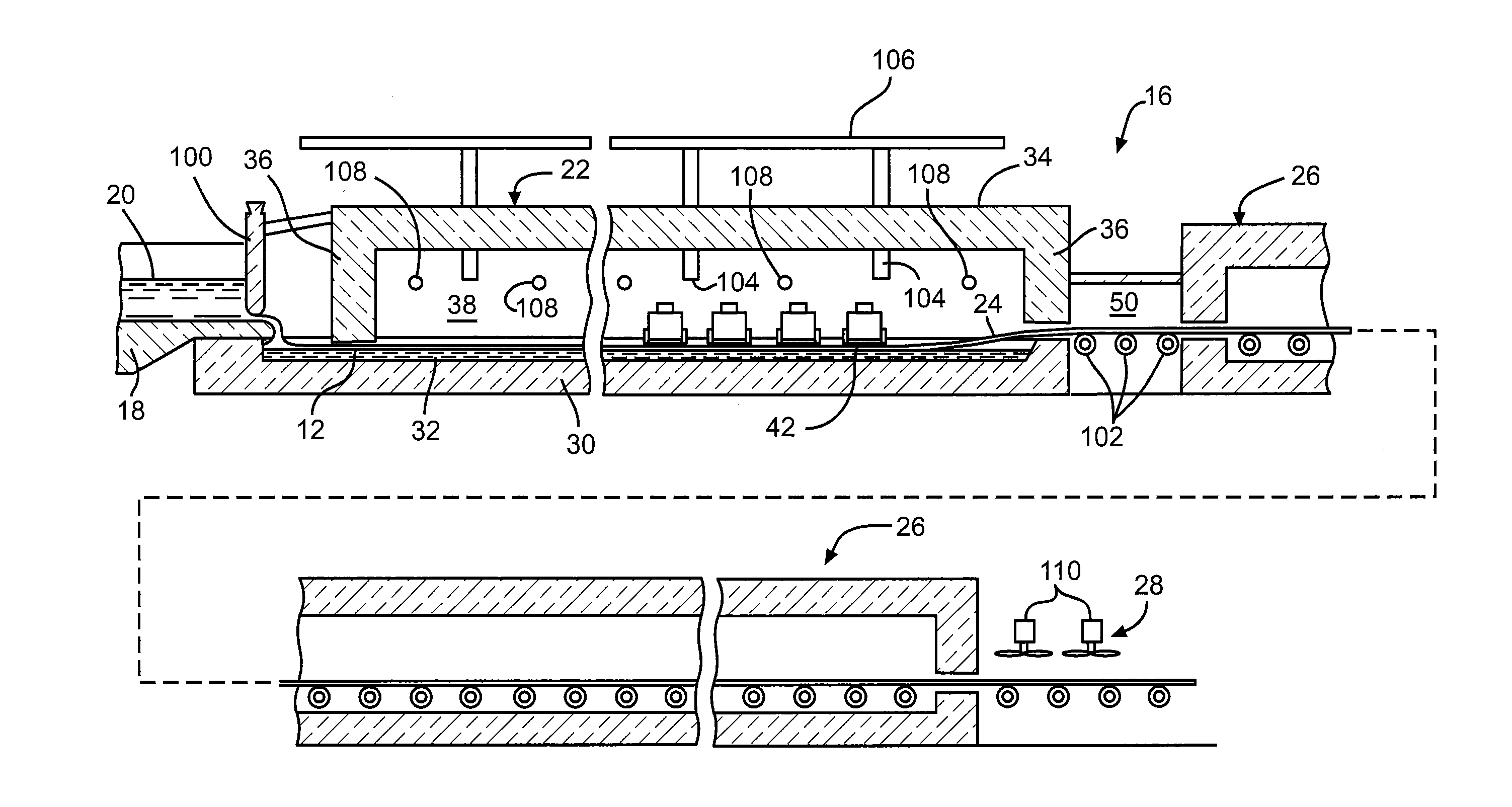

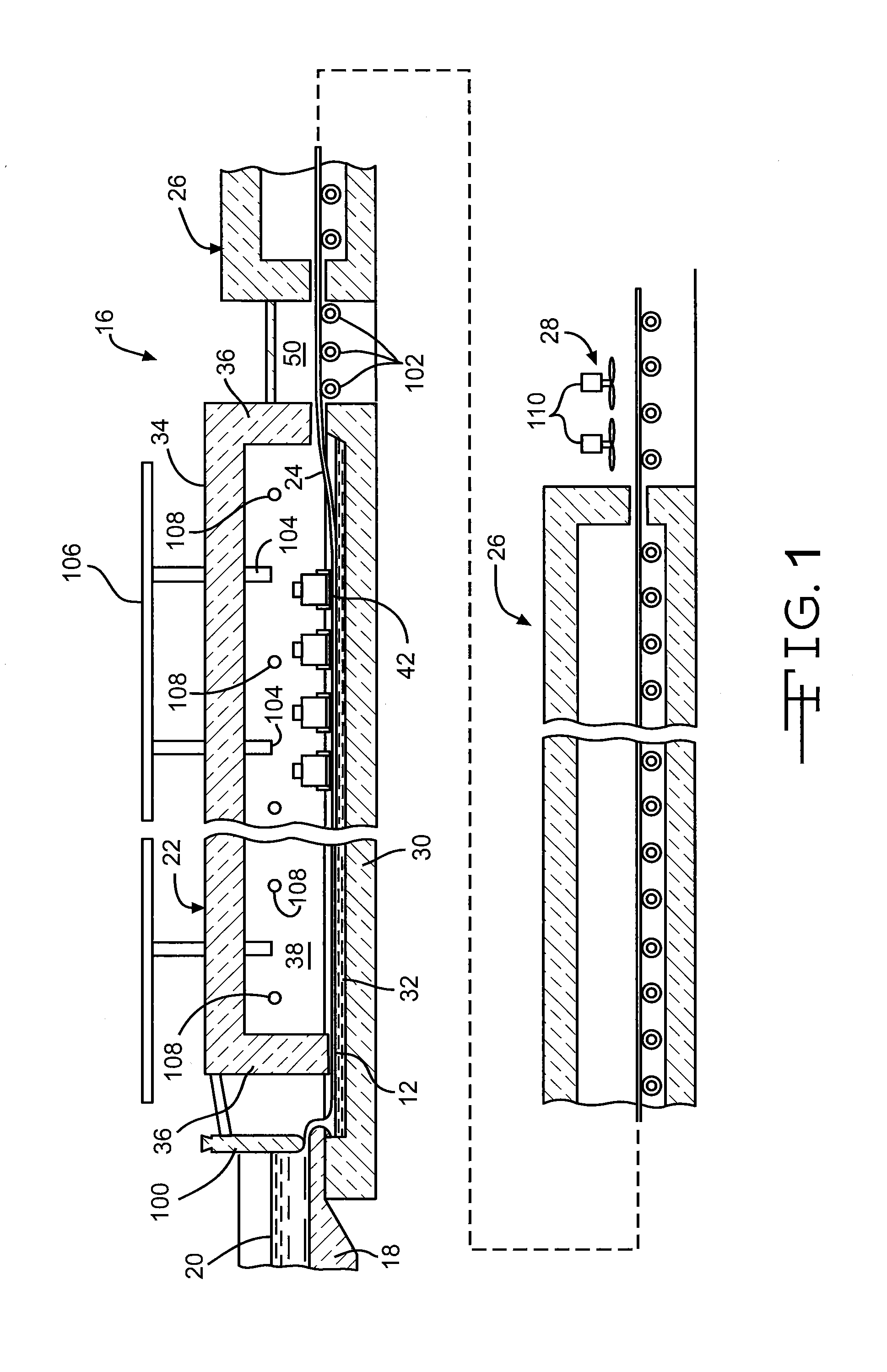

Computational pathology systems and methods for early-stage cancer prognosis

ActiveUS20170270666A1Reduce computing costInformed choiceImage enhancementImage analysisComputational pathologyLow risk group

The subject disclosure presents systems and computer-implemented methods for providing reliable risk stratification for early-stage cancer patients by predicting a recurrence risk of the patient and to categorize the patient into a high or low risk group. A series of slides depicting serial sections of cancerous tissue are automatically analyzed by a digital pathology system, a score for the sections is calculated, and a Cox proportional hazards regression model is used to stratify the patient into a low or high risk group. The Cox proportional hazards regression model may be used to determine a whole-slide scoring algorithm based on training data comprising survival data for a plurality of patients and their respective tissue sections. The coefficients may differ based on different types of image analysis operations applied to either whole-tumor regions or specified regions within a slide.

Owner:VENTANA MEDICAL SYST INC

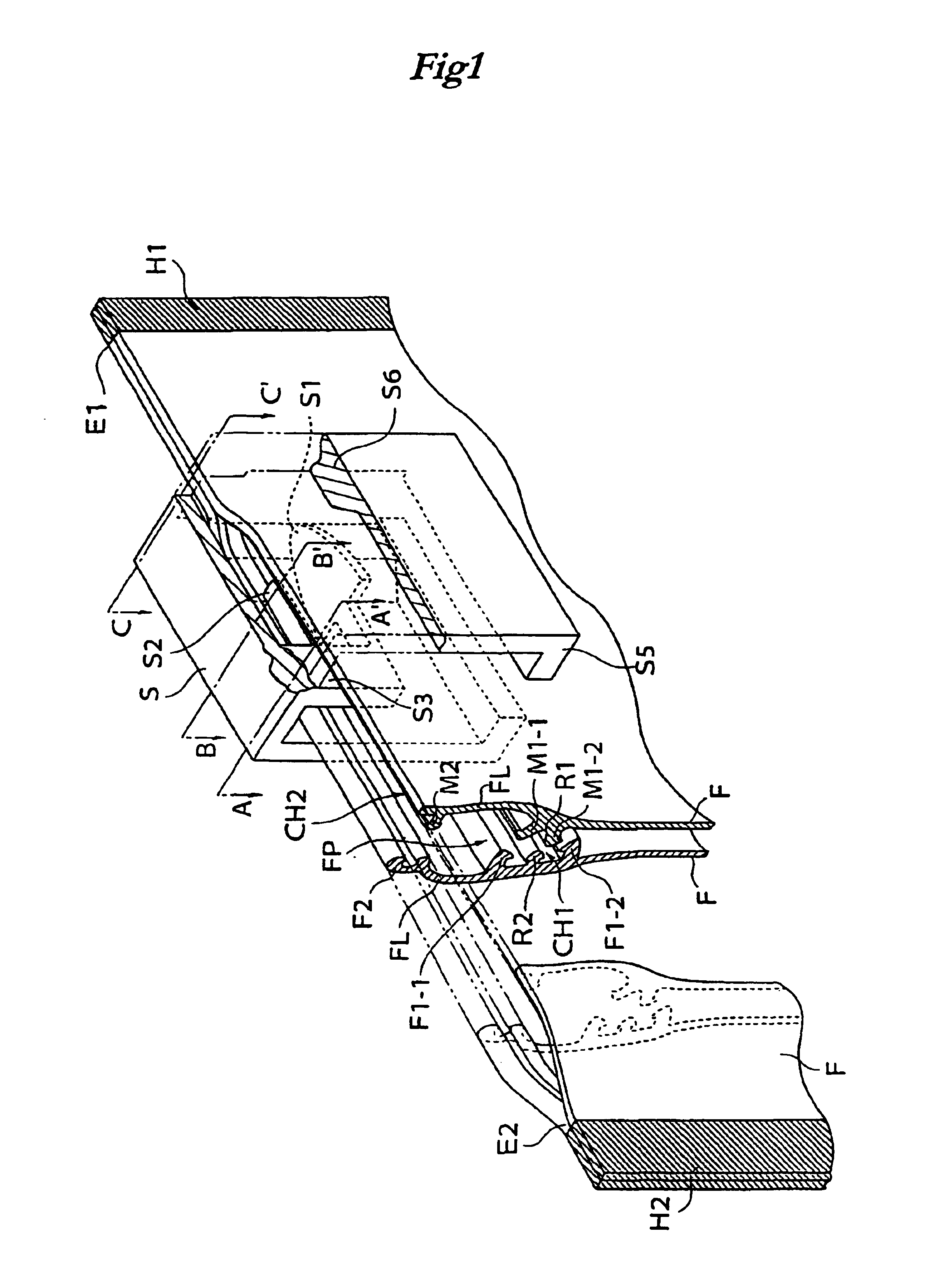

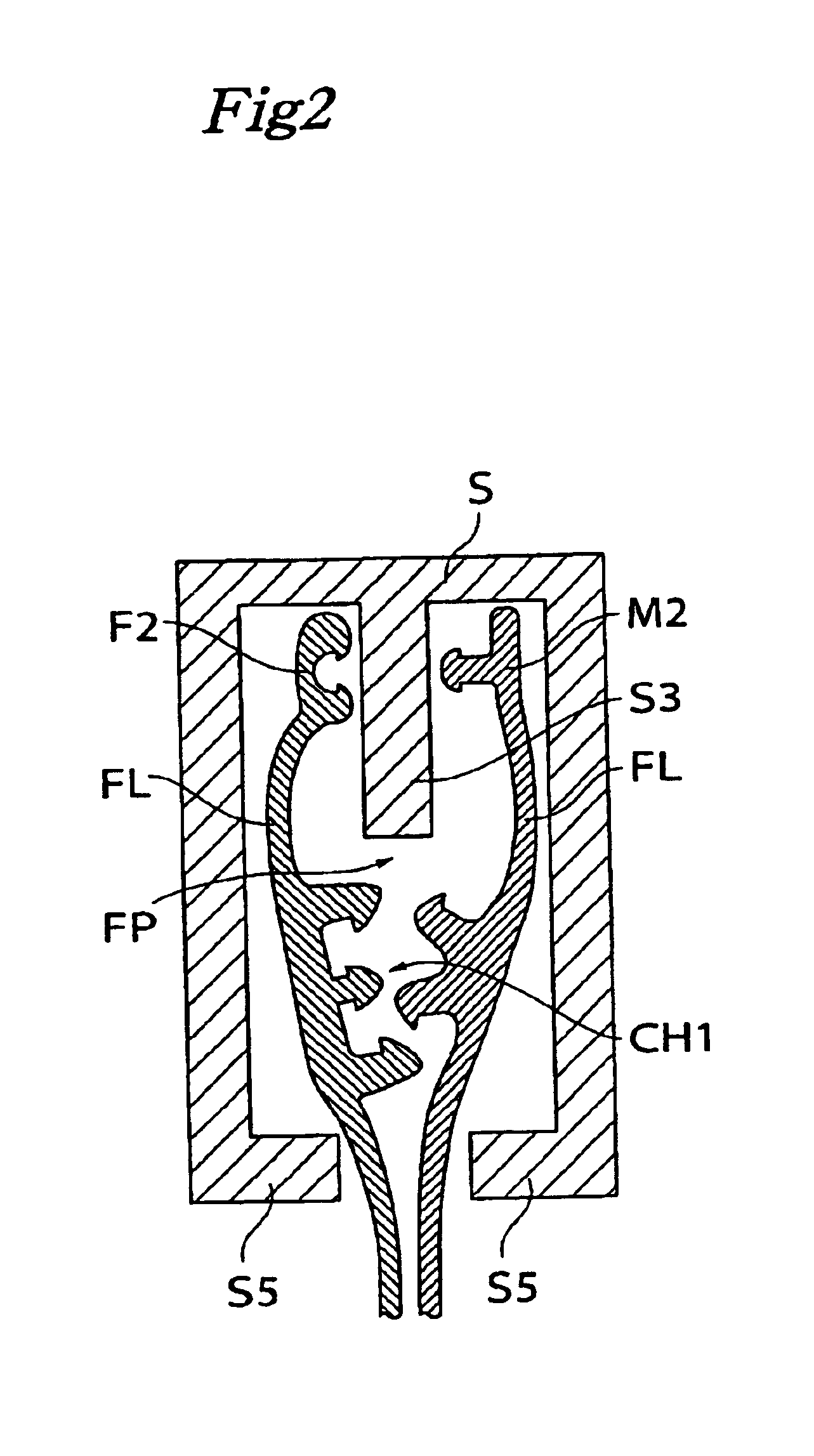

Plastic fastener with slider and bag body with plastic fastener

InactiveUS6915546B2Improve opening forceImpairing characteristicSnap fastenersSlide fastenersEngineeringFlange

A plastic zipper equipped with a slider, and a bag body equipped with the plastic zipper, the plastic zipper having a strong opening force despite its miniaturization. The hermetically sealing plastic zipper is equipped with a slider for opening and closing the zipper, and includes a pair of a male hook and a female hook, flanges on opening portion sides for each of the male and female hooks connectable at respective top end portions, and a wedged opening plate pressed into the inside of a closed plastic cylinder constituted of the connectable flange top end portions and extended to the zipper in an engaged state so that the zipper is firstly opened and after the zipper is opened, the top end portions of the flanges in a connected state are disconnected.

Owner:HIPACK

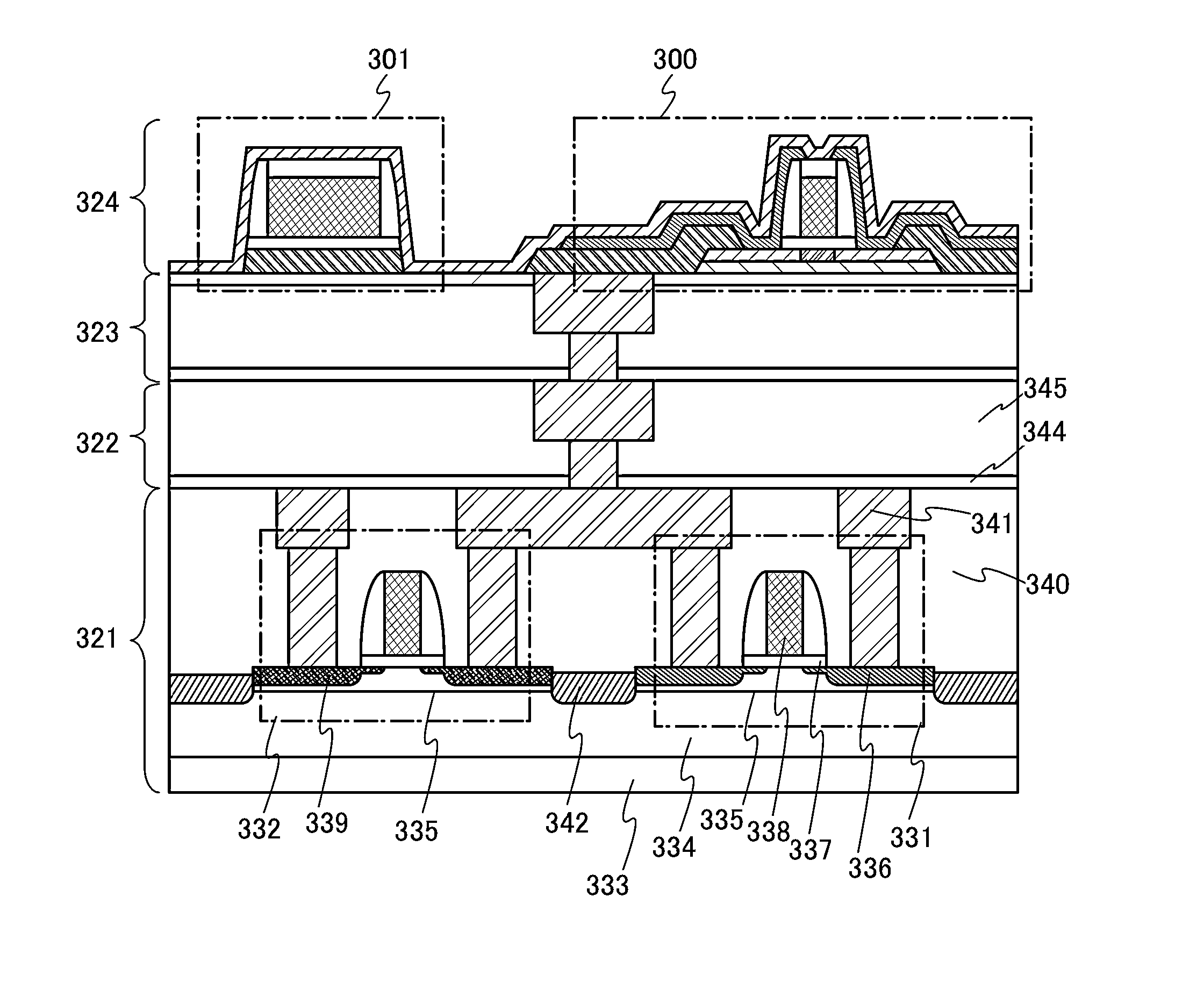

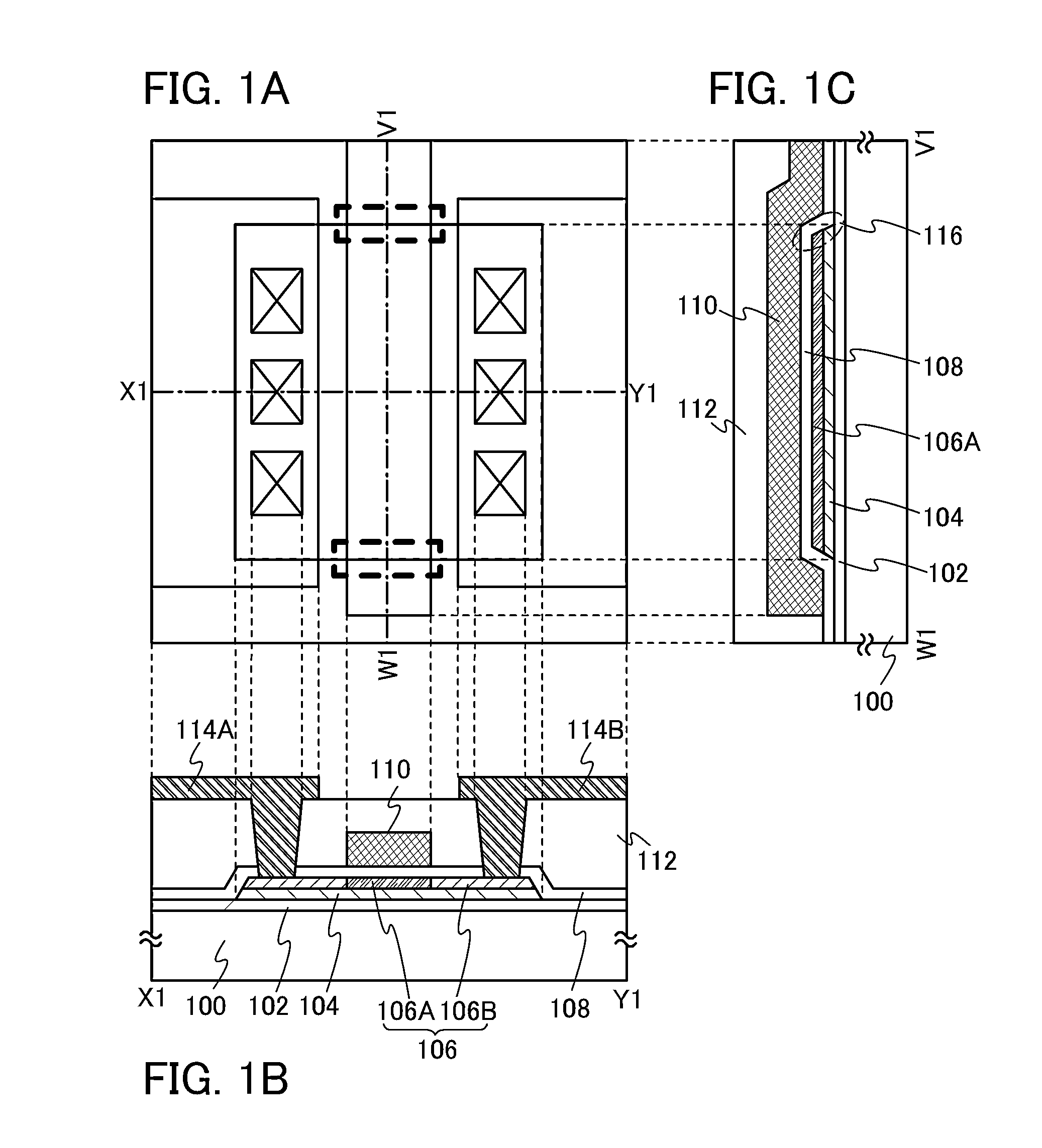

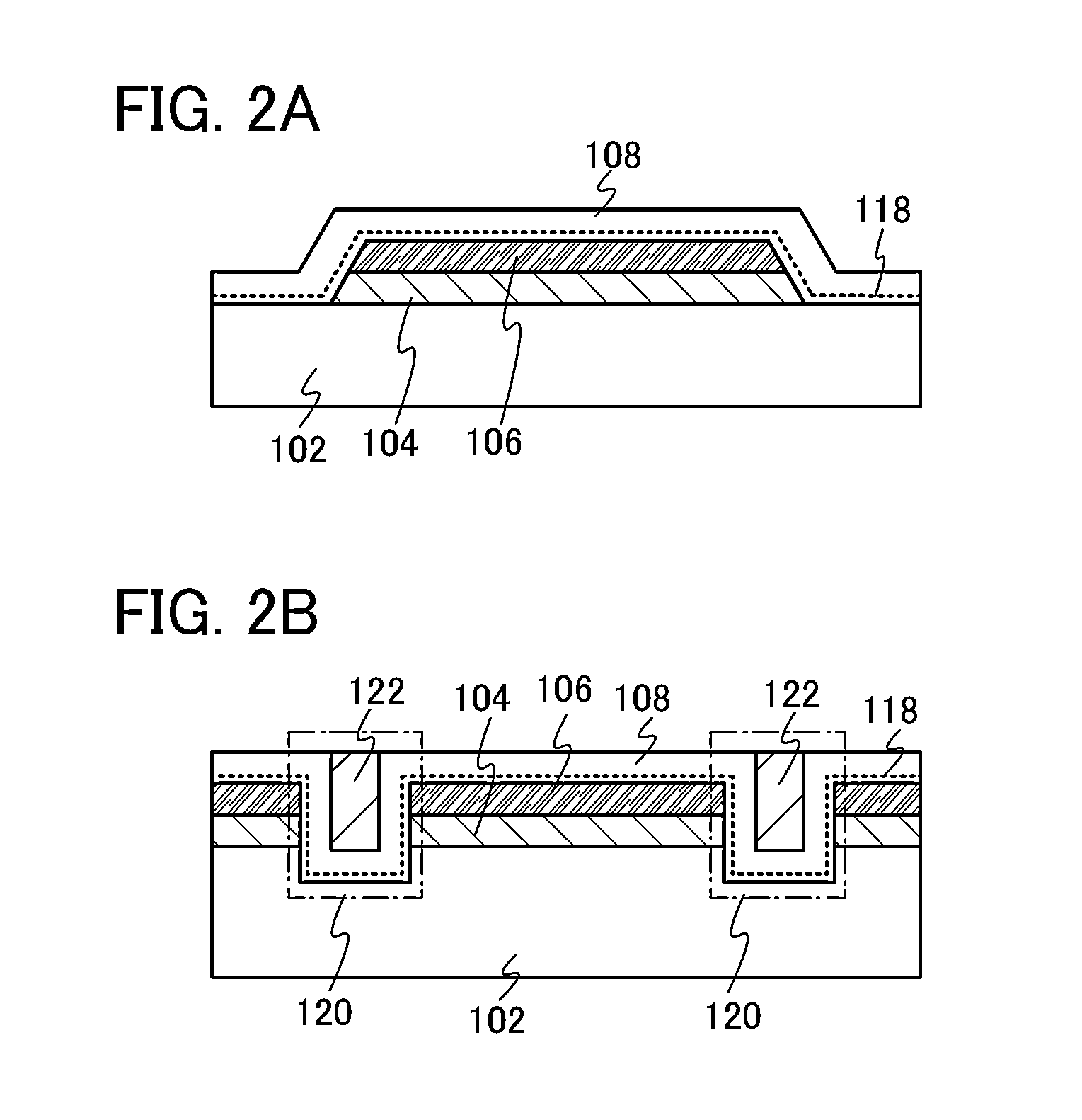

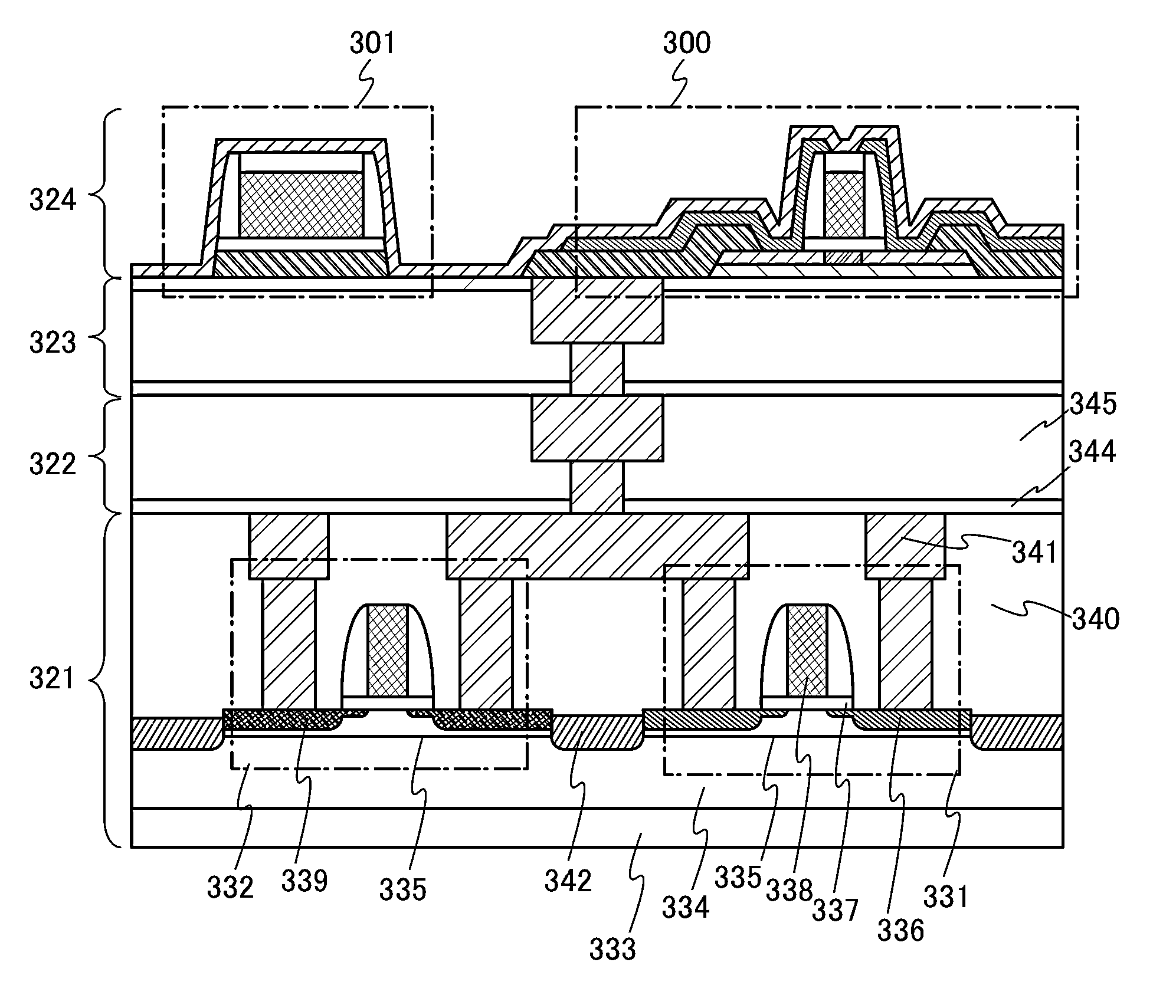

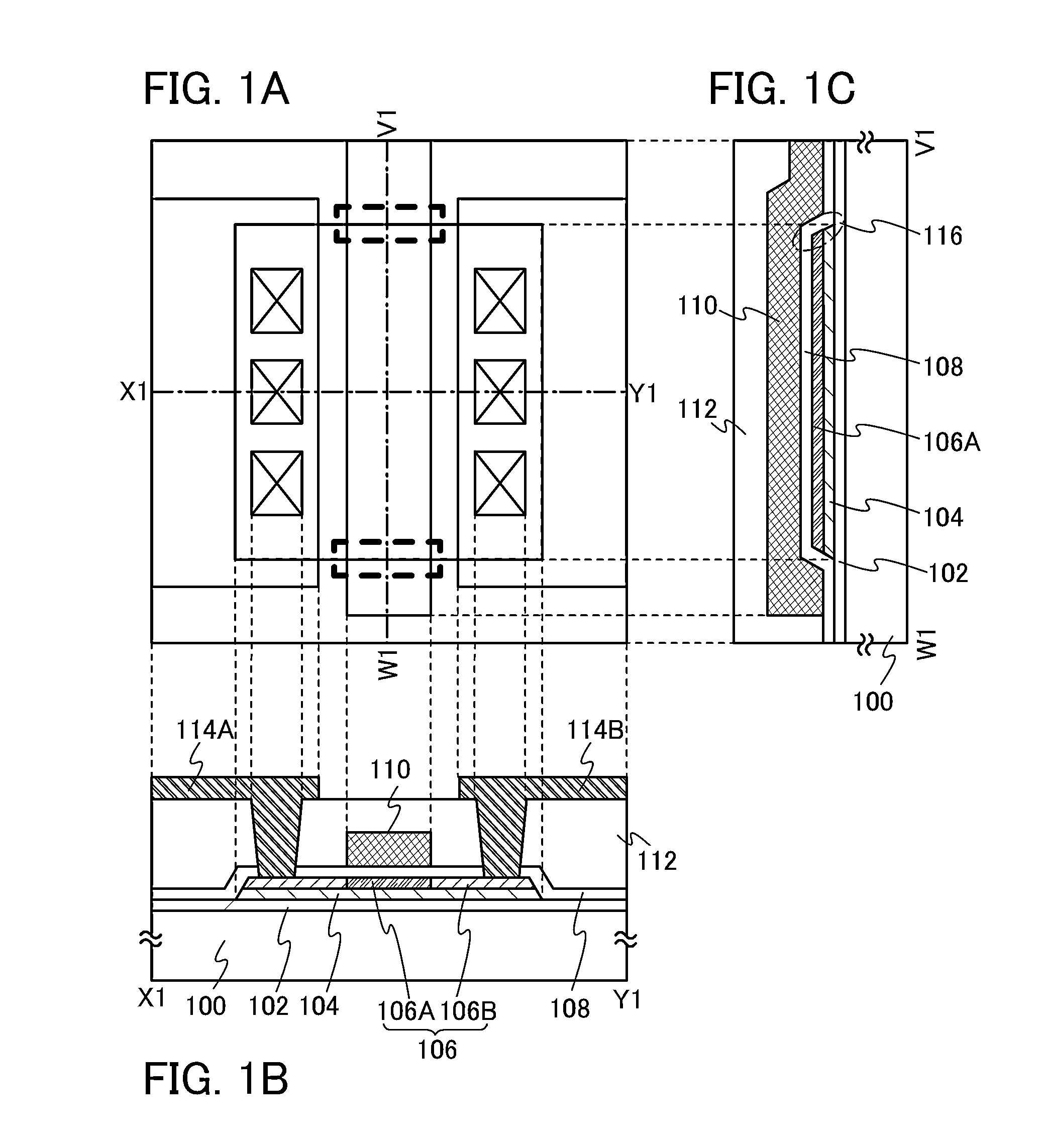

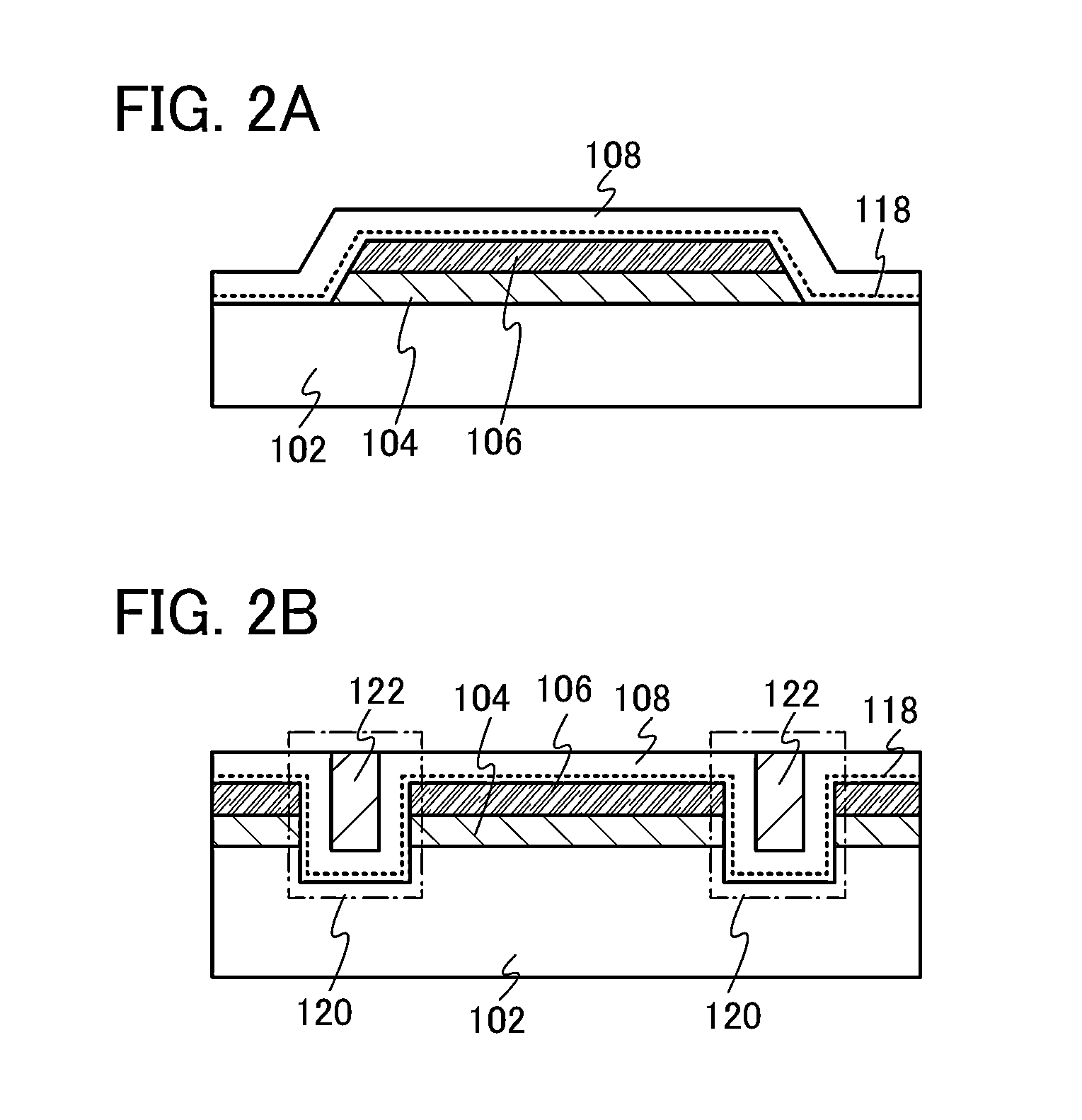

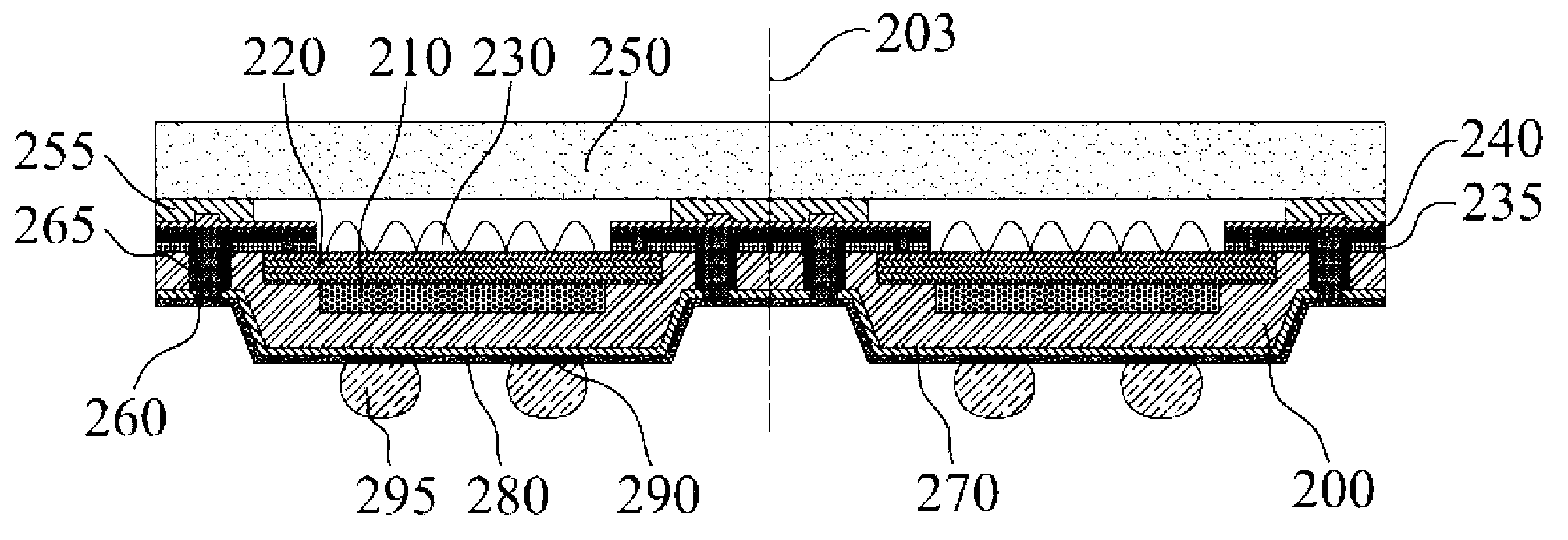

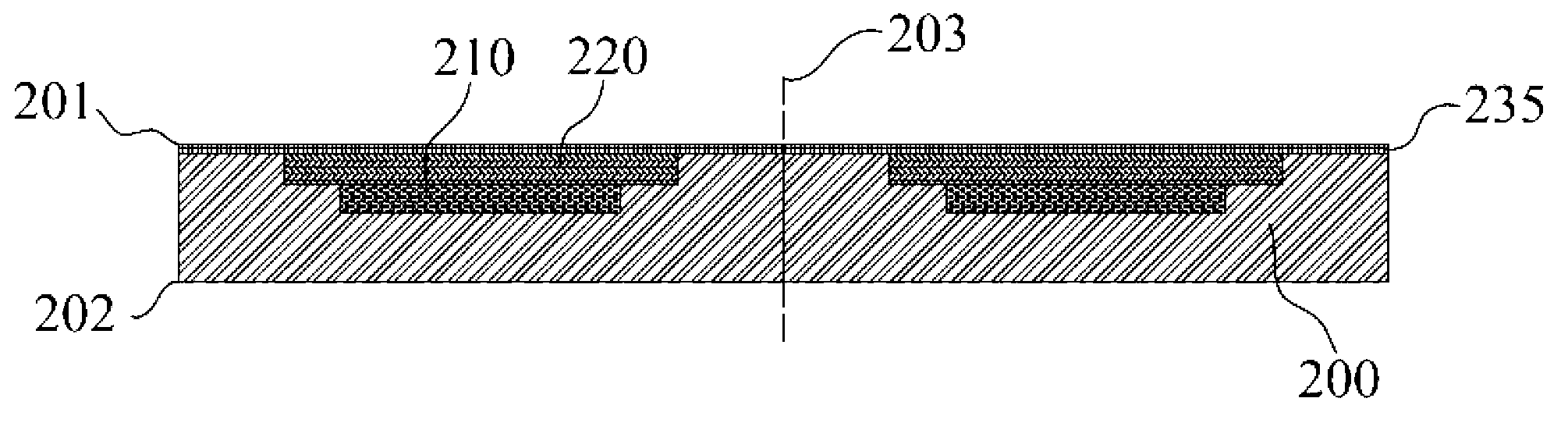

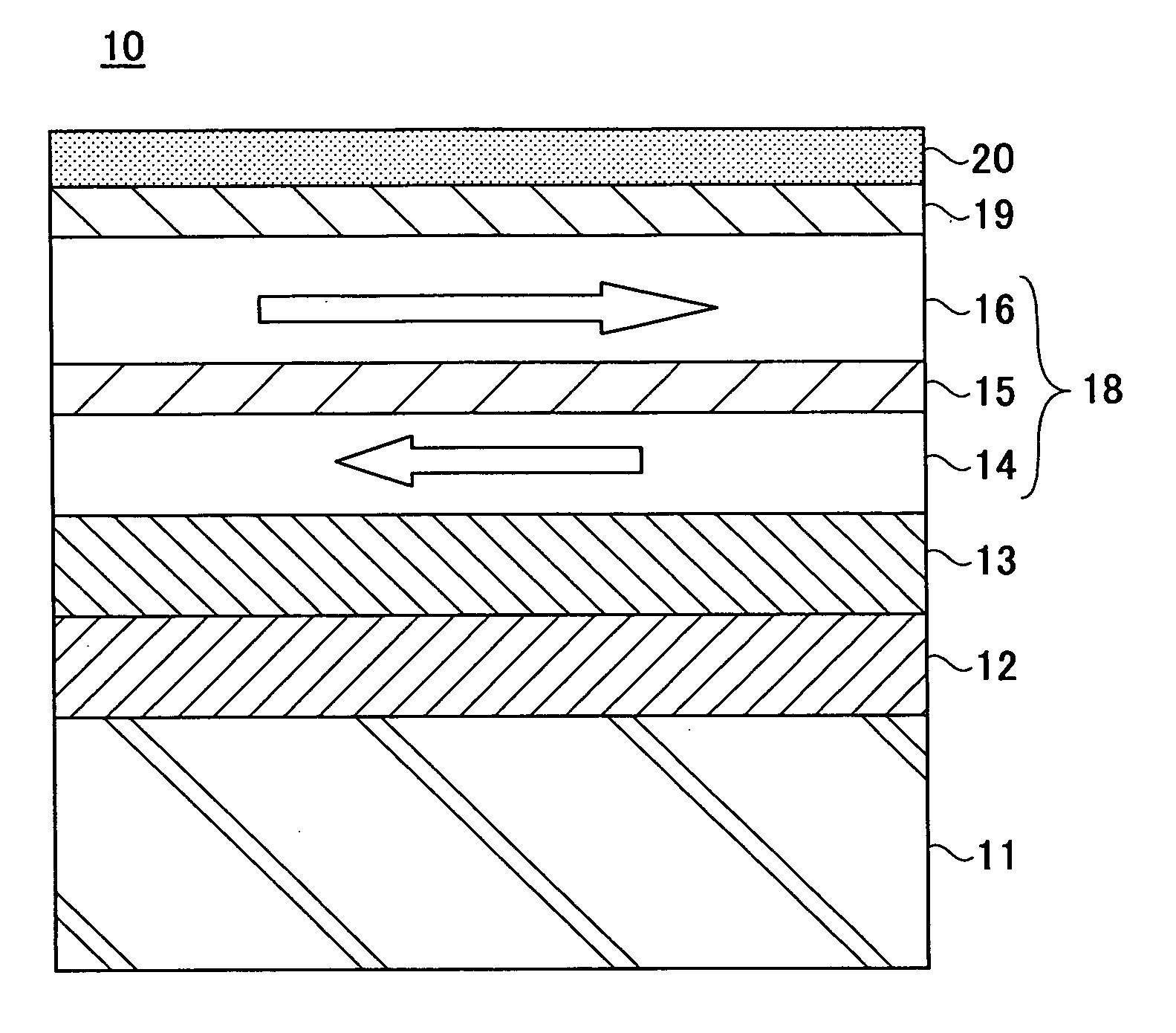

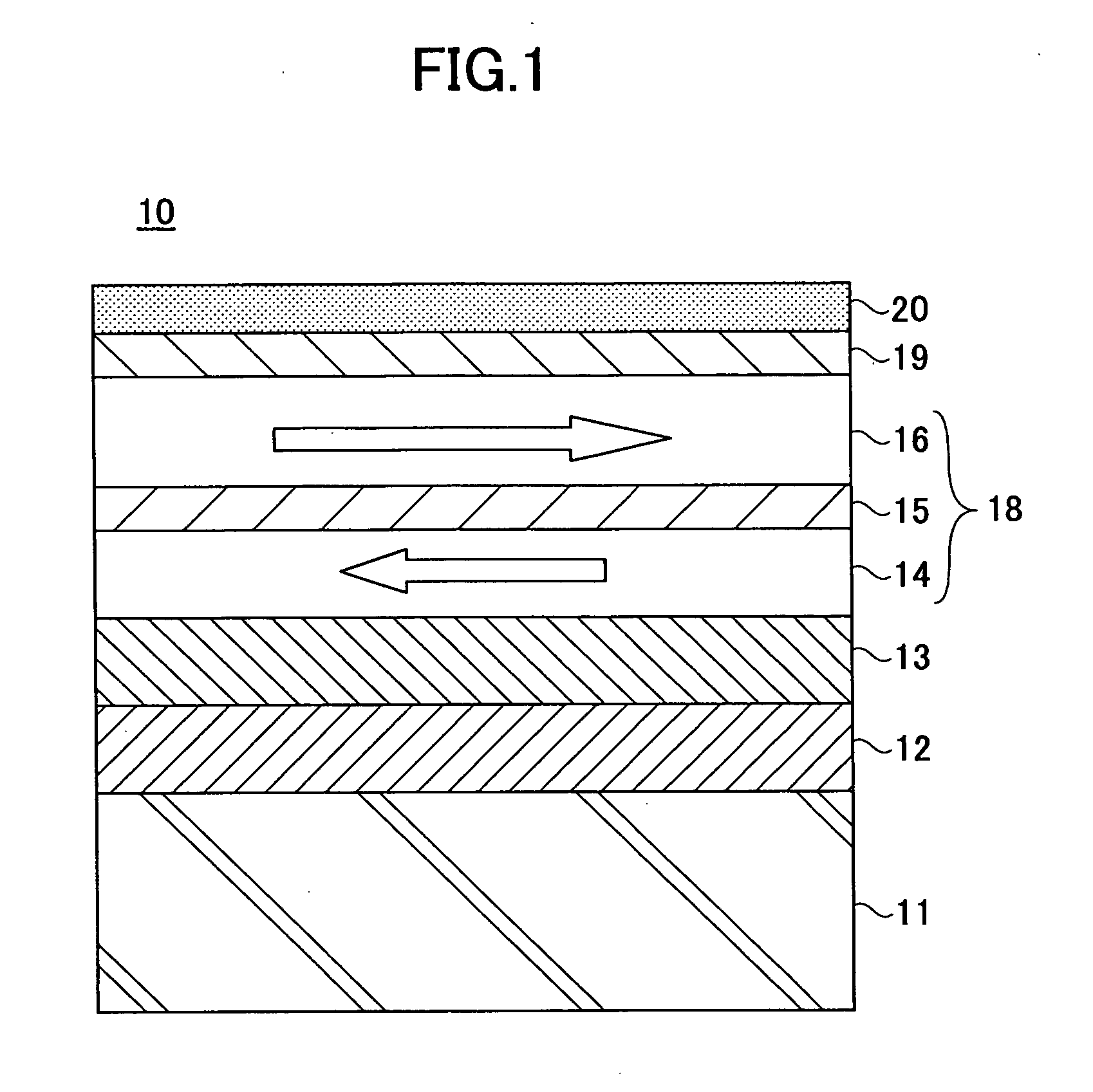

Semiconductor device

A semiconductor device in which release of oxygen from side surfaces of an oxide semiconductor film including c-axis aligned crystal parts can be prevented is provided. The semiconductor device includes a first oxide semiconductor film, a second oxide semiconductor film including c-axis aligned crystal parts, and an oxide film including c-axis aligned crystal parts. In the semiconductor device, the first oxide semiconductor film, the second oxide semiconductor film, and the oxide film are each formed using a IGZO film, where the second oxide semiconductor film has a higher indium content than the first oxide semiconductor film, the first oxide semiconductor film has a higher indium content than the oxide film, the oxide film has a higher gallium content than the first oxide semiconductor film, and the first oxide semiconductor film has a higher gallium content than the second oxide semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS8723176B2Easy to manufactureEasy to operateSolid-state devicesSemiconductor/solid-state device manufacturingIndiumSemiconductor

A semiconductor device in which release of oxygen from side surfaces of an oxide semiconductor film including c-axis aligned crystal parts can be prevented is provided. The semiconductor device includes a first oxide semiconductor film, a second oxide semiconductor film including c-axis aligned crystal parts, and an oxide film including c-axis aligned crystal parts. In the semiconductor device, the first oxide semiconductor film, the second oxide semiconductor film, and the oxide film are each formed using a IGZO film, where the second oxide semiconductor film has a higher indium content than the first oxide semiconductor film, the first oxide semiconductor film has a higher indium content than the oxide film, the oxide film has a higher gallium content than the first oxide semiconductor film, and the first oxide semiconductor film has a higher gallium content than the second oxide semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

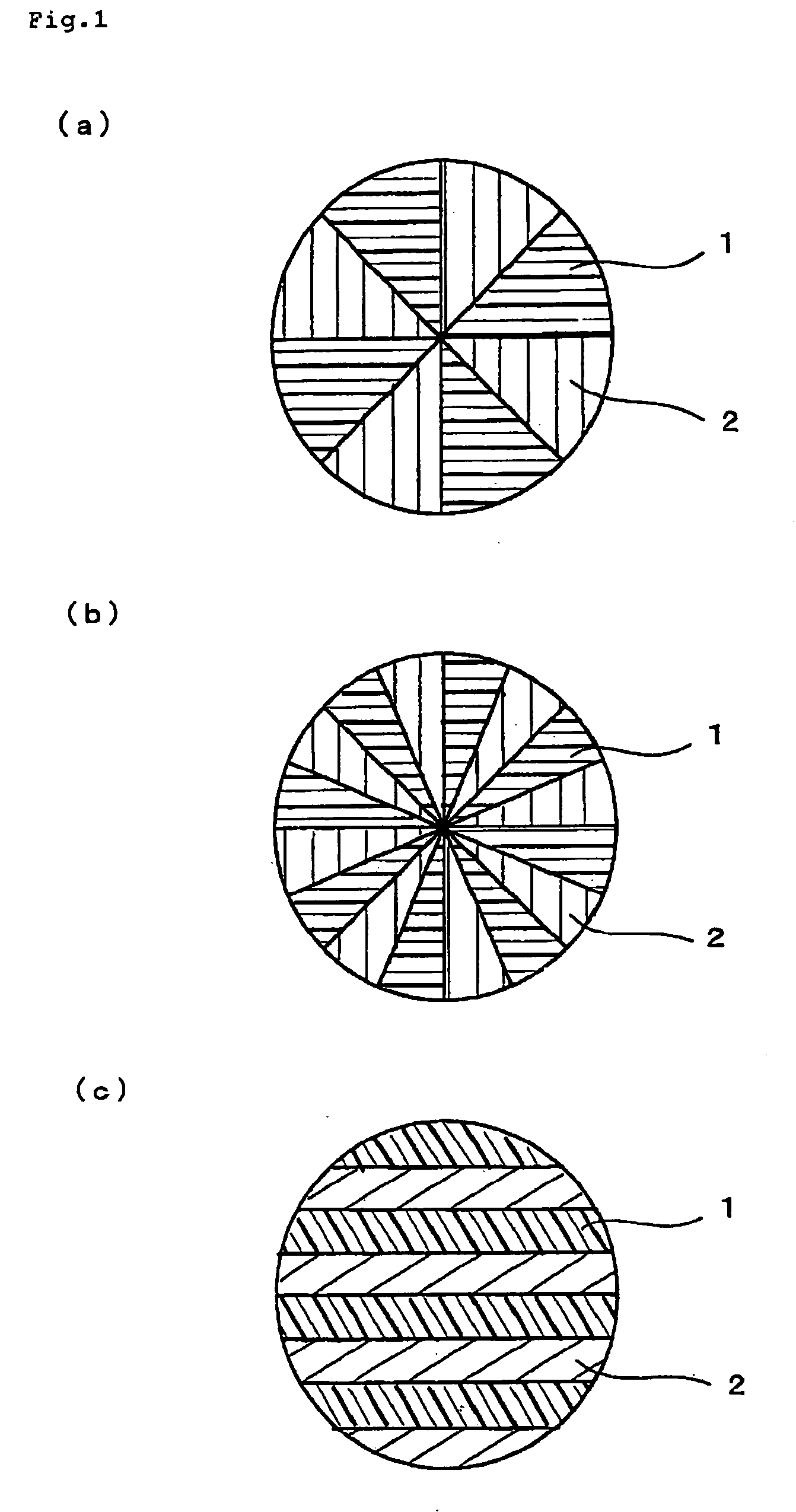

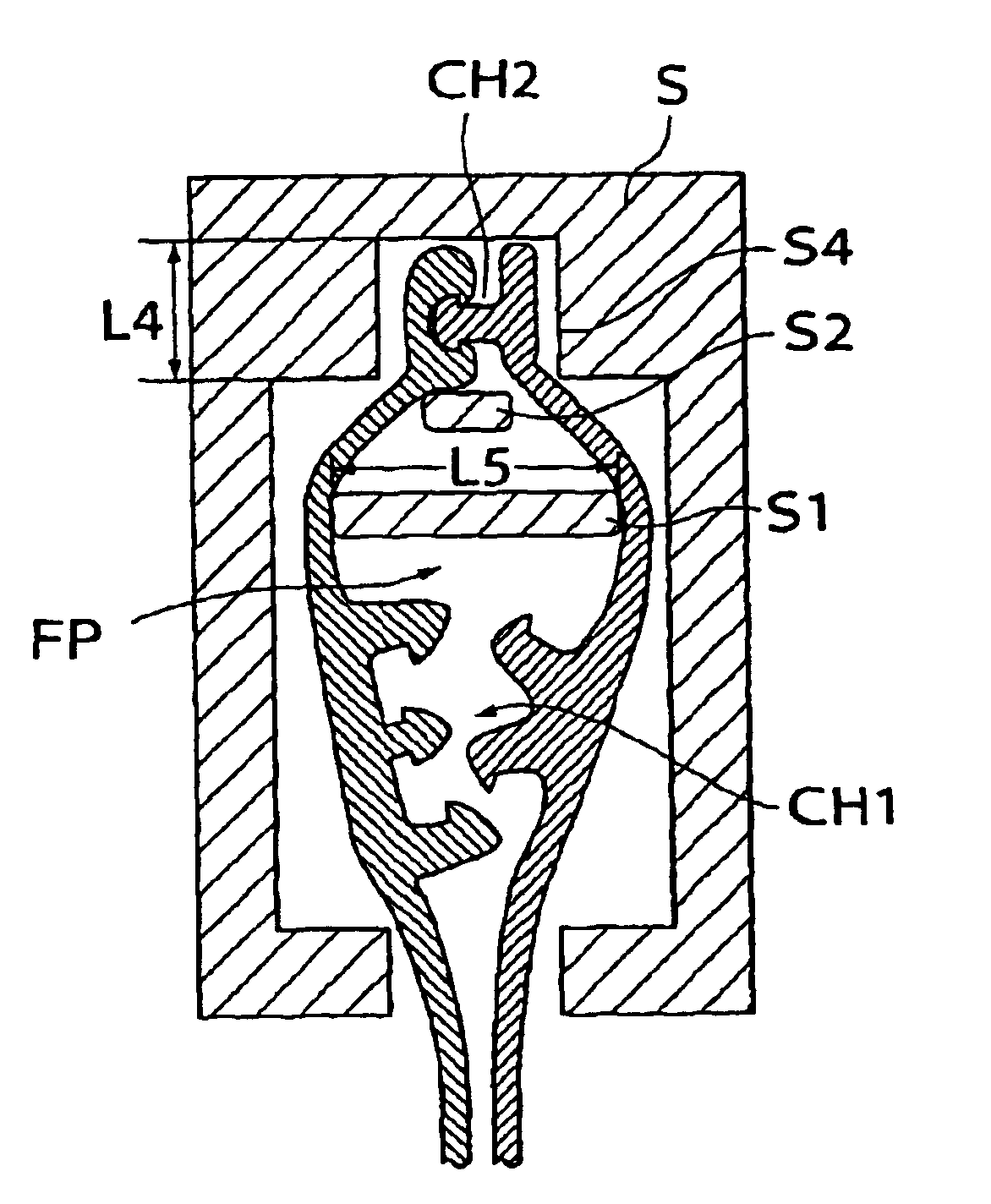

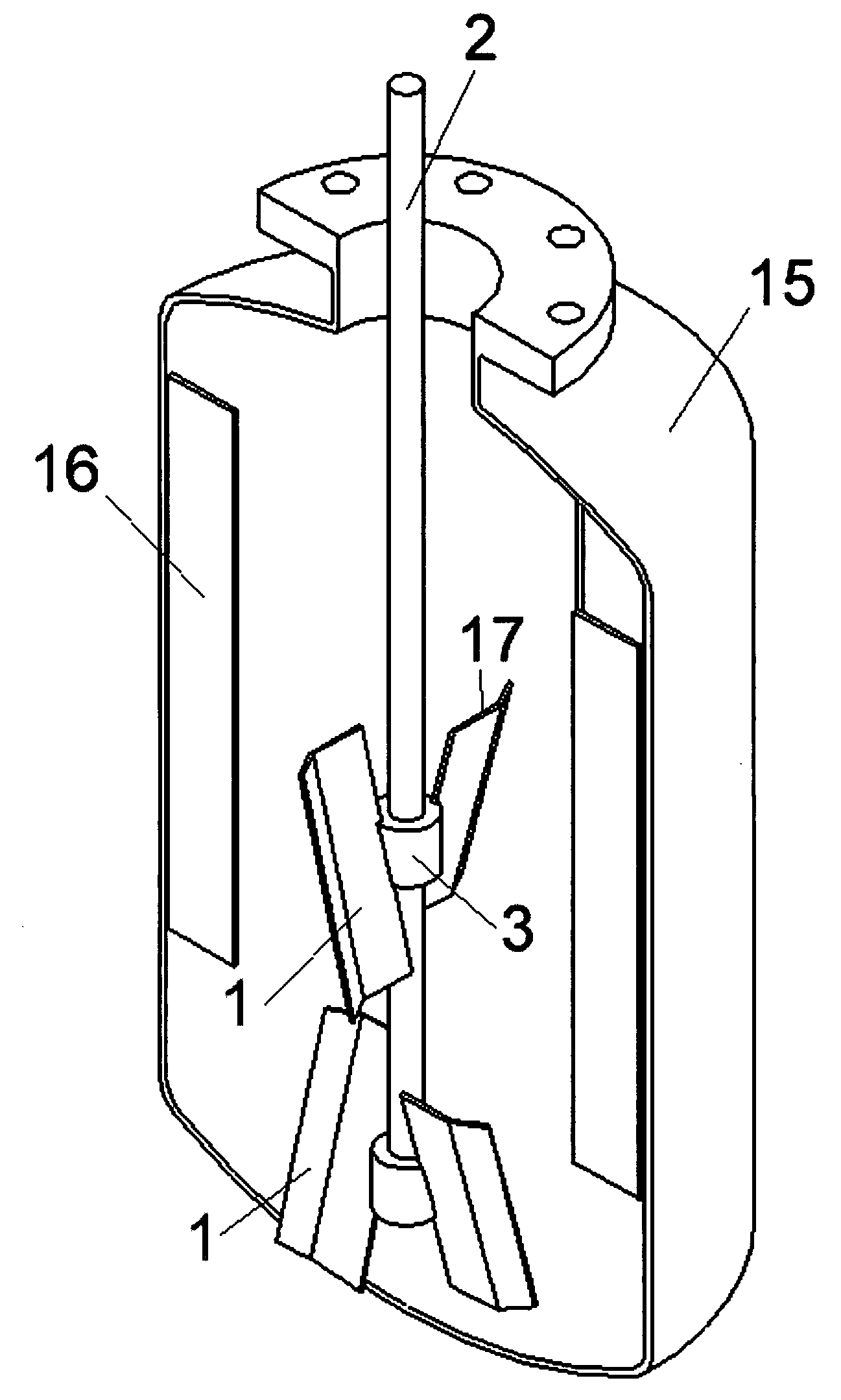

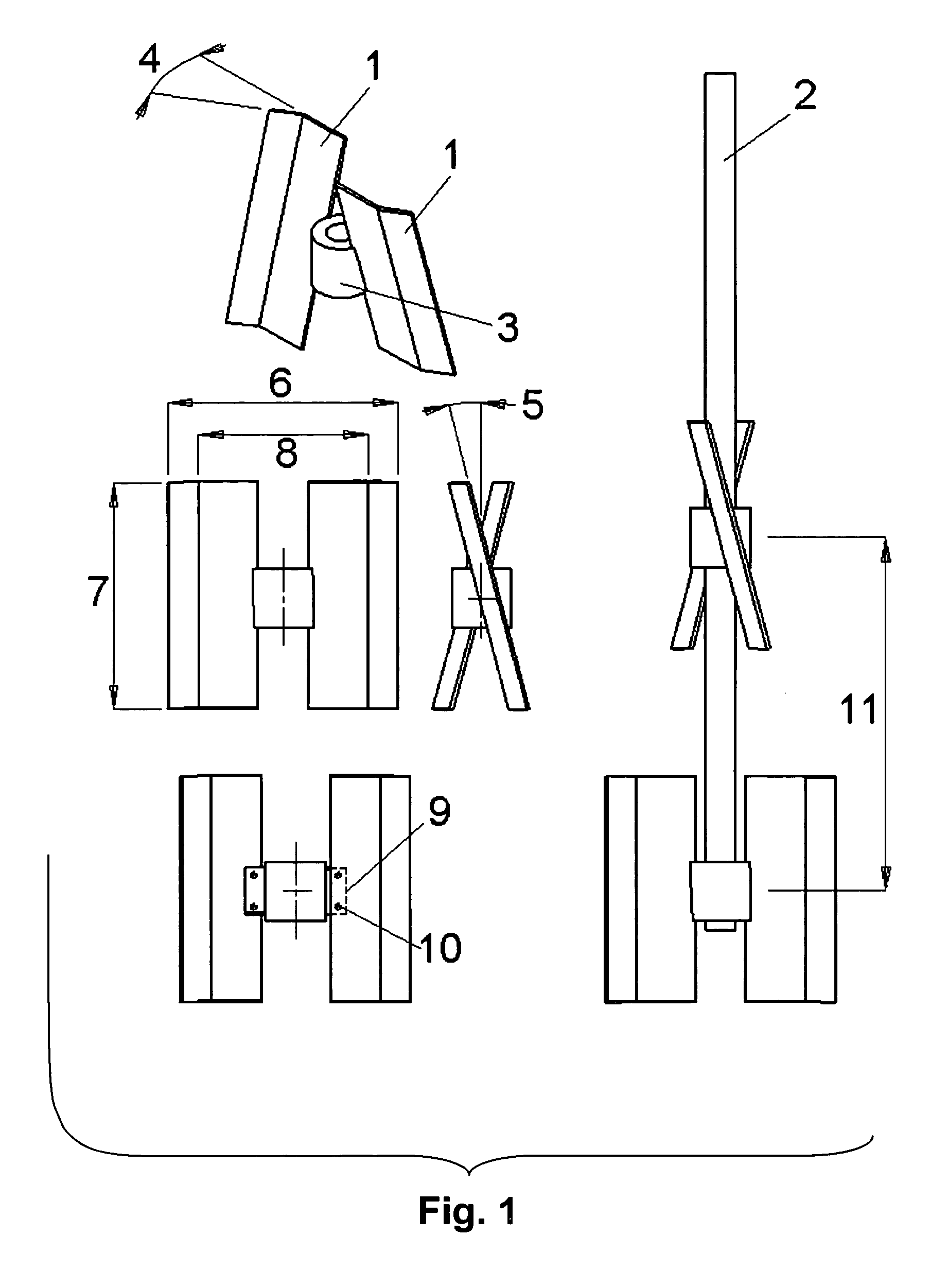

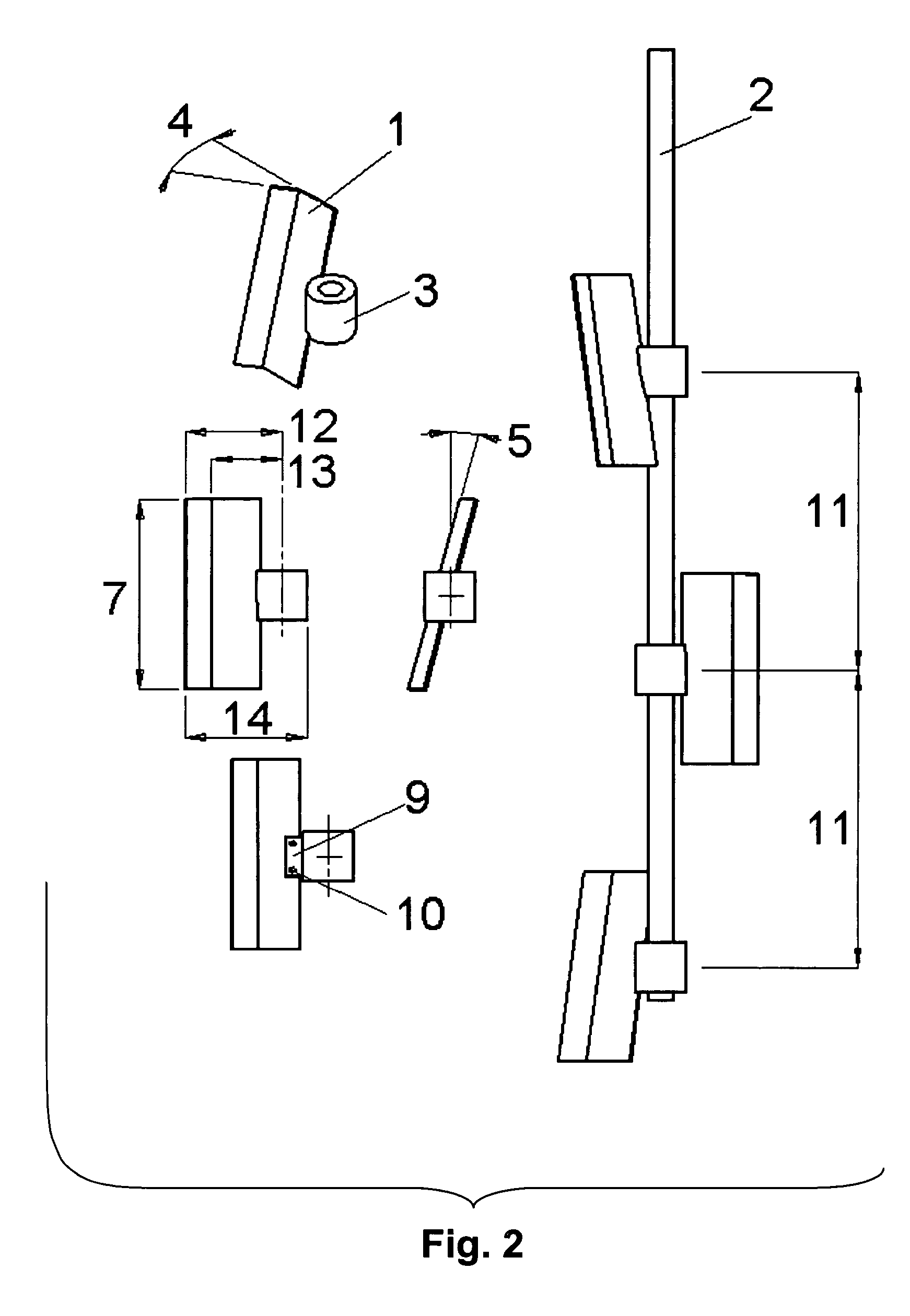

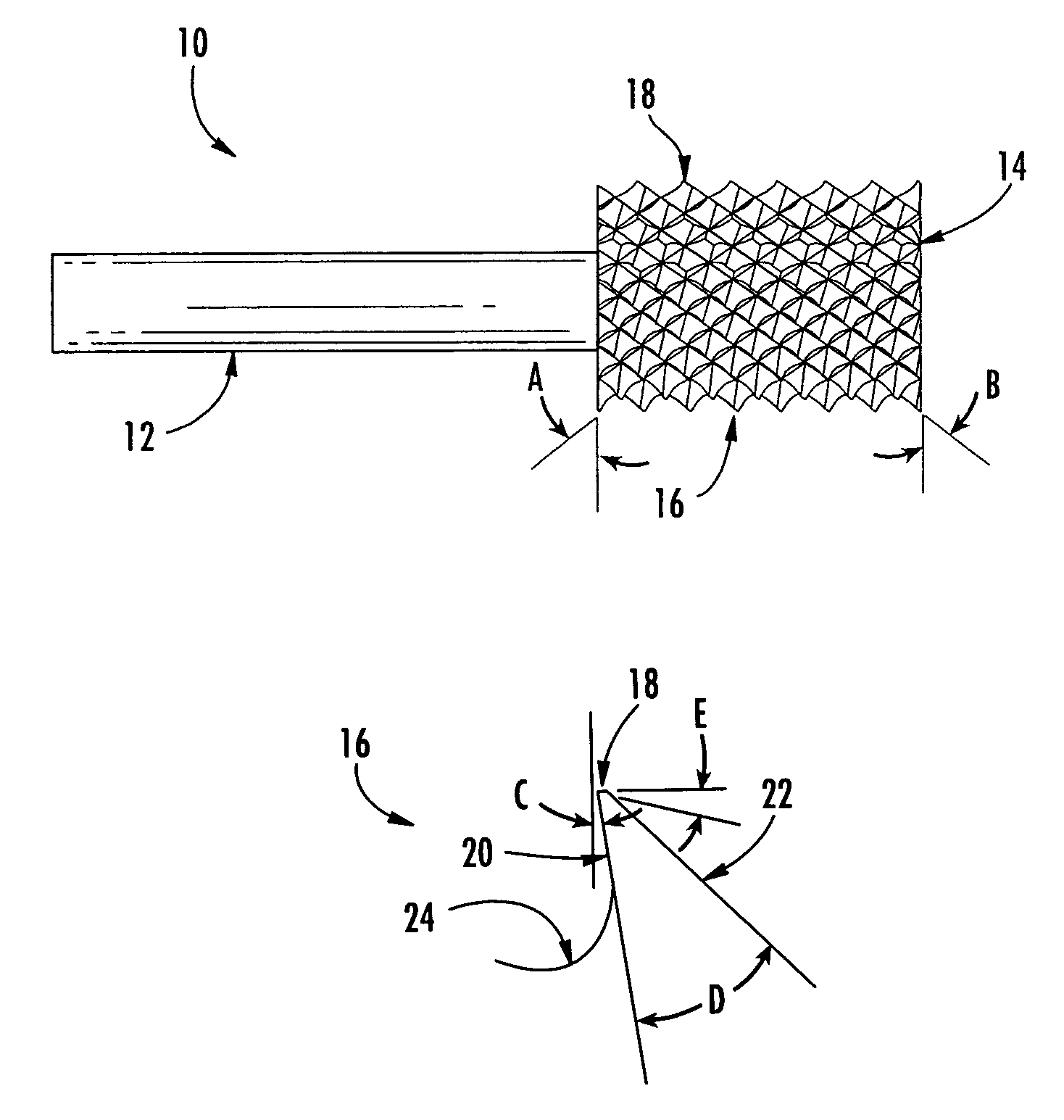

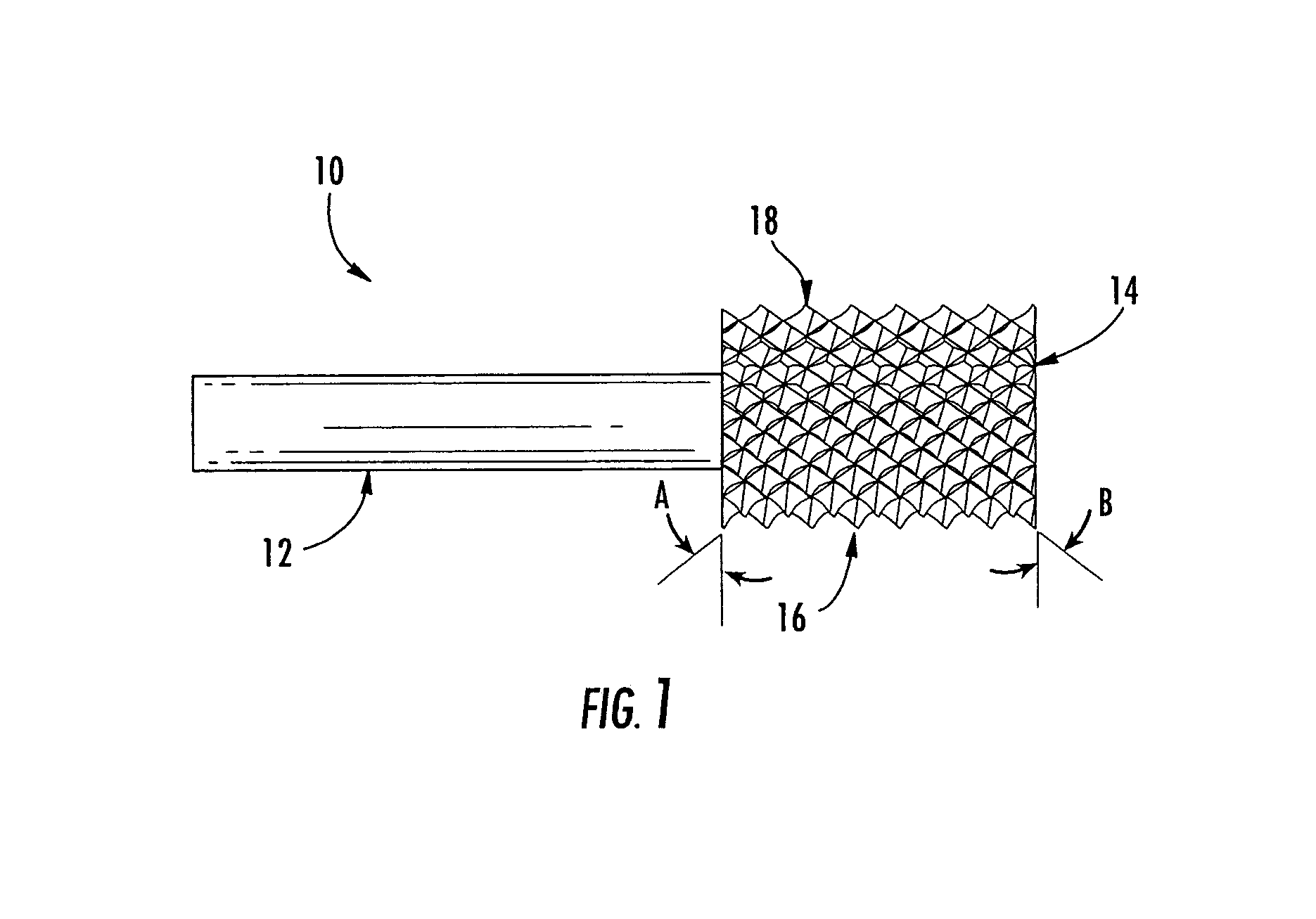

Low shear impeller

ActiveUS20050007874A1Promote stratificationImprove mixing efficiencyFlow mixersTransportation and packagingImpellerDrive shaft

One or more mixing impellers is carried on a driving shaft received in a mixing vessel. Impeller blades are angularly and / or axially distributed on the shaft and can be single staggered axially-spaced blades or groups of two or more placed angularly around the shaft, e.g., diametrically opposite. Each blade has a radially inner flat plate sloped to produce axial flow, preferably at about 15° from parallel to the rotation axis. An outer plate is joined to the inner plate at a bend line with an angle of about 20° located at about 70% of the outside diameter of the impeller path.

Owner:PHILADELPHIA GEAR

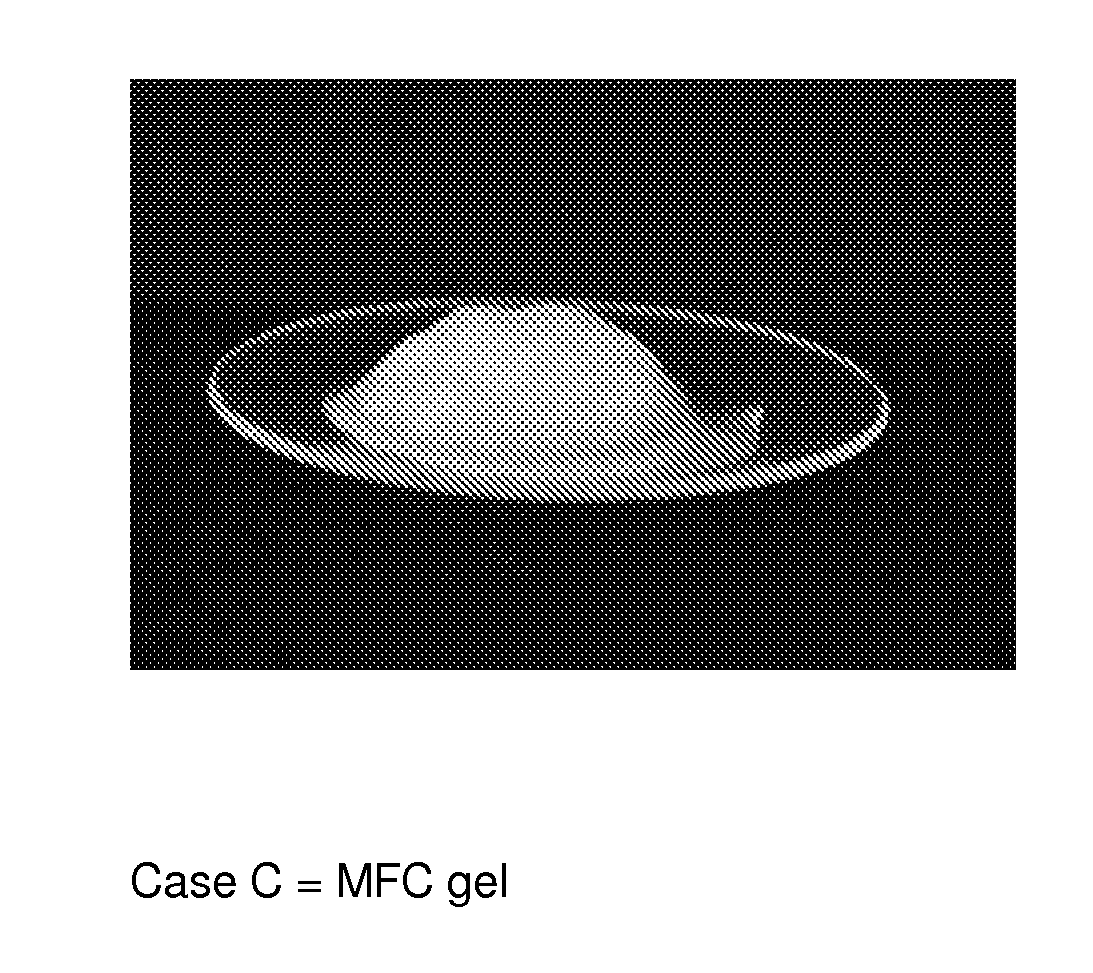

Method for providing a nanocellulose involving modifying cellulose fibers

ActiveUS20110036522A1Increases anionic charge densityReduce energy consumptionNanostructure manufacturePulp properties modificationAqueous electrolyteCellulose fiber

A method for the manufacturing of nanocellulose. The method includes a first modification of the cellulose material, where the cellulose fibres are treated with an aqueous electrolyte-containing solution of an amphoteric cellulose derivative. The modification is followed by a mechanical treatment. By using this method for manufacturing nanocellulose, clogging of the mechanical apparatus is avoided. Also the nanocellulose is manufactured in accordance with the method and uses of the cellulose.

Owner:INNVENTIA

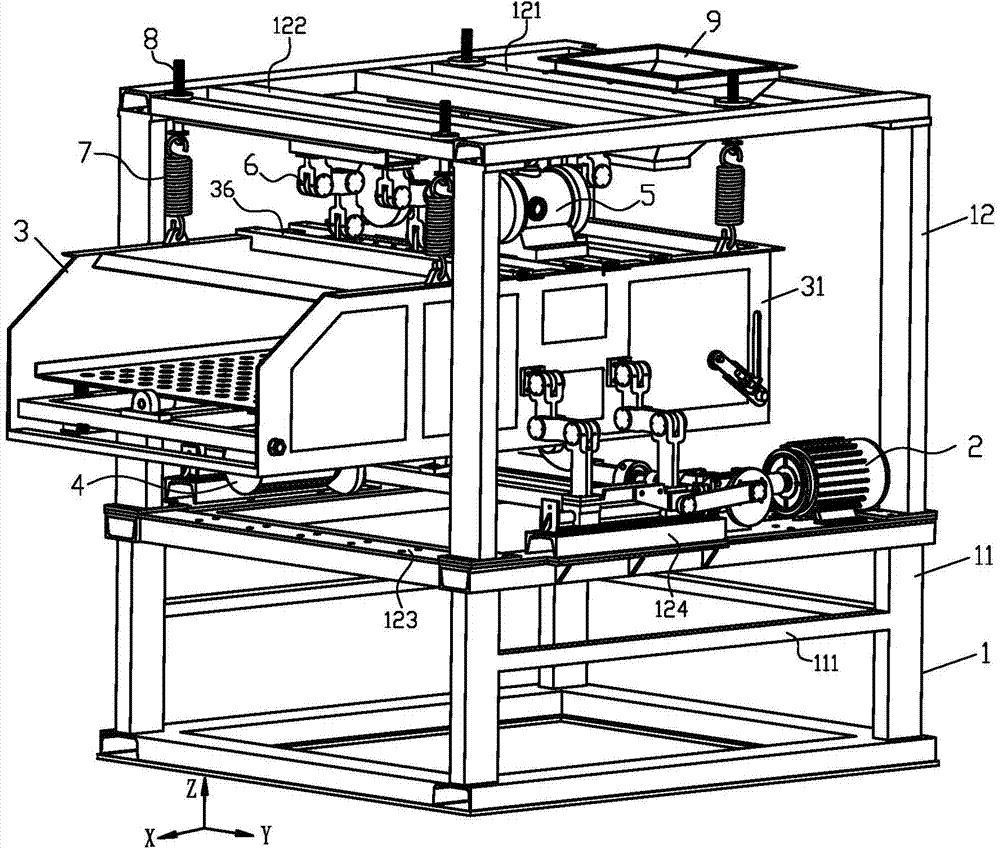

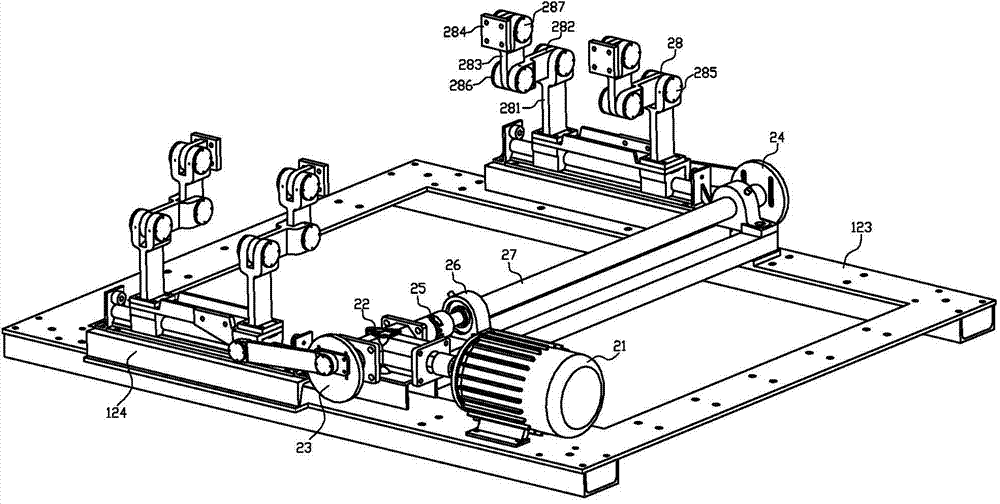

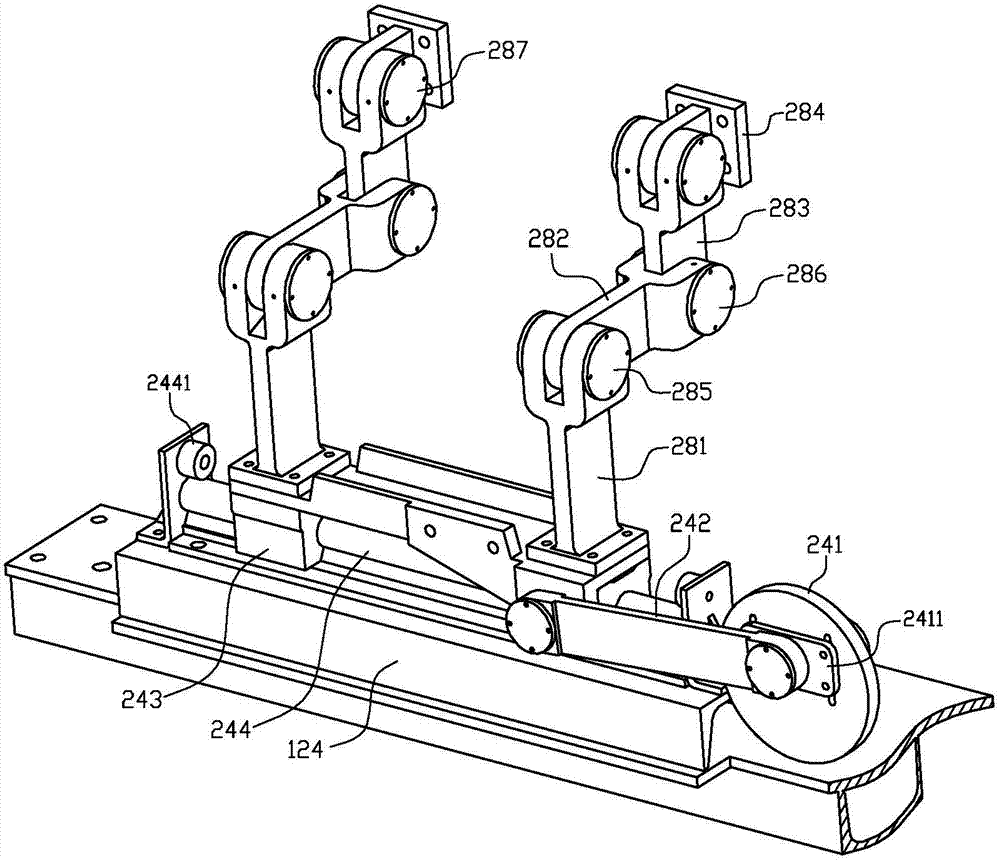

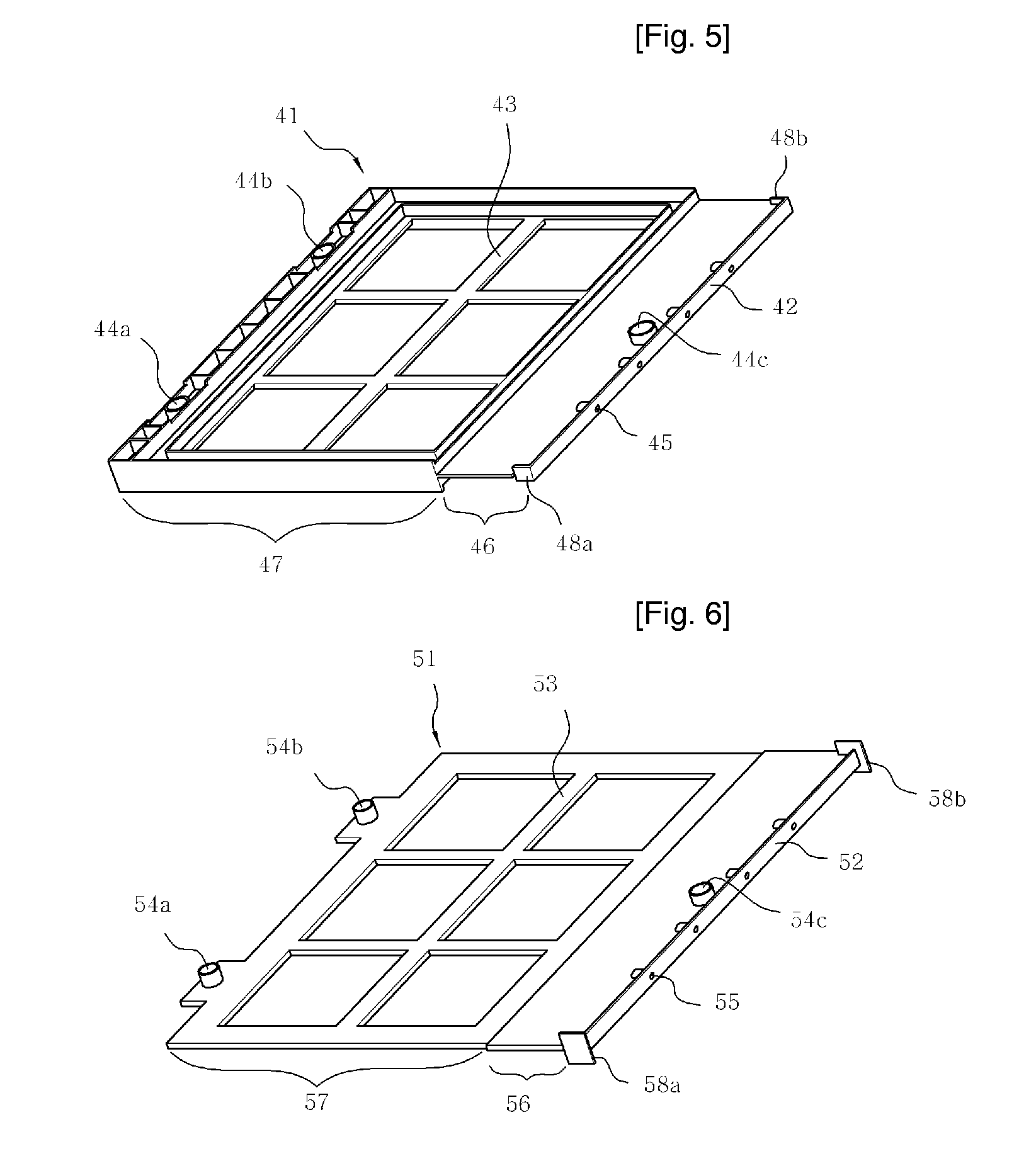

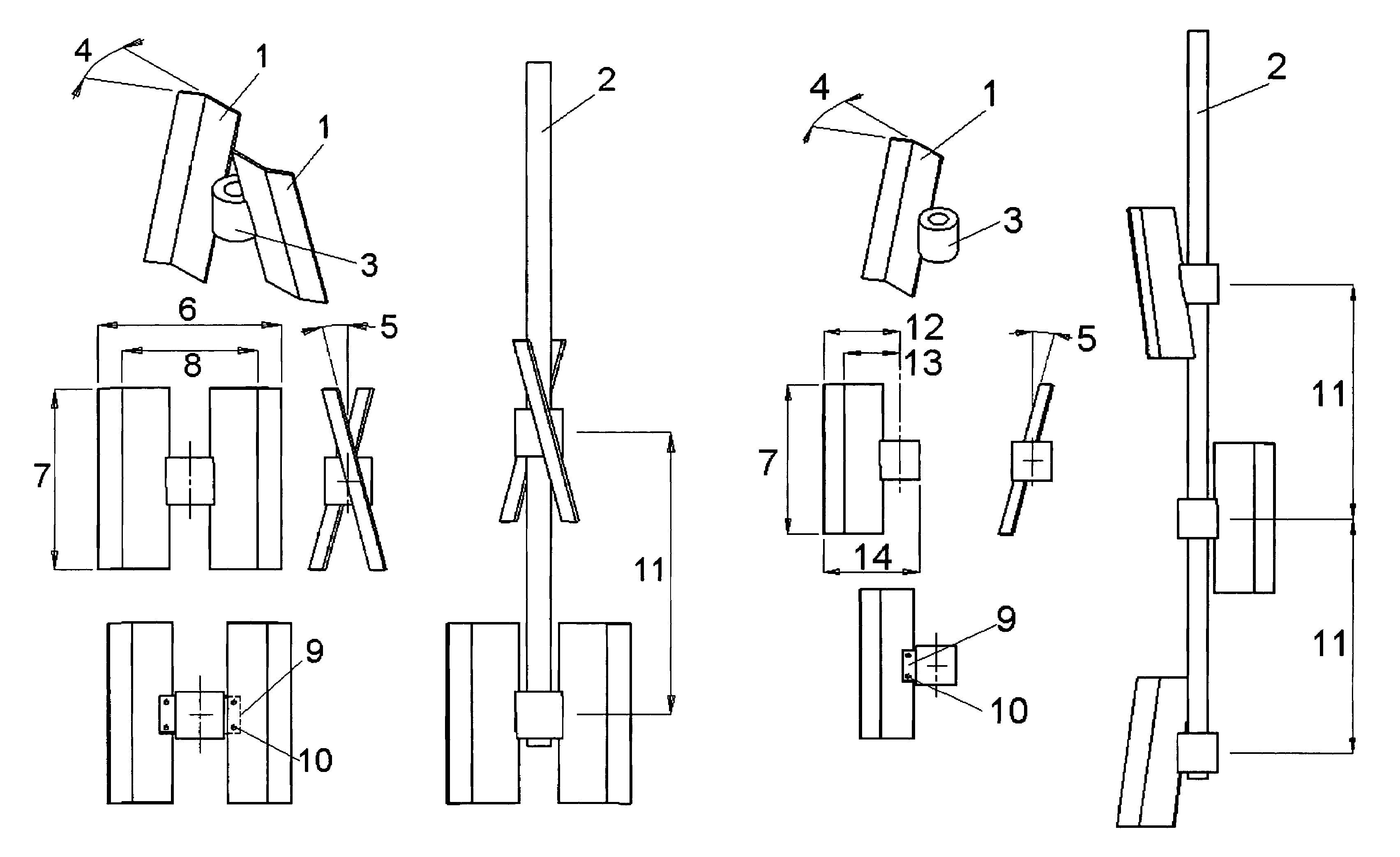

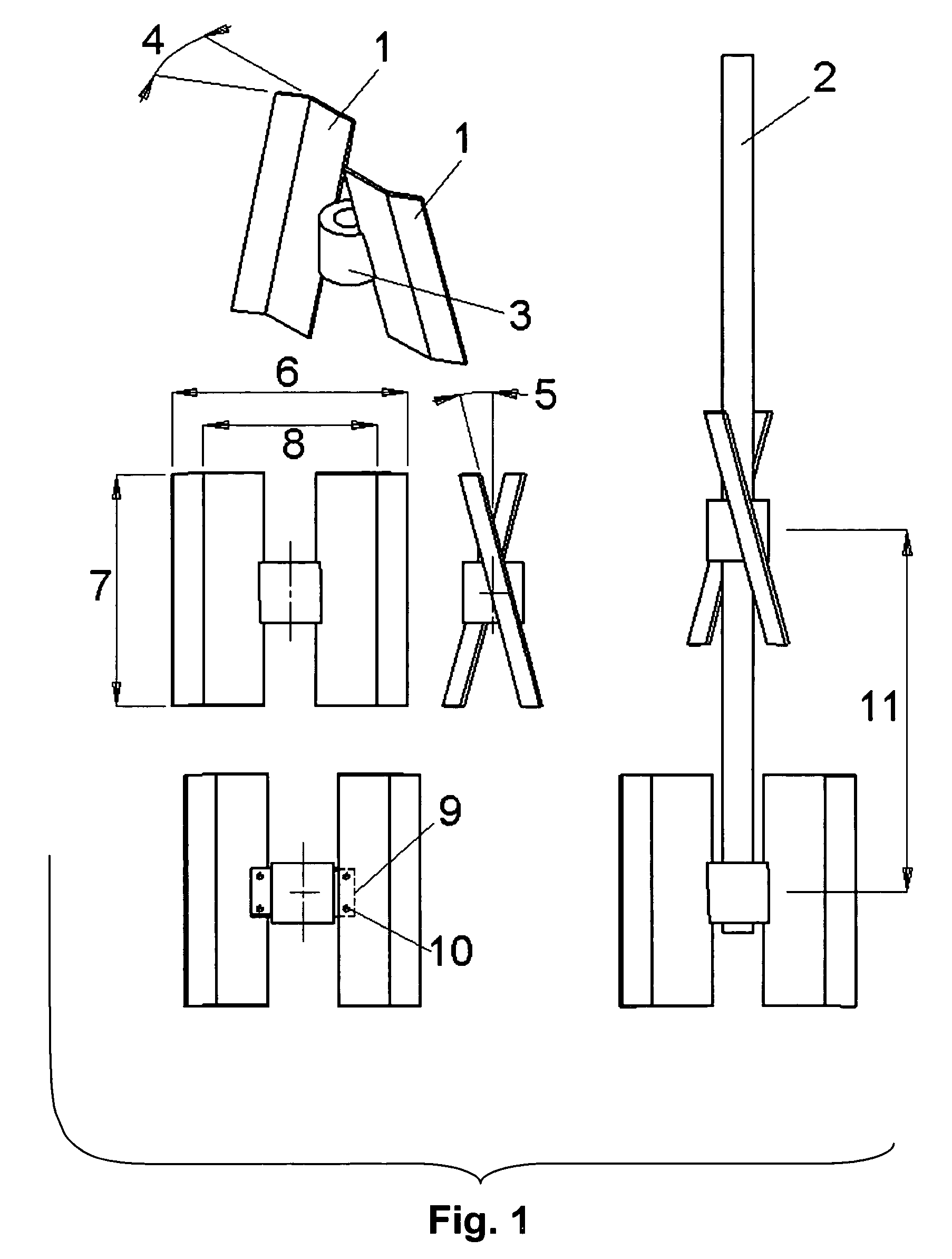

Two-horizontal-movement one-rotation three-freedom-degree series-parallel vibrating screen

ActiveCN104722482AImprove screening efficiencyReduce volumeSievingScreeningEngineeringPower consumption

The invention discloses a two-horizontal-movement one-rotation three-freedom-degree series-parallel vibrating screen. The two-horizontal-movement one-rotation three-freedom-degree series-parallel vibration screen comprises a supporting frame, a transverse excitation device, a screen body, a rotation excitation device, a vertical excitation device, auxiliary limiting chains, springs, lifting ring bolts and a hopper. A material box frame is arranged on the supporting frame, the screen body is suspended on the supporting frame through the springs and the lifting ring bolts, the transverse excitation device, the rotation excitation device and the vertical excitation device can make the screen body vibrate transversely in a reciprocating mode, swing around the horizontal axis in a reciprocating mode and vibrate vertically in a reciprocating mode, and the auxiliary limiting chains are used for limiting the movement freedom degree of the screen body and improve the movement stability. The screen body can achieve two-horizontal-movement one-rotation three-freedom-degree vibration at most, magnitudes, frequencies, screen surface leaning angles, freedom degrees and other parameters in all directions can be adjusted, the screening efficiency is high, and the handling capacity within per unit interval is large, and the two-horizontal-movement one-rotation three-freedom-degree series-parallel vibrating screen has the advantages of being compact in structure, stable and reliable in working, low in equipment cost and running power consumption, easy to control and the like.

Owner:江门市新会区金昌矽砂有限公司

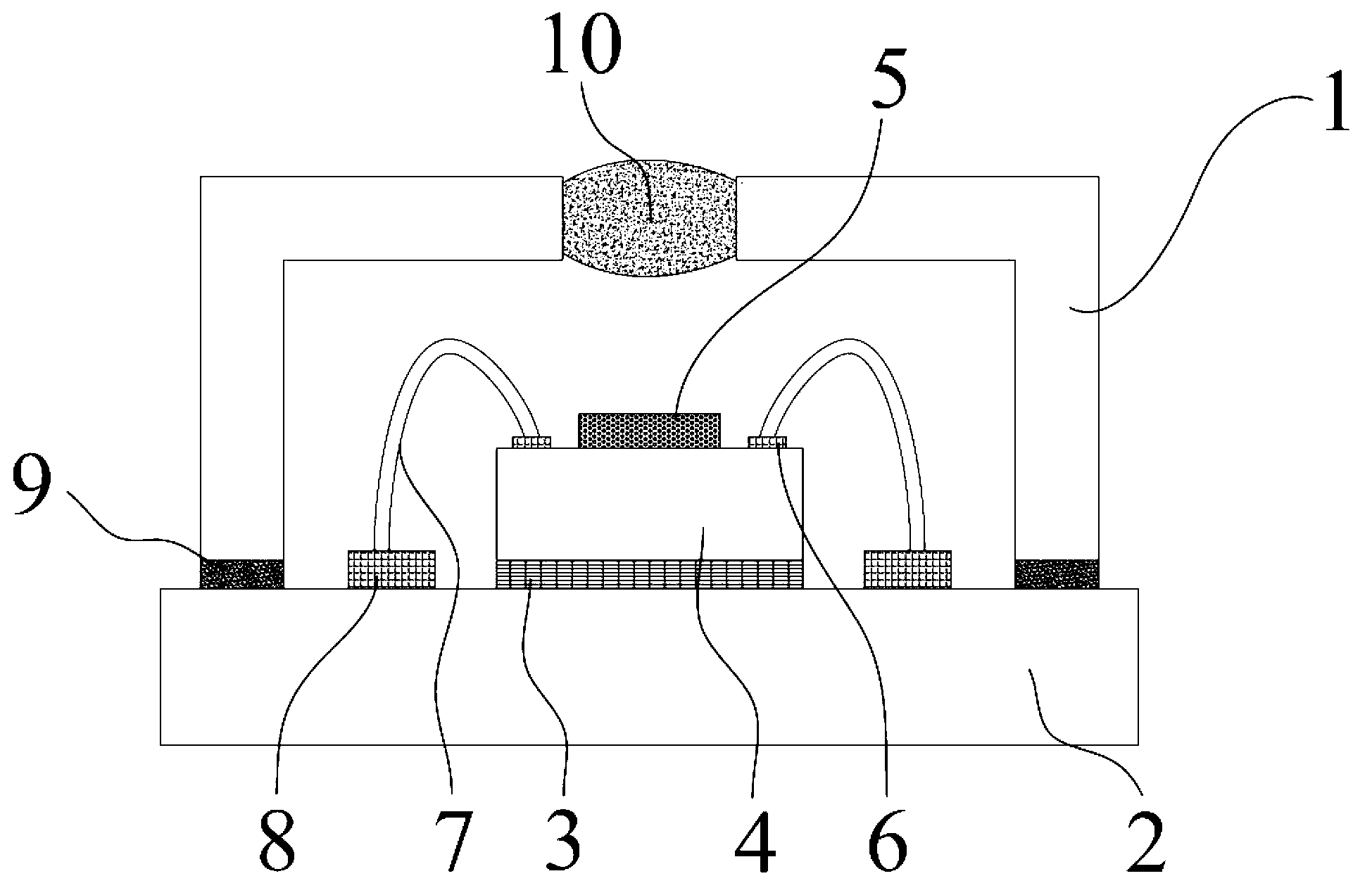

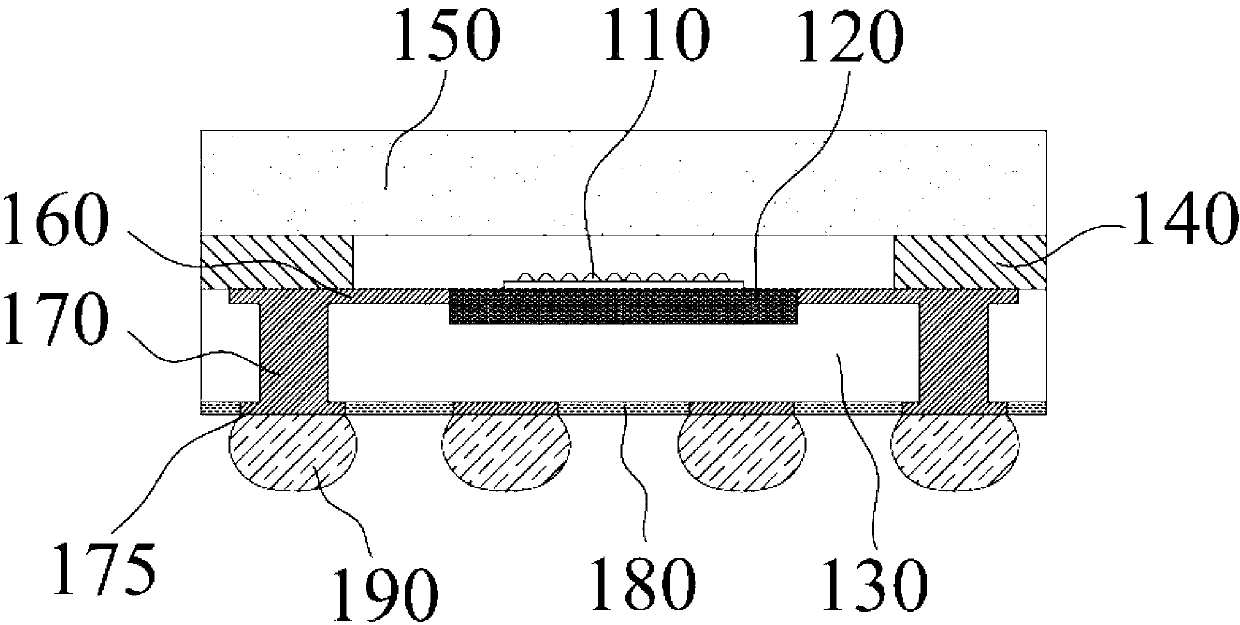

Wafer level chip size package and manufacturing method thereof

InactiveCN103021983AImprove bond strengthImprove layeringSemiconductor/solid-state device detailsSolid-state devicesMetalPolymer

The invention discloses a wafer level chip size package and a manufacturing method of the wafer level chip size package, belonging to the field of sensors. The wafer level chip size package comprises a wafer, wherein the positive surface of the wafer is a first surface which forms an image sensing region, the negative surface of the wafer is a second surface, and the first surface comprises a microlens, a metal interconnection layer and an optical interaction region from top to bottom; a silicon through hole which does not penetrate through a silicon substrate and a redistribution region are manufactured on the first surface, and I / Os at the periphery of the optical interaction region are connected with the silicon through hole; the wall of the silicon through hole is manufactured into a passivation layer and is filled; a polymer material is manufactured into a second protective layer on the redistribution region; the first surface is in bonding with a glass sheet, and a cavity is formed between the glass sheet and the wafer; the second surface is thinned and forms a groove structure through an etching process, and the silicon through hole is exposed; a line layer is manufactured on the second surface, and the silicon through hole is connected to a solder pad cushion; a welding prevention layer is manufactured on the line layer, and the solder pad cushion is exposed; and a solder ball is arranged on the solder pad cushion. With the adoption of the wafer level chip size package and the manufacturing method of the wafer level chip size package, the technological process is reduced, the reliability and the production efficiency of a product are improved, and the production cost is lowered.

Owner:BEIJING UNIV OF TECH

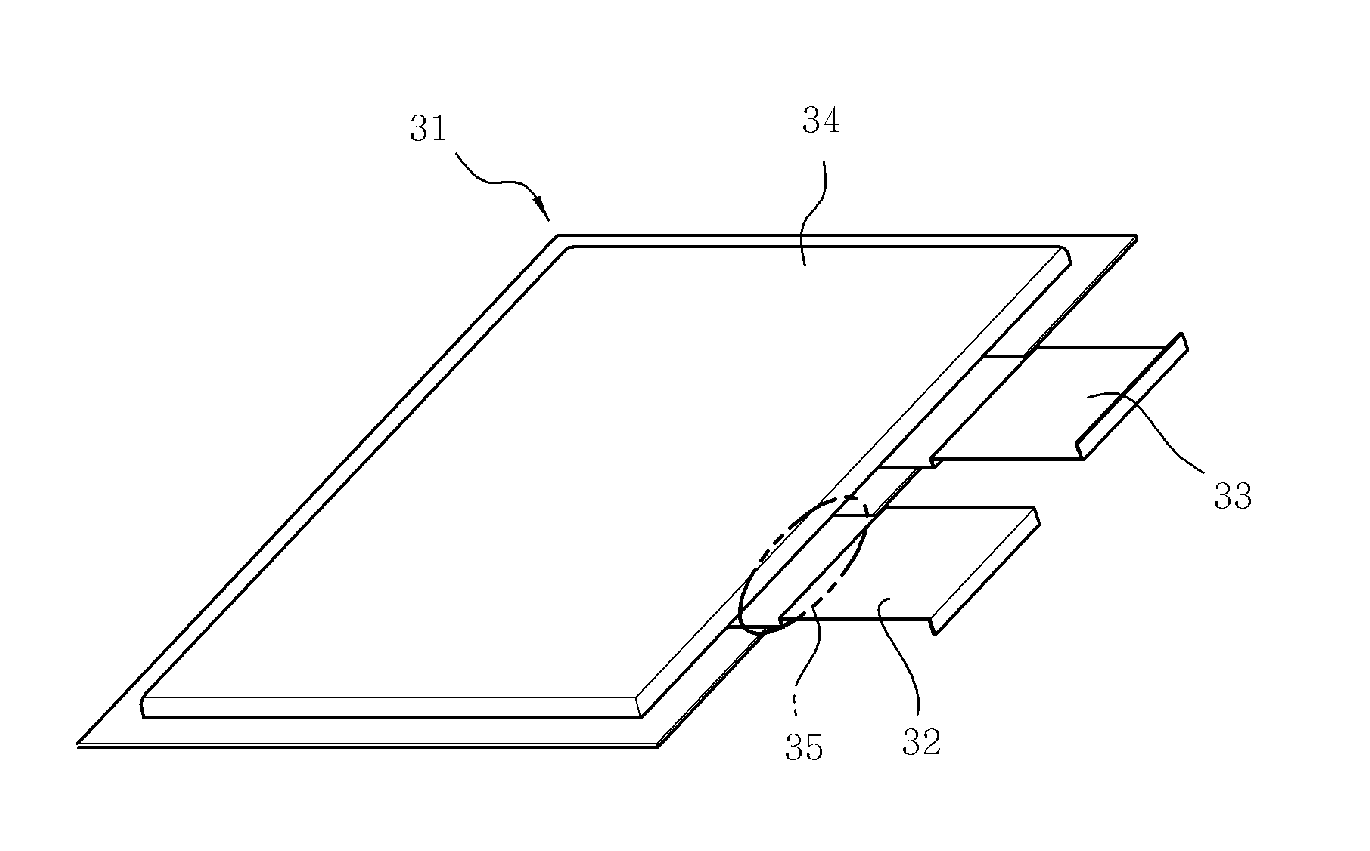

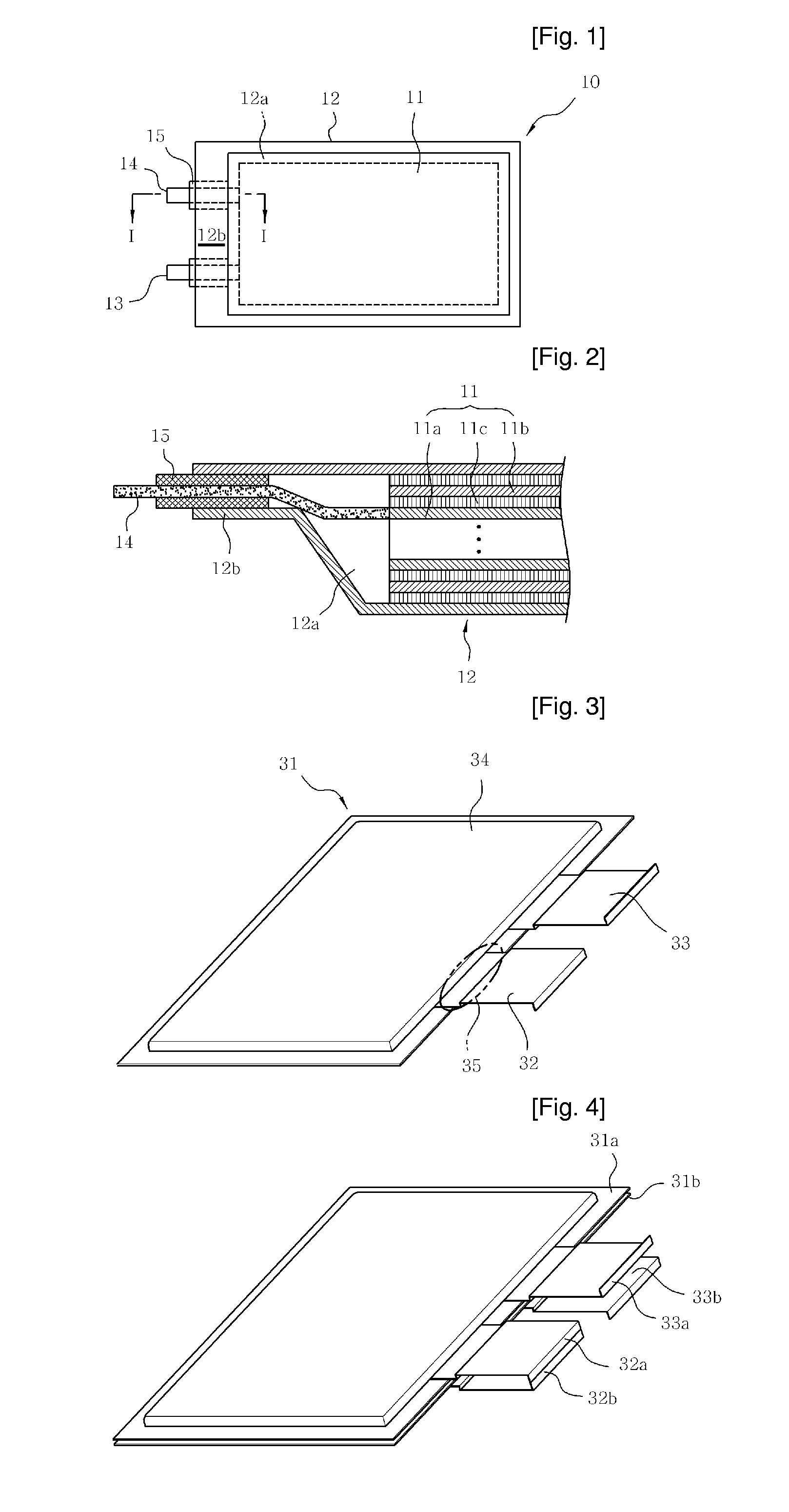

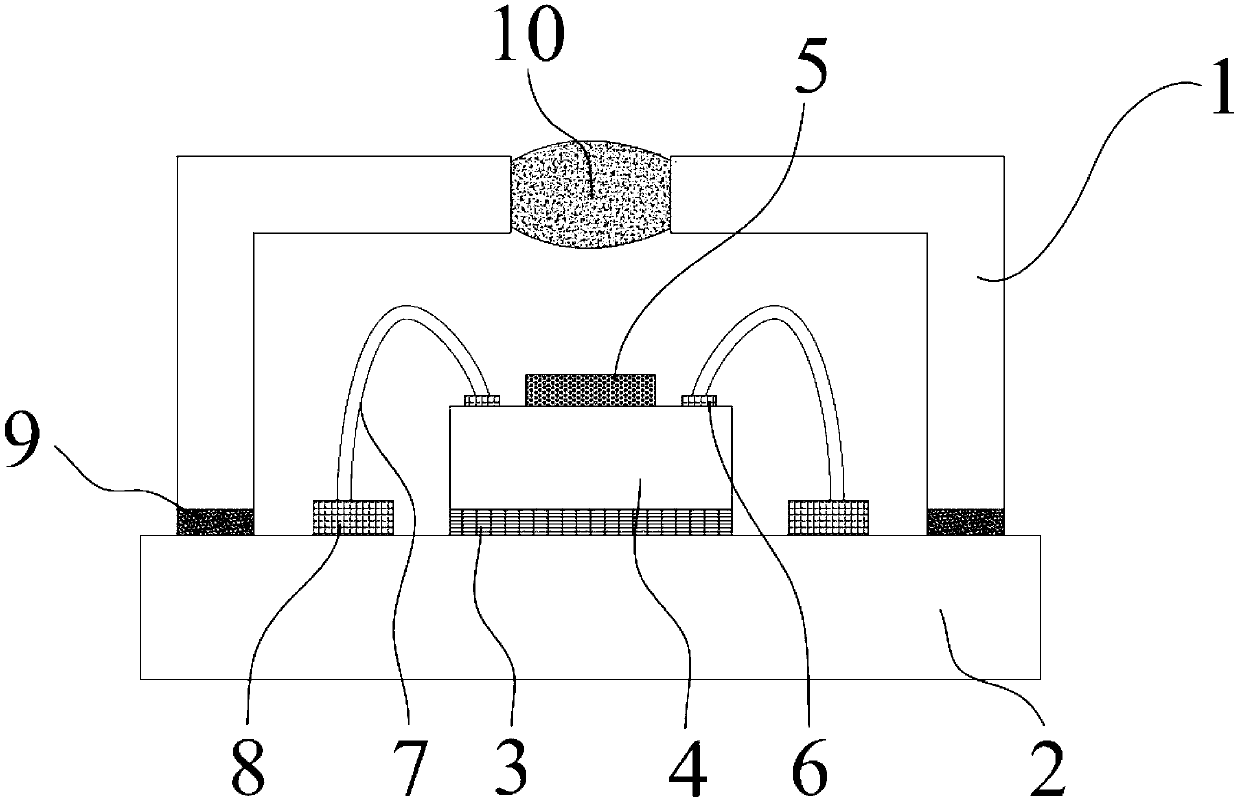

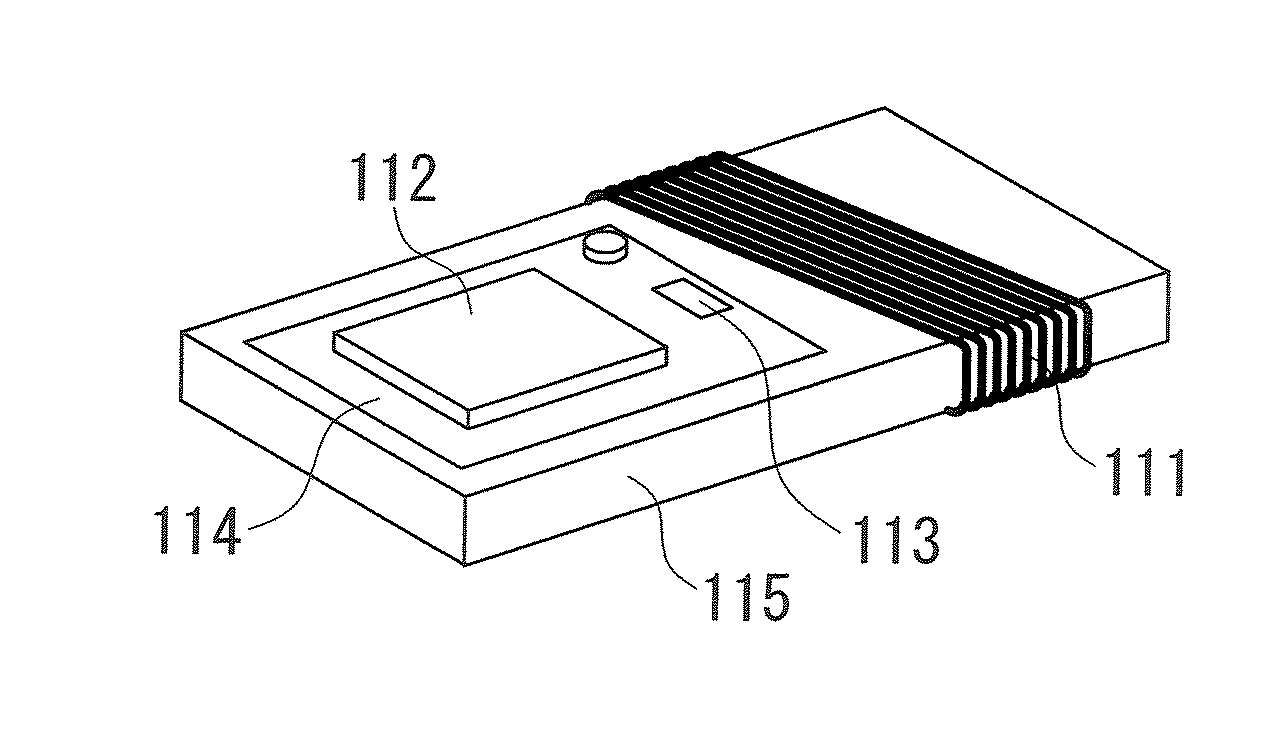

Case For High-Power Rechargeable Lithium Battery

Disclosed herein is a case which protects a plurality of flexible lithium polymer unit cells, has a compact structure to reduce volume, has a simple assembly process, and minimizes heat generated during a high-power charging or discharging operation. The battery case includes a pouch support frame to support a pouch of a unit cell having the pouch and electrode terminals. A heat radiating part having the shape of a shelf is provided on a surface of the pouch support frame, and defines a space for dispersing heat generated from the pouch. A terminal support having the shape of a wall is provided on an edge of the heat radiating part, thus supporting the electrode terminals of the unit cell.

Owner:SK ON CO LTD

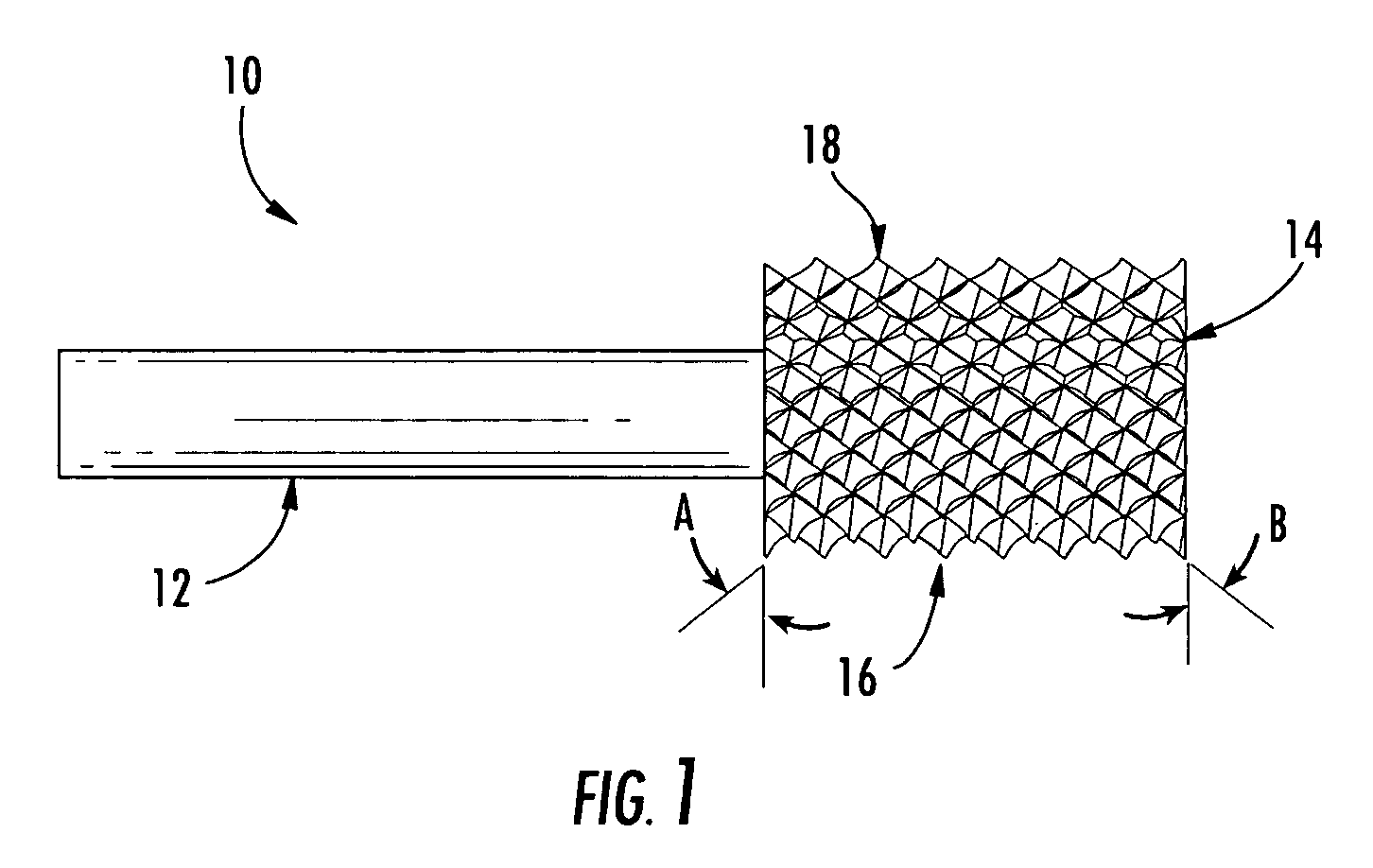

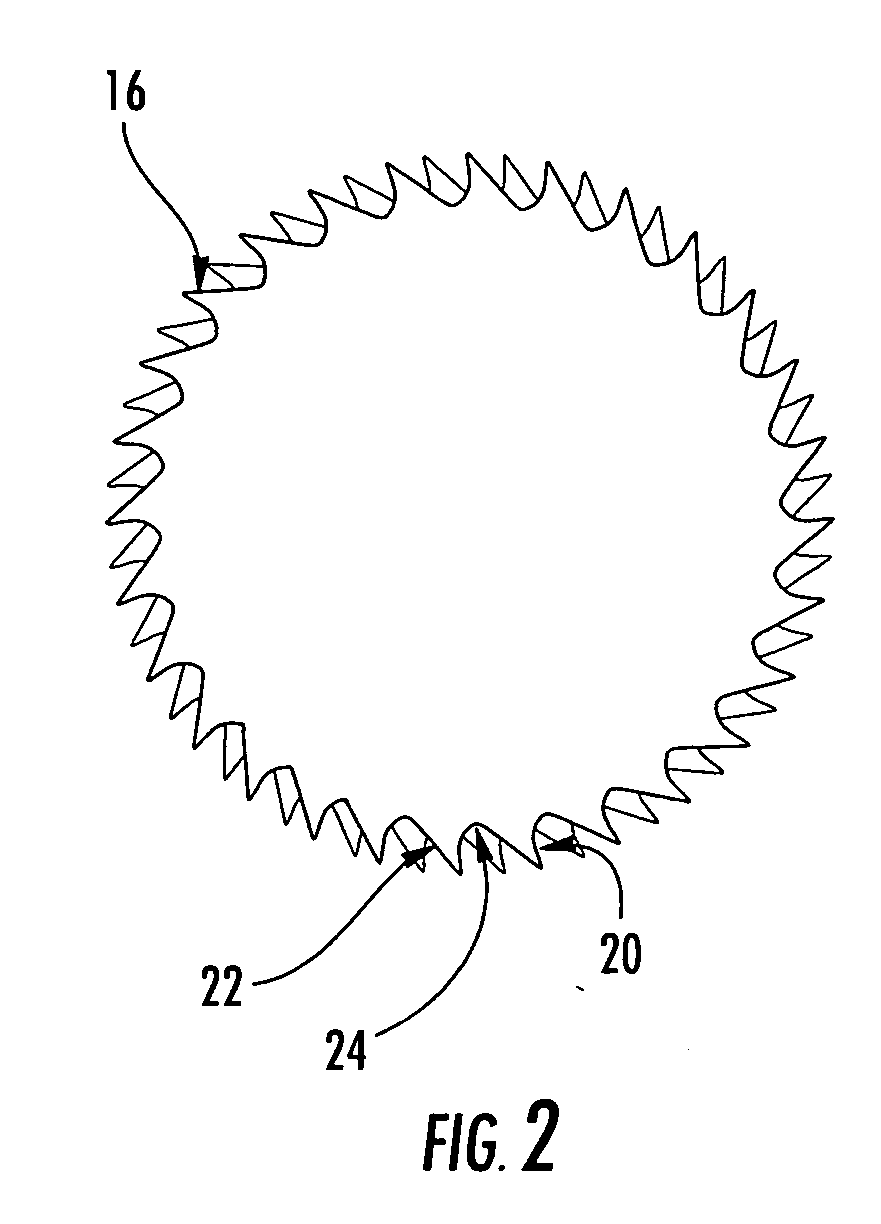

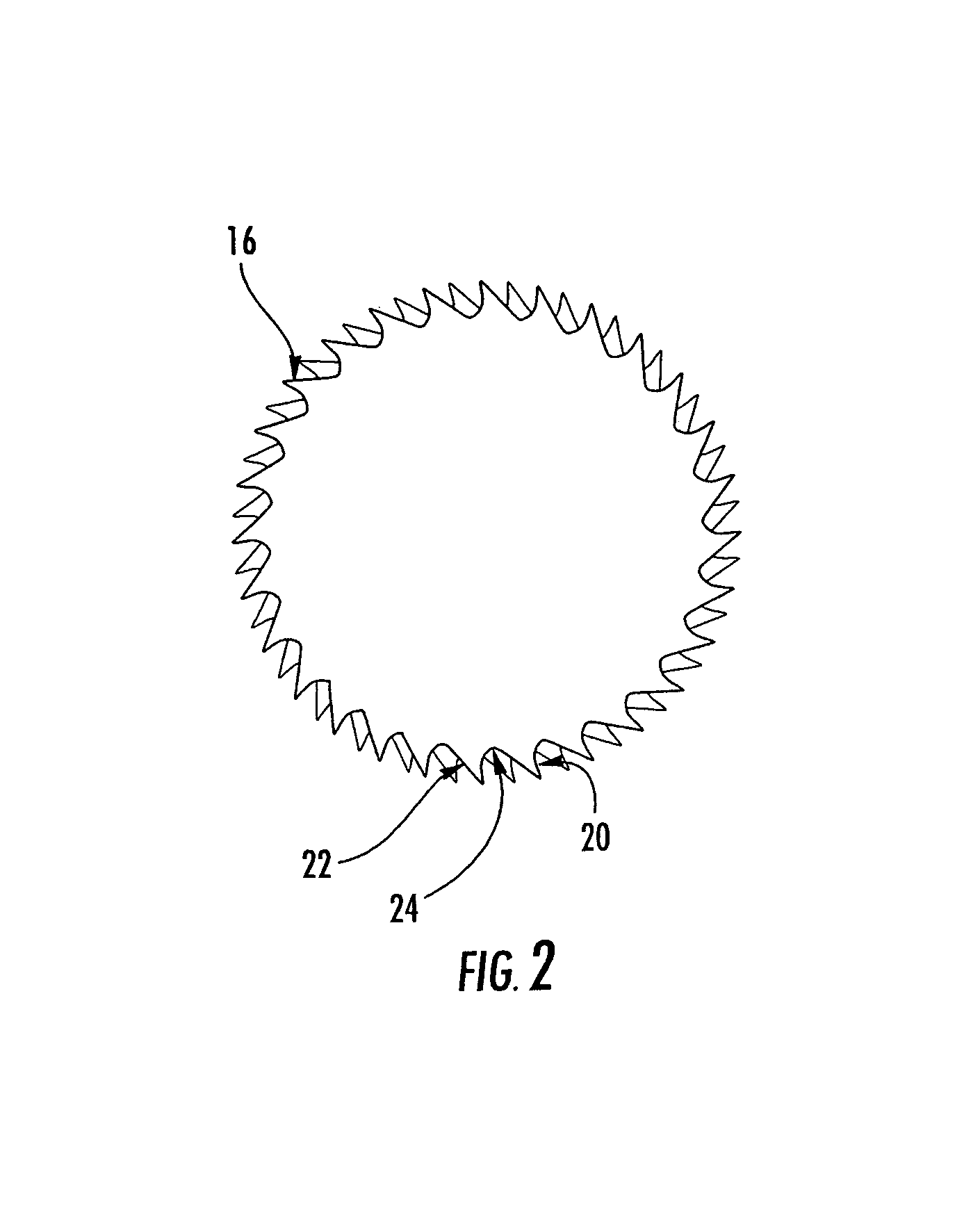

Shaper router and method

ActiveUS20050123363A1Reduce layeringHigh surface finishMilling cuttersFiling/rasping toolsMechanical engineeringHelix

A routing tool for cutting material and an associated apparatus and method are provided. The tool includes a substantially cylindrical shaft member having a shank portion and a cutting portion. The cutting portion includes a plurality of cutting teeth disposed peripherally about a first helix and an intersecting second helix. Each cutting tooth defines a first cutting clearance on a first cutting edge and a first clearance on a first non-cutting edge. The cutting tooth defines a second cutting clearance on a second cutting edge and a second clearance on a second non-cutting edge. A flat extends on each cutting tooth resulting in a circular land on an outside diameter of the cutting portion.

Owner:THE BOEING CO

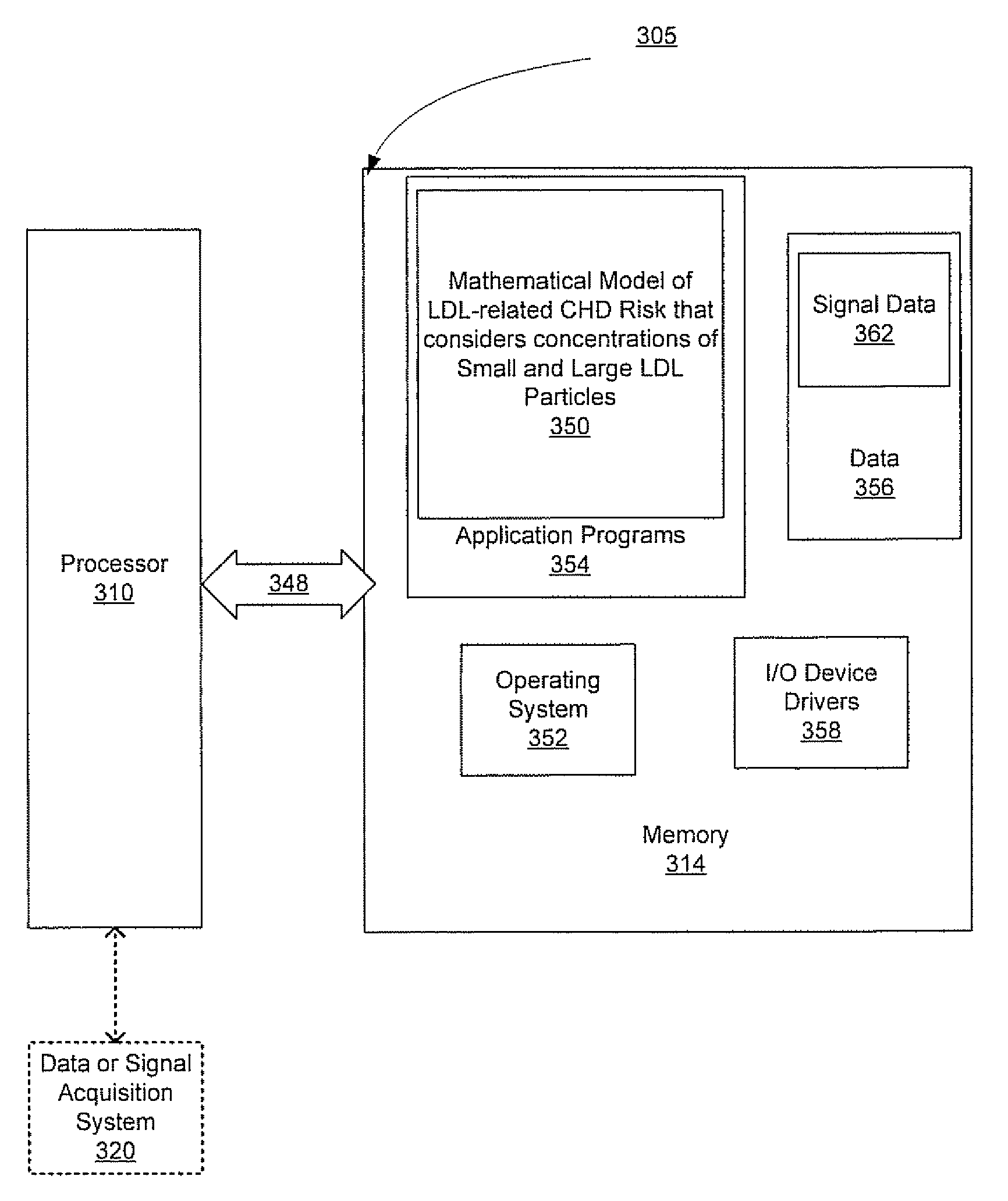

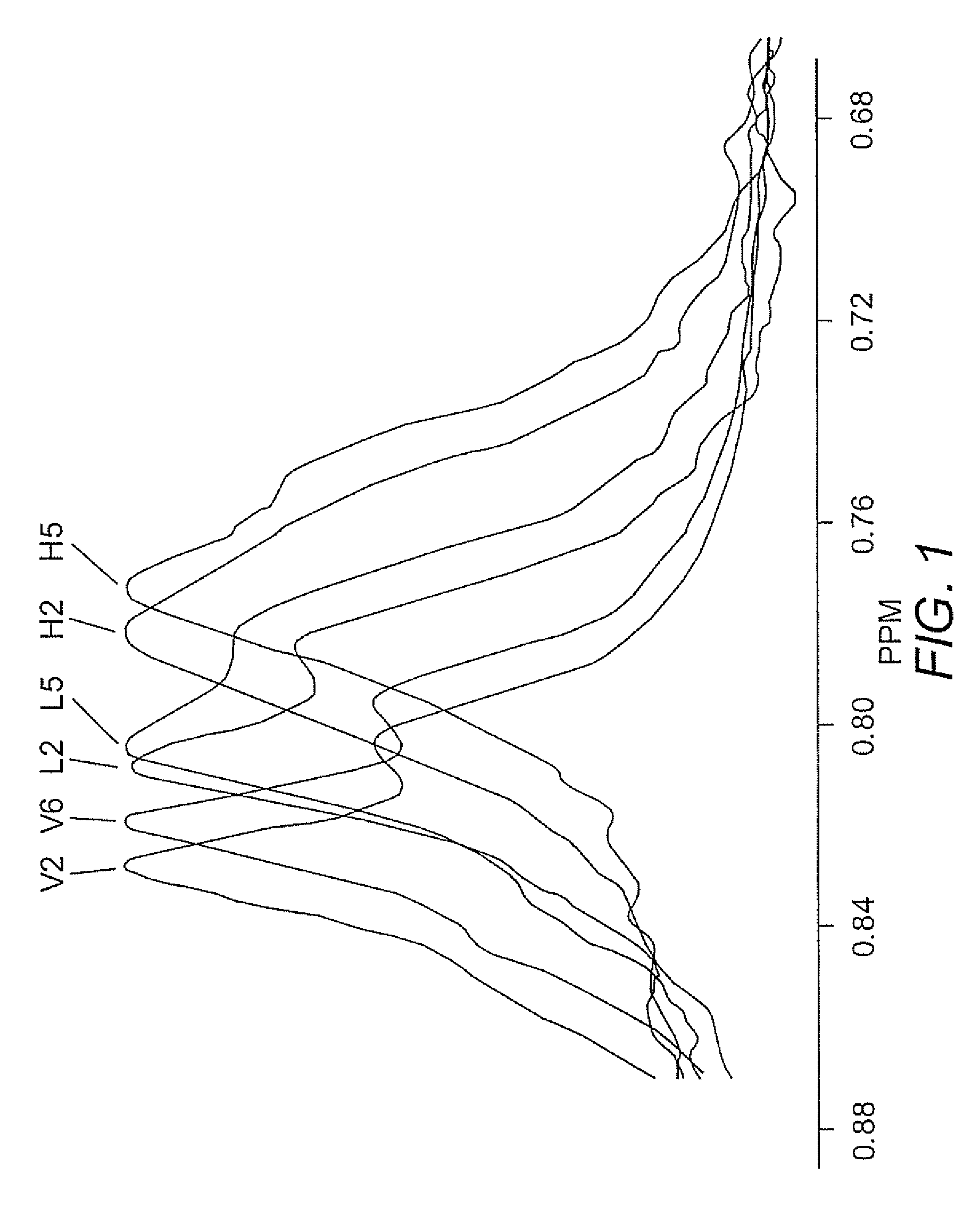

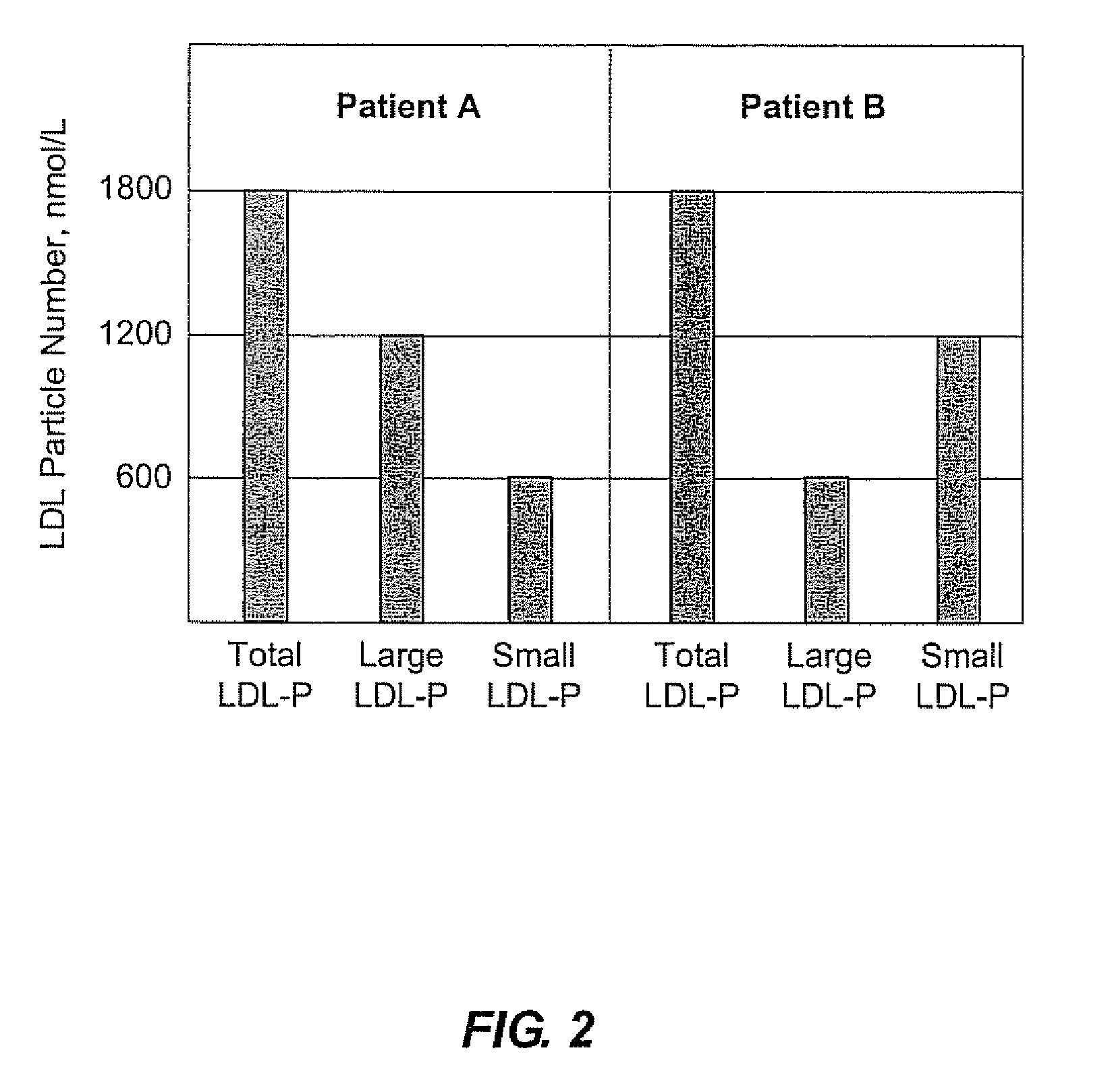

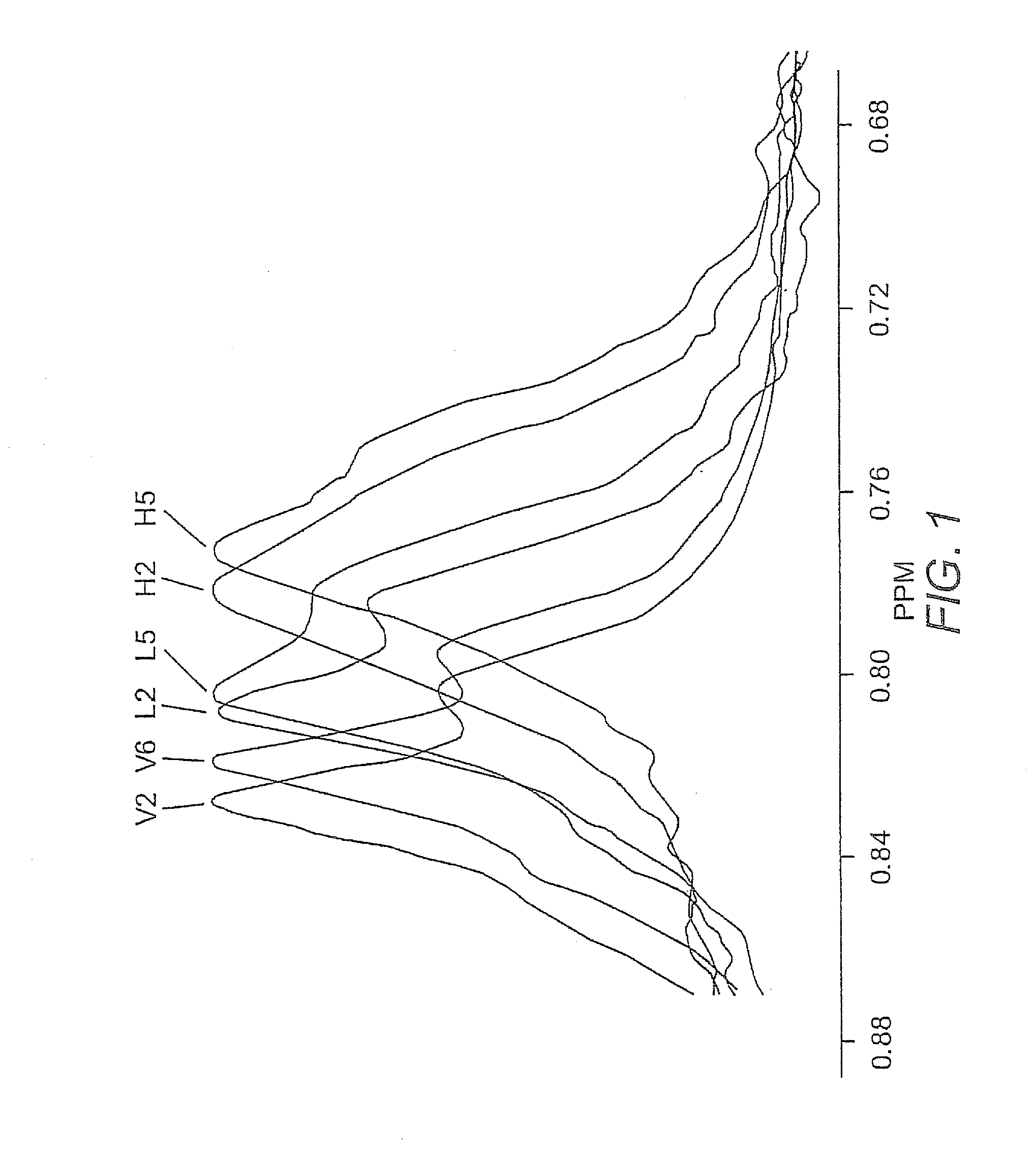

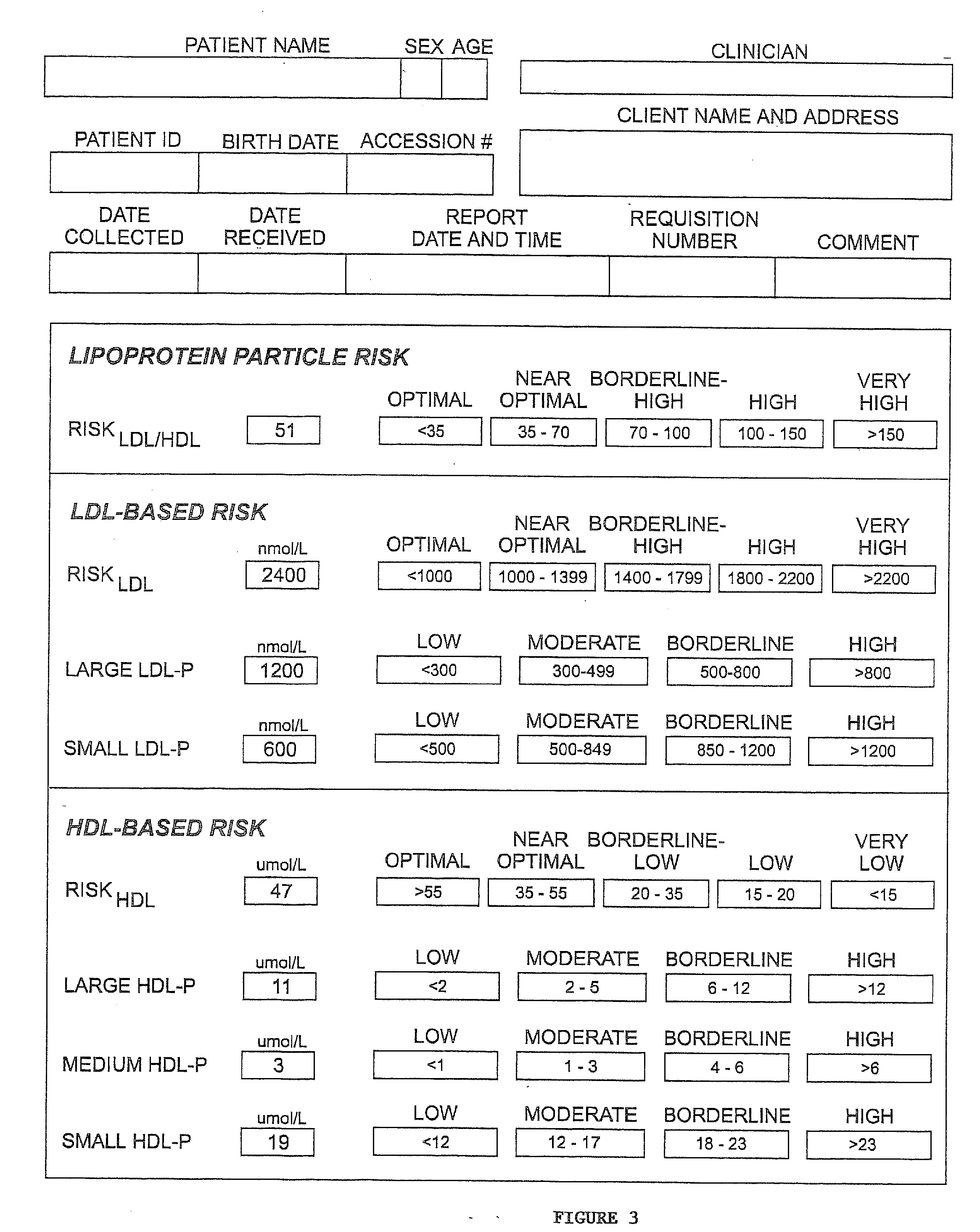

Methods, systems and computer programs for assessing CHD risk using adjusted LDL particle number measurements

InactiveUS7790465B2Reduce riskEasy to understandDisease diagnosisBiological testingMedicineMathematical model

Methods, computer program products and apparatus determine a subject's risk of having or developing CHD using a calculated LDL particle risk number and / or a mathematical model of risk associated with LDL particles that adjusts concentrations of at least one of small and large LDL particle measurements to reflect predicted CHD risk.

Owner:LIPOSCI

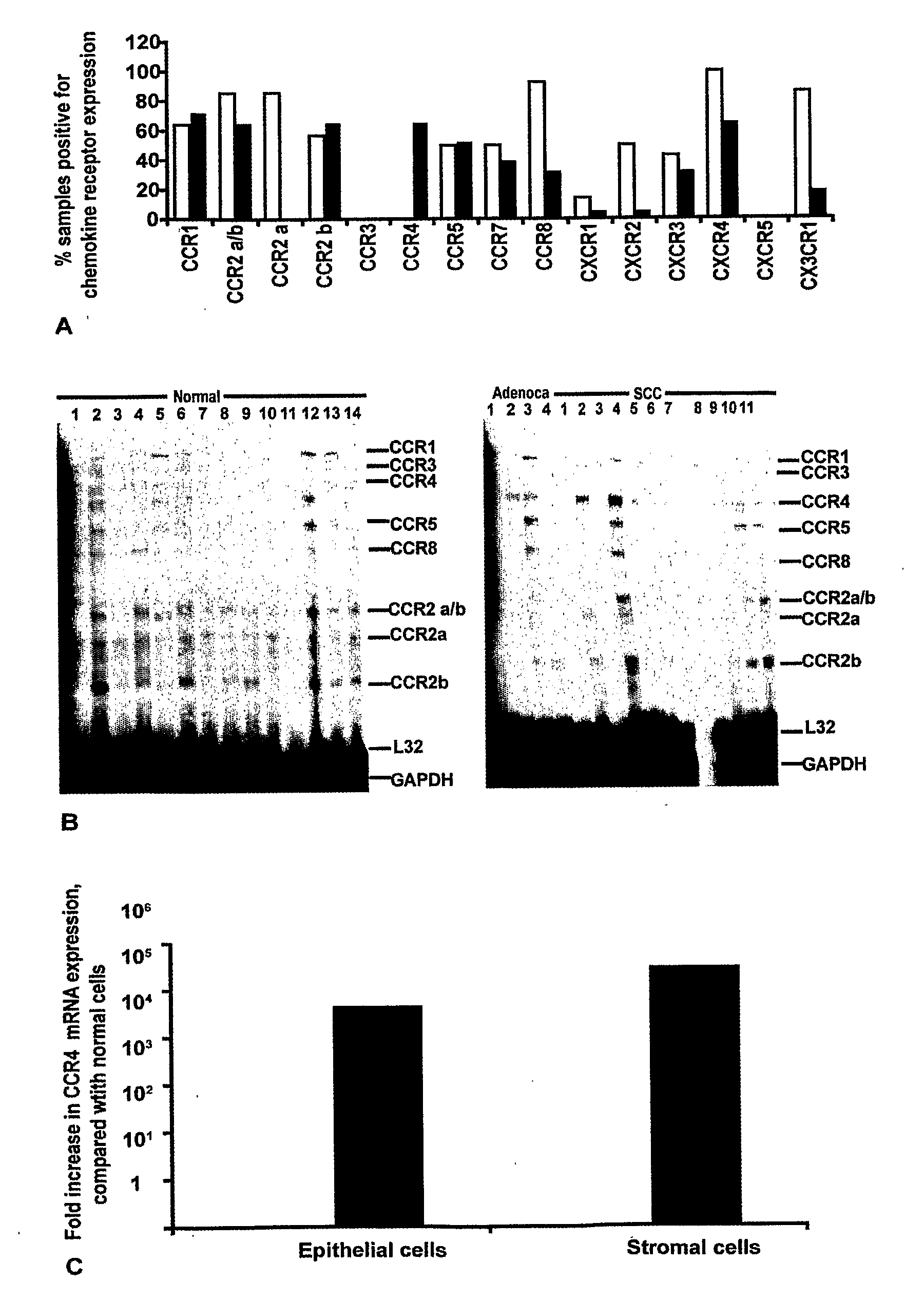

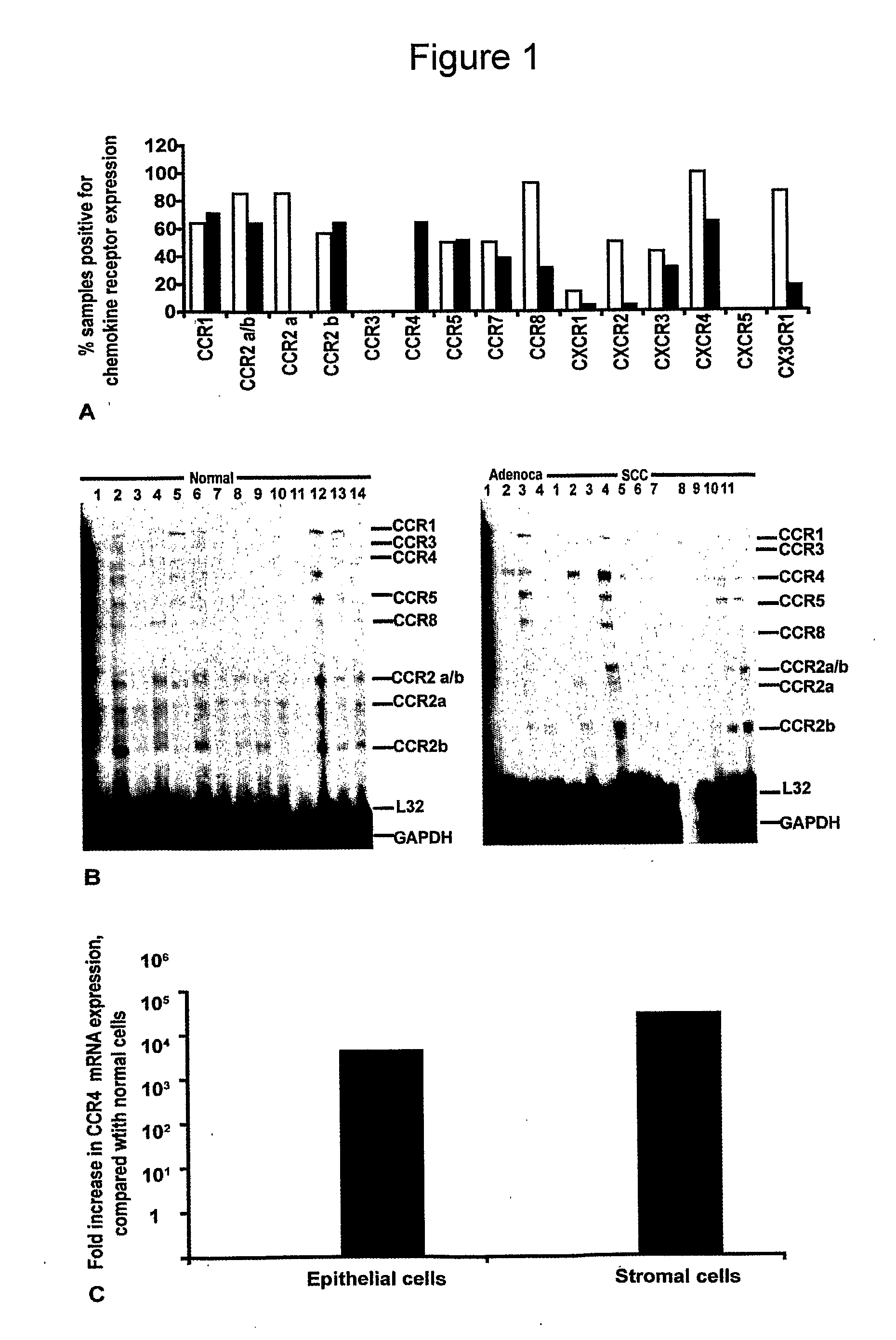

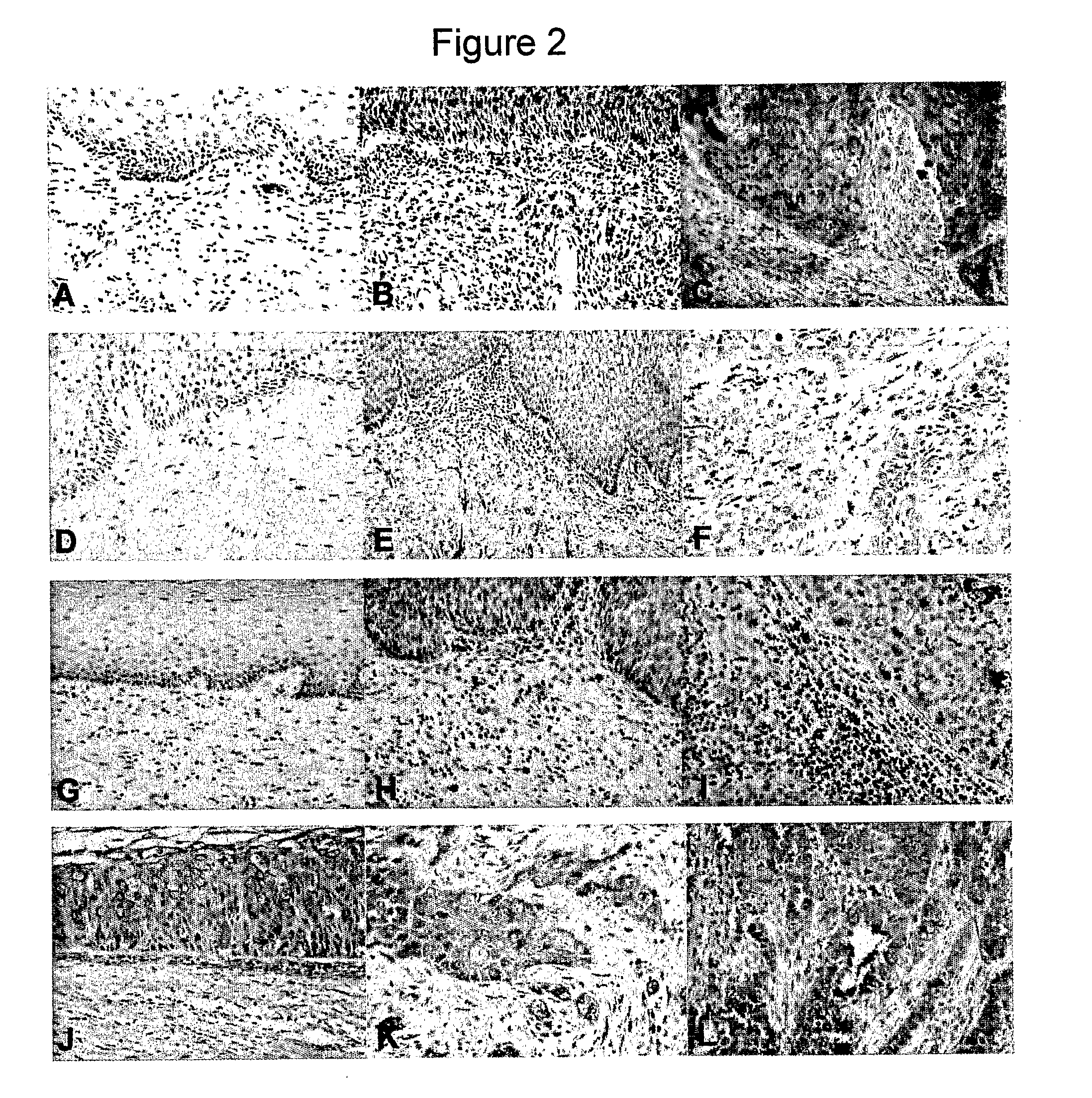

Cancer Marker and Therapeutic Target

InactiveUS20100278844A1Permit stratificationConvenient treatmentOrganic active ingredientsAntibody ingredientsOncologyDrug biological activity

Chemokine receptor CCR4 and its ligands CCL1 7 and CCL22 are used as markers for the identification and / or staging of cancer. The level of CCR4, CCL17 and CCL22 are found to increase during malignant tumour progression. CCR4, CCL17 and CCL22 are used as markers for the stratification of cancer patients according to their suitability for treatment with anti-cancer agents. Information of diagnostic character is provided by measuring the level of one or more of CCR4, CCL 17 and CCL22 present in a patient sample. Methods of treatment of cancer patients which agents that modulate the activity of CCR4, CCL17 and CCL22. Methods of screening for agents which modulate the biological activities of CCR4, CCL 17 and CCL22 provide anti-cancer agents.

Owner:CANCER RES TECH LTD

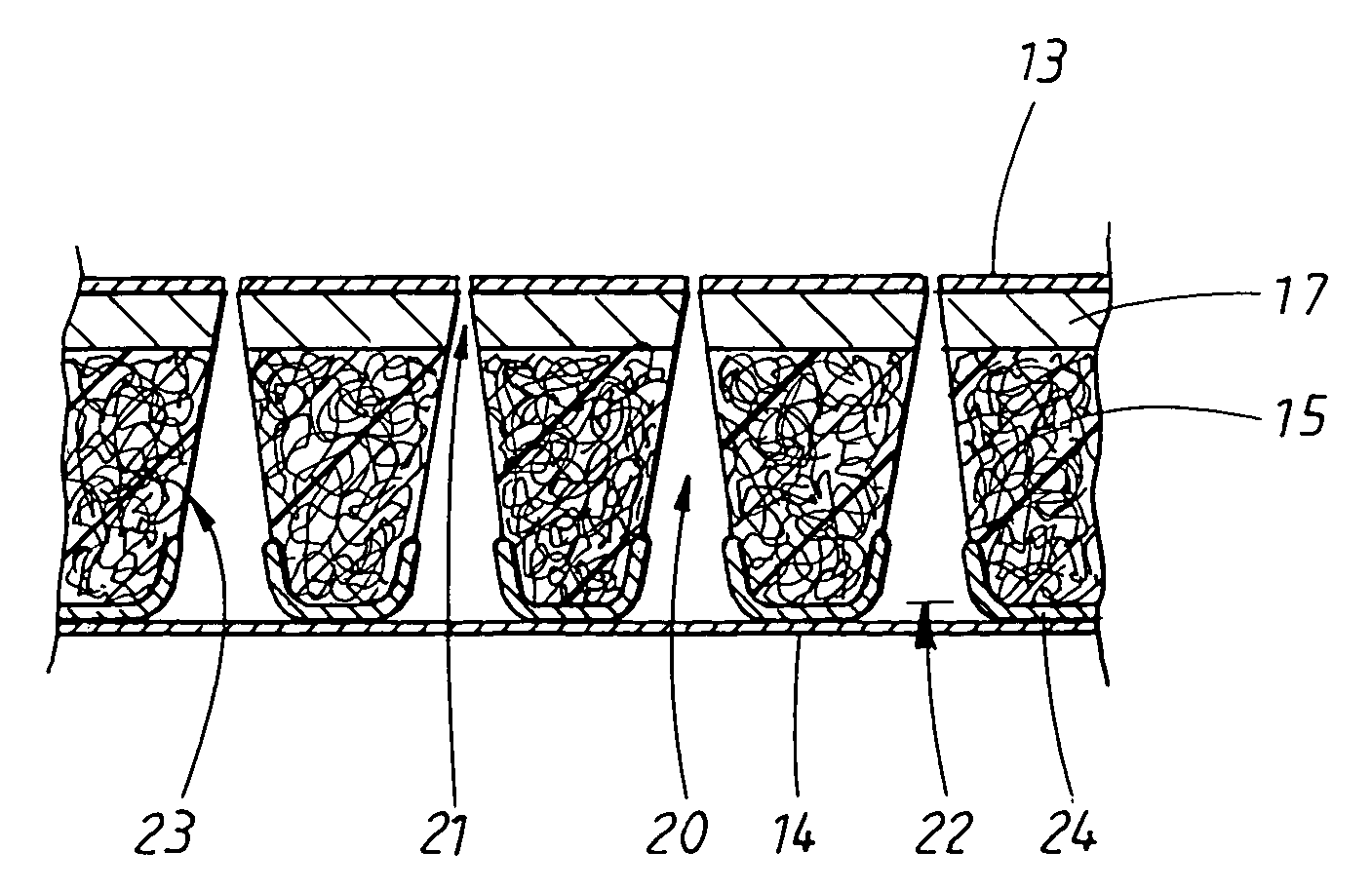

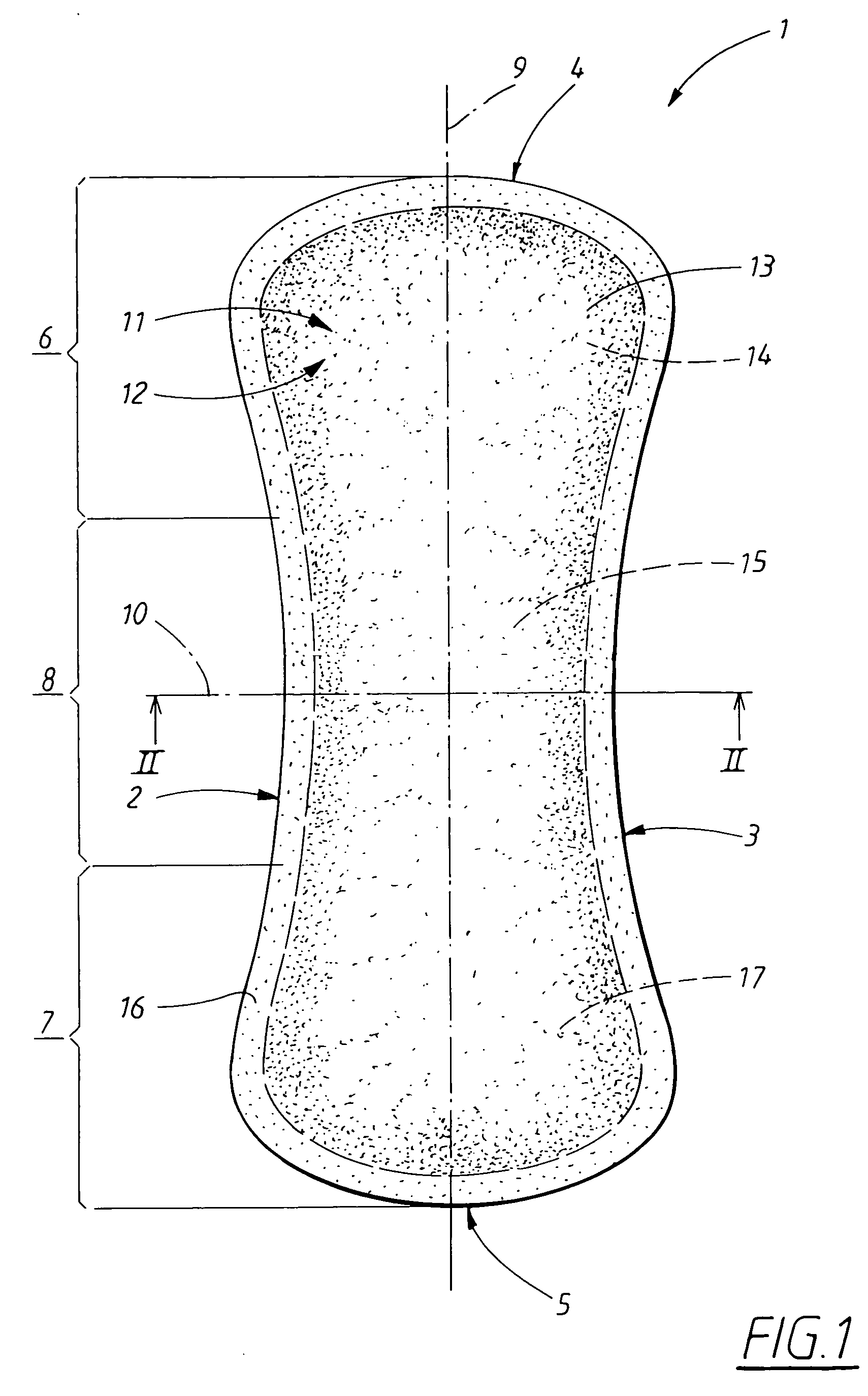

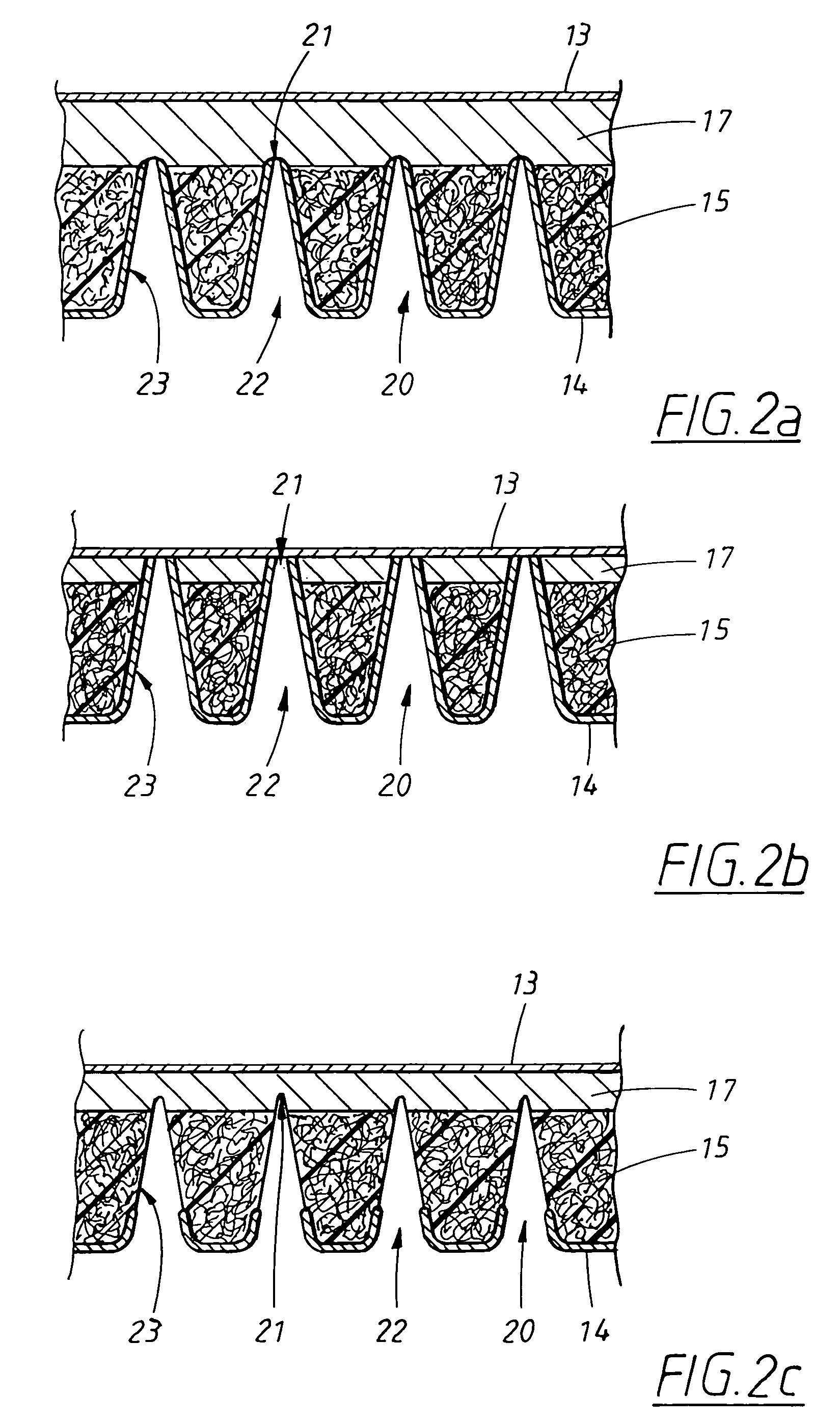

Absorbent article and method of production of an absorbent article

InactiveUS20060122569A1Avoid cavitiesImprove surface propertiesLayered productsBaby linensSurface layerEngineering

An absorbent article having a first essentially liquid permeable surface layer (13), a backing layer (14) and, located between said liquid permeable surface layer (13) and said liquid impermeable backing layer (14), an absorbent body (15). The absorbent body has cavities (20) which are essentially cone-shaped and extend at least through part of the absorbent body (15), said cavities (20) having a tip part (21) and a base (22), the tip part (21) being located towards or in the liquid permeable surface layer (13) and the base (22) being located away from the liquid permeable surface layer (13). The inner surface of said cavities (20) is treated with at least one functional substance.

Owner:ESSITY HYGIENE & HEALTH AB

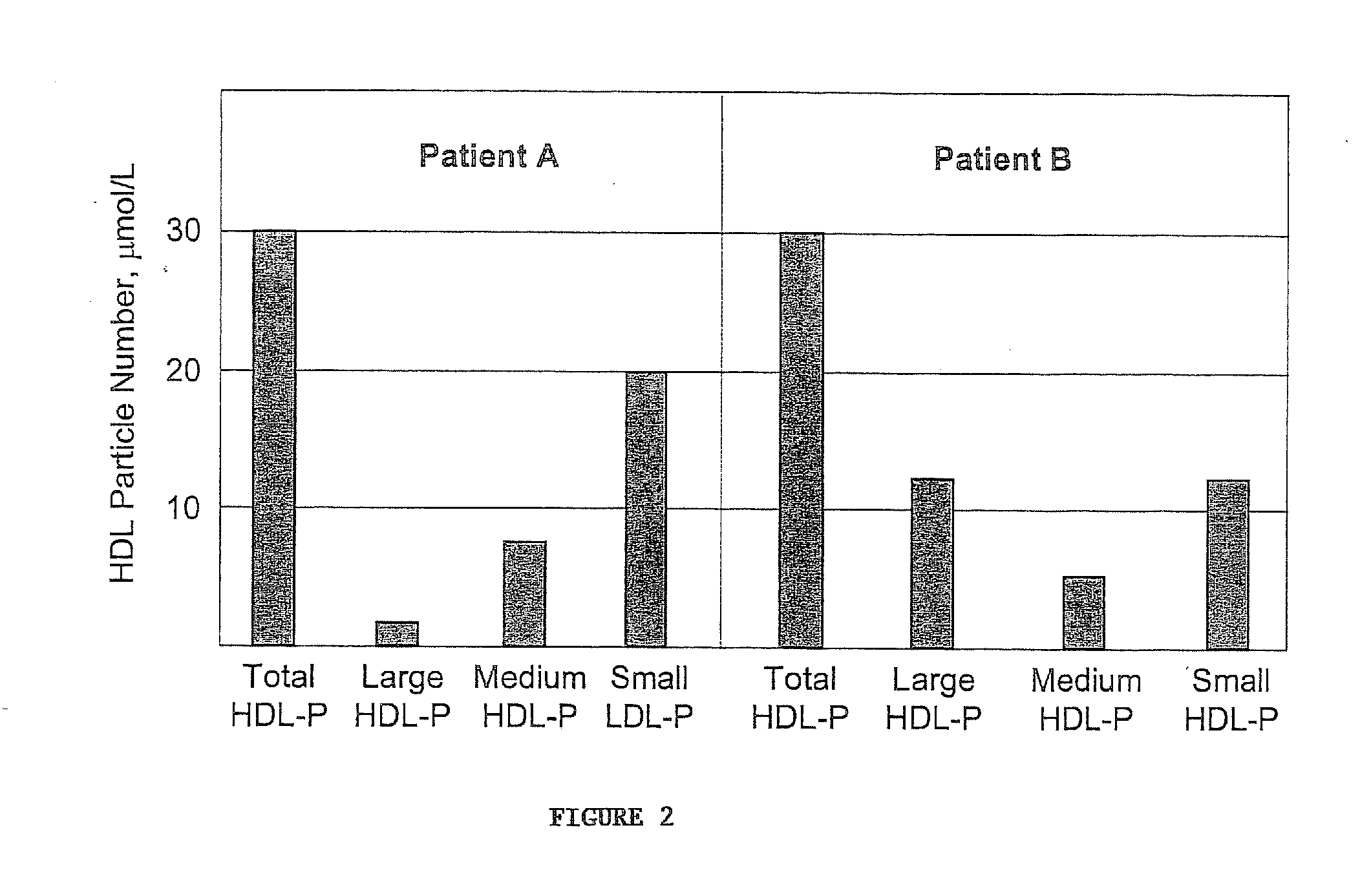

Methods, systems and computer programs for assessing chd risk using adjusted hdl particle number measurements

ActiveUS20070264677A1Facilitate patient risk stratificationEfficiently decideMagnetic measurementsTherapiesMathematical modelA lipoprotein

Methods, computer program products and apparatus determine a subject's risk of having or developing CHD using a calculated HDL particle risk number and / or a mathematical model of risk associated with HDL particles that adjusts concentrations of at least one of the subclasses of small, medium and large HDL particle measurements to reflect predicted CHD risk. A calculated LDL particle risk number may also be generated as well as a lipoprotein particle index derived from the ratio of RLDL / RHDL.

Owner:LIPOSCI

Shaper router and method

ActiveUS7090442B2Reduce layeringHigh surface finishMilling cuttersFiling/rasping toolsEngineeringMechanical engineering

A routing tool for cutting material and an associated apparatus and method are provided. The tool includes a substantially cylindrical shaft member having a shank portion and a cutting portion. The cutting portion includes a plurality of cutting teeth disposed peripherally about a first helix and an intersecting second helix. Each cutting tooth defines a first cutting clearance on a first cutting edge and a first clearance on a first non-cutting edge. The cutting tooth defines a second cutting clearance on a second cutting edge and a second clearance on a second non-cutting edge. A flat extends on each cutting tooth resulting in a circular land on an outside diameter of the cutting portion.

Owner:THE BOEING CO

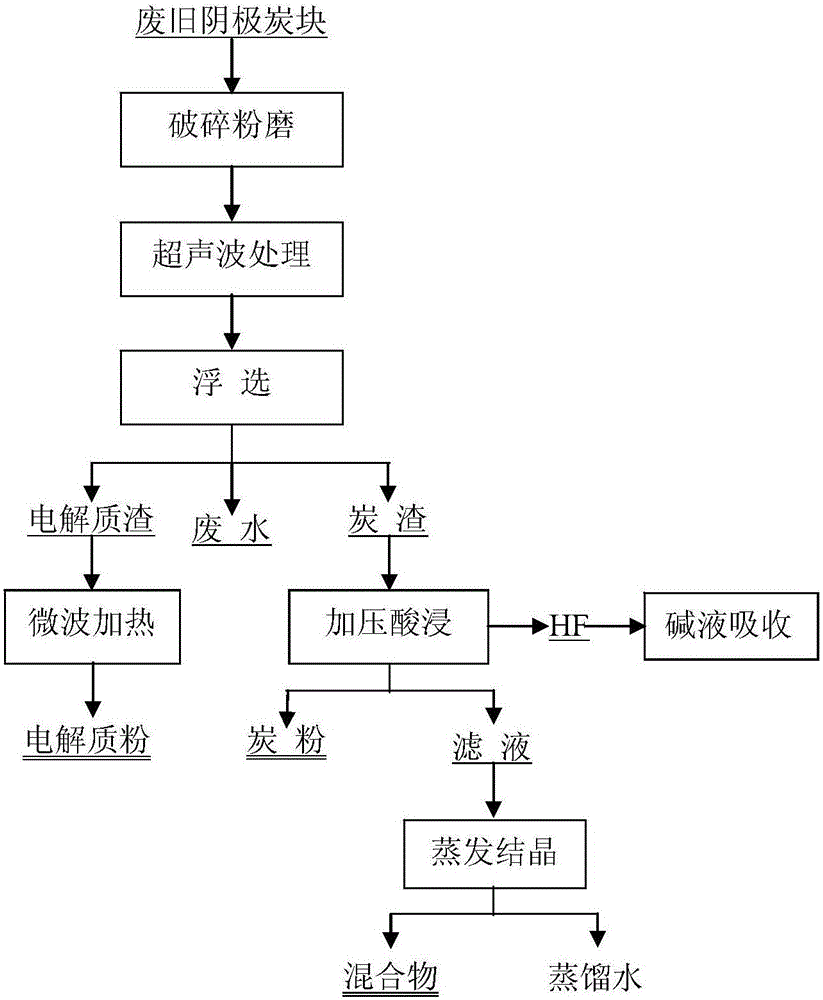

Method for comprehensively recovering aluminum electrolysis waste cathode carbon blocks through ultrasonic-assisted floatation and pressure acid leaching

InactiveCN106077037AEasy to separatePromote stratificationSolid waste disposalAluminiumAluminum electrolysis

The invention relates to a method for comprehensively recovering aluminum electrolysis waste cathode carbon blocks through ultrasonic-assisted floatation and pressure acid leaching, and belongs to the technical field of comprehensive utilization of aluminum electrolysis solid waste resources. The method comprises the steps of carrying out ultrasonic pretreatment after crushing and grinding the aluminum electrolysis waste cathode carbon blocks, carrying out floatation on pretreated powder to obtain electrolyte residues and carbon residues, and reusing the wastewater of floatation; removing carbon impurities after the electrolyte residues are subjected to microwave heating to obtain electrolyte powder with high purity, and carrying out pressure acid leaching on the carbon residues to remove solvend so as to obtain carbon powder with high purity; and carrying out absorption treatment on the gas generated during acid leaching with alkali liquor, carrying out evaporative crystallization on filter liquor to separate out sediment of sodium salt and aluminum salt, and reusing distilled water. According to the method, through collaborative assistance action among ultrasonic pretreatment, floatation, microwave heating and pressure acid leaching, the high-efficiency comprehensive recycling of aluminum electrolysis waste cathodes is achieved. The method for comprehensively recovering aluminum electrolysis waste cathode carbon blocks through ultrasonic-assisted floatation and pressure acid leaching is reasonable in technological design, high in recovery rate of valuable matter, high in processing capacity, short in production cycle, high in purity of obtained products, free of secondary pollutants and applicable to industrial large-scale application.

Owner:CENT SOUTH UNIV

A multiple functional group (methyl) acrylate synthesis and purification method

ActiveCN1733688AImprove density differenceEasy to handleOrganic compound preparationCarboxylic acid esters preparationPurification methodsAdhesive

The invention relates to a process for preparing multifunctional (methyl) acrylate, which can be widely applied in the fields of radiation solidified paint, printing ink, adhesive and polymer modification. The preparation comprises using mixed entrainer, subjecting the crude product to post-treatment and purification. The obtained product has a yield of greater than 95%, a purity above 99%, and a chromaticity (APHA) lower then 20.

Owner:SHANGHAI HUAYI NEW MATERIAL

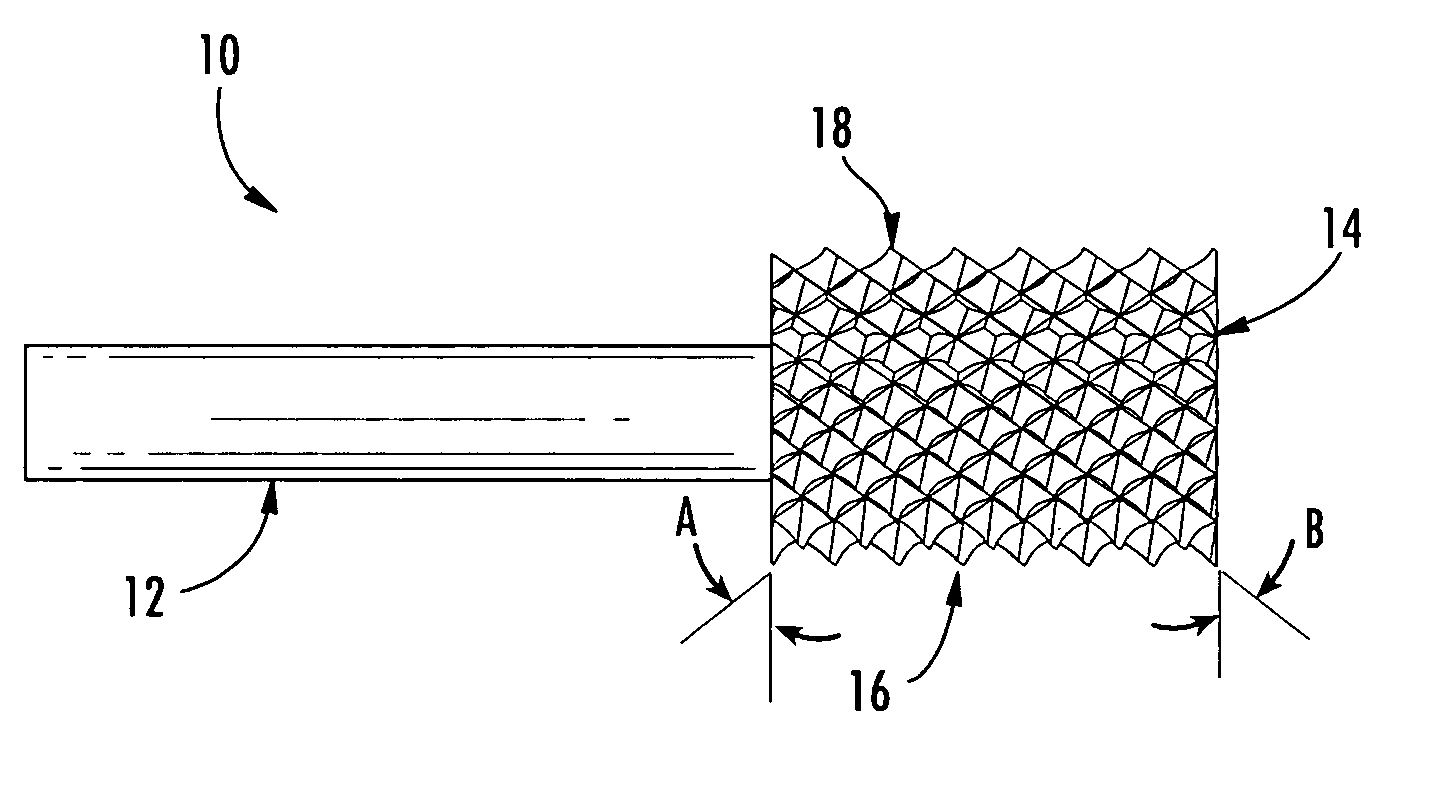

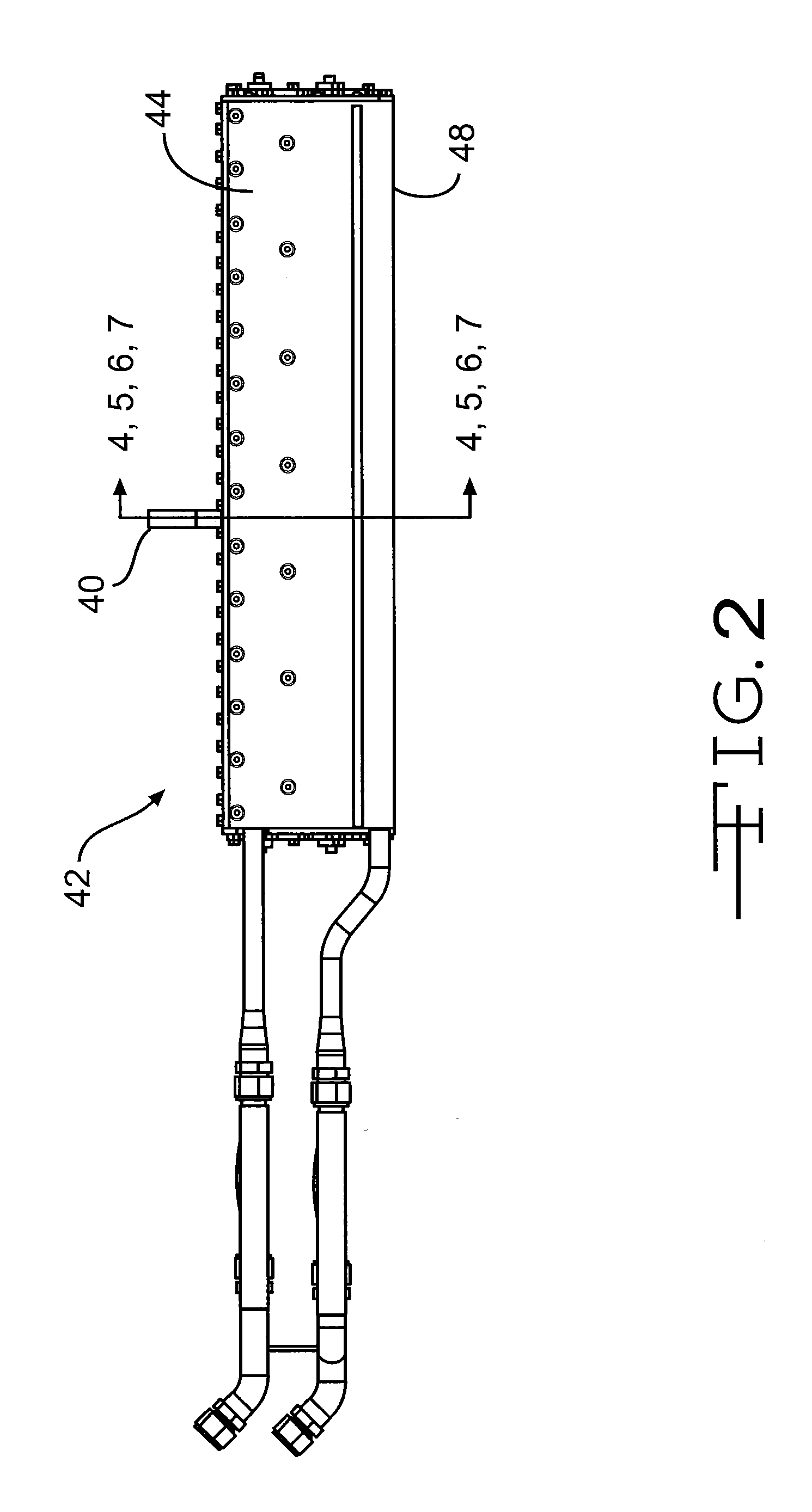

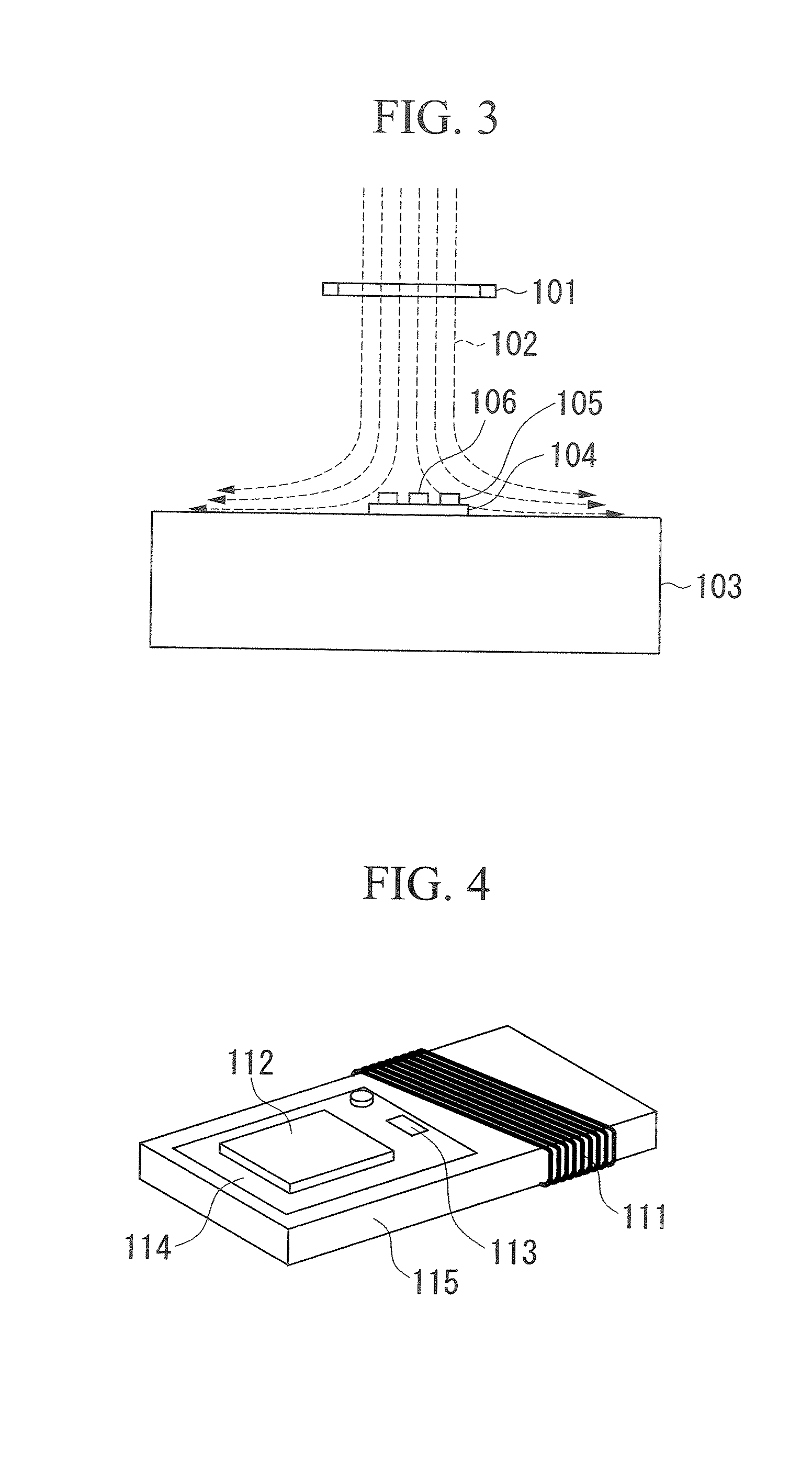

Method of depositing zinc oxide coatings by chemical vapor deposition

InactiveUS20120240634A1Promote stratificationChemical vapor deposition coatingGas phaseChemical vapor deposition

A chemical vapor deposition process for depositing zinc oxide coatings is provided. The process includes providing a glass substrate and a coating apparatus. The coating apparatus includes two or more separate flow pathways. Each flow pathway provides communication between an inlet opening and an outlet opening, and one or more flow conditioners disposed in each of the flow pathways. Gaseous precursor compounds are provided. The gaseous precursor compounds and the one or more inert gases are introduced as two or more streams into the inlet openings. The streams are directed through the two or more separate flow pathways and discharged from the outlet openings of the coating apparatus. The gaseous precursor compounds and one or more inert gases mix to form a zinc oxide coating on a surface of the glass substrate.

Owner:PILKINGTON GROUP LTD

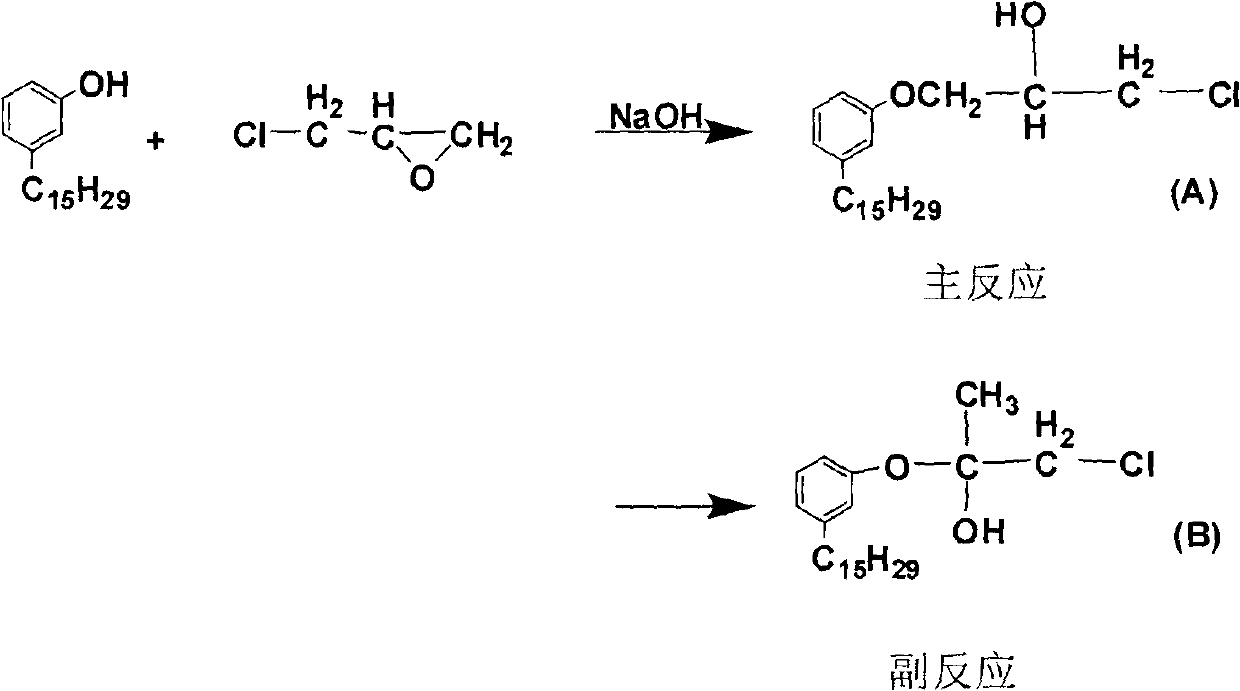

Preparation method of anacardol glycidol ether

The invention provides a preparation method of anacardol glycidol ether. The method comprises the following steps of: weighing substances including anacardol, epoxy chloropropane and sodium hydrate in the molar ratio of 1:(0.8-1.2):(0.7-1.2); adding the anacardol into a reaction container; stirring; introducing nitrogen gas and exhausting air; adding epoxy chloropropane 1-5 minutes later; continually stirring; controlling the temperature at 40-50 DEG C; adding sodium hydrate; dropwise adding, and raising the temperature to 70-100 DEG C; preserving heat for 4-9 hours; standing, settling and discharging; and centrifugally filtering to obtain a first batch of light color clarified transparent product serving as anacardol glycidol ether. According to the preparation method, the ratio of the epoxy chloropropane is lowered, and the color of an epoxy active diluent synthesized by using anacardol is lightened greatly. Meanwhile, delamination is quick, and operation is easier.

Owner:上海美东生物材料股份有限公司

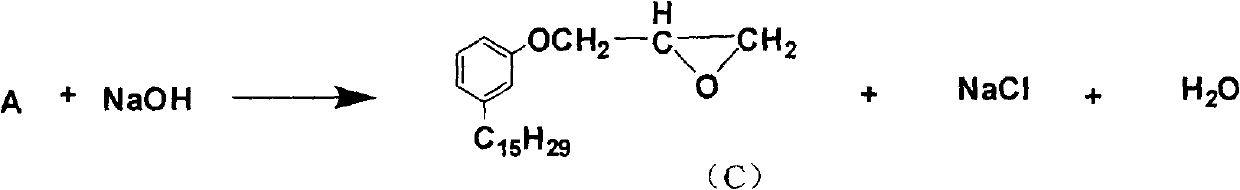

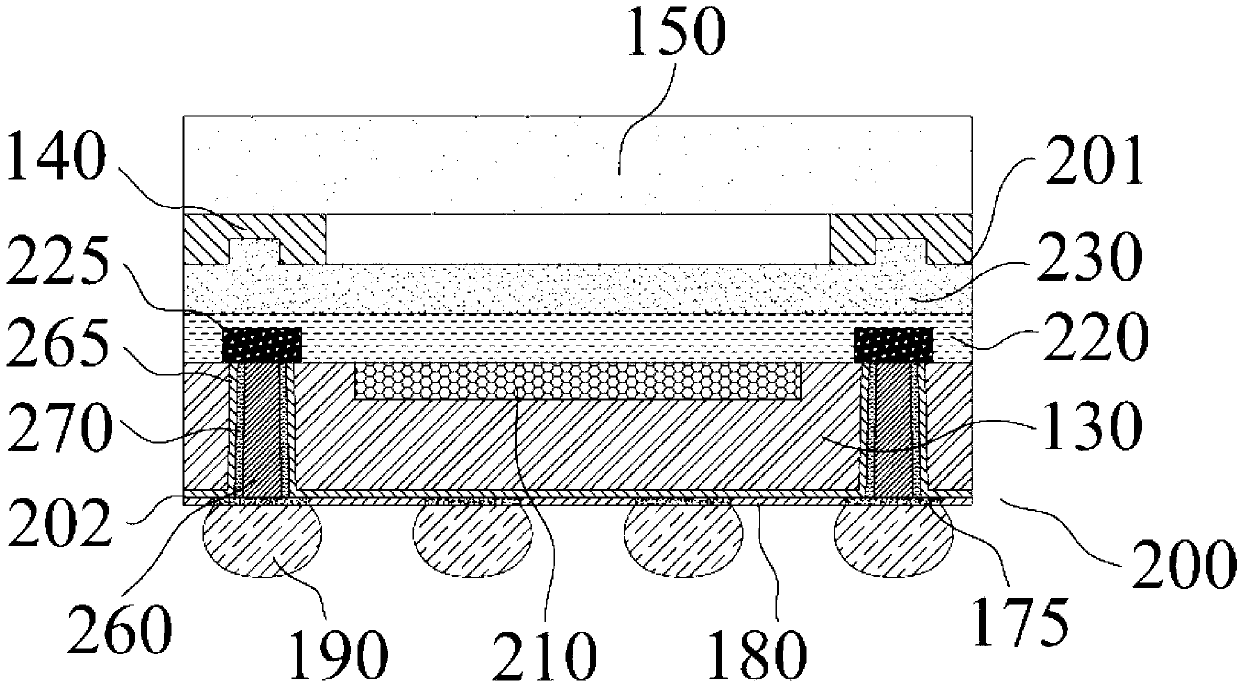

Large chip scale package and manufacturing method thereof

InactiveCN103000648AImprove bond strengthImprove layeringRadiation controlled devicesEngineeringInput/output

The invention provides large chip scale package and a manufacturing method thereof and belongs to the technical field of sensors. An optical interaction region is arranged at the center above a silicon substrate in a first surface of a wafer, one side provided with the optical interaction region is connected with a metal interconnection structure, and an input-output (I / O) around the optical interaction region on the silicon substrate is connected to an electrode pad through the metal interconnection structure. The surface of the metal interconnection structure is provided with a protective layer, and a stepped protrusion or groove structure is formed on the protective layer. The first surface of the wafer is bonded with a glass piece together, and a cavity is formed between the glass piece and the wafer. A second surface of the wafer is provided with a through silicon via (TSV) hole, the electrode pad penetrates through the silicon substrate through the TSV hole to be connected to a bonding pad on the second surface of the wafer, a passivation layer and a metal liner are sequentially manufactured on a hole wall of the TSV hole, and a polymer material is filled into the TSV hole. An anti-welding layer is manufactured on the second surface of the wafer, and a weld ball is manufactured on the bonding pad. By means of the large chip scale package and the manufacturing method, the layering problem of glass and the silicon substrate in an existing package structure is solved, and the packing reliability is improved.

Owner:BEIJING UNIV OF TECH

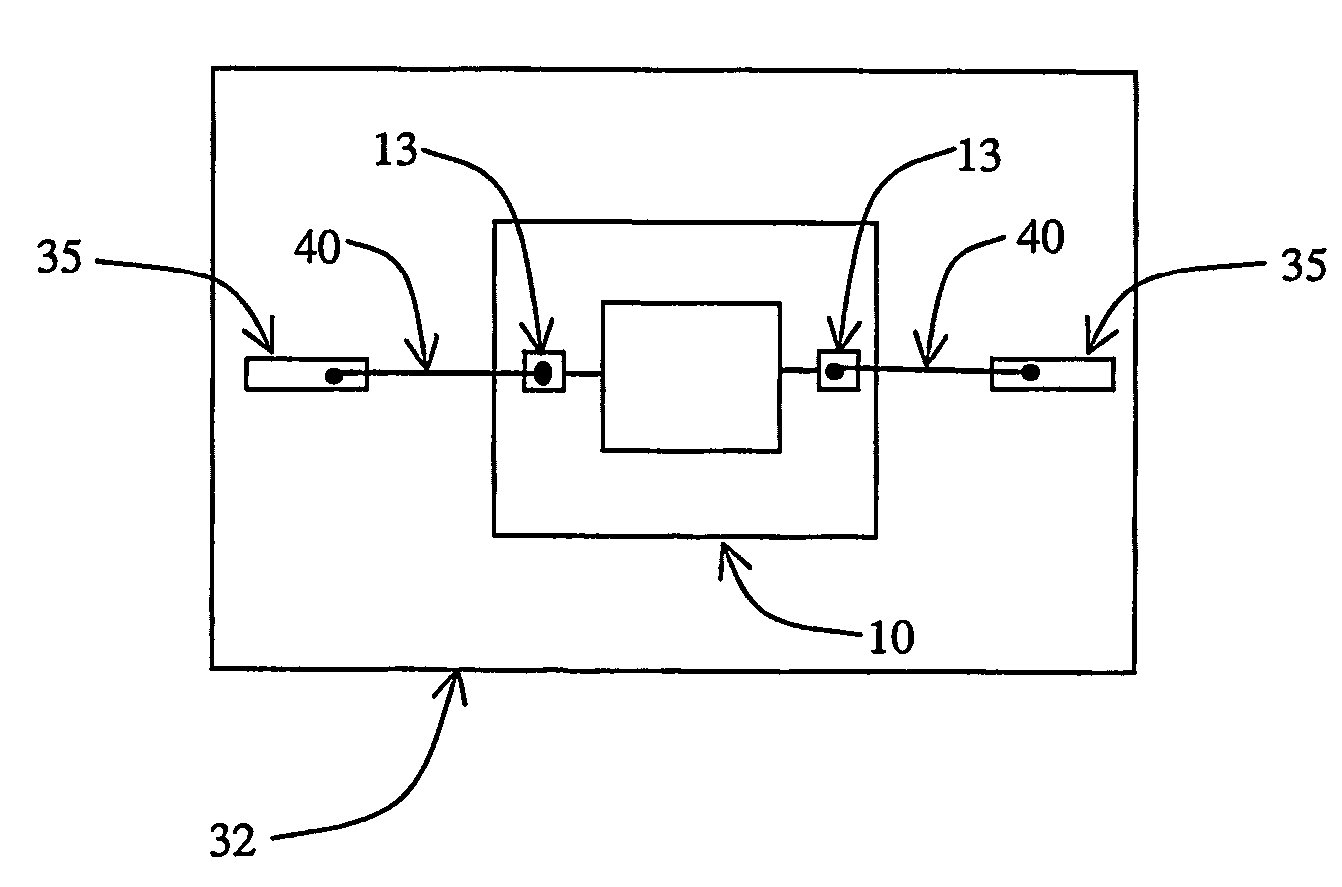

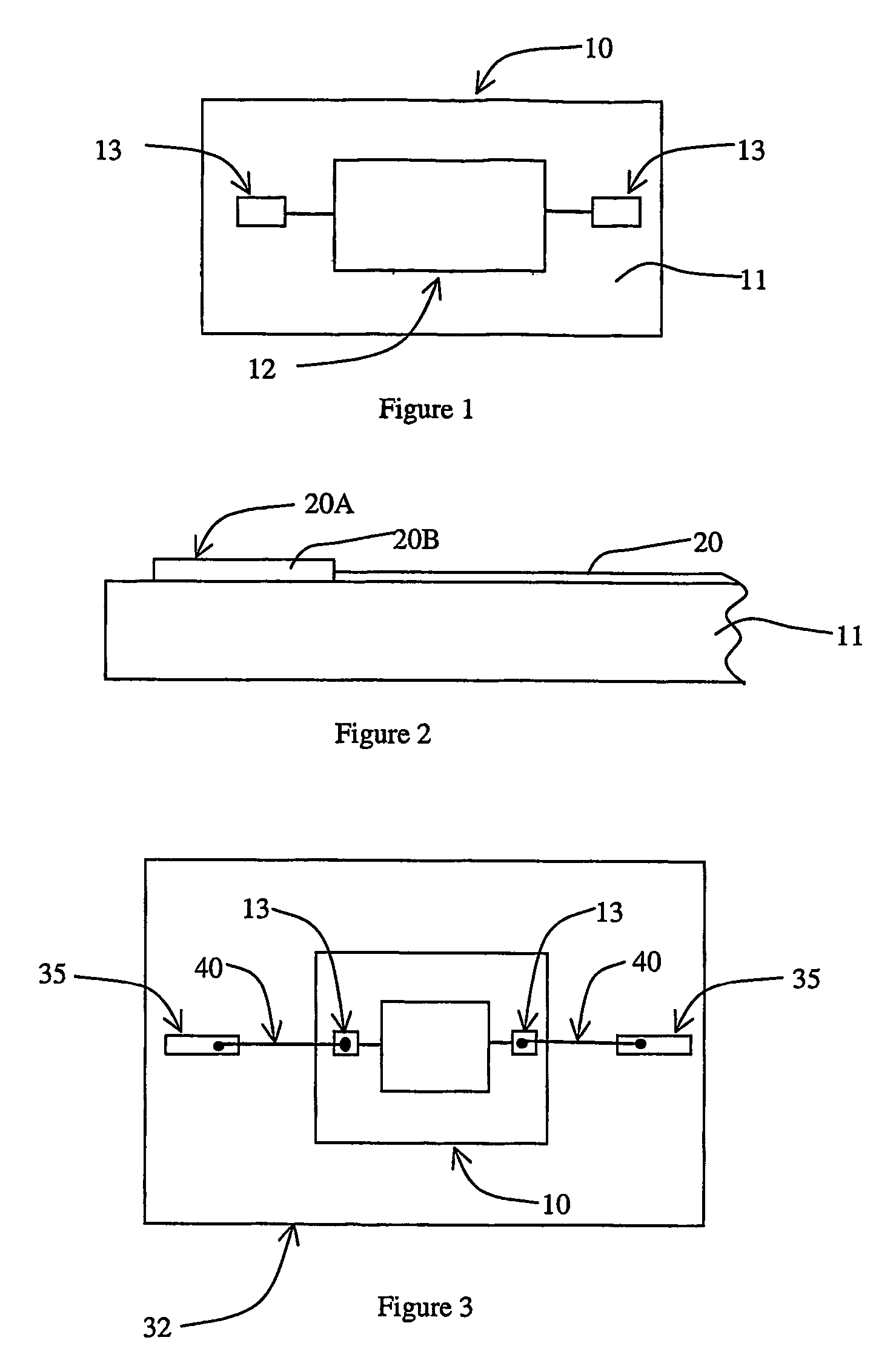

Noncontact Data Receiver/Transmiter

InactiveUS20080191028A1Promote generationLarge magnetic permeabilityTransformersInorganic material magnetismContact typeMicroparticle

A non-contact type data reception and transmission body has an inlet having a base substrate, and an antenna and an integrated circuit chip which are provided on one side surface of the base substrate, and connected to each other, and a magnetic substrate layer disposed so that the magnetic substrate layer covers at least one of the antenna and the integrated circuit chip which constitute the inlet, wherein the magnetic substrate layer has a main component of a resin including a filler made of magnetic microparticles.

Owner:TOPPAN MOORE CO LTD +1

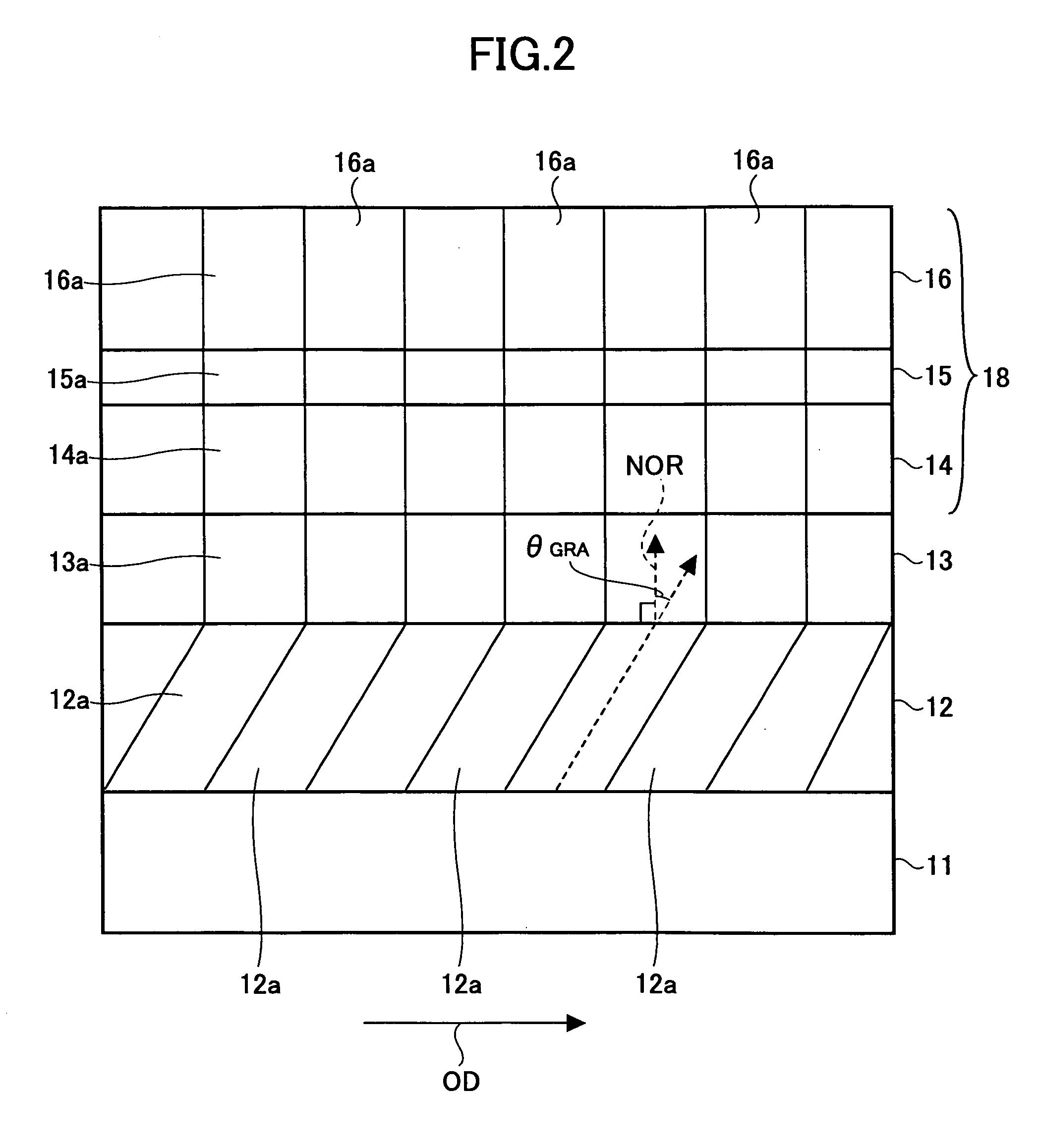

Magnetic recording medium, method of producing magnetic recording medium and magnetic storage apparatus

InactiveUS20050276998A1Promote stratificationIncrease magnetic densityBase layers for recording layersRecord information storageCrystalliteMagnetic storage

A magnetic recording medium has a seed layer provided on a substrate surface, an underlayer provided on the underlayer, and a recording layer provided on the underlayer. Information is recorded in the recording layer by magnetizing the recording layer in a recording direction. The seed layer is formed by a polycrystal of crystal grains made of an alloy material having a B2 crystal structure, and a [100] crystal orientation of the crystal grains are inclined towards one of two sides partitioned by a plane that is formed by the recording direction and a substrate normal which is normal to the substrate surface.

Owner:FUJITSU LTD

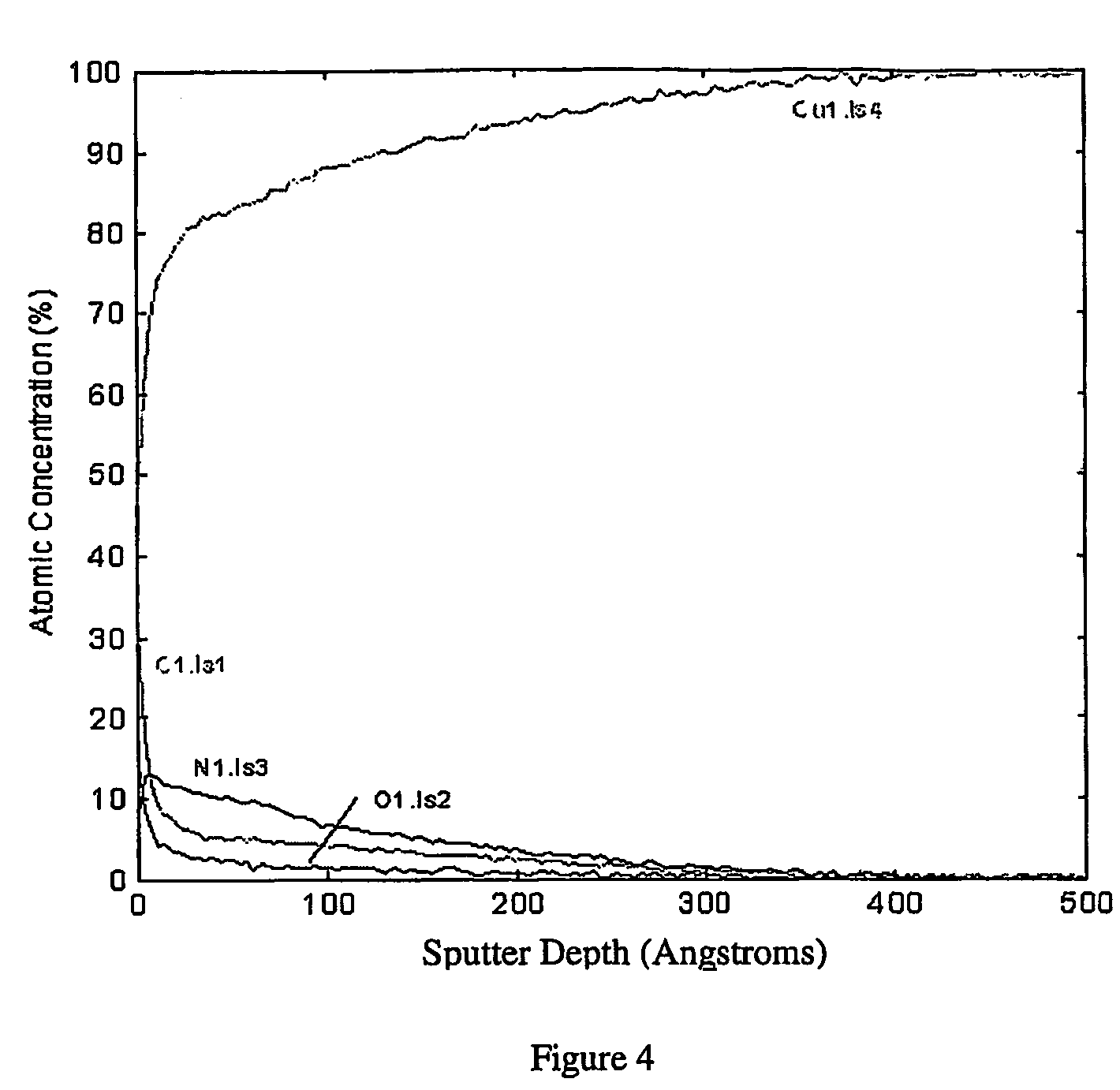

Electrical interconnect structures for integrated circuits and methods of manufacturing the same

InactiveUS7294217B2Effective of materialEfficient oxidationContact member manufacturingSemiconductor/solid-state device detailsConductive materialsCopper

Disclosed are interconnect structures and methods which utilize a bonding surface comprising copper nitride. The interconnect structures include a bonding surface comprising copper nitride which is effective at preventing oxidation and / or other unwanted corrosion of the underlying conductive material while providing the basis for a high conductivity bond. The copper nitride bonding surface provides a relatively non-conductive, corrosion-resistant bonding surface while at the same time being readily transformed into a conductive layer at or just prior to the time of bonding.

Owner:KULICKE & SOFFA IND INC

Low shear impeller

ActiveUS7172337B2Promote stratificationImprove mixing efficiencyFlow mixersRotary stirring mixersImpellerDrive shaft

Owner:PHILADELPHIA GEAR

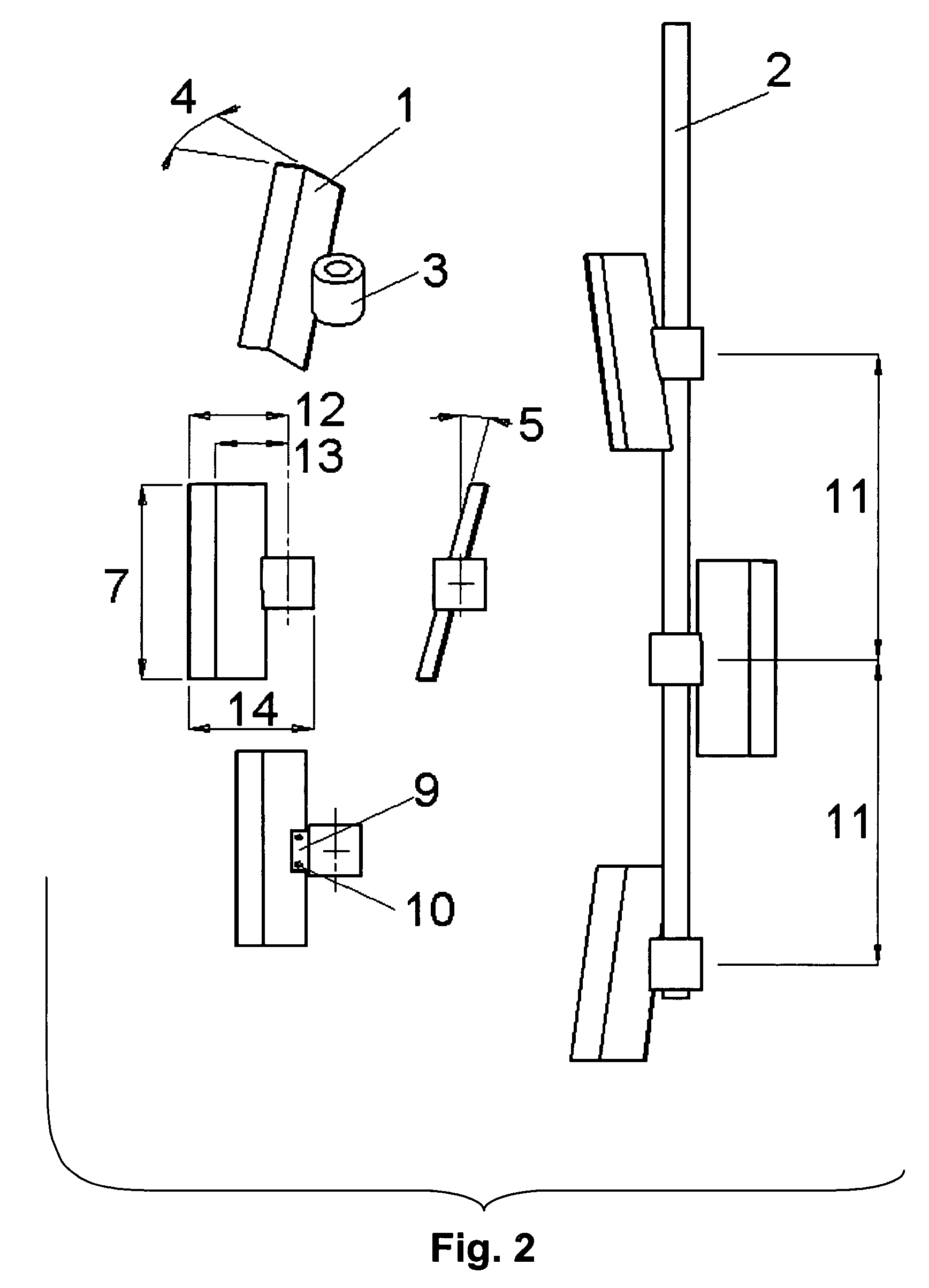

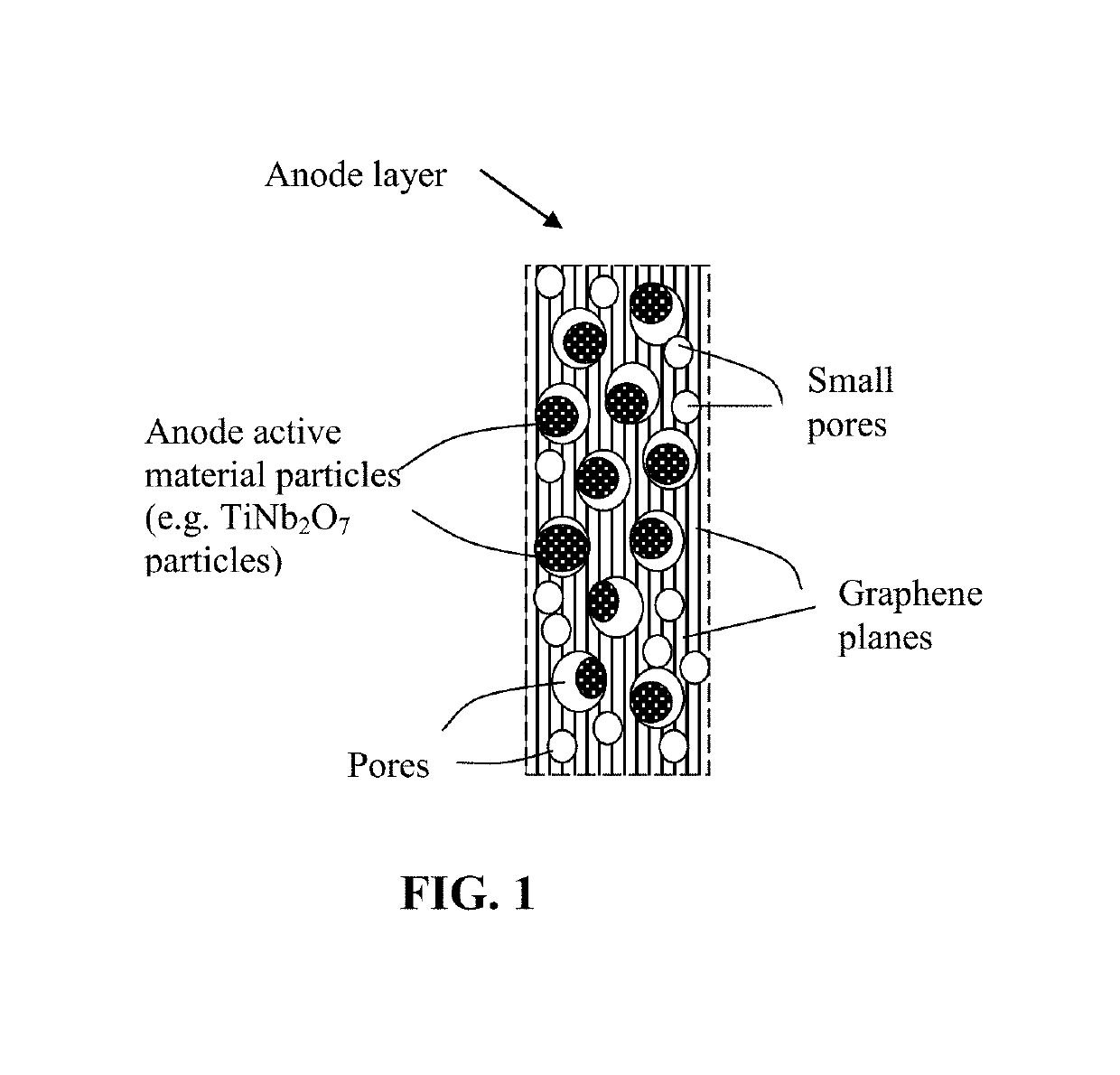

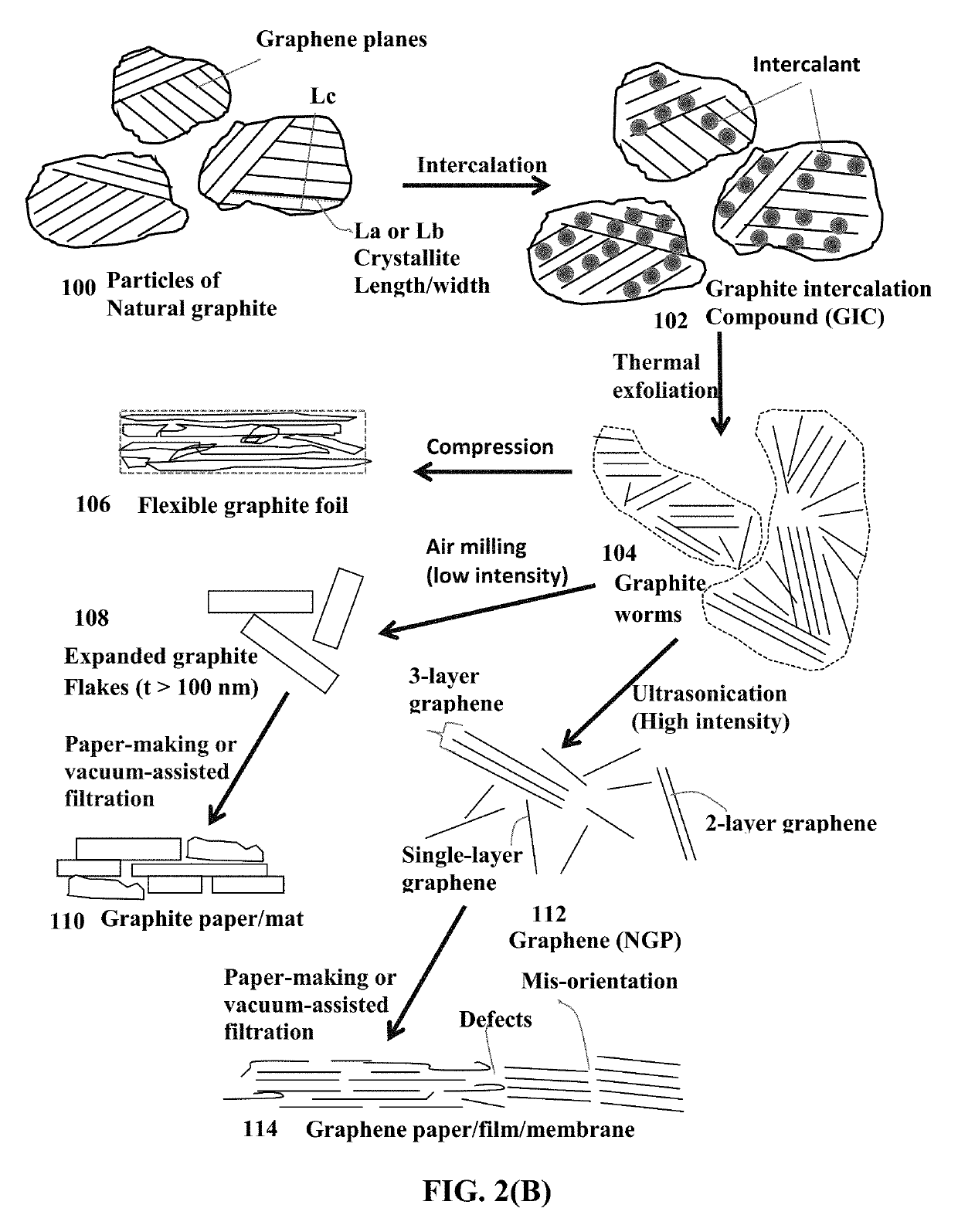

Graphene Foam-Protected Niobium-Based Composite Metal Oxide Anode Active Materials for Lithium Batteries

PendingUS20190165363A1High conductivityLarge electrode thicknessMolybdeum compoundsSingle layer grapheneSpecific gravityGraphene foam

A lithium-ion battery anode layer, comprising an anode active material embedded in pores of a solid graphene foam composed of multiple pores and pore walls, wherein (a) the pore walls contain a pristine graphene or a non-pristine graphene material; (b) the anode active material contains particles of a niobium-containing composite metal oxide and is in an amount from 0.5% to 99% by weight based on the total weight of the graphene foam and the anode active material combined, and (c) the multiple pores are lodged with particles of the anode active material. Preferably, the solid graphene foam has a density from 0.01 to 1.7 g / cm3, a specific surface area from 50 to 2,000 m2 / g, a thermal conductivity of at least 100 W / mK per unit of specific gravity, and / or an electrical conductivity no less than 1,000 S / cm per unit of specific gravity.

Owner:GLOBAL GRAPHENE GRP INC

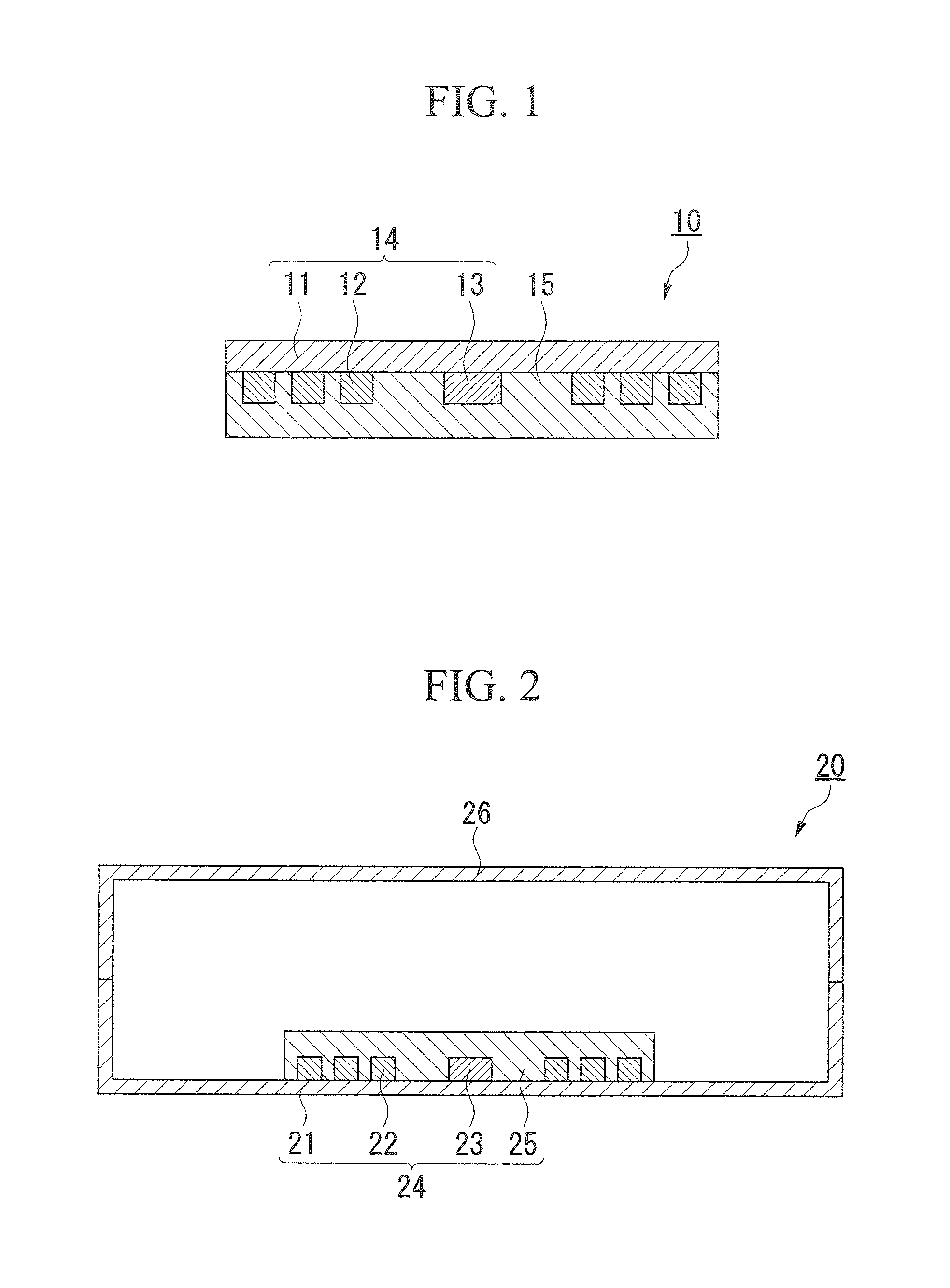

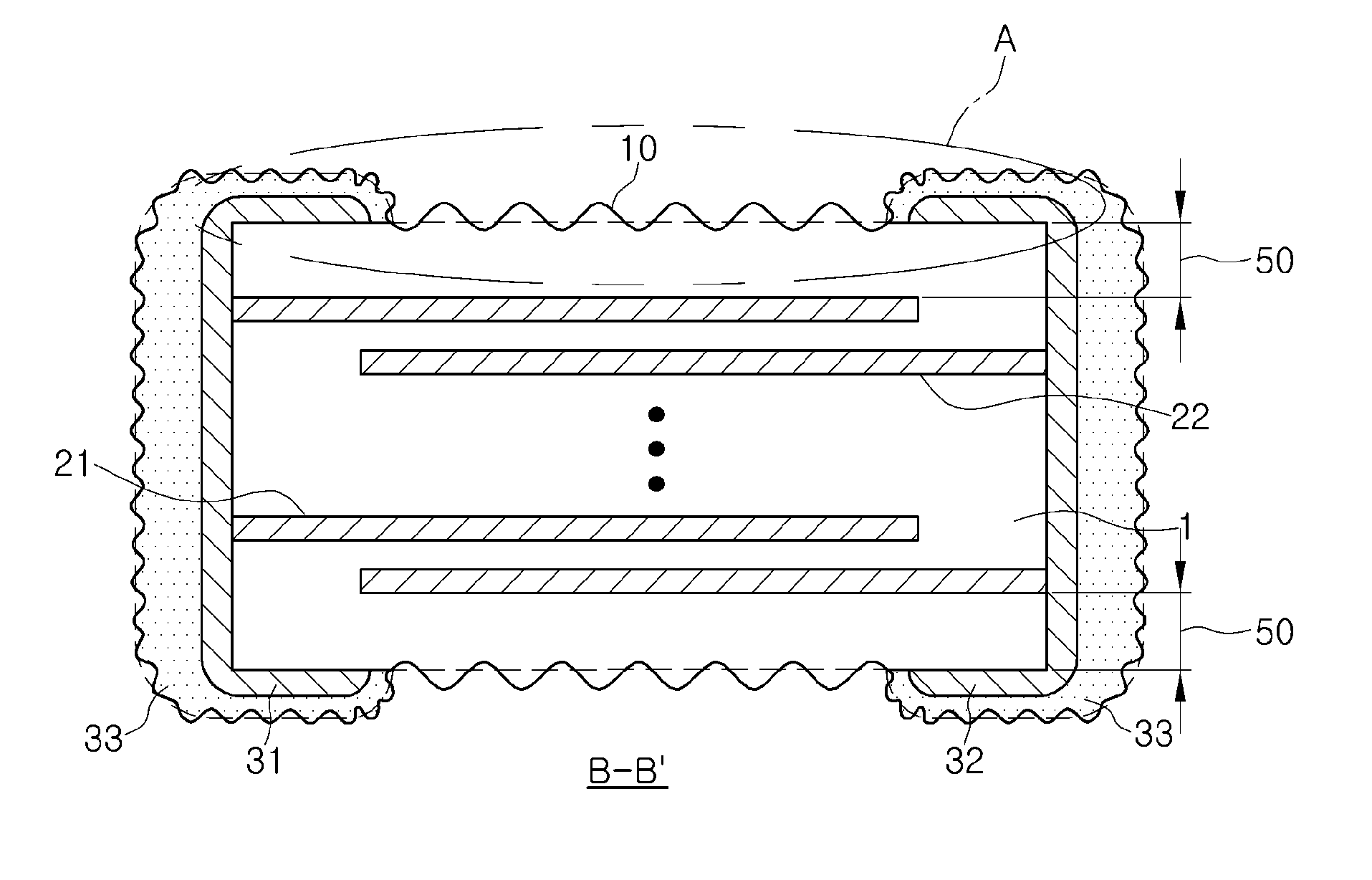

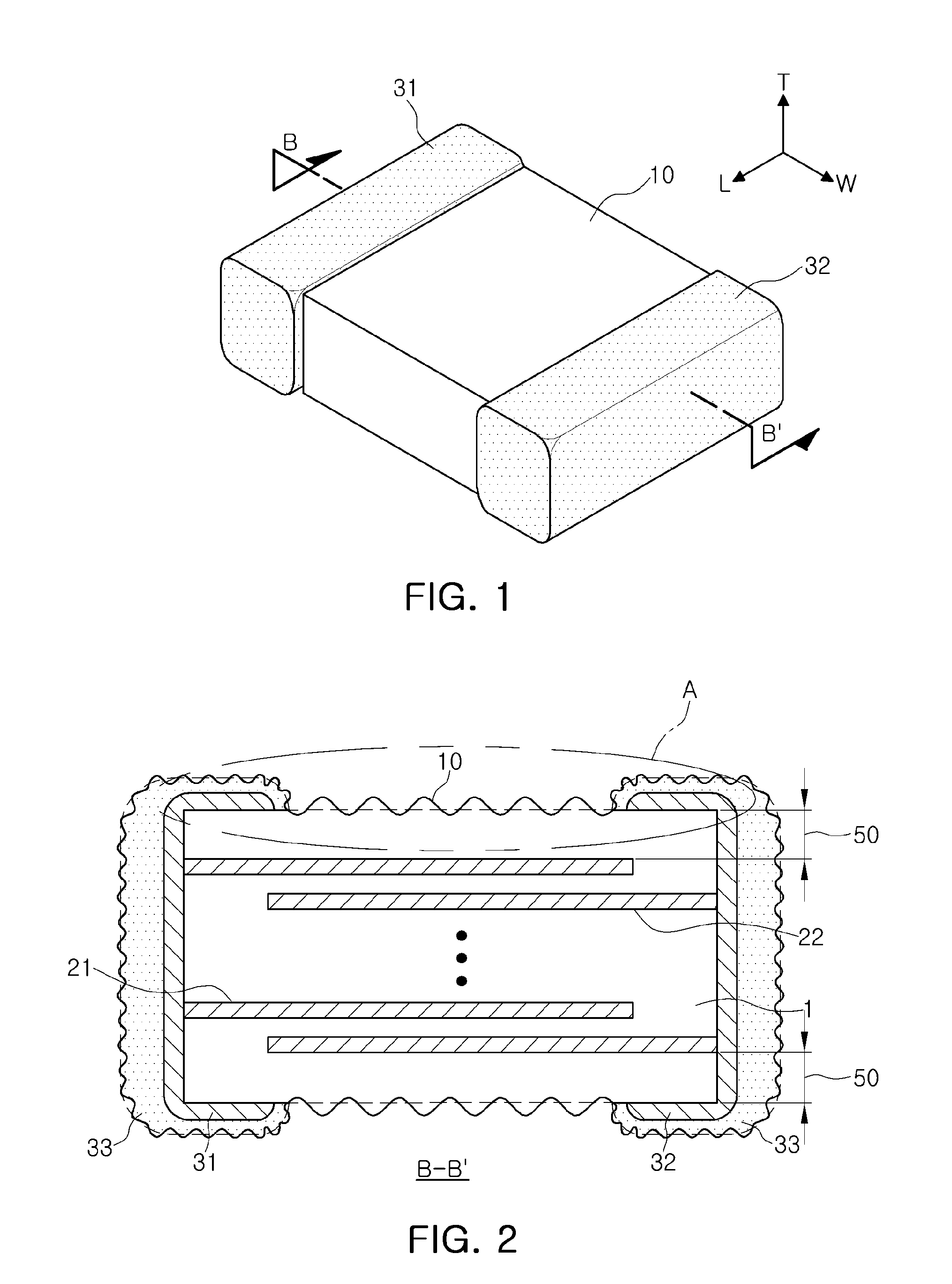

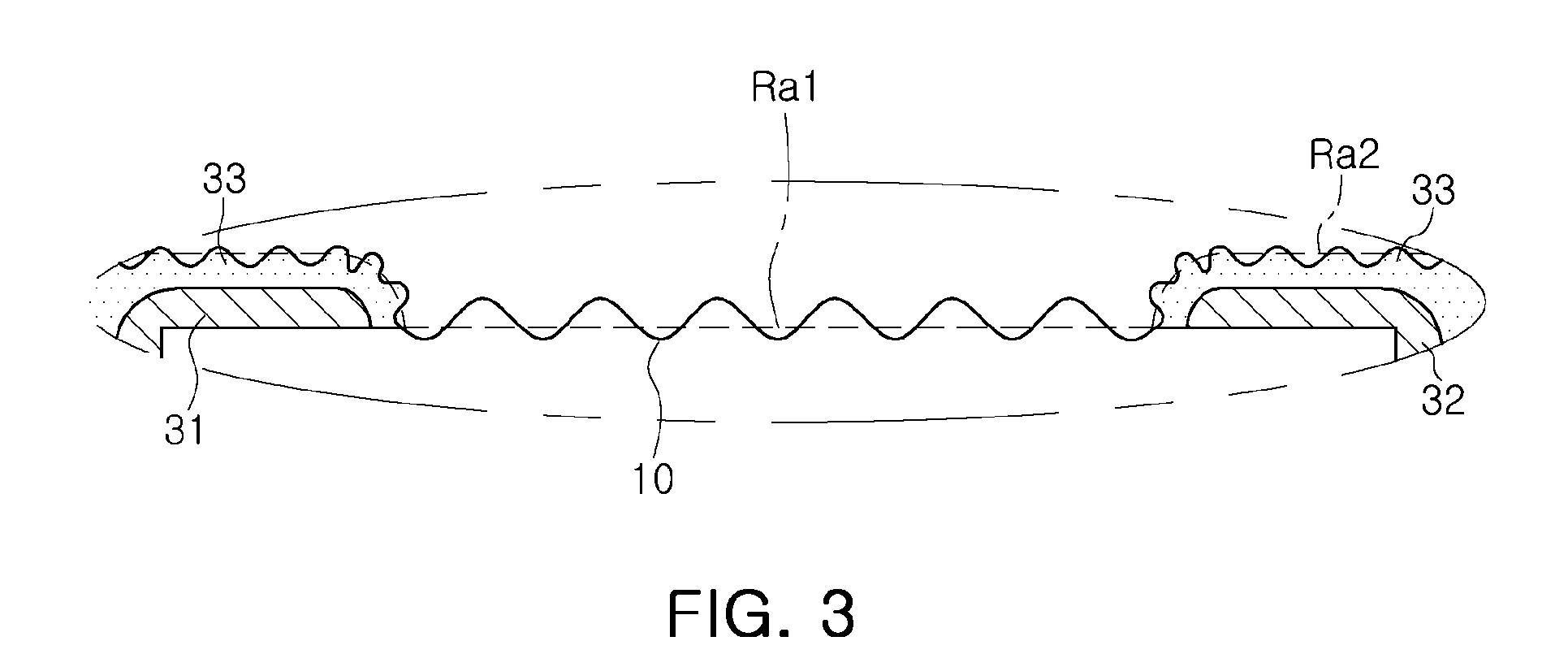

Embedded multilayer ceramic electronic component and method of manufacturing the same, and printed circuit board having embedded multilayer ceramic electronic component therein

InactiveUS20140151101A1Promote stratificationImprove featuresFinal product manufacturePrinted electric component incorporationMetallurgySurface roughness

There is provided an embedded multilayer ceramic electronic component, including: a ceramic body including dielectric layers; first and second internal electrodes facing each other with the dielectric layers interposed therebetween; a first external electrode and a second external electrode formed on external surfaces of the ceramic body, the first external electrode being electrically connected to the first internal electrodes and the second external electrode being electrically connected to the second internal electrodes; and a plating layer formed on the first external electrode and the second external electrode, wherein a surface roughness of the ceramic body is 500 nm or greater and not greater than a thickness of a ceramic cover sheet and a surface roughness of the plating layer is 300 nm or greater and not greater than a thickness of the plating layer.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

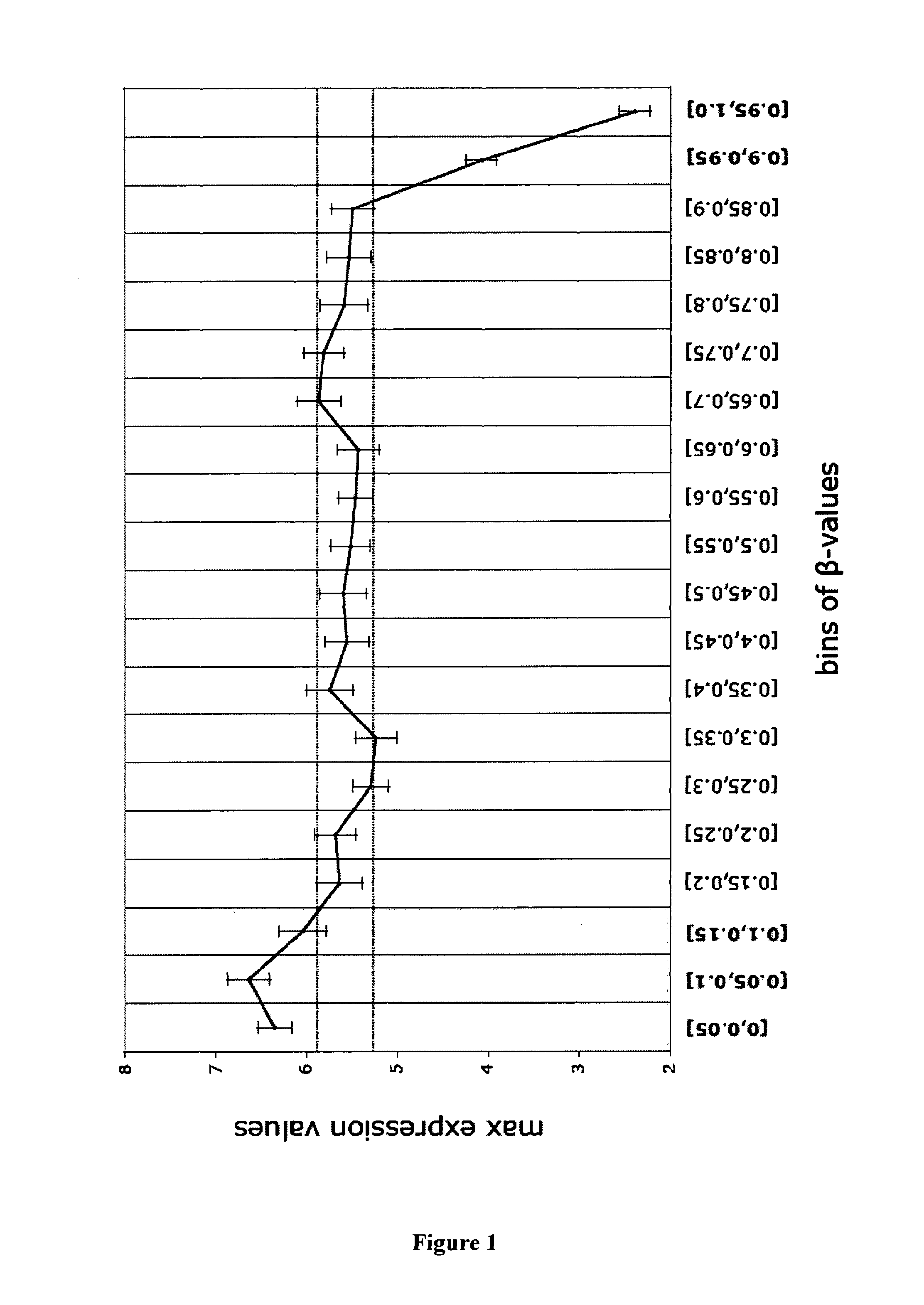

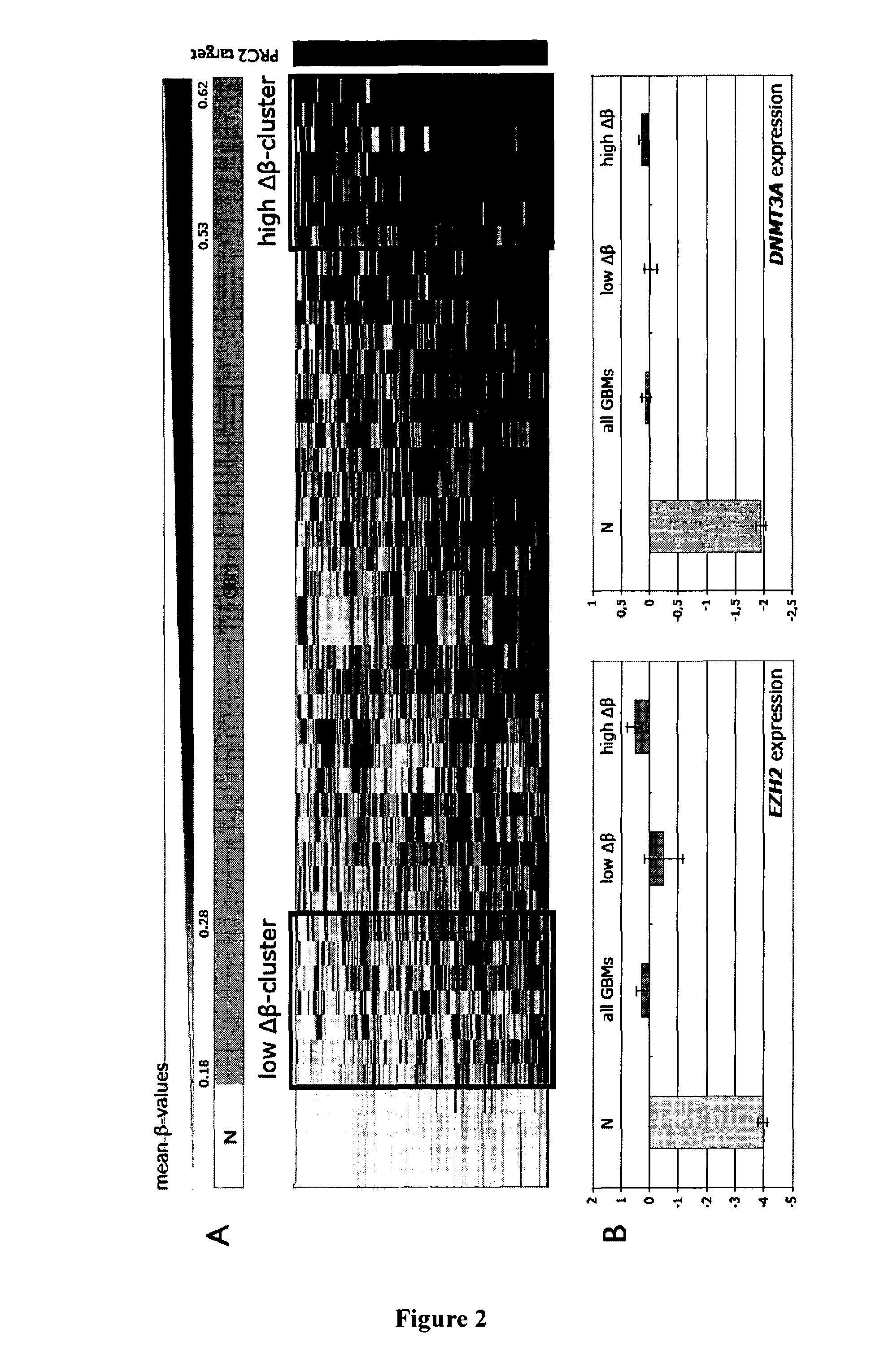

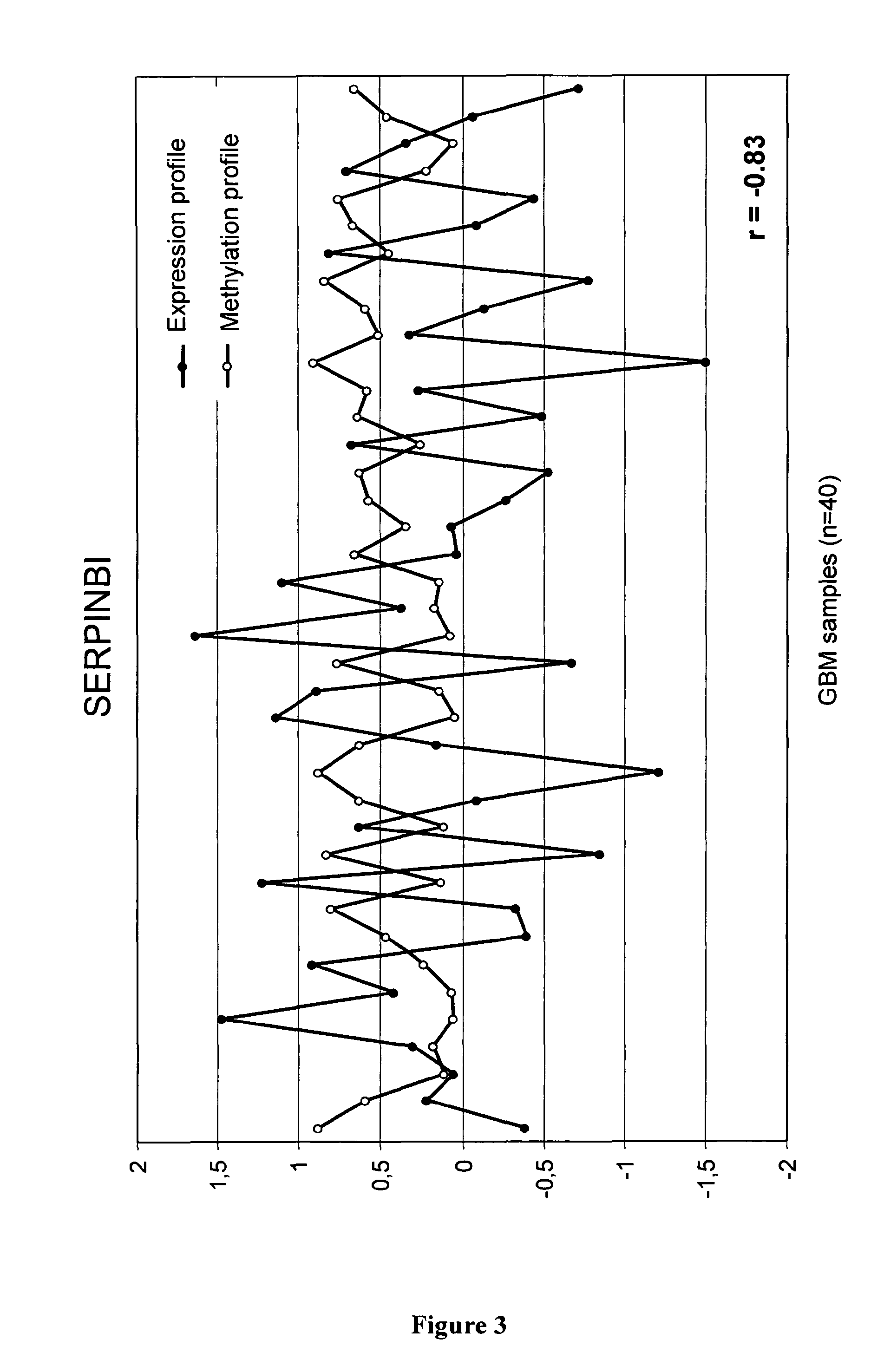

Biomarkers and methods for the prognosis of glioblastoma

InactiveUS20140011702A1Improve conventional MGMT stratificationPromote stratificationMicrobiological testing/measurementLibrary screeningGlioblastomaTreatment response

The present invention relates to gene promoters whose methylation status correlates with the clinical survival outcome of glioblastoma patients treated according to the Stupp protocol. More specifically, the invention provides methods and kits for the prognosis of survival outcome and / or treatment response in glioblastoma patients.

Owner:CENT HOSPITALER UNIV PONTCHAILLOU