Patents

Literature

151results about How to "Reduce the effect of jitter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

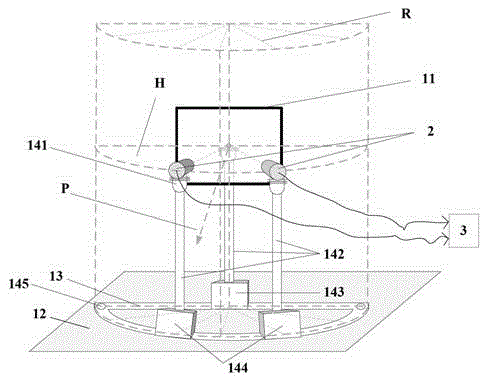

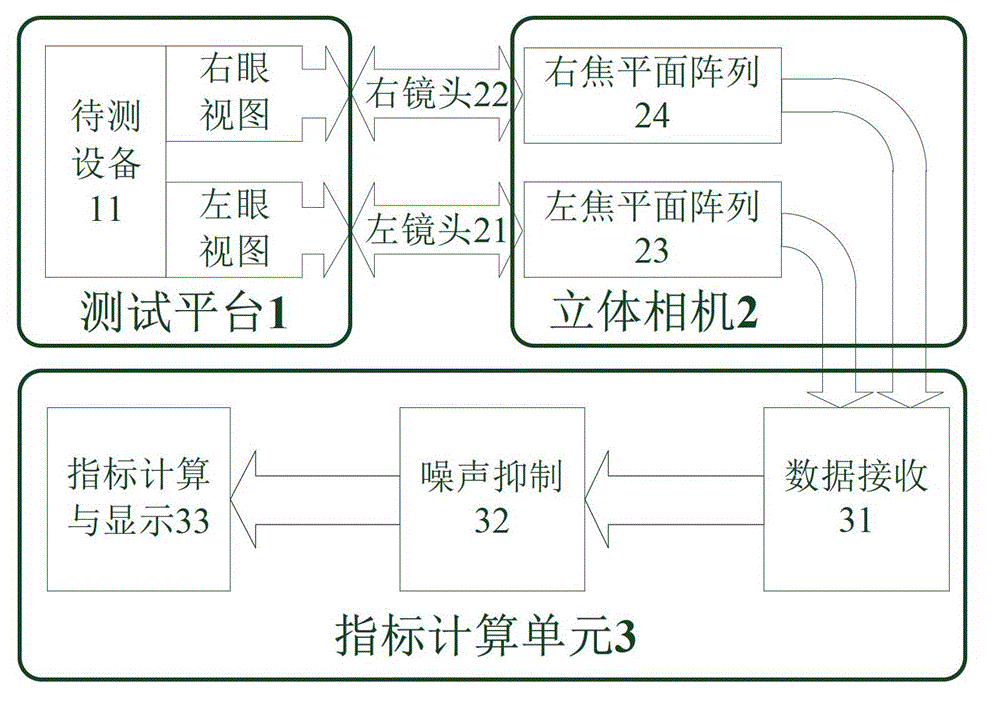

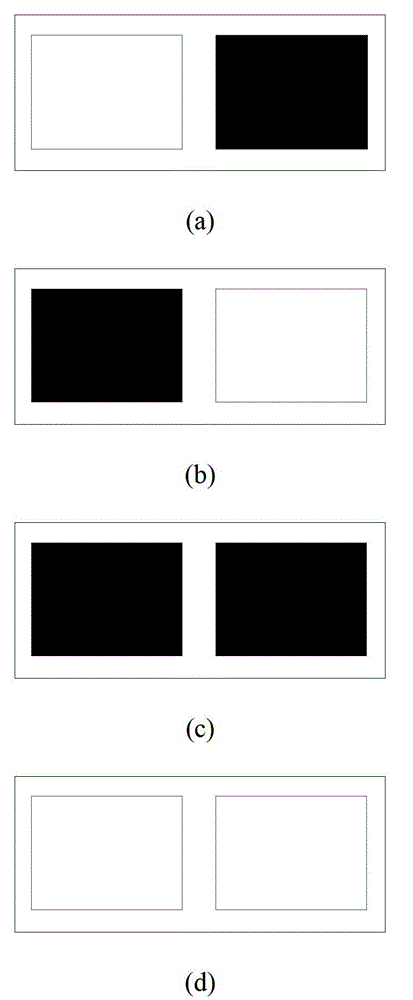

Method and system for testing performance indexes of naked-eye 3D (three dimension) display equipment

InactiveCN102724545AStandardize product qualityAvoid harmStatic indicating devicesTelevision systemsDesign objectiveDisplay device

The invention discloses a method and a system for testing performance indexes of naked-eye 3D (three dimension) display equipment. The method and the system mainly solve the problem that the existing testing technology can be only used for timesharing equipment and light splitting equipment, can only evaluate performances by depending on local information, and is failed to test performances of the naked-eye 3D display equipment. The technical scheme for realizing the method and the system includes designing objective evaluation indexes characterizing the performances of the 3D display equipment and measuring methods for the objective evaluation indexes according to the features of a human vision system for sensing dimensional images; computing to obtain seven indexes of the display performances of the naked-eye 3D display equipment by means of images acquired by a stereo camera, namely the left-passage luminance crosstalk level CTL, the right-passage luminance crosstalk level CTR, the left-passage luminance contrast ratio CL, the right-passage luminance contrast ratio CR, the luminance difference value dL, the luminance contrast difference value dC and the moir strength index dM, and testing the performances of the naked-eye 3D display equipment according to the above indexes. The method and the system for testing performance indexes of the naked-eye 3D display equipment can be used for quality checking and classification of the naked-eye 3D display equipment and guarantees that quality of the naked-eye 3D display equipment sold in the market can meet the standard.

Owner:XIDIAN UNIV

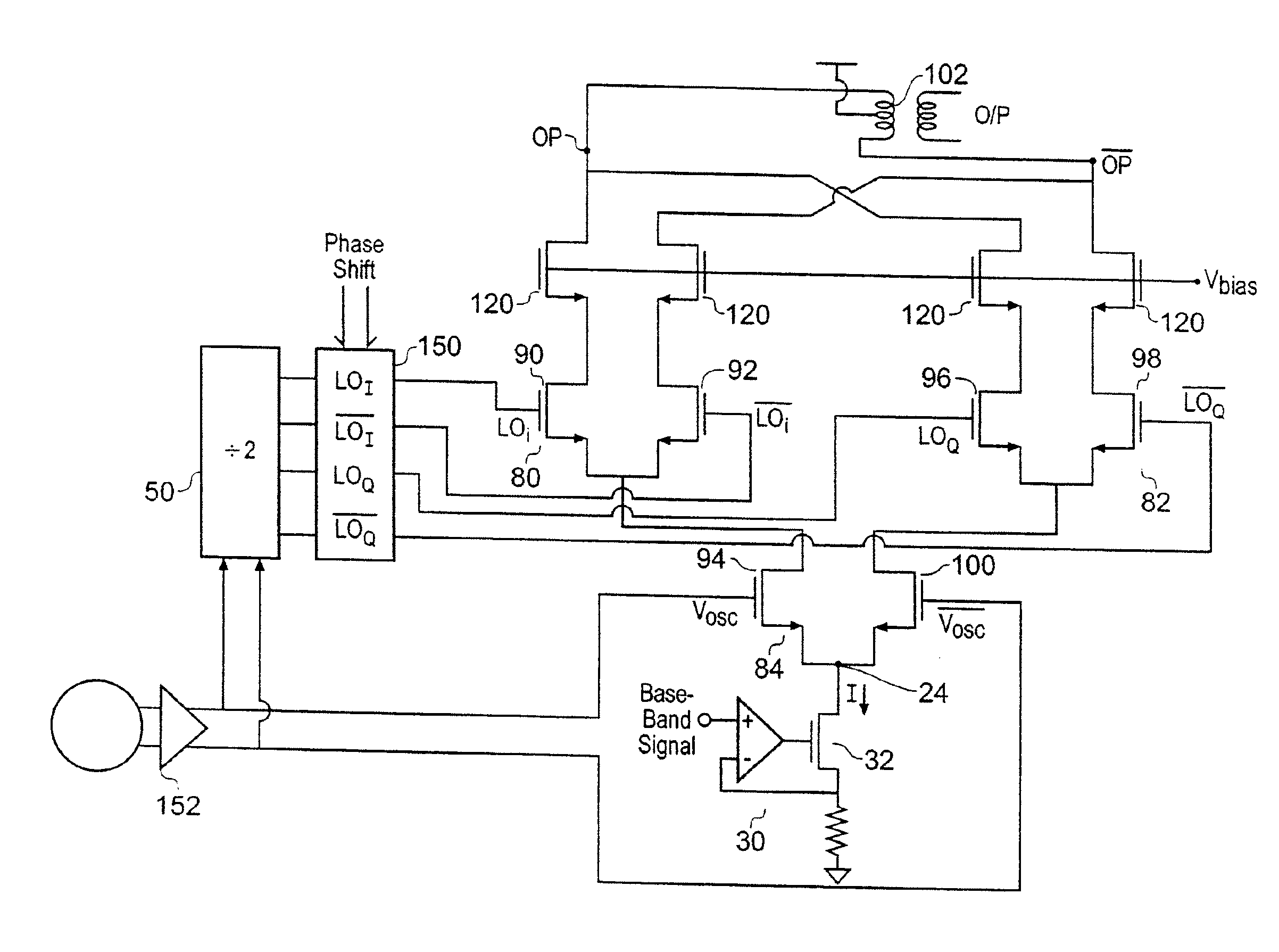

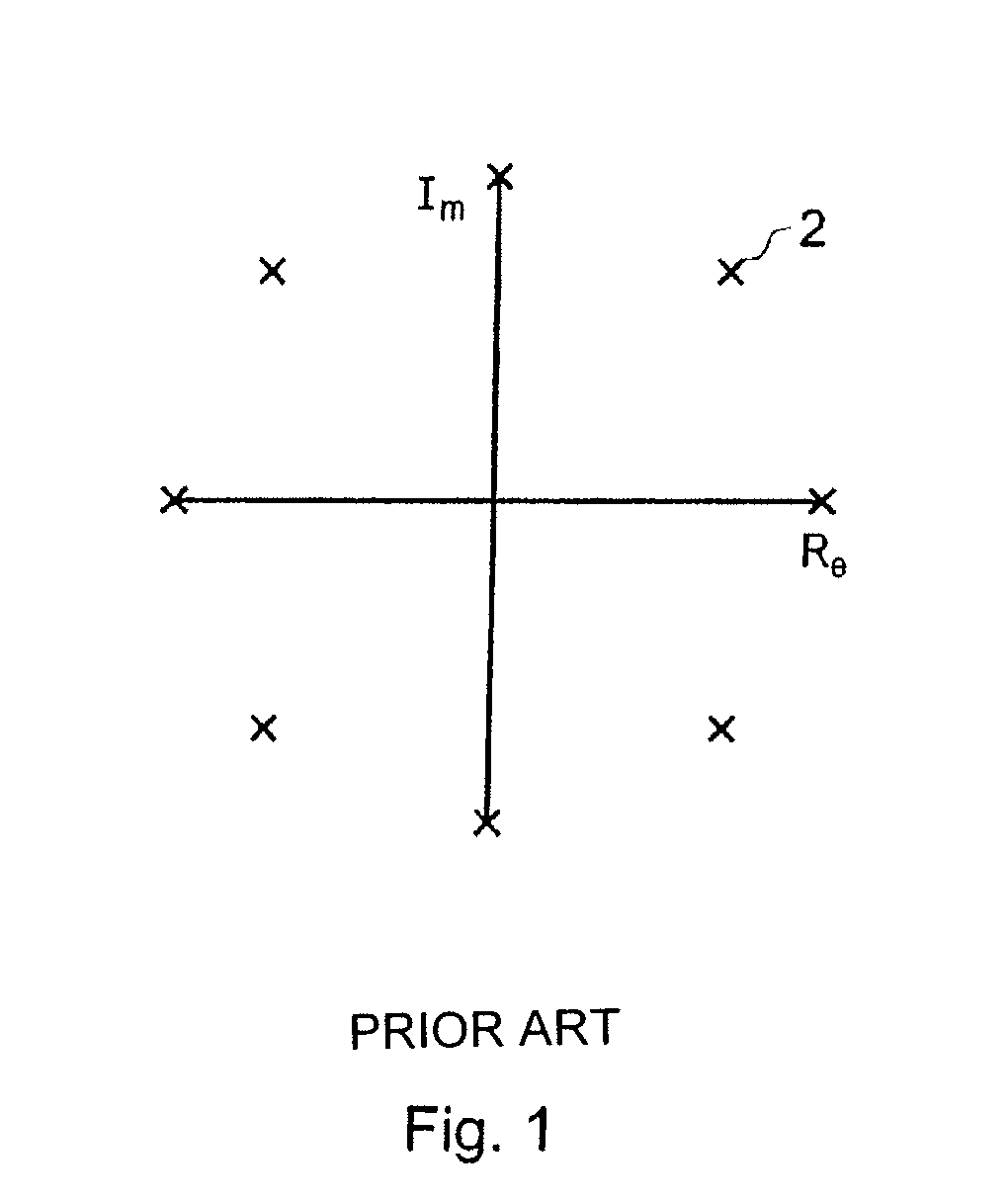

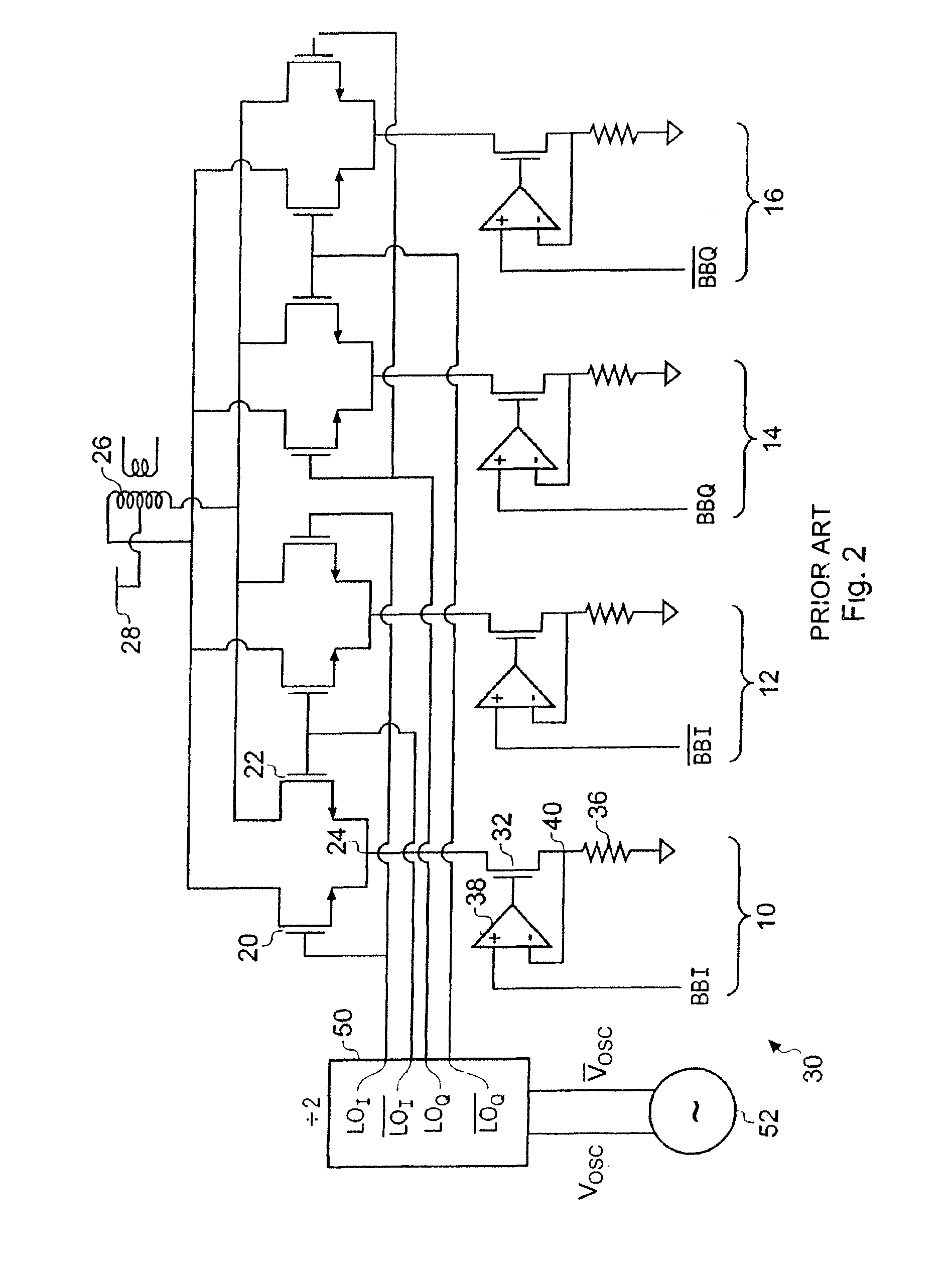

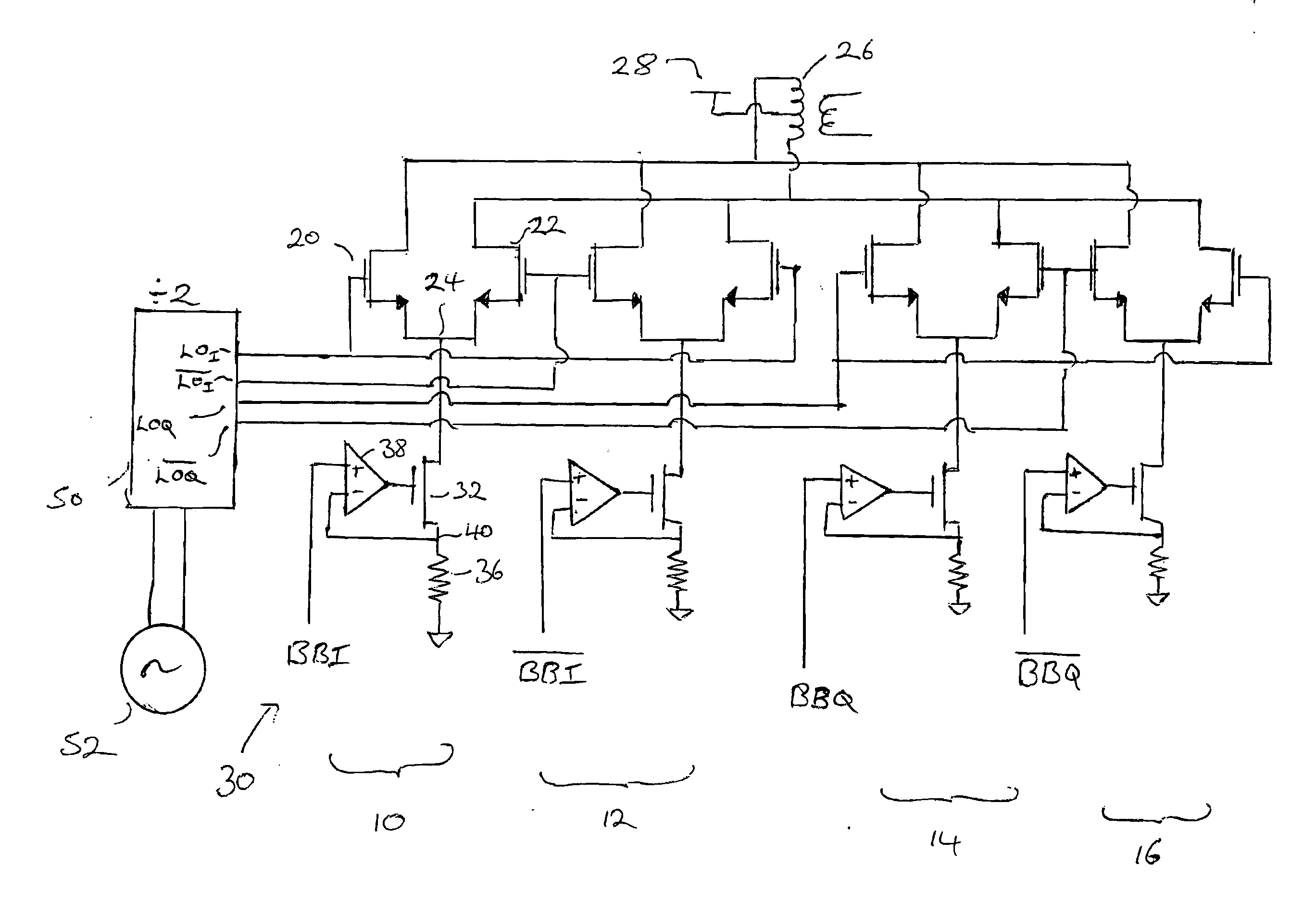

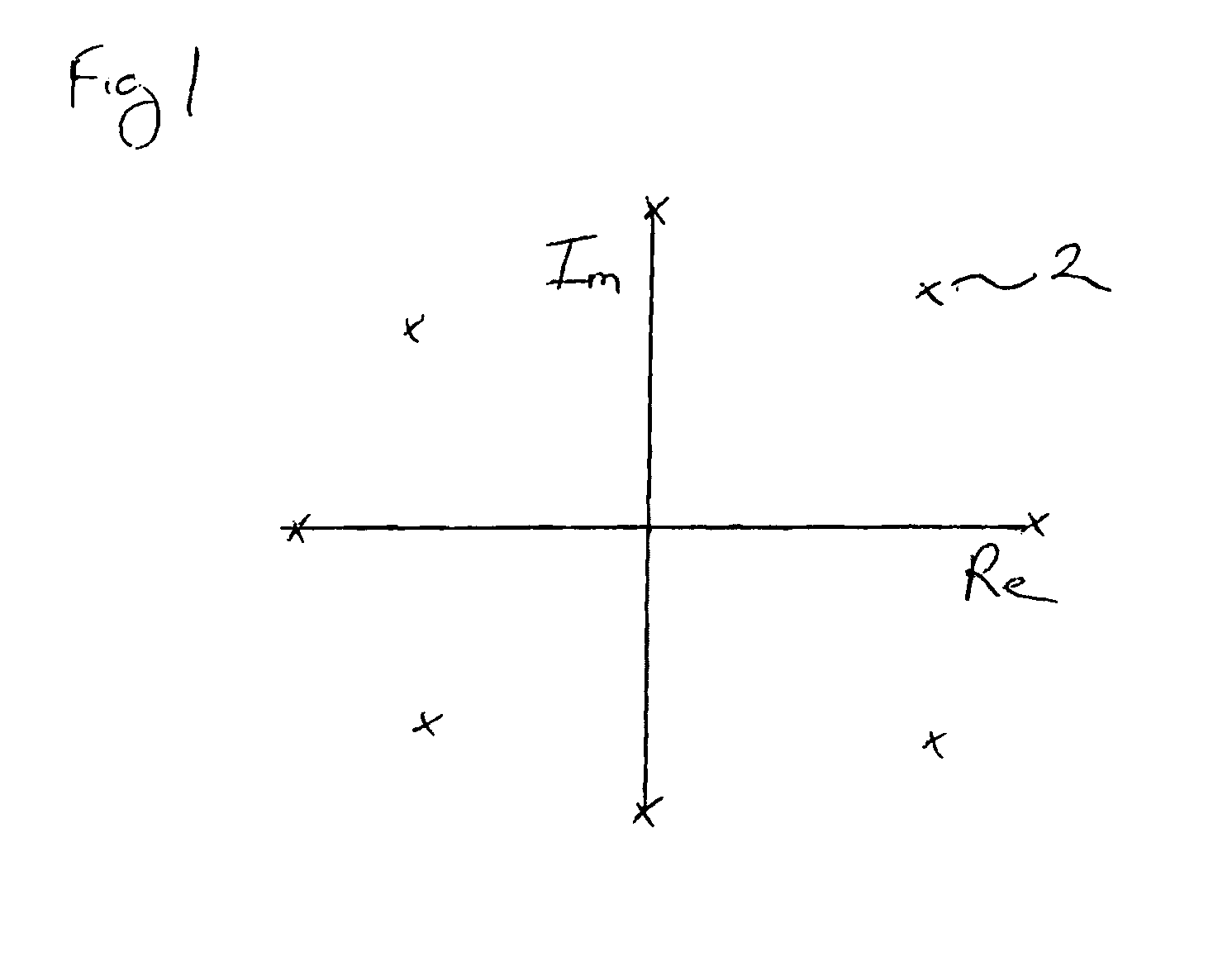

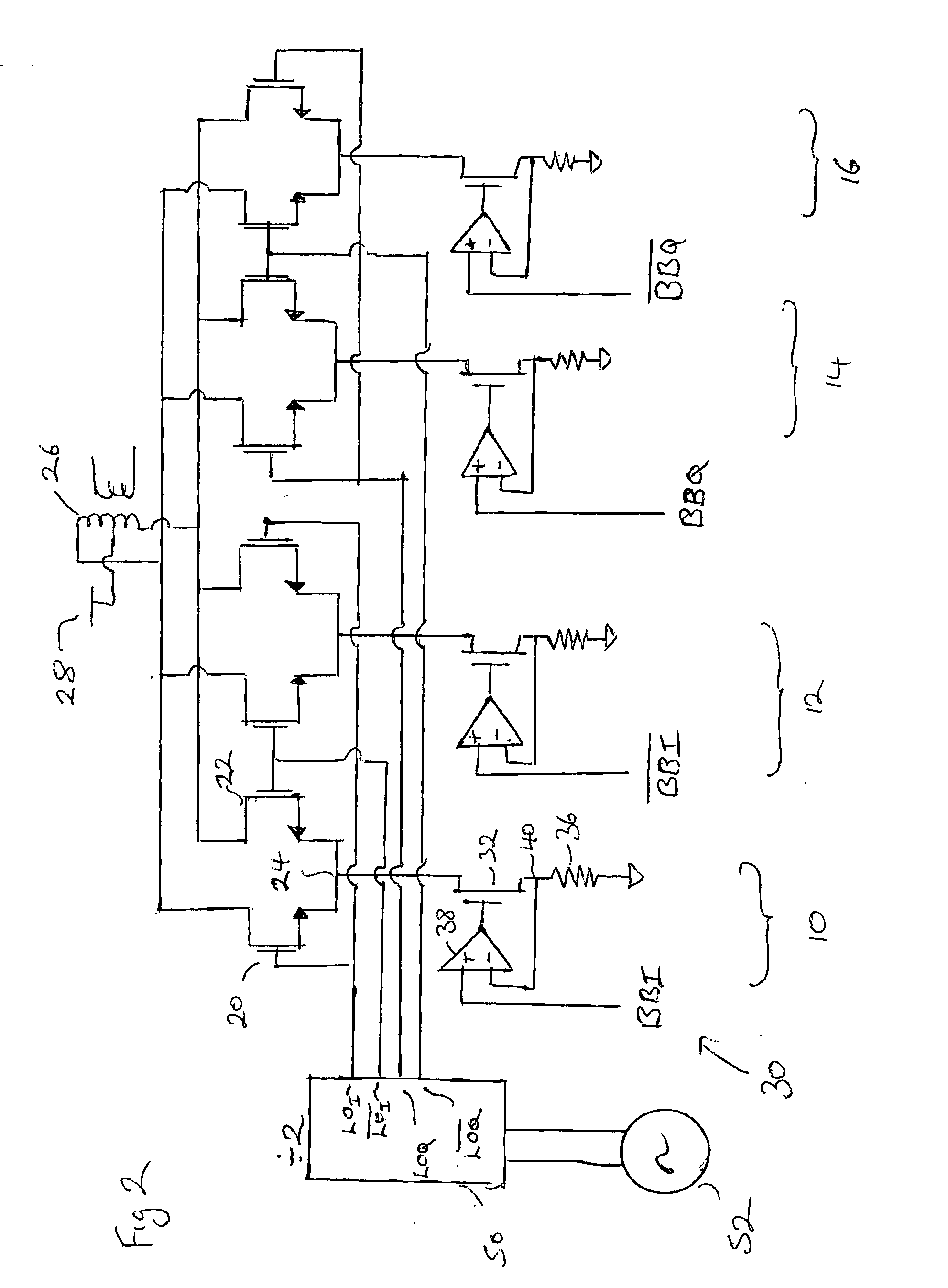

Switching circuit, and a modulator, demodulator or mixer including such a circuit

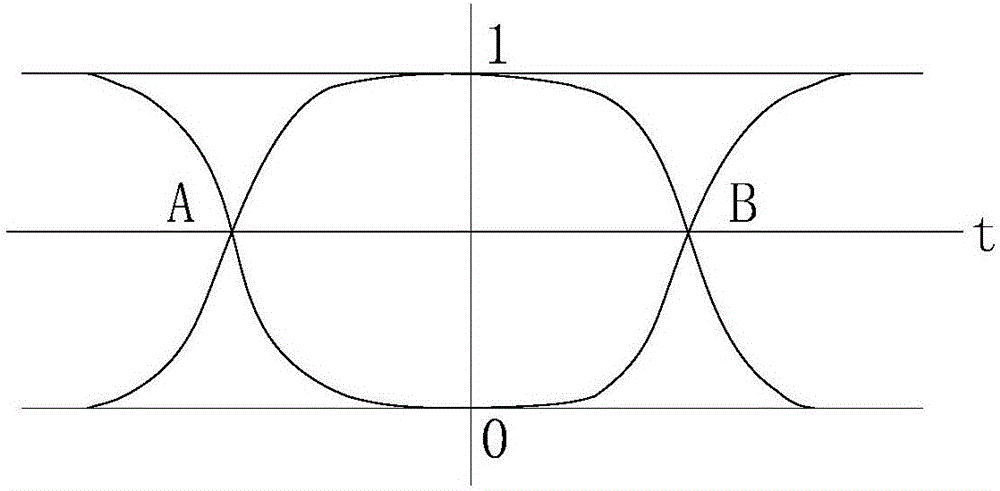

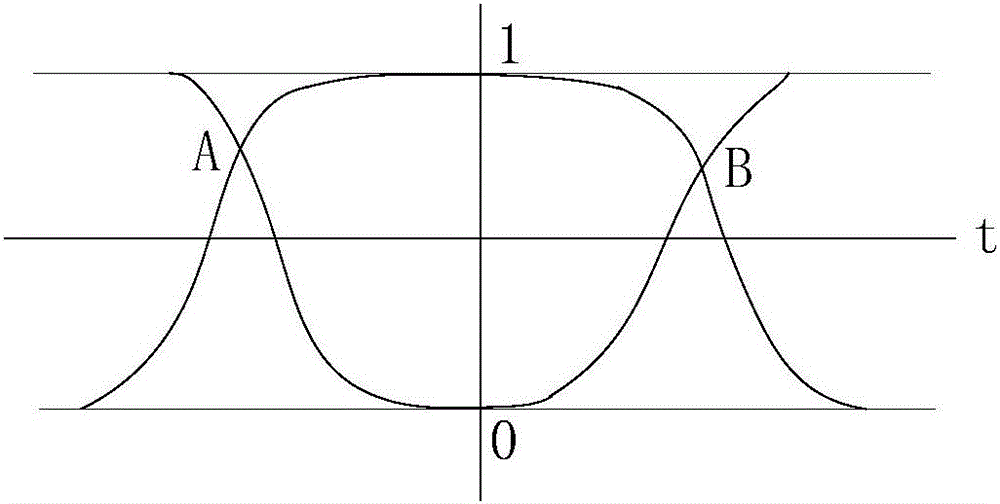

ActiveUS7750749B2Improve Noise PerformanceReduce the effect of jitterModulation transferenceComputations using contact-making devicesFrequency mixerControl signal

A switching circuit comprising: first and second steering switches operable to make or break a path between first and second terminals thereof, and each steering switch further having a control terminal for controlling the switch, the first and second steering switches having their control terminals driven by first and second switching signals, the first and second switching signals having a first frequency and the second switching signal being in anti-phase with the first switching signal and a first chopping switch operable to make or break a path between first and second terminals thereof and being connected in series with at least one of the first and second steering switches and receiving at its first terminal an input to be modulated, wherein the control terminal of the chopping switch is driven by a first switching control signal such that the chopping switch is non-conducting while the first and second steering switches are changing between being conducting and being non-conducting.

Owner:MEDIATEK INC

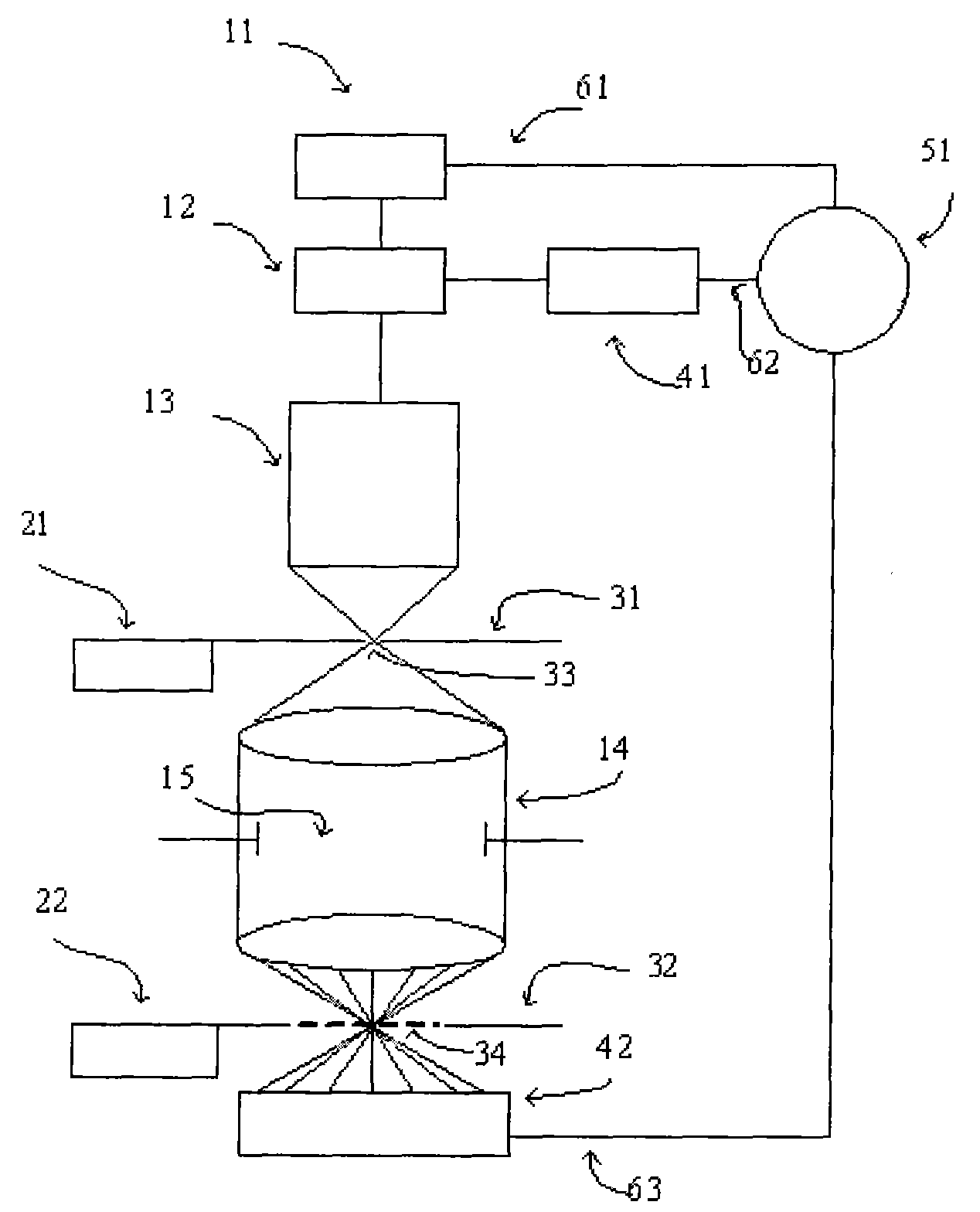

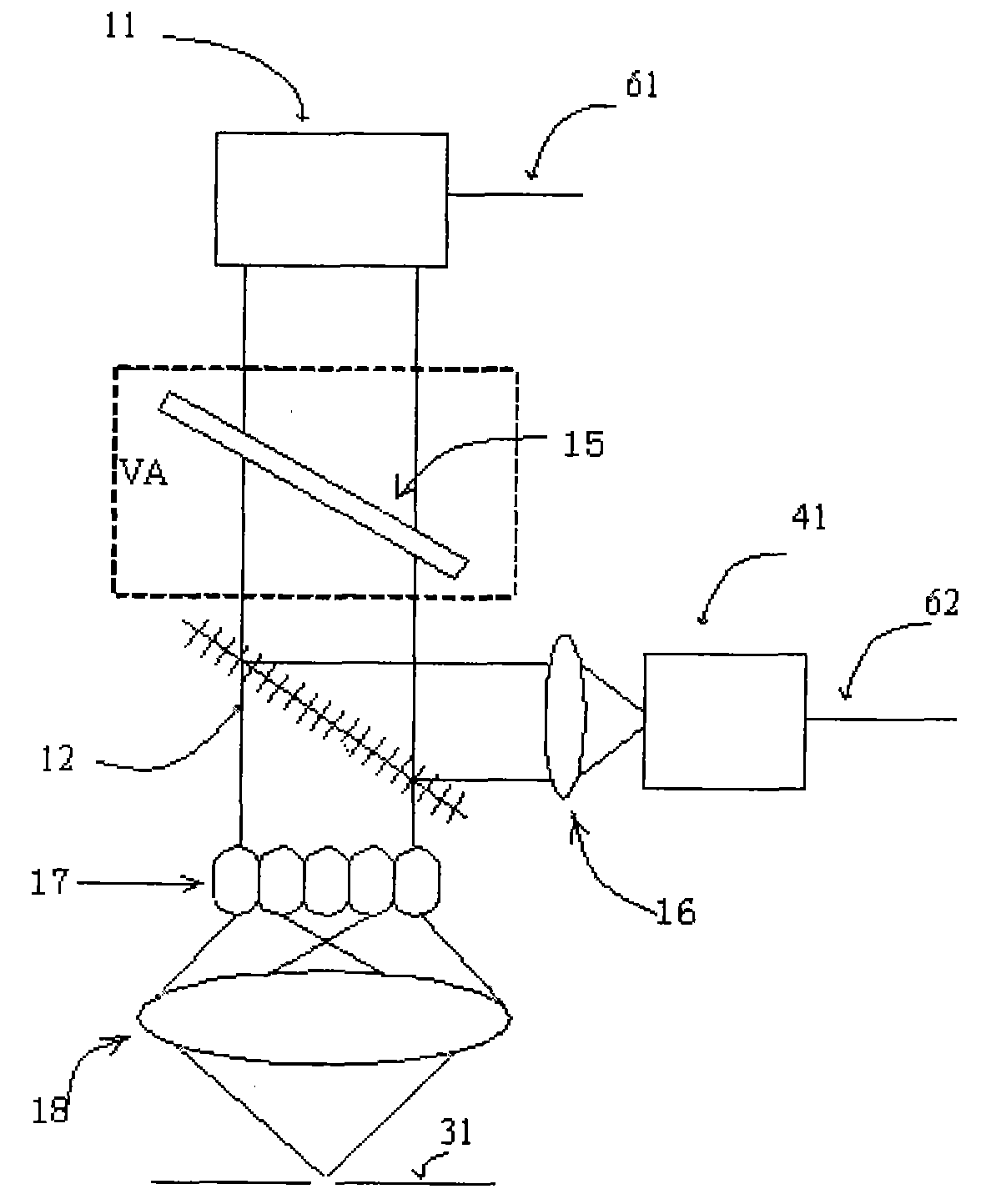

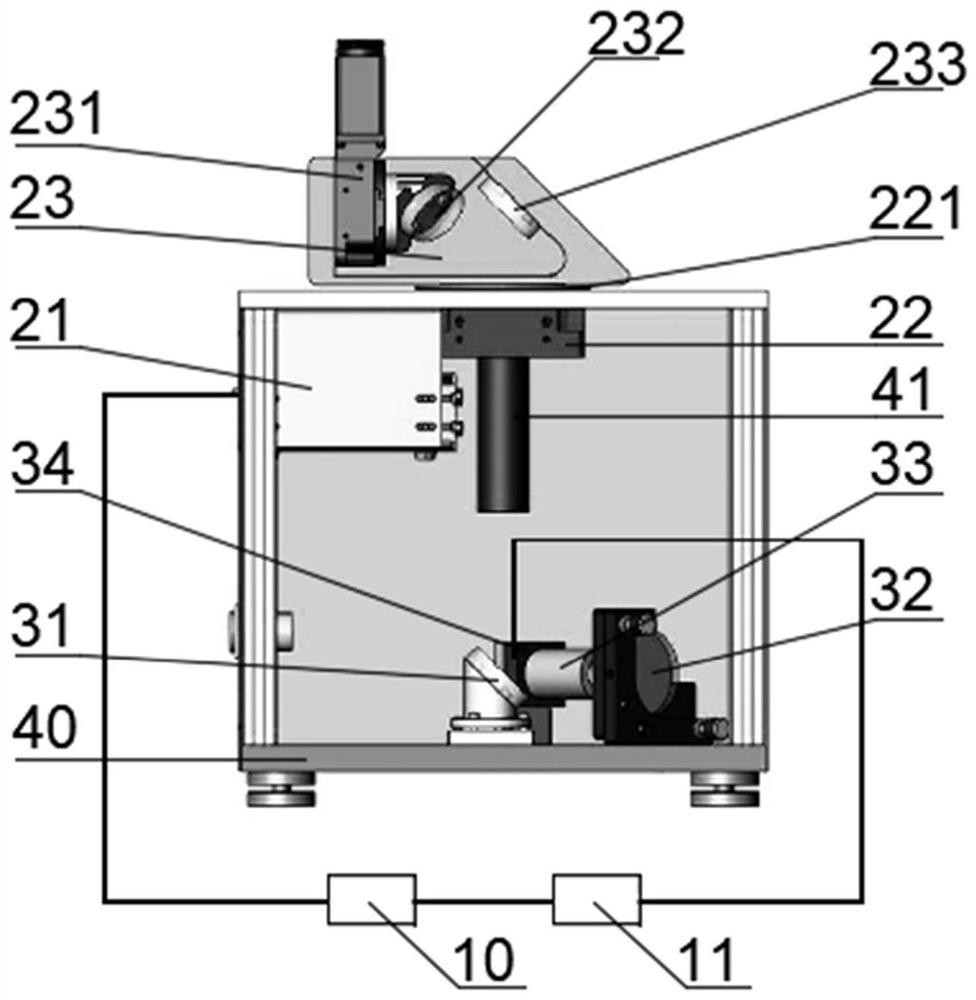

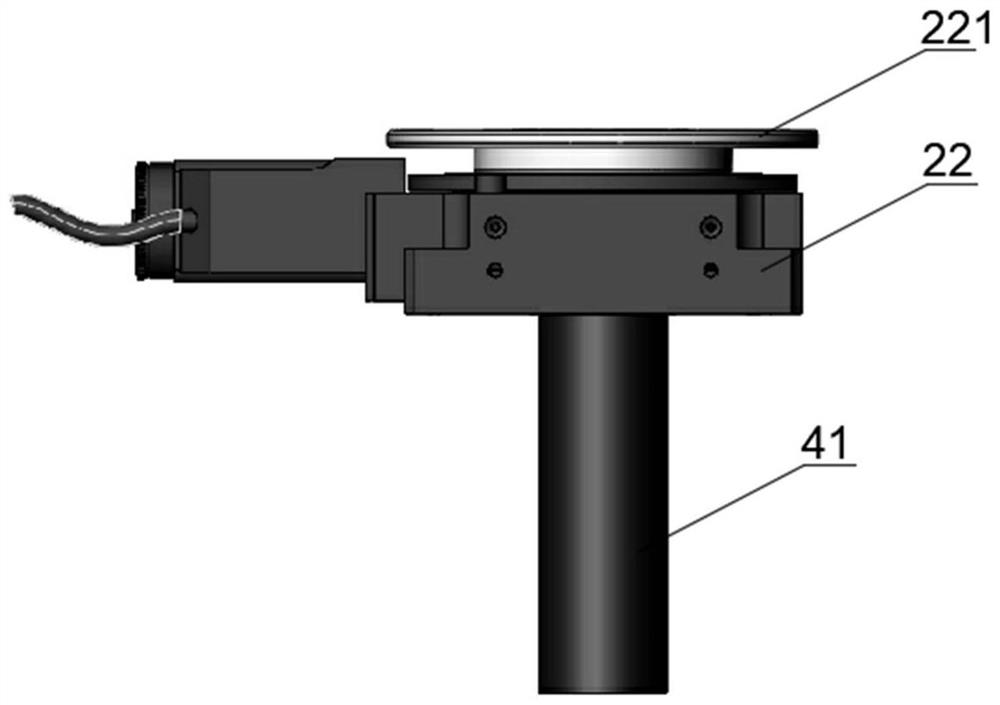

Real-time measuring device and method for wave aberration

ActiveCN102073217AReduce the effect of jitterImprove accuracyPhotomechanical exposure apparatusMicrolithography exposure apparatusBeam splitterGrating

The invention discloses a real-time measuring device for wave aberration, which comprises a light source, a beam splitter, a lighting system, an object surface pinhole, an objective lens system, a shearing grating, a two-dimensional array photosensitive element, an energy sensor, and a synchronous control and comparison part, wherein the beam splitter splits light emitted by the light source into a first light beam and a second light beam; the lighting system receives the first light beam emitted by the beam splitter; the object surface pinhole receives light emitted by the lighting system to form a probe light source; the objective lens system is used for imaging the pinhole; the shearing grating is positioned on the image surface of the objective lens system and diffracts probe light emitted by the pinhole; the probing surface of the two-dimensional array photosensitive element receives shearing interference fringes generated by the shearing grating and is conjugate with the pupilplane of an objective lens; the energy sensor receives the second light beam emitted by the beam splitter; and the synchronous control and comparison part is connected with the light source, the energy sensor and the two-dimensional array photosensitive element through signal wires. During measurement, the synchronous control and comparison part controls the energy sensor and the two-dimensional array photosensitive element to perform synchronous optical energy integral at the same time interval, and a measuring result of the two-dimensional array photosensitive element is calibrated by a measuring result of the energy sensor.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD

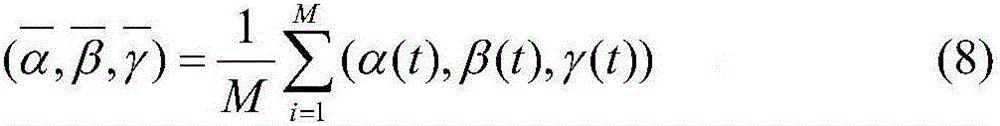

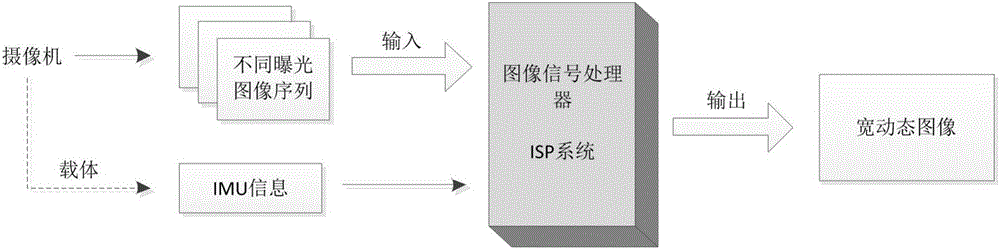

IMU information-based wide dynamic image fusion method

InactiveCN106060418AEliminate the effects of random jitterReduce the effect of jitterTelevision system detailsColor television detailsCamera response functionBased wide

The invention discloses an IMU information-based wide dynamic image fusion method. According to the method, different shutter time is set, the same scene is subjected to multiple times of long exposure and short exposure, and then three frames of images of which bright and dark area contrasts are relatively large are selected, including the shortest exposure image frame, the moderate exposure image frame, and the longest exposure image frame; the three frames of images are divided into M areas respectively, each area is subjected to Euler angle multi-data fusion attitude calculation based on information detected by an IMU sensor to obtain a motion vector of each area, and a motion vector mean is calculated to be used as a correcting value to perform registration correction on each image frame; and the different exposure images that are corrected are subjected to segmented linear fitting by adoption of the least square method in combination with a camera response function and a luminance mapping function, then wide dynamic images are obtained through mapping, and finally, the wide dynamic images are fused by a multi-frame accumulation method. Through adoption of the method, a phenomenon that a transition area generated by direct fusion of two frames of images is unnatural is optimized, and thus the clear and natural wide dynamic images are obtained.

Owner:深圳市优象计算技术有限公司

Switching circuit, and a modulator, demodulator or mixer including such a circuit

ActiveUS20070116015A1Improved noise performanceReduce jitterModulation transferenceData switching by path configurationControl switchSwitching signal

A switching circuit comprising: first and second steering switches operable to make or break a path between first and second terminals thereof, and each steering switch further having a control terminal for controlling the switch, the first and second steering switches having their control terminals driven by first and second switching signals, the first and second switching signals having a first frequency and the second switching signal being in anti-phase with the first switching signal and a first chopping switch operable to make or break a path between first and second terminals thereof and being connected in series with at least one of the first and second steering switches and receiving at its first terminal an input to be modulated, wherein the control terminal of the chopping switch is driven by a first switching control signal such that the chopping switch is non-conducting while the first and second steering switches are changing between being conducting and being non-conducting.

Owner:MEDIATEK INC

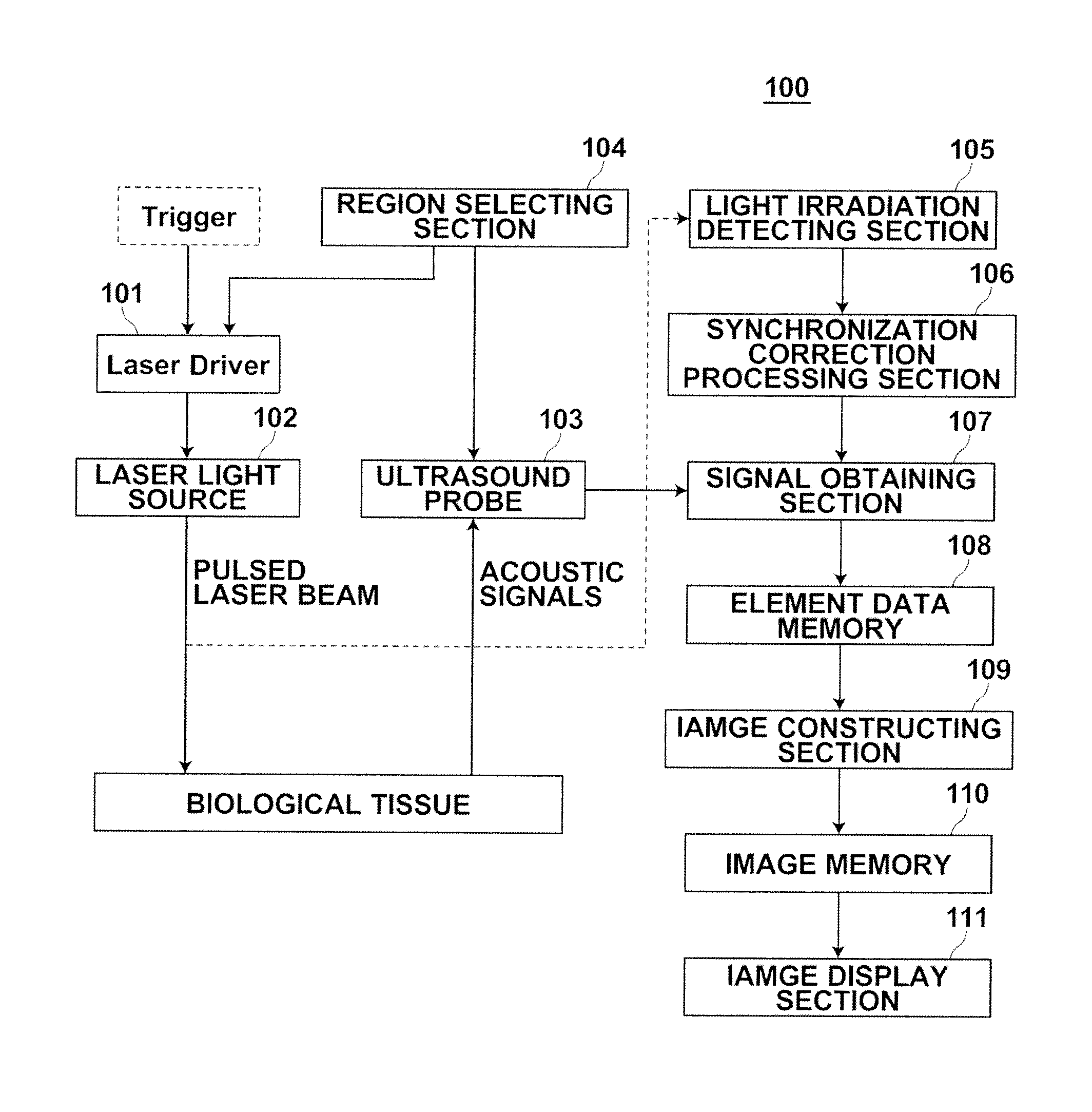

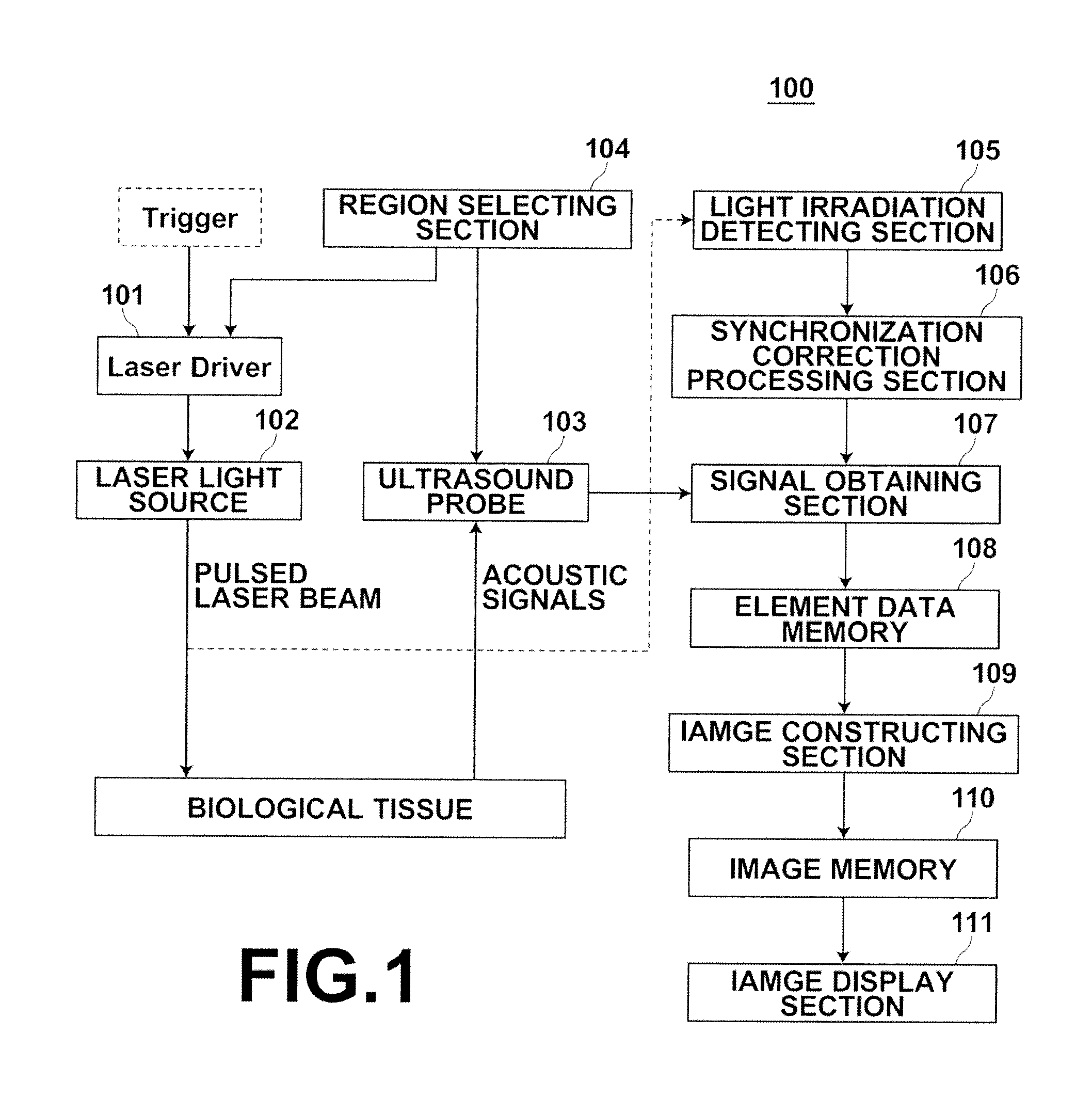

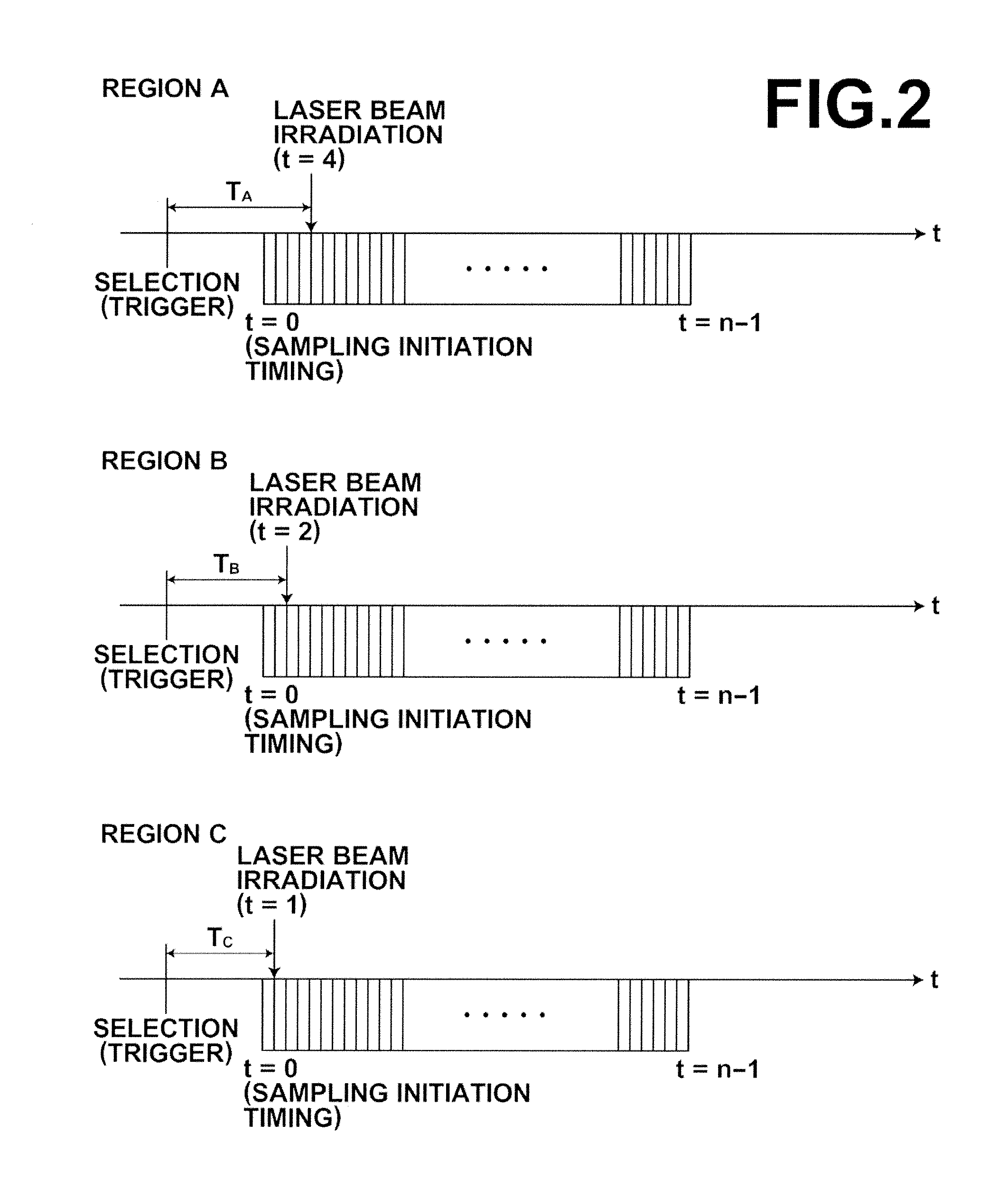

Photoacoustic imaging apparatus and photoacoustic imaging method

InactiveUS20110319744A1Improve image qualityReduce the impactUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsLaser lightTomographic image

A region selecting means sequentially selects a plurality of partial regions, into which a range to be imaged of a subject is divided. A light irradiation detecting section detects light which is irradiated onto the subject from a laser light source. A signal obtaining section samples acoustic signals detected by probe elements corresponding to the selected partial region, and stores the acoustic signals in an element data memory. An image constructing section constructs a tomographic image of the subject based on the data read out from the element data memory. A synchronization correction processing section obtains the differences in the timings at which the light irradiation detecting section has detected irradiation of light, and corrects the temporal axes of the sampled data in the element data memory based on the obtained timing differences.

Owner:FUJIFILM CORP

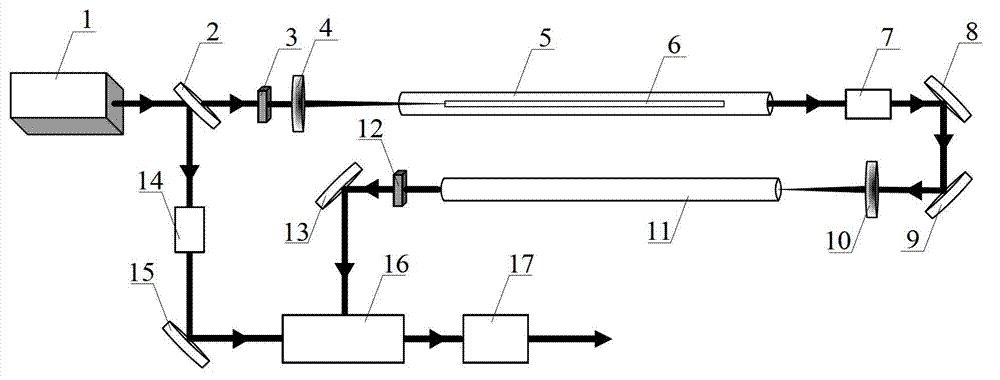

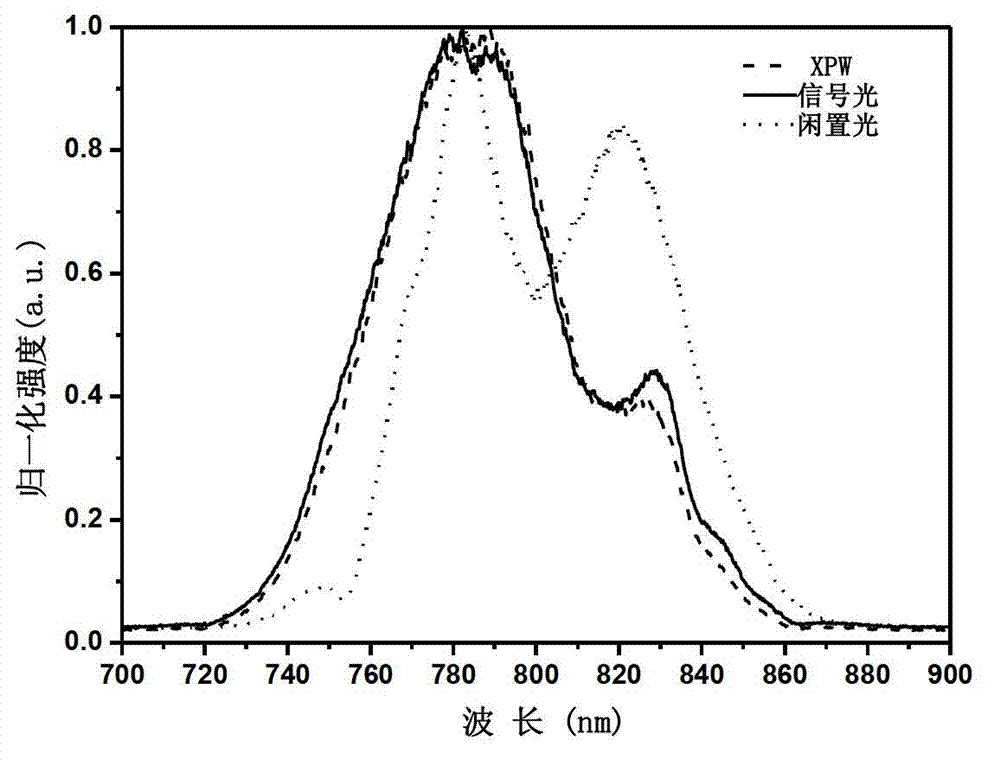

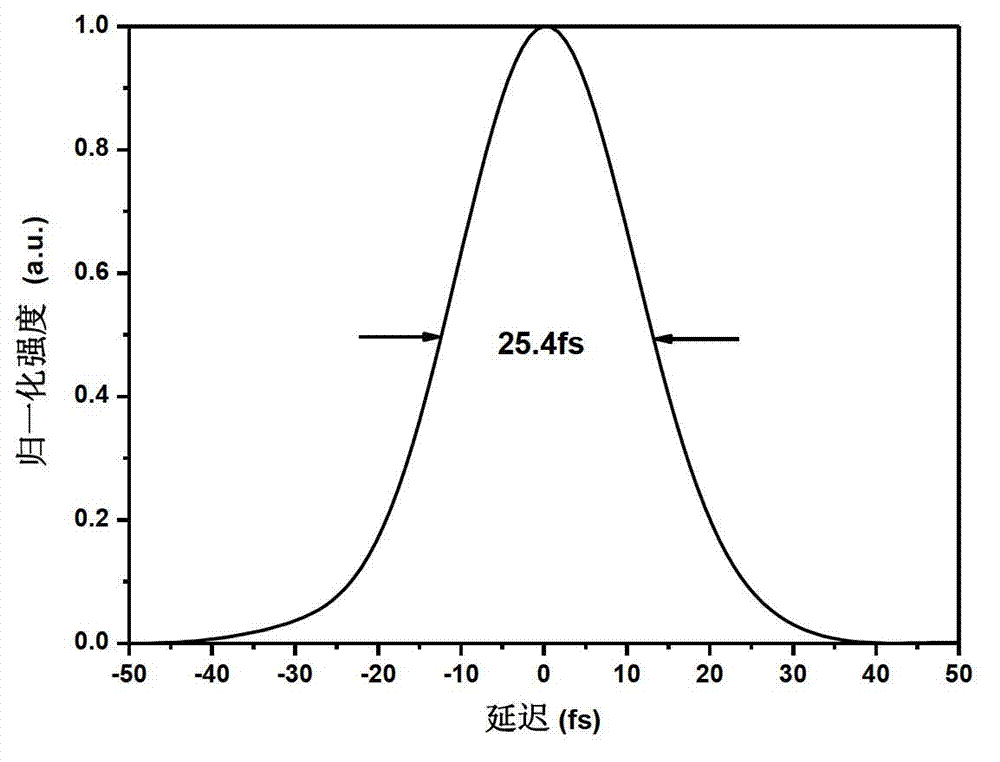

Stable high-contrast femtosecond laser pulse source

InactiveCN103208734AAvoid Serious Injury ProblemsHigh Pulse Time Domain ContrastLaser detailsNon-linear opticsHigh contrastPhysics

A stable high-contrast femtosecond laser pulse source comprises a pumping source, a spectrum broadening system, a laser pulse purification system, a parametric amplification system and a dispersion compensation system. The pulse is subjected to shaping filtering through hollow optical fibers, to pulse purification through a cross polarized wave generating device, to optical parametric amplification and pulse compression, finally, the output of the high-contrast femtosecond laser pulse is achieved. According to the high-contrast femtosecond laser pulse source, not only the problem of the serious damage to crystals due to cross polarized waves under large energy is avoided, but also the stable output of the high-contrast femtosecond laser pulse during long working time is achieved. The stable high-contrast femtosecond laser pulse source is widely applicable to attosecond pulse generation and the like.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

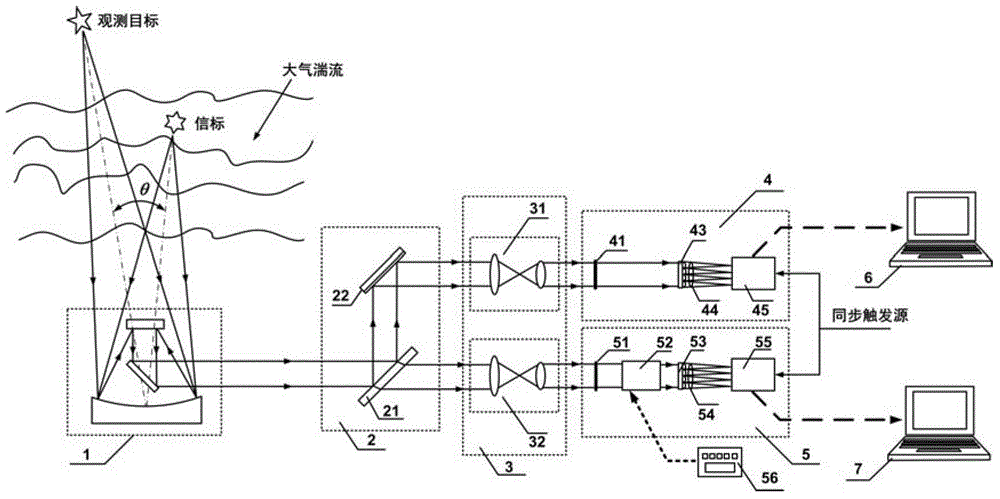

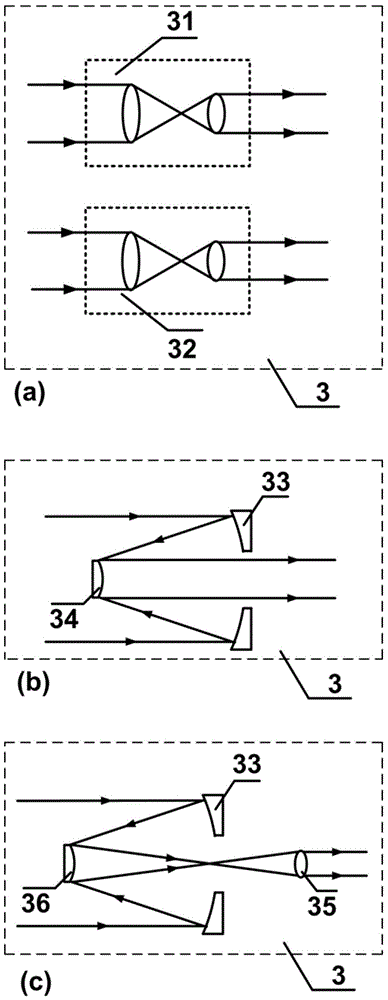

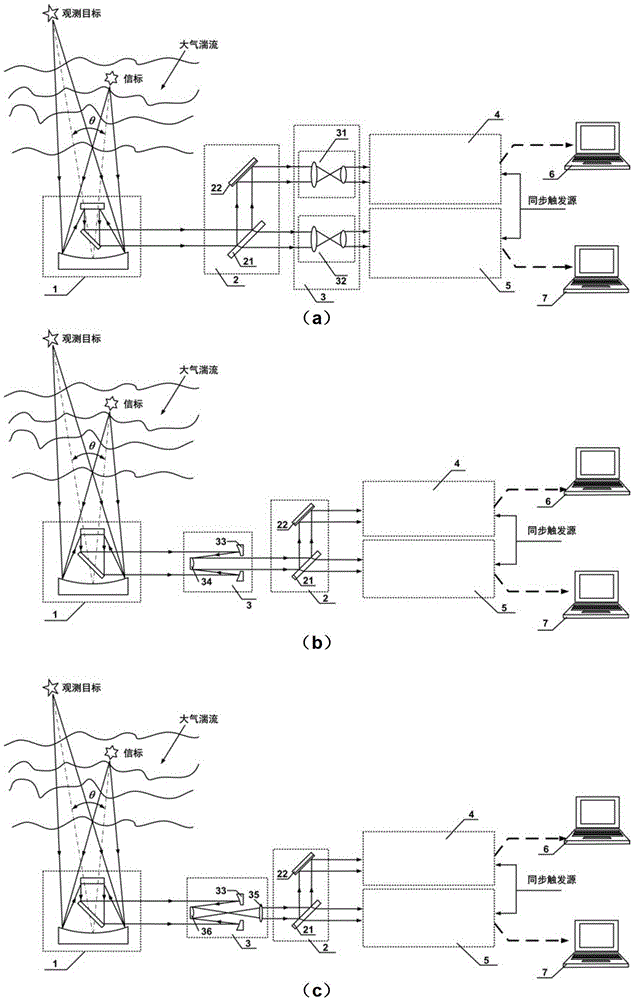

Device and method for measuring non-isoplanatism wave-front errors and turbulence characteristic parameters of atmosphere turbulence

ActiveCN103335950AReduce the effect of jitterSimple structureMaterial analysis by optical meansObservational errorMeasurement device

The invention provides a device and a method for measuring non-isoplanatism wave-front errors and turbulence characteristic parameters of an atmosphere turbulence. The method comprises the following steps: setting a beacon Hartmann sensor focusing distance according to a beacon mode; respectively receiving a target light wave imaging light spot pattern and a beacon light wave imaging light spot pattern by utilizing a target Hartmann sensor and a beacon Hartmann sensor; controlling a target Hartmann sensor CCD (Charge Coupled Device) and a beacon Hartmann sensor CCD to synchronously collect by an external synchronous triggering source; calculating an average slope of a time sequence target light wave and a beacon light wave in a sub-hole diameter of a micro-lens set, and carrying out difference operation by utilizing a wave-front processor; carrying out recovery on a difference average slope and a target light wave average slope and expanding a Zernike mode by utilizing a recovering algorithm to obtain counting characteristics including non-isoplanatism wave-front errors, target turbulence wave-front two-dimensional distribution, wave-front square errors, a P-V value, Zernike mode square errors, non-isoplanatism relative errors and the like, as well as the turbulence characteristic parameters including the coherence length, an isoplanatic angle, the beacon equivalent diameter and the like. The device and method disclosed by the invention have the advantages of high light energy utilization rate, small measurement errors and wide application prospect.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

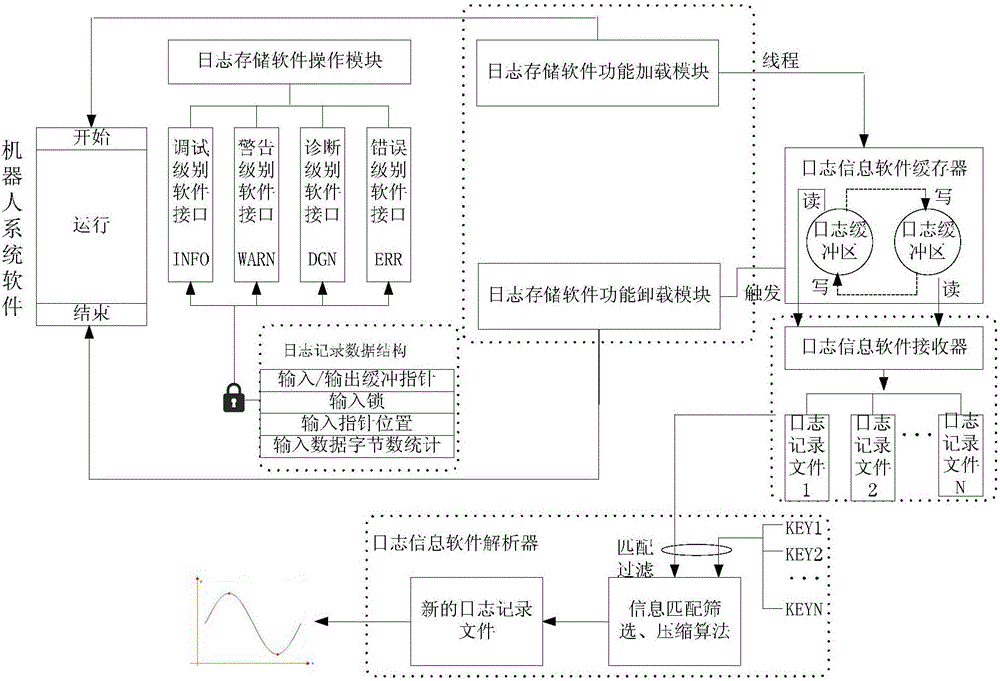

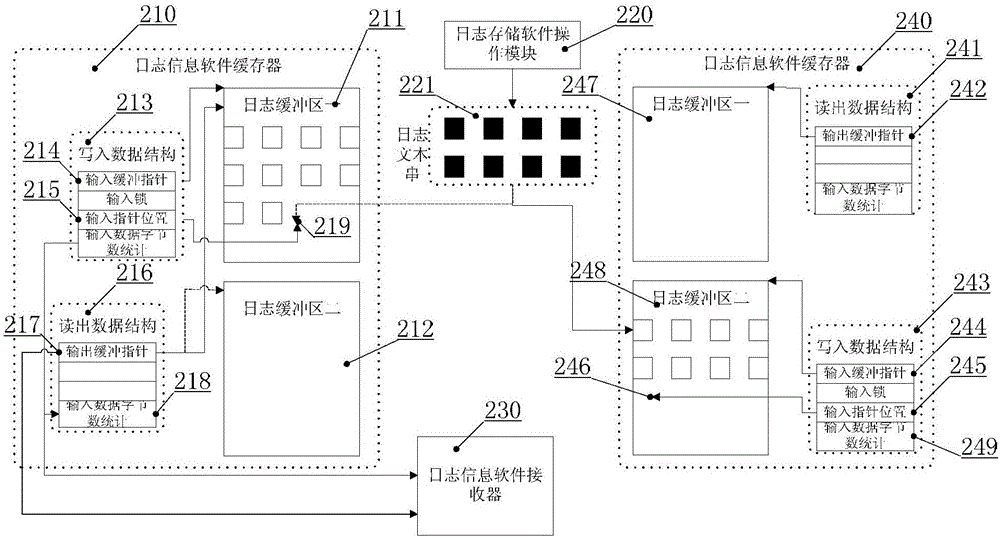

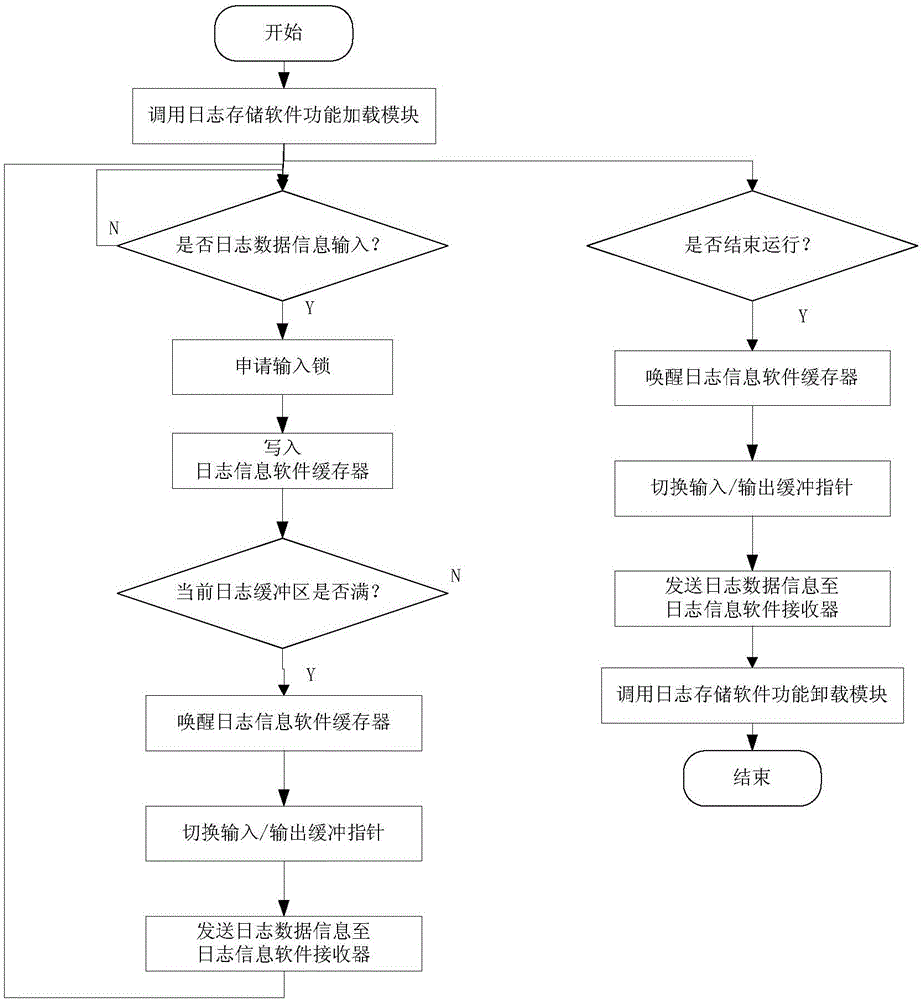

Double-buffering type robot software log storage method

The invention provides a double-buffering type robot software log storage method. The method is characterized by comprising the following steps of: setting a log storage software function loading module, a log storage software function unloading module, a log storage software operation module, a log information software buffer, a log information software receiver and a log information software analyzer, wherein the log information software buffer comprises two log buffer areas with same storage spaces; when one log buffer area is full of data, switching an input pointer to the other log buffer area so as not to delay the data input; pointing an output pointer to the log buffer area full of data, outputting the log data information in the log buffer area full of data, and setting the log buffer area to be in an idle state. According to the method, the log data information can be stored, and the overall operation load of robot system software can be greatly reduced, so that benefit is brought to improve the software defect check efficiency.

Owner:FOSHAN INST OF INTELLIGENT EQUIP TECH +1

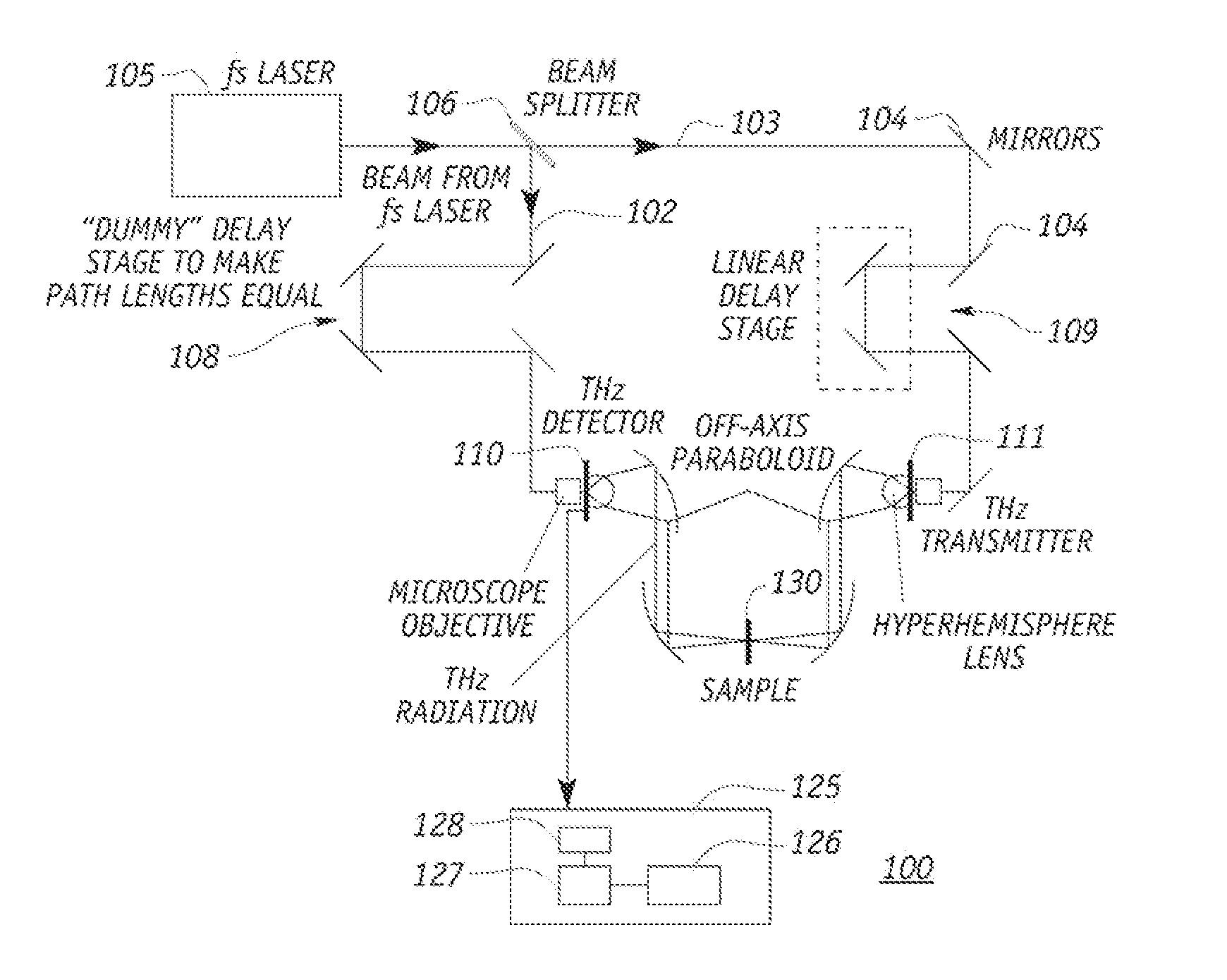

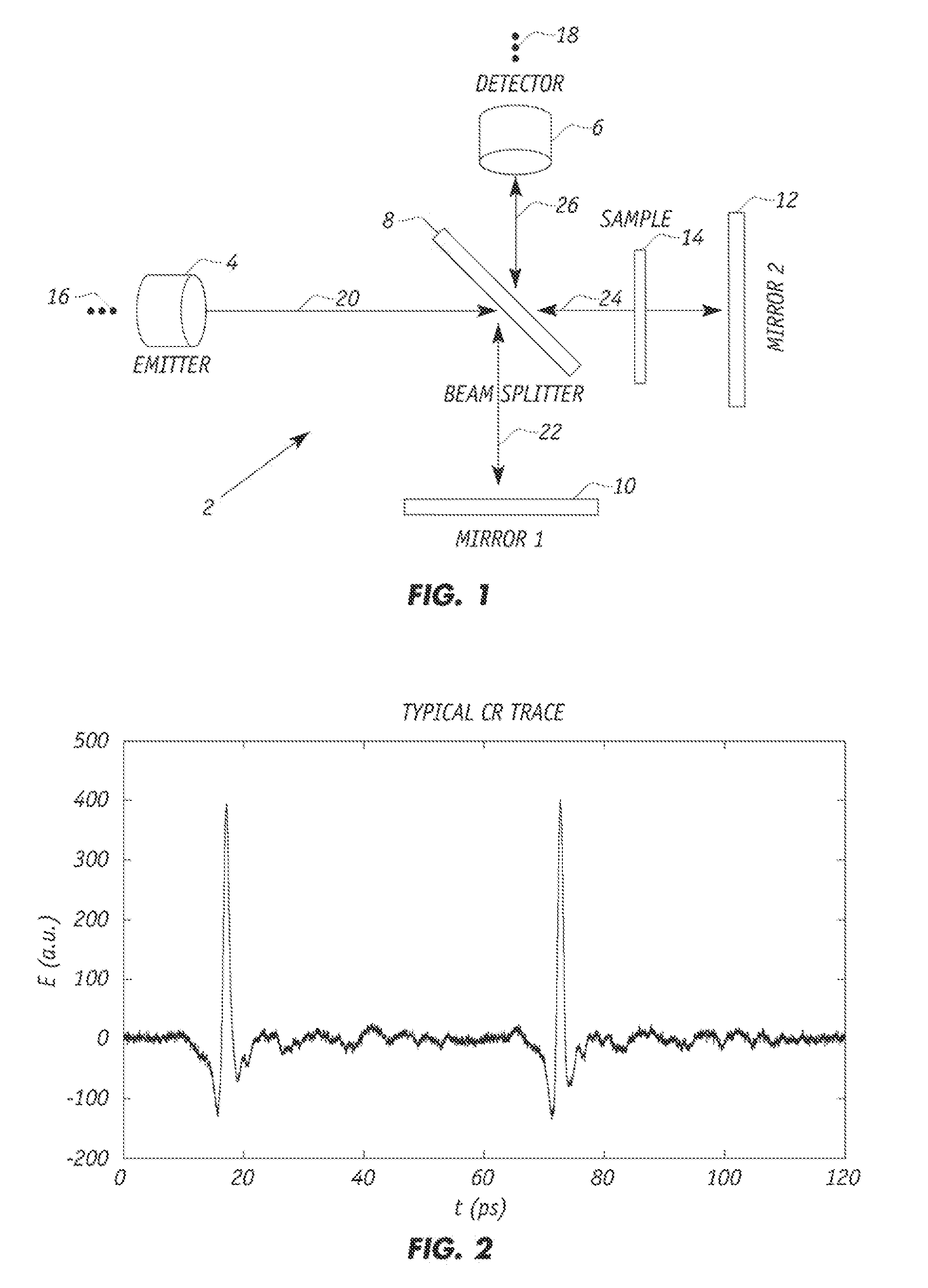

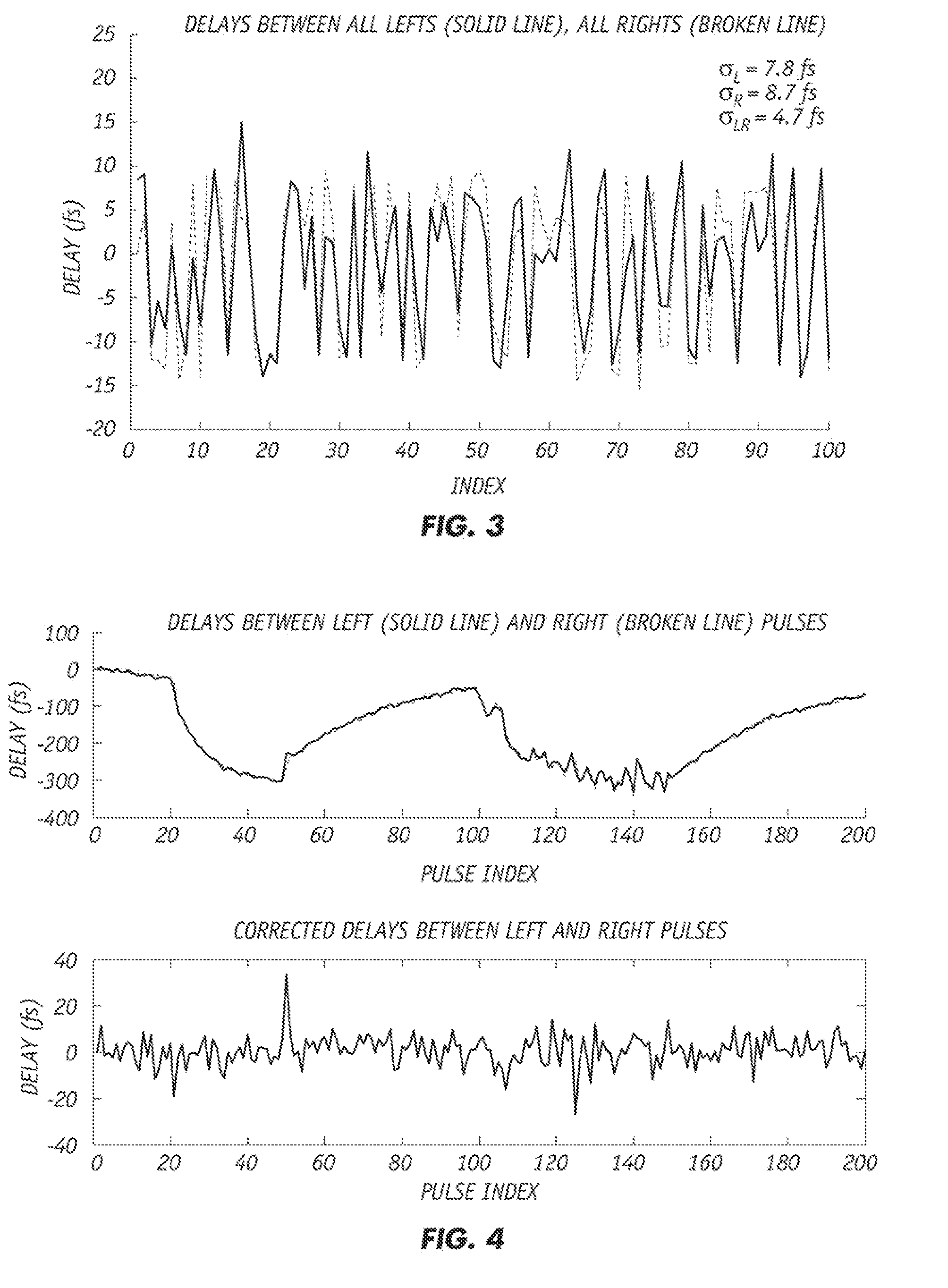

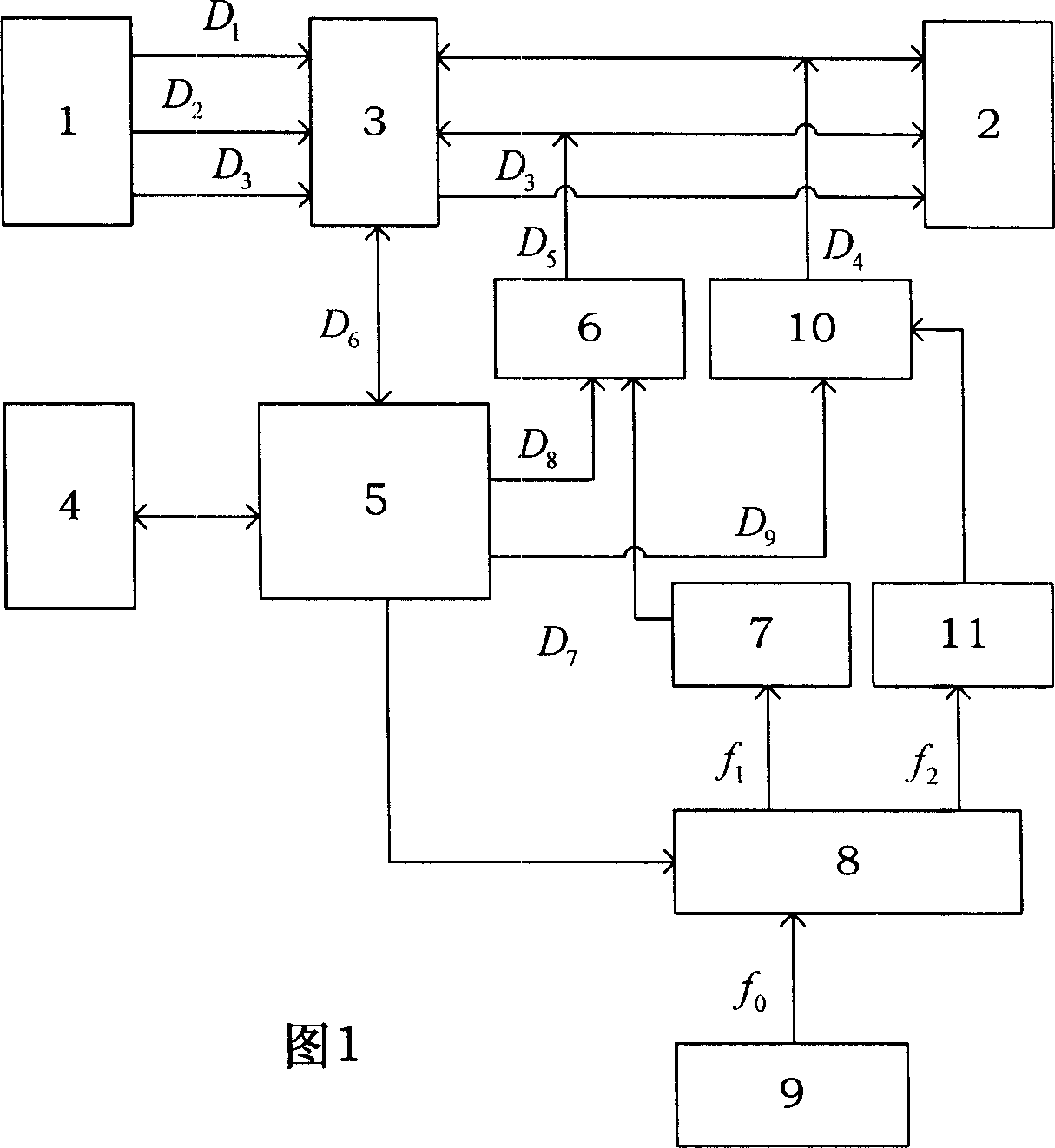

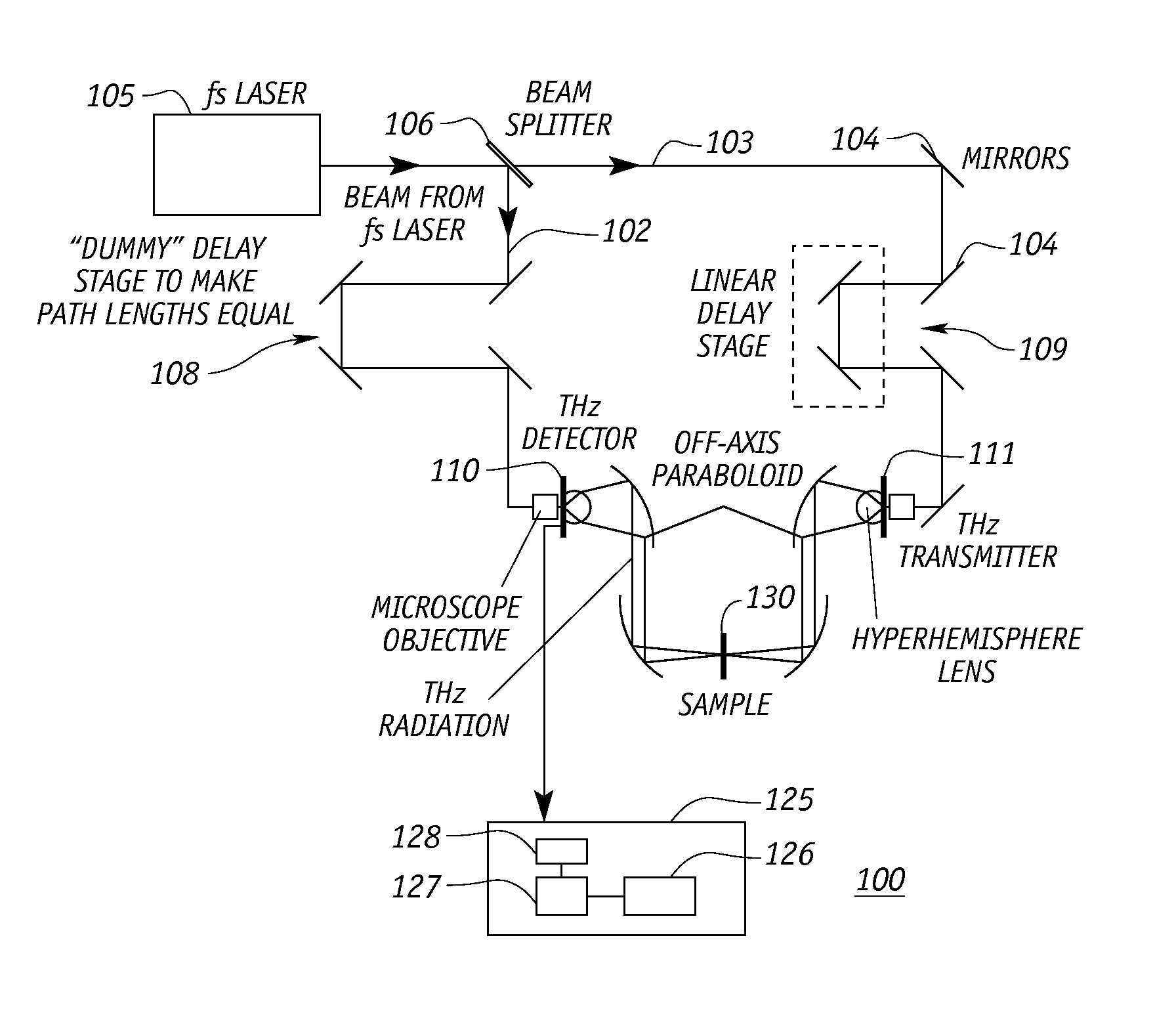

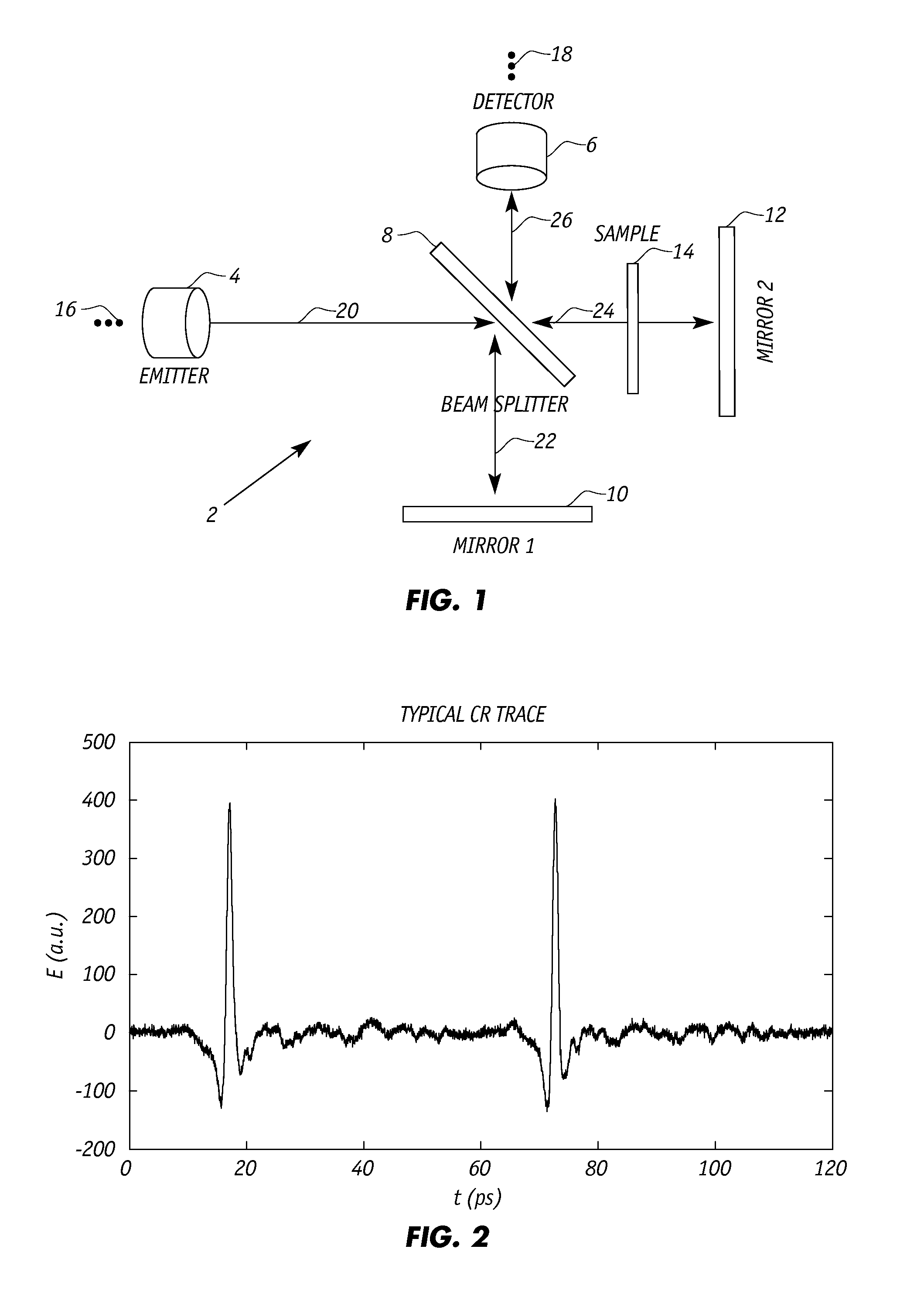

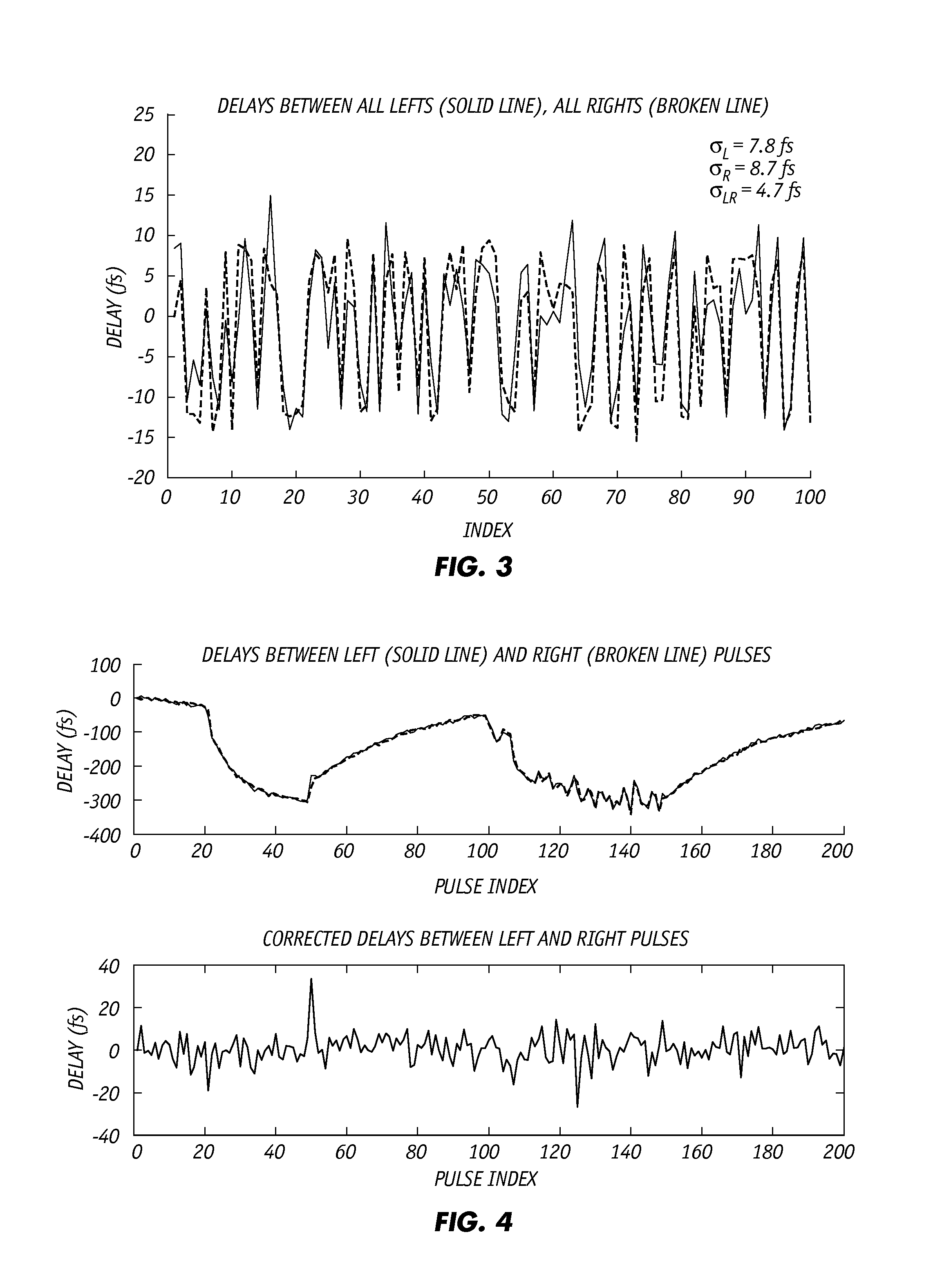

Continuous Referencing For Increasing Measurement Precision In Time-Domain Spectroscopy

ActiveUS20120049070A1Simple designReduce the effect of jitterRadiation pyrometryInvestigating moving sheetsTime domainBeam splitter

An apparatus for incorporation into time-domain spectroscopy systems that creates a continuous reference whereby a sample pulses' phase and amplitude can be tracked and corrected employs a beam splitter to generate sample and reference pulses. A detector is positioned for receiving the reference radiation pulses that do not interact with the sample. The same detector is also positioned for receiving the sample radiation pulses that emerge from the sample. The apparatus can be readily implemented by being configured between the emitter and detector of a terahertz time-domain spectrometer. The reference pulse is used to trace the changes in time and amplitude of the sample pulse. Since any changes in the reference pulse will most likely manifest in the sample pulse, the reference pulse is monitored and used to correct the sample pulse and thereby reduce the effects of jitter.

Owner:HONEYWELL ASCA INC

Rebuilt-up device for digital asynchronous clock

InactiveCN101001228AReduce the effect of jitterReduce absolute accuracy requirementsTransmitter/receiver shaping networksBandpass filteringPhase difference

This invention discloses a digital asynchronous clock reconstructing device composed of a digital signal input interface, digital signal output interface, an asynchronous FIFO storage, a non-volatile storage, a general processor, a first clock distributor, a second clock distributor, a first bandpass filter, a second bandpass filter, a digital frequency synthesizer and a high speed crystal oscillator, in which, the clock inputting digit signals is independent of the clock outputting digital signals, and an asynchronous buffer system is used to lag the output data behind the input data, so that, when short period of frequency or phase differences exists, the DDS is used to re-generate output clock to distribute chips to further improve qualities of the output clocks, a general processor is used to tune the output frequency of the DDS to eliminate long time of frequency difference between input and output digital signal clocks to avoid overflow of the asynchronous buffer or empty.

Owner:BEIHANG UNIV

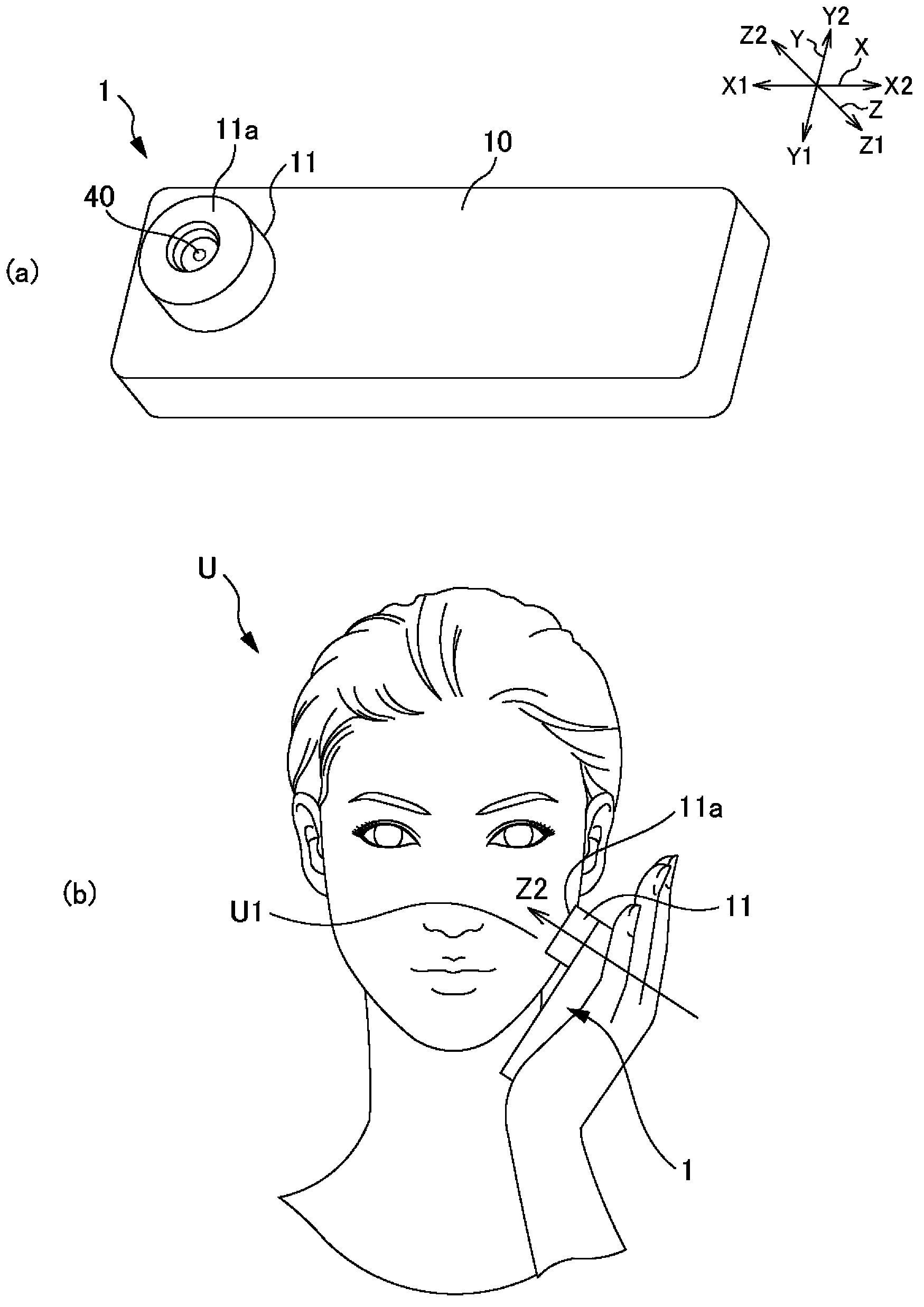

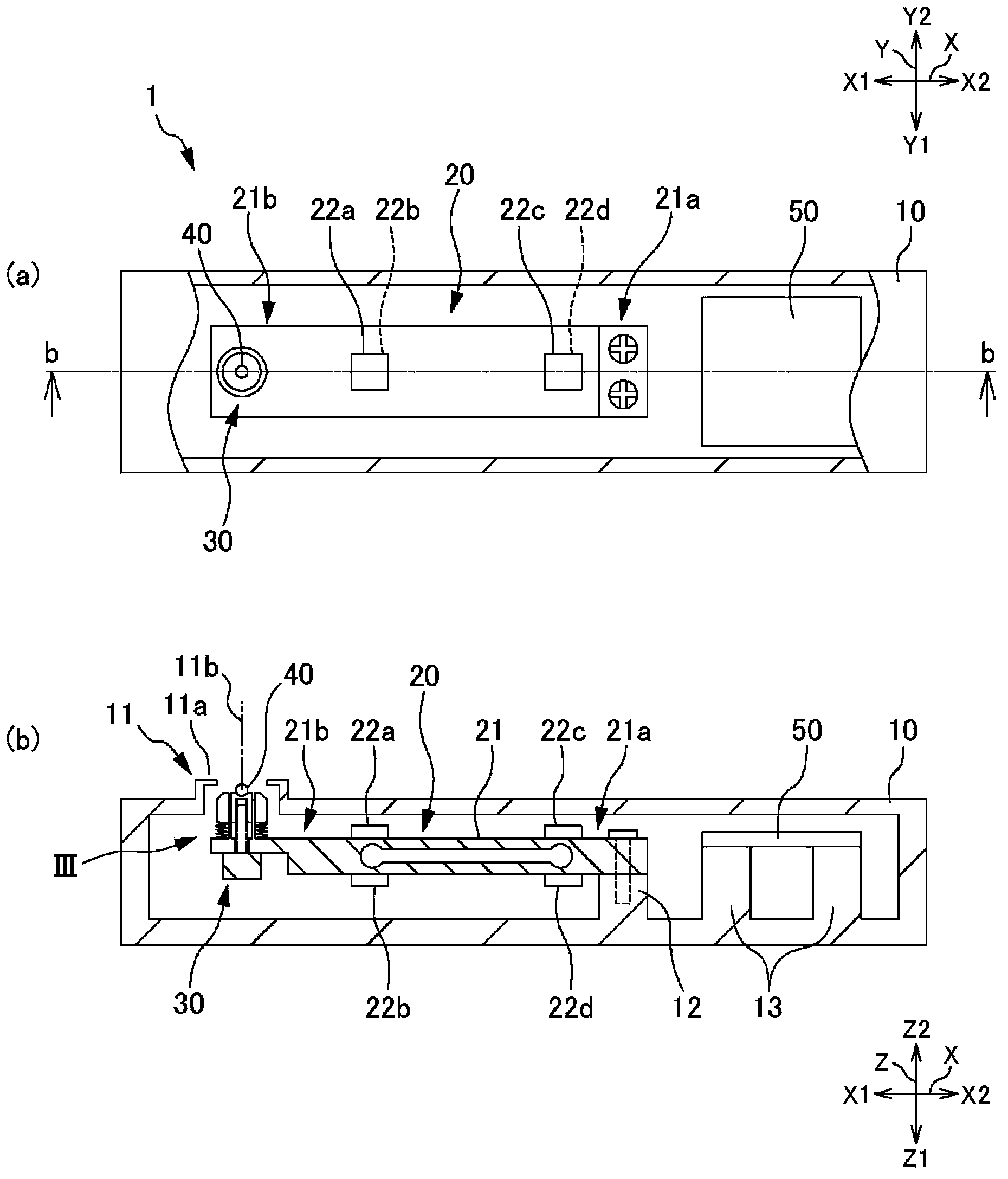

Viscoelasticity measuring apparatus

InactiveCN103565414ASmall driving forceReduce the effect of jitterDiagnostics using pressureForce measurementMeasurement deviceEngineering

A viscoelasticity measuring apparatus that measures viscoelasticity of a measurement target with high precision is provided. The measuring apparatus includes: a casing; a surface contact part provided in the casing and brought into surface contact with skin; a ball indenter that moves toward the skin more than the surface contact part and is pushed into the skin; a driving unit that supports the ball indenter and moves the ball indenter toward the skin; a load cell whose right end side is fixed to the casing and left end side supports the driving unit, the load cell detecting a pushing load that pushes the ball indenter into the skin; and a control unit that obtains displacement of the ball indenter.

Owner:TANITA CORP +1

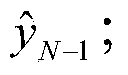

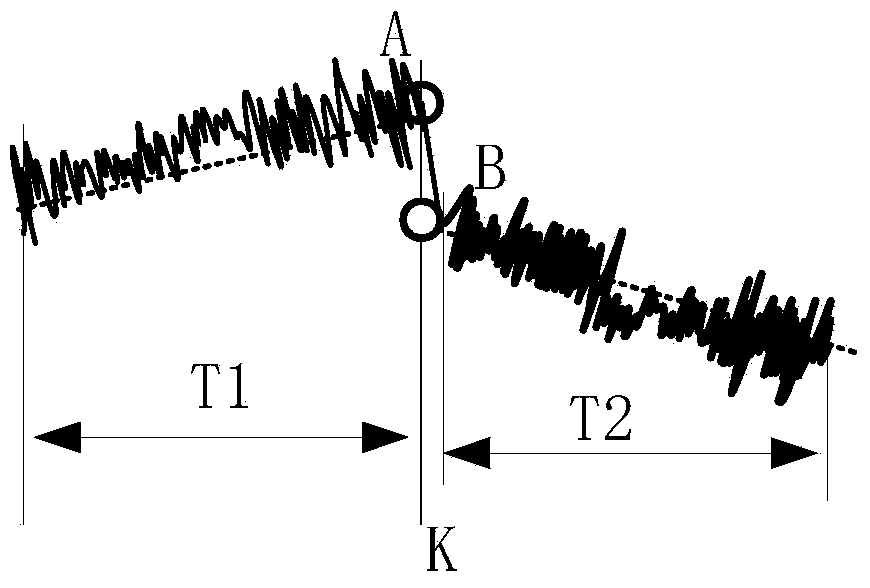

Method for testing phase and frequency change before and after switching primary and secondary clocks of navigation satellite

ActiveCN103424755AEfficient forecastingSuppression of measurement noiseSatellite radio beaconingMeasuring instrumentComputer science

Disclosed is a method for testing phase and frequency change before and after switching primary and secondary clocks of a navigation satellite. Phases of output signals of satellite clocks are measured by a phase measuring device, phase measuring data are acquired at equal time intervals, phase measuring data before and after output of on-off switching action of the satellite clocks are recorded for a long time, on-off switching time is recorded, phase testing data before and after switching are respectively subjected to curve-fitting by the least square method, and change quantities of the phases and frequency are calculated according to fitted values corresponding to the switching time before and after switching. By the method, the influence of frequency drift of the satellite clocks and measuring instruments on testing results can be reduced, and measuring precision is high.

Owner:BEIJING INST OF SPACECRAFT SYST ENG

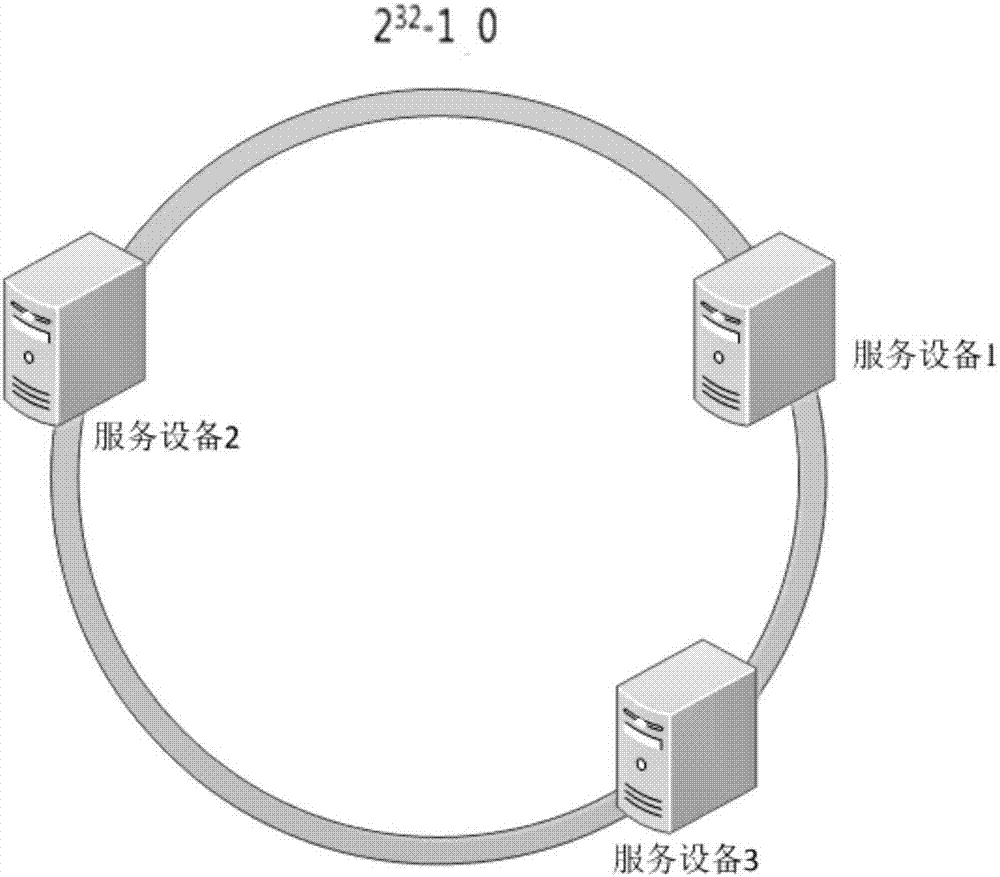

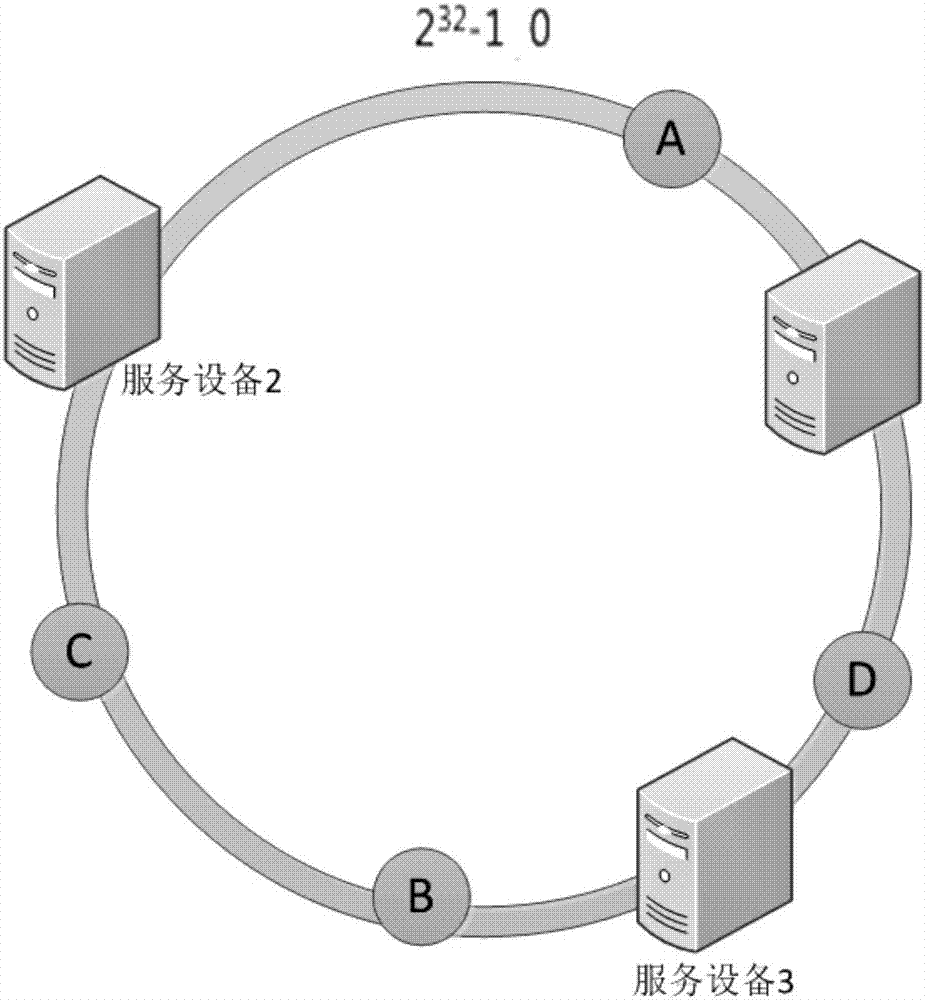

Method for realizing network flow load balancing by utilizing consistency Hash strategy

InactiveCN107171971AReduce the effect of jitterUninterrupted serviceData switching networksTraffic volumeIp address

The invention discloses a method for realizing network flow load balancing by utilizing a consistency Hash strategy. A DNS analyzes an ip address corresponding to a set of service devices; the set of devices externally provides services at the same time; the flow is distributed to the service devices corresponding to the set of service devices by utilization of the consistency Hash strategy of a switch according to a consistency Hash algorithm; a new load balancing device is not increased; the load balancing function is realized completely with the help of the routing function of the switch; when a fault occurs, because a device cluster bears the flow at the same time, services can be provided continuously; when the fault of a certain device is recovered, the device is re-added into the consistency Hash list of the switch; therefore, the flow is smoothly switched; and jitter is avoided.

Owner:北京云端智度科技有限公司

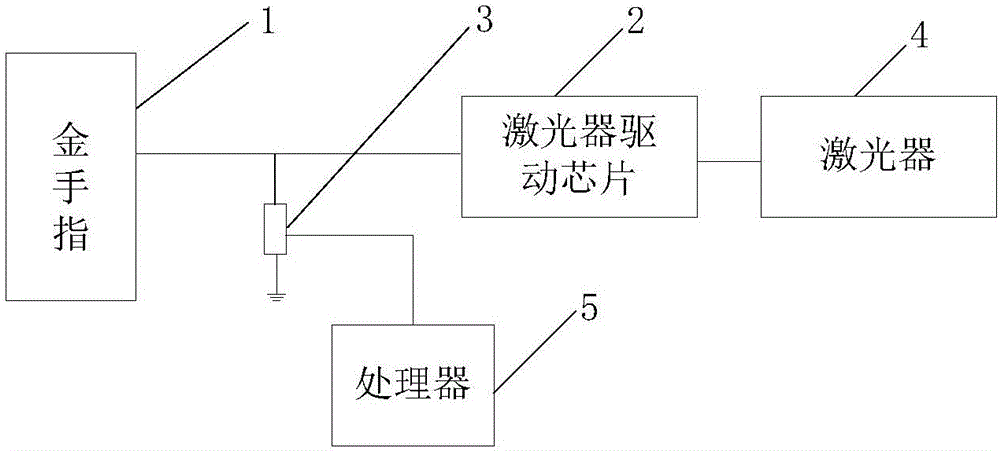

Optical module

InactiveCN106253975AThe amplitude of the voltage signal decreasesHigh level duration shortenedElectromagnetic network arrangementsCapacitancePower flow

The embodiment of the invention discloses an optical module, comprising a gold finger, a laser drive chip, a laser and a variable resistor. The gold finger is equipped with a signal interface and is used for outputting a current signal. The laser drive chip is equipped with a signal receiving end and a drive signal output end. The signal receiving end is connected with the signal interface. The drive signal output end is connected with the laser and is used for driving the laser to transmit an optical signal. The signal receiving end and one end of the variable resistor are connected with the signal interface. The other end of the variable resistor is grounded. When the duty cycle of the current single is overhigh, the variable resistor is adjusted, the resistance value of the variable resistor is reduced, the current input to the laser drive chip is reduced, a voltage signal amplitude is reduced, a high level part in the voltage signal is pulled down, the duty cycle is reduced, and an intersection in an optical eye diagram moves towards the middle position of the optical eye diagram. When the duty cycle of the input electric signal is changed, other resistance and capacitance in the optical module are not modified, so that jitter of the optical eye diagram is not influenced.

Owner:HISENSE BROADBAND MULTIMEDIA TECH

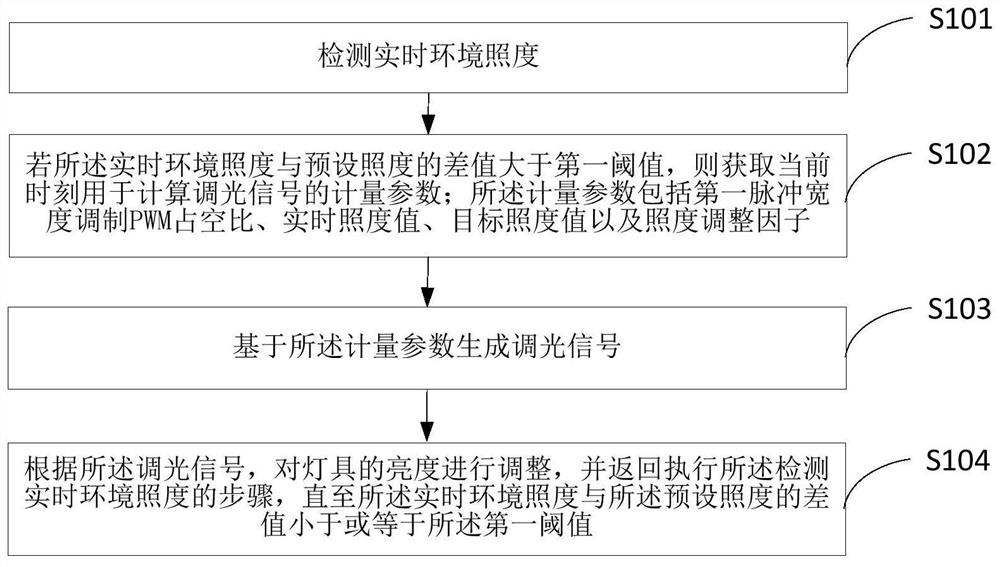

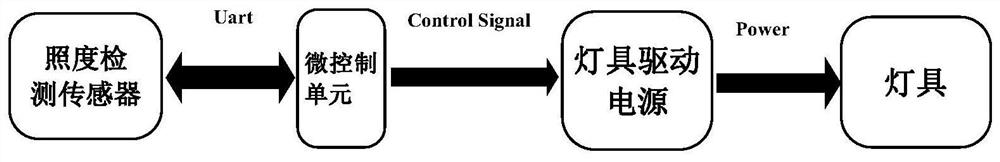

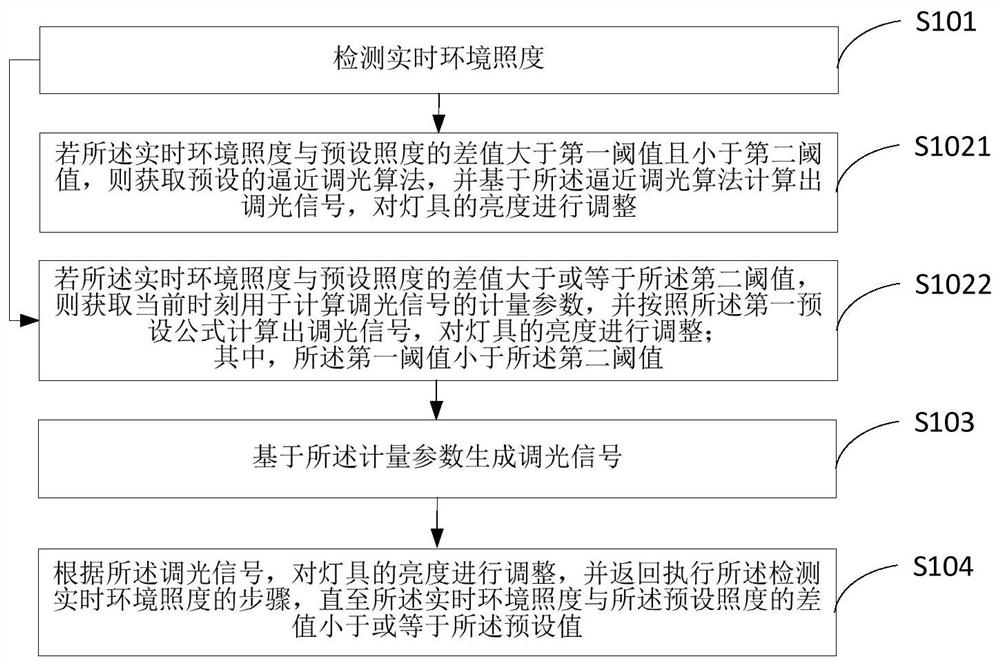

Control method and device for real-time environment illumination of lamp, terminal equipment and medium

PendingCN113329550AAccurate adjustment of constant illuminationRealize intelligent control of constant illuminationElectrical apparatusEnergy saving control techniquesIlluminanceTerminal equipment

The invention is suitable for the technical field of automatic intelligent control, and provides a control method and device for the real-time environment illumination of a lamp, terminal equipment and a medium. The method comprises the steps of detecting the real-time environment illumination, if the difference value between the real-time environment illumination and the preset illumination is greater than a first threshold value, obtaining a metering parameter used for calculating a dimming signal at the current moment, wherein the metering parameters comprise a first pulse width modulation duty ratio, a real-time illumination value, a target illumination value and an illumination adjustment factor, generating a dimming signal based on the metering parameter, and adjusting the brightness of the lamp according to the dimming signal, and returning to execute the step of detecting the real-time environment illumination until the difference value between the real-time environment illumination and the preset illumination is less than or equal to the first threshold value. Intelligent control of constant illumination of the lamp is realized, so that the constant illumination adjusting effect of the dimming signal can be more accurate and has higher stability; and meanwhile, the control efficiency of the real-time environment illumination of the lamp is improved.

Owner:LEEDARSON IOT TECH INC

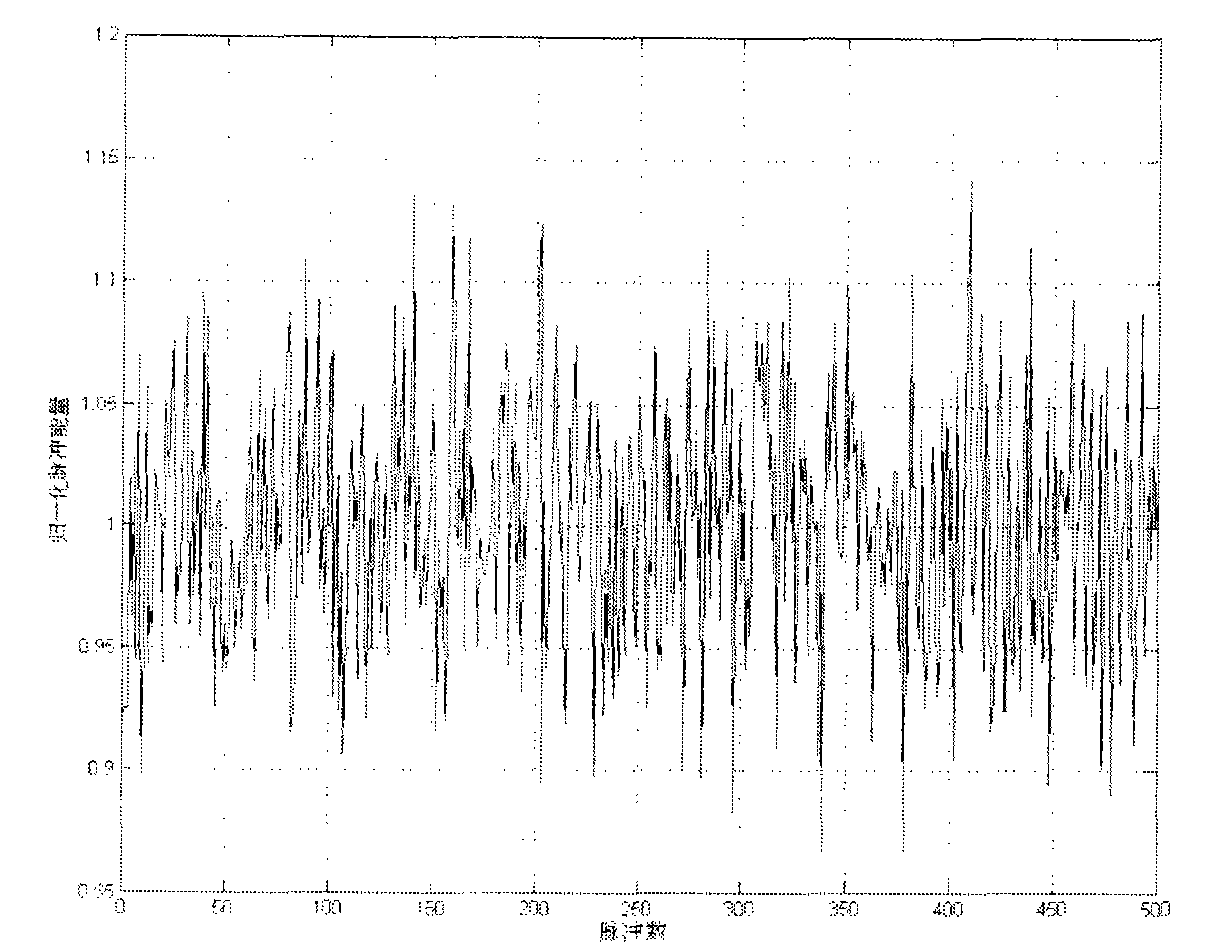

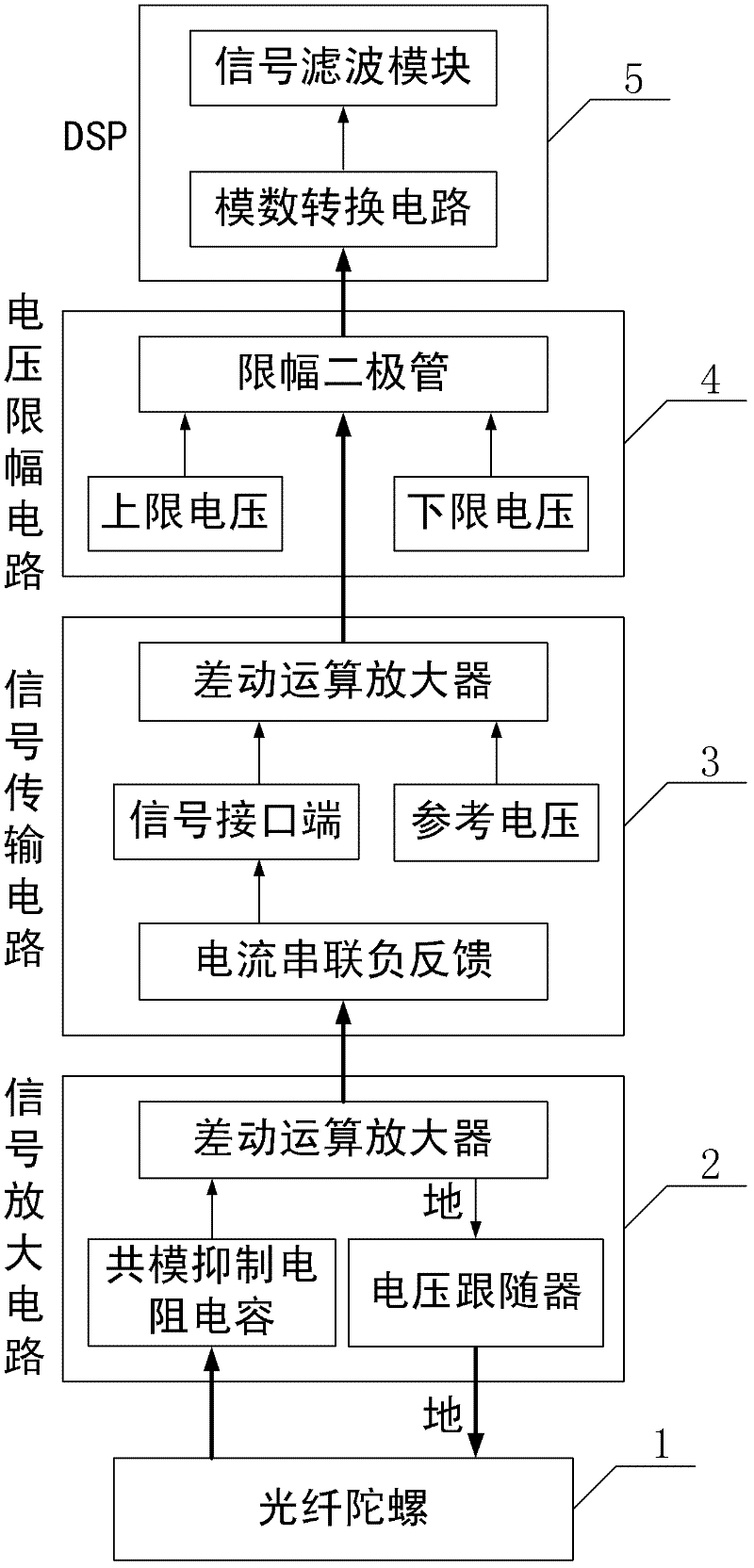

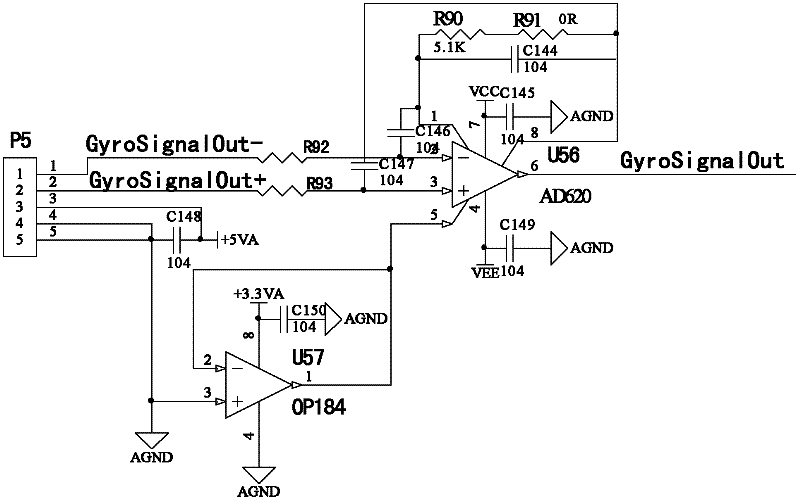

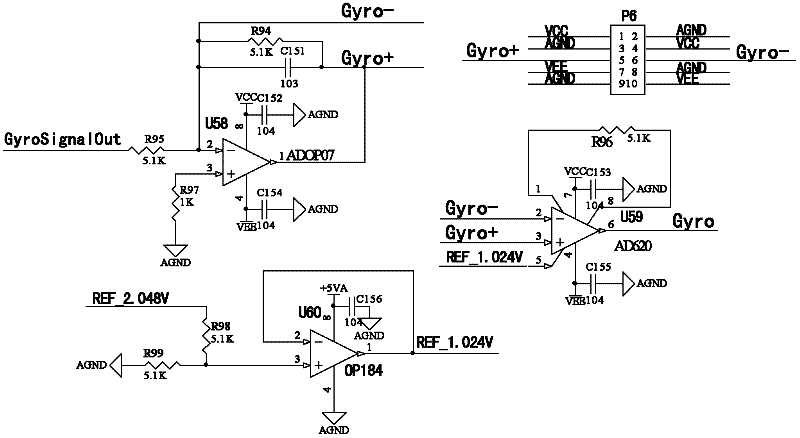

Gyro signal acquisition circuit and signal filtering system for three-axis inertially-stabilized platform

InactiveCN102506859AEfficient detectionSmoothingNavigation by speed/acceleration measurementsVoltage amplitudeAverage filter

The invention relates to a gyro signal acquisition circuit and a signal filtering system for a three-axis inertially-stabilized platform, which are used for realizing the high-precision acquisition of angular rate information of the three-axis inertially-stabilized platform and providing feedback reference for the high-precision control of the platform. The gyro signal acquisition circuit comprises a signal amplification circuit, a signal transmission circuit, a voltage amplitude limit circuit and an analog-to-digital (A / D) conversion circuit of a DSP (Digital Signal Processor); and a signal filtering module comprises a static factor calibration part and an online sliding average filter part. According to the gyro signal acquisition circuit and the signal filtering system for the three-axis inertially-stabilized platform, weak gyro voltage signals are appropriately amplified, filtered and converted into current signals, the current signals are subjected to voltage amplitude limit and then enter an AD channel of the DSP, the original analog signal acquisition is carried out, useful information is extracted by the signal filtering module, and thus, the gyro voltage signals are converted into the true value of the angular rate of a framework of the platform.

Owner:BEIHANG UNIV

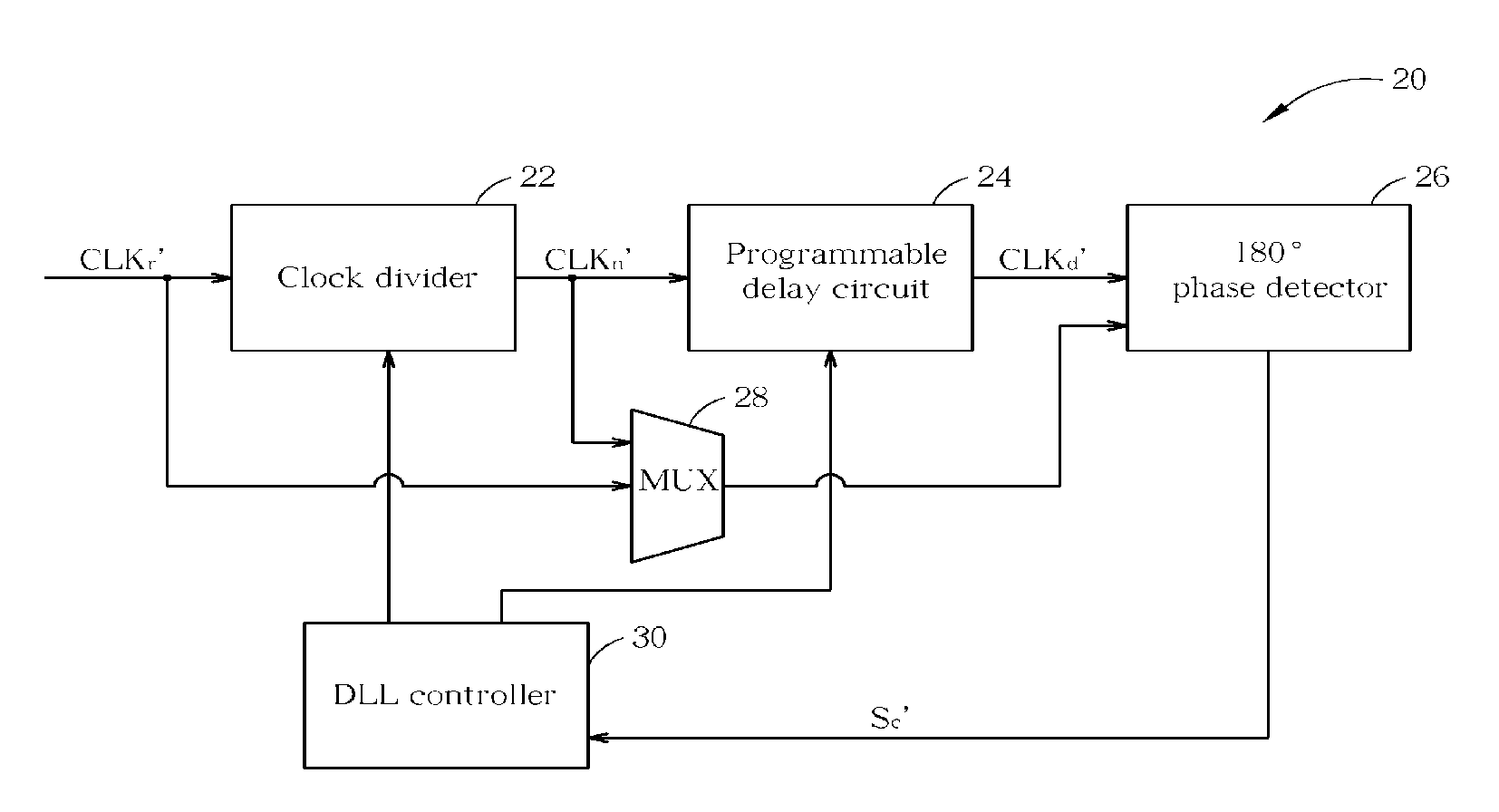

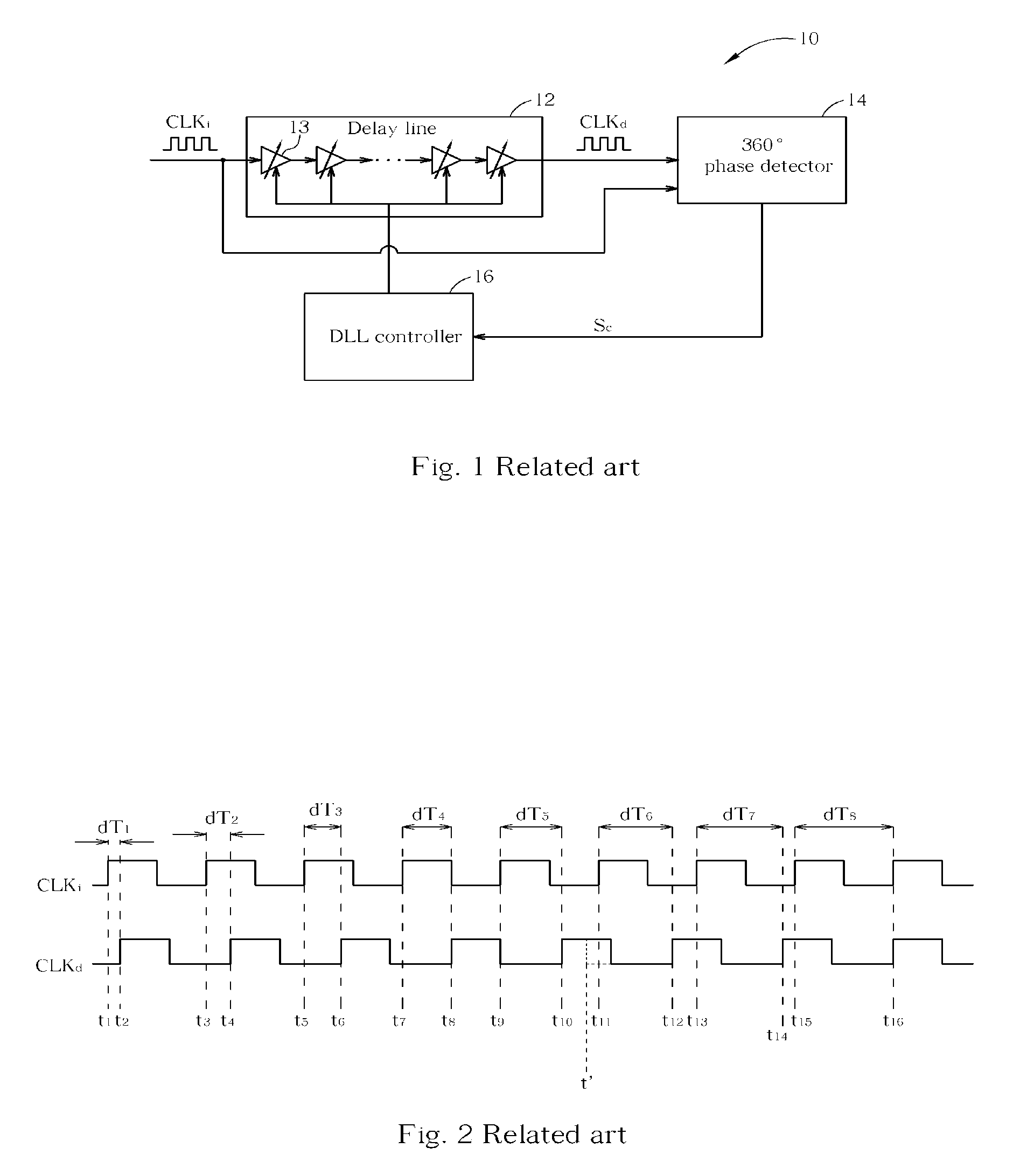

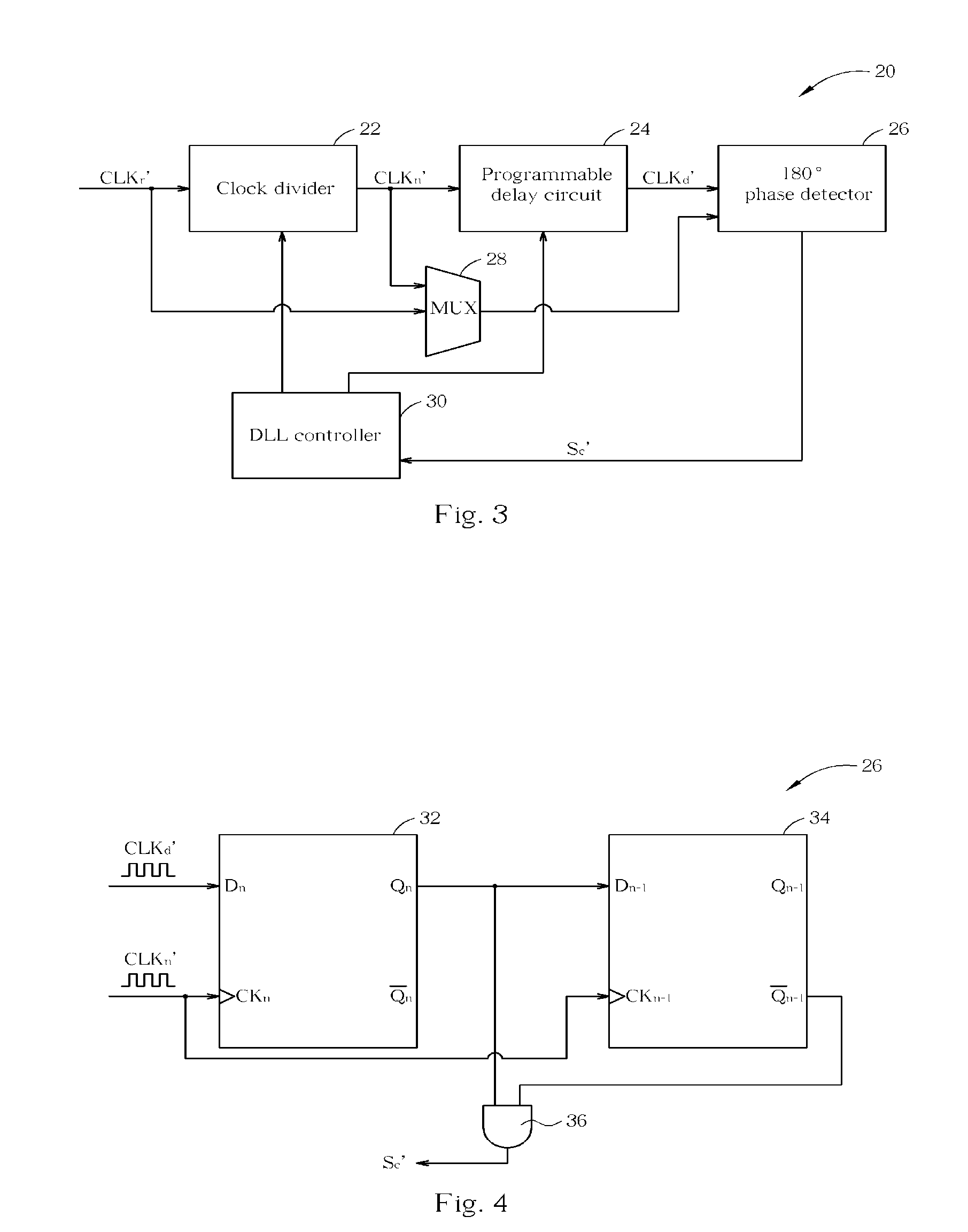

Jitter-resistive delay lock loop circuit for locking delayed clock and method thereof

InactiveUS20060055440A1Resisting jitterReduce the effect of jitterPulse automatic controlPhase detectorDelay-locked loop

A delay lock loop circuit for delaying a reference clock to lock a delayed clock. The delay lock loop circuit includes a clock divider for dividing a frequency of the reference clock by N to generate a frequency-divided clock, a programmable delay circuit electrically coupled to the clock divider for delaying the frequency-divided clock to generate the delayed clock, a 180° phase detector electrically coupled to the programmable delay circuit for detecting a phase change of the delayed clock, and a delay lock loop controller electrically coupled to the programmable delay circuit and the 180° phase detector for programming the programmable delay circuit to lock the delayed clock according to the phase change.

Owner:MEDIATEK INC

Method for eliminating shaking impact of rotation table during high precision inertial navigation system calibration

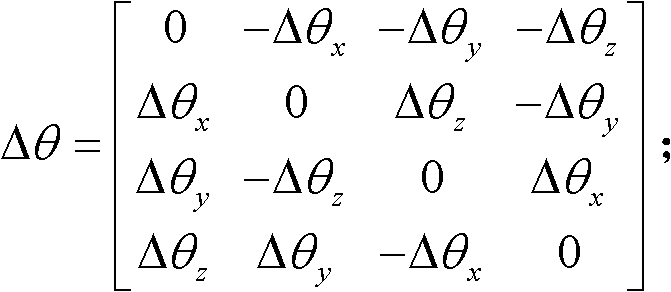

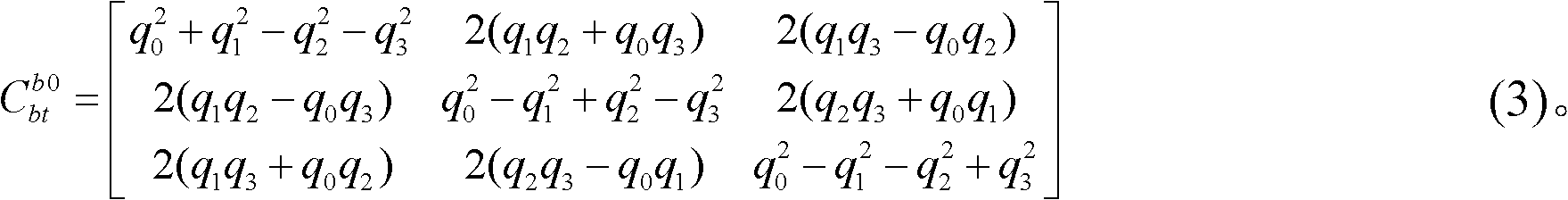

ActiveCN102997932AReduce the effect of jitterReduce adverse effectsMeasurement devicesGeographic coordinate systemAdverse effect

The present invention belongs to the technical field of inertial navigation calibration, and particularly relates to a method for eliminating shaking impact of a rotation table during high precision inertial navigation system calibration. The method comprises: firstly establishing a direction cosine matrix between a real-time vector coordinate system and a starting moment vector coordinate system; then constructing a direction cosine matrix between the starting moment vector coordinate system and a starting moment earth coordinate system; and obtaining an attitude matrix between the real-time vector coordinate system and a geographic coordinate system, wherein attitude information of a stationary state end moment is obtained. With the present invention, the technical problem of impact on calibration precision by the rotation table shaking factor during a system level calibration process of the high precision inertial navigation system is solved; and gyro output information is adopted to real timely track attitude change of the inertial navigation system due to rotation table shaking so as to eliminate adverse effects caused by the rotation table shaking, improve inertial navigation system calibration precision, and reduce requirements on rotation table locking precision during the calibration process.

Owner:BEIJING AUTOMATION CONTROL EQUIP INST

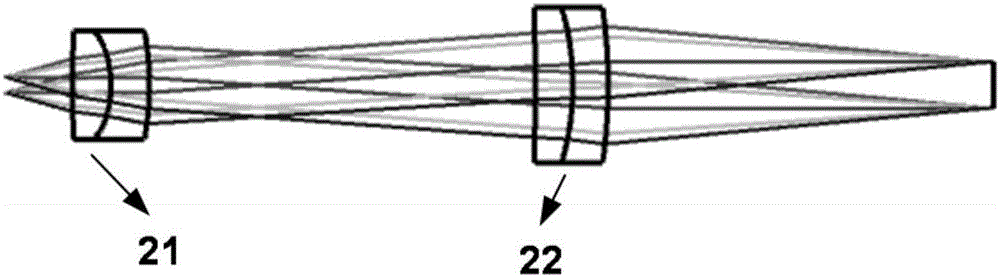

Laser scanning relay lens group and confocal laser endomicroscopy comprising relay lens group

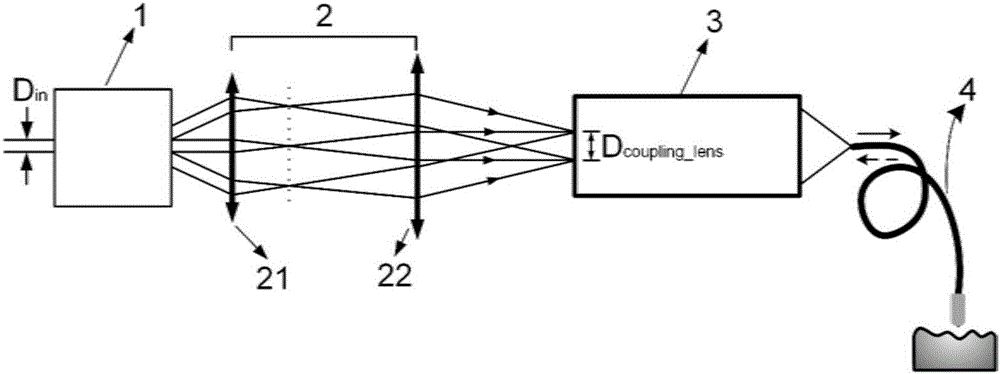

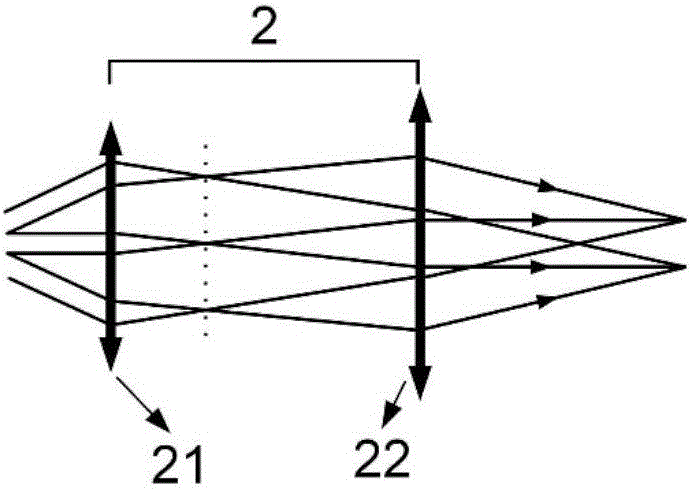

ActiveCN106802479AIncrease the angleReduce the effect of jitterSurgeryMicroscopesExit pupilLaser scanning

The invention discloses a laser scanning relay lens group used in a confocal laser endomicroscopy system. The laser scanning relay lens group is arranged between a two-dimensional laser scanning mechanism (1) used for deflecting excitation light beams and a coupling object lens (3) used for performing focusing and imaging on collimation light beams and coupling the light beams into an optical fiber bundle probe (4) in order to compress the deflected light beams. The laser scanning relay lens group is characterized in that the magnification M of the laser scanning relay lens group (2) is greater than 1. The invention also discloses a confocal laser endomicroscopy system comprising the above laser scanning relay lens group. According to the laser scanning relay lens group and the system, the condition that the exit pupil of emitted light beams and the entrance pupil of the coupling object lens are matched is guaranteed, the swing angle of a scanning vibrating mirror is employed to the maximum, the influence of positioning errors of the vibrating mirror on pixel jittering is reduced, and the system stability is improved.

Owner:JINGWEI SHIDA MEDICAL TECH WUHAN CO LTD

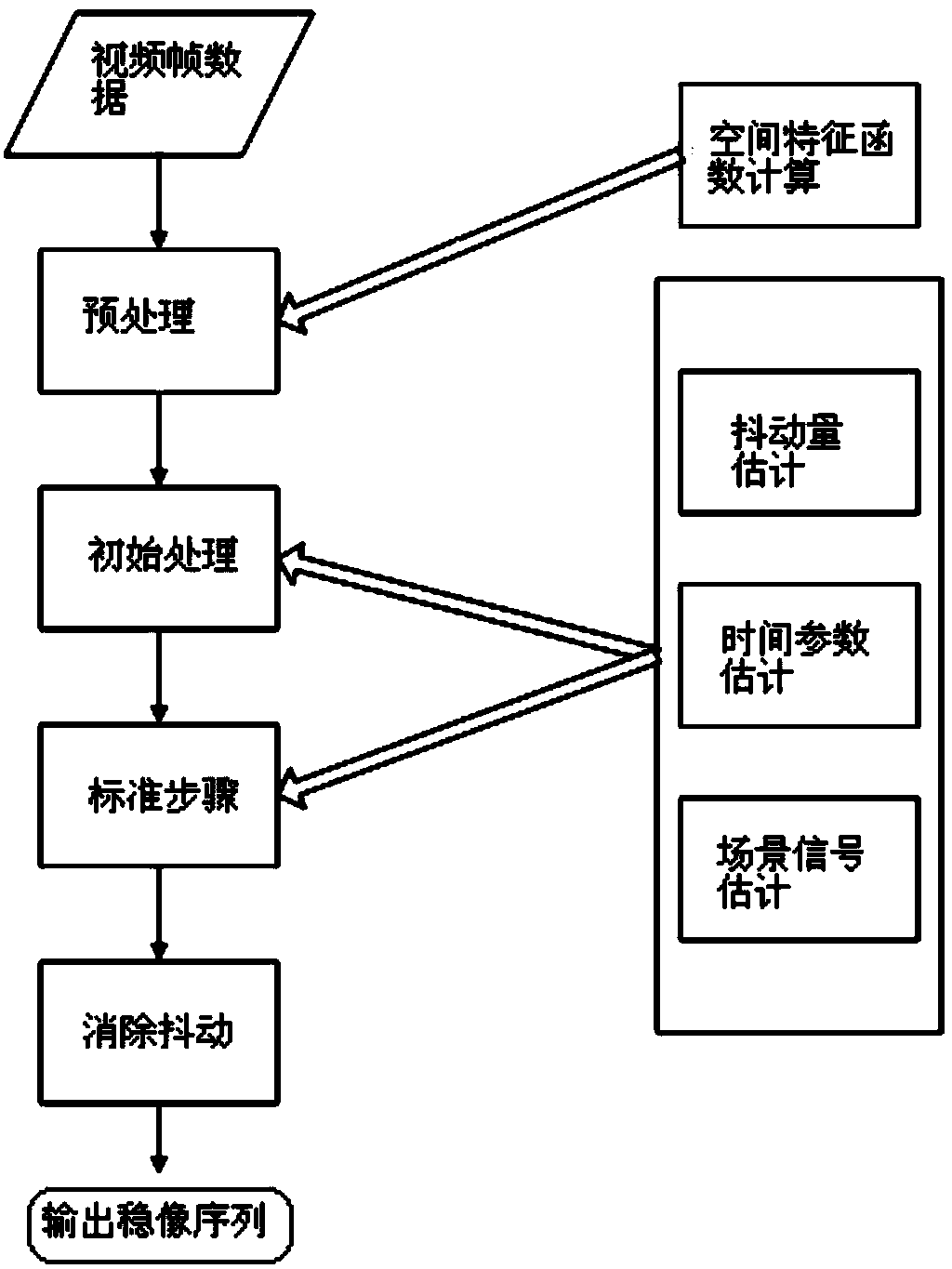

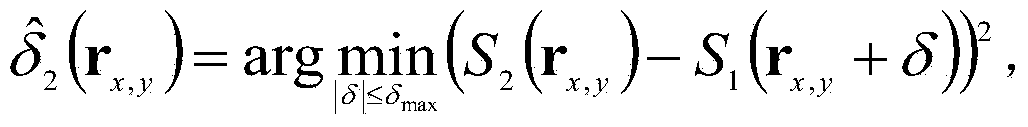

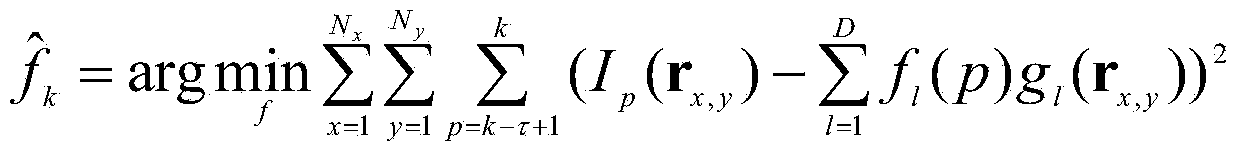

Video image stabilization method based on three-dimensional space-time image estimation technology

InactiveCN103442161AReduce the effect of jitterSolve the defect that it cannot handle the change of depth of fieldTelevision system detailsImage analysisFrame sequenceOriginal data

The invention discloses a video image stabilization method based on a three-dimensional space-time image estimation technology. Original data are collected through a vidicon, the collected original data are preprocessed to be sequential frame sequences, interframe movement conditions are estimated by means of space similarity between a current frame and a reference frame, the jitter amount of each frame is obtained by means of the minimum distance criterion, a set of jitter vectors can be obtained through multi-frame processing, and the obtained set of jitter vectors is used for representing the moving conditions of the vidicon in a time domain; according to all the jitter estimation information in each frame, the overall moving condition of the current frame is obtained comprehensively, space reconstruction is carried out on an original scene frame image through a motion estimation result, the jitter amount is eliminated, and a stabilized image sequence is obtained. The video image stabilization method is used for eliminating jitter influences, video contents are stabilized, the video image stabilization method is based on three-dimensional space-time image estimation, and the defect that field depth changes cannot be processed in a two-dimensional scene stabilization image can be effectively overcome.

Owner:HEFEI UNIV OF TECH

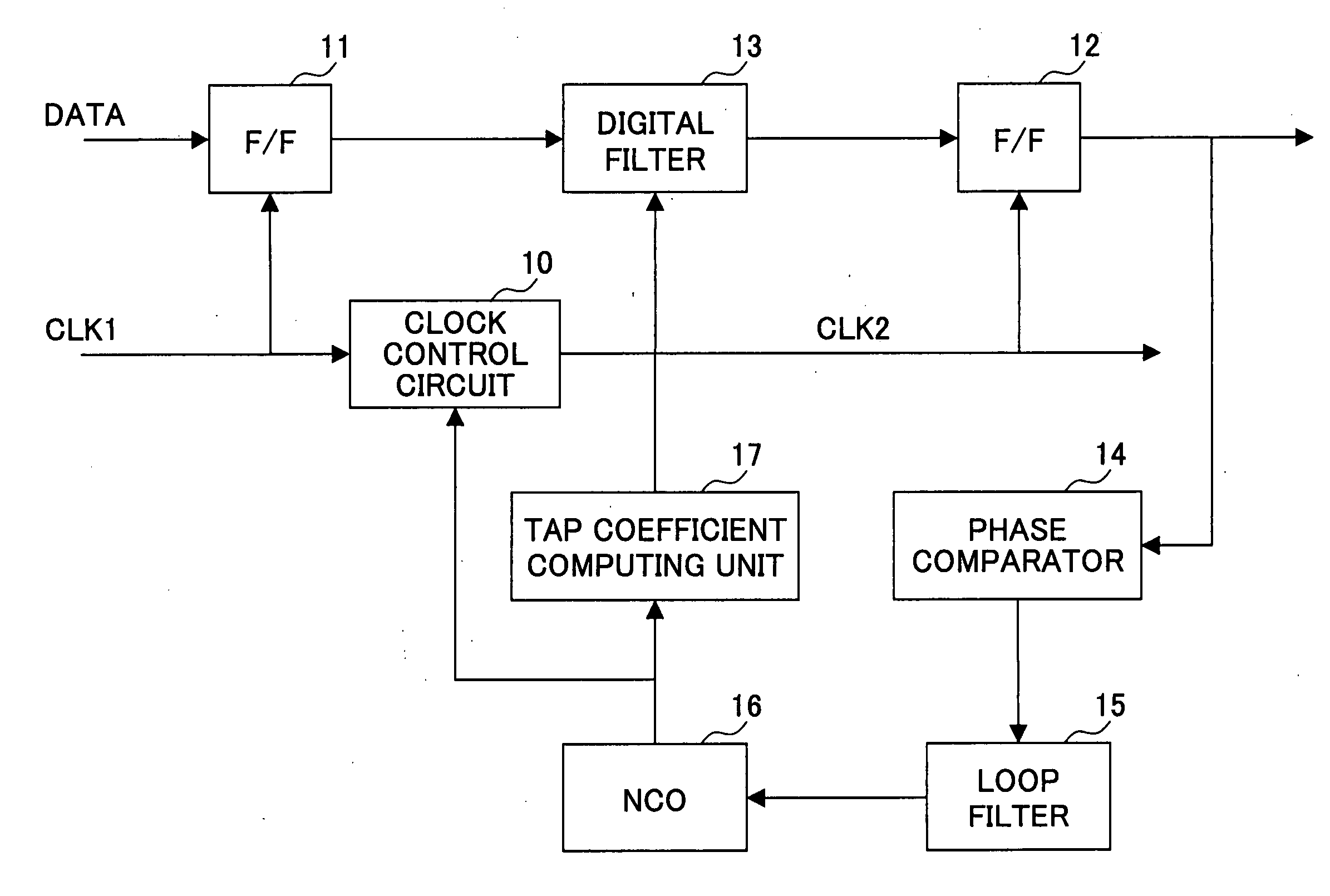

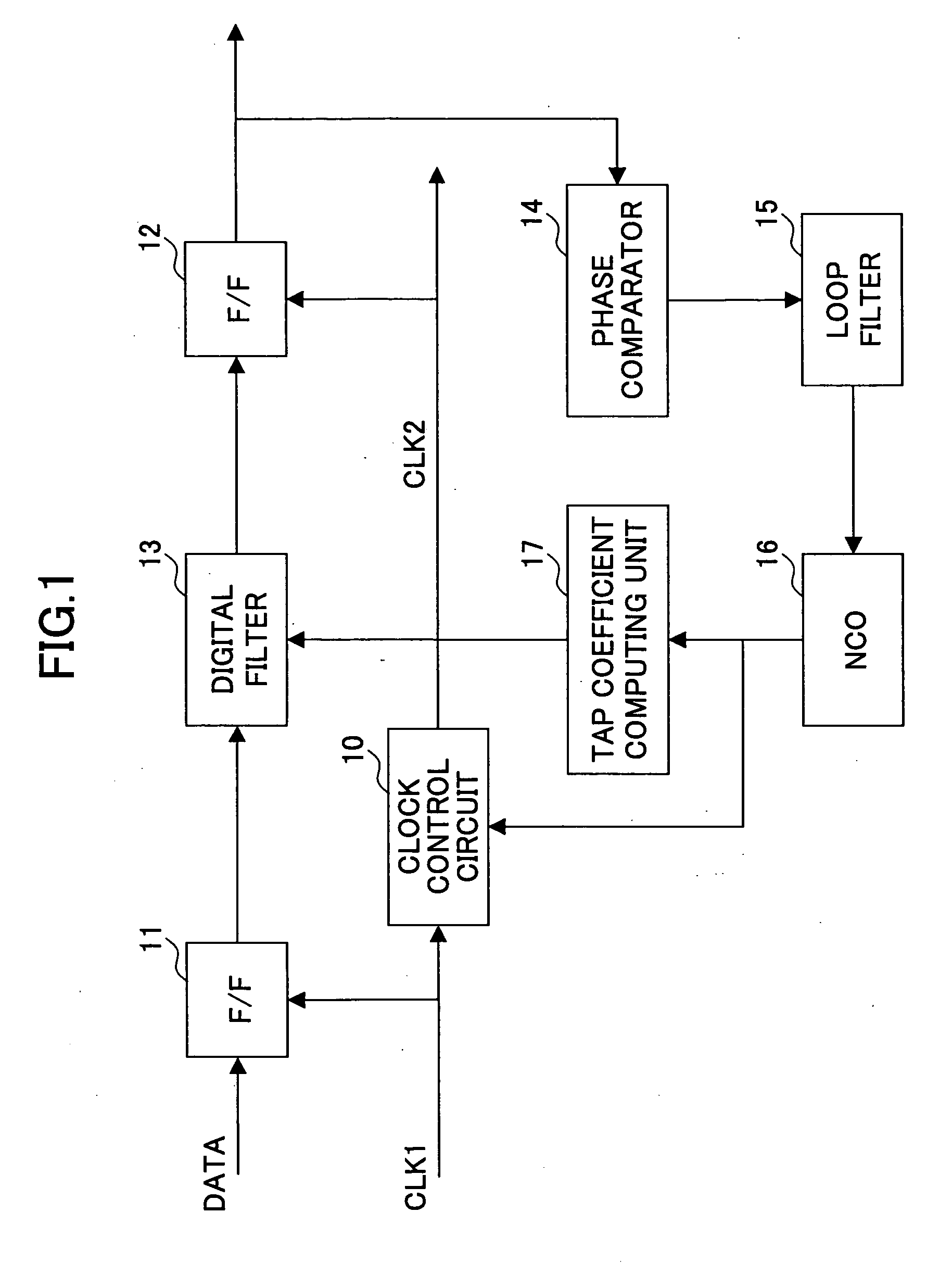

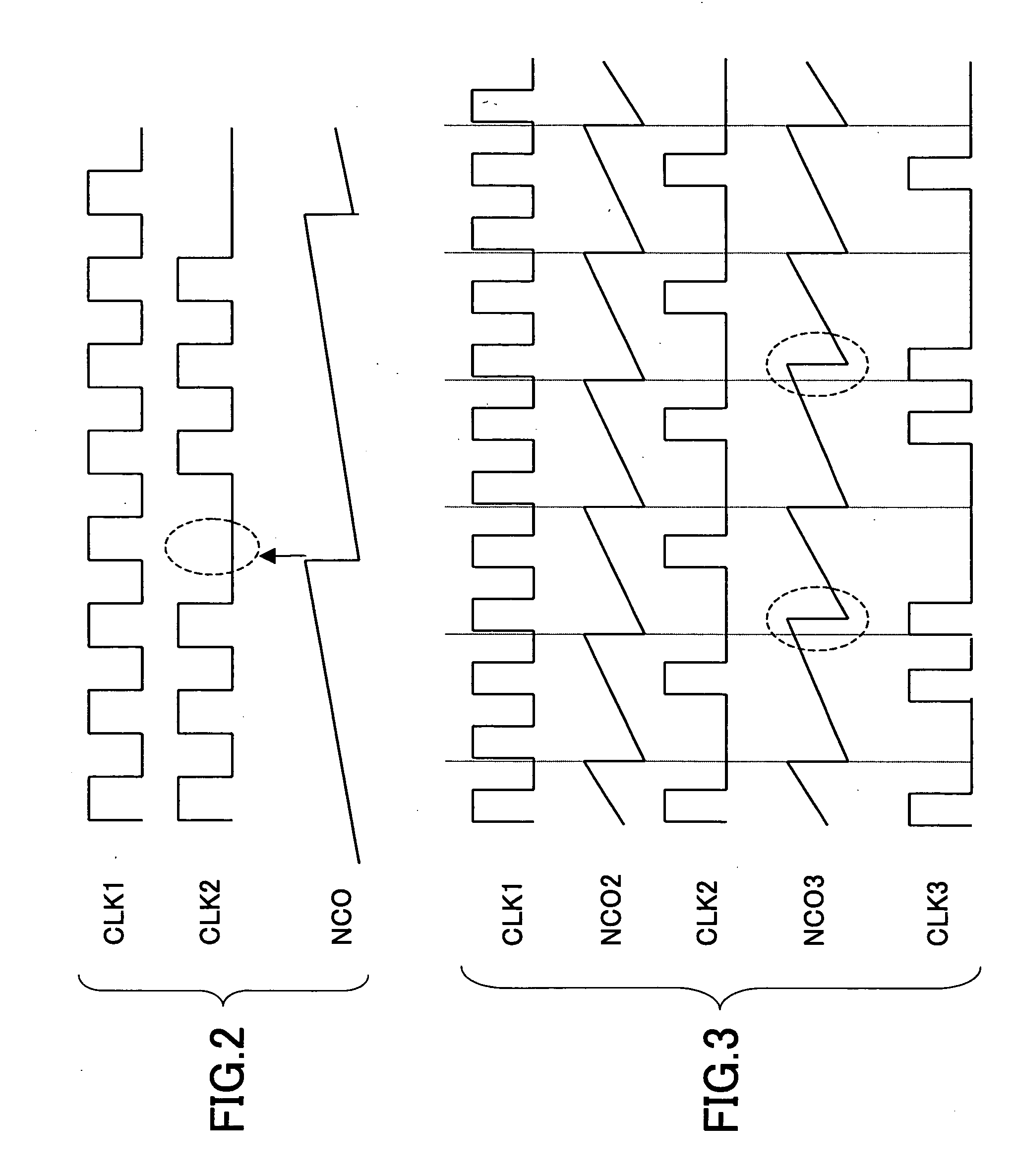

Timing recovery circuit with multiple stages

ActiveUS20060214825A1Decimation rate of decimation can be loweredReduce the effect of jitterSynchronisation information channelsCode conversionMultiple stagesClock signal

A timing recovery circuit includes a first oscillating circuit configured to produce a first timing signal, a second oscillating circuit configured to produce a second timing signal, a first decimation circuit coupled to a supply node of a first clock signal and to the first oscillating circuit to produce a second clock signal made by decimating pulses of the first clock signal in response to the first timing signal, and a second decimation circuit coupled to the first decimation circuit and to the second oscillating circuit to produce a third clock signal made by decimating pulses of the second clock signal in response to the second timing signal, wherein one of the first timing signal and the second timing signal has a fixed cycle, and another one has a cycle responsive to feedback control.

Owner:SOCIONEXT INC

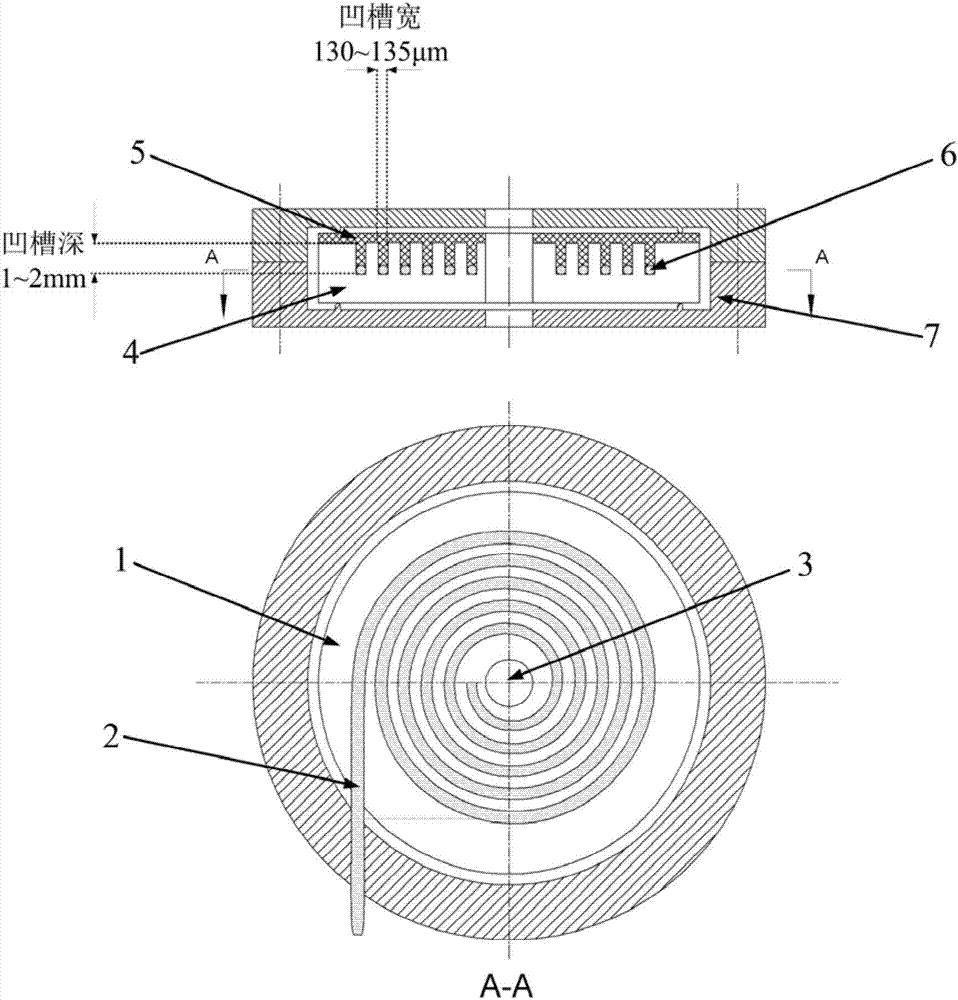

Novel large-wrapping sensing fiber and fiber sensing ring thereof

ActiveCN106950643AReduce motor vibrationGood temperature stabilityOptical fibre with polarisationCurrent measurements onlyOptoelectronicsPhotonic-crystal fiber

The invention relates to a novel large-wrapping sensing fiber and a fiber sensing ring thereof. The fiber is formed by twisting a long beat length polarized photonic crystal fiber from beginning to end, and the minimum pitch of the fiber after twisting is between 0.2 and 2mm. A wrapping of the fiber is between 300-800[mu]m. The sensing ring comprises a quartz substrate layer, a sensing fiber, a quartz upper wrapping, an external protection skeleton and the like. The ultra-fast laser processing technology is used to perform overall shaping of the integrated sensing fiber. After the stress is released by annealing, the rough part is grinded. A central through hole is drilled, and is placed in the external protection skeleton for fixed packaging. The expansion coefficient of the quartz substrate layer is close to that of the fiber. After the sensing ring is packaged, influences of external temperature and vibration on the integrated fiber polarization are reduced, and the integrated fiber is effectively fixed and protected. The manufacturing precision is high, and the usage is convenient.

Owner:HUBEI UNIV OF TECH

Continuous referencing for increasing measurement precision in time-domain spectroscopy

ActiveUS8378304B2Simple designReduce the effect of jitterRadiation pyrometryInvestigating moving sheetsTime domainBeam splitter

An apparatus for incorporation into time-domain spectroscopy systems that creates a continuous reference whereby a sample pulses' phase and amplitude can be tracked and corrected employs a beam splitter to generate sample and reference pulses. A detector is positioned for receiving the reference radiation pulses that do not interact with the sample. The same detector is also positioned for receiving the sample radiation pulses that emerge from the sample. The apparatus can be readily implemented by being configured between the emitter and detector of a terahertz time-domain spectrometer. The reference pulse is used to trace the changes in time and amplitude of the sample pulse. Since any changes in the reference pulse will most likely manifest in the sample pulse, the reference pulse is monitored and used to correct the sample pulse and thereby reduce the effects of jitter.

Owner:HONEYWELL ASCA INC

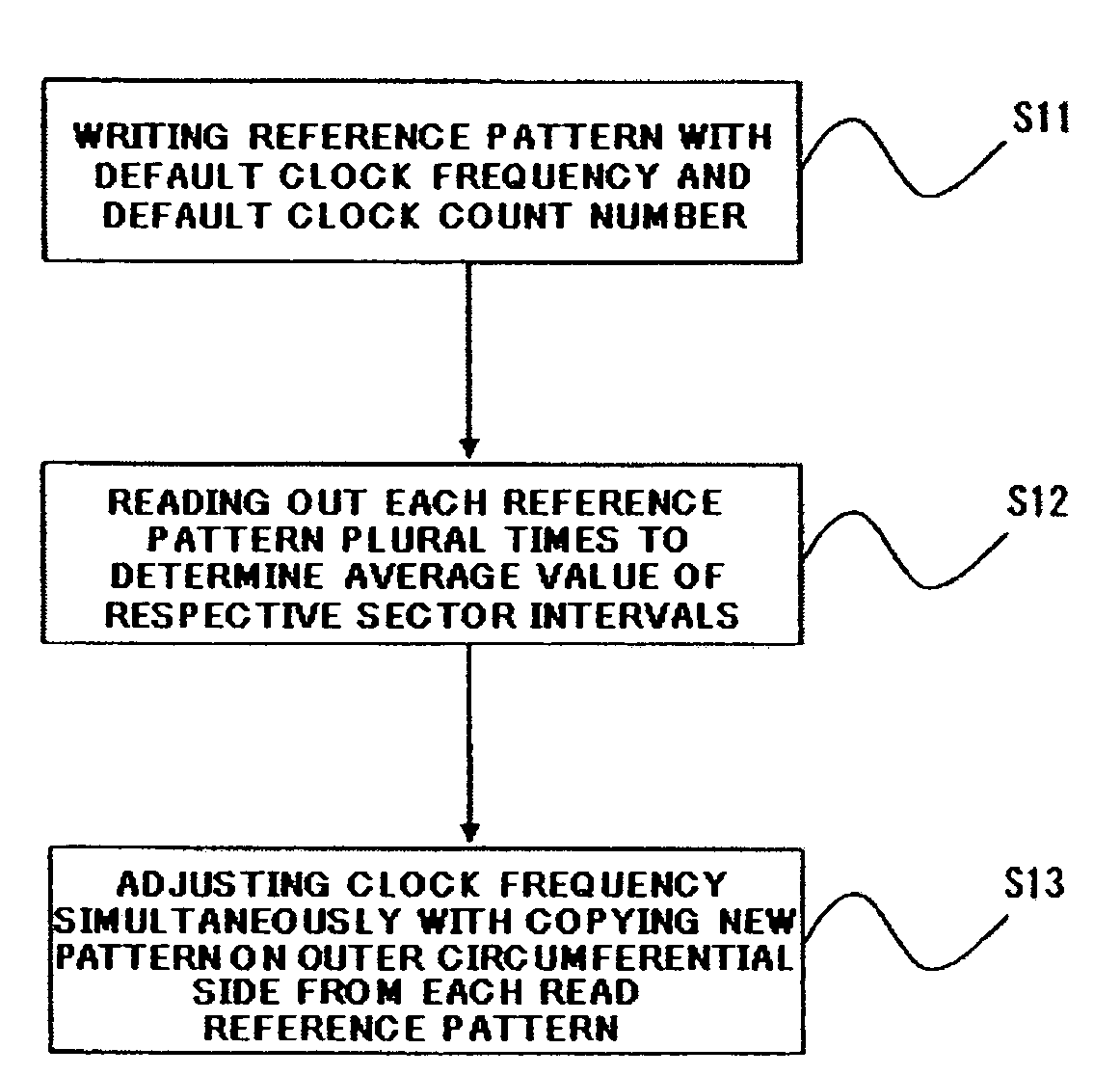

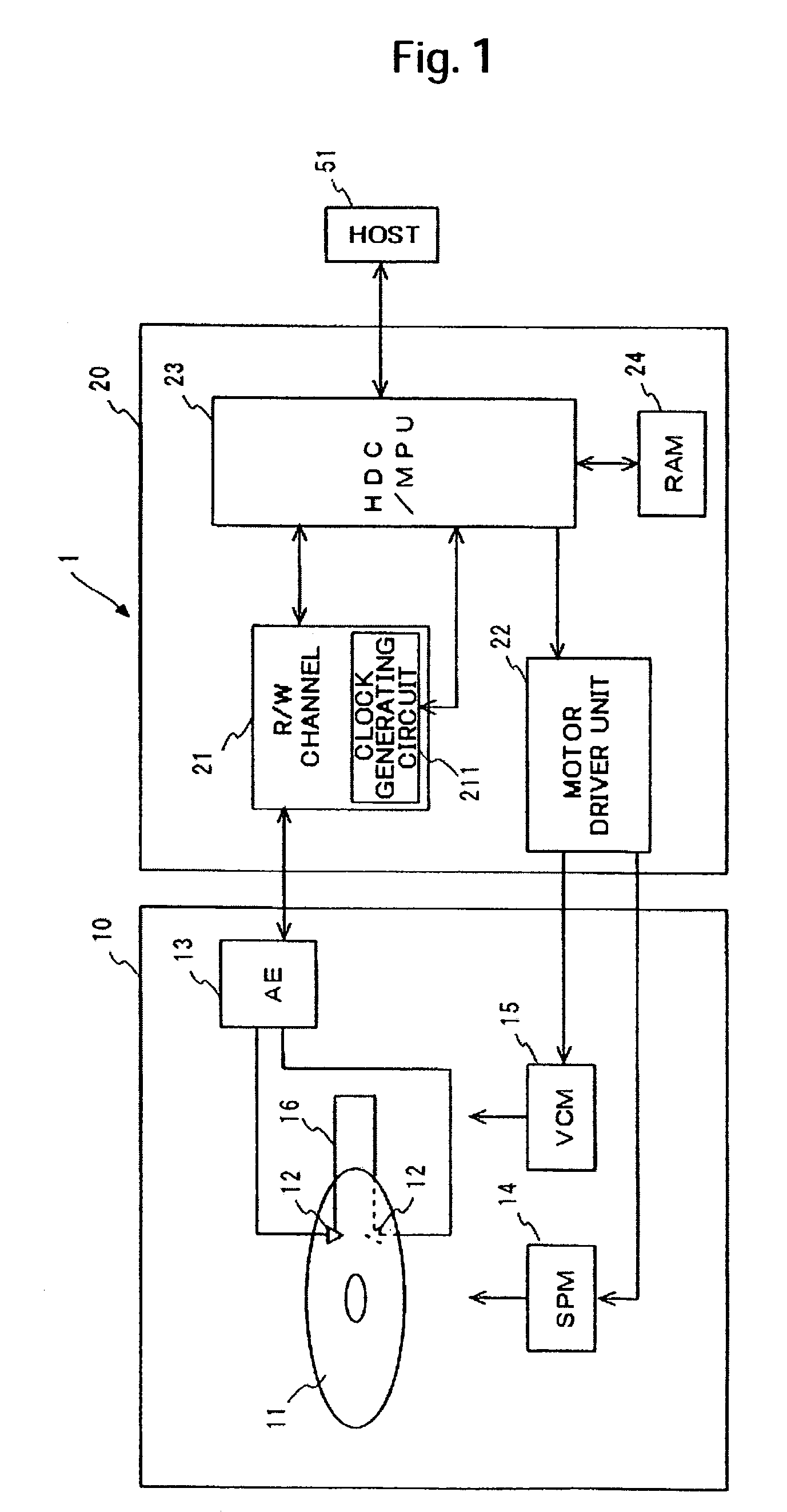

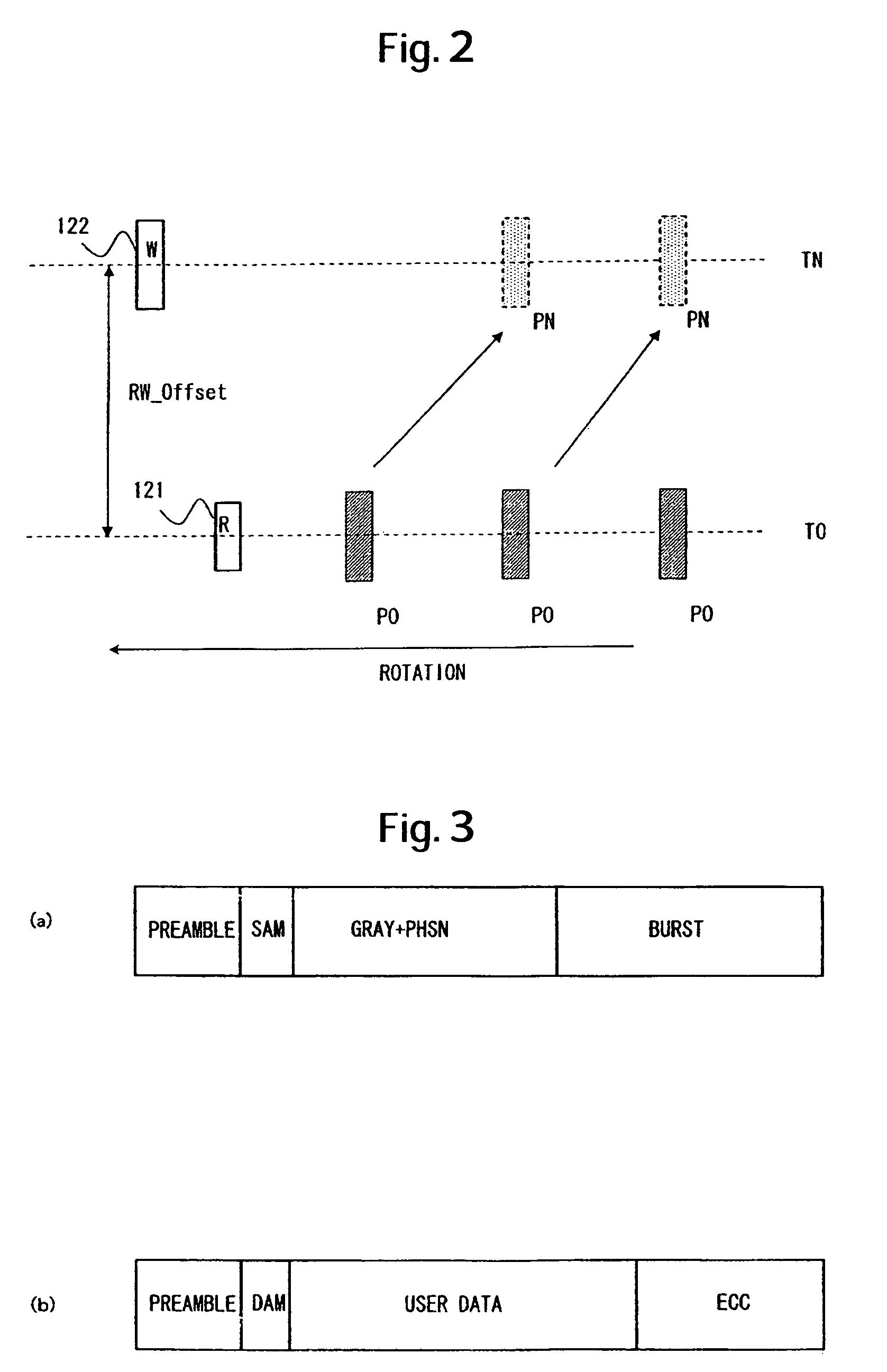

Method of writing pattern on media and data storage device

InactiveUS7532424B2Reduce the effect of jitterAccurate timingDriving/moving recording headsRecord information storageClock rateDelayed time

Embodiments of the invention reduce the effect of the rotational jitters to write a pattern in more accurate timing in self-writing a pattern on a magnetic disk. In an embodiment of the invention, respective patterns in N sectors are first written on an inner circumferential side track as reference patterns with a default clock frequency and a default clock number (a writing interval clock number between respective patterns). The respective reference patterns are then read out plural times for measuring intervals thereof to determine an average value of intervals between the respective sectors. Using the value, a target value is calculated in each sector, which is used in wiring new patterns on the outer circumferential side at even intervals. Then, the respective reference patterns on the inner circumferential side track are read out while the new patterns are written on the outer circumferential side. The respective outer circumferential side patterns are written with the modulated clock frequency after a delay time calculated for every sector has passed from the time when the reference patterns on the inner circumferential side track are detected.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

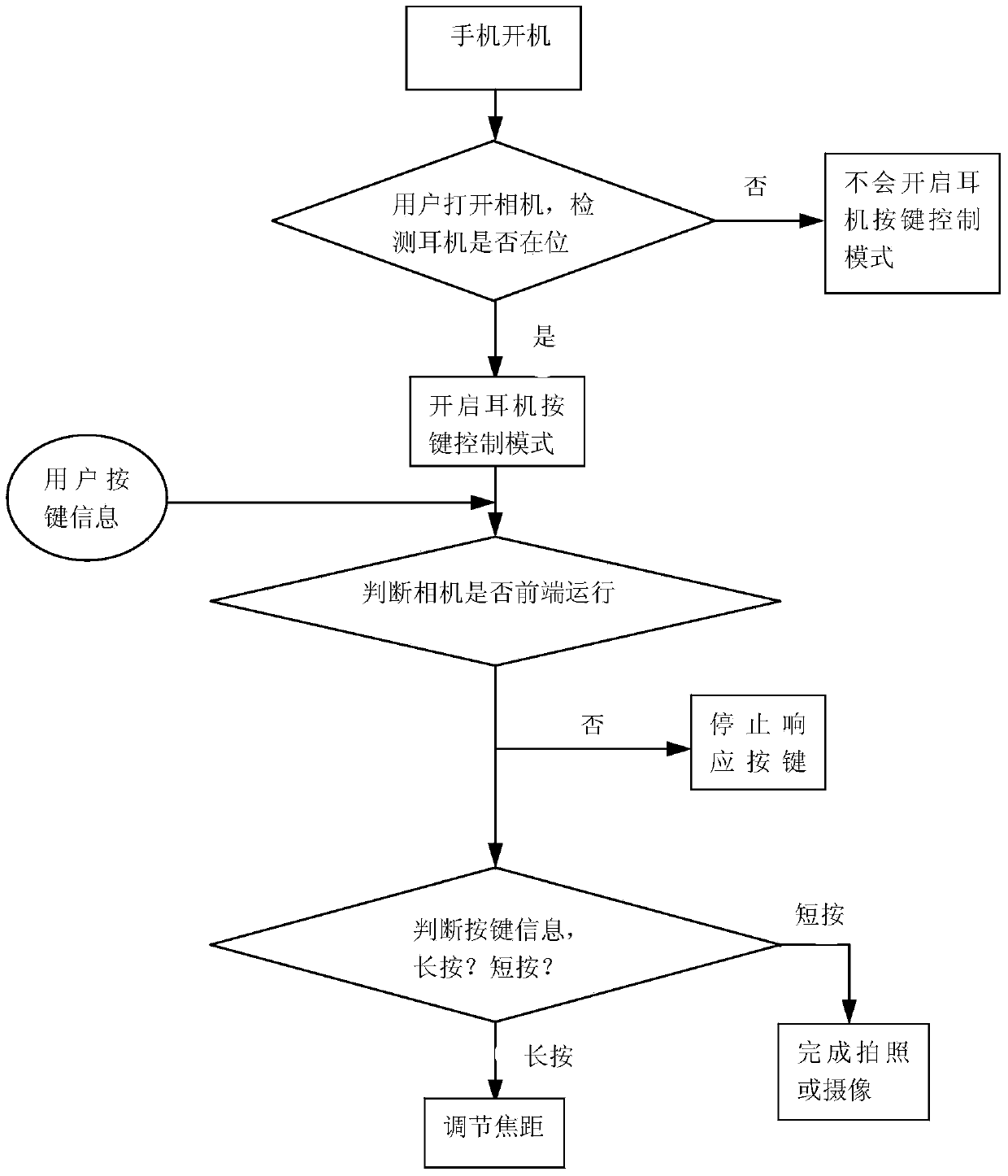

Method for controlling camera of mobile phone by using earphone

InactiveCN103747176AReduce the effect of jitterAccurate and smooth operationTelevision system detailsColor television detailsHeadphonesMobile phone

The invention provides a method for controlling a camera of a mobile phone by using an earphone. The problem that a camera of a conventional mobile phone is mainly operated with fingers, so that a viewing angle of the camera is easily influenced by the length of an arm, and the camera is easily jittered is mainly solved. According to the method for controlling the camera of the mobile phone by using the earphone, the camera of the mobile phone is controlled through keys of the earphone, so that the dependence of the mobile phone on the fingers is reduced, and human-computer interaction modes are expanded. The method for controlling the camera of the mobile phone by using the earphone comprises the following steps of 1, starting the camera of the mobile phone, detecting whether the earphone is connected or not, entering a step 2 for processing if the earphone is connected, and if the earphone is not connected, entering a screen touching photographing mode or entering the step 2 for processing after the earphone is connected; 2, operating the keys of the earphone to finish photographing.

Owner:西安乾易企业管理咨询有限公司

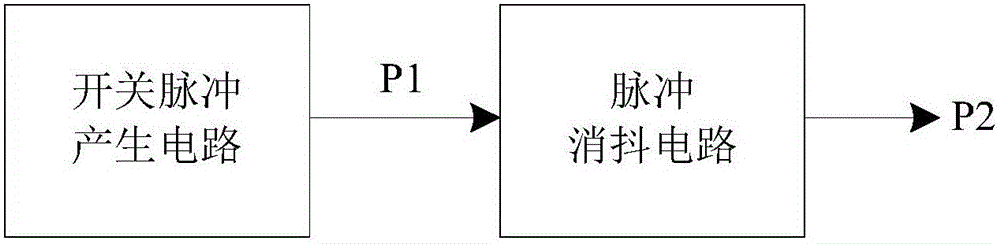

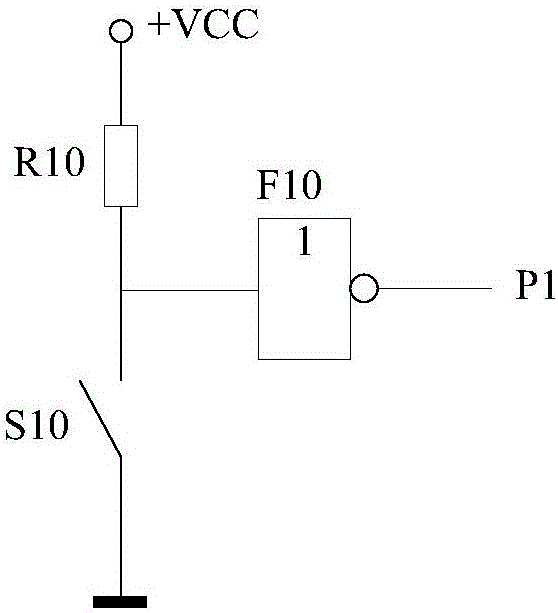

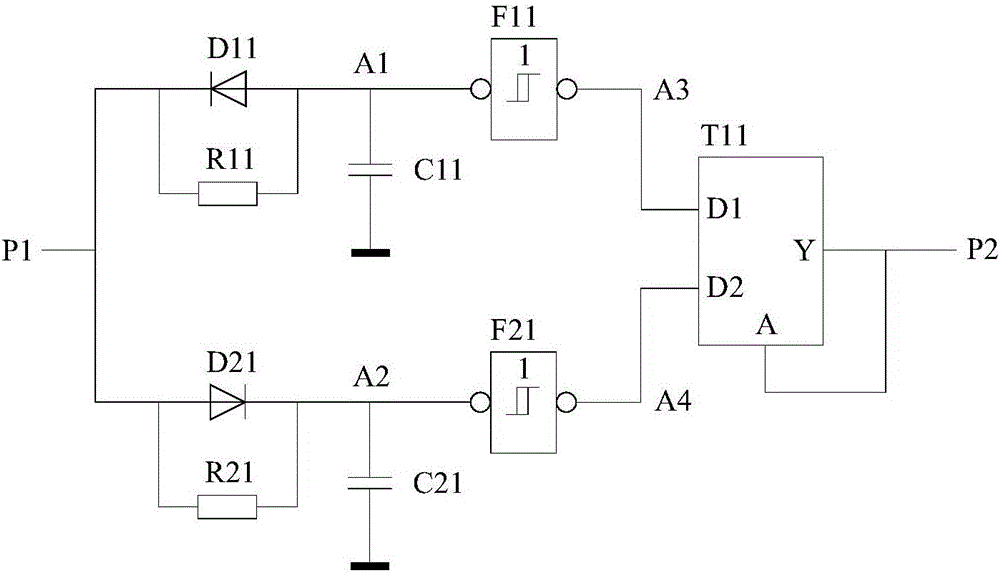

Anti-jitter circuit

ActiveCN106067789AReduce the effect of jitterQuick recovery of interfering signalsPulse manipulationMultiplexerTime constant

Provided is an anti-jitter circuit which comprises a switching pulse generating circuit, a forward anti-interference circuit, a backward anti-interference circuit, and a data selector. An output pulse controls the data selector in order to switch an output signal of either the forward anti-interference circuit or the backward anti-interference circuit as the output pulse. The anti-jitter circuit may automatically filter out a positive narrow pulse during a negative wide pulse and a negative narrow pulse during a positive wide pulse, especially may filter out key or switch contact jitter narrow pulse interference signal. The maximum widths of the positive narrow pulse and the negative narrow pulse required to be filtered out can be regulated by changing a charge time constant and a discharge time constant, respectively. The anti-jitter circuit can be used in the fields where a circuit is required to reliably remove key or switch pulse jitter influence.

Owner:邳州市景鹏创业投资有限公司

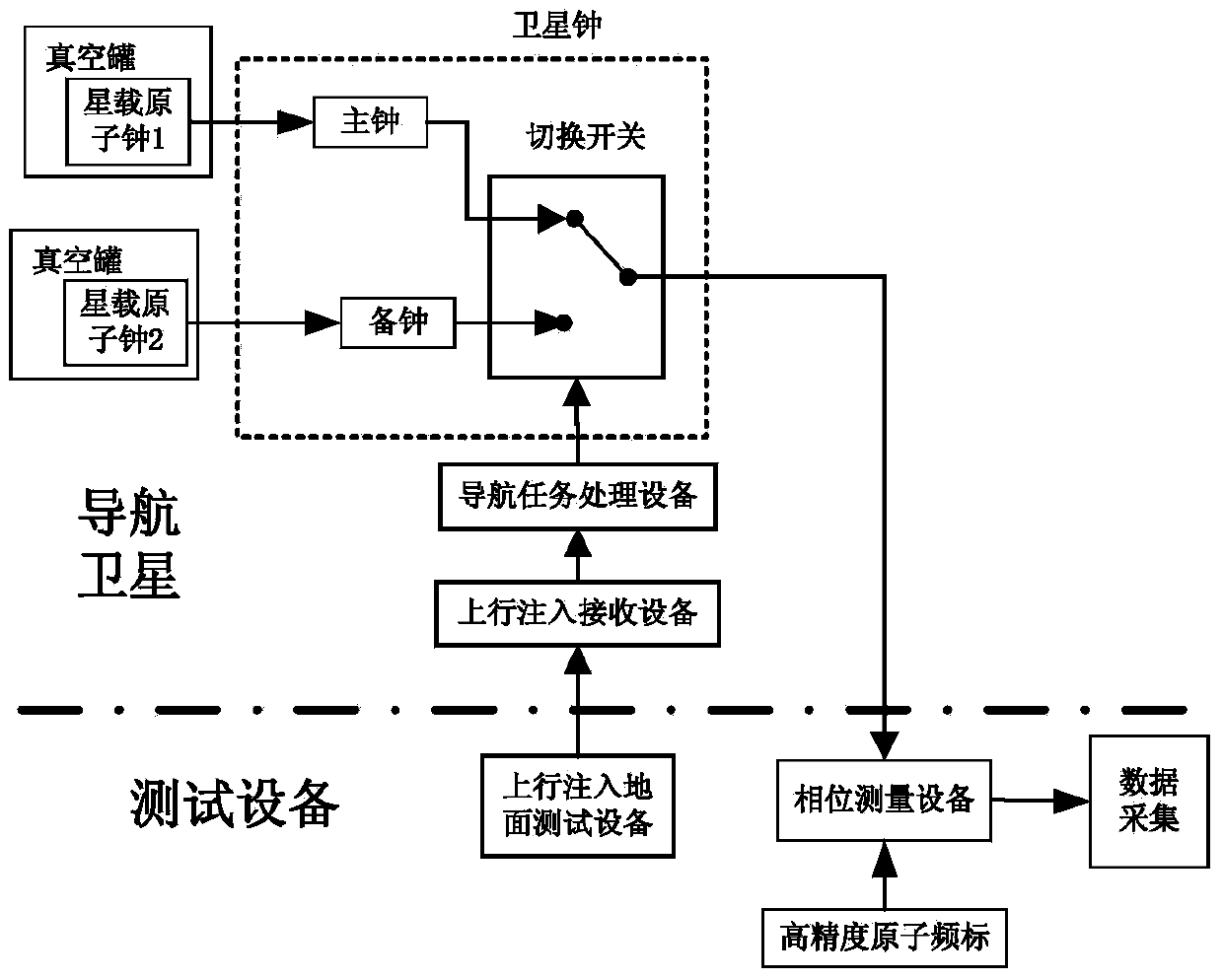

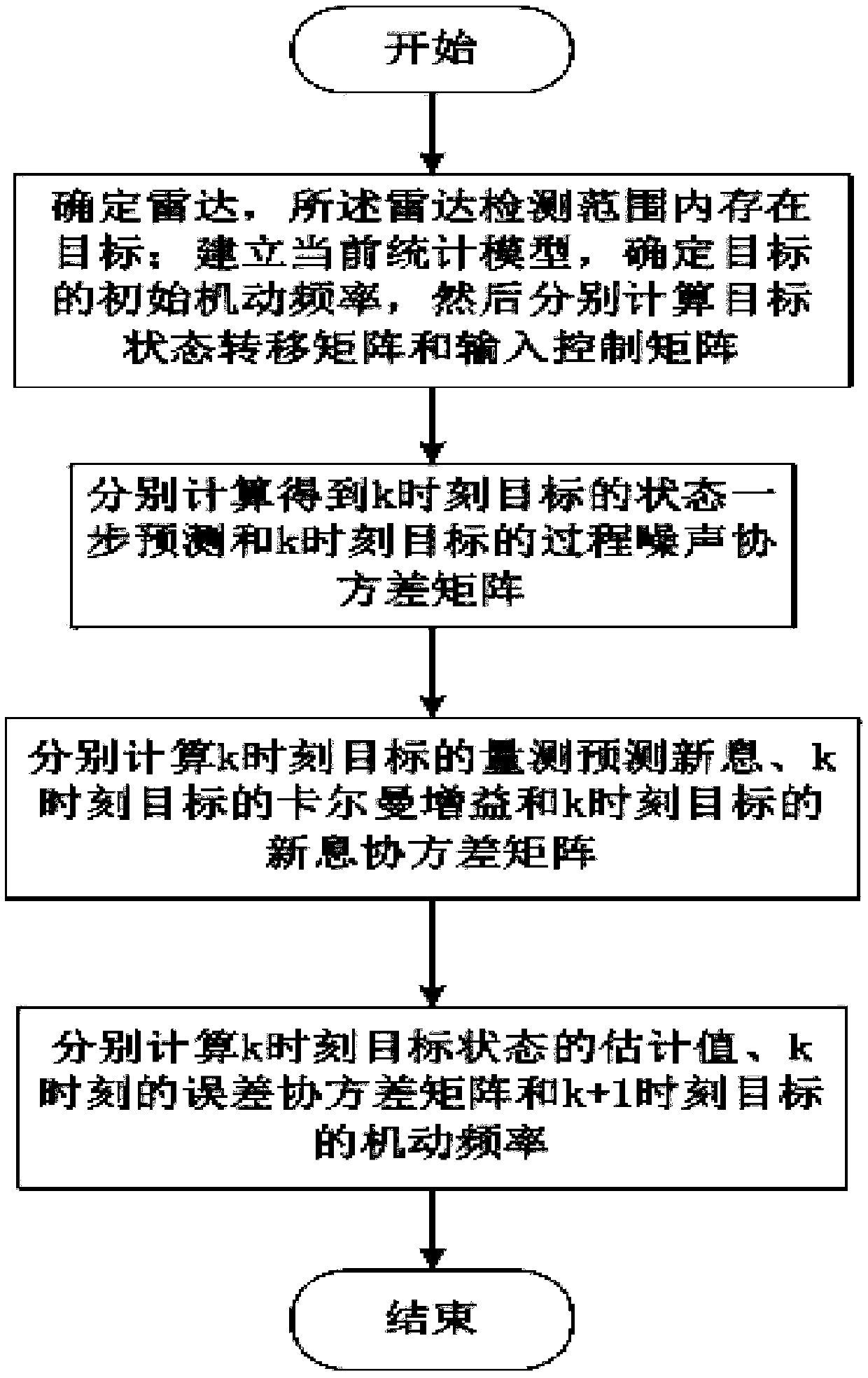

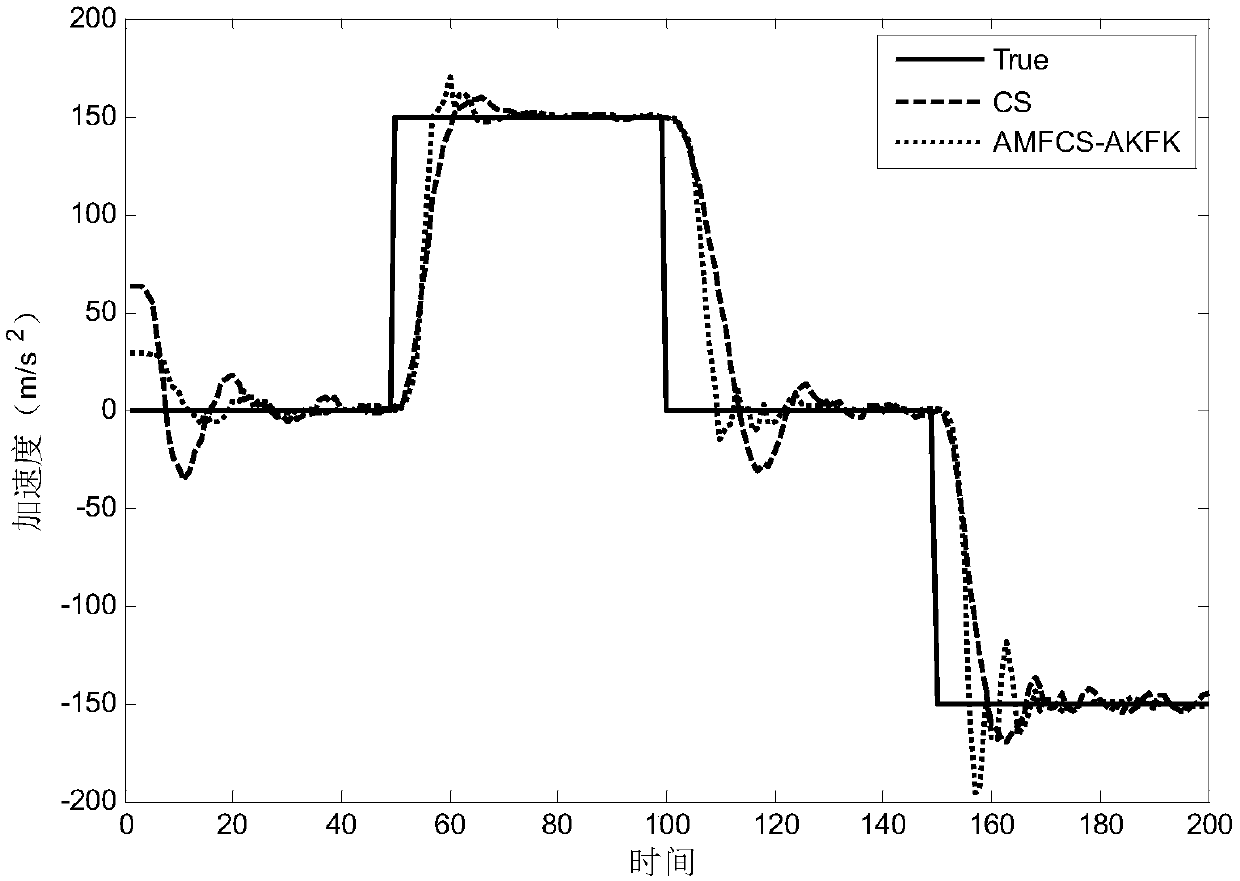

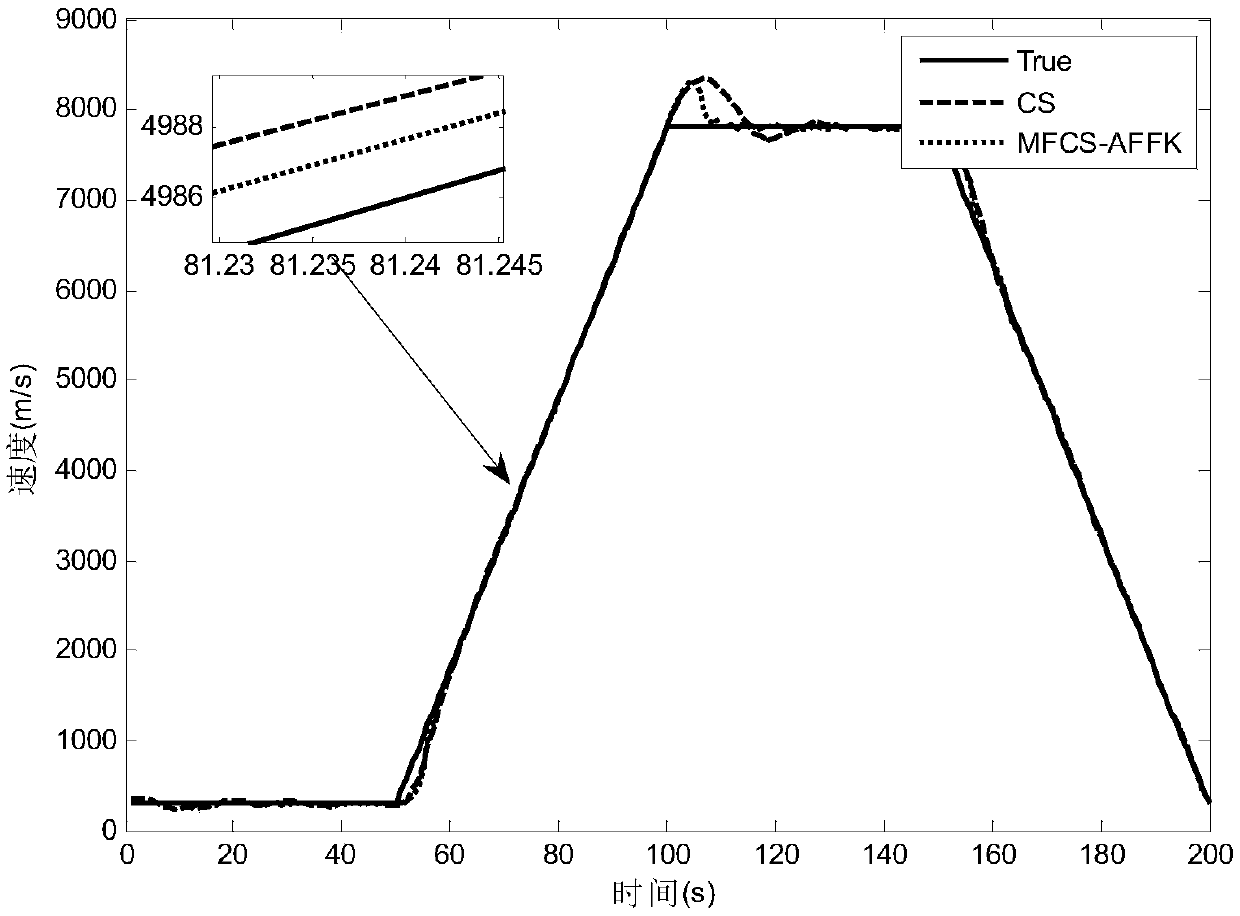

Radar maneuvering target tracking optimization method based on current statistical model

InactiveCN108646237ALower latencyImprove real-time performanceRadio wave reradiation/reflectionProcess noiseInput control

The invention discloses a radar maneuvering target tracking optimization method based on a current statistical model. The radar maneuvering target tracking optimization method based on a current statistical model includes the steps: determining a radar and determining that a target exists in the radar detection range; establishing a current statistical model, determining an initial maneuvering frequency alpha0, and respectively calculating a target state-transition matrix F and an input control matrix G; marking the state estimation of the target at the k-1 moment as X<^>(k-1|k-1), marking themaneuvering frequency of the target at the k moment as alphak, and respectively calculating the state one-step prediction X<^>(k|k-1) of the target at the k moment and the process noise covariance matrix Q(k) of the target at the k moment; respectively calculating the measurement prediction innovation v(k) of the target at the k moment, the kalman gain K(k) of the target at the k moment, and theinnovation covariance matrix S(k) of the target at the k moment; and respectively calculating the estimated value X<^>(k|k) of the state of the target at the k moment, the error covariance matrix P(k|k) of the target at the k moment, and the maneuvering frequency alphak+1 of the target at the k+1 moment, wherein the error covariance matrix P(k|k) of the target at the k moment, the estimated valueX<^>(k|k) of the state of the target at the k moment, and the maneuvering frequency alphak+1 of the target at the k+1 moment are the radar maneuvering target tracking optimization result based on thecurrent statistical model.

Owner:XIDIAN UNIV

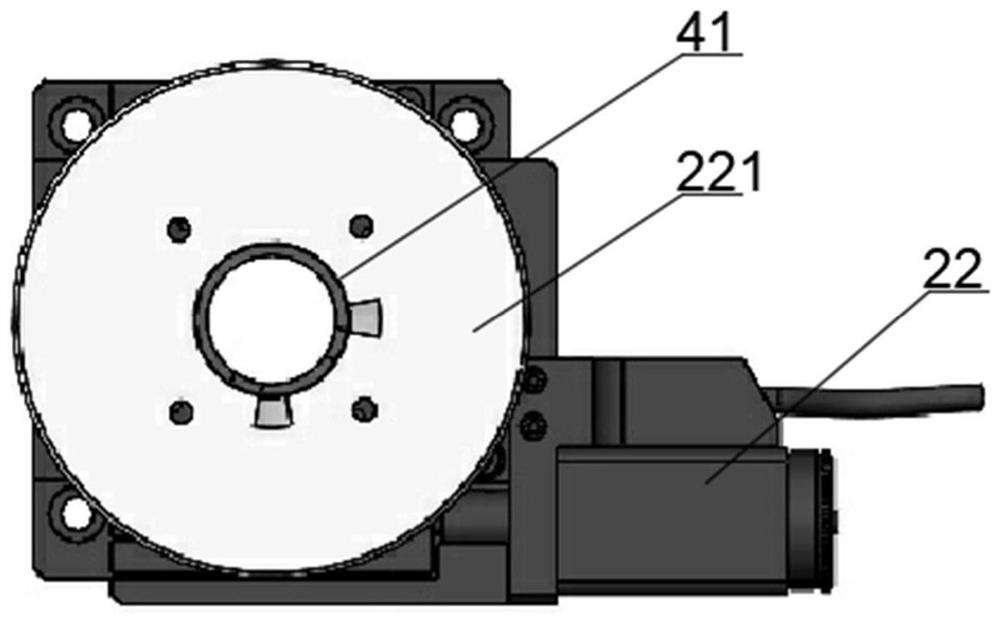

High-precision free space type sun tracker and tracking method thereof

PendingCN112212857AEliminate the effects of jitterEliminate the effects ofNavigation by astronomical meansPhotometry for measuring solar lightAutomatic controlOptical processing

The invention belongs to the field of automatic control, and particularly relates to a high-precision free space type sun tracker and a tracking method thereof. The system comprises a data processingsystem, a sun tracking system and an optical processing system, the data processing system comprises an upper computer program and an upper computer image processing program, and the upper computer program has a time and space position measuring and calculating function; the sun tracking system comprises a motor controller, a motor and a tracking part; the motor controller acquires an instructionfrom an upper computer program to control the motor to drive the tracking part to track the sun; the light processing system comprises a light emitting reflector, a window sheet, an imaging cylinder and a high-pixel CCD detector. The light processing system is used for collecting light spots of light collected by the sun tracking system and transmitting the light spots to an upper computer image processing program. The tracker is high in tracking precision, and can be used as a matching device of an intermediate infrared laser heterodyne technology to provide a detection signal light source for a laser heterodyne system.

Owner:HEFEI INSTITUTES OF PHYSICAL SCIENCE - CHINESE ACAD OF SCI

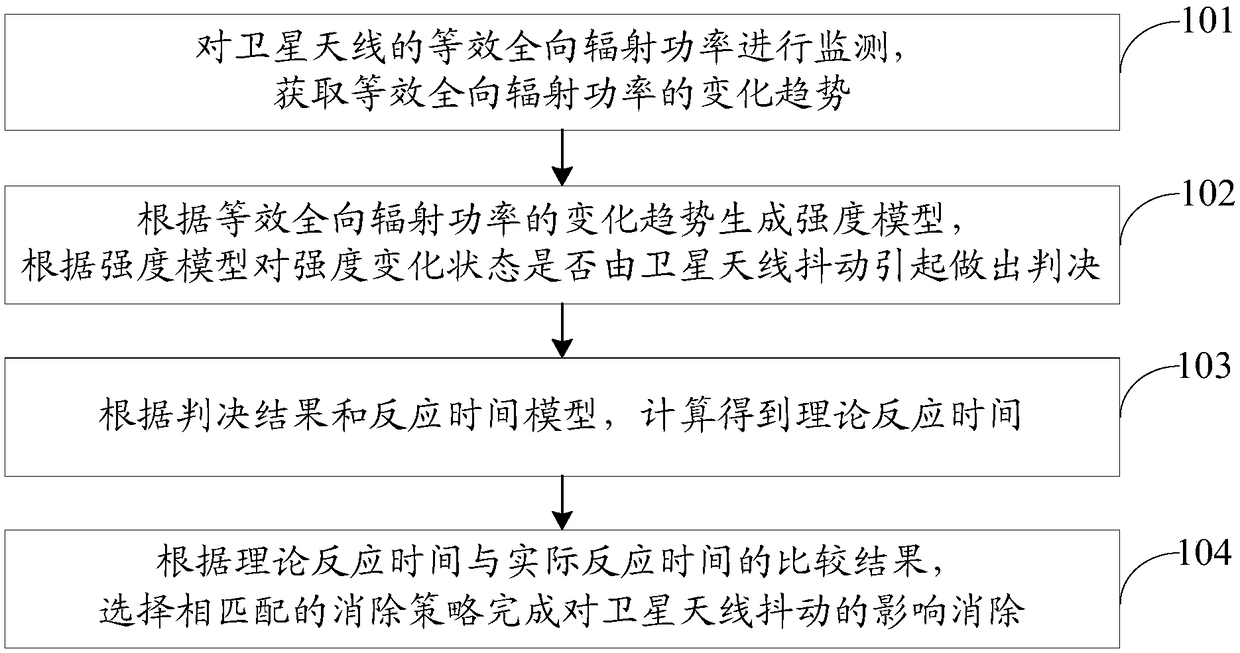

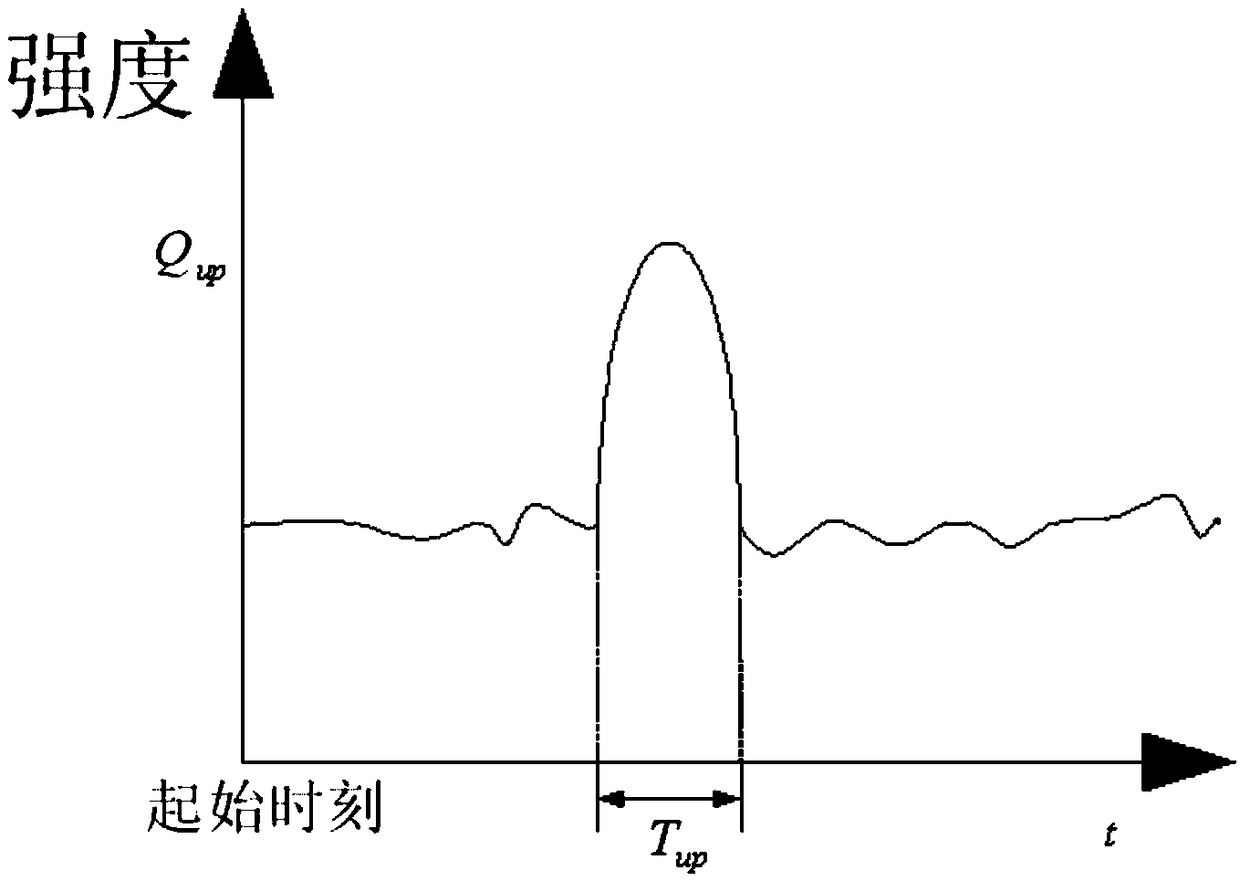

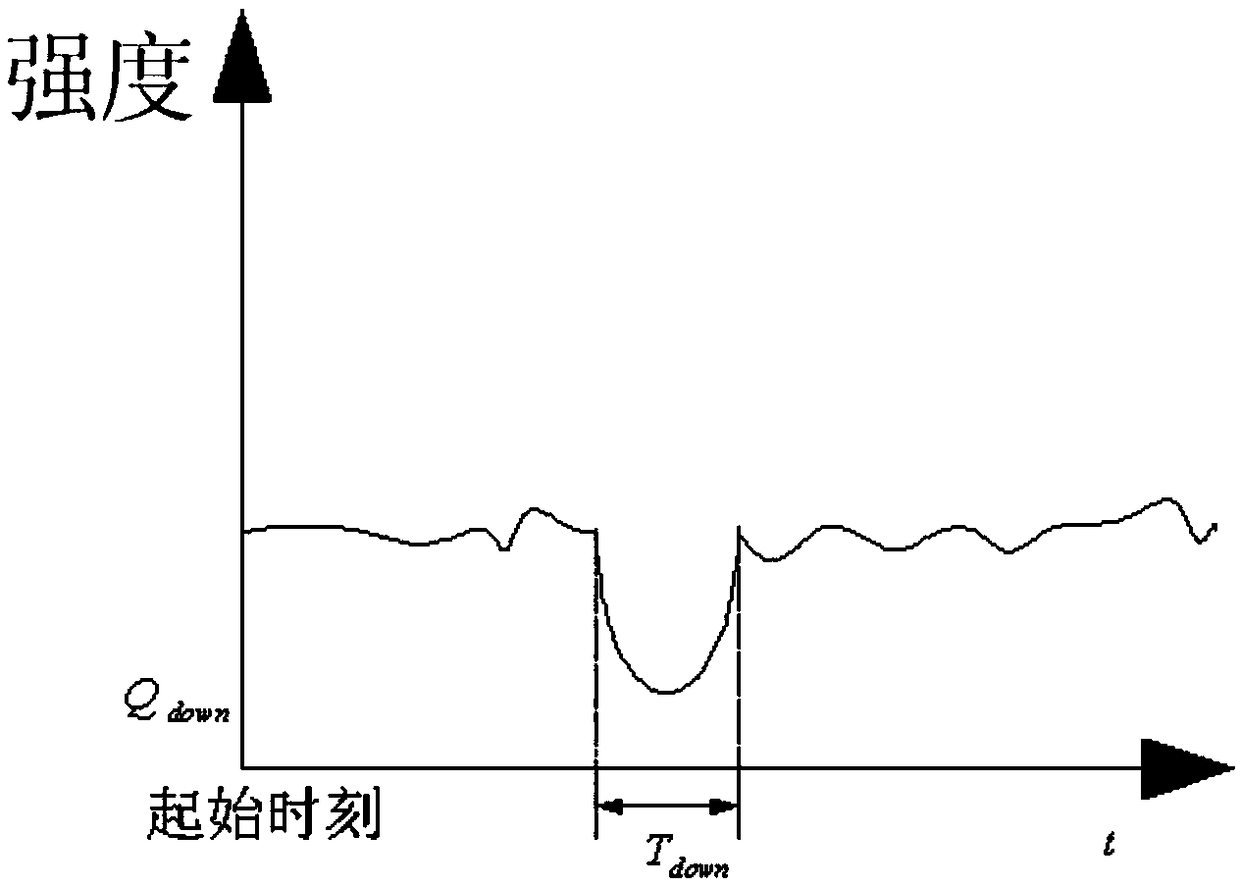

Satellite antenna jitter monitoring and influence elimination analysis method and system

ActiveCN108650012ATimely judgmentWork lessTransmitters monitoringRadio transmissionLimit valueGround station

The invention discloses a satellite antenna jitter monitoring and influence elimination analysis method and system. The method comprises the steps of monitoring equivalent omnidirectional radiation power of a satellite antenna and obtaining a change trend; generating an intensity model according to the change trend, and judging whether an intensity change state results from satellite antenna jitter or not; calculating theoretical response time according to a judgment result and a response time model; and selecting a matching elimination policy to finish eliminating the influence of the satellite antenna jitter according to a comparison result between the theoretical response time and practical response time. According to the method and the system, through monitoring of the satellite antenna radiation intensity threshold change condition, a response time limit value is calculated; the response time of a ground station or a user is taken as the most key technical index, and under the condition that a satellite signal and a parameter of the user or the ground station work normally or the satellite signal is not disconnected with the user or the ground station, a handover scheme and process for eliminating the influence of the antenna jitter on the signal intensity can be provided.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com