Patents

Literature

164 results about "Hydrogen annealing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Hydrogen Annealing is nothing but annealing or heating the component upto 200-300 degree celsius in ambient hydrogen atmosphere in the furnace. Hydrogen has a higher heat transfer coefficient than air or traditional Hydrogen + Nitrogen gas mixture.

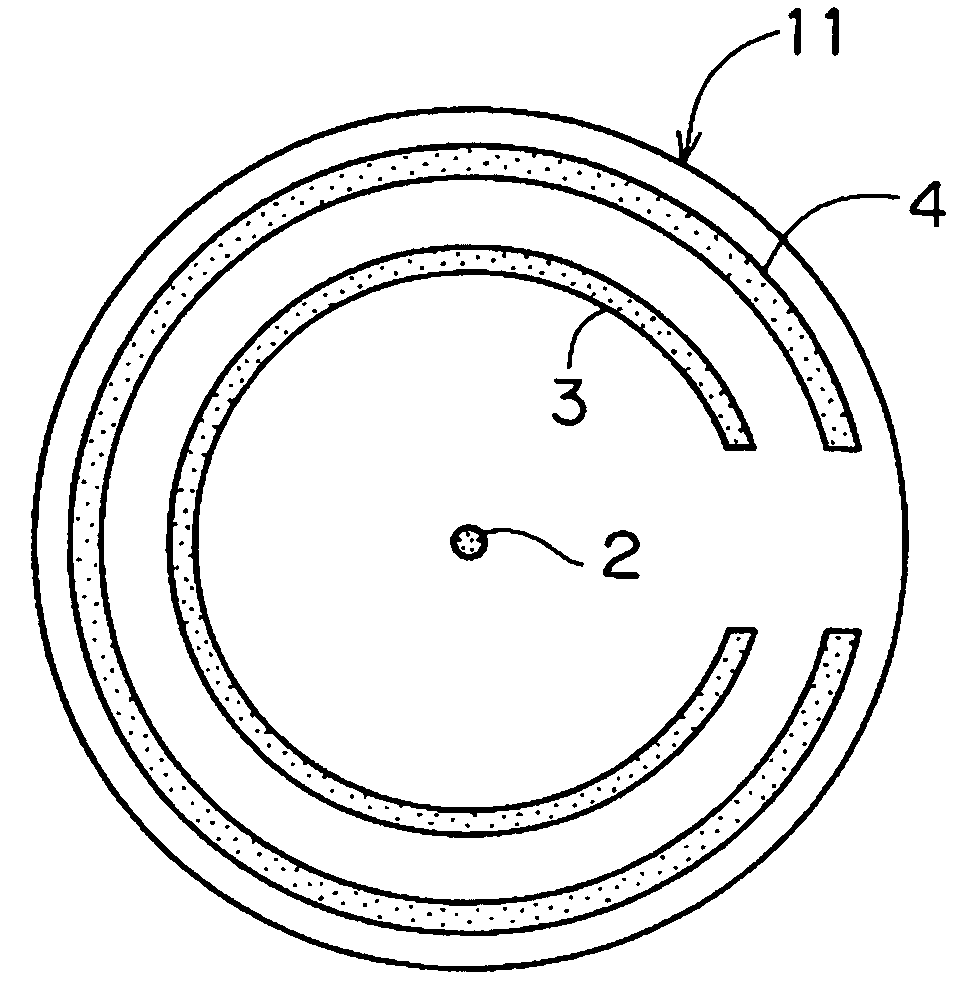

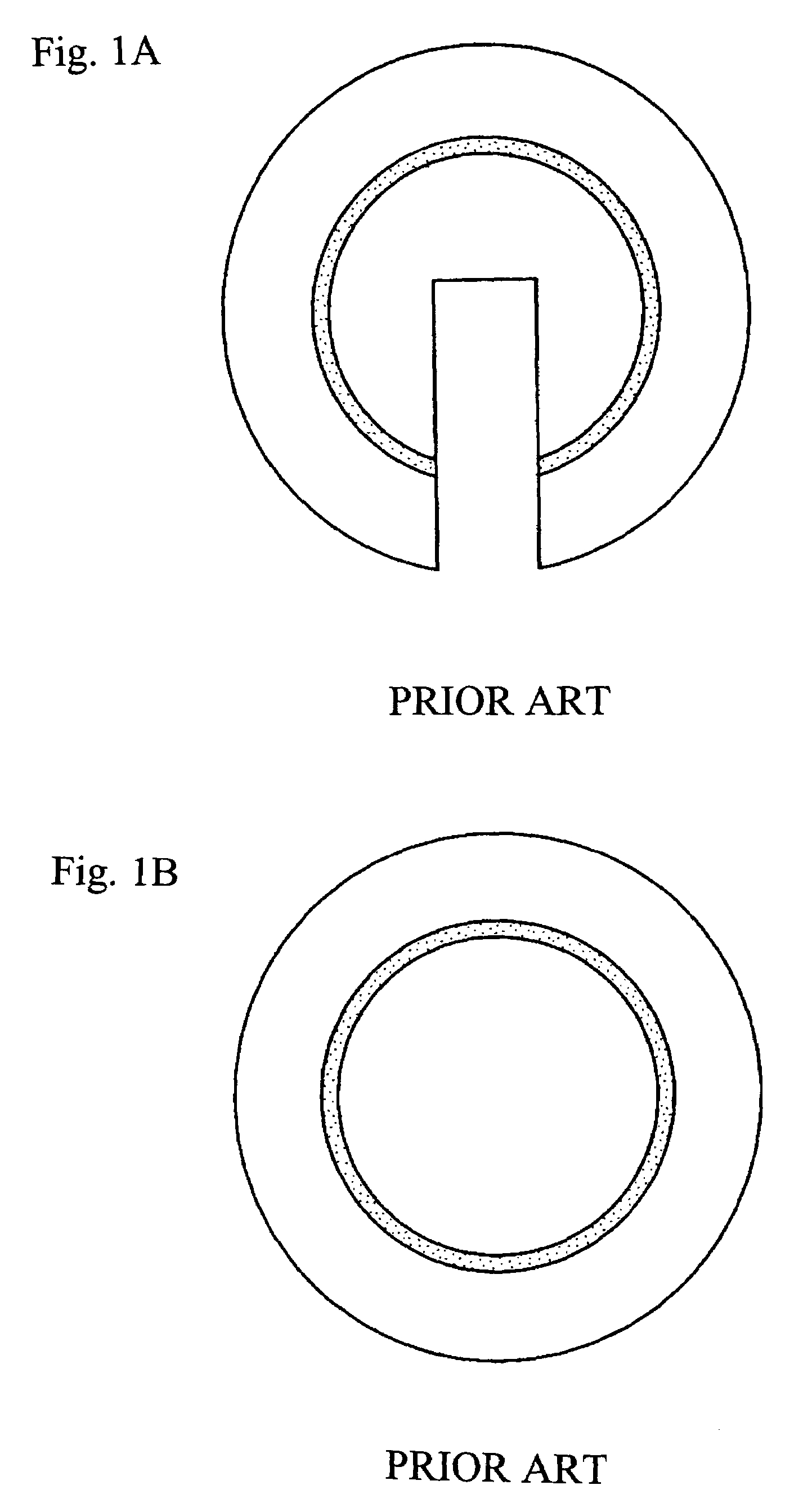

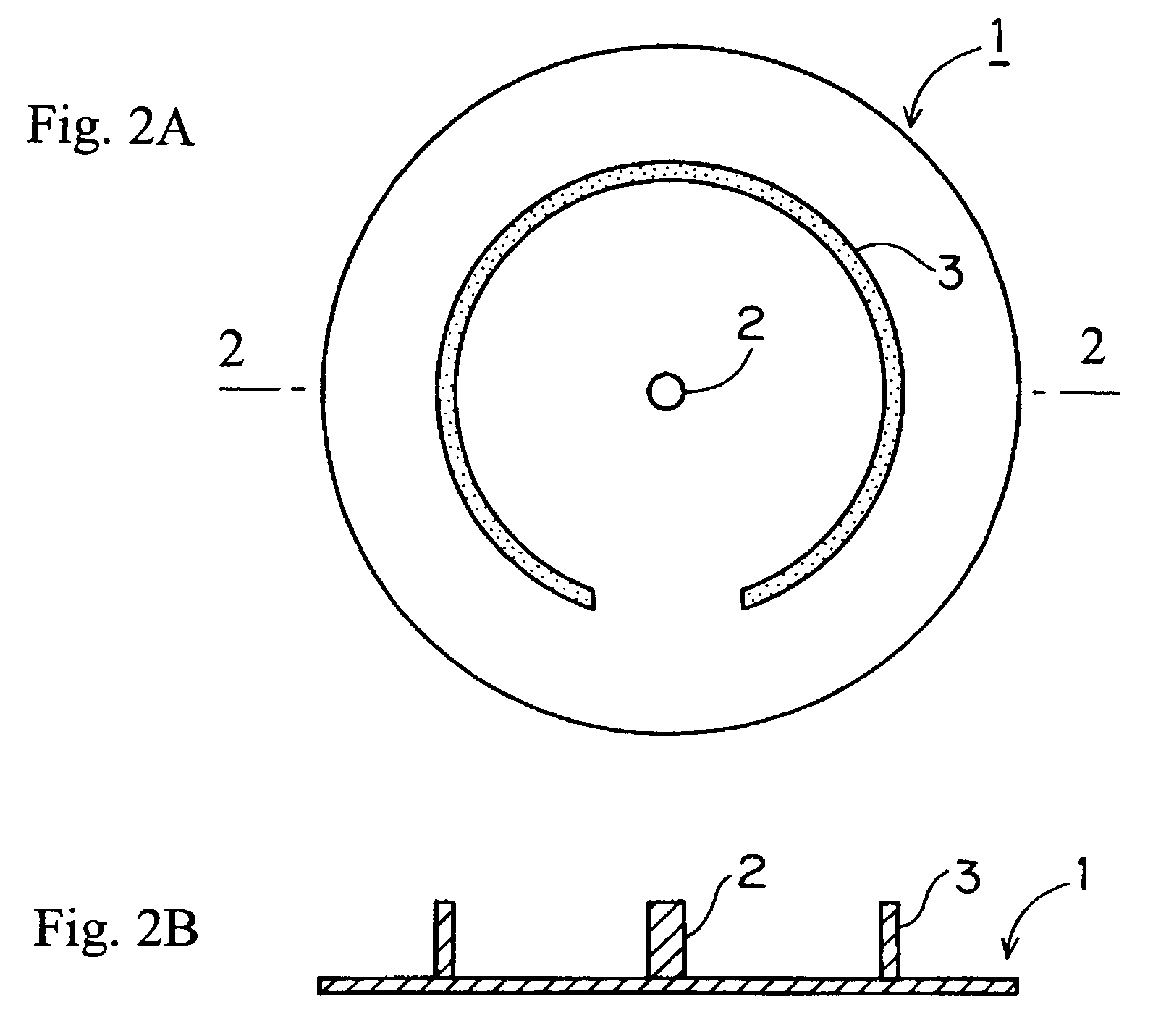

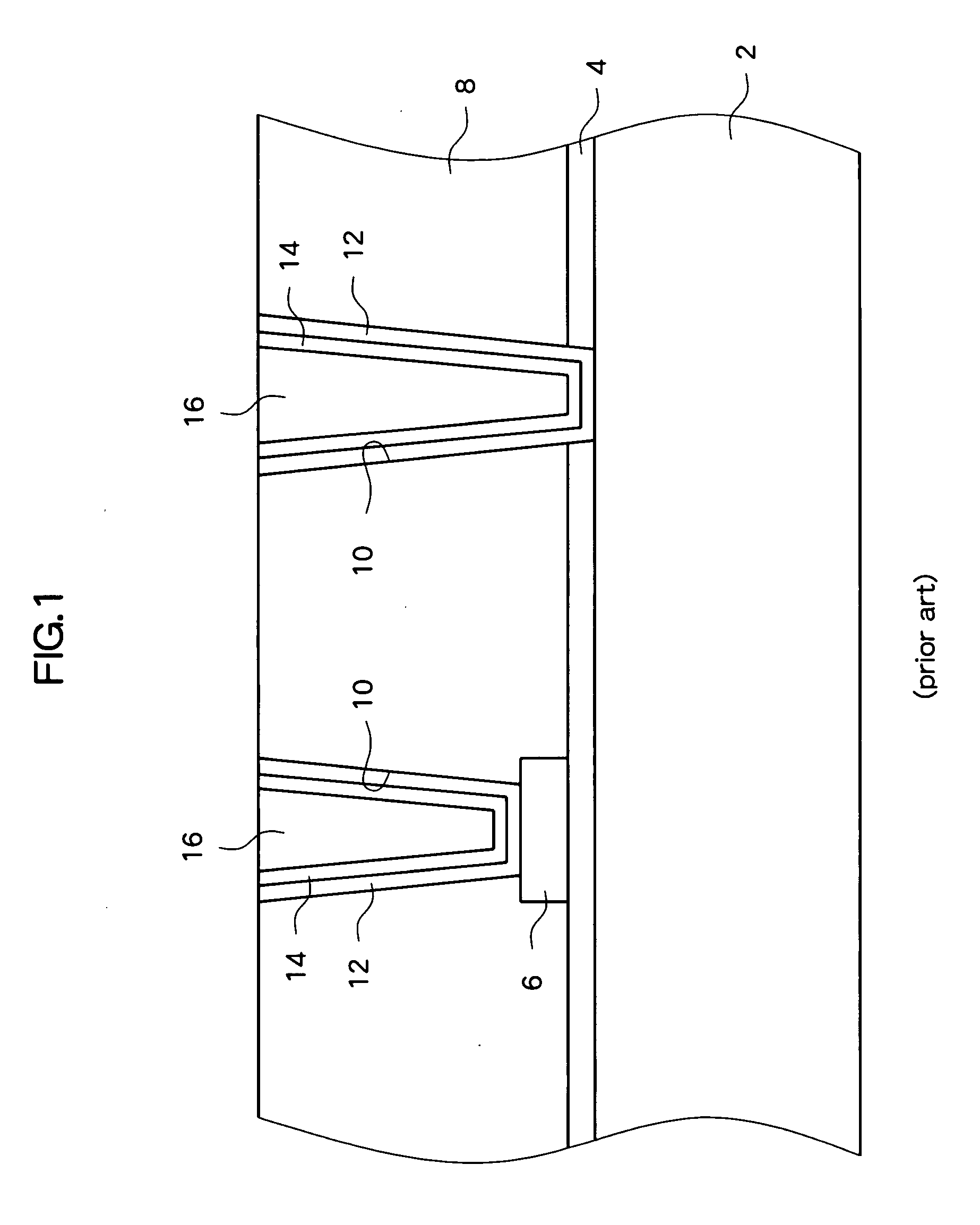

Heat treatment jig for semiconductor silicon substrate

ActiveUS7163393B2Charge supportsSemiconductor/solid-state device manufacturingDislocationHydrogen annealing

Owner:SUMITOMO MITSUBISHI SILICON CORP

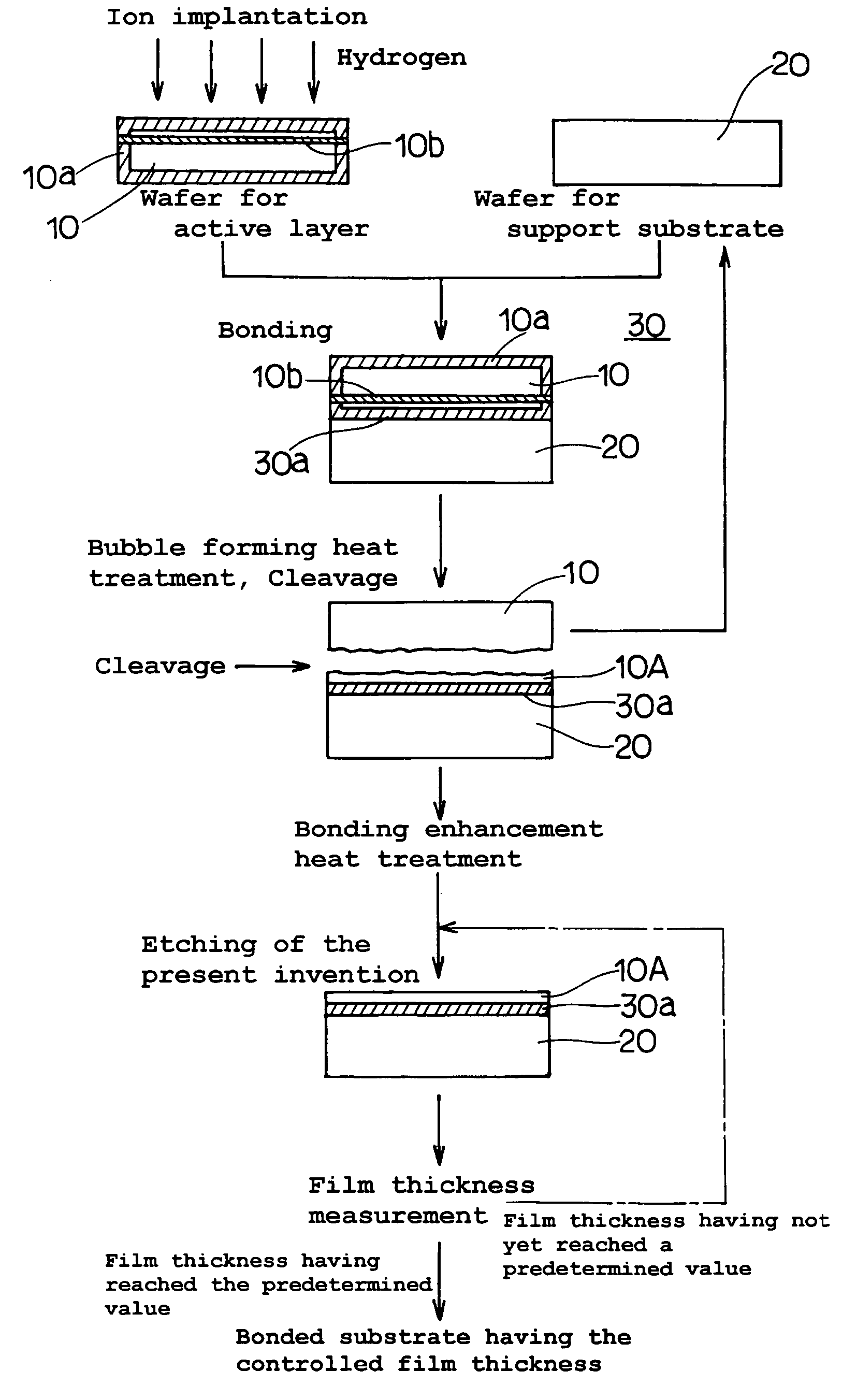

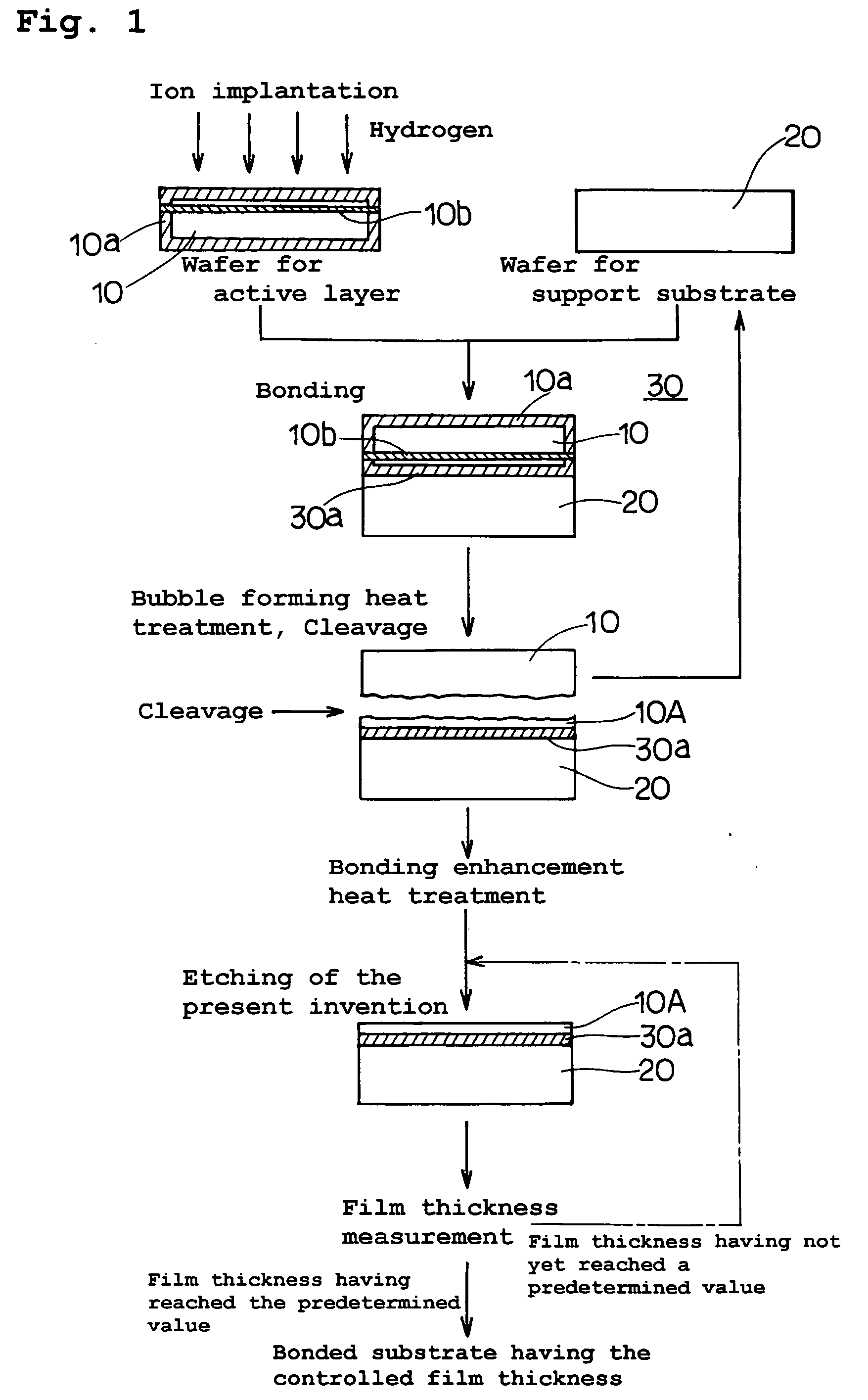

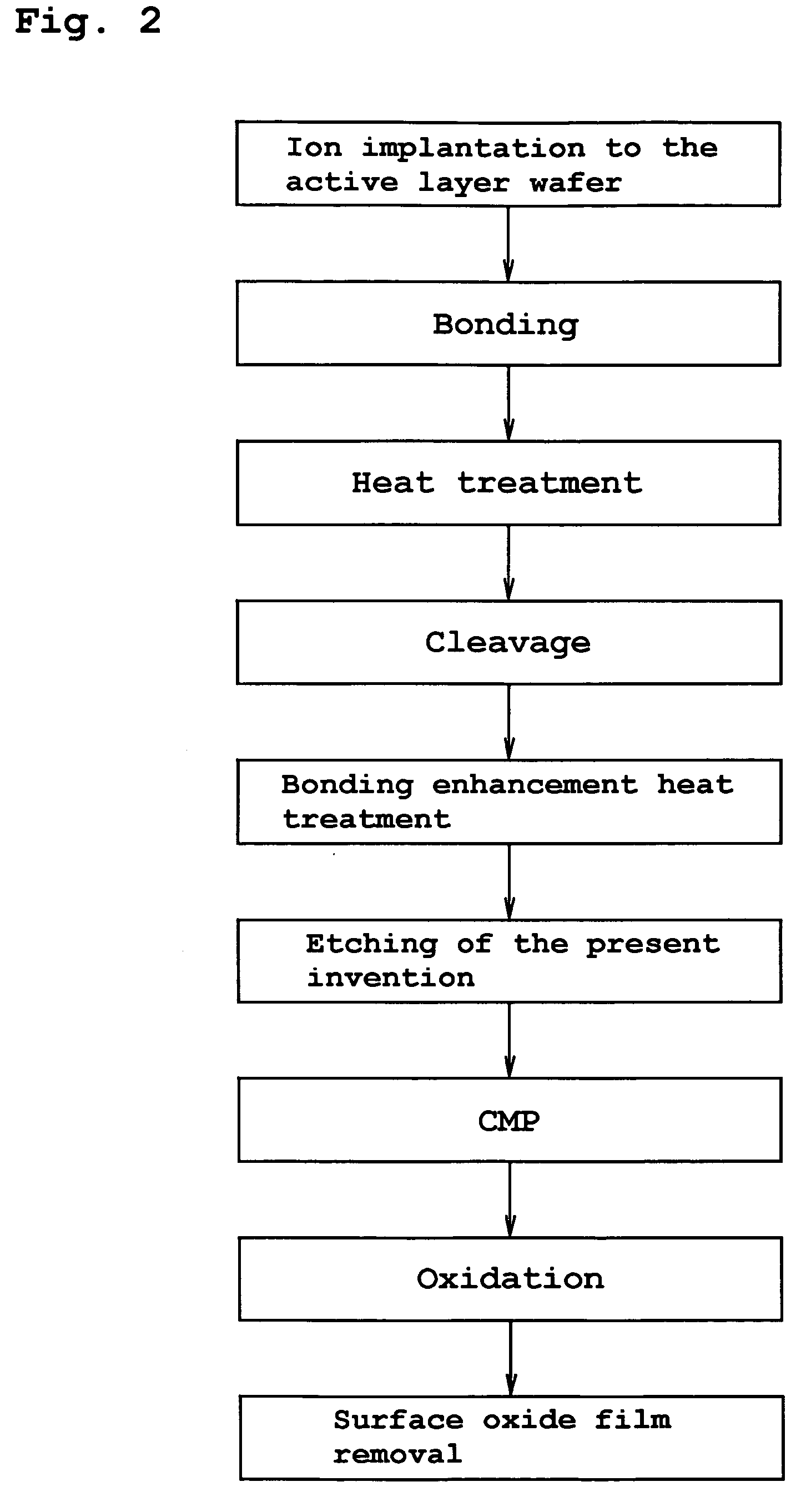

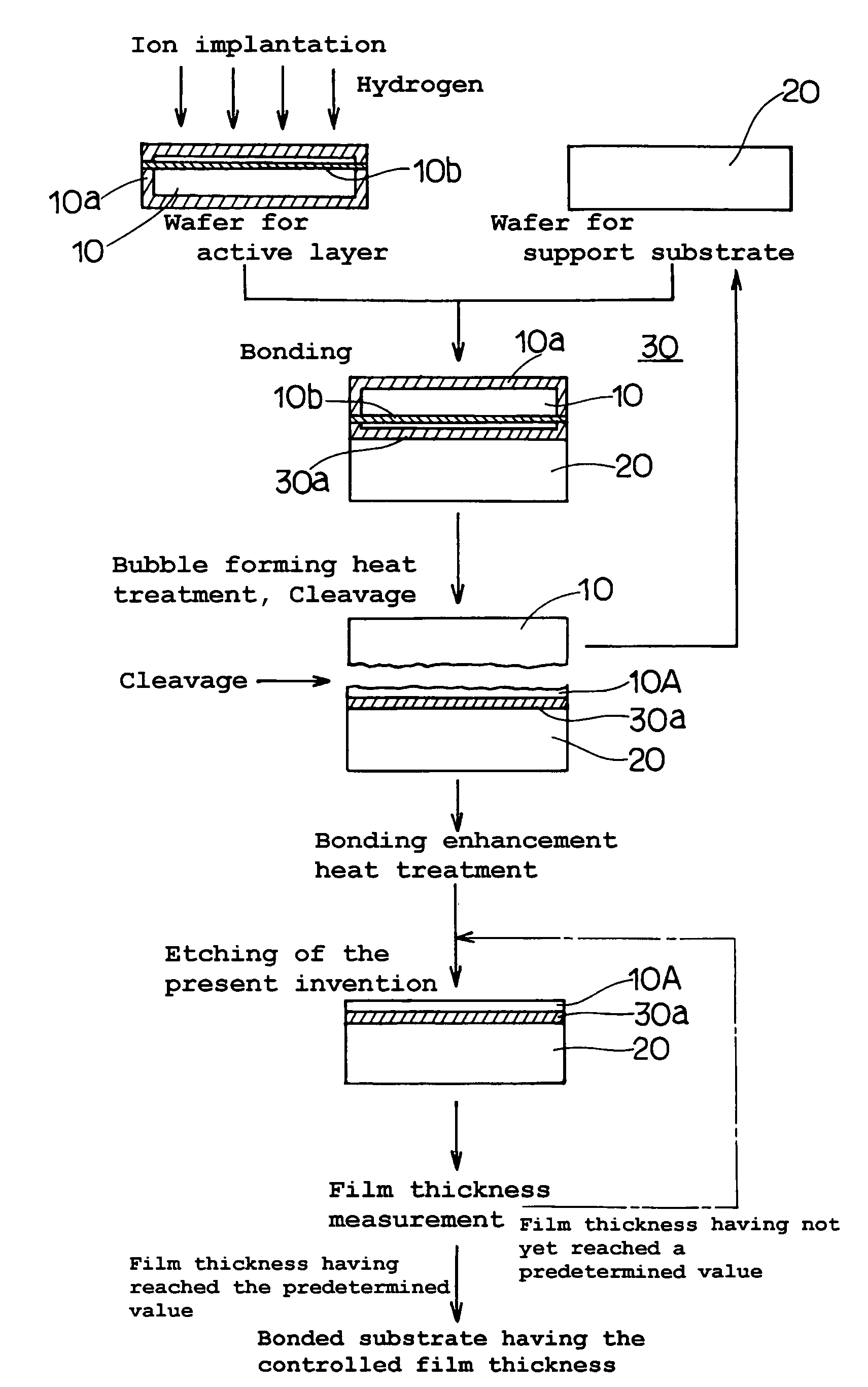

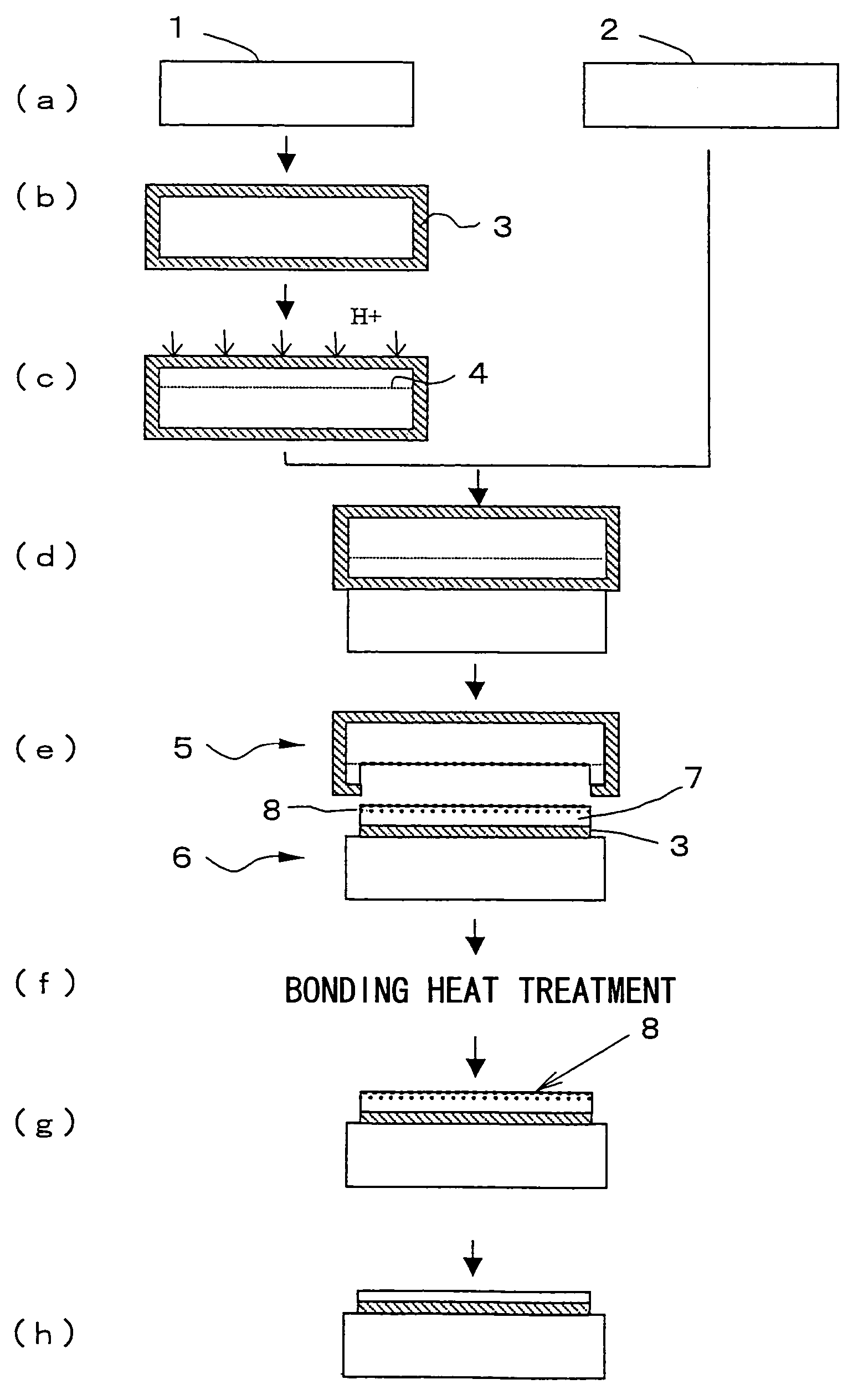

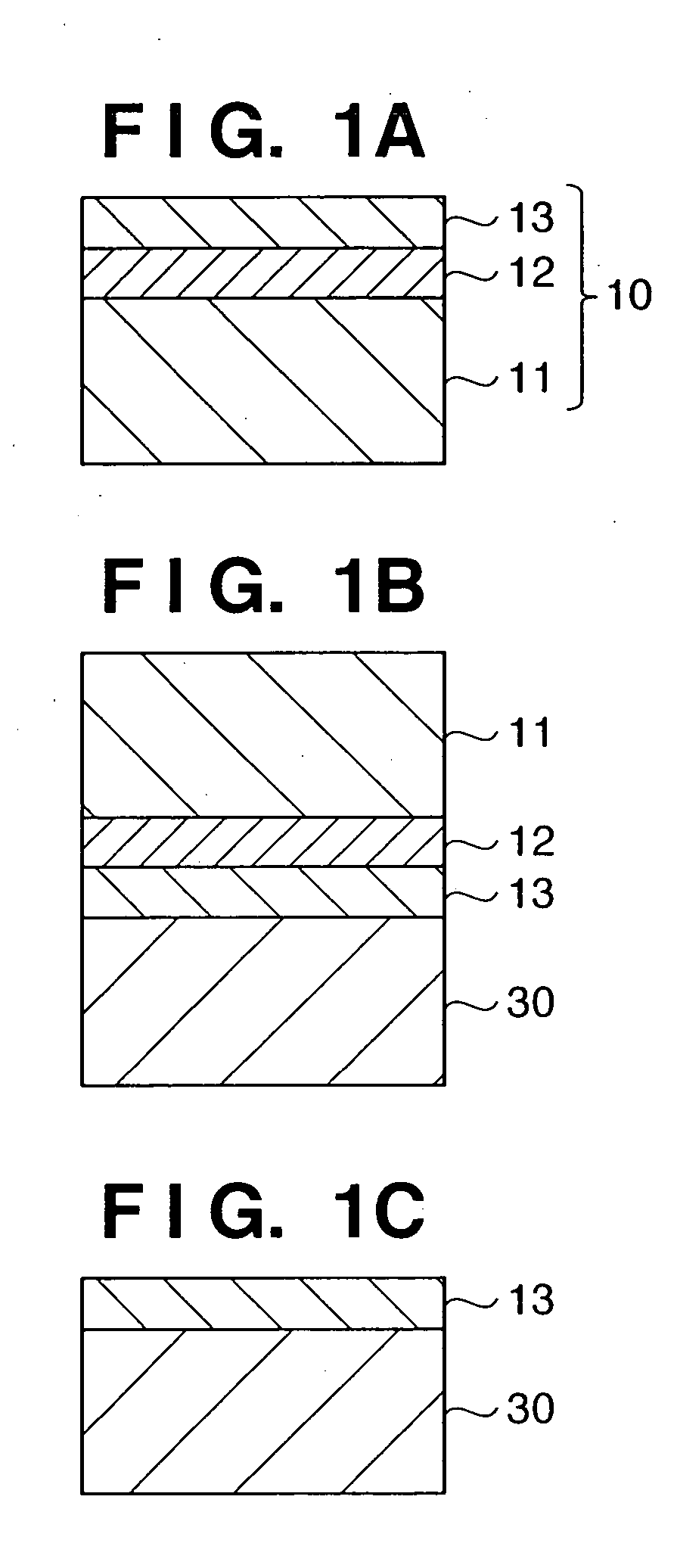

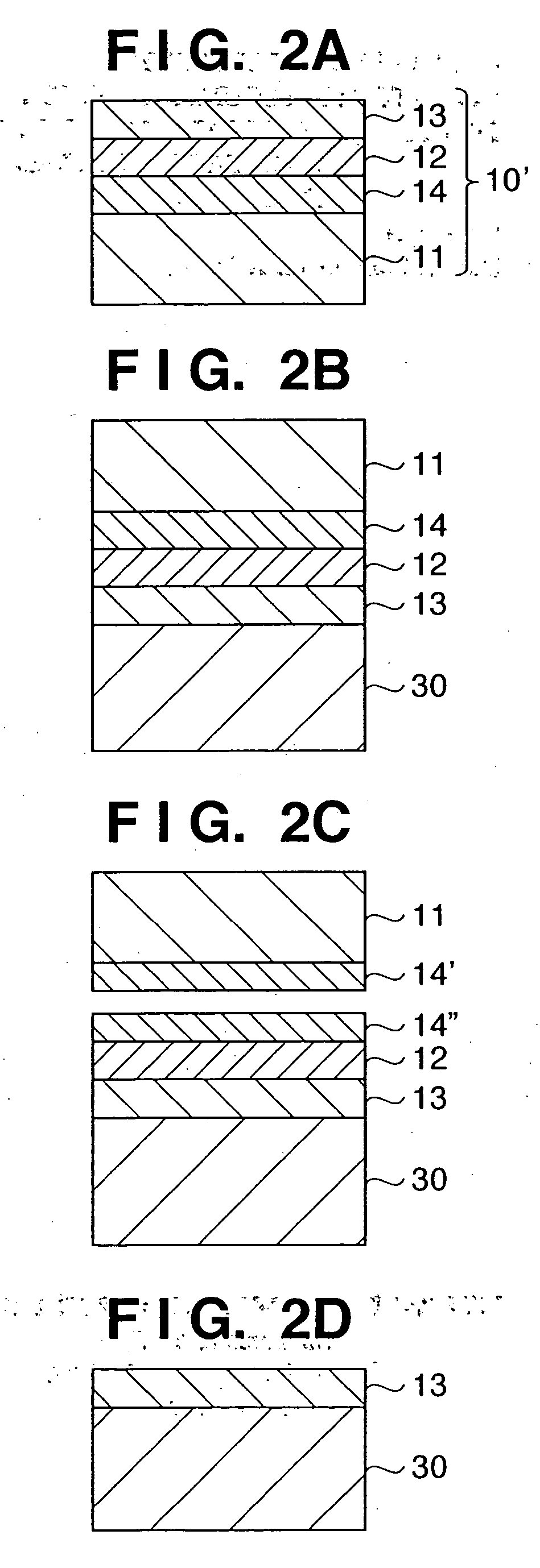

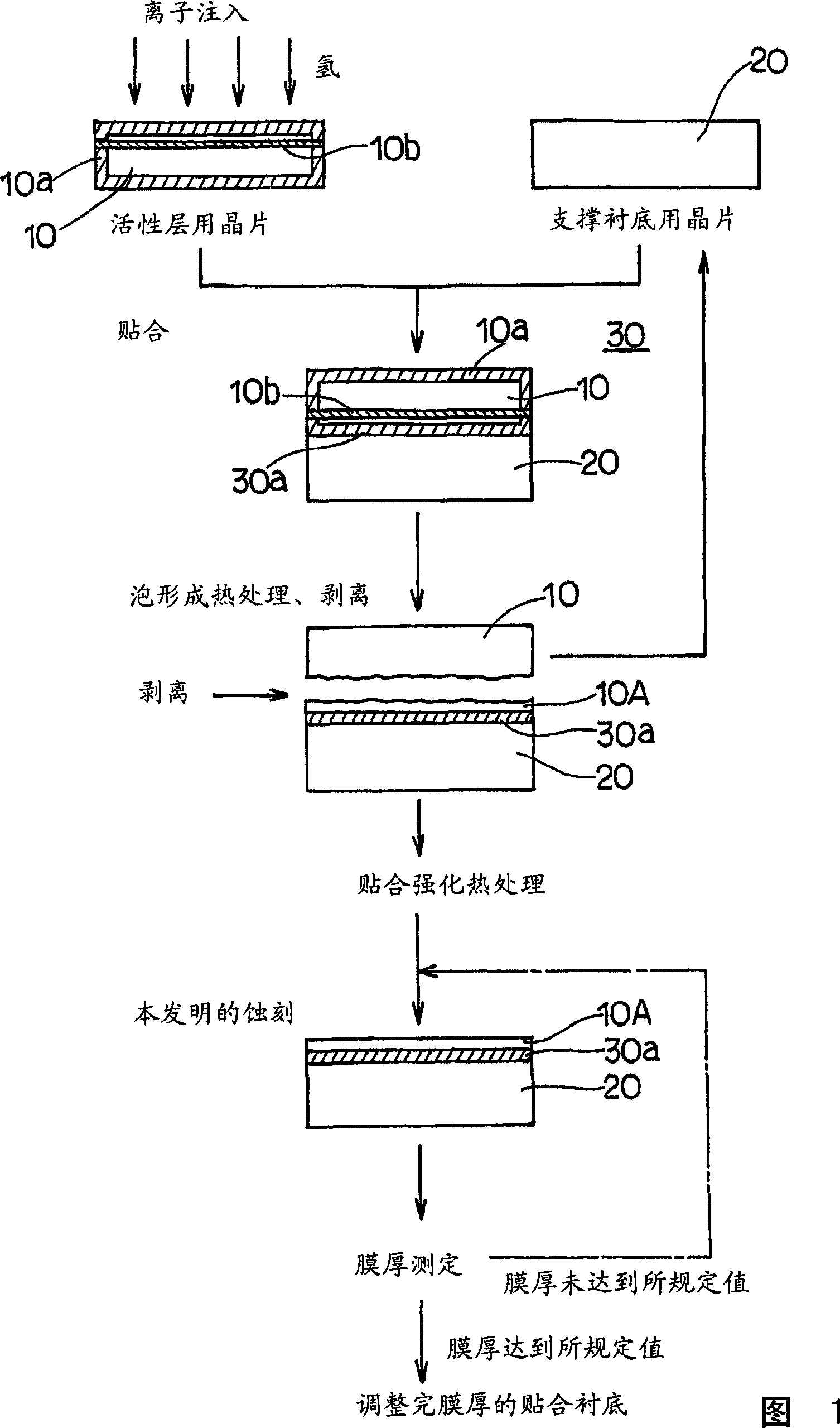

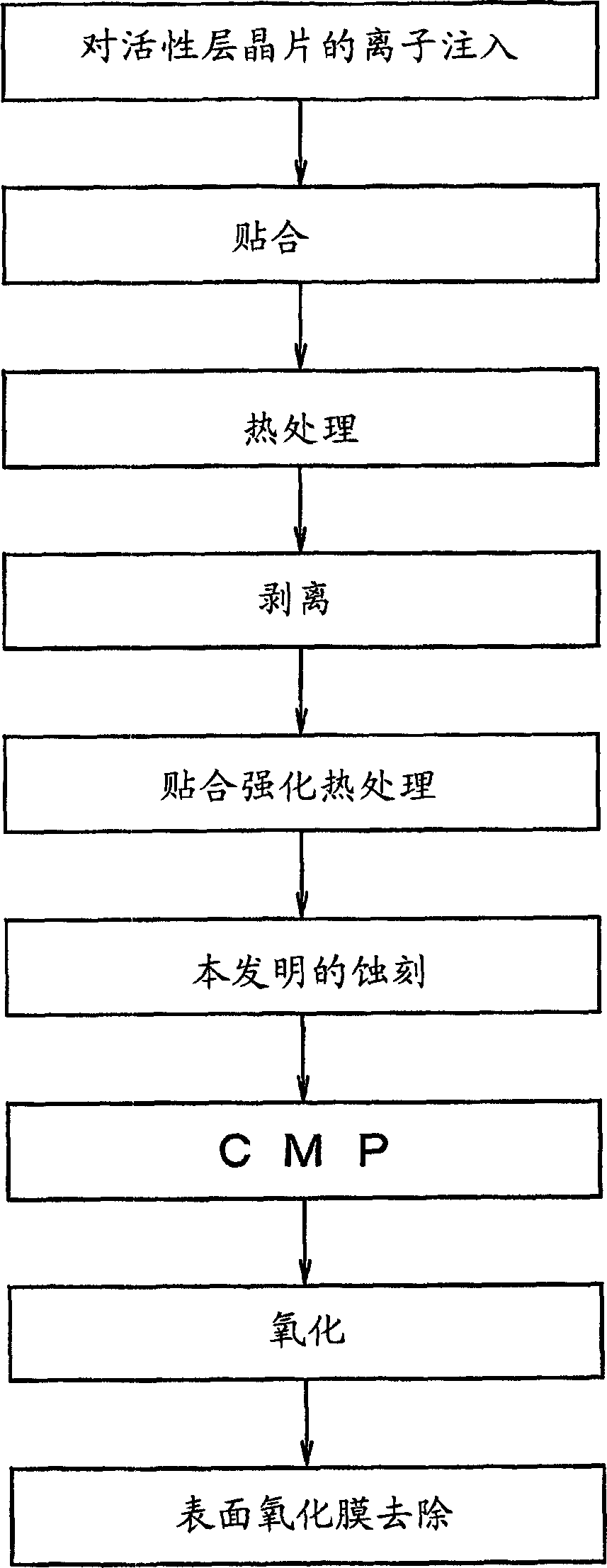

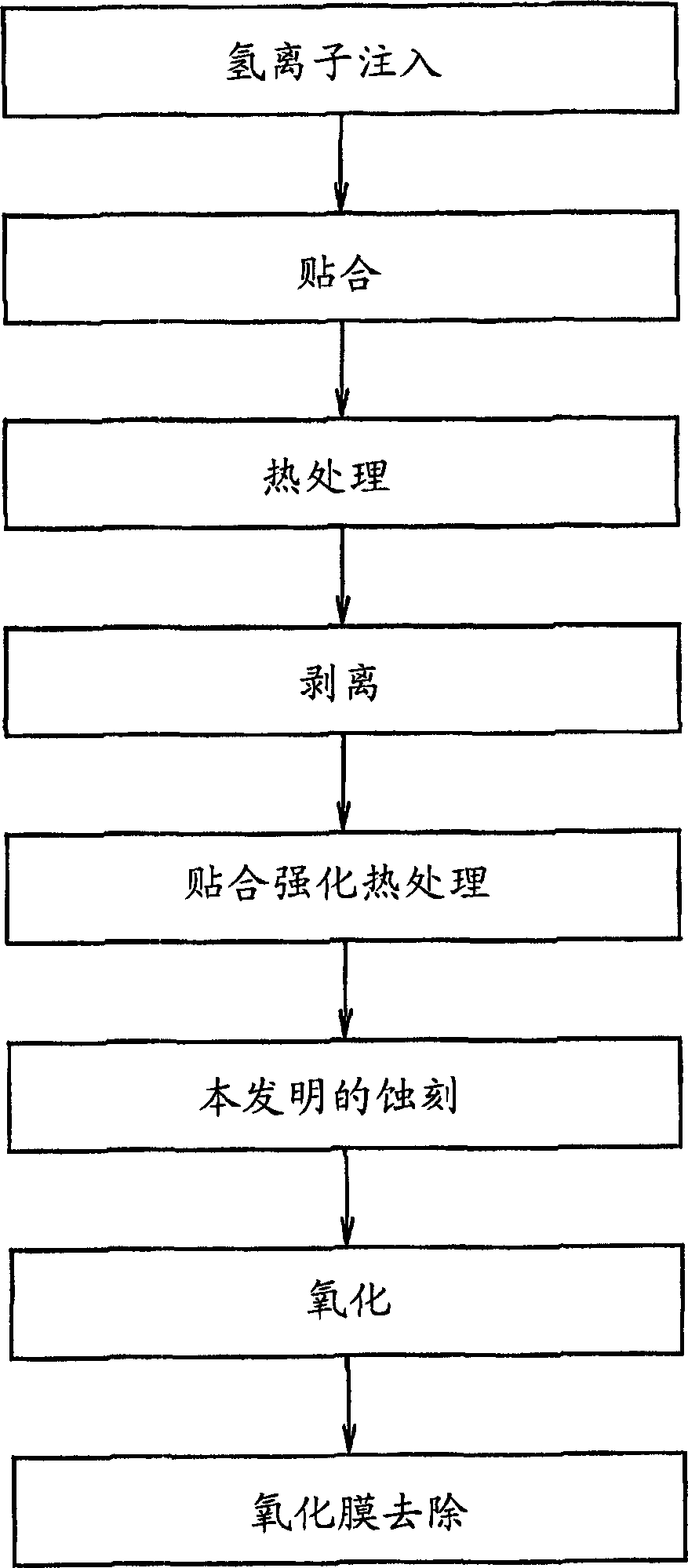

Laminated semiconductor substrate process for producing the same

InactiveUS20060118935A1Simple processReduce surface roughnessDecorative surface effectsSemiconductor/solid-state device detailsEtchingSurface roughness

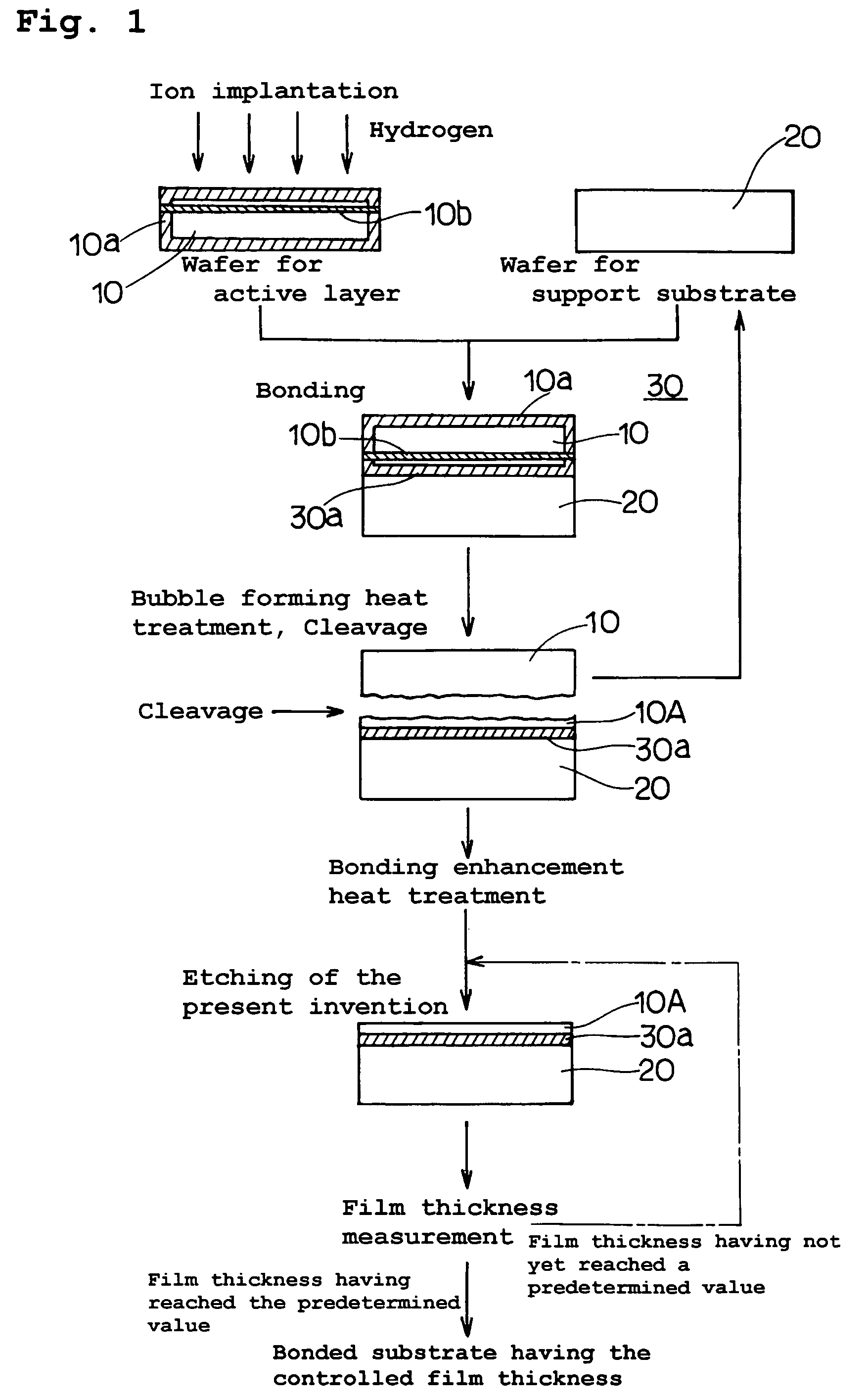

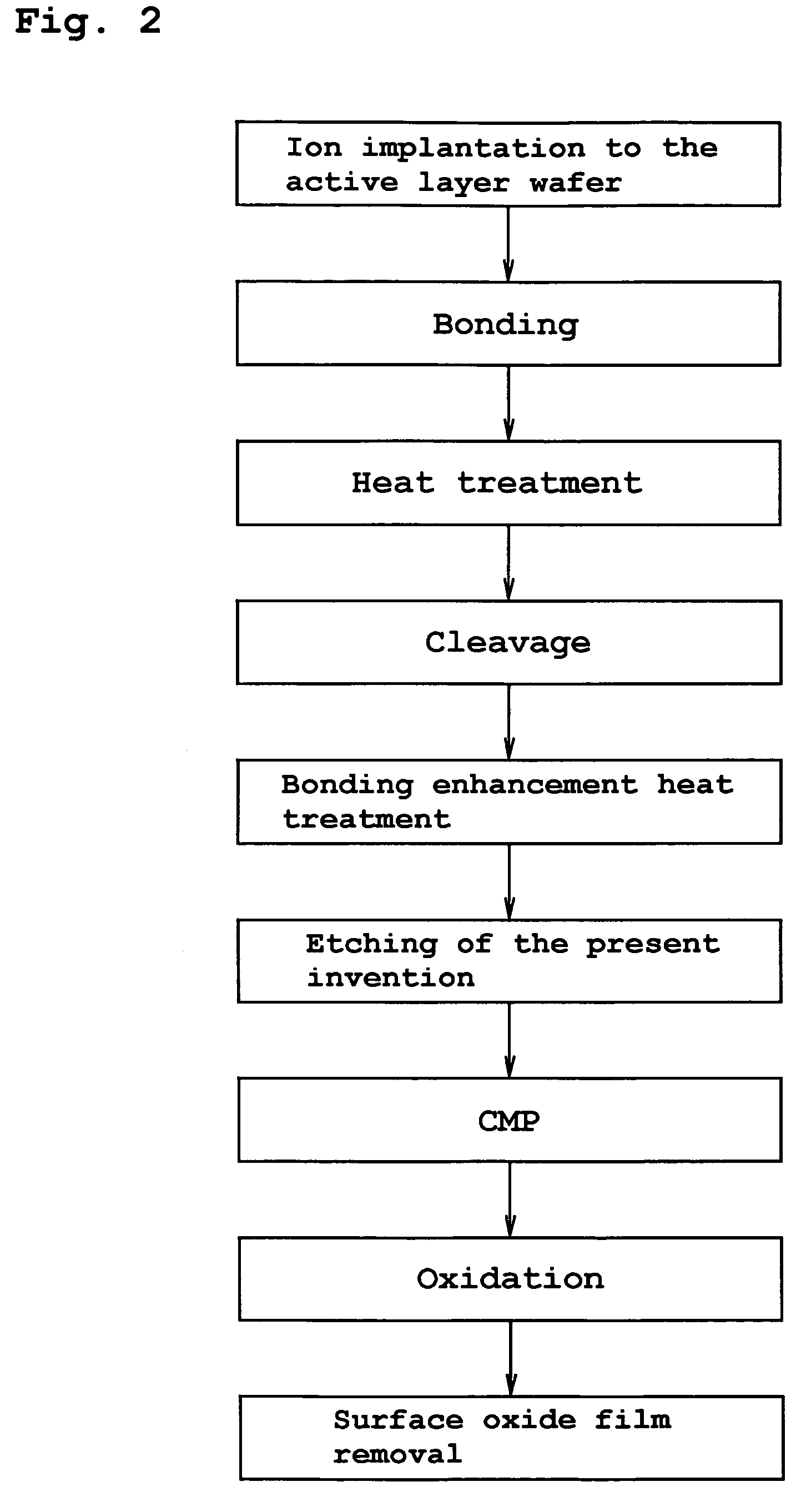

The present invention provides a bonded substrate fabricated to have its final active layer thickness of 200 nm or lower by performing the etching by only 1 nm to 1 μm with a solution having an etching effect on a surface of an active layer of a bonded substrate which has been prepared by bonding two substrates after one of them having been ion-implanted and then cleaving off a portion thereof by heat treatment. SC-1 solution is used for performing the etching. A polishing, a hydrogen annealing and a sacrificial oxidation may be respectively applied to the active layer before and / or after the etching. The film thickness of this active layer can be made uniform over the entire surface area and the surface roughness of the active layer can be reduced as well.

Owner:SUMCO CORP +1

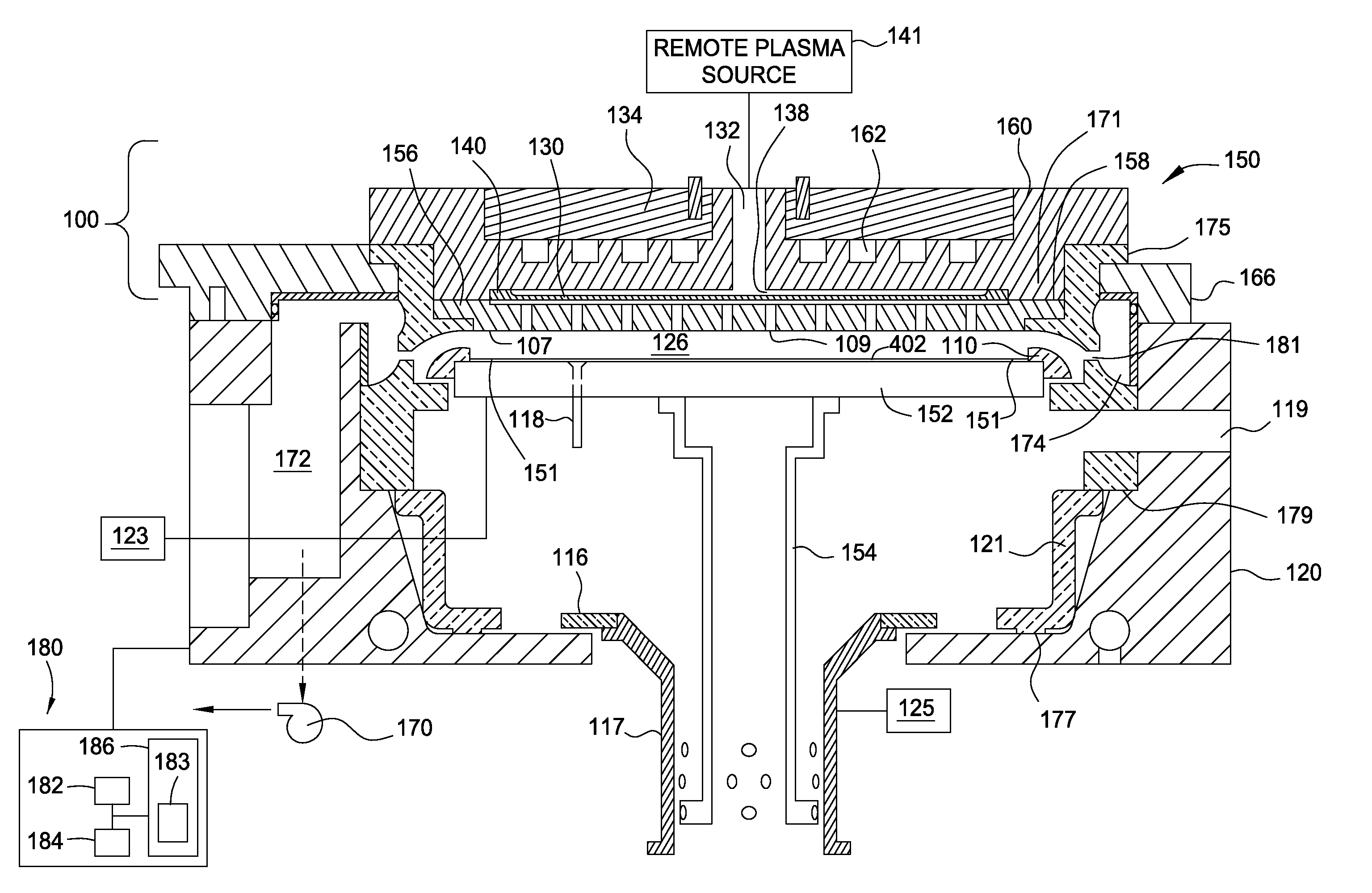

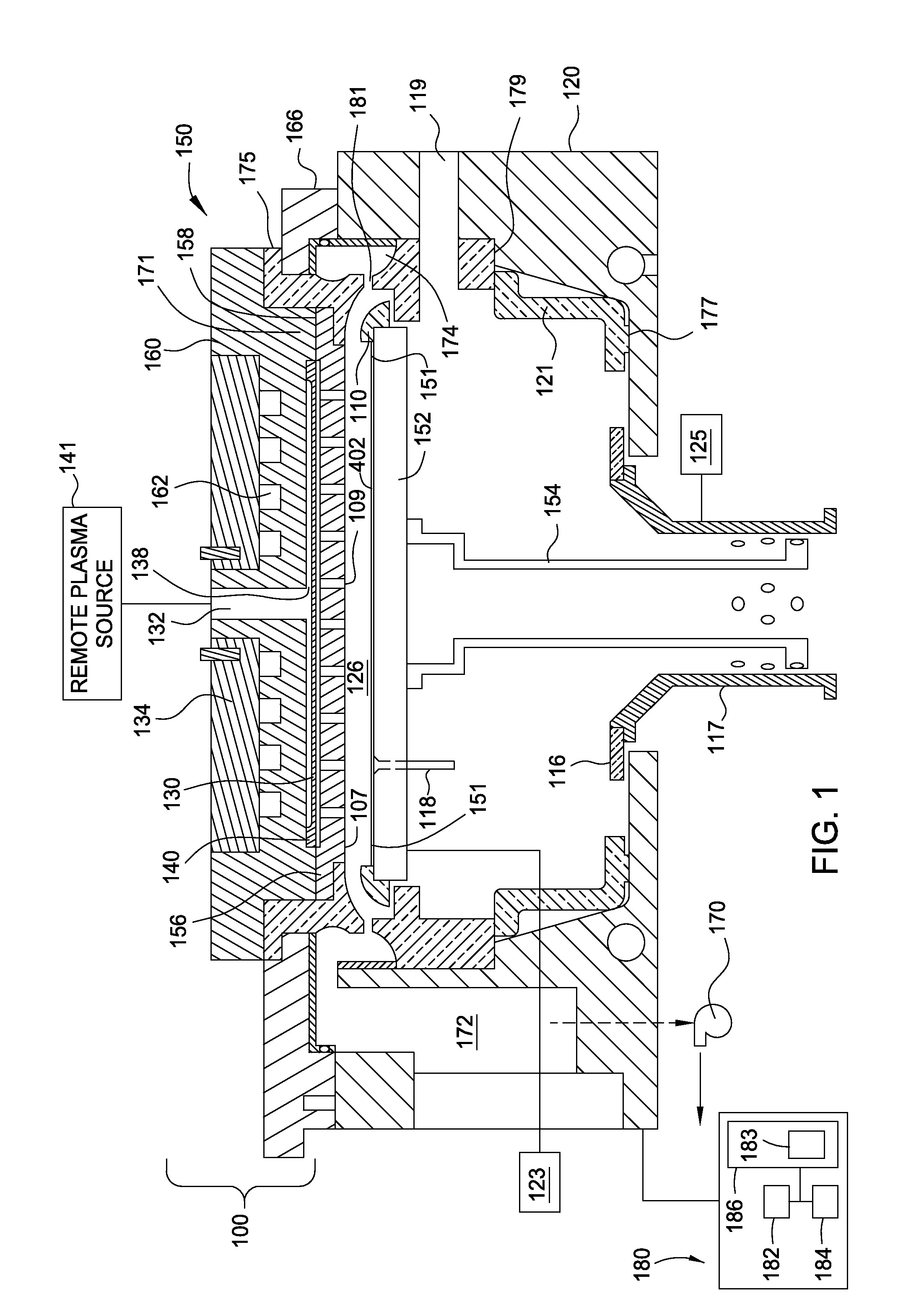

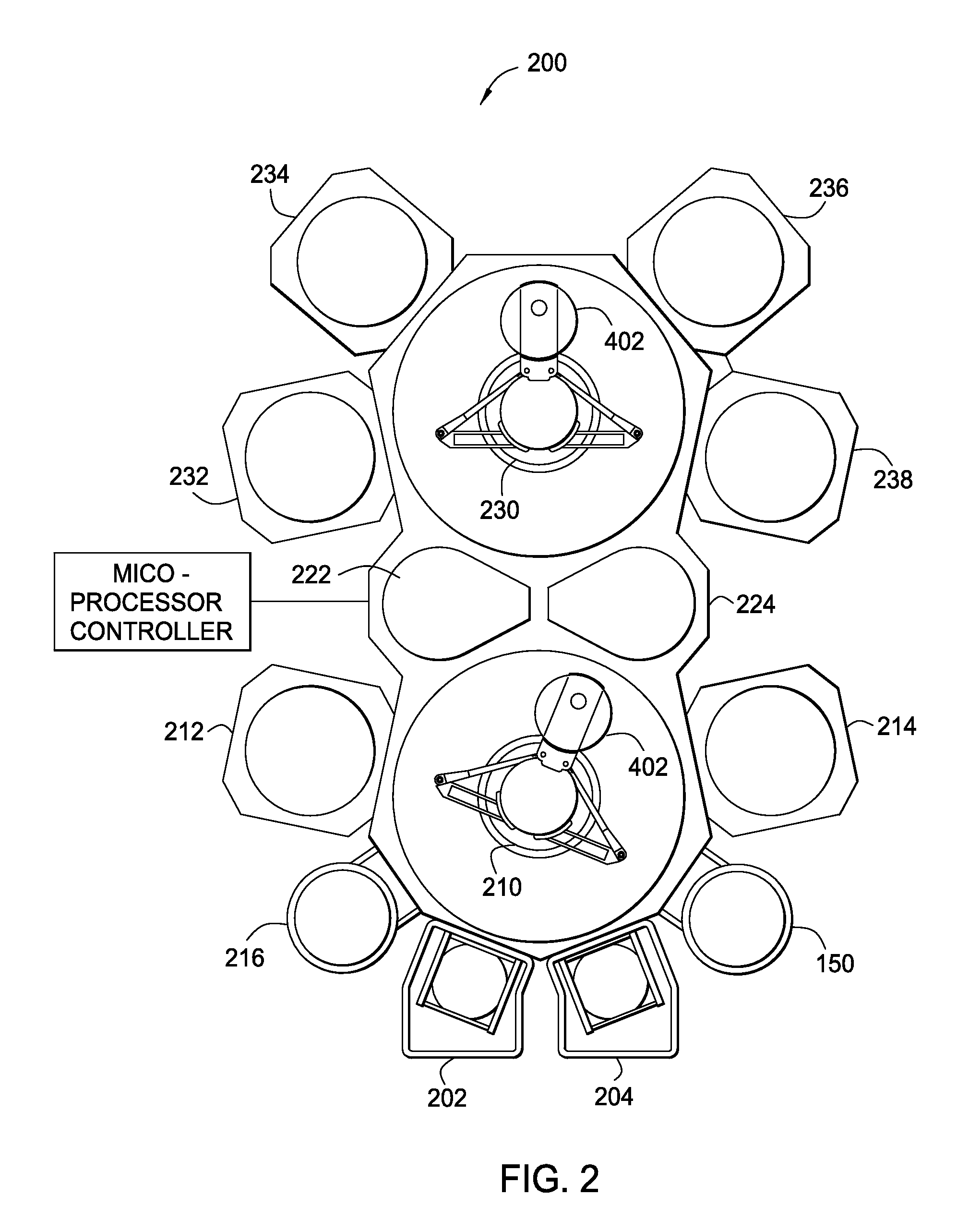

Method of enabling seamless cobalt gap-fill

ActiveUS20150093891A1Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingCobaltHydrogen annealing

Methods for depositing a metal layer in a feature definition of a semiconductor device are provided. In one implementation, a method for depositing a metal layer for forming a semiconductor device is provided. The method comprises performing a cyclic metal deposition process to deposit a metal layer on a substrate and annealing the metal layer disposed on the substrate. The cyclic metal deposition process comprises exposing the substrate to a deposition precursor gas mixture to deposit a portion of the metal layer on the substrate, exposing the portion of the metal layer to either a plasma treatment process or hydrogen annealing process and repeating the exposing the substrate to a deposition precursor gas mixture and exposing the portion of the metal layer to either a plasma treatment process or hydrogen annealing process until a predetermined thickness of the metal layer is achieved.

Owner:APPLIED MATERIALS INC

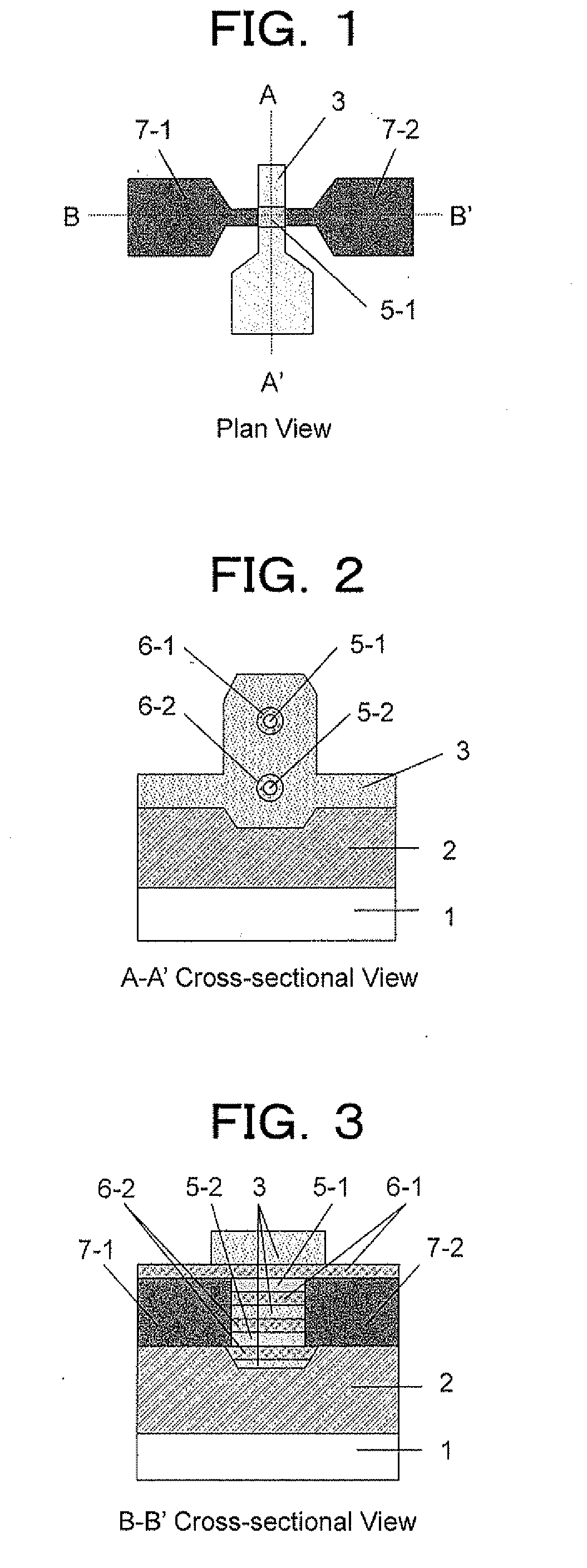

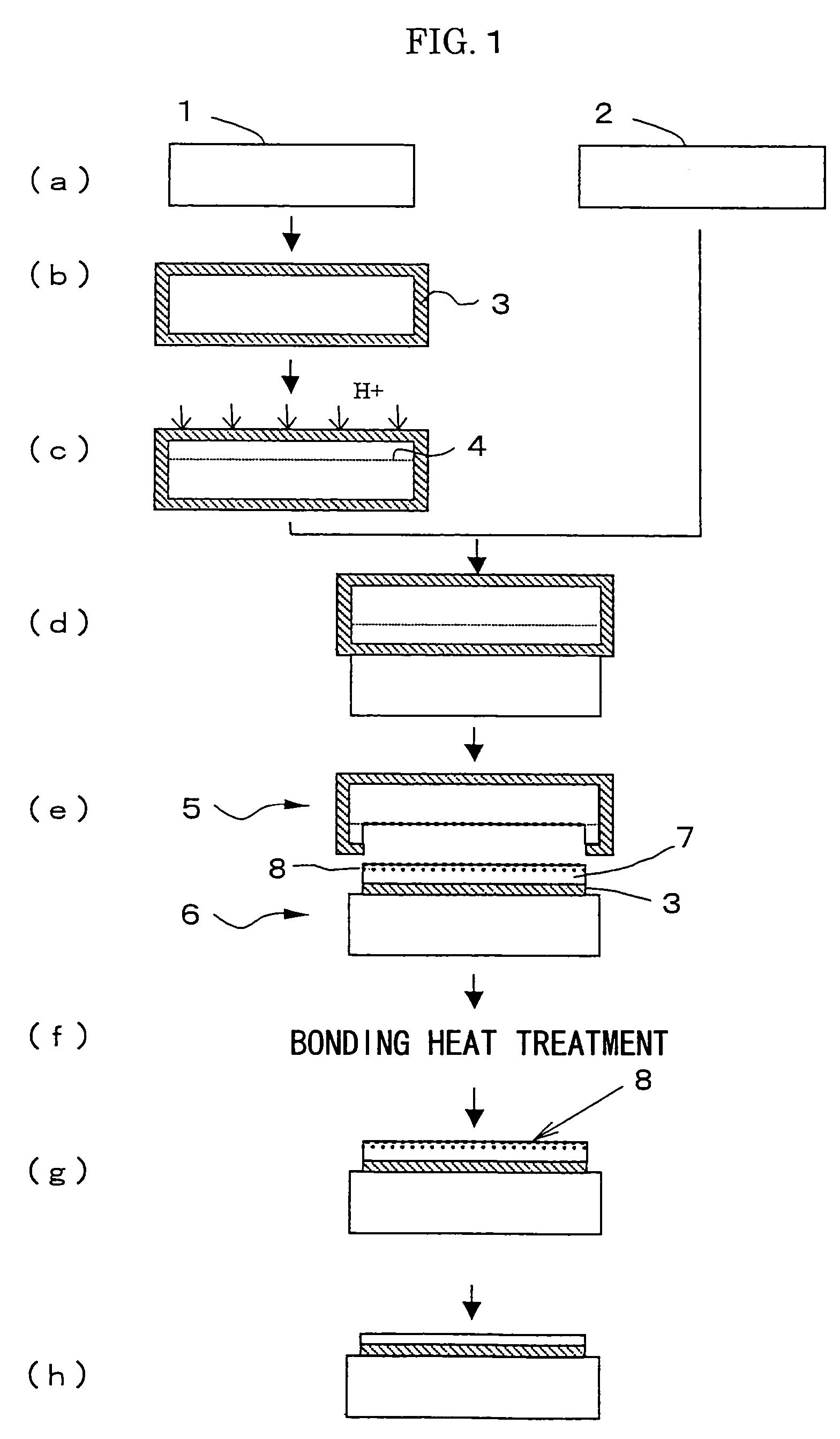

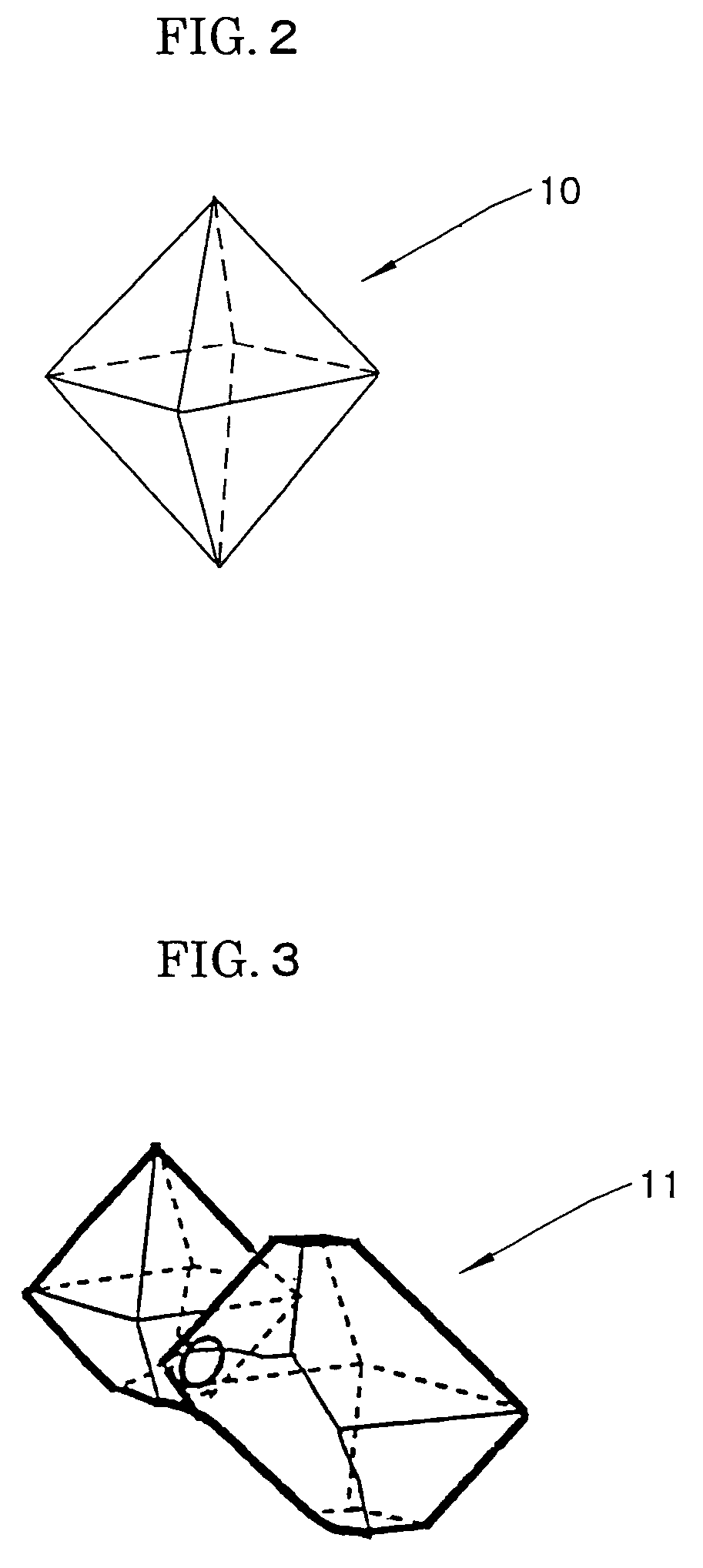

Nano-wire field effect transistor, method for manufacturing the transistor, and integrated circuit including the transistor

InactiveUS20110057163A1Superior in size reproducibility and uniformityNanoinformaticsSemiconductor/solid-state device manufacturingNanowireSoi substrate

Provided is a method for fabricating a nano-wire field effect transistor including steps of: preparing a nano-wire field effect transistor including two columnar members made of a silicon crystal configuring a nano-wire on a substrate are arranged on a substrate in parallel and one above the other, and an SOI substrate having a (100) surface orientation; processing a silicon crystal layer configuring the SOI substrate into a standing plate-shaped member having a rectangular cross-section; processing the silicon crystal by orientation dependent wet etching and thermal oxidation into a shape where two triangular columnar members are arranged one above the other with a spacing from each other as to face along the ridge lines of the triangular columnar members; and processing the triangular columnar member into a circular columnar member configuring a nano-wire by hydrogen-annealing or a thermal oxidation; and an integrated circuit including the transistor.

Owner:NAT INST OF ADVANCED IND SCI & TECH

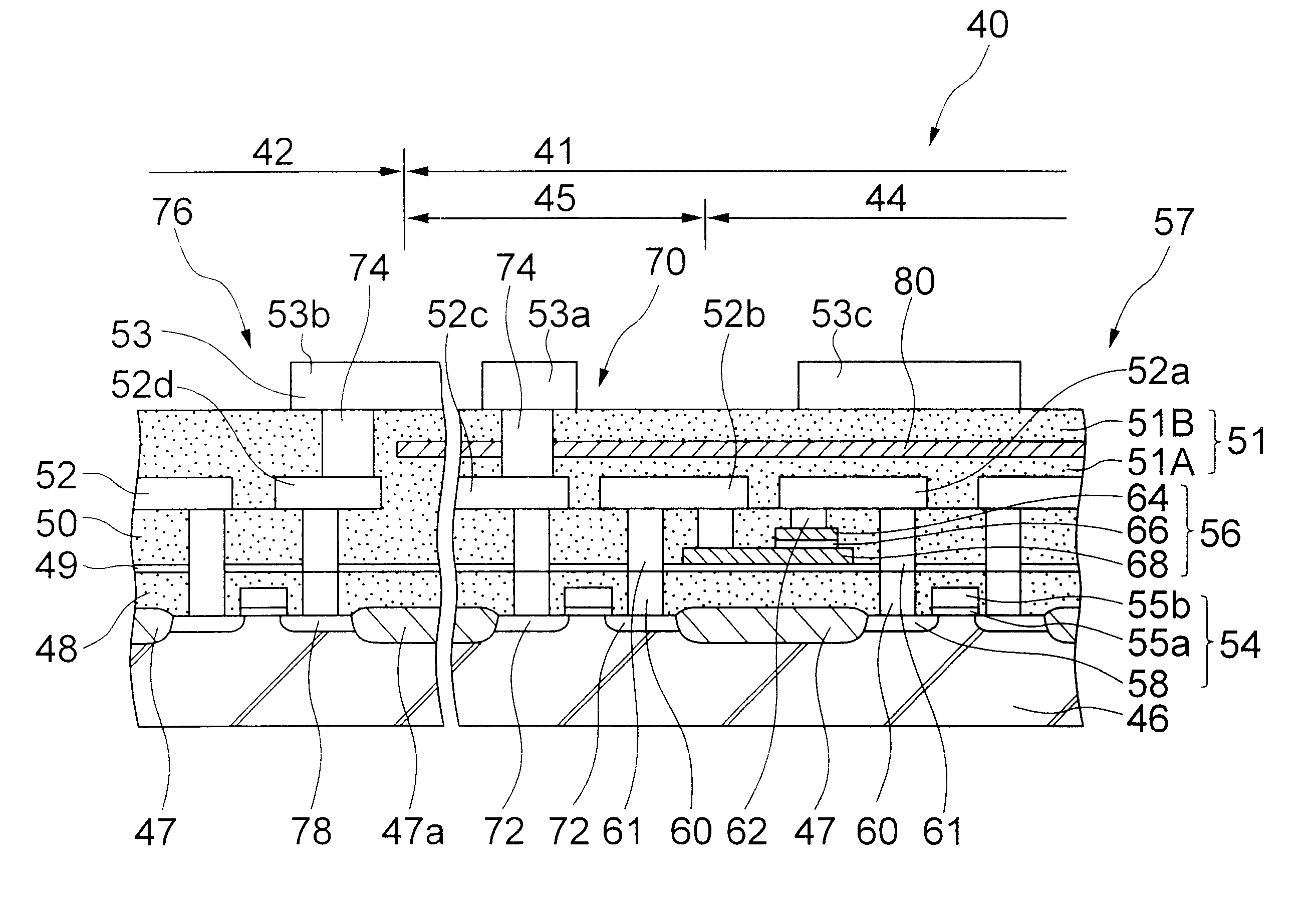

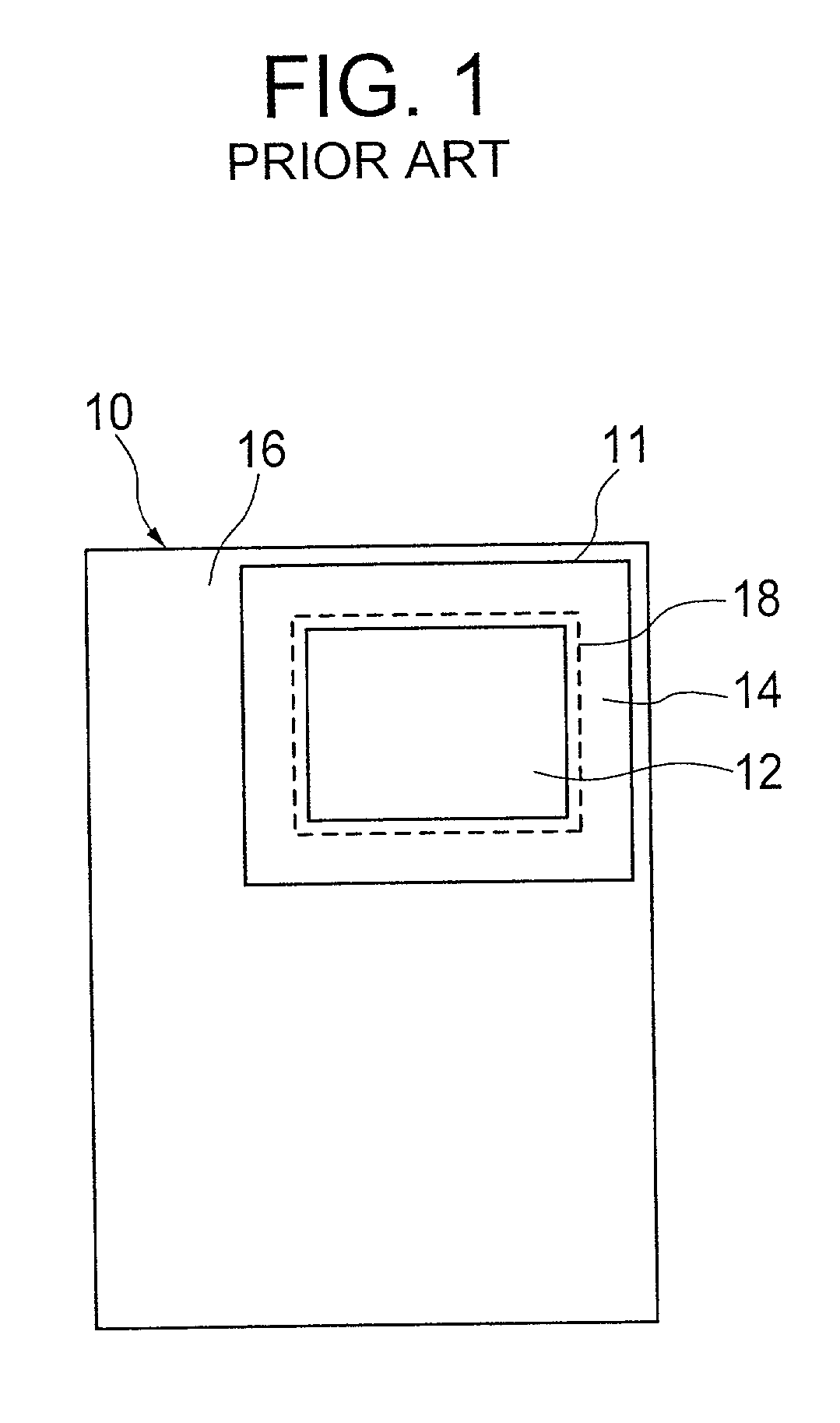

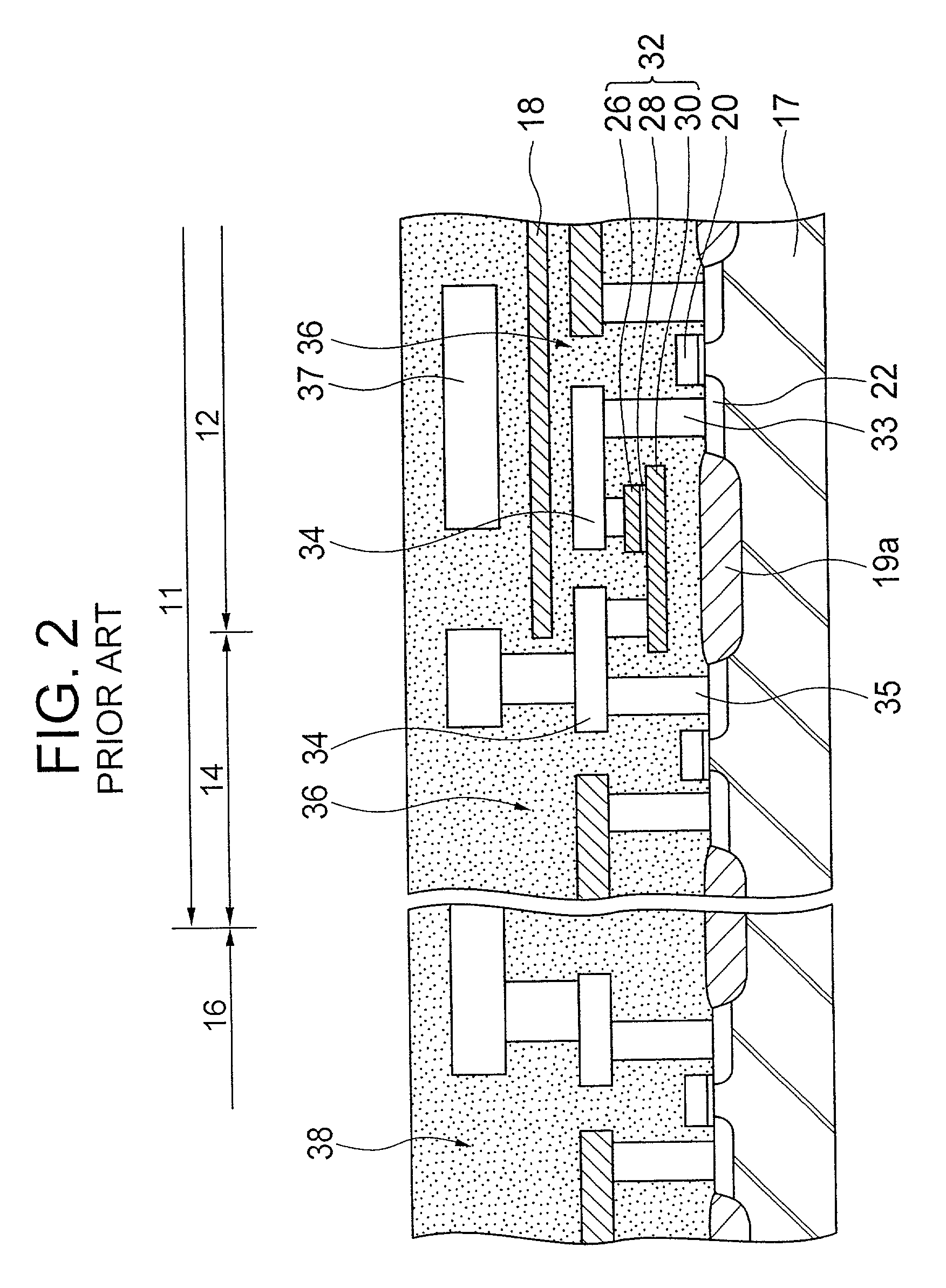

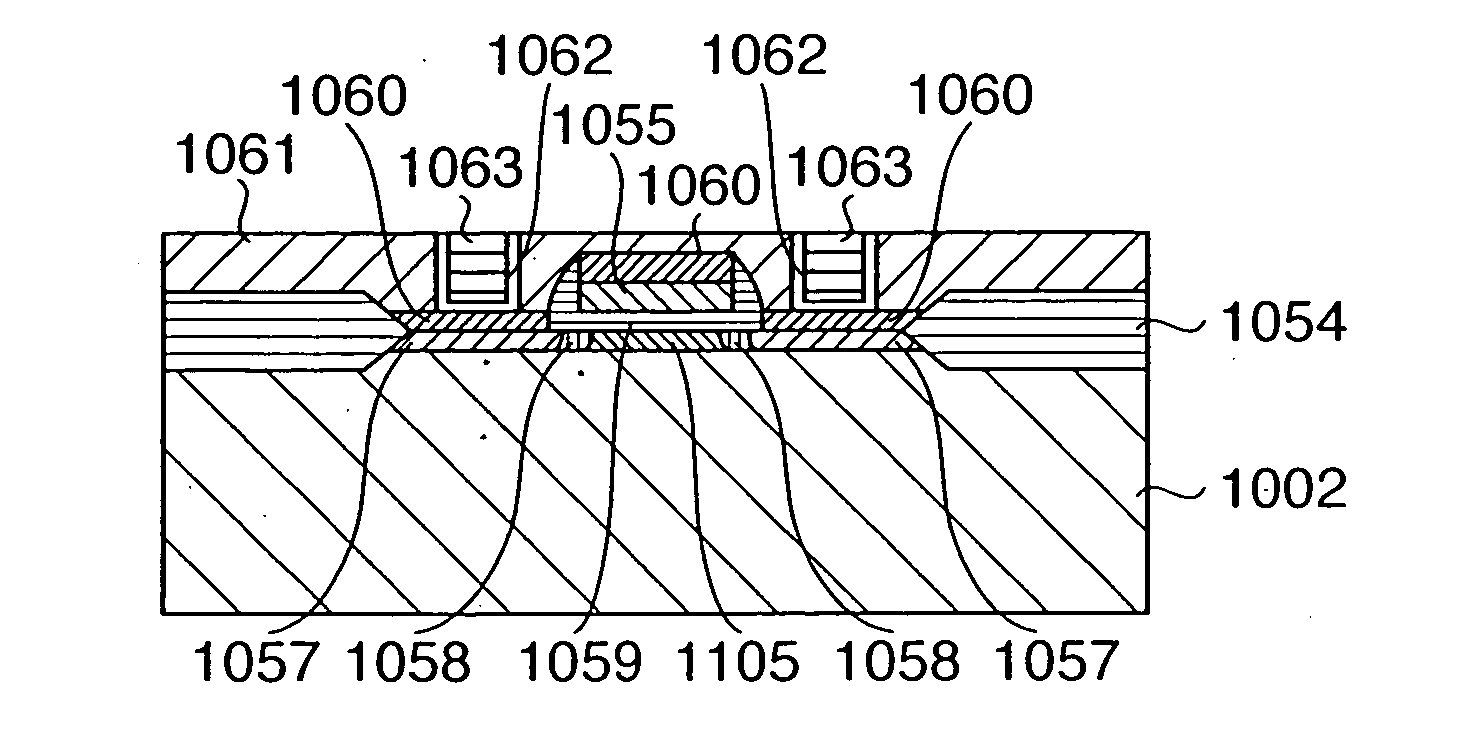

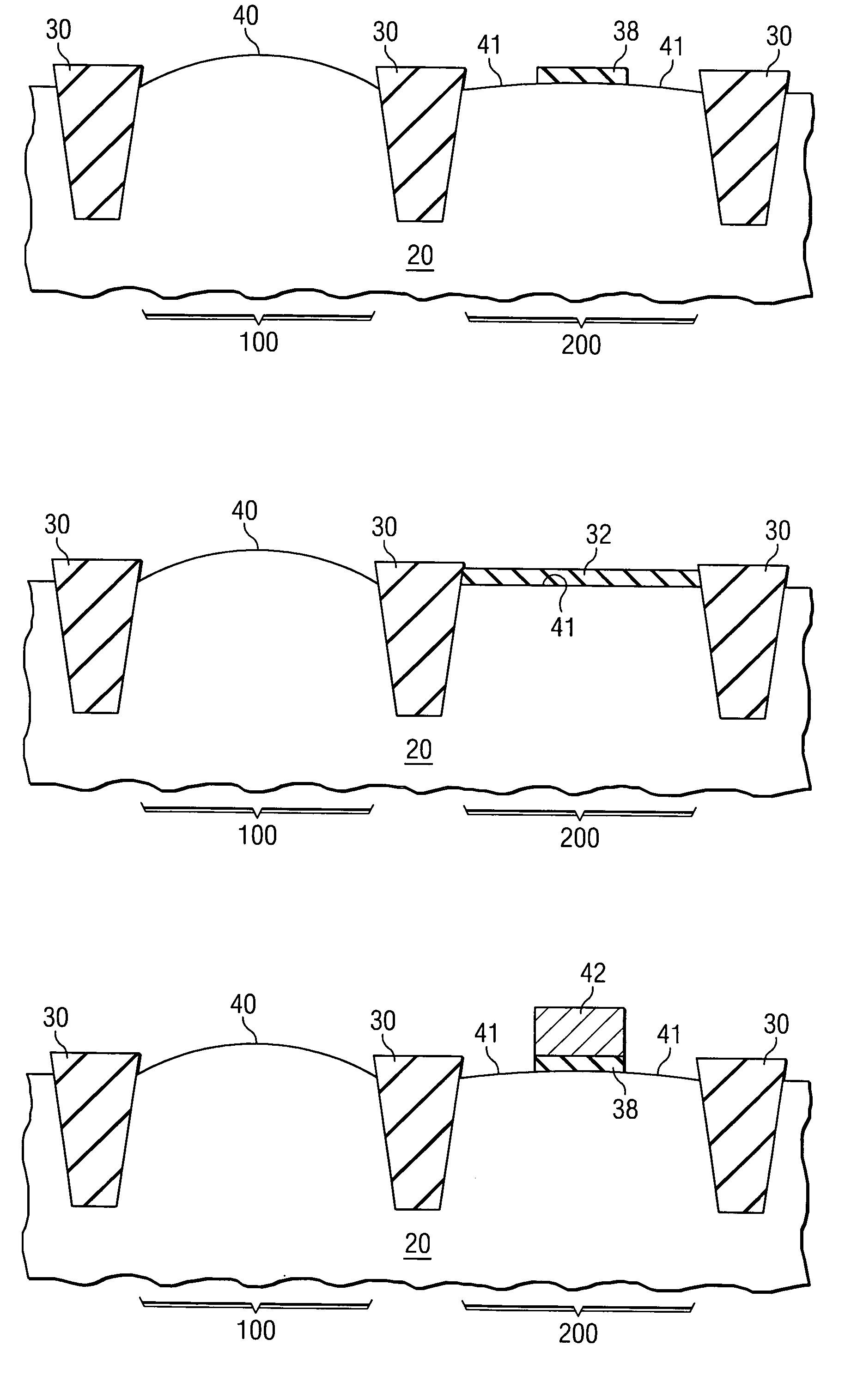

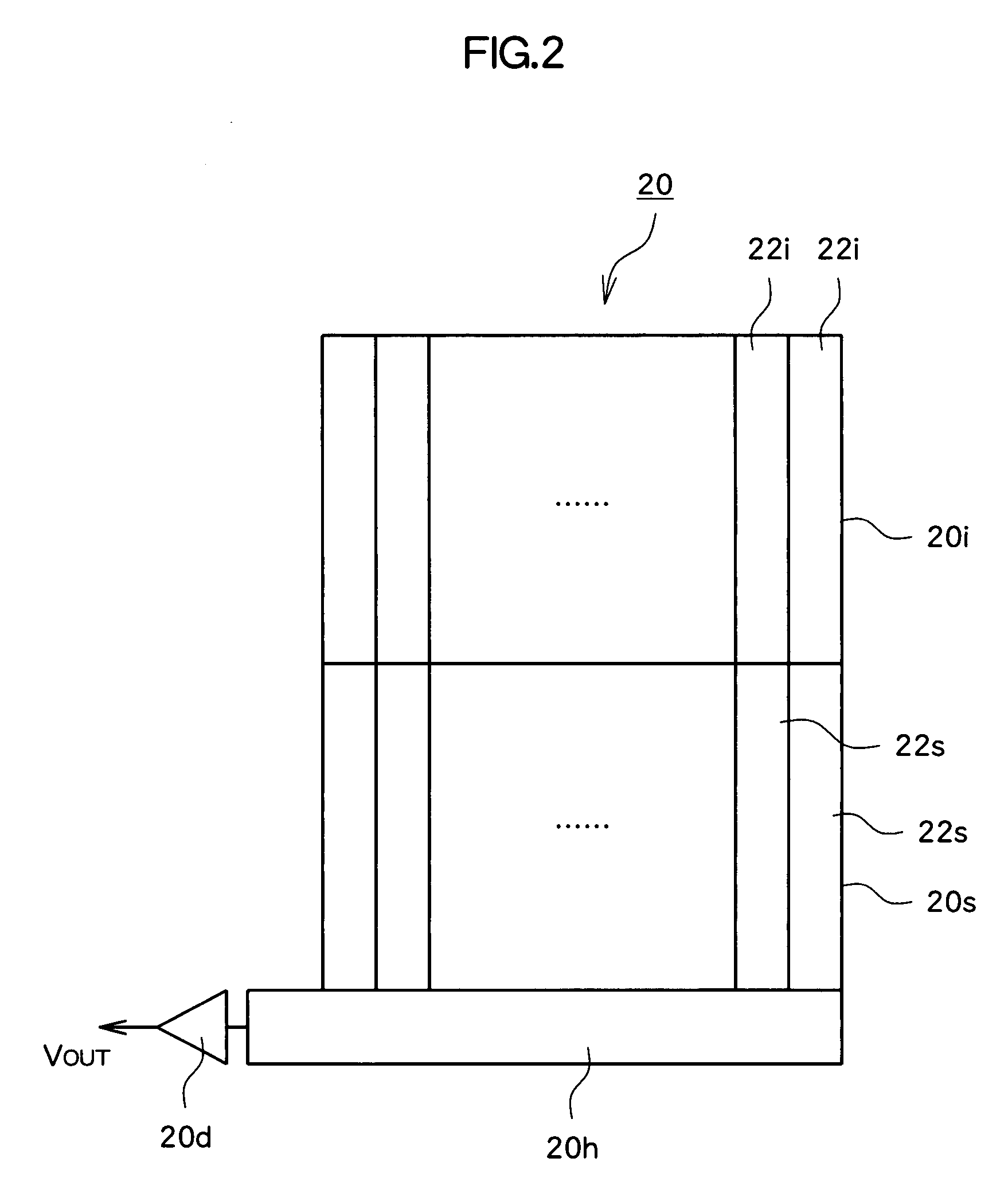

Embedded LSI having a FeRAM section and a logic circuit section

InactiveUS6218197B1Solid-state devicesSemiconductor/solid-state device manufacturingHydrogen annealingLogic circuitry

An embedded LSI includes a FeRAM macro block and an associated logic circuit section. A hydrogen barrier layer covers the FeRAM macro block as a whole and exposes the logic circuit section. The edge of the hydrogen barrier layer overlies the peripheral circuit of the FeRAM macro block and the boundary separating the FeRAM macro block from the logic circuit section. The ferroelectric capacitor is protected by the hydrogen barrier layer against hydrogen during a hydrogen-annealing process.

Owner:RENESAS ELECTRONICS CORP

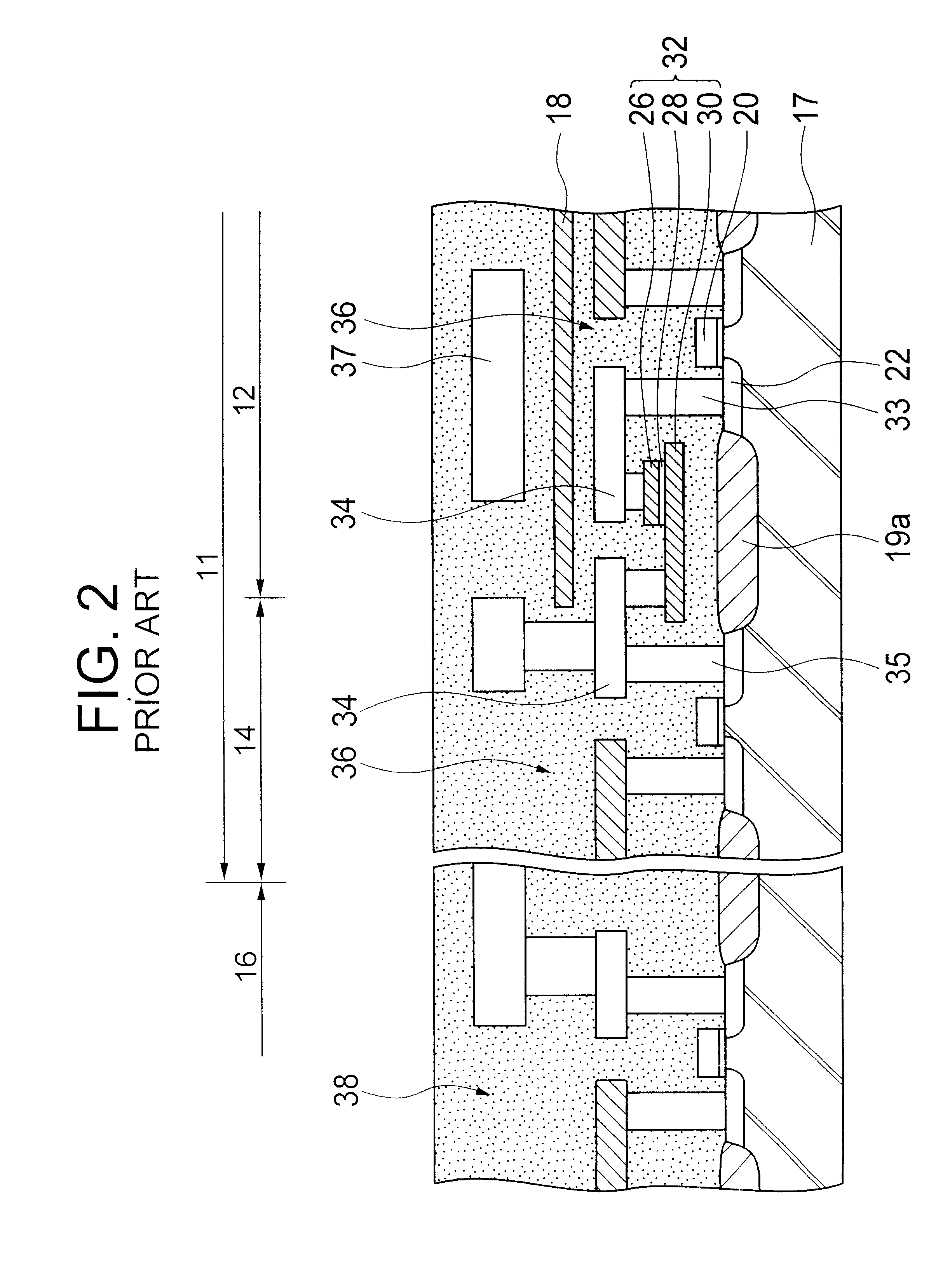

Process for manufacturing a semiconductor integrated circuit device

InactiveUS6165873ASolid-state devicesSemiconductor/solid-state device manufacturingDevice PropertiesCrystallographic defect

This invention relates to a process for manufacturing a semiconductor integrated circuit device comprising hydrogen annealing where a silicon substrate on which a device structure is formed and an interlayer insulating film is deposited is annealed in an atmosphere of hydrogen, comprising removing a substrate material on a substrate surface opposite to the surface on which a device structure is formed (substrate rear face), to make the substrate thinner before the hydrogen annealing; and processing the rear face for removing damages due to crystal defects and scratches generated on the rear face. According to this invention, hydrogen annealing can improve device properties and reliability, regardless of a device structure on the substrate surface, and a semiconductor integrated circuit device can be manufactured in a higher yield.

Owner:NEC ELECTRONICS CORP

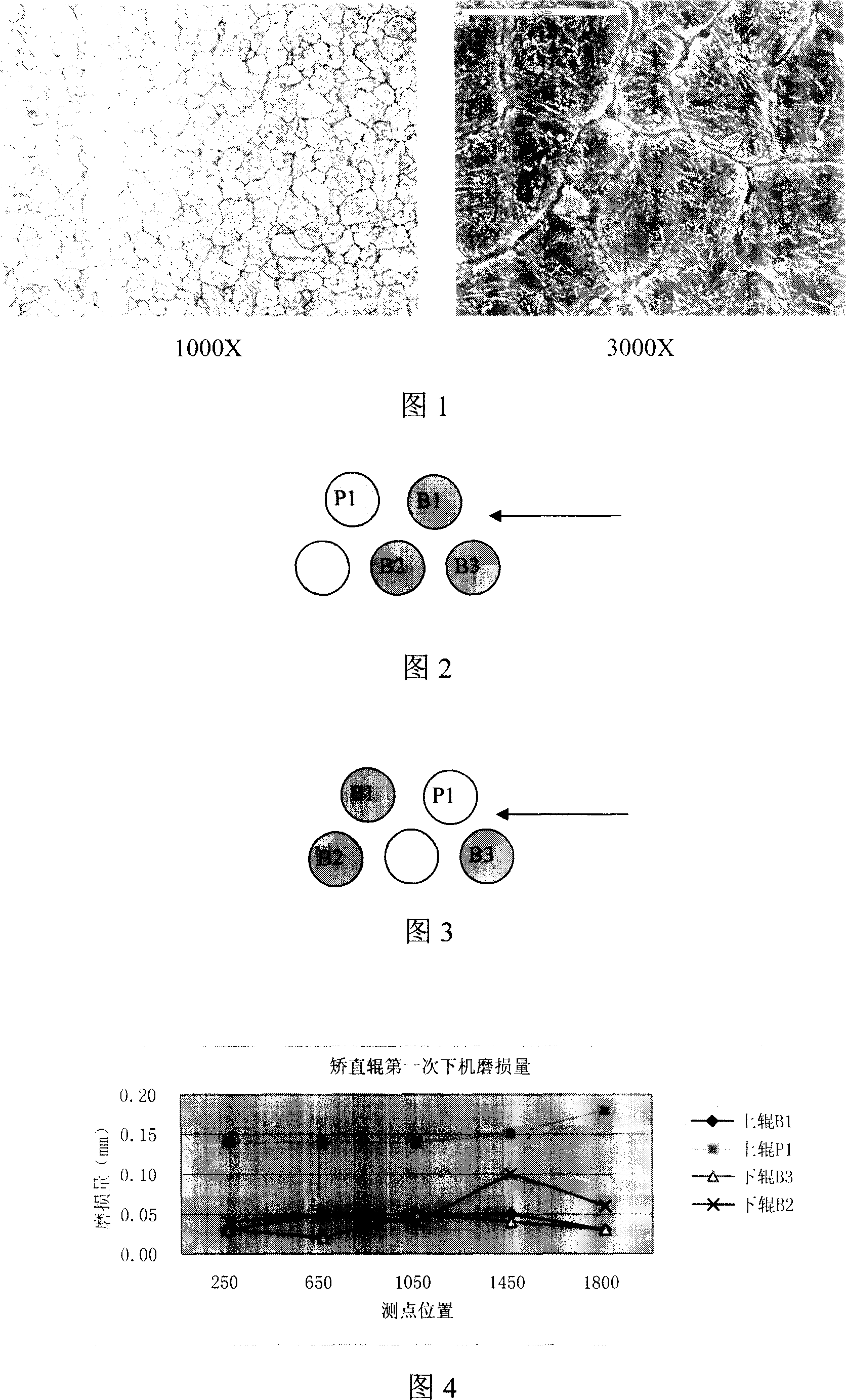

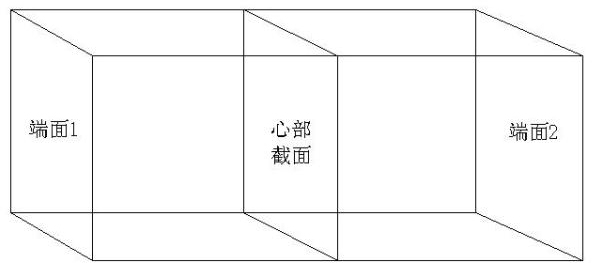

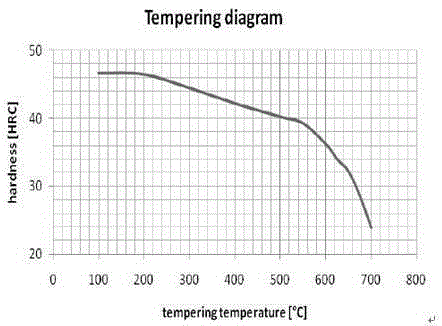

Leveler roll and manufacturing process thereof

ActiveCN101153377AReduce contentChange sizeIncreasing energy efficiencyFurnace typesStrip steelMachining

The invention relates to a straightening roll and the manufacturing process thereof, wherein, the composition of the roll includes 0.60wt percent to 1.10wt percent of C, 0.20wt percent to 1.0wt percent of Si, 0.20wt percent to 0.60wt percent of Mn, 0.20wt percent to 1.00wt percent of Ni, 4.00wt percent to 6.00wt percent of Cr, 0.20wt percent to 1.00wt percent of Mo, 0.10wt percent to 0.50wt percent of V, less than or equal to 0.02wt percent of P, less than or equal to 0.02wt percent of S and the rest, Fe and other inevitable impurities; the manufacturing process of the roll includes: electric furnace smelting to secondary refining to ingot casing to electrode rolling to electrode rough machining to electroslag remelting to ingot casing to hydrogen diffusion annealing to forging to conditioning treatment to ultrasonic flaw detection and microscopic and macroscopic test to rough machining to quenching and tempering heat treatment to semifinishing to final heat treatment to finish machining to finished product. The invention increases the service life of the straightening roll and the surface quality of strip steel and eliminates the bottleneck in straightening high strength plate during production.

Owner:BAOSHAN IRON & STEEL CO LTD

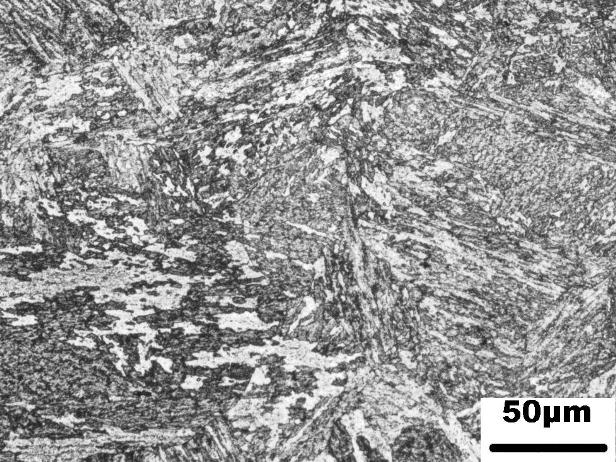

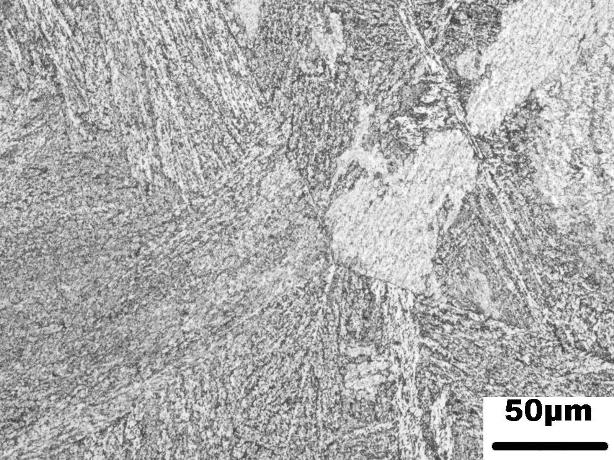

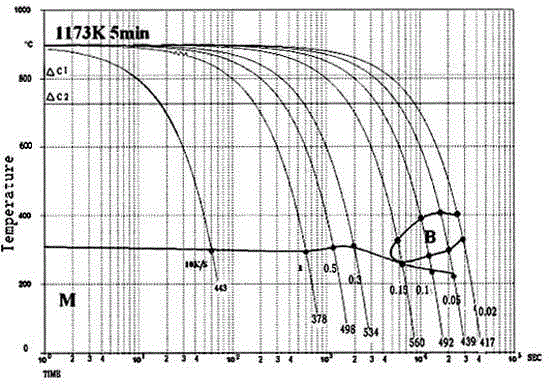

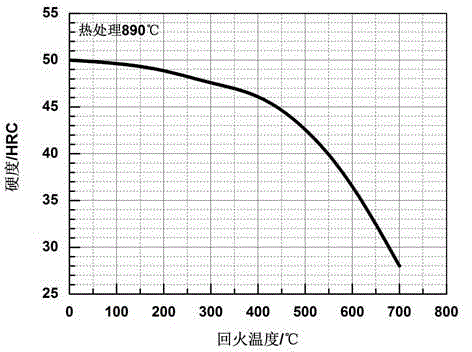

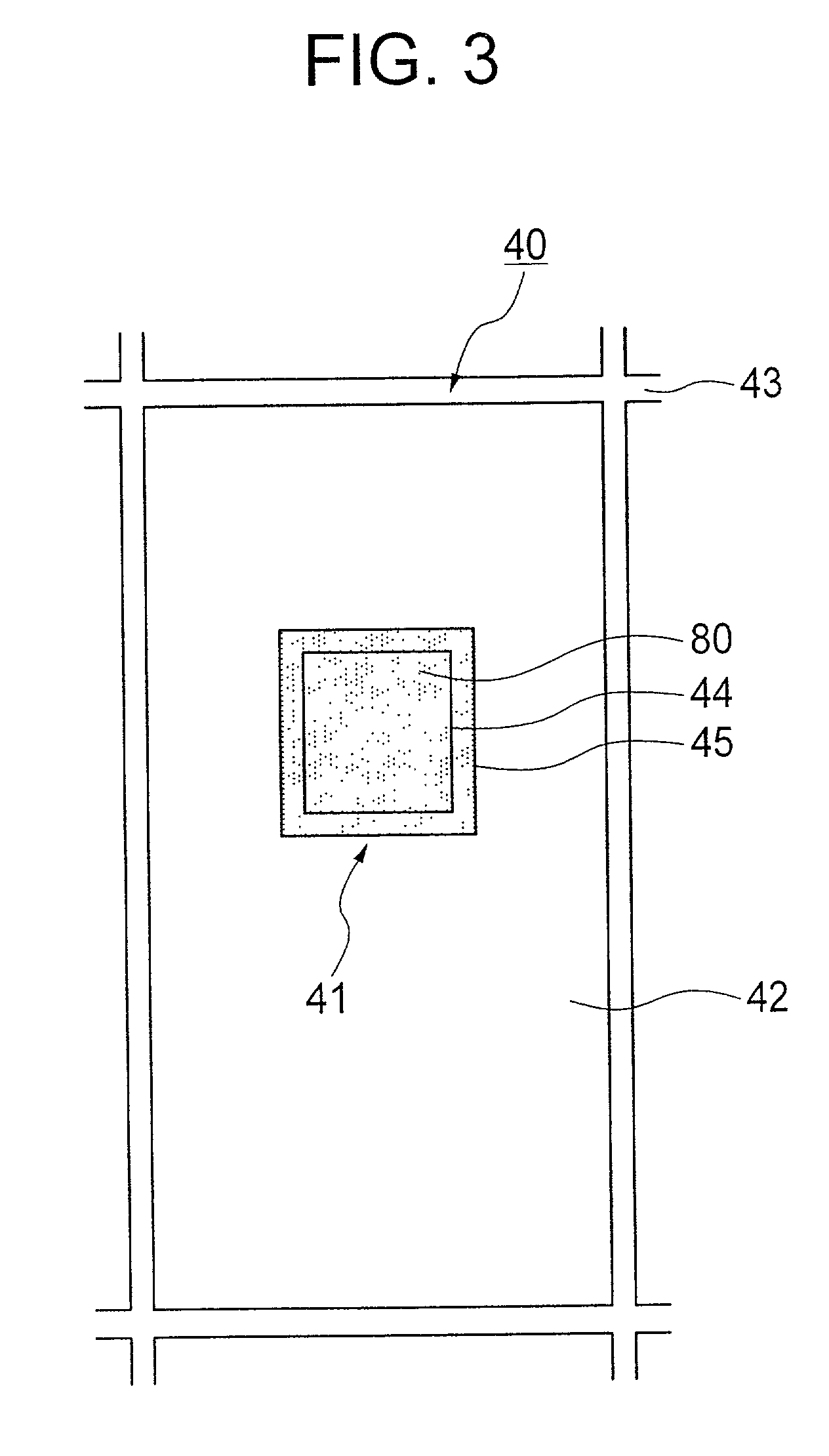

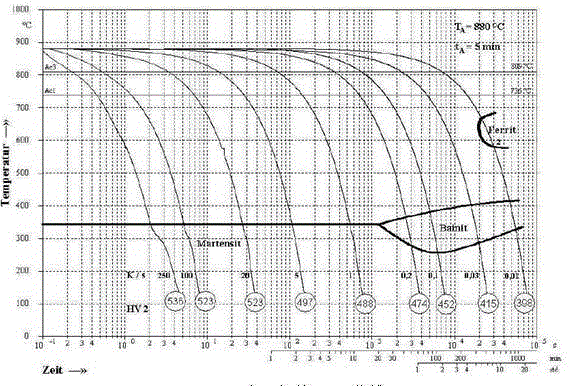

Bainite pre-hardening plastic mold steel and preparation method and heat treatment method thereof

The invention relates to bainite pre-hardening plastic mold steel and a preparation method and a heat treatment method thereof. Chemical components of the steel are optimized on the basis of P20 steel, the content of manganese (Mn) is appropriately increased, the content of the chromium (Cr) and molybdenum (Mo) is reduced, little niobium (Nb) is added, and no nickel (Ni) and vanadium (V) in expensive price are not contained. The preparation method of the plastic mold steel comprises the following steps of: compounding, smelting and casting; carrying out the multi-directional forging heat machining; carrying out the wind cooling and the air cooling; and finally carrying out the tempering heat treatment. The plastic mold steel has characteristics of large cross section, low cost, high hardenability, good hardness uniformity and the like and also has low susceptibility of flake formation, a diffusion hydrogen annealing process is omitted, in addition the post-forging normalizing is adopted to substitute a thermal refining process, so that the production period is greatly shortened, the domestication of the plastic mold steel with large cross section, long service life, top quality and short period can stride forward for a large step, and the existing domestic manufacturing concept of energy conservation, emission reduction, sustainability and economical type can be met.

Owner:SHANGHAI UNIV

Bonded semiconductor substrate manufacturing method thereof

InactiveUS7491342B2Simple processReduce surface roughnessDecorative surface effectsSemiconductor/solid-state device detailsEtchingSurface roughness

The present invention provides a bonded substrate fabricated to have its final active layer thickness of 200 nm or lower by performing the etching by only 1 nm to 1 μm with a solution having an etching effect on a surface of an active layer of a bonded substrate which has been prepared by bonding two substrates after one of them having been ion-implanted and then cleaving off a portion thereof by heat treatment. SC-1 solution is used for performing the etching. A polishing, a hydrogen annealing and a sacrificial oxidation may be respectively applied to the active layer before and / or after the etching. The film thickness of this active layer can be made uniform over the entire surface area and the surface roughness of the active layer can be reduced as well.

Owner:SUMCO CORP +1

High-hardness high-polishing pre-hardening plastic die steel and manufacture technology thereof

ActiveCN104532154AGrain refinementRefine the uniformity of ingredientsManufacturing technologyHardness

The invention relates to a high-hardness high-polishing pre-hardening plastic die steel and a manufacture technology thereof, which belongs to the technical field of alloy steel manufacture technology. The steel is characterized in that the alloy chemical component comprises the following alloy elements by mass percentages: 0.25-0.40% of C, 0.10-0.30% of Si, 1.50-2.00% of Mn, 1.50-2.50% of Cr, 0.50-1.00% of Mo, 0.10-0.30% of V, less than or equal to 0.025% of P, less than or equal to 0.005% of S, 0.60-1.50% of Ni, less than or equal to 0.15% of Nb, and the balance of Fe. The manufacture method comprises the following steps: burdening, smelting, pouring, performing hot delivery; performing high-temperature diffusing heat treatment, then performing multi-directional forging and hot processing, normalizing on fine grains and dehydrogenizing and annealing; and finally quenching and performing temper heat treatment to obtain the tempered structure with hardness of 38-42HRC. The steel of the invention has the advantages of low cost, high hardenability, high hardness, high polishing performance and dermatoglyph etching performance.

Owner:RUGAO HONGMAO HEAVY FORGING

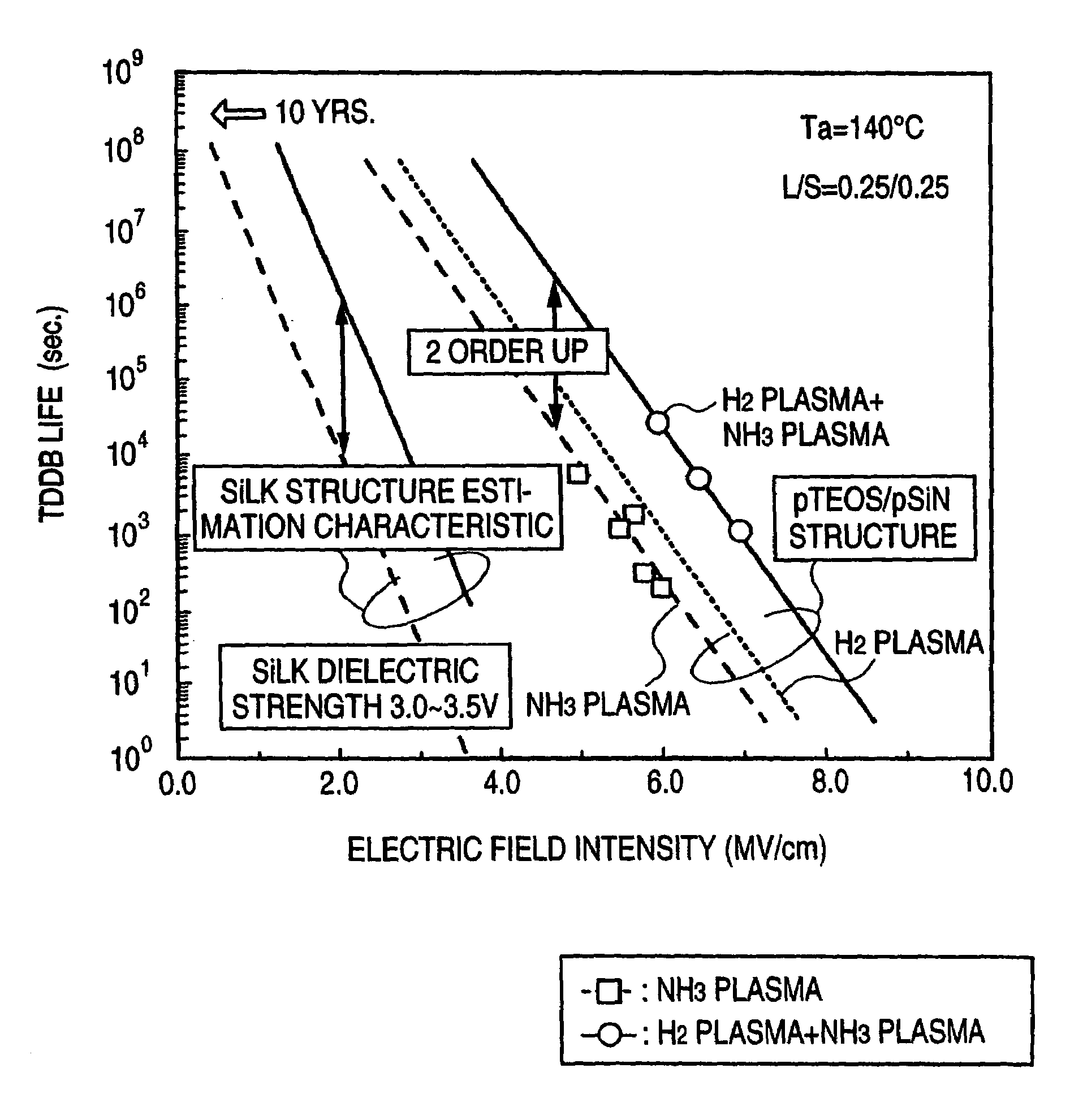

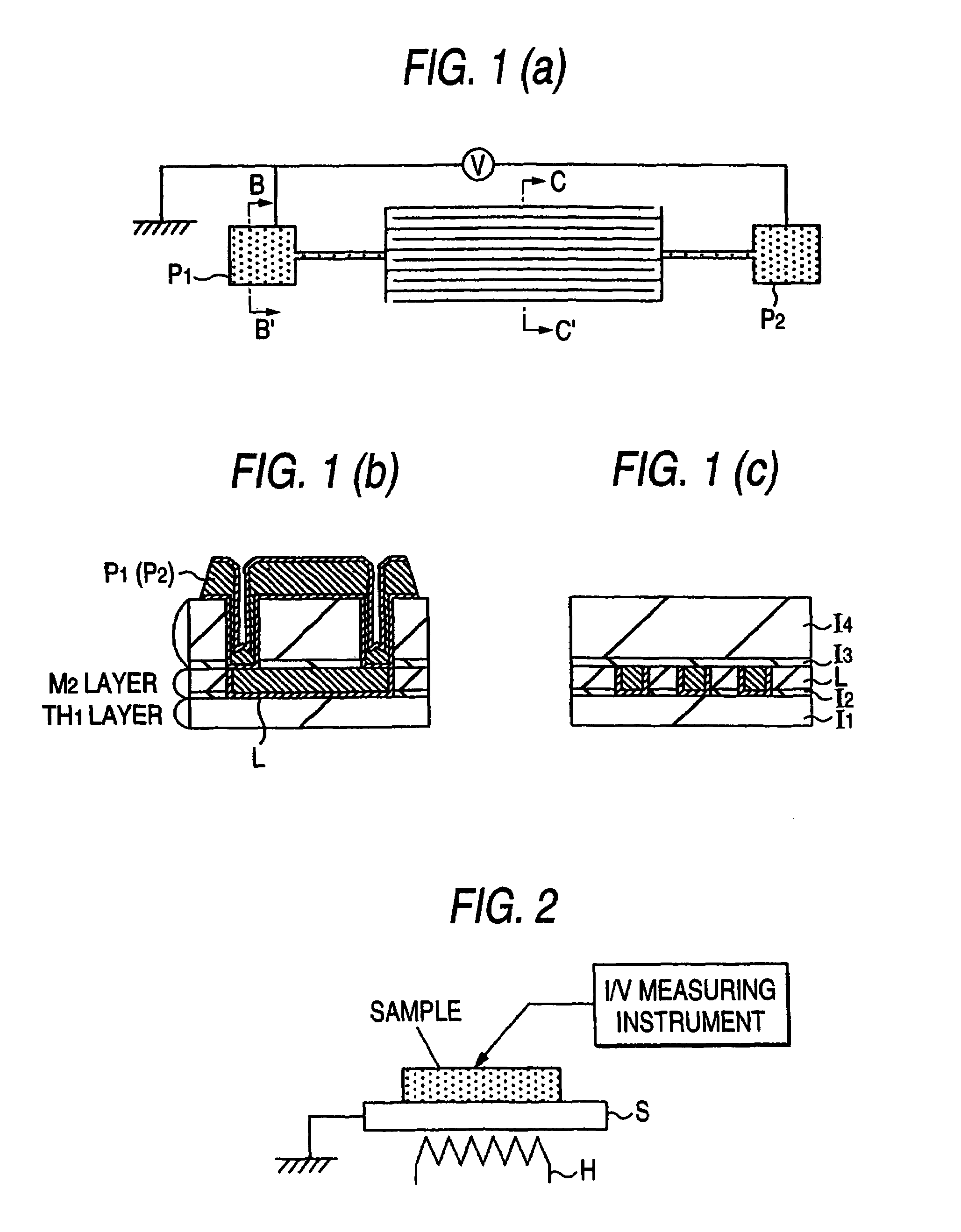

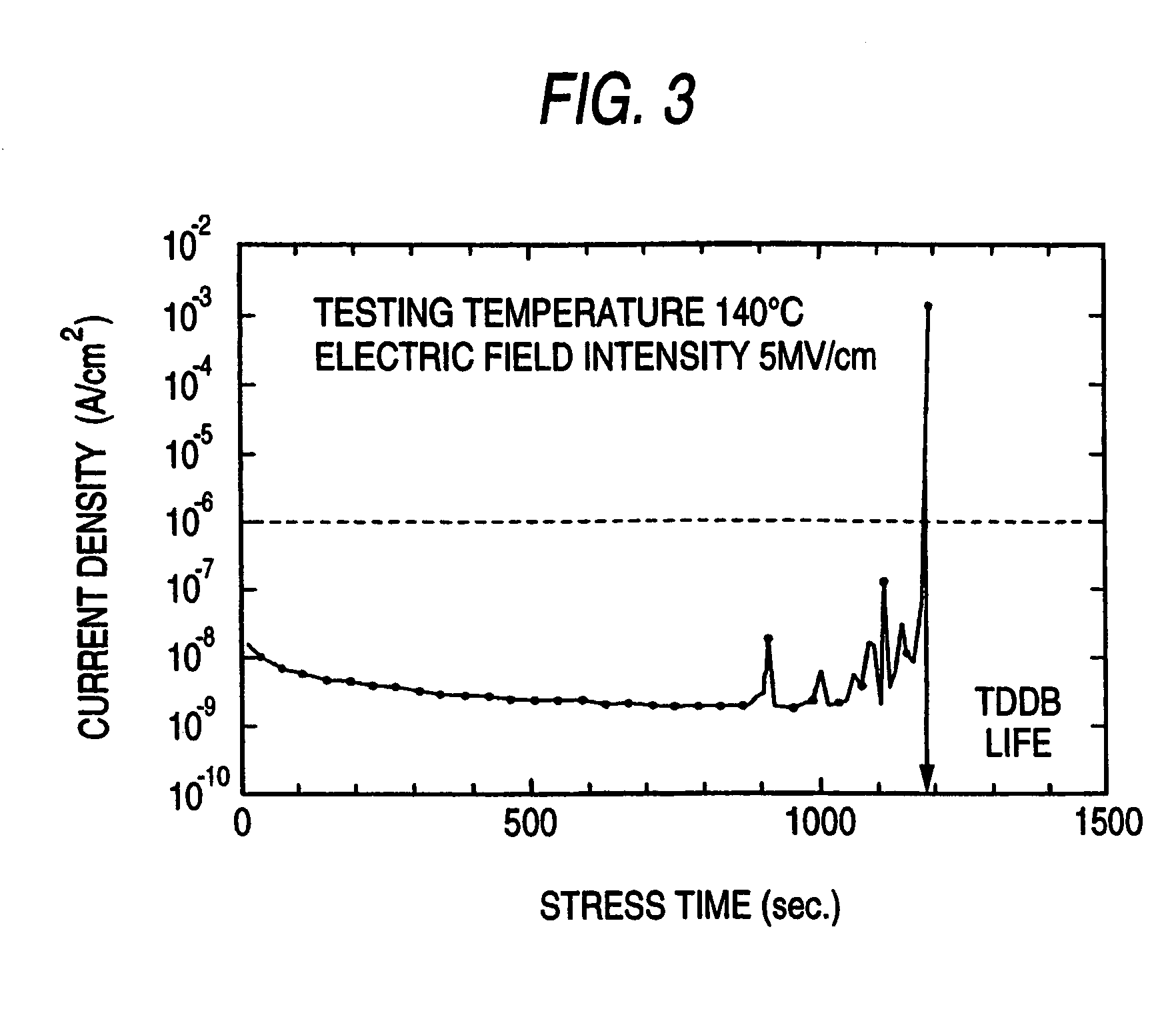

Fabrication method of semiconductor integrated circuit device

InactiveUS7084063B2Improve dielectric breakdown strengthIncrease resistanceTransistorSemiconductor/solid-state device detailsCopper interconnectDielectric breakdown strength

The copper interconnect formed by the use of a damascene technique is improved in dielectric breakdown strength (reliability). During post-CMP cleaning, alkali cleaning, a deoxidizing process due to hydrogen annealing or the like, and acid cleaning are carried out in this order. After the post-CMP cleaning and before forming an insulation film for a cap film, hydrogen plasma and ammonia plasma processes are carried out on the semiconductor substrate. In this way, a copper-based buried interconnect is formed in an interlayer insulation film structured of an insulation material having a low dielectric constant.

Owner:HITACHI LTD

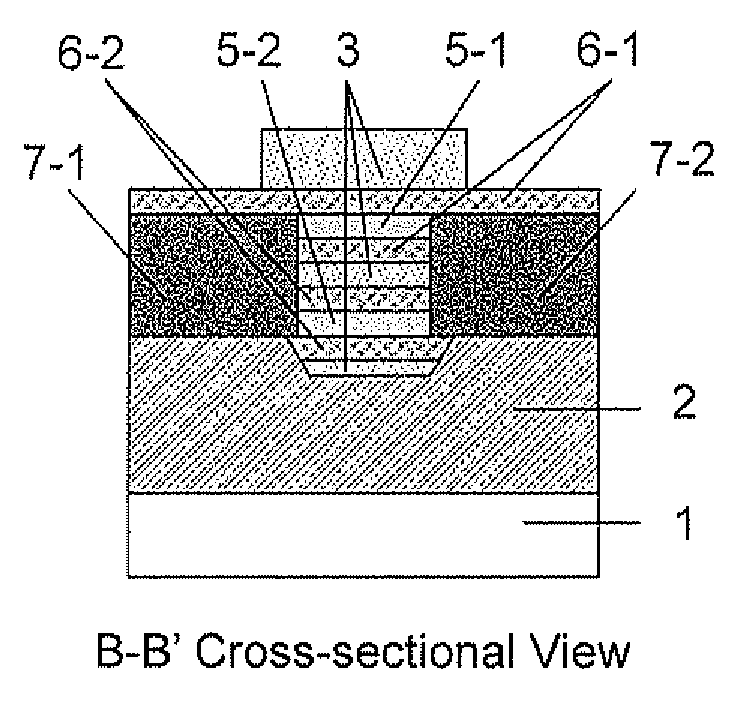

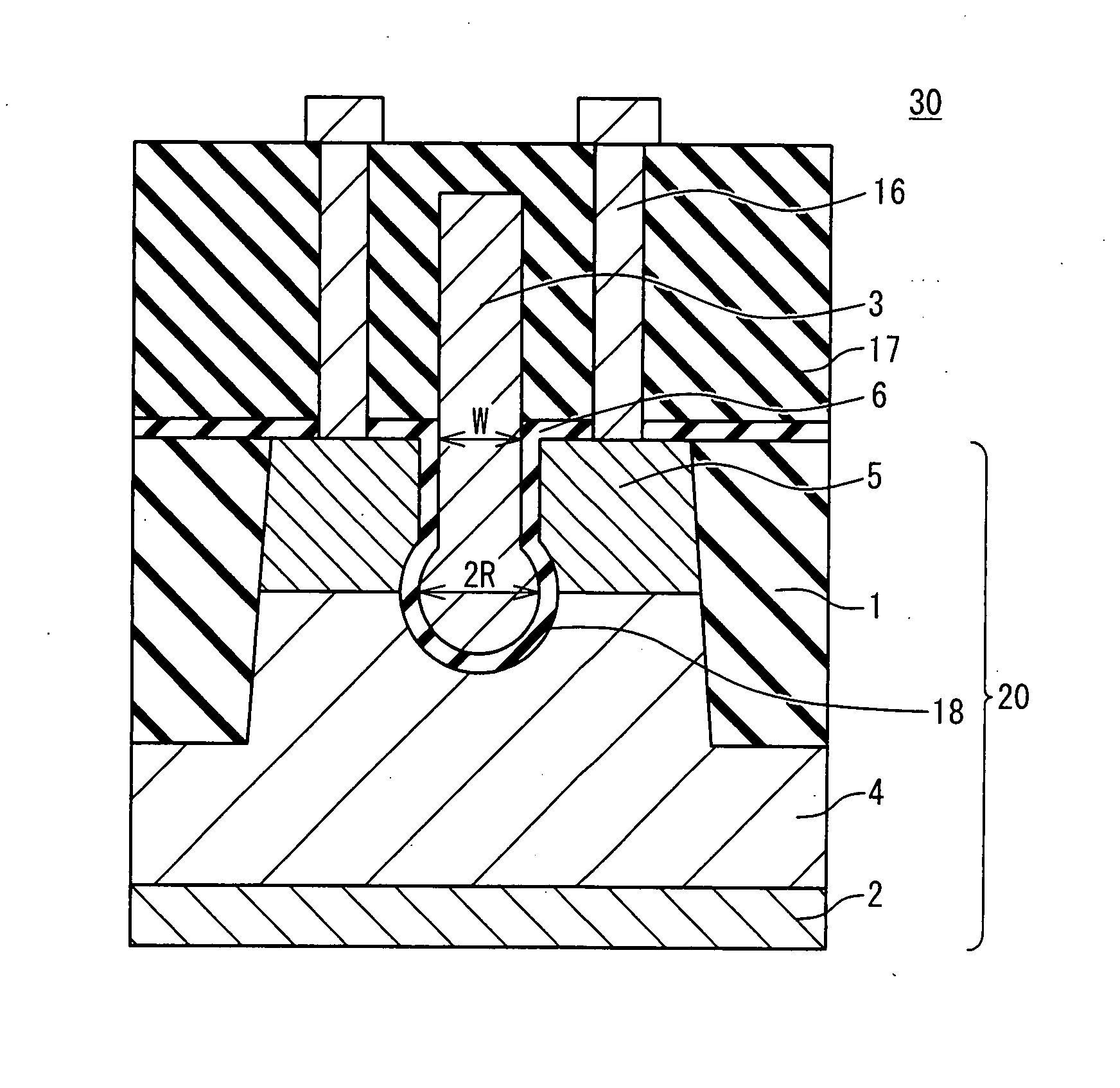

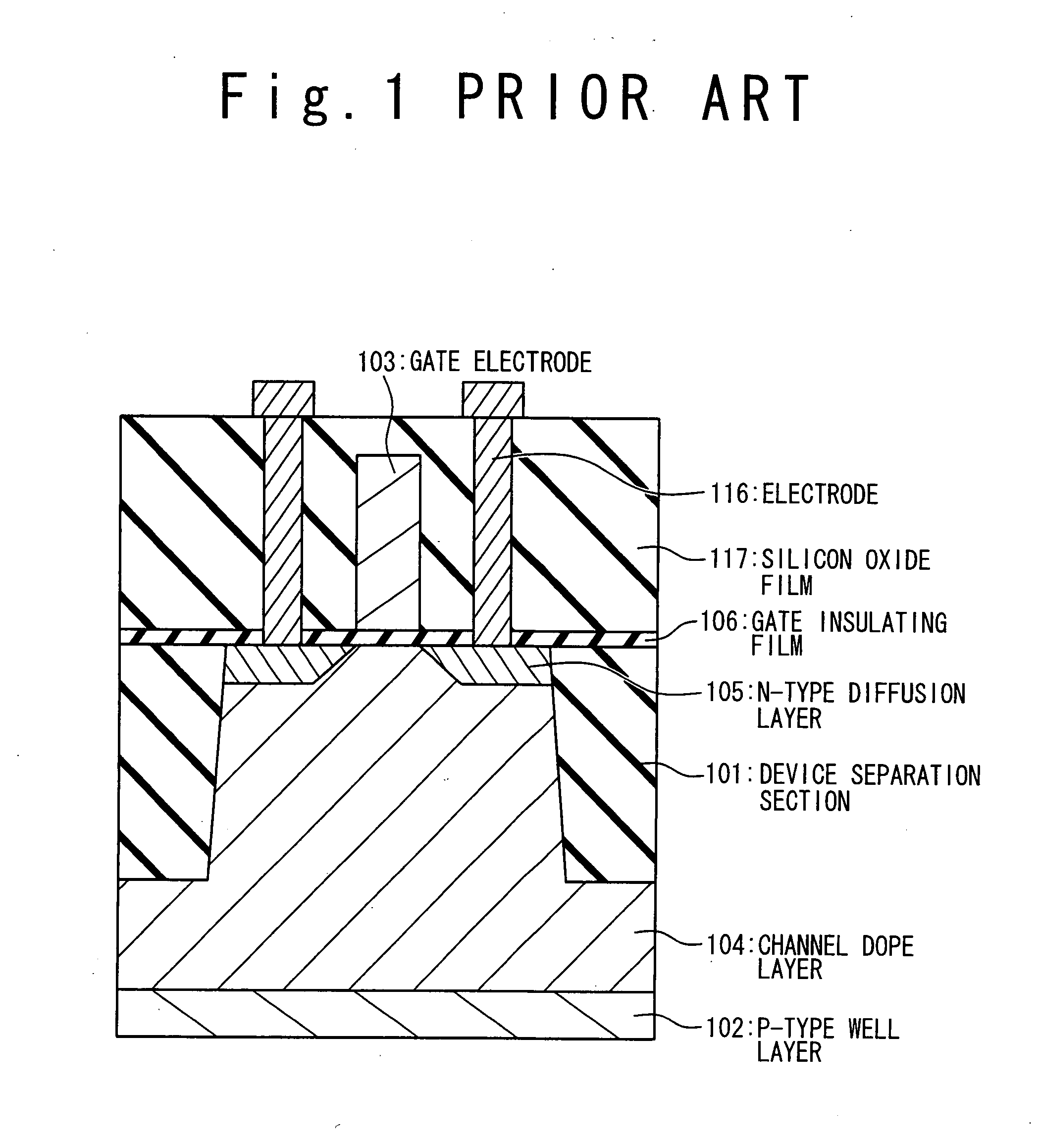

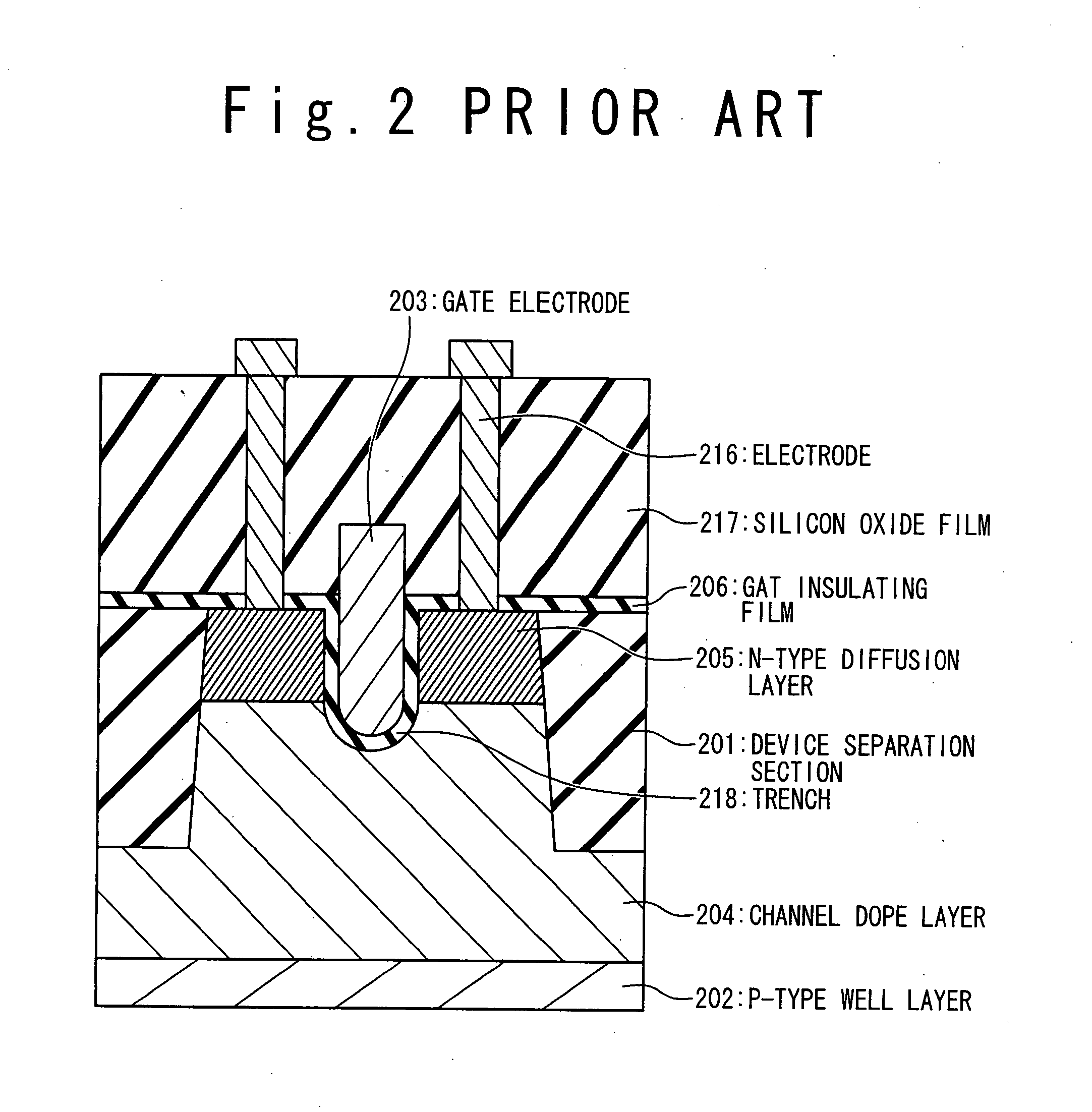

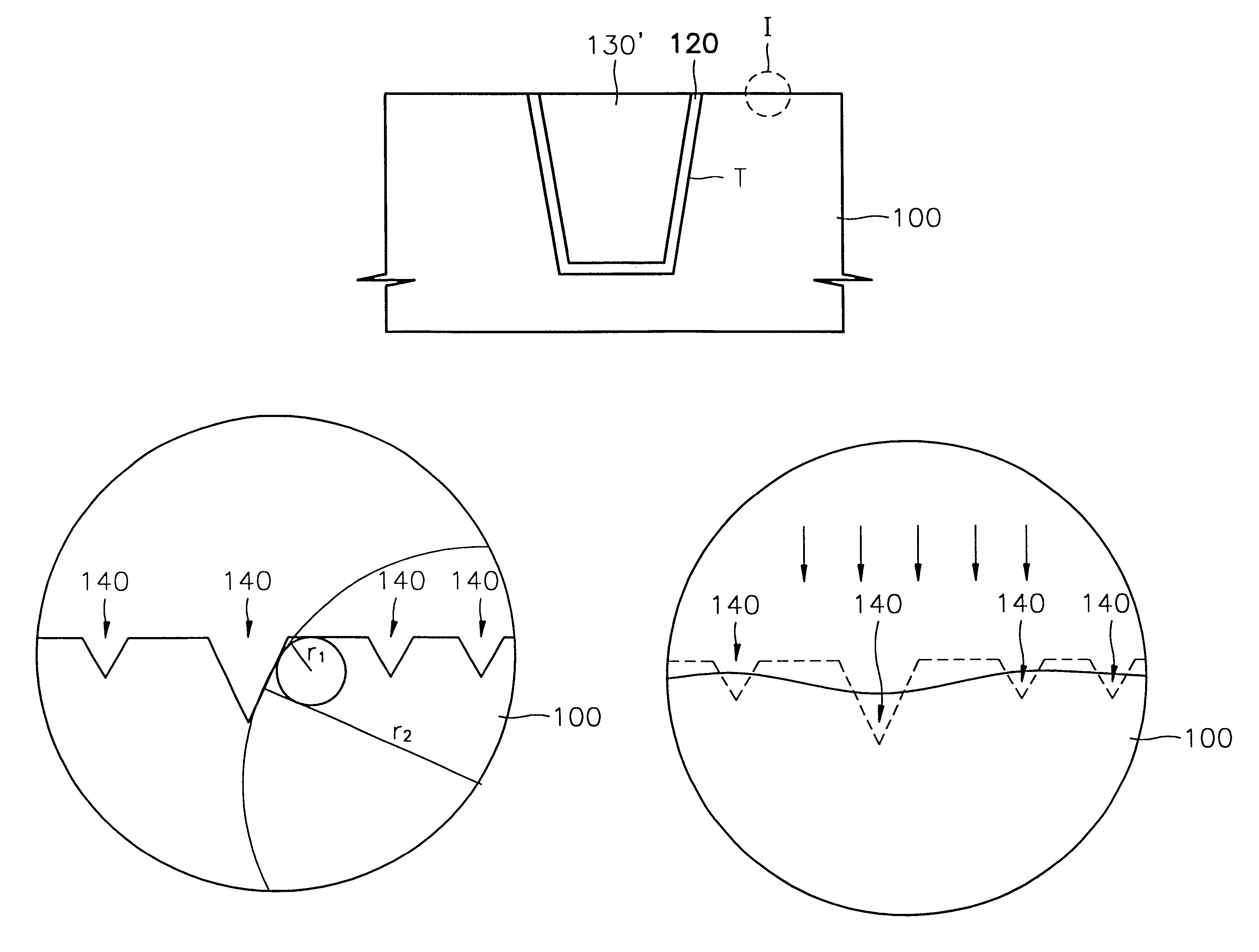

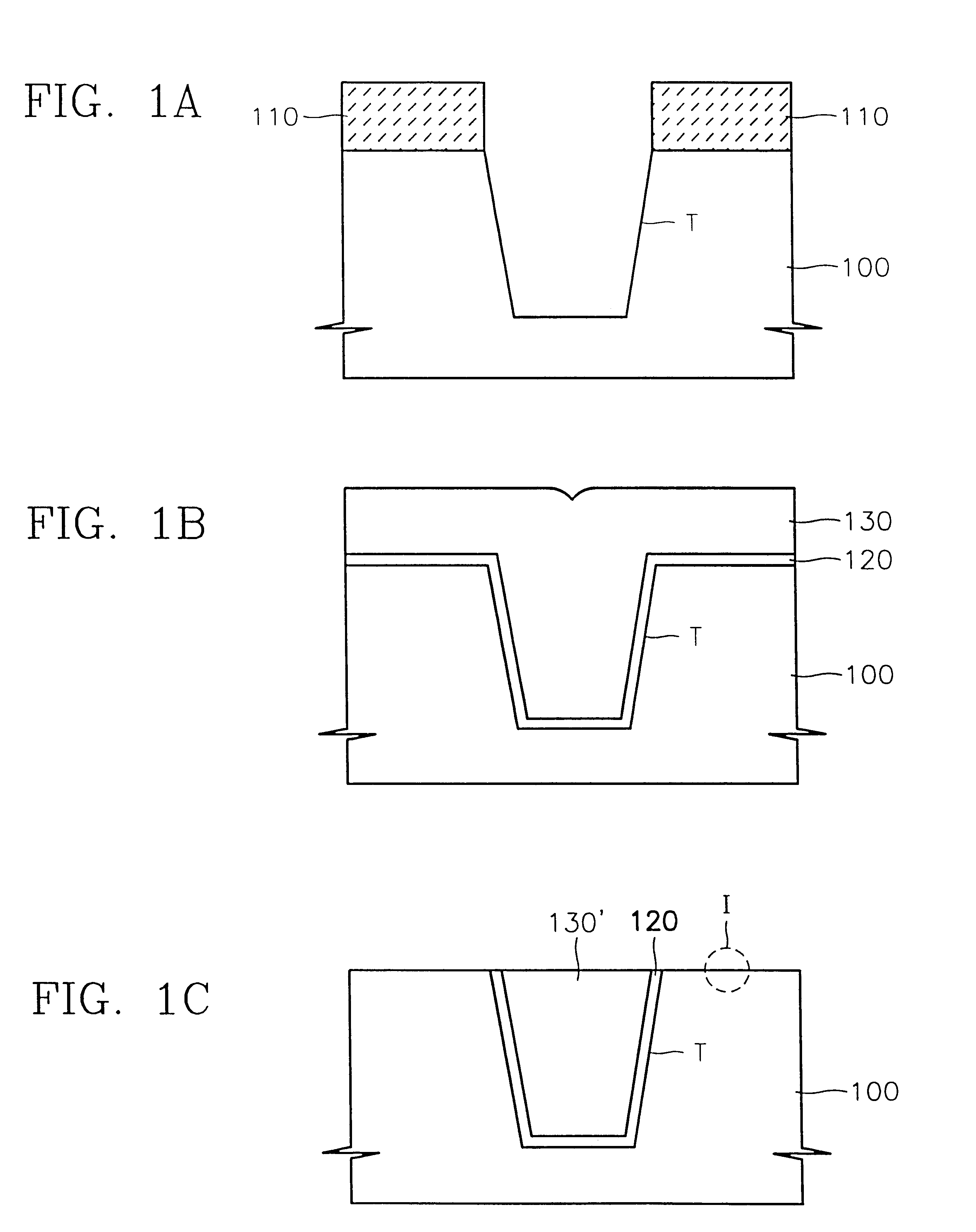

Semiconductor device and method of manufacturing the same

InactiveUS20070224763A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

In a method of manufacturing a semiconductor device, a trench is formed to have an upper quadrangular section and a lower circular section which is formed through a hydrogen annealing process, to extend in a depth direction of a semiconductor substrate. An insulating film is formed on a surface of the trench and a surface of the semiconductor substrate. A conductive film is formed to fill the trench whose surface is covered with the an insulating film. Source / drain regions are formed on both sides of the trench.

Owner:LONGITUDE SEMICON S A R L

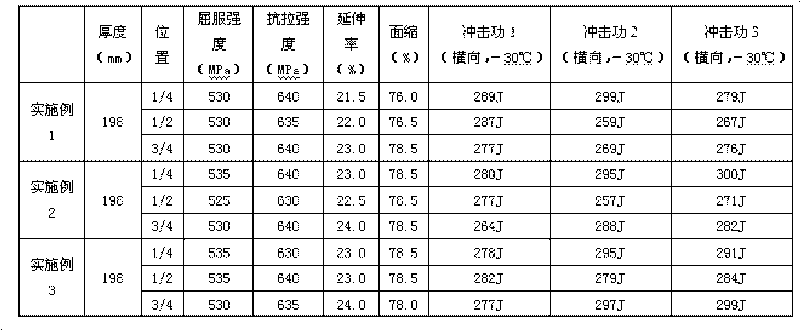

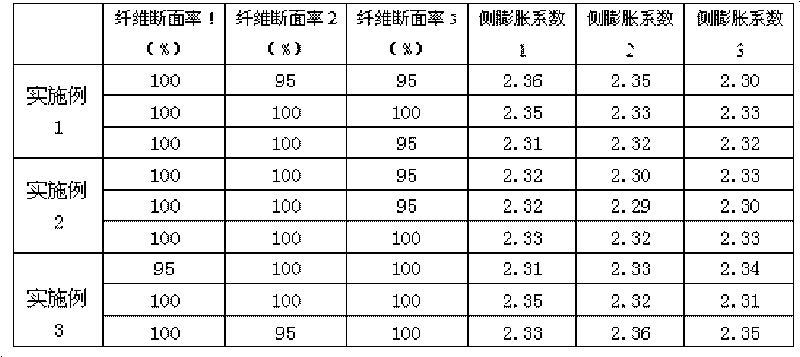

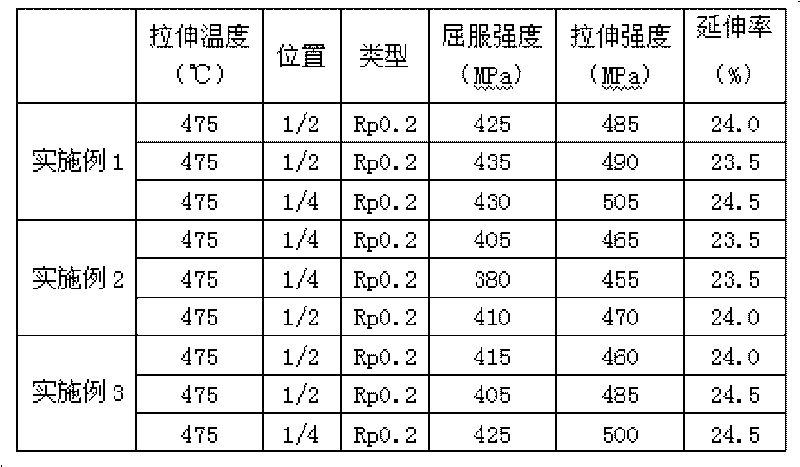

Large thickness steel plate for hydrogenation reaction chamber reeling equipment and production method thereof

InactiveCN101713054AImprove purityUniform compositionProcess efficiency improvementElectric furnaceSheet steelHydrogenation reaction

The invention discloses a large thickness steel plate for hydrogenation reaction chamber reeling equipment and a production method thereof. The steel plate takes Cr-Mo steel as the base, an amount of alloying elements, such as Ni, Cu, Al, Nb, Mn, Cr and the like are added, the contents of harmful elements, such as Sn, Sb, As, P, S and the like are controlled, and the finished large thickness steel is prepared by adopting the processes of electric furnace smelting, LF refining furnace refining, throwing down line stacking for slow-cooling, electroslag remelting, rolling and product forming, diffusion hydrogen annealing, normalizing and tempering heat treatment and the like. The thickness of the steel plate reaches 198 mm, the weight of single steel plate reaches 25 tons, the high temperature tensile strength and yield strength of the steel plate are good, the lower temperature toughness at minus 30 DEG C is good, the steel plate has good tempering embrittlement sensitivity coefficient, and the purity of the produced steel plate is high, the component is uniform, the inner part is compact, and the mechanical property is uniform. The steel plate can meet the operation requirement of hydrogenation reaction chamber reeling equipment, and is suitable for the production of the main structural parts of all hydrogenation reaction chamber reeling equipment.

Owner:WUYANG IRON & STEEL +1

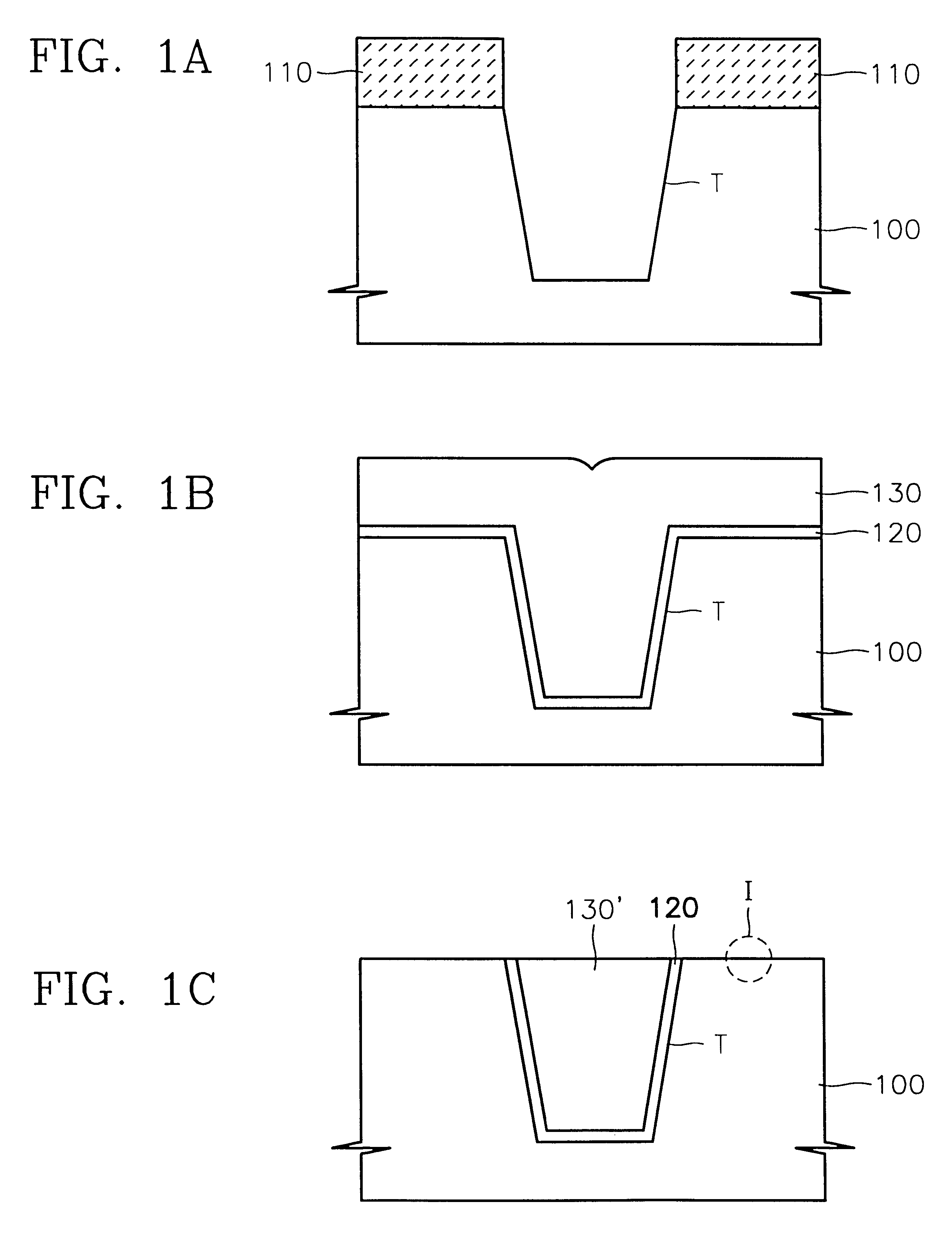

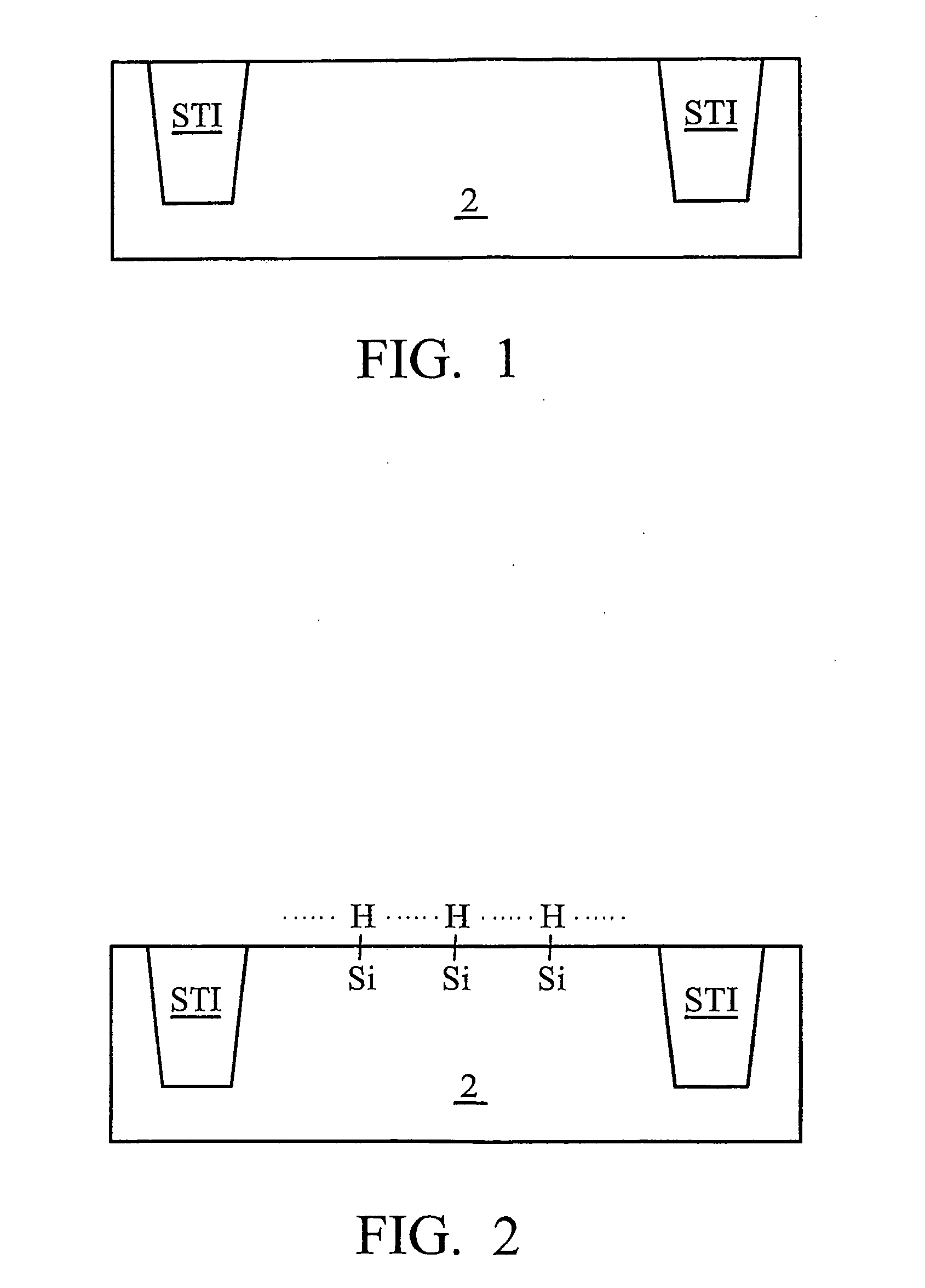

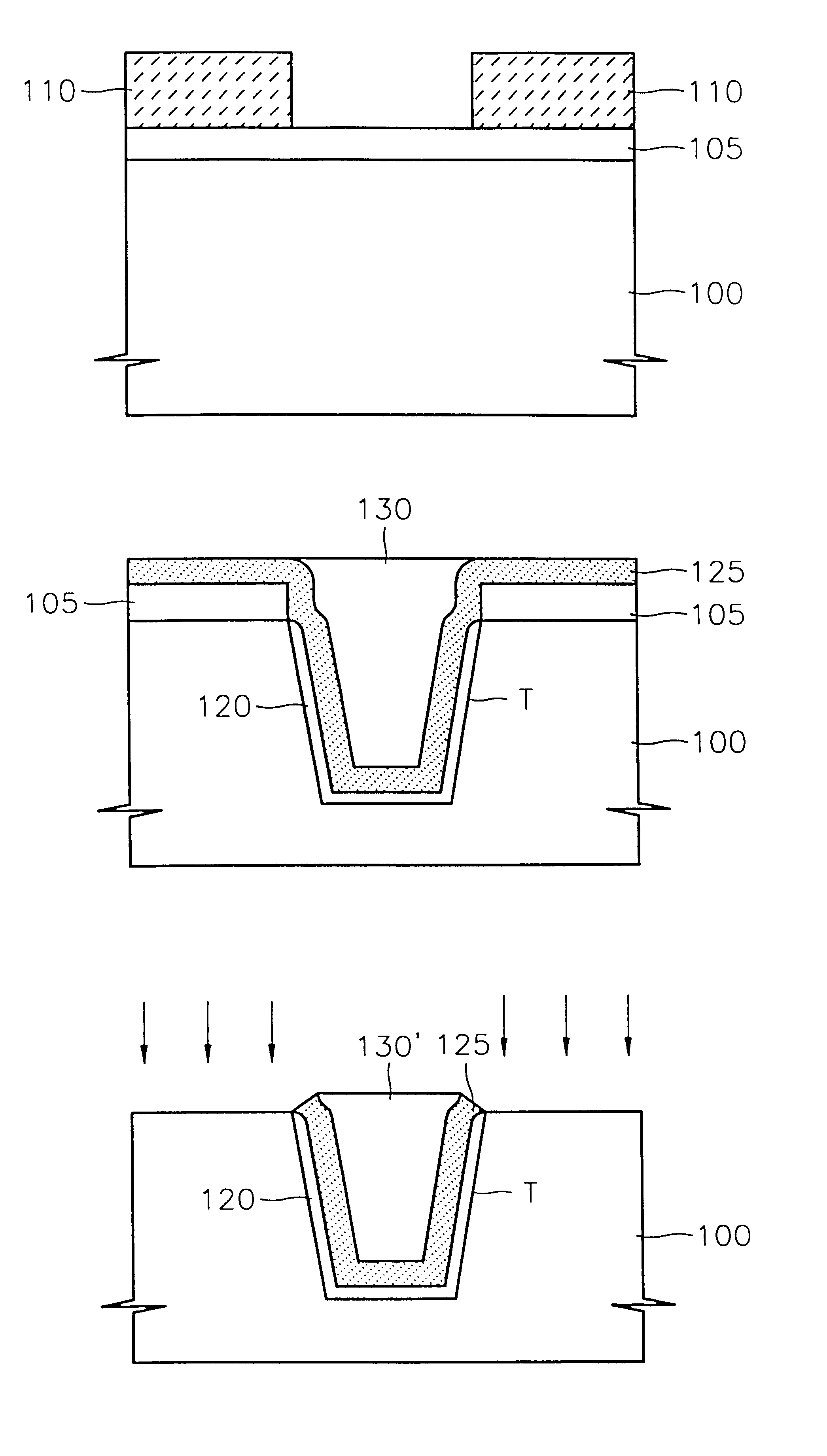

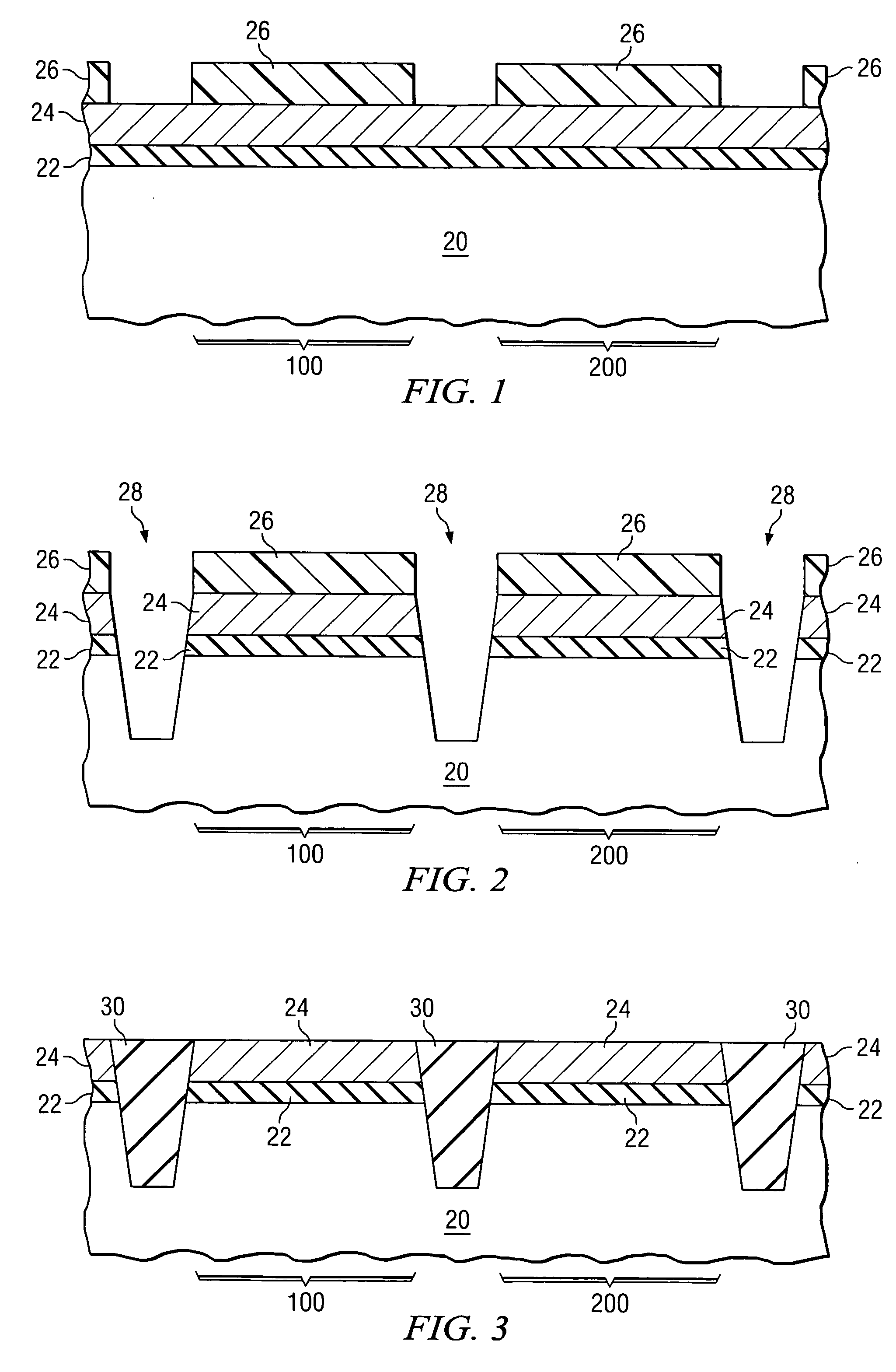

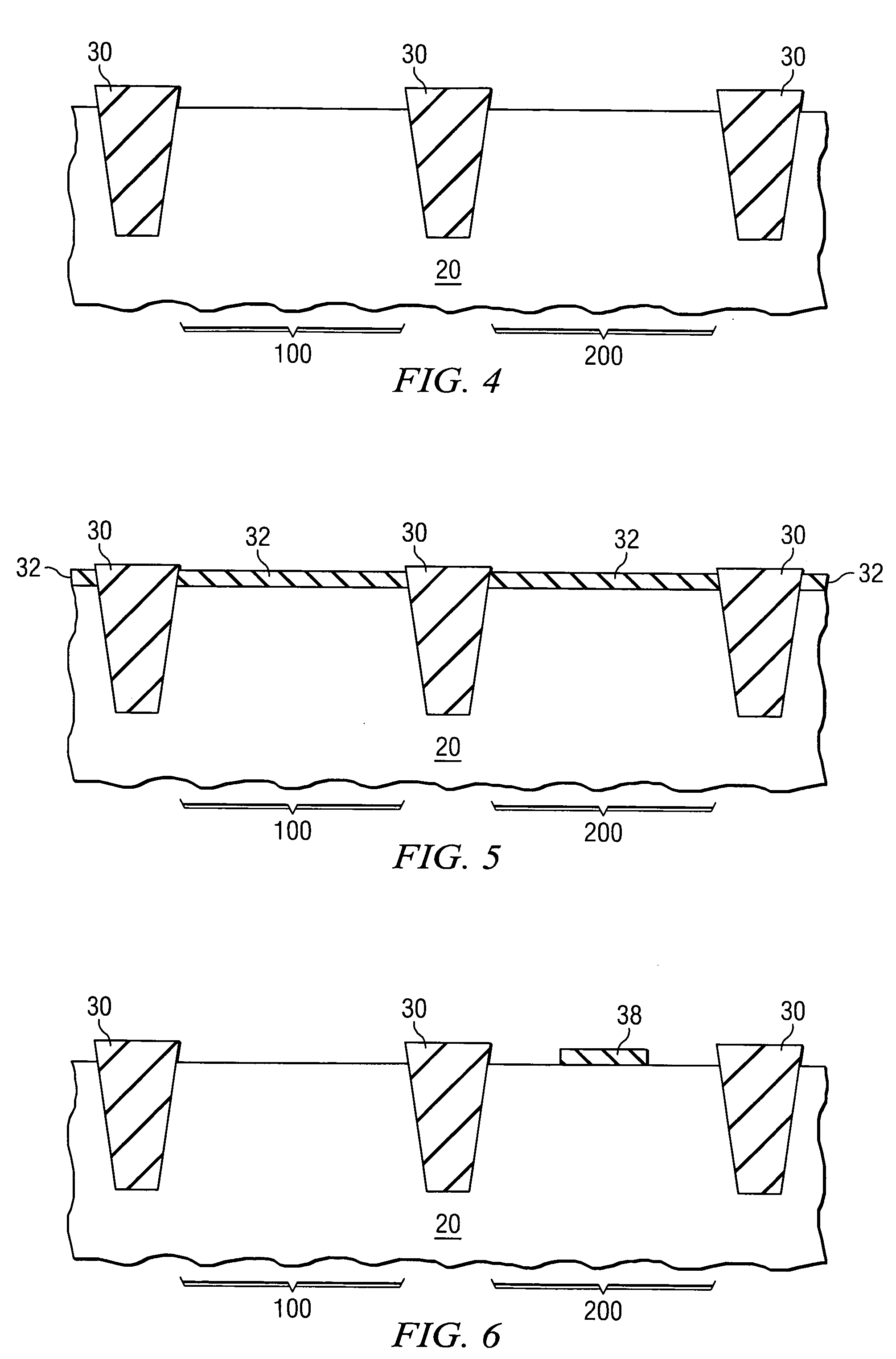

Method of fabricating a semiconductor device using trench isolation method including hydrogen annealing step

InactiveUS6511888B1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialHydrogen atmosphere

A method of fabricating a semiconductor device using a trench isolation method including a hydrogen annealing step, wherein a photoresist pattern is formed on a semiconductor substrate, a pad insulating layer may be formed before forming the photoresist pattern, the semiconductor substrate is etched using the photoresist pattern as an etching mask to form a trench, and an isolation layer is formed in the trench. To remove damages created in an active region defined by the isolation layer, the semiconductor substrate having the isolation layer is annealed in a hydrogen atmosphere.

Owner:SAMSUNG ELECTRONICS CO LTD

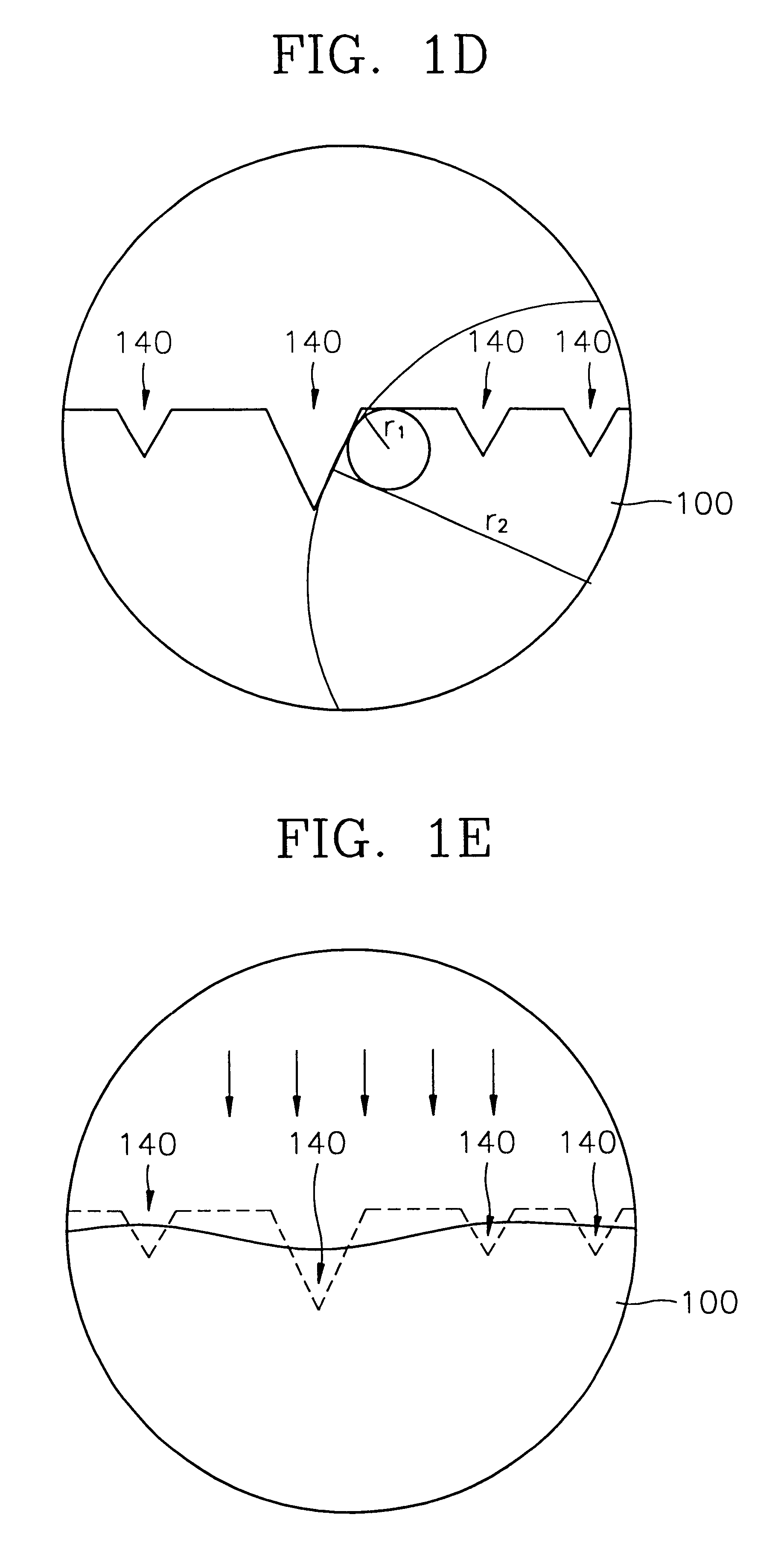

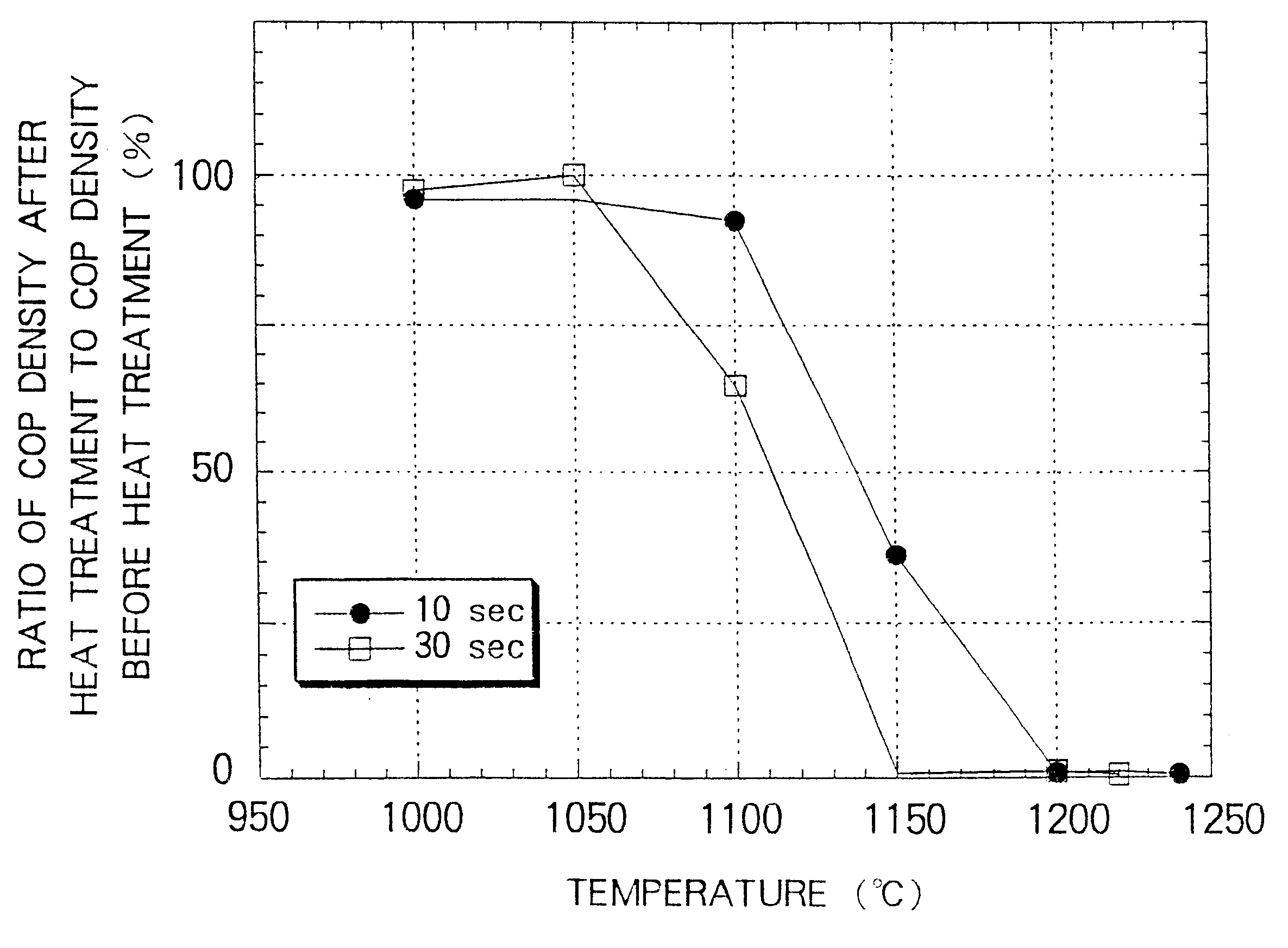

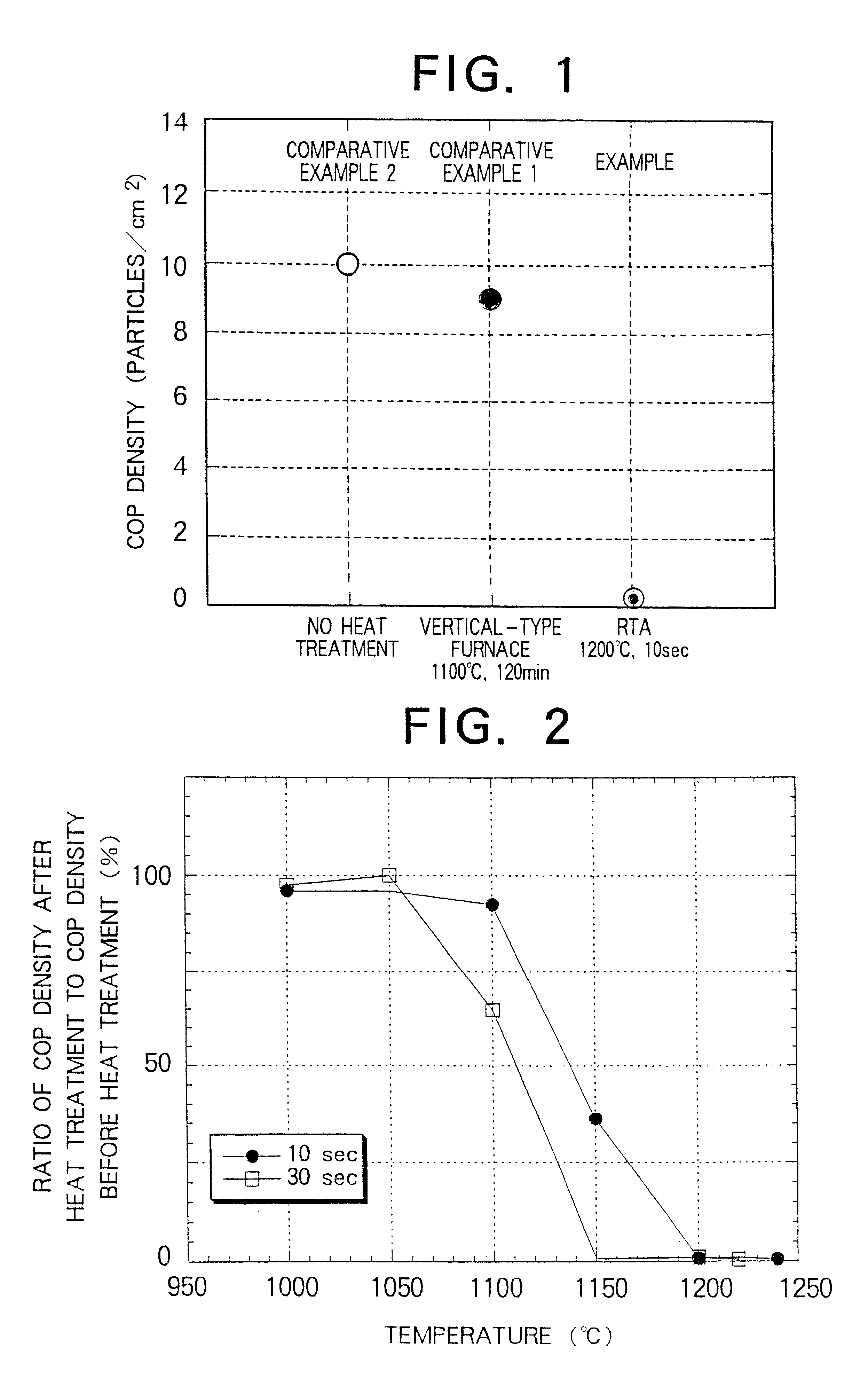

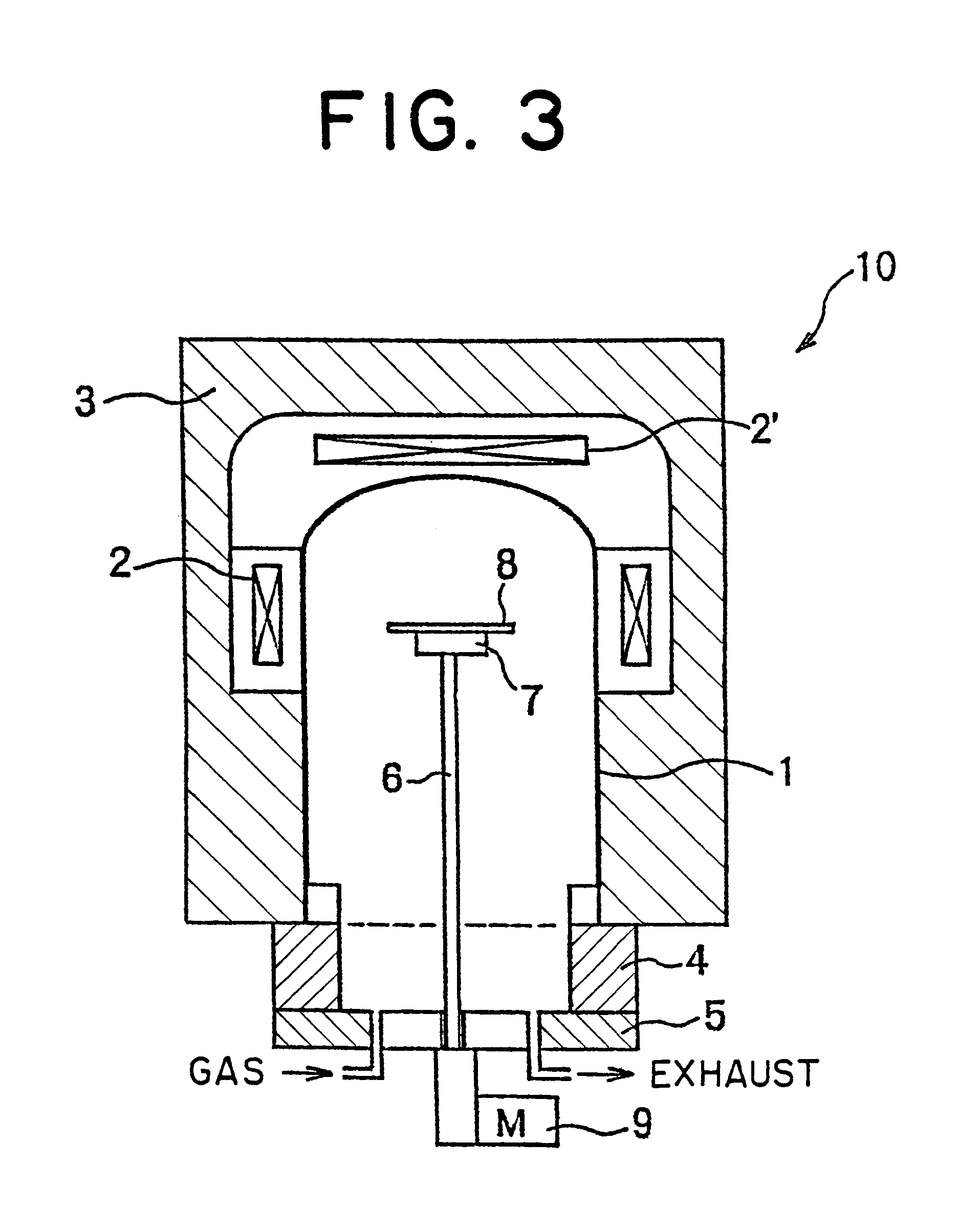

Method for heat treatment of SOI wafer and SOI wafer heat-treated by the method

InactiveUS6238990B1Excellent characteristicsHigh yieldSolid-state devicesSemiconductor/solid-state device manufacturingReducing atmosphereRapid thermal annealing

A method for heat-treating an SOI wafer in a reducing atmosphere, wherein the SOI wafer is heat-treated through use of a rapid thermal annealer at a temperature within the range of 1100.degree. C. to 1300.degree. C. for 1 sec to 60 sec. The reducing atmosphere is preferably an atmosphere of 100% hydrogen or a mixed gas atmosphere containing hydrogen and argon. The heat treatment is preferably performed for 1 sec to 30 sec. The method eliminates COPs in an SOI layer of an SOI wafer in accordance with a hydrogen annealing method, while preventing etching of the SOI layer and a buried oxide layer.

Owner:SHIN-ETSU HANDOTAI CO LTD

Method of manufacturing an SOI wafer where COP's are eliminated within the base wafer

InactiveUS7186628B2Quality improvementAccurately reflectSolid-state devicesSemiconductor/solid-state device manufacturingWaferingSingle crystal

When an SOI wafer is produced by using a bond wafer made of silicon single crystal to form an SOI layer and a base wafer made of silicon single crystal to be a support substrate, one silicon wafer selected from a group consisting of an epitaxial wafer, an FZ wafer, a nitrogen doped wafer, a hydrogen annealed wafer, an intrinsic gettering wafer, a nitrogen doped and annealed wafer, and an entire N-region wafer is used as the bond wafer. Thereby, even where a thin insulator film or a thin SOI layer is formed in the SOI wafer, COPs are hardly detected in inspection of the SOI layer after the SOI wafer was completed, and a high quality SOI wafer is provided.

Owner:SHIN-ETSU HANDOTAI CO LTD

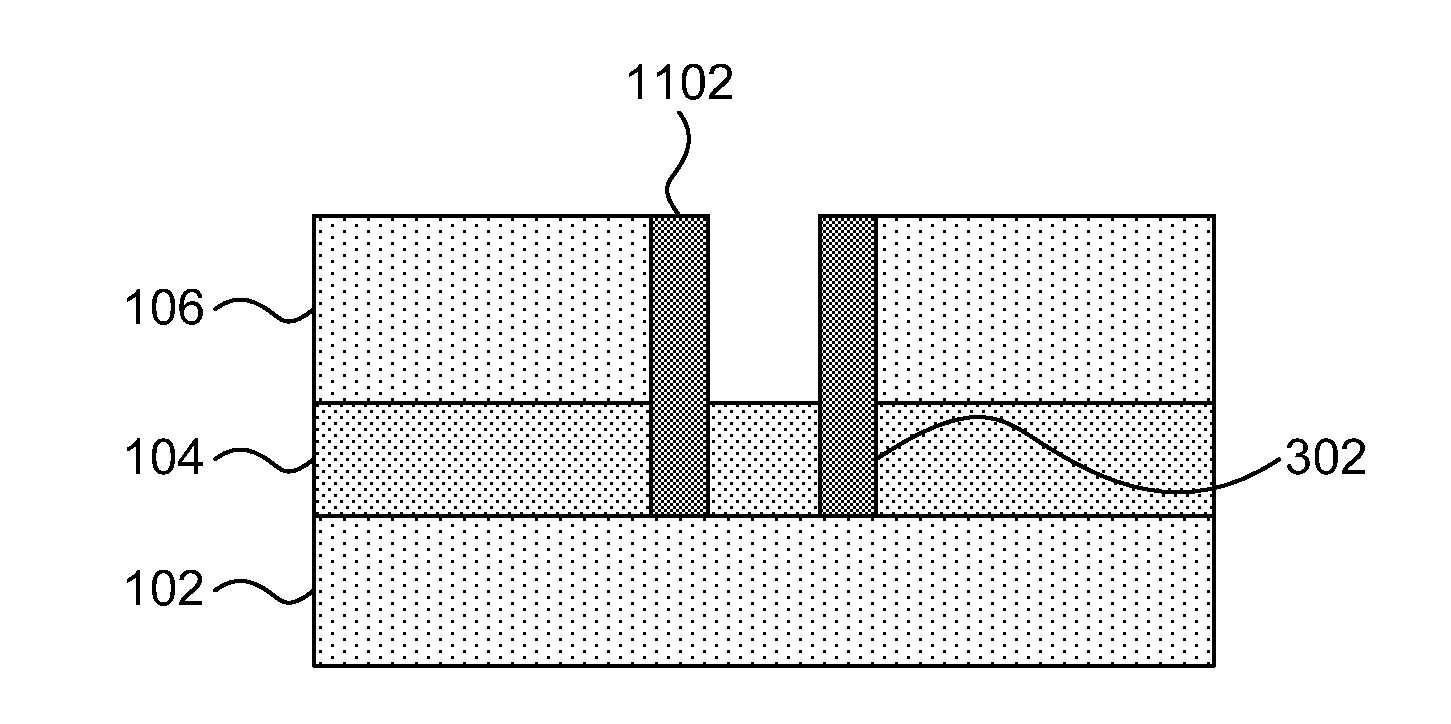

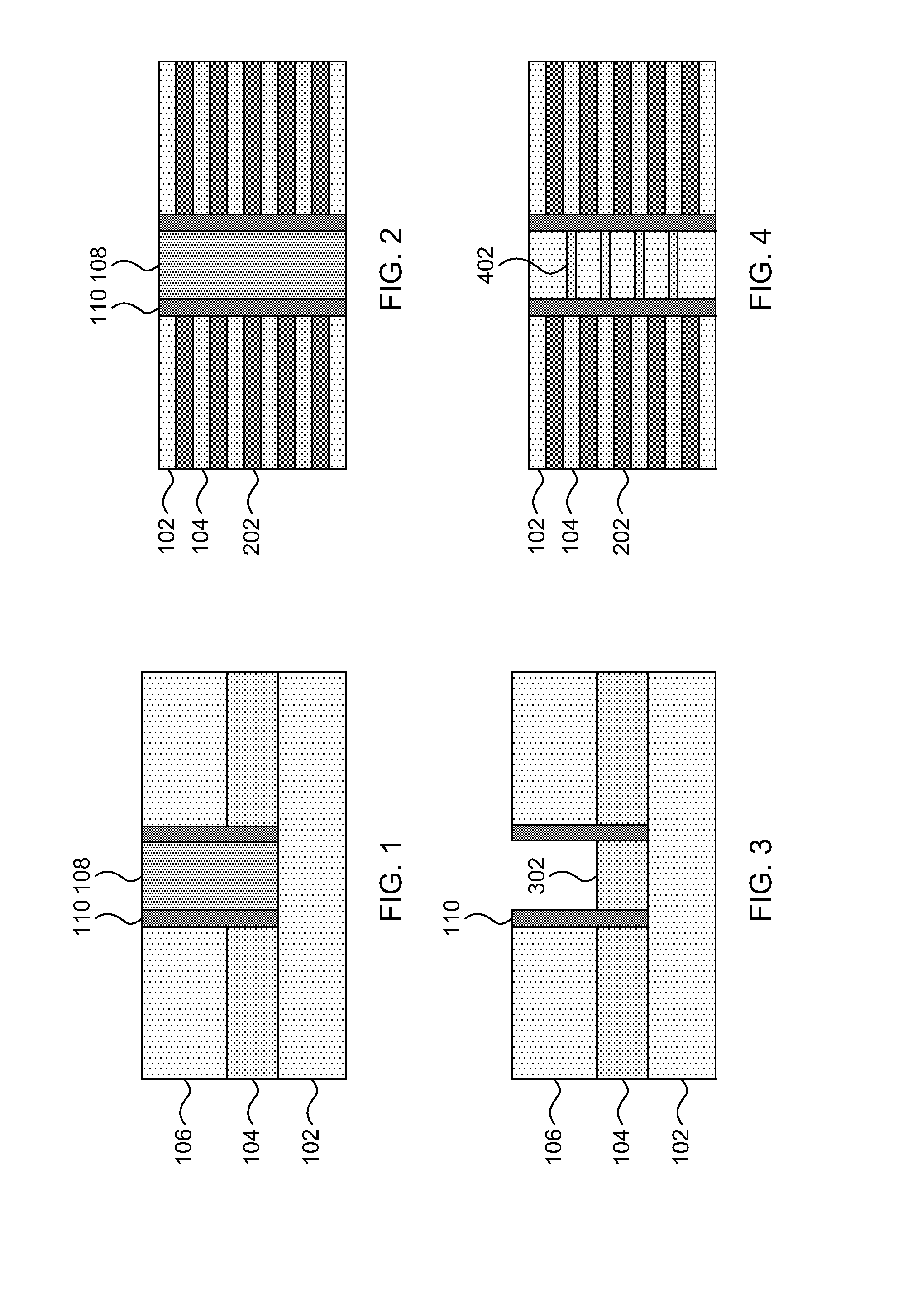

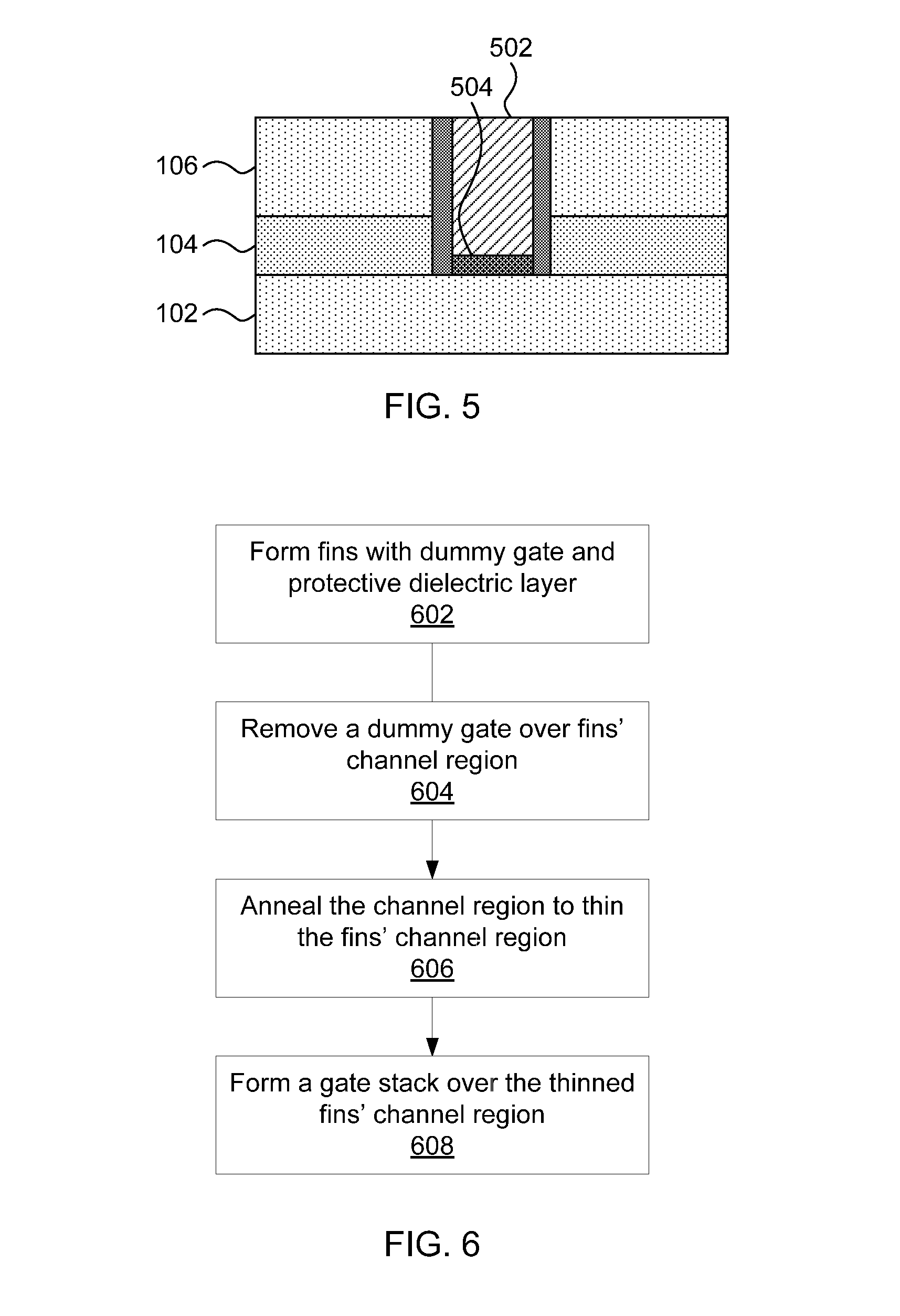

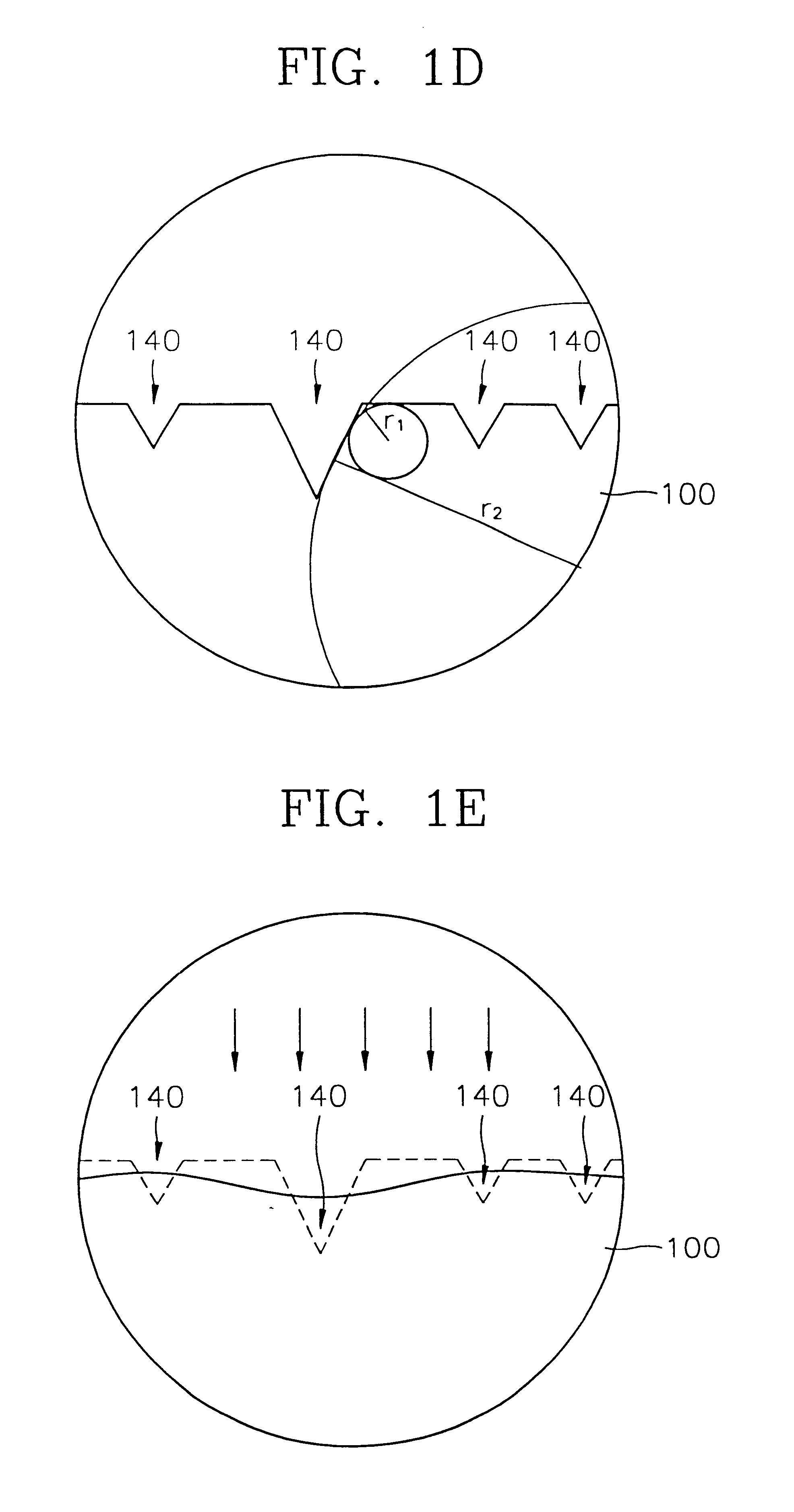

Localized fin width scaling using a hydrogen anneal

ActiveUS20140353735A1Reduce widthSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringProtection layer

Transistors and methods for fabricating the same include forming one or more semiconductor fins on a substrate; covering source and drain regions of the one or more semiconductor fins with a protective layer; annealing uncovered channel portions of the one or more semiconductor fins in a gaseous environment to reduce fin width and round corners of the one or more semiconductor fins; and forming a dielectric layer and gate over the thinned fins.

Owner:RENESAS ELECTRONICS CORP +1

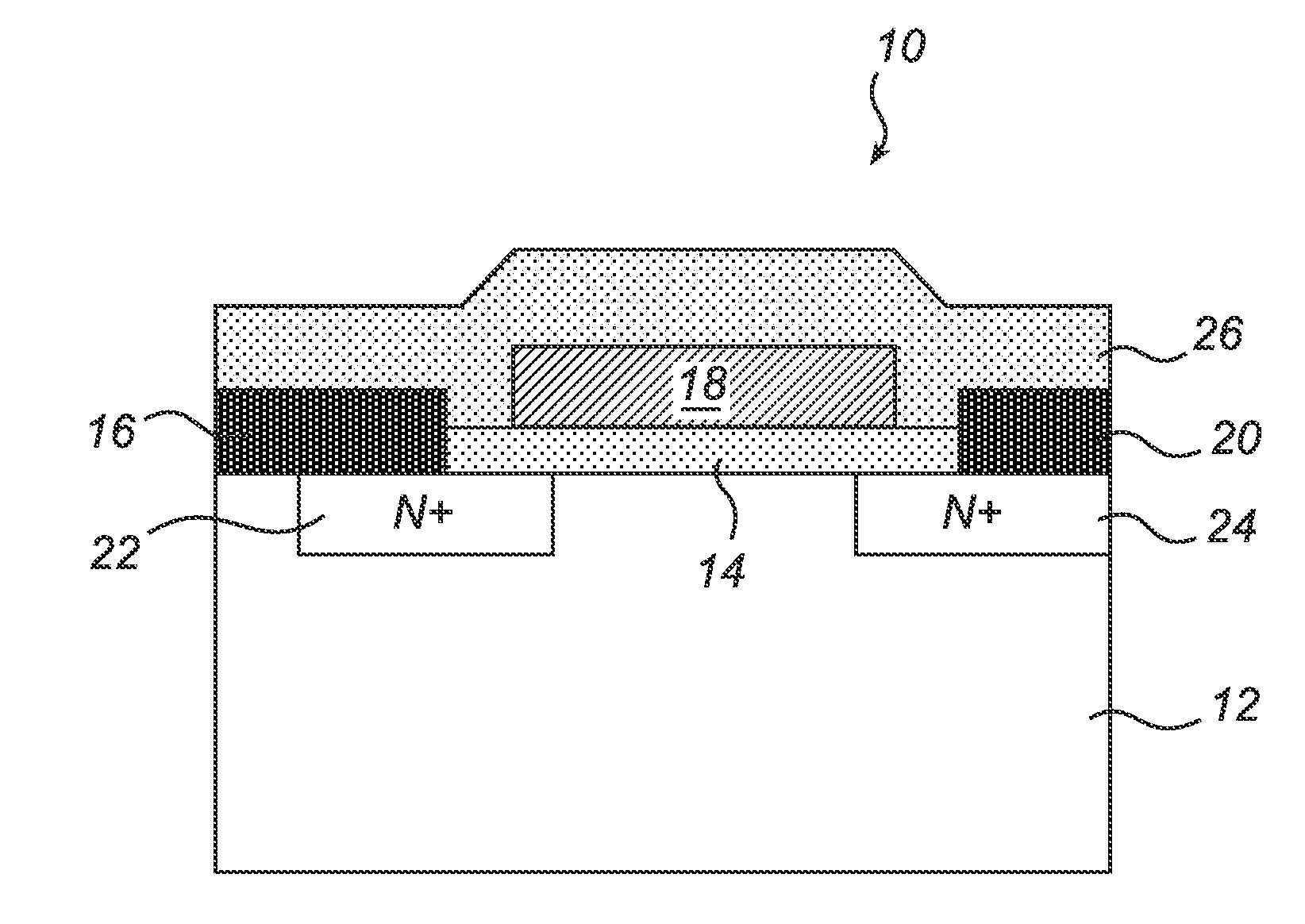

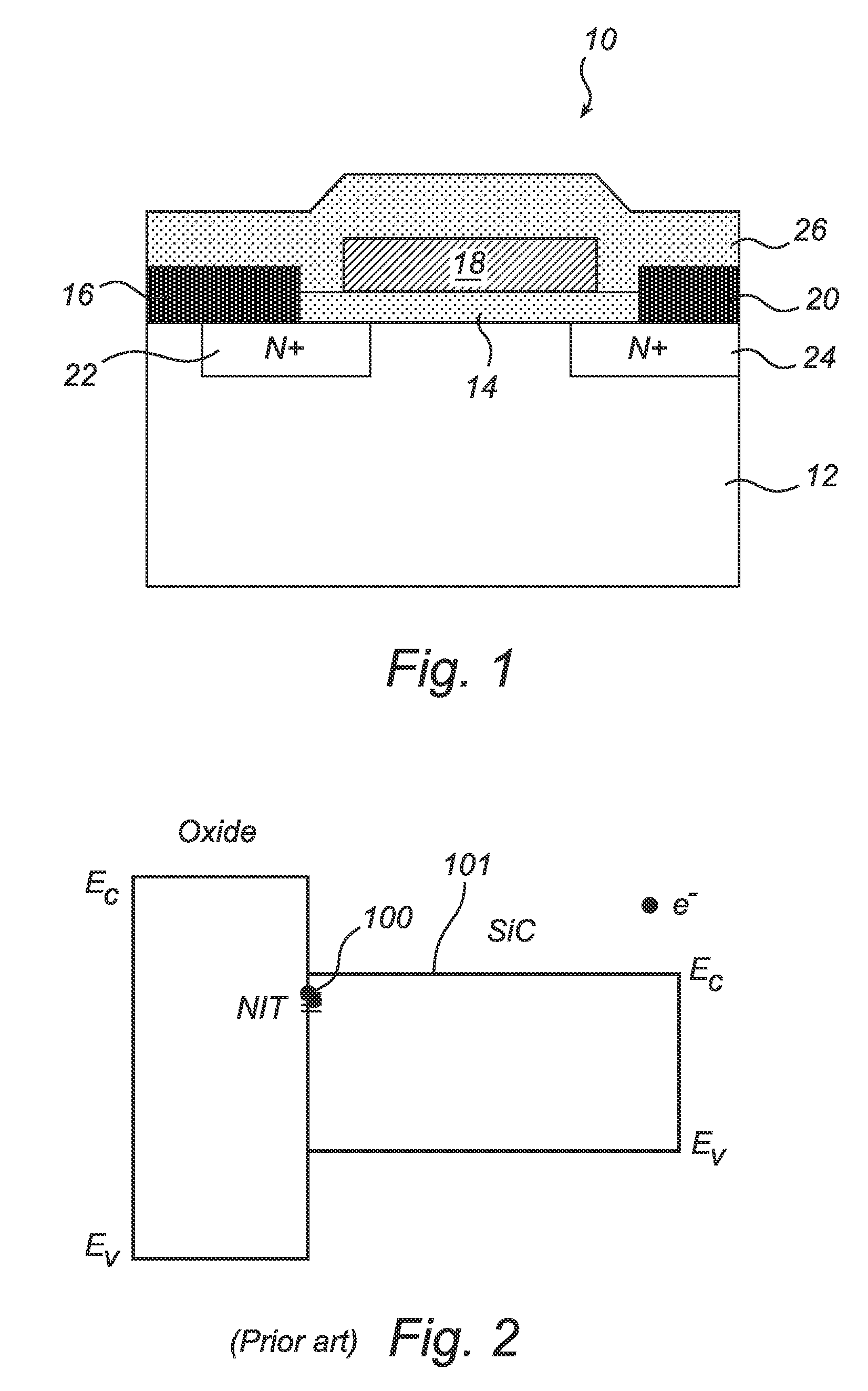

Method for improving inversion layer mobility in a silicon carbide mosfet

ActiveUS20100006860A1Improved inversion channel mobilityLower threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETHydrogen annealing

A method of manufacturing a semiconductor device based on a SiC substrate (12), comprising the steps of forming (201) an oxide layer (14) on a Si-terminated face of the SiC substrate (12) at an oxidation rate sufficiently high to achieve a near interface trap density below 5×1011 cm−2; and annealing (202) the oxidized SiC substrate in a hydrogen-containing environment, in order to passivate deep traps formed in the oxide-forming step, thereby enabling manufacturing of a SiC-based MOSFET (10) having improved inversion layer mobility and reduced threshold voltage. It has been found by the present inventors that the density of DTs increases while the density of NITs decreases when the Si-face of the SiC substrate is subject to rapid oxidation. According to the present invention, the deep traps formed during the rapid oxidation can be passivated by hydrogen annealing, thus leading to a significantly decreased threshold voltage for a semiconductor device formed on the oxide.

Owner:UNITED MICROELECTRONICS CORP

Base oxide engineering for high-K gate stacks

InactiveUS20070287199A1Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor structureGate stack

A method of forming a semiconductor structure includes providing a semiconductor substrate, performing a hydrogen annealing to the semiconductor substrate, forming a base oxide layer after the step of hydrogen annealing, and forming a high-k dielectric layer on the base oxide layer.

Owner:TAIWAN SEMICON MFG CO LTD

Embedded LSI having a FeRAM section and a logic circuit section

InactiveUS20010020708A1Solid-state devicesSemiconductor/solid-state device manufacturingHydrogen annealingLogic circuitry

An embedded LSI includes a FeRAM macro block and an associated logic circuit section. A hydrogen barrier layer covers the FeRAM macro block as a whole and exposes the logic circuit section. The edge of the hydrogen barrier layer overlies the peripheral circuit of the FeRAM macro block and the boundary separating the FeRAM macro block from the logic circuit section. The ferroelectric capacitor is protected by the hydrogen barrier layer against hydrogen during a hydrogen-annealing process.

Owner:RENESAS ELECTRONICS CORP

Highly polished pre-hardening plastic die steel and manufacturing process thereof

The invention relates to highly polished pre-hardening plastic die steel and a manufacturing process thereof and belongs to the technical field of alloy steel manufacturing processes. A base body of the highly polished pre-hardening plastic die steel is composed of, by mass, 0.10-0.30% of C, 0.00-0.30% of Si, 0.50-1.50% of Mn, 0.50-1.00% of Cr, 0.20-1.00% of W, 0.40-1.00% of Mo, 0.00-0.10% of V, 0.00-0.025% of P, 0.00-0.005% of S, 0.002-0.005% of B, 0.60-1.50% of Ni, 0.00-0.15% of Nb and the balance Fe. The manufacturing process of the die steel comprises the steps of burdening, smelting, casting, hot charging, high temperature heat diffusion heat treatment, multidirectional forging heat machining, post-forging fine crystalline normalizing and dehydrogenation annealing processing, and final quenching and tempering heat treatment to obtain a tempered martensite structure with the hardness of 38-42 HRC. The die steel has low cost, high hardenability, high hardness, high polishing performance and leather pattern etching performance.

Owner:RUGAO HONGMAO HEAVY FORGING

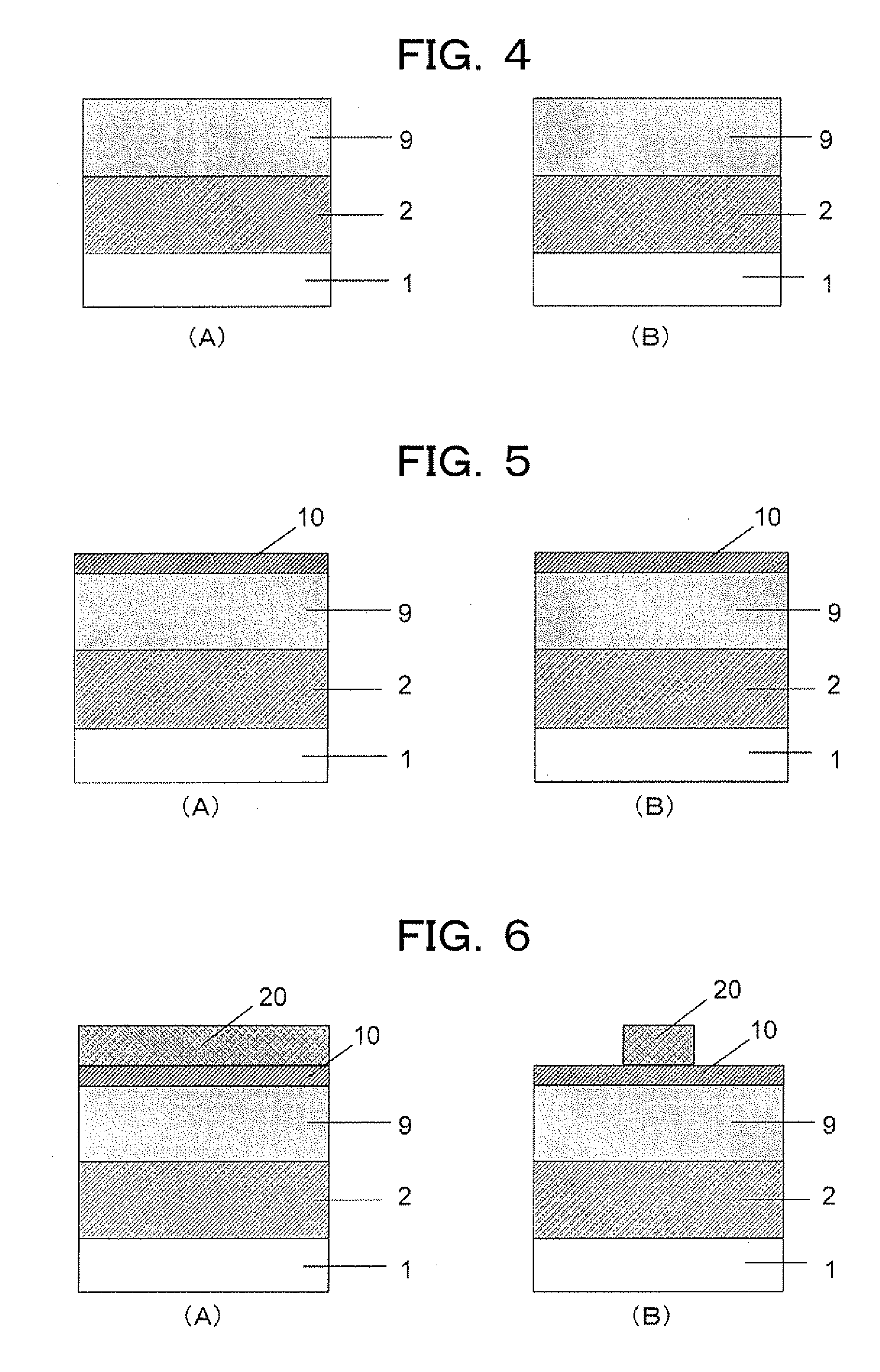

Semiconductor substrate, manufacturing method thereof, and semiconductor device

InactiveUS20060124961A1Improve channel mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialHydrogen annealing

A separation layer is formed on a silicon substrate. An SiGe layer serving as a strain induction layer and a silicon layer serving as a strained semiconductor layer are formed sequentially on the separation layer to prepare a first substrate. The first substrate is bonded to a second substrate made of the same material as the silicon layer of the strained semiconductor layer. The structure is separated into two parts at the separation layer. When the residue of the separation layer and the SiGe layer are removed, and the surface is planarized by hydrogen annealing, an Si substrate having a strained silicon layer on the uppermost surface is obtained.

Owner:CANON KK

Laminated semiconductor substrate and process for producing the same

InactiveCN1894795ASimple processLow costSolid-state devicesSemiconductor/solid-state device manufacturingEtchingSurface roughness

Owner:SUMCO CORP

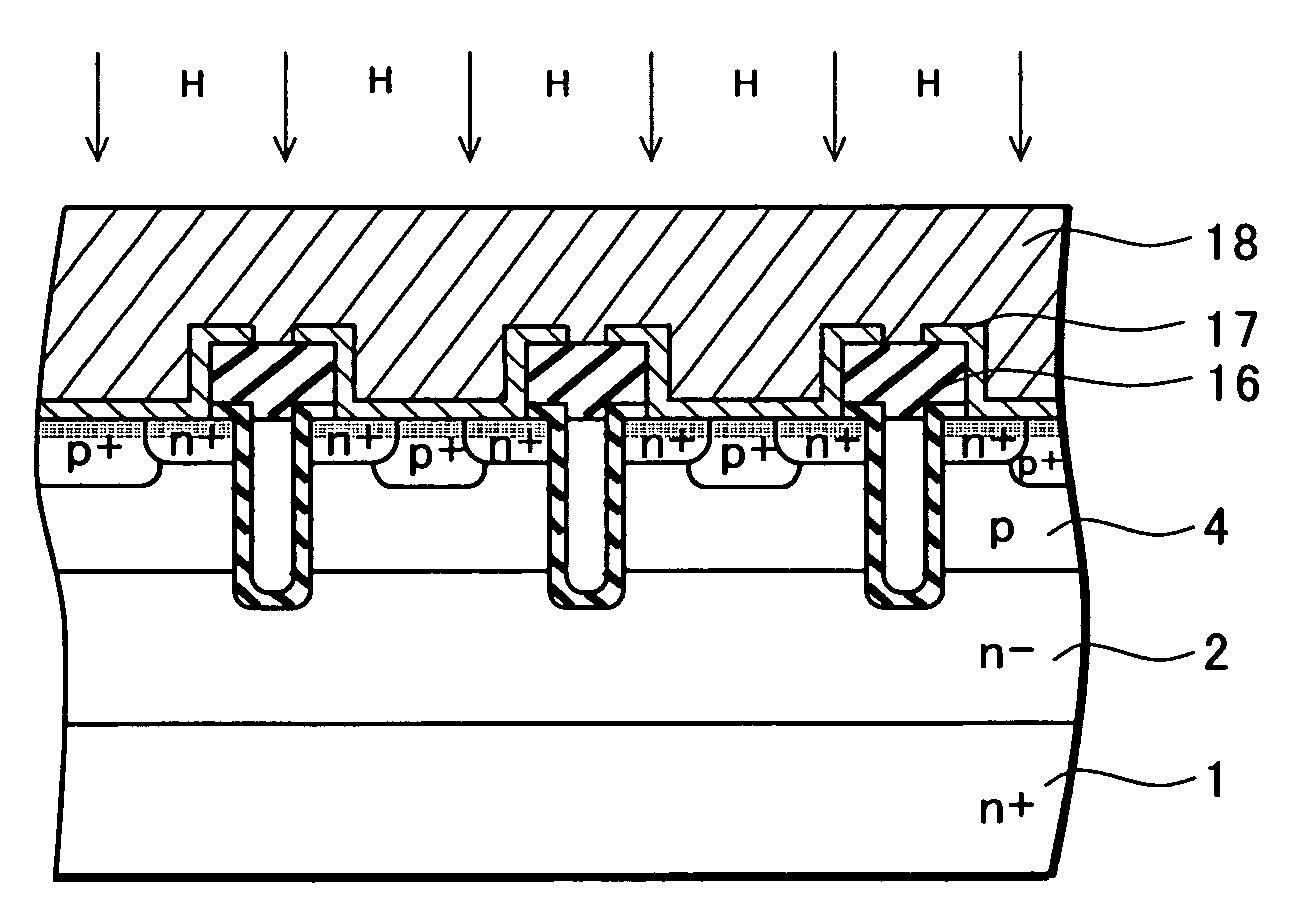

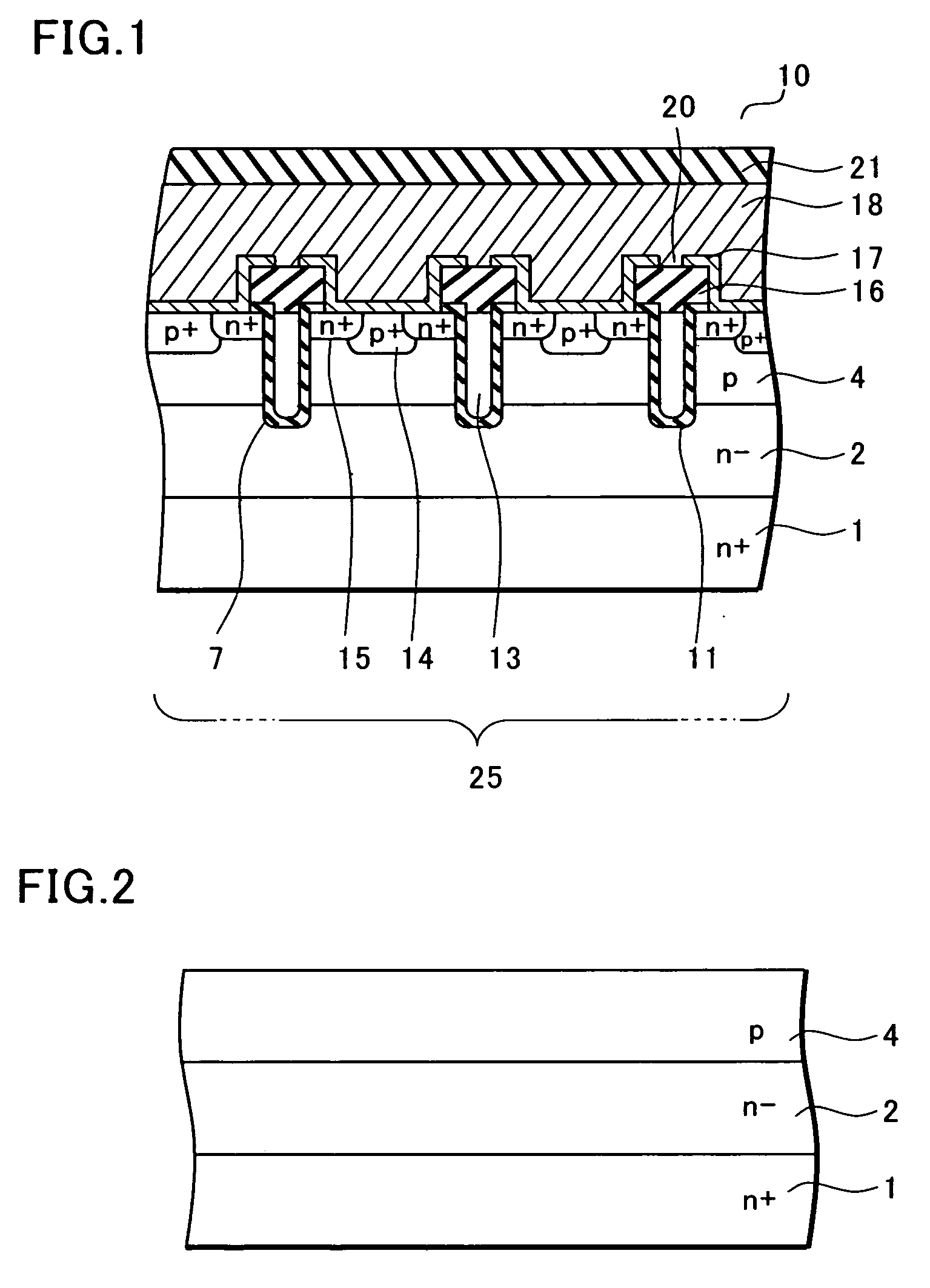

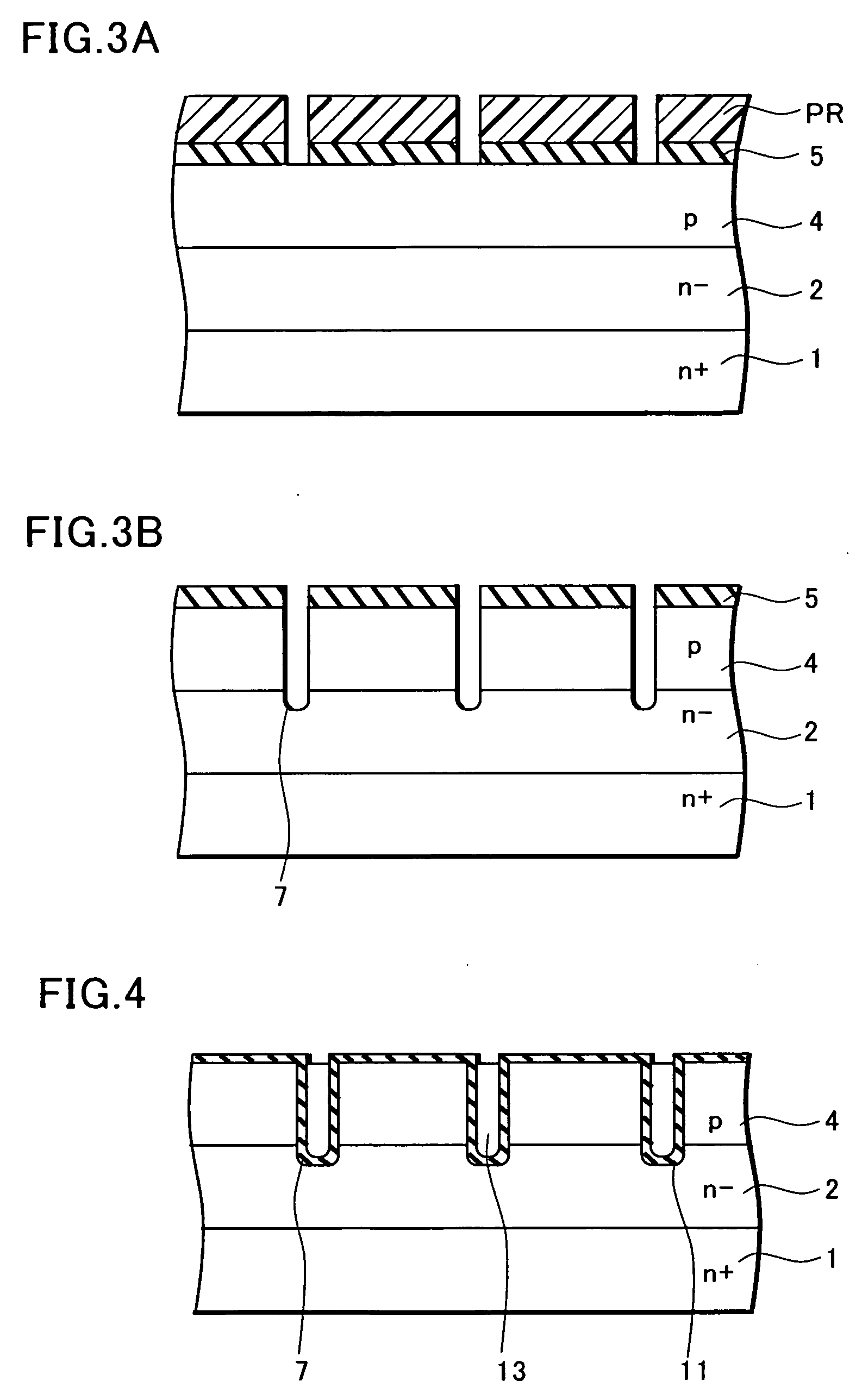

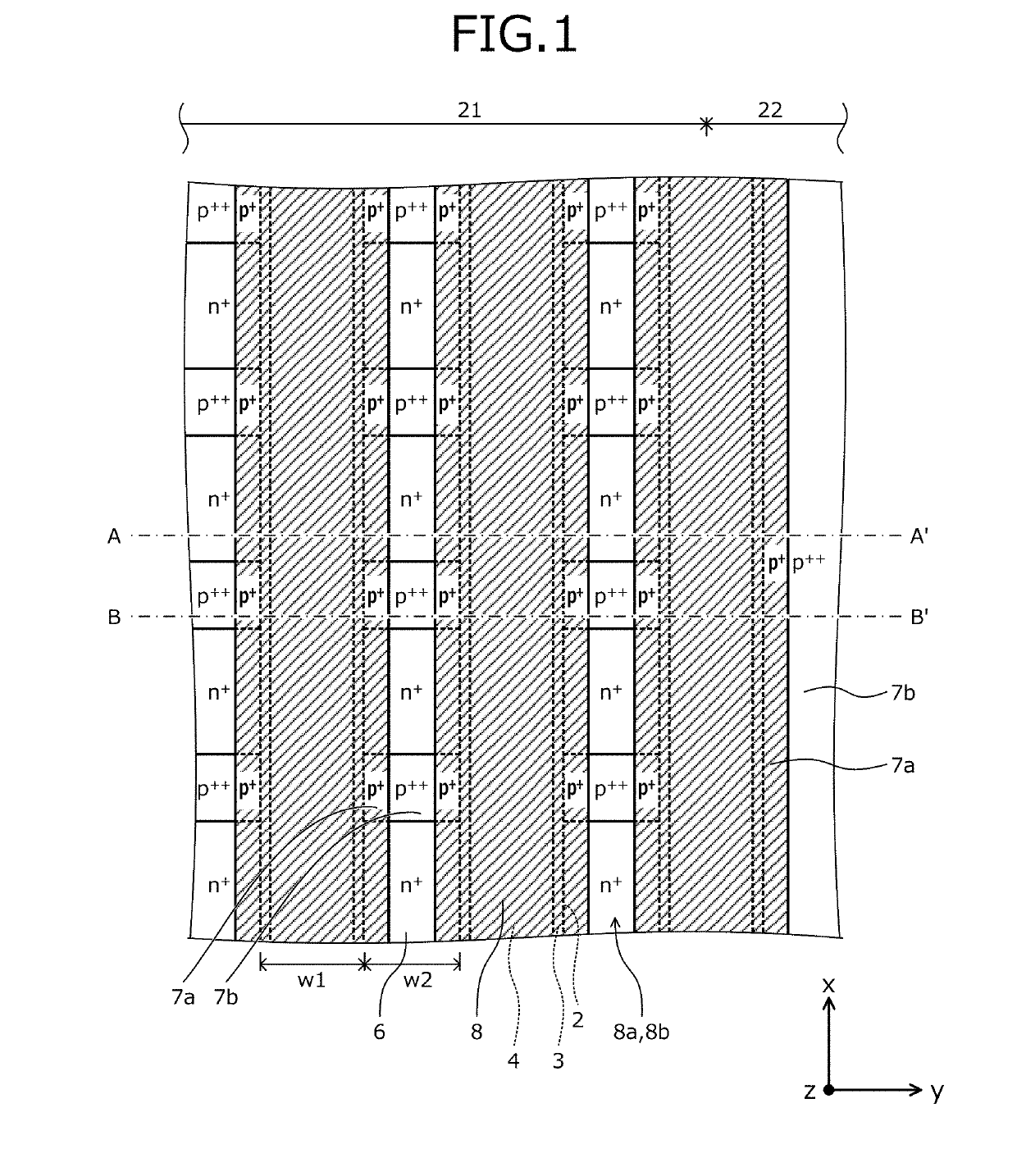

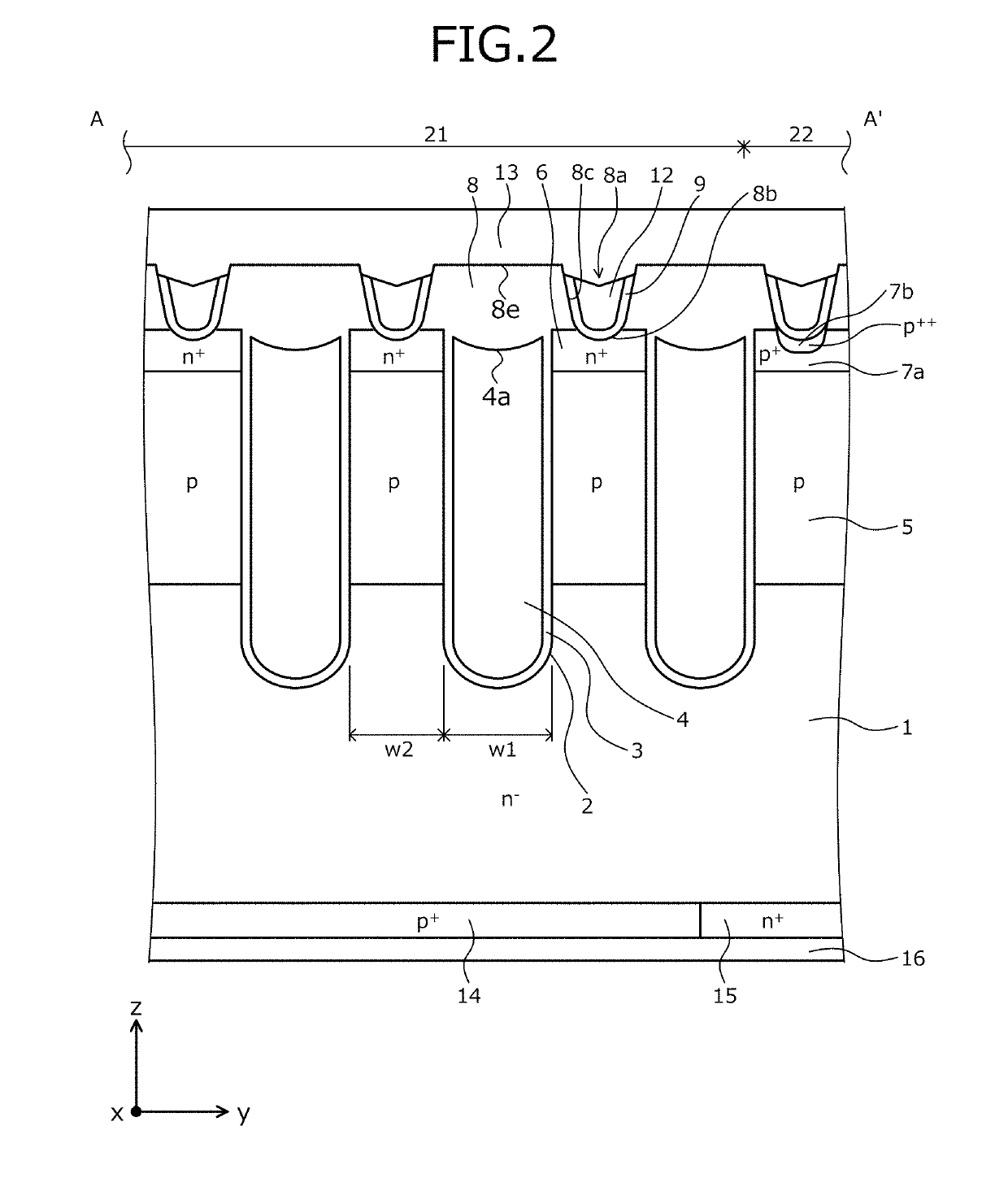

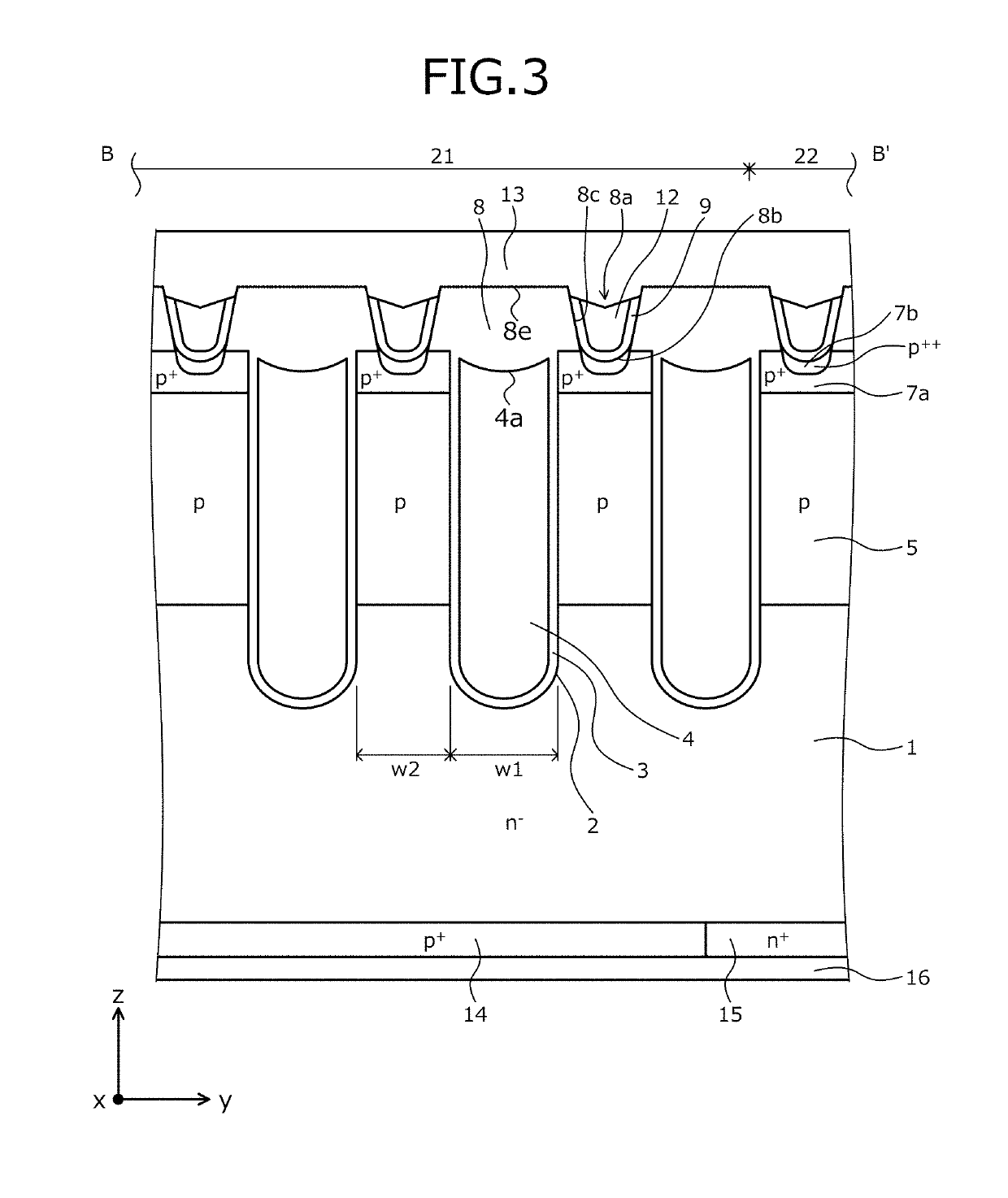

Method for manufacturing semiconductor device

ActiveUS20050255706A1Improvement and stability in characteristicLower on-resistanceThyristorSolid-state devicesMOSFETElectrical resistance and conductance

In a MOSFET, after an element region is formed, a wiring layer is formed subsequently to a barrier metal layer, and hydrogen annealing is performed. However, in the case of an n-channel MOSFET, a threshold voltage is lowered due to an occlusion characteristic of the barrier metal layer. Thus, an increased impurity concentration in a channel layer causes a problem that reduction in an on-resistance is inhibited. According to the present invention, after a barrier metal layer is formed, an opening is provided in the barrier metal layer on an interlayer insulating film, and hydrogen annealing treatment is performed after a wiring layer is formed. Thus, an amount of hydrogen which reaches a substrate is further increased, and lowering of a threshold voltage is suppressed. Moreover, since an impurity concentration in a channel layer can be lowered, an on-resistance is reduced.

Owner:SEMICON COMPONENTS IND LLC

Method of fabricating a semiconductor device using trench isolation method including hydrogen annealing step

InactiveUS6645866B2Semiconductor/solid-state device manufacturingSemiconductor devicesResistHydrogen atmosphere

A method of fabricating a semiconductor device using a trench isolation method including a hydrogen annealing step, wherein a photoresist pattern is formed on a semiconductor substrate, a pad insulating layer may be formed before forming the photoresist pattern, the semiconductor substrate is etched using the photoresist pattern as an etching mask to form a trench, and an isolation layer is formed in the trench. To remove damages created in an active region defined by the isolation layer, the semiconductor substrate having the isolation layer is annealed in a hydrogen atmosphere.

Owner:SAMSUNG ELECTRONICS CO LTD

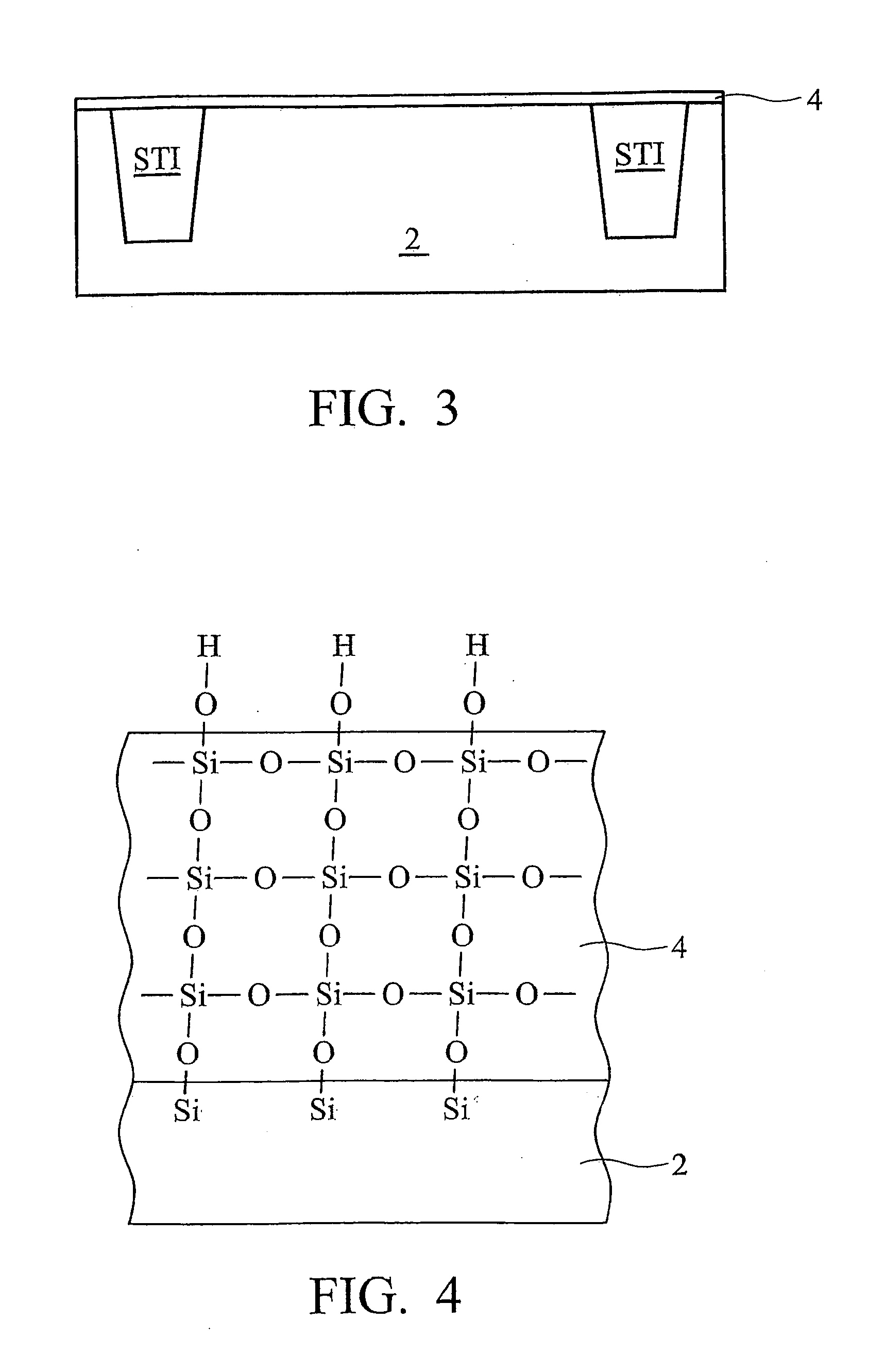

Pre-gate dielectric process using hydrogen annealing

ActiveUS20070166904A1Improve performanceImprove reliabilitySemiconductor/solid-state device manufacturingGate dielectricHydrogen annealing

The preferred embodiment of the present invention provides a novel method of forming MOS devices using hydrogen annealing. The method includes providing a semiconductor substrate including a first region and a second region, forming at least a portion of a first MOS device covering at least a portion of the first active region, performing a hydrogen annealing in an ambient containing substantially pure hydrogen on the semiconductor substrate. The hydrogen annealing is performed after the step of the at least a portion of the first MOS device is formed, and preferably after a pre-oxidation cleaning. The method further includes forming a second MOS device in the second active region after hydrogen annealing. The hydrogen annealing causes the surface of the second active region to be substantially rounded, while the surface of the first active region is substantially flat.

Owner:TAIWAN SEMICON MFG CO LTD

Method for manufacturing semiconductor device

InactiveUS20080124915A1Efficient executionSolid-state devicesSemiconductor/solid-state device manufacturingTrappingTitanium

An insulation film having an open part in which a silicon part is exposed at a bottom surface is formed on a silicon substrate for forming a semiconductor device. Titanium is deposited to form a titanium film on the bottom surface and side wall surfaces of the contact hole. The silicon substrate and the titanium film are reacted with each other by a first annealing process to form a titanium silicide film on the bottom surface. After the titanium film that remains on the side wall surfaces of the contact hole is removed, a hydrogen annealing process is performed. This hydrogen annealing reduces the density of the interface level in the interface between the silicon substrate, the gate insulation film on the substrate surface, or the like, and improves the characteristics of the semiconductor device. After the hydrogen annealing, tungsten is deposited in the remaining space of the contact hole to form a tungsten plug. According to this manufacturing method, since a barrier metal composed of a titanium film is not formed on the bottom surface and side wall surfaces of the contact hole, trapping of hydrogen by titanium is suppressed, and hydrogen annealing is effectively performed.

Owner:SANYO ELECTRIC CO LTD

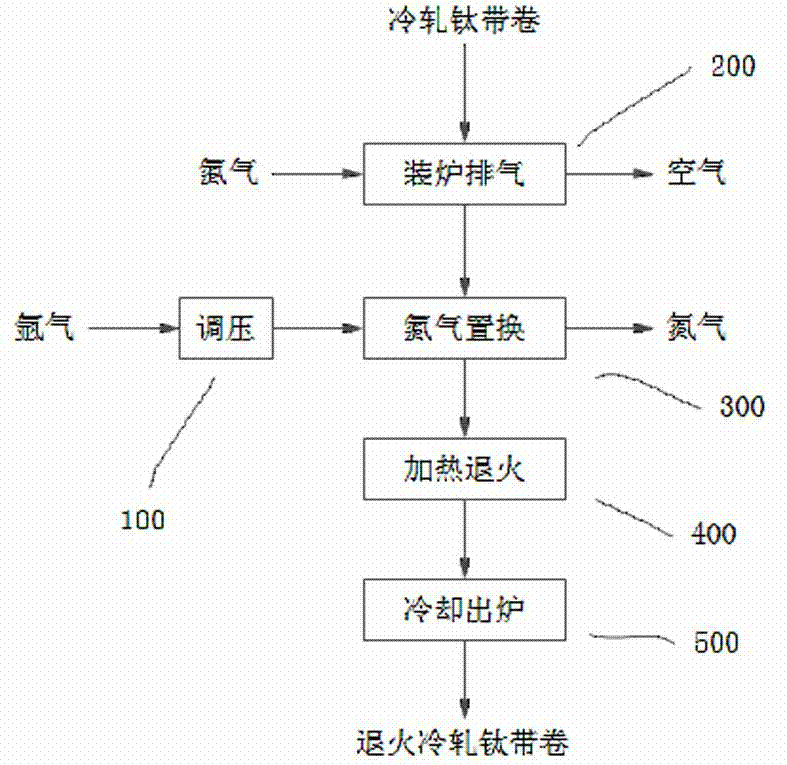

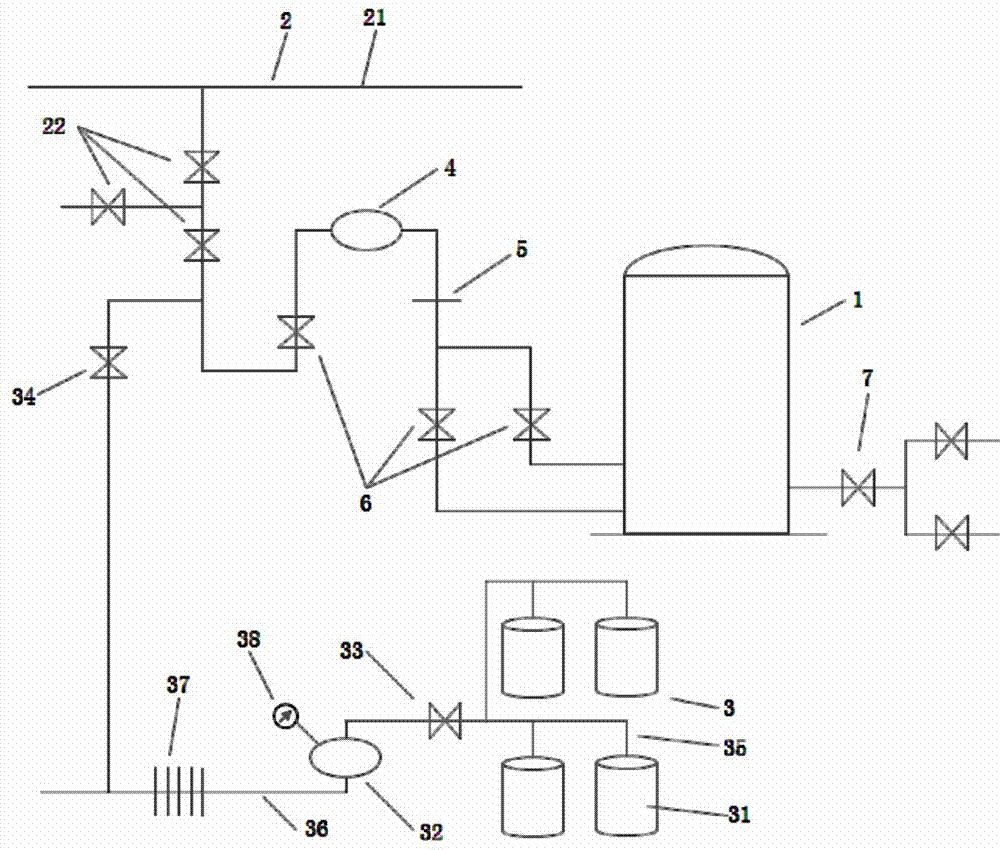

Method and device for performing inert gas protective cover type annealing on cold-rolled titanium strip coils

ActiveCN103205559AAchieve annealingImprove efficiencyFurnace typesHeat treatment furnacesTitaniumNitrogen gas

The invention discloses a method and a device for performing inert gas protective cover type annealing on cold-rolled titanium strip coils, and belongs to the technical field of nonferrous metallurgy. The annealing method comprises the following steps of: pressure adjustment, feeding and exhausting, nitrogen displacement, heating and annealing, cooling and discharging. The device comprises a cover type annealing furnace (1), a nitrogen supply device (2) and an argon supply device (3), wherein the nitrogen supply device (2) is communicated with the inner cover of the cover type annealing furnace (1); and the argon supply device (3) is communicated with the inner cover of the cover type annealing furnace (1). Based on the common full hydrogen or nitrogen-hydrogen annealing furnace, the argon supply device is additionally arranged, so that different annealing requirements of the common full hydrogen or nitrogen-hydrogen annealing furnace for cold-rolled steel strips and titanium strip coils are met; and the device has the advantages of high efficiency, process stability, convenience for transformation, multiple purposes and high reliability.

Owner:WUKUN STEEL

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20190097030A1Increase stickinessStablySemiconductor/solid-state device manufacturingSemiconductor devicesLattice defectsDevice material

A plug electrode is subject to etch back to remain in a contact hole and expose a barrier metal on a top surface of an interlayer insulating film. The barrier metal is subject to etch back, exposing the top surface of the interlayer insulating film. Remaining element structures are formed. After lifetime is controlled by irradiation of helium or an electron beam, hydrogen annealing is performed. During the hydrogen annealing, the barrier metal is not present on the interlayer insulating film covering a gate electrode, enabling hydrogen atoms to reach a mesa part, whereby lattice defects generated in the mesa part by the irradiation of helium or an electron beam are recovered, recovering the gate threshold voltage. Thus, predetermined characteristics of a semiconductor device having a structure where a plug electrode is provided in a contact hole, via barrier metal are easily and stably obtained when lifetime control is performed.

Owner:FUJI ELECTRIC CO LTD +1

Manufacturing technology of gate dielectric layer of silicon carbide semiconductor device

InactiveCN106571300AElimination of SiOxCy defectsElimination of SiOxCy defect generationSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricManufacturing technology

The invention relates to a manufacturing technology of a gate dielectric layer of a silicon carbide semiconductor device. The technology comprises the following steps of cleaning a silicon carbide surface, before a dielectric layer is deposited, removing oxygen atoms of the silicon carbide surface so that the surface taking silicon atoms as a main component is remained; using an atomic layer deposition method or a molecular beam epitaxy method to deposit a layer of silicon nitride (SiN) on the silicon carbide surface; then using the atomic layer deposition method or the molecular beam epitaxy method to deposit a layer of silicon; and using a CVD method to deposit a layer of polycrystalline silicon or amorphous silicon; and then using a thermal oxidation method to oxidize all the silicon above the SiN layer, wherein an oxidation layer and a silicon nitride layer commonly form the gate dielectric layer; and after the oxidation layer is formed, carrying out various kinds of high temperature annealing, such as hydrogen annealing, nitrogen annealing, phosphorus annealing, or annealing of various combinations of hydrogen+nitrogen+phosphorus and the like.

Owner:NANJING LISHENG SEMICON SCI & TECH CO LTD