Patents

Literature

53 results about "Hydrogen silsesquioxane" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

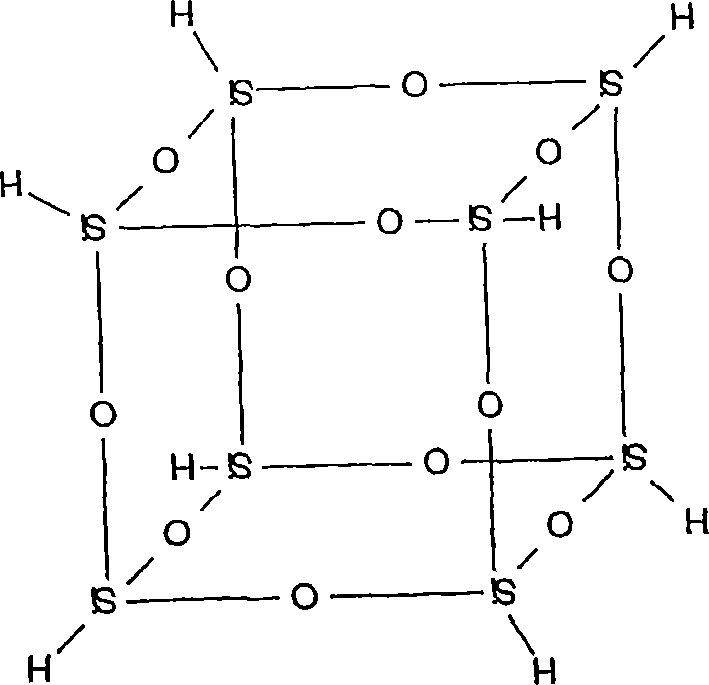

Hydrogen silsesquioxane (HSQ) is class of inorganic compounds with the chemical formula [HSiO₃⸝₂]ₙ. Such clusters are specific representatives of the family of silsesquioxanes with the formula [RSiO₃⸝₂]ₙ (R = alkyl, halide, alkoxide, etc.). The most widely studied member of the hydrogen silsesquioxanes is the cubic cluster H₈Si₈O₁₂.

Process to improve adhesion of HSQ to underlying materials

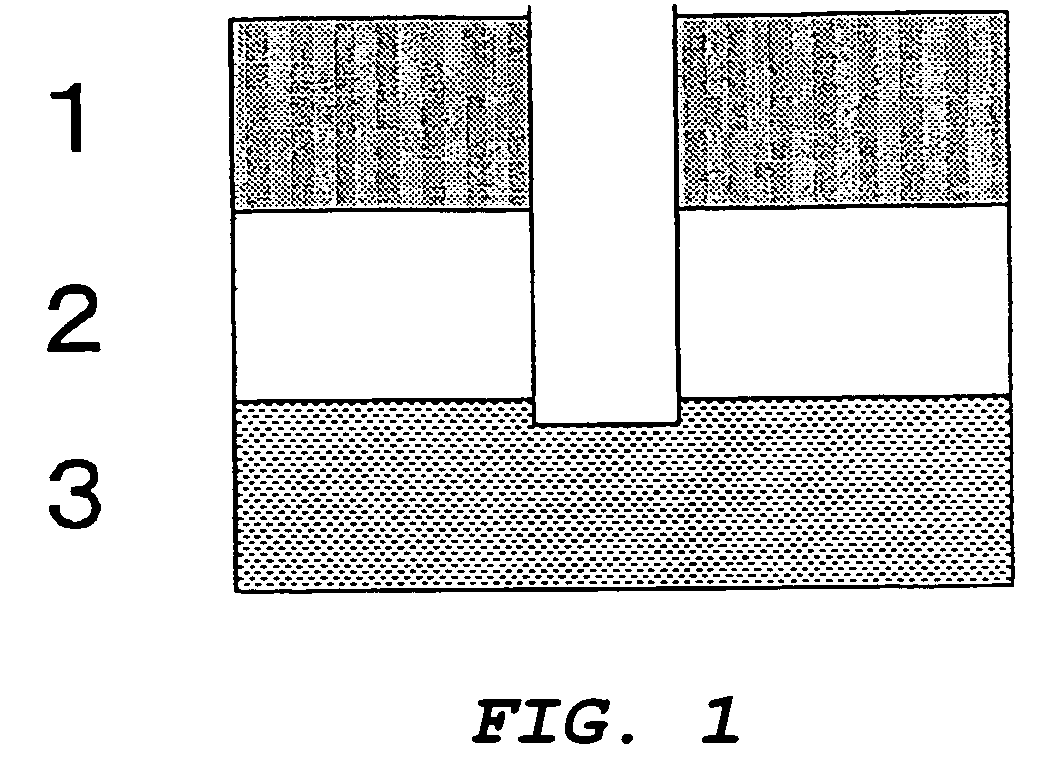

A process for forming an intermetal dielectric, (IMD), layer, comprised of an overlying silicon oxide layer, and an underlying low k dielectric layer, such as hydrogen silsesquioxane, (HSQ), has been developed. The process features the use of a series of plasma treatments, performed in a nitrogen containing ambient, used to improve the adhesion of the IMD layer, to underlying materials. A first plasma treatment is performed on a thin insulator layer, prior to application of the HSQ layer. The plasma treatment roughens the top surface of the thin insulator layer, resulting in improved adhesion of the HSQ layer to the thin insulator layer. A second plasma treatment is performed to the HSQ layer, prior to deposition of the overlying, thick silicon oxide layer, allowing improve adhesion of the thick silicon oxide layer, to the underlying HSQ layer, to be achieved.

Owner:TAIWAN SEMICON MFG CO LTD

Anode active material, method of preparing the same, and anode and lithium battery containing the material

ActiveUS20080166634A1Improving initial chargeImprove discharge efficiencyBio-organic fraction processingSilicaFull width at half maximumX-ray

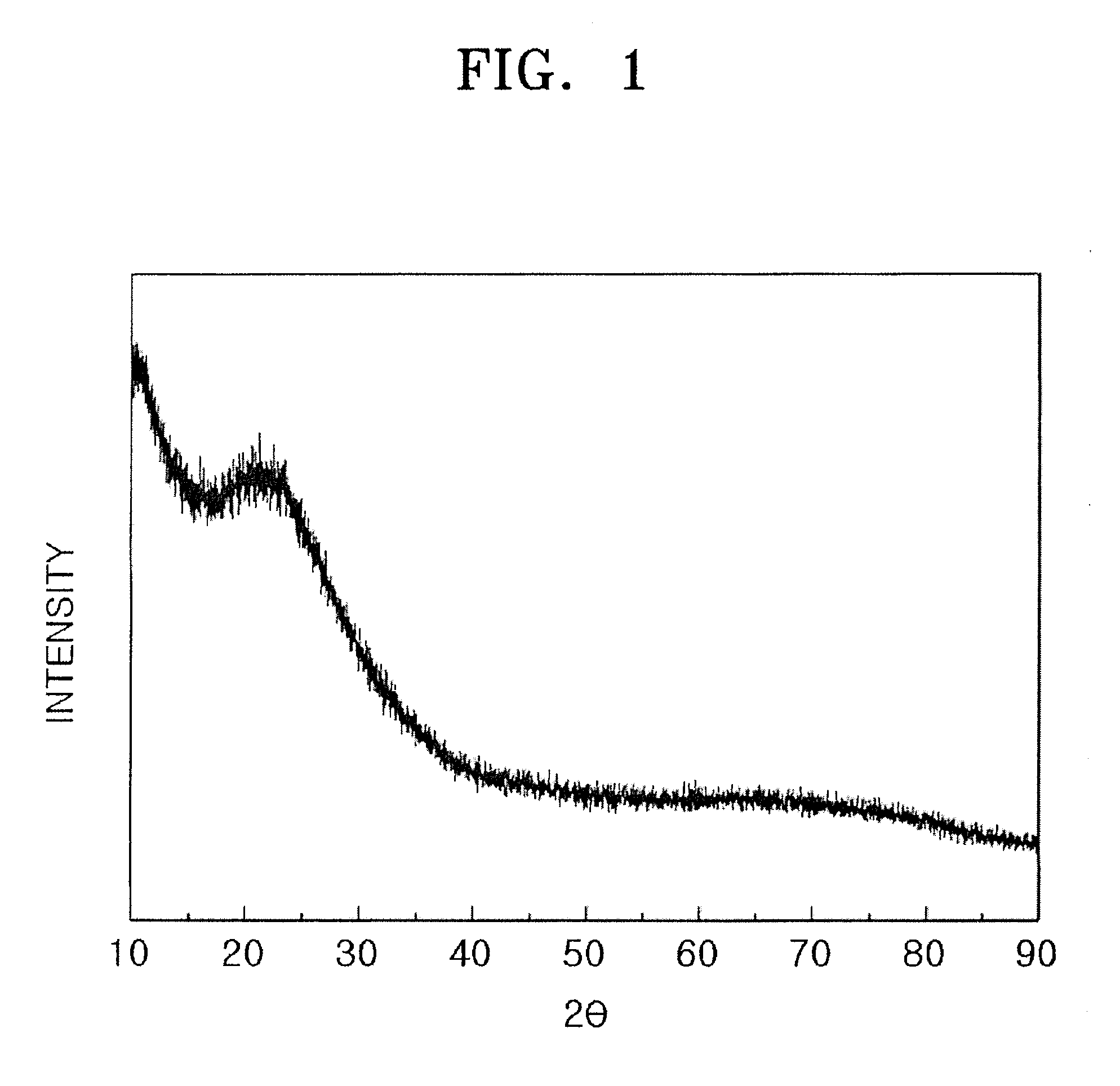

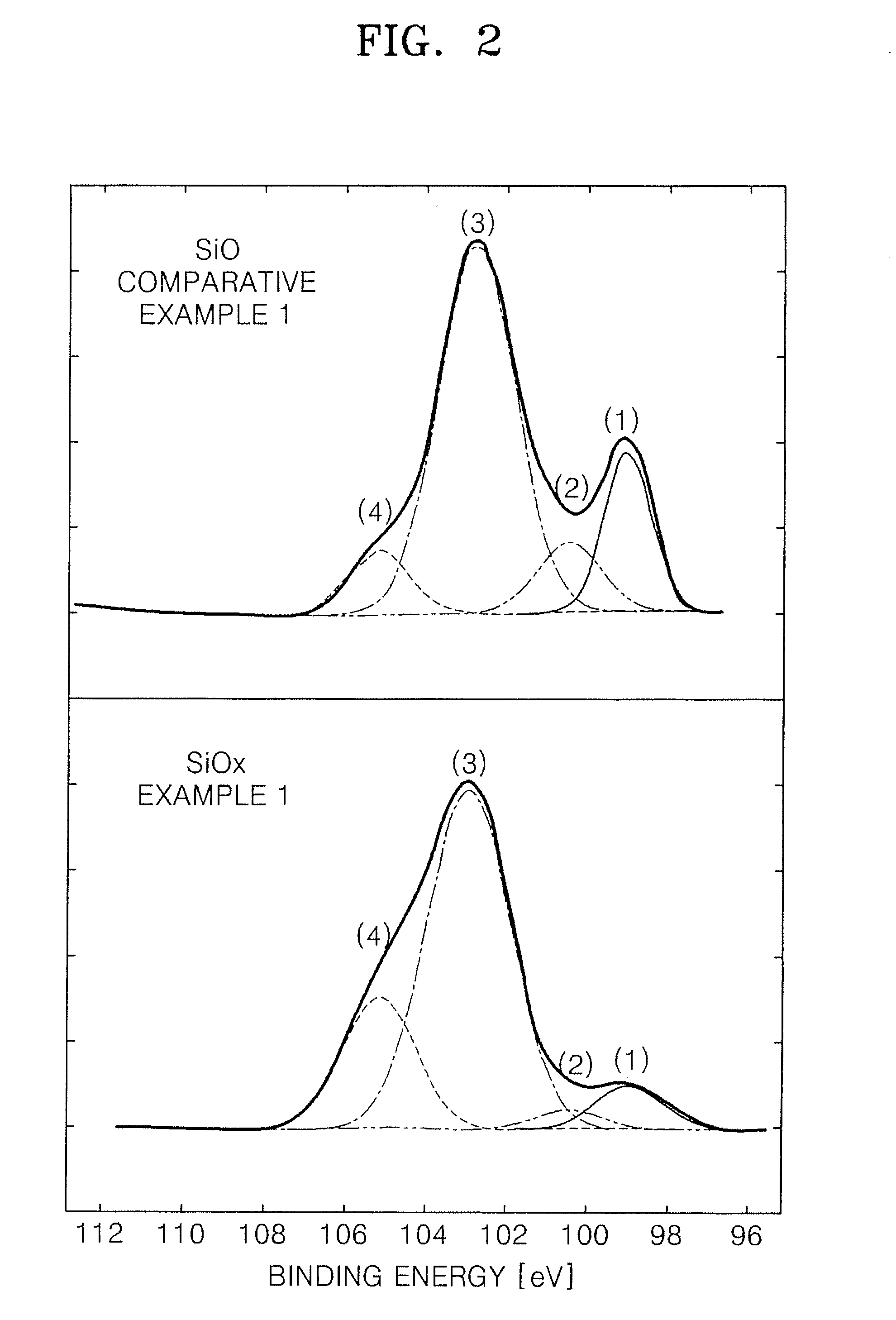

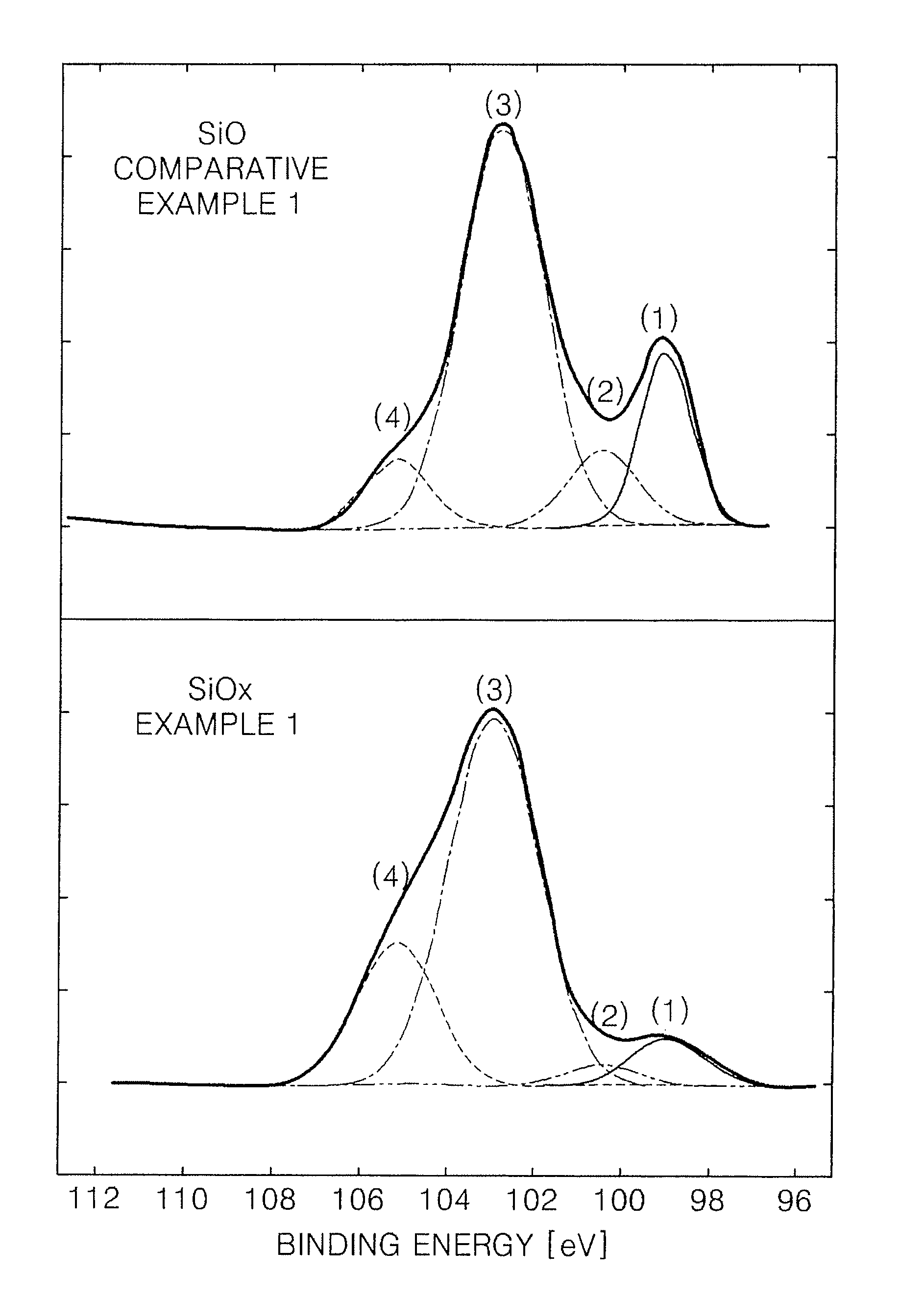

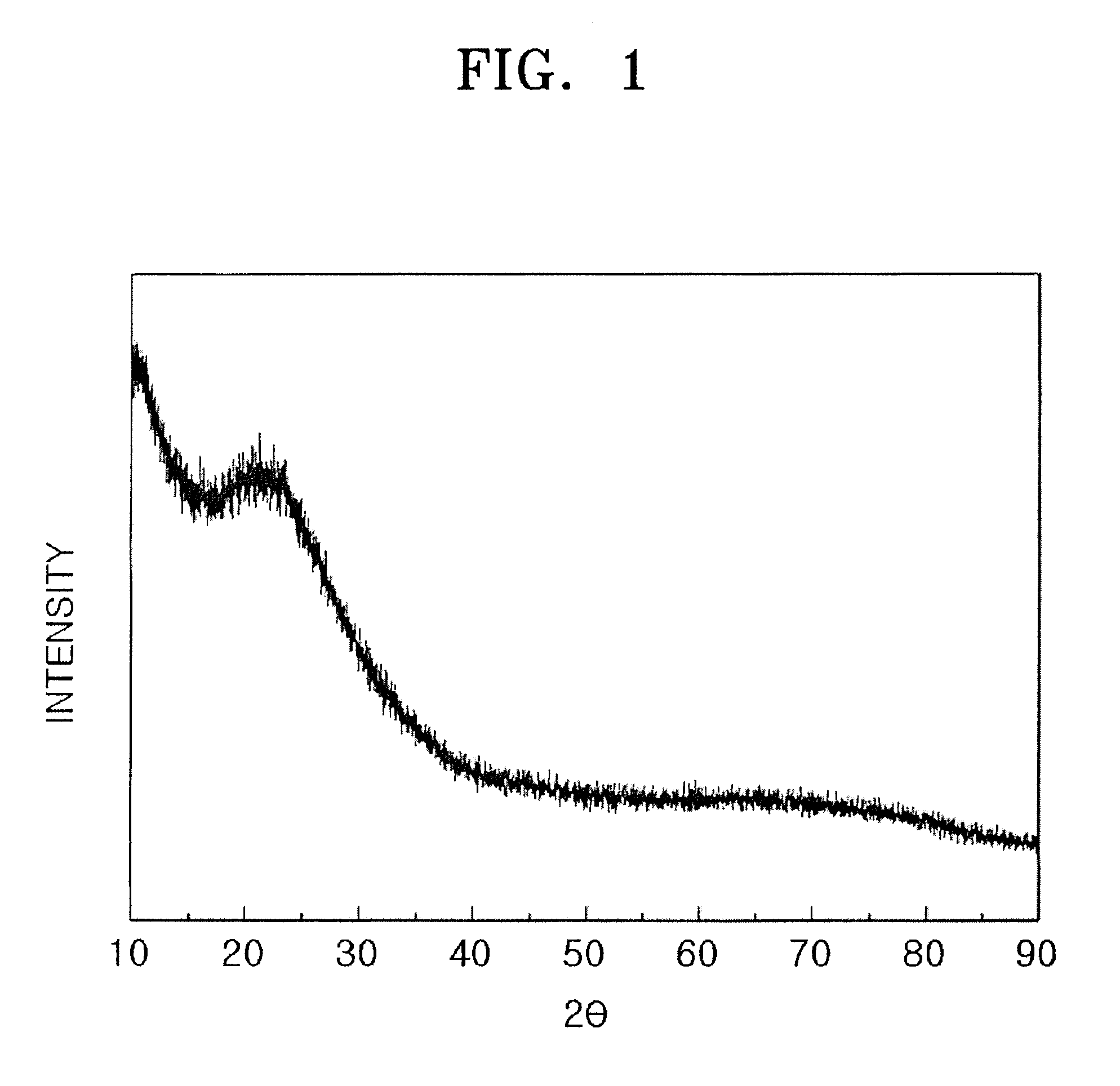

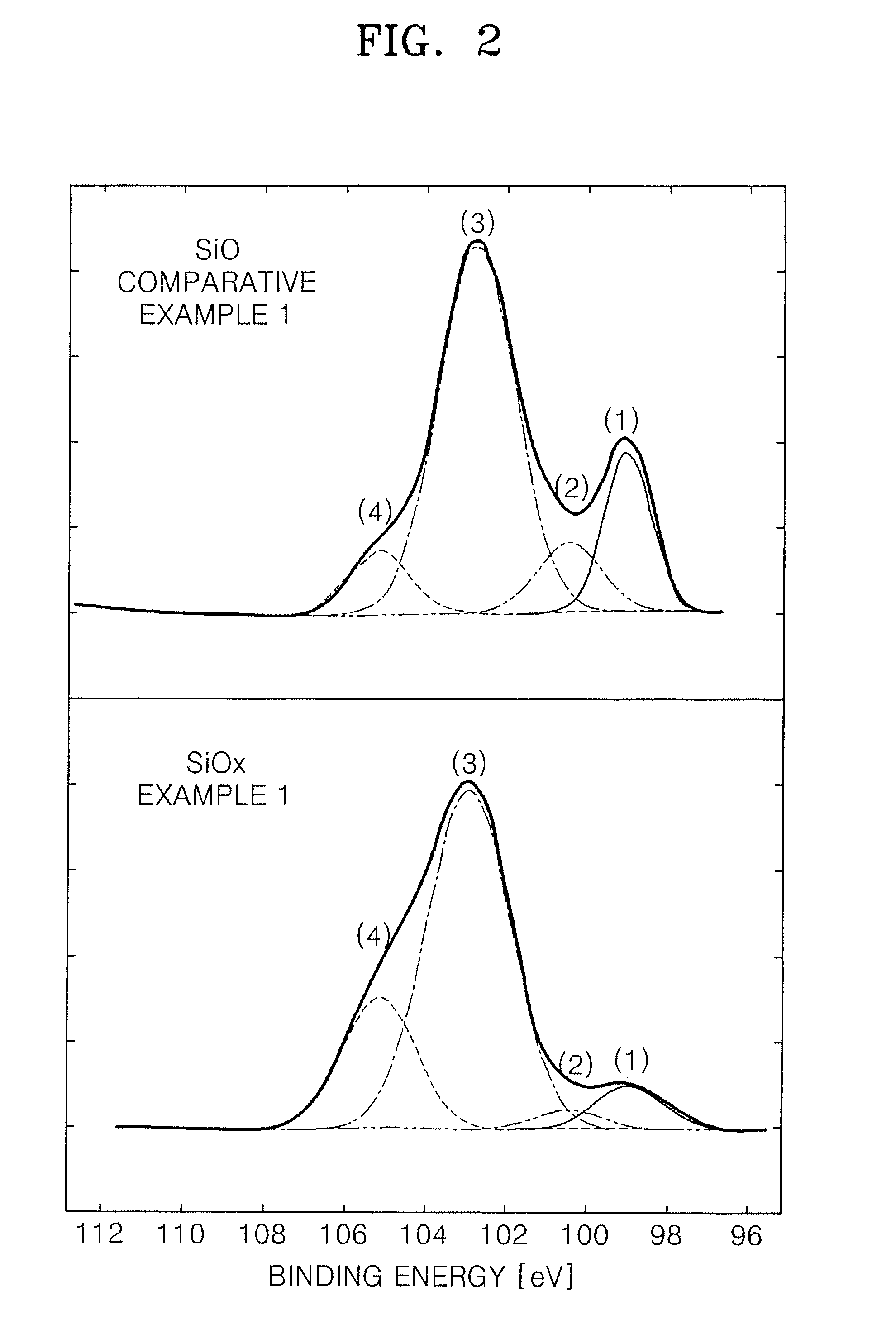

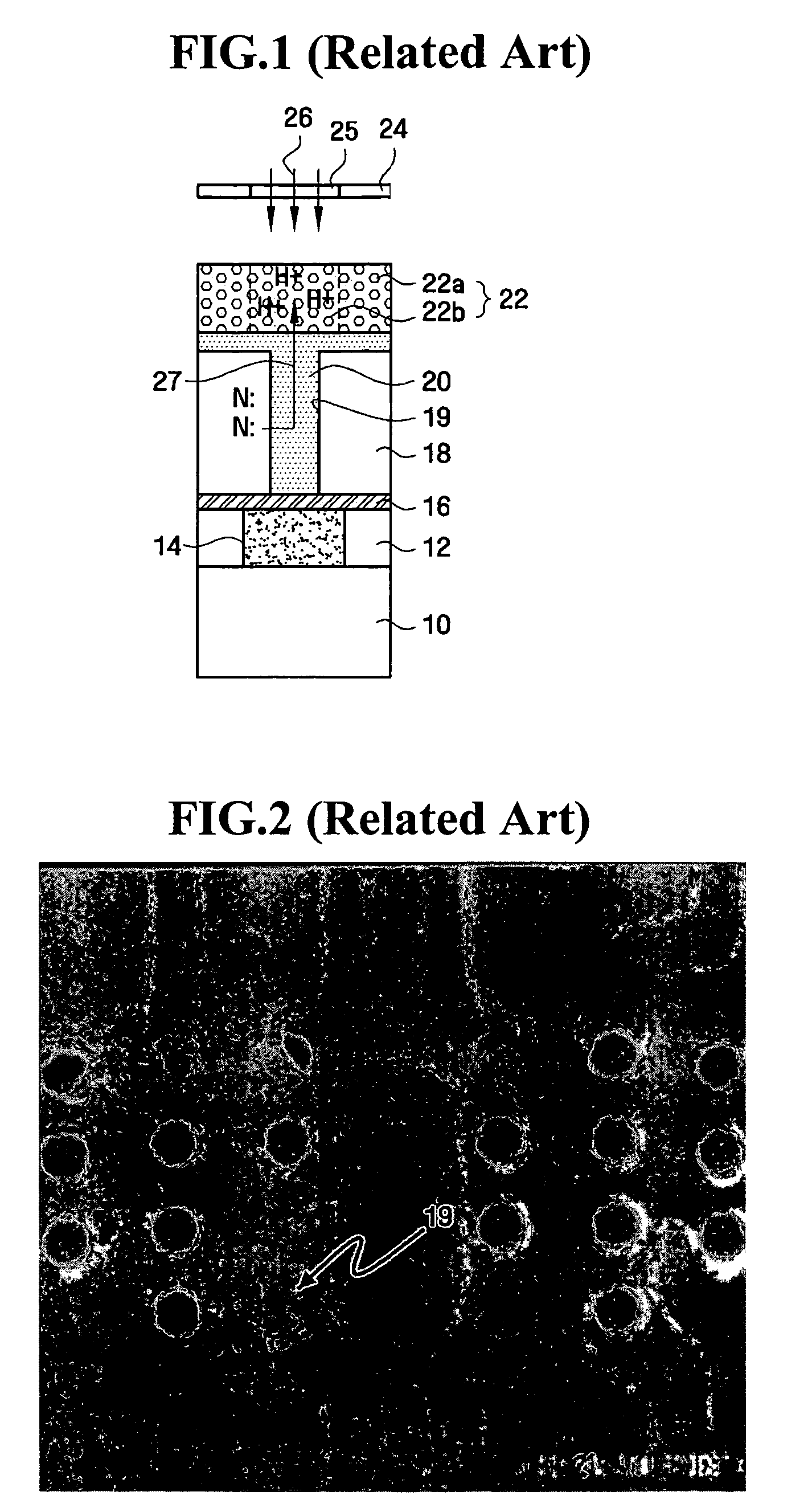

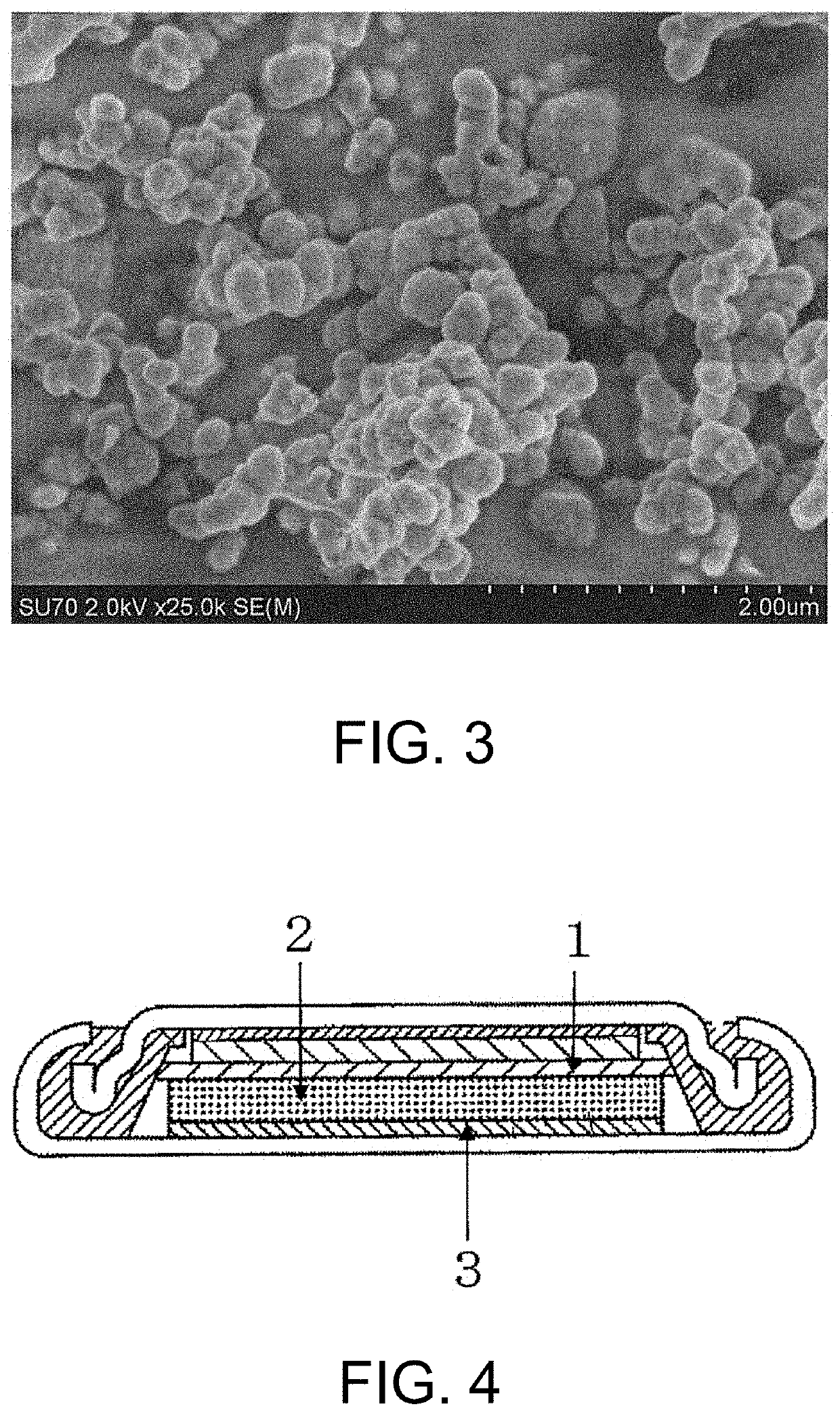

Silicon oxide based composite anode active materials including amorphous silicon oxides are provided. In one embodiment, the amorphous silicon oxide is represented by SiOx (where 0<x<2), has a binding energy of about 103 to about 106 eV, a silicon peak with a full width at half maximum (FWHM) ranging from about 1.6 to about 2.4 as measured by X-ray photoelectron spectrometry, and an atomic percentage of silicon greater than or equal to about 10 as calculated from an area of the silicon peak. The anode active material is a composite anode active material obtained by sintering hydrogen silsesquioxane (HSQ). Anodes and lithium batteries including the anode active material exhibit improved charge and discharge characteristics.

Owner:SAMSUNG SDI CO LTD

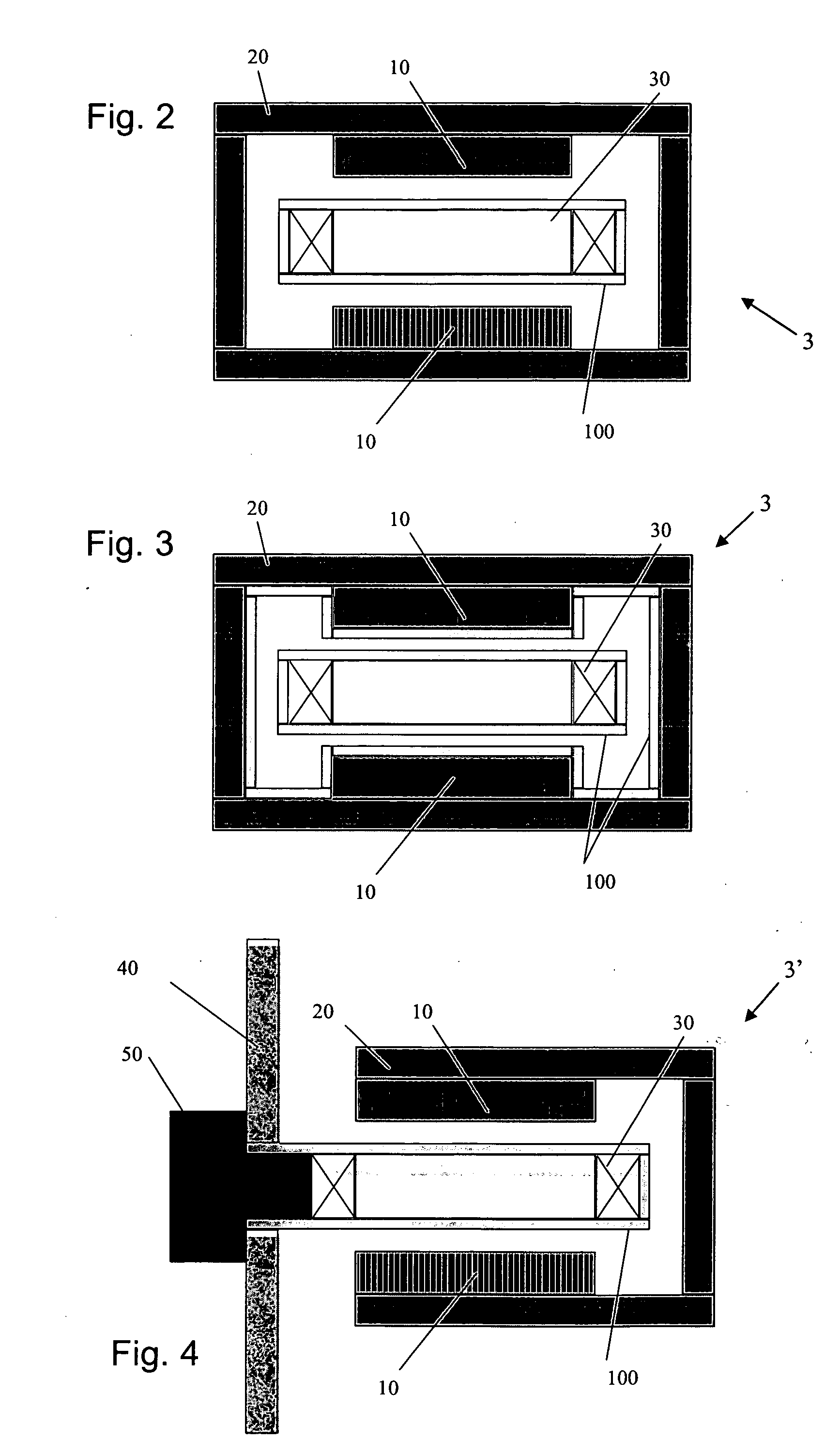

Method of fabricating dual damascene interconnections of microelectronic device using diffusion barrier layer against base material

ActiveUS20060063376A1Improve propertiesImprove performanceSemiconductor/solid-state device manufacturingDielectricInterconnection

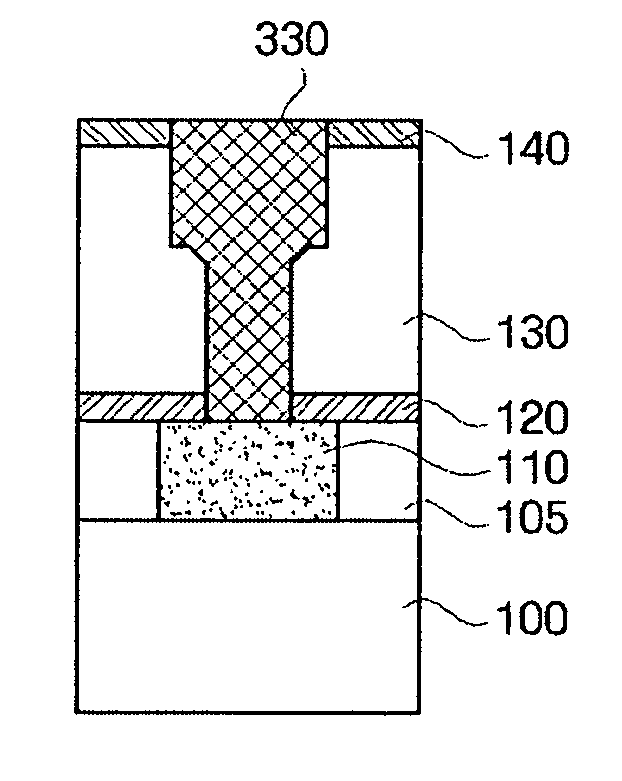

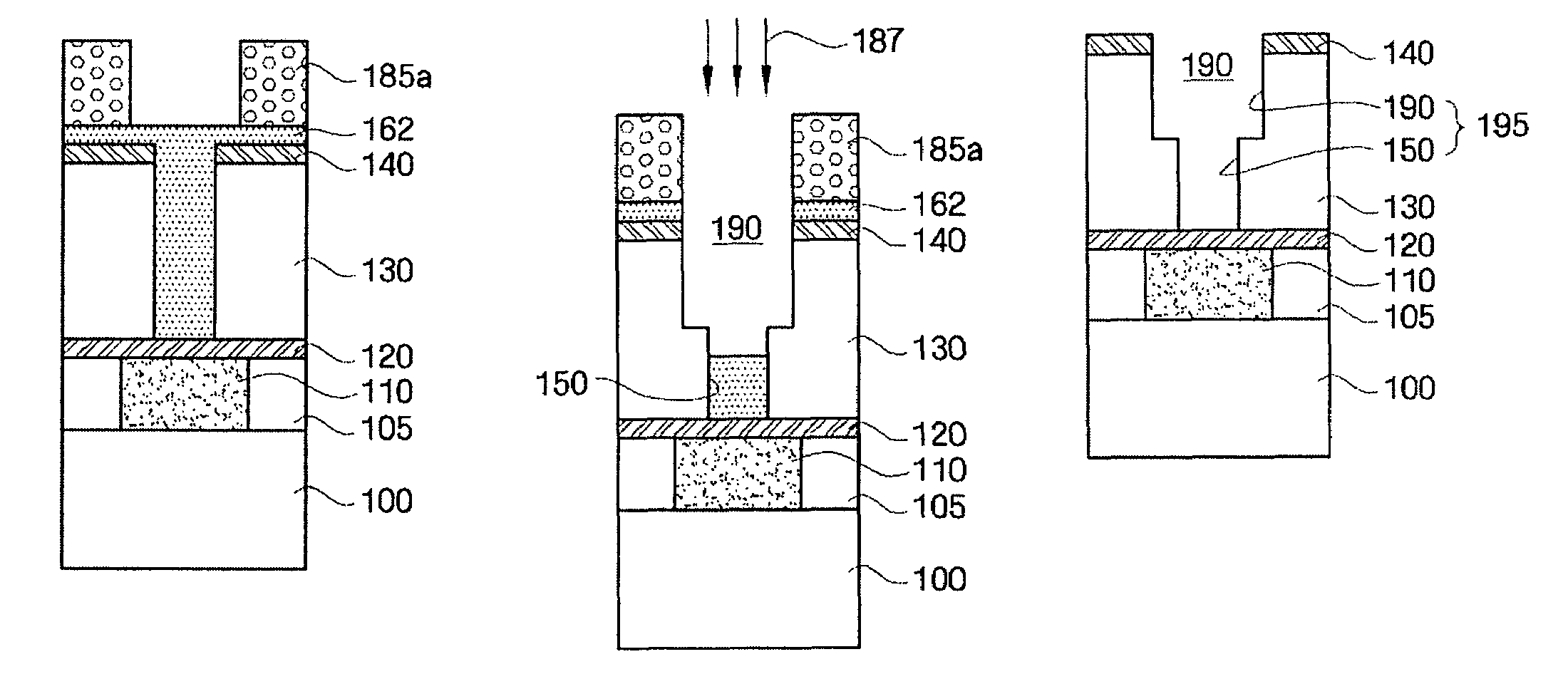

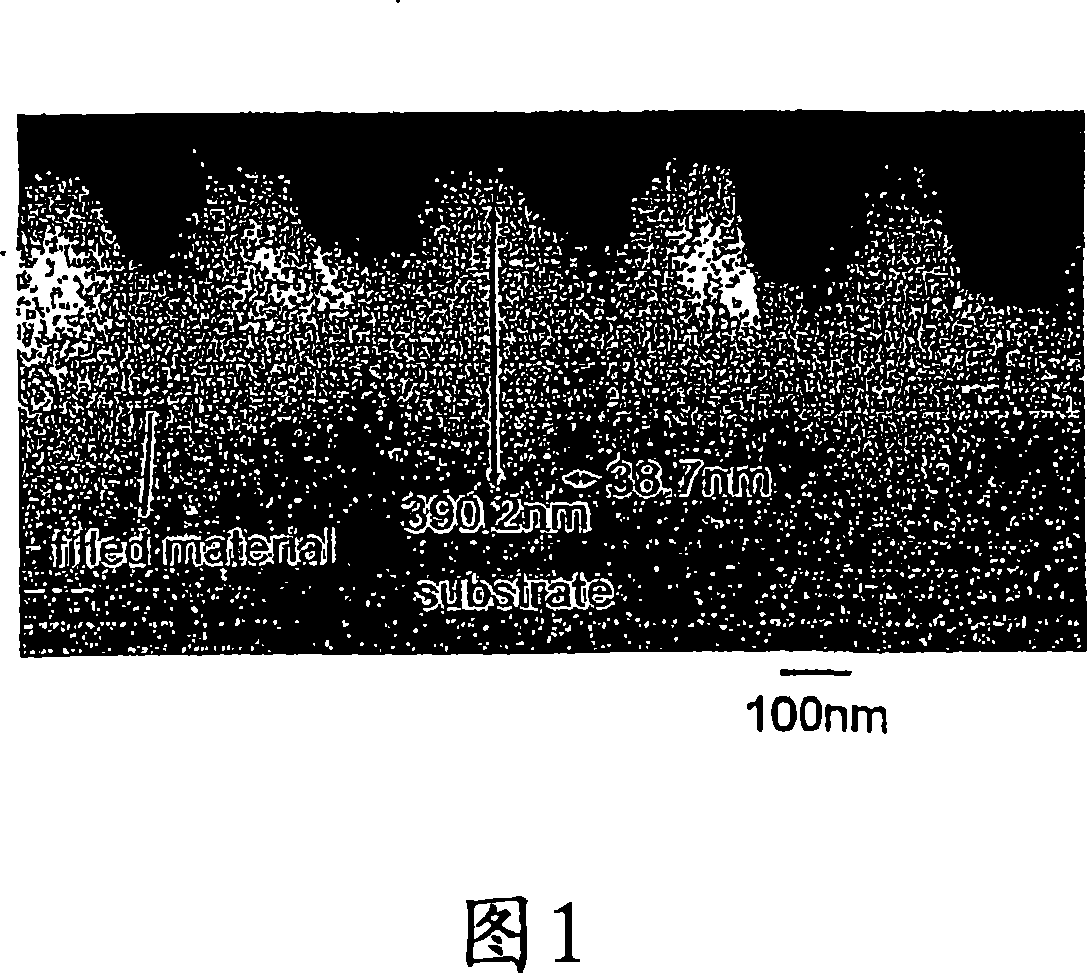

Methods of fabricating dual damascene interconnections suitable for use in microelectronic devices and similar applications using a diffusion barrier layer to protect against base materials during processing are provided. The methods include the steps of: filling a via with a hydrogen silsesquioxane (HSQ)-based filler as expressed by the general chemical formula: (RSiO3 / 2)x(HSiO3 / 2)y, wherein x and y satisfy the relationships x+y=1 and 0<x<y<1, and R is selected from C4-C24 alkyl, C4-C24 alkenyl, C4-C24 alkoxy, C8-C24 alkenoxy, substituted C4-C24 hydrocarbon, non-substituted C1-C4 hydrocarbon or substituted C1-C4 hydrocarbon; and, partially etching the filler filling the via and an interlayer dielectric to form a trench, which is connected to the via in the region where the dual damascene interconnections are to be formed. Then, the filler remaining in the via is removed, and the trench and the via are filled with an interconnection material to complete the dual damascene interconnections.

Owner:SAMSUNG ELECTRONICS CO LTD

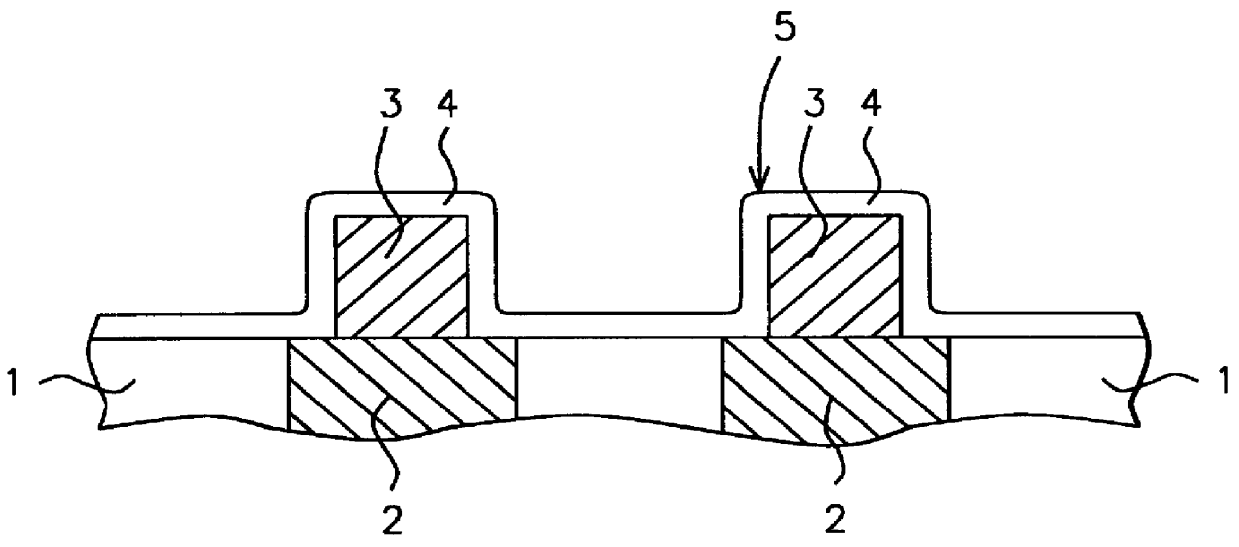

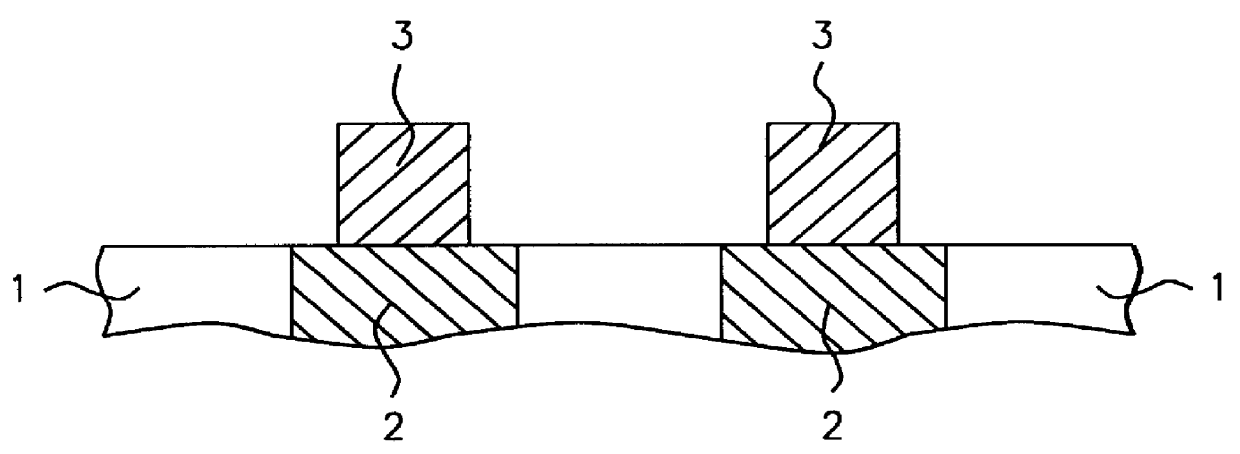

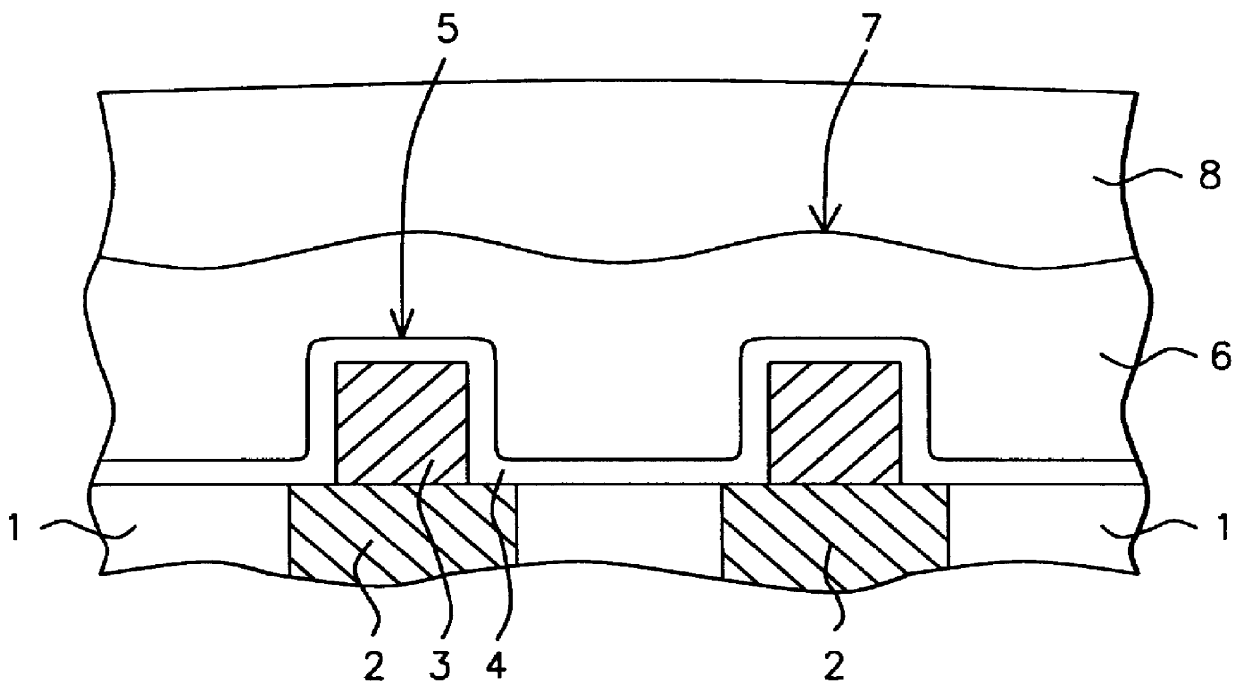

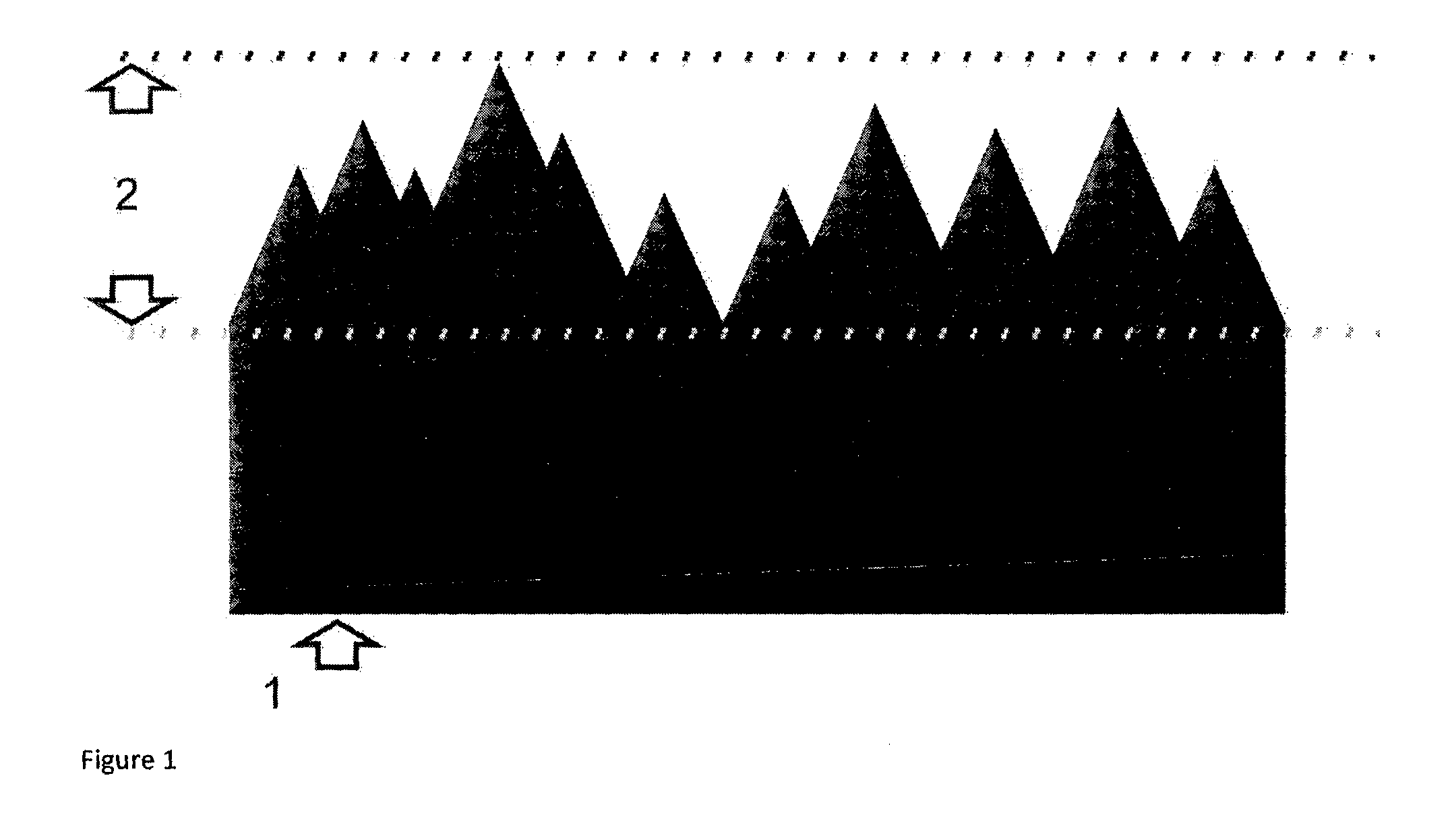

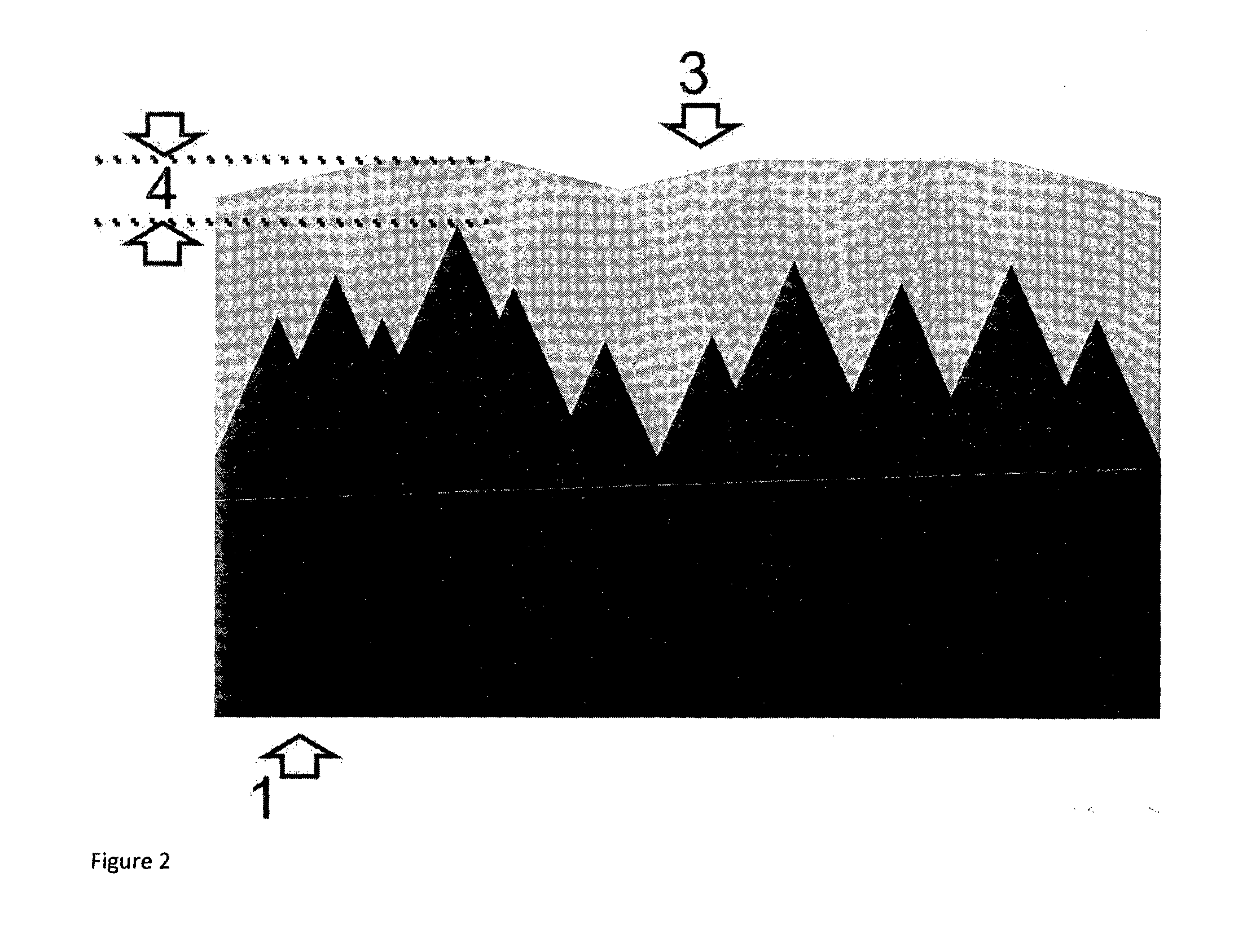

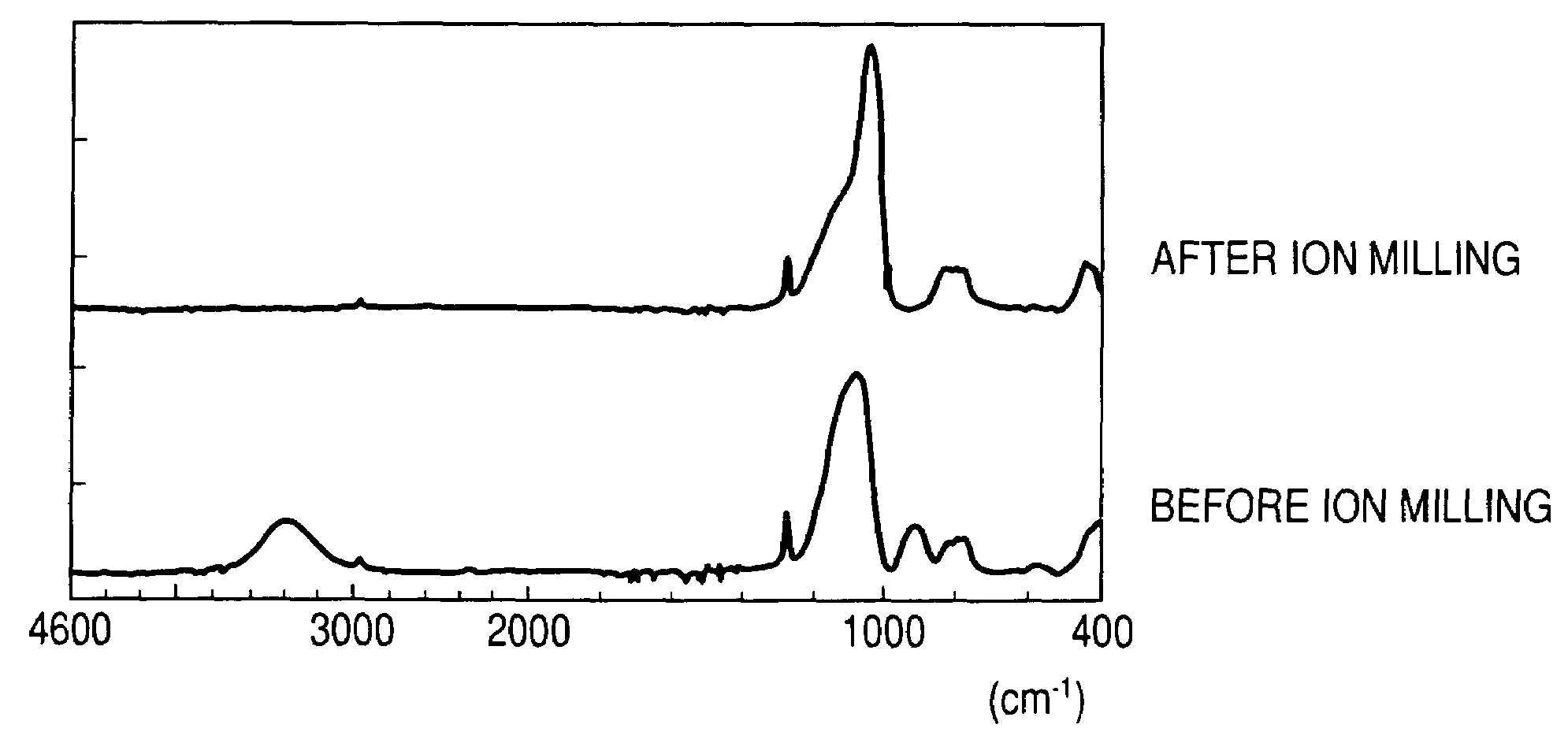

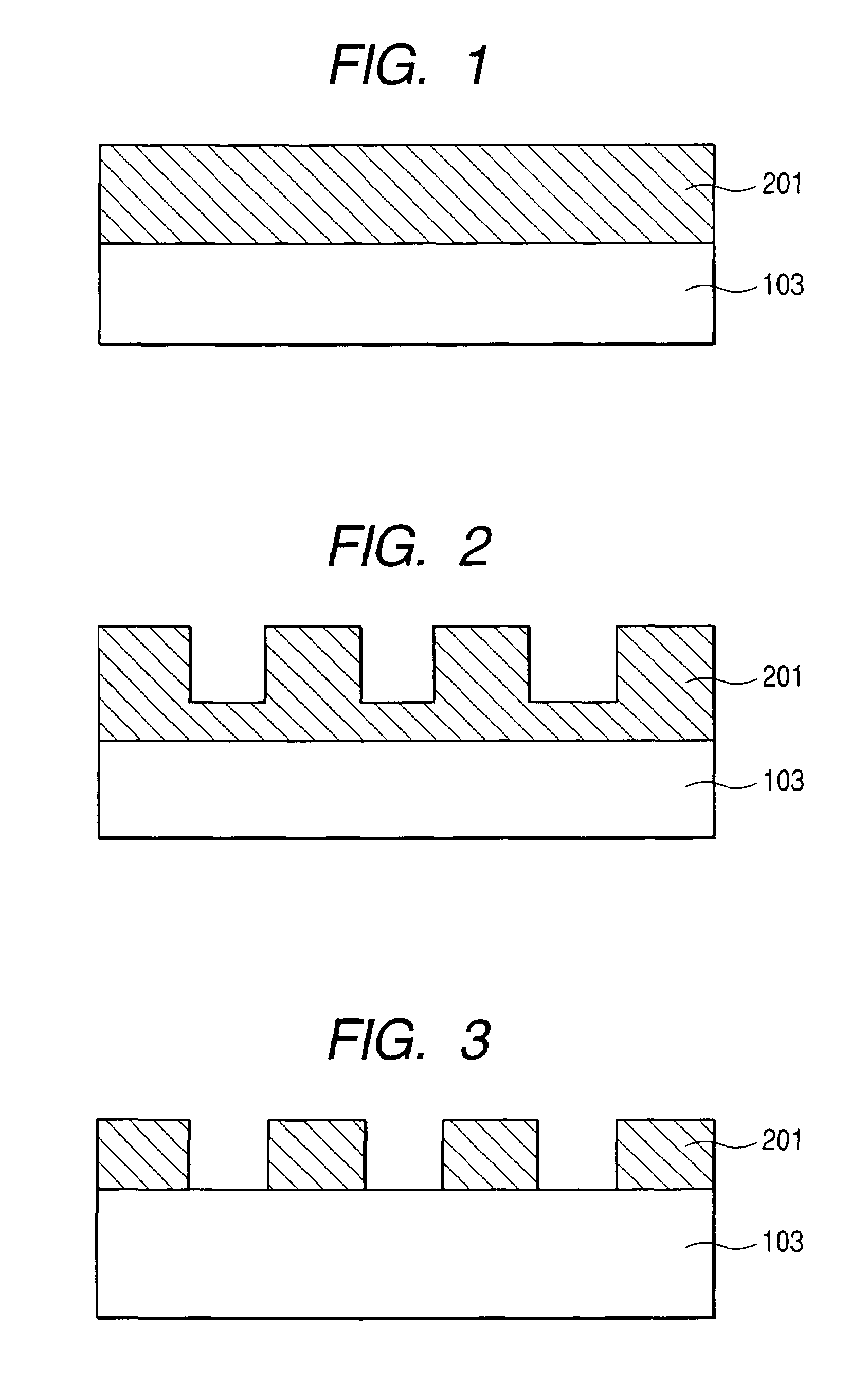

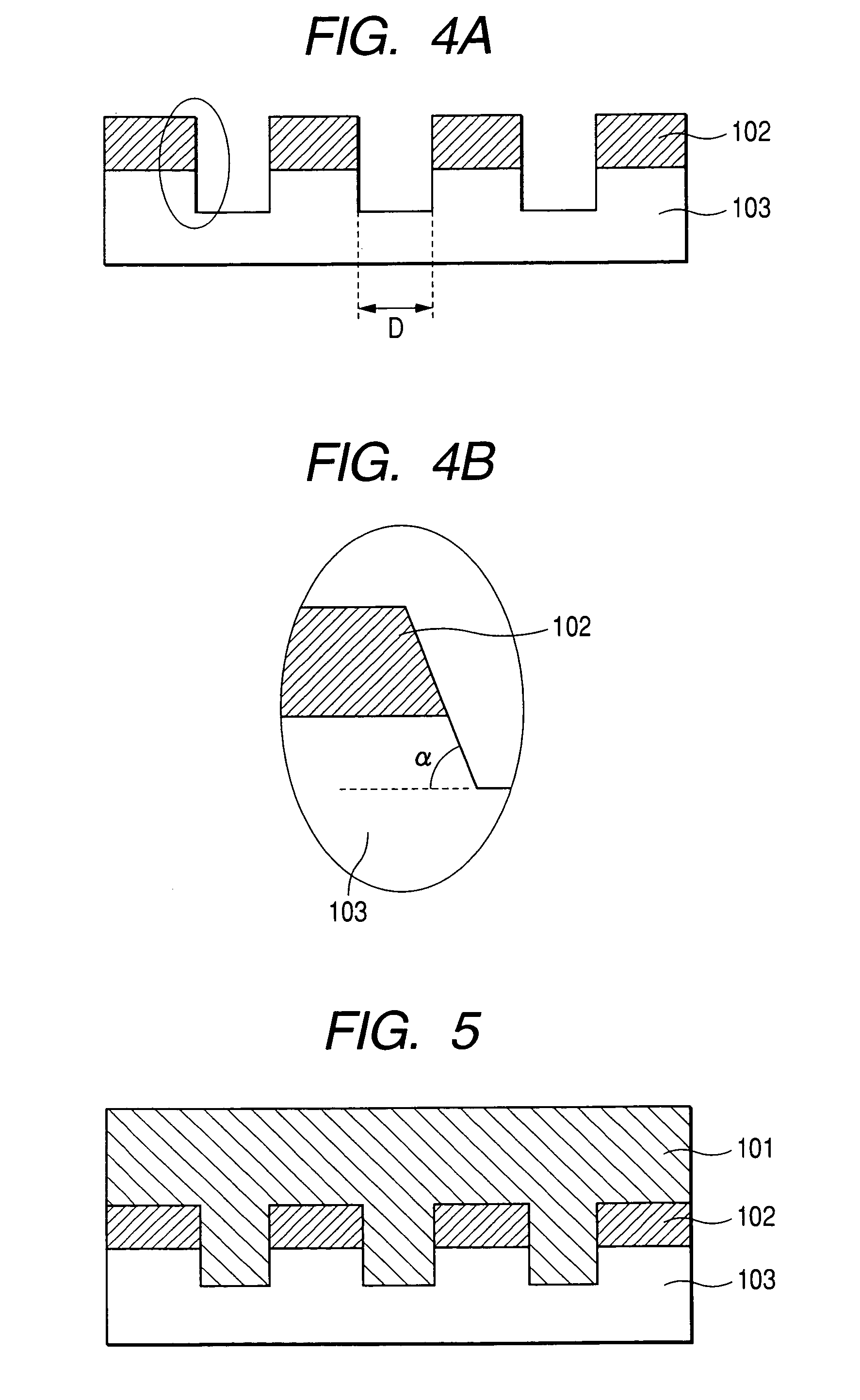

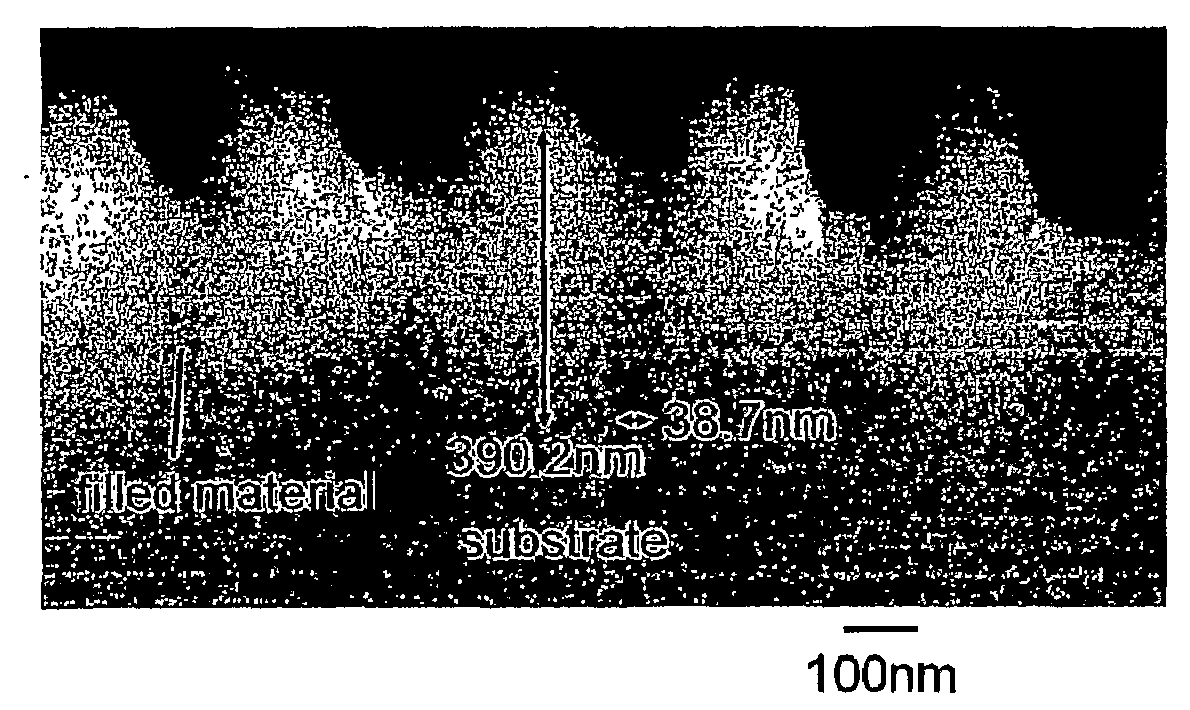

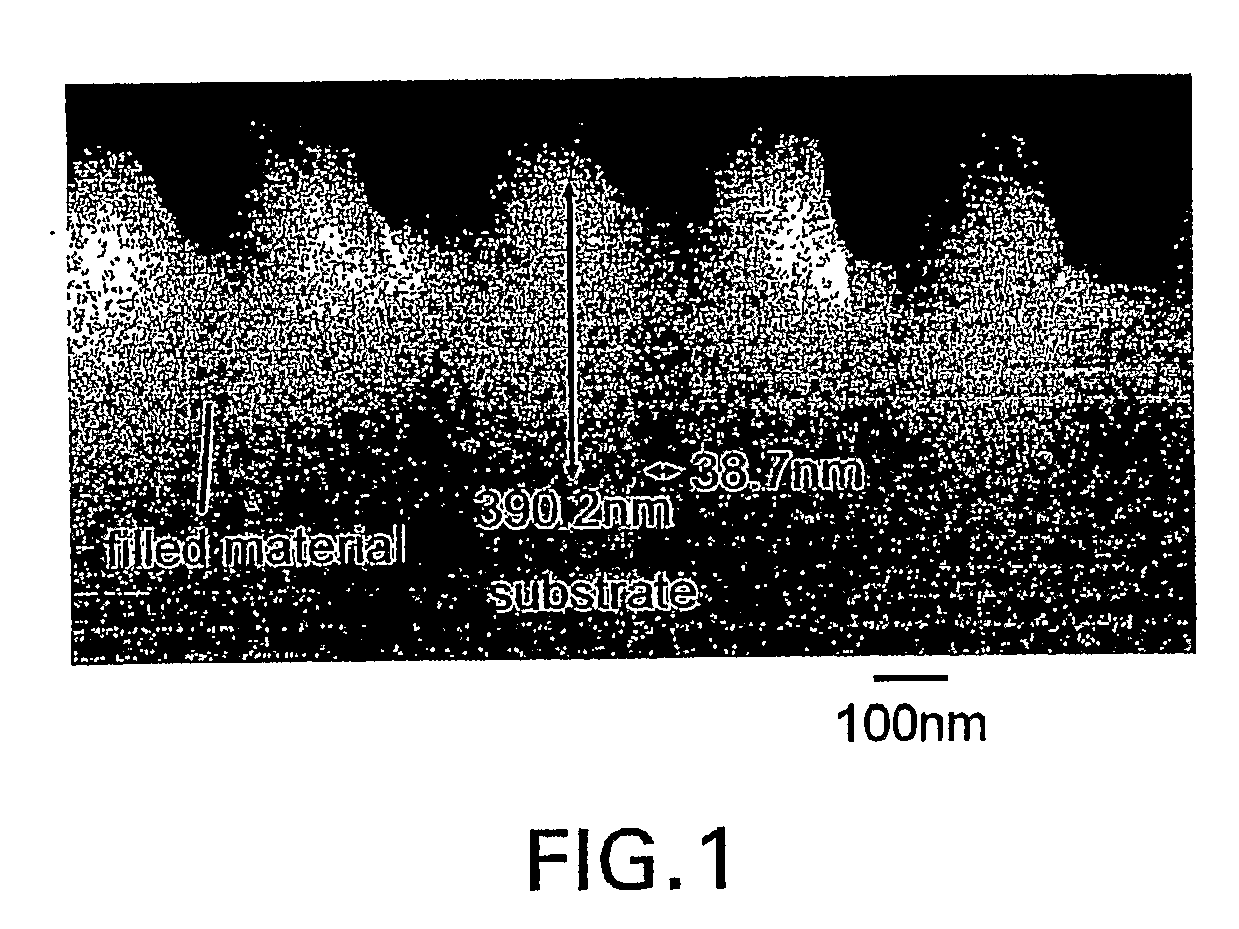

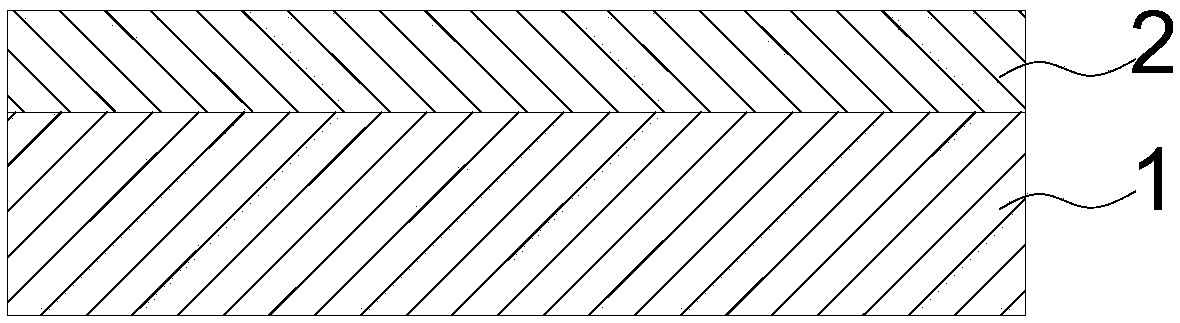

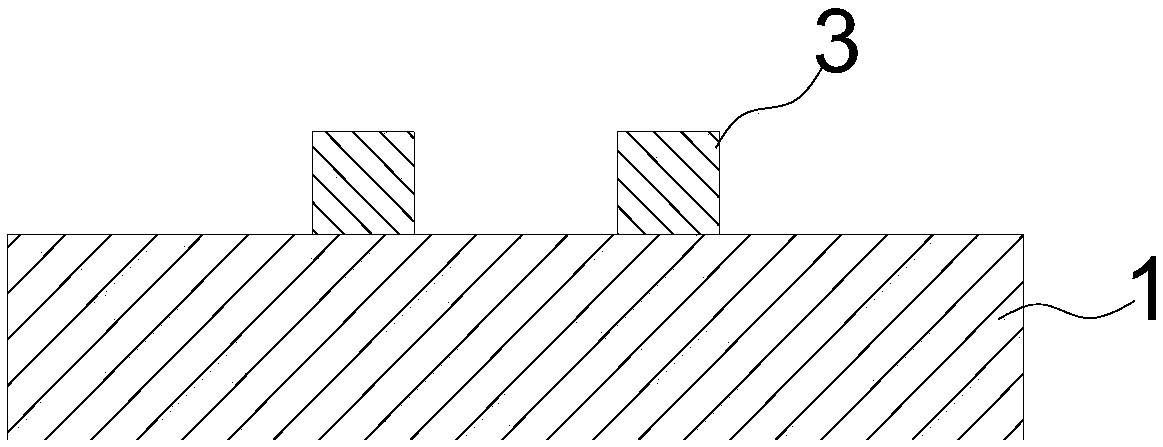

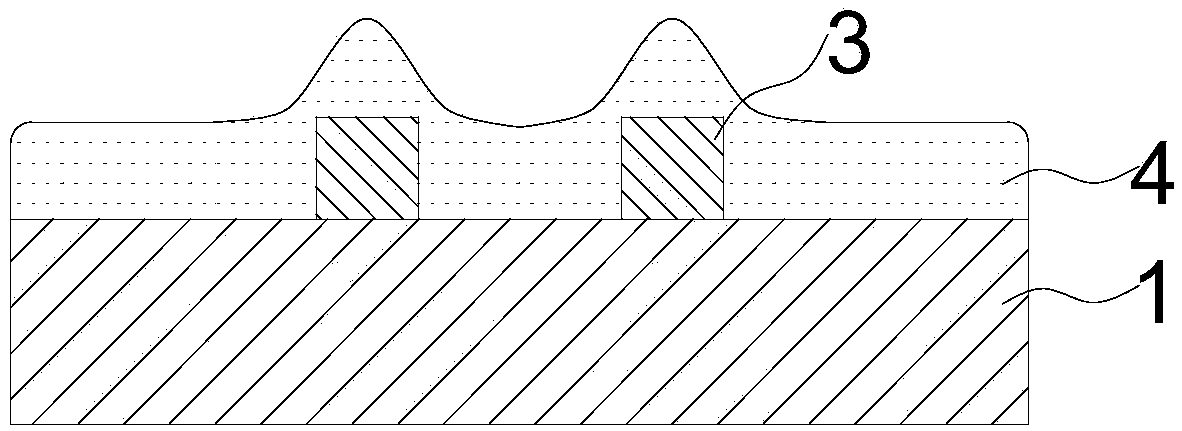

Method for producing magnetic recording medium

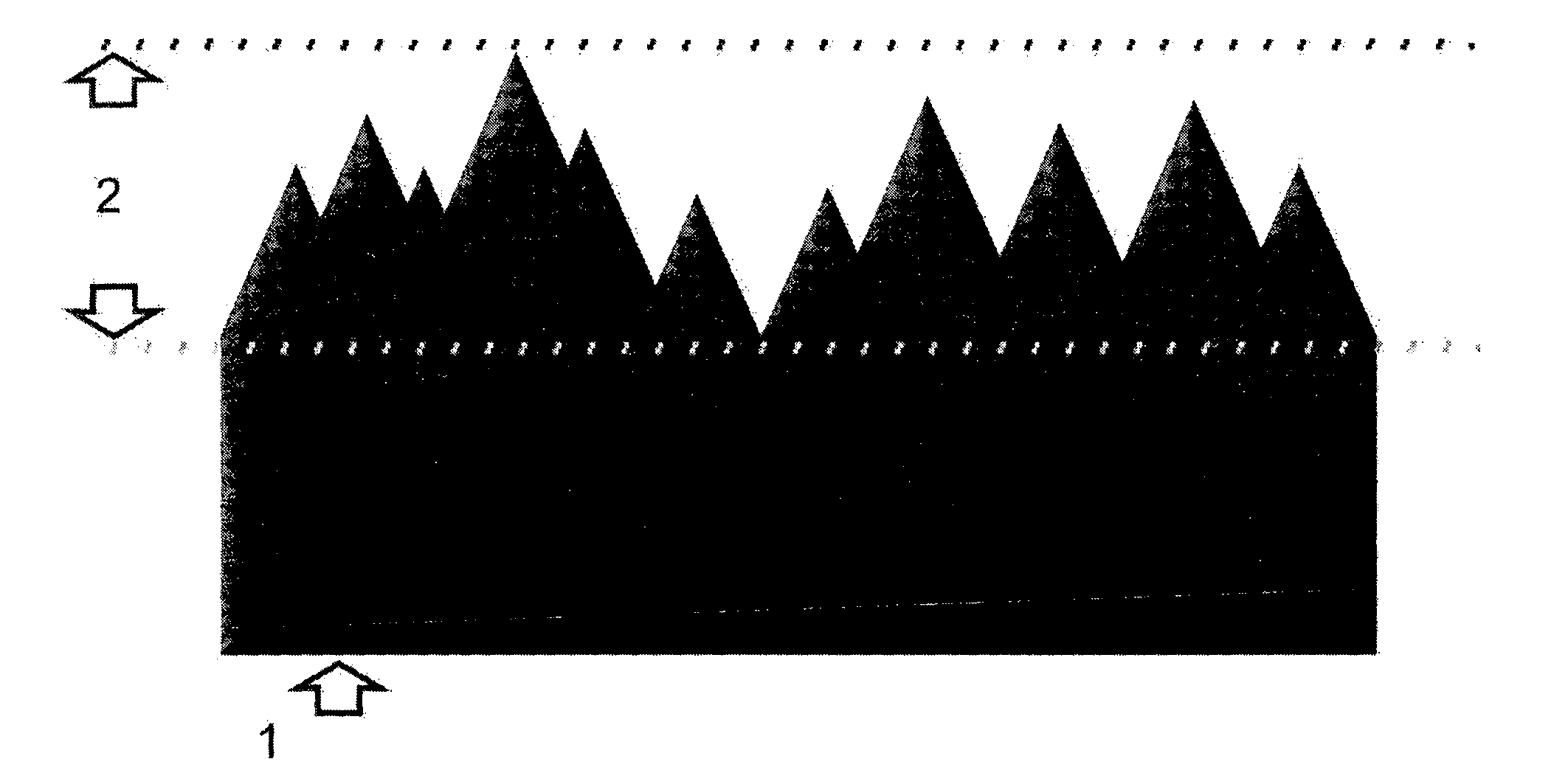

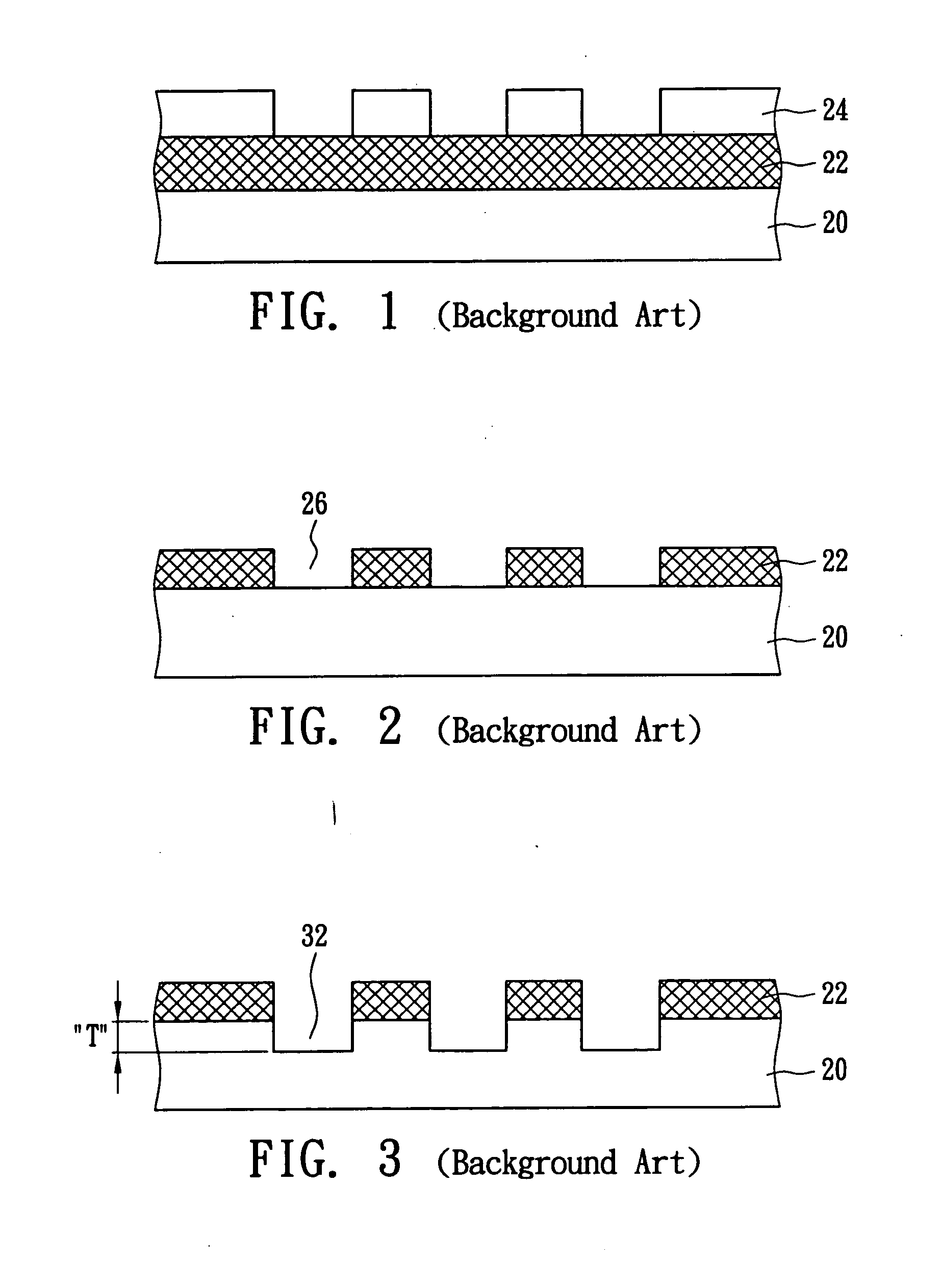

InactiveUS20060280861A1Magnetic material can be suppressedSuitable for processingDecorative surface effectsVacuum evaporation coatingConvex structureSilsesquioxane

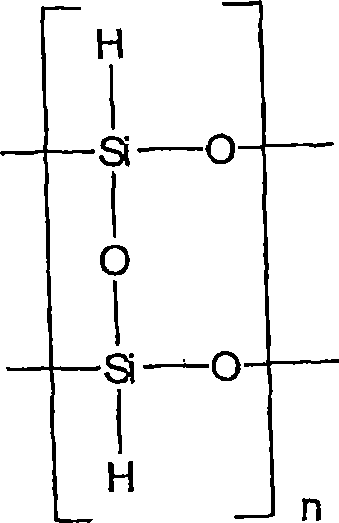

A method for producing a magnetic recording medium, includes: forming an SOG film on a surface of a magnetic layer; forming a concavo-convex structure in the SOG film comprising one selected from a group consisting of silica glass, alkylsiloxane polymer, methyl silsesquioxane polymer, hydrogen silsesquioxane polymer and hydro alkylsiloxane polymer; etching the SOG film to expose the surface of the magnetic layer; etching the exposed surface of the magnetic layer by ion milling; and forming a filling layer on the surface of the magnetic layer while leaving a portion of the magnetic layer having been subjected to the ion milling.

Owner:KK TOSHIBA

Anode active material, method of preparing the same, and anode and lithium battery containing the material

ActiveUS7833662B2Increase capacityEasy to chargeBio-organic fraction processingSilicaBinding energyFull width at half maximum

Silicon oxide based composite anode active materials including amorphous silicon oxides are provided. In one embodiment, the amorphous silicon oxide is represented by SiOx (where 0<x<2), has a binding energy of about 103 to about 106 eV, a silicon peak with a full width at half maximum (FWHM) ranging from about 1.6 to about 2.4 as measured by X-ray photoelectron spectrometry, and an atomic percentage of silicon greater than or equal to about 10 as calculated from an area of the silicon peak. The anode active material is a composite anode active material obtained by sintering hydrogen silsesquioxane (HSQ). Anodes and lithium batteries including the anode active material exhibit improved charge and discharge characteristics.

Owner:SAMSUNG SDI CO LTD

Spin-on-glass assisted polishing of rough substrates

InactiveUS20150197455A1Reduce polishing costsImprove the quality of anticorrosionDecorative surface effectsVacuum evaporation coatingOptical radiationPolymer science

A method produces a smooth surface on a rough substrate. The rough substrate is coated with a film or particles of spin-on-glass (SOG) dissolved in a solvent using spin coating, spray coating or dip coating. The SOG is made to reflow by using thermal melting and solvent thinning. The reflow is done in an atmosphere containing a partial pressure of the solvent. The reflow allows the SOG to partially melt and to decrease the surface roughnesss of the film. The SOG is cured by thermal curing or UV exposure radiation curing into a hard durable and chemical inert silicon dioxide film. The SOG can be hydrogen silsesquioxane or methyl silsesquioxane dissolved in either methyl isobutyl ketone or volatile methyl siloxanes. The method can include embossing, chemical mechanical polishing, etching and functionalizing the surface. The substrate can be a cast, mould or form for producing a polymer or a glass replica.

Owner:INMOLD BIOSYST

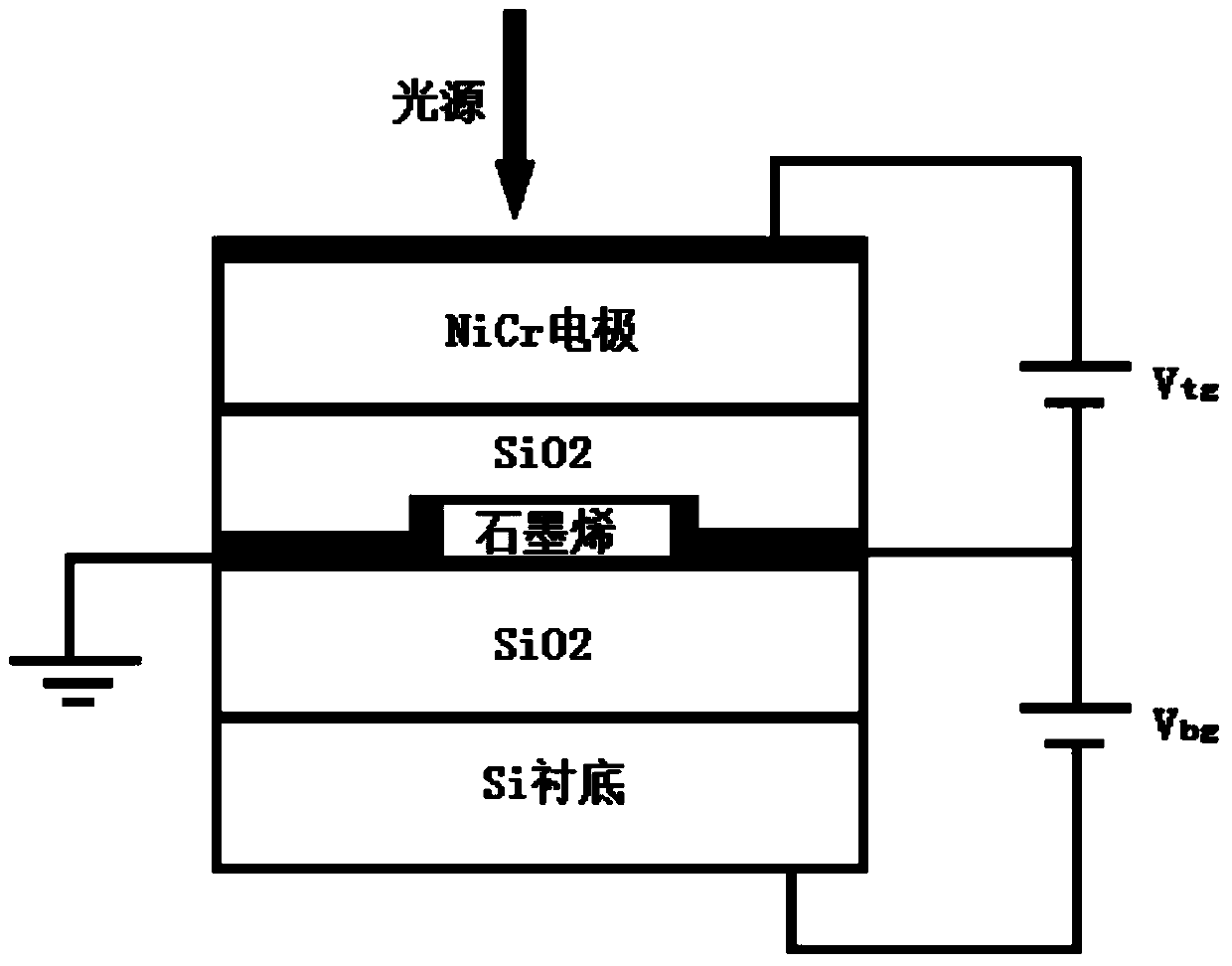

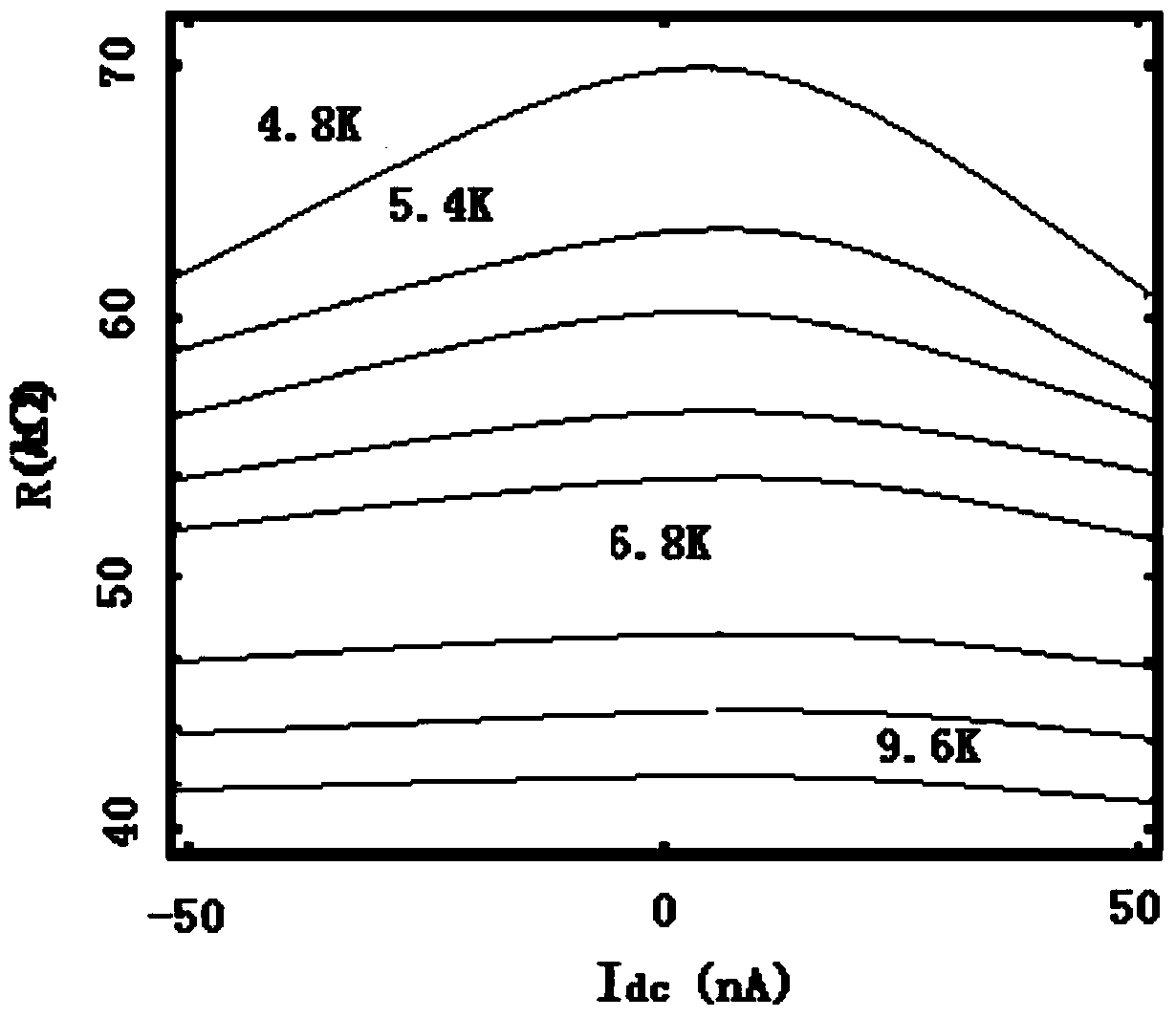

Graphene temperature sensor and preparing process thereof

InactiveCN103630254AThermometers using electric/magnetic elementsUsing electrical meansNi cr alloyCvd graphene

The invention discloses a graphene temperature sensor and a preparing process thereof. The structure of the graphene temperature sensor comprises a top gate electrode, a Ni-Cr alloy film, an upper SiO2 layer, hydrogen silsesquioxane, a dual-layer graphene and source and drain electrode, a lower SiO2 layer, a Si substrate and a back gate electrode from top to bottom. The method comprises the steps of depositing the dual-layer graphene obtained by mechanical stripping at the Si substrate with a SiO2 layer of 300nm thick, manufacturing electrodes at a source end and a drain end by an electronic beam photoetching technology, and thermally evaporating 5nmCr / 100nmAu. Compared with the existing sensor, the graphene temperature sensor has the advantages of very high sensitivity, lower intrinsic noise and very high detection speed and has well application prospect in the aviation field.

Owner:XIDIAN UNIV

Insulation film

InactiveUS7297360B2Semiconductor/solid-state device manufacturingLiquid/solution decomposition chemical coatingDielectricPolymer science

An insulation film comprising an organosilicon polymer and an organic polymer such as polyarylene, polyarylene ether, polyimide, and fluororesin is disclosed, wherein the organosilicon polymer has a relative dielectric constant of 4 or less and has a dry etching selection ratio of 1 / 3 or less to silicon oxide, fluorine-doped silicon oxide, organosilicate glass, carbon-doped silicon oxide, methyl silsesquioxane, hydrogen silsesquioxane, a spin-on-glass, or polyorganosiloxane. The insulation film is used as an etching stopper or a hard mask in a dry etching process of interlayer dielectric films for semiconductors and can produce semiconductors having excellent precision with minimal damages.

Owner:JSR CORPORATIOON

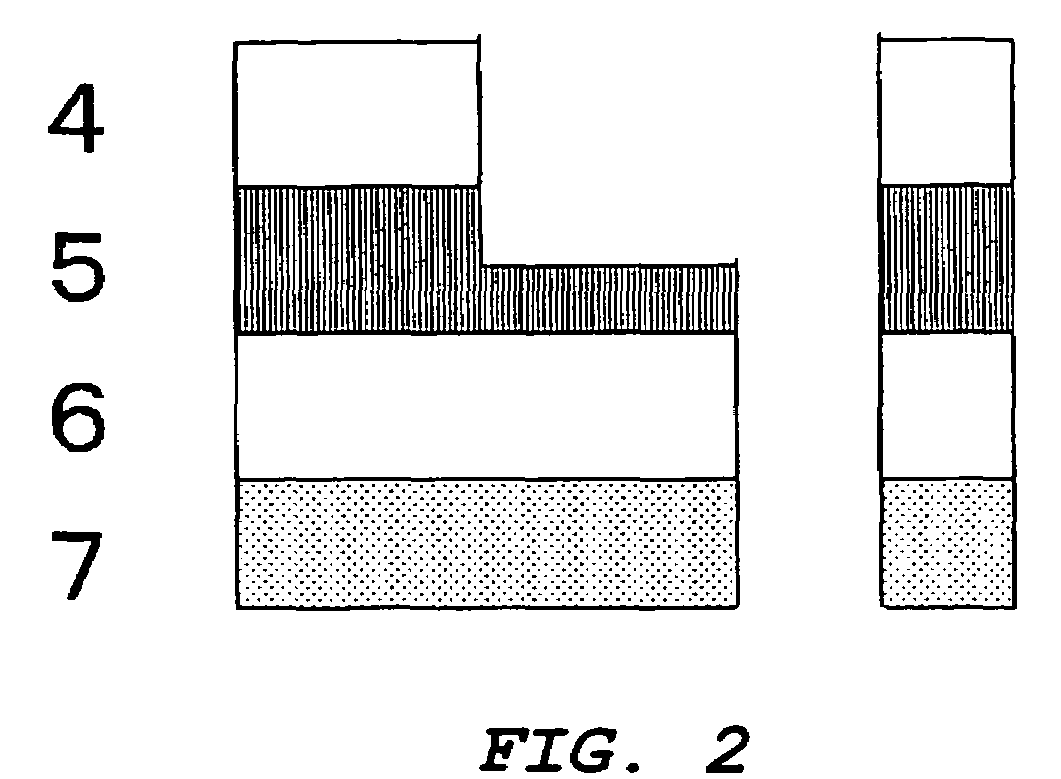

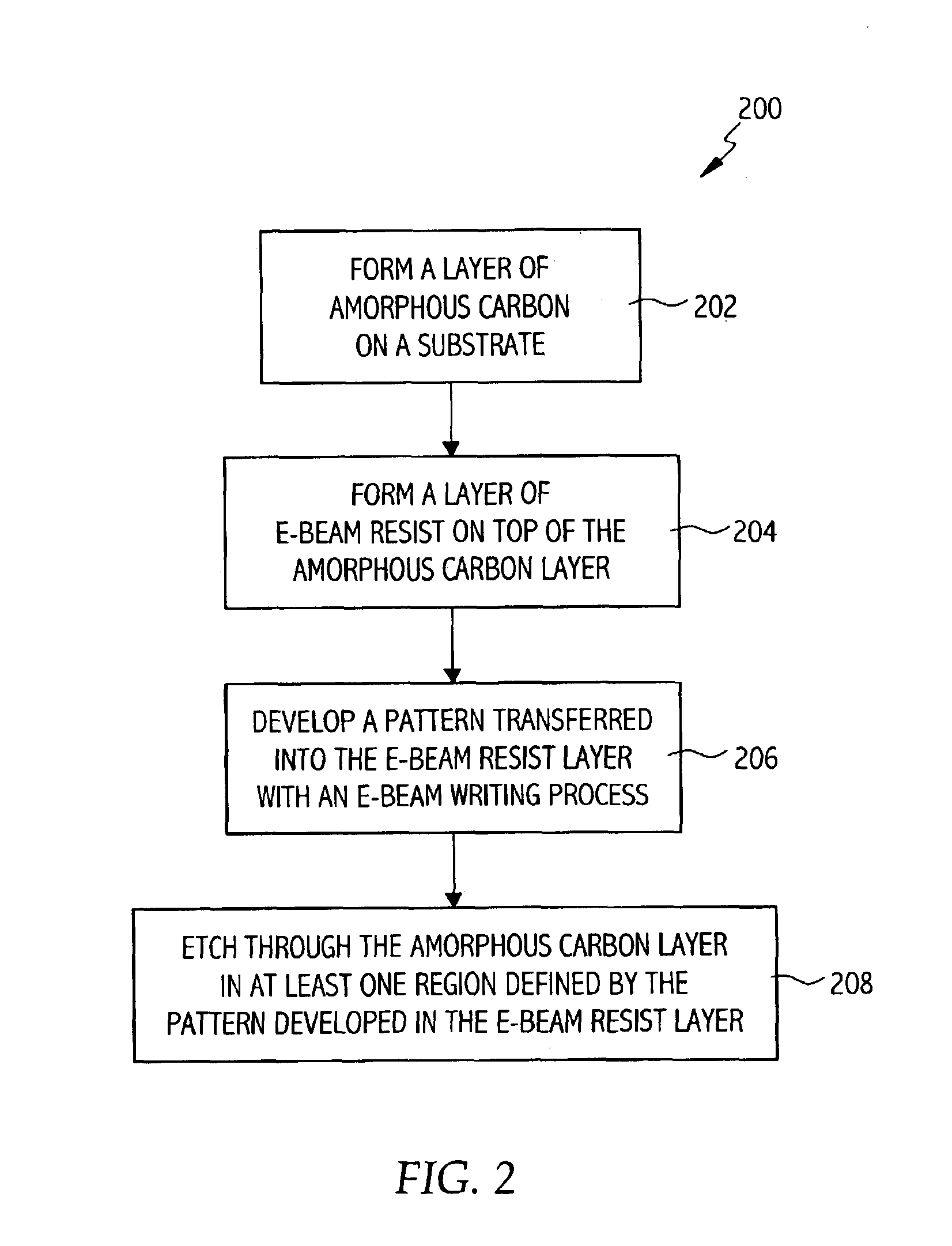

Conductive bi-layer e-beam resist with amorphous carbon

Methods for forming a patterned layer of amorphous carbon on a substrate are described. A layer of amorphous carbon may be formed on the substrate. A layer of electron sensitive resist may be formed on top of the amorphous carbon layer. A pattern transferred into the electron sensitive resist layer with an electron beam writing process is developed. During the electron beam writing process, electrons may be conducted away from the writing area through the amorphous carbon layer. The amorphous carbon layer may be etched through in at least one region defined by the pattern developed into the layer of electron sensitive resist material. For some embodiments, the amorphous carbon layer may be formed by chemical vapor deposition. For some embodiments, the layer of electron sensitive resist may be hydrogen silsesquioxane (HSQ).

Owner:APPLIED MATERIALS INC

Method for producing thick crack-free coatings from hydrogen silsesquioxane resin

InactiveUS6022625AIncrease coating thicknessShorter and low temperaturePretreated surfacesSemiconductor/solid-state device manufacturingCrack freePhysical chemistry

This invention pertains to a method for producing crack-free, insoluble, greater than 1.25 mu m thick coatings from hydrogen silsesquioxane resin compositions. The method for producing the coating comprises applying a fillerless hydrogen silsesquioxane resin composition onto a substrate and thereafter heating the hydrogen silsesquioxane resin at a temperature of less than 500 DEG C. for a controlled period of time to produce the crack-free coating having a thickness of greater than 1.25 mu m. The resins may be cured in an inert or oxygen containing environment.

Owner:DOW CORNING CORP

Method for producing magnetic recording medium

InactiveUS7662264B2Suitable for processingMagnetic material can be suppressedDecorative surface effectsVacuum evaporation coatingConvex structureSilsesquioxane

A method for producing a magnetic recording medium, includes: forming an SOG film on a surface of a magnetic layer; forming a concavo-convex structure in the SOG film comprising one selected from a group consisting of silica glass, alkylsiloxane polymer, methyl silsesquioxane polymer, hydrogen silsesquioxane polymer and hydro alkylsiloxane polymer; etching the SOG film to expose the surface of the magnetic layer; etching the exposed surface of the magnetic layer by ion milling; and forming a filling layer on the surface of the magnetic layer while leaving a portion of the magnetic layer having been subjected to the ion milling.

Owner:KK TOSHIBA

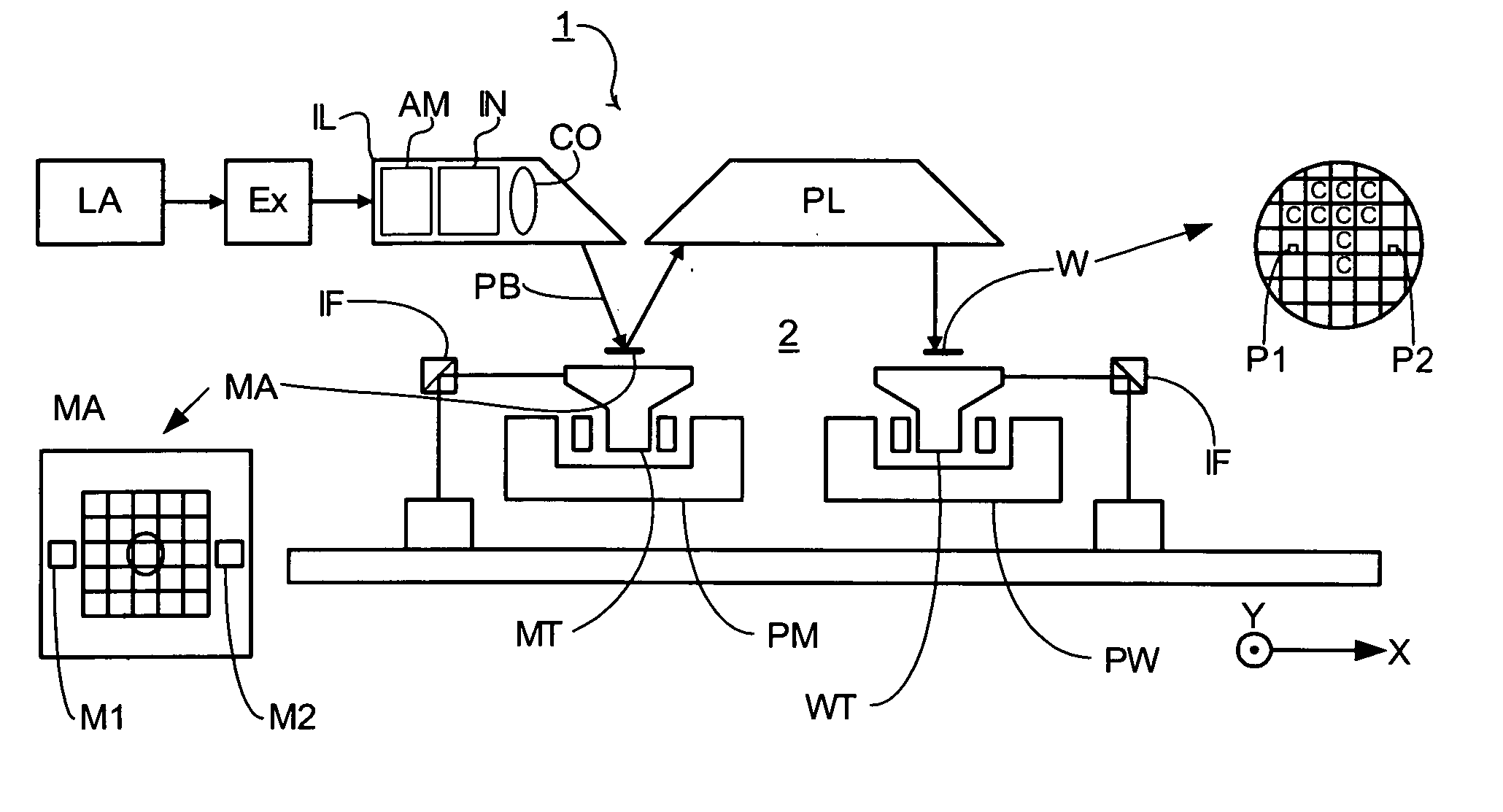

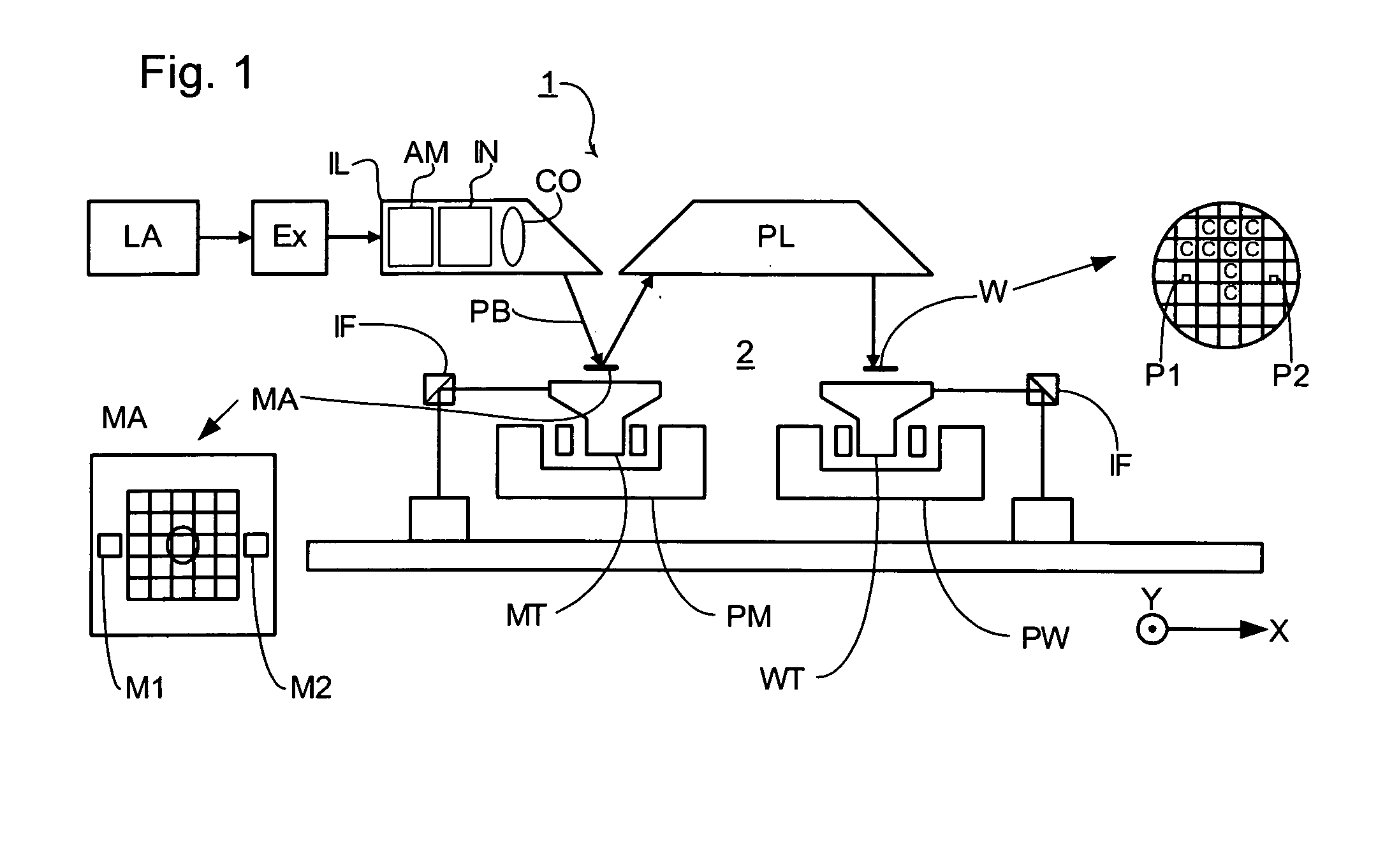

Method of preparing components, prepared component, lithographic apparatus and device manufacturing method

InactiveUS20050008978A1Reduce decreaseReduce pollutionSemiconductor/solid-state device manufacturingPhotomechanical exposure apparatusOutgassingHydrocotyle bowlesioides

A method of preparing components for use in a vacuum chamber of a lithographic apparatus is disclosed. The method includes coating the component with a non-metallic material. The method may further include treating the coating so as to harden the coating. Preferably, the coating material is a hydrogen silsesquioxane (HSQ), which may be applied via spraying, brushing, or spinning and can be treated by heating or by irradiation with an electron beam. The resulting components strongly reduce outgassing of water and hydrocarbons when subjected to a vacuum environment.

Owner:ASML NETHERLANDS BV

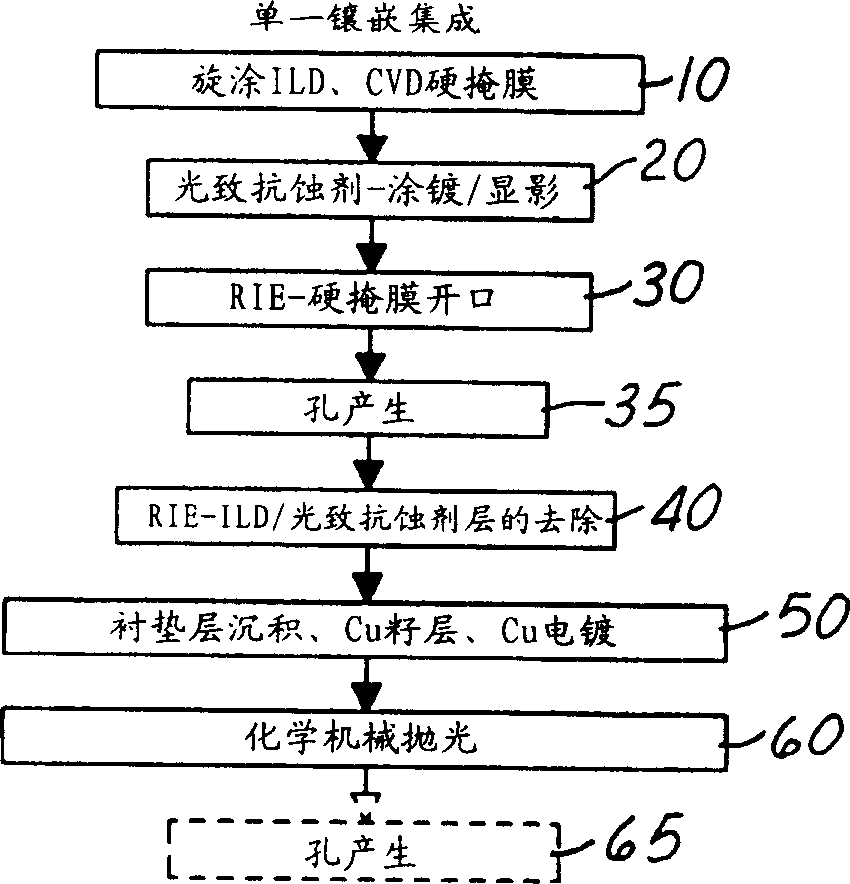

Method for forming porous dielectric material layer on semiconductor device and formed device

InactiveCN1427456ANot subject to erosionPorositySemiconductor/solid-state device detailsSolid-state devicesElectronic structureThermosetting polymer

A method for forming a porous dielectric material layer in an electronic structure and the structure formed are disclosed. In the method, a porous dielectric layer in a semiconductor device can be formed by first forming a non-porous dielectric layer, then partially curing, patterning by reactive ion etching, and final curing the non-porous dielectric layer at a higher temperature than the partial curing temperature to transform the non-porous dielectric material into a porous dielectric material, thus achieving a dielectric material that has significantly improved dielectric constant, i.e. smaller than 2.6. The non-porous dielectric material may be formed by embedding a thermally stable dielectric material such as methyl silsesquioxane, hydrogen silsesquioxane, benzocyclobutene or aromatic thermoset polymers with a second phase polymeric material therein such that, at the higher curing temperature, the second phase polymeric material substantially volatilizes to leave voids behind forming a void-filled dielectric material.

Method of fabricating dual damascene interconnections of microelectronic device using diffusion barrier layer against base material

ActiveUS7323407B2Improve performanceImprove propertiesSemiconductor/solid-state device detailsSolid-state devicesDielectricInterconnection

Methods of fabricating dual damascene interconnections suitable for use in microelectronic devices and similar applications using a diffusion barrier layer to protect against base materials during processing are provided. The methods include the steps of: filling a via with a hydrogen silsesquioxane (HSQ)-based filler as expressed by the general chemical formula: (RSiO3 / 2)x(HSiO3 / 2)y, wherein x and y satisfy the relationships x+y=1 and 0<x<y<1, and R is selected from C4-C24 alkyl, C4-C24 alkenyl, C4-C24 alkoxy, C8-C24 alkenoxy, substituted C4-C24 hydrocarbon, non-substituted C1-C4 hydrocarbon or substituted C1-C4 hydrocarbon; and, partially etching the filler filling the via and an interlayer dielectric to form a trench, which is connected to the via in the region where the dual damascene interconnections are to be formed. Then, the filler remaining in the via is removed, and the trench and the via are filled with an interconnection material to complete the dual damascene interconnections.

Owner:SAMSUNG ELECTRONICS CO LTD

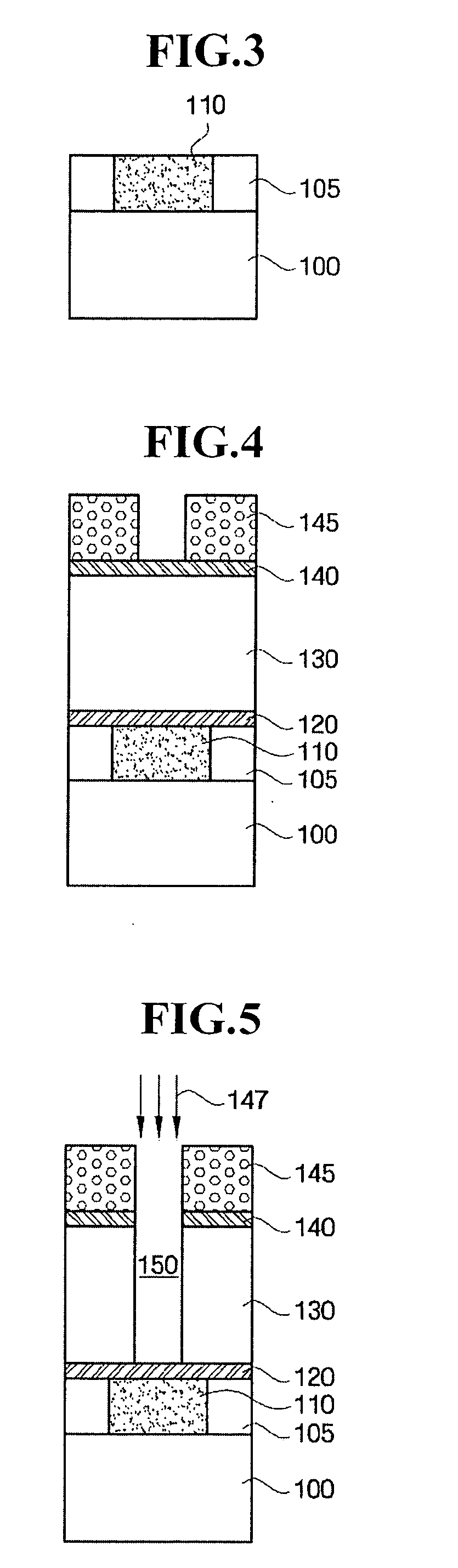

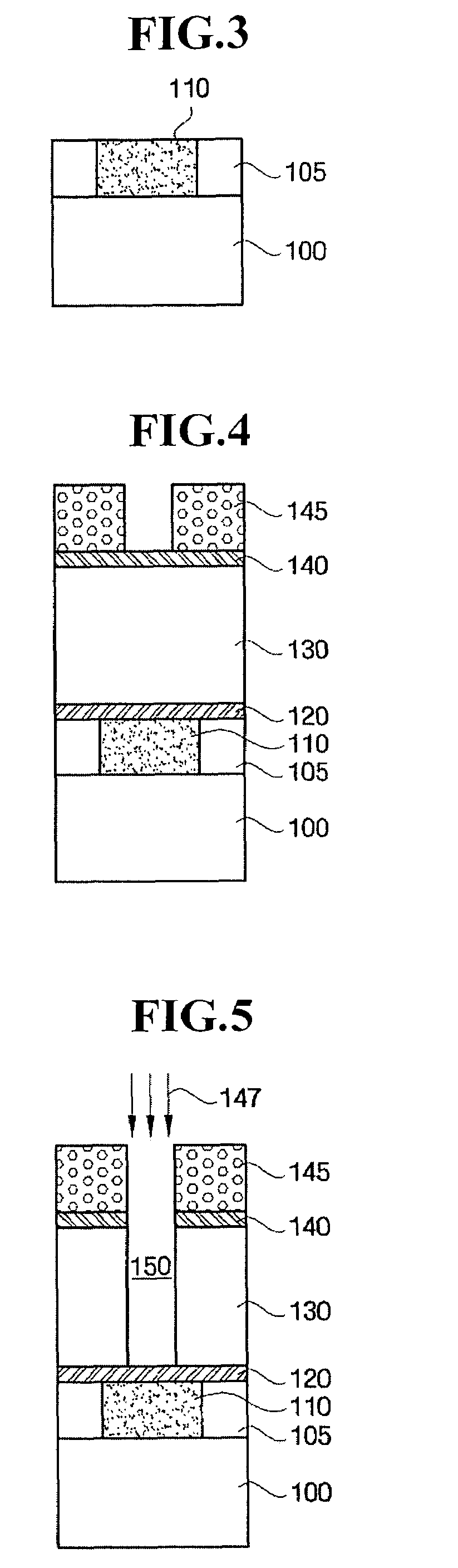

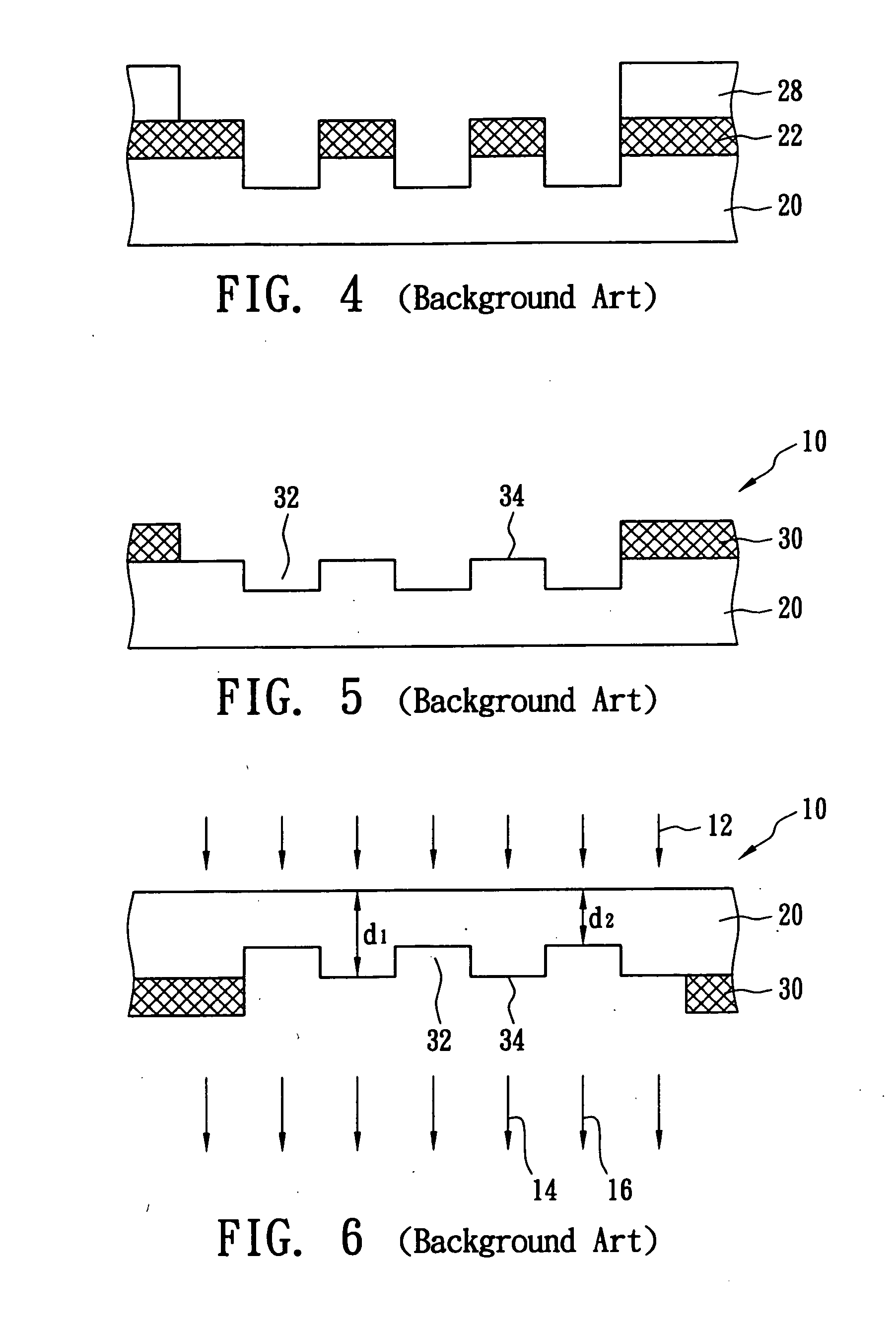

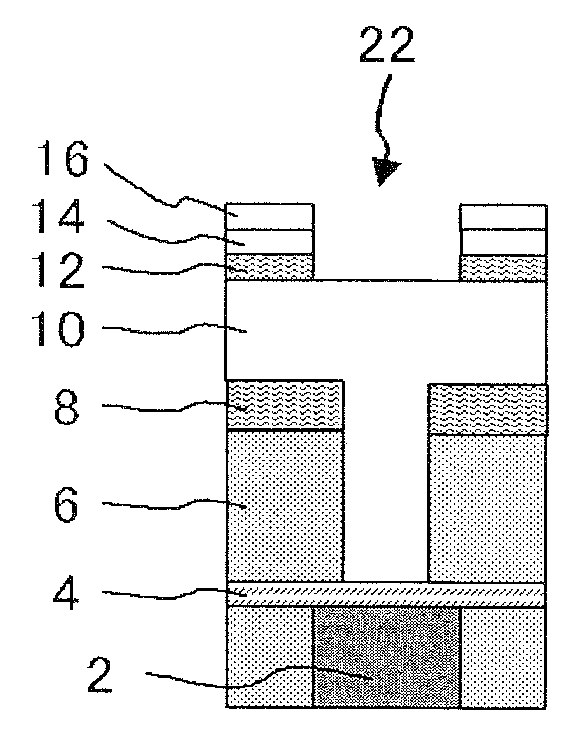

Method of curing hydrogen silsesquioxane and densification in nano-scale trenches

InactiveUS20090032901A1Semiconductor/solid-state device detailsSolid-state devicesSilsesquioxaneSemiconductor

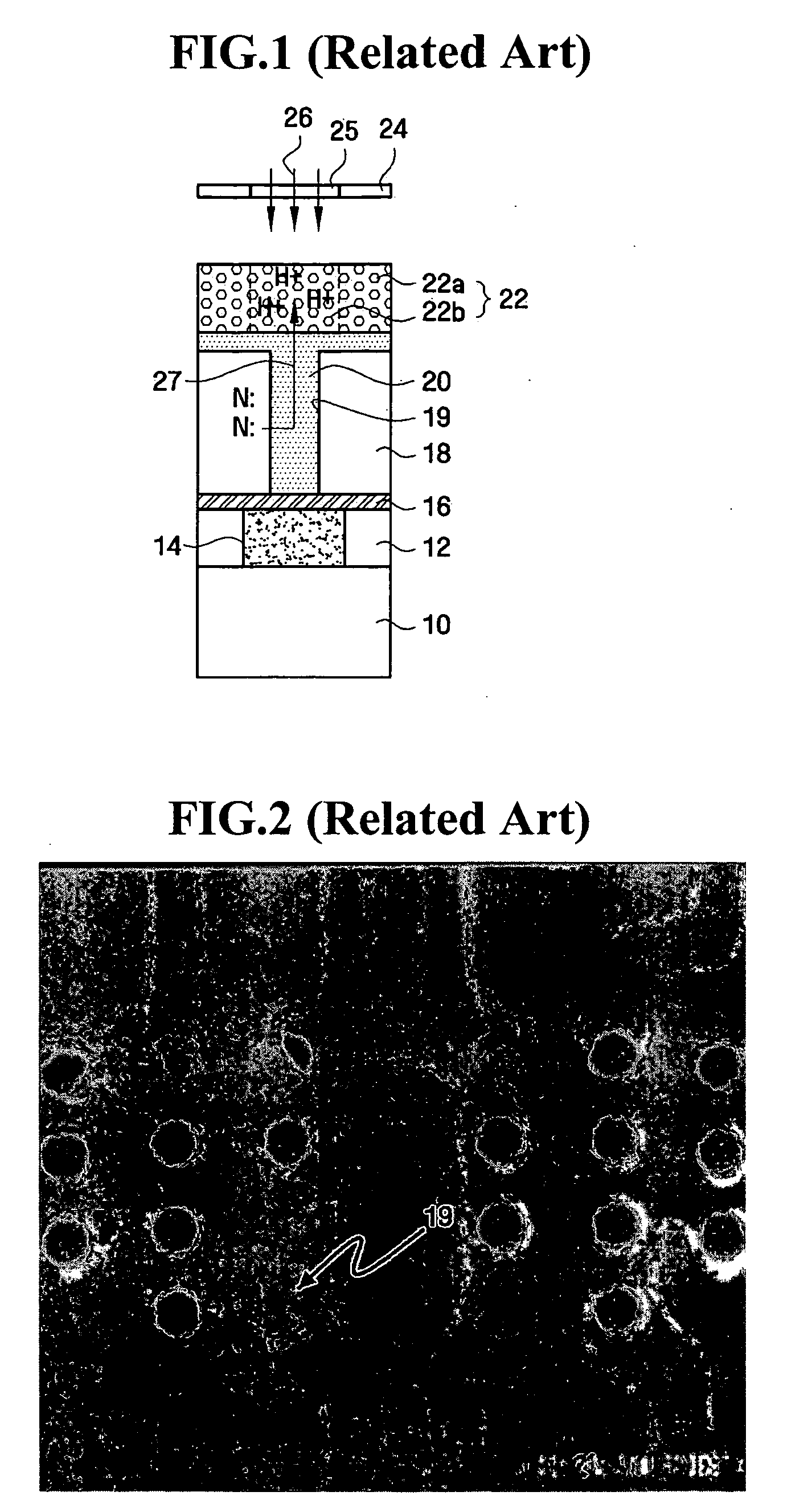

Trenches in a semiconductor substrate are filled by (i) dispensing a film forming material on the semiconductor substrate and into the trenches; (ii) curing the dispensed film forming material in the presence of an oxidant at a first low temperature for a first predetermined period of time; (iii) curing the dispensed film forming material in the presence of an oxidant at a second low temperature for a second predetermined period of time; (iv) curing the dispensed film forming material in the presence of an oxidant at a third high temperature for a third predetermined period of time; and (v) forming filled oxide trenches in the semiconductor substrate. The film forming material is hydrogen silsesquioxane.

Owner:CHEN WEI DA +5

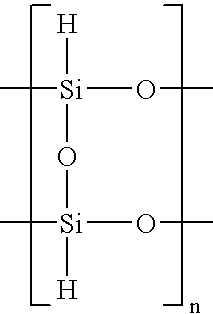

Boron-containing hydrogen silsesquioxane polymer, integrated circuit device formed using the same, and associated methods

ActiveUS20110027466A1Reducing and eliminating emissionSemiconductor/solid-state device detailsSolid-state devicesDevice formSilicon oxygen

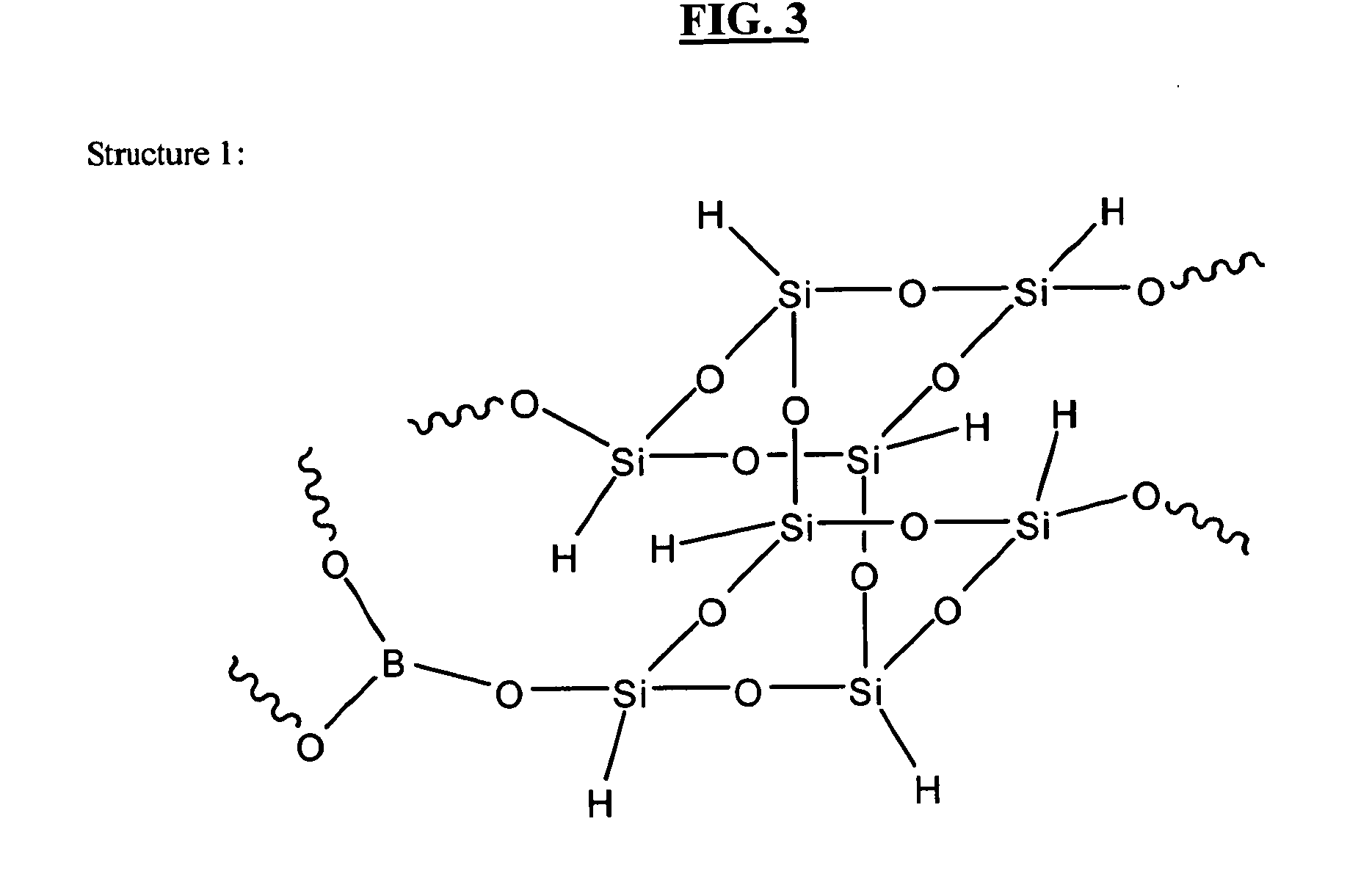

A composition includes a boron-containing hydrogen silsesquioxane polymer having a structure that includes: silicon-oxygen-silicon units, and oxygen-boron-oxygen linkages in which the boron is trivalent, wherein two silicon-oxygen-silicon units are covalently bound by an oxygen-boron-oxygen linkage therebetween.

Owner:CHEIL IND INC

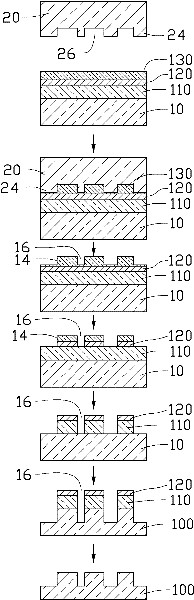

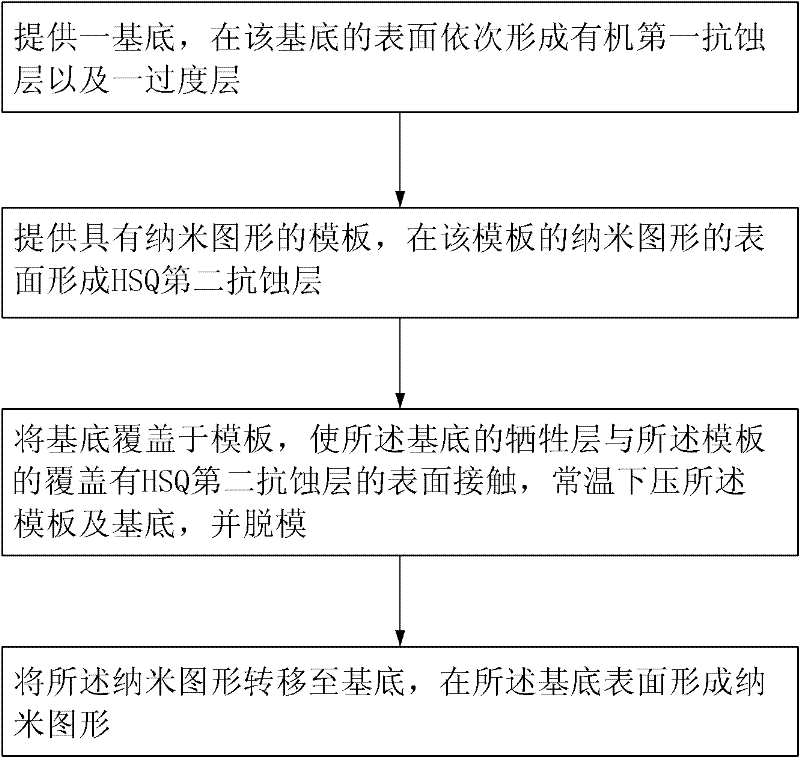

nanoimprint method

InactiveCN102279517AReduce adhesionIntegrity guaranteedNanoinformaticsPhotomechanical apparatusResistImage resolution

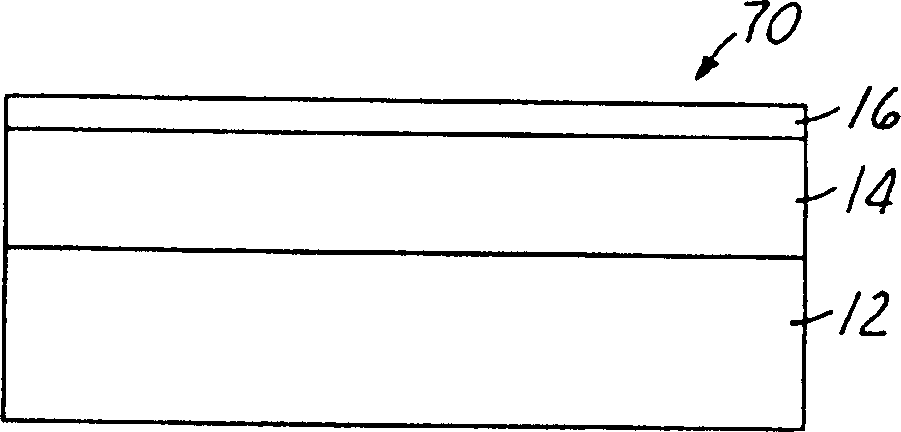

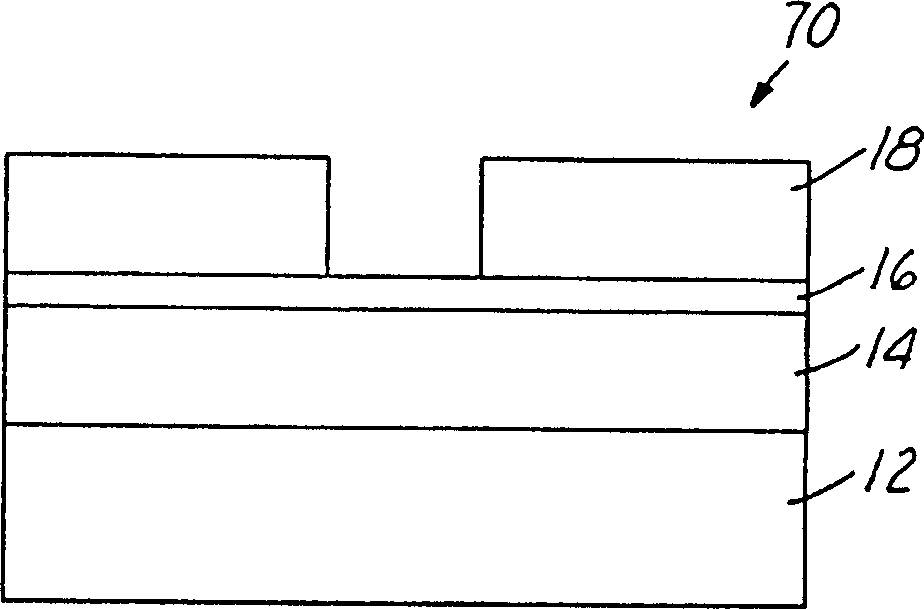

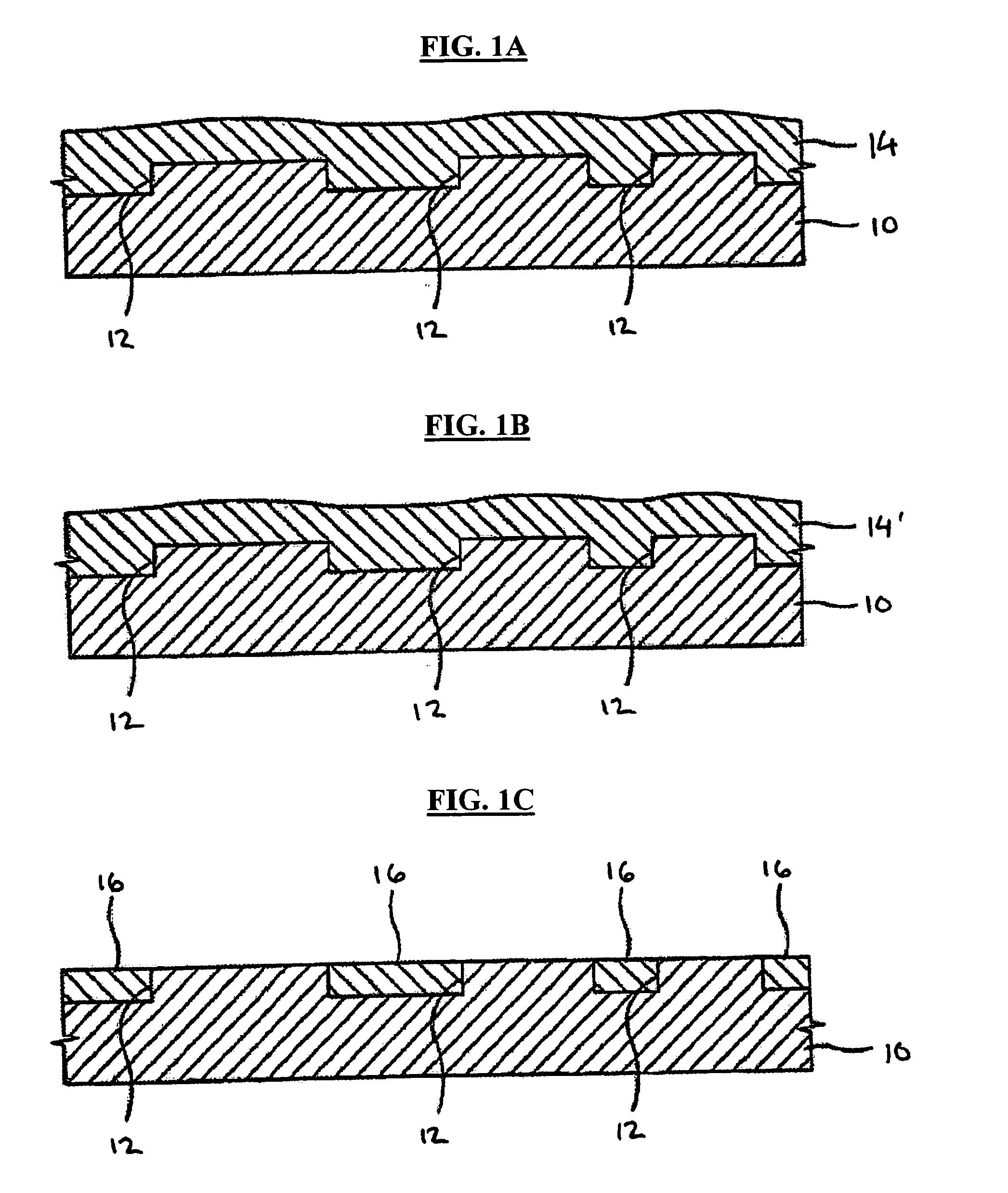

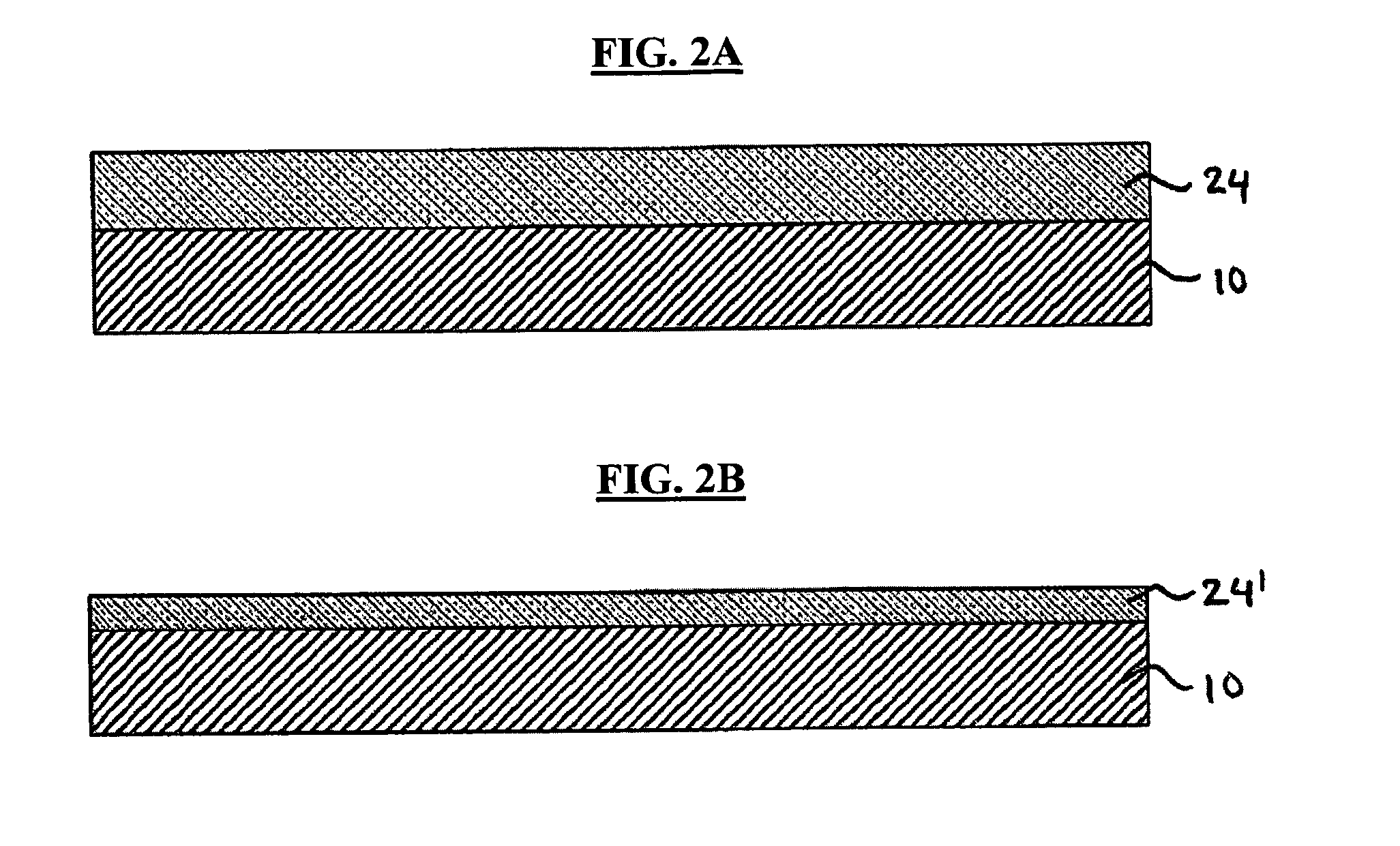

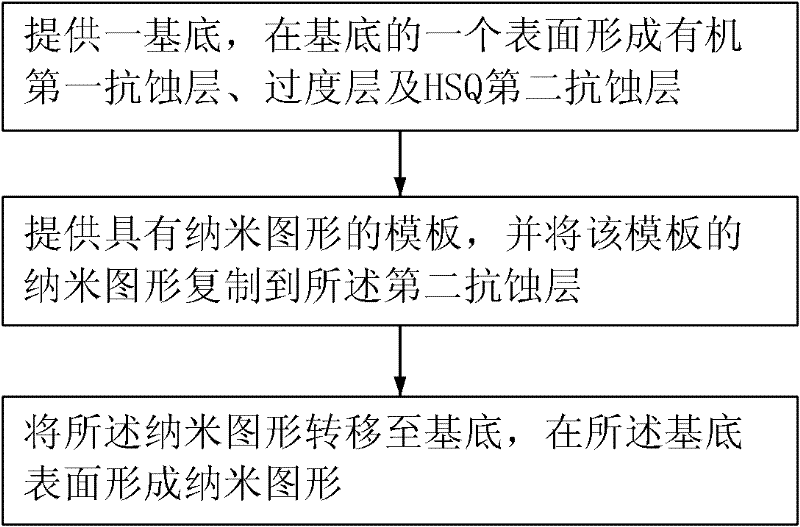

A nanoimprint method is provided. A substrate and a master stamp are first provided. The substrate has a first resist layer, a transition layer, and a second resist layer orderly formed thereon. The master stamp has a nanopattern defined therein. The second resist layer is a layer of hydrogen silsesquioxane. The nanopattern of the master stamp is then pressed into the second resist layer to form a nanopattern in the second resist layer at normal temperature which is in a range from about 20 centidegrees to about 50 centidegrees. Finally, the nanopattern of the second resist layer is transferred to the substrate.

Owner:TSINGHUA UNIV +1

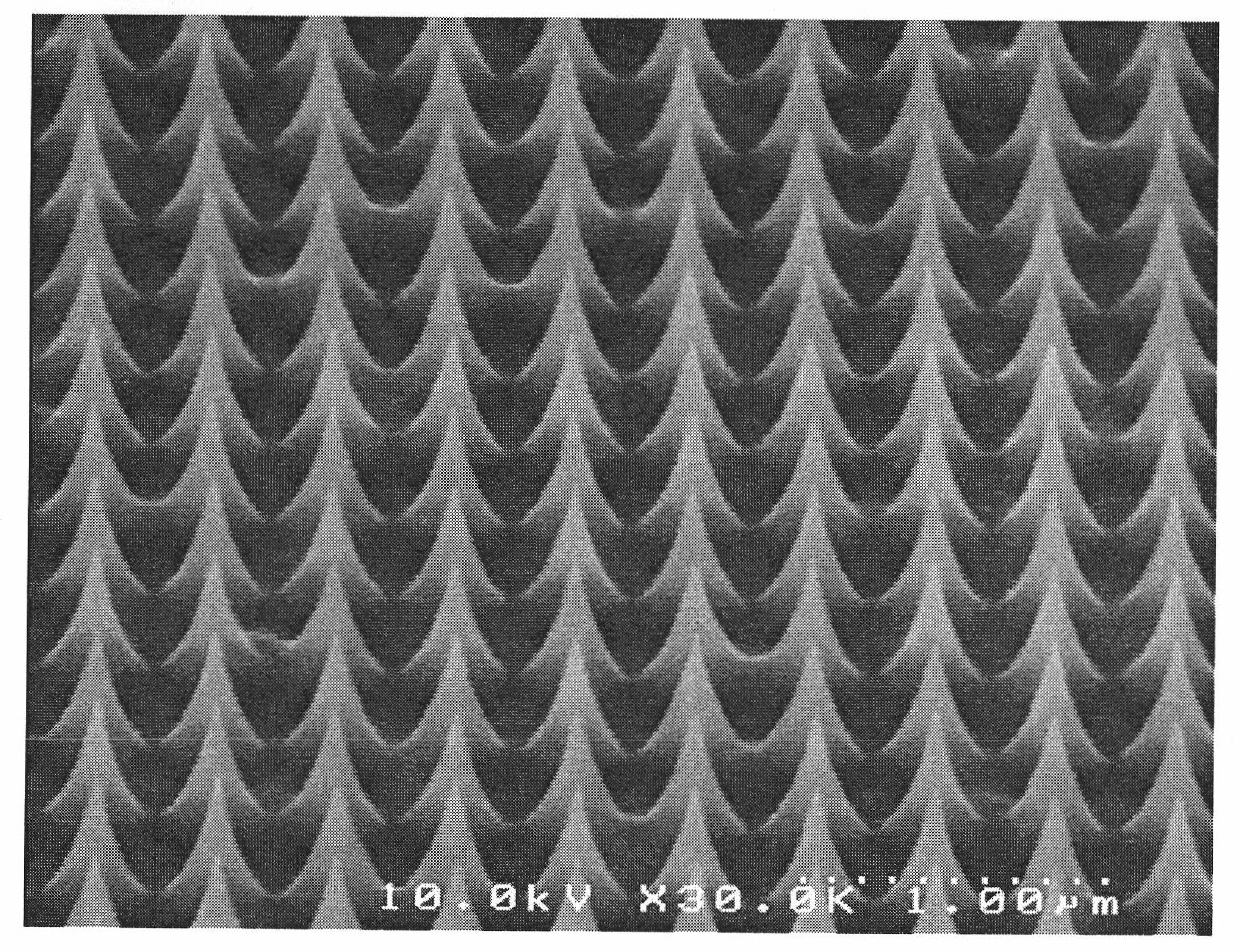

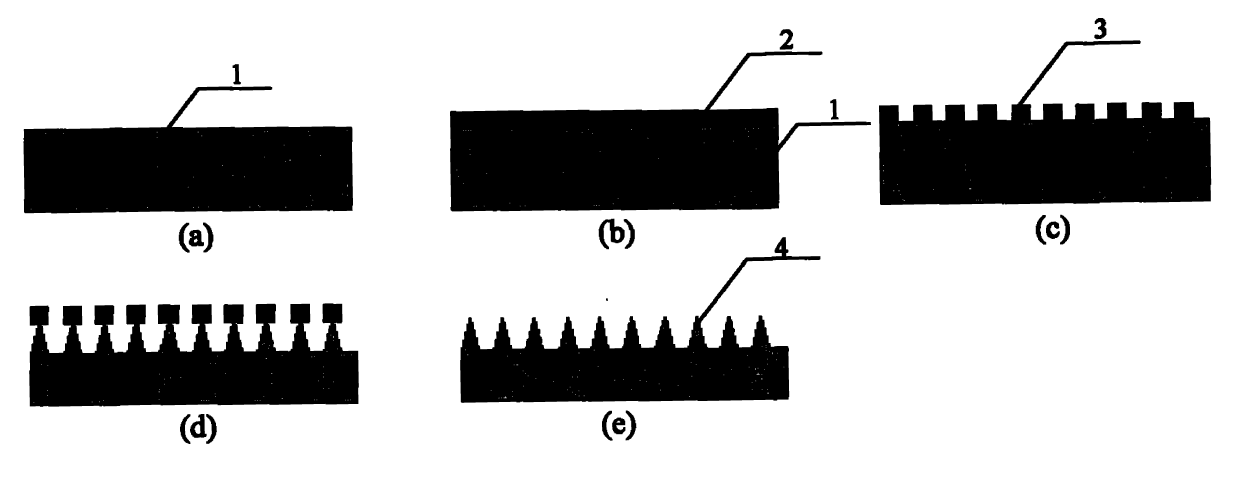

Method for preparing high-density super sharp silicon probe array

The invention provides a method for preparing a high-density super sharp silicon probe (tip) array by directly taking a hydrogen silsesquioxane (HSQ) electron beam resist as an etching mask. The hydrogen silsesquioxane (HSQ) electron beam resist is exposed by an electron beam photoetching method, and then developed to form a raster graphics of the HSQ; the silicon is subjected to isotropic etching by directly taking the HSQ as the mask; by controlling the etching conditions, the probe tip can be sharpest and the HSQ is about to fall off or automatically falls off simultaneously; the probe tip can reach several nanometers; and the additional oxidation, corrosion and other sharpening process are not needed, so the method is very simple. The method overcomes the inconvenience that the traditional preparation method needs an oxide layer to serve as a mask for secondary graphic transfer and requires additional oxidation and etching processes to sharpen the probe, and overcomes the difficulty in preparing submicron-period high-density silicon probe array, and can easily prepare the silicon probe array with the density more than 2.5*107 / mm<2>.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI +2

Preparation method for nanoscale negative structure with high depth-to-width ratio and high conformality

InactiveCN107857236AHigh aspect ratioHigh dimensional accuracySpecific nanostructure formationNanomedicineEtchingMetallic materials

The invention discloses a preparation method for a nanoscale negative structure with high depth-to-width ratio and high conformality. The preparation method comprises the following steps: spin-coatinga layer of hydrogen silsesquioxane (HSQ) onto a provided substrate by using a spin-coating process; subjecting a sample to exposing and developing by utilizing an electron beam exposure technology soas to obtain an expected HSQ columnar nanostructure; conformally depositing a layer of a functional material film onto the sample by utilizing a magnetron sputtering film-coating deposition technology; spin-coating a planarized layer of HSQ onto the magnetron-sputtered sample by utilizing a spin-coating manner; then placing the sample onto a hot plate, and carrying out baking at a low temperatureso as to remove a solvent in a planarized material; subjecting the sample to polishing treatment with an included angle less than 10 degrees by utilizing a beveling ion beam polishing device until ametal material on the upper surface of an HSQ column is completely removed; and treating the sample with hydrofluoric acid through wet etching for removal of an HSQ columnar structure so as to obtaina nanoscale negative structure with high depth-to-width ratio and high conformality required by the invention.

Owner:HUNAN UNIV

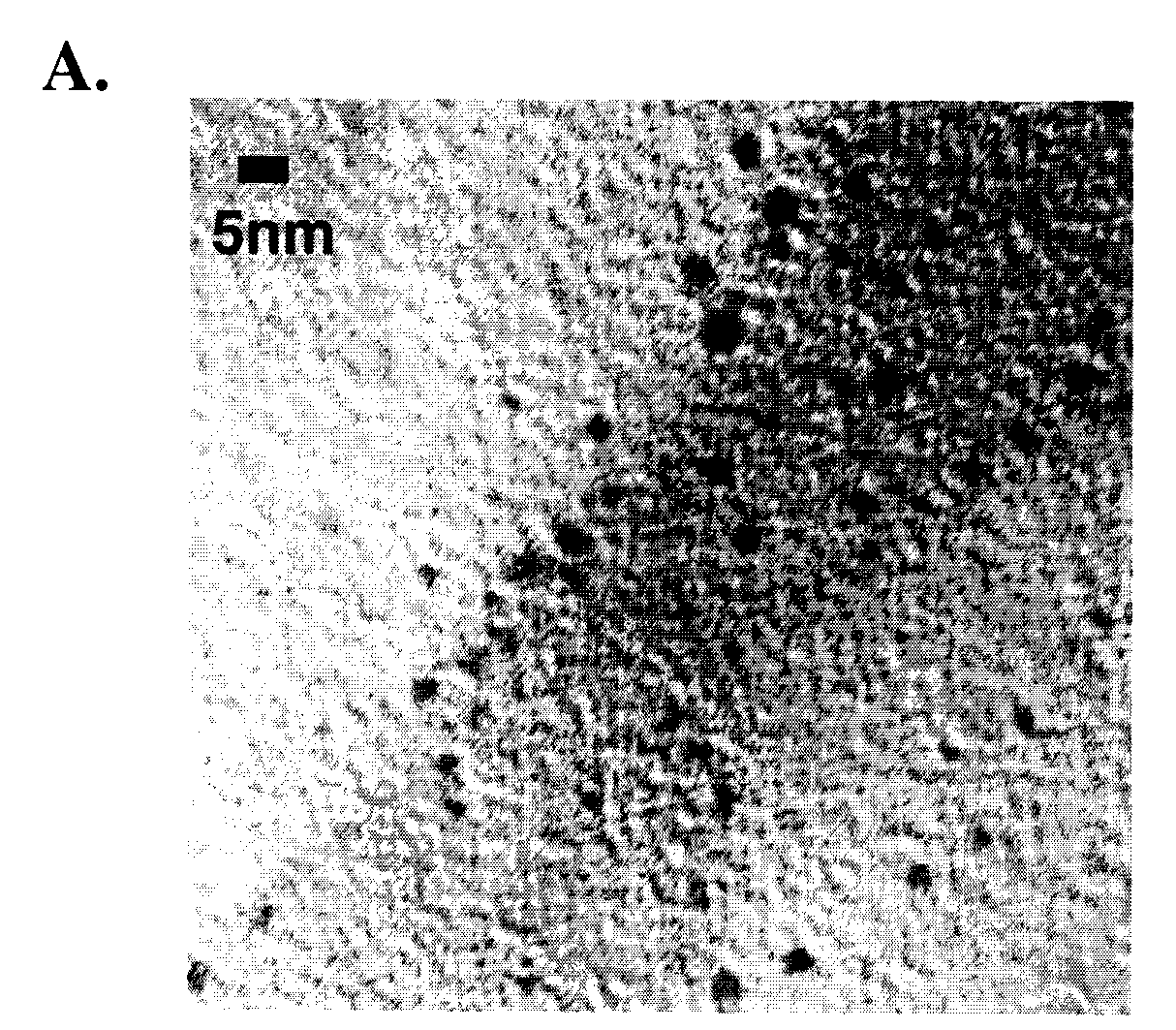

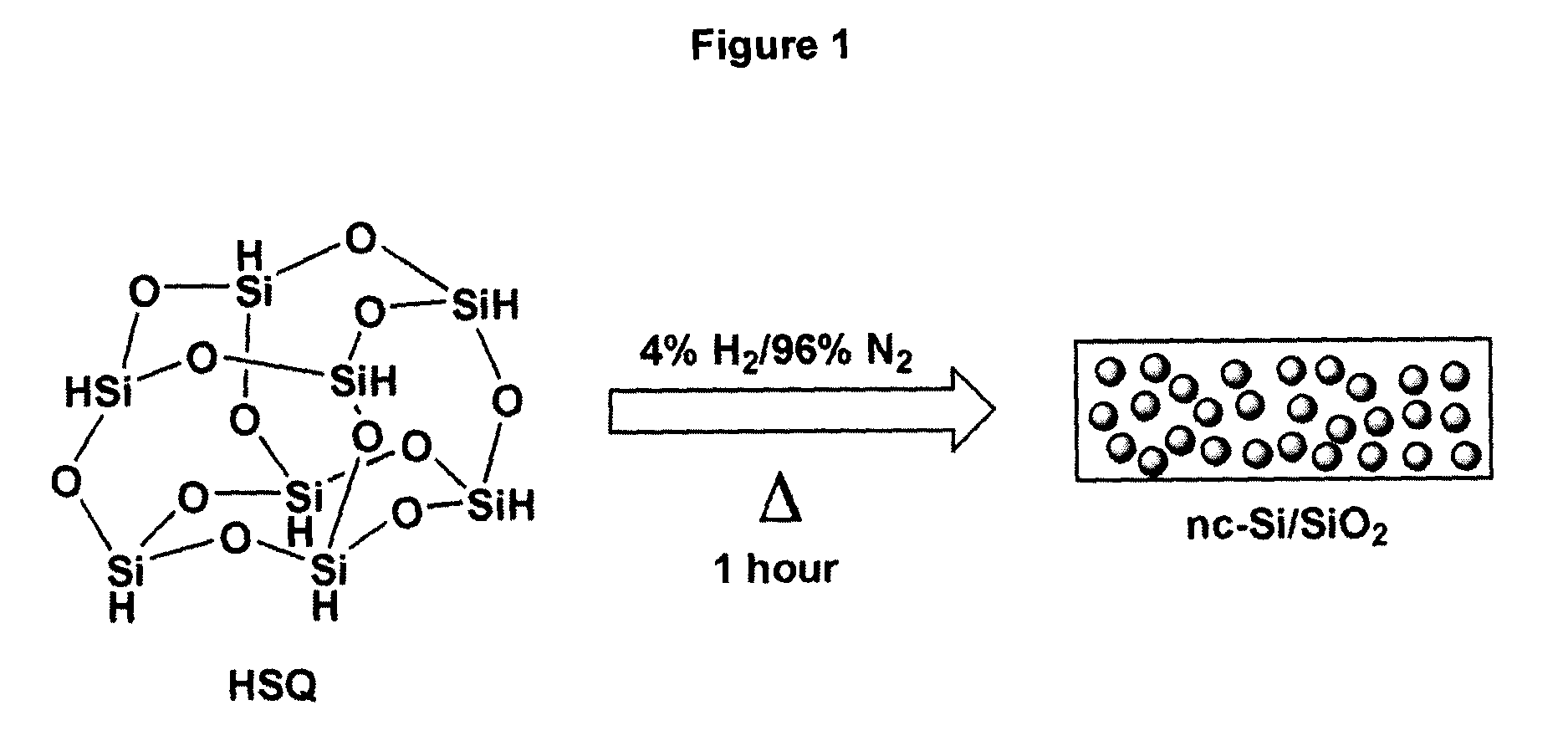

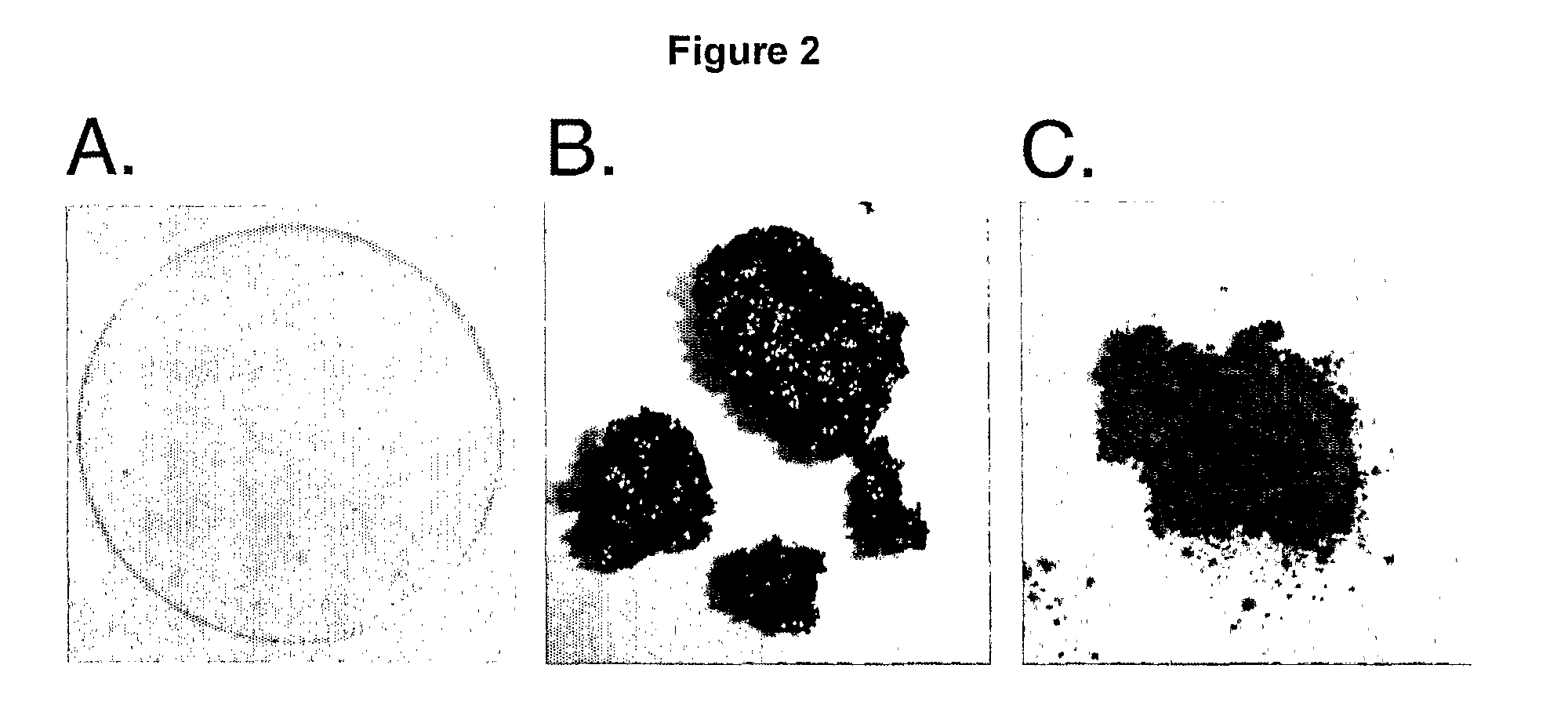

Method for preparing nanocrystalline silicon in sio2 and freestanding silicon nanoparticles

ActiveUS20090117392A1Nanostructure manufactureDecorative surface effectsAcid etchingNanocrystalline silicon

Methods for preparing nanocrystalline-Si / SiO2 composites by treating hydrogen silsesquioxane (HSQ) under reductive thermal curing conditions are described. Also described are methods of preparing silicon nanoparticles by acid etching the nanocrystalline-Si / SiO2 composites.

Owner:THE GOVERNORS OF THE UNIV OF ALBERTA

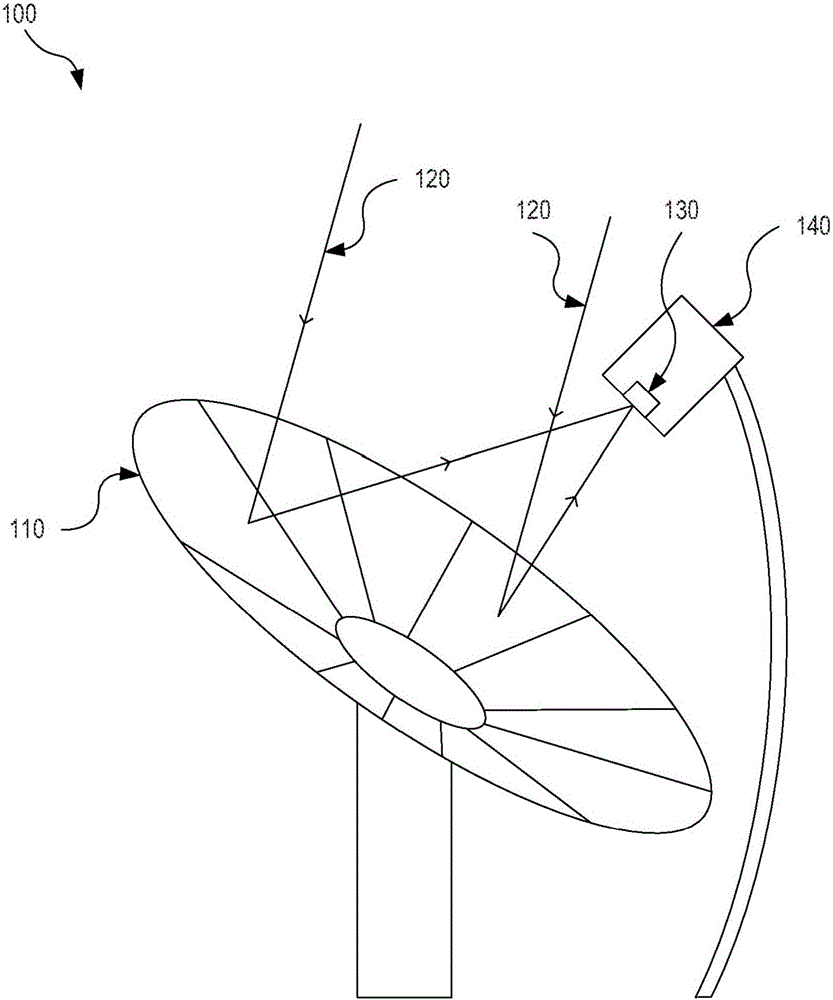

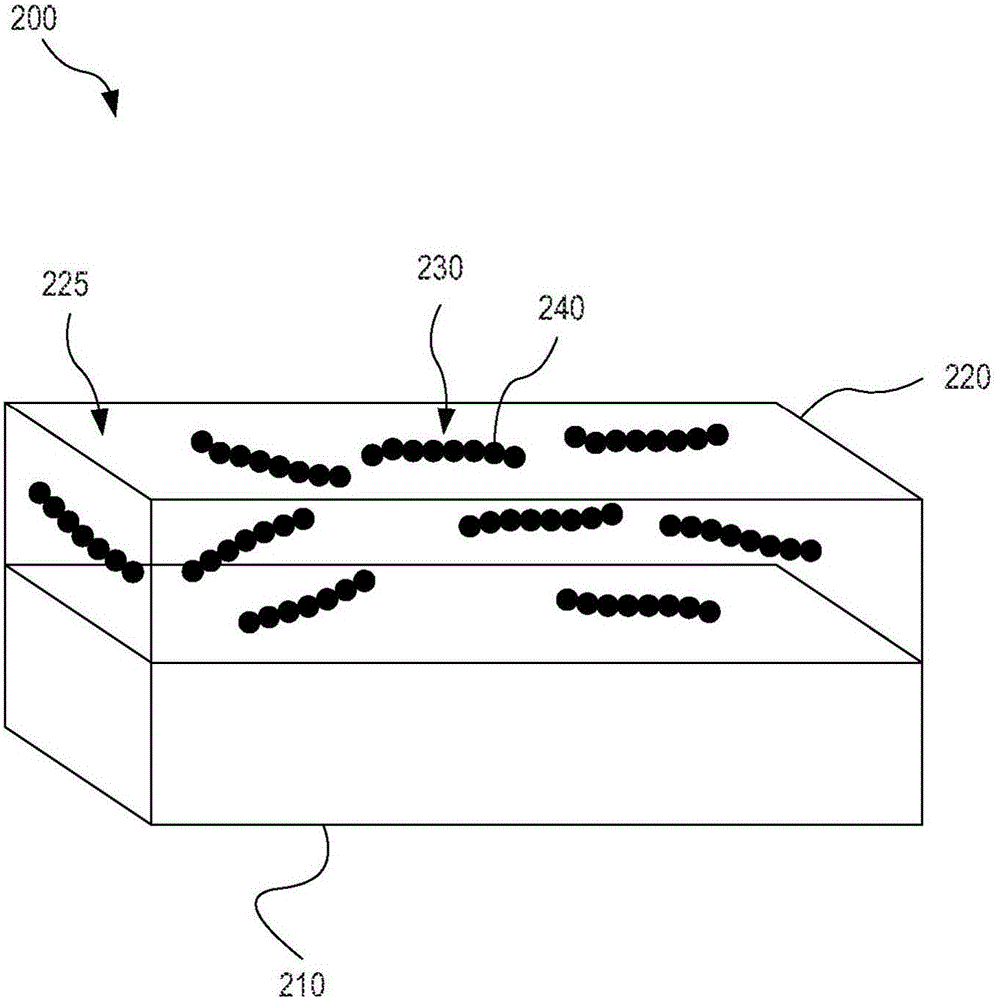

Systems and methods using metal nanostructures in spectrally selective absorbers

Solution-processed Ni nanochain-SiOx (x<2) and Ni nanochain-SiO2 selective solar thermal absorbers that exhibit a strong anti-oxidation behavior up to 600 degrees centigrade in air. The thermal stability is far superior to Ni nanoparticle-Al2O3 selective solar thermal absorbers. The SiOx (x<2) and SiO2 matrices are derived from hydrogen silsesquioxane (HSQ) and tetraethyl orthosilicate (TEOS) precursors, respectively. We find that both the excess Si and the stoichiometric SiO2 matrix contribute to antioxidation behavior. Methods of making the selective solar thermal absorbers are described. A system, and method of manufacture of the system, for spectrally selective radiation absorption includes a matrix that includes metal nanostructures, each metal nanostructure having spectrally selective radiation absorption properties, such that the matrix reflects a majority of light incident thereupon for wavelengths greater than a cutoff wavelength and absorbs a majority of light incident thereupon for wavelengths smaller than the cutoff wavelength.

Owner:达特茅斯学院托管理事会

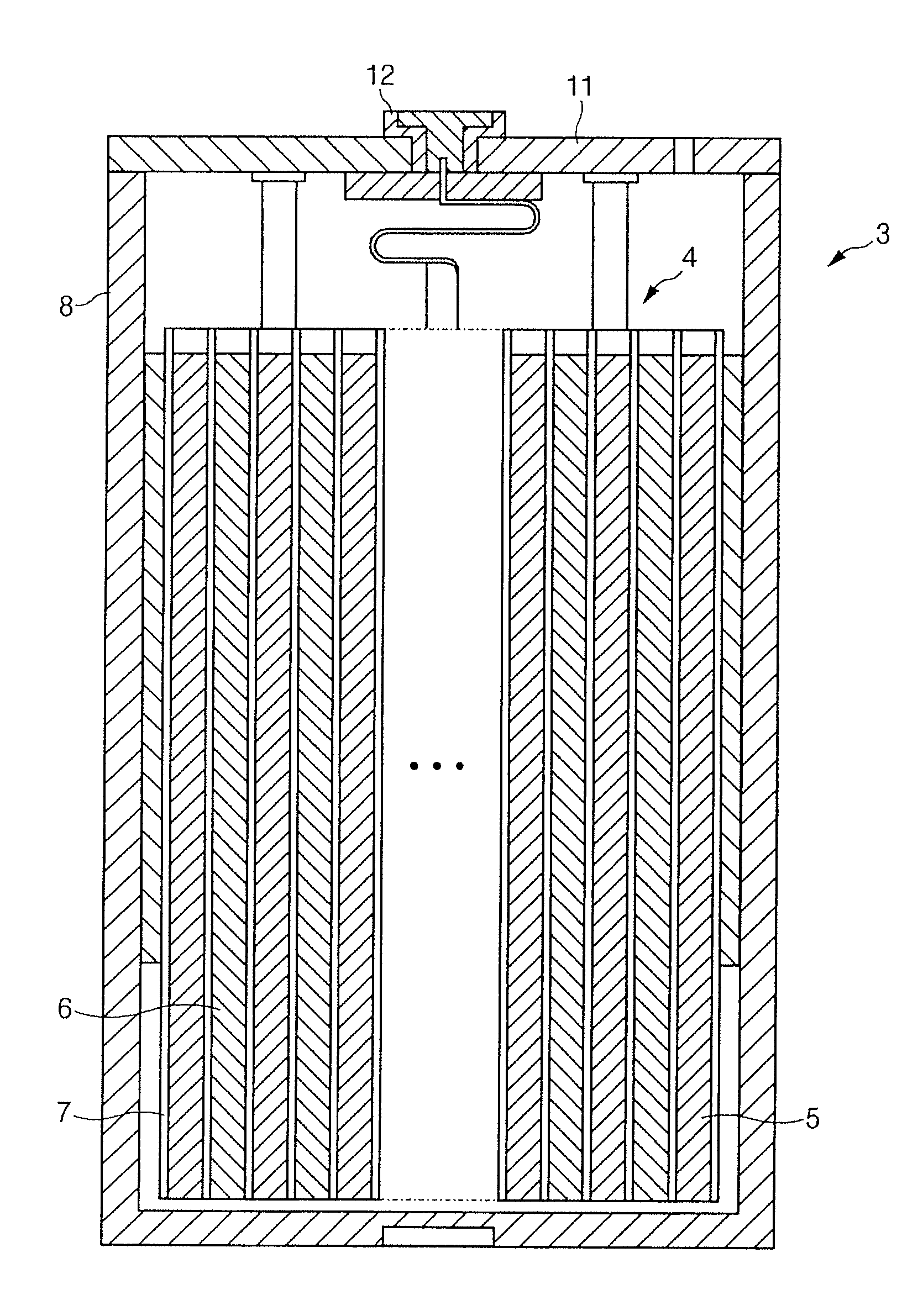

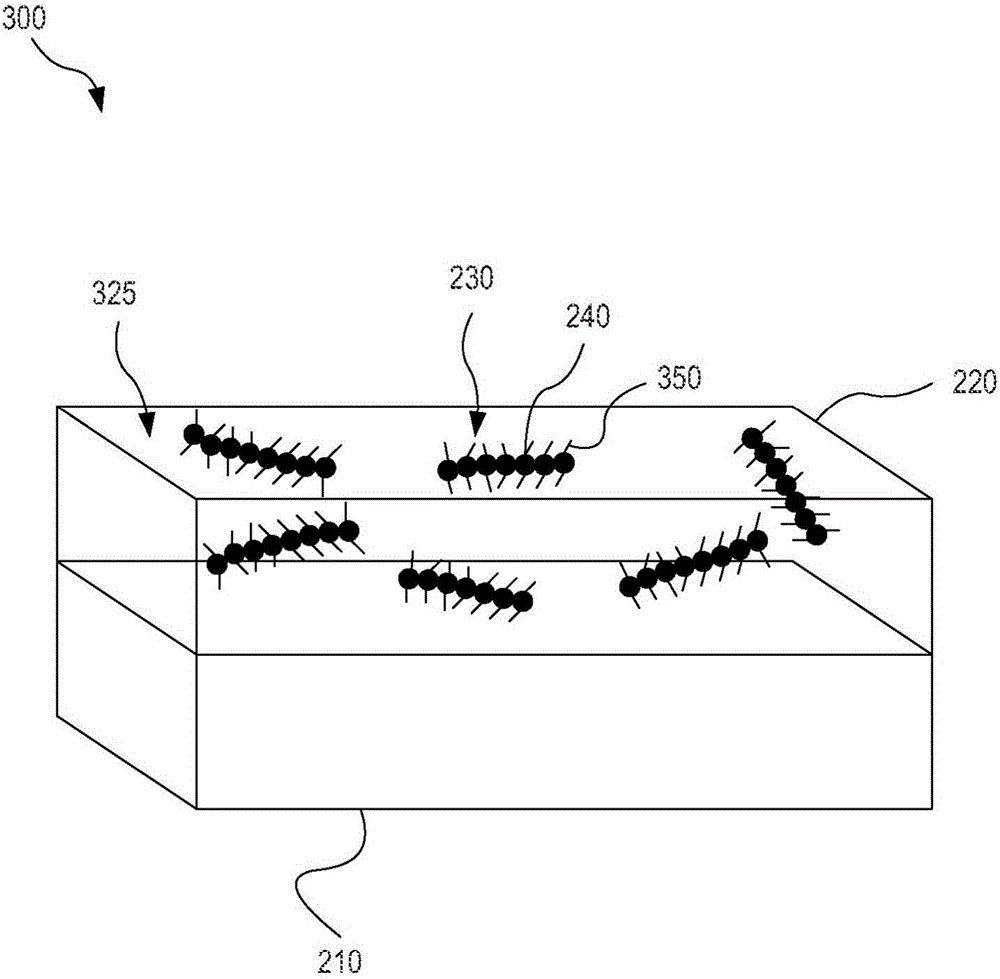

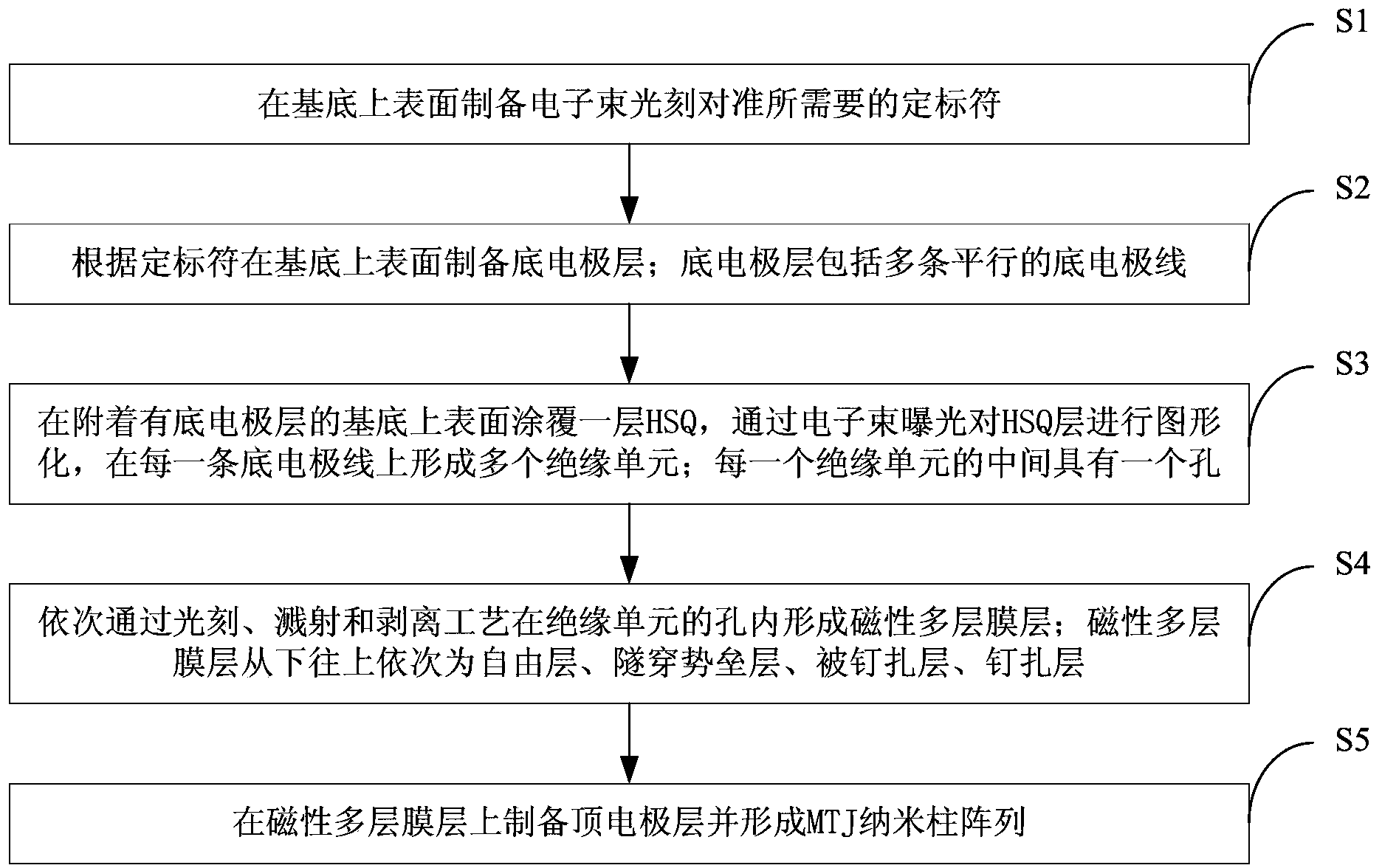

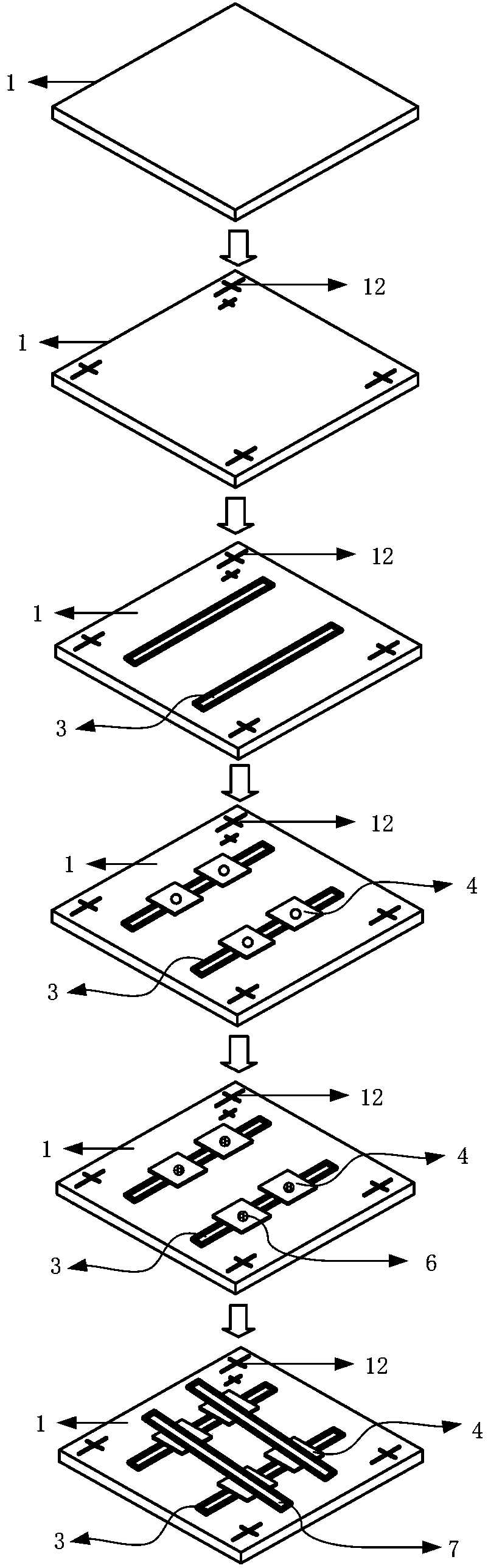

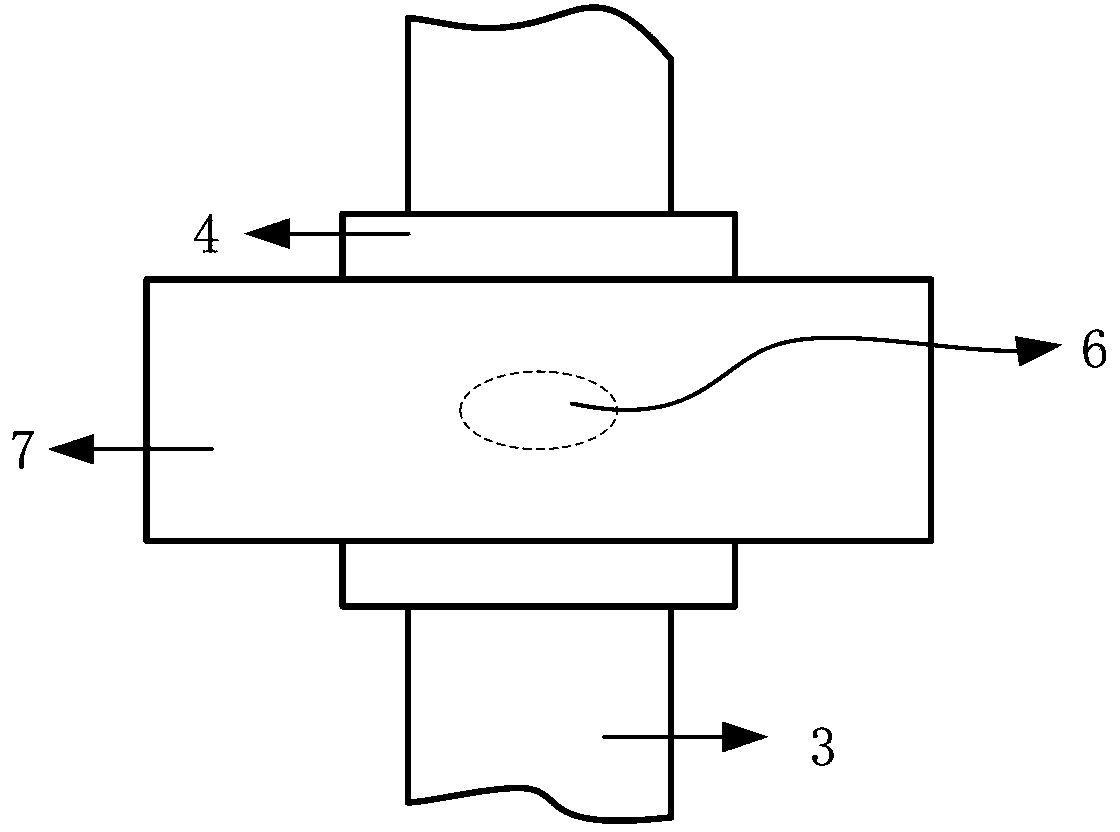

Method for preparing magnetic tunnel junction (MTJ) nano column array

ActiveCN103359683AStable mechanical propertiesIncreased etch resistanceDecorative surface effectsChemical vapor deposition coatingInsulation layerLithography process

The invention discloses a method for preparing a magnetic tunnel junction (MTJ) nano column array. The method comprises the following steps of: (1) preparing a calibrator required for electron beam lithography alignment on the surface of a substrate; (2) preparing a bottom electrode layer on the upper surface of the substrate according to the calibrator, wherein the bottom electrode layer comprises a plurality of parallel bottom electrode lines; (3) coating a hydrogen silsesquioxane (HSQ) layer on the upper surface of the substrate to which the bottom electrode layer is attached, imaging the HSQ layer through electron beam exposure, and forming a plurality of insulation units on each bottom electrode line, wherein a hole is formed in the middle of each insulation unit; (4) forming a magnetic multi-layer film layer in the hole of each insulation unit sequentially through a lithography process, a sputtering process and a peeling process, wherein each magnetic multi-layer film layer sequentially comprises a free layer, a tunneling barrier layer, a pinned layer and a pinning layer from bottom to top; (5) preparing a top electrode layer on each magnetic multi-layer film layer and forming the MTJ nano column array. An insulation layer is formed by the electron beam exposure of HSQ, so that process steps are simplified, the cost is greatly reduced, and process errors are reduced.

Owner:HUAZHONG UNIV OF SCI & TECH

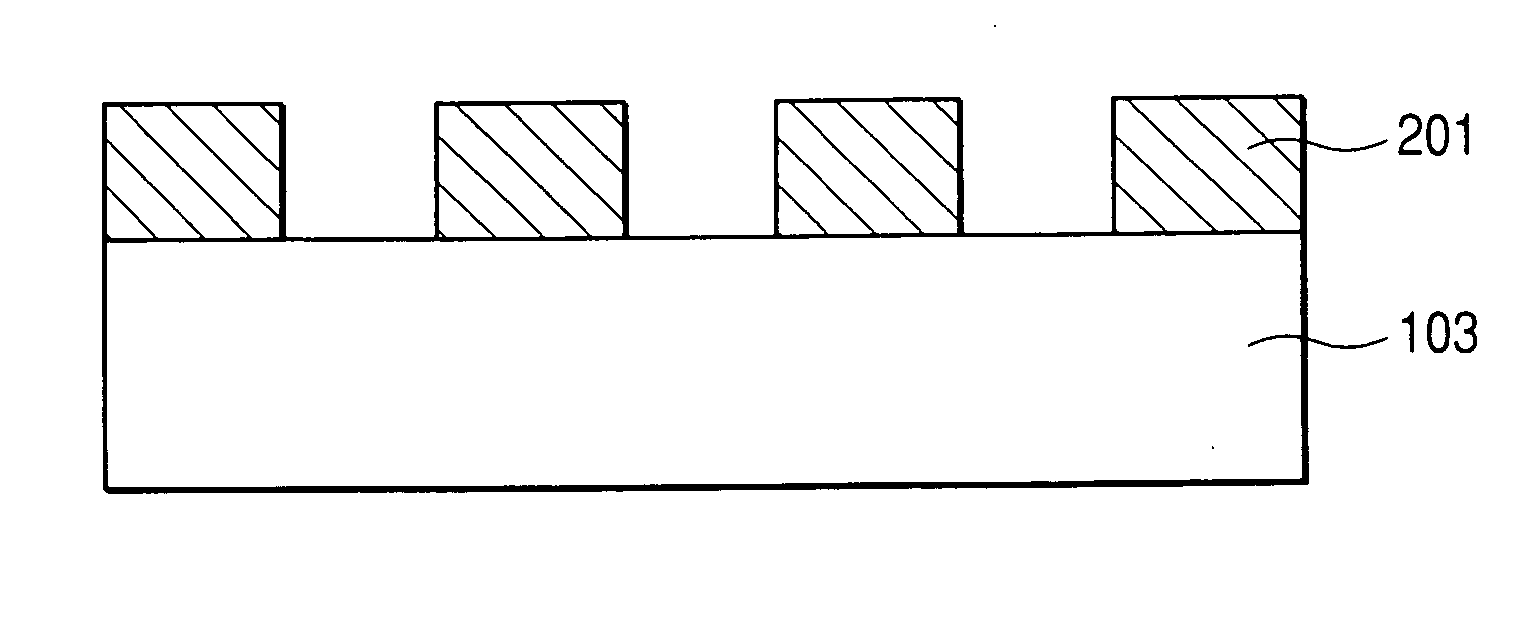

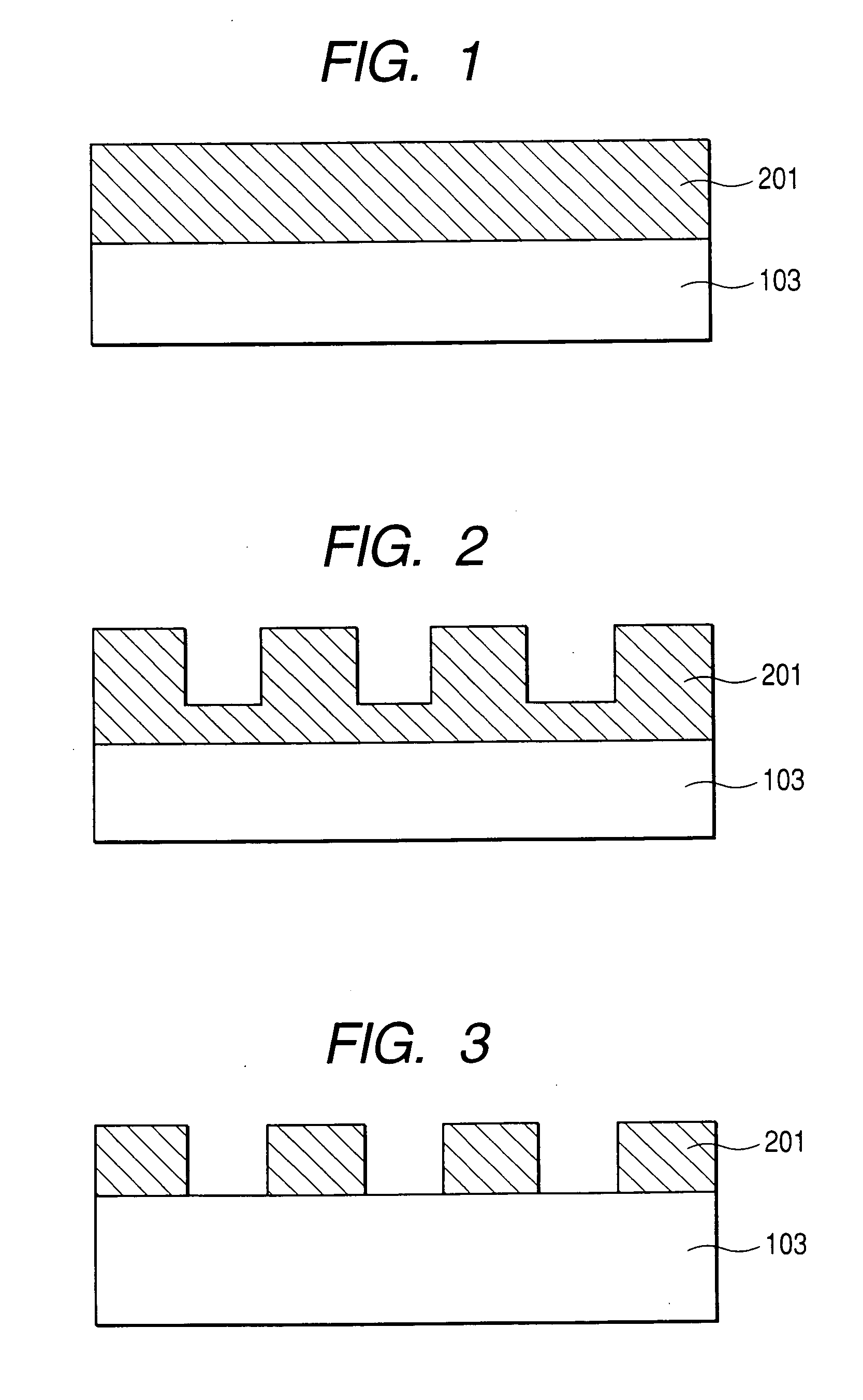

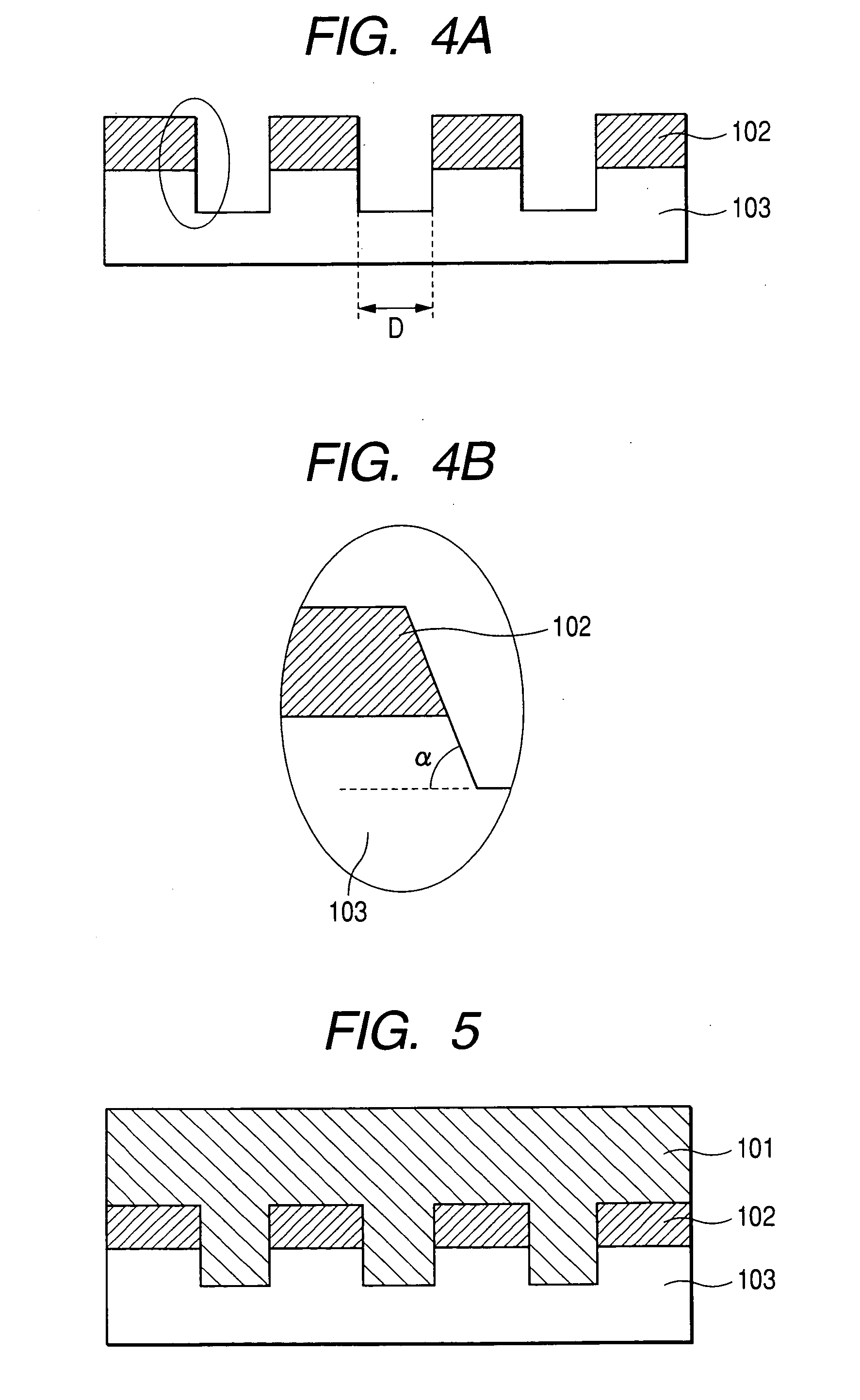

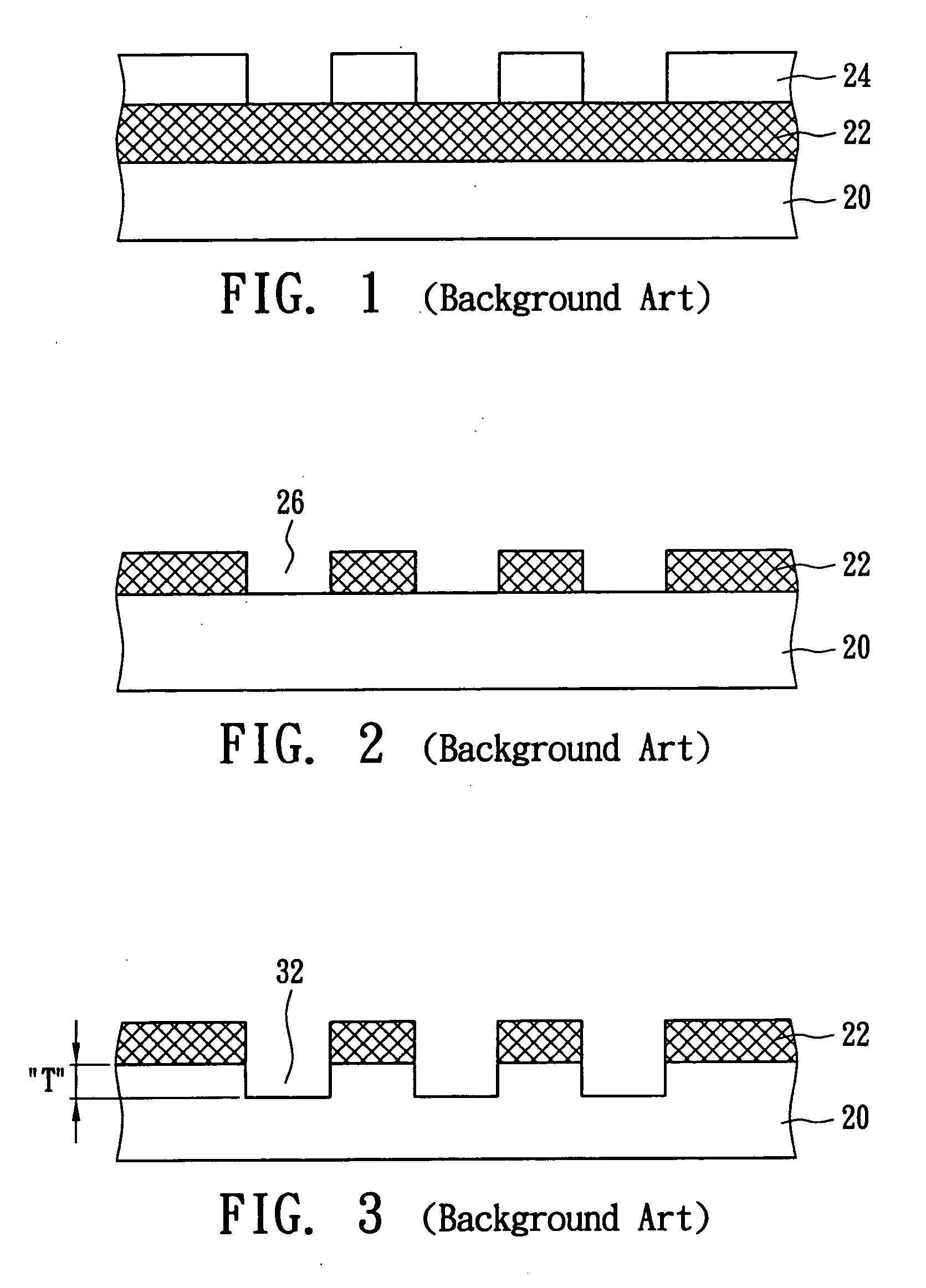

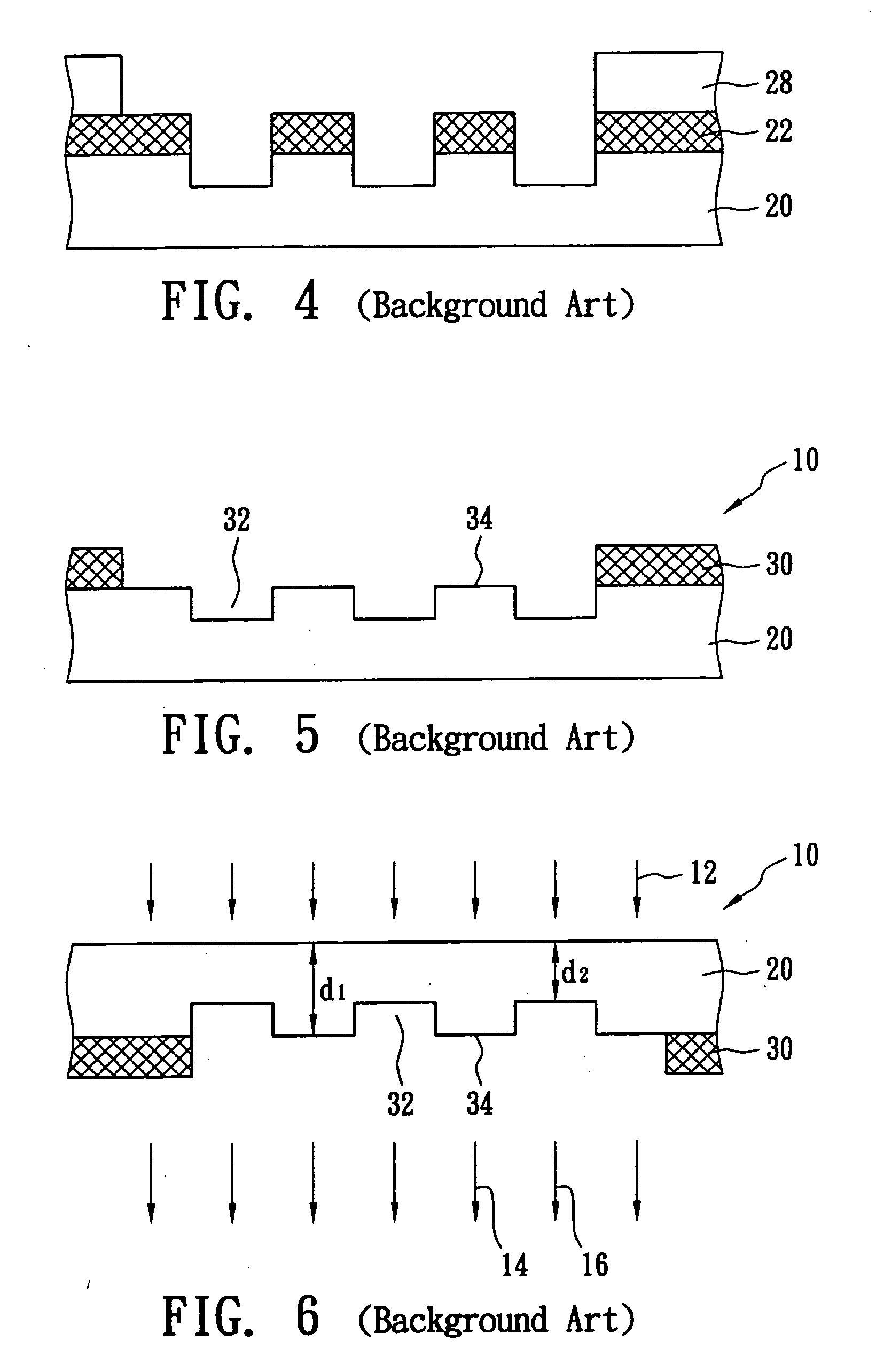

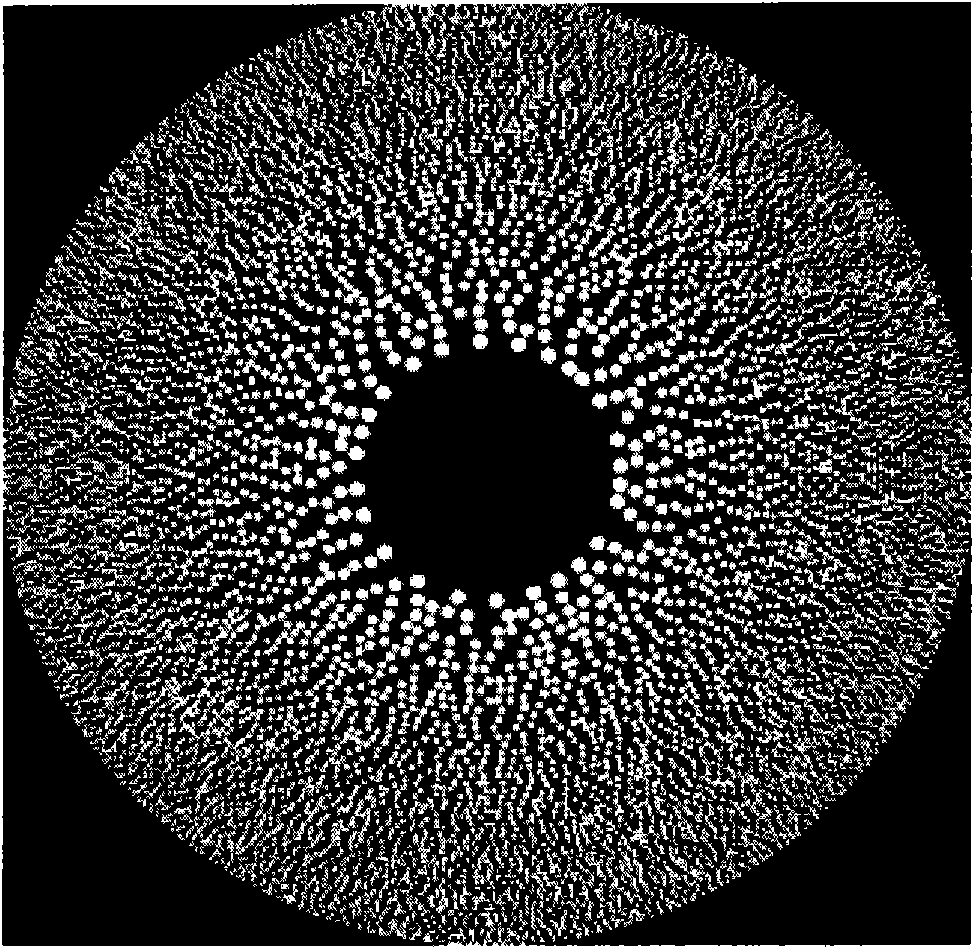

Phase-shifting mask

InactiveUS20070087271A1Increase mask throughputEliminate phase error problemPhotomechanical apparatusOriginals for photomechanical treatmentPresent methodEngineering

The present phase-shifting mask comprises a substrate and a plurality of phase-shifting patterns made of polymer material and positioned on the substrate in an array manner. Preferably, the space between phase-shifting patterns is smaller than the width of the phase-shifting pattern along a first direction, and the space between two line-shaped patterns consisting of phase-shifting patterns is substantially equal to the width of the line-shaped pattern along a second direction perpendicular to the first direction. The present method for preparing the phase-shifting mask comprises steps of forming a polymer layer on a substrate, changing the molecular structure the polymer layer in a plurality of predetermined regions, and removing a portion of the polymer layer outside these predetermined regions. The polymer layer can be made of hydrogen silsesquioxane, methylsilsesquioxane or hybrid organic siloxane polymer.

Owner:PROMOS TECH INC

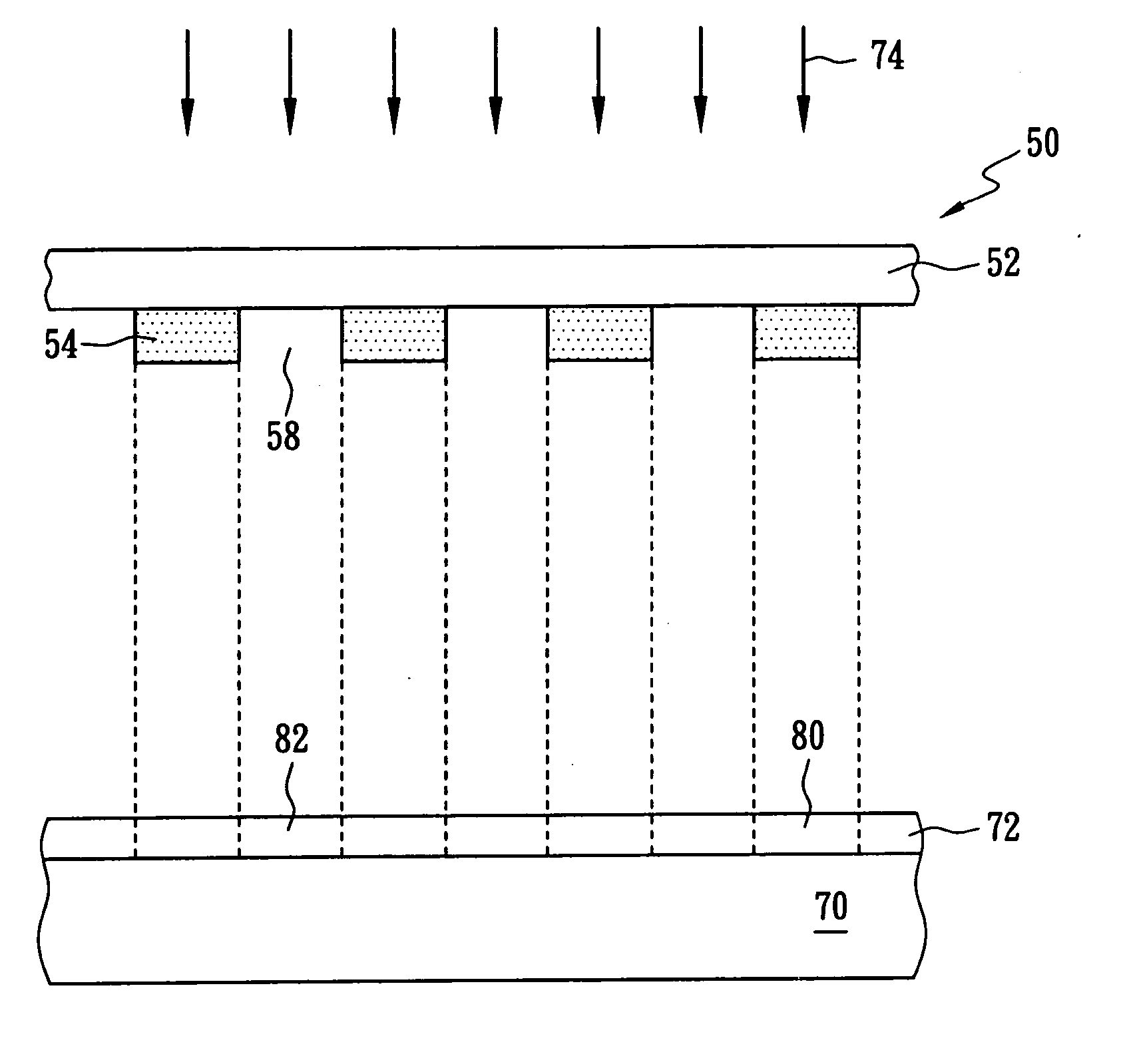

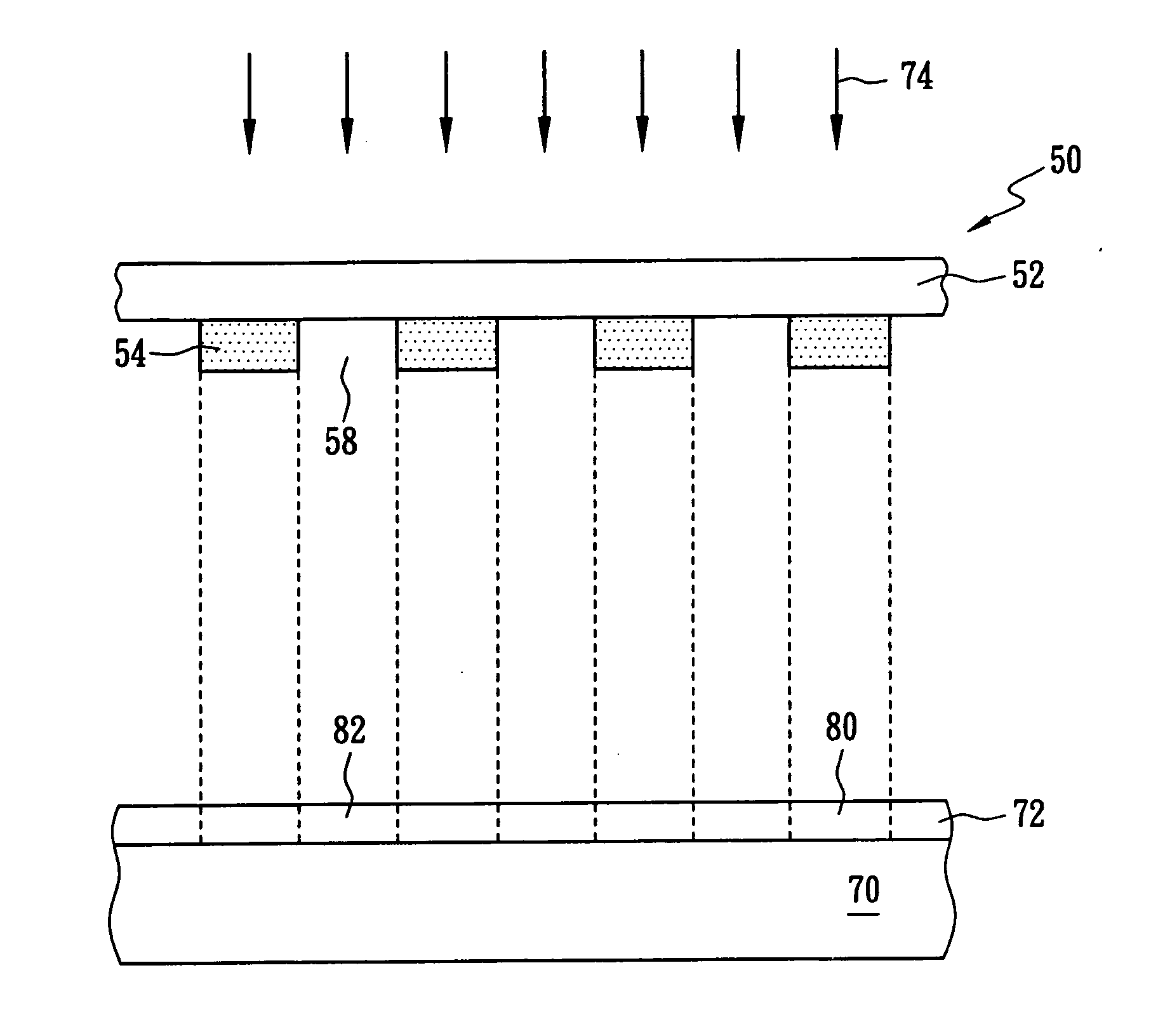

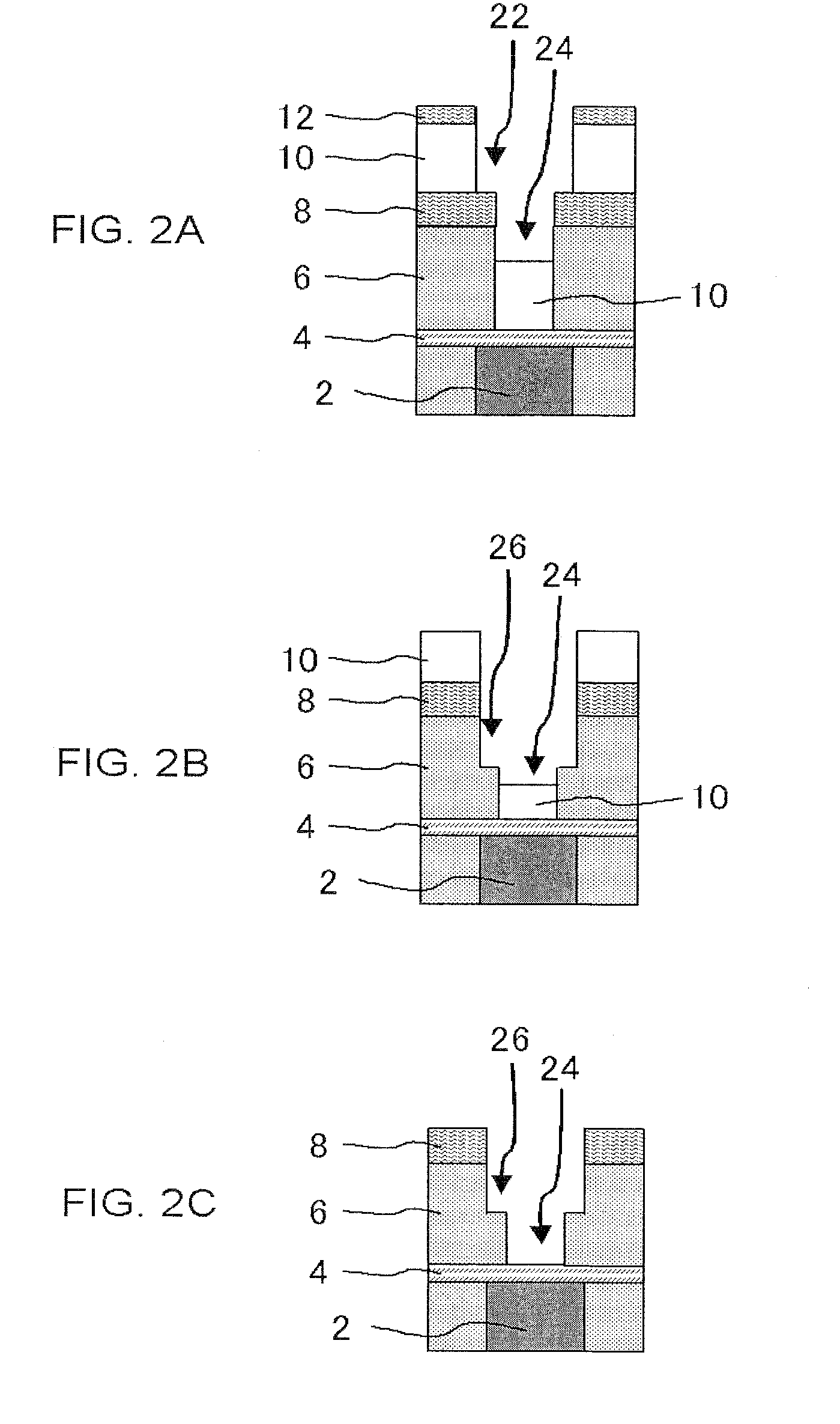

Method for preparing a phase-shifting mask and method for preparing a semiconductor device using the phase-shifting mask

InactiveUS20070087272A1Increase mask throughputEliminate phase error problemPhotomechanical apparatusOriginals for photomechanical treatmentPresent methodDevice material

A phase-shifting mask comprises a substrate and a plurality of phase-shifting patterns made of polymer material and positioned on the substrate in an array manner. Preferably, the space between phase-shifting patterns is smaller than the width of the phase-shifting pattern along a first direction, and the space between two line-shaped patterns consisting of phase-shifting patterns is substantially equal to the width of the line-shaped pattern along a second direction perpendicular to the first direction. The present method for preparing the phase-shifting mask comprises steps of forming a polymer layer on a substrate, changing the molecular structure the polymer layer in a plurality of predetermined regions, and removing a portion of the polymer layer outside these predetermined regions. The polymer layer can be made of hydrogen silsesquioxane, methylsilsesquioxane or hybrid organic siloxane polymer.

Owner:PROMOS TECH INC

Method of manufacturing a semiconductor device

InactiveUS20080057727A1Increase resistanceImprove an etching gradeSemiconductor/solid-state device manufacturingDevice materialNitrogen

Method of manufacturing a semiconductor device including arranging a substrate having a stacked film containing a first insulating film and a second insulating film formed thereon in an etching equipment, etching the first and second insulating film in the etching equipment, the first insulating film comprised of a nitrogen-containing film, and the second insulating film comprised of one or more kinds of films selected from a group consisting of an SiOCH film, an SiO2 film, a methyl silsesquioxane film, a hydrogen silsesquioxane film and a methyl hydrogen silsesquioxane film, while using as etching gas (a) gas including fluorocarbon represented by CxFy (x: an integer from 1 to 6, and y: an integer from 4 to 12), or (b) mixed gas of the fluorocarbon and one or more kinds of gas selected from a group consisting of O2, Ar and CO.

Owner:RENESAS ELECTRONICS CORP

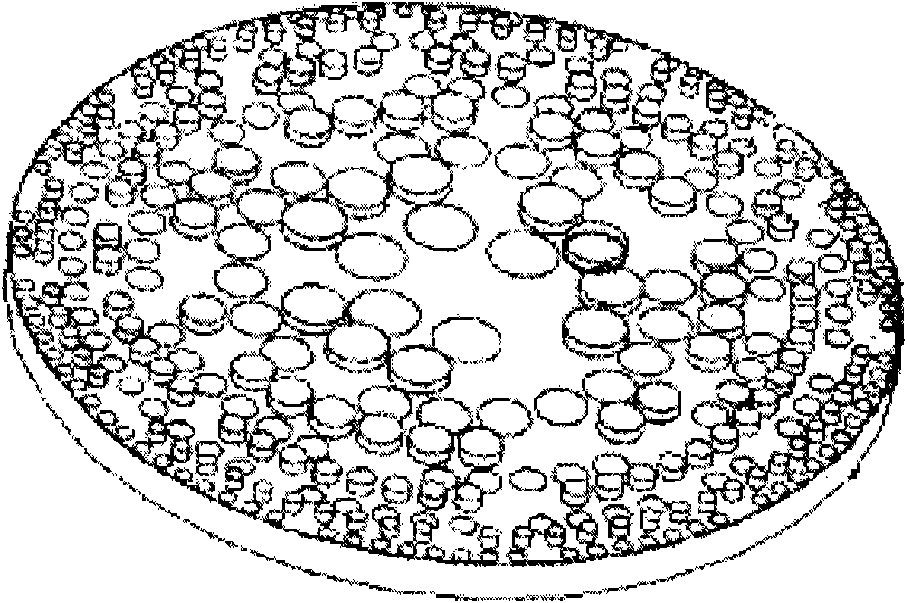

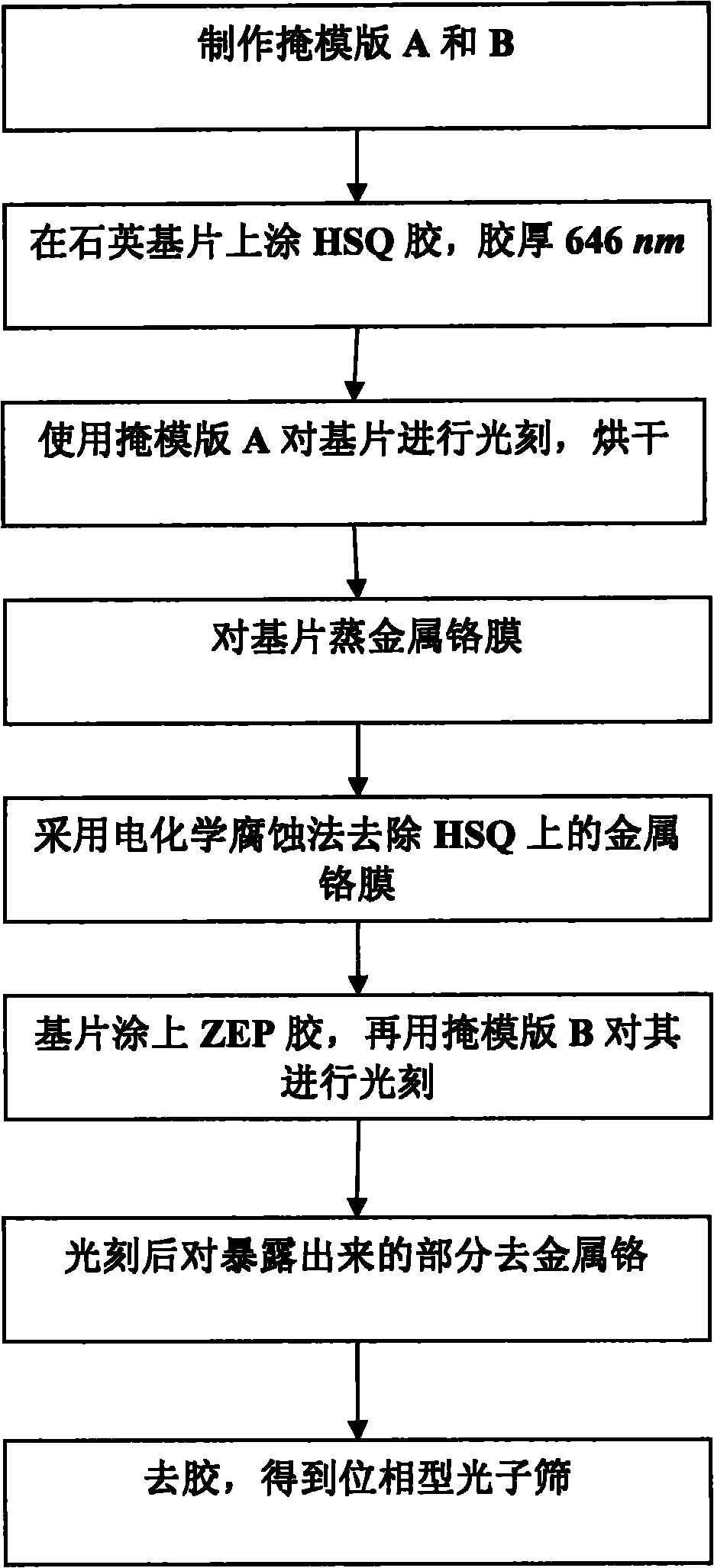

Method for manufacturing topological type binary diffractive optical element through HSQ (hydrogen silsesquioxane) process

InactiveCN102313917AHigh diffraction efficiencyAchieve preparationDiffraction gratingsEtchingImage resolution

The invention discloses a method for manufacturing a topological type binary diffractive optical element through an HSQ (hydrogen silsesquioxane) process, which comprises: A, preparing a mask plate of the binary diffractive optical element; B, coating hydrogen silsesquioxane glue on a substrate, photoetching the substrate with the mask plate, drying, and steaming a metal film; C, selectively removing the metal film on the substrate via electrochemical corrosion; and D, drying the substrate, and thus obtaining the topological type binary diffractive optical element. Compared with the traditional etching method, the invention has the advantages that the manufacturing process is simple, the cost is low, the stability is good, higher resolution can be achieved, and the large-scale promotion and application of the method can be facilitated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

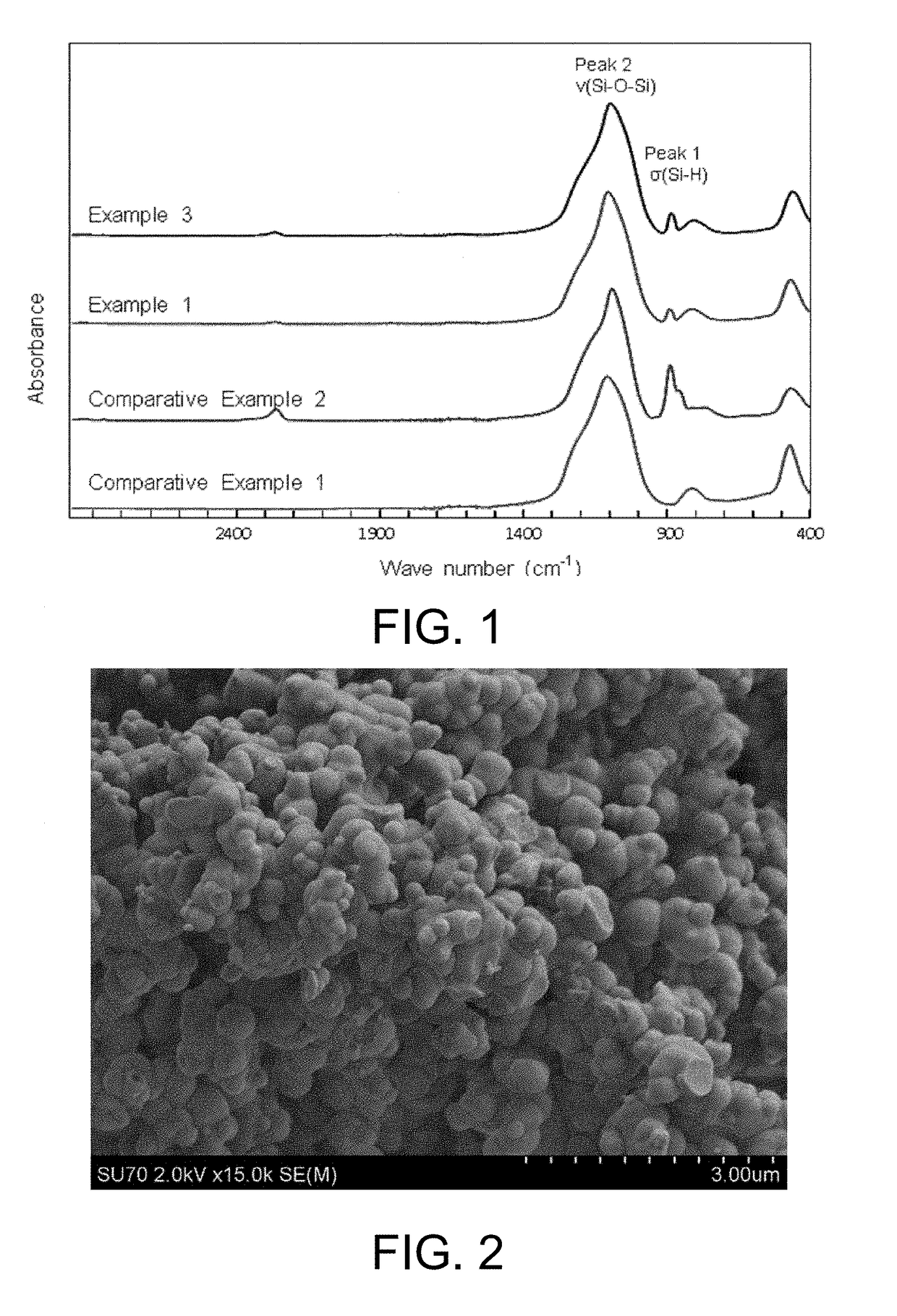

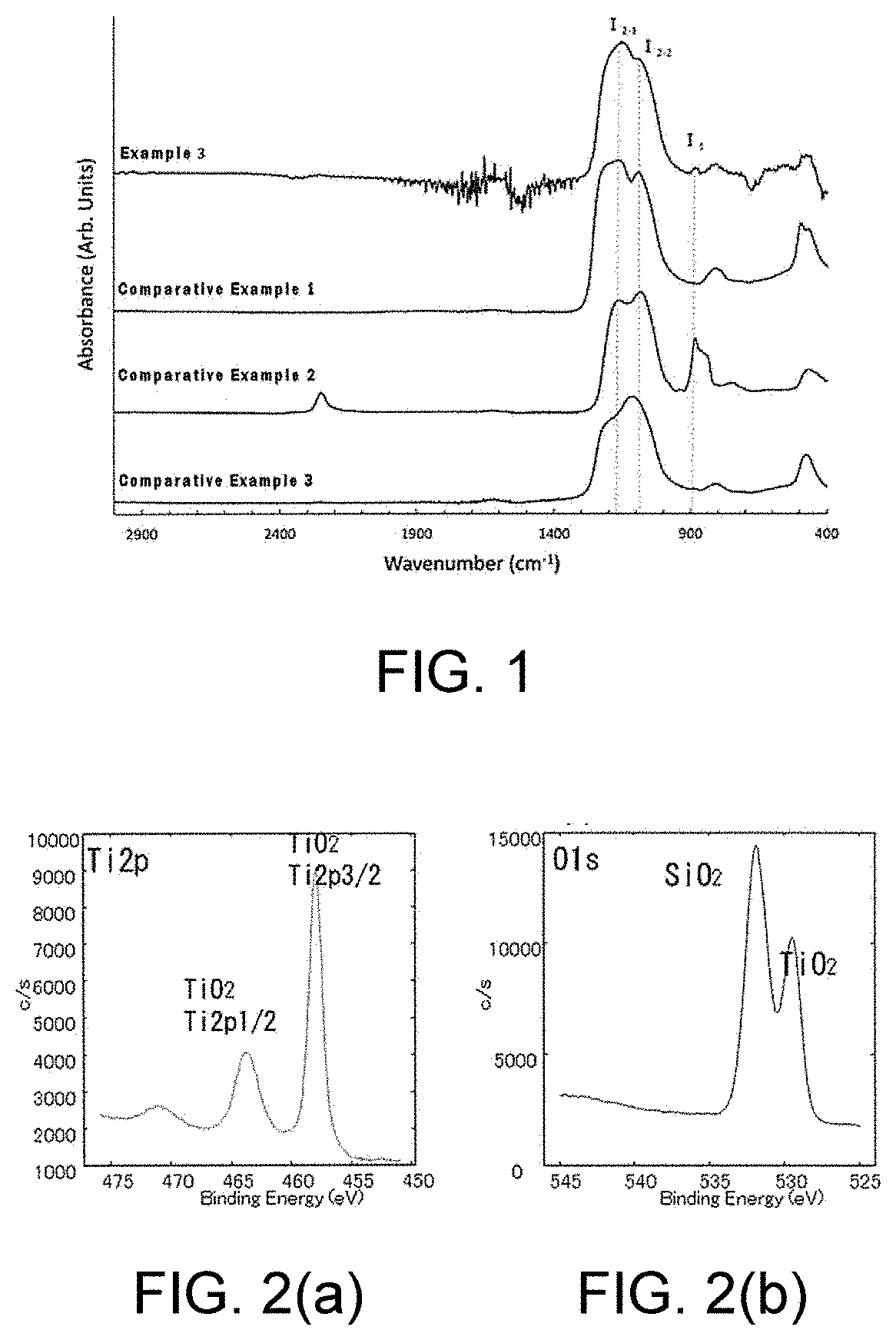

Negative electrode active material for lithium ion secondary battery and method for producing same

ActiveUS20180212228A1Low costImprove charge and discharge performanceSilicaCell seperators/membranes/diaphragms/spacersLithiumHydrogen

A negative electrode active material for the lithium ion secondary battery contains silicon oxide that is obtained by heat-treating, under an inert gas atmosphere, a hydrogen silsesquioxane polymer (HPSQ) obtained by allowing hydrolysis of a silicon compound represented by formula (1) and then a condensation reaction of the resulting material, contains Si, O and H, and has, in an infrared spectrum, a ratio (I1 / I2) in the range of 0.01 to 0.35 with regard to intensity (I1) of peak 1 at 820 to 920 cm−1 due to a Si—H bond to intensity (I2) of peak 2 at 1000 to 1200 cm−1 due to a Si—O—Si bond, and is represented by general formula SiOxHy (1<x<1.8, 0.01<y<0.4): HSi(R)3 (1), in which R is groups selected from hydrogen, alkoxy having 1 to 10 carbons and the like.

Owner:JNC CORP +1

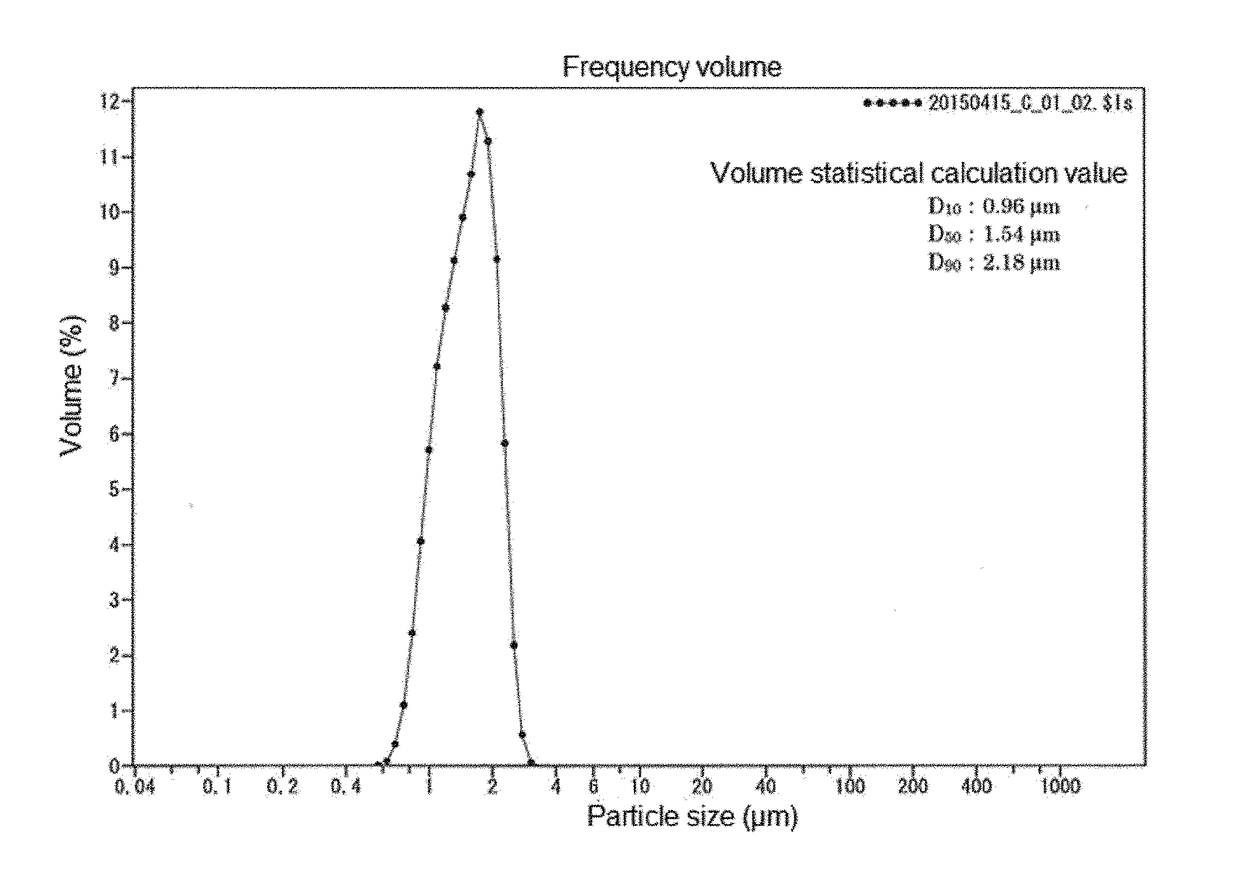

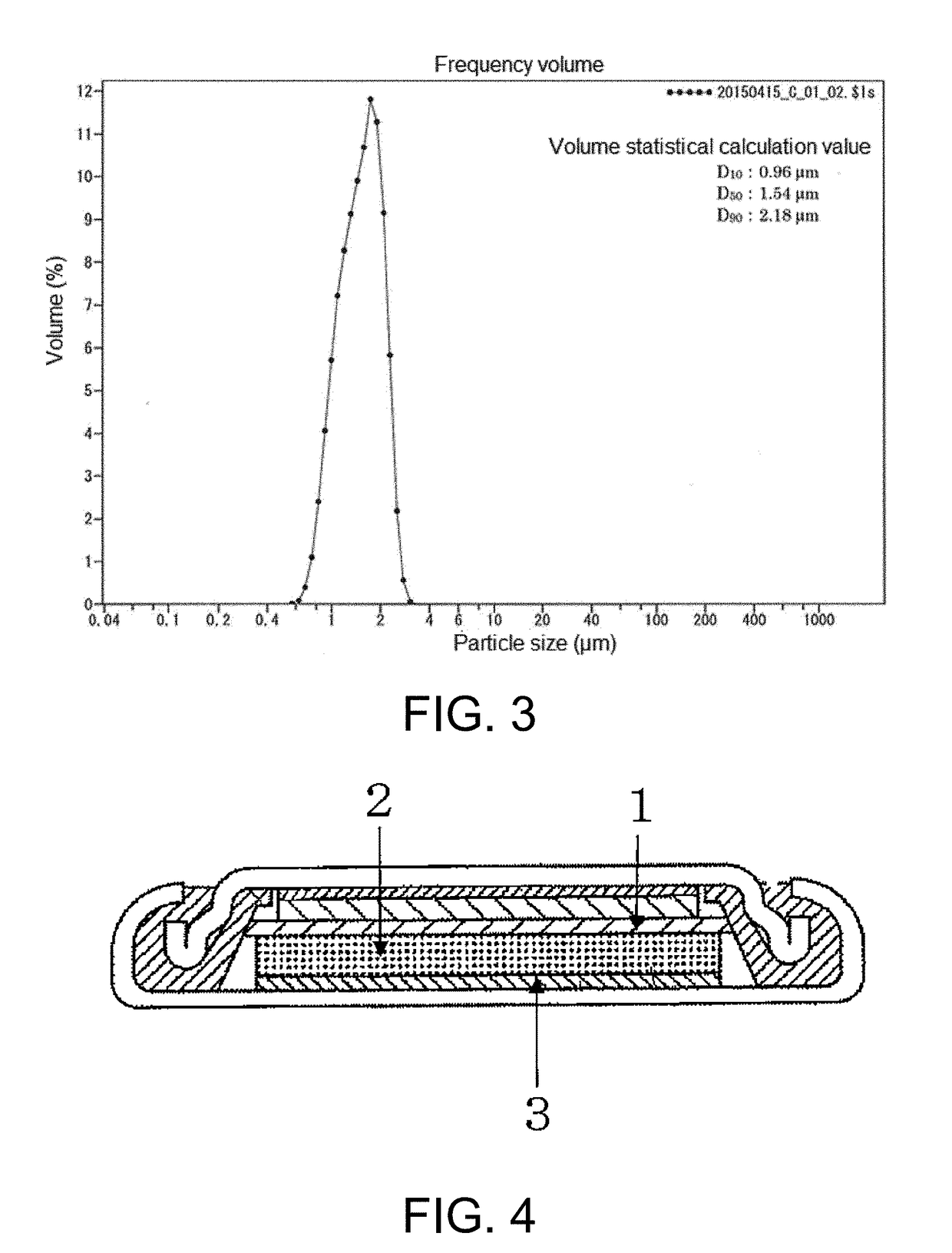

Silicon nanoparticle-containing hydrogen polysilsesquioxane calcined product-metal oxide complex and production method thereof, negative electrode active material for lithium ion battery, negative electrode for the lithium ion battery and lithium ion battery

ActiveUS20190363353A1High rate charge/discharge propertiesIncrease capacitySiliconNegative electrodesSilicon oxideLithium-ion battery

A silicon nanoparticle-containing hydrogen polysilsesquioxane sintered product-metal oxide complex comprising a silicon nanoparticle-containing hydrogen polysilsesquioxane sintered product and a metal oxide, wherein the silicon nanoparticle-containing hydrogen polysilsesquioxane sintered product contains 5 wt % to 95 wt % of silicon nanoparticles having a volume-based mean particle size of more than 10 nm but less than 500 nm, and a hydrogen polysilsesquioxane-derived silicon oxide structure that coats the silicon nanoparticles and is chemically bonded to the surfaces of the silicon nanoparticles. The silicon nanoparticle-containing hydrogen polysilsesquioxane sintered product is represented by the general formula SiOxHy (0.01<x<1.35, 0<y<0.35) and has Si—H bonds. The metal oxide consists of one or more metals selected from titanium, zinc, zirconium, aluminum, and iron.

Owner:JNC CORP +1

Method of curing hydrogen silses quioxane and densification in nano-scale trenches

InactiveCN101185160ASemiconductor/solid-state device manufacturingNanotechnologyHydrogenSilsesquioxane

Trenches in a semiconductor substrate are filled by (i) dispensing a film forming material on the semiconductor substrate and into the trenches; (ii) curing the dispensed film forming material in the presence of an oxidant at a first low temperature for a first predetermined period of time; (iii) curing the dispensed film forming material in the presence of an oxidant at a second low temperature for a second predetermined period of time; (iv) curing the dispensed film forming material in the presence of an oxidant at a third high temperature for a third predetermined period of time; and (v) forming filled oxide trenches in the semiconductor substrate. The film forming material is hydrogen silsesquioxane.

Owner:DOW CORNING CORP

Method for bonding and interconnecting semiconductor chips

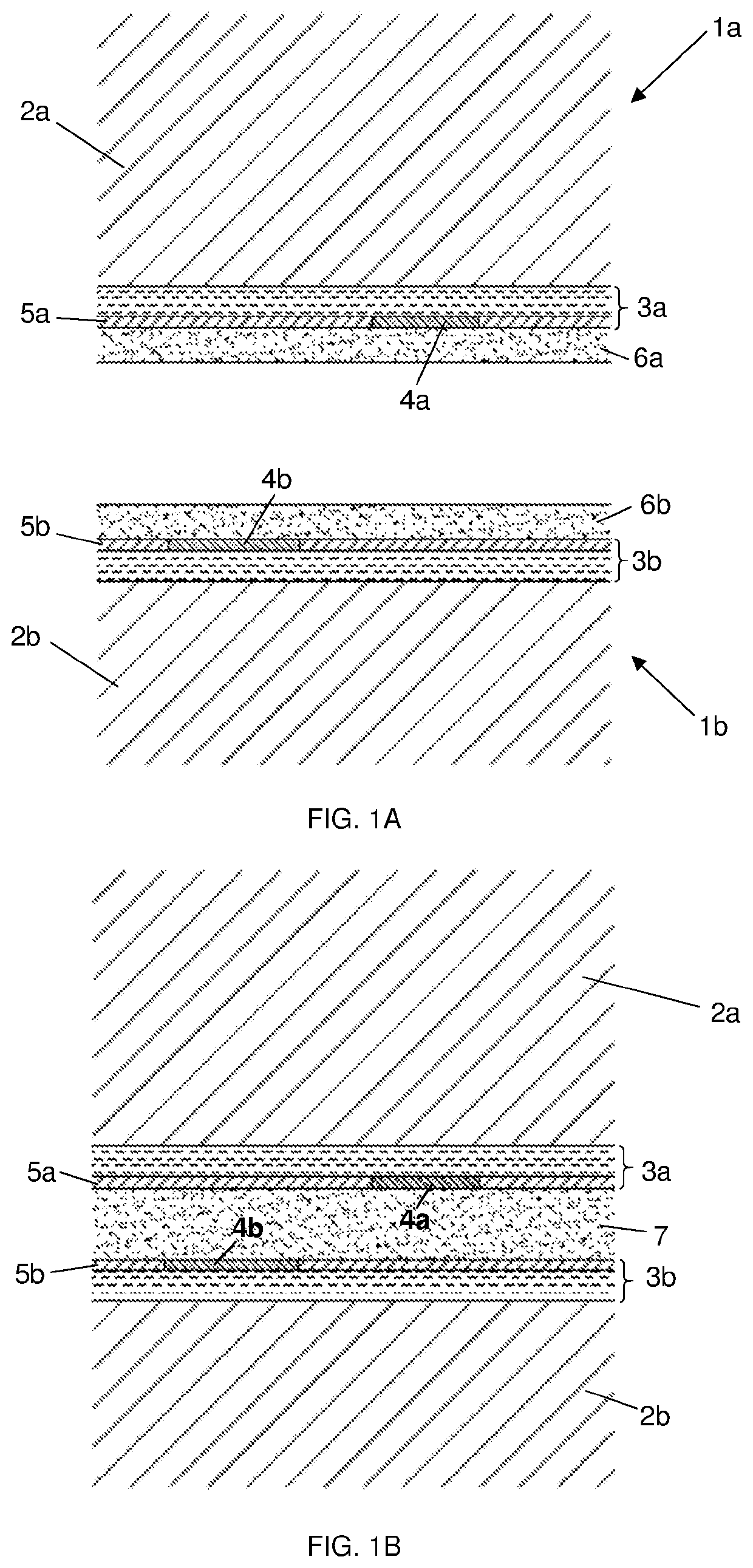

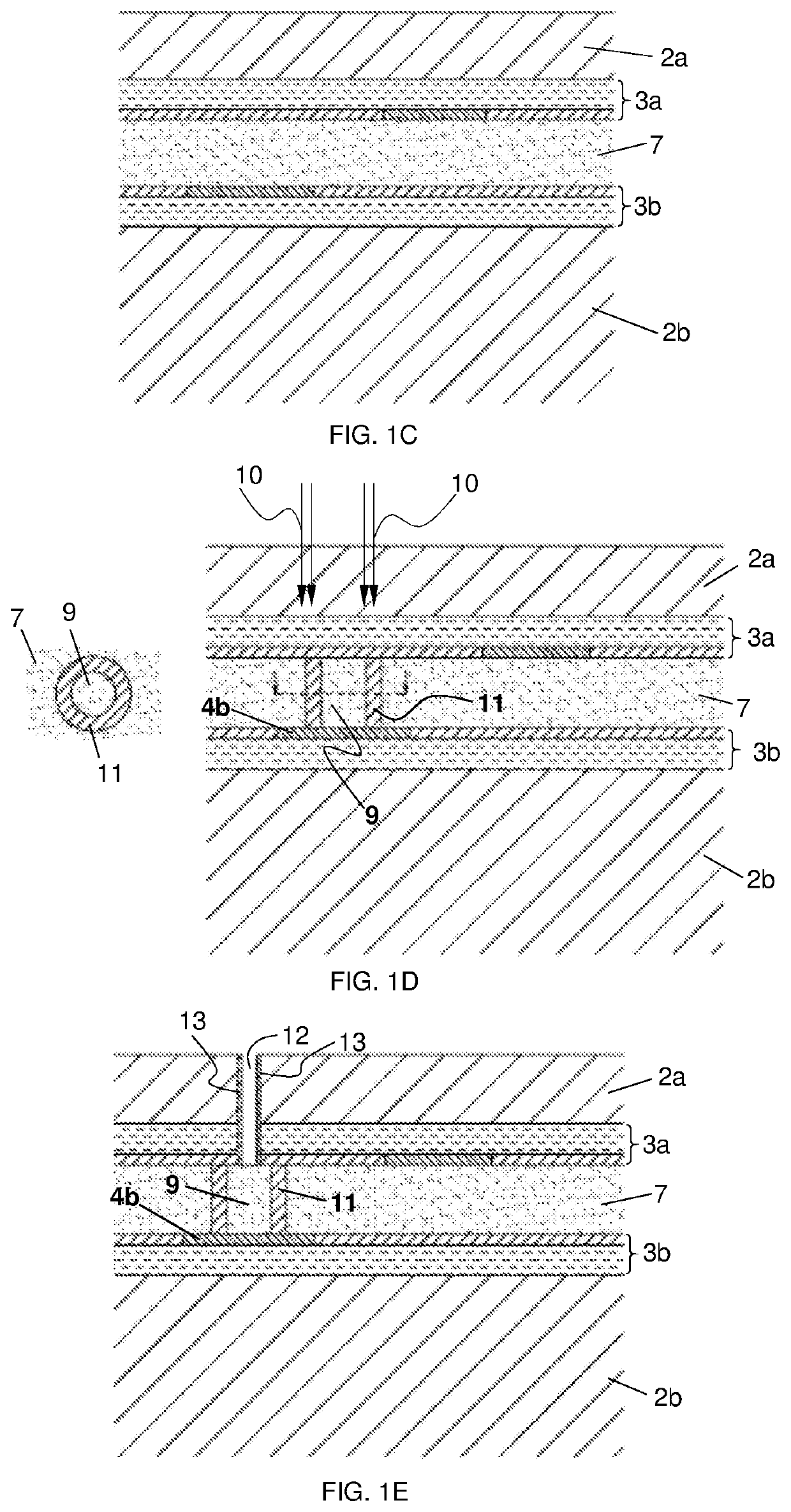

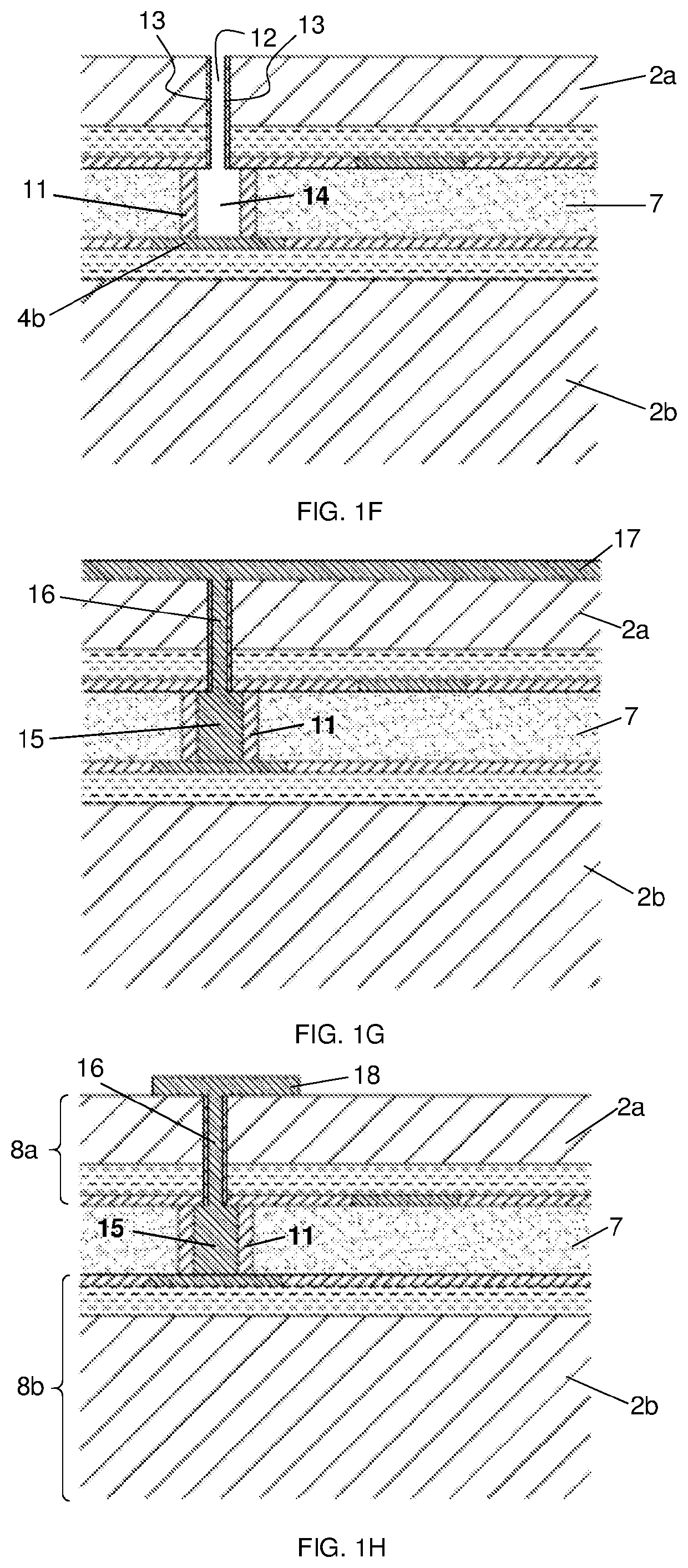

ActiveUS20200203224A1Suffer from disadvantageSemiconductor/solid-state device detailsSolid-state devicesWaferingSemiconductor chip

A method is provided for bonding and interconnecting two semiconductor chips arranged on semiconductor substrates. HSQ (Hydrogen Silsesquioxane) or an equivalent material is used as a bonding layer and after bonding and thinning one of the wafers (or first thinning and then bonding), the bond layer is locally irradiated by an e-beam through the thinned substrate, thereby locally transforming the bonding material into silicon oxide. Then a via opening is etched through the thinned substrate and an etch process selectively removes the oxide from an area delimited by the bonding material or vice versa. The filling of the via opening establishes an electrical connection between the bonded wafers, that is equivalent to a connection obtained by hybrid bonding, but that does not suffer from the disadvantages thereof.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)