Patents

Literature

38results about How to "Increase etch depth" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

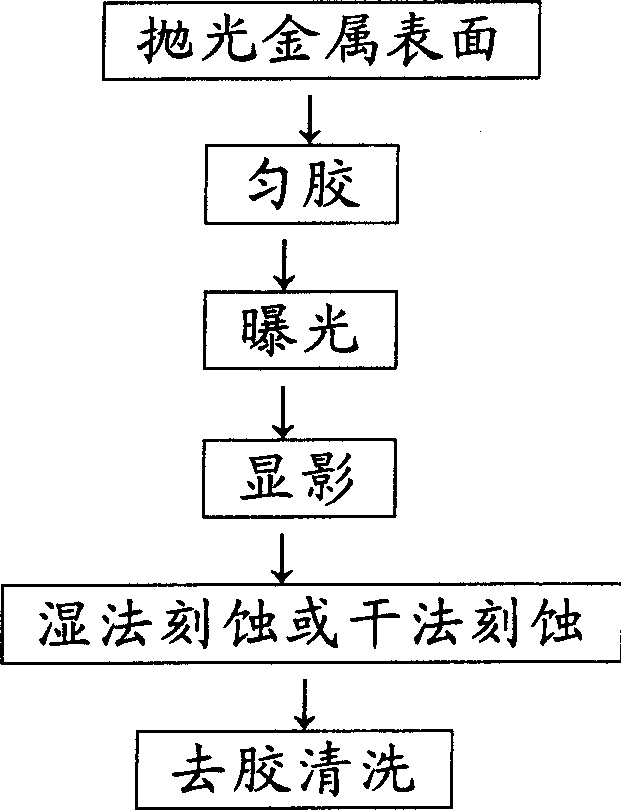

Metal grating template making process

The metal grating template making process includes photoetching comprising homogenizing photoresist, exposure, developing and other steps to form photoresist grating pattern; electrolytic etching via setting metal workpiece as positive electrode inside the electrolyte with the grating pattern side set opposite to the negative electrode to etch out the exposed the grating pattern to form grooves while protecting the photoresist masked metal surface; and taking out the metal template after reaching the required etching depth, eliminating photoresist and cleaning to obtain the metal grating template. The metal grating template making process of the present invention is simple, low in cost and fast, and etched pattern is smooth and precise.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

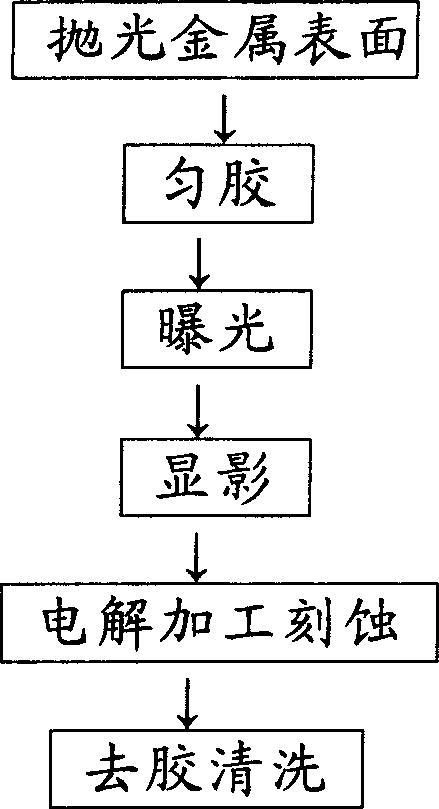

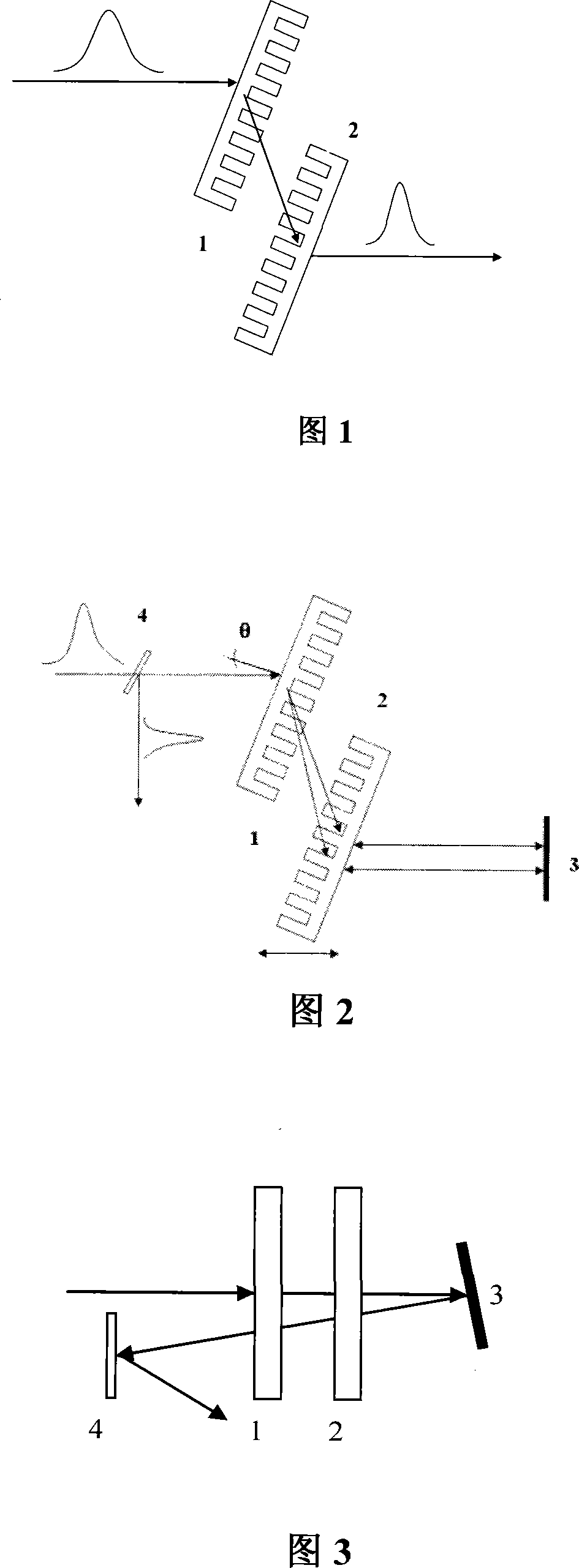

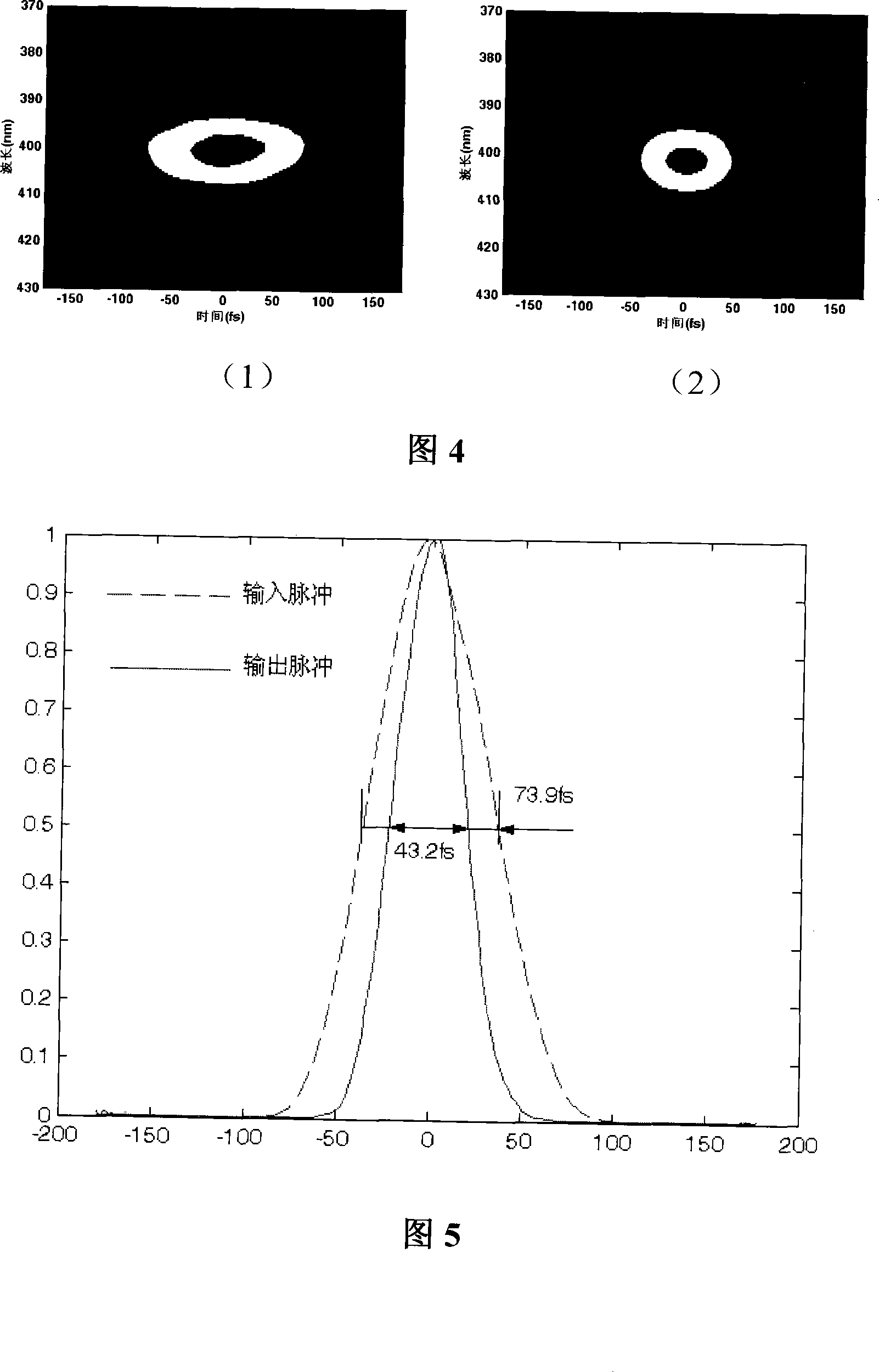

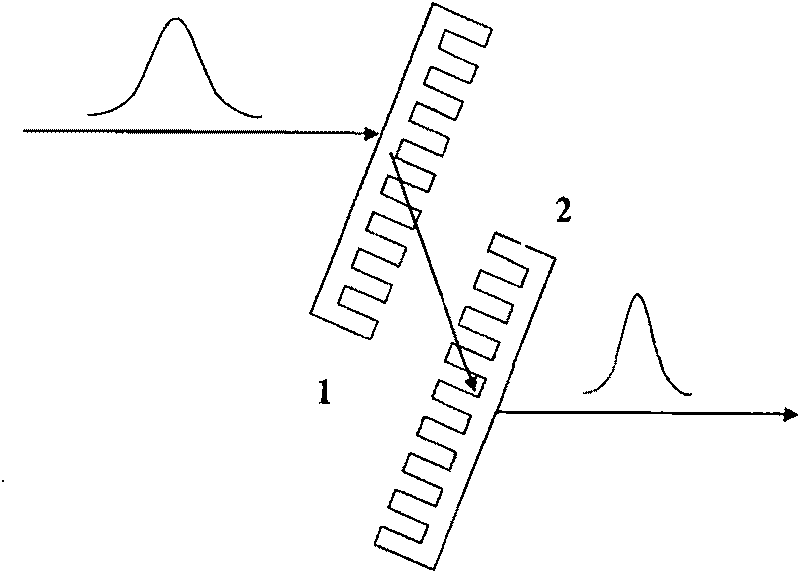

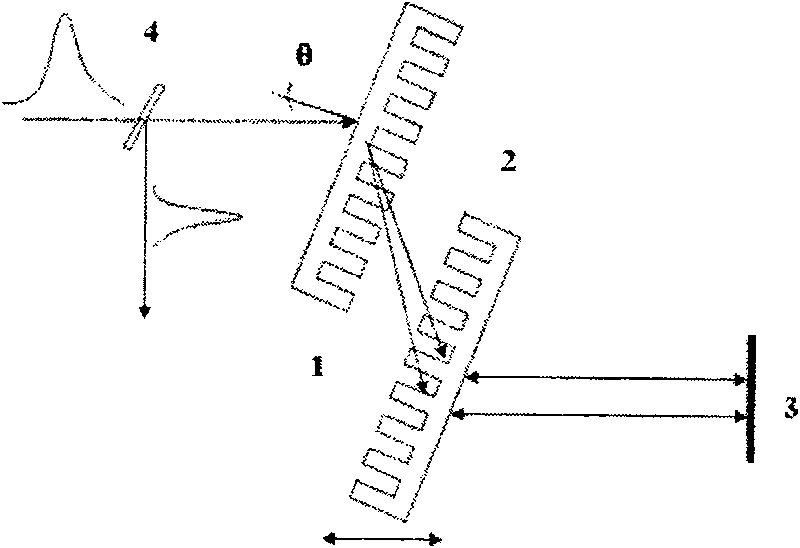

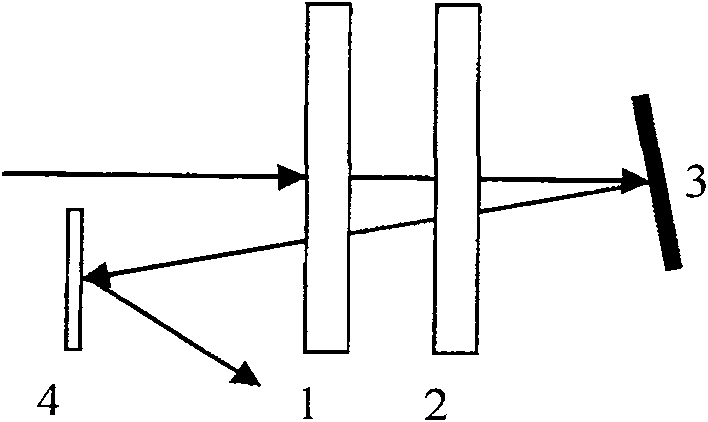

Femto second compression device

ActiveCN101187770AEasy to makeImprove efficiencyLaser detailsNon-linear opticsCompression deviceFemtosecond pulse

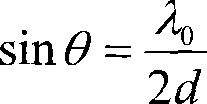

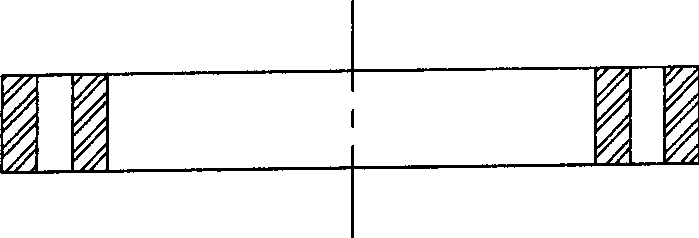

A femtosecond pulse compression device comprises a first grating and a second grating which are arranged in parallel, one surfaces of the two gratings which are provided with grating fringes are arranged on the inner side of the gratings, and the first grating and the second grating with the same structure are all sub-wavelength deep etching transmission gratings whose periodic times are d, the second grating is arranged on the second direction of the diffraction order of the transmission negative first order of the first grating, femtosecond laser pulse which needs to be compressed is incident to the first grating in a Bragg angle theta and meet the grating equation, sin theta= lambda0 / 2d, wherein theta is an incident angle, lambda0 is a center wavelength of the femtosecond laser pulse. The invention utilizes the sub-wavelength deep etching transmission gratings to constitute the femtosecond pulse compression device which has the advantages of compact structure and high efficiency.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

Transmissive metal grating and preparation method thereof

InactiveCN1790067AReduce processEasy to manufactureSemiconductor/solid-state device manufacturingDiffraction gratingsTransmittanceCopper

The invention discloses a transmission type metal raster, which comprises the following parts: metal base plate, raster bright fringe and raster dark fringe, wherein the raster bright fringe is the gap of metal base plate with 100 percent light transmittance ratio; the dark fringe is metal base plate itself without light transmission; the metal base plate is stainless steel, copper and aluminum film or metal ruler. The transmission type metal raster making method comprises the following steps: washing the metal base plate surface; coating even thickness photoresist on two sides of base plate; removing the dilute agent of photoresist by drying; placing the base plate in two same raster motherboards to align then exposing; developing through the developing liquid; corroding the toast hard film in the FeCl3 liquid; removing the photoresist; cleaning the base plate surface.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

Method for preparing hundred nano grade narrow line width holographic grating photoresist pattern with various features

ActiveCN101738662AElasticityThe degree of freedom becomes largerDiffraction gratingsPhotomechanical coating apparatusResistGrating

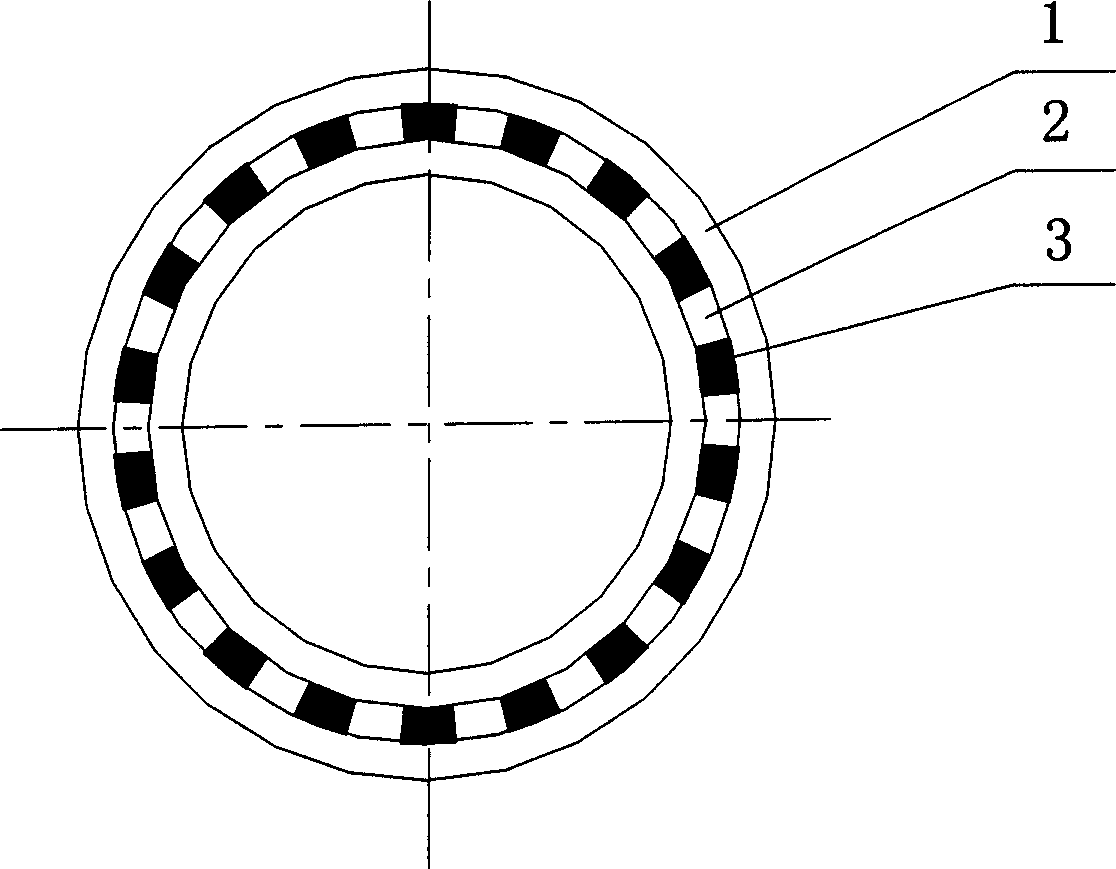

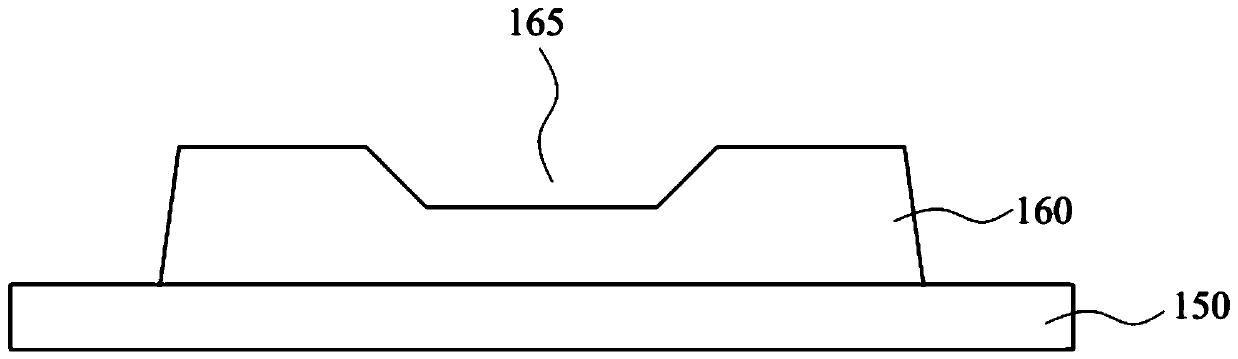

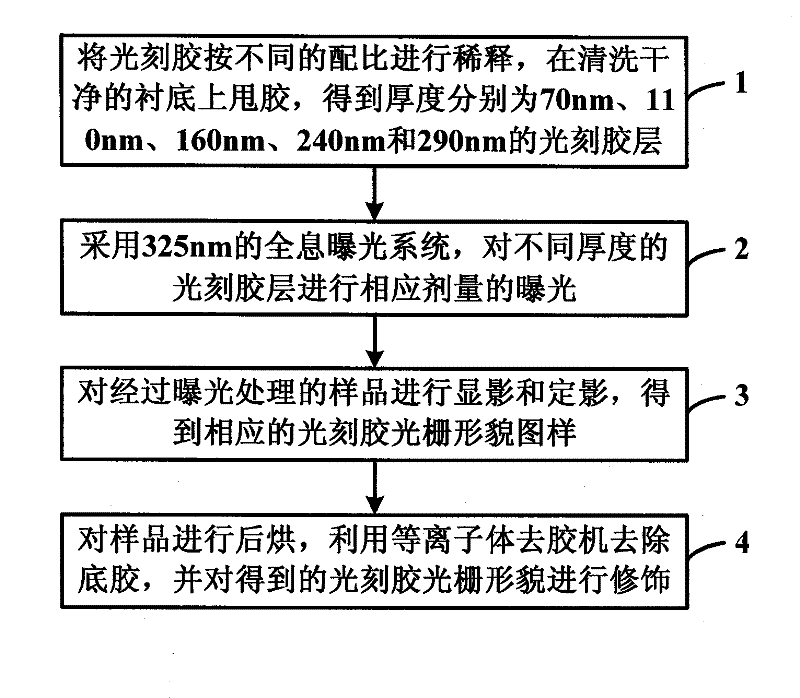

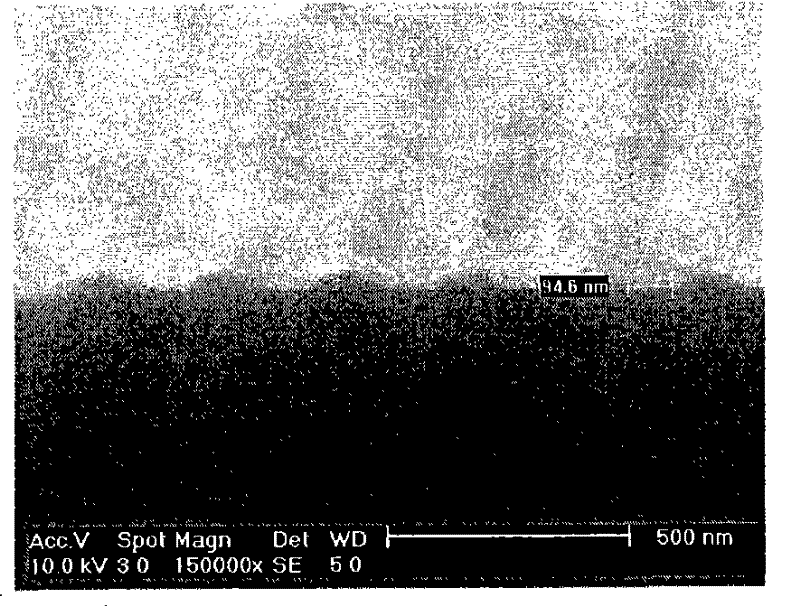

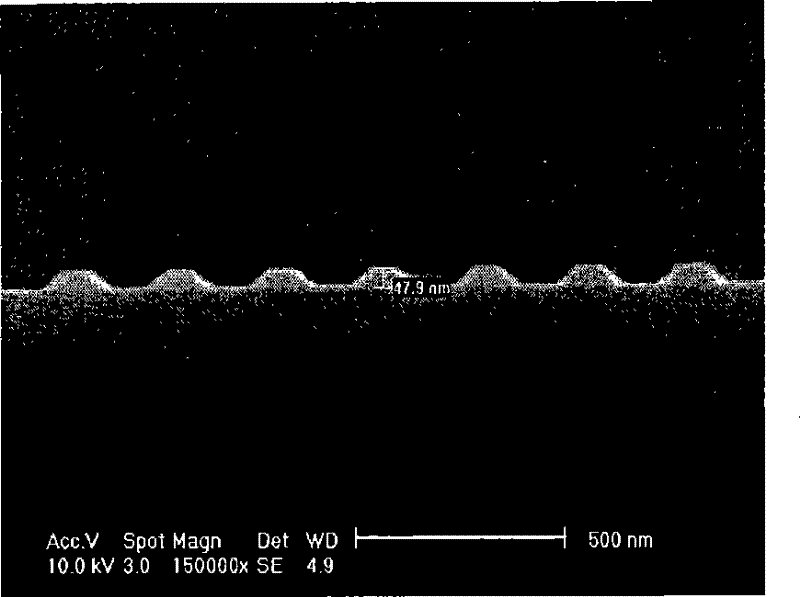

The invention discloses a method for preparing a hundred nano grade narrow line width holographic grating photoresist pattern with various features, which comprises the following steps of: 1. diluting photoresist according to different proportions and throwing the photoresist on a clean substrate to obtain photoresist layers with the respective thicknesses of 80nm, 120nm, 160nm, 200nm and 260nm; 2. carrying out the exposure of corresponding dosage on the photoresist layers with different thicknesses by a holographic exposure system with the thickness of 325nm; 3. carrying out development and photographic fixation on a sample after exposure processing to obtain a corresponding photoresist grating feature pattern; 4. after-baking the sample, removing a primer by a plasma resist removing machine and decorating the obtained photoresist grating feature. By utilizing the invention, the hundred nano grade narrow line width holographic grating photoresist pattern with various features is prepared.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

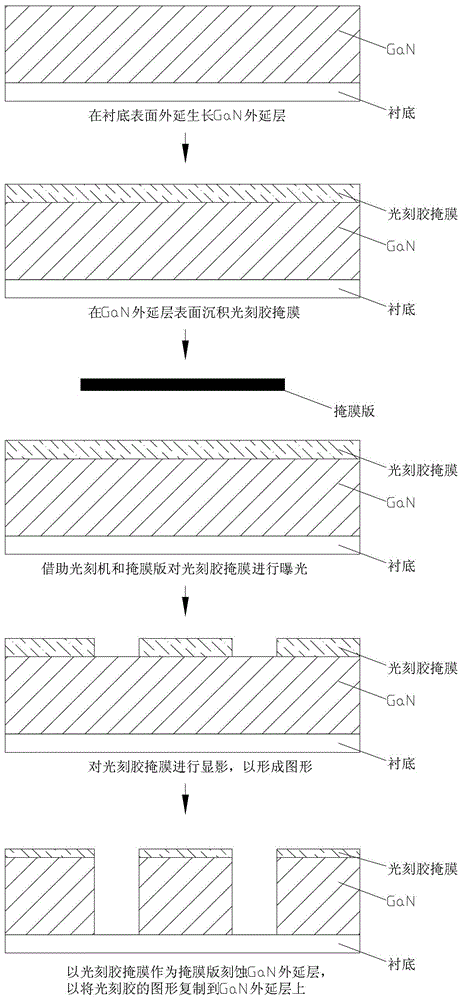

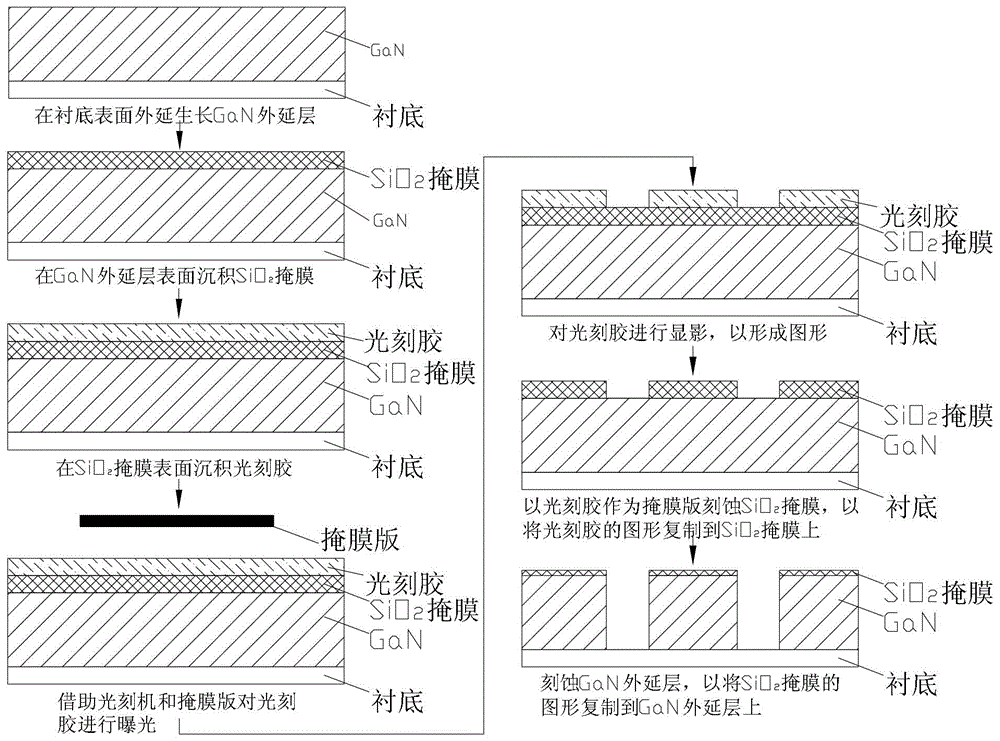

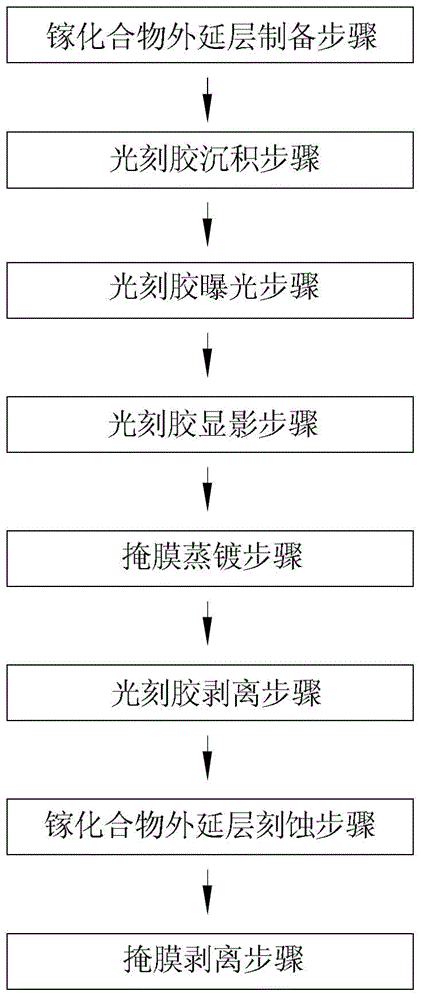

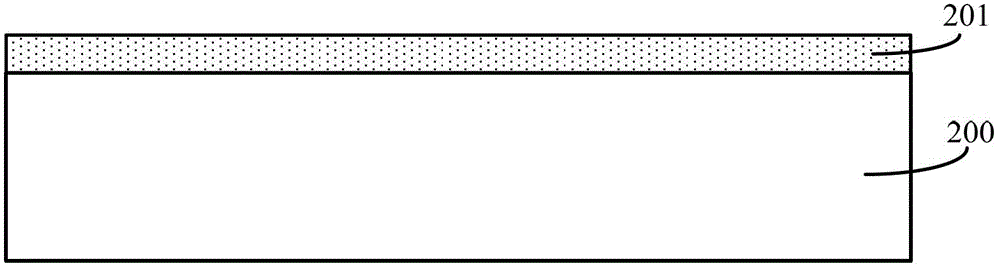

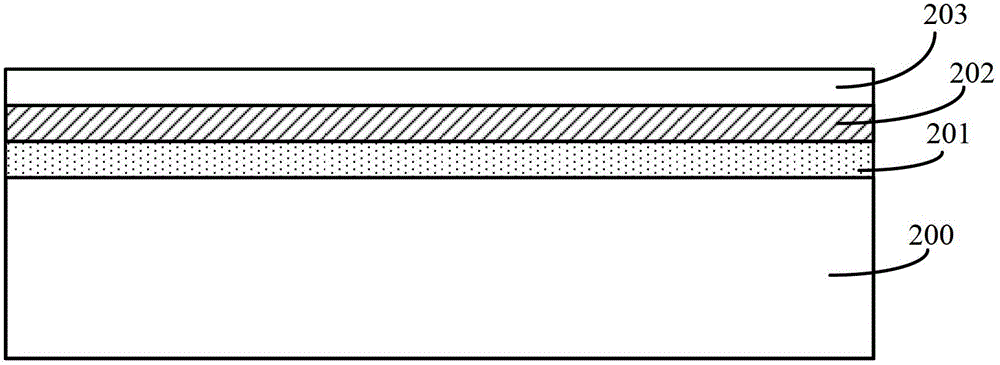

Method for preparing mask layer of III family compound substrate

ActiveCN104425224AImprove etch selectivityPrevent proliferationSemiconductor/solid-state device manufacturingSemiconductor devicesChemical compoundMetallic materials

The invention provides a method for preparing a mask layer of a III family compound substrate. The method comprises the following steps of depositing a photoresist, namely depositing the photoresist on the surface of an epitaxial layer of a gallium compound; exposing the photoresist; developing the photoresist, namely developing the exposed photoresist; evaporating the mask layer, namely evaporating at least one isolation layer on the surface of the photoresist and on the surface, uncovered by the photoresist, of the epitaxial layer of the gallium compound, and evaporating at least one metal layer on the surface of the isolation layer, wherein the isolation layer is made of a material capable of preventing a metal material of the metal layer from spreading to the epitaxial layer of the gallium compound, and the metal layer is made of a material capable of improving an etching selection ratio of the mask layer to the epitaxial layer of the gallium compound; peeling the photoresist, namely peeling the photoresist and the isolation layer and the metal layer on the photoresist. According to the method for preparing the mask layer of the III family compound substrate, the etching selection ratio of the mask layer to the epitaxial layer of the gallium compound is improved on the premise of not damaging the surface of the epitaxial layer of the gallium compound.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

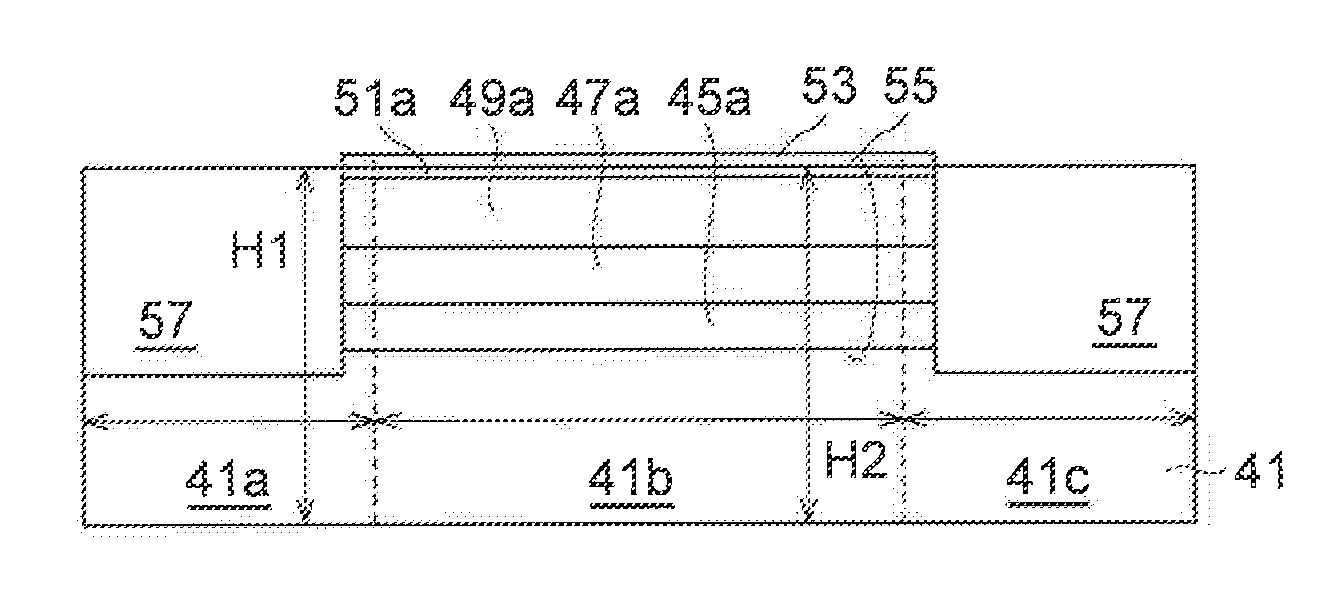

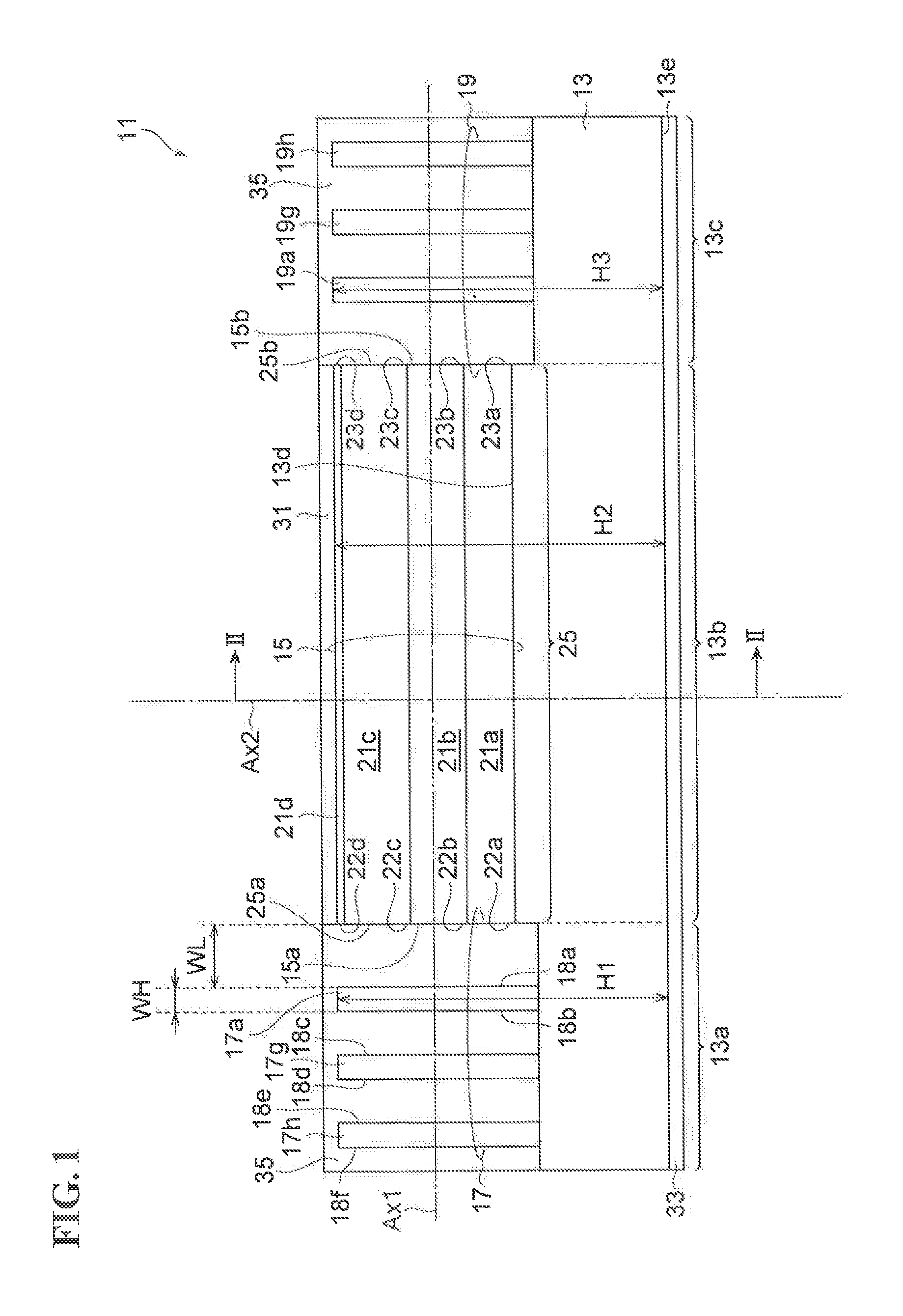

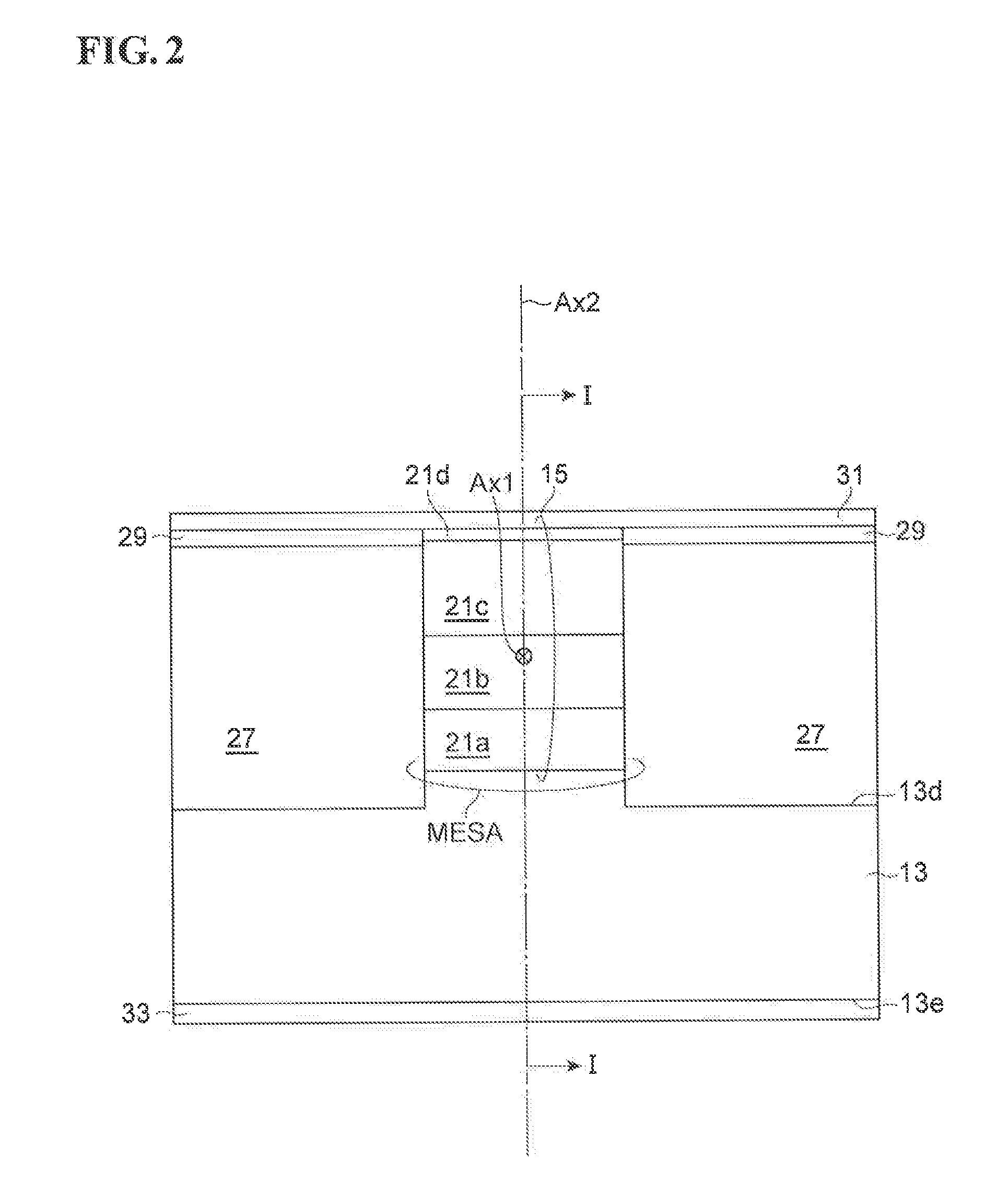

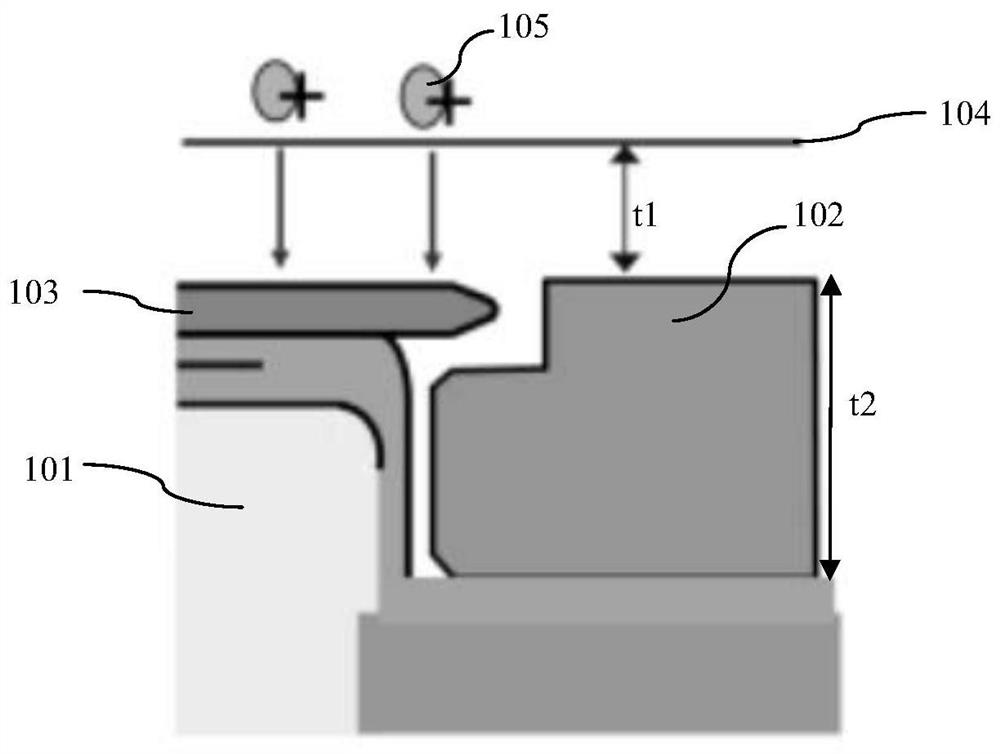

Quantum cascade laser

ActiveUS20160094015A1Large thicknessIncrease etch depthOptical wave guidanceLaser detailsSemiconductor materialsQuantum cascade laser

A quantum cascade laser includes a substrate having a principal surface including first and second regions arranged along a first axis; a laser structure disposed on the principal surface in the second region, the laser structure having an end facet intersecting the first axis, the laser structure including a stripe-shaped stacked semiconductor layer extending along the first axis; and a distributed Bragg reflection structure disposed on the principal surface in the first region, the distributed Bragg reflection structure including a semiconductor wall made of a single semiconductor material, the distributed Bragg reflection structure being optically coupled to the end facet of the laser structure. The semiconductor wall has first and second side surfaces that intersect the first axis and extend along a second axis intersecting the principal surface. The semiconductor wall is located away from the end facet of the laser structure.

Owner:SUMITOMO ELECTRIC IND LTD

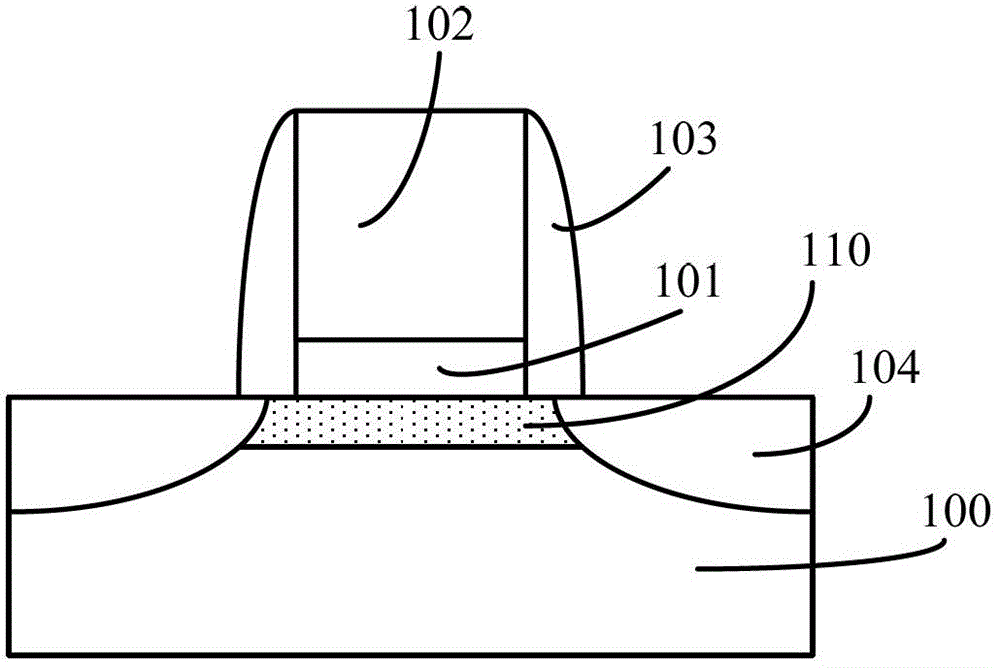

Transistor and formation method thereof

InactiveCN104064464APromote formationThreshold Voltage StabilitySemiconductor/solid-state device manufacturingSemiconductor devicesVoltage regulationSemiconductor

The invention discloses a transistor and a formation method thereof. The formation method of the transistor comprises: providing a semiconductor substrate, wherein the surface of the semiconductor substrate is provided with a threshold voltage adjusting film, the surface of the threshold voltage adjusting film is provided with a barrier film, the surface of the barrier film is provided with a channel film, the threshold voltage adjusting film is internally provided with doped irons, the channel film is at an intrinsic state, and the barrier film is used for preventing penetration by the doped irons in the threshold voltage adjusting film; forming a grid structure on the surface of the channel film; forming a first side wall on the surface of the channel film at the two sides of the grid structure; by taking the grid structure and the first side wall as masks, etching the channel film, the barrier film, the threshold voltage adjusting film and a part of the semiconductor substrate to form a channel layer, a barrier layer and a threshold voltage adjusting layer; and forming a doping layer on the surface of the semiconductor substrate at the two sides of the threshold voltage adjusting layer, the barrier layer, the channel layer and the grid structure, wherein the surface of the doping layer is not lower than the surface of the channel layer. The performance of the formed transistor is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

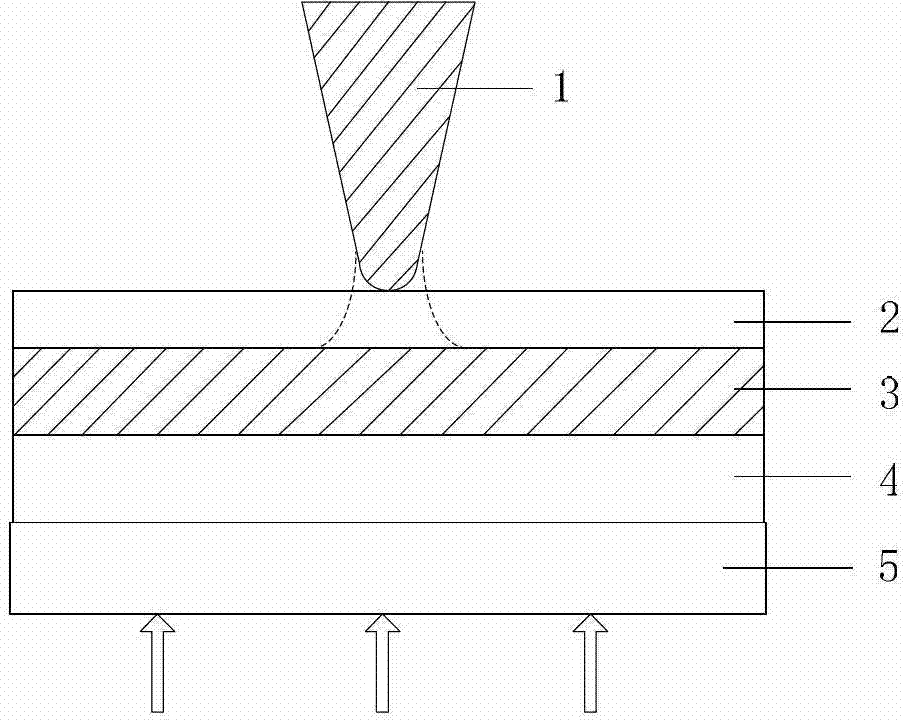

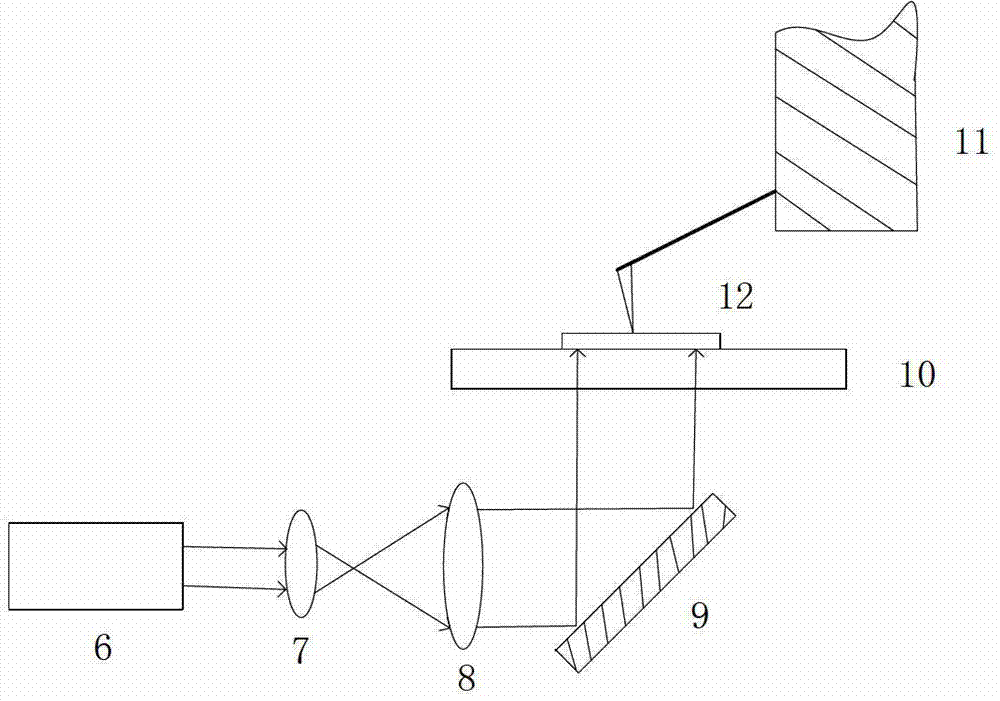

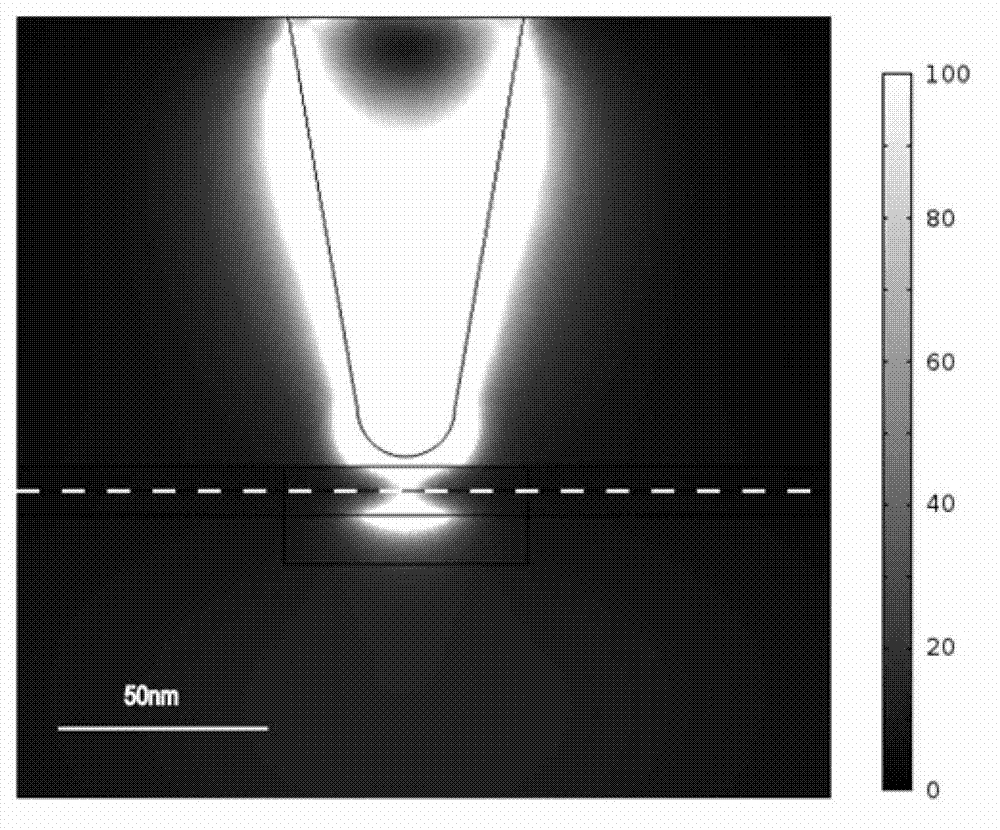

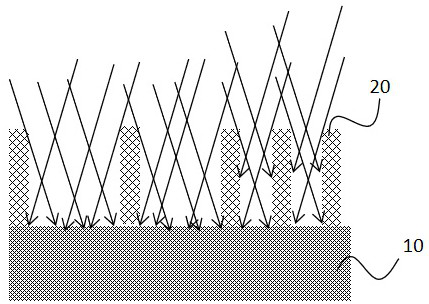

Surface plasma ultra-diffraction photoetching method based on tip-insulator-metal structure

InactiveCN102880010AConsistent sizeUniform energyPhotomechanical exposure apparatusMicrolithography exposure apparatusResonant cavityUltrasound attenuation

The invention provides a surface plasma ultra-diffraction photoetching method based on a tip-insulator-metal (TIM) structure. The surface plasma ultra-diffraction photoetching method is characterized in that a TIM resonant cavity structure is formed by tip-insulator-metal, a light is emitted in a substrate containing the resonant cavity in a normal incidence manner, a probe tip of a probe stimulates local surface plasmas (LSP), the waves of the stimulated local surface plasmas are reflected and coupled by a metal reflection layer in a downward attenuation propagation process and reflected for multiple times to cause resonance and form relatively-uniformly-distributed regular circular light spot modes in a longitudinal distribution manner in a medium recording layer clamped between a metal reflection layer and the probe. According to the surface plasma ultra-diffraction photoetching method based on the tip-insulator-metal structure, the problem that the write-through photoetching depth of a conventional probe is shallow is solved, the sizes of the light spots (full width at half maximum, FWHM) at different depths of the medium recording layer are identical, and the energies are uniform. According to the surface plasma ultra-diffraction photoetching method, the quality of the light spot photoetched by the conventional write-through probe is greatly improved; the structure adopted by the method is simple; and the photoetching line width can be greatly reduced.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI

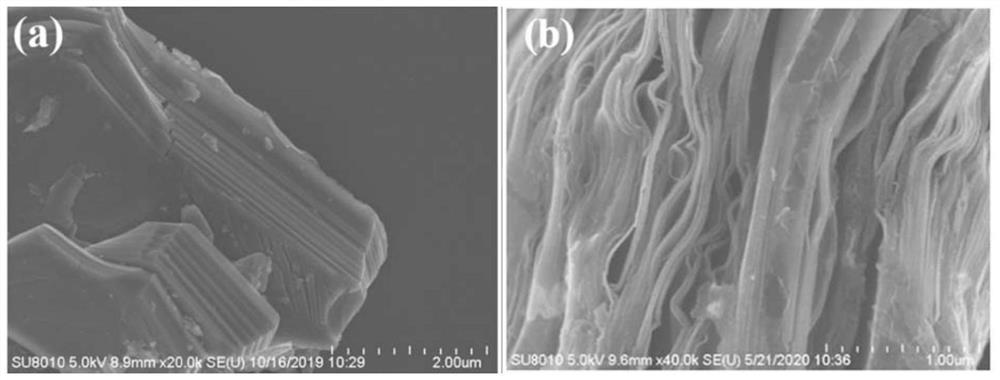

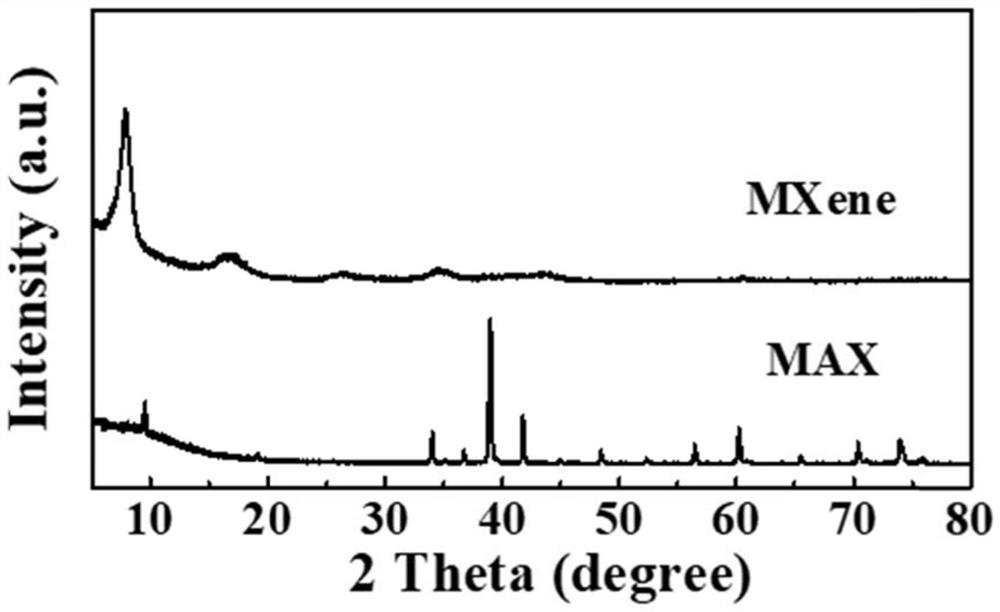

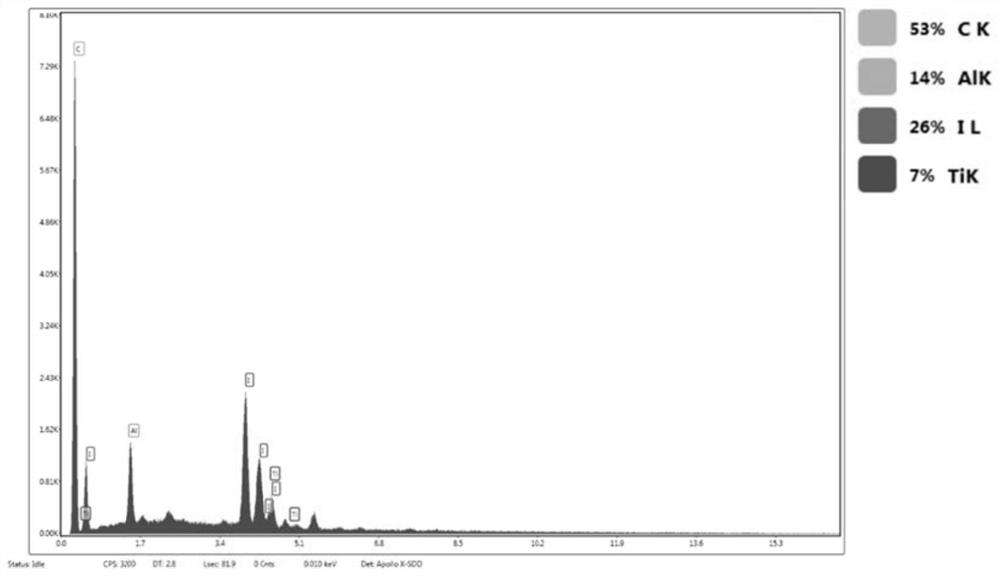

Simple and pollution-free method for preparing fluoride-free two-dimensional material MXene

ActiveCN111943207AEasy to operateRaw materials are easy to getNitrogen-metal/silicon/boron binary compoundsTitanium carbidePhysical chemistryRedox

The invention creatively provides a simple and pollution-free method for preparing a fluoride-free two-dimensional material MXene, which comprises the following steps: uniformly mixing an iodine cosolvent and an MAX phase, transferring the mixture into a sealed reaction bin, heating the mixture in an inert environment for reaction to obtain the MXene two-dimensional material. According to the method for preparing the two-dimensional material MXene, the principle is that the two-dimensional material MXene is prepared by etching MAX through iodine cosolvent steam, iodine steam is generated afterthe iodine cosolvent is heated, the iodine steam and A-layer elements are subjected to redox reaction etching at the high temperature, and the MXene is obtained. The method has the advantages of easily available raw materials, low cost, mild reaction conditions, simple operation, no fluorine, no solvation, no waste liquid generation, low toxicity, environmental protection, and realization of large-scale production.

Owner:XUZHOU LANOXENE INST CO LTD

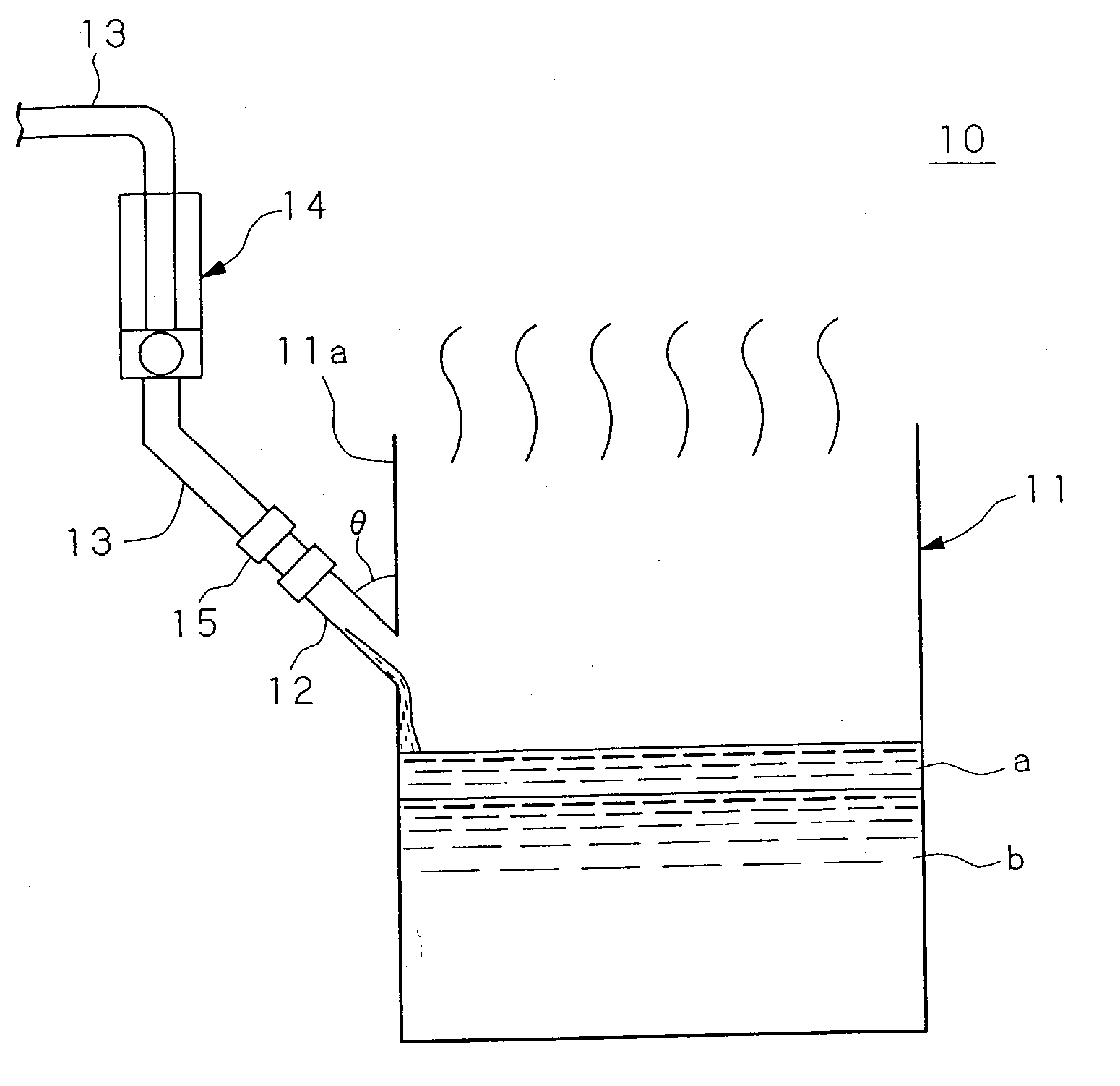

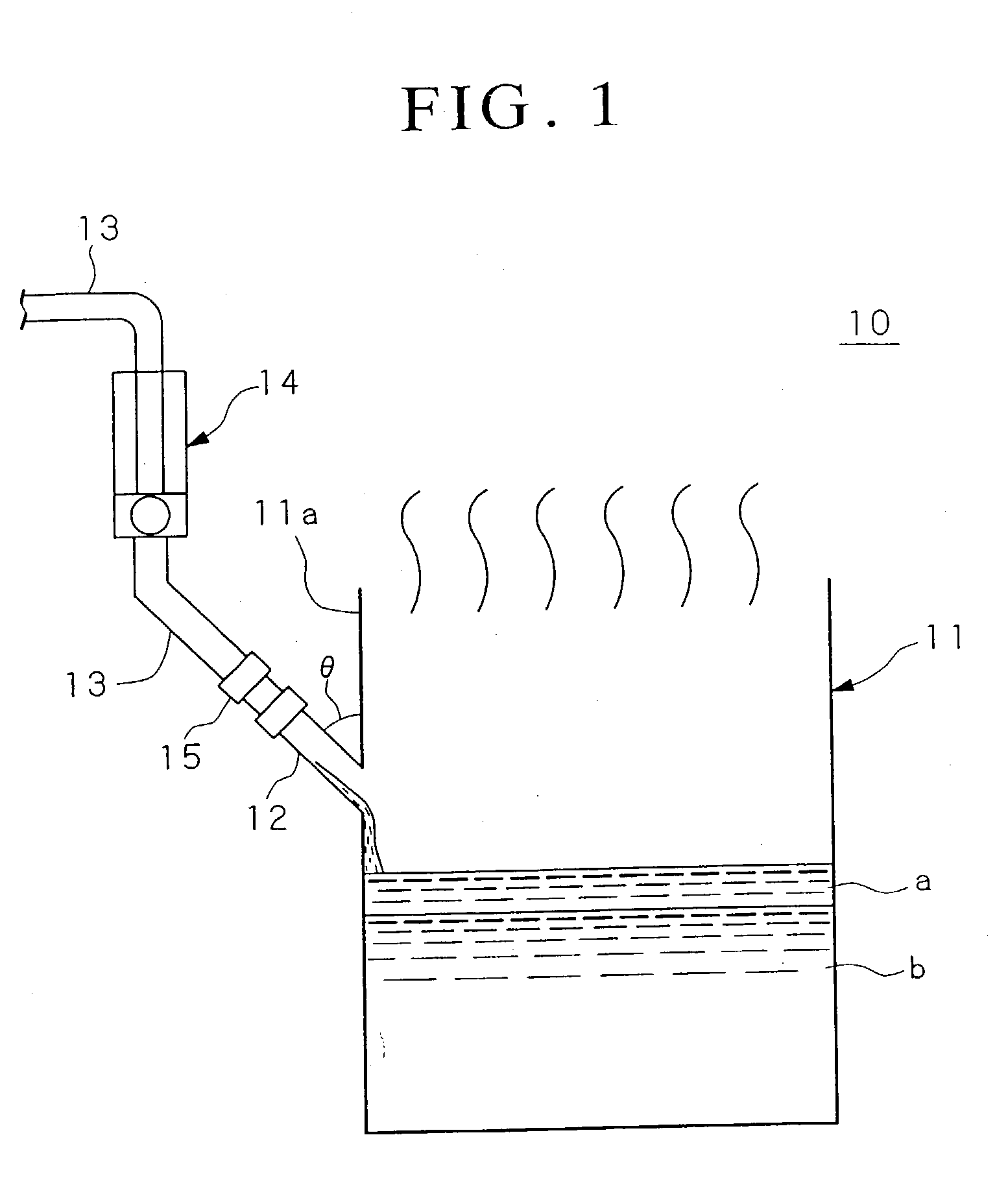

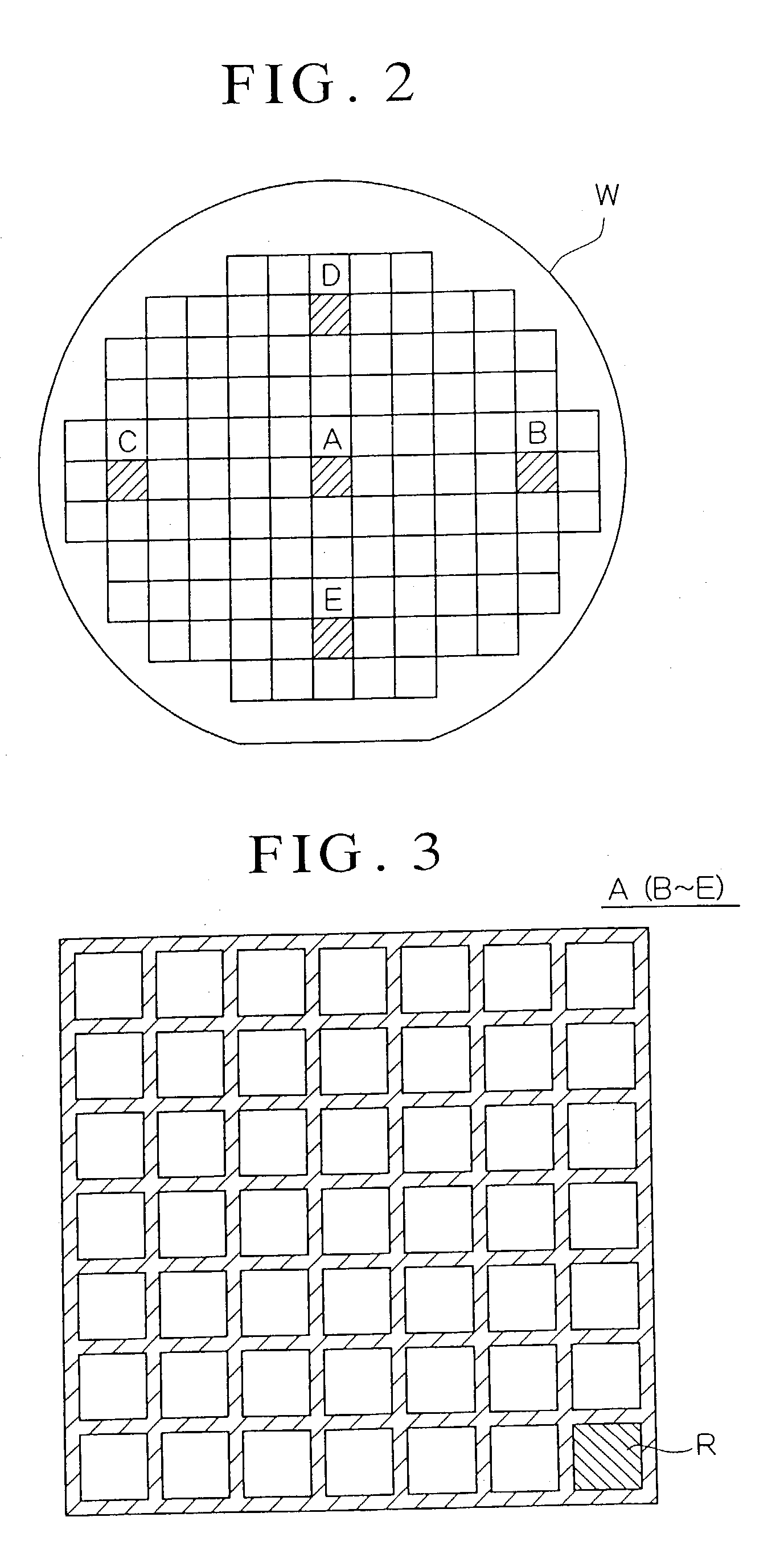

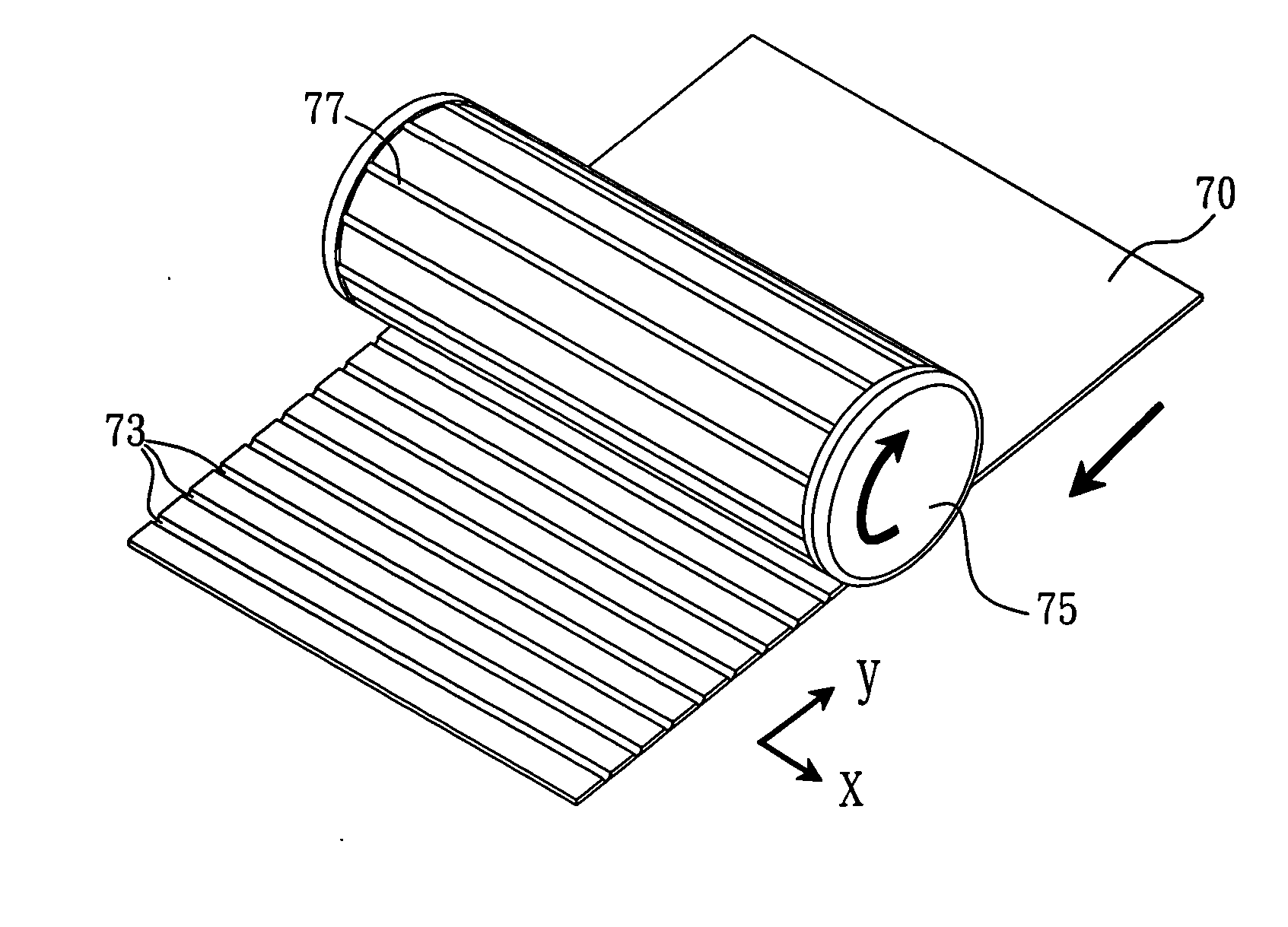

Anisotropic etching method and apparatus

InactiveUS20030124853A1Improving anisotropic etchingImproving the anisotropic etchingSemiconductor/solid-state device manufacturingEvaporationCirculating pump

An anisotropic etching method and apparatus is disclosed, by which the anisotropic etching of a wafer surface can be stably performed, the generation of mu pyramids generated on the etched surface of a semiconductor wafer can be reduced, and the etching depth can be uniform. Therefore, during the anisotropic etching, a replenishing etchant which compensates for the evaporation of a component from the surface of the anisotropic etchant is continuously supplied by an amount corresponding to the amount of the component evaporated. An anisotropic etching apparatus is also disclosed, by which the etchant is not contaminated, the evaporated component of the etchant does not catch fire, the composition of the etchant does not change and the characteristics of the anisotropic etching are stabilized, the generation of mu pyramids can be suppressed, and the etching depth is uniform over the wafer surface. In the apparatus, when a circulating pump is operated, a heating medium in a heating medium jacket is drawn into a heating medium circulating passage, and then is heated by a heating device in the middle of the passage and returned to the jacket. The anisotropic etchant in the anisotropic etching vessel is heated by the heat of the returned heating medium.

Owner:MITSUBISHI MATERIALS SILICON CORP

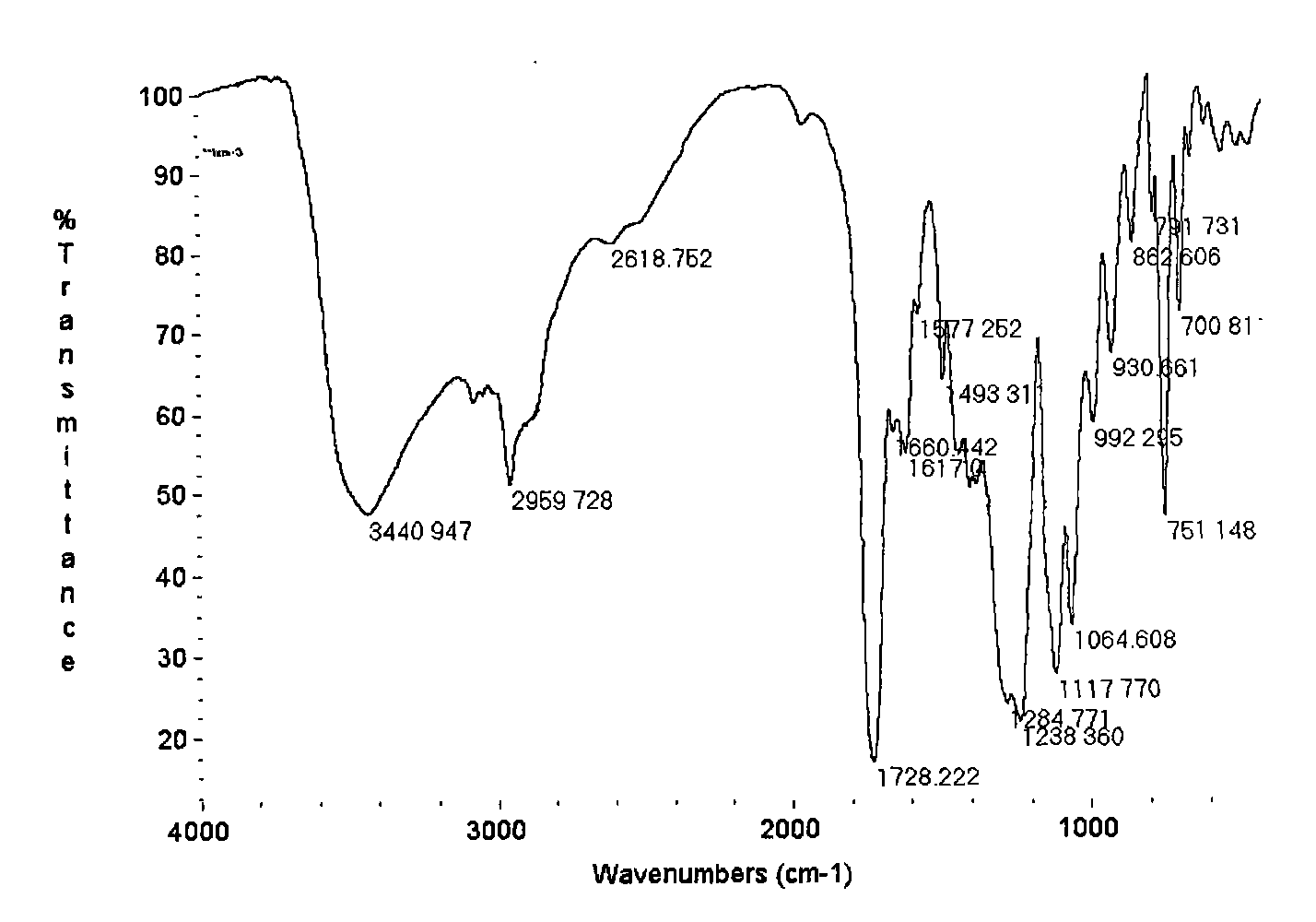

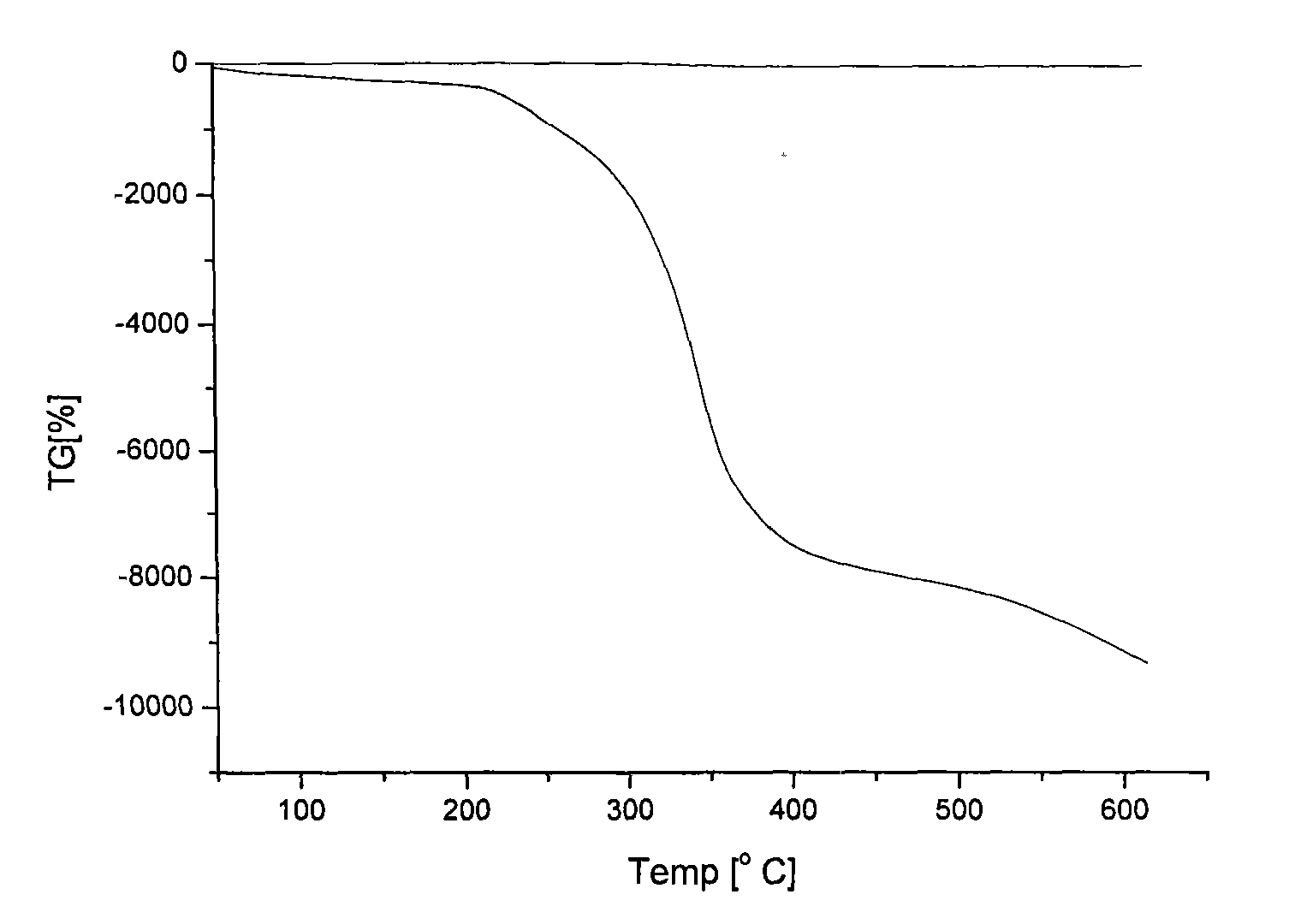

Hyperbranched polyester micro-optical photoresist

InactiveCN101799625AHigh activityHigh etching speedPhotosensitive materials for photomechanical apparatusCross-linkPolymer science

The invention relates to a hyperbranched polyester micro-optical photoresist, comprising a hyperbranched alkali-soluble photopolymer, an active diluent, a cross-linking agent, a photoinitiator, an auxiliary agent and the like. The photosensitive property, the corrosion performance, the linear range and the like of the hyperbranched polyester micro-optical photoresist can be adjusted through the hyperbranched polymer structure, the functional group at the tail end of the hyperbranched polymer molecule and the formula of the photoresist. The photoresist has easy preparation and great physicochemical property adjustability, and can be developed with aqueous developer, thereby having little influence to the environment in use. In addition, the photoresist has high light sensitivity and image definition, great corrosion depth and unique linear corrosion performance, and is especially suitable for photoetching process of micro-optical elements.

Owner:ZHANJIANG NORMAL UNIV

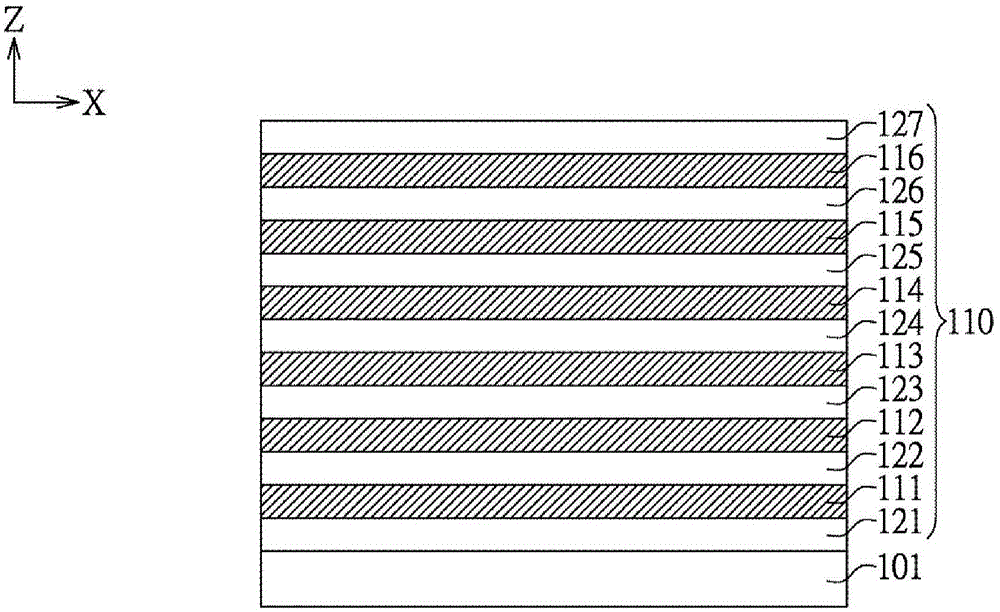

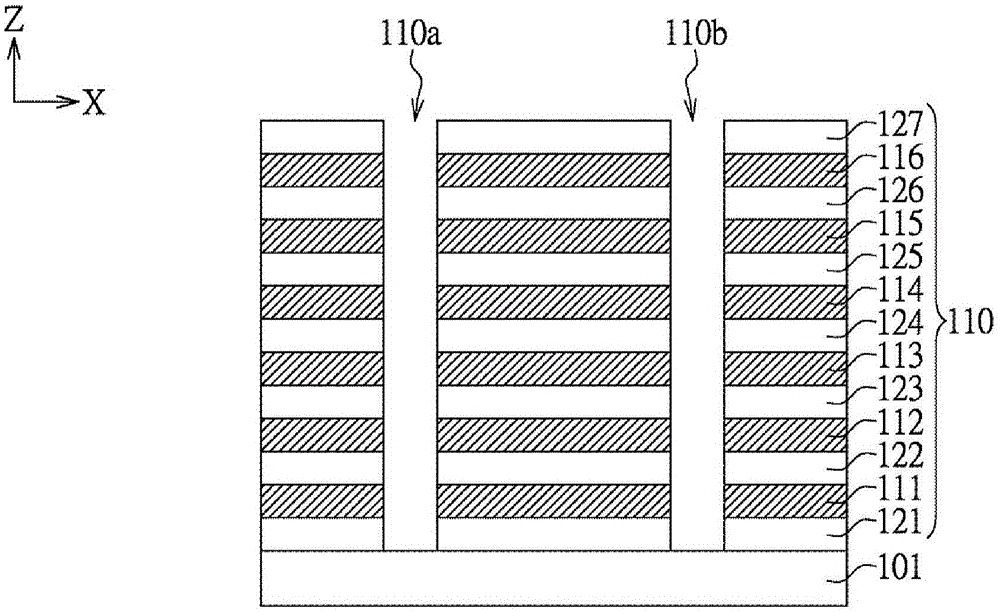

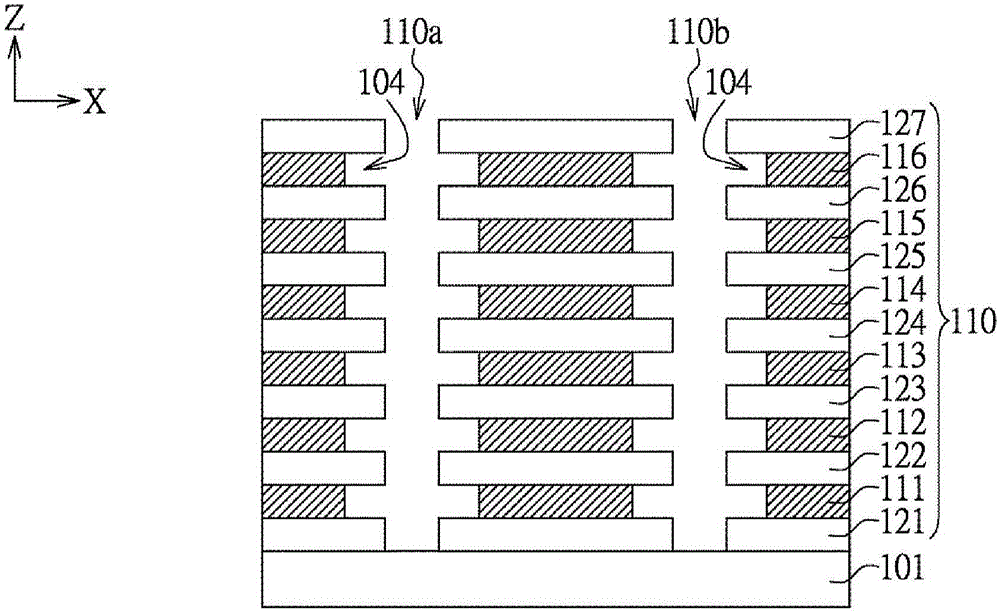

Memory and manufacturing method thereof

ActiveCN106409837AImprove reliabilityHigh densitySolid-state devicesSemiconductor devicesIsolation layerElectrical and Electronics engineering

The present invention discloses a memory and a manufacturing method thereof. A memory element comprises a first insulating layer, a second insulating layer, an isolation layer, a floating gate electrode, a control gate electrode, a channel layer and a tunneling oxide layer. The second insulating layer is adjacent to and parallel with the first insulating layer and defines an interlayer space with the first insulating layer, the isolation layer is located in the interlayer space, and the included angle of the isolation layer and the first insulating layer is a non-flat angle. The interlayer space is isolated into a first concave chamber and a second concave chamber, the floating gate electrode is located in the first concave chamber, and the control gate electrode is located in the second concave chamber. The channel layer is located at the outer side of the opening of the first concave chamber, the included angle of the channel layer and the first insulating layer is a non-flat angle, and the tunneling oxide layer is located between the channel layer and the floating gate electrode.

Owner:MACRONIX INT CO LTD

Fishing net thread use quality improvement processing process

InactiveCN107641955AImprove the effect of modified treatmentImprove physical and chemical propertiesPhysical treatmentFibre typesPhosphoric acidEngineering

The invention discloses a fishing net thread use quality improvement processing process. The process includes steps: (1) cleaning and deoiling treatment; (2) phosphoric acid solution soaking treatment; (3) treating fluid A soaking treatment; (4) ultraviolet irradiation treatment; (5) treating fluid B soaking treatment; (6) flushing and drying treatment. By special processing of fishing net threads, under joint actions in each step, the grafting effect of the fishing net threads is evidently improved, utilization characteristics of the fishing net threads are improved, and the finally treaded fishing net threads are high in coating compatibility, corrosion resistance, strength and comprehensive quality, thereby being high in popularization and utilization value.

Owner:CHAOHU JUNYE FISHING TACKLE CO LTD

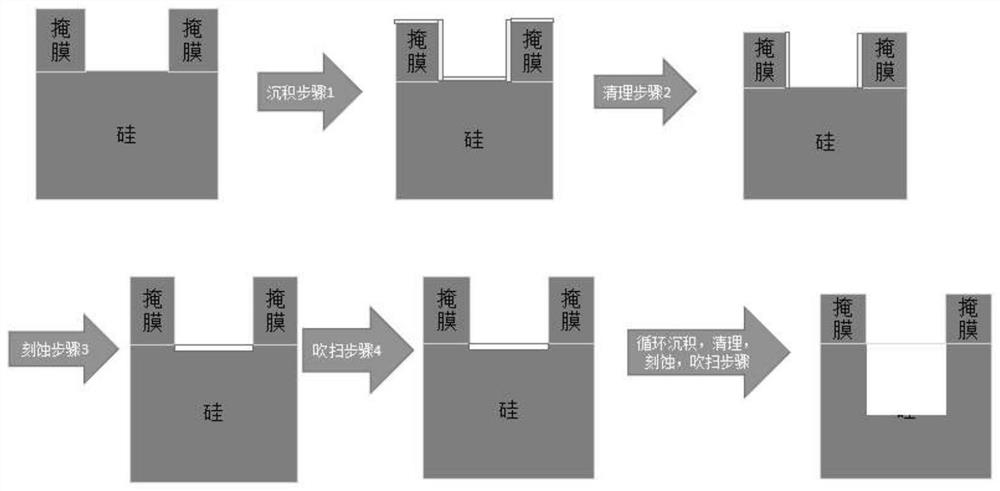

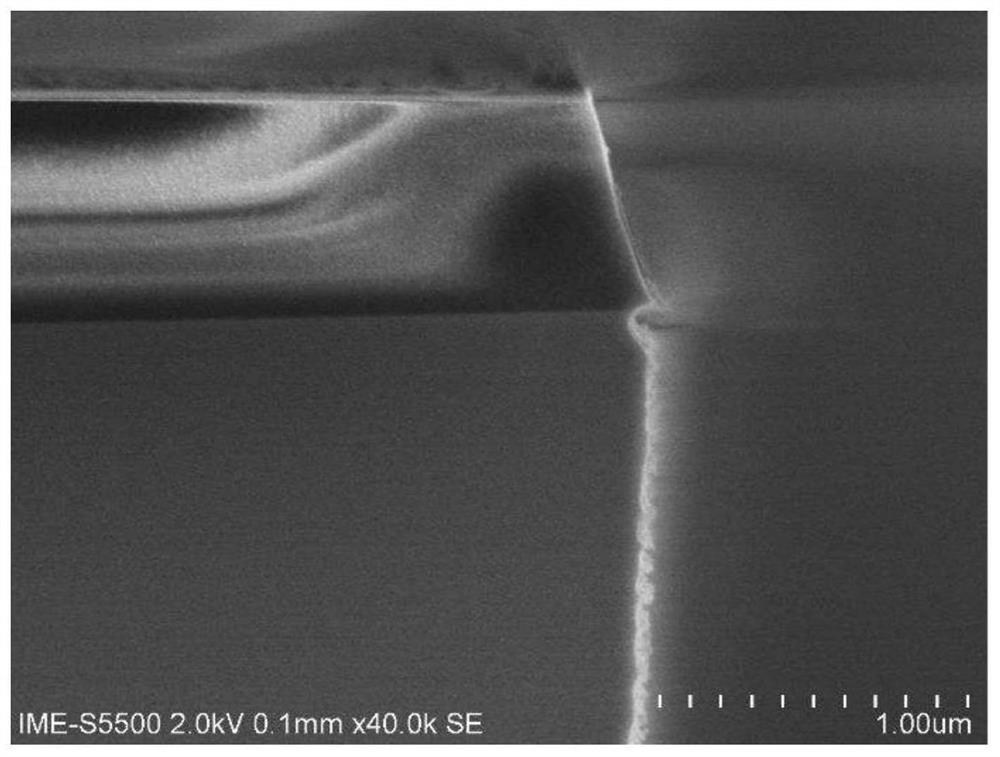

Deep silicon etching method based on SOG wafers

ActiveCN108447785AReduce collisionEasy accessDecorative surface effectsSemiconductor/solid-state device manufacturingRadio frequencyResist

The invention relates to a deep silicon etching method based on SOG wafers. The method comprises the steps of providing a SOG wafer and placing the SOG wafer on a flat plate; forming a hard mask layeron the silicon structure layer of the SOG wafer; forming a photo-resist layer on the hard mask layer, exposing and developing to expose one part of the hard mask layer; etching the exposed part of the hard mask layer to expose one part of the silicon structure layer; and subjecting the exposed part of the silicon structure layer to deep-induction coupling plasma dry etching in a chamber. The deep-induction coupling plasma dry etching comprises a first etching stage and a second etching stage. The first etching stage comprises a first passivation step, a first pre-etching step and a first etching step, wherein the first passivation step, the first pre-etching step and the first etching step are carried out circularly. The second etching stage comprises a second passivation step, a second pre-etching step and a second etching step, wherein the second passivation step, the second pre-etching step and the second etching step are carried out circularly. The pressure in the first etching step and the pressure in the second etching step are respectively 30 mTorr to 40 mTorr. The etching time and the radio frequency power at the flat plate in the first etching step and the second etchingstep are gradually increased along with the increase of the cycle period.

Owner:TSINGHUA UNIV

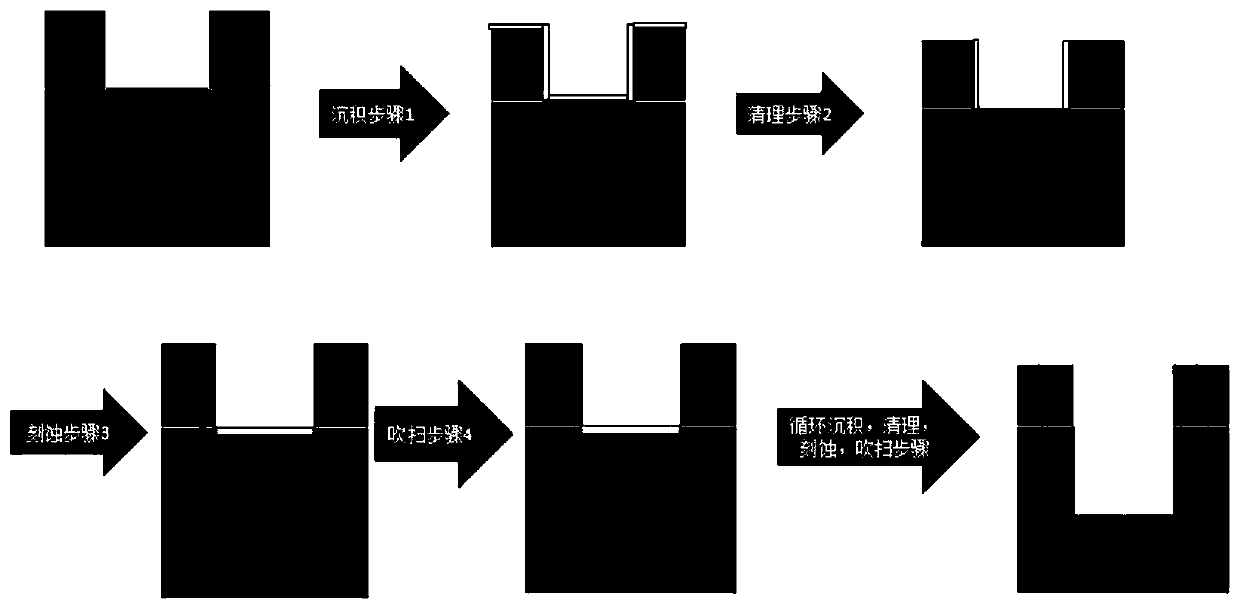

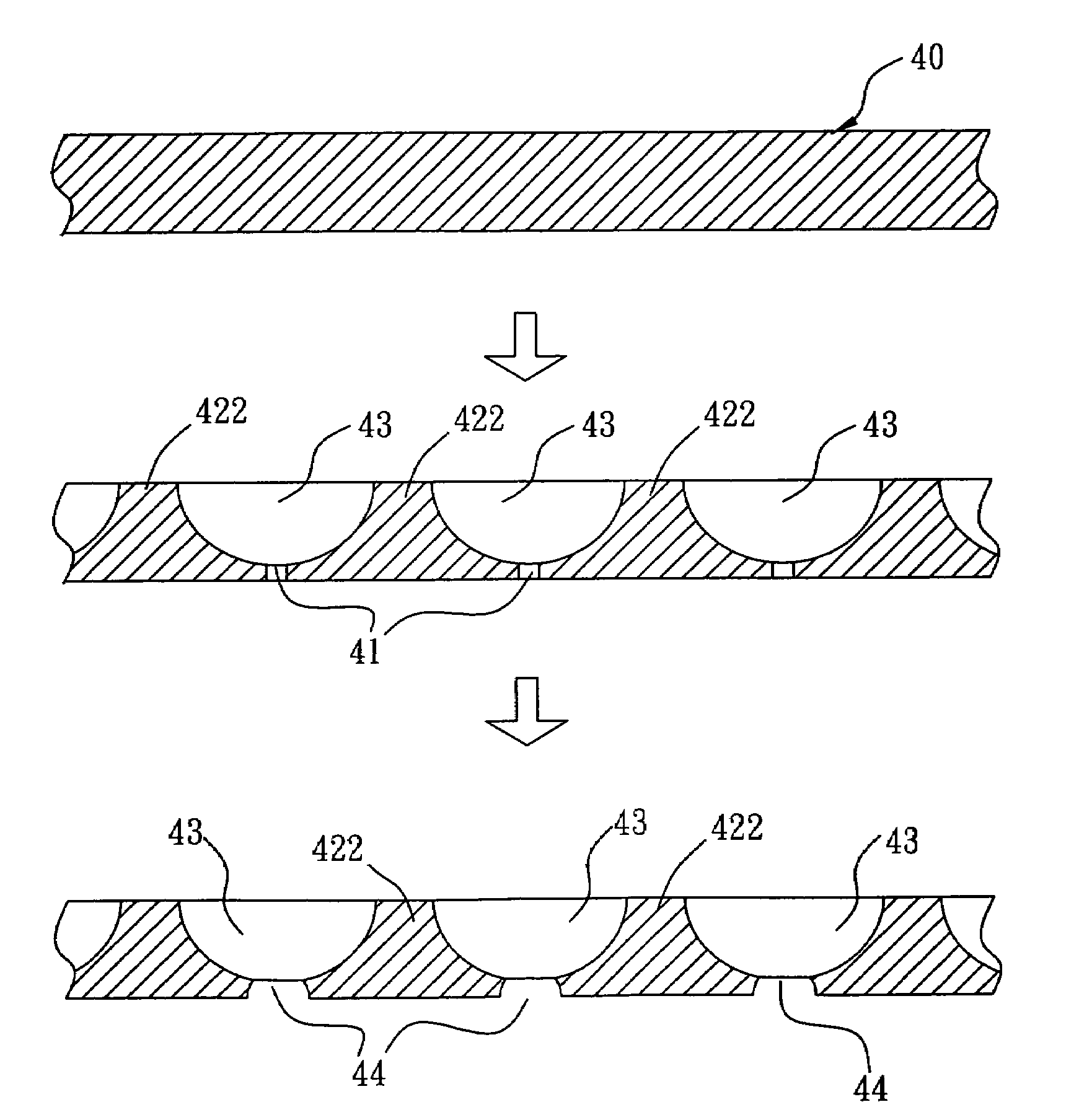

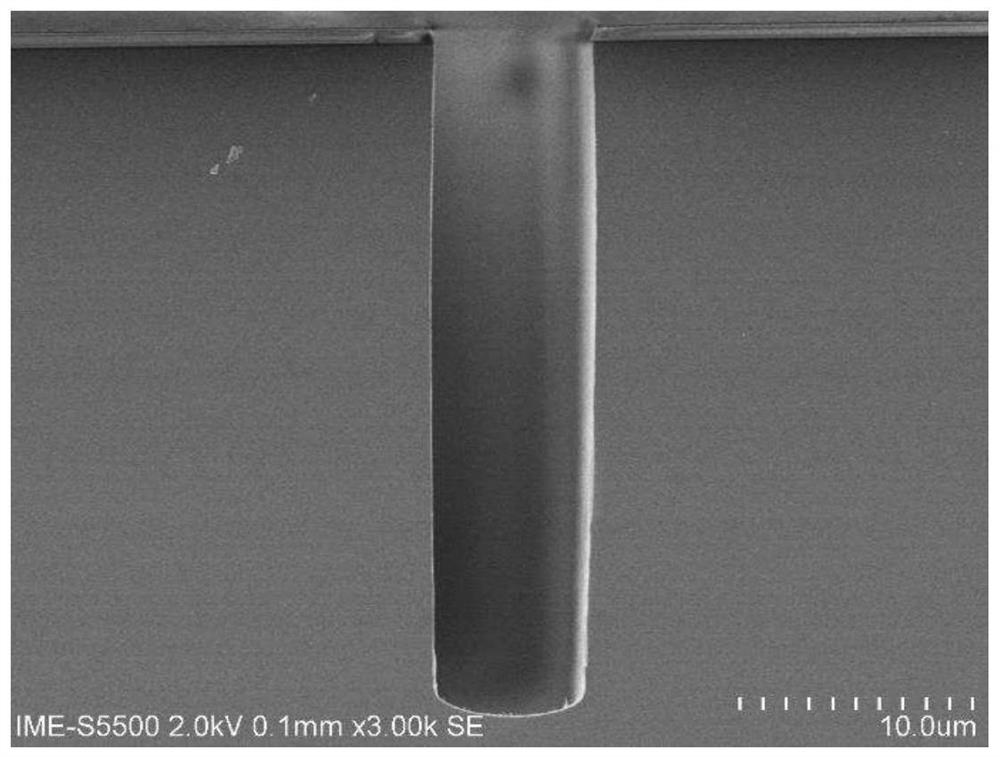

Deep silicon etching method for MEMS

ActiveCN110171802AIntegrity guaranteedMeet the needs of the designDecorative surface effectsChemical vapor deposition coatingLarge sizeSilicon etching

The invention provides a deep silicon etching method for an MEMS, and belongs to the technical field of deep silicon etching. According to the technical scheme, the deep silicon etching method of theMEMS comprises a deposition step, a cleaning step, an etching step, a purging step, a repeated deposition step, a repeated cleaning step, a repeated etching step and a repeated purging step, and is characterized in that side circulation is carried out through the deposition step, the cleaning step, the etching step and the purging step for multiple times, and a sample is vacuumized. The beneficialeffects of the deep silicon etching method are as follows: the deep silicon etching method disclosed by the invention can be applied to a large-scale integrated circuit industrial manufacturing environment; particularly, the integrity of sensing elements can be kept during long-time etching, the device design requirement can be met, the purging step is added, the temperature of the vacuum reaction chamber and the temperature of the sample table can be reduced, the vacuum reaction chamber is kept within a constant range, and the uniformity of large-size samples after being etched and the roughness of the side wall of the MEMS device can be easily provided.

Owner:JIANGSU LEUVEN INSTR CO LTD

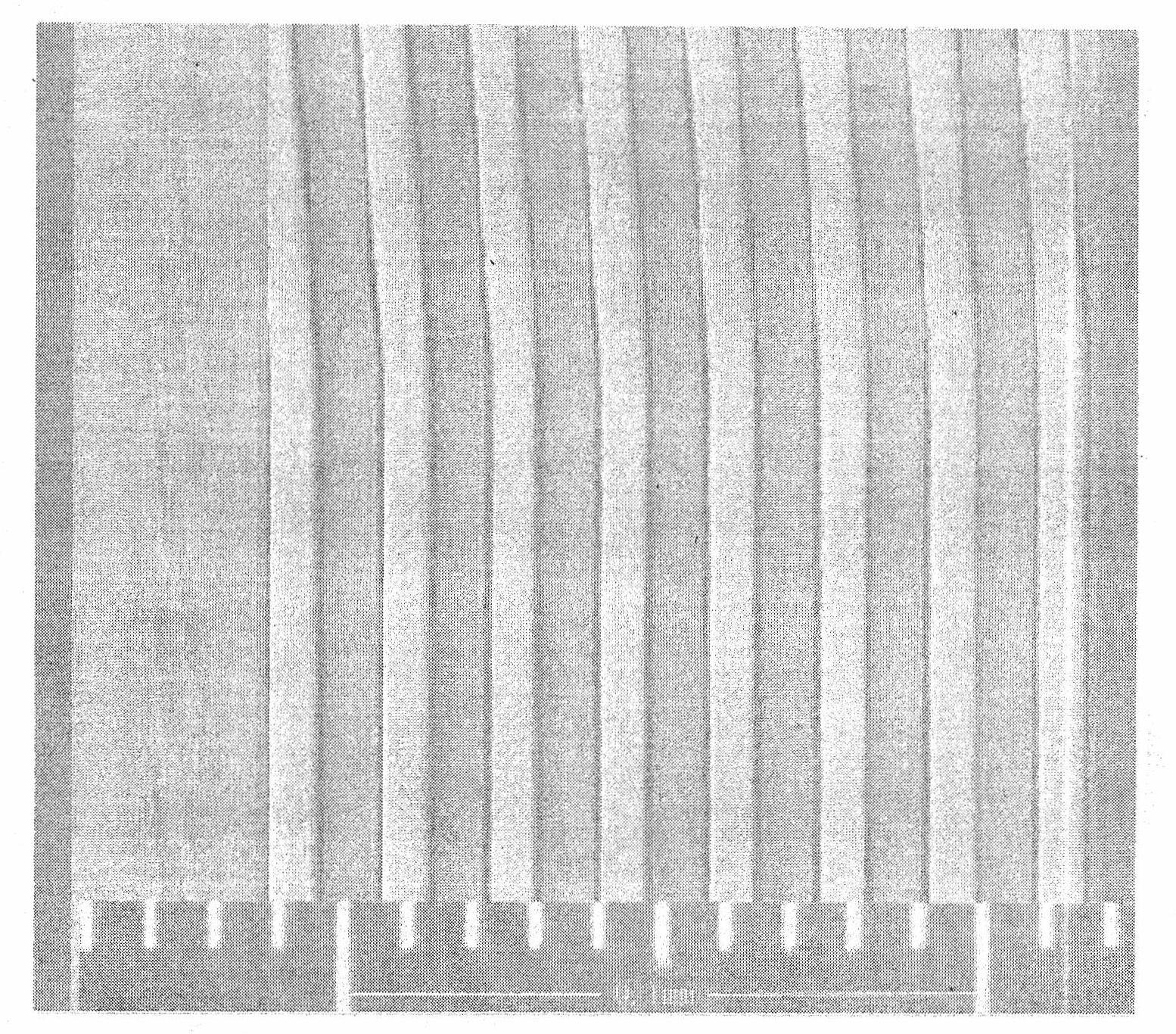

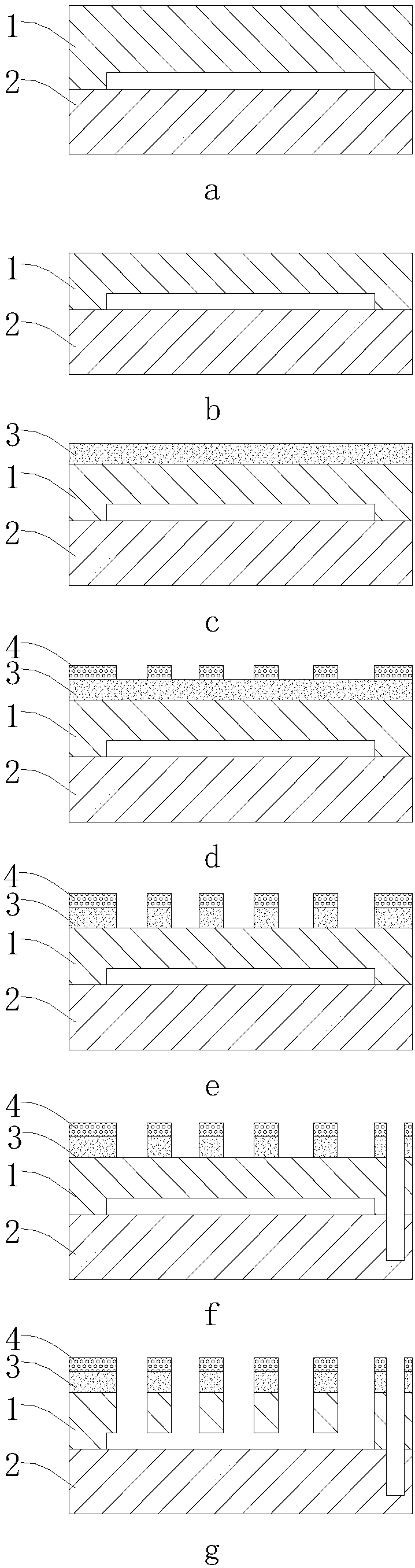

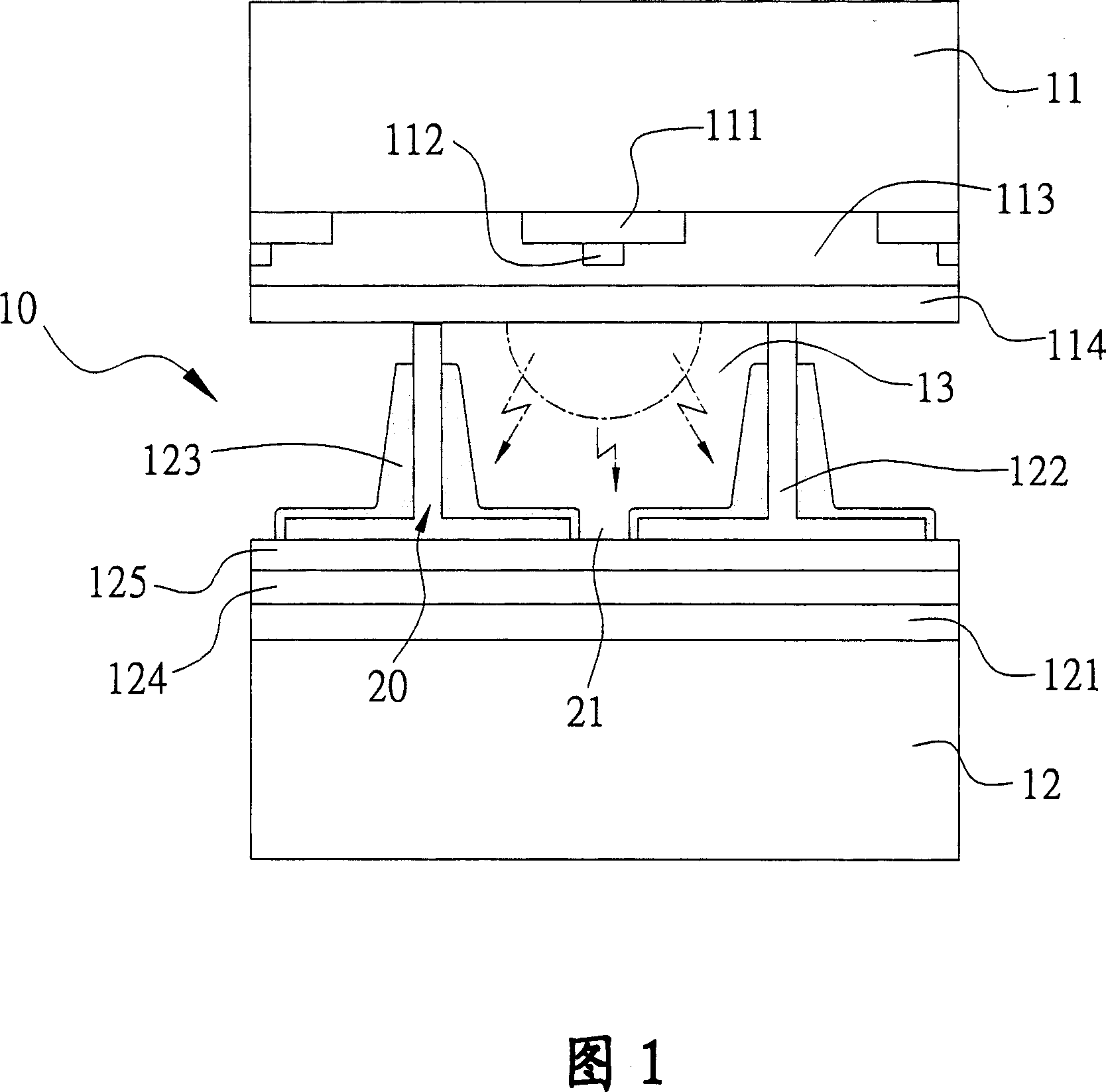

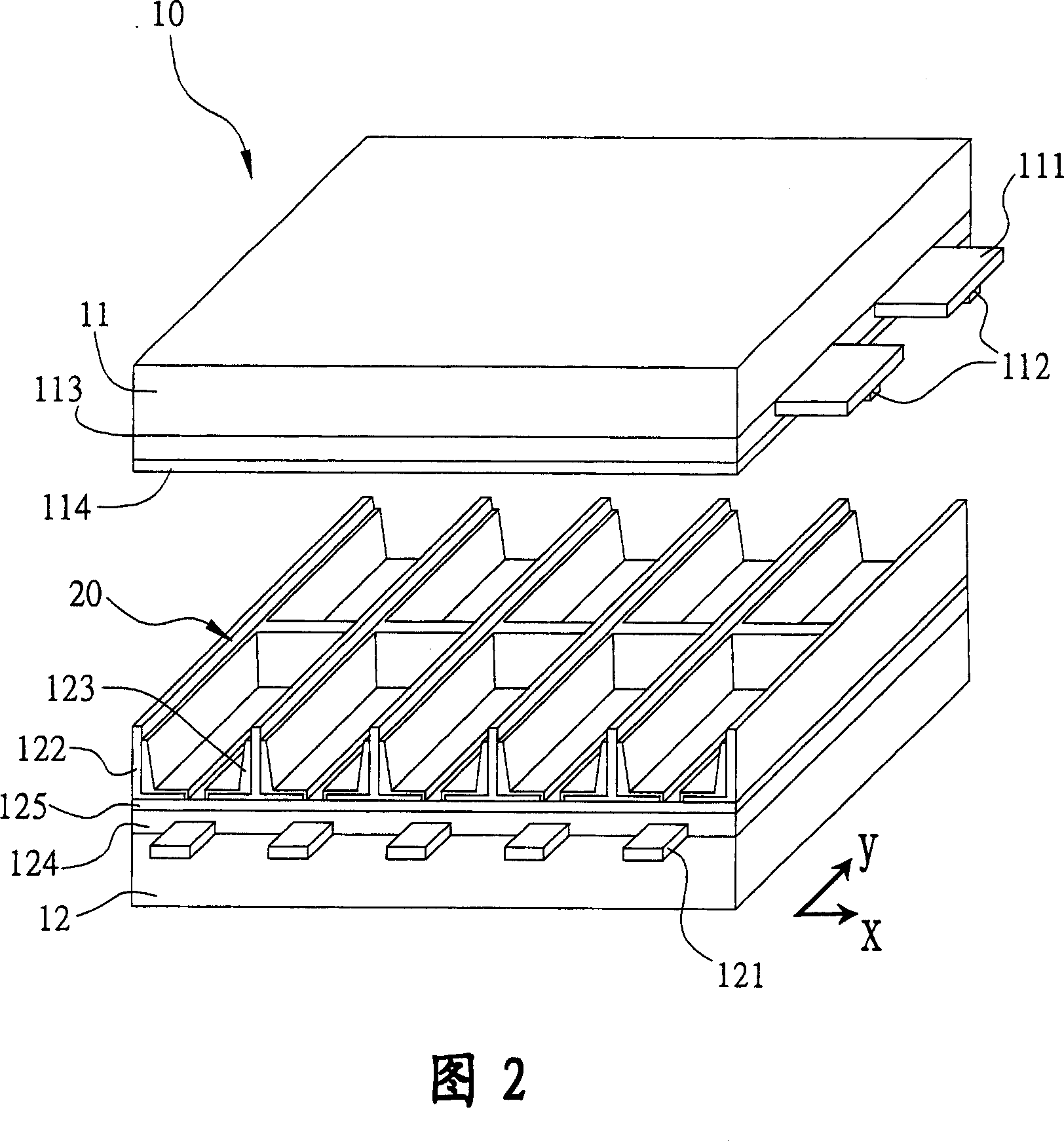

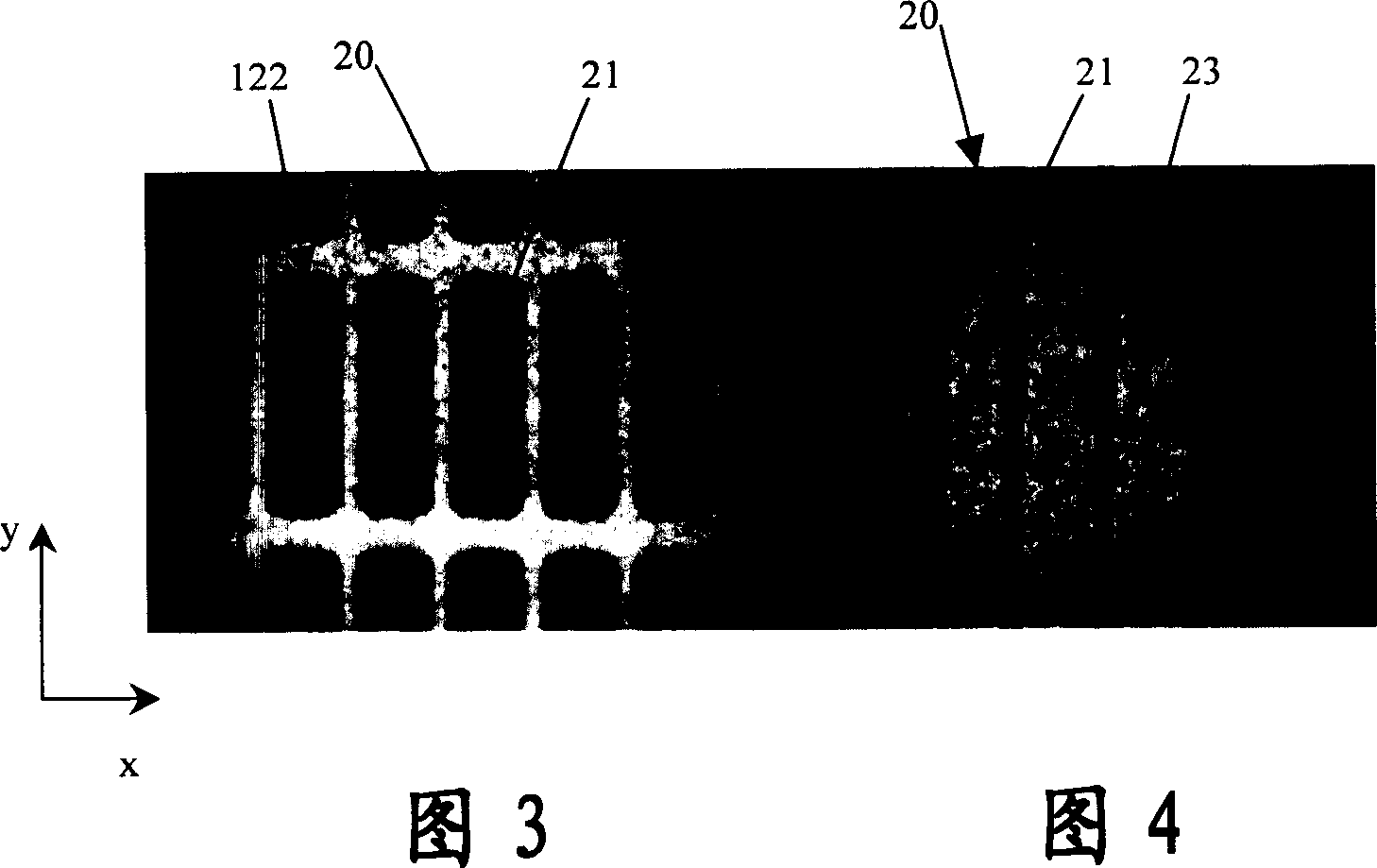

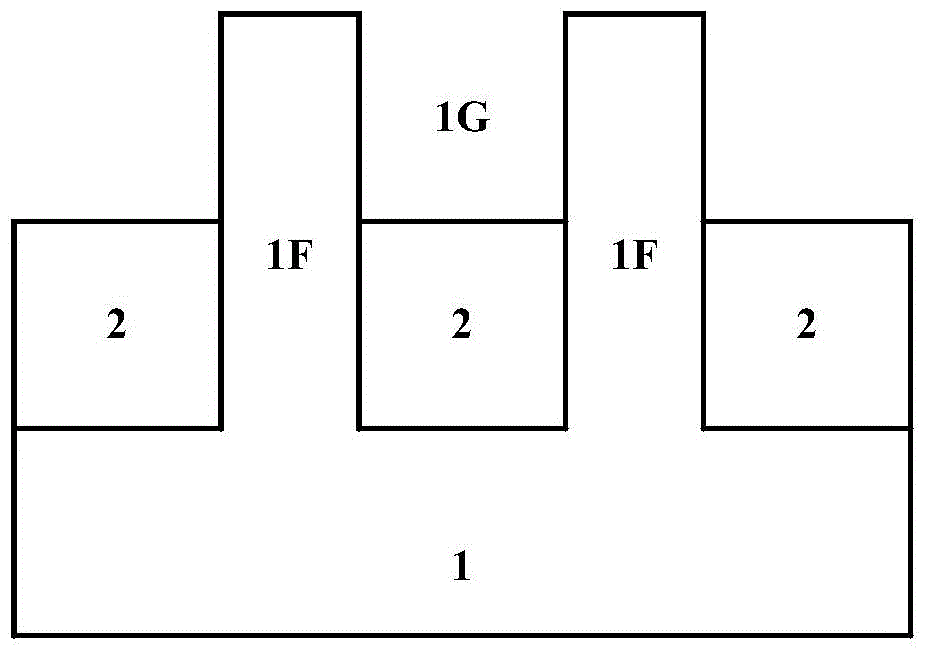

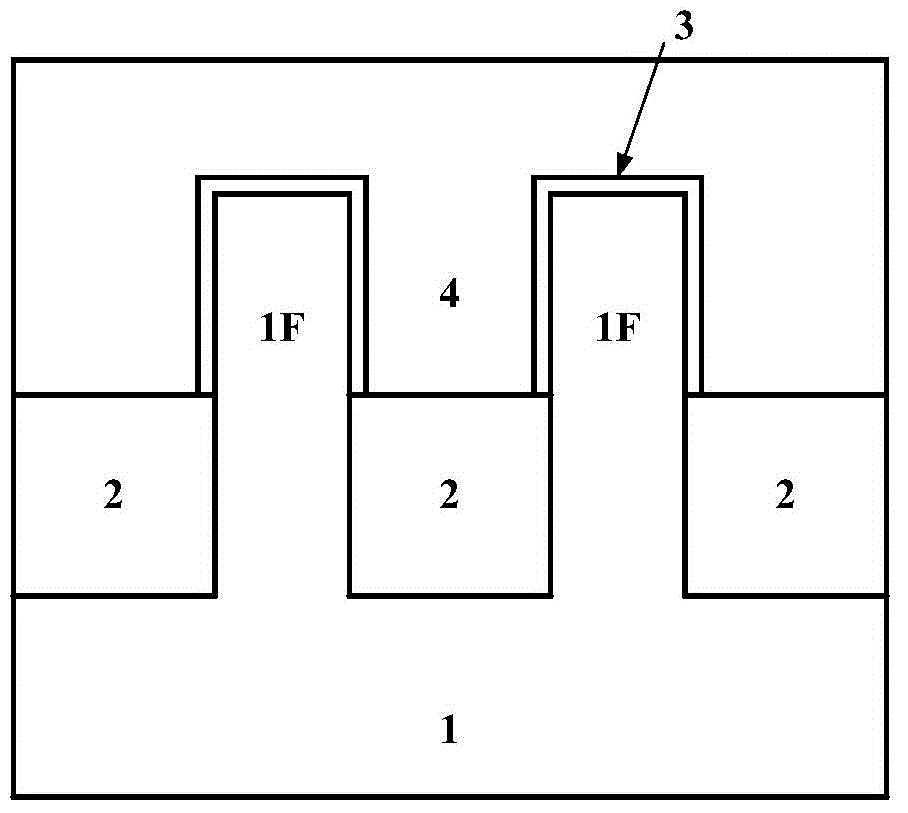

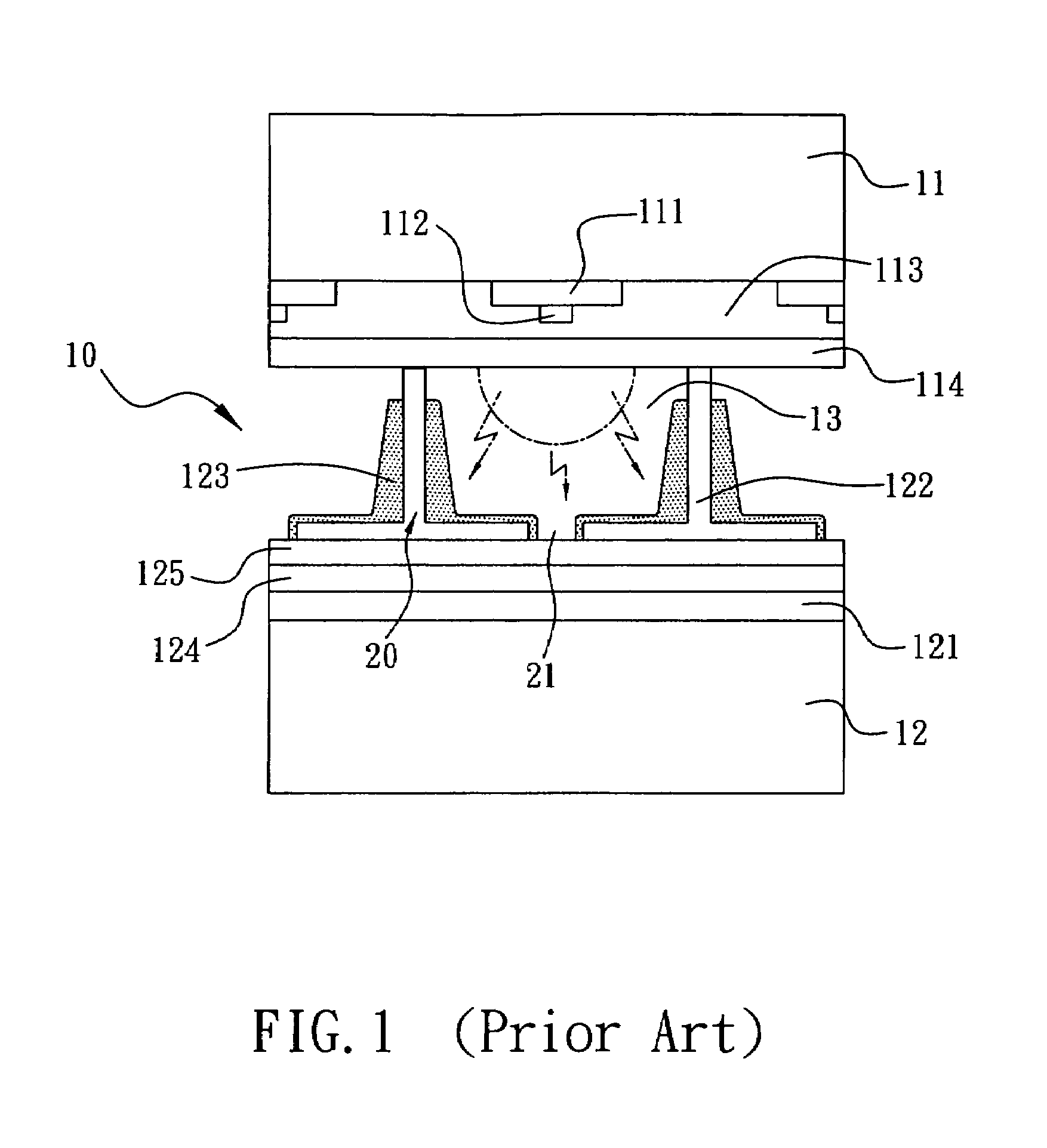

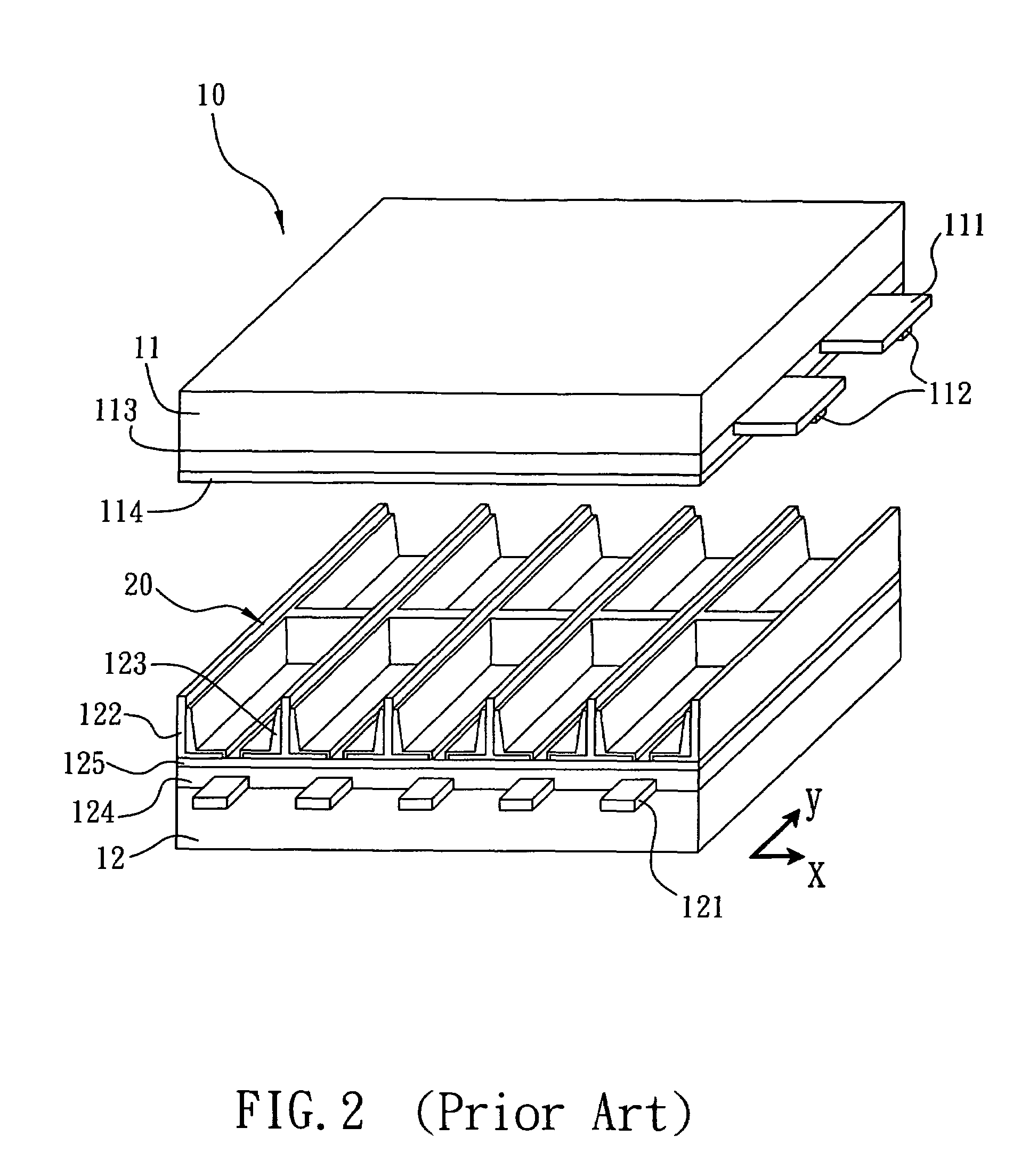

Method for making shadow mask of opposed-discharging type plasma plane display

InactiveCN1979722AIncrease etch depthImprove efficiencyNon-emitting electrodes manufactureEtchingMetal

The invention is for a making method for a kind of shield of plasma plane display of discharge type in opposite direction. The method is to take advantage of the etching process to etch respectively many obstructing walls that are parallel each other and with equidistant spacing on one side surface of one metal plate along the vertical and horizontal direction, and each four neighboring obstructing walls encloses a discharge unit, and a shading hole is etched in the center of each discharge unit whilst that runs through the metal plate; on the other side surface of the metal plate, at least a groove is made that puts through with the shading hole on the position of the relevant discharge unit by taking advantage of the rolling or punch process, and the neighboring grooves put through each other so as to form many air guide ditch on the other side surface. Thus, a shield that is necessary to the plasma plane display of discharge type in opposite direction is made simply and quickly, which can not only reduce the problems of the chemical pollutions caused by the traditional etching on both sides, but also improve the conformability rate of product as well as reduce the fabrication cost.

Owner:MARKETECH INT

Semiconductor device and manufacturing method therefor

ActiveCN105405881AImprove performanceImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesCharge carrier mobilitySemiconductor

The invention discloses a semiconductor device, and the device comprises a plurality of fins which extend in a first direction, a grid electrode which extends in a second direction and is across all the fins, source and drain regions which are located on fins at two sides of the grid electrode, and a grid electrode side wall. Each fin consists of a buffering layer and a trench layer made of high-migration-rate materials, and the buffering layers enclose the side and bottom surfaces of the trench layers. According to the invention, the device can locally form a high carrier mobility trench in a self-alignment manner on a needed fin structure through removing false grid stacking and increasing an etching depth and a lateral width, thereby effectively improving the carrier mobility of a fin trench region, and effectively improving the performance and reliability of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Method for making a shadow mask for an apposed discharge plasm display panel

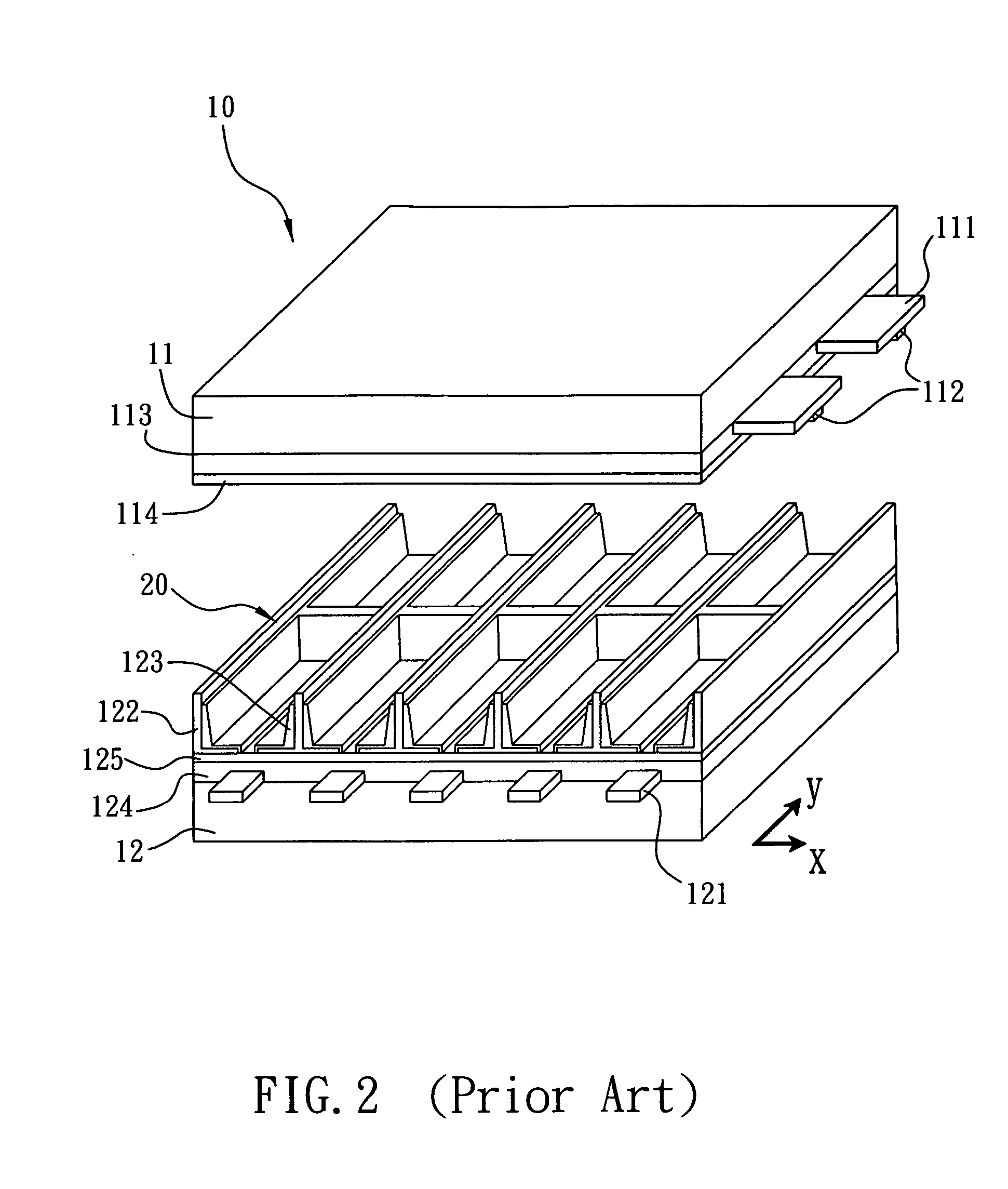

InactiveUS20070117241A1The way is simple and fastImprove production yieldDecorative surface effectsAlternating current plasma display panelsEtchingCompound (substance)

The present invention is to provide a method for making a shadow mask for an opposed discharge plasma display panel by etching one lateral surface of a metal slab to produce a plurality of parallel and equidistant barrier ribs along the vertical and horizontal directions on the lateral surface and a discharging cell by enclosing every four adjacent barrier ribs. A shadow hole is formed at the middle of each discharging cell and etched through the metal slab, and at least one groove interconnected to the shadow holes is produced on another lateral surface of the metal slab by utilizing a rolling process or a stamping process. The adjacent grooves are interconnected with each other, and a plurality of air guide channels is formed on another lateral side, such that a shadow mask can be made in a simple and fast manner, chemical pollutions caused by a traditional double-sided etching can be minimized, and the product yield rate and the manufacturing cost can be effectively improved and lowered.

Owner:MARKETECH INT

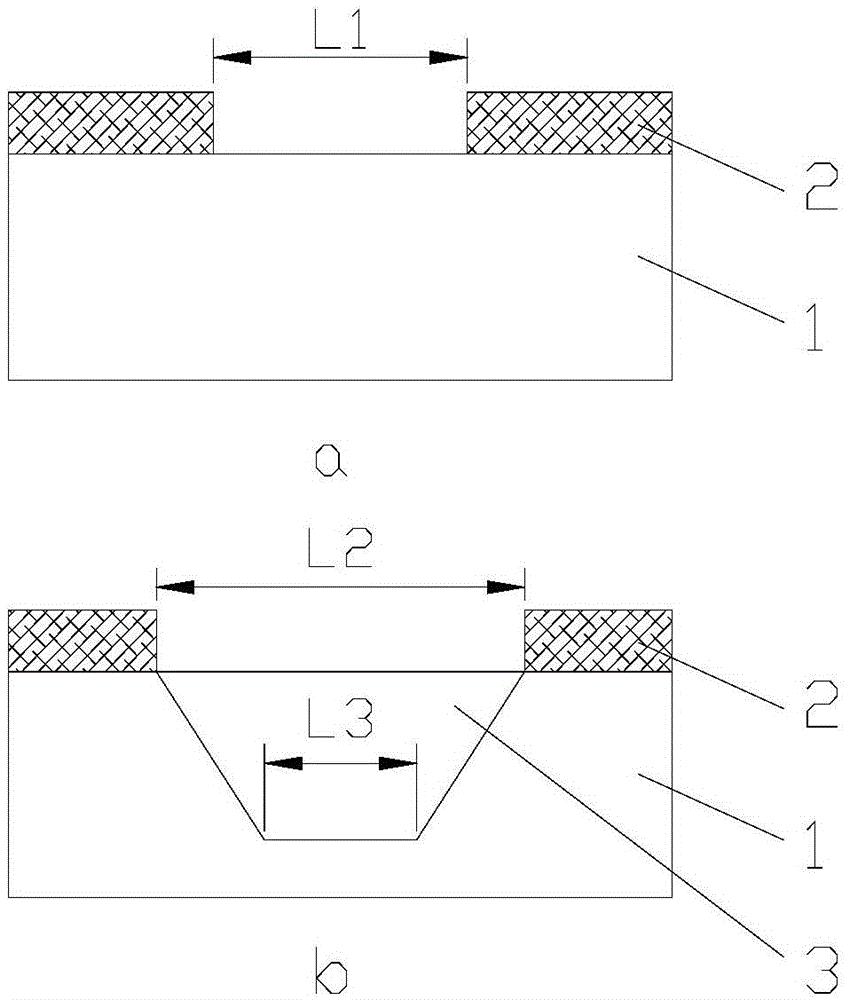

Substrate etching method

InactiveCN106783584AIncrease etch depthProtect the side walls of deep wellsSemiconductor/solid-state device manufacturingChemistryEtching rate

The present invention provides a substrate etching method. The method is configured to etch a deep hole at the surface to be etched of a silicon dioxide substrate, and comprises the following steps: an etching step: employing the fluorine-containing gas which has an etching product being gas as the main etching gas and employing the inert gas as auxiliary gas to perform anisotropic etching so as to increase the etching depth; a deposition step: employing the fluorocarbon gas as the deposition gas to respectively deposit one layer of polymer at the side wall of the deep hole and the bottom of the deep hole; and circulation of the two steps mentioned above until reaching the required total etching depth. The substrate etching method allows the etching of the deep hole to be performed at the consistent temperature so as to avoid the prolonging of the whole etching time caused by the temperature difference, improve the average etching rate and fit the technology volume production.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

Method for making a shadow mask for an opposed discharge plasma display panel

InactiveUS7393457B2The way is simple and fastPollution minimizationDecorative surface effectsAlternating current plasma display panelsEtchingEngineering

The present invention is to provide a method for making a shadow mask for an opposed discharge plasma display panel by etching one lateral surface of a metal slab to produce a plurality of parallel and equidistant barrier ribs along the vertical and horizontal directions on the lateral surface and a discharging cell by enclosing every four adjacent barrier ribs. A shadow hole is formed at the middle of each discharging cell and etched through the metal slab, and at least one groove interconnected to the shadow holes is produced on another lateral surface of the metal slab by utilizing a rolling process or a stamping process. The adjacent grooves are interconnected with each other, and a plurality of air guide channels is formed on another lateral side, such that a shadow mask can be made in a simple and fast manner, chemical pollutions caused by a traditional double-sided etching can be minimized, and the product yield rate and the manufacturing cost can be effectively improved and lowered.

Owner:MARKETECH INT

A deep silicon etching method for mems

ActiveCN110171802BIntegrity guaranteedMeet the needs of the designDecorative surface effectsChemical vapor deposition coatingEngineeringSilicon etching

The invention provides a MEMS deep silicon etching method, which belongs to the technical field of deep silicon etching. The technical solution is: a MEMS deep silicon etching method, including deposition steps, cleaning steps, etching steps, purging steps, repeated deposition steps, repeated cleaning steps, repeated etching steps and repeated purging steps, after several The deposition step, cleaning step, etch step and purge step are side-circulated, and the sample is out of vacuum. The beneficial effects of the present invention are: the deep silicon etching method of the present invention can be applied in the industrial manufacturing environment of large-scale integrated circuits, in particular, it can enable the sensor element to maintain the integrity of the device during long-term etching, and It can meet the needs of device design, adding a purge step can reduce the temperature of the vacuum reaction chamber and the sample stage, so that the vacuum reaction chamber can be kept in a constant range, which helps to provide the uniformity of large-scale samples after etching and the roughness of the sidewall of the MEMS device.

Owner:JIANGSU LEUVEN INSTR CO LTD

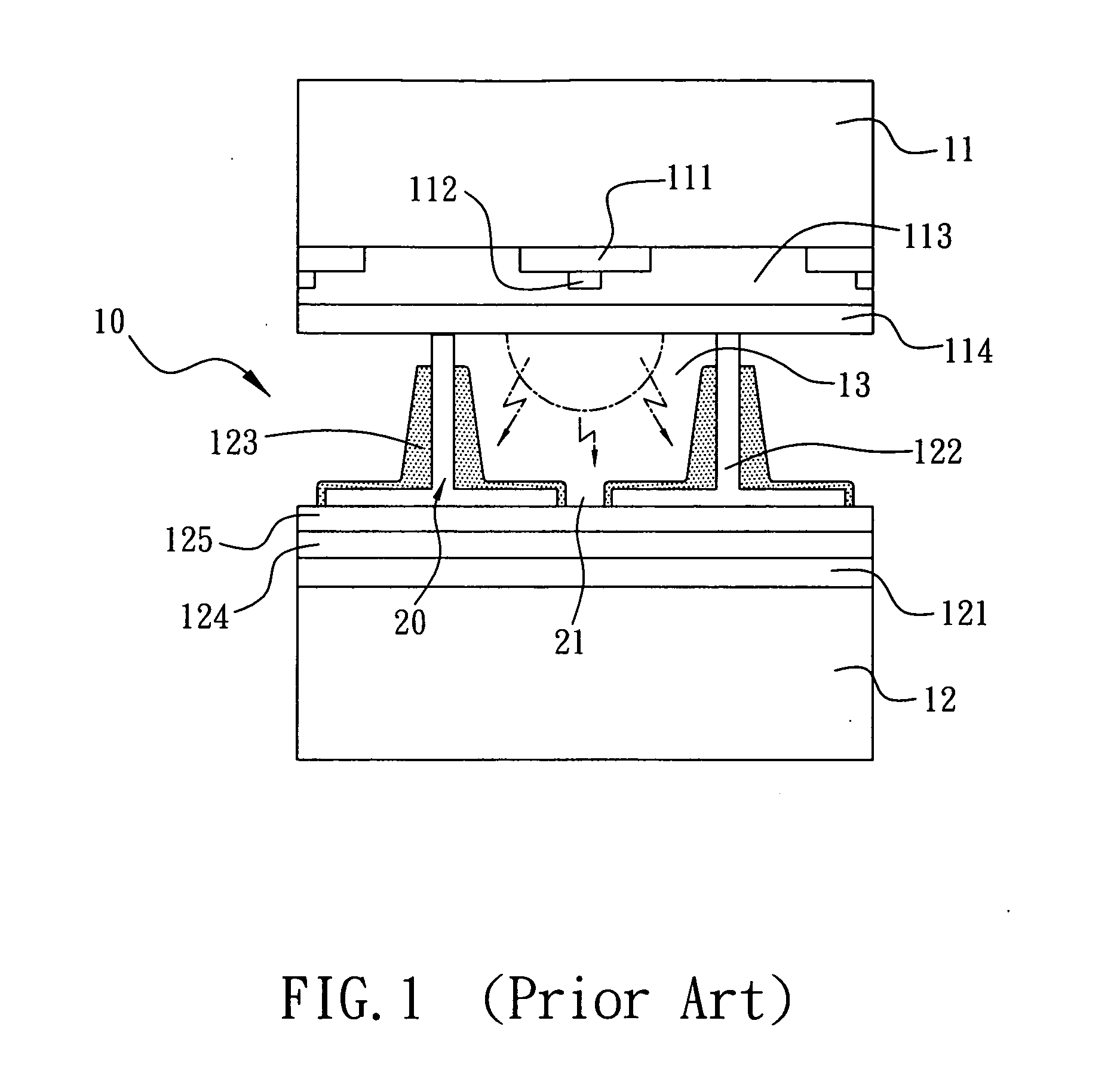

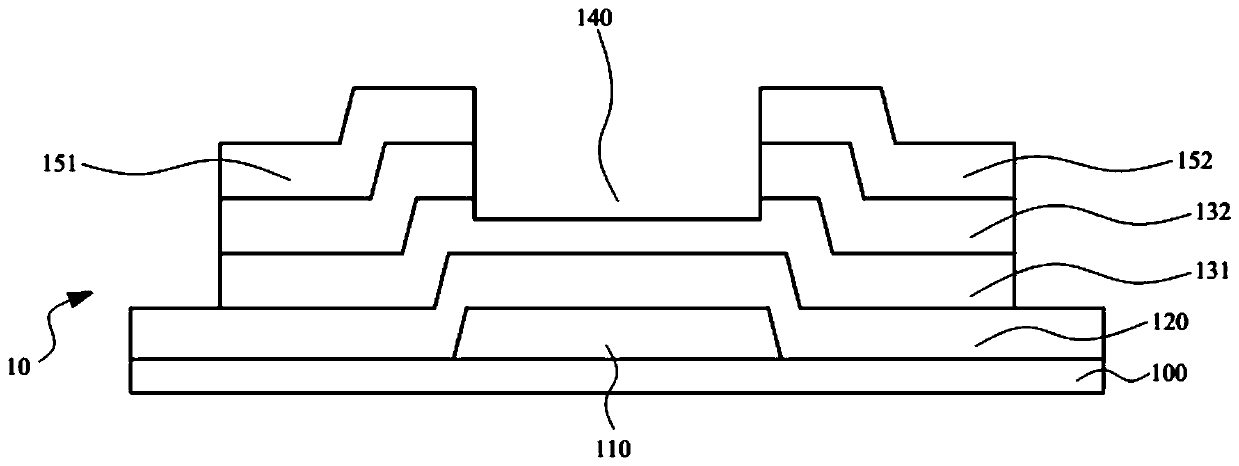

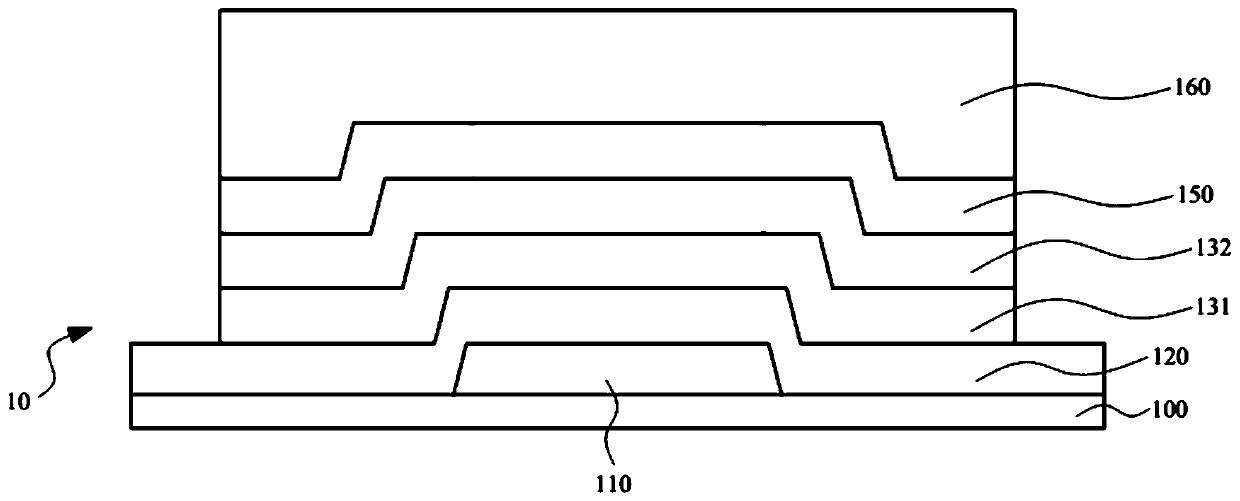

Manufacturing method of display panel and photomask of display panel

ActiveCN109786322ADon't change the widthAdjust exposureSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

The invention provides a manufacturing method of a display panel and a photomask of the display panel. The manufacturing method comprises the steps of: providing a first substrate; setting a grid layer on the first substrate; setting a grid insulation layer on the first substrate and the grid layer; setting a source layer and a drain layer on the grid insulation layer; and forming a channel regionbetween the source layer and the drain layer through the photomask, wherein the photomask is provided with a channel region pattern which is provided with a light supplementing pattern on the sourcelayer or the drain layer, and through the light supplementing pattern, the light of the photomask can reach the channel region.

Owner:HKC CORP LTD

Preparation method of holographic grating photoresist patterns with multiple shapes and narrow line widths of hundreds of nanometers

ActiveCN101738662BElasticityThe degree of freedom becomes largerDiffraction gratingsPhotomechanical coating apparatusLine widthPhotoresist

The invention discloses a method for preparing a holographic grating photoresist pattern with a narrow line width of 100 nanometers and various shapes. Drop glue on the bottom to obtain photoresist layers with thicknesses of 70nm, 110nm, 160nm, 240nm and 290nm respectively; Step 2: Use a 325nm holographic exposure system to expose the photoresist layers of different thicknesses with corresponding doses; Step 3 : develop and fix the exposed sample to obtain the corresponding photoresist grating topography pattern; step 4: post-bake the sample, remove the primer with a plasma degumming machine, and analyze the obtained photoresist grating The shape is modified. By using the invention, the holographic grating photoresist pattern with various shapes and narrow line widths in the order of 100 nanometers is prepared.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Etching processing method and device for high-quality alumina ceramics

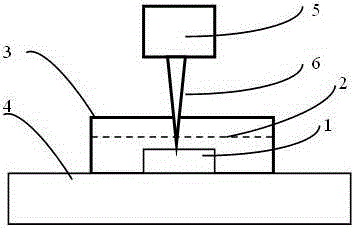

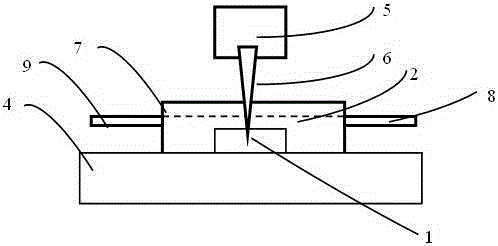

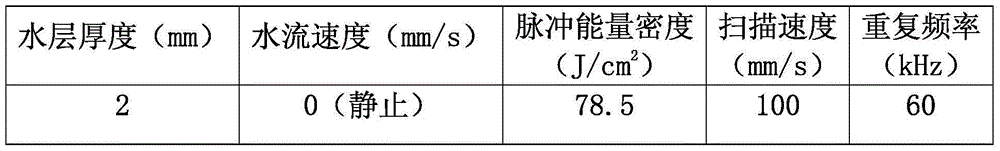

ActiveCN103894739BAvoid blackening and deteriorationIncrease etch depthWelding/soldering/cutting articlesLaser beam welding apparatusLaser etchingGalvanometer

The invention discloses a method and a device for etching and processing aluminum oxide ceramics. The method includes positioning the integral clean aluminum oxide ceramics in water; scanning, etching and processing the aluminum oxide ceramics by the aid of ultraviolet pulse laser. The distances from the surface of the water to the surfaces of aluminum oxide ceramic materials range from 2mm to 12mm. The surfaces of the etched and processed aluminum oxide ceramics are free of blackened deterioration layers and re-coagulation layers. The device comprises an ultraviolet laser device, a scanning galvanometer, a two-dimensional processing platform and a container. The container is used for accommodating the water and the to-be-processed aluminum oxide ceramics. The method and the device have the advantages that a 'water' factor is ingeniously introduced into the method and the device, cooling and slagging effects can be realized when the aluminum oxide ceramics are etched by the aid of the laser under the condition of a certain thickness or in the water with a certain flow rate, accordingly, blackening deterioration due to direct etching in the air can be effectively prevented, the etching depth can be increased, the etching quality and the laser etching and processing efficiency can be improved, and various three-dimensional complicated patterns with high dimensional precision can be etched and manufactured on the surfaces of the aluminum oxide ceramics by the aid of the method and the device.

Owner:武汉飞能达激光技术有限公司

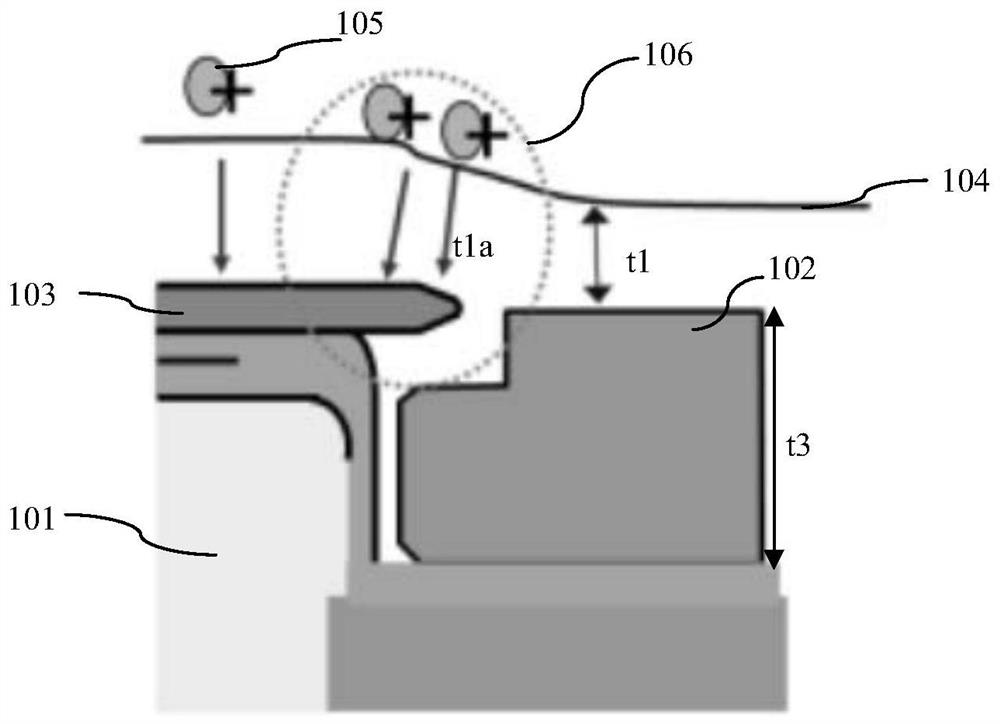

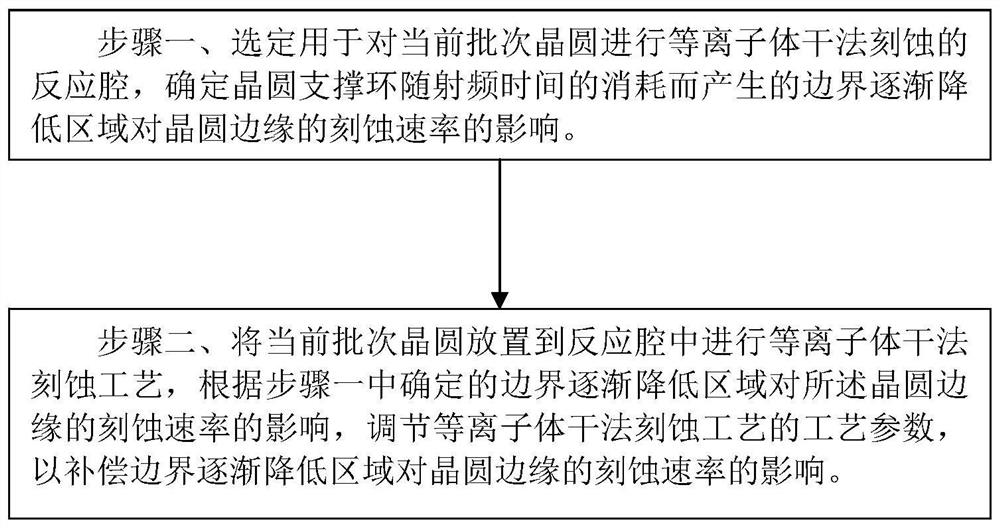

Control method of plasma dry etching process

ActiveCN112259452AEffect of increasing etch rateStable etch depthSemiconductor/solid-state device manufacturingTotal factory controlWaferEngineering

The invention discloses a method for controlling a plasma dry etching process, and the method comprises the following steps: 1, selecting a reaction cavity for performing plasma dry etching on a current batch of wafers, and determining the influence of a boundary gradually-reduced region generated by a wafer support ring along with the consumption of radio frequency time on the etching rate of theedge of the wafer; 2, placing the current batch of wafers into a reaction chamber to carry out a plasma dry etching process, and adjusting process parameters of the plasma dry etching process according to the influence of the boundary gradually-reduced area determined in the step 1 on the etching rate of the wafer edge, so that the influence of the area on the etching rate of the wafer edge is gradually reduced by the compensation boundary. The wafer edge etching depth can be kept stable, the service life of parts of the reaction cavity can be prolonged, and the process time between two timesof cavity opening can be prolonged, so the process cost is reduced, and the productivity of a machine table is improved.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

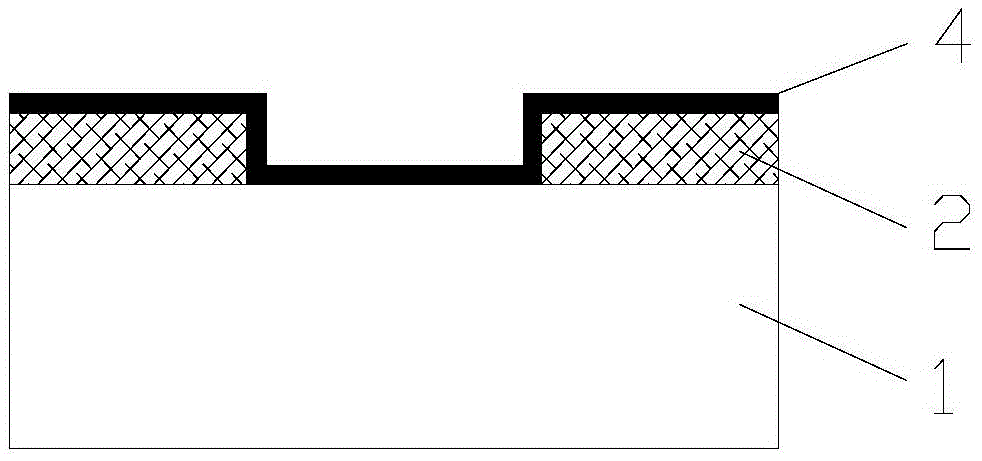

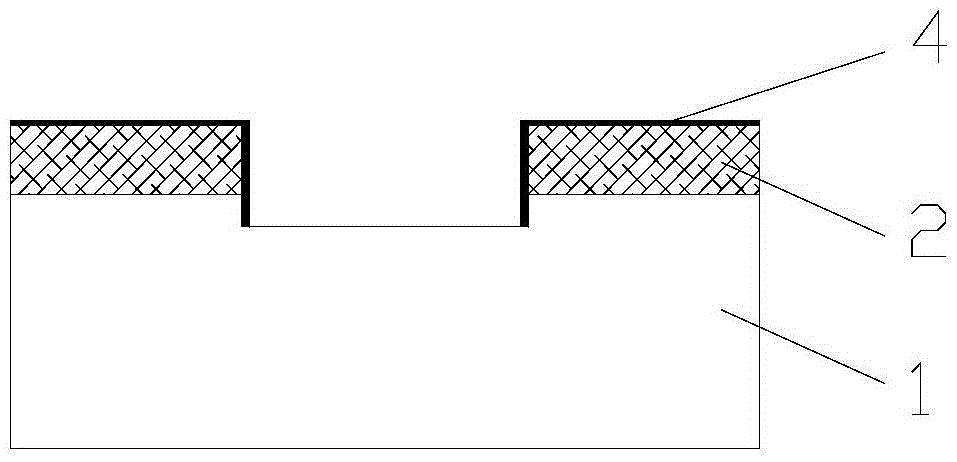

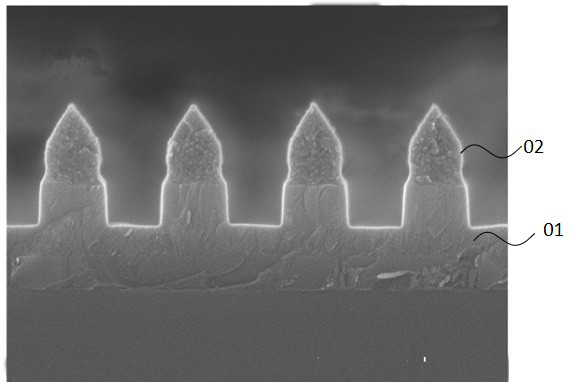

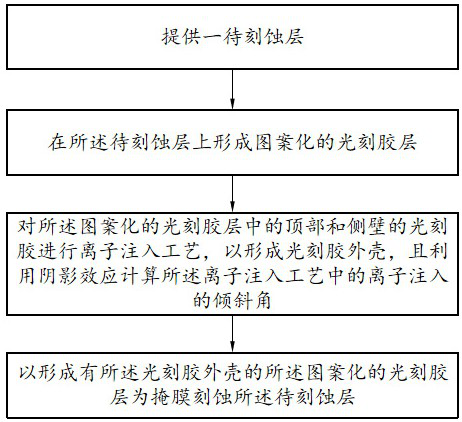

Etching method

ActiveCN111933525BSmall attenuationIncrease etch depthSemiconductor/solid-state device manufacturingEtchingPhotoresist

The invention provides an etching method, comprising: firstly, providing a layer to be etched; then, forming a patterned photoresist layer on the layer to be etched; The photoresist on the top and sidewalls in the glue layer is subjected to an ion implantation process to form a photoresist shell, and the tilt angle θ of the ion implantation in the ion implantation process is calculated using the shadow effect; finally, to form the The patterned photoresist layer of the photoresist shell is used as a mask to etch the layer to be etched. The present invention forms a photoresist shell by performing an ion implantation process on the top and sidewall photoresist in the patterned photoresist layer, which can reduce the attenuation of the patterned photoresist layer during the etching process, and Increase thickness selectivity of photoresist.

Owner:南京晶驱集成电路有限公司

Femto second compression device

ActiveCN101187770BCompact structureEasy to manufactureLaser detailsNon-linear opticsDiffraction orderGrating

A femtosecond pulse compression device comprises a first grating and a second grating which are arranged in parallel, and the surfaces of the two gratings, which are provided with grating fringes, arearranged on the inner side of the gratings, the first grating and the second grating with the same structure are all sub-wavelength deep etching transmission gratings whose periodic times are d, thesecond grating is arranged on the second direction of the diffraction order of the transmission negative first order of the first grating, femtosecond laser pulse which needs to be compressed is incident to the first grating in a Bragg angle theta and meet the grating equation, sin theta= lambda0 / 2d, wherein theta is an incident angle, lambda0 is a center wavelength of the femtosecond laser pulse.The invention utilizes the sub-wavelength deep etching transmission gratings to constitute the femtosecond pulse compression device which has the advantages of compact structure and high efficiency.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

Semiconductor device and manufacturing method thereof

ActiveCN105405881BImprove performanceImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialCharge carrier mobility

The invention discloses a semiconductor device, comprising: a plurality of fins extending along a first direction on a substrate, extending along a second direction and crossing the gate of each fin, The source-drain region and the side wall of the gate, wherein the fin is composed of a buffer layer and a channel layer made of high-mobility material, and the buffer layer surrounds the side surface and the bottom surface of the channel layer. According to the semiconductor device and its manufacturing method of the present invention, by removing the dummy gate stack while increasing the etching depth and lateral width, a high carrier mobility can be locally aligned on the desired fin structure channel, thereby effectively improving the carrier mobility in the channel region of the fin, thereby effectively improving device performance and reliability.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

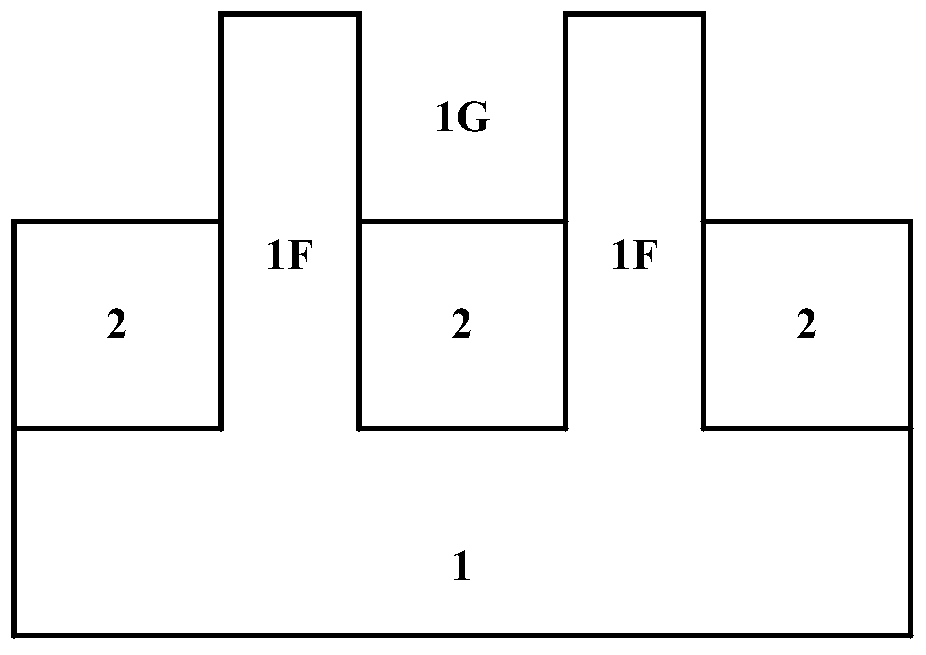

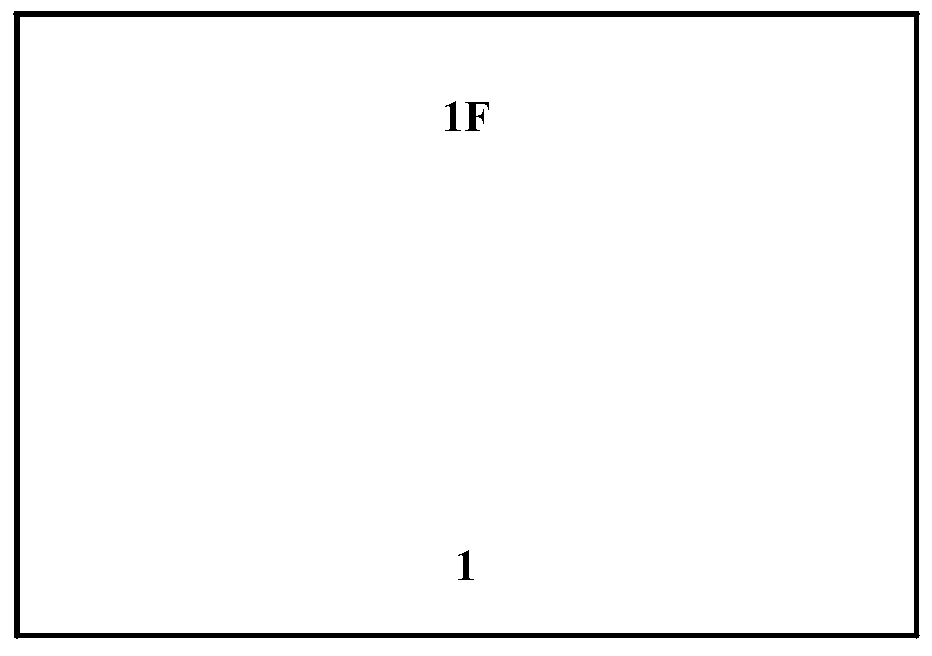

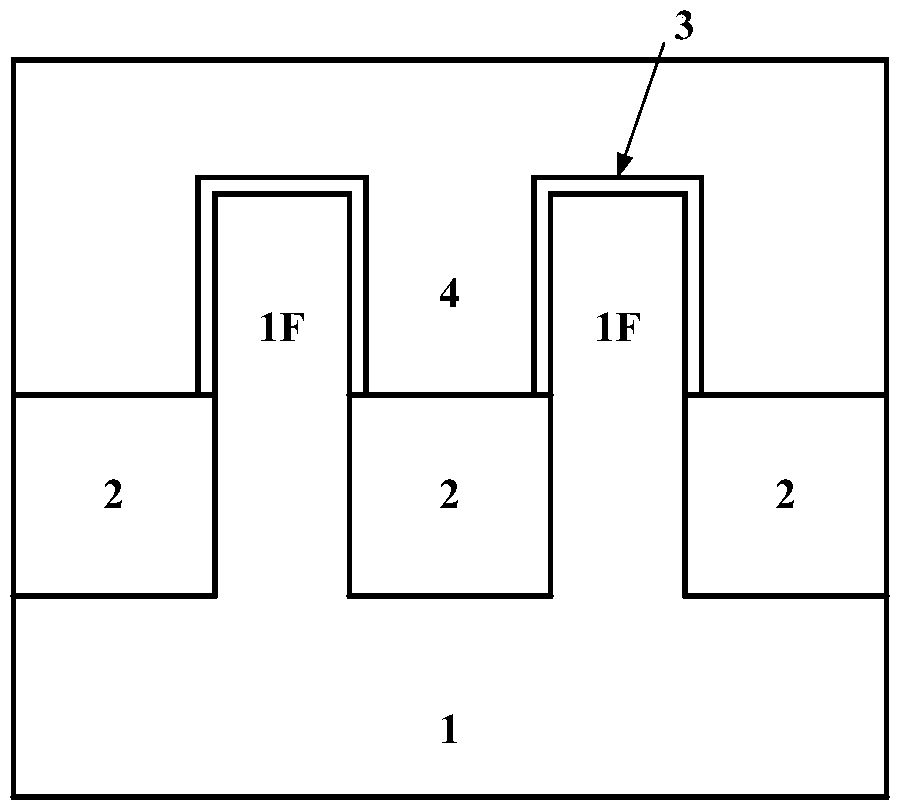

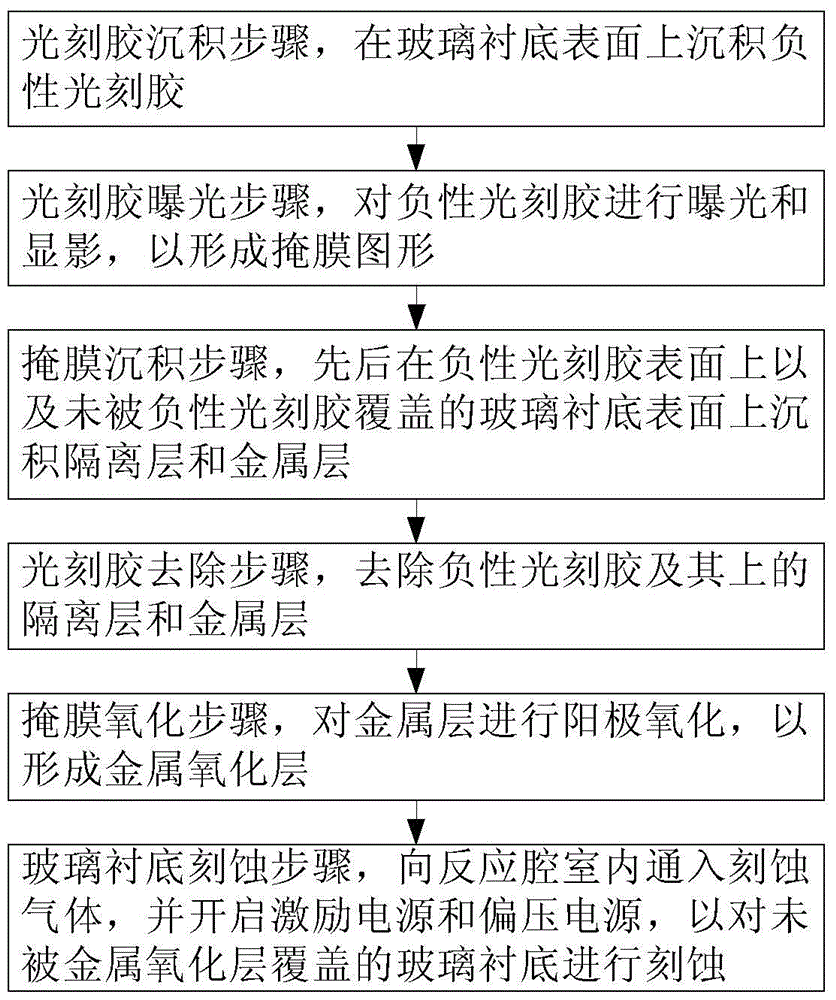

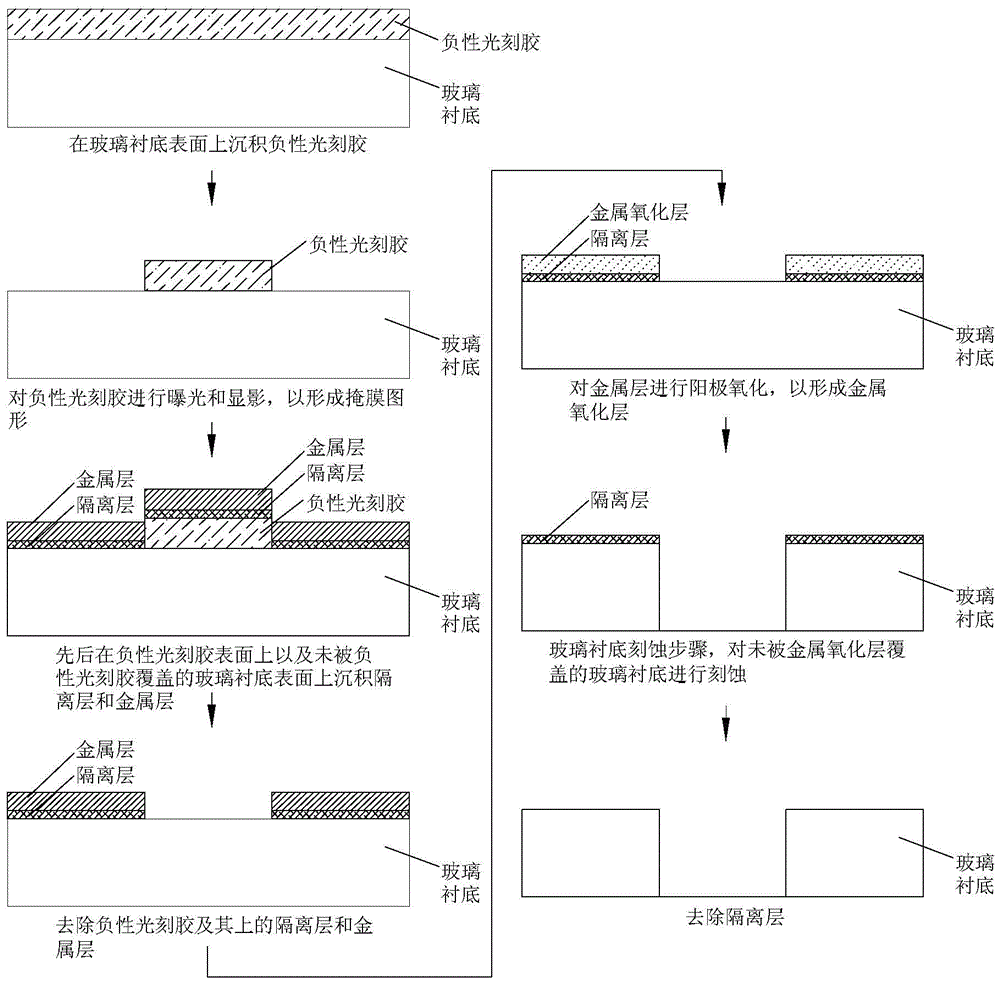

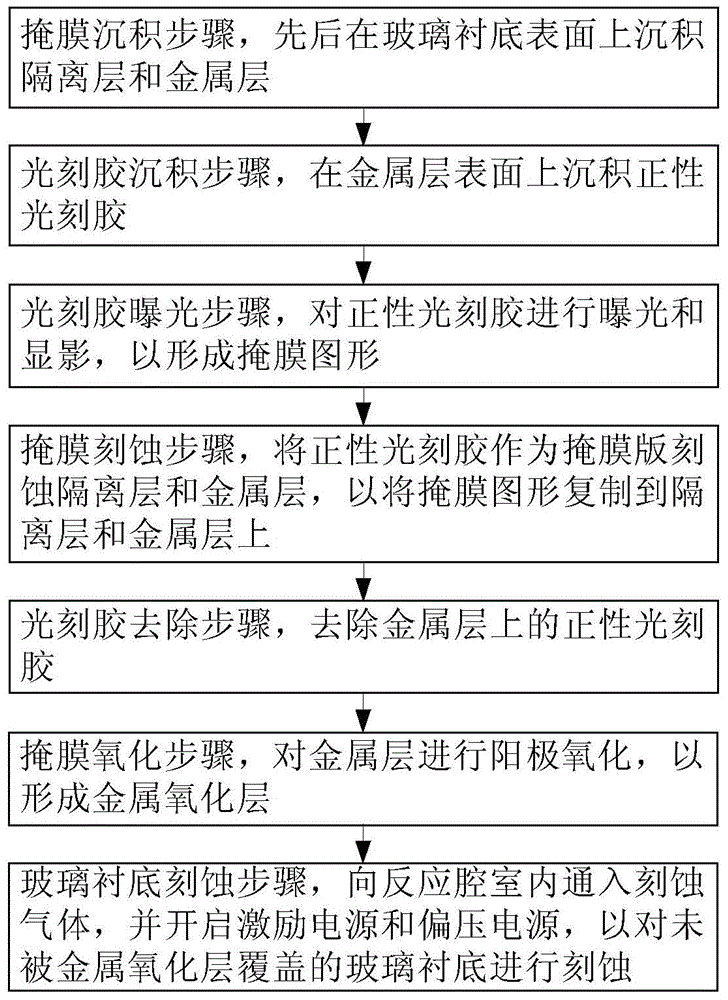

Process method of glass substrate

ActiveCN104743499BHard textureImprove etch selectivityDecorative surface effectsChemical vapor deposition coatingIsolation layerMetallic materials

The invention provides a technological method for a glass substrate. The method includes: a photoresist deposition step: depositing negative photoresist on a glass substrate surface; a photoresist exposure step: exposing and developing negative photoresist to form a mask pattern; a mask deposition step: depositing an isolation layer and a metal layer on the negative photoresist surface and the glass substrate surface not covered by the negative photoresist in order, wherein the isolation layer is prepared from an anti-anodic oxidation material, and the metal layer is prepared from a bivalent or trivalent metal material; a photoresist removal step: removing the negative photoresist and the isolation layer and the metal layer thereon; and a mask oxidation step: carrying out anodic oxidation on the metal layer to form the metal oxide layer. The technological method for the glass substrate provided by the invention can improve the etching selection ratio of the glass substrate to the mask.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

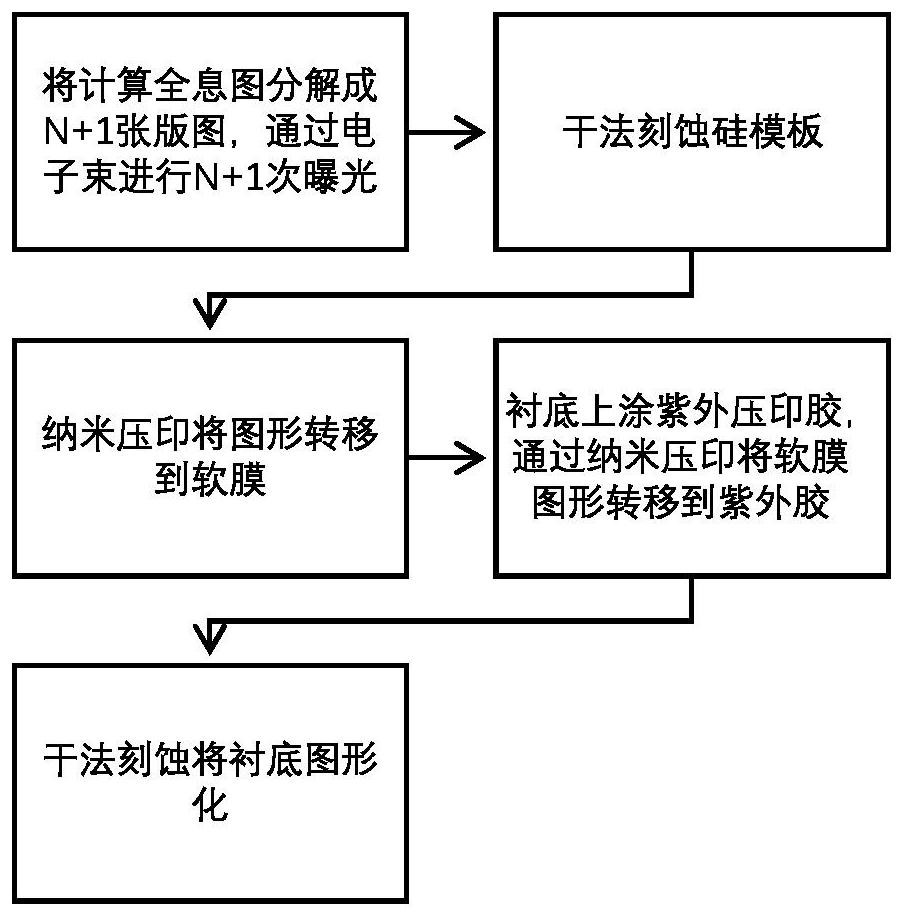

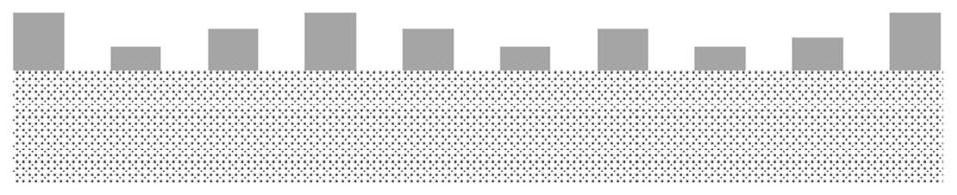

Method for preparing 2.5 D micro-nano structure through gray exposure

PendingCN113173559AImprove efficiencyGuaranteed Exposure AccuracyDecorative surface effectsPhotomechanical apparatusNano structuringSilicon chip

The invention discloses a method for preparing a 2.5 D micro-nano structure through gray exposure, and belongs to the technical field of microstructures in semiconducting science. The method comprises the steps of: dividing the height of the 2.5 D micro-nano structure into 2N levels, establishing corresponding N binary exposure layouts, wherein N is larger than I; acquiring a union set of the N binary exposure layouts, and establishing an additional compensation layout; carrying out N+1 times of layered exposure after spin-coating photoresist on the silicon wafer to obtain a photoresist layer containing 2N heights; and using the photoresist layer as a mask to perform dry etching to prepare a nanoimprint template, and realizing batch production through soft film thermocuring nanoimprint and secondary transfer printing of ultraviolet curing nanoimprint. The nanoimprint template is high in pattern precision and has 2N different heights, and the micro-nano structure prepared through soft film transfer printing, nanoimprint and dry etching is high in efficiency, high in yield and accurate in size.

Owner:HUAZHONG UNIV OF SCI & TECH