Patents

Literature

31results about How to "Alleviate the problem" patented technology

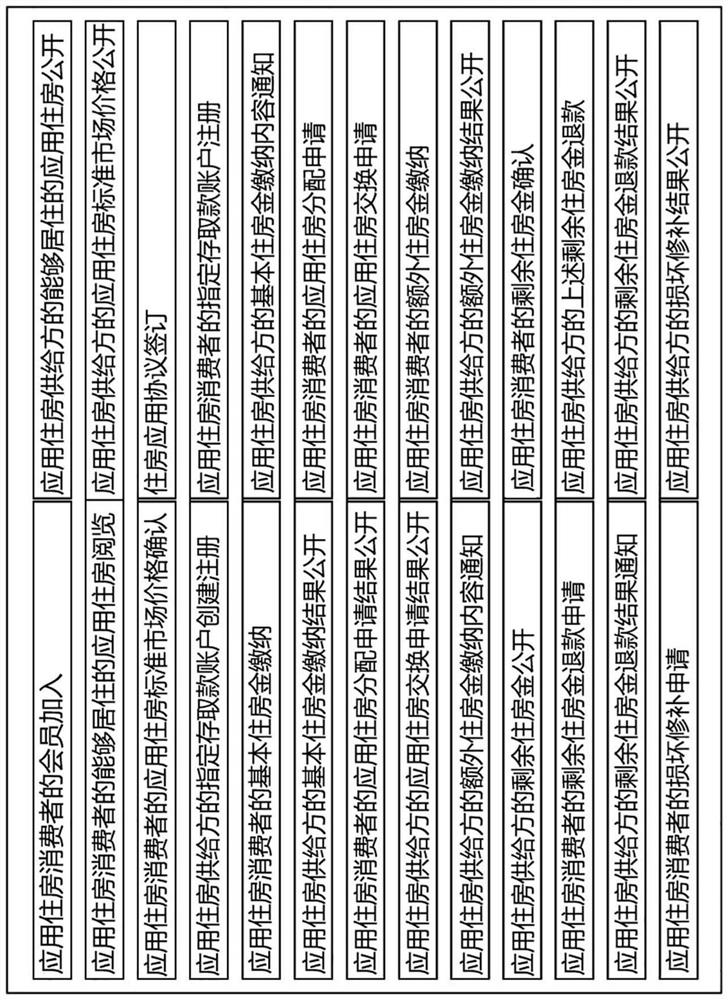

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

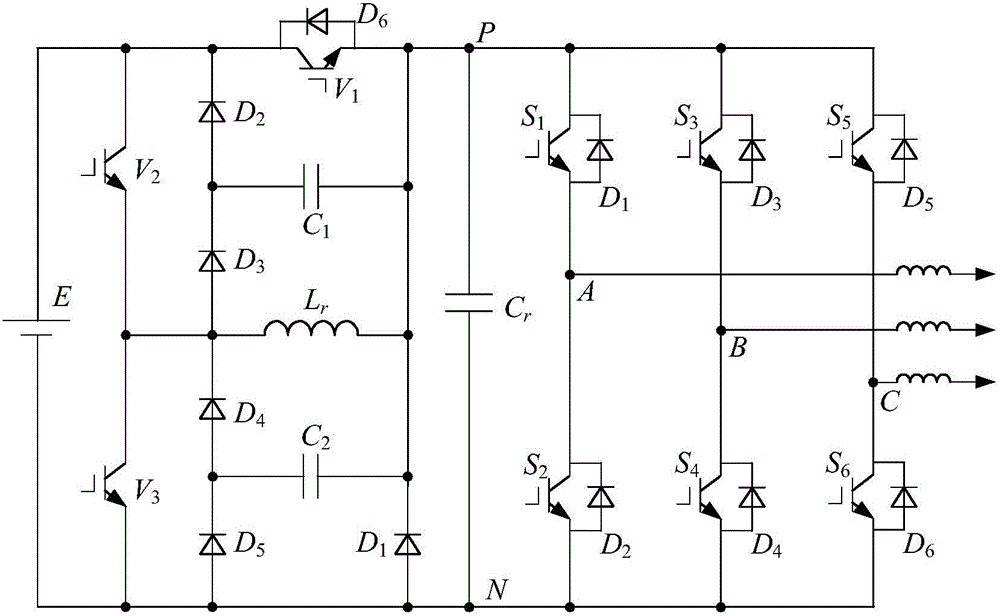

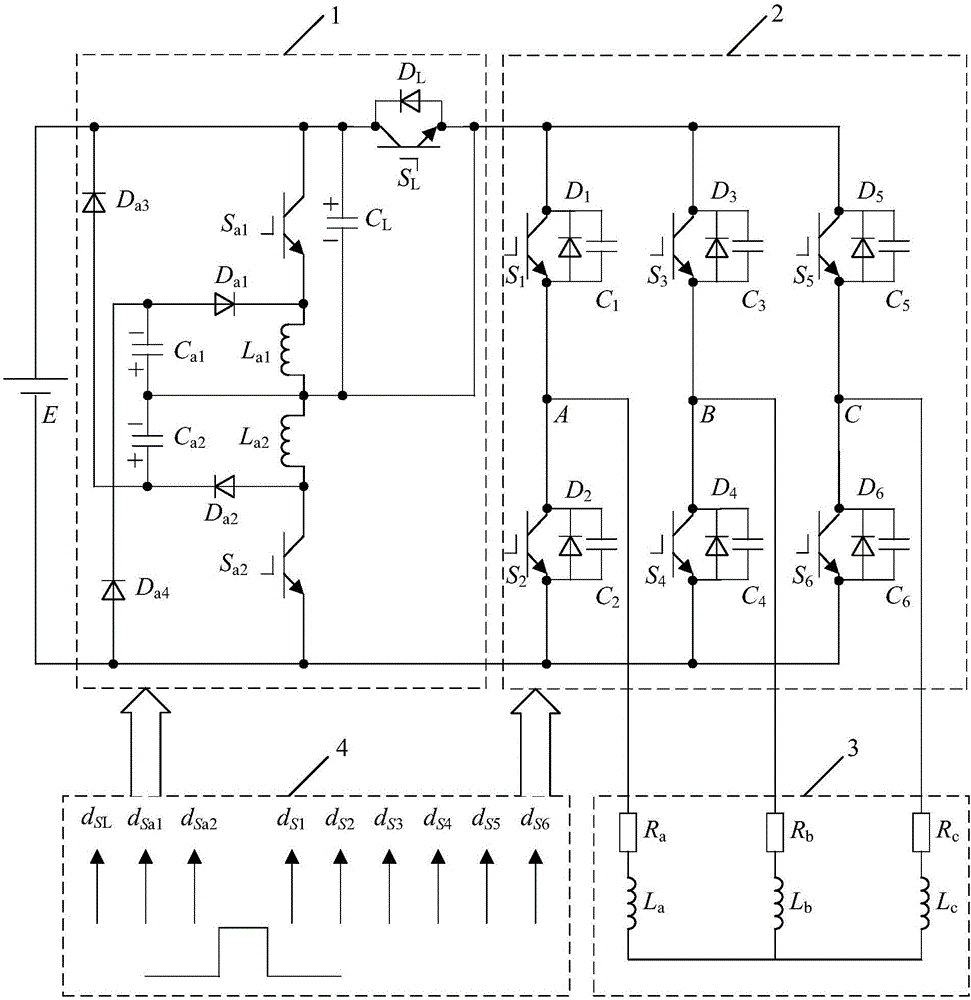

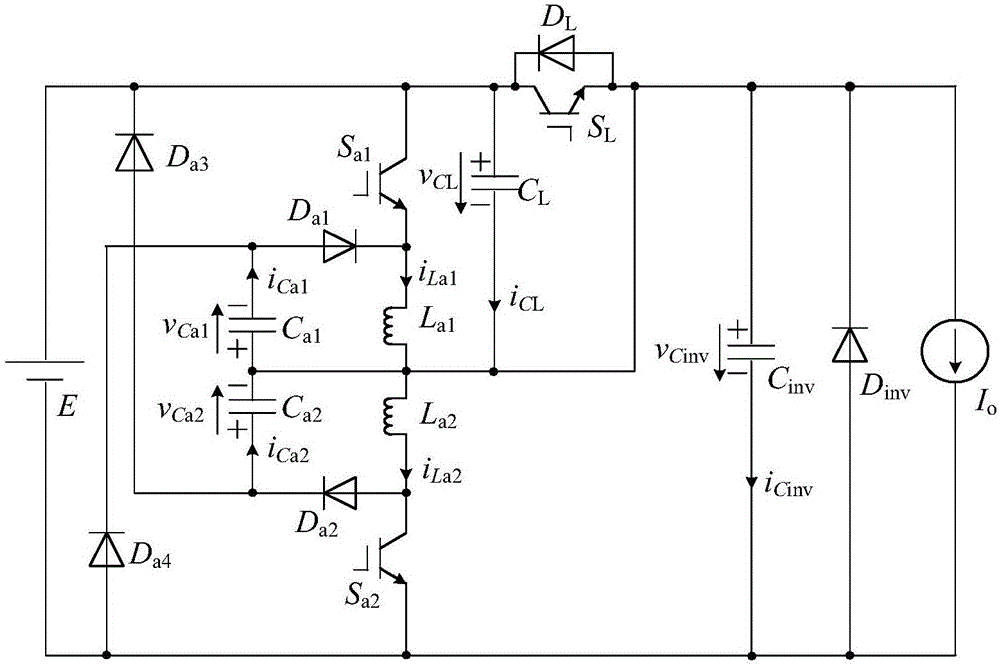

Novel resonant DC-link soft switching inverter and modulation method thereof

InactiveCN106533224AExtended service lifeAvoid stackingEfficient power electronics conversionDc-ac conversion without reversalLoad circuitPhase difference

The invention provides a novel resonant DC-link soft switching inverter and a modulation method thereof, and relates to the technical field of inverters. The inverter comprises an auxiliary resonant circuit, an inverter bridge, a load circuit and a DC power supply, wherein the auxiliary resonant circuit comprises a bus switch tube, two auxiliary switch tubes, two auxiliary resonant inductors, a primary resonant capacitor, two auxiliary resonant capacitors, an anti-parallel diode of the bus switch tube and four auxiliary diodes; the inverter bridge is of a three-phase bridge structure; the load circuit is a three-phase resistor-inductance load; and various main power switch tubes of the inverter bridge work in manners of sine pulse width modulation and complementary turn-on at a phase difference of 180 degrees. According to the novel resonant DC-link soft switching inverter, a zero-crossing reverse process of current of each auxiliary resonant inductor is avoided, the service life of the inverter is prolonged, and the current stress of the auxiliary switch tubes of the inverter, the conduction loss of the auxiliary resonant circuit and the switching losses of the bus switch tube and the auxiliary switch tubes are effectively reduced.

Owner:NORTHEASTERN UNIV

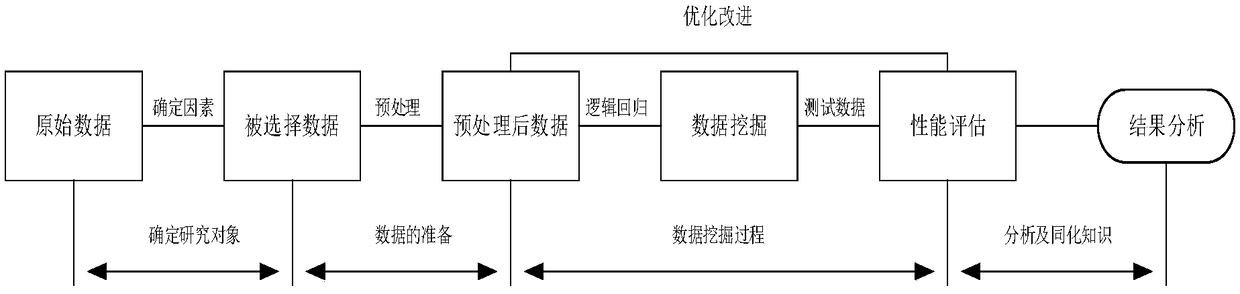

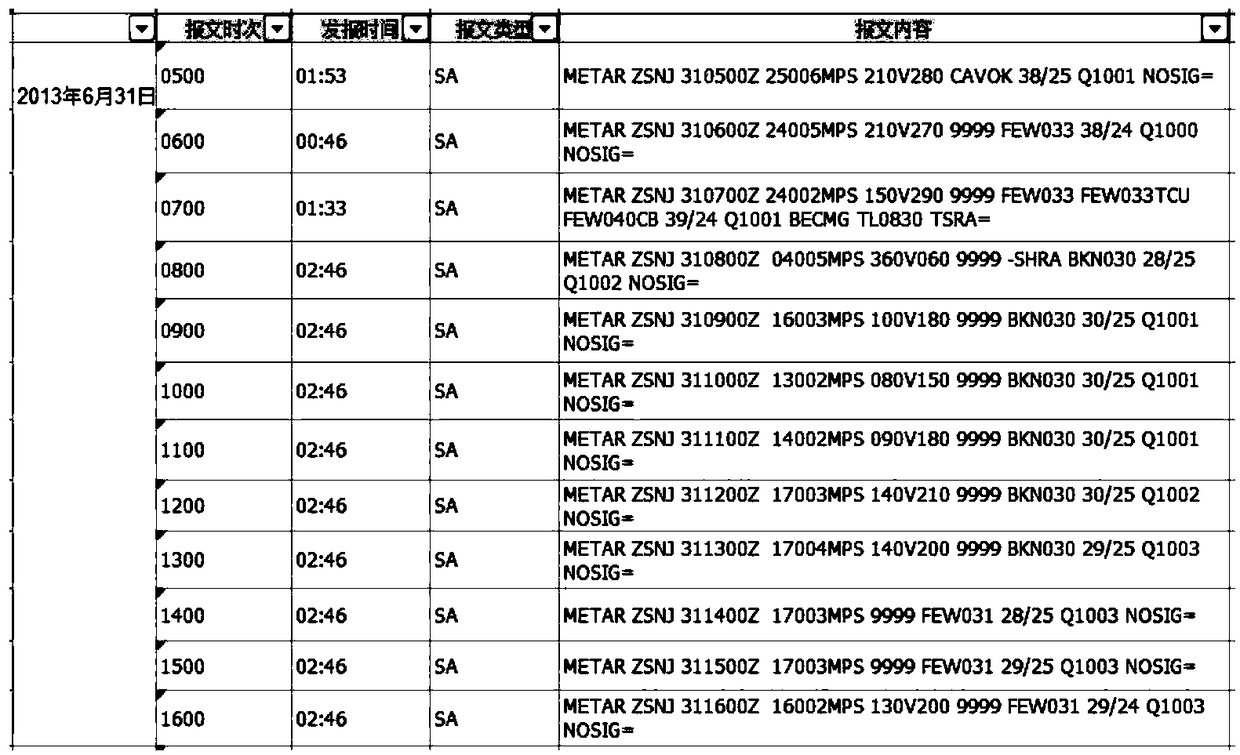

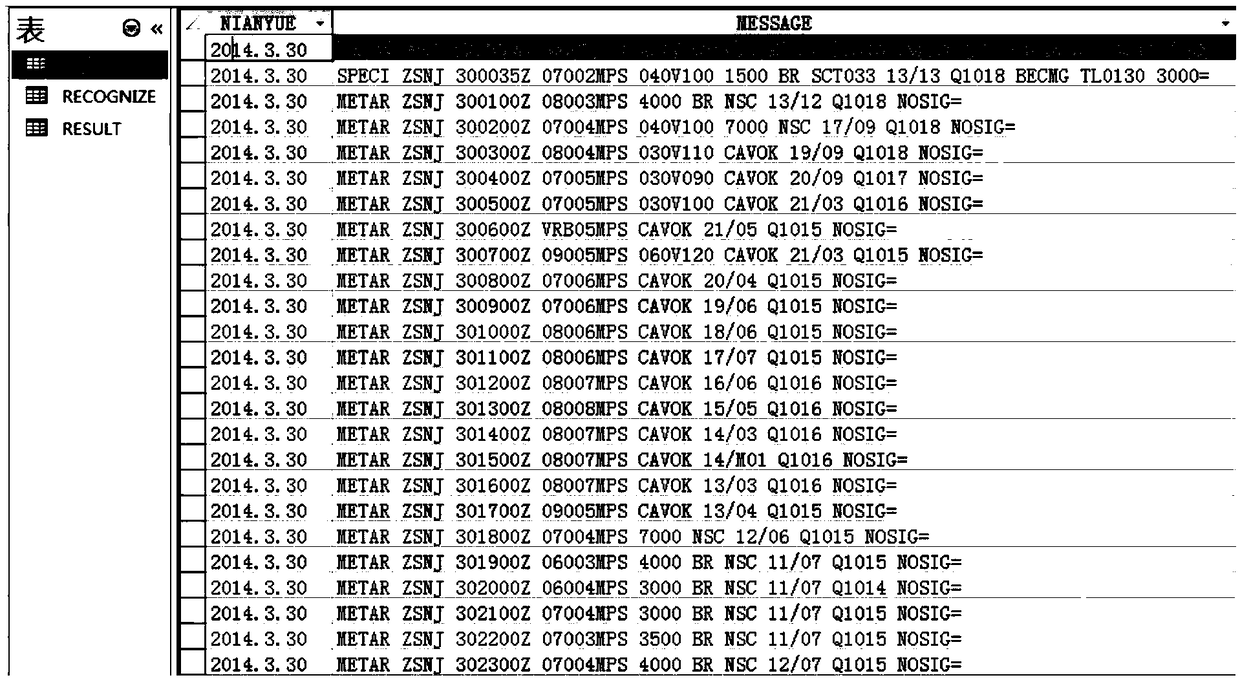

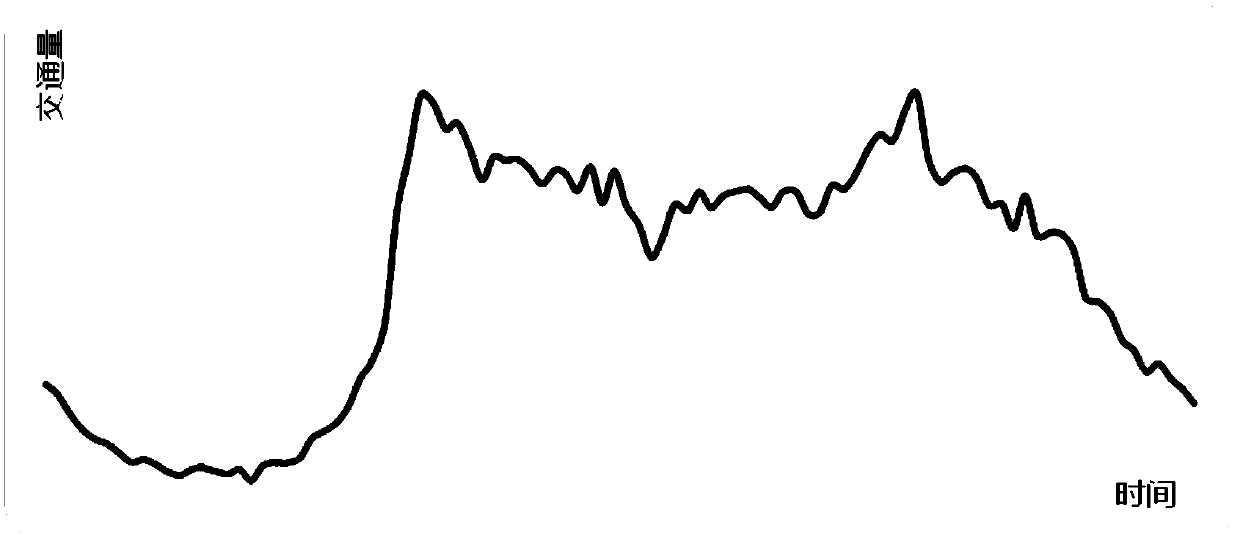

A forecasting method of airport traffic flow based on weather data mining

InactiveCN109409587AReal-time forecastRealize Now Forecast ModeForecastingNeural learning methodsNetwork modelTraffic flow

The invention discloses an airport traffic flow prediction method based on weather data mining, which comprises the following steps: extracting required weather information from the history data of aselected airport according to preset rules, and identifying the weather information according to preset conditions; Obtain the airport flow statistics data in a specific period of time of the selectedairport, and match the airport flow and weather information, in which, the airport flow is divided into take-off, landing and flying three types; Based on BP neural network, the matching informationof airport traffic is trained and learned respectively, and the influence relationship of different weather types on airport traffic is obtained. The influence relationship is analyzed and verified, and the corresponding BP neural network model is finally obtained. Finally, based on the trained BP neural network model and the forecast weather information, the airport's inflow and outflow are classified and forecasted. The method can effectively solve the normal operation of flights in complex weather and improve the air traffic safety level and efficiency of the terminal airspace.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

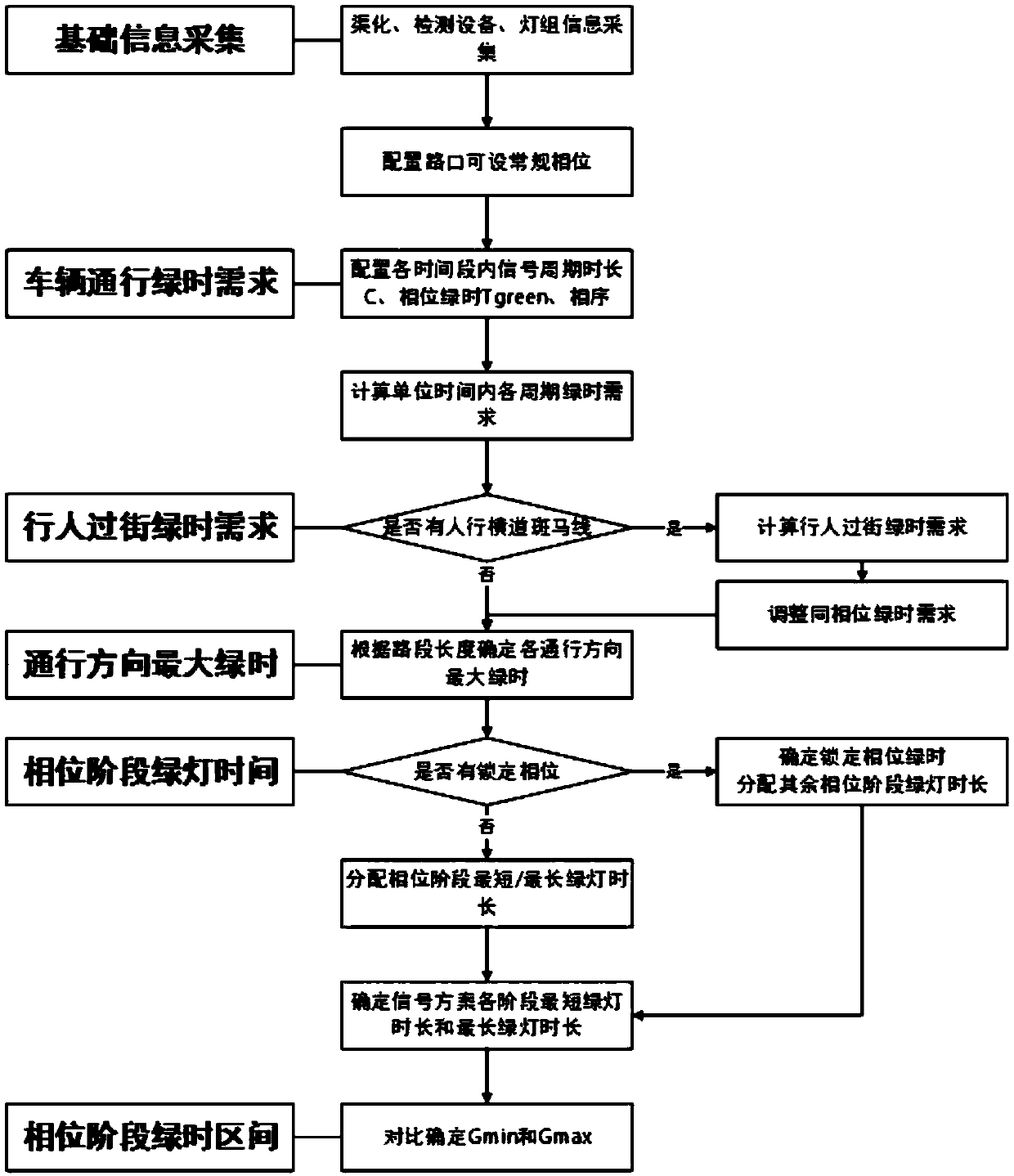

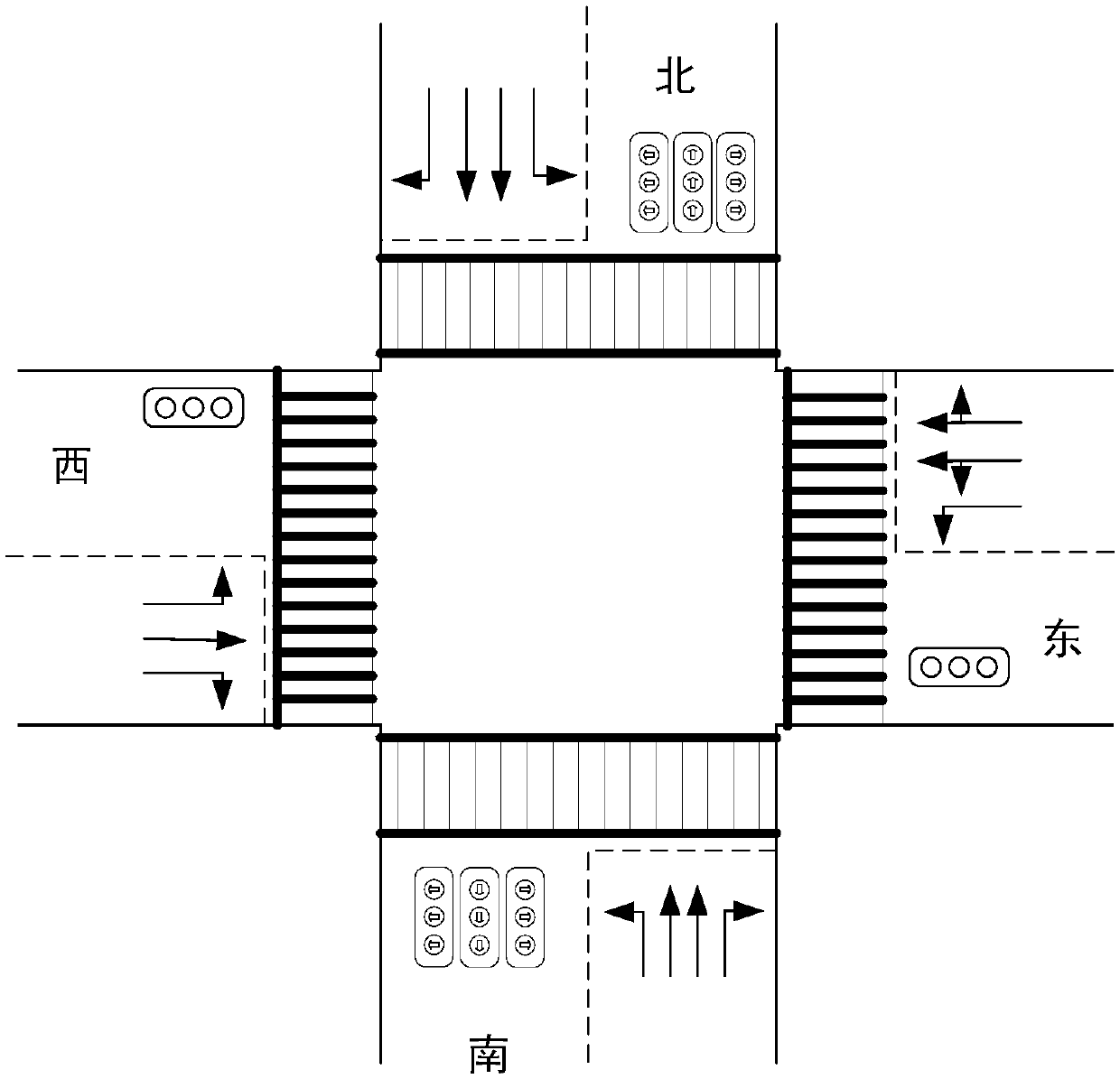

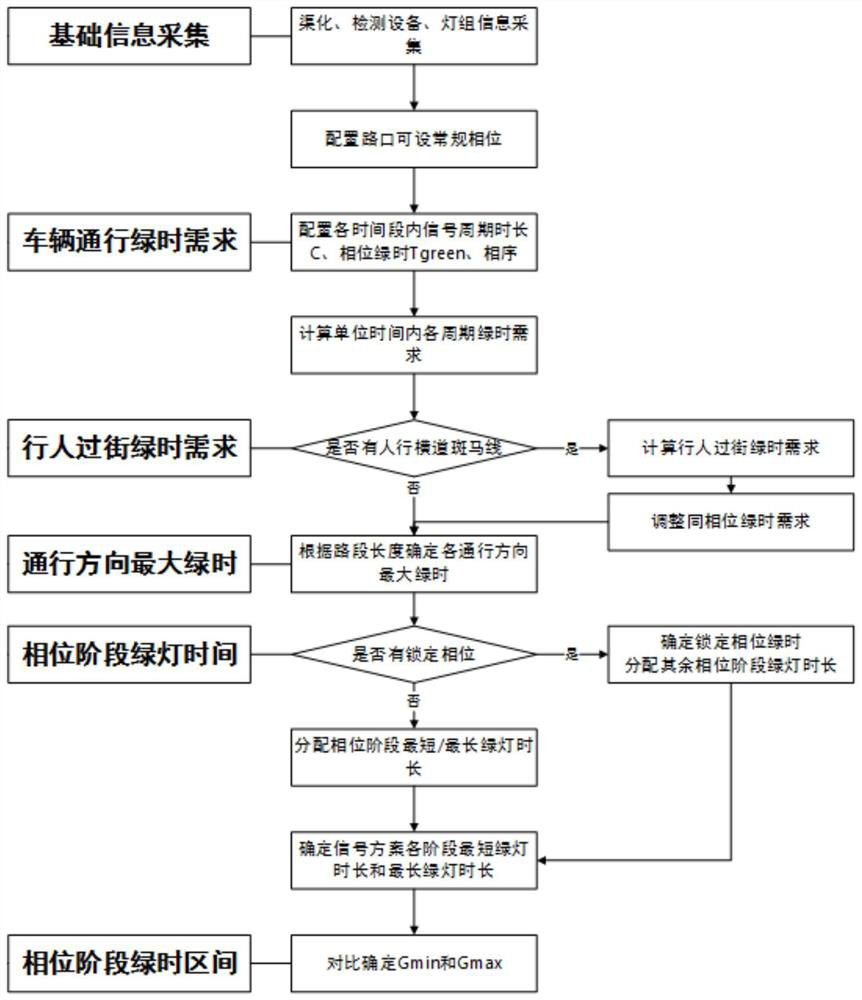

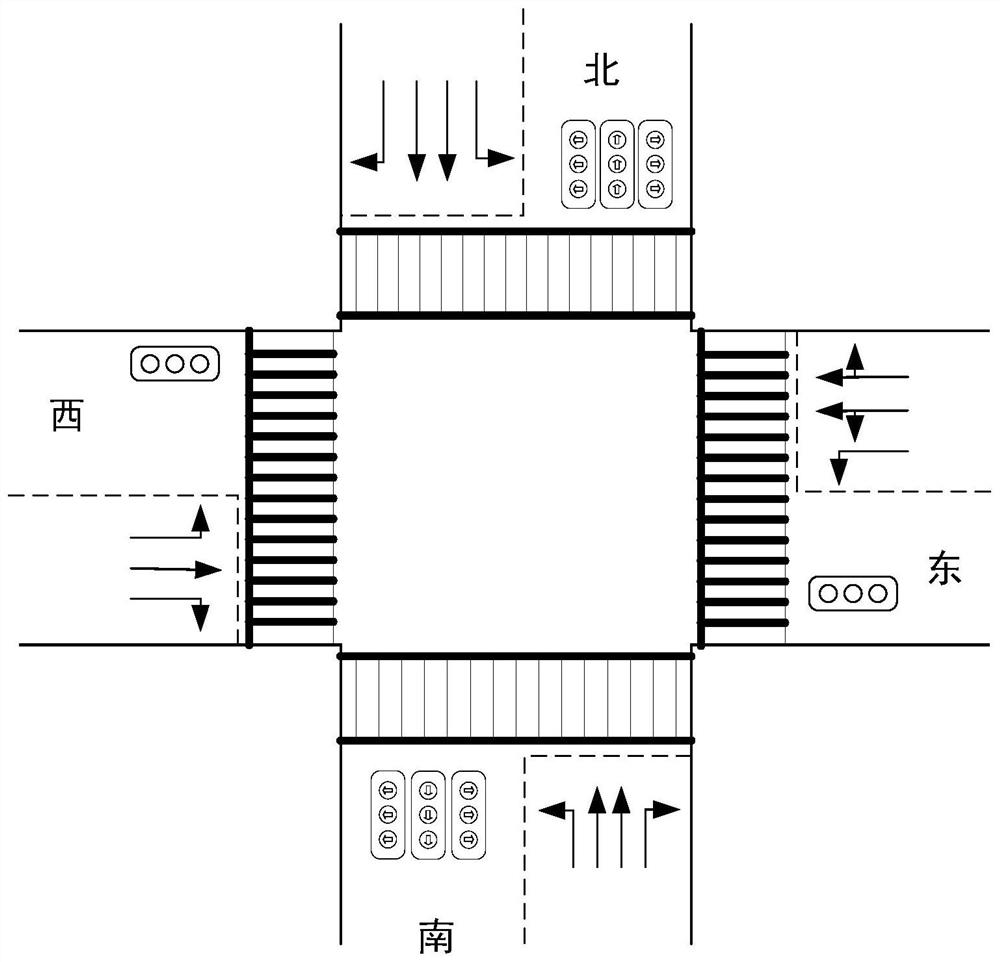

Optimal configuration method for signal control intersection phase green light time induction interval

ActiveCN109035780AImprove implementation efficiencyImprove green hour utilizationControlling traffic signalsDetection of traffic movementGreen timeControl signal

The invention provides an optimal configuration method for a signal control intersection phase green light time induction interval. According to a traffic flow, a signal scheme time period is divided,and the green time induction interval of each phase stage in each time period is subjected to distribution calculation on the basis of non-motor vehicle and pedestrian street crossing requirements, intersection vehicle passage requirements and traffic management requirements. By use of the method, minimum green light time requirements and maximum green light time requirements in the signal phasetime period are summarized, the street-crossing green light time requirements of non-motor vehicles and pedestrians in periodic time and a locking situation of a traffic control signal phase stage areconsidered, the green light time induction interval of each phase stage in the time period is subjected to optimal configuration, so that a green light time use ratio of the interaction traffic signal is effectively improved, intersection passage efficiency is improved, and a traffic user problem is alleviated.

Owner:JIANGSU ZHITONG TRANSPORTATION TECH

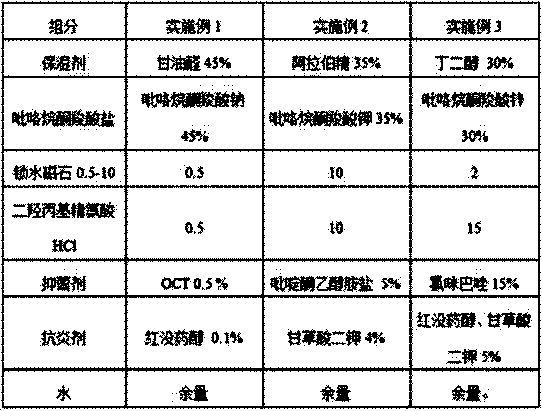

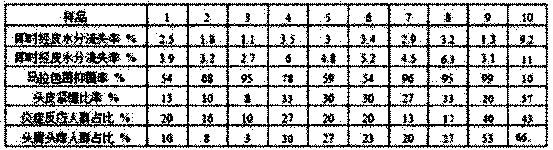

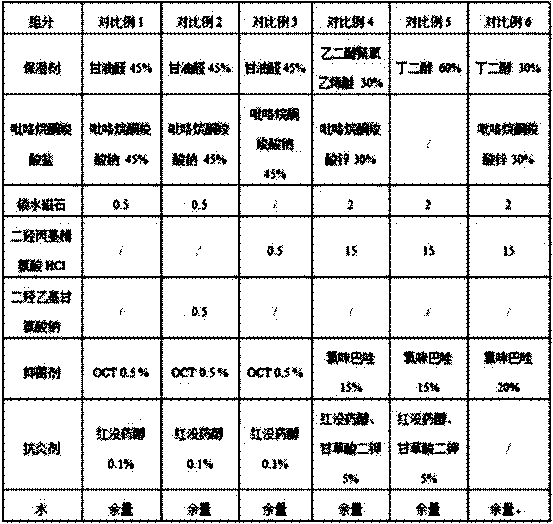

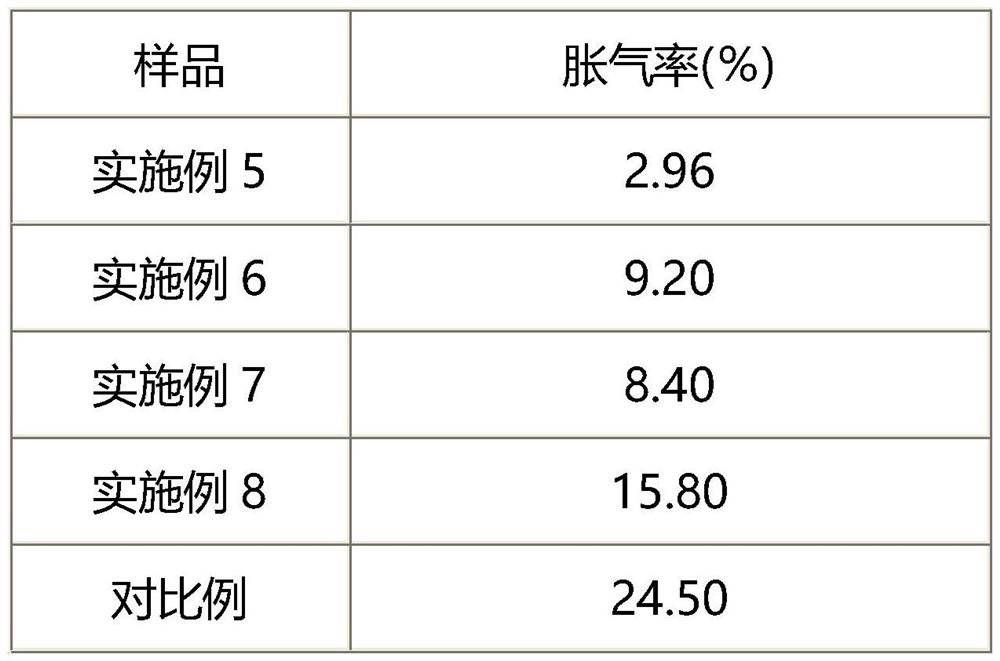

Scalp multidirectional nursing composition and application thereof

ActiveCN110859766AAvoid damageAdjustable antibacterial abilityCosmetic preparationsHair cosmeticsActive agentPyrrolidinones

The invention belongs to the field of daily chemicals, and relates to a scalp multidirectional nursing composition. The scalp multidirectional nursing composition is prepared from the following components: a polyhydroxy humectant with a carbon chain length of C3-C6, pyrrolidone carboxylate, a saccharide isomer, dihydroxypropyl arginine HCl, a bacteriostatic agent, an anti-inflammatory agent and water. The composition is mild in formula, has the effects of moisturizing, properly inhibiting bacteria, relieving inflammation, controlling oil and resisting dandruff, has a good scalp barrier repairing function, can help scalp resist the influence caused by external stimulation, grease peroxidation and surfactant residues, effectively relieves scalp problems such as scalp itching, scalp inflammation and scalp tightness, can soften hair and resist static electricity, and has good elasticity and glossiness.

Owner:OPAL COSMETICS HUIZHOU

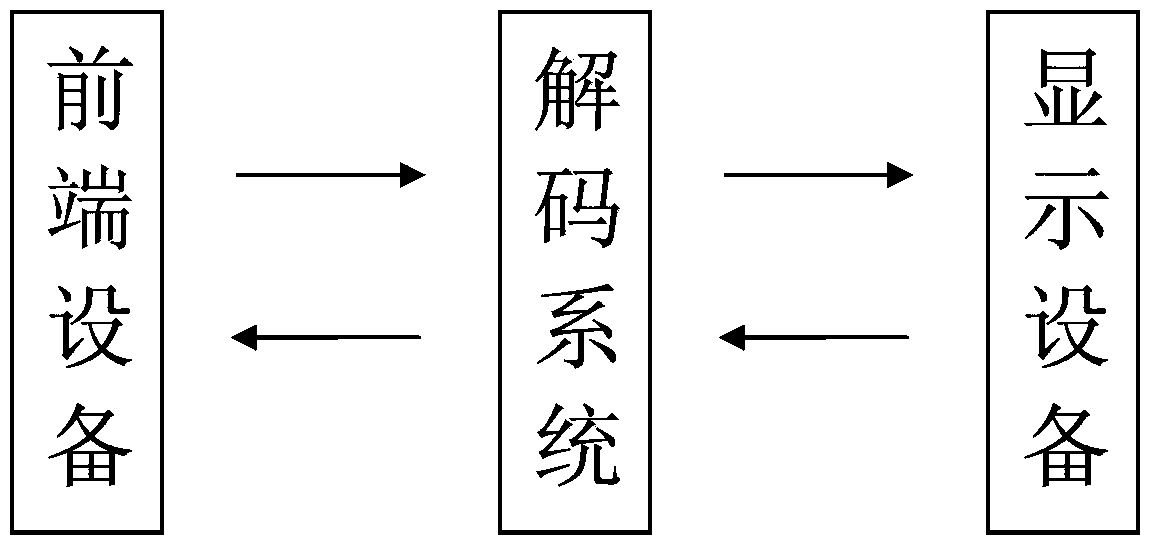

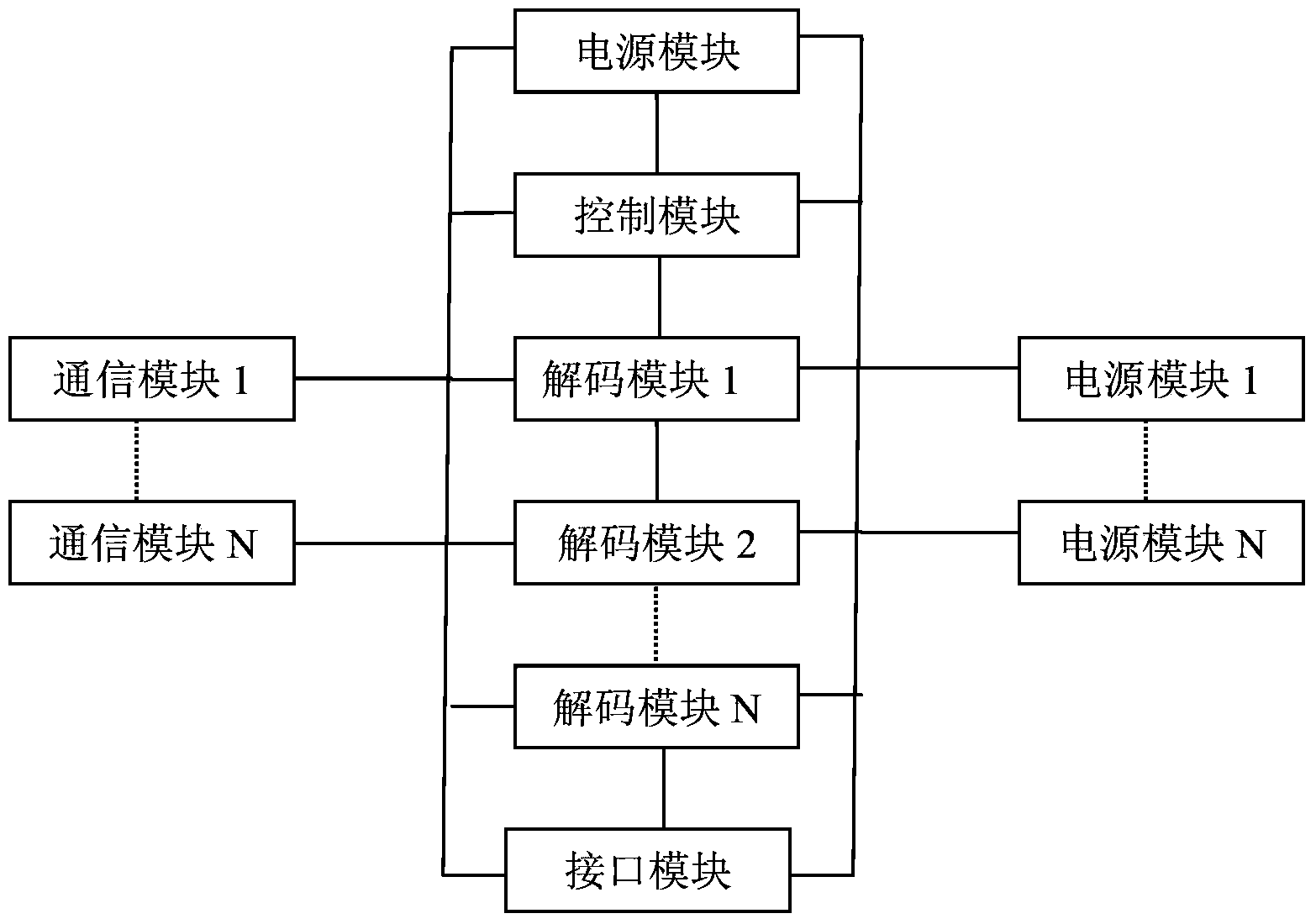

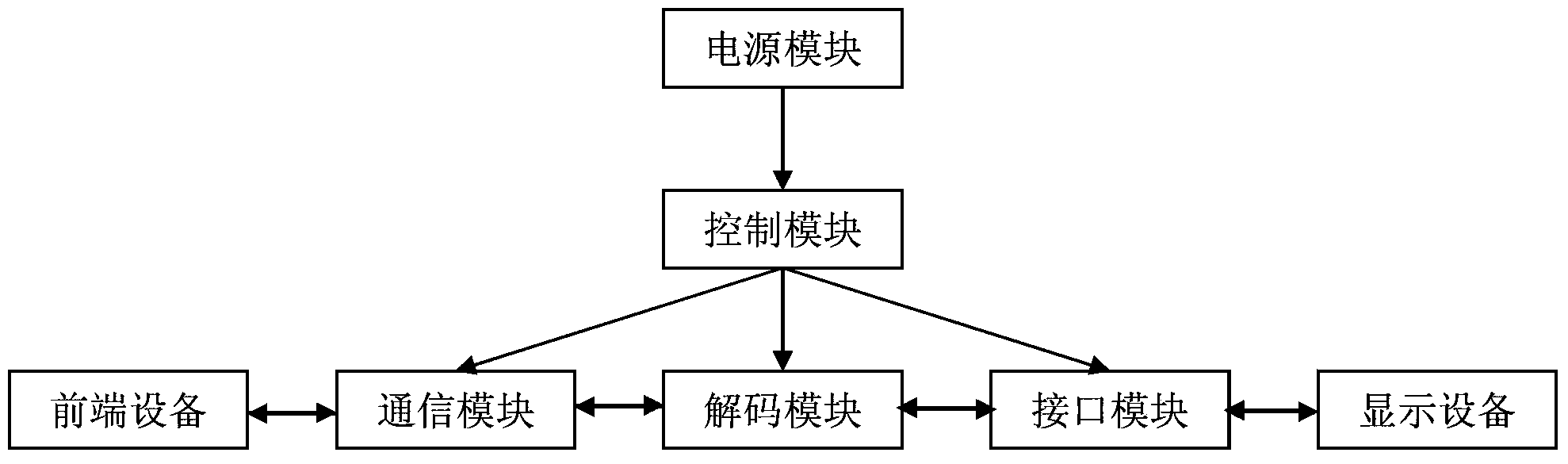

Audio and video decoding system and decoding method thereof

InactiveCN104349120AIncrease or decrease quantityDoes not affect normal operationClosed circuit television systemsDigital video signal modificationData exchangeVideo decoding

The invention provides an audio and video decoding system and a decoding method thereof. The system comprises at least one communication module which is used for data exchange between the audio and video decoding system and front-end equipment; at least one decoding module which is electrically connected with the communication module and used for acquiring the required audio and video data from the front-end equipment via the communication module and decoding the audio and video data; at least one interface module which is electrically connected with the decoding module and used for providing multiple audio and video output interfaces and outputting the audio and video data decoded by the decoding module to display equipment; a control module which is electrically connected with the communication module, the decoding module and the interface module and used for dynamically controlling loads of all the modules in a balancing way according to the existing loads of all the current modules in the audio and video decoding system and the loads capable of being borne by the system; and a power supply module which is used for supplying power to the audio and video decoding system.

Owner:BEIJING INST OF COMP TECH & APPL +1

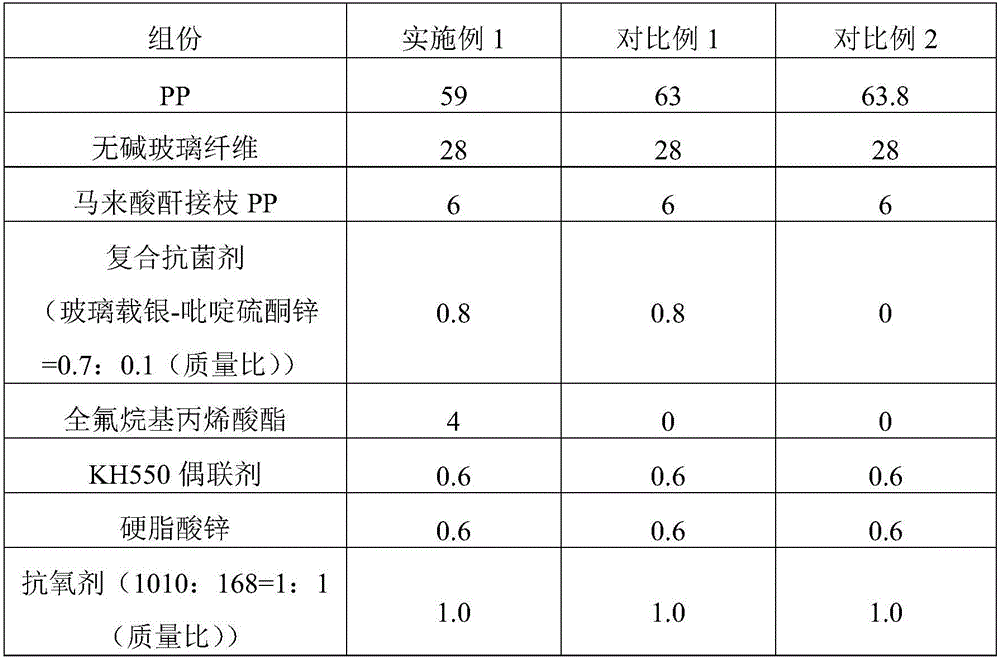

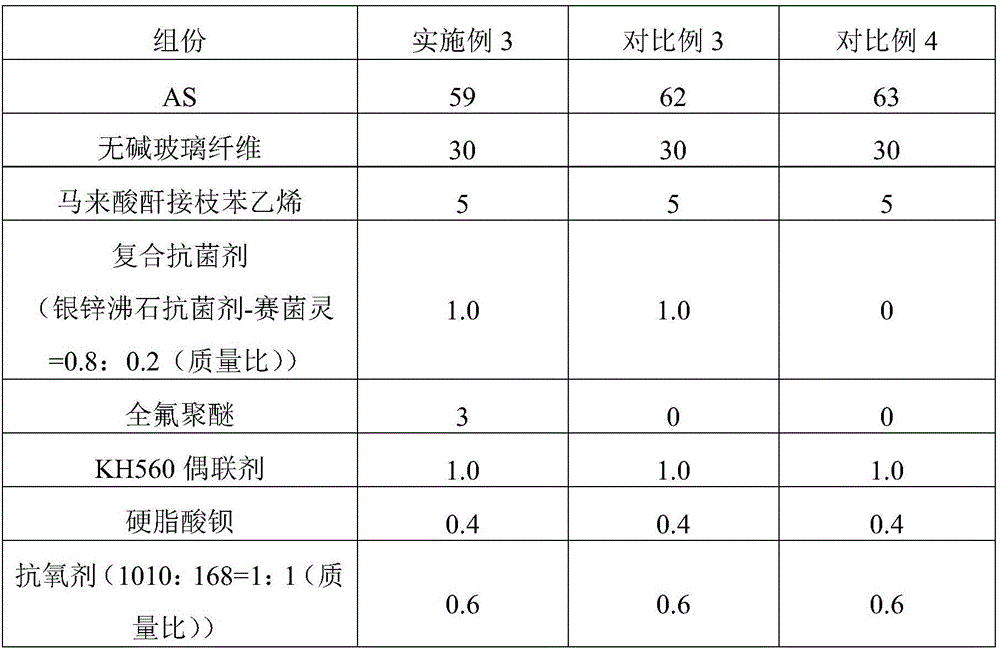

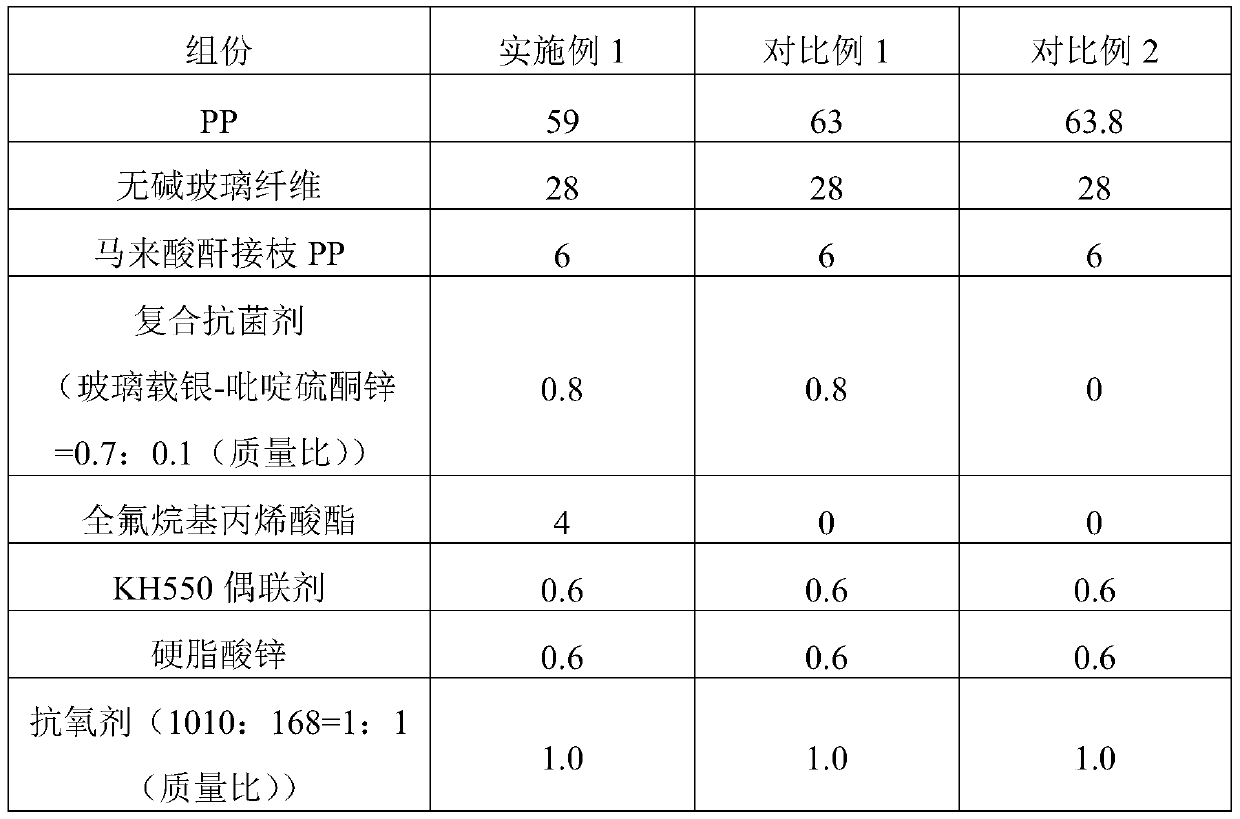

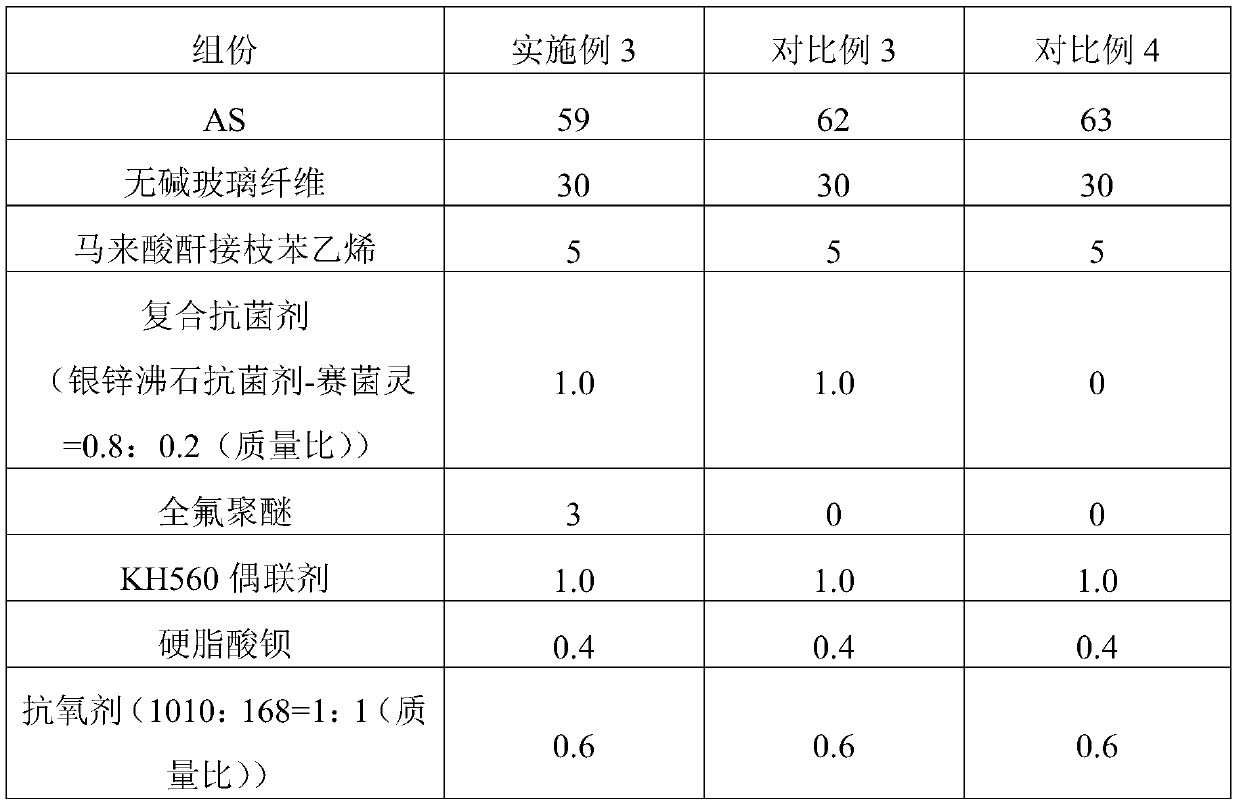

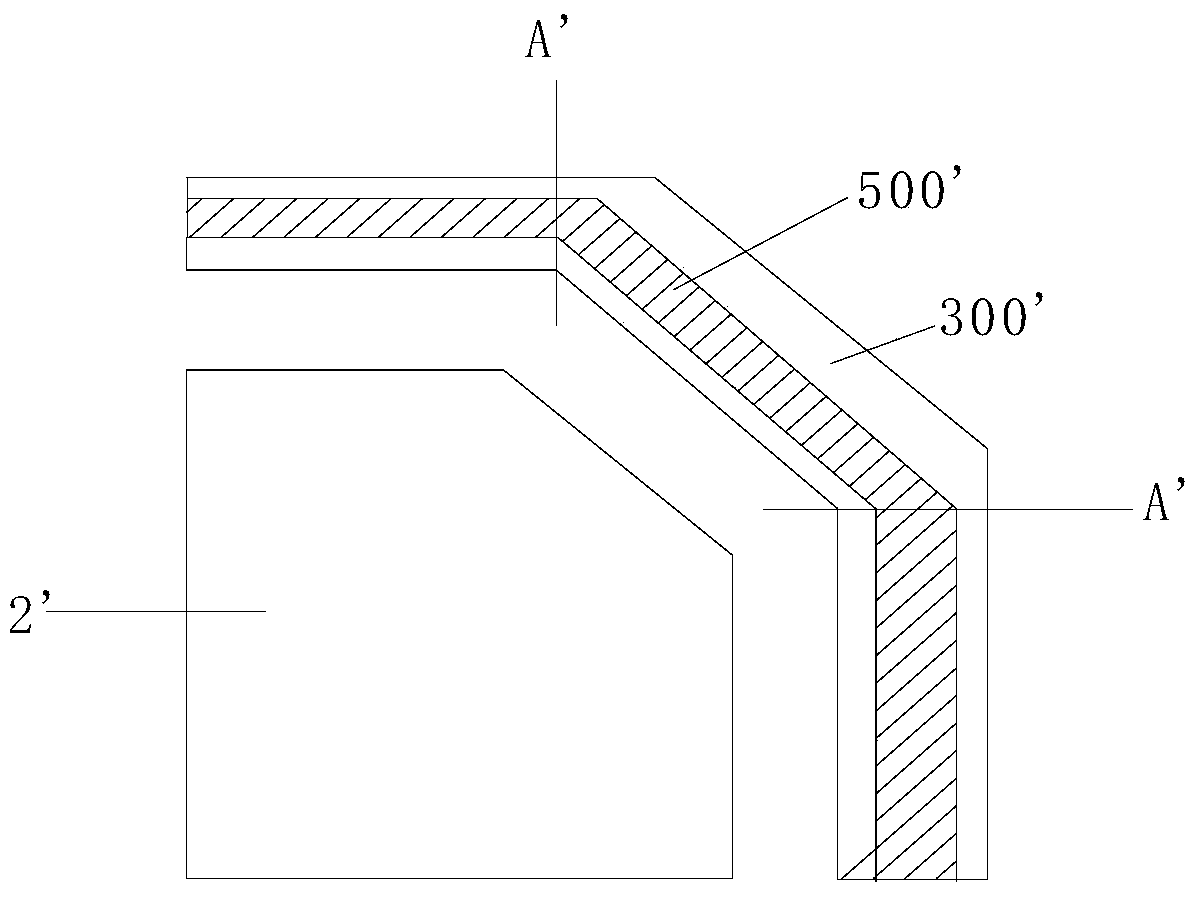

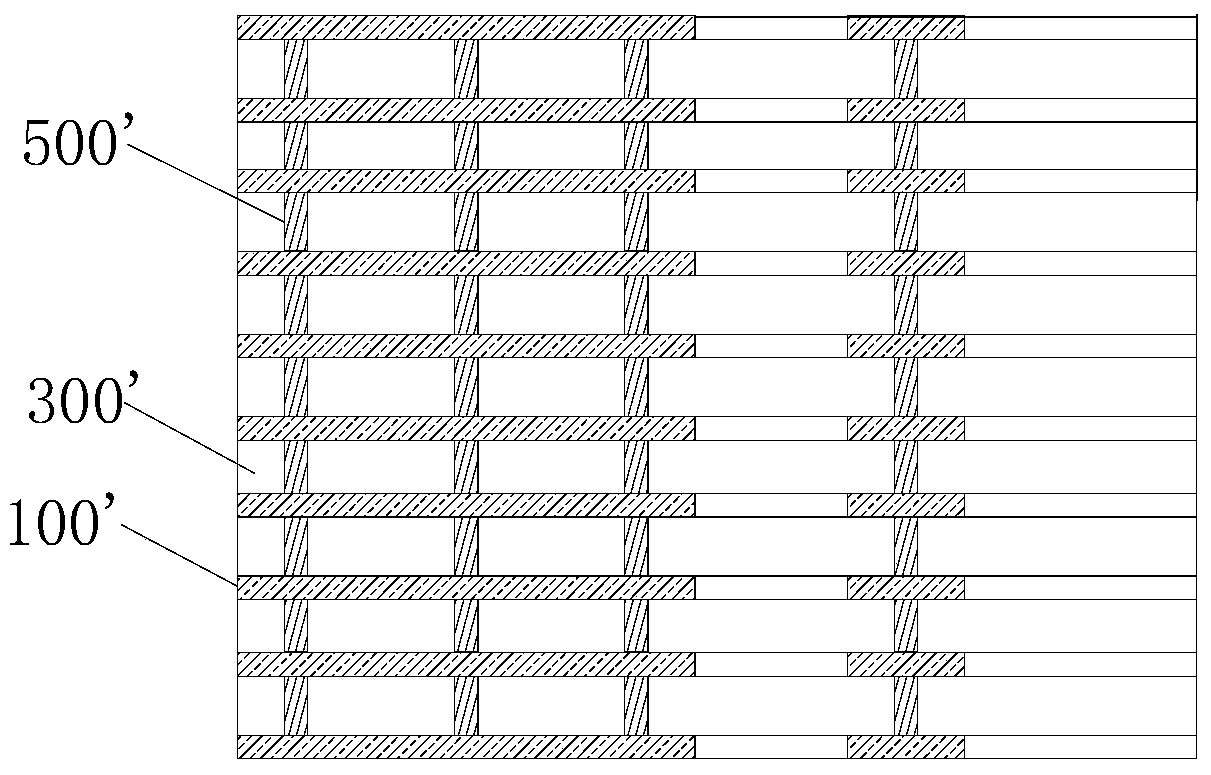

Air conditioner wind wheel material as well as preparation method and application thereof

ActiveCN106633399ASimple and fast operationEasy to controlMechanical apparatusLighting and heating apparatusEngineeringFluorine containing

The invention provides an air conditioner wind wheel material as well as a preparation method and application thereof. The air conditioner wind wheel material comprises an antibacterial agent and a fluorine-containing surface modifier. According to the air conditioner wind wheel material provided by the invention, the fluorine-containing surface modifier can reduce the surface energy of an air conditioner wind wheel, so that the attachment force of dust and microorganisms to the surface of the air conditioner wind wheel can be reduced; meanwhile, the antibacterial agent can also inhibit and kill attached microorganisms in time to further synergistically and effectively prevent attachment and increase of the dust and the microorganisms on the surface of the air conditioner wind wheel, so that the accumulation amount of the microorganisms and the dust on the surface of the wind wheel is reduced.

Owner:WUHAN REFRIGERATION EQUIP OF MIDEA GROUP +1

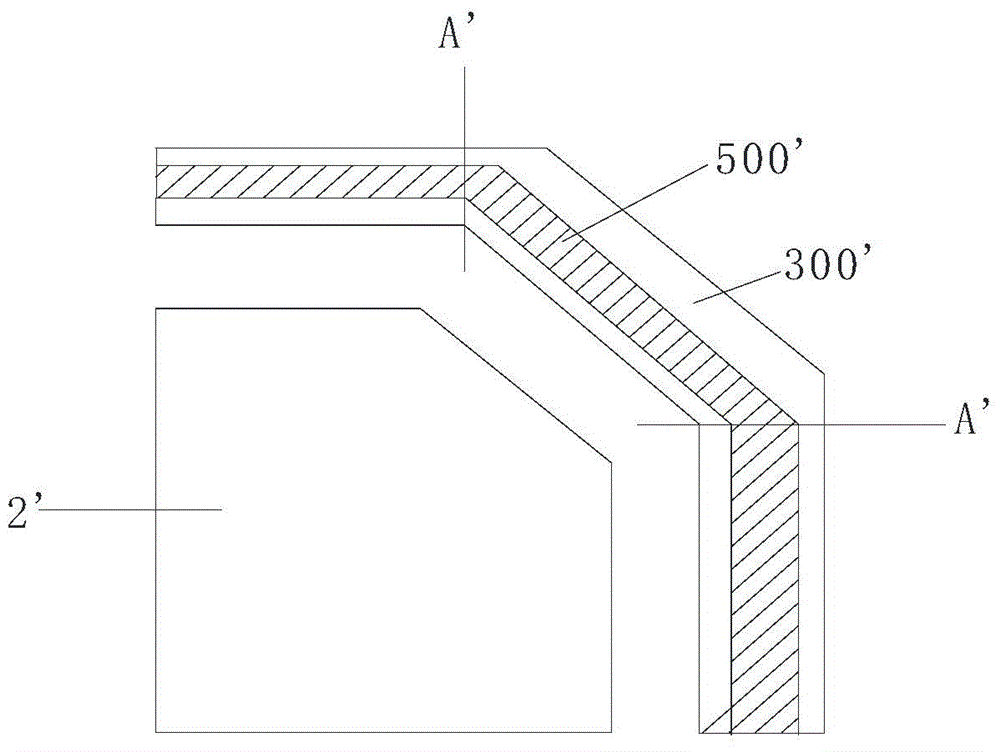

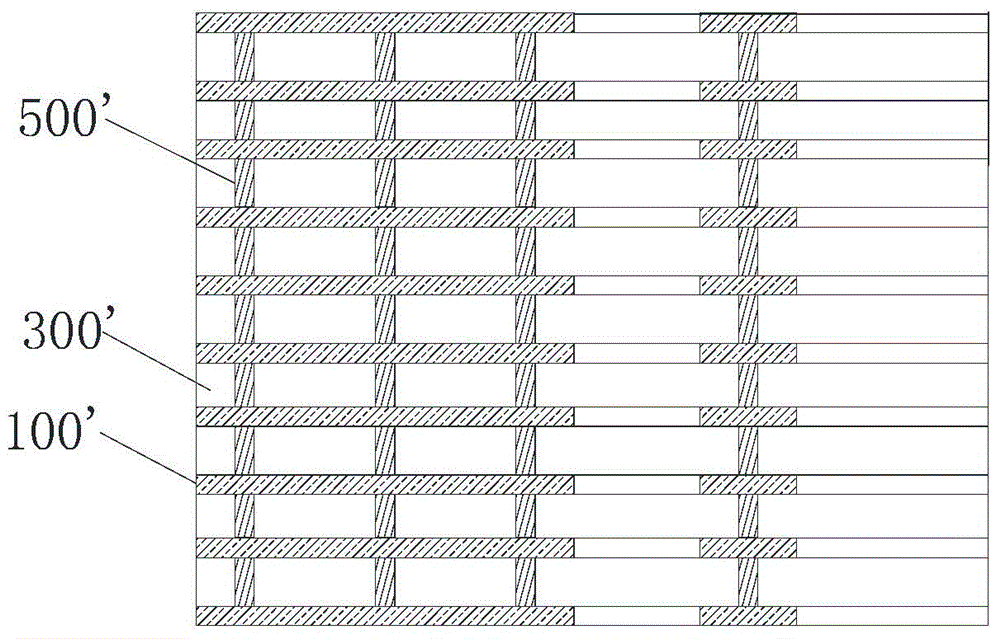

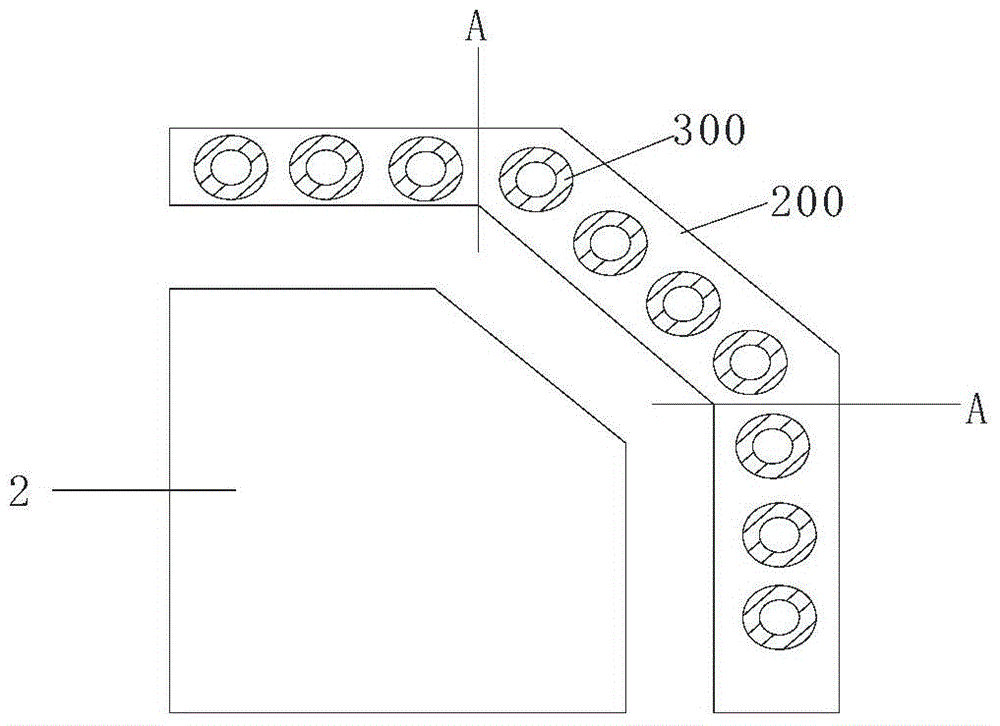

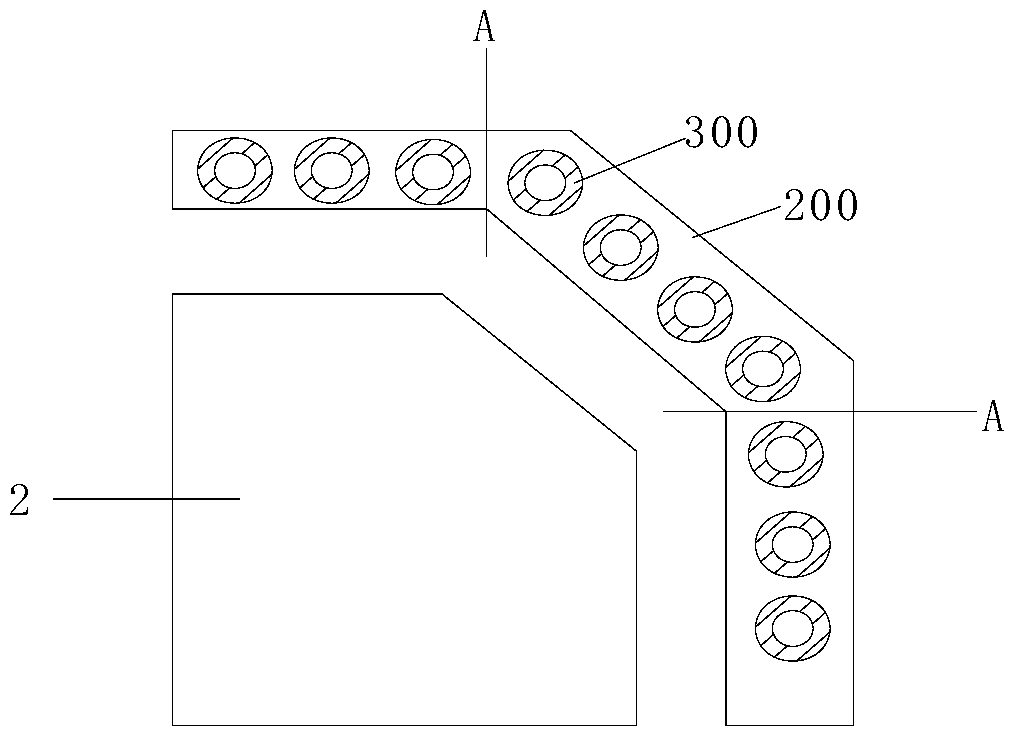

Sealing ring of chip

ActiveCN105990313AReduce rigidityAlleviate the problemSemiconductor/solid-state device detailsSolid-state devicesAdhesion forceDielectric layer

The invention provides a sealing ring of a chip. The sealing ring comprises one or more sealing units; each sealing unit comprises a first metal wiring layer, a second metal wiring layer, an interlayer dielectric layer, and one or more via hole groups; the first metal wiring layer surrounds the chip; the first metal wiring layer includes a first metal portion and a first dielectric material portion which are insulated from each other; the second metal wiring layer is opposite to the first metal wiring layer; the second metal wiring layer includes a second metal portion and a second dielectric material portion which are insulated from each other; the interlayer dielectric layer is arranged between the first metal wiring layer and the second metal wiring layer; the one or more via hole groups surround the chip, are arranged in the interlayer dielectric layer and are connected with the first metal portion and the second metal portion; and each via hole group includes a plurality of via holes which are independent from each other. A via hole formation mechanical stress breaks through the obstruction of an adhesion force between the first metal portion, the second metal portion and the via holes, so that the problem of delamination of the edge of the chip can be alleviated; and the rigidness of the via holes is decreased, so that the deformation ability of the via holes can be increased, and therefore, the delamination of the edge of the chip can be effectively prevented.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Drug for treating cervical spondylosis

InactiveCN103536847ASignificant effectEffective cureSkeletal disorderPlant ingredientsDrugCervical spondylosis

The invention discloses a drug for treating cervical spondylosis, belonging to the technical field of medicines. The drug comprises 30g of kudzuvine root, 15g of radix clematidis and 15g of zedoary. The drug disclosed by the invention has the advantages of effectively relieving a problem caused by spondylosis, being obvious in curative effect and effectively treating focus fundamentally.

Owner:袁辉

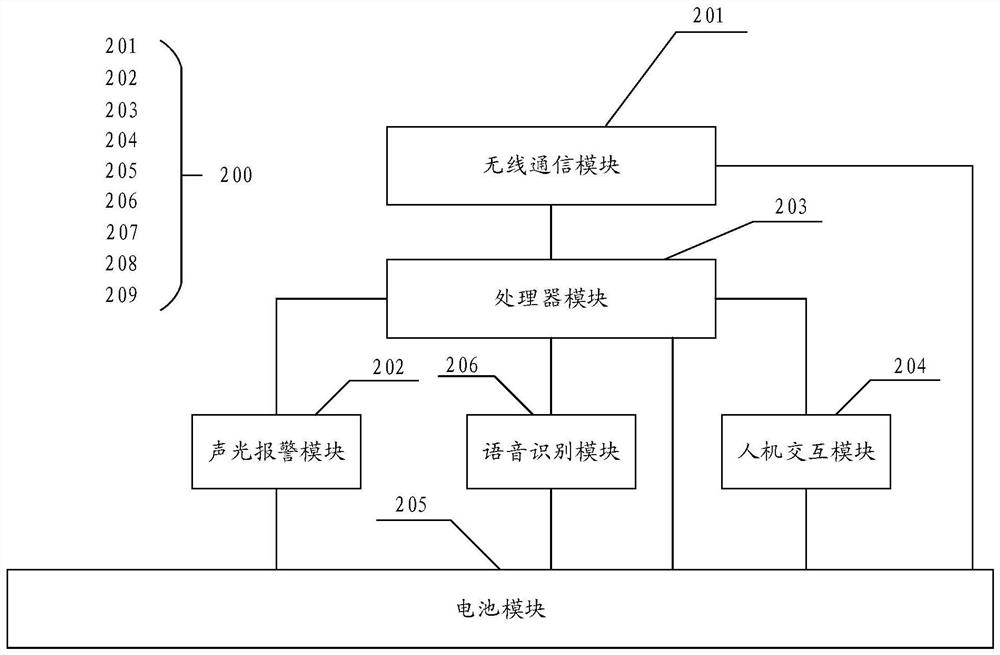

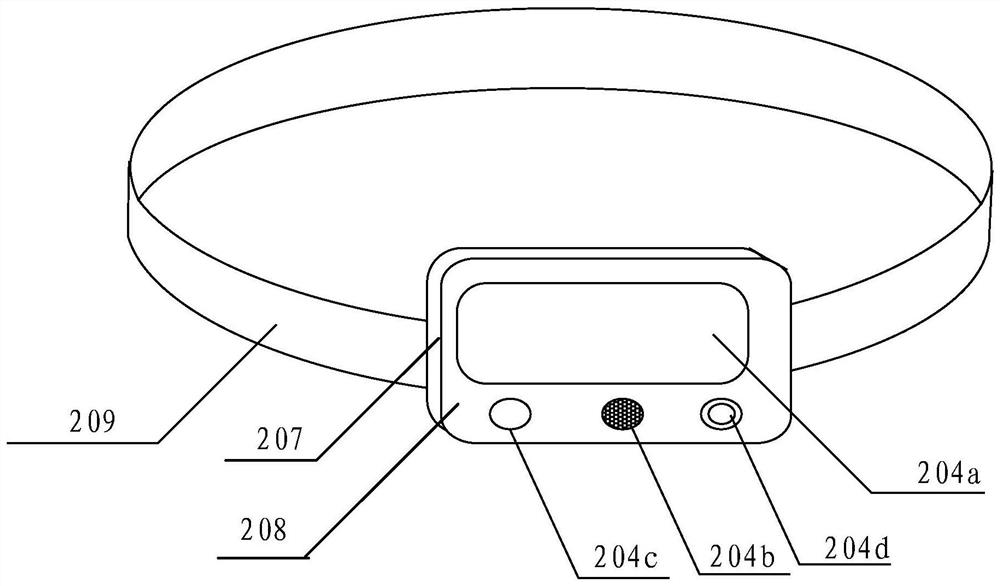

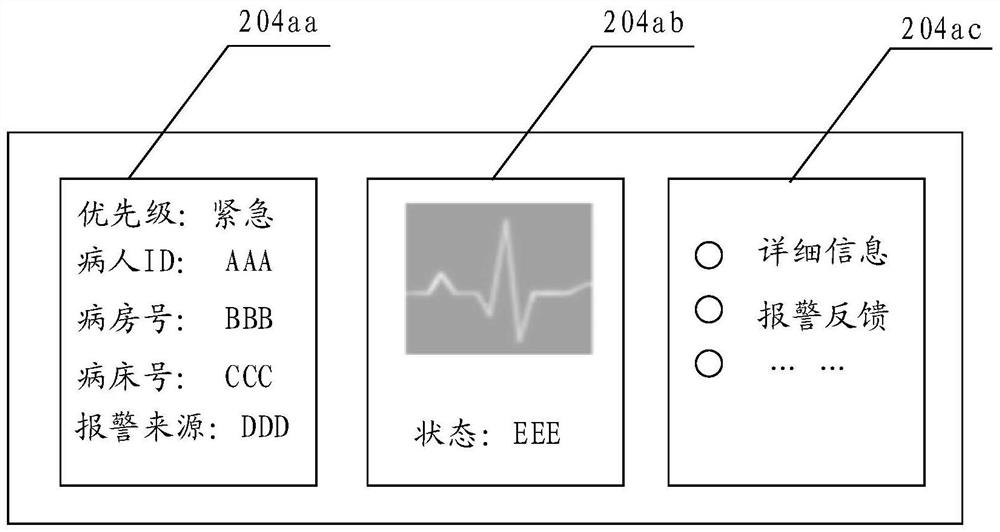

Auxiliary alarm device, system and method

PendingCN113129568ABig spaceExpand the effective receiving space after the medical alarm source equipment sends out the alarmAlarmsElectric transmission signalling systemsAlarm messageEmbedded system

The invention provides an auxiliary alarm device, system and method. The auxiliary alarm device comprises a processor module, and a wireless communication module, a sound-light alarm module and a man-machine interaction module which are connected with the processor module, and is in wireless communication connection with at least one medical alarm source device. The auxiliary alarm method comprises the following steps: receiving alarm information of the medical alarm source device; classifying the alarm information to obtain alarm parameters; presenting an alarm priority and medical care parameters of the alarm information in the form of image-text, sound and / or light according to the alarm mode, and finally sending the alarm feedback of the medical care personnel to the medical alarm source device. According to the auxiliary alarm device and method provided by the invention, a plurality of pieces of alarm information can be classified and filtered, and alarm feedback is provided; and therefore, more emergency alarm information is preferentially provided for a medical staff, and a more comprehensive, safer and more efficient alarm mechanism is provided for intelligent medical treatment.

Owner:SHANGHAI DRAEGER MEDICAL INSTRUMENT CO LTD

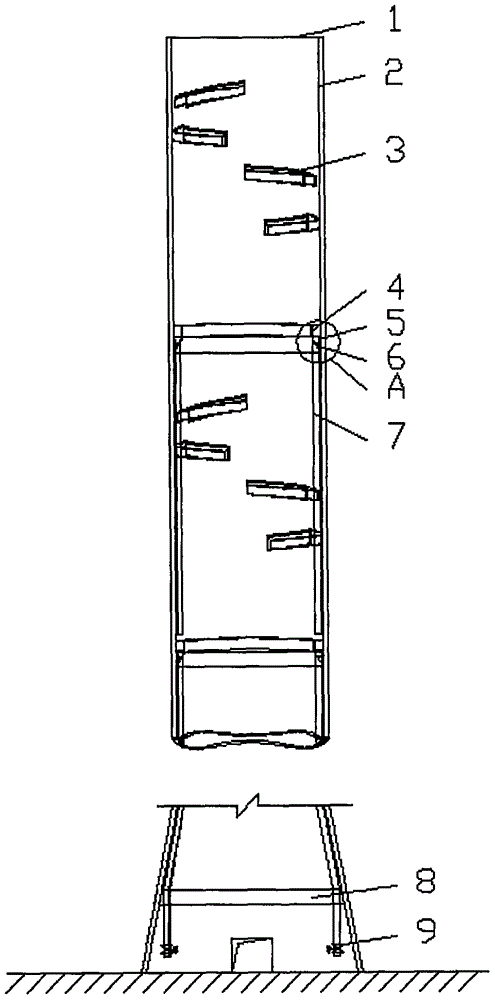

All-round collecting and discharging system for smoke liquid-state media

InactiveCN106122997ASolve corrosiveAlleviating the rain problemLighting and heating apparatusLiquid stateTreatment field

The invention relates to a flue gas liquid medium collection and discharge system, including: an active collection device, a passive collection device and a discharge device, wherein the active collection device collects the flue gas liquid medium near the inner wall of the chimney and the condensed acid attached to the inner wall of the chimney, and the passive mobile device collects The condensed acid collected at the corbel and the condensed acid flowing down the inner wall of the chimney are finally discharged to the acid collection pool at the bottom of the chimney through the glass fiber reinforced plastic acid discharge pipe of the discharge device or diverted to a designated discharge location outside the chimney. This device realizes "regional treatment and centralized discharge", and completely solves the problems of corrosion of the internal structure and lining of the chimney and leakage of the chimney caused by the large accumulation of condensed acid in the chimney anti-corrosion treatment, especially in the field of condensed acid collection and discharge. , and alleviate the chimney rain problem.

Owner:北京金汇中电力科技有限公司

Baking soda toothpaste

ActiveCN109199909AInhibit plaqueReduce gum rednessCosmetic preparationsToilet preparationsDecompositionGuar gum

The invention discloses baking soda toothpaste, which is prepared from the following raw materials in parts by weight: 67.0-67.2 wt% of nanometer sodium bicarbonate powder, 3.0-3.2 wt% of xylitol, 1.6-1.8 wt% of polyethylene glycol, 1.2-1.3wt% of calcium pyrophosphate, 2.8-3.0 wt% of poly (oxypropylene) olefinic ether sodium phosphate having a mass concentration of 30%, 0.2-0.3 wt% of sodium alginate, 0.2-0.3 wt% of guar gum, 0.2-0.3 wt% of stevioside, 0.1-0.11 wt% of sodium fluoride, an appropriate amount of perfume and 4-6% of fatty acid alkanolamide borate and potassium phosphate, with thebalance being water, wherein that weight part ratio of fatty acid alkanolamide ester to potassium phosphate is 3-5:1. The baking soda toothpaste provided by the invention adopts the unique dental baking soda formula, can inhibit dental plaque, reduce gingival swelling, bleeding, alleviate gingival problems, and strengthen gingiva and teeth. Can effectively prevent the formation of dental calculi,remove odor, prevent tooth decay. The baking soda toothpaste provided by the invention has stable property and does not cause baking soda decomposition after long-term storage.

Owner:浙江施维康生物医学材料有限公司

Ginger planting soil conditioner

InactiveCN108610174AImprove propertiesImprove fertilityCalcareous fertilisersAlkali orthophosphate fertiliserSoil propertiesRapeseed

The invention discloses a ginger planting soil conditioner which comprises the following raw materials in parts by weight: 4-9 parts of siliceous petrified powder, 4-9 parts of perlite powder, 3-8 parts of calcium magnesium phosphate fertilizer, 2-6 parts of microbial mixture, 0.3-0.8 parts of fulvic acid, 6-9 parts of perlite powder, 7-15 parts of rapeseed meal, 0.3-0.8 parts of sodium citrate, 5-10 parts of vitamin complex, 4-10 parts of borax, 0.2-0.7 parts of calcium hydroxide, 0.3-0.8 parts of sodium lignin sulfonate, 5-10 parts of plant ash, 3-7 parts of zeolite powder, 1-5 parts of bamboo powder, 4-8 parts of biological straw and 0.3-0.7 parts of disodium octoborate tetrahydrate. The conditioner has the advantages of improving soil properties, facilitating plant growth and achievinghigh and stable yields.

Owner:临泉县盈昌农副产品有限公司

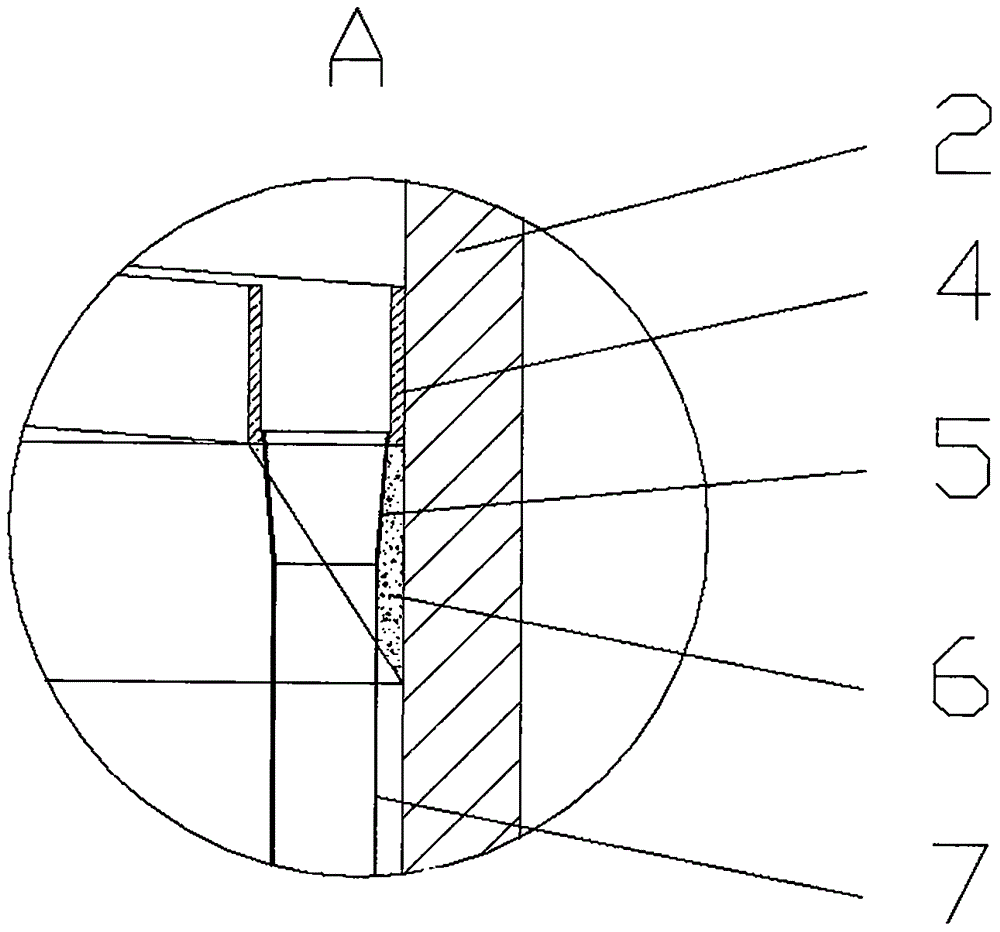

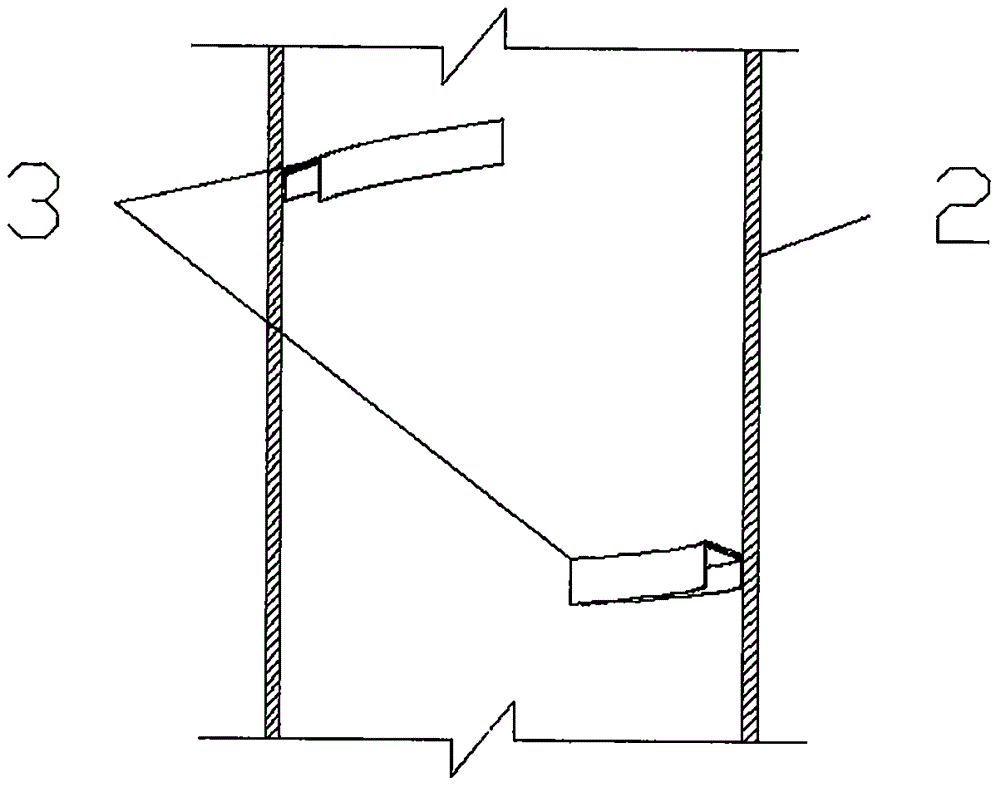

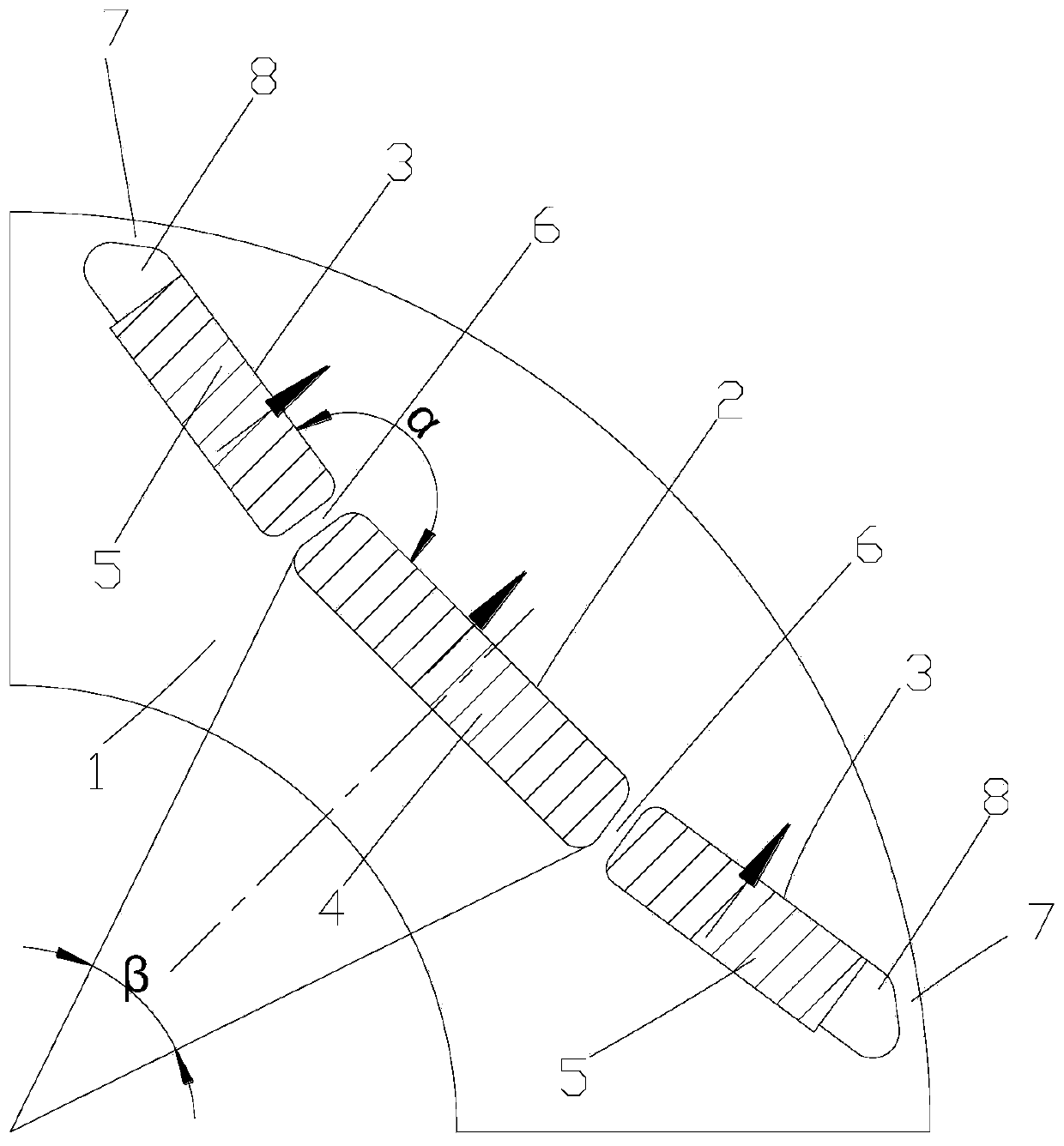

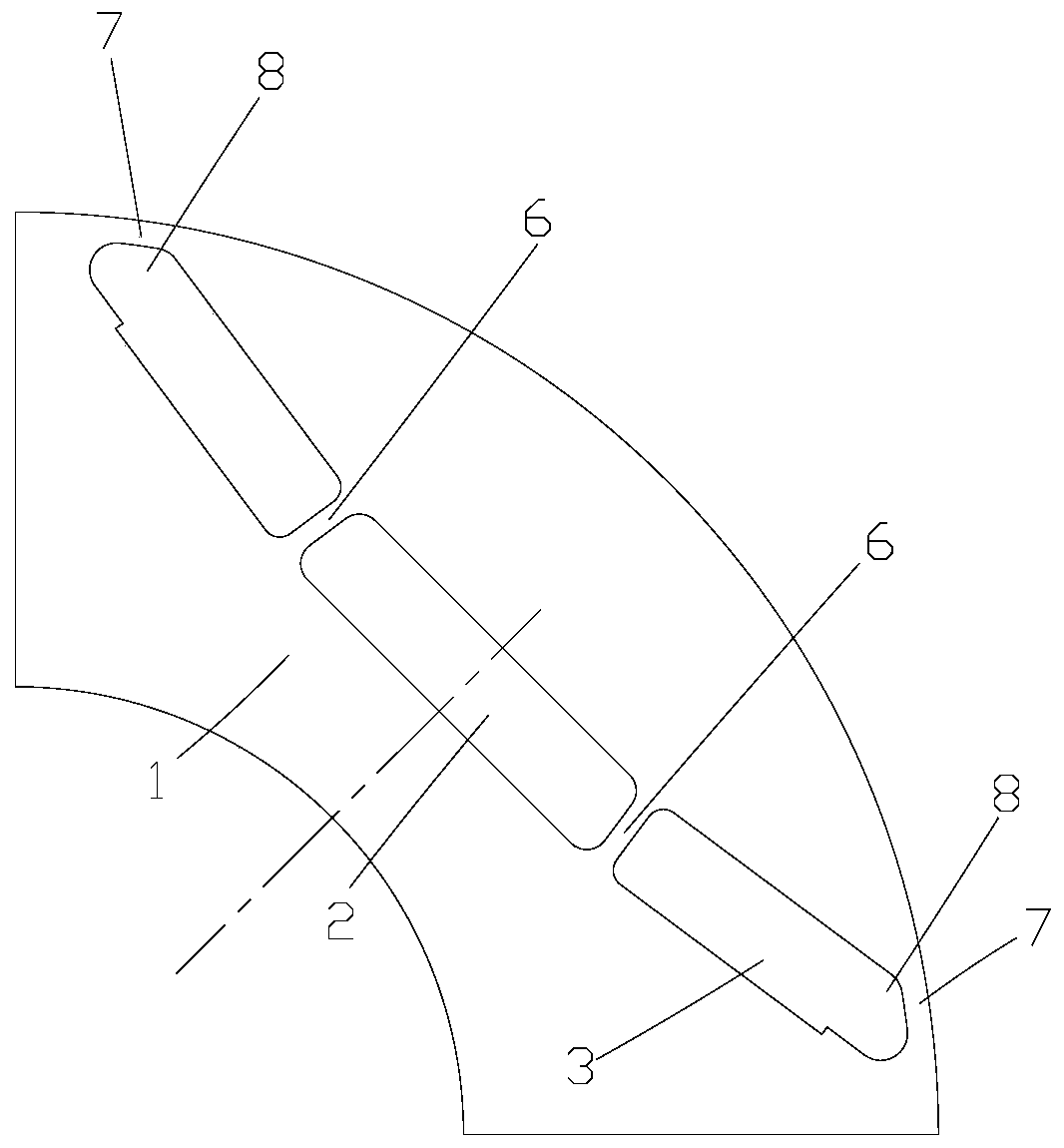

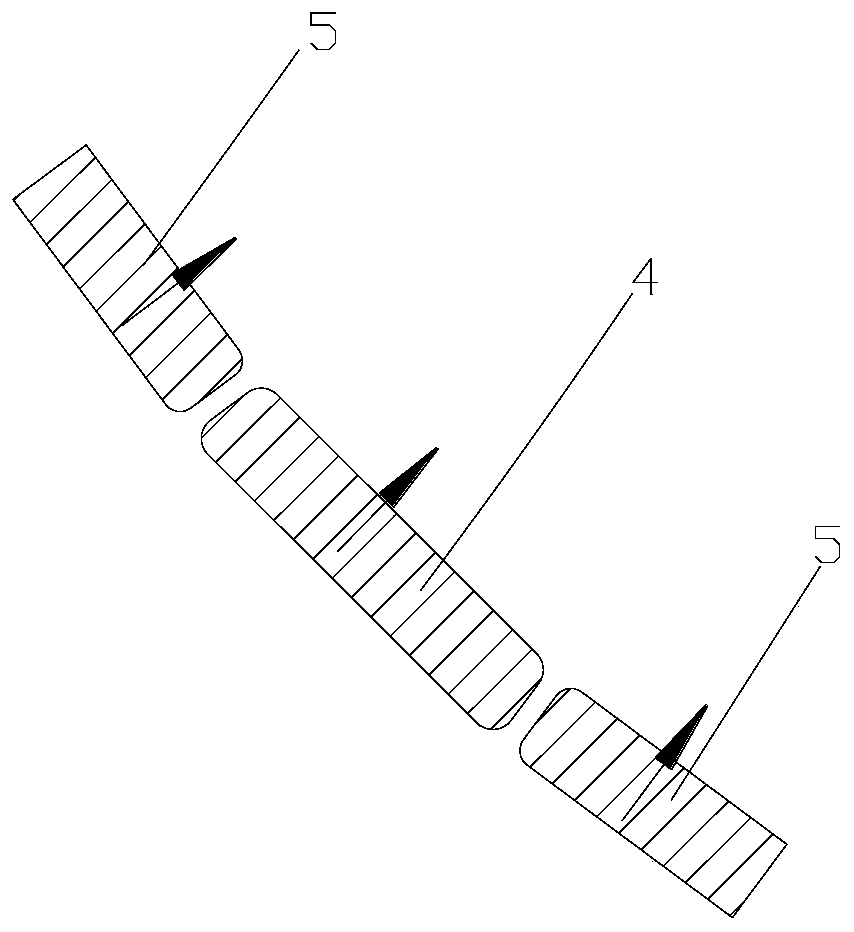

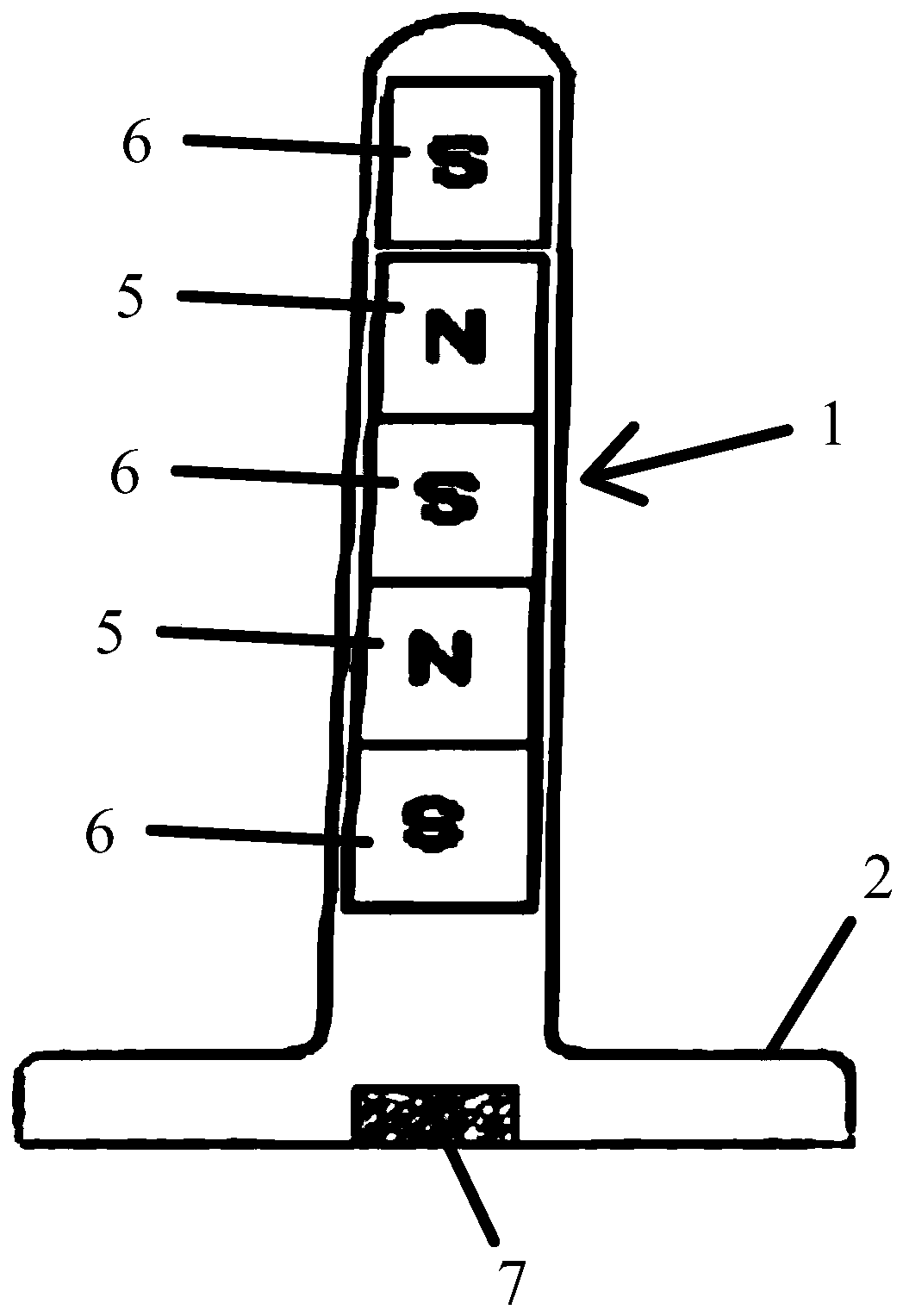

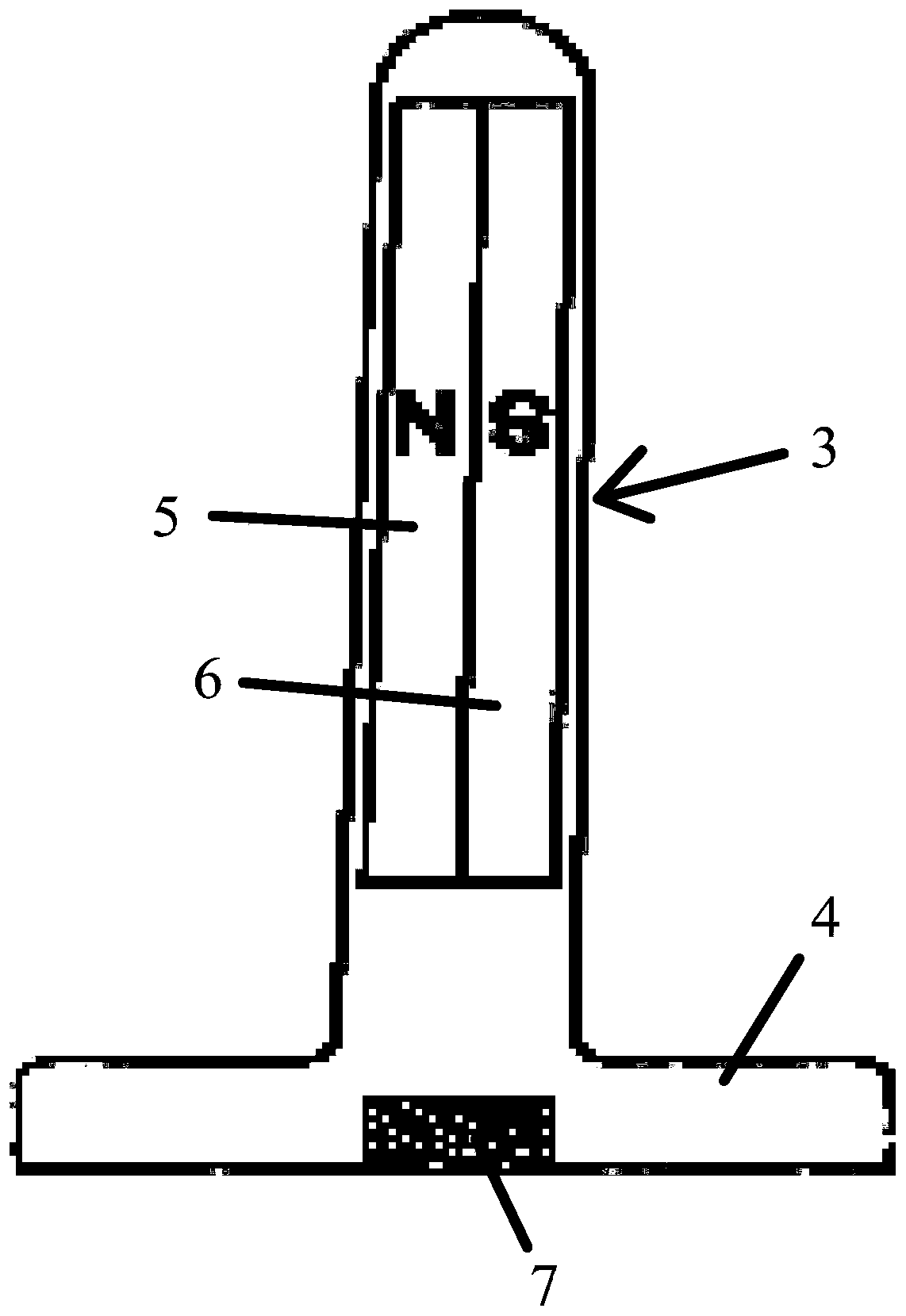

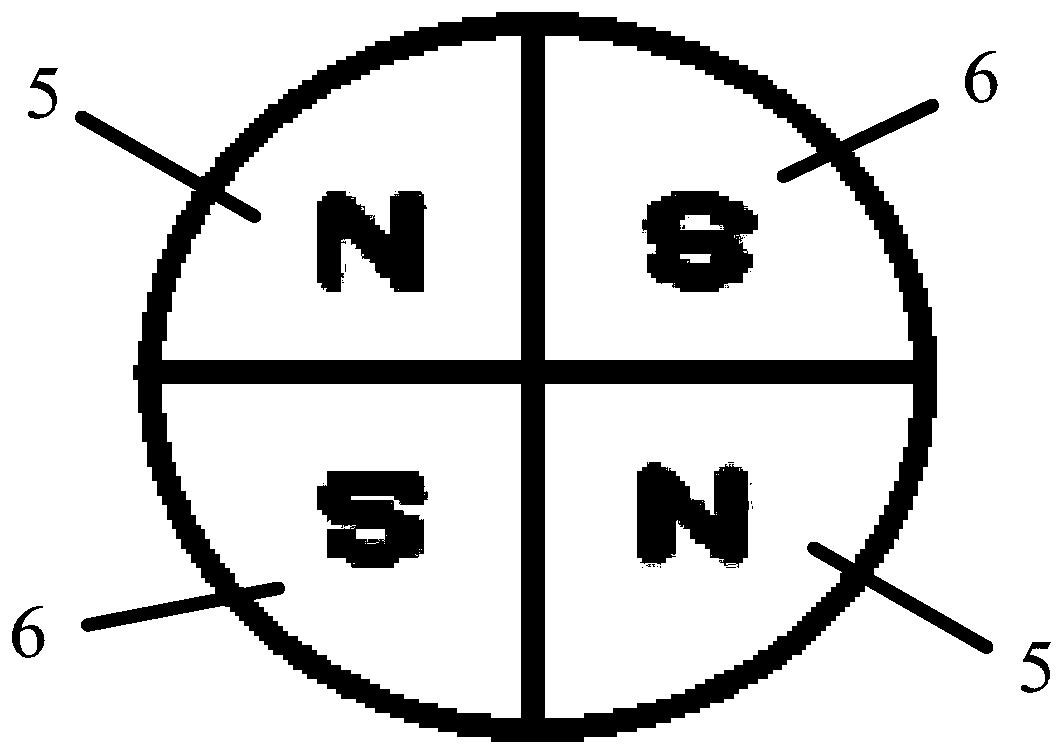

Motor rotor and motor

PendingCN111106688AImprove operational reliabilityIncrease output torqueMagnetic circuit rotating partsElectric machineEngineering

The invention provides a motor rotor and a motor. The motor rotor comprises a rotor core (1). The rotor core (1) is provided with a first installation groove (2) perpendicular to the d axis of the motor and two second installation grooves (3) located in the two sides of the first installation groove (2). A first permanent magnet (4) is arranged in the first installation groove (2). Second permanent magnets (5) are arranged in the second installation grooves (3). The two second installation grooves (3) are symmetrical about the d axis of the motor. An included angle alpha is formed between thefirst installation groove (2) and the second installation grooves (3), and alpha is larger than or equal to 155 degrees and smaller than or equal to 170 degrees. According to the motor rotor providedby the invention, the demagnetization resistance of the motor rotor can be effectively improved, and the output torque of the motor is ensured.

Owner:GREE ELECTRIC APPLIANCES INC

a baking soda toothpaste

ActiveCN109199909BGood dispersionEasy to disperse evenlyCosmetic preparationsToilet preparationsSodium phosphatesToothpaste

The invention discloses a baking soda toothpaste, which is prepared by the following raw materials in parts by weight: nanometer sodium bicarbonate powder 67.0-67.2wt%, xylitol 3.0-3.2wt%, polyethylene glycol 1.6-1.8wt%, Calcium pyrophosphate 1.2-1.3wt%, mass concentration is 30% poly(oxypropylene) oleyl ether sodium phosphate 2.8-3.0wt%, sodium alginate 0.2-0.3wt%, guar gum 0.2-0.3wt%, 0.2-0.3wt% of stevia, 0.1-0.11wt% of sodium fluoride, and 4-6wt% of fatty acid alkanolamide borate and potassium phosphate, wherein the weight ratio of fatty acid alkanolamide ester and potassium phosphate is 3- 5:1, and the right amount of essence, the balance of water. The baking soda toothpaste provided by the invention adopts a unique dental-grade baking soda formula, which can inhibit dental plaque, reduce gum swelling and bleeding, relieve gum problems, and strengthen gums and teeth. It can effectively prevent the formation of dental calculus, remove bad breath, and prevent tooth decay. The baking soda toothpaste provided by the invention has stable properties, and long-term storage will not cause the baking soda to decompose.

Owner:浙江施维康生物医学材料有限公司

Air conditioner wind wheel material and its preparation method and application

ActiveCN106633399BSimple and fast operationEasy to controlMechanical apparatusLighting and heating apparatusEngineeringAir conditioning

The invention provides an air conditioner wind wheel material as well as a preparation method and application thereof. The air conditioner wind wheel material comprises an antibacterial agent and a fluorine-containing surface modifier. According to the air conditioner wind wheel material provided by the invention, the fluorine-containing surface modifier can reduce the surface energy of an air conditioner wind wheel, so that the attachment force of dust and microorganisms to the surface of the air conditioner wind wheel can be reduced; meanwhile, the antibacterial agent can also inhibit and kill attached microorganisms in time to further synergistically and effectively prevent attachment and increase of the dust and the microorganisms on the surface of the air conditioner wind wheel, so that the accumulation amount of the microorganisms and the dust on the surface of the wind wheel is reduced.

Owner:WUHAN REFRIGERATION EQUIP OF MIDEA GROUP +1

A sealing ring for a chip

ActiveCN105990313BReduce rigidityAlleviate the problemSemiconductor/solid-state device detailsSolid-state devicesAdhesion forceDielectric layer

The invention provides a sealing ring of a chip. The sealing ring comprises one or more sealing units; each sealing unit comprises a first metal wiring layer, a second metal wiring layer, an interlayer dielectric layer, and one or more via hole groups; the first metal wiring layer surrounds the chip; the first metal wiring layer includes a first metal portion and a first dielectric material portion which are insulated from each other; the second metal wiring layer is opposite to the first metal wiring layer; the second metal wiring layer includes a second metal portion and a second dielectric material portion which are insulated from each other; the interlayer dielectric layer is arranged between the first metal wiring layer and the second metal wiring layer; the one or more via hole groups surround the chip, are arranged in the interlayer dielectric layer and are connected with the first metal portion and the second metal portion; and each via hole group includes a plurality of via holes which are independent from each other. A via hole formation mechanical stress breaks through the obstruction of an adhesion force between the first metal portion, the second metal portion and the via holes, so that the problem of delamination of the edge of the chip can be alleviated; and the rigidness of the via holes is decreased, so that the deformation ability of the via holes can be increased, and therefore, the delamination of the edge of the chip can be effectively prevented.

Owner:SEMICON MFG INT (SHANGHAI) CORP

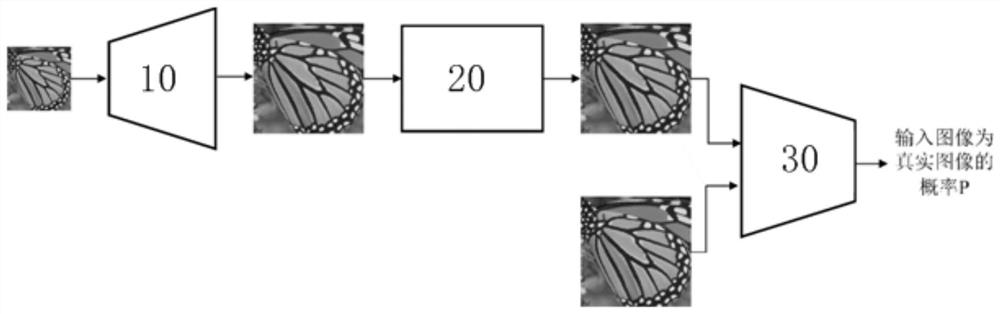

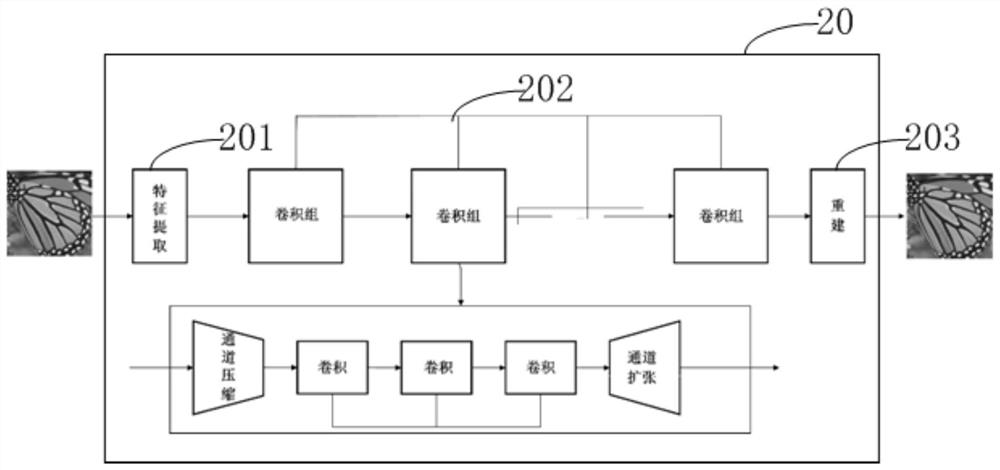

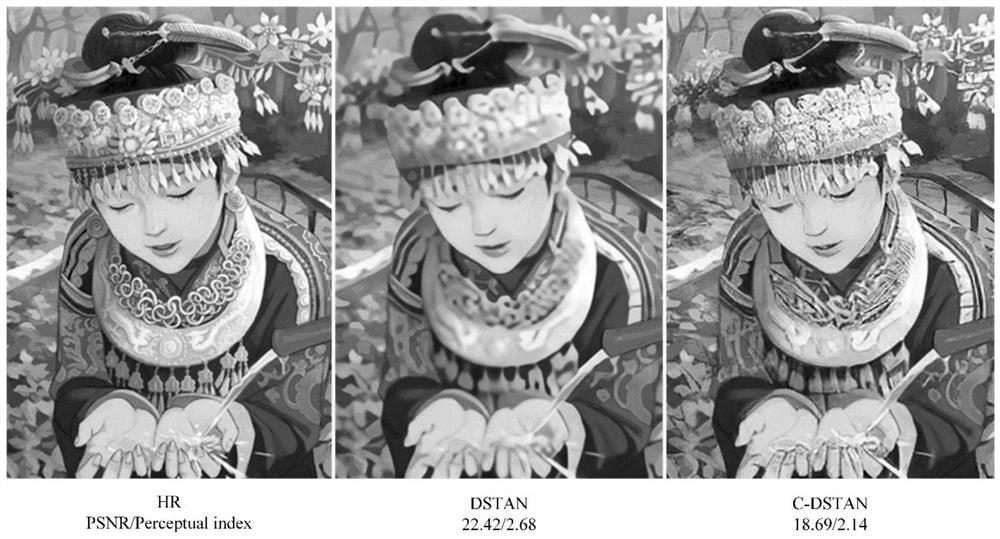

Image super-resolution method based on cascade network framework and cascade network

PendingCN112116527AImprove sensory lossAlleviate the problemGeometric image transformationEnergy efficient computingImage resolutionImage based

The invention relates to an image super-resolution method based on a cascade network framework and a cascade network, and the method comprises the steps: obtaining a preliminary upsampling result of atarget image based on a basic super-resolution network; and based on the detail refinement network, obtaining a super-resolution image result according to the preliminary up-sampling result. Two networks are cascaded, a task facing a peak signal-to-noise ratio and a task facing subjective feeling are separated and are respectively processed by two models, a basic super-resolution network firstlycompletes preliminary up-sampling, and the result of the preliminary up-sampling ensures content consistency with an original high-resolution image to a great extent; then, a preliminary up-sampling result is sent to a refinement network to further improve sensory loss, and the refinement network has the input of the preliminary up-sampling result, so that the content consistency of the whole super-resolution result is not excessively sacrificed; in addition, the training difficulty of a refinement network and a discriminator is reduced through refinement on a preliminary up-sampling result, the training speed is increased, and the problem of an existing model is effectively relieved.

Owner:HANGZHOU INNOVATION RES INST OF BEIJING UNIV OF AERONAUTICS & ASTRONAUTICS

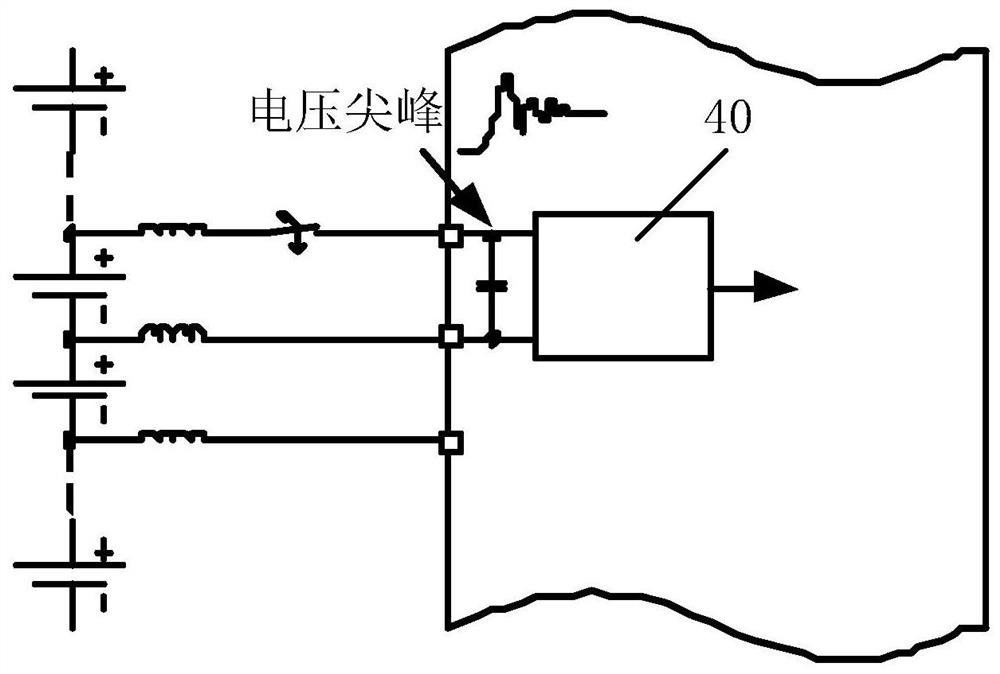

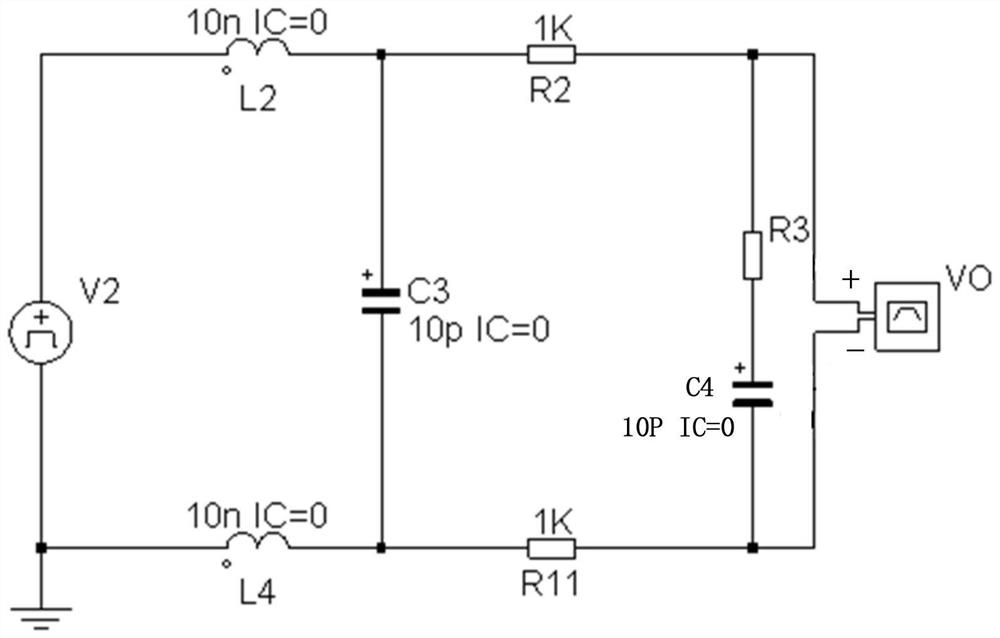

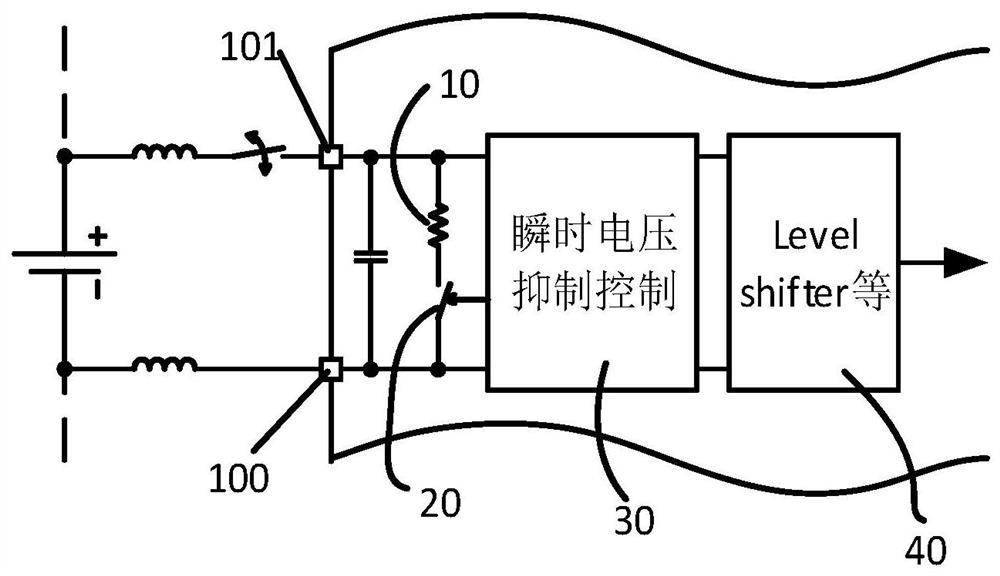

Voltage spike suppression circuit and battery protection circuit

PendingCN112968426AAlleviate the problemIncrease resistanceElectric powerArrangements for several simultaneous batteriesVoltage spikeElectrical battery

The invention provides a voltage spike suppression circuit and a battery protection circuit. The voltage spike suppression circuit comprises a first resistor unit, a first switch unit and a voltage comparison unit; the first resistor unit is connected between a first end and a second end of a load; the first switch unit is connected in series or parallel with the first resistor unit; the voltage comparison unit is connected between the first end and the second end of the load; the voltage comparison unit is electrically connected with the first switch unit; and the voltage comparison unit is used for controlling the state change of the first switch unit under the condition that the difference value between an instantaneous voltage and an average voltage is larger than a preset voltage, so that current can pass through the first resistor unit, wherein the instantaneous voltage is an instantaneous sampling voltage between the first end of the load and the second end of the load, and the average voltage is the average value of the voltage between the first end of the load and the second end of the load in a certain time window. The circuit plays a better role in suppressing oscillation for the voltage spike of a chip.

Owner:JOULWATT TECH INC LTD

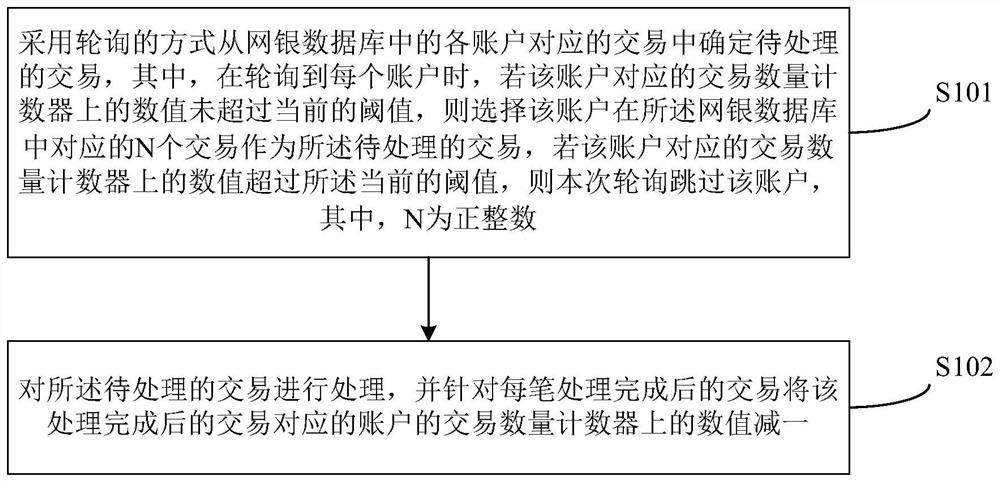

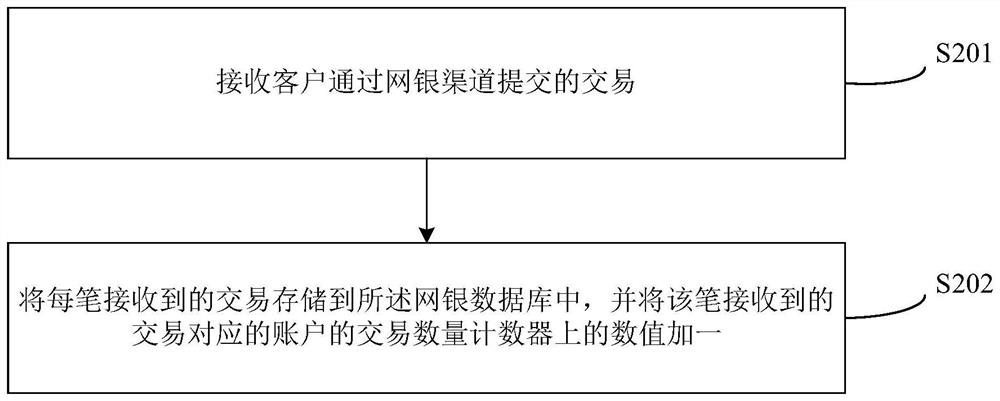

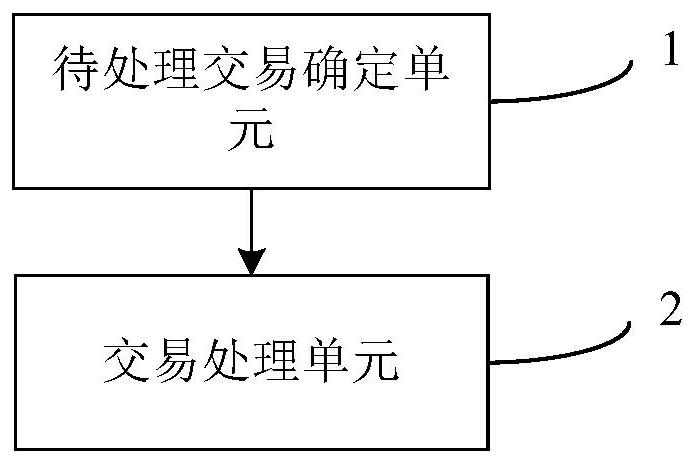

Transaction processing method and device

PendingCN114860407AAlleviate the problemCircumstances that reduce processing speedProgram initiation/switchingFinanceFinancial transactionData mining

The invention discloses a transaction processing method and device which can be used in the financial field or other fields, and the method comprises the steps: determining a to-be-processed transaction from transactions corresponding to all accounts in an online banking database in a polling mode, and when each account is polled, determining the to-be-processed transaction according to the to-be-processed transaction; if the numerical value on the transaction quantity counter corresponding to the account does not exceed the current threshold value, N transactions corresponding to the account in the online banking database are selected as the transactions to be processed, if the numerical value on the transaction quantity counter corresponding to the account exceeds the current threshold value, the account is skipped in the polling, and if the numerical value on the transaction quantity counter corresponding to the account exceeds the current threshold value, the N transactions corresponding to the account in the online banking database do not exceed the current threshold value. N is a positive integer; and processing the to-be-processed transaction, and subtracting one from the numerical value on the transaction quantity counter of the account corresponding to the processed transaction for each processed transaction. According to the method, the problem of the hotspot account is effectively relieved, and the situation that the processing speed of a core accounting system is slowed down by the hotspot account is effectively reduced.

Owner:BANK OF CHINA

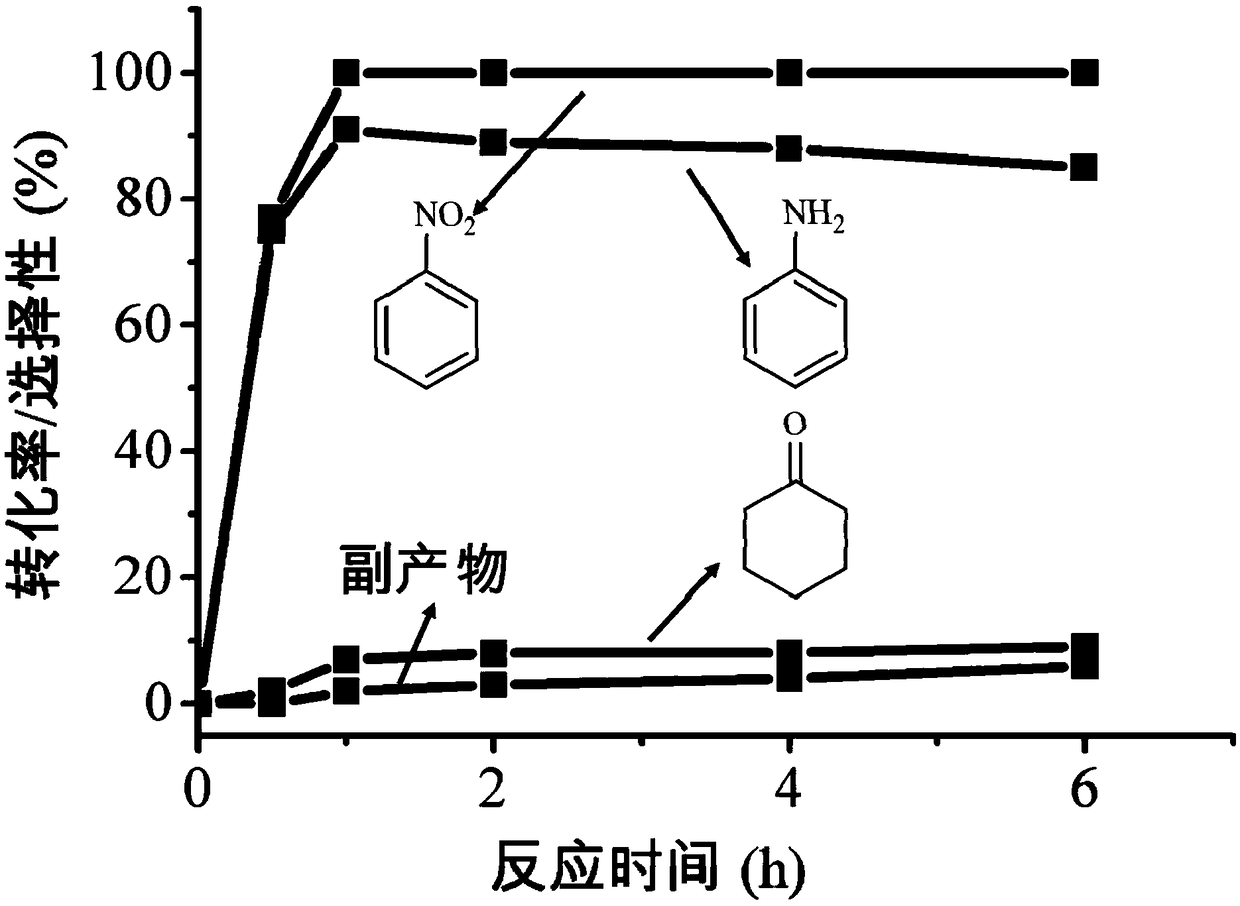

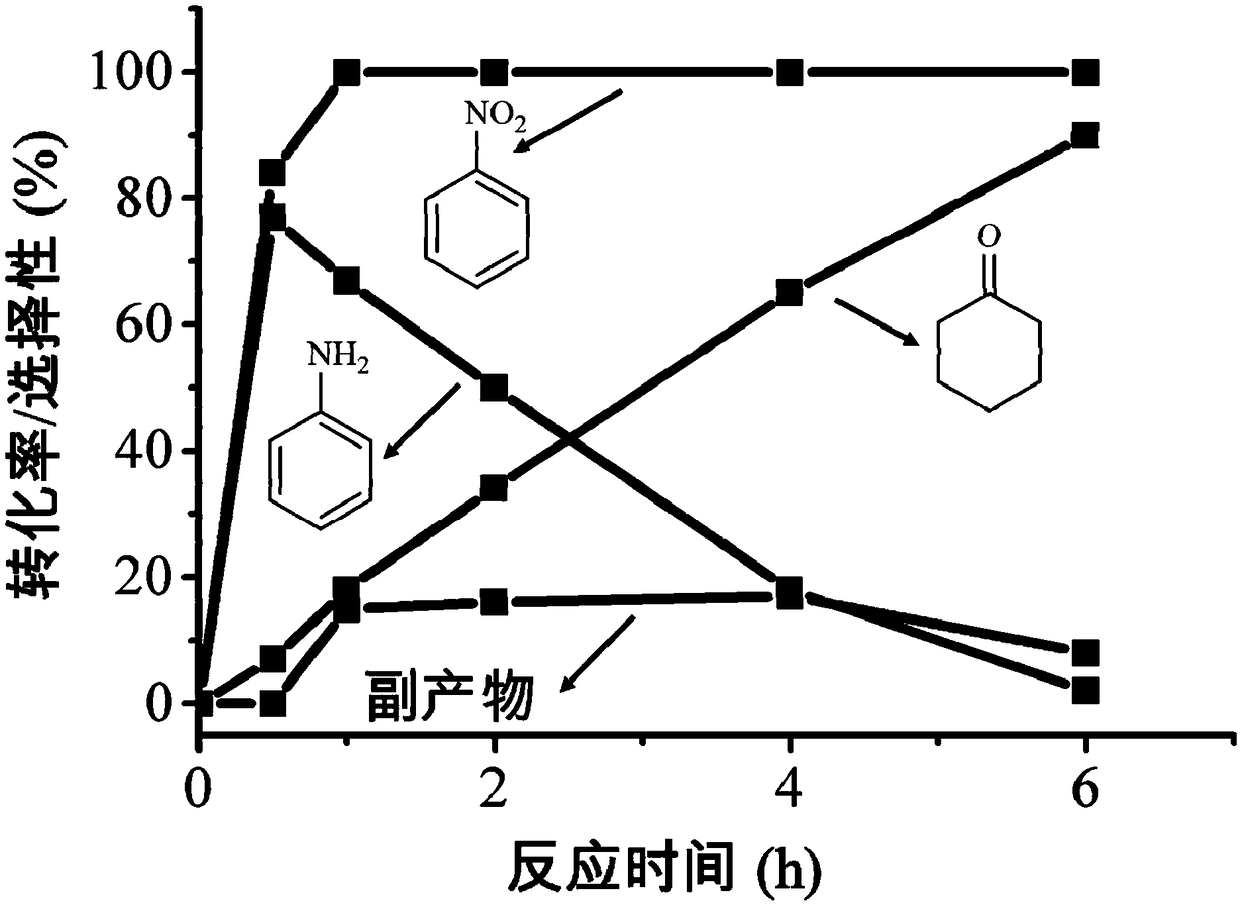

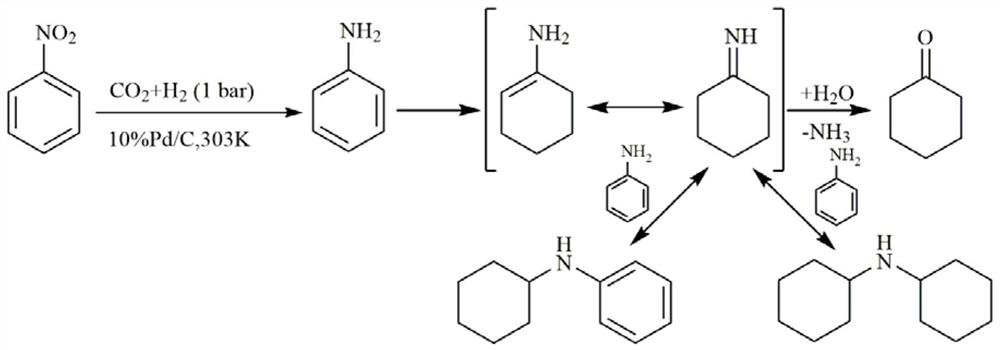

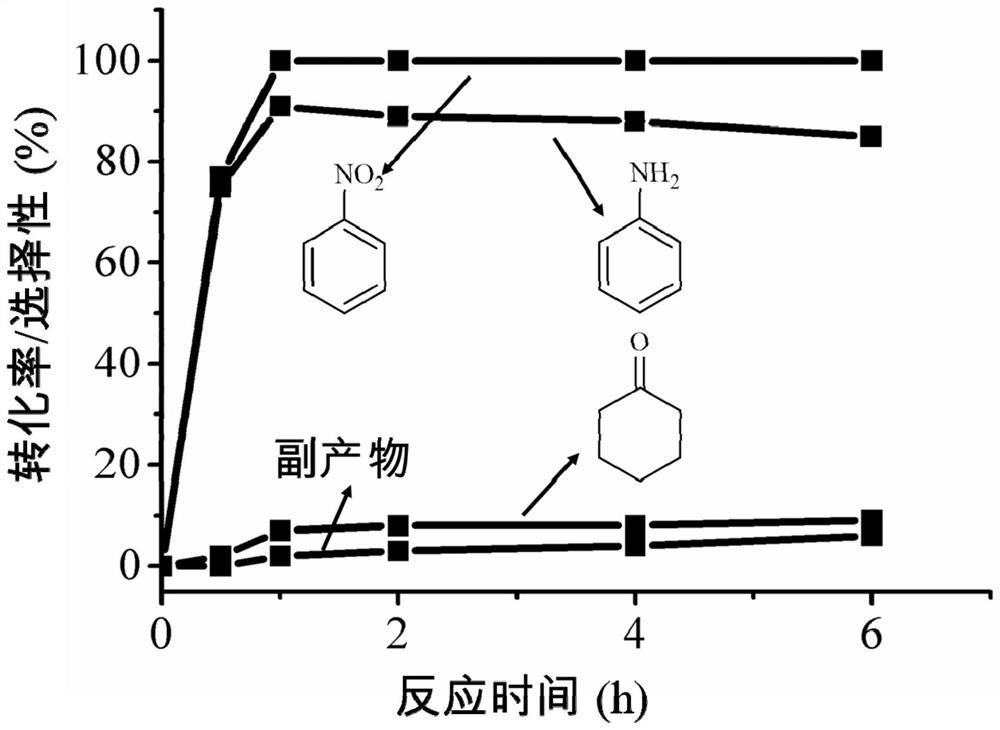

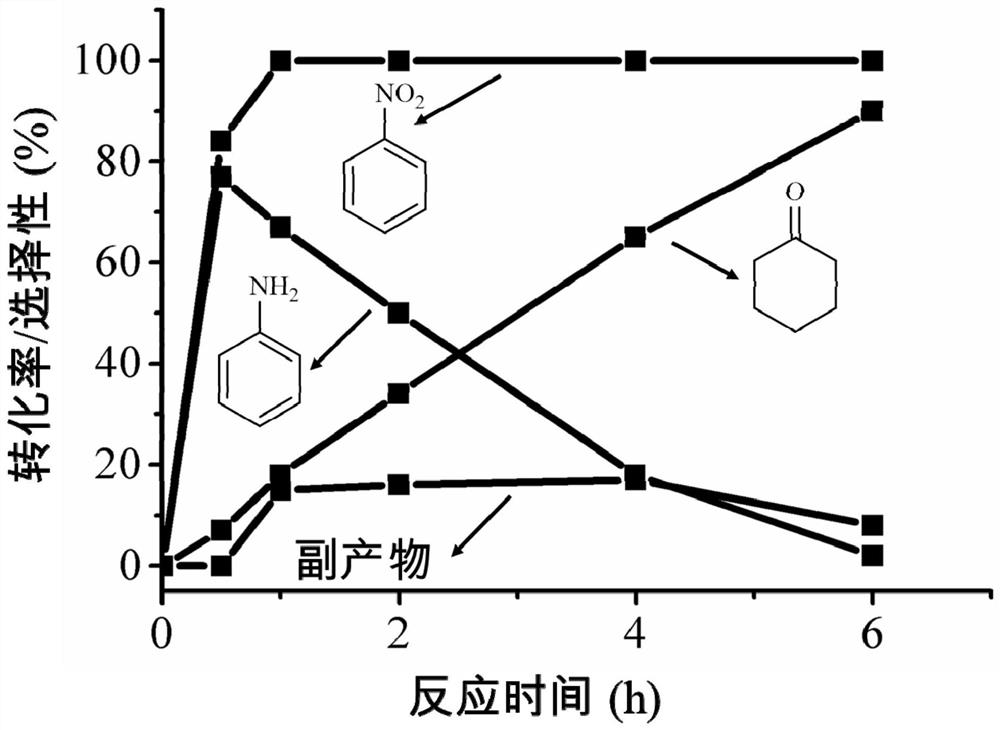

Method for synthesizing cyclohexanone by accelerating hydrogenation of aromatic compounds with carbon dioxide

ActiveCN109180444AMitigate environmental problemsSimple process operationOrganic compound preparationCarbonyl compound preparationNitrobenzeneNitro compound

The invention relates to a method for synthesizing cyclohexanone by accelerating hydrogenation of aromatic compounds with carbon dioxide. The method comprises the following steps: dissolving CO2 in water to produce H2CO3 molecules, further forming hydrogen bonds through aromatic nitro compounds (such as nitrobenzene), accelerating to be adsorbed onto the surface of metal nanoparticles, activatinghydrogen by the metal nanoparticles, and reducing into corresponding cyclohexanone. According to the method, the greenhouse gas CO2 is effectively utilized, and the wastes are changed into valuable materials. The method disclosed by the invention has the characteristics of being simple in process operation, green, safe and low in cost, can realize large-scale continuous production, and has obviouseconomic benefits and environmental benefits.

Owner:SHANGHAI JIAO TONG UNIV

Prostate magnet therapy rod assembly and use method thereof

PendingCN111202910AEffectively regulates the biomagnetic fieldAdjust biomagnetic fieldElectrotherapyMagnetotherapy using permanent magnetsHyperaemiaUrethra

Owner:李少华

Novel compound fertilizer and preparation method thereof

InactiveCN107266263AAlleviate the problemPromote absorptionAlkali orthophosphate fertiliserExcrement fertilisersAbsorption capacityRetention time

The invention relates to a novel compound fertilizer and a preparation method thereof. The novel compound fertilizer is prepared from, by weight, 10-15 parts of ammonium phosphate, 8-12 parts of phosphorus nitrate, 2-6 parts of TBHQ, 3-5 parts of potassium nitrate, 3-5 parts of monopotassium phosphate, 20-25 parts of urea, 3-5 parts of monopotassium phosphate, 2-5 parts of diammonium phosphate, 20-25 parts of rape seed cakes, 10-20 parts of tea seed cakes, 10-20 parts of chicken manure and 3-8 parts of fermentation powder. The novel compound fertilizer is easy in material acquisition, low in cost, sufficient, rich in nutrition component, less prone to causing soil acidification and basification and effective in alleviation of soil problems, absorption capacity of crops is improved, growth acceleration and yield increase are realized, and freeness of caking, easiness in decomposition and absorption, high oxidation resistance, stability improvement and long retention time are realized.

Owner:马鞍山中粮生物化学有限公司

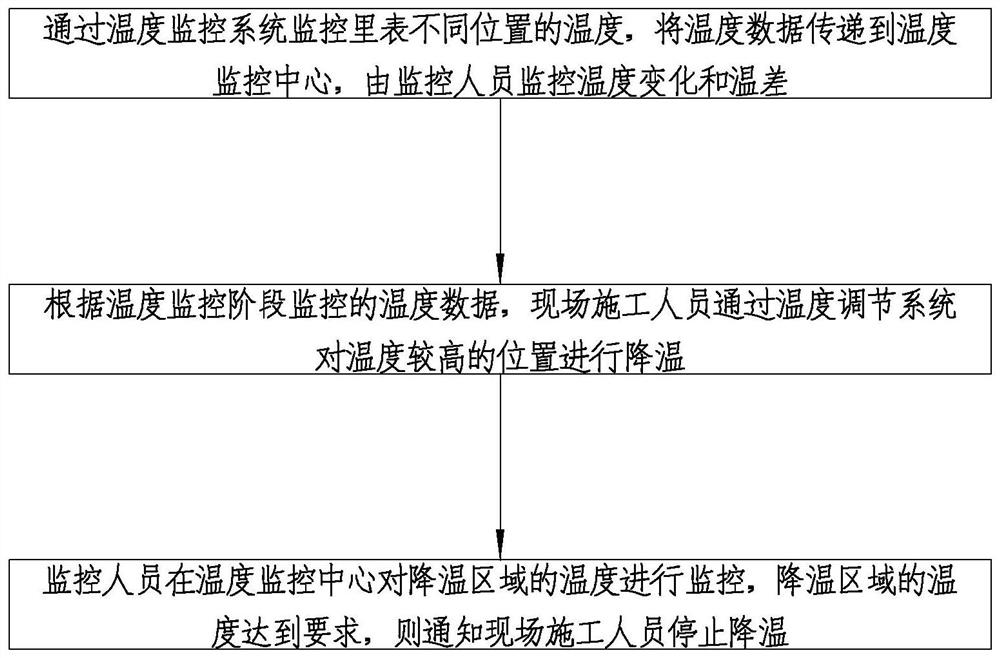

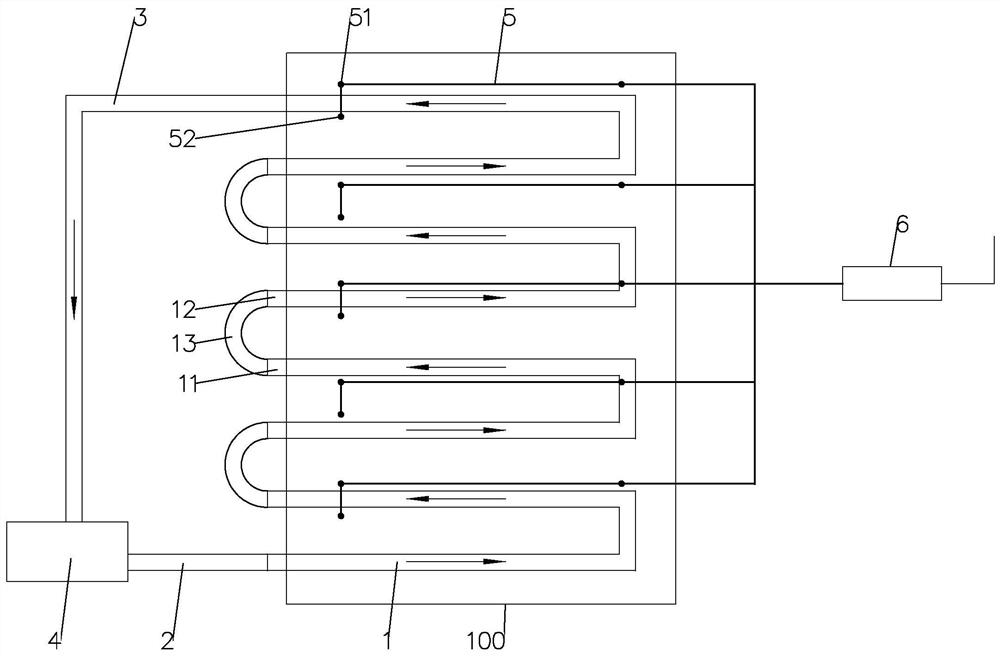

A kind of mass concrete temperature control method

ActiveCN113152468BAlleviate the problemImprove control efficiencyFoundation engineeringBuilding material handlingTemperature controlMonitoring temperature

The present application relates to a temperature control method for mass concrete, including a temperature monitoring stage and a temperature adjustment stage; in the temperature monitoring stage, the temperature at different positions on the inner surface is monitored through a temperature monitoring system, and the temperature data is transmitted to a temperature monitoring center, which is monitored by monitoring personnel Temperature change and temperature difference; in the temperature adjustment stage, according to the temperature data monitored in the temperature monitoring stage, the temperature adjustment system is used to cool the location with higher temperature; the temperature adjustment system includes multiple sets of cooling water pipes set in the mass concrete, connected to The water inlet and return pipes at both ends of the water pipe, as well as the water source connected to the water inlet and the return pipe, the cooling water pipes are distributed in a serpentine shape from top to bottom in the mass concrete, and the cooling water pipes pass through cooling water to cool the position with higher temperature . The present application can reduce the difficulty of temperature control of mass concrete and improve the precision of temperature control.

Owner:北京路鹏达建设发展有限责任公司

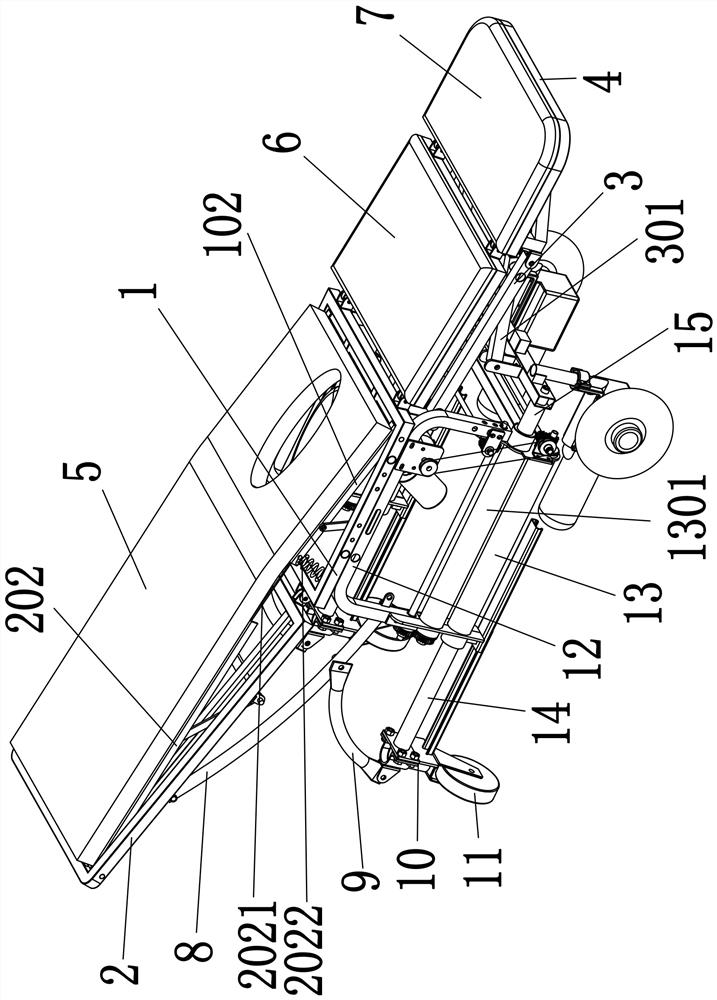

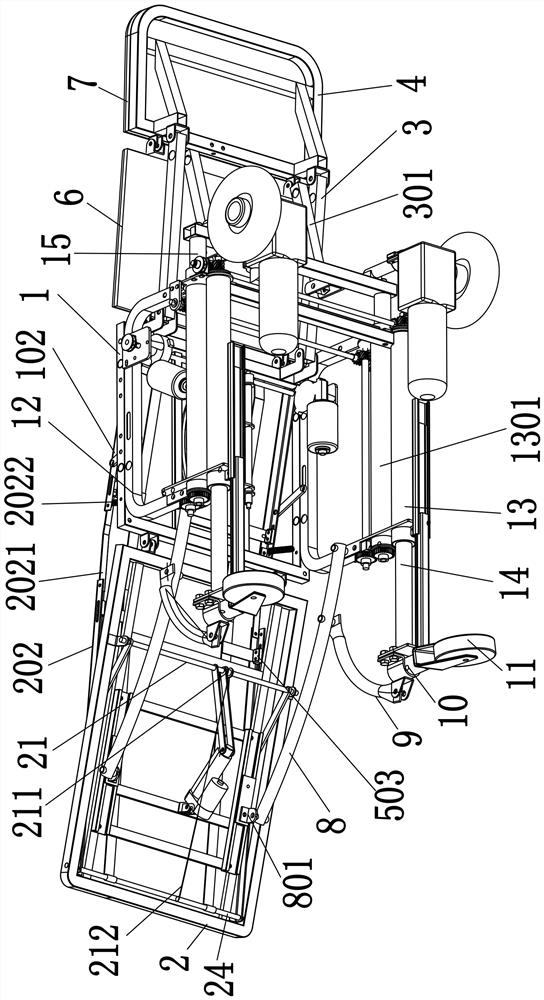

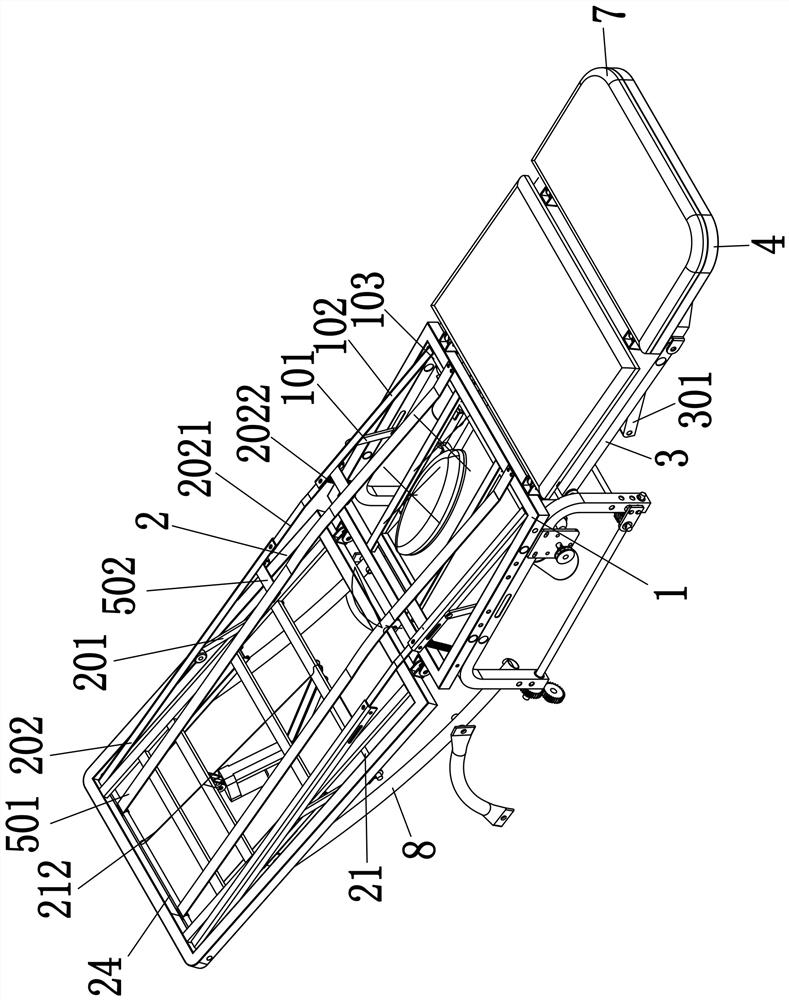

Bedsore-preventing defecation-assisting automatic bed trolley

PendingCN112932841AAlleviate the problemRelieve pressureWheelchairs/patient conveyanceNursing bedsElectric machineryCushion

The invention particularly relates to a bedsore-preventing defecation-assisting automatic bed trolley. A first cushion body is installed on the upper surfaces of a seat frame and a back frame. A first pushing frame and a first connecting rod are arranged on the seat frame. A first rotating shaft is arranged on the back frame. The first pushing frame is connected with the first connecting rod. A second connecting rod and a second pushing frame are arranged on the back frame. The second pushing frame is connected with a second connecting rod, the other end of the first pushing frame is connected with the other end of the second pushing frame through a force-bearing flexible belt, the other end of the second connecting rod is connected with a rotating rod, the rotating rod is connected with a second motor, and one end of the second motor is fixed to the back frame. A tough drawstring is arranged on the bottom surface of the first cushion body, one end of the tough drawstring is connected to the first rotating shaft, and the other end of the tough drawstring is connected to the seat frame. The automatic bed trolley has the beneficial effects that through combined use of the back frame, the second connecting rod, the second pushing frame, the rotating rod and the motor, the first cushion body is in an arched state, contact between a human body and the first cushion body is reduced, and therefore the bedsore problem is relieved.

Owner:佛山市顺德区新大通工艺电器有限公司

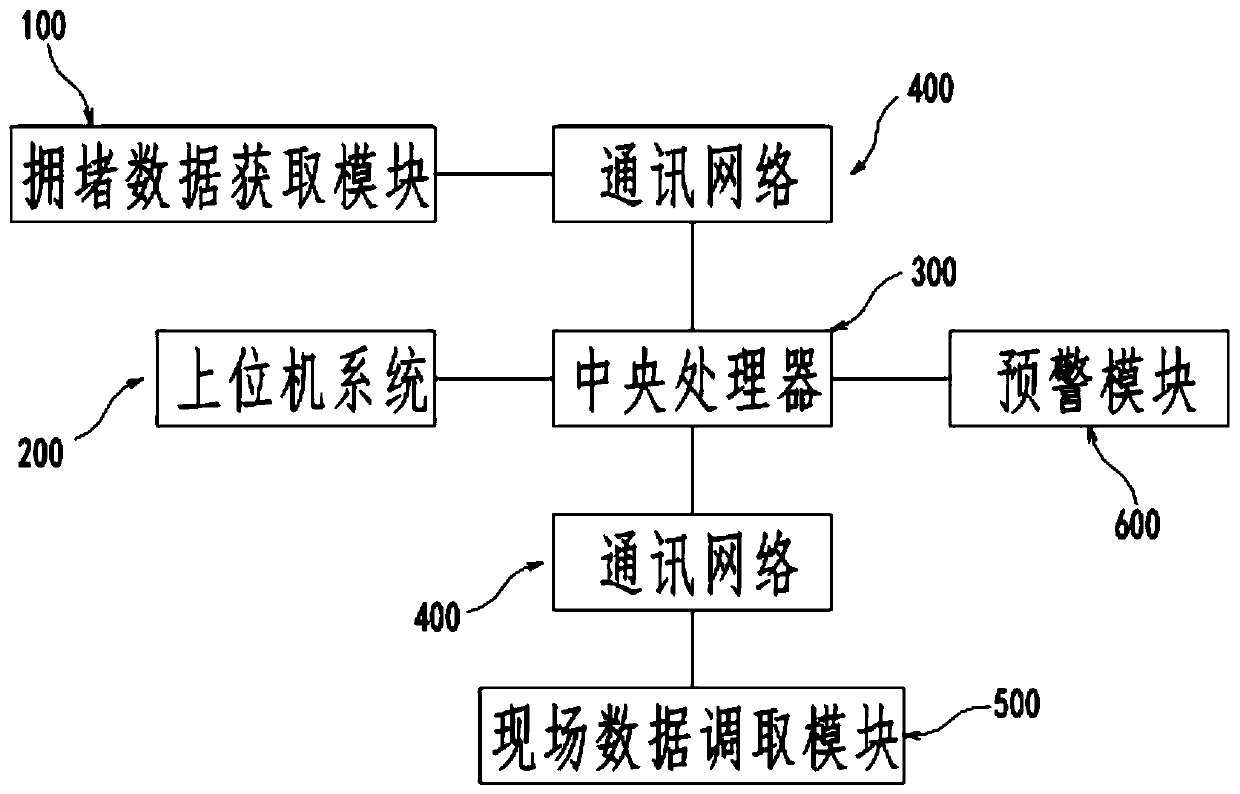

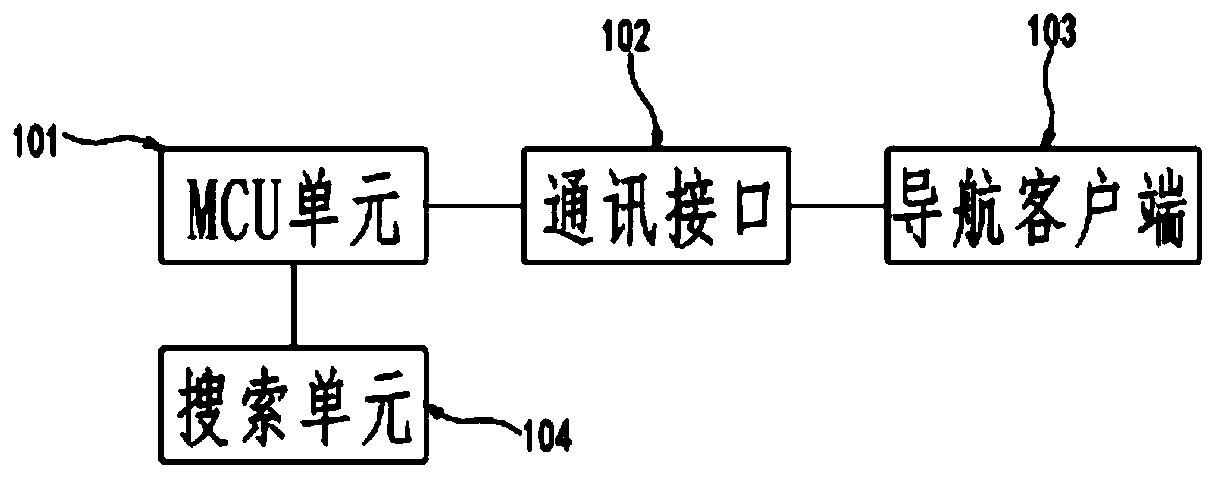

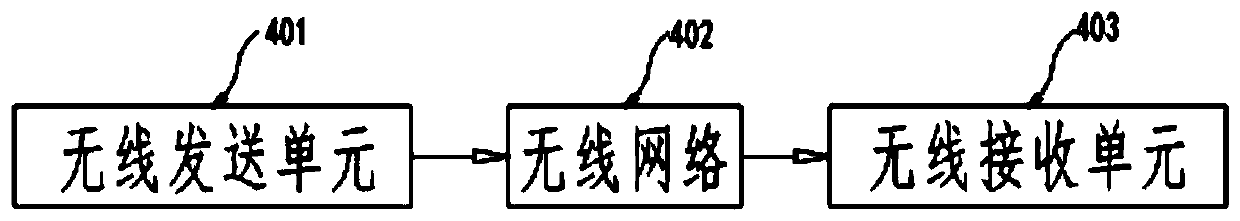

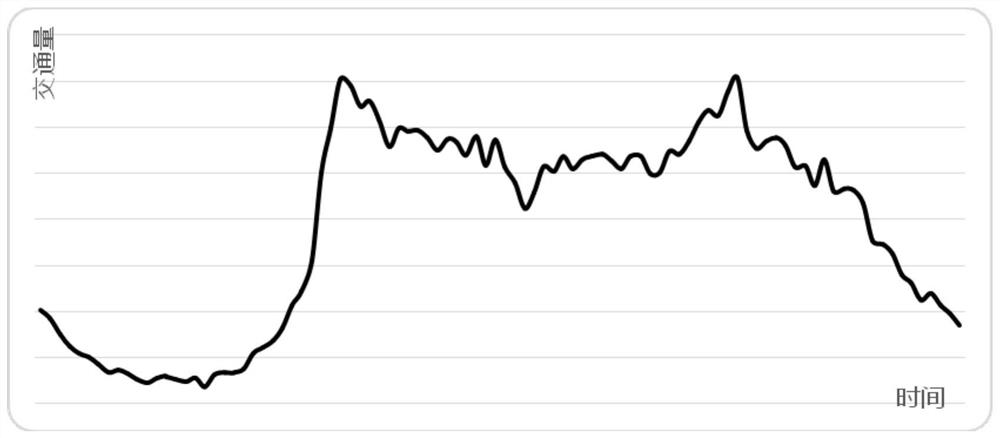

Intelligent traffic management system capable of alleviating traffic congestion

InactiveCN110580807AEase traffic congestionAlleviate the problemDetection of traffic movementTraffic congestionData acquisition module

The invention discloses an intelligent traffic management system capable of alleviating traffic congestion. The system comprises a congestion data acquisition module, an upper computer system, a central processing unit and a field data calling module. The field data calling module communicates with the central processing unit through a communication network, and is used for acquiring video information of a congestion site to enable personnel to judge the cause and position of congestion. The congestion data acquisition module communicates with the central processing unit through the communication network. The beneficial effect of the system is as follows: the congestion condition of a certain road section is acquired through a navigation client, the central processing unit immediately acquires video information of a congestion site through the field data calling module after receiving alarm information, the field personnel at the upper computer system judges the cause and position of congestion according to the situation and generates a decision (for example, police at the congestion position is immediately notified to rush to the site for handling the congestion), the police can quickly judge the cause of an accident and handle the accident, and thus, the problem of traffic congestion can be alleviated.

Owner:HANGZHOU SIYUAN INFORMATION TECH CO LTD

Optimal configuration method of sensing interval when signal control intersection phase is green

ActiveCN109035780BImprove green hour utilizationImprove traffic efficiencyControlling traffic signalsDetection of traffic movementRoad traffic controlGreen time

The present invention provides an optimal configuration method for signal-controlled intersection phase green-time sensing intervals. According to traffic flow, signal scheme time sections are divided, and based on non-motor vehicle and pedestrian crossing requirements, intersection vehicle traffic requirements, and traffic management requirements, each time period is determined. The green time induction interval of each phase stage is allocated and calculated. The present invention summarizes the minimum green hour demand and the maximum green hour demand in the signal phase time period, considers the green hour demand of non-motor vehicles and pedestrians crossing the street within the cycle time and the phase locking situation of the traffic control signal phase, and analyzes each phase in the time period Optimizing the configuration of the green light sensing interval in the phase, so as to effectively improve the utilization rate of the traffic signal at the intersection when it is green, improve the efficiency of intersection traffic, and alleviate the problem of traffic users.

Owner:JIANGSU ZHITONG TRANSPORTATION TECH

Method for synthesizing cyclohexanone by accelerated hydrogenation of aromatic compounds using carbon dioxide

ActiveCN109180444BImprove adsorption capacityReaction impactOrganic compound preparationCarbonyl compound preparationCyclohexanoneNitro compound

The present invention relates to the method for using carbon dioxide to accelerate the hydrogenation of aromatic compounds to synthesize cyclohexanone, the method is by CO 2 Soluble in water to form H 2 CO 3 Molecules, and then by forming hydrogen bonds with aromatic nitro compounds (such as nitrobenzene), it accelerates the adsorption to the surface of metal nanoparticles, and then the metal nanoparticles activate hydrogen to reduce it to the corresponding cyclohexanone. The method efficiently utilizes the greenhouse gas CO 2 , turning waste into treasure, the method involved in the invention not only has the characteristics of simple process operation, green safety and low cost, but also can realize large-scale continuous production, and has obvious economic and environmental benefits.

Owner:SHANGHAI JIAO TONG UNIV

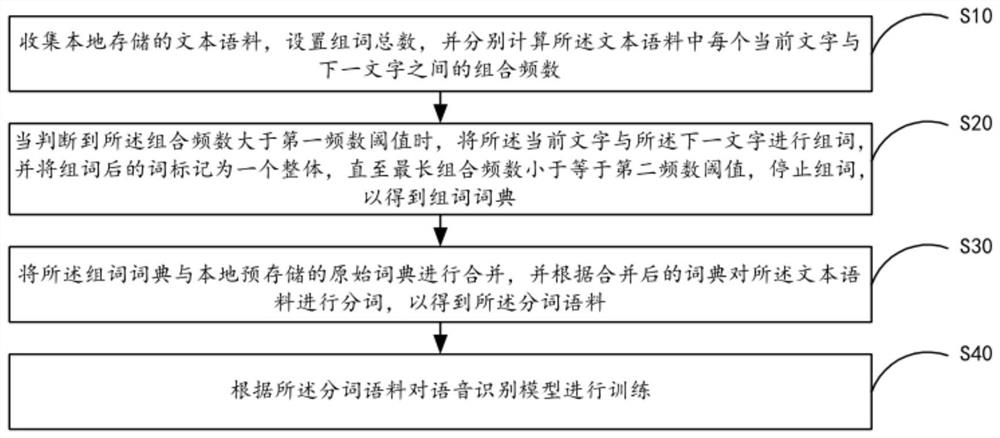

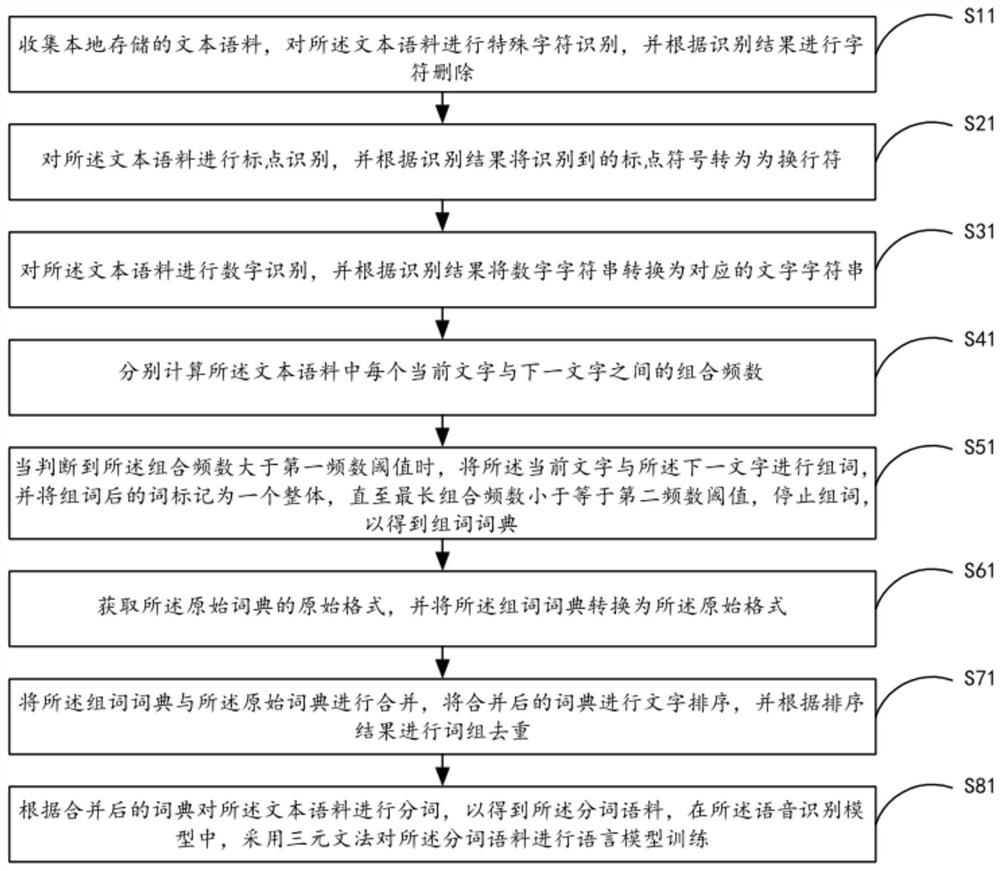

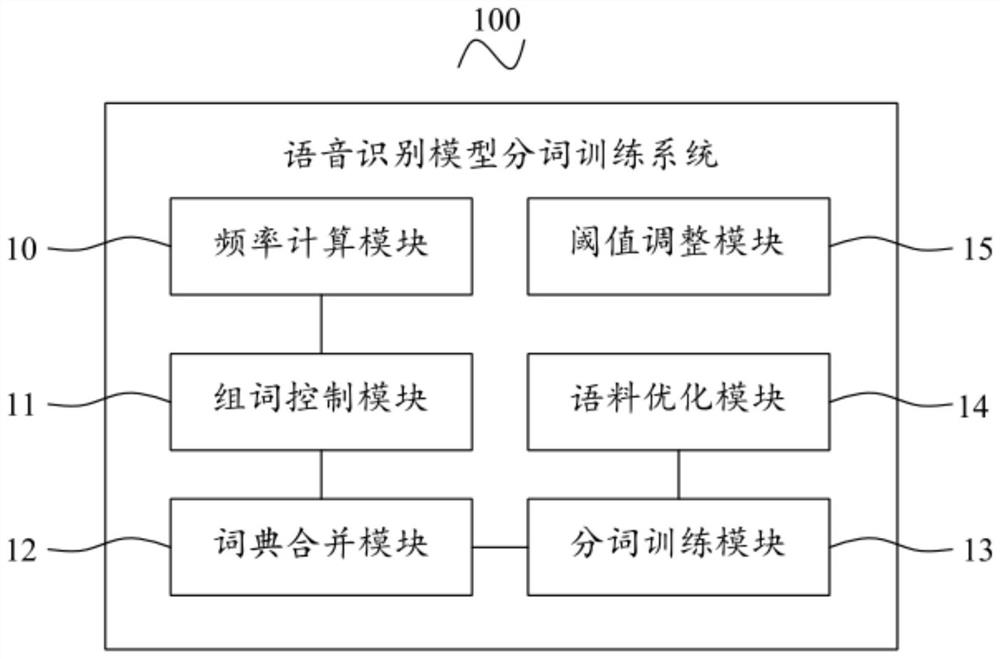

Speech recognition model word segmentation training method, system, mobile terminal and storage medium

ActiveCN110853625BAlleviate the problemEasy to identifySpeech recognitionSpeech soundSubvocal recognition

The present invention is applicable to the technical field of speech recognition, and provides a speech recognition model word segmentation training method, system, mobile terminal and storage medium. The method includes: collecting locally stored text corpus, setting the total number of word groups, and calculating the sum of each current text and Combination frequency between the next text; when it is judged that the combination frequency is greater than the first frequency threshold, the current text and the next text are combined and marked as a whole, until the longest combination frequency is less than or equal to the second frequency threshold, stop forming words , to obtain a word dictionary; merge the word dictionary with the original dictionary, and perform word segmentation on the text corpus according to the merged dictionary to obtain word segmentation data; train the speech recognition model according to the word segmentation data. The present invention expands the original dictionary by constructing a word-group dictionary, so that there is no need to additionally collect training corpus for substring labeling learning, and it is not necessary to perform manual word segmentation in advance or use other word segmentation algorithms for word segmentation.

Owner:XIAMEN KUAISHANGTONG TECH CORP LTD

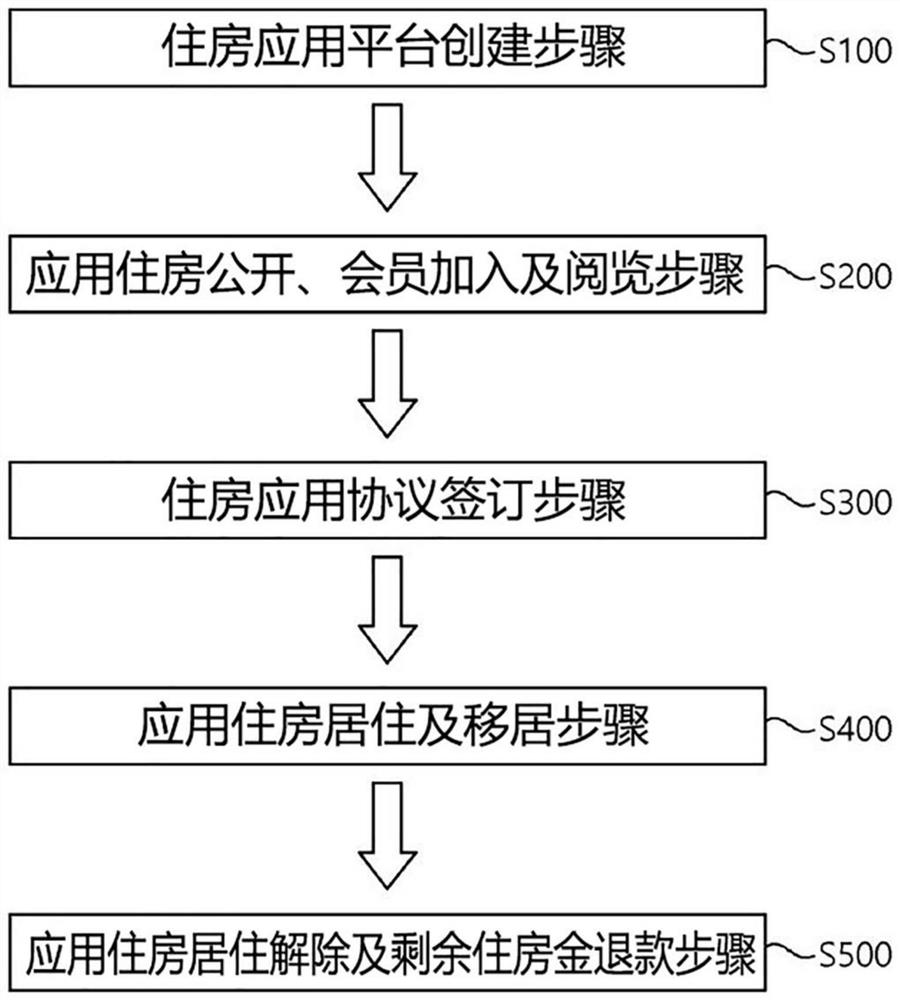

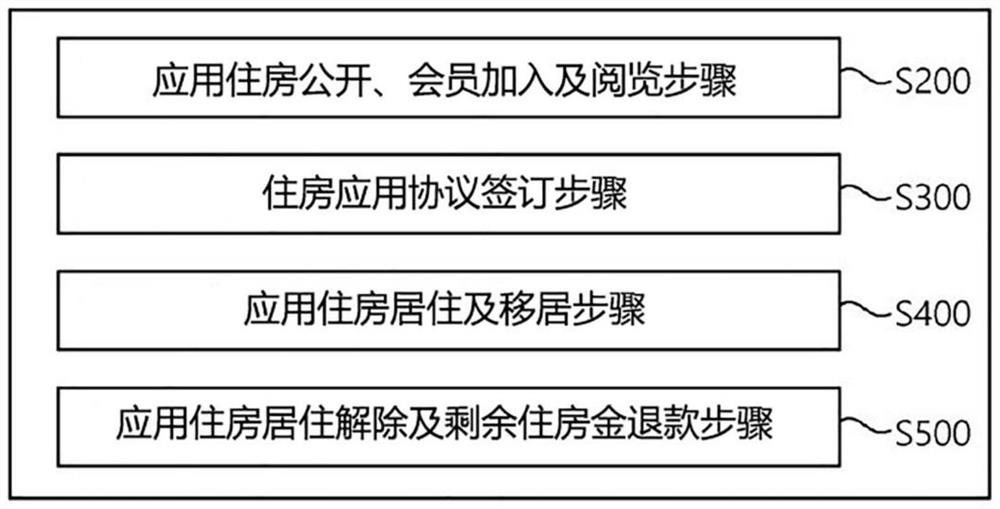

Public application method of housing

InactiveCN114207658AImprove convenienceGuaranteed quick liquidityMarket predictionsOperations managementSystems engineering

The present invention relates to a public application method of a housing, comprising: a housing application platform creation step of creating a housing application platform operated and managed by an application housing supplier; an application housing disclosure and reading step in which the application housing of the application housing supplier is disclosed on the created housing application platform so that the application housing consumer who joins the member can read the disclosed application housing; and a housing application agreement signing step in which a housing application agreement is signed between the application housing supplier and each of the plurality of application housing consumers on the basis of the application housing viewing result, thereby enabling the housing supplier to obtain stable earnings and supply stable housing to the housing consumers and facilitating free residence transfer.

Owner:元哲镐

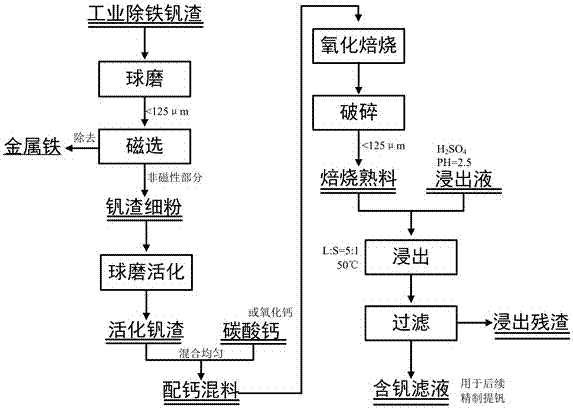

A method for strengthening the calcification of converter vanadium slag to extract vanadium

ActiveCN105886786BRaise the firing temperatureImprove oxidation roasting efficiencyProcess efficiency improvementSlagCalcification

The invention discloses a method for strengthening vanadium extraction from vanadium slags of a converter through calcification. The method comprises the following steps of crushing vanadium-containing slags which are used as raw materials after industrial iron separation, and then performing magnetic separation so as to obtain fine vanadium slag powder; then performing ball milling and activation on the fine vanadium slag powder so as to obtain activated vanadium slags; then adding powdery calcium-containing compound powder to the activated vanadium slags in a matching manner, and performing uniform mixing so as to obtain calcium matching mixed materials; then performing oxidizing roast on the calcium matching mixed materials in an oxidizing roaster, and then performing air cooling and crushing so as to obtain roasted clinker; and leaching the roasted clinker in a weak acid solution so as to obtain a vanadium-containing leaching solution, wherein the vanadium-containing leaching solution is used for subsequent purification and vanadium extraction. Through the adoption of the method disclosed by the invention, the oxidizing roast temperature of the vanadium slags of the converter can be reduced, and the leaching rate of vanadium in the roasted clinker is increased.

Owner:CHONGQING UNIV