Patents

Literature

83results about How to "Guaranteed crystal quality" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

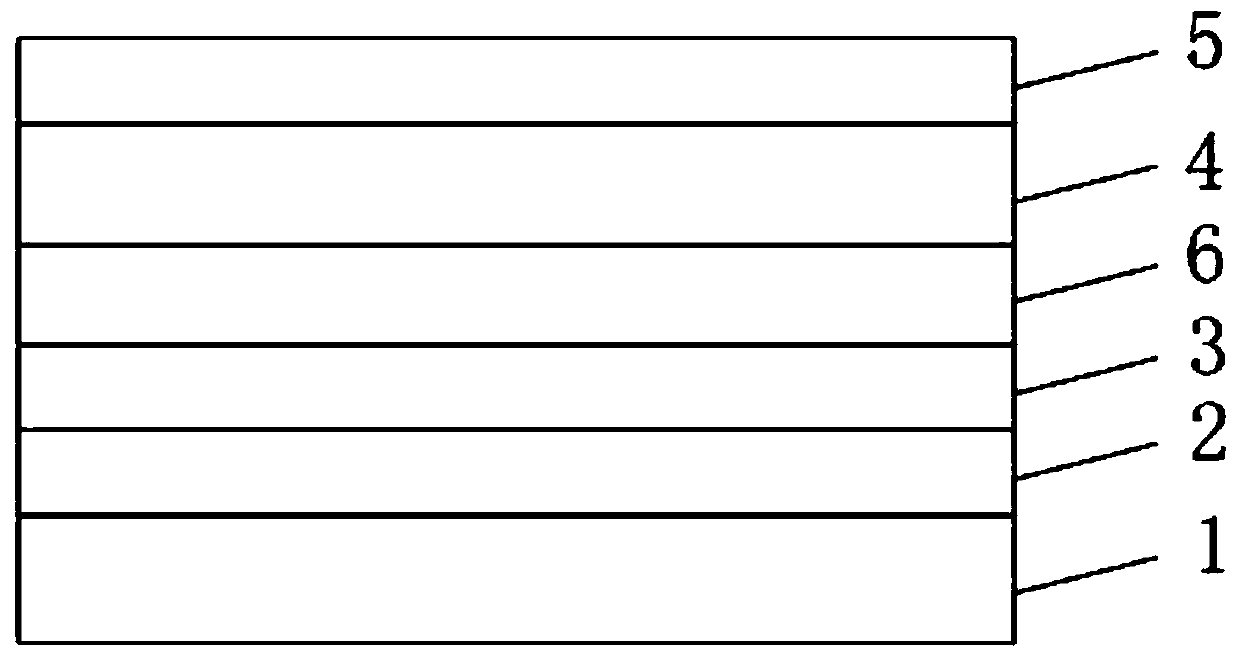

Solar cell

InactiveCN101866967AReduce manufacturing costImprove conductivityFinal product manufacturePhotovoltaic energy generationThermal expansionSolar cell

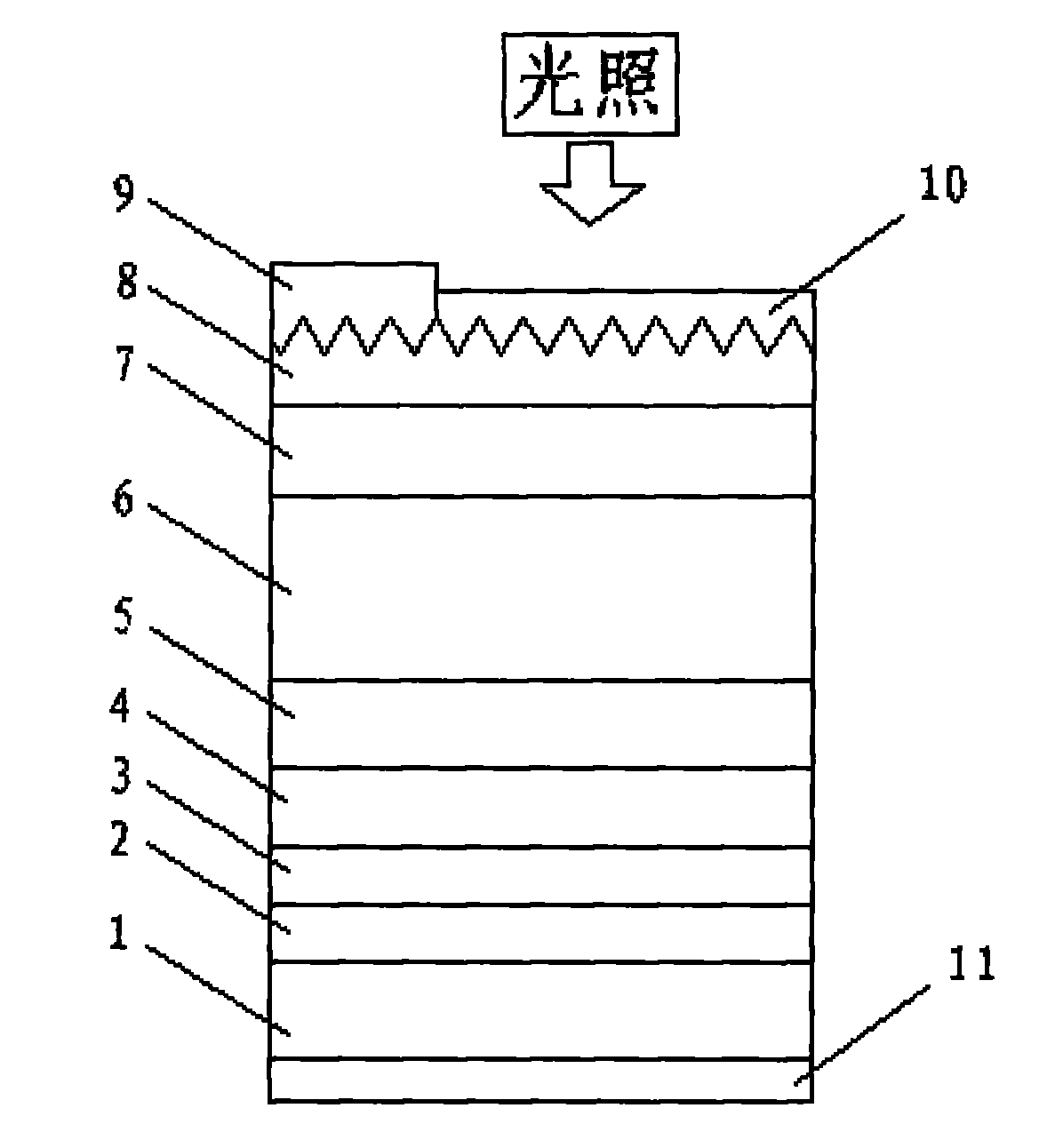

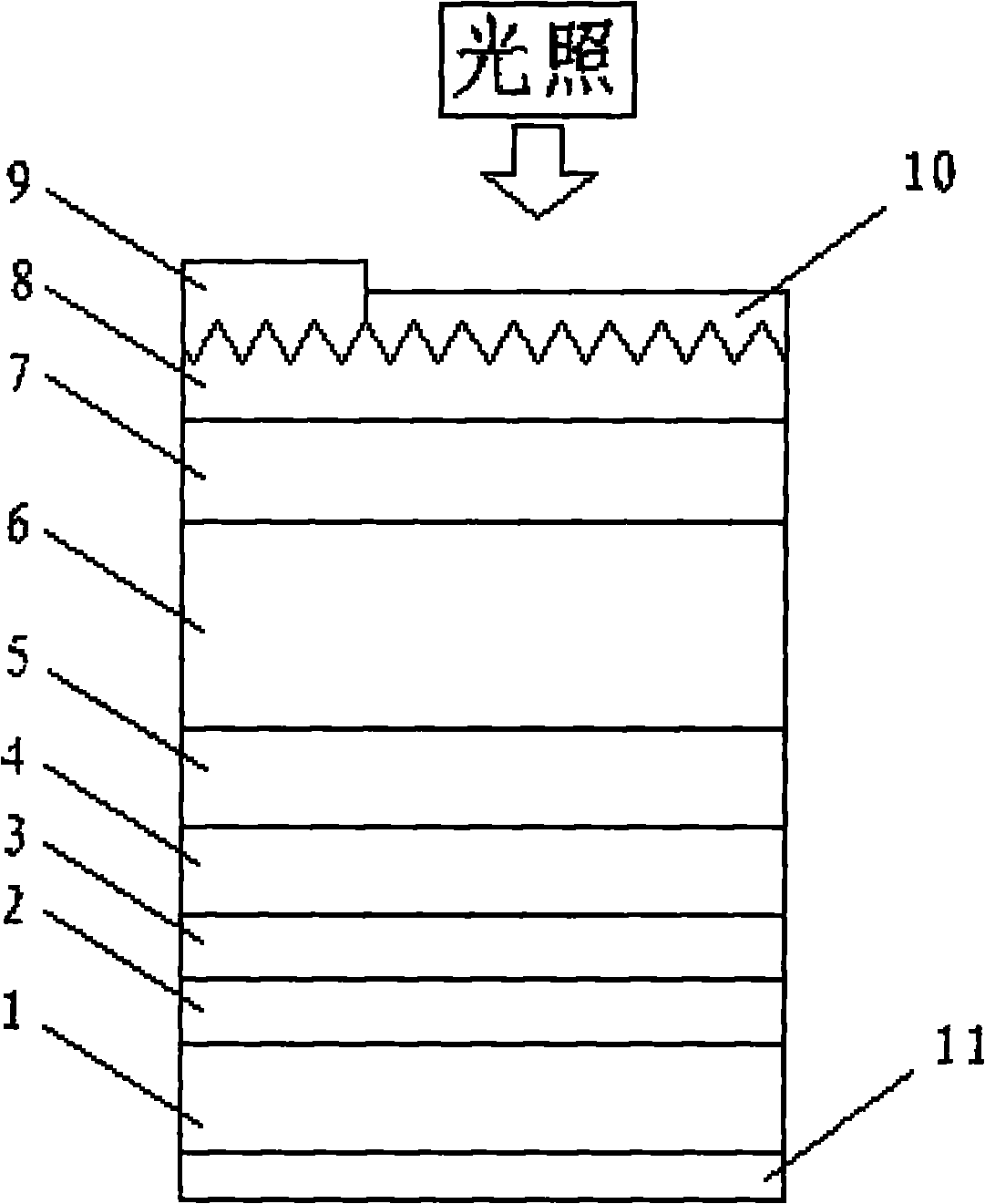

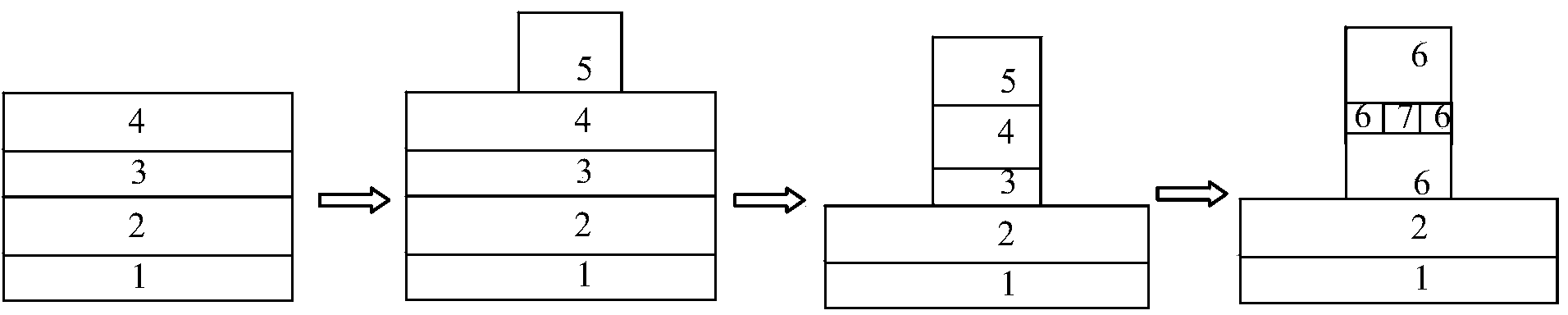

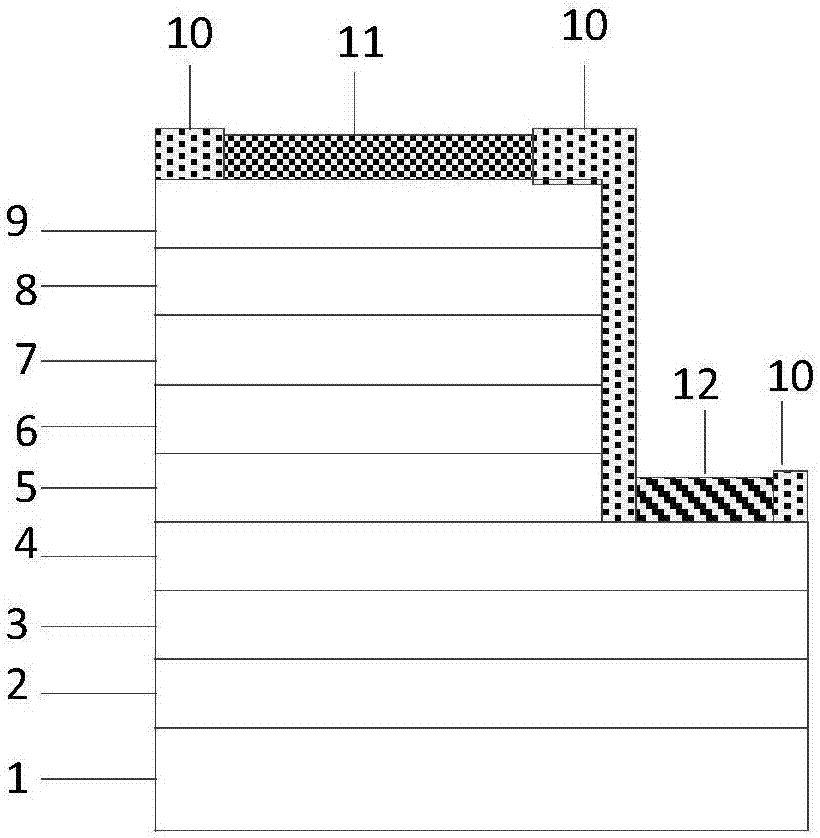

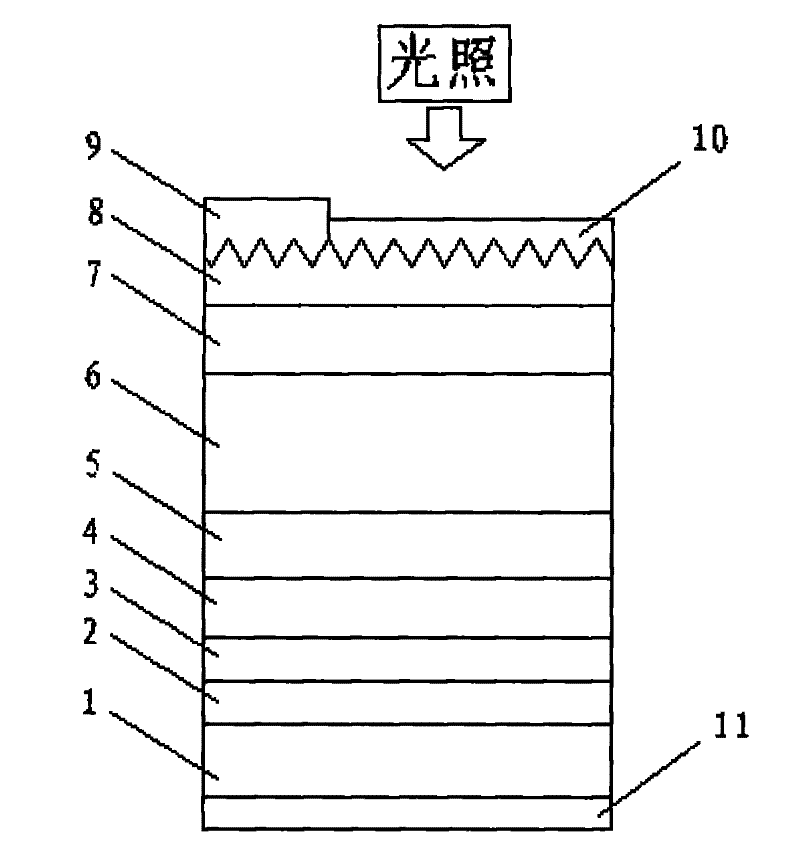

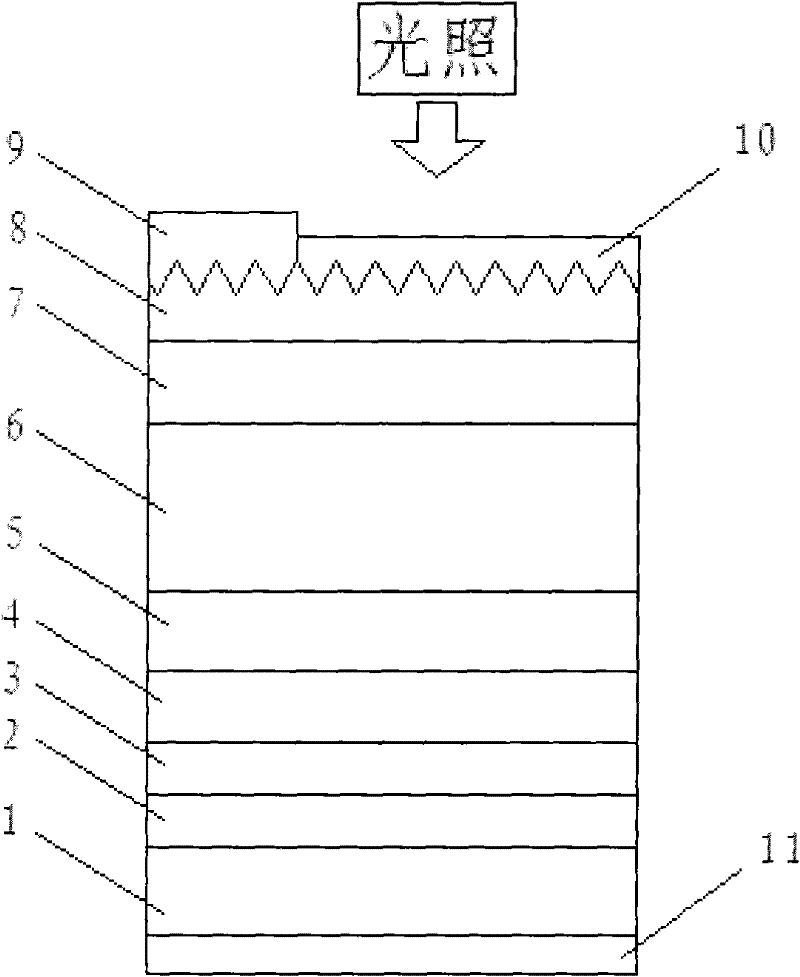

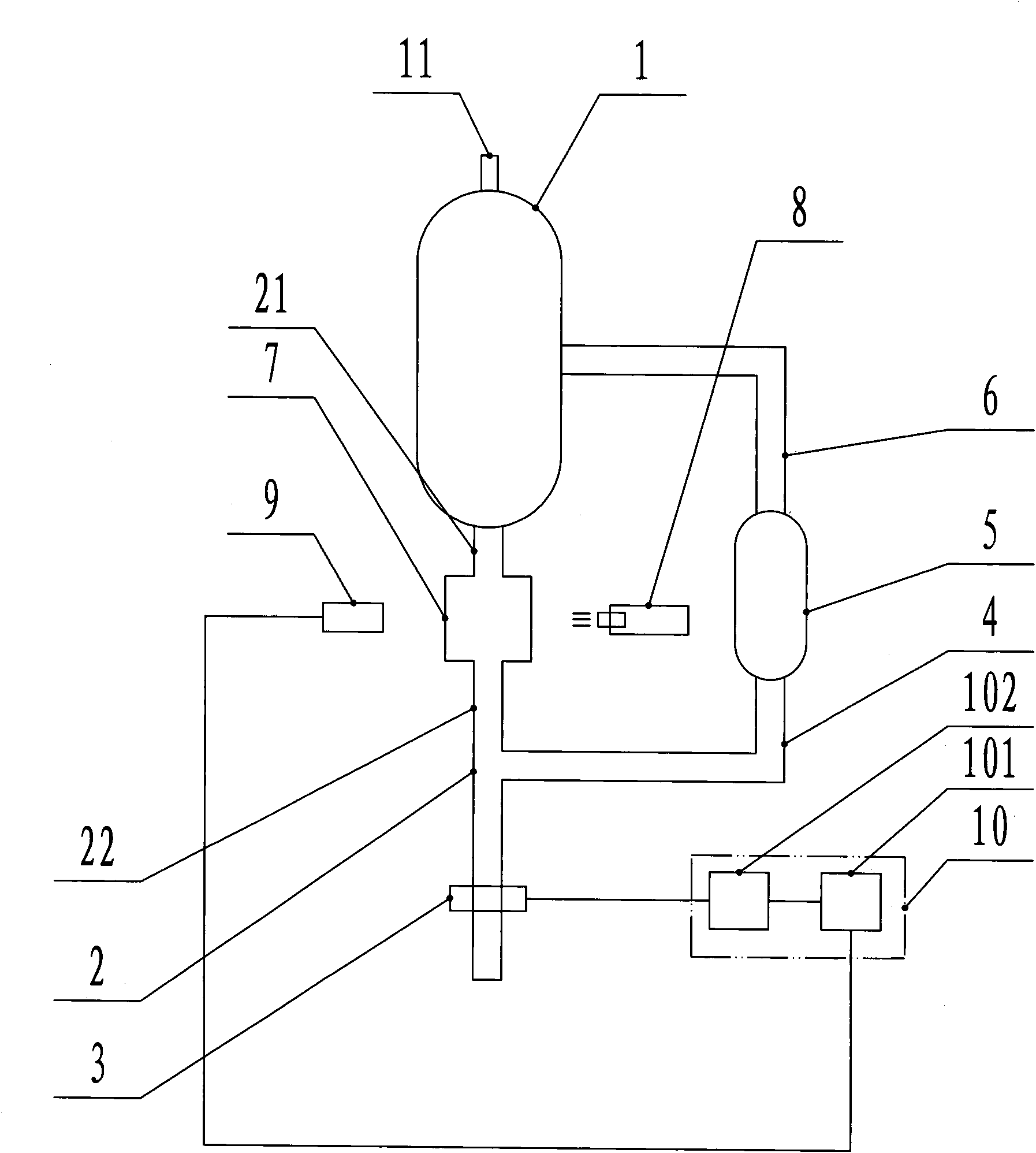

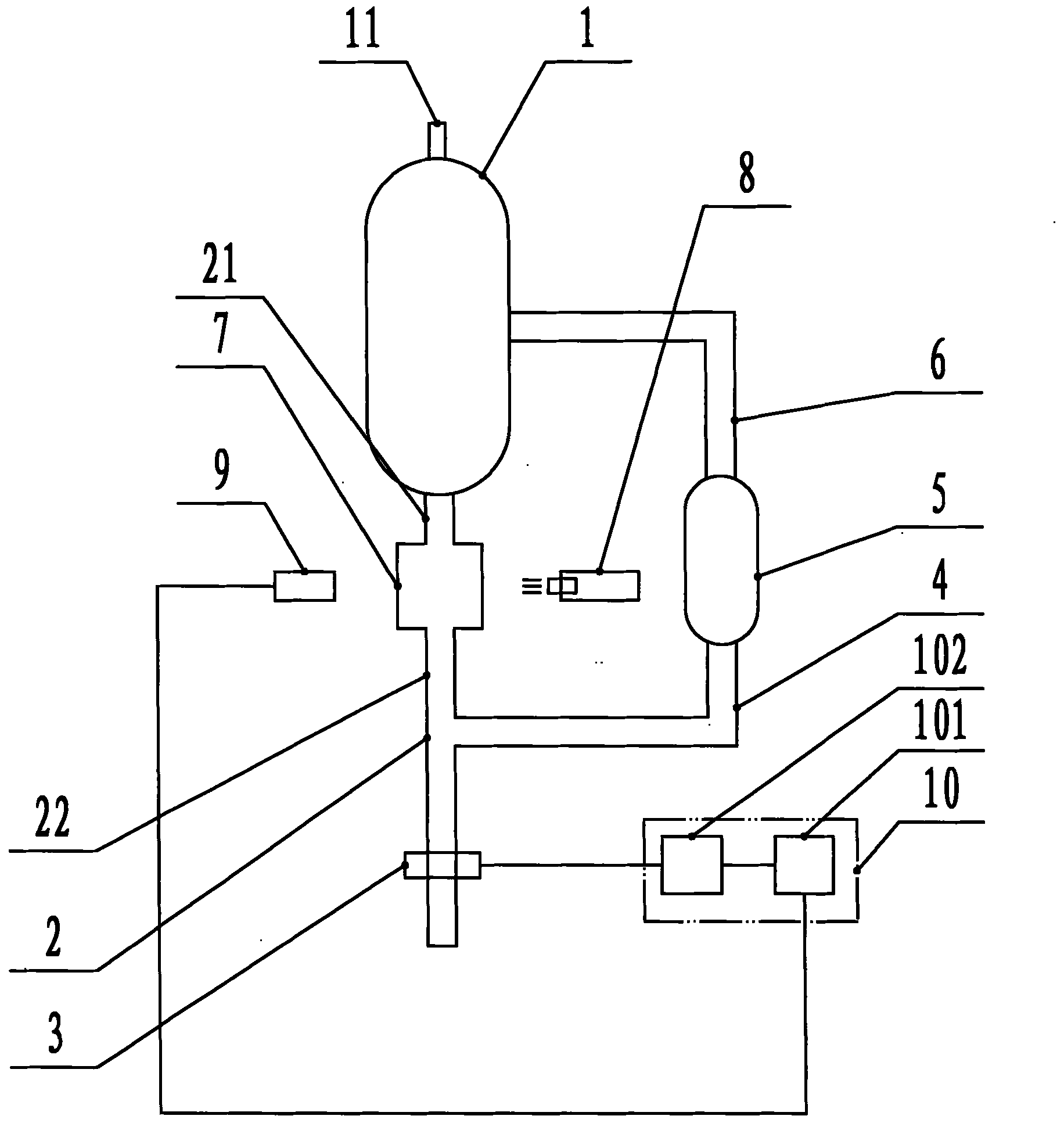

The invention relates to a silicon-based single-junction gallium indium nitride solar cell which comprises a back electrode (11), a silicon substrate (1), a seed crystal layer (2), a buffer layer (3), an n-type doped GaN buffer layer (4), an InaGal-aN layer (5), an unintentional doped InbGal-bN layer (6), a p-type doped IncGal-cN layer (7), a window layer (8), a positive electrode (9) and an anti-reflection conductive film (10) which are arranged from bottom to top, wherein the silicon substrate and the InaGal-aN layer is are an n-type doped structure, the seed crystal layer and the buffer layer are made of ZnO material, the window layer is made of p-type heavily doped GaN, and the anti-reflection conductive film covers areas of the window layer other than the positive electrode. The solar cell can quite effectively solve the problems of lattice matching, thermal expansion coefficient matching and the like encountered when a GaN film extends from the silicon substrate, and has the advantages of low manufacturing cost, high sunlight absorbability and the like.

Owner:HUAZHONG UNIV OF SCI & TECH

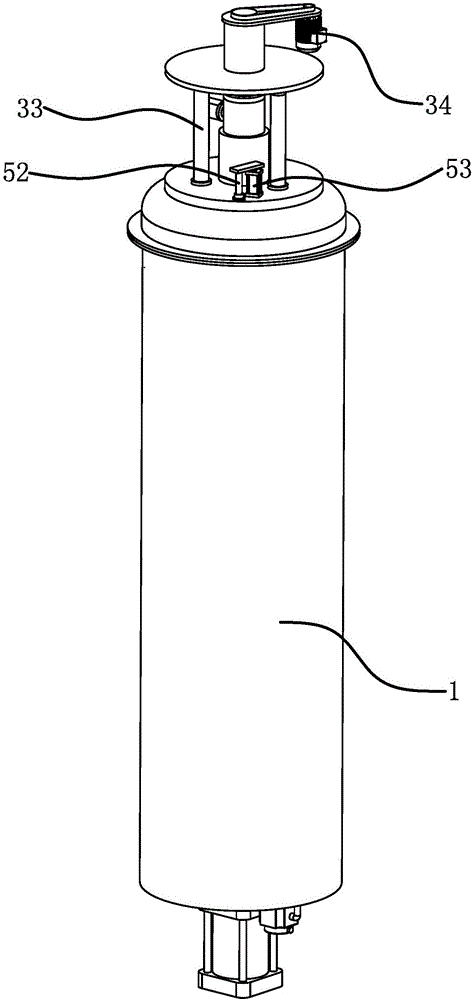

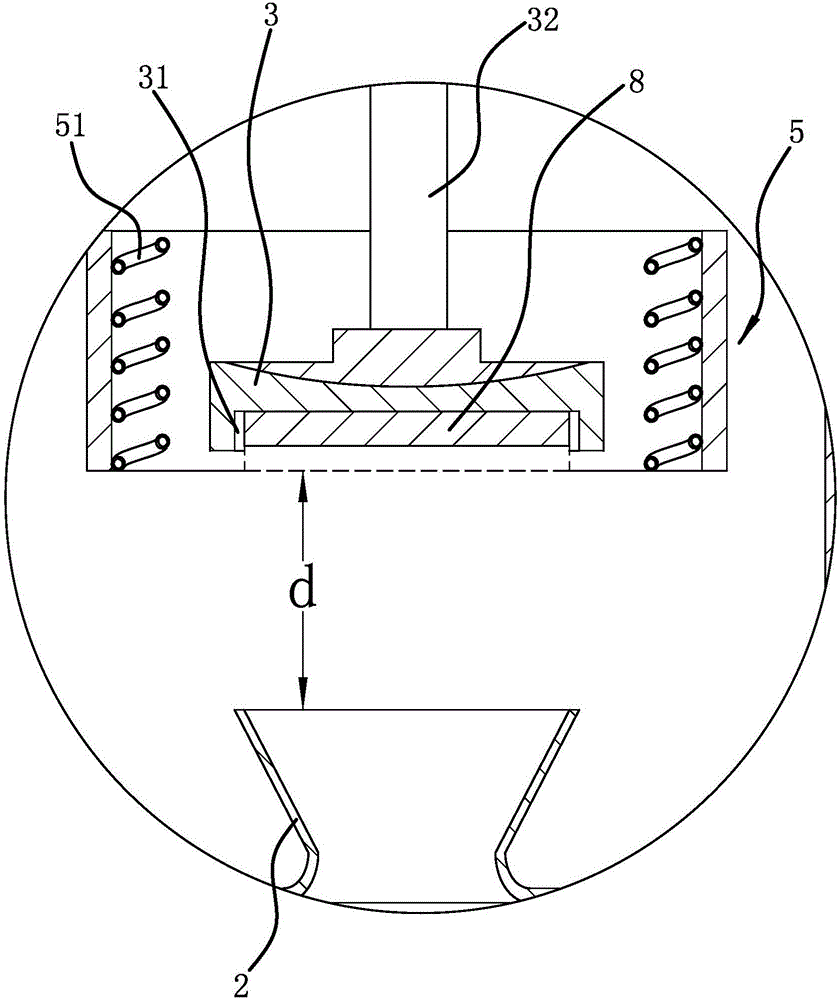

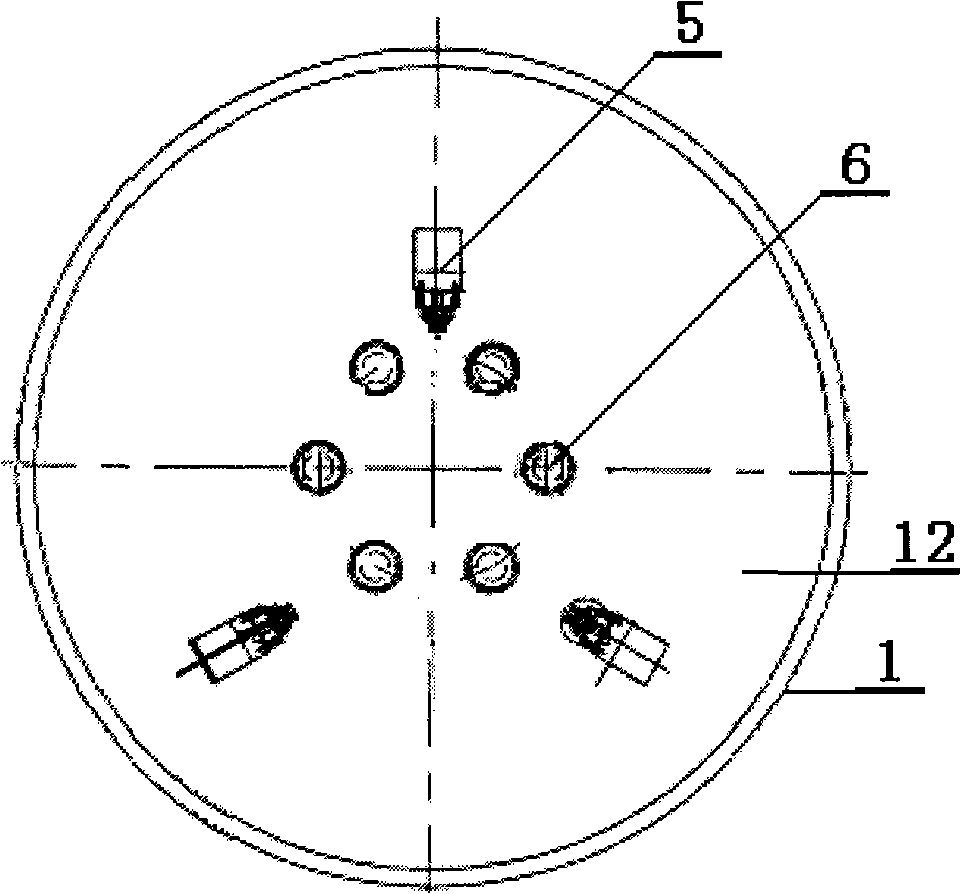

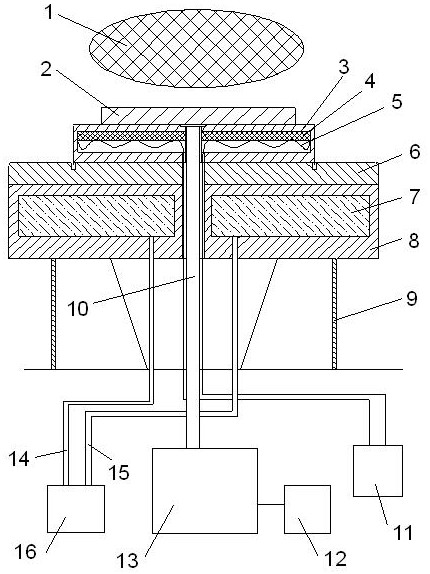

Silicon carbide single crystal manufacturing device

InactiveCN106119954AReduce stressReduce lossesPolycrystalline material growthSemiconductor/solid-state device manufacturingCrucibleMechanical equipment

Owner:TAIZHOU BEYOND TECH

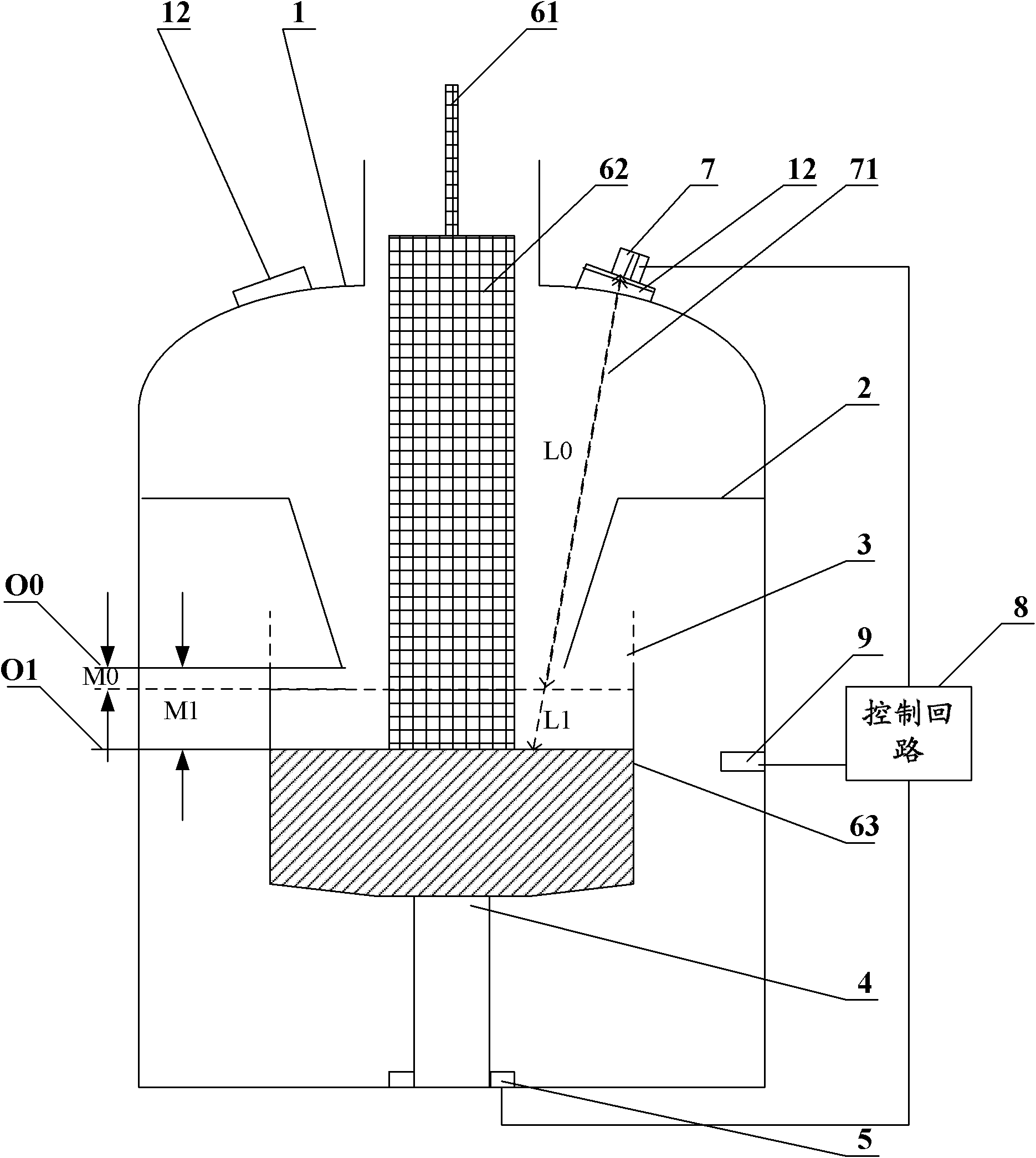

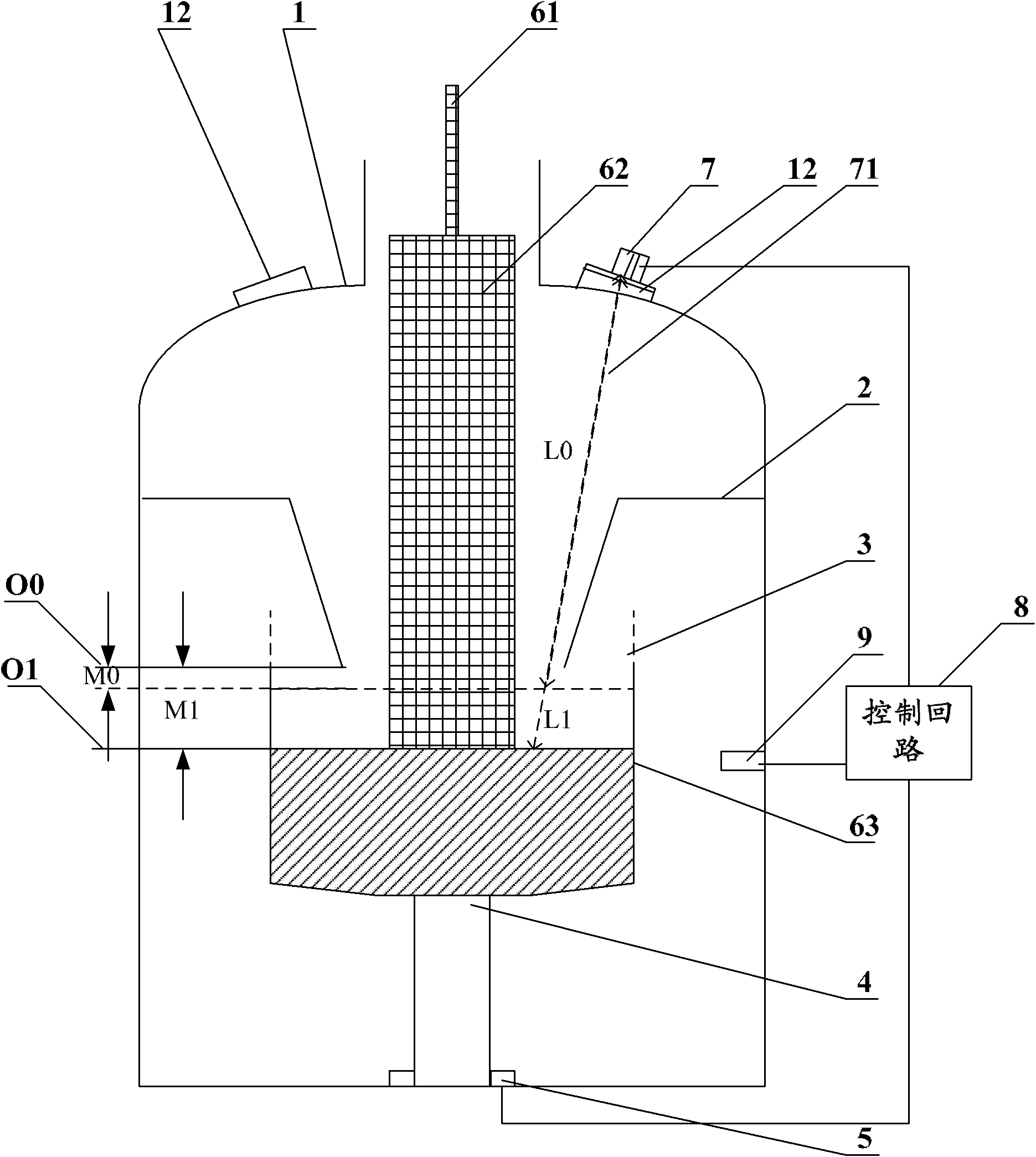

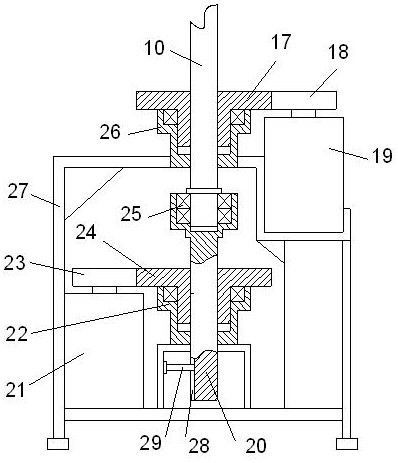

Position control method and device for silicone liquid level of czochralski crystal grower

InactiveCN101982569AQuality assuranceGuaranteed crystal qualityPolycrystalline material growthBy pulling from meltMotor speedCrucible

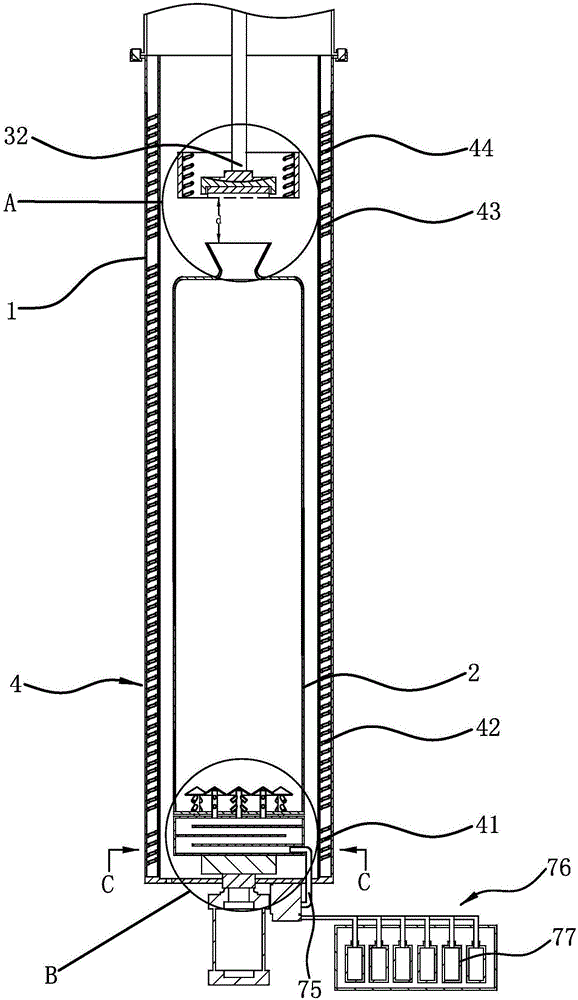

The embodiment of the invention discloses a position control method for the silicone liquid level of a czochralski crystal grower, which comprises the following steps: A, storing a target distance value between an observation window of the czochralski crystal grower and the silicone liquid level in advance; B, measuring the actual distance value between the observation window and the silicone liquid level; and C, comparing the target distance value with the actual distance value to obtain the comparative value, and controlling the motor speed according to the comparative value. In the method of the embodiment of the invention, the motor speed is adjusted in real time by detecting the distance between the window and the silicone liquid level, thereby controlling the following ratio of a crucible, keeping the single crystals in the growing process in an appropriate growing environment, and ensuring the crystal quality. The embodiment of the invention also discloses a position control device for the silicone liquid level of the czochralski crystal grower.

Owner:ZHEJIANG YUHUI SOLAR ENERGY SOURCE

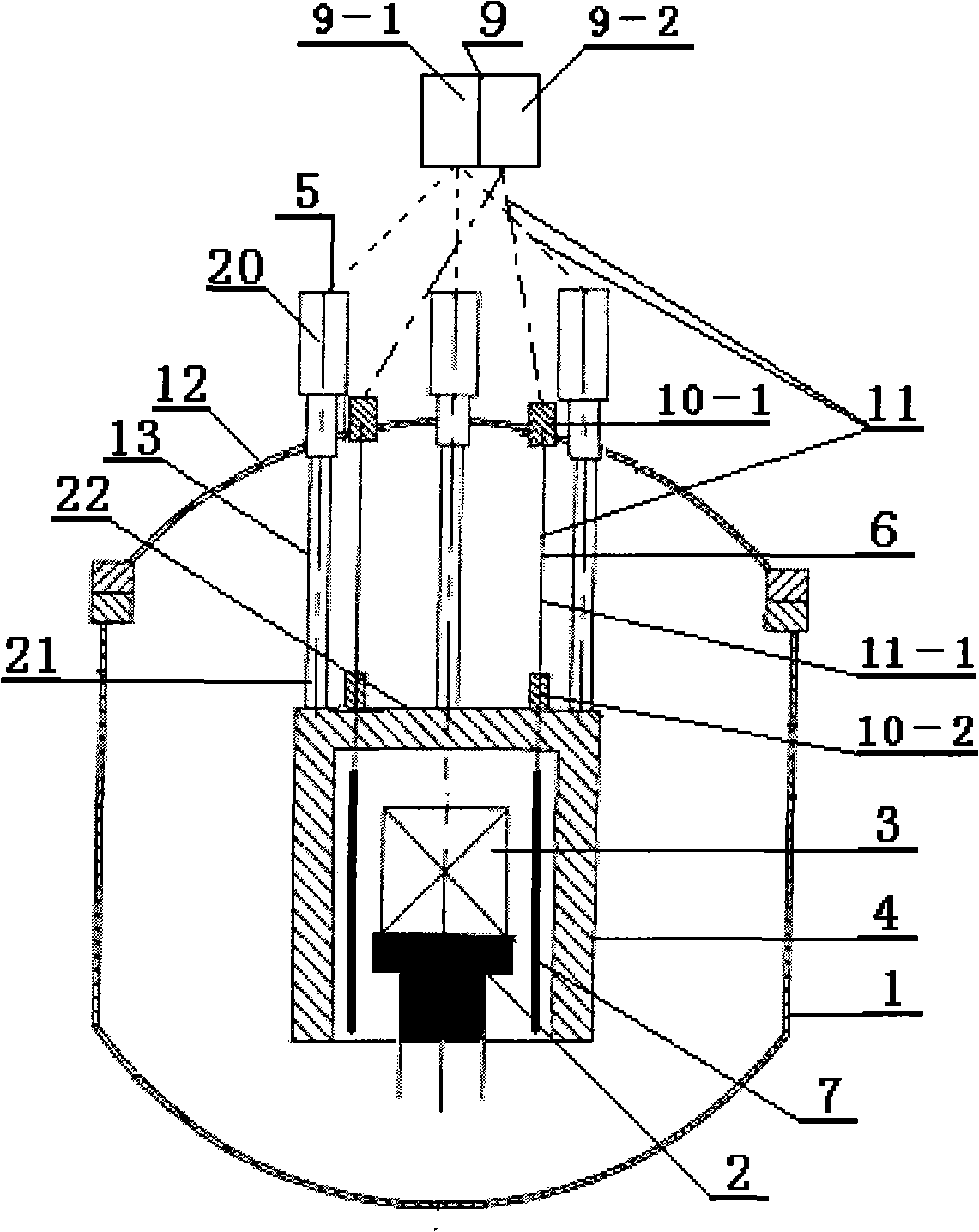

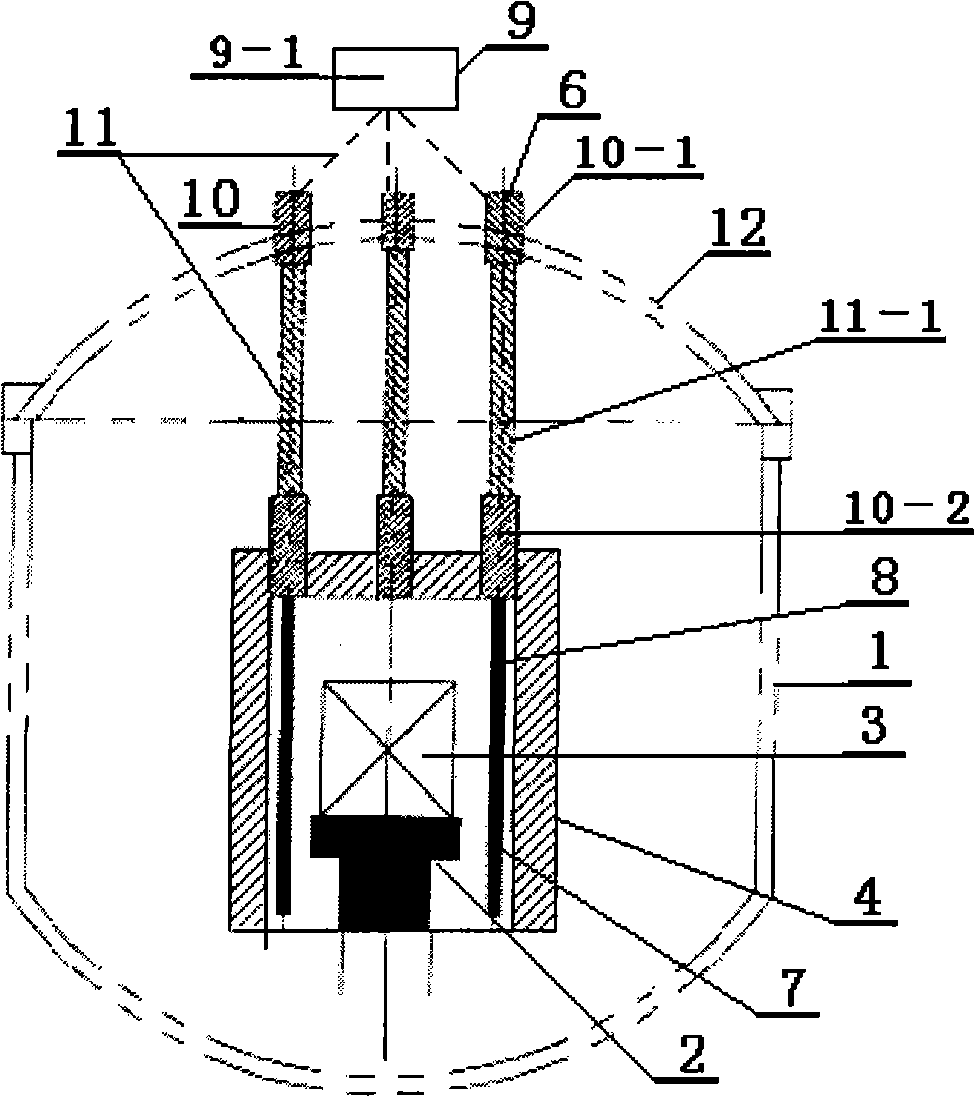

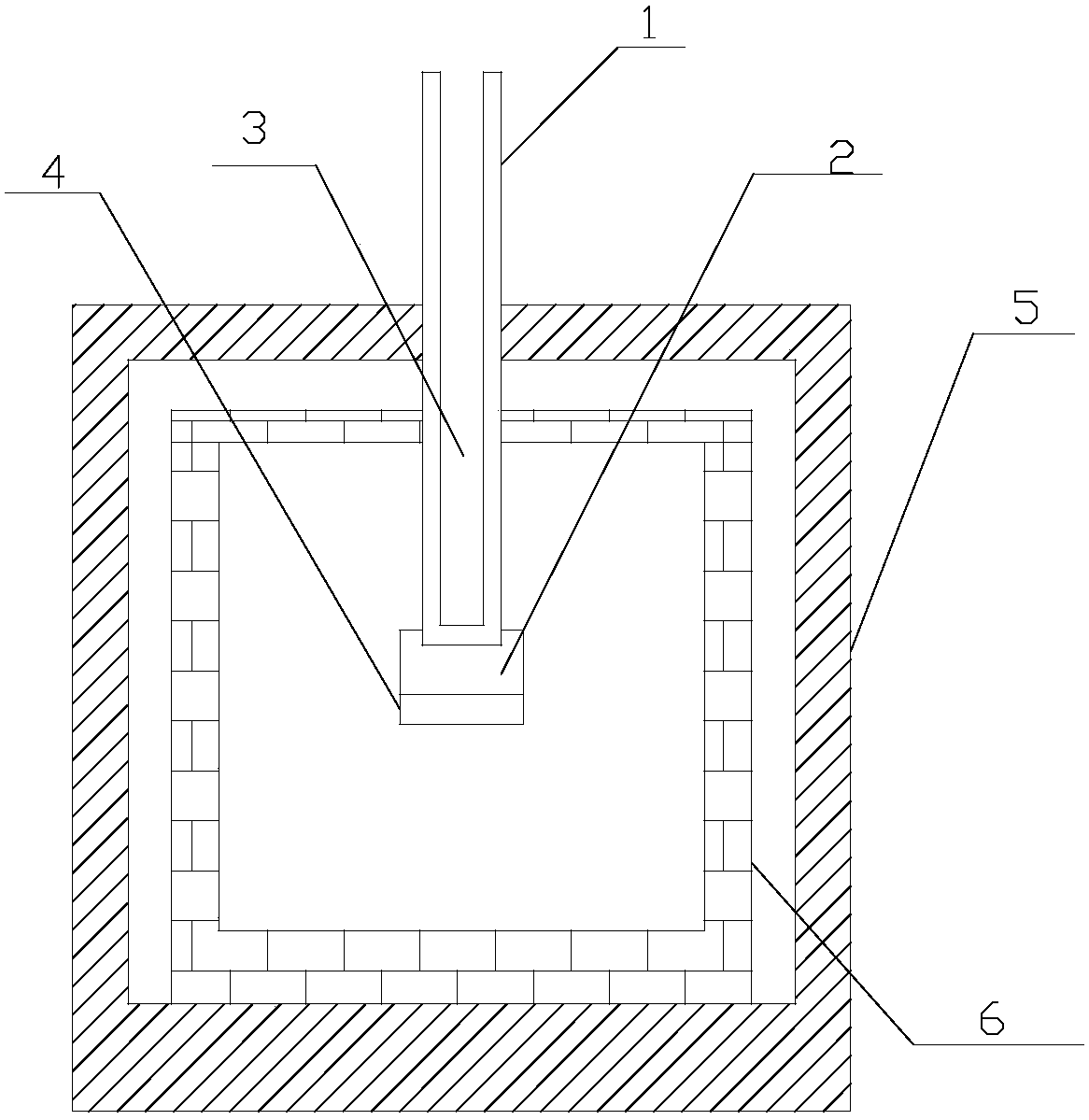

Vacuum furnace suitable for preparing large-diameter high-purity polysilicon ingot

InactiveCN101311343AScientific and reasonable structureImprove product qualityPolycrystalline material growthFrom frozen solutionsEngineeringWorking interference

The invention relates to an ingot vacuum furnace which is suitable for making polysilicon with large size and high purity. An insulating cover is designed to be a lifting type. A main body of a lifting mechanism consisting of a servo linear motion mechanism and a continuous-motion bar is arranged on a furnace cover, wherein, one end of the continuous-motion bar is fixedly arranged on the top of the insulating cover. An electrode of a power supply part is a water cooling type. A transmission cable in the furnace is a flexibility water cooling type. As a material platform and a crucible are free from the working interference of the lifting mechanism, a fixed type of the crystallization quality is beneficial to being ensured. The volume size in the crucible is only related to the bearing ability of the material platform; therefore, the crucible with large capacity is easy to be arranged. Furthermore, the water cooling type of the upper and lower electrodes and the water cooling type of the flexibility cable are adopted to ensure the reliable service life, thus ensuring the free lifting of the insulating cover. The ingot vacuum furnace has the advantages of scientific and reasonable structure, reliable working, long service life, stable product quality and high purity, which is suitable for producing polysilicon with large size and high purity and has strong practicability.

Owner:SHANGHAI CHEN HUA ELECTRIC FURNACE CORP

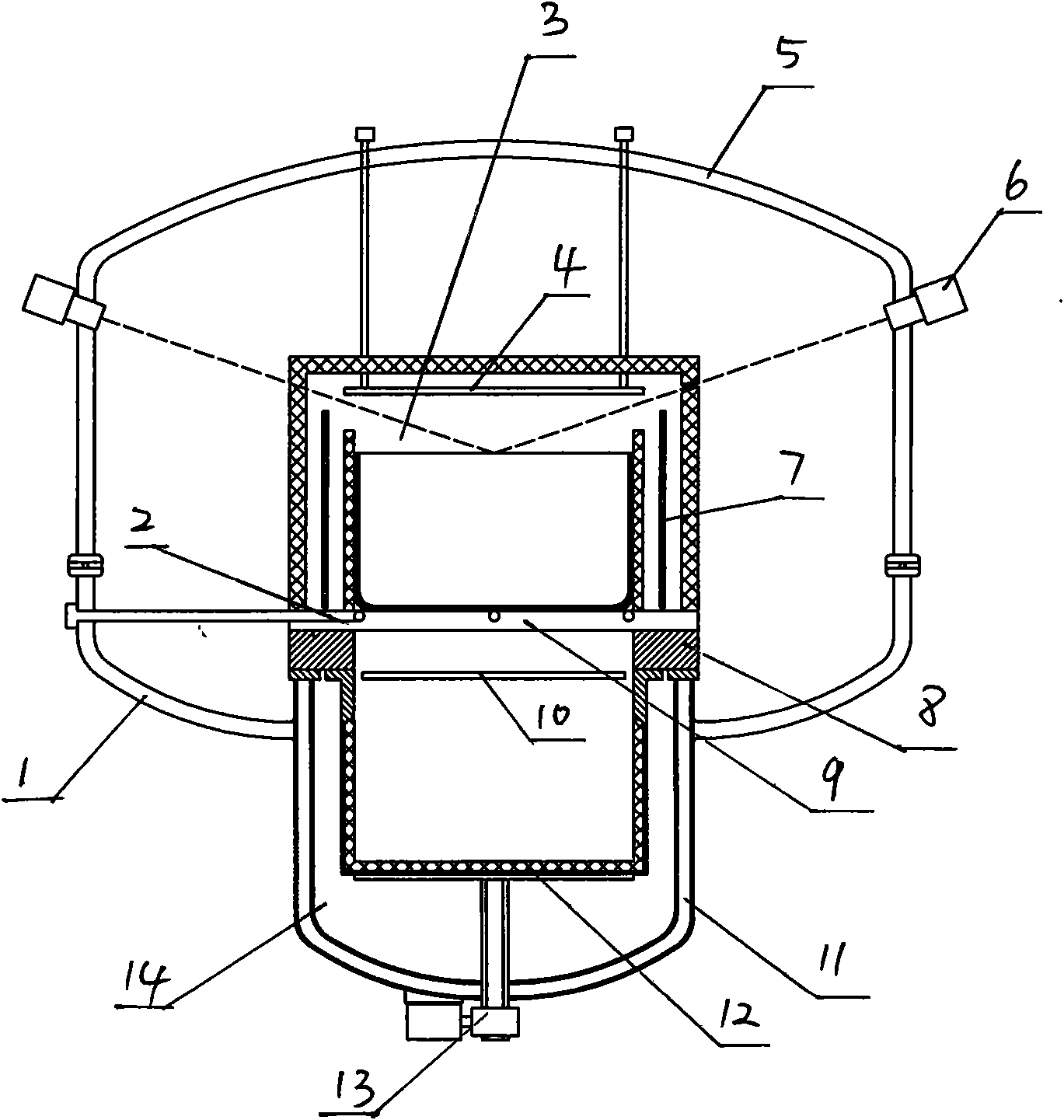

Polysilicon growth ingot furnace

InactiveCN101624187AGuaranteed growth qualityGuaranteed crystal qualityPolycrystalline material growthSilicon compoundsCrucibleIngot

The invention discloses a polysilicon growth ingot furnace. The polysilicon growth ingot furnace is provided with an upper furnace body and a lower furnace body, the upper furnace body is fixed at the upper part of a stand, the lower furnace body is arranged at the lower part of the stand through an opening device, a fixed upper heating chamber is arranged in the upper furnace body, a bearing plate buckled with four walls of the upper heating chamber is arranged at the lower side of a heat conduction plate, a hole is arranged in the centre of the lower furnace body, the hole part is provided with a lower heat field container, the lower heat field container is provided with a container wall with a separate circulating cooling system, a silicon liquid overflow container is arranged in the lower heat field container, and the lower end of the lower heat field container is connected with a container wall of the lower heat field container through a lifting device. Surrounding heating bodies, the upper heating body, the lower heating body, the upper heating field and the lower heating field are separately controlled to realize that gradients of the upper heating field and the lower heating field are conveniently operated so as to carry out directional solidification to produce large-scale polysilicon ingots. The silicon liquid overflow container can effectively prevent a silicon liquid from damaging the furnace body after the overflow of silicon liquid caused by cracking a crucible or other reasons, therefore, the invention has safe and reliable production .

Owner:管悦

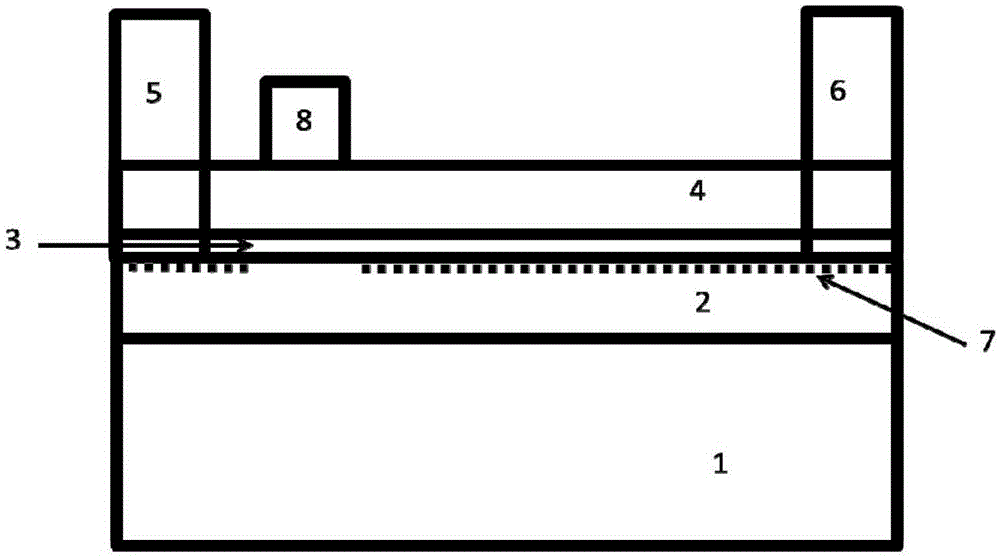

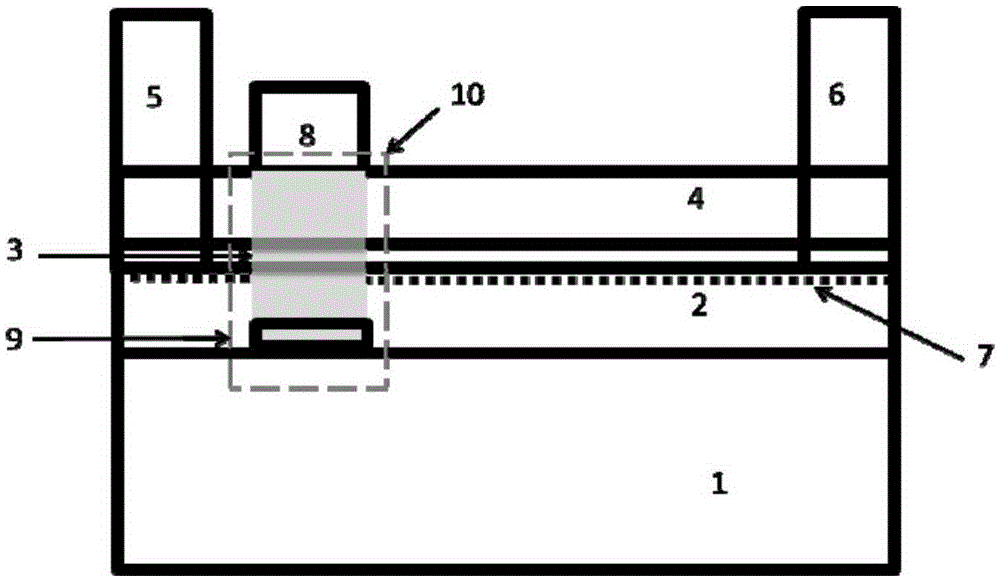

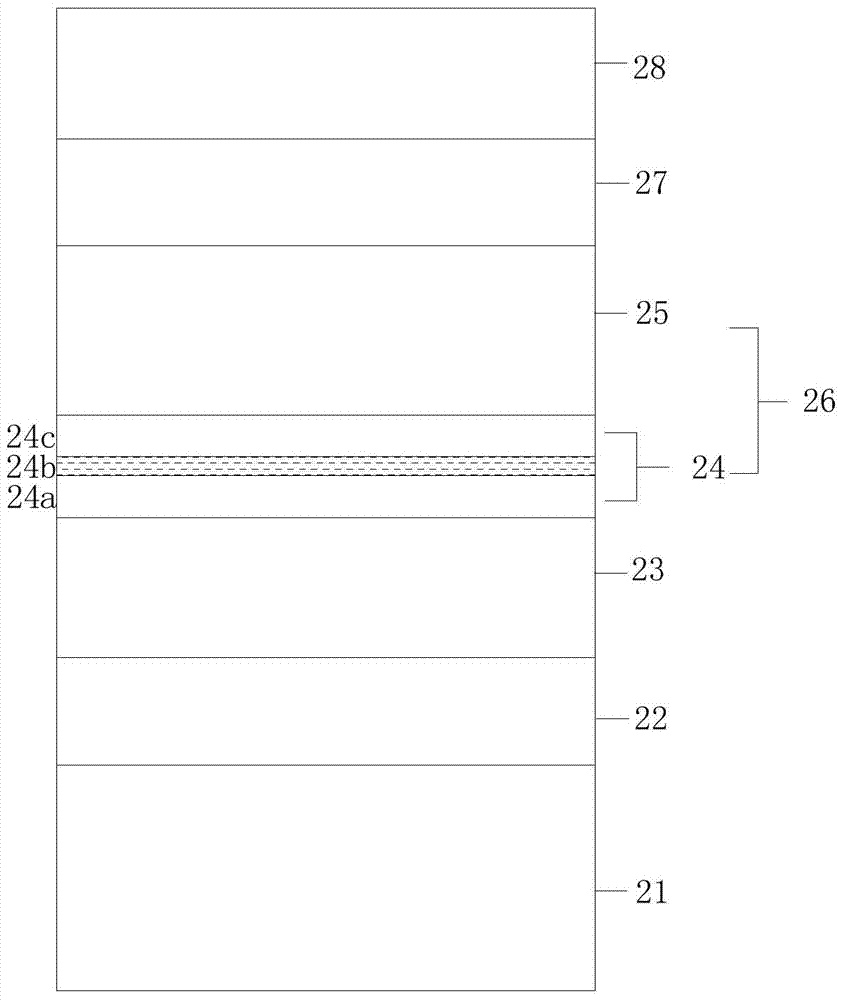

Method for achieving enhanced HEMT through polarity control and enhanced HEMT

InactiveCN106531789AGuaranteed crystal qualityPerformance impactSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorRepeatability

The invention discloses an enhanced HEMT, which comprises a heterostructure, a source electrode, a drain electrode and a gate electrode, wherein the heterostructure mainly comprises a first semiconductor layer and a second semiconductor layer; the source electrode, the drain electrode and the gate electrode are connected with the heterostructure; the source electrode and the drain electrode are electrically connected through a two-dimensional electron gas formed in the heterostructure; the gate electrode is distributed between the source electrode and the drain electrode; and component materials distributed in local areas of the first semiconductor layer and the second semiconductor layer below the gate electrode have set polarity, so that accumulation of the two-dimensional electron gas in the local area of the heterostructure below the gate electrode is avoided when zero bias is applied to the gate electrode or no bias is applied to the gate electrode, and the two-dimensional electron gas can be formed in the local area of the heterostructure below the gate electrode when voltage of the gate electrode is greater than threshold voltage. The invention further discloses a method for achieving the enhanced HEMT through polarity control. The method has the advantages of being simple in process and high in repeatability, the performance of a device is stable and excellent, the cost is low and large-scale production is easy to implement.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

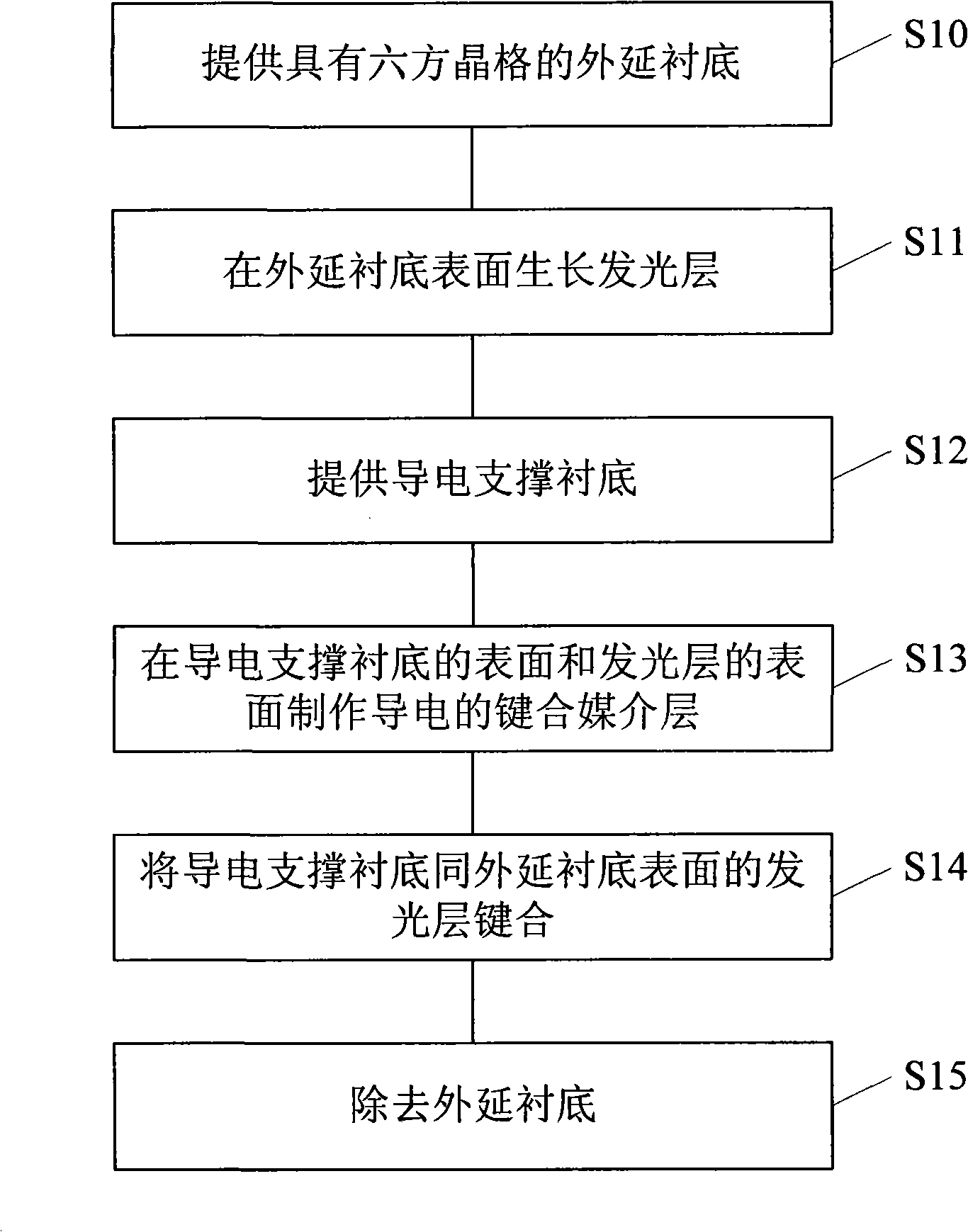

Method for preparing LED

The invention relates to a manufacturing method of a light emitting diode (LED), which comprises the following steps: an extending substrate with hexagonal lattices is adopted; an emitting layer is grown on the surface of the extending substrate; conductive supporting substrates are adopted; the conductive supporting substrates are bonded with the emitting layer on the surface of the extending substrate; the extending substrate is then removed. The manufacturing method has the advantages that: the extending substrate with hexagonal lattices is adopted to grow the emitting layer, thus ensuring the crystal quality of the emitting layer; by adopting the method of bonding conductive supporting substrates and then peeling off the extending substrate, the technical problems that the extending substrate is not conductive and vertical structures cannot be made can be solved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

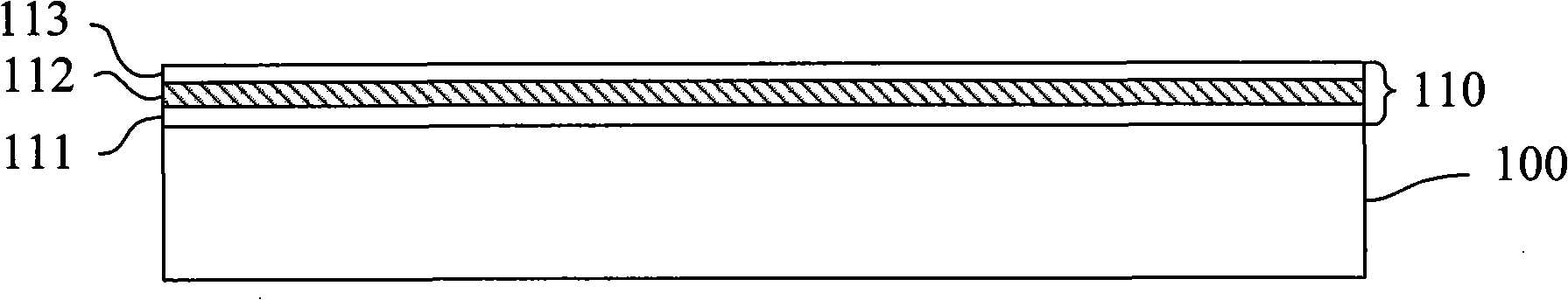

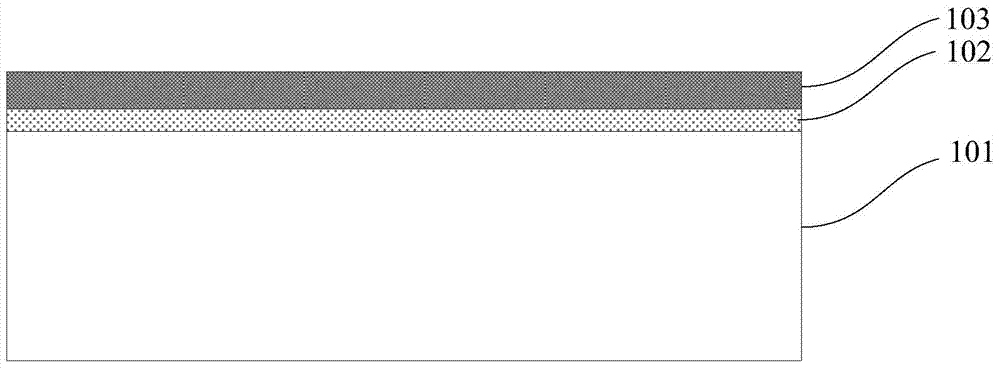

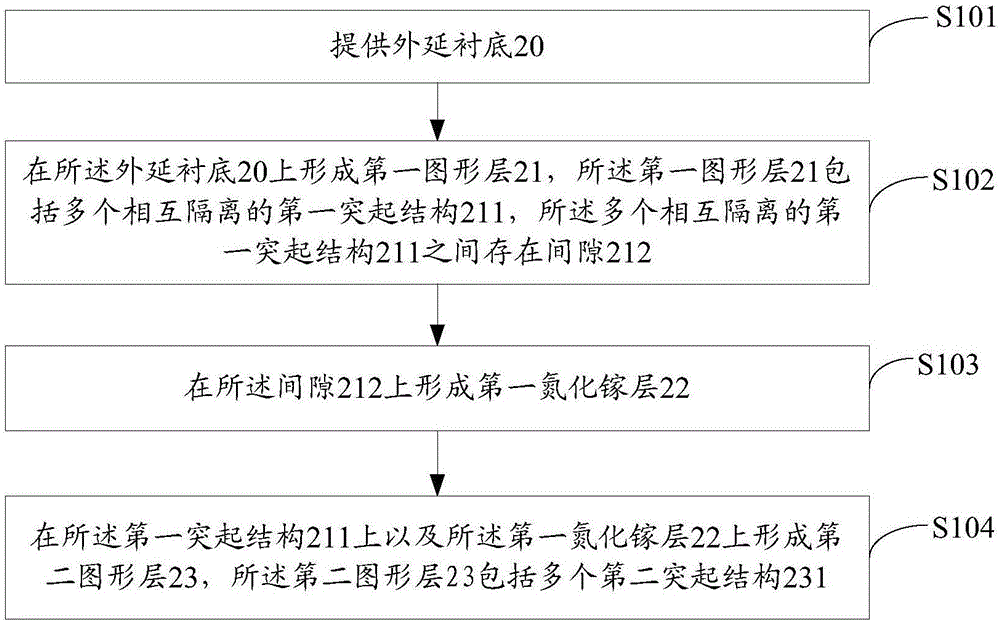

Manufacturing method of composite substrate structure used for nitride growth

InactiveCN103840041AImprove light extraction efficiencyGuaranteed crystal qualitySemiconductor devicesManufacturing cost reductionComposite substrate

The invention provides a manufacturing method of a composite substrate structure used for nitride growth. The manufacturing method comprises the steps that (1) a buffer layer used for growth of a subsequent luminous epitaxial structure is formed on the surface of a growth substrate; (2) an SiO2 layer is formed on the surface of the buffer layer; (3) a mask layer with a plurality of hole-shaped windows which are arranged at intervals is formed on the surface of the SiO2 layer; (4) the hole-shaped windows are used for etching the SiO2 layer to form a plurality of hole-shaped structures in the SiO2 layer, and the parts, below the hole-shaped structures, of the buffer layer are exposed out. According to the manufacturing method, a BN material layer or an AlN layer or an AlxGal-xN layer with a hexagonal lattice structure is manufactured first to serve as the buffer layer for growth of the luminous epitaxial structure, and then the hole-shaped structures which are arranged at intervals are manufactured in the SiO2 layer through an ICP etching technology. The buffer layer and the SiO2 layer with the hole-shaped structures can guarantee the quality of crystals with grown luminous epitaxial structures, and can also improve the light emitting efficiency of a light-emitting diode. The manufacturing method of the composite substrate structure used for nitride growth is simple in technology, beneficial for lowering the manufacturing cost and applicable to industrial production.

Owner:EPILIGHT TECH

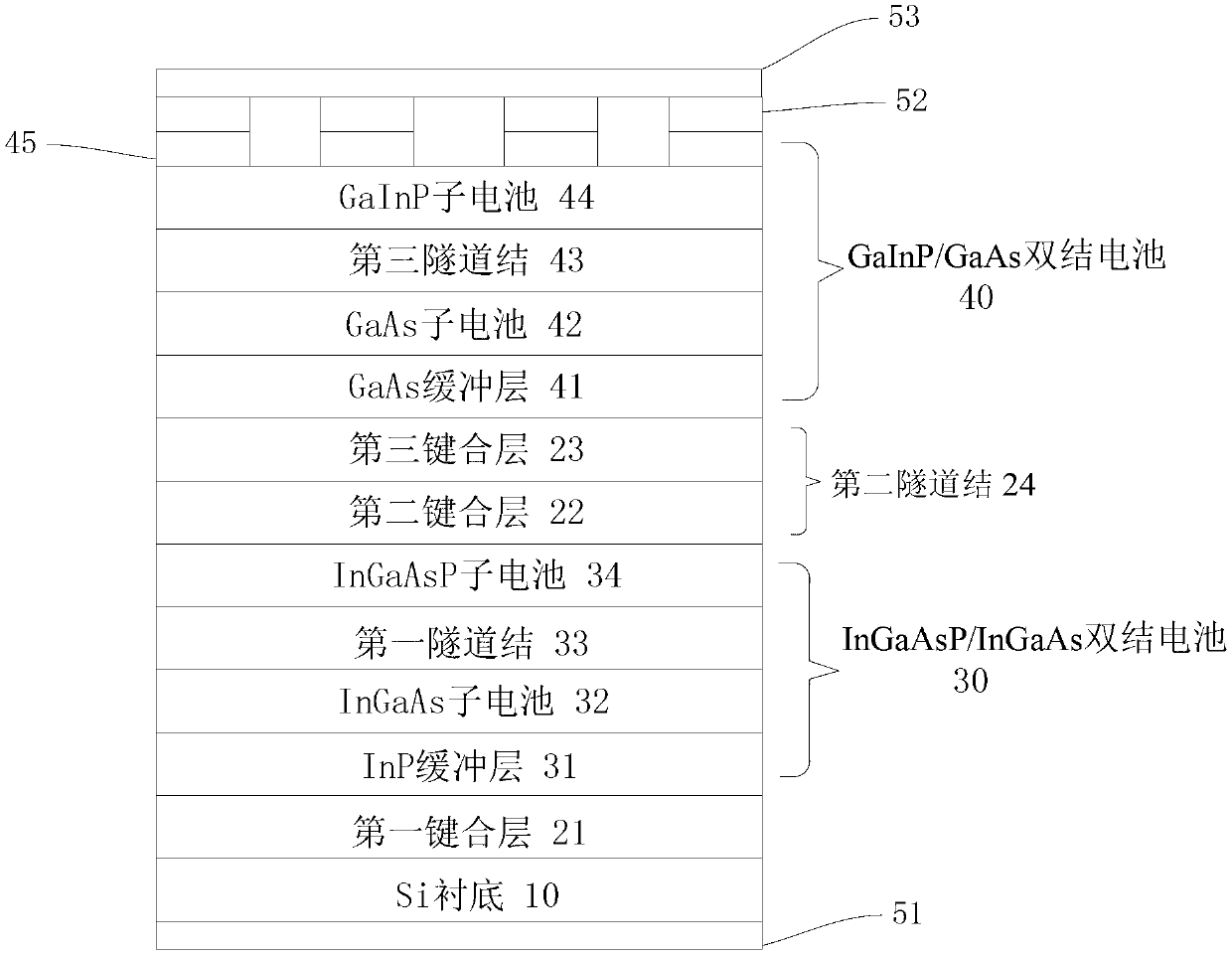

Four-knot cascade solar cell with Si substrate and preparation method thereof

ActiveCN103346190AHigh mechanical strengthAchieve matching growthFinal product manufacturePhotovoltaic energy generationLattice mismatchThin layer

The invention relates to the field of a semiconductor technology, in particular to a four-knot cascade solar cell which comprises a first bonding layer, an InGaAsP / InGaAs double-knot cell, a second bonding layer, a third bonding layer and a GaInP / GaAs double-knot cell, wherein the first bonding layer, the InGaAsP / InGaAs double-knot cell, the second bonding layer, the third bonding layer and the GaInP / GaAs double-knot cell are arranged from bottom to top in sequence on a Si substrate. The InGaAsP / InGaAs double-knot cell and the GaInP / GaAs double-knot cell are connected in series on the Si substrate. The invention further provides a preparation method for the solar cell. The Si substrate used as the supporting substrate has good mechanical strength. Meanwhile, the method that the double-knot cells are subjected to bonding and then growing thin layers are assembled on the double-knot cells is adopted, the GaAs and InP thin layer bonding method achieves lattice match growth of the four-knot cell, and the crystalline quality of materials is guaranteed compared with lattice mismatch growth.

Owner:SUZHOU INST OF NANO TECH & NANO BIONICS CHINESE ACEDEMY OF SCI

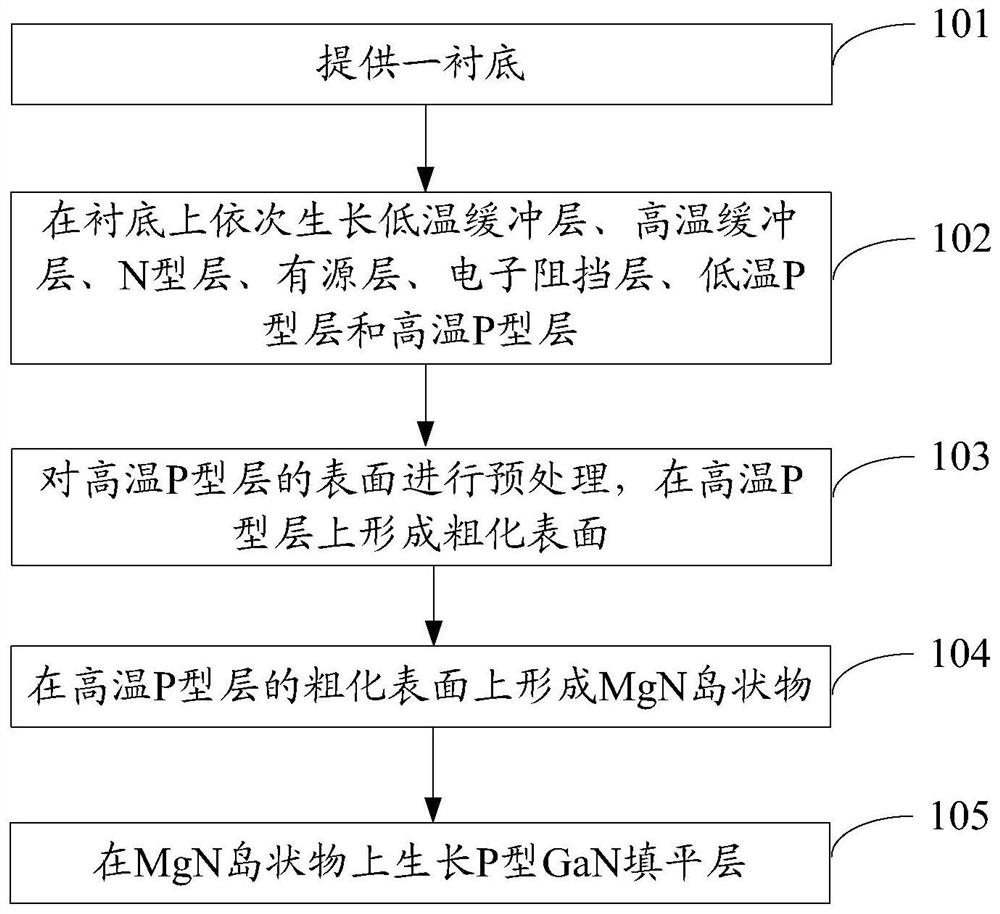

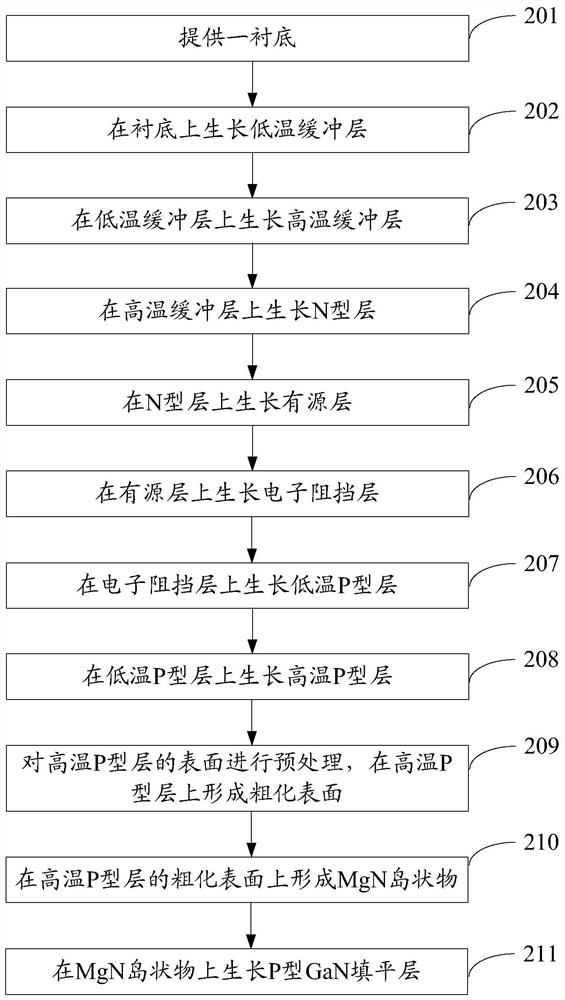

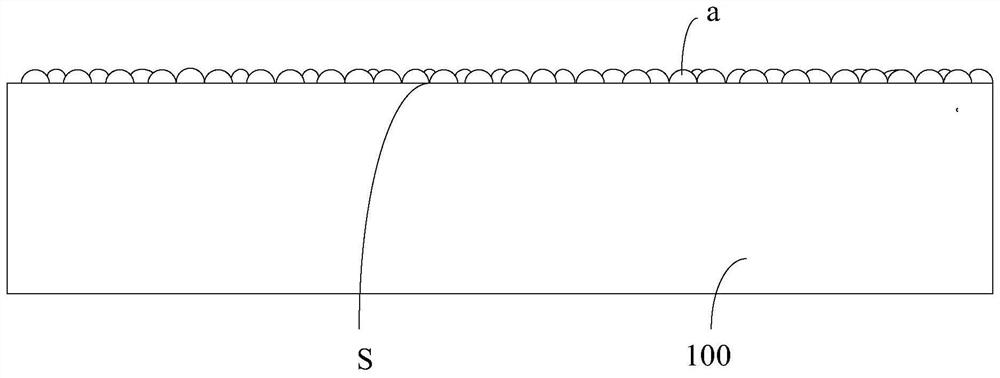

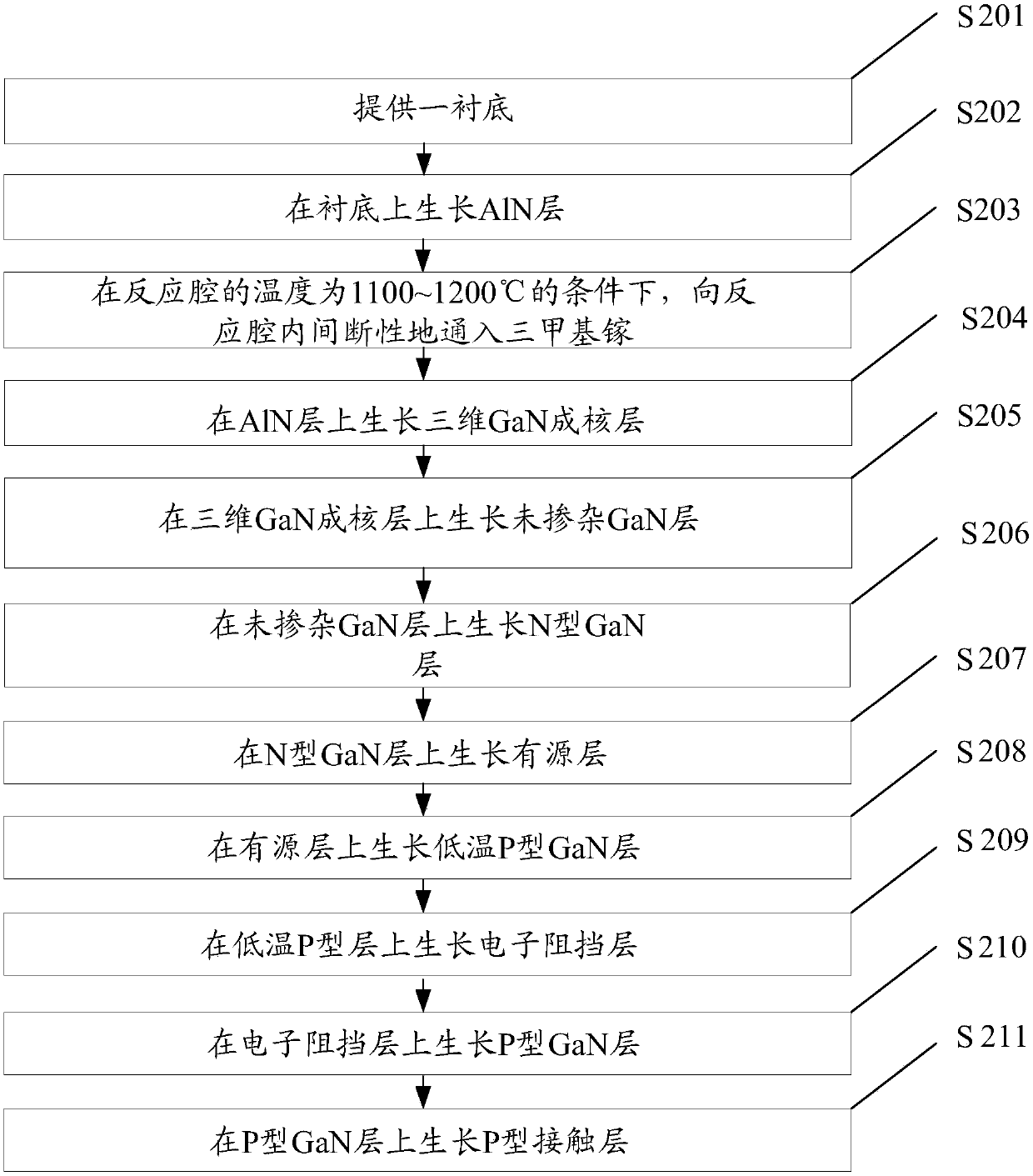

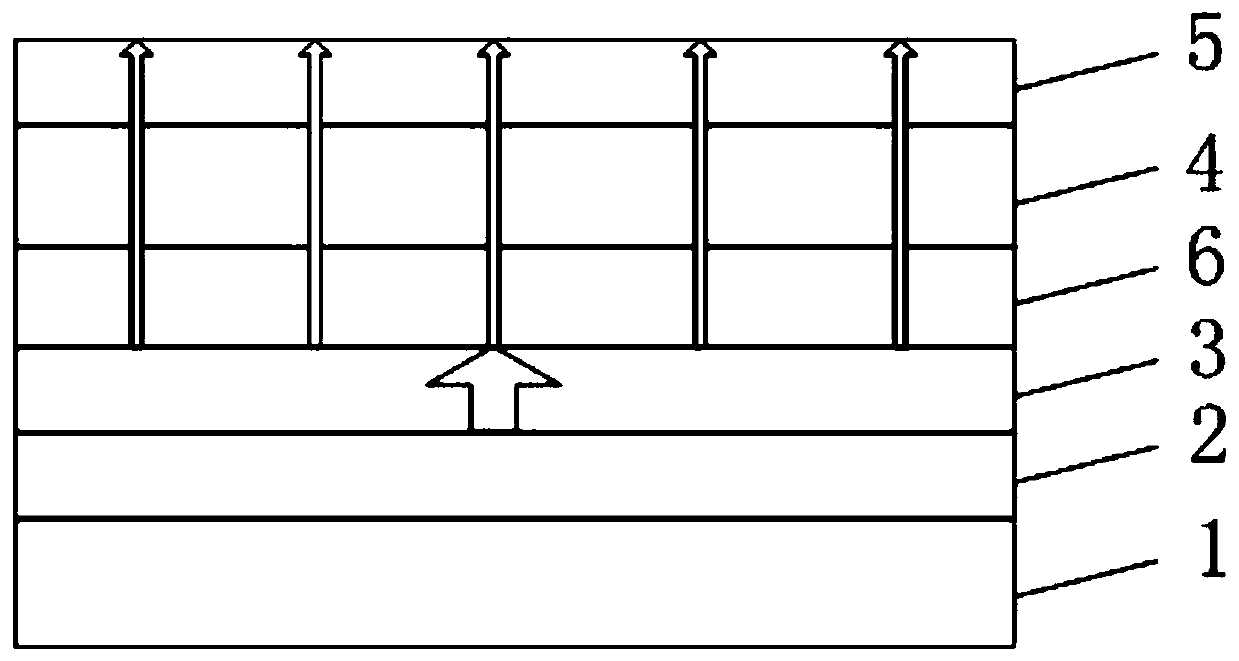

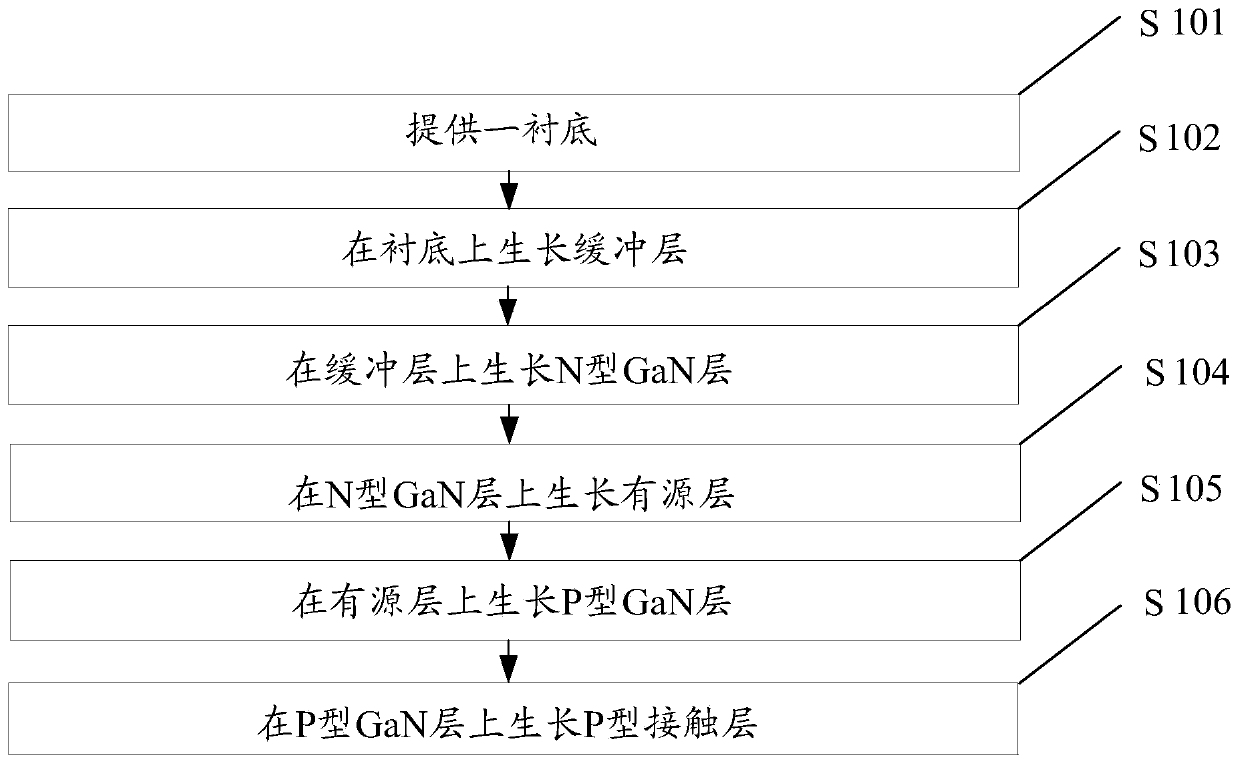

Growth method of light-emitting diode epitaxial wafer

ActiveCN112133797AImprove surface roughnessImprove transmittanceSemiconductor devicesPhysical chemistryElectron blocking layer

The invention provides a growth method of a light-emitting diode epitaxial wafer, and belongs to the technical field of semiconductors. The growth method comprises the following steps: providing a substrate; sequentially growing a low-temperature buffer layer, a high-temperature buffer layer, an N-type layer, an active layer, an electron blocking layer, a low-temperature P-type layer and a high-temperature P-type layer on the substrate; after the high-temperature P-type layer completely grows, pretreating the surface of the high-temperature P-type layer, and forming a roughened surface on thehigh-temperature P-type layer; forming an MgN island-shaped object on the roughened surface of the high-temperature P-type layer; and growing a P-type GaN filling and leveling layer on the MgN island-shaped object. According to the growth method, a two-layer coarsened structure can be formed, the total reflection of photons between the high-temperature P-type layer and the air interface is reduced, and the light extraction efficiency of the high-temperature P-type layer is improved.

Owner:HC SEMITEK ZHEJIANG CO LTD

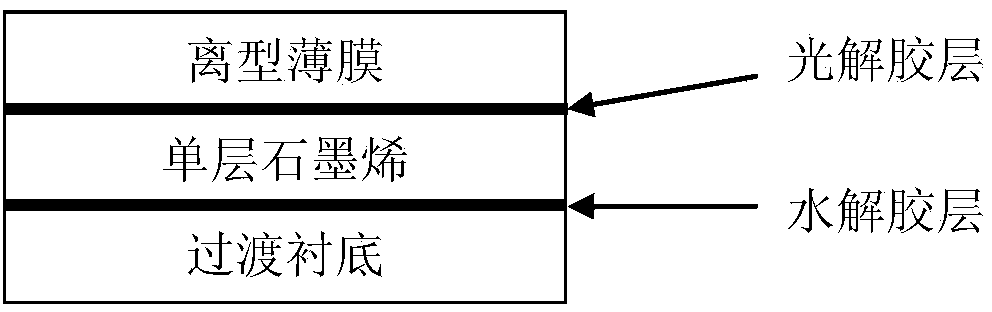

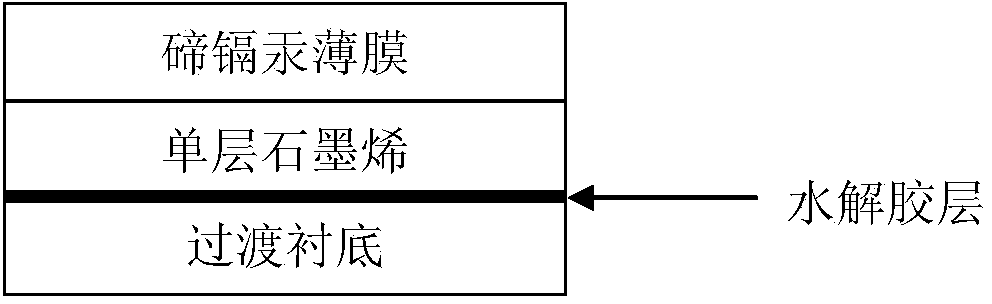

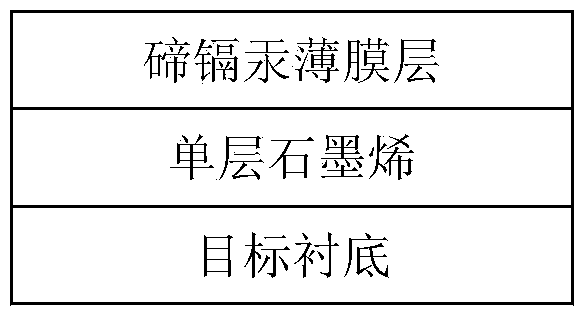

Preparing method of transferable Te-Cd-Hg film

InactiveCN103700731AGuaranteed crystal qualityGuaranteed stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesCooking & bakingOptoelectronics

The invention relates to a preparing method of a transferable Te-Cd-Hg film. The method comprises the steps of performing vapor deposition on a metal substrate to obtain a graphene layer, adhering the obtained structural material with a release film of which the surface is uniformly coated with a photolysis glue into a whole by proper heating and baking, then corroding the metal substrate off, rinsing the rest ''graphene+photolysis glue+release film structural material with deionized water, drying and adhering the structural material with a hard transparent high-temperature resistant substrate into a whole with a hydrolysis glue to form a ''transition substrate+hydrolysis glue layer+graphene+photolysis glue layer+release film'' structure material; releasing the photolysis glue and removing the release film to obtain the ''transition substrate+hydrolysis glue layer+graphene'' structural material, depositing a Te-Cd-Hg film with a laser molecular beam epitaxy method, releasing the hydrolysis glue, removing the transition substrate, and moving the ''graphene+Te-Cd-Hg'' structural material onto a target substrate material. The crystalline state Te-Cd-Hg film can be obtained on amorphous state inorganic substrate and organic substrate materials.

Owner:SHANDONG NORMAL UNIV

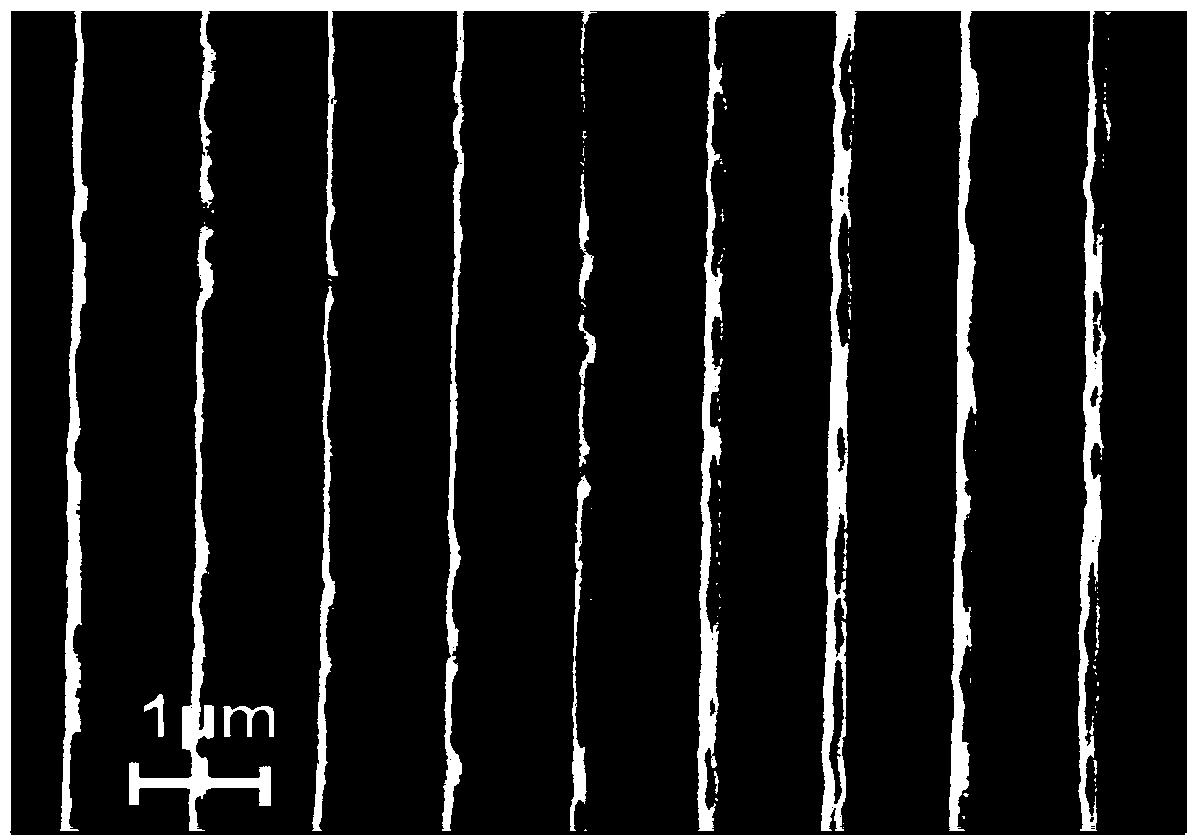

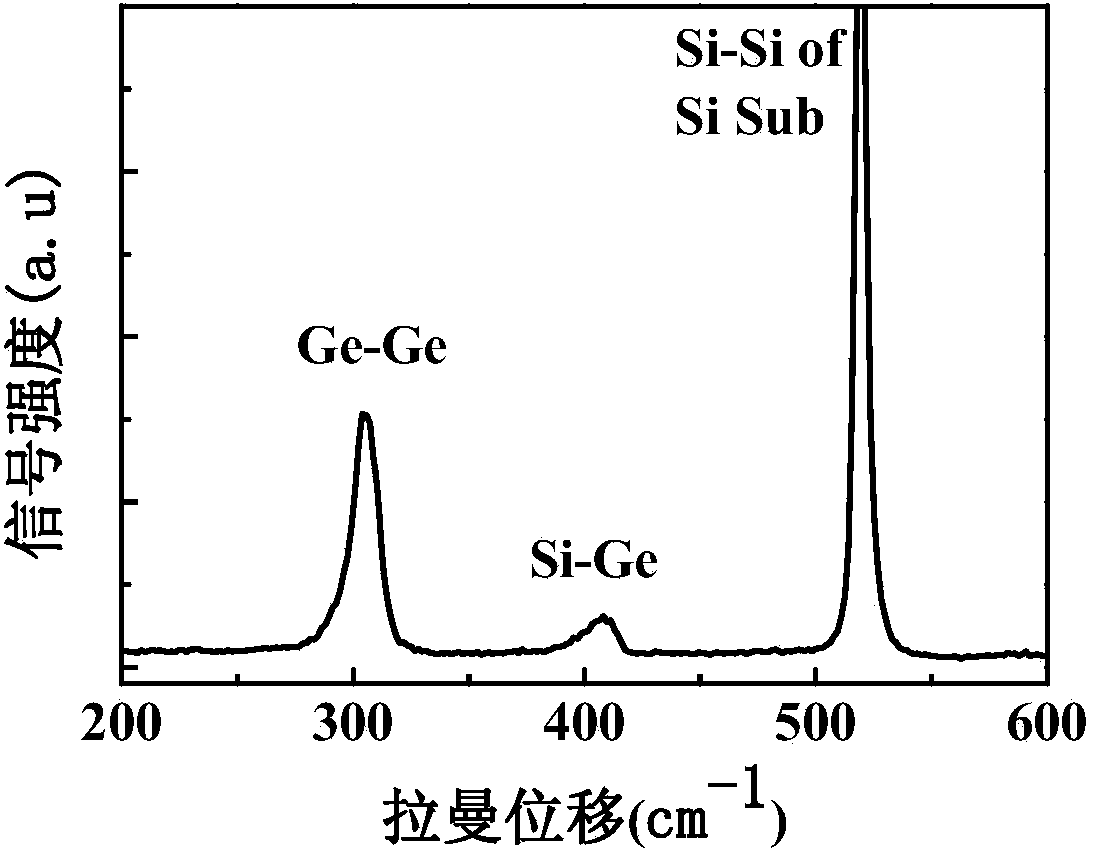

Method for preparing Ge component and bandwidth regulated SiGe nanobelt

ActiveCN103441062AGuaranteed crystal qualityQuality assuranceSemiconductor/solid-state device manufacturingNanotechnologyGratingSemiconductor materials

The invention discloses a method for a preparing Ge component and bandwidth regulated SiGe nanobelt and relates to a nano-material. The method comprises the following steps: generating a Si / SiGe / Si structure on an SOI substrate by using a molecular beam epitaxy method or a chemical vapor deposition method; performing exposing and developing on an obtained sample by using holographic laser interferometry, obtaining an optical grating array with a period below 1 [mu] m, etching a pattern by using an ICP dry method and a wet method, and etching a buried layer SiO2 layer with a depth reaching the SOI substrate; and performing selective oxidation and annealing on the sample by using a conventional resistor type heating oxidation furnace, and obtaining the Ge component and bandwidth regulated SiGe nanobelt with a bandwidth reaching below 200 nm. According to the Ge component and bandwidth regulated SiGe nanobelt, the epitaxial Si and SiGe on the SOI substrate are oxidated through a local selective oxidation mode, so that the bandwidth is reduced, Ge components are regulated for preparing and generating a semiconductor material with nanometer scale, and the method is simple, low-cost, and compatible with a silicon conventional process.

Owner:XIAMEN UNIV

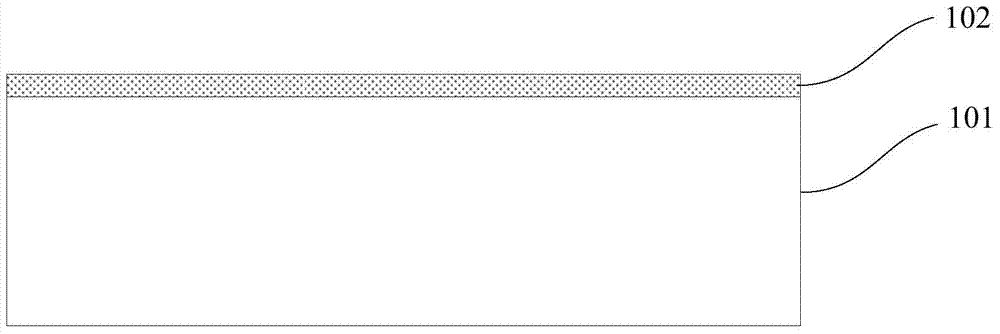

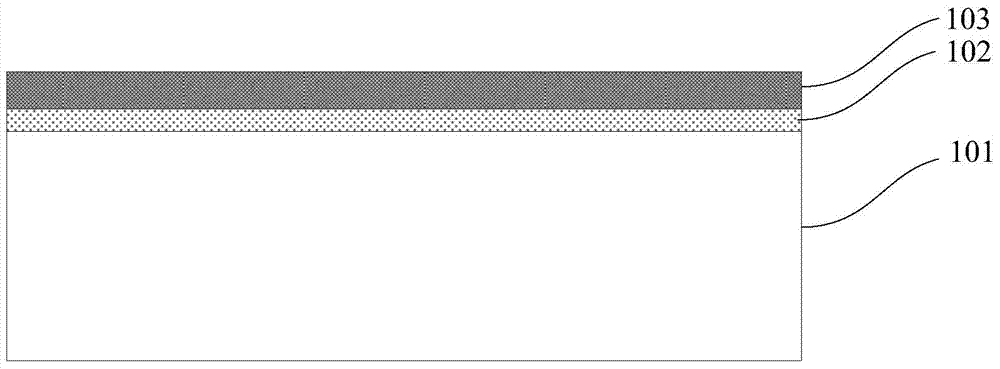

Manufacturing method of substrate structure used for III-V group nitride growth

InactiveCN103840051AGuaranteed crystal qualityImprove light extraction efficiencySemiconductor devicesTwo stepLight-emitting diode

The invention provides a manufacturing method of a substrate structure used for III-V group nitride growth. The manufacturing method comprises the following steps that (1) a buffer layer growth of a subsequent luminous epitaxial structure is formed on the surface of a growing substrate; (2) an SiO2 layer is formed on the surface of the buffer layer; (3) a plurality of SiO2 protrusions which are arranged at intervals are etched on the SiO2 layer through the inductive coupling plasma etching technology, and SiO2 base layers with a preset thickness are kept between the SiO2 protrusions; (4) the SiO2 base layers are etched by the adoption of the wet etching technology until the parts, located between the SiO2 protrusions, of the buffer layer are exposed out. According to the manufacturing method, a BN material layer or an AlN layer or an AlxGal-xN layer with a hexagonal lattice structure is manufactured first to serve as the buffer layer for growth of the luminous epitaxial structure, the SiO2 protrusions are manufactured through the two-step etching method, and the parts, located below the SiO2 protrusions, of the buffer layer can be well protected. The buffer layer and the SiO2 protrusions can guarantee the quality of crystals with grown luminous epitaxial structures and can also improve the light emitting efficiency of a light-emitting diode.

Owner:EPILIGHT TECH +1

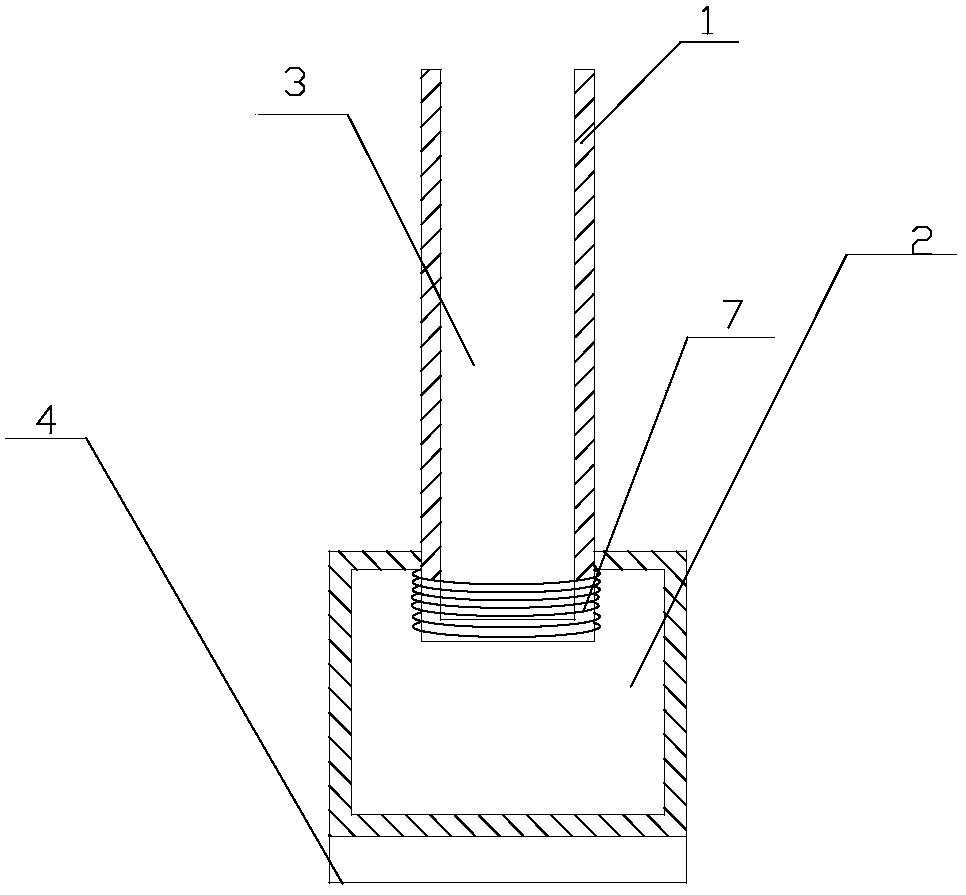

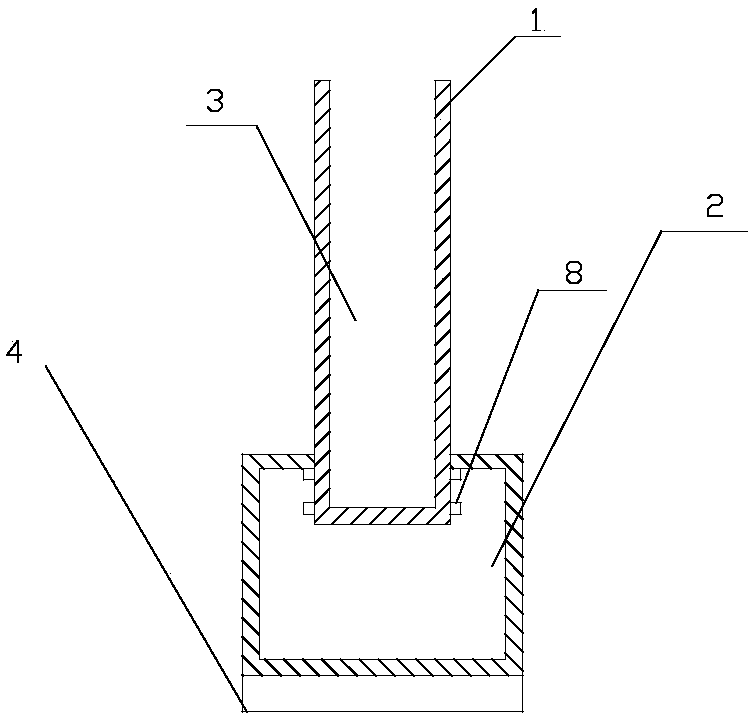

A seed crystal axis and method for growing silicon carbide in liquid phase

ActiveCN106012021BTemperature Gradient RegulationGuaranteed growth ratePolycrystalline material growthBy pulling from meltGraphiteSeed crystal

The invention relates to a seed crystal shaft and a method for liquid phase growth of silicon carbide, and belongs to the technical field of silicon carbide growth. The seed crystal shaft provided by the invention comprises a graphite shaft; the lower end of the graphite shaft is connected with a graphite shaft cap; the graphite shaft cap is of a hollow structure. According to the seed crystal shaft and the method for the liquid phase growth of the silicon carbide, the problems of polytypes, inclusions and stress caused by high-speed growth of a conventional method are solved; the temperature gradient can be regulated and controlled conveniently, so that the growth speed of a crystal is ensured, and meanwhile, the quality of the crystal can also be ensured.

Owner:SICC CO LTD

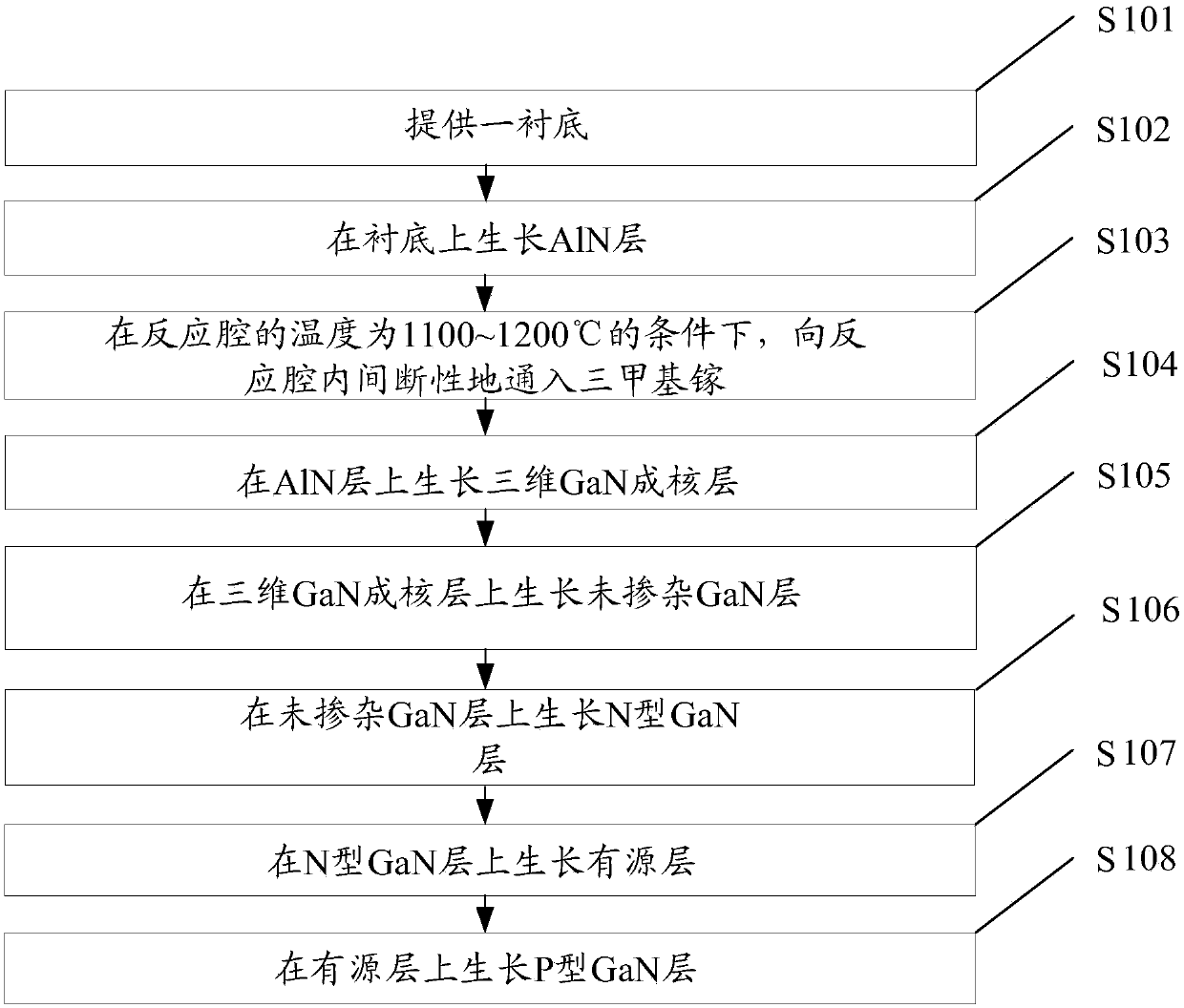

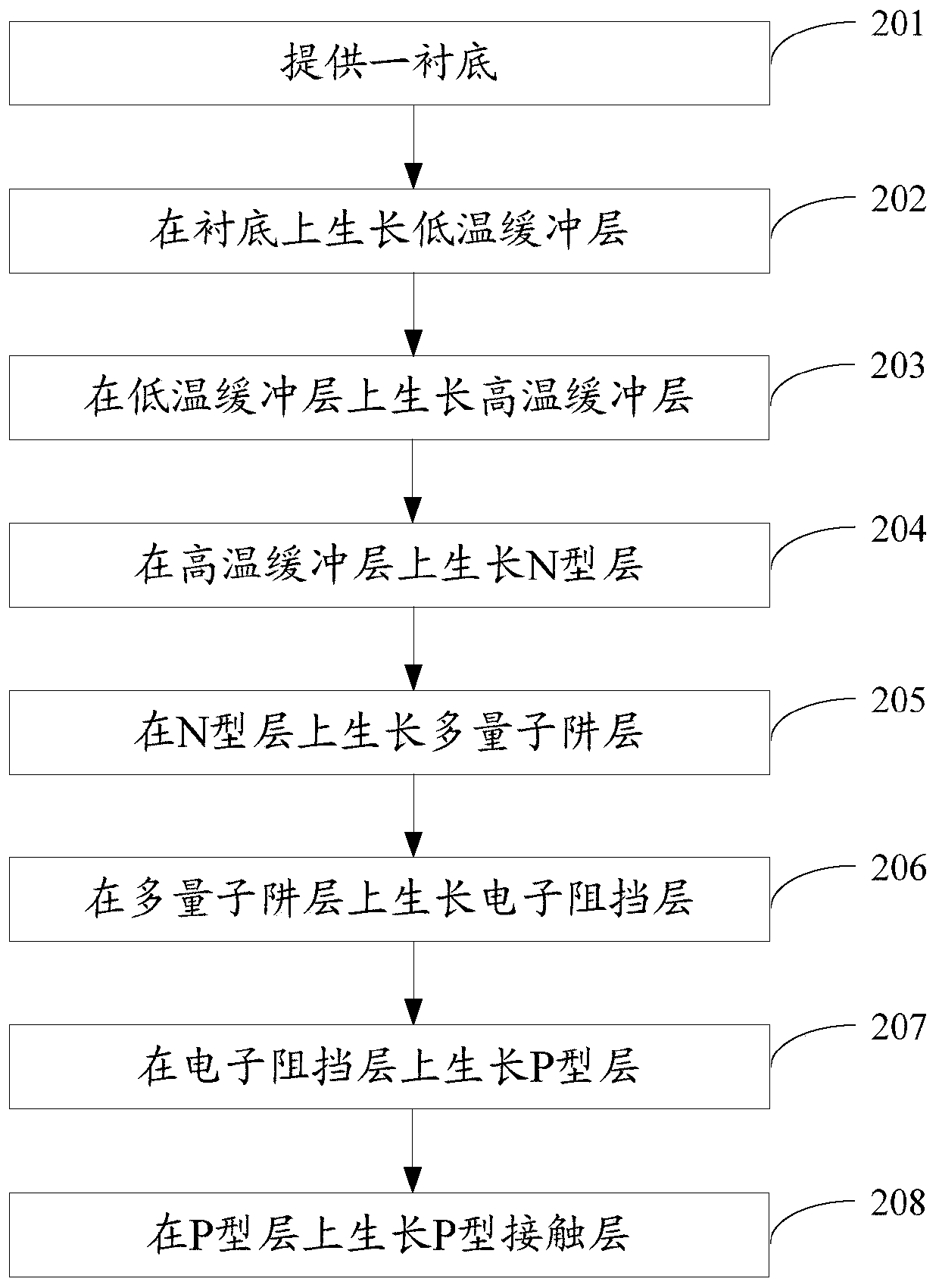

Preparation method of epitaxial wafer of light-emitting diode

The invention discloses a preparation method of an epitaxial wafer of a light-emitting diode, and belongs to the field of light-emitting diode manufacturing. The preparation method comprises the following steps: trimethyl gallium is introduced into a reaction cavity, wherein the trimethyl gallium acts on an AlN layer, gallium atoms in the trimethyl gallium are attracted by micro-pits with lower potential energy on the surface of the AlN layer far away from the substrate, and the gallium atoms are filled into the micro-pits on the AlN layer, so that the surface of the AlN layer is relatively flat; the trimethyl gallium is intermittently introduced, so that the protrusion at the micro-pits due to excessive gallium atom filling can be avoided, the roughness of the surface of the AlN layer faraway from the substrate is reduced, the surface flatness of a three-dimensional GaN nucleation layer grown on the AlN layer is ensured, and the surface flatness of the whole epitaxial wafer is further ensured, which is beneficial to improving the light-emitting uniformity of the light-emitting diode. The gallium atoms fill the micro-pits on the AlN layer, so that the defect of the AlN layer at the micro-pits can be prevented from being transferred to the three-dimensional GaN nucleation layer, the quality of the three-dimensional GaN nucleation layer is improved, the crystal quality of the epitaxial wafer is ensured, and the luminous efficiency of the light-emitting diode is improved.

Owner:HC SEMITEK ZHEJIANG CO LTD

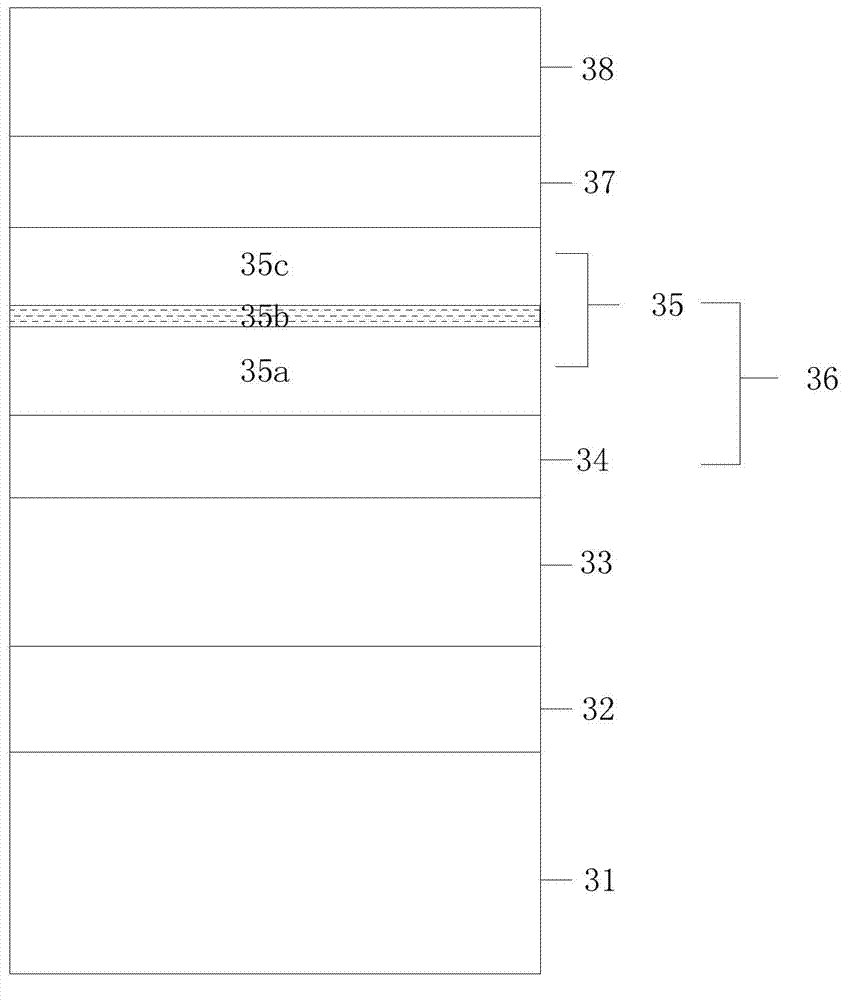

Deep ultraviolet LED epitaxial structure and fabrication method thereof

PendingCN106981548AGuaranteed crystal qualityImprove luminous efficiencySemiconductor devicesChemistryUltraviolet

The invention discloses a deep ultraviolet LED epitaxial structure and a fabrication method thereof. The deep ultraviolet LED epitaxial structure comprises a substrate, wherein a nucleating layer is grown on the substrate, a buffer layer is grown on the nucleating layer, an n-type AlGaN layer, a periodic structure AlGa<1-a>N / GaN current extension layer, a periodic structure AlGa<1-b>N / Al<c>Ga<1-c>N light-emitting layer, a periodic structure AlN / Al<d>Ga<1-d>N barrier layer, a periodic structure Al<e>Ga<1-e>N / GaN barrier layer and a p-type GaN layer are sequentially grown on the buffer layer, a Al<e>Ga<1-e>N layer in a Al<e>Ga<1-e>N / GaN barrier layer 8 is a unintentional doping layer, and a GaN layer is a Mg-doped layer. The periodic structure Al<e>Ga<1-e>N / GaN barrier layer is employed, Al<e>Ga<1-e>N is the unintentional doping layer, the GaN layer is the Mg-doped layer, holes are successfully introduced to the light-emitting layer by a memory effect of Mg and hole tunneling, electrons can be limited in the light-emitting layer by the barrier layer, the crystal quality of the barrier layer is also ensured, and the light-emitting efficiency is higher.

Owner:ZEARAY WUHAN OPTOELECTRONICS TECH CO LTD

Epitaxial growth method of high-resistance GaN thin film

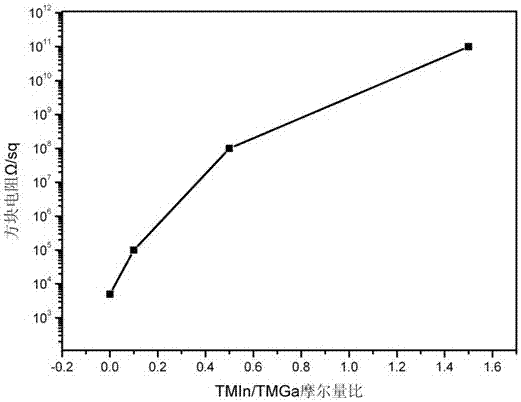

ActiveCN107887255AFree installationImprove economySemiconductor/solid-state device manufacturingHigh resistanceImpurity doping

The invention relates to an epitaxial growth method of a high-resistance GaN thin film. The method is performed in MOCVD equipment and includes a substrate baking stage, a nucleation stage and an epitaxial growth stage. The method is characterized in that a metal organic matter trimethylindium is used as a C impurity doping source during the epitaxial growth stage. With the method adopted, the high resistance of the GaN thin film can be achieved; the TMIn is unlikely to form In-N bonds in crystal lattices under high temperature, and therefore, high growth temperature can assist in avoiding theformation of InGaN alloys and ensuring the integrity of the lattice structure of the GaN thin film; the concentration of C impurities in a GaN epitaxial layer can be effectively controlled by changing the flow rate of the dopant TMIn, and therefore, doping efficiency is high, and repeatability is stable; and a doping source pipeline is not required to be added into an MOCVD system, other C dopingsources are not required to be installed, and therefore, the resources of existing device can be fully utilized. The method is of simplicity and easy to operate. The epitaxial material has good performance. The high-quality and low-cost growth of the high-resistance GaN thin film can be realized.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

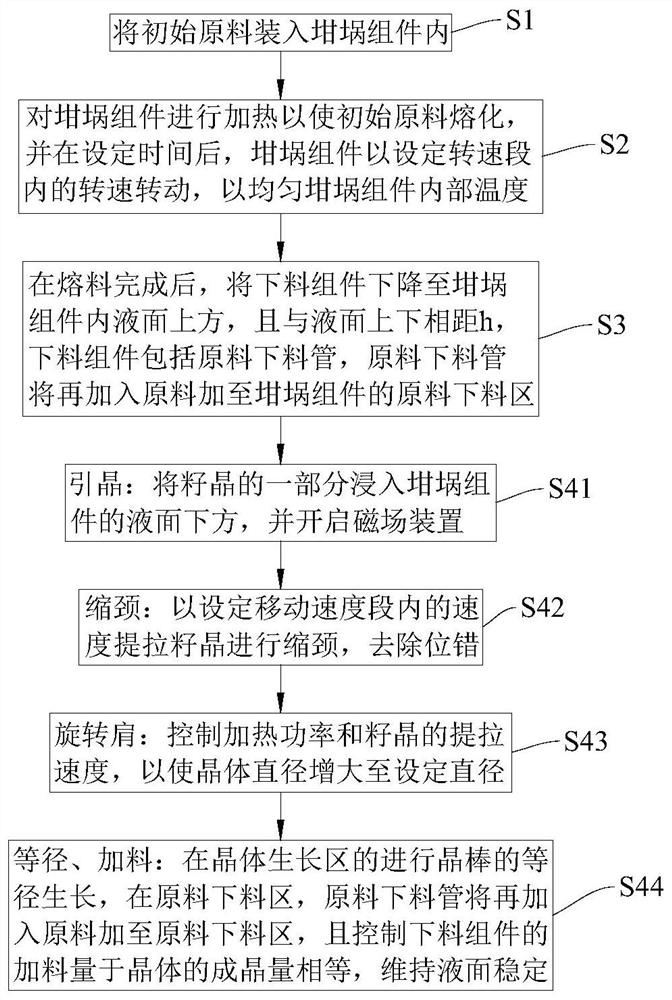

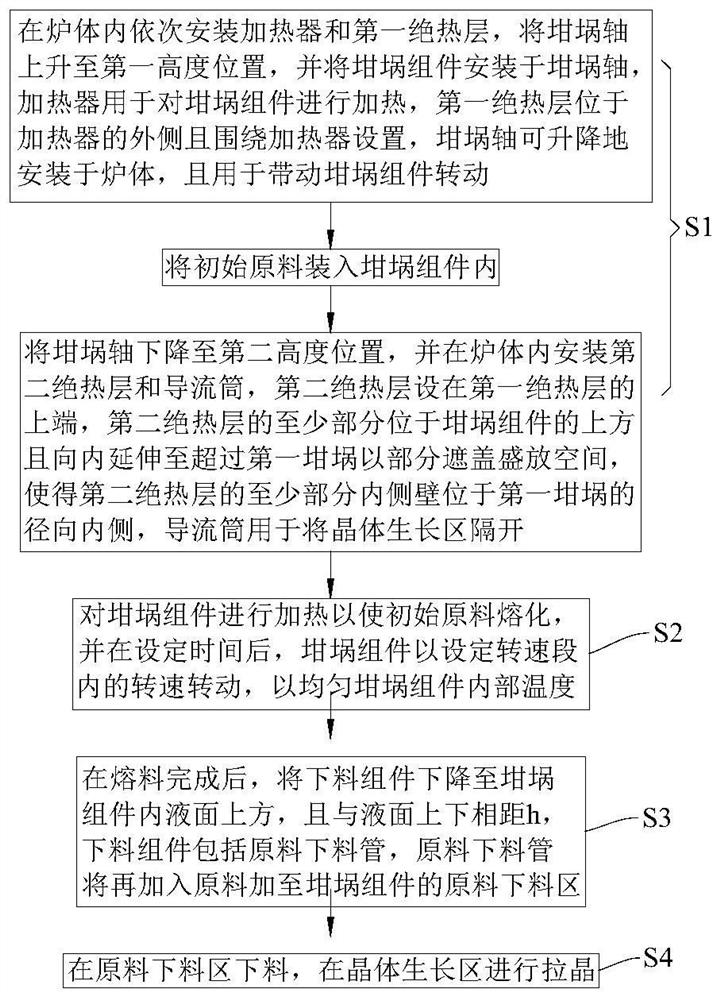

Crystal production process

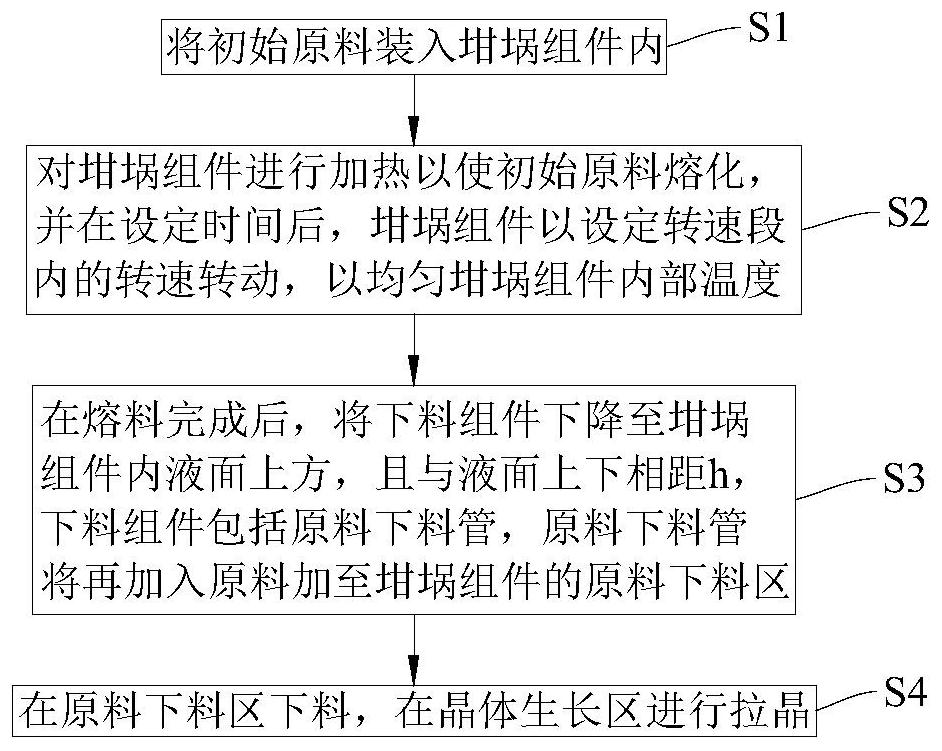

PendingCN112210820AGuaranteed Crystal QualityUniform internal temperatureBy pulling from meltAfter-treatment apparatusChemistryEngineering

The invention discloses a crystal production process. The crystal production process comprises the following steps: S1, putting an initial raw material into a crucible assembly; s2, the crucible assembly is heated to melt the initial raw materials, and after set time, the crucible assembly rotates at the rotating speed within the set rotating speed section; s3, after material melting is completed,a discharging assembly descends to the position above the liquid level in the crucible assembly, the distance between the discharging assembly and the liquid level is h, the discharging assembly comprises a raw material discharging pipe, and the raw material discharging pipe adds the readded raw materials into a raw material discharging area of the crucible assembly; and S4, blanking is conductedin the raw material blanking area, crystal pulling is conducted in the crystal growth area, in the step S1, the initial raw materials are loaded into a first cavity, a second cavity and a third cavity correspondingly, and the particle diameter of the initial raw materials in the first cavity is larger than the particle diameter of the initial raw materials in the second cavity and the particle diameter of the initial raw materials in the third cavity. According to the crystal production process, molten liquid in the crucible assembly can be more uniform, and the crystal quality can be improved.

Owner:XUZHOU XINJING SEMICON TECH CO LTD

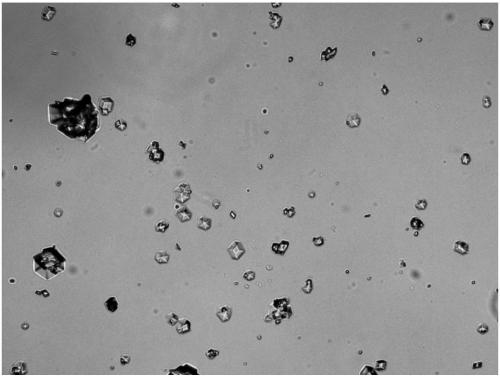

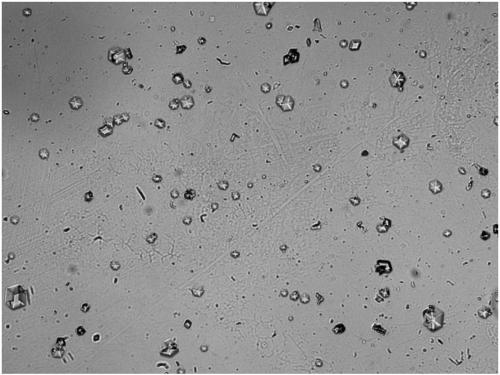

Preparation method for glycine-lysine-proline insulin crystals

ActiveCN109957001AReduce the amount addedReduce contentPeptide preparation methodsInsulinsGlycineLysine / Proline

The invention discloses a preparation method for glycine-lysine-proline insulin crystals. The method includes the step of adding Zn ions to a crystalline solution containing glycine-lysine-proline insulin in a method of two or more steps for two or more steps of crystallization, wherein according to the mass ratio of Zn to glycine-lysine-proline insulin, the amount of the Zn ions added in the first step of crystallization is 0.1%-0.8%, the amount of the Zn ions added in other steps of crystallization is 0.1% or more, and the total amount of the Zn ions added in all the steps is 0.4% or more. The preparation method can prepare high-quality and high-yield glycine-lysine-proline insulin crystals, and is prone to industrialized production of glycine-lysine-proline insulin.

Owner:GAN&LEE PHARMA

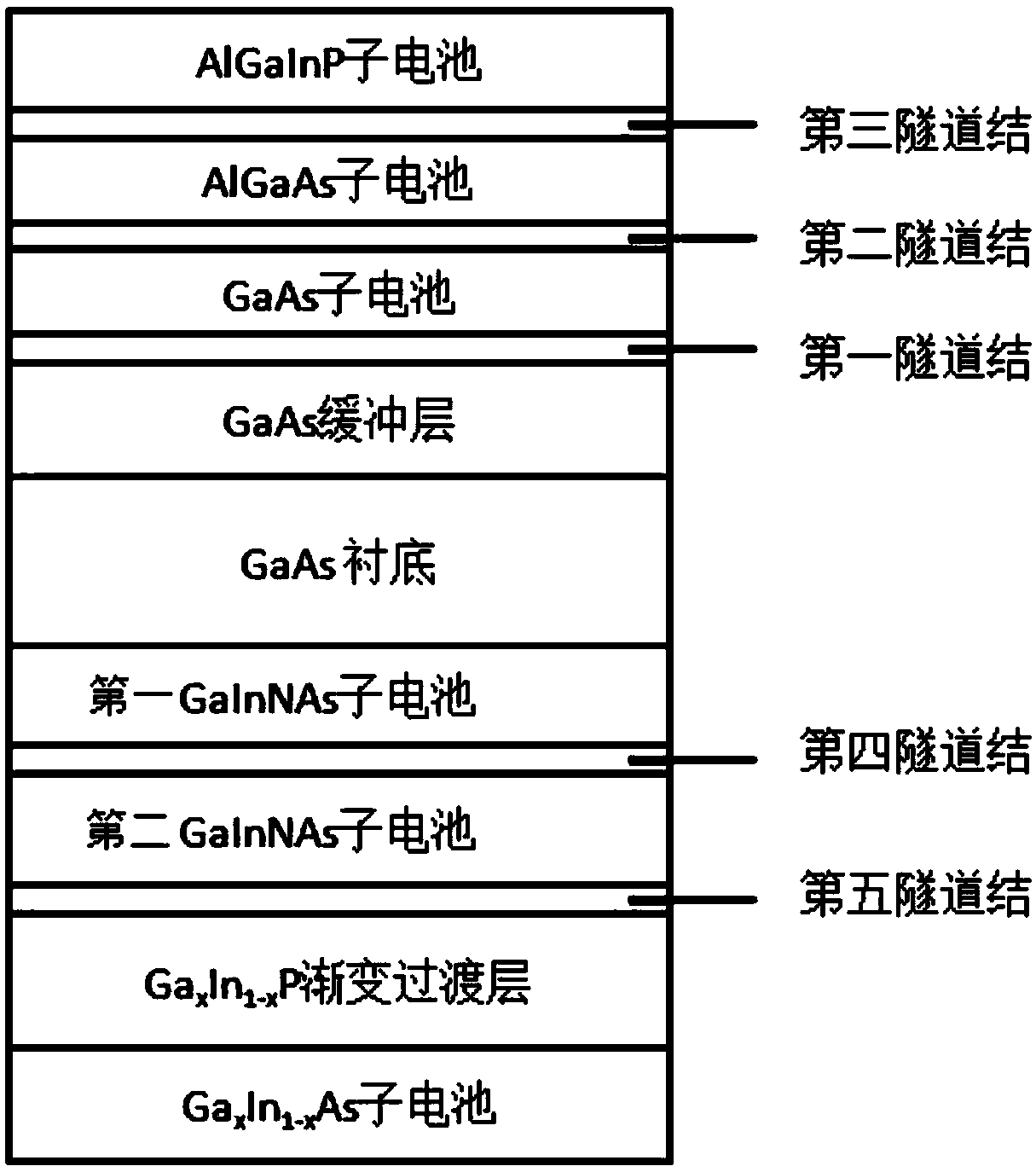

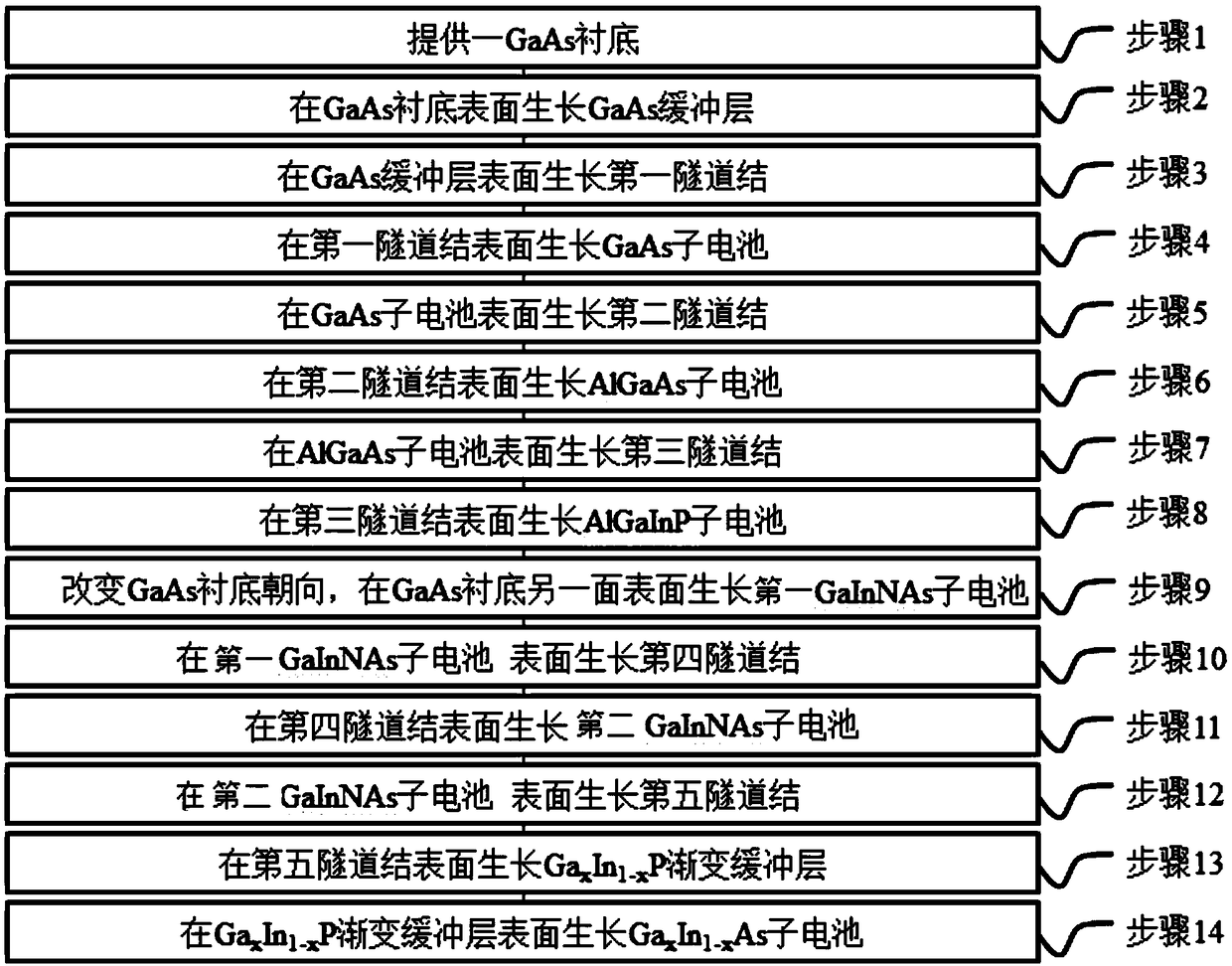

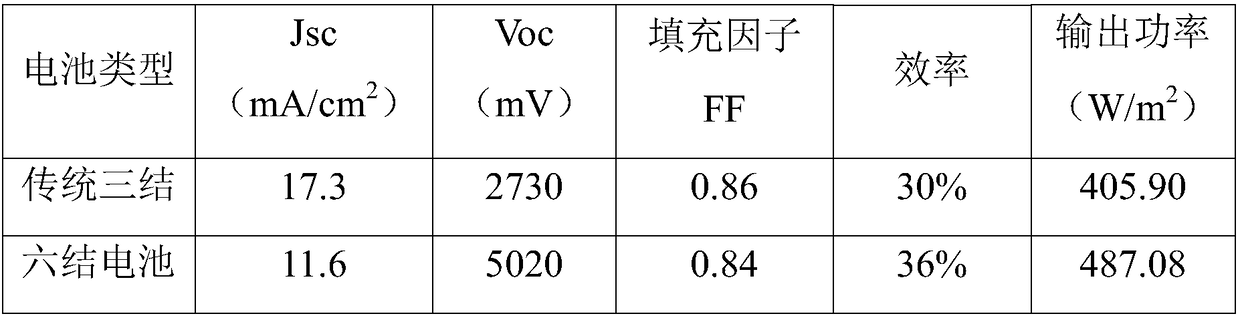

An efficient six-junction solar cell grown on double sides and a preparation method thereof

ActiveCN109148621AImprove photoelectric conversion efficiencyImprove photoelectric conversion performanceFinal product manufacturePhotovoltaic energy generationThermal energySingle crystal

The invention discloses a efficient six-junction solar cell grown on double sides and a preparation method thereof, by means of metal organic chemical vapor deposition, based on a double-sided polished n-type GaAs single crystal wafer, a GaAs buffer layer, a GaAs sub-cell, an AlGaAs sub-cell and an AlGaInP sub-cell are sequentially arranged on the first surface of the GaAs substrate from bottom totop, the second side of the GaAs substrate is sequentially provided with a first GaInNAs sub-cell, a second GaInNAs sub-cell, and a GaxIn<1-x>P Gradient Transition Layer and GaxIn<1-x>As sub-batteryfrom top to bottom, each sub-battery being connected through a tunnel junction. The band gaps of the six-junction solar cells are 2.2 eV, 1.7 eV, 1.42 eV, 1.1 eV, 0.9 eV and 0.7 eV, respectively. Thecurrent mismatch of each sub-cell is small, which reduces the heat loss in the photoelectric conversion process, increases the open-circuit voltage of the cell and improves the photoelectric conversion efficiency.

Owner:ZHONGSHAN DEHUA CHIP TECH CO LTD

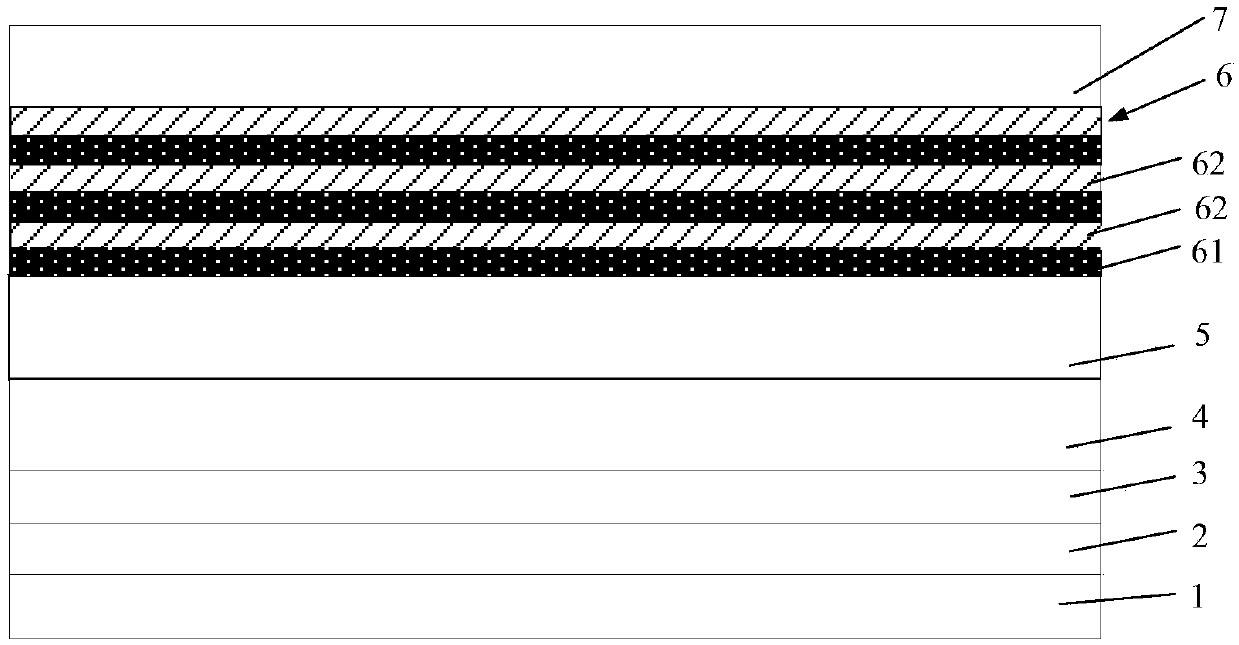

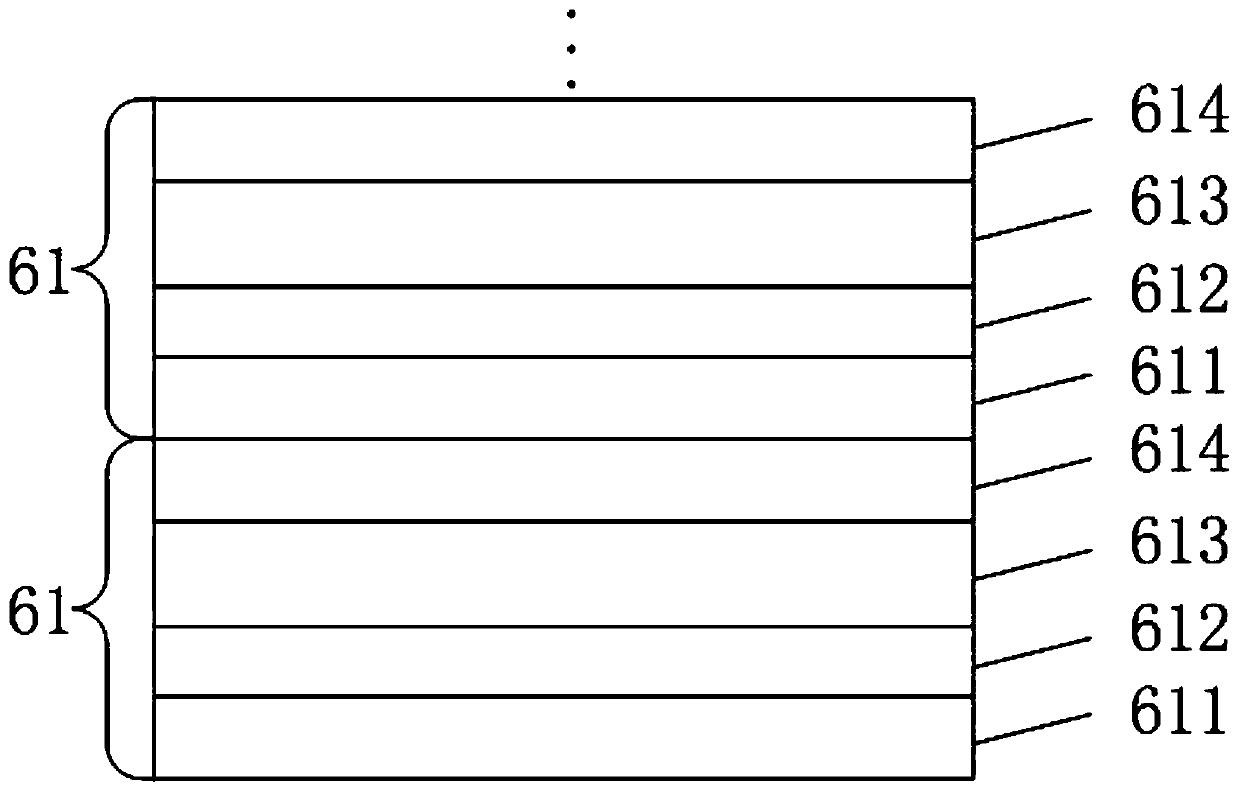

GaN-based light-emitting diode and manufacturing method thereof

ActiveCN103794690AGuaranteed crystal qualityImprove luminous efficiencySemiconductor devicesQuantum wellCrystal

The invention provides a GaN-based light-emitting diode and a manufacturing method of the GaN-based light-emitting diode. A quantum well of the light-emitting diode comprises a well layer and a barrier layer. The well layer is an InxGa1-xN well layer, and the barrier layer is an InyGa1-yN barrier layer, wherein y<x<1, 0<x<1 and 0<=y<1. At least one GaN tunneling layer is arranged in the well layer and / or the barrier layer. Due to the fact that the GaN tunneling layer is added, before the well layer or the barrier layer grows to a certain thickness and In gathering occurs, the GaN tunneling layer is grown, and therefore the In gathering phenomenon of the well layer and / or the barrier layer is avoided. The crystalline quality of the quantum well is improved, and therefore the light-emitting efficiency of the light-emitting diode is improved.

Owner:FOSHAN NATIONSTAR SEMICON

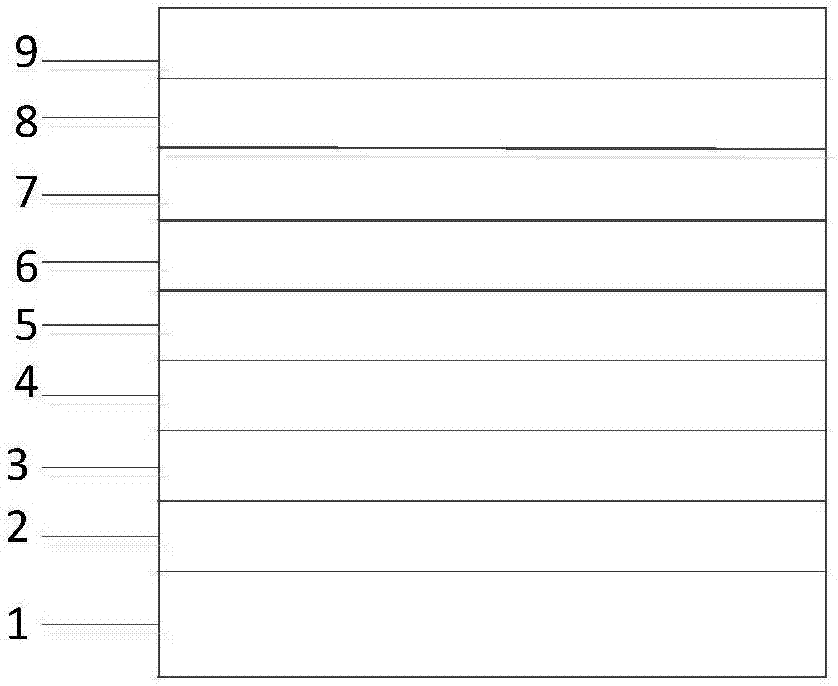

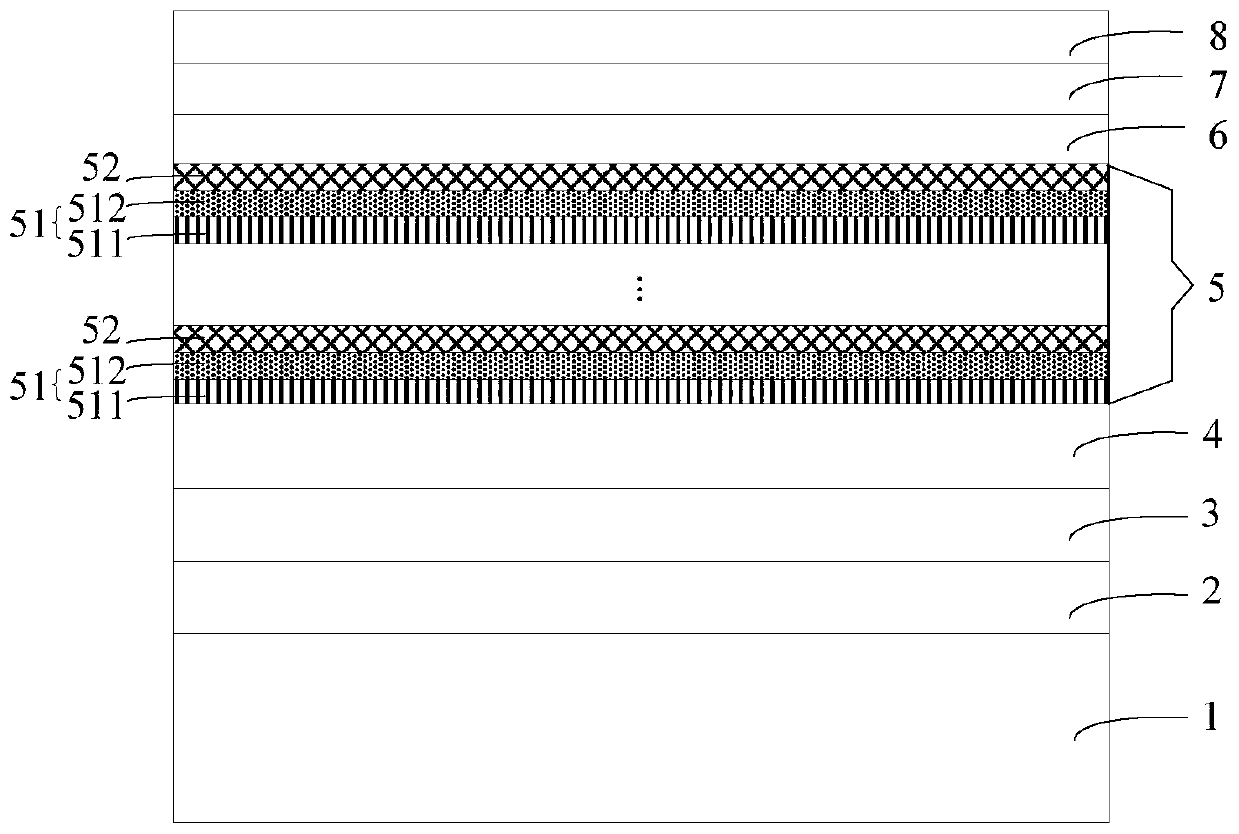

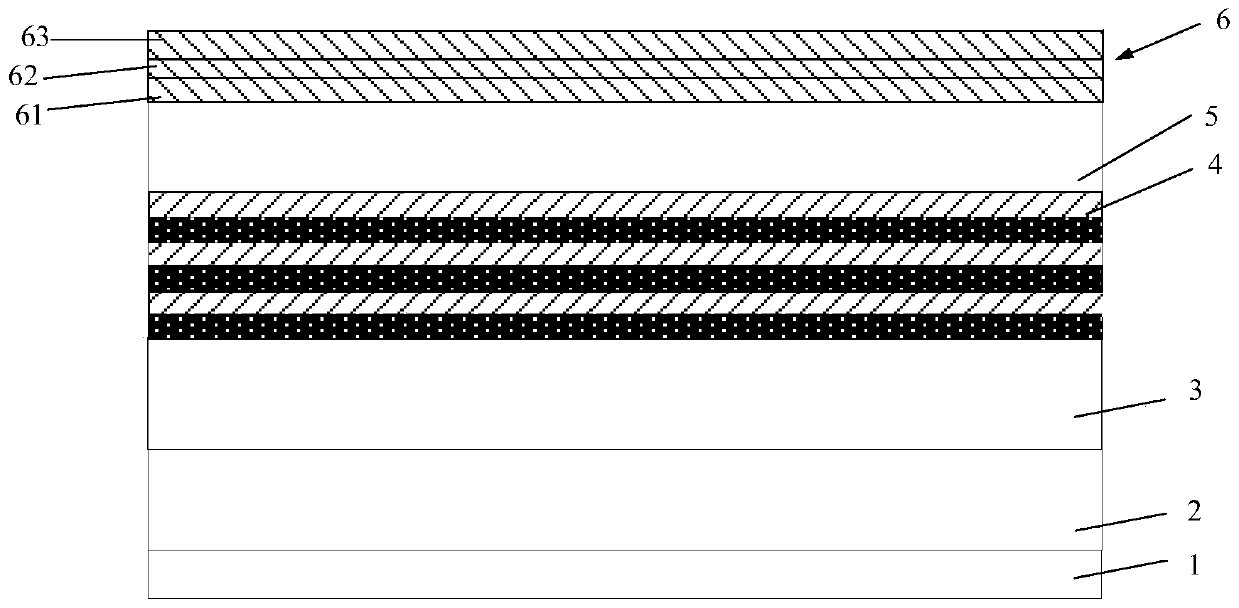

Antistatic epitaxial structure and manufacturing method thereof

PendingCN110364603AImprove electrostatic propertiesPrevent breakdownSemiconductor devicesActive layerSilicon

The invention discloses an antistatic epitaxial structure and a manufacturing method thereof. The epitaxial structure comprises a buffer layer, an N-type GaN layer, an active layer and a P-type GaN layer which are sequentially arranged on a substrate, characterized in that it is characterized in that it comprises, a composite layer is arranged between the N-type GaN layer and the active layer; thecomposite layer comprises a plurality of silicon concentration changing GaN layers. The silicon concentration change GaN layer comprises a first GaN layer, a second GaN layer arranged on the first GaN layer, a third GaN layer arranged on the second GaN layer, and a fourth GaN layer arranged on the third GaN layer. Wherein the doping concentration of silicon in the first GaN layer is zero, and thedoping concentration of silicon in the second GaN layer and the fourth GaN layer is smaller than the doping concentration of silicon in the third GaN layer. According to the invention, the compositelayer is arranged between the N-type GaN layer and the active layer, and the current can be uniformly distributed to the whole epitaxial structure after passing through the composite layer, so that the current cannot be concentrated on a certain region or point, the antistatic capability of the epitaxial structure is improved, and the active layer is prevented from being broken down by static electricity.

Owner:FOSHAN NATIONSTAR SEMICON

Light emitting diode epitaxial wafer and manufacturing method thereof

ActiveCN110993753AIncreased spontaneous emission intensityLarge effective band widthSemiconductor devicesLight-emitting diodeEffective energy

The invention provides a light emitting diode epitaxial wafer and a manufacturing method thereof, and belongs to the technical field of semiconductors. The light emitting diode epitaxial wafer comprises a substrate, and a low-temperature buffer layer, a high-temperature buffer layer, an N-type layer, a multi-quantum well layer and a P-type layer which are stacked on the substrate in sequence. Themulti-quantum well layer comprises a plurality of quantum well layers and quantum barrier layers which grow periodically and alternately, each quantum well layer comprises a first sub-layer and a second sub-layer growing on the first sub-layer, the first sub-layer is an InGaN layer, and the second sub-layer is a Si-doped InN layer. By doping Si into the second sub-layer, the enrichment of In in the quantum well layer is facilitated, so that the spontaneous radiation intensity in the quantum well layer is increased, and the effective energy band width is increased, and accordingly the drop effect can be reduced, and the light-emitting efficiency of the diode is improved.

Owner:HC SEMITEK SUZHOU

Chemical vapor deposition method and device for submicron diamond film

ActiveCN112779599AImprove growth efficiencyGuaranteed uniformityPolycrystalline material growthFrom chemically reactive gasesThin membraneChemical vapor deposition

The invention discloses a microwave plasma chemical vapor deposition method and device for a submicron diamond film. The method comprises the following steps: placing a seed crystal substrate on a pad, placing the pad in a growth chamber of MPCVD equipment, adjusting the pressure in the growth chamber, operating a microwave source, adjusting the temperature of the pad, and adjusting the pad to a height required by growth along with the rise of the seed crystal substrate; the device comprises a cushion plate, a tray, a quartz window and a cushion plate movement mechanism, the cushion plate, the tray, a cooling plate and the quartz window are sequentially arranged from top to bottom, and the cushion plate is connected to the power output end of the cushion plate movement mechanism; and a heating device is arranged in the cushion plate. The height and the rotation rate of a growth pad are adjusted through the pad movement mechanism, the epitaxial thin film deposition efficiency is controlled in a pad heating mode, the deposition rate of each epitaxial area is optimized, the height of the pad is dynamically adjusted along with the increase of the height of the seed crystal substrate in the growth process, rotation is conducted, the growth continuity and uniformity of the same seed crystal substrate can be ensured, and the crystal quality is ensured.

Owner:JINAN ZHONGWU NEW MATERIALS CO LTD

Compound substrate, preparation method of compound substrate and preparation method of light emitting diode chip

ActiveCN106816509AEasy corrosion strippingImprove crystal qualitySemiconductor devicesGallium nitrideLight-emitting diode

The invention discloses a compound substrate, a preparation method of the compound substrate, and a preparation method of a light emitting diode chip with a vertical structure based on the compound substrate. According to the compound substrate, the thickness of a first gallium nitride layer clamped between a first graph layer and a second graph layer is less than the height of first bulge structures, so that the first bulge structures on the first graph layer can be connected with and communicate with the second bulge structures on the second graph layer; and the second bulge structures on the second graph layer are connected together, so that the first graph layer and the second graph layer can form a whole mutually connected graph capable of being corroded with a wet corrosive solution. Once the wet corrosive solution begins to corrode the graph layers from the side face of the compound substrate, the wet corrosive solution can permeate and etch each bulge structure better, so that the wet corrosion stripping of a subsequent epitaxial substrate is facilitated. In addition, the compound substrate can further ensure crystal mass of a subsequent epitaxial layer.

Owner:XIAMEN CHANGELIGHT CO LTD

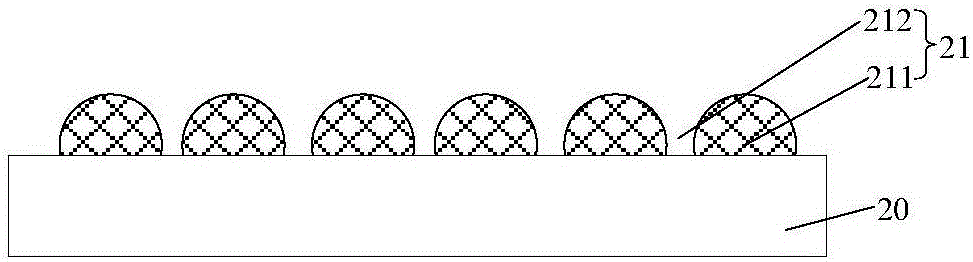

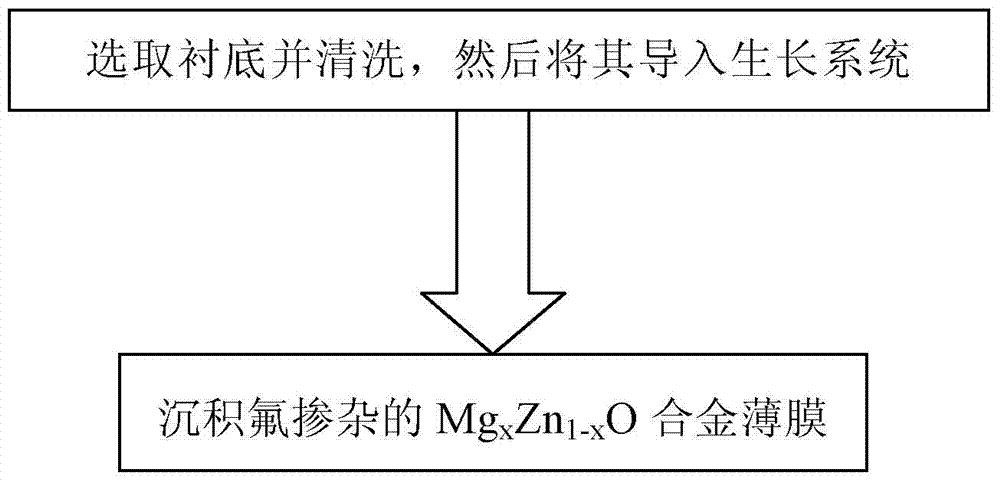

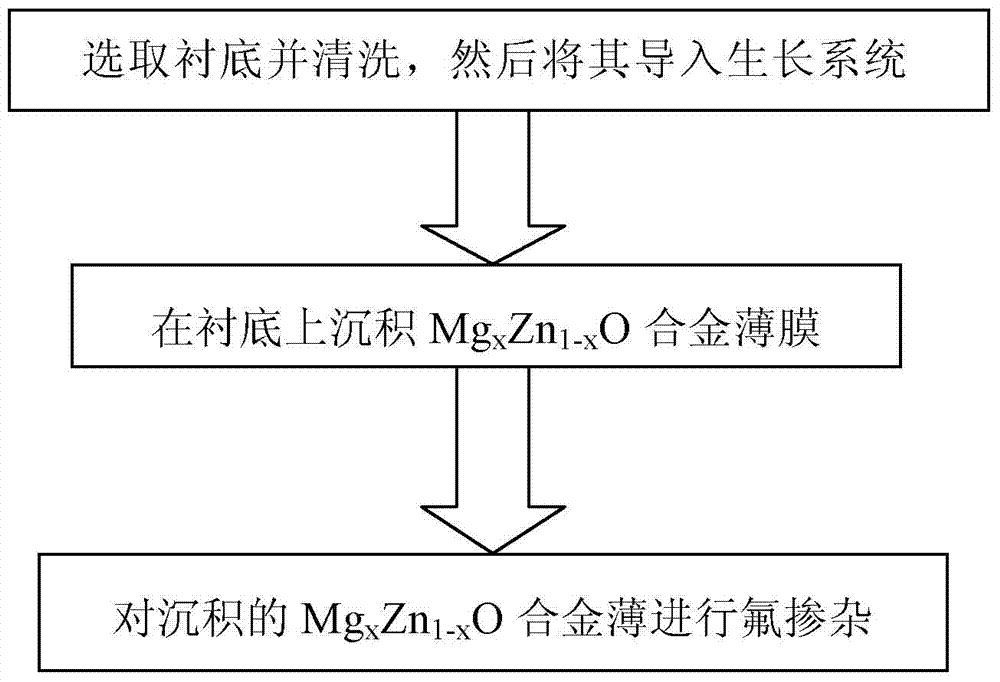

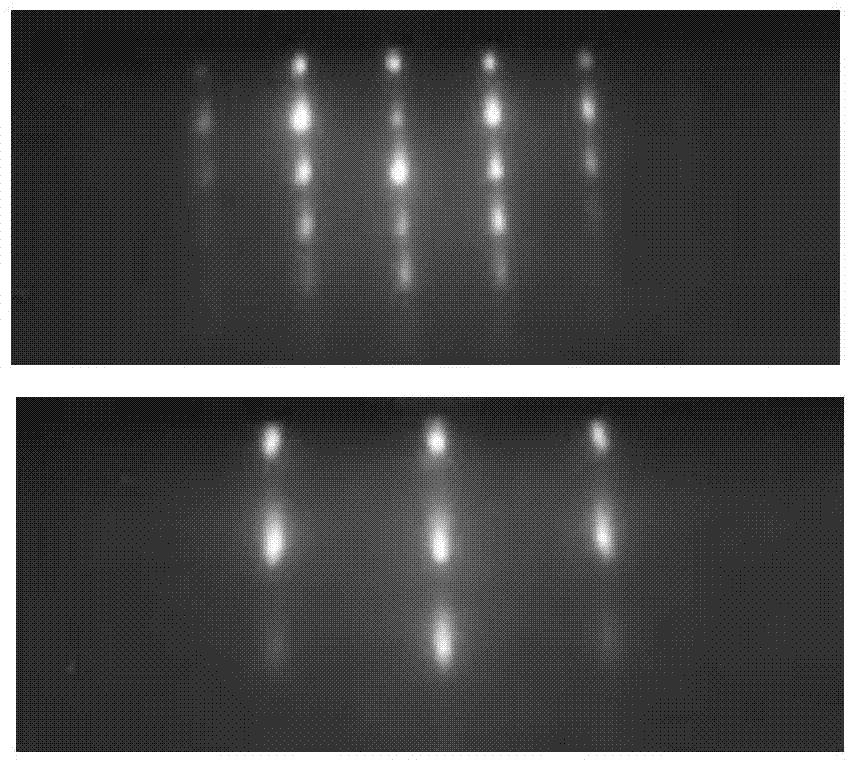

Method for improving the conductivity of MgxZn(1-x)O and application of MgxZn(1-x)O in photoelectronic device

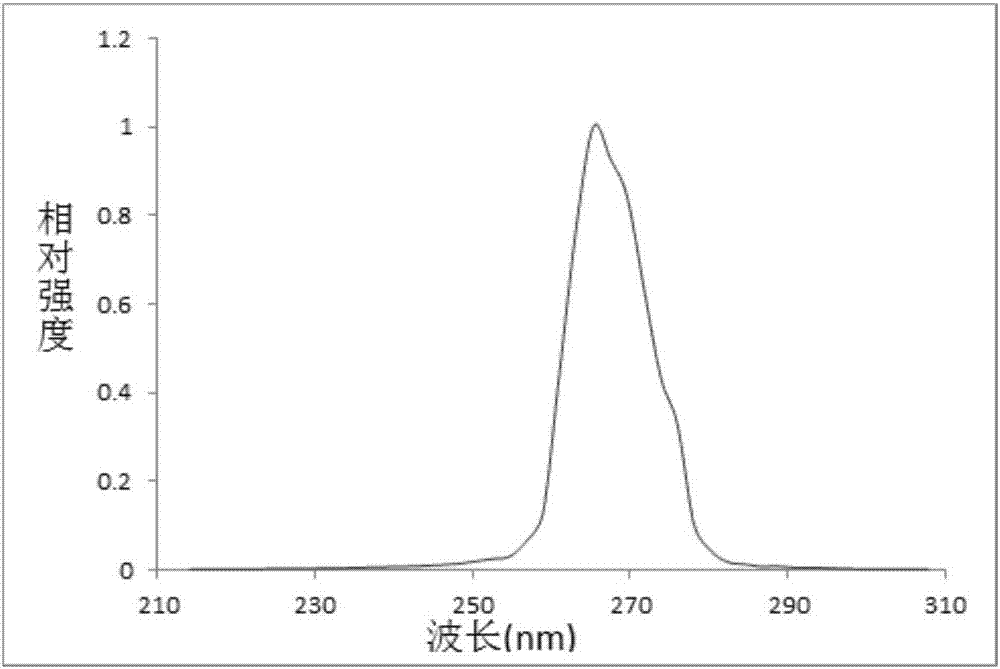

ActiveCN104779308AGood electrical propertiesGuaranteed crystal qualityFinal product manufactureSemiconductor devicesUltravioletElectrical control

The invention provides a method for improving the conductivity of MgxZn(1-x)O and an application of MgxZn(1-x)O in a photoelectronic device. The method for improving the conductivity of MgxZn(1-x)O comprises the step of doping a MgxZn(1-x)O film with fluorine to obtain a fluorine-doped MgxZn(1-x)O film or directly preparing a fluorine-doped MgxZn(1-x)O film. The photoelectronic device of the invention comprises an active layer and a metal electrode layer arranged on the active layer, wherein the active layer comprises a fluorine-doped MgxZn(1-x)O film. Electrical control on MgxZn(1-x)O including deep ultraviolet is realized by fluorine doping. Excess carriers are provided through effective doping of fluorine atoms, and therefore, an n-type conductivity MgxZn(1-x)O film with greatly improved electrical performance is obtained.

Owner:INST OF PHYSICS - CHINESE ACAD OF SCI

Solar cell

InactiveCN101866967BReduce manufacturing costImprove conductivityFinal product manufacturePhotovoltaic energy generationThermal expansionSolar cell

The invention relates to a silicon-based single-junction gallium indium nitride solar cell which comprises a back electrode (11), a silicon substrate (1), a seed crystal layer (2), a buffer layer (3), an n-type doped GaN buffer layer (4), an InaGal-aN layer (5), an unintentional doped InbGal-bN layer (6), a p-type doped IncGal-cN layer (7), a window layer (8), a positive electrode (9) and an anti-reflection conductive film (10) which are arranged from bottom to top, wherein the silicon substrate and the InaGal-aN layer is are an n-type doped structure, the seed crystal layer and the buffer layer are made of ZnO material, the window layer is made of p-type heavily doped GaN, and the anti-reflection conductive film covers areas of the window layer other than the positive electrode. The solar cell can quite effectively solve the problems of lattice matching, thermal expansion coefficient matching and the like encountered when a GaN film extends from the silicon substrate, and has the advantages of low manufacturing cost, high sunlight absorbability and the like.

Owner:HUAZHONG UNIV OF SCI & TECH

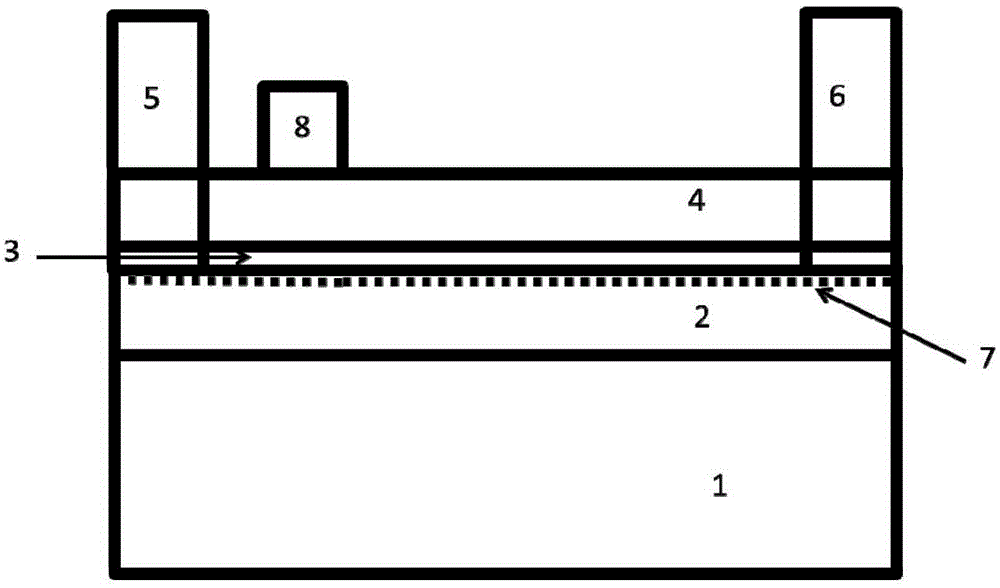

Falling-film crystallizer

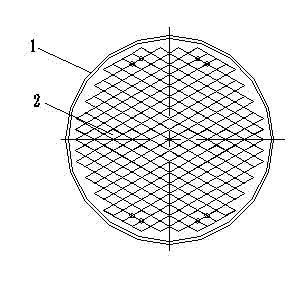

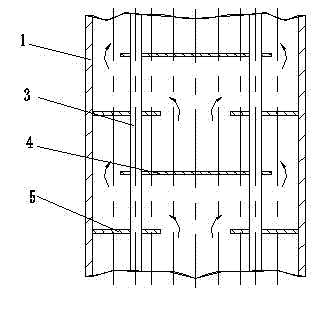

InactiveCN103191577AEven by forceSpeed up the flowSolution crystallizationHalogenated hydrocarbon preparationEngineeringMaterial distribution

The invention relates to a falling-film crystallizer, comprising a falling-film distributor and a material heat exchange device arranged in series. The falling-film distributor comprises a cylinder body and a material distribution channel arranged in the cylinder body and formed by a plurality of continuous square holes; and the material heat exchange device comprises a cylinder body and a plurality of heat exchange tubes arranged in the cylinder body, and the cylinder body is provided with annular baffle plates perpendicular to the heat exchange tubes. The invention provides a falling-film crystallizer with good crystallization efficiency and quality.

Owner:JIANGSU PENGYU CHEM

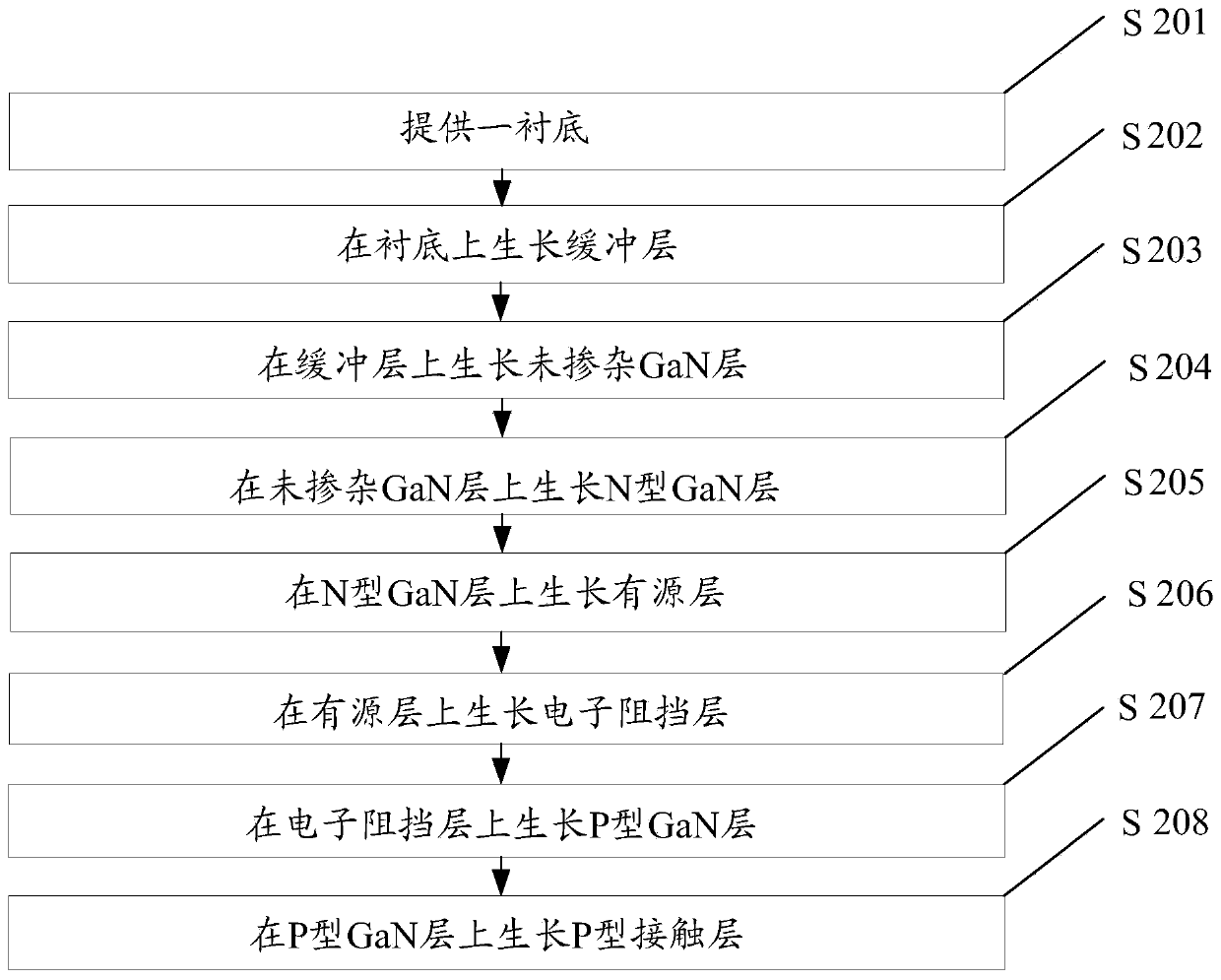

Preparation method of epitaxial wafer of light emitting diode

InactiveCN109802024AImprove luminous efficiencyGuaranteed crystal qualitySemiconductor devicesCarbon impuritiesOhmic contact

The invention discloses a preparation method of an epitaxial wafer of a light emitting diode, which belongs to the field of light emitting diode manufacturing. The growth temperature of a second P-type contact sub-layer in a P-type contact layer is 650-750 DEG C. The growth can increase the amount of Mg doped in the second P-type contact sub-layer, increase the number of holes in the P-type contact layer, increase the number of holes injected into an active layer and improve the luminescence efficiency of the light emitting diode. The increase of the amount of Mg doped in the second P-type contact sub-layer enables a good ohmic contact to be formed between the P-type contact layer and a P electrode, increases current expansion and reduces the working voltage of the light emitting diode. The growth temperature of a first P-type contact sub-layer is higher than that of the second P-type contact sub-layer, which can ensure the quality of the second P-type contact sub-layer. The growth temperature of a third P-type contact sub-layer is higher than that of the second P-type contact sub-layer, which can reduce the amount of carbon impurities doped in the third P-type contact sub-layer, reduce the overall light absorption of the P-type contact layer and improve the luminescence efficiency of the light emitting diode.

Owner:HC SEMITEK ZHEJIANG CO LTD

Chemical product concentration and crystallization device with detector

The invention relates to a chemical product concentration and crystallization device with a detector, which can detect the concentration and crystallization degree of chemical material in the chemical material concentration and crystallization process. The chemical product concentration and crystallization device comprises a crystallizing tank and a heater, wherein the top of the crystallizing tank is provided with an air outlet pipe; the bottom of the crystallizing tank is provided with a discharge pipe; the discharge pipe is provided with a valve and a plate glass sight glass which divides the discharge pipe into an upper discharge pipe and a lower discharge pipe; two ends of the plate glass sight glass are respectively connected with the upper discharge pipe and the lower discharge pipe; one side of the plate glass sight glass is provided with a light source of which the light ray exactly faces the plate glass sight glass; the other side of the plate glass sight glass is provided with a photomultiplier signal collector; the light source, the plate glass sight glass and the photomultiplier signal collector are arranged on the same straight line; and the photomultiplier signal collector is connected with a signal processor. The invention is suitable for chemical enterprises to carry out concentration and crystallization to chemical materials.

Owner:南通宏信化工有限公司