Patents

Literature

83 results about "Solid phase crystallization" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

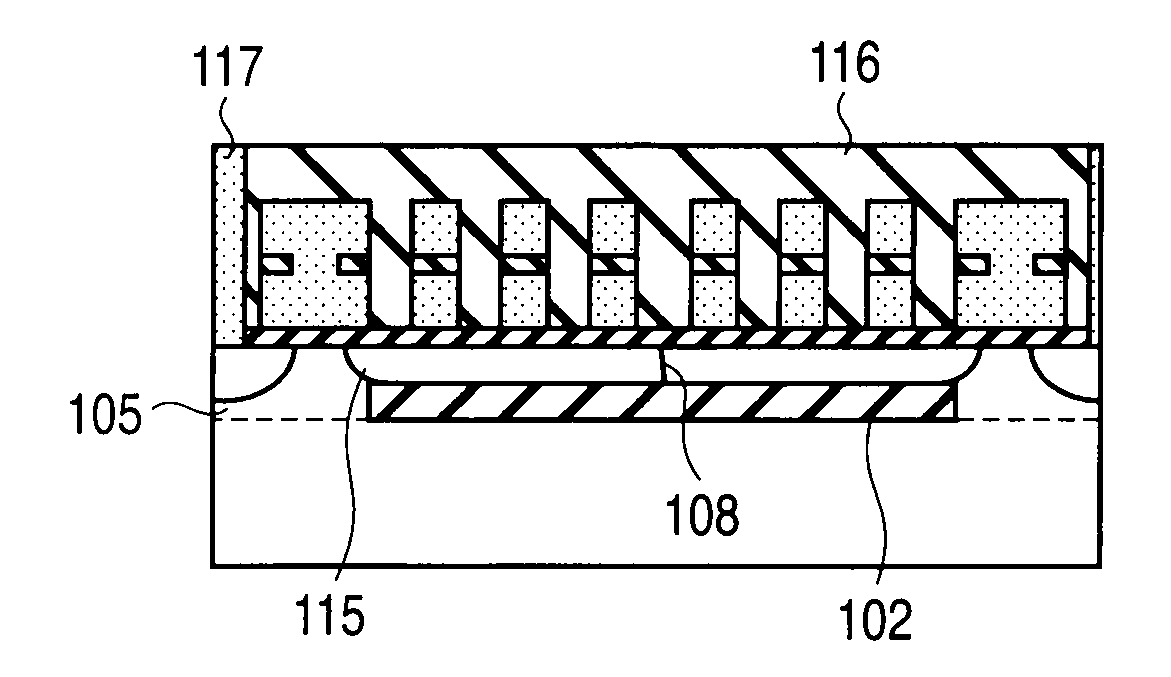

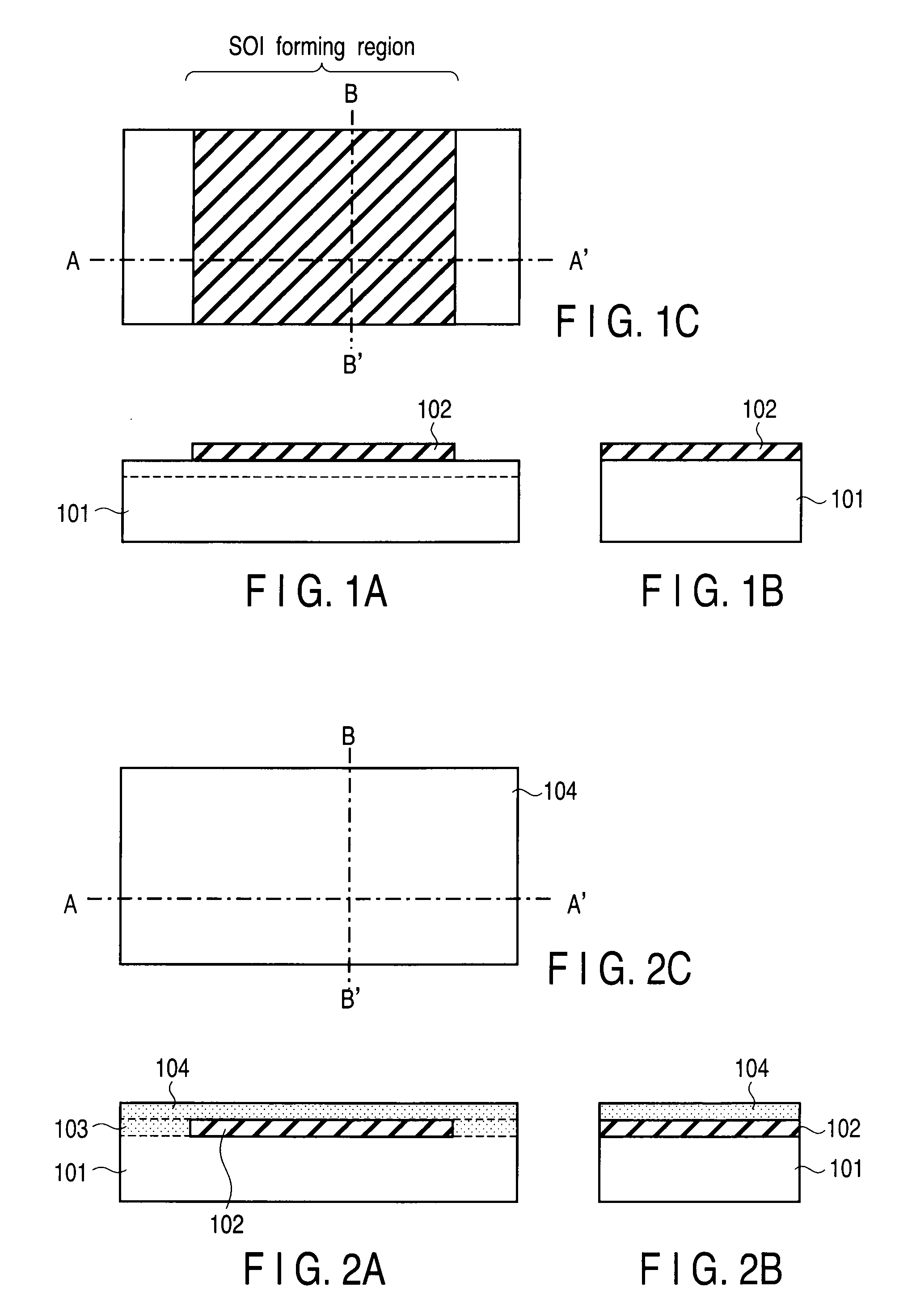

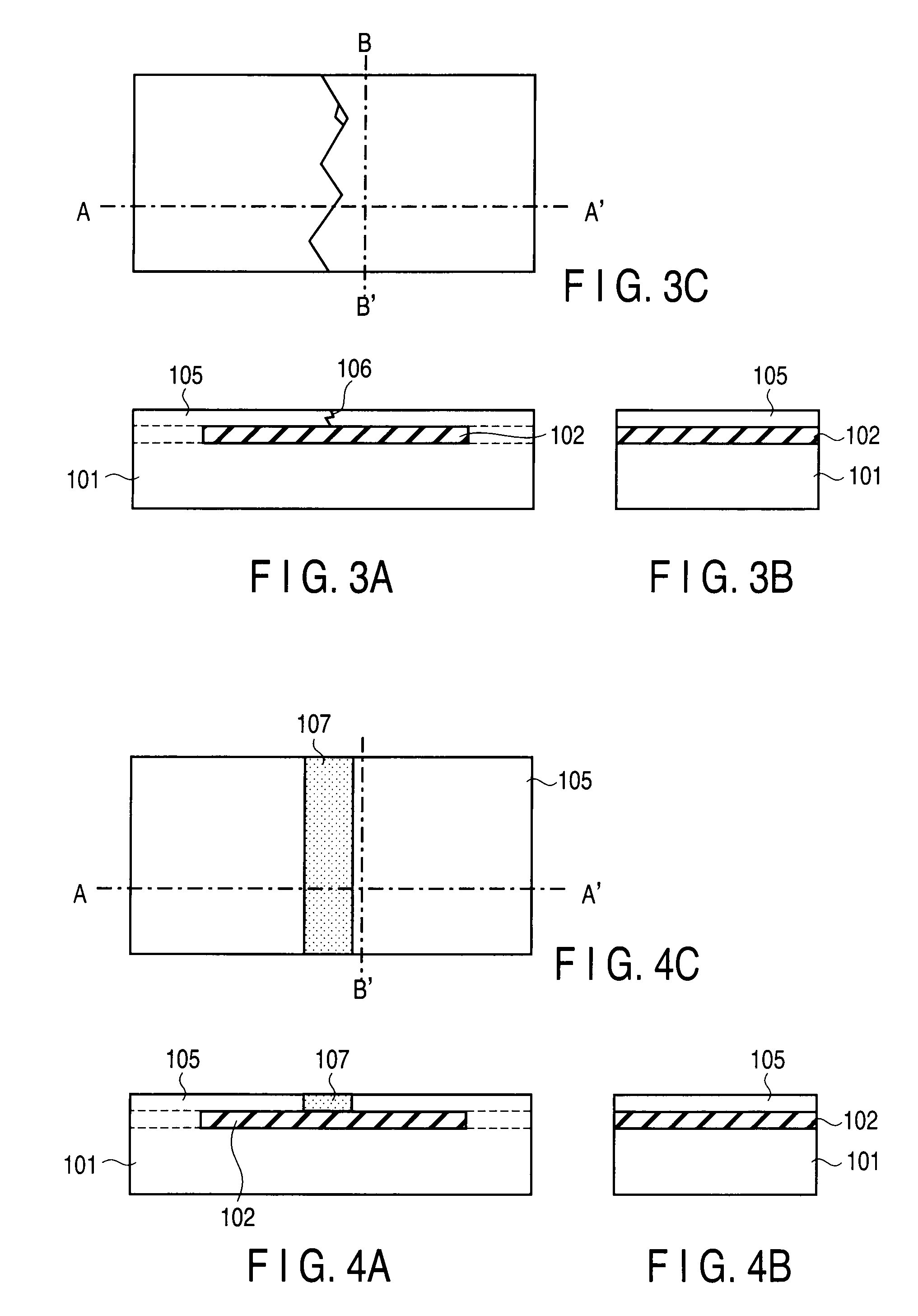

Method of manufacturing semiconductor storage device

ActiveUS20090004833A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor storage devicesSingle crystal

A method of manufacturing a semiconductor storage device includes providing an opening portion in a plurality of positions in an insulating film formed on a silicon substrate, and thereafter forming an amorphous silicon film on the insulating film, in which the opening portions are formed, and in the opening portions. Then, trenches are formed to divide the amorphous silicon film, in the vicinity of a midpoint between adjacent opening portions, into a portion on one opening portion side and a portion on the other opening portion side. Next, the amorphous silicon film, in which the trenches are formed, is annealed and subjected to solid-phase crystallization to form a single crystal with the opening portions used as seeds, and thereby a silicon single-crystal layer is formed. Then, a memory cell array is formed on the silicon single-crystal layer.

Owner:KIOXIA CORP

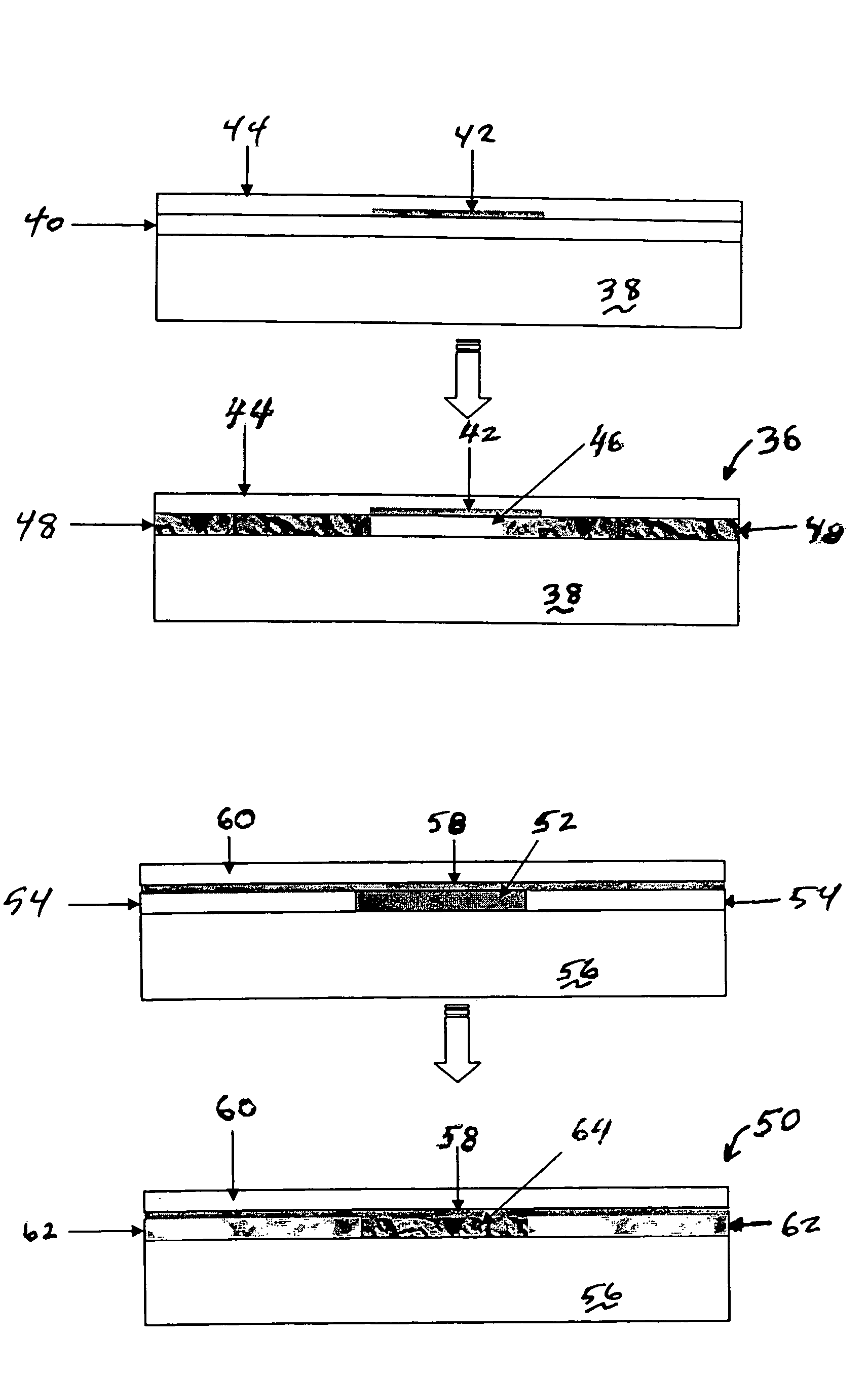

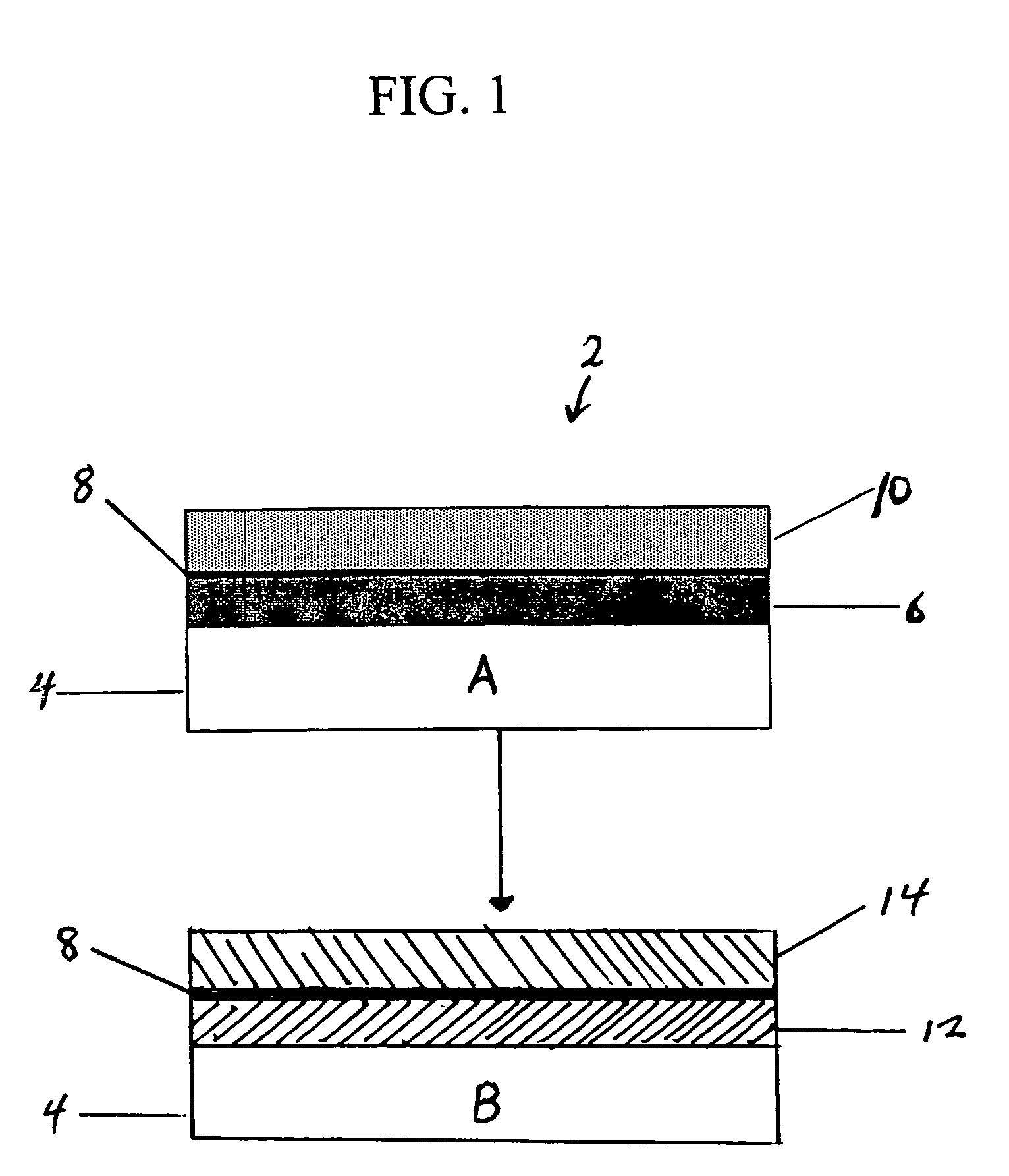

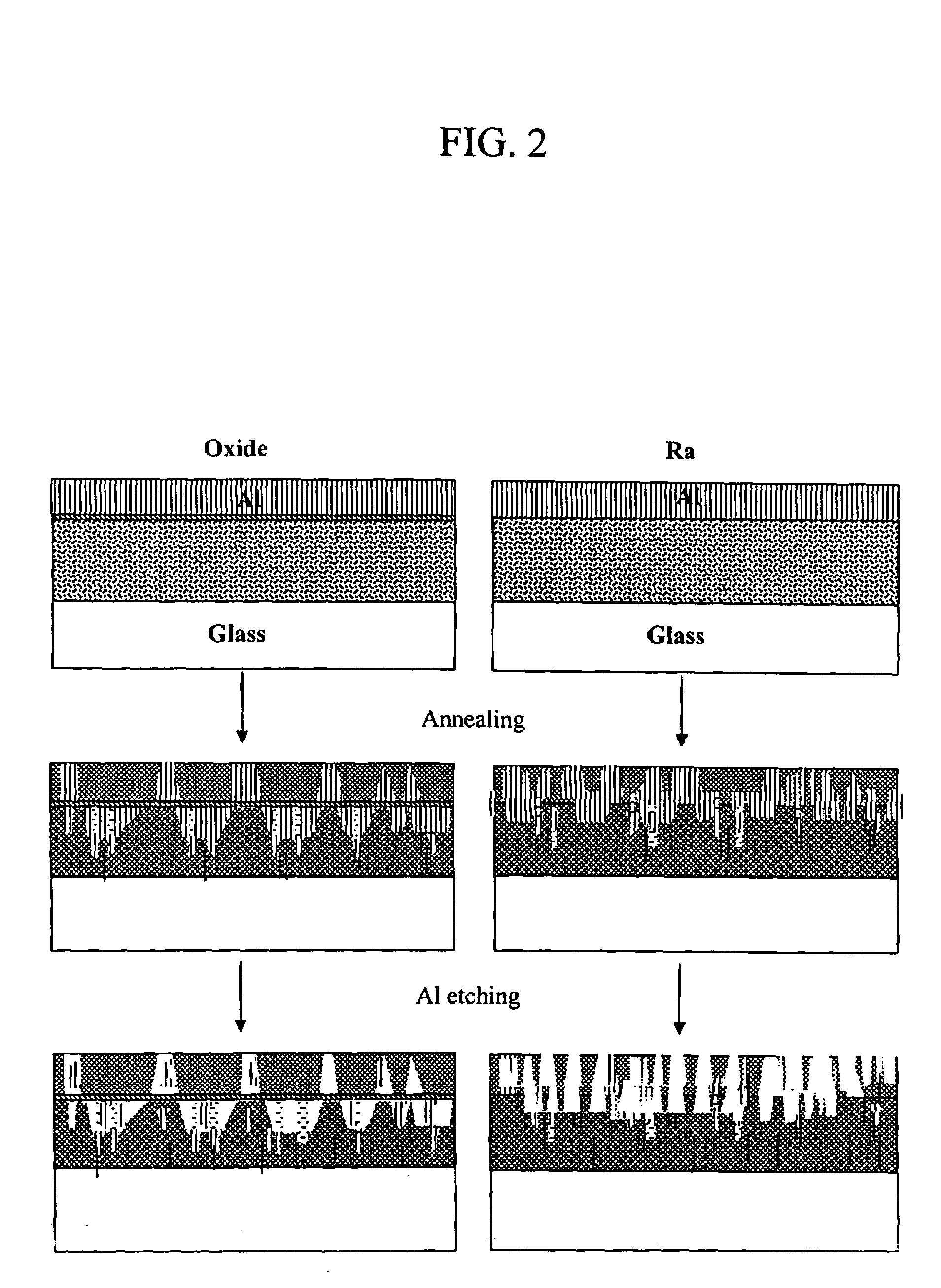

Low temperature production of large-grain polycrystalline semiconductors

InactiveUS7202143B1Final product manufactureSemiconductor/solid-state device manufacturingSolar cellSilicon dioxide

An oxide or nitride layer is provided on an amorphous semiconductor layer prior to performing metal-induced crystallization of the semiconductor layer. The oxide or nitride layer facilitates conversion of the amorphous material into large grain polycrystalline material. Hence, a native silicon dioxide layer provided on hydrogenated amorphous silicon (a-Si:H), followed by deposited Al permits induced crystallization at temperatures far below the solid phase crystallization temperature of a-Si. Solar cells and thin film transistors can be prepared using this method.

Owner:THE BOARD OF TRUSTEES OF THE UNIV OF ARKANSAS

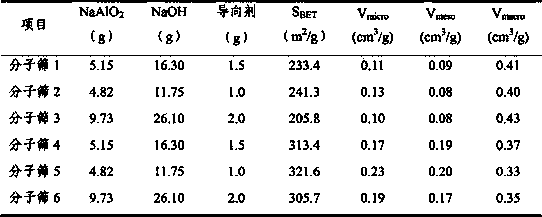

Preparation method for zeolite-immobilized photocatalyst

ActiveCN106362787ALow priceEasy to makeWater/sewage treatment by irradiationMolecular sieve catalystsNatural substanceSingle crystal

The invention relates to preparation technology of a photocatalyst and aims to provide a preparation method for a zeolite-immobilized photocatalyst. The preparation method comprises the following steps: dispersing a photocatalyst in deionized water, then adding a silicon source and carrying out a reaction under stirring; taking a reaction product out for washing and drying, subjecting the dried reaction product to mixing with a template and an aluminum source and then carrying out grinding; filling a reaction vessel with a mixture obtained in the previous step and carrying out solid-phase crystallization so as to produce a carrier with a zeolite structure; and washing and drying the carrier and then carrying out sintering in a muffle furnace to remove the template so as to obtain the zeolite-immobilized photocatalyst. According to the method, the usage amount of the template is low; due to improvement of the preparation method, the photocatalyst can be perfectly enveloped in a zeolite monocrystal, and the content of the photocatalyst is controllable; raw materials used in the method is low, and preparation process is simple; and in subsequent application, the utilization rate of the photocatalyst is high, the yield of the zeolite-immobilized photocatalyst is high, and the zeolite-immobilized photocatalyst has high organic pollutant degradation rate and exerts good protection effect on natural substances.

Owner:ZHEJIANG UNIV

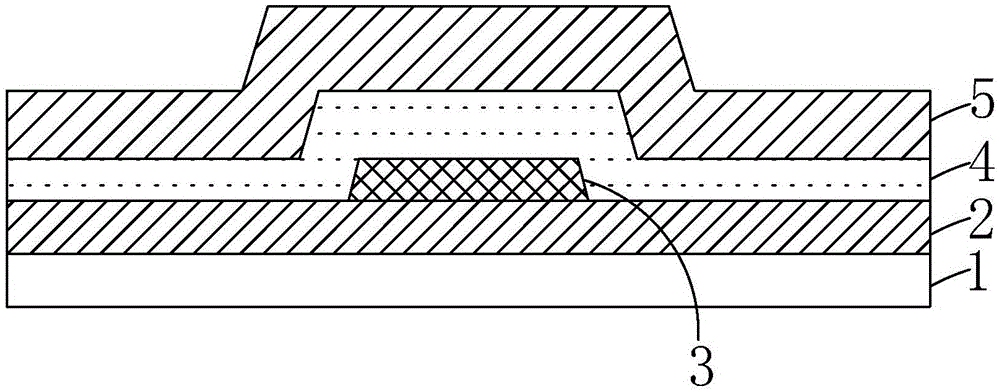

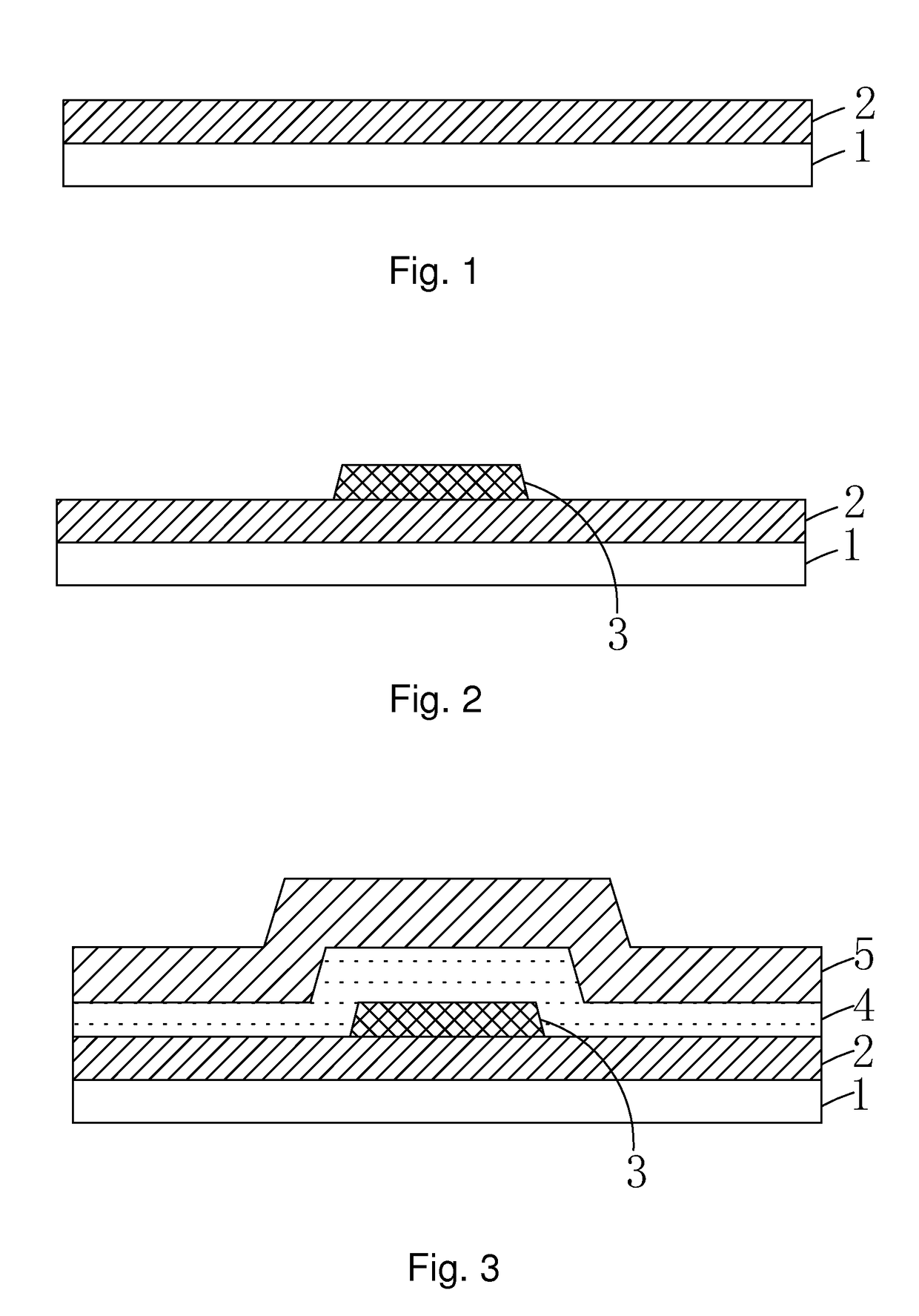

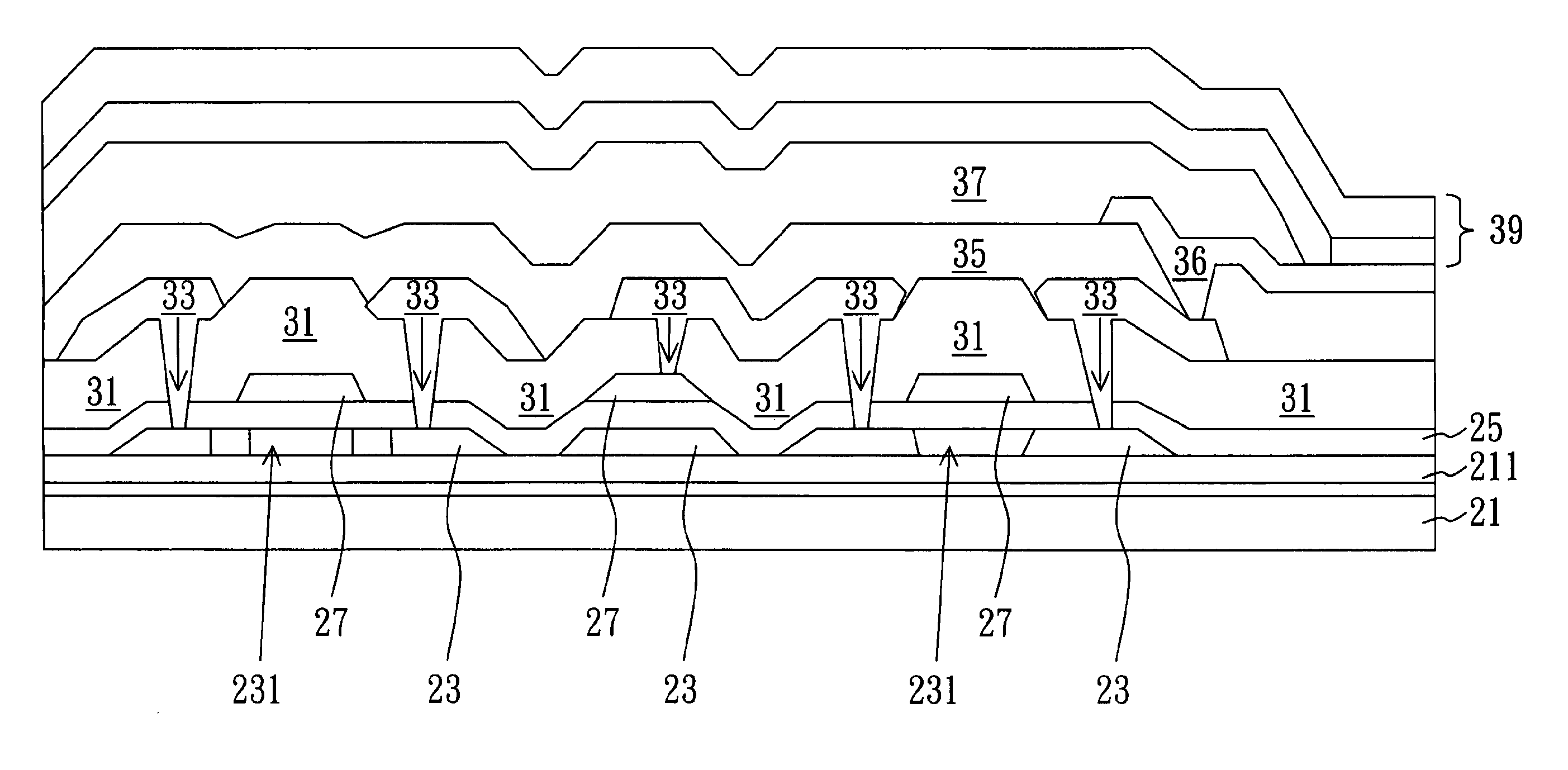

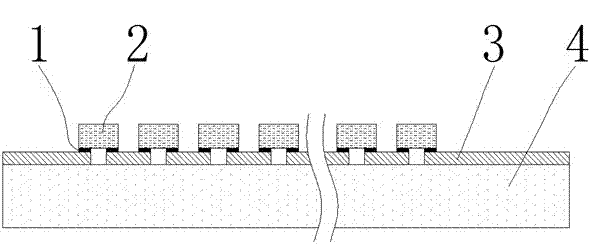

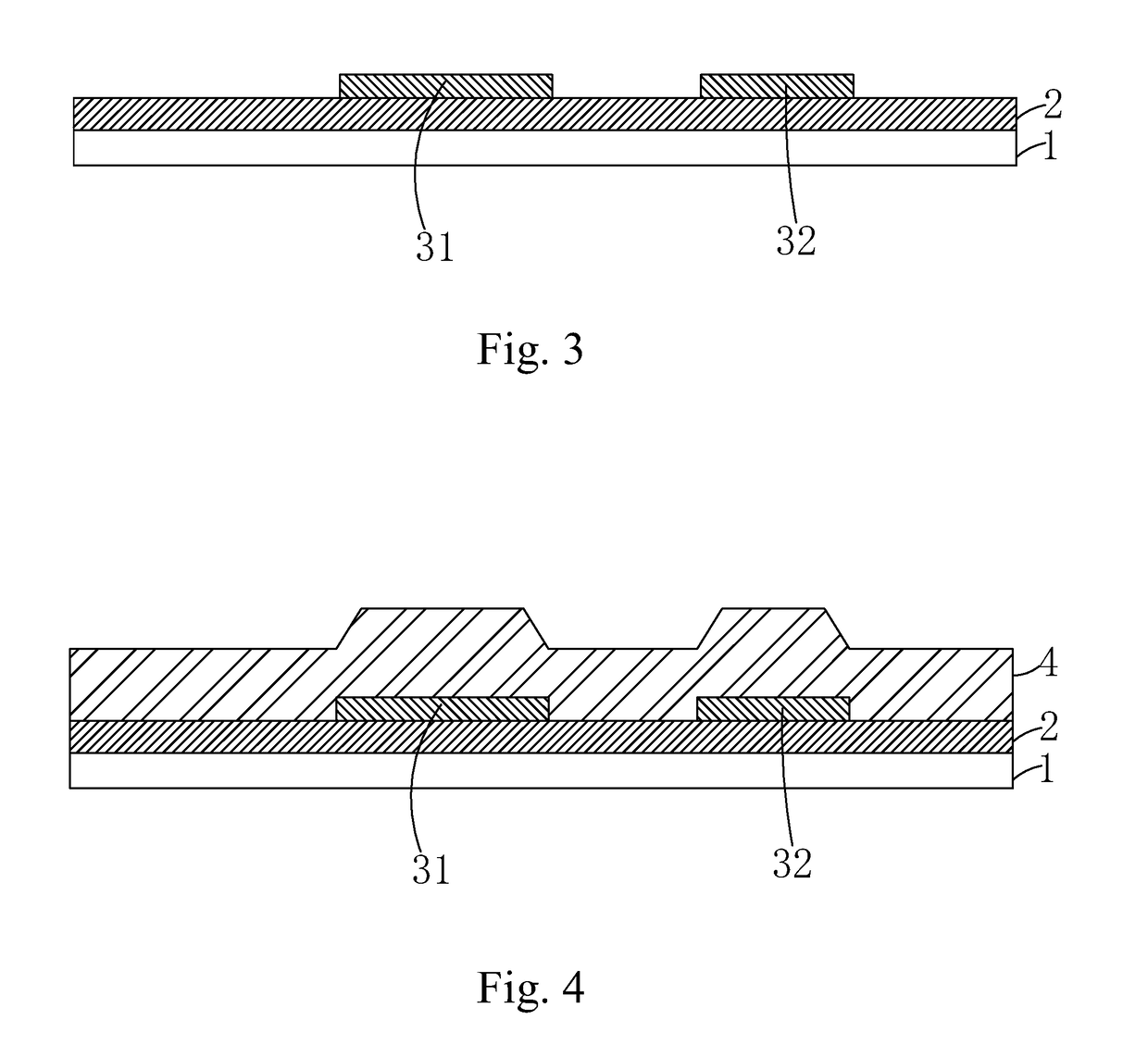

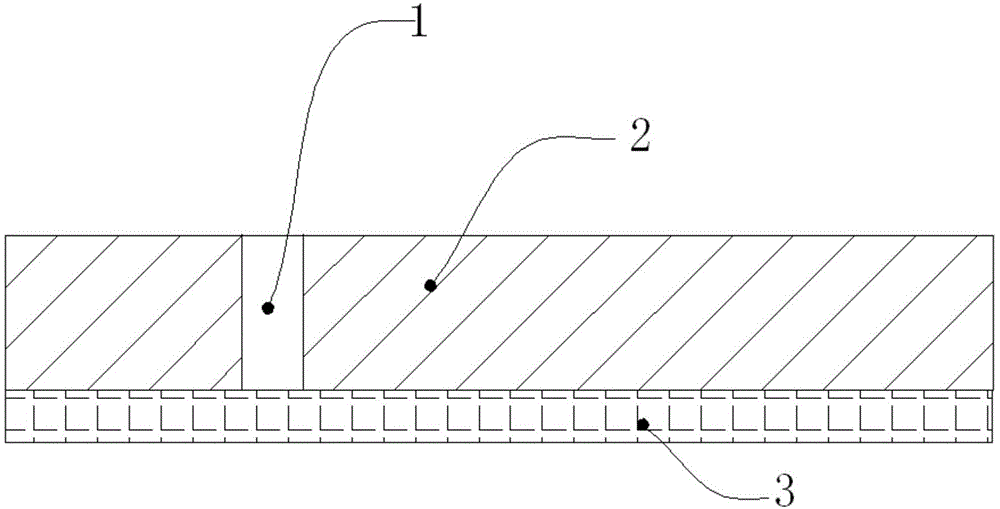

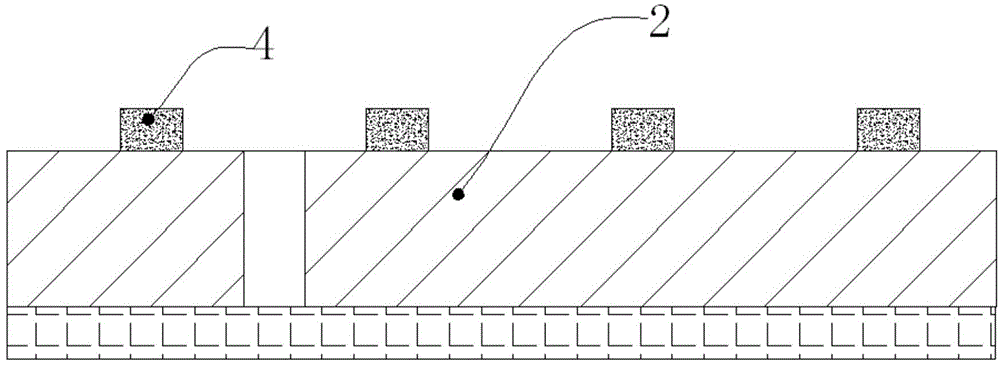

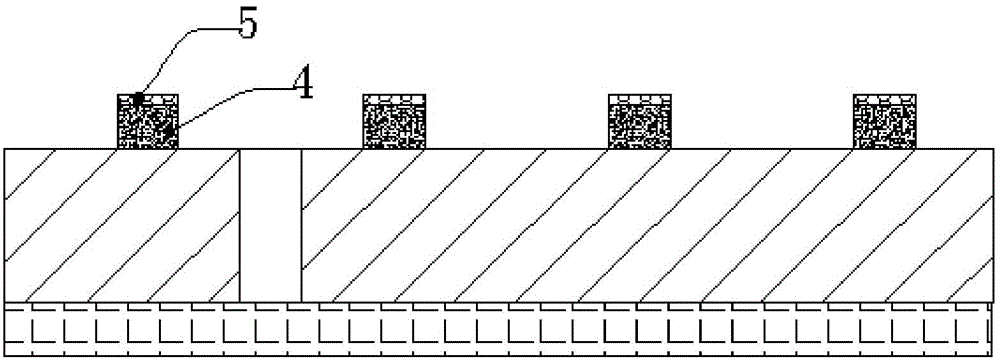

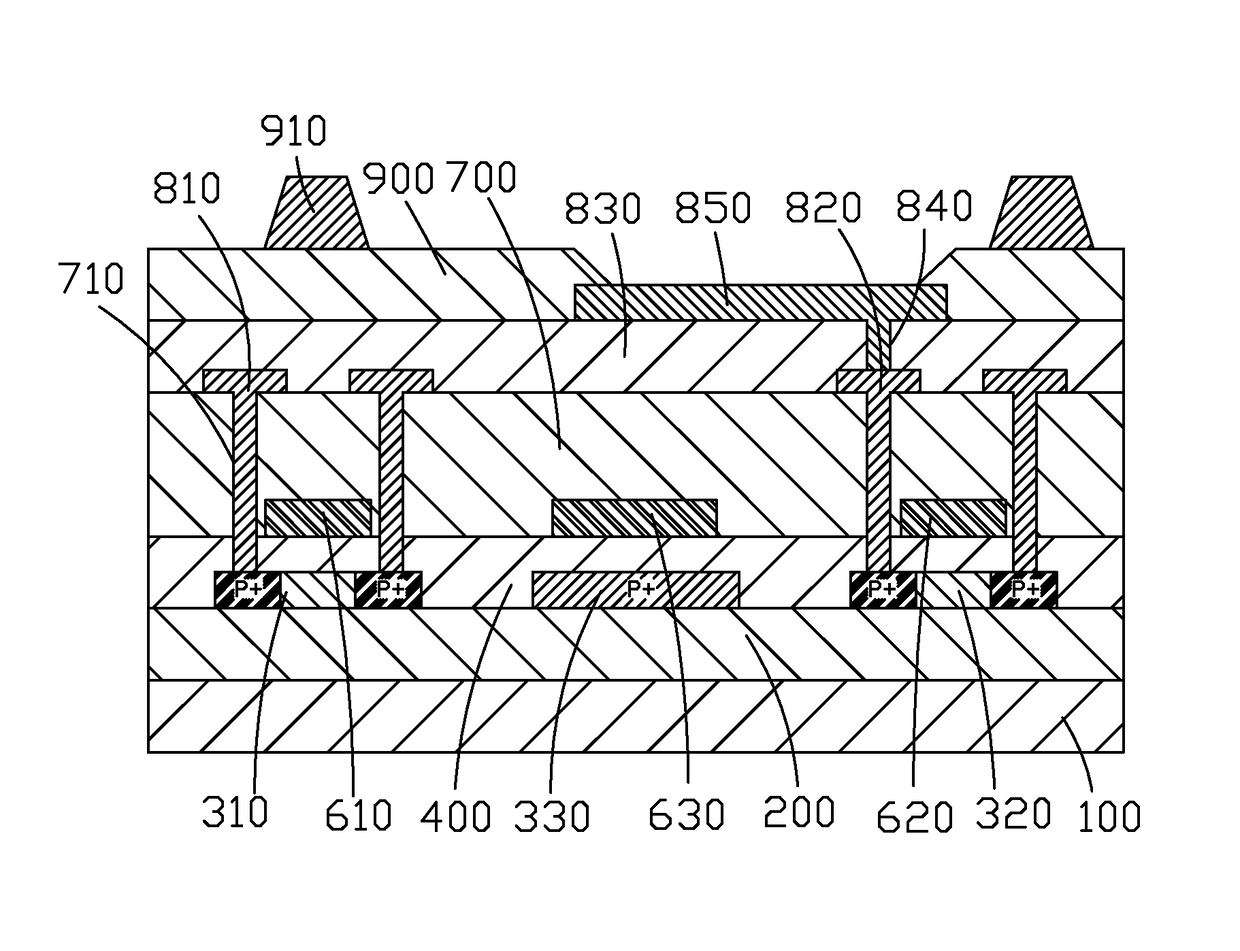

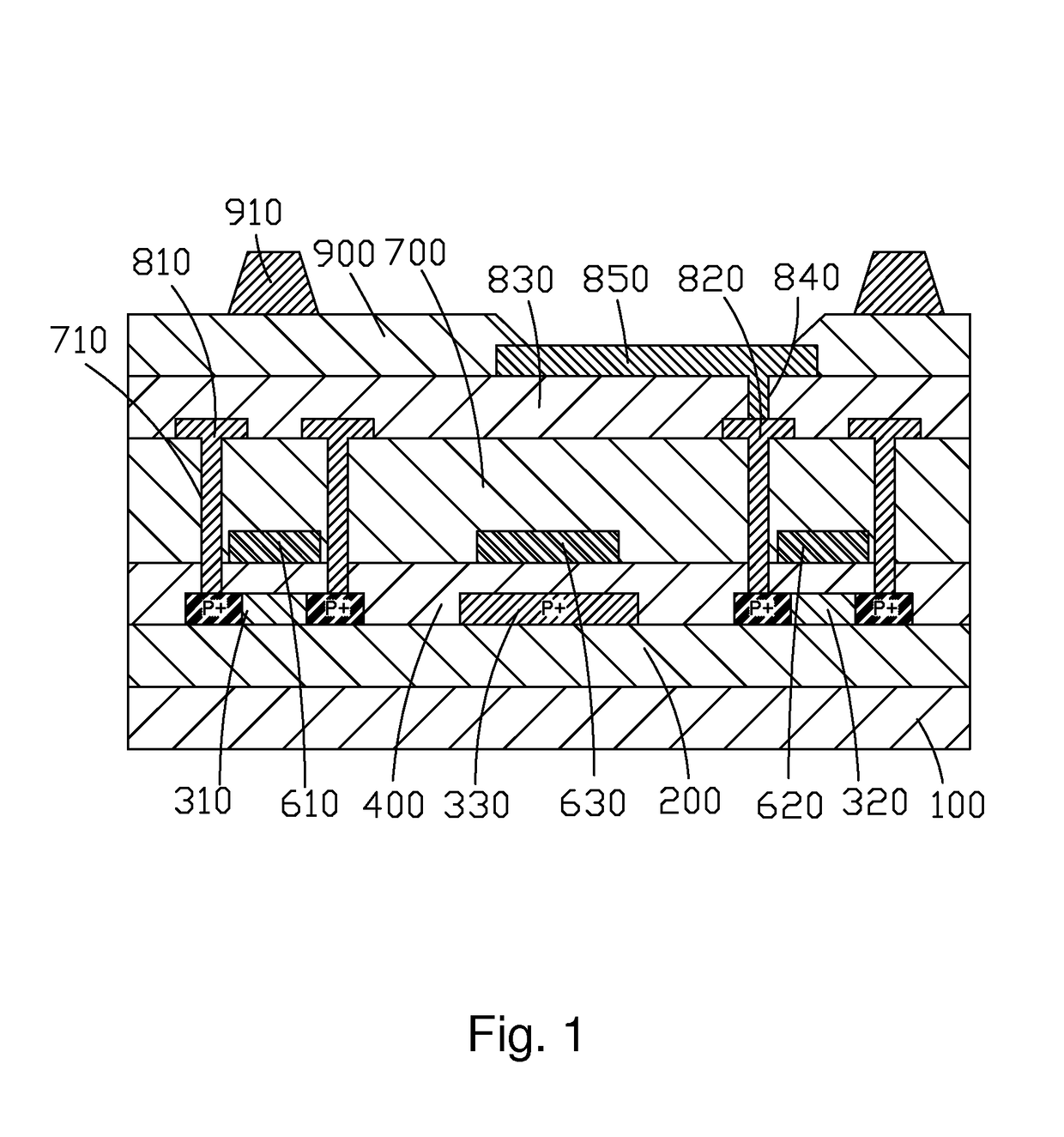

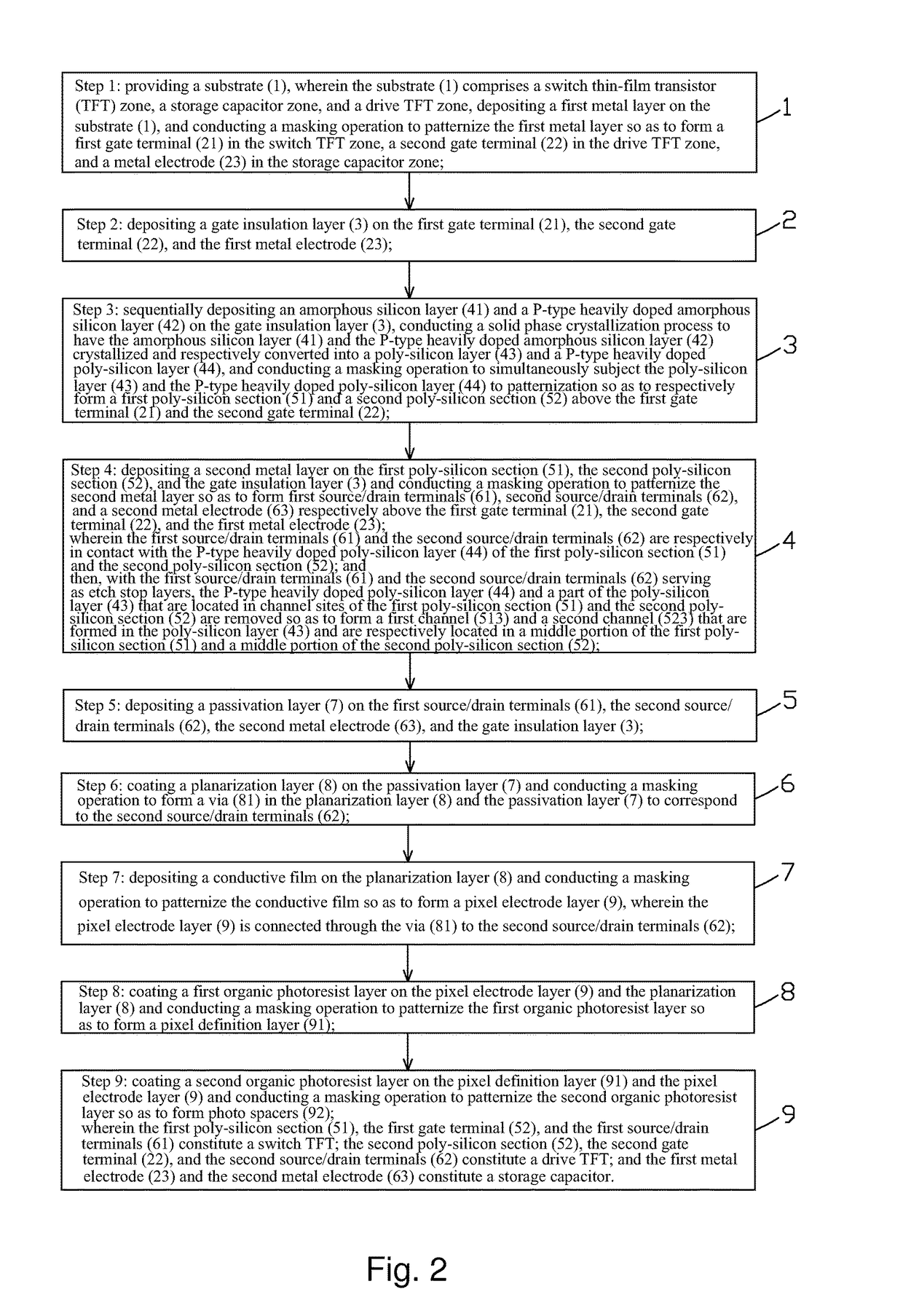

TFT substrate manufacturing method and TFT substrate

InactiveCN105070724ALow electricityImprove uniformityTransistorSolid-state devicesMaterials sciencePhotochemistry

The invention provides a TFT substrate manufacturing method and a TFT substrate. The method employs the SPC (Solid Phase Crystallization) technology to prepare an LTPS (Low Temperature Poly-Silicon) layer, and can reduce costs and form crystalline grains with better uniformity compared with the excimer laser crystallization technology; meanwhile, a bigrid structure is introduced, thereby enhancing the control of grids to channels, increasing the on state current of a film transistor, reducing off state current, inhibiting warping effects, reducing a threshold voltage and a subthreshold gradient, and improving the driving capability of the film transistor; besides, top grids can cover light, and reduce channel photoinduced electric leakage. The invention provides the TFT substrate, the LTPS layer of which is prepared through the SPC technology, and the TFT is low in production costs; in addition, the TFT substrate is provided with the bigrid structure, allowing the film transistor to have better electric property and strong driving capability, and not easy to generate channel photoinduced electric leakage.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

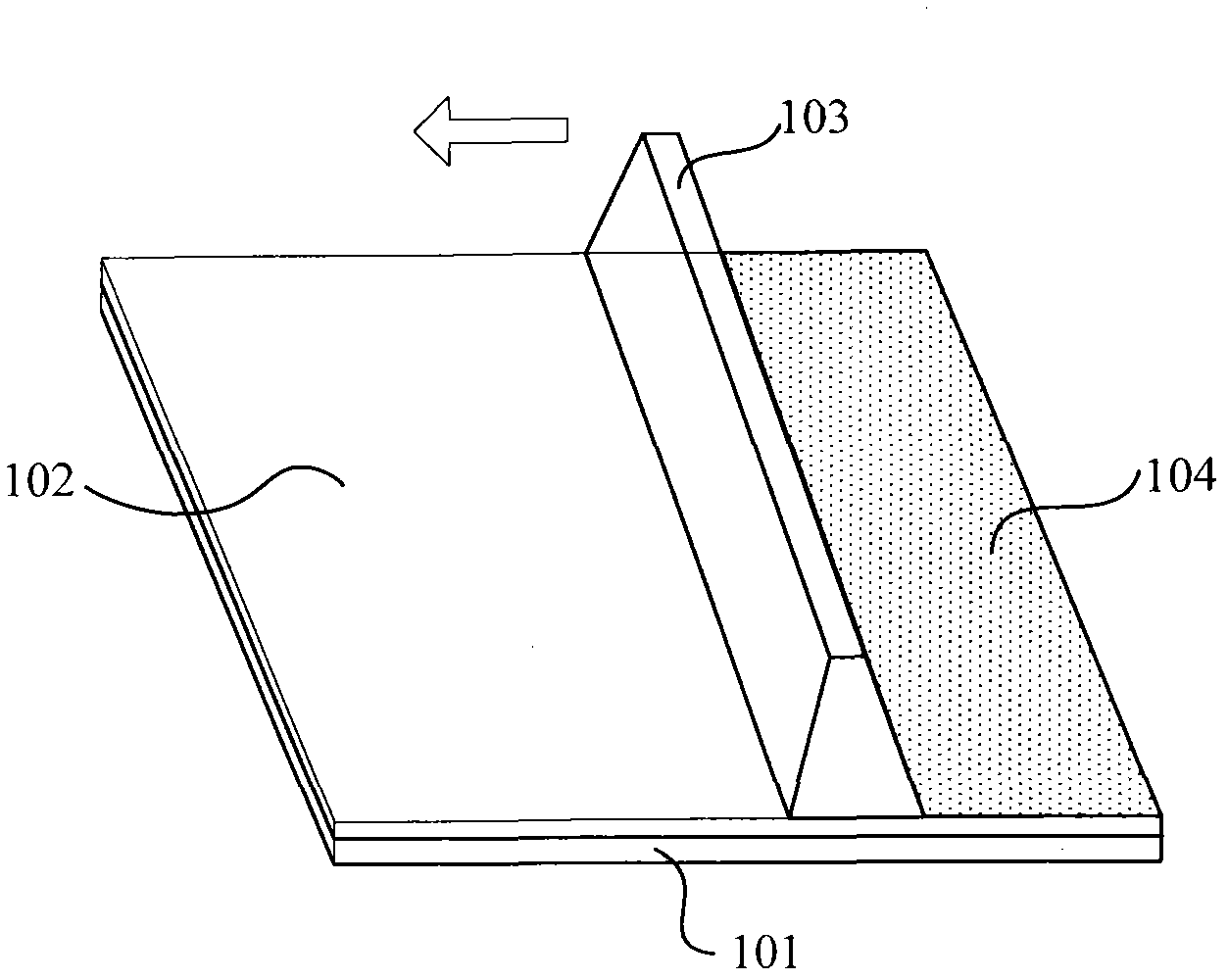

Manufacturing method of active matrix organic light-emitting display array base plate

ActiveCN102034746AReduce consumptionIncrease production capacitySolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSolid phase crystallization

The invention relates to a manufacturing method of an active matrix organic light-emitting display array base plate, in particular to a manufacturing method of a low-temperature polysilicon thin film transistor array base plate. In the technical scheme provided by the invention, solid-phased crystallization is carried out on a noncrystalline silicon layer, and then a switch region is irradiated by a dot matrix laser source so that the carrier mobility for switching on or off a thin film transistor is improved, different requirements of an active matrix organic light-emitting display on the characteristics of driving and switching on or off the thin film transistor are met, meanwhile, the consumption on laser sources is reduced, the production capacity is improved and the method is free from the limit of the size of the array base plate.

Owner:KUNSHAN NEW FLAT PANEL DISPLAY TECH CENT

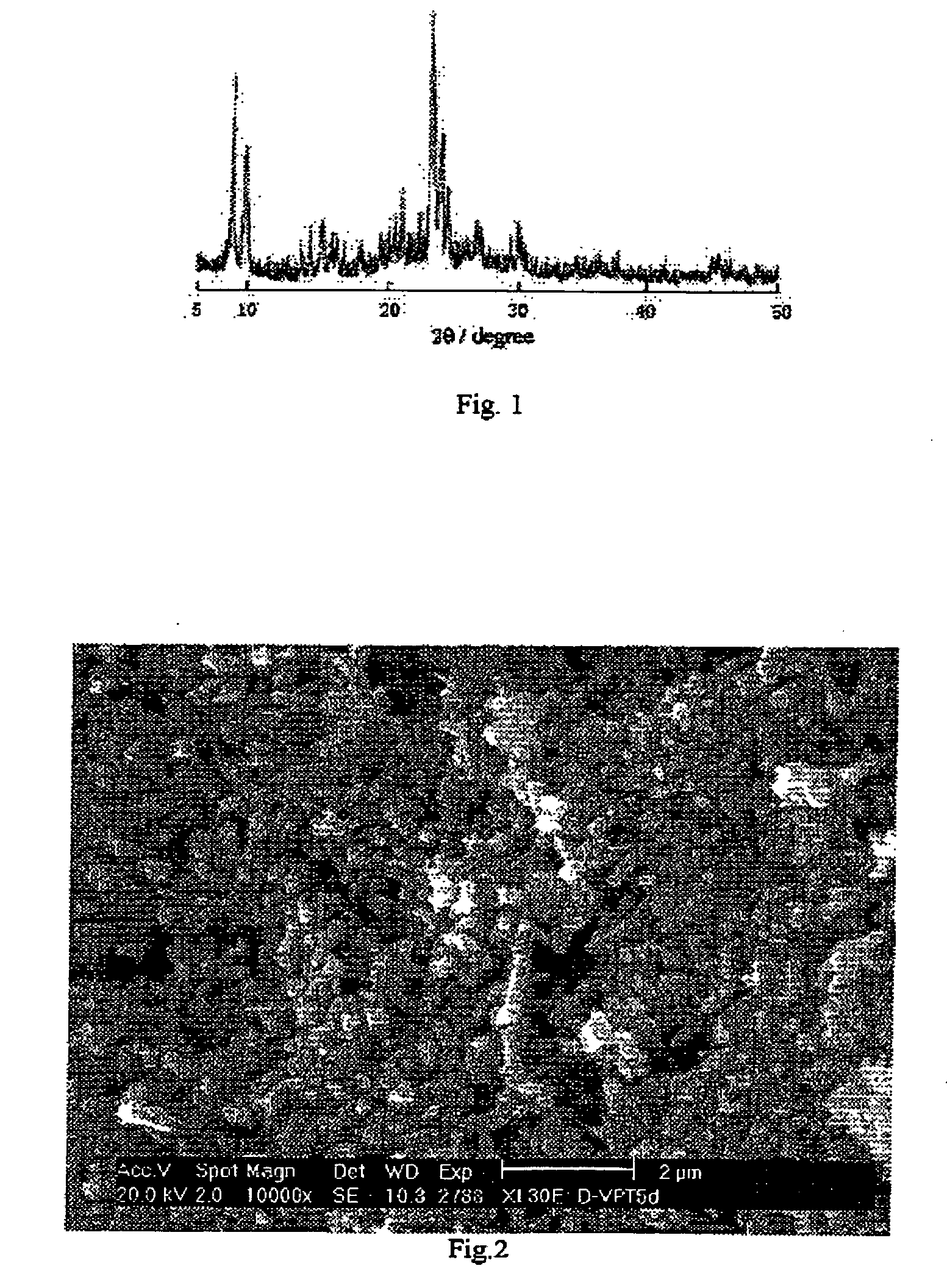

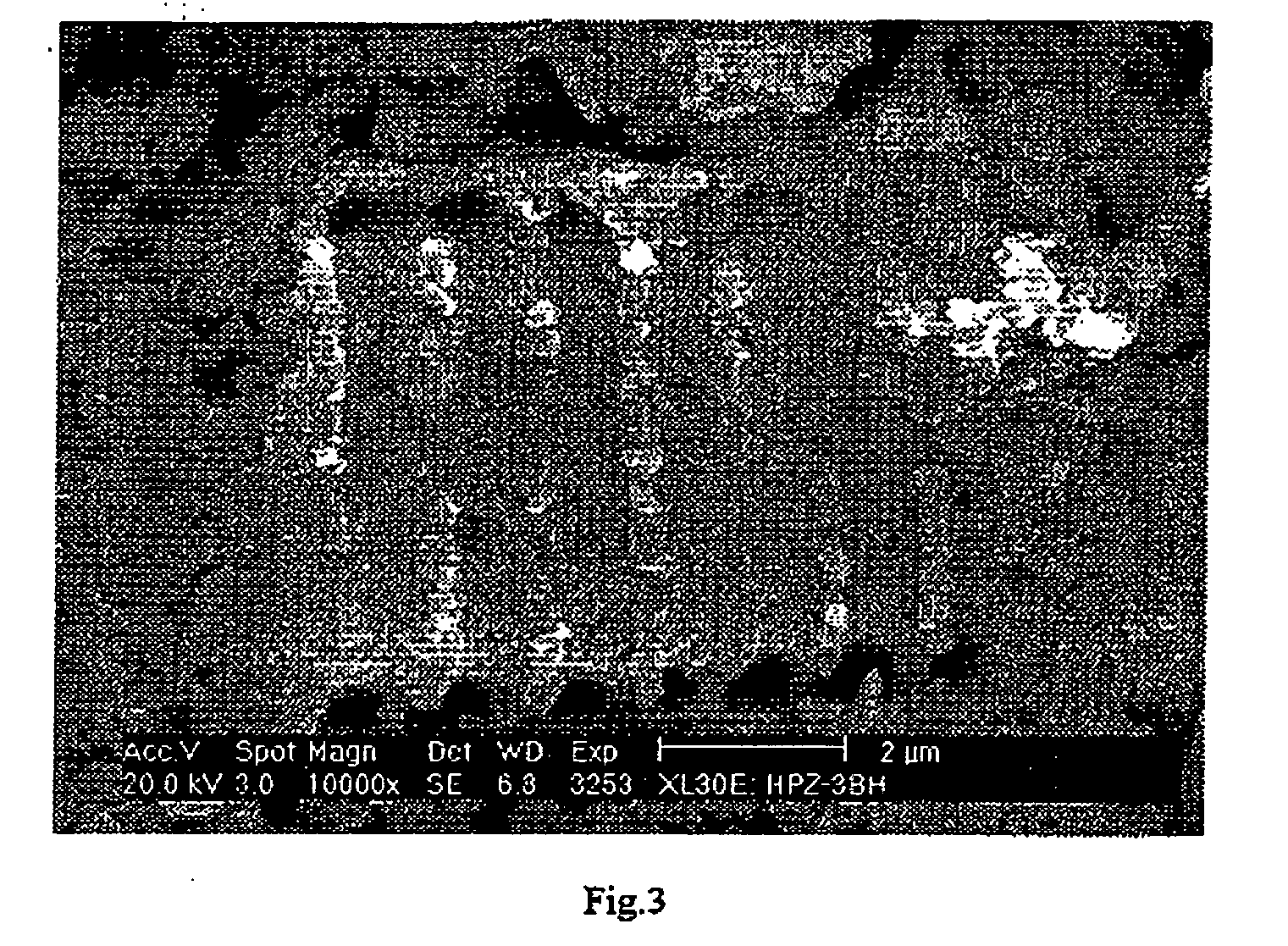

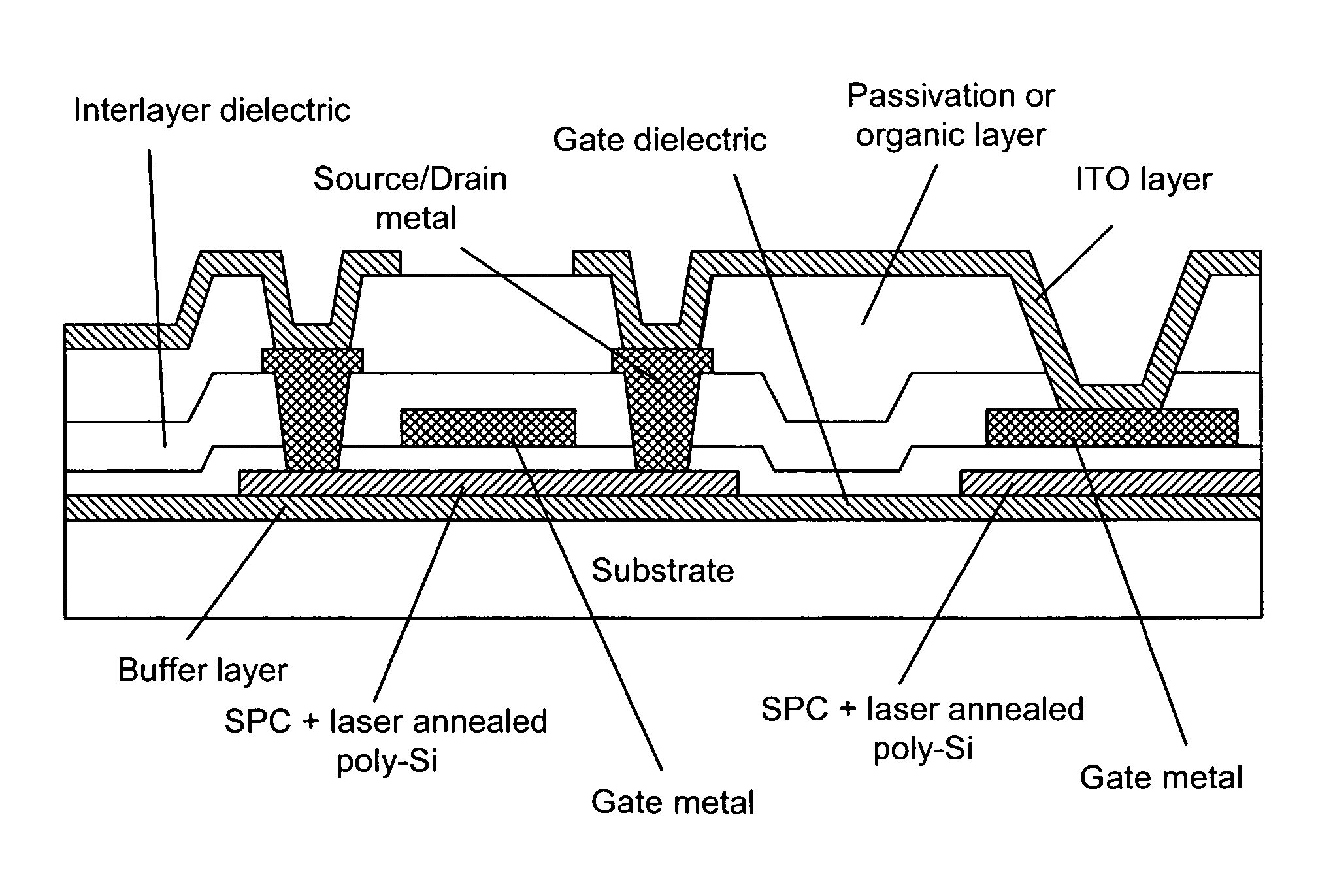

Process for producing binder-free ZSM-5 zeolite in small crystal size

ActiveUS7601330B2Readily availableLarge crystal sizeAluminium compoundsMolecular sieve catalystsEffective surfaceWater vapor

The present invention relates to a process for producing a binder-free ZSM-5 zeolite in small crystal size. The invention is primarily used for solving the problems in the practical application, e.g., the zeolite powder is difficult to be recovered and easily inactivates and aggregates, and the addition of the binder in the shaping process will result in the reduction of effective surface areas and introduce the diffusional limitation. Said problems are better solved in the present invention by using diatomite or silica aerogel as the main starting material, adding a seed crystal orienting agent, a silica sol and sodium silicate for kneading and shaping, and then converting to integrative ZSM-5 in small crystal size by vapor-solid phase crystallization with organic amine and water vapor. Said process can be used in the industrial preparation of ZSM-5 molecular sieve catalyst in small crystal size.

Owner:CHINA PETROCHEMICAL CORP +1

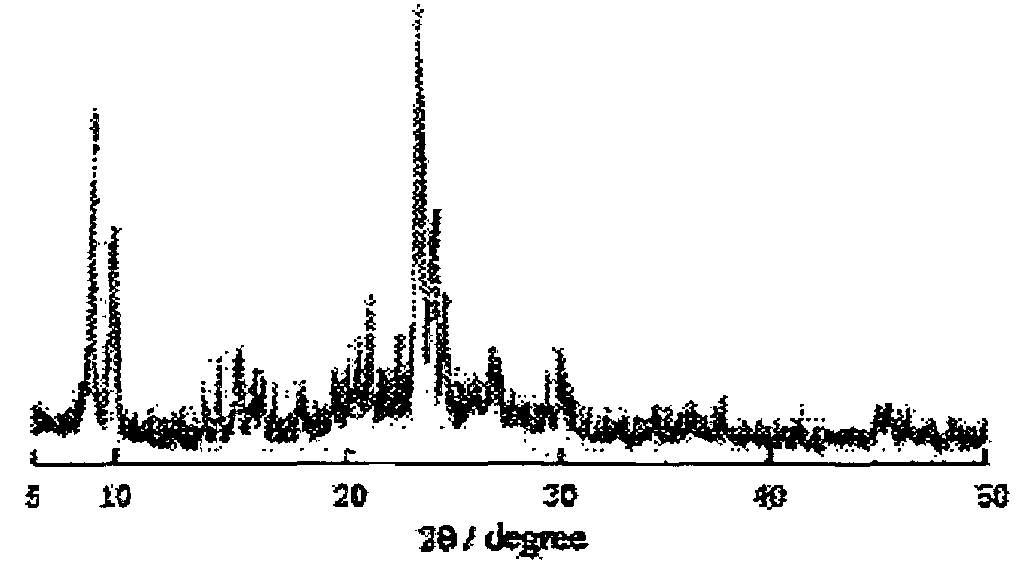

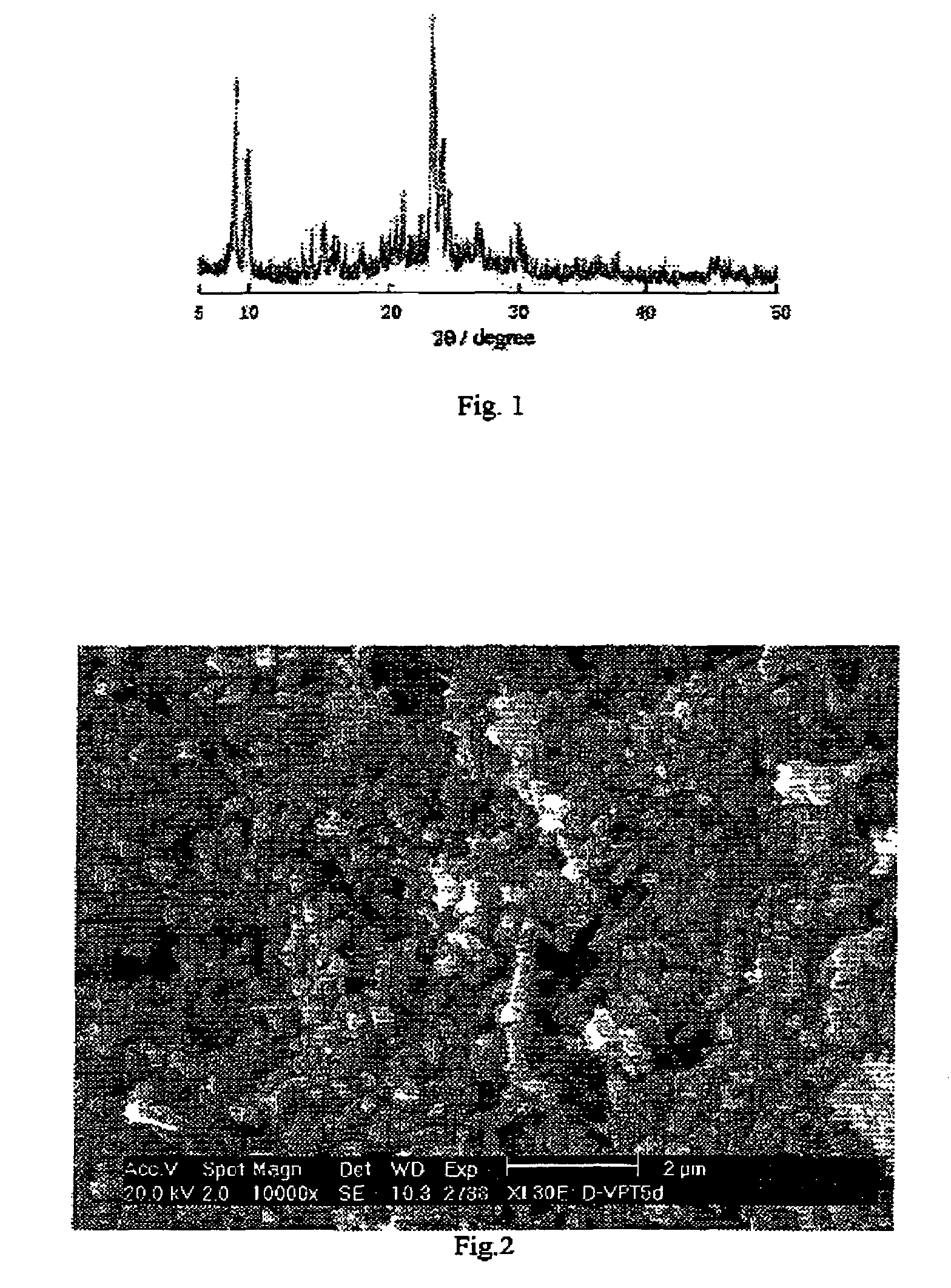

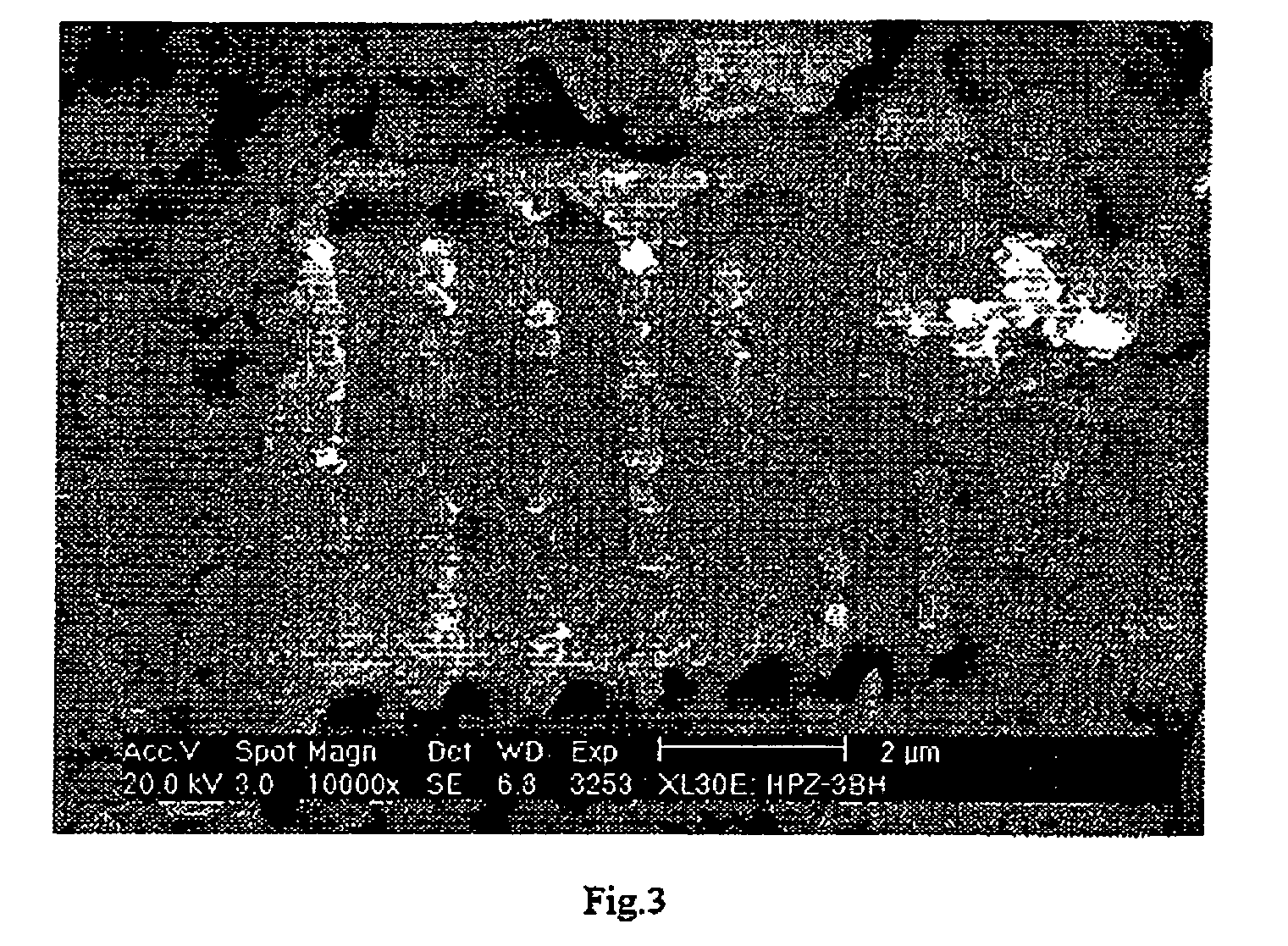

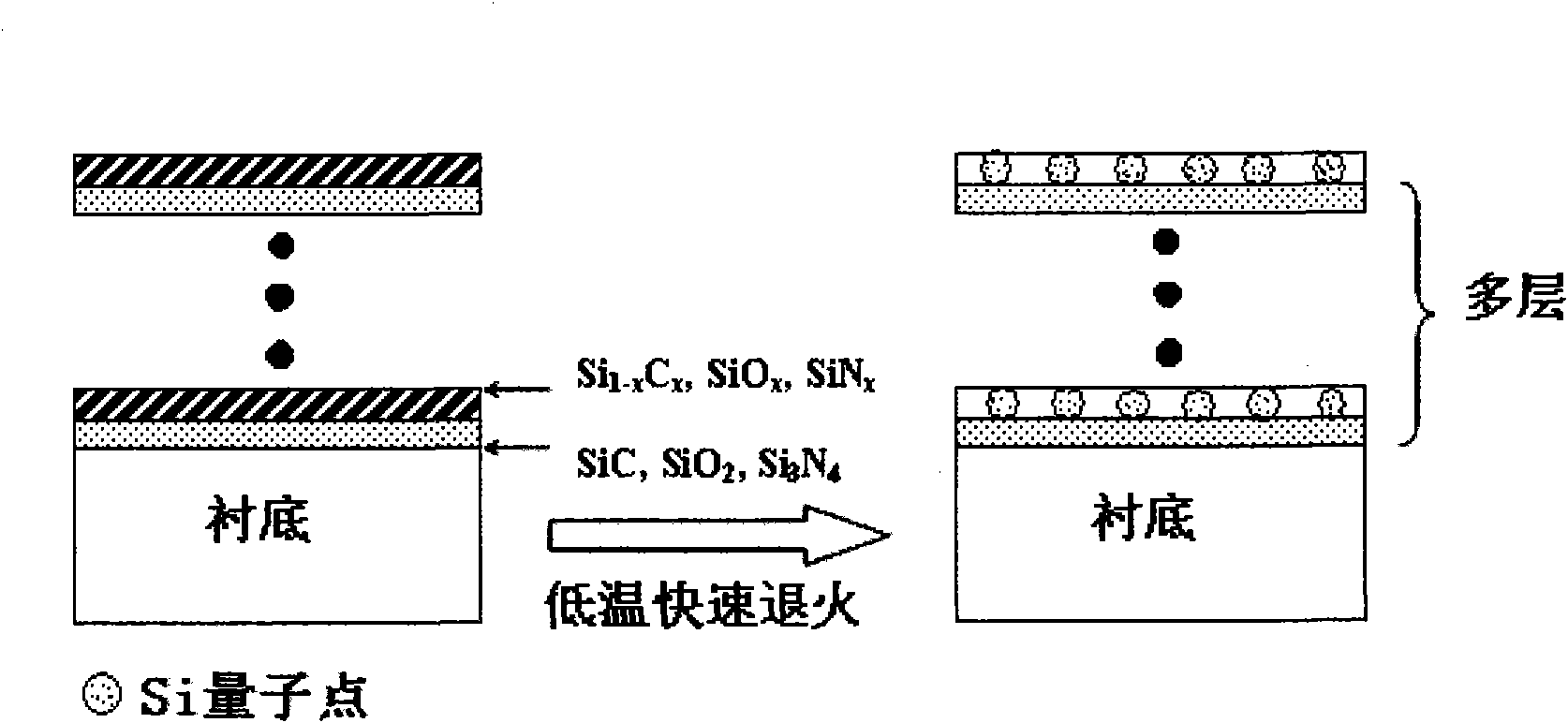

Low-temperature growth method of silicon quantum dots for solar battery

InactiveCN101626048AIncrease flexibilityImprove uniformityFinal product manufactureSemiconductor devicesGas phaseSolar battery

The invention relates to a low-temperature growth method of silicon quantum dots for a solar battery, which belongs to the technical field of silicon quantum dot material. The method comprises the following steps: alternately growing a silicon compound dielectric layer of the stoichiometric proportion and a silicon compound layer containing Si which is several nanometers thick in stoichiometric ratio on a silicon wafer or a quartz sheet or a glass sheet or a stainless steel sheet or high-temperature resistant polymer substrate material at the temperature lower than 450 DEG C by using the plasma chemical vapour deposition (PCVD) technology; carrying out post annealing treatment at the temperature lower than or equal to 550 DEG C by using the rapid photo-thermal annealing technology, so that the residual Si in the silicon compound layer containing Si generates diffusion transfer and solid phase crystallization to form the Si quantum dots, wherein the formed Si quantum dots are arranged in a layered mode, the size of each Si quantum dot is controlled by the thickness of the originally-grown silicon compound layer containing Si, and the density of each Si quantum dot is determined by the content of Si in the original SiN<x> layer containing Si. The invention has the advantages of low depositing temperature, quick speed and good technology controllability and repeatability, thus the uniformity of the grown silicon quantum dot material is good; and the invention is favorable for integrated manufacture and cost reduction of devices.

Owner:YUNNAN NORMAL UNIV

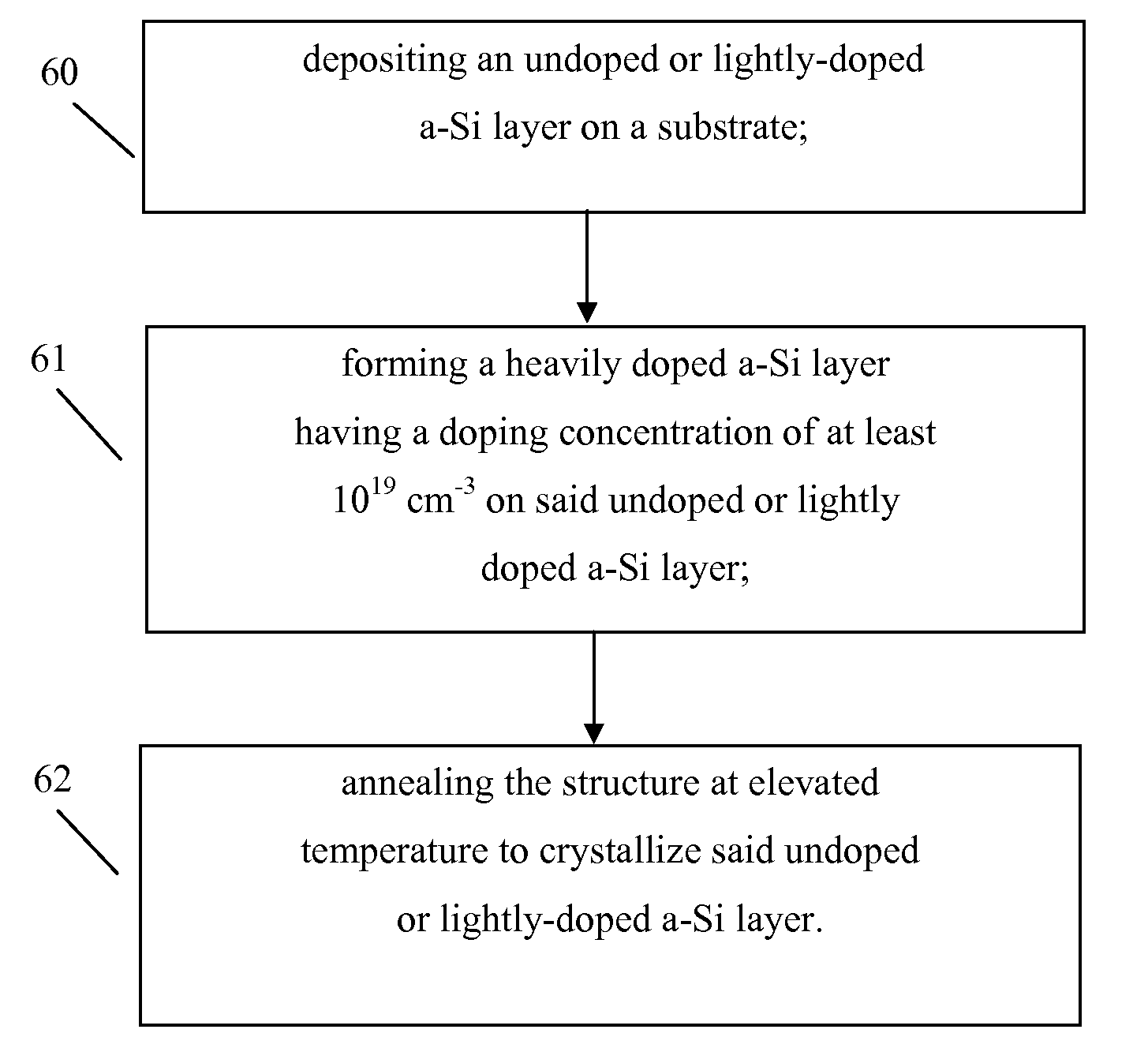

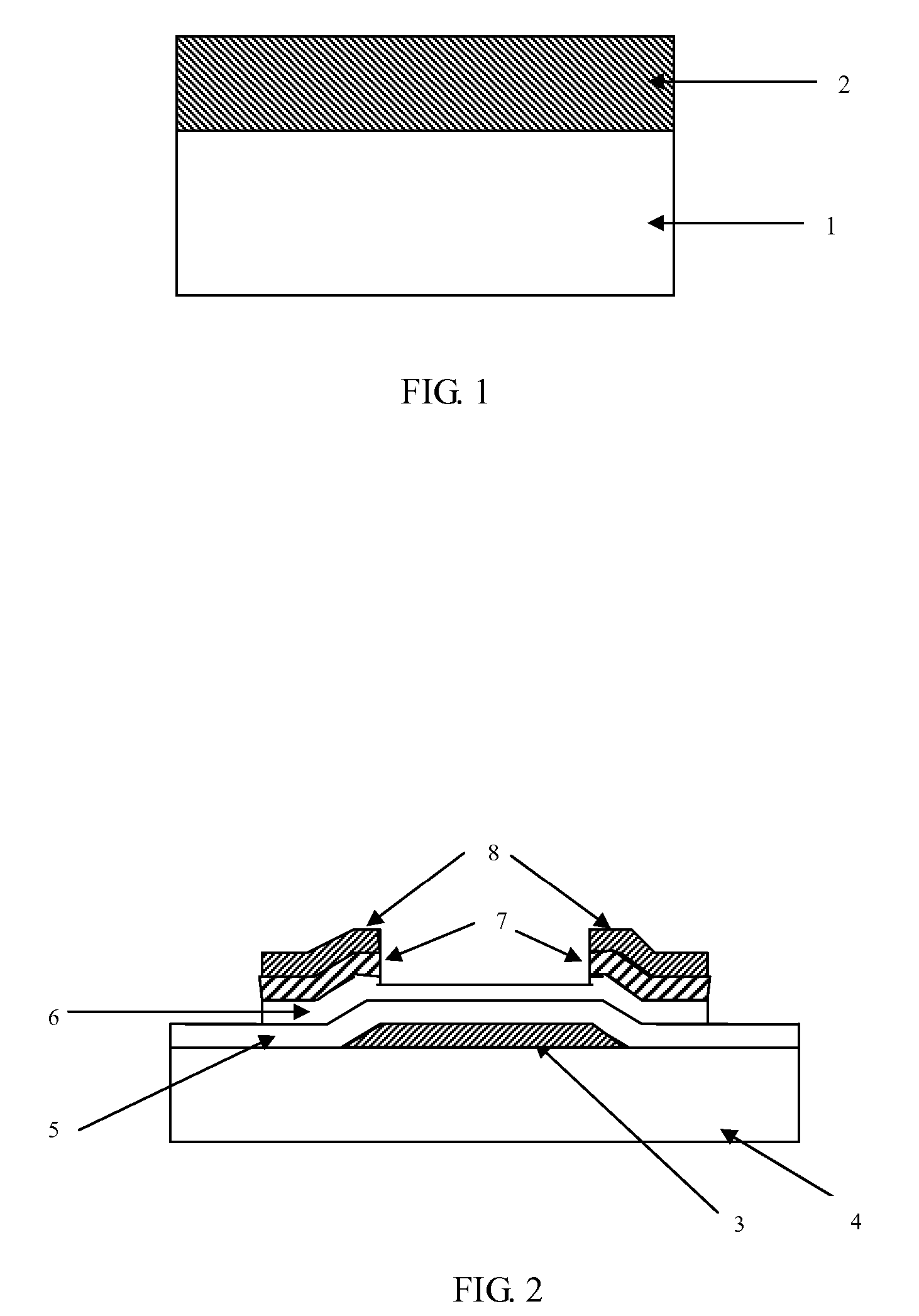

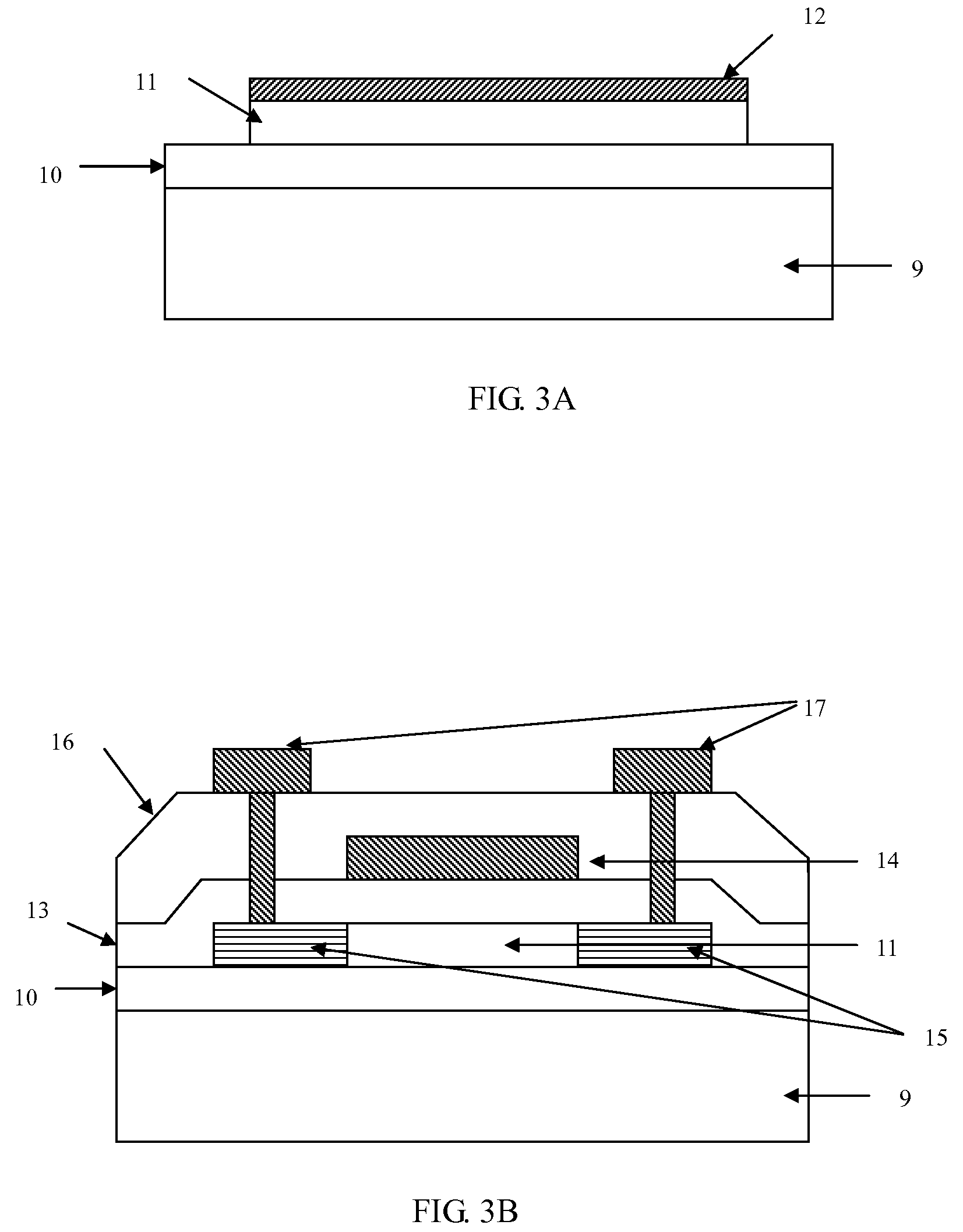

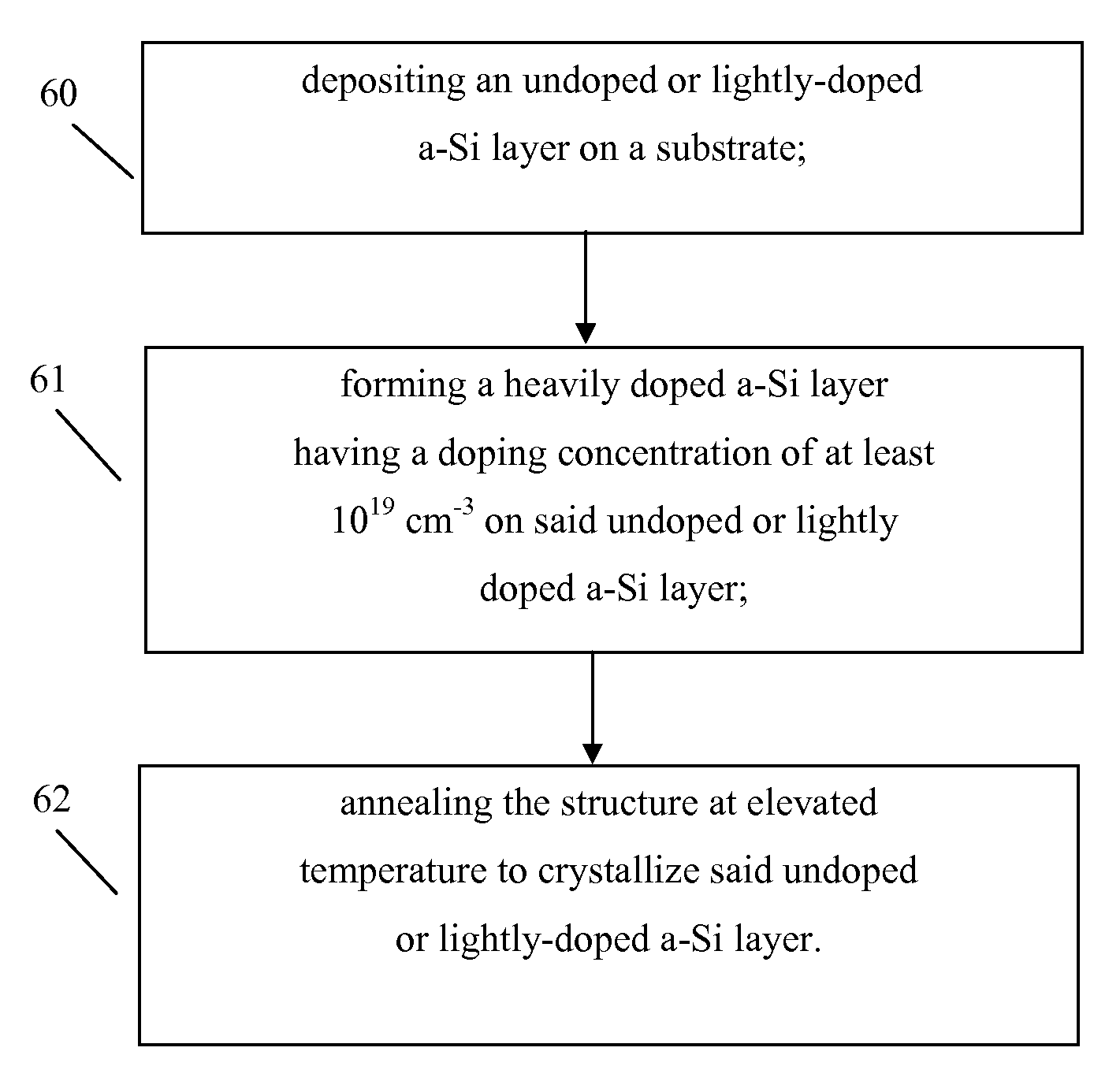

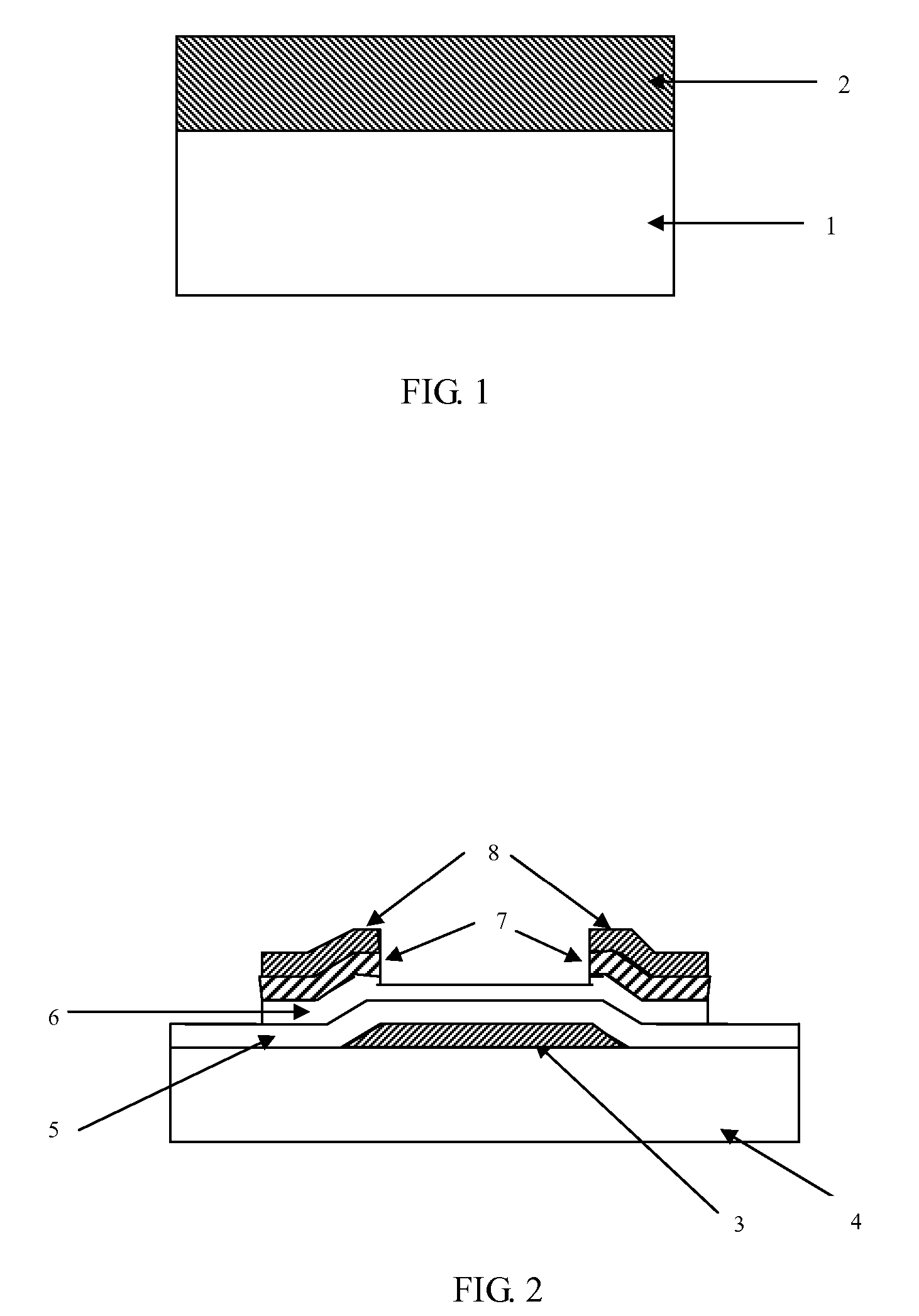

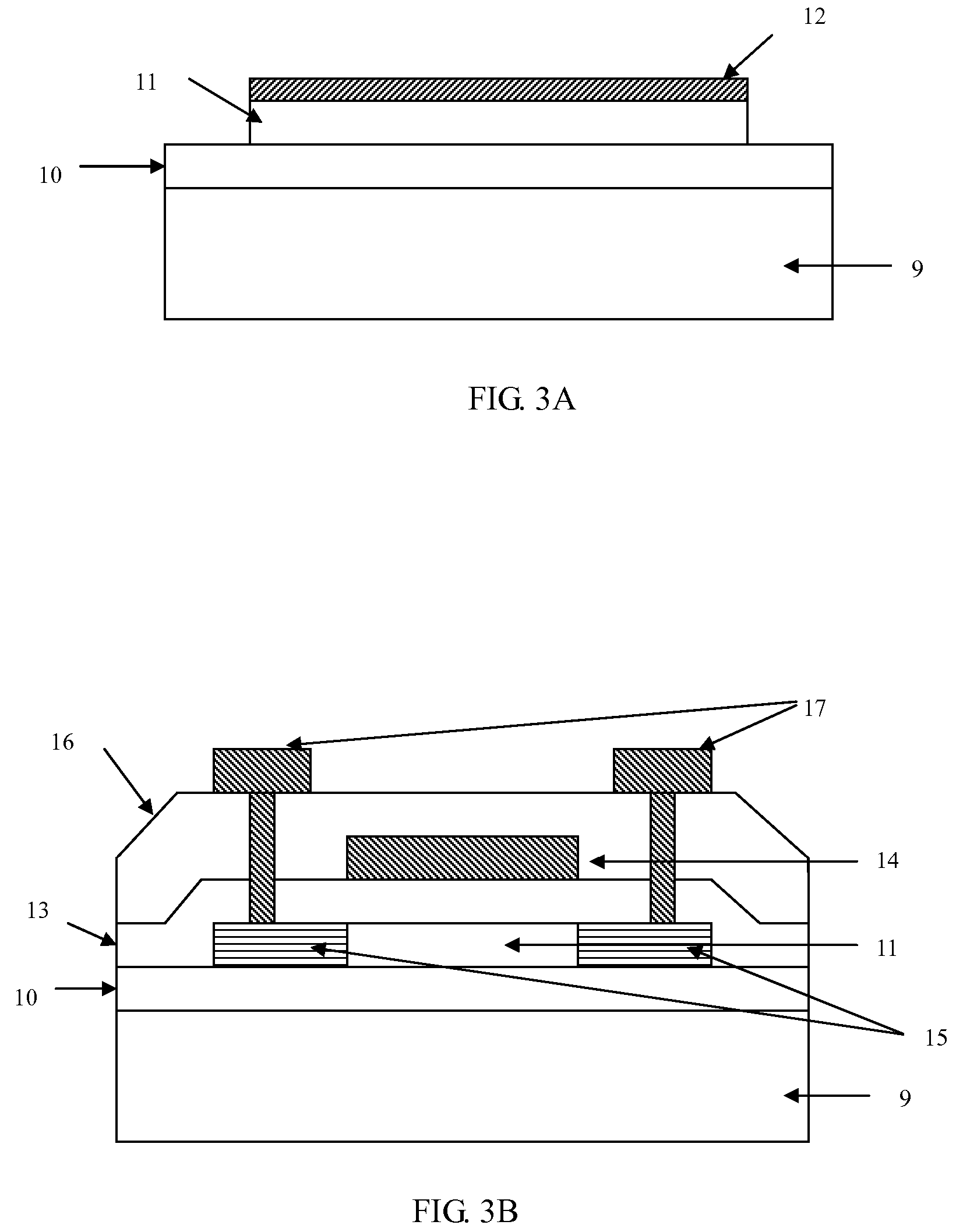

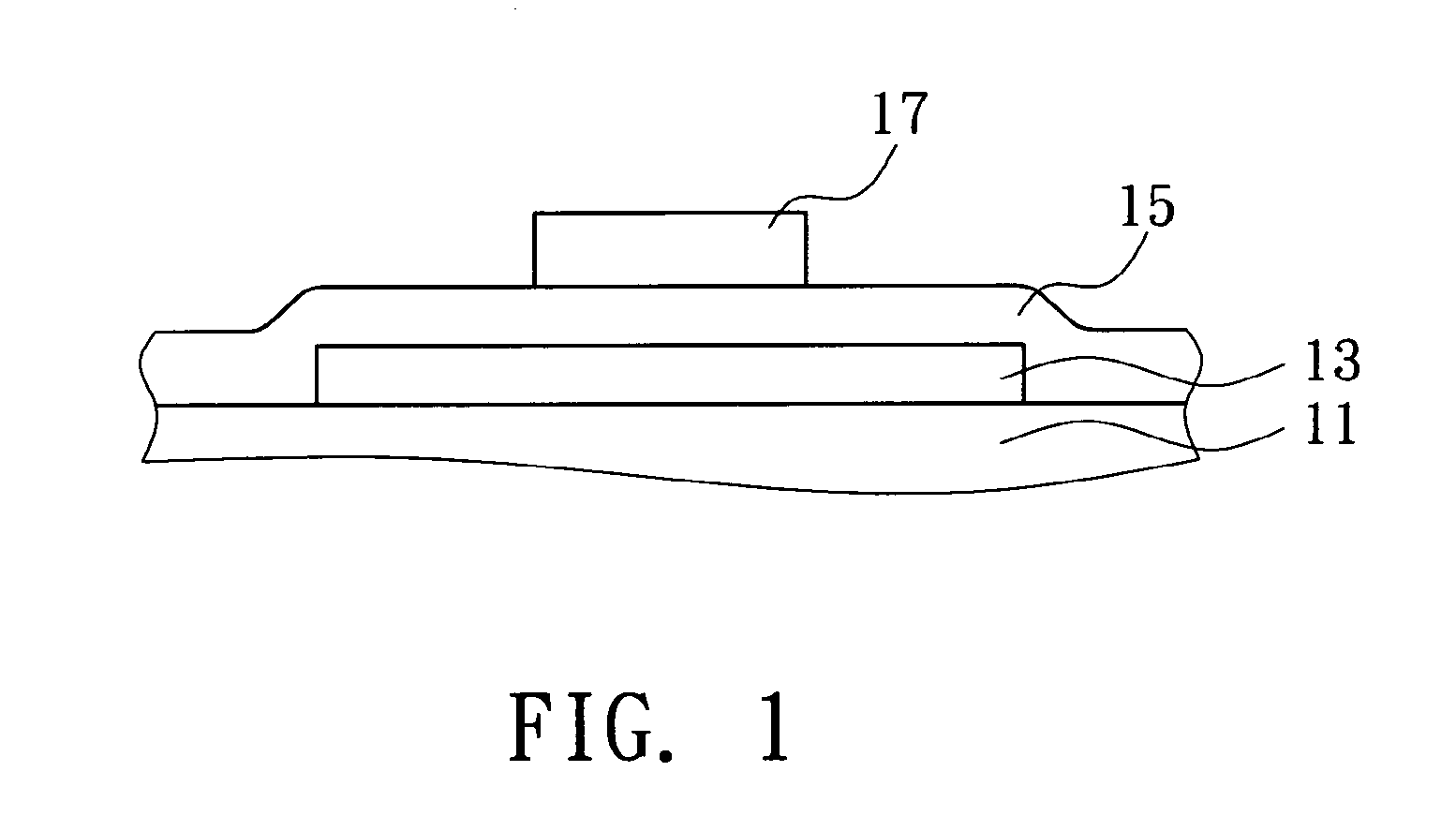

Methods of Fabricating Crystalline Silicon Film and Thin Film Transistors

ActiveUS20070004185A1Budget is reducedSolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsSilicon thin film

A method by which solid phase crystallization (SPC) thermal budget for crystallizing an undoped (or a lightly doped) amorphous Si (a-Si) is significantly reduced. First, a composite layer structure consisting of an undoped (or a lightly doped) a-Si layer and a heavily doped (either p-type or n-type) a-Si layer is formed and it is subsequently annealed at an elevated temperature. The solid phase crystallization starts from the heavily doped amorphous silicon layer at a substantially reduced thermal budget and proceeds to crystallize the undoped amorphous silicon layer in contact with the heavily doped film at reduced thermal budget. The method can be applied to form poly silicon thin film transistor at reduced thermal budgets.

Owner:KAKKAD RAMESH

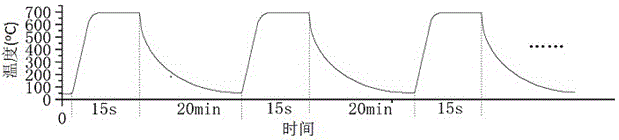

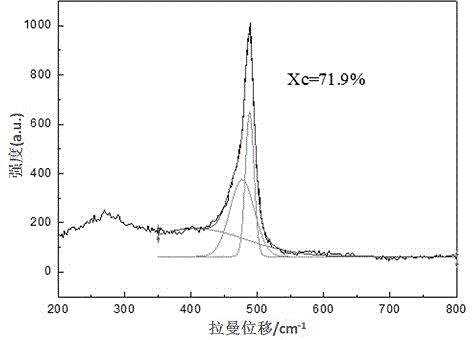

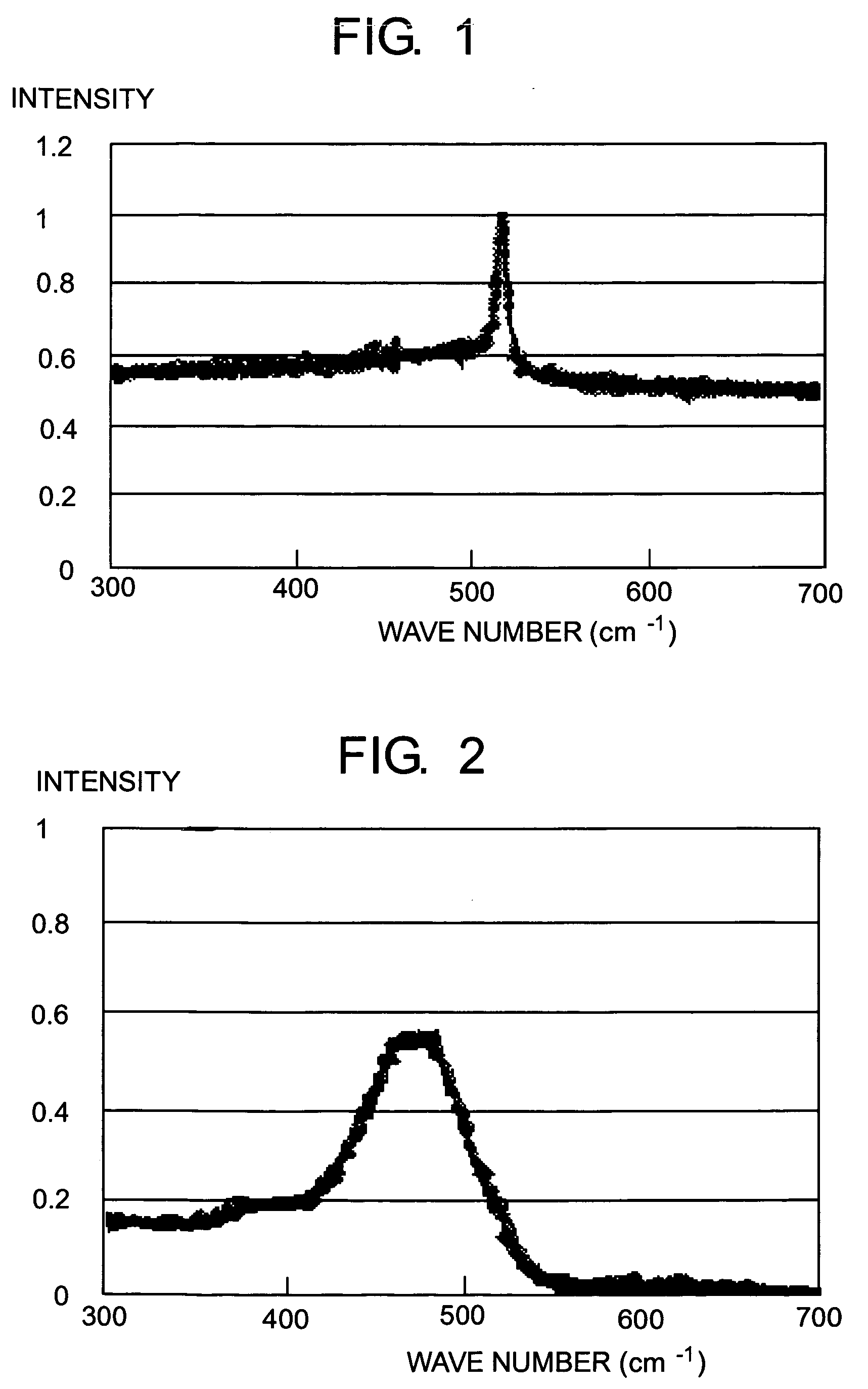

Multi-cycle rapid thermal annealing method of amorphous silicon film

InactiveCN102978590AShorten the annealing timeIncrease the number of annealingChemical vapor deposition coatingSolar cellRapid thermal annealing

The invention relates to a multi-cycle rapid thermal annealing method of an amorphous silicon film, belonging to the technical field of preparation technology of a polycrystalline silicon film. The method comprises the following steps of: depositing an amorphous silicon film on a common glass slide substrate by a vapor deposition method; performing rapid thermal treatment, wherein the heating rate is about 150-200 DEG C / s; after the film sample is heated to 640 DEG C from room temperature, keeping the temperature for a while, and cooling naturally; when the film temperature reaches room temperature, performing next cycle; and after rapid thermal annealing is carried out several times, crystallizing the amorphous silicon film. Through the method, a polycrystalline film with crystallization rate being about 71.9% can be prepared. Compared with the traditional solid-phase crystallization technology of an amorphous silicon film, the method provided by the invention reduces requirements on the substrate, shortens the treatment time and has the characteristics of simple preparation technology, little pollution, low cost and the like. The polycrystalline silicon film prepared by using the method provided by the invention can be applied to the manufacture field of microelectronics such as thin-film transistors and solar cells.

Owner:SHANGHAI UNIV

Methods of fabricating crystalline silicon film and thin film transistors

ActiveUS7507648B2Budget is reducedSolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsSilicon thin film

A method by which solid phase crystallization (SPC) thermal budget for crystallizing an undoped (or a lightly doped) amorphous Si (a-Si) is significantly reduced. First, a composite layer structure consisting of an undoped (or a lightly doped) a-Si layer and a heavily doped (either p-type or n-type) a-Si layer is formed and it is subsequently annealed at an elevated temperature. The solid phase crystallization starts from the heavily doped amorphous silicon layer at a substantially reduced thermal budget and proceeds to crystallize the undoped amorphous silicon layer in contact with the heavily doped film at reduced thermal budget. The method can be applied to form poly silicon thin film transistor at reduced thermal budgets.

Owner:KAKKAD RAMESH

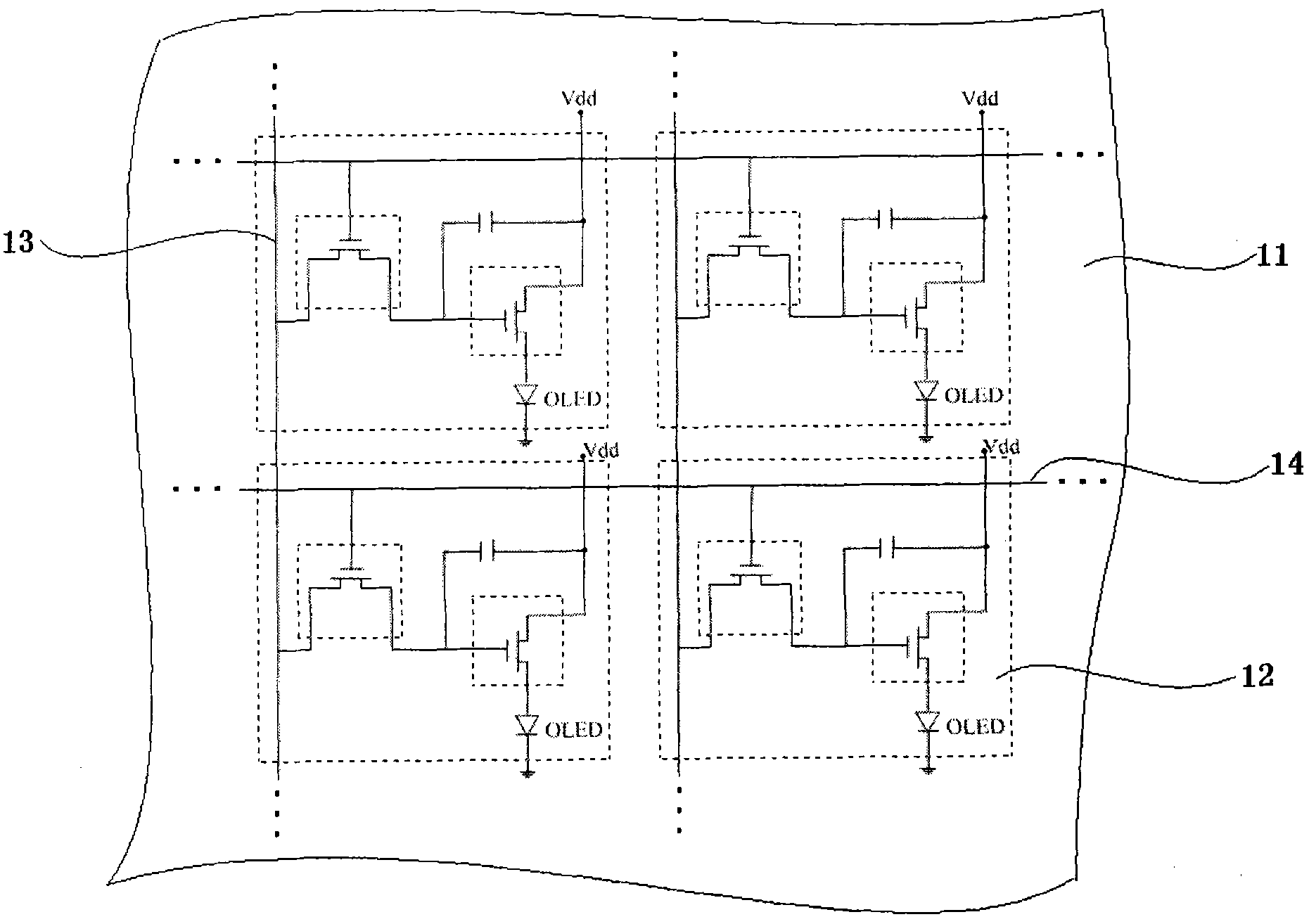

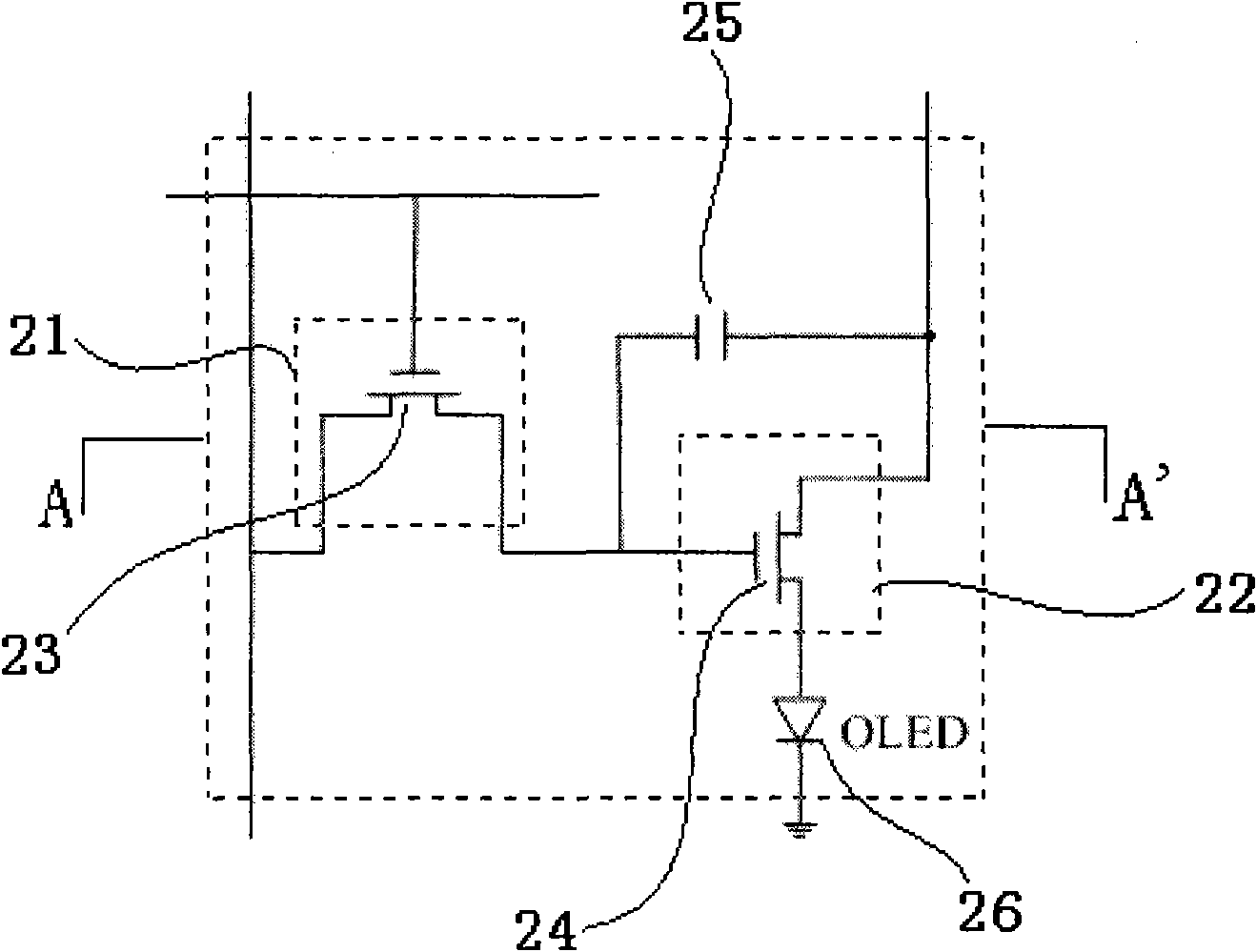

Active matrix/organic light emitting display and manufacturing method thereof

InactiveCN101924070AImprove performanceHigh carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingActive matrixLaser crystallization

The invention relates to an active matrix / organic light emitting display and a manufacturing method thereof, in particular to a low-temperature polysilicon display panel and a manufacturing method thereof. In the technical scheme of the invention, a switch thin-film transistor (TFT) with high carrier mobility is obtained in a switch area in a pixel and a drive TFT with good consistency is obtained in a drive area by way of double crystallization, namely solid-phase crystallization and local laser crystallization, thus realizing improvement of the overall property of the active matrix / organic light emitting display.

Owner:KUNSHAN NEW FLAT PANEL DISPLAY TECH CENT +2

Method for preparing large-area polycrystalline film

InactiveCN101908471AImprove mobilityReduce defectsFinal product manufactureSemiconductor/solid-state device manufacturingLaser crystallizationMetal

The invention discloses a method for preparing a large-area polycrystalline film, which comprises the following steps of: (1) depositing a layer of amorphous silicon film on a glass substrate; (2) exposing a strip window on the amorphous silicon film by adopting a photo-etching process; (3) sputtering a layer of metal on the amorphous silicon film in the window by adopting a magnetron sputtering method; (4) irradiating the window by adopting a laser device to prepare the polycrystalline film; and (5) removing the residual nickel metal by using acid. The invention provides the new method for preparing the polycrystalline film by combining a conventional metal-induced solid phase crystallization method and a laser crystallization technique; the prepared polycrystalline film has the effects on preferred orientation of the metal-induced solid phase crystallization method and high mobility and few defects of the laser crystallization method; and meanwhile, the method can prepare the large-area polycrystalline film by combining the photo-etching technology and the metal-induced transverse crystallization property, and provides convenience for industrialization.

Owner:江苏华创光电科技有限公司

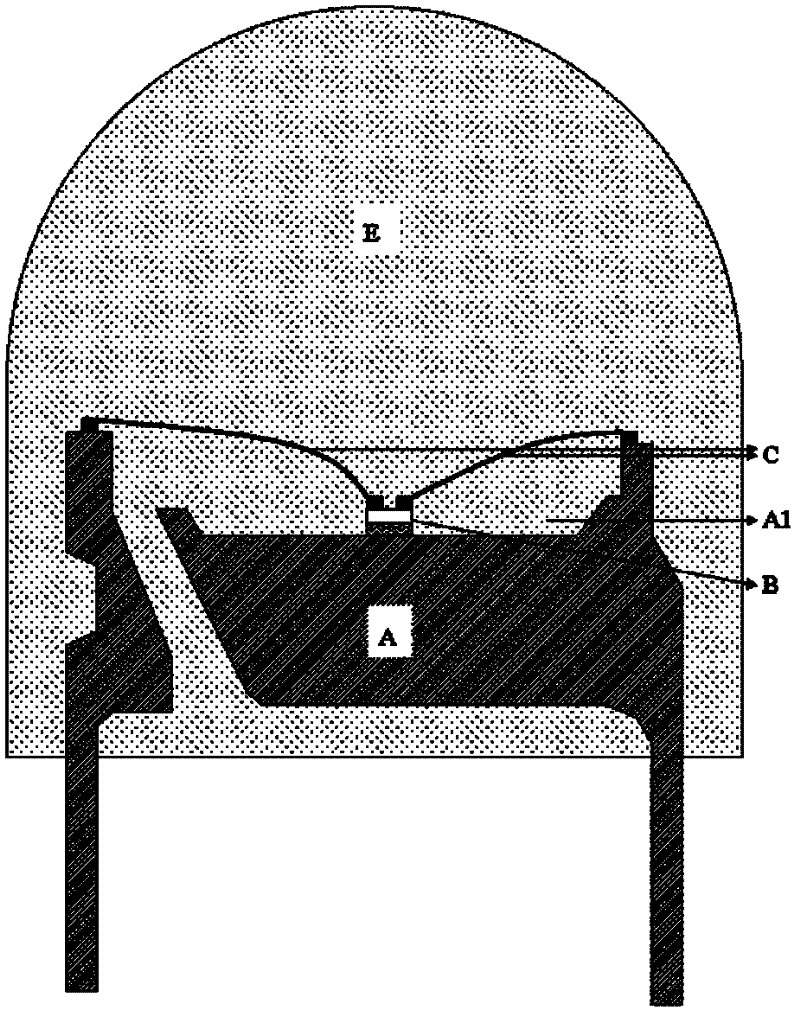

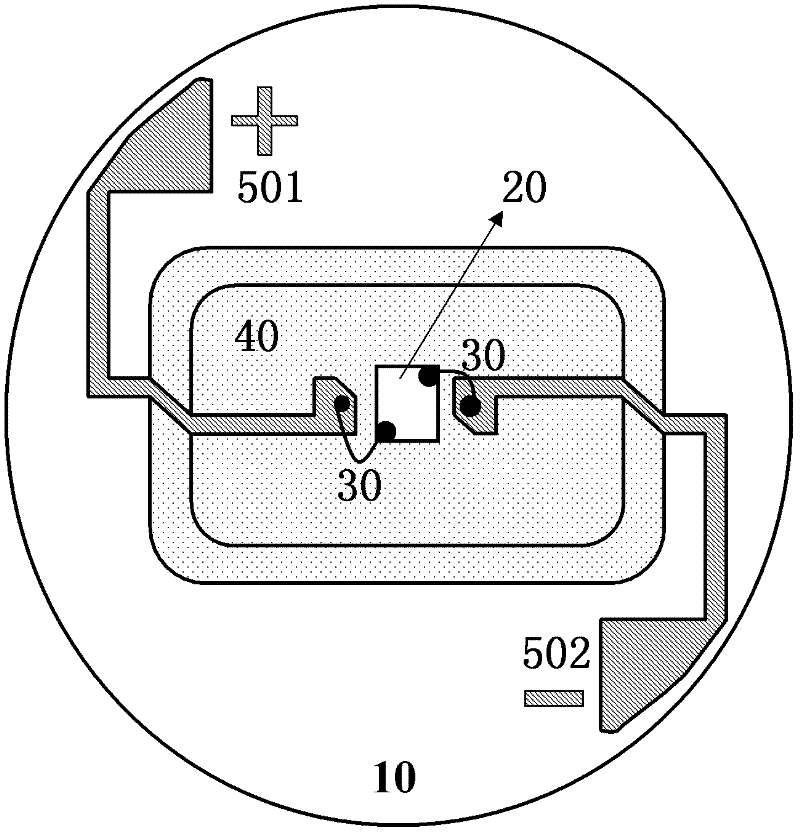

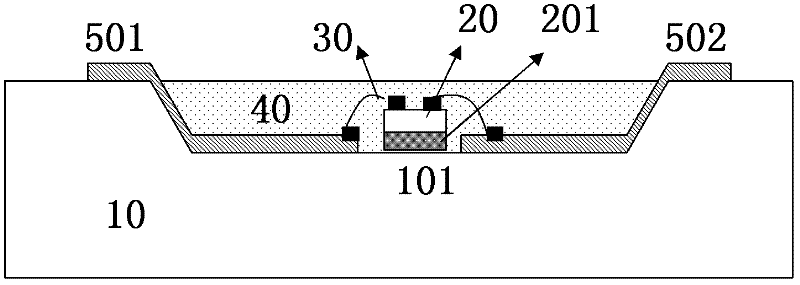

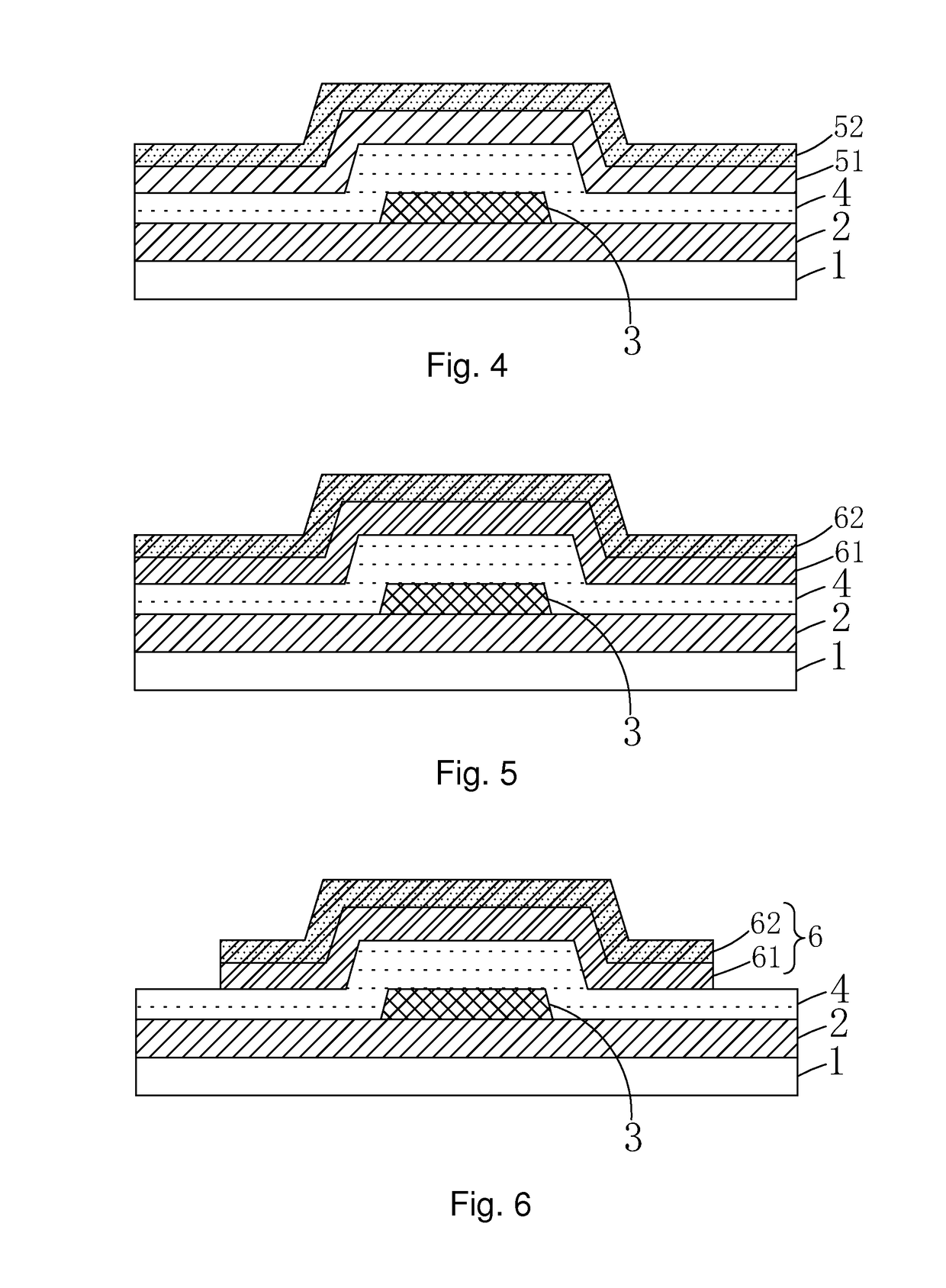

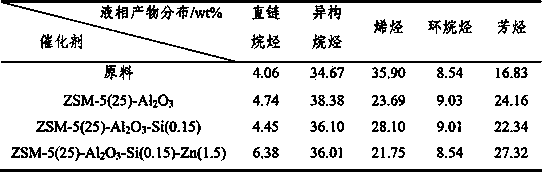

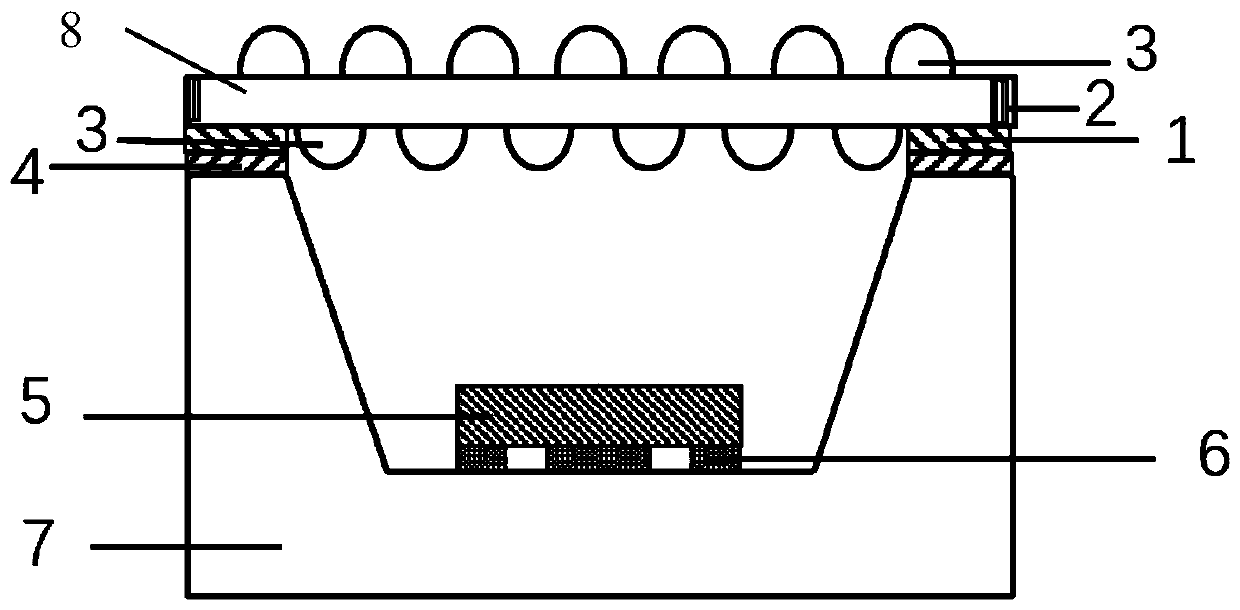

LED (Light Emitting Diode) packaging structure using rear earth element doped transparent ceramic as base

InactiveCN102569597AImprove insulation performanceMeet packaging requirementsSolid-state devicesSemiconductor devicesEpoxySilica gel

The invention relates to an LED (Light Emitting Diode) packaging structure using rear earth element-doped transparent ceramic as a base and emitting white light from two sides. The LED packaging structure is characterized in that: an LED chip (20) is arranged on the surface of the transparent ceramic base (10) through a solid phase crystallization manner and is electrically connected with patterned electrodes (501 and 502); and phosphor-mixed transparent silica gel or epoxy resin glue (40) is covered on the base (10) and the LED chip (20). Through the LED packaging scheme, blue light emitted from the back and side of the LED chip to the base can be absorbed by YAG (Yttrium Aluminum Garnet) ceramic, then converted into white light and emitted out from the back, so that the LED packaging structure emitting white light from the two sides is formed.

Owner:FUJIAN INST OF RES ON THE STRUCTURE OF MATTER CHINESE ACAD OF SCI

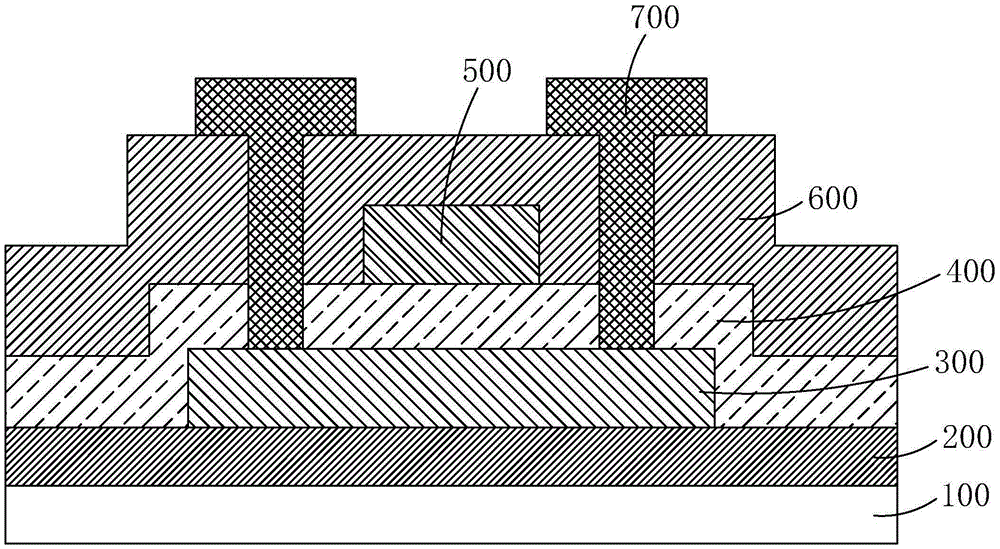

Method for manufacturing TFT substrate and TFT substrate manufactured thereof

ActiveUS20170154773A1Reliable controlIncreasing open currentTransistorSolid-state devicesEngineeringLow-temperature polycrystalline silicon

The invention provides a method for manufacturing a TFT substrate and a TFT substrate manufactured thereof. In the above TFT substrate, the low temperature poly-silicon layer is produced by solid phase crystallization, the cost of production is under budget, and the TFT substrate is a double-grid structure that can guarantee the electrical characteristics of the thin film transistor and better the capacity of drive, and leakage phenomenon caused by groove light seldom happens.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

LED (Light-Emitting Diode) light-emitting element

InactiveCN102969437AIncrease cooling areaImprove cooling effectSolid-state devicesSemiconductor devicesAdhesiveHeat conducting

The invention relates to an LED (Light-Emitting Diode) light-emitting element. The LED light-emitting element comprises LED chips and a glass substrate, wherein the LED chips and a metal conductive circuit are fixed on the glass substrate; the connecting surfaces of the glass substrate and the LED chips are coated with aluminum nitride coatings, and the LED chips are coated with fluorescent powder adhesives; a plurality of the LED chips are connected in series and arranged on thin-film circuits of the aluminum nitride coatings in a solid-phase crystallization way; the surfaces of the LED chips are coated with fluorescent powder so that white-light devices are formed; aluminum nitride coating thin-films are grown on the glass substrate in a magnetron sputtering film-forming way; and fluorescent powder adhesive protective layers coated at the outer layers of the LED chips can be formed into needed shapes according to the light-emitting shapes of the LED chips. The LED light-emitting element disclosed by the invention increases the radiating area by coating the aluminum nitride coating thin-films as heat-conducting insulated layers on the LED chips and the glass substrate, thereby realizing optimal radiation.

Owner:SHANGHAI DANGOO ELECTRONICS TARDING

A thin-film solar cell and method for preparing same

InactiveCN1547260AImprove absorption and utilizationImprove photoelectric conversion efficiencyFinal product manufacturePhotovoltaic energy generationIndiumQuenching

The invention discloses a kind of film solar energy battery and the manufacturing method. The battery is made up of a substrate, polar, a p-type copper indium selenium layer, an n-type cadmium sulfide layer, a p-type multi-crystal silicon layer, an n-type multi-crystal silicon layer and the polar stack. The manufacturing method of the invention is carried on with following steps: 1. uses magnetic control splattering and vacuum selenide quenching method to produce p-type copper indium selenium (GIS) film; 2. n-type cadmium sulfide (CdS) is generated on the p-type copper indium selenium (CIS) with vacuum evaporating method and forms the copper indium selenium / cadmium sulfide (CIS / CdS) compound structure; 3. The p-type multi-crystal silicon layer and the n-type multi-crystal silicon layer are formed on the compound structure with PCVD process and metal leading solid phase crystallization method; 4. The film solar energy battery of multi-crystal silicon-copper indium selenium compound structure is formed.

Owner:SOUTH CHINA UNIV OF TECH

Low temperature polysilicon thin film transistor display and method of fabricating the same

InactiveUS20080206938A1Improve display characteristicsImprove featuresTransistorSolid-state devicesGate dielectricDisplay device

Owner:AU OPTRONICS CORP

Catalyst for aromatization and quality modification of catalytic gasoline

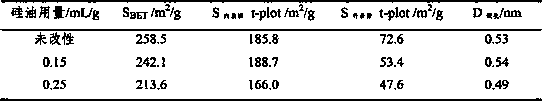

The invention discloses a catalyst for aromatization and quality modification of FCC (fluid catalytic cracking) gasoline. The catalyst is obtained by modifying stepped hole ZSM-5 by solid-phase crystallization of a molecular sieve by taking solid silica gel or kieselguhr as a silicon source. The modification process comprises the following steps: firstly, carrying out surface silicon coating modification on the molecular sieve by adopting silicon oil with certain molecular weight, then depositing a certain amount of metal ions on the inner surface of the molecular sieve by a dipping method, and compounding the modified molecular sieve with the silicon-coated outer surface and metal-deposited inner surface with a certain amount of aluminum oxide and silicon oxide, thereby obtaining the catalyst provided by the invention. Because the adopted molecular sieve has a smooth mesoporous structure, and is subjected to outer-surface silicon coating modification and inner-surface metal modification, the catalyst provided by the invention has the properties of good aromatization performance and high carbon deposit resistant capability, and is especially suitable for production of clean gasoline with high fluid yield in a modification process of the catalytic gasoline.

Owner:BC P INC CHINA NAT PETROLEUM CORP +1

Full-inorganic LED packaging structure and preparation method thereof

InactiveCN109786537AImprove stabilityHigh light transmittanceSemiconductor devicesInorganic leadState of art

The invention belongs to the field of LED devices, and discloses a full-inorganic LED packaging structure. The full-inorganic LED packaging structure comprises a box dam type copper coated ceramic substrate, an LED chip in the copper coated ceramic substrate, plane quartz glass at the top of the copper coated ceramic substrate and a first metal layer on the lower surface of the plane quartz glass,wherein the first metal layer has a size equal to the size of a contact area between the plane quartz glass and the copper coated ceramic substrate; the first metal layer comprises Cr, Pt and Au metal layers in sequence from top to bottom; and the total thickness of the first metal layer is 0.9-2 microns. The invention furthermore discloses a preparation method of the full-inorganic LED packagingstructure, and the preparation method comprises the steps of carrying out solid phase crystallization on the LED chip, preparing the first metal layer and completing LED packaging. The invention aimsat solving the technical problem that the LED devices obtained through LED packaging technologies in the prior art are low in reliability and easy to permeate air and moisture.

Owner:EZHOU INST OF IND TECH HUAZHONG UNIV OF SCI & TECH +1

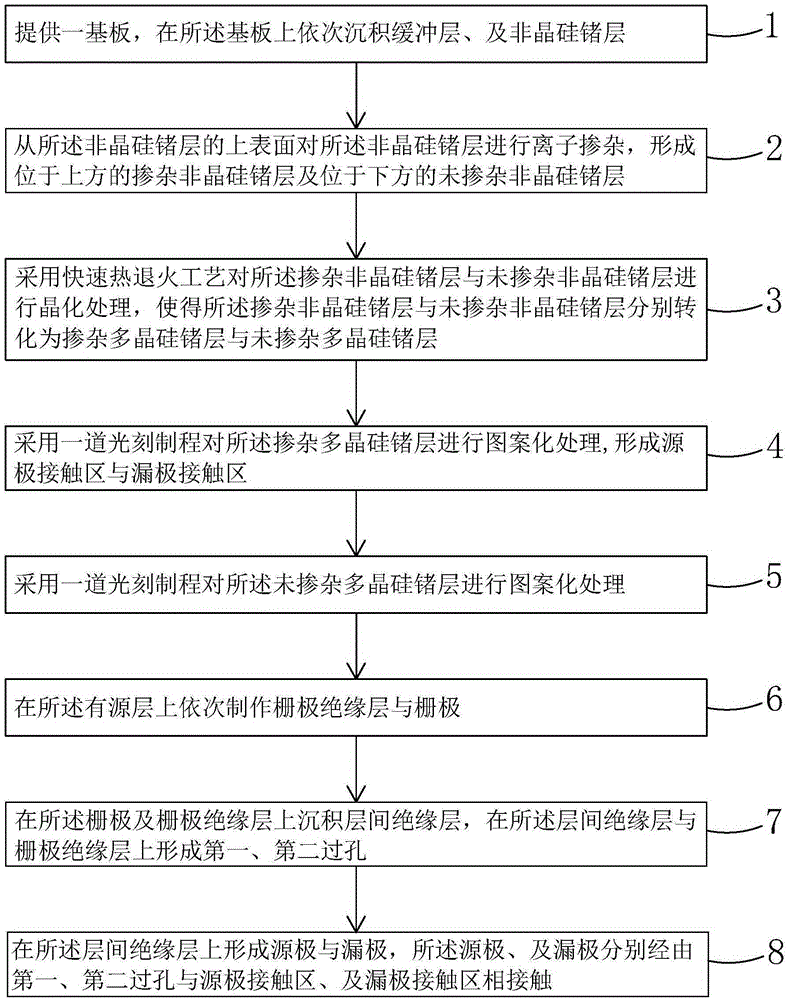

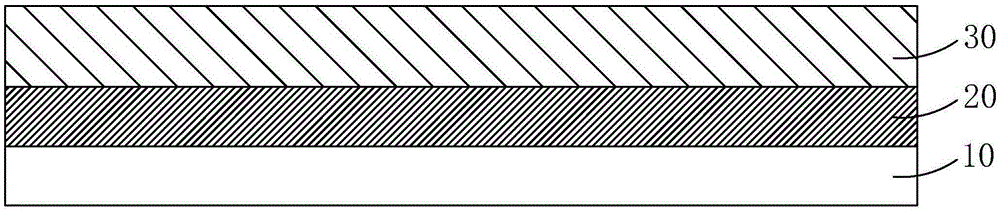

TFT substrate manufacturing method and TFT substrate

ActiveCN105355593AImprove electrical performanceShorten crystallization timeSolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsCrystallization temperature

The invention provides a TFT substrate manufacturing method and a TFT substrate. The TFT substrate manufacturing method comprises the steps of depositing a buffer layer and an amorphous silicon germanium layer on a substrate; implanting doped ions at the upper portion of the amorphous silicon germanium layer so as to form a doped amorphous silicon germanium layer; employing a rapid thermal annealing process for crystallization processing on the doped amorphous silicon germanium layer and the un-doped amorphous silicon germanium layer. Because the crystallization process begins from the doped amorphous silicon germanium layer and the crystallization temperature of the doped amorphous silicon germanium layer is low, the crystallization process can be carried out at a low temperature; because the un-doped amorphous silicon germanium layer in contact with the doped amorphous silicon germanium layer can be crystallized continuously at the low temperature, the doped polysilicon germanium layer and the un-doped polysilicon germanium layer can be obtained; compared with prior art, like existing solid phase crystallization, the crystallization process of the present invention can be carried out at a lower temperature, and the crystallization time can be shortened; the crystallization effect can be improved; and larger and more uniform crystal grains can be obtained.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

LED (Light-Emitting Diode) wafer modularized packaging process

InactiveCN102969433AEfficient packaging manufacturing processHigh speedSolid-state devicesSemiconductor devices for light sourcesIndium tin oxideChipset

The invention relates to an LED (Light-Emitting Diode) wafer modularized packaging process which particularly comprises the following steps of: firstly connecting single or multiple LED chips in upright or reverse structures in series and in parallel to form an LED chipset; and then mounting the LED chipset to a substrate or a support frame by using LED chip mounting equipment. After the single or multiple LED chips are connected in series and in parallel to form the LED chipset, a metal wire and a metal film wire or a transparent indium tin oxide wire are adopted as outgoing wires, wherein the upright LED chips are welded on the outgoing wires by using gold wires and ball welding spots, and the reverse LED chips are welded on the outgoing wires by using eutectic welding spots; and the LED chip mounting equipment is a solid-phase crystallization machine or a chip mounting machine. The LED wafer modularized packaging process disclosed by the invention ensures that the packaging and manufacturing processes of the LED chips are more efficient; and compared with the traditional LED packaging mode, the LED wafer modularized packaging process disclosed by the invention adopts the simplest chip mounting manufacturing mode of a chip mounting resistor, thereby greatly increasing the speed of LED packaging and manufacturing, enhancing the productivity and reducing the cost.

Owner:SHANGHAI DANGOO ELECTRONICS TARDING

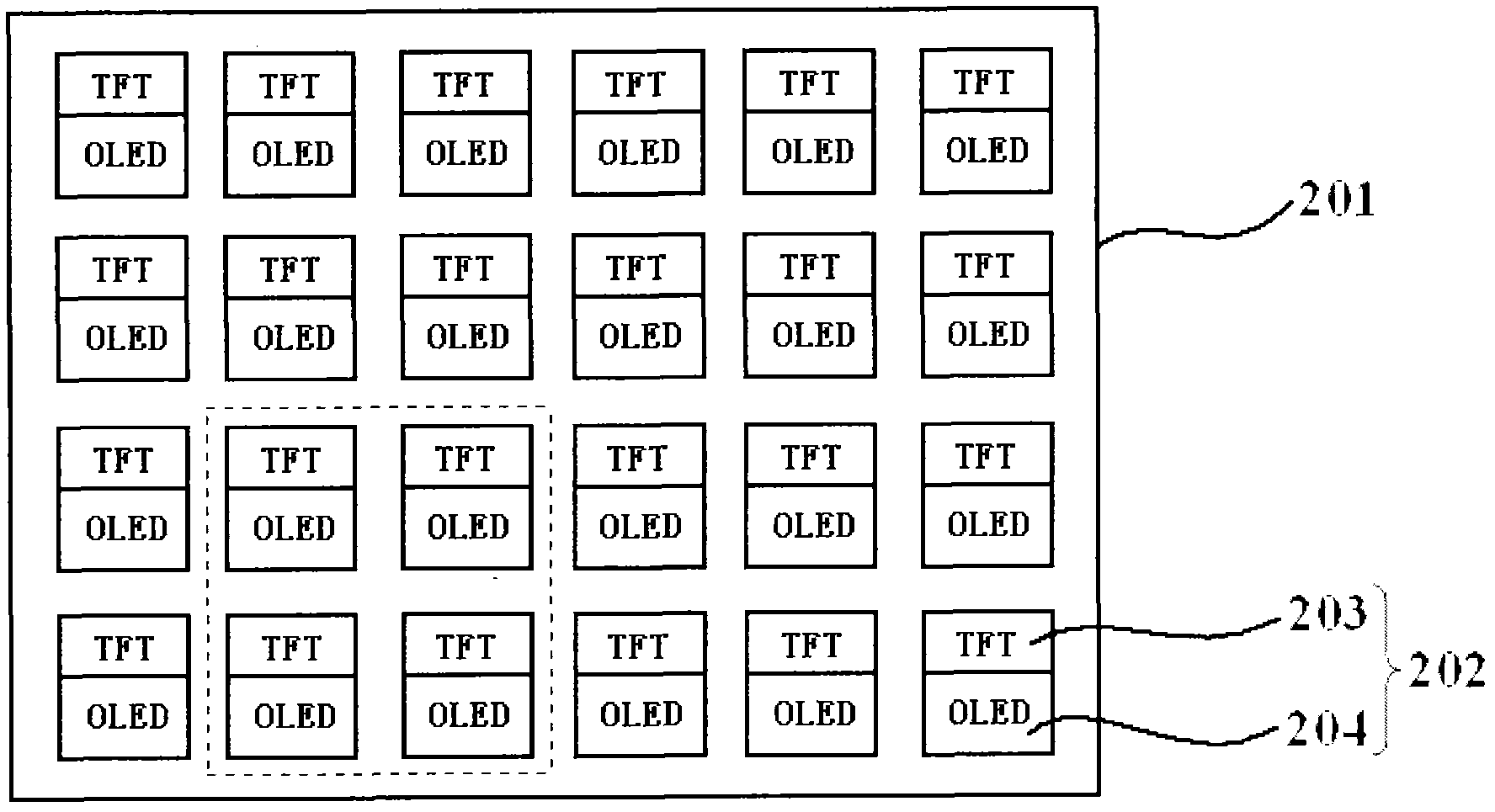

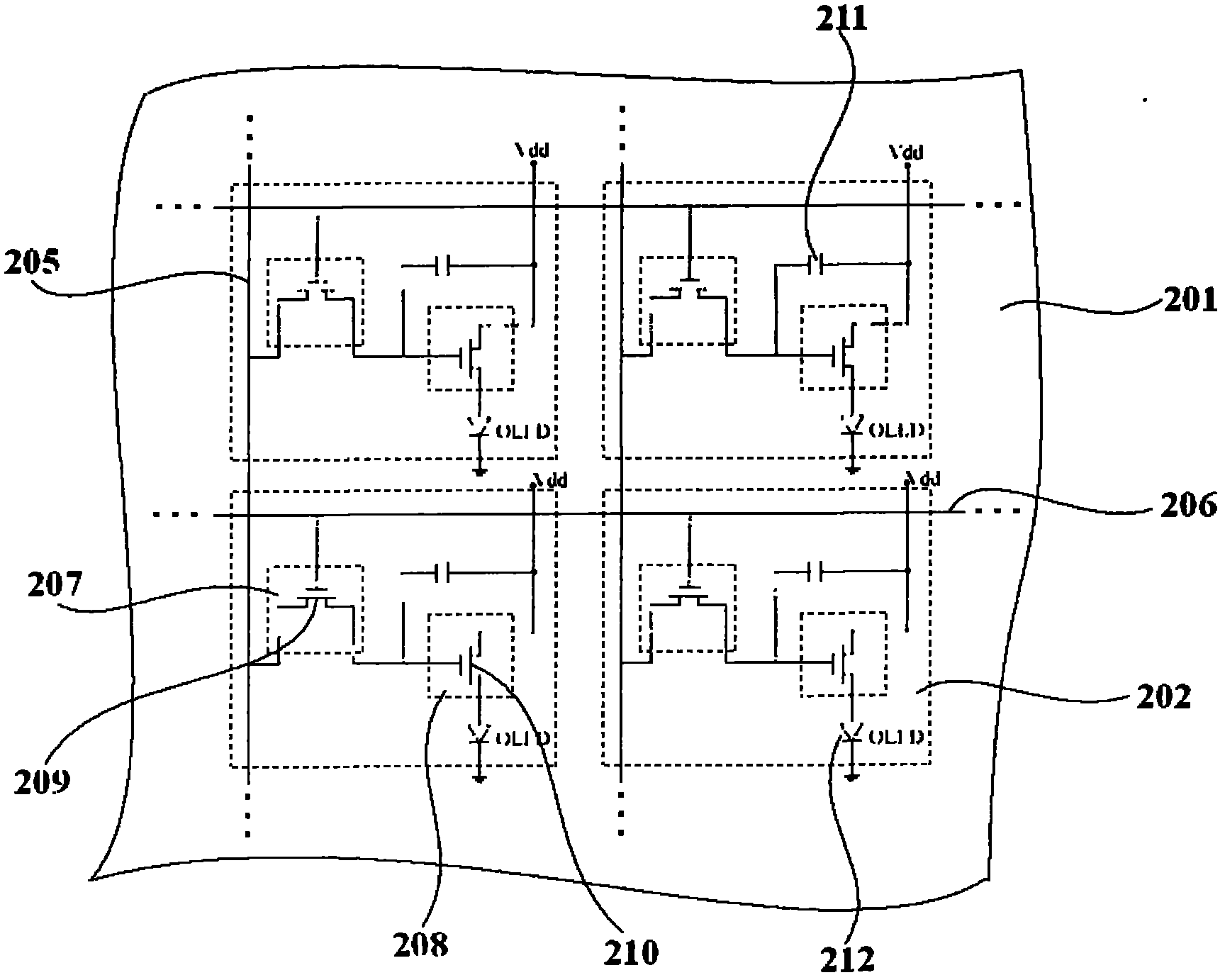

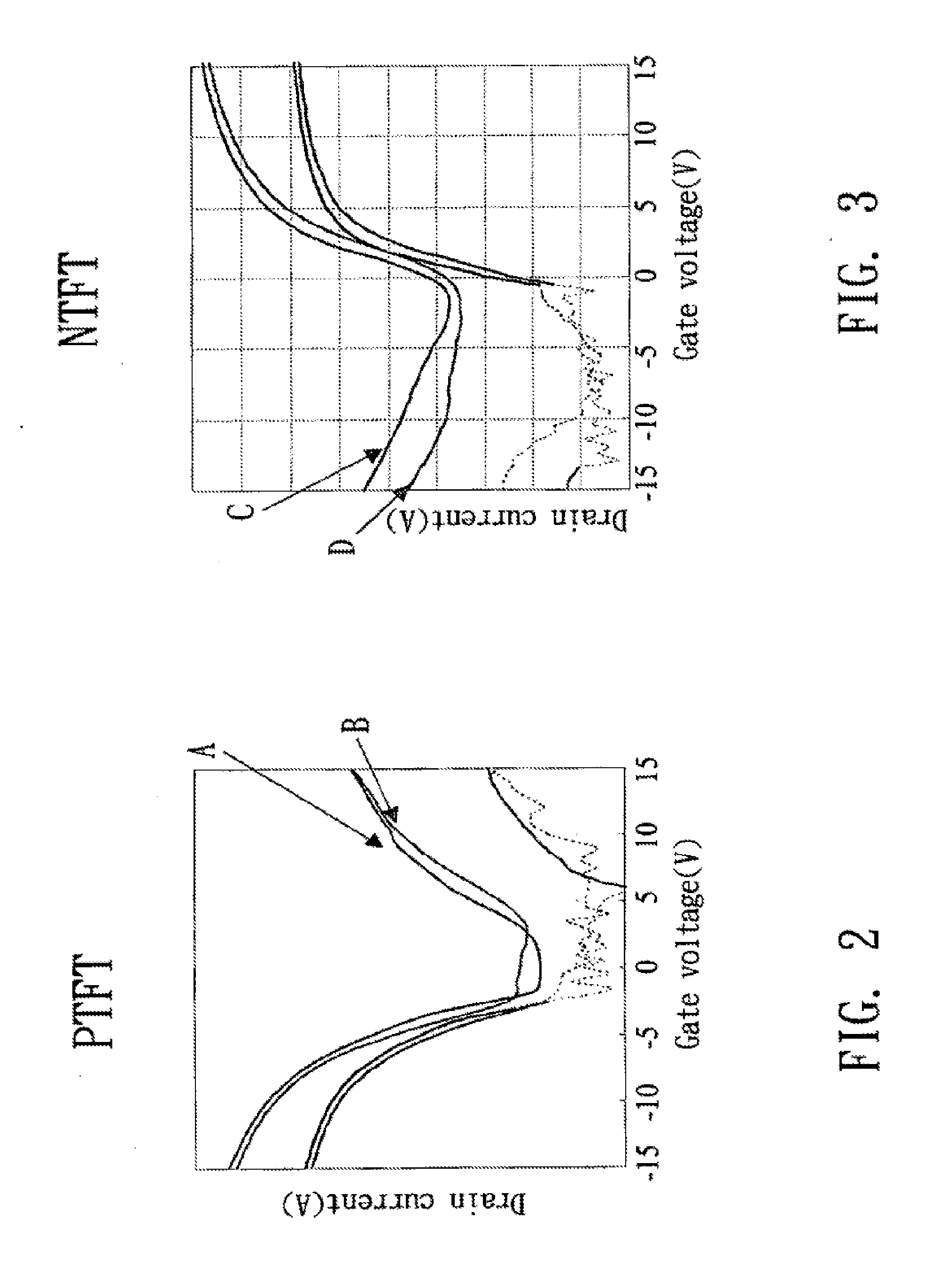

Manufacture method of amoled pixel drive circuit

ActiveUS20180204897A1Reduce leakage currentImprove mobilityTransistorFinal product manufactureParasitic capacitanceEngineering

The present invention provides a manufacture method of an AMOLED pixel driving circuit. The method utilizes the oxide semiconductor thin film transistor to be the switch thin film transistor of the AMOLED pixel driving circuit to reduce the leakage current of the switch thin film transistor, and the P type polysilicon thin film transistor manufactured by utilizing the Solid Phase Crystallization is employed to be the drive thin film transistor of the AMOLED pixel driving circuit to promote the mobility, the equality and the reliability of the drive thin film transistor, and utilizing the P type thin film transistor to be the drive thin film transistor can form the constant current type OLED element, which is more stable than the source follower type OLED formed by the N type thin film transistor, and meanwhile, the parasitic capacitance is decreased with the top gate structure.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

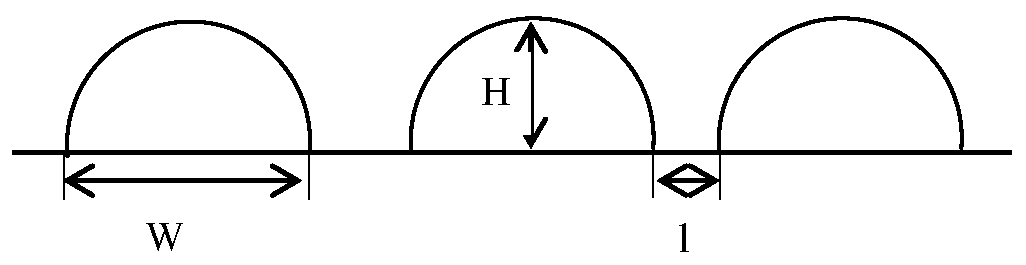

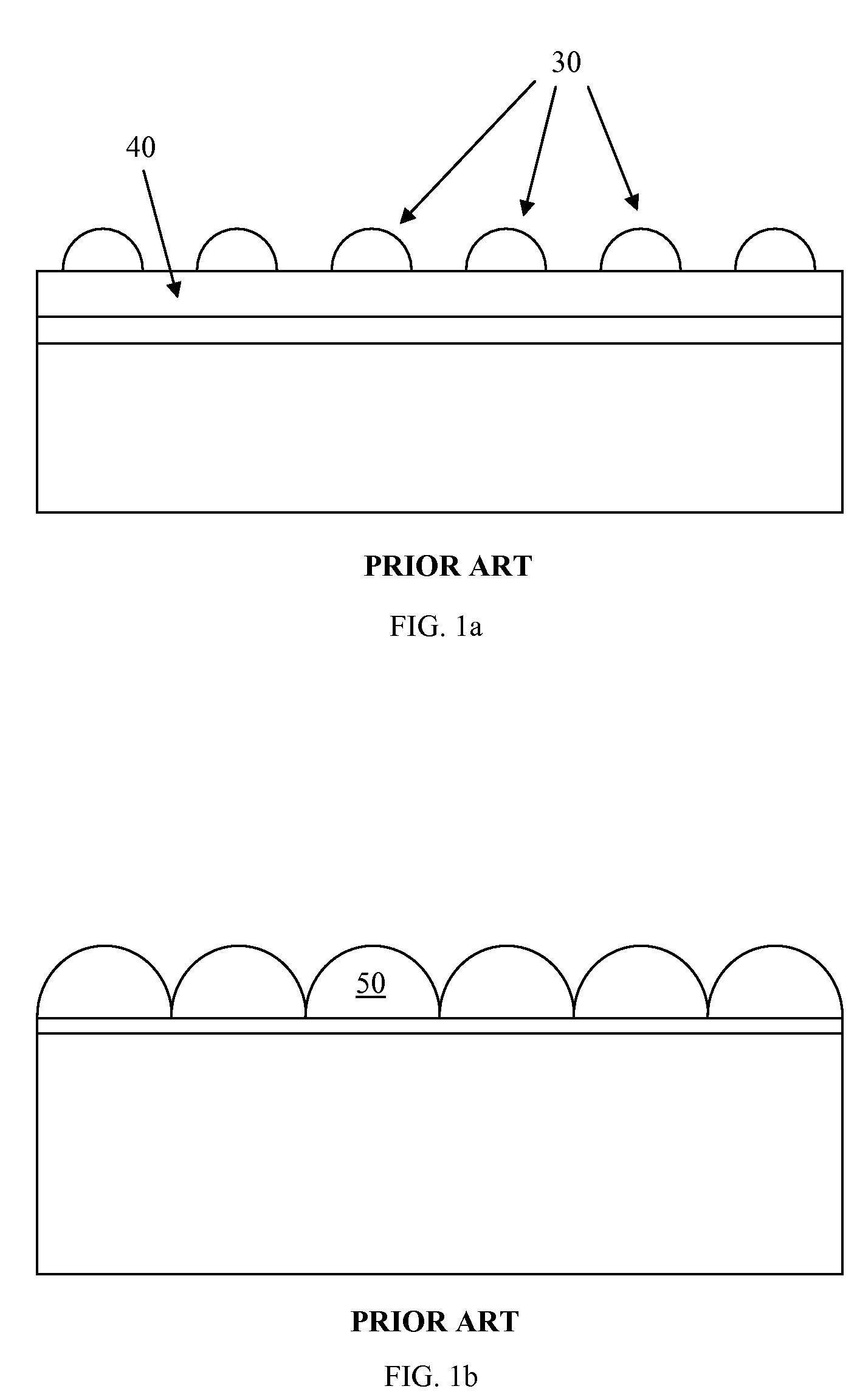

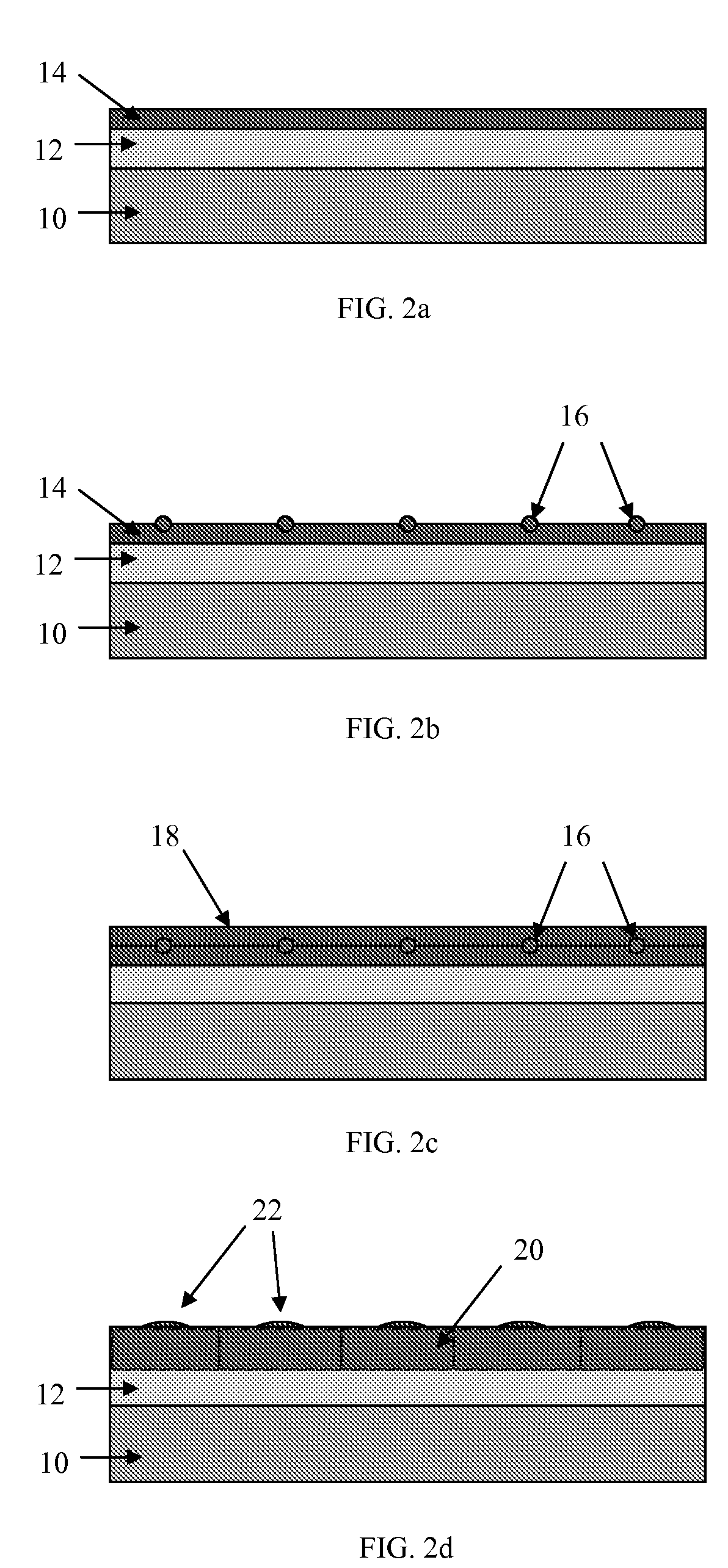

Method to form large grain size polysilicon films by nuclei-induced solid phase crystallization

A method to enhance grain size in polysilicon films while avoiding formation of hemispherical grains (HSG) is disclosed. The method begins by depositing a first amorphous silicon film, then depositing silicon nuclei, which will act as nucleation sites, on the amorphous film. After deposition of silicon nuclei, crystallization, and specifically HSG, is prevented by lowering temperature and / or raising pressure. Next a second amorphous silicon layer is deposited over the first layer and the nuclei. Finally an anneal is performed to induce crystallization from the embedded nuclei. Thus grains are formed from the silicon bulk, rather than from the surface, HSG is avoided, and a smooth polysilicon film with enhanced grain size is produced.

Owner:SANDISK TECH LLC

Process for producing binder-free ZSM-5 zeolite in small crystal size

ActiveUS20070042900A1Simple preparation procedureReadily availableAluminium compoundsMolecular sieve catalystsEffective surfaceWater vapor

The present invention relates to a process for producing a binder-free ZSM-5 zeolite in small crystal size. The invention is primarily used for solving the problems in the practical application, e.g., the zeolite powder is difficult to be recovered and easily inactivates and aggregates, and the addition of the binder in the shaping process will result in the reduction of effective surface areas and introduce the diffusional limitation. Said problems are better solved in the present invention by using diatomite or silica aerogel as the main starting material, adding a seed crystal orienting agent, a silica sol and sodium silicate for kneading and shaping, and then converting to integrative ZSM-5 in small crystal size by vapor-solid phase crystallization with organic amine and water vapor. Said process can be used in the industrial preparation of ZSM-5 molecular sieve catalyst in small crystal size.

Owner:CHINA PETROCHEMICAL CORP +1

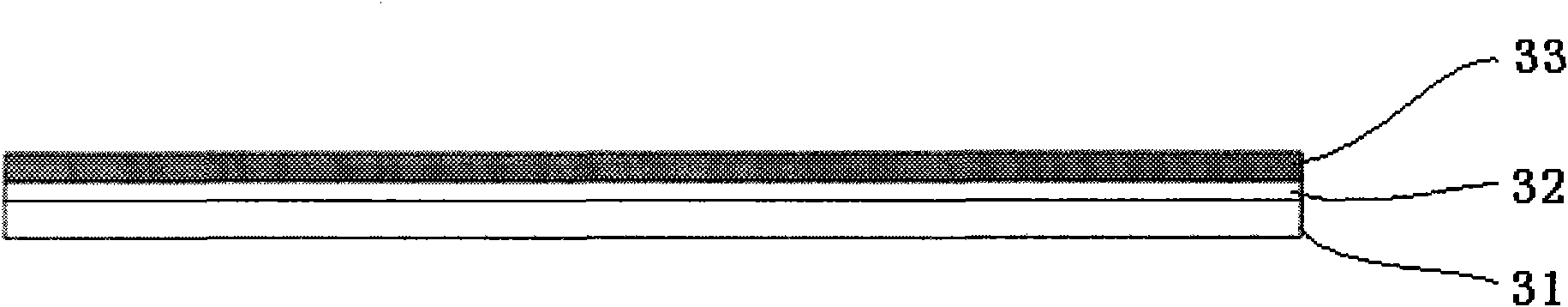

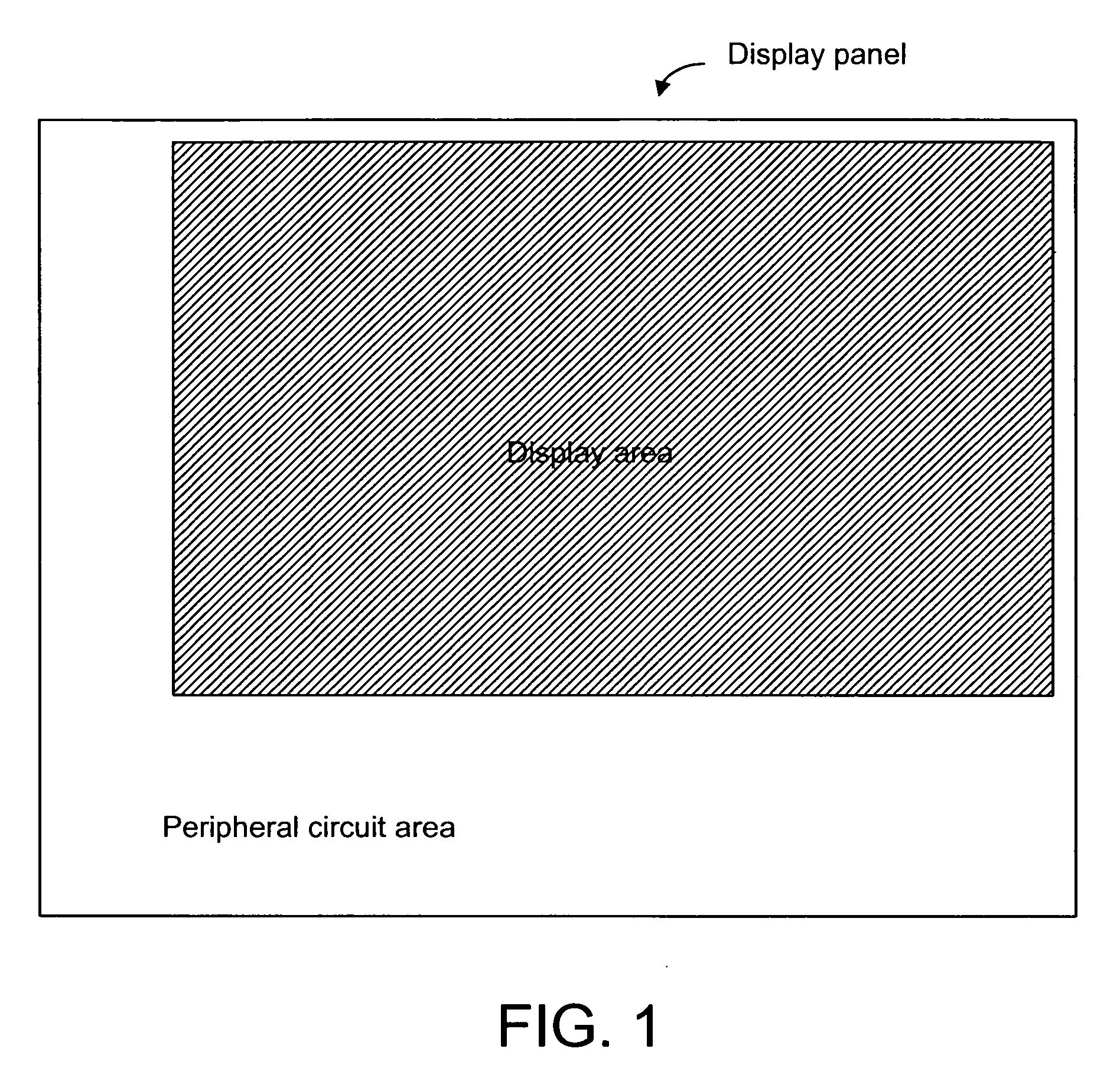

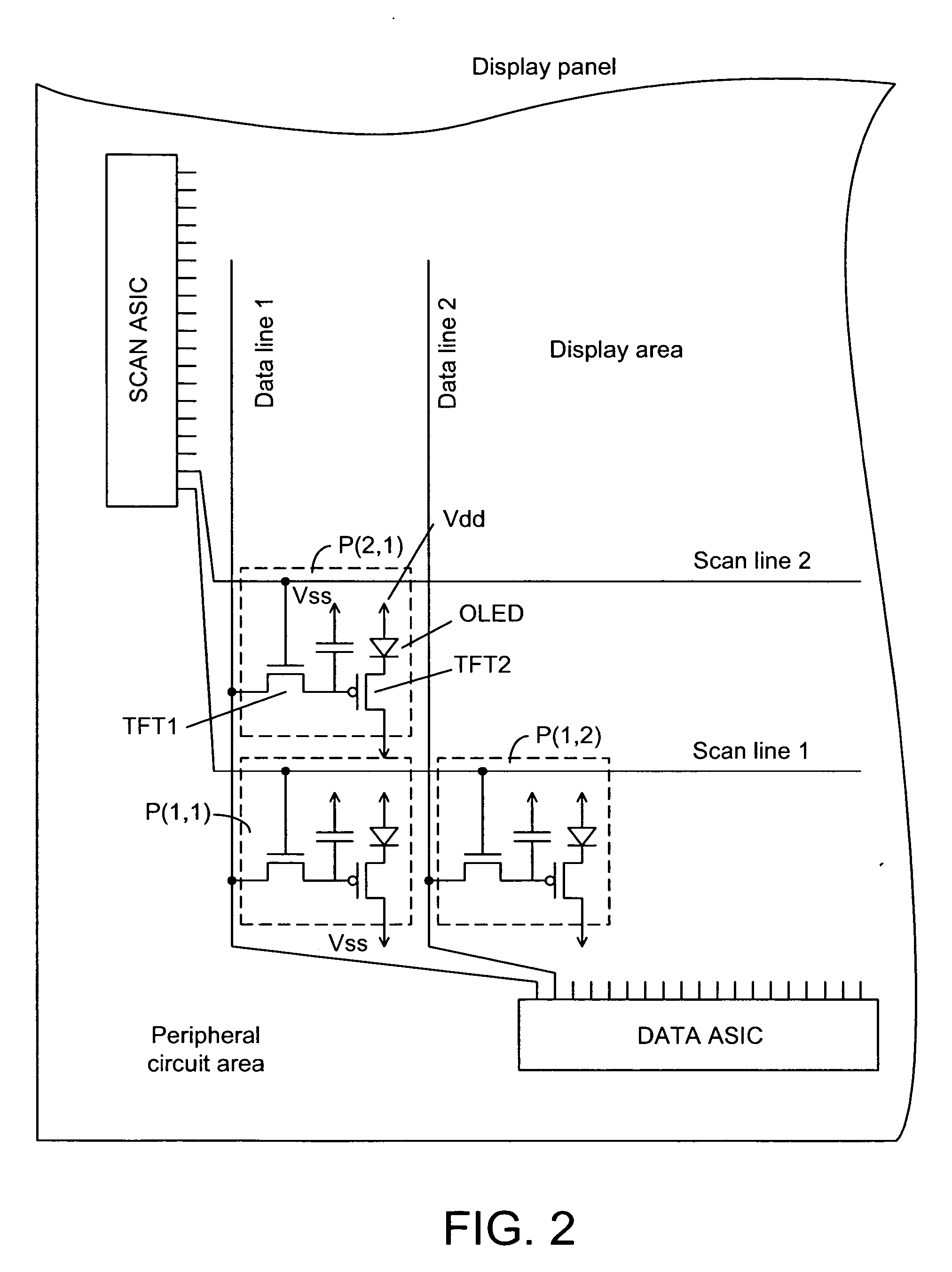

Low-temperature polysilicon display and method for fabricating same

ActiveUS20070105287A1High electron mobilityUniform layersSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceHigh electron

A display panel comprising at least one display area and one peripheral circuit area having electronic components for driving the display components in the display area. The electronic components in the display area are fabricated substantially on a polysilicon layer converted from amorphous silicon by a solid phase crystallization process, whereas the electronic components in the peripheral circuit area are fabricated substantially on a polysilicon layer converted from amorphous silicon first by the solid phase crystallization process and then by laser annealing. As such, display area has a more uniform poly-Si layer substantially free of defects associated with laser annealing, and the peripheral circuit has a poly-Si layer with higher electron mobility.

Owner:OPTRONIC SCI LLC

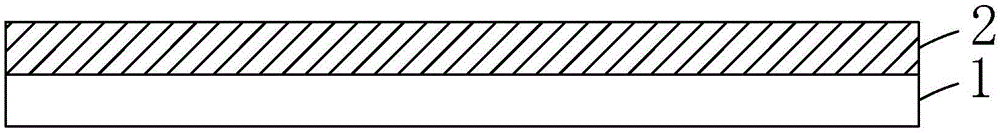

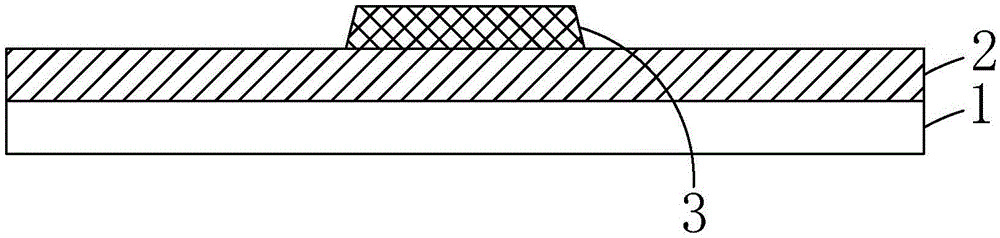

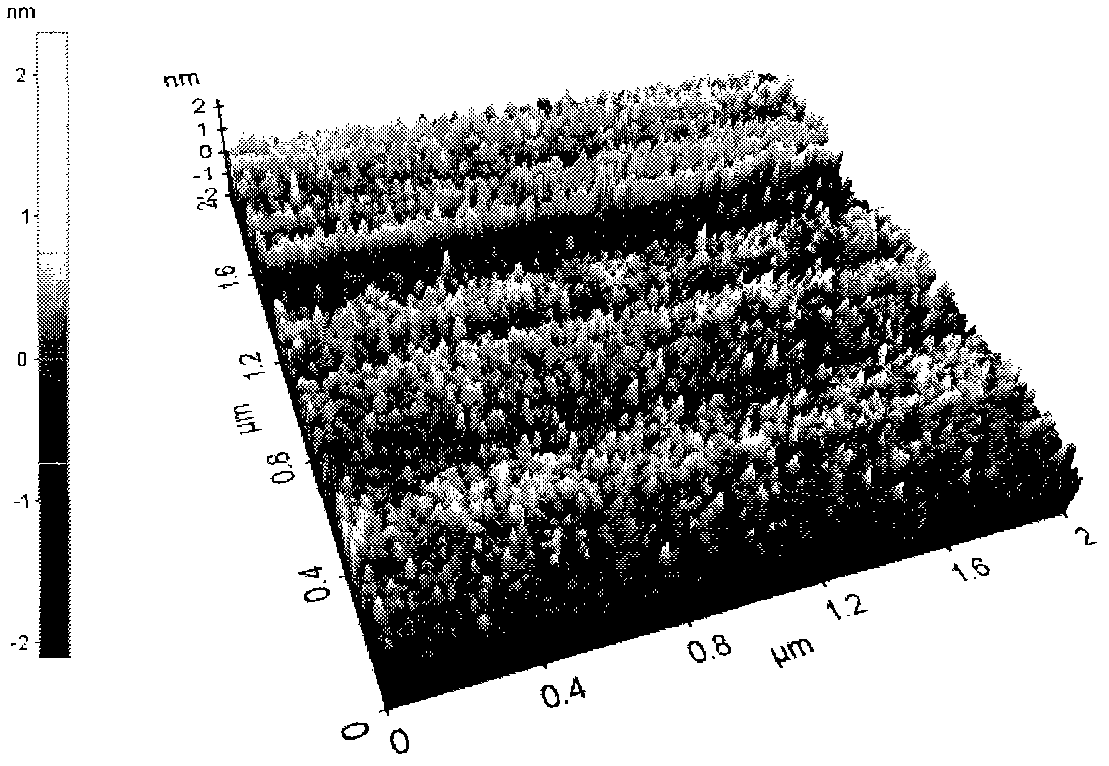

Method of fabricating polysilicon thin film and thin film transistor using polysilicon fabricated by the same method

ActiveUS20050186720A1High crystallinityPrevents the substrate from being bentTransistorPolycrystalline material growthFilm resistanceSilicon membrane

A method of fabricating a polysilicon thin film produces a polysilicon thin film which is used to make a thin film transistor. The method includes depositing a silicon film containing amorphous silicon on a substrate, and performing thermal treatment on the silicon film at a predetermined temperature in an H2O atmosphere. Accordingly, the crystallization temperature and thermal treatment time are decreased when the amorphous silicon is crystallized by a solid phase crystallization method, and this prevents the substrate from being bent due to application of a thermal treatment process for a long time and at a high temperature. As a result of the invention, a polysilicon thin film having superior crystallization properties is obtained. Use of the polysilicon thin film in a thin film transistor results in the reduction of defects in the thin film resistor.

Owner:SAMSUNG DISPLAY CO LTD

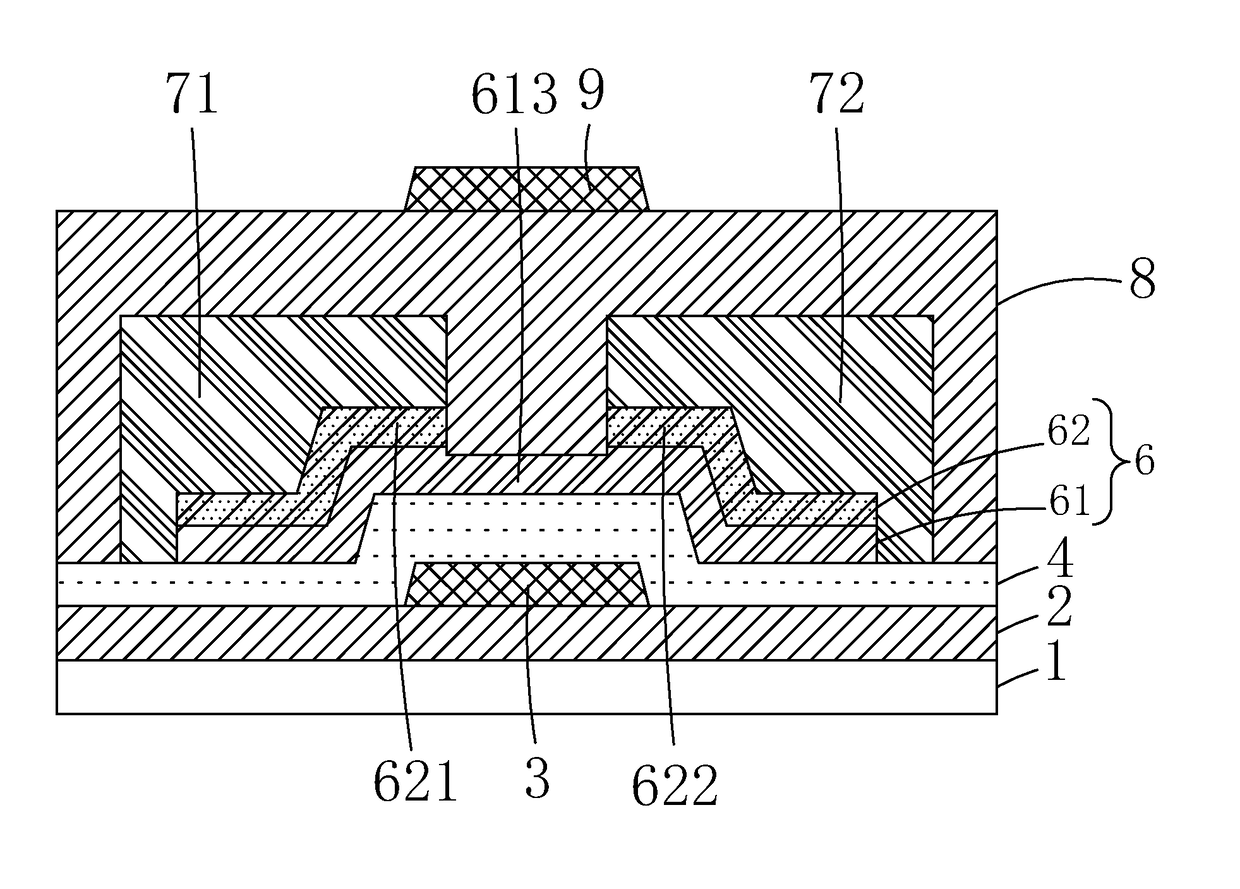

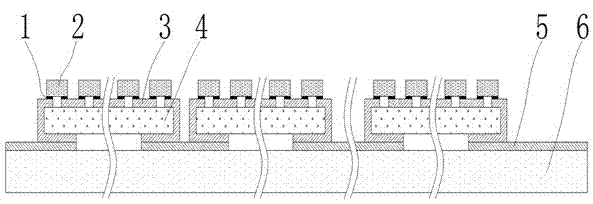

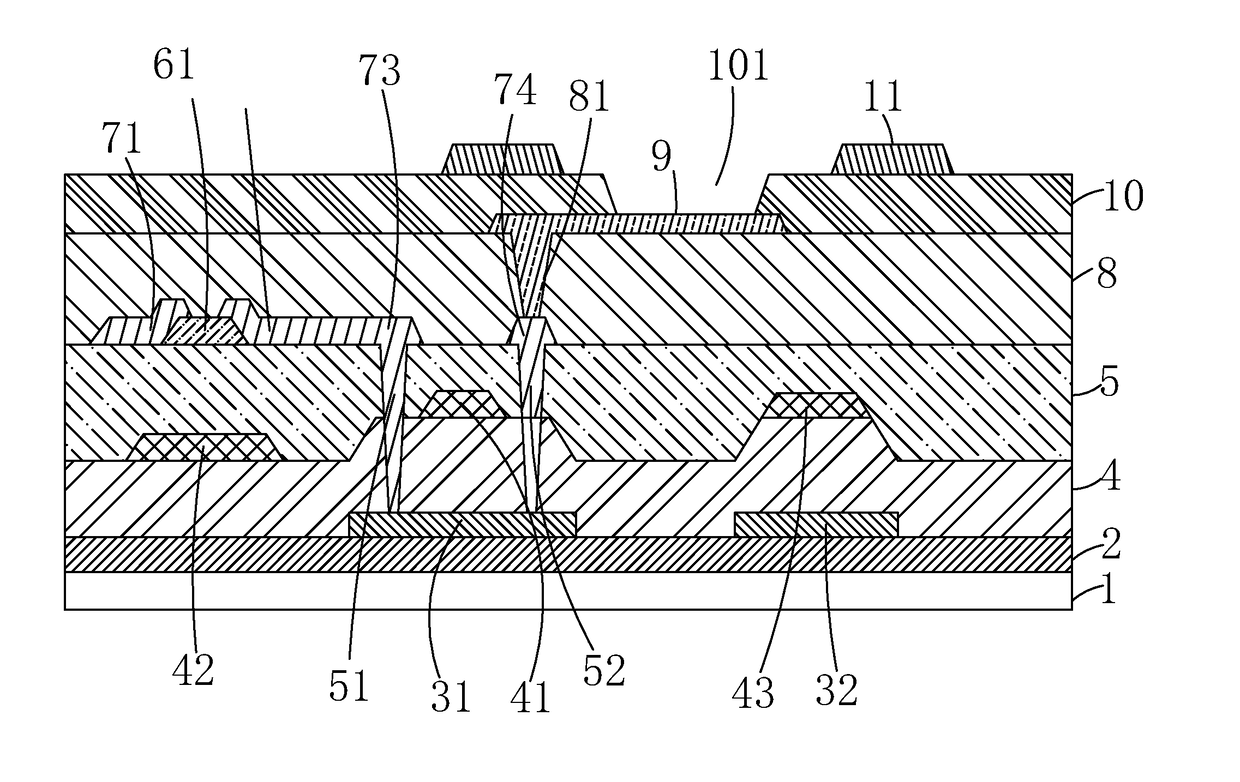

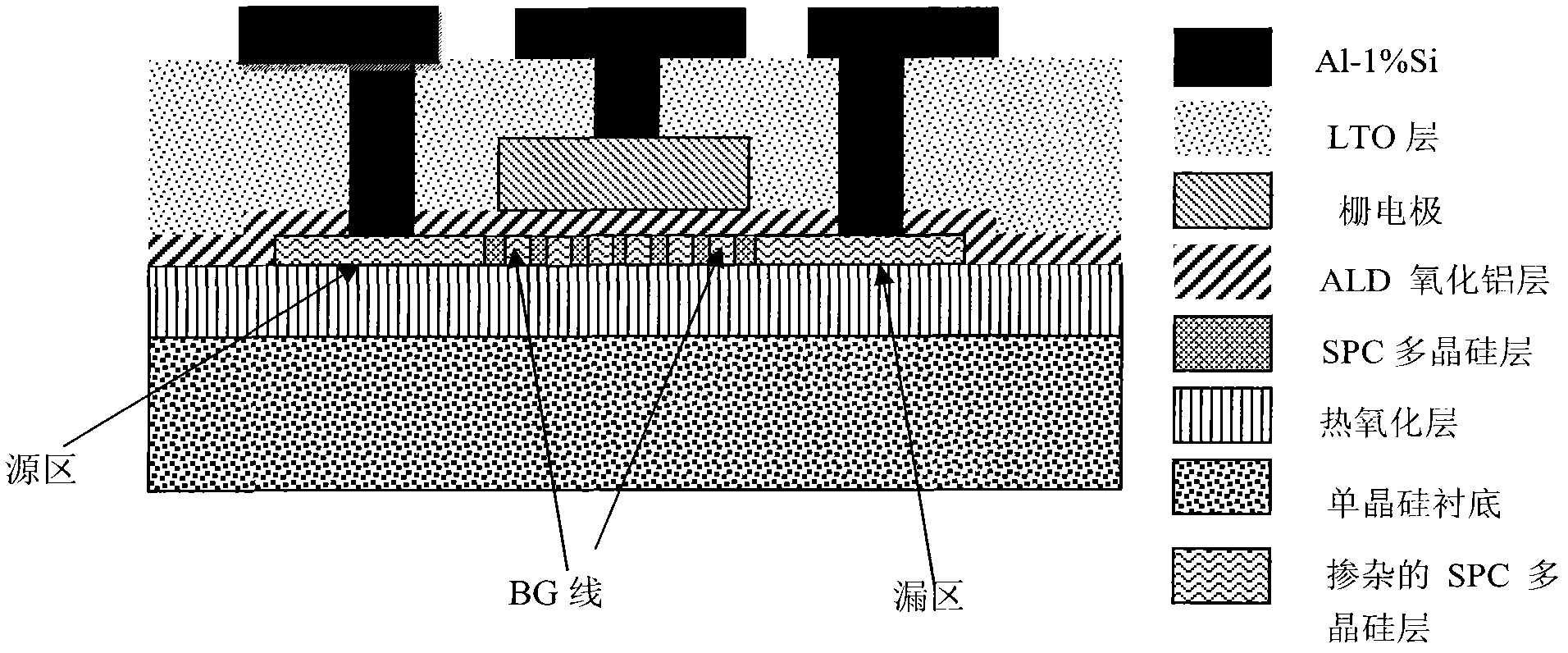

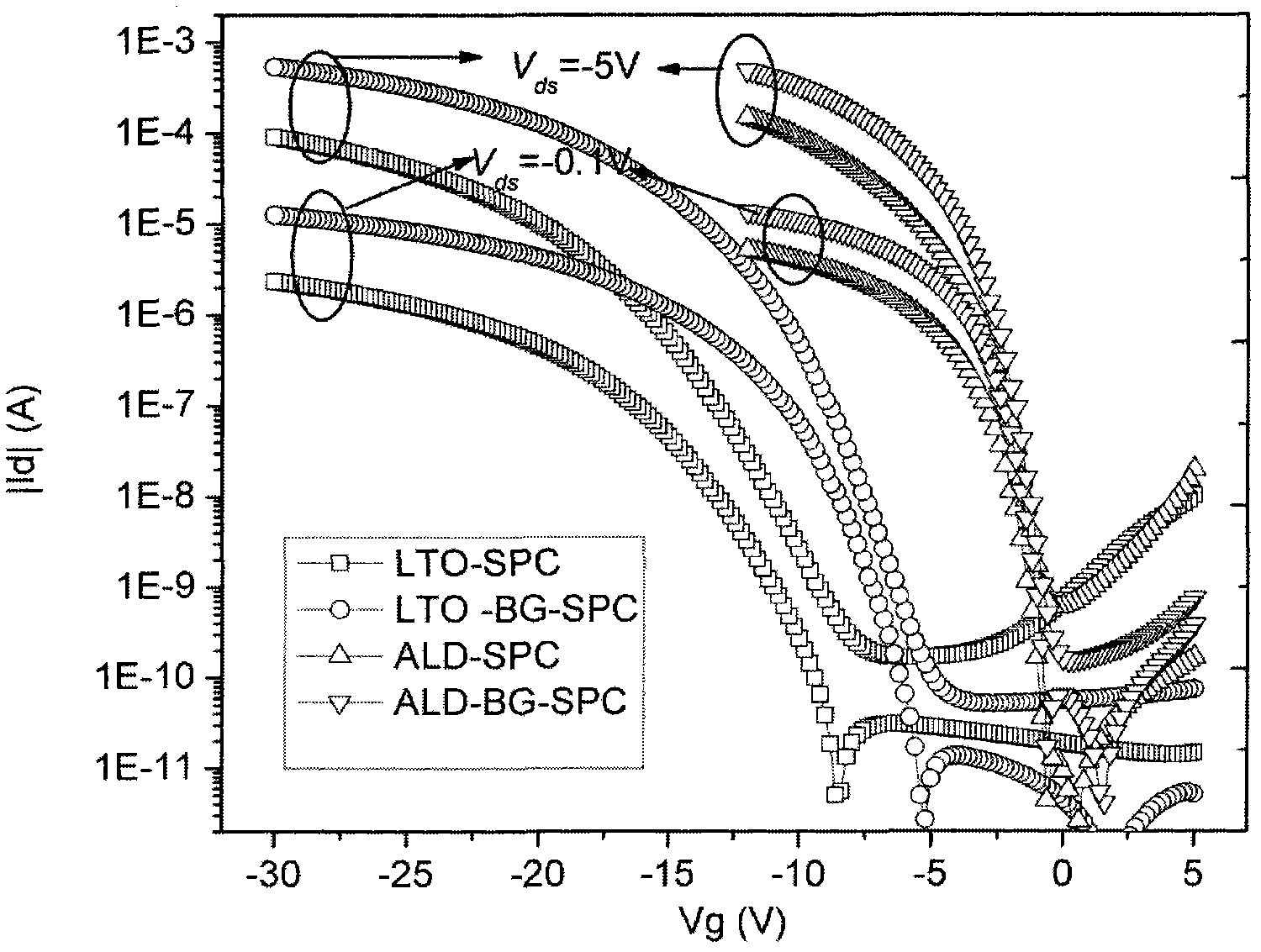

Polycrystalline silicon thin film transistor based on solid-phase crystallization technology and manufacturing method thereof

InactiveCN103258855ARaise the threshold voltageLow costTransistorSemiconductor/solid-state device manufacturingOptoelectronicsActive layer

The invention provides a polycrystalline silicon thin film transistor which comprises a substrate, an insulating layer on the substrate, a polycrystalline silicon active layer, an aluminum oxide layer and a gate electrode, wherein the polycrystalline silicon active layer is manufactured through a solid-phase crystallization method, parallel bridging crystalline grain lines, a source region and a drain region are arranged in the polycrystalline silicon active layer, the aluminum oxide layer is deposited through ALD and arranged on the polycrystalline silicon active layer and used for serving as a gate medium layer, and the gate electrode is arranged on the aluminum oxide layer.

Owner:GUANGDONG SINODISPLAY TECH

Method for encapsulating LED device with metal substrate

ActiveCN104362246AAvoid the possibility of destructionNo cost increaseSemiconductor devicesColloidEngineering

The invention discloses a method for encapsulating an LED device with a metal substrate. The method is used for solving the problems that a hollowed-out metal substrate deforms in the encapsulating process, and residual glue exists on the back face and the hollowed-out parts of the metal substrate. The method for encapsulating the LED device comprises the steps of film attaching, wherein an attaching film is attached to the back face of the hollowed-out metal substrate; conducting solid phase crystallization, wherein LED chips are fixed to the metal substrate, and solid phase crystallization is conducted on weld lines to form circuits; manufacturing fluorescent layers, wherein the fluorescent layers are manufactured on the LED chips; conducting encapsulating, wherein encapsulating layers are manufactured on the LED chips, and the LED chips are encapsulated; film removing, wherein the attaching film is removed; conducting slicing, wherein the metal substrate is cut, and each LED chip forms an independent unit. By means of the technology, glue cannot remain on the back of the metal substrate, the phenomenon of loose contact can be avoided, and the additional process for removing the residual glue is not needed.

Owner:FUJIAN TIANDIAN OPTOELECTRONICS CO LTD

Method for manufacturing amoled backplane and structure thereof

ActiveUS20170141355A1Simple processReduce the number of masksSolid-state devicesSemiconductor/solid-state device manufacturingState of artManufacturing technology

The present invention provides a method for manufacturing an AMOLED backplane and a structure thereof. The method uses a solid phase crystallization process to crystallize and convert amorphous silicon into poly-silicon so as to prevent the issue of mura on a display device caused by excimer laser annealing and adopts a back channel etching structure to effectively reduce the number of masks used. The method for manufacturing the AMOLED backplane according to the present invention needs only seven masking operations and, compared to the prior art, saves two masking operations, thereby simplifying the manufacturing process, improving the manufacturing efficiency, and saving costs.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

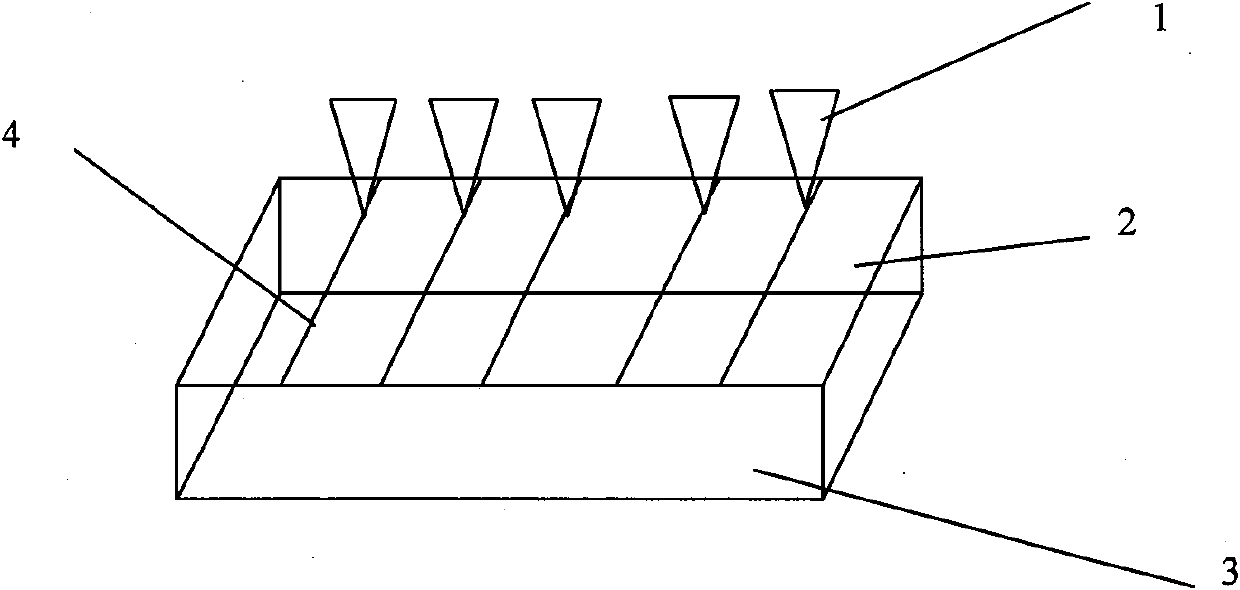

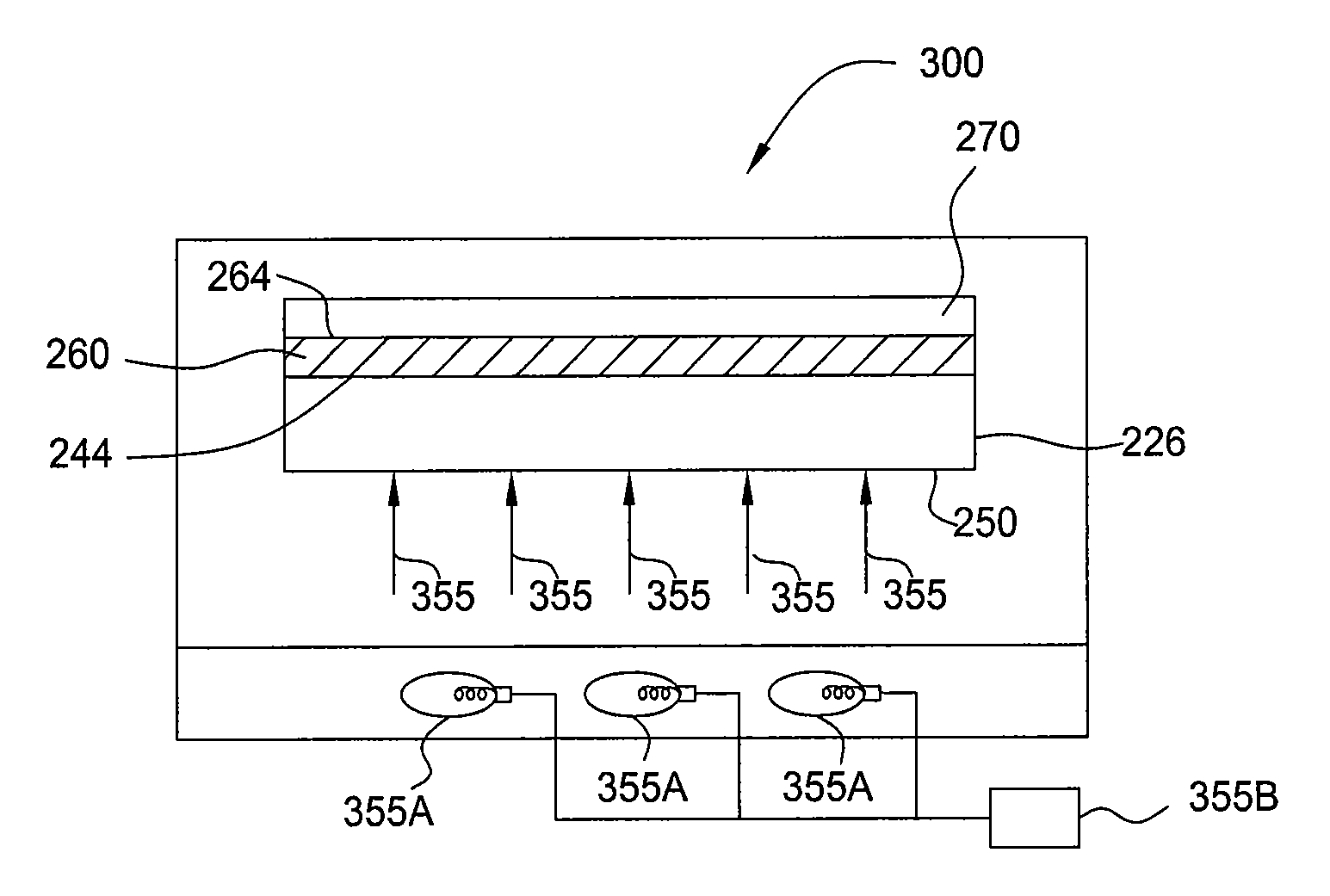

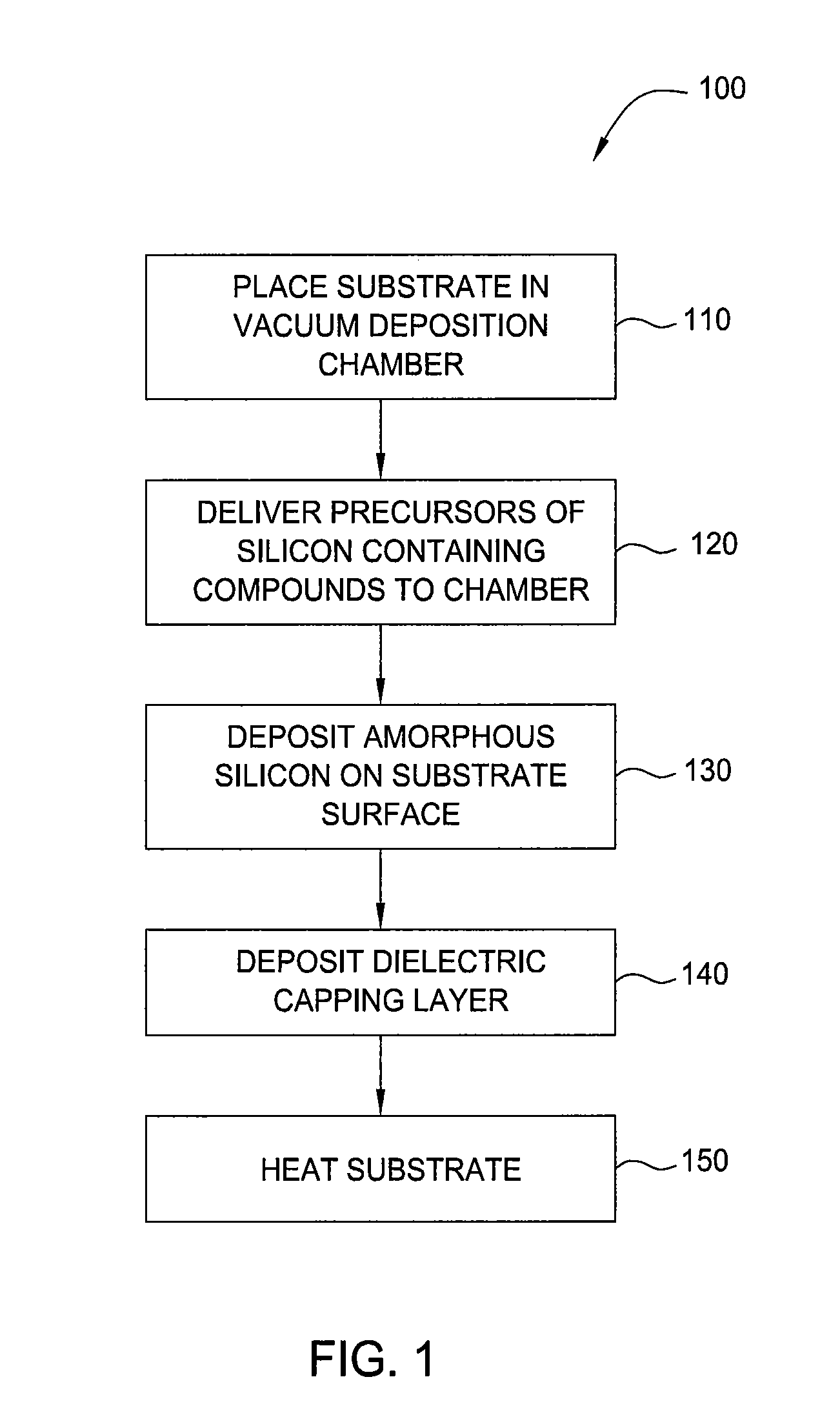

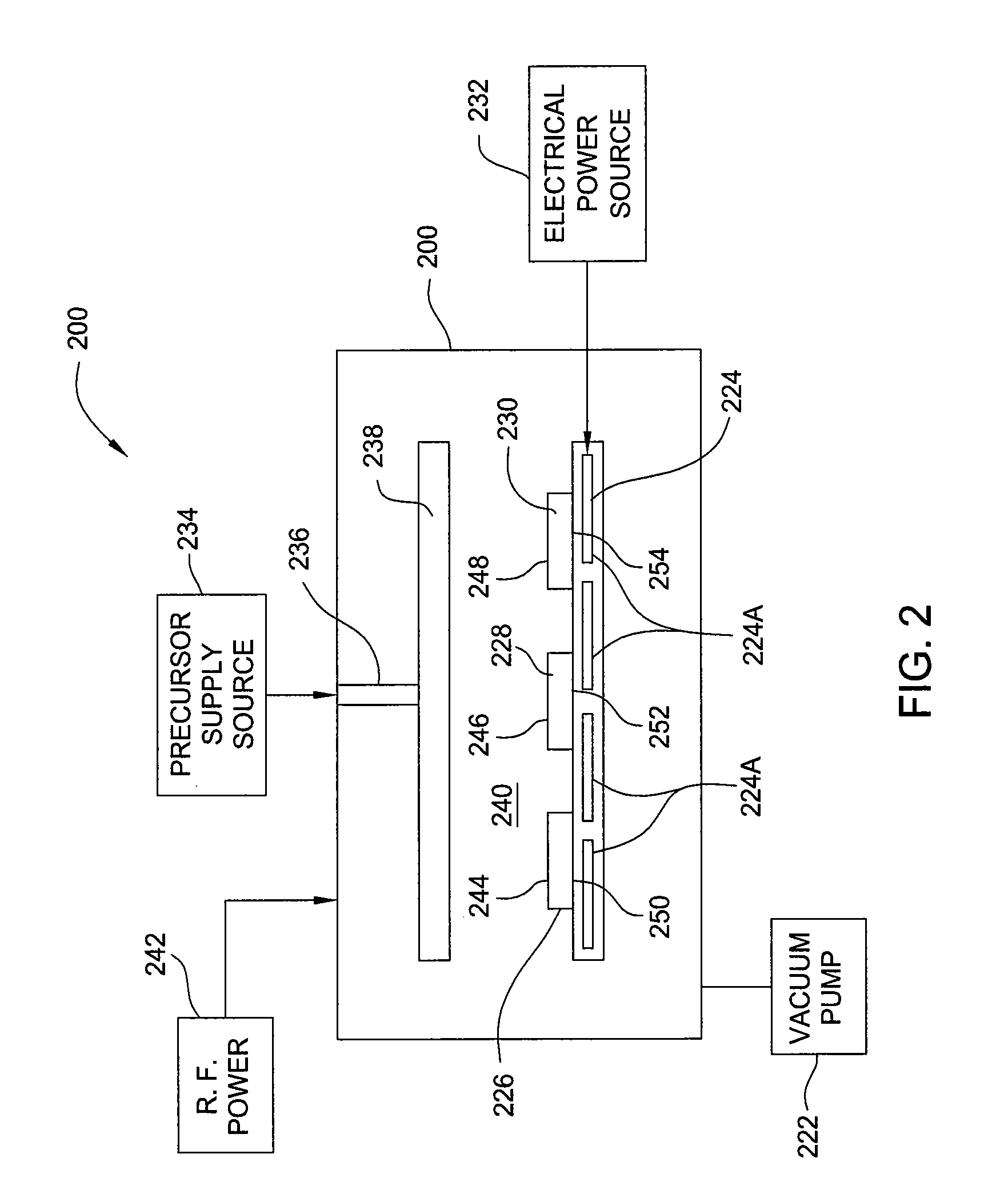

Directional solid phase crystallization of thin amorphous silicon for solar cell applications

Embodiments of the invention provide a system for heat treating a substrate which includes a first processing chamber having a first processing region coupled with a precursor source assembly configured to deliver a silicon containing gas to an upper surface of a substrate disposed within the first processing region in order to form an amorphous silicon film on the upper surface. The system further includes a substrate support having a heating element configured to heat the substrate to a temperature sufficient to crystallize the amorphous silicon film by solid phase crystallization and to create a temperature gradient in which a temperature at the lower surface of the substrate is greater than a temperature at the upper surface of the amorphous silicon film and the temperature gradient is within a range from about 2° C. to about 10° C.

Owner:APPLIED MATERIALS INC