Patents

Literature

89results about How to "Realized area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

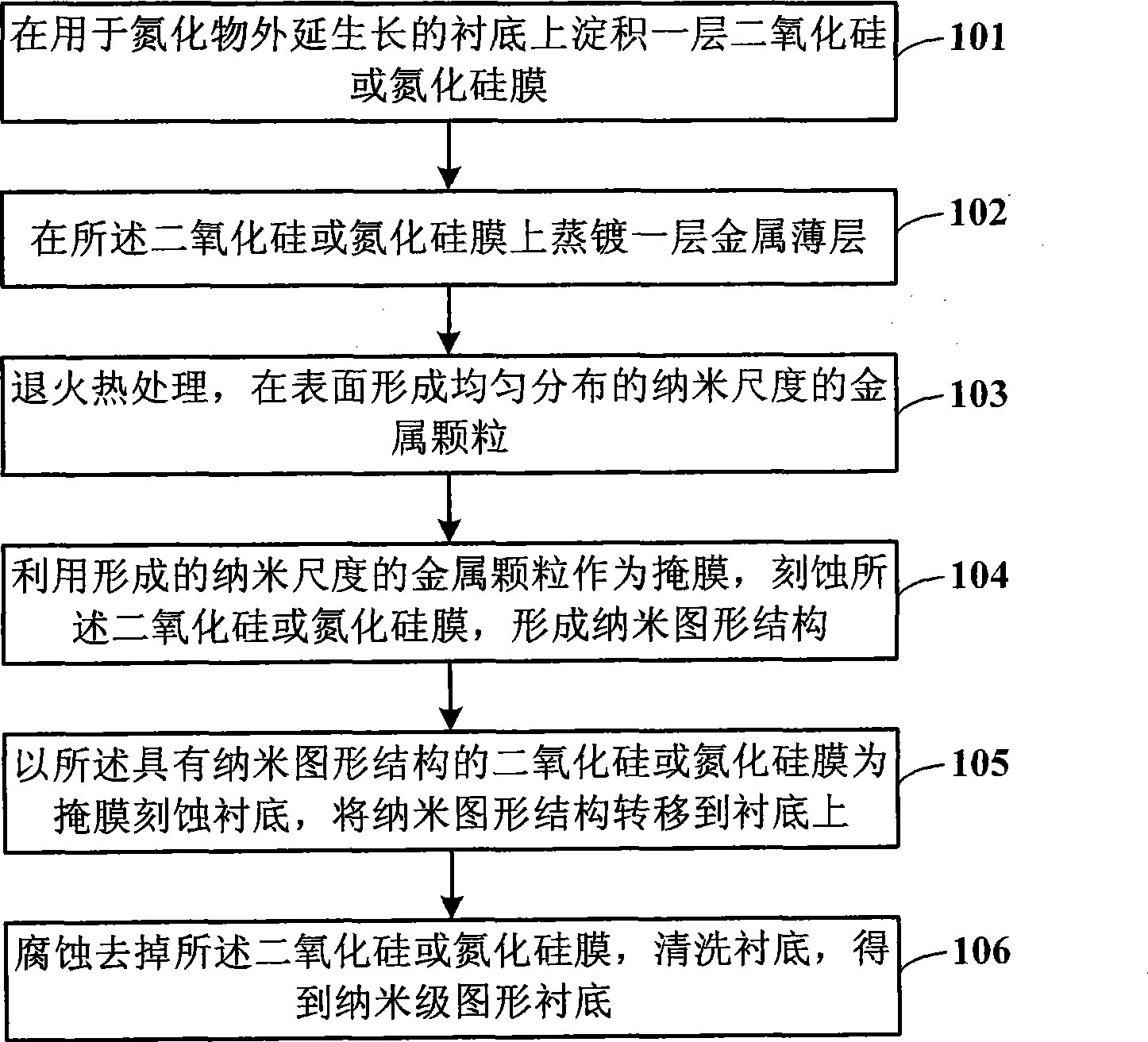

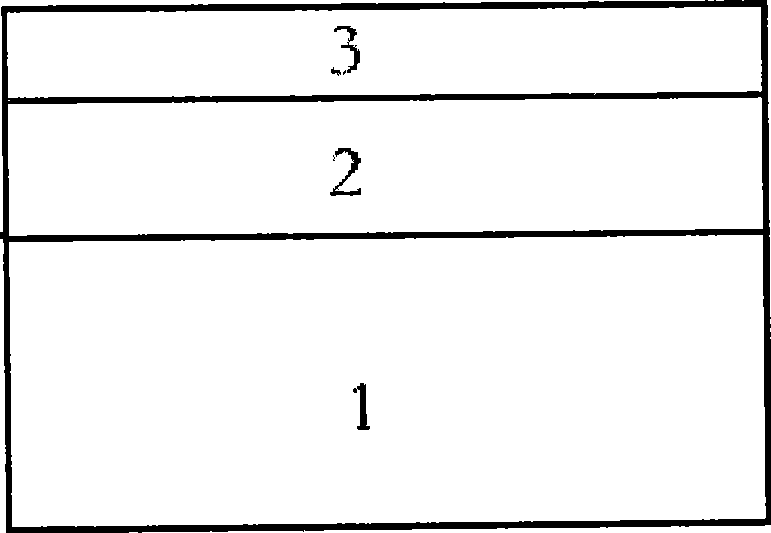

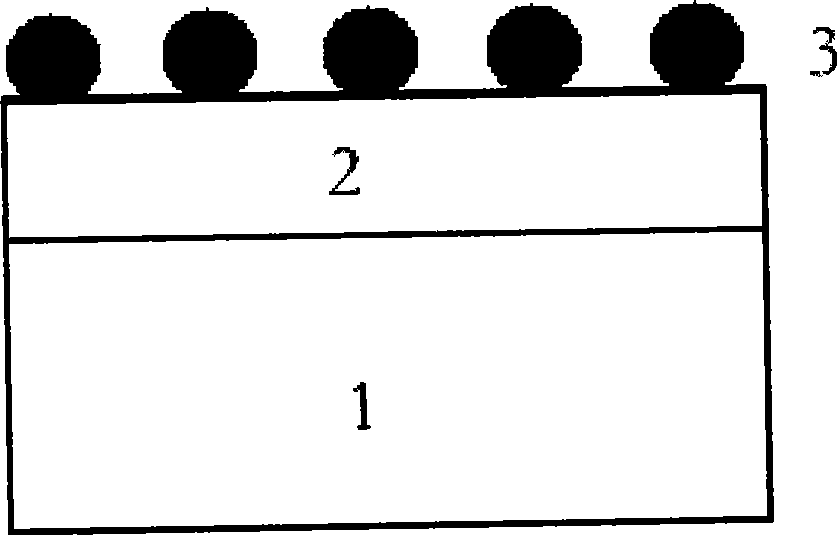

Method for preparing nano-scale pattern substrate for nitride epitaxial growth

InactiveCN101373714AReduce dislocation densityImprove crystal qualitySemiconductor/solid-state device manufacturingThin metalEpitaxial material

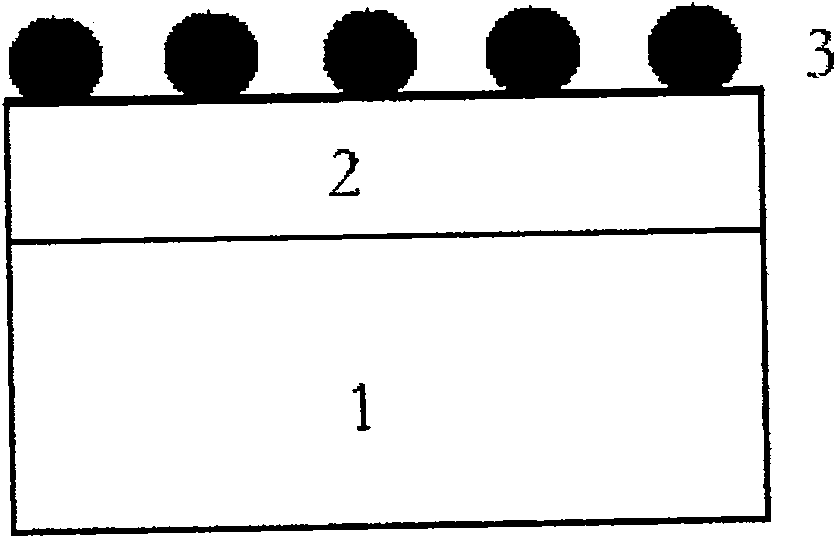

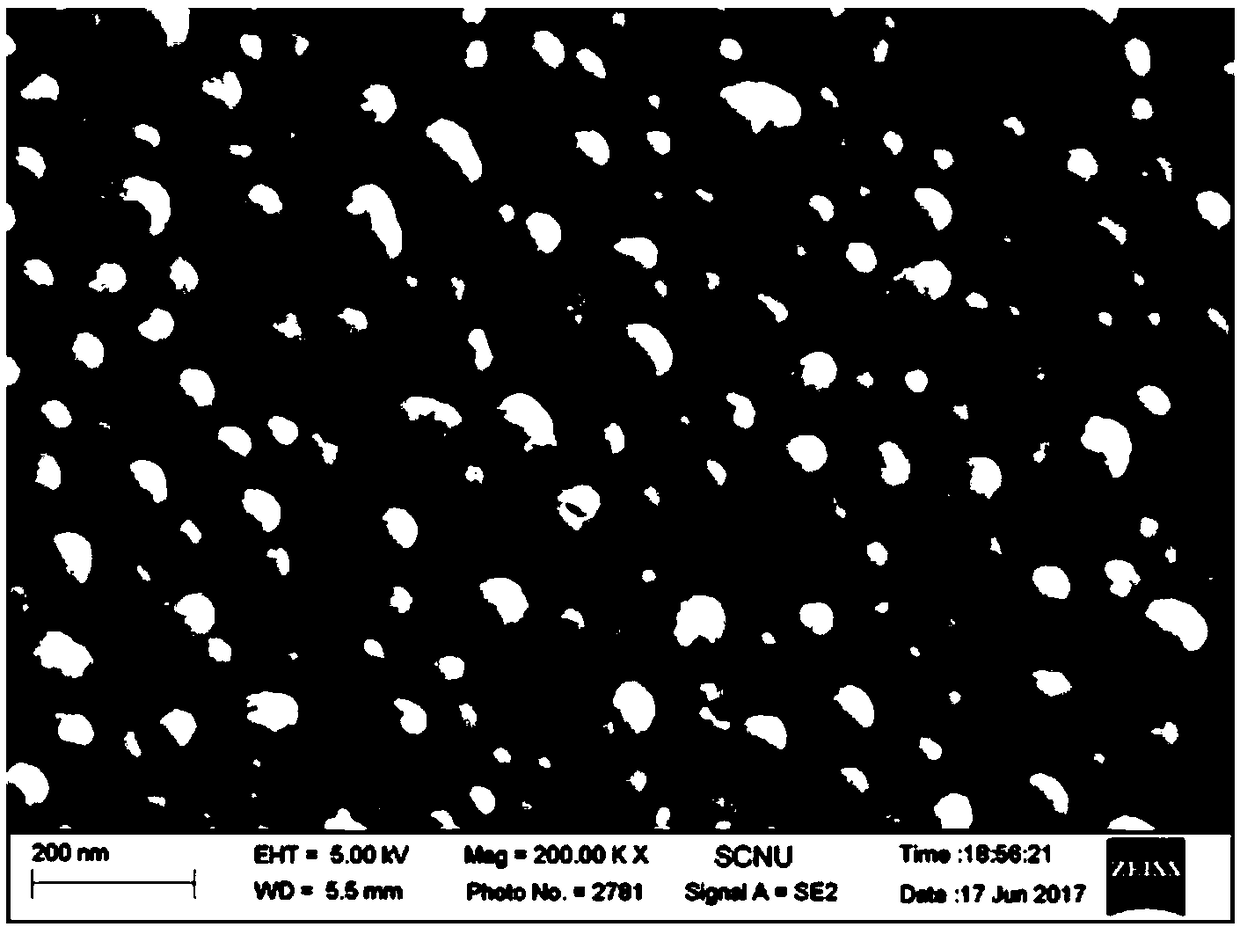

The invention relates to the semiconductor technical field and discloses a method for manufacturing a nanometer pattern substrate used for the epitaxial growth of a nitride. The method comprises the followings steps: settling a layer of silicon dioxide or silicon nitride film on a substrate used for the epitaxial growth of the nitride; the silicon dioxide or silicon nitride film is coated with a layer of thin metal layer through vapor deposition; conducting the annealing heat treatment, and forming uniformly distributed nano-scaled metal particles; utilizing the formed nano-scaled metal particles as masks to etch the silicon dioxide or silicon nitride film so as to form a nanometer pattern structure; using the silicon dioxide or silicon nitride film with the nanometer pattern structure as a mask etching substrate to transfer the nanometer pattern structure of the substrate; and etching to remove the silicon dioxide or silicon nitride film, cleaning the substrate, and obtaining the nanometer pattern substrate. The invention can reduce the dislocation density in the epitaxial layer of the nitride, improve the crystal quality of epitaxial materials, improve the performance of devices and help to realize the scaled and large area manufacture.

Owner:UNILUMIN GRP

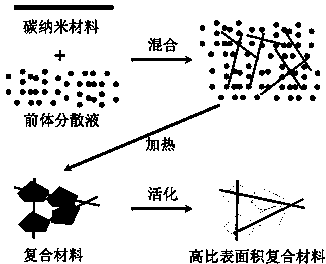

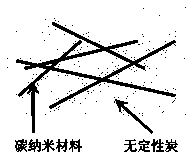

Carbon composite material, and preparation method and application thereof

InactiveCN104176721ATo achieve an organic combinationRaw materials are easy to getMaterial nanotechnologyOther chemical processesFiberCarbon composites

The invention discloses a carbon composite material. The carbon composite material comprises 0.1-35wt% of a carbon nanomaterial and 99.9-65wt% of amorphous carbon with a high surface area; the carbon nanometer is one or a mixture of more of carbon nanotubes, carbon fibers, graphene oxide and graphene; and the specific surface area, the pore volume and the conductivity of the composite material are not lower than 800m<2> / g, not lower than 0.3cm<3> and not lower than 4S / cm respectively, and the aperture of the composite material is 0.5-10nm. The carbon composite material has the respective characteristics of the carbon nanomaterial and the amorphous carbon, realizes the organic combination of the carbon nanomaterial and the amorphous carbon in functions, has high surface area and high conductivity, and can provide superior capacity and rate performance as an excellent electrode and conductive material of super capacitors, lithium ion capacitors, fuel batteries and lead carbon battery electrodes. The carbon composite material can remove impurities in water as an electrode material in water treatment devices.

Owner:JIANGSU JF ADVANCED TECH

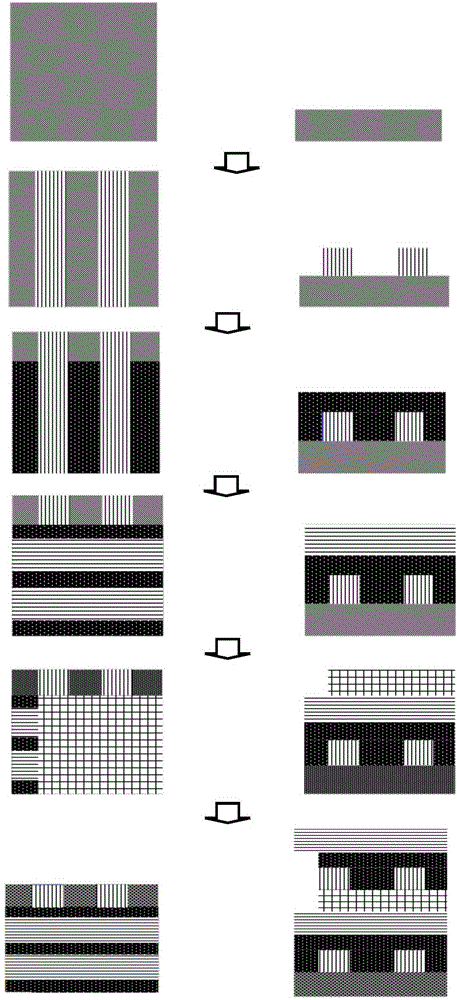

Method for preparing GaN-based pattern substrate template

InactiveCN101814427AEvenly distributedImprove orderSemiconductor/solid-state device manufacturingMicrosphereNitride

The invention relates to a method for preparing a GaN-based pattern substrate template. The method comprises the following steps of: growing a layer of GaN-based template on a substrate for epitaxial growth of nitrides; laying microspheres on the surface of the GaN-based template by using a microsphere solution to form a microsphere layer with a monomolecular layer structure; evaporating metals on the substrate, depositing the evaporated metals on the surface of the GaN-based template through the voids among the microspheres; removing the microsphere layer with a monomolecular layer structure by supersonic vibration to obtain a pattern metal layer; transferring patterns on the metal layer to the GaN-based template with an etching method by using the metal layer as a mask; and removing the metal layer to obtain the GaN-based material pattern substrate template. The method has the advantages of simple process, low cost and adjustable pattern pit size and space. The method can be used for preparing a micron-grade semiconductor substrate pattern.

Owner:SUN YAT SEN UNIV

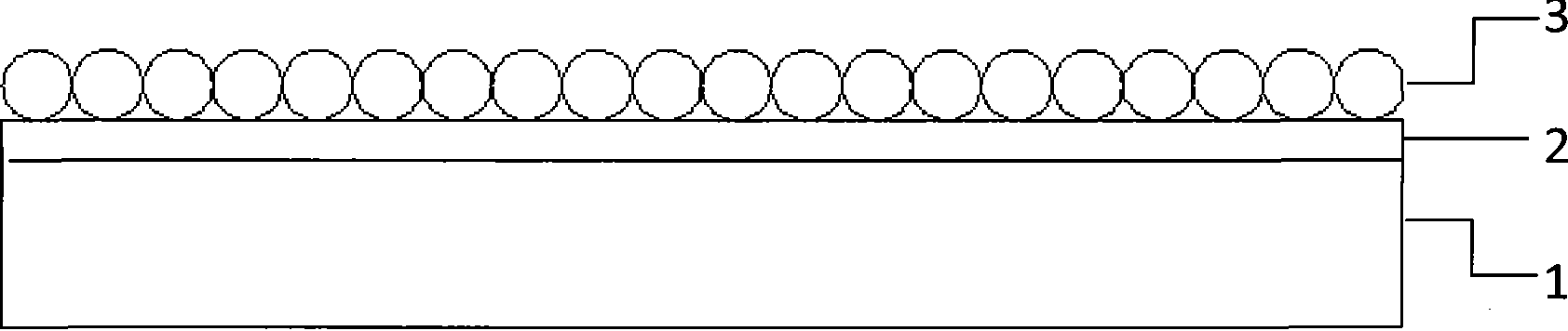

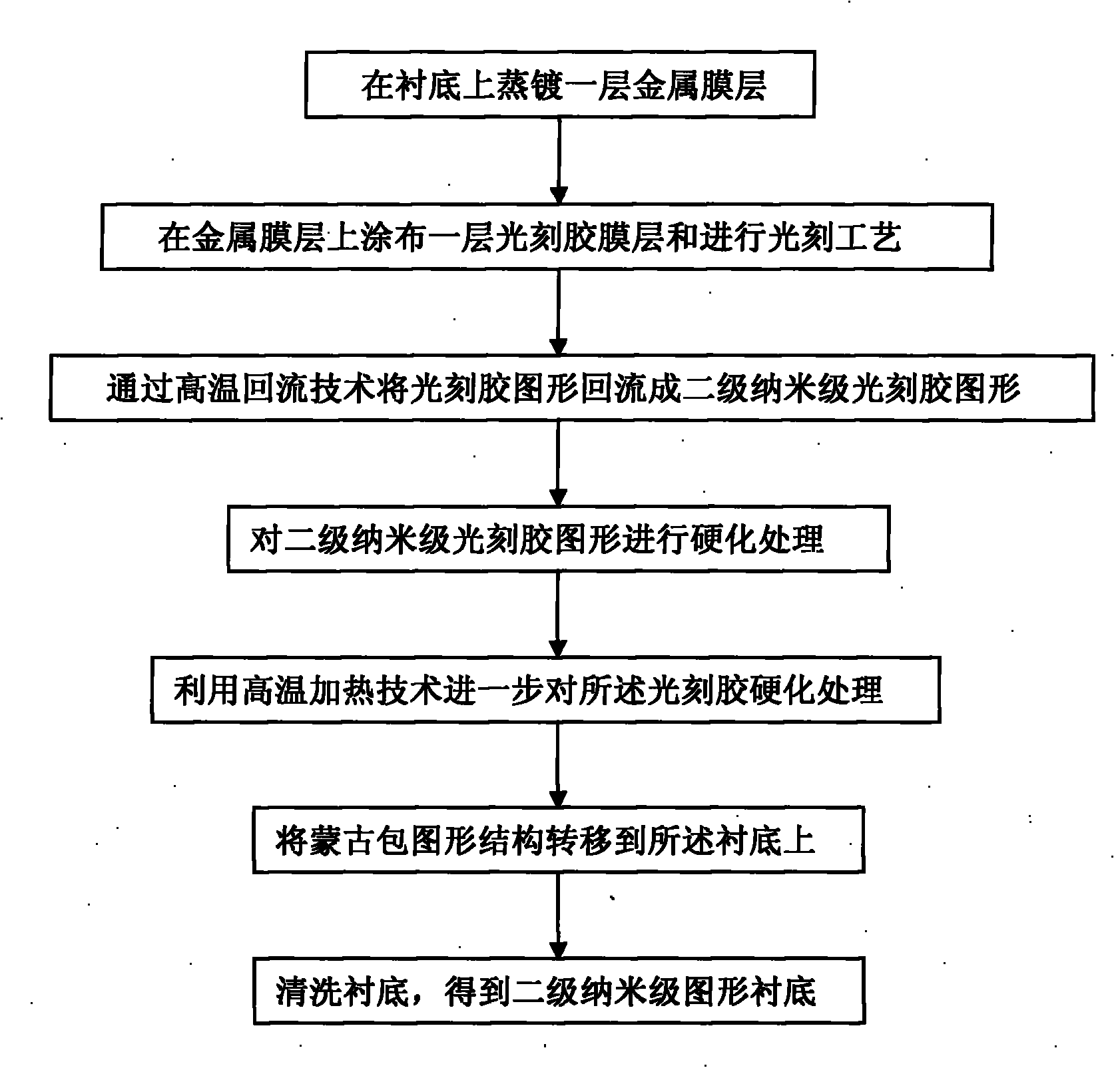

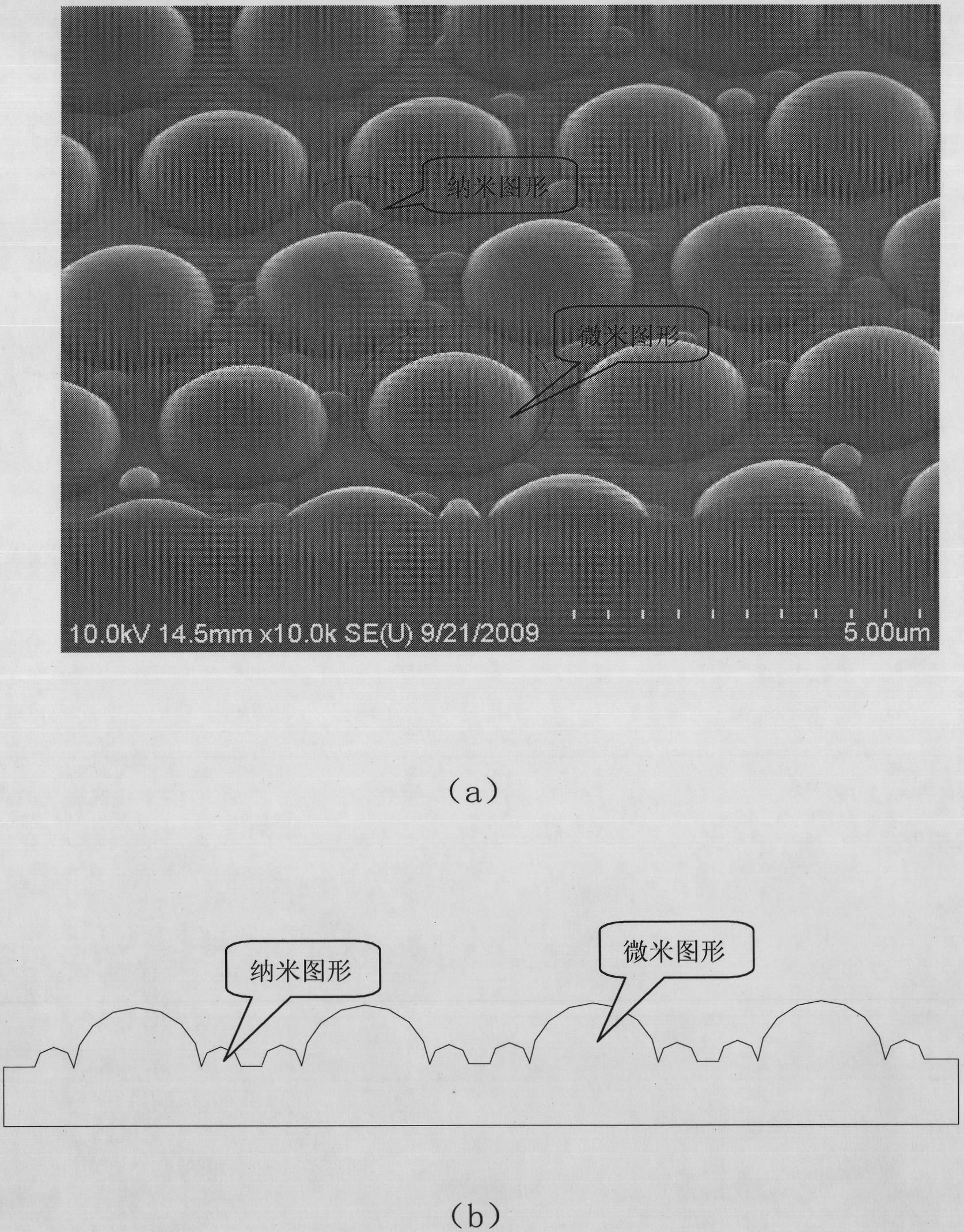

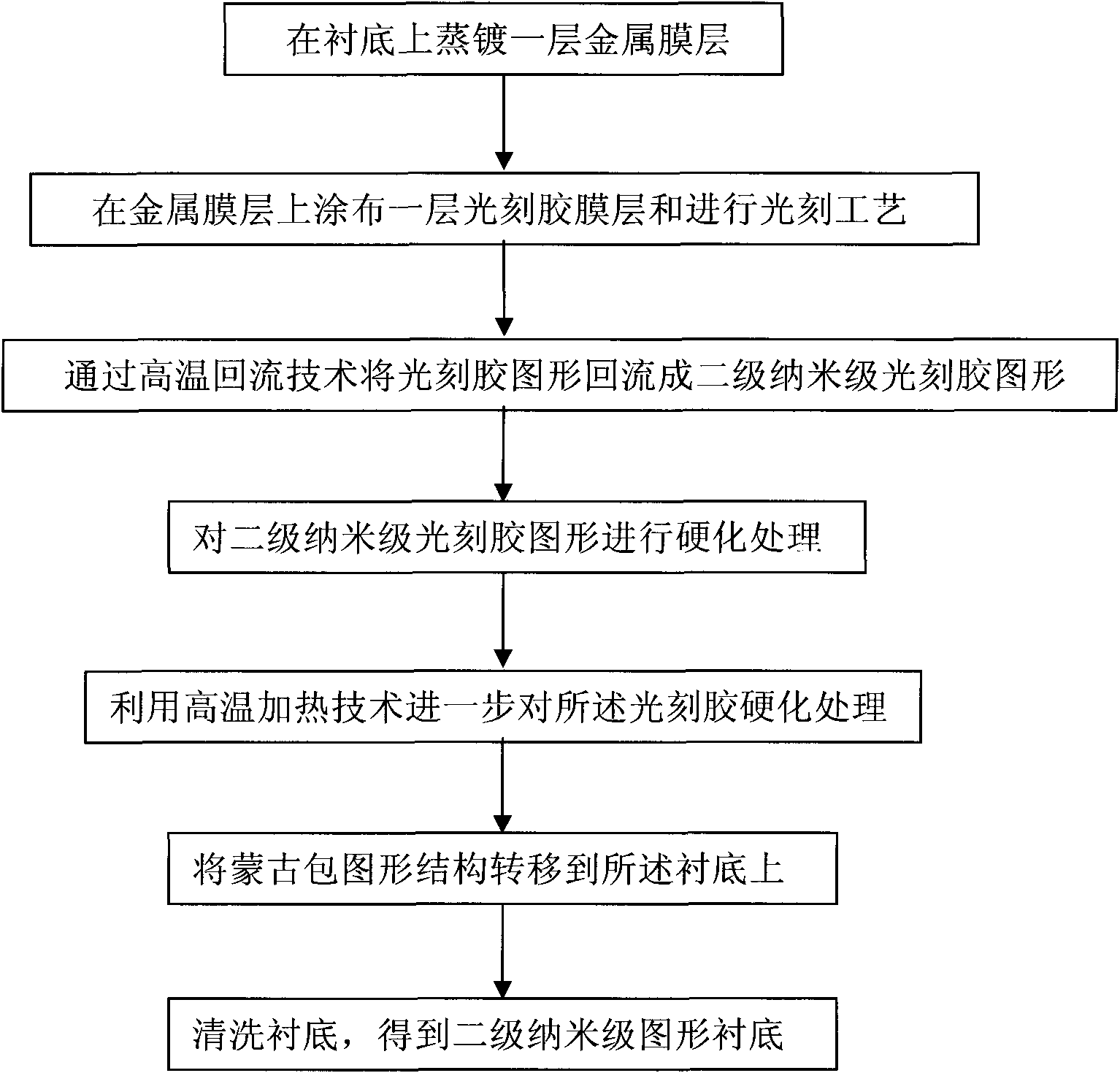

Method for preparing epitaxial growing nano pattern substrate of nitride

InactiveCN101814564AReduce dislocation densityStress effective relaxationSemiconductor devicesRefluxPhotoresist

The invention discloses a method for preparing an epitaxial growing nano pattern substrate of a nitride, which comprises the following steps of: evaporating a metal film layer on a substrate; coating a photoresist film layer on the metal film layer; developing nano-size photoresist patterns on the substrate by a photomask technology and retaining a layer of thin photoresist between the patterns; forming two stages of nano-grade photoresist patterns by a high-temperature reflux technology, wherein one stage of nano-grade photoresist pattern is a micron-size pattern, and the other stage of nano-grade photoresist pattern is a nano-size pattern; carrying out hardening processing on the two stages of nano-grade photoresist patterns; further hardening the photoresist patterns by utilizing a photoresist heating and baking technology; transferring the photoresist pattern structures on the substrate by utilizing the two formed stages of nano-grade photoresist patterns as mask films through a dry etching technology; and cleaning the substrate to obtain two stages of nano-grade pattern substrates. The invention can improve the crystal quality of materials and the corresponding device performance.

Owner:EPILIGHT TECH

Write-once read-many disc internal memory

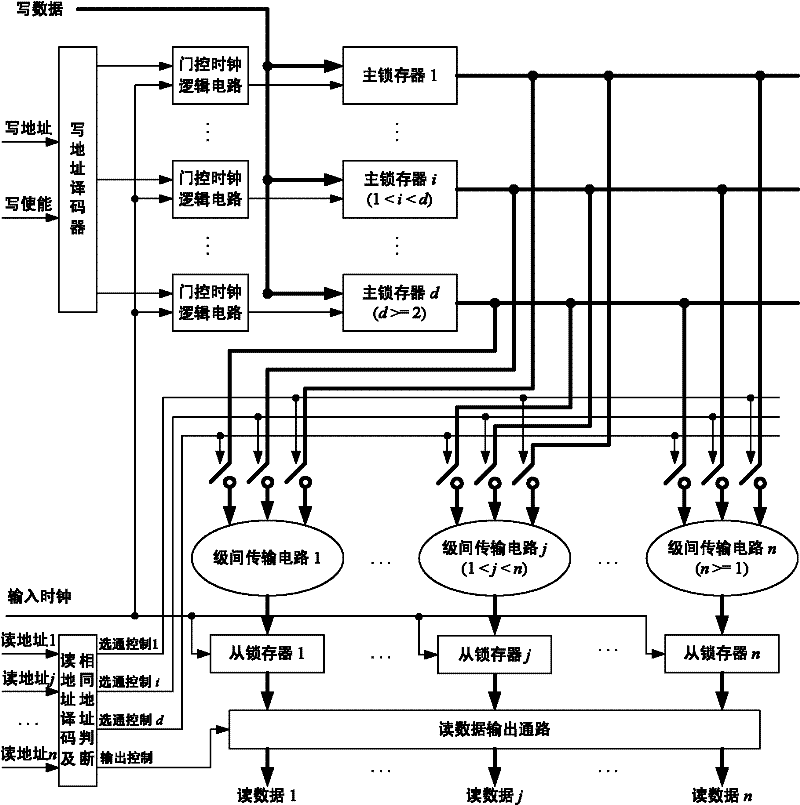

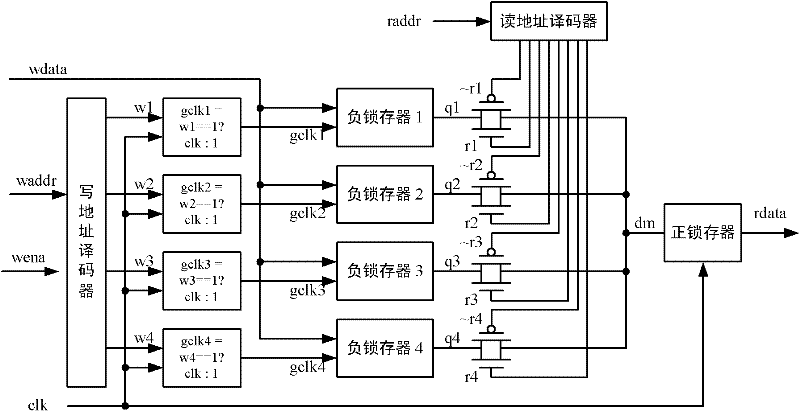

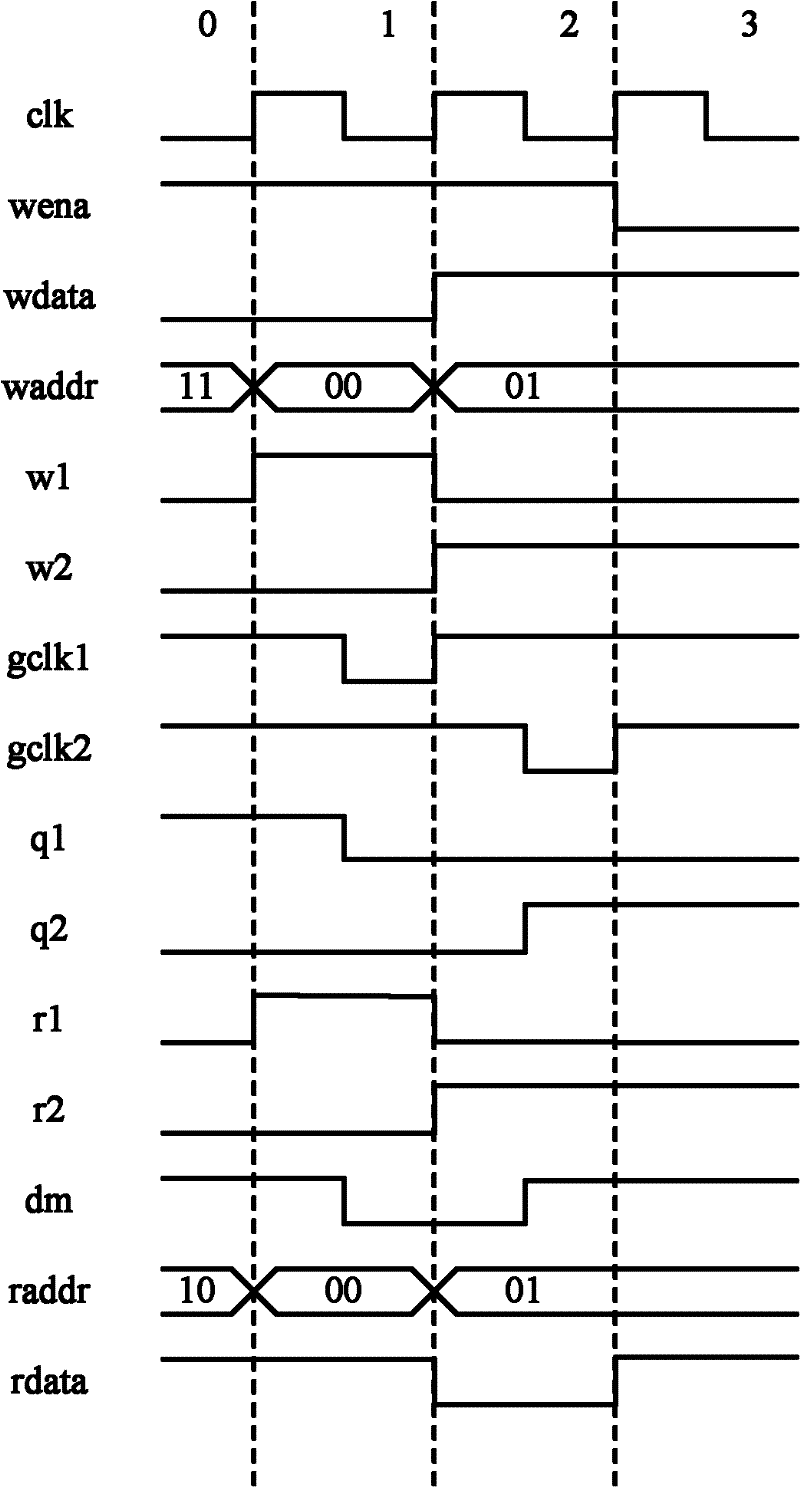

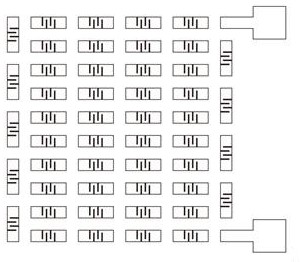

ActiveCN102610269AKeep reading and writing characteristicsReduce areaDigital storageInternal memoryAddress decoder

The invention discloses a write-once read-many disc internal memory, comprising a write address decoder, d (d>1) gate clock logic circuits, d first level main latches, n d input inter-stage transmission circuits, n second-level sub latches, a read data output path, and a read address decoding and same address judging module, wherein if the d first-level main latches are negative latches, the n second-level sub latches are positive latches; and if the d first-level main latches are positive latches, the n second-level sub latches are negative latches. The area of the memory unit close to the latches is realized, simultaneously the reading and writing features of the file in a register are held, that is, the same memory unit can be accessed by any reading port and any writing port in a same clock period.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

Reverse sanding process

The invention provides a reverse sanding process comprising the following steps that: (1) a ceramic anilox roller with 80-120 wires is utilized, and the requirements are as follows: in the area with one square meter, more than 40000 ink cells exist, the angle of each ink cell is 60 degrees, and the depth of each ink cell is 13-33micrometers; (2) the temperature of a production environment is kept between 22 DEG C-29 DEG C, and the humidity is controlled between 45 degrees-65 degrees; (3) single-set colorless transparent ultraviolet (UV) light curing oil ink and single-set colorless transparent UV light curing UV are selected, and the viscosity is 45-60PaS; (4) five 15KW UV lamps are selected, the wavelengths of ultraviolet rays of the UV lamps are 200-400, the first group of control power and the second group of control power are 50%, and the control power of the three UV lamps of a paper absorbing drying channel is 100%; and (5) the printing is conducted according to an existing offset print operation procedure. According to the reverse sanding process provided by the invention, the printing and sanding process of printing materials with six colors or less then six colors can be completed at one time, the large-area sanding and surface mirror effects can be realized, and the printing precision problem can be solved effectively.

Owner:富康集团有限公司

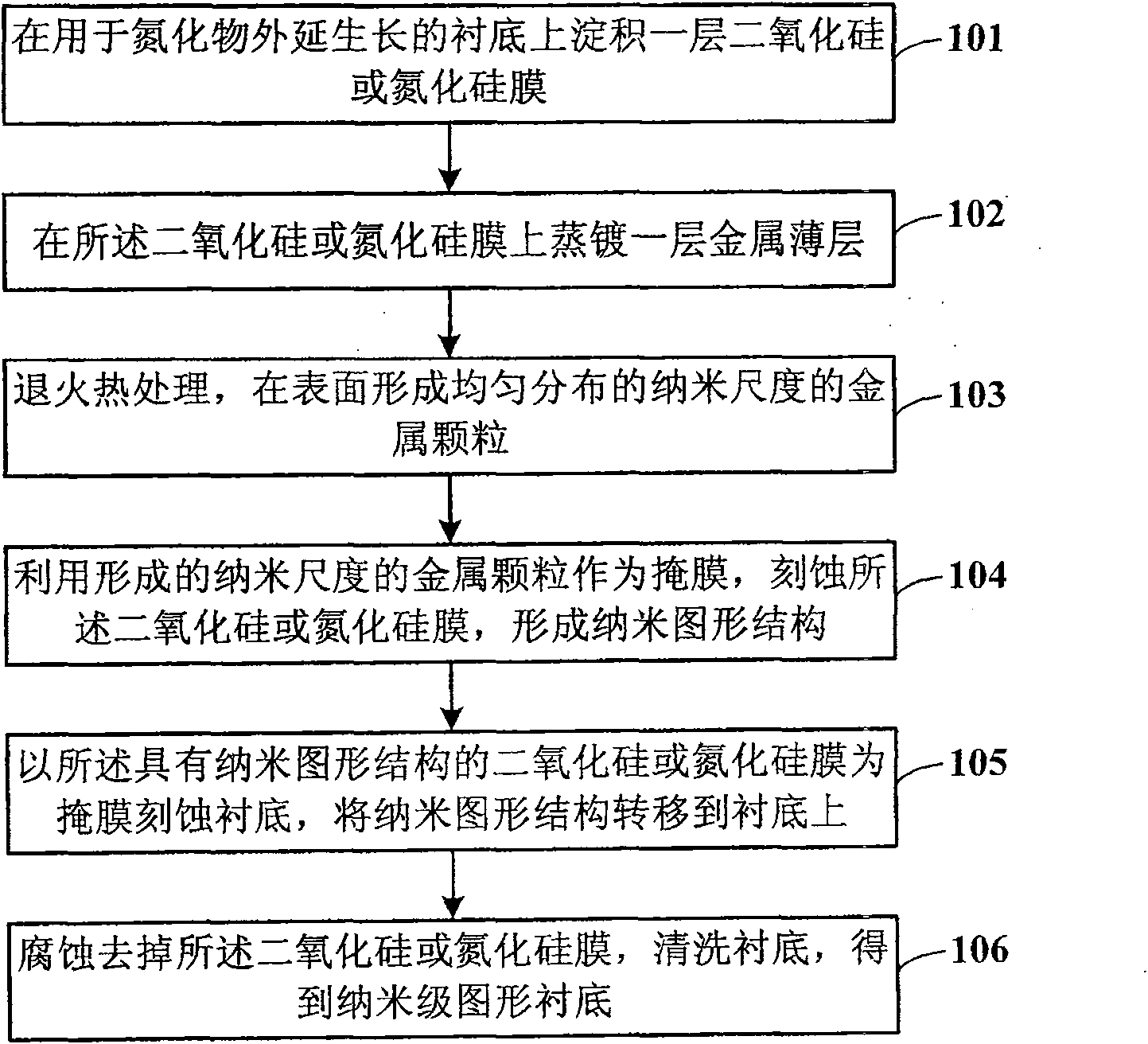

Method for preparing nano-scale pattern substrate for nitride epitaxial growth

InactiveCN100587919CReduce dislocation densityImprove crystal qualitySemiconductor/solid-state device manufacturingThin metalEpitaxial material

The invention relates to the semiconductor technical field and discloses a method for manufacturing a nanometer pattern substrate used for the epitaxial growth of a nitride. The method comprises the followings steps: settling a layer of silicon dioxide or silicon nitride film on a substrate used for the epitaxial growth of the nitride; the silicon dioxide or silicon nitride film is coated with a layer of thin metal layer through vapor deposition; conducting the annealing heat treatment, and forming uniformly distributed nano-scaled metal particles; utilizing the formed nano-scaled metal particles as masks to etch the silicon dioxide or silicon nitride film so as to form a nanometer pattern structure; using the silicon dioxide or silicon nitride film with the nanometer pattern structure asa mask etching substrate to transfer the nanometer pattern structure of the substrate; and etching to remove the silicon dioxide or silicon nitride film, cleaning the substrate, and obtaining the nanometer pattern substrate. The invention can reduce the dislocation density in the epitaxial layer of the nitride, improve the crystal quality of epitaxial materials, improve the performance of devicesand help to realize the scaled and large area manufacture.

Owner:UNILUMIN GRP

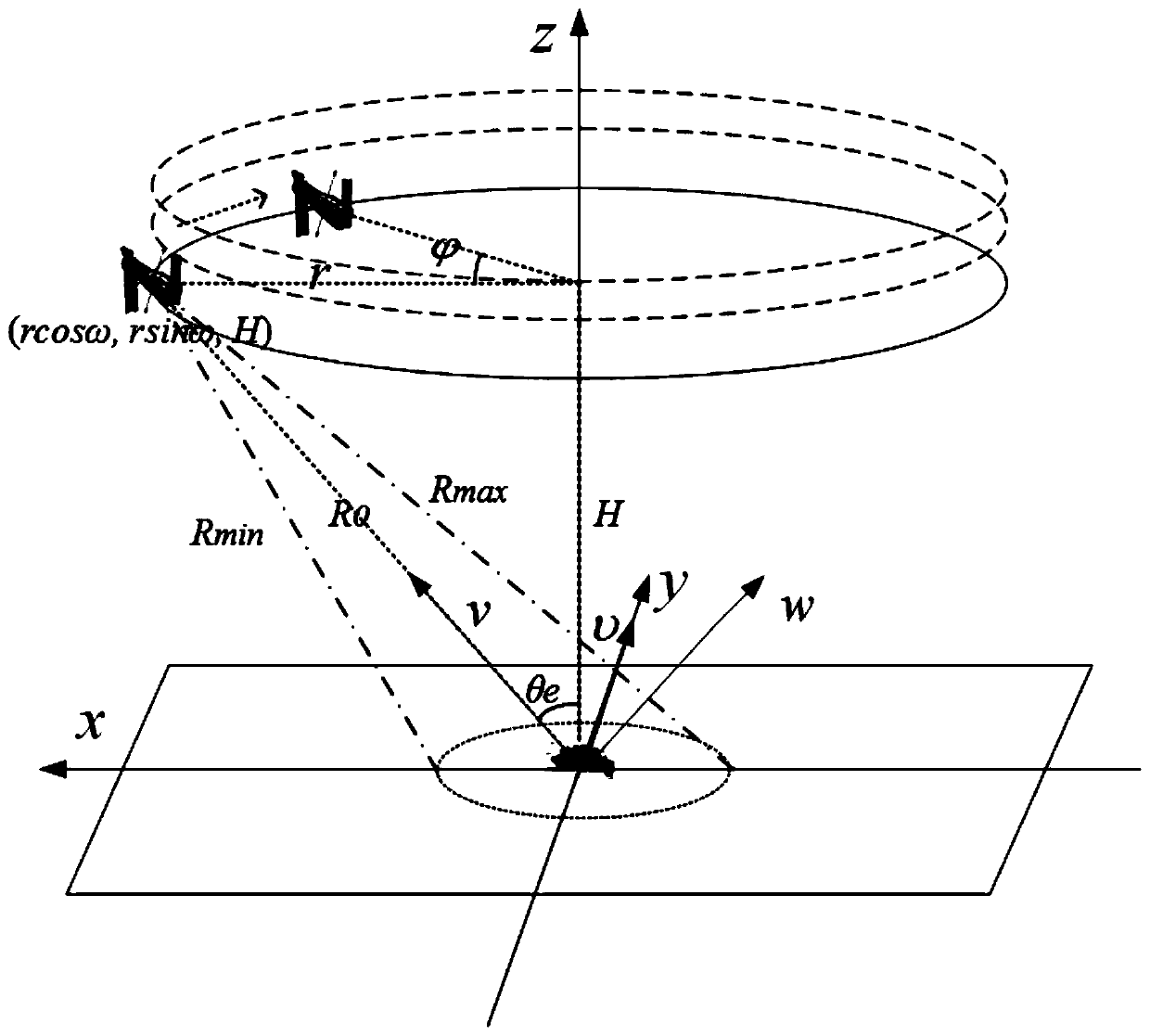

Spaceborne multi-baseline holographic SAR imaging method

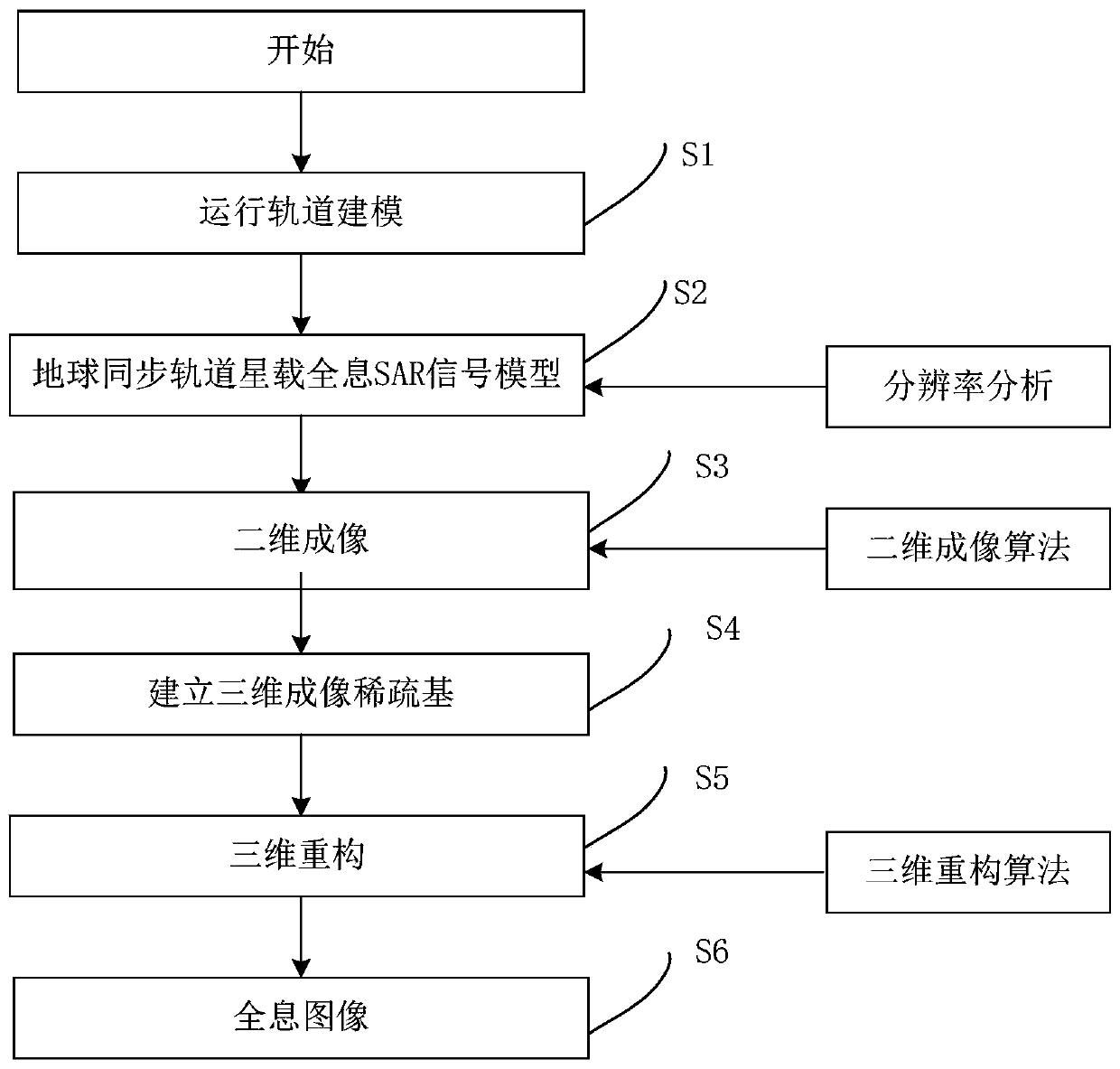

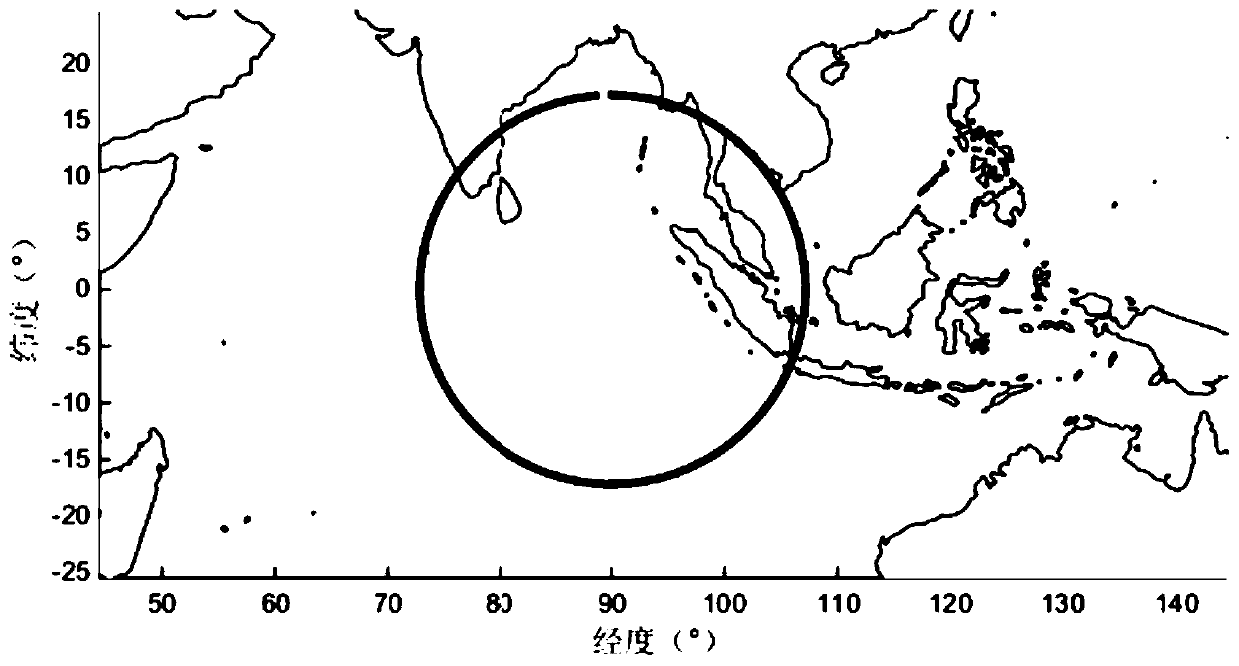

InactiveCN110488294ASolution rangeSolve the limited detection areaRadio wave reradiation/reflectionGeosynchronous orbitHolographic imaging

The invention discloses a spaceborne multi-baseline holographic SAR imaging method, which realizes 360-degree omnibearing imaging based on multiple navigation geosynchronous orbit baselines. The method comprises the following steps: S1, an orbit model for geosynchronous orbit spaceborne holographic SAR imaging is constructed; S2, based on the orbit model and an imaging geometric model of the geosynchronous orbit spaceborne holographic SAR imaging, a geosynchronous orbit spaceborne holographic SAR echo signal model is constructed; S3, two-dimensional holographic imaging is carried out; S4, a three-dimensional imaging sparse basis is constructed through constructing an altitude sparse basis; S5, the altitude of a ground target is reconstructed by using a compressed sensing reconstruction algorithm; and S6, a holographic image is displayed. The problems that the airborne platform has a small detection range, the detection area is limited, and the holographic imaging quality is affected bythe movement of a carrier and the like can be solved.

Owner:SHANGHAI RADIO EQUIP RES INST

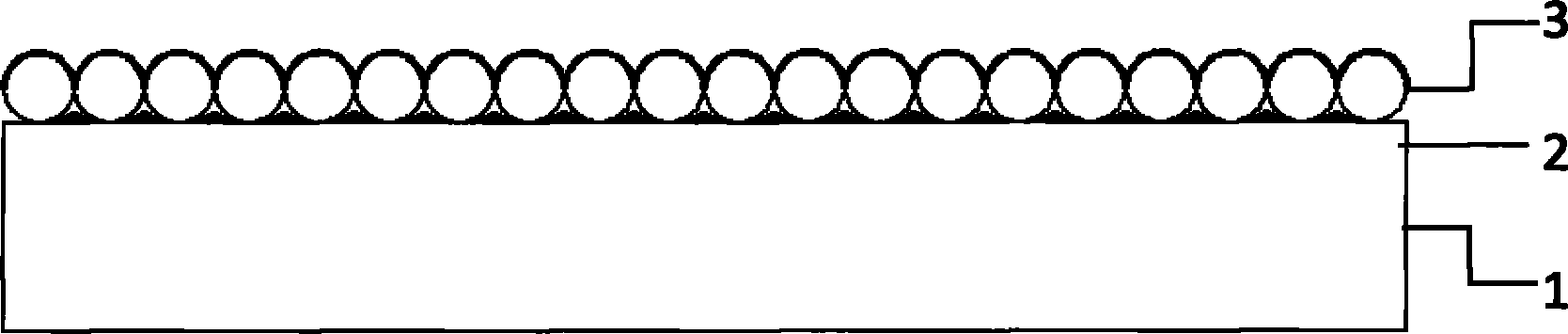

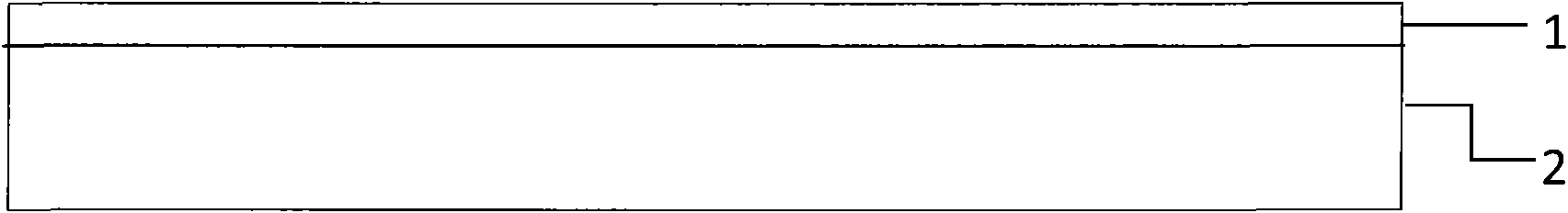

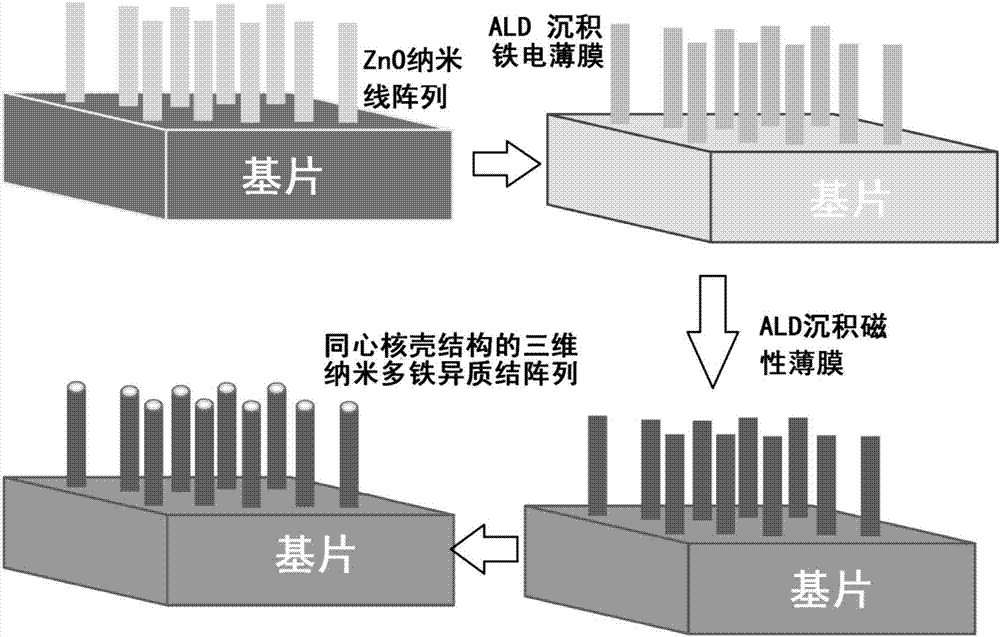

Method for constructing concentric nuclear-shell three-dimensional nano multi-ferroic heterojunction array by ALD

ActiveCN107425053AHighly integratedEasy to operateMaterial nanotechnologyNanoinformaticsHeterojunctionSputtering

The invention discloses a method for constructing a concentric-nuclear-shell three-dimensional nano multi-ferroic heterojunction array by an ALD. A ZnO nano-wire array grows on a piece of conductive glass; a ferroelectric thin films and a magnetic thin film are deposited successively by using the ZnO nano-wire array as a template according to an atomic layer deposition (ALD) method; and after the ferroelectric thin films and the magnetic thin film that are formed on the top of the ZnO nano-wire array are etched, a metal electrode layer is sputtered on the top of the ZnO nano-wire array, so that a three-dimensional nano multi-ferroic heterojunction array having a concentric nuclear-shell structure is obtained. Therefore, technical problems that the existing multi-ferroic heterojunction only has the planar structure and microminiaturization can not be realized are solved. The method is compatible with the existing leading three-dimensional microelectronic device process and can be operated simply; the price is low; the safety is high and the non-toxic and pollution-free performances are good; and batched production is realized. On the basis of the effective technical scheme and the solution, transition of the multi-ferroic heterojunction from the planar structure to the three-dimensional structure is realized, so that the bottleneck breakthrough of transition from the macro dimension to the micro dimension is realized.

Owner:XI AN JIAOTONG UNIV

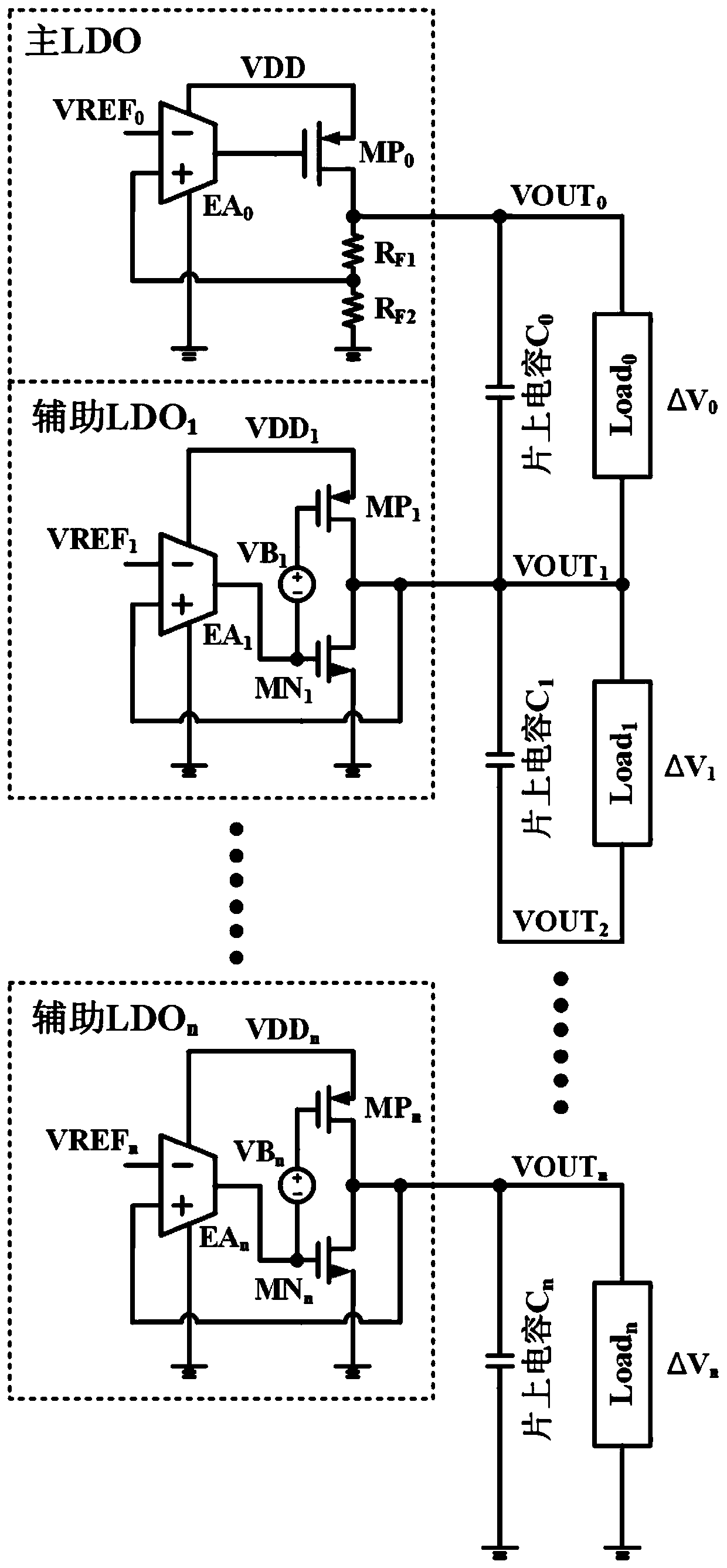

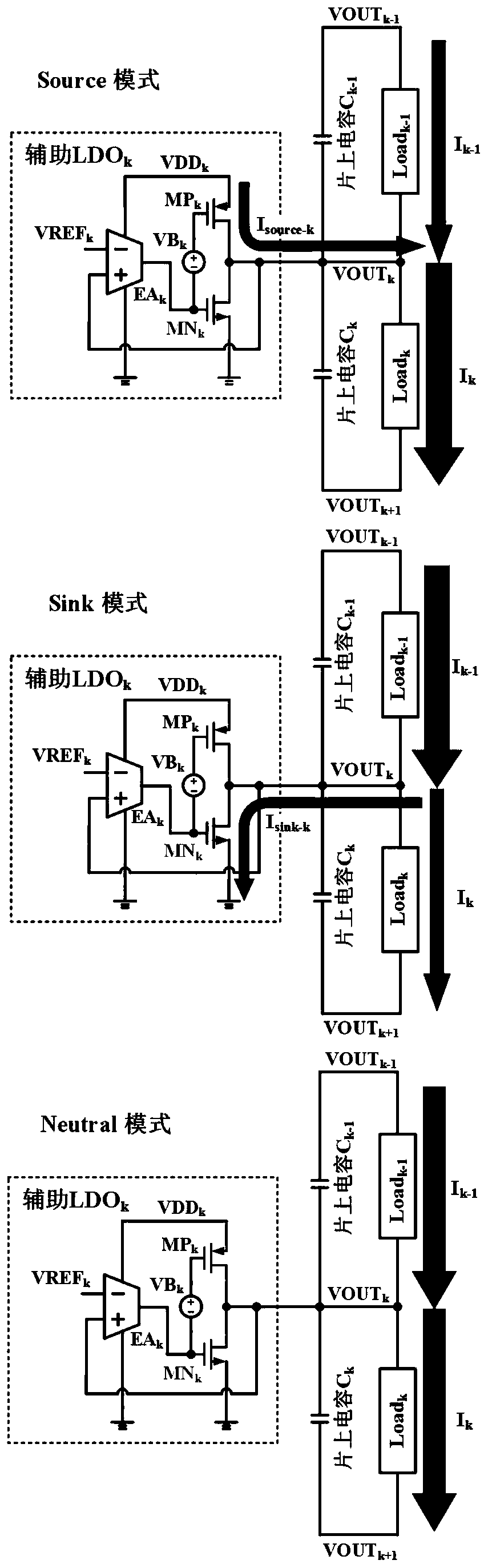

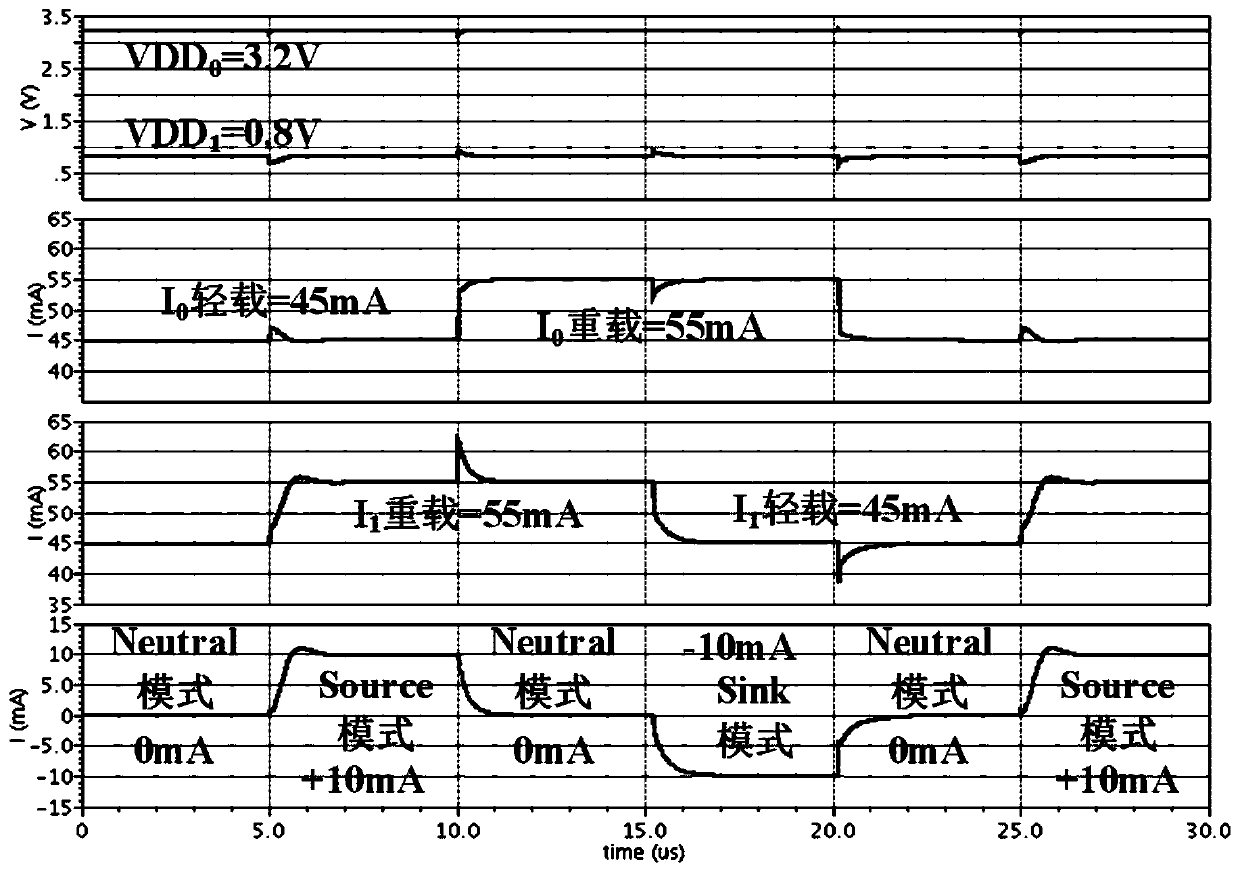

Fully integrated multi-output stackable low-dropout regulator (LDO)

ActiveCN109725673AImprove dynamic performanceAchieving a fully integrated structureElectric variable regulationSystem integrationComputer module

The invention discloses a fully integrated multi-output stackable low-dropout regulator (LDO). The fully integrated multi-output stackable low-dropout regulator (LDO) comprises a main LDO and an auxiliary LDO<k>; k is 1,2...n; the main LDO is connected with an on-chip capacitor C<k> and a load Load<k> on an auxiliary LDO<k> circuit through an on-chip capacitor C<0> and a load Load<0> in series, sothat a stacked structure is formed; the main LDO is used for providing current required by the load; the auxiliary LDO<k> is used for stabilizing VOUT<k> voltage; and, when the load current is not same, a I<source> current flowing from VDD<k> to VOUT<k> through MP<k> or a I<sink> current flowing from VOUT<k> to GND through MN<k> is generated. According to the stacked structure in the invention, the output voltage value and the output voltage number can be flexibly adjusted according to load requirements; relatively flexible load requirements are satisfied; due to the three working modes of the auxiliary LDO<k>, voltage current fluctuation due to mismatching between loads can be rapidly adjusted; the dynamic performance of a power supply system is improved; due to the fully integrated structure, system integration is easily carried out; the cost is easily reduced; all output ends, particularly an output end near the GND, have good PSR characteristic; and thus, the LDO is suitable for amodule sensitive to a power supply.

Owner:XI AN JIAOTONG UNIV

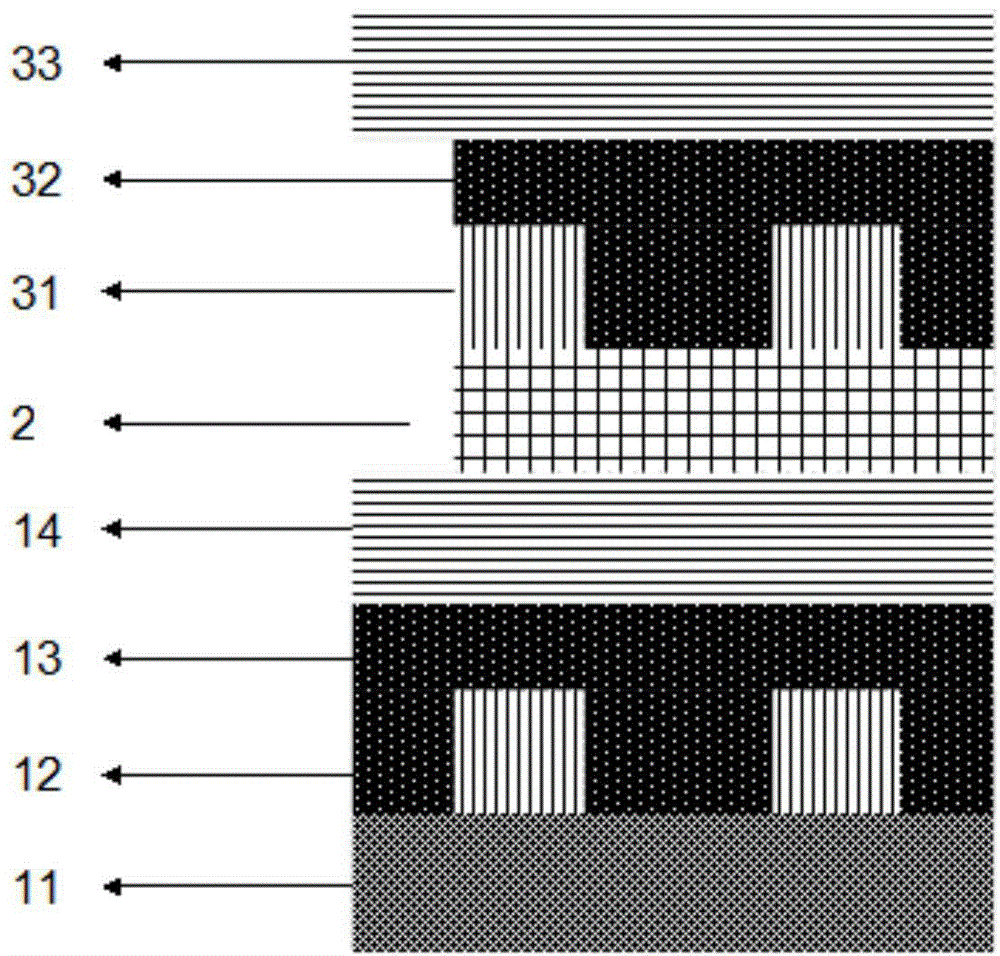

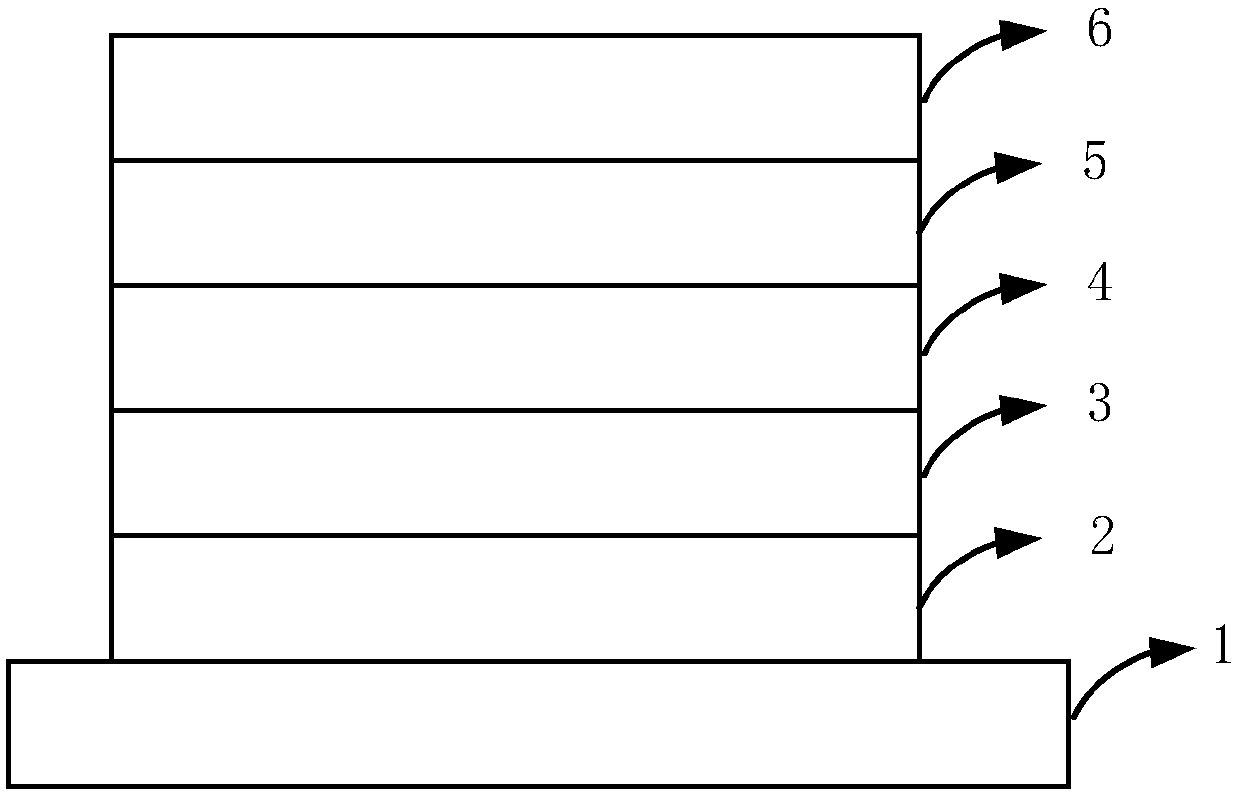

Three-dimensional array-intersected array resistive random access memory and method for manufacturing the memory

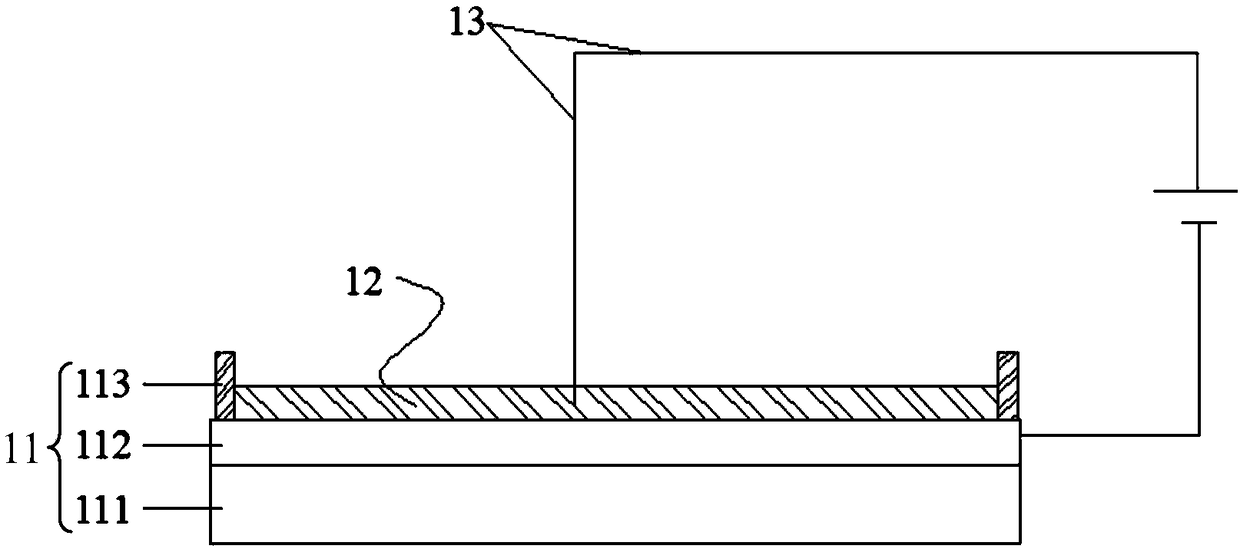

InactiveCN104701454ALow manufacturing costAchieve transparencySolid-state devicesSemiconductor devicesTransparent electronicsComputer science

The invention discloses a three-dimensional array-intersected array resistive random access memory and a method for manufacturing the memory. The three-dimensional array-intersected array resistive random access memory comprises a first resistive random access memory layer region, a second resistive random access memory layer region and a medium separation layer, wherein the medium separation layer is arranged on the first resistive random access memory layer region; the second resistive random access memory layer region is arranged on the medium separation layer; the first resistive random access memory layer region comprises a first transparent glass substrate, a first transparent oxide bottom electrode film layer, a first transparent oxide resistance change layer and a first transparent oxide top electrode film layer; the second resistive random access memory layer region comprises a second transparent oxide bottom electrode film layer, a second transparent oxide resistance change layer and a third transparent oxide top electrode film layer. The memory and the method are low in manufacturing cost, convenient to process, and high in large-area integration level, thus the large-scale three-dimensional array-intersected array resistive random access memory can be manufactured and applied to the transparent electronics.

Owner:PEKING UNIV

Preparation method of metal nanoparticles

ActiveCN108315769AReduce manufacturing costEasy to operateNanotechnologyElectrolysisHazardous substance

The invention discloses a preparation method of metal nanoparticles. The preparation method comprises the steps: electrolyzing a conductive solution contacted with metal oxides by utilizing an electrochemical technique, and reacting the conductive solution with the metal oxides, thereby obtaining the metal nanoparticles. The metal nanoparticles prepared by the method have controllable particle size and morphology and controllable area coverage in which the nanoparticles exist. Moreover, the preparation method is simple, the cost is low, large-scale production can be realized, any hazardous substance is not produced in the whole process, and the green production principle is met.

Owner:SOUTH CHINA NORMAL UNIVERSITY

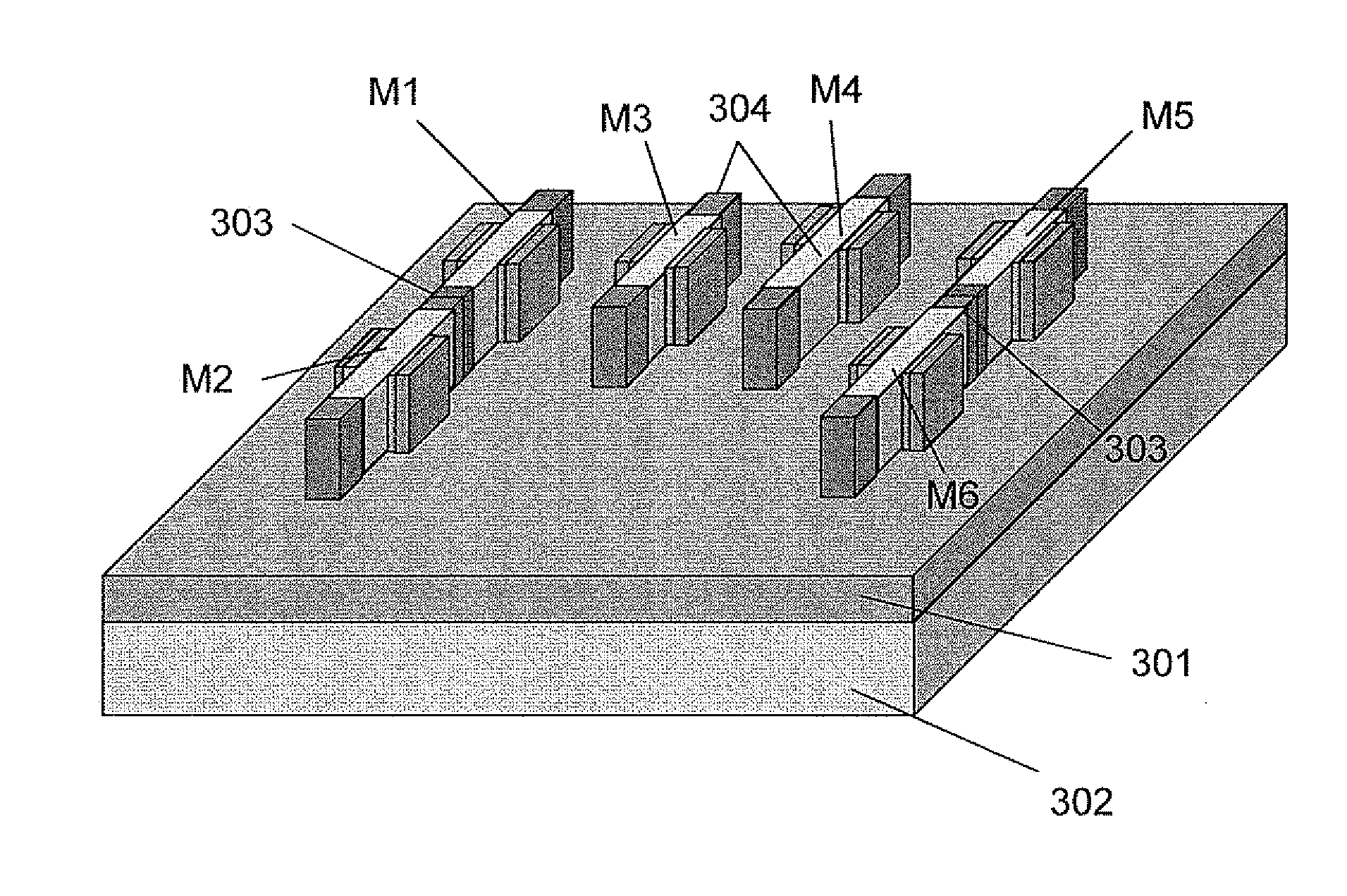

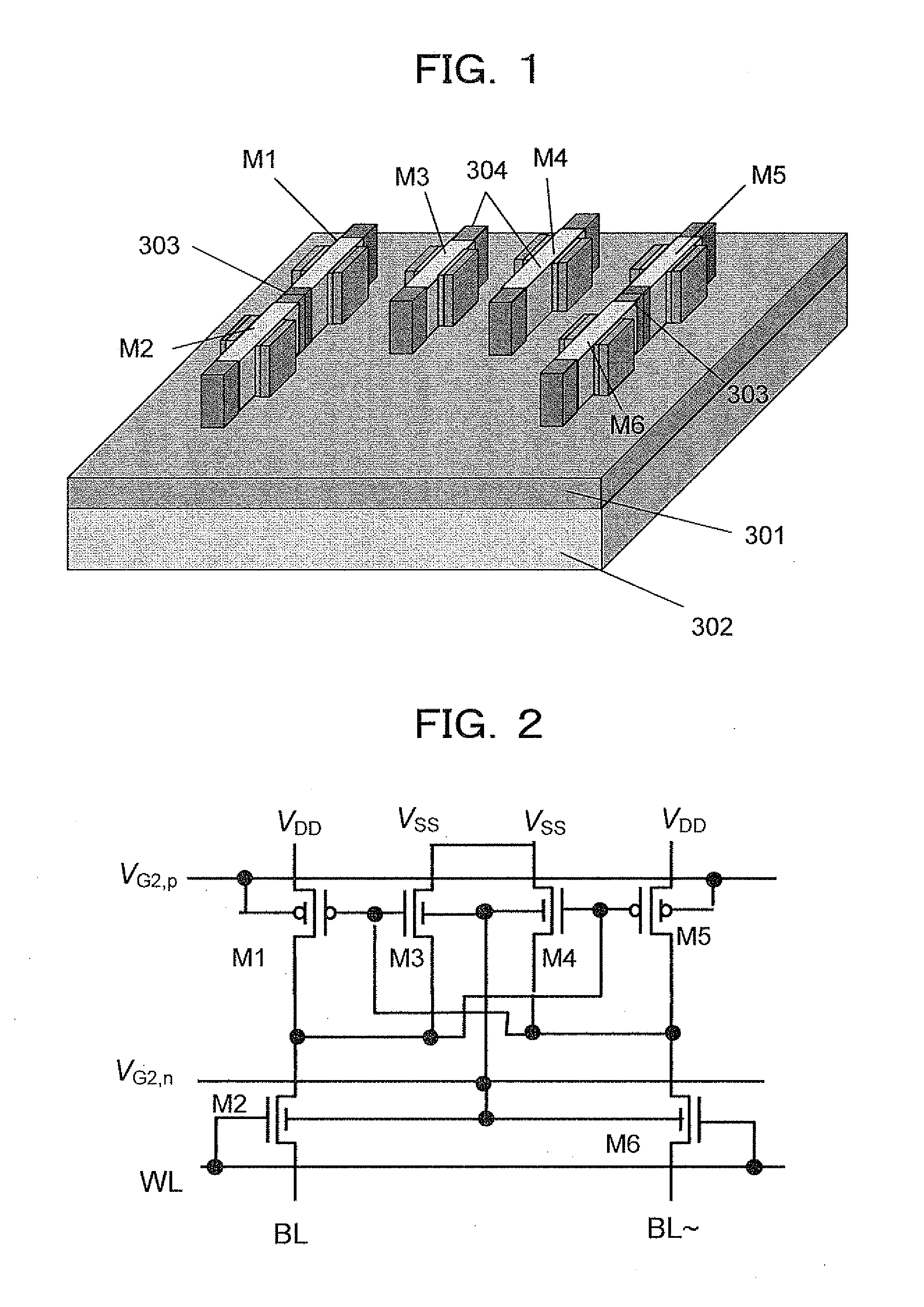

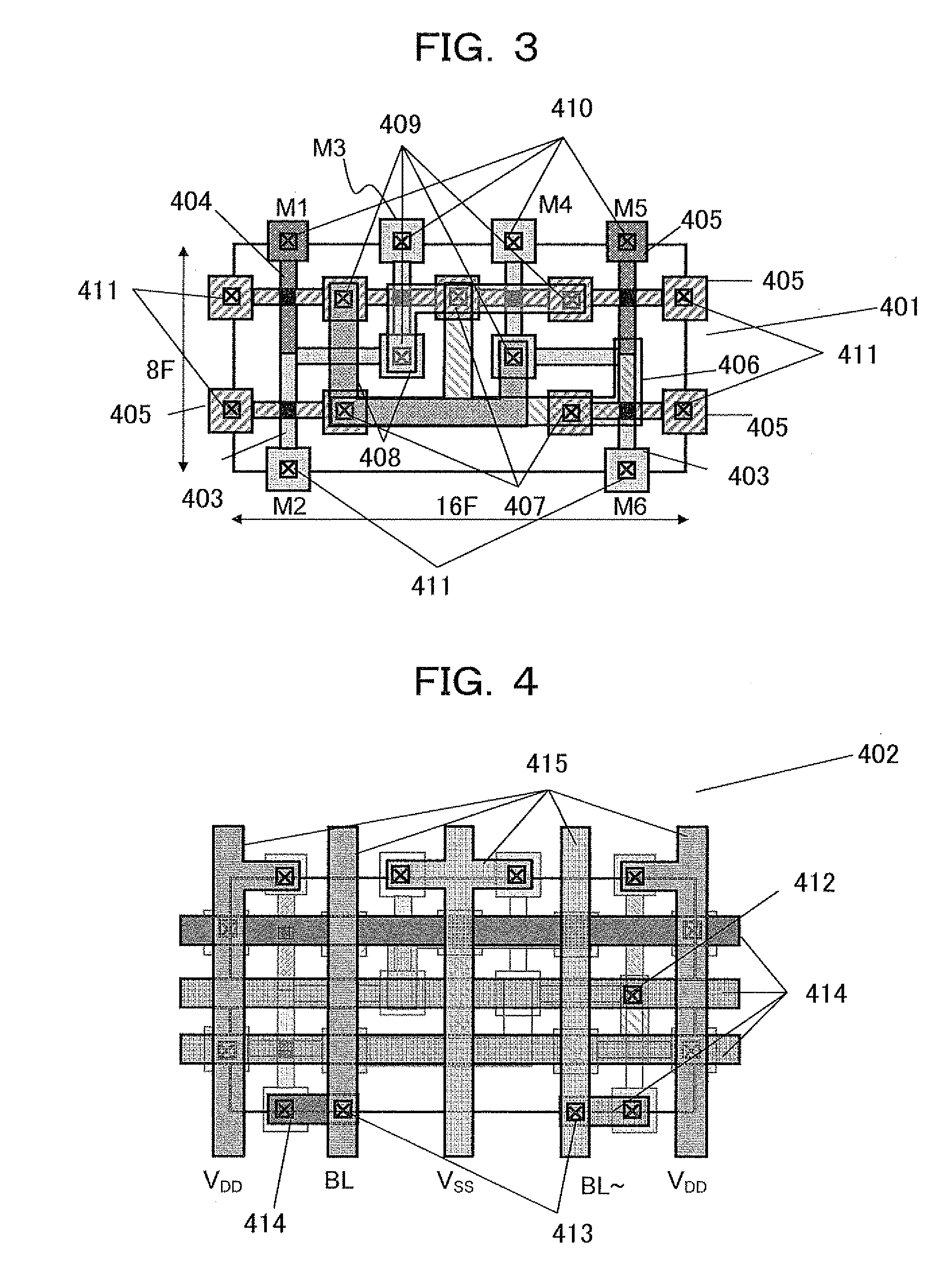

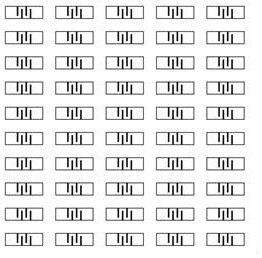

SRAM cell and SRAM device

InactiveUS20110024844A1Increase spacingCell area be saveTransistorSolid-state devicesSram cellEngineering

An SRAM cell comprising a first to fourth semiconductor thin plates standing on a single substrate and sequentially arranged parallel to each other, on the first semiconductor thin plate a first four-terminal double gate FET with a first conduction type and a second four-terminal double gate FET with a second conduction type being formed and connected in series to each other, on the second semiconductor thin plate a third four-terminal double gate FET with the second conduction type being formed, on the third semiconductor thin plate a fourth four-terminal double gate FET with the second conduction type is formed, on the fourth semiconductor thin plate a fifth four-terminal double gate FET with the first conduction type and a sixth four-terminal double gate FET with the second conduction type being formed and connected in series to each other. The second and sixth four-terminal double gate FETs constitute select transistors with logic signal input gates thereof being connected to a word line. The first and third four-terminal double gate FETs and the fourth and the fifth four-terminal double gate FETs respectively constitute cross-coupled complementary inverters to realize a flip-flop. The SRAM cell is characterized in that the first four-terminal double gate FET and the third four-terminal double gate FET are neighboring with each other and logic signal input gates thereof are formed on the side surfaces facing to each other of the respective semiconductor thin plates; the fourth four-terminal double gate FET and the fifth four-terminal double gate FET are neighboring with each other and logic input gates thereof are formed on the side surfaces facing to each other of the respective semiconductor thin plates; the third four-terminal double gate FET and the fourth four-terminal double gate FET are neighboring with each other and a threshold voltage control gates thereof are formed on the side surfaces facing to each other of the respective semiconductor thin plates; the second four-terminal double gate FET and the sixth four-terminal double gate FET are neighboring with each other sandwiching the second and third semiconductor thin plates and threshold voltage control gates thereof being formed on side surfaces facing to each other of the respective semiconductor thin plate; the threshold voltage control gates of the second, third, fourth, and sixth four-terminal double gate FETs are connected in common to a first bias wiring; threshold voltage control gates of the first and fifth four-terminal double gate FETs are connected in common to a second bias wiring; and the word line and the first and second bias wirings are arranged in a direction perpendicular to the alignment direction of the first to the fourth semiconductor thin plates.

Owner:NAT INST OF ADVANCED IND SCI & TECH

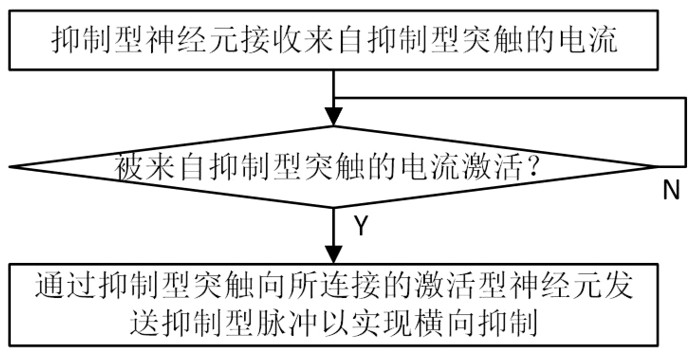

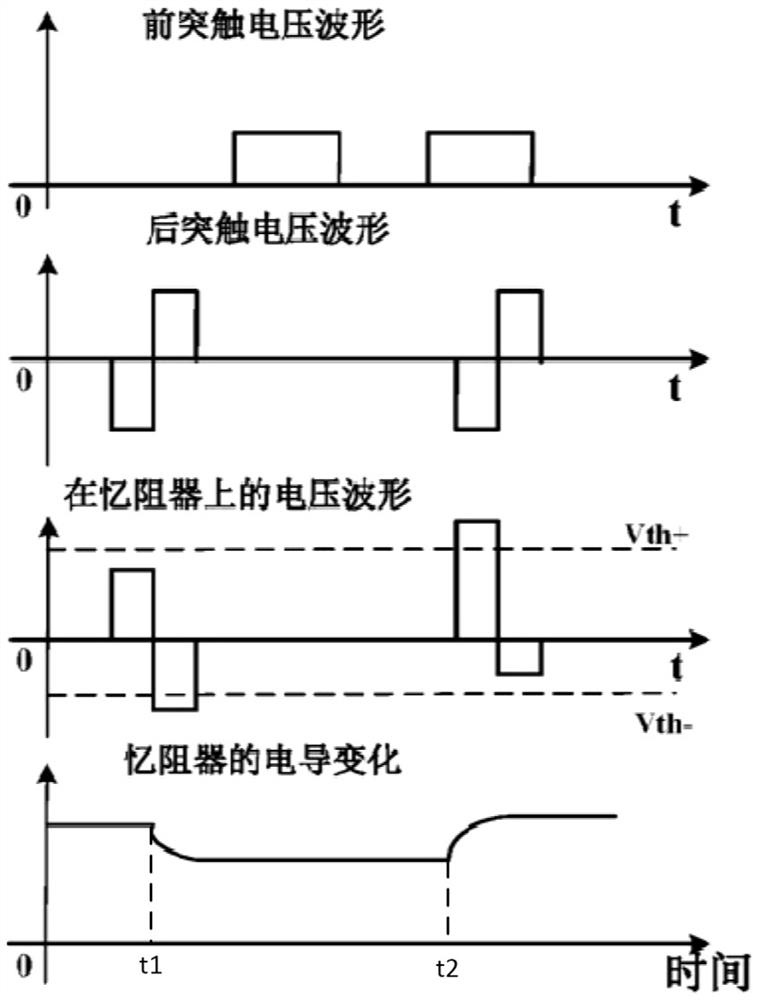

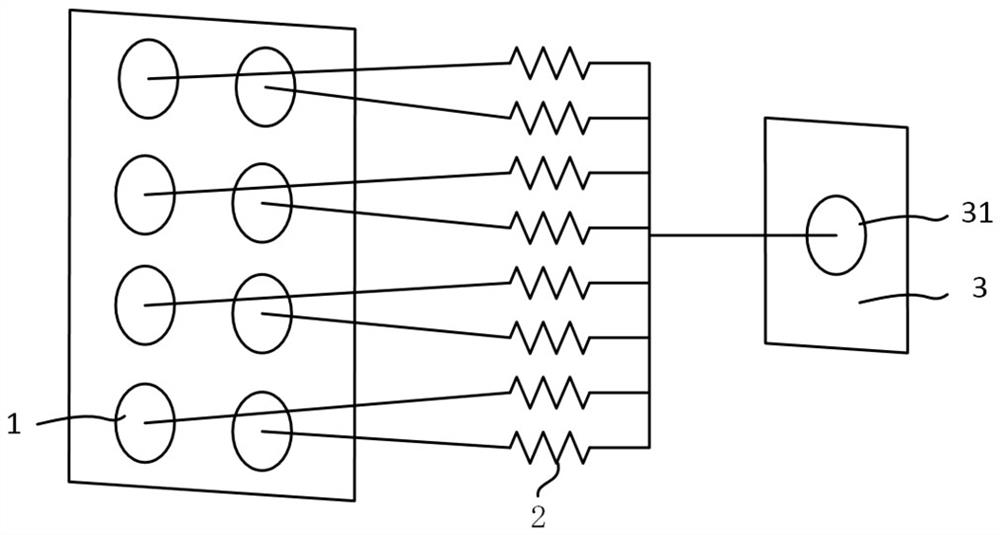

Method and system for realizing competitive learning mechanism of spiking neural network based on memristor

PendingCN111882064AAchieving Lateral InhibitionRealized areaPhysical realisationNeural learning methodsSynapseLearning machine

The invention discloses a method and system for realizing a competitive learning mechanism of a spiking neural network based on a memristor, and the method comprises the steps: enabling an activated neuron of a learning layer in the spiking neural network to receive a pulse from an input layer, and carrying out the learning under an STDP rule; the method further comprises a step of performing lateral suppression through a synapse realized based on a memristor and a suppression-type neuron connected with one or more activation-type neurons: if the suppression-type neuron is activated by currentfrom the synapse, enabling the suppression-type neuron to send a suppression-type pulse to the connected activation-type neuron through the synapse so as to realize lateral suppression. According tothe invention, the memristor is used as a synapse to realize a transverse suppression and balance mechanism, the expandability of the network can be improved, and the inherent device advantages of thememristor are effectively utilized to reduce the hardware complexity and power consumption of the unsupervised SNN network.

Owner:NAT UNIV OF DEFENSE TECH

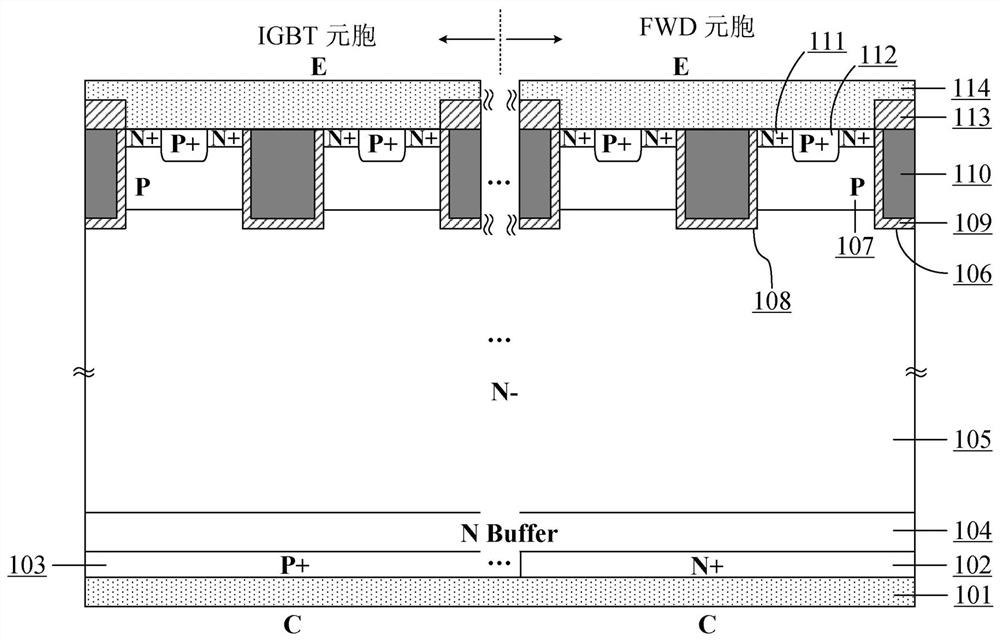

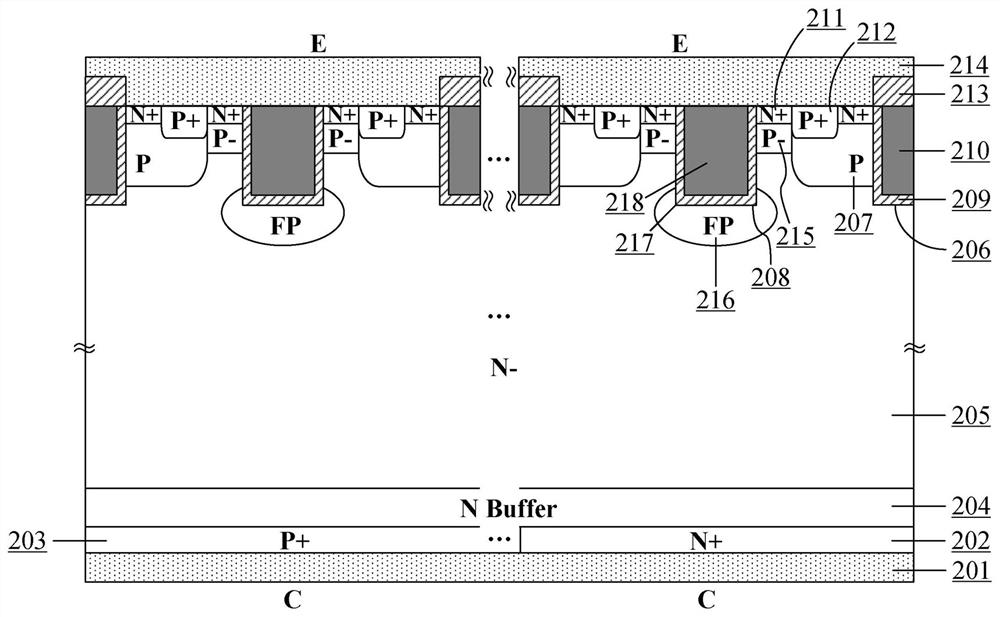

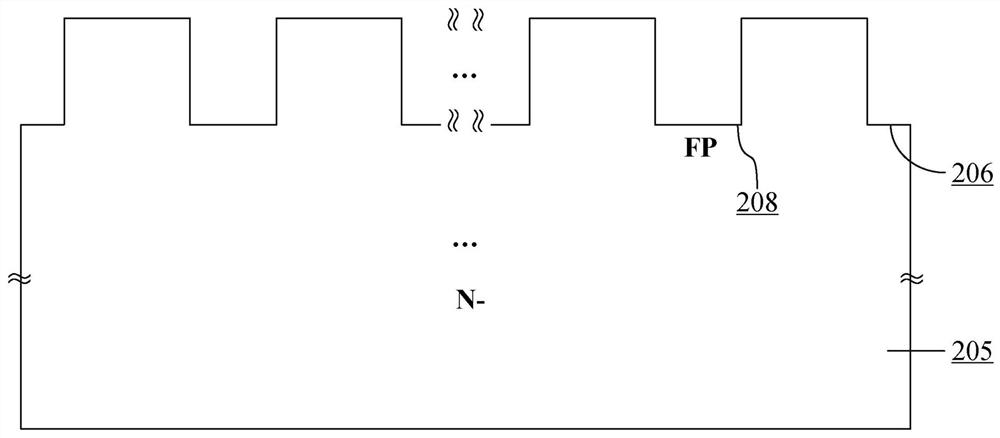

Power semiconductor device and preparation method thereof

ActiveCN114551589AEasy to adjustReduce lossEfficient power electronics conversionSemiconductor/solid-state device manufacturingPower semiconductor deviceElectron hole

The invention discloses a power semiconductor device and a preparation method thereof, and belongs to the field of power semiconductor devices. A punch-through triode structure for extracting electrons in a drift region is introduced, so that the injection efficiency of a front hole is reduced, an emitter hole current is converted into an electron drift current, and the conduction voltage drop is not obviously increased; in addition, adjustment of punch-through area and position is realized by changing density and morphology of the front grooves, so that efficiency of electron extraction and front hole injection is changed, and design flexibility and design dimension of the device are improved.

Owner:安建科技(深圳)有限公司

Surveying and mapping method and device, computer equipment and storage medium

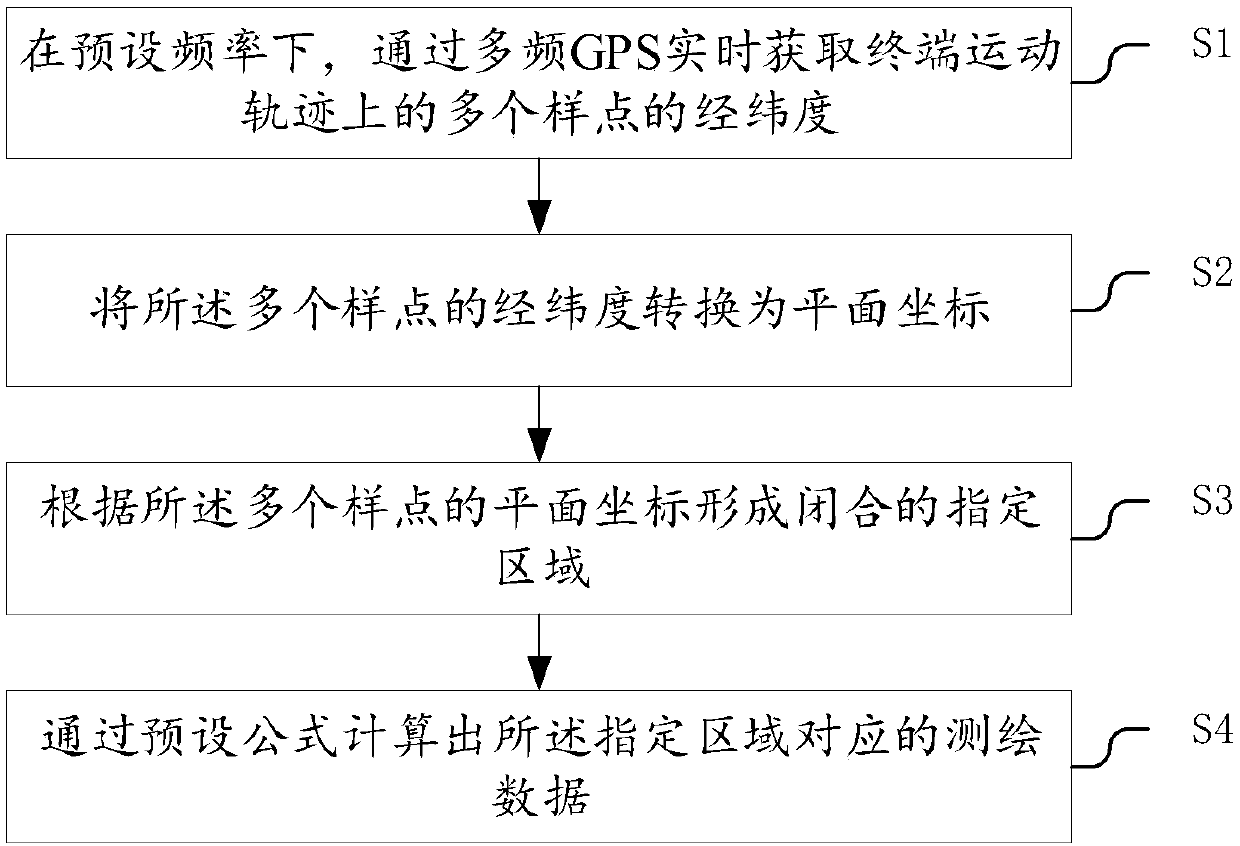

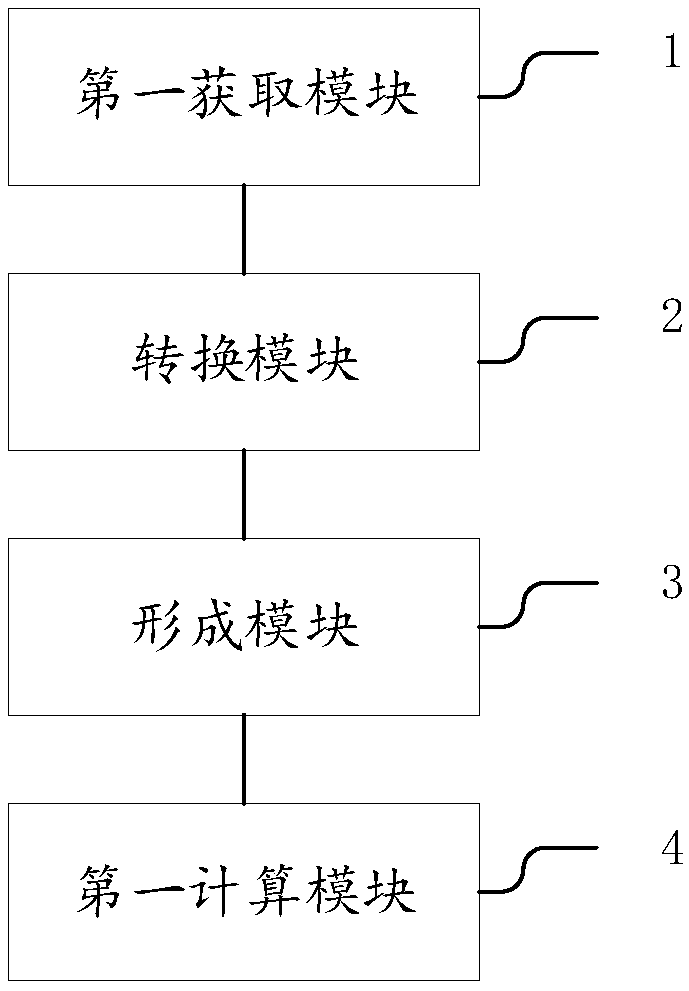

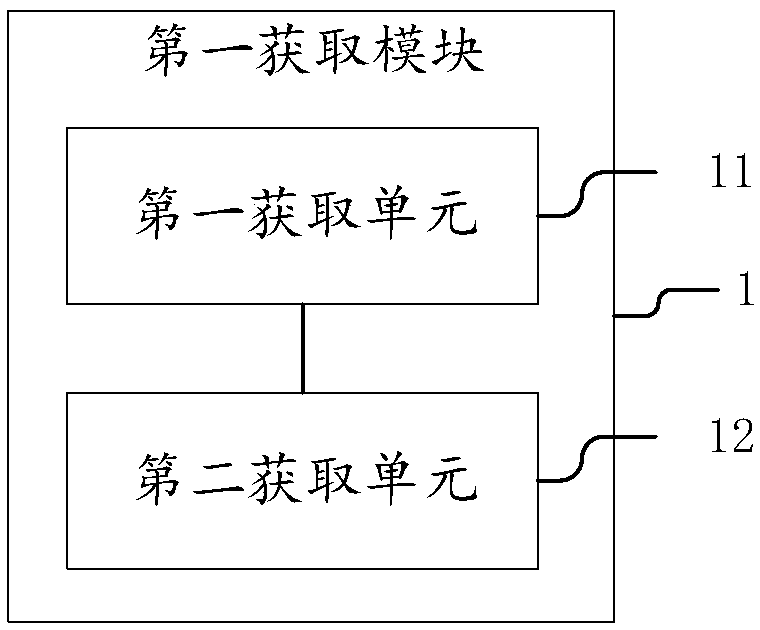

ActiveCN109631750ARealized areaReduce mistakesElectric/magnetic area measurementsLongitudeComputer terminal

The invention discloses a surveying and mapping method and device, computer equipment and a storage medium. The method comprises the following steps that: under preset frequency, through a multi-frequency GPS (Global Positioning System), obtaining the longitudes and latitudes of a plurality of sample points on a terminal movement locus; converting the longitudes and latitudes of the plurality of sample points into plane coordinates; according to the plane coordinates of the plurality of sample points, forming a closed appointed zone; and through a preset formula, calculating surveying and mapping data corresponding to the appointed zone. By use of the method, the built-in multi-frequency GPS of an intelligent terminal is used for realizing sub-meter level positioning, sample points with ahighest amount in the appointed zone are collected, the plurality of collected sample points are fit into a polygonal appointed zone, and therefore, the area and the perimeter of the polygonal appointed zone are calculated.

Owner:SHENZHEN WATER WORLD INFORMATION CO LTD

Stretchable flexible thermoelectric device and manufacturing method thereof

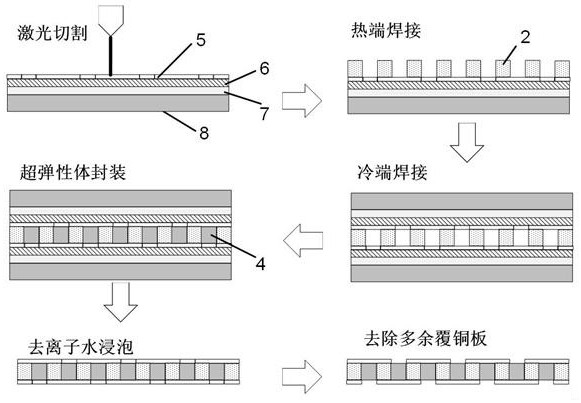

ActiveCN113517384AImprove processing efficiencyImprove adaptabilityThermoelectric device with peltier/seeback effectThermoelectric device manufacture/treatmentElectrode arrayMechanical engineering

The invention discloses a stretchable flexible thermoelectric device and a manufacturing method thereof. A hot-end or cold-end stretchable electrode array of the stretchable flexible thermoelectric device comprises a plurality of hot-end or cold-end stretchable electrodes arranged in an array. Each hot-end or cold-end stretchable electrode is a flexible copper-clad plate of a sheet-shaped structure. Each hot-end or cold-end stretchable electrode is divided into three parts, the two ends are of structures with the same shape as the bottom surface of the hot end or the cold end of a P-type thermoelectric block or a N-type thermoelectric block, and the middle is of a staggered gap structure. According to the stretchable flexible thermoelectric device and the manufacturing method thereof, the alternate kerf structures are designed and manufactured on the hot-end electrode array and the cold-end electrode array of the flexible thermoelectric device, so that the thermoelectric device has good stretchability; and meanwhile, according to the manufacturing method of the stretchable flexible thermoelectric device, large-area integrated manufacturing and positioning welding of the electrode array are innovatively achieved, the manufacturing cost of the stretchable flexible thermoelectric device is reduced, and the processing efficiency of the flexible thermoelectric device is improved.

Owner:XIDIAN UNIV

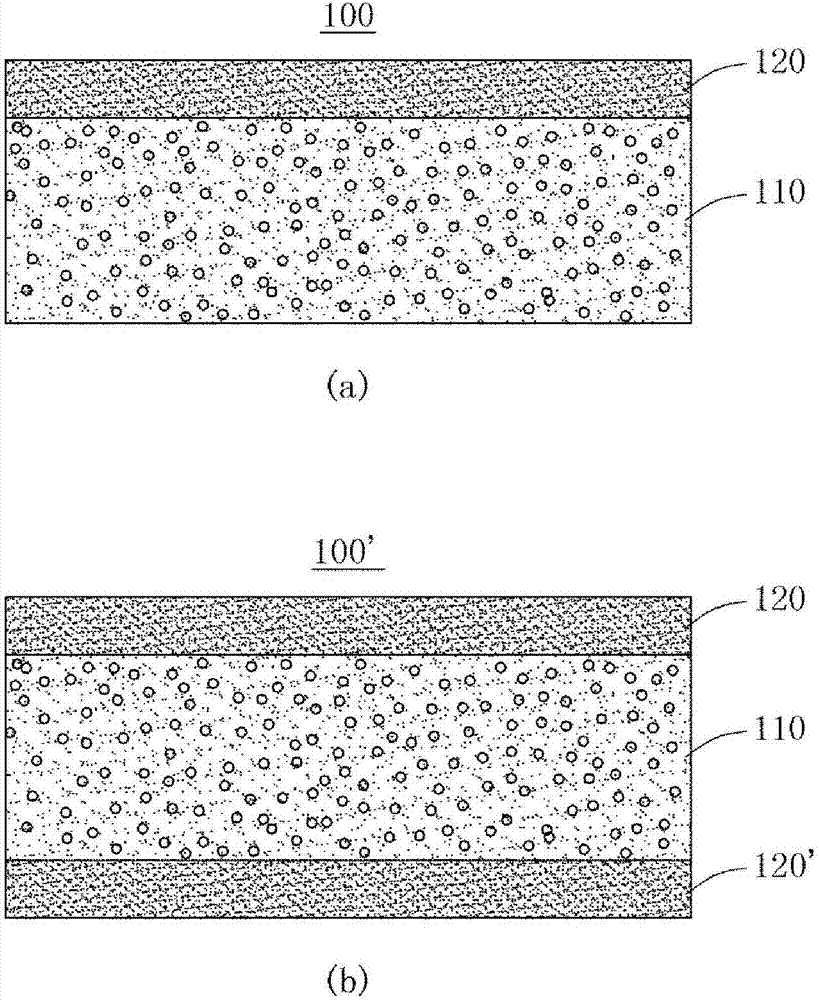

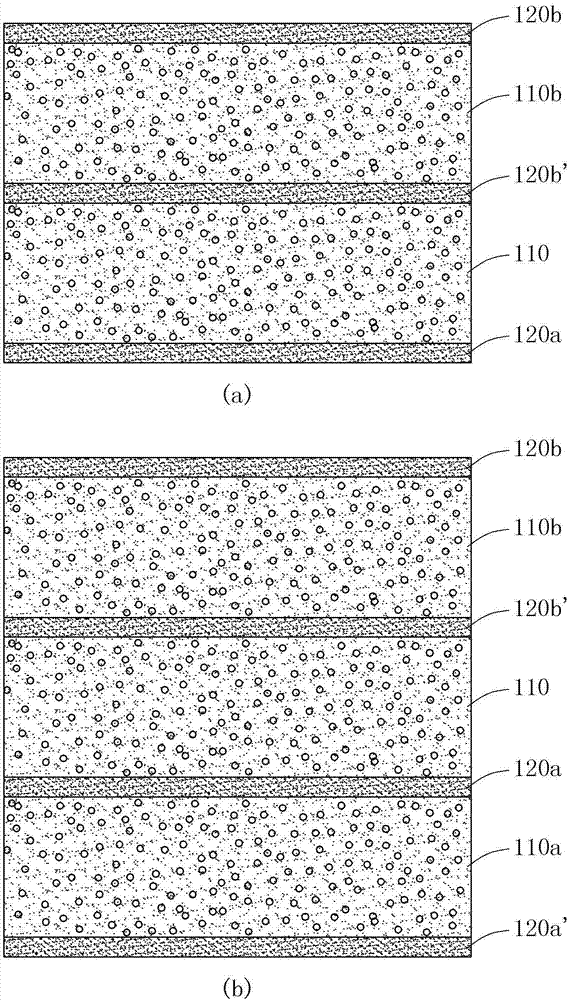

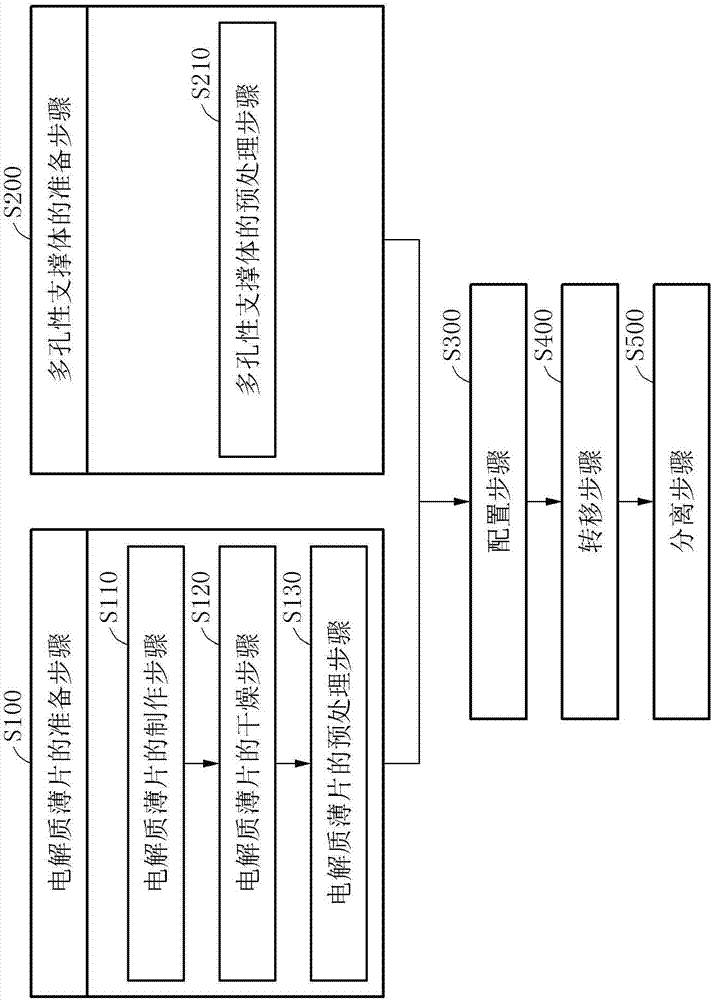

Reinforced composite membranes and method for manufacturing the same

ActiveCN107009706AImprove Interface StabilityImprove performanceFinal product manufactureSynthetic resin layered productsOptoelectronicsElectrolyte

Provided are a reinforced composite membrane and a method of manufacturing the reinforced composite membrane, and more particularly, a reinforced composite membrane including a porous support layer; and an electrolyte membrane layer formed on one surface or each of both surfaces of the porous support layer, at least a portion of the porous support layer being impregnated with an electrolyte, and a method of manufacturing the reinforced composite membrane. The reinforced composite membrane may enhance an interfacial adhesive force between a support and the electrolyte membrane layer, and may be manufactured on a continuous mass production.

Owner:KOREA INST OF ENERGY RES

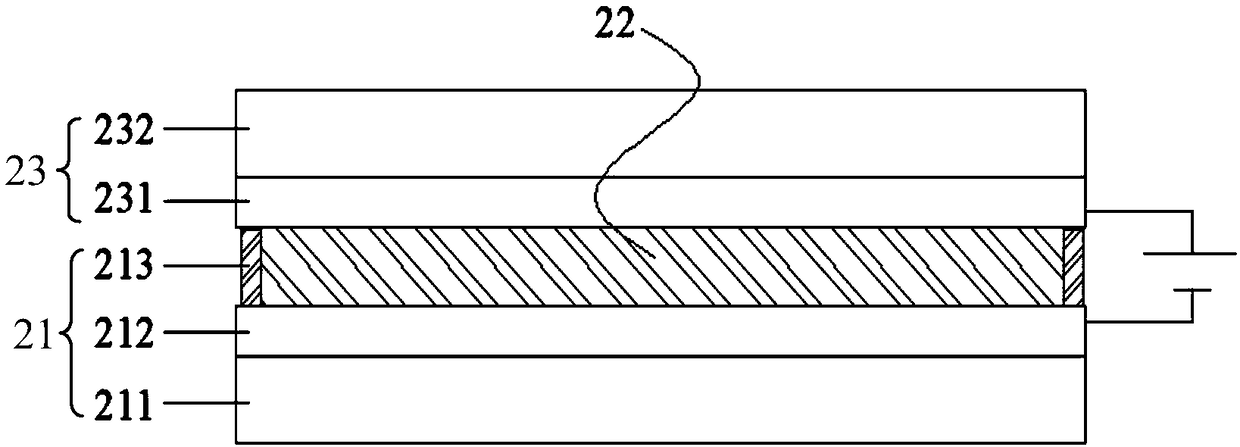

Zinc oxide film and preparation method thereof, and luminescent device

ActiveCN109695028AReduce internal oxygen vacancies and surface oxygen defectsRadiation combination reductionLiquid/solution decomposition chemical coatingSemiconductor devicesOxygen vacancyOxide

The invention belongs to the field of display devices, and provides a zinc oxide film and a preparation method thereof, and a luminescent device. Peroxide can be added after the complexing of a zinc precursor salt solution and mixing; a zinc oxide crystal particle solution can be obtained through reaction; and the film forming of the zinc oxide crystal particle solution can be performed on a substrate so that the zinc oxide film can be obtained, and therefore, the internal oxygen vacancy and surface oxygen deficiency of the zinc oxide film can be reduced, the radiation combination of electronhole pairs can be decreased, and electronic transmission performance can be enhanced. The preparation method is simple in technology and low in cost, so that large area and large-scale production canbe realized.

Owner:TCL CORPORATION

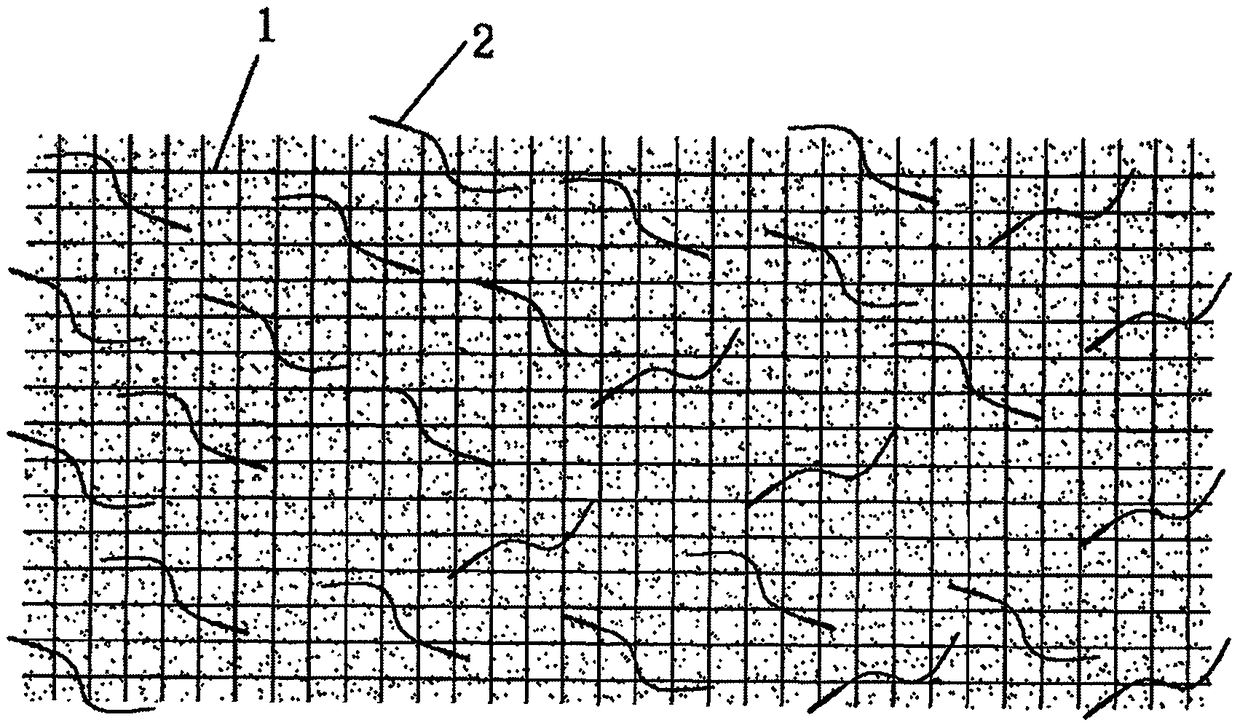

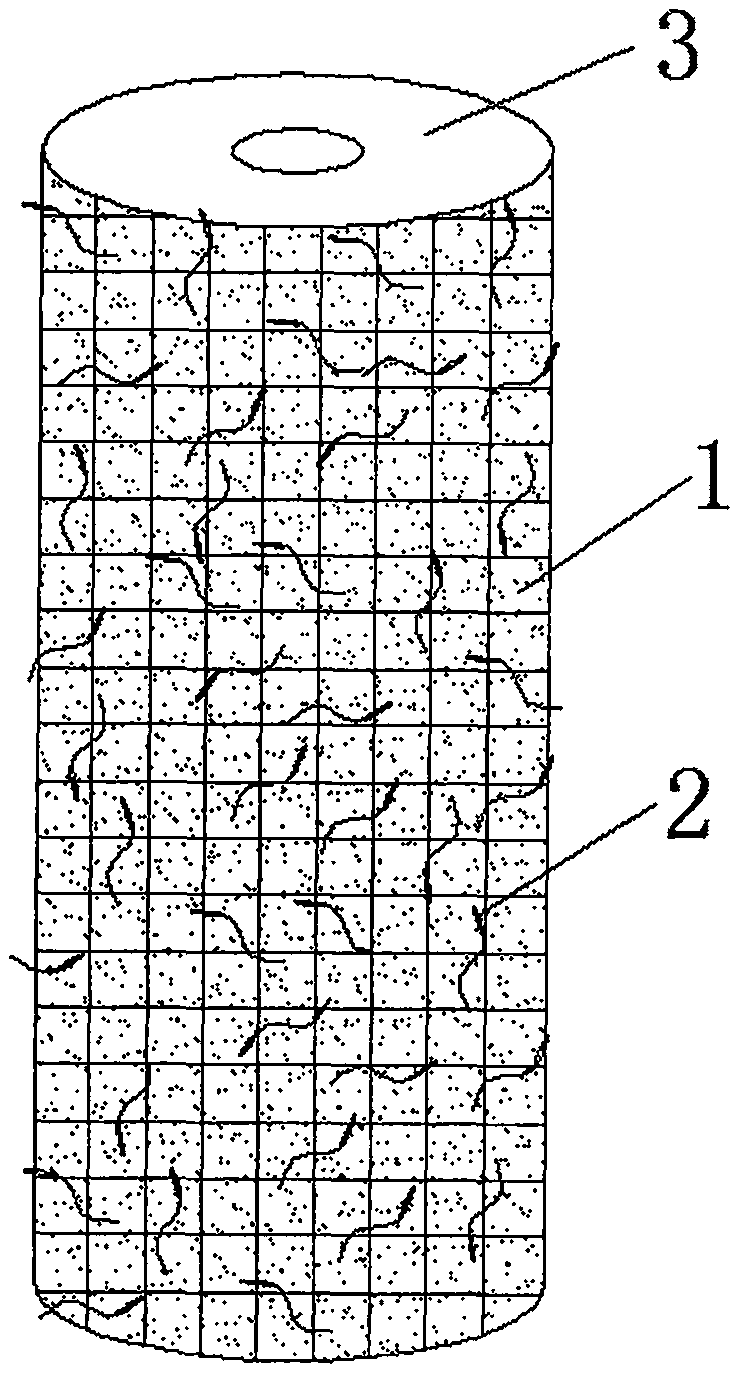

Manufacturing method of Stipa plant seed roll and seed roll spreading and sowing method

InactiveCN108207174ASolve the low seedling preservation rate at the seedling stageSolve problems such as intolerance to direct sunlightSeed arrangmentsYarnPlanting seed

The invention discloses a manufacturing method of a Stipa plant seed roll and a seed roll spreading and sowing method. A Stipa collecting net is a seed sticking net formed by weaving multiple coarse wool yarn, short fluff is arranged on the wool yarn for weaving the seed sticking net, a manufactured Stipa collecting net is dragged on the grass, and Stipa seeds are attached to the Stipa collectingnet by long awn of Stipa plant seeds and hard barbs at bottoms of the seeds; the Stipa collecting net with the Stipa seeds is rolled into a cylindrical seed roll with height of 1 m. The seed roll is spread on the surface of finished soil, soil coverage is performed with depth of 1 cm, and irrigating is performed after soil coverage; sowing is selected in the rainy season in areas without irrigation conditions, waiting for precipitation is performed after sowing, and the soil surface is covered with non-woven fabric. Harvesting and sowing of the Stipa plant seeds in a large area are made possible, the problems that the Stipa plant seeds are intolerant to drought at seedling stage, the seedling protection rate is low and the like in production practice are solved, and technical guarantee forrestoration of degraded Stipa steppe is provided.

Owner:GRASSLAND RES INST OF CHINESE ACAD OF AGRI SCI

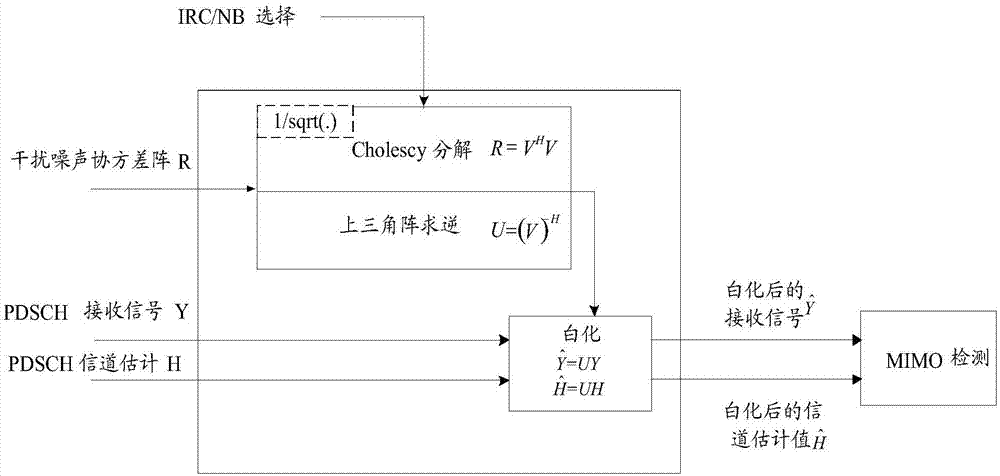

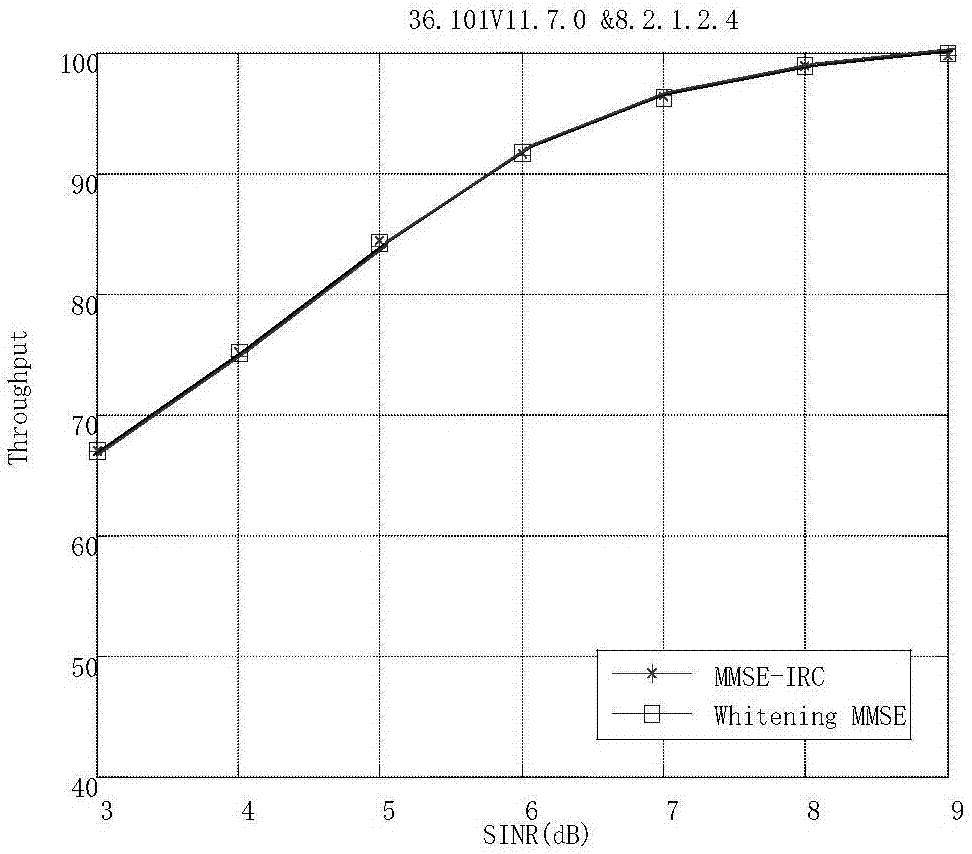

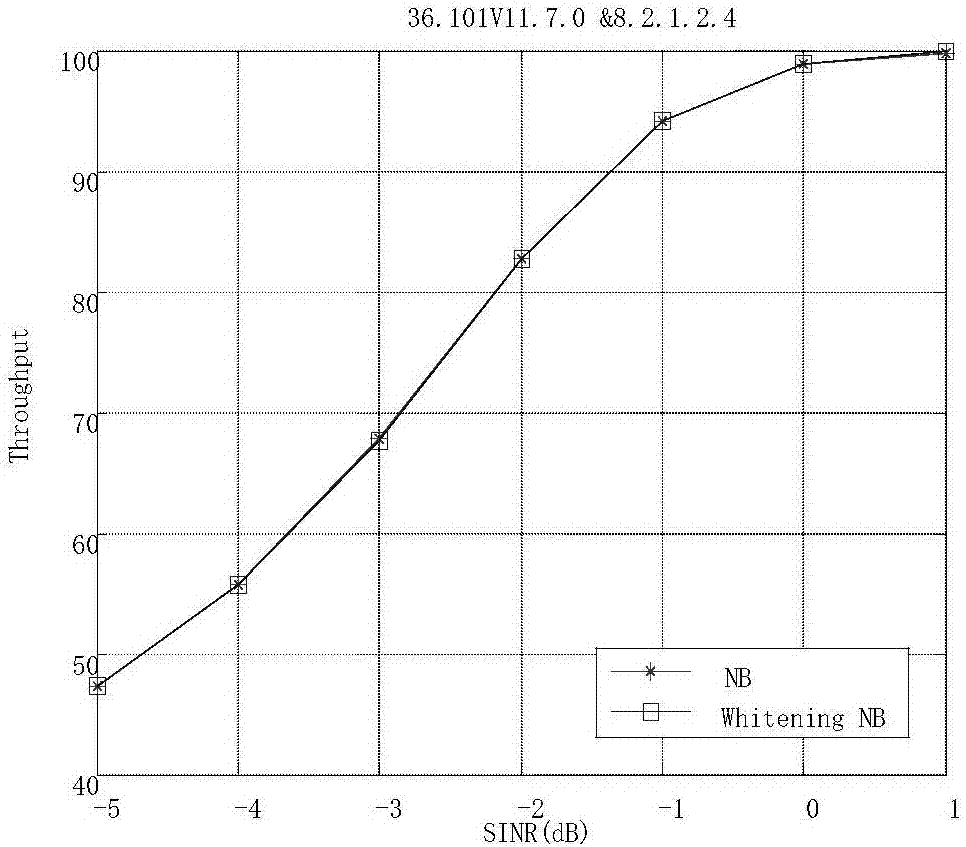

Interference suppression combining and noise balancing combined processing method and device

InactiveCN107306141AReduce processing complexityReduce power consumptionSpatial transmit diversityHigh level techniquesComputer scienceUltimate tensile strength

Owner:SANECHIPS TECH CO LTD

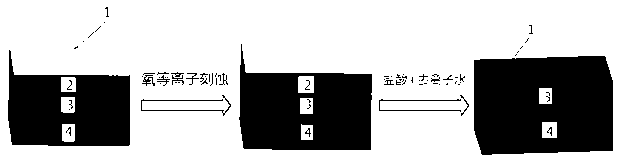

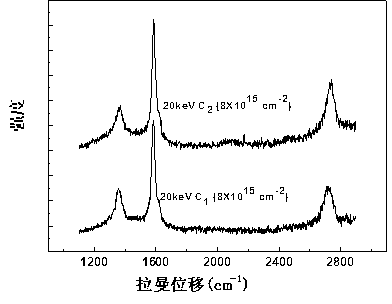

Method for directly preparing graphene on SiO2/Si substrate

The invention discloses a method for directly preparing graphene on a SiO2 / Si substrate. The method comprises the following steps of: preparing graphene on a transitional metal film of the transitional metal SiO2 / Si substrate by using an ion implantation method; and then sequentially removing the graphene and the transitional metal film from the surface of the transitional metal film, thus obtaining the graphene on the SiO2 / Si substrate. The method is simple and convenient and can be used for directly obtaining the graphene film with low defect level and high quality on the SiO2 / Si substrate.

Owner:WUHAN UNIV

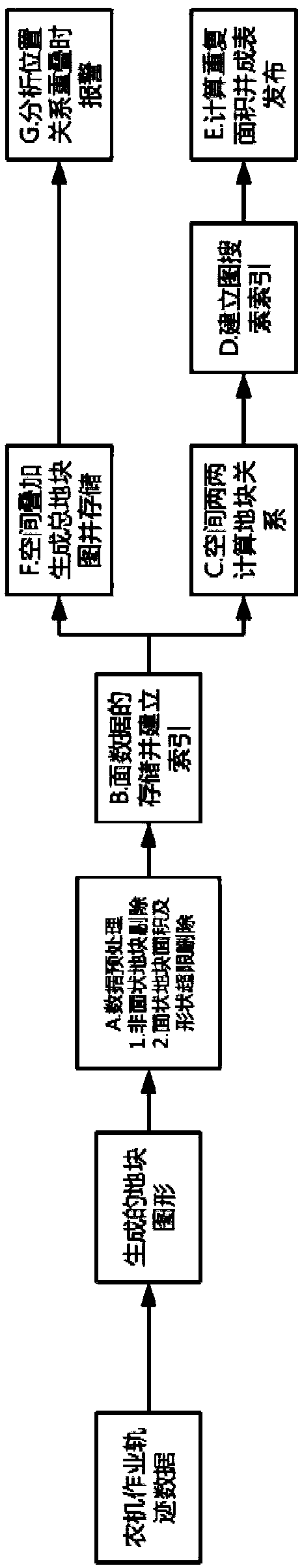

Repetitive operation area calculation and alarm method

ActiveCN111336980AAvoid wasting multiple jobsProvide repeat job alarmMeasurement devicesAgricultural engineeringFarm machine

The invention discloses a repetitive operation area calculation and alarm method, and belongs to the technical field of big data. The method comprises the steps: firstly, preprocessing operation trackdata of an agricultural machine; taking the preprocessed plot graph as surface data; storing the surface data and establishing an index; calculating a plot graphic relationship in pairs; calculatingthe relationship between the paired plot graphs; calculating the repetition area, and generating and issuing a repeated area table; reading raster data of all the surface data; deleting duplicated data, and generating a raster data general table; extracting positioning coordinates of the agricultural machine from the agricultural machine track real-time positioning table; mapping the positioning coordinates into the surface data table, judging the repeated tillage phenomenon, and sending repeated alarm information, thereby solving the technical problem of providing repeated tillage area and repeated tillage alarm service for agricultural departments and agricultural users, avoiding repeated operation waste of agricultural machinery, and eradicating repeated tillage fraud subsidy.

Owner:江苏北斗卫星应用产业研究院有限公司

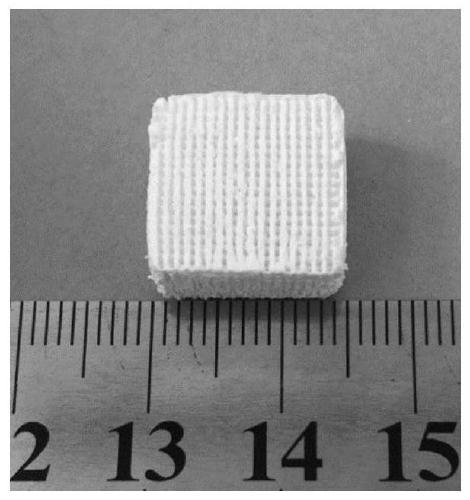

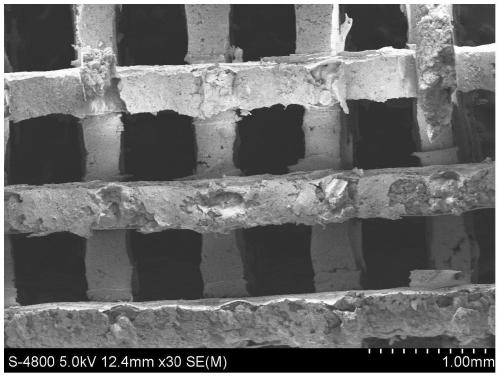

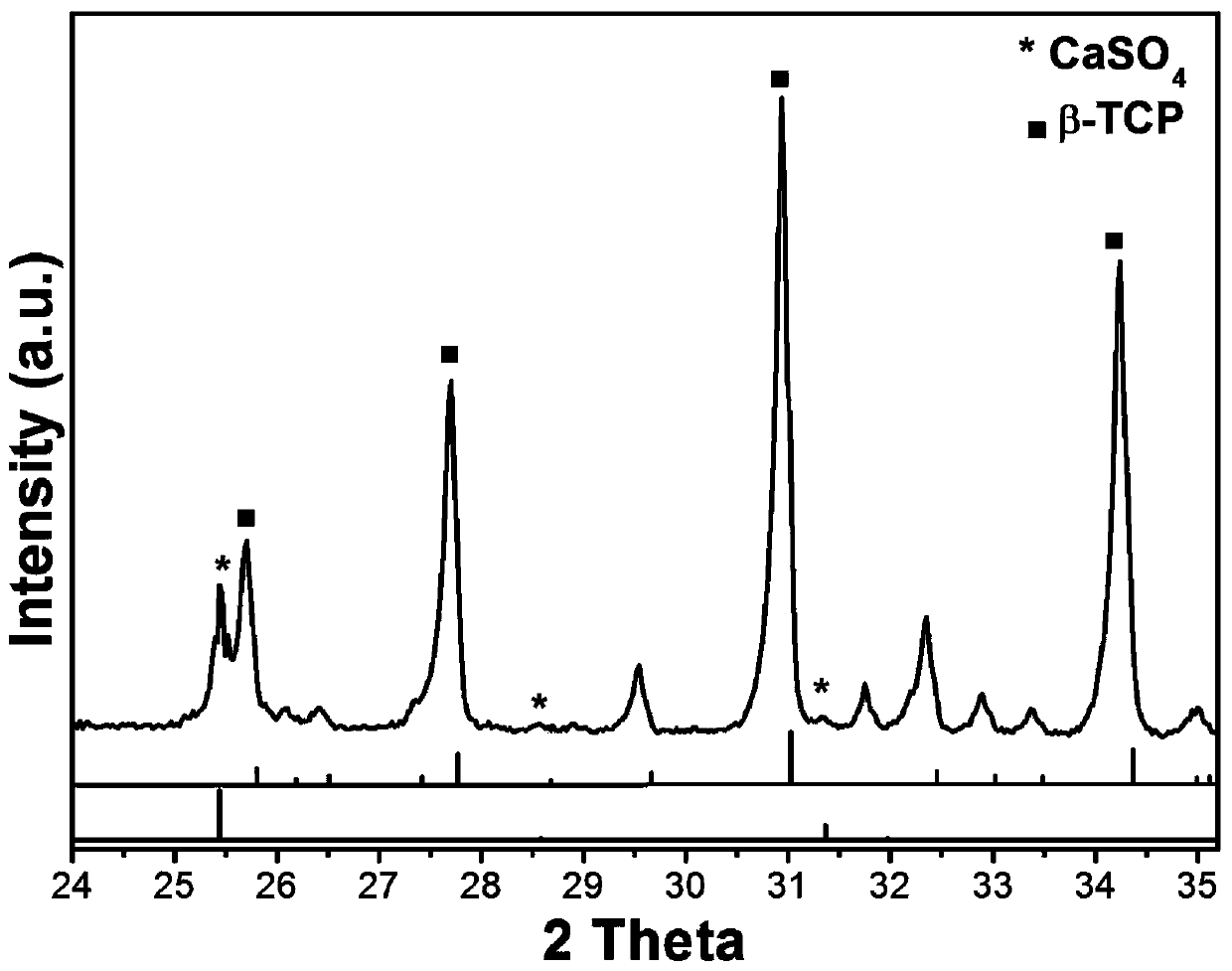

Porous composite ceramic capable of guiding bone regeneration and preparation method of porous composite ceramic

PendingCN110251723APromote ingrowthHigh strengthTissue regenerationCeramicwareSpatial directionS system

The invention discloses porous composite ceramic capable of guiding bone regeneration. The porous composite ceramic is formed by the combination of calcium sulfate and calcium phosphate in any other way except the coating to form a porous structure of an arbitrary shape, the pore pattern of pores with at least one dimensional direction in the three-dimensional spatial direction of the porous structure is regular, the distance from the center of each pore to the edge is 50-2000 microns, and all the pores are mutually communicated. The invention further provides a preparation method of the porous composite ceramic. The functional defect of a single composite is well overcome, cells and blood vessels are facilitated to grow into the ceramic to regenerate new bone, and new bone tissue is beneficial to the formation of dense bone with Huffler's system structure; meanwhile, the porous composite ceramic has the advantages that the pore shape rules are controllable, which is beneficial to unify the quality standard of the product and also facilitates the detection and quality control of the product; therefore, the porous composite ceramic is quite suitable for commercial and mass production applications.

Owner:陶合体科技(苏州)有限责任公司

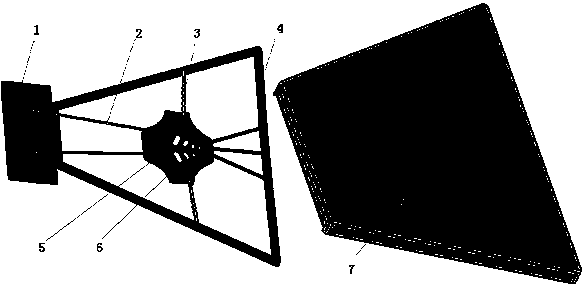

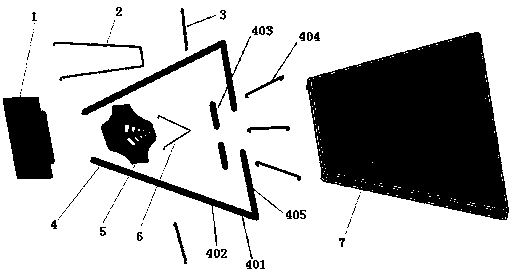

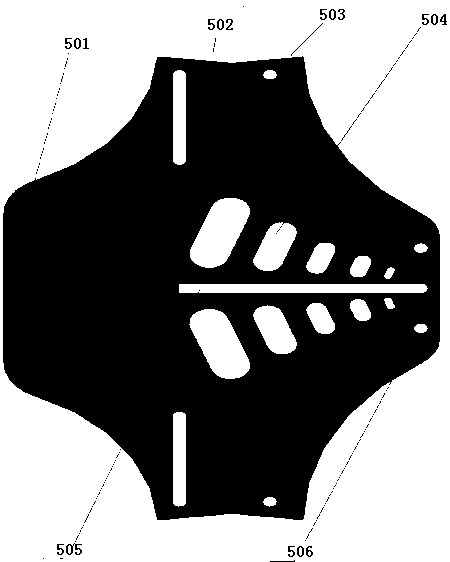

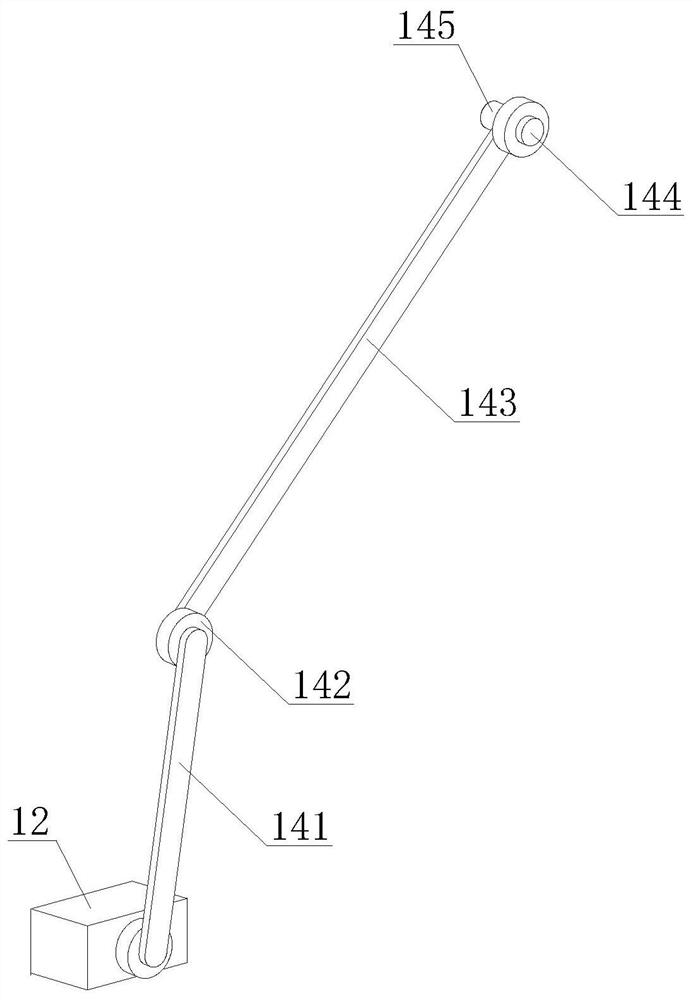

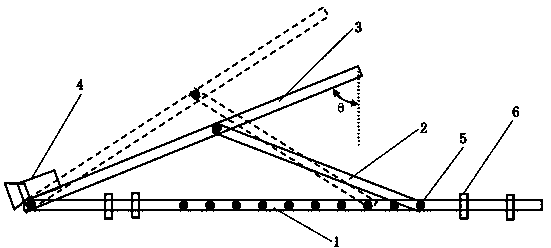

Adaptive variable-area tail fin underwater propulsion device

ActiveCN109292065AAchieving Adaptive ChangesPolymorphic swimmingPropulsive elements of non-rotary typeOcean explorationEngineering

The invention relates to the technical field of biomimicry, in particular to an adaptive variable-area tail fin underwater propulsion device. The adaptive variable-area tail fin underwater propulsiondevice comprises a tail fin mounting plate, wherein first shape memory metal is embedded in the tail fin mounting plate, and the other end of the first shape memory metal is fixed to a supporting plate; and the tail fin mounting plate is further connected with a tail fin deformation part, the tail fin deformation part is in an isosceles triangle shape integrally, the tail fin deformation part is provided with waist rods and a bottom rod, and two tail end motion rod parts are connected to the middle part of the bottom rod. The supporting plate is connected to the bottom rod of the tail fin deformation part through two pull rods, one ends of the pull rods are fixed into tip connecting fixing holes of the supporting plate, and the other ends of the pull rods are fixed to the joints of the bottom rod of the tail fin deformation part and the end motion rod parts. According to the adaptive variable-area tail fin underwater propulsion device, various scientific research and production activities such as ocean exploration, ocean protection are facilitated for human beings in the future.

Owner:JIANGSU UNIV OF SCI & TECH

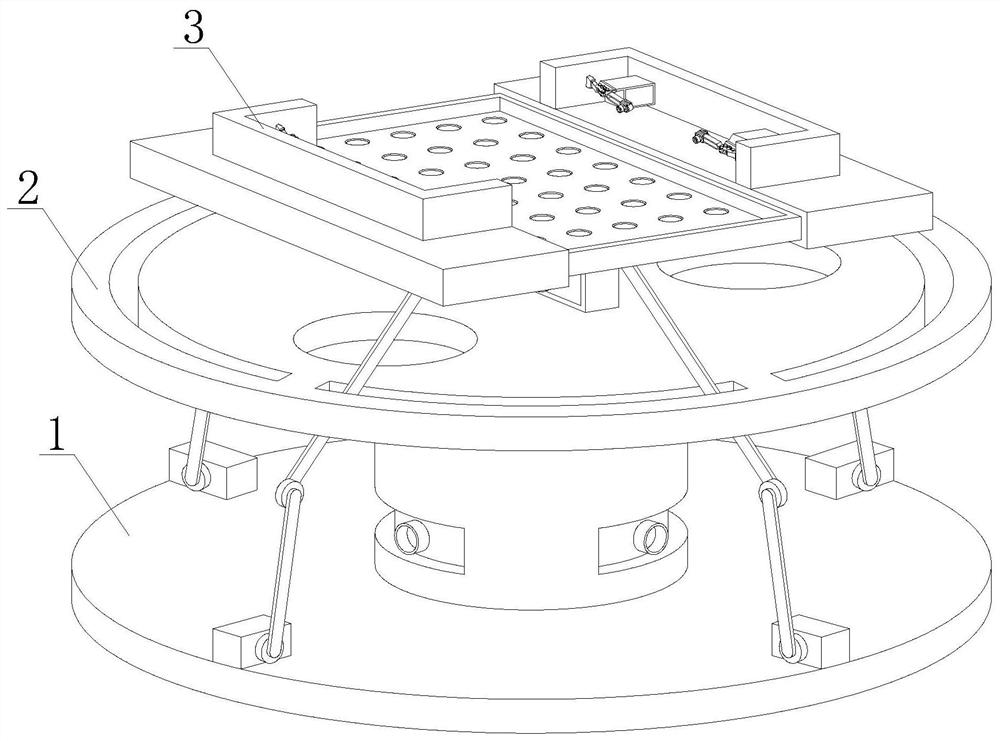

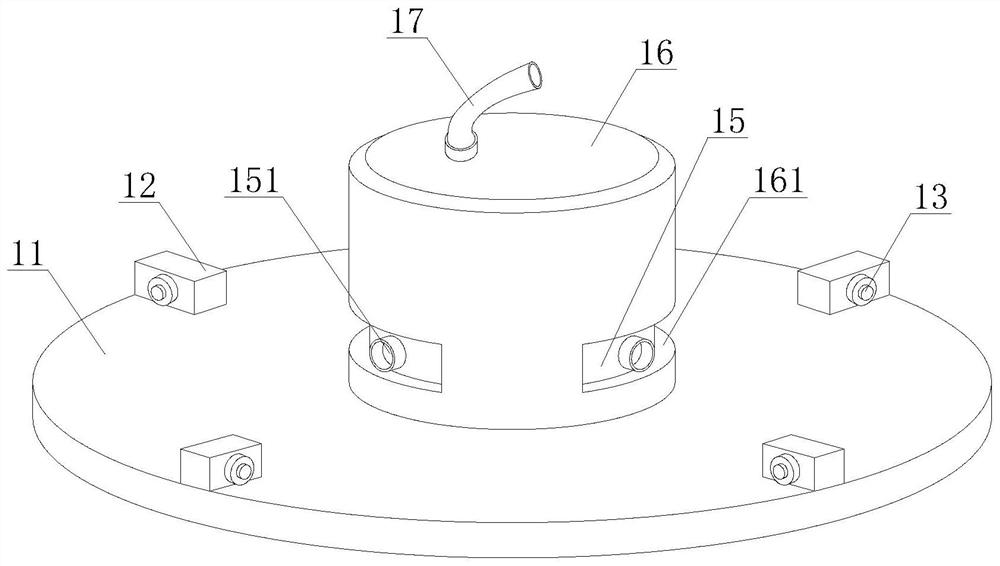

Steel structure special-shaped curved surface welding equipment

ActiveCN113333988ARealized areaRealize regulationWelding/cutting auxillary devicesAuxillary welding devicesCold airWeld seam

The invention relates to the technical field of steel structure welding, in particular to steel structure special-shaped curved surface welding equipment. The steel structure special-shaped curved surface welding equipment comprises a dynamic welding base, a welding platform frame and a welding table, the dynamic welding base is connected with the welding platform frame, and the welding table is arranged above the welding platform frame. A machine box drives a driving rotating shaft to rotate to enable a lower connecting rod to be overturned outside, a left welding rack and a right welding rack are driven to move towards the two sides and move downwards at the same time, the area and the position of the welding table are adjusted, and one-key operation is achieved. The structure is simple, adaptability is high, a switch is triggered after a middle connecting plate is pressed downwards, cold air overflows upwards from an air hole, a special-shaped curved surface steel structure in welding from bottom to top is cooled, the cooling speed of the welding face is increased, sliding of a welding seam material caused by the fact that the special-shaped curved surface steel structure is affected by gravity of different faces in the welding process is prevented, welding seam flatness is optimized, and welding quality is improved; and the position stability of the special-shaped curved surface steel structure is achieved through synchronous stretching and retracting of the output end of a telescopic rod mounting box, and practicability is higher.

Owner:青岛昊宇重工有限公司

Method for artificially culturing fungus tabasheer

The invention discloses a method for artificially culturing fungus tabasheer. The method comprises the following steps of (1) scraping tabasheer spores onto clean filter paper for later use in the tabasheer generating reason; (2) preparing the stored tabasheer spores into a tabasheer inoculum; (3) in mid-to-late March, selecting a tabasheer host bamboo, and injecting 8 to 12 mu.L of tabasheer inoculum into a leaf sheath along the handle of a bamboo leaf which is grown in the last year to obtain a tabasheer source; and (4) collecting the tabasheer spores from the tabasheer seed source obtained by the step (3), storing the tabasheer spores, preparing the stored tabasheer spores into a tabasheer inoculum, spraying the tabasheer inoculum into the host bamboo to be inoculated, and finally obtaining tabasheer stroma. The tabasheer spores which are naturally grown are collected, and the tabasheer spores are prevented from being affected by an adverse environment through indoor storage, so that the maximal activity of the tabasheer spores is kept; and a protecting agent is added into the tabasheer spores in a proper season to inoculate to obtain the tabasheer seed source, the tabasheer seed source is used for expanding cultivation to obtain a large number of tabasheer stroma, and then tabasheer is manually cultivated in a large area and popularized.

Owner:贵州省生物技术研究所

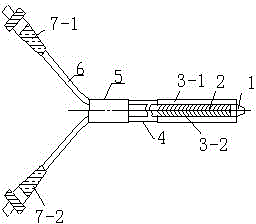

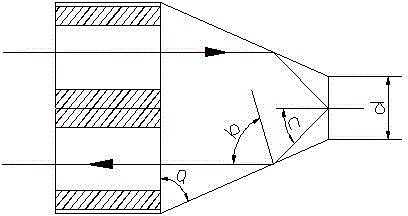

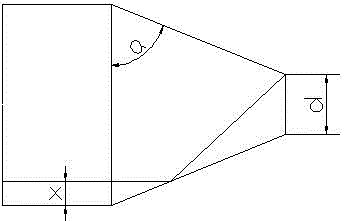

Intermediate-infrared hollow optical fiber ATR coupling probe

ActiveCN104535539AFlexible operationEasy to operateMaterial analysis by optical meansCouplingPhotonics

The invention discloses an intermediate-infrared hollow optical fiber ATR coupling probe and belongs to the technical fields of biomedical photonics and molecular spectrometric measurement and devices. The intermediate-infrared hollow optical fiber ATR coupling probe comprises an ATR crystal probe (1), an incident optical fiber (2-1), an emergent optical fiber (2-2), a handle cover (3), a dual-optical-fiber protective layer (4), a single-optical-fiber protective layer (6), a connecting sleeve (5), an incident optical fiber jumper (7-1) and an emergent optical fiber jumper (7-2). With the adoption of a method for coupling an intermediate-infrared hollow optical fiber and a ZnSe crystal probe, the probe is flexible and convenient due to reasonable design, small-area single-point detection and in-situ measurement can be realized, spectral deformation caused by factors such as light scattering is avoided, the infrared spectroscopy quality is improved, the probe is suitable for in-vivo detection or living body detection and has wide application prospects in the field of biomedicines, and the application range of the ATR spectral measurement technology in the field of biomedical engineering is widened.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

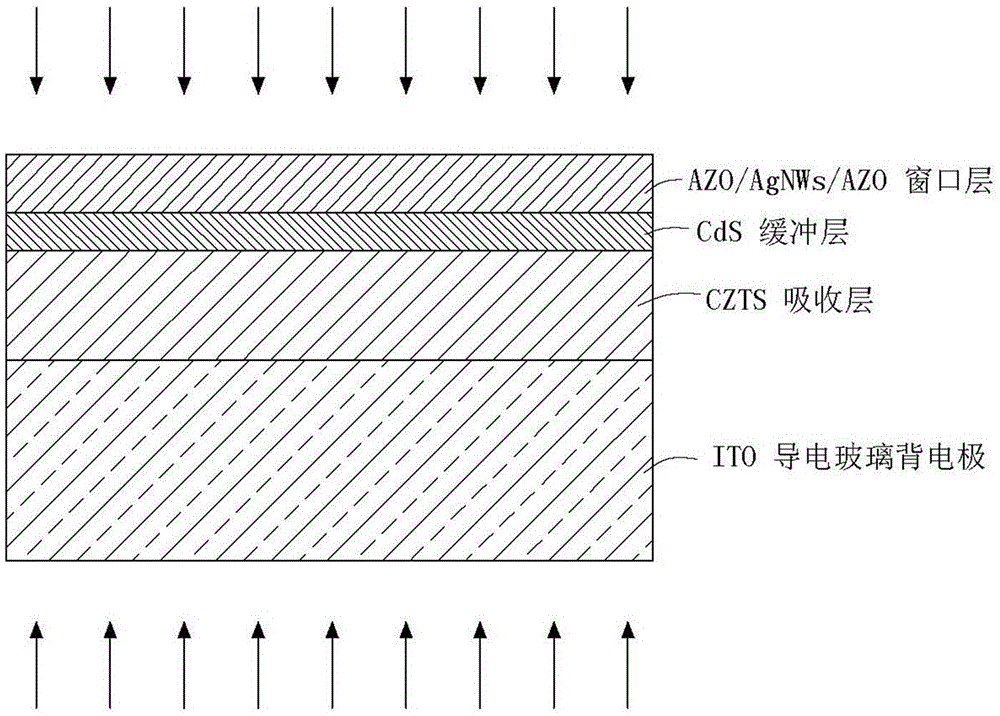

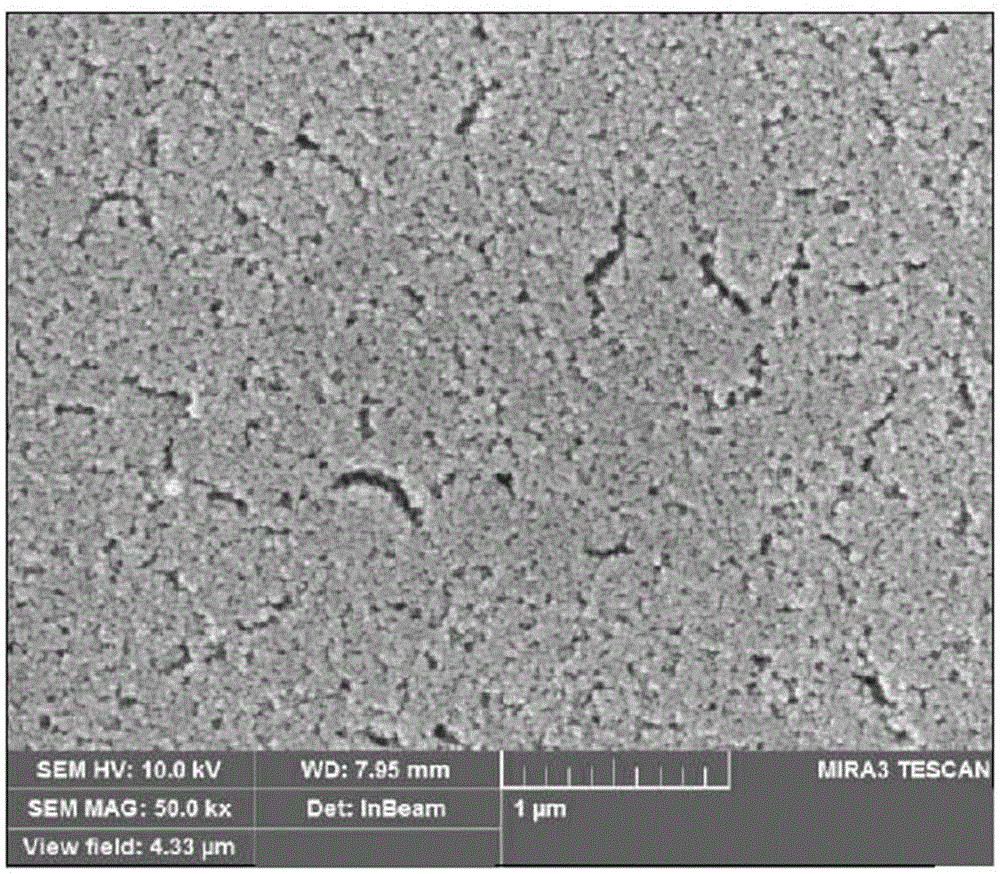

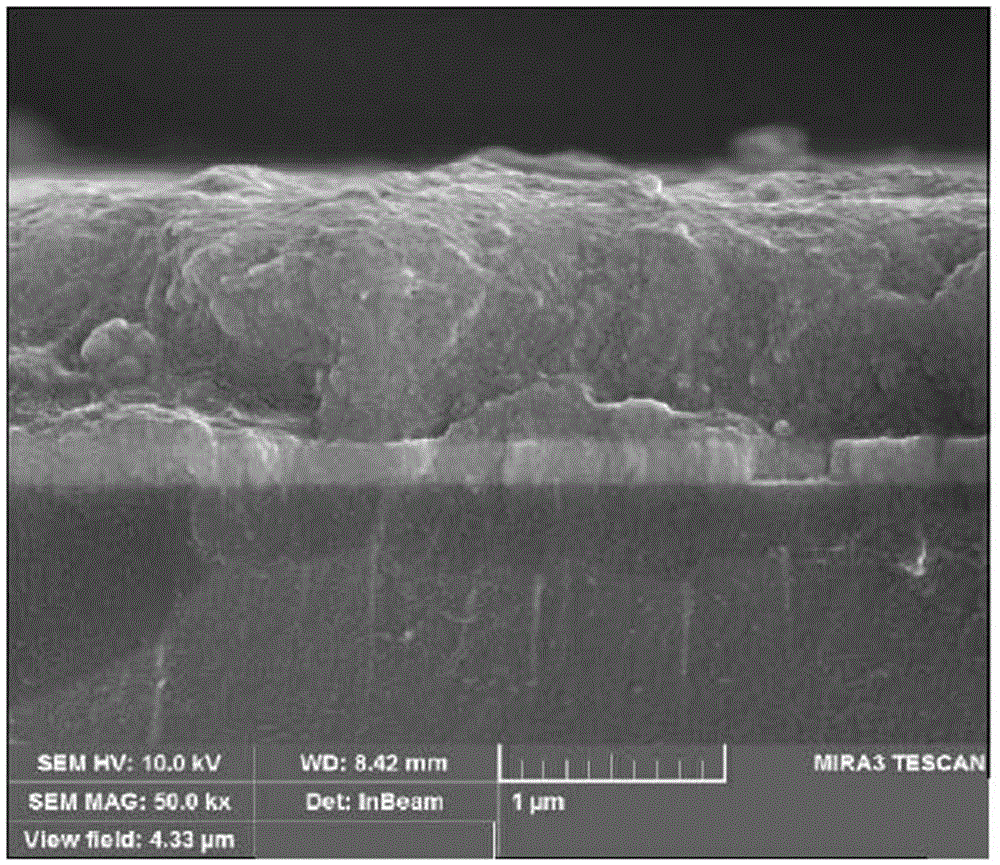

Copper zinc tin sulfur thin film solar cell and preparation method thereof

ActiveCN105576053AAvoid chemical thermal instability problemsPrevent thermal instabilityFinal product manufacturePhotovoltaic energy generationVulcanizationThermal instability

The invention provides a copper zinc tin sulfur thin film solar cell. The copper zinc tin sulfur thin film solar cell comprises an indium tin oxide conductive glass back electrode layer, a copper zinc tin sulfur thin film light absorption layer, a cadmium sulfide buffer layer and an aluminum-doped zinc oxide / silver wire / aluminum-doped zinc oxide composite transparent conductive window layer which are sequentially laminated, in the aluminum-doped zinc oxide / silver wire / aluminum-doped zinc oxide composite transparent conductive window layer, a layer of silver wire thin film is sandwiched between two layers of aluminum-doped zinc oxide thin films. In the copper zinc tin sulfur thin film solar cell, indium tin oxide conductive glass is adopted to substitute a Mo back electrode, and the thermal instability characteristics of the Mo back electrode and the copper zinc tin sulfur thin film during the vulcanization process are prevented; meanwhile, double-surface transmitting can be achieved, and the device efficiency of the copper zinc tin sulfur thin film solar cell is improved; moreover, the aluminum-doped zinc oxide / silver wire / aluminum-doped zinc oxide composite transparent conductive window layer prepared by a solution method is adopted to substitute an indium tin oxide / aluminum-doped zinc oxide (ITO / AZO) conductive window layer deposited by a vacuum method, the manufacturing cost of the copper zinc tin sulfur thin film solar cell is reduced, and the copper zinc tin sulfur thin film solar cell is very friendly to a surrounding environment.

Owner:RESEARCH INSTITUTE OF TSINGHUA UNIVERSITY IN SHENZHEN

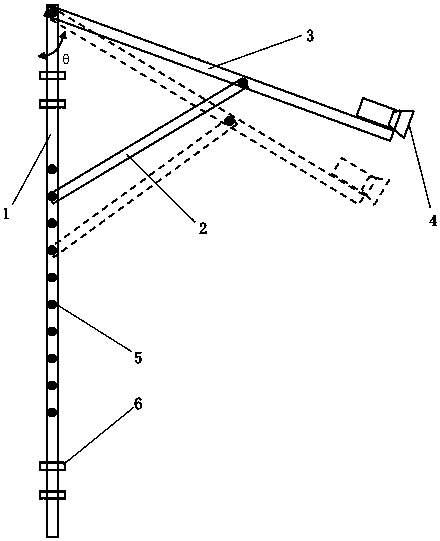

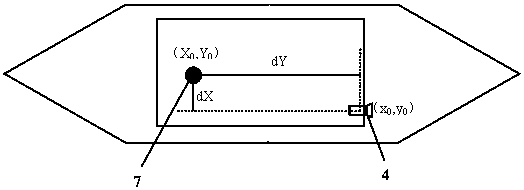

A sea surface observation device and method with adjustable ship-borne field of view

ActiveCN103791892BRealized areaHigh practical valuePhotogrammetry/videogrammetryOpen water surveyInformation processingSurface ocean

The invention discloses a ship-mounted sea surface observation device and method with adjustable field of view. Through the design of ship-mounted positioning device, high-definition camera and fixed mechanism, a ship-mounted sea surface observation device and method with adjustable field of view is established, which is realized through steps such as time synchronization, device installation, field of view adjustment, observation and information processing. The invention is based on high-definition camera technology and high-precision positioning technology, and designs a fixed mechanism with adjustable field of view, proposes an information processing method, and realizes sea surface observation and area estimation. The invention can exert great practical value in the on-site positioning observation and area estimation of marine phenomena and processes such as sea surface red tides, oil spills, fronts and underwater reefs.

Owner:SECOND INST OF OCEANOGRAPHY MNR