Patents

Literature

181results about How to "Easy processing conditions" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

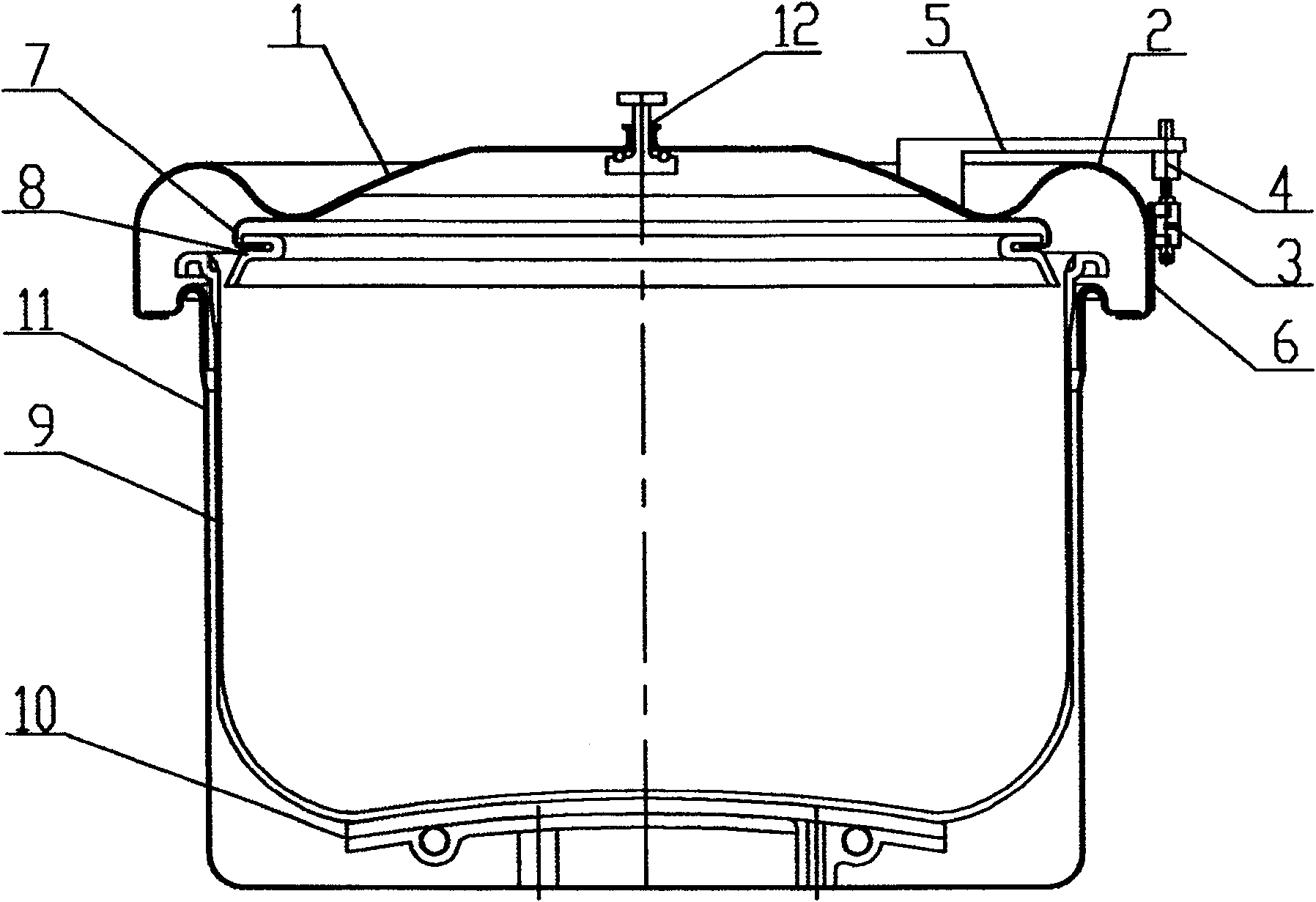

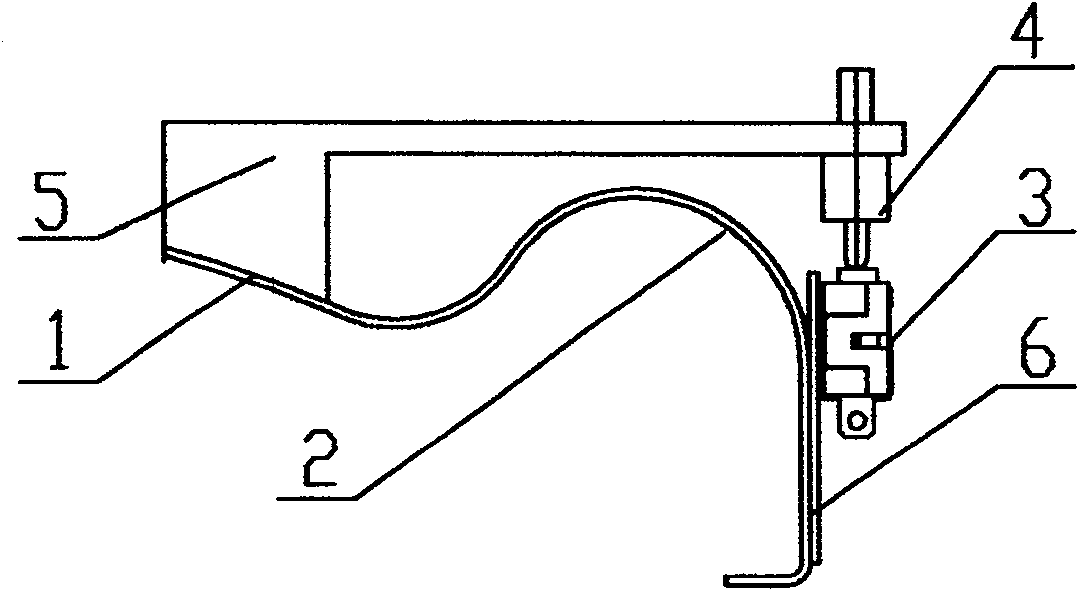

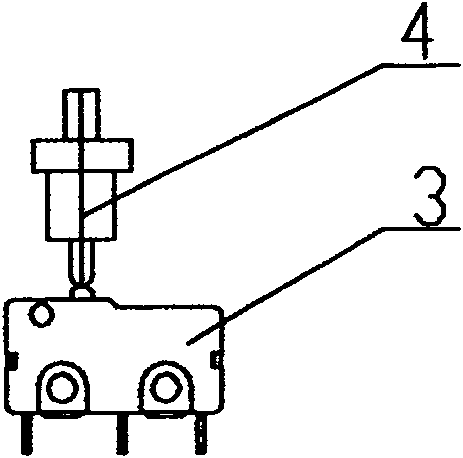

Moving-cover type electric pressure cooker

The invention relates to a movable cover electric pressure cooker, which belongs to kitchen electric appliances, and is a patented technology of electric rice cooker pressurization that controls and limits the pressure inside the cooker through an elastic cooker cover. It includes a pot cover, an elastic element, a switch, a sealing ring, an inner pot, an electric heater, and an outer pot; the edge of the inner pot sits on the edge of the outer pot; The outer pot is movable and rigidly connected; the elastic element controls the on-off of the switch by the elastic displacement generated under the pressure in the pot, and the elastic displacement is transmitted to the corresponding device through the transmission part arranged at the displacement or static position of the elastic element. on the switch. The invention can solve the problems in the integrated design and mechanical connection of the elastic element and other parts in the prior art, improve the utilization rate of materials, simplify the production process and reduce the production cost.

Owner:王永光

Galactomannan based well treating fluids

ActiveUS20050272612A1Low polymer contentHigh molecular weightFluid removalFlushingPolymer scienceFracturing fluid

A well fracturing fluid is shown which includes an aqueous base fluid, a hydratable polymer, such as a guar gum, and a suitable crosslinking agent for crosslinking the hydratable polymer to form a polymer gel. The hydratable polymer has a higher molecular weight which is achieved by improvements in the processing of the guar split. The higher molecular weight polymer provides improved performance in well fracturing operations.

Owner:BAKER HUGHES INC

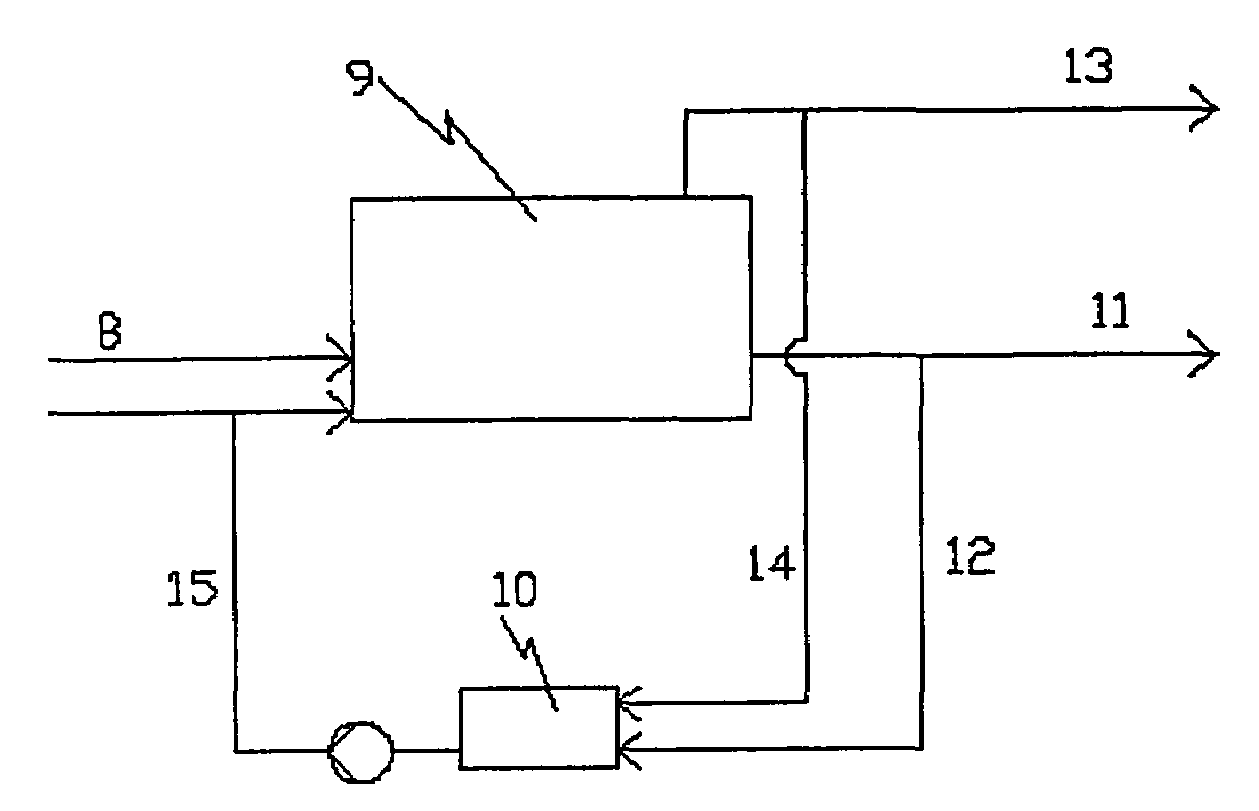

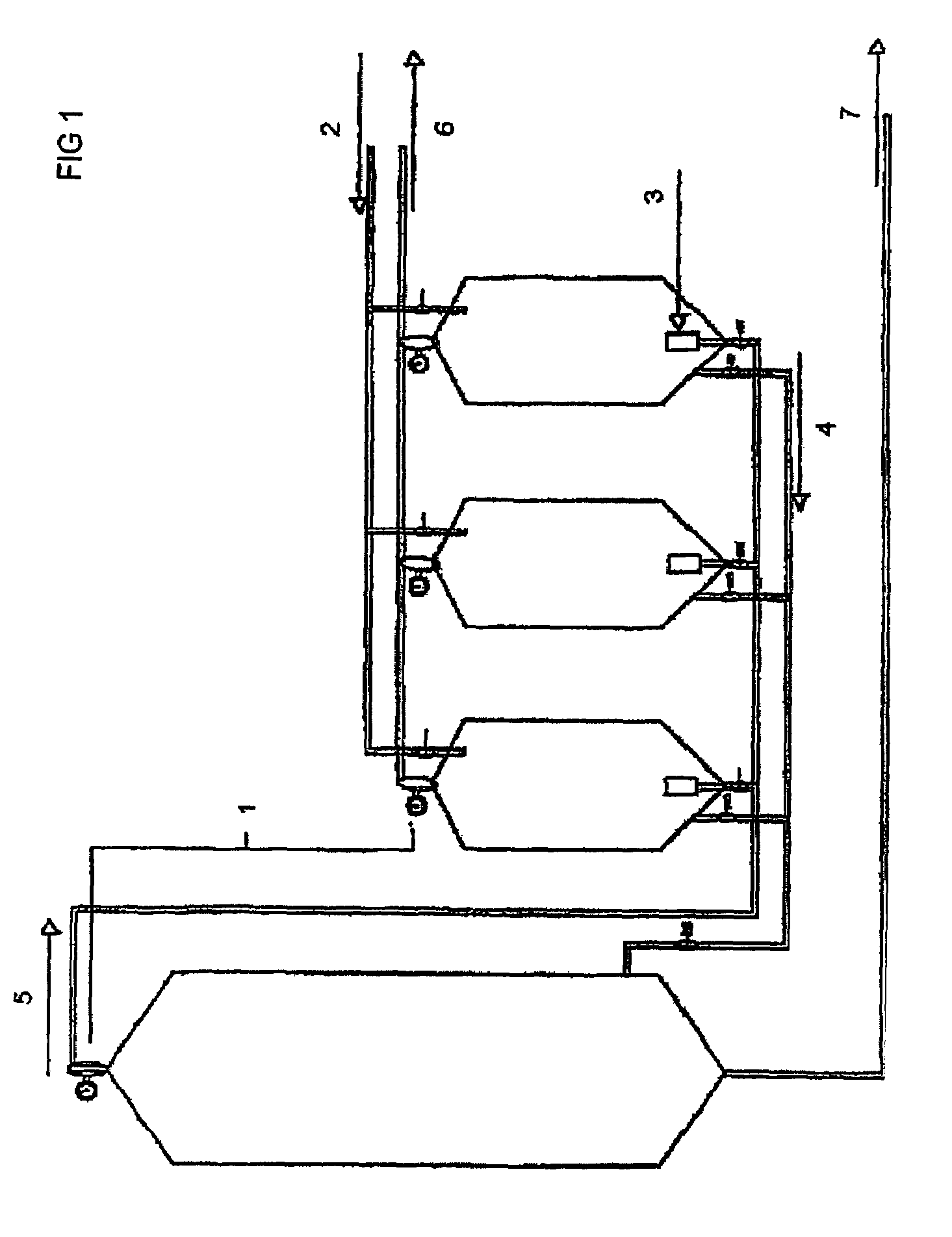

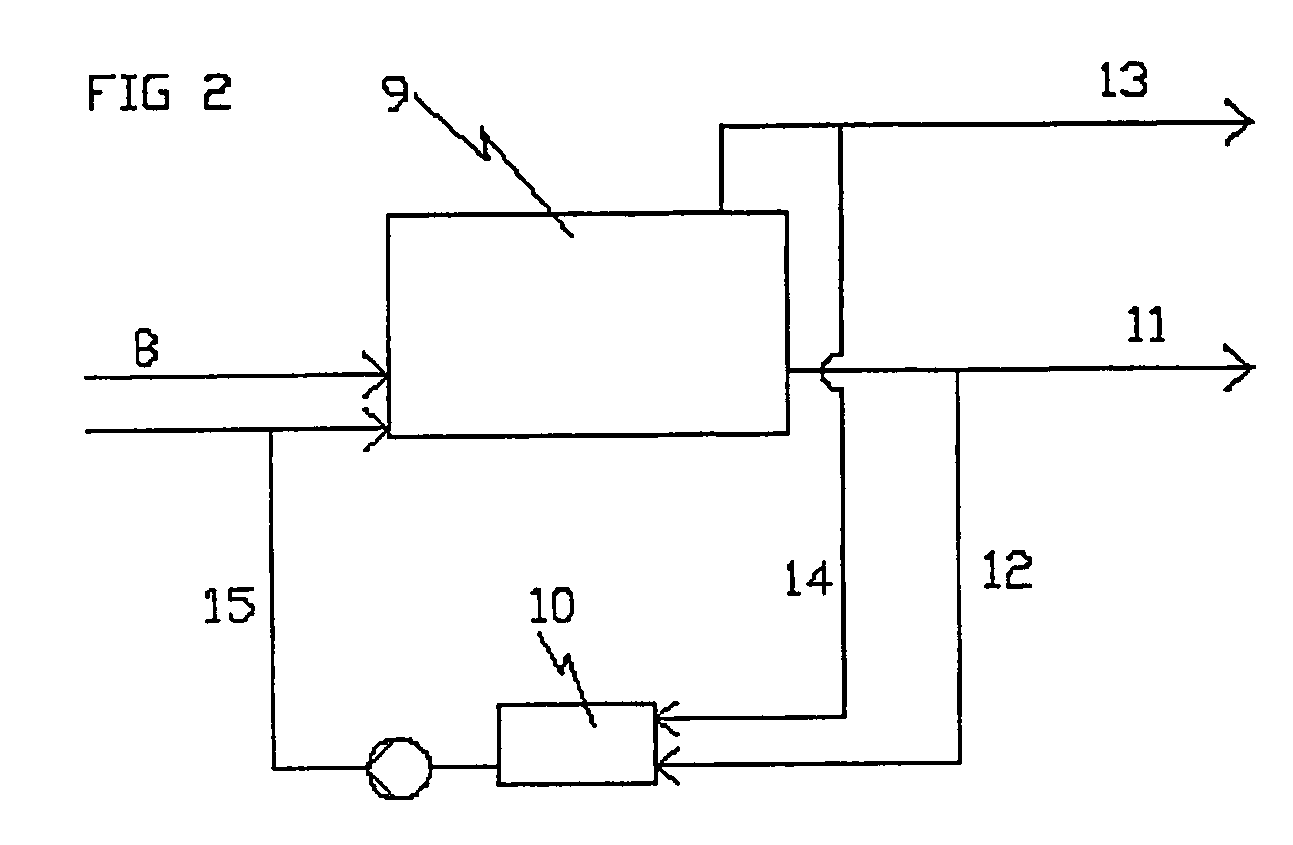

Method and equipment for processing organic material

InactiveUS7160456B2Organic material longerEasy to storeBio-organic fraction processingAnimal corpse fertilisersBuffer solutionAmmonia

A method for processing organic material, in which method bioconversion is performed on the organic material in at least one first reactor, the biogas formed in the bioconversion is treated with ammonia in at least one second reactor and buffer solution produced in the second reactor is recycled to the bioconversion in the first reactor. Thus, the carbon dioxide of the mixed methane / carbon dioxide gas reacts with the ammonia and forms a buffer compound, such as ammonium bicarbonate and / or ammonium carbonate.

Owner:PRESECO

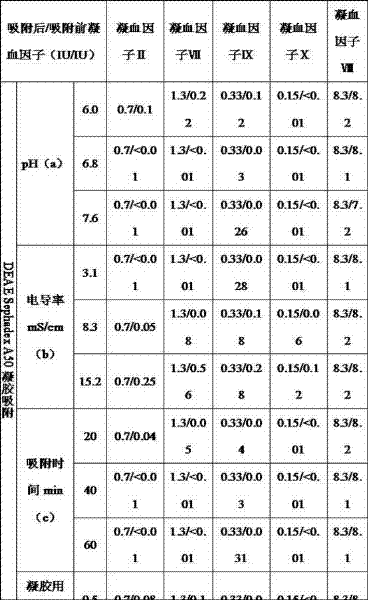

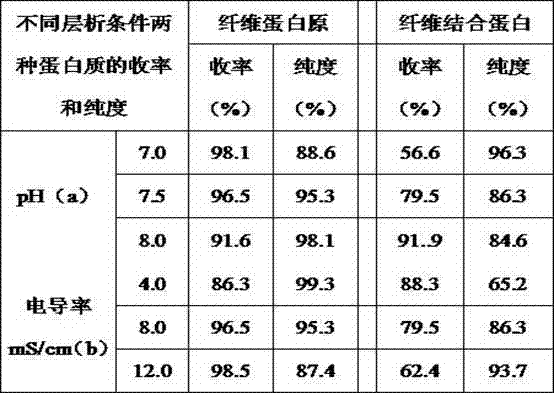

Method for preparing blood coagulation factor ⅷ, fibrinogen and fibronectin by cryoprecipitation

ActiveCN102295696AIncrease profitHigh yield and purityFactor VIIConnective tissue peptidesFibrinBlood plasma

The invention relates to the field of blood products, in particular to a process method for preparing three kinds of blood products from cryoprecitation, and aims to provide a complete separation and purification process for respectively and sequentially preparing the three kinds of blood products, i.e. a coagulation factor VIII, fibrinogen and fibronectin, from the cryoprecitation. The process method is implemented by the following technical scheme that the process method comprises the preparation steps of cryoprecitation dissolution, gel adsorption, precipitation of the fibrinogen and the fibronectin, two-step ion exchange chromatography and glycin / sodium chloride precipitation and inactivation of virus. The process method has the beneficial effects that the three kinds of useful blood products, i.e. the coagulation factor VIII, the fibrinogen and the fibronectin, can be separated and extracted from the cryoprecitation sequentially; and the utilization rate of blood plasma is greatly improved.

Owner:SHANDONG TAIBANG BIOLOGICAL PROD CO LTD

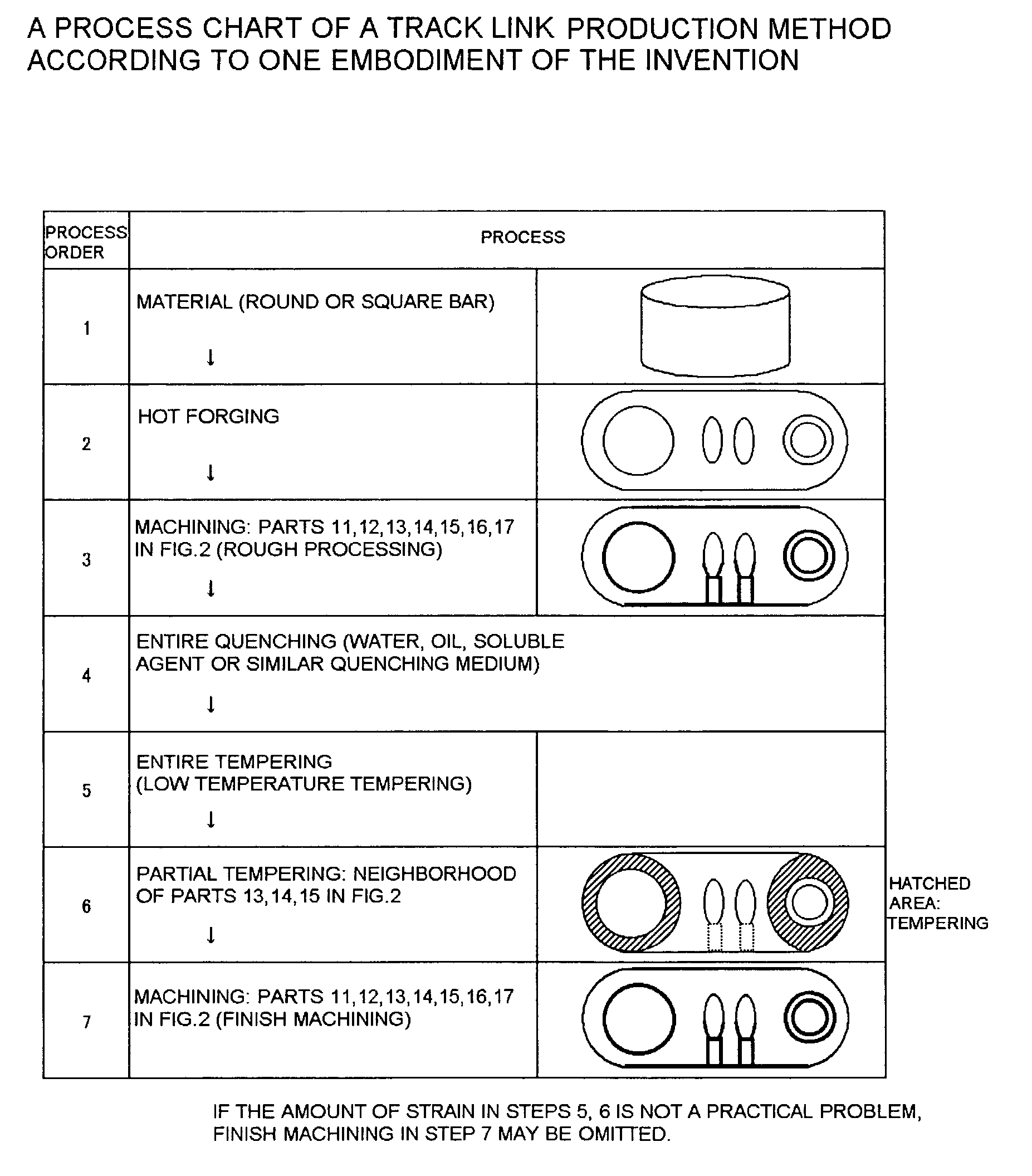

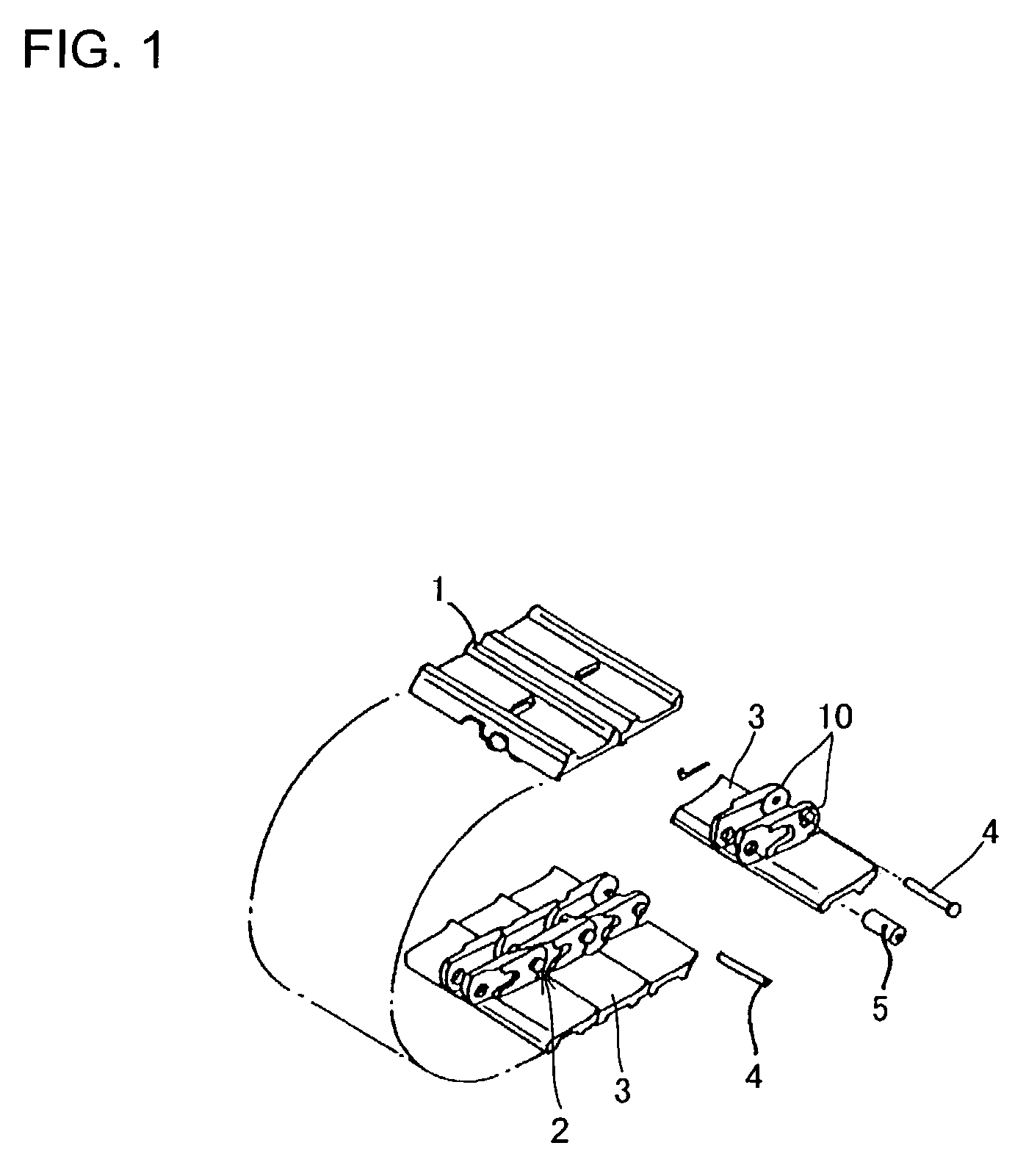

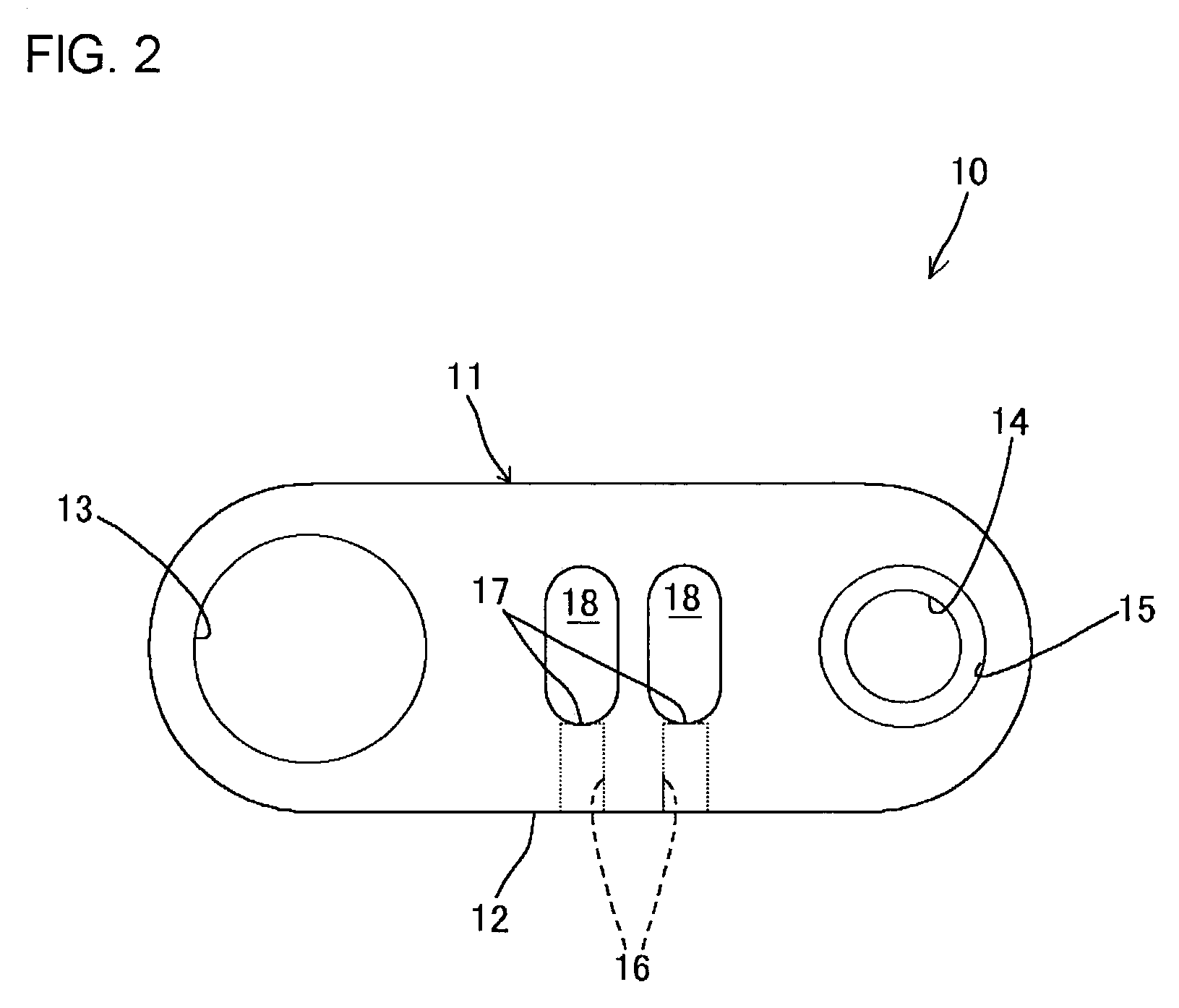

Track link production method and track link produced by the same

InactiveUS7040080B2Delayed failureIncrease pressureConnecting rodsMetal-working apparatusHigh dimensionalMachining process

There are proposed a track link production method capable of providing markedly improved wear life with good cost performance and a track link produced by this method. To this end, the track link production method includes a heat treatment process (Steps 4, 5) of applying quenching and low temperature tempering treatment to a whole link material after hot forging (Step 2), and is designed such that desired machining is applied to the link material (Step 3) before the heat treatment process (Steps 4, 5) and such that after the heat treatment process (Steps 4, 5), tempering (Step 6) and finish machining (Step 7) are sequentially applied to some of the parts which have undergone the machining process, the some parts including at least parts where high dimensional accuracy is required.

Owner:KOMATSU LTD

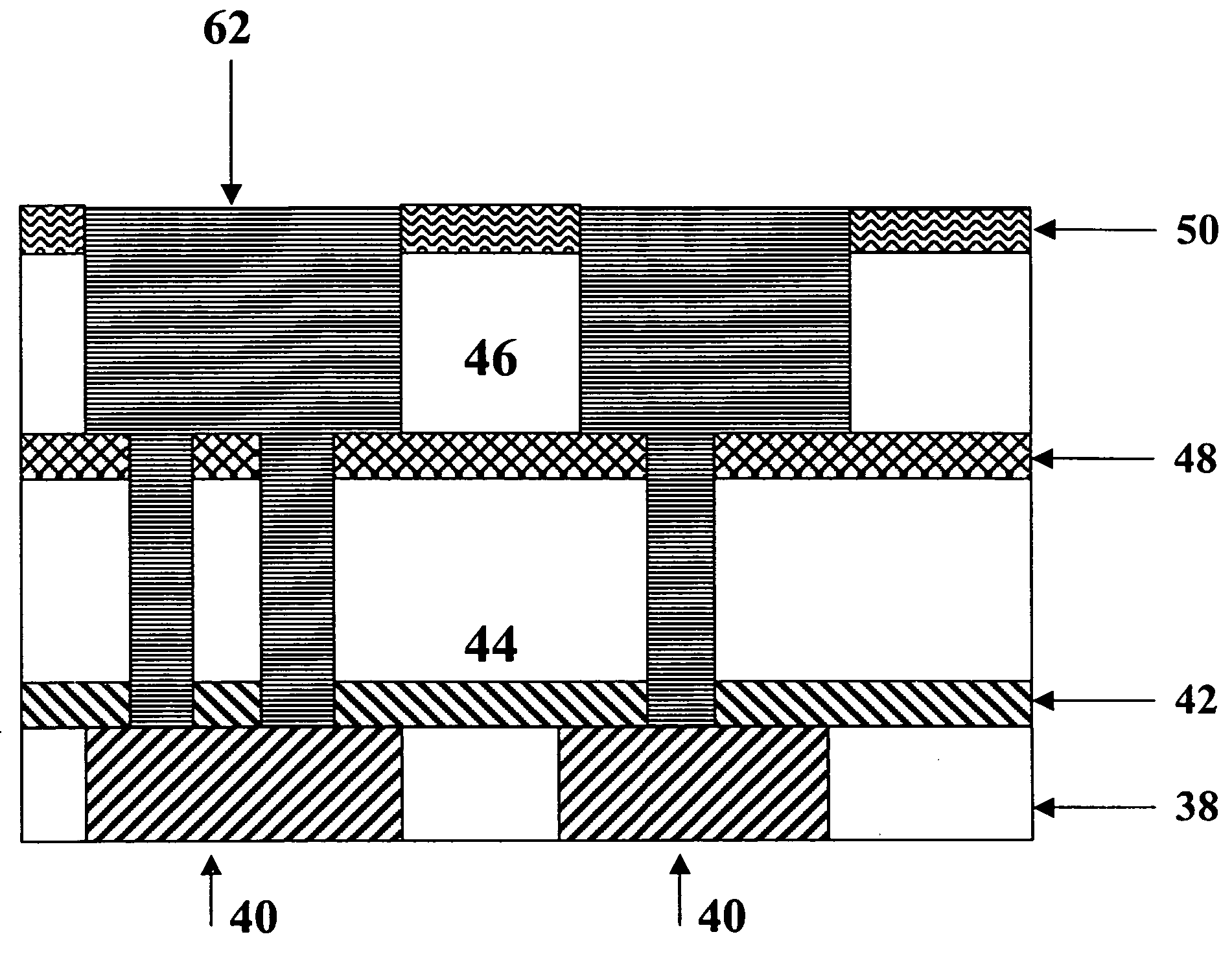

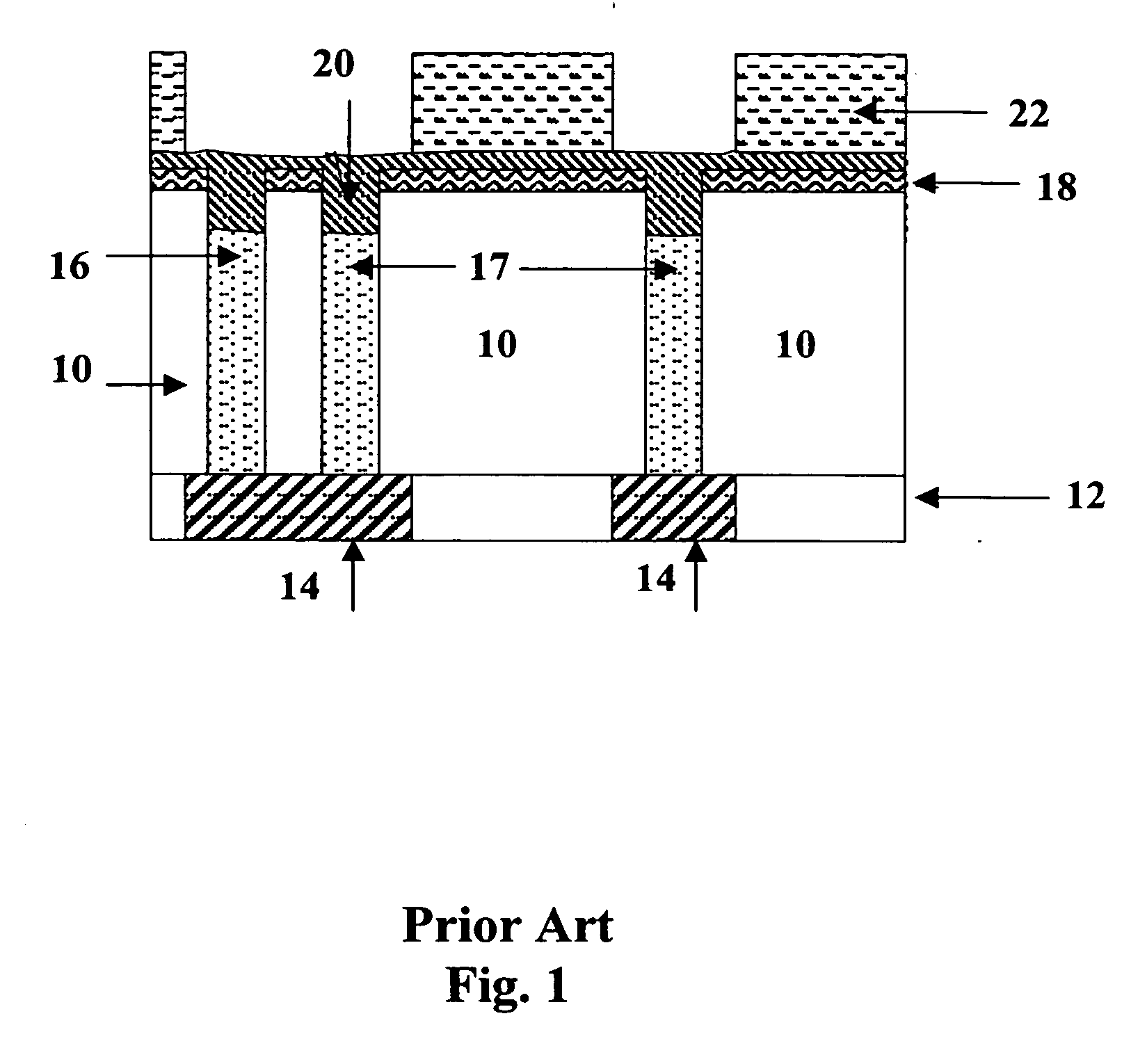

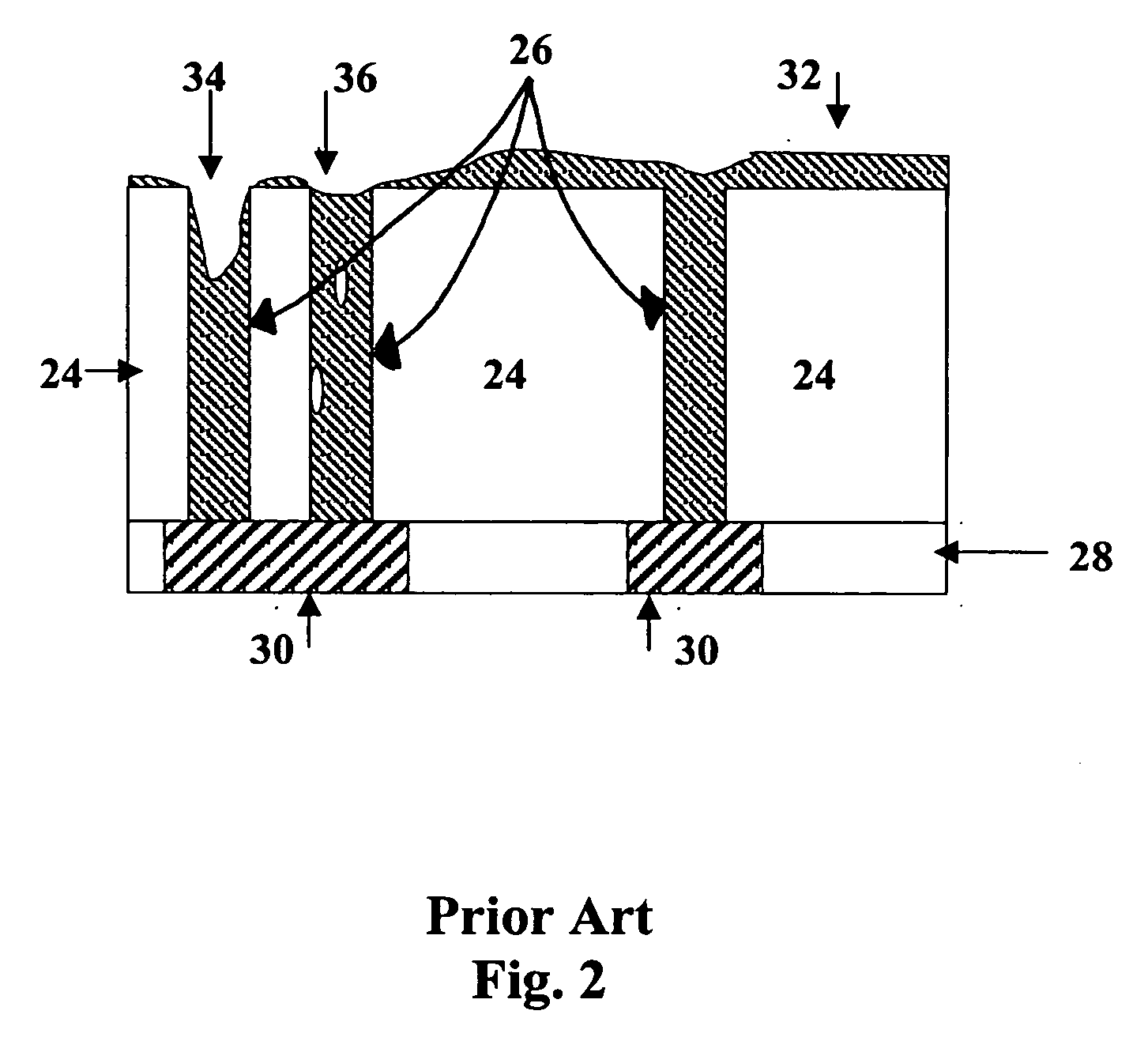

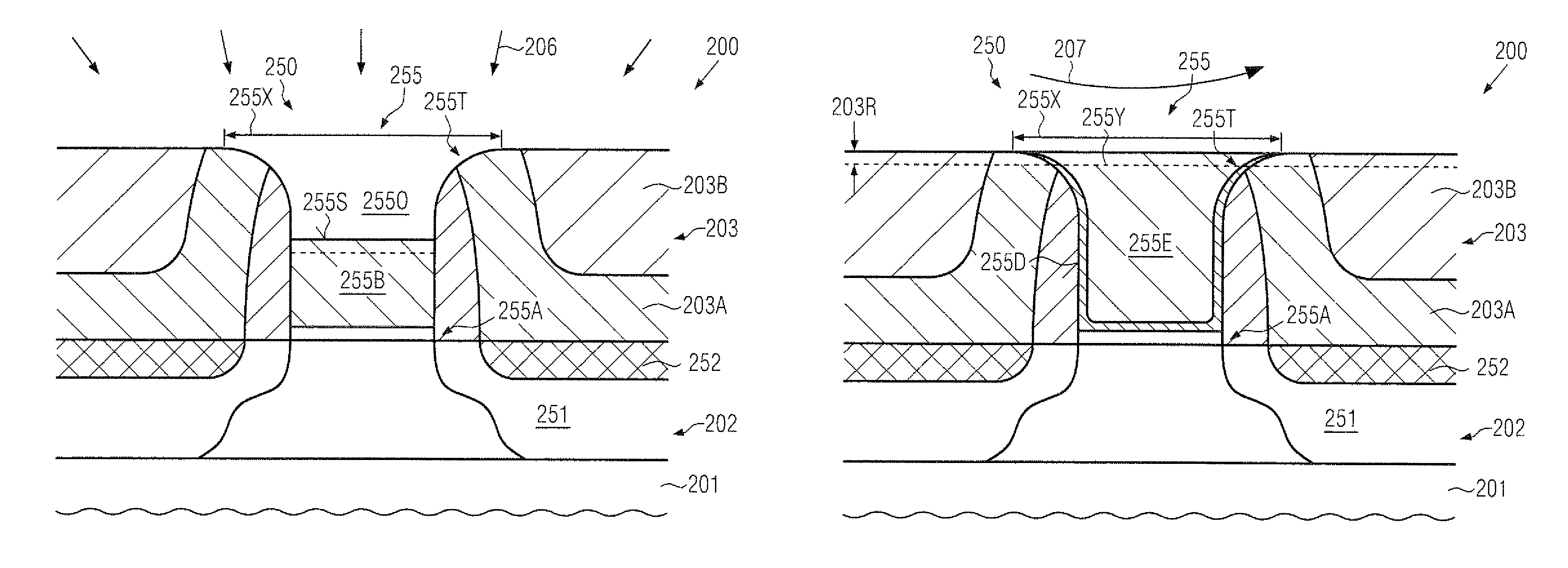

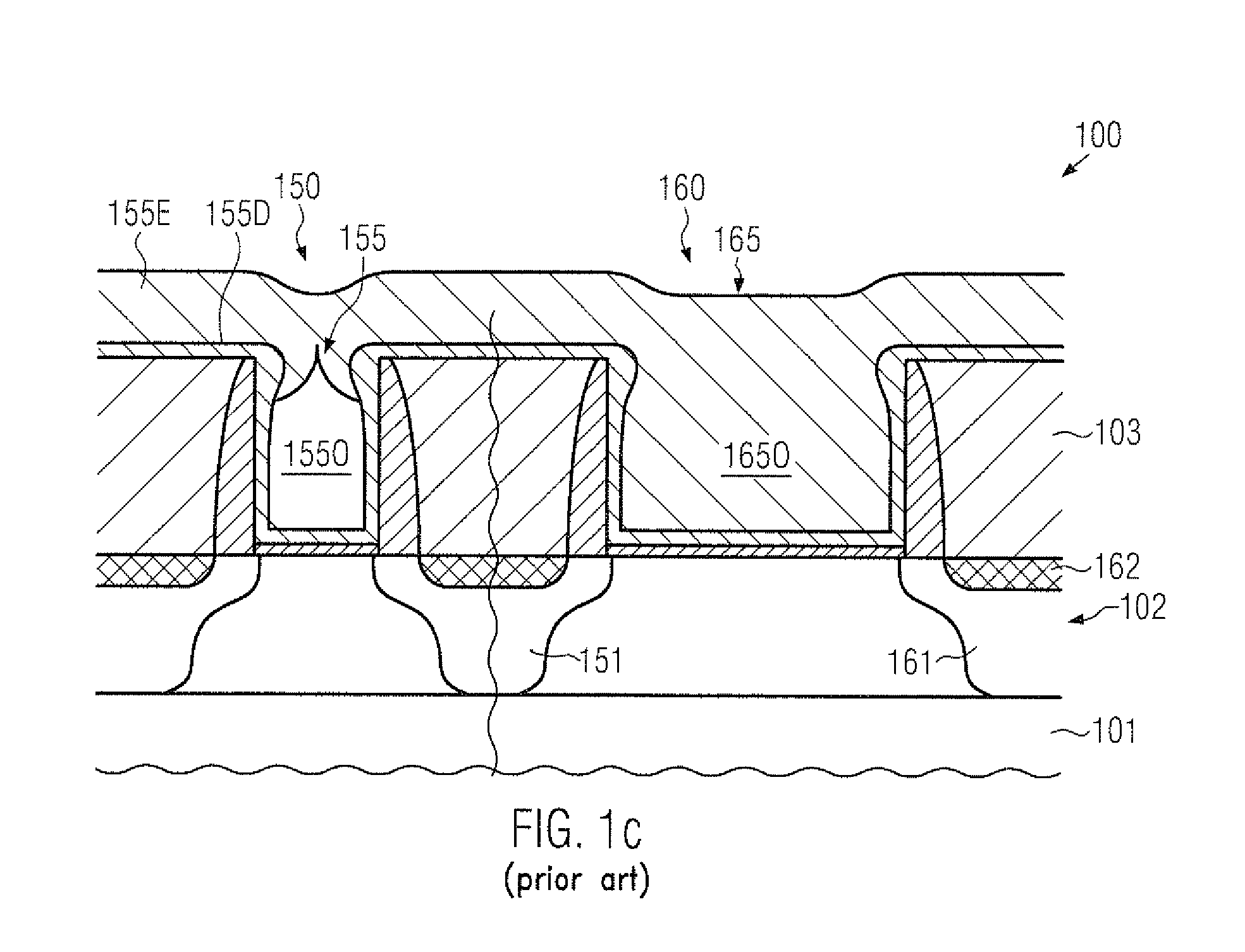

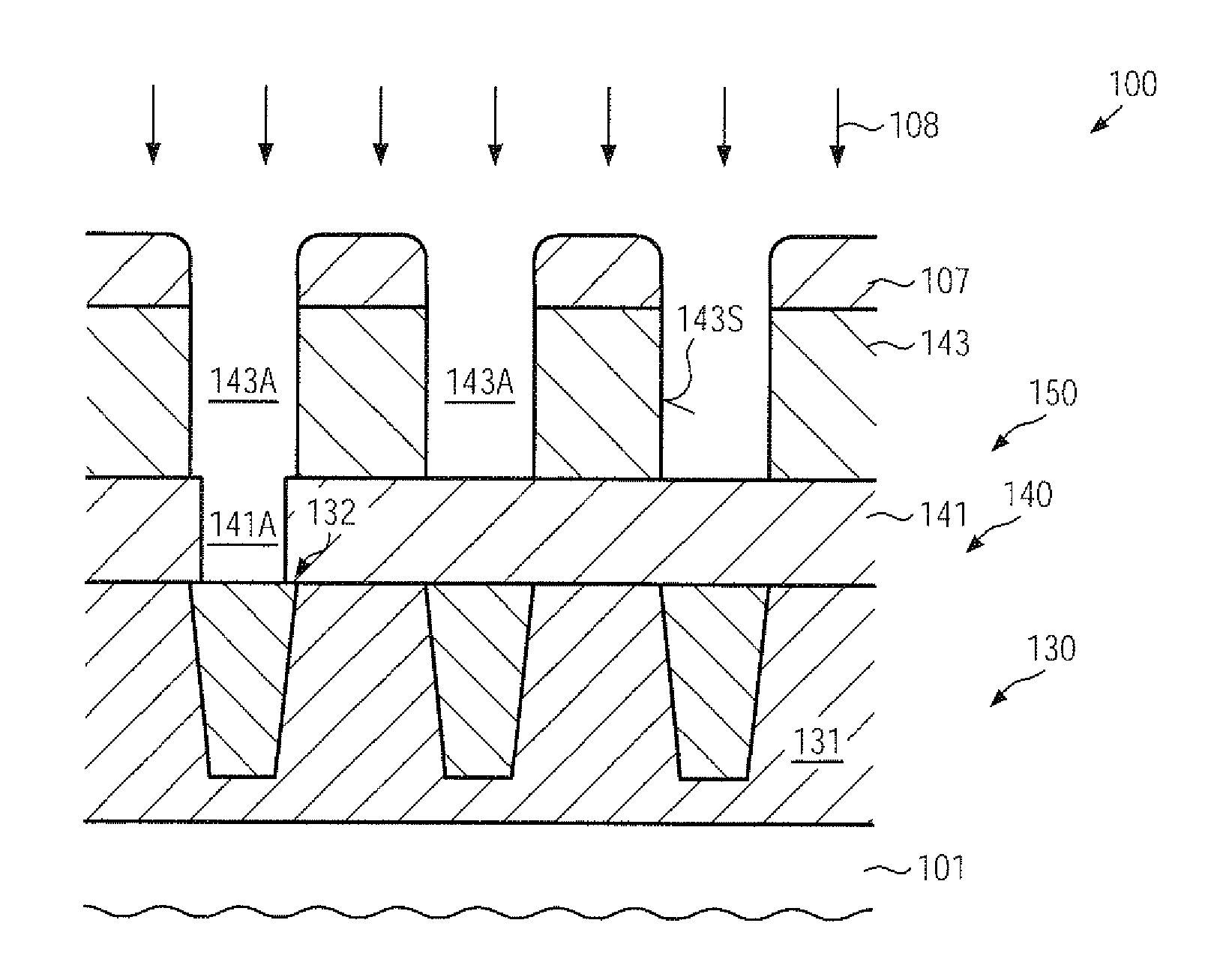

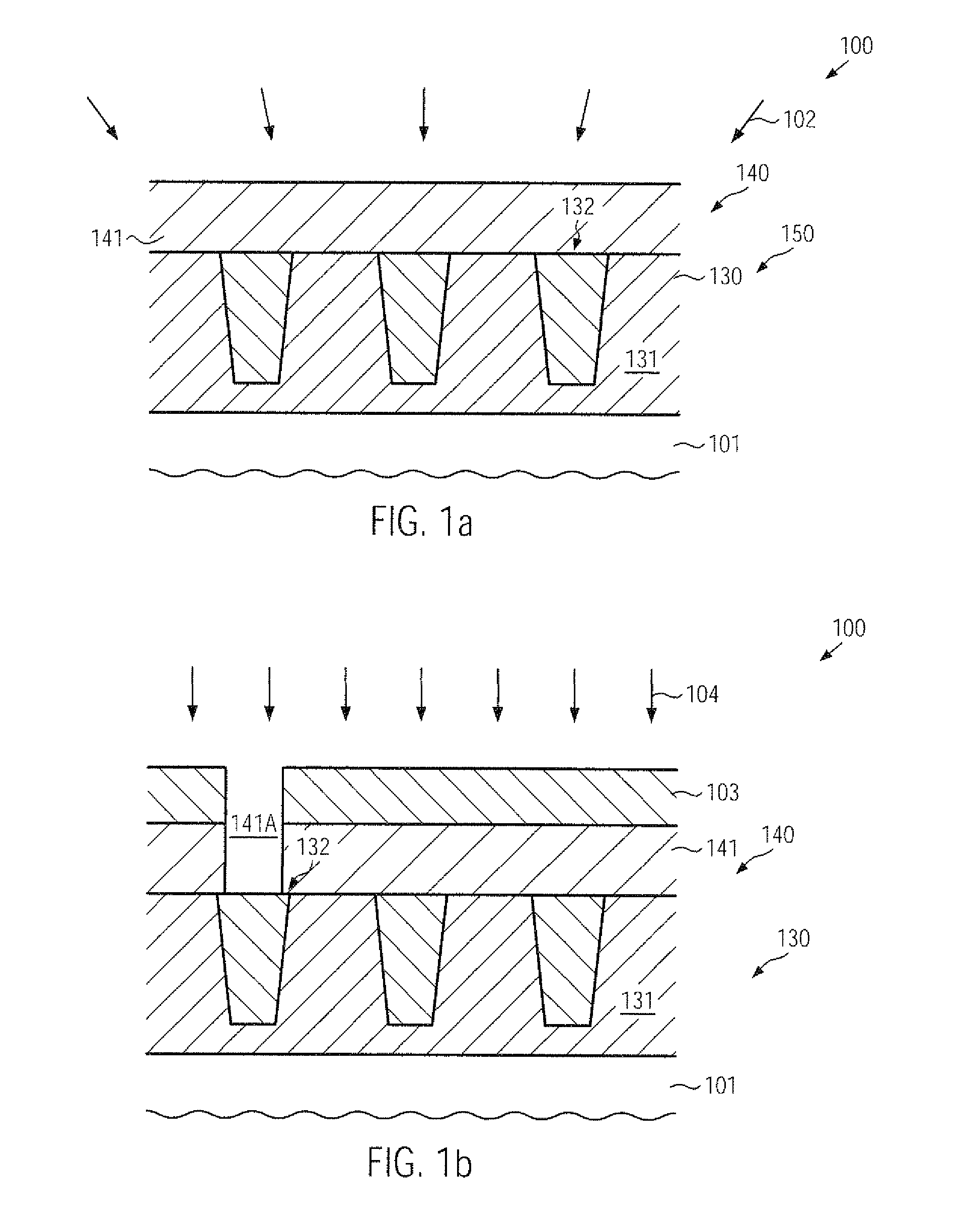

Method of filling structures for forming via-first dual damascene interconnects

ActiveUS20050118800A1Reduce biasEasy processing conditionsSolid-state devicesSemiconductor/solid-state device manufacturingAnti-reflective coatingContact time

A method of forming via-first, dual damascene interconnect structures by using a gap-filling, bottom anti-reflective coating material whose thickness is easily controlled by a solvent is provided. After application to a substrate, the bottom anti-reflective coating is partially cured by baking at a low temperature. Next, a solvent is dispensed over the coated wafer and allowed to contact the coating for a period of time. The solvent removes the bottom anti-reflective coating at a rate controlled by the bottom anti-reflective coating's bake temperature and the solvent contact time to yield a bottom anti-reflective coating thickness that is thin, while maintaining optimum light-absorbing properties on the dielectric stack. In another possible application of this method, sufficient bottom anti-reflective coating may be removed to only partially fill the vias in order to protect the bottoms of the vias during subsequent processing. The solvent is removed from the wafer, and the bottom anti-reflective coating is cured completely by a high-temperature bake. The wafer is then coated with photoresist, and the trench pattern exposed. The bottom anti-reflective coating material used maintains a greater planar topography for trench patterning, eliminates the need for an inorganic light-absorbing material layer on the top of the dielectric stack, protects the bottom of the vias during the trench etch, and prevents the formation of fencing problems by using a solvent to control the thickness in the vias.

Owner:BREWER SCI

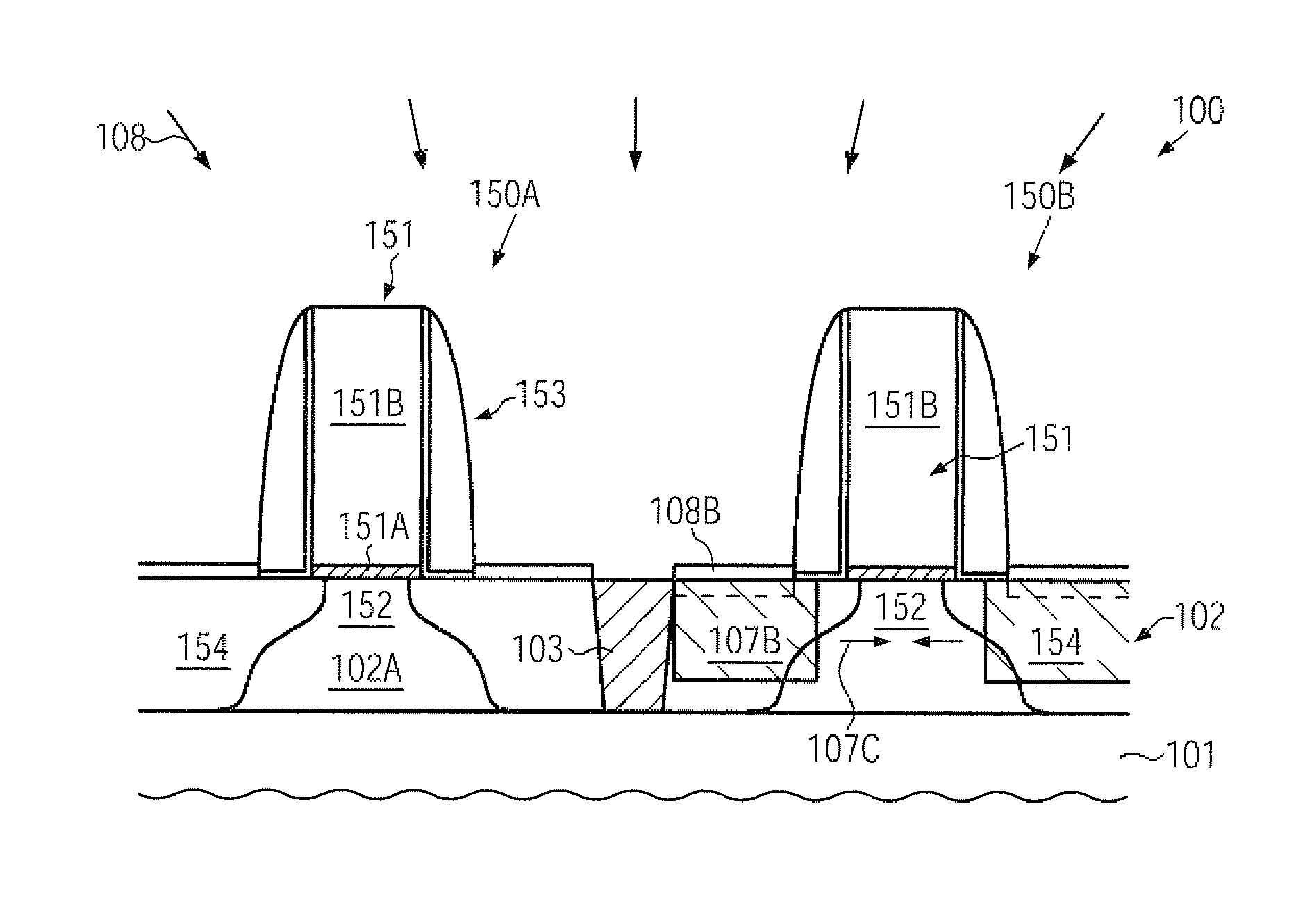

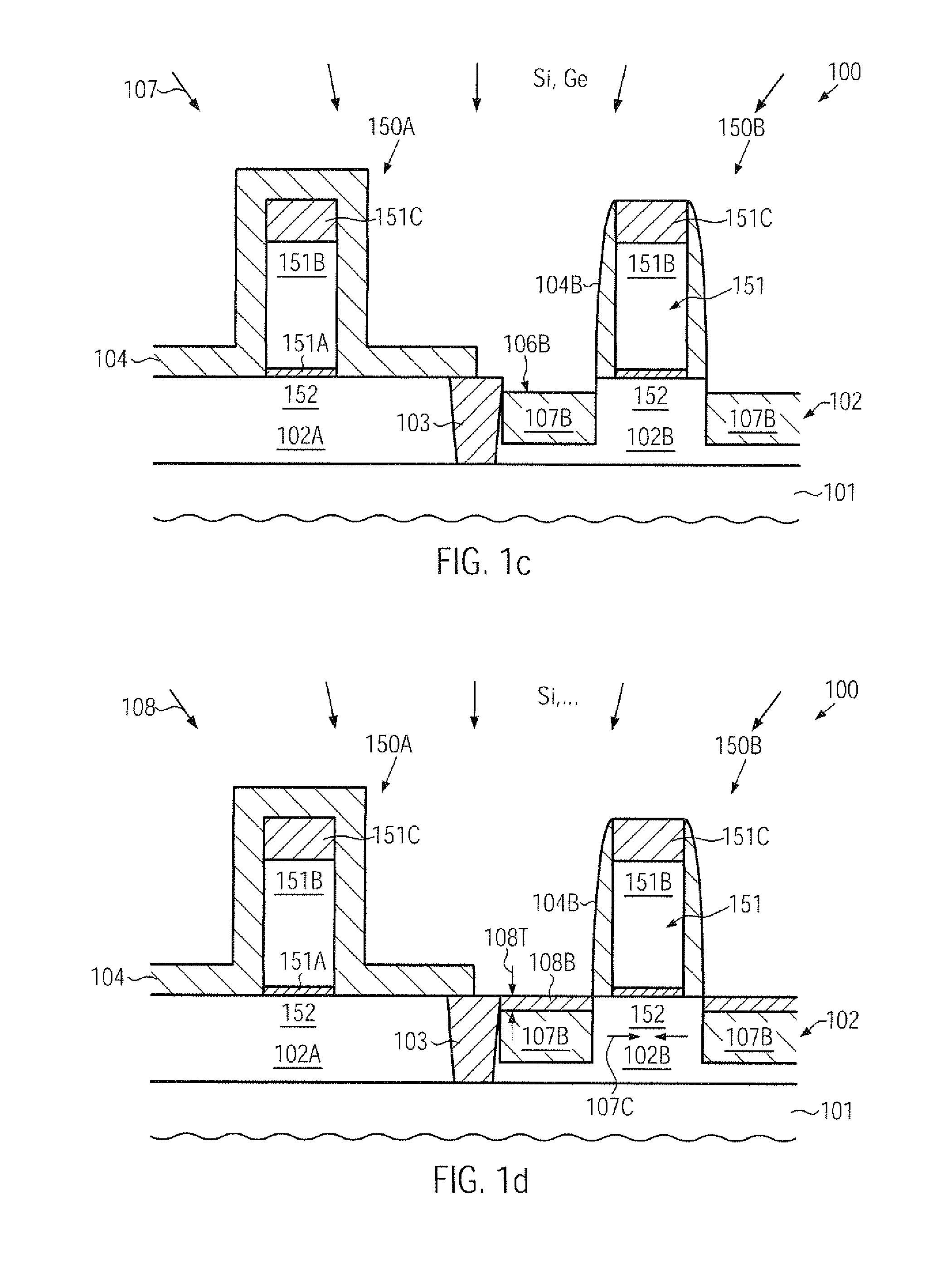

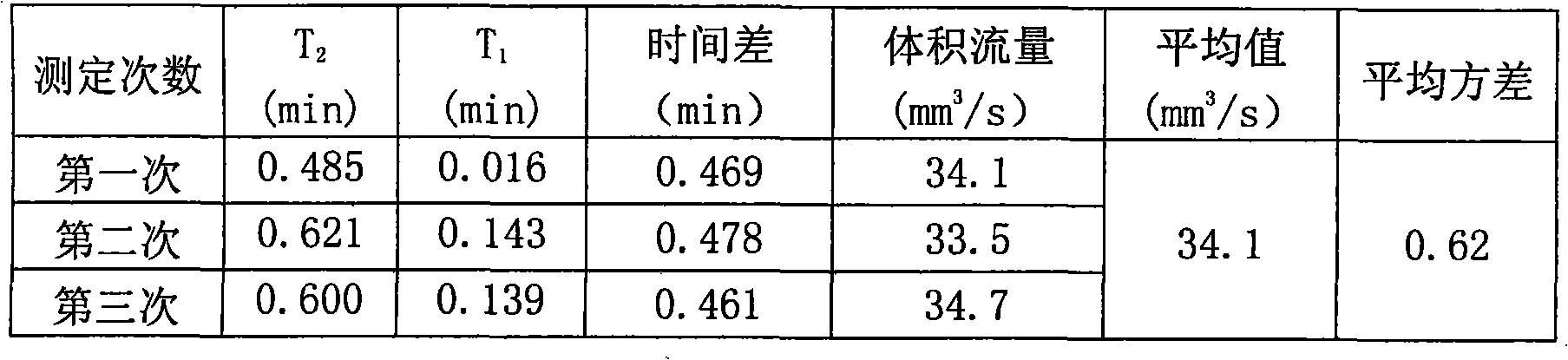

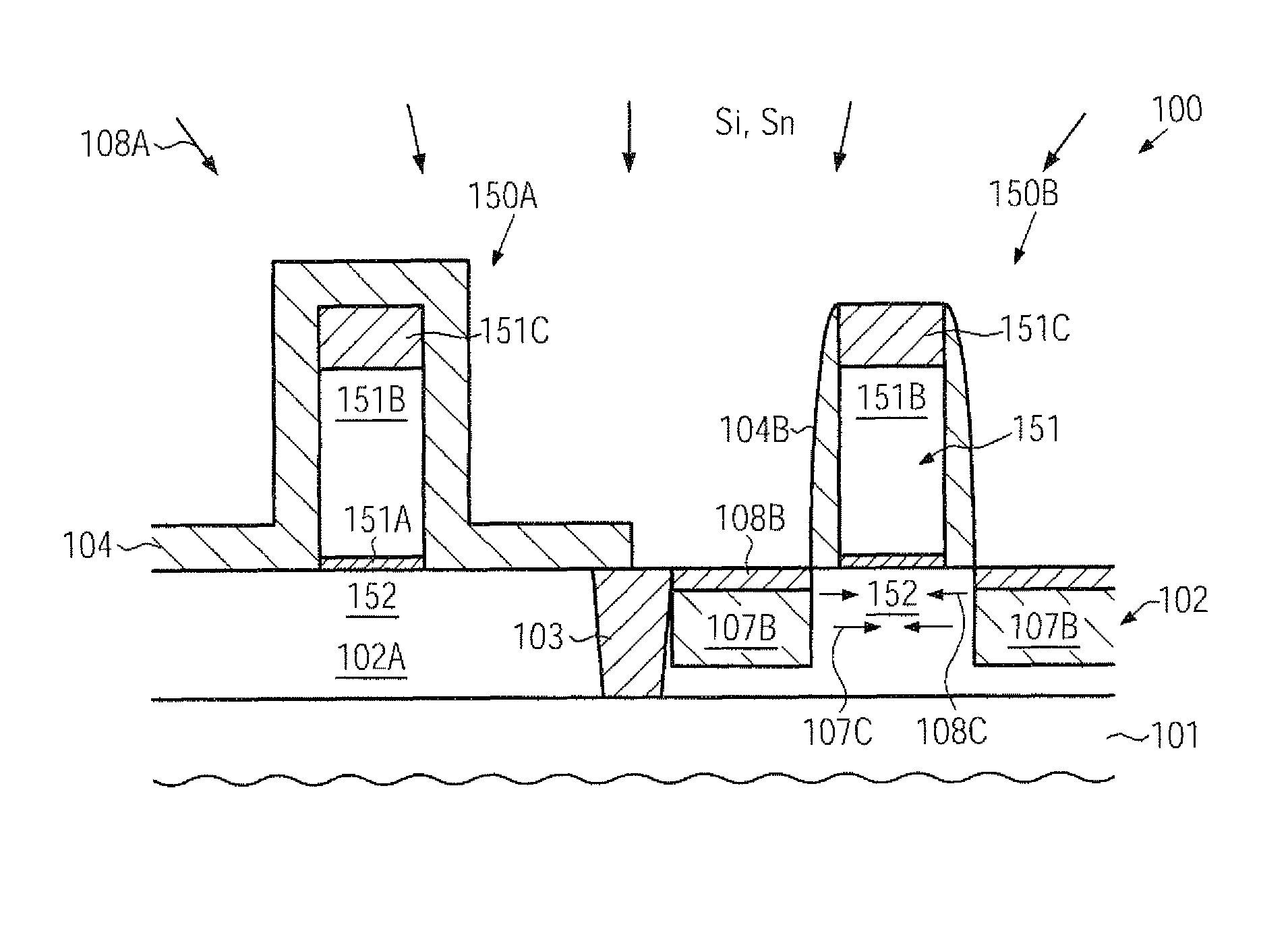

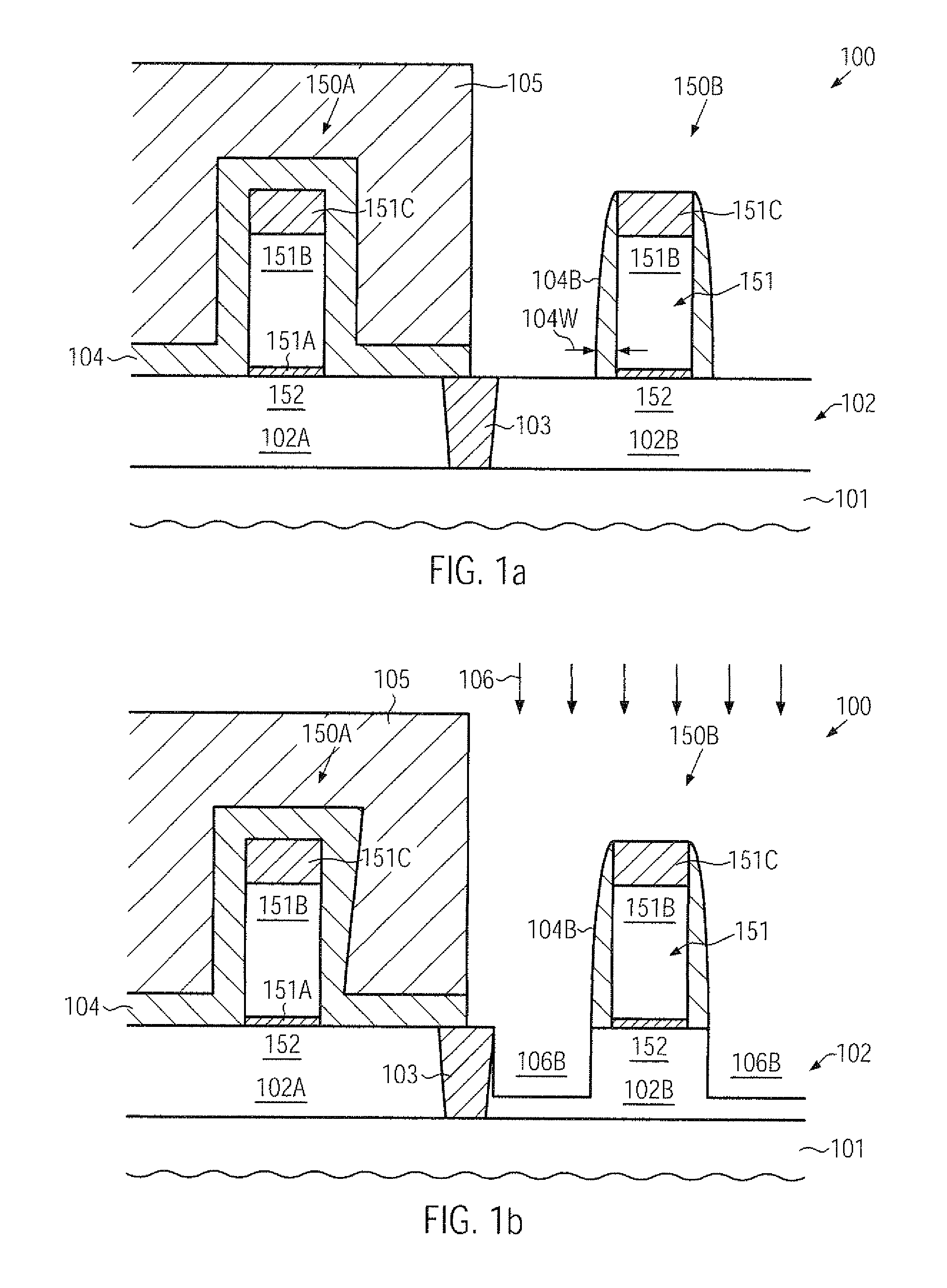

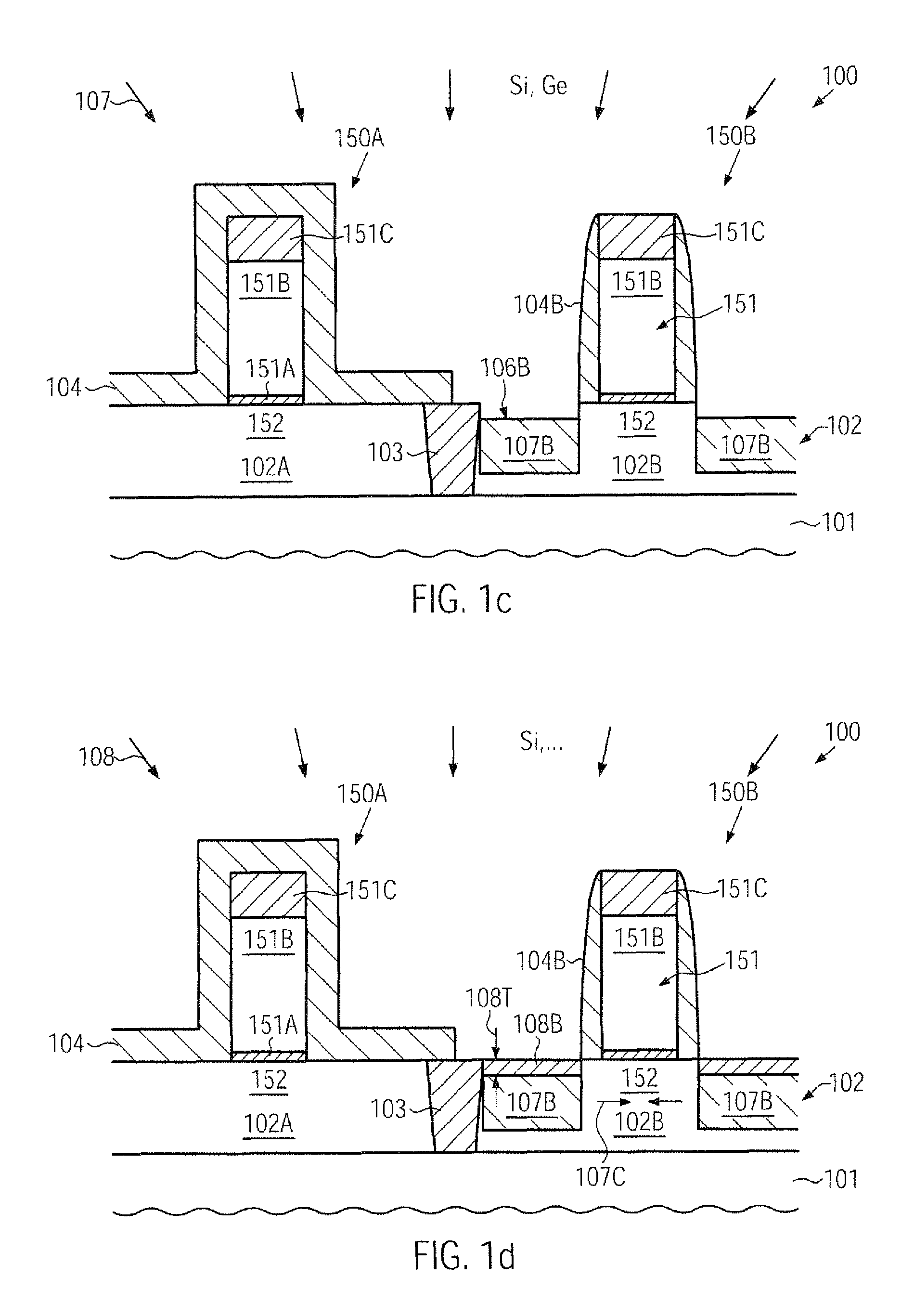

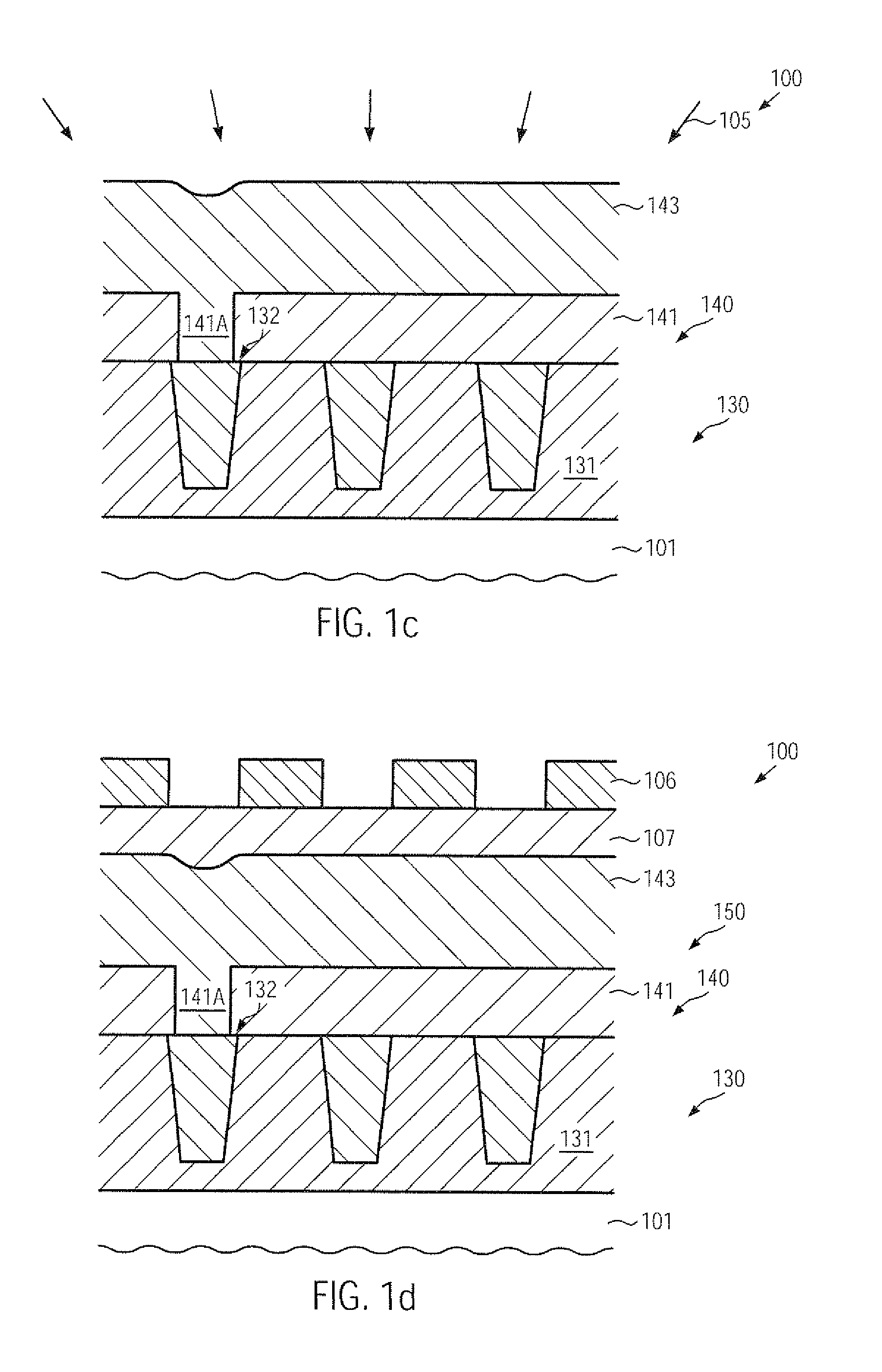

Reducing silicide resistance in silicon/germanium-containing drain/source regions of transistors

ActiveUS20100244107A1Reducing process irregularityReduced germanium concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesHigh strainP channel

In sophisticated P-channel transistors, a high germanium concentration may be used in a silicon / germanium alloy, wherein an additional semiconductor cap layer may provide enhanced process conditions during the formation of a metal silicide. For example, a silicon layer may be formed on the silicon / germanium alloy, possibly including a further strain-inducing atomic species other than germanium, in order to provide a high strain component while also providing superior conditions during the silicidation process.

Owner:GLOBALFOUNDRIES US INC

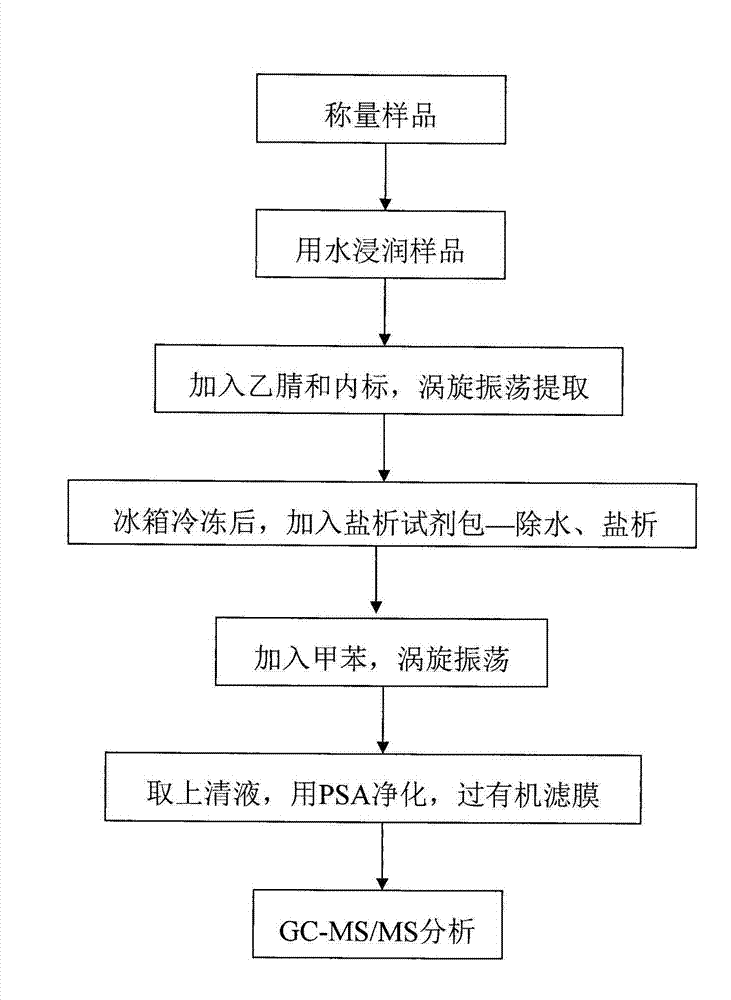

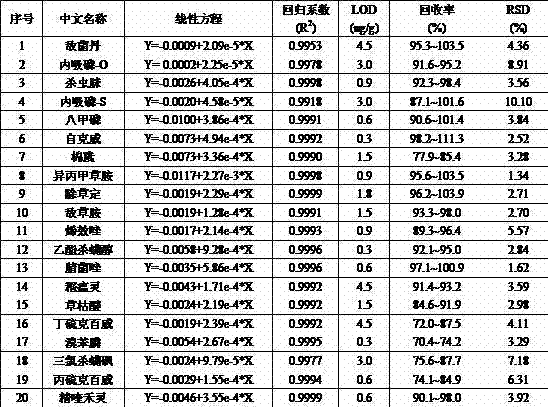

Gas chromatography-mass spectrometer (GC-MS)/MS measuring method for 20 pesticide residues in tobaccos and tobacco products

ActiveCN102866215AEasy to handleEasy processing conditionsComponent separationPesticide residueOrganosolv

Owner:CHINA NAT TOBACCO QUALITY SUPERVISION & TEST CENT

Process for producing a polymer and a polymer for wire and cable applications

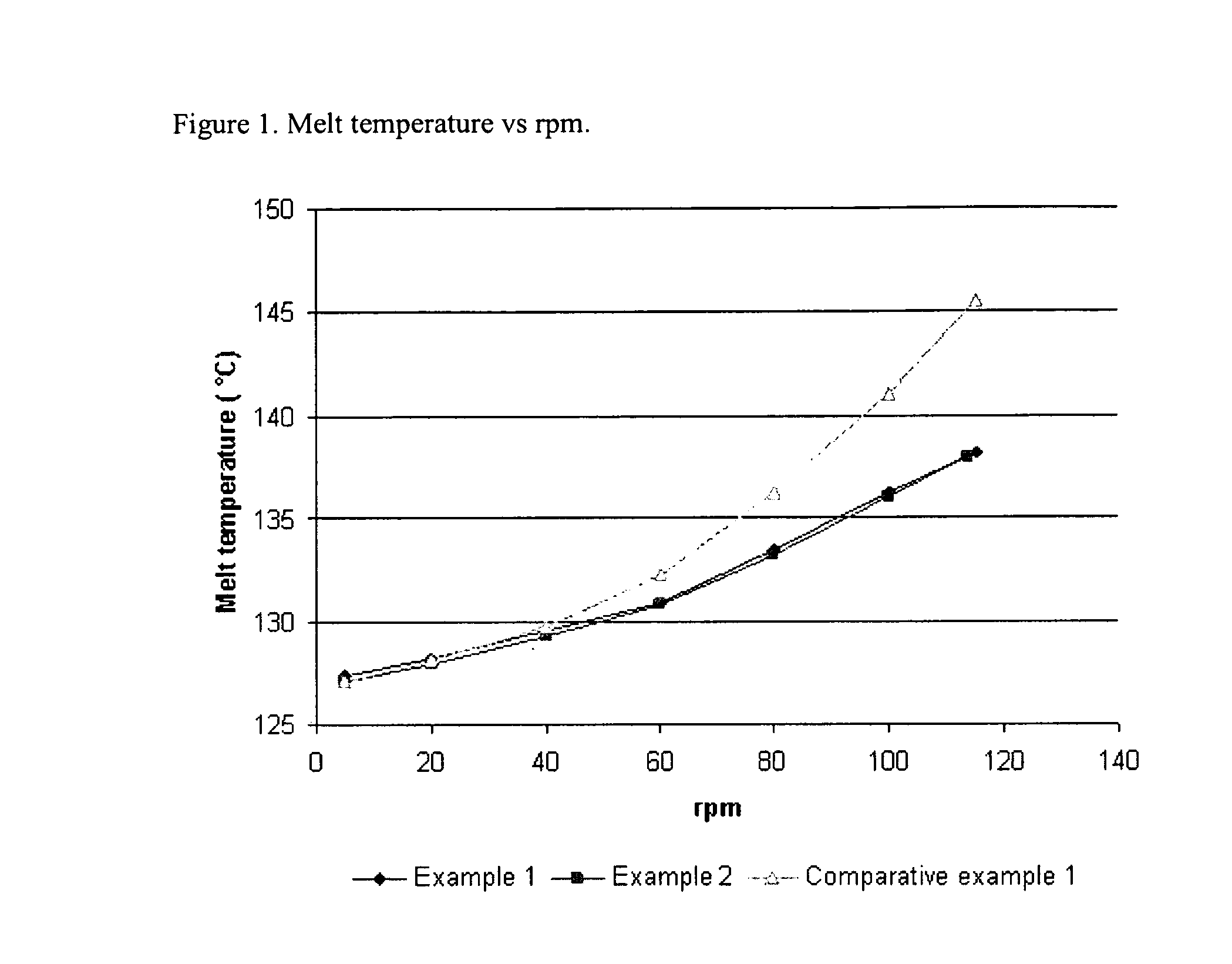

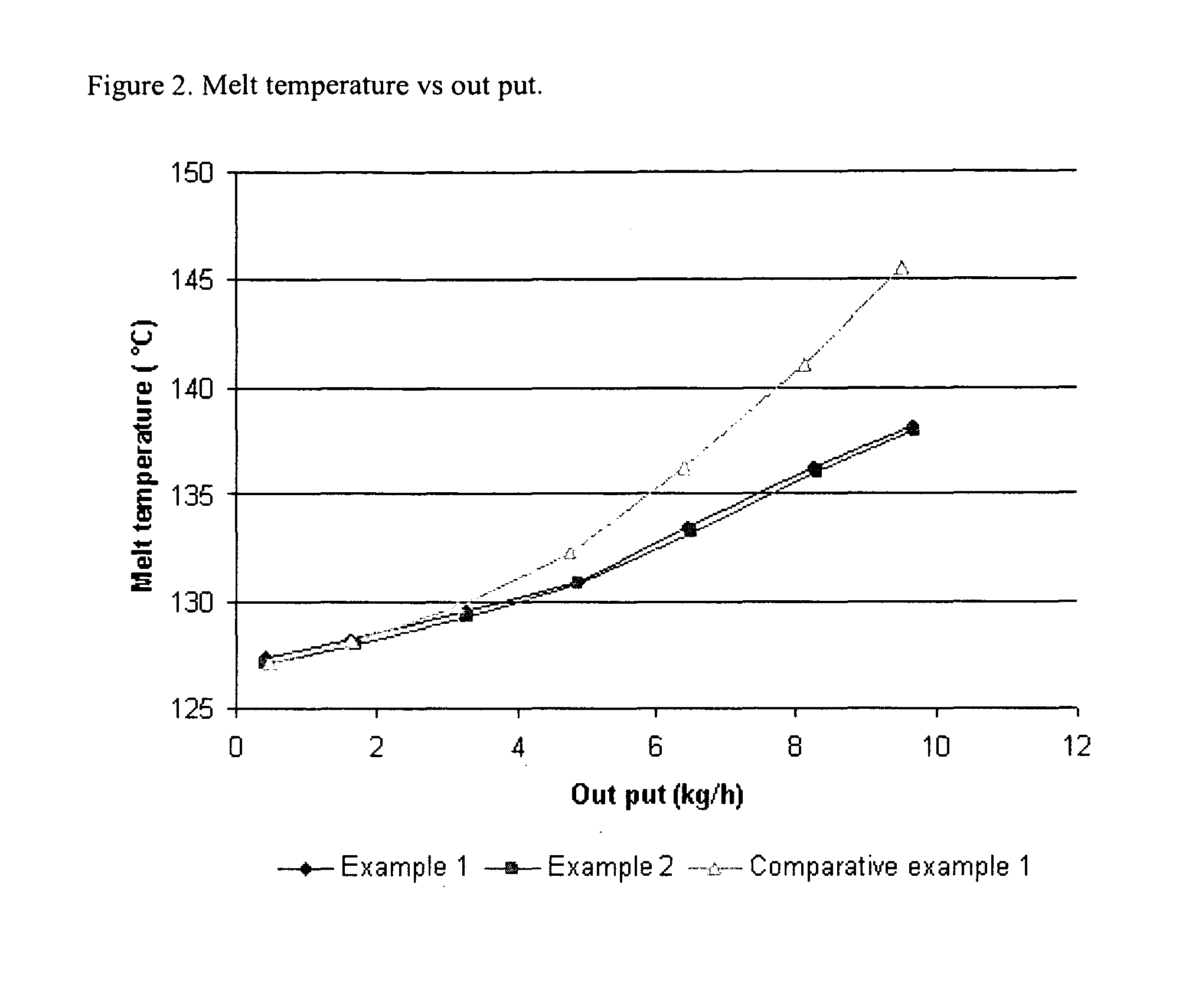

InactiveUS20110162869A1Excellent processability propertyImprove processing conditionPlastic/resin/waxes insulatorsSynthetic resin layered productsEngineeringPolymer composition

The invention relates to a process for producing a cable in a continuous vulcanization (CV) line, which cable comprises a conductor surrounded by one or more layers,wherein the process comprises the steps ofi) applying on a conductor one or more layers by using a polymer composition which comprisesA) at least one unsaturated polymer, andB) optionally a crosslinking agent;to form at least one of said cable layers surrounding the conductor.

Owner:BOREALIS AG

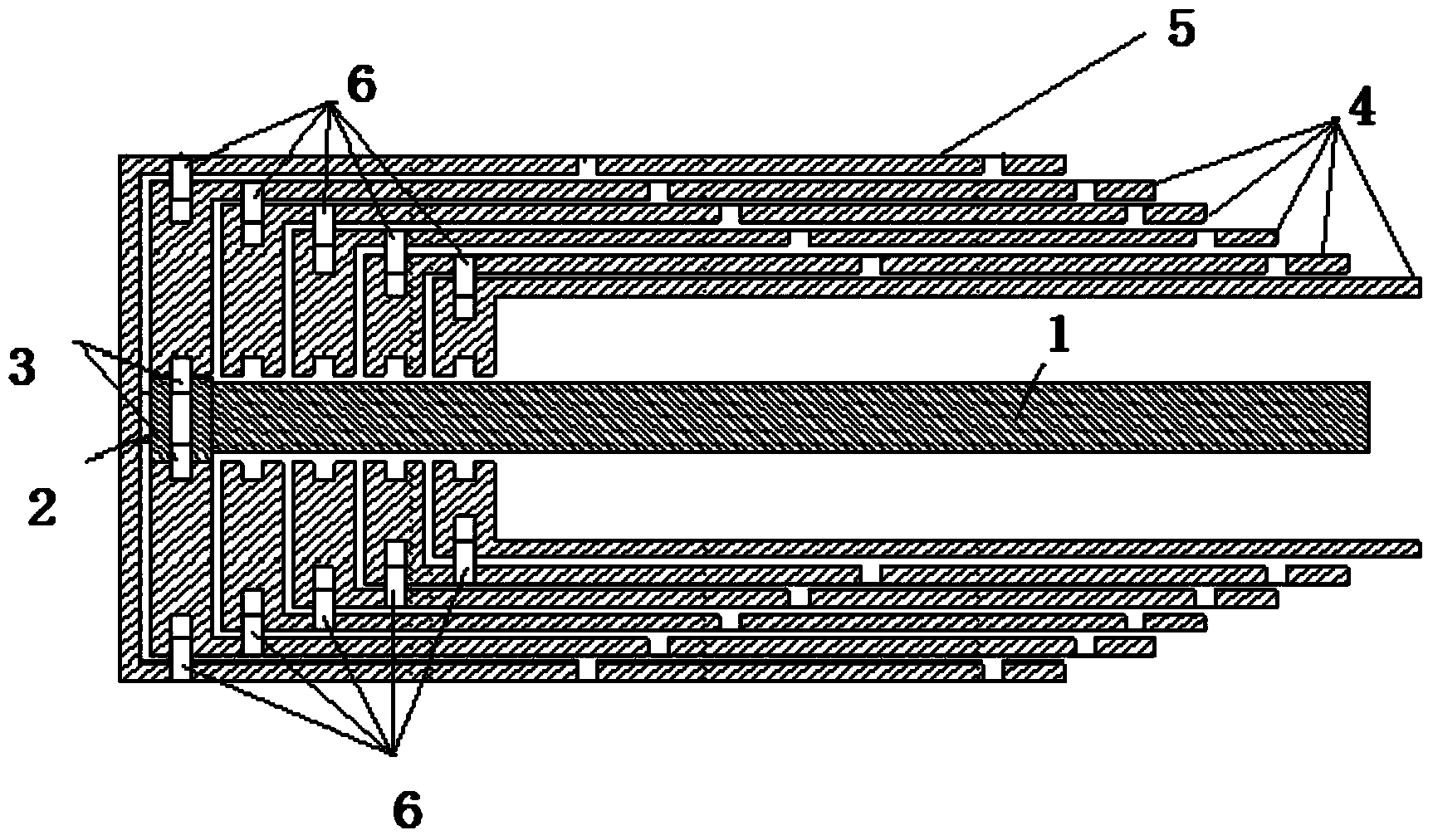

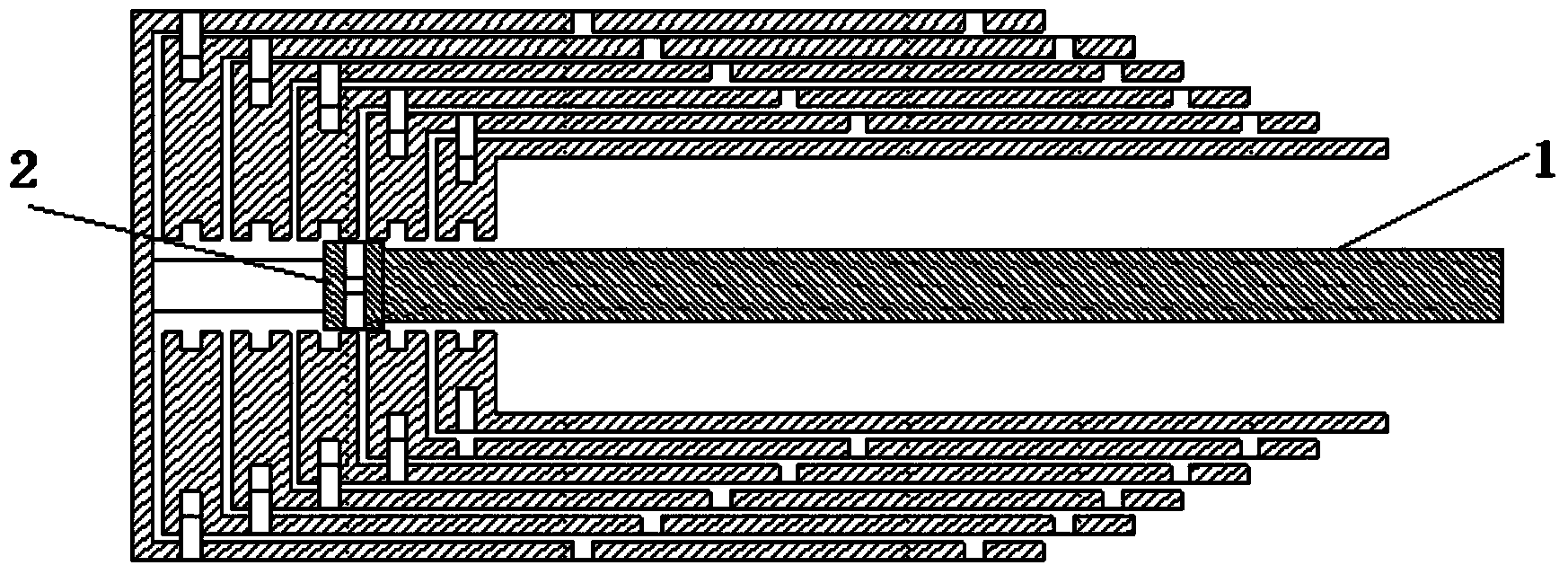

Single-cylinder plug pin type telescopic arm, crane and telescoping method of single-cylinder plug pin type telescopic arm

The invention relates to a single-cylinder plug pin type telescopic arm, a crane and a telescoping method of the single-cylinder plug pin type telescopic arm. The single-cylinder plug pin type telescopic arm comprises a basic arm and at least one section of telescopic arm which is sleeved in the basic arm, wherein coaxial central holes are formed in the tails of the telescopic arms; a telescopic oil cylinder is arranged in the central holes and comprises a cylinder rod and a cylinder barrel; at least two cylinder heads are fixedly sleeved outside the cylinder barrel in the longitudinal direction; at least three arm pin holes are respectively formed in the basic arm and the telescopic arm in the longitudinal direction. The single-cylinder plug pin type telescopic arm provided by the invention adopts the telescopic oil cylinder and the at least two cylinder heads; each cylinder head can be used for locking and unlocking the telescopic oil cylinder and any one telescopic arm; in a relay manner, the telescopic arms stretch or shrink; telescoping of the single-cylinder plug pin type telescopic arm is realized; the length of the oil cylinder is reduced; the cylinder diameter and the rod diameter of the oil cylinder are reduced; the cost of the oil cylinder is lowered; the loading weight is reduced; the hoisting capability is improved; the design capability of the crane is improved.

Owner:XUZHOU HEAVY MASCH CO LTD

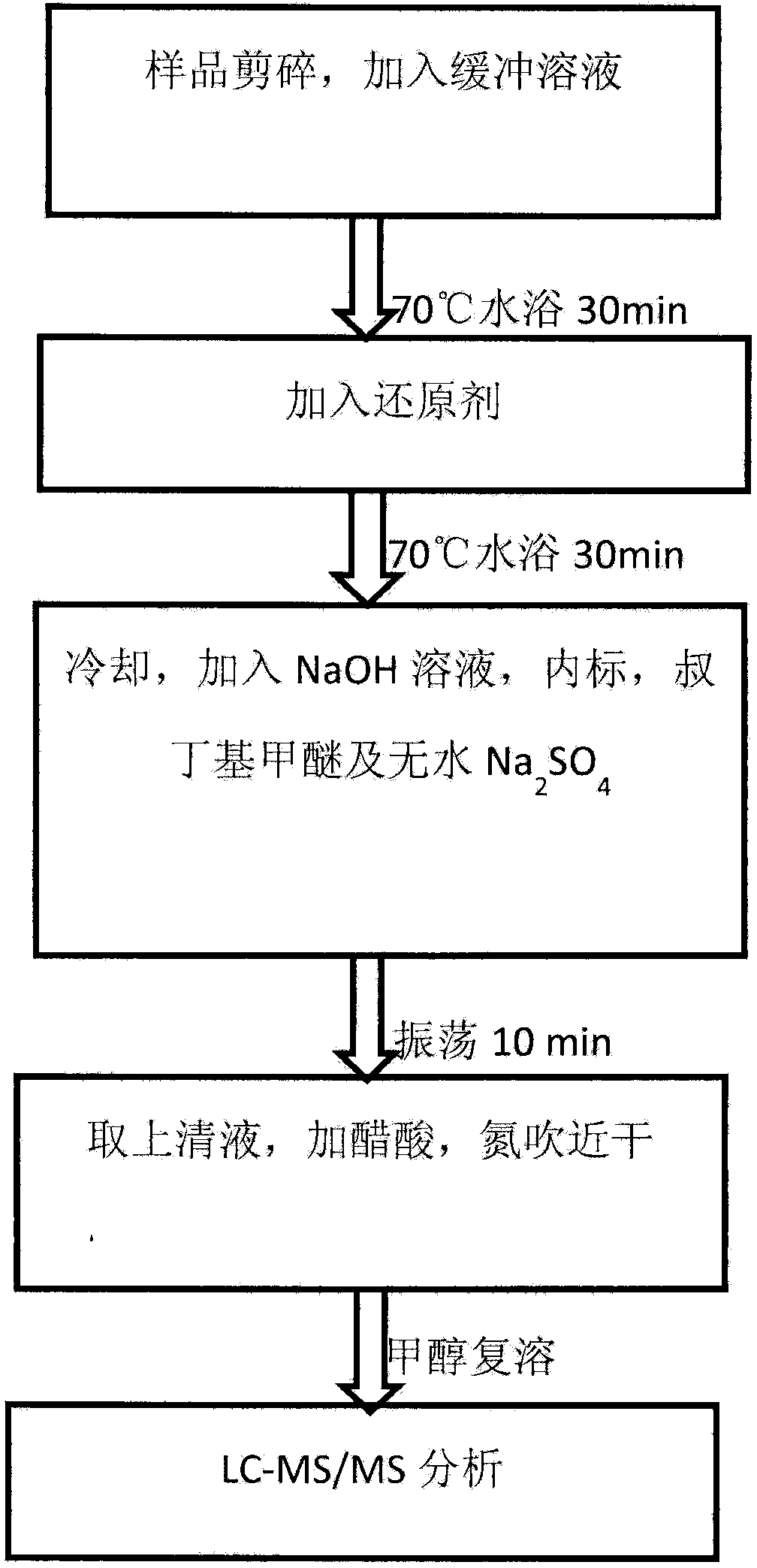

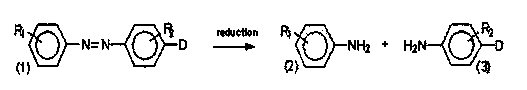

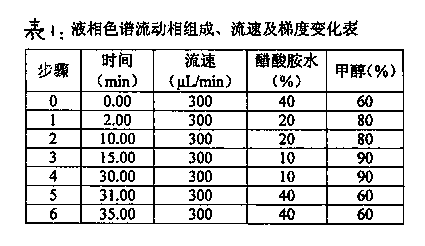

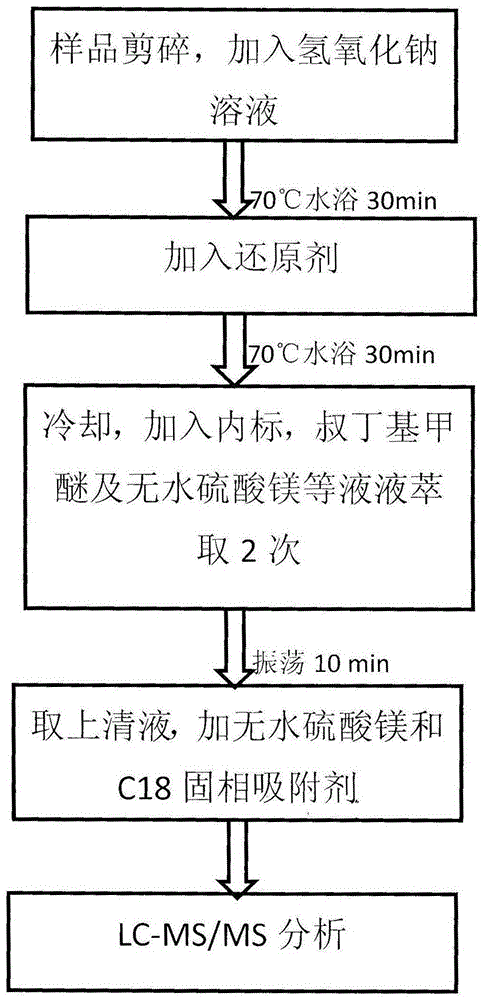

Test method of banned azo-dye in cigarette paper

ActiveCN103760288AEasy to handleEasy processing conditionsComponent separationSodium dithioniteHazardous substance

The invention discloses a test method of a banned azo-dye in cigarette paper and belongs to the technical field of physical and chemical inspection of harmful substance residues in lined paper, tipping paper and carton packaging paper for cigarettes. The test method is characterized by comprising the following steps: cutting a cigarette paper sample, adding a reduction solution, reducing an azo substance into aromatic amine by sodium hydrosulfite in a citric acid buffer solution, extracting aromatic amine from the solution by a liquid-liquid extraction method, concentrating, redissolving by methanol, testing by a liquid chromatography-tandem mass spectrometry combined instrument, and quantifying by an internal standard method. According to the method, the deficiencies of a sample treatment method in the prior art are overcome, and a sample pre-treatment method and instrument test conditions are optimized for the tipping paper, the lined paper and the carton packaging paper for the cigarettes; as a solid-phase extraction column does not need to be passed, cumbersome purification and concentration steps such as rotary evaporation are not required, and the method has the advantages of accuracy for operation, high recovery rate, quickness, simplicity, convenience, high sensitivity and the like.

Owner:CHINA NAT TOBACCO QUALITY SUPERVISION & TEST CENT

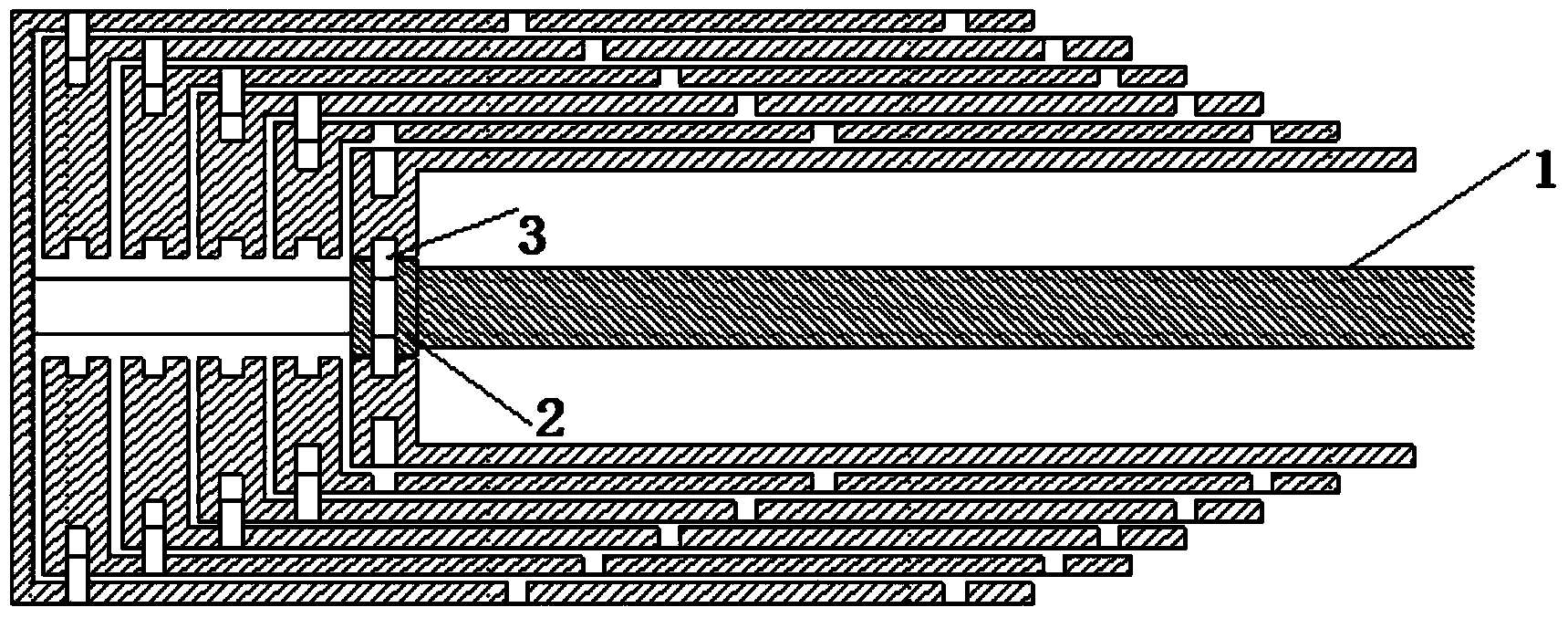

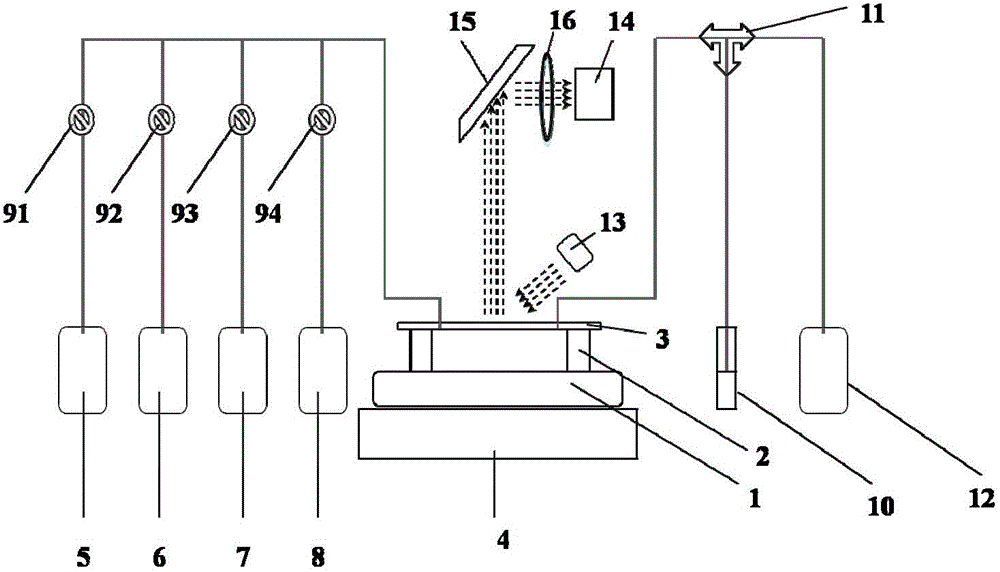

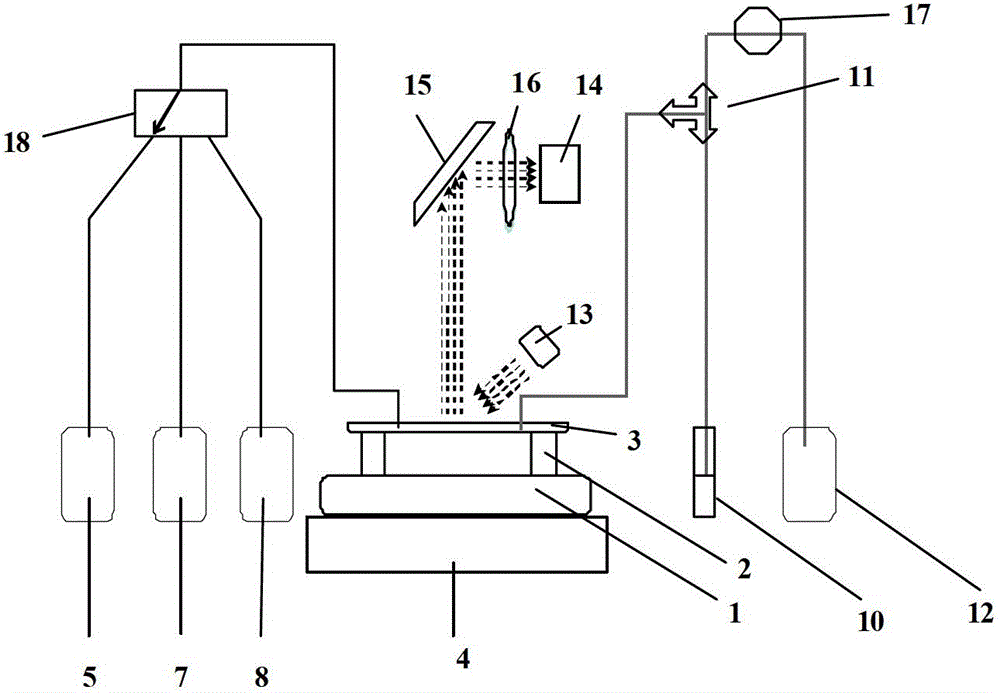

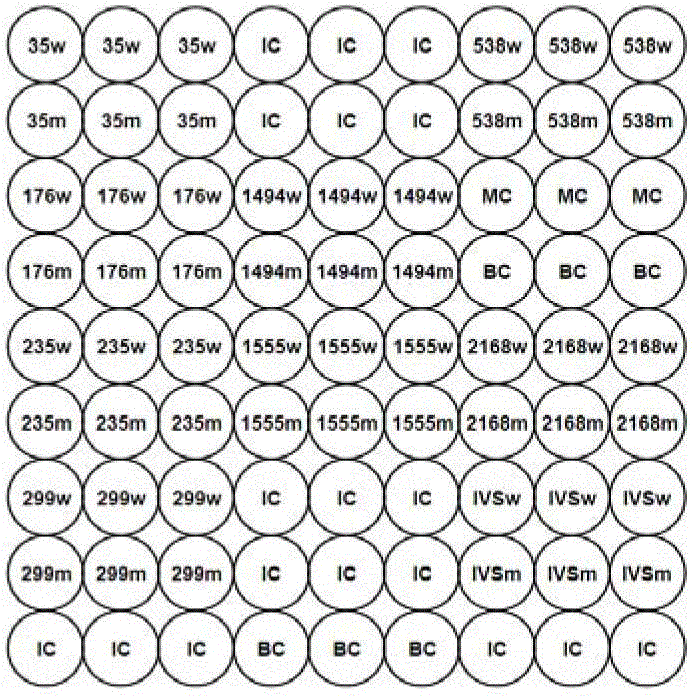

Hybridization system for real-time monitoring parsing process of micro array chip

ActiveCN102719357ARealize dynamic hybridizationEasy processing conditionsBioreactor/fermenter combinationsBiological substance pretreatmentsTemperature controlMagnetic bead

The invention discloses a hybridization system for real-time monitoring parsing process of a micro array chip, which comprises a hybridization cavity body, a temperature control device, a peripheral flow path and a real-time imaging module, wherein the hybridization cavity body is composed of the micro array chip, a cavity body cofferdam and a cover plate, and a fluid inlet and a fluid outlet are formed on the cover plate; the temperature control device is connected with the hybridization cavity body; the peripheral flow path is communicated with the hybridization cavity body by the fluid inlet and the fluid outlet; and the real-time imaging module comprises a light source and a photodetection device, and the light of the light source irradiates the surface of the micro array chip, reflected by the surface of the micro array chip and then projected to the photodetection device. The micro array chip hybridization system can realize dynamic hybridization, cleaning, drying and other flows of the chip; and the real-time imaging module can realize real-time monitoring on the magnetic bead intensity of the processing flows of the chip. According to the signal change condition, the chip processing condition is optimized; and the hybridization system can also be used for studying the dynamic problems of solid-liquid phase hybridization.

Owner:BOAO BIOLOGICAL CO LTD +1

Method for recycling valuable resources of waste glass fiber reinforced plastics and waste circuit boards

InactiveCN102441554AEliminate pollutionLow distillation rangeSolid waste disposalProcess efficiency improvementRecovery methodGlass fiber

The invention provides a method for carrying out splitting according to pollution-free microwave radiation of waste glass fiber reinforced plastics and waste circuit boards and recycling aromatic hydrocarbon organic components from a splitting process. The method has the advantages of simple treatment process, no pollution, low cost and high recycling efficiency.

Owner:宋党记

Preparation method of bamboo dissolving pulp

InactiveCN102121201AHigh removal rateReduce pollution loadPulp bleachingPulping with inorganic basesSulfateDissolving pulp

The invention discloses a preparation method of bamboo dissolving pulp. The method comprises the following steps of: (1) preparing materials; (2) stewing with sulfate; (3) bleaching with OO-X-D1-E-D2; and (4) treating with acid. The purity and the content of type A cellulose in the bamboo dissolving pulp prepared with the preparation method of the bamboo dissolving pulp are increased in a certain degree compared with those in the prior art, the purity and the content of alpha cellulose are increased by 1.5-2.5 percent compared with those in the prior art, the yield can be further increased, the dosage of chemical preparations and energy consumption are reduced, and environmental pollution can be further reduced.

Owner:FUJIAN AGRI & FORESTRY UNIV

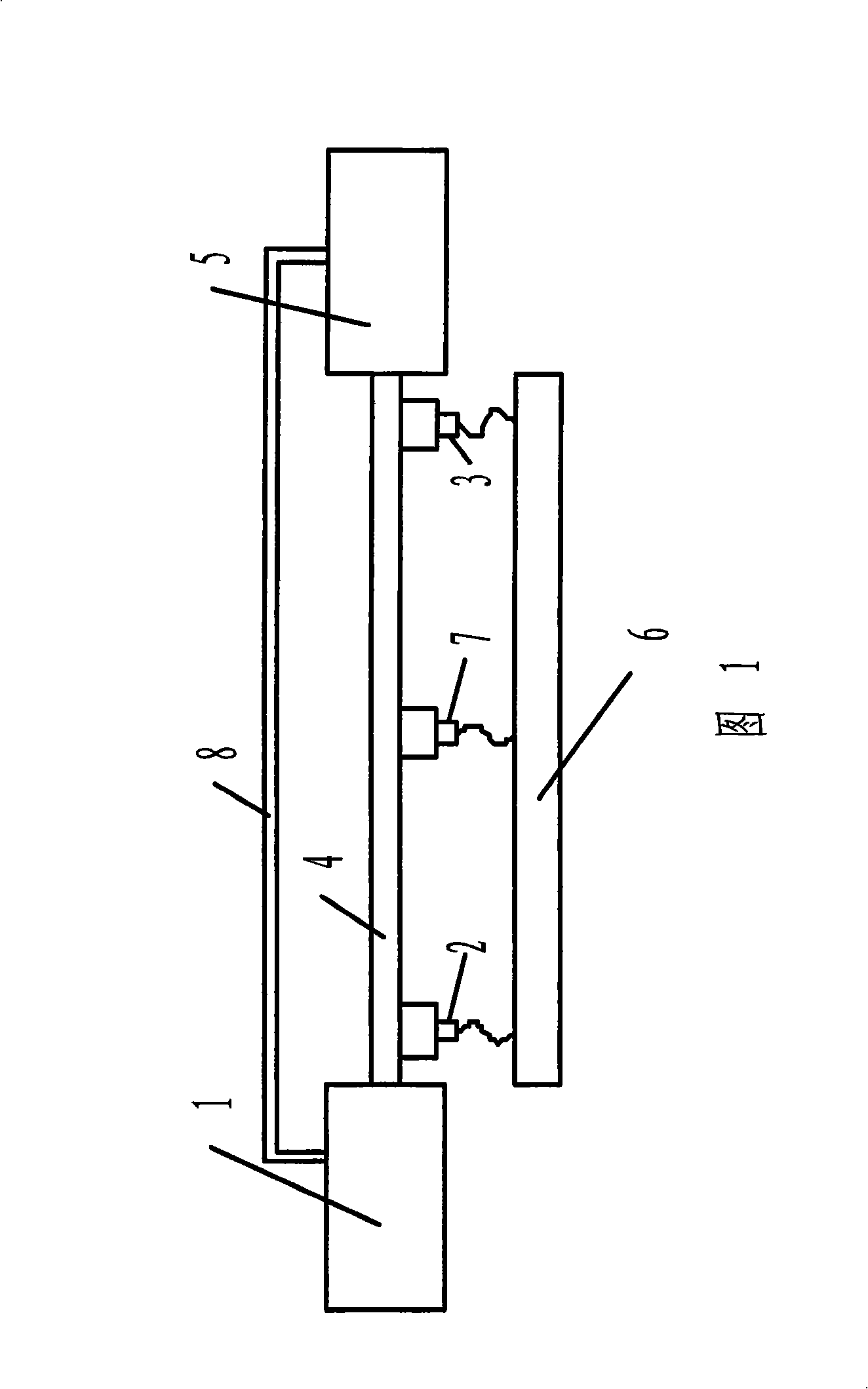

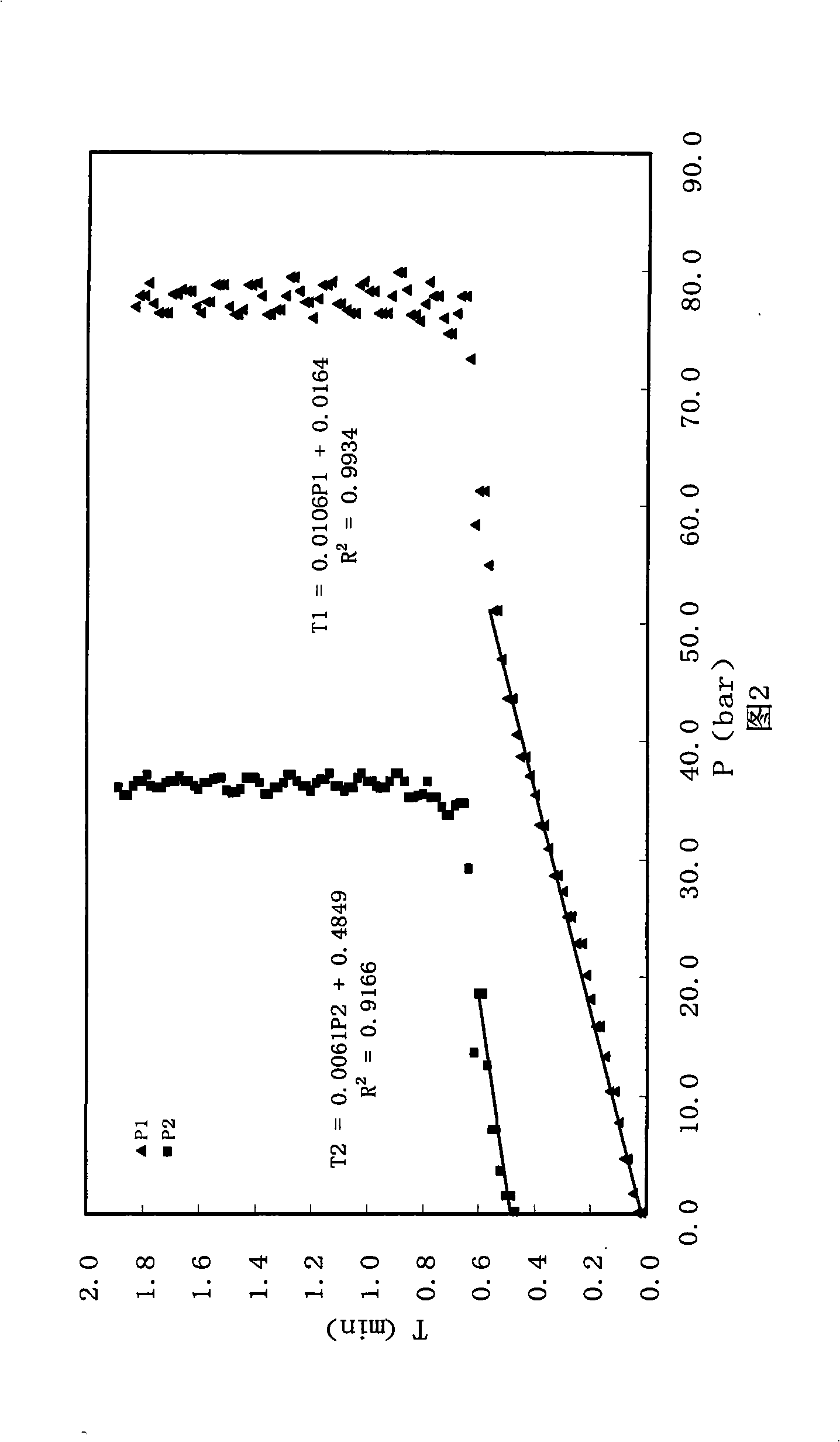

Method and device for measuring high polymer molten volume flow

ActiveCN101408443AEliminate measurement error interferenceAccurate Indirect Determination CalculationsVolume/mass flow measurementDirect flow property measurementEngineeringMeasurement precision

The invention discloses a measuring device for high polymer fusant volume flow and a measuring method thereof. The invention is characterized in that one end of a slit flow passage or a conduit flow passage (4) is connected with a flow passage actuating unit (1), the other end thereof is connected with a fusant external flow passage (5), the external flow passage is connected with the flow passage actuating unit by a loop flow passage (8), the slit flow passage or the conduit flow passage is provided with a temperature sensor (7) and a plurality of pressure sensors (2, 3), and the temperature sensor and a plurality of pressure sensors are respectively connected with a collecting and processing system (6) for temperature and data. The actuating unit pushes the high polymer fusant to enter the flow passage at a certain speed, and the passing time of fluid is measured by two pressure sensors, therefore, the volume flow of the high polymer in the flow passage can be obtained according to the physical dimension of the flow passage and the passing time. The measuring device of the invention can measure the volume flow of the high polymer fusant in the flow passage without the influence of the change of the pressure and the dimension of the flow passage. In addition, the invention provides a method which can improve and enhance the rheological measurement precision of the high polymer.

Owner:浙江博发新材料股份有限公司

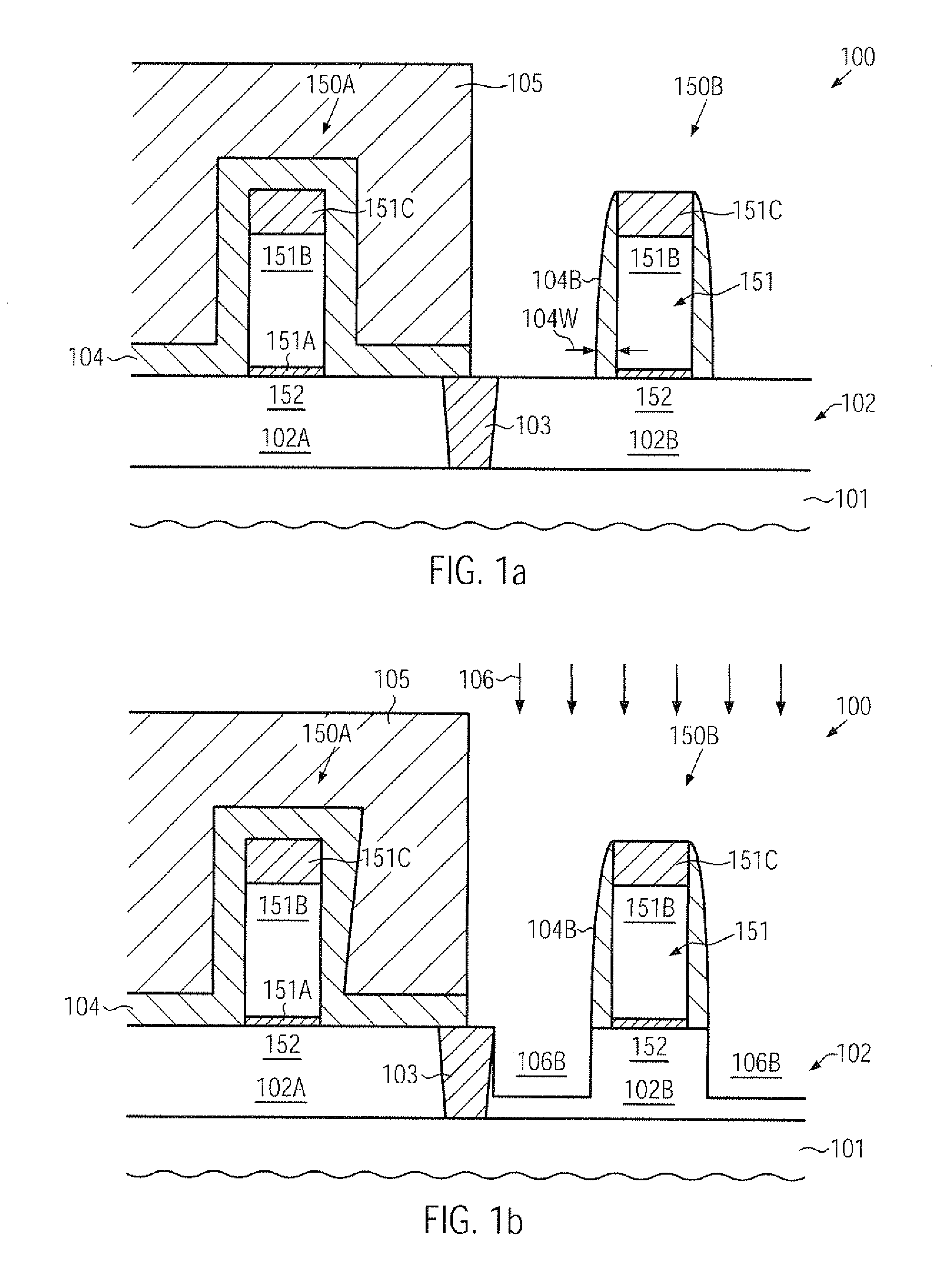

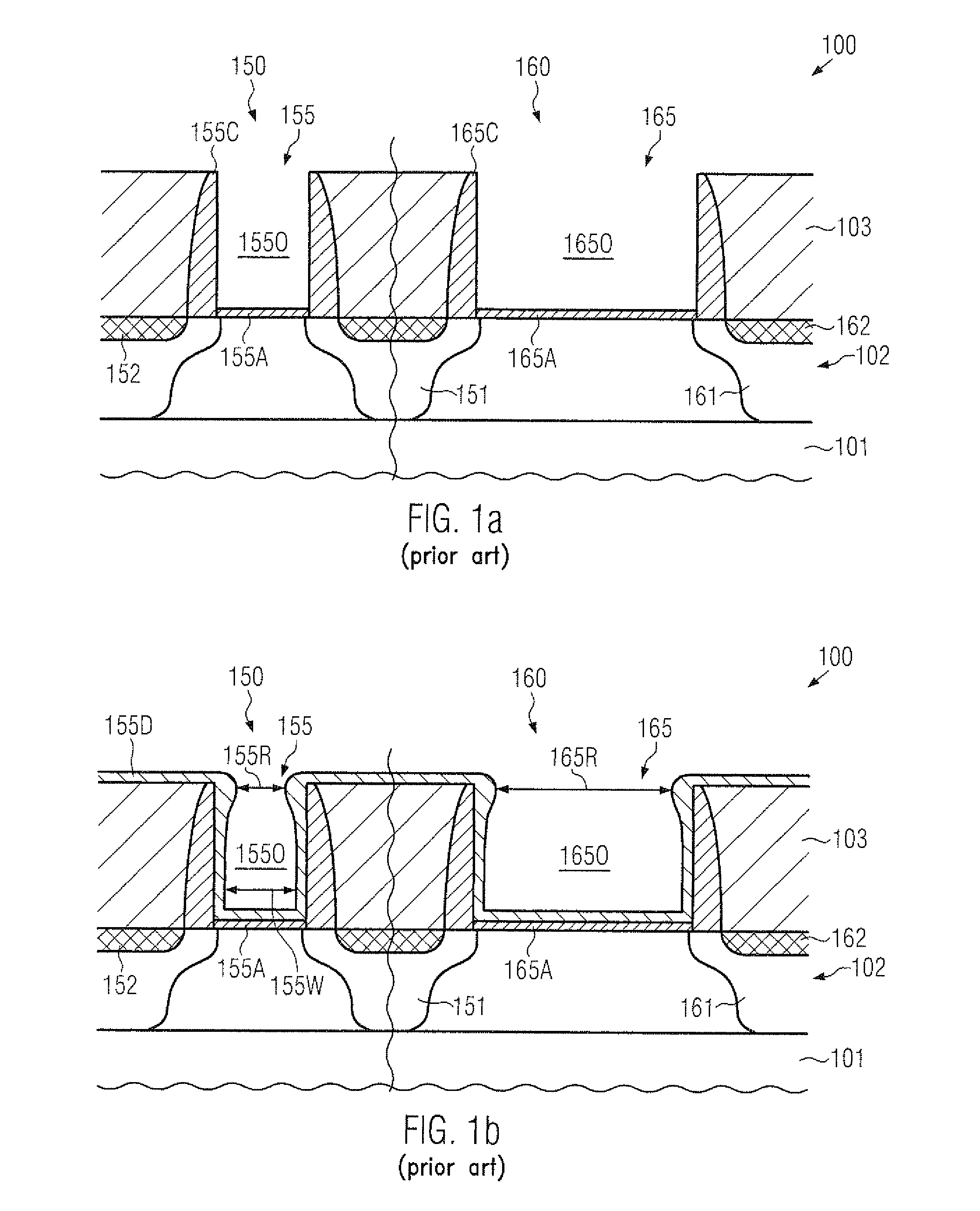

Superior fill conditions in a replacement gate approach by corner rounding prior to completely removing a placeholder material

InactiveUS8048792B2Efficient removalIncrease of a gate openingSemiconductor/solid-state device manufacturingSemiconductor devicesMaterial ErosionIntermediate state

In a replacement gate approach, a superior cross-sectional shape of the gate opening may be achieved by performing a material erosion process in an intermediate state of removing the placeholder material. Consequently, the remaining portion of the placeholder material may efficiently protect the underlying sensitive materials, such as a high-k dielectric material, when performing the corner rounding process sequence.

Owner:GLOBALFOUNDRIES INC

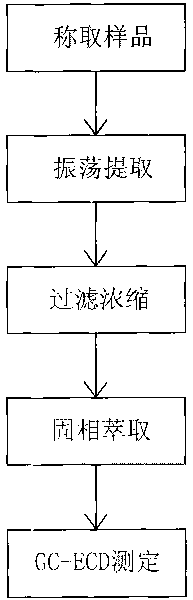

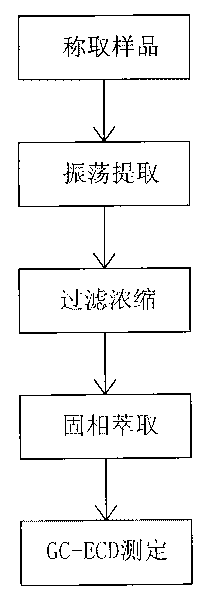

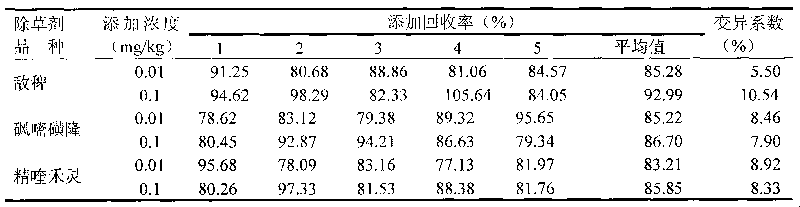

Method for simultaneously measuring residual quantity of three types of herbicide in vega soil

InactiveCN101718756AOptimizationEasy to handleComponent separationPreparing sample for investigationPretreatment methodElectron capture detector

The invention discloses a method for simultaneously measuring residual quantity of three types of herbicide in vega soil, belonging to the technical field of physicochemical detection of pesticide residue in vega soil. Specifically, acetonitrile is used for extraction, Florisil is carried out with solid phase extraction, a gas chromatograph is matched with an electron capture detector to directly measure the residual quantity of three types of herbicide, such as propanil, Rimsulfuron, quizalofop-p-ethyl and the like in vega soil. The invention overcomes the restriction of the defect and the condition of the prior art to optimize the pretreatment method and the instrument detection condition of vega soil samples. Compared with the prior art, the invention has the following favorable advantages that the invention can detect three types of herbicide all at once and has the advantages of simple pretreatment process, high detection sensitivity and good accuracy and reproducibility.

Owner:HUNAN TOBACCO CHENZHOU

Ultraviolet-visible light full-wavelength scanning sewage quality online rapid detection method and application thereof

PendingCN111351762AAccurate Water Quality TestingShort detection timeGeneral water supply conservationTesting waterWater qualityPhysical chemistry

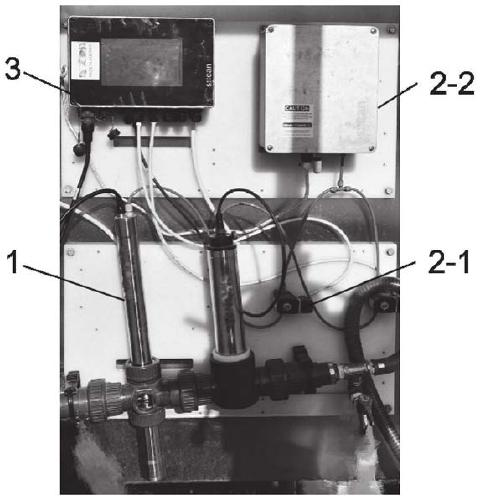

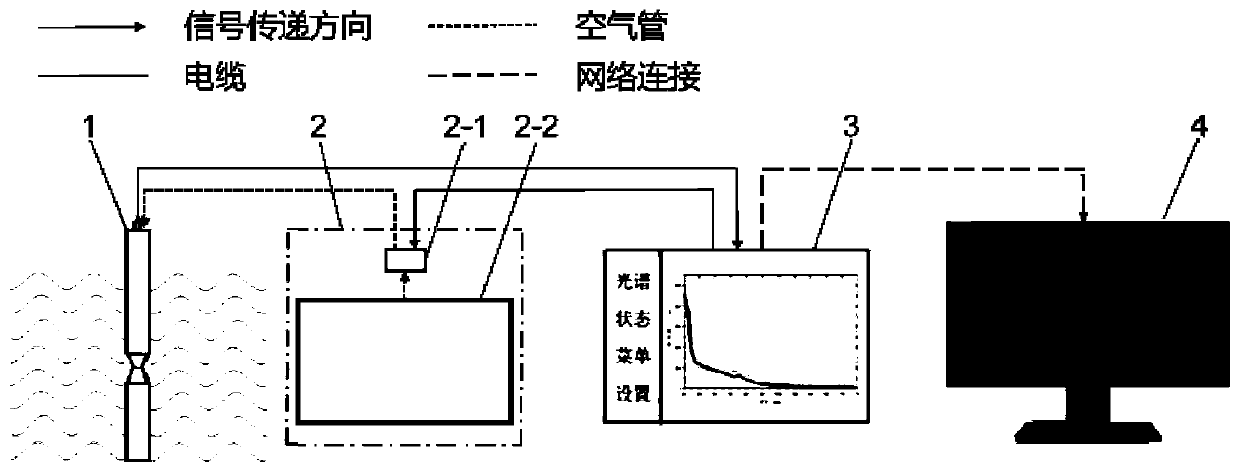

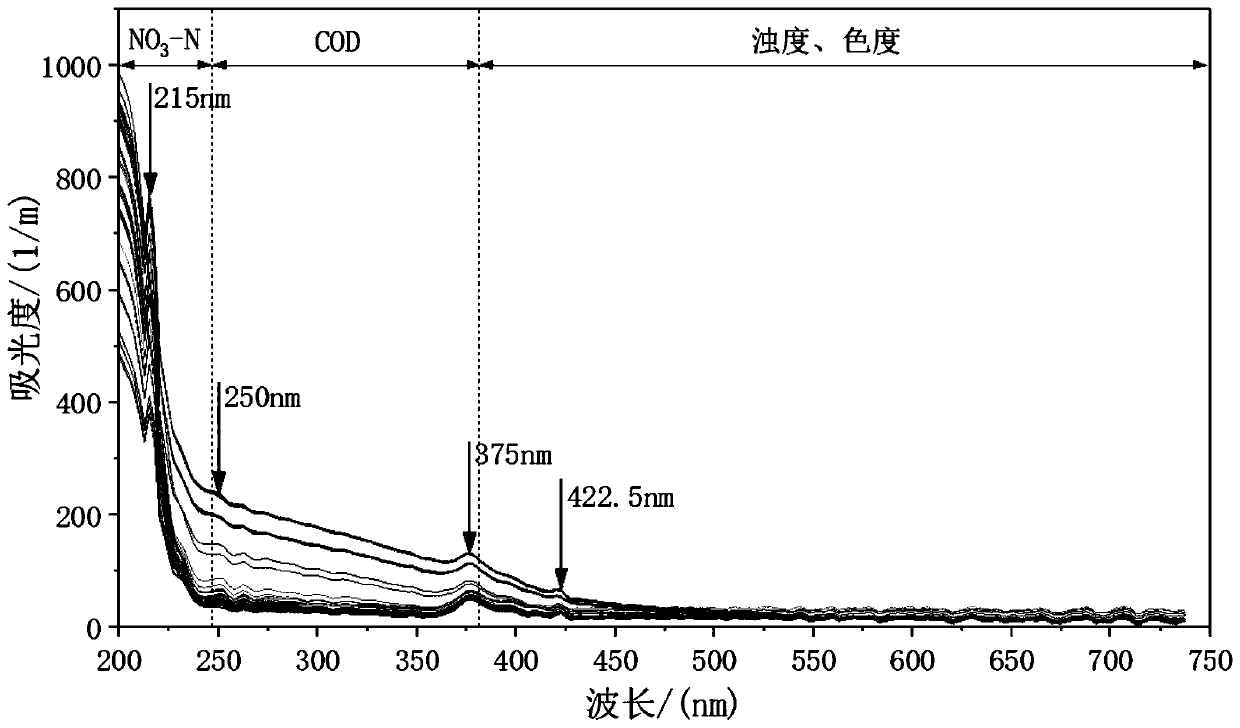

The invention relates to an ultraviolet-visible light full-wavelength scanning sewage quality online rapid detection method and an application thereof. A full-waveband spectrum detection system is used for carrying out full-waveband scanning on sewage, a water body is directly scanned in an immersion mode, and obtained spectral absorption information of the sewage is transmitted to the full-waveband spectrum detection system; an absorption full-spectrum chart of the sewage is calculated by utilizing the full-waveband spectrum detection system; a multiple regression equation of each to-be-detected substance is obtained by fitting through a multiple regression equation model by utilizing the full-waveband spectrum detection system, wherein the multiple regression equation model is as follows: Yn = A1 * x1 + A2 * x2 +... + A210 * x210 +... + An * xn (n = 215-217), Yn is a target parameter prediction value, and A1 to An are respectively a coefficient of a wavelength corresponding to each model. The full-waveband spectrum detection system is used for detecting water quality parameter values. The simultaneous detection of various substances is realized, the detection time is short and is15 seconds, and the result can be obtained.

Owner:QINGDAO TECHNOLOGICAL UNIVERSITY

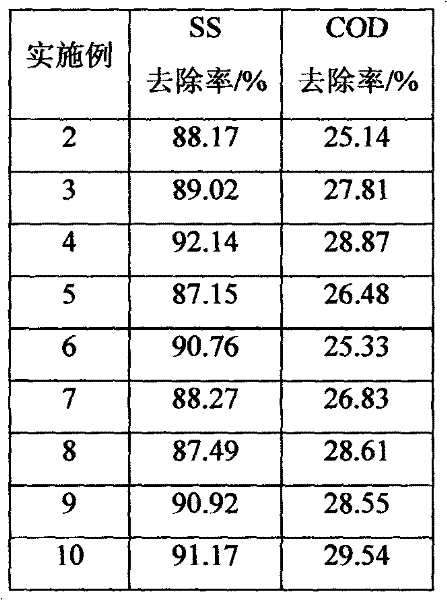

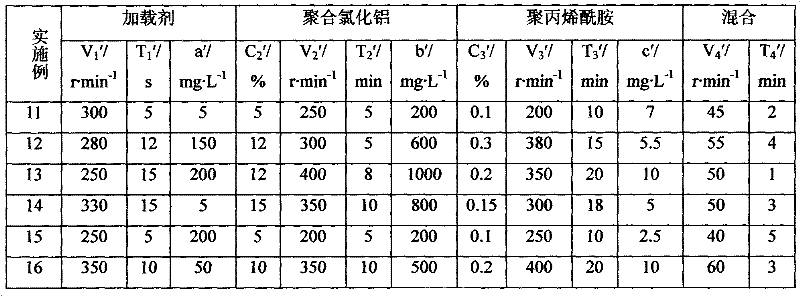

Loading flocculation pretreatment method of antibiotic fermentation wastewater

ActiveCN102351368AImprove flocculation effectImprove collision efficiencyMultistage water/sewage treatmentChemistryPolyacrylamide

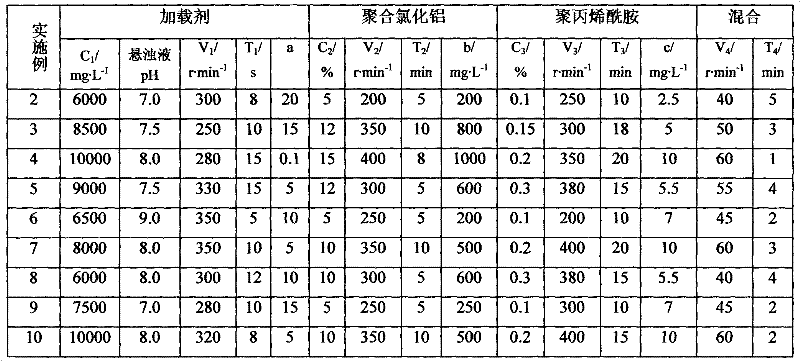

The invention discloses a loading flocculation pretreatment method of antibiotic fermentation wastewater and is suitable for processing mixed wastewater discharged during each antibiotic fermentation technological section. By the adoption of the loading flocculation technology, flocculation pretreatment is carried out on mixed wastewater of a crystallization solution, waste mother liquor, dona tub washing wastewater and washing wastewater for a fermentation cylinder during the antibiotic production process. A flocculating agent contains polyaluminum chloride and polyacrylamide; and the addition sequence of the flocculating agent is to add polyaluminum chloride at first and then add polyacrylamide. A loading agent contains one or two mixtures selected from active carbon, fly ash, activatedsludge and settling sludge. By the adoption of the method provided by the invention, the flocculation treatment can be effectively carried out on high-density organic wastewater generated during the antibiotic fermentation production. The method provided by the invention is simple, requires low cost and has a stable effect. By the adoption of the method, the treated wastewater can reach the requirement of subsequent biochemical treatment.

Owner:河北协同环境科技有限公司

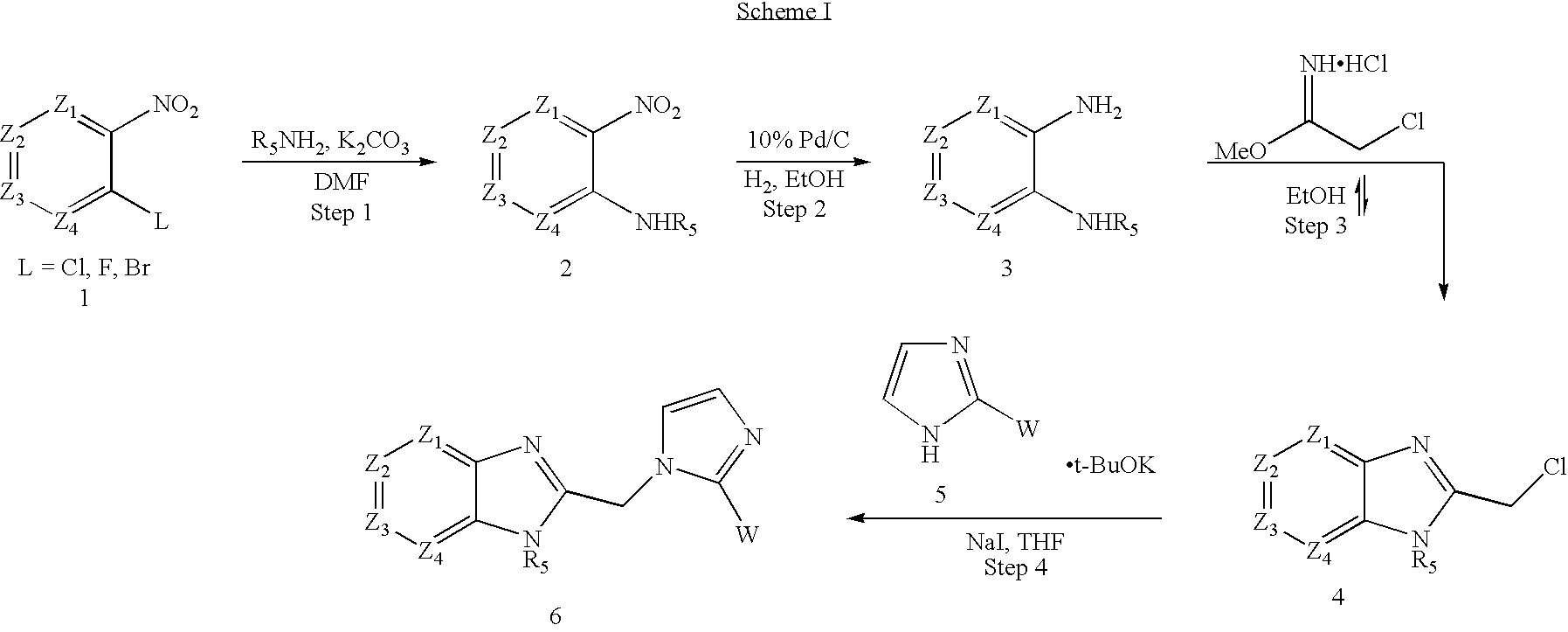

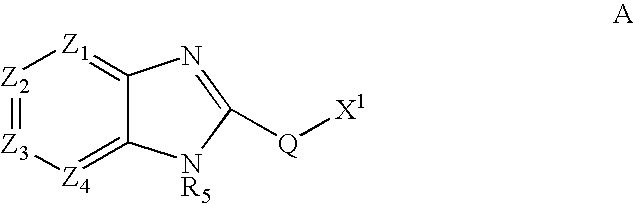

Process for preparing haloalkyl pyrimidines

InactiveUS20040063938A1Avoid instabilityEasy processing conditionsNervous disorderOrganic chemistryBenzodiazepineGABAA receptor

The invention is a process for producing haloalkyl pyrimidines as intermediates in the production of benzimidazole and / or pyridylimidazole derivatives having high selectivity and / or high affinity to the benzodiazepine site of GABAA receptors.

Owner:PFIZER INC +1

Reducing silicide resistance in silicon/germanium-containing drain/source regions of transistors

ActiveUS8124467B2Reduce concentrationReduce probabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSalicideMetal silicide

In sophisticated P-channel transistors, a high germanium concentration may be used in a silicon / germanium alloy, wherein an additional semiconductor cap layer may provide enhanced process conditions during the formation of a metal silicide. For example, a silicon layer may be formed on the silicon / germanium alloy, possibly including a further strain-inducing atomic species other than germanium, in order to provide a high strain component while also providing superior conditions during the silicidation process.

Owner:GLOBALFOUNDRIES U S INC

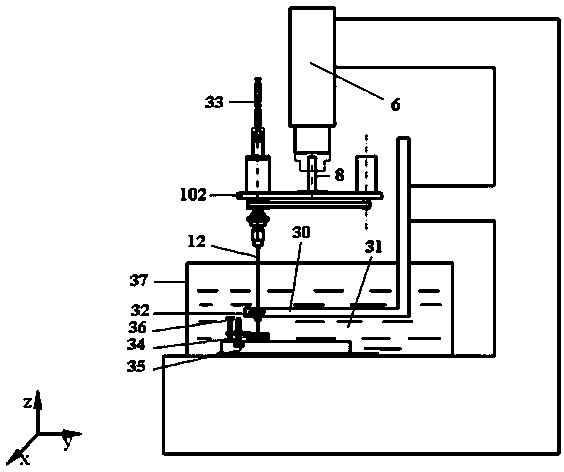

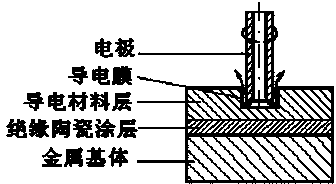

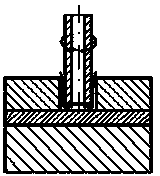

Self-inductive-internal flushing liquid electric spark processing method for metal with insulating ceramic coating

ActiveCN103433576AEasy processing conditionsGood chip removal effectChemical reactionCeramic coating

The invention relates to a self-inductive-internal flushing liquid electric spark processing method for metal with an insulating ceramic coating, belonging to the technical field of electric spark processing and forming. In order to solve the technical problem that the metal with the insulating ceramic coating cannot be processed with high quality and high efficiency, the invention provides the self-inductive electric spark processing method, and on the basis, a processing form of the internal flushing liquid of a rotating electrode is adopted. The whole processing process is carried out in an oil-base working liquid. The tubular electrode rotates around the axis and is assisted by a high pressure flushing liquid in an inner hole of the electrode, and flushing by the working liquid has good chip removal effect. A conductive material is arranged on the surface of the insulating ceramic coating, and the conductive material is connected to the positive electrode of a power supply. In the initial processing stage, according to the thermal chemical reaction of electrical discharge processing, a workpiece discharging area is self-induced to generate conductive films which are continuously produced in the processing process, and the process is continuously carried out, so that the insulating ceramic is processed. According to the self-inductive-internal flushing liquid electric spark processing method for the metal with an insulating ceramic coating provided by the invention, micropores of the metal material with the insulating ceramic coating can be processed with high precision and high efficiency.

Owner:HARBIN INST OF TECH

Method of extracting and separating soybean protein

InactiveCN1740189AReduce usageReduce manufacturing costPeptide preparation methodsPlant peptidesFiberEmulsion

The method of extracting and separating soybean protein includes the following steps: 1. adding water in 12-18 times at 45-55 deg.c into crushed soybean dregs, adding sodium hydroxide solution to regulating pH value to 8-9 and stirring to form protein emulsion; 2. filtering the protein emulsion in plate-frame filter to eliminate insoluble dreg and fiber; 3. membrane system separation and concentration to obtain liquid protein with water content of 85 %; 4. adding small amount of hydrochloric acid solution into the liquid protein to regulate pH value to 7; and 5. spray drying the neutralized liquid protein to produce soybean protein. The present invention has the advantages of no protein denaturation, low production cost, high protein yield, and high production efficiency.

Owner:WUHAN SAIPU FILM TECH

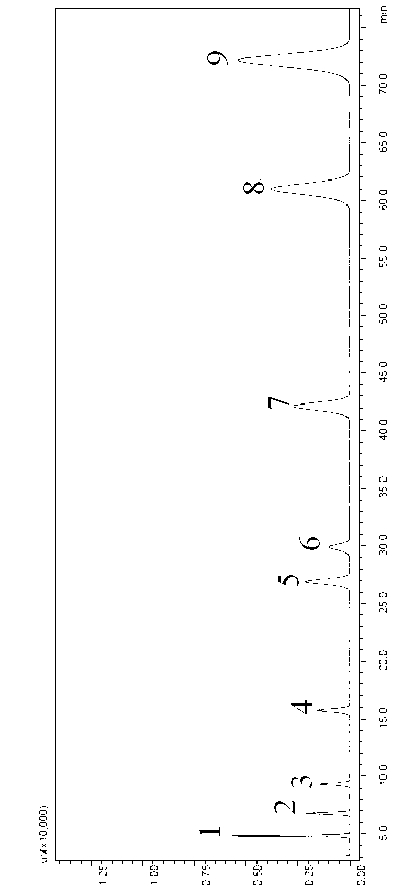

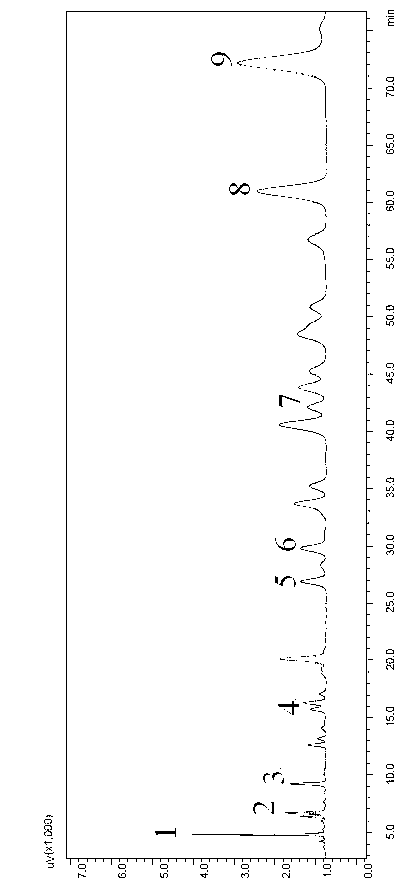

Method for simultaneous determination of caffeic acid and 8 flavonoids in propolis by using high performance liquid chromatography

InactiveCN103257201AEasy to handleEasy processing conditionsComponent separationPropolisQuantitative determination

The invention relates to a method for simultaneous determination of caffeic acid and 8 flavonoids in propolis by using high performance liquid chromatography. Simultaneous quantitative determination of flavonoids and caffeic acid has not been reported so far. The method provided by the invention is characterized in that a high performance liquid chromatograph is used for determination, the method comprises the procedures consisting of preparation of standard stock solutions, preparation of standard intermediate solutions, preparation of standard working solutions, drafting of standard curves, treatment of samples and determination of the samples, and in the procedure of preparation of the standard stock solutions, a caffeic acid standard stock solution, a rutin standard stock solution, a quercetin standard stock solution, a myricetin standard stock solution, an apigenin standard stock solution, a kaempferol standard stock solution, a pinocembrin standard stock solution, a chrysin standard stock solution and a galangin standard stock solution can be obtained. According to the invention, high performance liquid chromatography is employed for simultaneous determination of caffeic acid and 8 flavonoids in propolis, and pre-treatment of samples is easy and convenient and is rapid to operate.

Owner:杭州蜂之语蜂业股份有限公司

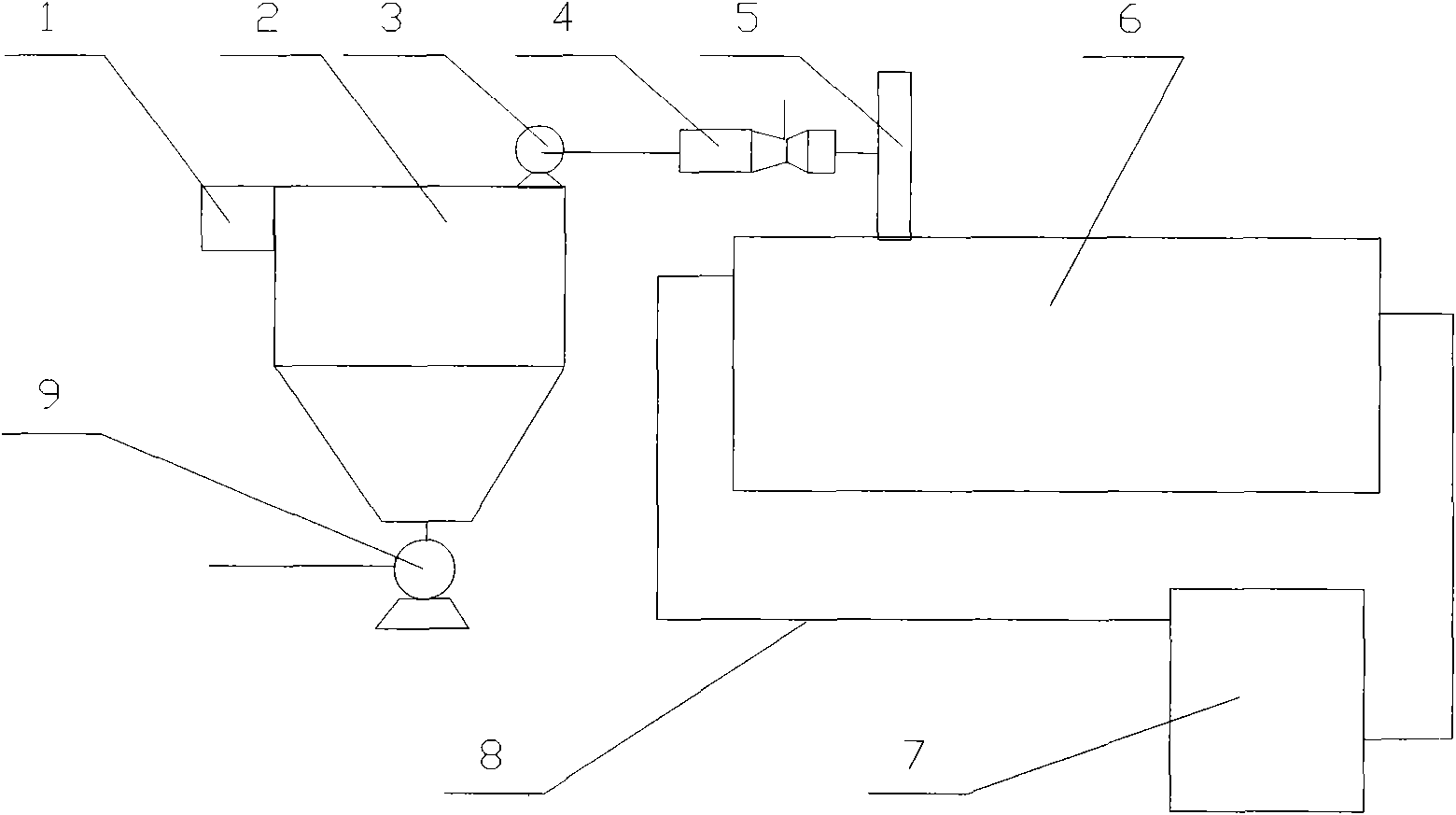

Artificial wetland high-efficiency pre-aeration sewage treatment system

InactiveCN101585641AEasy processing conditionsImprove responseMultistage water/sewage treatmentSustainable biological treatmentConstructed wetlandWater storage tank

The invention relates to an artificial wetland high-efficiency pre-aeration sewage treatment system, which comprises a bar screen, a primary sedimentation tank, a venturi, a splash board and an artificial wetland connected in turn, wherein the bar screen is positioned in the front of the primary sedimentation tank; the inlet of the gradually reducing part of the venturi is connected with the upper part of the primary sedimentation tank through a high-pressure pump, the throat part is connected with the atmosphere through an air inlet pipe, and the outlet of the gradually expanding part is provided with a jet pipe extending forwards; and the splash board is positioned above the artificial wetland in front of the jet pipe. The artificial wetland adopts a horizontal baffling structure, the water outlet is provided with a water storage tank, and the water storage tank is provided with a backflow pipe connected with the water inlet end of the artificial wetland. The artificial wetland high-efficiency pre-aeration sewage treatment system has a simple structure and reasonable process, and through the high-efficiency aeration of the venturi and the splash board, the artificial wetland high-efficiency pre-aeration sewage treatment system improves the biochemical reaction types and the reaction speed in the artificial wetland, improves the surrounding environment, and is helpful to improve the purification degree of the yielding water of the artificial wetland. The artificial wetland high-efficiency pre-aeration sewage treatment system has the advantages of simple structure, convenient operation and good adaptability, allows the sewage quantity to have large range of variation, and is mainly adapted to the treatment of domestic sewage.

Owner:HAISIBOTE BEIJING SCIENE & TECH

Method of measuring residual amount of 4-aminoazobenzene in paper for cigarettes

ActiveCN105181876AReduce distractionsAvoid matrix effectsComponent separationTert-butyl methyl etherSolid phases

The invention belongs to the technical field of physical and chemical inspection of harmful substance residues in inner liners, tipping paper and carton packaging paper for cigarettes, and particularly relates to a method of measuring the residual amount of 4-aminoazobenzene in paper for the cigarettes. The method specifically comprises the following steps: reducing an azo substance into aromatic amine by sodium dithionite in an alkaline solution; then extracting the aromatic amine in the solution by using tert-butyl methyl ether; carrying out solid-phase dispersion extraction, and then measuring by using a liquid chromatography-tandem mass spectrometry; carrying out internal standard method determination. According to the method disclosed by the invention, the defects of a sample processing method in the prior art are overcome; a sample pretreatment method and instrument detection conditions are optimized, aiming at the tipping paper and the inner liners for the cigarettes, cigarette strips and carbon packaging paper samples. Since a solid-phase extraction column is not needed to pass, instead the simpler and more convenient solid-phase dispersion extraction is used, and the tedious purification and concentration steps, such as rotary evaporation is not needed, the method disclosed by the invention has the advantages of accuracy in operation, high recovery rate, high sensitivity and the like and is rapid, simple and convenient.

Owner:CHINA NAT TOBACCO QUALITY SUPERVISION & TEST CENT

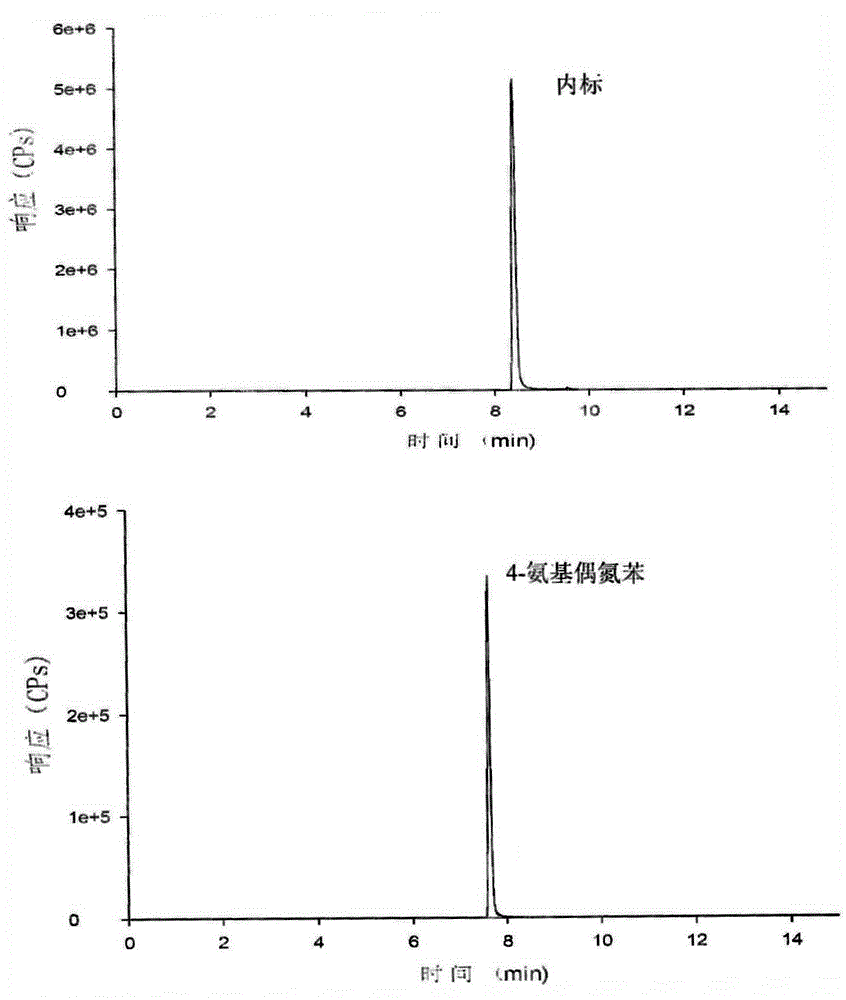

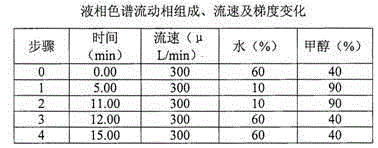

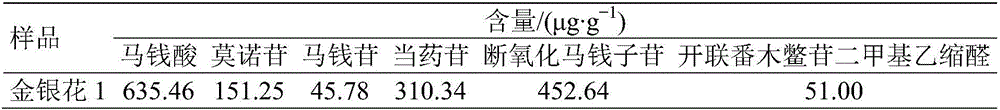

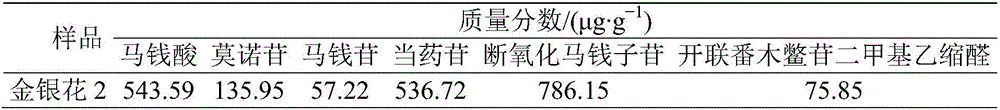

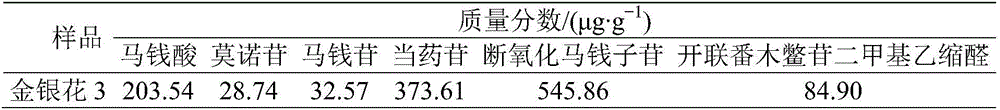

Honeysuckle quality evaluation method

ActiveCN106248817AEasy to handleEasy processing conditionsComponent separationChlorogenic acidDimethyl acetal

The invention discloses a honeysuckle quality evaluation method. According to the honeysuckle quality evaluation method, chlorogenic acid, galuteolin and six iridoid glycoside ingredients in honeysuckle are determined, wherein the six iridoid glycoside ingredients are loganic acid, morroniside, loganin, chiratin, secoxyloganin and secologanin dimethyl acetal. The honeysuckle quality evaluation method disclosed by the invention has the advantages that the iridoid glycoside ingredients in the honeysuckle are included in a honeysuckle quality evaluation system for the first time, six representative iridoid glycoside ingredients in the honeysuckle are selected and determined at the same time for guaranteeing reliability and effectiveness of the quality evaluation method, and a dispersive solid phase extraction-high performance liquid chromatography (DSPE-HPLC) is established for the first time and used for detecting the six iridoid glycoside ingredients of different structures, so that reliability and effectiveness of honeysuckle quality evaluation are obviously improved, quality control level of traditional Chinese medicine honeysuckle and related patent medicines is further improved, and the honeysuckle quality evaluation method disclosed by the invention is significant on guidance of clinical application.

Owner:SHANDONG ANALYSIS & TEST CENT

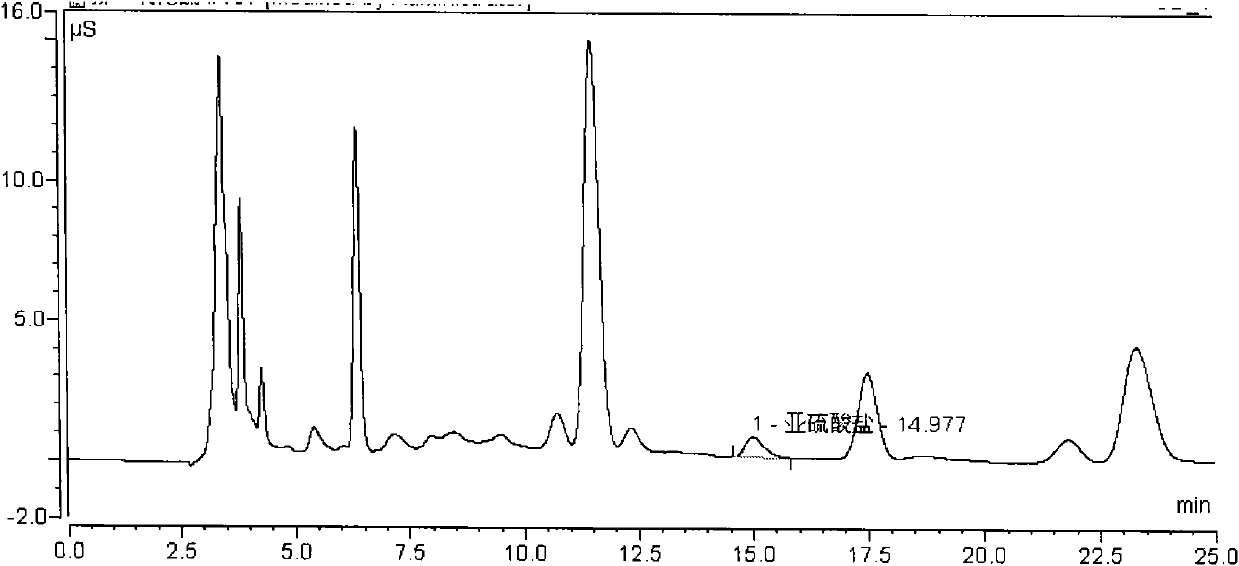

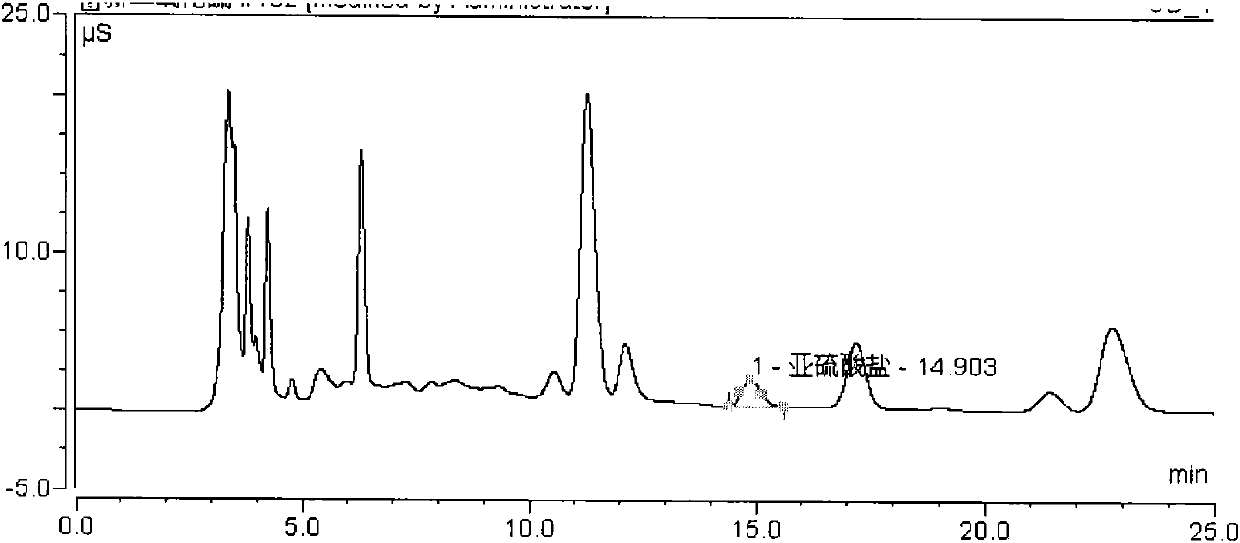

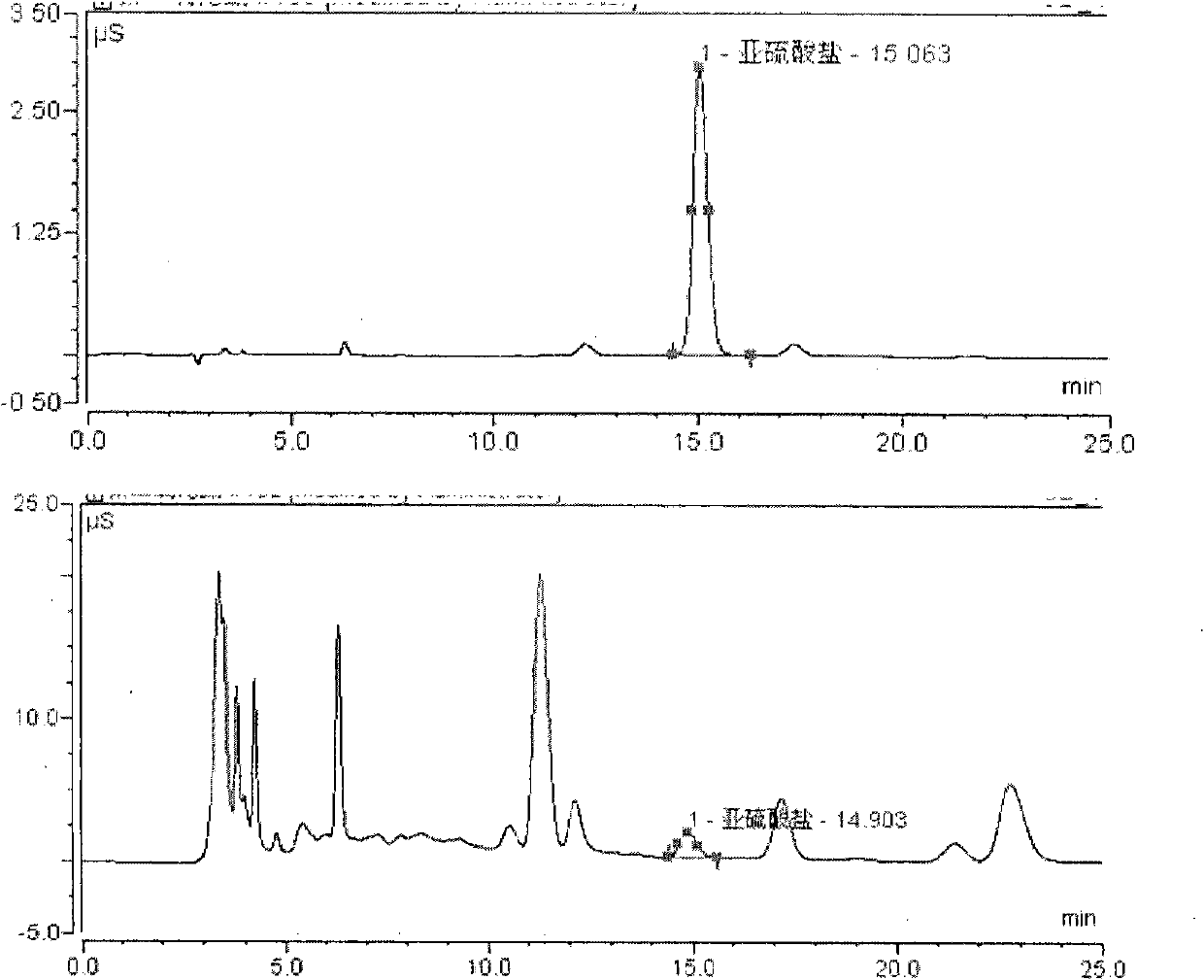

Method for detecting sulfur dioxide content in shitake mushrooms

The invention discloses a method for detecting sulfur dioxide content in shitake mushrooms, which comprises the following steps of: 1) preparing standard solution, namely preparing standard stock solution from anhydrous sodium sulfite, formaldehyde solution, NaOH solution, and deionized water, preparing the standard stock solution into the standard solution at step concentration , filtering, injecting by adopting ion chromatography, and drawing a standard curve according to the concentration and peak appearance area; 2) treating samples, namely taking dried shitake mushrooms as samples, injecting the obtained supernatant by adopting ion chromatography, substituting the peak appearance area obtained under the same peak appearance time in the step 1) into the standard curve obtained in the step 1), and obtaining sulfur dioxide content c of the injected solution; and 3) obtaining the sulfur dioxide content in the shitake mushrooms. The method for detecting the sulfur dioxide content in the shitake mushrooms has the characteristics of accurate result and convenient use.

Owner:丽水蓝城农科检测技术有限公司

Microstructure device including a metallization structure with self-aligned air gaps formed based on a sacrificial material

InactiveUS8048796B2Increase flexibilityHigh degree of processingSemiconductor/solid-state device detailsSolid-state devicesProcess conditionsDielectric layer

In a sophisticated metallization system of a semiconductor device, air gaps may be formed in a self-aligned manner on the basis of a sacrificial material, such as a carbon material, which is deposited after the patterning of a dielectric material for forming therein a via opening. Consequently, superior process conditions during the patterning of the via opening and the sacrificial material in combination with a high degree of flexibility in selecting appropriate materials for the dielectric layer and the sacrificial layer may provide superior uniformity and device characteristics.

Owner:GLOBALFOUNDRIES INC

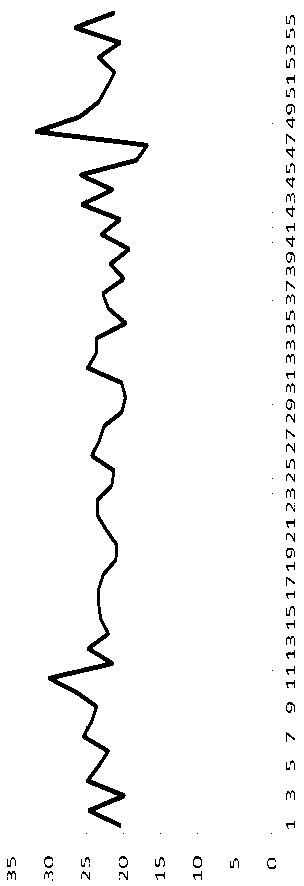

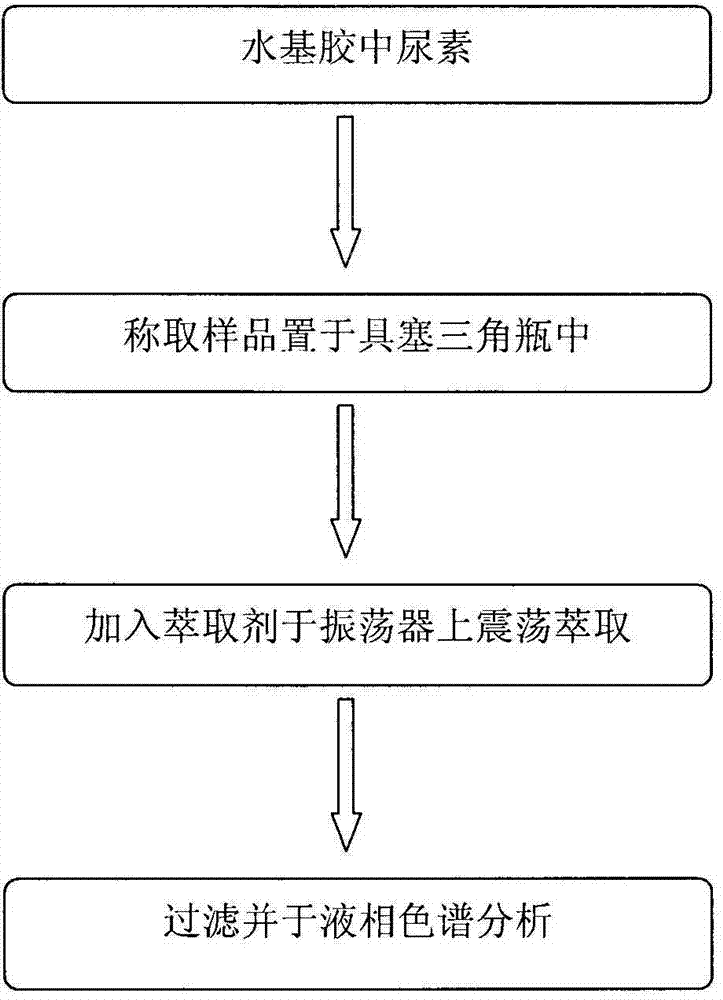

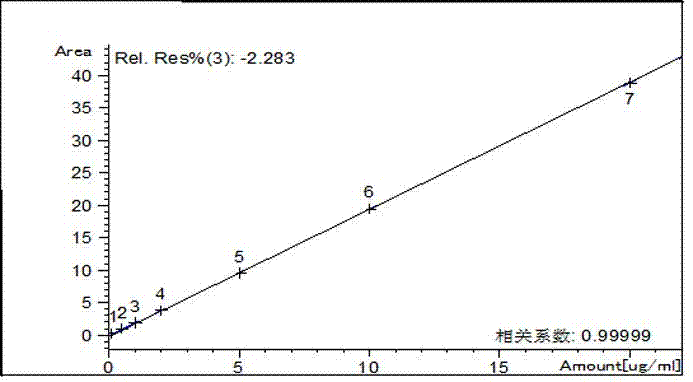

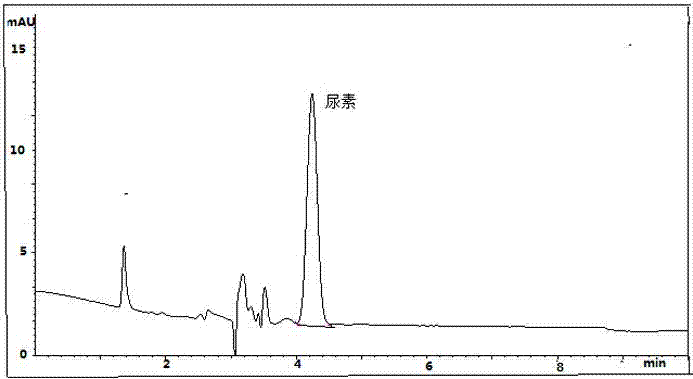

Determination method of content of urea in water-based adhesive

ActiveCN104122346AEasy to handleEasy processing conditionsComponent separationWater basedRelative standard deviation

The invention relates to a determination method of the content of urea in water-based adhesive. The determination method of the content of urea in water-based adhesive comprises the following steps: preparing a sample solution, analyzing by liquid chromatogram, calculating the determination result and the like. A detection method after optimization has the advantages of short detection time, simplicity and convenience in operation, high flexibility, high recovery rate, good repeatability and the like. The chromatographic condition of the method provided by the invention enables the separation of the chromatographic peak of urea and the chromatographic peak of impurities to be favorable, and has good relevancy. The detection limit is 2.34 micrograms / g; the average recovery rate is 92.01%; the average relative standard deviation of the sample testing result is 0.33%.

Owner:CHINA NAT TOBACCO QUALITY SUPERVISION & TEST CENT