Patents

Literature

50results about How to "Not easy to oxidize and corrode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

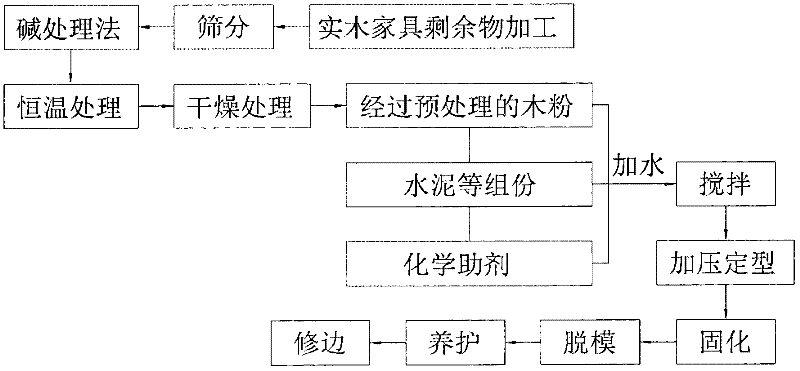

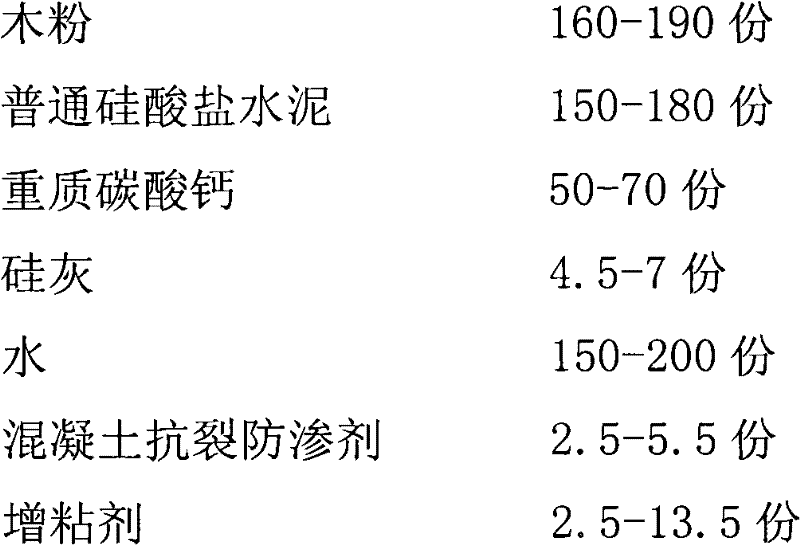

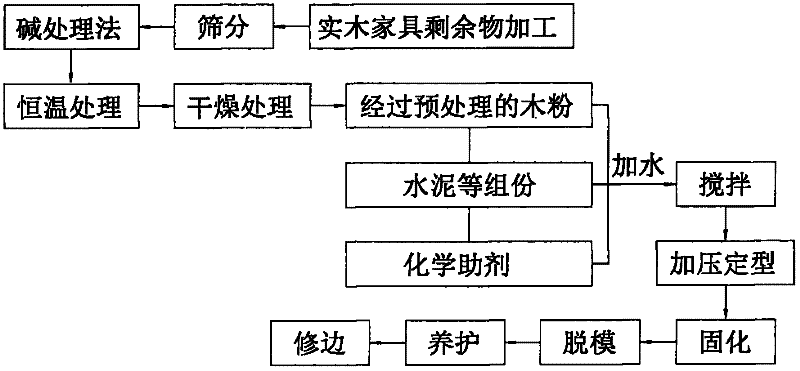

Cement-based wood fiber artificial board and manufacturing method thereof

InactiveCN102531492AReduce pollutionSave resourcesSolid waste managementCeramic shaping apparatusSolid woodFiber

The invention discloses a cement-based wood fiber artificial board and a manufacturing method thereof. According to the invention, the cement-based wood fiber artificial board is obtained by taking cement as a gel material and taking wood fibers as an organic reinforcing material, doping a certain amount of chemical addition agent, and carrying out steps of batching, agitating, pressurizing, curing, de-molding and maintaining. The artificial board provided by the invention is a novel material with water resistance, anti-oxidation, corrosion resistance and flame retardant property. The wood fiber raw material is selected from leftovers in the production of solid wood furniture and is mixed with cement slurry after being classified, machined and treated, so that the cost of the cement-based wood fiber artificial board is low; and bonding glue is not used so that the pollution to the environment is reduced while timber resources are protected and saved. The cement-based wood fiber artificial board and the manufacturing method thereof, provided by the invention, are applicable to lightweight wall materials for buildings, indoor and outdoor decorative sheet materials, and furniture decorative sheet materials.

Owner:LANGFANG HUARI FURNITURE CO LTD

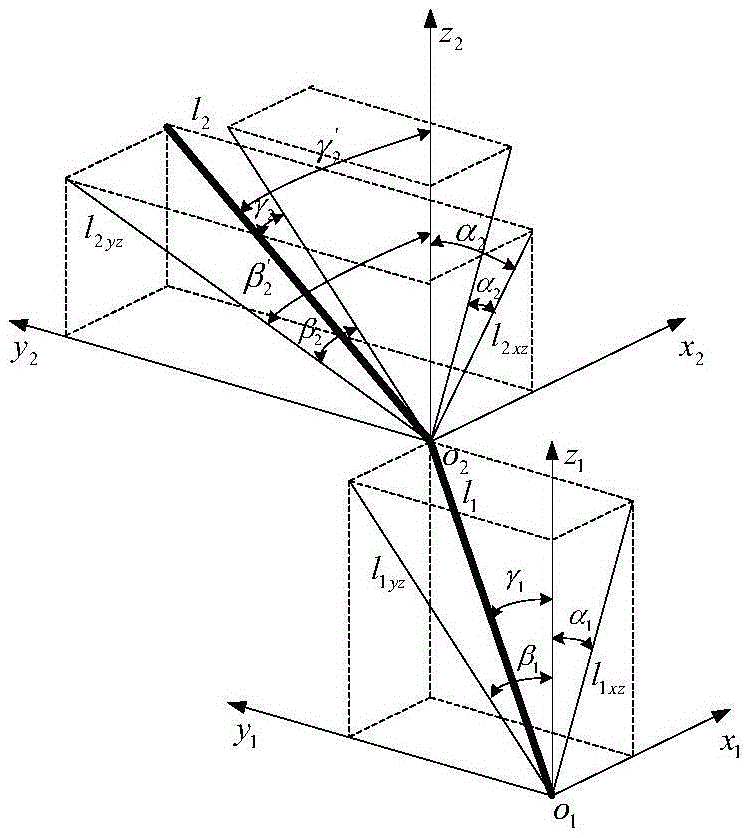

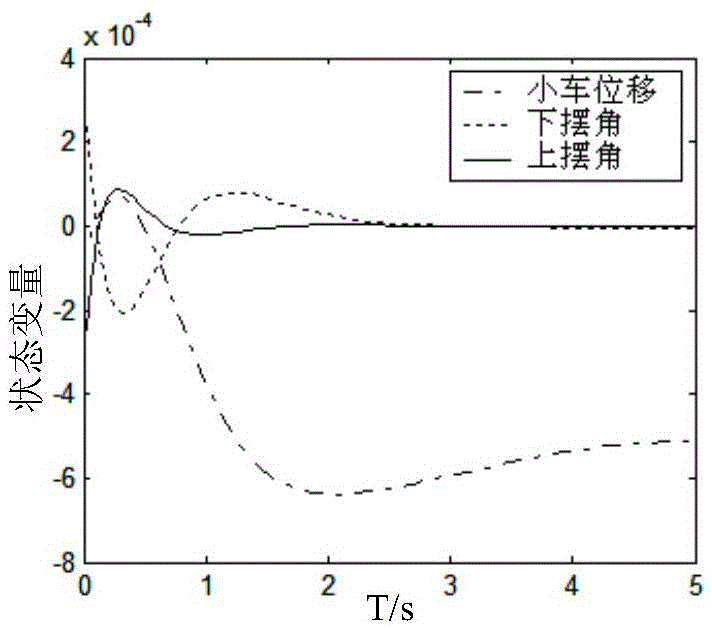

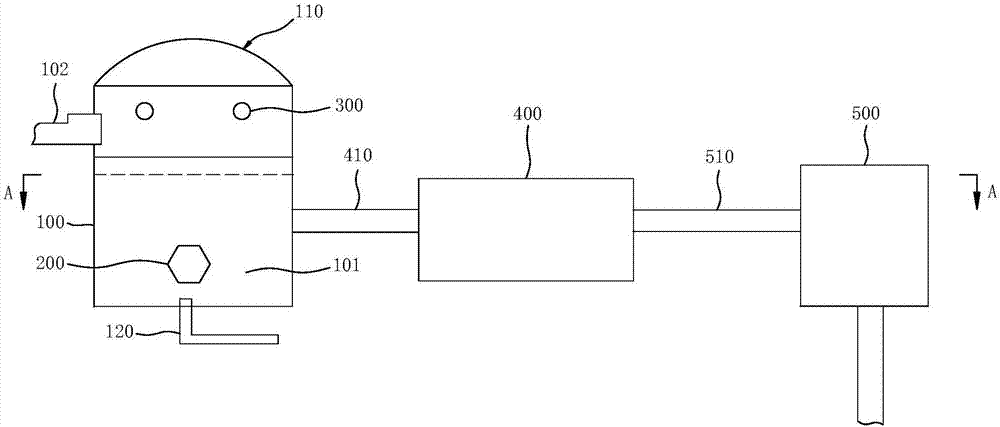

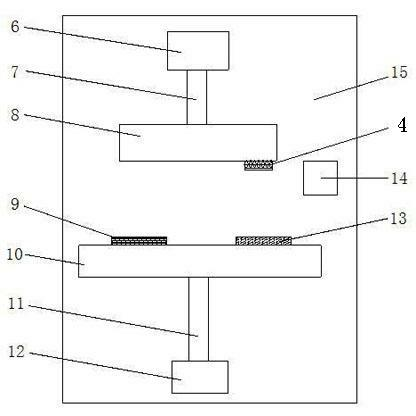

Generation method for self-adaptive sliding mode controller of uncertainty plane inverted pendulum system

InactiveCN105573124AImprove robustnessImprove performanceAdaptive controlHandoff controlControl system

The invention provides a generation method for a self-adaptive sliding mode controller of an uncertainty plane inverted pendulum system. The generation method comprises the steps that step 1, the sliding mode control law is generated for a linear time-invariant system with uncertainty items; and step 2, fuzzy system h<^> approximation switching control epsilonsgn(s) is adopted for the uncertainty items. The beneficial effects of the generation method are listed as follows: the self-adaptive fuzzy sliding mode controller is designed for the inverted pendulum system with the uncertainty items, the uncertainty inverted pendulum system is theoretically proved to be stable, and the designed control system is verified to be great in rapidity and robustness through simulation experiment.

Owner:HENAN POLYTECHNIC UNIV

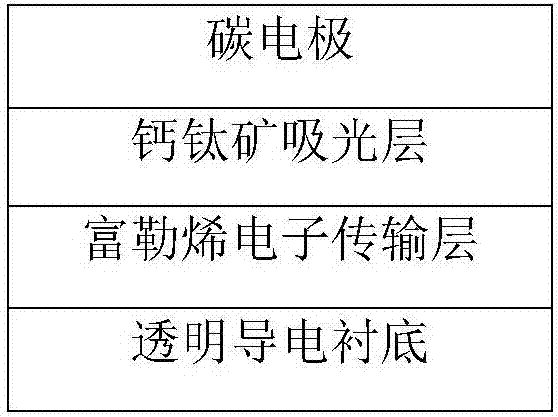

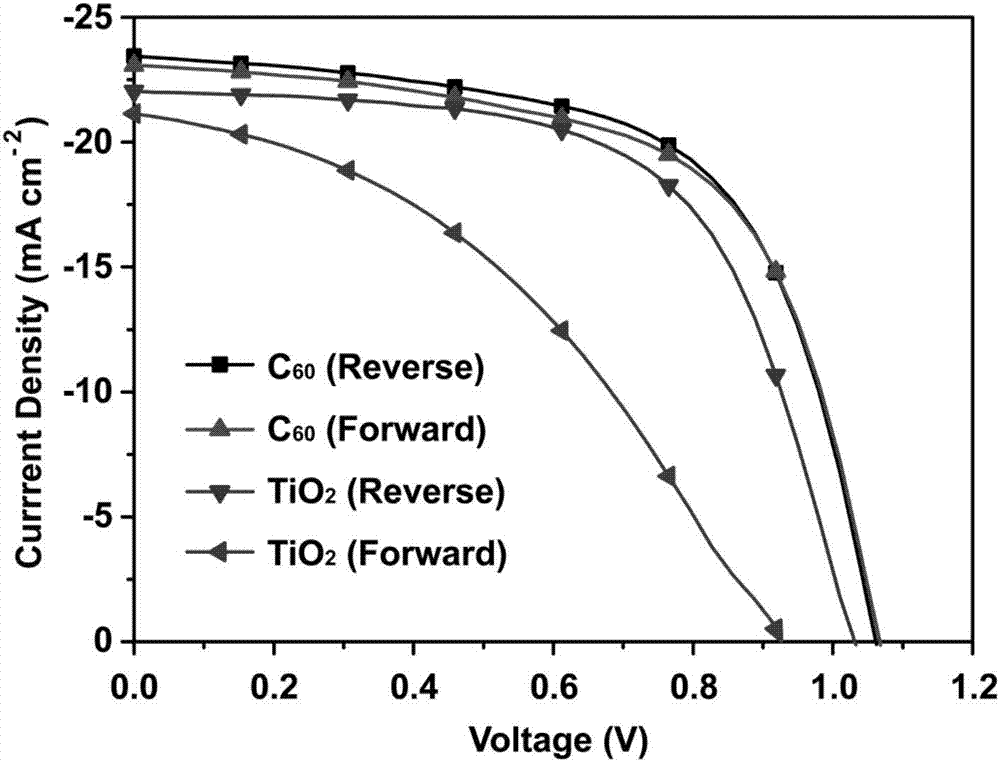

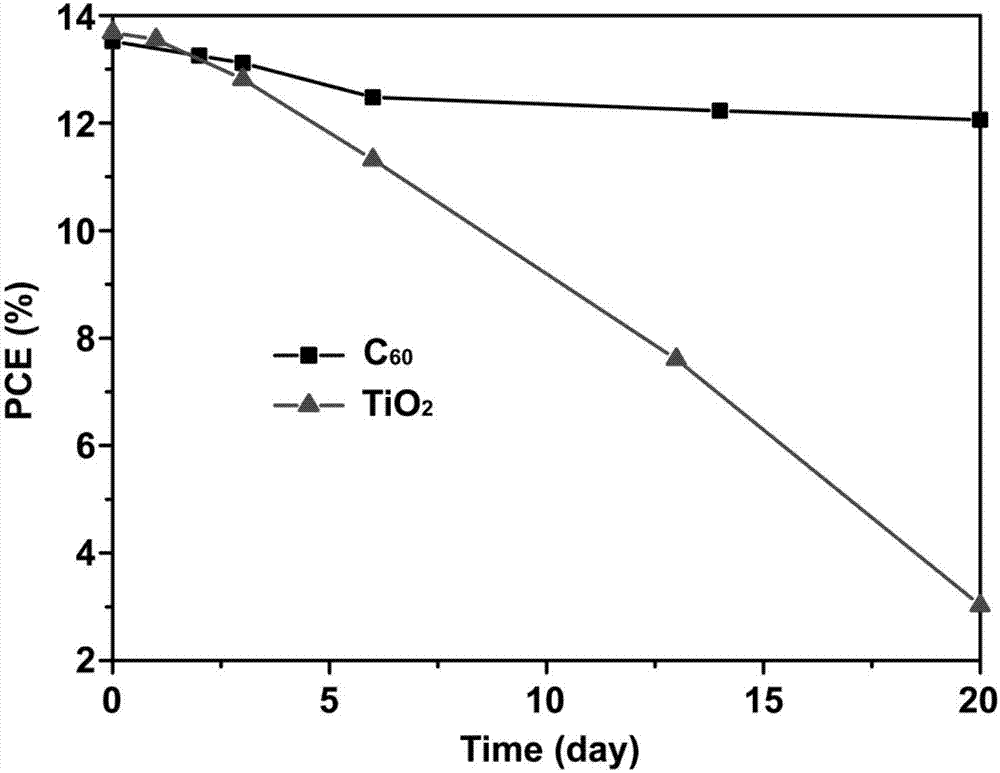

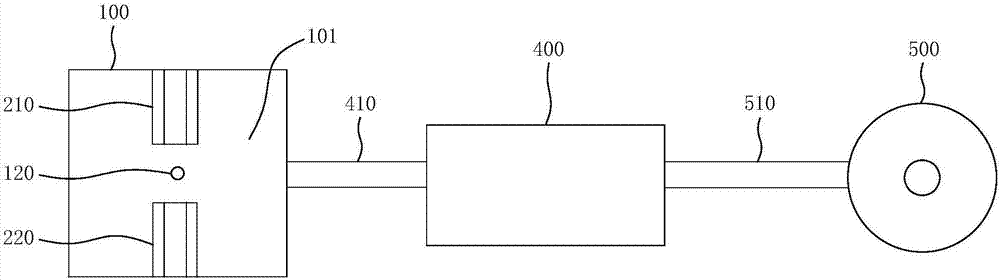

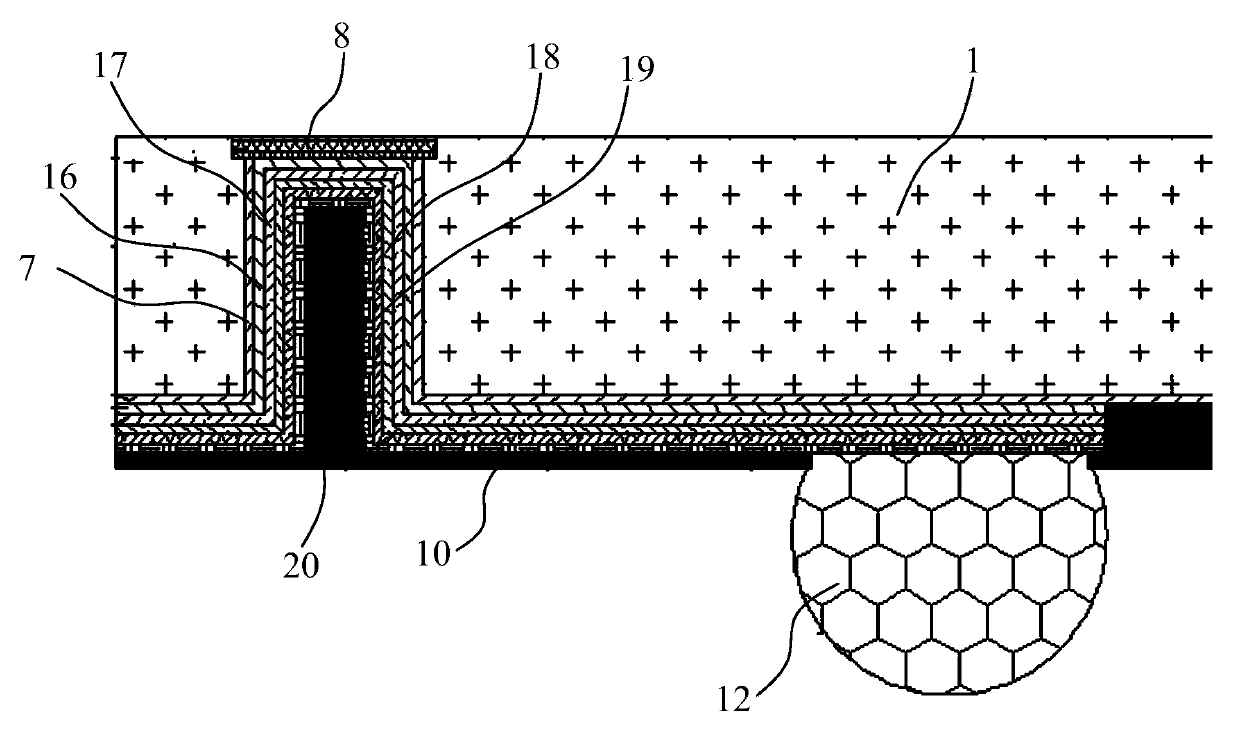

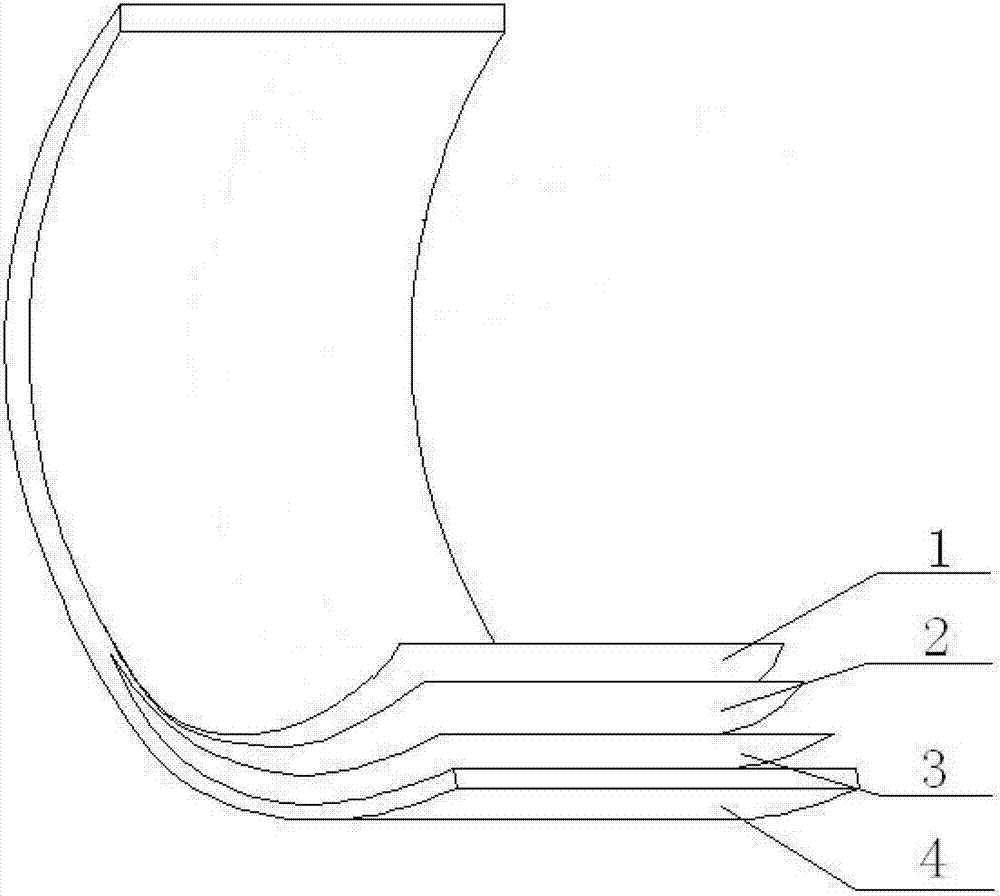

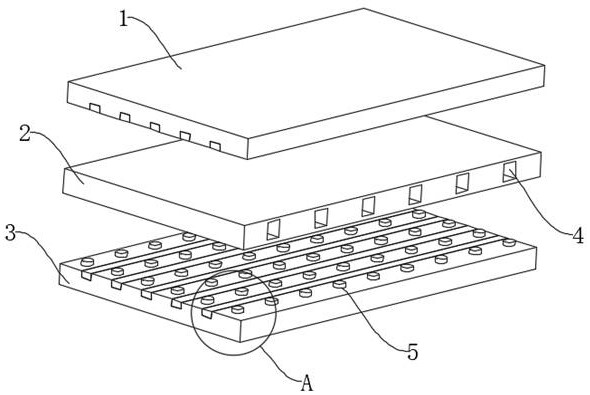

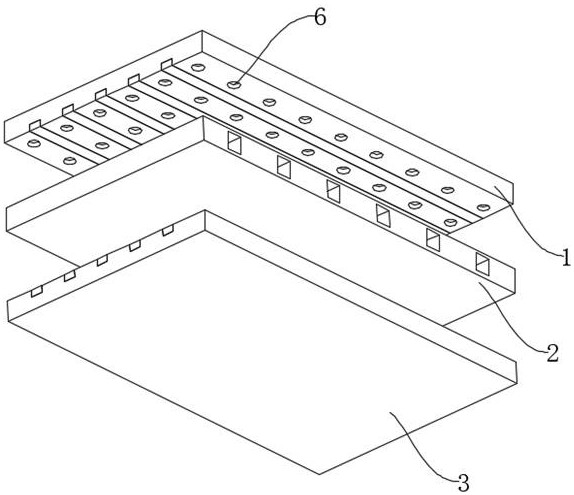

Full-carbon-base perovskite solar energy cell and preparation process

InactiveCN107154460AImprove photostabilityStable in natureSolid-state devicesSemiconductor/solid-state device manufacturingElectronic transmissionPerovskite solar cell

The invention discloses a full-carbon-base perovskite solar energy cell and a preparation process. The perovskite solar energy cell comprises a substrate, a transparent electrode, fullerene or fullerene derivative, a perovskite light-absorption layer and a charcoal electrode which are sequentially laminated, wherein the fullerene or the fullerene derivative is taken as an electronic transmission layer, and the perovskite light-absorption layer is prepared by a photovoltaic material having a perovskite structure. And the preparation process comprises sequentially preparing the transparent electrode, the fullerene electronic transmission layer, the perovskite light-absorption layer and the charcoal electrode on the substrate. The full-carbon-base perovskite solar energy cell is advantaged in that the preparation process is simple, cost is low, cell stability is high, and cell industrialization production can be realized.

Owner:BEIJING UNIV OF CHEM TECH

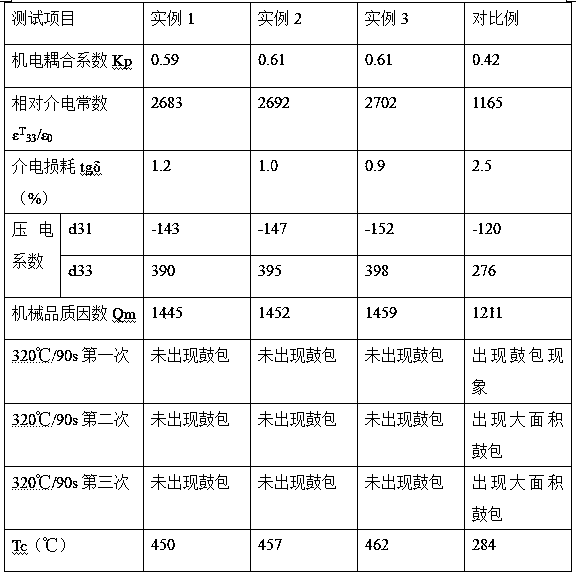

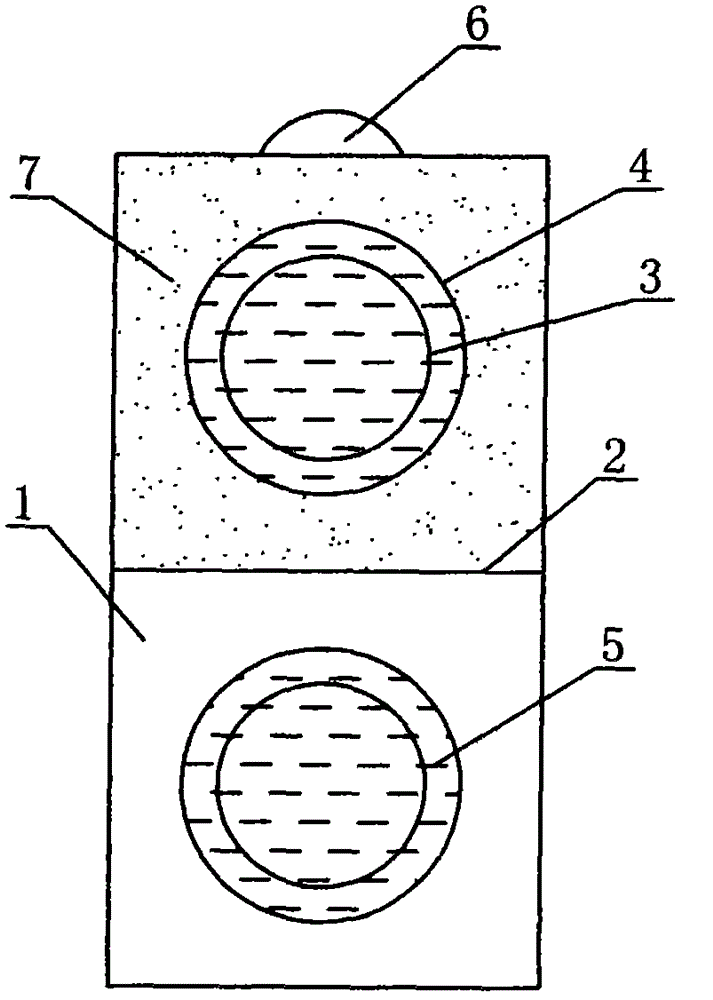

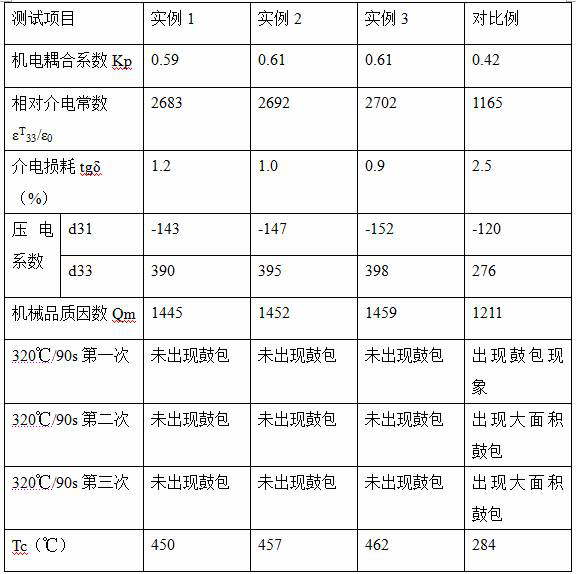

Method for preparing BCZT-based leadless piezoelectric ceramics

ActiveCN108546124AImprove adhesionLow thermal conductivityPiezoelectric/electrostrictive/magnetostrictive devicesChemistryMagnetic powder

The invention relates to the technical field of preparation of electronic components and devices and particularly relates to a method for preparing BCZT-based leadless piezoelectric ceramics. The method comprises the steps of dissolving citric acid in ethylene glycol, adding anhydrous ethanol diluted butyl titanate to obtain a compounding solution, dropwise adding a barium acetate solution, a calcium nitrate solution and a zirconium nitrate solution into the compounding solution, carrying out uniform mixing so as to obtain a BCZT-based polymer precursor, mixing NdFeB nano-powder with ferrum nano-powder so as to obtain magnetic powder slurry, mixing hard magnetic powder and core-shell structured ferrum / cobalt nano powder, then, carrying out high-speed dispersing treatment, and carrying outmold loading, spark plasma sintering and demolding, thereby obtaining the piezoelectric ceramics. Dense cobalt powder particles can be used for protecting ferrous powder from oxidation, tetrabutyl titanate reacts with citric acid to form a network structure, zirconium-calcium-barium titanate based materials are free of Pb and have little harm to human and environment, elemental cobalt will be slightly softened at high temperature, thus, the binding power of magnetic materials is enhanced, the coefficient of thermal conductivity of the magnetic materials is reduced, the magnetic materials can stably work in high-temperature environments, and the application prospect is broad.

Owner:景德镇市鑫惠康电子有限责任公司

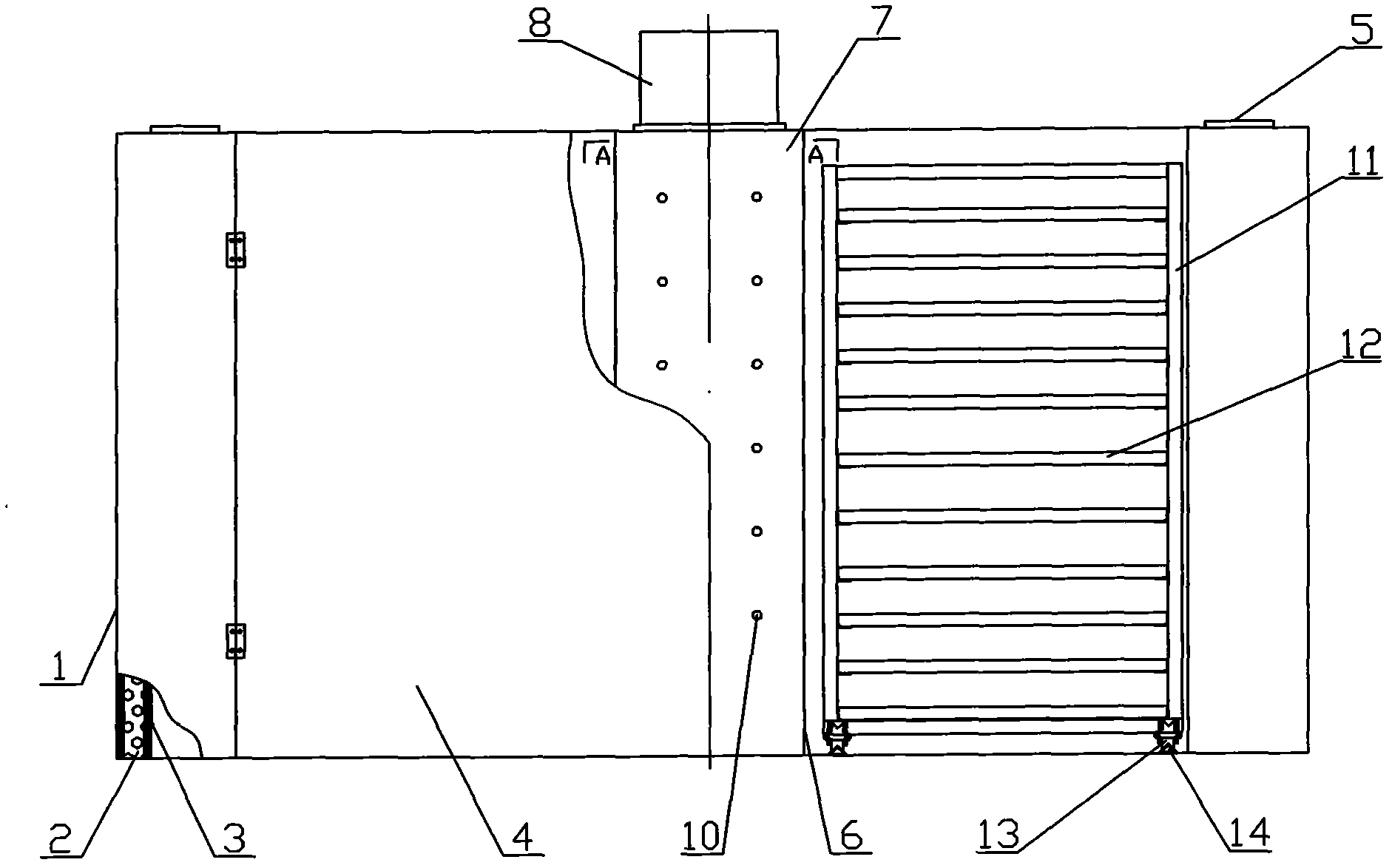

Electric dry oven for Chinese herbal medicine

InactiveCN102305522AEven and efficient thermal cycleEnsure indoor temperature uniformityDrying gas arrangementsDrying machines with local agitationElectricityEngineering

The invention discloses an electric dry oven for a Chinese herbal medicine. The electric dry oven comprises a box body, a door and a temperature controller, wherein a hot air chamber consisting of heat insulation plates and an insulation plate is arranged in the middle in the box body; an air blower is arranged on the top of the hot air chamber; air outlets are uniformly formed on the heat insulation plates on the left side and the right side of the hot air chamber; and the insulation plate is provided with a plurality of electrothermal tubes from top to bottom. By the electric dry oven, the shortcomings of one-directional heat cycle, non-uniform heating range and non-uniform drying degree in the prior art are overcome; and the electric dry oven has the characteristics of low energy consumption, low cost, high efficiency and convenience for maintenance and regulation.

Owner:安徽九天生态农业开发有限公司

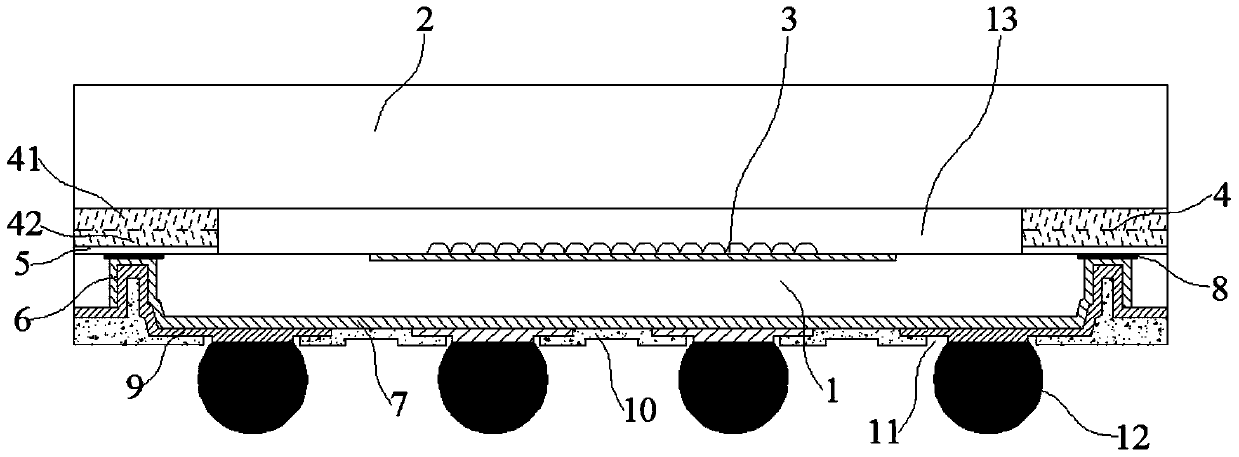

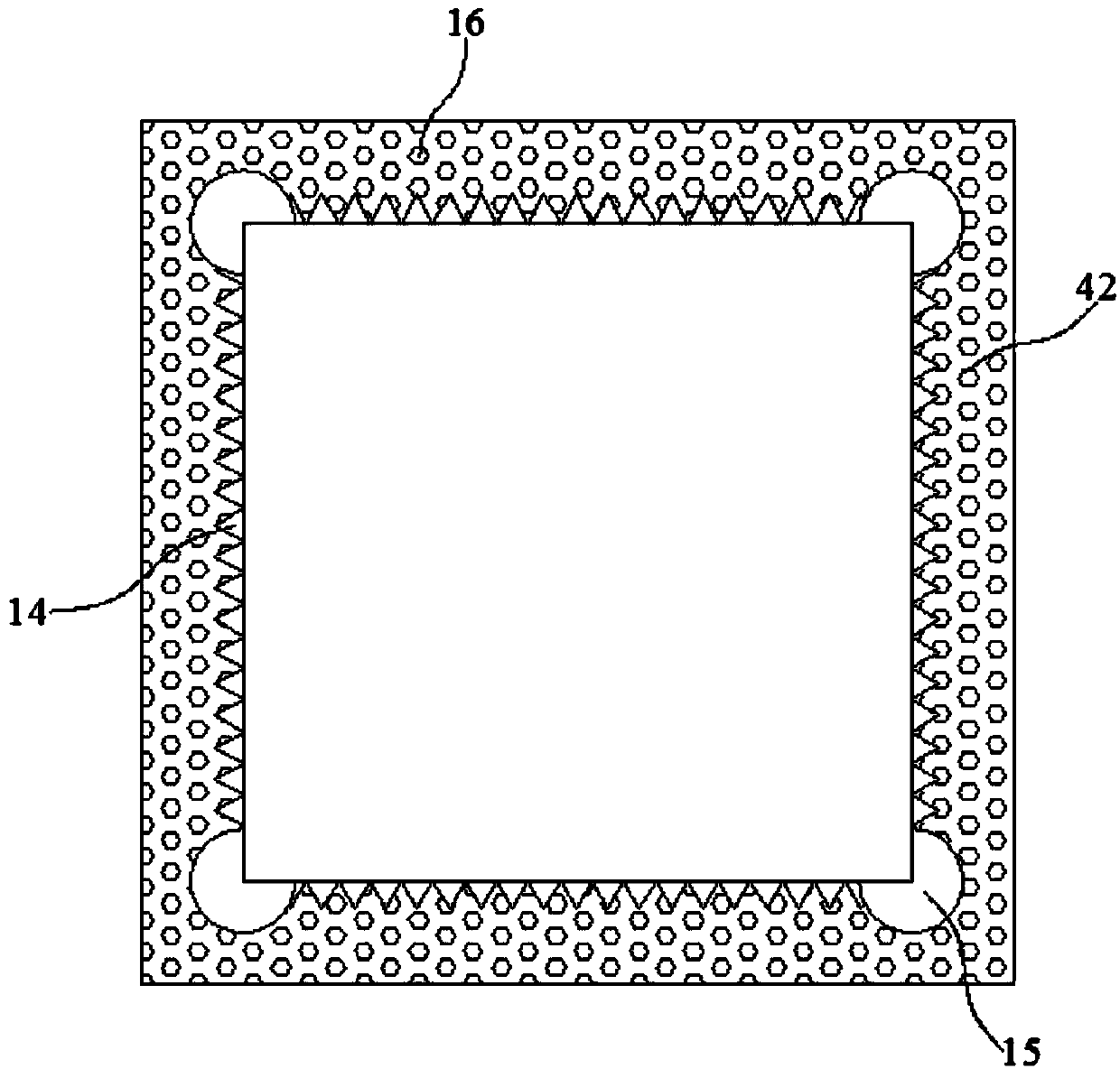

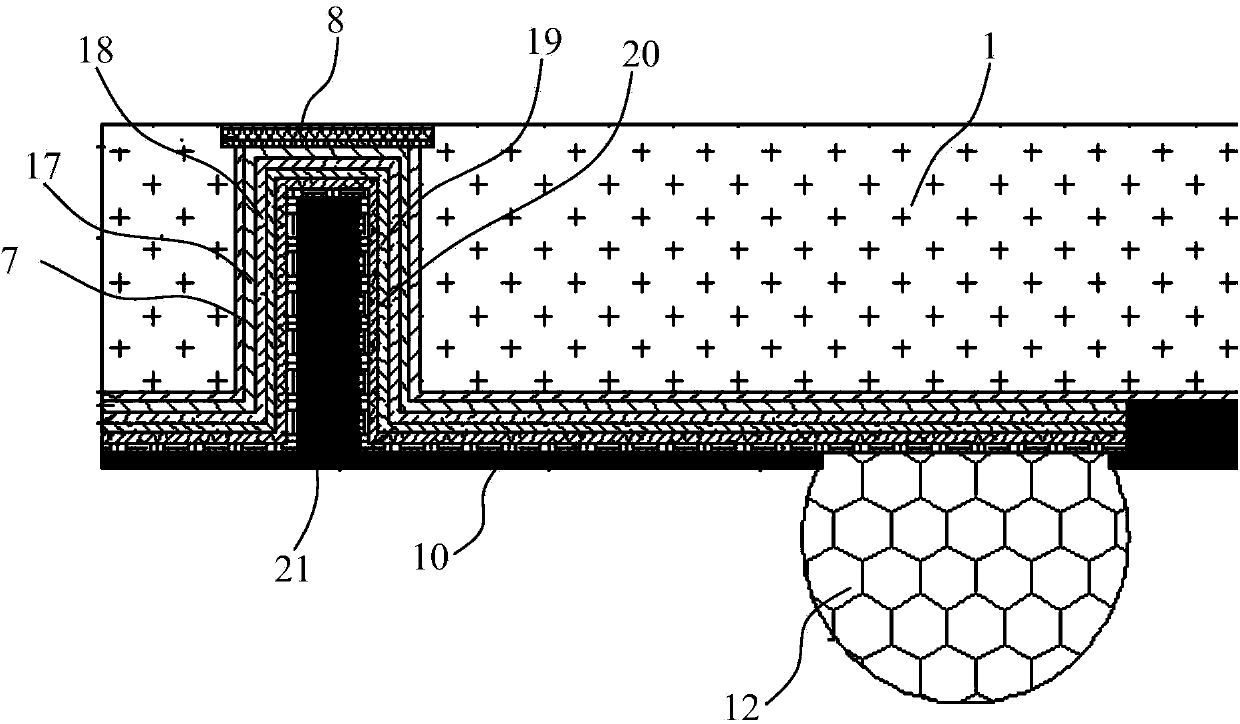

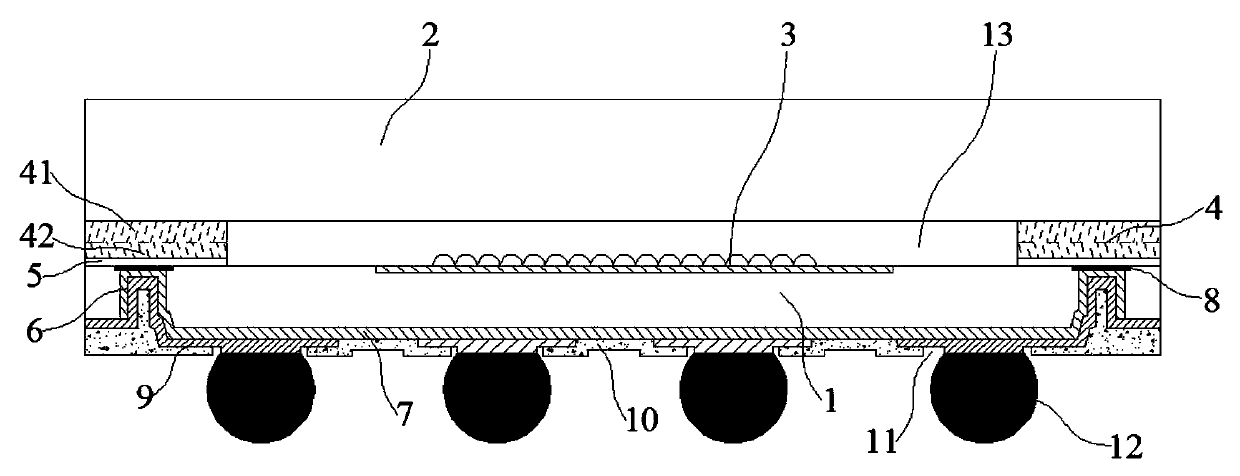

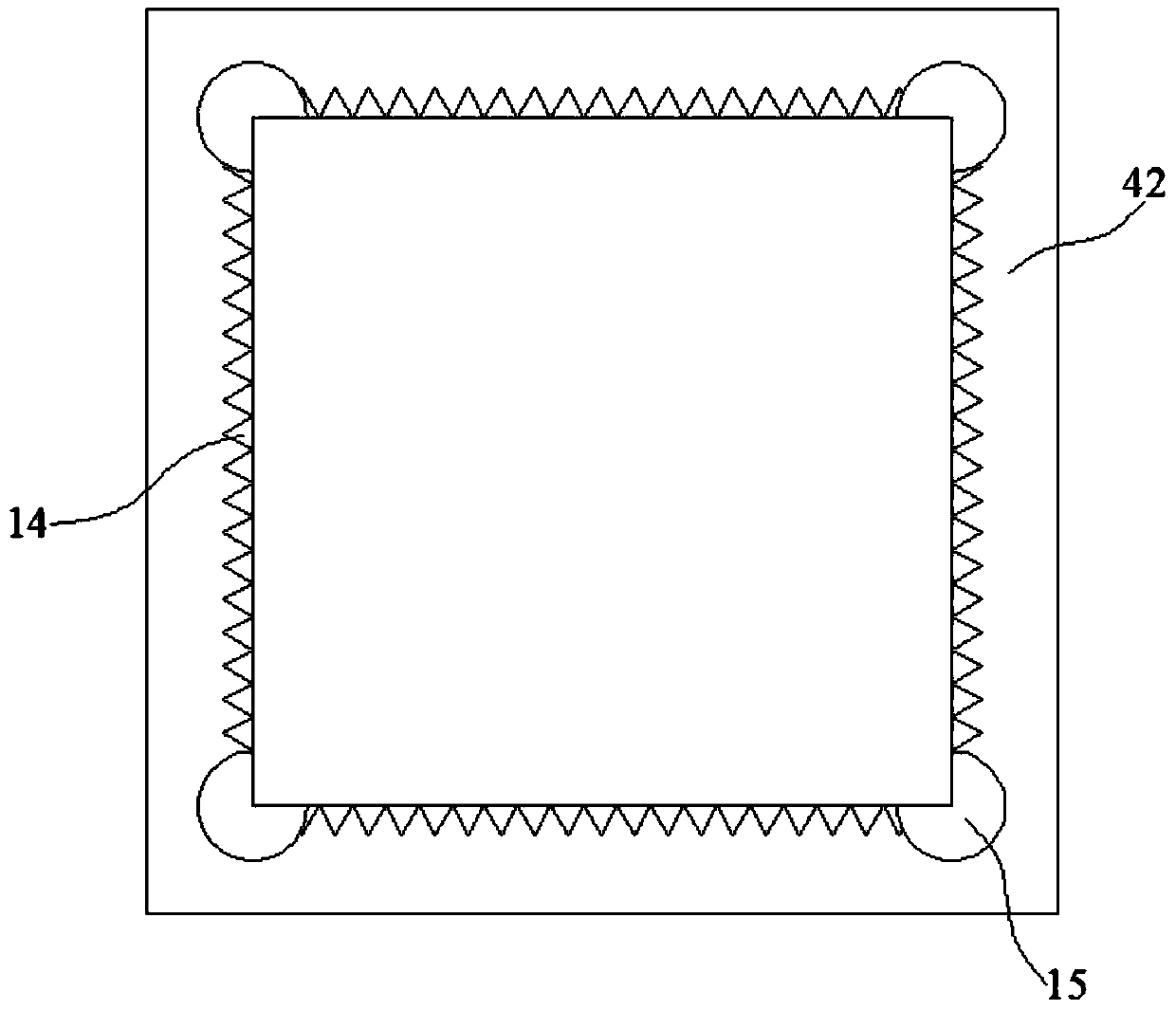

Wafer-level chip packaging structure

The invention discloses a wafer-level chip packaging structure. The wafer-level chip packaging structure comprises an image sensing chip and a transparent cover plate, wherein metal conductive pattern layers electrically connected with pin bonding pads are arranged on the surface, with the back towards the image sensing chip, of a passivation layer and blind holes respectively. Each supporting cofferdam is composed of a first supporting cofferdam layer and a second supporting cofferdam layer which are placed in a vertically stacked mode, a plurality of continuously arranged V-shaped notched are formed in the inner side face of each second supporting cofferdam layer, arc-shaped notches are formed in the four corners of each second supporting cofferdam layer respectively, a plurality of holes are evenly formed in the surface, in contact with the image sensing chip, of each supporting cofferdam, each metal conductive pattern layer is formed by placing a titanium layer, a copper layer, a nickel layer and a palladium layer in a stacked mode in sequence, and the titanium layers are in contact with the passivation layer. According to the wafer-level chip packaging structure, stress is relieved, the structure is not prone to oxidation corrosion, the response time of a device is shortened, the reliability of a product is improved, and the requirement for continuously covering the inner wall of a deep hole with a high aspect ration with a metal layer can be met.

Owner:苏州科阳半导体有限公司

Metal product polishing liquid and preparation method thereof

The invention discloses metal product polishing liquid. The polishing liquid is prepared from, by weight, 20-30 parts of citric acid, 50-100 parts of glacial acetic acid, 2-10 parts of 2-ethylimidazole, 5-12 parts of salicylic acid, 10-20 parts of glycolic acid, 8-15 parts of 1H-benzotriazole, 20-80 parts of polyethylene glycol 8000, 100-150 parts of tetrahydrofurfuryl alcohol, 50-150 parts of ethyl alcohol, 80-100 parts of butyl acetate, 5-12 parts of oleic alcohol polyoxyethylene ether, 5-12 parts of ethylenediamine, 4-6 parts of nano-silicon dioxide, 3-9 parts of nano-zinc oxide and 30-80 parts of auxiliaries. The metal product polishing liquid contains the auxiliaries, the auxiliaries contain rice bran and mango skin, an oxide layer on the surface of a metal product can be effectively removed by means of extraction, tea seed powder can remove blots on the surface of the metal product, effective substances in a polishing agent can easily make direct contact with the oxide layer on the surface of the metal product, the efficiency is improved when the polishing agent removes the oxide layer, and after being modified through iron powder, latex powder and natural resin can form a layer of compact protective film on the surface layer of the metal product after being polished.

Owner:广西钱隆投资管理有限公司

Glass manufacture device and manufacture method for high-transmittance optical glass

ActiveCN107298521AReduce oxidation rateReduce the degree of oxidationCharging furnaceGlass furnace apparatusMelting tankVitreous Humors

The invention belongs to the technical field of glass manufacture, particularly discloses a glass manufacture device and a manufacture method for high-transmittance optical glass, and aims to solve the problem that an electrode easily generates corrosion to influence the quality of produced glass in a traditional glass manufacture device use process. The glass manufacture device comprises a melting tank and an electrode, wherein a melting cavity is arranged in the melting tank; the electrode is arranged on the side wall of the melting cavity; the upper edge of the electrode is positioned below the upper limit of the liquid level of vitreous humour. The manufacture method for high-transmittance optical glass adopts the glass manufacture device to manufacture the high-transmittance optical glass. Since the electrode is under the liquid level of vitreous humour in a production process and only the vitreous humour is in contact with the electrode, the chemical property of the electrode is stable, oxide etch is unlikely to generate, and service life is prolonged; in addition, when a glass raw material is continuously or intermittently supplied to the melting tank, since a bare electrode is not arranged above the vitreous humour, the electrode is prevented from being subjected to powerful thermal shock, and the fatigue or damage of the electrode due to thermal shock can be avoided.

Owner:CDGM OPTICAL GLASS

Semiconductor device of novel package structure

The invention discloses a semiconductor device of a novel package structure. The semiconductor device comprises an image sensing chip and a transparent cover plate. A metal conductive pattern layer which is electrically connected with a pin bonding pad is arranged in a blind hole and on the surface, opposite to the image sensing chip, of a passivating layer. A supporting cofferdam is composed of a first supporting cofferdam layer and a second supporting cofferdam layer which are overlapped up and down. The first supporting cofferdam layer is in contact with the transparent cover plate. The second supporting cofferdam layer is in contact with the image sensing chip. A plurality of V-shaped continuous notches are formed in the inner side face of the second supporting cofferdam layer. Arc notches are formed in the four corners of the second supporting cofferdam layer respectively. The metal conductive pattern layer is formed by sequentially overlapping a titanium layer, a copper layer, a nickel layer and a palladium layer. The titanium layer and the passivating layer are in contact. The semiconductor device relieves stress, is exposed in the environment, and can not be easily oxidized and corroded, stress deformation of metal on the two sides of the blind hole under the cold and hot environments is effectively buffered, the response time of the semiconductor device is shortened, and the requirement that the metal layer continuously covers the inner wall of the deep hole with a high aspect ratio is met.

Owner:苏州科阳半导体有限公司

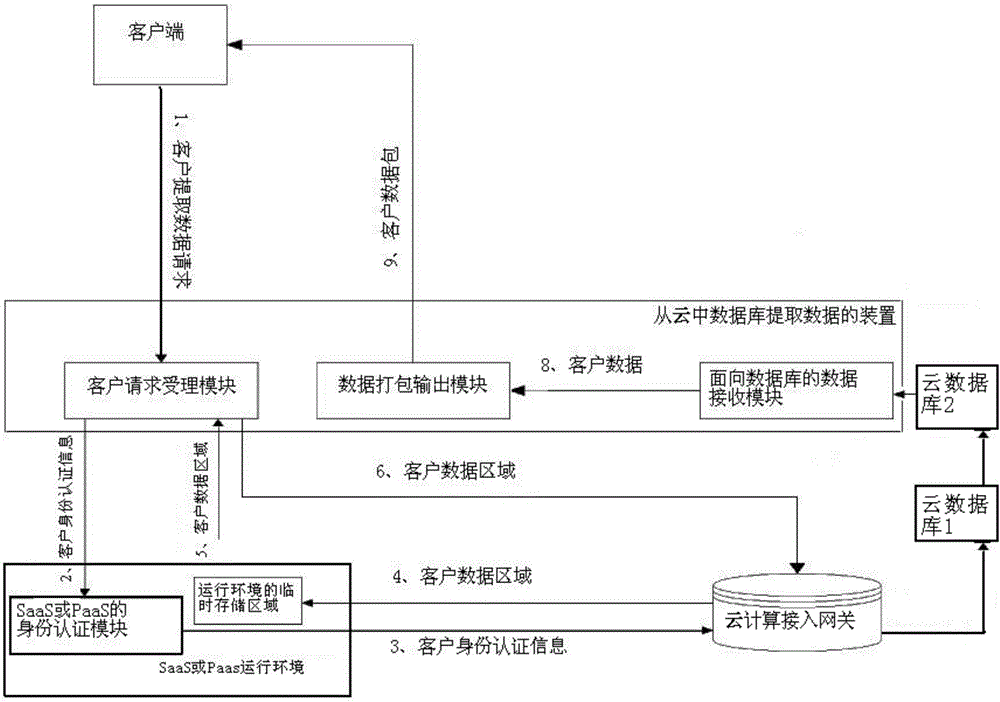

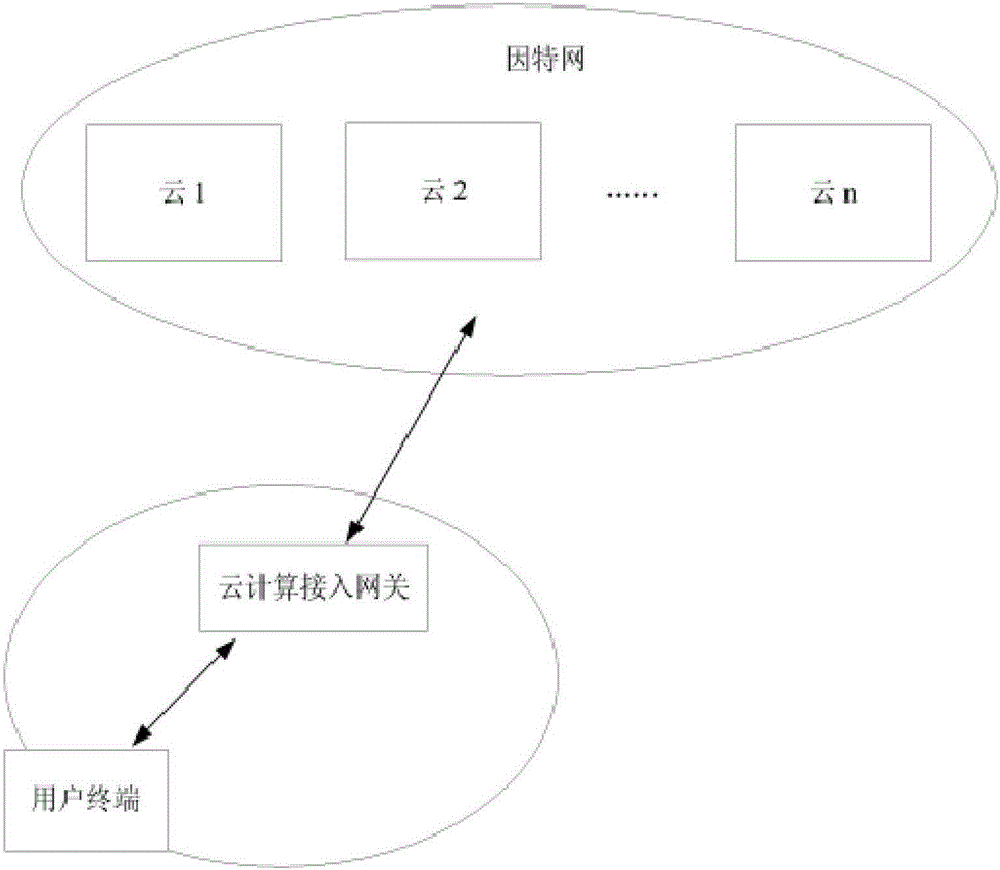

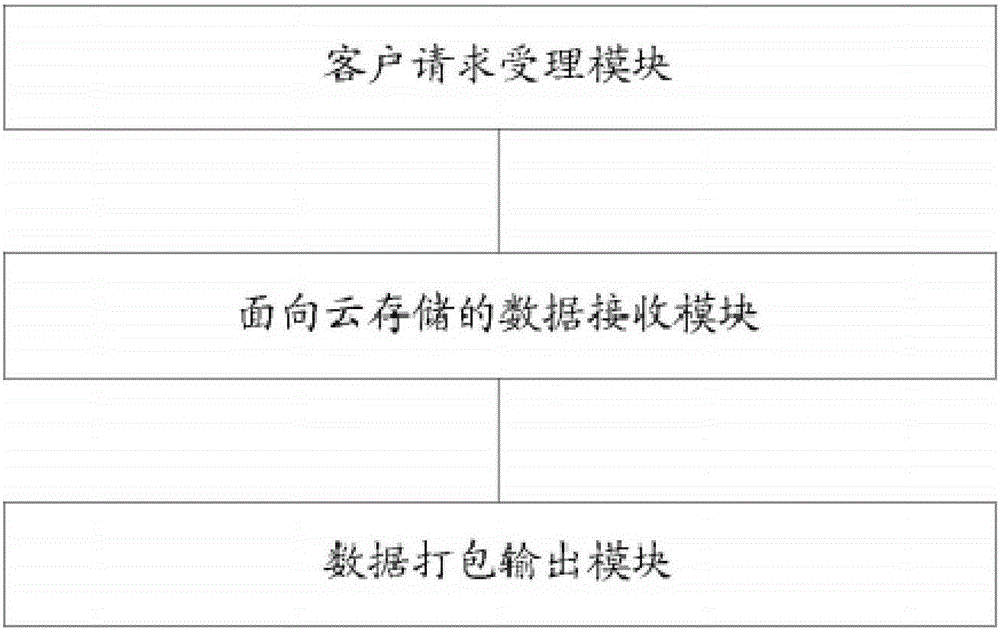

Cloud computing access gateway

InactiveCN105978877ASafe storageImprove performanceNetwork connectionsCloud service providerTarget database

The invention provides a cloud computing access gateway. A user can transfer data to a new cloud service provider via an original application account between that the service period is ended and that the application account of the user is destroyed. The user data can be transferred from a cloud source database to a target database rapidly and timely via the cloud computing access gateway. According to the invention, the user can select different cloud service providers freely and rapidly, historical data of the original cloud service provider can be provided for the new cloud service provider directly and rapidly, and rapid and convenient cloud access and storage services are provided for the user.

Owner:JIANGSU ELECTRIC POWER CO +1

Coating process for improving performance of reflection cup

InactiveCN108796502ANo pollution in the processNot easy to fall offVacuum evaporation coatingSputtering coatingPower flowIon current

The invention provides a coating process for improving performance of a reflection cup. The coating process for improving the performance of the reflection cup comprises the following steps that step1, a workpiece is placed in a processing furnace cavity, after vacuumizing is carried out, the processing furnace cavity is filled with argon gas, and the surface of the workpiece is cleaned by ion current bombardment; step 2, the workpiece is coated with a dimethyl silicone oil base film under the condition of ion current bombardment by a chemical vapor deposition method; step 3, the workpiece iscoated with an aluminum film by an evaporation mode, and the workpiece is subjected to evaporation by pure aluminum at a high temperature of 1100-1200 DEG C, wherein the purity of the pure aluminum is 99.99 %; and step 4, the workpiece is coated with a dimethyl silicone oil protective film under the condition of ion current bombardment by a chemical vapor deposition method. The coating process for improving the performance of the reflection cup has high light efficiency, high film layer stability, less material consumption and reduced cost.

Owner:中山市达尔科光学有限公司

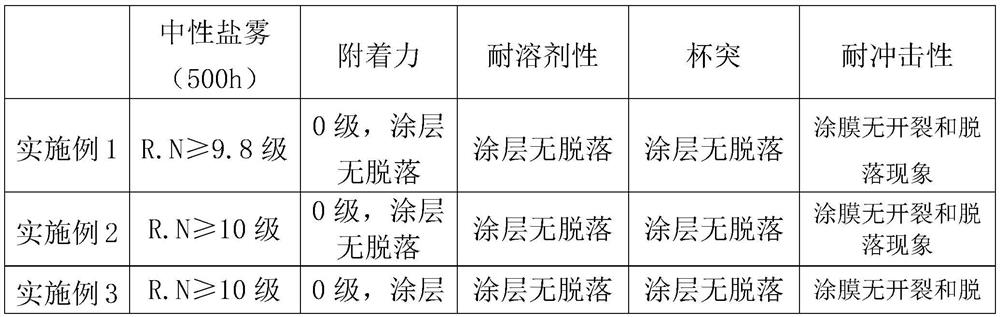

Water-based paint for anticorrosion treatment of copper pipes of two devices of air conditioner and preparation method of water-based paint

PendingCN113174172AImprove anti-corrosion performanceImprove bindingAnti-corrosive paintsEpoxy resin coatingsAcrylic resinFirming agent

The invention provides a water-based paint for anticorrosion treatment of copper pipes of two devices of an air conditioner. The paint, including 100 parts wholly, comprises the following components in parts by weight: 15-30 parts of water-based epoxy modified acrylic resin, 0.2-0.5 part of organic amine, 8-15 parts of a low-temperature baking curing agent, 1-6 parts of an adhesion promoter, 0.05-0.5 part of a wetting agent, 0.05-0.5 part of a flatting agent and the balance of water, wherein the water-based epoxy modified acrylic resin is prepared from the following components in parts by weight: 50 to 70 parts of water-soluble acrylic resin, 5 to 15 parts of epoxy resin, 3 to 5 parts of acrylic acid, 2 to 5 parts of phosphorus-containing monomer, 0.2 to 0.5 part of peroxide initiator, 2 to 5 parts of ethylene glycol butyl ether and 1 to 3 parts of isoparaffin solvent. The anticorrosive treatment water-based paint for the copper pipes of the two devices of the air conditioner is good in wetting and leveling effect on the surfaces of the copper pipes, good in adhesion performance and good in anticorrosive effect. The invention also provides a preparation method of the water-based paint for the anticorrosion treatment of the copper pipes of the two devices of the air conditioner.

Owner:韶关瑞和环保科技有限公司

5G filter cover plate 6M61 aluminum alloy base material and preparing technology thereof

The invention relates to a 5G filter cover plate 6M61 aluminum alloy base material. The 5G filter cover plate 6M61 aluminum alloy base material comprises following components including, by weight percent, 0.50%-0.65% of Si, smaller than or equal to 0.30% of Fe, 0.15%-0.25% of Cu, smaller than or equal to 0.10% of Mn, 0.90%-1.10% of Mg, 0.15%-0.25% of Cr, smaller than or equal to 0.10% of Zn, 0.002%-0.035% of Ti, AL and other inevitable elements, the content of other inevitable single elements is smaller than or equal to 0.05%, and the sum is smaller than or equal to 0.15%. After the above element mixtures are smelted and cast in a smelting furnace into an aluminum alloy ingot, uniform thermalization treatment is conducted, hot rolling and cold rolling are conducted to intermediate annealing, repeated cold rolling is conducted, stretch bending straightening cleaning and plate form stretching straightening are conducted, and then an aluminum alloy plate meeting the requirement is manufactured. The aluminum alloy plate prepared through the technology has good machining performance and oxidation performance, and the 5G filter cover plate 6M61 aluminum alloy base material is suitable for machining during filter cover plate production.

Owner:河南明晟新材料科技有限公司

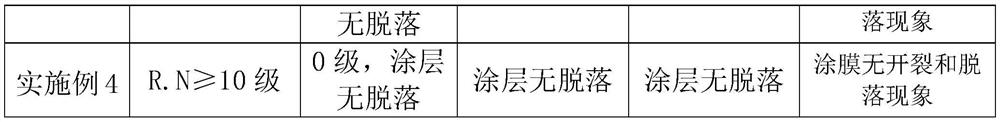

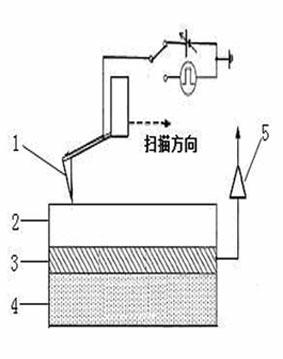

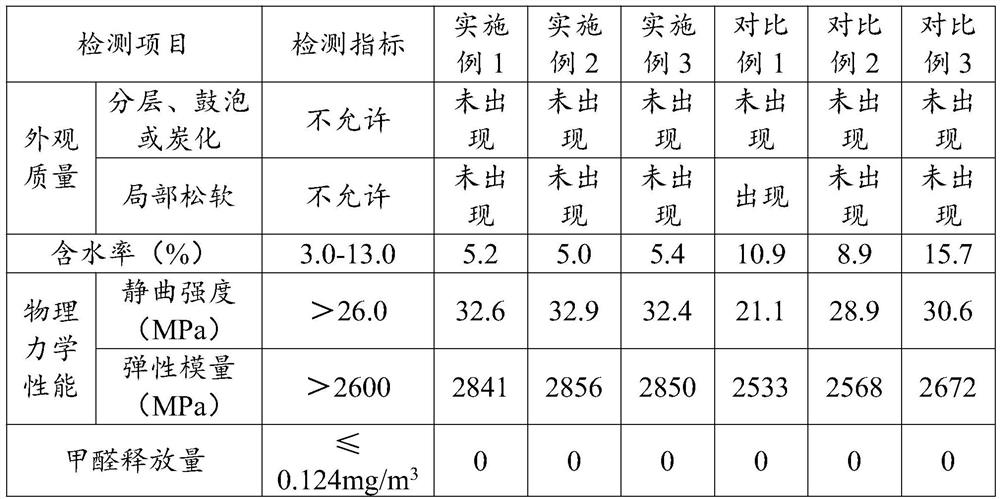

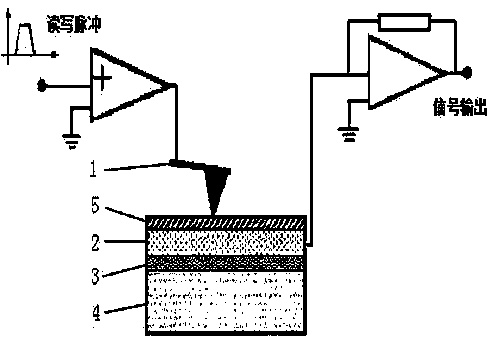

Multilayer phase-change film for ultrahigh density probe storage and preparation method thereof

InactiveCN102627004AReduce roughnessImprove surface qualityVacuum evaporation coatingSputtering coatingCarbon filmDiamond-like carbon

The invention discloses a multilayer phase-change film for ultrahigh density probe storage and a preparation method thereof. The multilayer phase-change film has a top layer which is a diamond-like carbon film protective layer having the thickness of 8 to 12nm, a bottom layer which is a copper-tungsten alloy film electrode layer having the thickness of 10 to 15nm and a copper-tungsten weight ratio of 15: 85, and a middle layer which is a tellurium-based alloy film phase-change layer having the thickness of 25 to 45nm. The preparation method is characterized in that 1, an electrode layer and a phase-change layer are prepared by direct current-radio frequency magnetron sputtering integrated equipment; 2, a rotating disk is rotated so that a substrate is located right above a target material; a vacuum chamber is subjected to a vacuum-pumping process and argon is fed into the vacuum chamber; after sputtering, a vacuum-pumping process is carried out again; a heating resistor is started and a heating process is carried out; and after the heating process, an in-situ annealing process is carried out; and 3, the substrate sputtered with the electrode layer and the phase-change layer is taken out and then is put into a plasma-enhanced chemical vapor deposition chamber; methane and borane are put into the plasma-enhanced chemical vapor deposition chamber and a vapor deposition process is carried out; and after the growth of a diamond-like carbon film is finished, the diamond-like carbon film is taken out, then is put into an annealing furnace having a temperature of 180 DEG C and is annealed. The preparation method can effectively prevent conducting layer oxidation, improves surface quality, storage density, a storage life and power consumption of a multilayer nanoscale film, and improves preparation efficiency.

Owner:JIANGSU UNIV

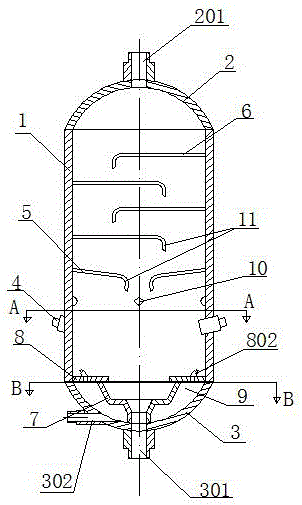

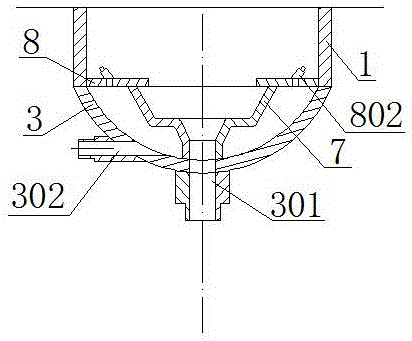

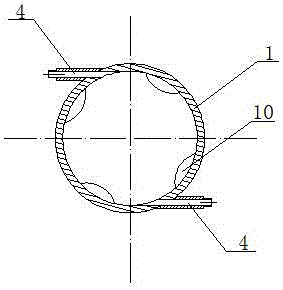

Ozone mixing reactor

InactiveCN106215656AIncrease profitAvoid direct impactAntifouling/underwater paintsDispersed particle separationEnvironmental engineeringUtilization rate

The invention discloses an ozone mixing reactor which comprises a chamber, wherein a plurality of gas inlet tubes are arranged on the side face of the chamber; the gas inlet tubes are eccentric tangential inclined insertion tubes; at least one downwards inclined sloping baffle is arranged above the gas inlet tubes in the chamber; and a plurality of baffle plates are sequentially arranged above the sloping baffle at intervals according to the axis direction of the chamber. The gas inlet tubes are set as the eccentric tangential inclined insertion tubes, and waste gases and ozone form eddy flow so as to be fully mixed and in full contact with each other, so that the ozone utilization rate is improved, the waste gases and ozone are prevented from directly impacting the wall surface of the chamber, the stress environment of the stainless steel chamber is improved, the stainless steel chamber has low probability of oxidation corrosion, and the problem that the stainless steel chamber is short in life is effectively solved. Due to coordination between the sloping baffle and baffle plates, lots of waste gases are fully treated, the ozone utilization rate is further improved, and the ozone mixing reactor is suitable for treatment of lots of waste gases.

Owner:CHENGDU 90 DEGREE IND PROD DESIGN CO LTD

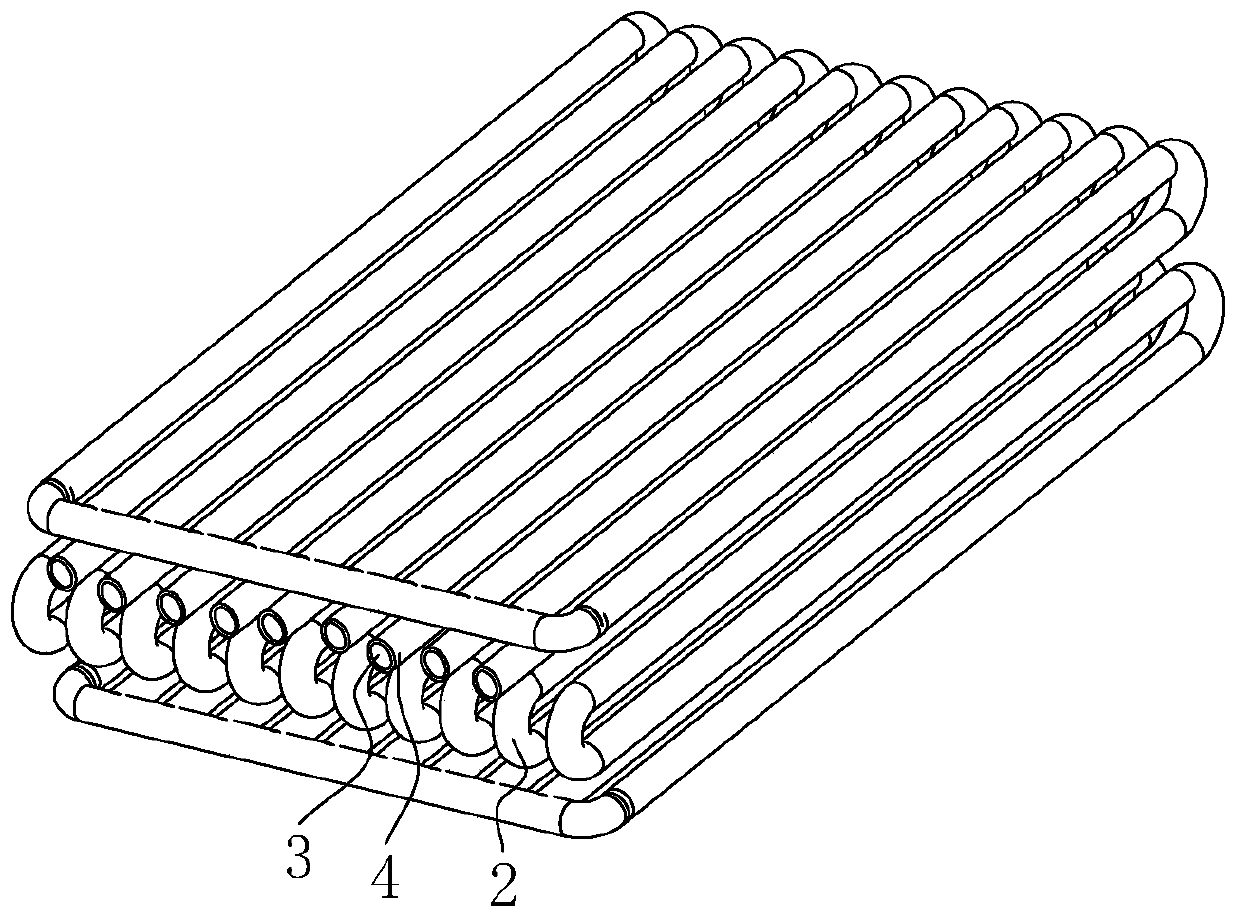

Preparation method of anti-corrosion rare earth permanent magnet material

ActiveCN107983960AImprove thermal stabilityIncrease working temperatureTransportation and packagingMetal-working apparatusMagnetic powderCurie temperature

The invention relates to the technical field of preparation of rare earth permanent magnet materials, in particular to a preparation method of an anti-corrosion rare earth permanent magnet material. According to the preparation method, after alkalization of a sodium borohydride solution, the sodium borohydride solution is mixed with a ferrous sulfate solution, and nanometer iron powder is obtainedafter treating and is dispersed in cyclohexane; the alkalized sodium borohydride solution is added in; iron / cobalt nanometer powder of a core-shell structure is obtained through treating; the nanometer NdFeB powder and the nanometer iron powder are mixed according to proportion, and dispersion media and surface active substances are added in; magnetic powder slurry is obtained through ball-milling; the magnetic powder slurry is treated, and hard magnetic powder is obtained; after the magnetic powder slurry is mixed with the iron / cobalt nanometer powder of the core-shell structure, treating isperformed, and the rare earth permanent magnet material is obtained; under the high temperature work condition, the iron powder can be protected against oxidization by cobalt, the anti-corrosion performance of the permanent magnet material is improved; under the high temperature work condition, the expanding coefficient of the NdFeB powder is small, the saturation magnetic flux density is improved, the Curie temperature of the NdFeB powder is increased, and therefore the work temperature of the rare earth permanent magnet material rises, and the application prospects are wide.

Owner:NANTONG CHENGTAI MAGNETIC MATERIAL TECH CO LTD

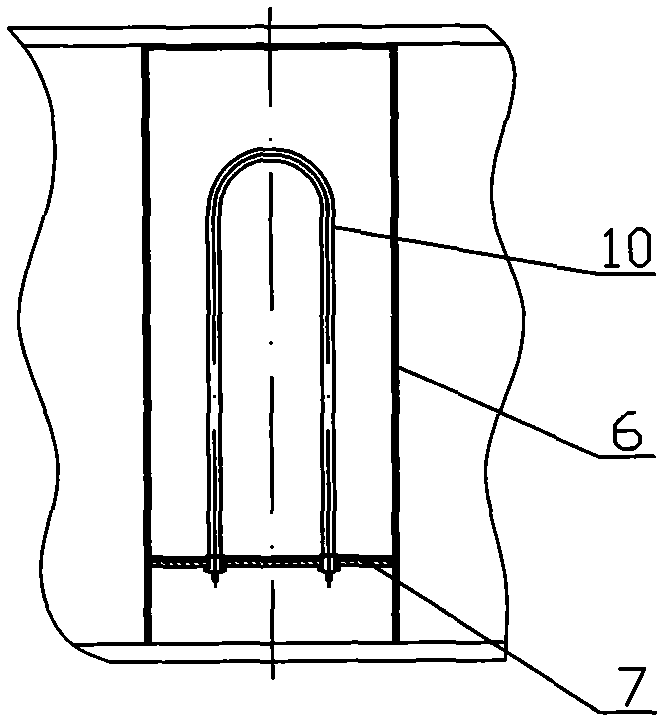

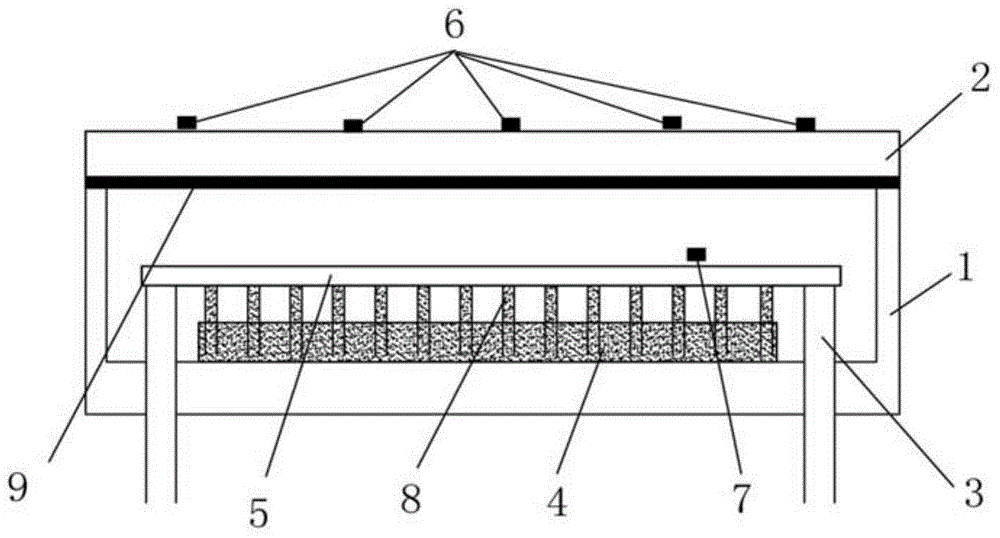

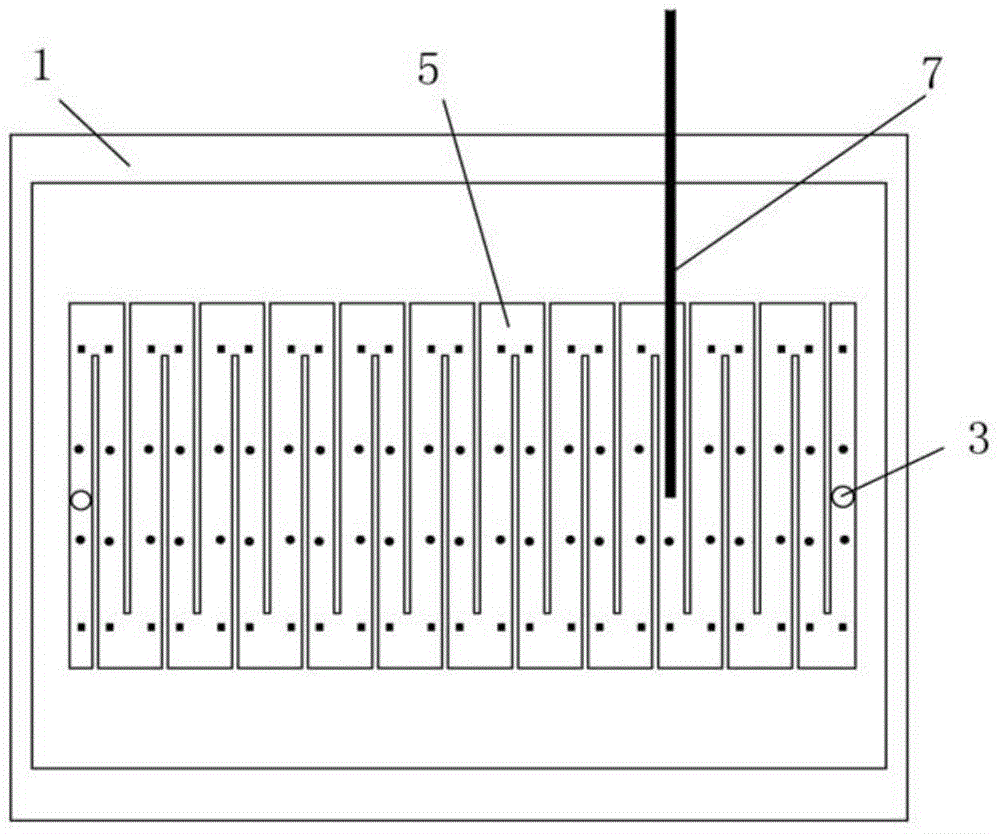

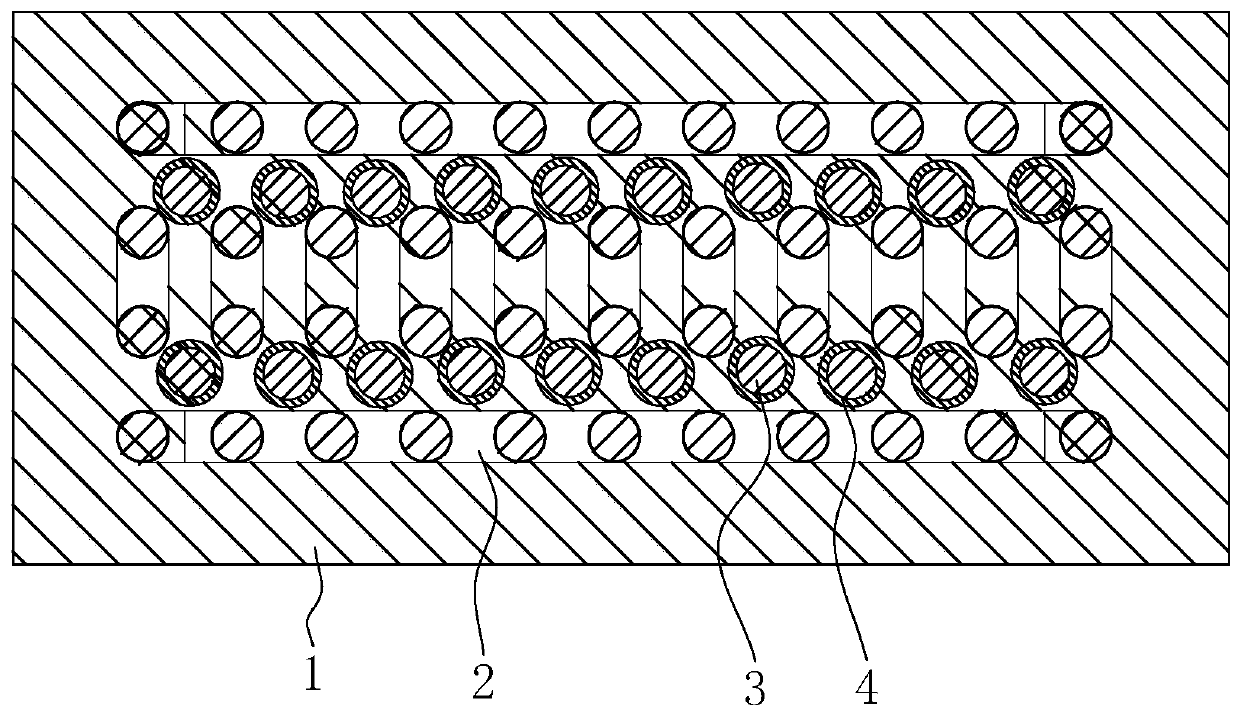

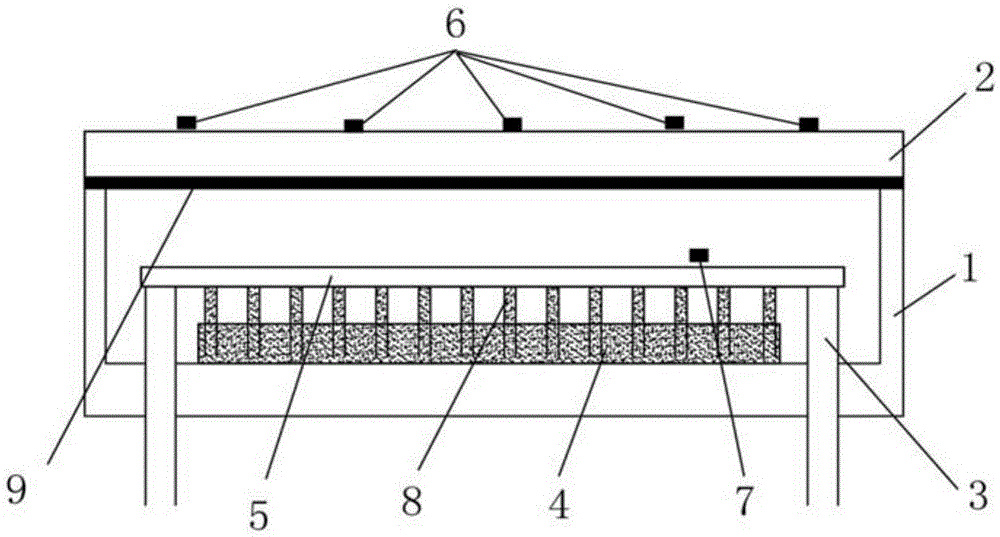

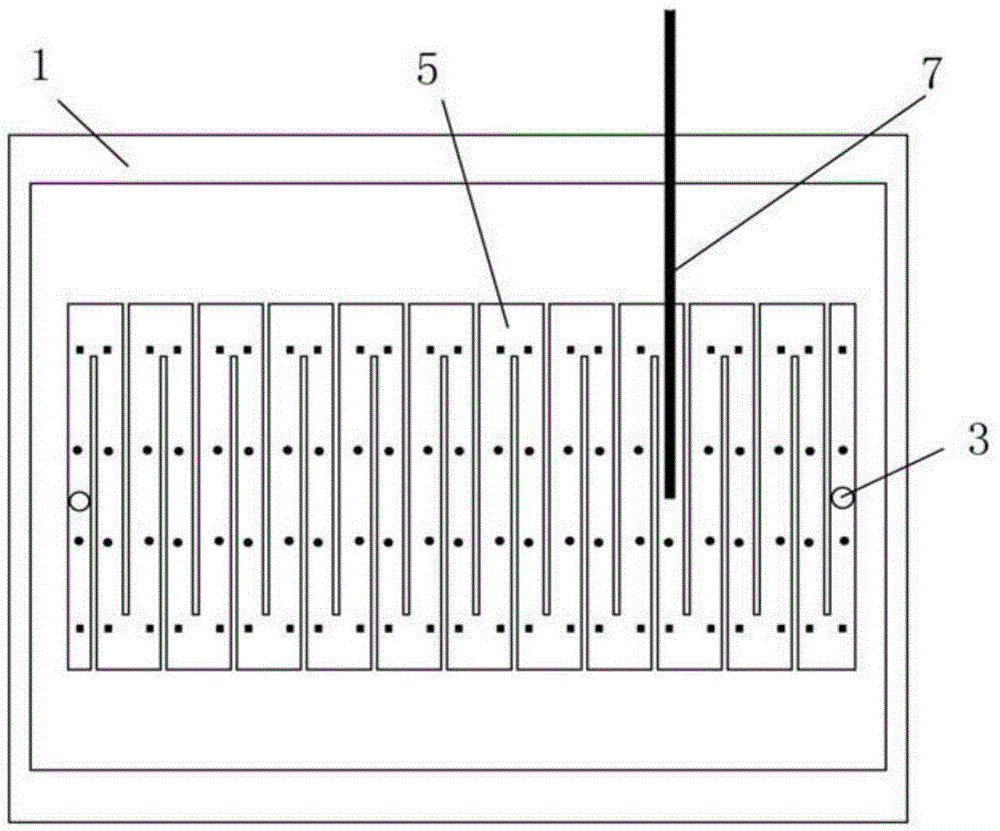

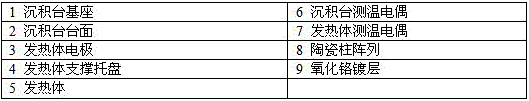

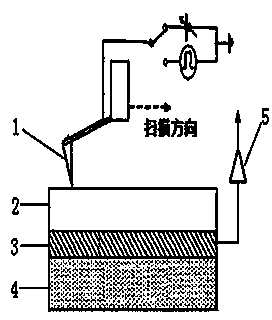

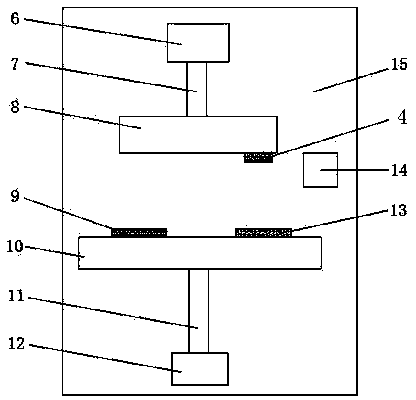

High-temperature heating deposition table for chemical vapor deposition (CVD)

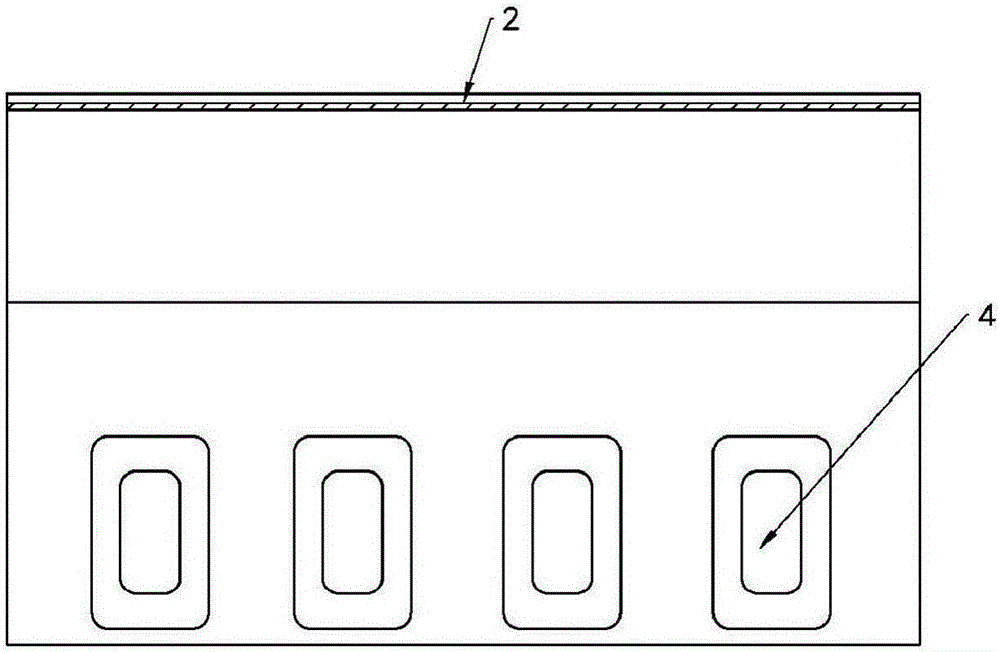

ActiveCN103556131ANot easy to oxidize and corrodeAvoid deformationChemical vapor deposition coatingGas phaseThermal radiation

The invention discloses a high-temperature heating deposition table for chemical vapor deposition (CVD), belonging to the field of preparation and production of materials. The design of the heating deposition table is improved, a 100nm chromium oxide film is coated on the inner surface of a deposition table top, and the efficiency of the deposition table top for receiving heat radiation can be improved by utilizing the black body coefficient, namely 0.8, of chromium oxide. In addition, for a heating body sealed inside the deposition table, an insulating body supporting piece is designed as a ceramic column array, so that the heat dissipation efficiency of the heating body can be improved while the supporting function is not influenced. Through the improvements, the heating efficiency and stability of the novel high-temperature heating deposition table can be greatly improved, the high-temperature heating deposition table can continuously and stably work in the temperature segment of 700 DEG C to 1000 DEG C, and fills a technical gap of the heating type deposition table on a high-temperature segment.

Owner:BEIJING TECHNOL SCI

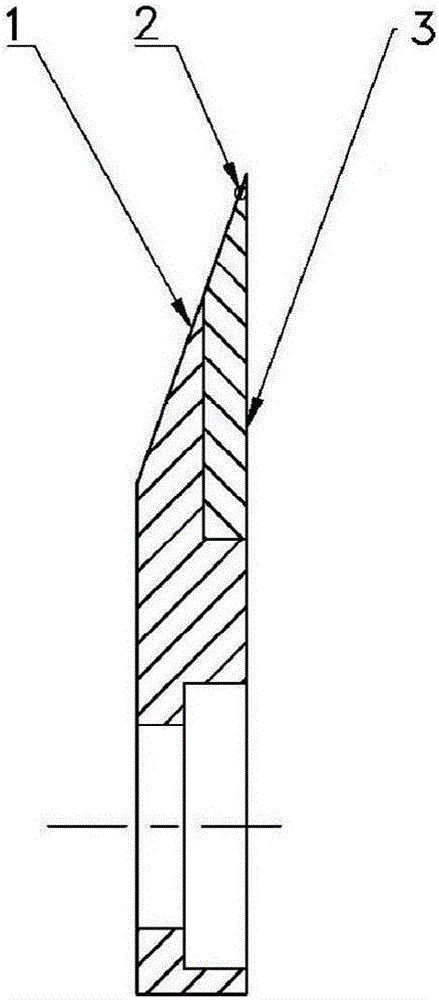

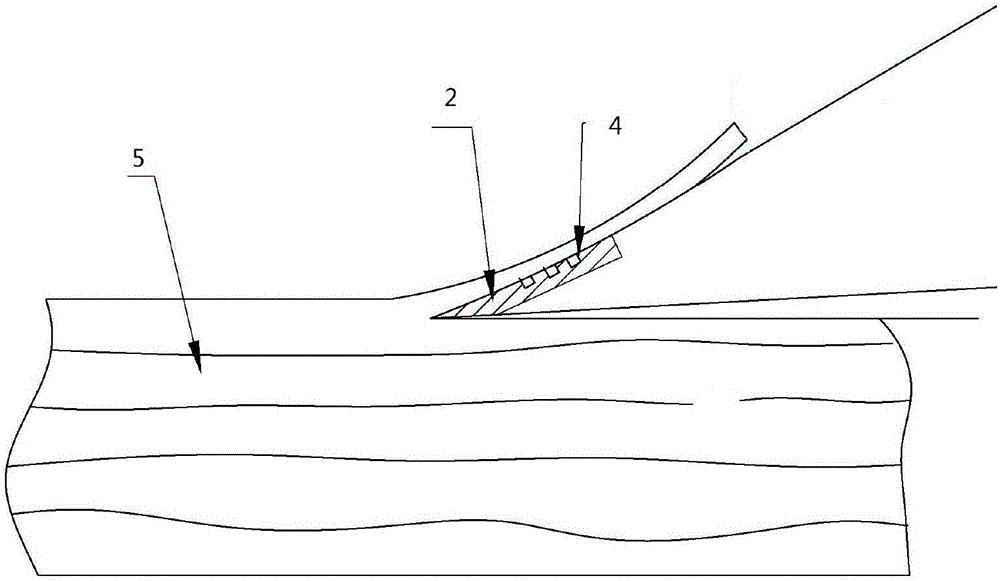

Woodworking tool for reducing friction coefficient during cutting of woodworking tool and manufacturing method of woodworking tool

ActiveCN105922377AImprove work efficiencyExtended service lifeCoverings/external coatingsCoatingsEngineeringWoodworking

The invention provides a woodworking tool for reducing the friction coefficient during cutting of the woodworking tool and a manufacturing method of the woodworking tool. The woodworking tool comprises a tool body. The tool body comprises a front tool face and a rear tool face. An inclined cutting edge is formed between the front tool face and the rear tool face. A microstructure texture is formed at the position, close to the cutting edge, of the front tool face. The manufacturing method comprises the step that the microstructure texture is generated at the position, close to the cutting edge, of the front tool face of the woodworking tool through a laser or tiny abrasive particle jetting or a micro-electronic mechanical system method.

Owner:INST OF WOOD INDUDTRY CHINESE ACAD OF FORESTRY

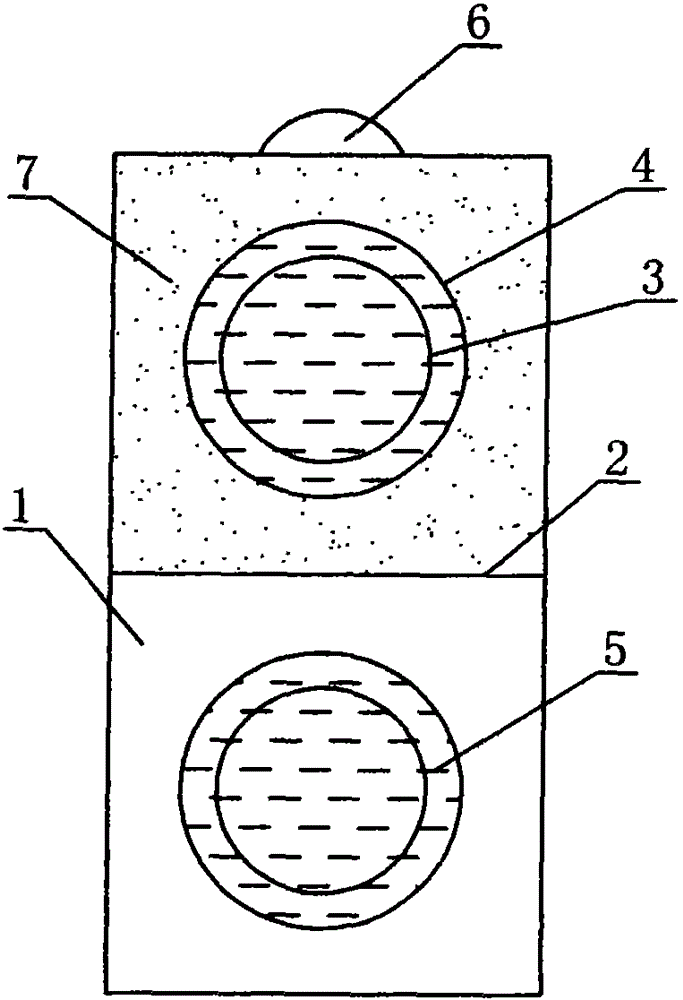

Construction waste recycling method

InactiveCN111574118AStable structureImprove stabilitySolid waste managementCeramic shaping apparatusBrickMaterial type

The invention relates to the technical field of construction waste treatment, in particular to a construction waste recycling method which comprises the following steps of: S1, performing classifyingand recycling, namely, performing classifying according to material types obtained by splitting on a construction site, and obtaining waste steel bars and concrete blocks; S2, performing high-temperature smelting on the waste steel bars, and performing cooling to form a brick framework; S3, crushing selected concrete blocks to form recycled aggregate; S4, doping the recycled aggregate into cementmortar to form aggregate slurry; and S5, placing the brick framework in a brick mold, pouring the aggregate slurry, and forming a recycled brick through solidification. With the method adopted, construction waste can be reasonably utilized, and the recycled brick can be produced. The recycled brick has the advantages of light weight, firm structure and better sound insulation and thermal insulation properties.

Owner:深圳市绿悦环保科技有限公司

Bearing bush alloy layer working surface fluoride-free and lead-free double-layer alloy plating structure and plating technology

InactiveCN102758231AStable structure and performanceNot easy to oxidize and corrodeBearing componentsRolling resistance optimizationAlloyCopper

The invention discloses a bearing bush alloy layer working surface double-layer alloy plating structure and a plating technology; and after an electroplating technology is adopted, double Tin-Cu alloy plating layers are plated on the bearing bush inner circle, wherein the Cu content of the inner plating layer is more than that of the outer plating layer. Therefore, the service life of a bearing bush is effectively prolonged, and the performance of the bearing bush is improved.

Owner:WUHU MEIDA MECHANICAL & ELECTRONICS INDAL

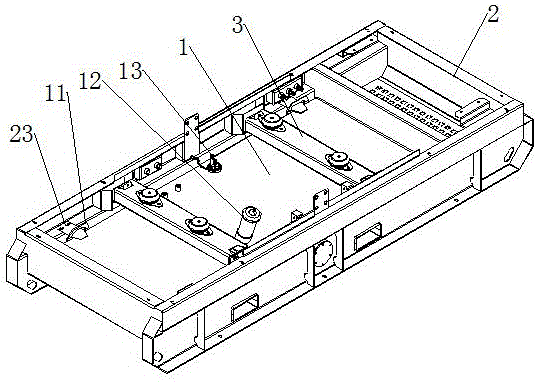

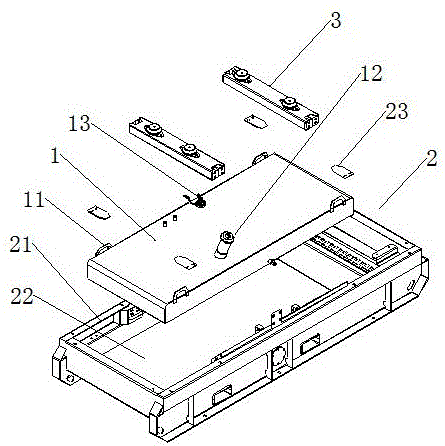

Detachable chassis fuel tank structure

InactiveCN106762272AEasy to useEasy to disassemble and repairMachines/enginesLiquid fuel feedersFuel tankEngineering

The invention discloses a detachable chassis fuel tank structure. The detachable chassis fuel tank structure comprises a chassis fuel tank body and a rectangular chassis frame used for mounting the chassis fuel tank body, wherein protection side plates are arranged at the periphery of the rectangular chassis frame, a chassis protection plate is arranged on the lower end face of the rectangular chassis frame, a handle convenient for carrying the chassis fuel tank body is fixedly arranged on the upper end face of the chassis fuel tank body, a fuel tank fixing plate corresponding to the handle is mounted on the protection side plate of the rectangular chassis frame by virtue of bolts, the chassis fuel tank body is placed on the chassis protection plate in the rectangular chassis frame and is fixed by virtue of the fuel tank fixing plated clamped on the handle, and thus the chassis fuel tank body is avoided from shaking in the rectangular chassis frame. The detachable chassis fuel tank structure is convenient for disassembly, maintenance and cleaning, and the protection plate is arranged at the periphery, so that oxidation corrosion is hardly caused.

Owner:雷天动力设备(苏州)有限公司

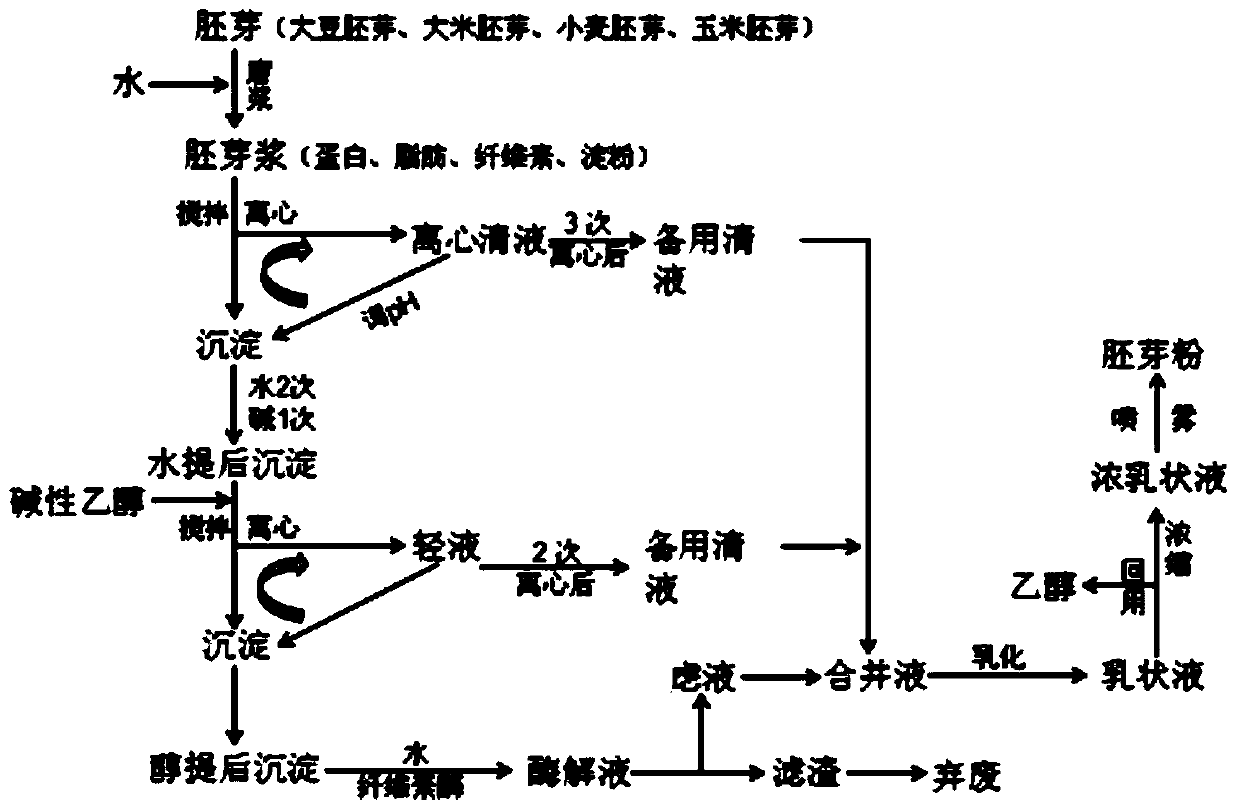

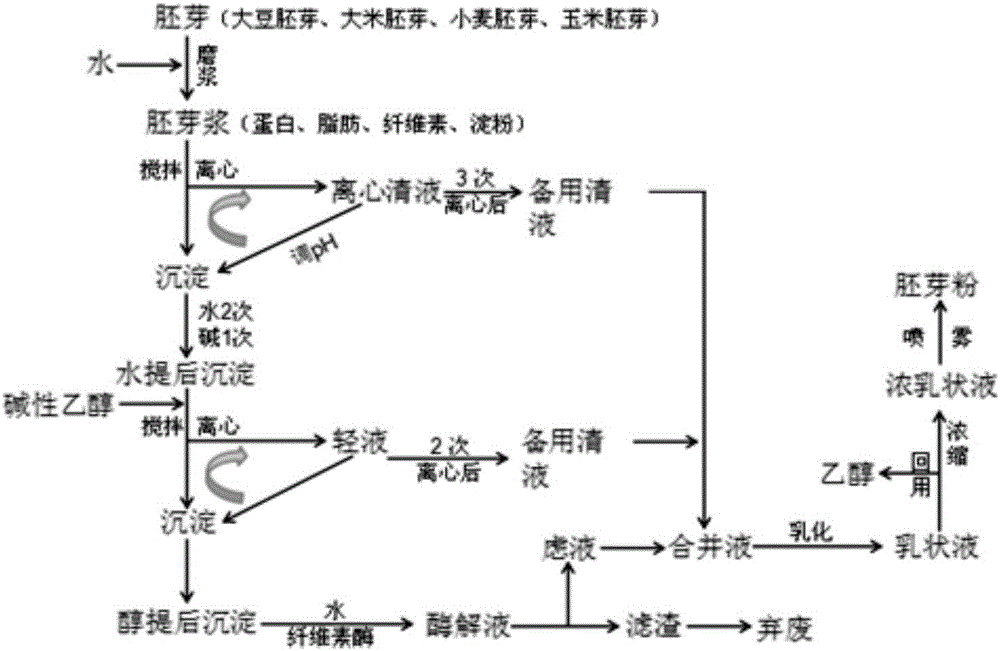

A method for recombining cereal germ components

InactiveCN105995549BIncrease profitSolve the problem of comprehensive utilizationMolten spray coatingNatural extract food ingredientsBiotechnologyMicrobiology

The invention provides a method for recombining grain germ components, comprising: a grinding step; a separation and extraction step; a second separation and extraction step; The invention continuously separates and concentrates the beneficial components in the grain germ, and at the same time reorganizes the separated beneficial components; the invention continuously separates, concentrates and reorganizes the beneficial components in the germ through cheap, simple and efficient means, Produces a delicious whole germ meal.

Owner:湖北斯味特粉体食品有限公司

Method for recombining cereal germ components

InactiveCN105995549AIncrease profitSolve the problem of comprehensive utilizationMolten spray coatingNatural extract food ingredientsChemistry

Owner:湖北斯味特粉体食品有限公司

A high-temperature heating deposition platform for chemical vapor deposition

ActiveCN103556131BNot easy to oxidize and corrodeAvoid deformationChemical vapor deposition coatingGas phaseHeat deposition

The invention discloses a high-temperature heating deposition platform for chemical vapor deposition, which belongs to the field of material preparation and processing. The invention improves the design of the heating deposition platform, coats a layer of 100nm chromium oxide thin film on the inner surface of the deposition platform, and improves the efficiency of the deposition platform to receive heat radiation by using the black body number of 0.8 of the chromium oxide. At the same time, for the heating body sealed inside the deposition table, its insulator support is designed as an array of ceramic pillars, which improves the heat dissipation efficiency of the heating body without affecting the support function. These improvements have greatly improved the heating efficiency and stability of this new type of high-temperature heating deposition platform, and can continue to work stably in the temperature range of 700 ° C to 1000 ° C, filling the technical gap of the heating deposition platform in the high temperature section.

Owner:BEIJING TECHNOL SCI

Self-adhesive coin collection paper clip processing method and finished product thereof

ActiveCN104605592AEasy to watch and collectNot easy to oxidize and corrodePursesMoney bagsPaperboardPulp and paper industry

The invention discloses a self-adhesive coin collection paper clip processing method and a finished product thereof. The self-adhesive coin collection paper clip processing method comprises the following steps: forming symmetrical holes in the two sides of a paperboard impression through pressing, covering the holes with concentric PP films, and forming concentric circular impressions through pressing. After a paperboard is folded and adhered along the impressions, by utilizing the deformation bulges of the circular impressions, the influence of collected coin thickness on adhesive surface reactive force is effectively eliminated, the reliability of adhesion is guaranteed, and the durability of a paper clip is improved. Through the laminating design of double-faced holes, a collected coin is convenient to view from two surfaces; moreover, a good sealing property is also formed, the oxidation of the collected coin is prevented, the long-term collection requirement is met, and the paper clip is a good guarantee for coin collection.

Owner:徐明

A kind of preparation method of bczt-based lead-free piezoelectric ceramics

ActiveCN108546124BNot easy to oxidize and corrodePrevent oxidationPiezoelectric/electrostrictive/magnetostrictive devicesBarium titanateGlycol synthesis

The invention relates to the technical field of preparation of electronic components, in particular to a preparation method of BCZT-based lead-free piezoelectric ceramics. In the present invention, citric acid is dissolved in ethylene glycol, and butyl titanate diluted with absolute ethanol is added to obtain a composite solution, and barium acetate solution, calcium nitrate solution and zirconium nitrate solution are added dropwise to the composite solution and mixed to obtain BCZT-based polymerization The material precursor is mixed with nano-NdFeB powder and nano-iron powder to obtain a magnetic powder slurry, and the hard magnetic powder is mixed with iron / cobalt nano-powder with a core-shell structure and then dispersed at a high speed. Electric ceramics, dense cobalt powder particles, can protect iron powder from oxidation, tetrabutyl titanate reacts with citric acid to form a network structure, zirconium perbarium calcium titanate-based material does not contain Pb, and has little harm to human body and environment. Elemental cobalt will soften at high temperature, which will enhance the bonding force of magnetic materials and reduce the thermal conductivity of magnetic materials. It can work stably in high temperature environments and has broad application prospects.

Owner:景德镇市鑫惠康电子有限责任公司

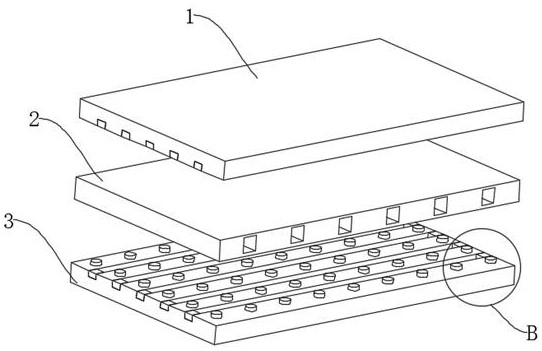

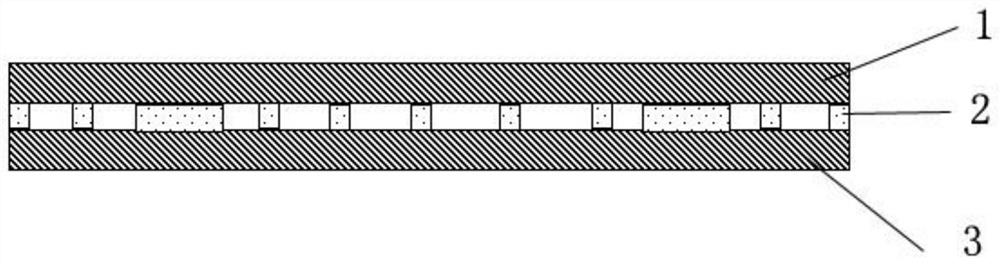

Production process of diatom formaldehyde-removing environment-friendly plate

PendingCN114683641AExtended service lifeIncrease the areaLamination ancillary operationsLaminationManufacturing engineeringWood plank

The invention discloses a production process of a diatom formaldehyde-removing environment-friendly board, and relates to the field of diatom formaldehyde-removing environment-friendly boards, the diatom formaldehyde-removing environment-friendly board comprises an upper-layer board, a diatomite board and a lower-layer board which are arranged from top to bottom, and the production process of the diatom formaldehyde-removing environment-friendly board comprises the following steps of S1, raw material preparation, S2, surface processing, and S3, surface treatment. The method comprises the following steps of S1, primary slotting machining, S4, hot pressing and fixing, S5, secondary slotting machining and S6, follow-up treatment. When the upper-layer wood board or the lower-layer wood board is attached to the position, located on one side of the cutting frame body, of the surface of the second pressing plate, the upper-layer wood board and the lower-layer wood board can be pushed to move along the surface of the second pressing plate through a pushing mechanism, and therefore an upper deformation groove and a lower deformation groove are formed in the surface of the upper-layer wood board and the surface of the lower-layer wood board correspondingly.

Owner:山东福茂装饰材料有限公司

Novel high-strength furniture board and preparation method and application thereof

The invention discloses a novel high-strength furniture board, which is prepared from the following raw materials in parts by weight: 100-150 parts of wood fibers, 100-200 parts of ordinary Portland cement, 70-80 parts of PVC resin powder, 20-30 parts of light calcium carbonate, 5-10 parts of a concrete waterproofing agent, 5-10 parts of a wood adhesive, 1-3 parts of an antibacterial agent, 1-3 parts of an antioxidant, 0.5-1.5 parts of PE wax and 0.5-1.5 parts of stearic acid. The preparation method comprises the following steps: (1) weighing the raw materials; (2) mixing the raw materials, adding 200-300 parts of water, and uniformly mixing; and (3) pouring the mixture into a mold, and then heating, extruding and molding by mold equipment to obtain the novel high-strength furniture board. The novel high-strength furniture board has the advantages of being high in strength, firm in structure, excellent in water resistance, excellent in flame retardant property, not prone to oxidation corrosion and the like, is free of formaldehyde and pollution and long in service life, and is an environment-friendly product.

Owner:郭卫科

Multilayer phase-change film for ultrahigh density probe storage and preparation method thereof

InactiveCN102627004BReduce roughnessImprove surface qualityVacuum evaporation coatingSputtering coatingCarbon filmDiamond-like carbon

The invention discloses a multilayer phase-change film for ultrahigh density probe storage and a preparation method thereof. The multilayer phase-change film has a top layer which is a diamond-like carbon film protective layer having the thickness of 8 to 12nm, a bottom layer which is a copper-tungsten alloy film electrode layer having the thickness of 10 to 15nm and a copper-tungsten weight ratio of 15: 85, and a middle layer which is a tellurium-based alloy film phase-change layer having the thickness of 25 to 45nm. The preparation method is characterized in that 1, an electrode layer and a phase-change layer are prepared by direct current-radio frequency magnetron sputtering integrated equipment; 2, a rotating disk is rotated so that a substrate is located right above a target material; a vacuum chamber is subjected to a vacuum-pumping process and argon is fed into the vacuum chamber; after sputtering, a vacuum-pumping process is carried out again; a heating resistor is started and a heating process is carried out; and after the heating process, an in-situ annealing process is carried out; and 3, the substrate sputtered with the electrode layer and the phase-change layer is taken out and then is put into a plasma-enhanced chemical vapor deposition chamber; methane and borane are put into the plasma-enhanced chemical vapor deposition chamber and a vapor deposition process is carried out; and after the growth of a diamond-like carbon film is finished, the diamond-like carbon film is taken out, then is put into an annealing furnace having a temperature of 180 DEG C and is annealed. The preparation method can effectively prevent conducting layer oxidation, improves surface quality, storage density, a storage life and power consumption of a multilayer nanoscale film, and improves preparation efficiency.

Owner:JIANGSU UNIV

Processing method and finished product of self-adhesive coin collection paper clip

ActiveCN104605592BEasy to watch and collectNot easy to oxidize and corrodePursesMoney bagsPaperboardStructural engineering

The invention discloses a self-adhesive coin collection paper clip processing method and a finished product thereof. The self-adhesive coin collection paper clip processing method comprises the following steps: forming symmetrical holes in the two sides of a paperboard impression through pressing, covering the holes with concentric PP films, and forming concentric circular impressions through pressing. After a paperboard is folded and adhered along the impressions, by utilizing the deformation bulges of the circular impressions, the influence of collected coin thickness on adhesive surface reactive force is effectively eliminated, the reliability of adhesion is guaranteed, and the durability of a paper clip is improved. Through the laminating design of double-faced holes, a collected coin is convenient to view from two surfaces; moreover, a good sealing property is also formed, the oxidation of the collected coin is prevented, the long-term collection requirement is met, and the paper clip is a good guarantee for coin collection.

Owner:徐明

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com