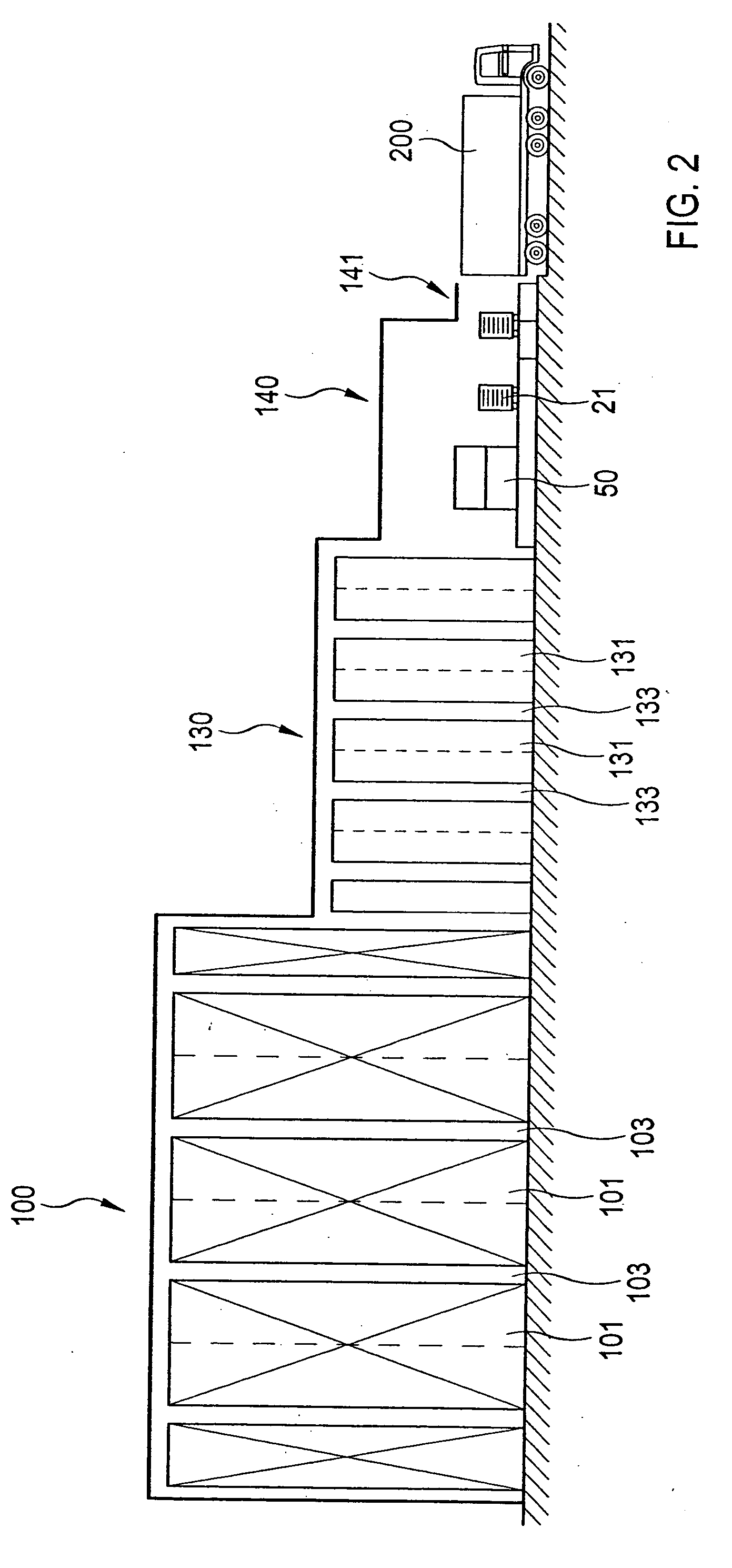

Patents

Literature

646results about How to "Strong load" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

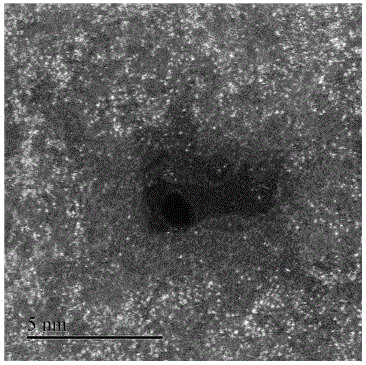

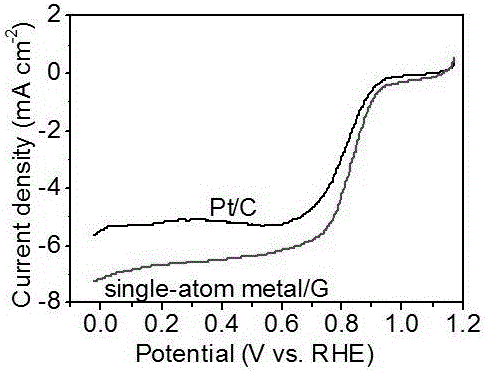

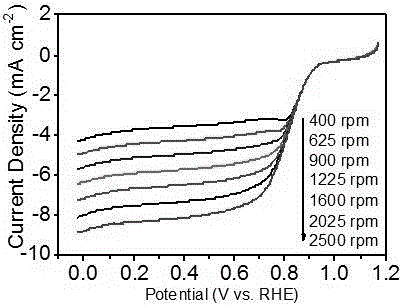

Monodisperse metal atom/graphene composite catalyst and preparation method and application thereof

ActiveCN106694007ALow costSimple stepsCell electrodesCatalyst activation/preparationCvd grapheneChemistry

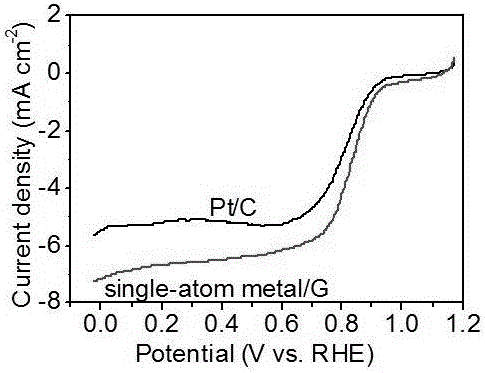

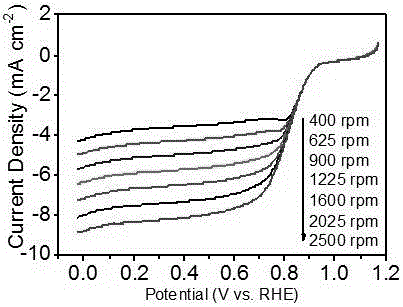

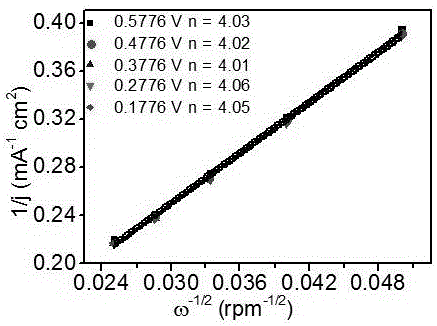

The invention discloses a monodisperse metal atom / graphene composite catalyst and a preparation method and application thereof. The catalyst is formed by loading monodisperse metal atoms on / in graphene, wherein the content of the monodisperse metal atoms is 0.0001wt%-5.0wt%; the content of heteroatom doped graphene is 95wt%-99.9999wt%; and the content of heteroatom in graphene is 0wt%-90wt%. The monodisperse metal atom / graphene composite catalyst is obtained through an electrochemical method, and the preparation method is simple, easy to operate and control, low in cost, high in efficiency, good in quality, high in security and favorable for industrial production. The composite catalyst has the characteristics of high activity and good stability when being applied to electro-catalytic oxygen reduction, and has better comprehensive performance and good application prospects relative to commercial 20wt% of Pt / C.

Owner:SHANXI INST OF COAL CHEM CHINESE ACAD OF SCI

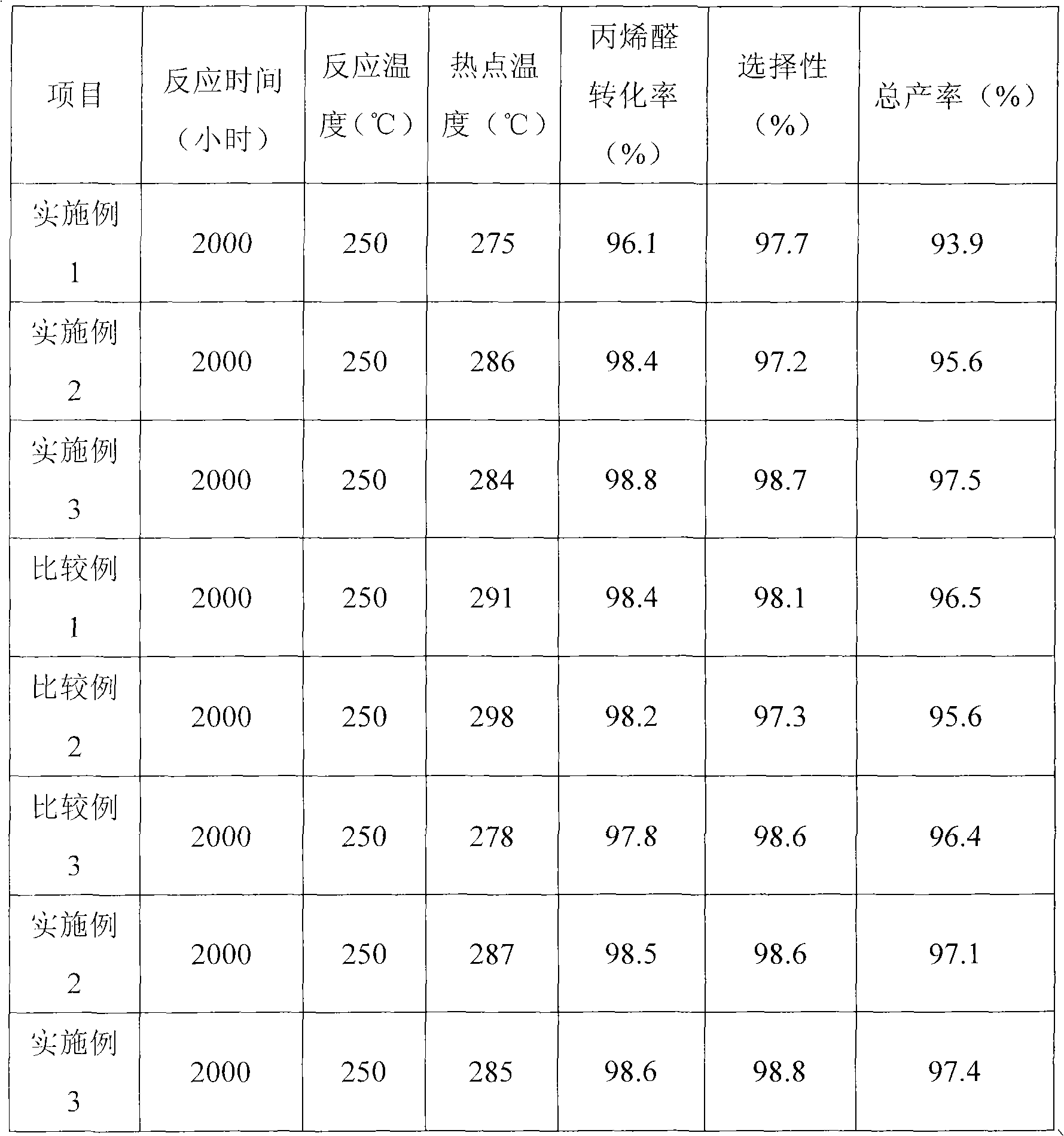

Preparation method of catalyst for acrylic acid by oxidizing acraldehyde

ActiveCN102039143ALarger than surfaceStrong loadOrganic compound preparationCarboxylic compound preparationAdhesiveSlurry

The invention relates to a preparation method of a catalyst for acrylic acid by oxidizing acraldehyde, which is characterized by comprising the following steps of: dispersing water soluble metal salts containing the components of Mo, V, W, Cu and Sb into a water / organic phase mixed system at the temperature of 30-100DEG C; maintaining the weight ratio of an organic solvent to water as 5-50 percent; reacting to generate composite oxide precursor serum; separating water by a distilling process under the condition of continuously supplementing organic phases at the temperature of 20-120DEG C, wherein the water content of distillate is not greater than 10 percent; then, pelleting by a spray drying process and roasting at the temperature of 200-600DEG C to prepare catalyst active components; mixing primary roasting powder, a forming additive and a strength improver; coating the active components on the surface of an inert carrier by using an adhesive, wherein the carrying capacity occupies5-70 percent of the total quantity of the catalyst; drying a formed product for 5-48 hours at room temperature; and then, roasting the formed product for 1-15 hours at the temperature of 200-600DEG Cto obtain a spherical catalyst with the active components carried on the inert carrier.

Owner:CHINA NAT OFFSHORE OIL CORP +1

Method for preparing monodisperse metal atom/graphene composite material employing electrochemical dissolved graphite

ActiveCN106654300ALow costSimple stepsCell electrodesMetal/metal-oxides/metal-hydroxide catalystsGraphiteElectrochemistry

The invention discloses a method for preparing a monodisperse metal atom / graphene composite material employing electrochemical dissolved graphite. The method comprises the steps of (1) preparing an electrode from a graphite-based material; (2) electrolyzing the prepared electrode in an electrolytic cell, carrying out solid-liquid separation and recycling an electrolyte; (3) further stripping the solid obtained by separation and carrying out solid-liquid separation to obtain a crude monodisperse metal atom / graphene composite material; (4) separating and purifying the crude monodisperse metal atom / graphene composite material; and (5) carrying out thermal treatment on the composite material obtained in the step (4) under inert atmosphere protection and cooling and drying the material to obtain a monodisperse metal atom / graphene composite catalyst. The preparation method is simple in process steps, high in efficiency and low in energy consumption, and massive production can be achieved.

Owner:SHANXI INST OF COAL CHEM CHINESE ACAD OF SCI

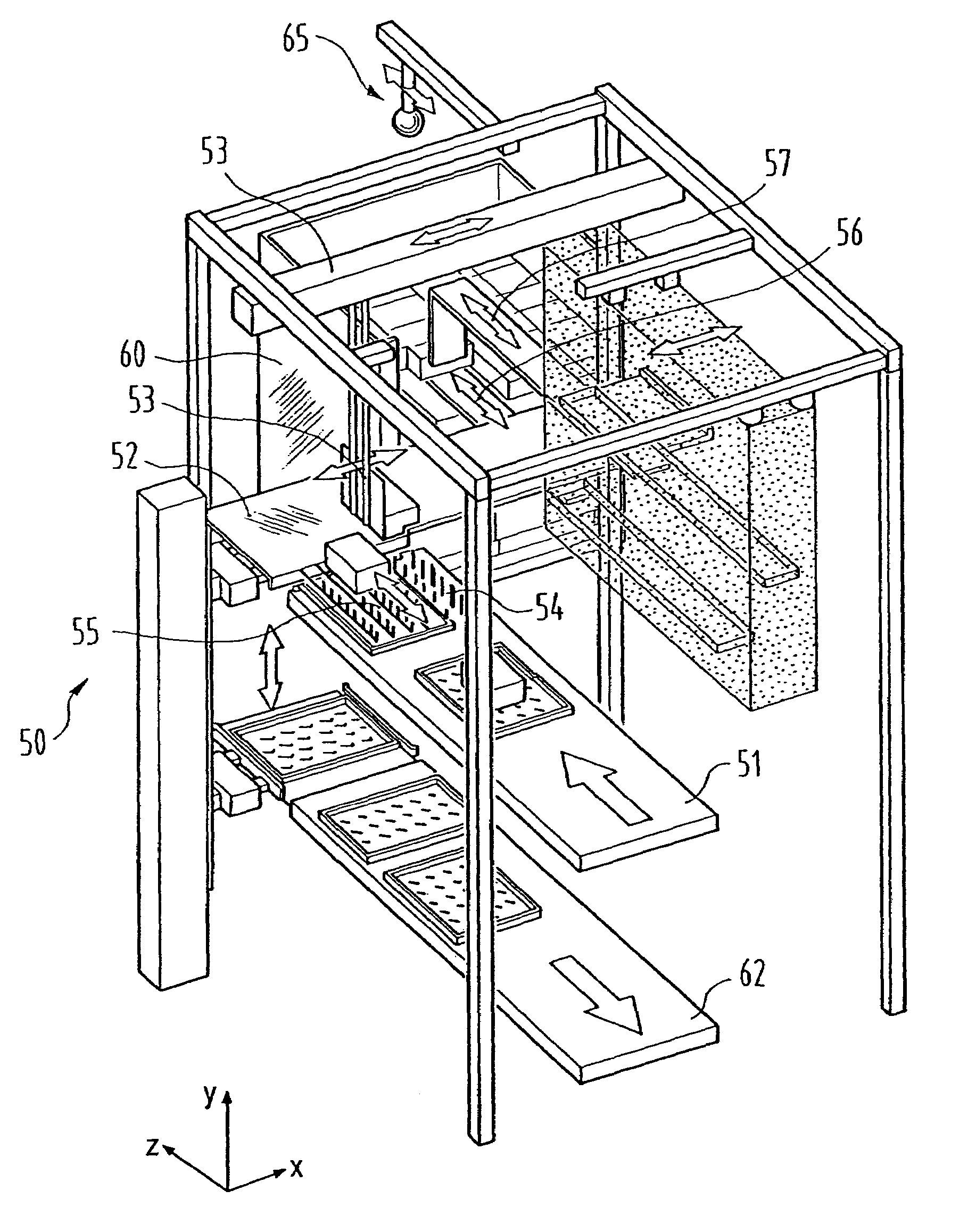

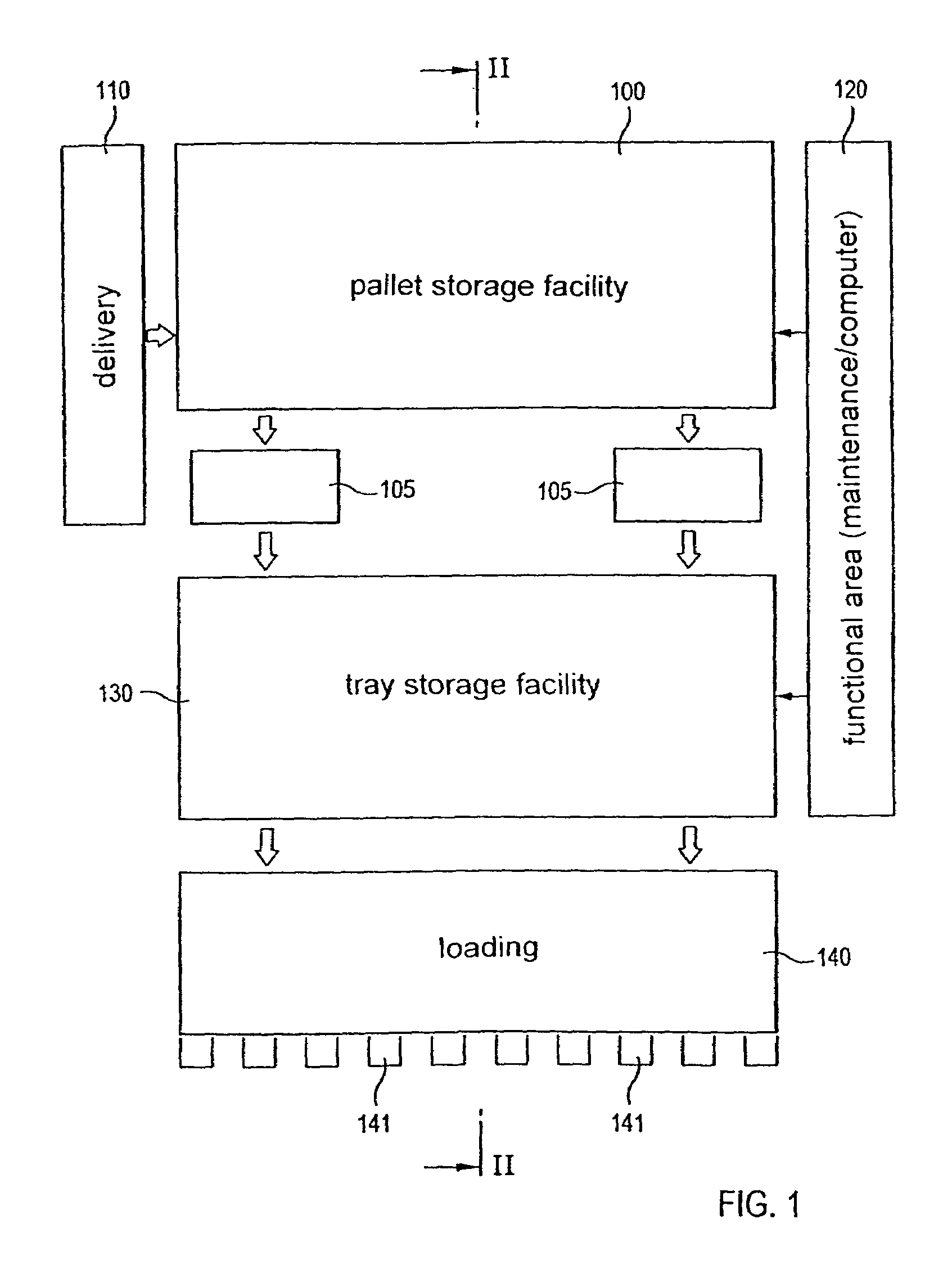

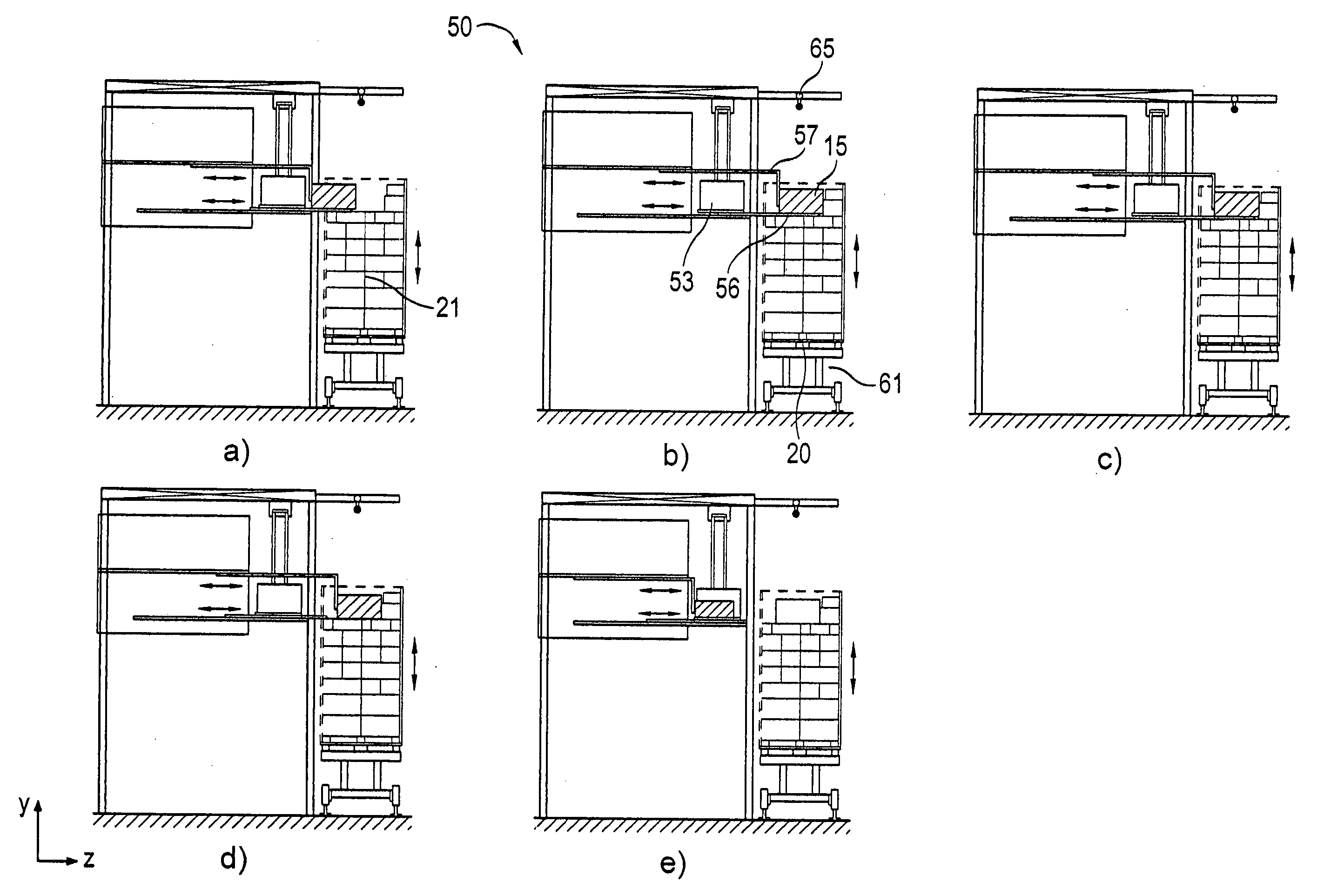

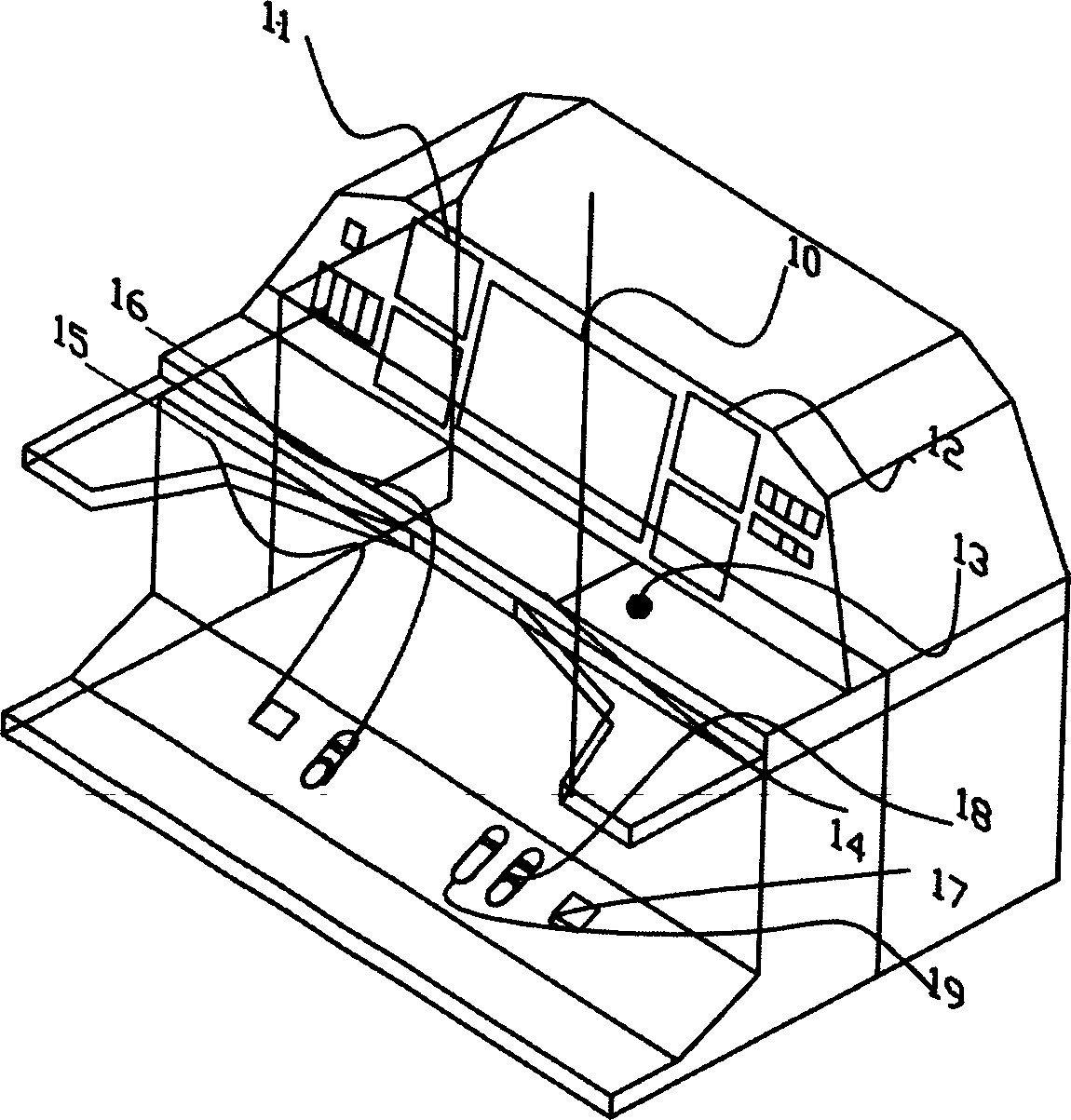

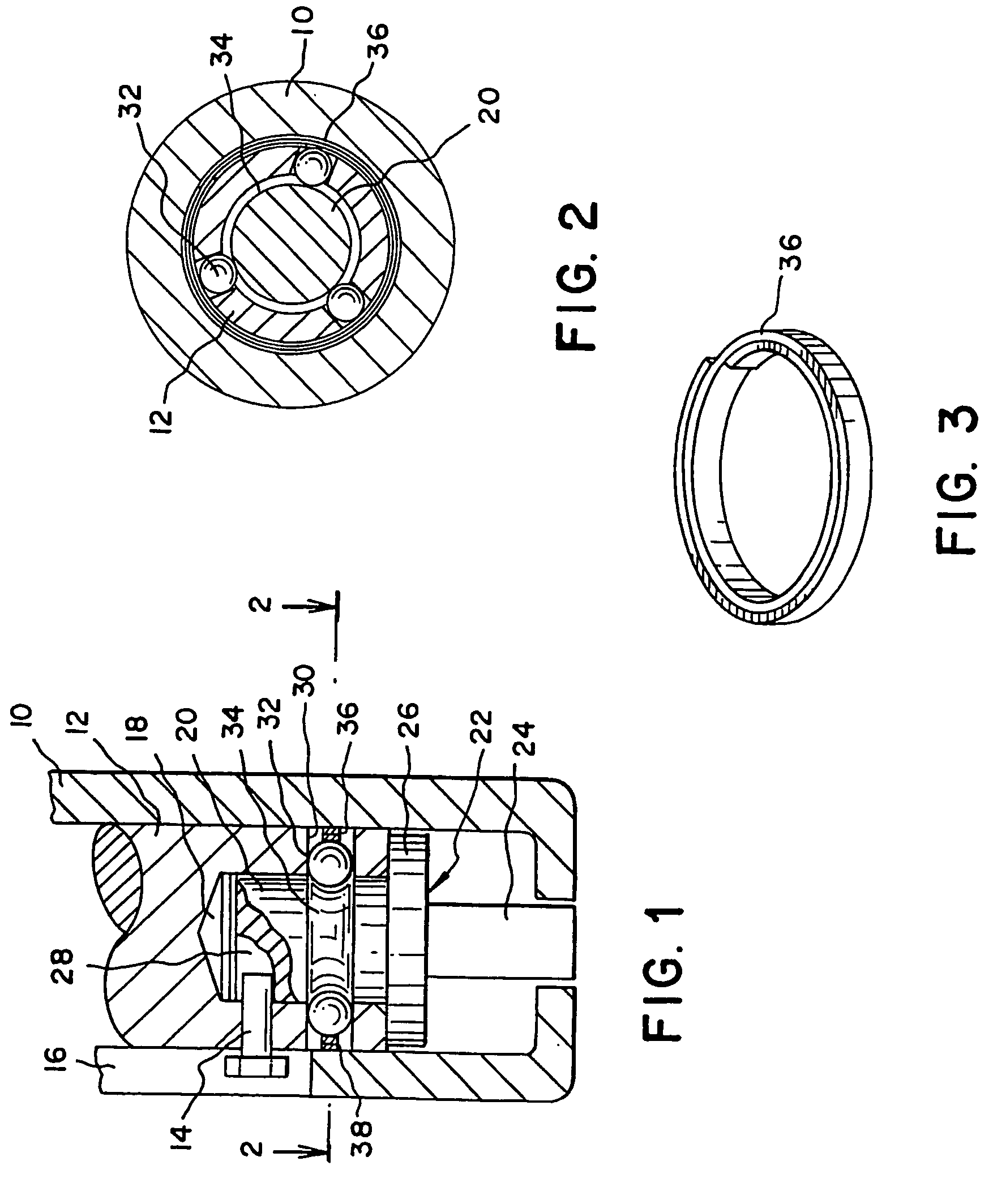

Apparatus for depositing a packing unit at a desired position on a load carrier

InactiveUS7047710B2Strong loadLoaded safely and reliablyWrappers shrinkageConveyorsEngineeringMaterial quality

A machine for loading a load carrier (20) such as a pallet with packing units (cardboard boxes, collis etc.), which form a load stack (21) on the load carrier, is presented. The machine includes handling and support mechanism (52–57), that allows a packing unit (15) to be loaded. The handling and support mechanism supports the load from below throughout the operation of loading from a feed device (51) onto the load stack. By virtue of the handling and support mechanism, the packing unit may be deposited at any selectable spatial position on the load stack. It is therefore possible to form an optimized load stack on the load carrier in which the packing units are always supported from below, with the result that the loading is not dependent upon the material quality of the packaging of the packing unit.

Owner:LOGISTIK INFORMATIK

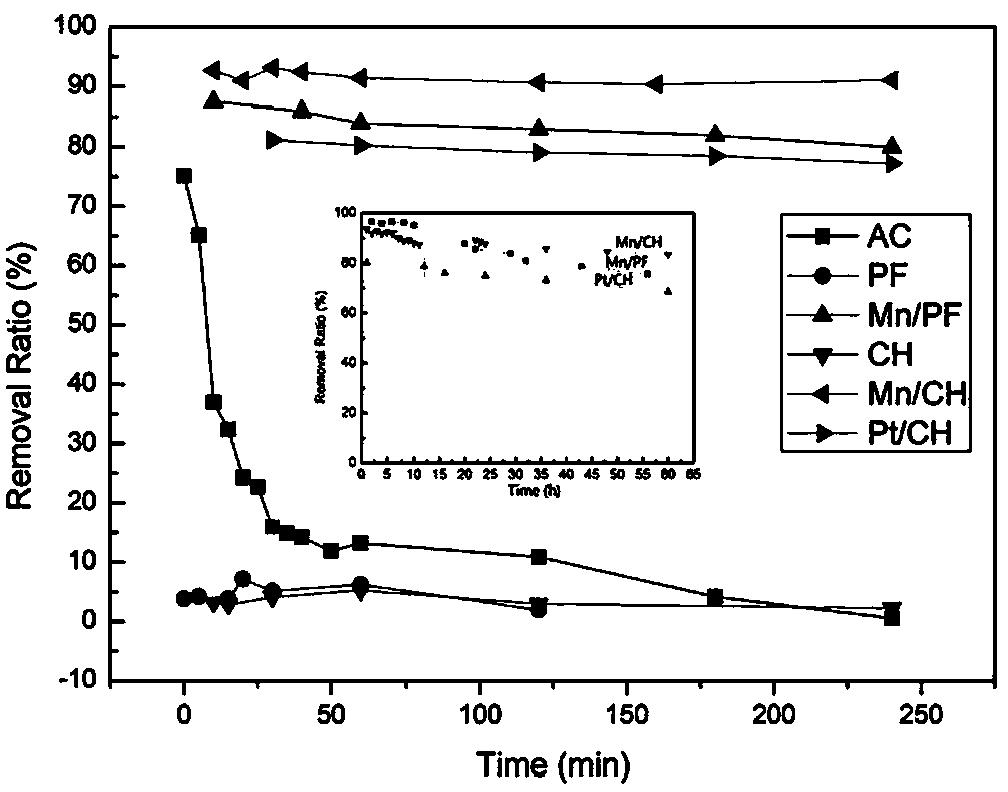

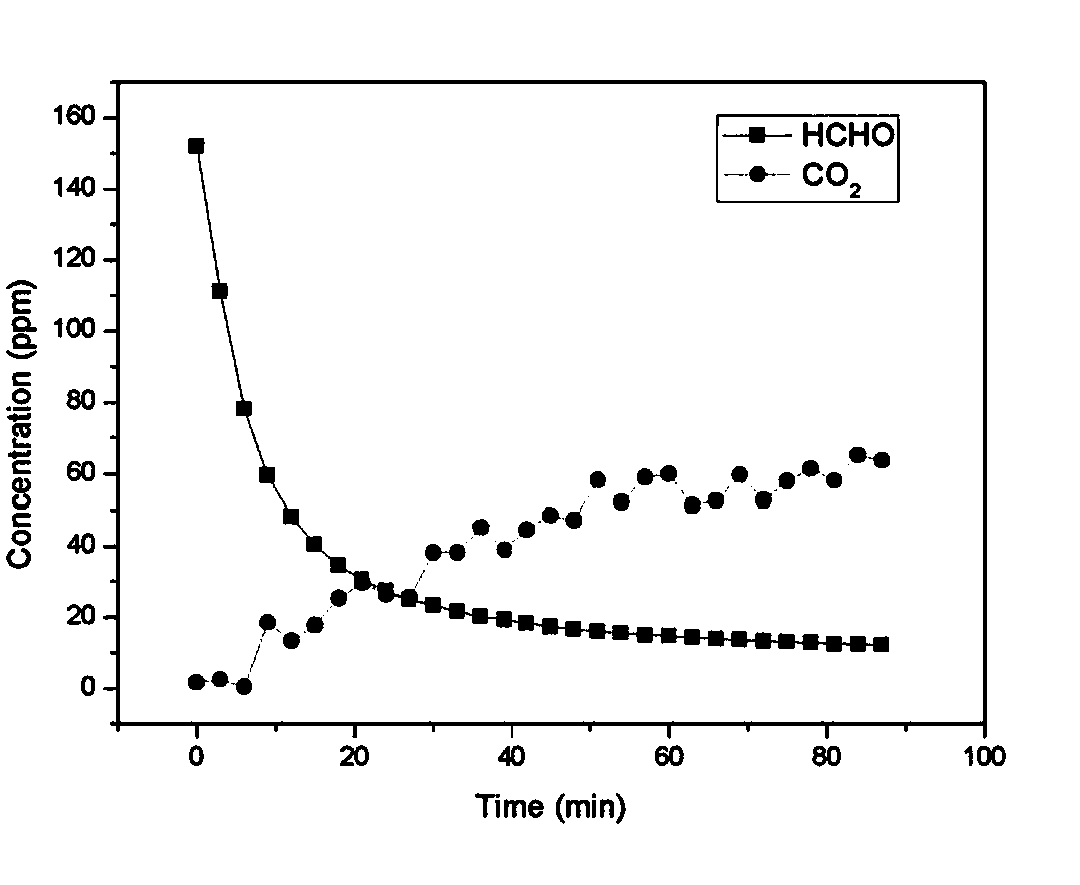

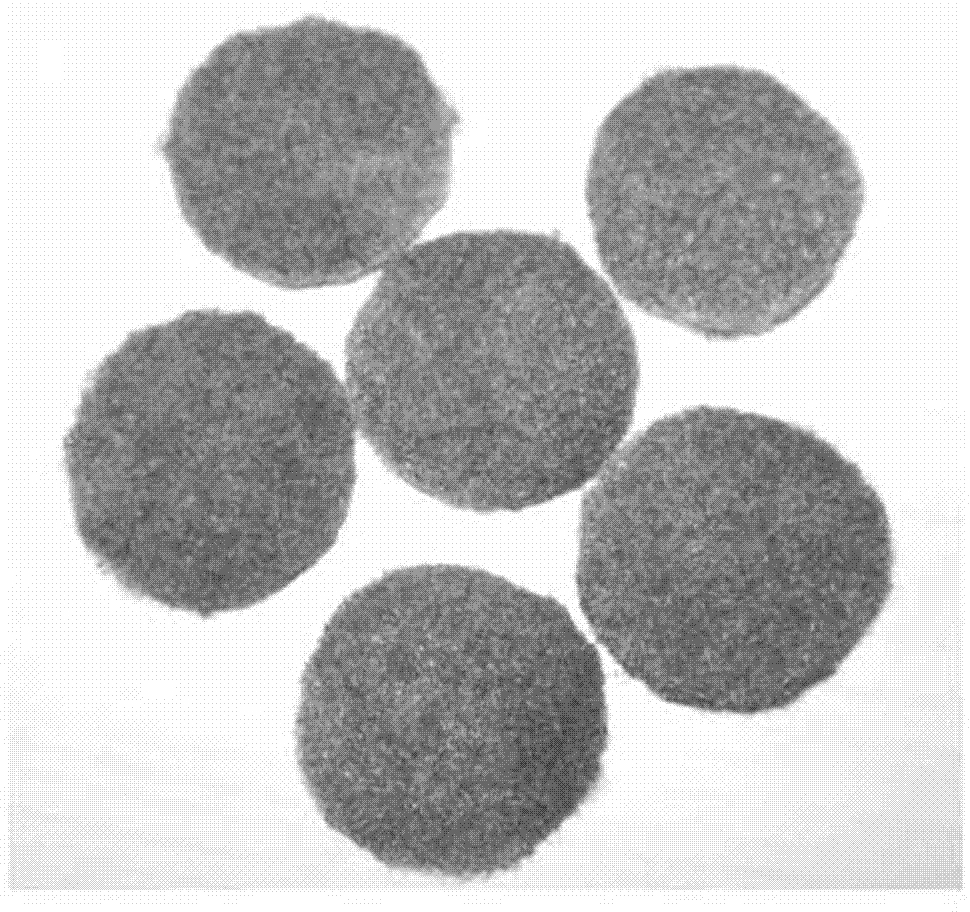

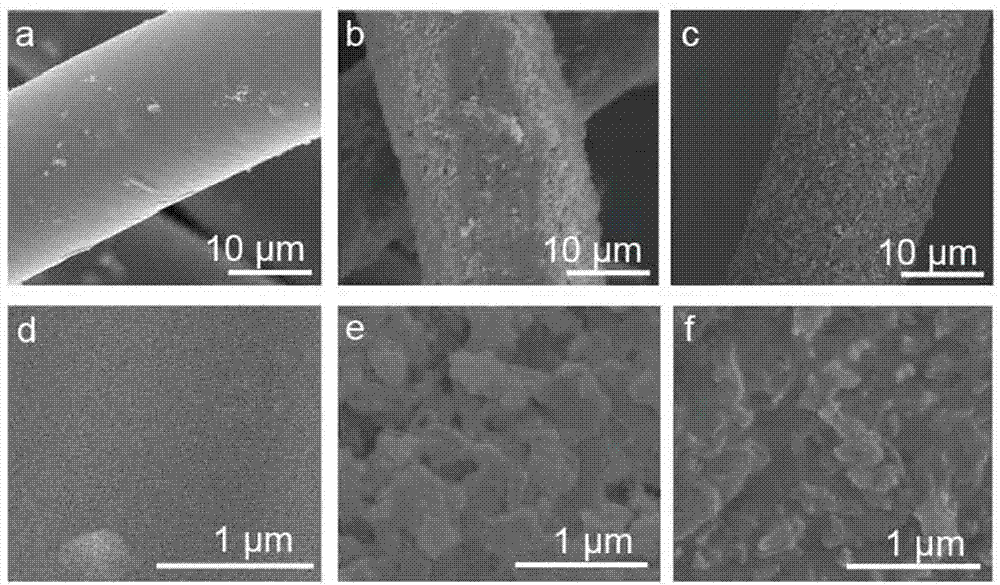

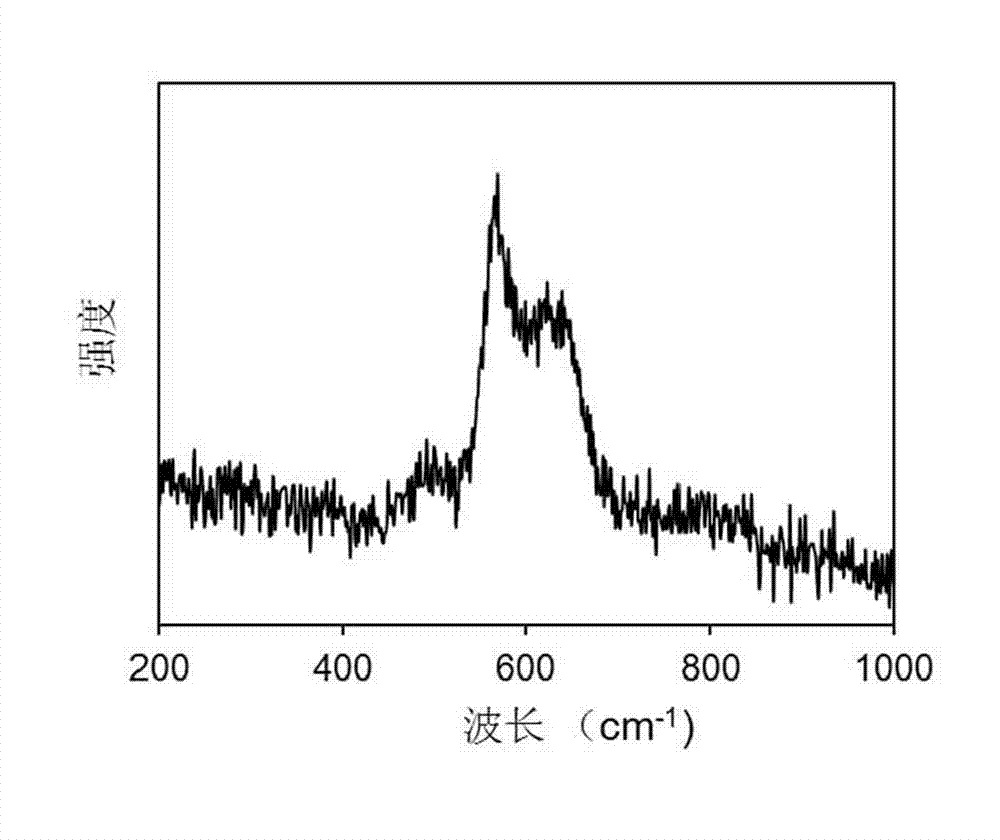

Air purification material and preparation method and application thereof

ActiveCN104190251AEfficient decompositionQuick removalDispersed particle separationFiberParticulates

The invention relates to an air purification material and a preparation method and application thereof, belonging to the technical field of chemical catalytic decomposition, in particular belonging to the technical field of decomposition of formaldehyde pollutants in environment air. The air purification material comprises a base material and manganese oxide, wherein the manganese oxide is supported on the base material, the base material is honeycomb ceramics or a fiber material with a particle filtering function, and the manganese oxide is birnessite manganese oxide prepared from permanganate and oxalate. The air purification material can effectively decompose formaldehyde pollutants in indoor air and can rapidly and constantly remove the formaldehyde pollutants in indoor air at room temperature. The air purification material can be regenerated through heating, so that the service life of the material is prolonged and the practical application is facilitated.

Owner:TSINGHUA UNIV

Air cleaning material, and preparation method and application thereof

ActiveCN103480267ASimple preparation processLow costDispersed particle separationMetal/metal-oxides/metal-hydroxide catalystsFiberParticulates

The invention relates to an air cleaning material, and a preparation method and an application thereof, and belongs to the technical field of chemical catalytic decomposition. The air cleaning material comprise a base material and a manganese oxide loaded on the base material; the manganese oxide is a birnessite type manganese oxide prepared by performing in-situ reduction on a permanganate and a reducing agent; and the base material is filter cotton, non-woven fabrics, cotton cloth, gauze, or fiber with particle filtering function. The preparation method comprises the following steps: step 1, dissolving a quaternary ammonium salt and the permanganate in water, adding the base material; step 2, adding the reducing agent into the solution obtained in the step 1, mixing uniformly; step 3, heating the solution obtained in the step 2 at a constant temperature; and step 4, taking out the base material and drying to obtain the finished product. According to the technical scheme, the manganese oxide is simple loaded on the fiber material base material such as filter cotton and the like, so that the obtained low-wind-resistance cleaning material is capable of continuously rapid degrading formaldehyde and ozone in the air at room temperature; and the preparation method of the air cleaning material is simple and low in cost, and no other pollutions are introduced.

Owner:TSINGHUA UNIV

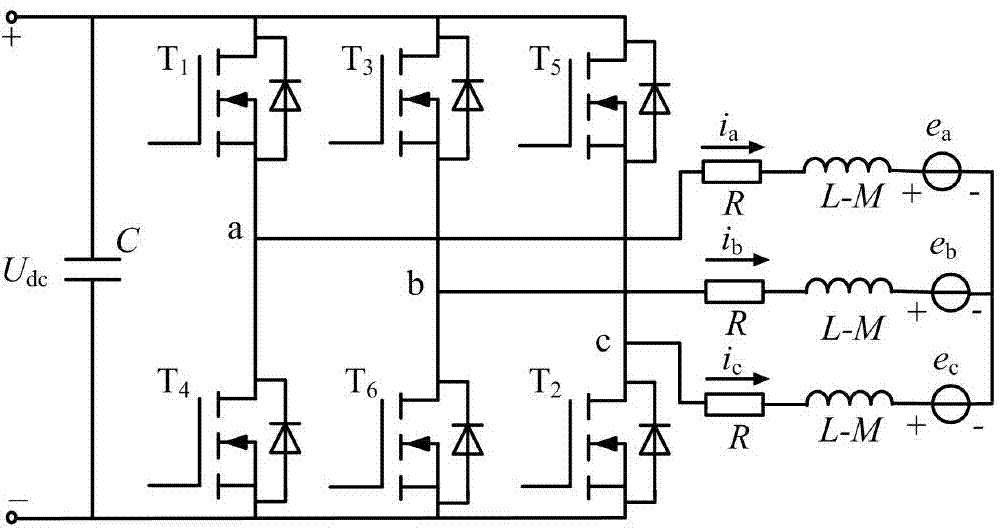

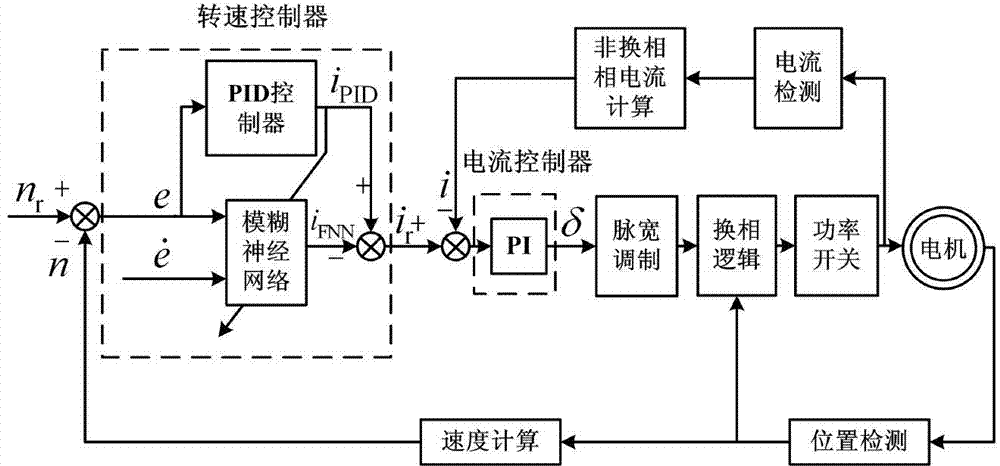

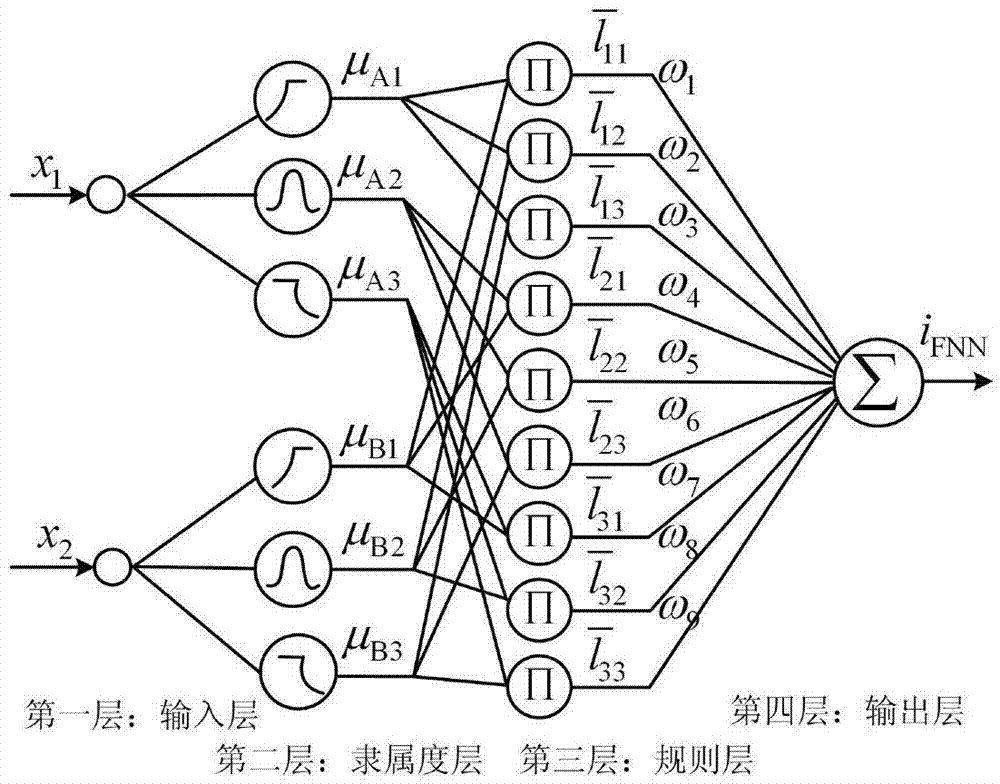

Motor rotating-speed tracking control method based on self-adaptive fuzzy neural network

The invention relates to a motor rotating-speed tracking control method based on a self-adaptive fuzzy neural network, wherein rotating-speed and current double closed-loop control is adopted, an outer ring is a rotating-speed ring, a sliding-mode control theory-based fuzzy neural-network controller (SMFNN) is designed, an inner ring is a current ring, and a PI (Proportional-Integral) controller is adopted; a fuzzy neural-network rotating-speed controller comprises two parts, wherein one part is a PID (Proportional-Integral-Derivative) controller, and the other part is the fuzzy neural network, online real-time learning is carried out through the fuzzy neural network by utilizing a parameter correcting method designed on the basis of the sliding-mode control theory, and the two parts jointly act to obtain the output ir of the rotating-speed controller, i.e. a difference obtained by subtracting the output iFNN of the fuzzy neural network from the output iPID of the PID controller is used as the output ir of the rotating-speed controller. The control precision and the anti-interference performance of a motor speed-adjusting system can be improved through the control strategy of the motor rotating-speed tracking control method.

Owner:TIANJIN UNIV

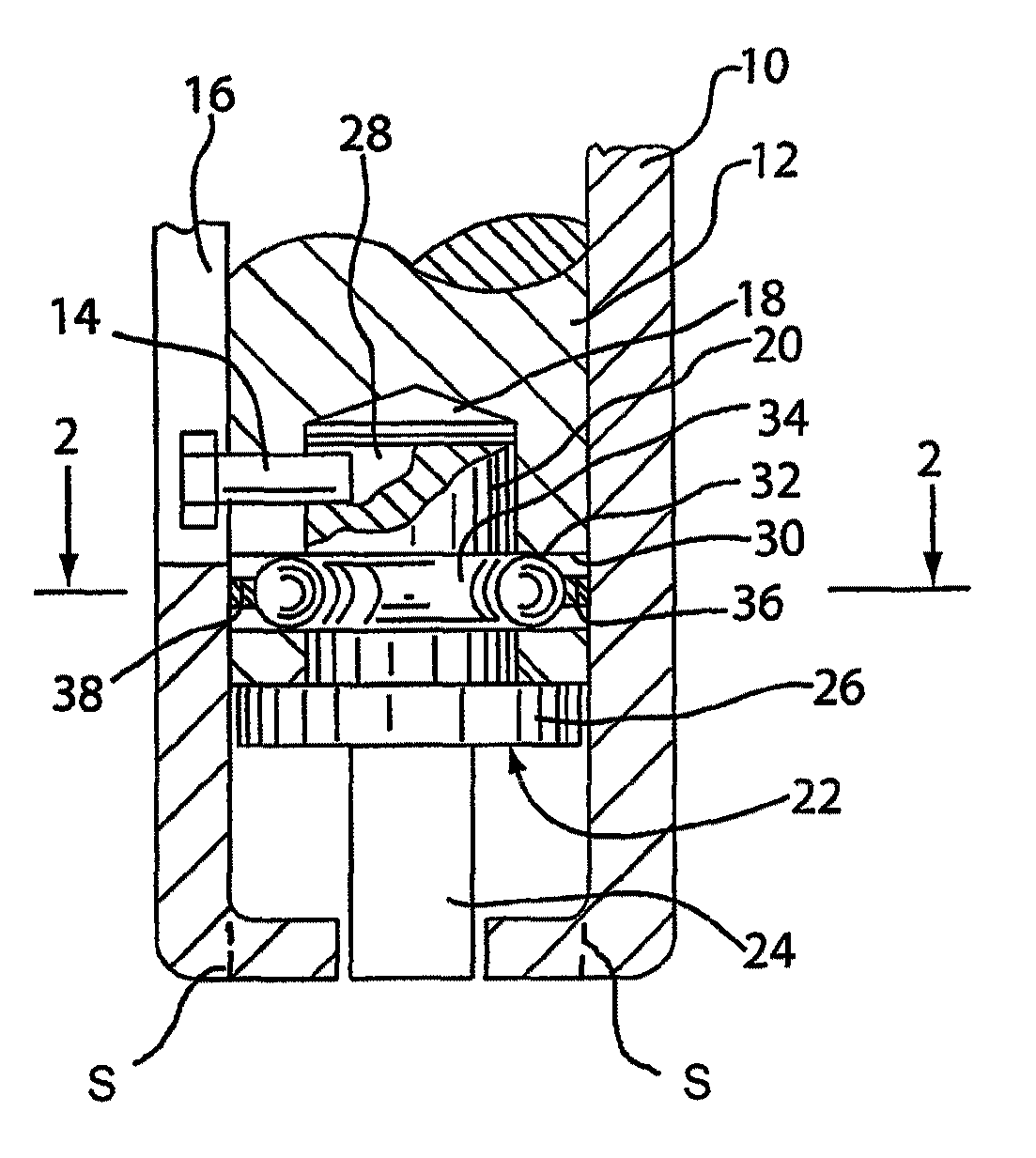

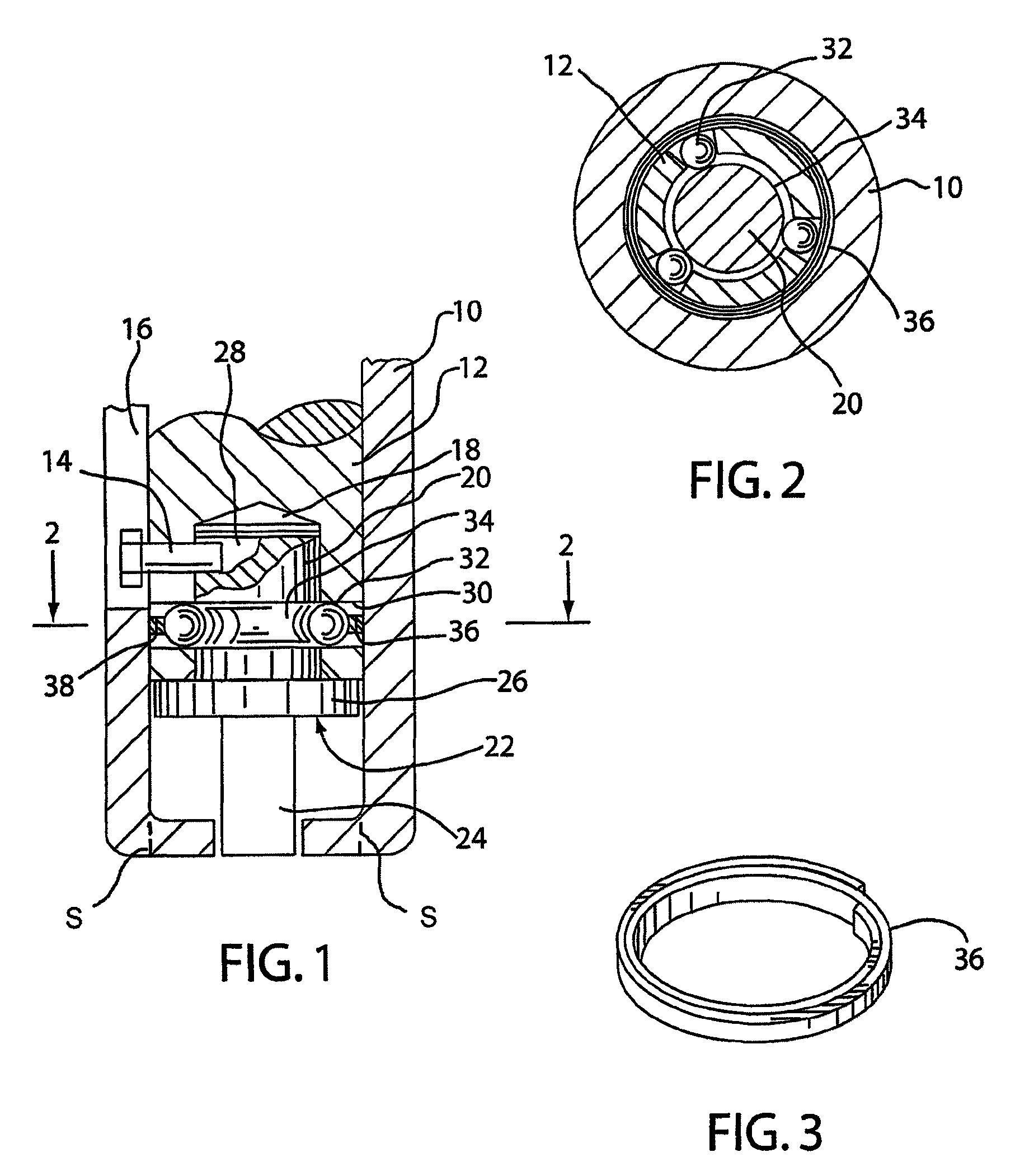

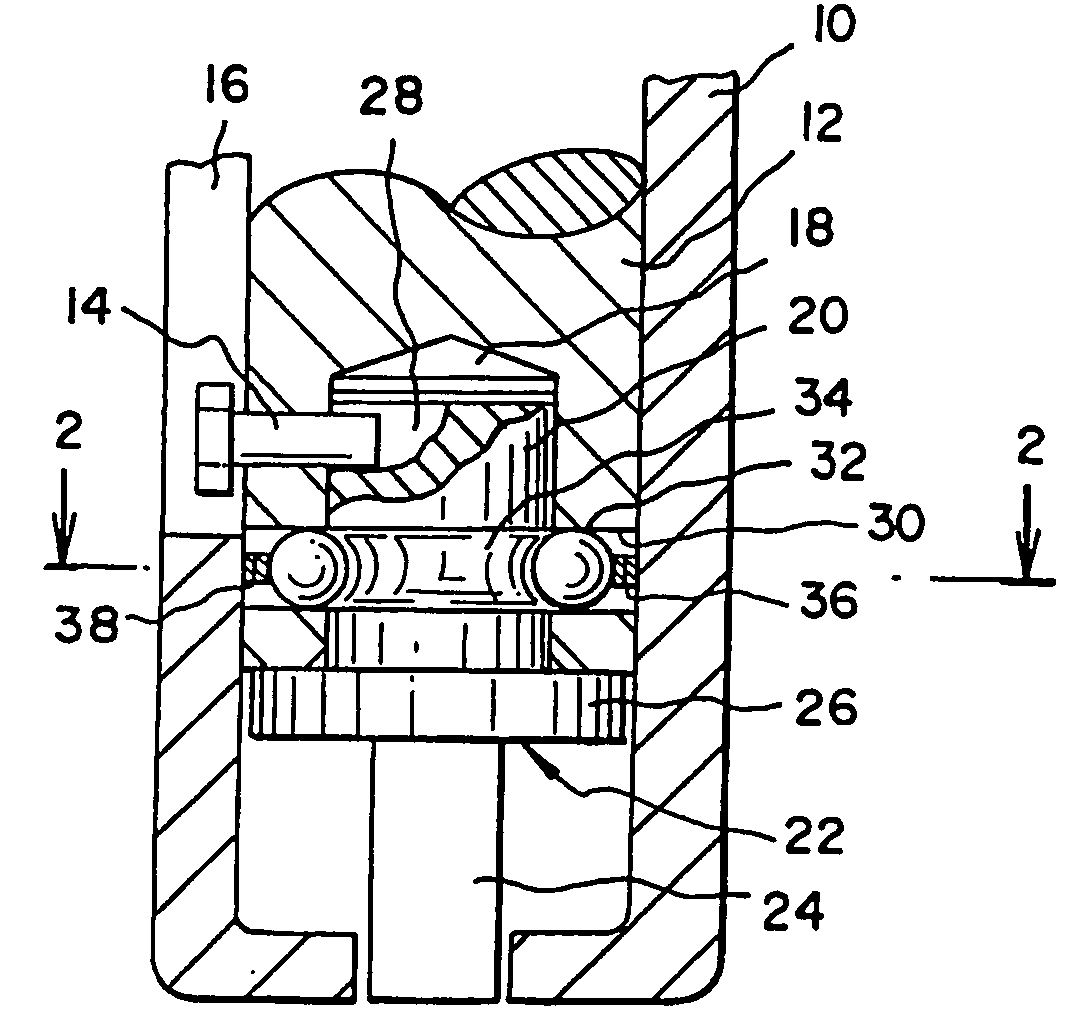

Punching tool

ActiveUS7975587B2Simple and rapid separationEasy to separatePerforating toolsMetal working apparatusPunchingPlunger

A punching tool has a guided, axially displaceable die plunger, which is fixed against relative rotation, in a guide bushing. In a bore in its front end a punching die is seated. During the punching stroke the punching die rests against a front face of the die plunger and is axially fixed in place by means of one or several snap-in balls each of which is seated in a transverse bore, which snap-in balls are maintained in engagement with an annular groove by means of a resilient ring in the die plunger. The outer diameter of the resilient ring is only slightly less in the engagement position than the inner diameter of the guide bushing and can be resiliently widened for releasing the punching die outside of the guide bushing.

Owner:MATE PRECISION TOOLING

Foam metal hydrogenating catalyst and its preparing method and use

ActiveCN1781595ALow densityHigh catalytic activityCatalyst activation/preparationMetal/metal-oxides/metal-hydroxide catalystsPorosityChemical plating

The present invention discloses hydrogenating catalyst of foam metal and its preparation process and application. The hydrogenating catalyst includes foamed metal carrier and active noble metal component in effective amount supported onto the carrier, the carrier is prepared through powder metallurgical process, and the active component is supported via chemical plating process and distributed homogeneously on the port surfaces of the foamed carrier. The catalyst has the advantages of high catalytic activity, firm combination between the active component and the carrier, high stability, simple preparation process, high porosity of the carrier, great specific surface area, etc. in addition, the catalyst provides sufficient gas-liquid contact area, is favorable to mass transfer between gas phase and liquid phase, may be used in catalytic rectification and possesses both reaction and separation effects.

Owner:CHINA PETROLEUM & CHEM CORP +1

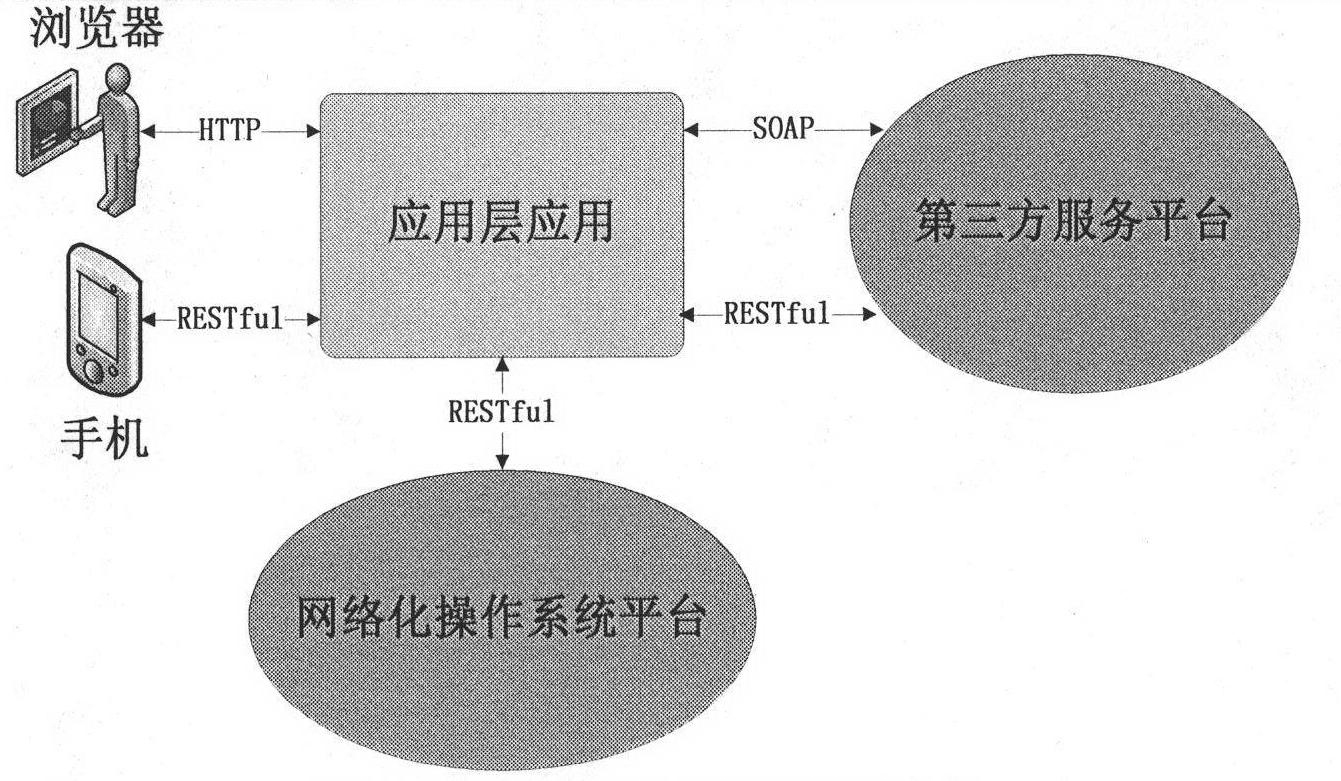

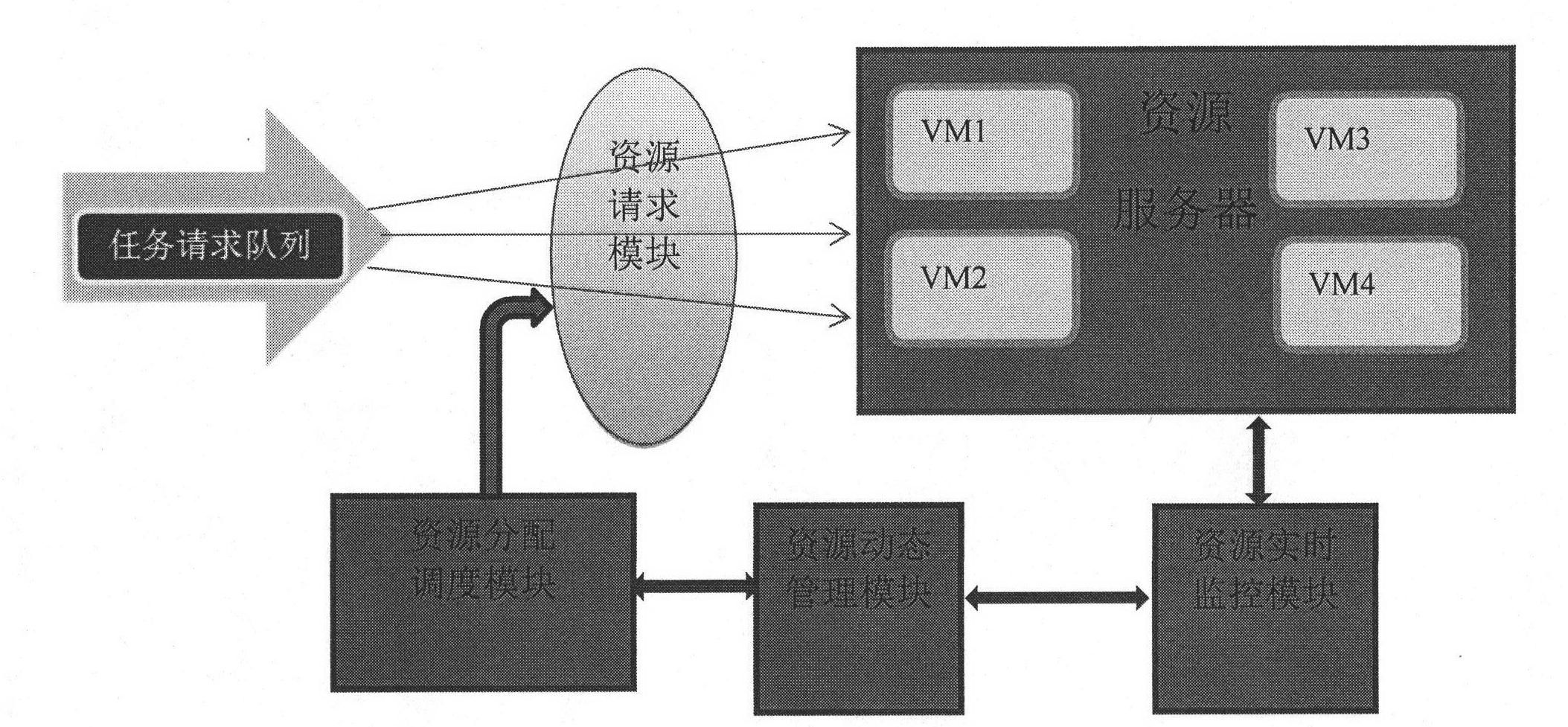

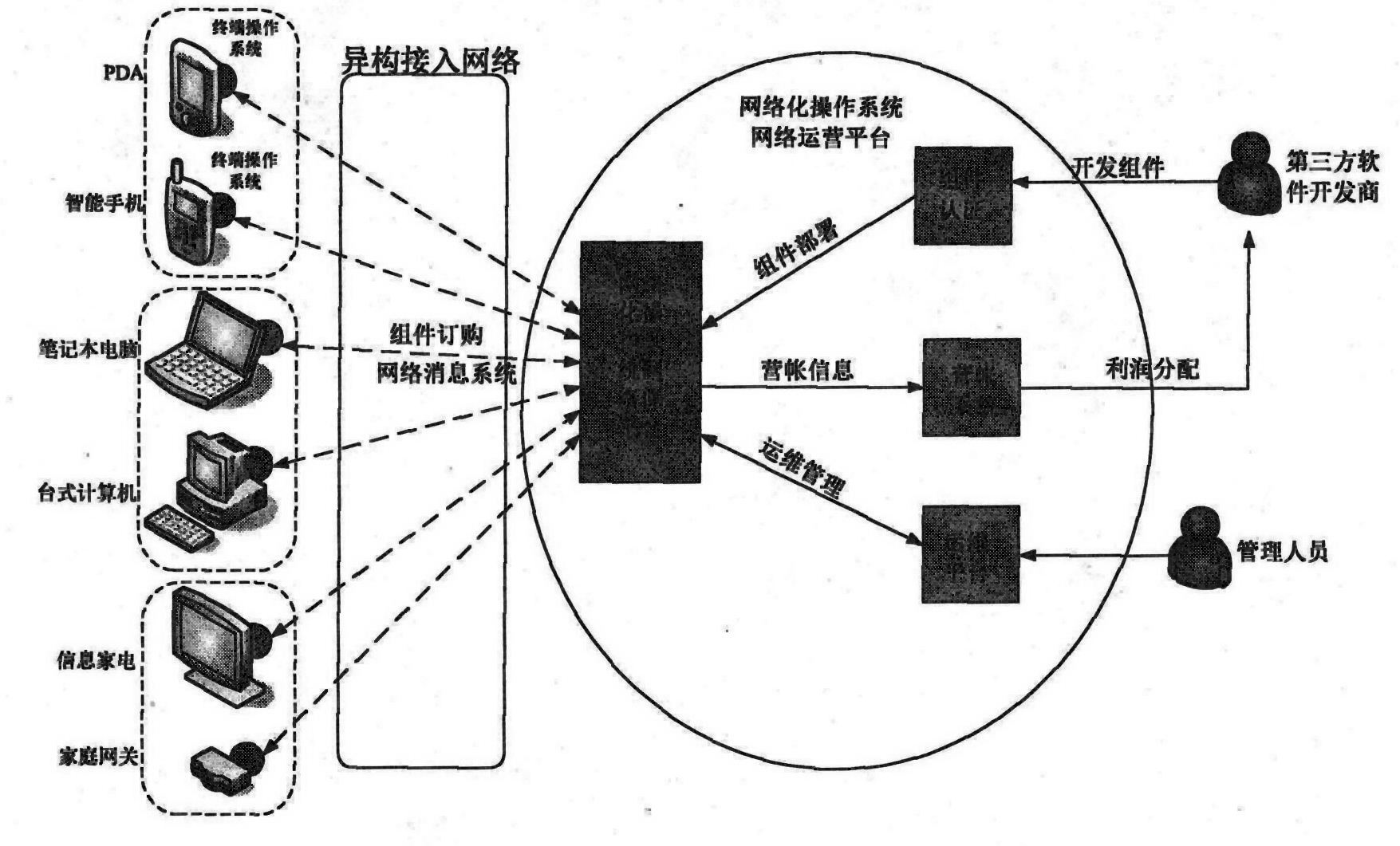

Virtual resource dynamic feedback balanced allocation mechanism for network operation system

InactiveCN102223419APrevent overloadAchieve reasonable utilizationTransmissionSoftware simulation/interpretation/emulationOperational systemDynamic management

The invention relates to a virtual resource dynamic feedback balanced allocation mechanism for a network operation system. The mechanism comprises a resource request module, a resource real-time monitoring module, a resource dynamic management module and a resource allocating and scheduling module. The mechanism can be used for monitoring, predicating and performing dynamic and balanced allocation on the virtual resources of the whole network operation system so as to achieve the purposes of fully utilizing resources and realizing reliable service. By adopting the method, a favorable effect of improving the utilization ratio and the stability of the system resources is achieved.

Owner:BEIJING UNIV OF POSTS & TELECOMM

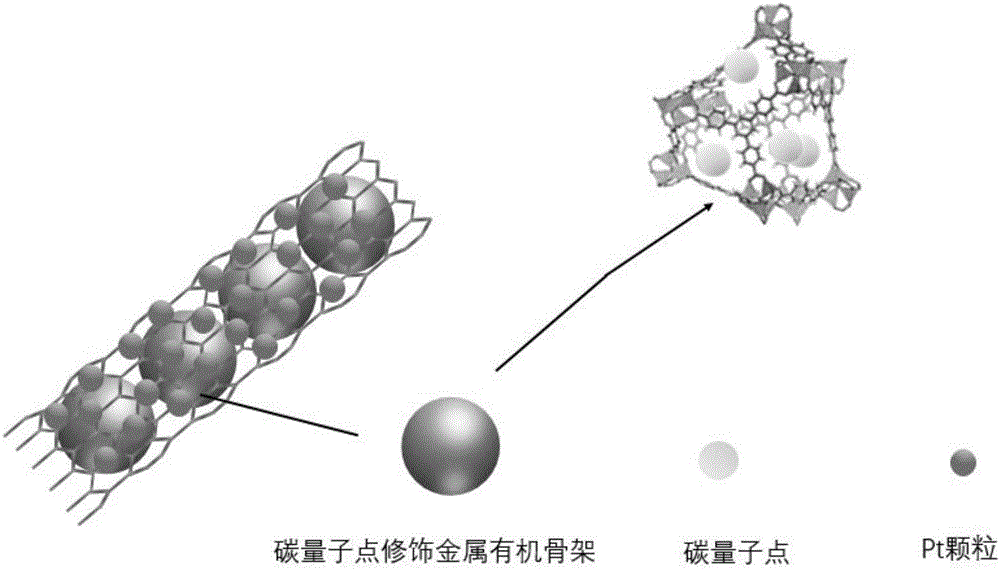

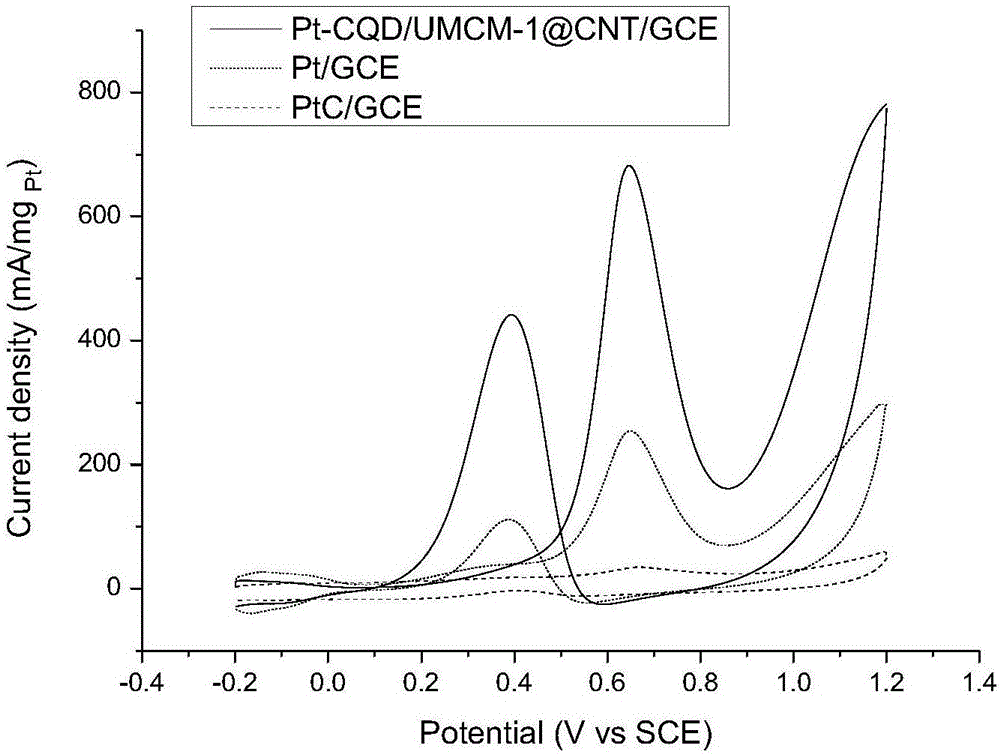

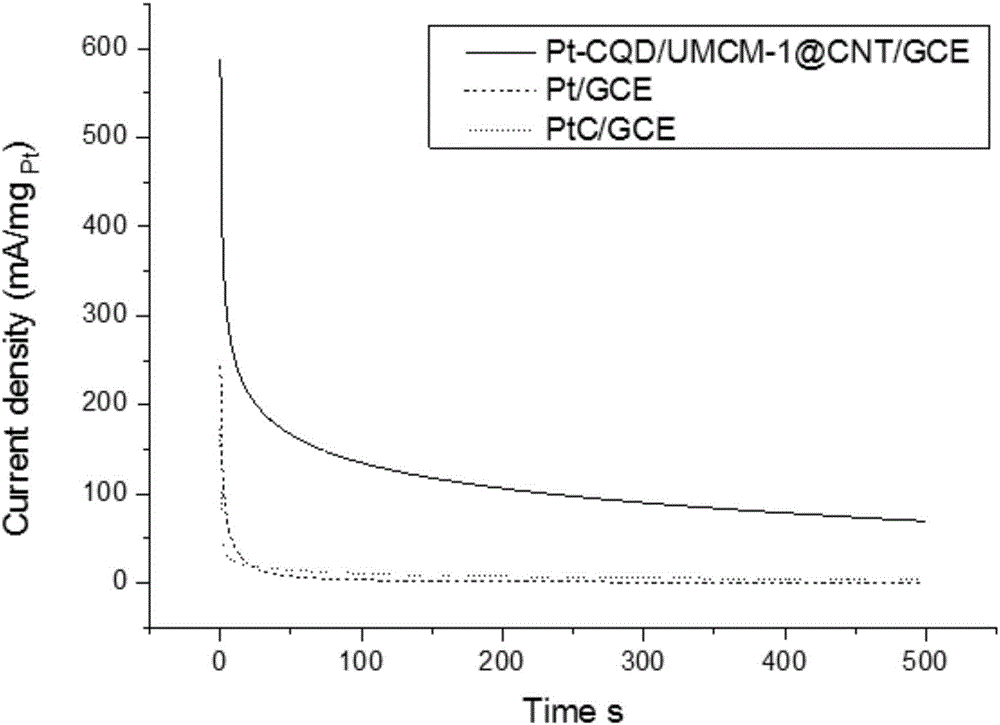

Preparation of carbon nanotube material embedded with quantum-dot modified metal organic framework

The invention provides preparation of a carbon nanotube material embedded with a quantum-dot modified metal organic framework. The preparation comprises the following steps of firstly, adding a certain amount of powder quantum dots to a formed metal organic framework precursor solvent so that the quantum dots of which the diameters are matched with the sizes of pore passages are embedded into the pore passages of the formed metal organic framework; secondly, uniformly mixing the obtained quantum-dot modified metal organic framework and melamine powder, and performing high-temperature processing to obtain a composite material (QD / UMCM-1@CNT) in a carbon nanotube embedded with the quantum-dot modified metal organic framework; and finally, enabling Pt to be loaded on a surface of the composite material carbon nanotube (Pt / QD / UMCM-1@CNT) by microwave radiation heating to be used as a positive electrode catalyst of a methanol fuel cell. Compared with a traditional hydrothermal method for synthesis of the carbon nanotube, the quantum-dot modified metal organic framework obtained by high-temperature processing is embedded into the composite material in the carbon nanotube, the structural aspects such as the length and the diameter of the carbon nanotube are more consistent, and a catalyst substrate with a unified structure is easier to form.

Owner:QINGDAO UNIV

Nanometer photocatalyst material supported embedded composite film and preparation method and application thereof

ActiveCN104084053AImprove hydrophilicityImprove throughputSemi-permeable membranesWater/sewage treatment by irradiationNano catalystComposite film

The invention discloses a method for preparing a nanometer photocatalyst material supported embedded composite film. The method comprises the following steps: dissolving an organic polymer base film material, a pore-forming agent and a nanometer catalyst in a solvent, stirring and standing to prepare a casting film solution; dispersing the nanometer photocatalyst in the solvent to obtain dispersion liquid, spreading the dispersion liquid on a plate to prepare a spreading solution, and drying the spreading solution to obtain a spreading film; and covering the spreading film with the casting film solution, scraping a liquid film by utilizing a film scraper, immersing the scraped liquid film in a constant temperature gel bath, and curing the liquid film to prepare the nanometer photocatalyst material supported embedded composite film. The invention also provides the nanometer photocatalyst material supported embedded composite film and application thereof. According to the method, a nanometer photocatalyst coating is uniformly, effectively, stably and firmly supported on the surface of the embedded composite film. Moreover, according to the composite film, the removal rate of pollutants is effectively improved, and film pollution is reduced.

Owner:SHANGHAI JIAO TONG UNIV

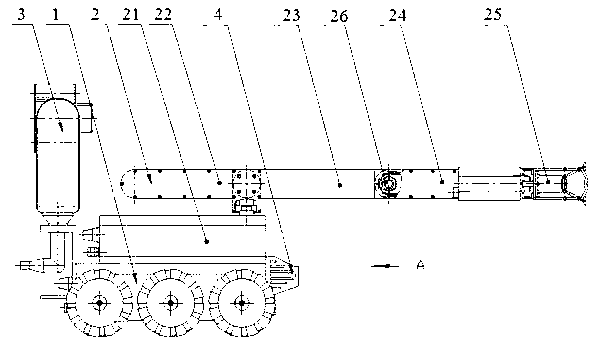

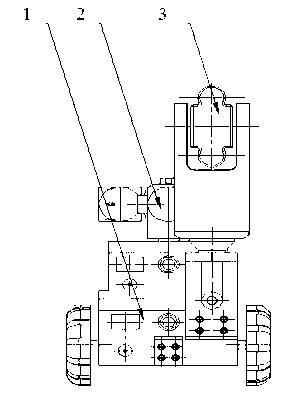

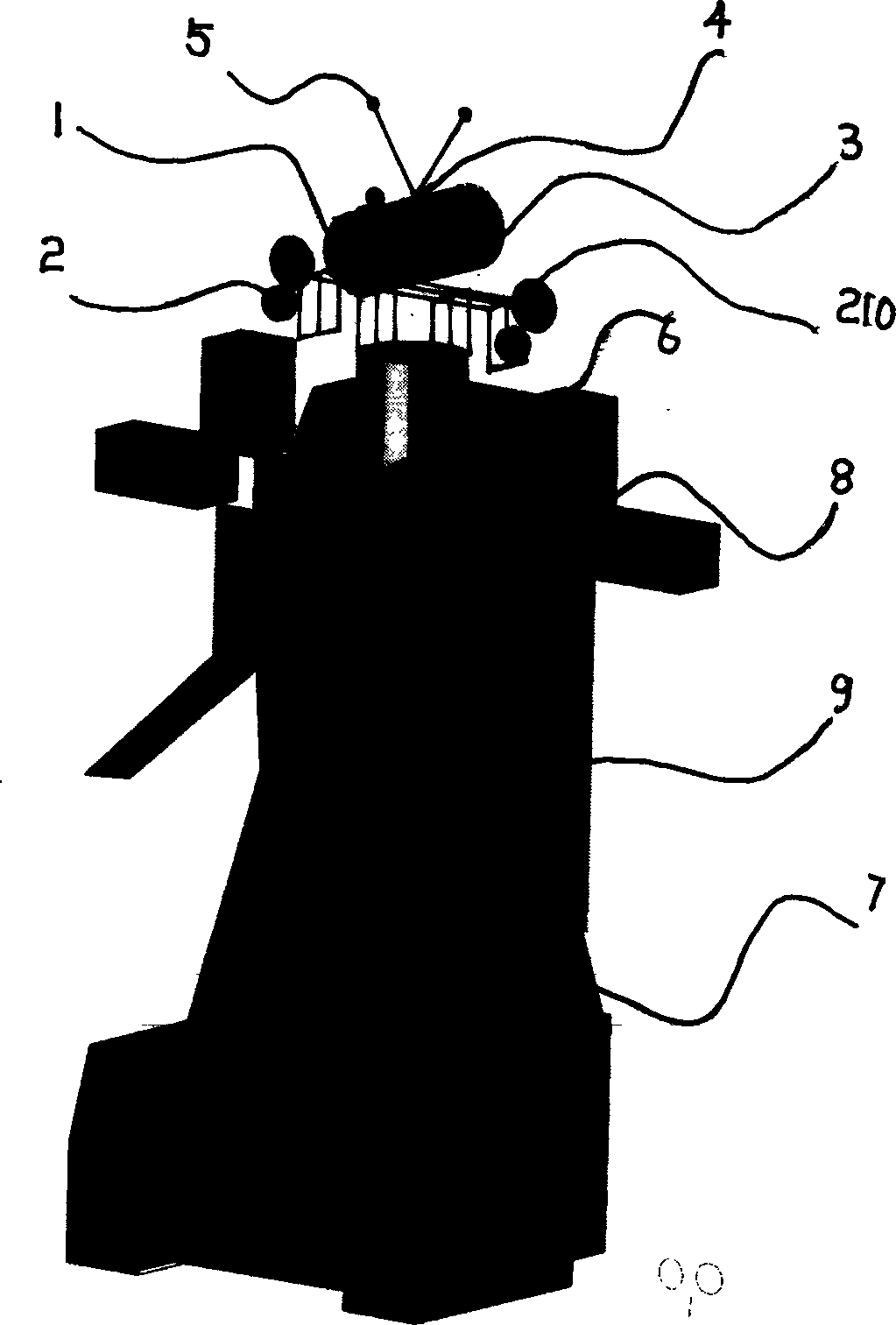

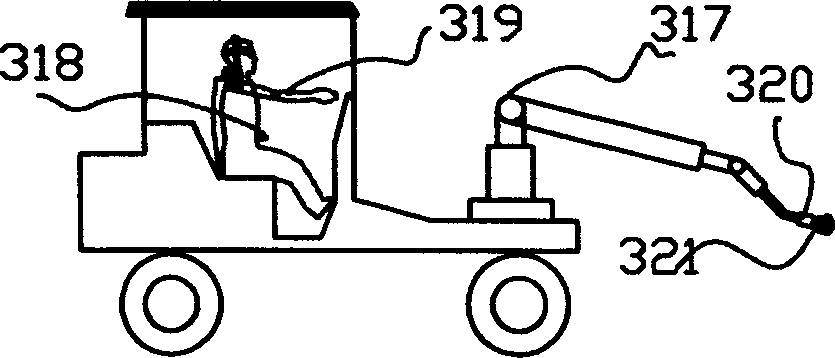

Underwater working robot

ActiveCN103303449AStrong radiation resistancePowerfulProgramme-controlled manipulatorUnderwater equipmentLead plateManipulator

The invention discloses an underwater working robot which is characterized by mainly comprising a vehicle body module, a manipulator module or / and an underwater camera module, a functional component module and a control module, wherein the modules are completely isolated mechanically and electrically; the vehicle body module mainly comprises a six-wheel and six-drive sealing vehicle body, a vehicle body direct current servo motor, a vehicle body motor driver, a vehicle body underwater ultrasonic sensor, a vehicle body temperature pressure sensor, an underwater lighting lamp, a vehicle body waterproof plug, a vehicle body inflating valve and a vehicle body anti-radiation lead plate; the manipulator module mainly comprises a base, a waist part, a large arm, a small arm and a tail end executer; the base, the waist part, the large arm and the small arm are connected with one another through hollow joints; air is filled into a manipulator, and wires are arranged in the manipulator; the underwater camera module mainly comprises an underwater camera, an underwater camera lighting lamp and a bidimensional tripod; the functional component module mainly comprises a storage box, an underwater dust remover and an underwater cutter; and the control module mainly comprises a main control console and a hand-control box.

Owner:HEBEI UNIV OF TECH +1

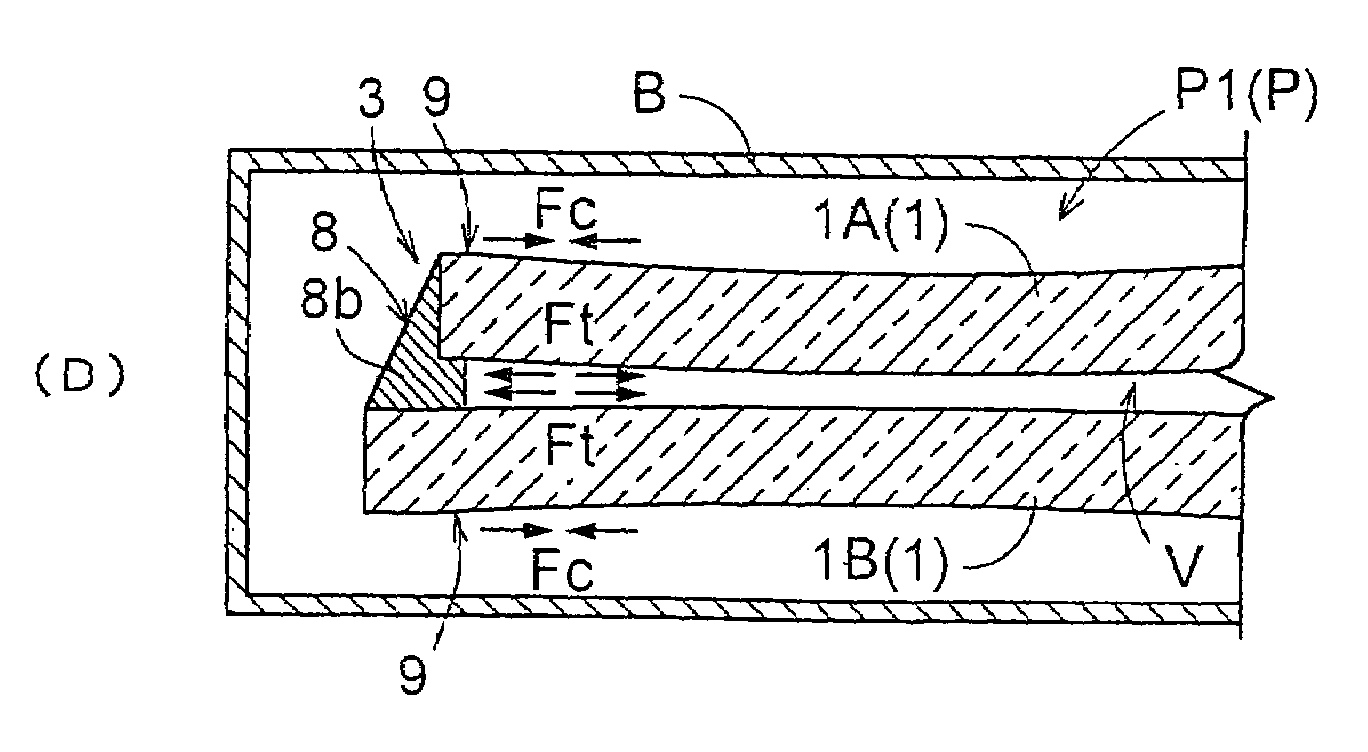

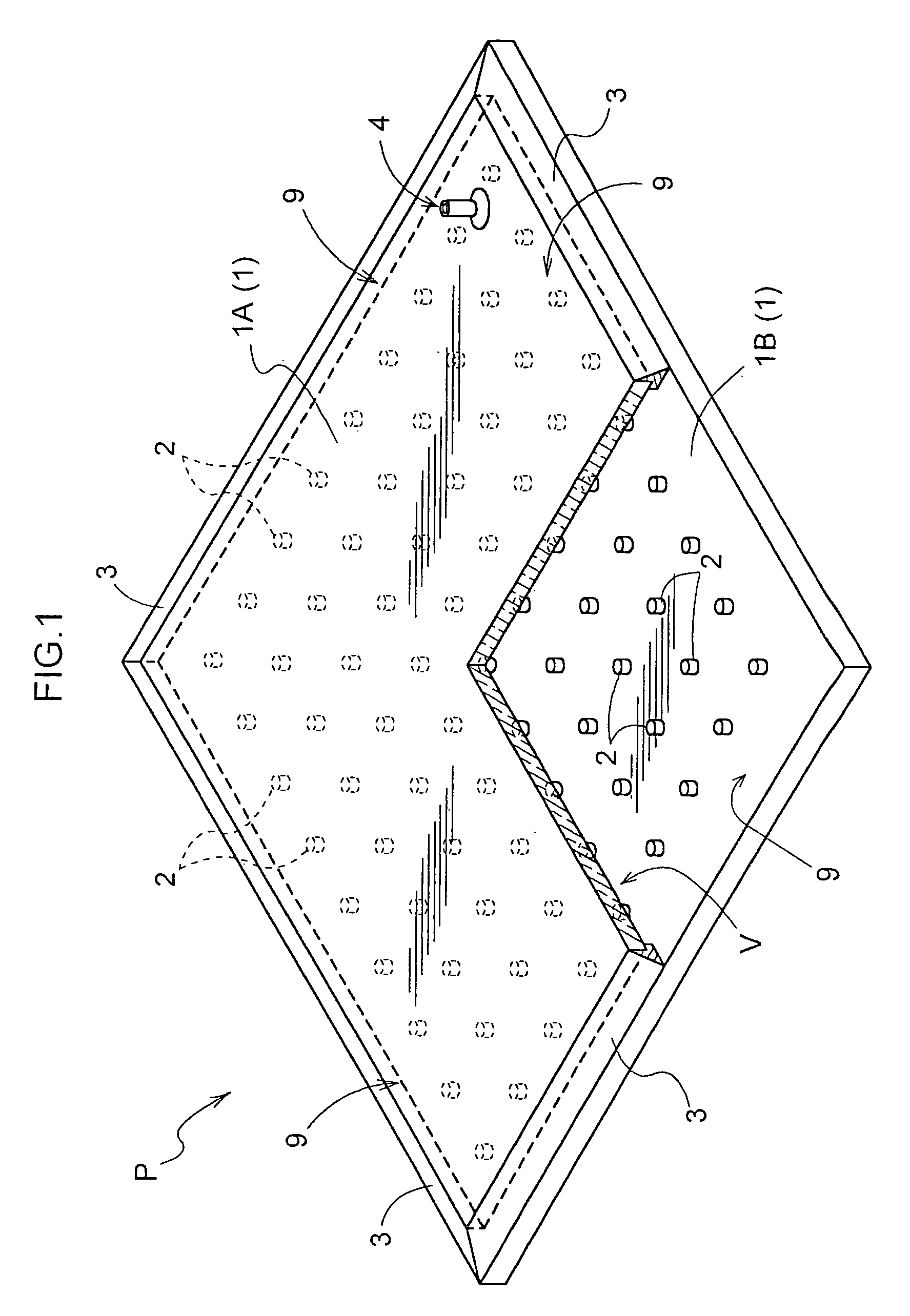

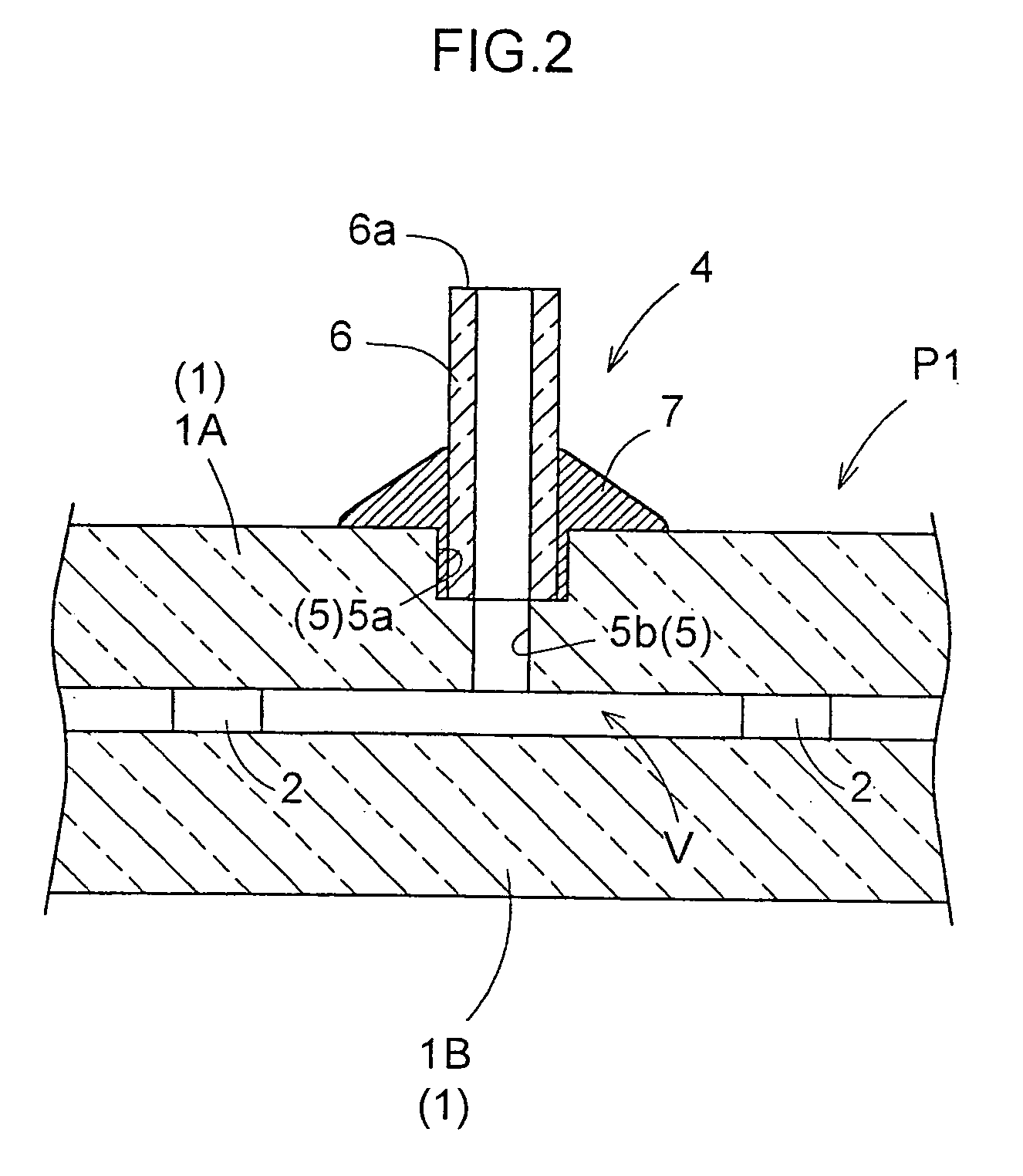

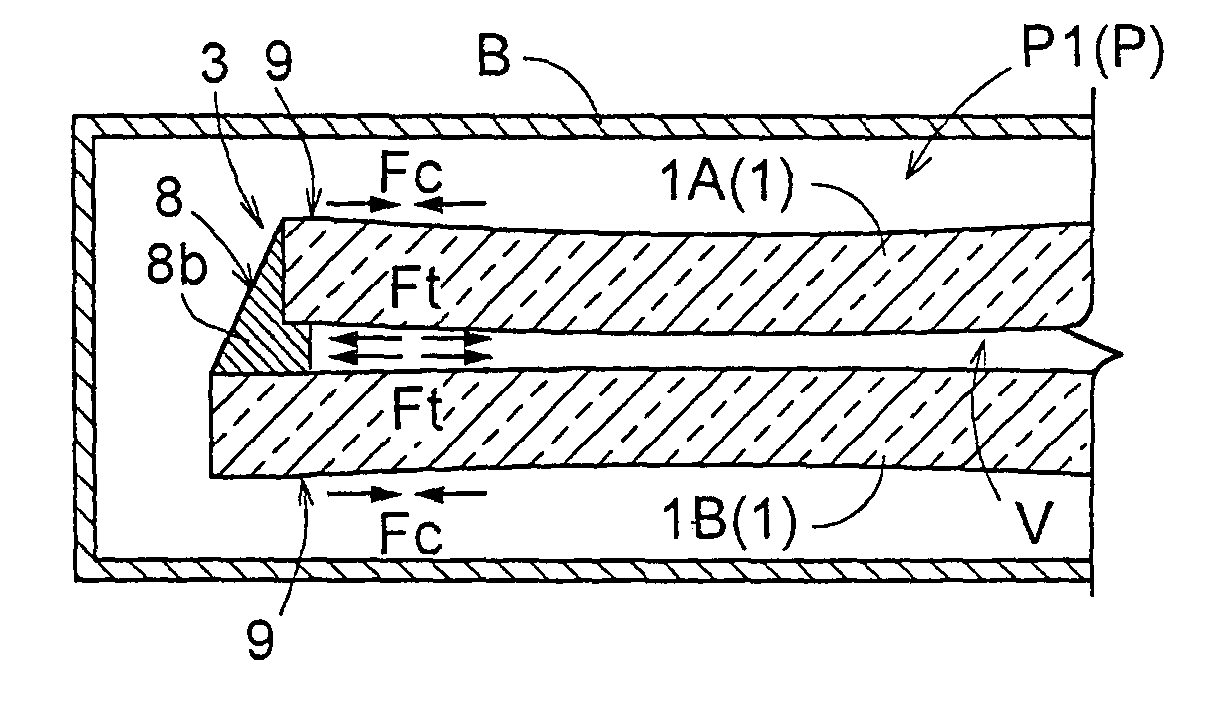

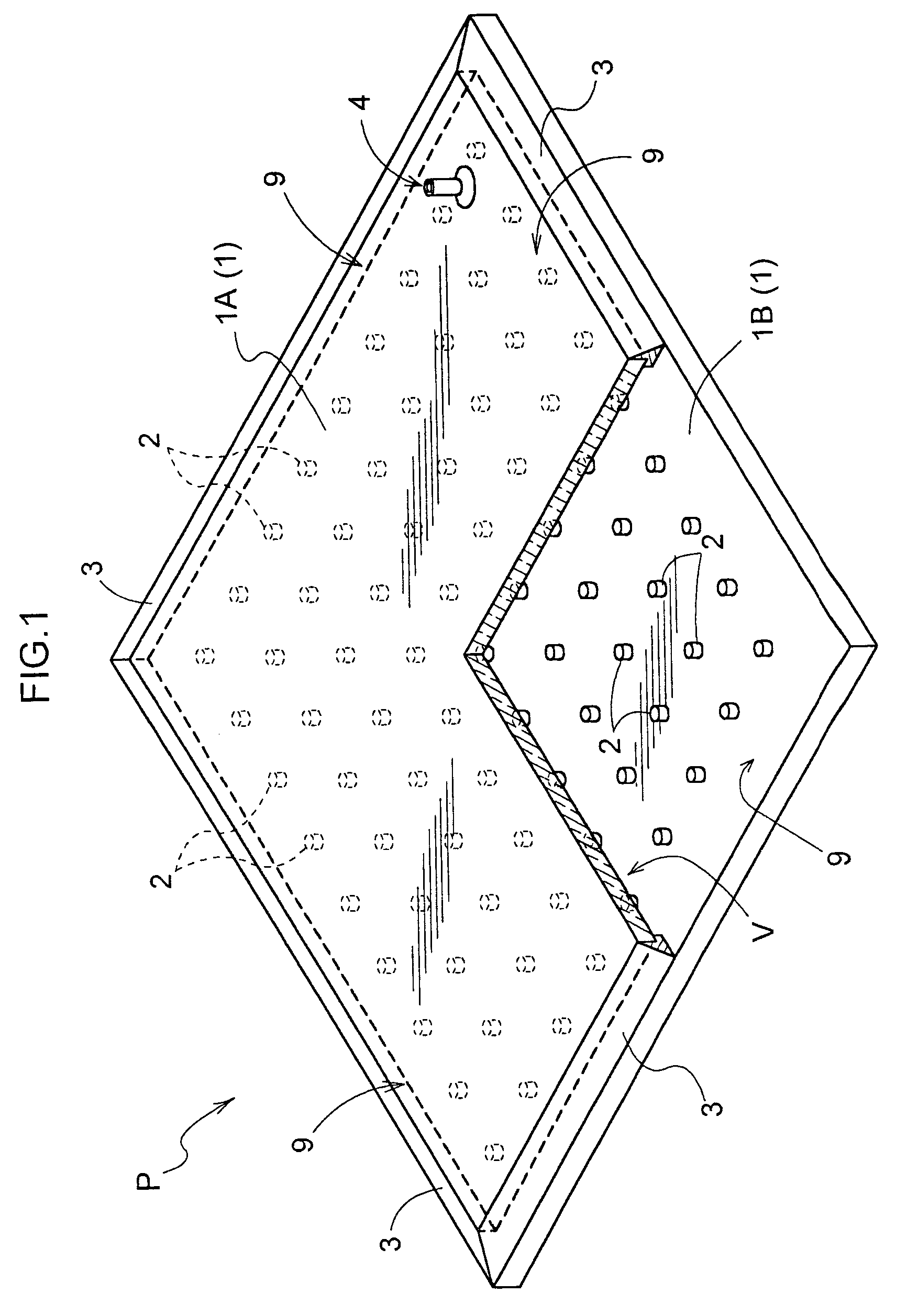

Glass panel

InactiveUS7141130B2Avoid crackingCut surfaceClimate change adaptationInsulation improvementAtmospheric pressureGlass sheet

A glass panel (P) comprising a pair of glass plates (1A, 1B) opposed to each other, spacers (2) disposed between the pair of glass plates for maintaining a gap therebetween, and a sealing member (3) having a lower melting point than the glass plates (1) for sealing the pair of glass plates (1A, 1B) at outer peripheries (9) thereof to form a decompression void (V) between the pair of glass plates (1A, 1B), wherein a compressive force Fc is allowed to remain at outer surfaces of the outer peripheries (9) of the glass plates (1), with the decompression void (V) being in atmospheric pressure condition.

Owner:NIPPON SHEET GLASS CO LTD

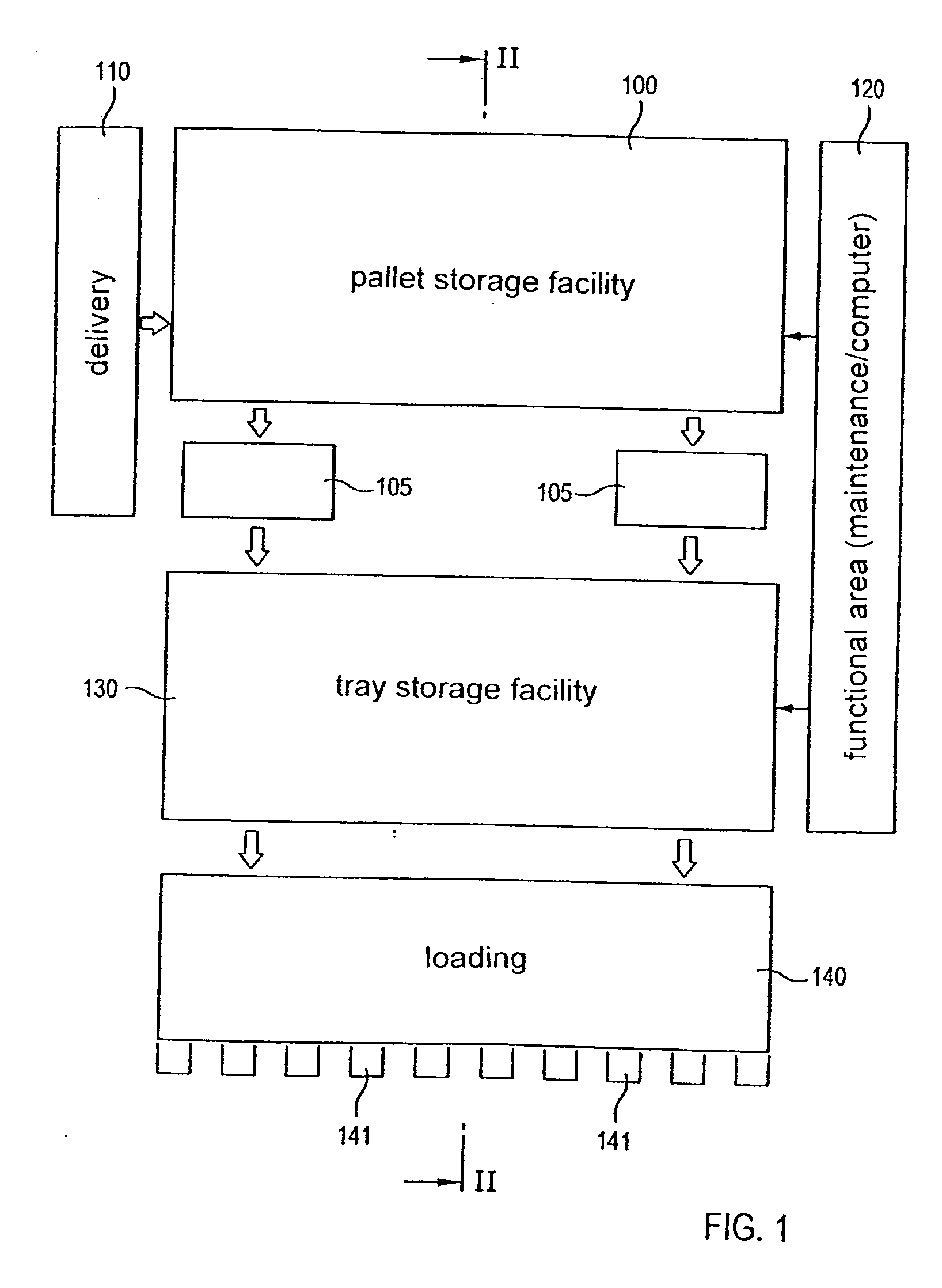

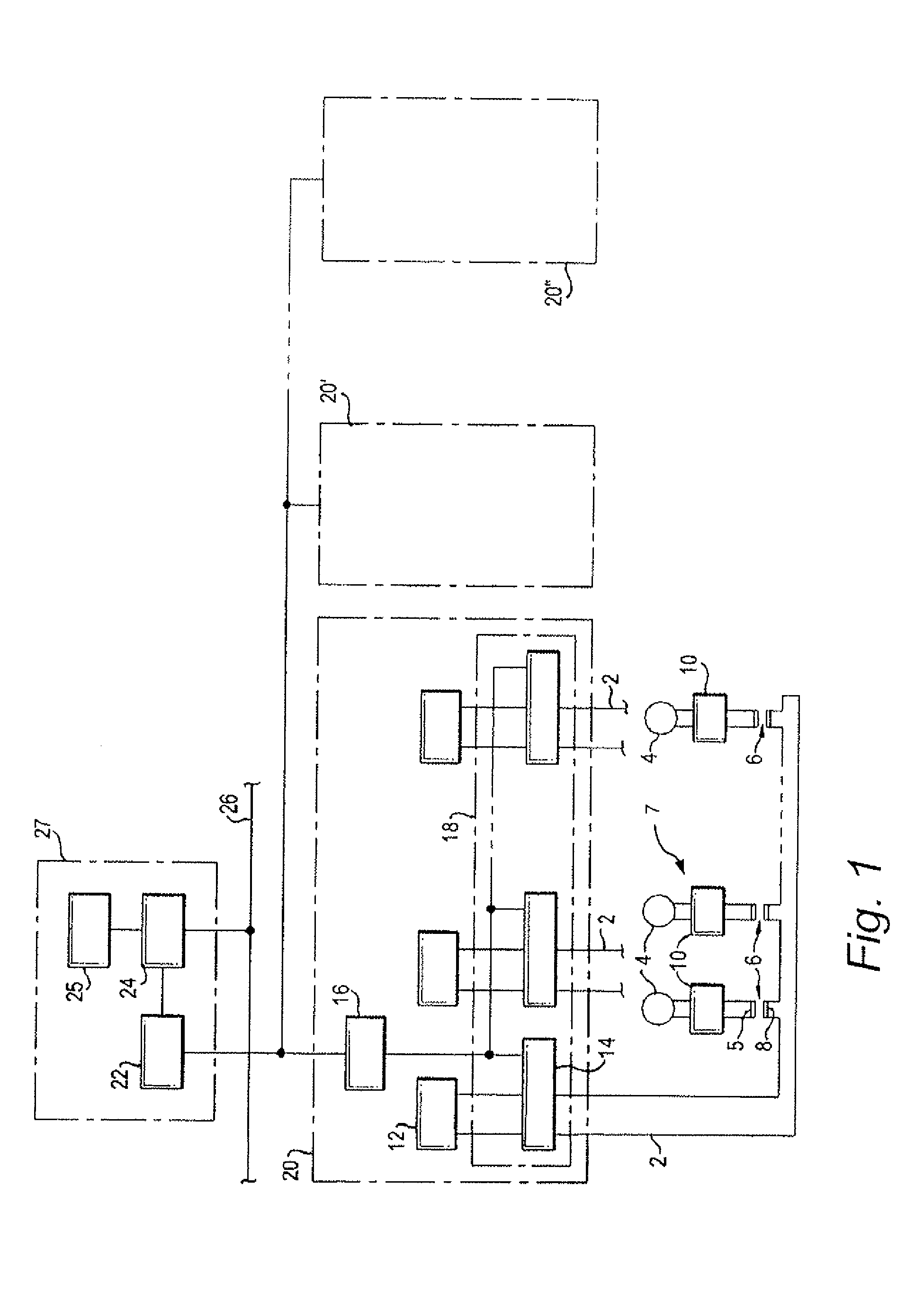

Load-carrier loading apparatus

ActiveUS20040191049A1Strong loadLoaded safely and reliablyWrappers shrinkageConveyorsMaterial qualityPallet

A machine for loading a load carrier (20) such as a pallet with packing units (cardboard boxes, collis etc.), which form a load stack (21) on the load carrier, comprises handling and support means (52-57), by means of which a packing unit (15) to be loaded is supported from below throughout the operation of loading from a feed device (51) onto the load stack. By virtue of the handling and support means the packing unit may be deposited at any selectable spatial position on the load stack. According to the invention it is therefore possible to form an optimized load stack on the load carrier, wherein the packing units are always supported from below, with the result that the loading is not dependent upon the material quality of the packaging of the packing unit.

Owner:LOGISTIK INFORMATIK

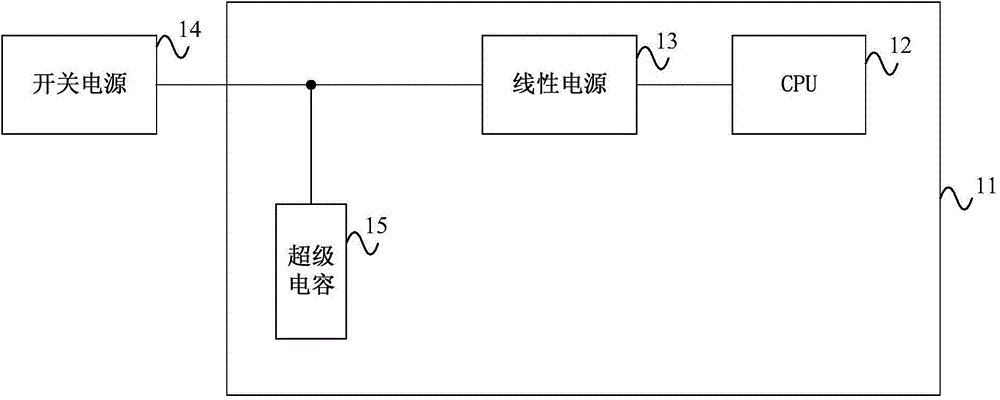

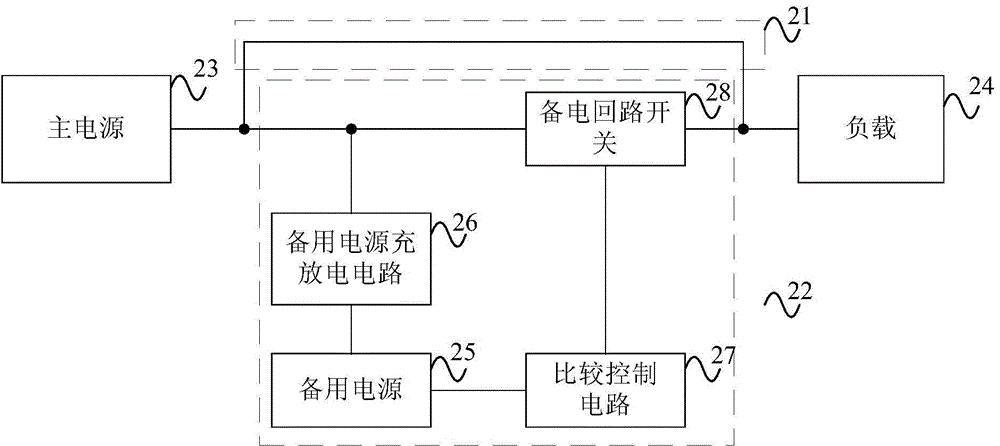

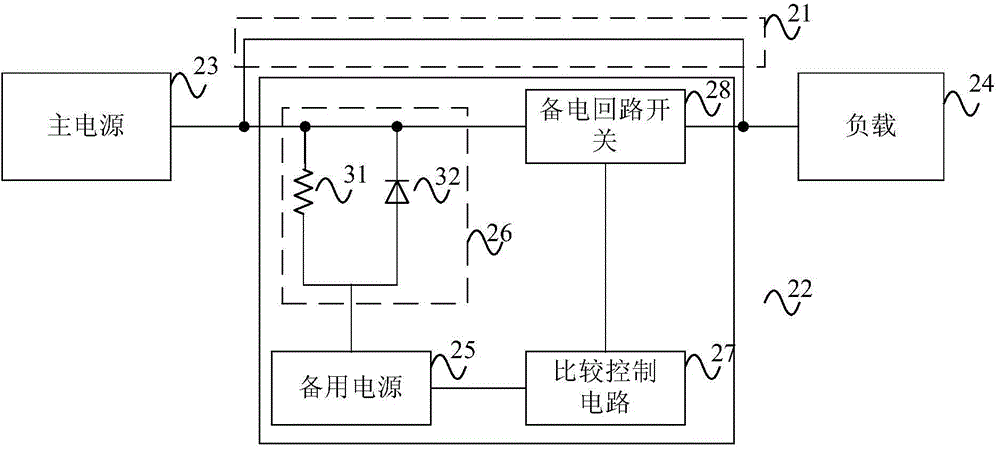

Switch control method and apparatus for reserve power supply

ActiveCN104935072AStrong loadPower network operation systems integrationInformation technology support systemReserve powerStandby power

An embodiment of the invention provides a switch control method and apparatus for a reserve power supply. The switch control apparatus for the reserve power supply comprises a main power supply loop and a reserve power supply loop; a main power supply and loads are connected respectively through the main power supply loop and the reserve power supply loop; the reserve power supply loop comprises a reserve power supply, a reserve power supply charge-discharge loop, a comparison control circuit and a reserve power supply loop switch; the main power supply charges the reserve power supply through the reserve power supply charge-discharge loop; the comparison control circuit is connected with the reserve power supply; the reserve power supply charge-discharge loop is connected with the loads through the reserve power supply loop switch; the comparison control circuit detects voltage of the reserve power supply; when the voltage of the reserve power supply is higher than a first voltage threshold value, the comparison control circuit controls the reserve power supply loop switch to be switched on; and when the voltage of the reserve power supply is lower than a first voltage threshold value, the comparison control circuit controls the reserve power supply loop switch to be switched off. The switch control method and apparatus for the reserve power supply provided by the embodiment of the invention are used for improving the stability when the reserve power supply is used for supplying power to the loads.

Owner:HUAWEI TECH CO LTD

Biological information follow-up instant-teaching control robot

InactiveCN1676286AEasy to operate and controlEasy to operateProgramme-controlled manipulatorThe InternetDriven element

The present invention relates to an electromechanical integral equipment capable of utilizing bioligical information to control movement. It is characterized by utilizing various sensors to collect various biological informations and transferring these biological informations into central computer to control various drive elements. The transmission of signal can use wired, wireless and Internet transmission mode.

Owner:李朝辉

Glass panel

InactiveUS7114306B2Avoid crackingCut surfaceClimate change adaptationInsulation improvementEngineeringAtmospheric pressure

A glass panel (P) comprising a pair of glass plates (1A, 1B) opposed to each other, spacers (2) disposed between the pair of glass plates for maintaining a gap therebetween, and a sealing member (3) having a lower melting point than the glass plates (1) for sealing the pair of glass plates (1A, 1B) at outer peripheries (9) thereof to form a decompression void (V) between the pair of glass plates (1A, 1B), wherein a compressive force Fc is allowed to remain at outer surfaces of the outer peripheries (9) of the glass plates (1), with the decompression void (V) being in atmospheric pressure condition.

Owner:NIPPON SHEET GLASS CO LTD

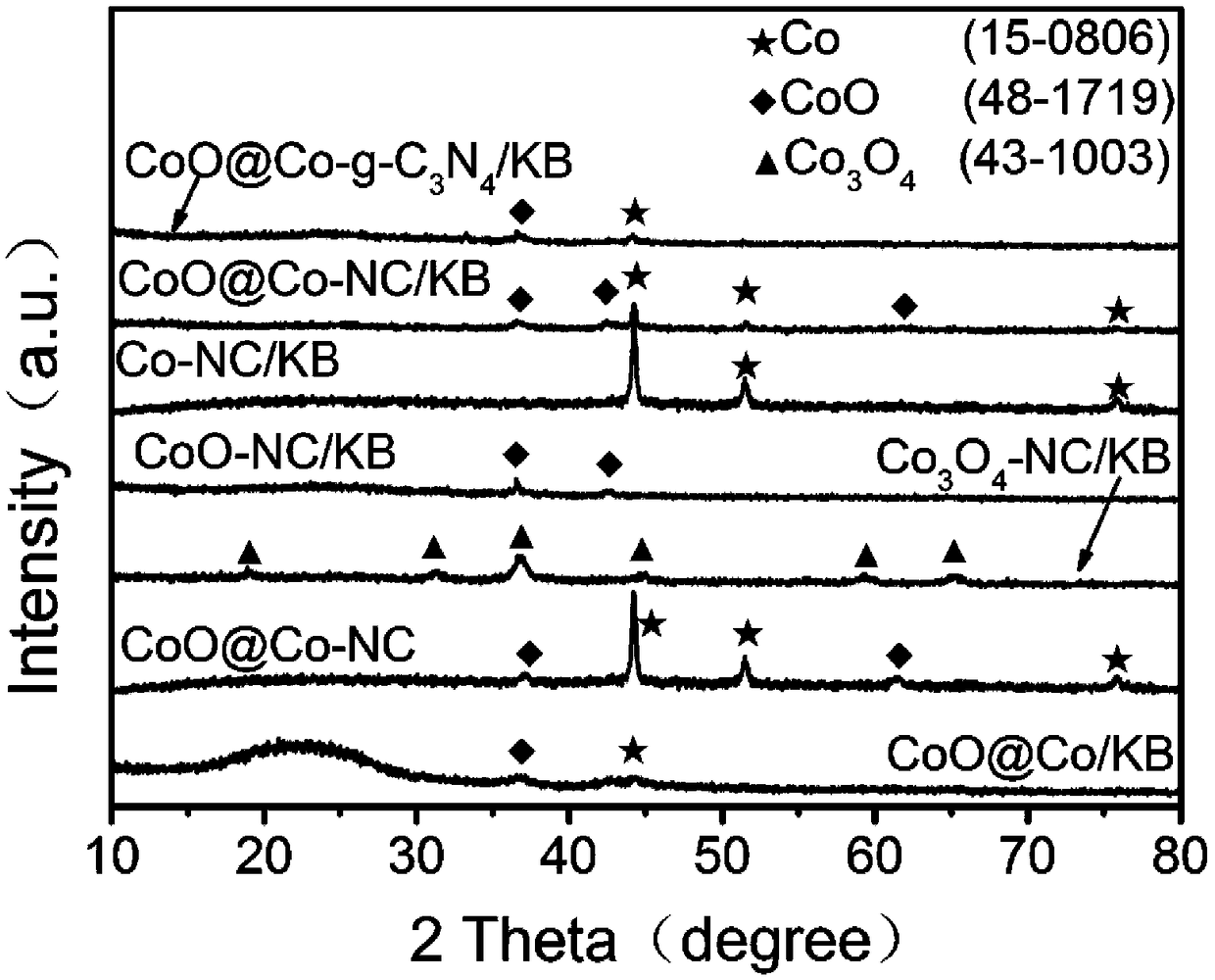

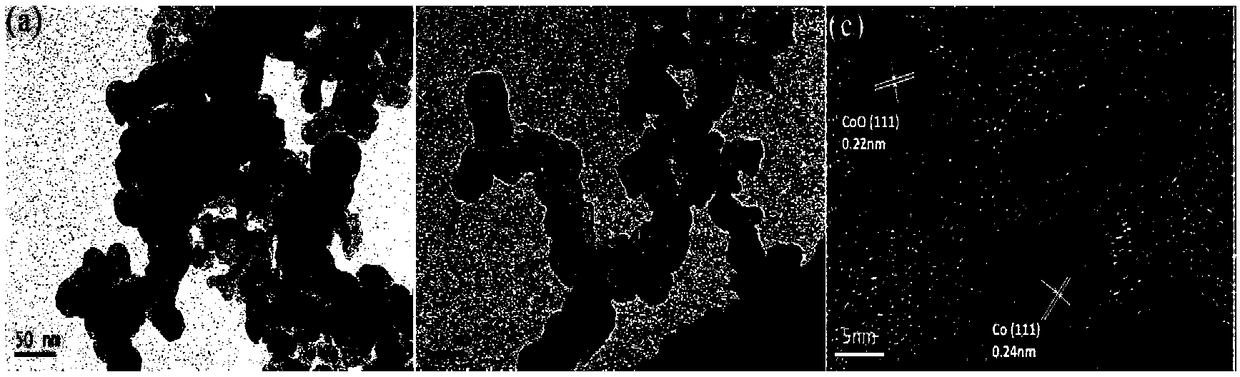

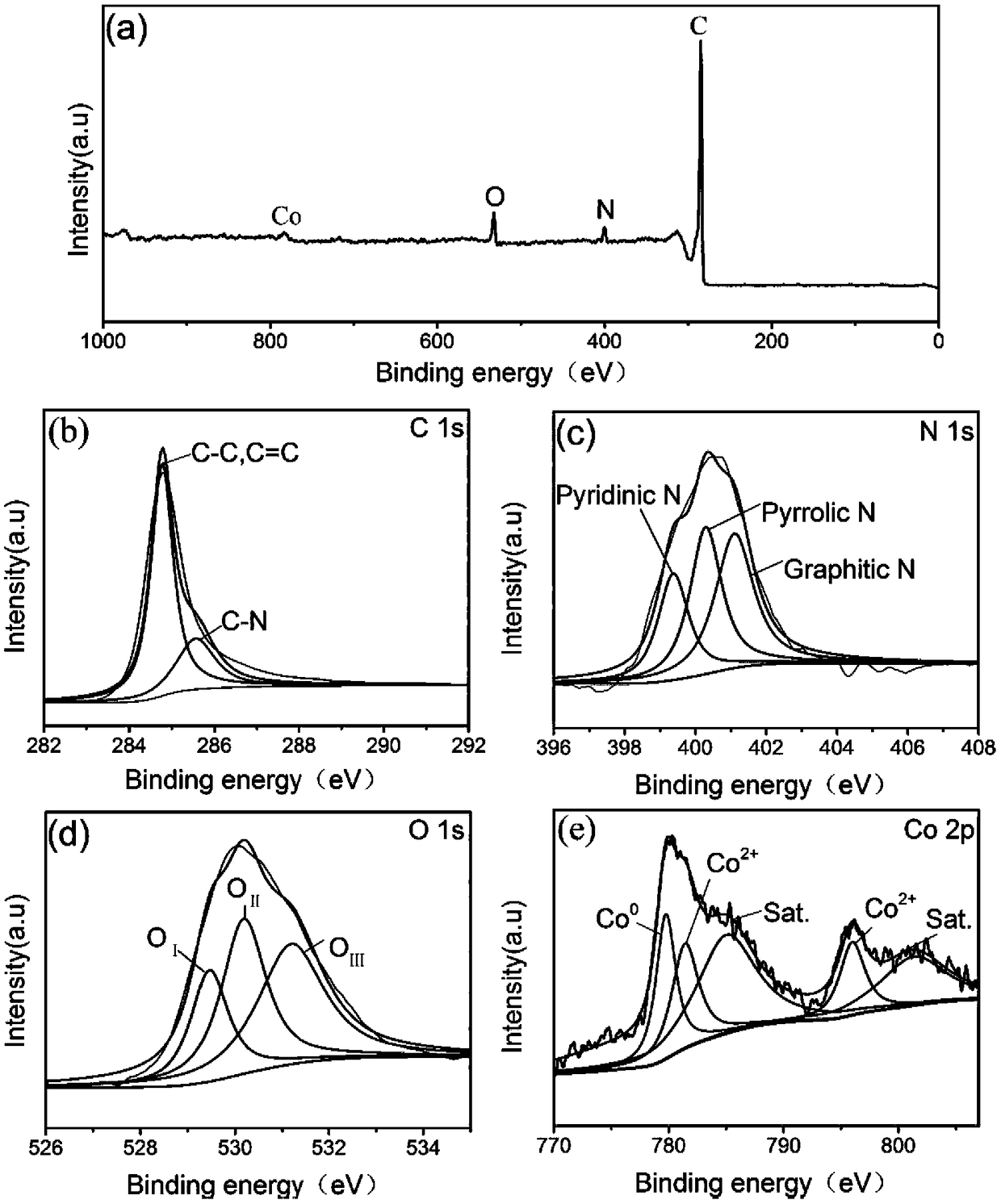

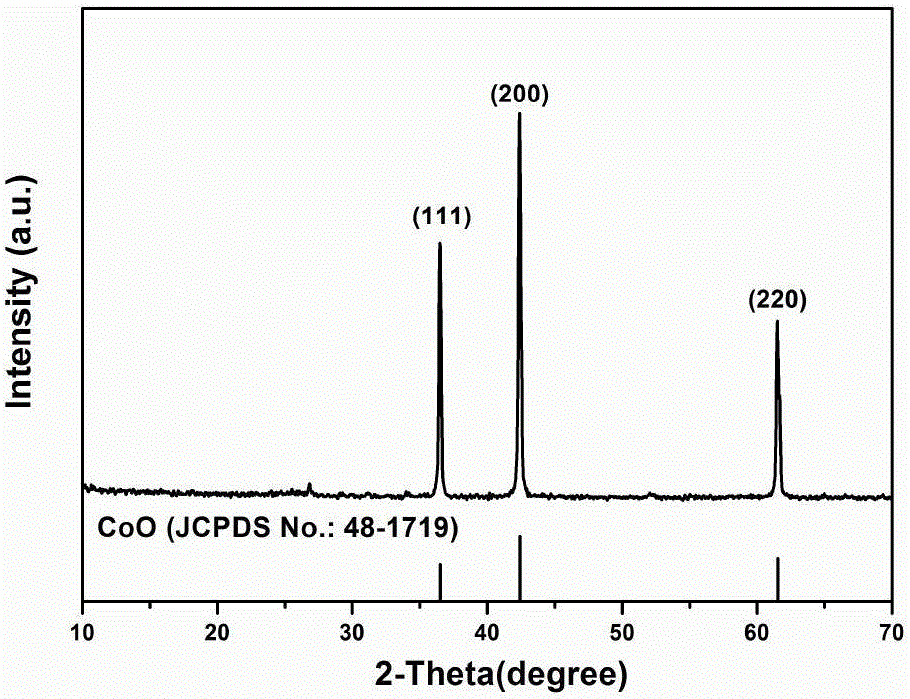

High-performance oxygen evolution CoO@Co-NC/C composite catalyst as well as preparation method and application thereof

ActiveCN108855184AImprove stabilityImprove catalytic performancePhysical/chemical process catalystsElectrodesChemistryOrganic acid

The invention discloses a high-performance oxygen evolution CoO@Co-NC / C composite catalyst as well as preparation method and application thereof. The composite catalyst is prepared by loading Co-coated CoO nano particles and nitrogen doped carbon on a carbon material; the preparation method comprises the following steps: mixing a nitrogen-containing organic small molecule compound, the carbon material and organic acid cobalt salt through a liquid phase, and performing evaporation and drying to obtain mixed powder; putting the mixed powder in a protection atmosphere, and performing two-stage roasting treatment to obtain the CoO@Co-NC / C composite catalyst. The preparation method is simple, low in cost and favorable for industrial production; the prepared CoO@Co-NC / C composite catalyst is applied to water decomposition or the storage and conversion system of renewable resources such as metal-air secondary batteries, and has the characteristics of high activity and high stability; comparedwith a RuO2 commercial catalyst, the CoO@Co-NC / C composite catalyst has better comprehensive performance and shows a good application prospect.

Owner:CENT SOUTH UNIV

Sponge composite metallic organic framework material for adsorption separation

ActiveCN110038540AStrong loadHigh load rateGas treatmentOther chemical processesFragilityMetal-organic framework

The invention relates to a sponge composite metallic organic framework material for adsorption separation and belongs to the technical field of materials. According to the invention, a two-step in-situ growth method is adopted for loading MOFs (metallic organic framework material) into a duct in a sponge carrier. The MOFs is synthesized from following organic ligands and metal salts, wherein the organic ligands include pyrazine, trimesic acid, terephthalic acid, 2,5-dihydroxyterephthalic acid, and the metal salts include cupric fluosilicate, magnesium nitrate, zirconium chloride, cupric nitrate, chromic nitrate, ferric nitrate, aluminum nitrate and hydrates thereof. According to a preparation method provided by the invention, a large amount of MOFs loaded in the duct in the sponge carriercan be realized; MOFs load rate is high; load is stable; the defects of fragility and easiness in loss of MOFs powder can be overcome; a breakthrough experiment proves that the material provided by the invention has the characteristics of high CO2-absorbing capacity, high adsorption separation selectivity, stable adsorption separation property, and the like.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

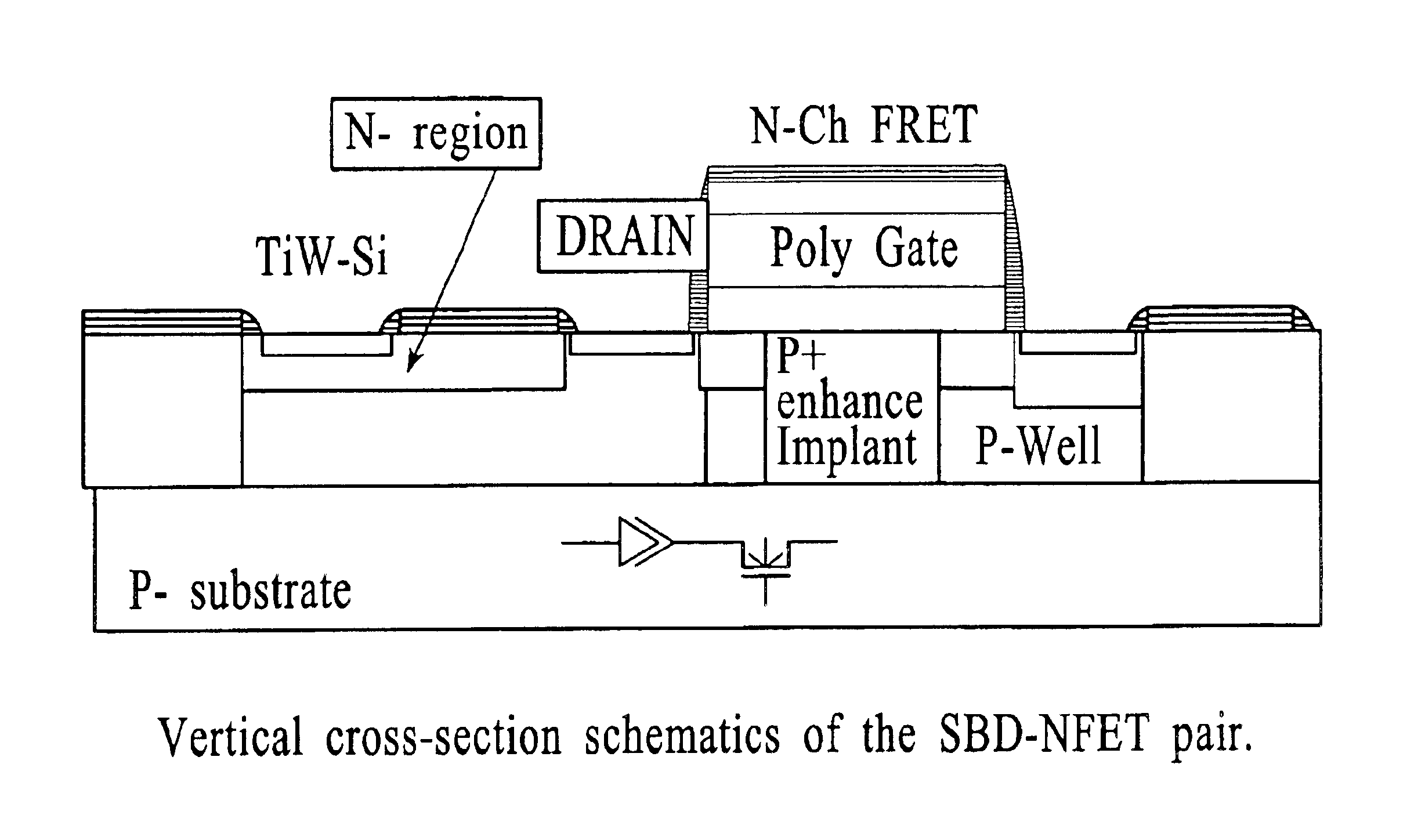

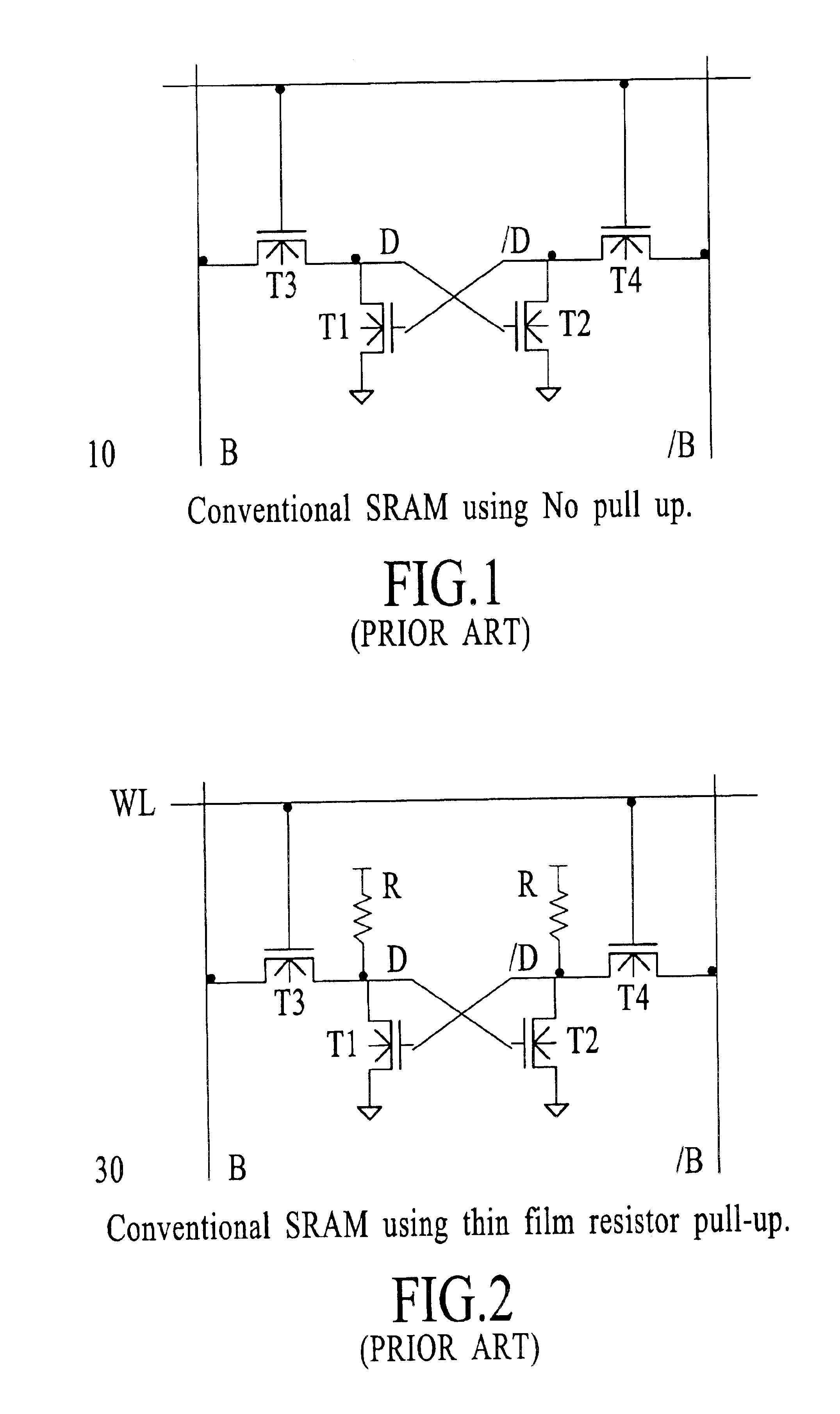

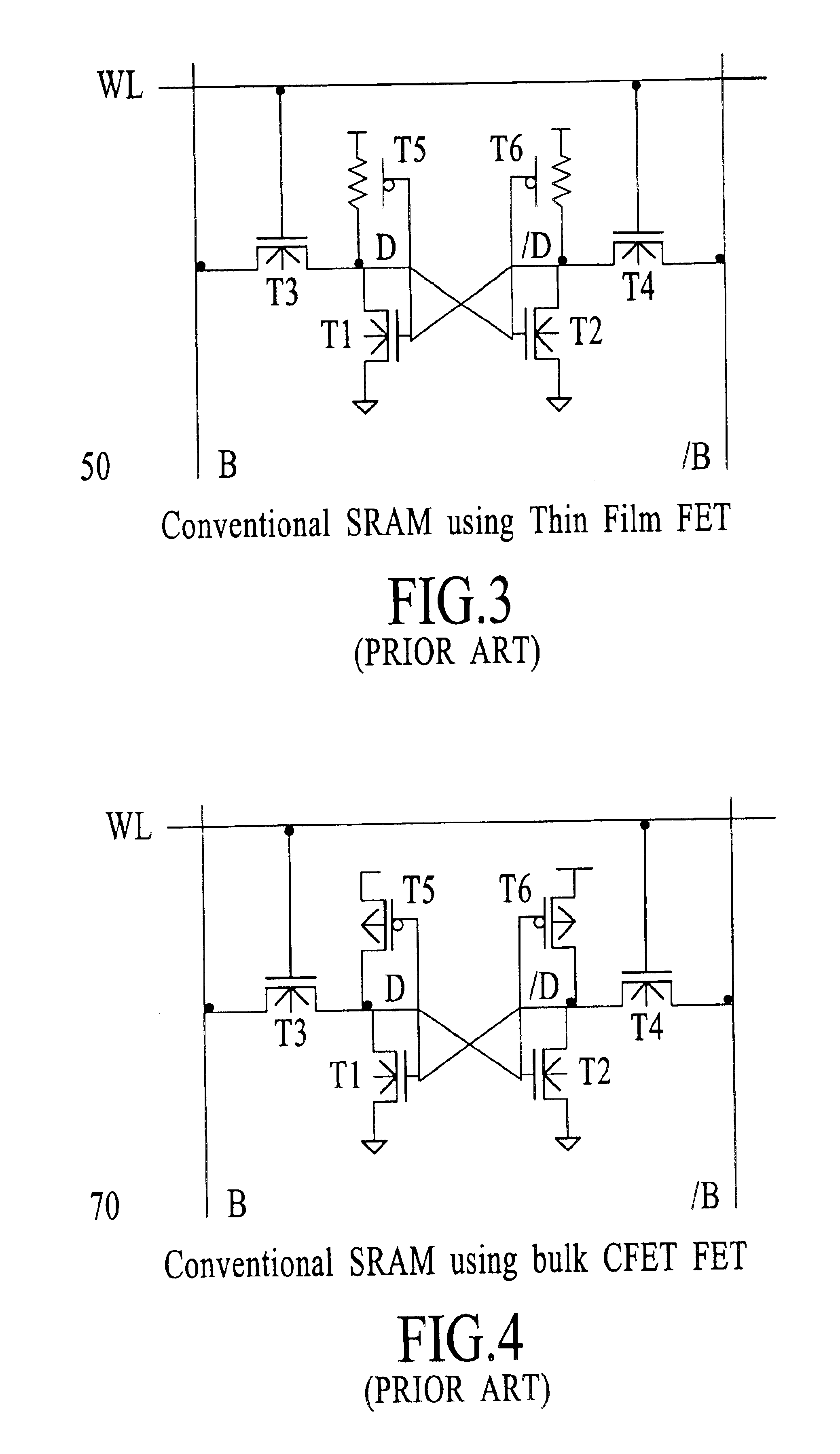

Schottky diode static random access memory (DSRAM) device, a method for making same, and CFET based DTL

InactiveUS6852578B2Stable load curveRapid designTransistorSemiconductor/solid-state device manufacturingCapacitanceLevel shifting

A high speed, low power Static Random Access Memory (SRAM) Array, which includes a 4T cell with two integrated Schottky Barrier Diodes (SBD) is provided. In a preferred embodiment, the cell bulk area and speed advantage is 30%, and AC power saving is 75% compared with the 6T CFET cell. The physical construct of the 4T cell saves capacitance in all critical nodes intra or inter cell wise, eliminates pass transistors, reduces the well noises. Typical embodiment uses a 0.15-um-rule based layout, and 1.5V supports operation at 5 ns cycles. SBD are used extensively with CFET to form a CMOS version of the Diode Transistor Logic circuitry. Generic control functions can be implemented including NAND / NOR gates, level shifting, decoding, voltage generator, ESD and latch-up protection, leakage control, and dynamic VT setting while in operation. Product applications include DRAM, SRAM, PLD, DRAM, CAM, Flash, Computing, Networking, and Communication devices as standalone system component or embedded into any ASIC.

Owner:SCHOTTKY LSI

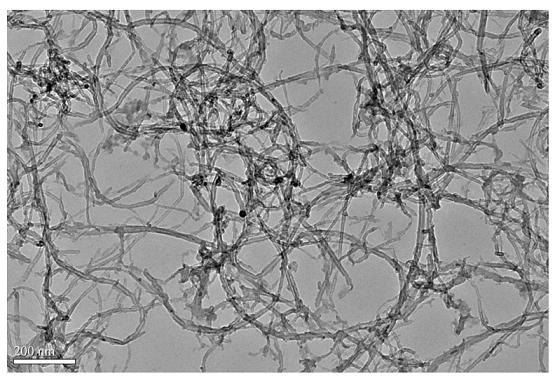

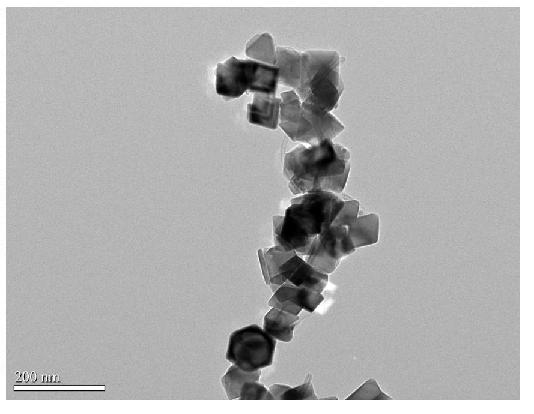

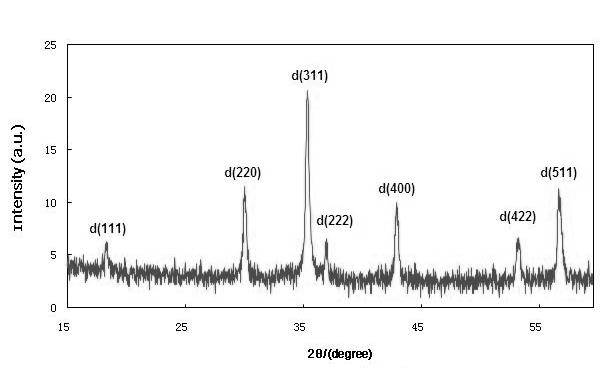

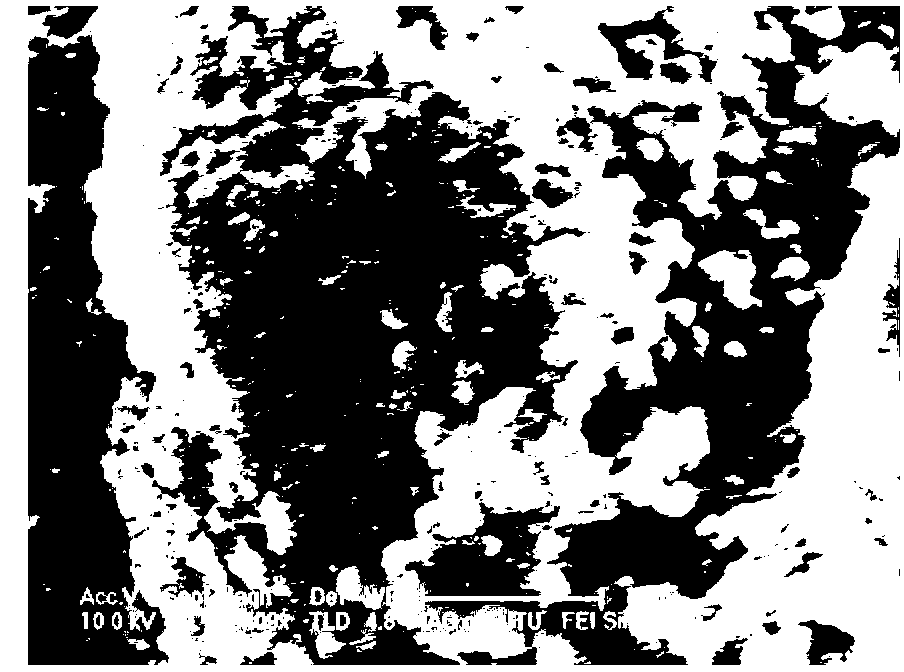

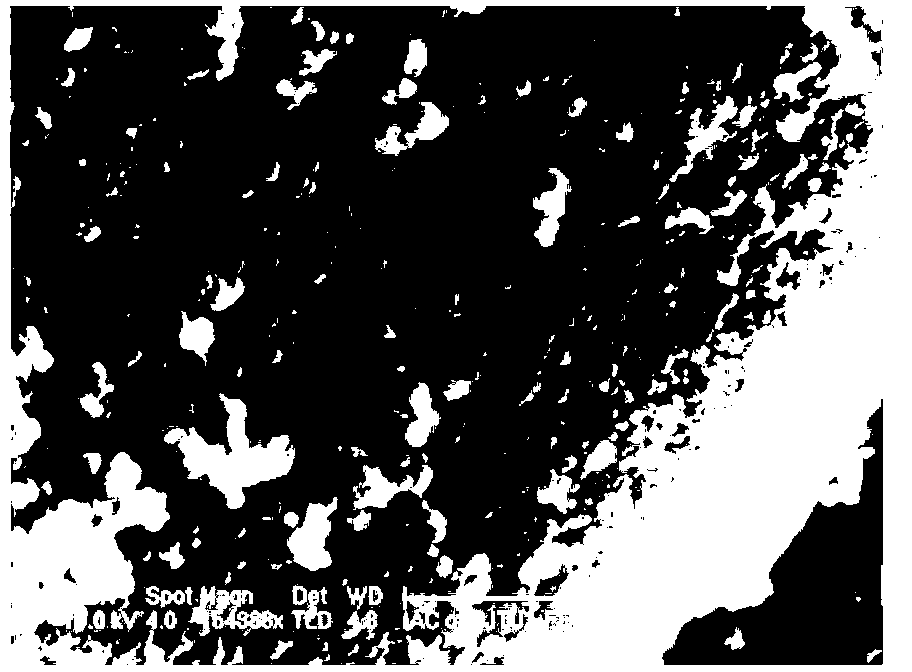

Ferroferric oxide nano crystal loaded on acid-modified carbon nano tube and preparation method thereof

InactiveCN102489252ALoad method is simpleReduce energy consumptionOther chemical processesAlkali metal oxides/hydroxidesModified carbonCarbon nanotube

The invention discloses a magnetic ferroferric oxide nano crystal loaded on an acid-modified carbon nano tube and a preparation method thereof and belongs to the field of nano crystals. The preparation method comprises the following steps of: carrying out ultrasonic modification treatment on the carbon nano tube in mixed acid composed of nitric acid and sulfuric acid; then dispersing the modified carbon nano tube in aqueous solution; under the condition of introducing inert gas and stirring, adding ferrous ions; and under the condition of hot-water bathing, adding a strongly-alkaline solution of nitrate, and growing the magnetic ferroferric oxide nano crystal with a regular structure directly on the carbon nano tube. The preparation method is simple and practicable, the conditions are easily controlled, roasting is not needed, the energy consumption is lower and industrial production can be achieved. The combination of the loaded ferroferric oxide crystal and the carrier carbon nano tube is compact, and the structure is stable. The prepared magnetic nano composite material is an excellent out-phase Fenton catalyst which has a function of absorbing organic pollutants and is convenient in separation, and simultaneously can be used for manufacturing chemical sensors and electromagnetic material devices.

Owner:NANJING UNIV

Magnetic carbon-based iron oxide compound material and preparation method thereof

ActiveCN103280577AHigh degree of crystallizationStrong loadCell electrodesWater/sewage treatment by magnetic/electric fieldsMagnetic carbonIron oxide

The invention discloses a magnetic carbon-based iron oxide compound material and a preparation method of the magnetic carbon-based iron oxide compound material. Particularly, the invention discloses a prepraation method of the magnetic carbon-based iron oxide compound material. The preparation method comprises the following steps of: (a) providing a mixture comprising a carbon-based precursor, elemental iron and a solvent; and (b) carrying out heating reaction on the mixture in the step (a), thus obtaining the carbon-based iron oxide compound material. The method has the advantages that materials are common and are easily available, and the process is simple, safe and effective and the like. The obtained compound material has stable magnetism, and is wide in application.

Owner:SHANGHAI JIAO TONG UNIV

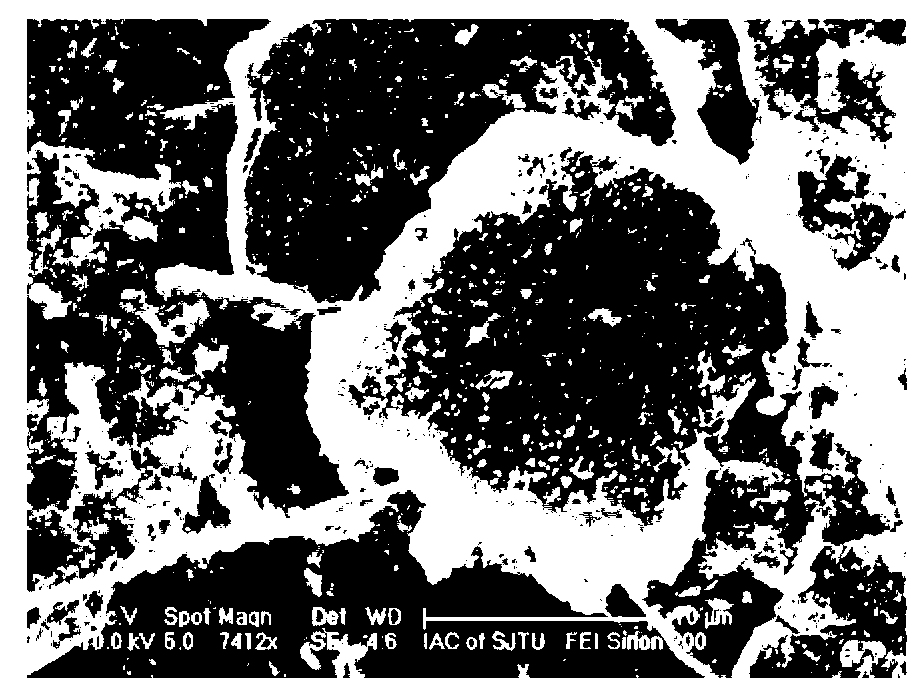

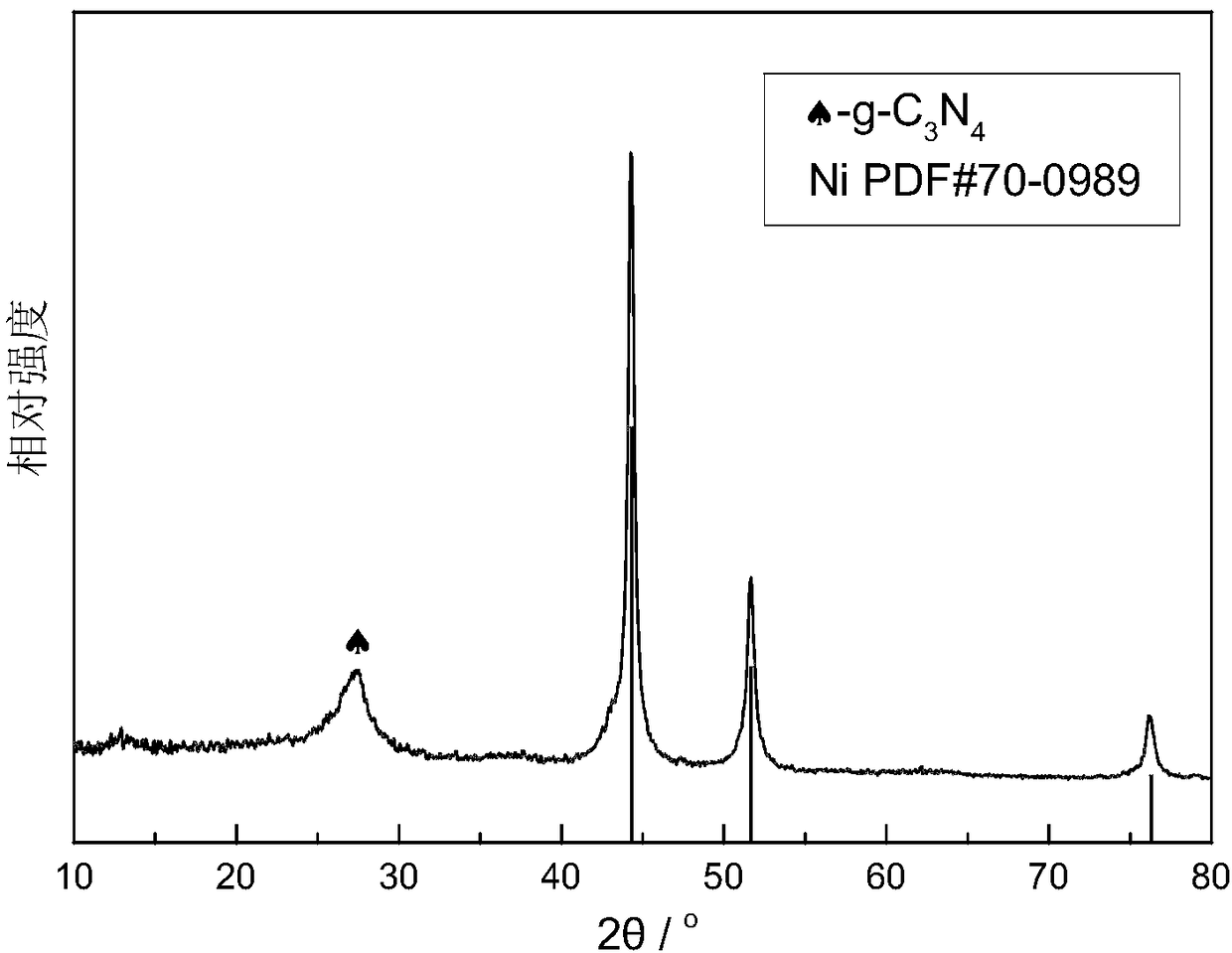

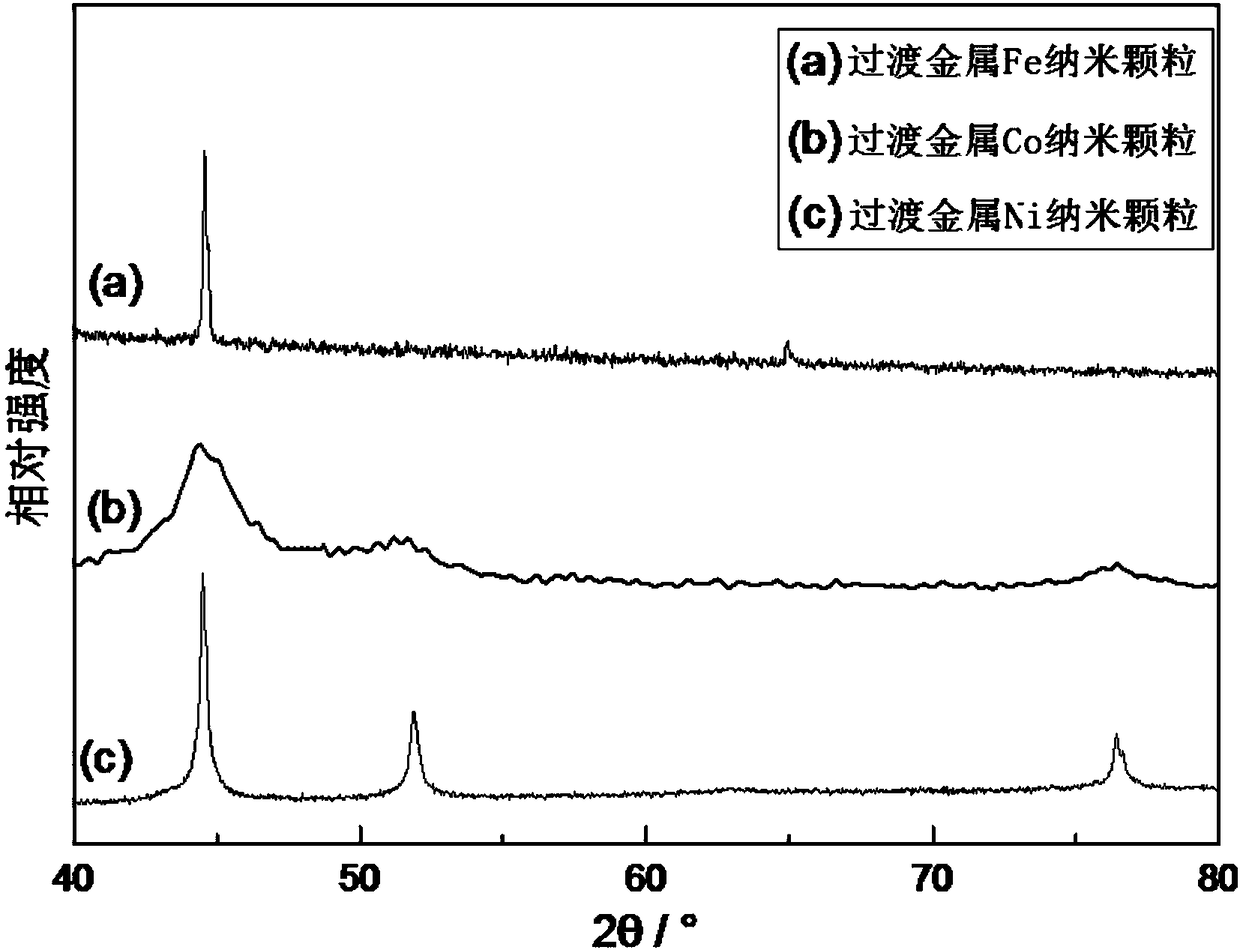

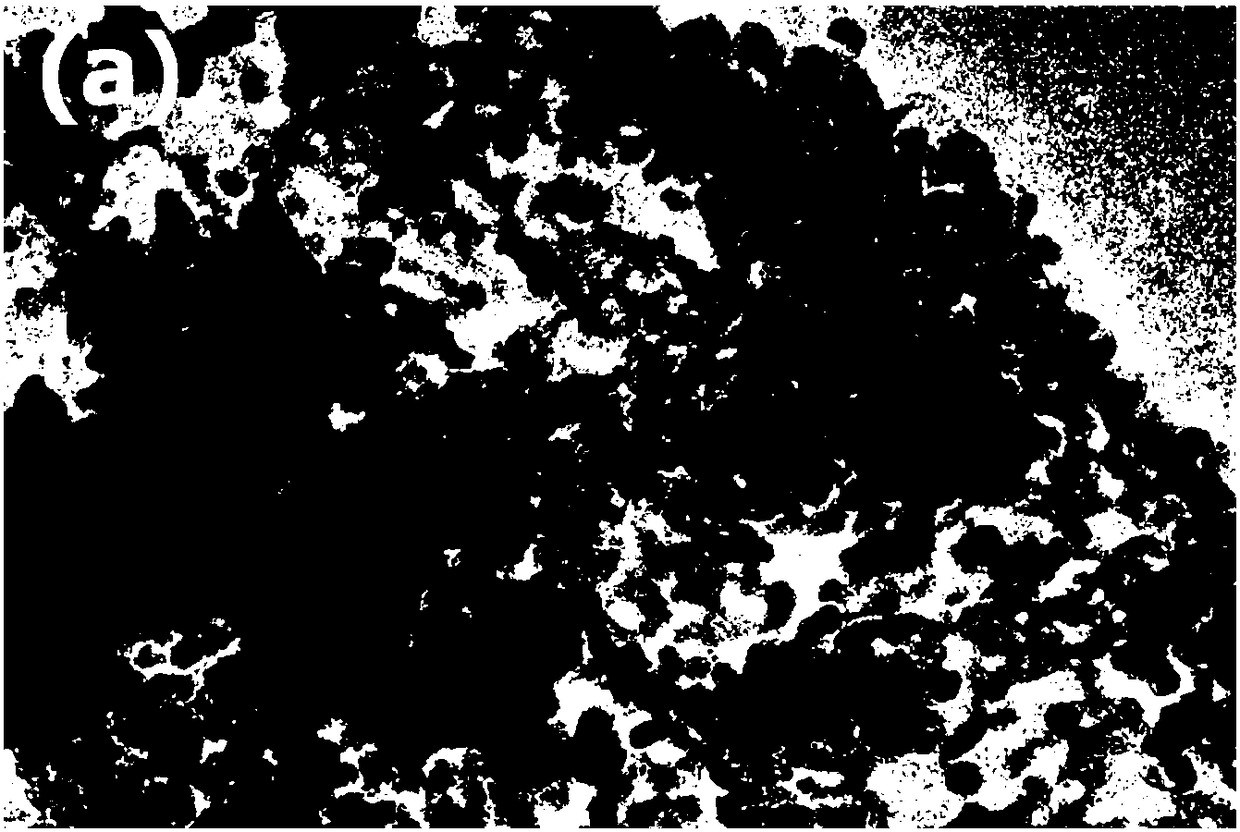

Transition metal complex nano-catalyst and preparation method and application thereof

InactiveCN108246333AAvoid uneven loadStrong loadPhysical/chemical process catalystsReversible hydrogen uptakeNano catalystSolvent

The invention discloses a transition metal complex nano-catalyst. The transition metal complex nano-catalyst comprises transition metal nanoparticles and a carrier, wherein the loading capacity of thetransition metal nanoparticles is 5-50%; and the carrier is g-C3N4. The preparation method comprises the following steps: (1) preparing urea as a precursor; and roasting under the temperature of 500-600 DEG C to obtain lamella shaped g-C3N4; (3) carbonizing a metal organic frame MOF-74-M under the temperature of 600-800 DEG C in protection atmosphere; and performing in-situ synthesizing on the carbon loaded transition metal nanoparticles, wherein M is Fe, Co or Ni; and (3) adding the transition metal nanoparticles and g-C3N4 to a solvent; and processing by stirring, ultrasonic wave and removing solvent to obtain the transition metal complex nano-catalyst. According to the method, the transition metal nanoparticles are loaded on the lamella shaped g-C3N4, so that the catalytic hydrogen production effect is improved; and the catalyst can be widely applied to the catalyzing field.

Owner:ZHEJIANG UNIV

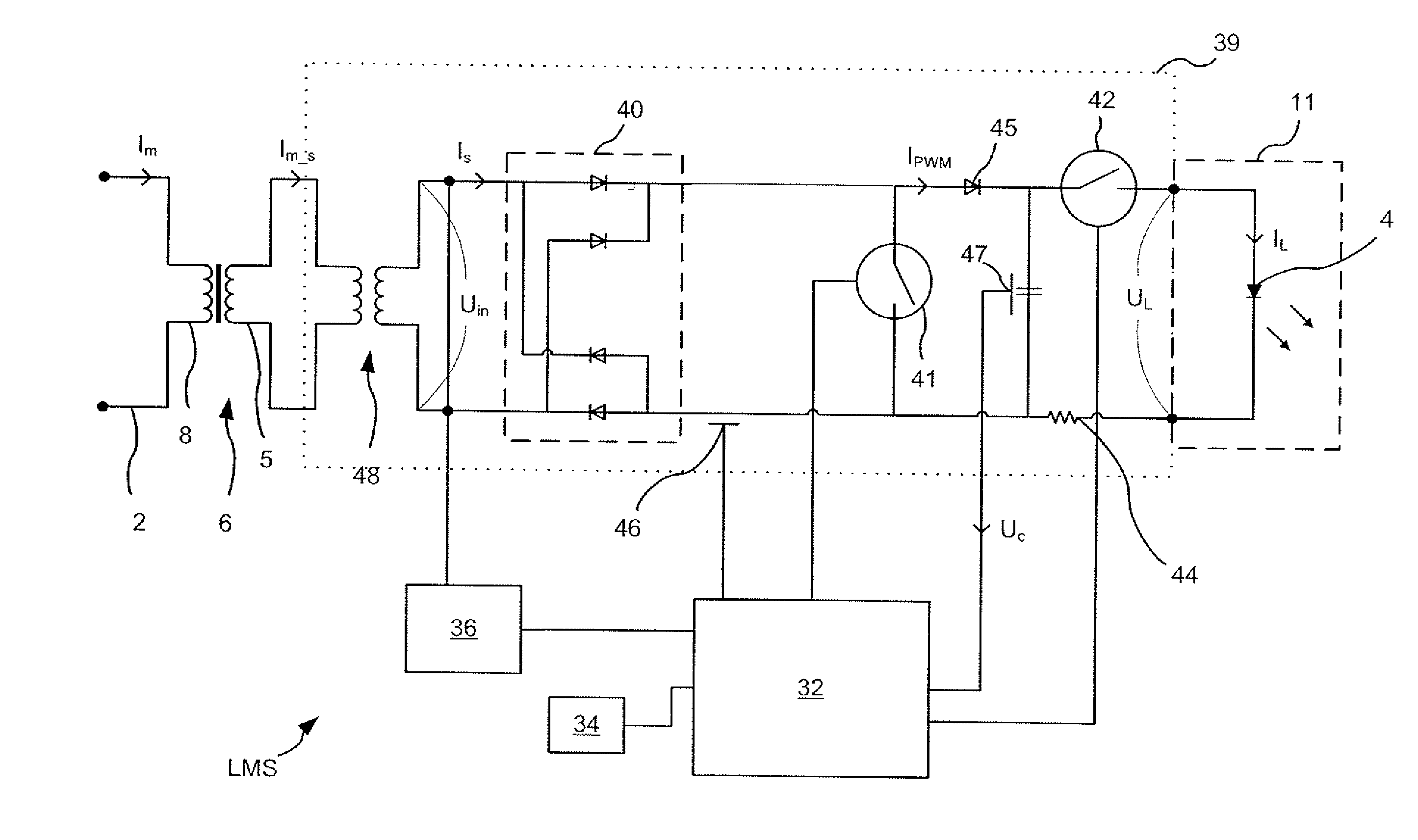

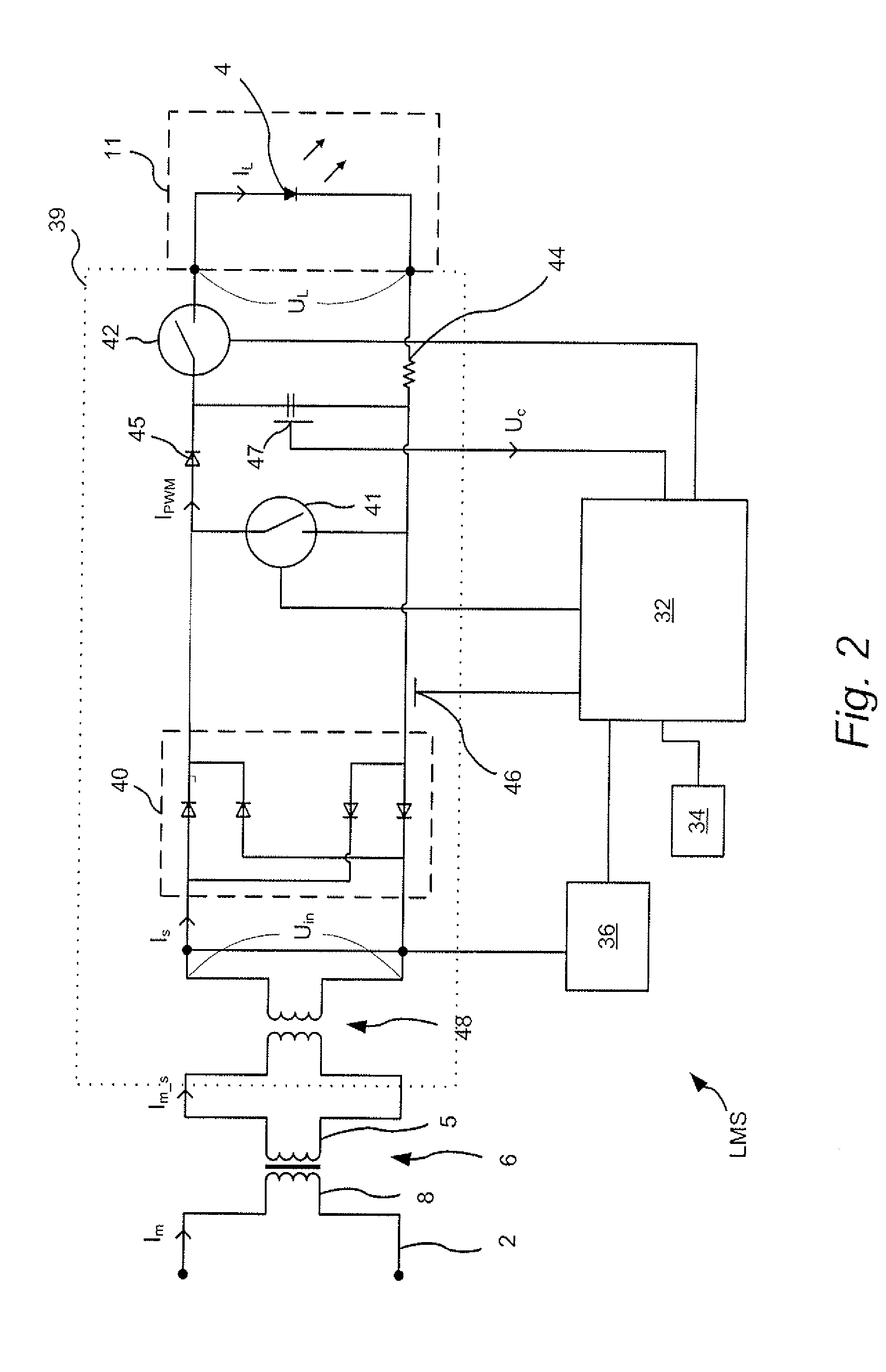

Airfield lighting with LED

InactiveUS20090091268A1Resistive characteristicStrong loadElectrical apparatusElectroluminescent light sourcesPulse width modulatedElectrical and Electronics engineering

A method of feeding electric power to an LED (4) in an airfield lighting unit (7). The method comprises the steps of: feeding a constant alternating current (Is) to a rectifier (40), rectifying the alternating current (Is) to a rectified current (Ir), pulse width modulating the rectified current (Ir), charging a capacitor (43) with the pulse width modulated rectified current (Ir), and feeding the LED (4) with power from the capacitor (43).

Owner:SAFEGATE INT

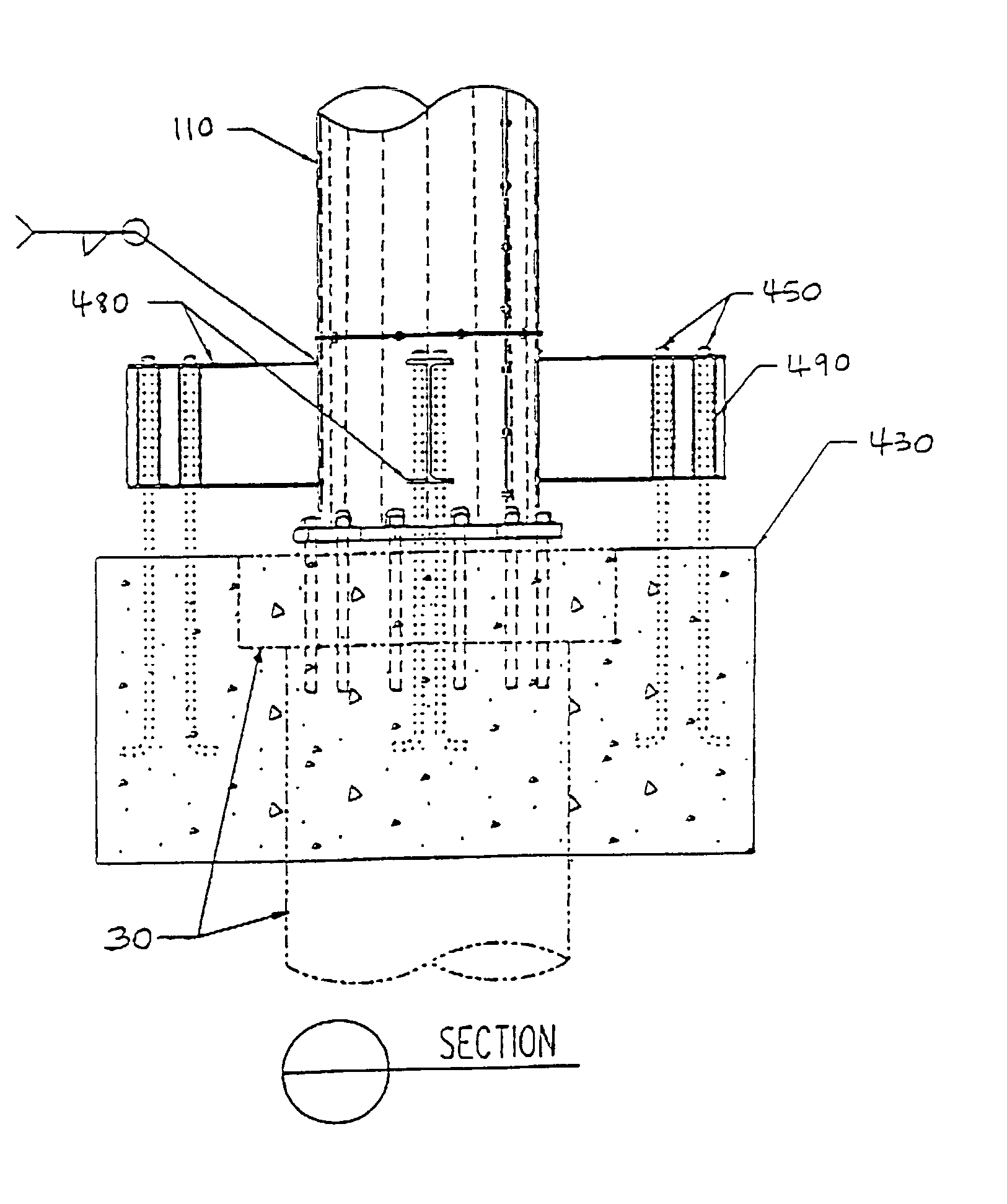

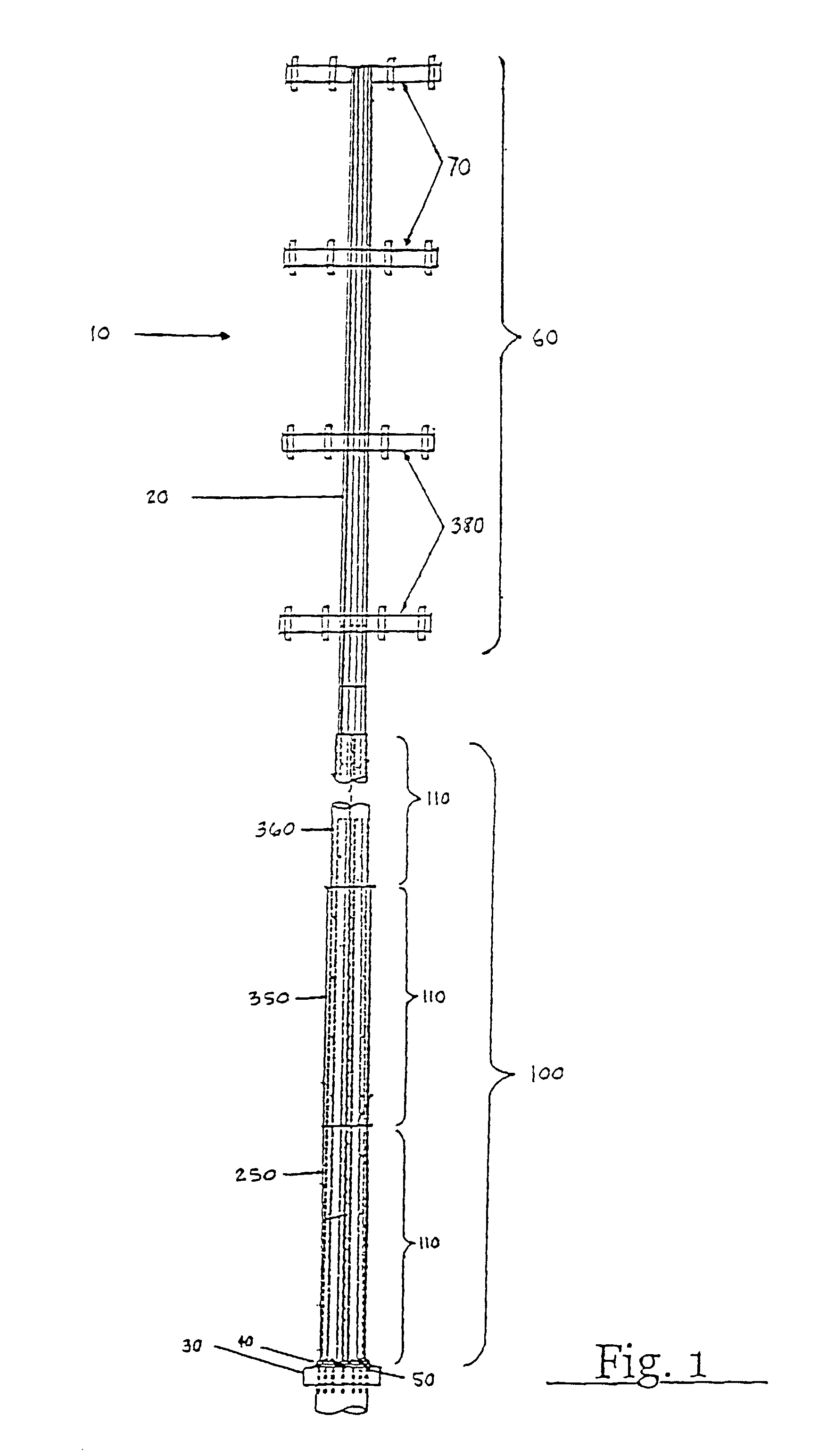

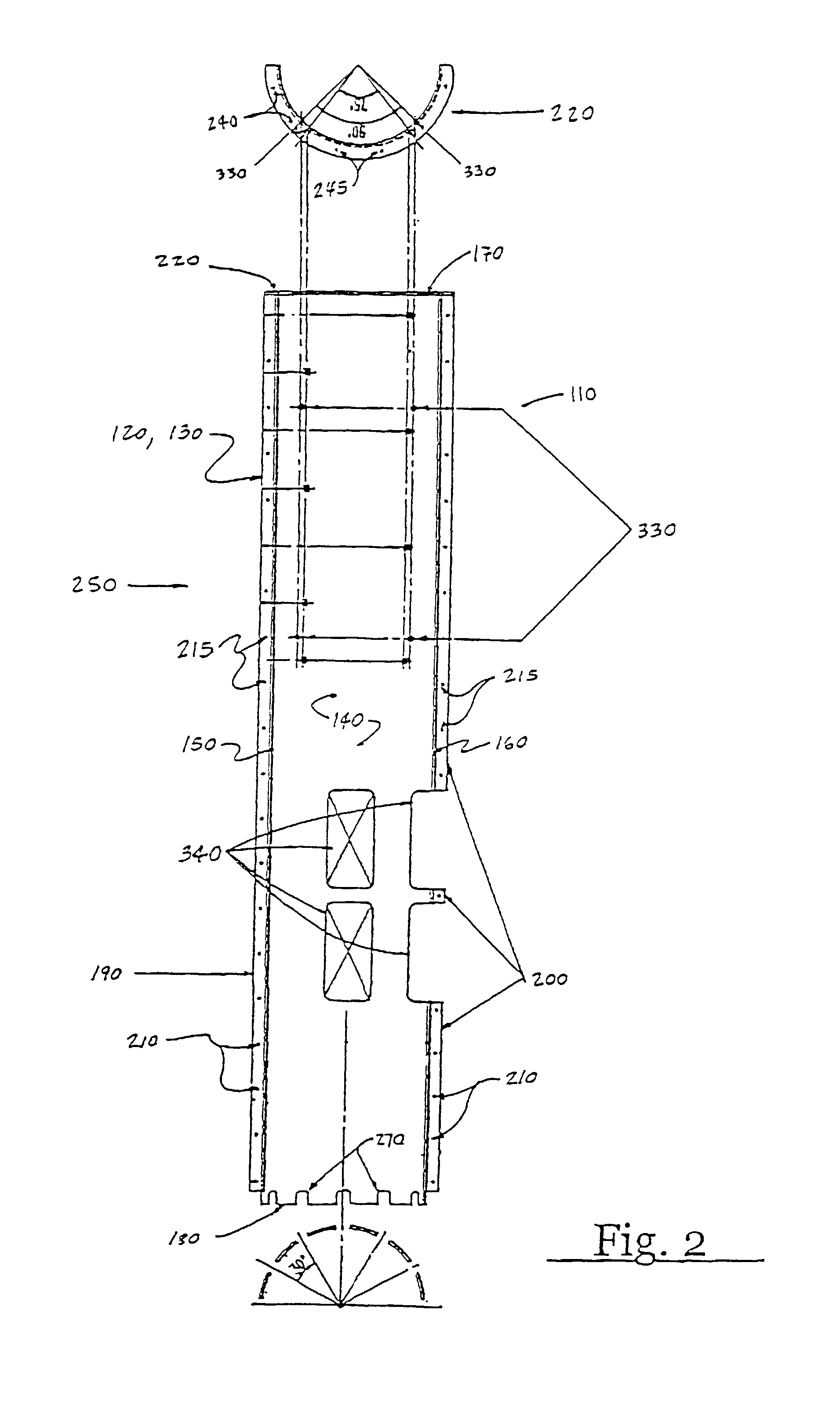

Method and apparatus for increasing the capacity and stability of a single-pole tower

A support structure for use with an existing single pole tower. The single pole tower has a pole anchored to a foundation and supports a first load. The support structure has a number of sleeves surrounding the pole. A first one of the sleeves is anchored to the foundation. A second load is attached to a second one of the sleeves.

Owner:RITZ TELECOMM

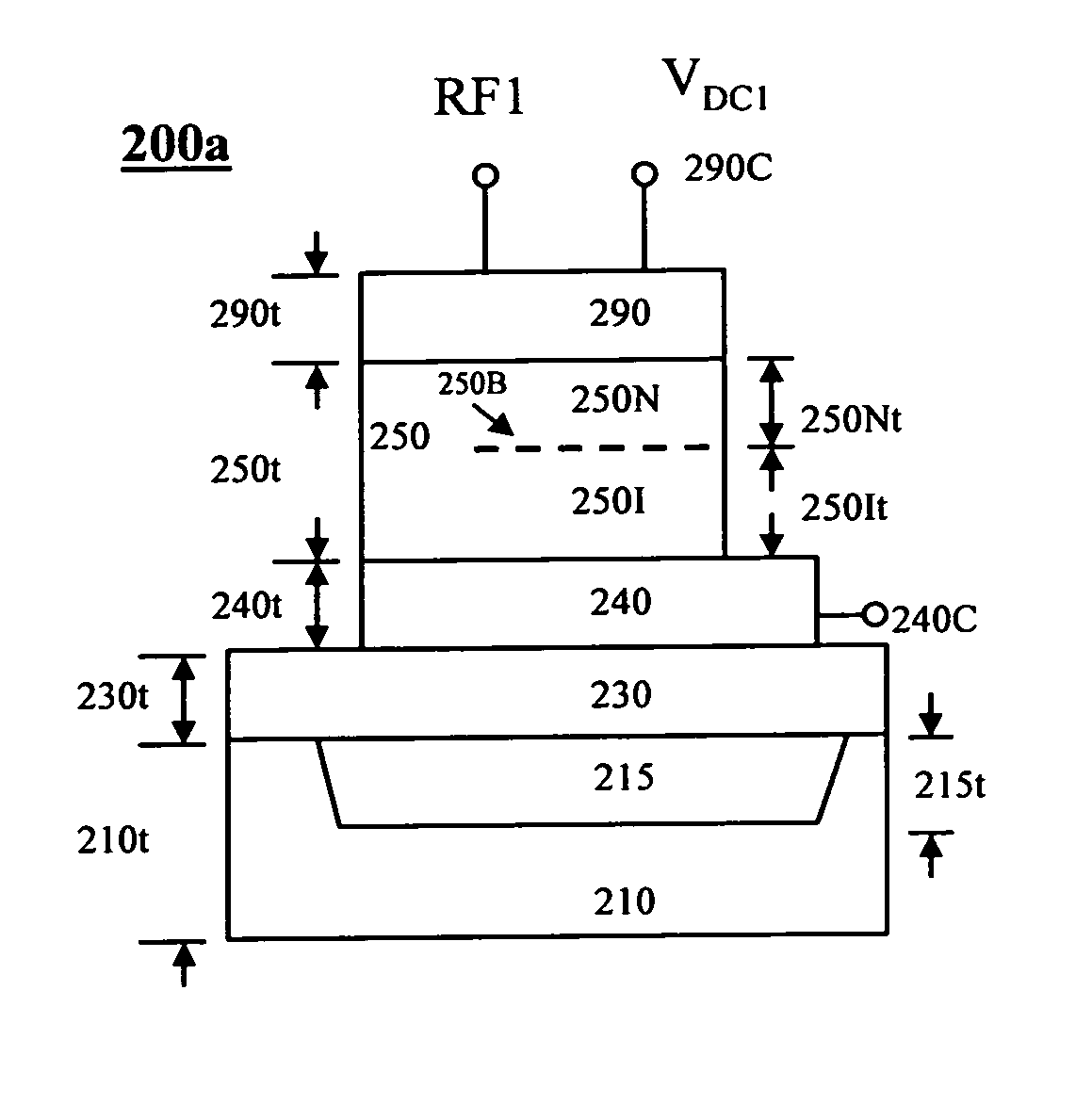

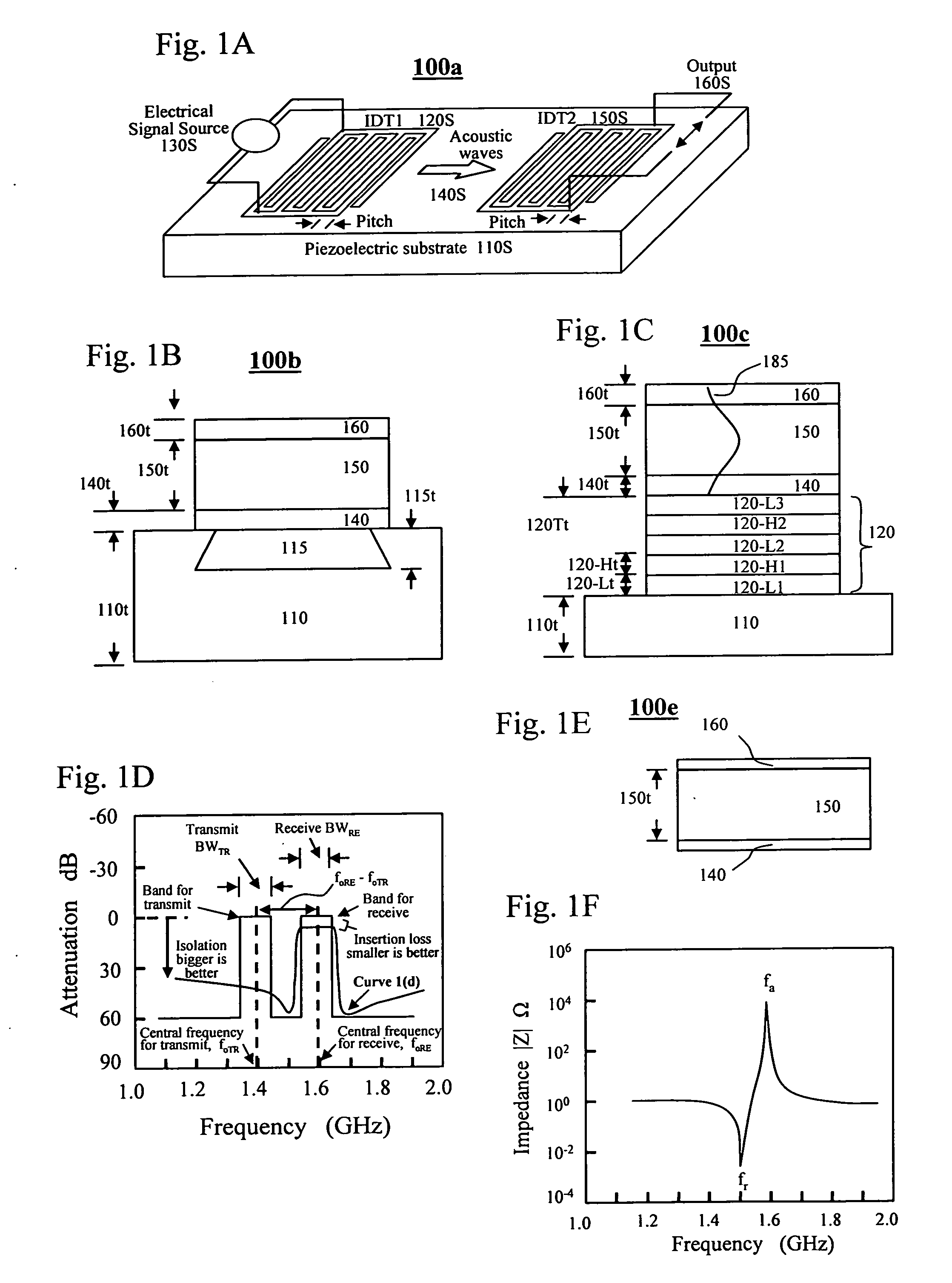

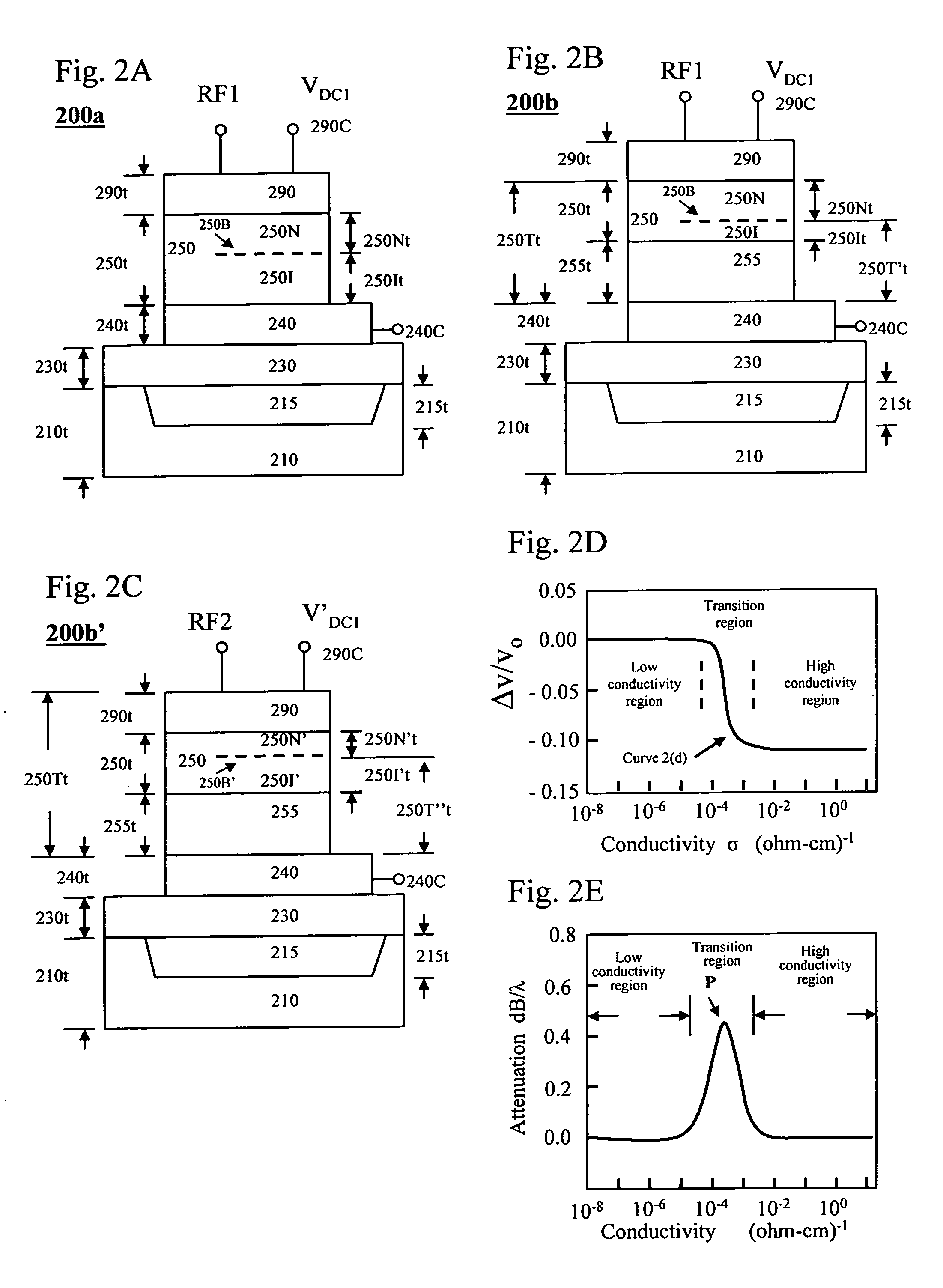

Tunable film bulk acoustic resonators and filters

ActiveUS20170025596A1Decrease in piezoelectric active layer thicknessReduce load effectImpedence networksPiezoelectric/electrostrictive/magnetostrictive devicesCommunication unitResonance

In wireless communications, many radio frequency bands are used. For each frequency band, there are two frequencies, one for transmitting and the other for receiving. As the band widths are small and separation between adjacent bands is also small, many band pass filters with different band pass frequencies are required for each communication unit such as mobile handset. The invention provides tunable film bulk acoustic resonators TFBARs containing semiconducting piezoelectric layers and methods for tuning and adjusting the resonant properties. When a DC biasing voltage is varied, both the depletion region thickness and neutral region thickness associated in the semiconducting piezoelectric layers varies leading to changes in equivalent capacitances, inductance and resistances and hence the resonance properties and frequencies. A plurality of the present TFBARs are connected into a tunable oscillator or a tunable and selectable microwave filter for selecting and adjusting of the bandpass frequency by varying the biasing voltages.

Owner:QIU CINDY X +5

Punching tool

ActiveUS20060048623A1Simple and rapid separationReliable lockingPerforating toolsMetal working apparatusPunchingPlunger

A punching tool has a guided, axially displaceable die plunger, which is fixed against relative rotation, in a guide bushing. In a bore in its front end a punching die is seated. During the punching stroke the punching die rests against a front face of the die plunger and is axially fixed in place by means of one or several snap-in balls, each of which is seated in a transverse bore, which snap-in balls are maintained in engagement with an annular groove by means of a spring washer in the die plunger. The outer diameter of the spring washer is only slightly less in the engagement position than the inner diameter of the guide bushing and can be elastically widened for releasing the punching die outside of the guide bushing.

Owner:MATE PRECISION TOOLING

Method for preparing anode material of three-dimensional porous carbon skeleton/CoO composite structured lithium ion battery

ActiveCN105845915AImprove cycle performanceImproved magnification performanceCell electrodesSecondary cellsElectrochemical responseChemical reaction

The invention relates to a method for preparing an anode material of a three-dimensional porous carbon skeleton / CoO composite structured lithium ion battery. Parenchymatous tissue of plants is used as the biomass carbon material; the biomass carbon material is immersed through acid, such that a pre-carbonized precursor is obtained; then, the precursor and alkali are mixed and sufficiently grinded, and then thermally treated in a tube furnace, such that a three-dimensional porous carbon skeleton is obtained; the three-dimensional porous carbon skeleton is immersed in solution including cobalt salt; then, suction filtration and drying are carried out; and finally, the mixture is thermally treated in the tube furnace, such that a CoO loaded three-dimensional porous carbon skeleton composite is obtained. The composite is applied to the lithium ion battery, such that the lithium ion battery has good cycle performance and rate performance; the porous carbon skeleton, prepared by using the parenchymatous tissue of plants as the biomass carbon material, has a steady structure for supporting load of CoO; the porous carbon skeleton having different pore diameters can be obtained by controlling the addition amount of urea; due to the porous carbon skeleton, the CoO structure can be stabilized; simultaneously, the electrical conductivity of CoO is also improved; therefore, the electron transmission rate is increased; the electrochemical reaction is accelerated; and the rate performance is improved easily.

Owner:SHAANXI UNIV OF SCI & TECH

Preparation method of low-mercury catalyst for preparing vinyl chloride

ActiveCN102151573ALow costHigh activityPreparation by halogen halide additionMetal/metal-oxides/metal-hydroxide catalystsEnvironmental resistanceEvaporation

The invention provides a novel preparation method of a low-mercury catalyst for preparing vinyl chloride from acetylene. In the method, treated coal carbon is taken as a carrier, the vacuum impregnation method is used for loading a small amount of mercury chloride and other auxiliaries on the carrier, and rotary evaporation and other drying ways are performed to obtain the novel catalyst. Compared with a high-mercury catalyst and a precious metal catalyst which is researched and developed currently, the carrier coal carbon, and the auxiliaries related to the catalyst disclosed by the invention are lower in cost, the catalyst is safer and more environment-friendly, the adopted process is simple, and the production period is short. In the application of preparing vinyl chloride by hydrochlorinate of acetylene, the low-mercury catalyst represents excellent activity and selectivity and can be regarded as an excellent substitute for the current mainstream high-mercury catalyst.

Owner:NANKAI UNIV